Patents

Literature

123results about How to "Low Power Features" patented technology

Efficacy Topic

Property

Owner

Technical Advancement

Application Domain

Technology Topic

Technology Field Word

Patent Country/Region

Patent Type

Patent Status

Application Year

Inventor

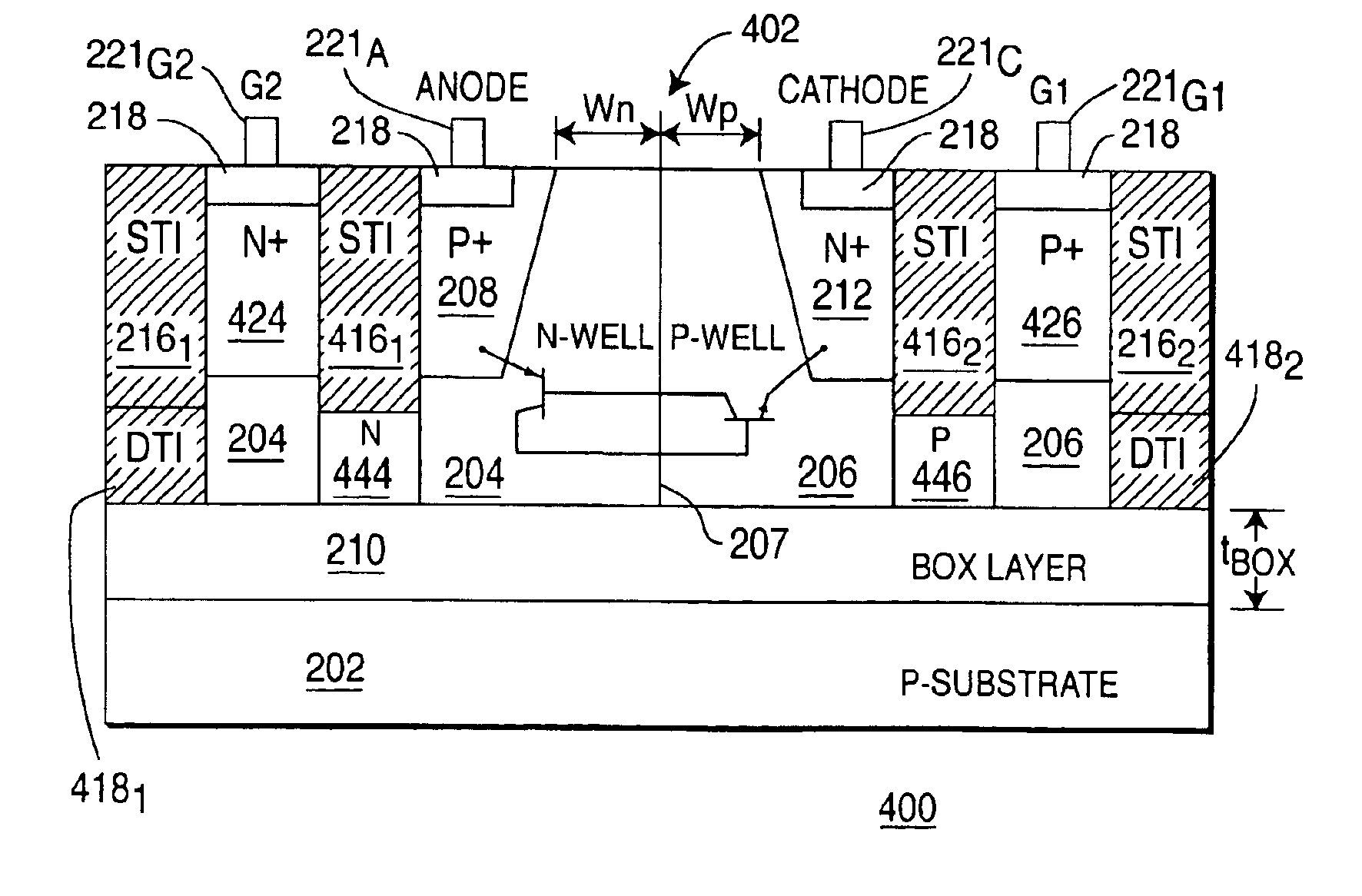

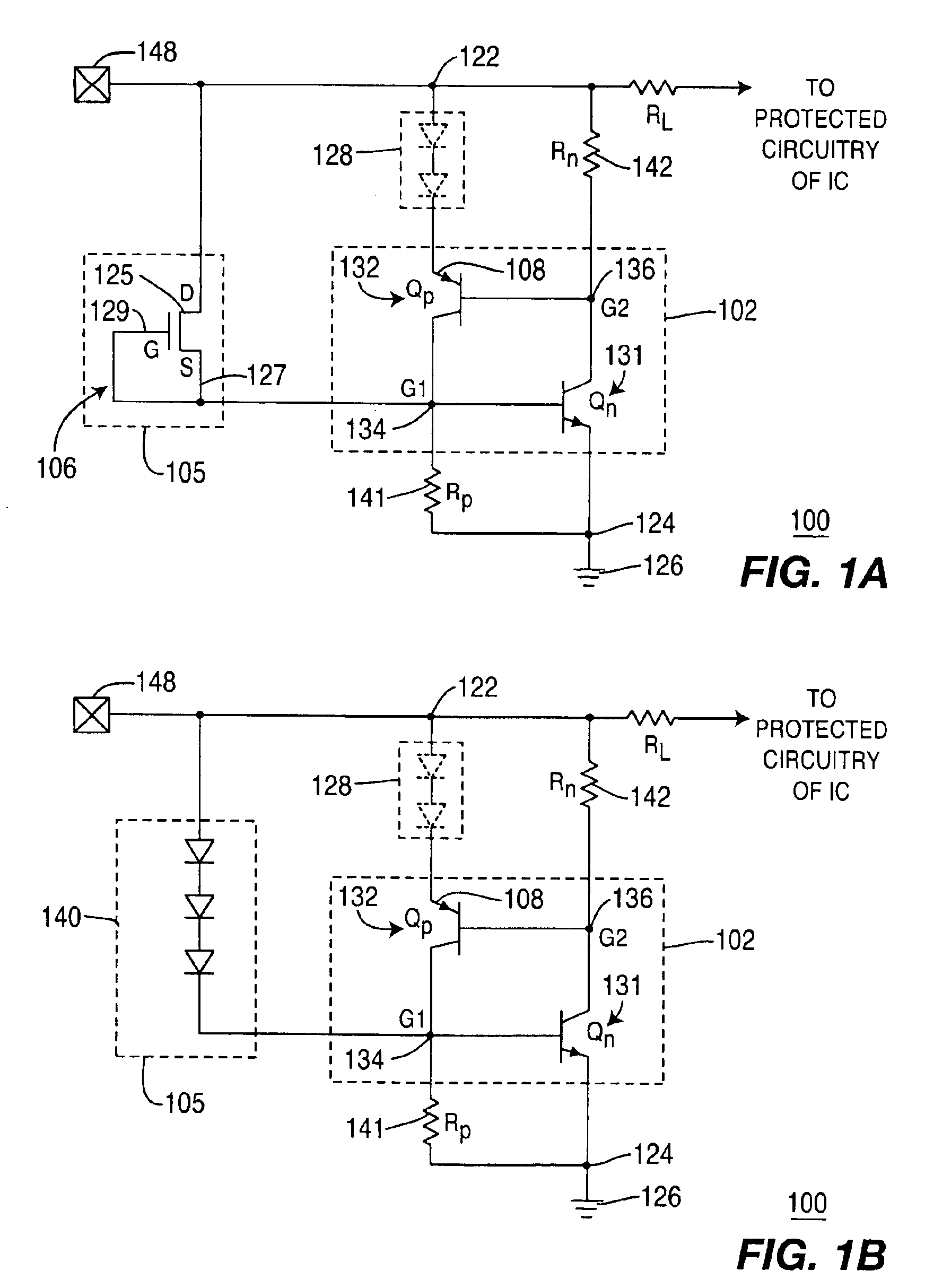

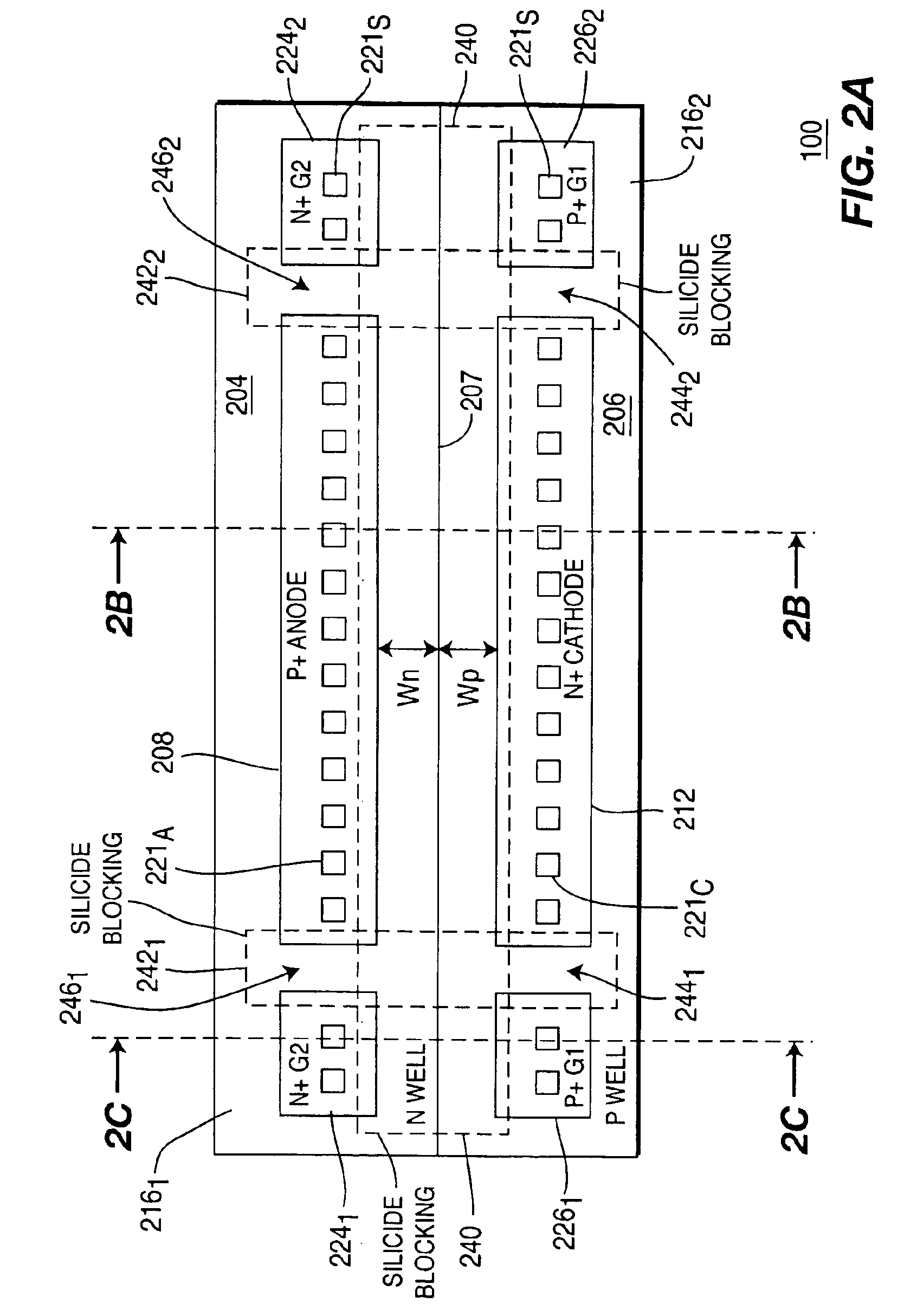

Low voltage silicon controlled rectifier (SCR) for electrostatic discharge (ESD) protection of silicon-on-insulator technologies

ActiveUS6909149B2Low triggeringLow holding voltageTransistorThyristorSilicon-controlled rectifierLow voltage

A silicon-on-insulator (SOI) electrostatic discharge (ESD) protection device that can protect very sensitive thin gate oxides by limiting the power dissipation during the ESD event, which is best achieved by reducing the voltage drop across the active (protection) device during an ESD event. In one embodiment, the invention provides very low triggering and holding voltages. Furthermore, the SOI protection device of the present invention has low impedance and low power dissipation characteristics that reduce voltage build-up, and accordingly, enable designers to fabricate more area efficient protection device

Owner:SOFICS BVBA

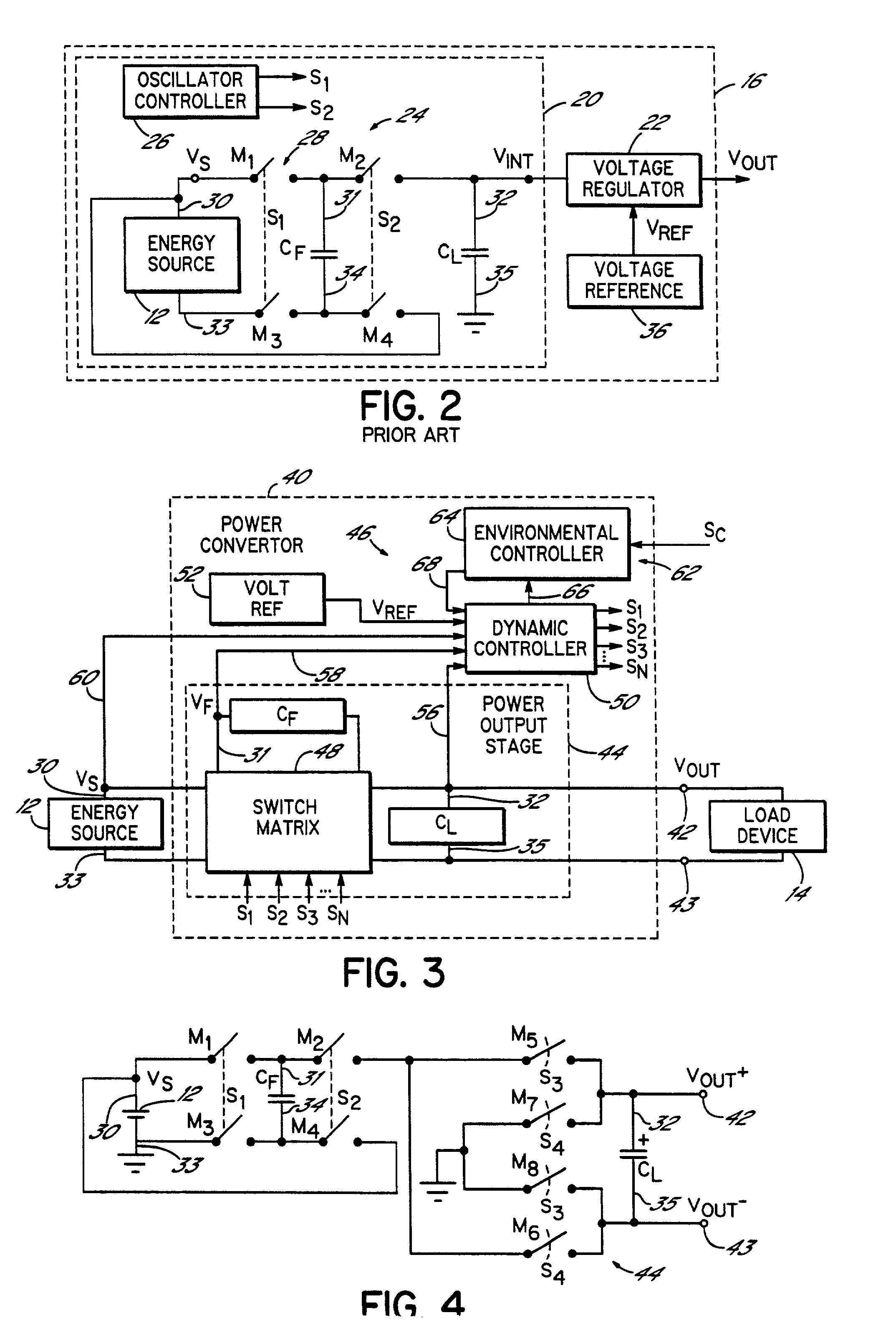

Progressive start-up circuit for activating a charge pump

InactiveUS20010033501A1Enhance battery service lifeHigh energyBatteries circuit arrangementsEfficient power electronics conversionClosed loopPower MOSFET

A charge pump power converter efficiently provides electrical power by dynamically controlling a switch matrix of the charge pump. Instead of open-loop oscillator-based control, a dynamic controller provides power upon demand by sensing the output voltage and changing the operating frequency of the charge pump in response. Moreover, this closed-loop dynamic control intrinsically voltage regulates the output voltage of the charge pump power converter without the inefficient addition of a step-down voltage regulator, downstream of the power converter. In addition, this closed-loop dynamic control allows for maintaining a desired output voltage even with variations in the input voltage. Also, the dynamic control accommodates the advantages of using ultra-capacitors in the charge pump. The power converter is capable of operating with a sub-one volt input voltage incorporating low-threshold, low on-resistance power MOSFET switches in the switch matrix of the charge pump. A progressive start-up circuit further allows the power converter to start from a discharged state even with a sub-one volt input voltage.

Owner:THE BOARD OF TRUSTEES OF THE UNIV OF ILLINOIS

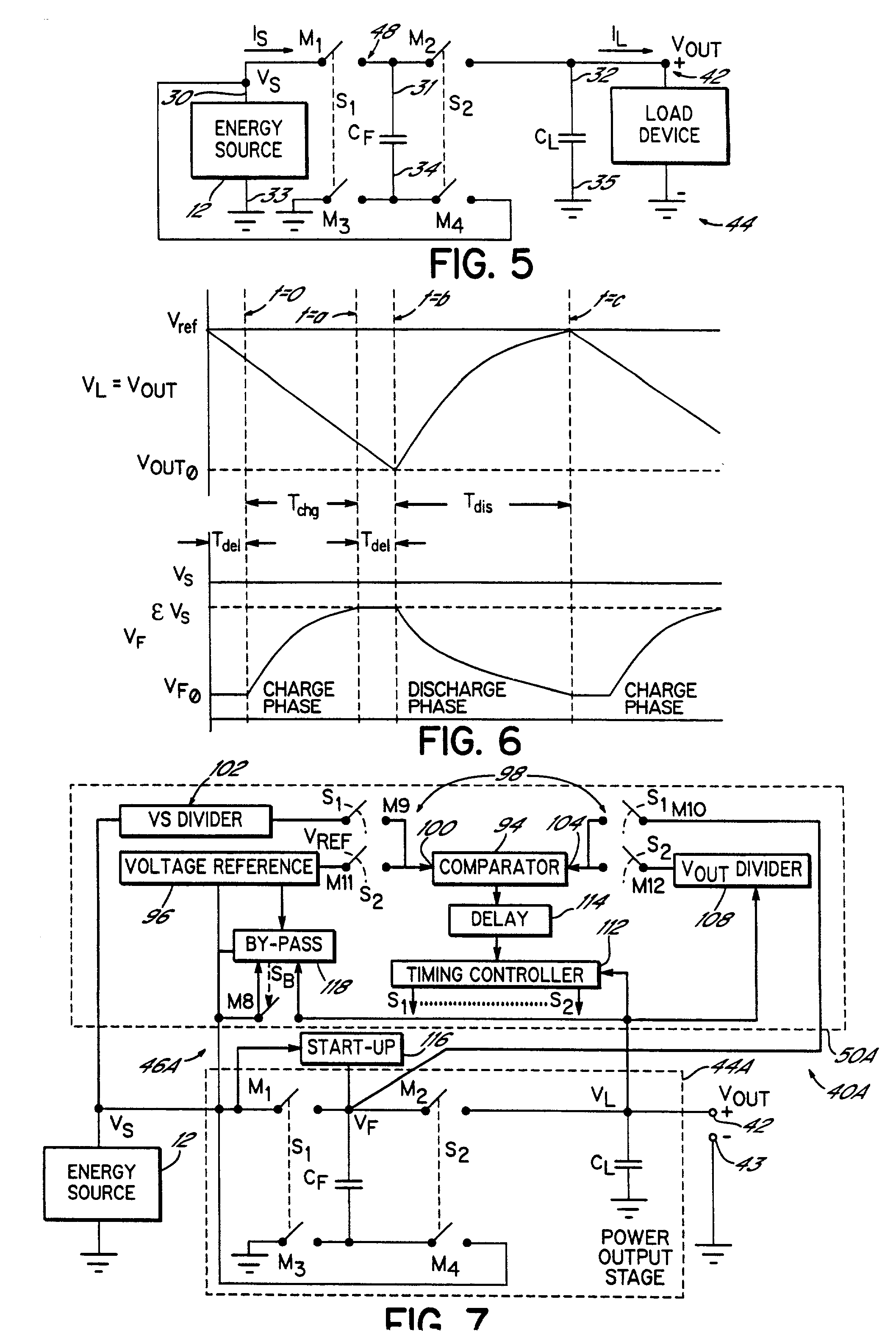

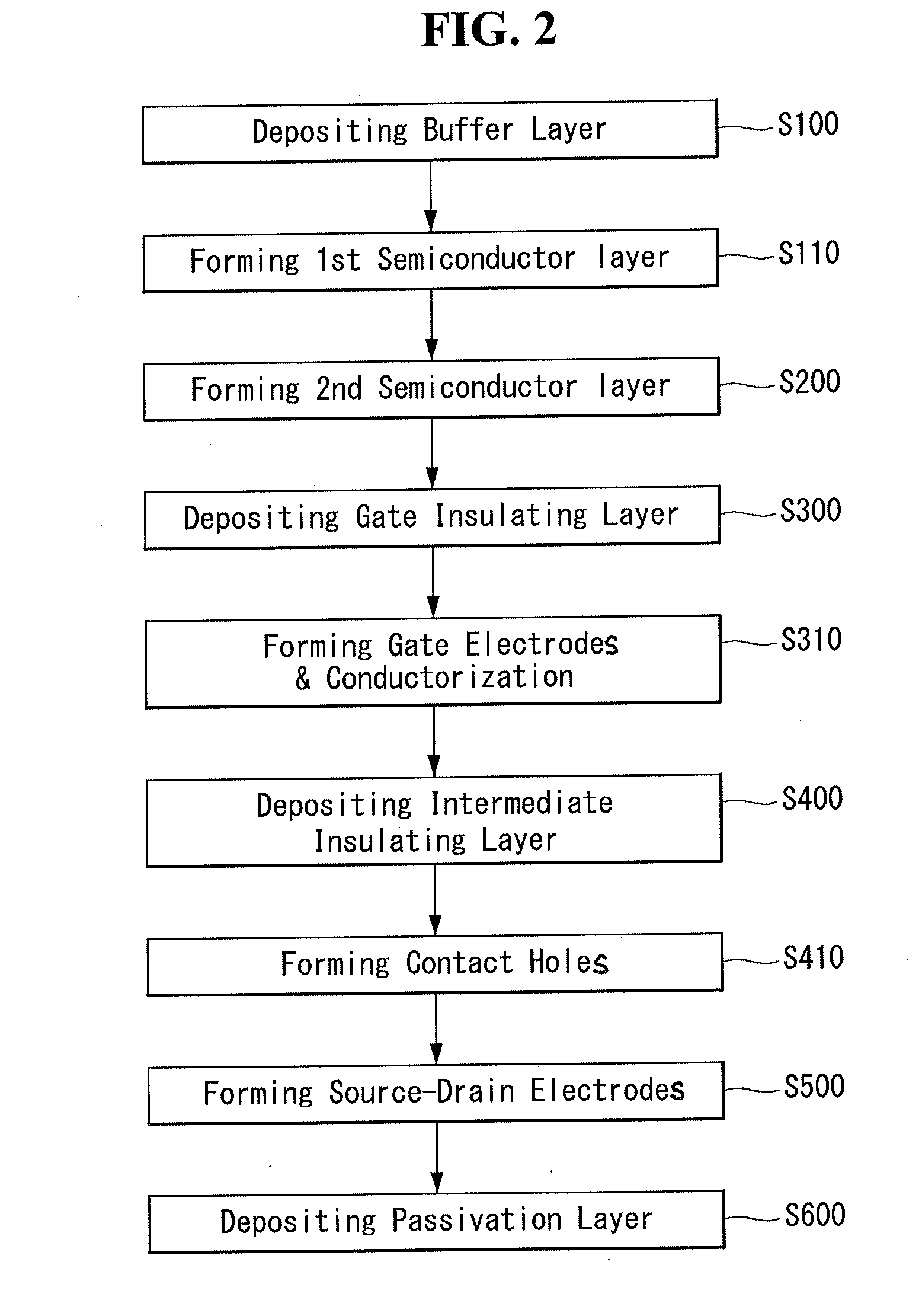

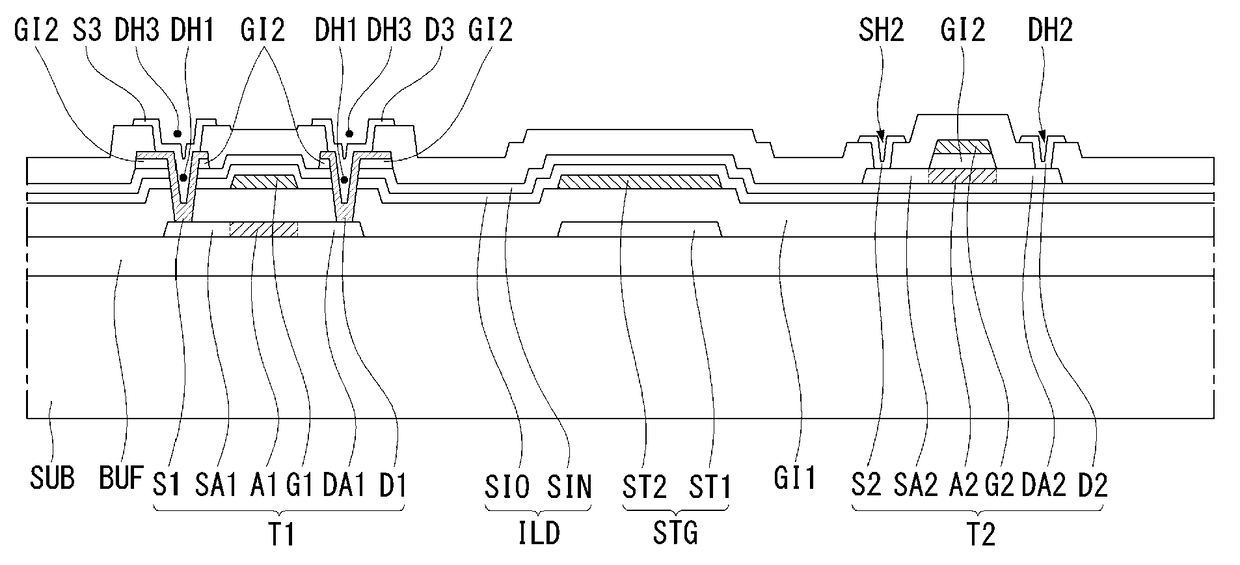

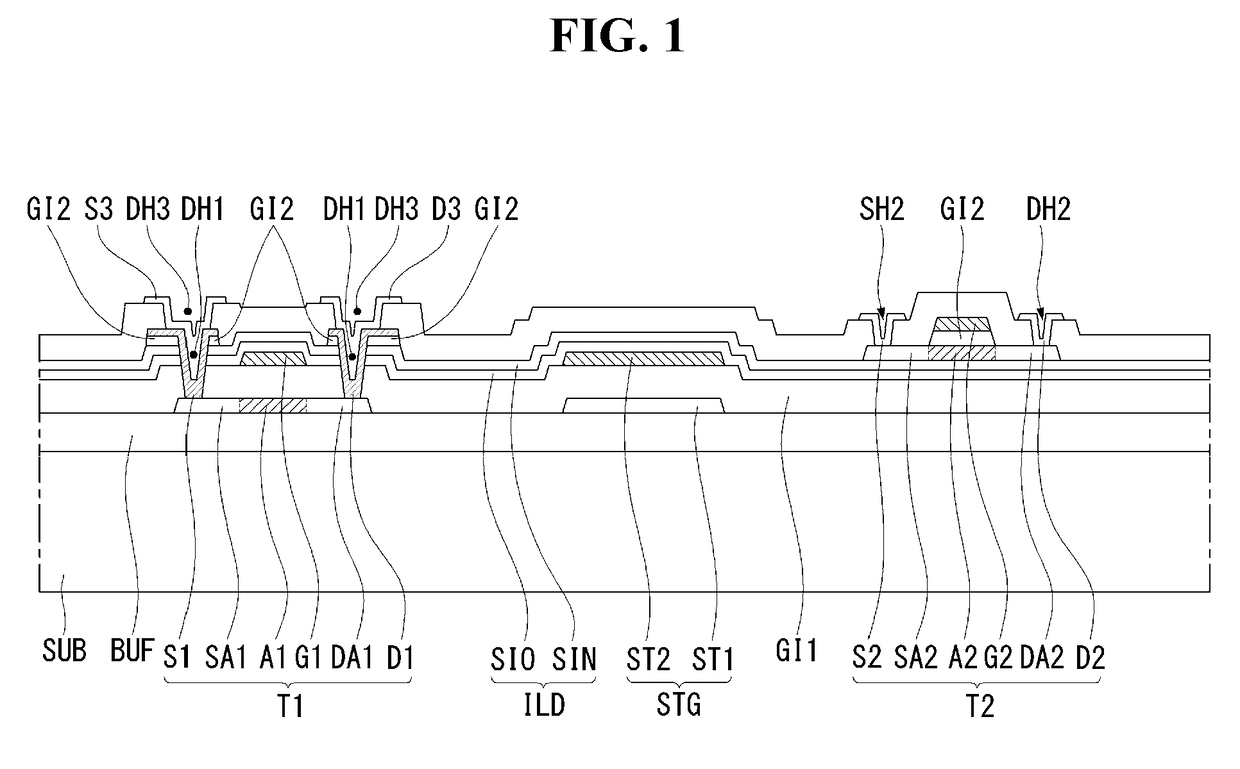

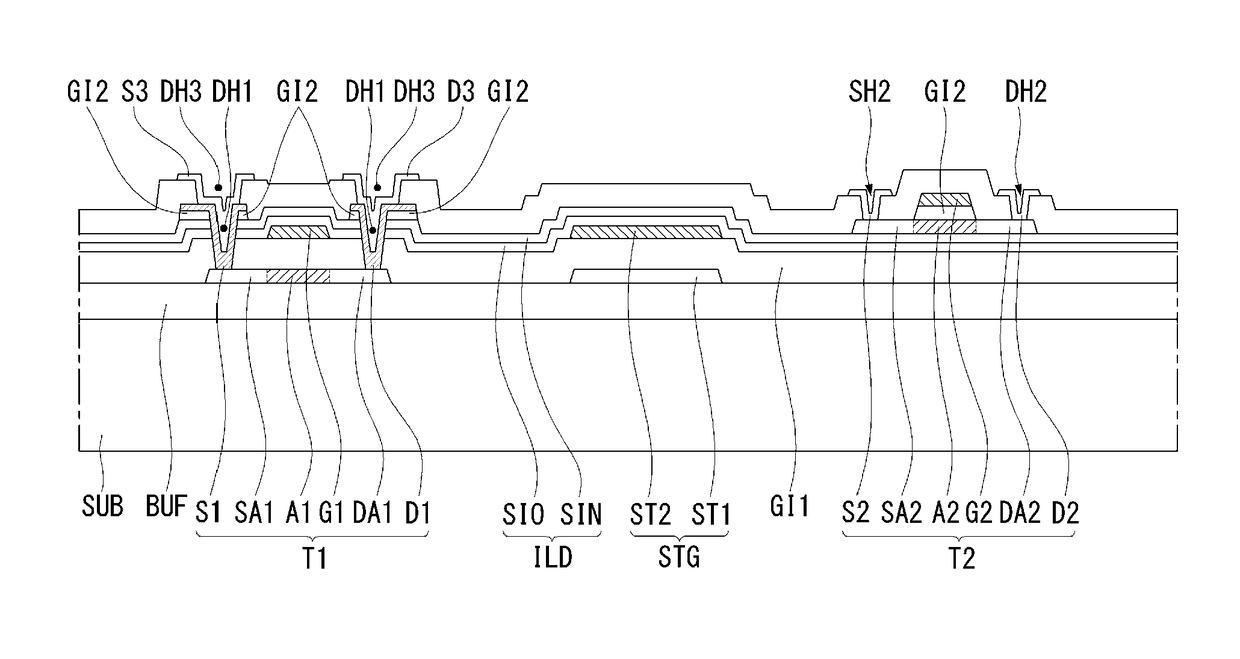

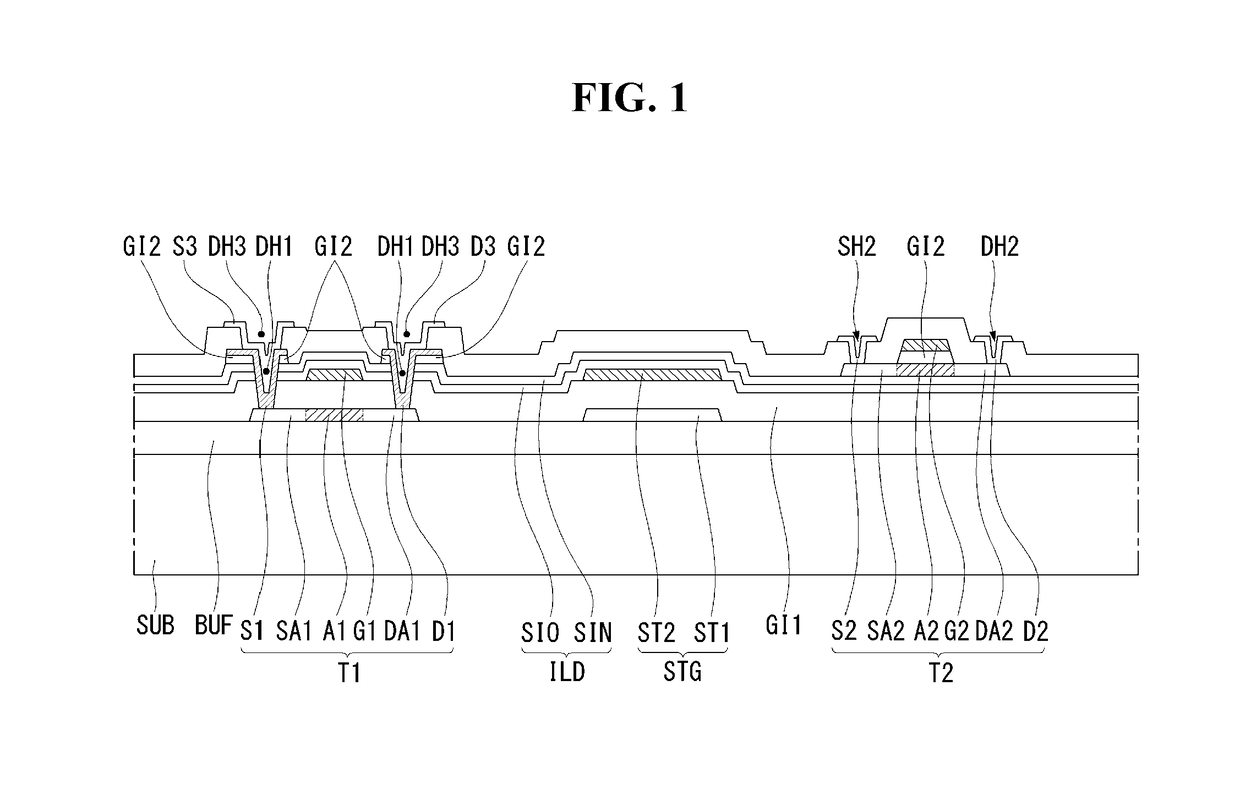

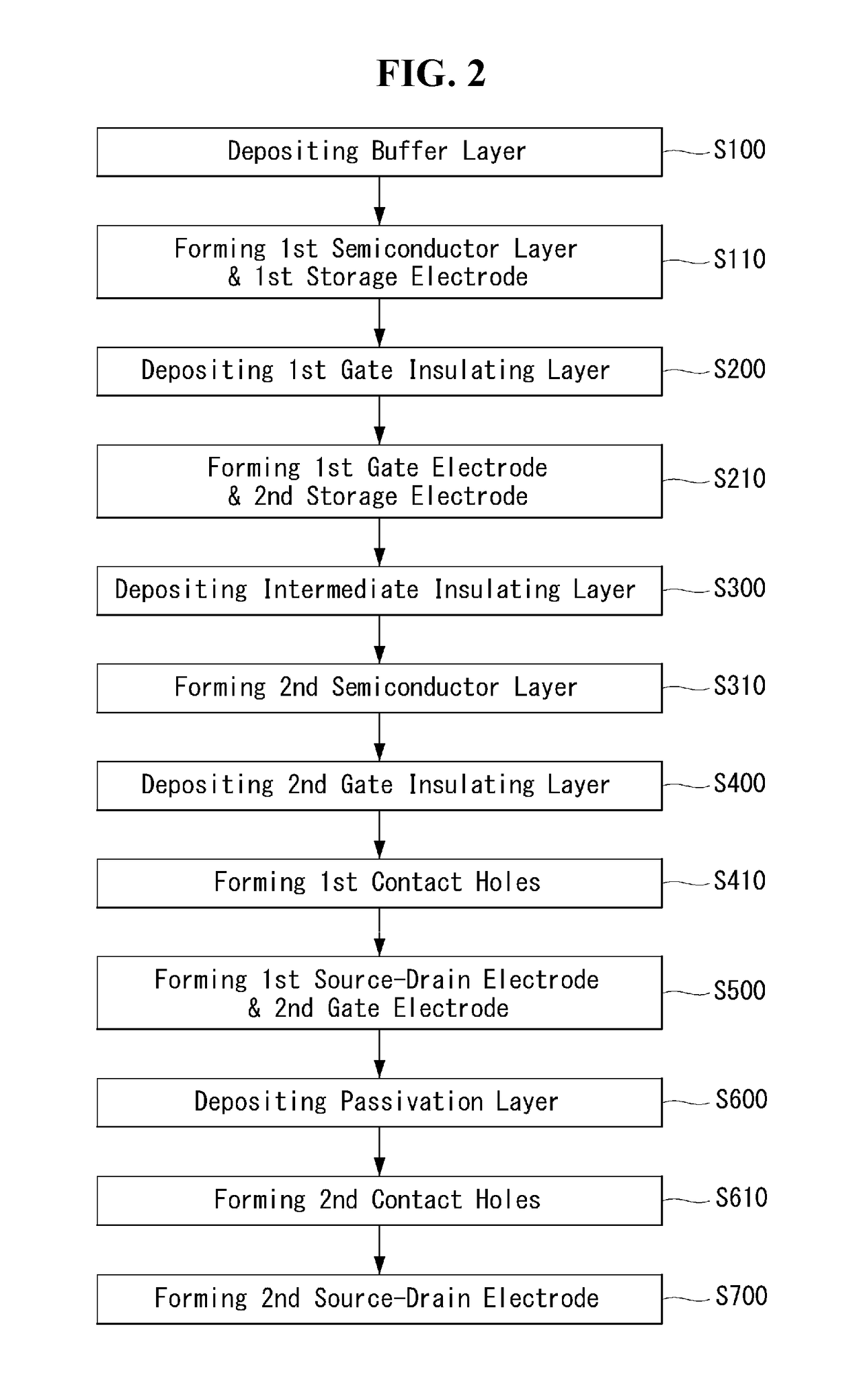

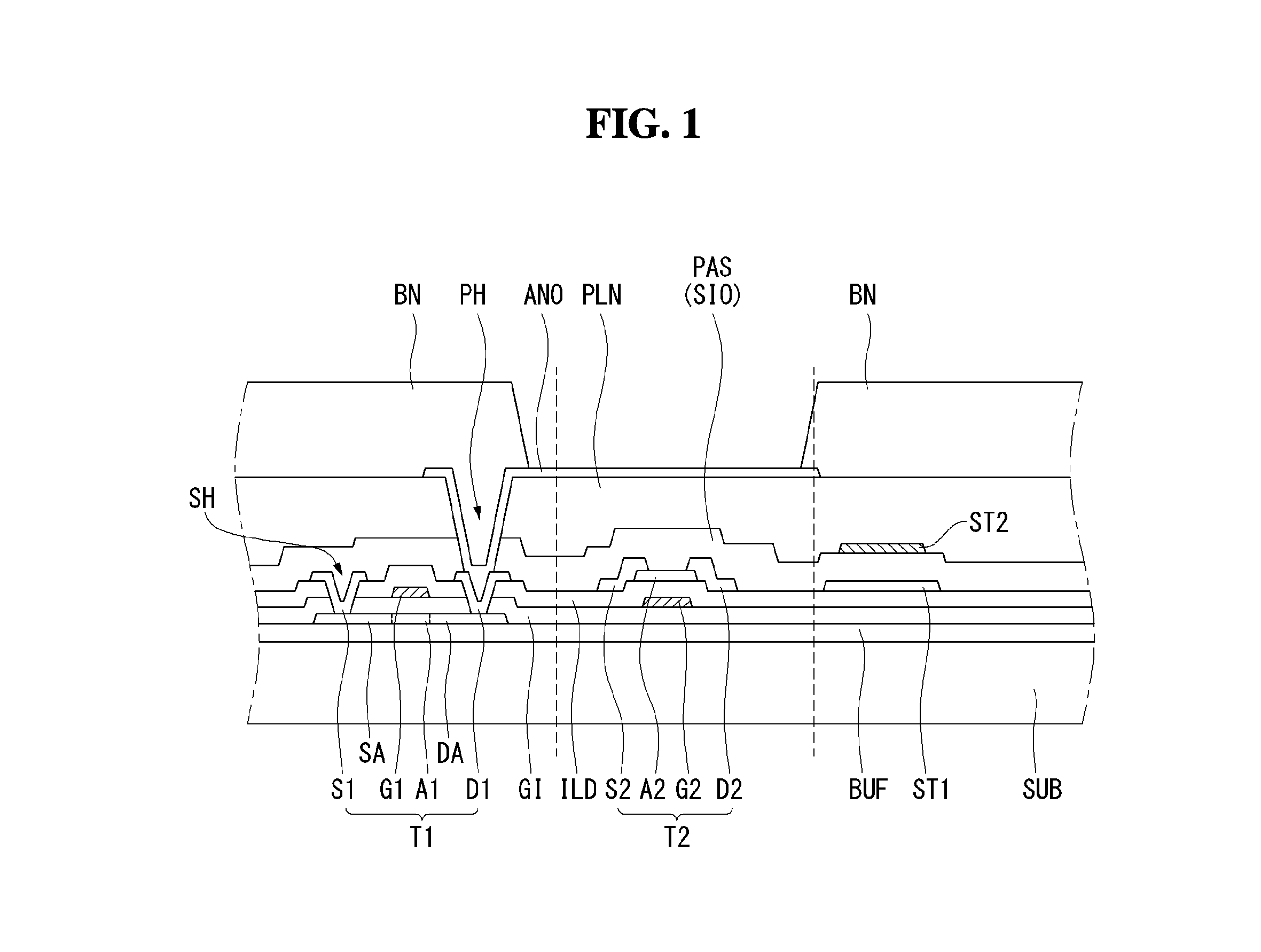

Thin film transistor substrate and display using the same

ActiveUS20160064465A1Simple preparation processReduce in quantityTransistorSolid-state devicesSemiconductor materialsDisplay device

The present invention relates to a thin film transistor substrate having two different types of semiconductor materials on the same substrate, and a display using the same. A disclosed display may include a substrate, a first thin film transistor having a polycrystalline semiconductor material on the substrate and a second thin film transistor having an oxide semiconductor material on the substrate.

Owner:LG DISPLAY CO LTD

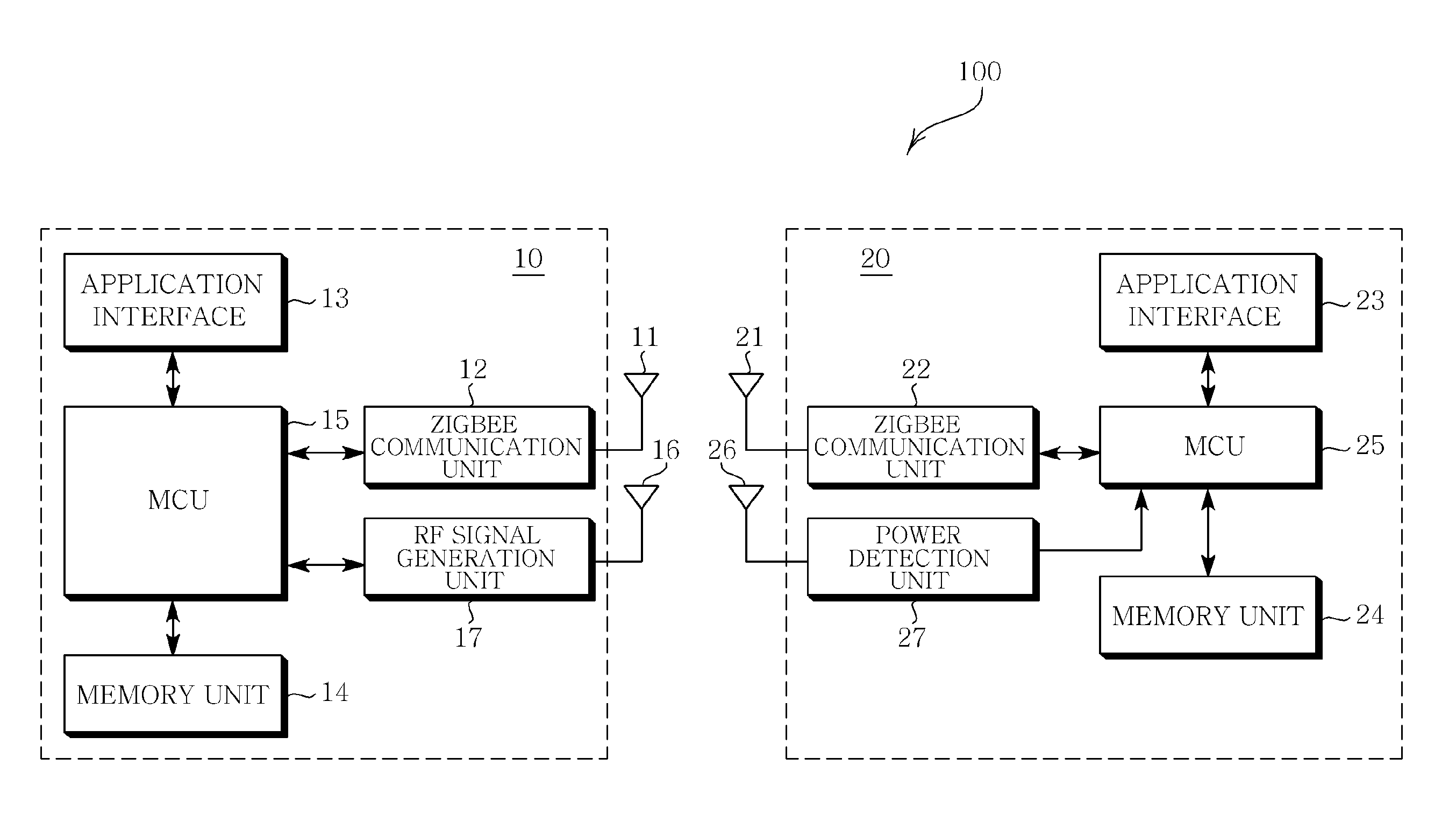

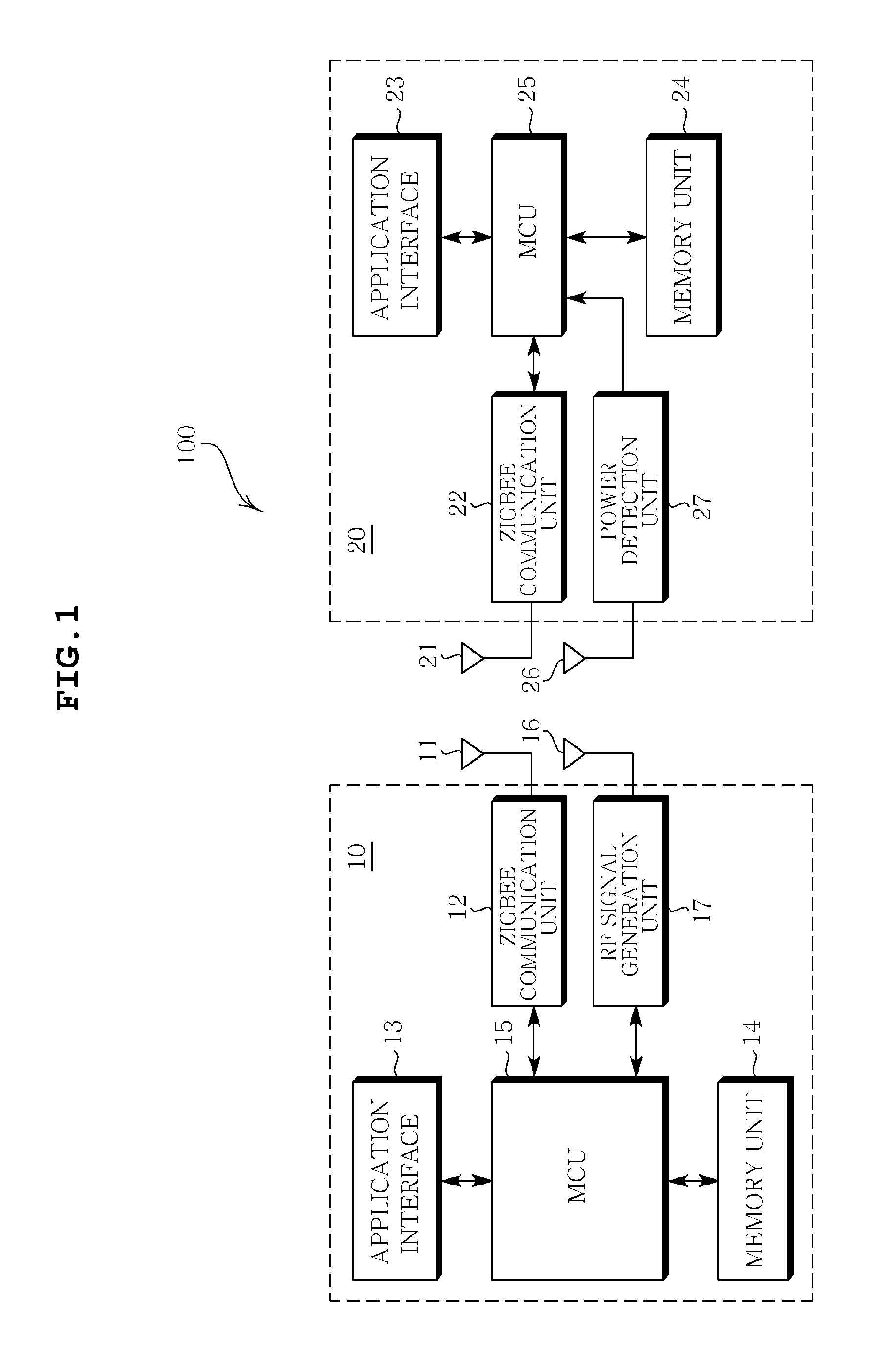

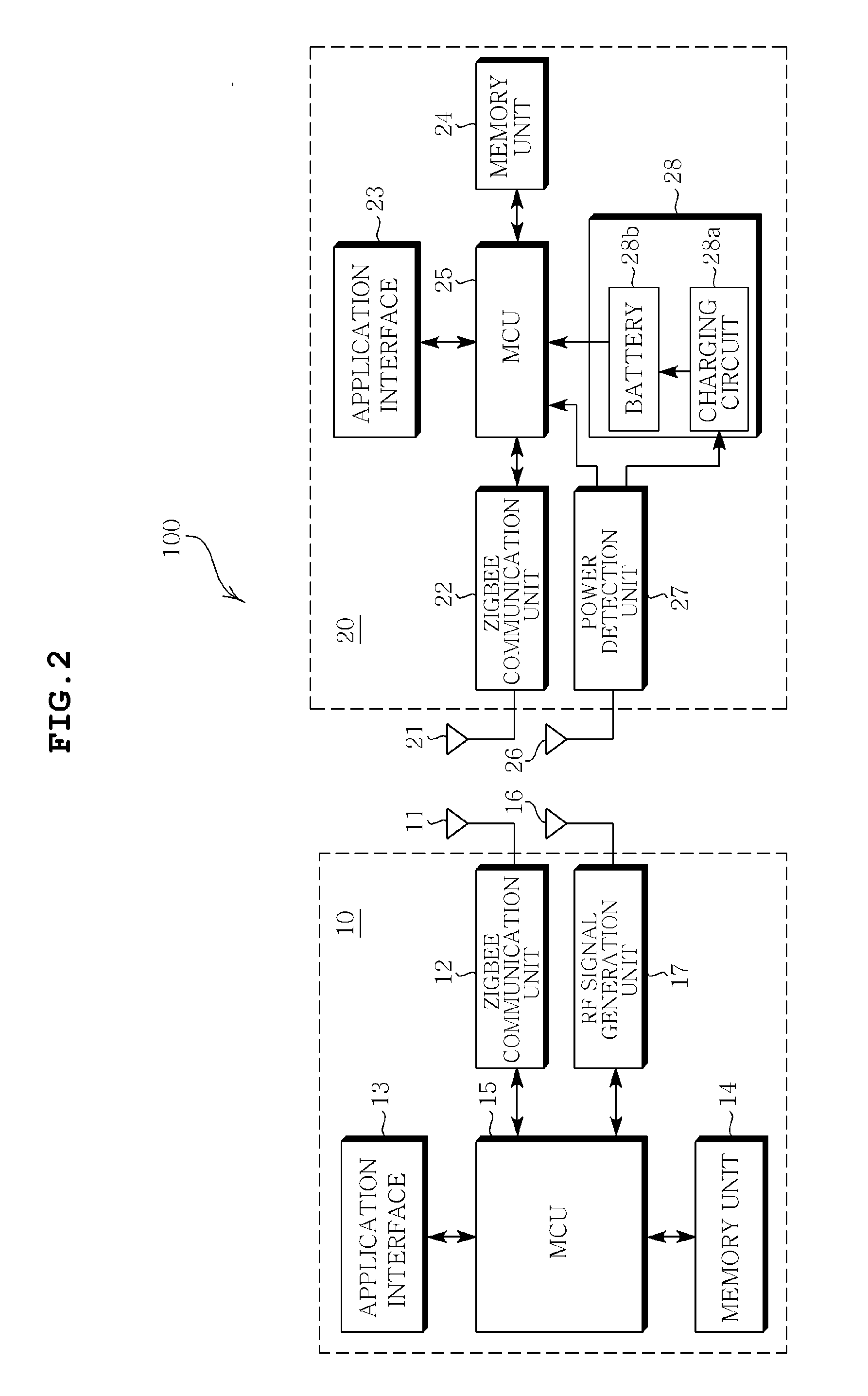

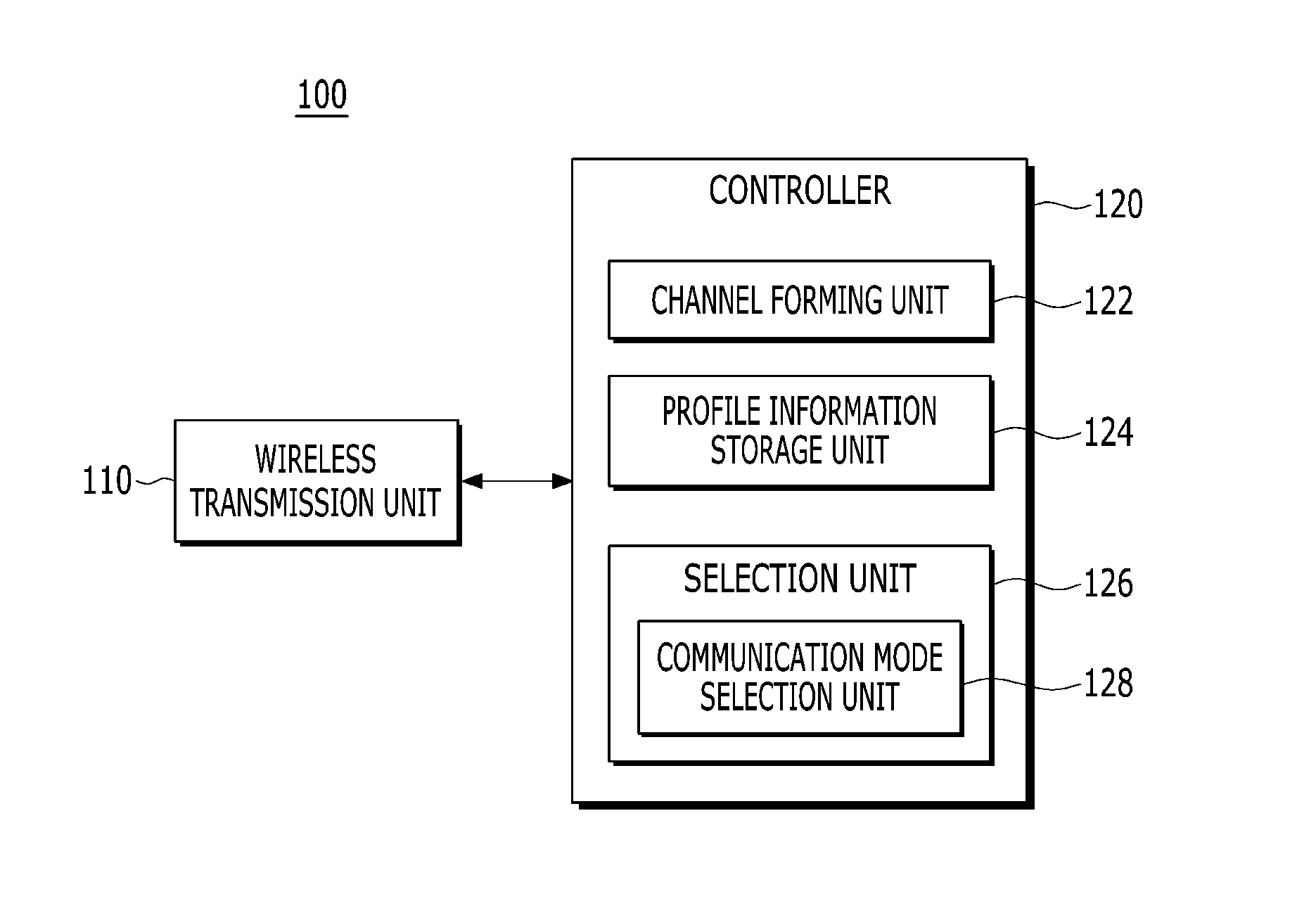

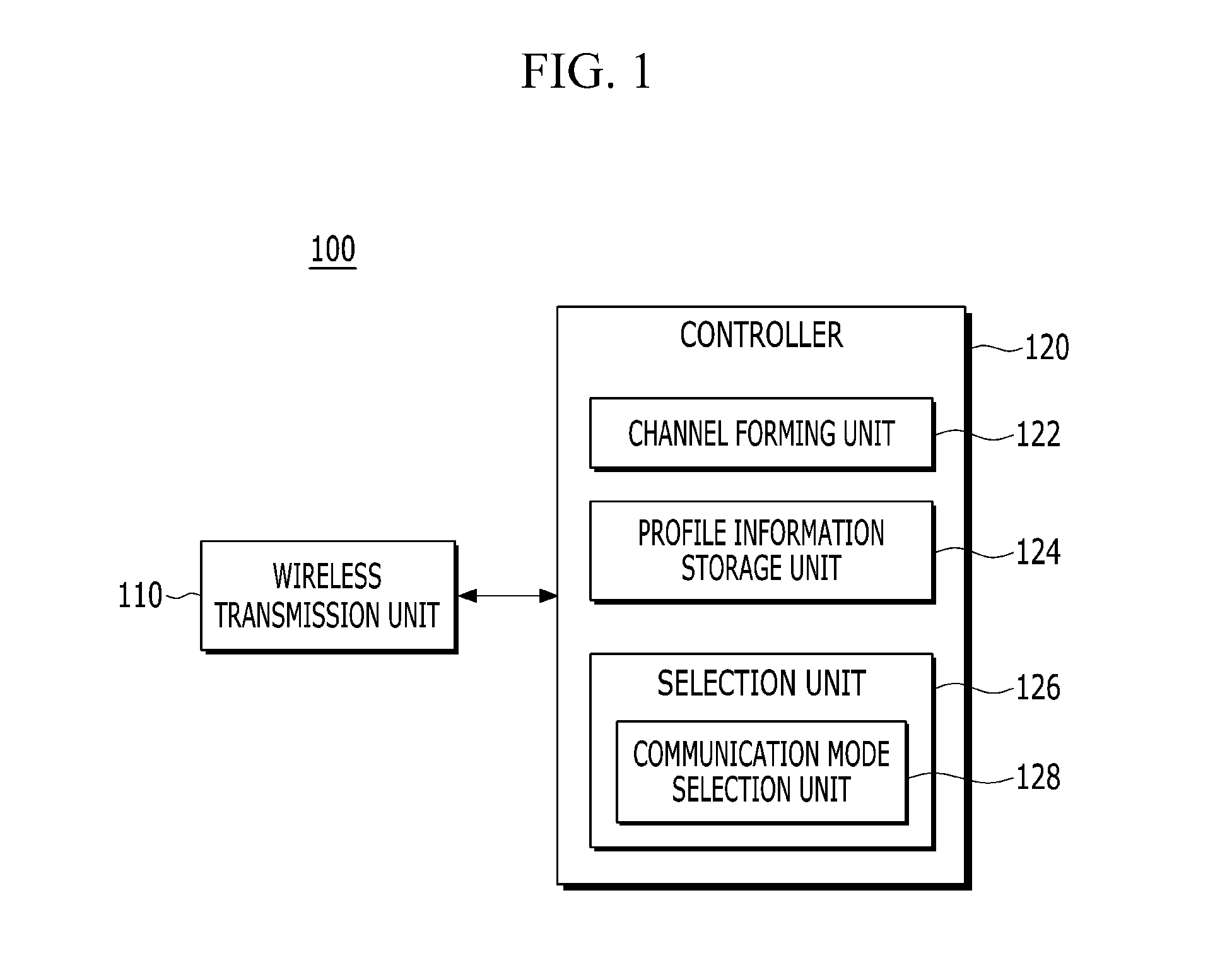

Apparatus and method for low power local area communication using event signal control

ActiveUS20110164595A1Low powerLow Power FeaturesPower managementEnergy efficient ICTPower savingReal-time computing

Disclosed herein is an apparatus and method for low power local area communication using event signal control. The low power local area communication apparatus includes at least one coordinator and a plurality of network device. The network coordinator transmits a periodic beacon signal based on the preset beacon period of a superframe and a continuous RF event signal, receives a first signal including a Service Set Identifier (SSID) and a second signal including the SSID and an event detection code, and performs the transmission or reception of data when authentication has been completed. Each of the network devices generates and transmits the first and second signals, performs the transmission and reception of data after authentication has been completed, and is thereafter switched to power saving mode or OFF mode. Accordingly, the construction of the system is simplified, and the cost of the system is reduced.

Owner:SAMSUNG ELECTRO MECHANICS CO LTD

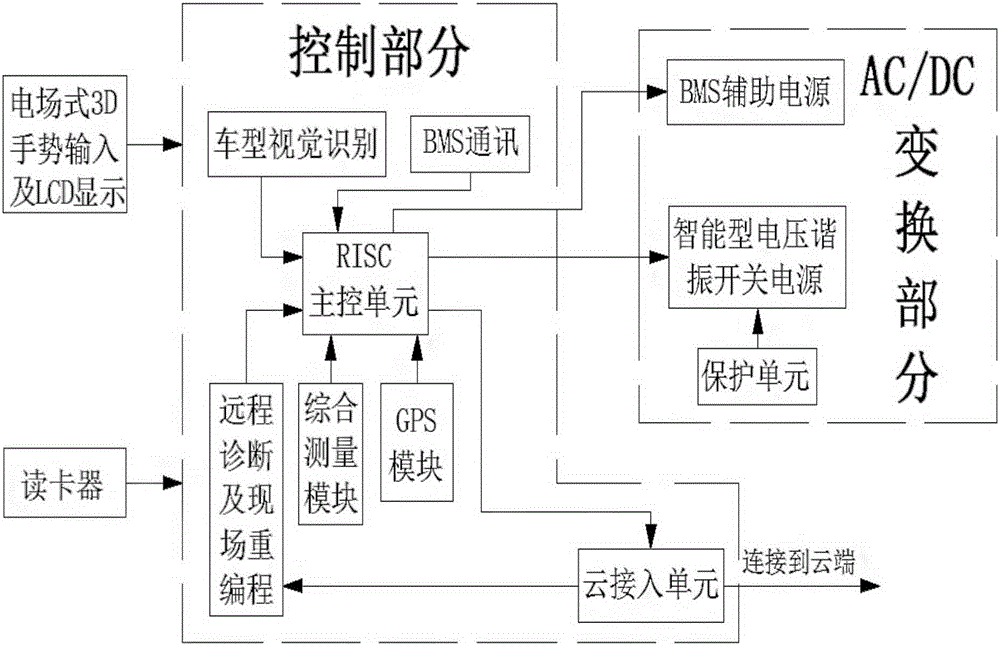

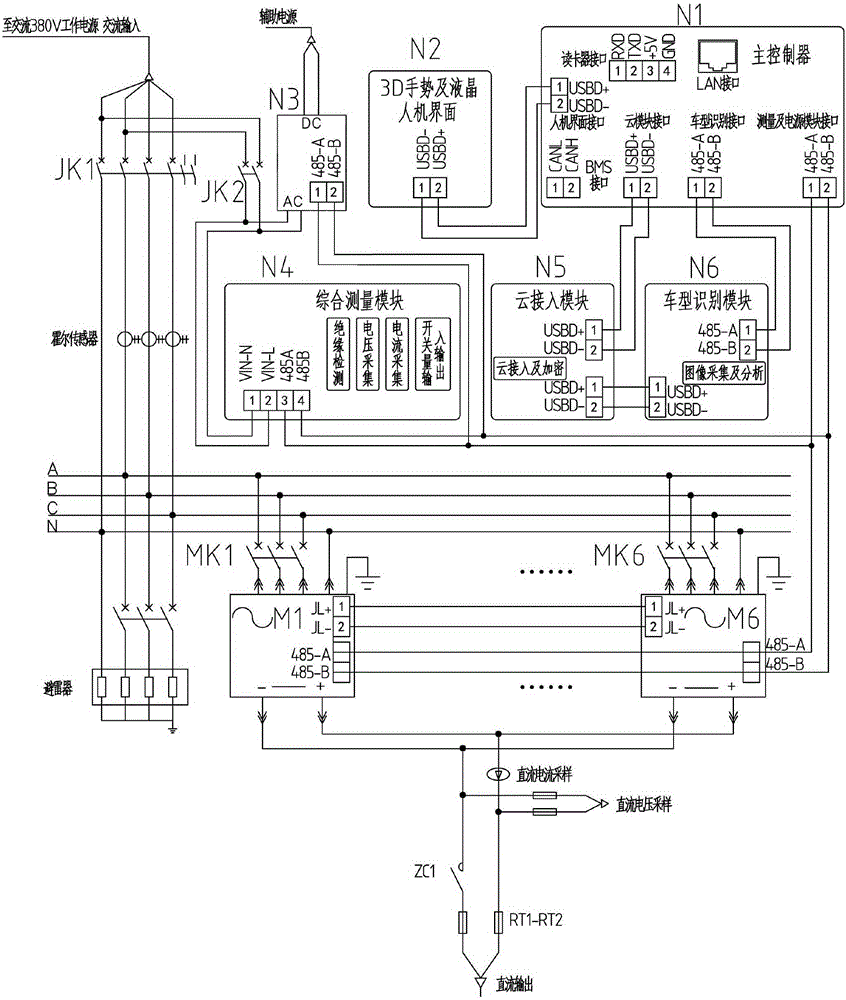

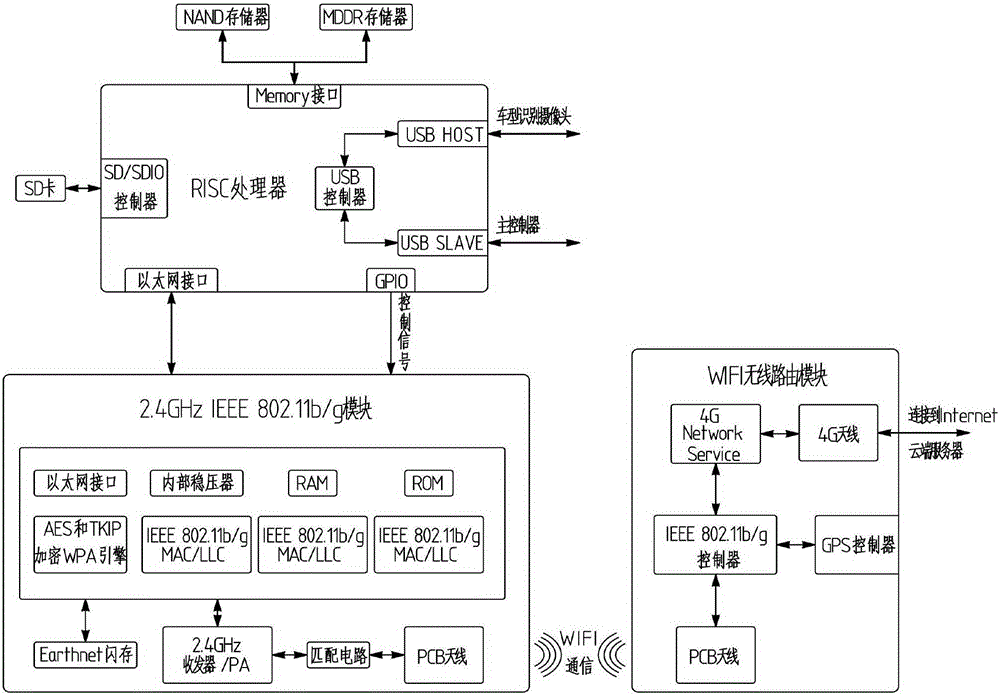

Non-vehicle-mounted intelligent DC charging pile

ActiveCN105337382AWith cloud access functionImprove reliabilityBatteries circuit arrangementsElectric powerVisual recognitionElectric cars

The invention relates to a non-vehicle-mounted intelligent DC charging pile, and the charging pile comprises an electric-field type 3D gesture input and LCD display interface, a card reader, a control part, and an AC / DC conversion part. The AC / DC conversion part is an executing mechanism for generating DC power supplied to an electric car, and consists of a BSM auxiliary power supply, an intelligent-type voltage resonance switching power supply, and a protection unit. The card reader achieves the confirmation of a user identity and a payment function. The control part consists of an RISC main control unit, a vehicle type recognition system, a BMS communication system, a GPS module, a comprehensive measurement module, and a cloud access unit. The vehicle type recognition system achieves the visual recognition and confirmation of the type of a to-be-charged car, and transmitting the recognition results to the RISC main control unit, thereby determining a power supply voltage level needed by the BMS of the car, and controlling the BSM auxiliary power supply of the AC / DC conversion part to generate direct current at the power supply voltage level for reliably supplying power to the BMS of the electric car. The image information of the vehicle type recognition system is uploaded to a remote cloud terminal through a cloud access unit.

Owner:STATE GRID TIANJIN ELECTRIC POWER +2

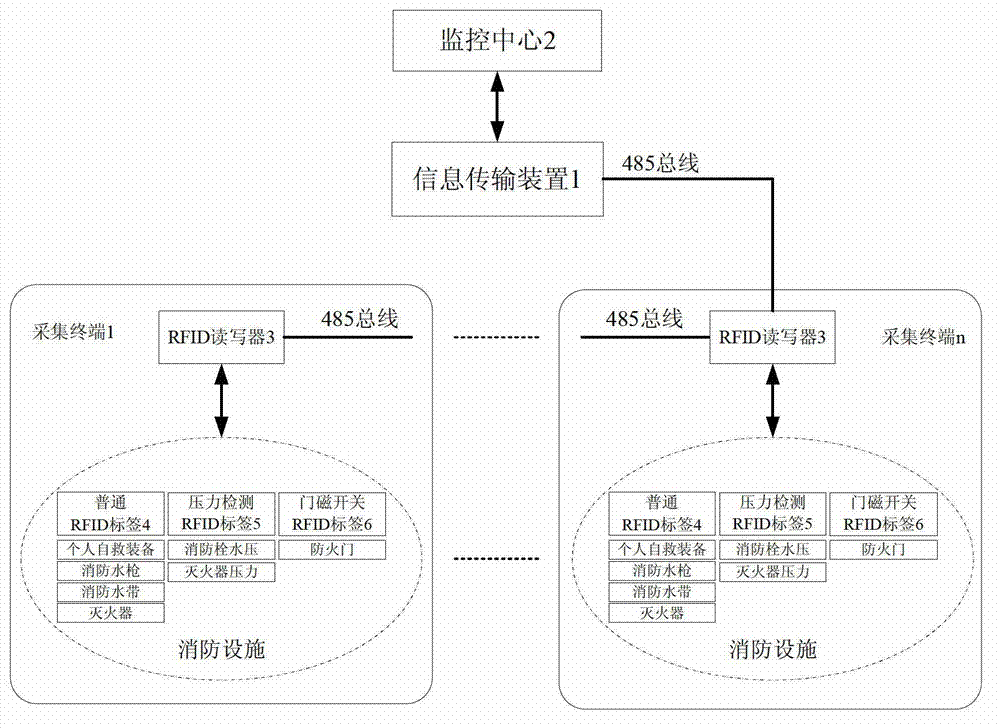

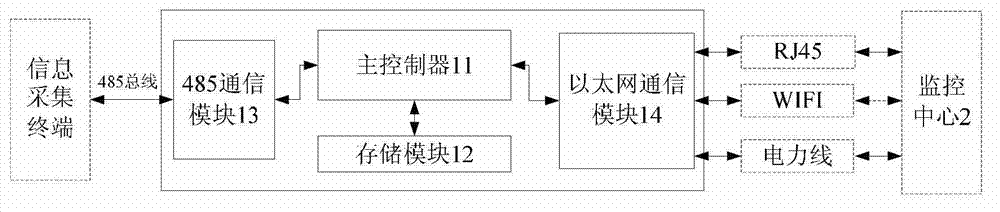

System and method for monitoring state of indoor passive fire-fighting equipment

The invention relates to the field of the internet of things for building fire protection, and particularly relates to a system and a method for monitoring the state of indoor passive fire-fighting equipment. The system comprises a plurality of state information acquisition terminals, an information transmission device and a monitor center, wherein the state information acquisition terminal comprises fire-fighting equipment for loading a common RFID (radio frequency identification) tag, a pressure detection RFID tag and a door magnetic switch RFID tag, and an RFID reader; the RFID reader is connected with the information transmission device through an RS485 bus; and the information transmission device transmits data to the monitor center in a wired or wireless manner. The system can be in communication with the monitor center by fully utilizing the existing wired communication network, the wireless communication network or an in-phase power line, and has the characteristics of diverse network access manners, few layouts, high network transmission real-time performance, high stability and the like. The system fills the blank for realizing real-time monitoring of the existing passive fire-fighting equipment, and has low power consumption; and the tag battery has a service life of 2 to 3 years.

Owner:SHENYANG FIRE RES INST OF MEM

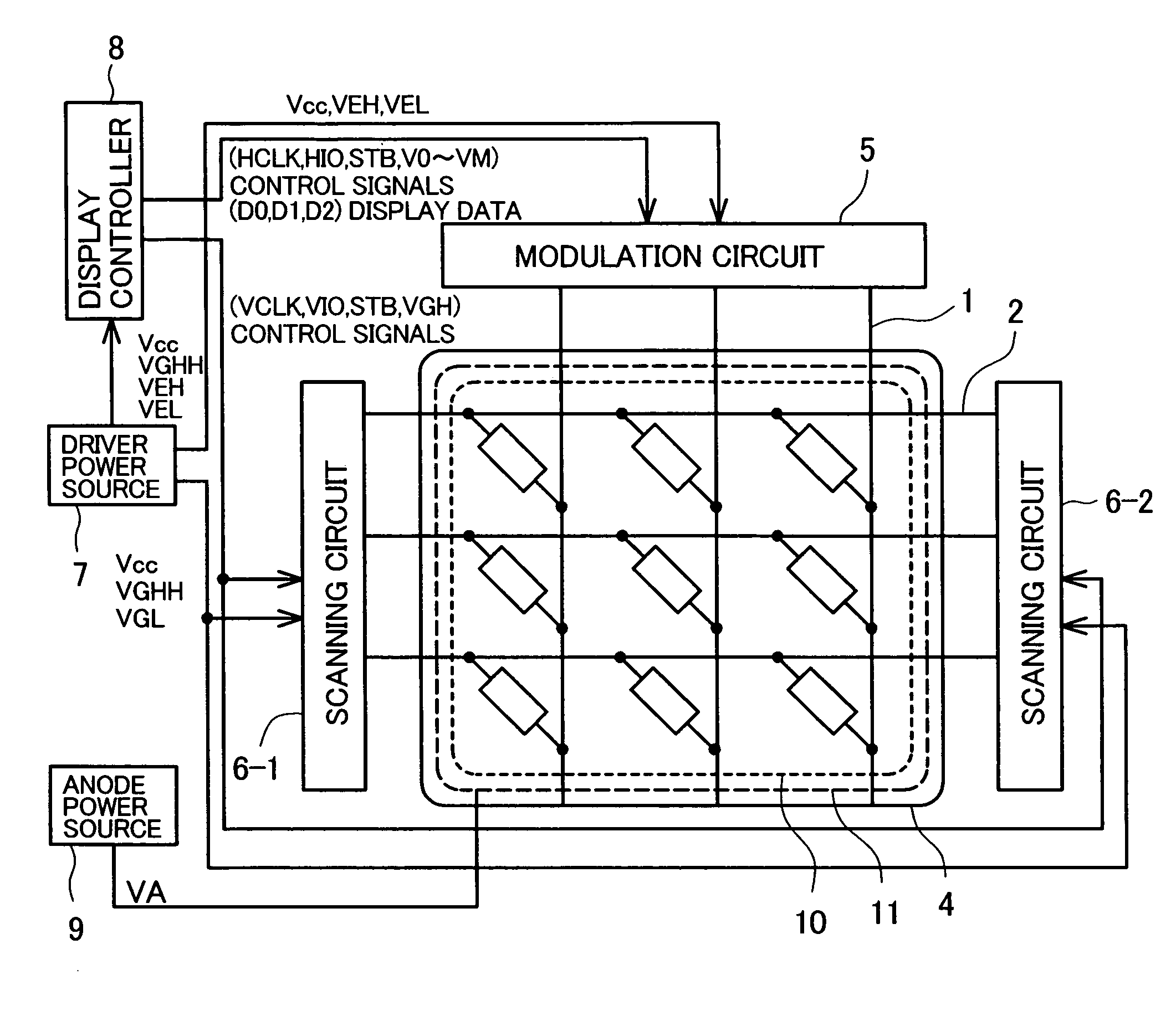

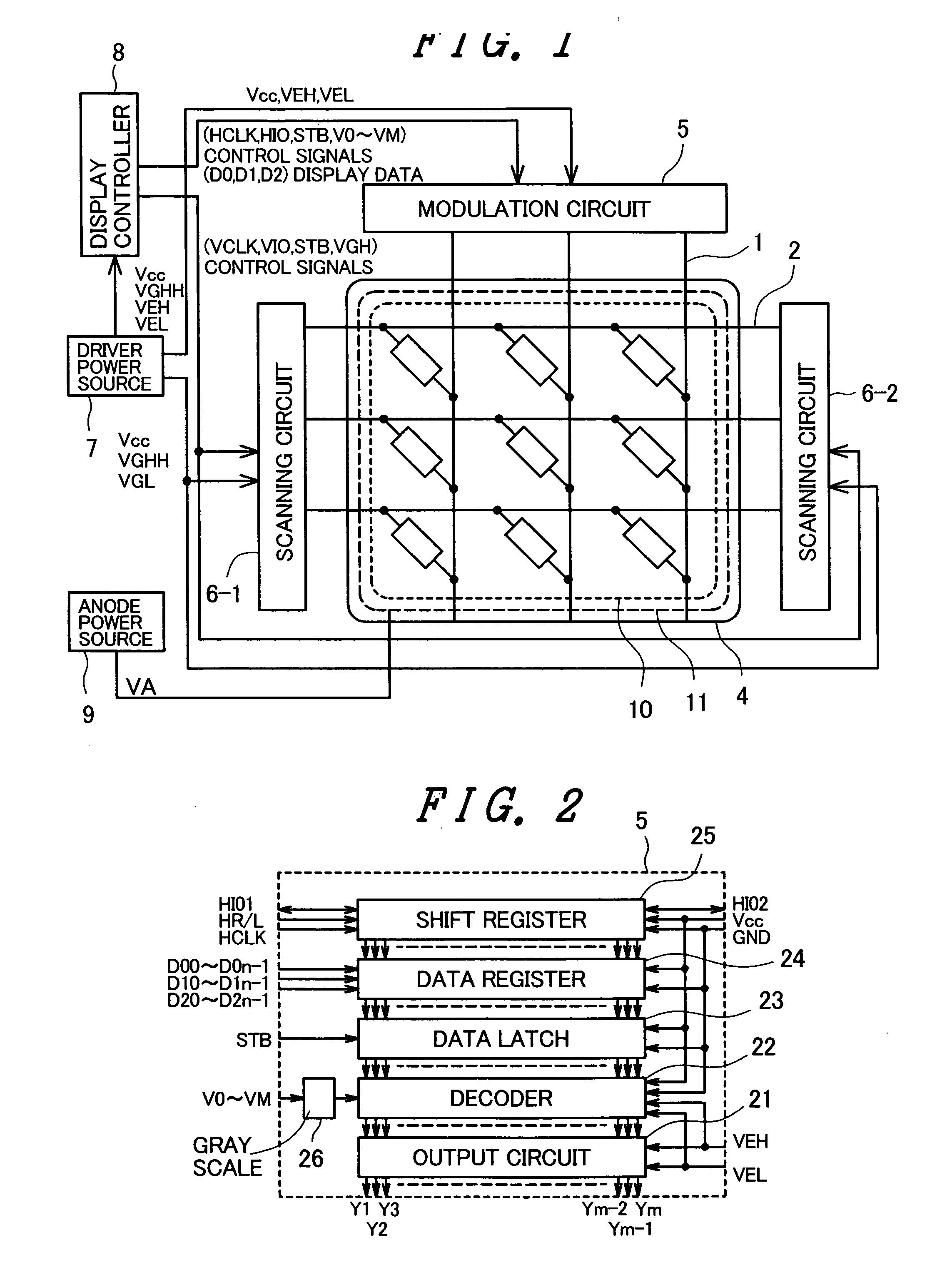

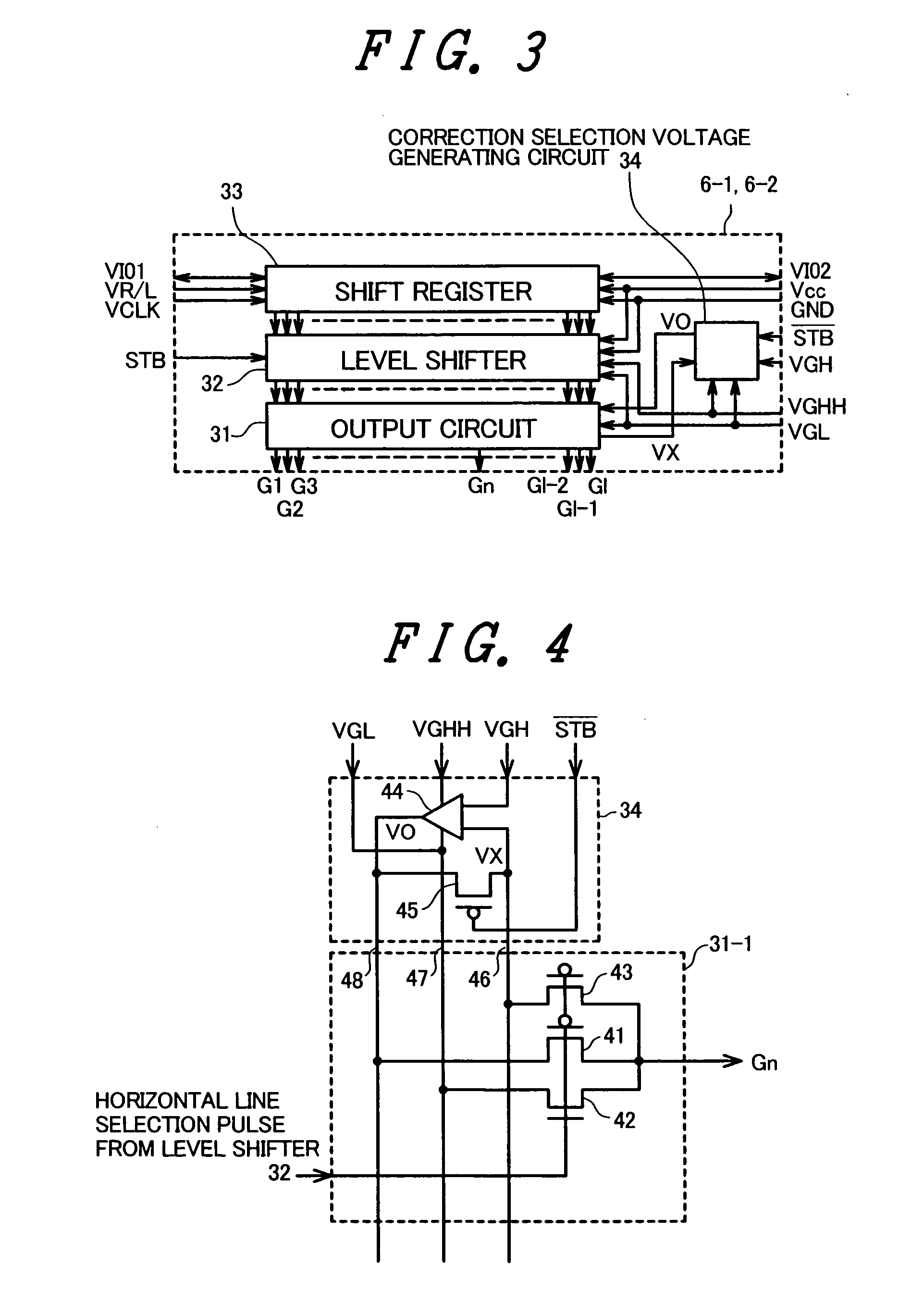

Display device

InactiveUS20060208671A1Reduce stepsInhibit deteriorationElectrode and associated part arrangementsCathode-ray tube indicatorsDisplay deviceVoltage drop

A display device of the invention includes horizontal lines, longitudinal lines, electron emission elements, and a scanning circuit which performs the selection of the horizontal lines. The scanning circuit includes a non-selection voltage switch, a correction selection voltage switch, and an output voltage detection switch for the selected horizontal line for every horizontal line. The display device also includes a differential amplifier which is connected to a correction selection voltage input line, a horizontal line selection voltage line, and a correction selection voltage output line for every plurality of horizontal lines. The invention can suppress a voltage drop of the horizontal lines and, at the same time, can suppress the brightness irregularities of the display device.

Owner:HITACHI DISPLAYS

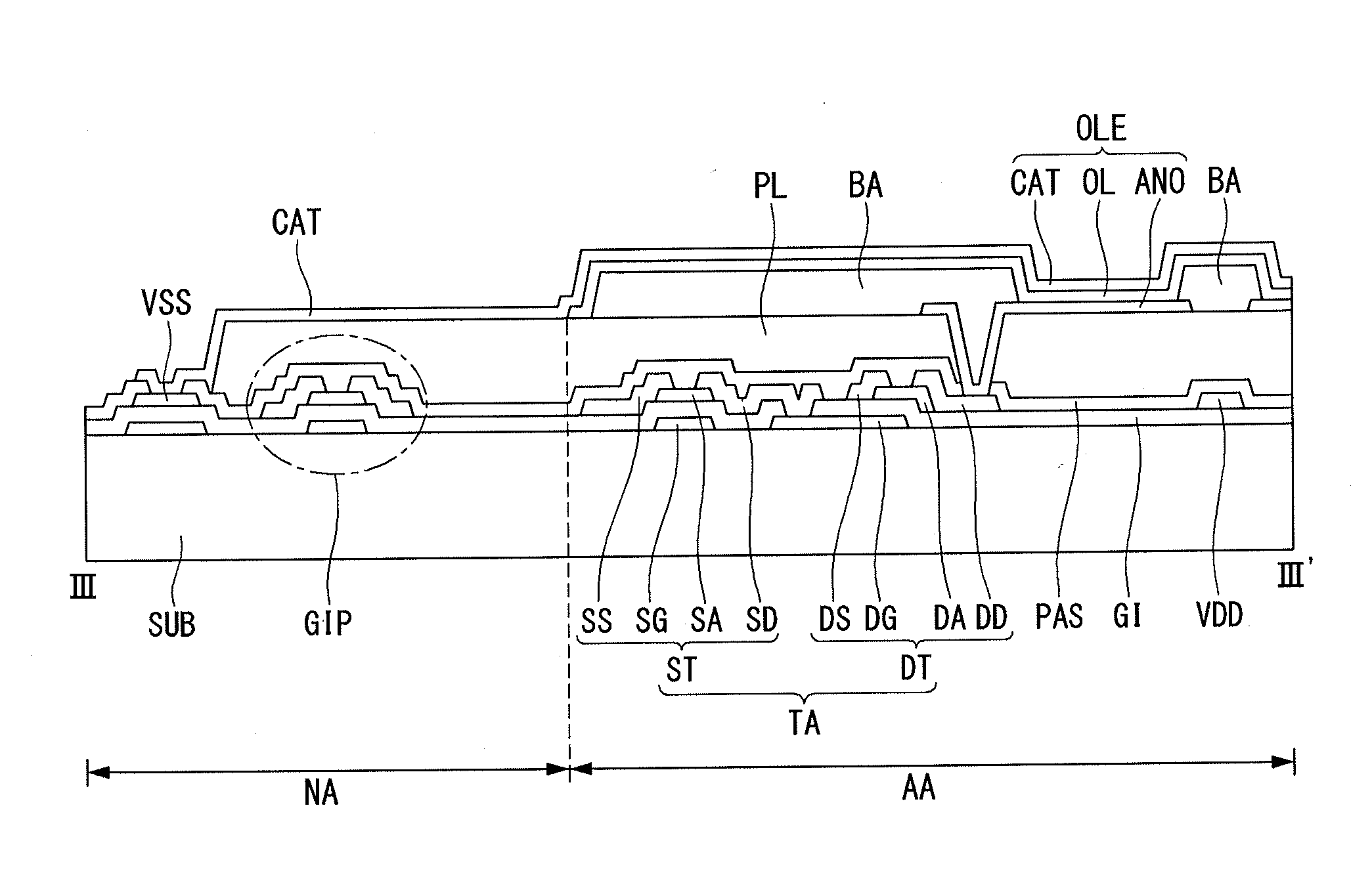

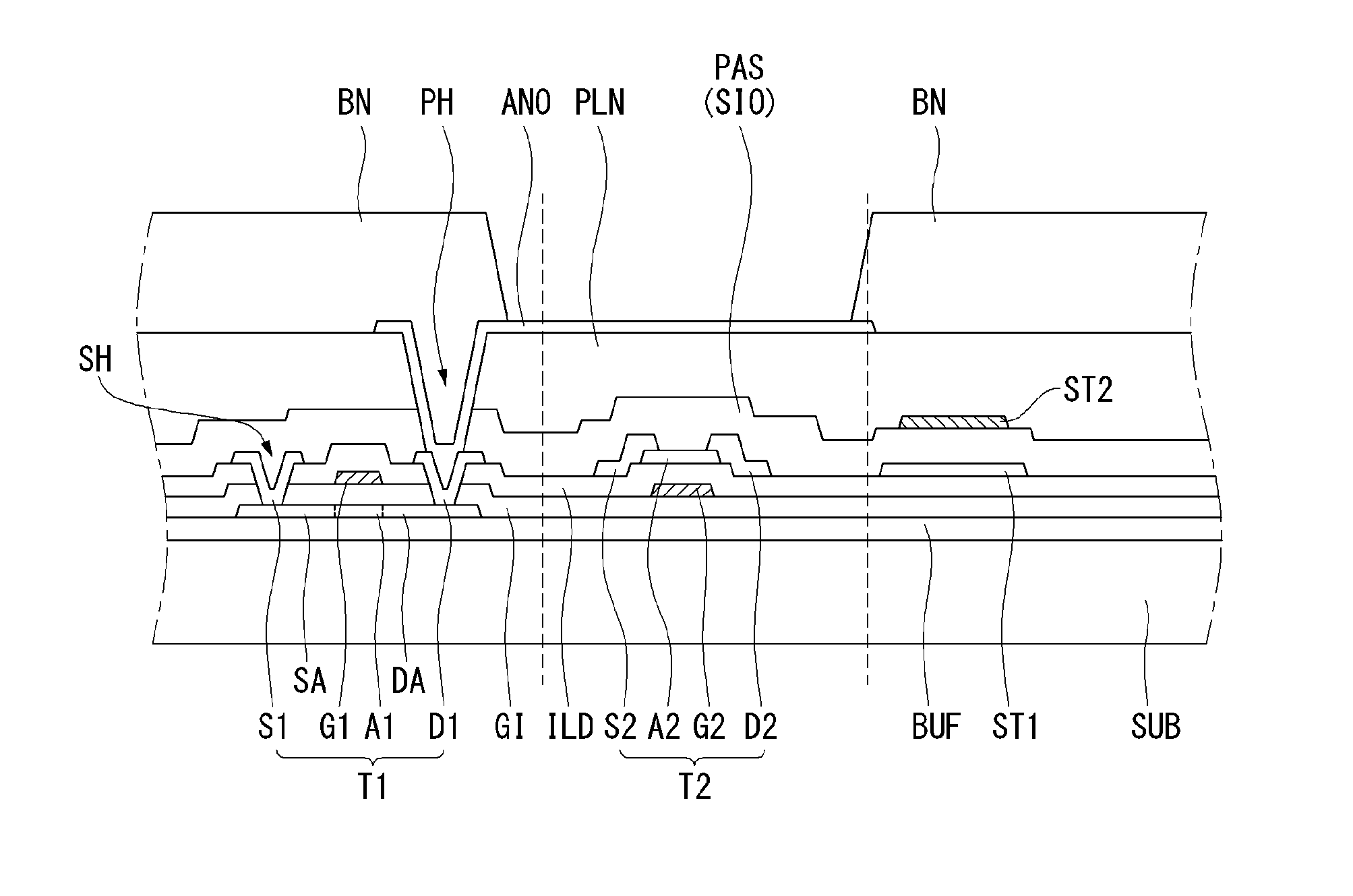

Thin film transistor substrate and display using the same

ActiveUS20170155000A1Low frequencyLow power consumption propertyTransistorSolid-state devicesOxide semiconductorDisplay device

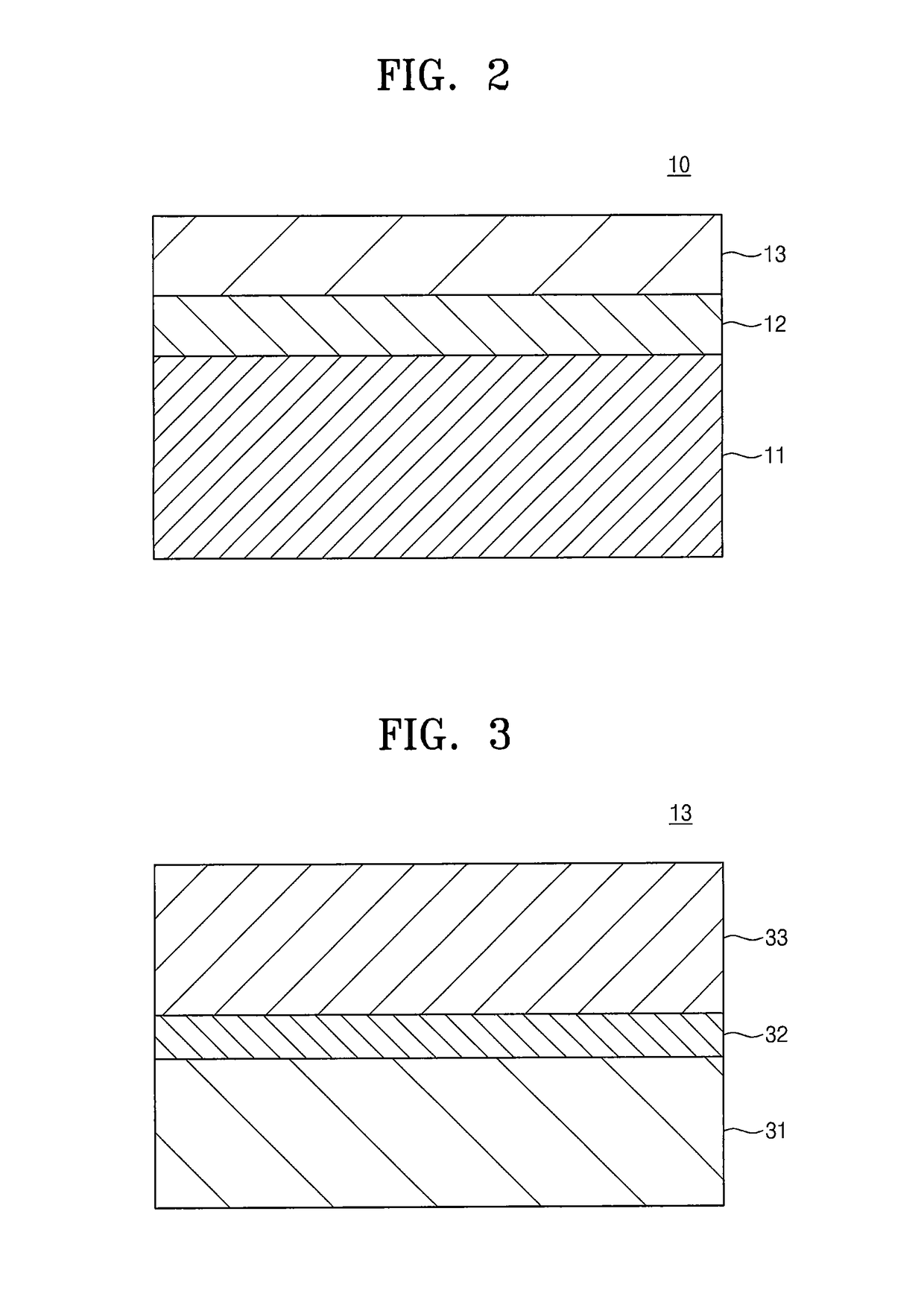

A thin film transistor substrate includes a first thin film transistor disposed having a polycrystalline semiconductor layer, a first gate electrode on the polycrystalline semiconductor layer, a first source electrode and a first drain electrode; a first gate insulating layer between the polycrystalline semiconductor layer and the first gate electrode; a second thin film transistor disposed having an oxide semiconductor layer on the first gate electrode, a second gate electrode on the oxide semiconductor layer, a second source electrode and a second drain electrode; an intermediate insulating layer disposed on the first gate electrode and under the oxide semiconductor layer; and a second gate insulating layer on the intermediate insulating layer and under the first source electrode, the first drain electrode and the second gate electrode.

Owner:LG DISPLAY CO LTD

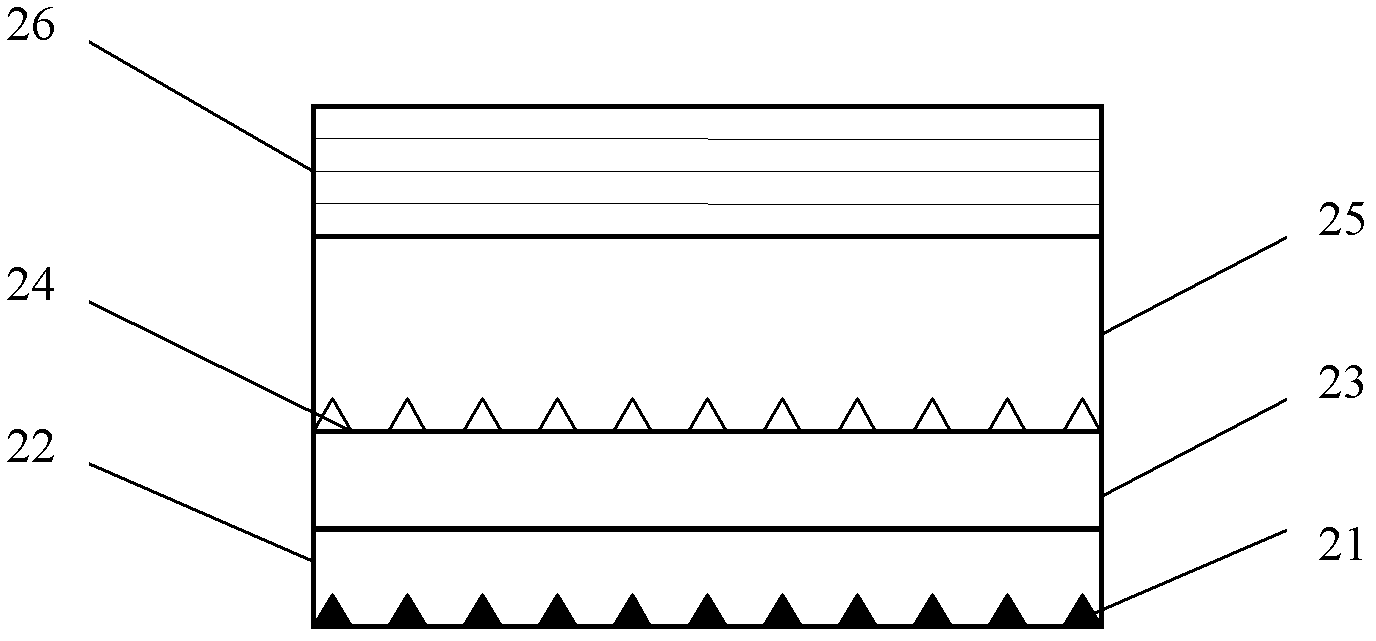

Antimonide transistor with high electron mobility and manufacturing method thereof

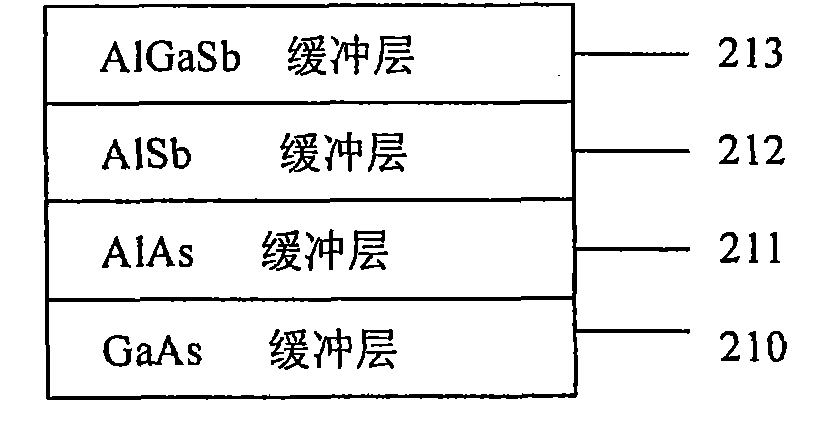

InactiveCN102054862AQuality improvementImprove output characteristicsSemiconductor/solid-state device manufacturingSemiconductor devicesIsolation layerHigh electron

The invention discloses an antimonide transistor with high electron mobility, which comprises a substrate, a composite buffer layer, an antimonide lower barrier layer, a channel layer, an antimonide isolated layer, a doping layer, an upper barrier layer and a cap layer, wherein the composite buffer layer grows on the substrate; the antimonide lower barrier layer grows on the composite buffer layer; the channel layer grows on the antimonide lower barrier layer; the antimonide isolated layer grows on the channel layer; the doping layer grows on the antimonide isolated layer; the upper barrier layer grows on the doping layer; and the cap layer grows on the upper barrier layer. The invention discloses a method for manufacturing the antimonide transistor with the high electron mobility. In the antimonide transistor, by adopting the composite buffer layer, the quality of transistor structural materials is improved greatly, the electronic transport characteristic of a channel is better, the output characteristic of the device is improved, the characteristics of high frequency, high speed and low power consumption of the device is fully played, and the stability and reliability of the device are improved effectively.

Owner:INST OF SEMICONDUCTORS - CHINESE ACAD OF SCI

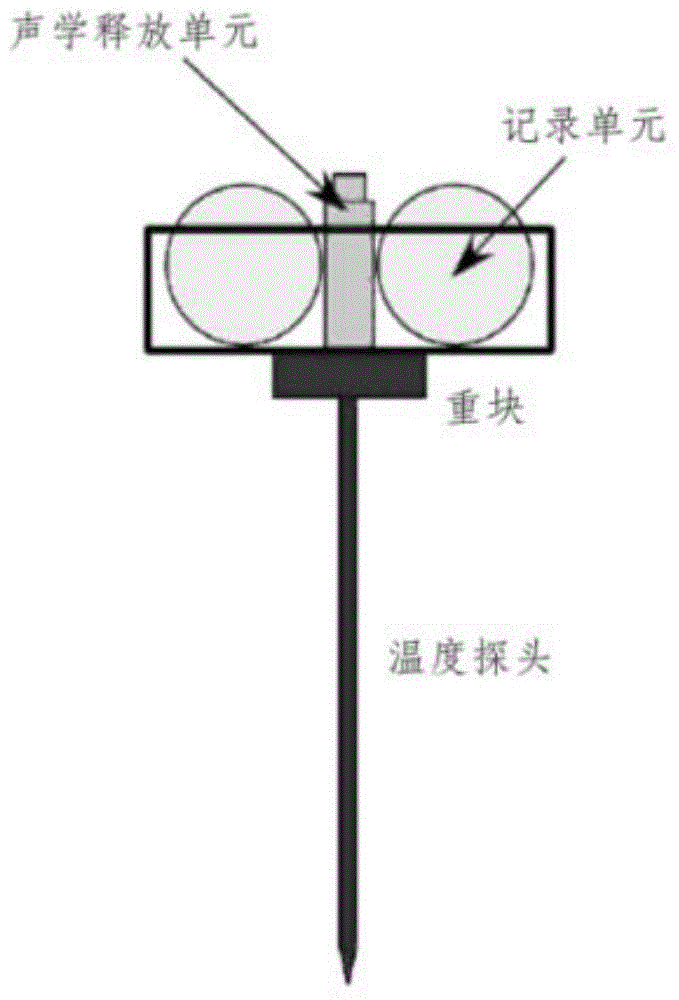

Seabed heat flow long-term observation probe based on underwater robot platform

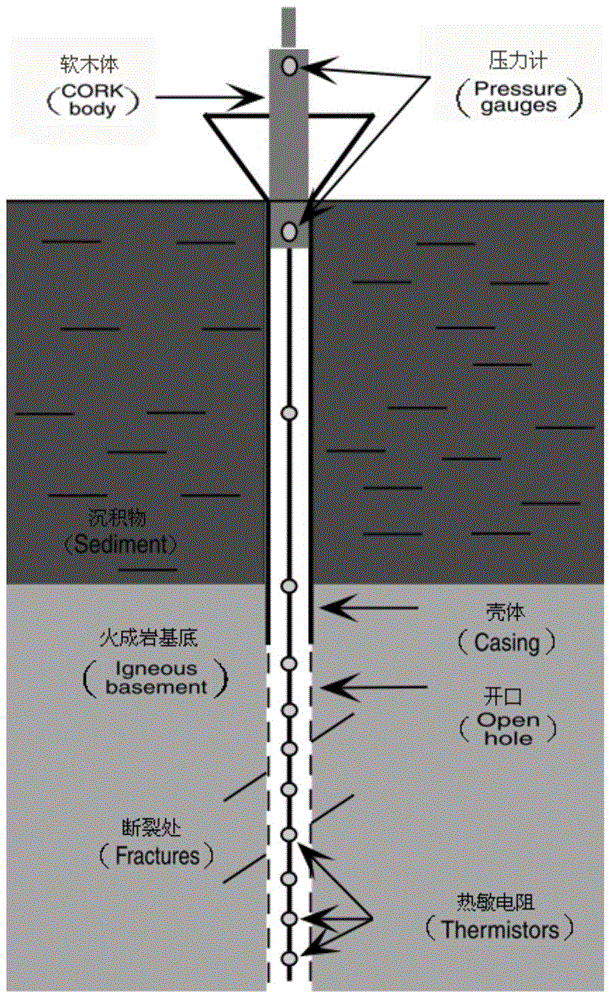

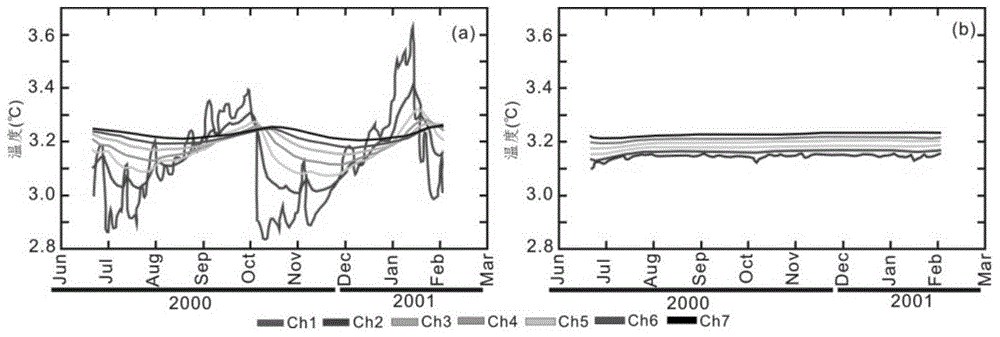

InactiveCN104950344AClose contactSensing temperature changesTemperature measurement of flowing materialsGeological measurementsSeabed sedimentCapacitance

The invention discloses a seabed heat flow long-term observation probe based on an underwater robot platform. The seabed heat flow long-term observation probe comprises a support probe lever and a plurality of self-capacitance temperature measuring units. The self-capacitance temperature measuring units are helically distributed at equal distance and fixed on the support probe lever to form a distributed multipoint temperature measuring structure, and temperature fluctuation of sediments in different depths of the seabed is observed in the long term. Each self-capacitance temperature measuring unit comprises a housing, a battery, a temperature measuring circuit board, a sensor packaging probe and a temperature sensor, wherein the battery and the temperature measuring circuit board are mounted in the housing, the sensor packaging probe is fixed at one end of the housing, and the temperature sensor is mounted in the sensor packaging probe and electrically connected with the temperature measuring circuit board. The temperature sensors closely contact with the sediments in the seabed, the self-capacitance temperature measuring units helically distributed guarantee that each temperature sensor can contact undisturbed sediments, and fastness and accuracy in temperature measurement of the sediments are guaranteed to the greatest extent.

Owner:SOUTH CHINA SEA INST OF OCEANOLOGY - CHINESE ACAD OF SCI

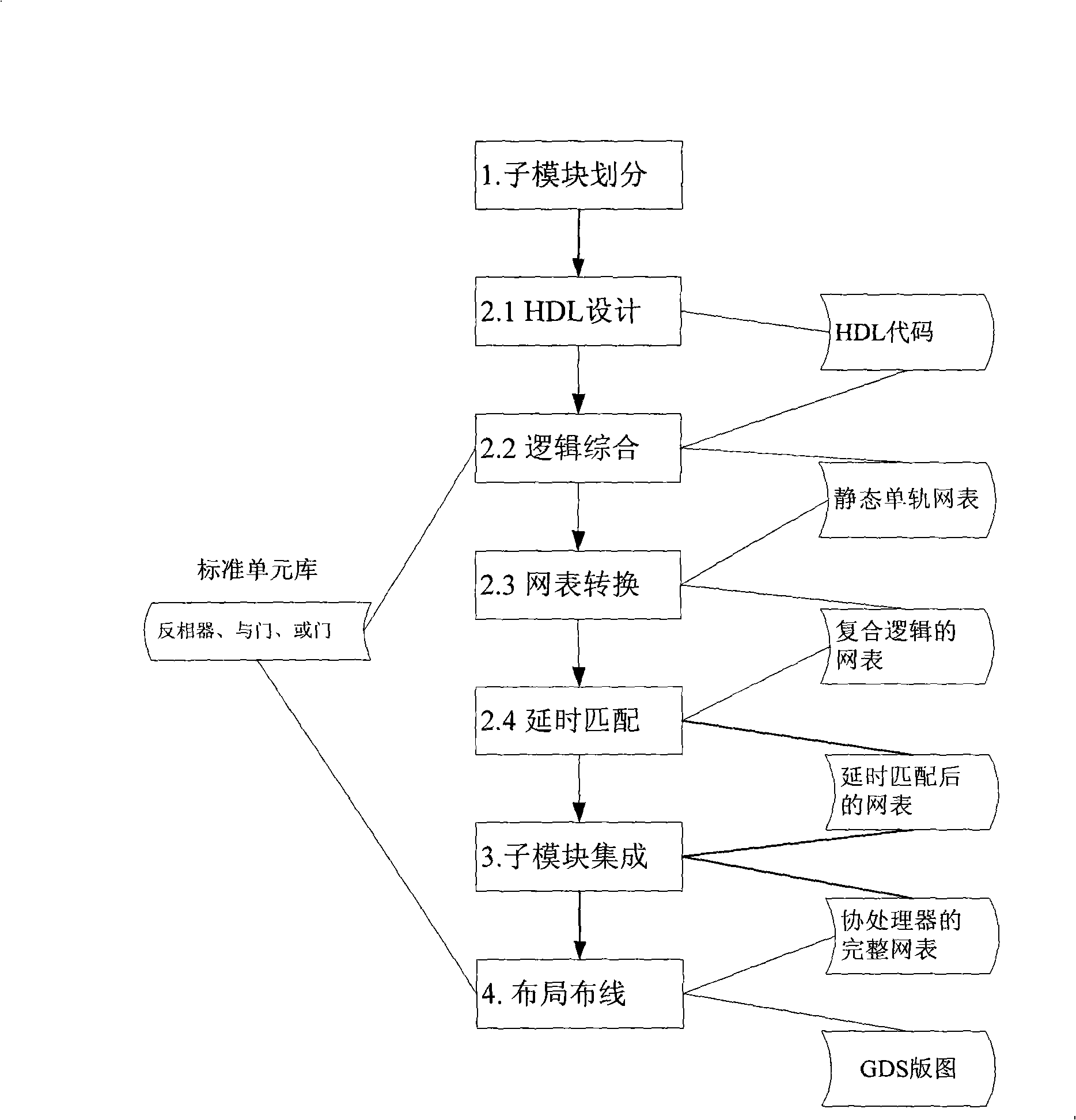

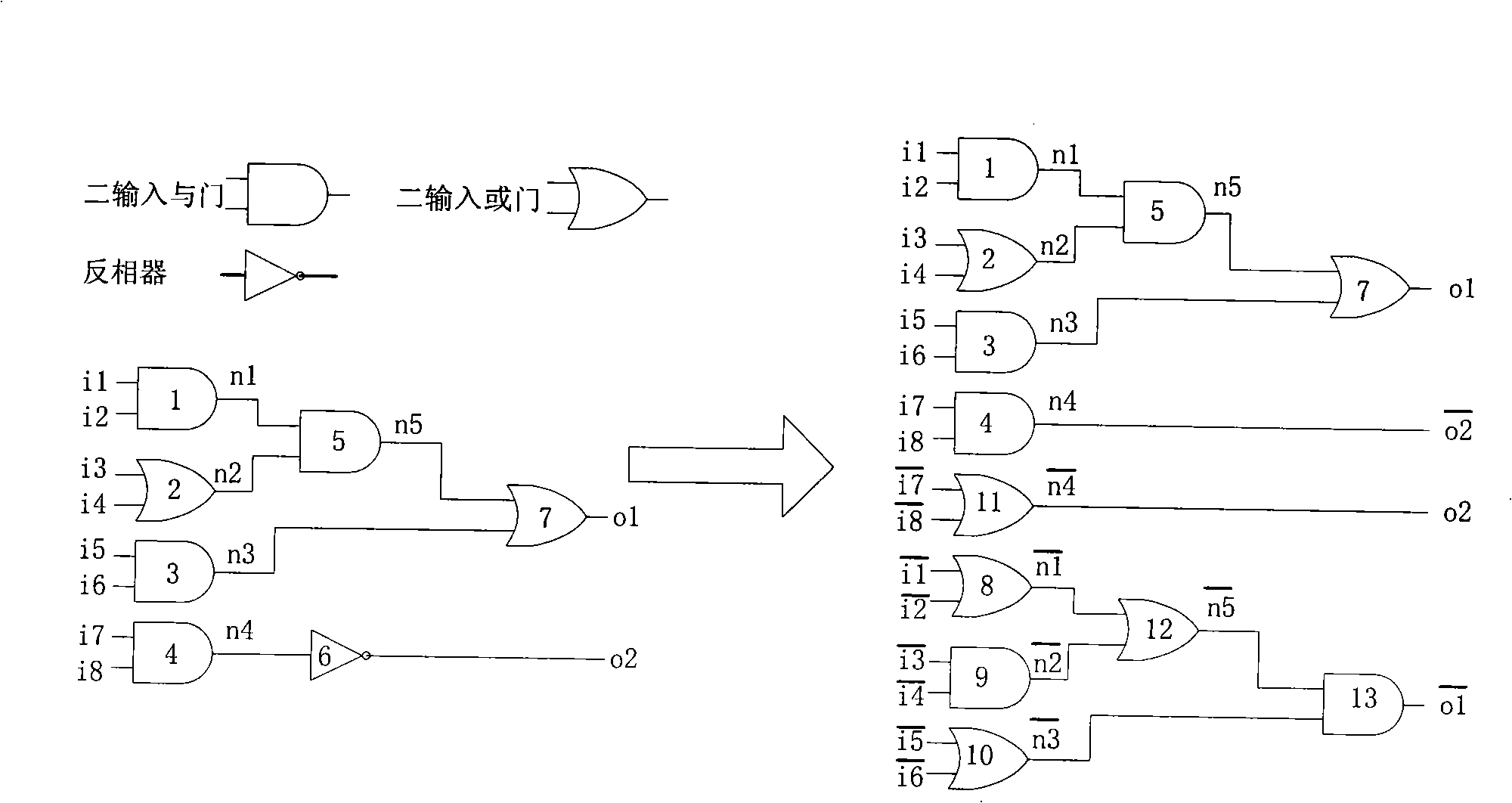

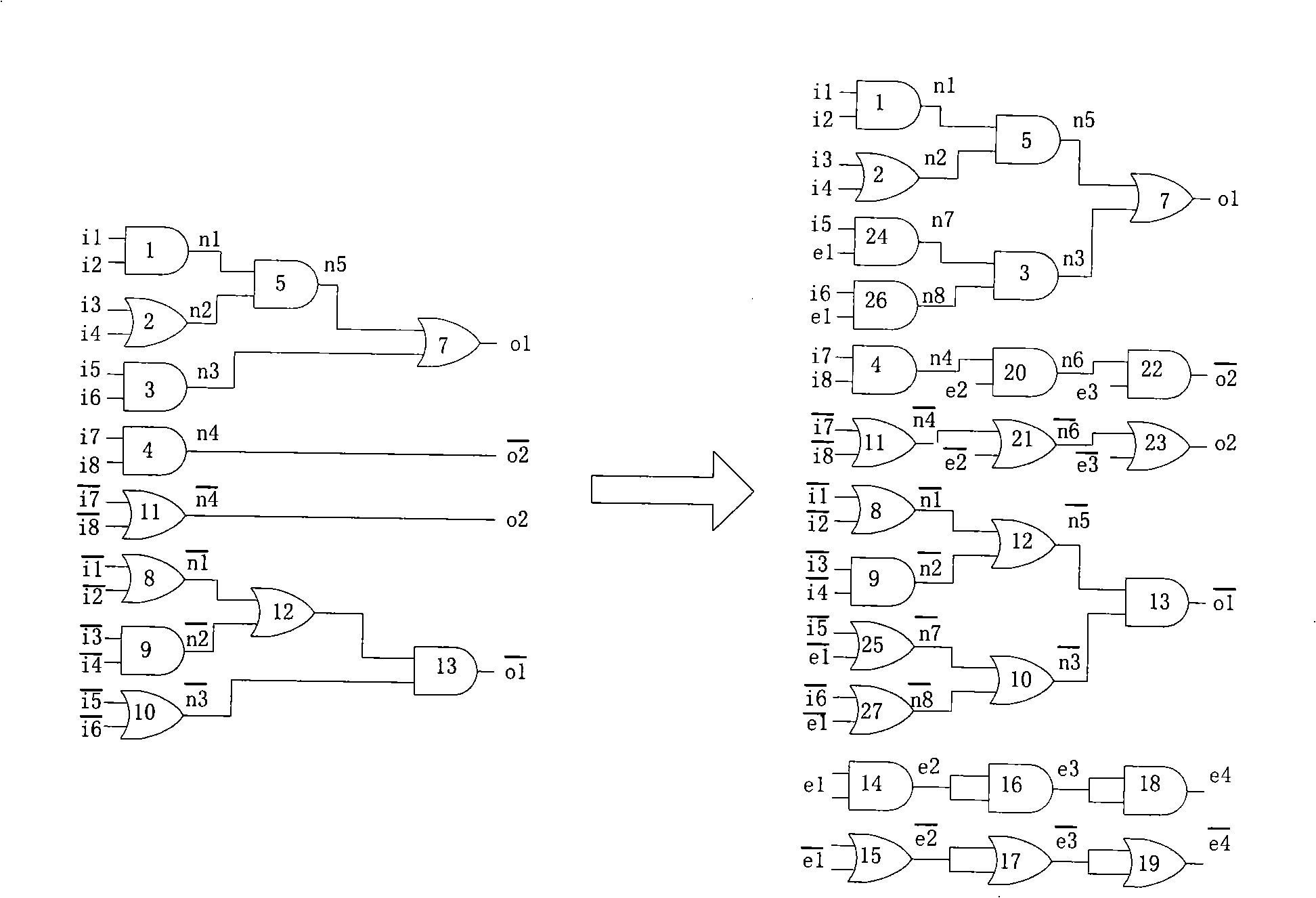

Design method of asynchronous block cipher algorithm coprocessor

InactiveCN101350038AHigh anti-power consumption attack protection capabilityGood constant power consumptionEncryption apparatus with shift registers/memoriesSpecial data processing applicationsCoprocessorMonorail

The invention discloses a method for designing an asynchronous block cipher algorithm coprocessor, wherein the technical problem which should be solved is to provide the method for designing the asynchronous block cipher algorithm coprocessor. The technical scheme comprises: taking each round of iteration in the block cipher algorithm as an independent submodule, adopting HDL to design each submodule, carrying out logic synthesis to each submodule, obtaining a static monorail net list, transforming the static monorail net list into a composite logic net list which is composed of two inputs which are complementary and doors and / or the doors, carrying out delay matching to each submodule, adding a delay matching module with same delay with the submodule, guaranteeing that the delays of signal input to signal output of each submodule are same, guaranteeing that the input reach time with the doors and / or the doors is same, connecting each submodule in turn, obtaining a complete net list, carrying out rear placement and routing, and obtaining a GDS layout. The coprocessor which is designed through adopting the method has higher power consumption attack resisting and protection ability and simultaneously has high operation performance and low power consumption features.

Owner:NAT UNIV OF DEFENSE TECH

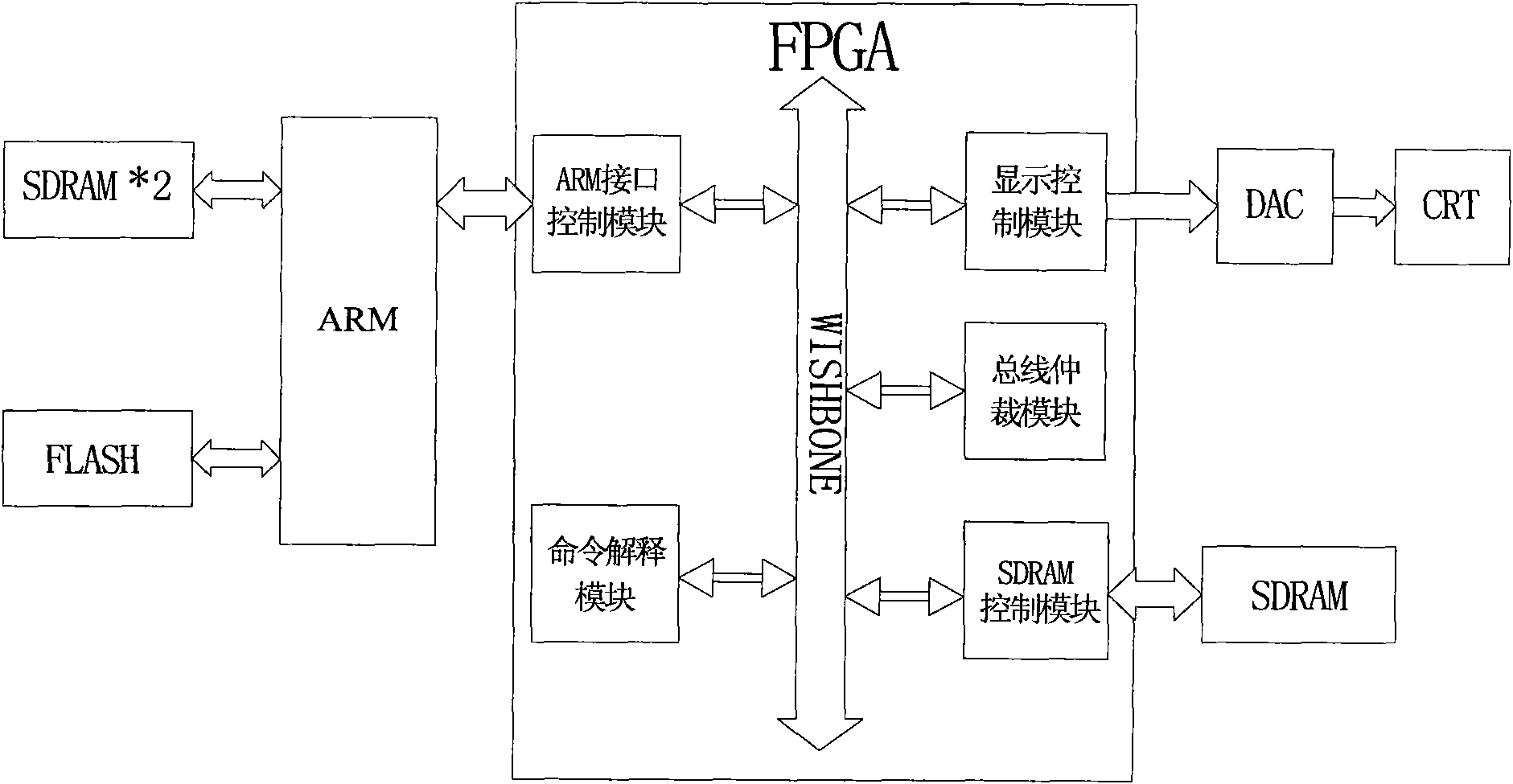

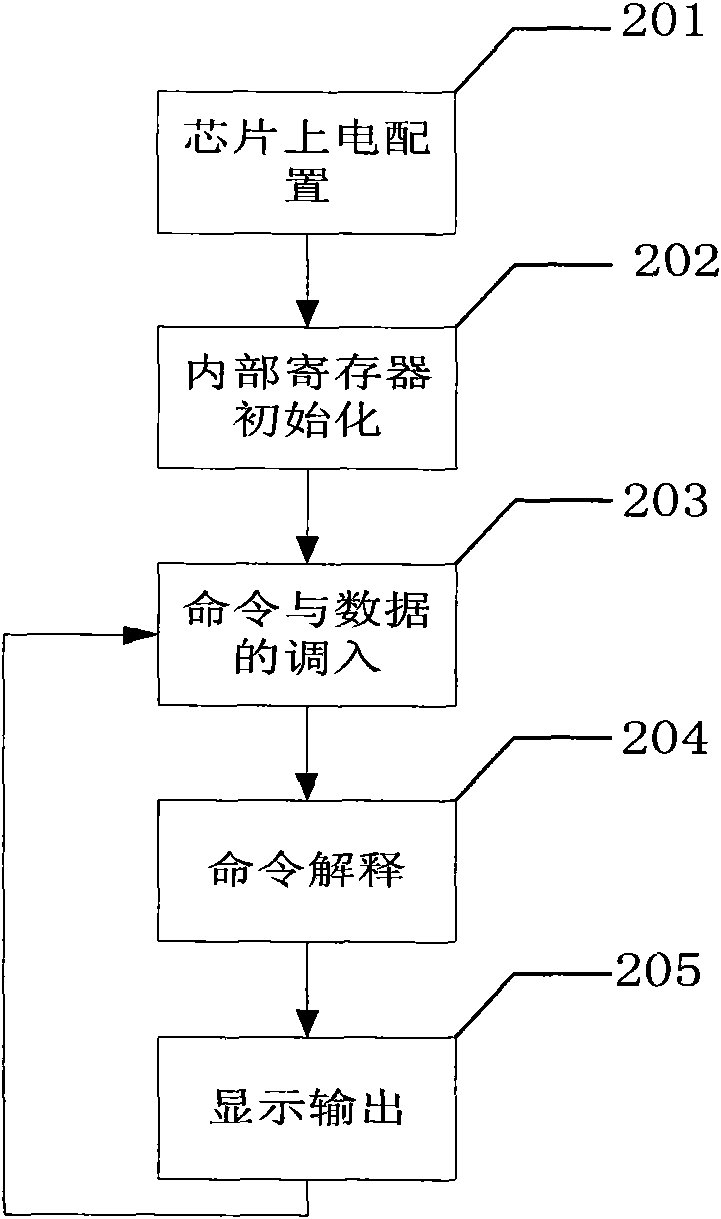

Image processing system based on FPGA

InactiveCN101625754AImprove performanceLow Power FeaturesProcessor architectures/configurationImaging processingMaster controller

The invention discloses an image processing system based on FPGA, comprising an image processing chip FPGA module; the FPGA includes an ARM interface module, an SDRAM control module, a command interpretation module, a display control module and a bus arbitration module, wherein the ARM interface module of the FPGA is also connected with a main controller which is an ARM microprocessor. The image processing system not only utilizes the ARM microprocessor so as to have the characteristics of having rich command sets and flexible programming, but also develops the advantages of the FPGA in the aspects of speed and parallel arithmetic, thus having and developing the advantages of the ARM microprocessor and the FPGA, and improving the efficiency, the flexibility and the upgradability of the system.

Owner:黄以华

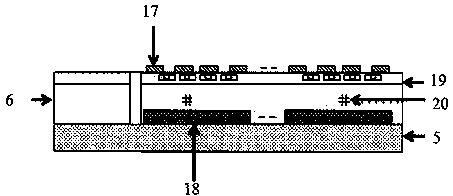

A low profile miniaturize phased array antenna

PendingCN109216938AMinimize RF tracesUltra Low Profile AchievementAntenna arraysDifferentiatorMicrowave

The invention relates to the field of radar communication, in particular, a low profile miniaturized phased array antenna is realized in a three-dimensional integrated manner, comprises an antenna TRmodule and a power supply and differentiator module, the high frequency signal interconnection between the antenna tr module and the power supply and differentiator module is implemented using radio frequency vertical interconnection, A low frequency interconnect is implement using a low frequency pin, the antenna TR module comprises an antenna TR module cavity, Antenna TR module printed circuit board and wave control PCB board, A printed circuit board of the antenna TR module and a waveform control PCB are respectively arranged on both sides of the cavity of the antenna TR module, As that microwave multilayer PCB board is use, the vertical interconnection between layers is realize, thereby realizing ultra-small longitudinal dimension integration, vertical interconnection blind insertion mode is adopted between the soft substrate part of the summer module and the prin circuit board of the antenna TR module, and the radio frequency traces are reduced by using the vertical interconnection between layers inside the microwave multilayer board.

Owner:CHENGDU RDW TECH CO LTD

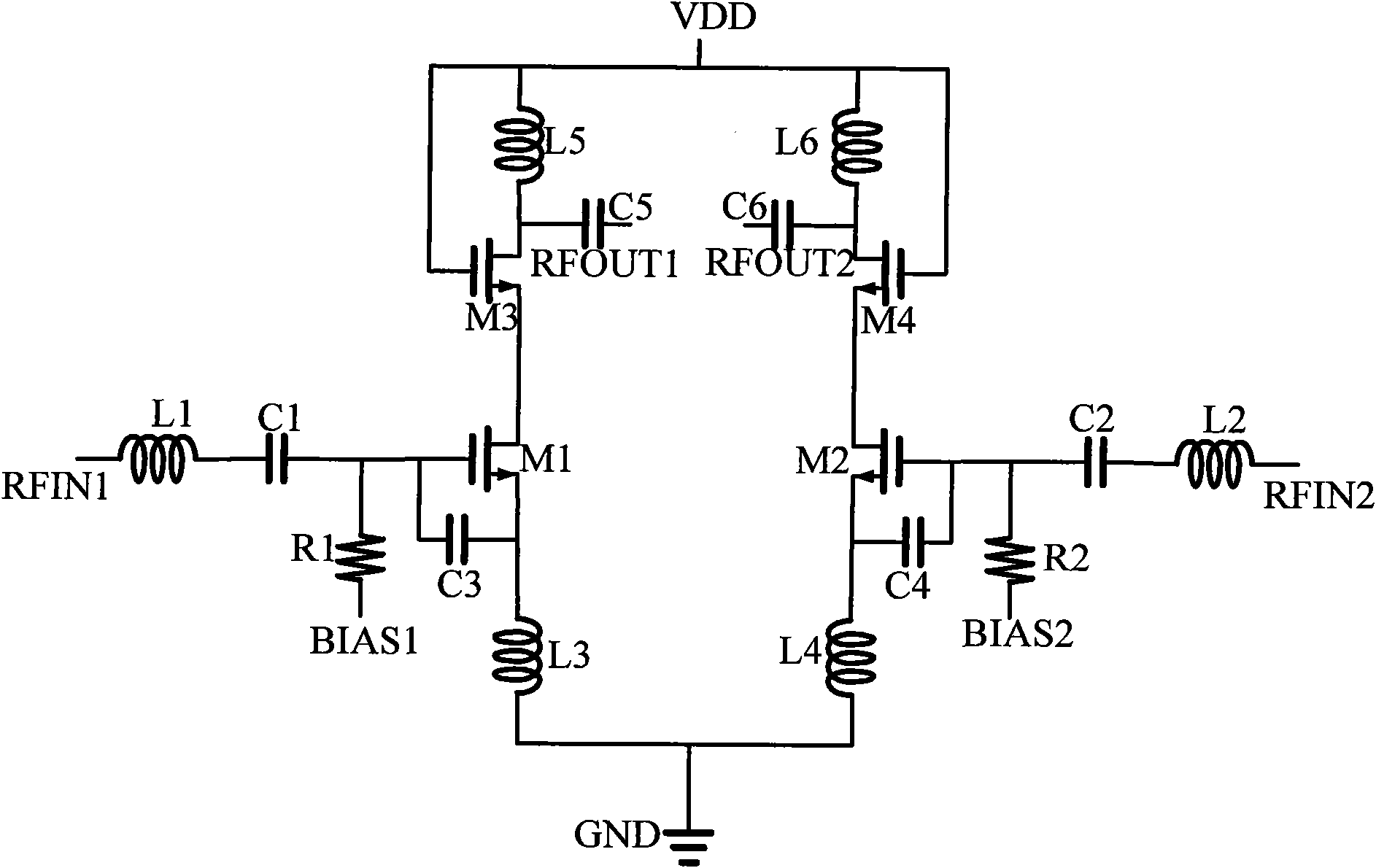

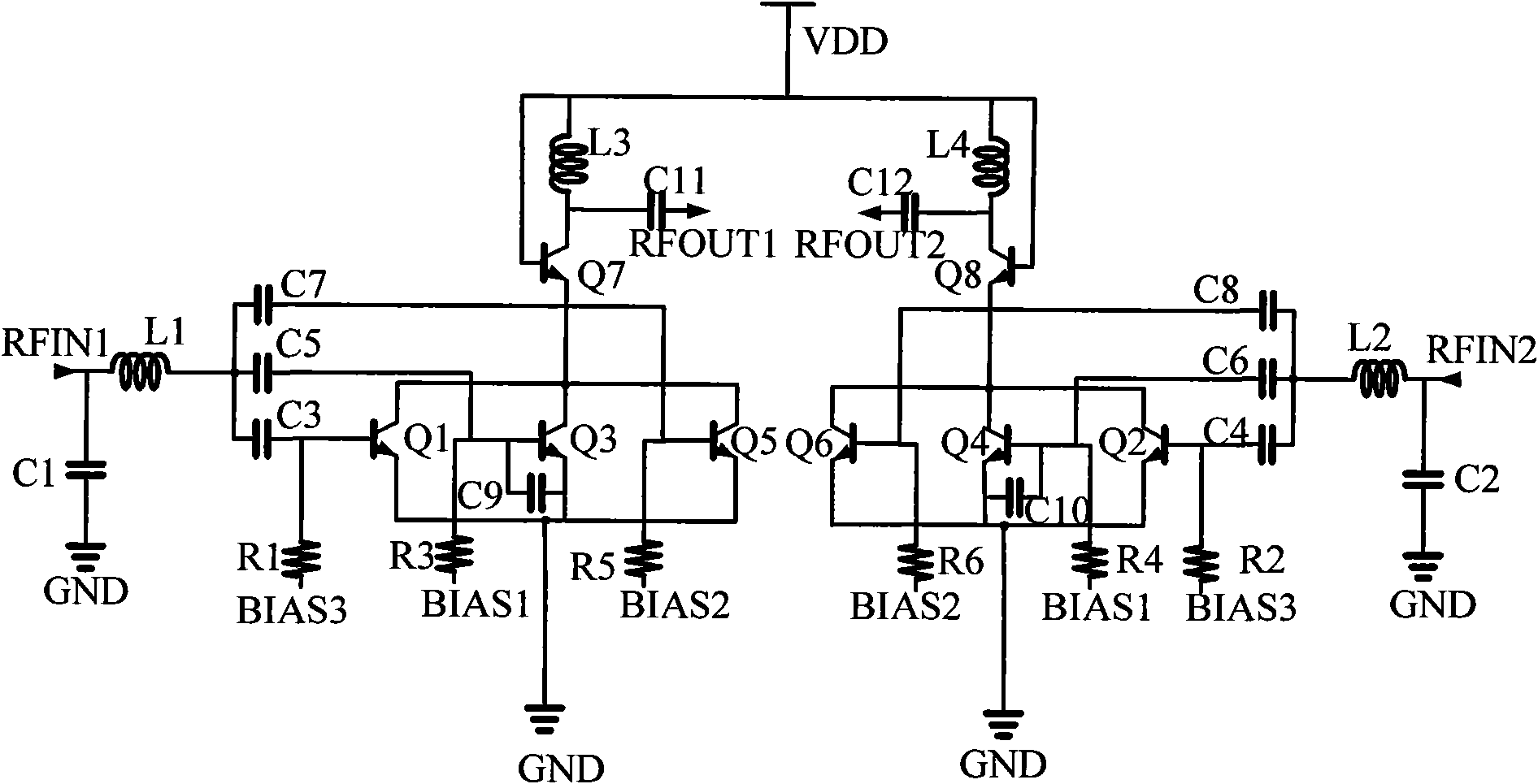

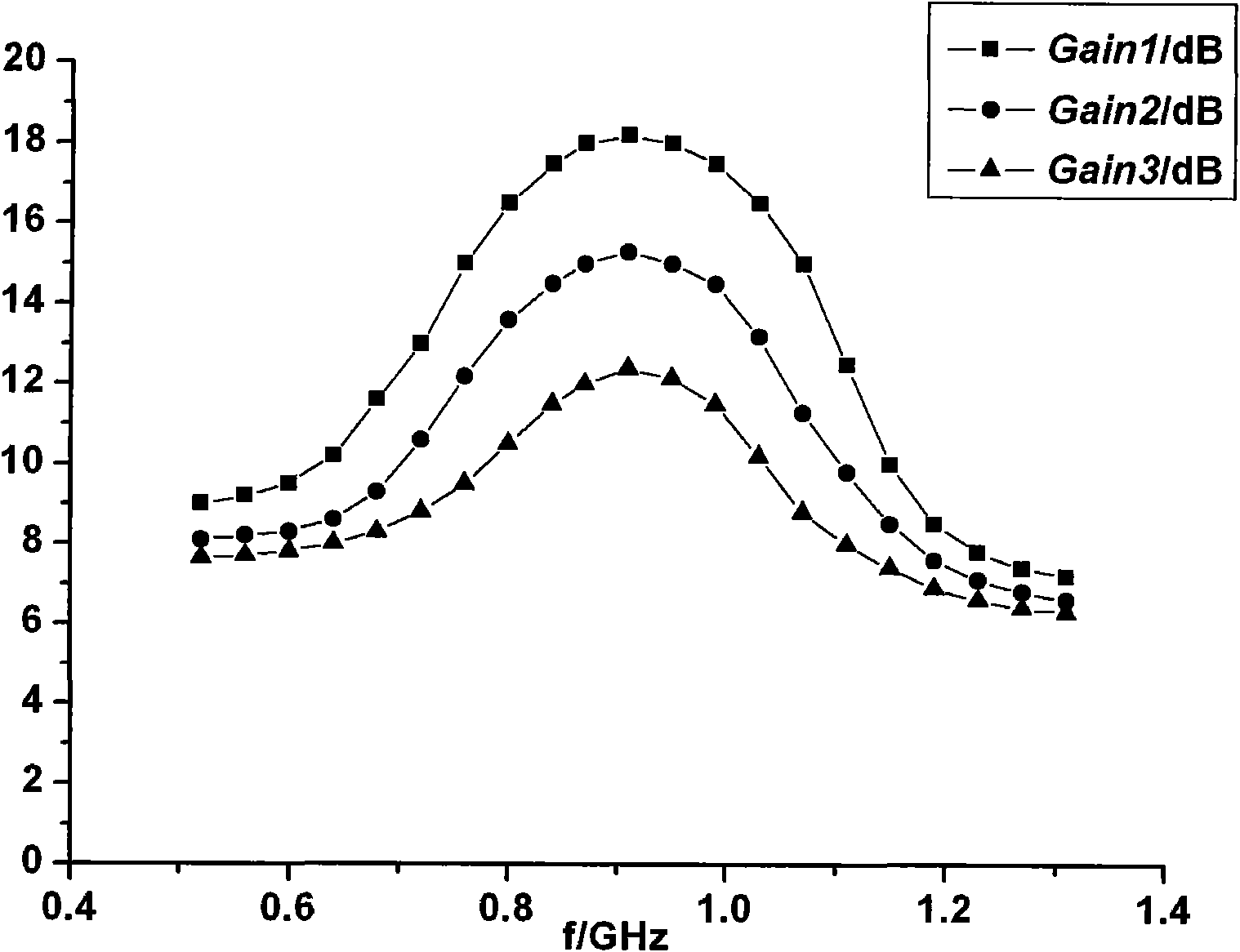

Variable gain low-noise driving amplifier

InactiveCN101944888AHigh variable gainGood input and output matchingDifferential amplifiersDc-amplifiers with dc-coupled stagesLow noiseExternal bias

The invention discloses a variable gain low-noise driving amplifier. The amplifier has a fully differential cascode structure, wherein a common gate consists of three side-by-side silicon germanide bipolar transistors; the central silicon germanide bipolar transistor adopts parallel capacitive feedback, a reasonable input / output matching circuit is adopted, a high variable gain is provided for a circuit, and the noise coefficient is reduced; a cascade circuit provides a high variable gain and increases the reverse isolation of the circuit at the same time; and a common source amplifying circuit further improves the gain of the circuit. By controlling the selection of an external bias, the variable gain with a 3dB step length is obtained. The variable gain low-noise driving amplifier has the characteristics of high variable gain, low noise and low power consumption.

Owner:EAST CHINA NORMAL UNIV

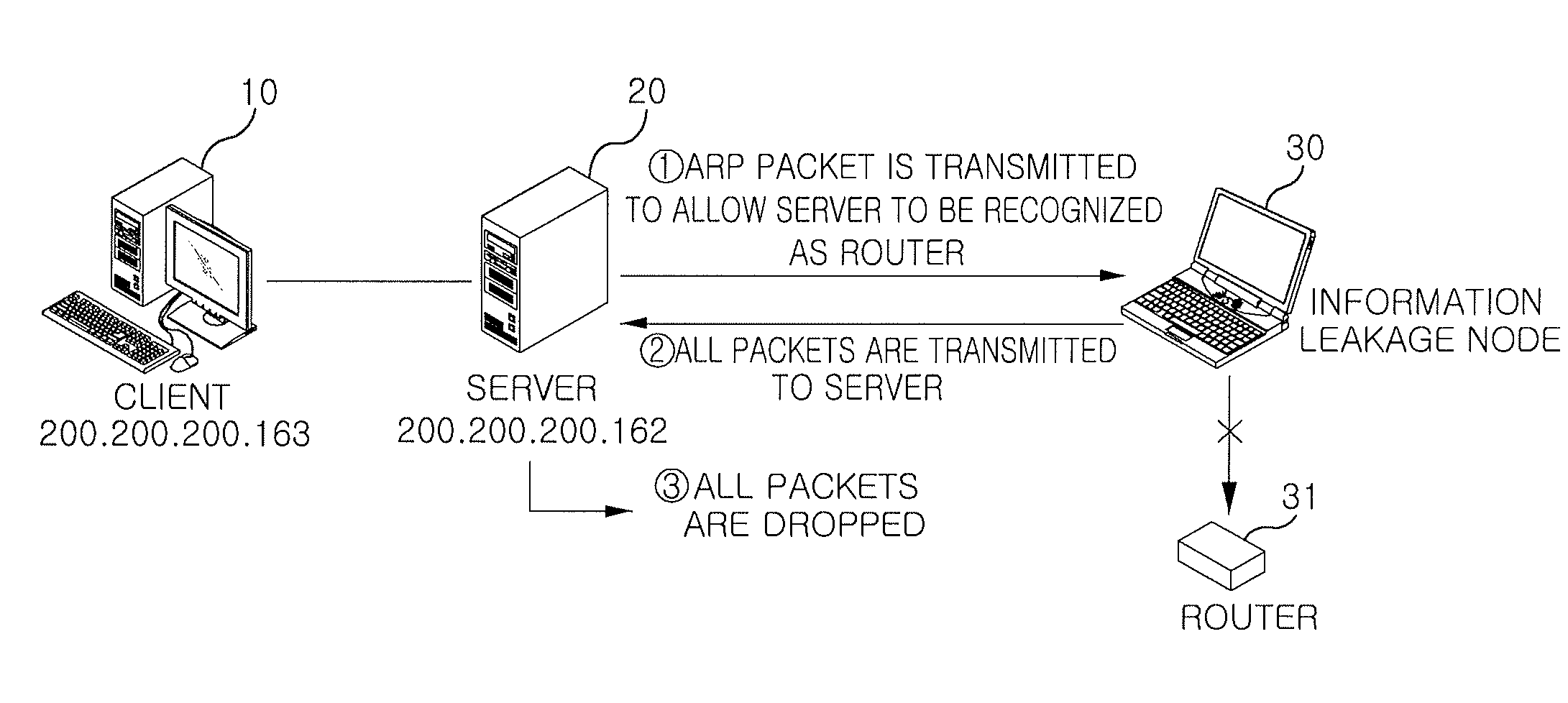

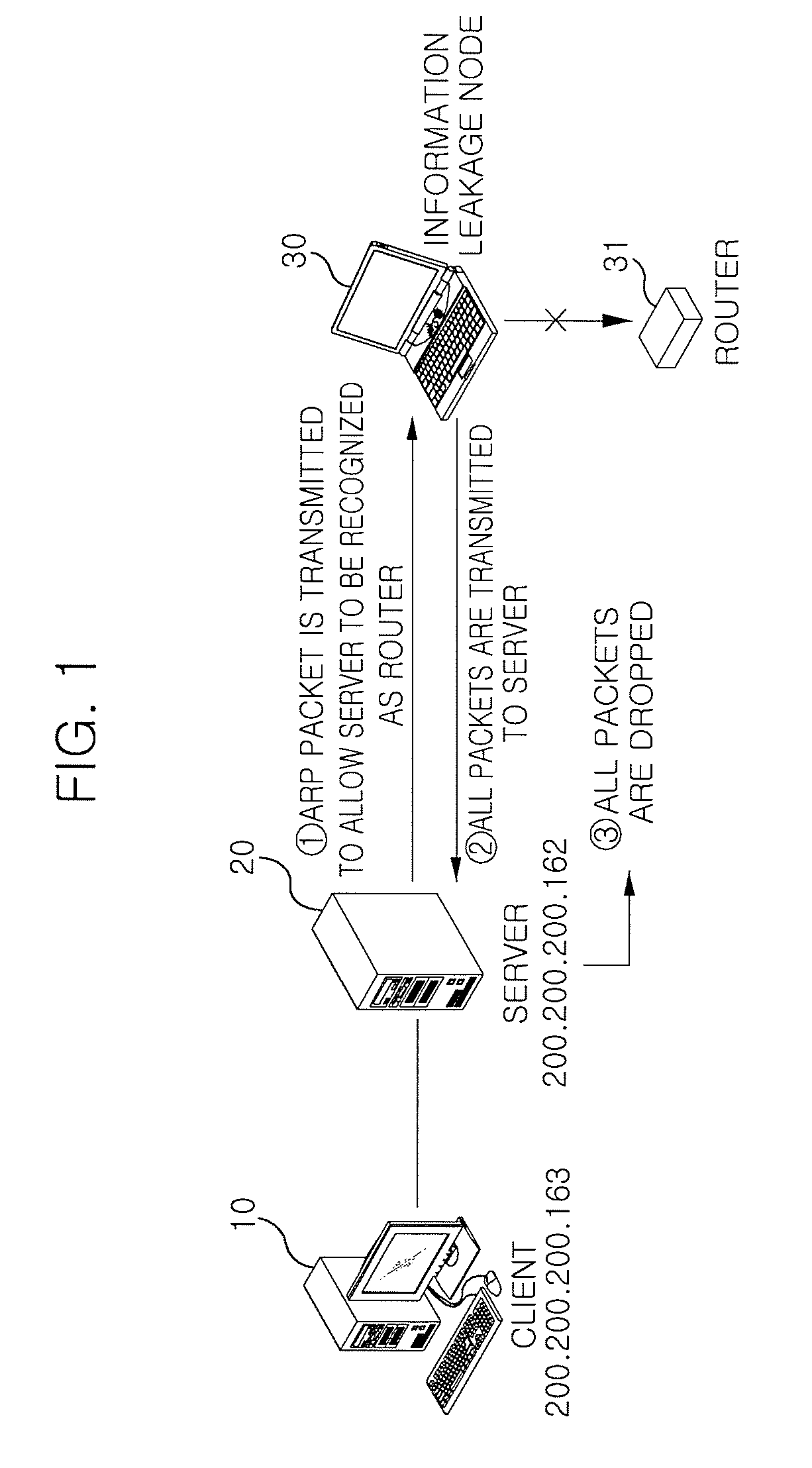

System and method for preventing private information from leaking out through access context analysis in personal mobile terminal

InactiveUS20090119745A1Low Power FeaturesData taking preventionComputer security arrangementsInformation analysisInformation leakage

A system for preventing private information from leaking out through access context analysis in a personal mobile terminal includes a private information manager that receives a private information leakage prevention policy, divides the policy into a plurality of private information leakage prevention rules, and transmits the plurality of rules to individual modules, respectively; a context analyzer that performs access context information analysis to obtain context information, when detecting a packet corresponding to a first rule, and transmits the context information; a packet analyzer that receives the context information, monitors packets transmitted to the outside through packet analysis, and transmits filtering information when detecting a packet corresponding to a second rule; and a private information leakage preventing unit that receives the filtering information and determines whether to allow or drop a packet corresponding to a third rule.

Owner:ELECTRONICS & TELECOMM RES INST

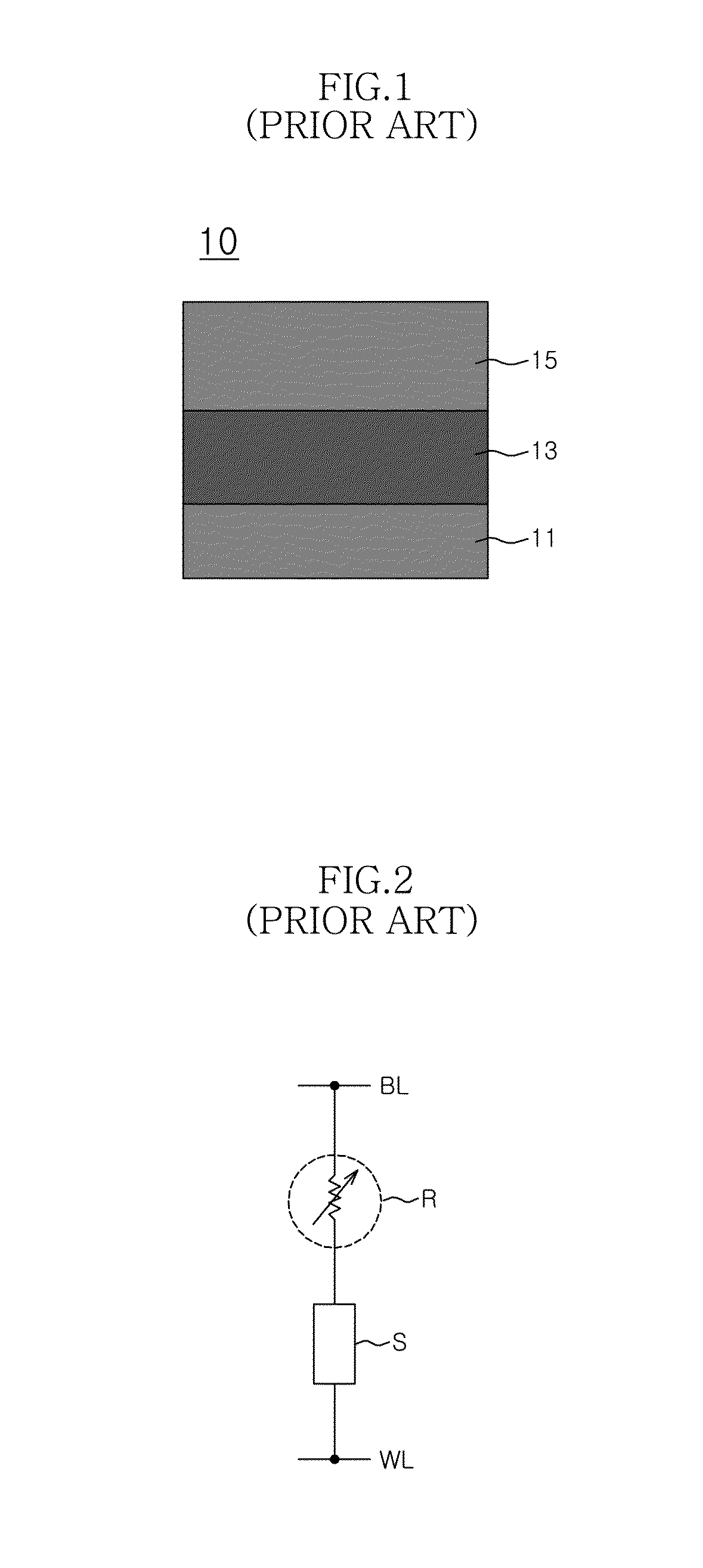

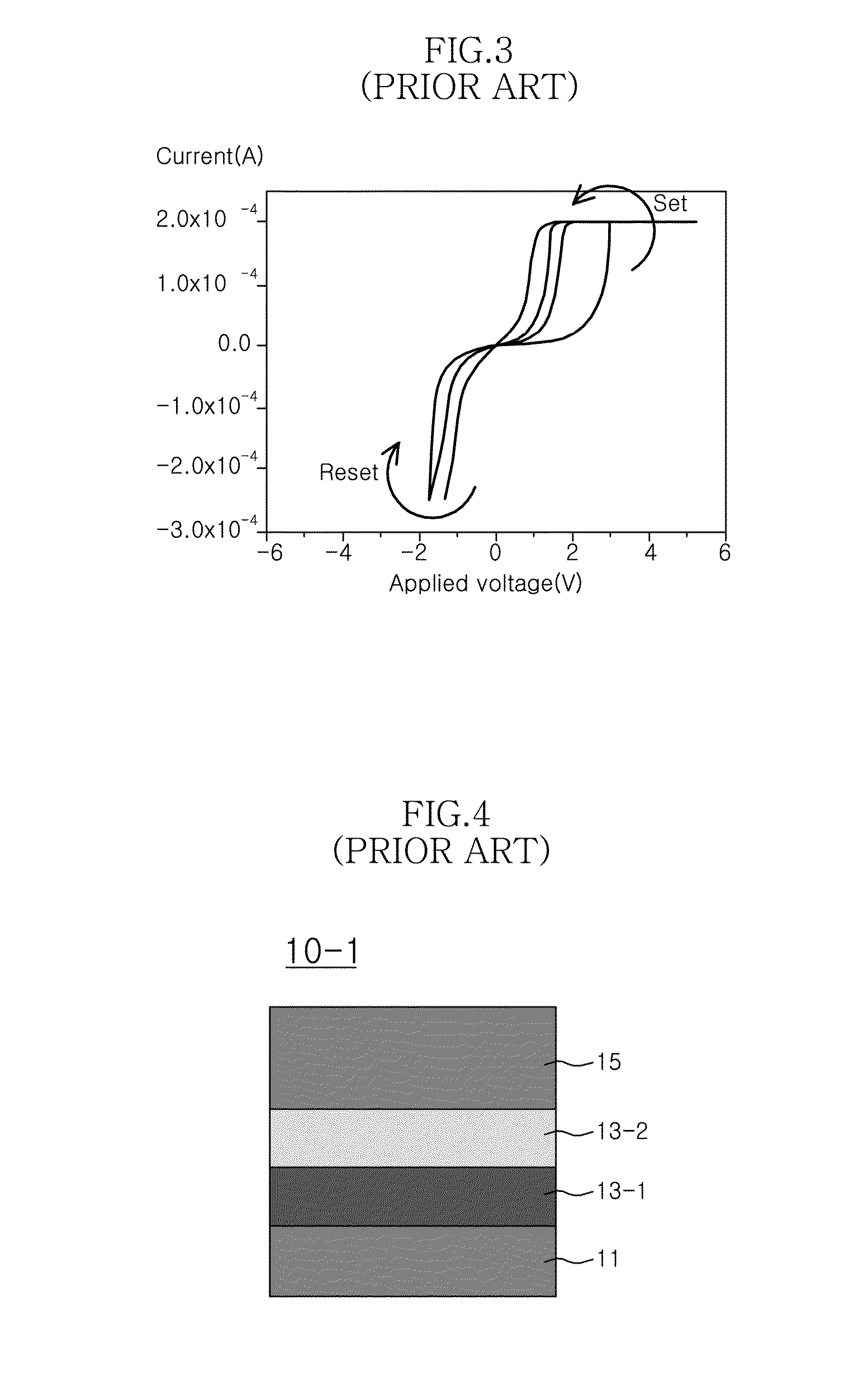

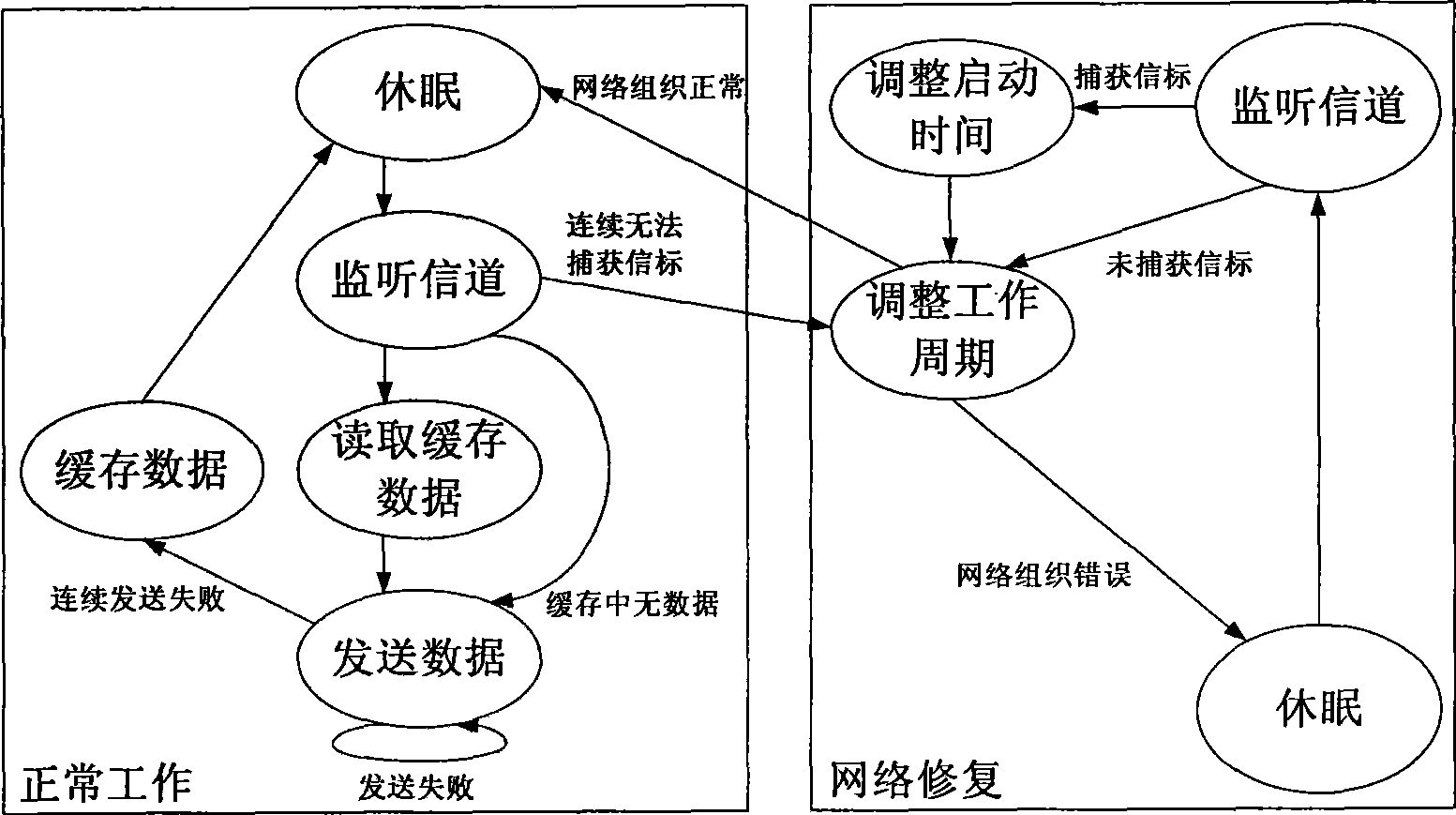

Resistive memory device and memory apparatus and data processing system having the same

InactiveUS20140097397A1High resistivityLow Power FeaturesDigital storageBulk negative resistance effect devicesData processing systemElectric resistivity

A resistive memory device includes a first electrode layer, a second electrode layer, and a first variable resistive layer and a second variable resistive layer stacked at least once between the first electrode layer and the second electrode layer. The first variable resistive material layer may include a metal nitride layer having a resistivity higher than that of the first electrode layer or the second electrode layer and less than or equal to that of an insulating material.

Owner:SK HYNIX INC

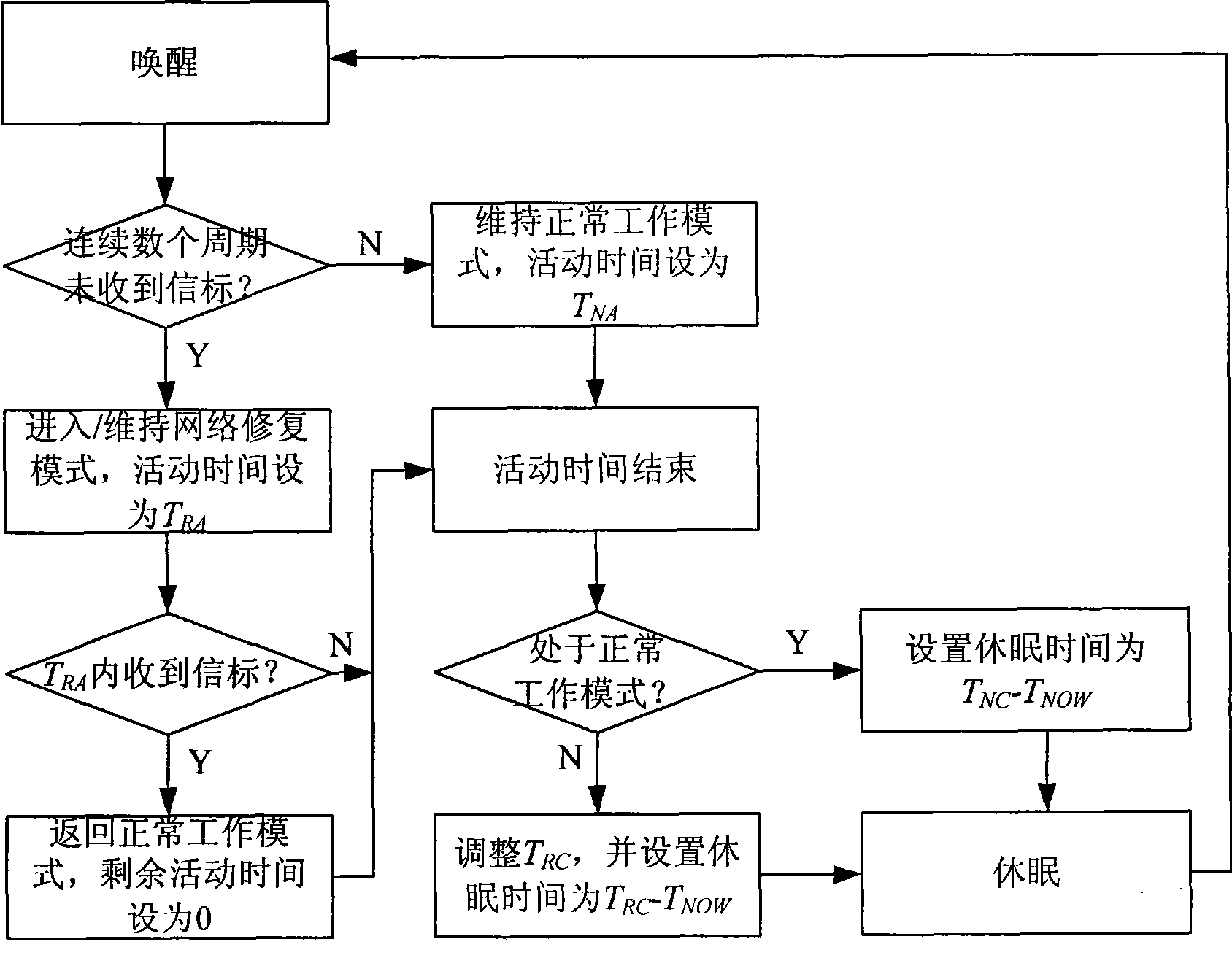

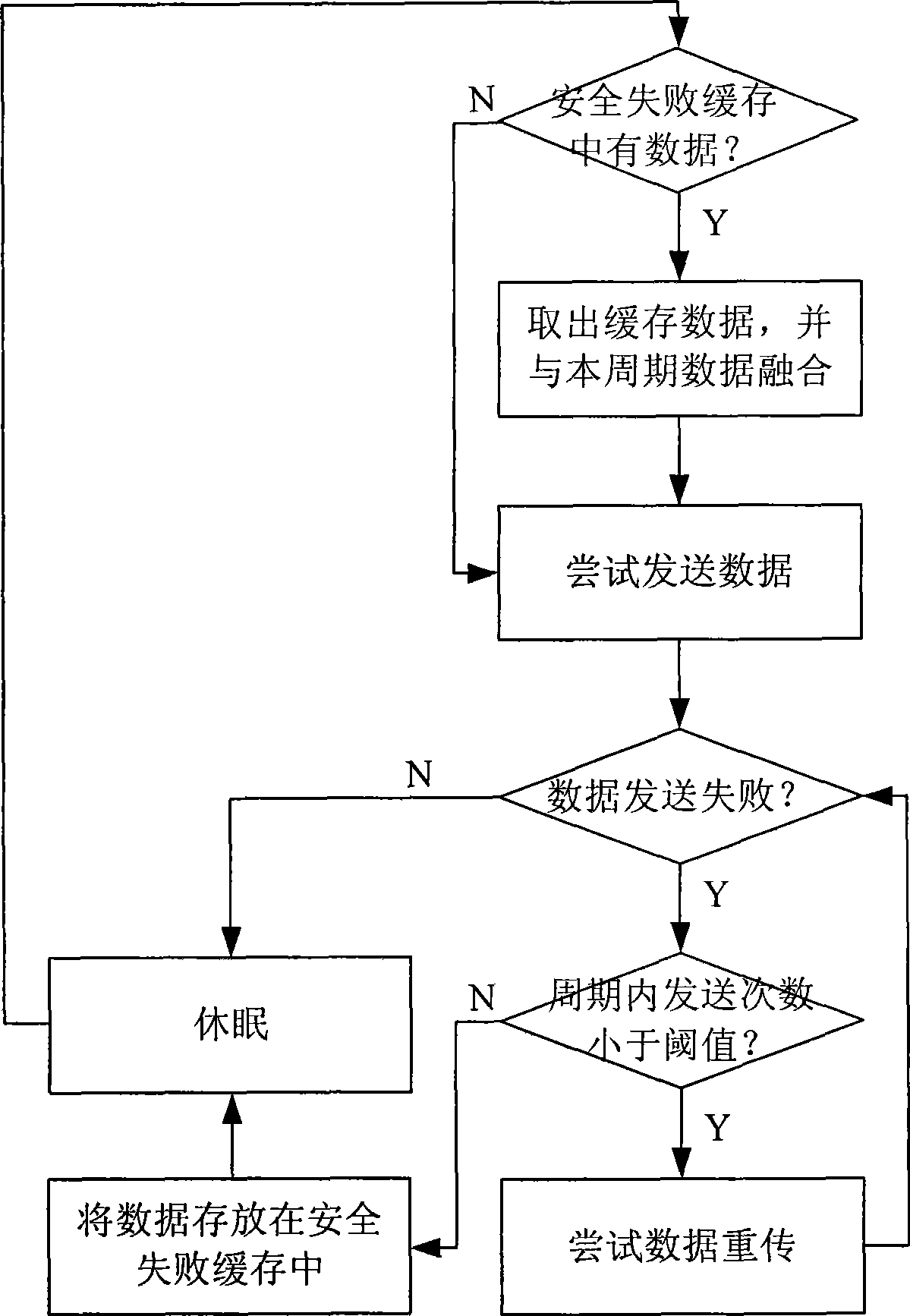

Data collection transmission reliable guarantee method in wireless sensor network

InactiveCN101459978AImprove repair abilityLow Power FeaturesEnergy efficient ICTError prevention/detection by using return channelWork periodData integrity

The invention discloses a method for guaranteeing the reliability of data collection transmission in a wireless sensor network, which comprises: adopting a high reliable network organizing method on the basis of dynamic working period adjustment by each sensor node in a sensor network and adopting a high reliable data transmission method on the basis of 2 phase retransmission between sensor nodes and between convergent nodes in the sensor network. On the aspect of network organization reliability guarantee, working modes of the sensor nodes are divided into two modes of normal work and network repair, intermittent working of the nodes under the two modes can be guaranteed through the dynamic working period adjustment, thereby guaranteeing the node lower power consumption characteristics and rapid network repair ability simultaneously. On the aspect of data transmission reliability guarantee, the high reliable data transmission method on the basis of 2 phase retransmission is adopted to guarantee the data integrity when data transmission errors and even chain interruption appear, and the influence of the data transmission errors on the data real time performance is lowered to the minimum.

Owner:ZHEJIANG UNIV

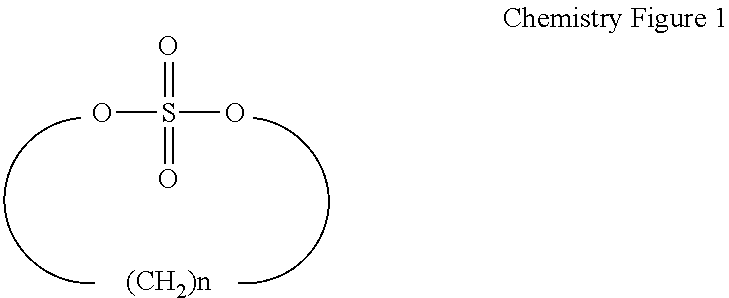

Non-Aqueous Electrolyte Solution For Lithium Secondary Battery And Lithium Secondary Battery Comprising The Same

ActiveUS20120009487A1Improve performanceLow Power FeaturesOrganic electrolyte cellsLi-accumulatorsSulfatePhysical chemistry

A non-aqueous electrolyte solution for a lithium secondary battery includes a non-aqueous solvent and a lithium salt dissolved in the non-aqueous solvent. The lithium salt includes LiN(CF3SO2)2. The non-aqueous electrolyte solution further includes a sulfate-based compound and vinylene carbonate. A lithium secondary battery having the above non-aqueous electrolyte solution may keep overall high temperature performance in a high level and also improve low temperature power characteristics.

Owner:LG ENERGY SOLUTION LTD

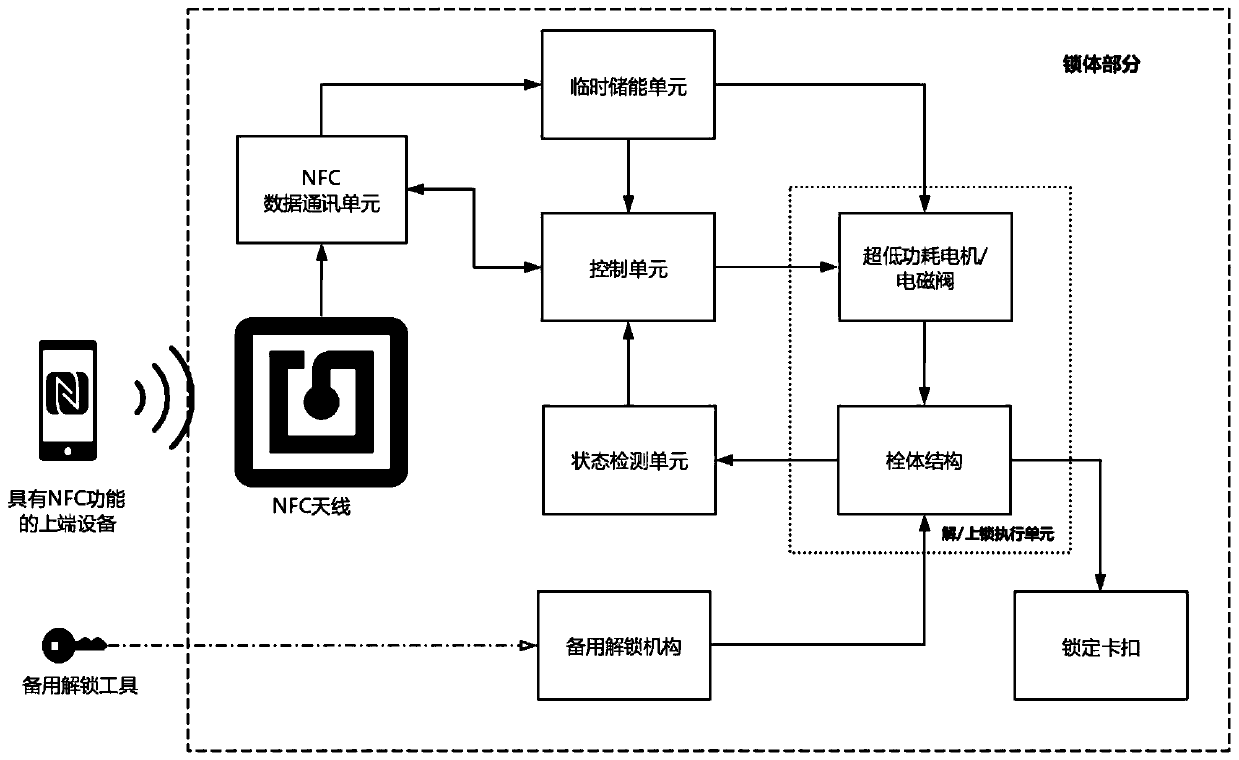

Passive intelligent electronic lock based on NFC electromagnetic field charging

InactiveCN110533803AExtended service lifeImprove use reliabilityCircuit arrangementsIndividual entry/exit registersCapacitanceElectricity

The invention relates to a passive intelligent electronic lock based on NFC (Near-Field Communication) electromagnetic field charging, and is designed by aiming at the technical problem that an existing intelligent lock product using an NFC technology needs battery or external power supply. The passive intelligent electronic lock consists of a casing, an NFC antenna, a circuit board and a switch lock executing mechanism, wherein the NFC antenna is arranged on the casing; the circuit board is arranged in the casing and is connected with the NFC antenna; and the switch lock executing mechanism is connected with the circuit board. The passive intelligent electronic lock is characterized in that the casing is made of non-metallic materials; the NFC antenna is arranged at the surface of the casing; the circuit board is provided with a control unit, an NFC data communication unit and temporary energy storage units; the switch lock executing mechanism comprises an unlocking / locking executingunit, a state detection unit, a locking clamp buckle and a standby unlocking mechanism; and the temporary energy storage units are conventional capacitors and circuits thereof, so that in the communication connection process, the NFC data communication unit performs energy collection and storage on an NFC signal electromagnetic field provided by upper end equipment with an NFC function, and provides energy for the action of the unlocking / locking executing unit.

Owner:宁波生久科技有限公司

Large-mismatch silicon-based substrate antimonide transistor with high electron mobility and manufacturing method thereof

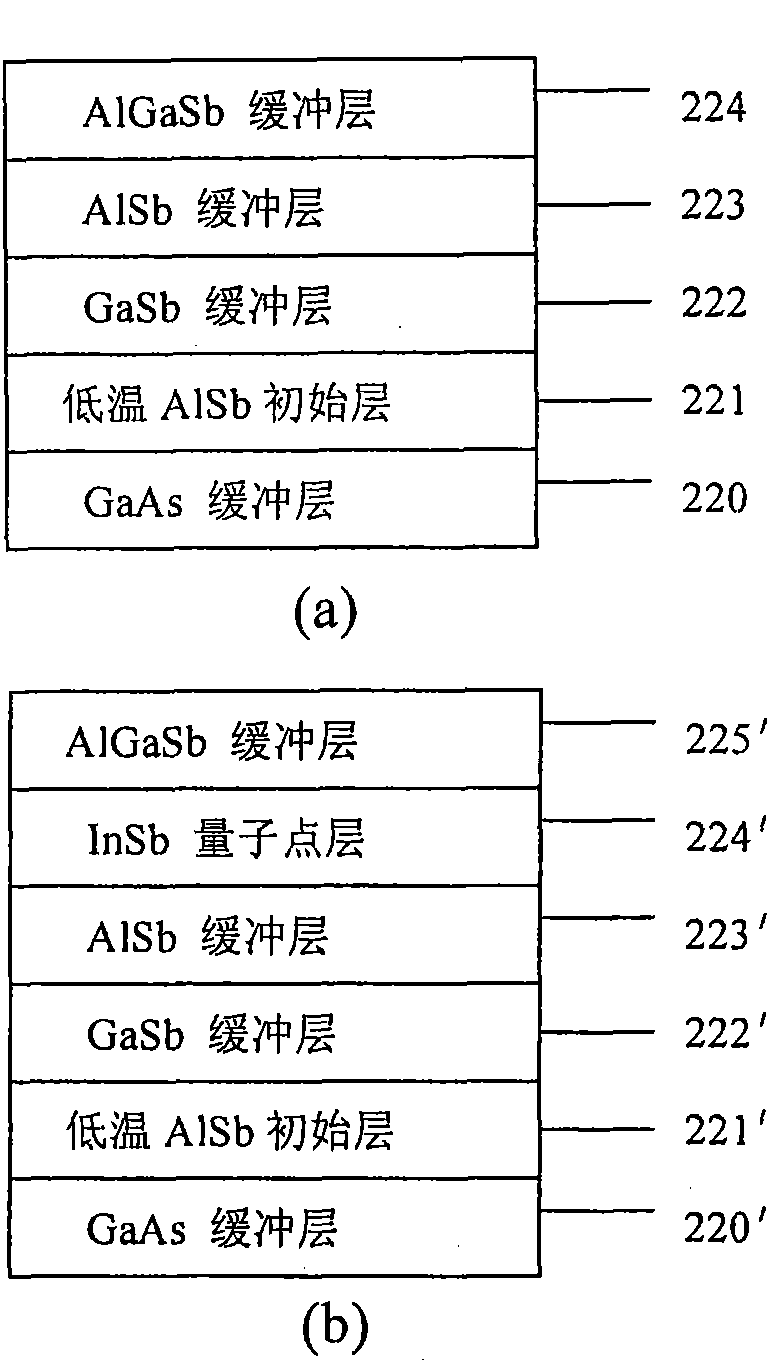

ActiveCN102324436AImprove output characteristicsLow Power FeaturesSemiconductor/solid-state device manufacturingSemiconductor devicesDelta dopingIsolation layer

The invention provides a large-mismatch silicon-based substrate antimonide transistor with high electron mobility. The large-mismatch silicon-based substrate antimonide transistor comprises a substrate, a composite buffering layer growing on the substrate, an insert layer growing on the composite buffering layer, an AlSb isolation layer growing on the insert layer, a sub channel layer growing on the AlSb isolation layer, an antimonide lower potential barrier layer growing on the sub channel layer, an InAs channel layer growing on the antimonide lower potential barrier layer, an antimonide isolation layer growing on the InAs channel layer, a doping layer growing on the antimonide isolation layer, wherein the doping layer is InAs doped with a Si plane or delta doping of Te; an upper potential barrier layer growing on the doping layer, wherein the upper potential barrier layer is a composite potential barrier layer consisting of an AlSb layer and an InAlAs layer; and an InAs cap layer growing on the upper potential barrier layer, wherein the InAs cap layer is an unintentionally doped InAs or n type doped InAs.

Owner:INST OF SEMICONDUCTORS - CHINESE ACAD OF SCI

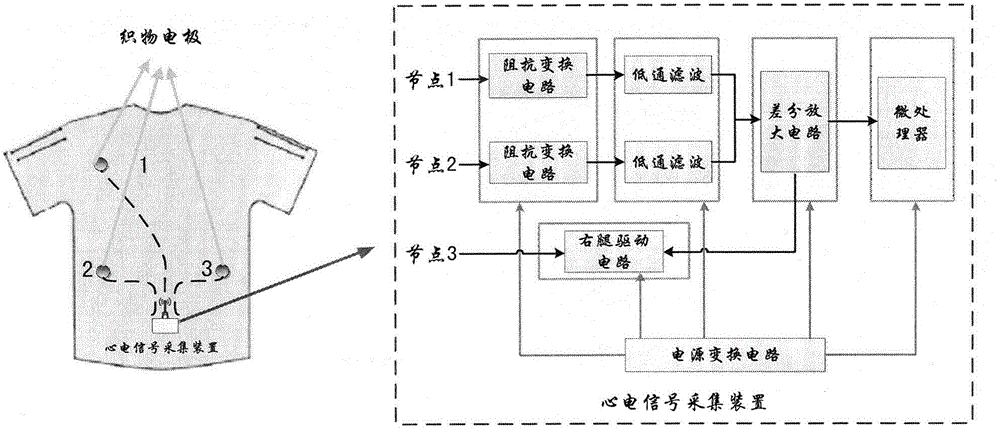

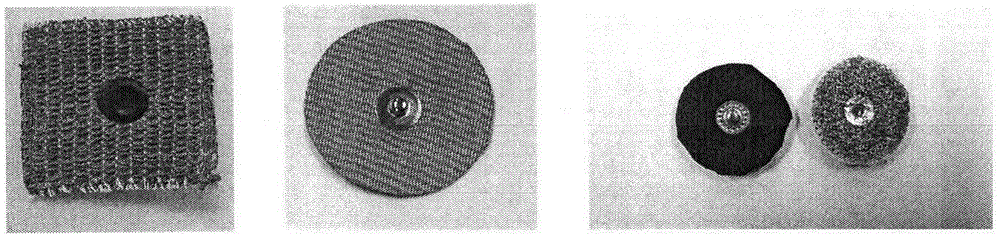

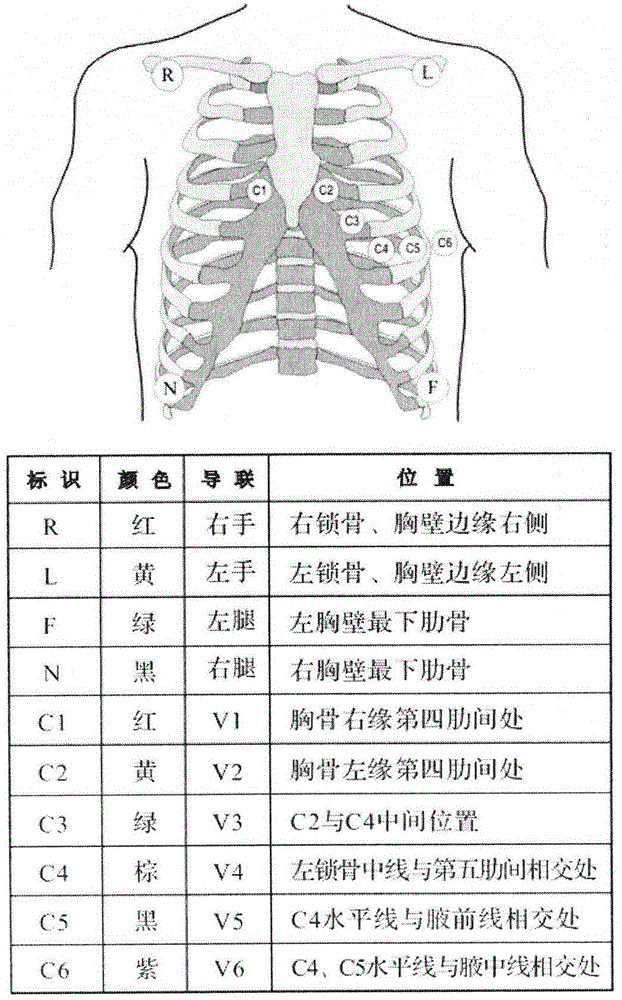

Wearable electro-cardio signal collection device based on fabric electrode

InactiveCN106606359ARealize transmissionEnables continuous monitoringDiagnostic recording/measuringSensorsEcg signalData set

The invention discloses a wearable electro-cardio signal collection device based on a fabric electrode. The device can carry out complete collection of electro-cardio signals of a human body aiming at the fabric electrode which is a novel flexible electrode. The device is characterized in that input impedance conversion of the fabric electrode could be achieved by an impedance conversion circuit, so the problem about high input impedance of the fabric electrode could be solved; common mode rejection and differential amplification are completed by a low-pass filtering circuit and a differential circuit; and finally, AD sampling and data set package transmission could be achieved. In comparison with a traditional electro-cardio collection circuit, the device disclosed by the invention is characterized in that the impedance conversion circuit is added at the fabric electrode part; power is supplied by a single power source; and an operational amplifier with a high signal to noise ratio and high input impedance is selected. In this way, the puzzle that signals are incomplete when the traditional electro-cardio collection circuits are used to extract the electro-cardio signals of the human body with application of the fabric electrode could be solved. The device is characterized by good performance, the small size and low power consumption. The device can be widely applied to wearable electro-cardio signal collection based on the fabric electrode; and comfort and convenience of use are enhanced.

Owner:SCI RES TRAINING CENT FOR CHINESE ASTRONAUTS

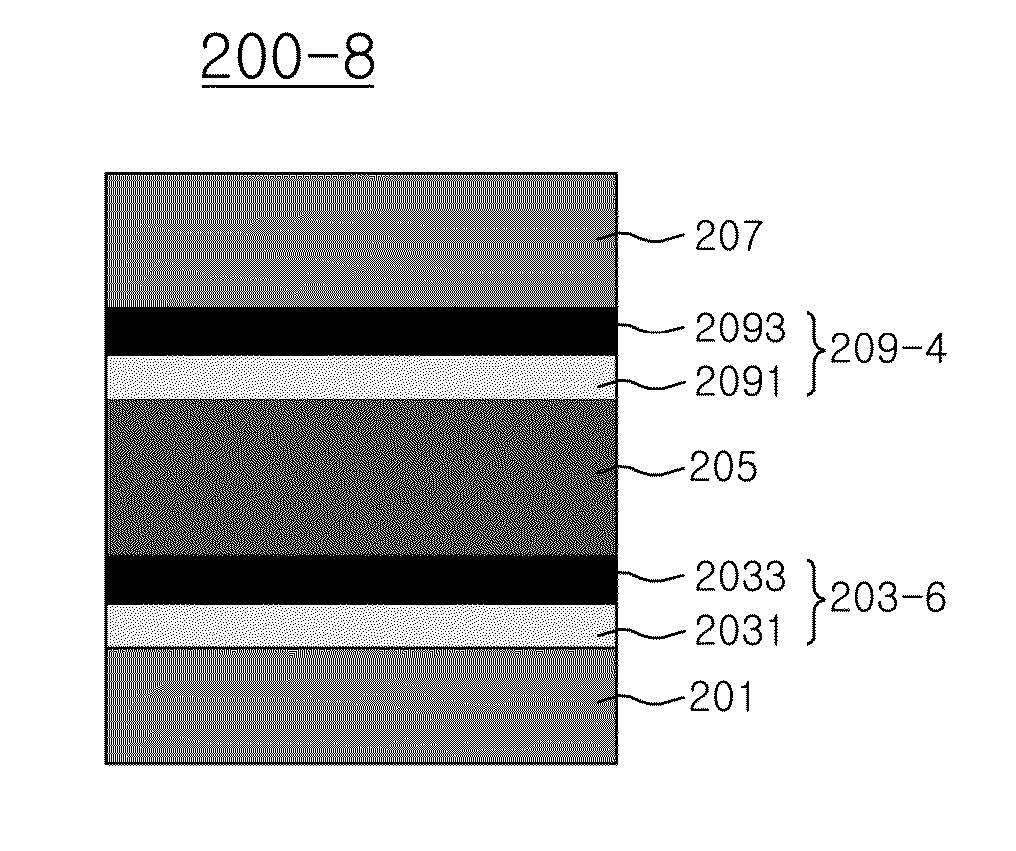

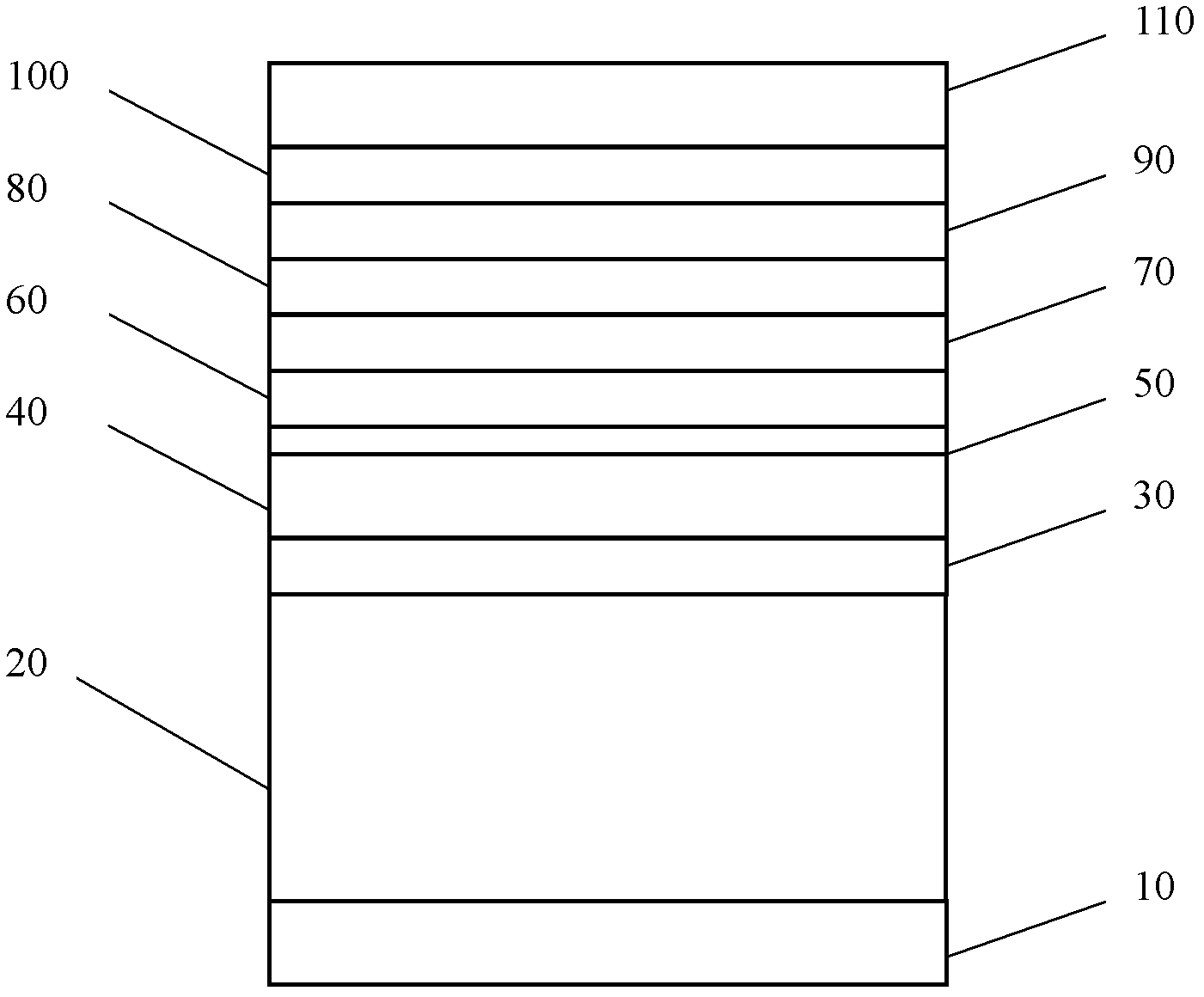

Thin film transistor substrate and display using the same

ActiveUS10121899B2Minimize the numberSimple processTransistorSolid-state devicesDisplay deviceOxide semiconductor

A thin film transistor substrate includes a first thin film transistor disposed having a polycrystalline semiconductor layer, a first gate electrode on the polycrystalline semiconductor layer, a first source electrode and a first drain electrode; a first gate insulating layer between the polycrystalline semiconductor layer and the first gate electrode; a second thin film transistor disposed having an oxide semiconductor layer on the first gate electrode, a second gate electrode on the oxide semiconductor layer, a second source electrode and a second drain electrode; an intermediate insulating layer disposed on the first gate electrode and under the oxide semiconductor layer; and a second gate insulating layer on the intermediate insulating layer and under the first source electrode, the first drain electrode and the second gate electrode.

Owner:LG DISPLAY CO LTD

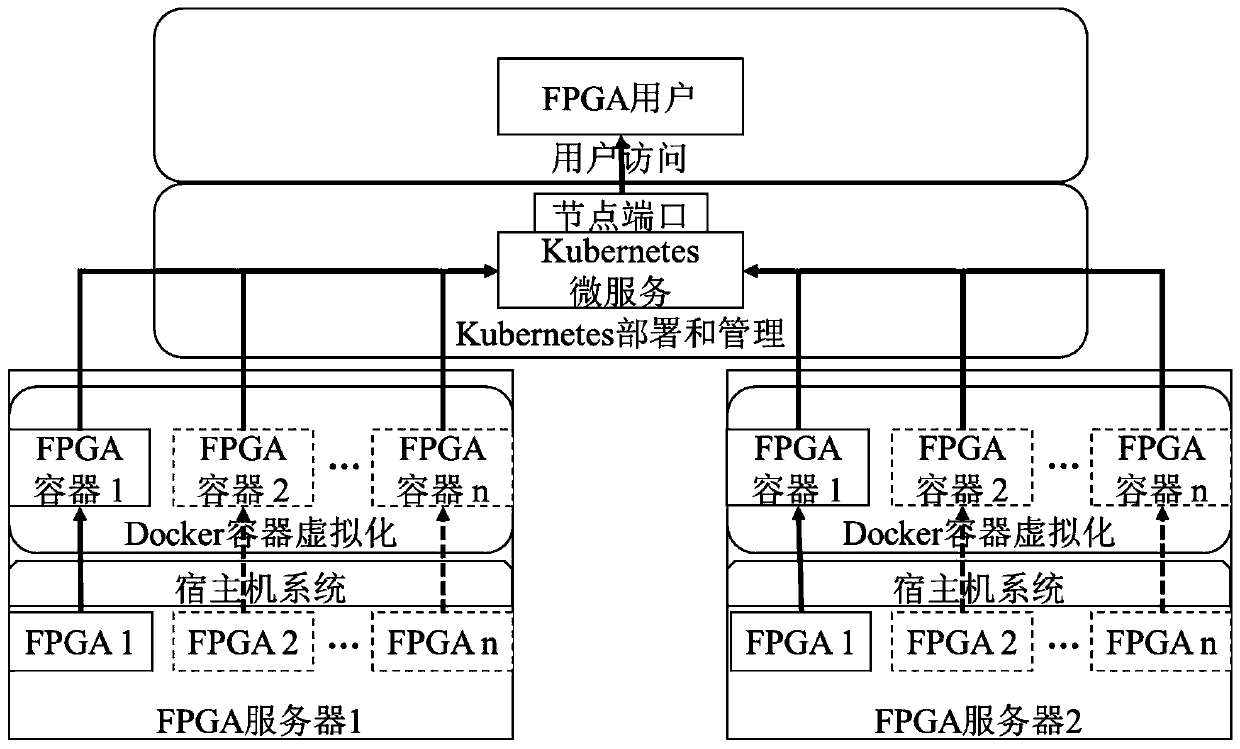

Method for realizing high-speed and safe server cluster management through FPGA virtualization deployment

PendingCN111124607AHigh-speed secure data processingHigh speed data processingDigital data authenticationSoftware simulation/interpretation/emulationVirtualizationOperational system

The invention discloses a method for realizing high-speed and safe server cluster management through FPGA virtualization deployment, and belongs to the field of high performance data processing, whichcan improve the speed, the reliability and the safety of services such as access, programming and calculation of small and medium-sized enterprise server clusters for externally deploying FPGA resources a. The method is characterized in that a Docker container engine and a Kubernetes cluster container orchestration engine management system are adopted to construct FPGA virtualization deployment;available virtualized FPGA resources are automatically provided for users outside the cluster in a micro-service mode; then, when a user accesses the virtualized FPGA container, the user can obtain access permission to all resources of FPGA hardware, that is, an operating system kernel of the host machine is directly used to process mass data, and after the user finishes using, the system can automatically release and recycle the resources for next resource allocation and use.

Owner:SHANGHAI UNIV

Wireless communication device using common control channel and wireless communication method using the same

ActiveUS20140286216A1Prevent unnecessary power wasteLow Power FeaturesPower managementFrequency-division multiplex detailsTelecommunicationsControl channel

A wireless communication method using a control channel between wireless communication devices including: exchanging profile information between a node and intermediate relay nodes therearound so as to allow the node to transmit / receive data to / from a destination node; determining, by the node, a first intermediate relay node using the profile information and determining a wireless communication mode with the first intermediate relay node; and transmitting / receiving data between the node and the first intermediate relay node by the determined wireless communication mode is provided.

Owner:ELECTRONICS & TELECOMM RES INST

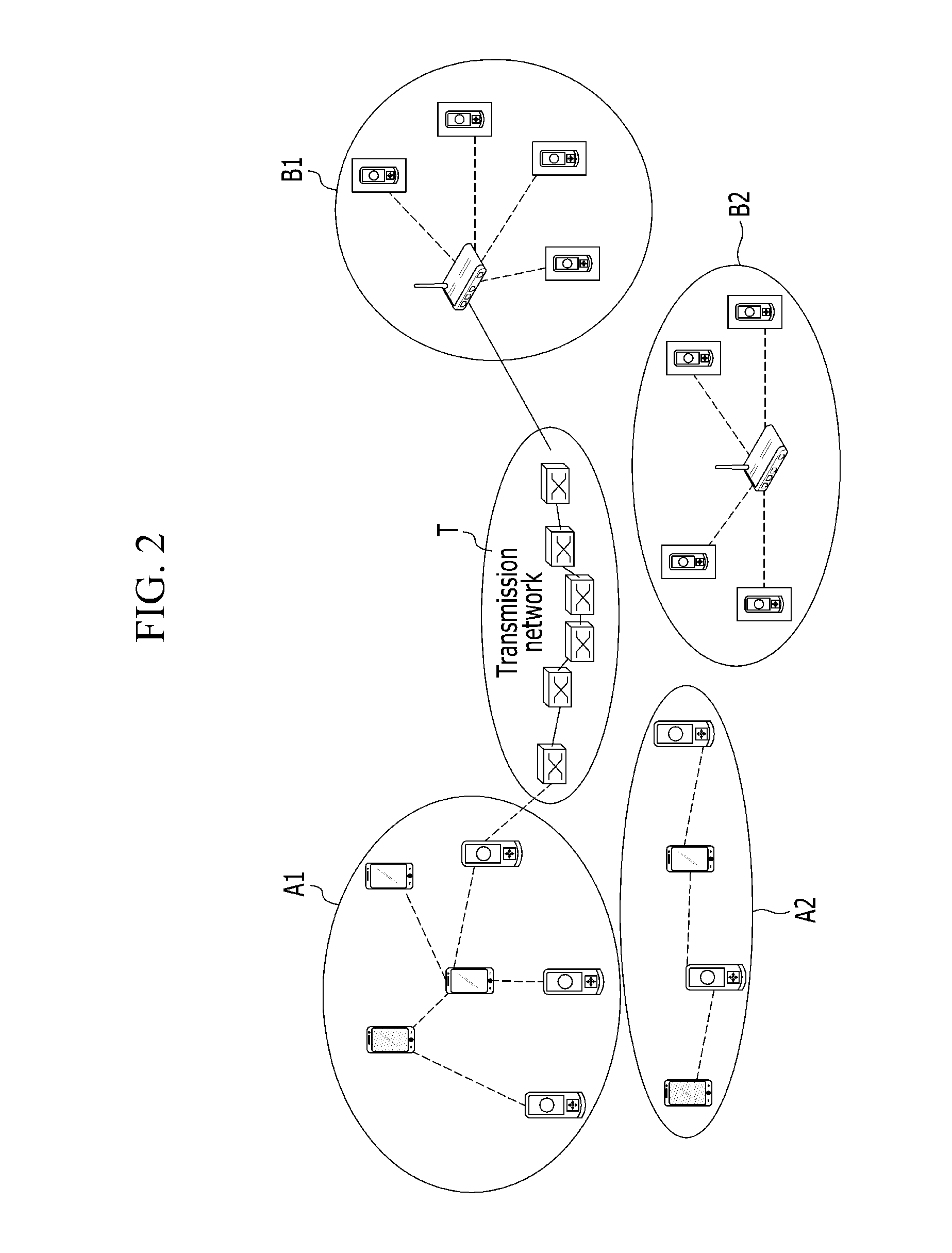

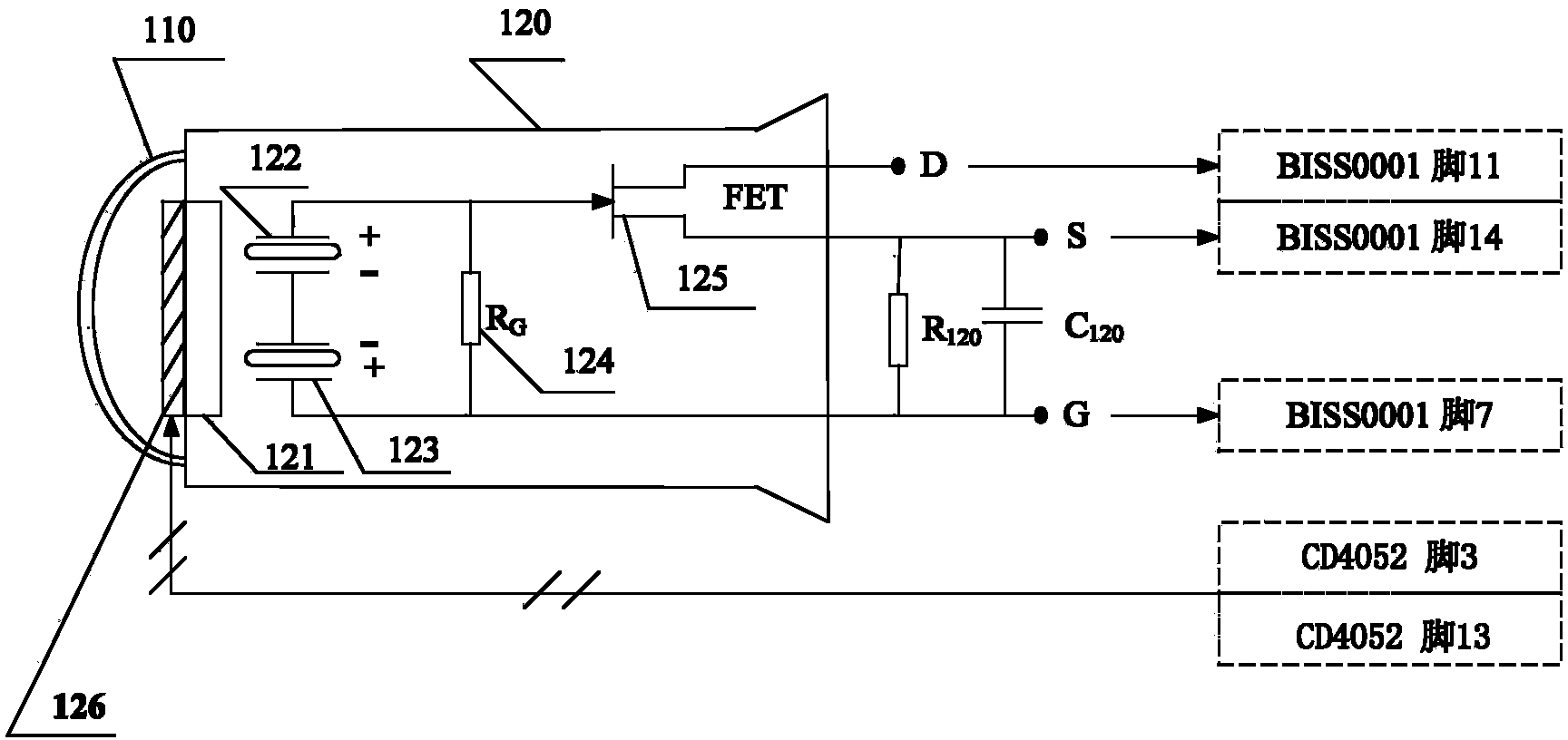

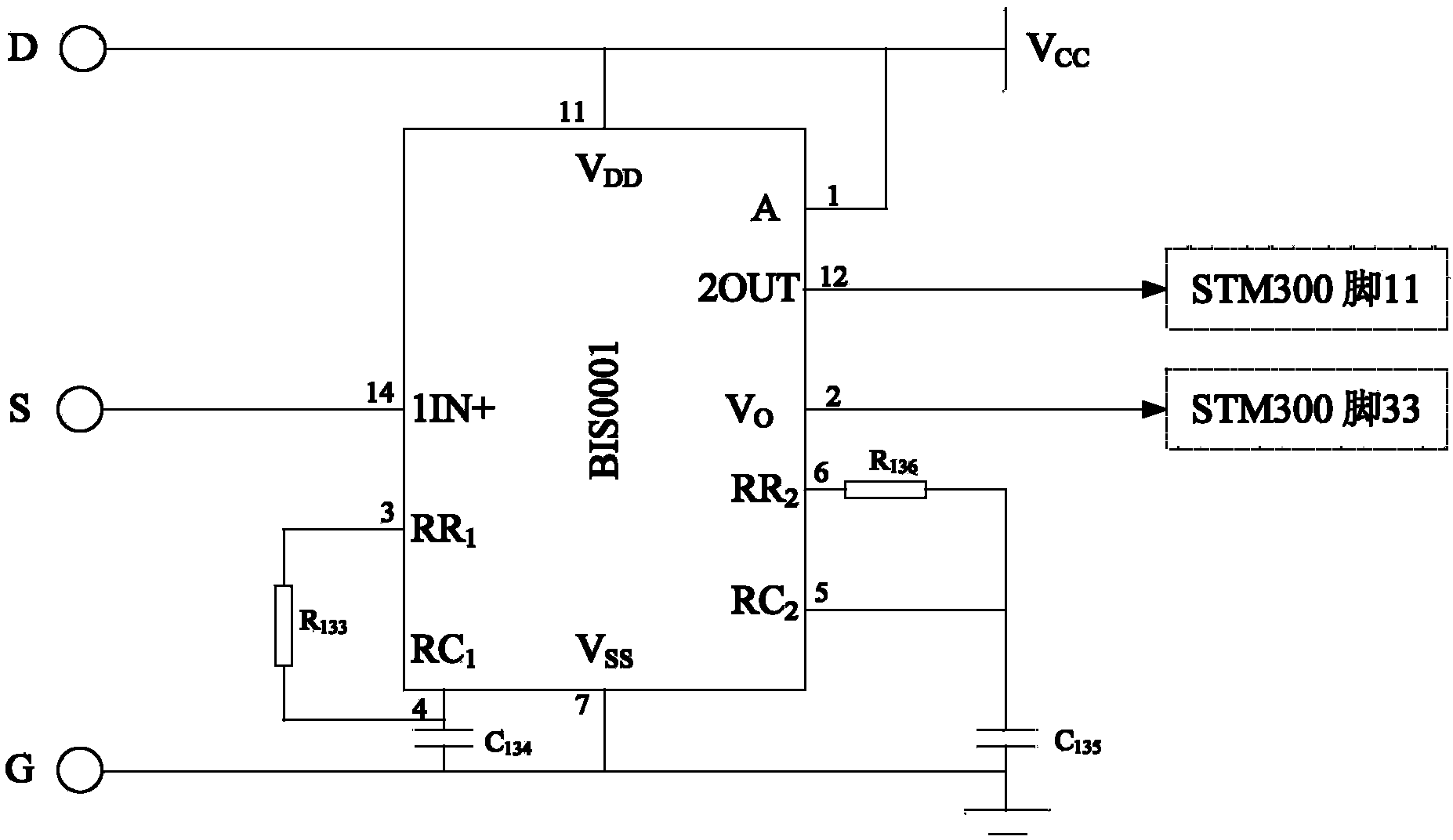

Self-energy-obtaining dynamic and static human body detector and micropower low-false-positive and low-false-negative method

InactiveCN103884433AImprove usabilityImprove effectivenessPyrometry using electric radation detectorsElectrical batteryLiquid crystal light valve

The invention discloses a self-energy-obtaining dynamic and static human body detector and a micropower low-false-positive and low-false-negative method. The human body detector comprises a monitoring detector body and an environment detector body, and the structure of the monitoring detector body and the structure of the environment detector body are similar; the monitoring detector body comprises a Fresnel lens, a pyroelectric infrared sensor, a signal modulation module, a bistable liquid crystal light valve executing module and a signal collecting, processing, communication, control and self-energy-obtaining module. The pyroelectric infrared sensor sleeved with the Fresnel lens is sequentially connected with the signal modulation module, the signal collecting, processing, communication, control and self-energy-obtaining module and the bistable liquid crystal light valve executing module. A self-energy-obtaining technology overcomes defects of battery / wired power supply, and by means of bright and dark conversion of a liquid crystal light valve, service objects of the human body detector are extended to static people. A differential data algorithm that environment interference is removed from signals of the monitoring detector body through medium-station filtering and by means of the environment detector body enables the false positive rate and the false negative rate to be reduced, and application of micropower improves usability of the human body detector.

Owner:ZHEJIANG UNIV

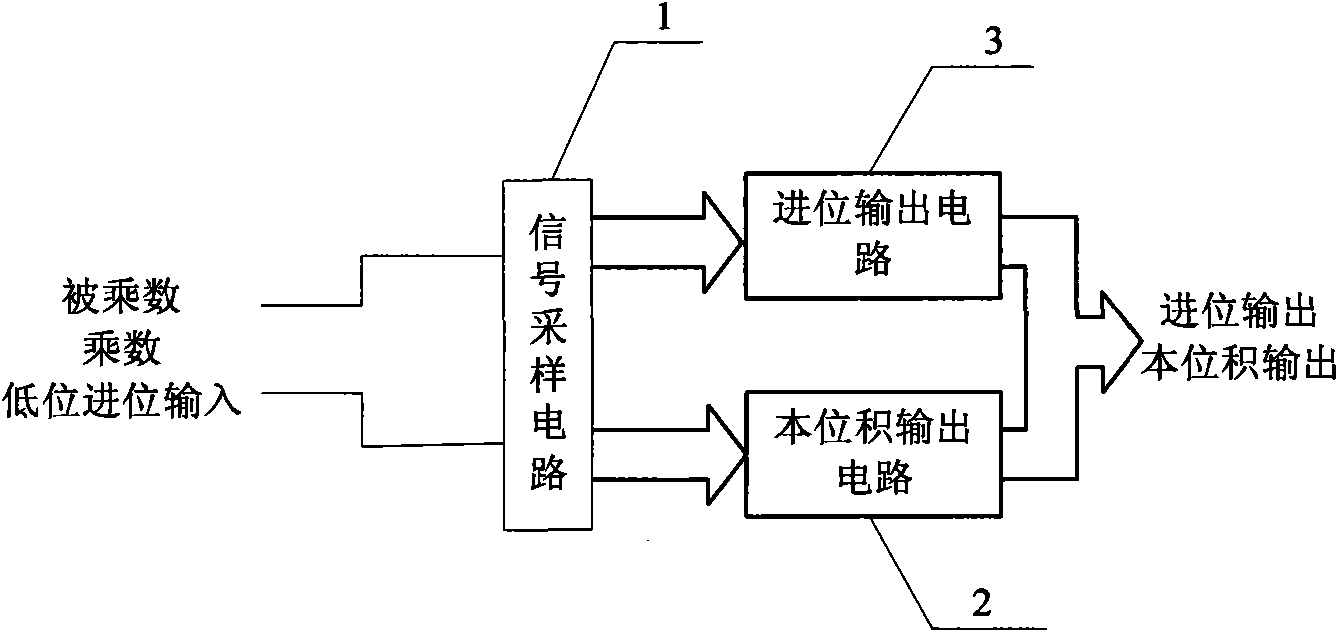

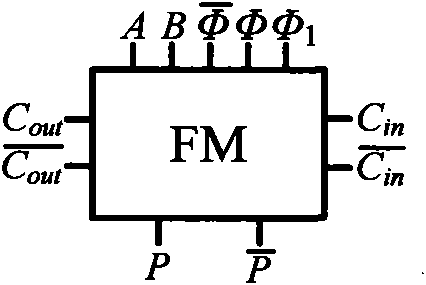

Tri-valued, thermal-insulating and low-power multiplier unit and multiplier

InactiveCN101833433ACorrect logic functionLow Power FeaturesComputation using non-contact making devicesBinary multiplierEngineering

The invention discloses a tri-valued, thermal-insulating and low-power multiplier unit and a multiplier. The multiplier unit controls each NMOS tube in an input signal sampling circuit to sample input signals by using a clock-controlled clock signal; four corresponding integrating circuit modules and carry output circuits with cross storage-type structures are constructed by sampled values according to required realized multiplication logic relationship through the bootstrap operation of the NMOS tube; power clocks phi1 and phi complete the evaluation and energy recovery of the output load to realize correct logic function; and compared with a DPL tri-valued multiplier, the four-digit tri-valued thermal-insulating and low-power multiplier can save energy consumption by about 91 percent in 0.9 microsecond and has distinct low-power characteristics.

Owner:NINGBO UNIV

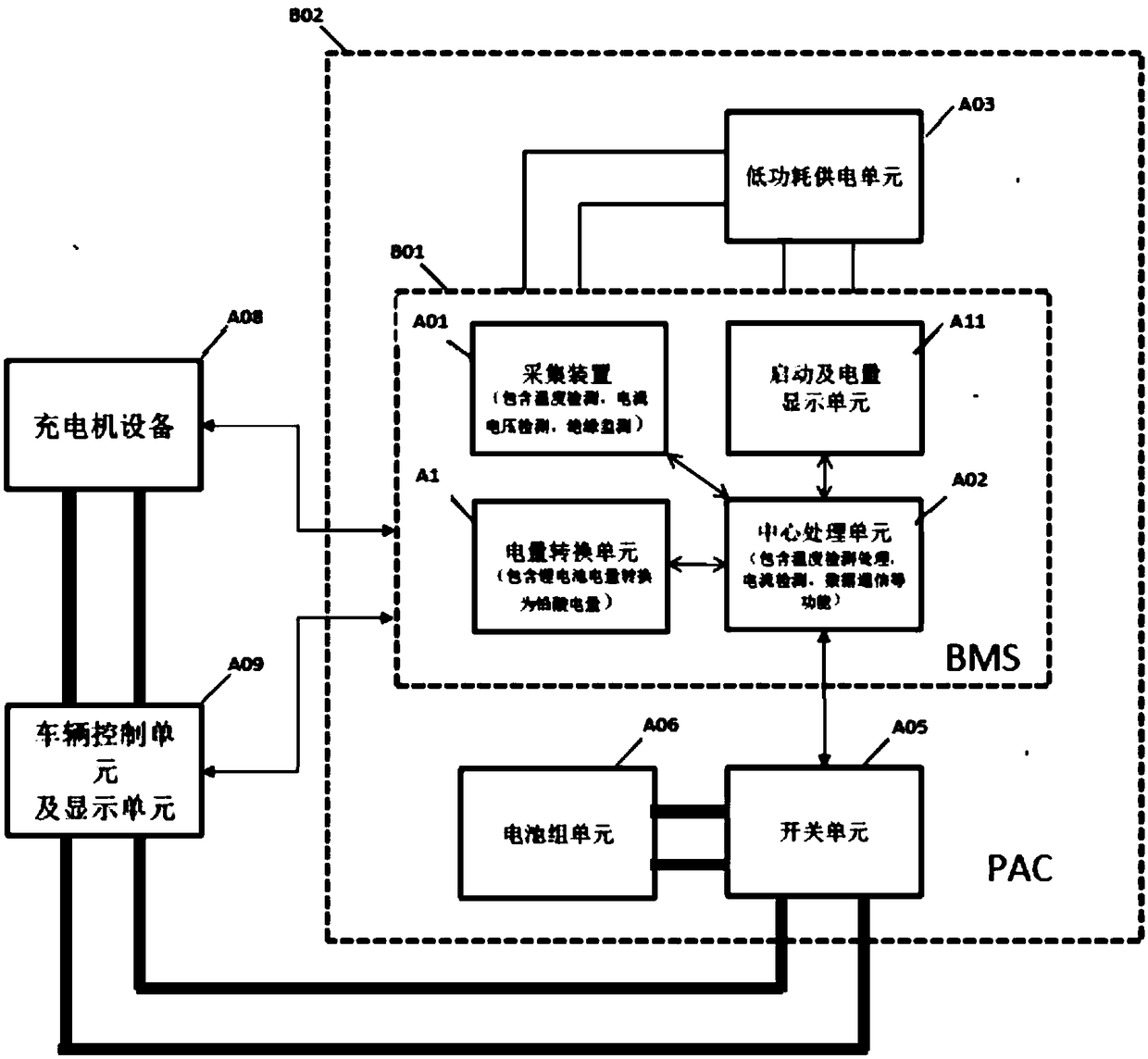

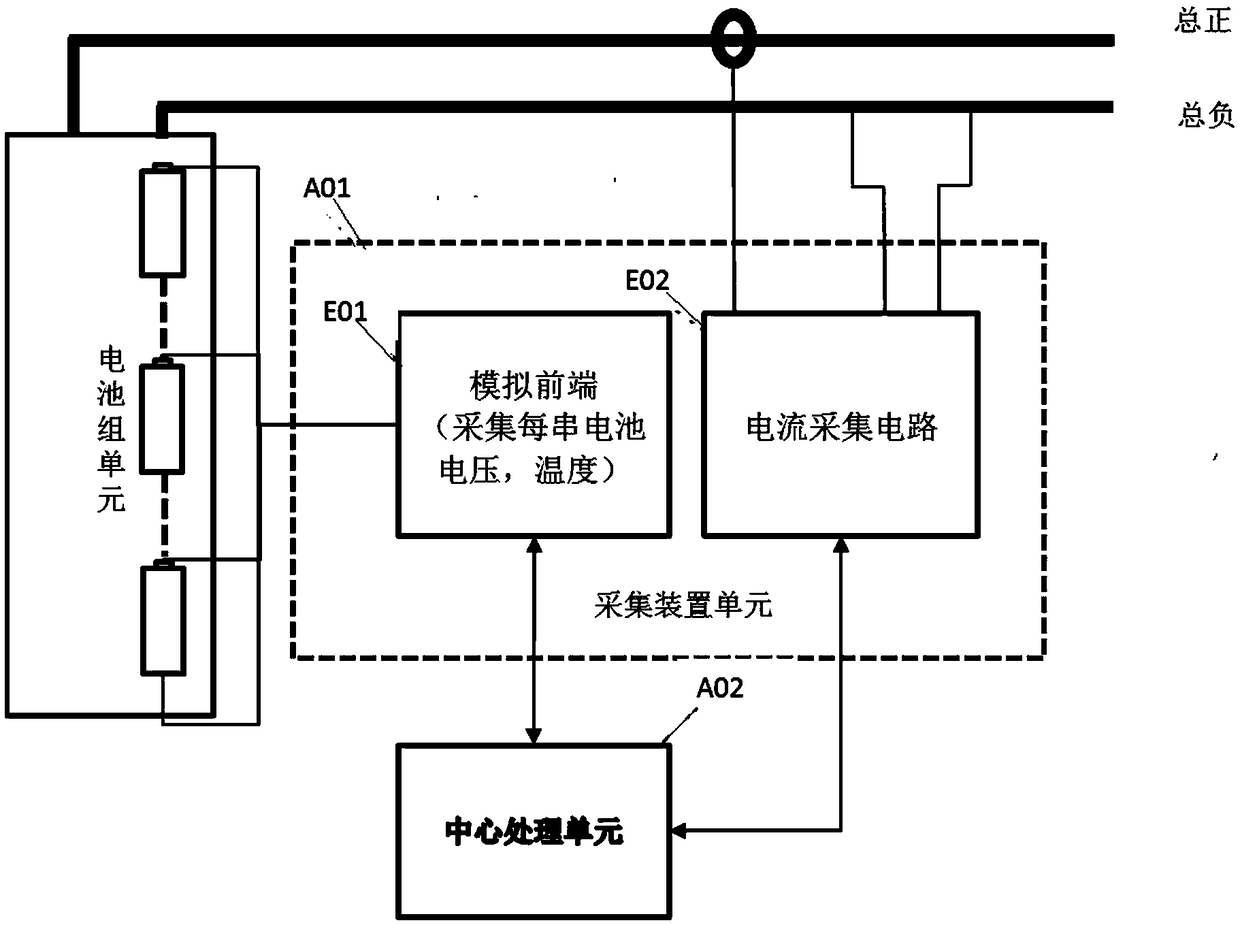

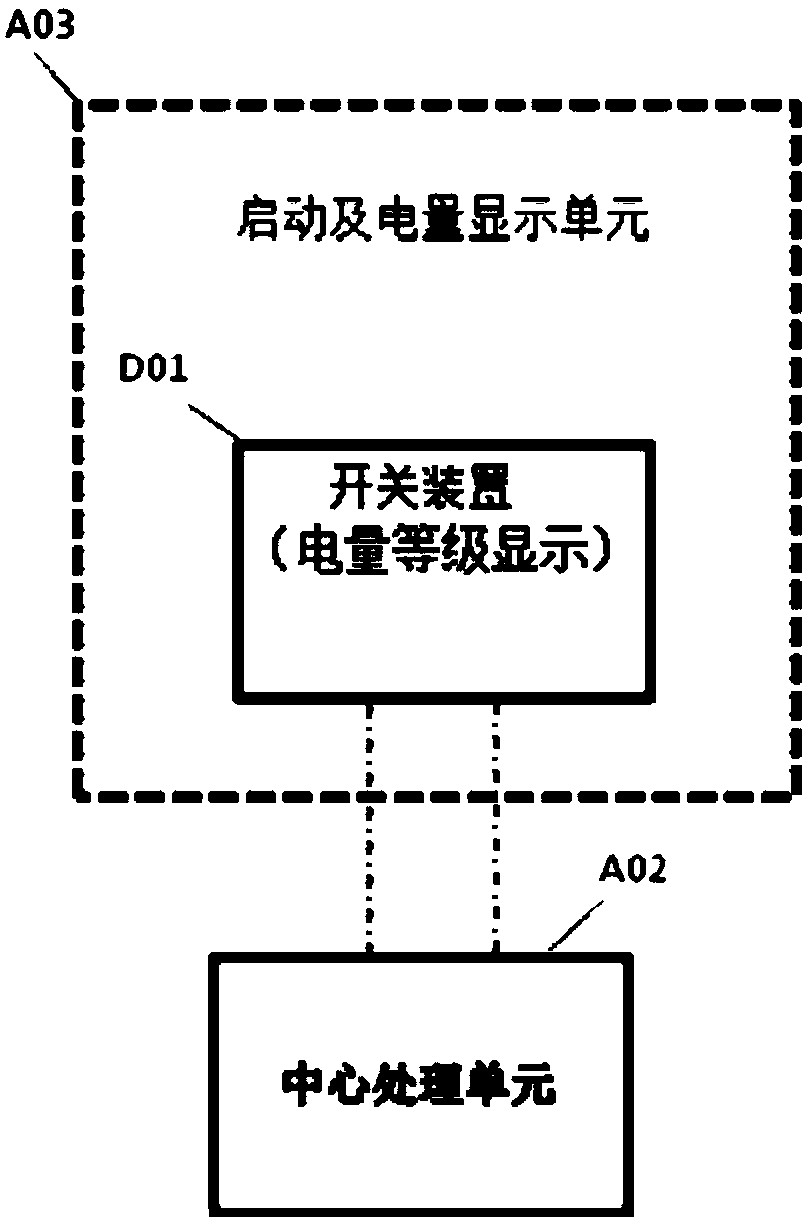

Lithium battery replacing lead-acid battery intelligent BMS architecture and use method

PendingCN109273783AStable power supplySafe and reliable power supplyCells structural combinationElectrical batteryEngineering

The invention discloses an intelligent BMS structure of lithium battery replacing lead acid battery, which comprises a central processing unit, a collection device, a startup and electric quantity display unit and an electric quantity conversion unit, which are respectively bidirectionally connected with the central processing unit. The collecting unit collects and processes the battery pack unitvoltage, current, temperature and insulation parameters of the battery pack, and uploads them to the central processing unit for data processing. The startup and electric quantity display unit is provided with an auxiliary switch for controlling the closing and opening of the switch unit of the battery pack. The electric quantity conversion unit causes the whole vehicle to accept and display the correct electric quantity value; The switch used in the switch unit of the battery pack is a relay switch. The invention is more suitable for the working condition of high load and high current of theelectric energy demand terminal, and ensures low power consumption, safety and stable operation. The invention provides a method for converting the electric quantity display so as to realize that theelectric quantity can be displayed correctly after the electric energy demand end of the lead-acid battery of the original device is replaced by the lithium battery.

Owner:众声物联(天津)科技有限公司

Thin Film Transistor Substrate and Display Using the Same

ActiveUS20170062490A1Simple manufacturing processHigh suppression characteristicsSolid-state devicesSemiconductor devicesCapacitanceDisplay device

A display is disclosed which includes a substrate, a first thin film transistor, a second thin film transistor, a first storage capacitor electrode, an oxide layer, a nitride layer, a second storage capacitor electrode, a planar layer and a pixel electrode. The first thin film transistor is disposed in a first area on the substrate. The second thin film transistor is disposed in a second area on the substrate. The first storage capacitor electrode is disposed in a third area on the substrate. The oxide layer covers the first thin film transistor and the second thin film transistor, and exposes the first storage capacitor electrode. The nitride layer is disposed on the oxide layer and covers the first storage capacitor electrode. The second storage capacitor electrode includes a first metal layer and a second metal layer, and overlaps with the first storage capacitor electrode on the nitride layer. The planar layer covers the first thin film transistor, the second thin film transistor and the second storage capacitor electrode. The pixel electrode is disposed on the planar layer.

Owner:LG DISPLAY CO LTD

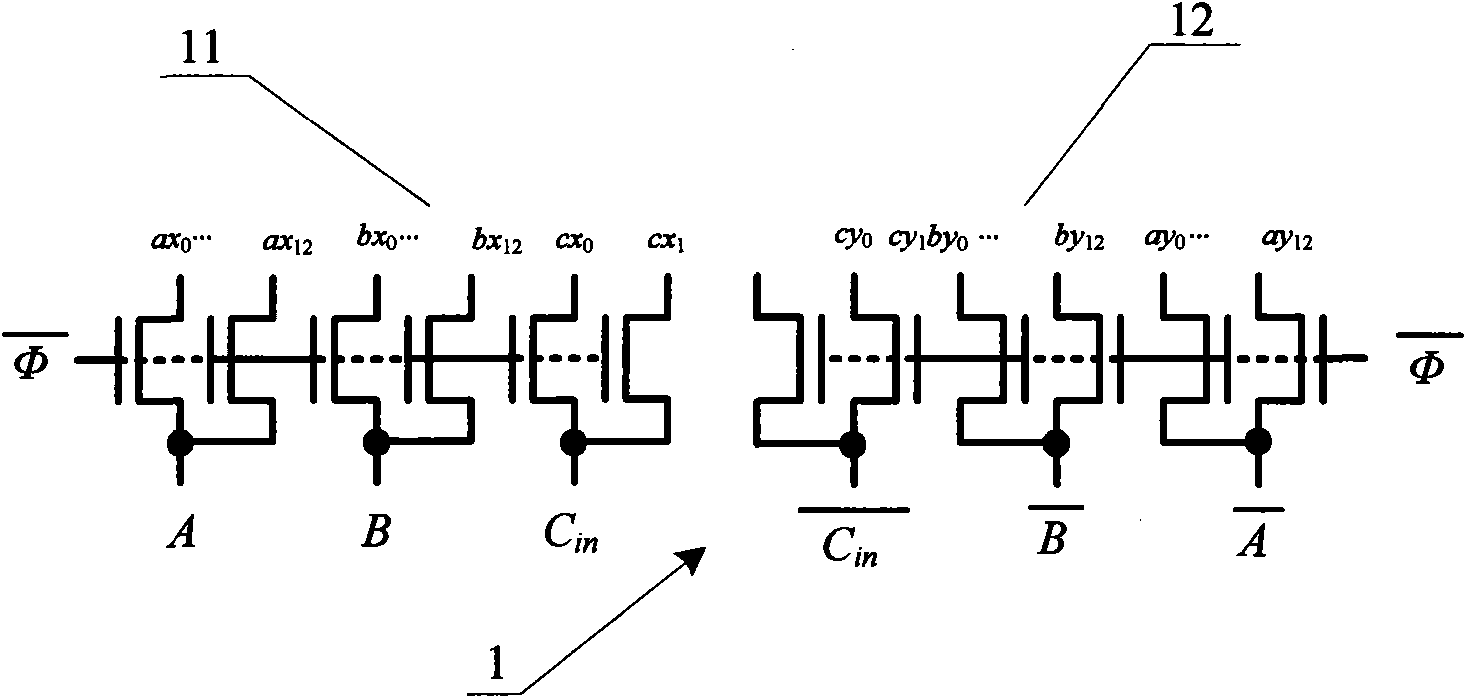

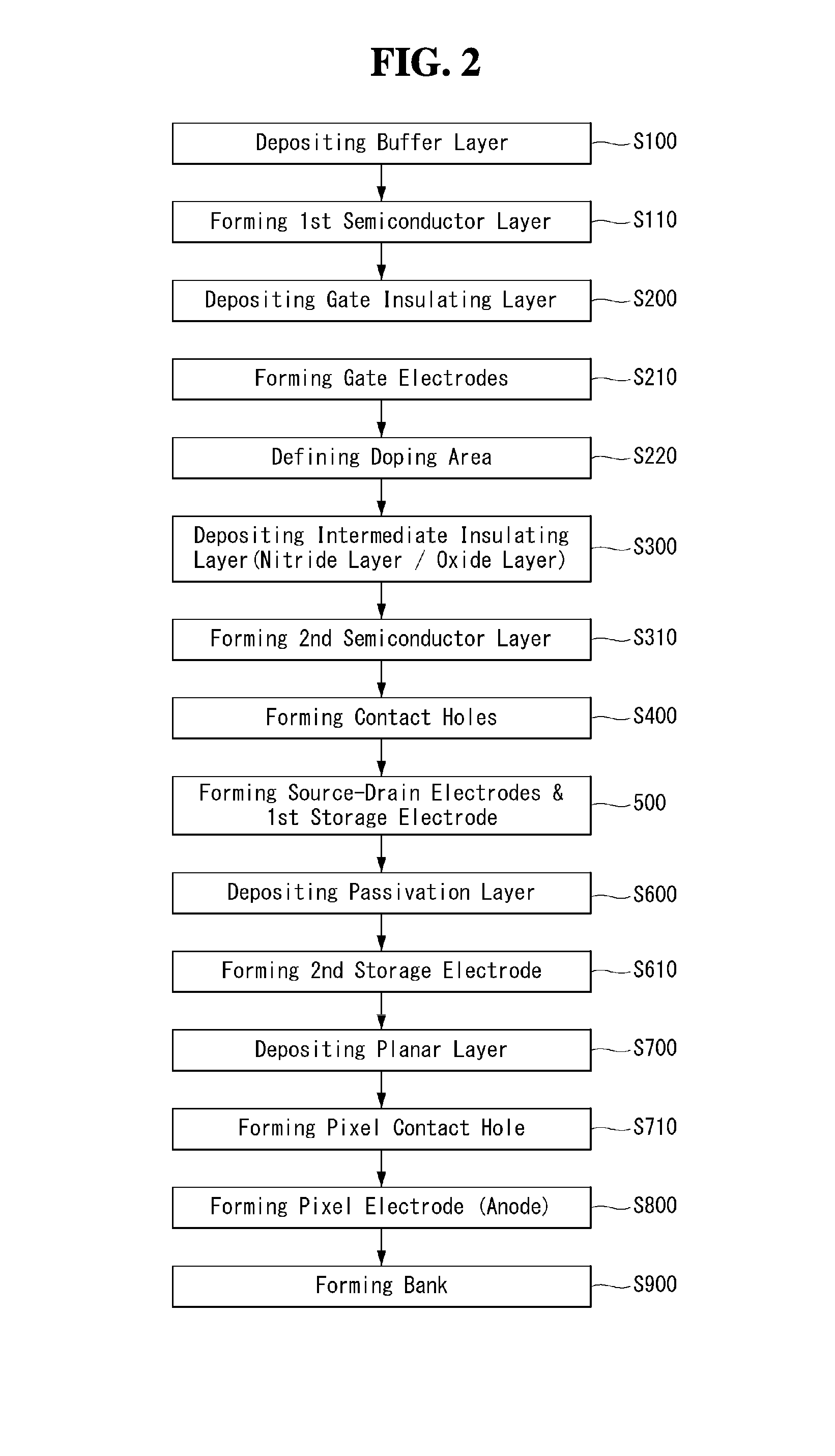

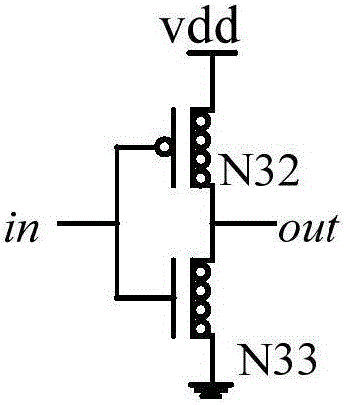

CNFET type double-edge pulse type JKL trigger

ActiveCN106100611AIncrease work rateCorrect circuit logicElectric pulse generatorMulti valuedEngineering

The invention discloses a carbon nanotube field effect transistor (CNFET) type double-edge pulse type JKL trigger. The CNFET type double-edge pulse type JKL trigger comprises a double-edge pulse signal generator, thirty-first CNFET tubes, six NTI gate circuits with the same circuit structure, six PTI gate circuit with the same circuit structure, a first ternary phase inverter and a second ternary phase inverter, wherein the first ternary phase inverter and the second ternary phase inverter have the same circuit structure. The CNFET type double-edge pulse type JKL trigger has the advantages: a clock signal is generated by utilizing the double-edge pulse signal generator; by combining switching operation of a multi-value logic circuit and high-speed low-power features of CNFET, a purpose of reducing the power consumption is achieved when the working speed of the JKL trigger is improved; and based on experiment results, the JKL trigger provided by the invention has a correct logic function and remarkable characteristic of low power consumption.

Owner:NINGBO UNIV