Tri-valued, thermal-insulating and low-power multiplier unit and multiplier

A low-power multiplier technology, applied in the field of ternary adiabatic low-power multiplier units and multipliers, can solve the problems of complex circuit structure and high power consumption

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment 1

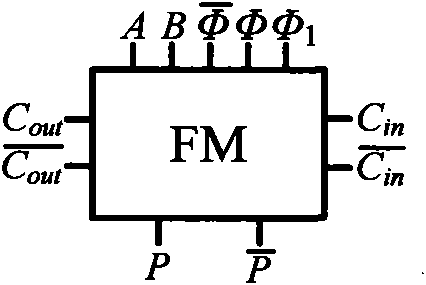

[0047] In the binary logic circuit, the multiplication of two signals is realized by AND gate, and no carry is generated. However, in a three-valued logic circuit, the product of two signals may exceed the value range (2×2=4), thereby generating a carry like an adder unit (ie, a full adder), so the three-valued multiplier unit (ie, Three-valued full multiplier) in addition to having the multiplicand A, the multiplier B and the original product output P, will also have a carry input C in and Carry Out C out , as the truth table shown in Table 1.

[0048] Table 1 The truth table of the ternary multiplier unit

[0049]

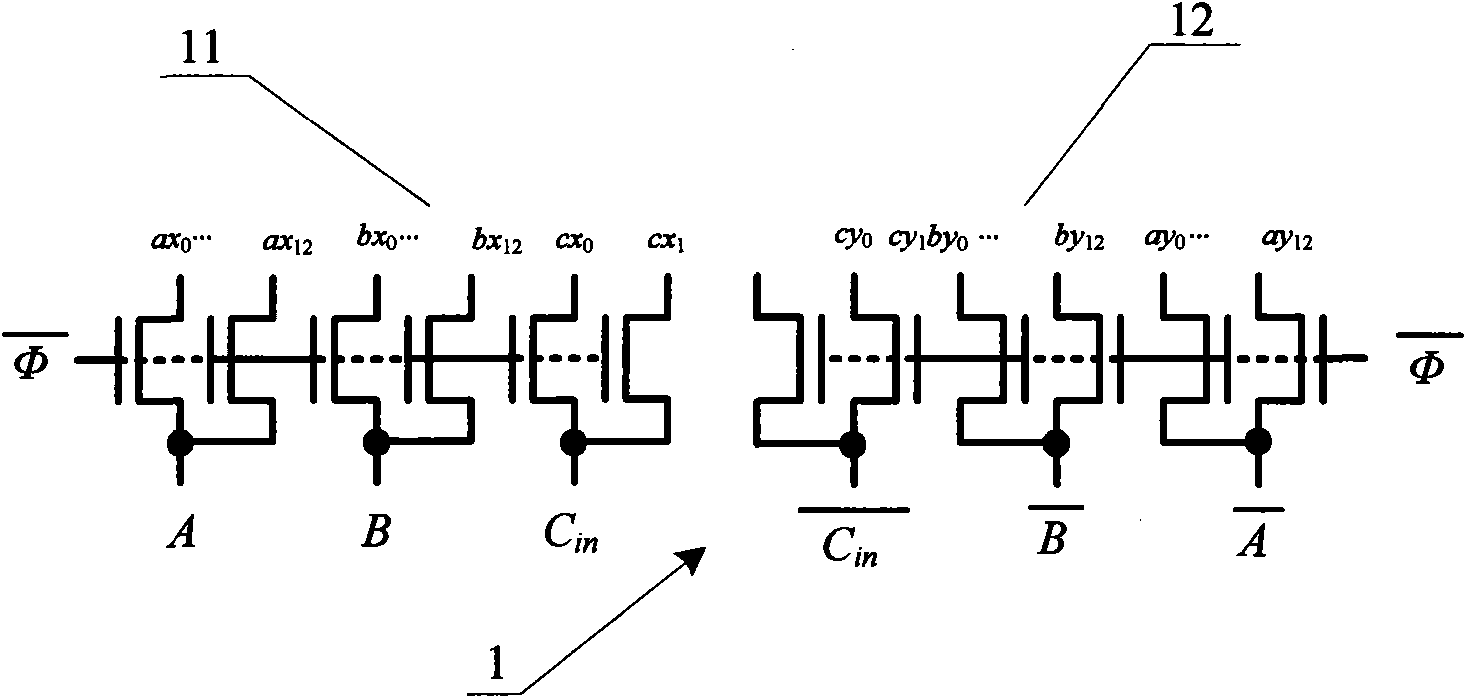

[0050] The present invention combines "Design of a DTCTGAL circuit and its application" (authors: Wang Pengjun, Li Kunpeng, Mei Fengna) disclosed in the Chinese Journal of Semiconductors on the basis of analyzing the truth table of Table 1 [Journal of Semiconductors, "Based on Double DTCTGAL circuit design and application of power clock", Wang Pengjun, Li...

Embodiment 2

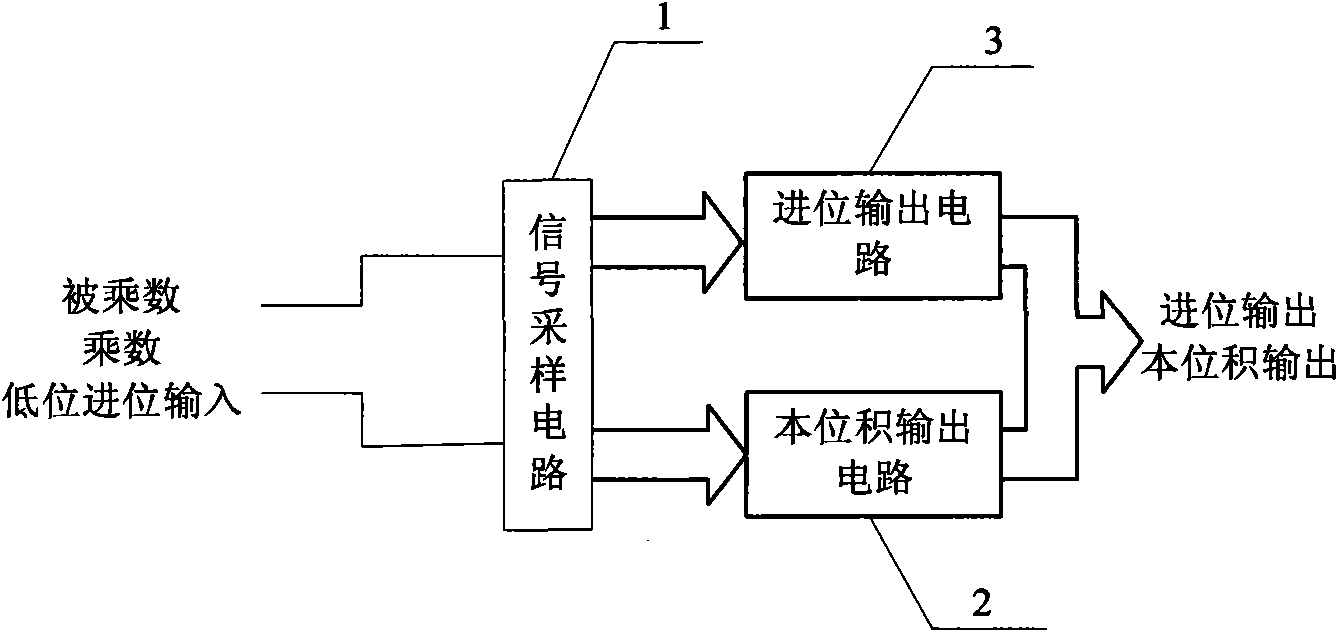

[0064] A ternary adiabatic low power consumption multiplier composed of the ternary adiabatic low power consumption multiplier unit given in Embodiment 1, such as Figure 9 As shown, it includes a 4-bit three-value adiabatic low-power multiplier unit, the first three-value adiabatic low-power multiplier unit FM0 is used to input the input terminal of the low-order carry input signal to input 0, that is, C in =0, the first three-value adiabatic low-power multiplier unit FM0 is used to input the input terminal of the complementary low-order carry input signal to access the clocked clock signal whose amplitude level corresponds to logic 2 which is The first three-value adiabatic low-power multiplier unit FM0 is used to output the output terminal C of the carry output signal 0 It is connected with the input end of the second ternary adiabatic low power consumption multiplier unit FM1 for inputting the low-order carry input signal, and the first ternary adiabatic low power consu...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More