A double-edge d flip-flop based on n-type sabl logic

A double-edge, flip-flop technology, applied in electrical pulse generator circuits, pulse generation, electrical components, etc., can solve the problems that SABL logic circuits cannot directly use D flip-flops, and single-edge flip-flops do not have balanced power consumption. , to achieve the effect of constant power consumption and balanced power consumption

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment

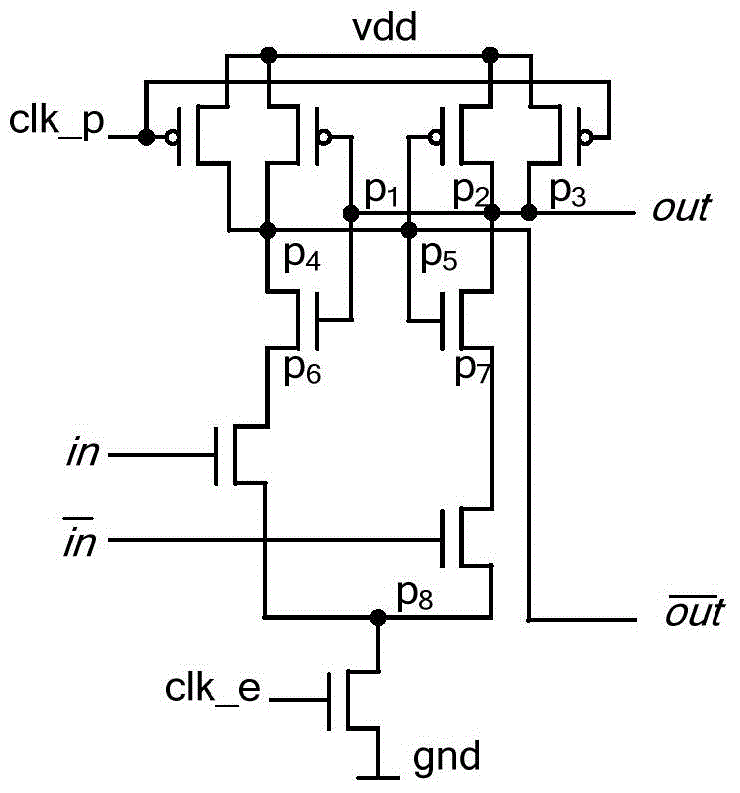

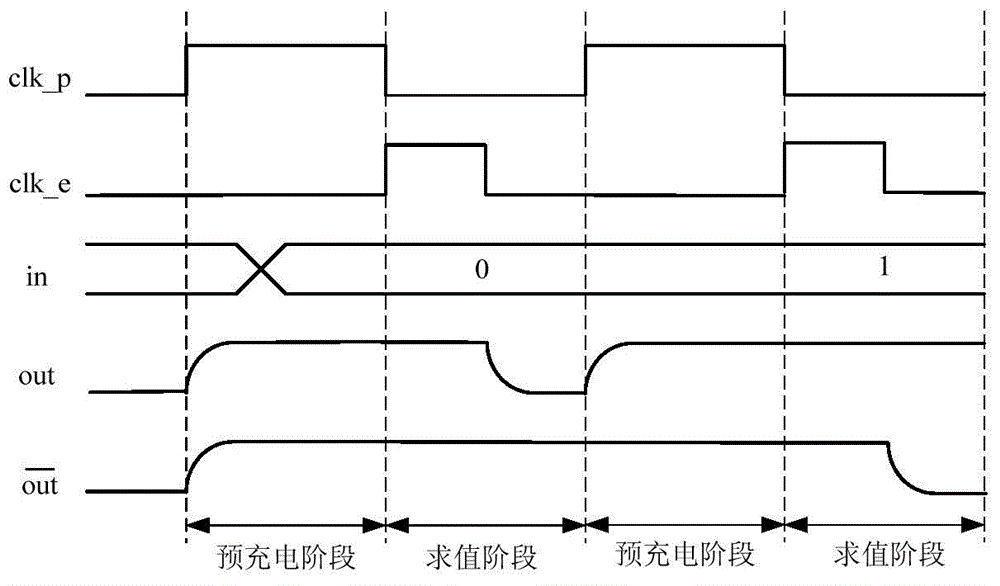

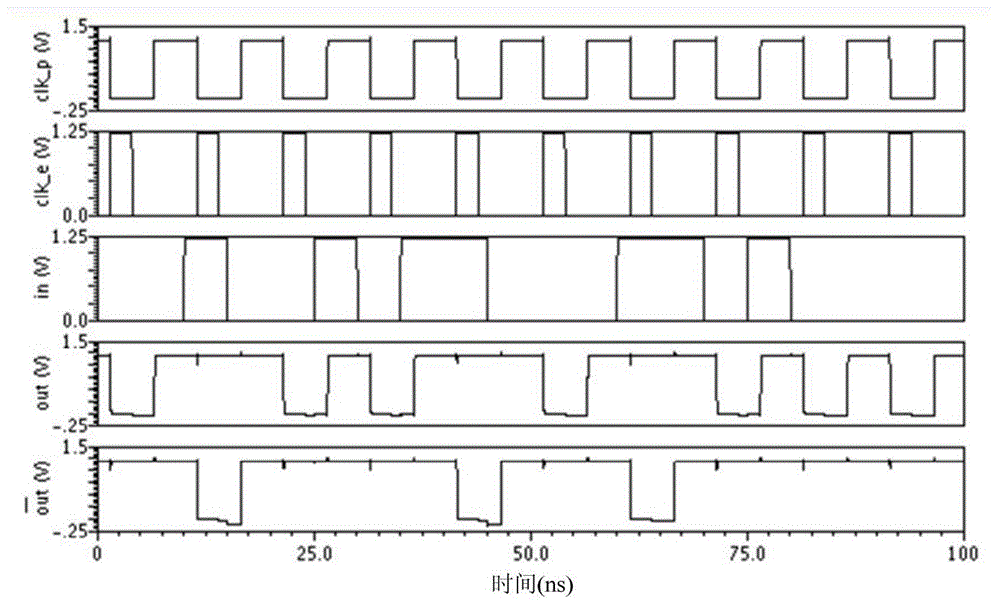

[0019] Example: such as Figure 4 As shown, a double-edge D flip-flop based on N-type SABL logic includes a first transmission gate T1, a second transmission gate T2, a third transmission gate T3, a fourth transmission gate T4, a fifth transmission gate T5, a sixth transmission gate Transmission gate T6 and two N-type SABL logic units, the two N-type SABL logic units are respectively the first N-type SABL logic unit and the second N-type SABL logic unit, the first N-type SABL logic unit and the second N-type SABL logic unit The logic unit respectively has a signal input terminal, a complementary signal input terminal, a signal output terminal, a complementary signal output terminal, a power signal input terminal, a first clock signal input terminal and a second clock signal input terminal, and the signal of the first N-type SABL logic unit The input terminal is connected to the signal input terminal of the second N-type SABL logic unit and its connection terminal is the signal...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More