Semiconductor power device with ultralow power consumption and preparation method

A power device and ultra-low power consumption technology, which is applied in the field of ultra-low power semiconductor power devices and their preparation, can solve problems such as low withstand voltage, complex device structure and process, and increased process levels, and achieve low forward voltage drop , save area, and reduce the cost of tape-out

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

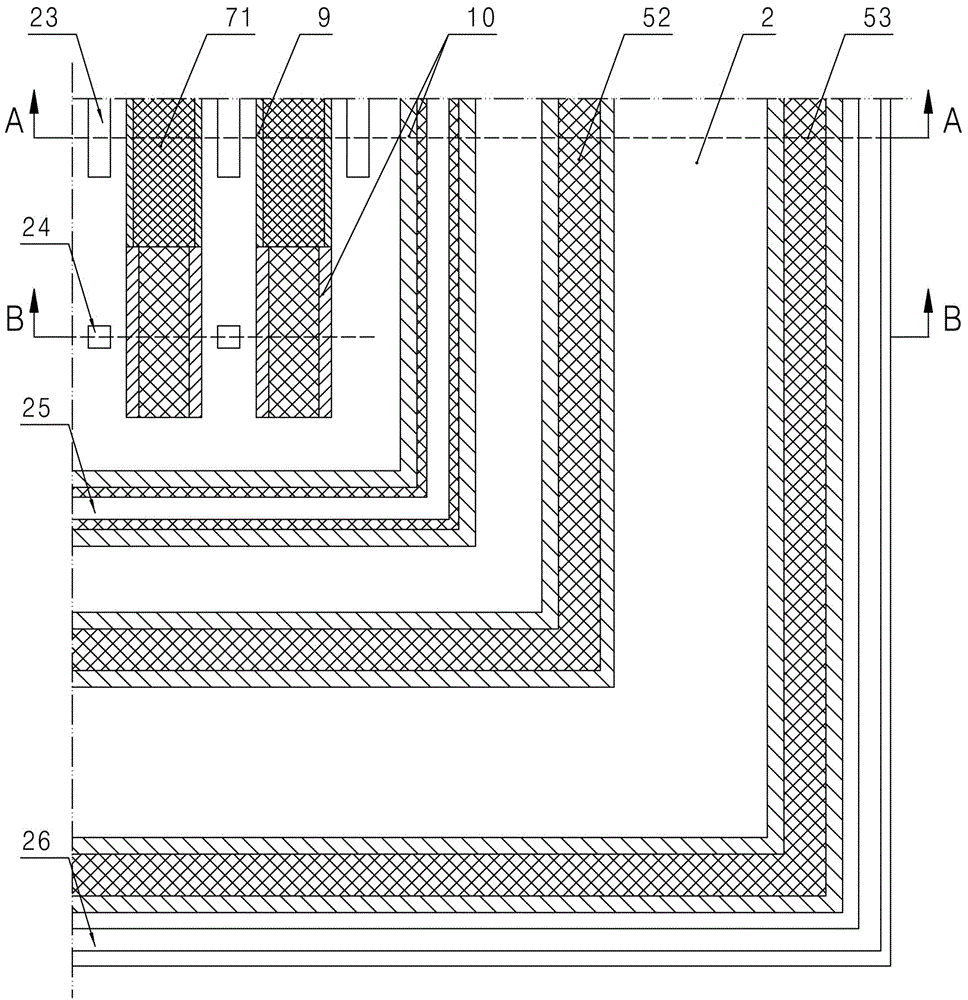

[0035]First, combined with the Figure 18 , taking an N-channel structure as an example to describe in detail a specific implementation of an ultra-low power consumption semiconductor power device of the present invention.

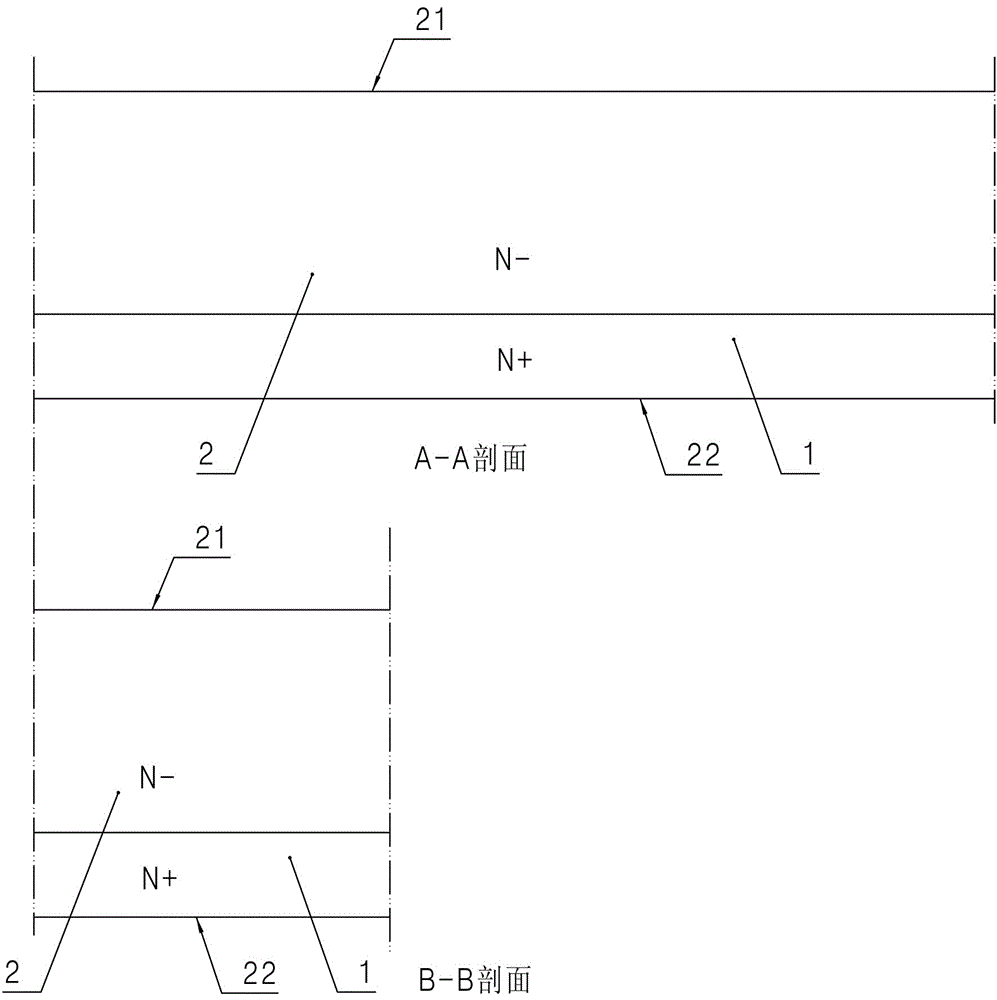

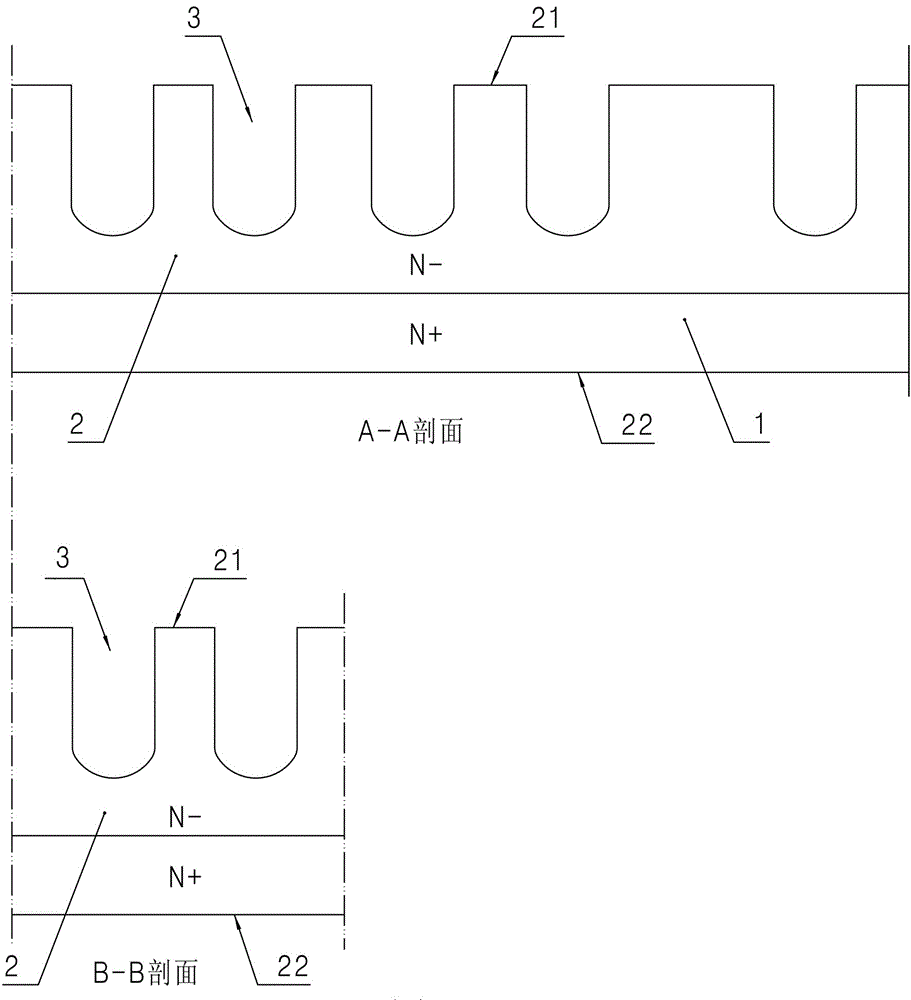

[0036] Such as Figure 18 As shown, a kind of ultra-low power consumption semiconductor power device described in the present invention comprises: semiconductor substrate, and semiconductor substrate comprises: N-type substrate 1 (also referred to as N+ substrate) and be arranged on N-type substrate 1 N-type epitaxial layer 2 (also called N- epitaxial layer), the surface of N-type epitaxial layer 2 is the first main surface 21, and the surface of N-type substrate 1 is the second main surface 22—see figure 2 As shown; the first main surface 21 includes: a cell area provided with cells and a terminal protection area located on the periphery of the cell area;

[0037] The specific structure of the cell includes: the first groove 3 set in the cell area, tha...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More