Patents

Literature

69results about How to "Improve short circuit performance" patented technology

Efficacy Topic

Property

Owner

Technical Advancement

Application Domain

Technology Topic

Technology Field Word

Patent Country/Region

Patent Type

Patent Status

Application Year

Inventor

Lithium ion battery and its prescription of anode material

InactiveCN101101987AImprove thermal stabilityImprove short circuit performanceActive material electrodesSecondary cellsGraphiteThermal stability

The invention is concerned with the description of the anode lithium ion battery material to improve its battery thermal stability, and the proportions are: lithium cobaltoxide 65%-72%, Li(Mn1 / 3Co1 / 3Ni1 / 3)O2 15%-18%, conductive graphite 5%-8%, vinylidene fluoride 2%-4% and the rest are impurity. The anode lithium ion battery is with high heat stability and short-circuits ability.

Owner:JIANGSU TENPOWER LITHIUM

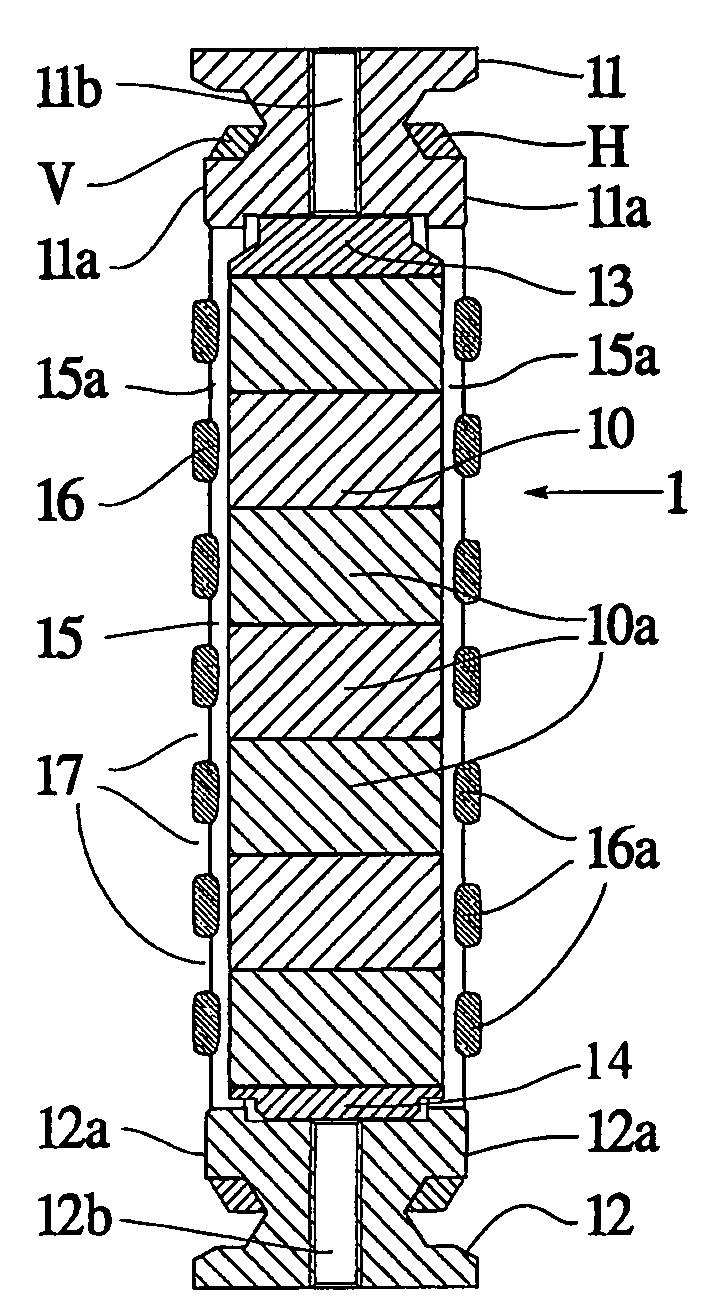

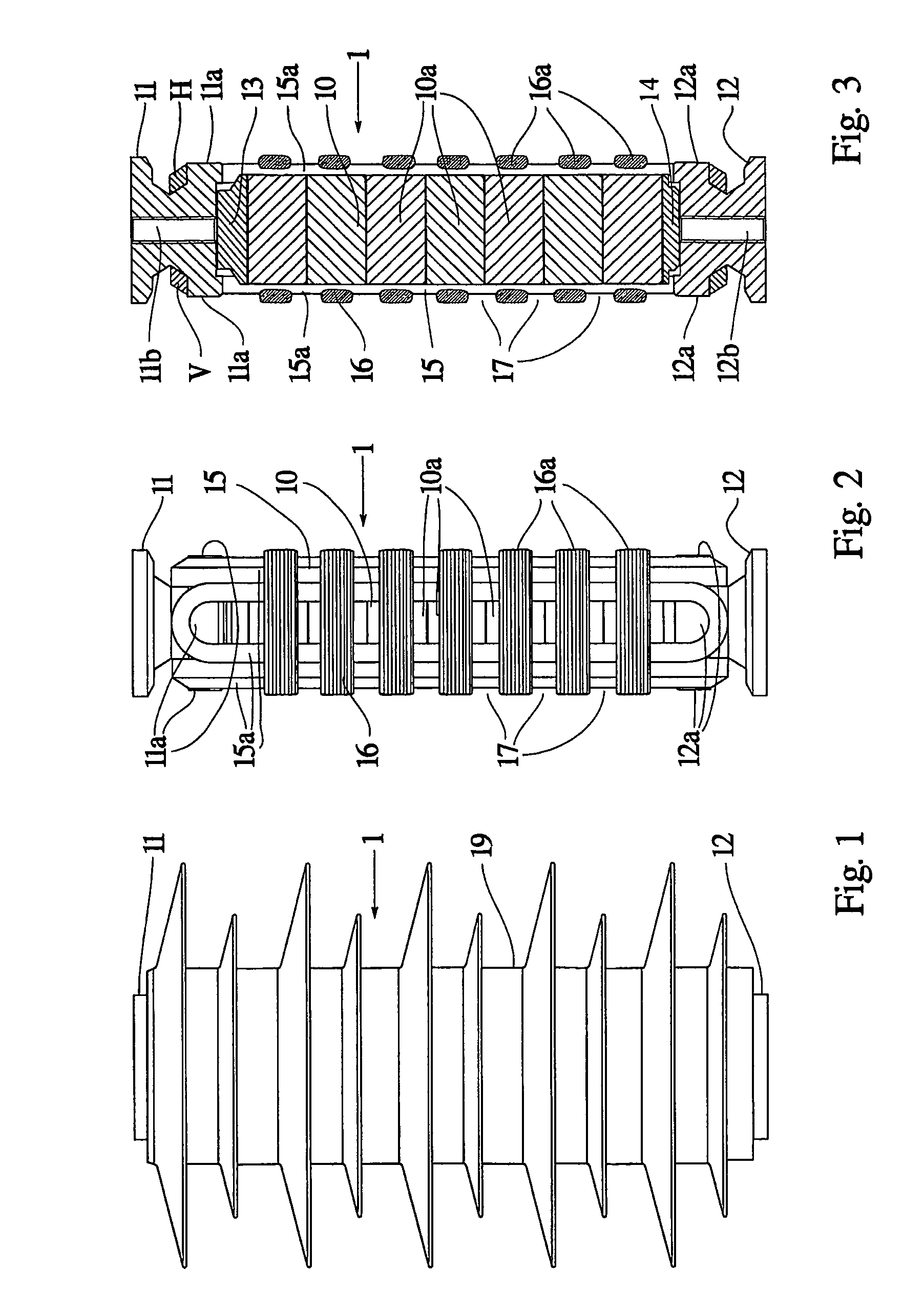

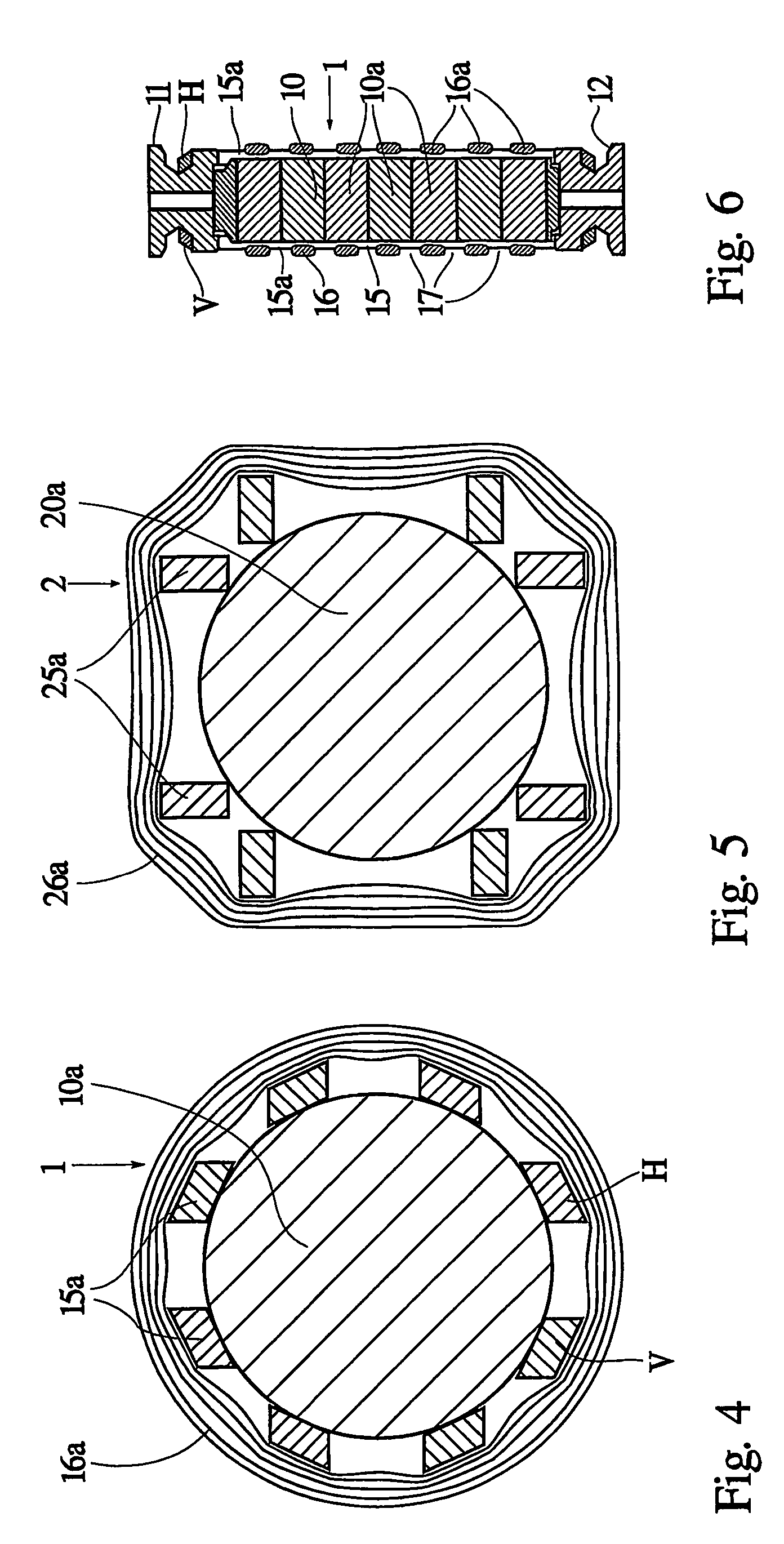

Electronic transformer

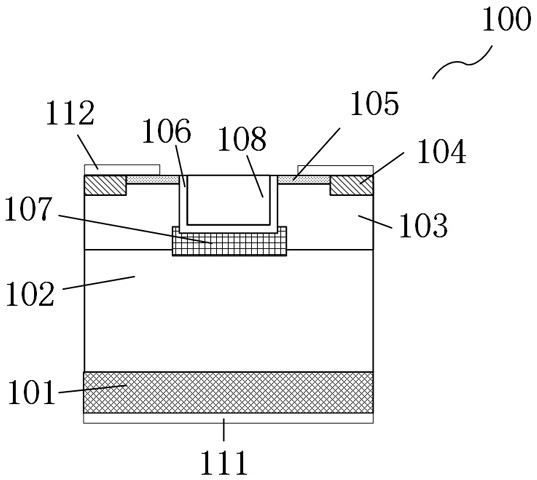

InactiveCN102013308AImprove short circuit performanceNot easy to damageTransformers/inductances coils/windings/connectionsTransformers/inductances magnetic coresTransformerShort circuit

The invention relates to an electronic transformer. The electronic transformer comprises an iron core, a primary coil, a secondary coil and an insulator, wherein the primary coil and the secondary coil are wound on the iron core, are oppositely arranged and are arranged along the iron core at a certain interval; the insulator is arranged on the secondary coil side of the iron core and is positioned between the iron core and the secondary coil to separate the iron core and the secondary coil. The electronic transformer improves the short circuit performance and has a simpler structure and a compacter shape on the premise of ensuring the insulativity of the electronic transformer.

Owner:OSRAM GMBH

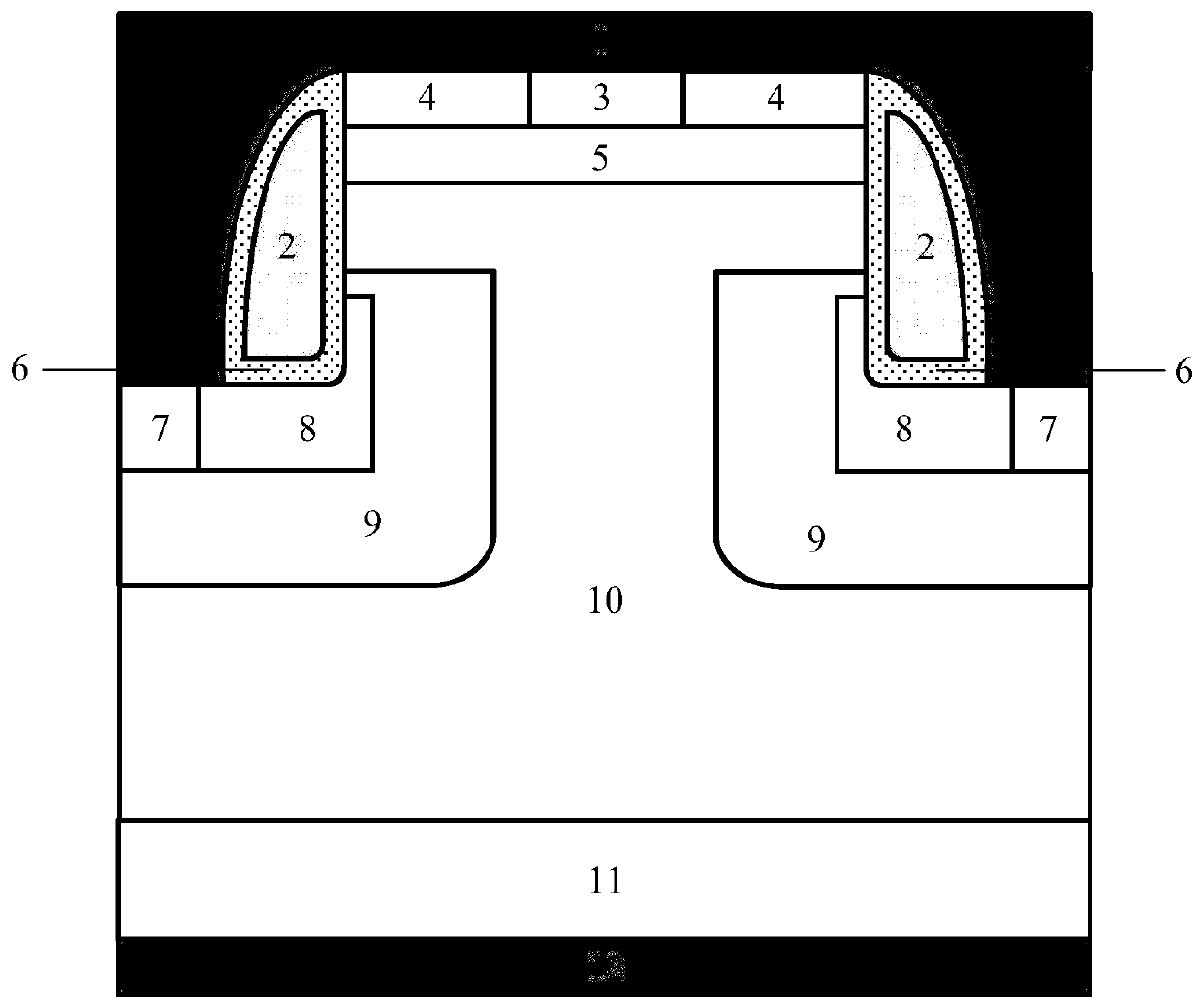

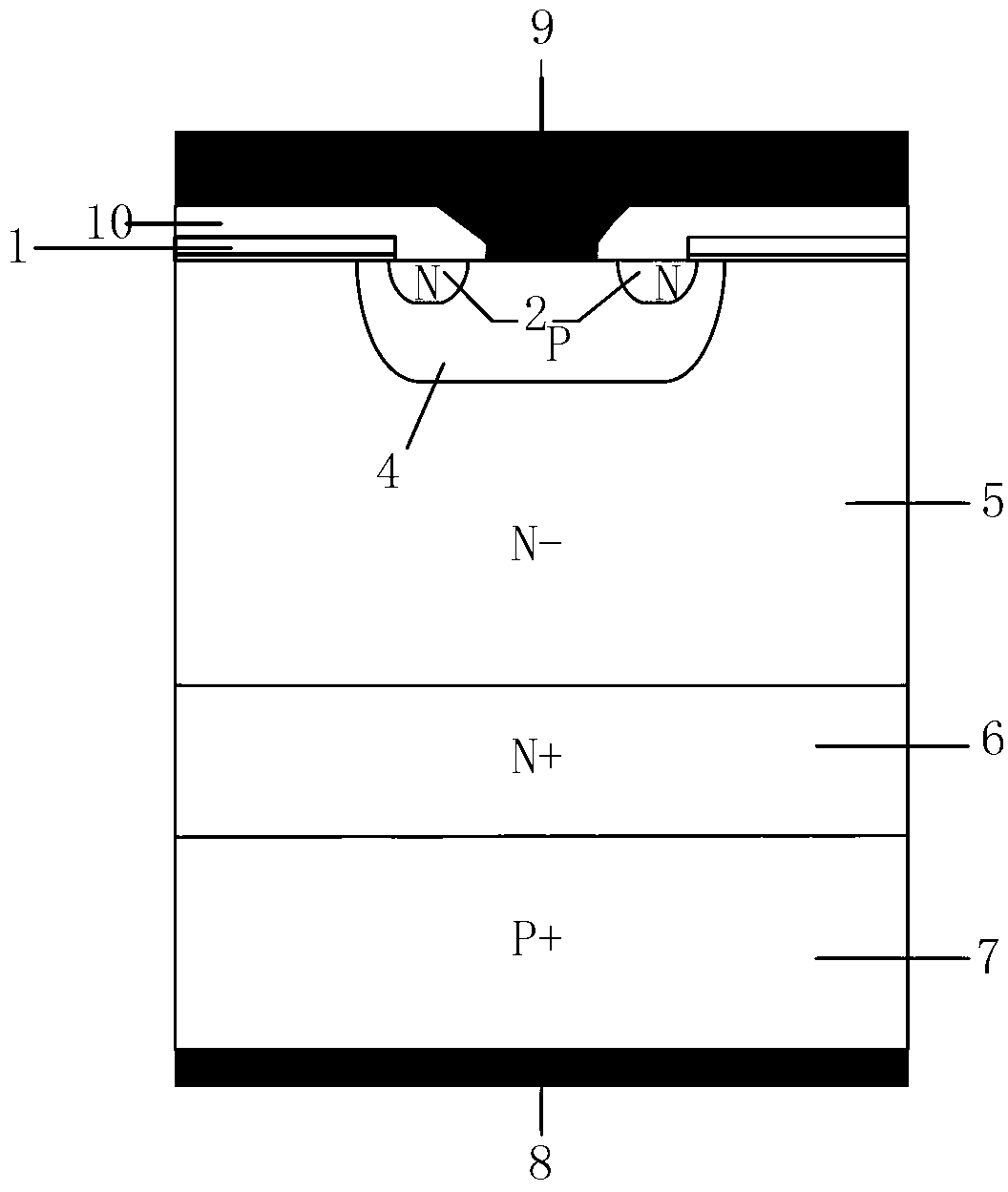

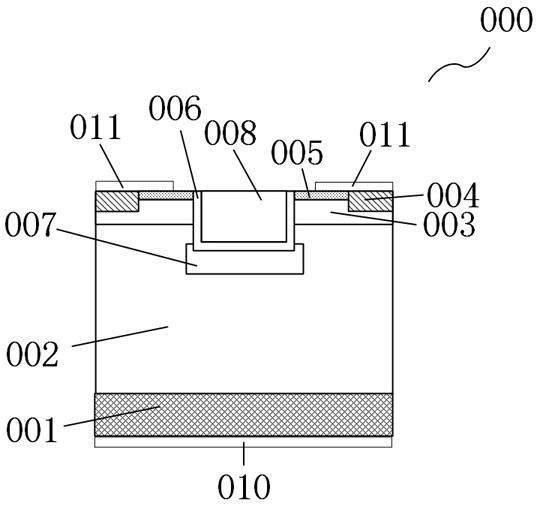

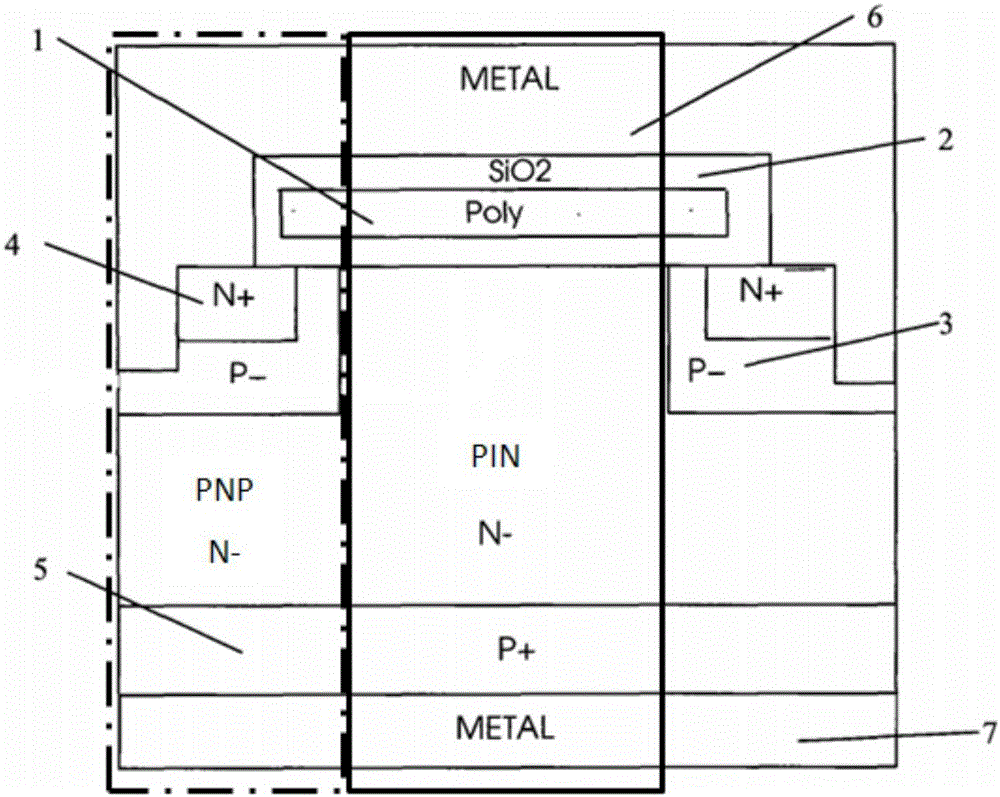

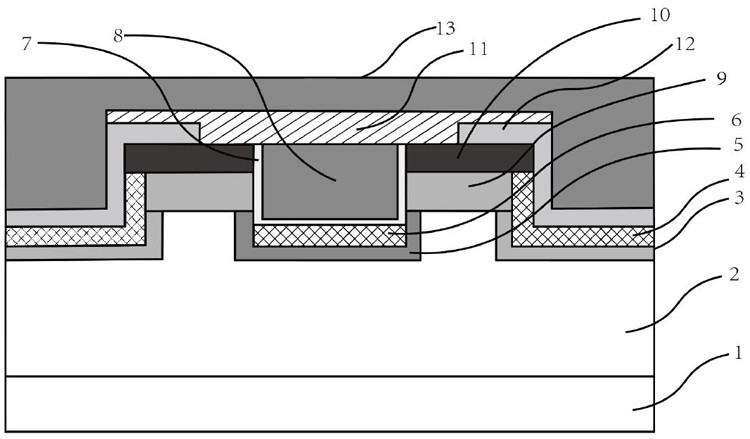

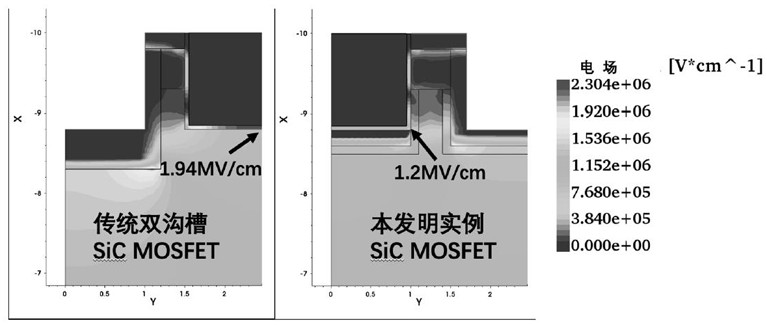

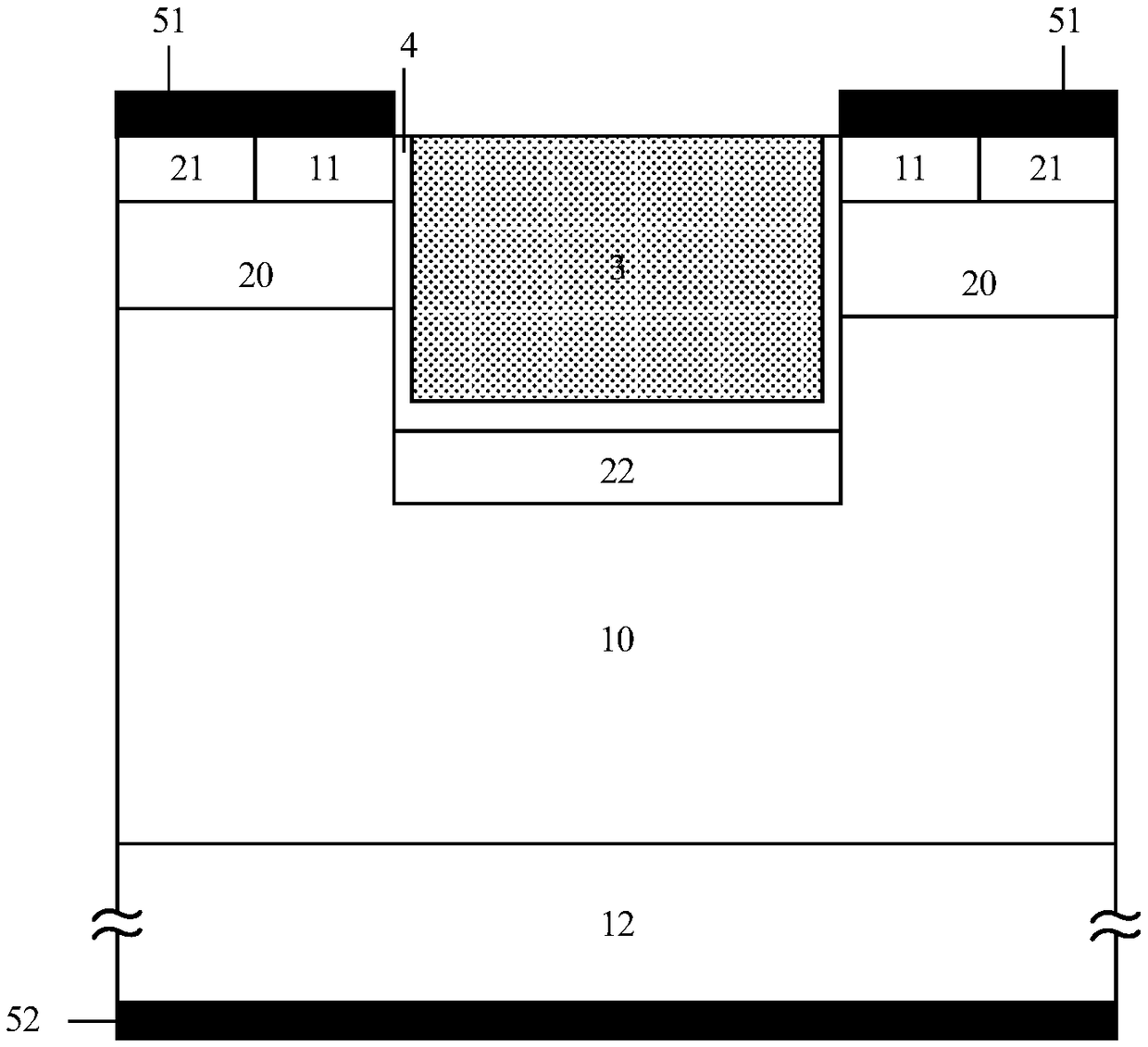

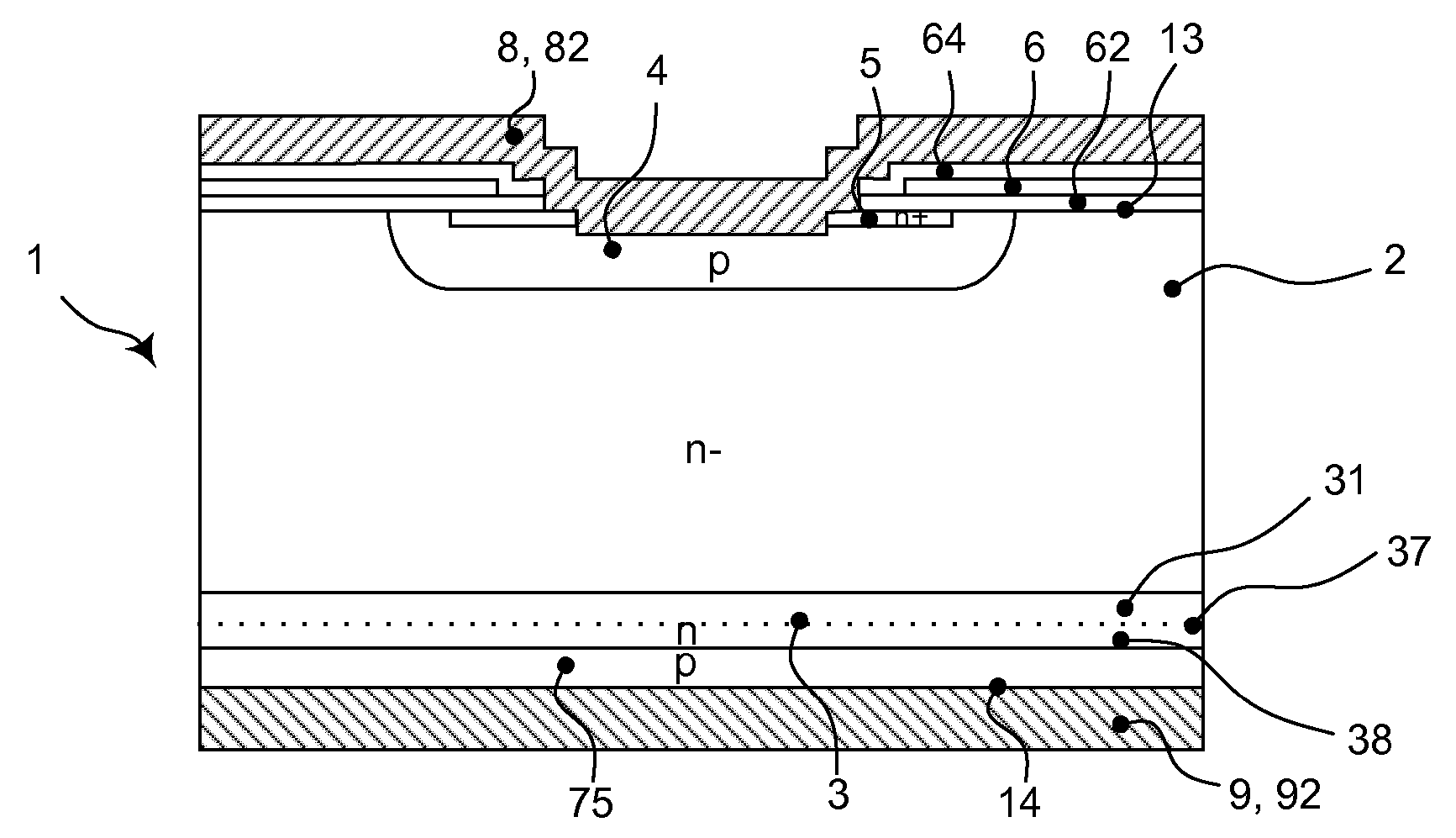

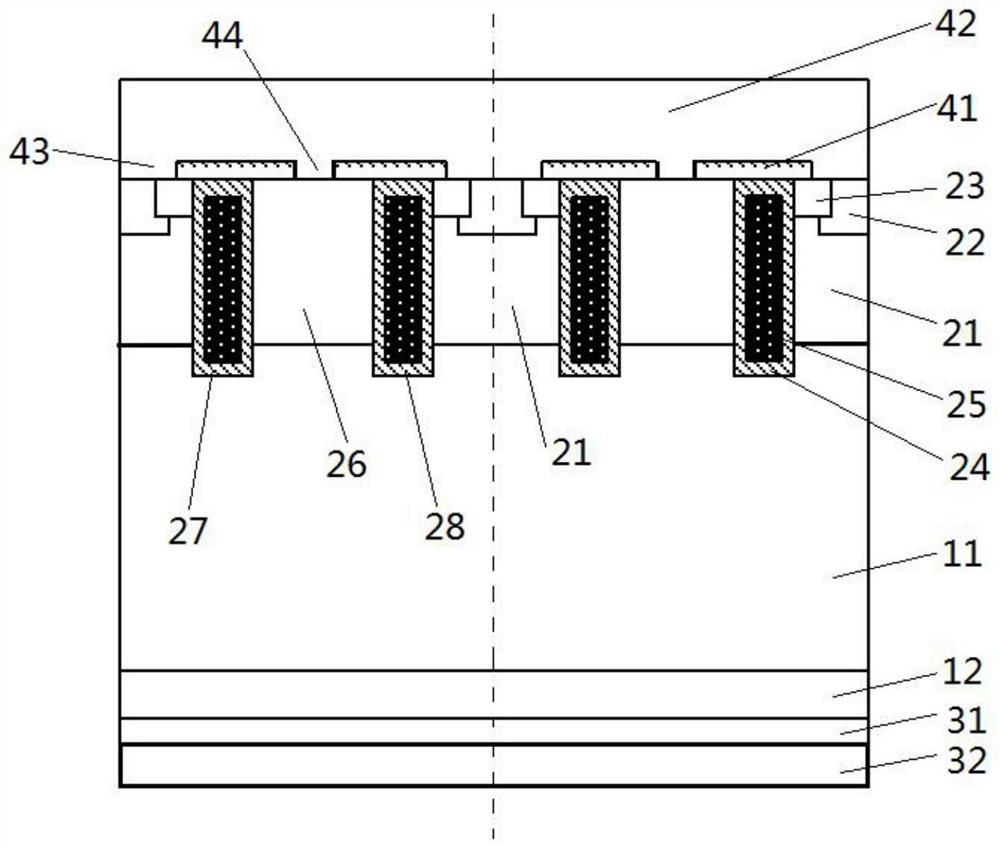

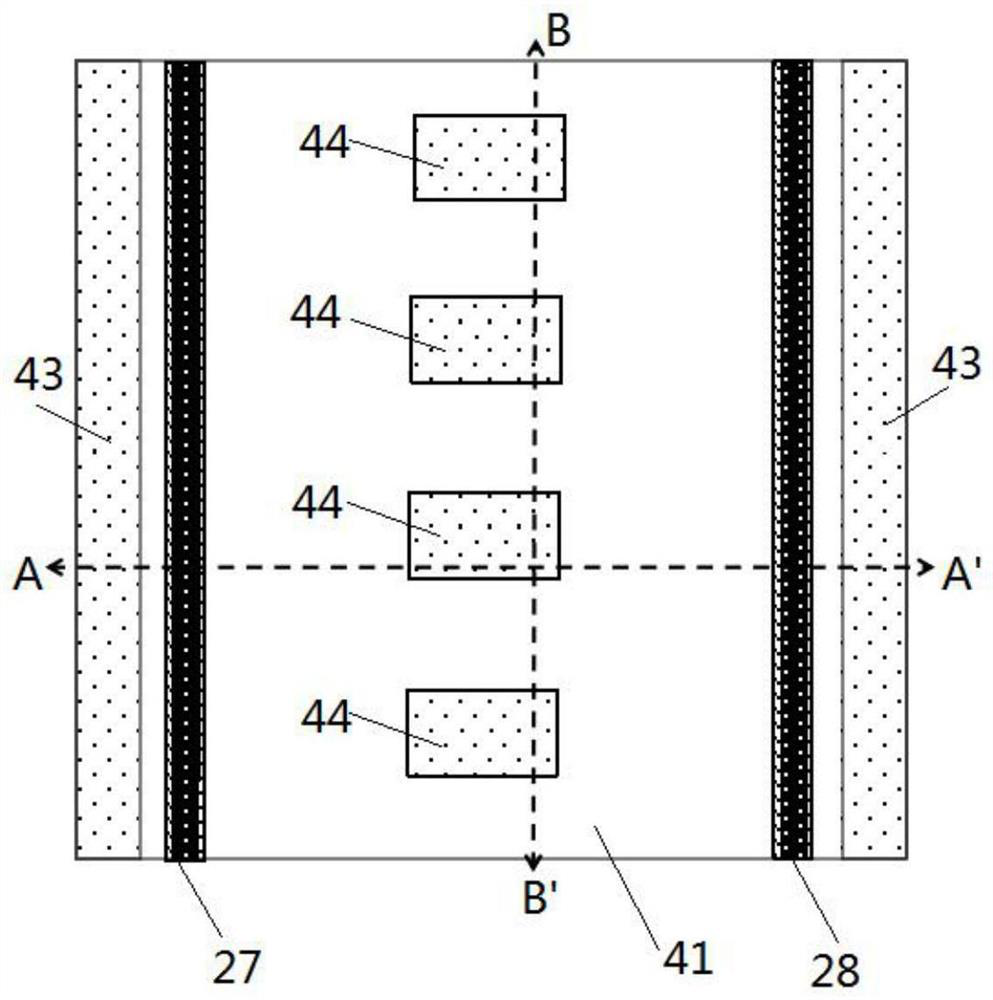

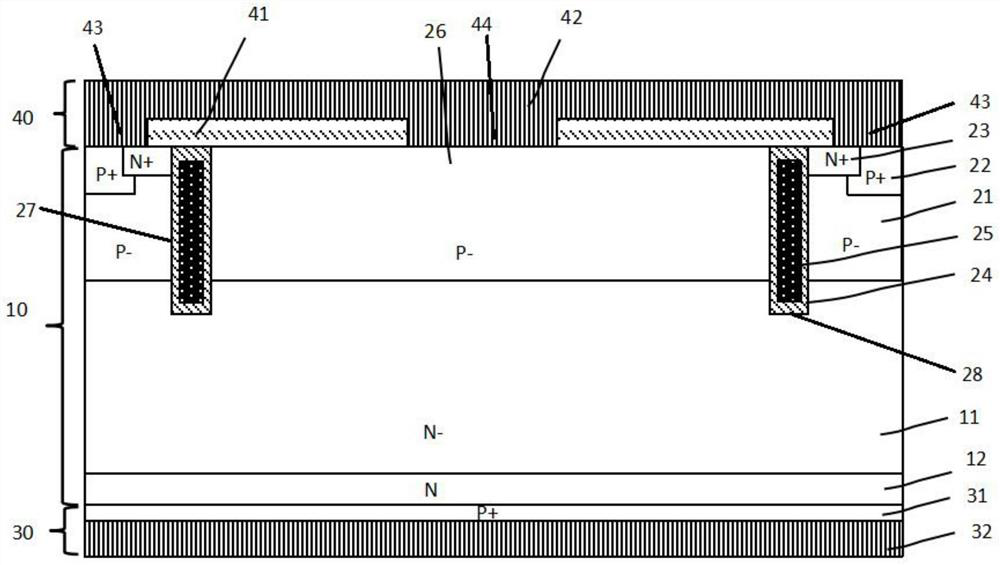

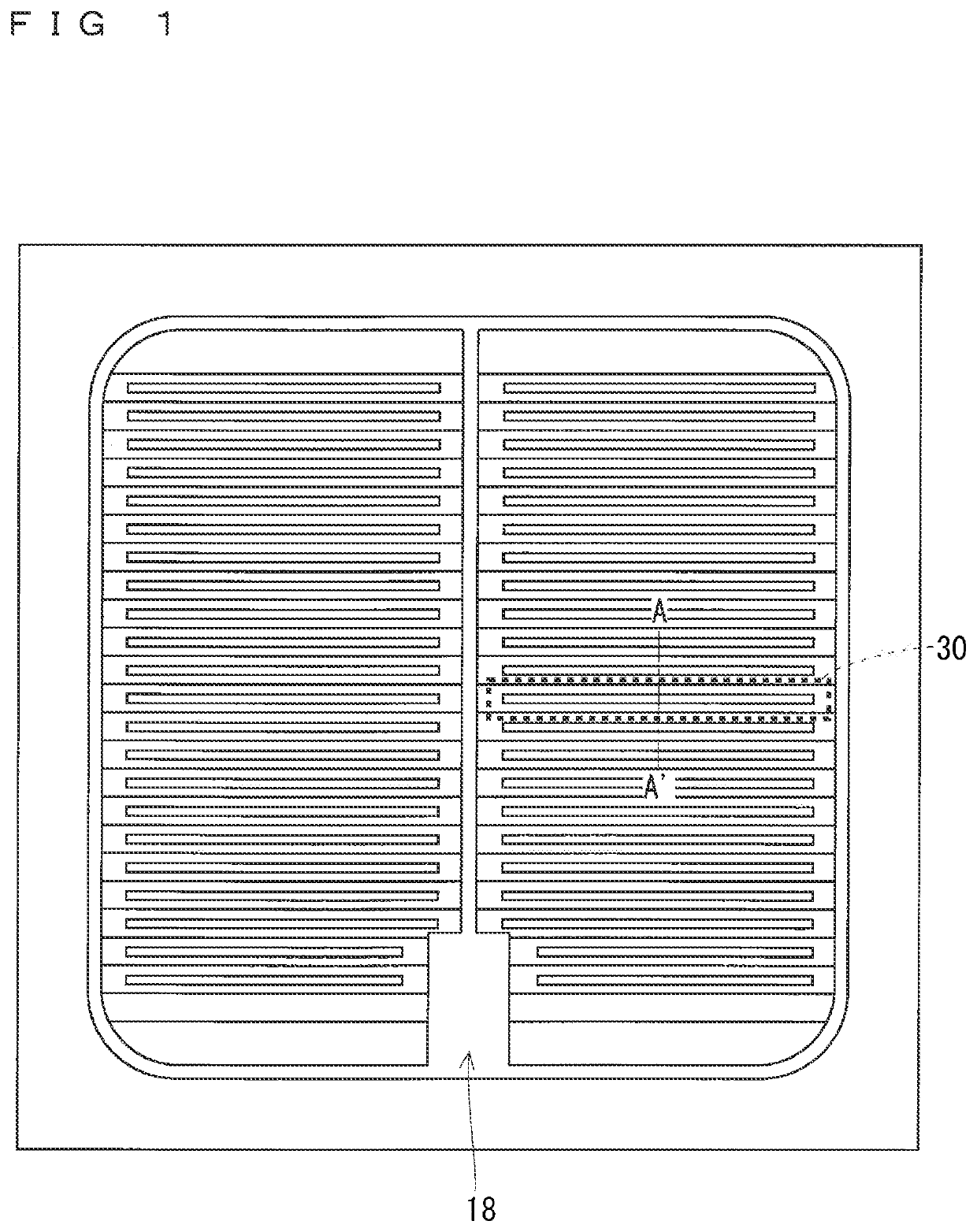

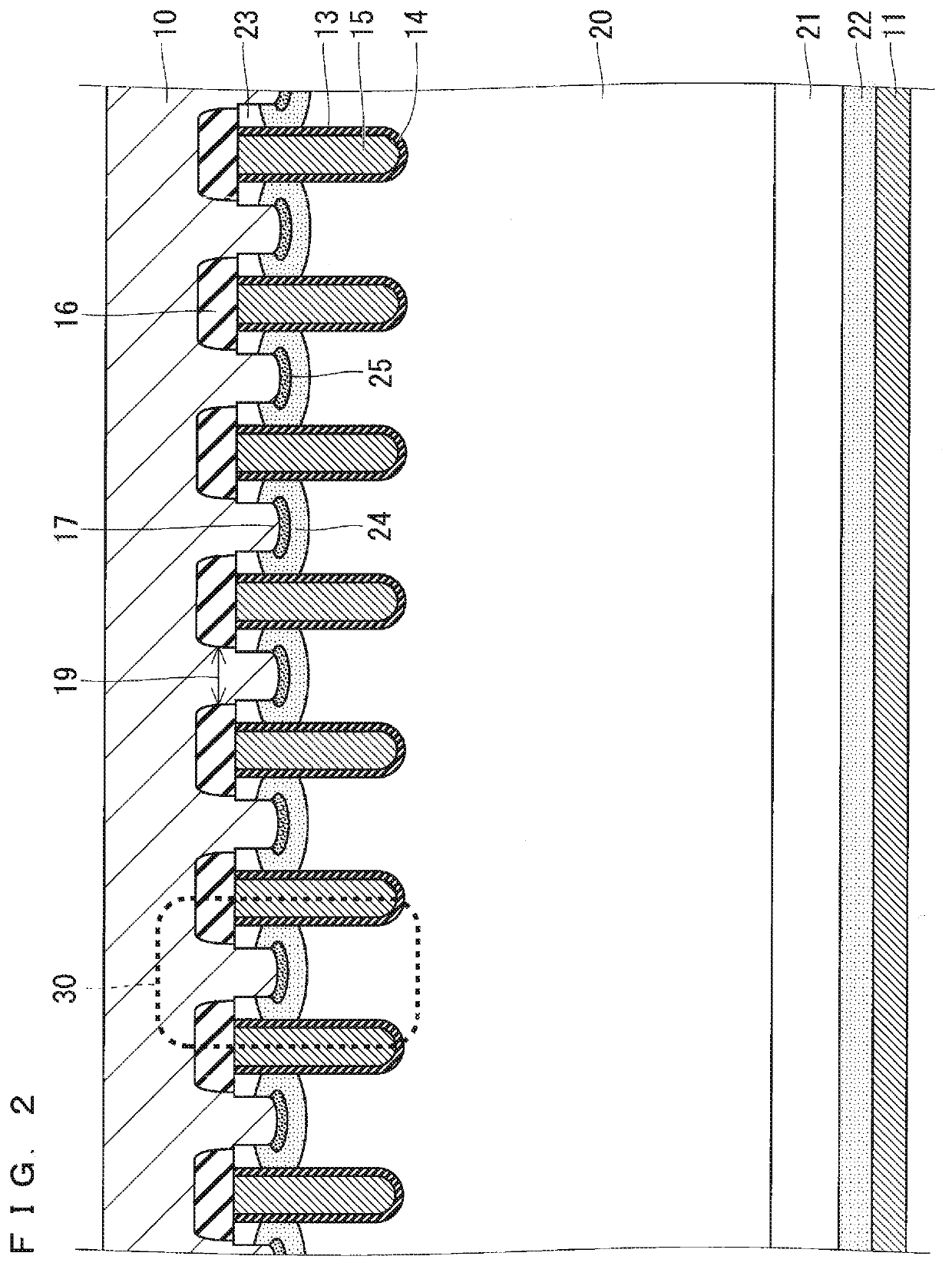

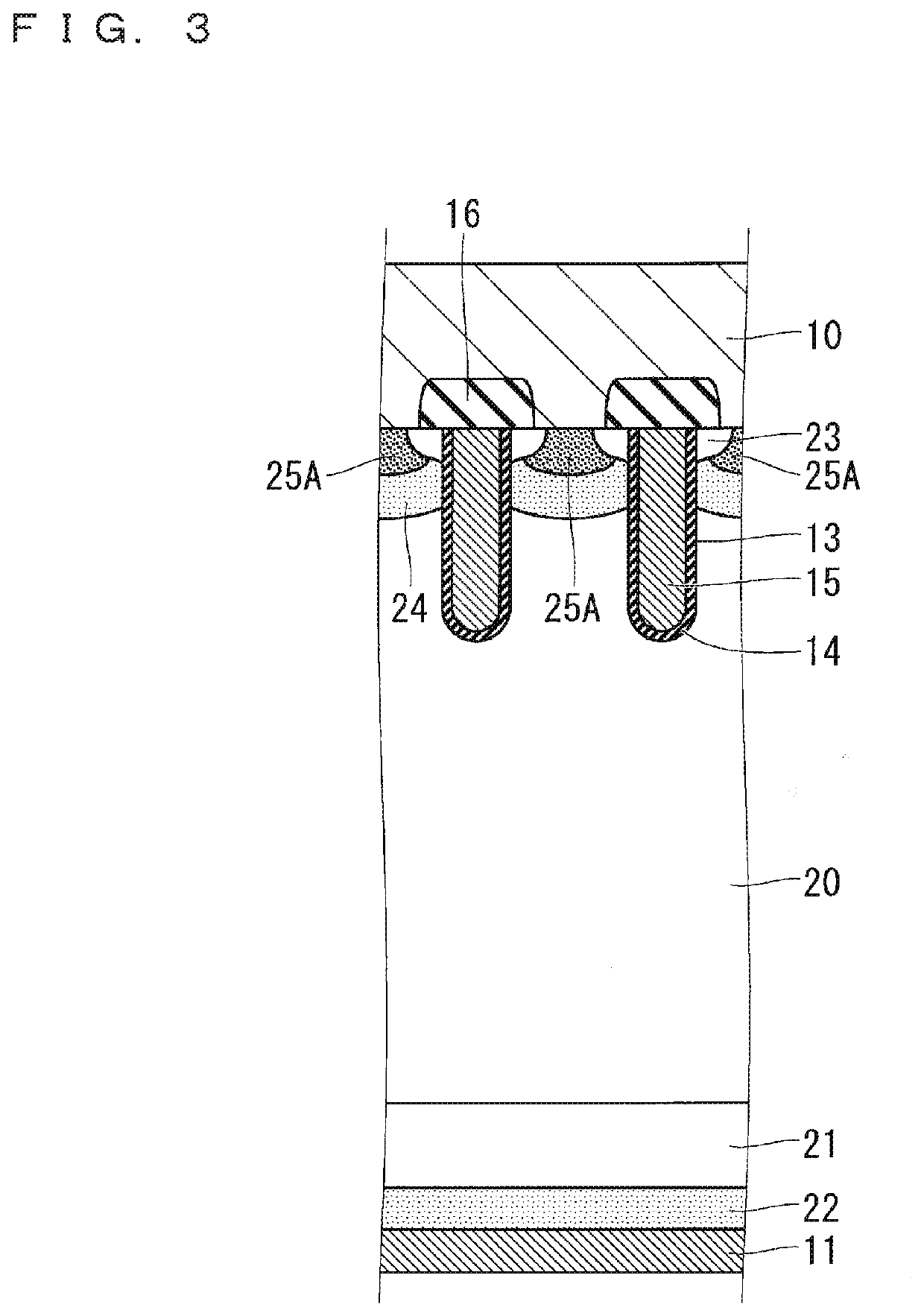

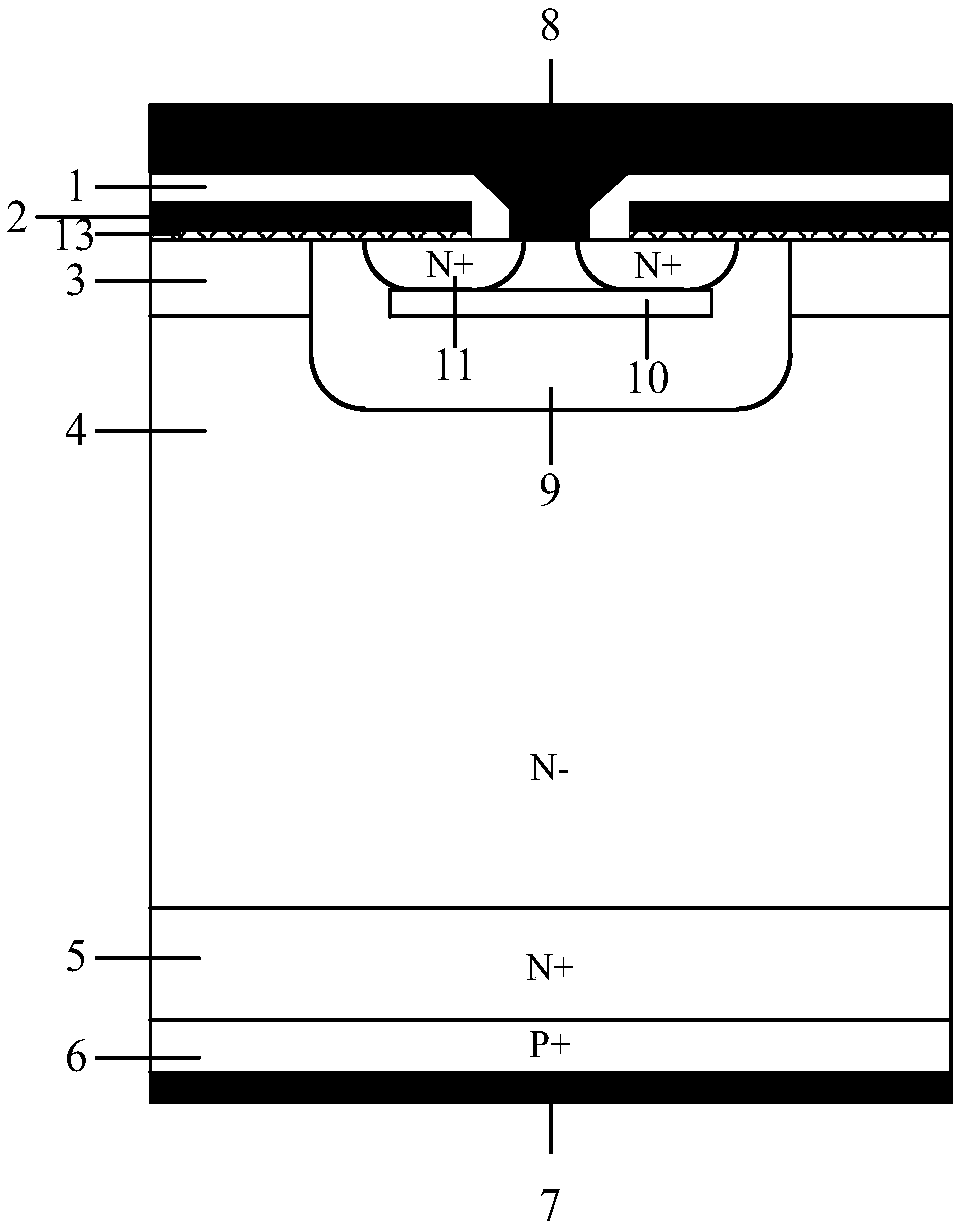

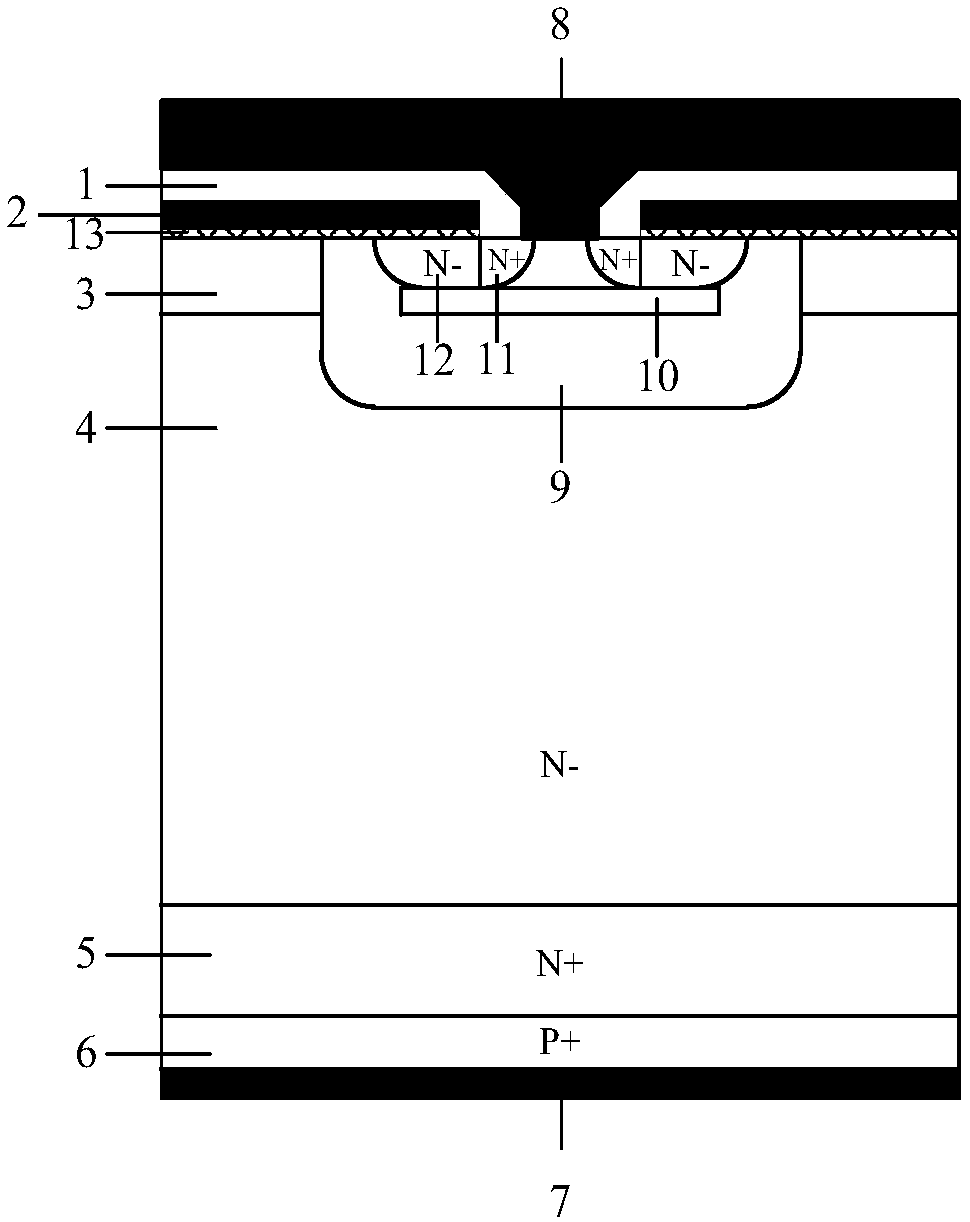

Low-power-consumption and high-reliability trench silicon carbide MOSFET device

ActiveCN110518065AReduce switching lossesImprove short circuit performanceSemiconductor devicesDiodeCapacitanceMOSFET

The invention provides a low-power-consumption and high-reliability trench silicon carbide MOSFET device which comprises an N-type substrate, an N-type epitaxial layer, a first P-Body region, first P+ contact region, a first N + contact region, a second P- body region, a second P + contact region, a second N + contact region, an oxide layer, a groove grid, a metal electrode and drain electrode. According to the SiC MOSFET device, the on-resistance can be significantly reduced through the parallel connection of four channels, and the reliability of the oxide layer of the device can be enhancedand partial gate leakage capacitance can be shielded through wrapping and protection of the second P- body to the groove grid so that the switching loss of the device can be reduced. When the deviceis short-circuited, the JFET region formed by the first P- body region and the Second P- body region is cut off so as to reduce the saturation current of the device and improve its short-circuit capability.

Owner:UNIV OF ELECTRONICS SCI & TECH OF CHINA

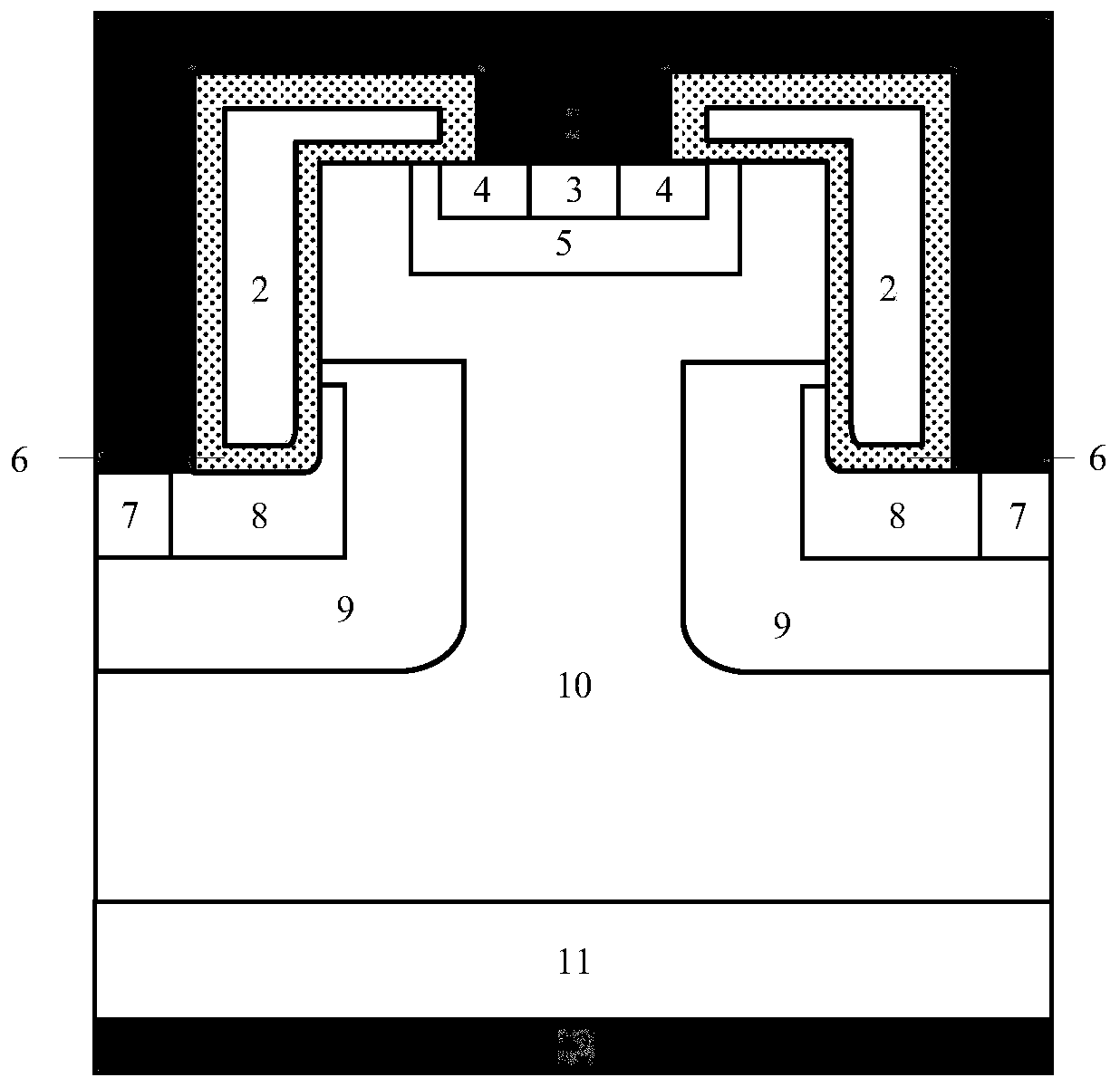

Insulated gate bipolar transistor (IGBT) device with positive temperature coefficient emitter ballast resistance

InactiveCN103258848AImprove short circuit performanceImproves latch-up resistanceSemiconductor/solid-state device manufacturingSemiconductor devicesCompensation effectEngineering

The invention discloses an insulated gate bipolar transistor (IGBT) device with positive temperature coefficient emitter ballast resistance (EBR), and belongs to the technical field of power semiconductor devices. In a conventional IGBT device of an EBR structure, the EBR is composed of a strip-shaped N<+> emitter region strip, the resistance value of the EBR generally represents a negative-temperature coefficient, namely, the higher the temperature is, the smaller the resistance value is, saturation current of the IGBT is increased, and the short-circuit capacity of the IGBT device with the positive temperature coefficient EBR will be remarkably reduced in high-temperature environments. According to the IGBT device with the positive temperature coefficient EBR, deep energy level acceptor impurities, including In or Ti or Co or Ni, are doped into the N<+> emitter region, holes produced after ionization of the deep energy level acceptor impurities have a certain compensation effect on N-type impurities, positive temperature coefficient EBR is achieved, thus the resistance value of the EBR is increased along with rise of the temperature of the IGBT device, and the short circuit capacity and latch resistant capacity of the IGBT are improved.

Owner:UNIV OF ELECTRONICS SCI & TECH OF CHINA +1

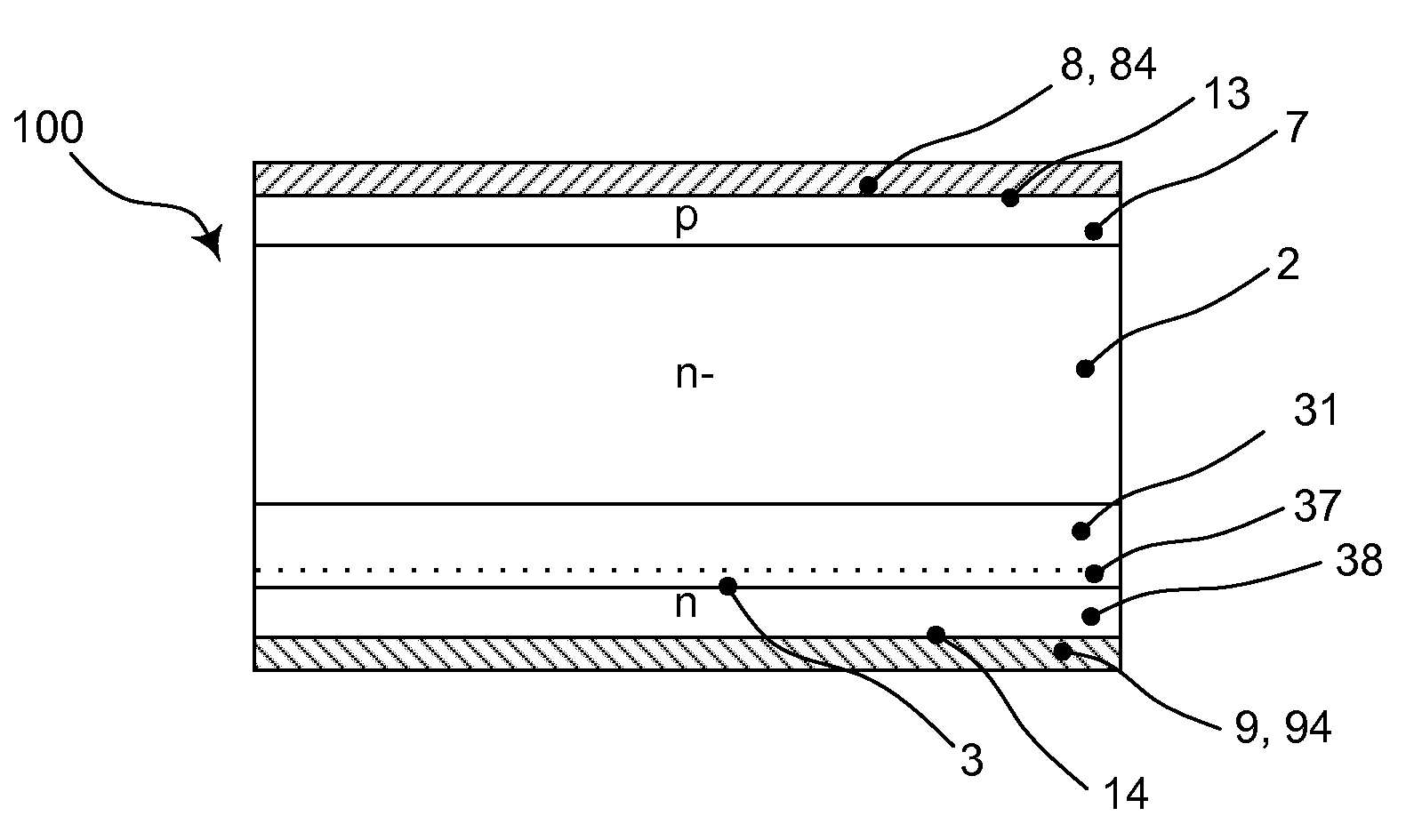

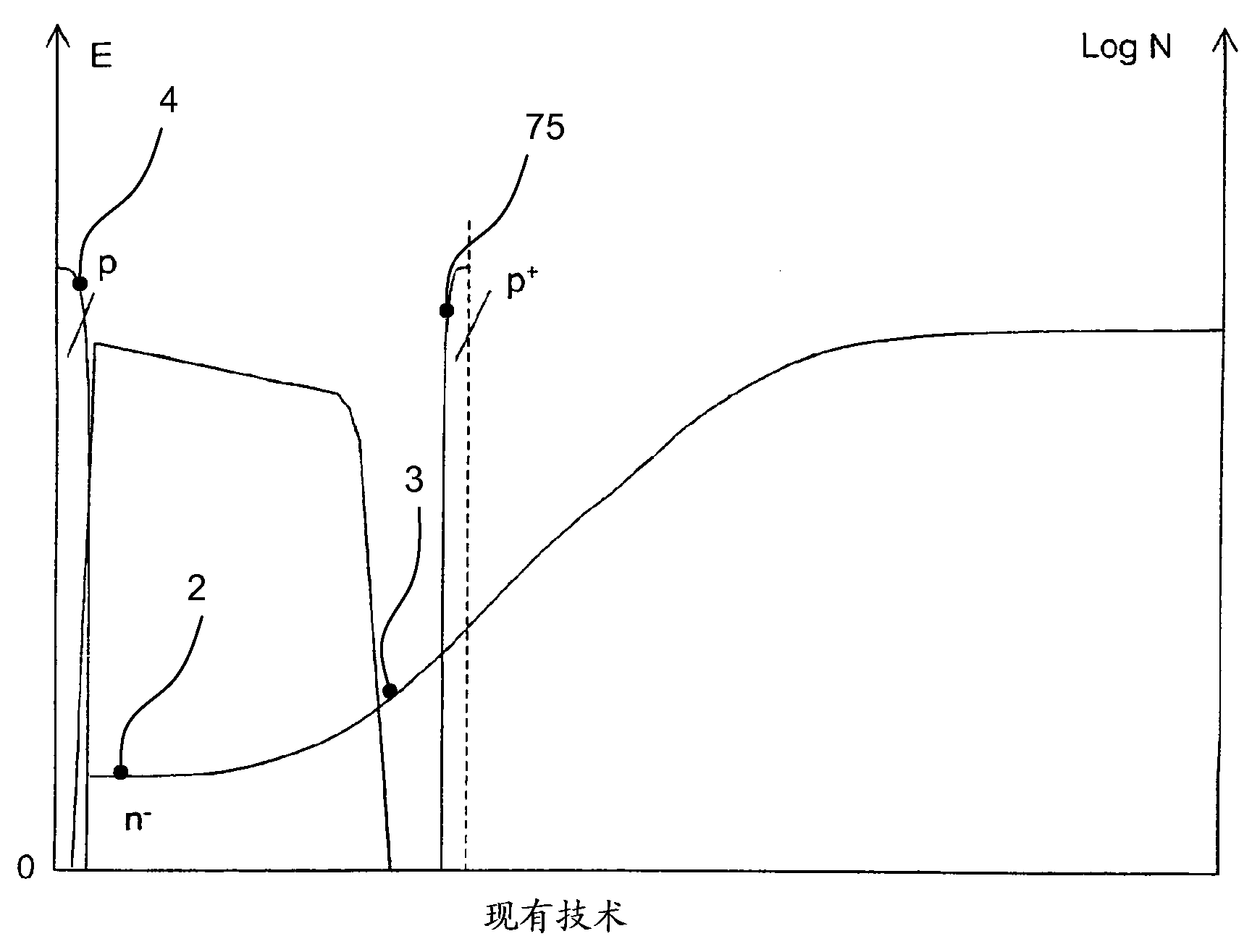

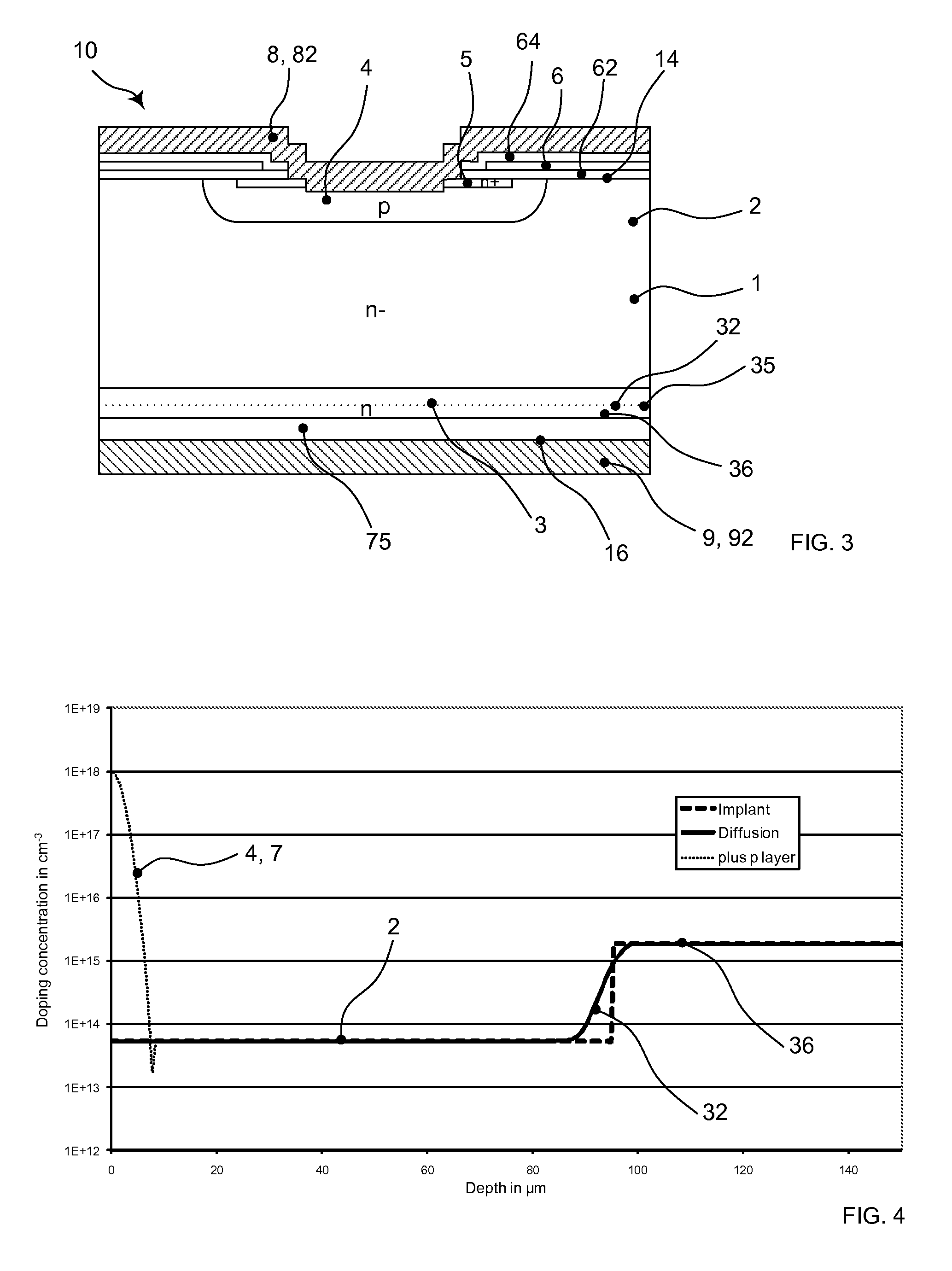

Bipolar punch-through semiconductor device and method for manufacturing such a semiconductor device

ActiveUS20140034997A1Reduce concentrationEasy to adaptTransistorSemiconductor/solid-state device manufacturingPower semiconductor deviceSemiconductor

A method for manufacturing a bipolar punch-through semiconductor device is disclosed, which includes providing a wafer having a first and a second side, wherein on the first side a high-doped layer of the first conductivity type having constant high doping concentration is arranged; epitaxially growing a low-doped layer of the first conductivity type on the first side; performing a diffusion step by which a diffused inter-space region is created at the inter-space of the layers; creating at least one layer of the second conductivity type on the first side; and reducing the wafer thickness within the high-doped layer on the second side so that a buffer layer is created, which can include the inter-space region and the remaining part of the high-doped layer, wherein the doping profile of the buffer layer decreases steadily from the doping concentration of the high-doped region to the doping concentration of the drift layer.

Owner:HITACHI ENERGY SWITZERLAND AG

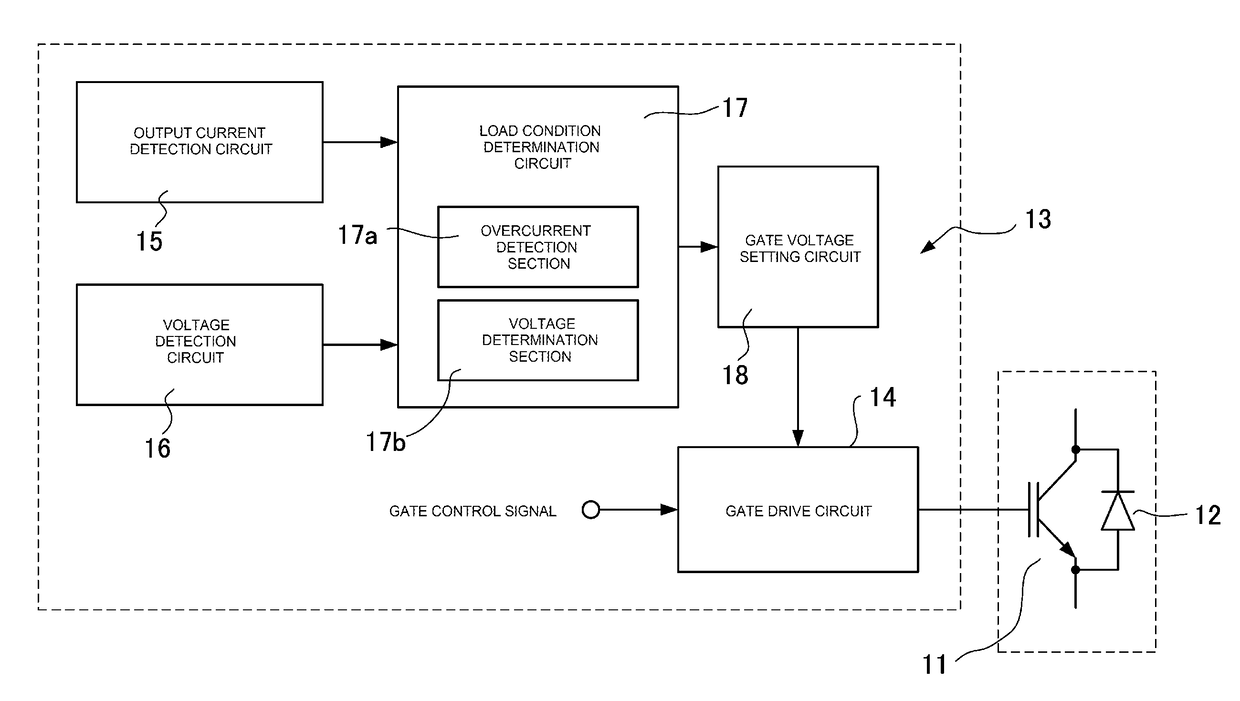

Insulated gate semiconductor device

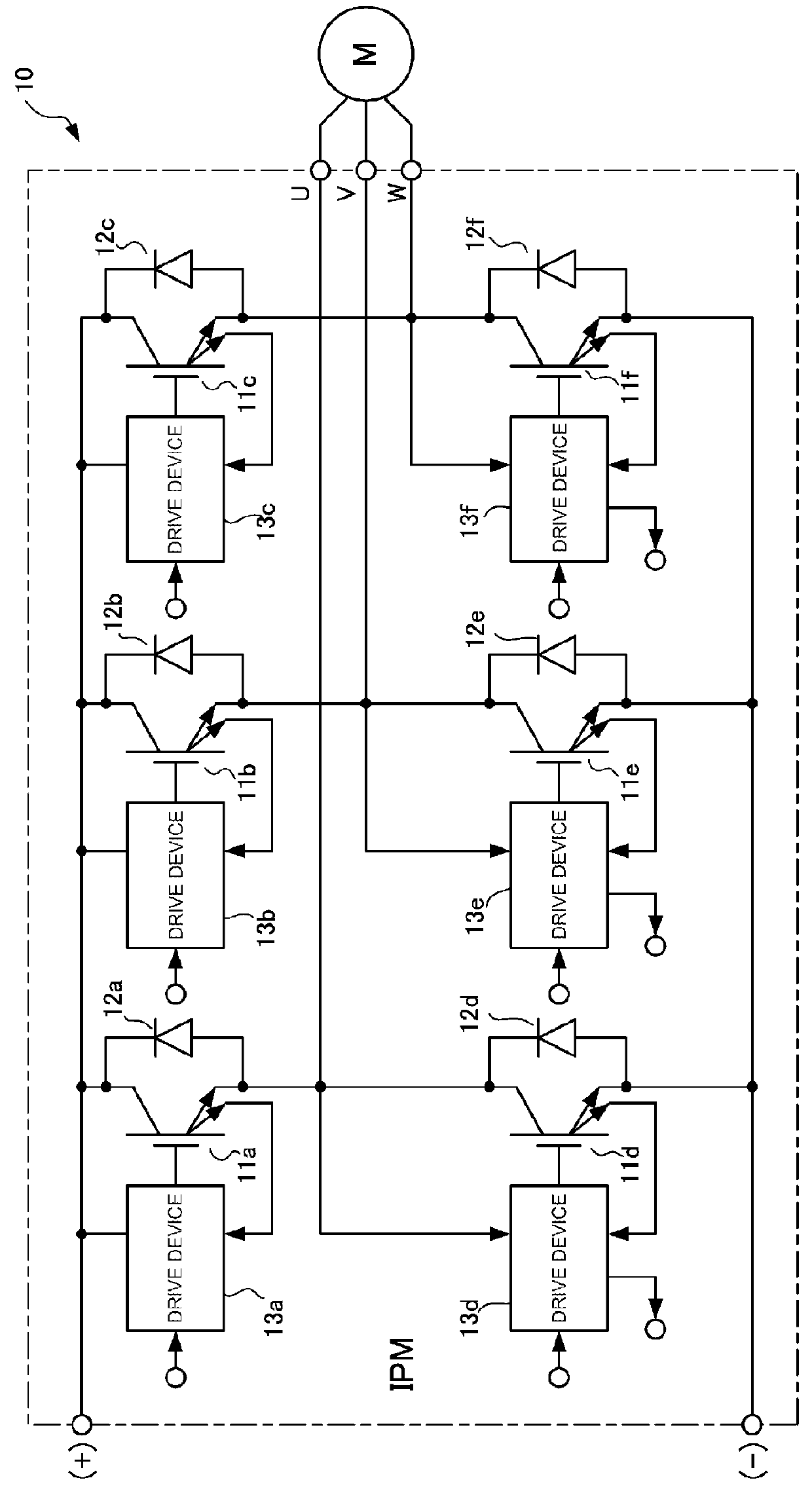

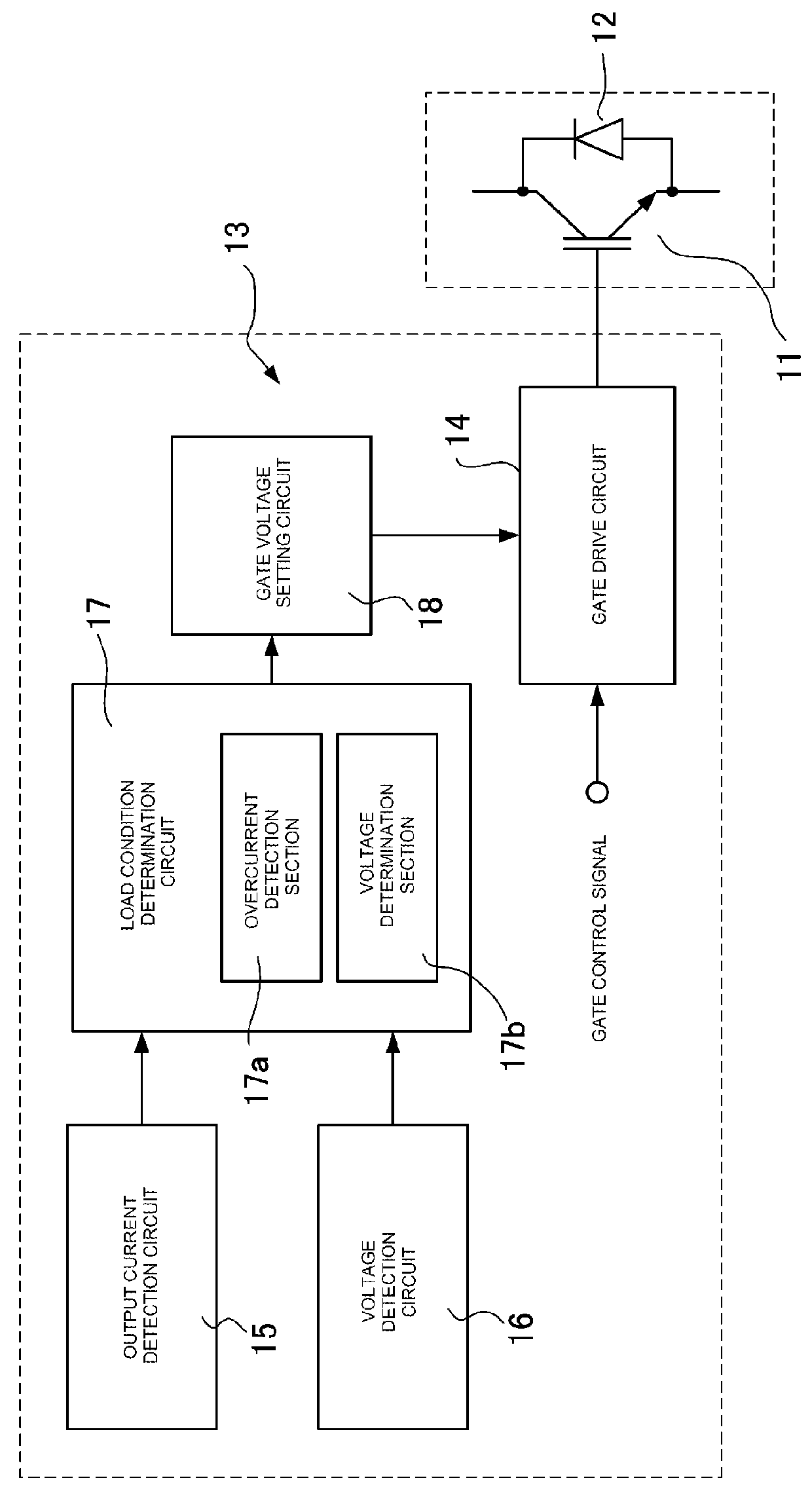

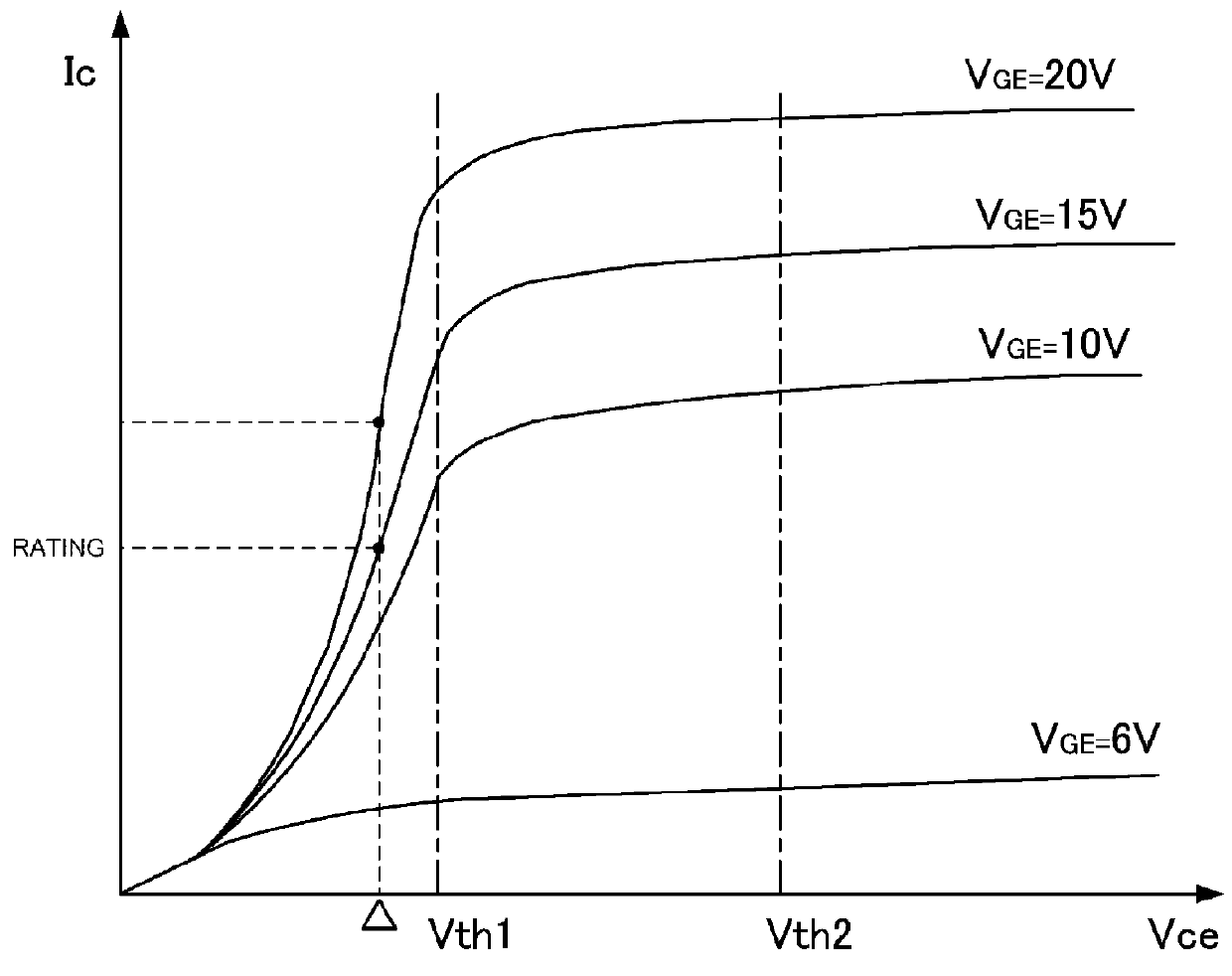

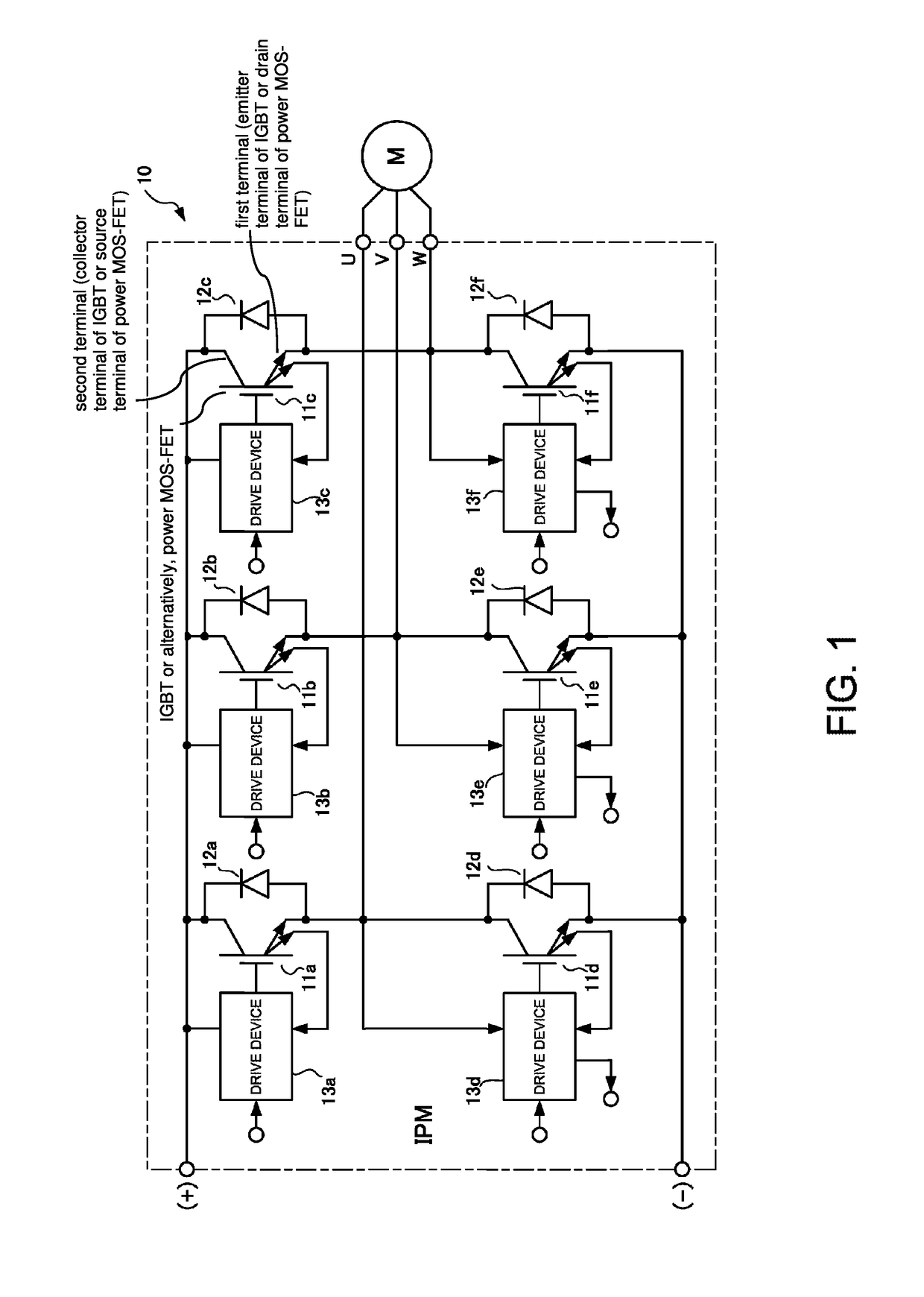

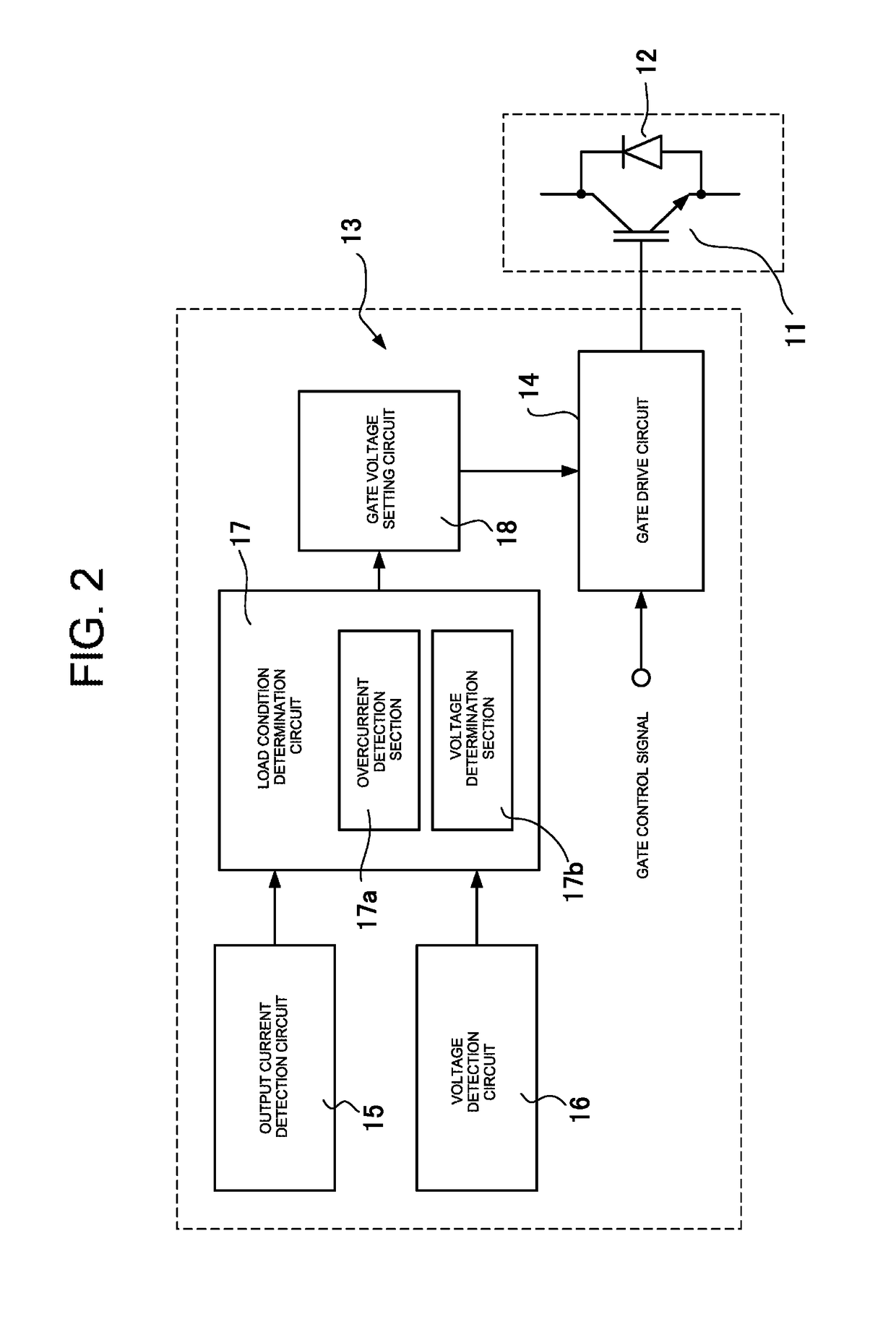

ActiveUS20160036316A1Avoid feverAvoid destructionAc-dc conversion without reversalElectronic switchingPower semiconductor devicePower flow

An insulated gate semiconductor device includes an insulated gate semiconductor element, an output current detection unit, a voltage detection unit, and a heat generation amount suppression unit. The insulated gate semiconductor element on-operates by receiving a first gate voltage at a control terminal, and switches and outputs an input voltage to a load. The output current detection unit detects an output current to the load. The voltage detection unit detects an on-voltage of the insulated gate semiconductor element. The heat generation amount suppression unit sets a gate voltage to be applied to the control terminal of the insulated gate semiconductor element higher than the first gate voltage in response to the output current exceeding a rated current value and the on-voltage being lower than a first threshold voltage.

Owner:FUJI ELECTRIC CO LTD

Surge arrester

ActiveUS7522399B2Less variation of performanceImprove short circuit performanceEmergency protective arrangement detailsOvervoltage protection resistorsGlass fiberFiber

Owner:HITACHI ENERGY LTD

Silicon carbide trench gate MOSFET and manufacturing method thereof

ActiveCN113690321AIncreasing the thicknessImprove breakdown voltageSemiconductor/solid-state device manufacturingSemiconductor devicesMOSFETGate dielectric

The invention provides a silicon carbide trench gate MOSFET and a manufacturing method thereof. The silicon carbide trench gate MOSFET comprises a substrate with a first doping type, an epitaxial layer which is formed on the substrate and has the first doping type, an epitaxial well region which is formed above the epitaxial layer and has a second doping type, a first source contact region which is formed in the epitaxial well region and has a first doping type, a second source contact region which has a second doping type, atrench gate, a source electrode and a drain electrode, wherein thetrench gate comprises a gate dielectric and a gate electrode. The silicon carbide trench gate MOSFET is characterized by comprising a concave injection type current diffusion region which wraps the bottom of a trench gate and has a first doping type, and the bottom of the injection type current diffusion region is not higher than the bottom of an epitaxial well region. The injection type current diffusion region is reasonably arranged, the saturation current of the device can be limited, meanwhile, the electric field peak value and the current position can be separated, the heating power is reduced, and the short-circuit capacity of the device is improved.

Owner:ZHEJIANG UNIV HANGZHOU GLOBAL SCI & TECH INNOVATION CENT

High-impedance combined-type transformer

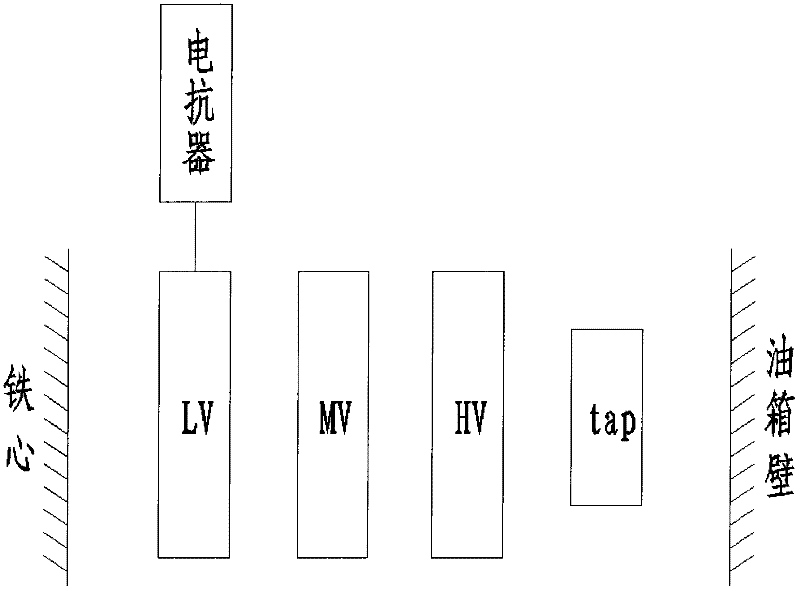

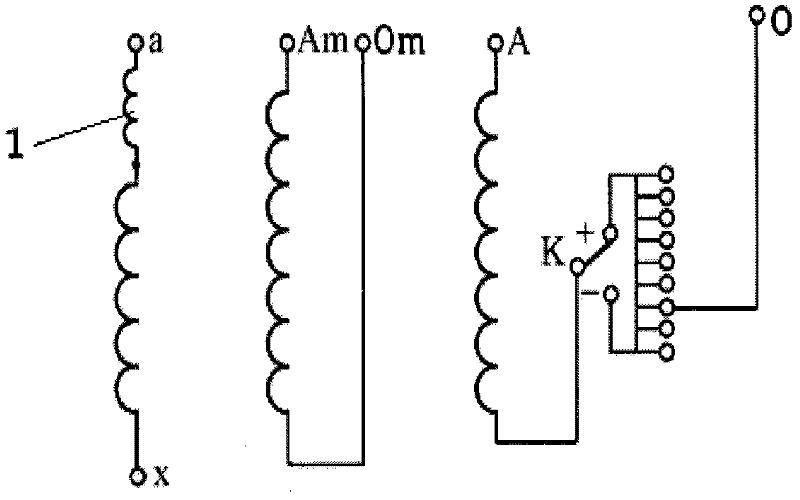

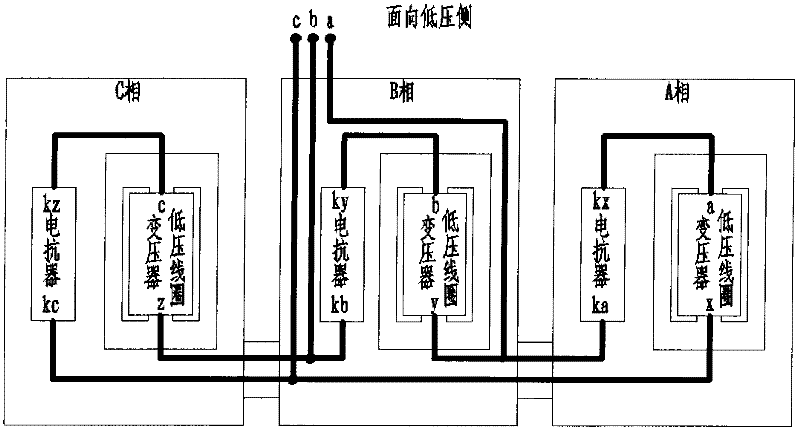

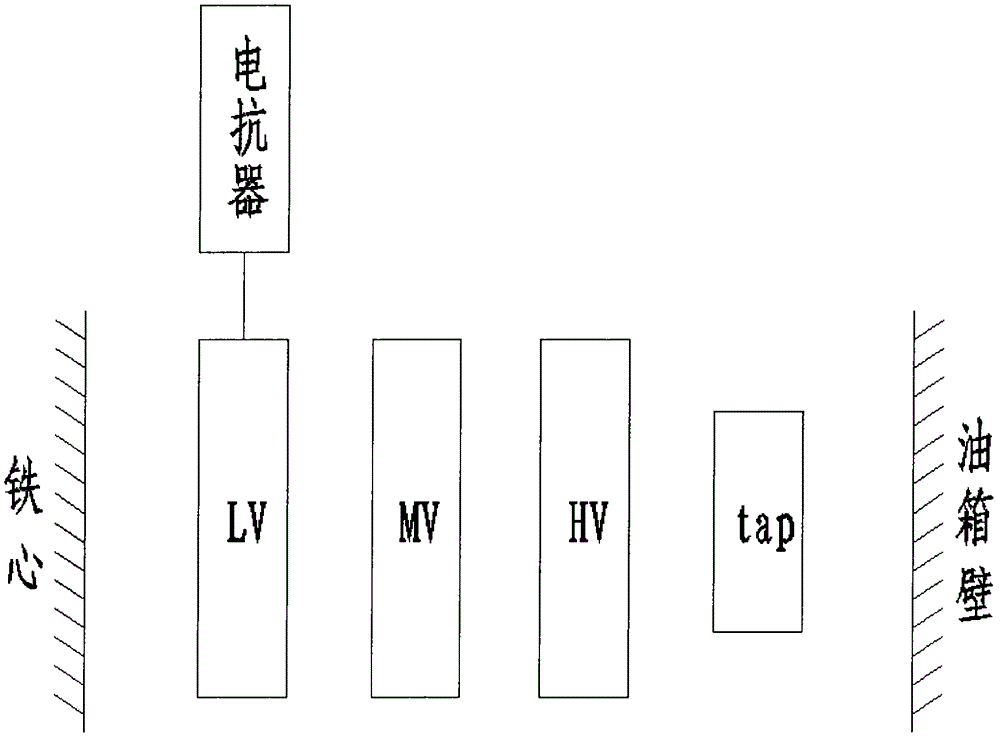

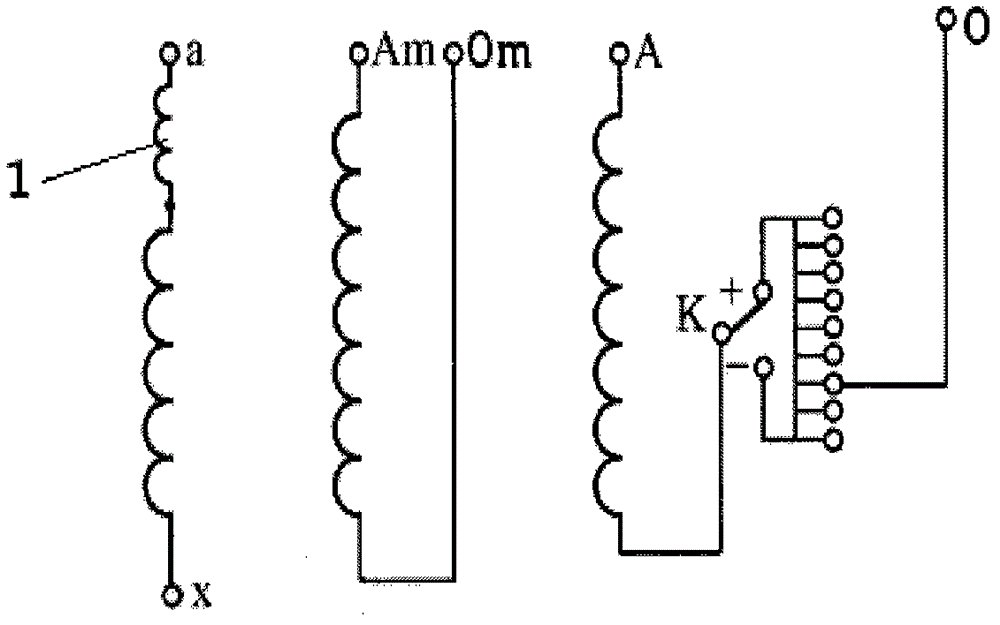

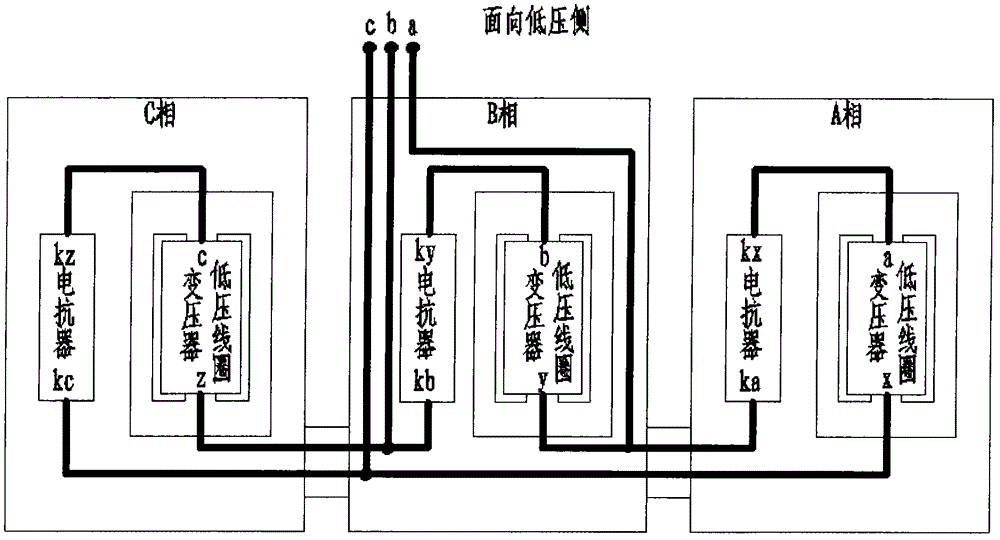

ActiveCN102543406AReduce short circuit currentImprove short circuit capabilityTransformers/inductances coils/windings/connectionsFixed transformersSingle phaseHigh impedance

The invention provides a high-impedance combined-type transformer which comprises three single-phase transformers and three transformer oil tanks, wherein the three single-phase transformers are respectively arranged in the three transformer oil tanks; the three single-phase transformers are combined to form a three-phase transformer; in the three-phase transformer, each phase of transformer comprises a low-voltage winding, a medium-voltage winding and a high-voltage winding; a reactor is arranged in each transformer oil tank; and the low-voltage winding of each phase of transformer is connected in series with the reactor of the transformer oil tank where the phase transformer is positioned. The high-impedance combined-type transformer can be in high-impedance operation and in split-type transportation, and has high performance-price ratio.

Owner:TBEA HENGYANG TRANSFORMERS

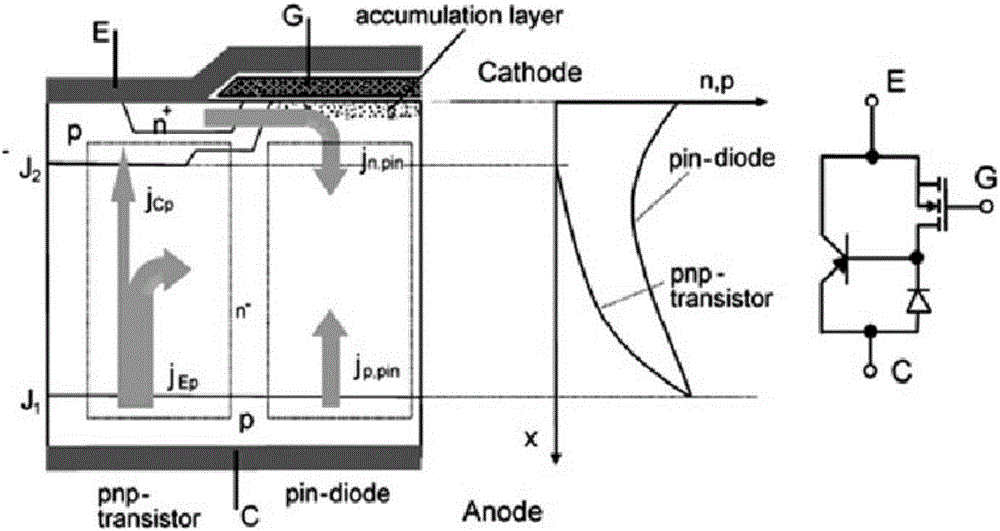

Low on-state loss insulated gate bipolar translator (IGBT) and manufacturing method thereof

ActiveCN105047706AIncrease the area of the PIN areaEnhanced conductance modulation effectTransistorSemiconductor/solid-state device manufacturingCell regionEngineering

The invention provides a low on-state loss insulated gate bipolar translator (IGBT) and a manufacturing method thereof. The IGBT comprises an active region, a terminal region and a gate region, wherein the active region comprises an N-substrate region, a gate oxidation layer, a polycrystalline silicon gate, a P-base region, an N+ emitter region, a P+ collector region, emitter metal and collector metal; the active region is a cell region; a dummy cell structure is formed in the active region; the dummy cell structure is formed by sacrificing a cellular local channel; and the cellular local channel is sacrificed by changing one or combination of more of a pressure ring layer, a field oxide layer, a polycrystal layer and a contact hole layer. According to the manufacturing method provided by the invention, an invalid cell is introduced into the active region; the PIN / PNP region distribution of the active region is changed; the conductivity modulation effect of the cell of the IGBT is optimized; the saturation voltage of the IGBT is reduced; the current density of the IGBT is improved; and the on-state loss of the IGBT is reduced. The IGBT chip manufactured by the method has advantages in the field of high power density and low on-state loss application.

Owner:GLOBAL ENERGY INTERCONNECTION RES INST CO LTD +2

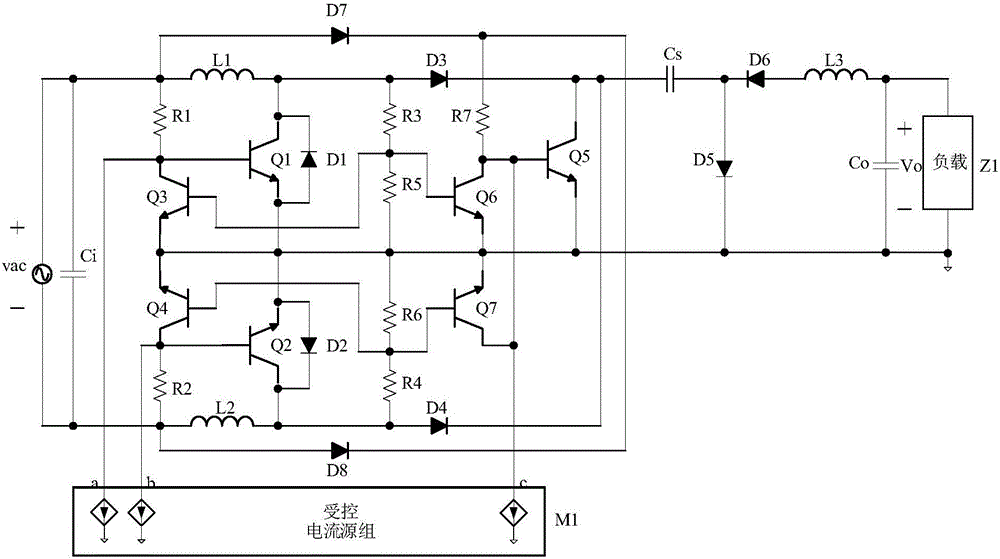

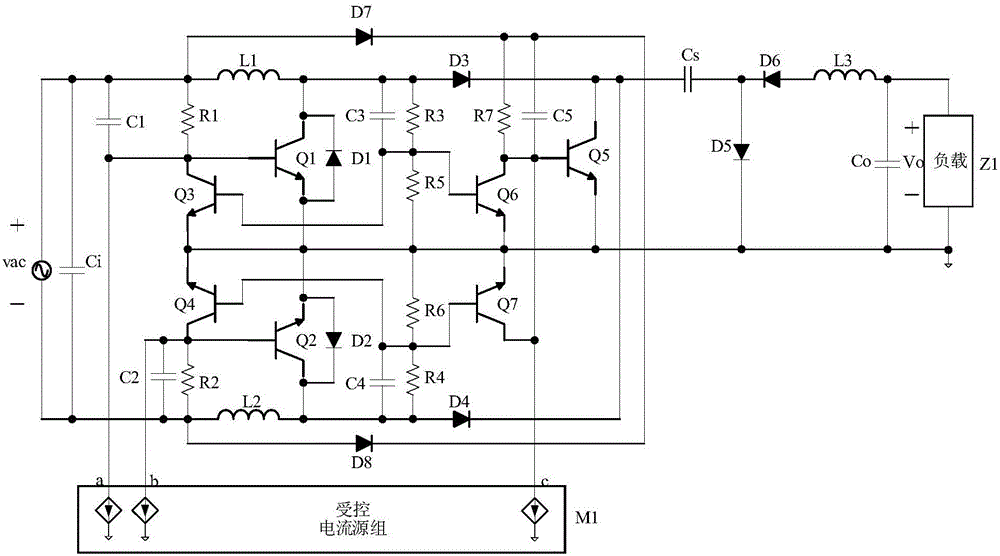

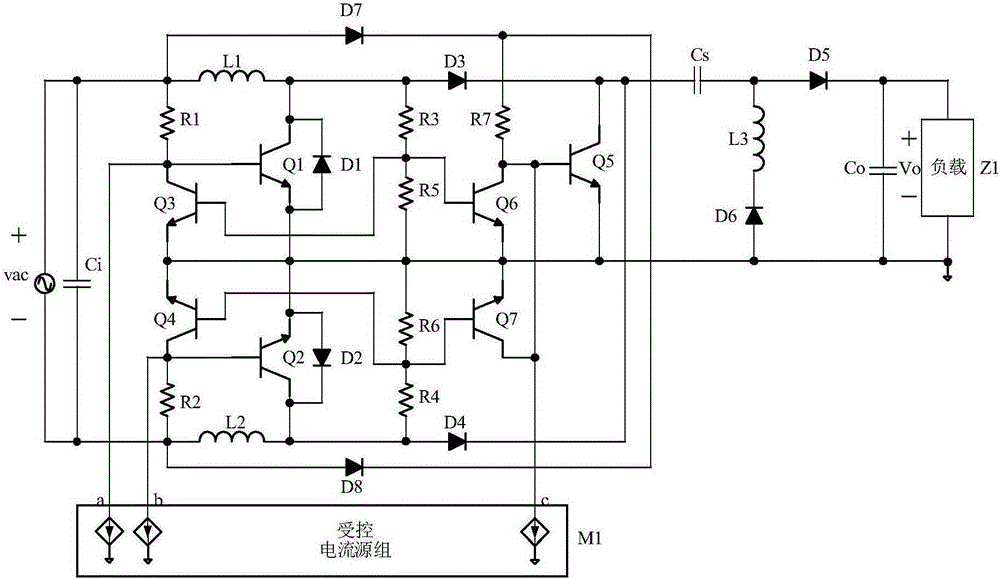

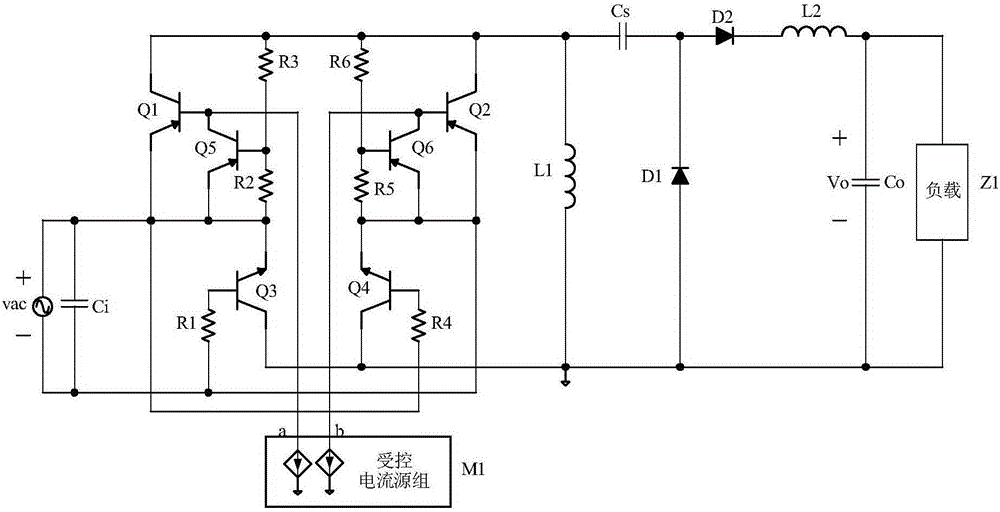

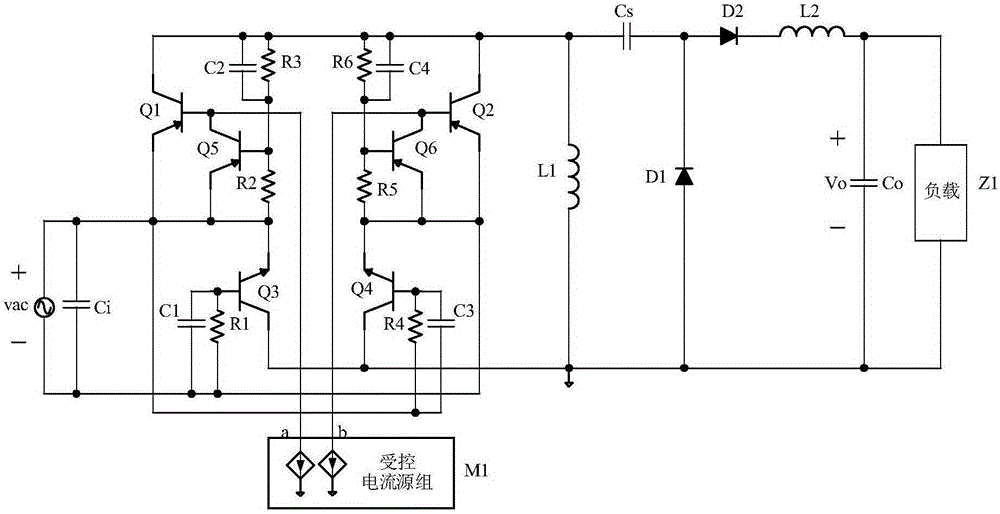

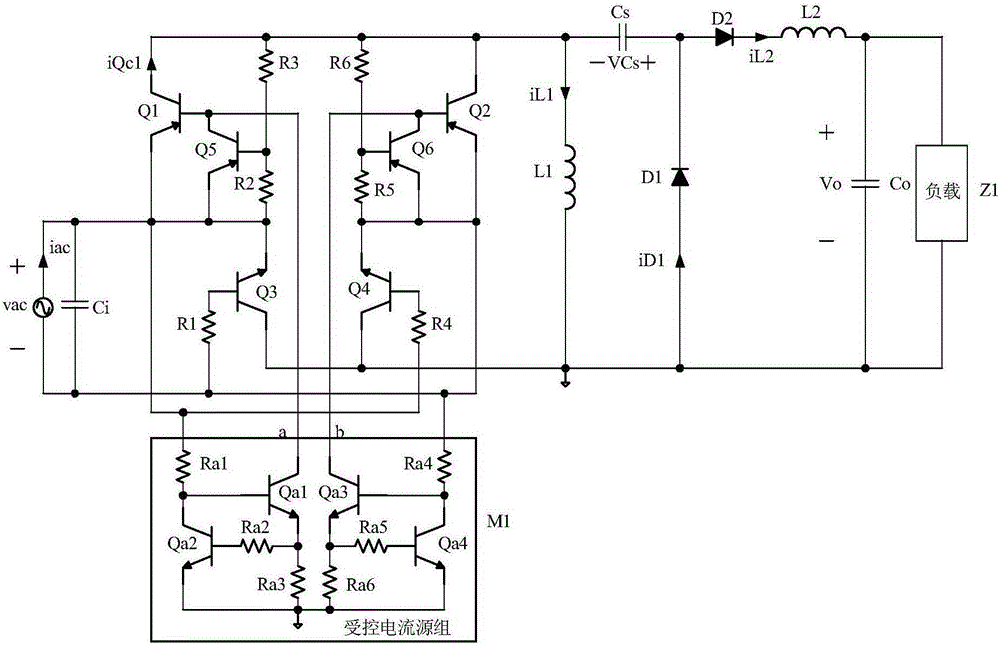

Self-excited BJT type bridgeless Cuk PFC rectification circuit

Provided is a self-excited BJT type bridgeless Cuk PFC rectification circuit. The rectification circuit comprises an input capacitor Ci, an NPN type BJT transistor Q1, an NPN type BJT transistor Q2, an NPN type BJT transistor Q3, an NPN type BJT transistor Q4, an NPN type BJT transistor Q5, an NPN type BJT transistor Q6, an NPN type BJT transistor Q7, a diode D1, a diode D2, a diode D3, a diode D4, a diode D5, a diode D6, a diode D7, a diode D8, an inductor L1, an inductor L2, an inductor L3, a capacitor Cs, an output capacitor Co, a resistor R1, a resistor R2, a resistor R3, a resistor R4, a resistor R5, a resistor R6, a resistor R7, and a controlled current source group M1. According to the rectification circuit, the structure of a driving circuit is simplified, the driving efficiency is high, and easy self-running performance is obtained.

Owner:南陵县建设投资有限责任公司

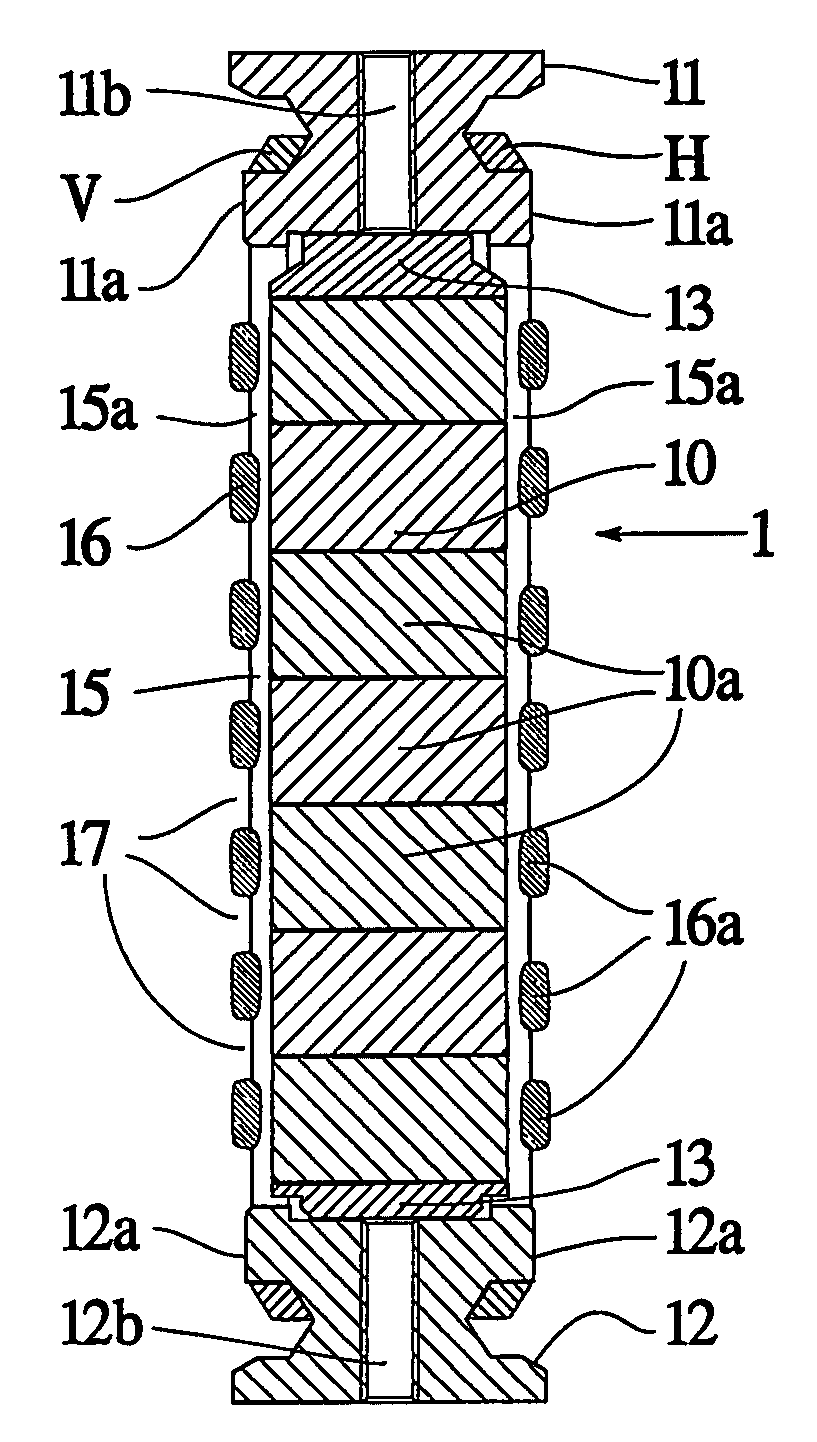

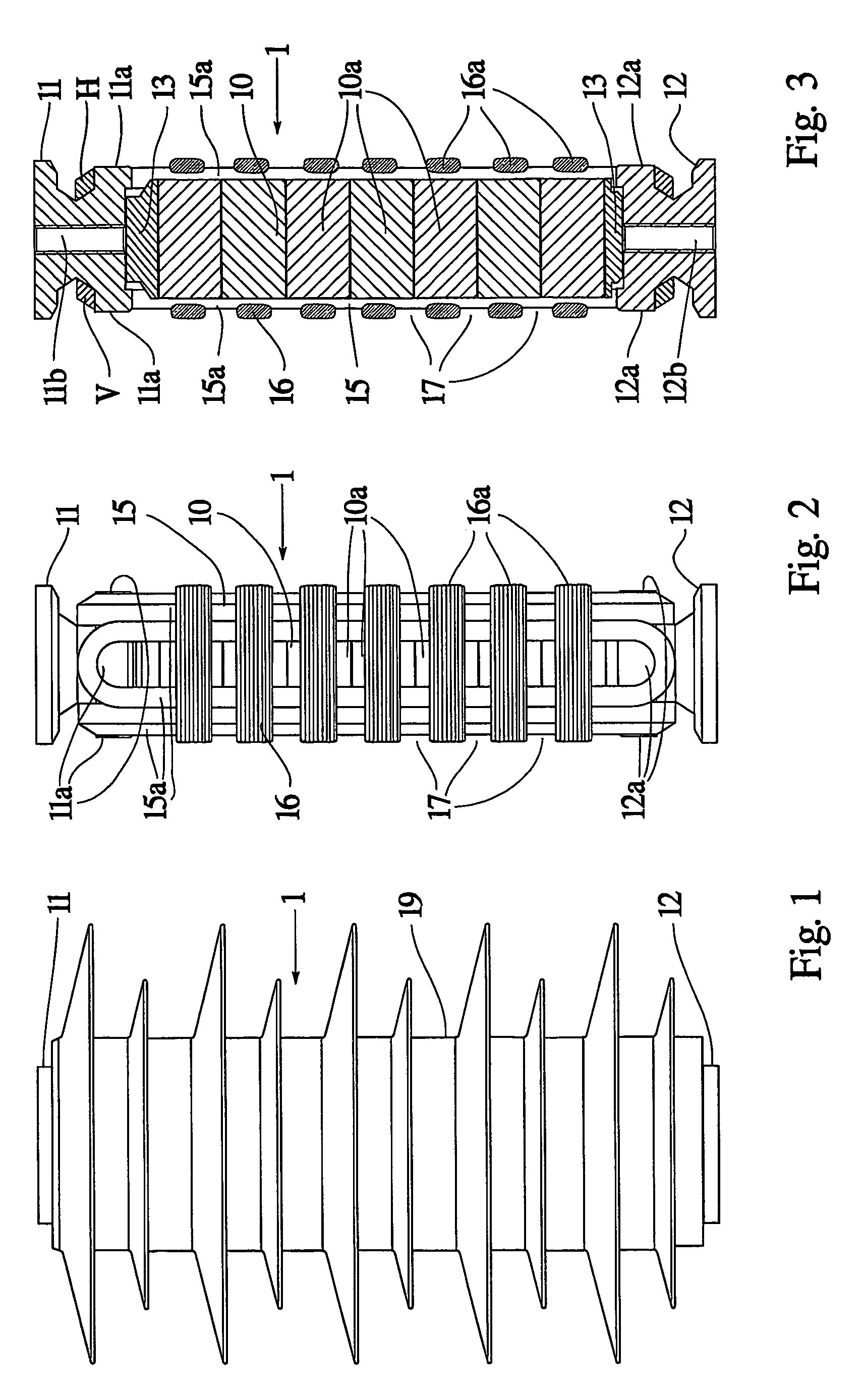

Surge arrester

ActiveUS20060227484A1Less variation of performanceImprove short circuit performanceEmergency protective arrangement detailsOvervoltage protection resistorsGlass fiberFiber

A surge arrester including a stack of a plurality of cylindrical varistor blocks that are arranged one after the other in the axial direction of the varistor blocks between an upper end electrode and a lower end electrode. Arranged around the stack are clamping members of an insulating material including at least three loops of continuously wound fiber that connect the upper end electrode to the lower end electrode as well as a bursting-protective bandage in the form of a plurality of rings wound of fiber, and a surrounding, electrically insulating, outer casing of rubber or other polymeric material. The loops are wound from glass fiber and exhibit an asymmetrical cross section.

Owner:HITACHI ENERGY SWITZERLAND AG

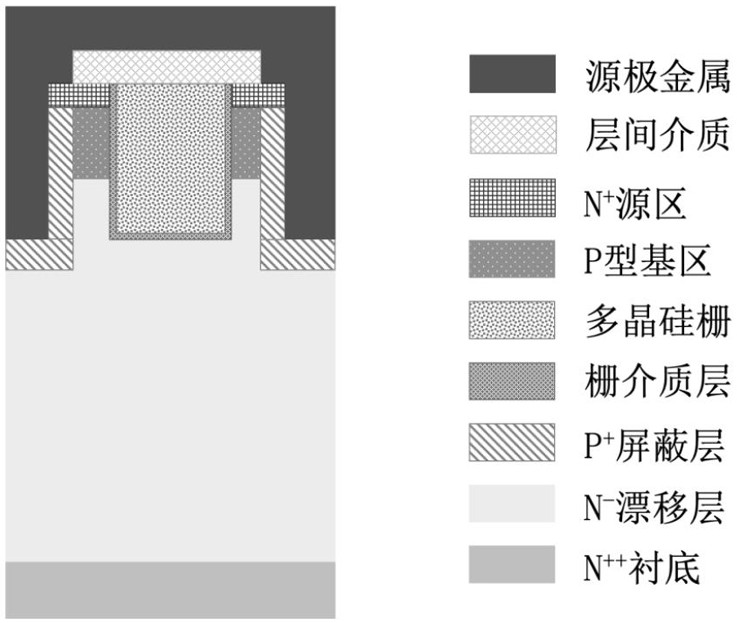

Double-groove type SiC MOSFET cellular structure, device and manufacturing method

InactiveCN114267739AImprove shielding effectReduce gate-to-drain capacitanceSemiconductor/solid-state device manufacturingSemiconductor devicesMOSFETCapacitance

The invention discloses a double-groove type SiC MOSFET cellular structure and device and a manufacturing method thereof, the double-groove type SiC MOSFET cellular structure comprises an N + + type SiC substrate, an N-type SiC drift layer, a P type base region and an N + type source region, the N-type SiC drift layer is located above the N + + type SiC substrate and is provided with a source electrode groove and a grid electrode groove, and the bottom of the source electrode groove is provided with an N type hole blocking layer and a source electrode P + type shielding layer; an N-type current conducting layer and a grid P + type shielding layer are arranged at the bottom of the grid groove, and a grid dielectric layer and a grid electrode are arranged in the grid groove; the P-type base region and the N + type source region are located on the N-type SiC drift layer between the source trench and the gate trench and are arranged from bottom to top. Shielding of the drain voltage is further enhanced, the electric field peak value and the gate-drain capacitance of the gate dielectric layer are reduced, the reliability of the gate dielectric layer and the working frequency of the device are improved, the on-resistance of the device can be reduced, and the short-circuit capability of the device can be enhanced.

Owner:北京昕感科技有限责任公司

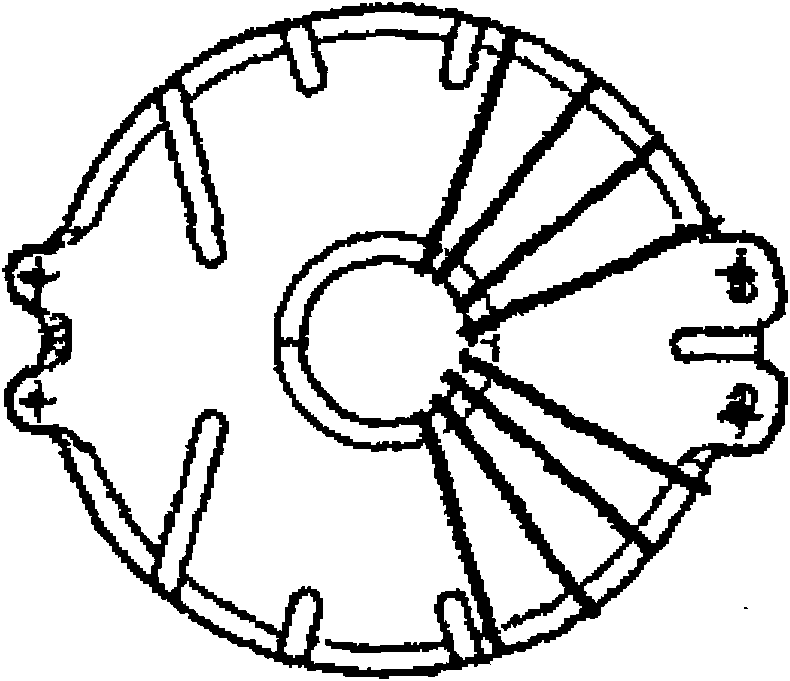

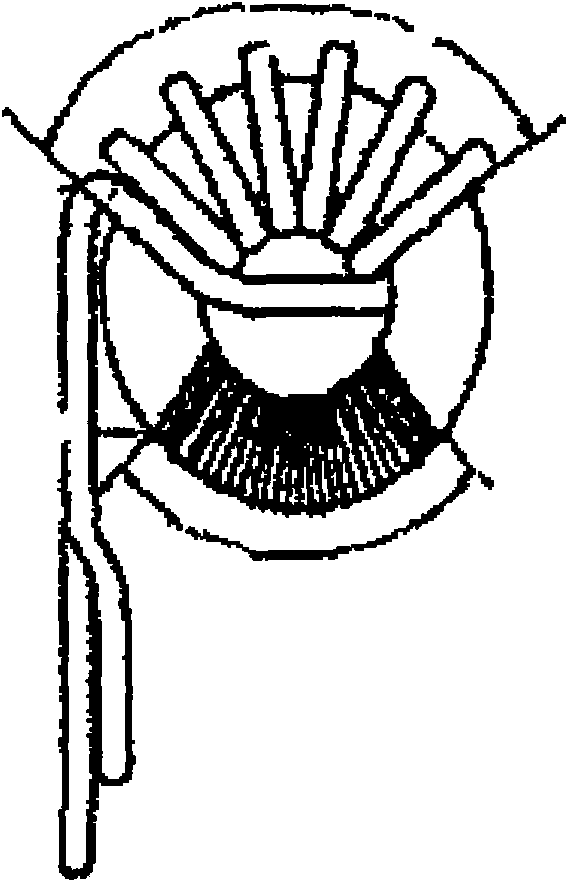

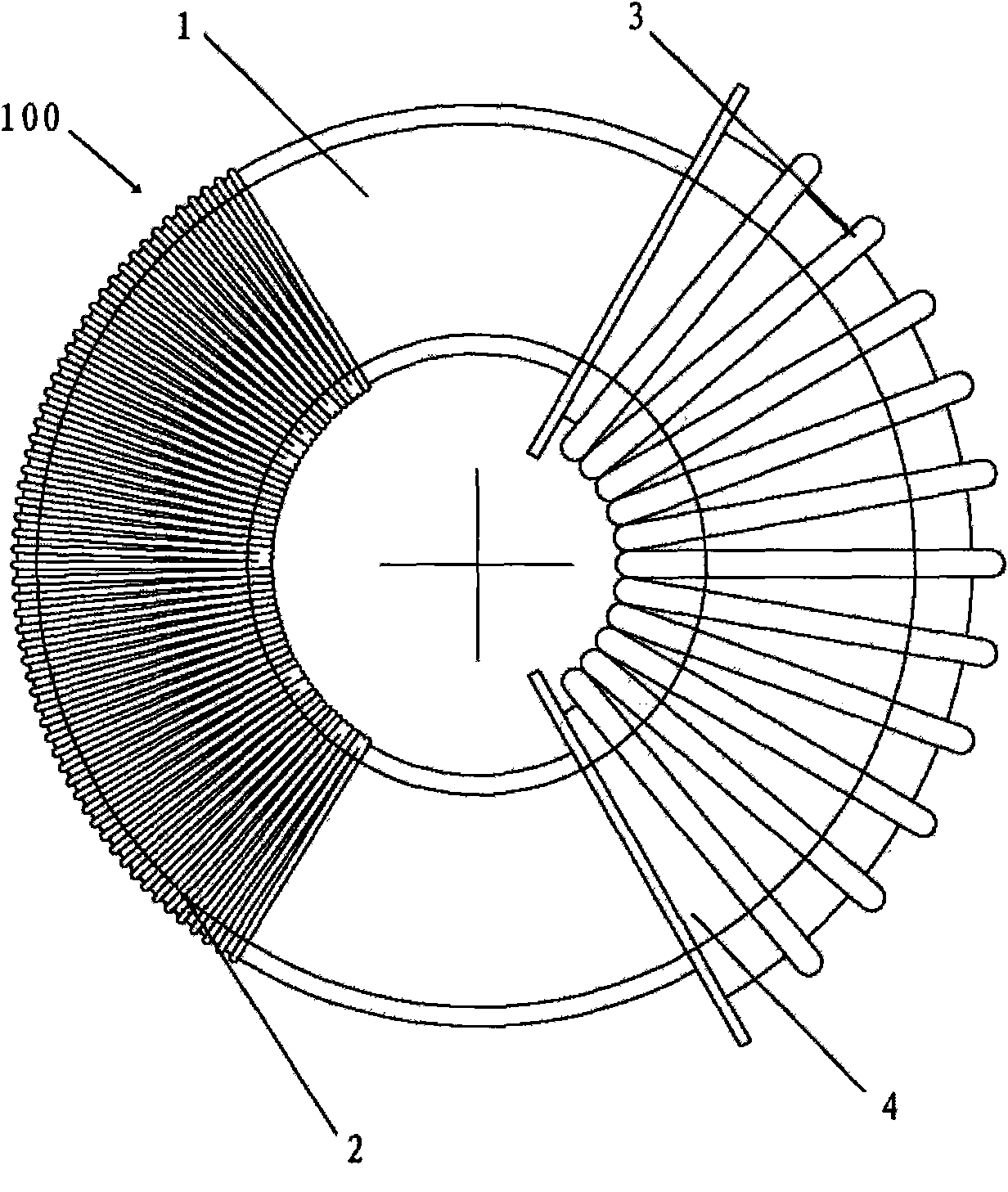

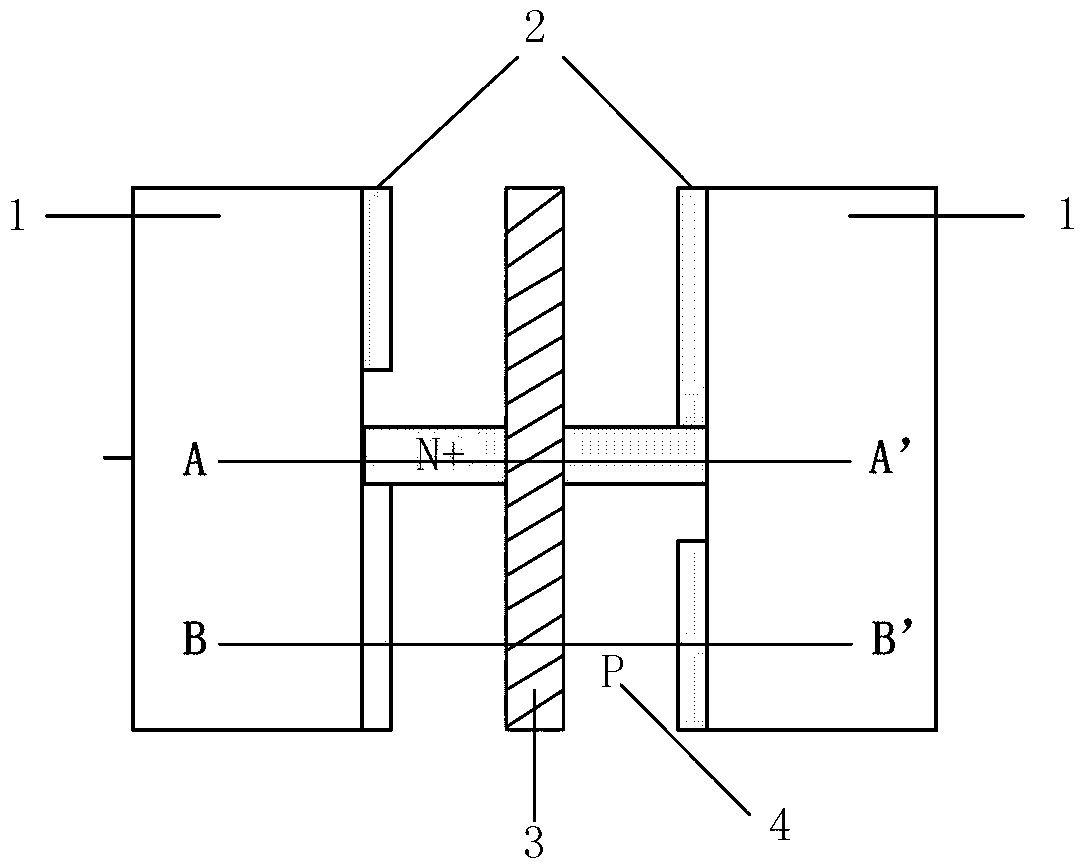

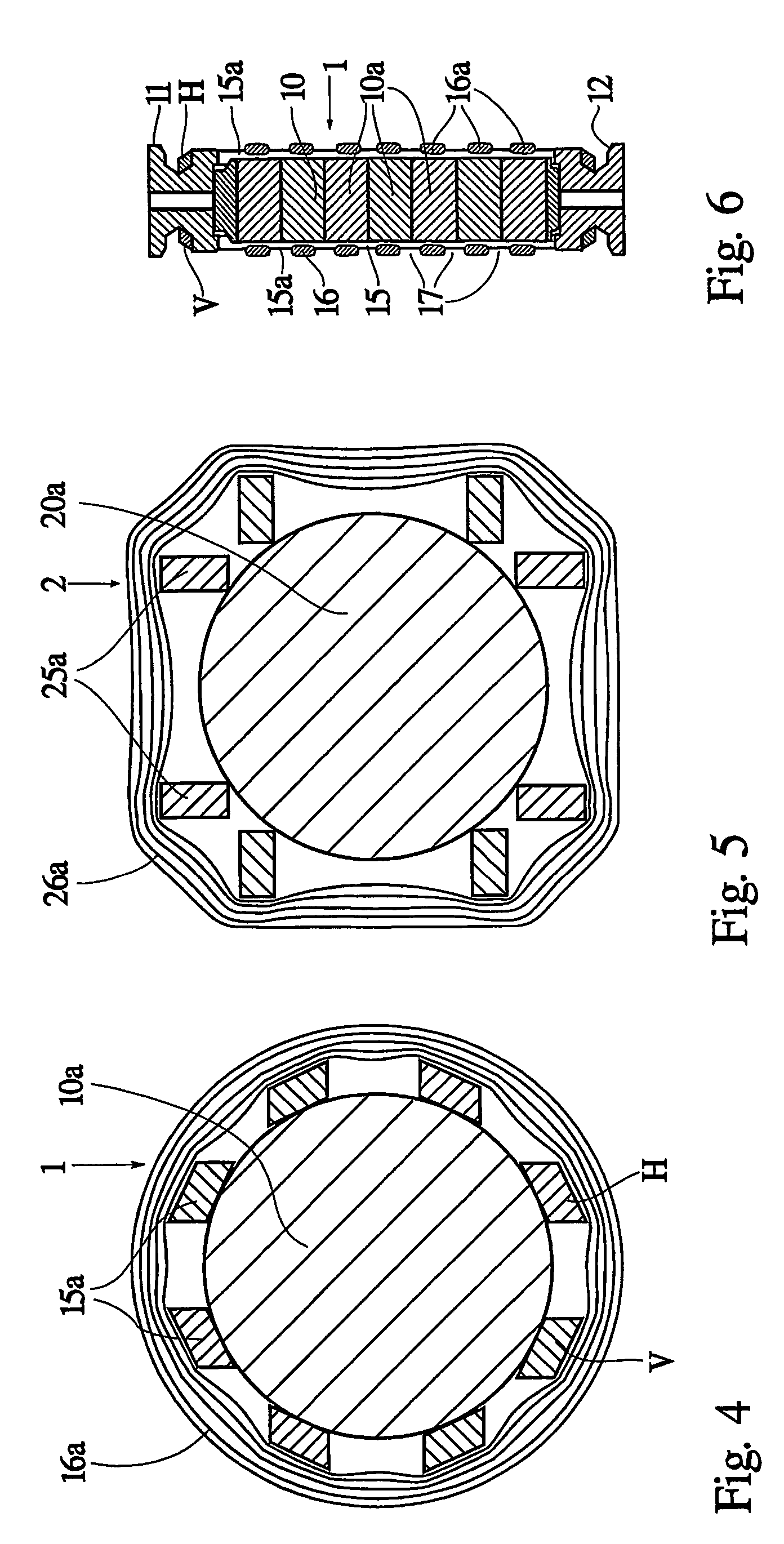

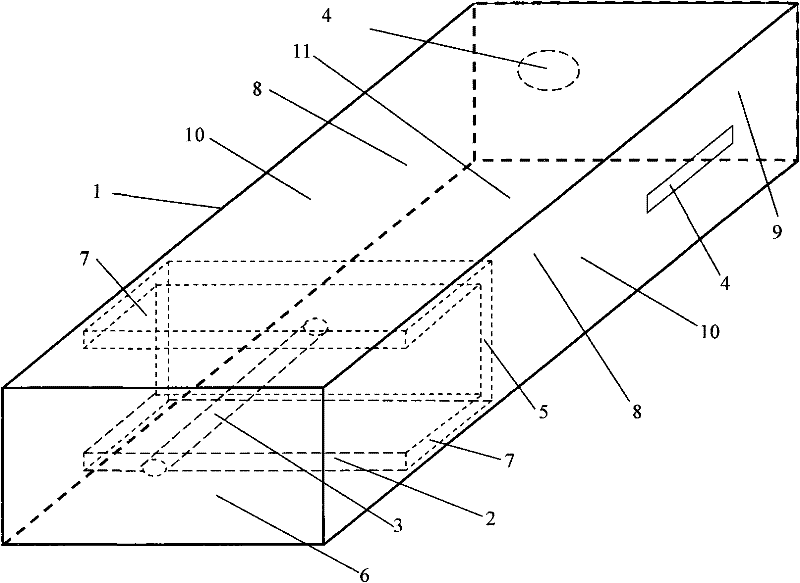

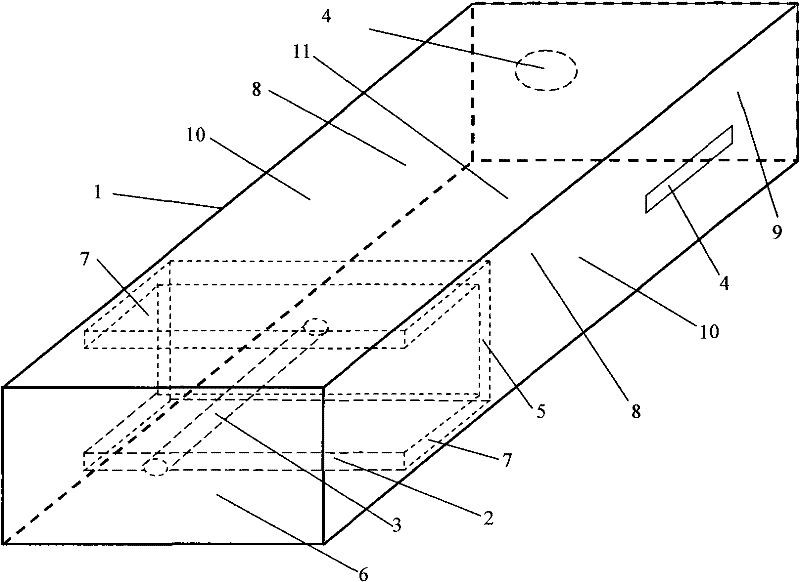

Rectangular waveguide resonant cavity of U-shaped temperature compensated short circuiter

InactiveCN101752641AGood electrical contactImprove short circuit performanceResonatorsCavity wallResonant cavity

The invention relates to a rectangular waveguide resonant cavity of a U-shaped temperature compensated short circuiter, which can remarkably reduce the influences of temperatures to the TE101mode and Tem0n mode resonant frequencies of the resonant cavity. The ultralow temperature floating U-shaped rectangular waveguide resonant cavity comprises a metal cavity (1), a U-shaped short circuiter (2), a supporting body (3) and one or more input and output coupling devices (4), wherein the U-shaped short circuiter (2) is positioned in the metal cavity (1), one head of the supporting body (3) is connected with a top surface cavity wall (6) of the metal cavity (1), the other head of the supporting body (2) is connected with a bottom surface (5) of the U-shaped short circuiter (2); the U-shaped short circuiter (2), a top surface cavity wall (9) of the metal cavity (1), two side surface cavity walls (10) and upper and lower surface cavity walls (8) of the metal cavity form a resonant space (11) of electromagnetic waves; and the input and output coupling devices (4) are positioned on the top surface cavity wall (9) or the narrow surface cavity wall (10) or the wide surface cavity wall (8) of part of the metal cavity (1) of the resonant space (11).

Owner:SOUTHEAST UNIV

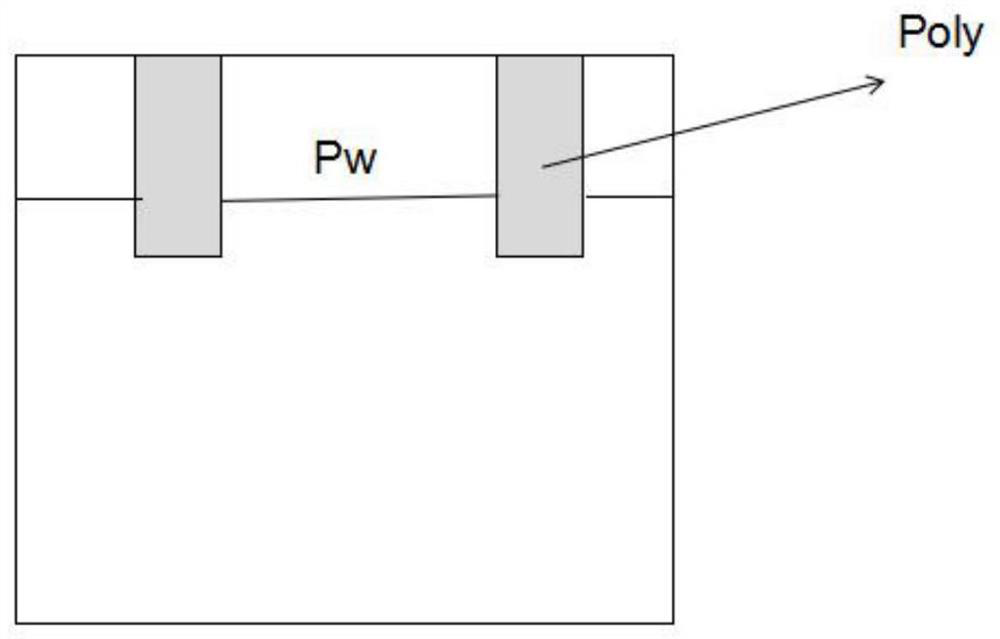

Diagonal through-flow square cell IGBT and manufacturing method thereof

ActiveCN112164652AReduce generationImprove short circuit performanceFinal product manufactureSemiconductor/solid-state device manufacturingMetallic electrodeCell region

The invention relates to the technical field of power devices, in particular to a diagonal through-flow square-cell IGBT (Insulated Gate Bipolar Transistor) and a manufacturing method thereof, aims tosolve certain problems existing in the short-circuit capability of devices in the prior art, and is technically characterized by comprising the following steps: S1, selecting a wafer substrate, depositing an initial oxide layer on the surface of the wafer substrate, opening an area needing to be etched, and forming a protection ring region; S2, removing the oxide layer to open the cell region; S3, forming a deep groove structure on the surface of the substrate; S4, forming a gate oxide layer on the surface of the substrate, depositing Polysilicon, and forming a Pw region on the surface of thesubstrate; S5, forming an Nplus region in the deep groove of the substrate; S6, forming an ILD dielectric layer on the surface of the substrate, and etching the dielectric layer to form a contact hole; S7, leading out a metal Emitter electrode; S8, forming a FieldStop layer and a Colletor layer on the back surface of the wafer substrate, and depositing a metal layer to lead out a Colletor electrode. Under the condition that conductive channels are not reduced, the distribution of the conductive channels is controlled, and at most two conductive channels are controlled to be connected, so thatthe generation of current wires is reduced.

Owner:JIANGSU HAIDONG SEMICON TECH CO LTD

SiC MOSFET device with good third quadrant performance

InactiveCN109244138AImprove third-quadrant performanceExcellent electrical propertiesSemiconductor devicesMOSFETConduction loss

The invention provides a SiC MOSFET device with good third quadrant performance, comprising an N-type substrate, an N-type epitaxial layer, a P- Body region, an N-type accumulation layer, an N + contact region, an oxide layer, a side gate, a metal electrode and a drain electrode. That SiC MOSFET device provide by the invention can improve the performance of the third quadrant of the SiC MOSFET, realize low reverse turn-on voltage and conduction loss, and avoid the problem of bipolar degradation. When the device is turned off, P-Body region can not only shield the electric field at the chamferof groove gate, but also protect the Schottky interface at the bottom of groove, which can effectively restrain the phenomena of excessive electric field at these two places, and improve the overall electrical characteristics and reliability of the device, the introduction of N-type accumulation layer and JFET pinch-off between the P-body regions effectively improves the short-circuiting capability of the device.

Owner:UNIV OF ELECTRONICS SCI & TECH OF CHINA

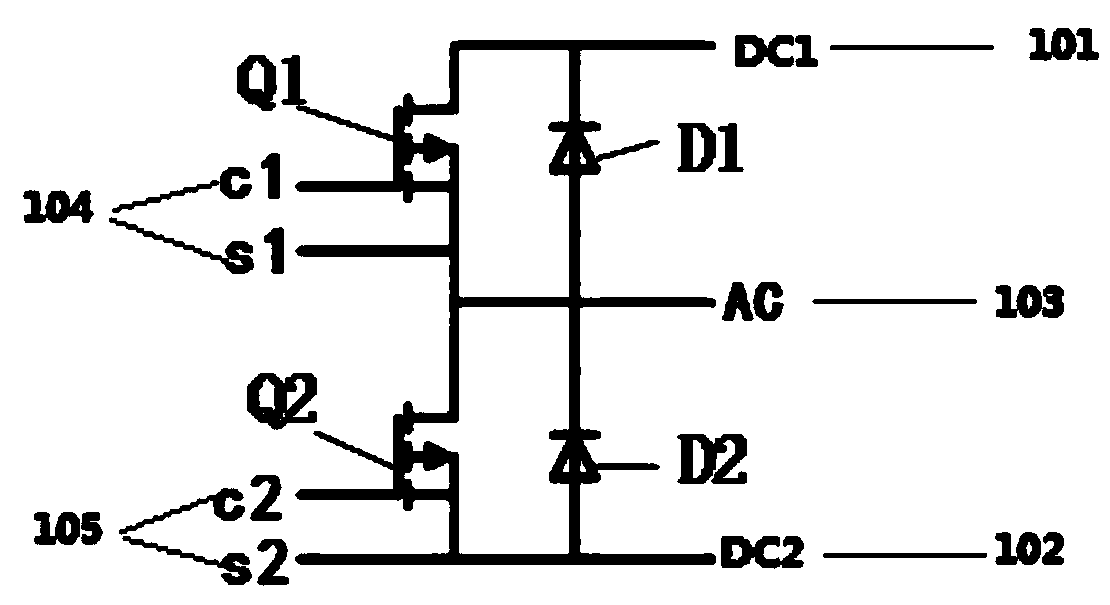

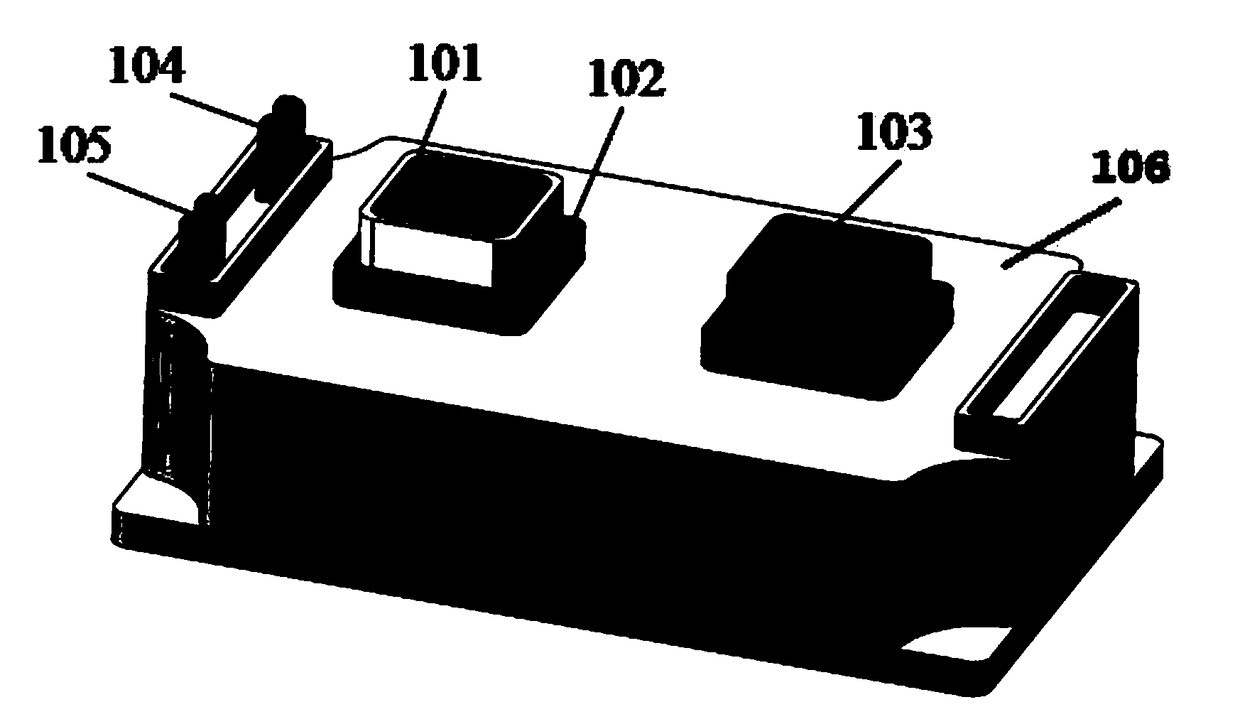

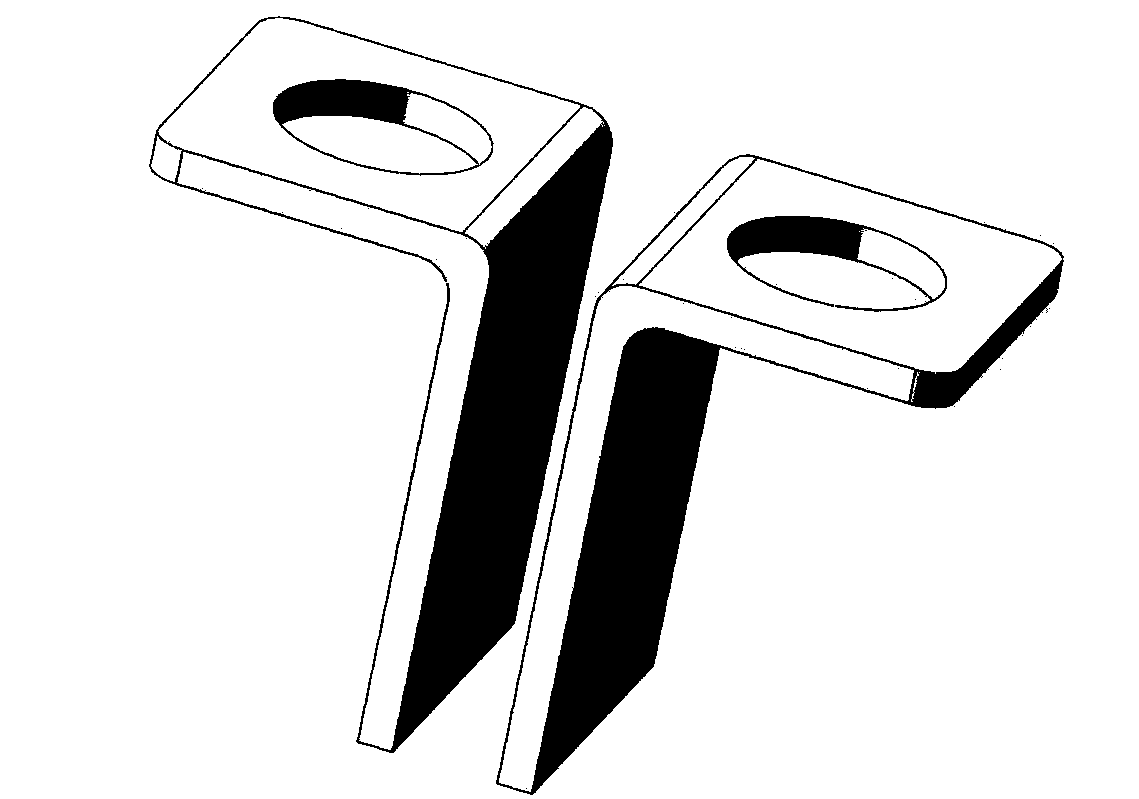

Novel power module of packaging structure

PendingCN108598074AReduce package inductanceIncrease package inductanceSemiconductor/solid-state device detailsSolid-state devicesVoltage overshootCoupling

The invention discloses a novel power module of a packaging structure. The power module comprises a first direct-current side terminal, a second direct-current side terminal, an alternating-current side terminal, a first drive terminal, a second drive terminal, a first silicon carbide metallic oxide semiconductor field-effect tube, a second silicon carbide metallic oxide semiconductor field-effecttube, a diode and a base, wherein the first direct-current side terminal, the second direct-current side terminal, the alternating-current side terminal, the first drive terminal and the second driveterminal are arranged on the upper surface of the base; and the first direct-current side terminal and the second direct-current side terminal are positioned on the same axis. According to the direct-current side terminals of coaxial structures provided by the invention, the distance between the direct-current side terminals can be reduced effectively, the coupling area is increased, the mutual inductance of the direct-current side terminals is increased, the packaging inductance of the power module is reduced, the voltage overshoot of the silicon carbide MOSFETs inside the power module in switching transient and short-circuited conditions is further reduced, and the switching loss of the power module is reduced.

Owner:NORTH CHINA ELECTRIC POWER UNIV (BAODING)

Insulated gate semiconductor device including switchable insulated gate semiconductor element

ActiveUS10003249B2Improve short circuit performanceIncrease output powerAc-dc conversion without reversalElectronic switchingPower semiconductor devicePower flow

An insulated gate semiconductor device includes an insulated gate semiconductor element, an output current detection unit, a voltage detection unit, and a heat generation amount suppression unit. The insulated gate semiconductor element on-operates by receiving a first gate voltage at a control terminal, and switches and outputs an input voltage to a load. The output current detection unit detects an output current to the load. The voltage detection unit detects an on-voltage of the insulated gate semiconductor element. The heat generation amount suppression unit sets a gate voltage to be applied to the control terminal of the insulated gate semiconductor element higher than the first gate voltage in response to the output current exceeding a rated current value and the on-voltage being lower than a first threshold voltage.

Owner:FUJI ELECTRIC CO LTD

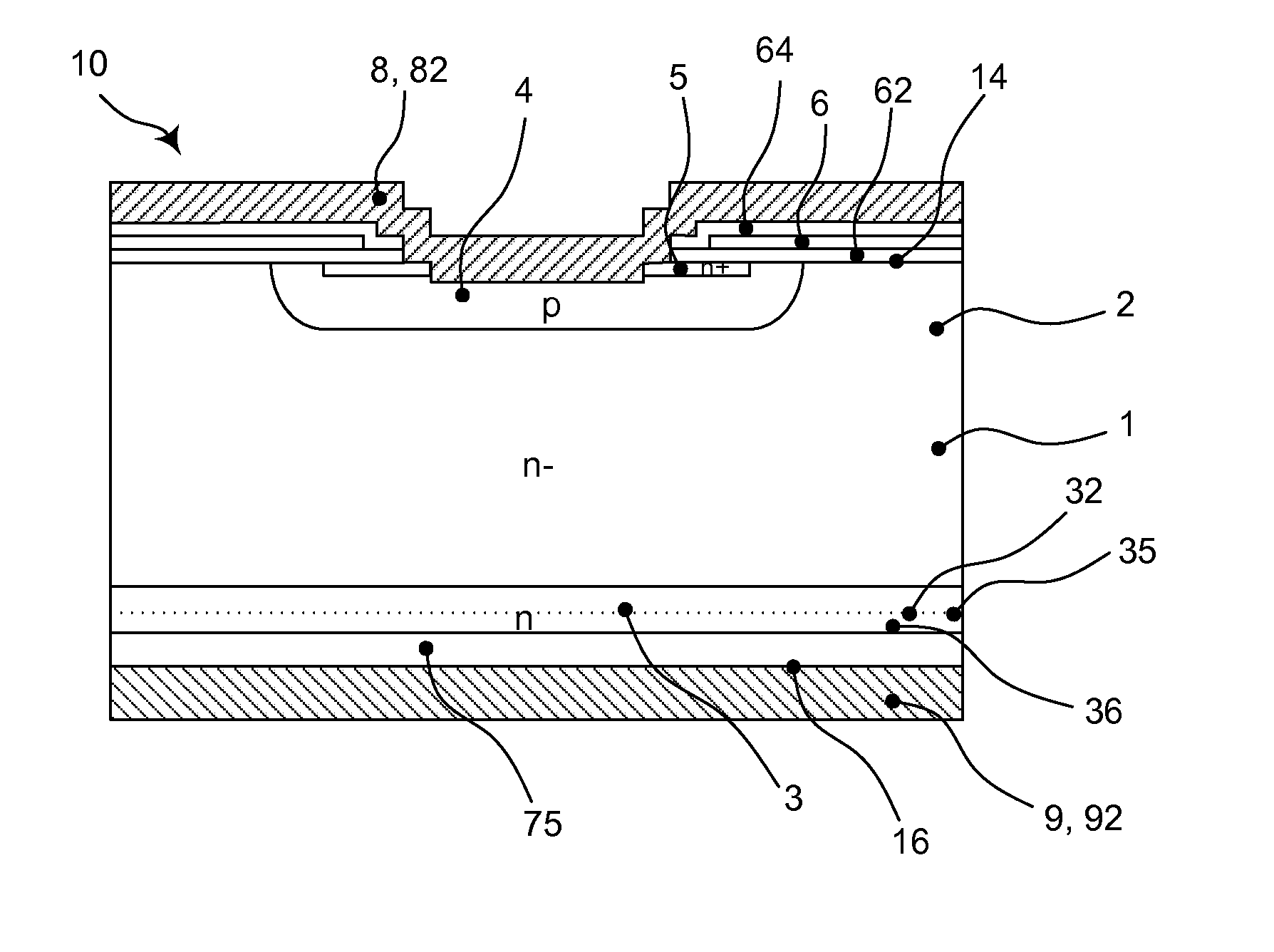

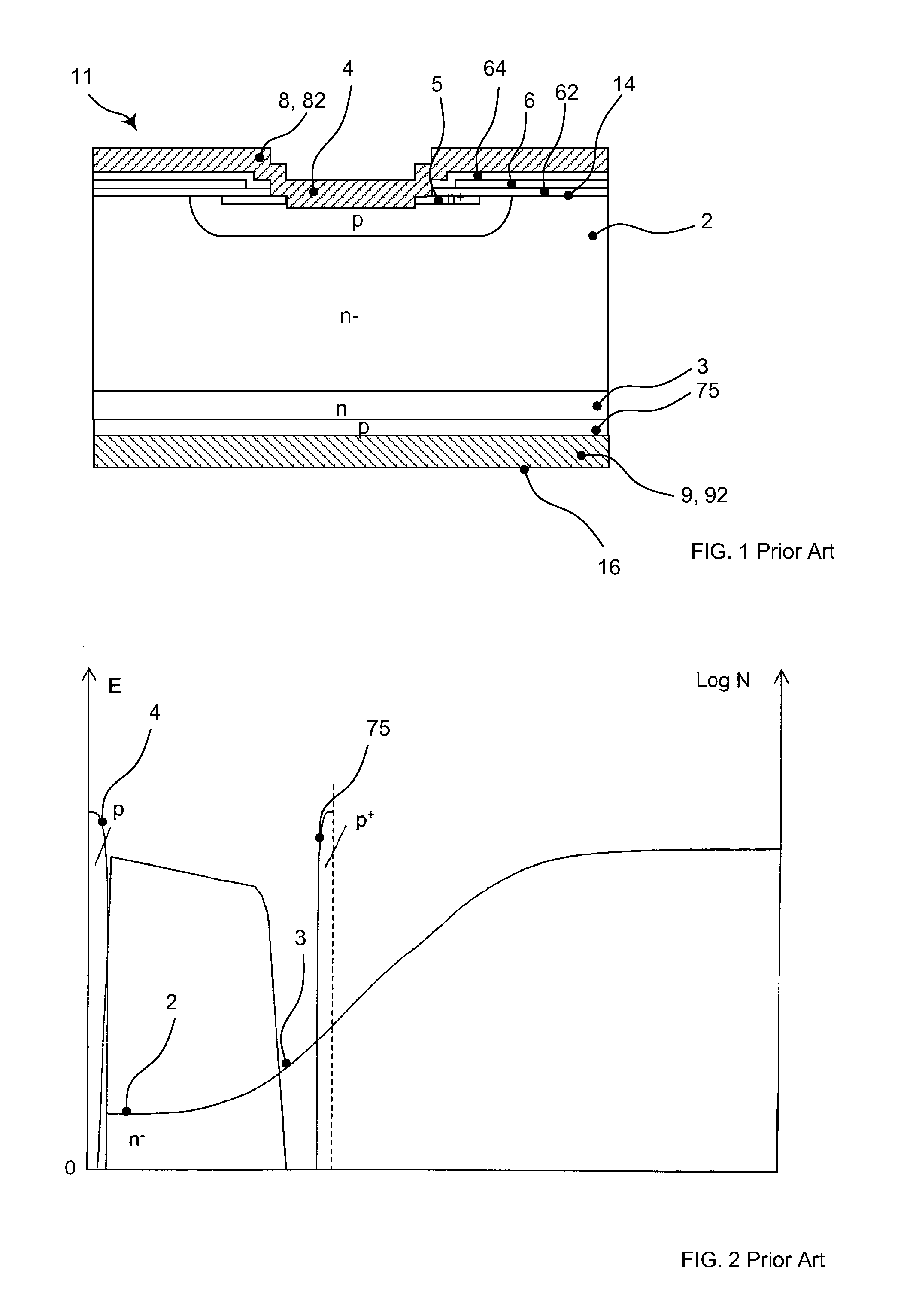

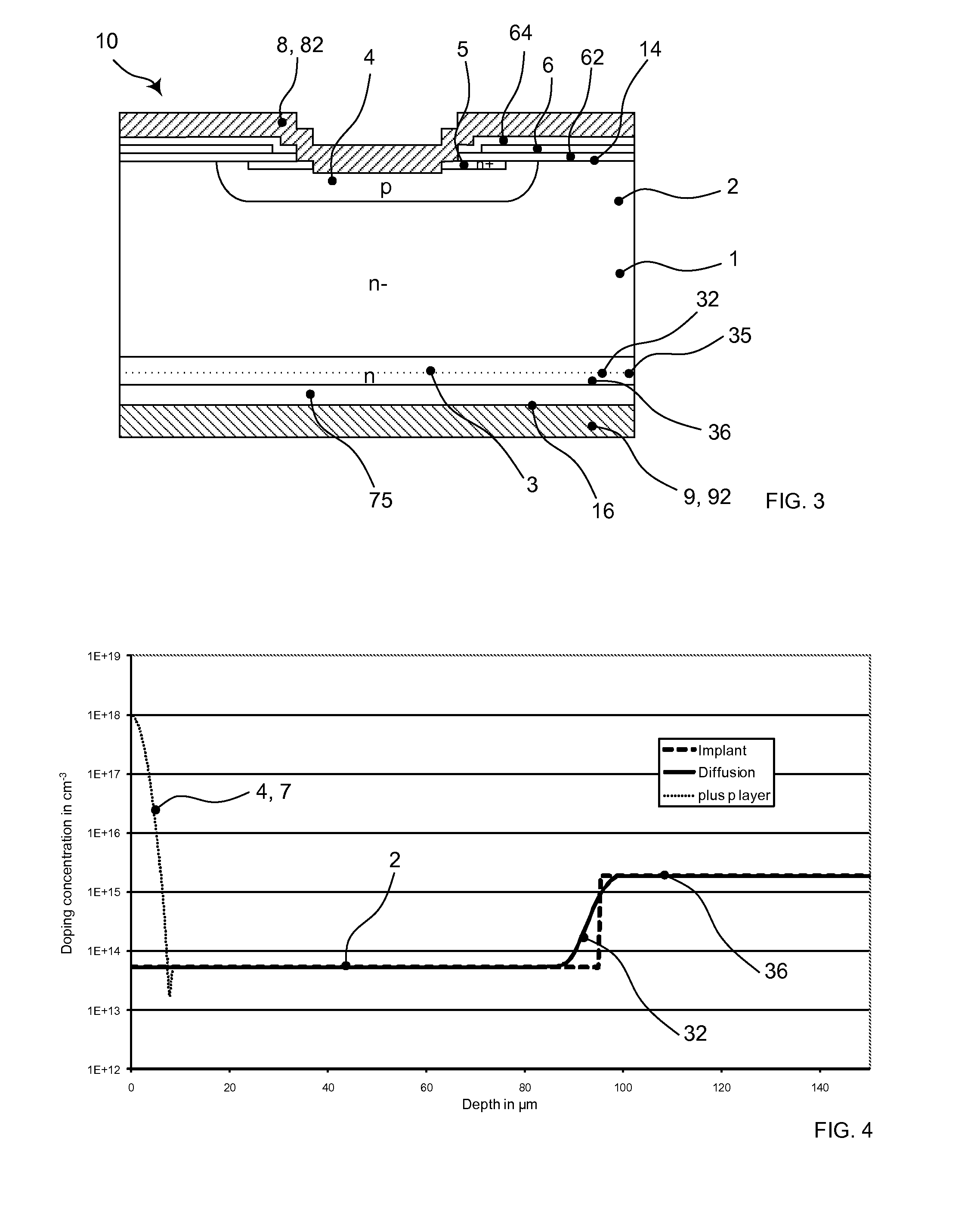

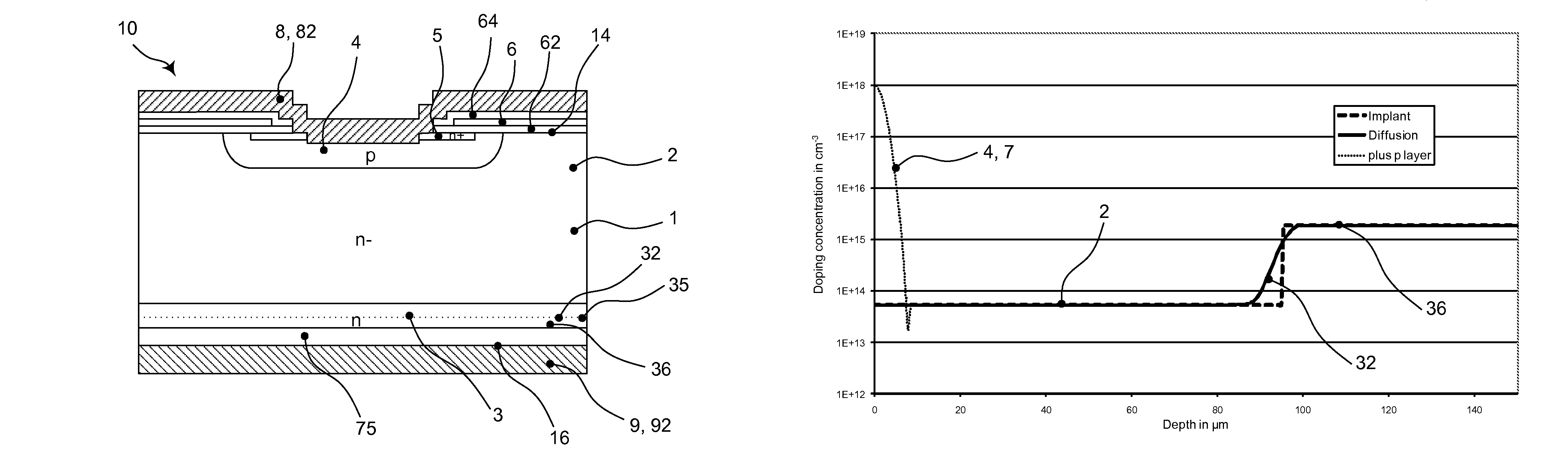

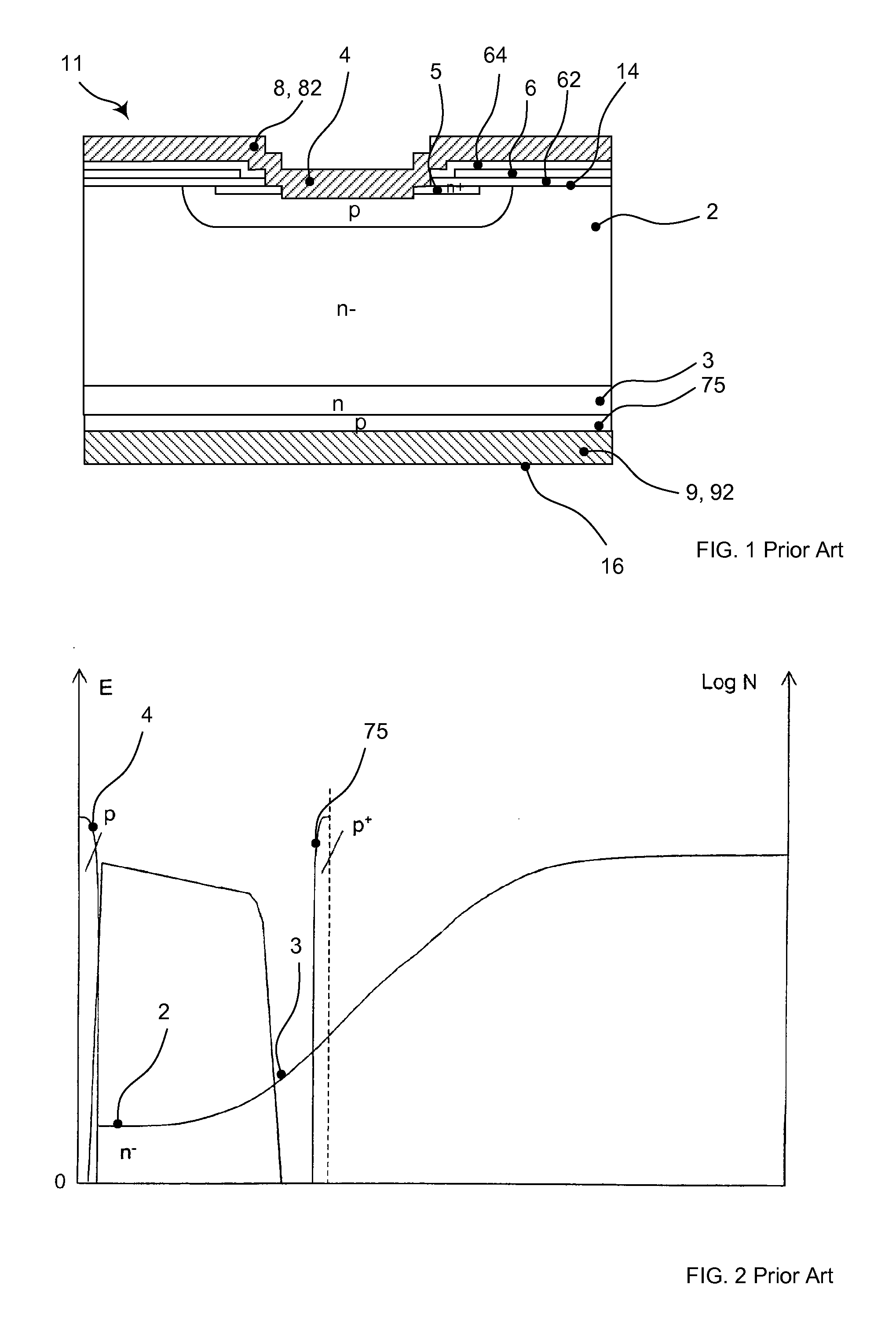

Bipolar punch-through semiconductor device and method for manufacturing such a semiconductor device

ActiveCN103518252AProcess step controlImprove controllabilitySemiconductor/solid-state device manufacturingSemiconductor devicesDevice formEngineering

A method for manufacturing a bipolar punch-through semiconductor device is provided, wherein the following steps are performed (a)providing a first high-doped wafer (10) having a first and a second side (11, 2), which is doped at least on the first side (11) with first particles of the first conductivity type, (b)providing a second low-doped wafer (20) of the first conductivity type having a third and a fourth side, (c)creating a wafer laminate having a wafer laminate thickness by bonding the first wafer (10) on its first side (11) and the second wafer (20) on its fourth side (22) together, (d)performing afterwards a diffusion step,thereby creating a diffused inter- space layer (31), which comprises first sided parts of the first wafer (10) and fourth sided parts of the second wafer (20), wherein that part of the second wafer having unamended doping concentration in the finalized device forms a drift layer (2), (e)afterwards creating at least one layer of the second conductivity type on the third side (21), (f)afterwards reducing the wafer laminate thickness from the second side (12) within the inter-space layer (31) and within the second wafer (20) such that a buffer layer(3) is created, which comprises the remaining part of the wafer laminate on the fourth side (22) having higher doping concentration than the drift layer (2).

Owner:HITACHI ENERGY SWITZERLAND AG

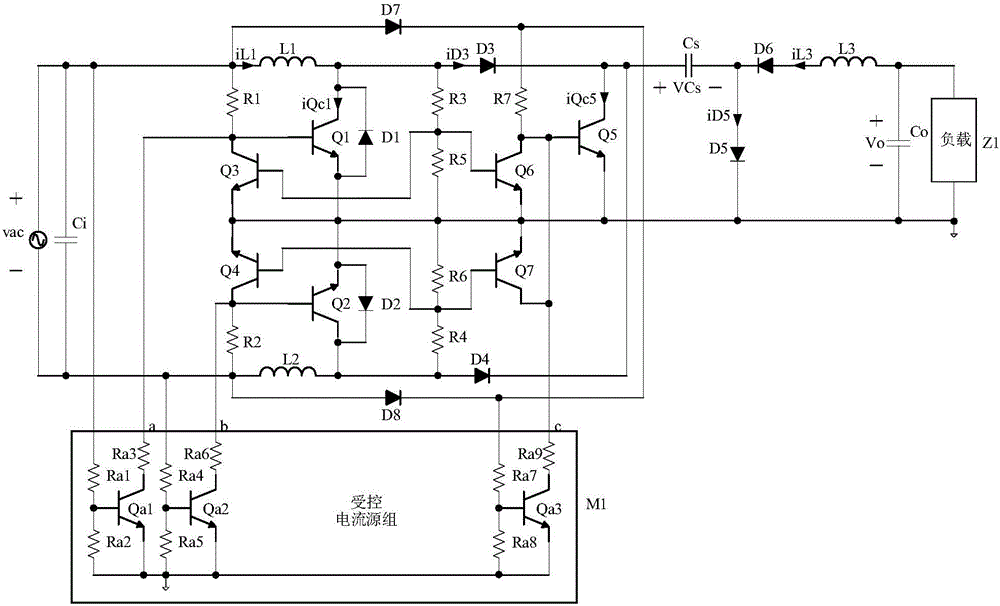

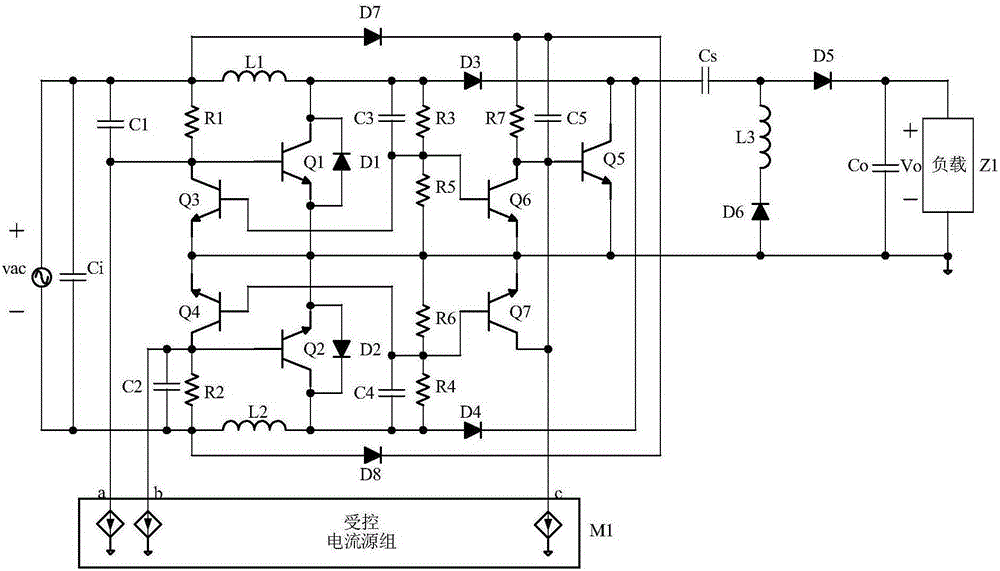

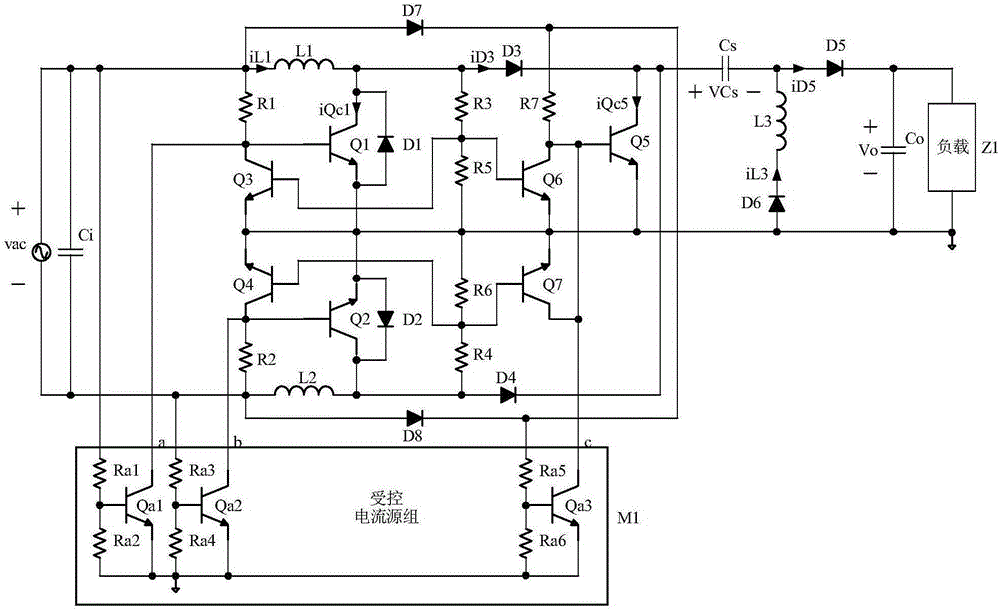

Self-excited type BJT type bridgeless Sepic PFC rectifying circuit

A self-excited type BJT type bridgeless Sepic PFC rectifying circuit is disclosed. The rectifying circuit comprises an input capacitor Ci, an NPN type BJT tube Q1, an NPN type BJT tube Q2, an NPN type BJT tube Q3, an NPN type BJT tube Q4, an NPN type BJT tube Q5, an NPN type BJT tube Q6, an NPN type BJT tube Q7, a diode D1, a diode D2, a diode D3, a diode D4, a diode D5, a diode D6, a diode D7, a diode D8, an inductor L1, an inductor L2, an inductor L3, a capacitor Cs, an output capacitor Co, a resistor R1, a resistor R2, a resistor R3, a resistor R4, a resistor R5, a resistor R6, a resistor R7 and a controlled power supply source group M1. The invention provides the self-excited type BJT type bridgeless Sepic PFC rectifying circuit with simplified driving circuit structure, higher driving efficiency and good self-starting performance.

Owner:SHANGHAI XINLONG SEMICON TECH CO LTD

High-impedance combined-type transformer

ActiveCN102543406BImprove short circuit performanceEasy to splitTransformers/inductances coils/windings/connectionsFixed transformersLow voltageFuel tank

The invention provides a high-impedance combined-type transformer which comprises three single-phase transformers and three transformer oil tanks, wherein the three single-phase transformers are respectively arranged in the three transformer oil tanks; the three single-phase transformers are combined to form a three-phase transformer; in the three-phase transformer, each phase of transformer comprises a low-voltage winding, a medium-voltage winding and a high-voltage winding; a reactor is arranged in each transformer oil tank; and the low-voltage winding of each phase of transformer is connected in series with the reactor of the transformer oil tank where the phase transformer is positioned. The high-impedance combined-type transformer can be in high-impedance operation and in split-type transportation, and has high performance-price ratio.

Owner:TBEA HENGYANG TRANSFORMERS

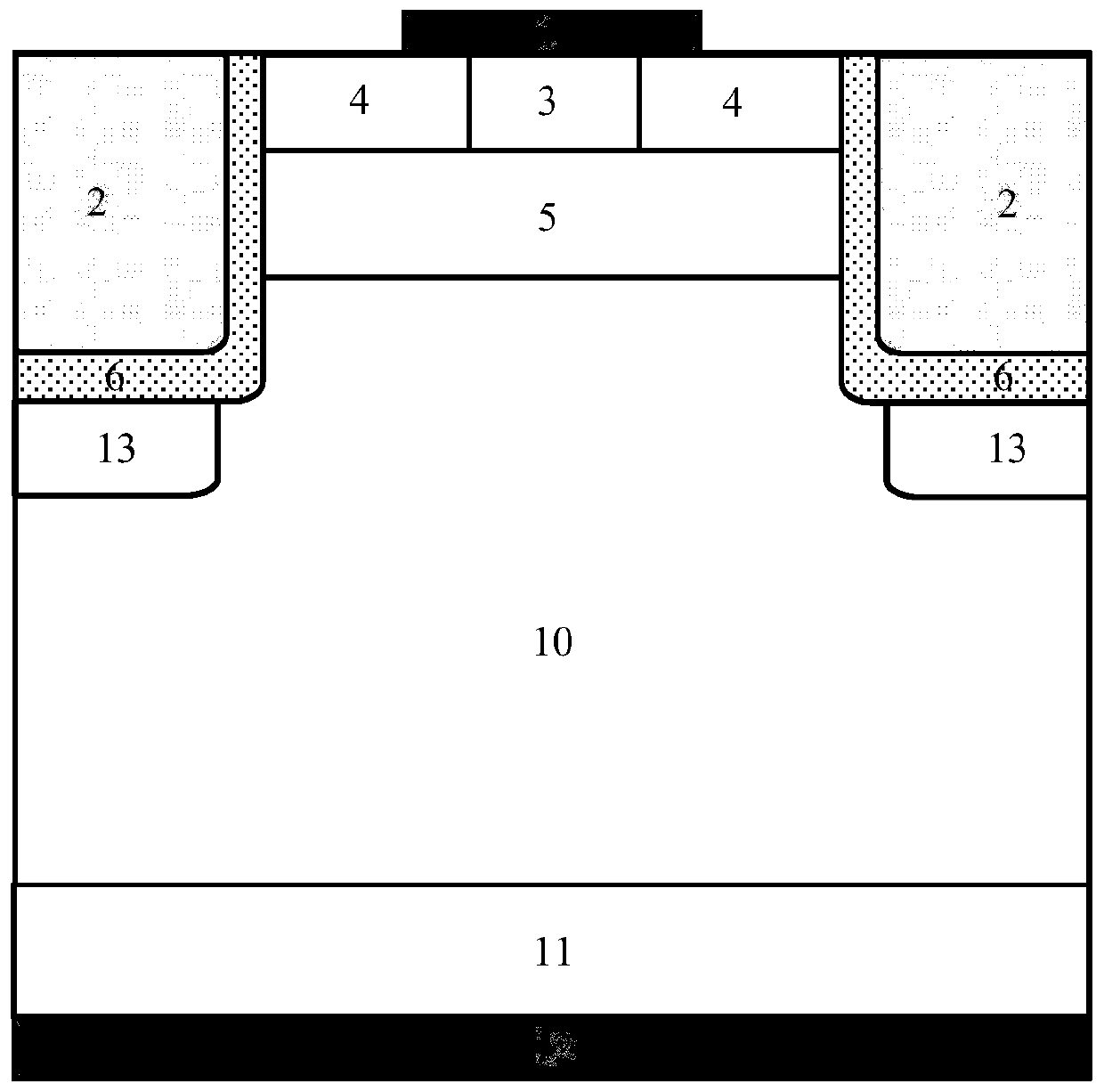

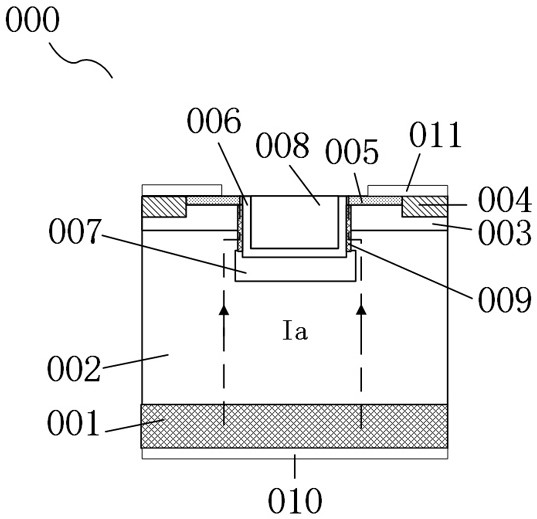

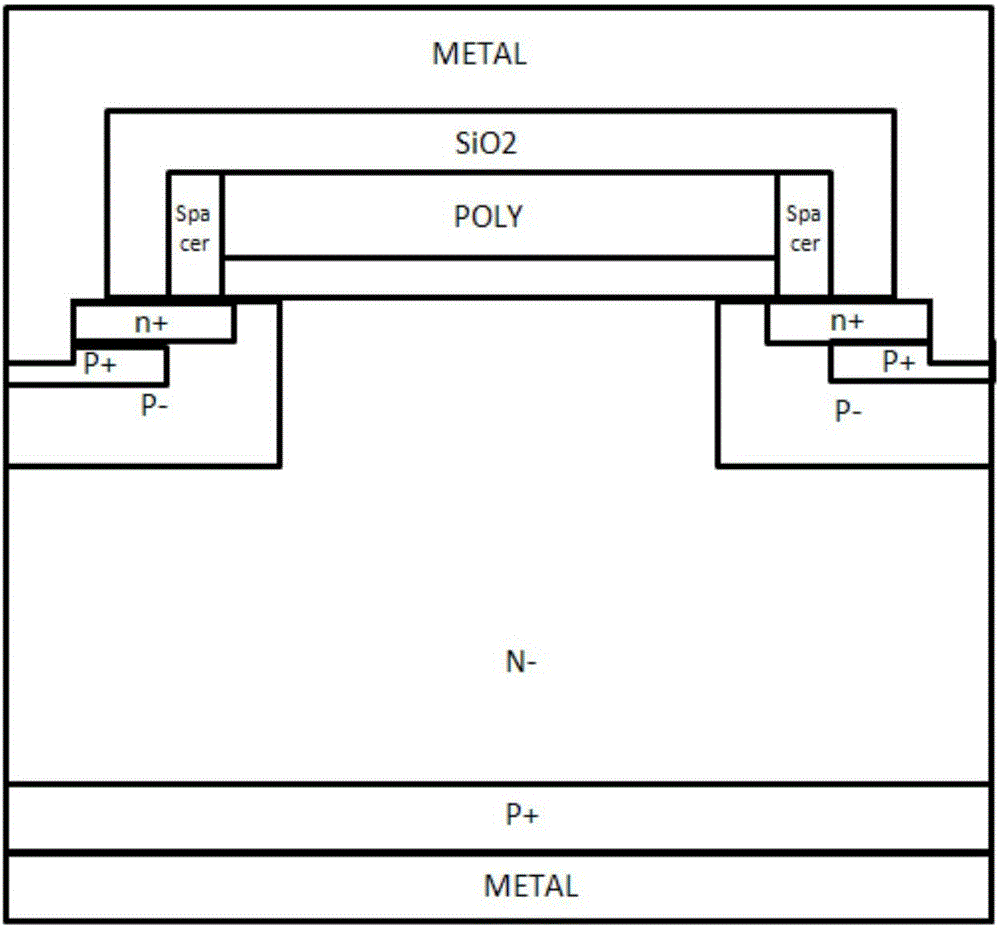

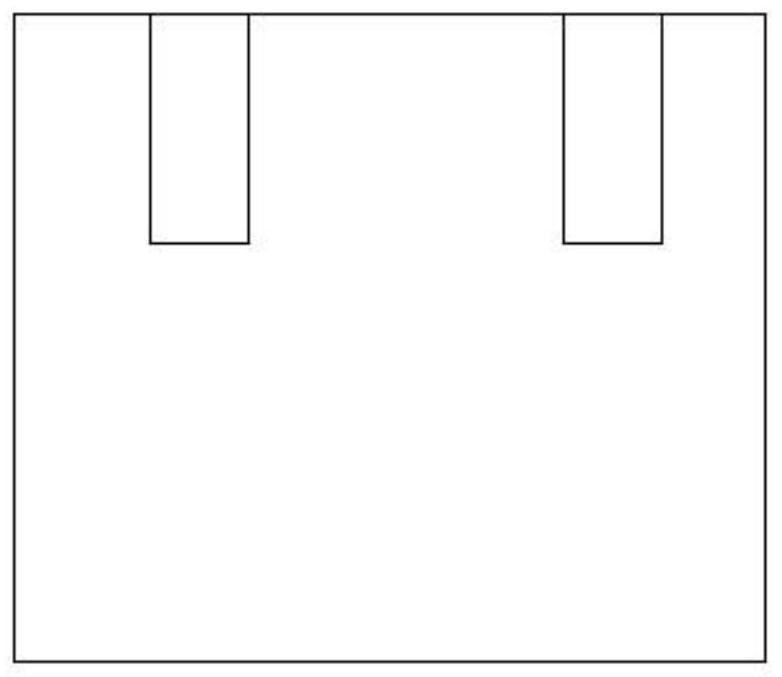

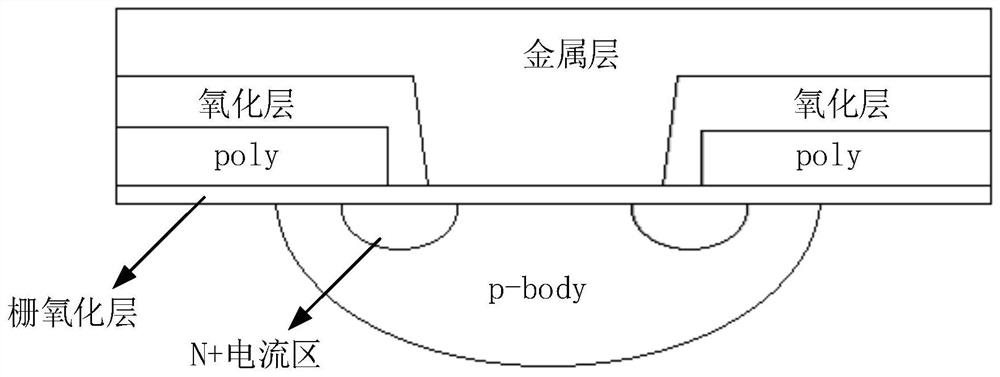

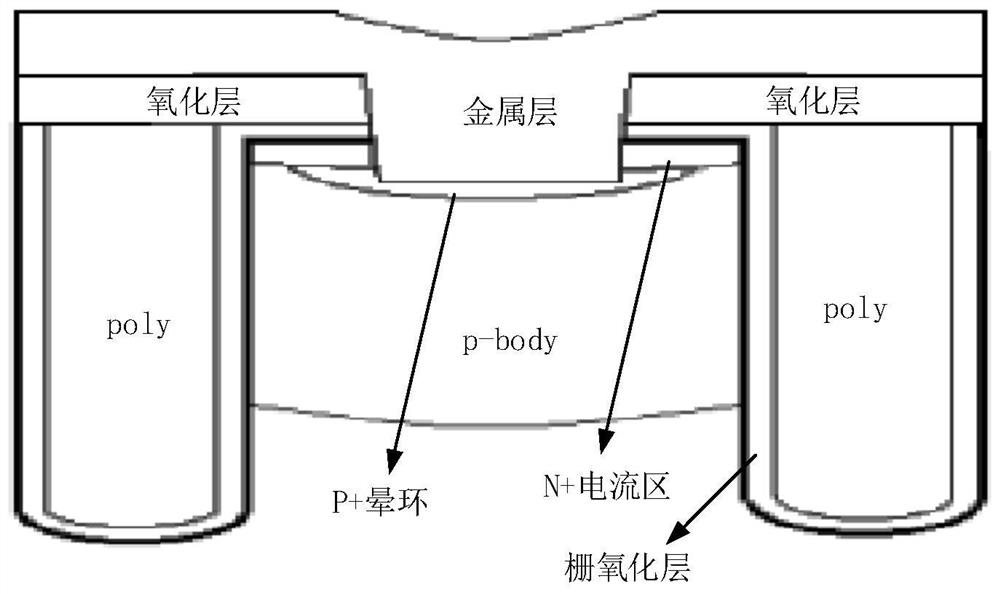

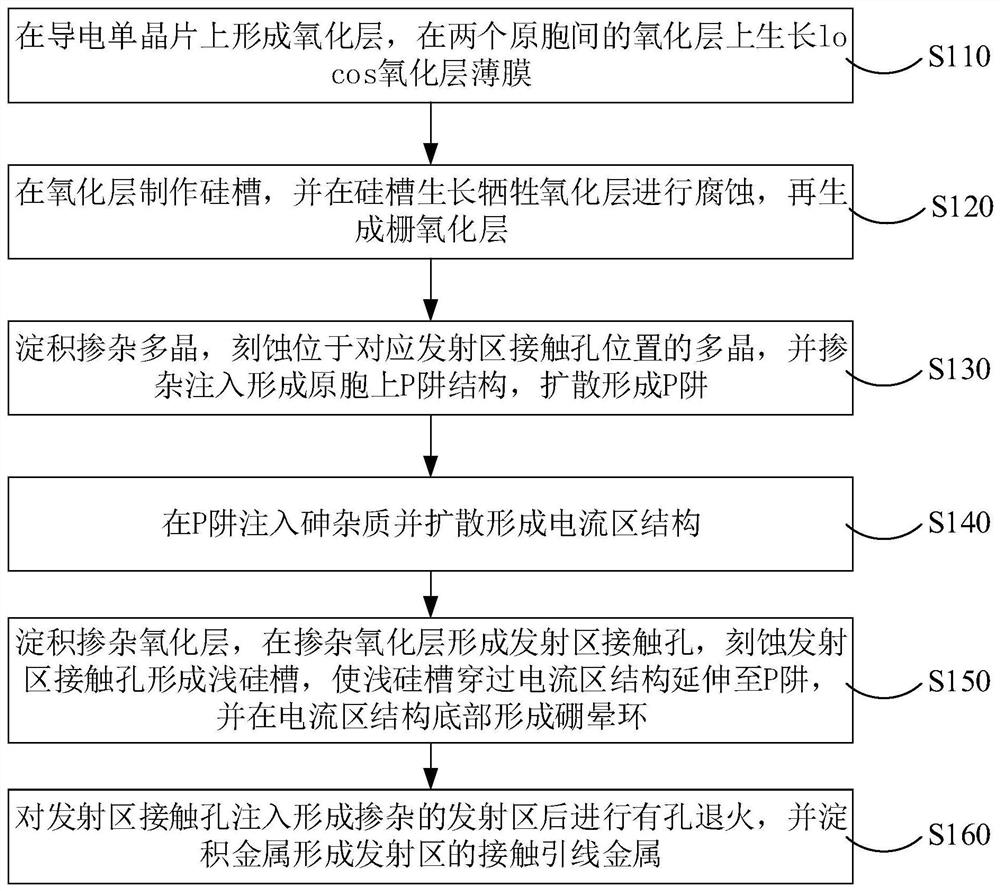

Groove type IGBT primitive cell structure manufacturing method and groove type IGBT primitive cell structure

PendingCN113193039AImprove short circuit performanceIncrease spacingSemiconductor/solid-state device manufacturingSemiconductor devicesChemical physicsLOCOS

The invention relates to a trench-type IGBT primitive cell structure manufacturing method and a trench-type IGBT primitive cell structure, and the method comprises the steps: forming an oxide layer on a conductive single crystal wafer, and growing a locos oxide layer film on the oxide layer between two primitive cells; manufacturing a silicon groove by using the deposited oxide layer as a hard mask, growing a sacrificial oxide layer in the silicon groove for corrosion, and generating a gate oxide layer; depositing doped polycrystals, etching the polycrystals at the positions corresponding to the emitter region contact holes, doping and injecting to form a P well structure on the primitive cell, and diffusing to form a P well; injecting the arsenic impurities into the P well and diffusing the arsenic impurities to form a current region structure; depositing a doped oxide layer, forming an emitter region contact hole in the doped oxide layer, etching the emitter region contact hole to form a shallow silicon groove, enabling the shallow silicon groove to penetrate through the current region structure to extend to the P well, and injecting boron ions at the bottom of the current region structure for doping to form a boron halo ring; carrying out hole annealing after a halo ring is injected into the contact hole of the emitter region, and depositing the metal to form contact lead metal of the emitter region.

Owner:深圳深爱半导体股份有限公司

Bipolar punch-through semiconductor device and method for manufacturing such a semiconductor device

ActiveUS9006041B2Easy to adaptSignificant processingTransistorSemiconductor/solid-state device manufacturingSemiconductorDoping profile

A method for manufacturing a bipolar punch-through semiconductor device is disclosed, which includes providing a wafer having a first and a second side, wherein on the first side a high-doped layer of the first conductivity type having constant high doping concentration is arranged; epitaxially growing a low-doped layer of the first conductivity type on the first side; performing a diffusion step by which a diffused inter-space region is created at the inter-space of the layers; creating at least one layer of the second conductivity type on the first side; and reducing the wafer thickness within the high-doped layer on the second side so that a buffer layer is created, which can include the inter-space region and the remaining part of the high-doped layer, wherein the doping profile of the buffer layer decreases steadily from the doping concentration of the high-doped region to the doping concentration of the drift layer.

Owner:HITACHI ENERGY LTD

IGBT (Insulated Gate Bipolar Translator) chip with novel structure and preparation method

PendingCN114566539AAvoid gatheringReduce input capacitanceTransistorSolid-state devicesMetallic electrodeEngineering

The invention relates to an IGBT (Insulated Gate Bipolar Translator) chip with a novel structure and a preparation method. The IGBT chip with the novel structure comprises a plurality of cellular structures, each single cellular structure sequentially comprises a chip surface area, a chip internal area and a chip back area from top to bottom; wherein the chip surface region comprises an emitter region and an oxide layer; the internal region of the chip comprises a polycrystalline silicon layer, a gate oxide layer, an N + emitter region, a P + region, a P base region, a P floating region, an N-drift region and an N-buffer region. The chip back area comprises a P + collector and a back metal electrode; a single cellular structure is an axisymmetric structure; and a plurality of shunting holes which are arranged at equal intervals are etched in the central area of the oxide layer. According to the invention, a plurality of shunt holes arranged at equal intervals are etched in the central area of the oxide layer, a hole channel is provided above the P floating region, hole carriers are prevented from gathering in the P floating region, and the short-circuit capability of the IGBT is improved under the condition of ensuring the stability of breakdown voltage.

Owner:上海睿驱微电子科技有限公司

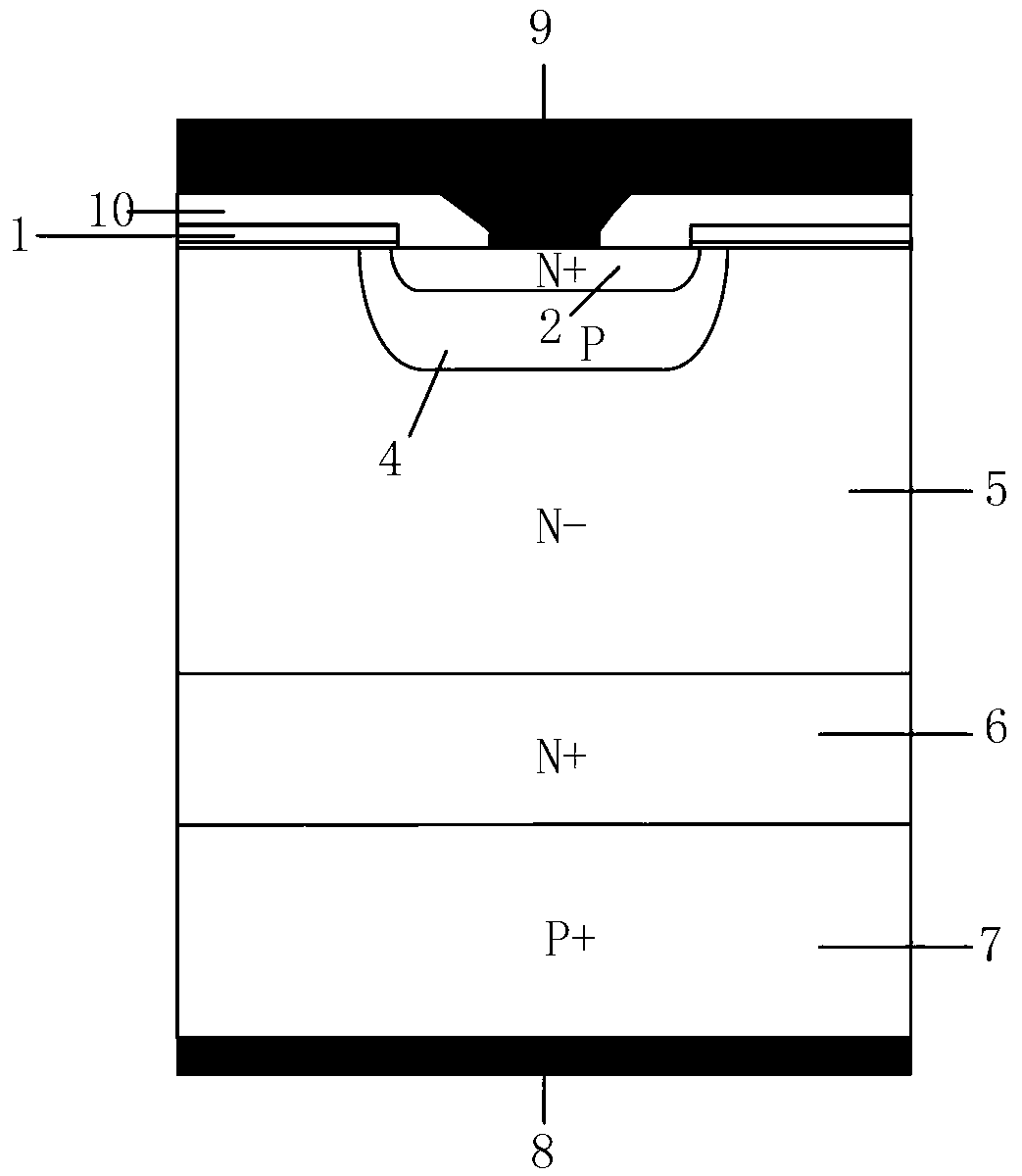

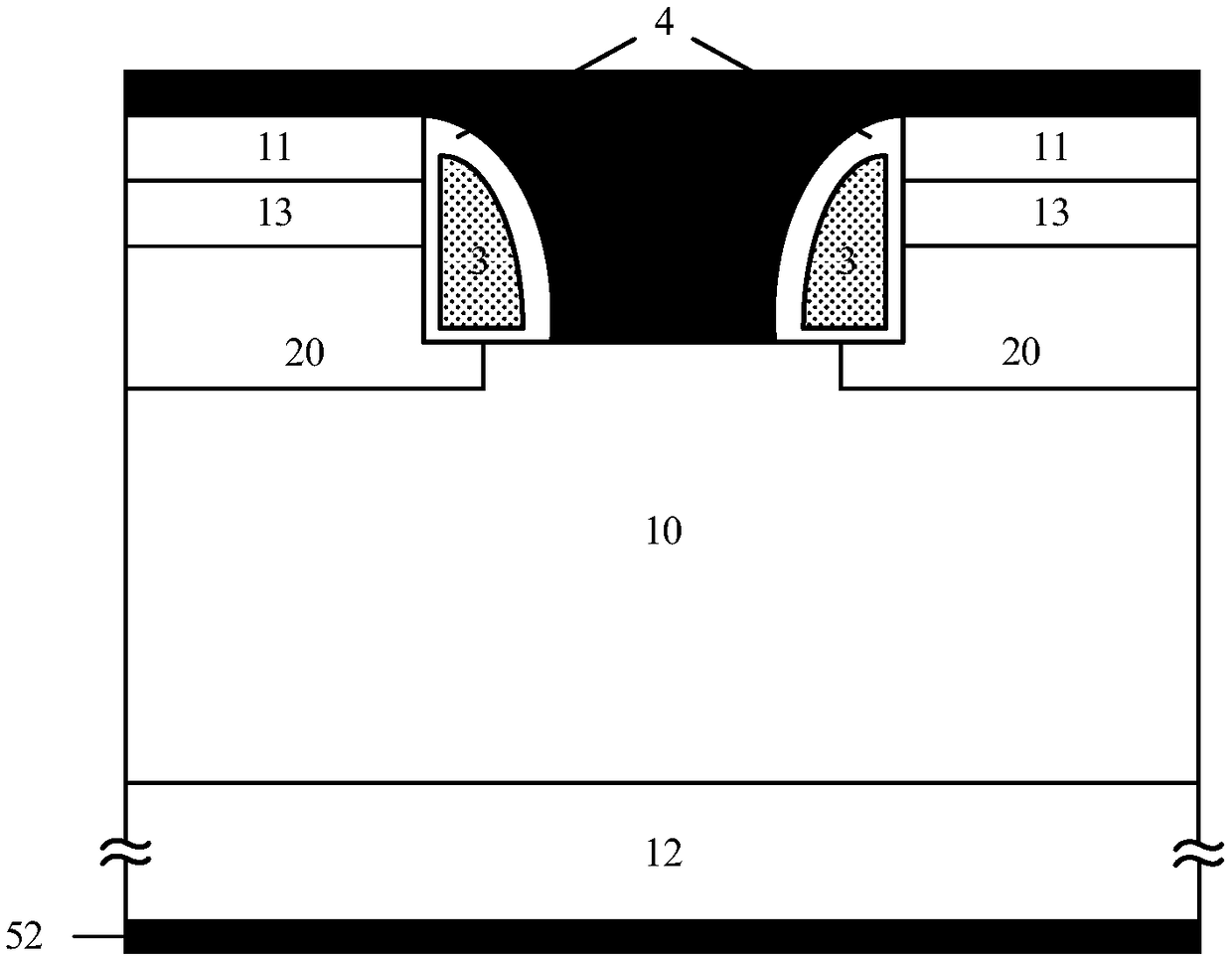

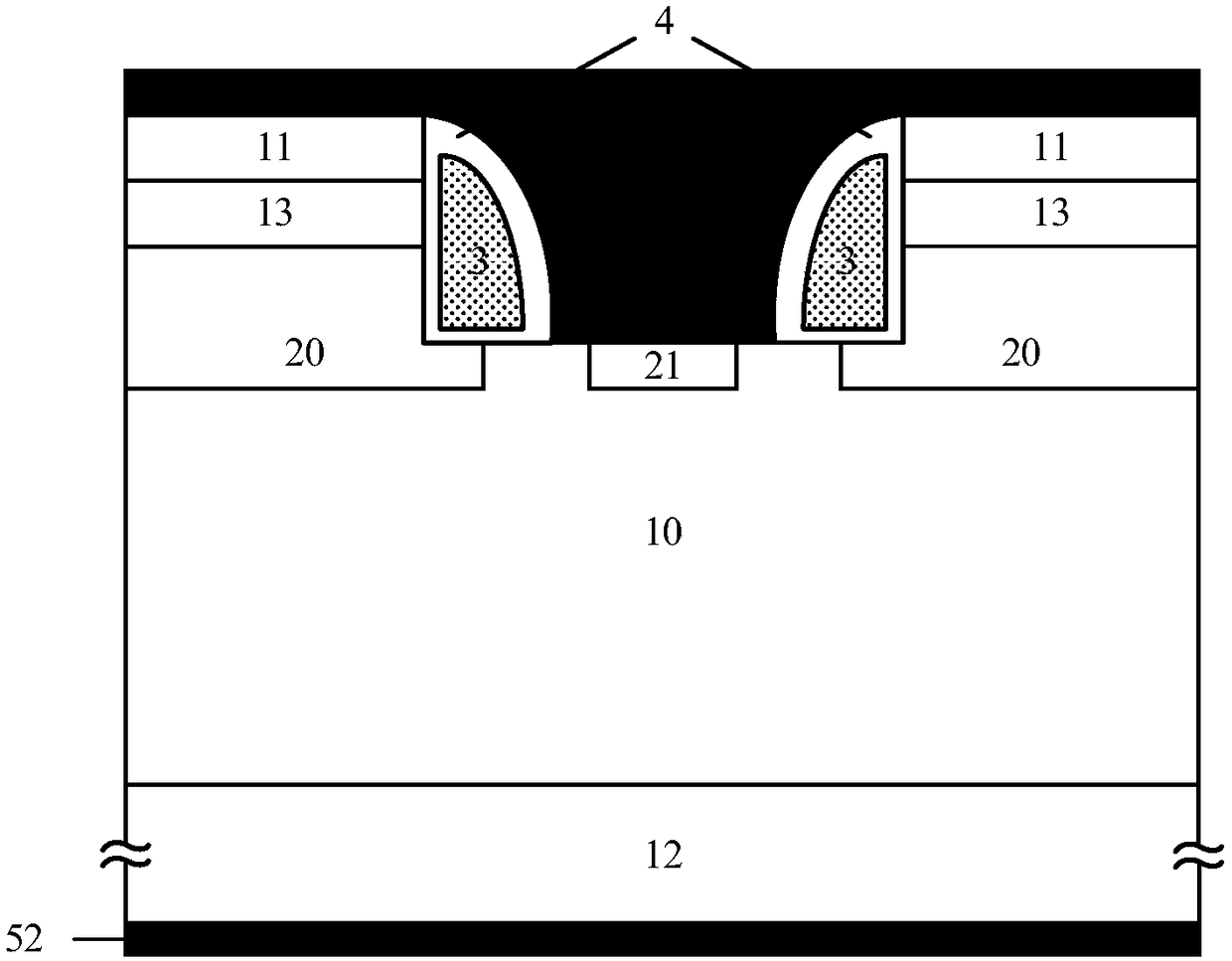

Semiconductor device

ActiveUS20200194574A1Improve short circuit performanceSolid-state devicesSemiconductor devicesDevice materialEngineering physics

A semiconductor device includes: a second semiconductor layer in a surface layer of a first semiconductor layer; a third semiconductor layer in a surface layer of the second semiconductor layer; a first trench penetrating the second semiconductor layer and the third semiconductor layer to reach an inside of the first semiconductor layer; a second trench penetrating, from an upper surface of the first semiconductor layer, the third semiconductor layer to reach an inside of the second semiconductor layer, and a fourth semiconductor layer in contact with a bottom of the second trench.

Owner:MITSUBISHI ELECTRIC CORP

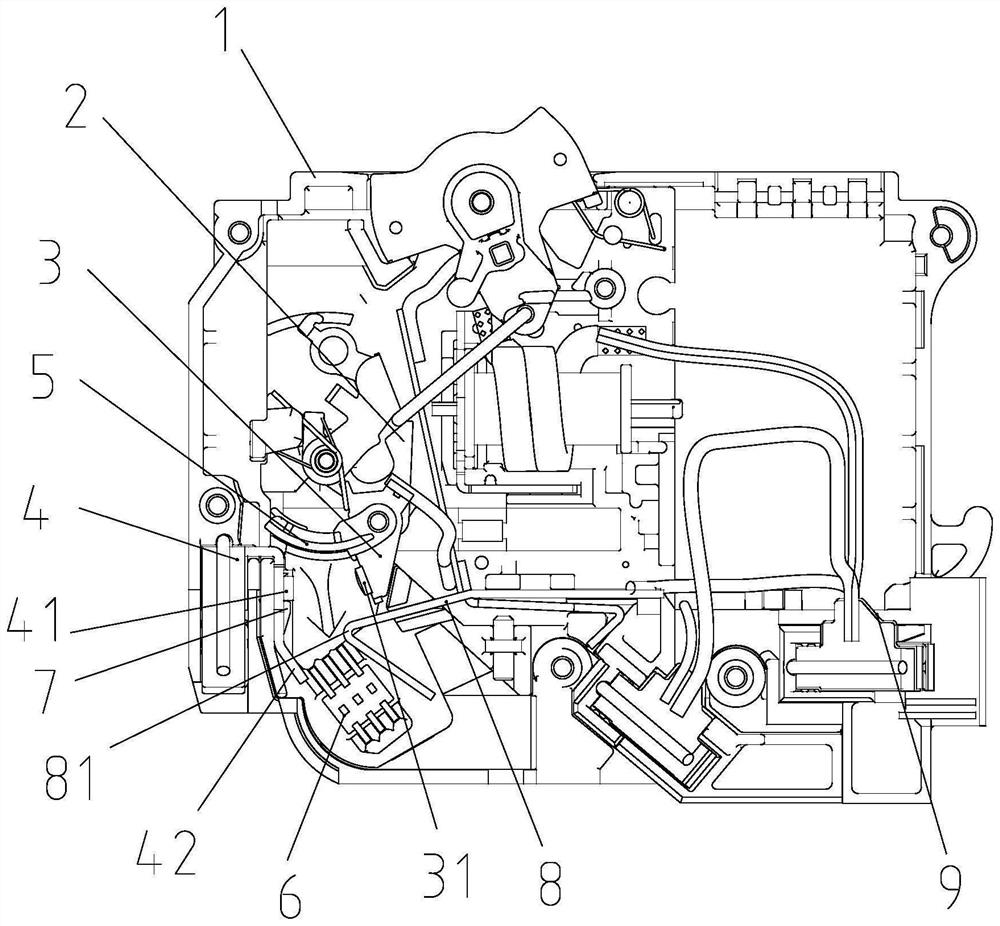

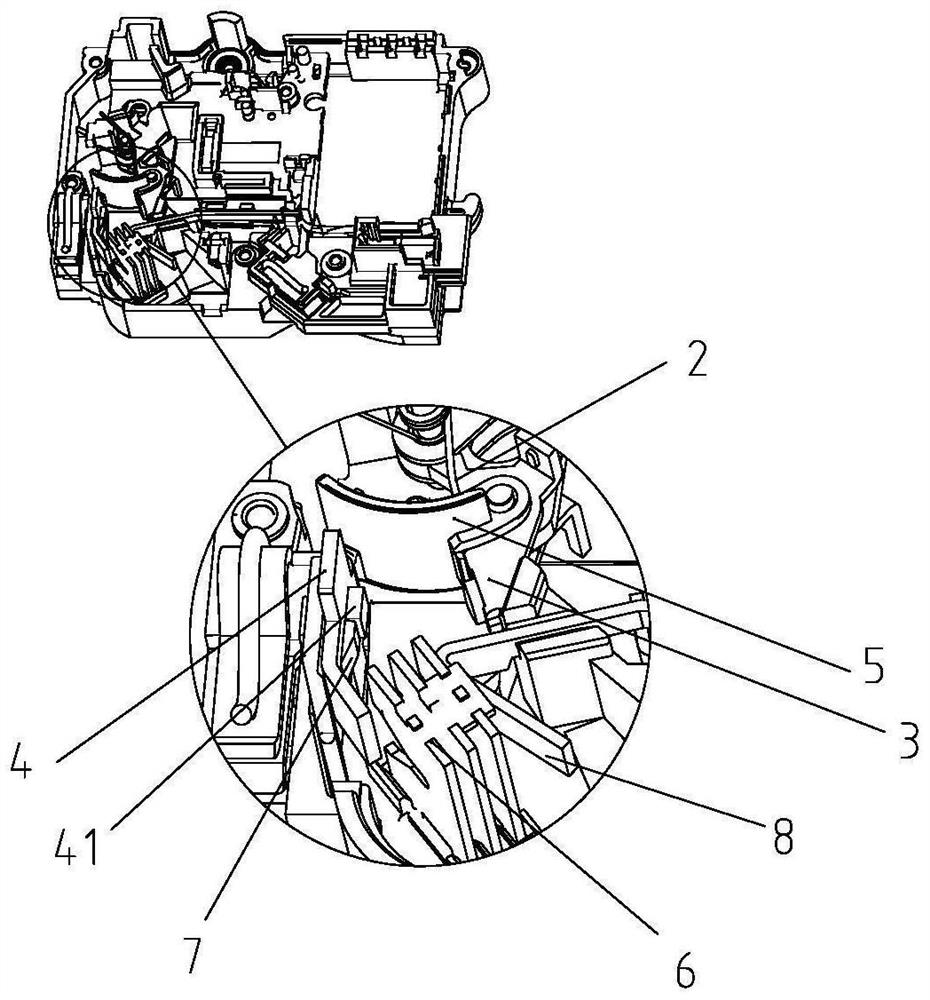

Circuit breaker

PendingCN114724901AShorten burn timeImprove short circuit performanceCircuit-breaking switch detailsEngineeringArc extinction

The invention relates to a circuit breaker which comprises a base, a mechanism, a contact assembly and an arc extinguish chamber, the arc extinguish chamber is arranged on one side of the contact assembly, the contact assembly comprises a static contact with a static contact point and a moving contact with a moving contact point, and the moving contact has a moving stroke for achieving connection or disconnection of the circuit breaker relative to the static contact. The mechanism is in linkage connection with a moving contact, a gas traveling path of gas blast arc extinguishing is formed from the contact assembly to the arc extinguishing chamber, a gas baffle plate moving along with the movement of the moving contact is attached to the moving contact or the mechanism, and when the moving contact is disconnected relative to a static contact, the gas baffle plate moves along with the movement of the moving contact. The gas baffle blocks the upstream of the gas traveling path along with the moving stroke of the moving contact, so that the vast majority of gas generated by the electric arc between the moving contact and the static contact can move towards the arc extinguish chamber, and the electric arc is accelerated to enter the arc extinguish chamber.

Owner:XIAMEN HONGFA ELECTRICAL SAFETY & CONTROLS CO LTD

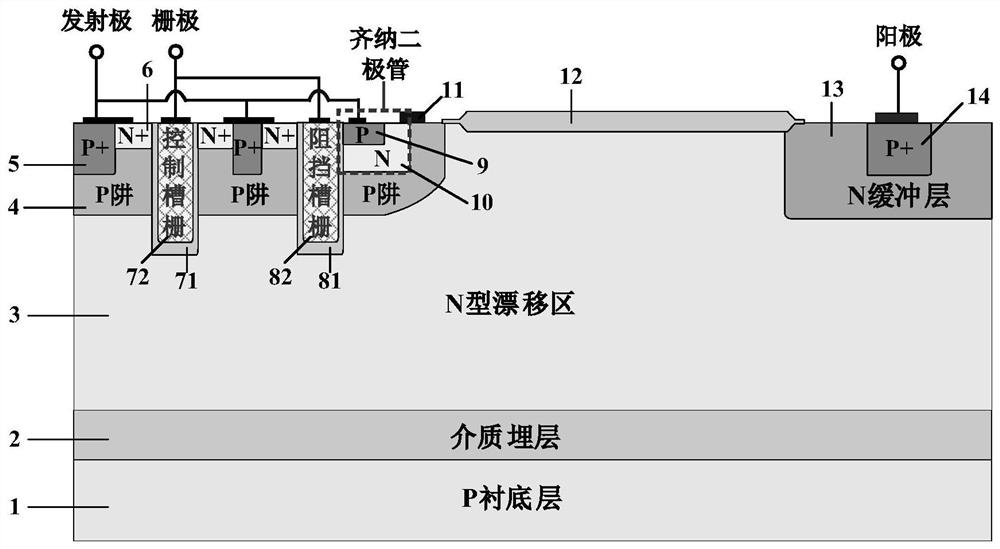

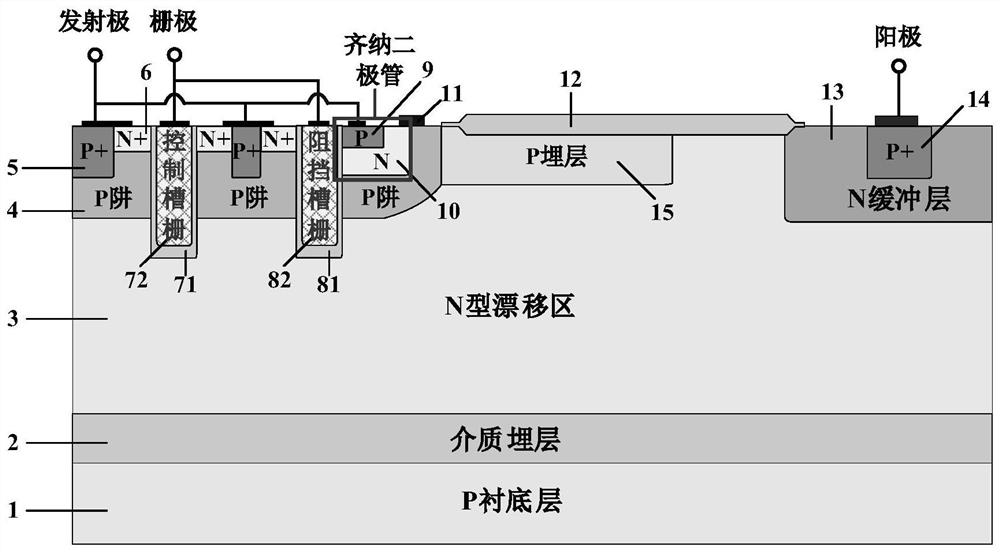

SOI LIGBT device integrated with Zener diode

ActiveCN111834450AImprove compromiseReduced Miller CapacitanceSemiconductor devicesCapacitanceZener diode

The invention belongs to the technical field of power semiconductors, and particularly relates to an SOI LIGBT device integrated with a Zener diode. Compared with a traditional LIGBT, the Zener diodeis introduced into a P well region at an emitter end of a new device, the P-type region of the Zener diode is electrically connected with the emitter of the device, and the N-type region of the Zenerdiode is electrically connected with the P well region through floating ohmic metal. When the voltage of a collector electrode is continuously increased, the Zener diode is reversely broken down and conducted, so that the potential of the P well region is clamped, the gate capacitance of the device can be reduced, the saturation current can be reduced to improve the short-circuit capability of thedevice when the device is conducted, and a hole extraction path can be provided in the turn-off process to reduce the turn-off time and the turn-off loss. Compared with a traditional LIGBT structure,the novel LIGBT structure provided by the invention has the advantages that a better compromise relationship between conduction voltage drop and turn-off loss is obtained, and the short-circuit resistance of the device is improved.

Owner:UNIV OF ELECTRONICS SCI & TECH OF CHINA

Series converter based on Si IGBT/SiC MOS hybrid parallel devices, and fault operation control method thereof

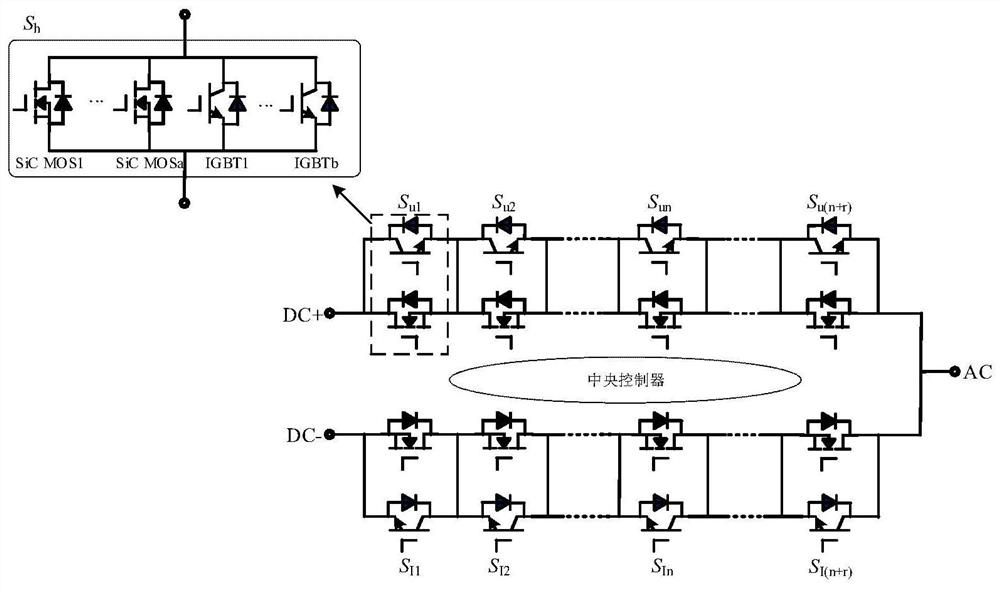

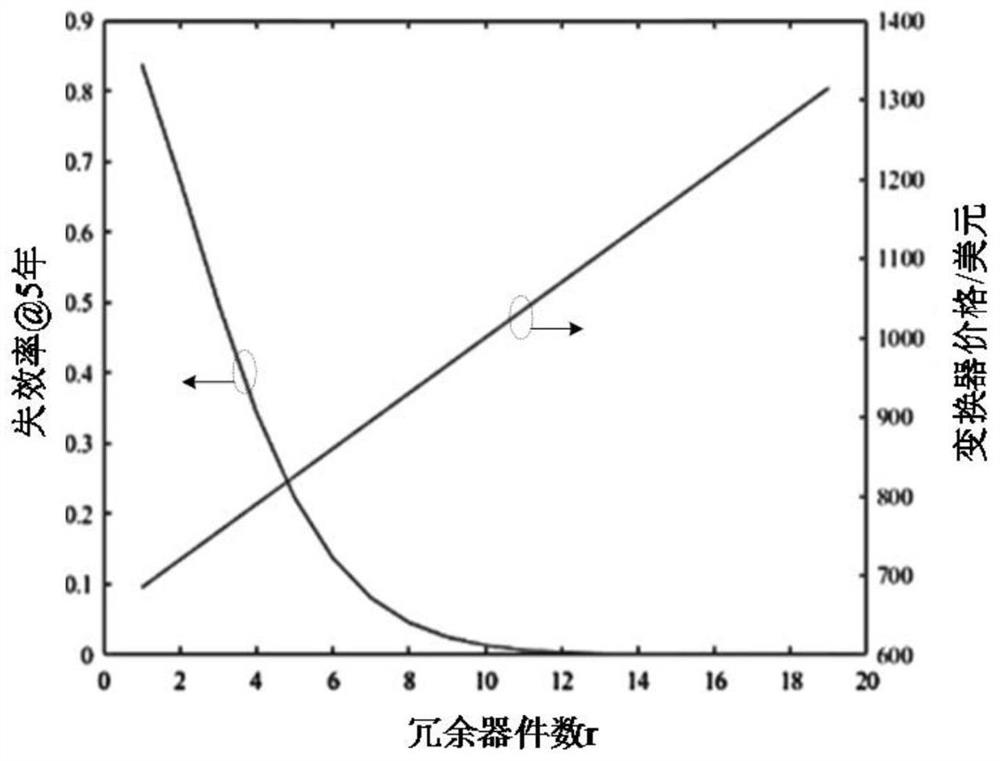

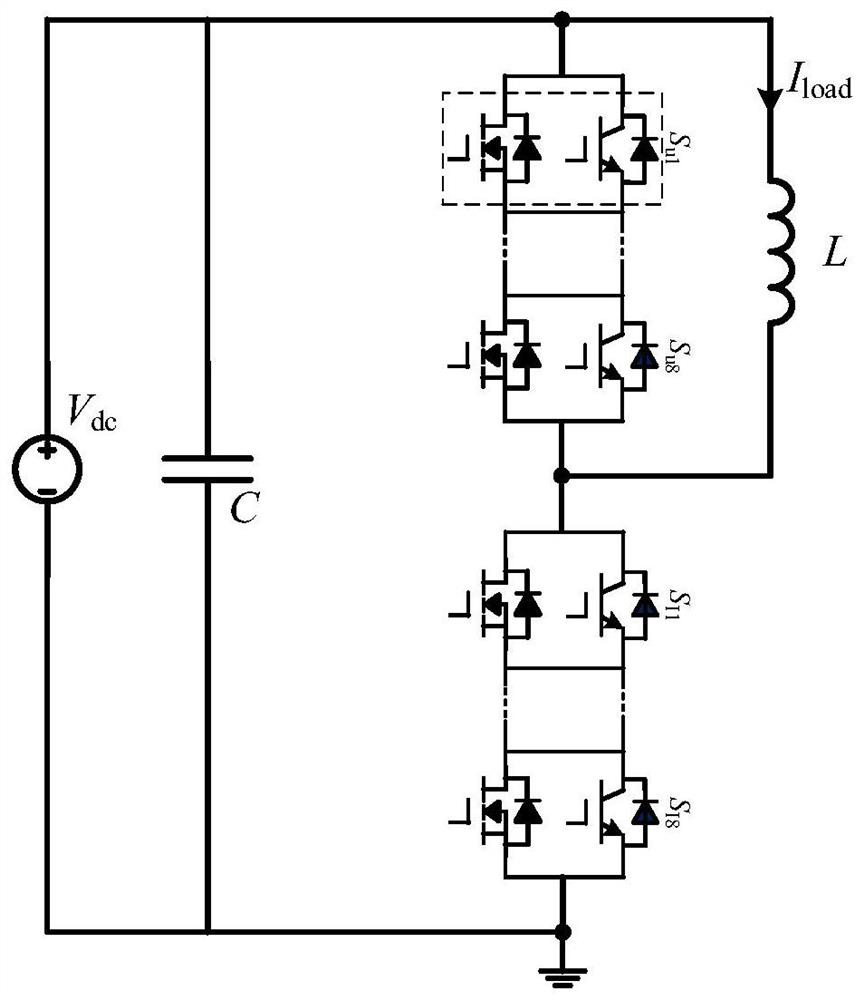

InactiveCN112701893AIncrease the voltage power levelMeet the needs of industrial applicationsEfficient power electronics conversionPower conversion systemsFault toleranceMonitoring and control

The invention discloses a series converter based on Si IGBT / SiC MOS hybrid parallel devices, and a fault operation control method thereof. The converter is of a half-bridge structure, an upper bridge arm and a lower bridge arm are each formed by connecting (n + r) hybrid parallel devices in series, n devices maintain normal operation, r devices are used as redundancy, each hybrid parallel device is formed by connecting a SiC MOSs and b IGBTs in parallel, each IGBT / SiC MOS comprises a driver, and the converter comprises a total central controller and is responsible for driving sequence, state monitoring and control strategy adjustment of devices. If a certain power device in the converter fails, the fault operation control strategy can judge the failure position in a switching period, uploads the operation condition of the converter, and adopts the control strategy to maintain normal operation. The converter provided by the invention considers the advantages of high voltage, high power, high frequency and high power density, and the provided fault control strategy can ensure that the converter continues to operate normally under the condition of device faults, so that the fault tolerance of the system is improved.

Owner:POWERCHINA HUADONG ENG COPORATION LTD

Self-exciting BJT type bridge-free Zeta PFC rectifier circuit

ActiveCN105207464AImprove driving efficiencyEasy to startEfficient power electronics conversionAc-dc conversionCapacitancePower flow

A self-exciting BJT type bridge-free Zeta PFC rectifier circuit comprises an input capacitor Ci, a PNP type BJT tube Q1, a PNP type BJT tube Q2, an NPN type BJT tube Q3, an NPN type BJT tube Q4, a PNP type BJT tube Q5, a PNP type BJT tube Q6, a diode D1, a diode D2, an inductor L1, an inductor L2, a capacitor Cs, an output capacitor Co, a resistor R1, a resistor R2, a resistor R3, a resistor R4, a resistor R5, a resistor R6 and a controllable current source group M1, wherein the controllable current source group M1 is used for controlling base current of the PNP type BJT tube Q1 through a port so as to control the working state of the PNP type BJT tube Q1 and controlling base current of the PNP type BJT tube Q2 tube through a port b so as to control the working state of the PNP type BJT tube Q2. By means of the self-exciting BJT type bridge-free Zeta PFC rectifier circuit, a driving circuit structure is simplified, the driving efficiency is higher, and the performance of easy self start is obtained.

Owner:沛县度创科技发展有限公司

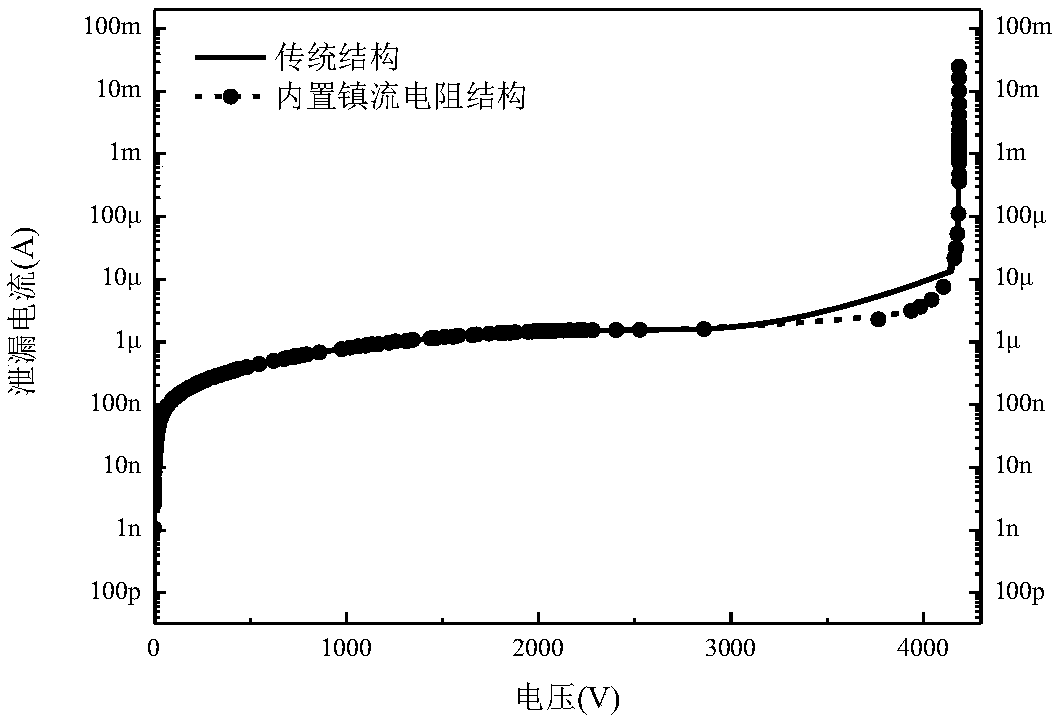

High-voltage IGBT device with a built-in ballast resistor

ActiveCN108172610AImprove short circuit performanceImprove thermal stabilitySemiconductor devicesHigh voltage igbtEngineering

The invention provides a high-voltage IGBT device with a built-in ballast resistor. A cell structure includes a first conductivity type semiconductor P+ collector region, a metal collector, a second conductivity type semiconductor buffer layer, a second conductivity type semiconductor N-drift region, a first conductivity type semiconductor P type base region, a heavily doped first conductivity type semiconductor P+ doping region, a second conductivity type semiconductor built-in ballast resistance region, and a heavily doped second conductivity type semiconductor N+ emitter region. The secondconductivity type semiconductor built-in ballast resistance region is used for replacing the part, extending horizontally towards the space below the gate structure, of the second conductivity type semiconductor N+ emitter region, so that the second conductivity type semiconductor built-in ballast resistance region is located in the gate voltage control region. On the basis of the positive temperature characteristic of the ballast resistance value at a high temperature, the short-circuit capability of the device is improved; and the thermal stability of the device in the forward blocking stateis enhanced.

Owner:UNIV OF ELECTRONICS SCI & TECH OF CHINA