SiC MPS diode device and preparation method thereof

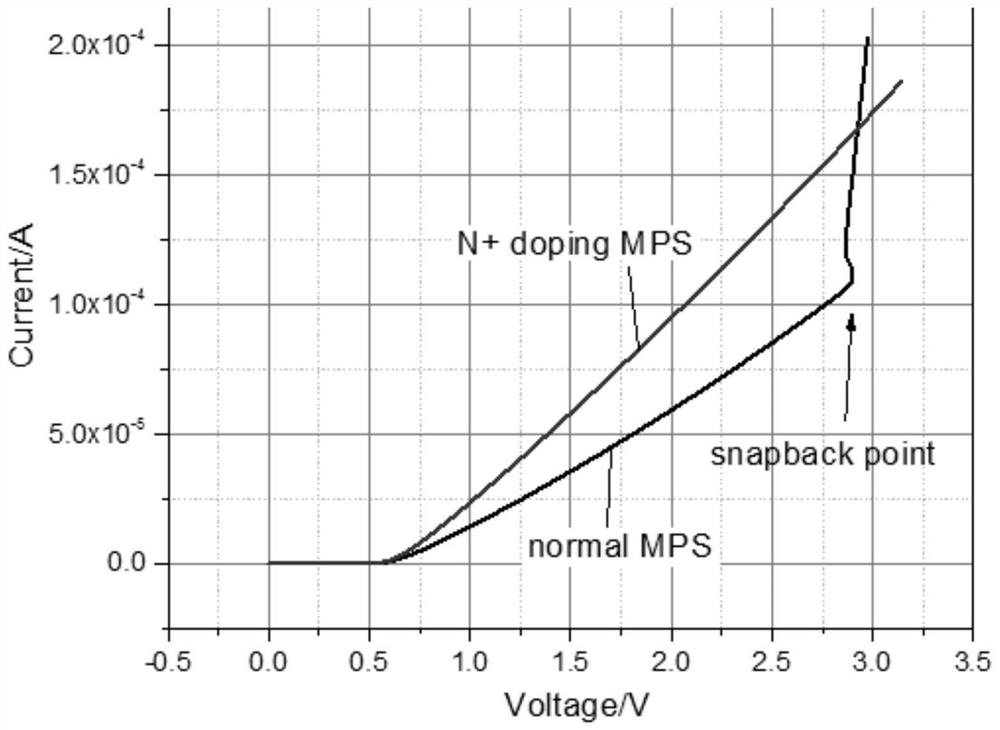

A diode and device technology, applied in the field of SiCMPS diode devices and their preparation, can solve the problems of device forward function degradation, forward current rebound, etc.

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

preparation example Construction

[0032] The preparation method of the above-mentioned SiC MPS diode device comprises the following steps:

[0033] S1: An N- epitaxial layer 4 is formed by epitaxial growth on the N+ substrate 5; the overall structure forming the N- epitaxial layer is usually called an epitaxial wafer;

[0034] S2: Preparation of SiO on N-epitaxial layer 4 2 The mask layer is formed with a mask pattern by a photolithography process, and an N+ implantation region 3 is formed by means of N ion implantation;

[0035] S3: cleaning off the implantation mask layer, forming a new mask layer on the surface, forming a mask pattern by photolithography, and forming a P+ implantation region 2 by means of Al ion implantation;

[0036] S4: cleaning off the implanted mask layer, forming a new mask layer on the surface, forming a mask pattern by photolithography, and then forming a trench structure 7 by ICP etching;

[0037] S5: Protect the surface of the epitaxial layer with a carbon film, activate the impl...

Embodiment 1

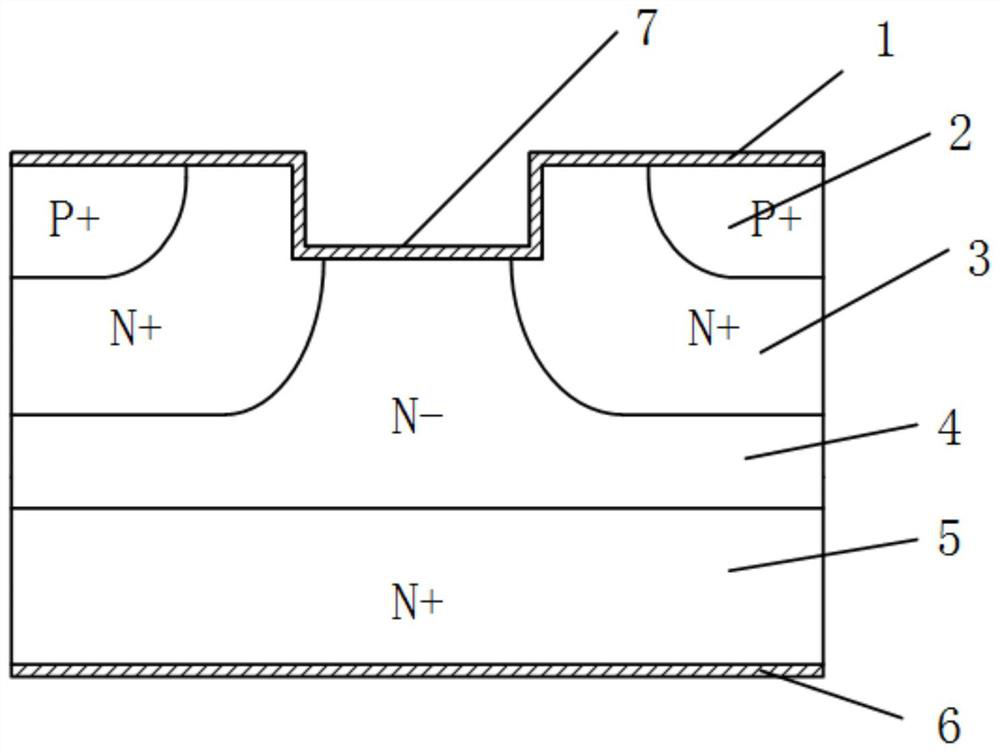

[0043] figure 1 A schematic cross-sectional view of a trench type SiCMPS diode device structure that has carried out N+ implantation for the present invention, combined below figure 1 Describe in detail the apparatus of the present invention;

[0044] A trench-type SiC MPS diode device structure with N+ implantation: including an N+ substrate 5 with a doping concentration of 5×10 18 atom / cm 3 Made of SiC material with a thickness of 350 μm, the lightly doped N- epitaxial layer 4 is located above the substrate layer 5; the cathode 6 is located below the substrate; the surface of the N- epitaxial layer 4 is provided with a trench structure 7; the P+ implantation region 2 is located in the trench The surface of the N- epitaxial layer 4 around the trench structure 7; the N+ implantation region 3 is located around the P+ implantation region 2, and the anode covers the entire surface of the P+ implantation region 2 and the surface of the trench structure 7.

[0045] The process s...

Embodiment 2

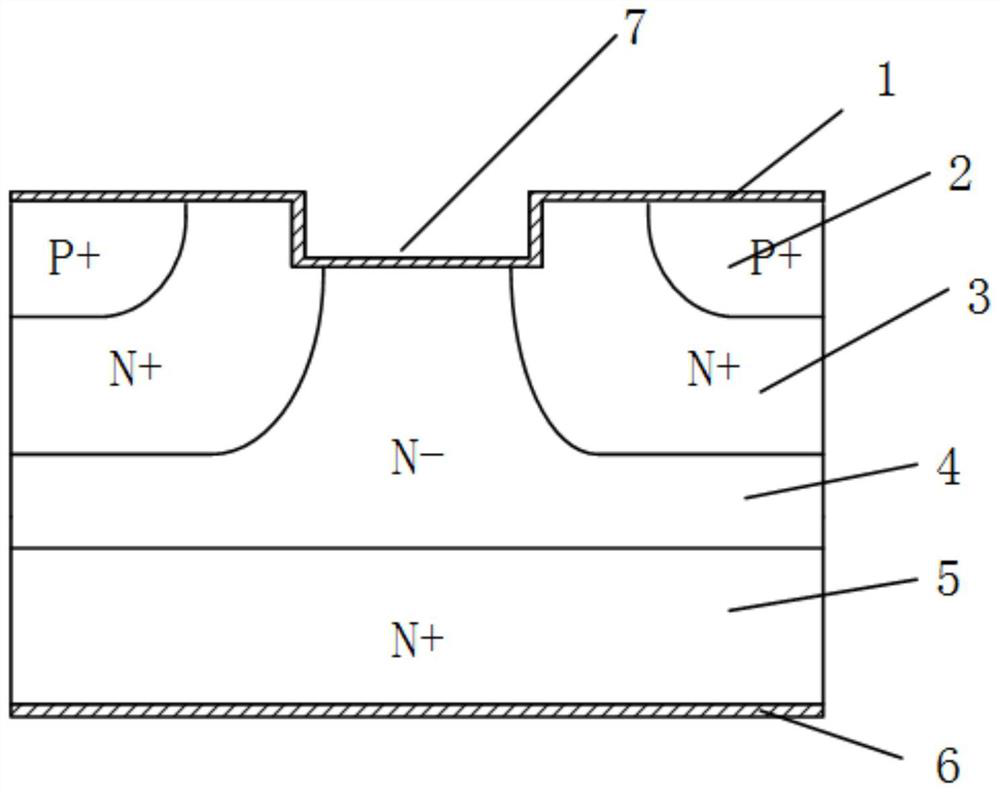

[0055] figure 2 It is a schematic cross-sectional view of the structure of a trench type SiC MPS diode device with N+ implantation in the present invention, combined below figure 2 Describe in detail the apparatus of the present invention;

[0056] A trench type SiC MPS diode device structure with N+ implantation: including N+ substrate 5, with a doping concentration of 5×10 18 atom / cm 3 Made of SiC material with a thickness of 350 μm; the lightly doped N- epitaxial layer 4 is located above the substrate layer 5; the cathode 6 is located below the substrate; the surface of the N- epitaxial layer 4 is provided with a trench structure 7; the P+ implantation region 2 is located in the trench The surface of the N- epitaxial layer 4 around the trench structure 7; the N+ implantation region 3 is located around the P+ implantation region 2, and the anode covers the entire surface of the P+ implantation region 2 and the surface of the trench structure 7.

[0057] The process step...

PUM

| Property | Measurement | Unit |

|---|---|---|

| width | aaaaa | aaaaa |

| depth | aaaaa | aaaaa |

| depth | aaaaa | aaaaa |

Abstract

Description

Claims

Application Information

Login to View More

Login to View More