Lateral power device with mixed conduction mode and method of making same

A lateral power device and mode technology, applied in semiconductor/solid-state device manufacturing, semiconductor devices, electrical components, etc., can solve the problems of reduced device loss characteristics, low turn-on voltage drop, large turn-off loss, etc. Turn-on voltage drop, improved breakdown voltage, and low turn-off loss

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment 1

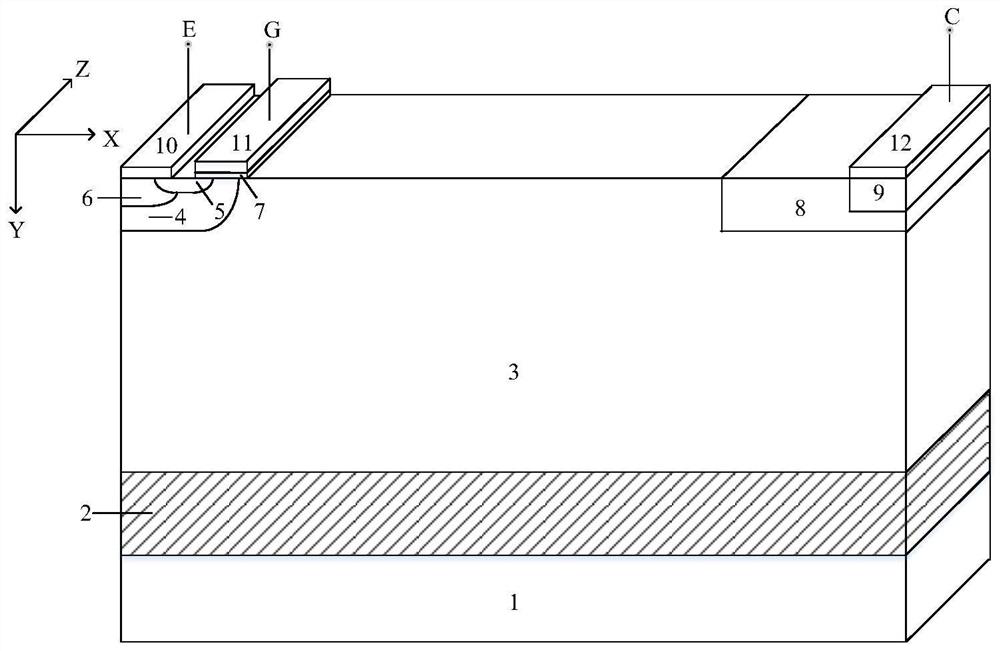

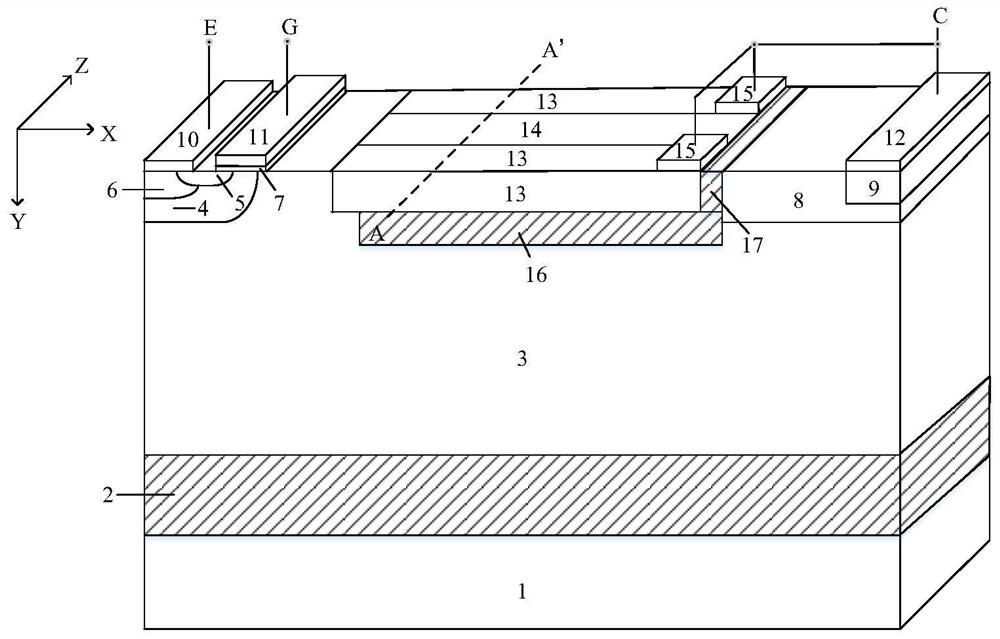

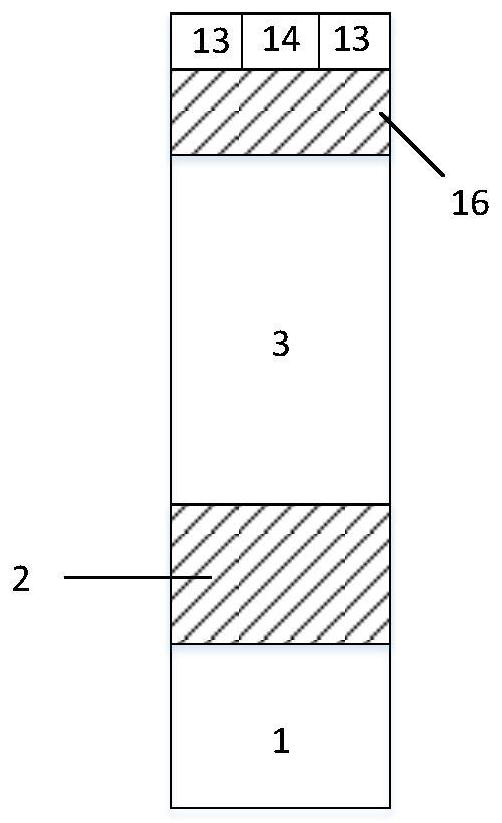

[0040] Such as figure 2 , image 3 As shown, a lateral power device with a mixed conduction mode includes a P-type substrate 1, a buried oxide layer 2, and an N-type drift region 3 arranged sequentially from bottom to top; one end of the N-type drift region 3 is provided with a P Type base area 4, the other end is provided with N-type buffer area 8; Described P-type base area 4 inner top is provided with N-type source area 5 and P-type contact area 6, and described N-type buffer area 8 inner top is provided with P type collector region 9; emitter 10 above the P-type contact region 6 and part of the N-type source region 5; part of the upper surface of the P-type collector region 9 has a collector electrode 12; above the P-type base region 4 A gate dielectric layer 7 is also provided, and a gate electrode 11 is arranged above the gate dielectric layer 7. The length of the gate structure formed by the gate dielectric layer 7 and the gate electrode 11 is greater than the length ...

Embodiment 2

[0049] Such as Figure 4 As shown, the difference between this example and Example 1 is that the N-type drift region 3 is composed of a first doped region 31 and a second doped region 32 whose concentration increases from left to right. Compared with Embodiment 1, this embodiment can further increase the breakdown voltage of the device, increase the turn-off speed of the device, and reduce the turn-off loss.

Embodiment 3

[0051] Such as Figure 5 As shown, the difference between this example and Example 1 is that there is a P-type RESURF buried layer 18 under the dielectric buried layer 16 in the N-type drift region 3 . The depth of the P-type RESURF buried layer from the dielectric buried layer 16 is 1-4 microns, and the thickness is 0.5-2 microns. Compared with Example 1, through the 3-dimensional RESURF effect of the P-type RESURF buried layer and the 3-dimensional expansion of the depletion layer, this embodiment can further increase the breakdown voltage of the device, and at the same time further increase the turn-off speed of the device, reducing turn-off loss.

PUM

| Property | Measurement | Unit |

|---|---|---|

| thickness | aaaaa | aaaaa |

| thickness | aaaaa | aaaaa |

| width | aaaaa | aaaaa |

Abstract

Description

Claims

Application Information

Login to View More

Login to View More