Semiconductor device modeling method

A device modeling and semiconductor technology, applied in instruments, special data processing applications, electrical digital data processing, etc., can solve problems such as complex formulas and slow simulation speed, and achieve simple models, elevated substrate pressure drop, and good convergence Effect

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0030] Various embodiments of the invention will be described in more detail below with reference to the accompanying drawings. In the various drawings, the same elements are denoted by the same or similar reference numerals. For the sake of clarity, various parts in the drawings have not been drawn to scale.

[0031] The specific implementation manners of the present invention will be further described in detail below in conjunction with the accompanying drawings and embodiments.

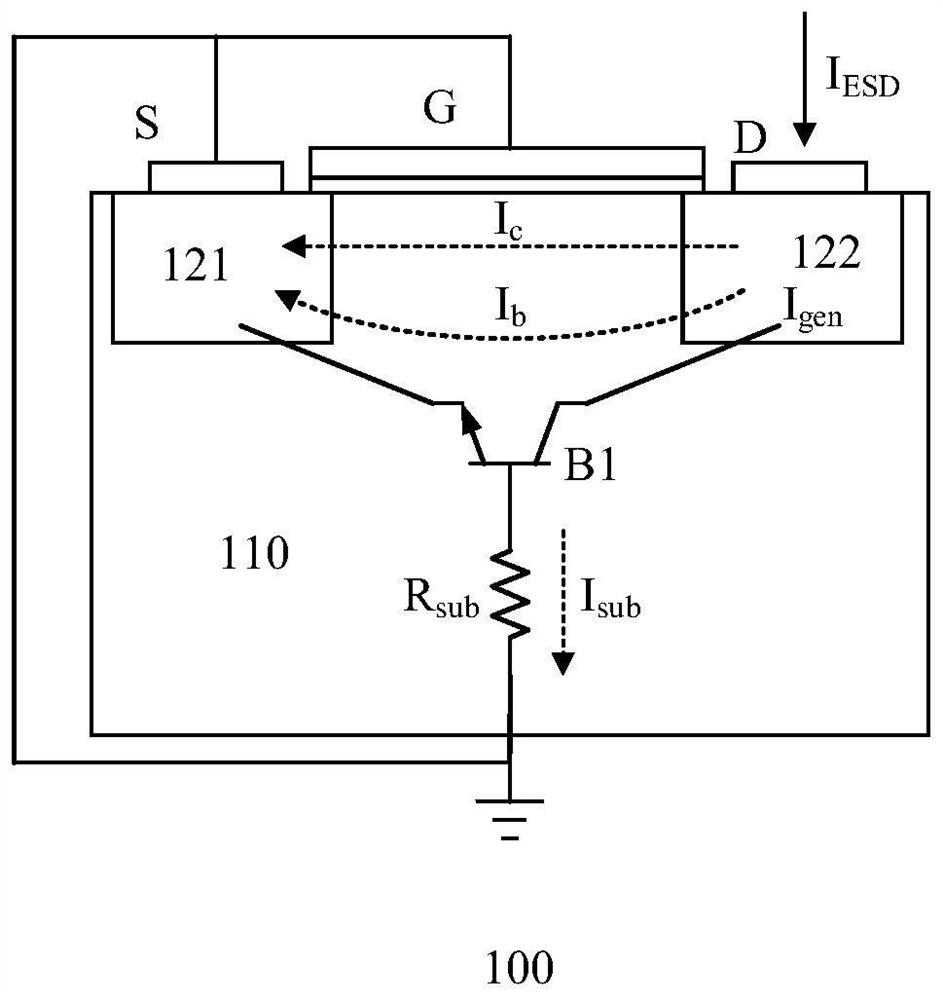

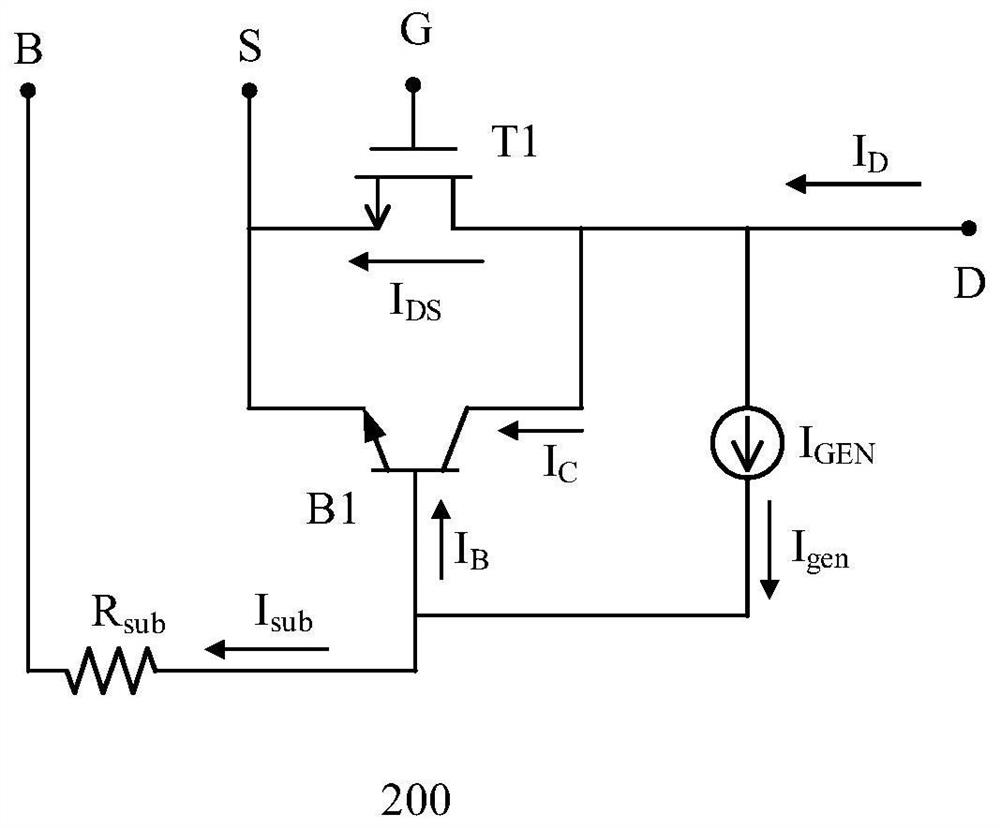

[0032] Figure 4 A schematic circuit structure diagram showing a GGNMOS model of a semiconductor device modeling method according to an embodiment of the present invention.

[0033] like Figure 4 As shown, the GGNMOS model of the embodiment of the present invention divides the whole device into native transistor T2 (native transistor model), parasitic transistor B2 (parasitic transistor model), substrate resistance R sub , source resistance R s and the drain resistor R d .

[0034] The subs...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More