IGBT device structure and preparation method thereof

A technology of device structure and junction area, applied in semiconductor/solid-state device manufacturing, semiconductor devices, electrical components, etc., can solve problems such as negative resistance snapback, and achieve the effect of ensuring device withstand voltage, improving insulation, and suppressing the phenomenon of snapback.

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0028] The following are specific embodiments of the present invention and in conjunction with the accompanying drawings, the technical solutions of the present invention are further described, but the present invention is not limited to these embodiments.

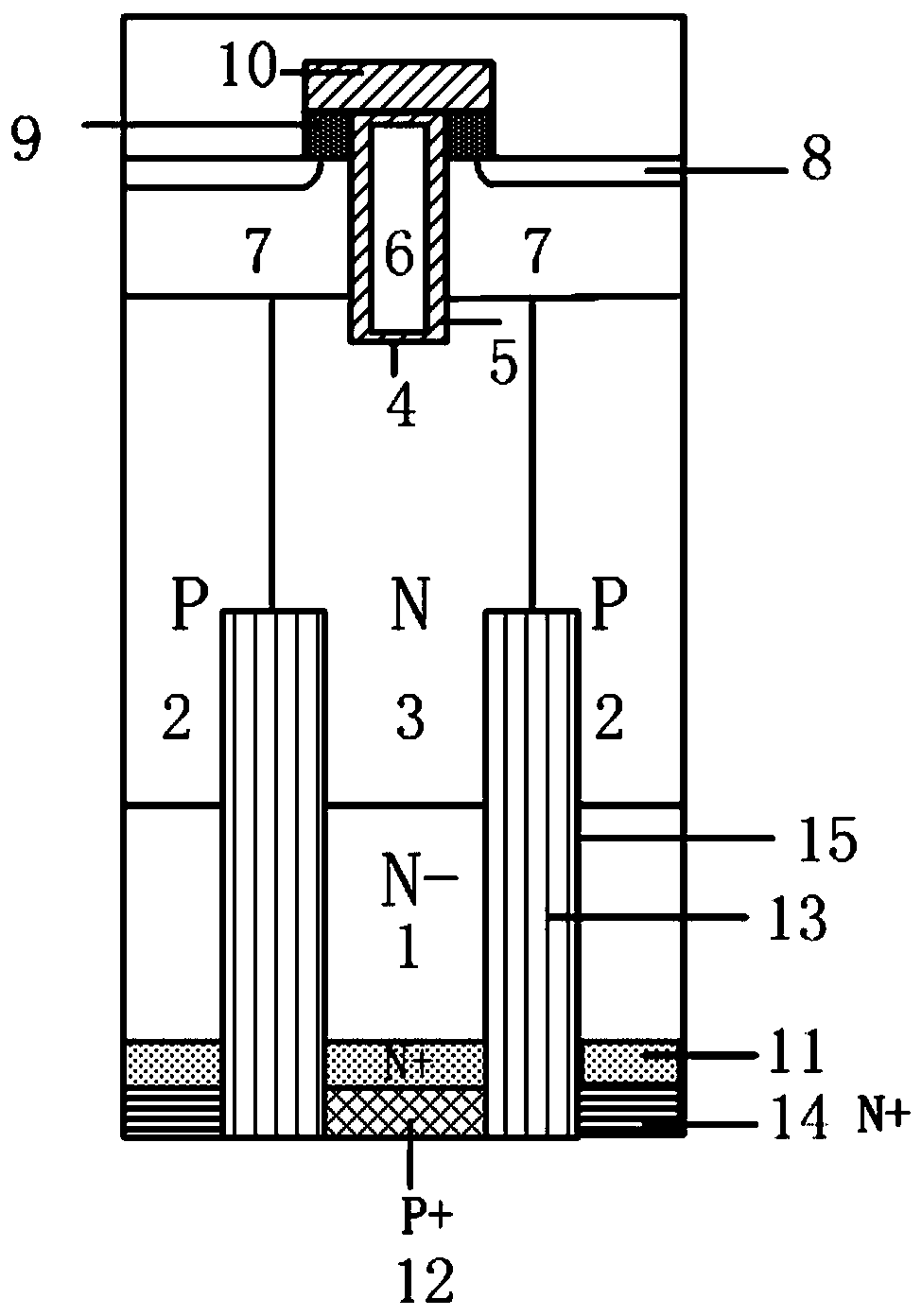

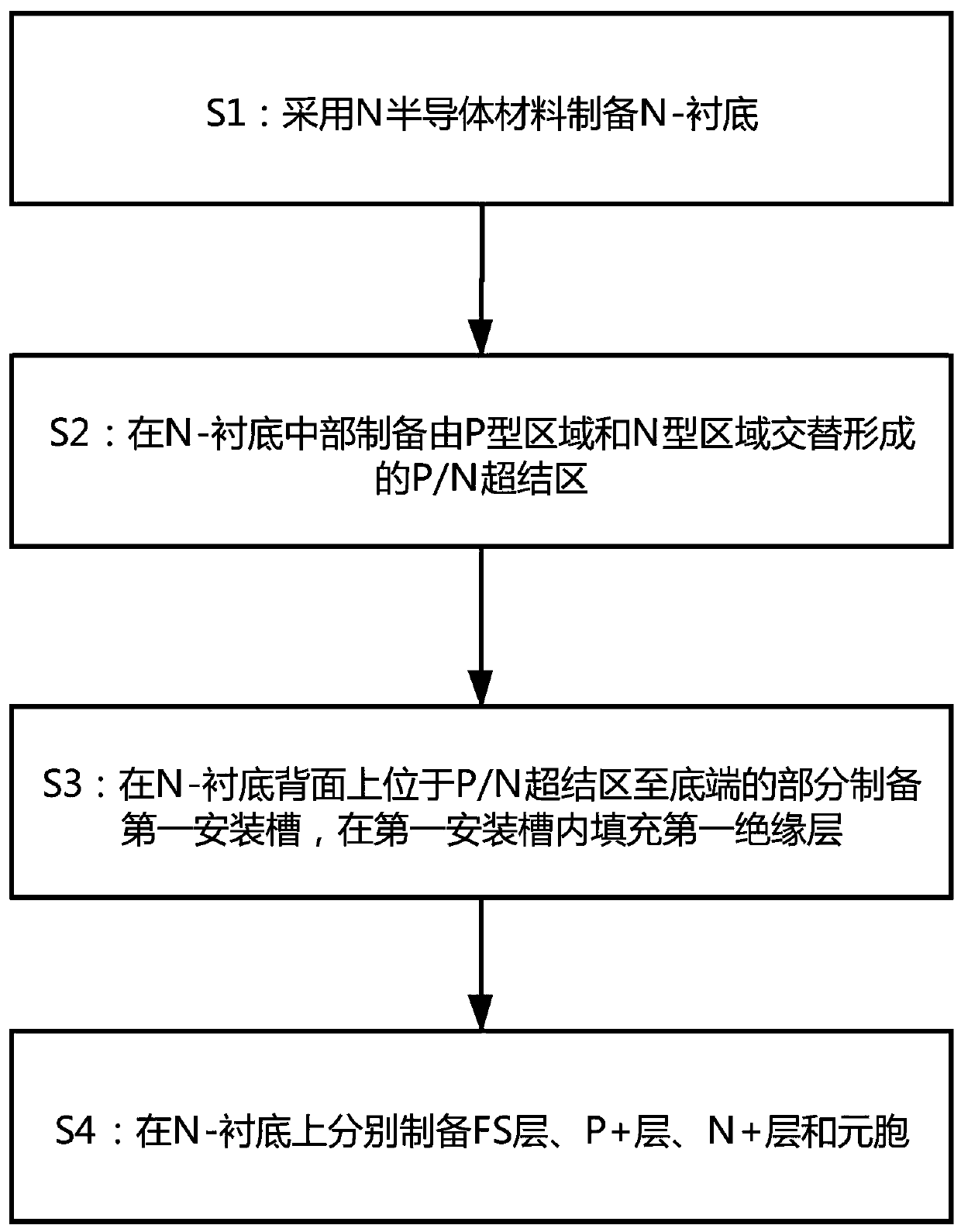

[0029] see Figure 1-2 , the IGBT device structure in this embodiment includes an N-substrate 1, a super junction region disposed on the N-substrate 1, a cell disposed on the upper end of the super junction region, and a FS disposed on the lower end of the N-substrate 1 layer 11, the P+ layer 12 disposed on the lower end of the N-substrate 1, the N+ layer 14 disposed on the lower end of the N-substrate 1, and the filling layer disposed on the N-substrate 1, the filling layer includes 1, and the first insulating layer 13 filled in the first installation groove 15.

[0030] Here, the N-substrate 1, the superjunction region, the cell, the FS layer 11, the P+ layer 12, and the N+ layer 14 can ensure the withstand voltage of t...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More