Patents

Literature

377results about "Pulse position modulation" patented technology

Efficacy Topic

Property

Owner

Technical Advancement

Application Domain

Technology Topic

Technology Field Word

Patent Country/Region

Patent Type

Patent Status

Application Year

Inventor

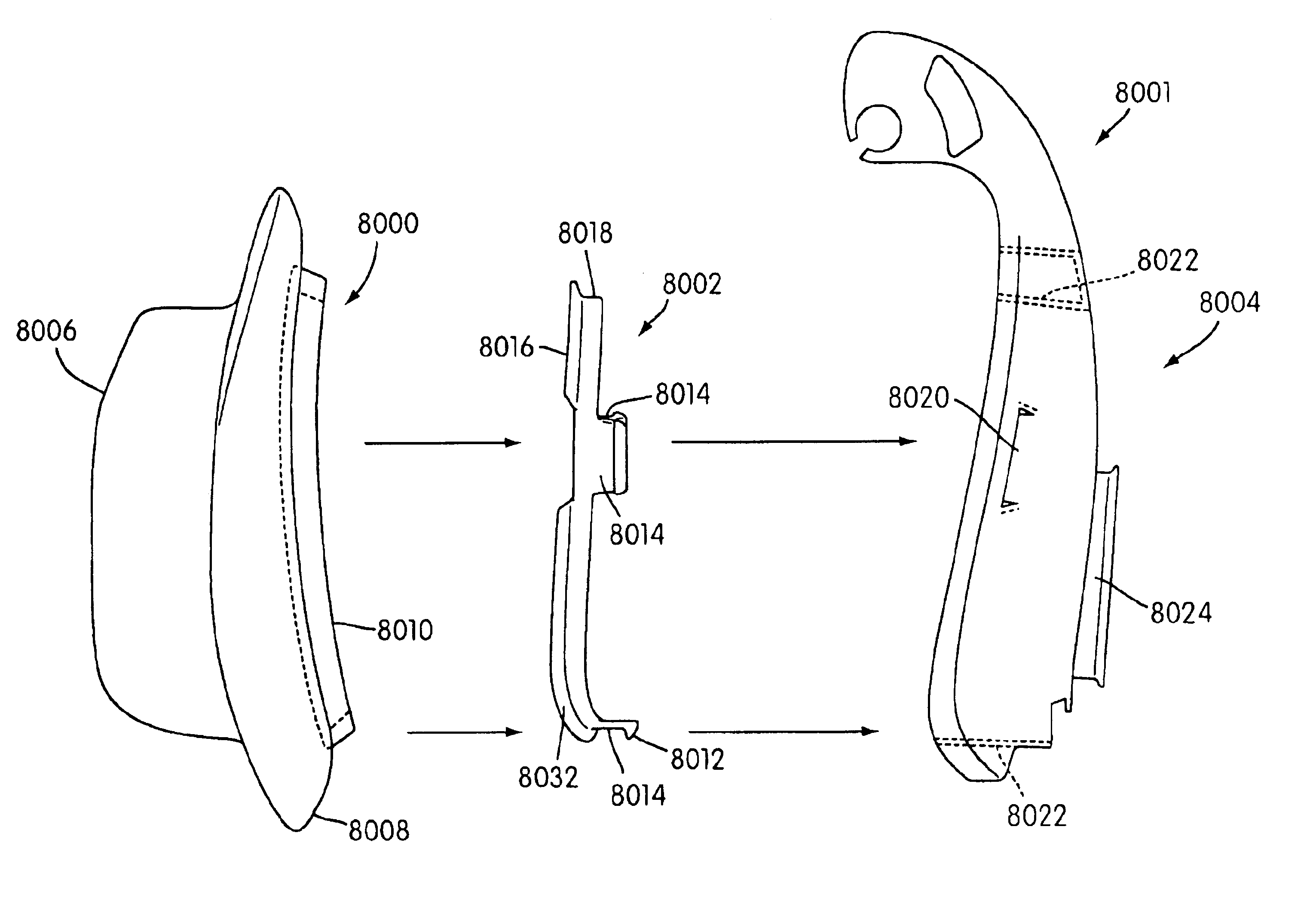

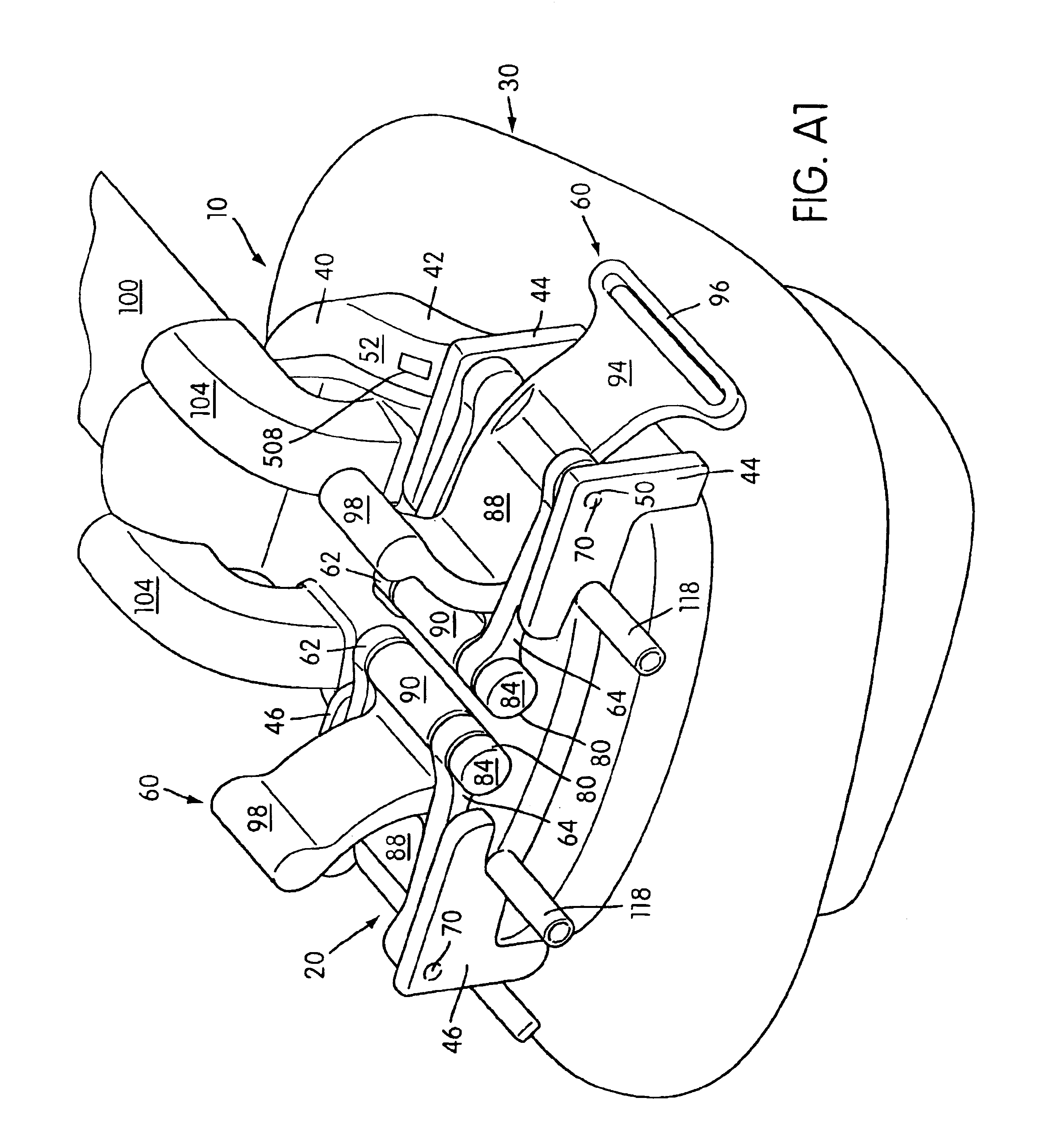

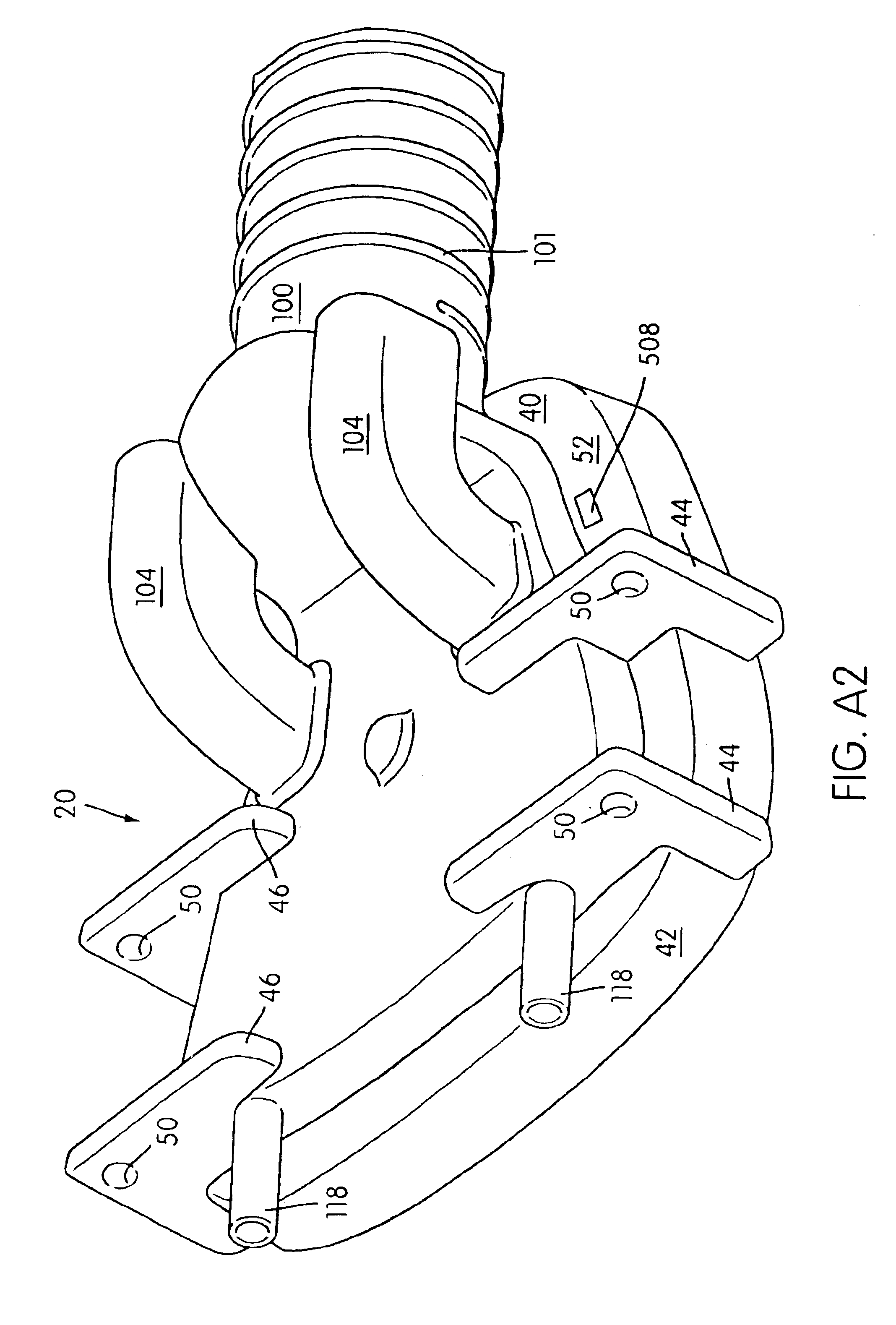

Mask assembly

A respiratory mask assembly for use in the delivery of non-invasive positive airway pressure to a user. The assembly includes a rigid shell having a channel portion defined by an inner wall, an outer wall and a channel floor, a face-contacting cushion acting to space the shell away from the user's face and a sealing tab extending from the cushion to engage a portion of the shell to provide a continuous airtight seal between the cushion and the shell. A retaining ring within the mask assembly is configured to secure the cushion to the shell. The retaining ring has a first portion including at least one clip configured to pass through at least one slot portion such that an underside surface of the at least one clip engages a section of the shell when the retaining ring is positioned within the channel.

Owner:RESMED LTD

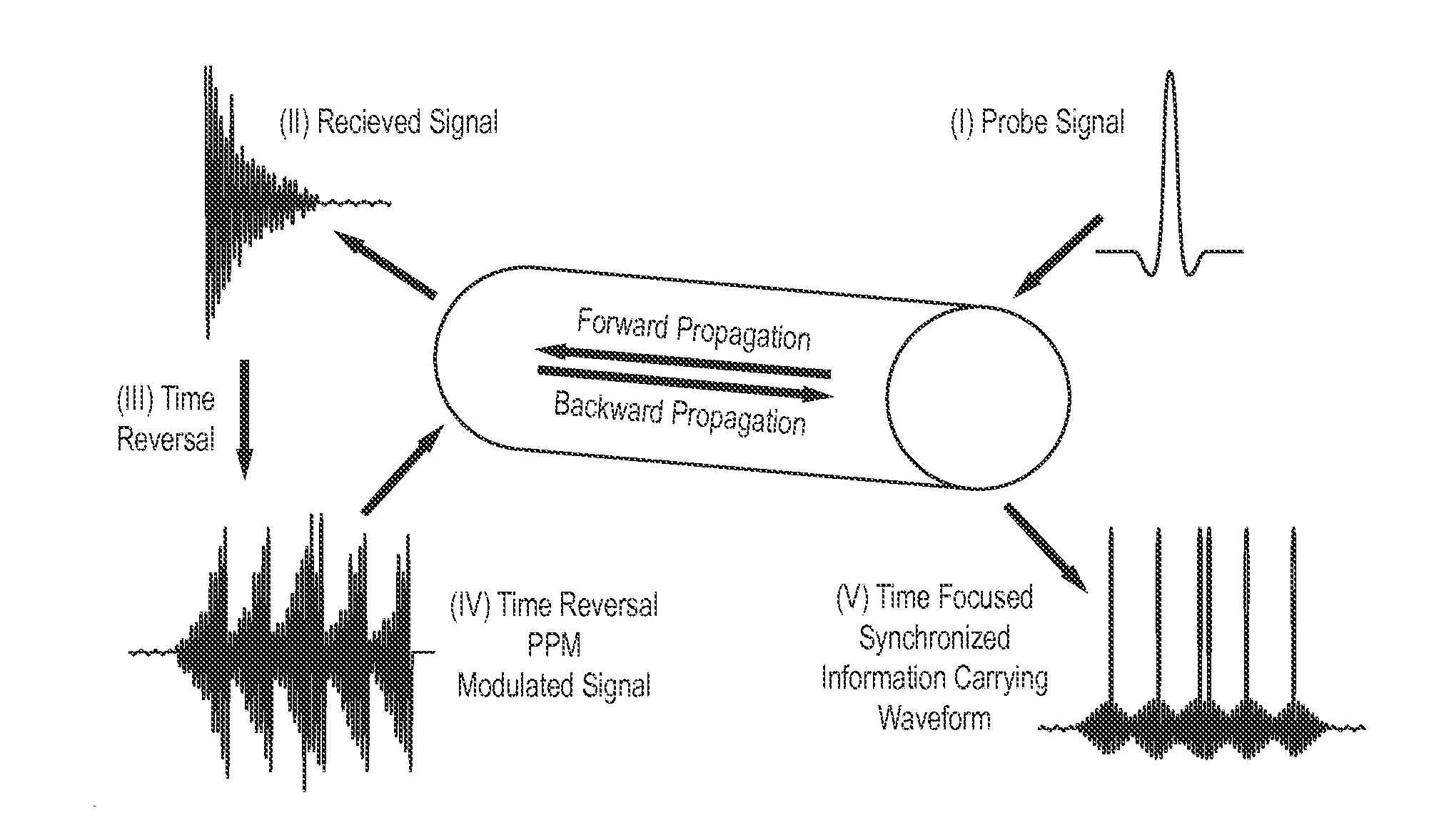

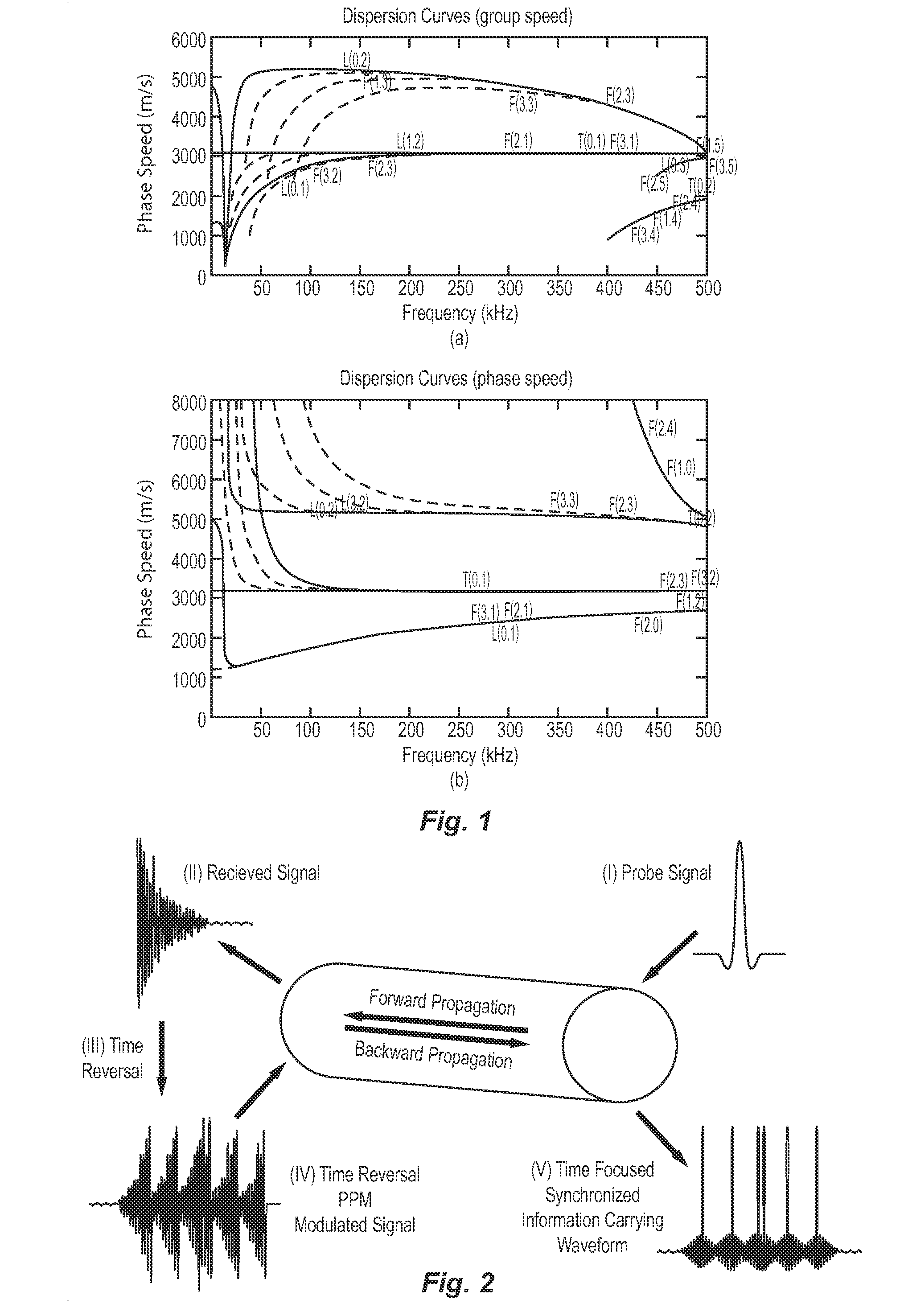

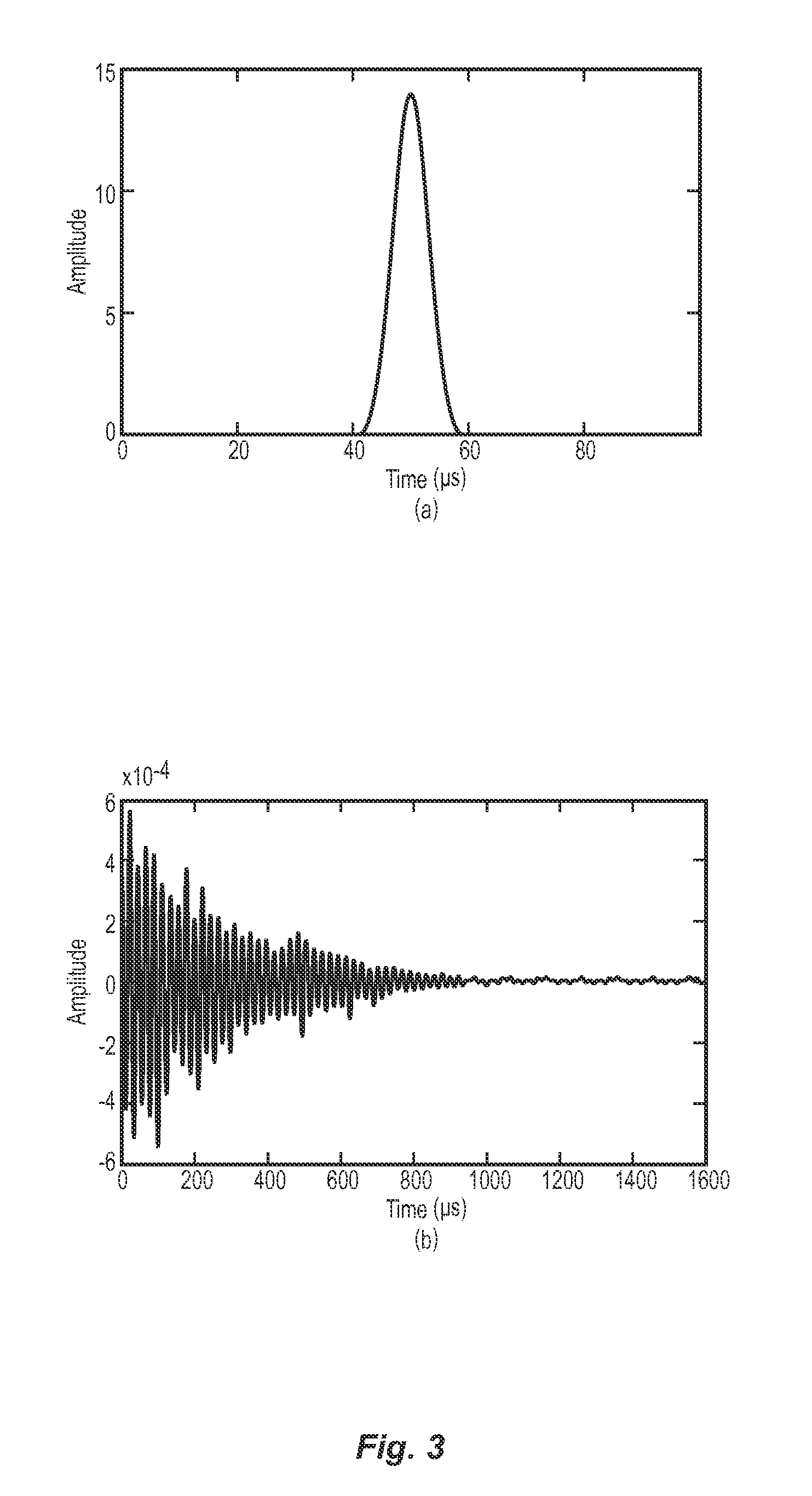

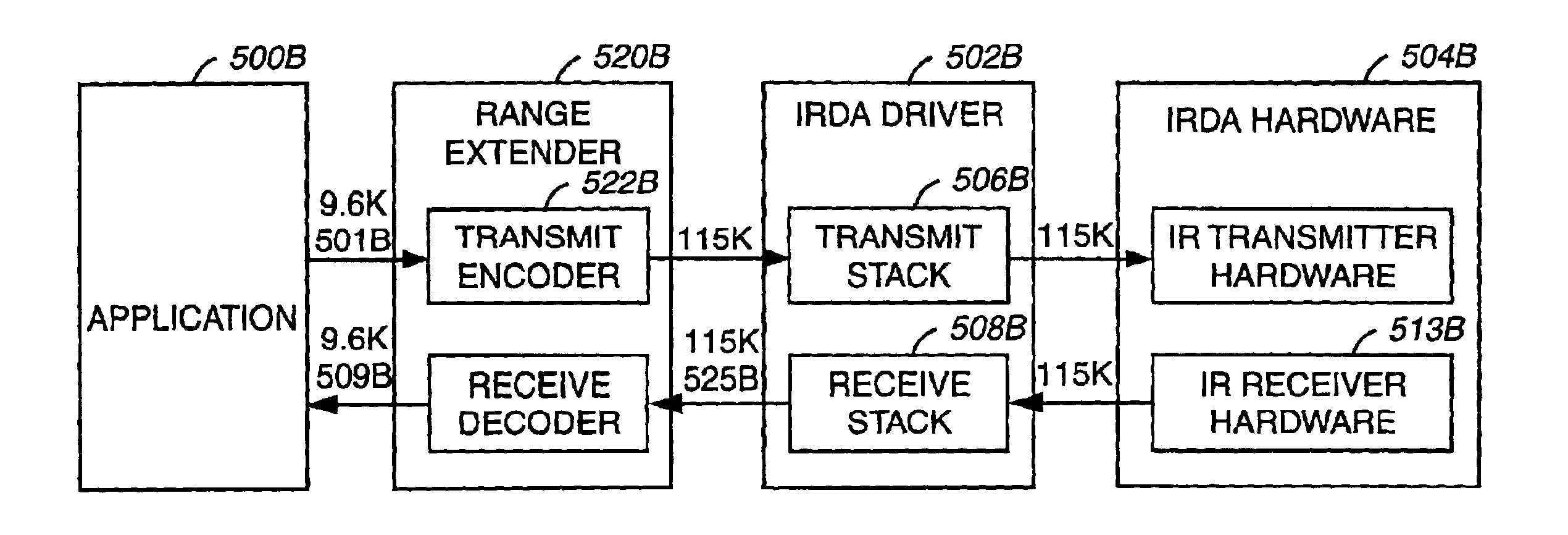

System and method for time reversal data communications on pipes using guided elastic waves

ActiveUS20130279561A1Efficient communicationClean signals for demodulationFrequency/rate-modulated pulse demodulationPosition-modulated pulse demodulationDiagnostic Radiology ModalityStructural health monitoring

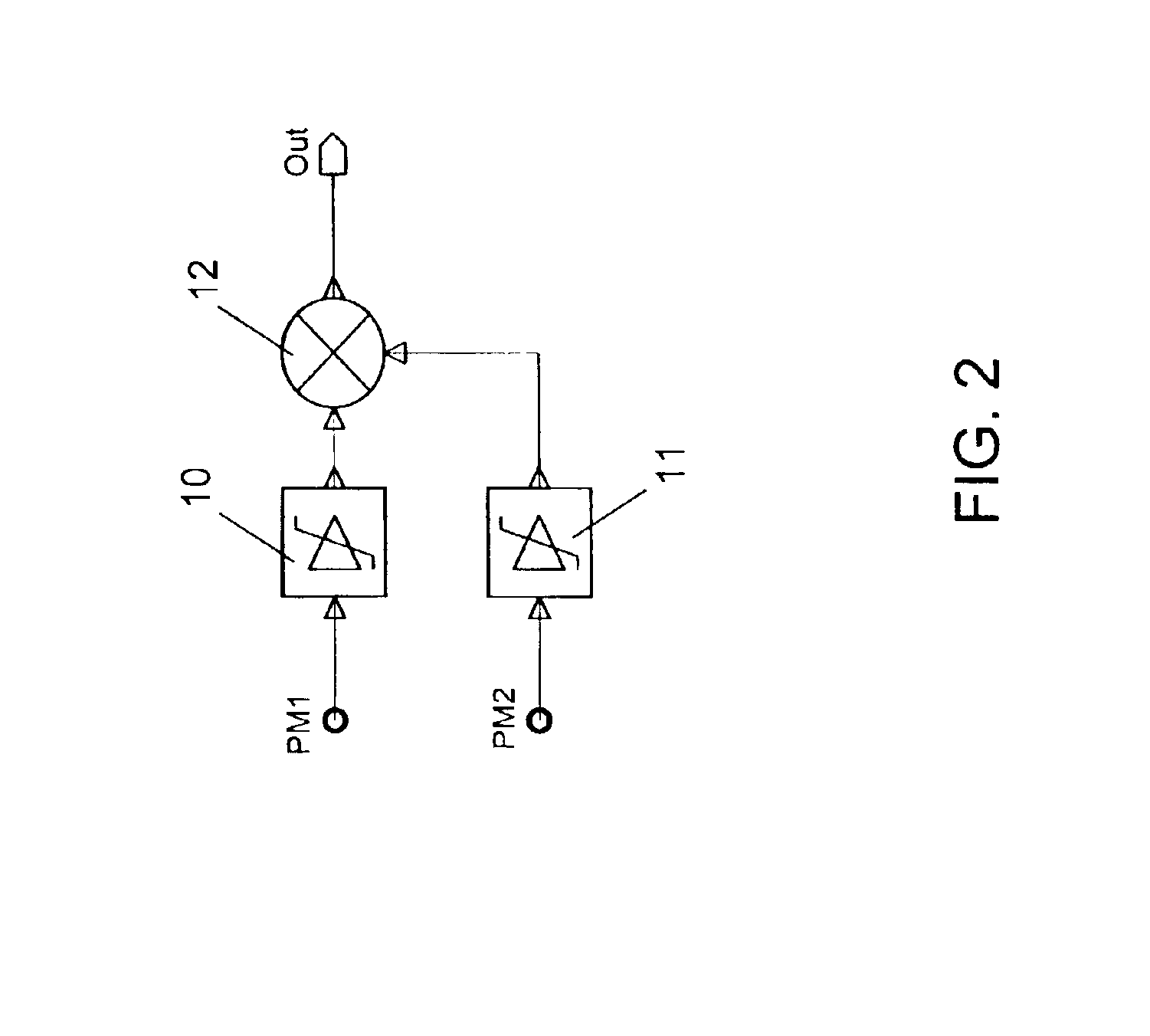

Embedded piezoelectric sensors in large civil structures for structural health monitoring applications require data communication capabilities to effectively transmit information regarding the structure's integrity between sensor nodes and to the central processing unit. Conventional communication modalities include electromagnetic waves or acoustical waves. While guided elastic waves can propagate over long distances on solid structures, their multi-modal and dispersive characteristics make it difficult to interpret the channel responses and to transfer useful information along pipes. Time reversal is an adaptive transmission method that can improve the spatiotemporal wave focusing. The present disclosure presents the basic principles of a time reversal based pulse position modulation (TR-PPM) method and demonstrates TR-PPM data communication by simulation. The present disclosure also experimentally demonstrates data communication with TR-PPM on pipes. Simulated and experimental results demonstrate that TR-PPM for data communications can be achieved successfully using guided elastic waves.

Owner:UNIV OF MARYLAND EASTERN SHORE +1

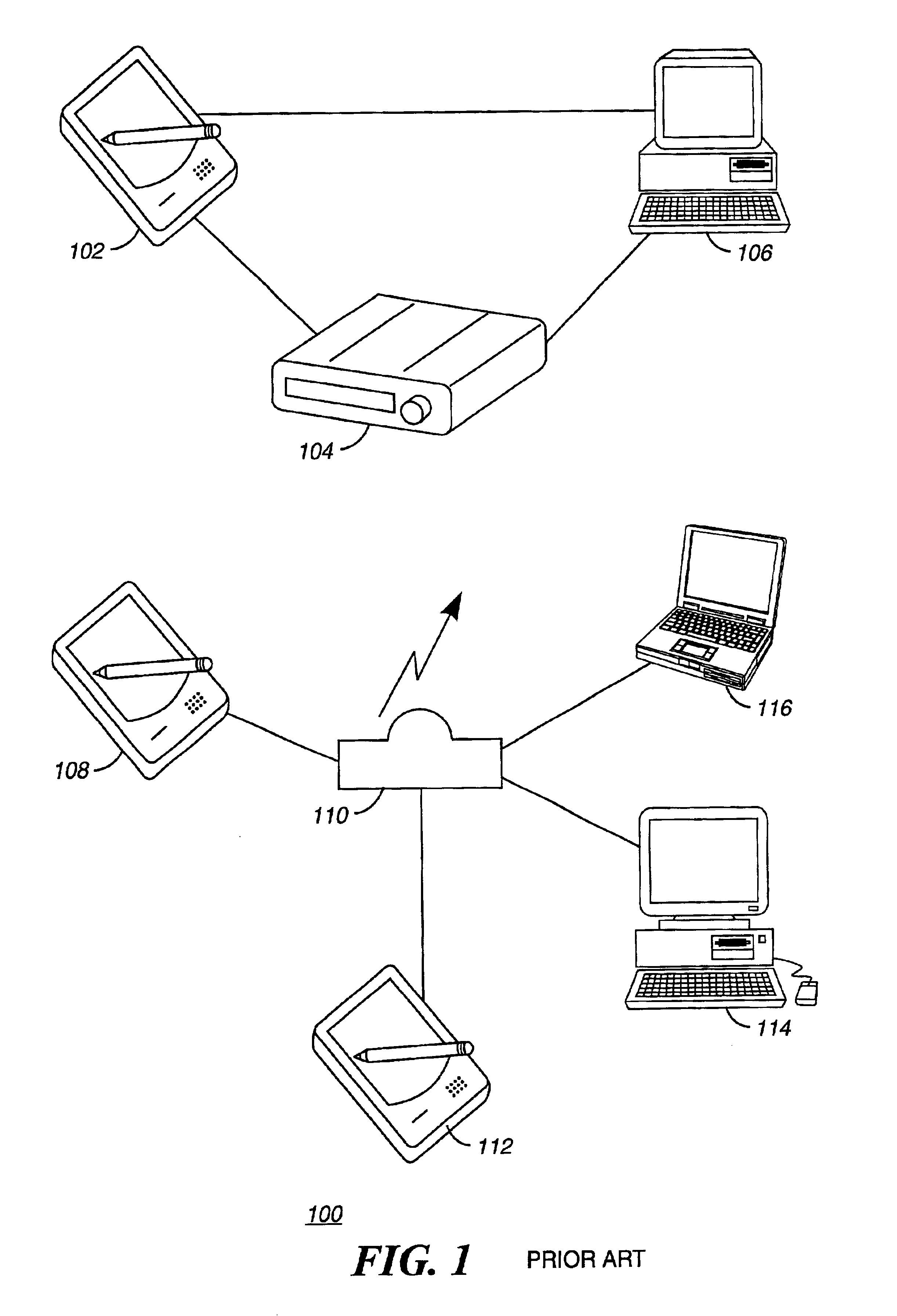

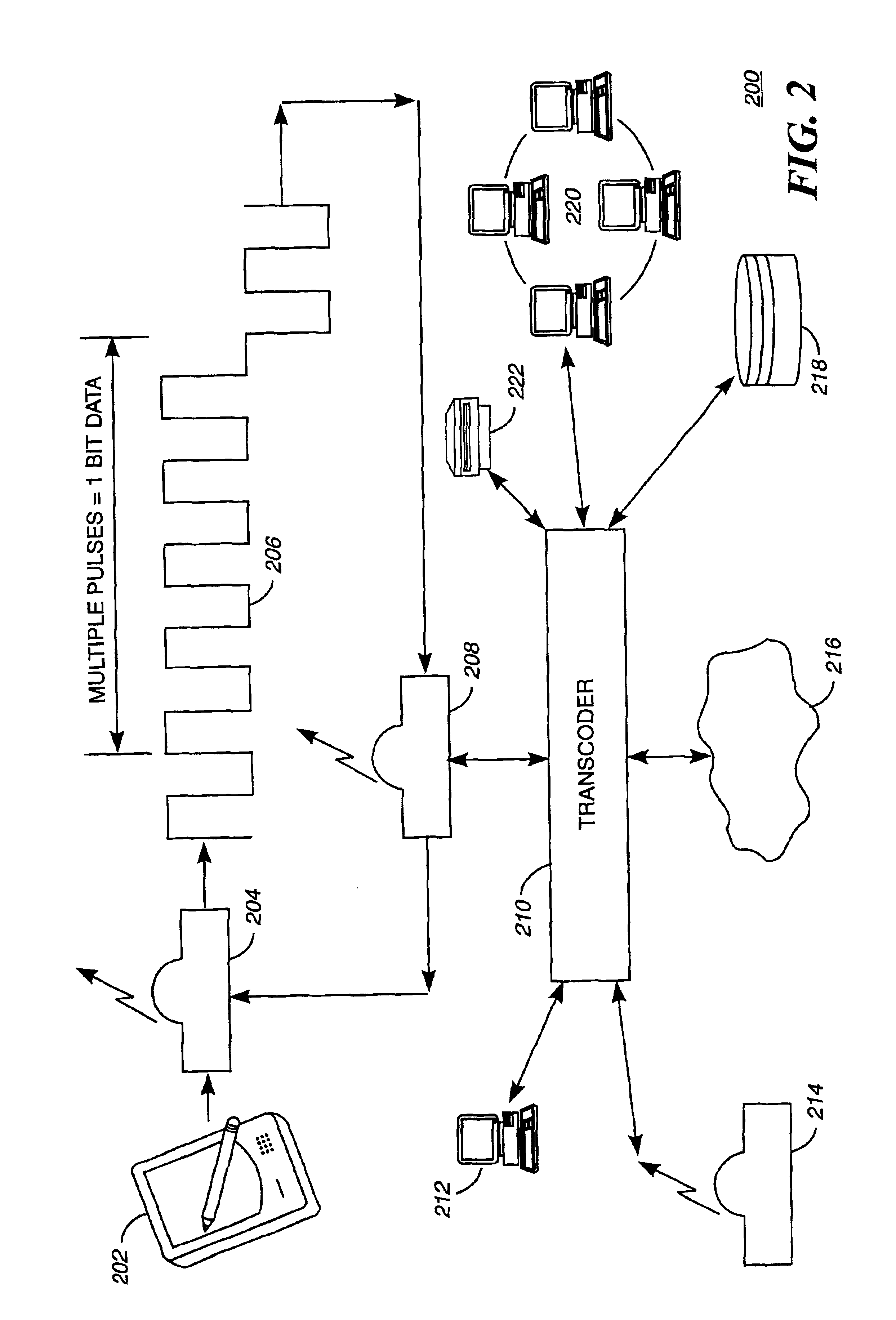

System and method for remote optical digital networking of computing devices

InactiveUS6920289B2Widely distributedIncrease rangeElectric signal transmission systemsFrequency/rate-modulated pulse demodulationData transmissionMobile device

This invention extends the range of optical data of mobile device by trading speed for distance as well as integrating a plurality of pulses over time to define a single bit of information. The present invention uses a number of integrated pulses to represent a single bit instead of utilizing a one to one correspondence between pulses and bits. The present invention executes a range extender application which executes on the mobile device without any hardware modification to the mobile device. The range extender application causes the optical transmitter to “stutter” or repetitively emanate the identical pulse representing a bit of information. Sufficient photons are thereby gathered at a receiver to reach a predetermined threshold. A tradeoff of the data transmission frequency in this invention is that a signal intensity drops by a factor of 100 when distance increases by a factor of 10 yielding a distance / intensity ratio of {fraction (1 / 10)}.

Owner:GLOBALFOUNDRIES US INC

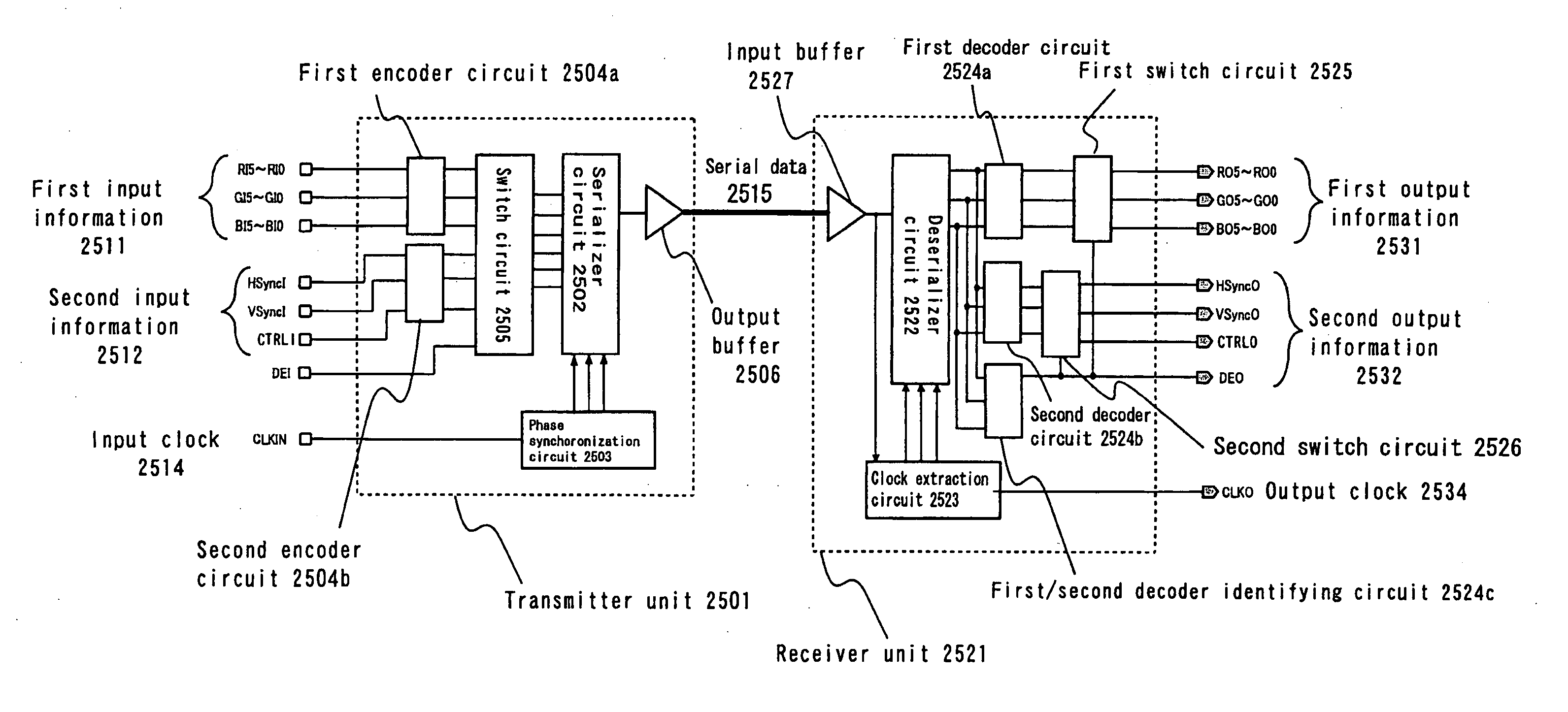

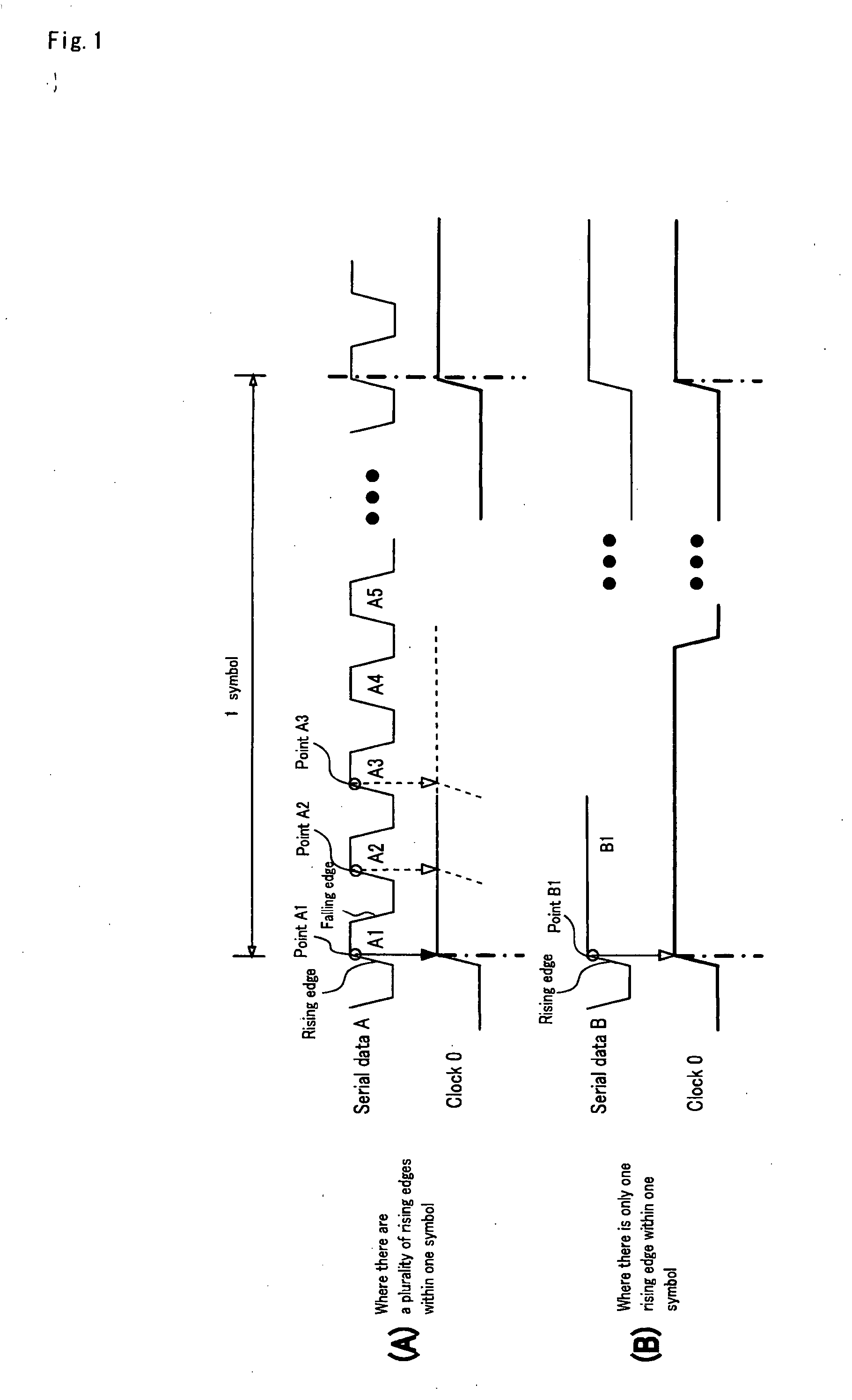

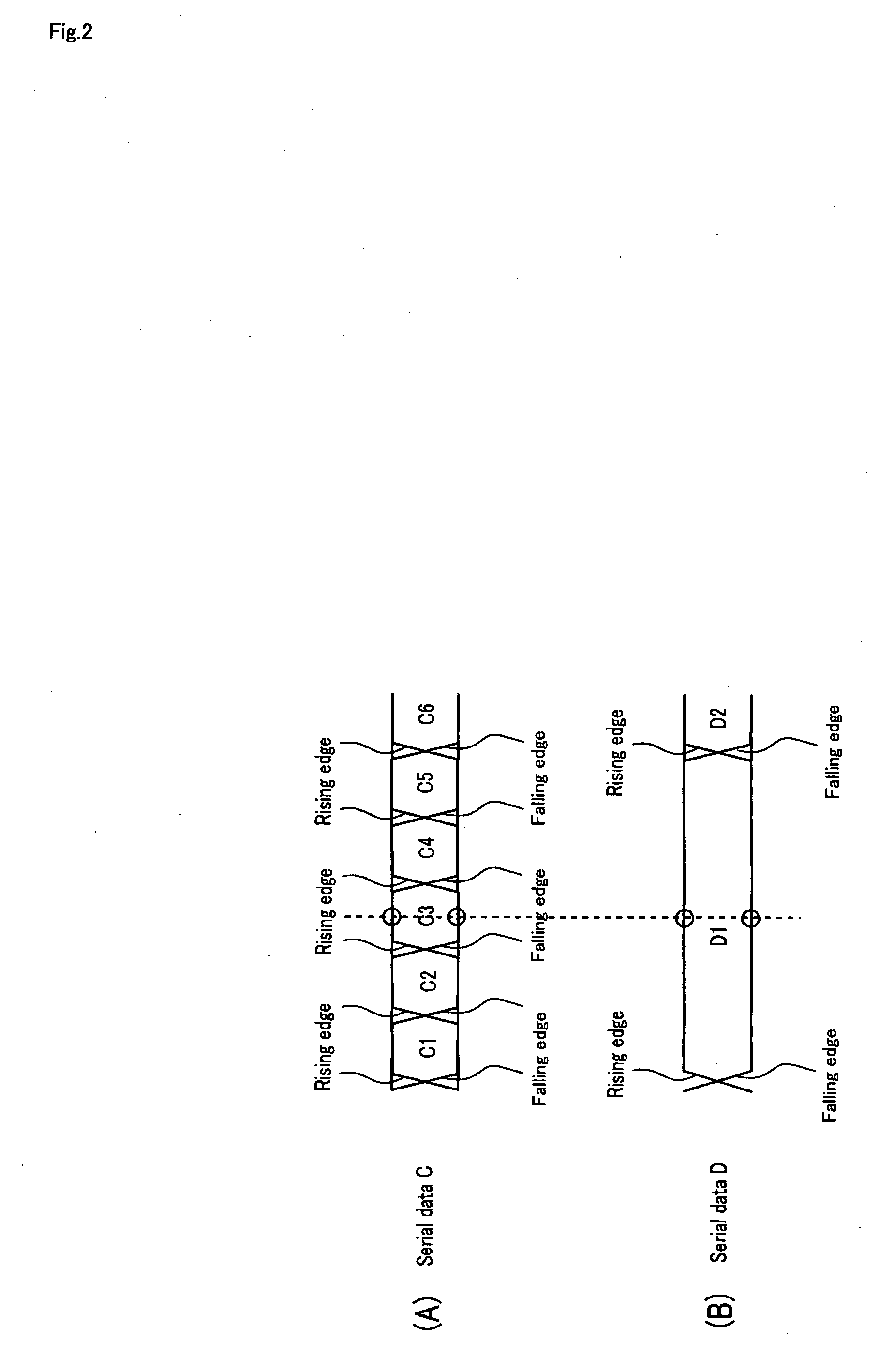

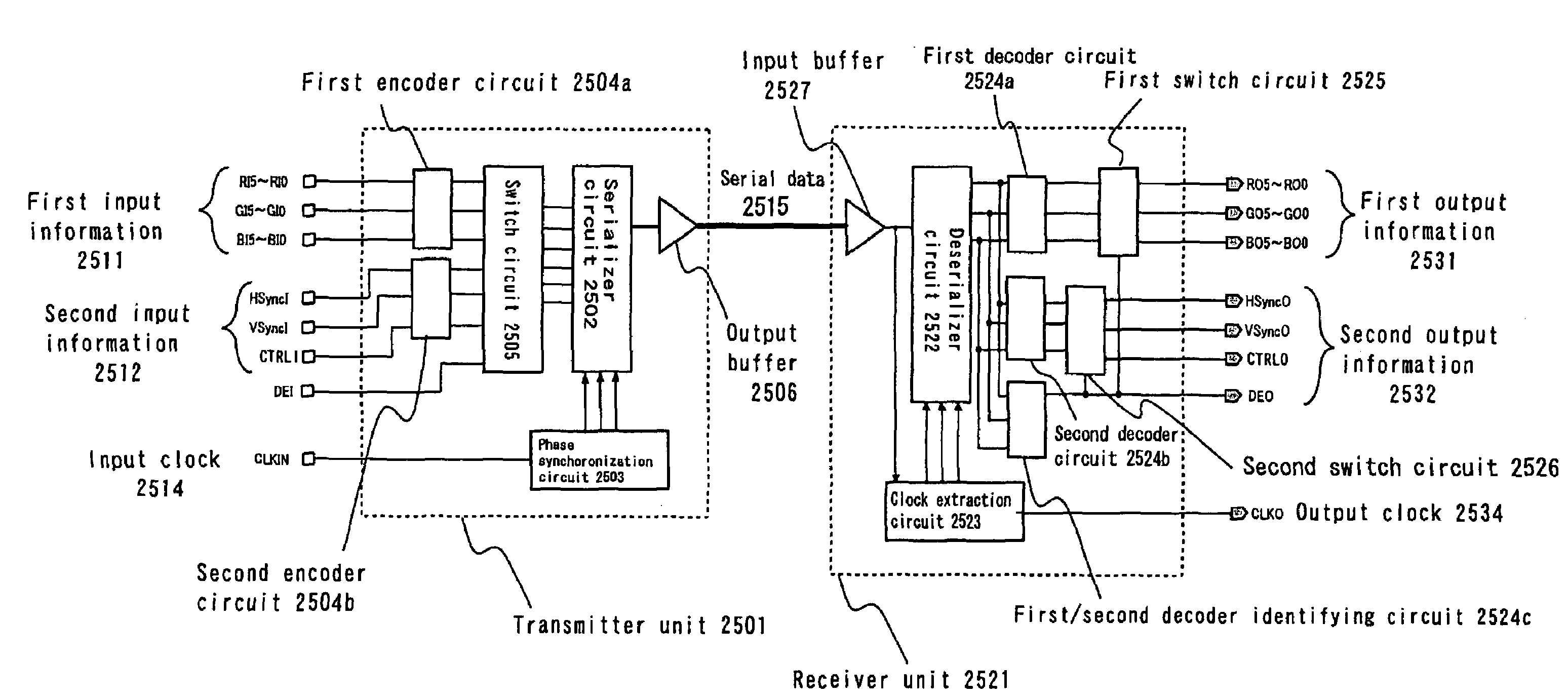

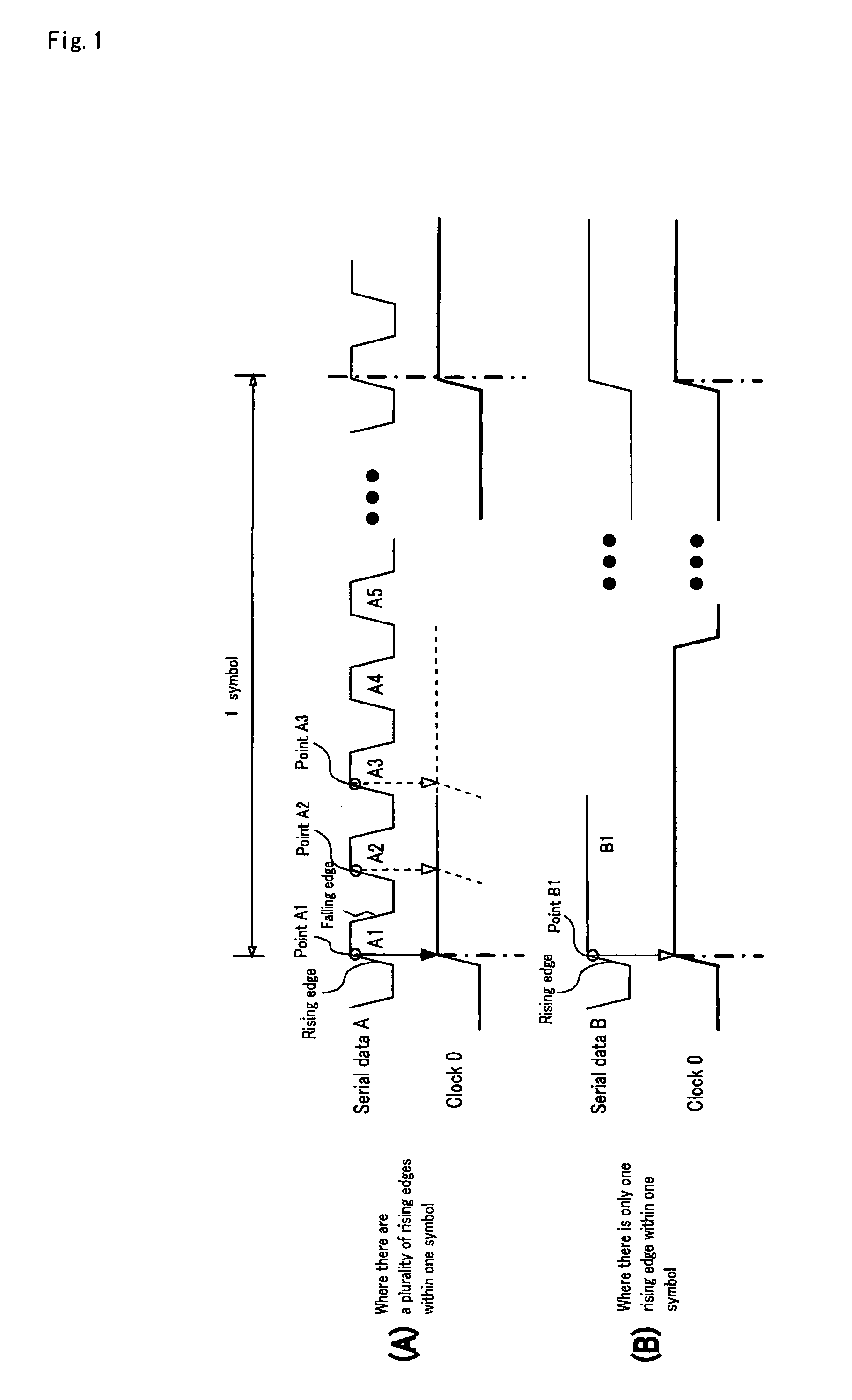

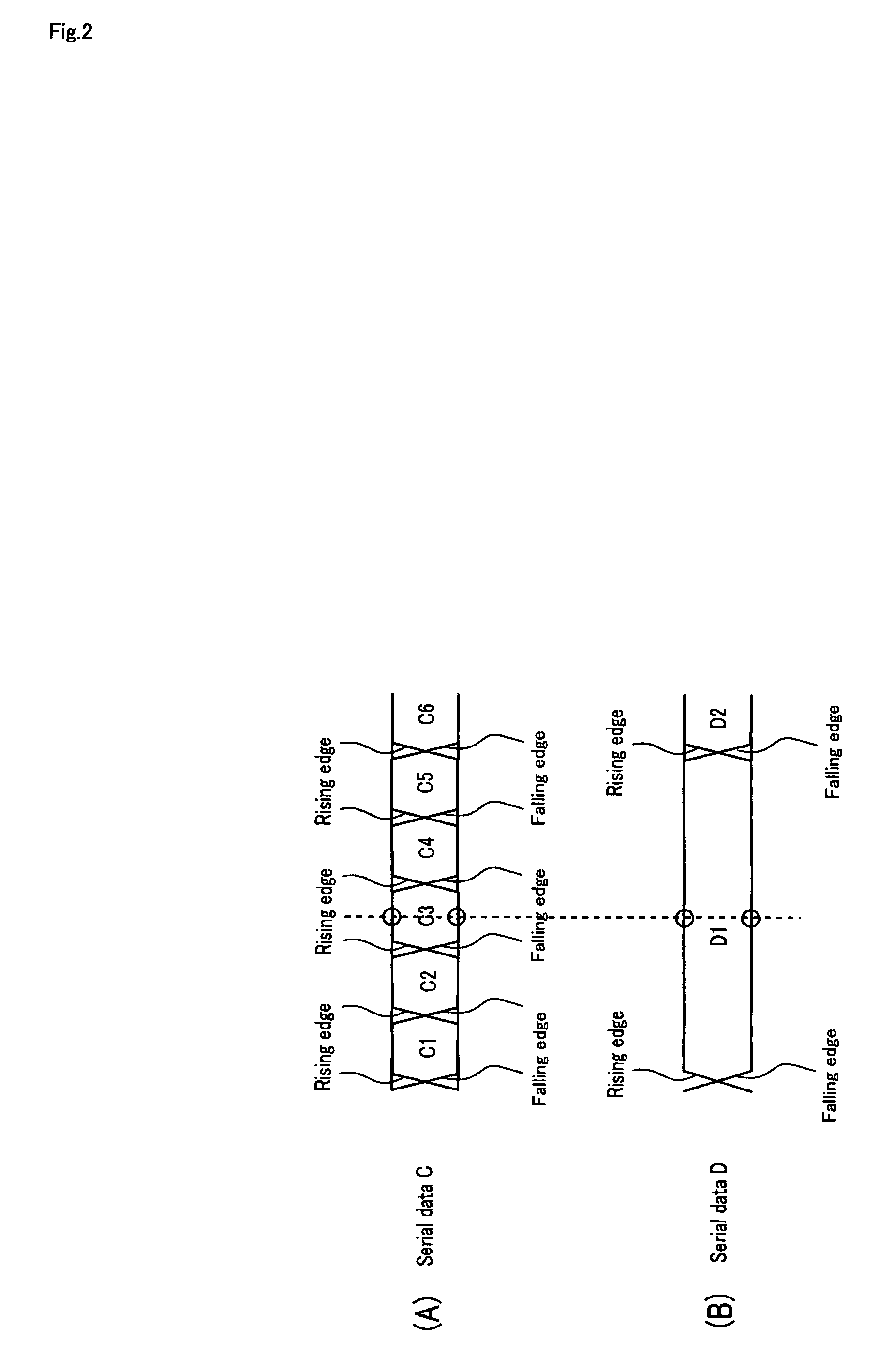

Transmitter circuit, receiver circuit, clock data recovery phase locked loop circuit, data transfer method and data transfer system

ActiveUS20050286643A1Reduce errorsData transmission is stableTelevision system detailsFrequency/rate-modulated pulse demodulationDigital dataPhase locked loop circuit

[Problems] To realize a reliable and stable transfer of digital data that does not require a reference clock and a handshake operation. [Means for Solving the Problem] The present invention provides a digital data transfer method for alternately and periodically transferring first information and second information respectively in a first period and in a second period, wherein: an amount of information of the first information per unit time in the first period is greater than an amount of information of the second information per unit time in the second period; and the second information in the first period is transferred as pulse-width-modulated serial data.

Owner:THINE ELECTRONICS

Transmitter circuit, receiver circuit, clock data recovery phase locked loop circuit, data transfer method and data transfer system

ActiveUS7535957B2Reduce errorsData transmission is stableTelevision system detailsFrequency/rate-modulated pulse demodulationDigital dataPhase locked loop circuit

[Problems] To realize a reliable and stable transfer of digital data that does not require a reference clock and a handshake operation.[Means for Solving the Problem] The present invention provides a digital data transfer method for alternately and periodically transferring first information and second information respectively in a first period and in a second period, wherein: an amount of information of the first information per unit time in the first period is greater than an amount of information of the second information per unit time in the second period; and the second information in the first period is transferred as pulse-width-modulated serial data.

Owner:THINE ELECTRONICS

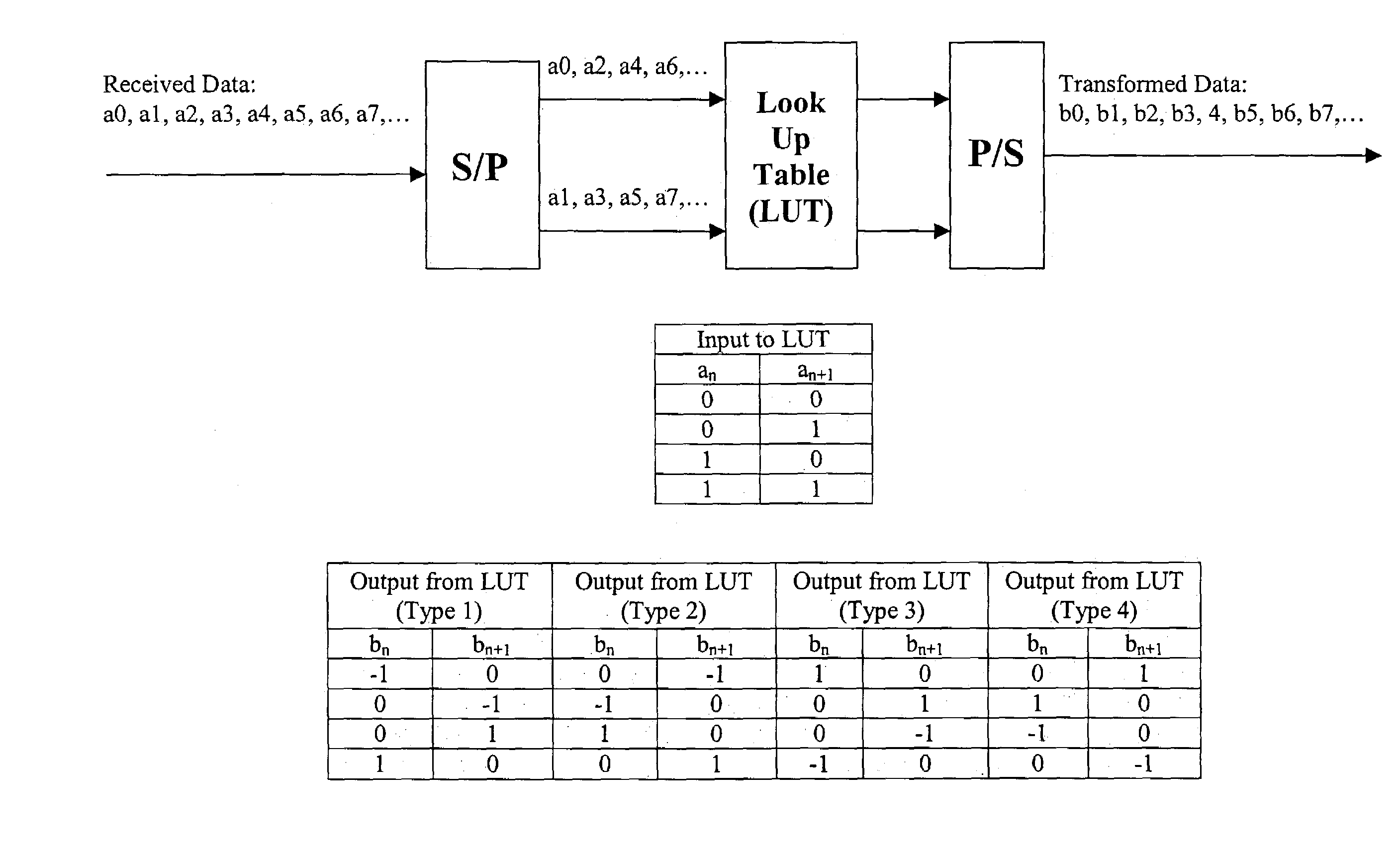

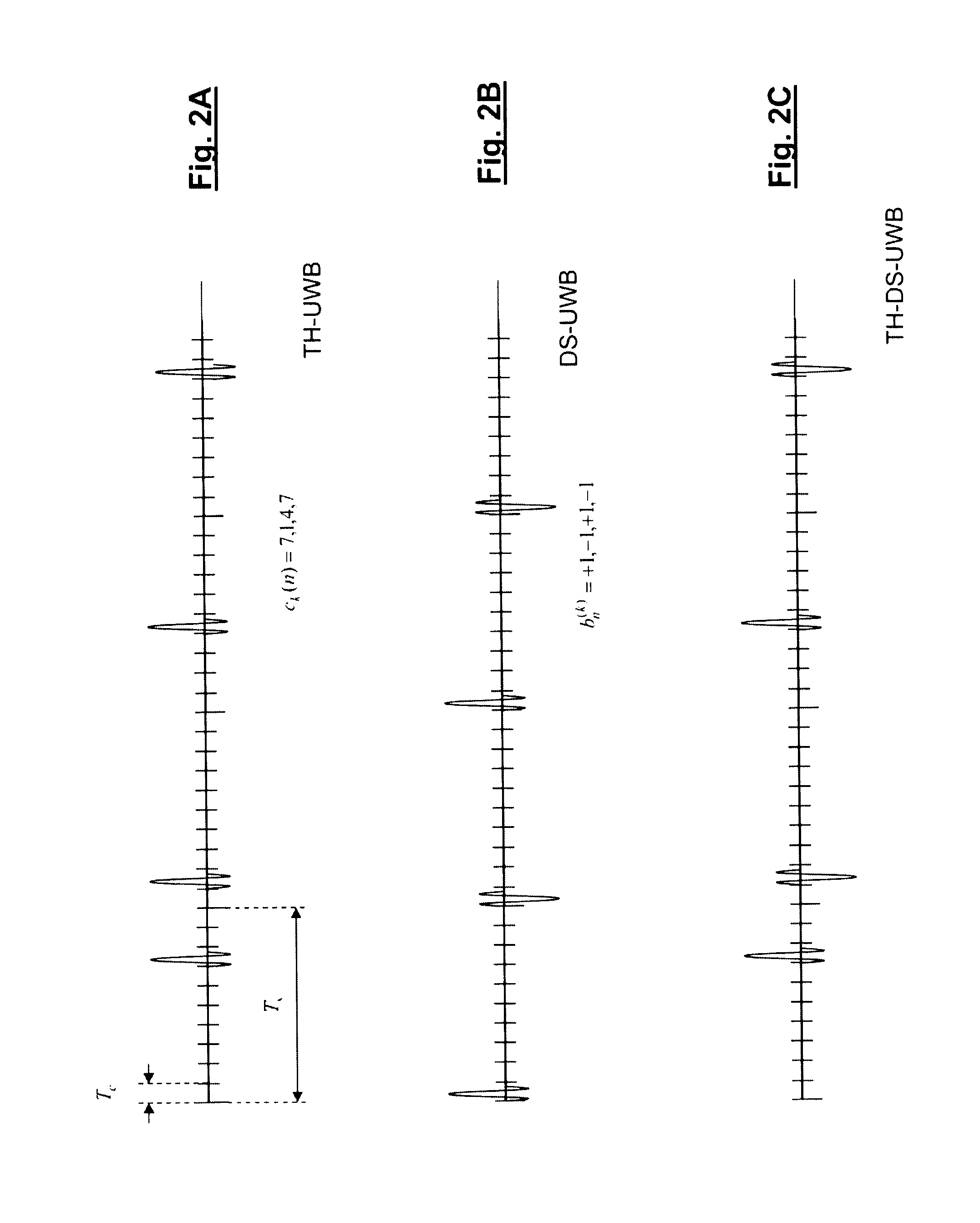

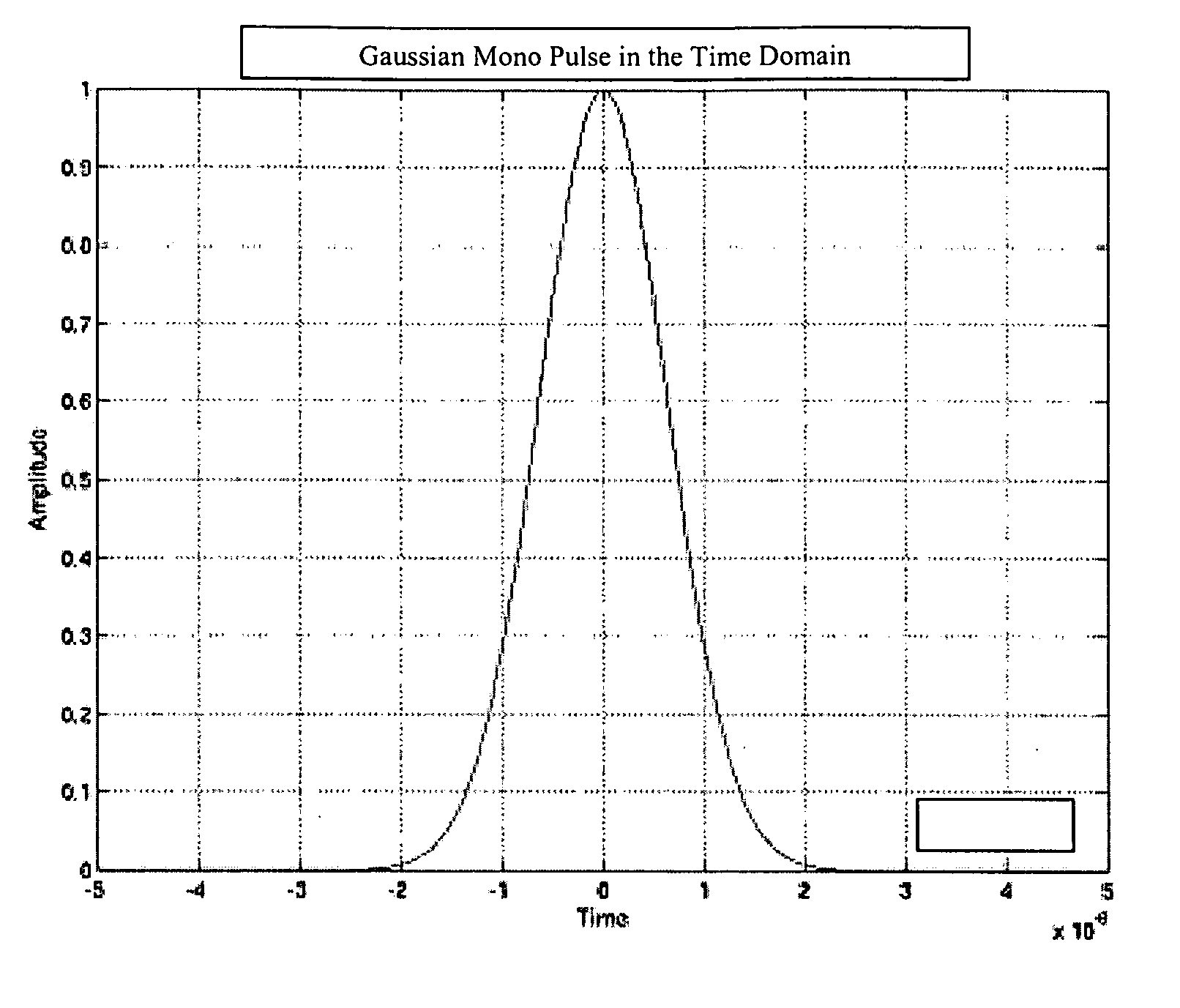

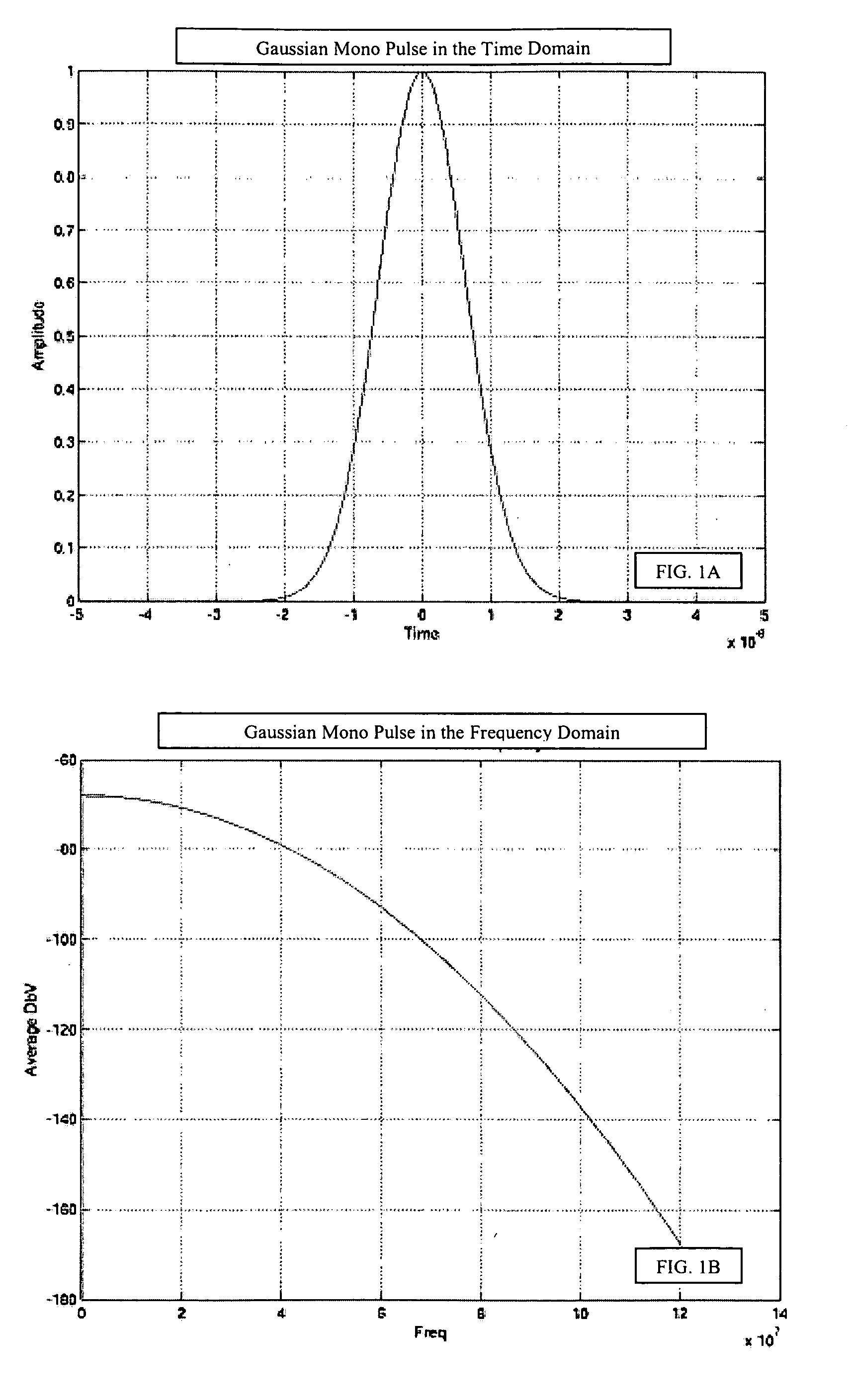

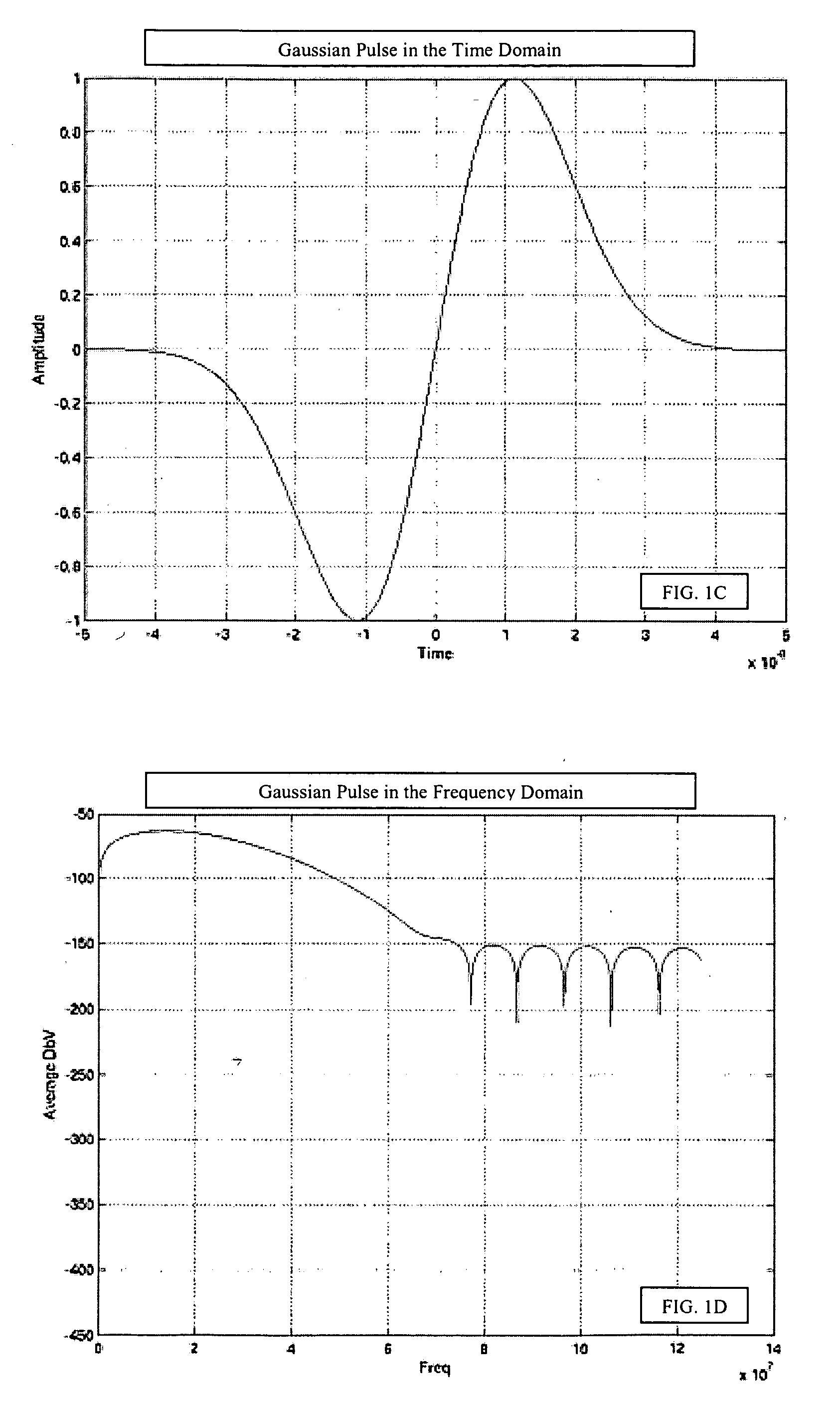

Ultra-wideband pulse modulation system and method

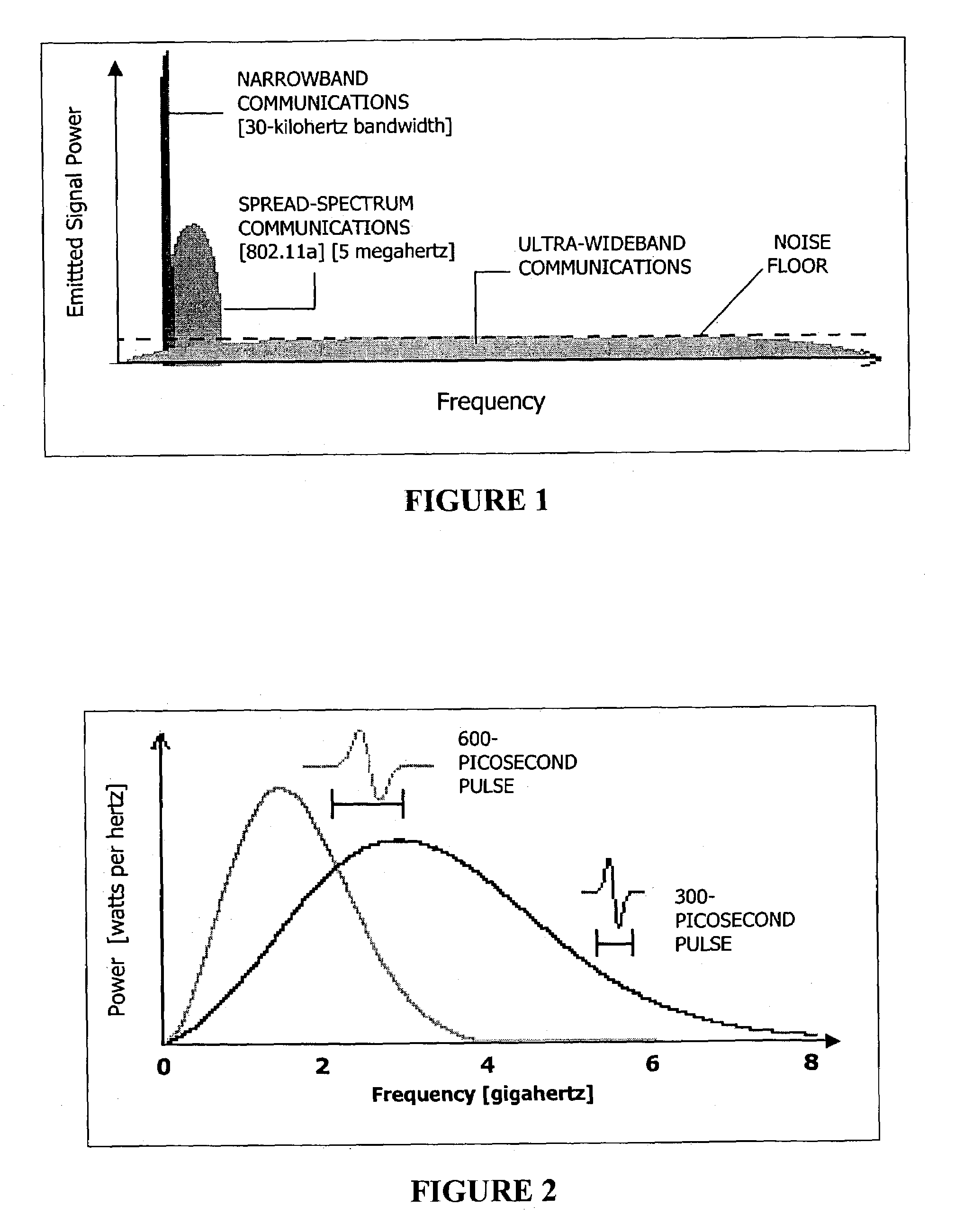

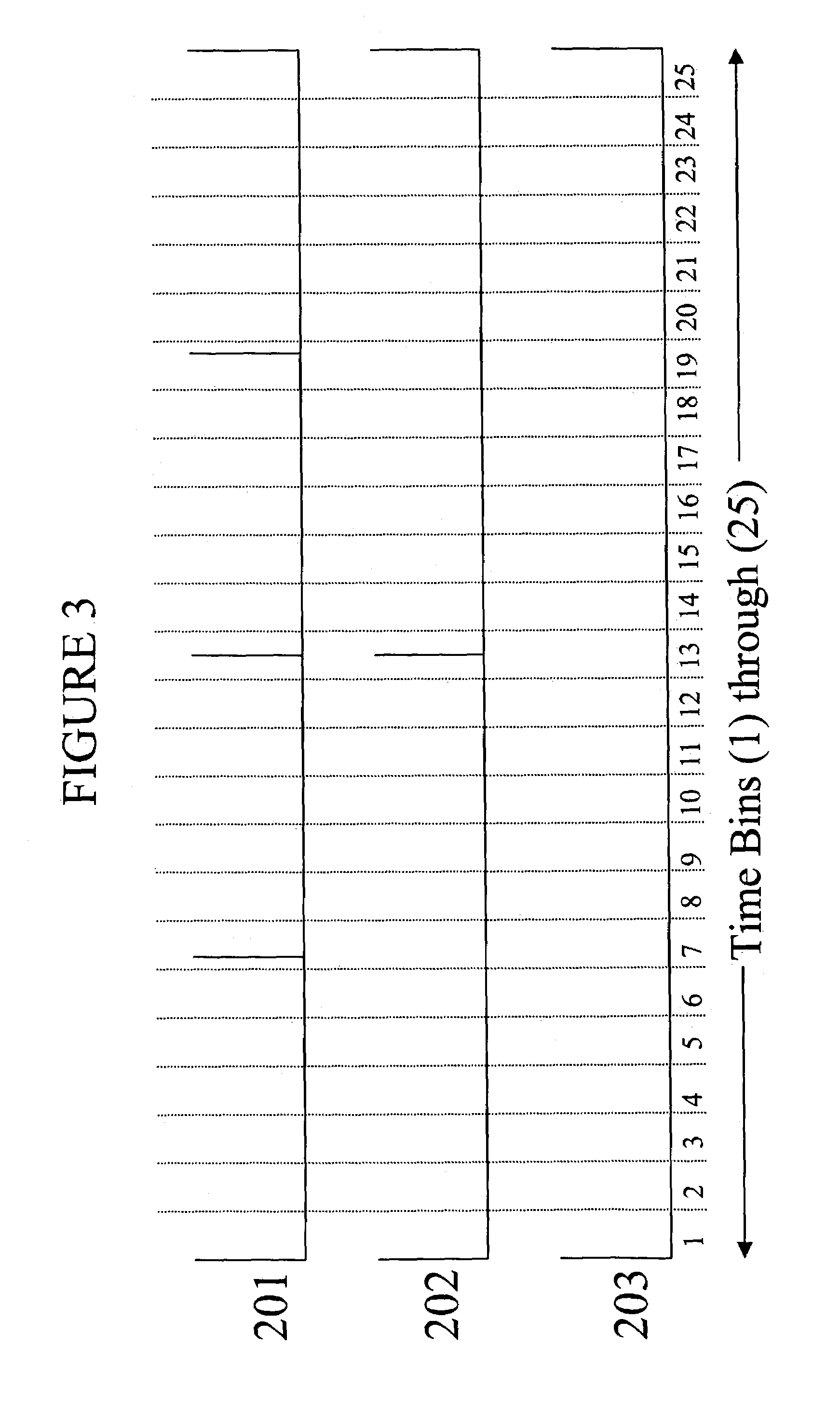

InactiveUS7190722B2Available bandwidth of communicationIncrease powerFrequency/rate-modulated pulse demodulationIndividual digits conversionUltra-widebandFiber

An ultra-wideband pulse modulation system and method is provided. One method of the present invention includes transforming data into a ternary data set with data being represented with states of zero, positive one and negative one. The modulation and pulse transmission method of the present invention enables the simultaneous coexistence of the ultra-wideband pulses with conventional carrier-wave signals. The present invention may be used in wireless and wired communication networks such as hybrid fiber-coax networks. This Abstract is provided for the sole purpose of complying with the Abstract requirement rules that allow a reader to quickly ascertain the subject matter of the disclosure contained herein. This Abstract is submitted with the explicit understanding that it will not be used to interpret or to limit the scope or the meaning of the claims.

Owner:INTELLECTUAL VENTURES HLDG 73

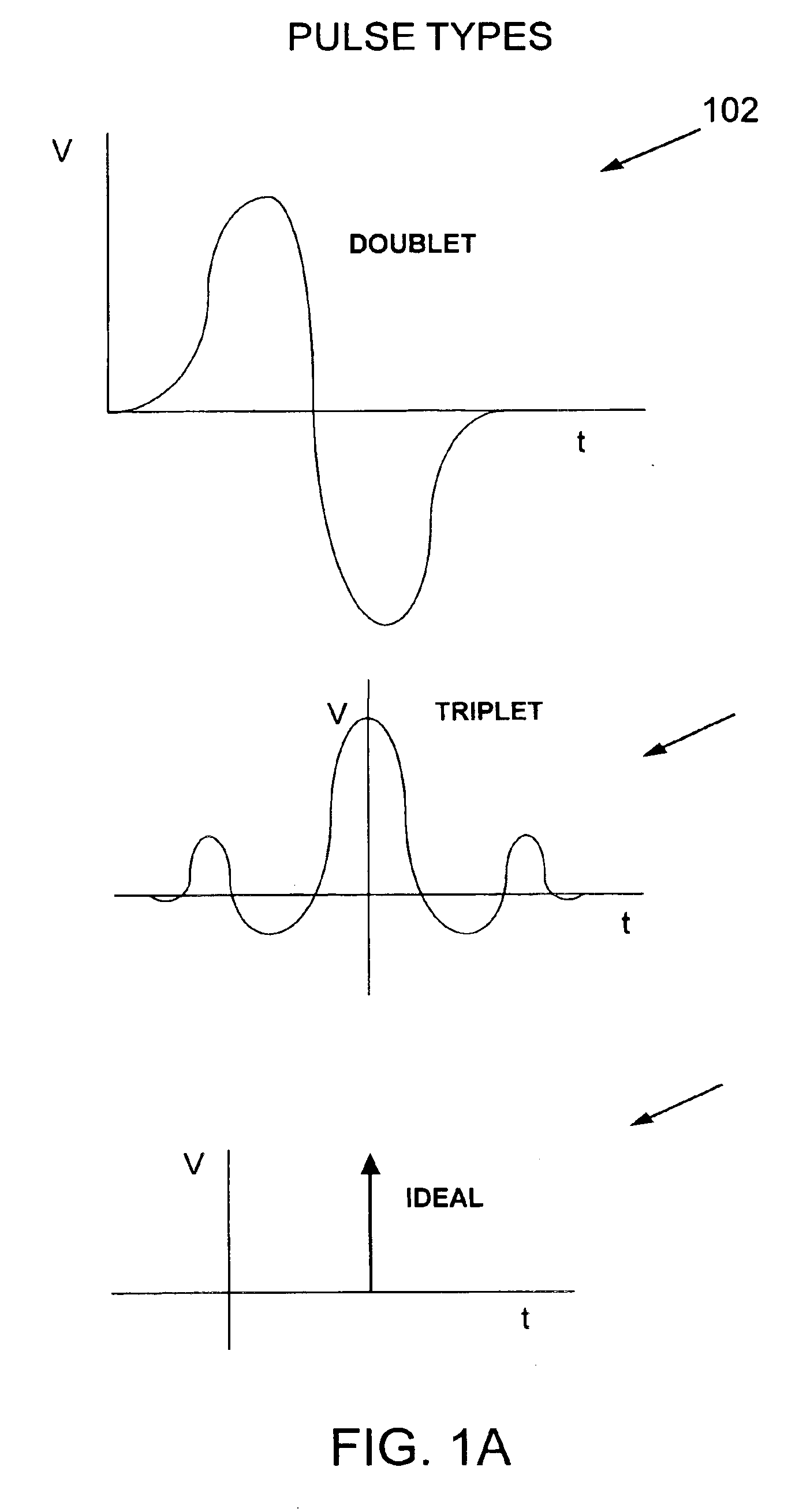

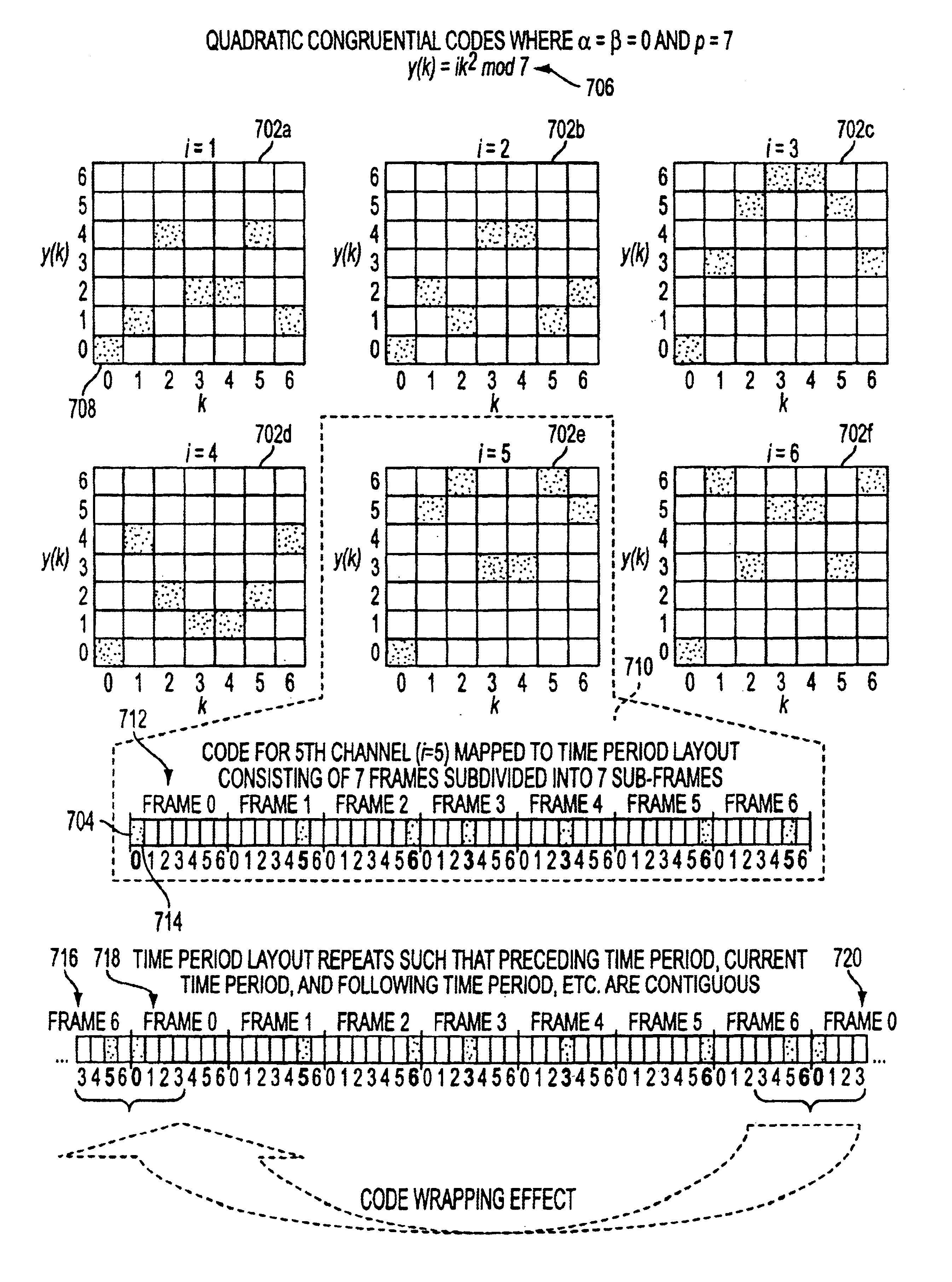

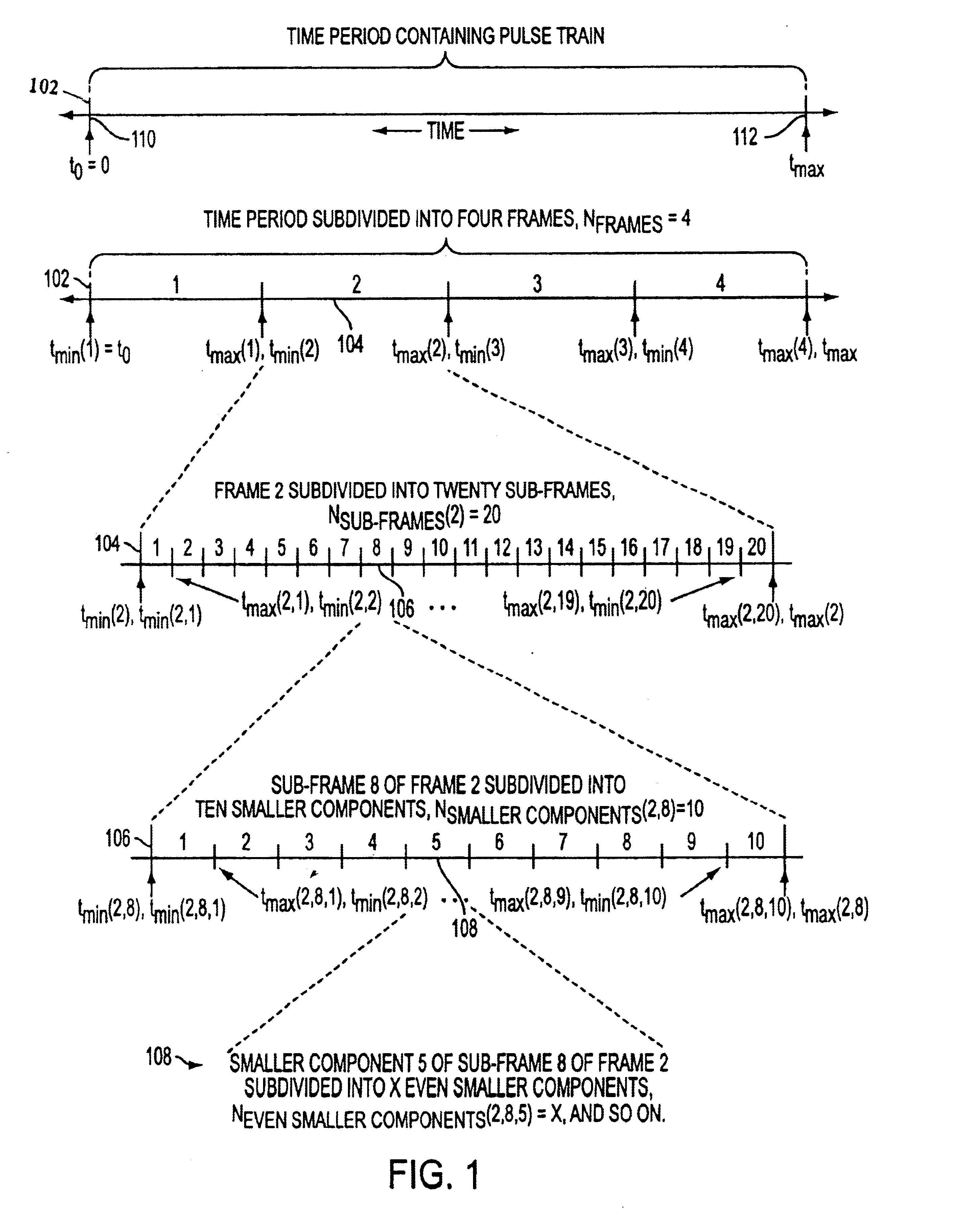

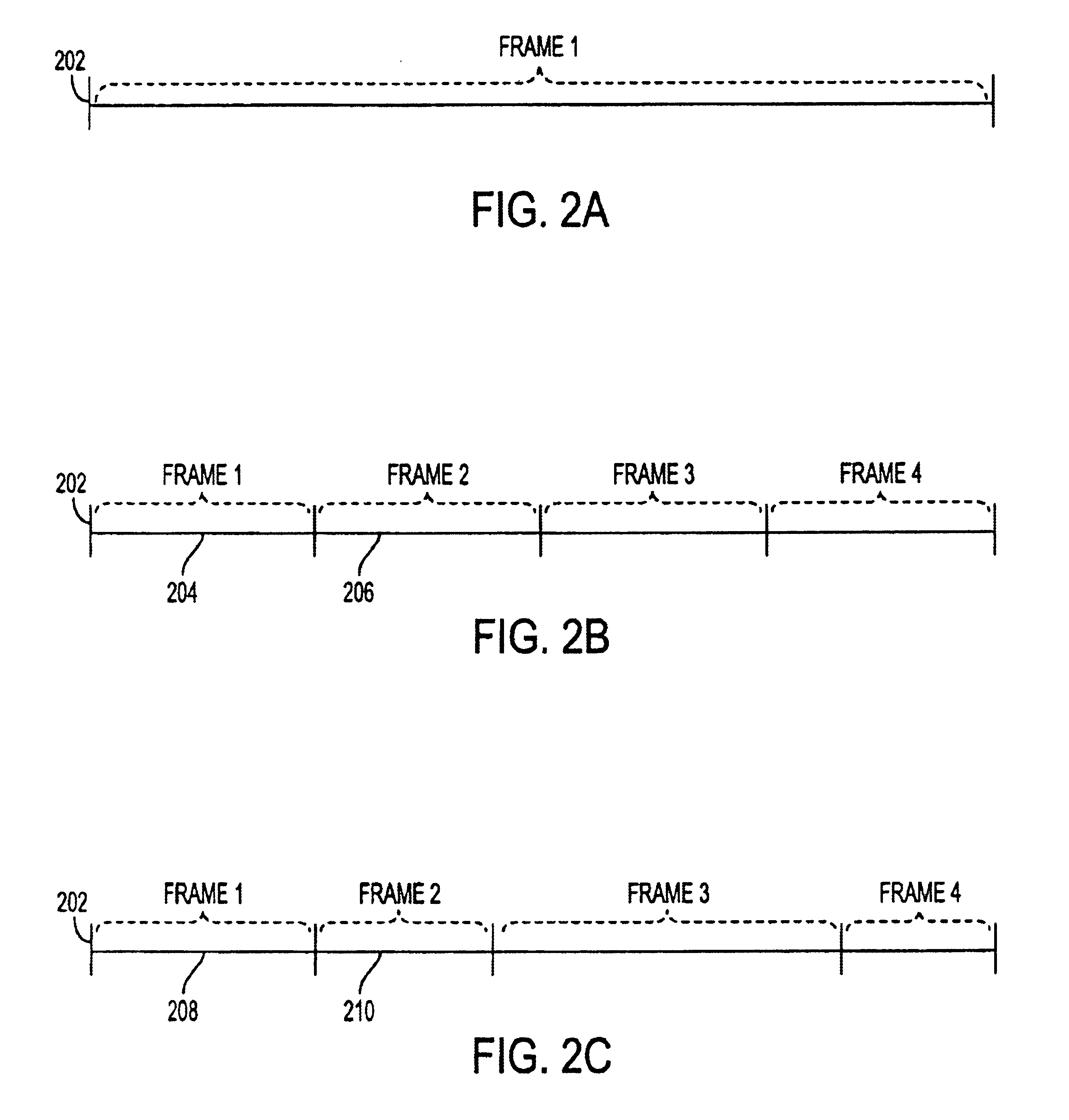

System and method for positioning pulses in time using a code that provides spectral shaping

InactiveUS6937639B2Minimizing the code spectrumDifferenceBeacon systems using radio wavesFrequency/rate-modulated pulse demodulationRadar systemsFrequency spectrum

A system, method and computer program product for positioning pulses, including positioning pulses within a specified time layout according to one or more codes to produce a pulse train having one or more predefined spectral characteristics where a difference in time position between adjacent pulses positioned to produce a spectral characteristic differs from another difference in time position between other adjacent pulses positioned to produce the spectral characteristic. The present invention may include shaping a code spectrum according to a spectral template in order to preserve a pre-defined code characteristic. A pre-defined code characteristic can include desirable correlation, or spectral properties. A transmitter incorporating the present invention can avoid transmitting at a particular frequency. Similarly, a receiver can avoid interference with a signal transmitting at a particular frequency. A radar system, can avoid a radar jammer attempting to jam a particular frequency.

Owner:HUMATICS CORP

Apparatus and method for envelope tracking power amplifier in wireless communication system

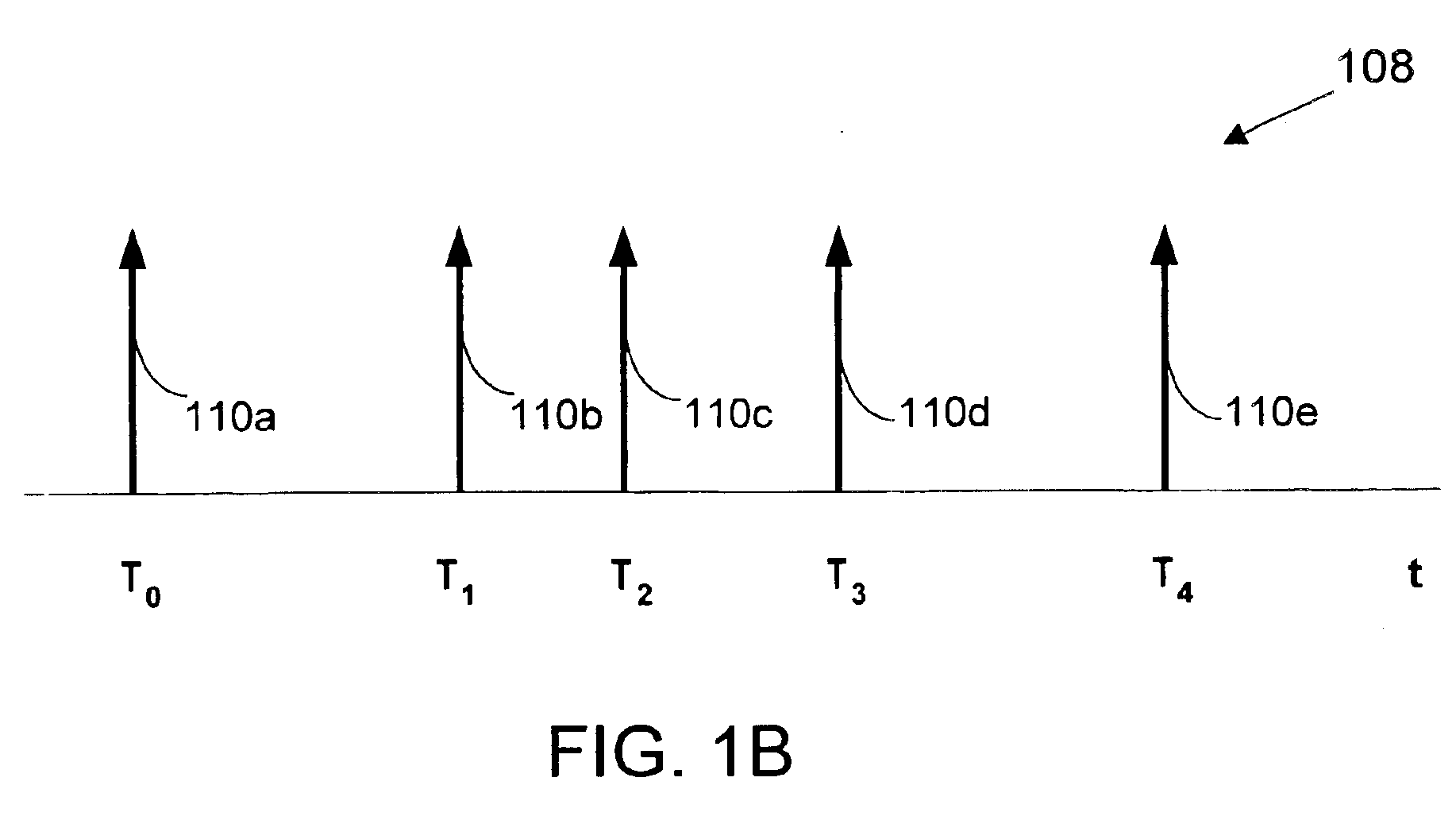

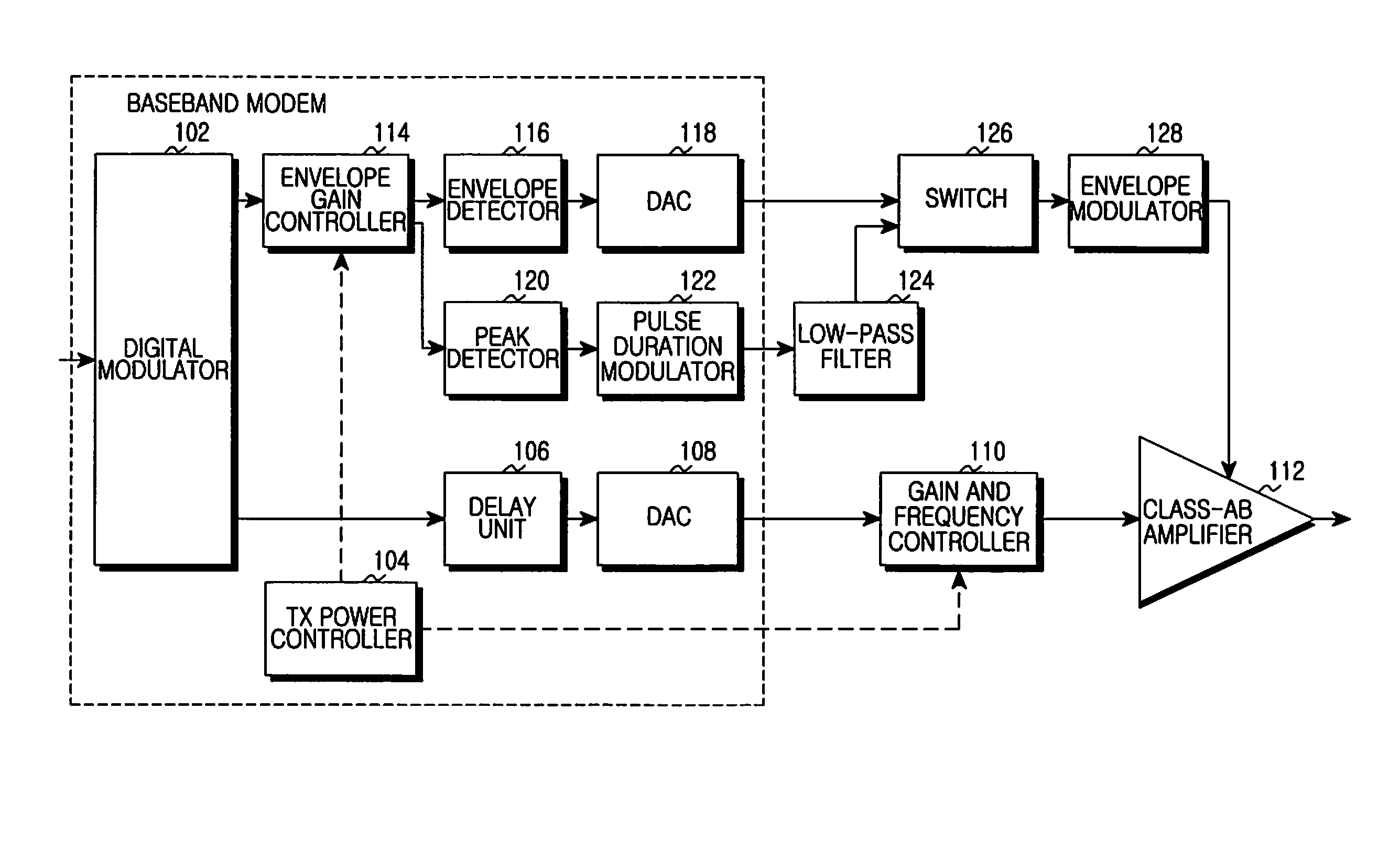

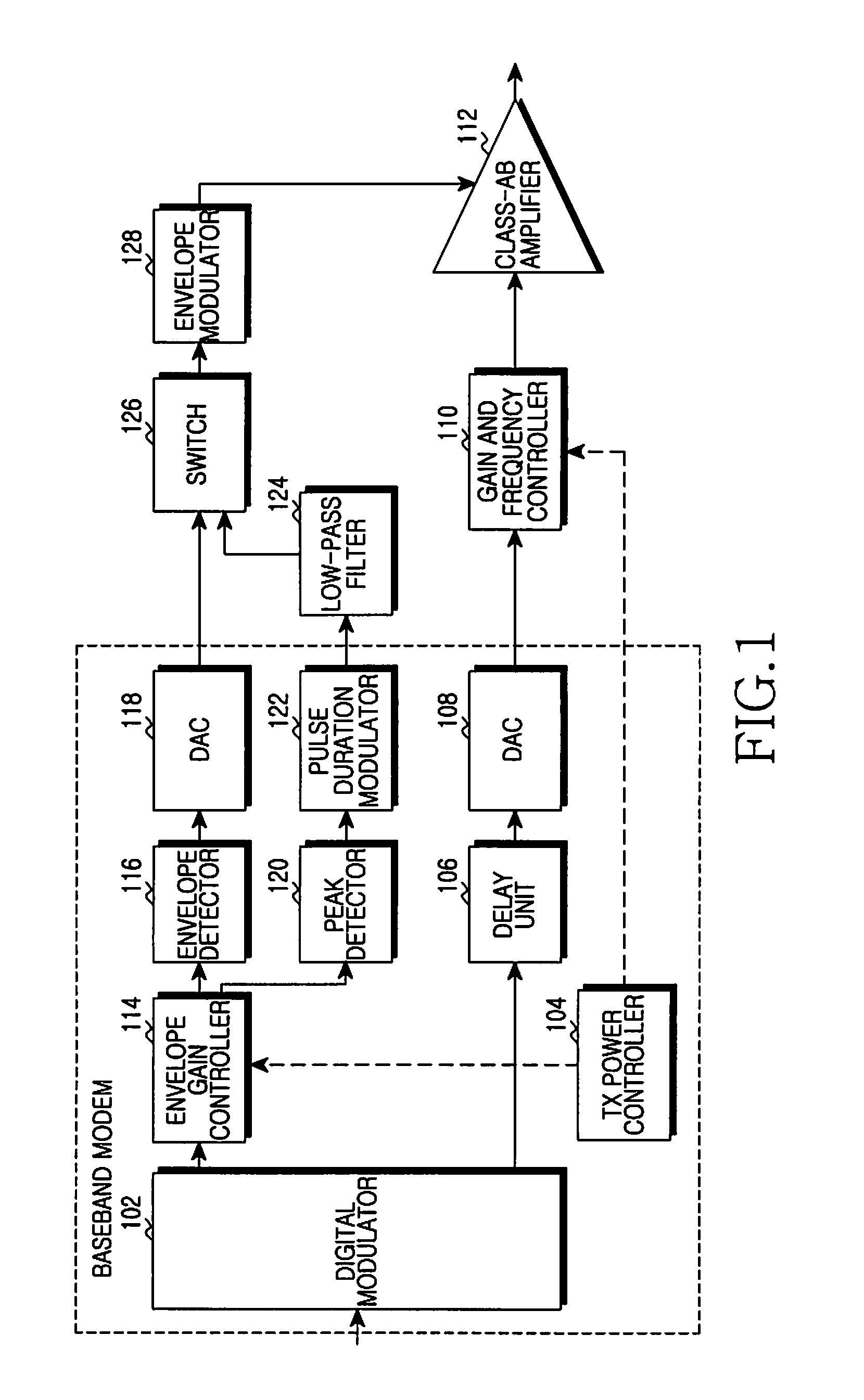

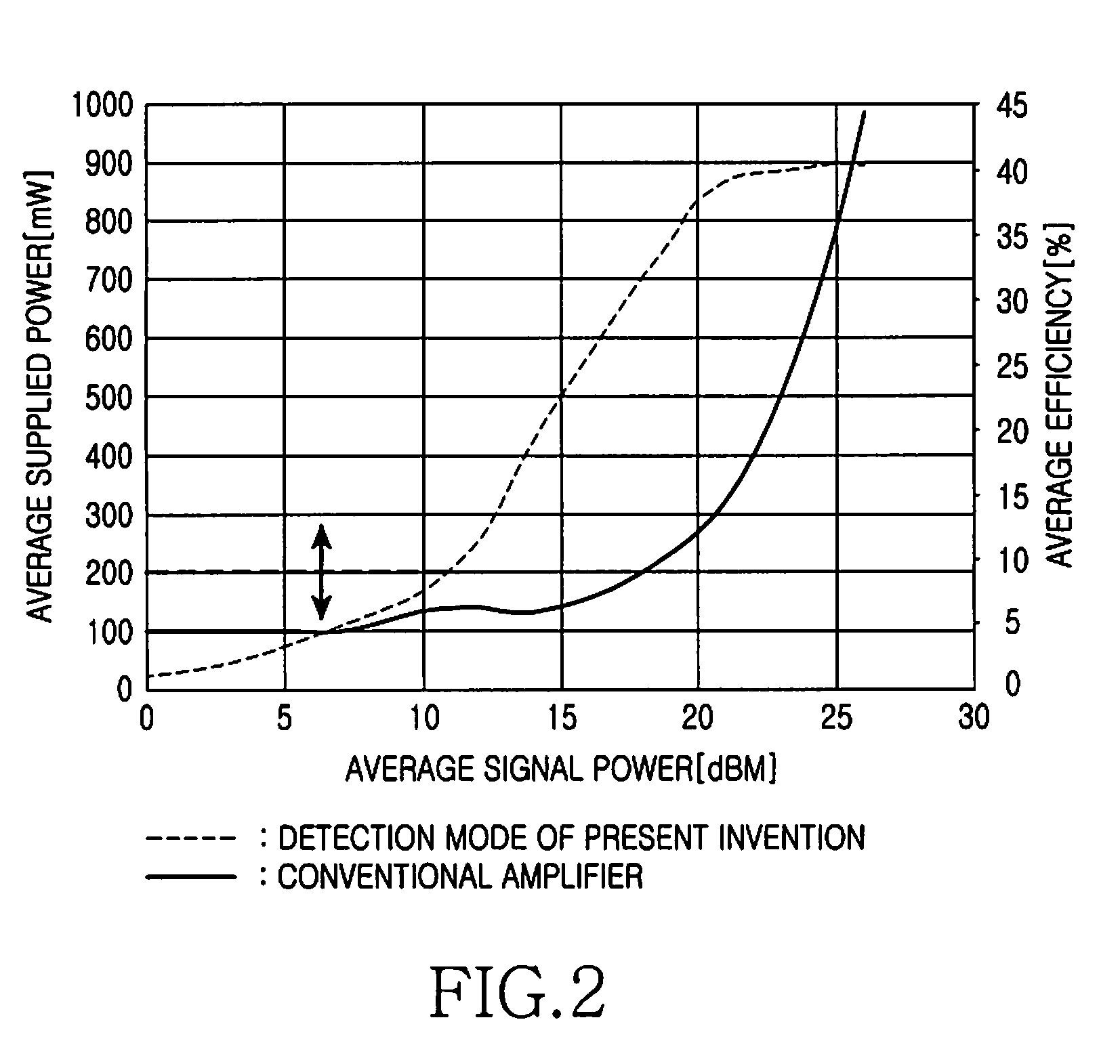

ActiveUS20110058601A1Enhanced signalPulse automatic controlModulated-carrier systemsCommunications systemAudio power amplifier

An apparatus and method for amplifying a Transmit (Tx) signal according to an Envelope Tacking (ET) scheme in a wireless communication system are provided. A transmitting end apparatus includes an envelope gain controller for controlling a gain of a digital baseband Tx signal in accordance with power control, a detector for detecting an envelope signal from the digital baseband Tx signal whose gain is controlled, and for shaping on the envelope signal, a first Digital to Analog Converter (DAC) for converting the shaped envelope signal into an analog signal, and an envelope modulator for generating a drain bias of a power amplifier that amplifies a Radio Frequency (RF) Tx signal by using the analog envelope signal. Accordingly, a digital-based ET scheme is implemented, and by using a plurality of shaping tables, efficiency of the ET scheme can be maximized in a transmitting end that uses power control.

Owner:SAMSUNG ELECTRONICS CO LTD

Method and apparatus for positioning pulses in time

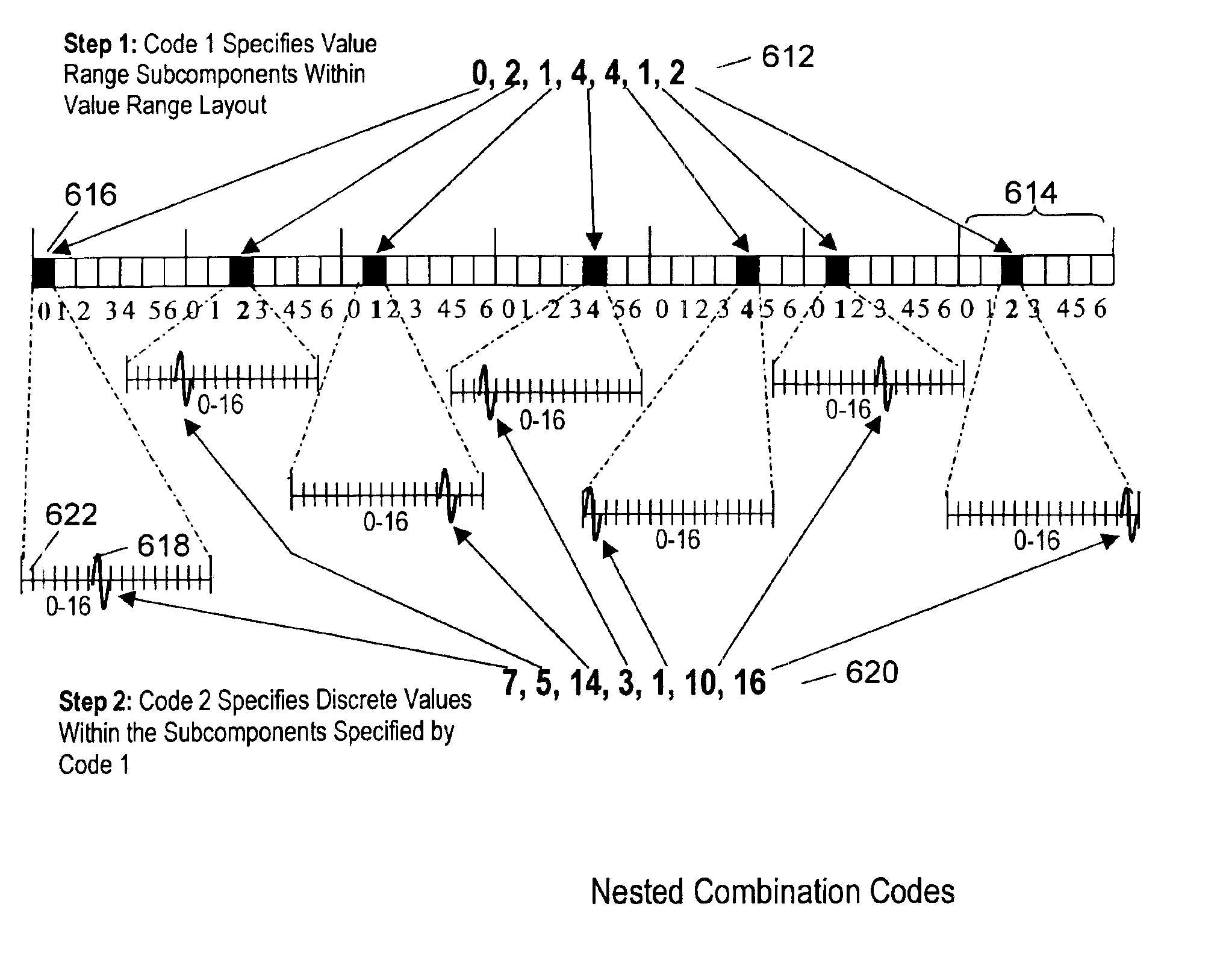

InactiveUS6959032B1Frequency/rate-modulated pulse demodulationPosition-modulated pulse demodulationPositioning systemSpectral properties

A coding method specifies pulse positioning over time according to a time layout about a time reference where a pulse can be placed at any location within the time layout. The method generates time-hopping codes having predefined properties, and a coded pulse train based on the time-hopping codes and the time layout. The time reference may be fixed or non-fixed and can be a time position of a preceding or a succeeding pulse. In addition, the predefined properties can be autocorrelation, cross-correlation, or spectral properties.

Owner:HUMATICS CORP

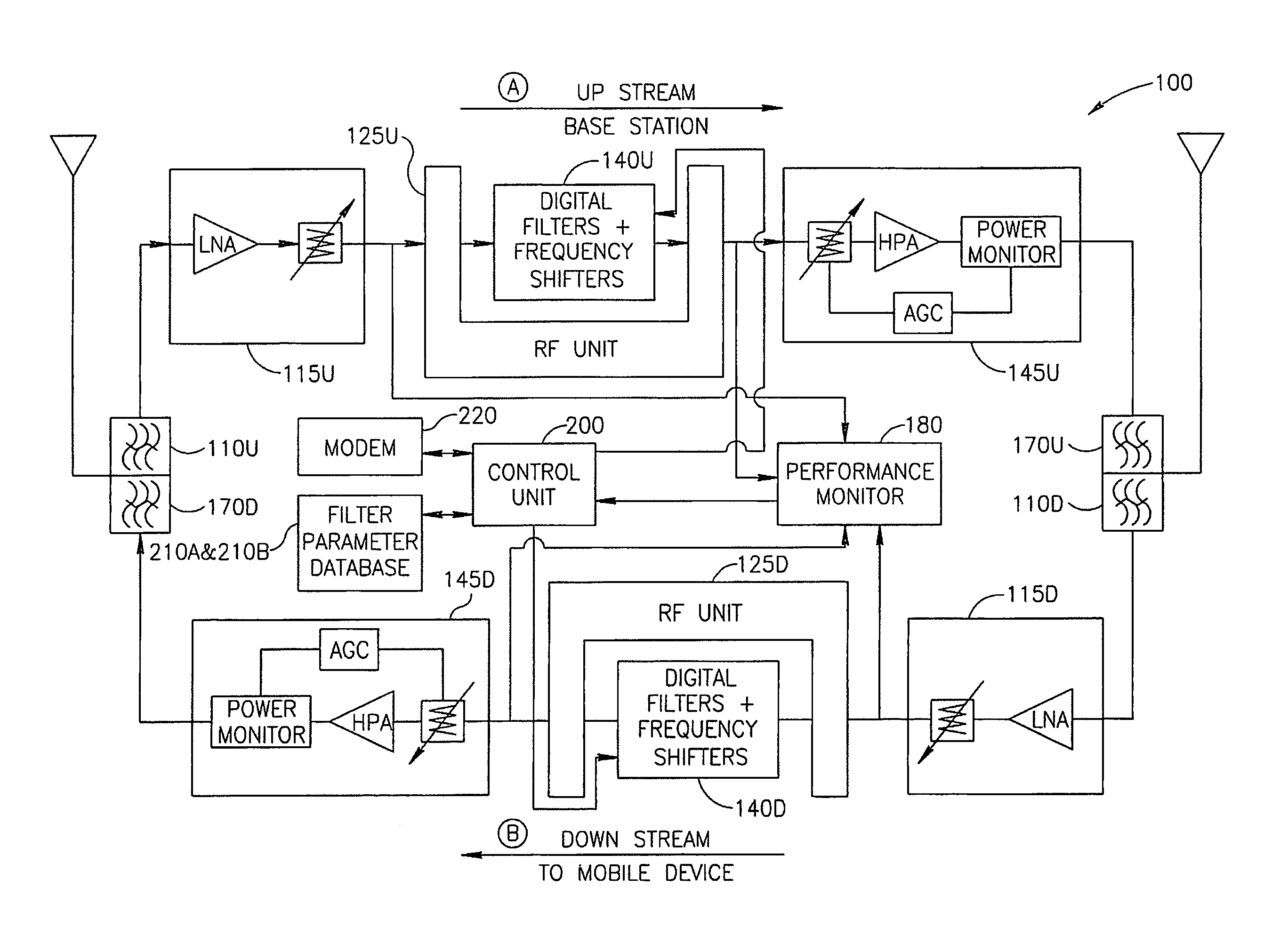

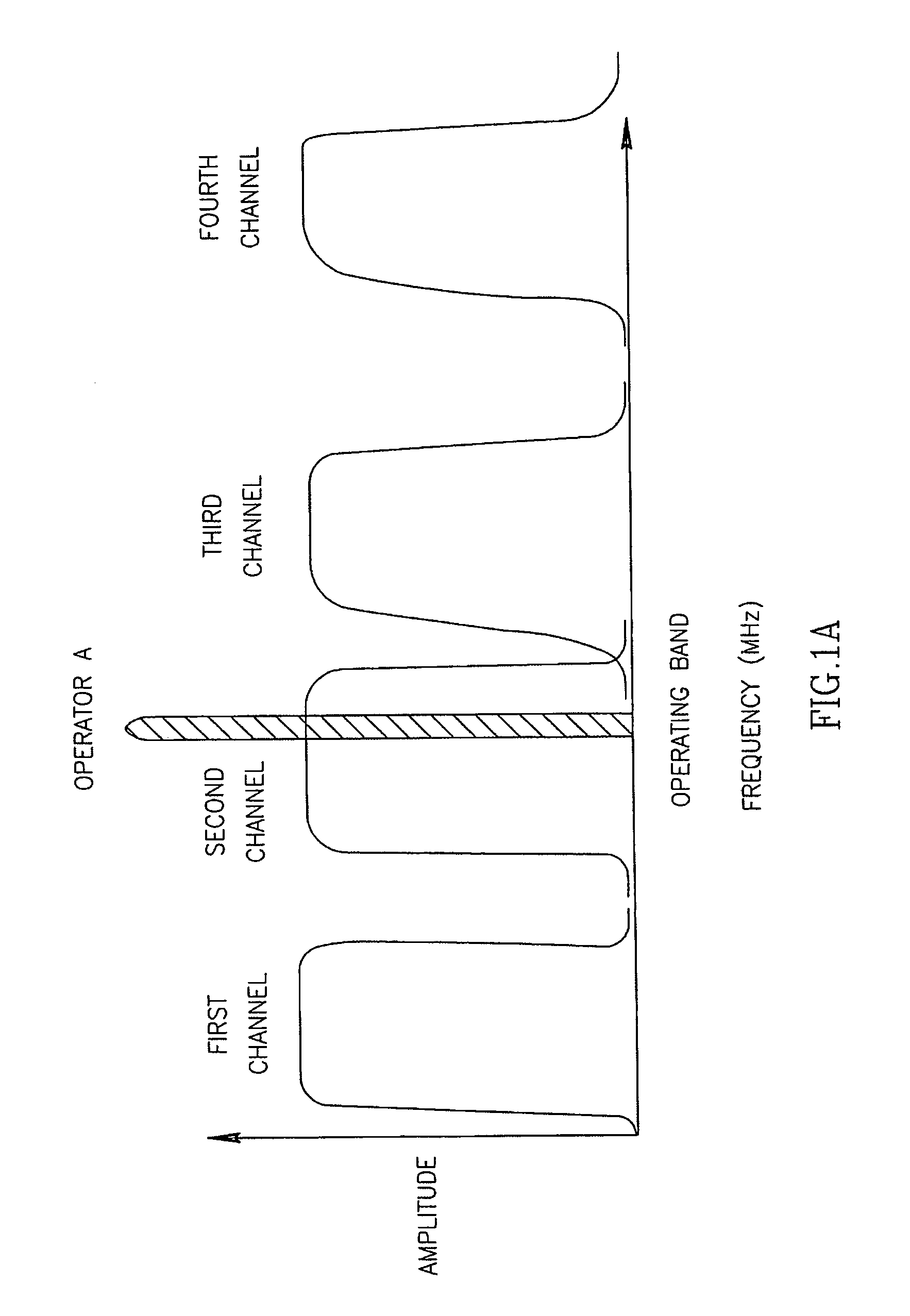

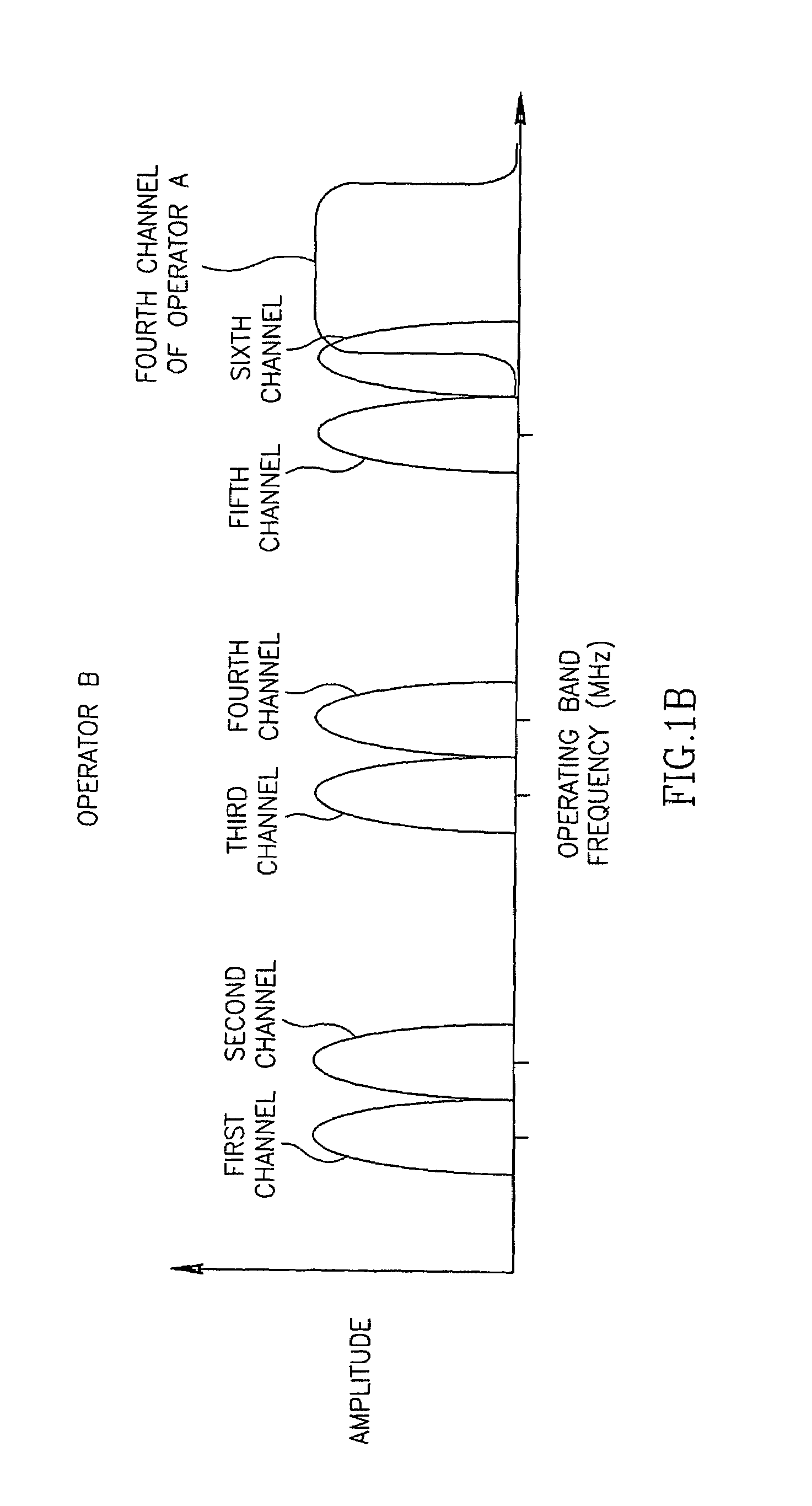

System and method for excluding narrow band noise from a communication channel

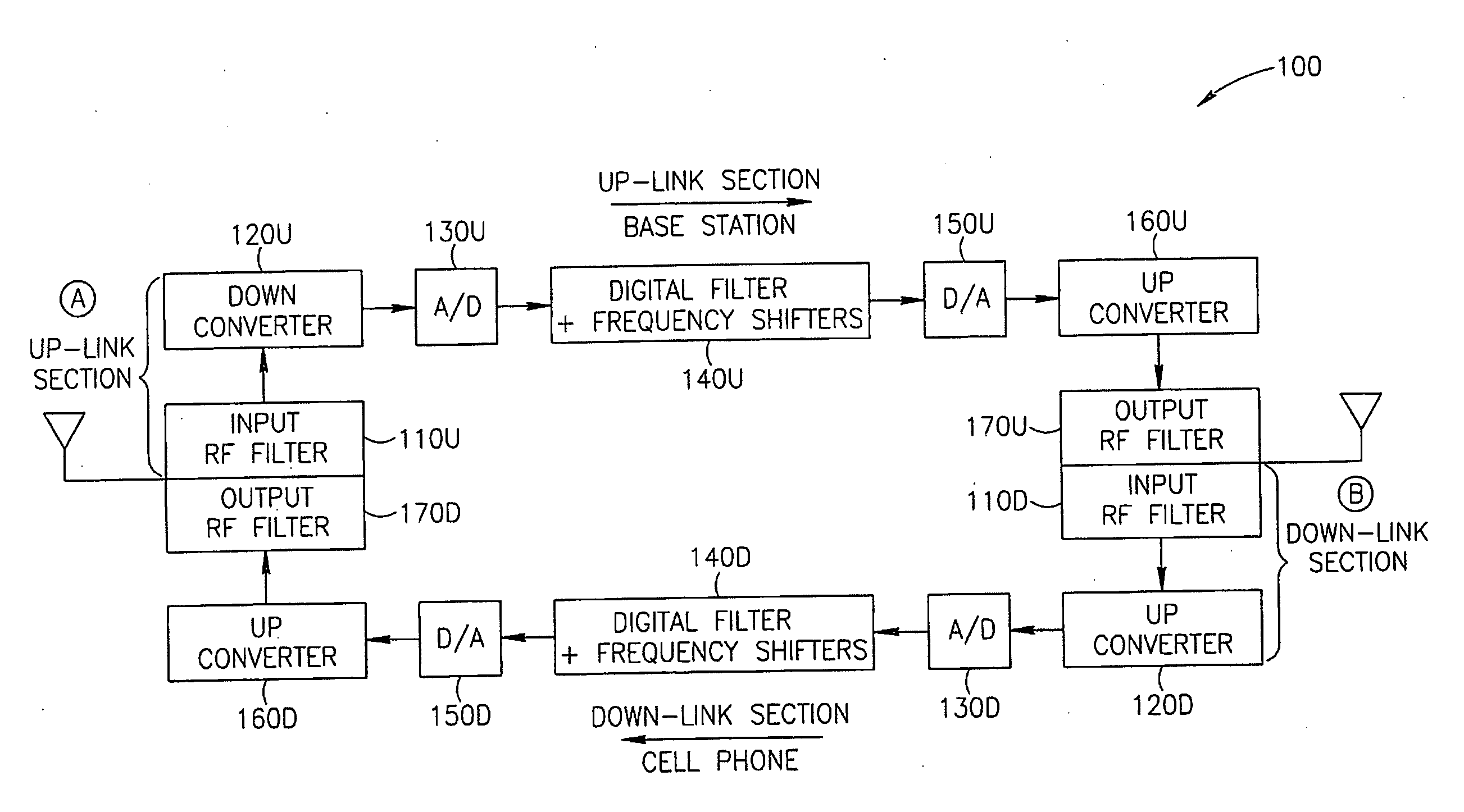

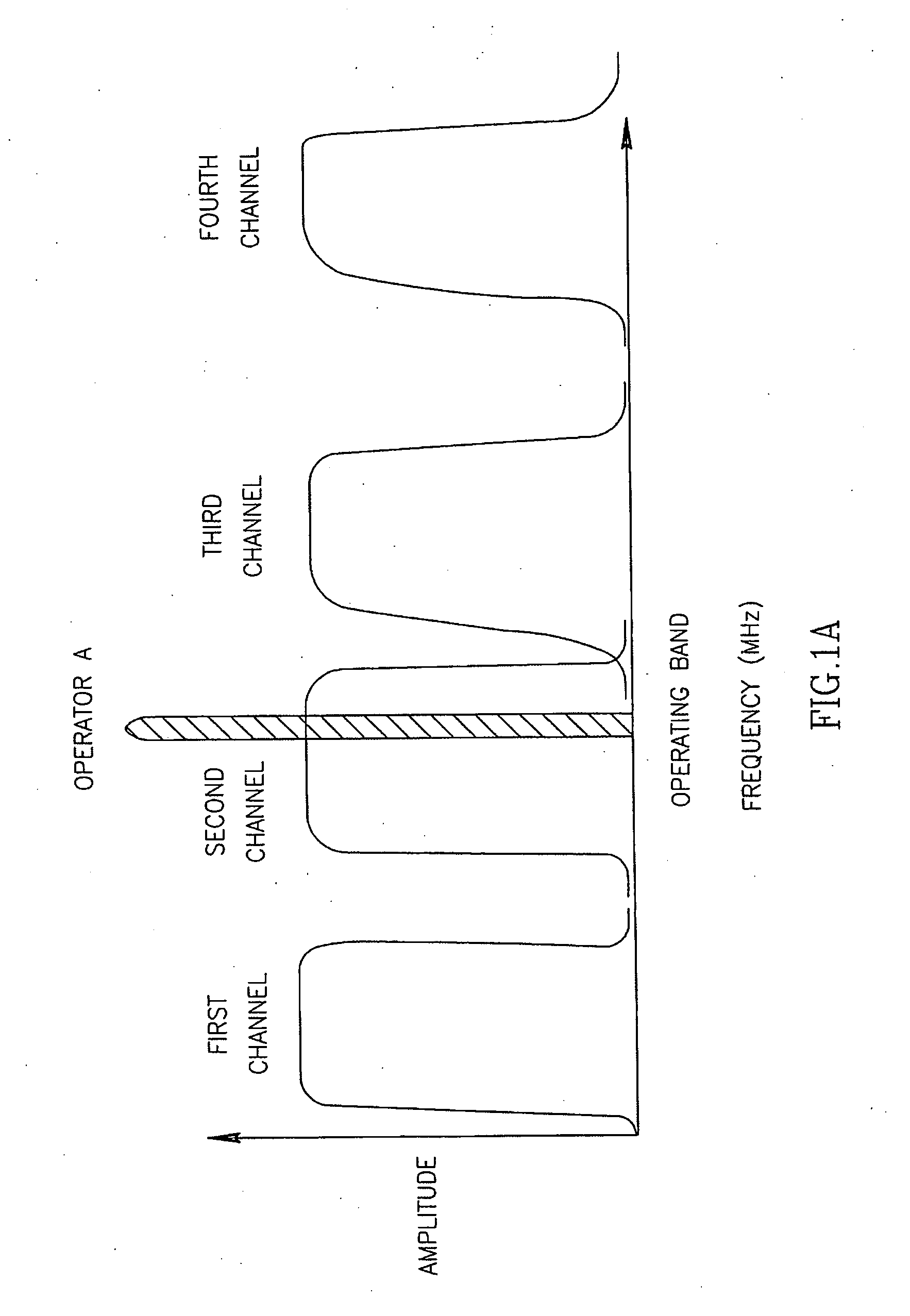

InactiveUS7460831B2Easy to operateFrequency/rate-modulated pulse demodulationPosition-modulated pulse demodulationData streamModem device

A signal filtering system and method that may be used in conjunction with a repeater or an input stage of a base-station. The system may include an analog to digital converter adapted to sample a received signal and to produce a data stream corresponding to the received signal in the time domain, a filtering block having one or more digital filter elements, wherein each of said one or more filter elements is adapted to filter one or more sets of frequency bands associated with one or more communication channel, and a controller adapted to configure said one or more digital filter elements based on parameters stored on a database and / or based on parameters received via a modem.

Owner:AXELL WIRELESS

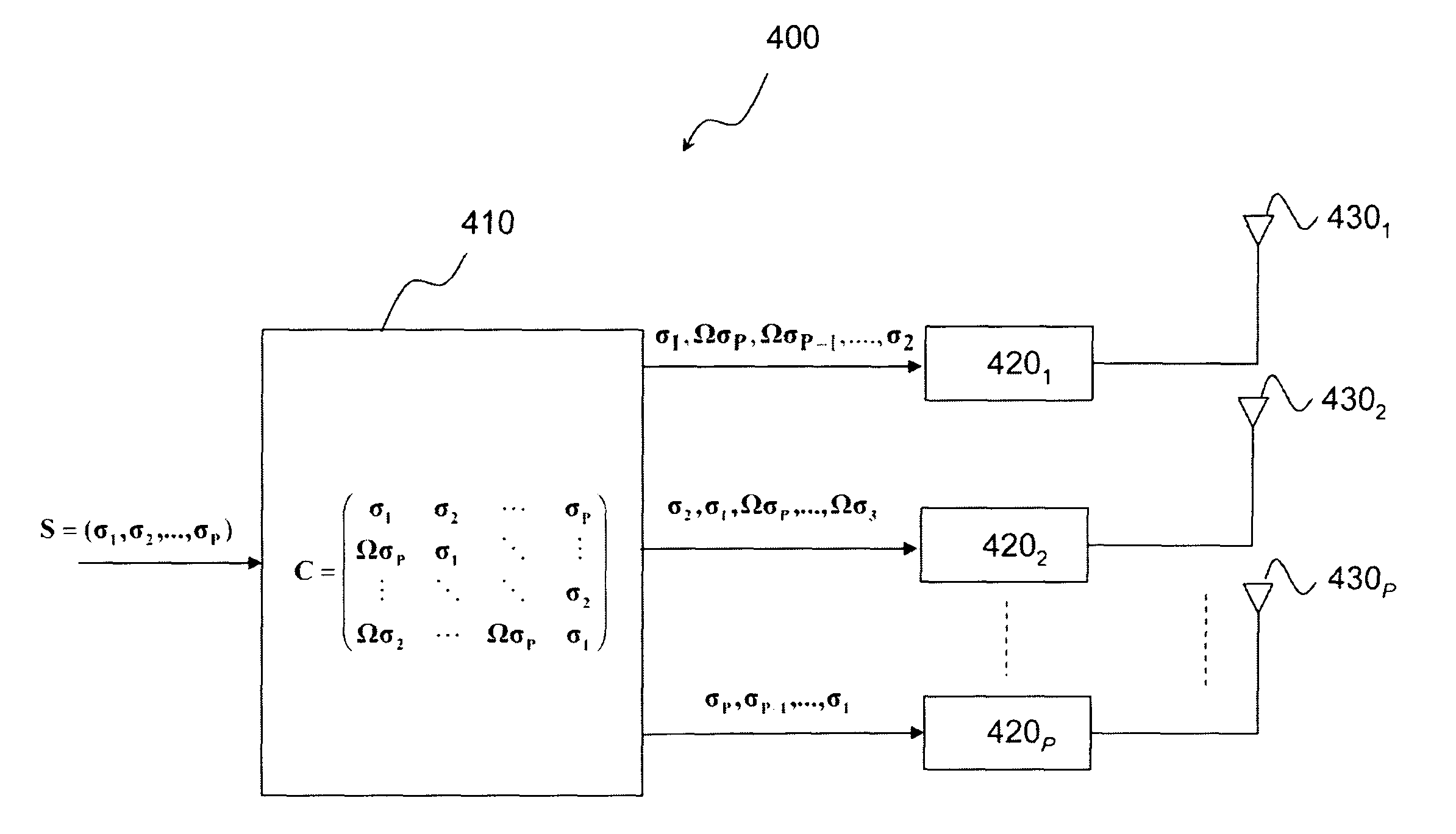

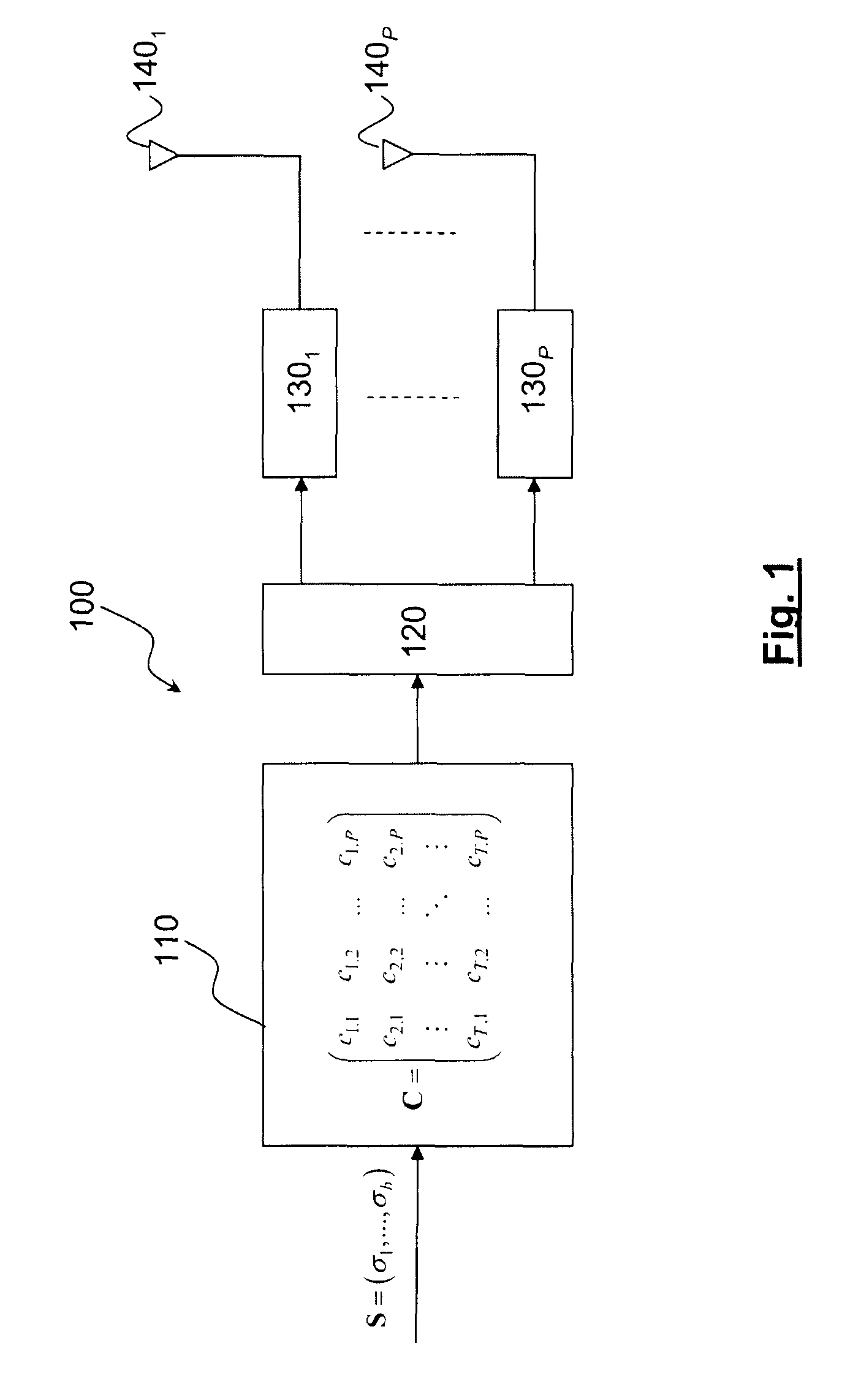

Method of space time coding with low papr for multiple antenna communication system of the UWB pulse type

InactiveUS8218670B2Polarisation/directional diversityFrequency/rate-modulated pulse demodulationCommunications systemTransmission channel

A method of space time coding for UWB transmission system including a plurality of radiative elements, the method coding a block of information symbols S=(σ1, σ2, . . . , σP) belonging to a M-PPM-M′-PAM modulation alphabet, as a sequence of vectors obtained from elements of the matrix:C=(σ1σ2…σPΩσPσ1⋱⋮⋮⋱⋱σ2Ωσ2…ΩσPσ1)a row of the matrix corresponding to a use of the transmission channel and a column of the matrix corresponding to a radiative element, the matrix C being defined to within a permutation of its rows and / or its columns and Ω being defined as the combination of a permutation (ω) of the modulation positions of the M-PPM alphabet and a symmetry operation (π) of the M′-PAM modulation alphabet for one of the modulation positions (m±).

Owner:COMMISSARIAT A LENERGIE ATOMIQUE ET AUX ENERGIES ALTERNATIVES

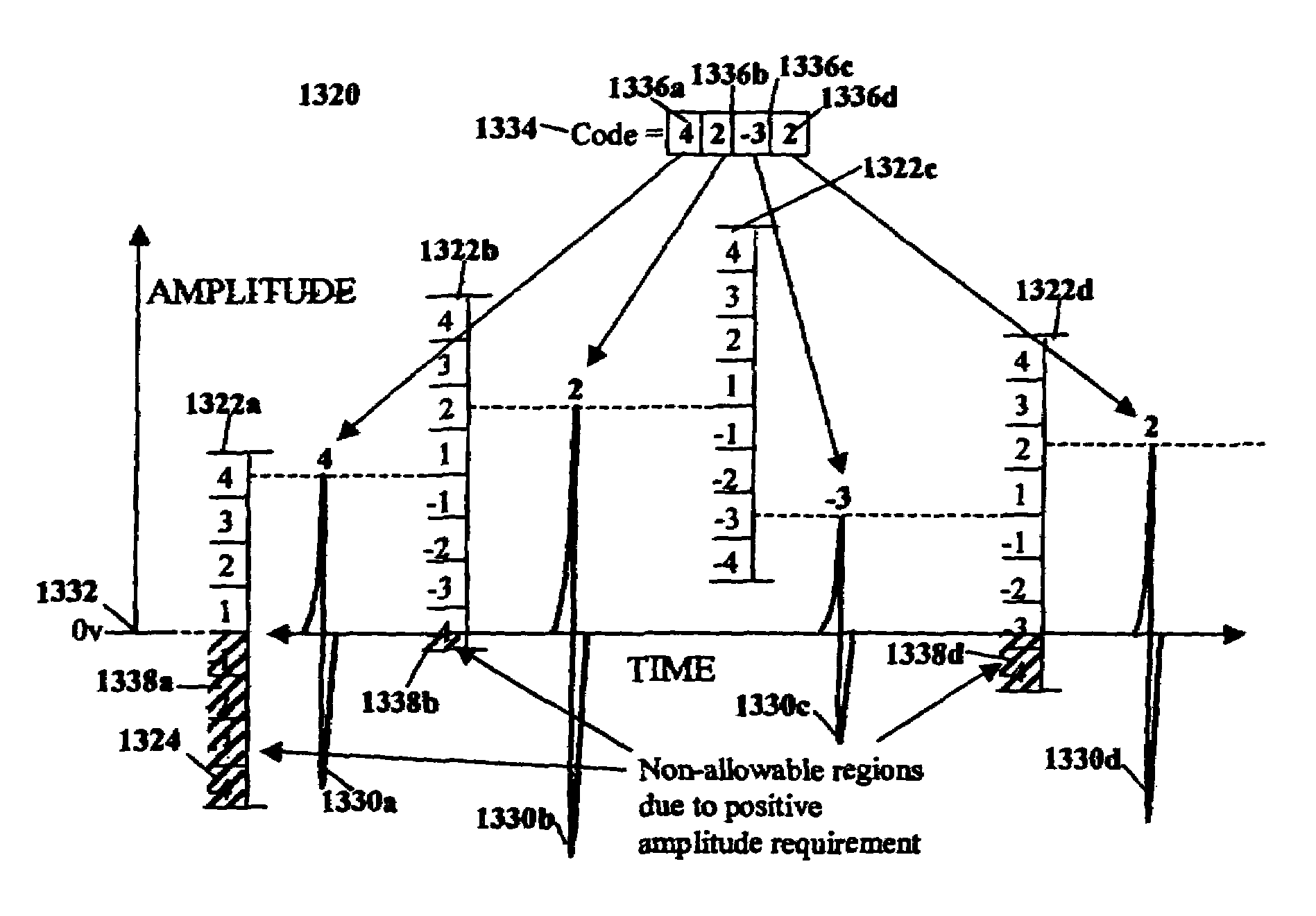

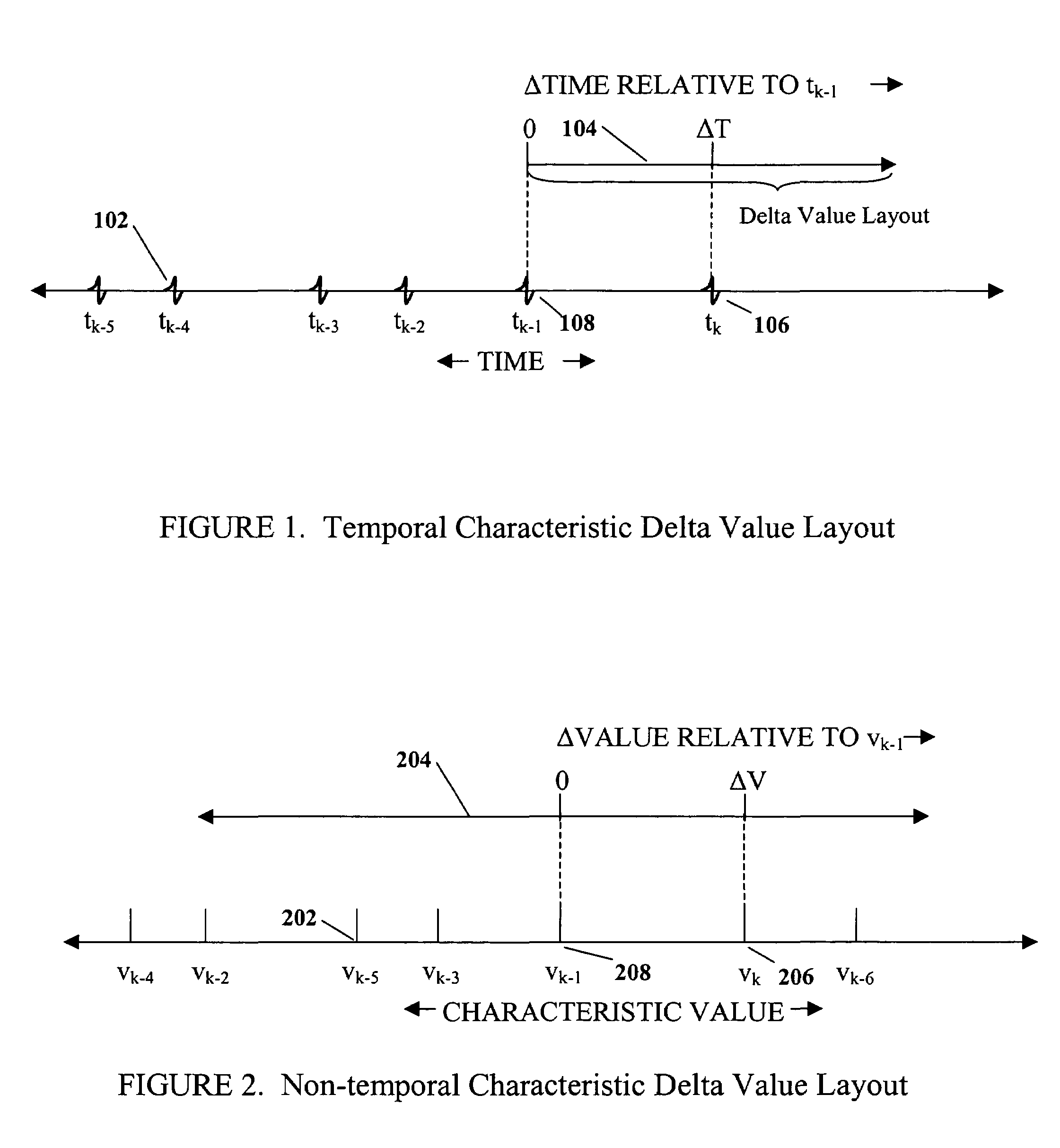

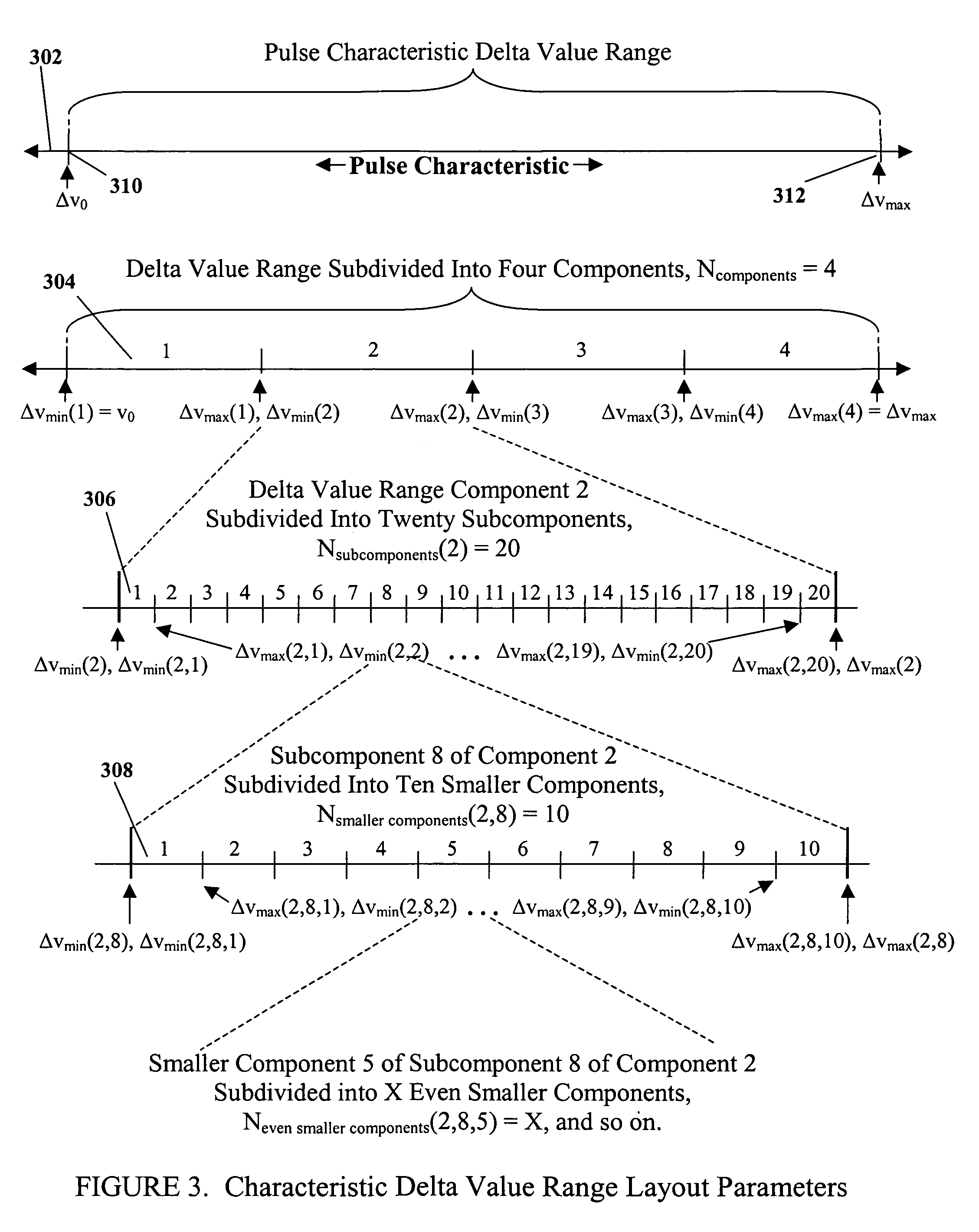

Method and apparatus for mapping pulses to a non-fixed layout

InactiveUS7145954B1Frequency/rate-modulated pulse demodulationPosition-modulated pulse demodulationPulse characteristicsPhysics

A coding method, specifies temporal and / or non-temporal pulse characteristics, where pulse characteristic values are relative to one or more non-fixed reference characteristic values within at least one delta value range or discrete delta value layout. The method allocates allowable and non-allowable regions relative to the one ore more non-fixed references. The method applies a delta code relative to the allowable and non-allowable regions. The allowable and non-allowable regions are relative to one or more definable characteristic values within a characteristic value layout. The one or more definable characteristic values are relative to one or more characteristic value references. In addition, the one or more characteristic value references can be a characteristic value of a given pulse such as a preceding pulse or a succeeding pulse.

Owner:TDC ACQUISITION HLDG

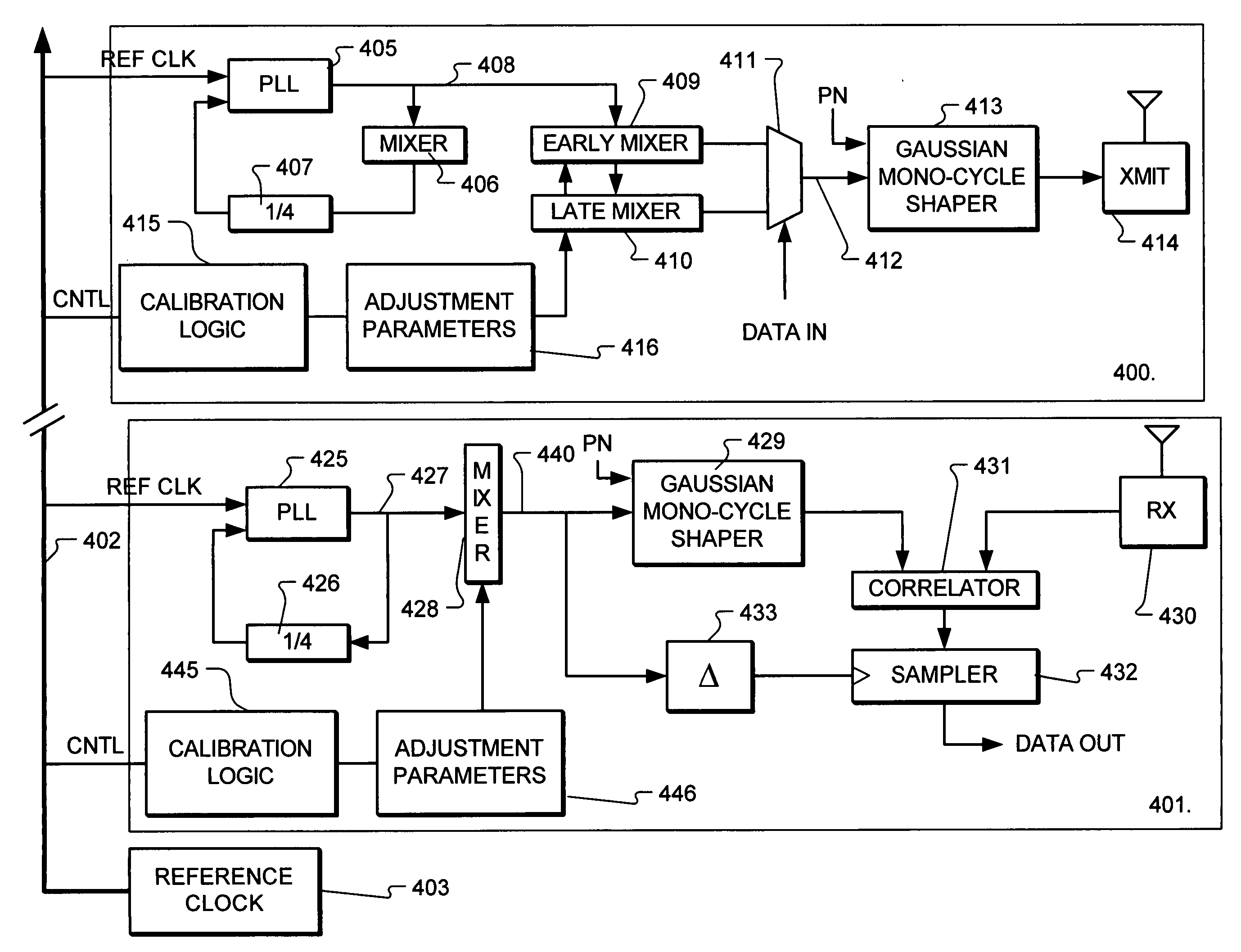

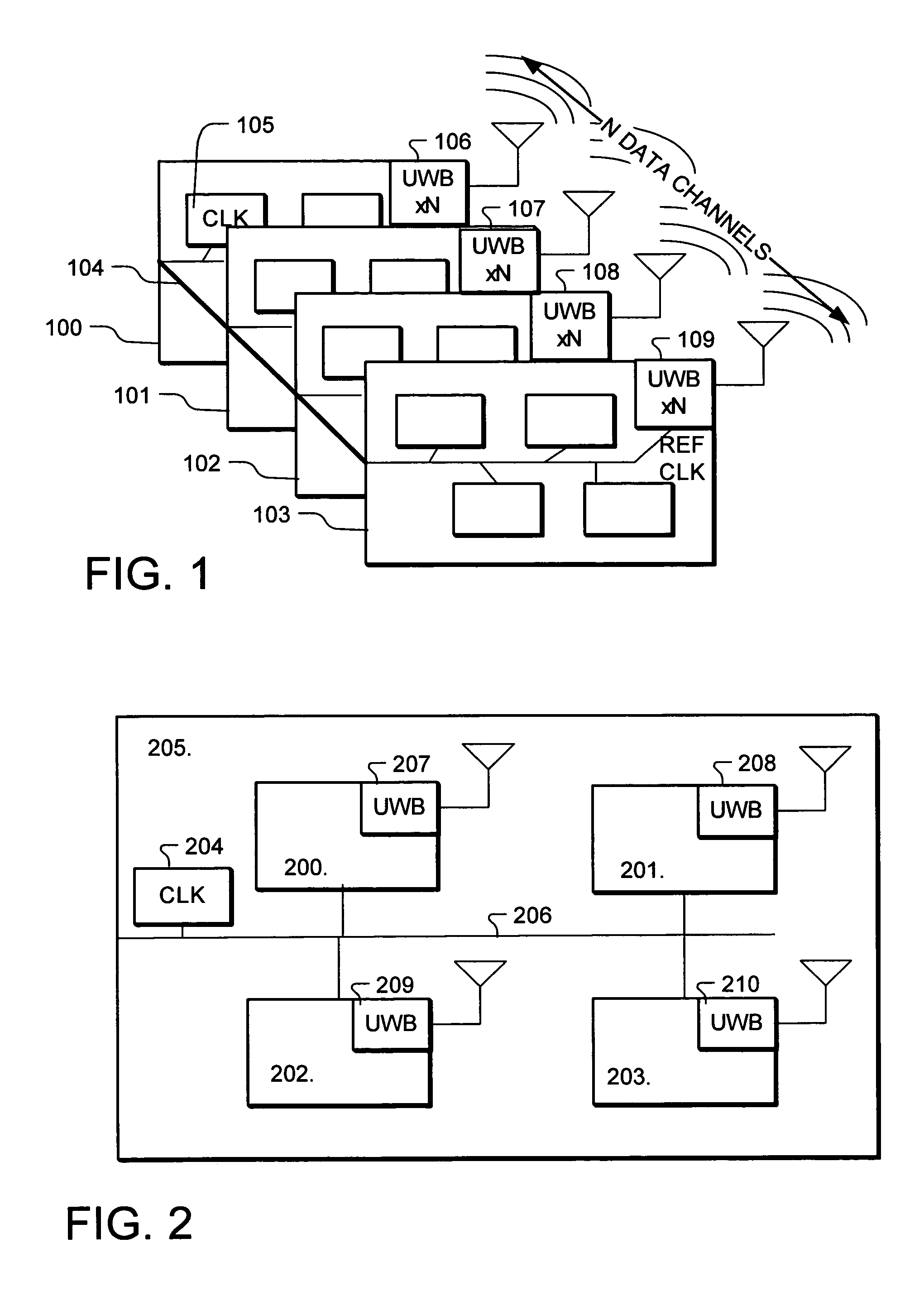

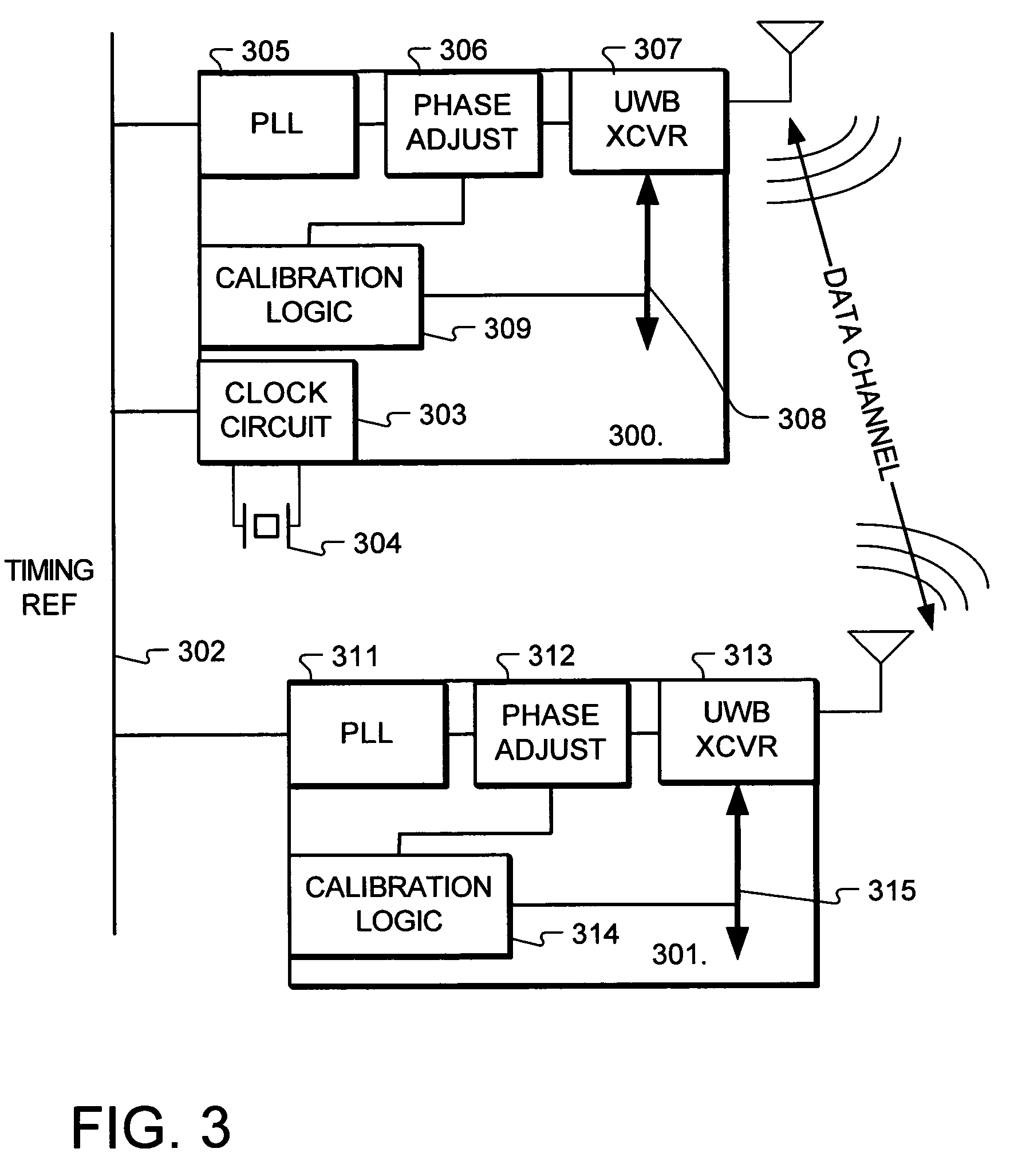

Hybrid wired and wireless chip-to-chip communications

InactiveUS7535958B2Precise timing alignment and mesochronous synchronizationLarge capacityModulated-carrier systemsFrequency/rate-modulated pulse demodulationUltra-widebandTransceiver

A hybrid wireless and wired system distributes precise timing and synchronization information among the nodes over a wired interconnect structure while data is transmitted wirelessly using ultra-wideband radio over short distances. The timing information communicated over the wired interconnect structure is used to establish a baseline timing reference for the wireless transmitters, receivers and transceivers on the nodes of the communication network. Using a common timing reference, a mesochronous communication system is established for chip-to-chip wireless data transmission.

Owner:RAMBUS INC

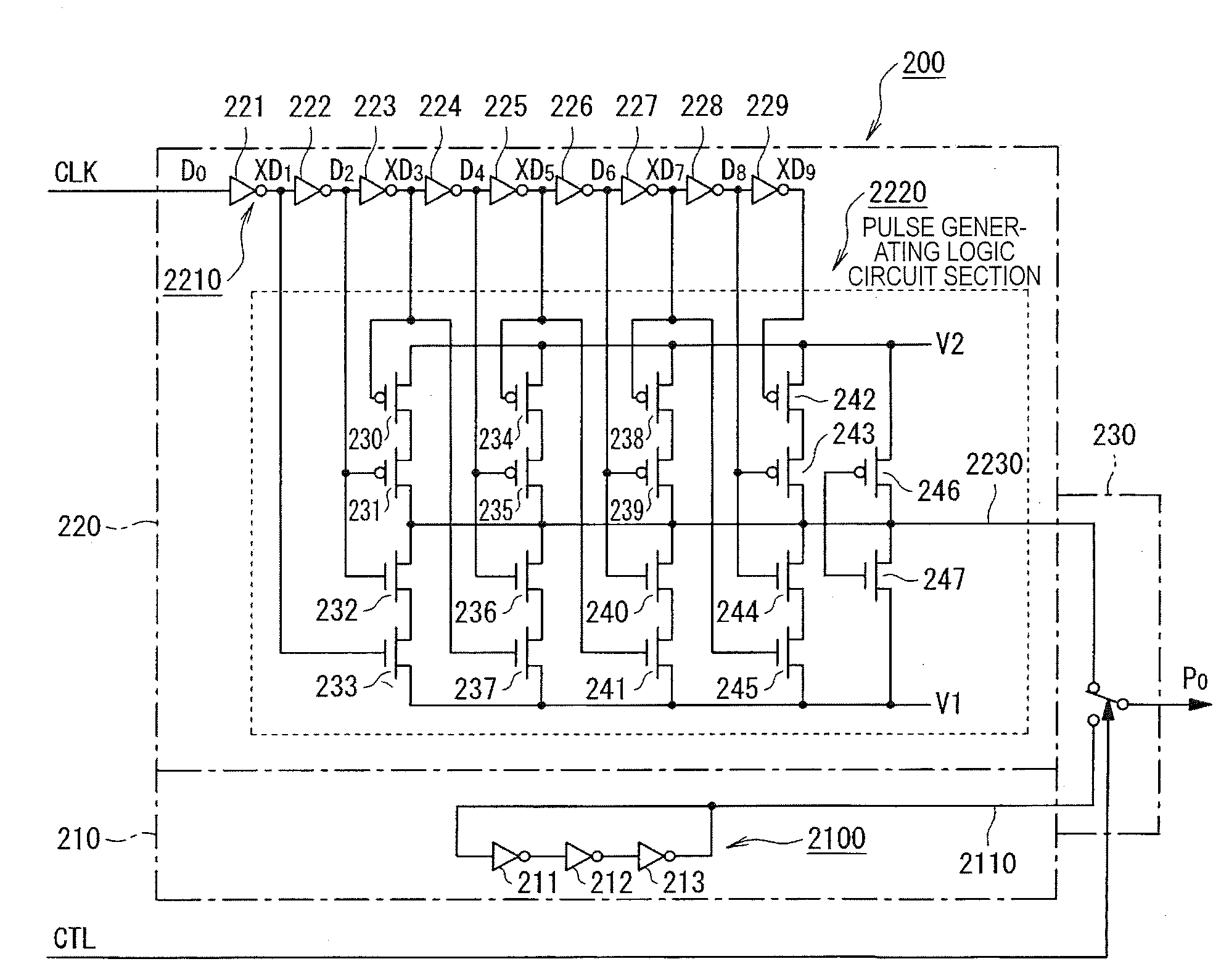

Template pulse generating circuit, communication device, and communication method

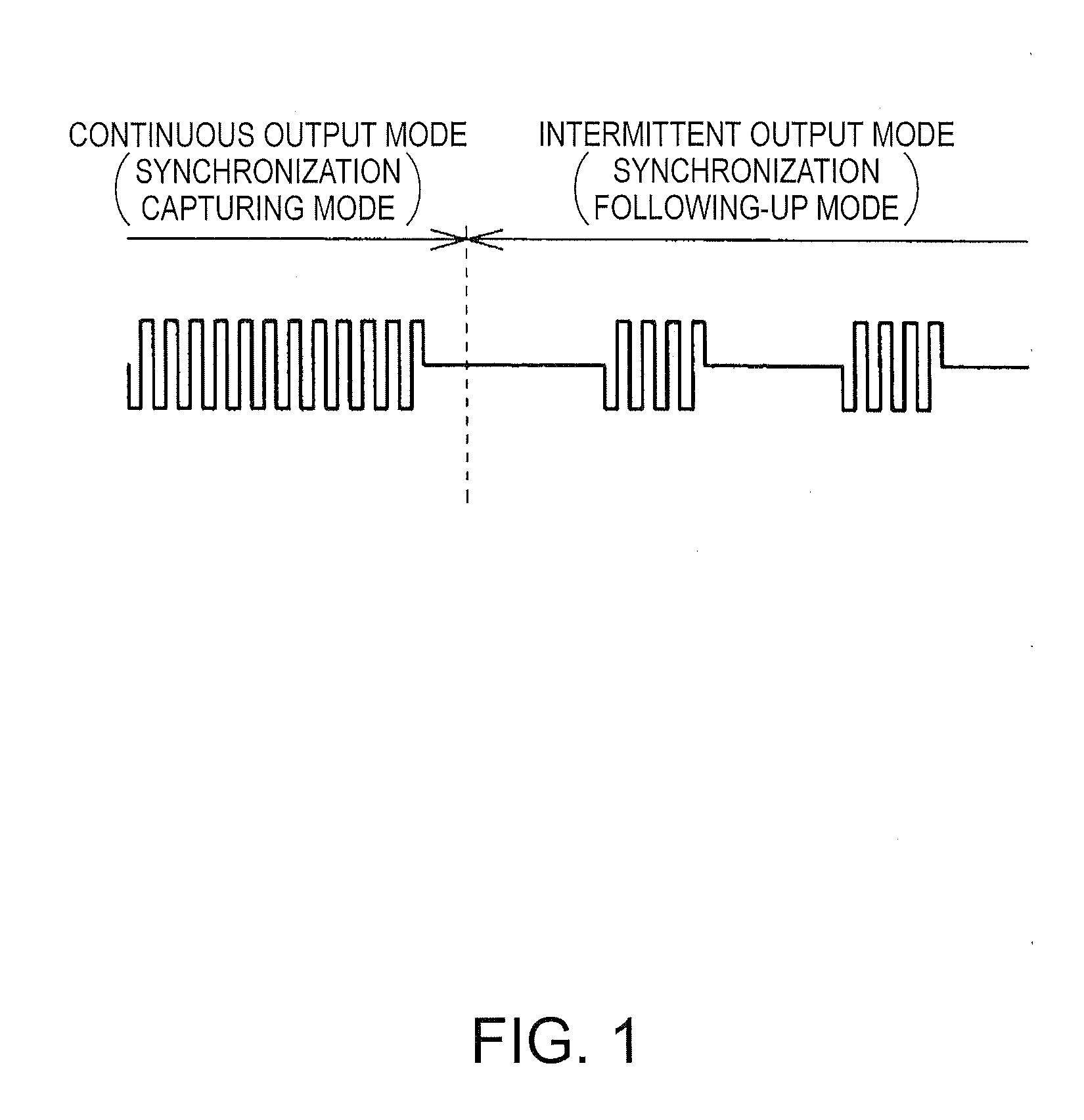

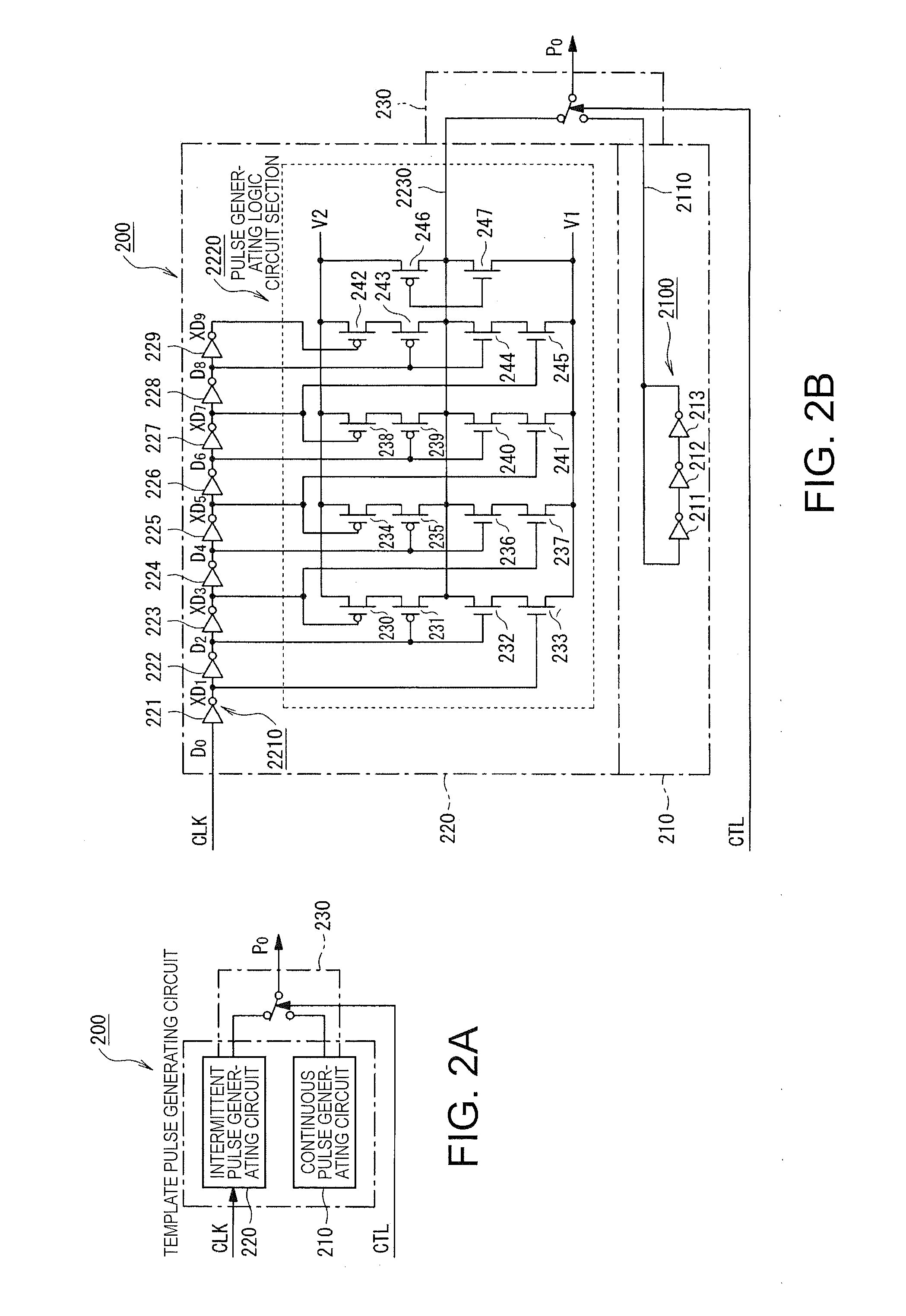

ActiveUS20080205559A1Reduce power consumptionDuration/width modulated pulse demodulationAmplitude-modulated carrier systemsControl signalEngineering

A template pulse generating circuit that generates a template pulse used for detection of a received pulse in pulse communication includes an output mode switching circuit for switching an output mode in accordance with a supplied control signal between a continuous output mode that continuously outputs the template pulses and an intermittent output mode that intermittently outputs the template pulses so that the template pulse is generated in either one of the continuous output mode and the intermittent output mode.

Owner:138 EAST LCD ADVANCEMENTS LTD

System and method for excluding narrow band noise from a communication channel

ActiveUS20060019604A1Interfere with detectionEasy to operateFrequency/rate-modulated pulse demodulationPosition-modulated pulse demodulationTime domainData stream

A signal filtering system and method that may be used in conjunction with a repeater or an input stage of a base-station. The system may include an analog to digital converter adapted to sample a received signal and to produce a data stream corresponding to the received signal in the time domain, a filtering block having one or more digital filter elements, wherein each of said one or more filter elements is adapted to filter one or more sets of frequency bands associated with one or more communication channel, and a controller adapted to configure said one or more digital filter elements based on parameters stored on a database and / or based on parameters received via a modem.

Owner:AXELL WIRELESS

Encoding and decoding ultra-wideband information

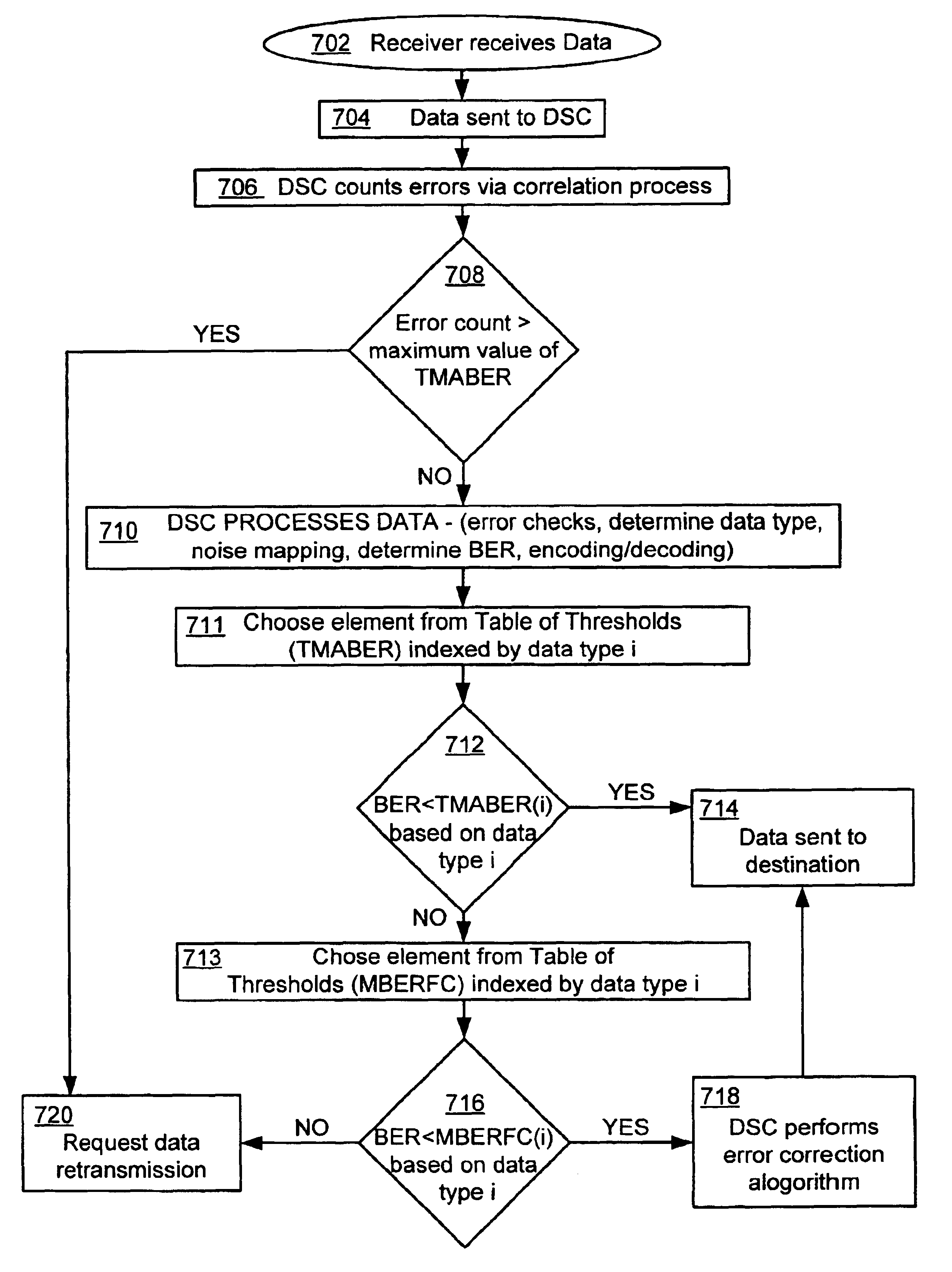

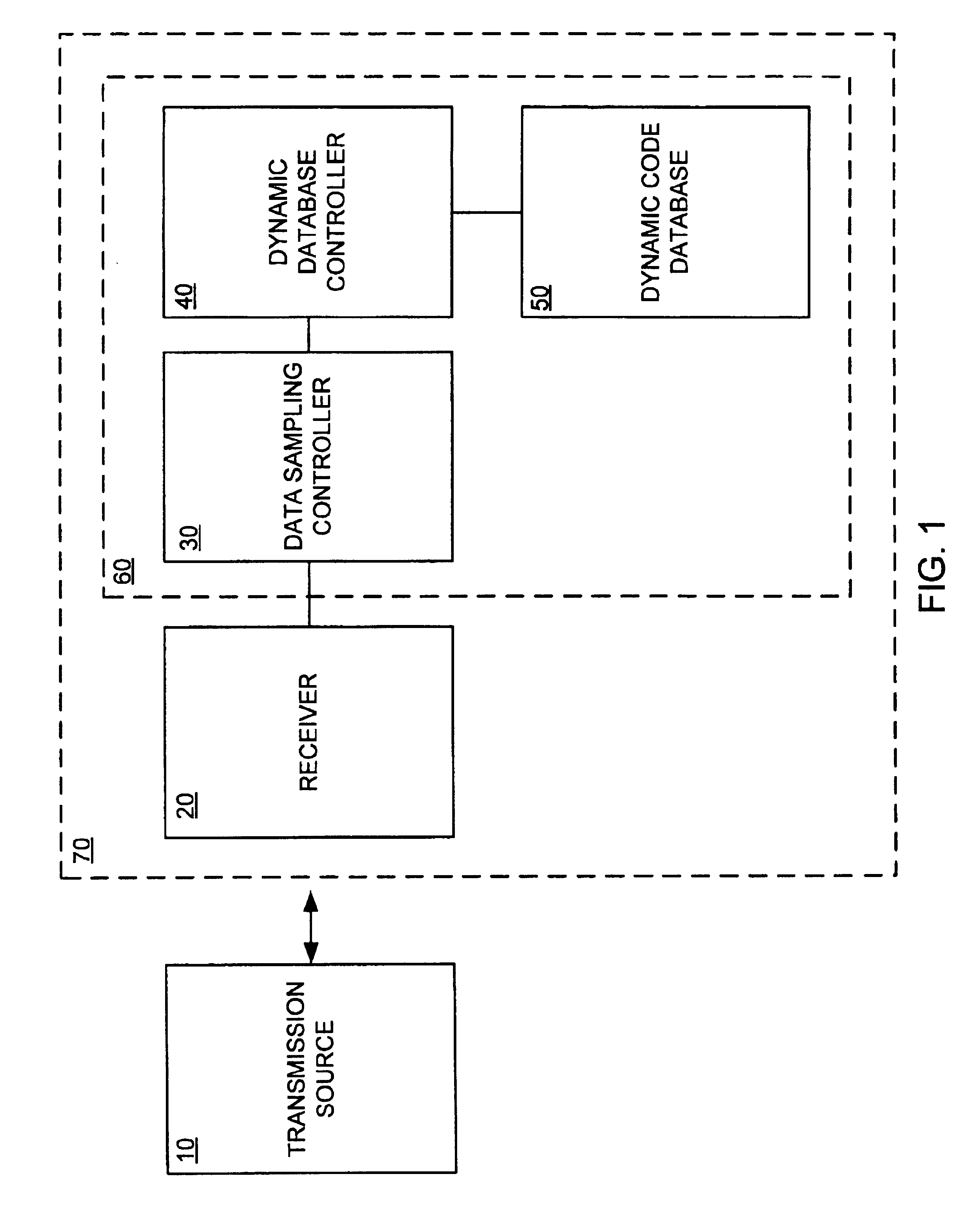

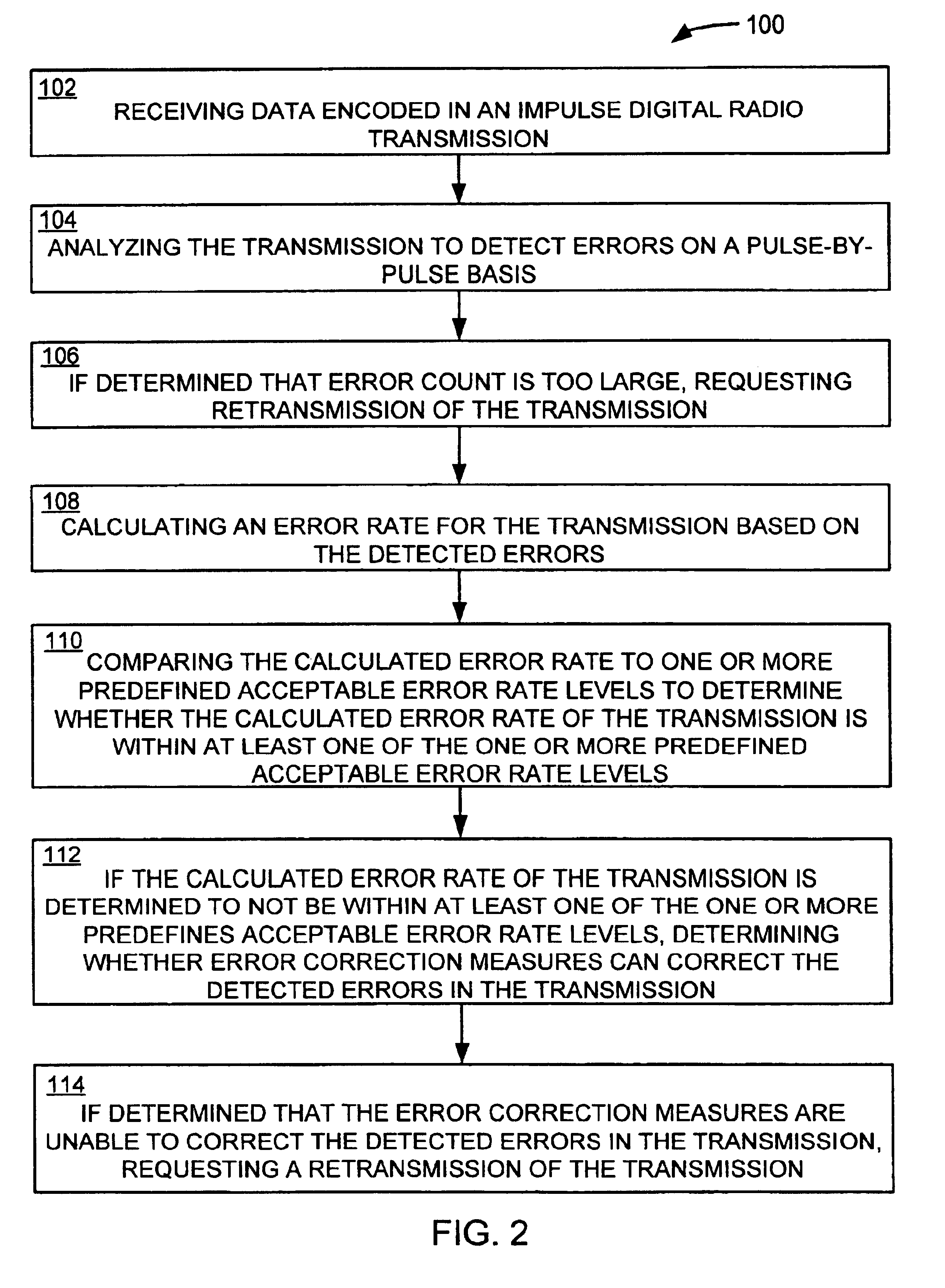

InactiveUS6947492B2Reduce disadvantagesDetection errorError prevention/detection by using return channelError detection/prevention using signal quality detectorUltra-widebandBroadband transmission

A system and a method for encoding and decoding ultra-wideband information are provided. An ultra-wideband transmission is encoded by positioning bipolar pulse pairs. The bipolar pulse pairs assist in detecting errors in the ultra-wideband transmission, before the entire transmission has been received. The transmission is analyzed for errors and an error rate is calculated. The calculated error rate is compared to one or more predefined acceptable error rate levels to determine whether the calculated error rate of the transmission is within at least one of the predefined acceptable error rate levels.

Owner:INTELLECTUAL VENTURES HLDG 73

Nonlinear inversion

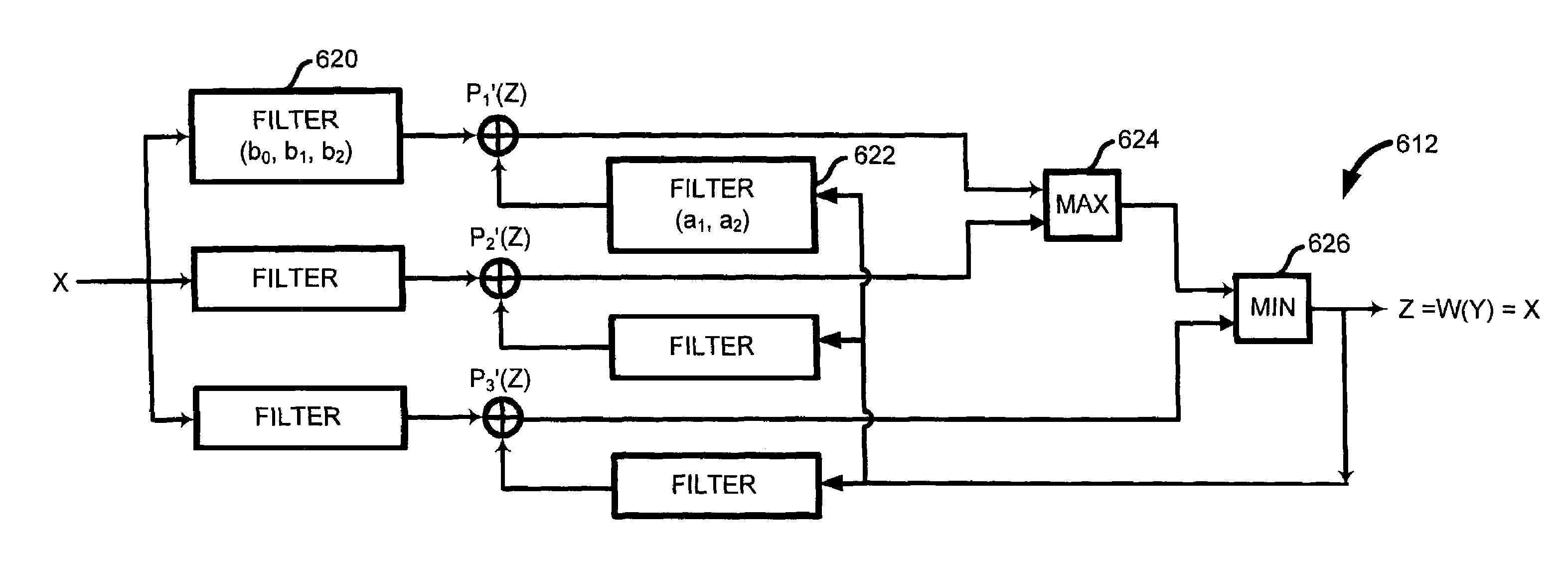

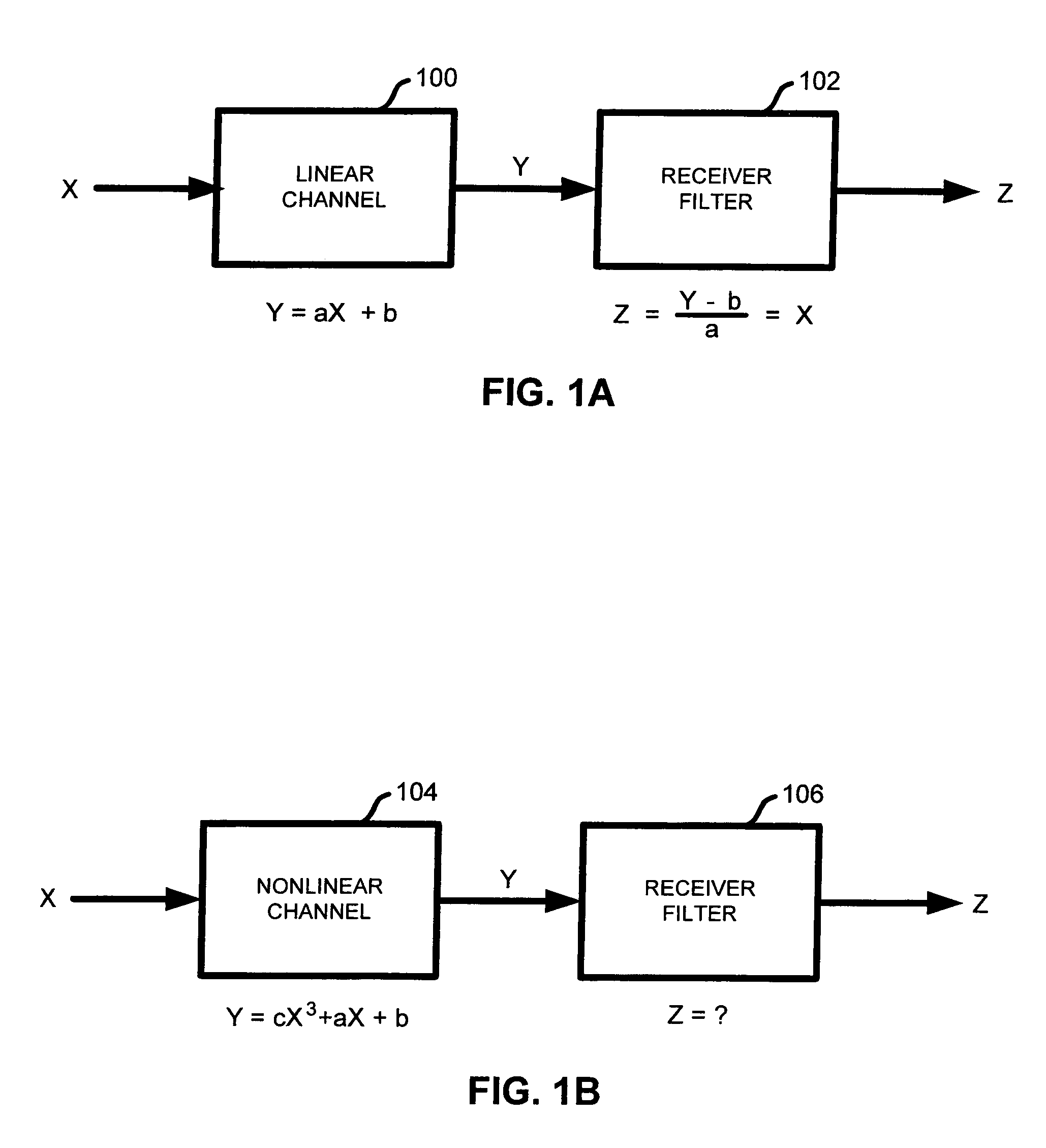

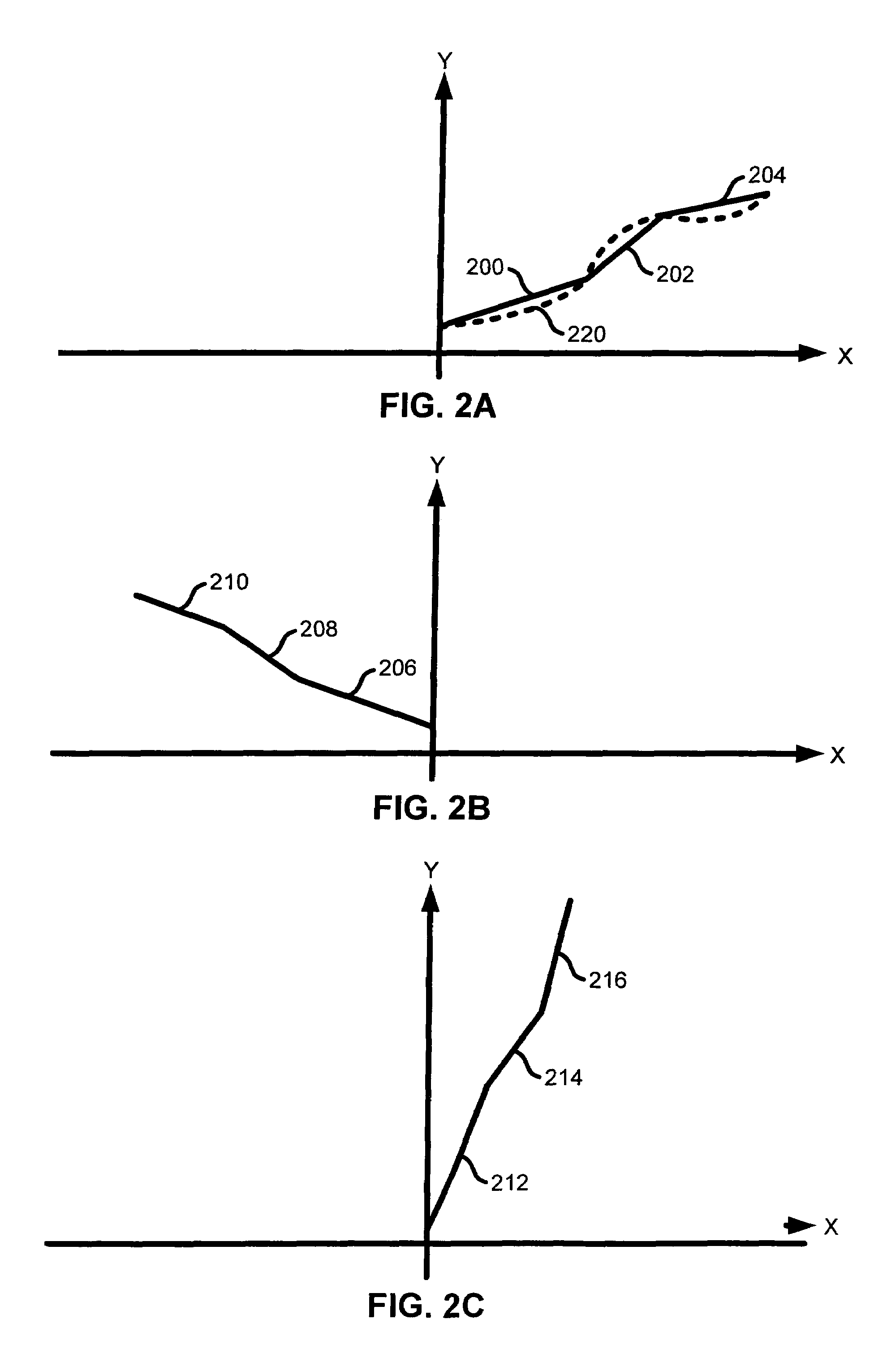

InactiveUS6999510B2Multiple-port networksDigital technique networkNonlinear inversionNonlinear channel

A method for processing a signal propagated through a nonlinear channel is disclosed. The method comprises modeling the channel characteristics to produce a linearized channel model, wherein the linearized channel model has a linearized transfer function that includes a plurality of first order polynomials and nonlinear operators. The method further comprises deriving an inverse linearized channel model from the linearized channel model and filtering the signal using the inverse linearized channel model.

Owner:AVAGO TECH WIRELESS IP SINGAPORE PTE

System and method for transmission of combined data stream

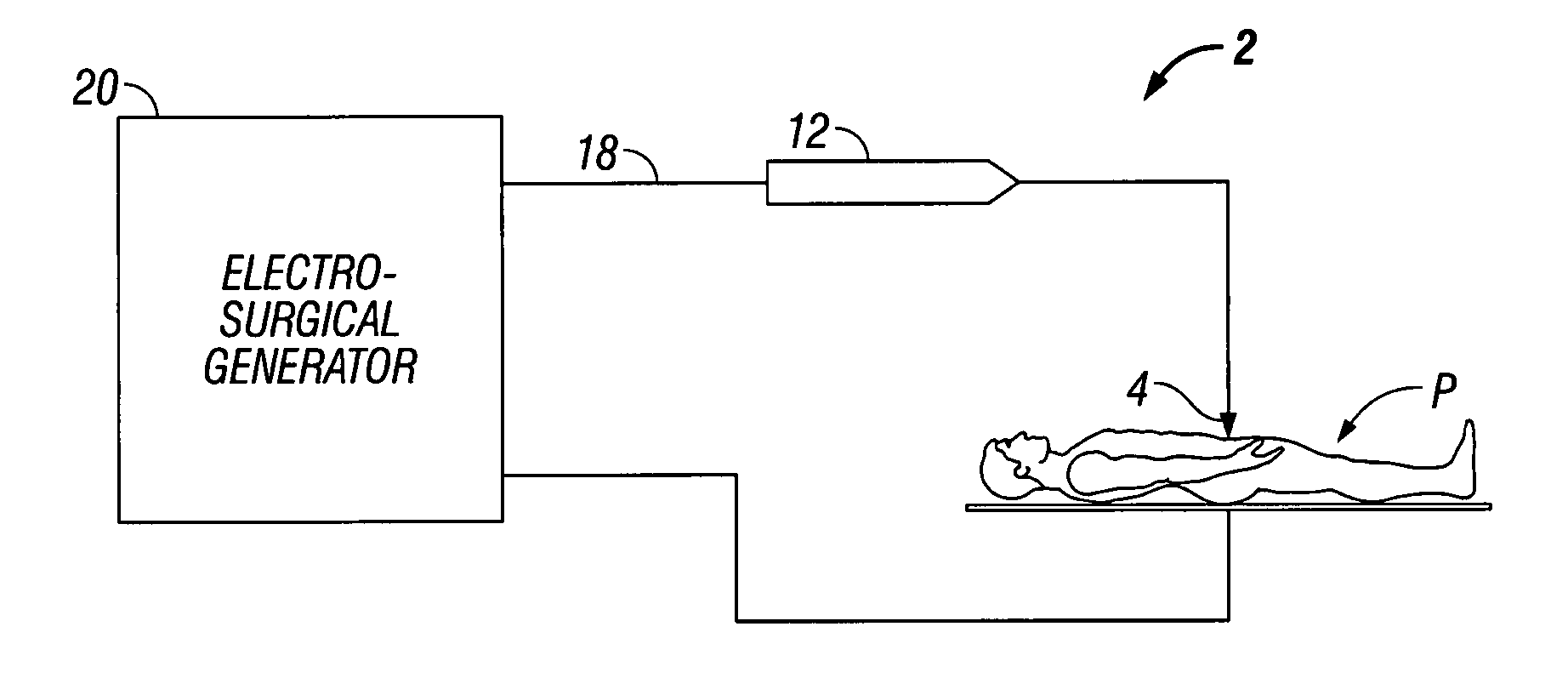

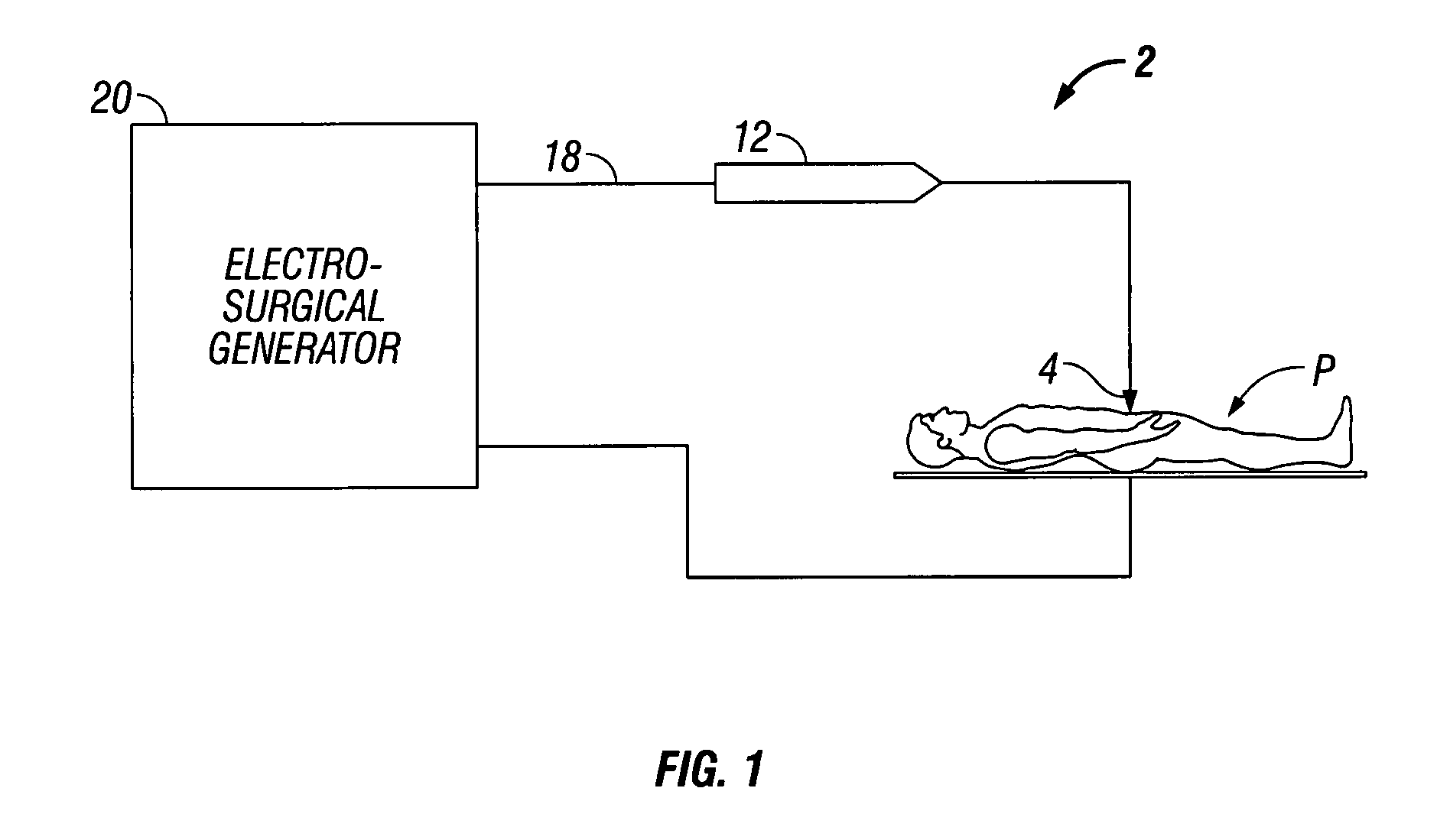

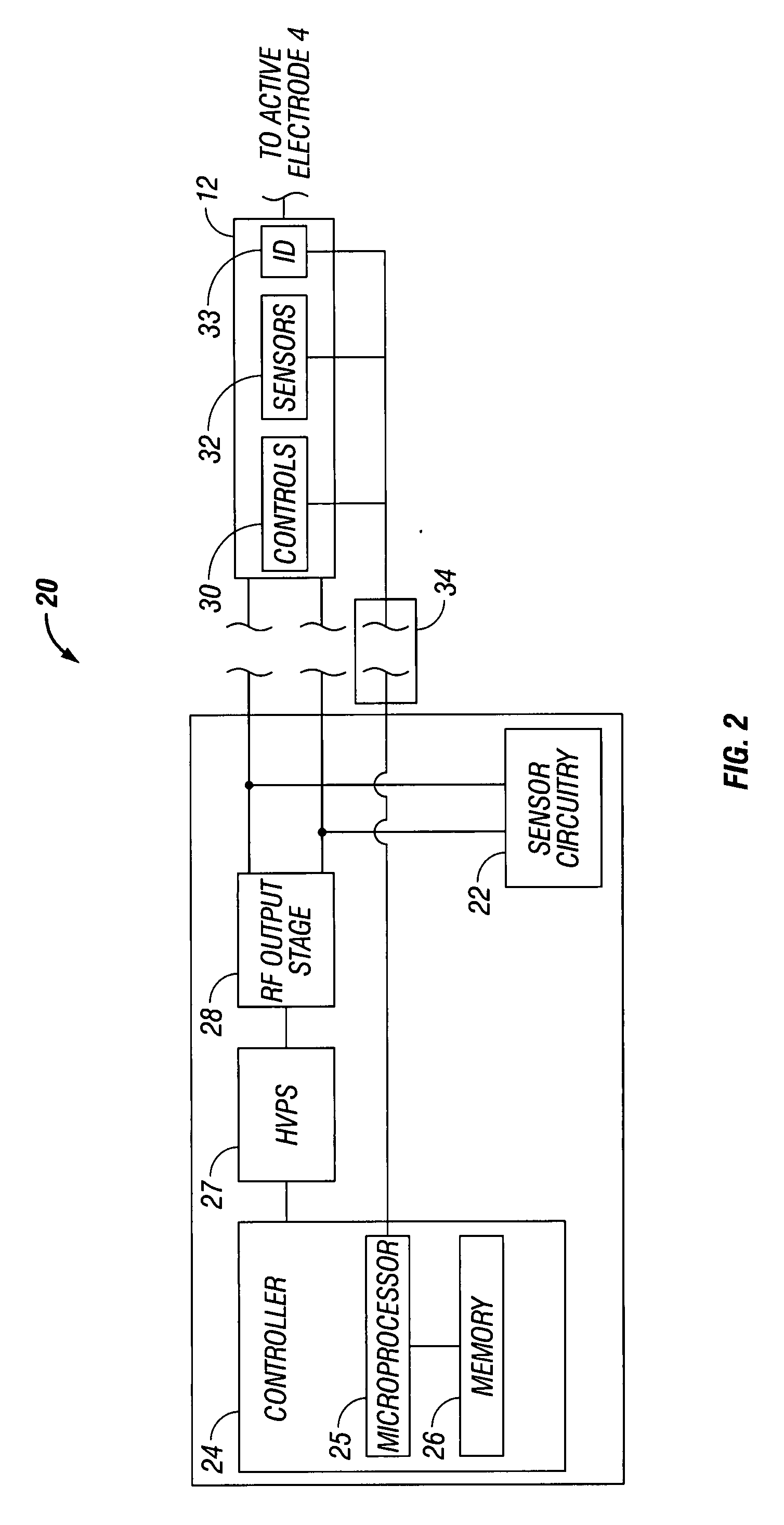

ActiveUS20090069801A1Modulated-carrier systemsFrequency/rate-modulated pulse demodulationElectricityData stream

An electrosurgical system is disclosed. The electrosurgical system includes an electrosurgical instrument configured to generate a first and second data streams and a transmission circuit configured to convert the first and second data streams into a pulsed transmission signal. The first signal property of the transmission signal is representative of the first data stream and the second signal property of the transmission signal is representative of the second data stream. The transmission circuit is further configured to process the transmission signal to decode the first signal property into the first data stream and the second signal property into the second data stream.

Owner:TYCO HEALTHCARE GRP LP

Method and system for a generation of a two-level signal

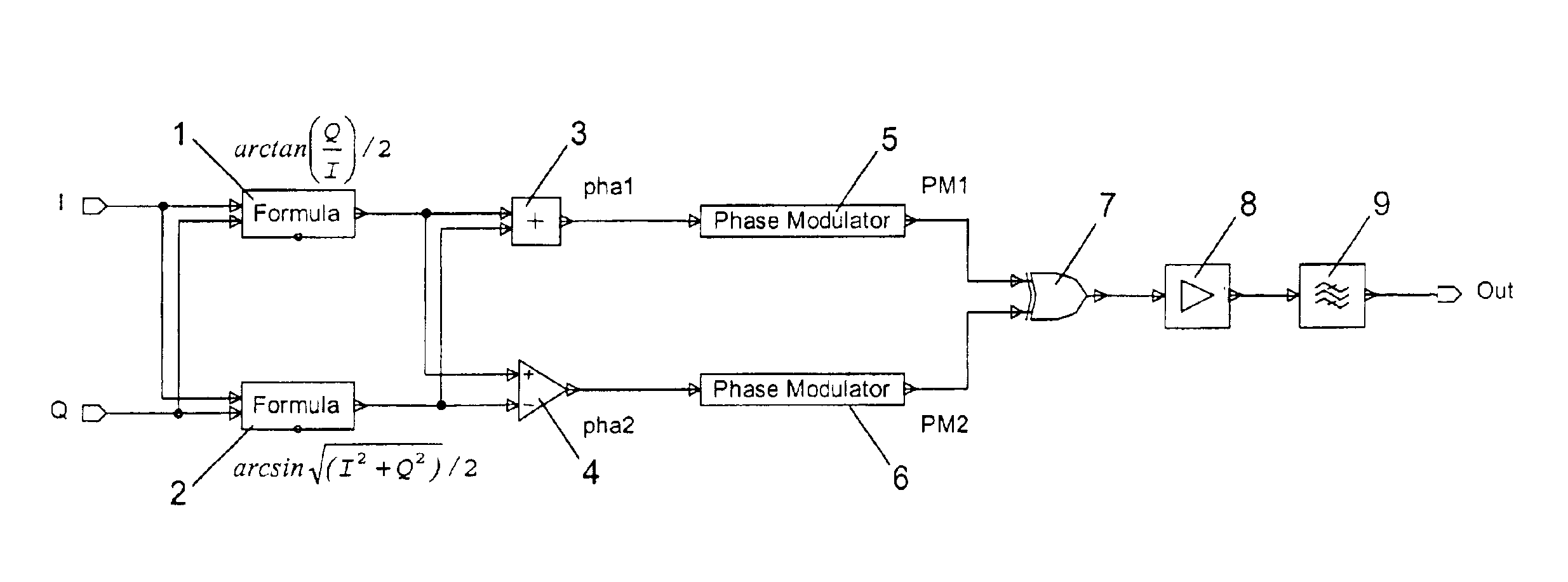

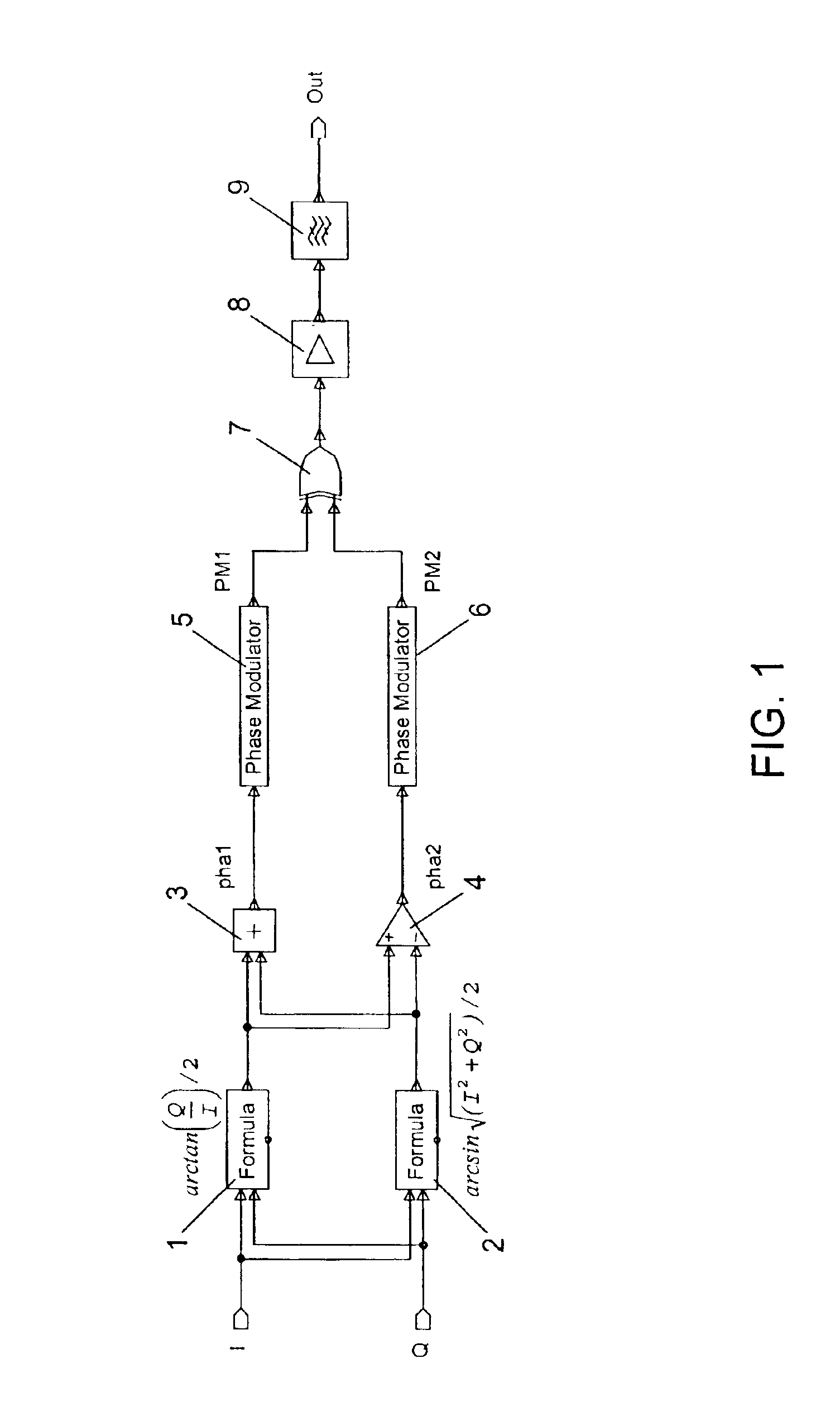

InactiveUS6975177B2Improve linearityImprove power efficiencyModulation with suppressed carrierFrequency/rate-modulated pulse demodulationAudio power amplifierControl signal

In a modulation system, in order to provide a two-level signal with a desired modulation which is suited to be amplified by a switching mode power amplifier, the modulation system may include a first constant envelope modulator modulating a signal according to a first control signal, a second constant envelope modulator modulating a signal according to a second control signal, and a combining portion combining the output signal of the first and said second constant envelope modulator to a single, two-level pulse-width-modulated signal. The information which is to be represented by the modulation of the single, two-level pulse-width-modulated signal is coded in the first and the second control signals. The invention relates equally to a corresponding method for generating a modulated signal.

Owner:NOKIA CORP

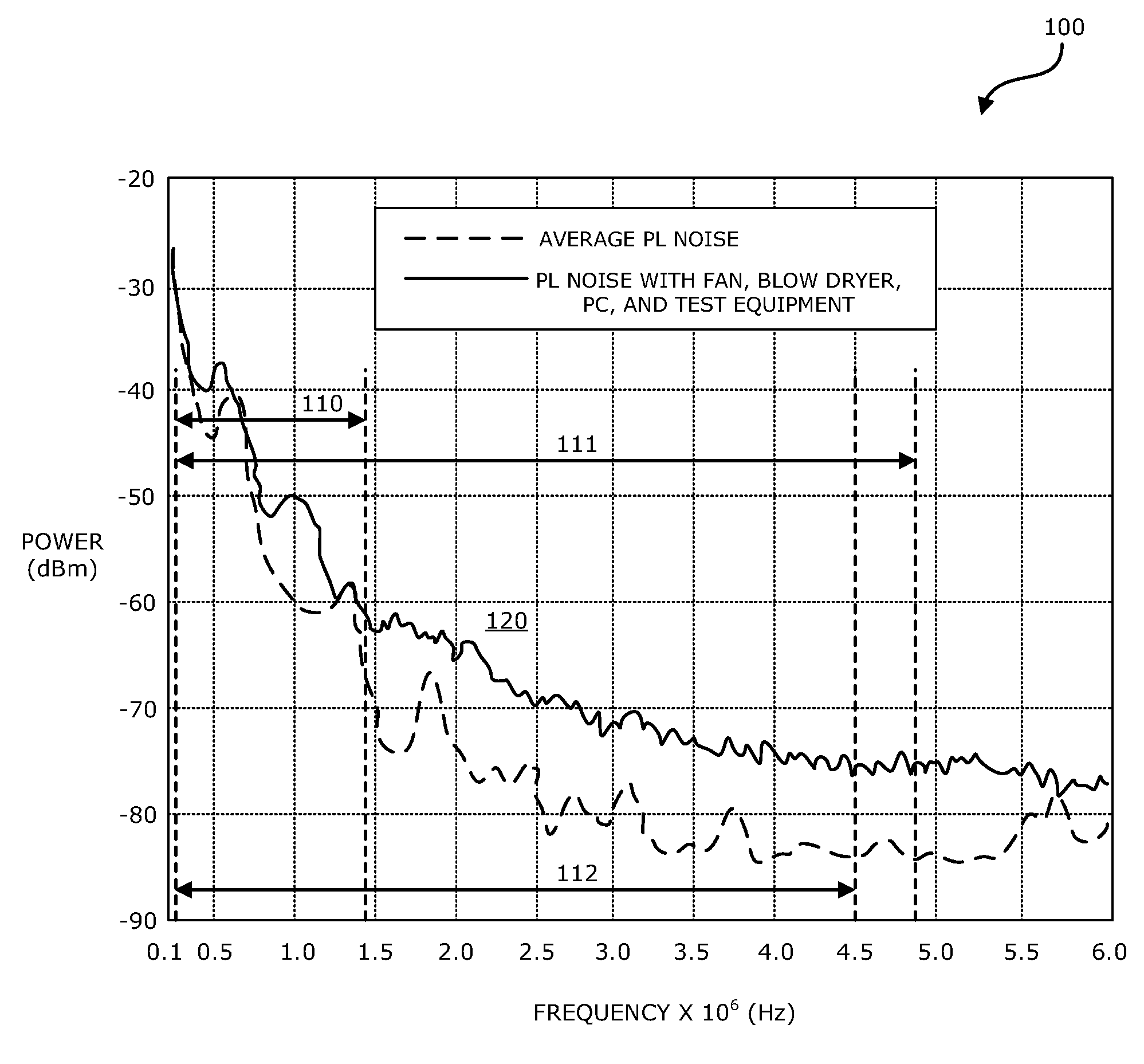

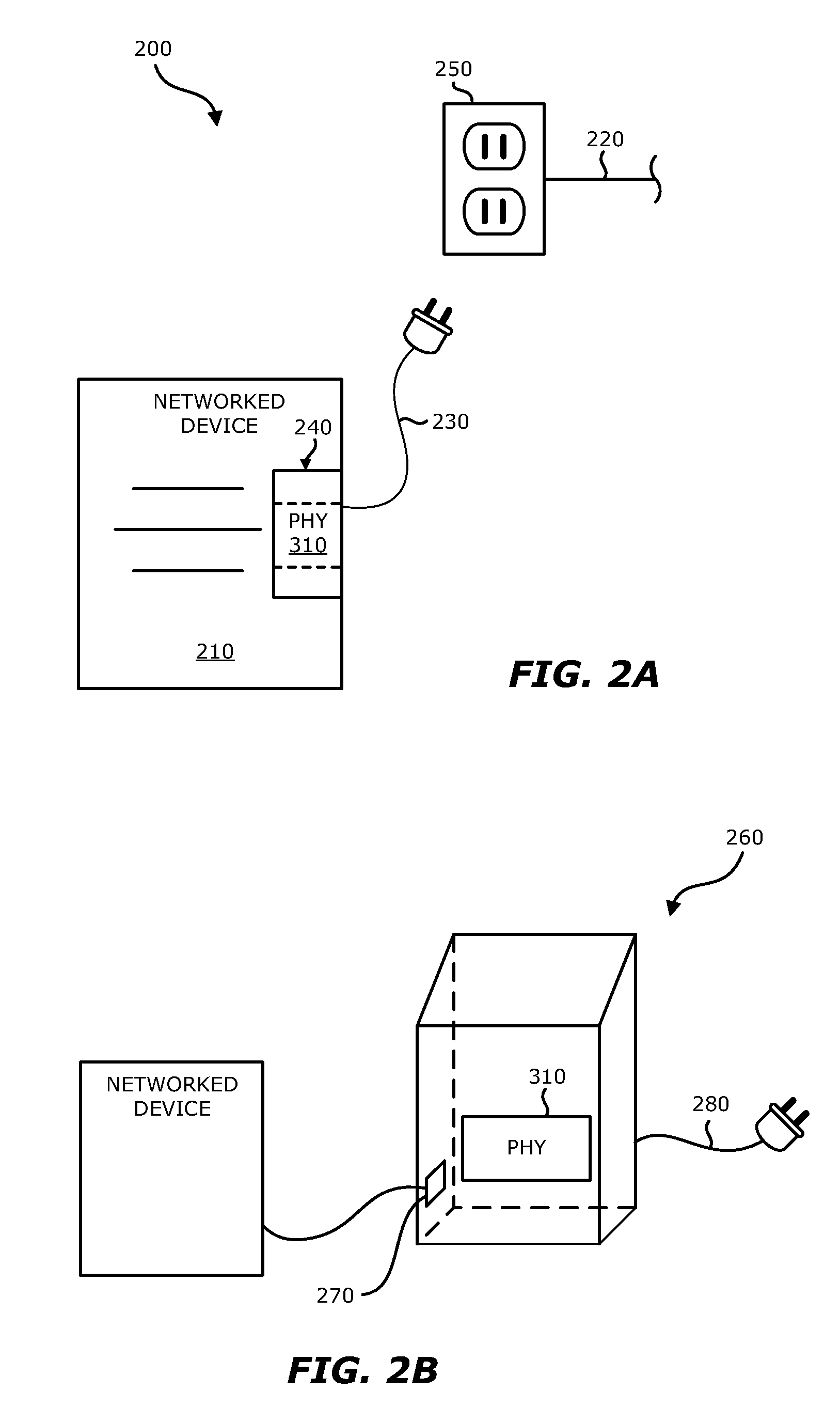

Transmitter and method for applying multi-tone OFDM based communications within a lower frequency range

ActiveUS20100316140A1Power distribution line transmissionFrequency/rate-modulated pulse demodulationFrequency spectrumMultiple modes

According to one embodiment of the invention, an integrated circuit comprises an encoding module, a modulation module and a spectral shaped module. The encoding module includes an interleaver that adapted to operate in a plurality of modes including a first mode, a second mod and a third mode. The interleaver performs repetitive encoding when placed in the second mode and even greater repetitive encoding when placed in the third mode.

Owner:MAXIM INTEGRATED PROD INC

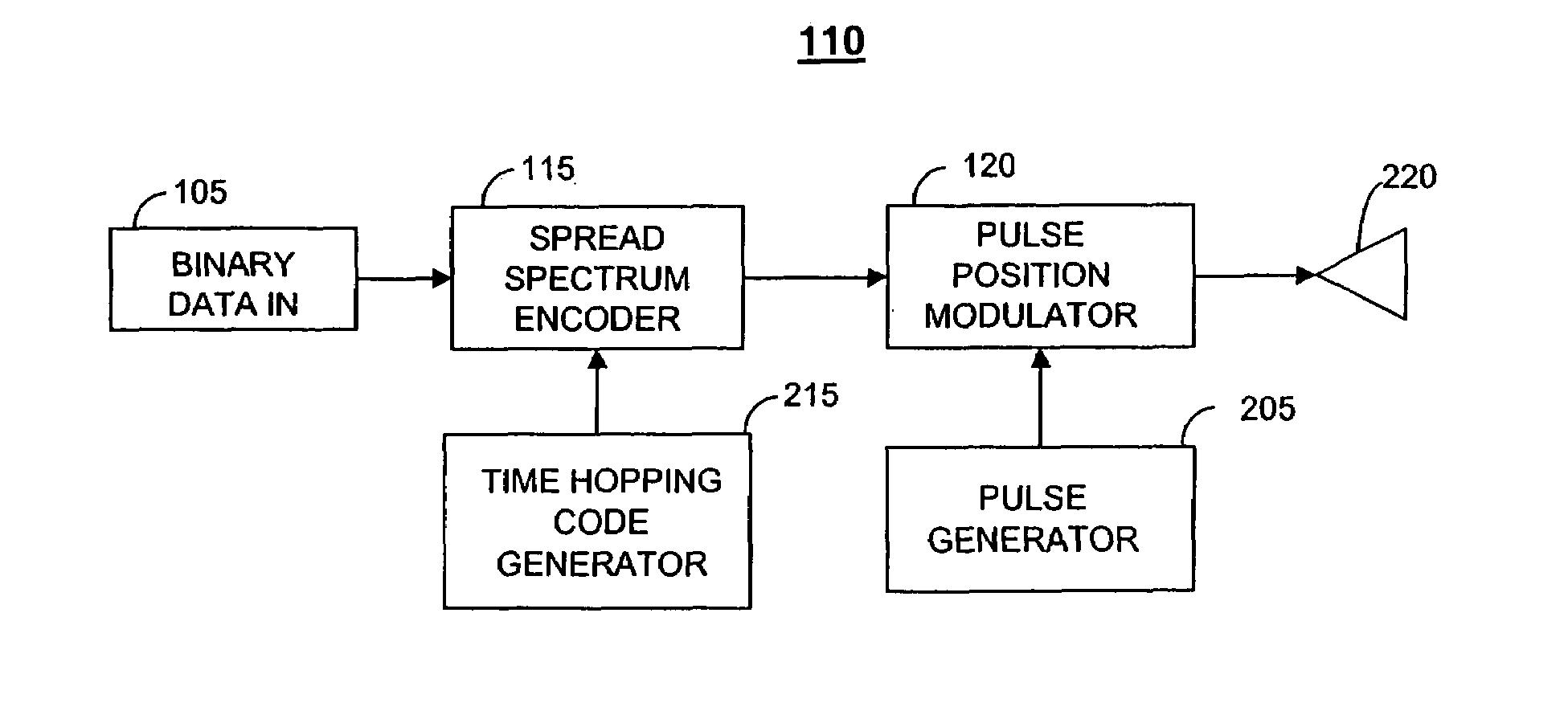

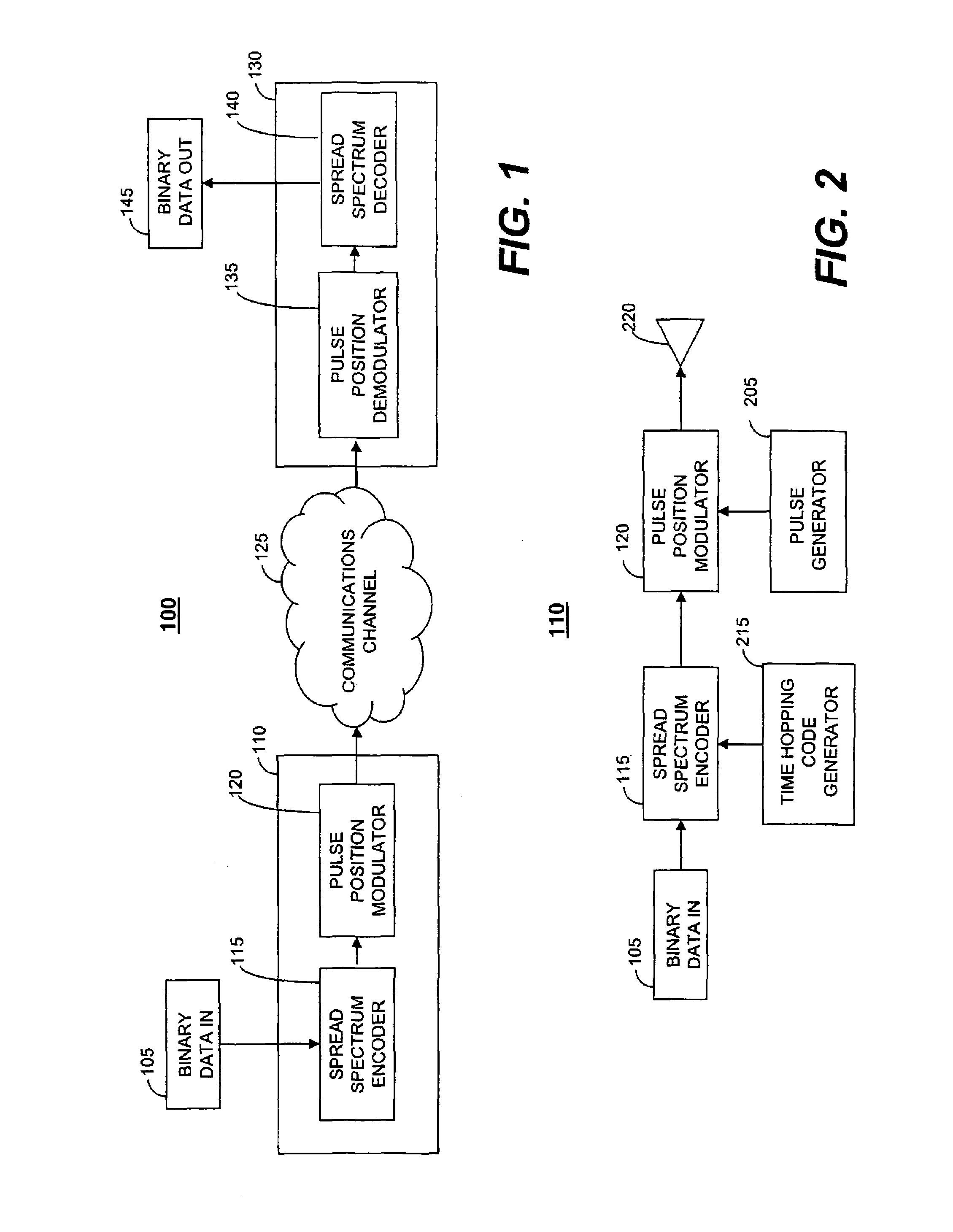

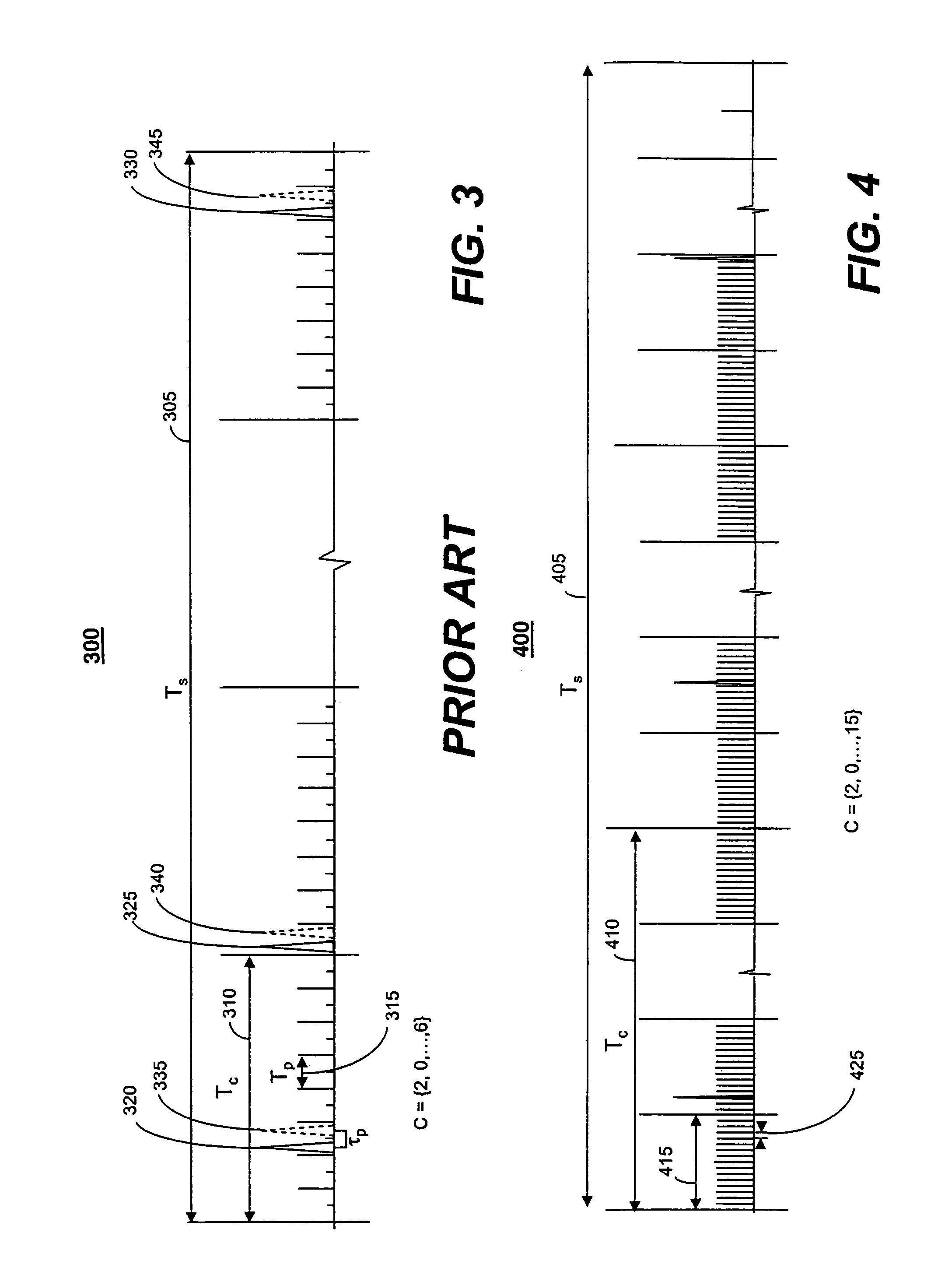

Variable spacing pulse position modulation for ultra-wideband communication links

ActiveUS7082153B2Improve throughputReduce riskFrequency/rate-modulated pulse demodulationPosition-modulated pulse demodulationUltra-widebandData stream

Methods and systems for generating a variable spacing pulse position modulated (VSPPM) signal for transmission across an ultra-wideband communications channel. The variable pulse position modulated spread spectrum signal is created by encoding every M input data bits from an input data stream into a symbol consisting of Nc chips. Each chip is divided into 2M sub-chips and each sub-chip is further divided into Np time slots. A pulse is transmitted for each chip in the symbol. During each chip period, the pulse is placed in the sub-chip corresponding to the binary M-tuple (or symbol) value. A time hopping code sequence consisting of Nc elements with a one-to-one chip association is then applied to each symbol so that the position of each pulse is shifted to the appropriate time slot that corresponds to the time hopping code value.

Owner:WSOU INVESTMENTS LLC +1

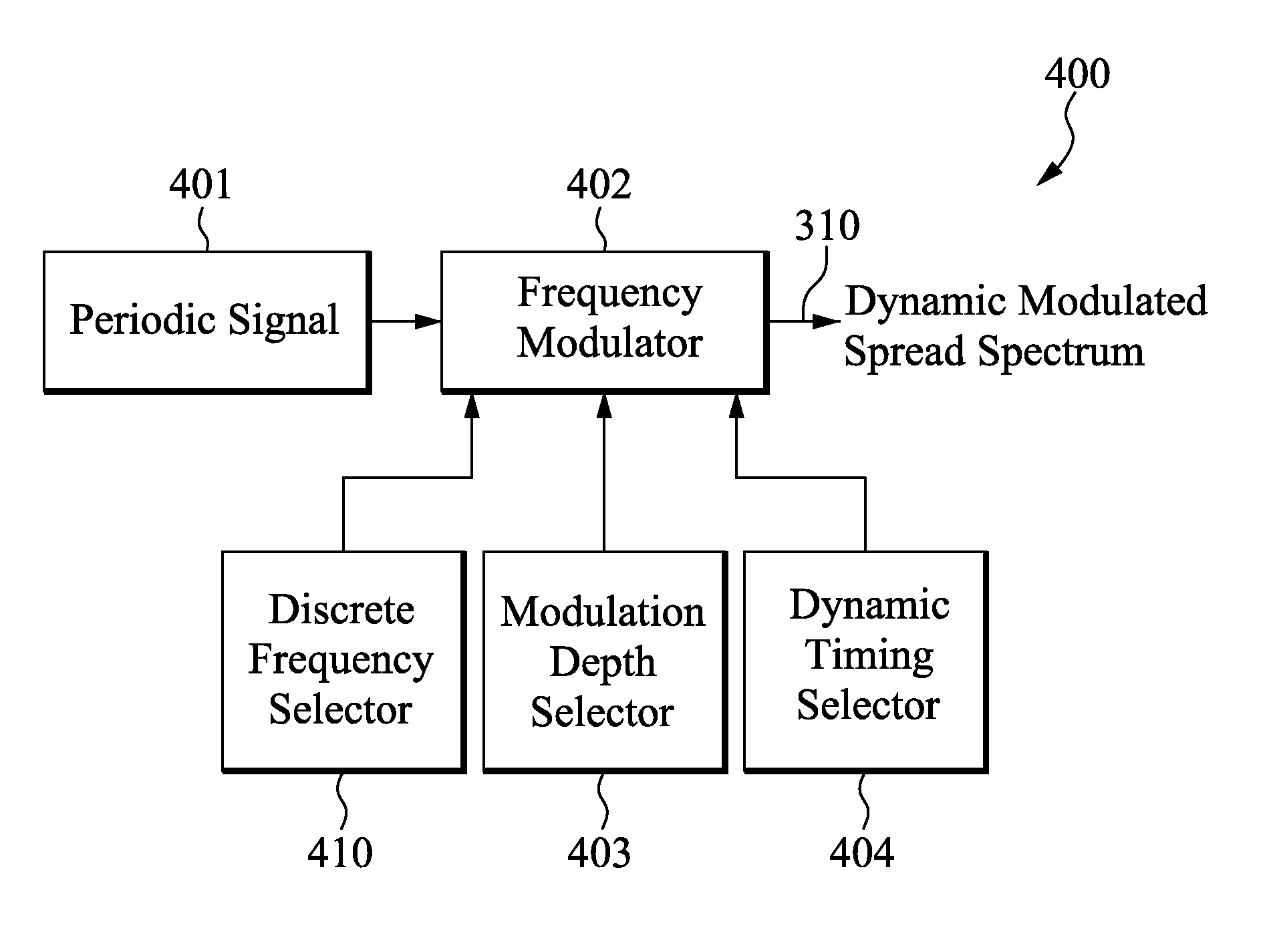

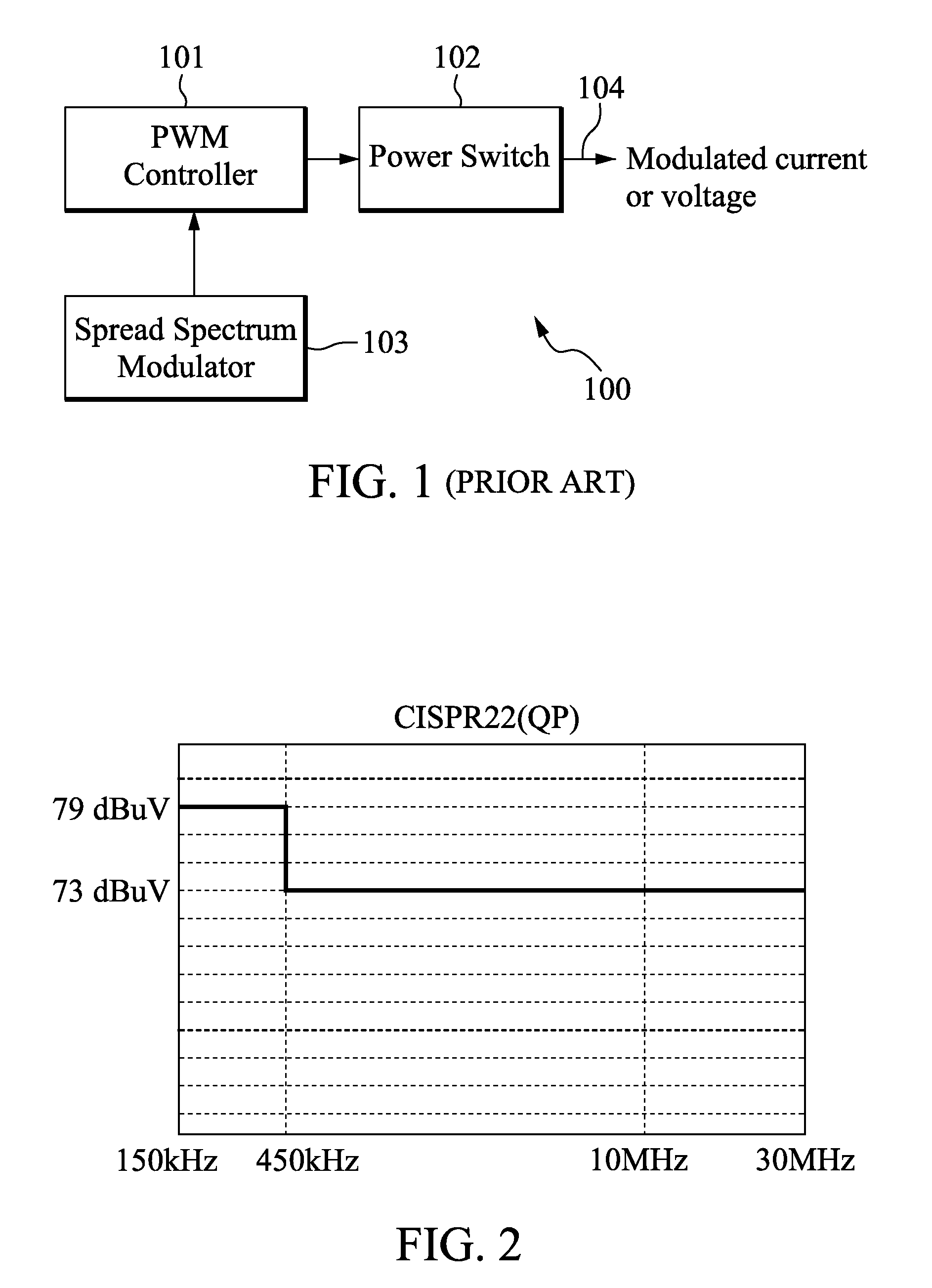

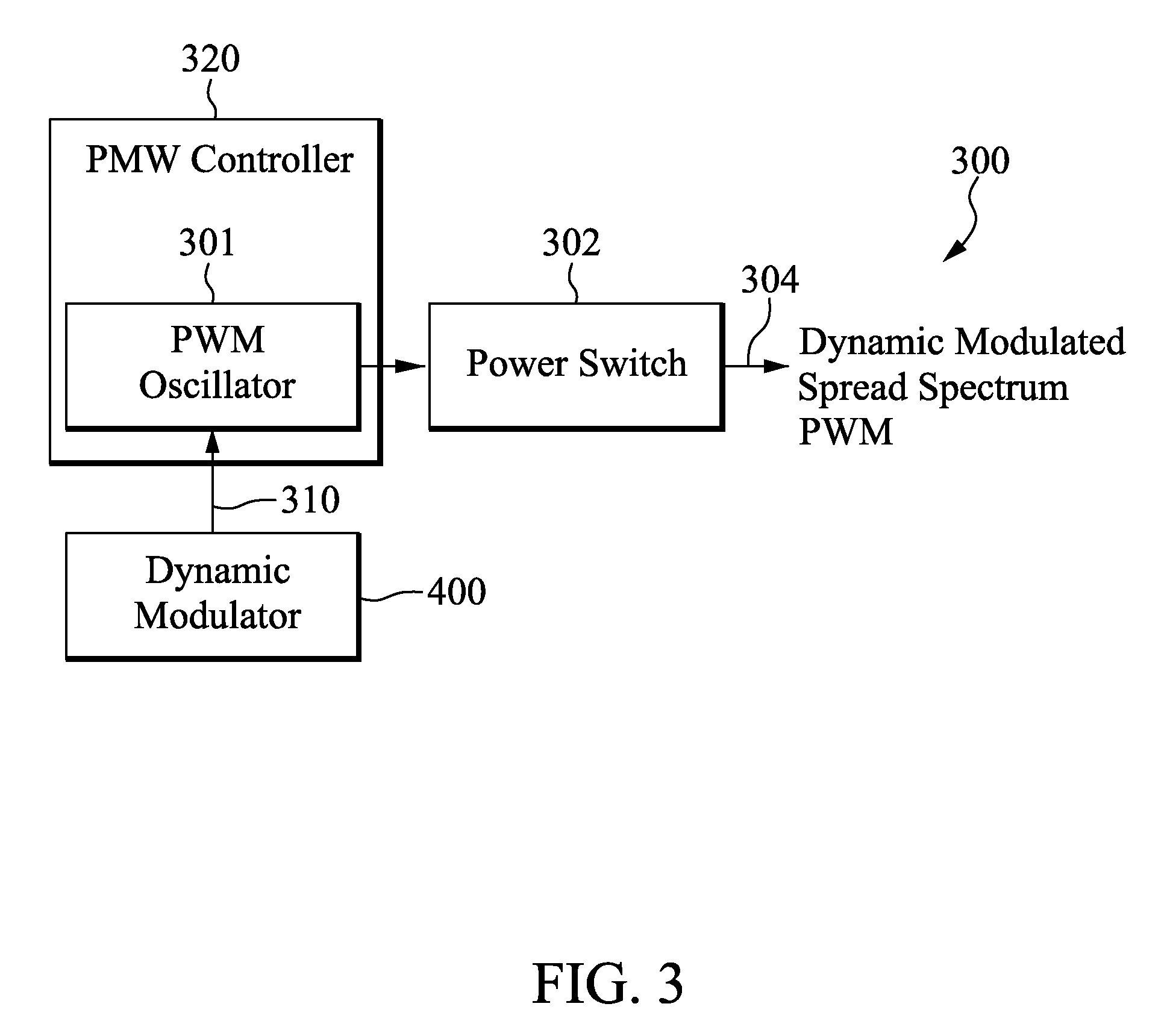

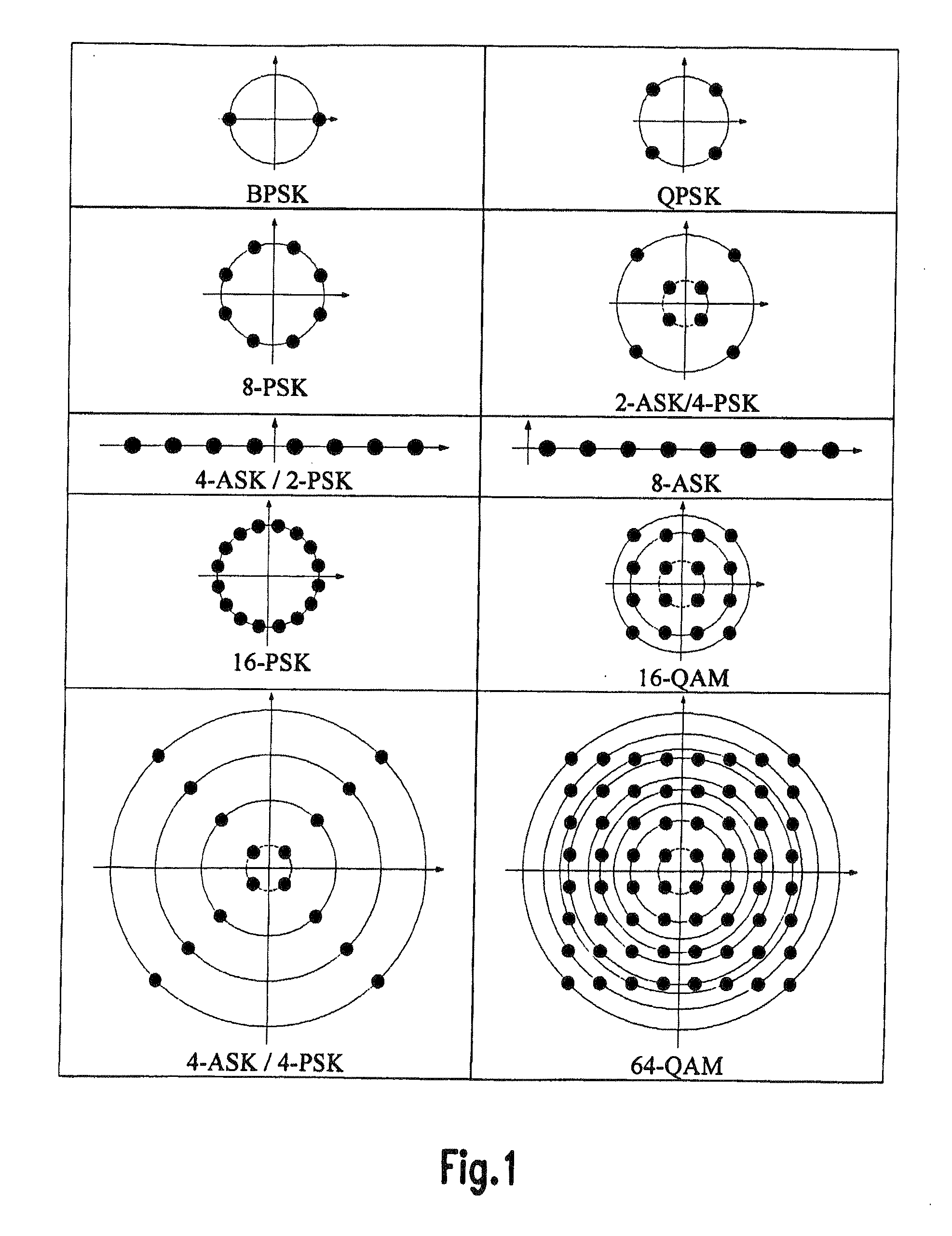

Method and apparatus for dynamic modulation

InactiveUS8085106B2Angle modulation detailsFrequency/rate-modulated pulse demodulationFrequency spectrumHarmonic

Circuits and methods of dynamic modulation are disclosed. A dynamic modulator is used to reduce measurable conducted and / or radiated electromagnetic interference (EMI). The dynamic modulator is configured to generate either a set of optimal frequency modulation depths or discrete frequencies or both, and dynamically selects them to use over a series of programmable time durations (dwell time). Together with the utilization of Peak, Average or Quasi-Peak (QP) method of measurement, the dynamic modulator can reduce the spectral amplitude of EMI components, in particular the lower harmonics, to effectively pass regulatory requirements. In alternative embodiments, the dynamic modulator is used in a closed loop system to continuously adjust the frequency and the duty cycle of a PWM signal to reduce conducted and / or radiated EMI.

Owner:HUDA MUZAHID BIN +1

High bandwidth data transport system

InactiveUS20050131922A1High bandwidthIncrease data rateModulated carrier system with waveletsTransmission/receiving by adding signal to waveUltra-widebandFiber

The present invention provides for a methods, system, and apparatus relating to data transmission. One method of the present invention includes representing data using at least one ultra wideband pulse, sending the at least one ultra wideband pulse over an electrically conductive guided media, and recovering the data from the at least one ultra wideband pulse. The present invention can be used in conjunction with telephony applications, cable TV applications, power line applications, fiber optic applications, and data bus applications.

Owner:LIGHTWAVES SYST

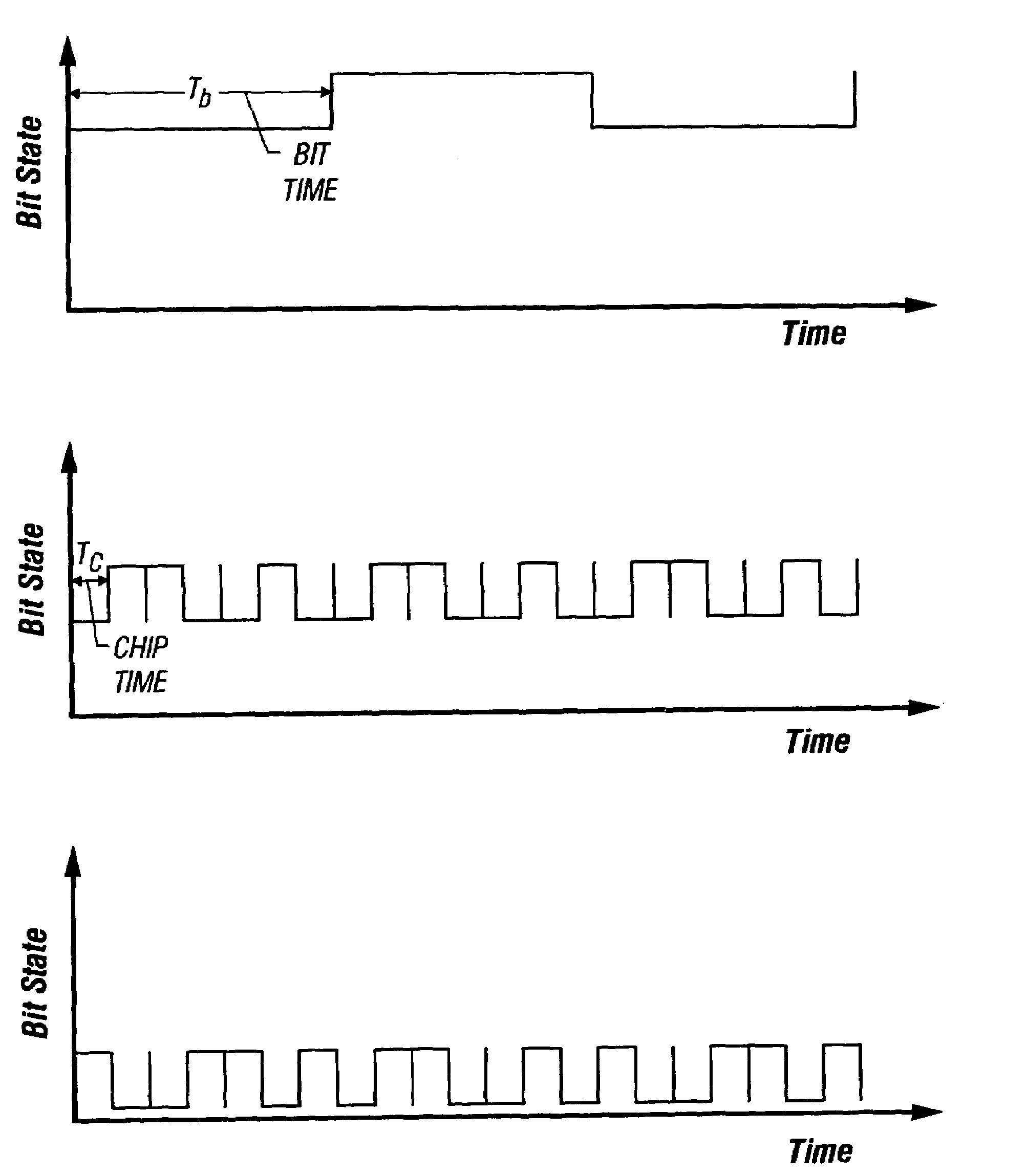

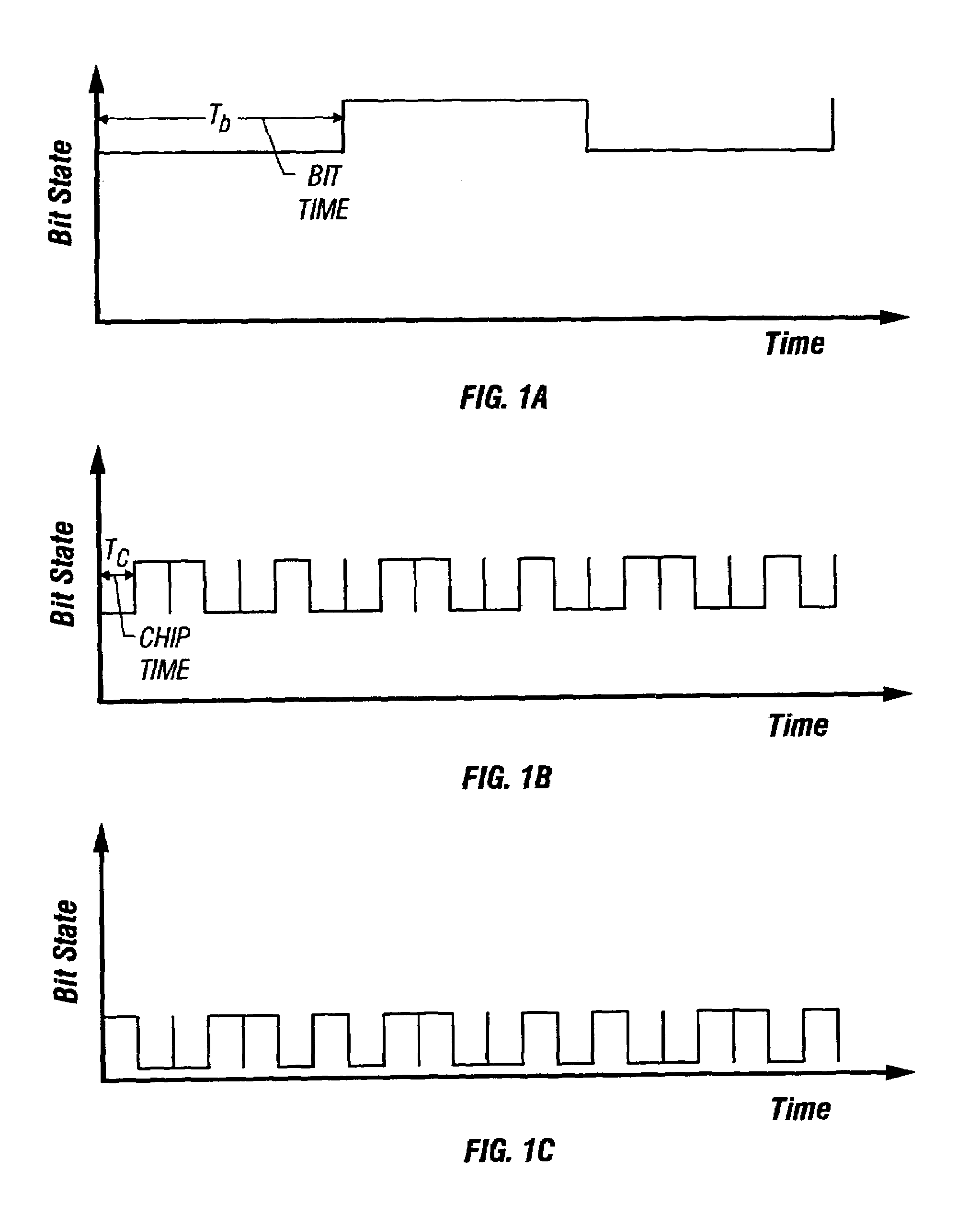

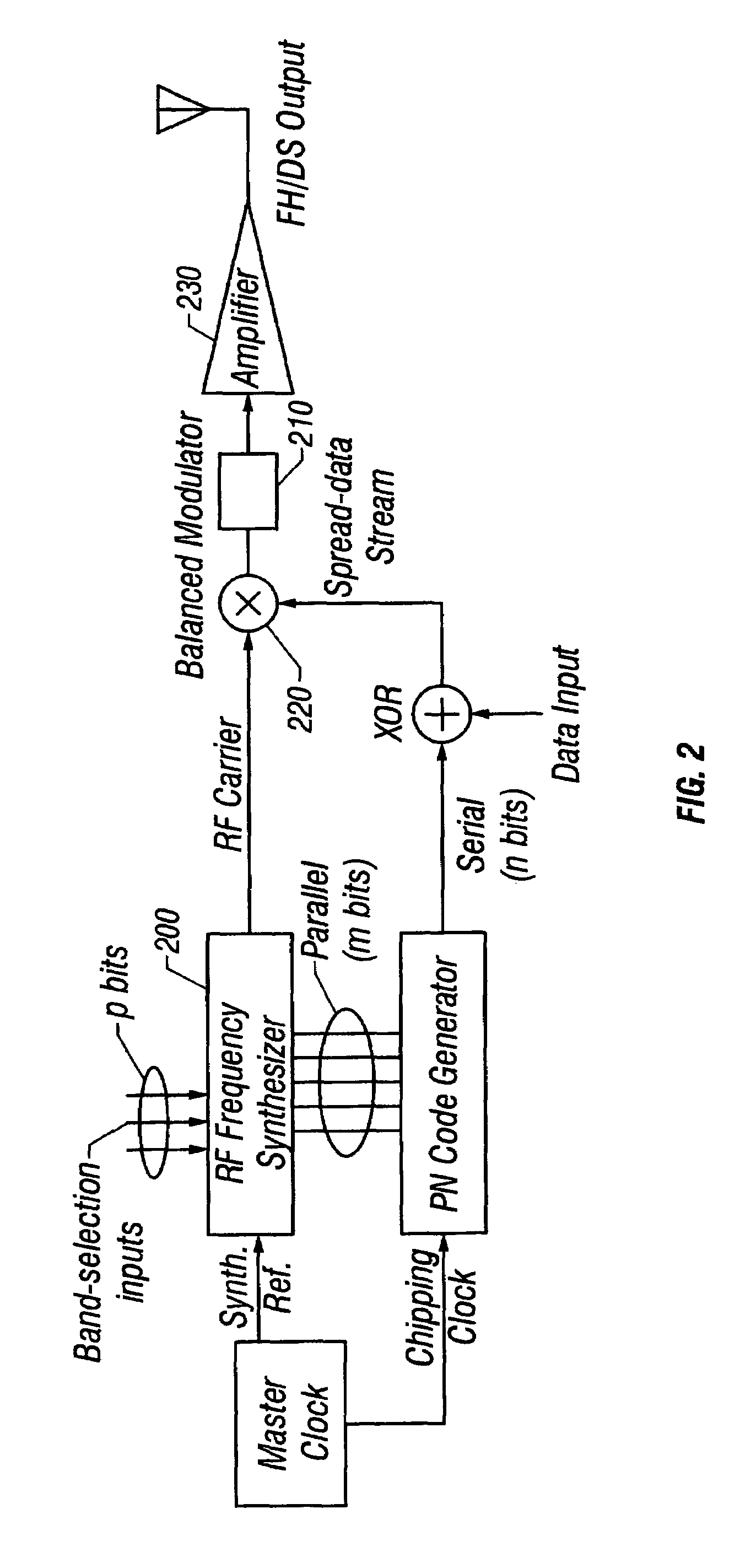

Hybrid spread-spectrum technique for expanding channel capacity

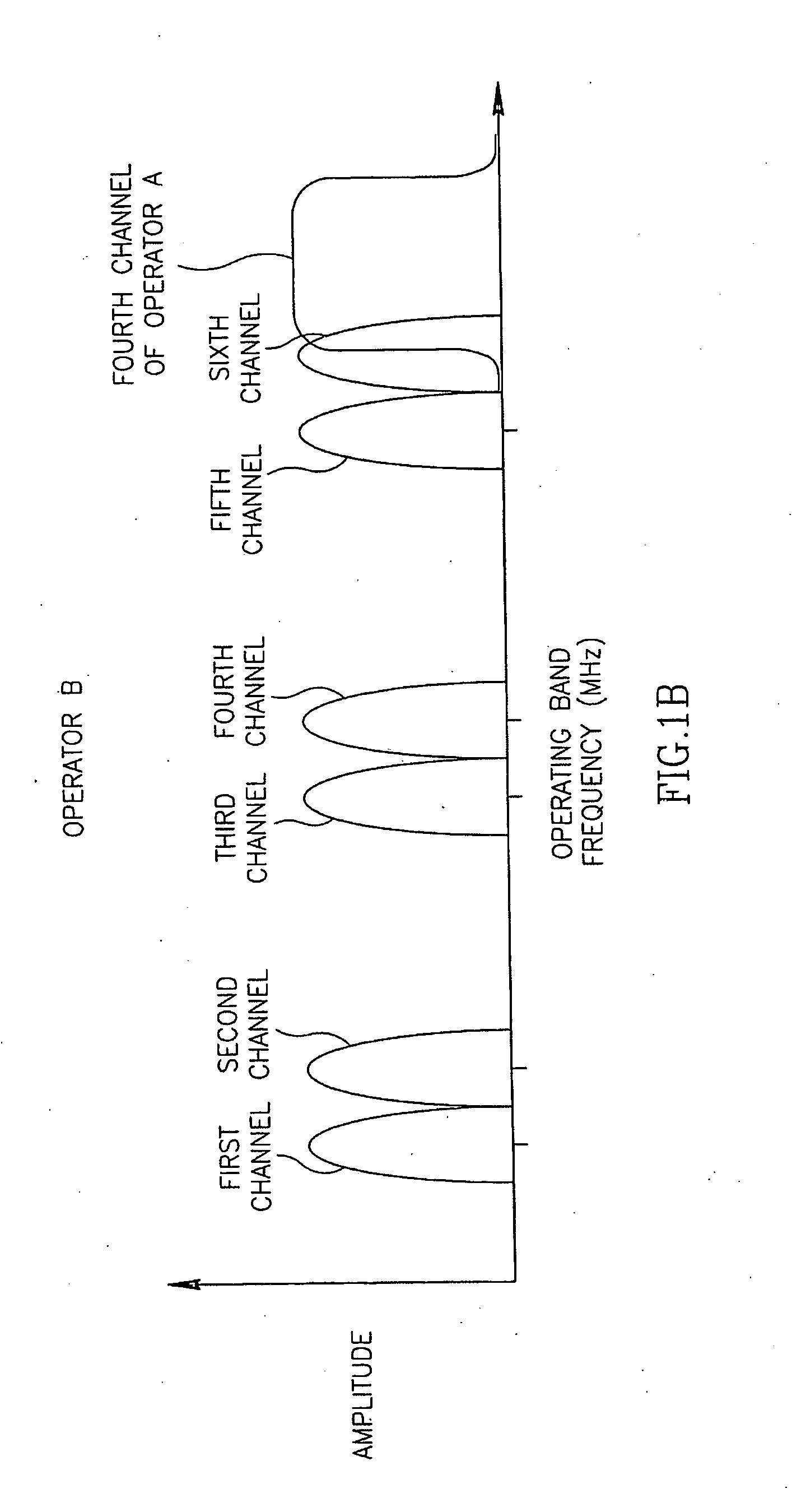

InactiveUS7092440B1Increase the number ofTime-division multiplexFrequency-division multiplexFrequency spectrumEngineering

Methods, systems and devices are described for a direct-sequence spread-spectrum communication scheme that increases the number of users by utilizing a plurality of closely spaced orthogonal carriers that produce overlapping spectra. A method includes overlapping a plurality of direct-sequence spread-spectrum signals using carrier frequencies that are orthogonally spaced relative to a bit rate. The methods, systems and devices provide advantages because they can accommodate an increase in the number of normalized users and can optimize the loading of users across multiple frequency channels.

Owner:UT BATTELLE LLC

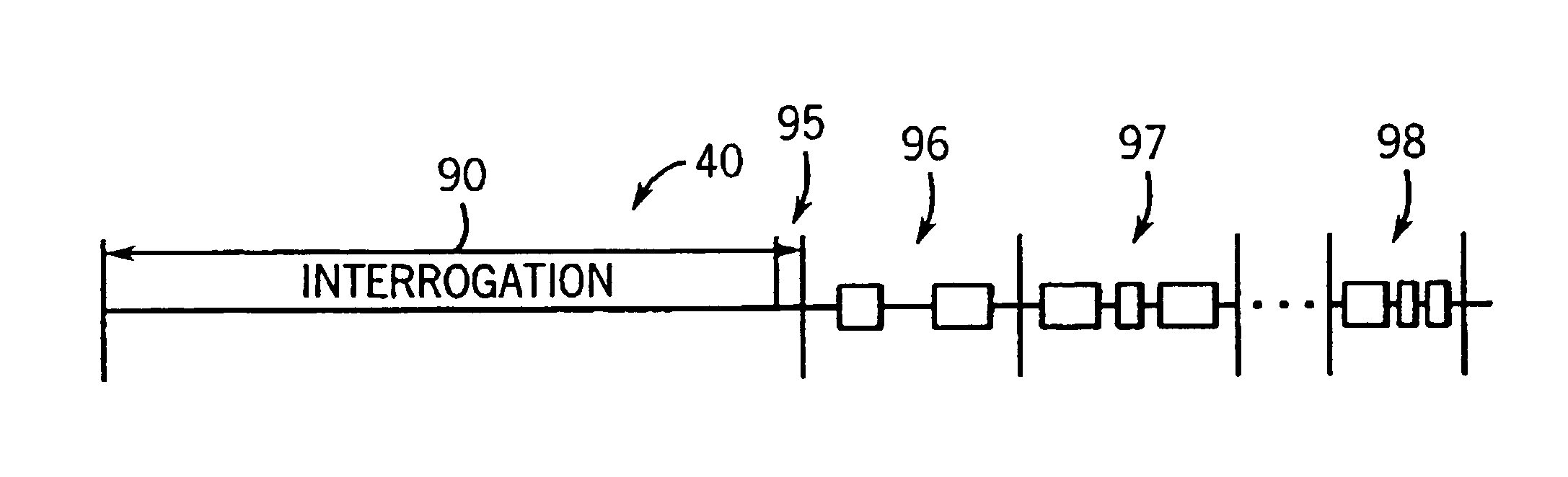

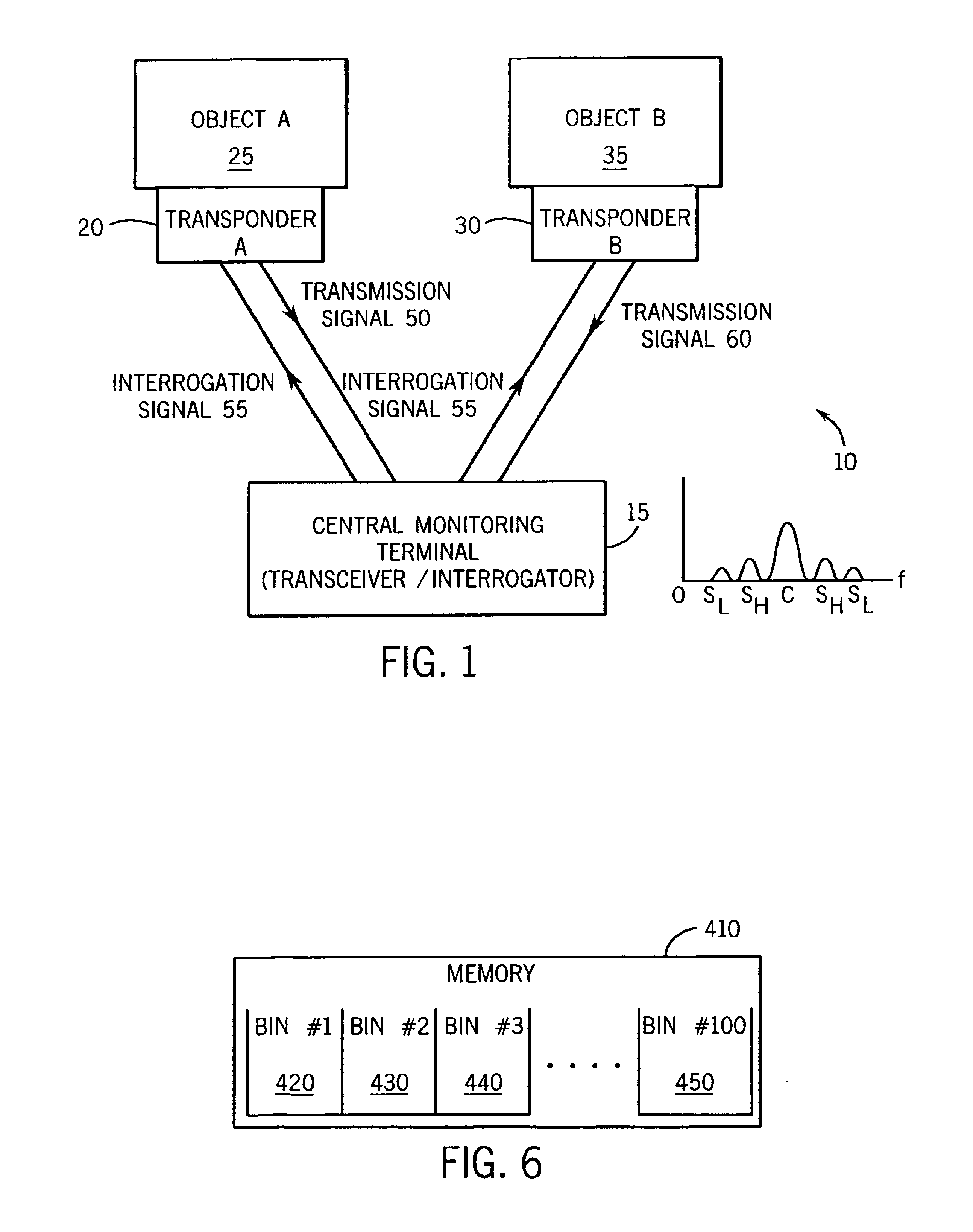

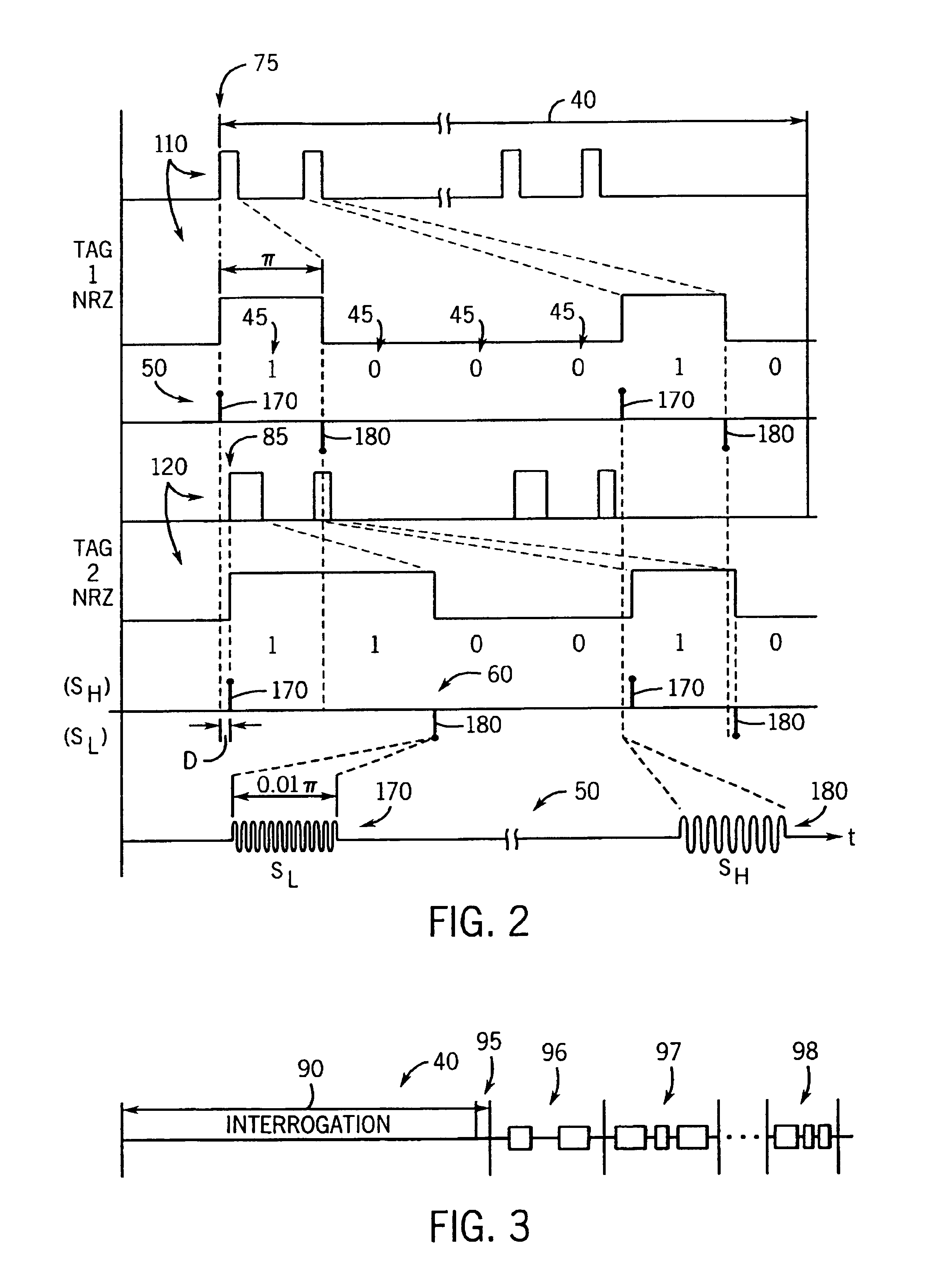

Method for communication between central terminal and multiple transponders

InactiveUS6975206B2Electric signal transmission systemsMemory record carrier reading problemsStart timeComputer terminal

A method of communicating information from first and second transponders (or multiple transponders) to a central monitoring device, and a communications apparatus, are disclosed. The method includes receiving a starting indication at the transponders, determining start times for the transponders in response to that indication, and transmitting first and second sets of bursts from the first and second transponders, respectively. The bursts of the first set occur at at least some of a first set of potential transmission times within an interrogation period, and the bursts of the second set occur at at least some of a second set of potential transmission times during that period. Each of the potential transmission times of the burst sets are respectively determined in relation to the start times of the respective transponders. The potential transmission times of the respective burst sets are separated from one another by one of a bit-cell period and a multiple thereof.

Owner:INTPROP LLC

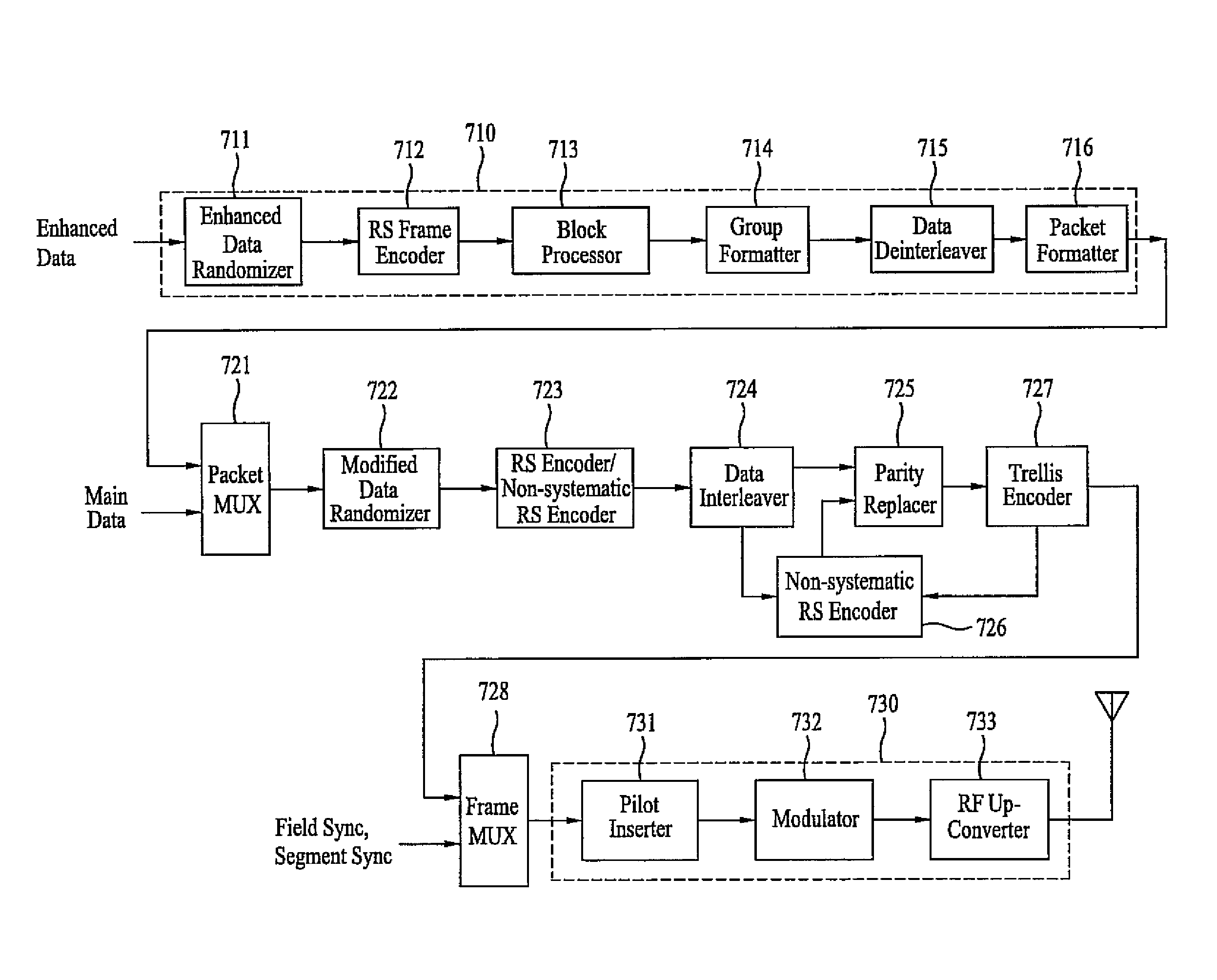

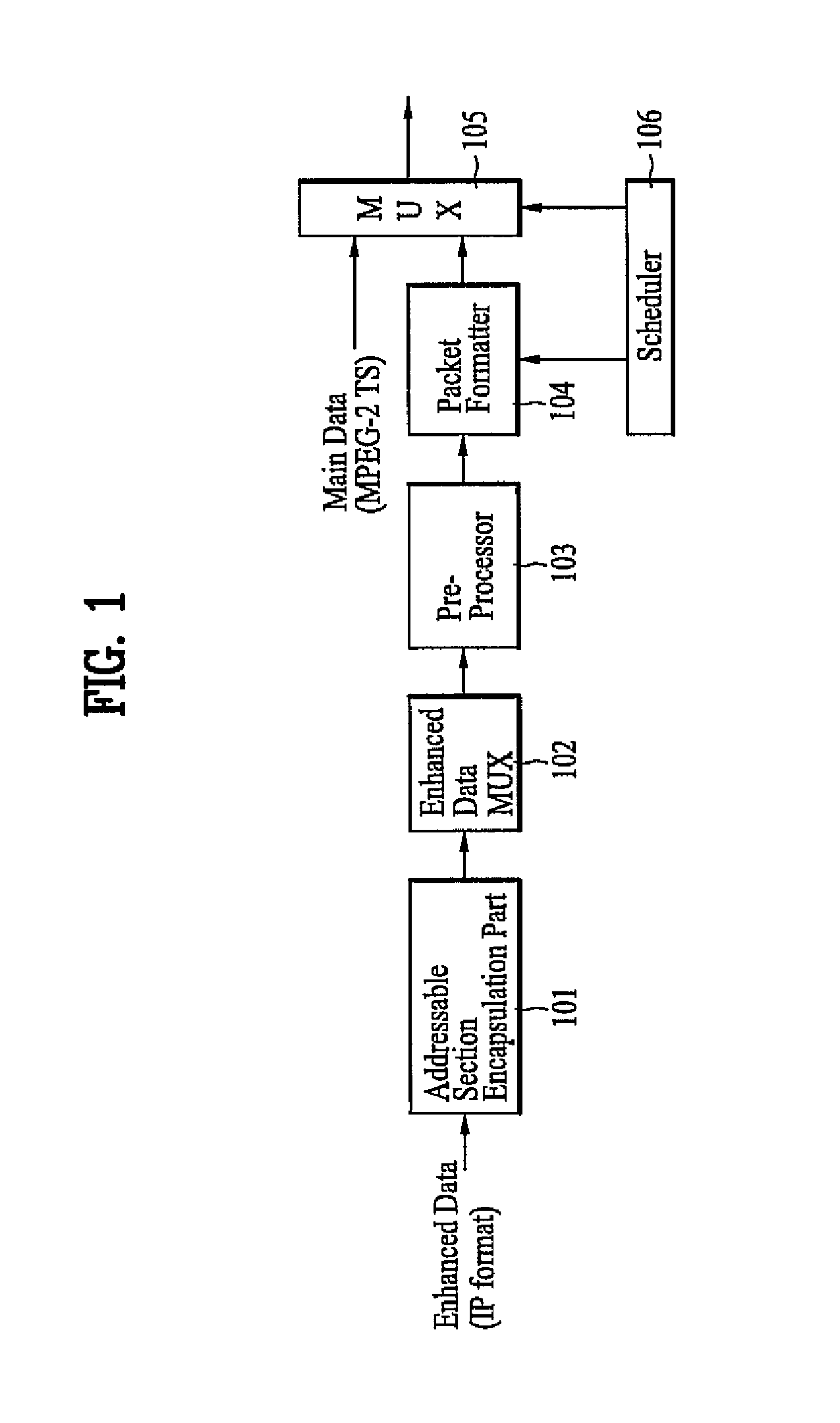

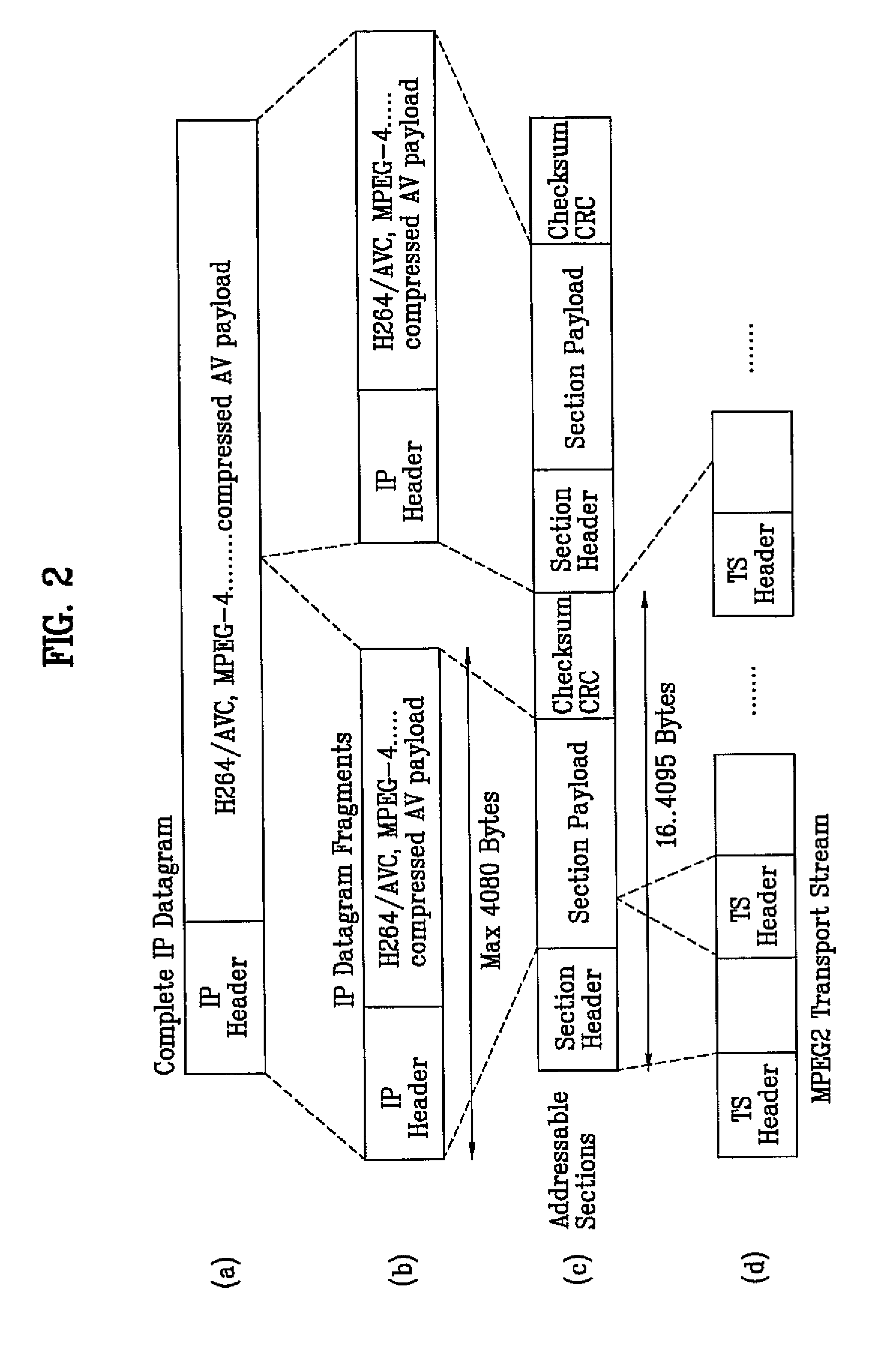

DTV transmitter and method of coding data in DTV transmitter

ActiveUS8094727B2Improve reception performanceData representation error detection/correctionPulse modulation television signal transmissionTime informationMultiplexing

A DTV transmitter includes an encapsulation unit which encapsulates enhanced data having an internet protocol (IP) format into a plurality of addressable sections. The encapsulation unit inserts burst time information into each addressable section. The DTV transmitter further includes a first multiplexer multiplexing the encapsulated enhanced data with program and system information, a pre-processor pre-processing the multiplexed enhanced data, a data formatter generating enhanced data packets including the pre-processed data and inserting the known data into the enhanced data packets, and a second multiplexer generating one or more bursts of data by multiplexing the enhanced data packets.

Owner:LG ELECTRONICS INC

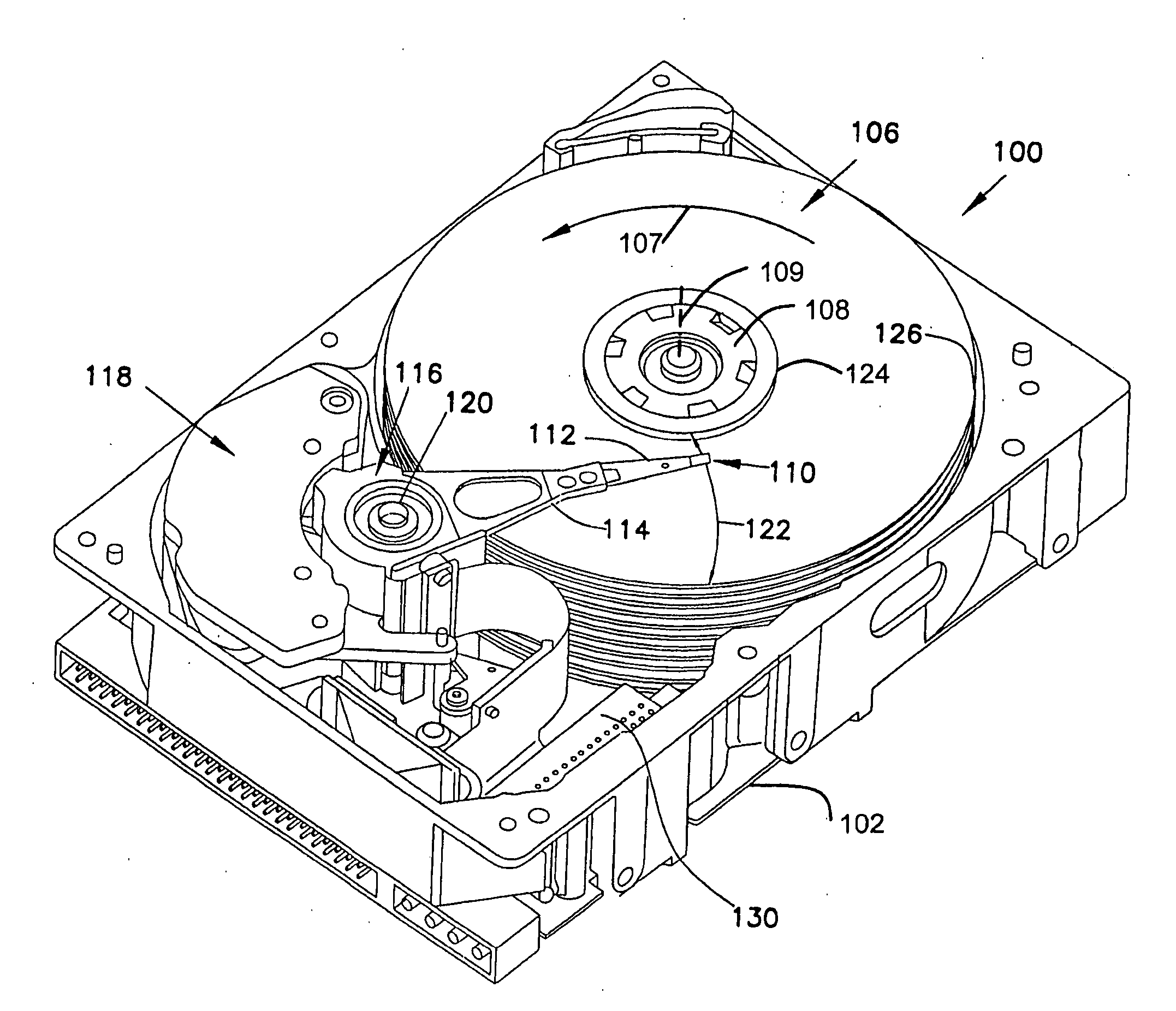

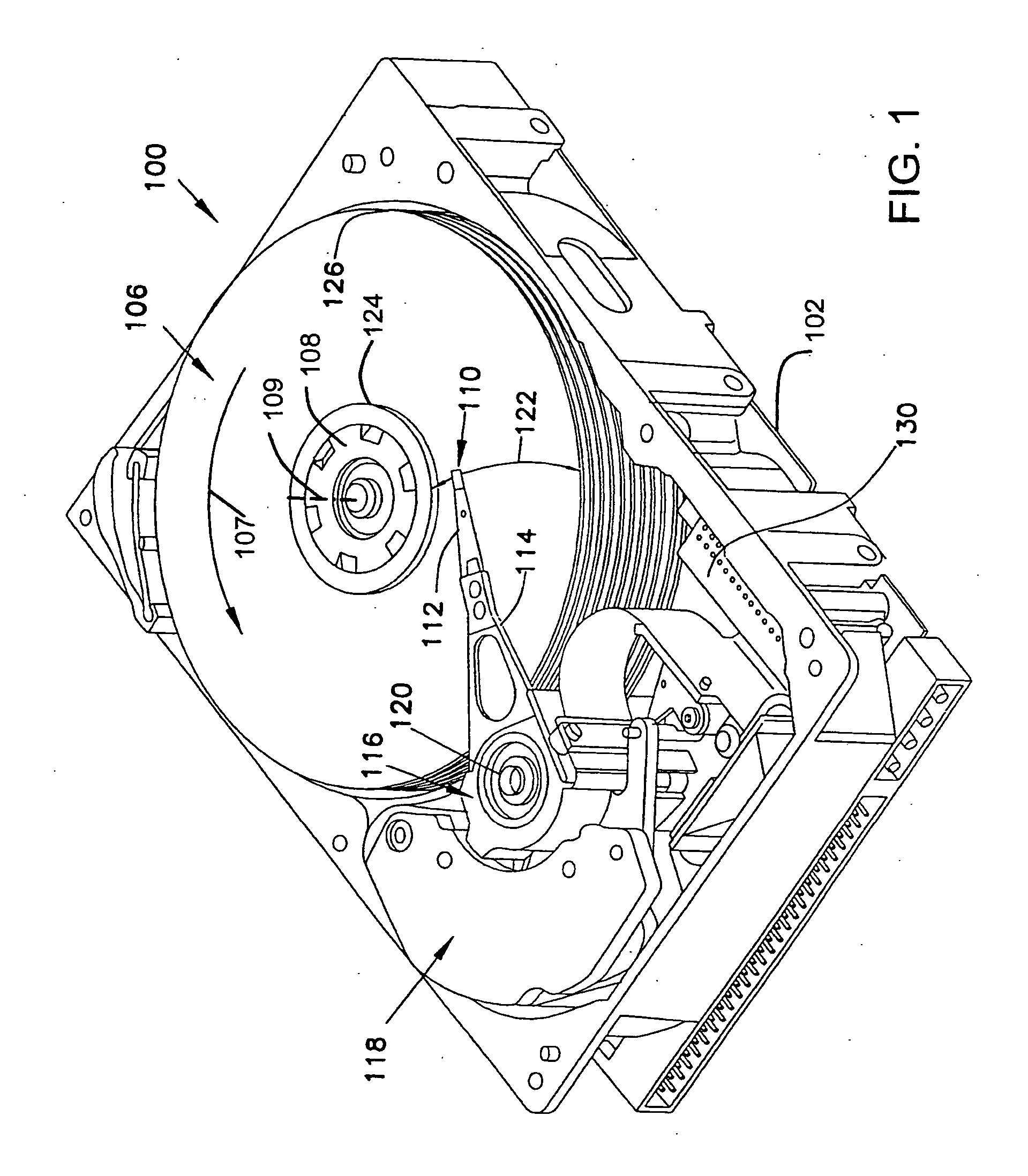

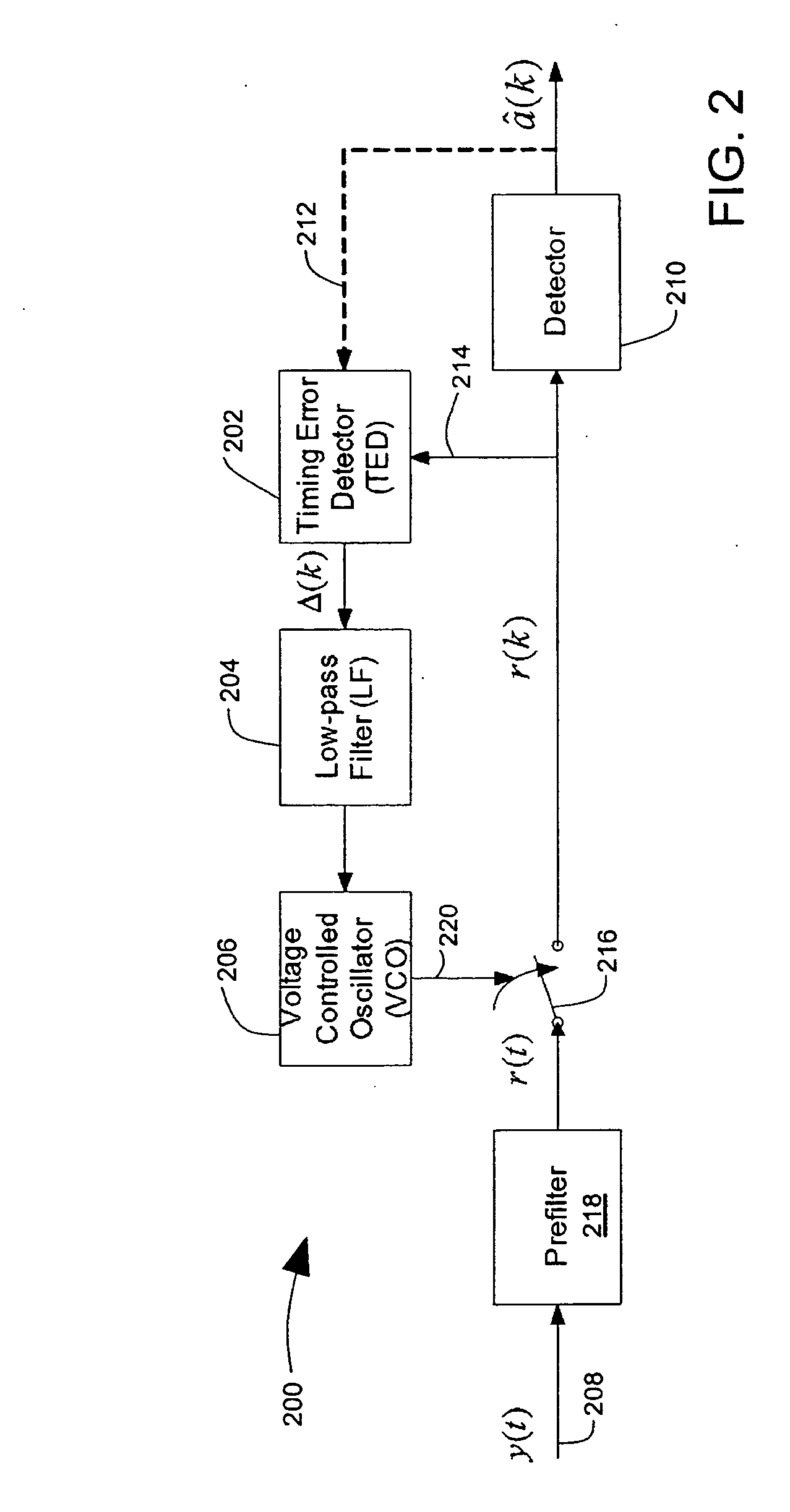

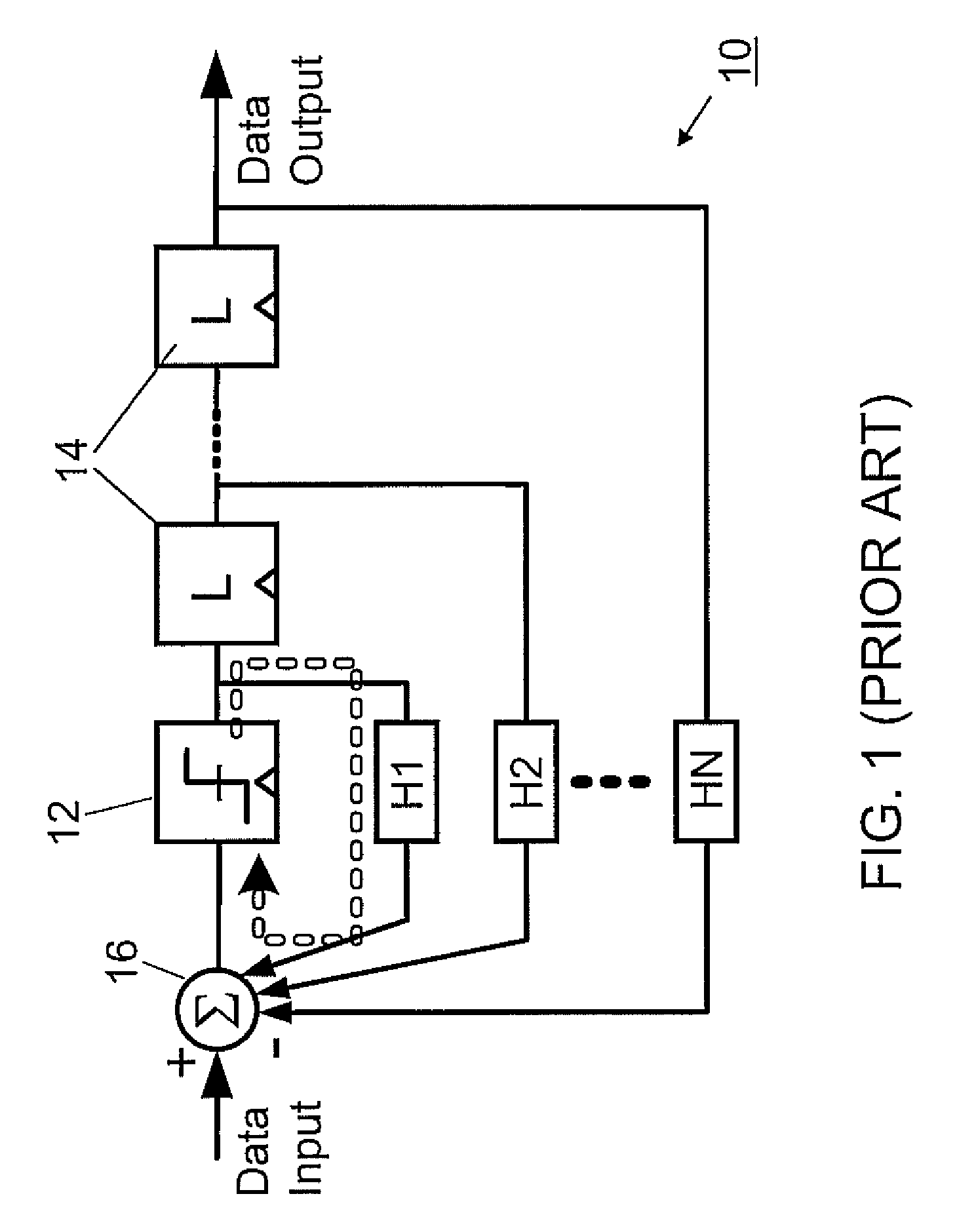

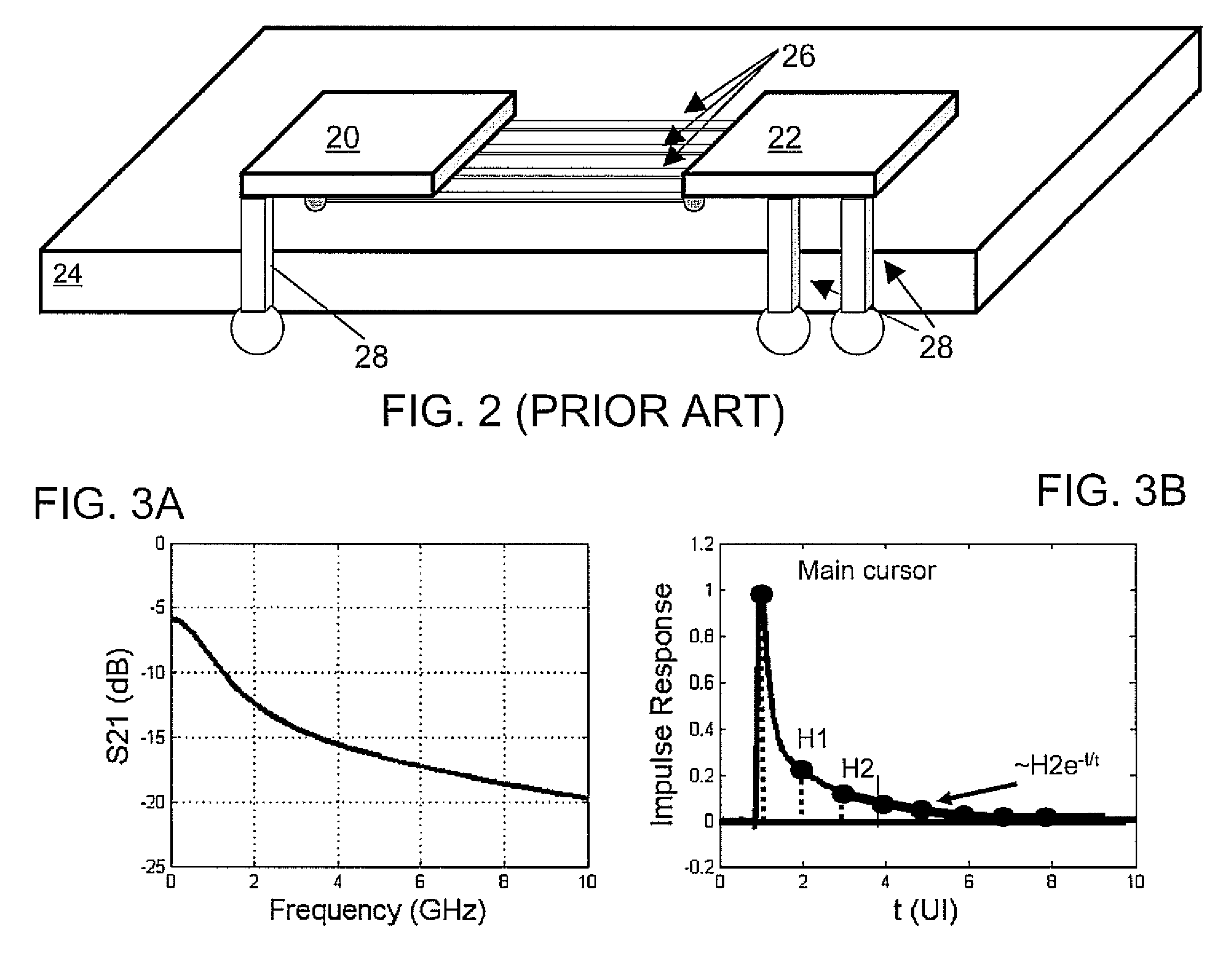

Timing recovery in a parallel channel communication system

ActiveUS20060210002A1Modification of read/write signalsSynchronisation error detectionCommunications systemDiscrete-time signal

A parallel channel timing recovery circuit. The parallel timing recovery circuit comprises multiple prefilters receiving parallel channel outputs and providing prefilter outputs. Multiple sampling filters receive the prefilter outputs and provide multiple discrete time signal samples. A self-timing circuit has multiple inputs receiving the multiple discrete time signal samples. The self-timing circuit provides a sampling control output to the sampling filters. The sampling control output is based on a composite of the multiple discrete time signal samples. Each of the sampling filters generates a discrete time signal sample based on the sampling control output and the prefilter outputs.

Owner:SEAGATE TECH LLC

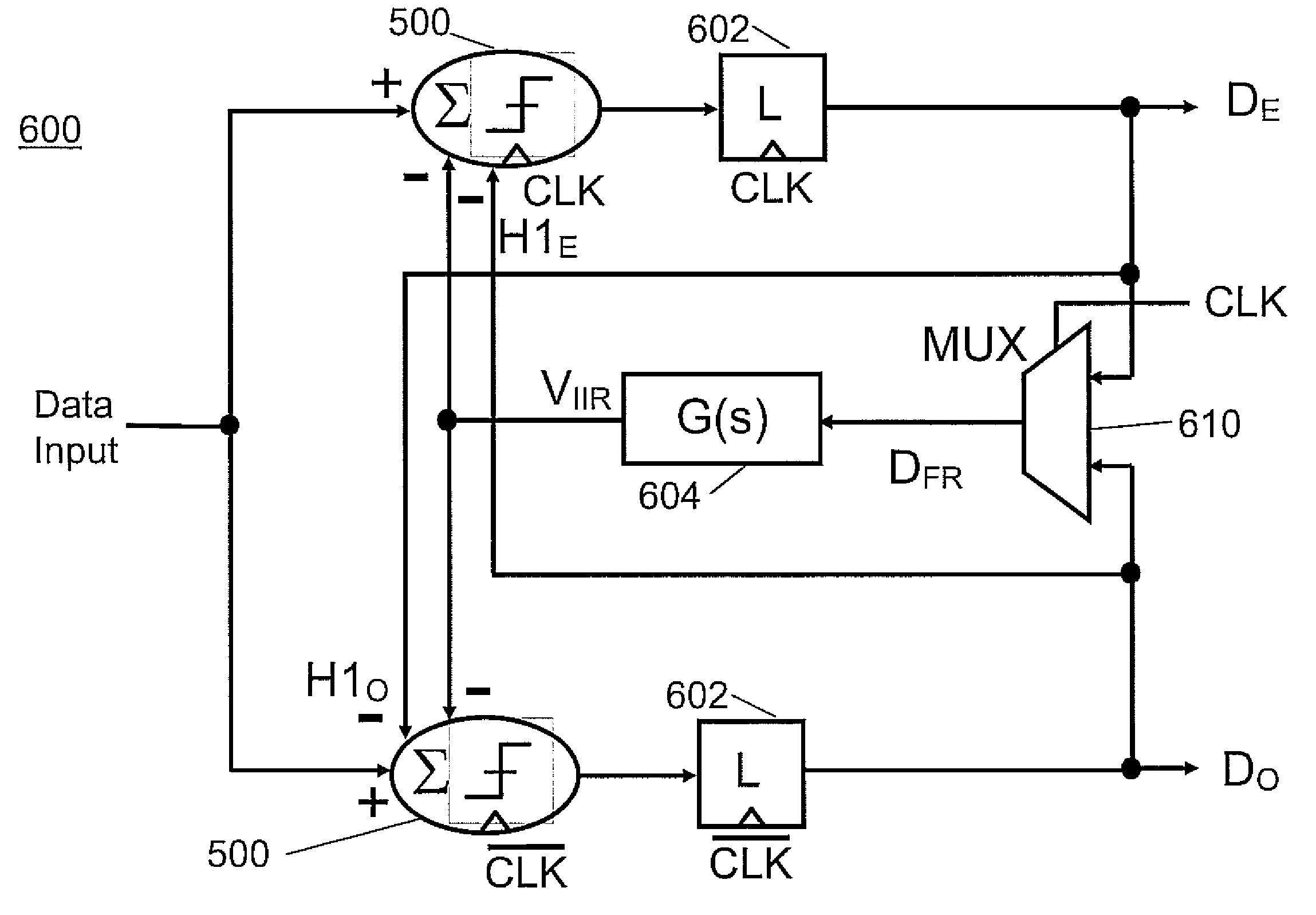

Circuits and methods for dfe with reduced area and power consumption

ActiveUS20100202506A1Increase speedHigh sensitivityMultiple-port networksFrequency/rate-modulated pulse demodulationMultiplexingMultiplexer

A 1 / n-rate decision feedback equalizer (DFE) and method include a plurality of branches. Each branch includes a summer circuit configured to add a feedback signal to a received input, and a latch configured to receive an output of the summer circuit in accordance with a clock signal. A feedback circuit includes a multiplexer configured to receive as input, an output of each branch, the multiplexer having a clocked select input and configured to multiplex the output of each branch to assemble a full rate bit sequence, and a filter configured to provide cancellation of intersymbol interference (ISI) from the received input to be provided to the summer circuit of each branch.

Owner:IBM CORP

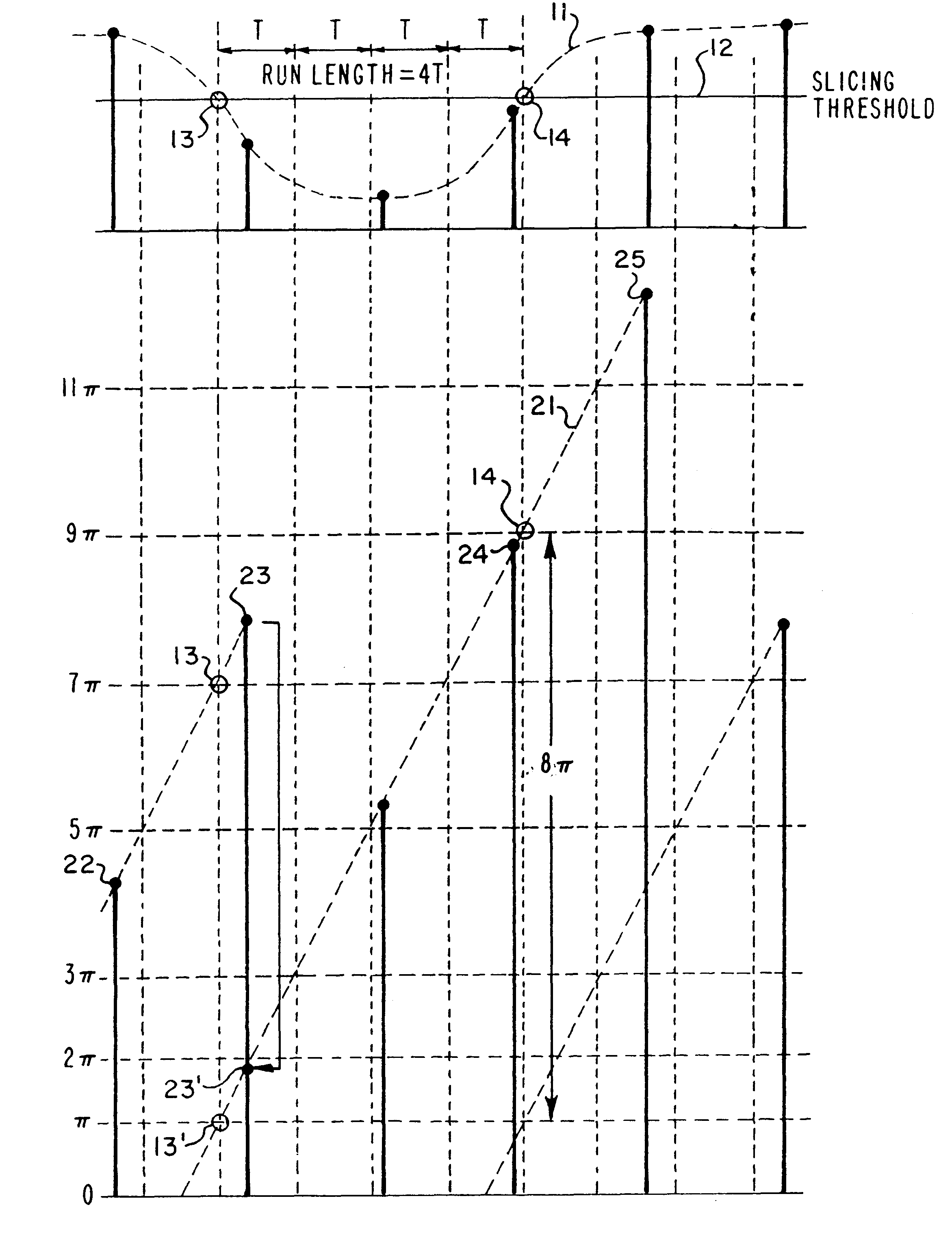

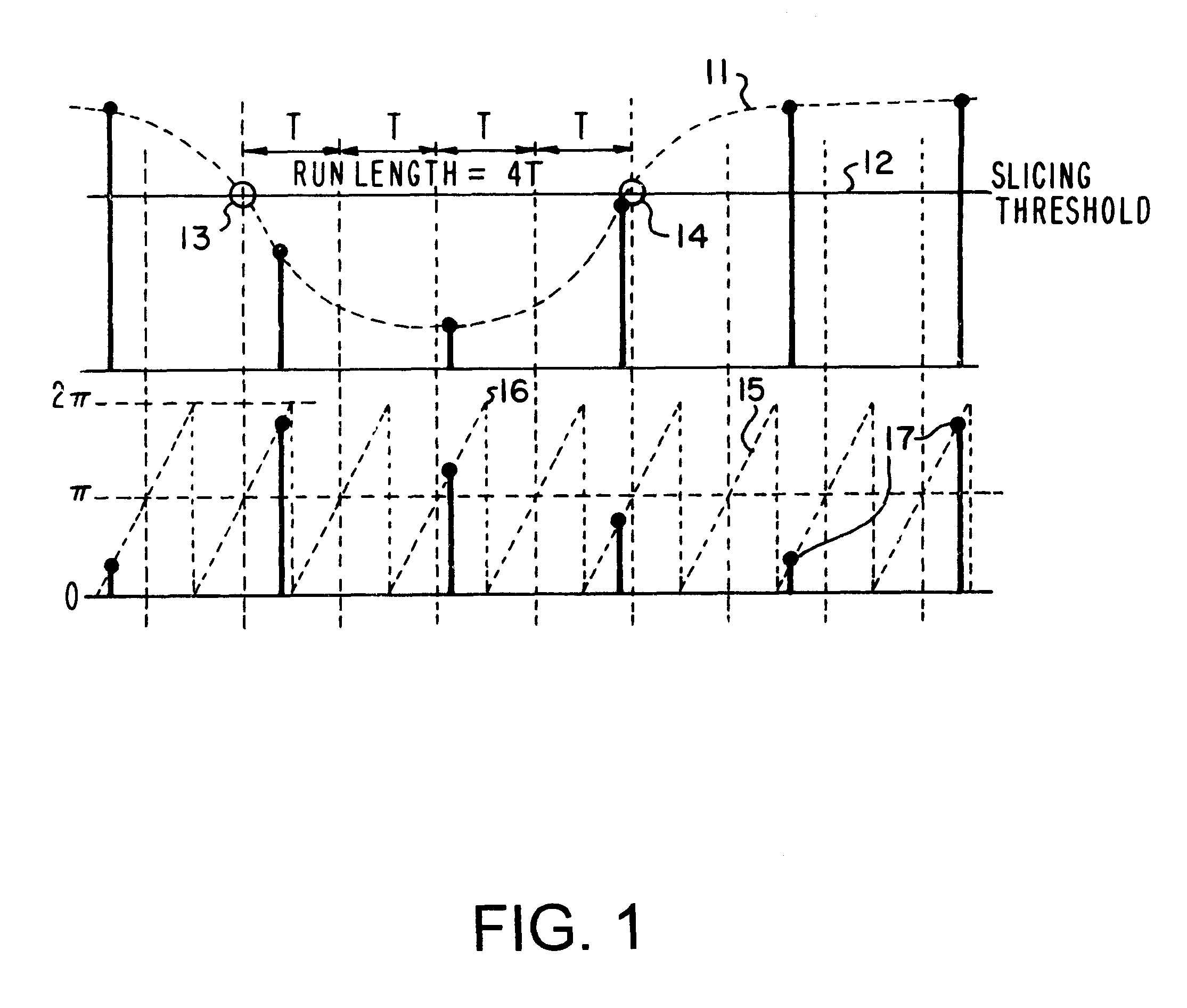

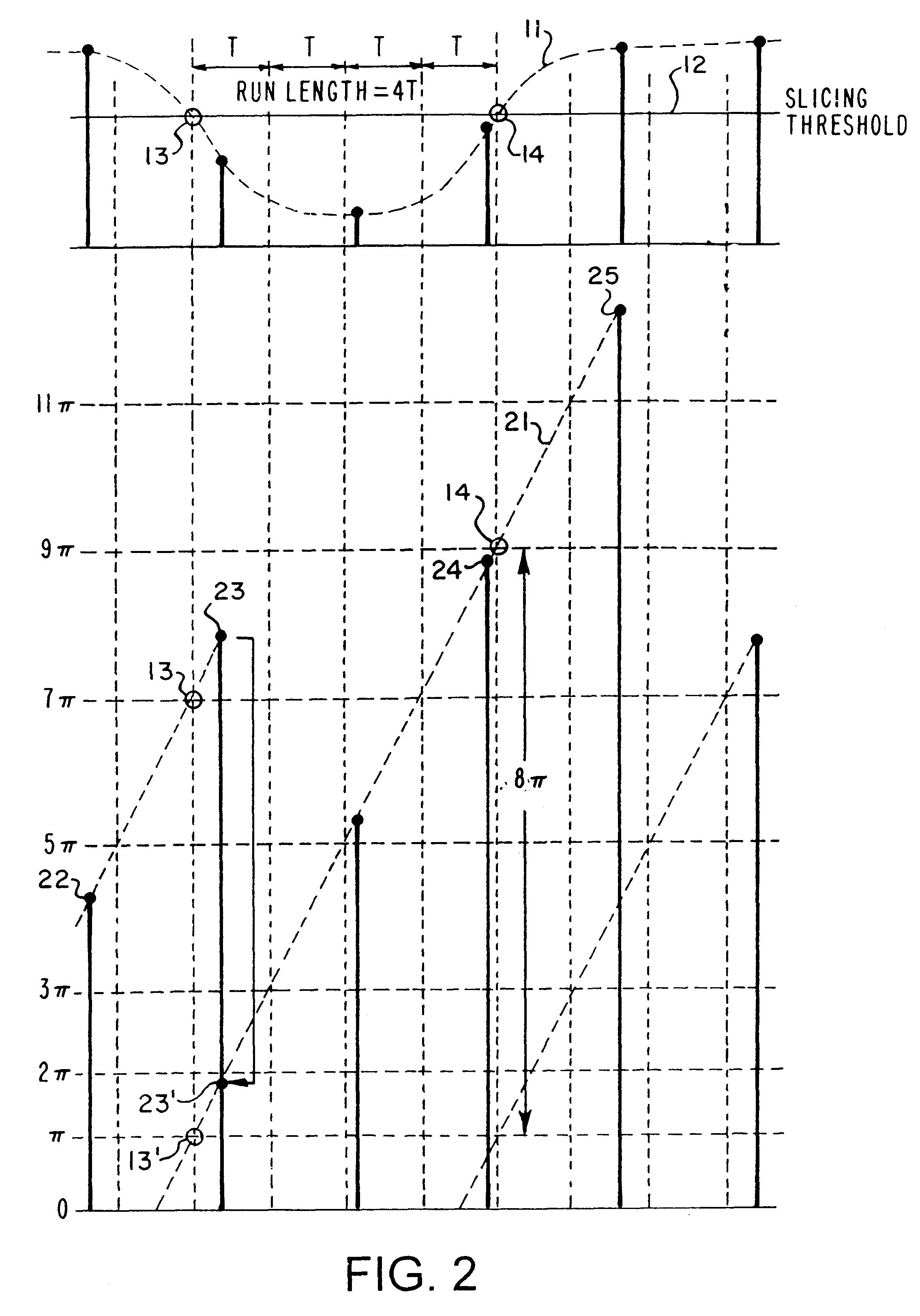

Pulse run-length measurement for HF data signal by dividing accumulated phase difference between first and second zero-crossings by single-cycle range using multiple cycle range sawtooth waveform

InactiveUS6389548B1Modulated-carrier systemsDigital data processing detailsPhase differenceLength measurement

A system and method for accurately measuring a pulse run length in a high frequency (HF) data signal while utilizing a low analog-to-digital conversion (ADC) sampling rate. Four bits are added to the most significant end of an oscillator's accumulator register so that the oscillator generates a sawtooth clock waveform ranging in phase from zero (0) to 32pi radians. An interpolator detects a first zero-crossing transition of the HF data signal at the leading edge of the pulse run length, and a phase detector measures a first phase increment at that time. The MSBs of the accumulator register is then initialized to place the measured first phase increment in a range between zero (0) and 2pi radians. The accumulator register then accumulates phase increments until the interpolator detects a second zero-crossing transition of the HF data signal at the trailing edge of the pulse run length, and the phase detector measures a second phase increment when the second zero-crossing transition is detected. An accumulated phase difference is calculated by subtracting the initialized first phase increment from the measured second phase increment. The pulse run length is then obtained by dividing the accumulated phase difference by 2pi.

Owner:CEVA IRELAND +1

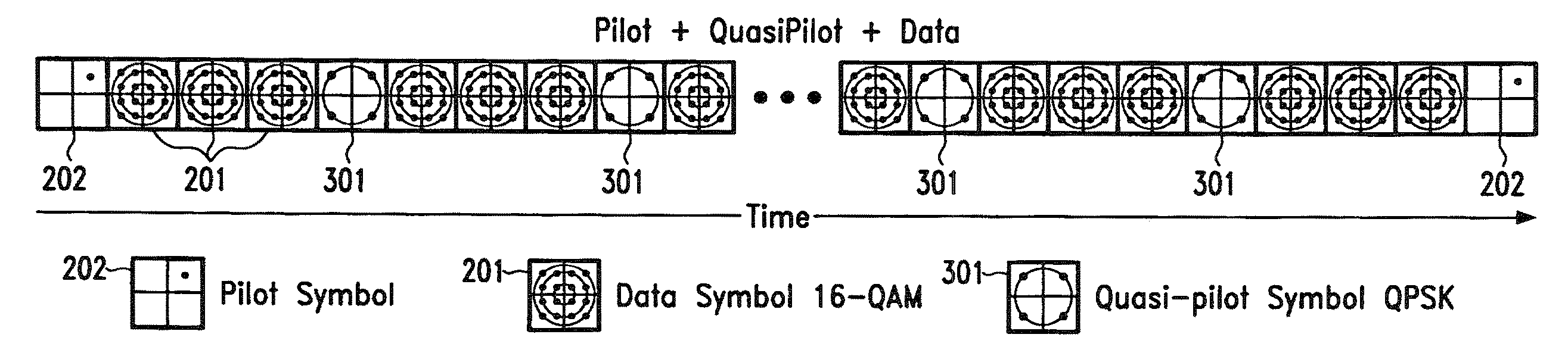

Quasi-Pilot Symbol Substitution

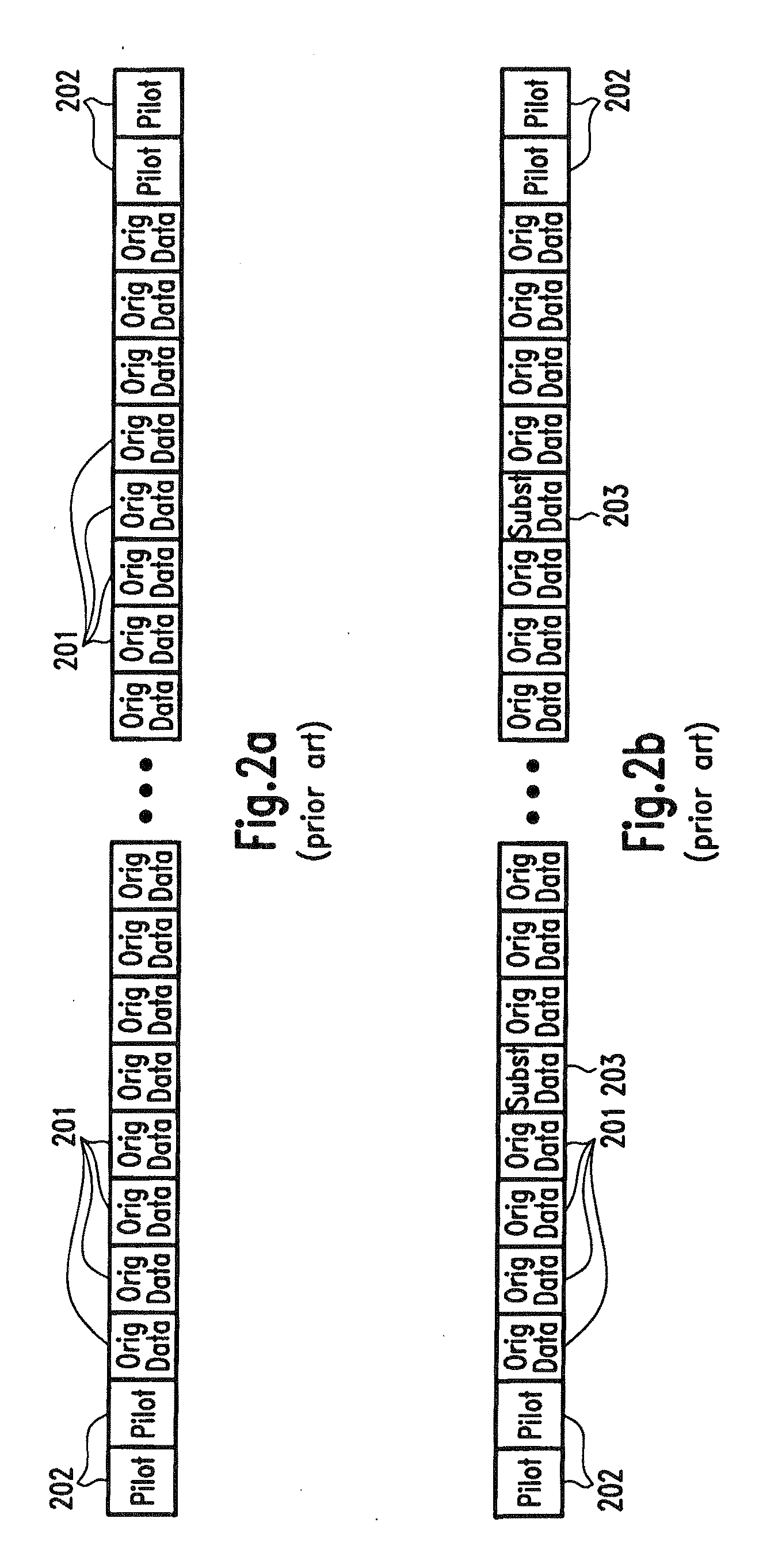

InactiveUS20080151989A1Easy to useReliable channel estimationFrequency/rate-modulated pulse demodulationSecret communicationData streamOriginal data

To improve the reliability of channel estimation, data symbols at determined positions of the transmitted data stream are replaced by quasi-pilot symbols. The quasi-pilot symbols carry data modulated onto the carrier with a different modulation scheme than the original symbols. The modulation scheme for the quasi-pilot symbols has a lower amplitude and / or phase ambiguity than the modulation scheme for the original data symbol.

Owner:OPTIS WIRELESS TECH LLC