Clock data recovery and serial-parallel conversion circuit based on over sampling

A clock data recovery and conversion circuit technology, applied in electrical components, digital transmission systems, automatic power control, etc., can solve problems such as jitter performance degradation, phase boundary control unit offset, etc.

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0019] The technical solution and working principle adopted by the present invention will be described in detail below in conjunction with the accompanying drawings.

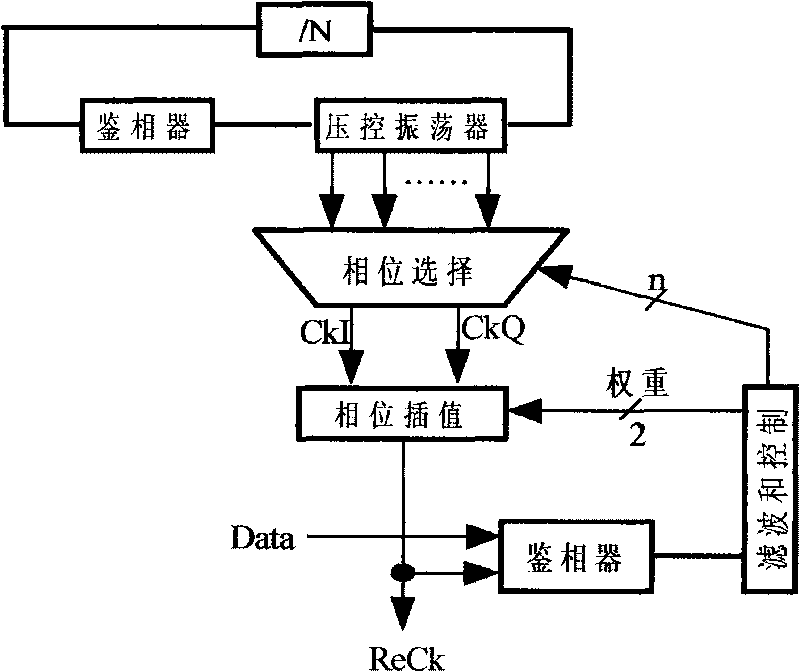

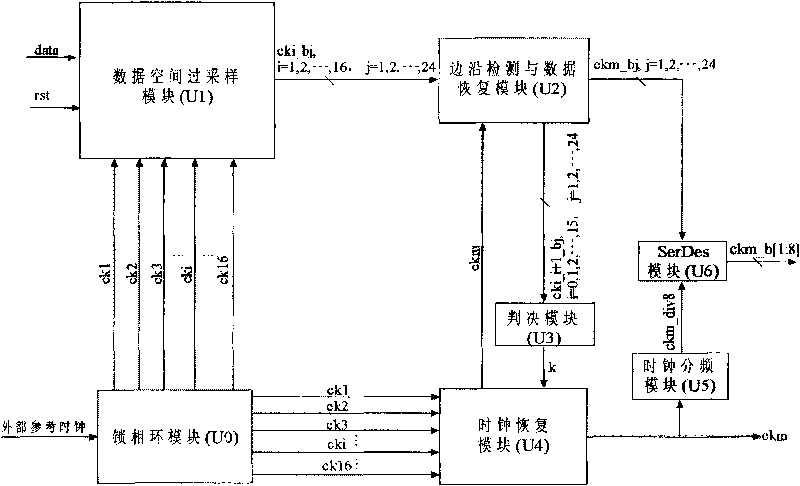

[0020] A clock data recovery and serial-to-parallel conversion circuit based on oversampling for the receiving end of a high-speed serial transceiver, including a phase-locked loop module U0, a data space oversampling module U1, an edge detection and data recovery module U2, a Judgment module U3, a clock recovery module U4, a clock frequency division module U5 and a SerDes module U6;

[0021] Firstly, the interface signals of each module of the circuit are described. The circuit signal flow diagram of the present invention is as image 3 shown. The description of the input and output interfaces of the module is shown in Table 1; the description of the input and output interfaces of the data space oversampling module (U1) is shown in Table 2; the description of the input and output interfaces of the edge detect...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More