Patents

Literature

612 results about "Phase selection" patented technology

Efficacy Topic

Property

Owner

Technical Advancement

Application Domain

Technology Topic

Technology Field Word

Patent Country/Region

Patent Type

Patent Status

Application Year

Inventor

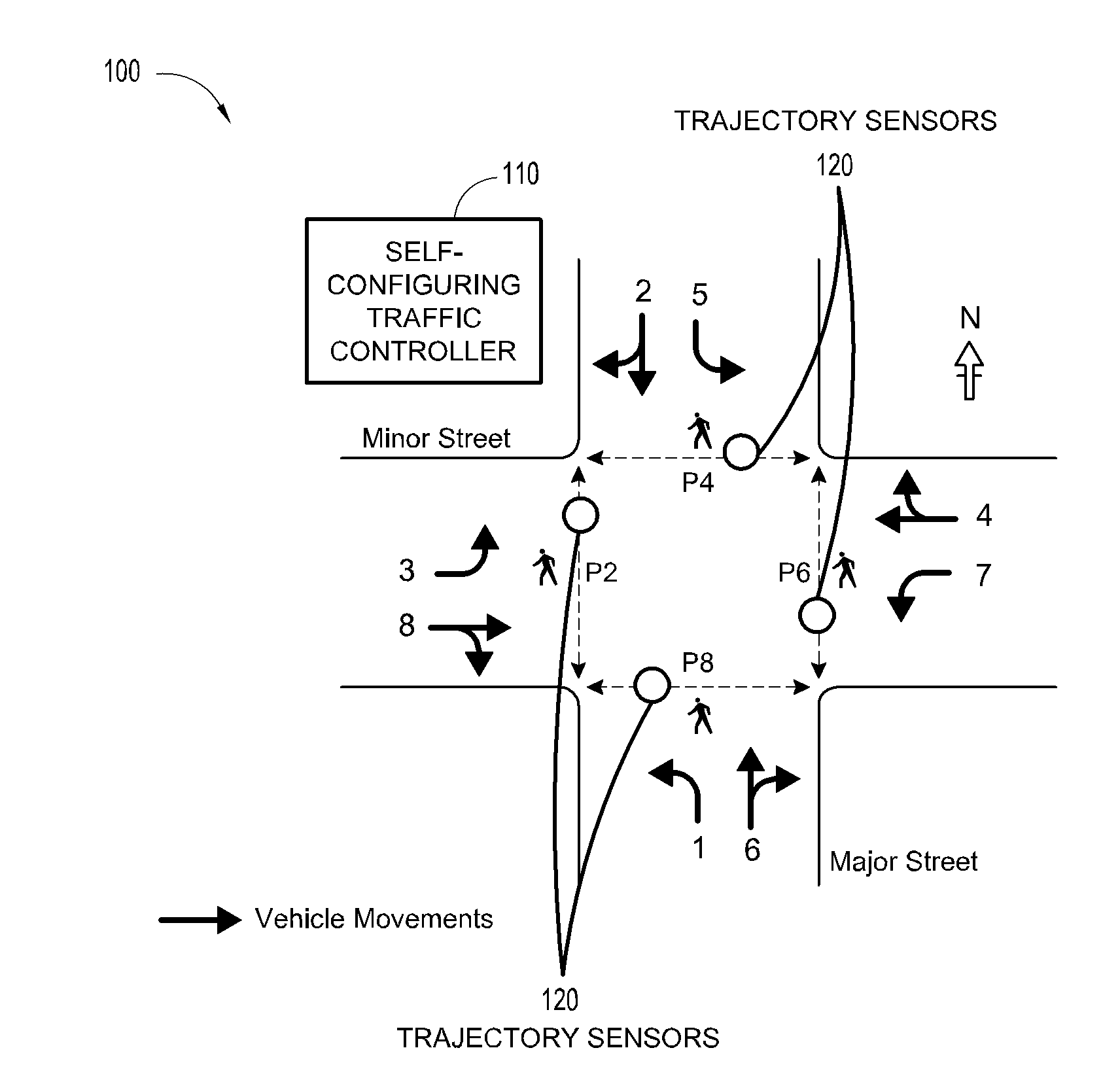

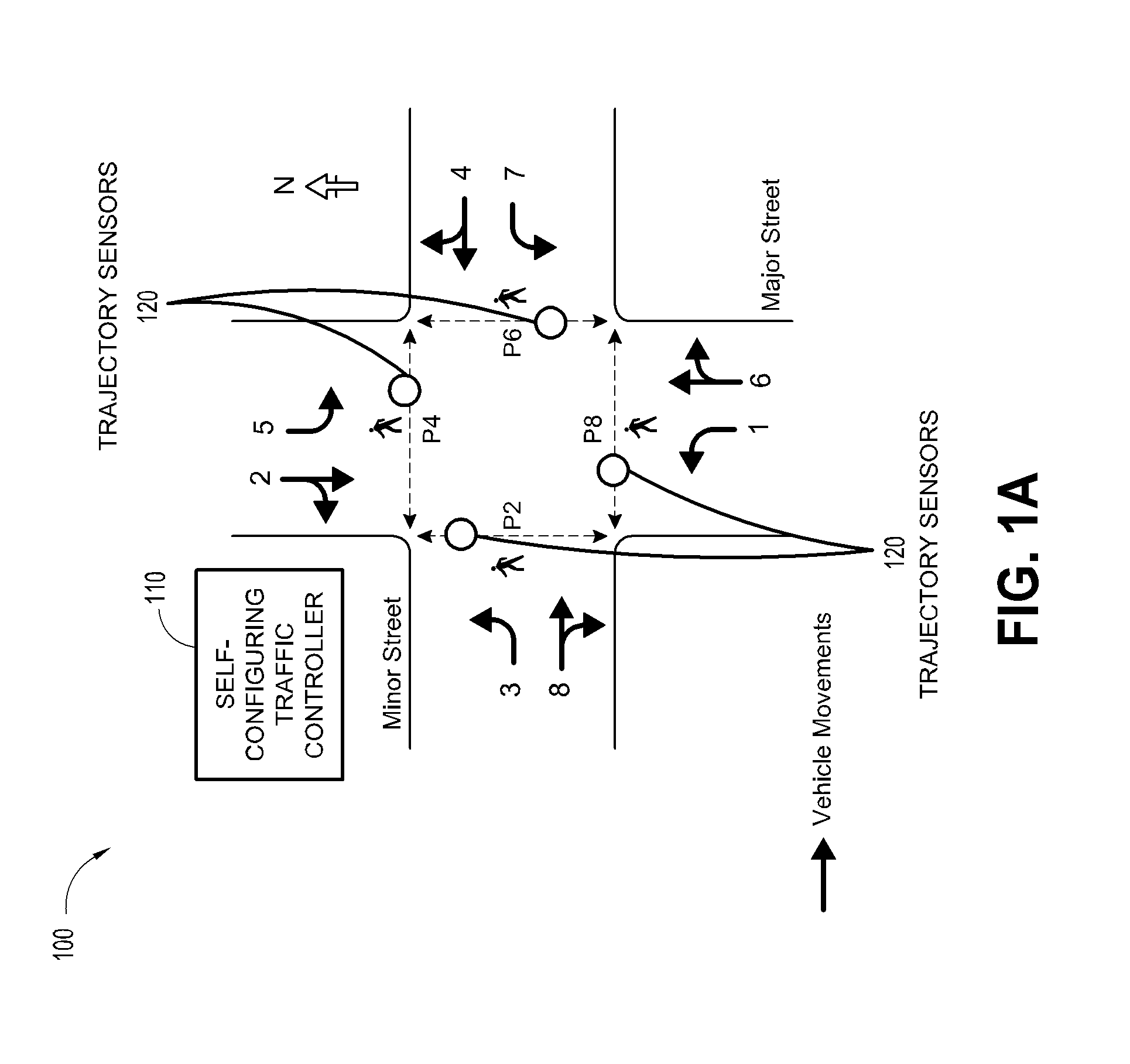

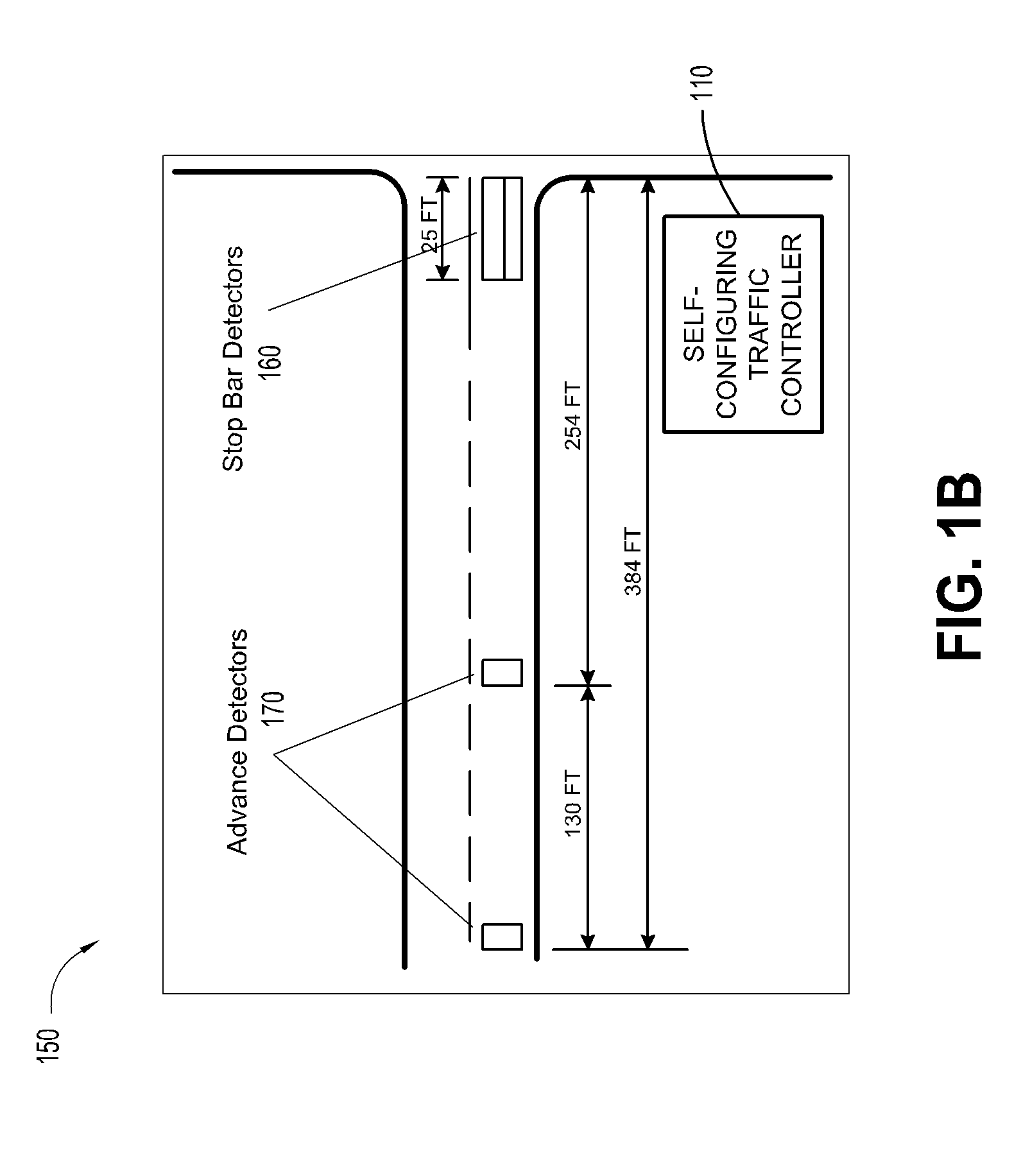

Self-configuring traffic signal controller

Embodiments describe new mechanisms for signalized intersection control. Embodiments expand inputs beyond traditional traffic control methods to include awareness of agency policies for signalized control, industry standardized calculations for traffic control parameters, geometric awareness of the roadway and / or intersection, and / or input of vehicle trajectory data relative to this intersection geometry. In certain embodiments, these new inputs facilitate a real-time, future-state trajectory modeling of the phase timing and sequencing options for signalized intersection control. Phase selection and timing can be improved or otherwise optimized based upon modeling the signal's future state impact on arriving vehicle trajectories. This improvement or optimization can be performed to reduce or minimize the cost basis of a user definable objective function.

Owner:ECONOLITE GRP

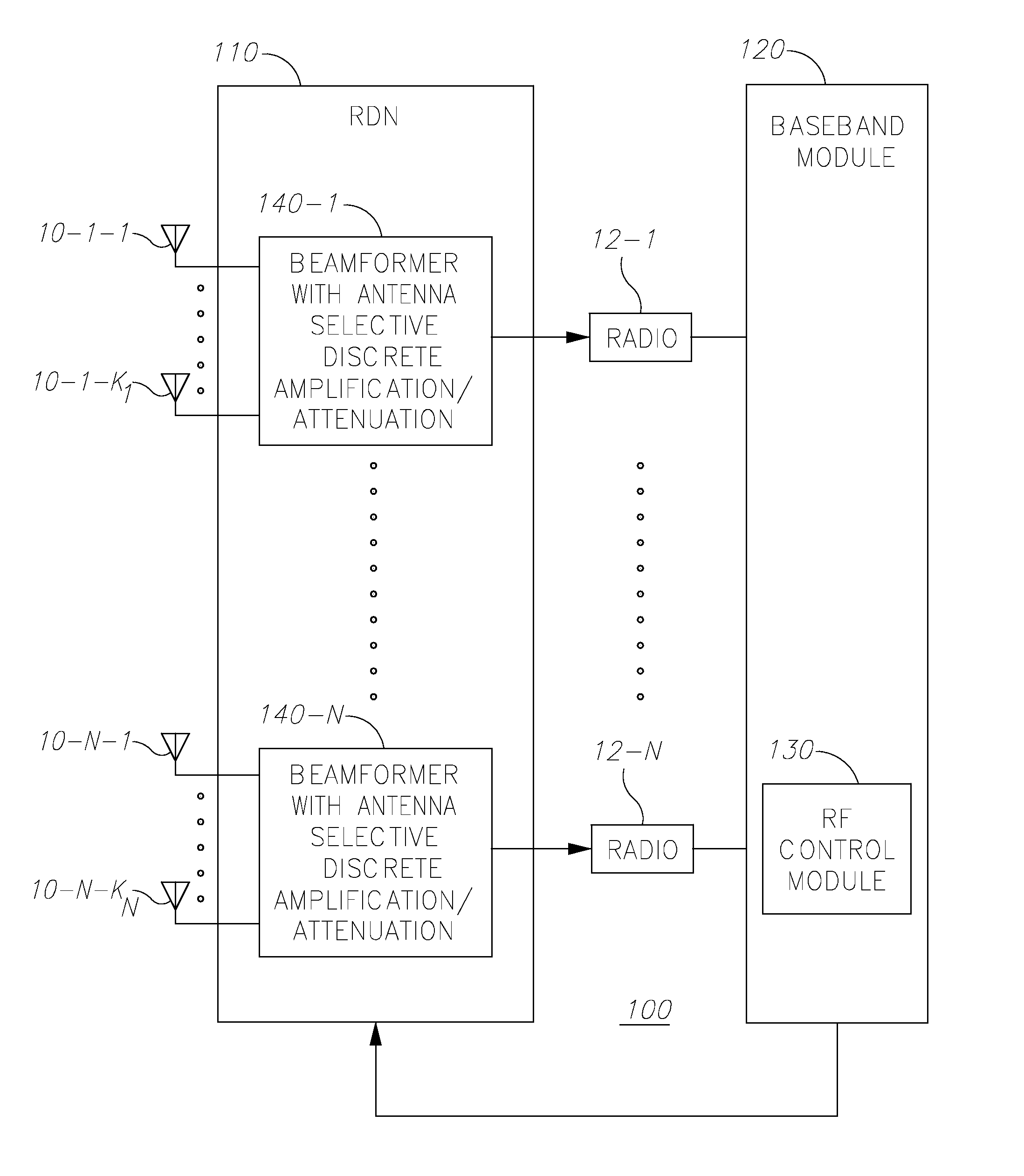

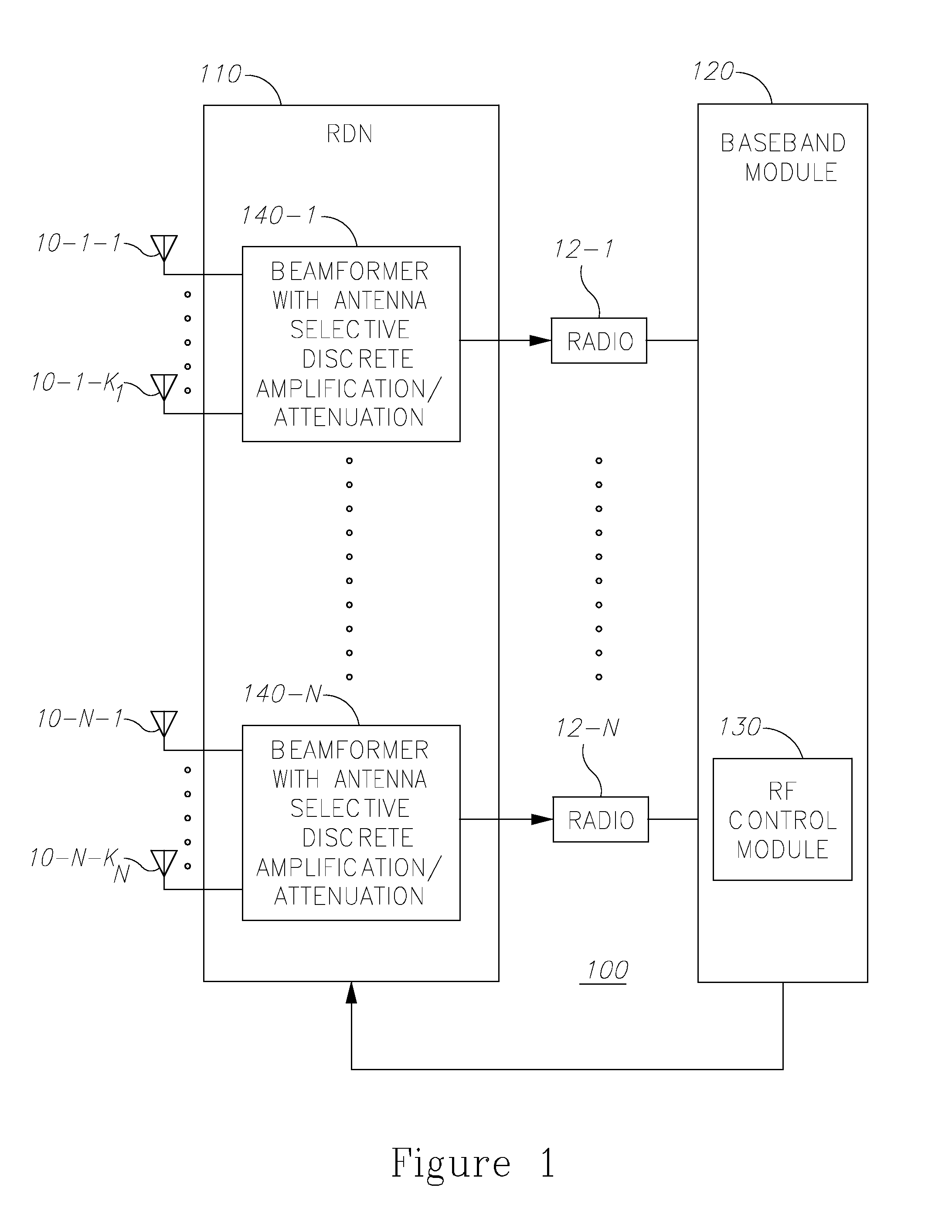

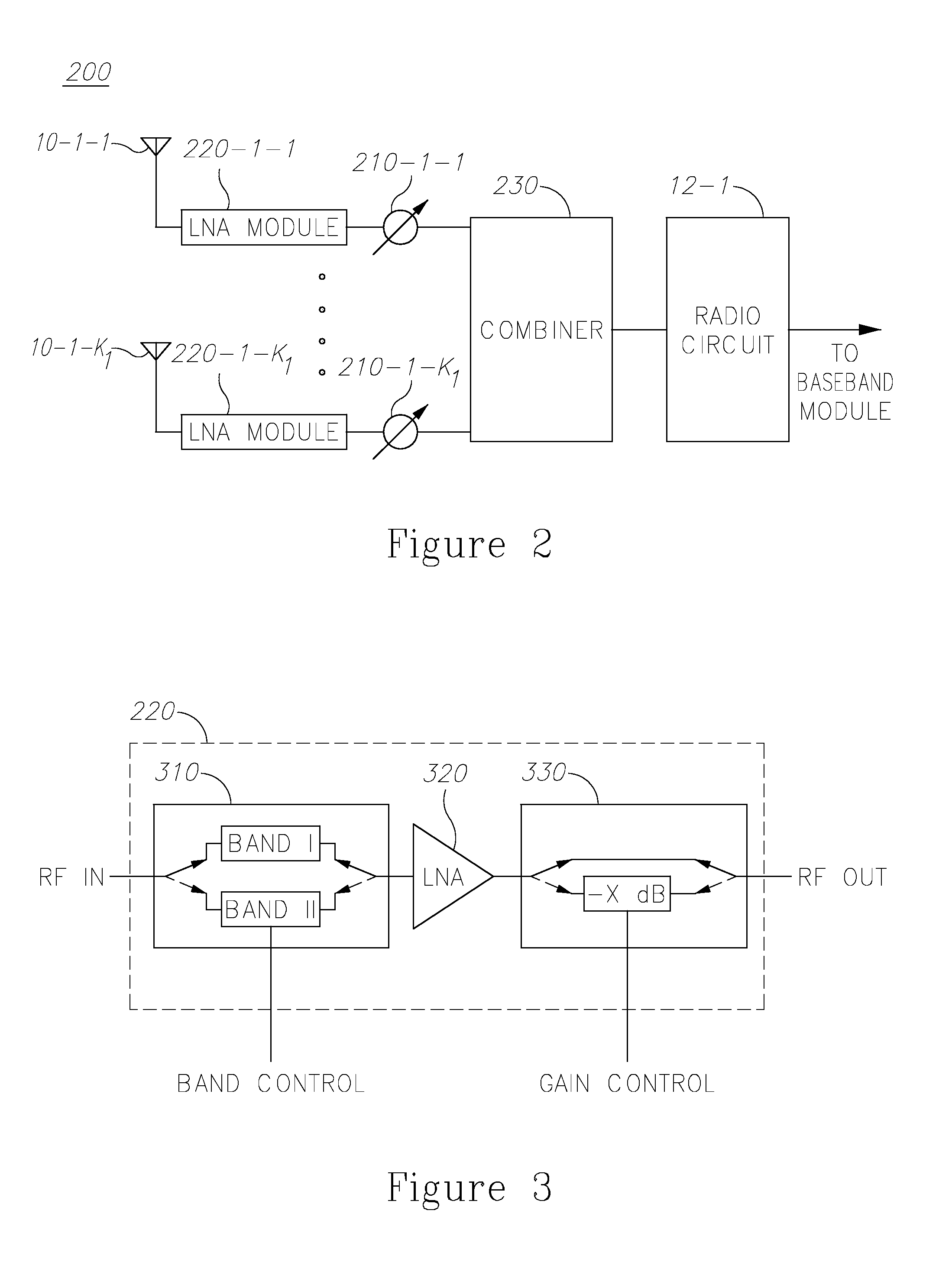

System and method for discrete gain control in hybrid MIMO RF beamforming for multi layer MIMO base station

A multiple-input-multiple-output (MIMO) receiving system configured for receiving multiple transmission layers is provided herein. The system includes a plurality of beamformed tunable receiving antennas configured to receive a plurality of transmitted layers; and a control module configured to select for the beamformed antennas a single set of discrete weights for tuning said antennas for all of the transmitted layers so that the weights are selected for optimal performance of said receiving system, wherein said selection is carried out based on an extended Maximal Ratio Combining (MRC) metric or other quality metric measured by the MIMO baseband module, and using said measured metric separately for each beamformed antenna to determine gain or attenuation independently of phase selection.

Owner:MAGNOLIA BROADLAND INC

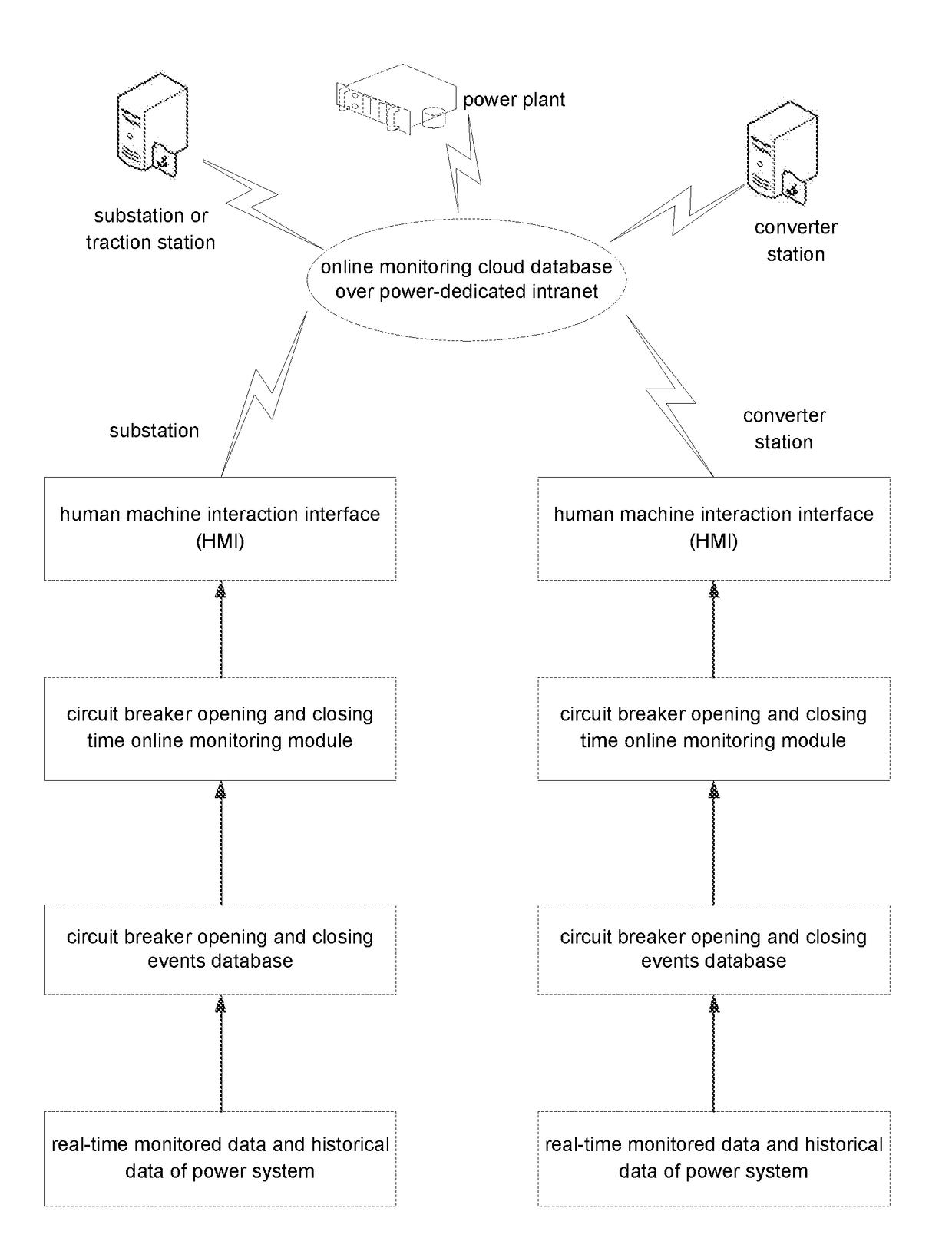

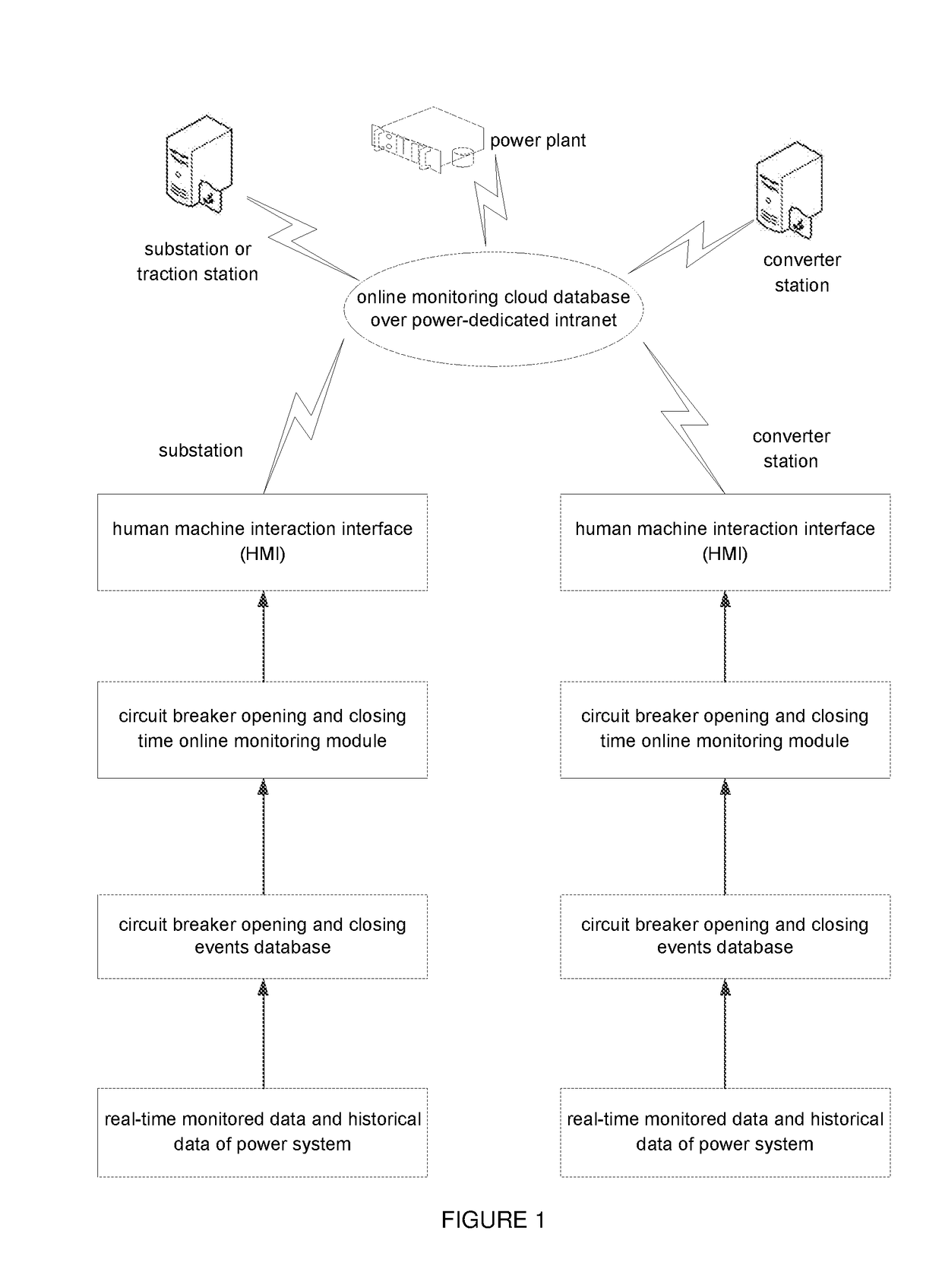

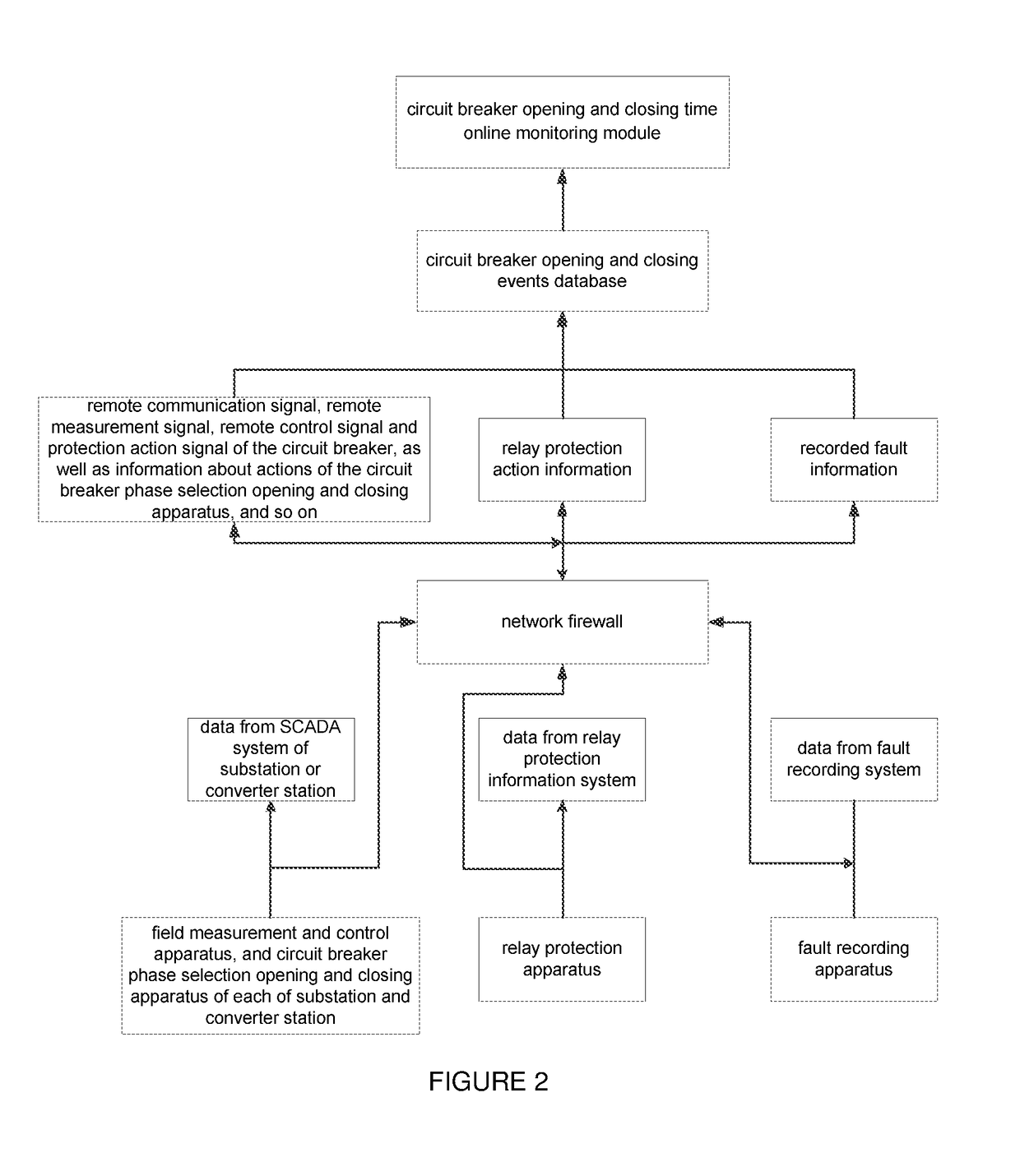

High-voltage circuit breaker opening and closing time online monitoring apparatus, smart multi-dimensional big data analyzing expert system for high-voltage circuit breaker in power grid and method therefor

ActiveUS20180059186A1Electric switchesEmergency protection data processing meansEngineeringMulti dimensional

Provided are a high-voltage circuit breaker opening and closing time online monitoring apparatus, a smart multi-dimensional big data analyzing expert system for a high-voltage circuit breaker in a power grid, and methods therefor. The opening and closing time online monitoring apparatus includes a circuit breaker opening and closing events database, a circuit breaker opening and closing time online monitoring module, and a human machine interaction interface. Data in the circuit breaker opening and closing events database is derived from a SCADA and a measurement and control apparatus thereof, a circuit breaker phase selection opening and closing apparatus, a relay protection apparatus and a relay protection information system, and a fault recording apparatus and a fault recording system of each of a substation and a converter station. The circuit breaker opening and closing time online monitoring module includes various modules, and cloud databases for such online monitoring are created.

Owner:YANG QIBEI

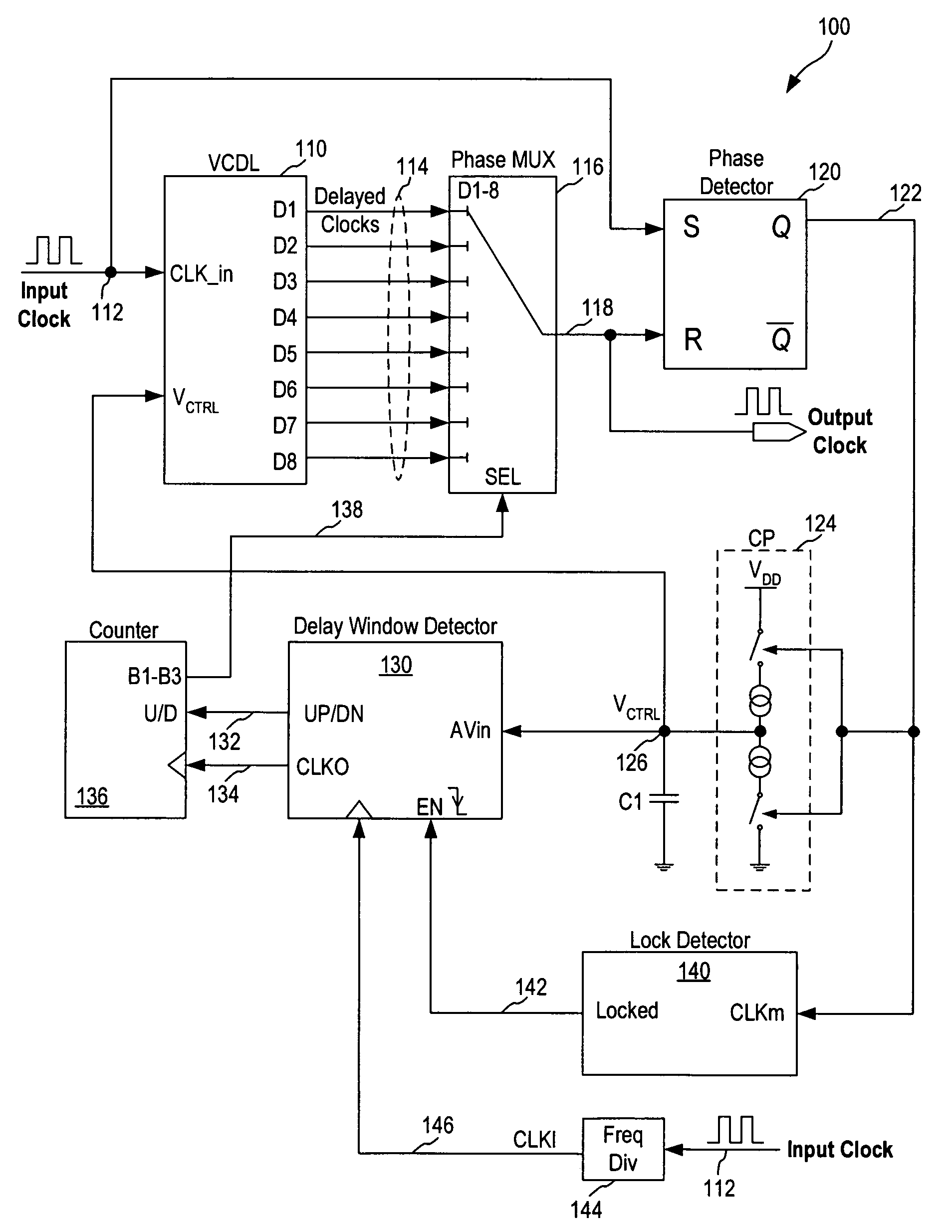

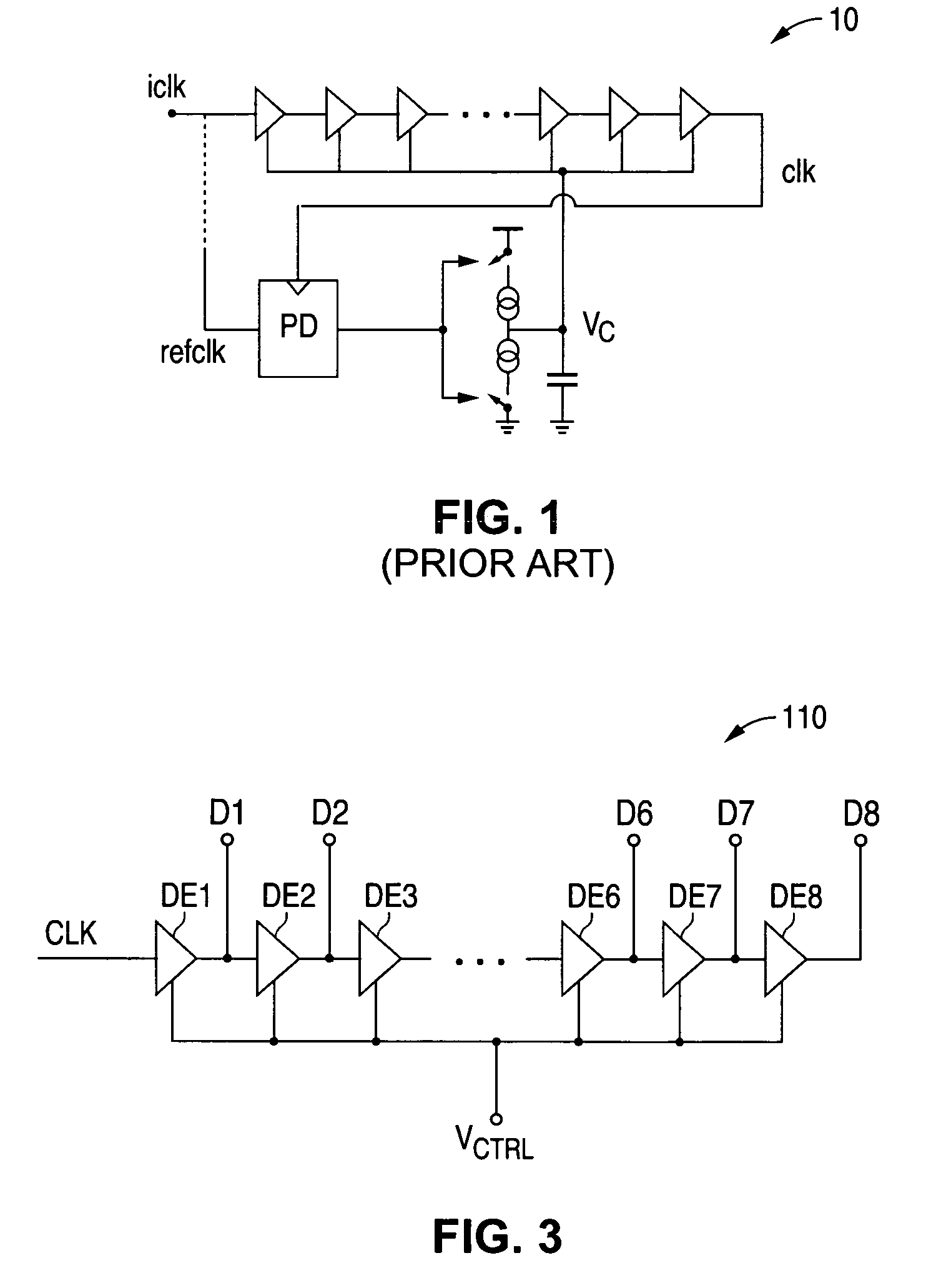

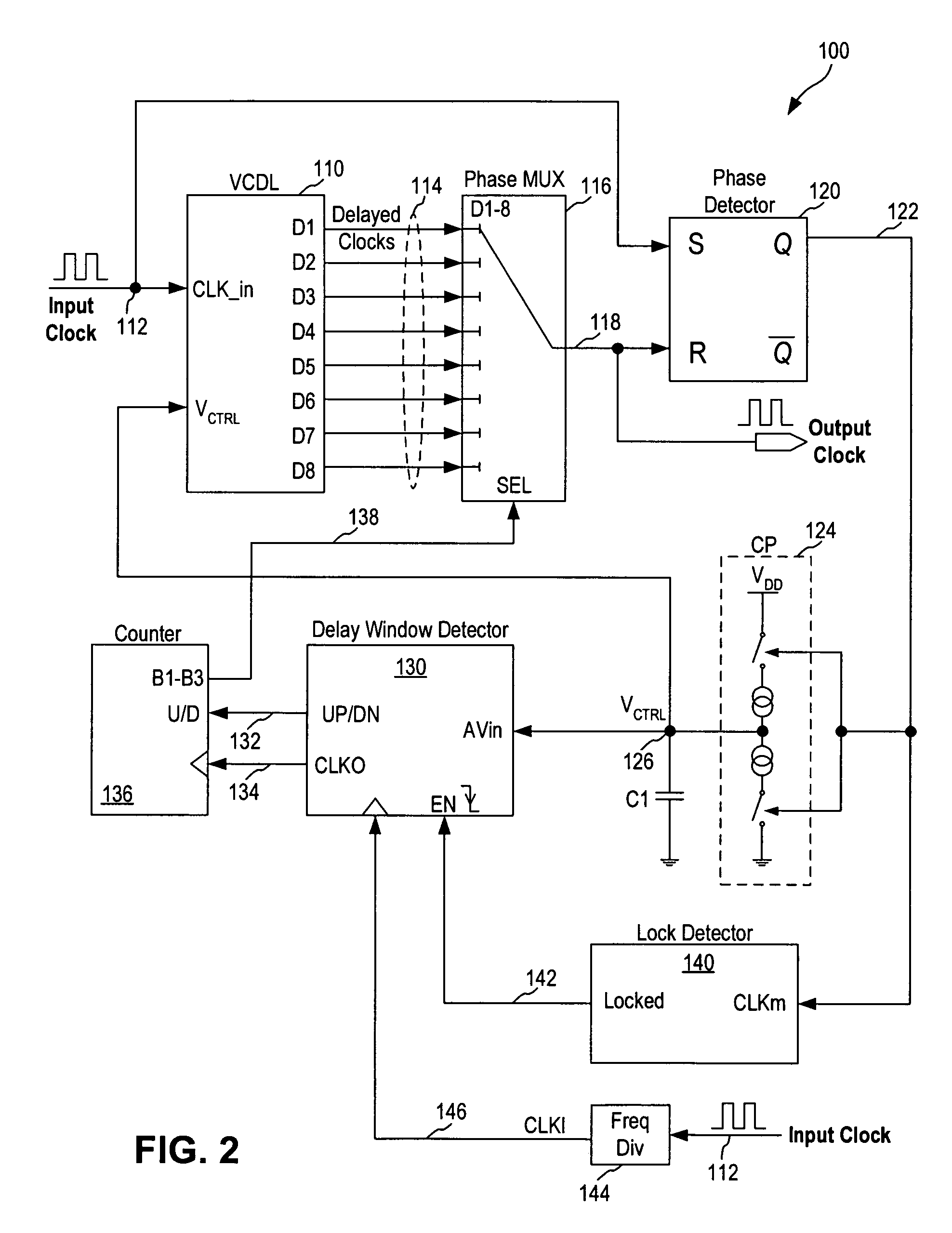

Adaptive frequency variable delay-locked loop

A delay-locked loop circuit receiving an input clock signal and generating an output clock signal whose delay is locked to the input clock includes a voltage controlled delay line (VCDL), a multiplexer, a phase detection control loop and a phase selection control loop. The VCDL generates a set of multi-phase delayed clock signals. The multiplexer selects one of the delayed clock signals as the output clock signal based on a select signal. The phase detection control loop measures the phase difference between the input and output clock signals and generate a control voltage for driving the VCDL. The phase selection control loop measures the control voltage and generates the select signal based on the control voltage, causing the multiplexer to select a delayed clock signal with increased or decreased amount of phase delay relative to the currently selected delayed clock signal or to hold the currently selected delayed clock signal.

Owner:NAT SEMICON CORP

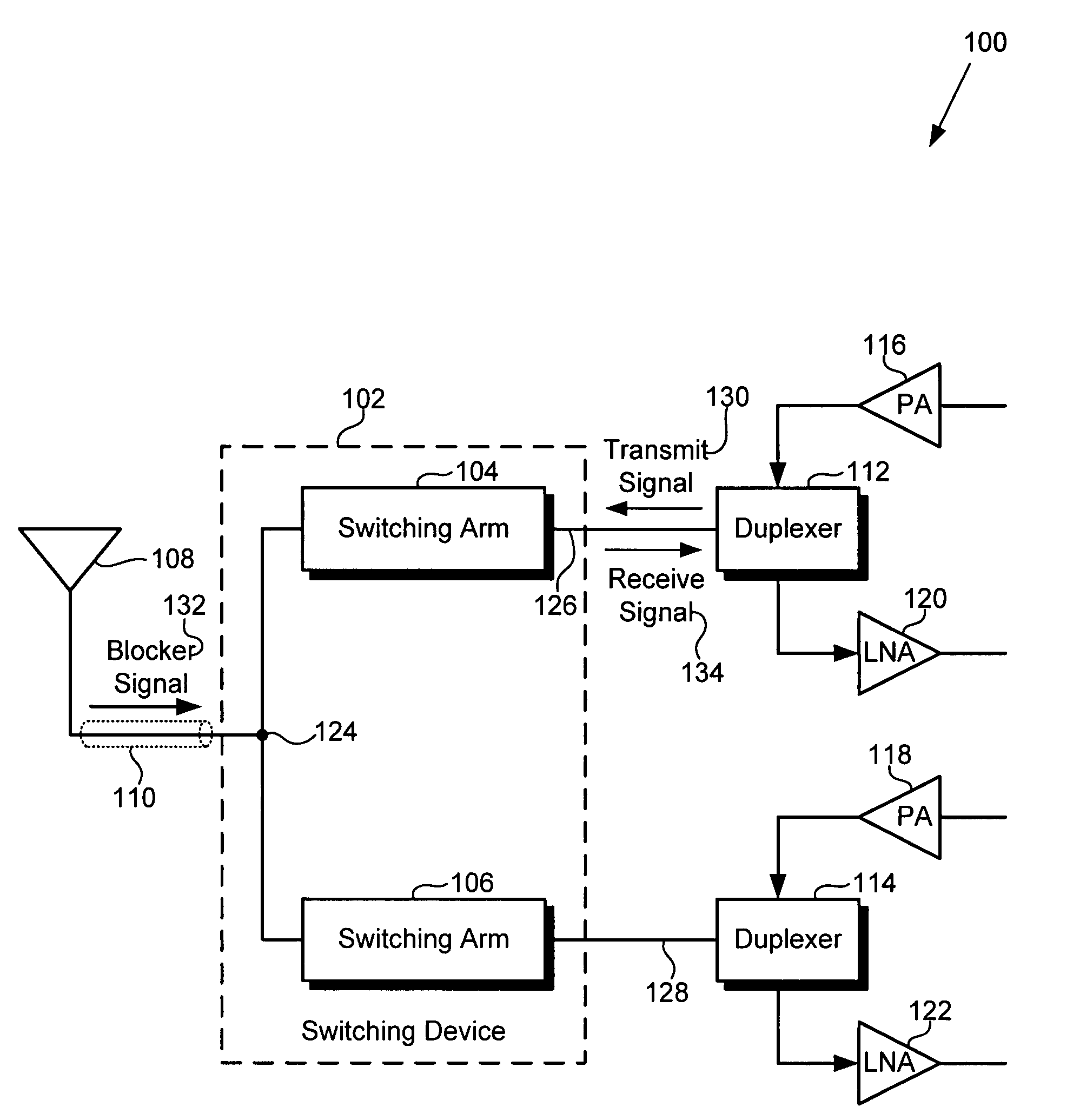

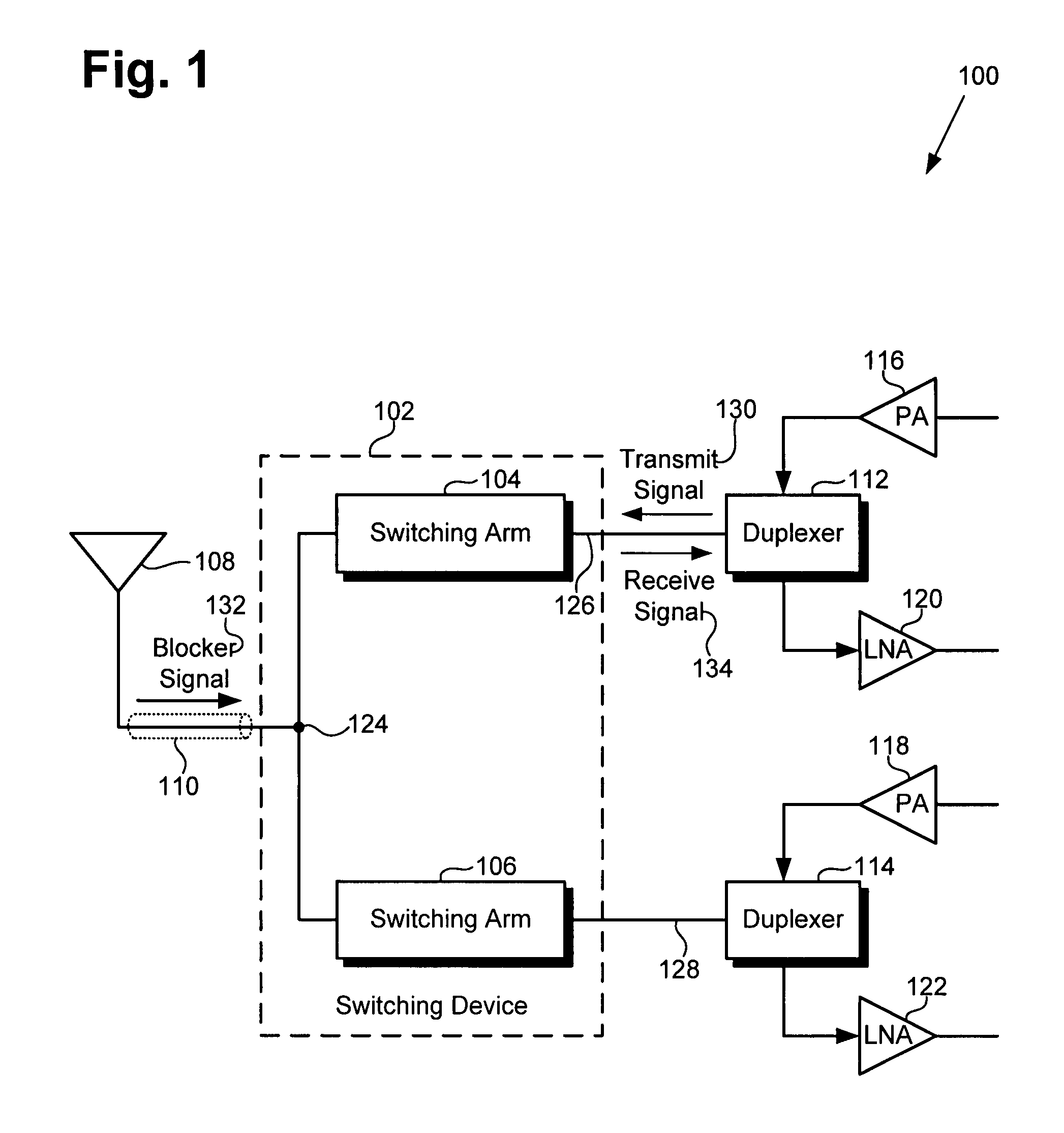

Switching device with reduced intermodulation distortion

According to one exemplary embodiment, a switching device with phase selection terminals to select between at least two phase shifting modes to reduce intermodulation distortion in the switching device includes a first phase selection terminal to select a first phase shifting mode of the switching device by enabling a first phase shifter in a first phase shifting switching branch coupled to an input of the switching device. The switching device further includes a second phase selection terminal to select a second phase shifting mode of the switching device by enabling a second phase shifting switching branch coupled to the switching device input. The intermodulation distortion in the switching device is reduced by selecting one of the first and second phase shifting modes. The switching device may further include a number of FETs coupled in series between an output of the switching device and the first and second phase shifting switching branches.

Owner:SKYWORKS SOLUTIONS INC

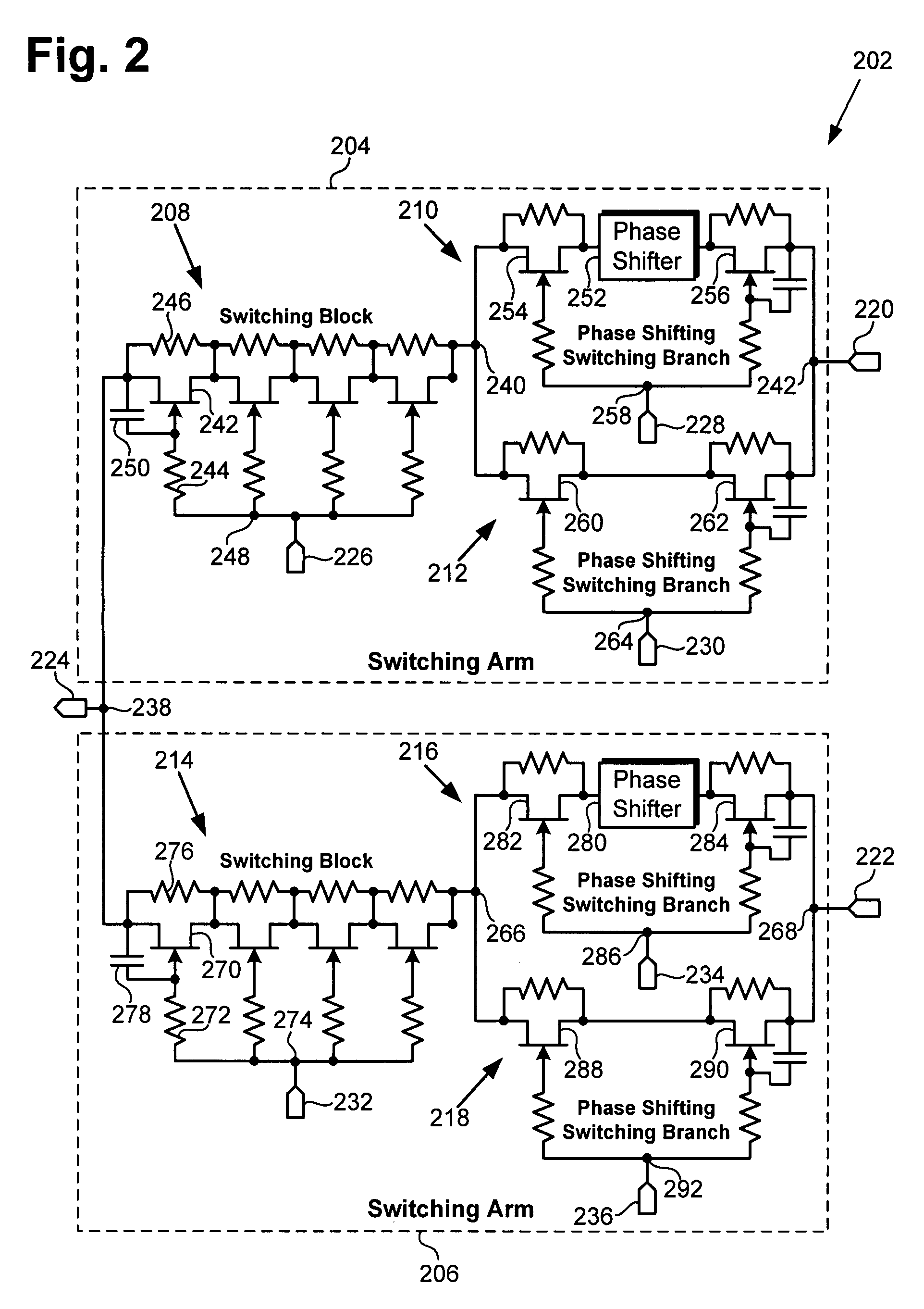

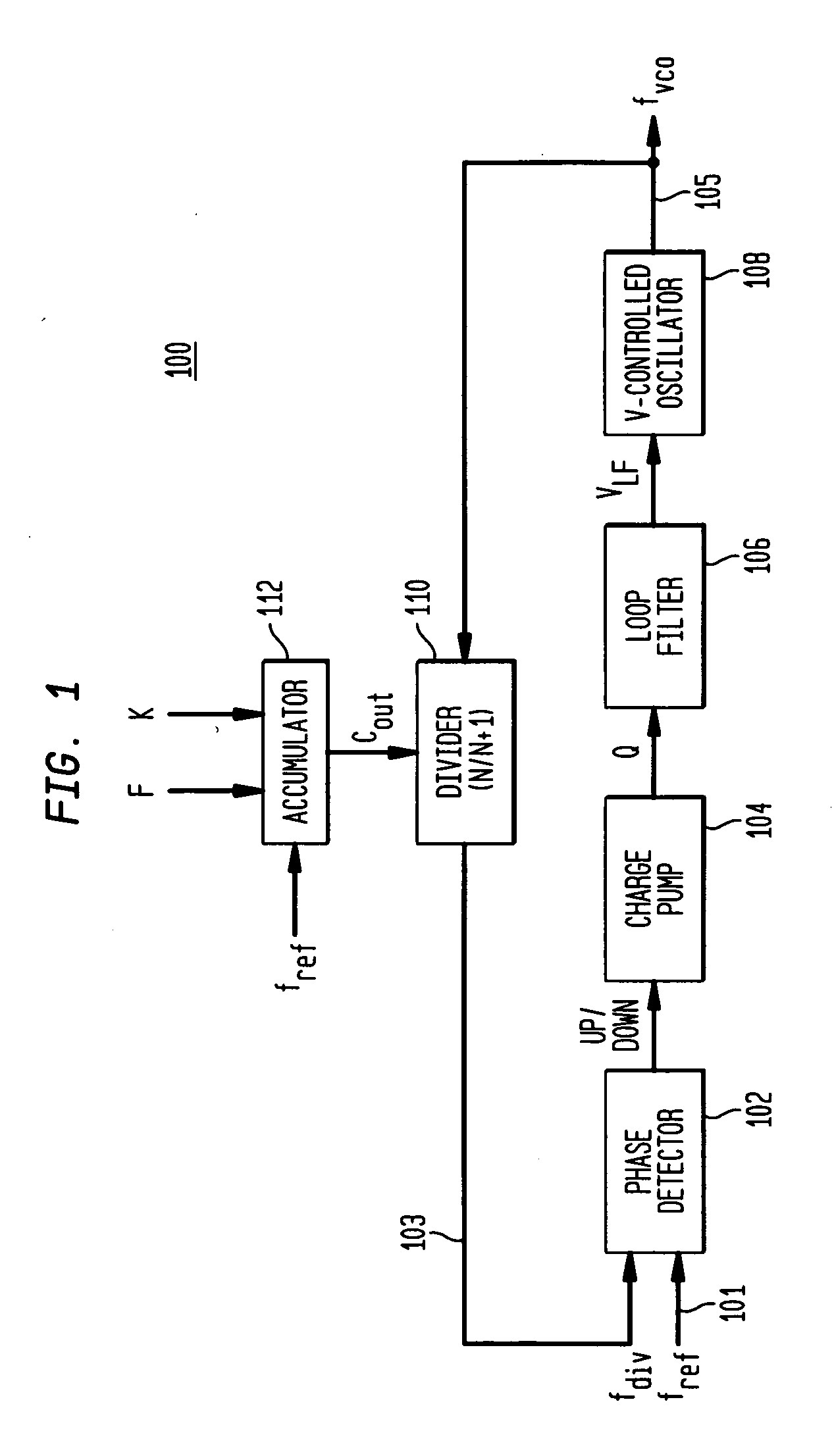

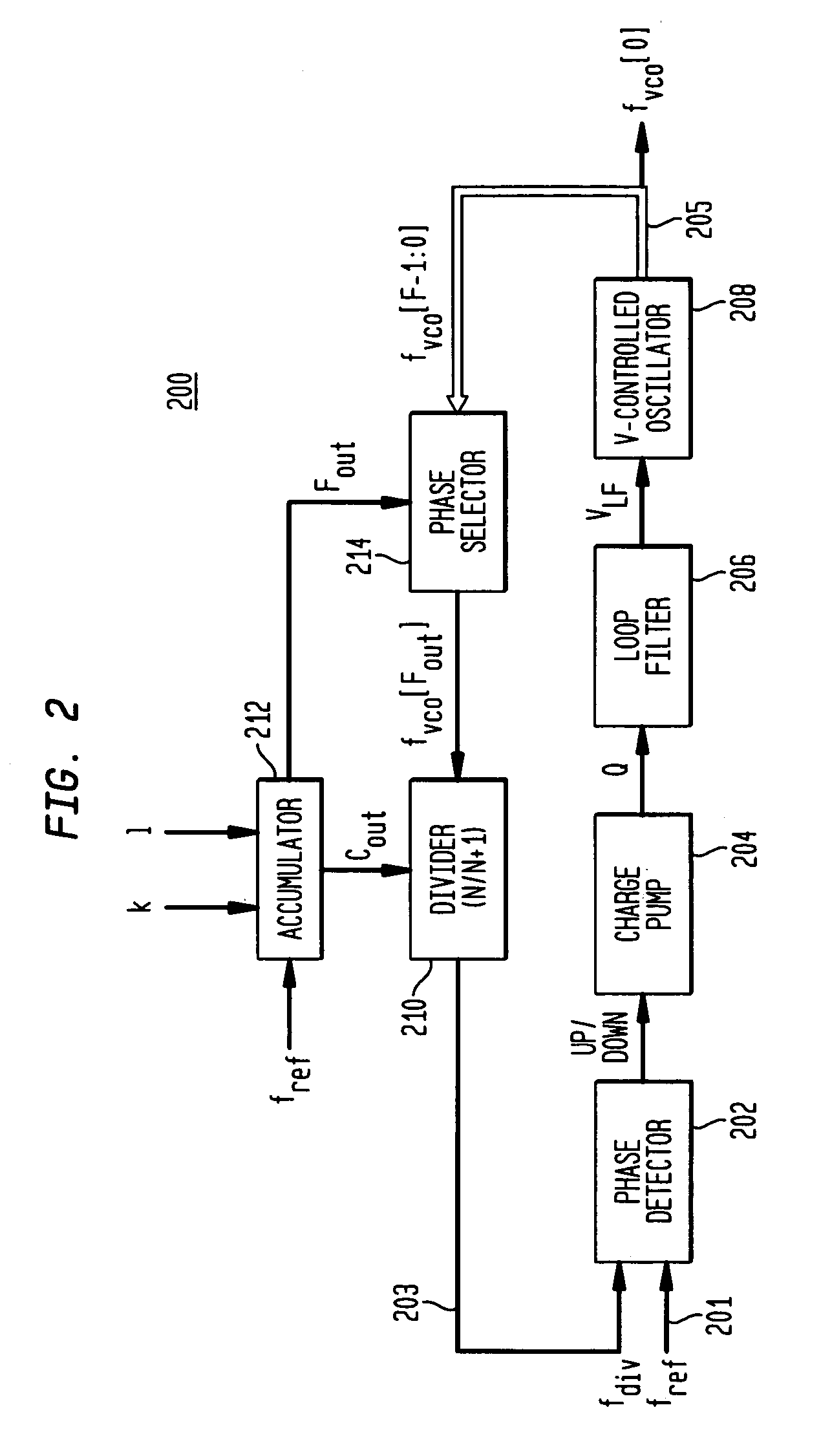

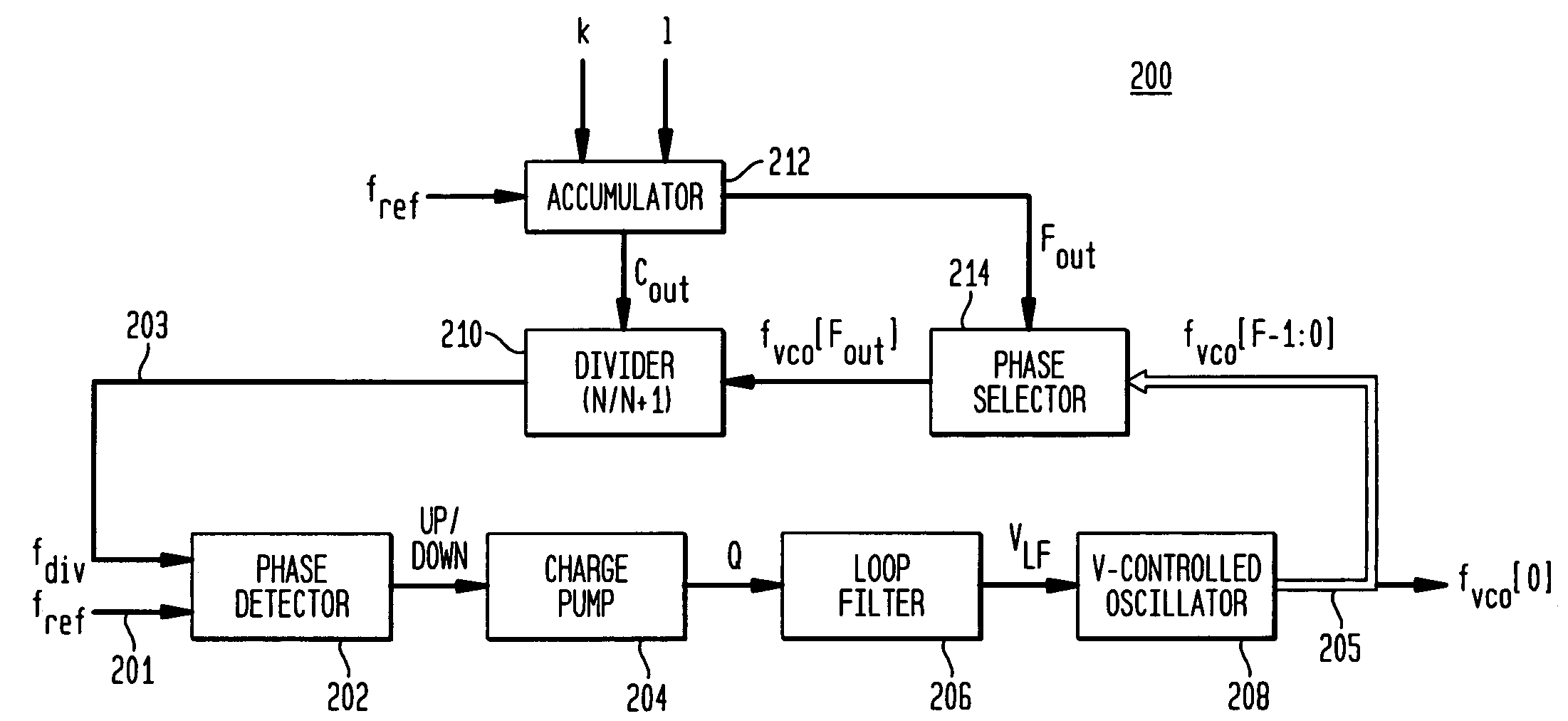

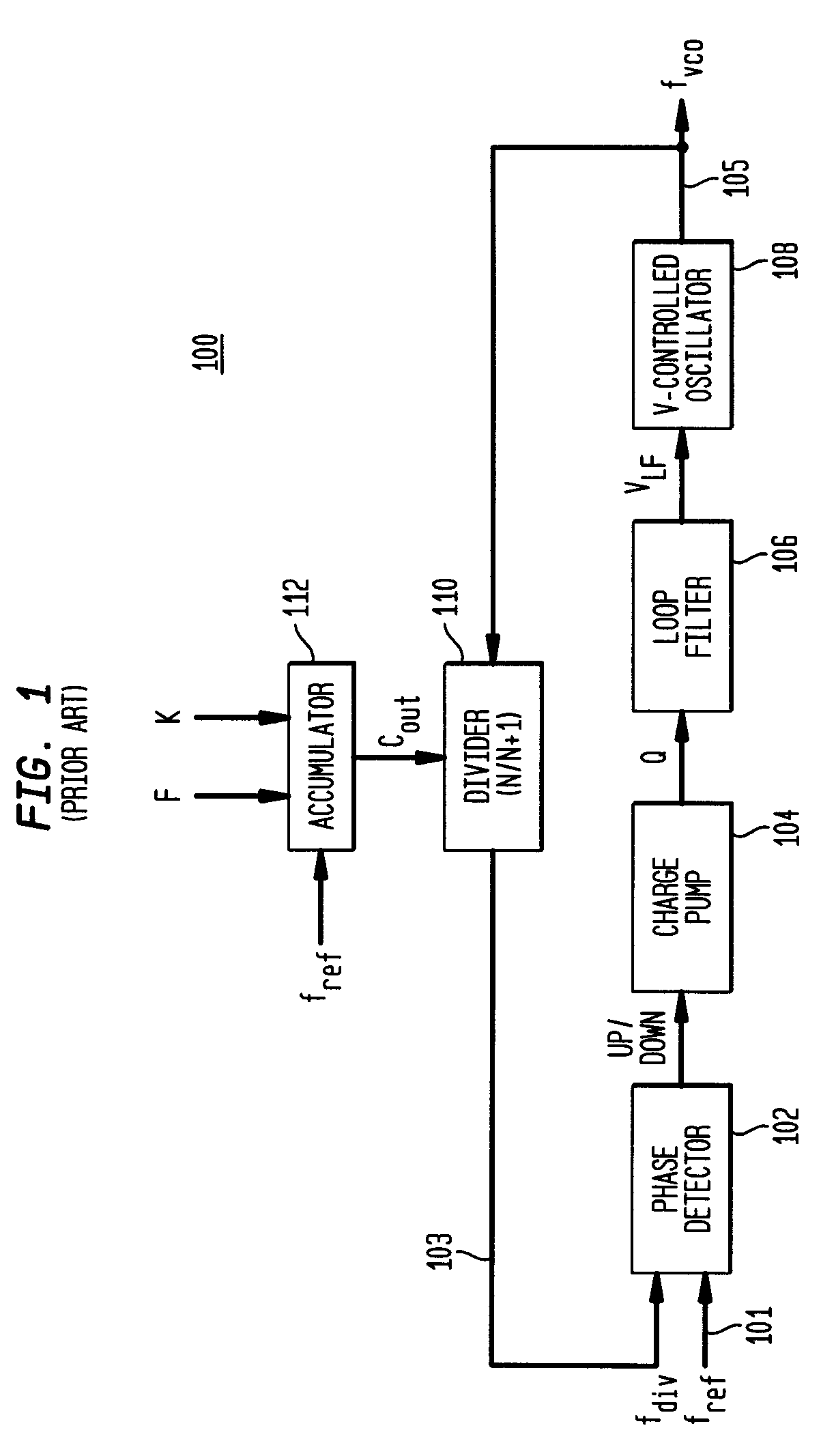

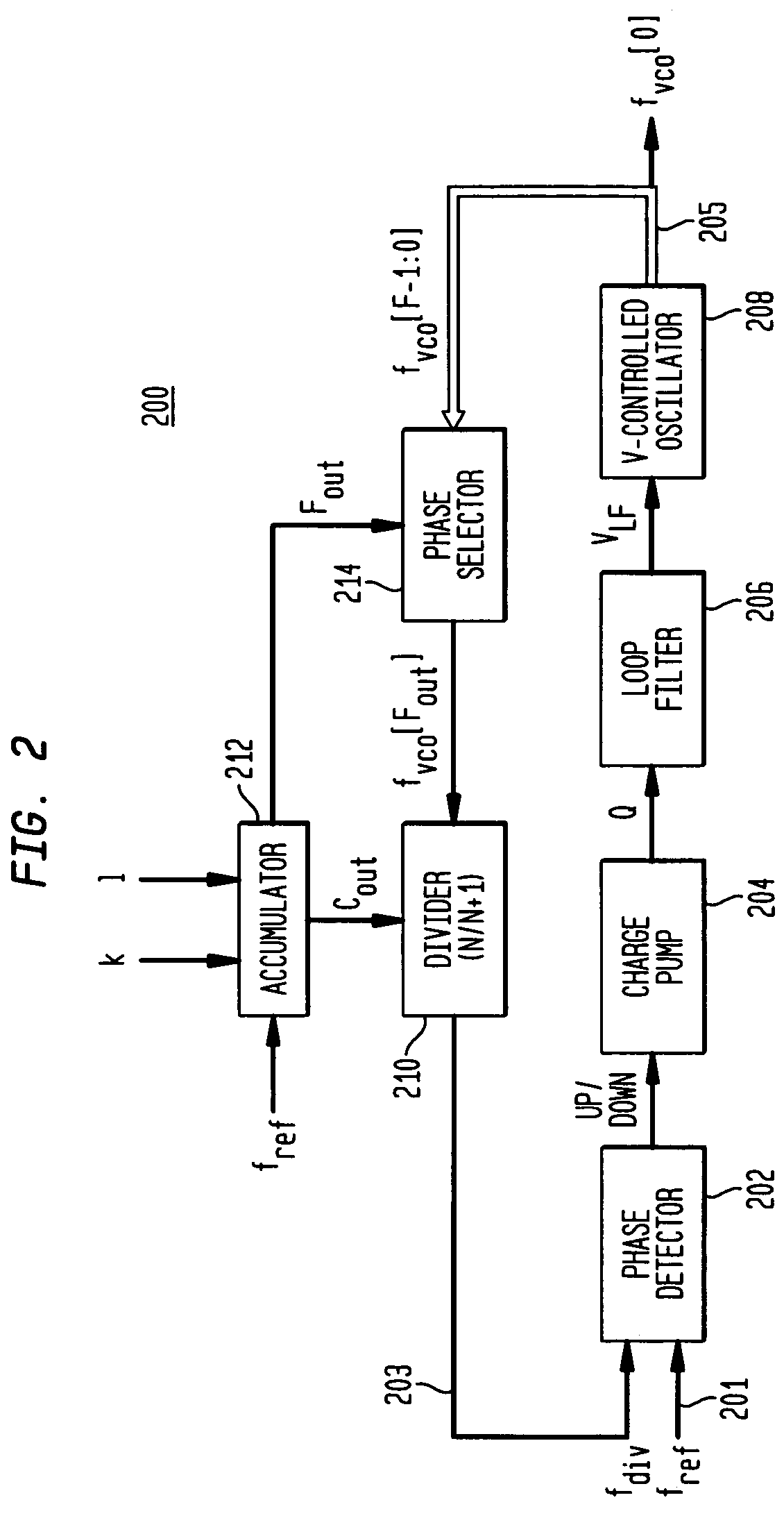

Phase-locked loop using multi-phase feedback signals

InactiveUS20060245531A1Pulse automatic controlAngle demodulation by phase difference detectionPhase shiftedControl signal

A signal generator, such as a fractional-N PLL, has, in its feedback signal path, a divider, a phase circuit, and a fractional accumulator that generates control signals for the divider and the phase circuit. The divider control signal controls the divisor value applied by the divider. In one embodiment, a phase selector selects, based on the phase-circuit control signal, one of a plurality of phase-shifted output signals generated by the PLL's main signal path (e.g., by a multi-phase VCO) and the divider generates the feedback signal for the PLL from the selected signal. In another embodiment, the divider generates a divided signal from one of the phase-shifted output signals, and a phase mixer generates, from the divided signal, a plurality of phase-shifted divided signals and selects, based on the phase-circuit signal, one of the phase-shifted divided signals as the PLL's feedback signal.

Owner:AVAGO TECH INT SALES PTE LTD

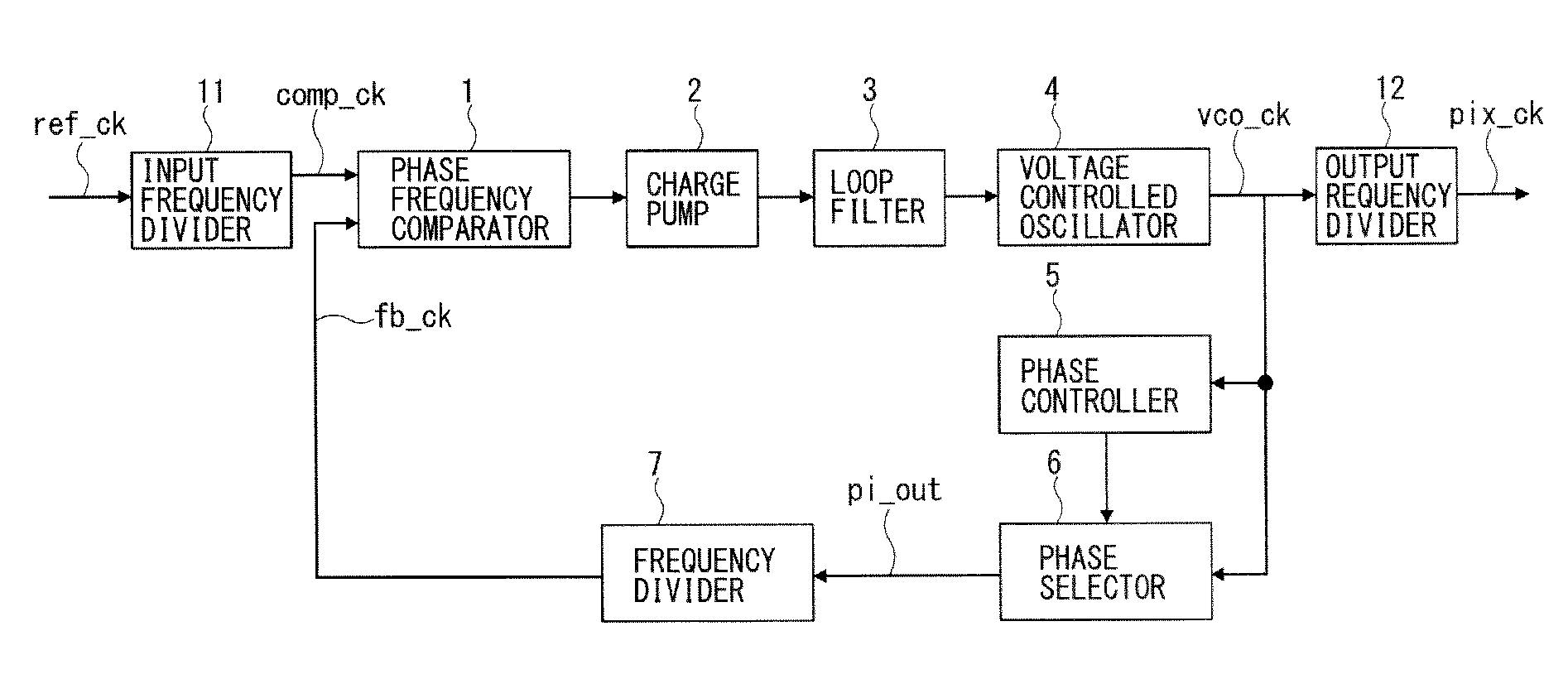

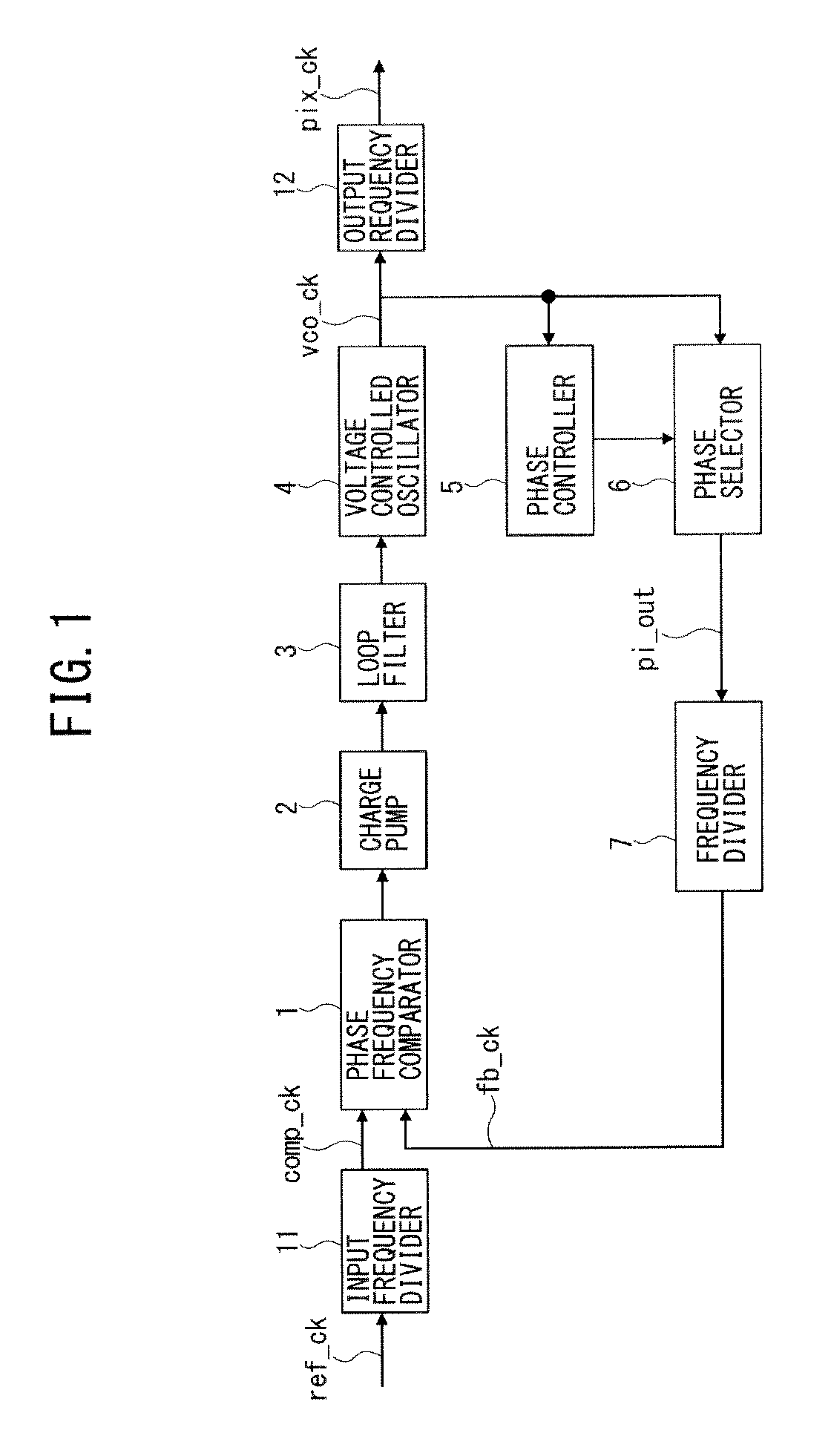

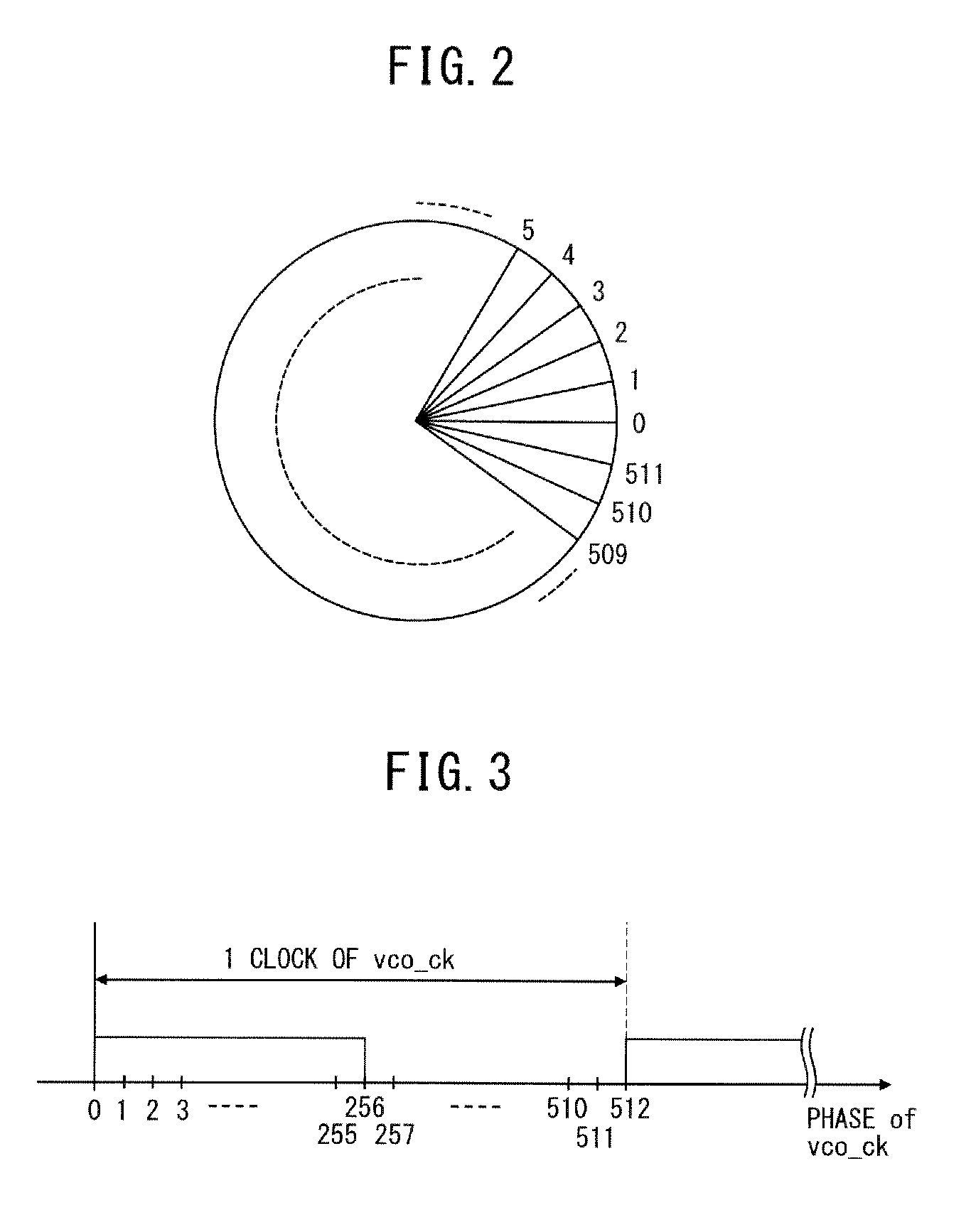

Spread spectrum clock generator

A spread spectrum clock generator includes a phase comparator to detect a phase difference between a reference input clock signal and a feedback signal and output a control voltage, a voltage controlled oscillator to generate an output clock signal with a frequency in line with the control voltage, a phase selector to select any of equally divided phases of one cycle of the output clock signal, generate and transmit a phase shift clock signal to the phase comparator as the feedback signal, and a phase controller to decide a phase of the rising edge of the phase shift clock signal and control the phase selector to select the decided phase, and generate a second phase shift amount, decide the rising edge of the phase shift clock signal to and subject the output clock signal to spread spectrum modulation by the second phase shift amount.

Owner:RICOH KK

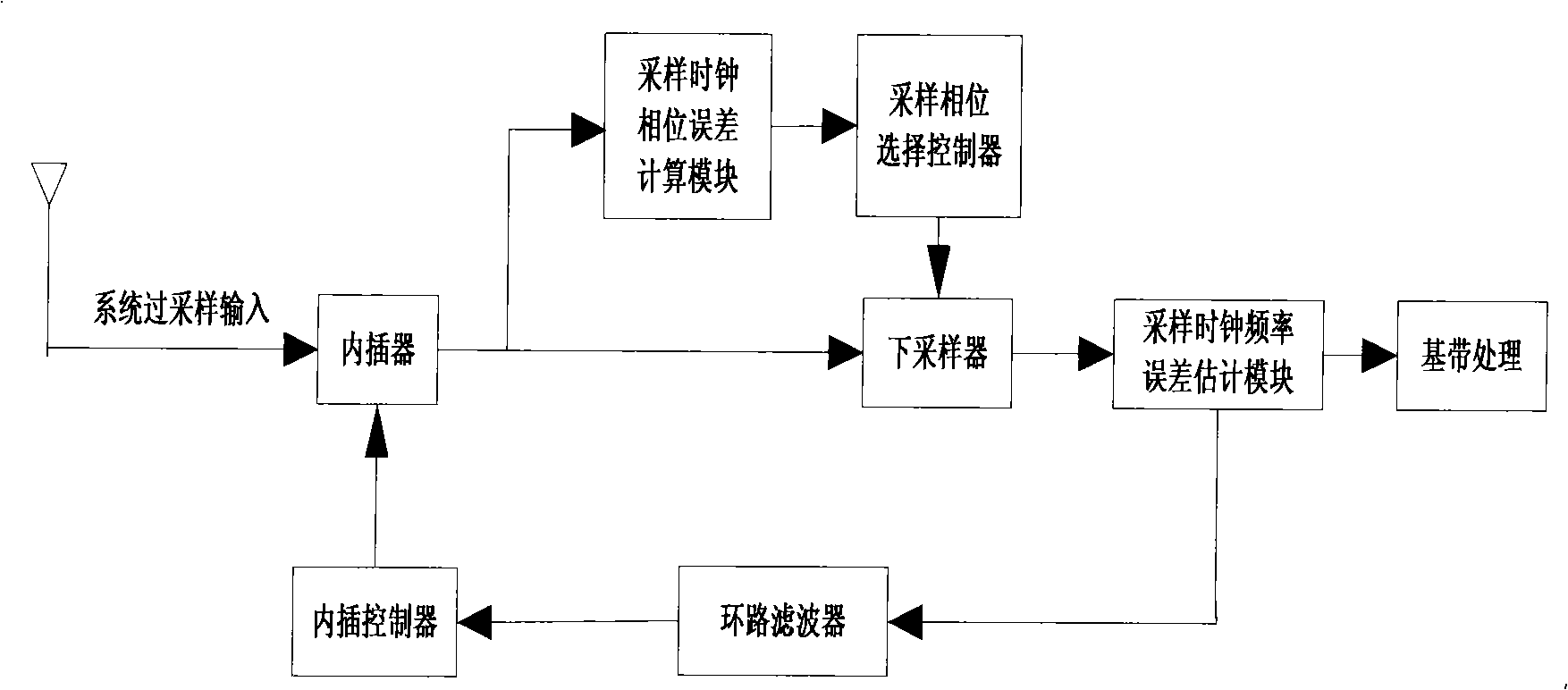

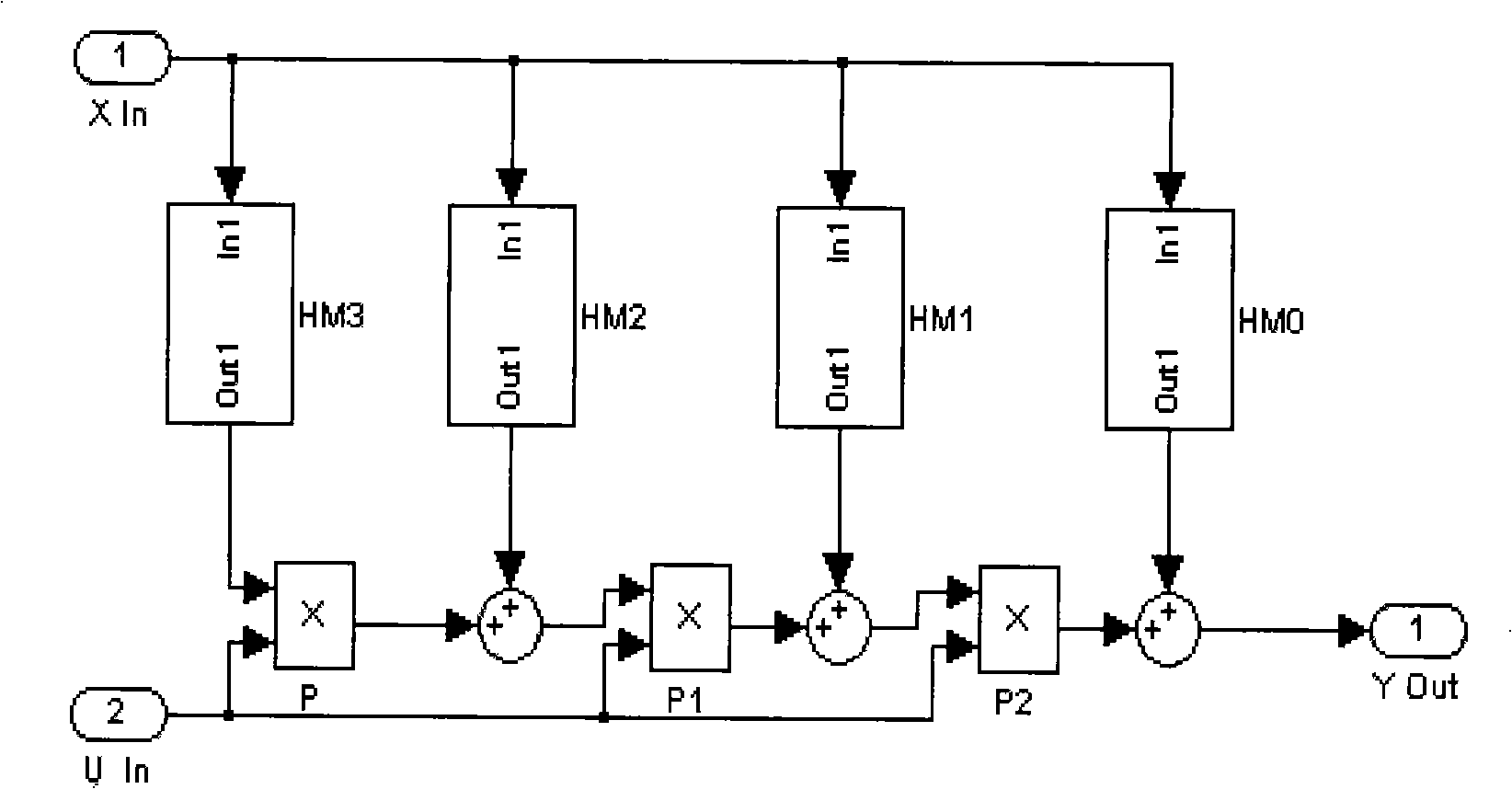

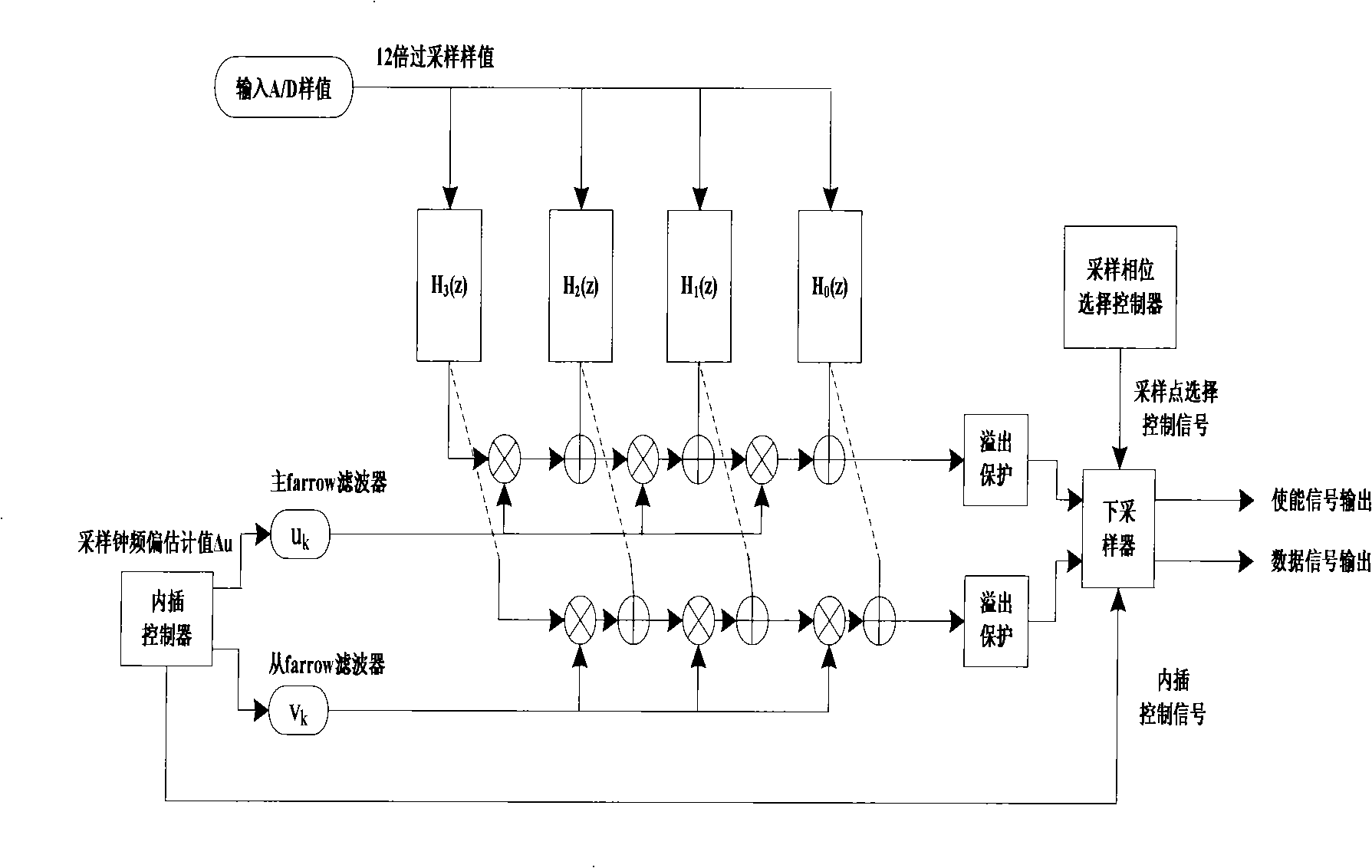

Symbol timing synchronizing apparatus for complete digital receiver

InactiveCN101299657AHigh precisionImprove performanceFrequency-division multiplex detailsSynchronising arrangementLoop filterCommunications system

A complete digital receiver symbol timing synchronizing apparatus of the digital communication technique domain, includes an interpolator, a sampling clock frequency error estimation module, a loop filter, an interpolation controller, a sampling clock phase error calculation module and a sampling phase selection controller, wherein, the sample value of the system over-sampling is taken as the input of the interpolator; the sample value result after the regulation of the interpolator output is taken as the input of the sampling clock frequency error estimation module, for finding the correct sampling point position; the sampling phase selection controller sends out commands to control a lower sampling device, thereby making the lower sampling device complete sampling in the optimum time; the output result of the lower sampling device is taken as the input of the sampling clock frequency error estimation module, for calculating the sampling clock frequency bias; the interpolation controller controls the work process of the interpolator according to the sampling clock frequency bias fed in from the loop filter, for implementing the exactness correction to the sampling values. The loop circuit structure of the invention is quite simple, and is realized by hardware in the digital domain.

Owner:SHANGHAI JIAO TONG UNIV

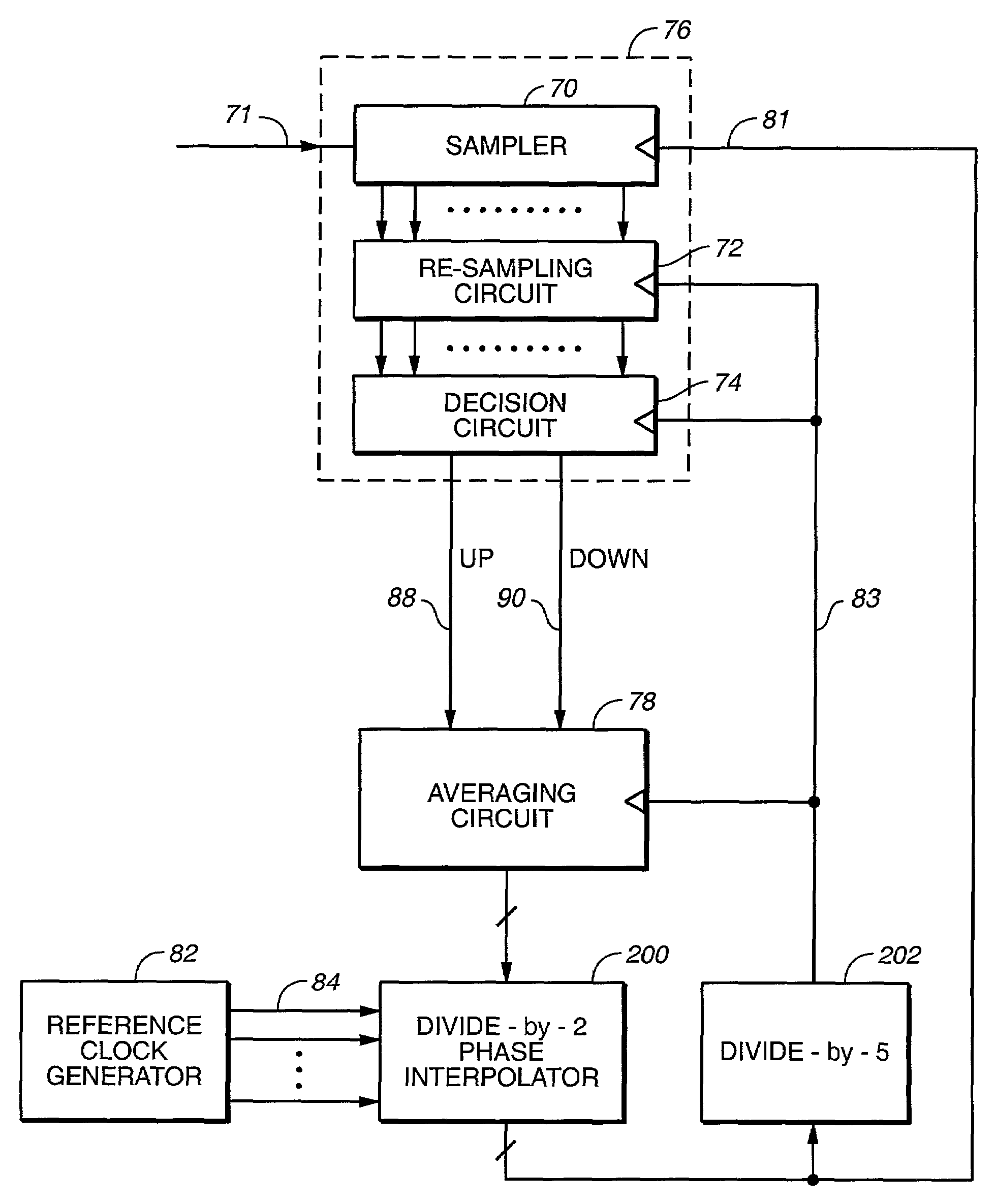

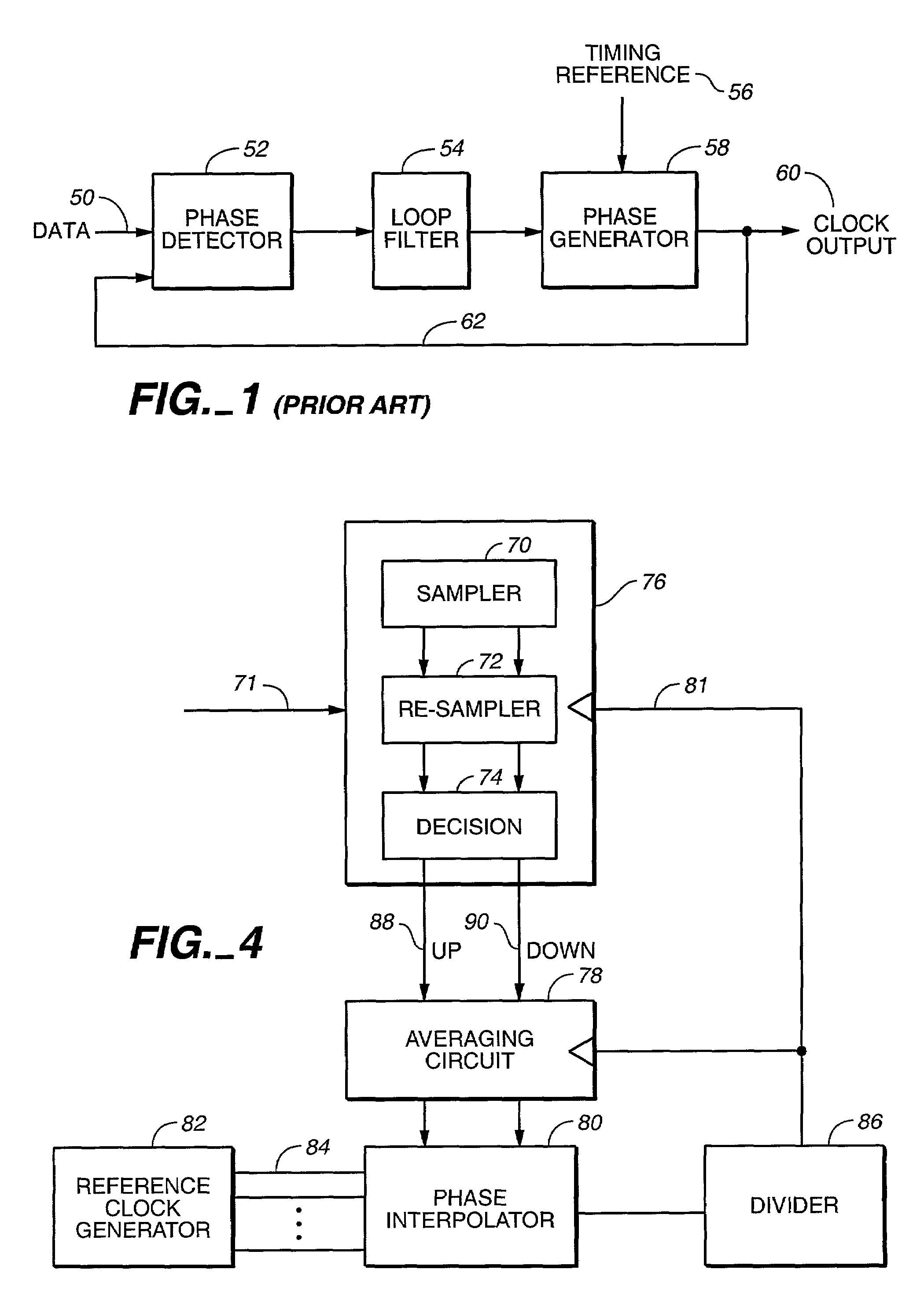

Method and apparatus for high-speed clock data recovery using low-speed circuits

InactiveUS7020227B1Reduces processing frequency requirementPulse automatic controlAngle demodulation by phase difference detectionLow speedData stream

A clock data recovery (CDR) circuit that can be used for recovering data from a high-speed serial transmission using components that operate at a fraction of the data speed. The CDR consists of a phase detector, an averaging circuit and a phase interpolator. The phase detector samples each data bit at its midpoint and at its transitional region and then compares the two samples to determine whether the sampling clock, which is generated by a phase interpolator, is leading or lagging the data stream. The averaging circuit filters out the high frequency jitters in the phase detector output and then passes the filtered signals on to the phase interpolator for phase selection. The phase interpolator uses the filtered signals from the averaging circuit as a guide in the selection of an output clock phase that minimizes the phase difference between the output clock and the incoming data.

Owner:ACARD TECH CORP

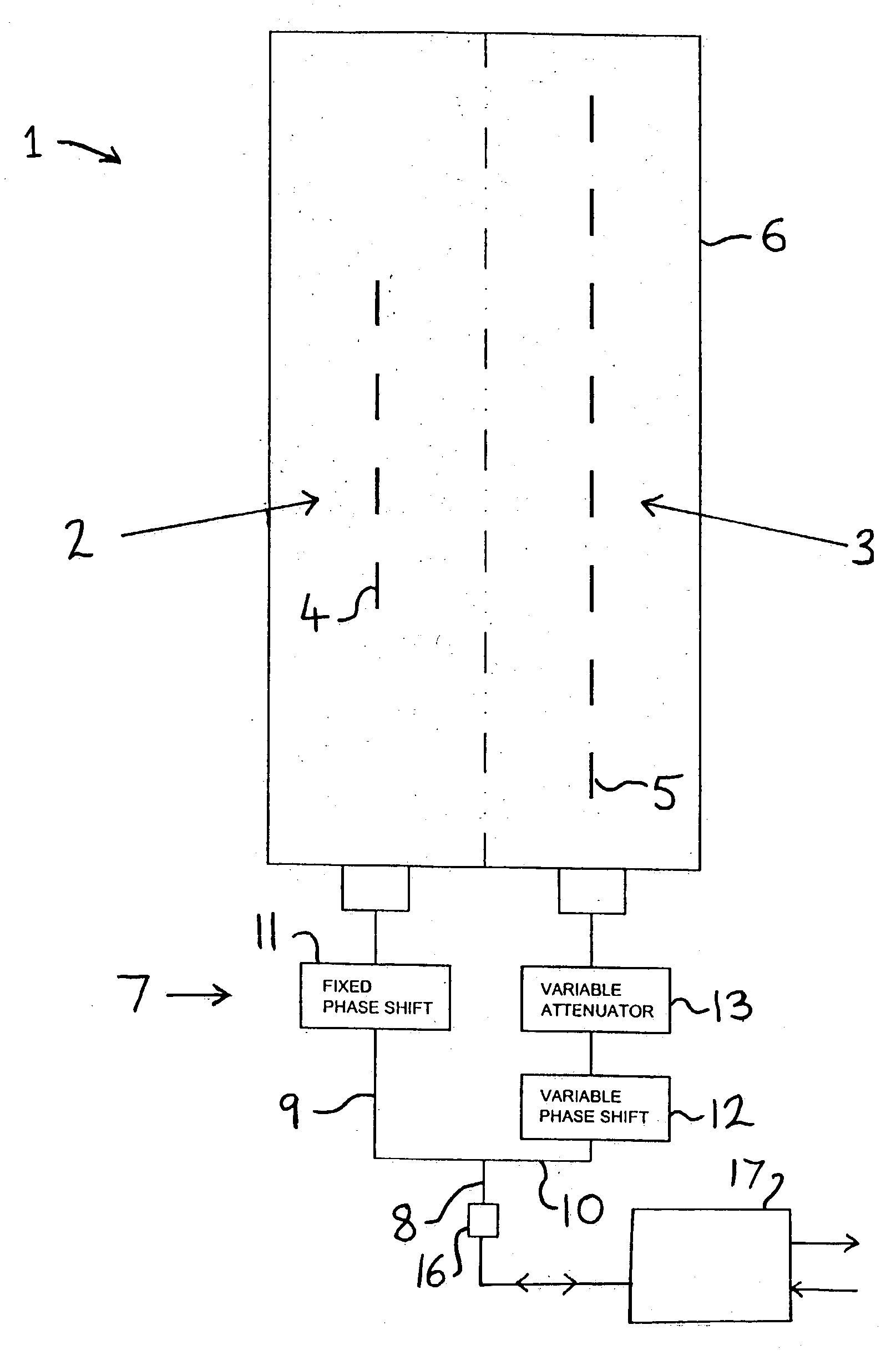

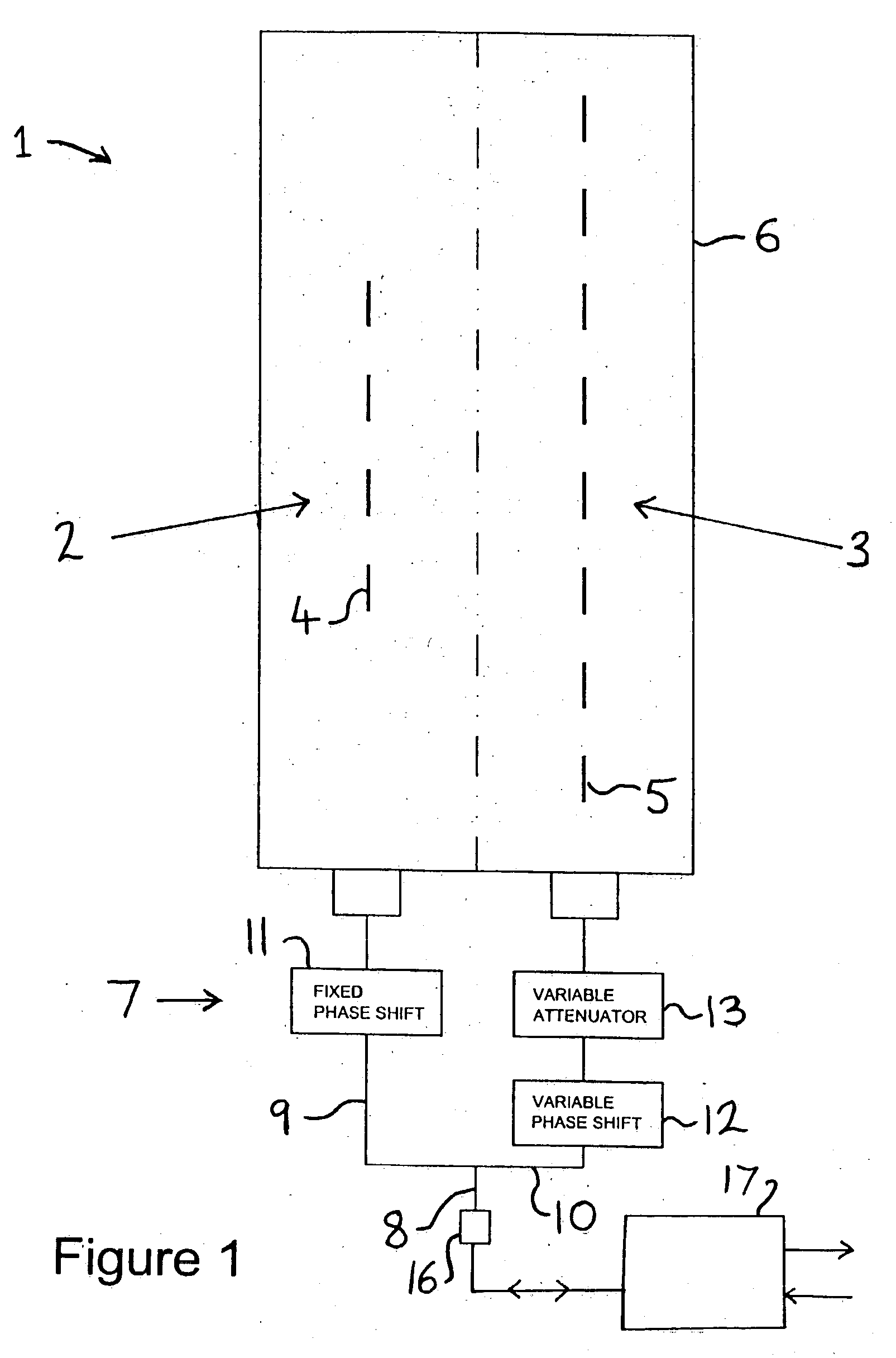

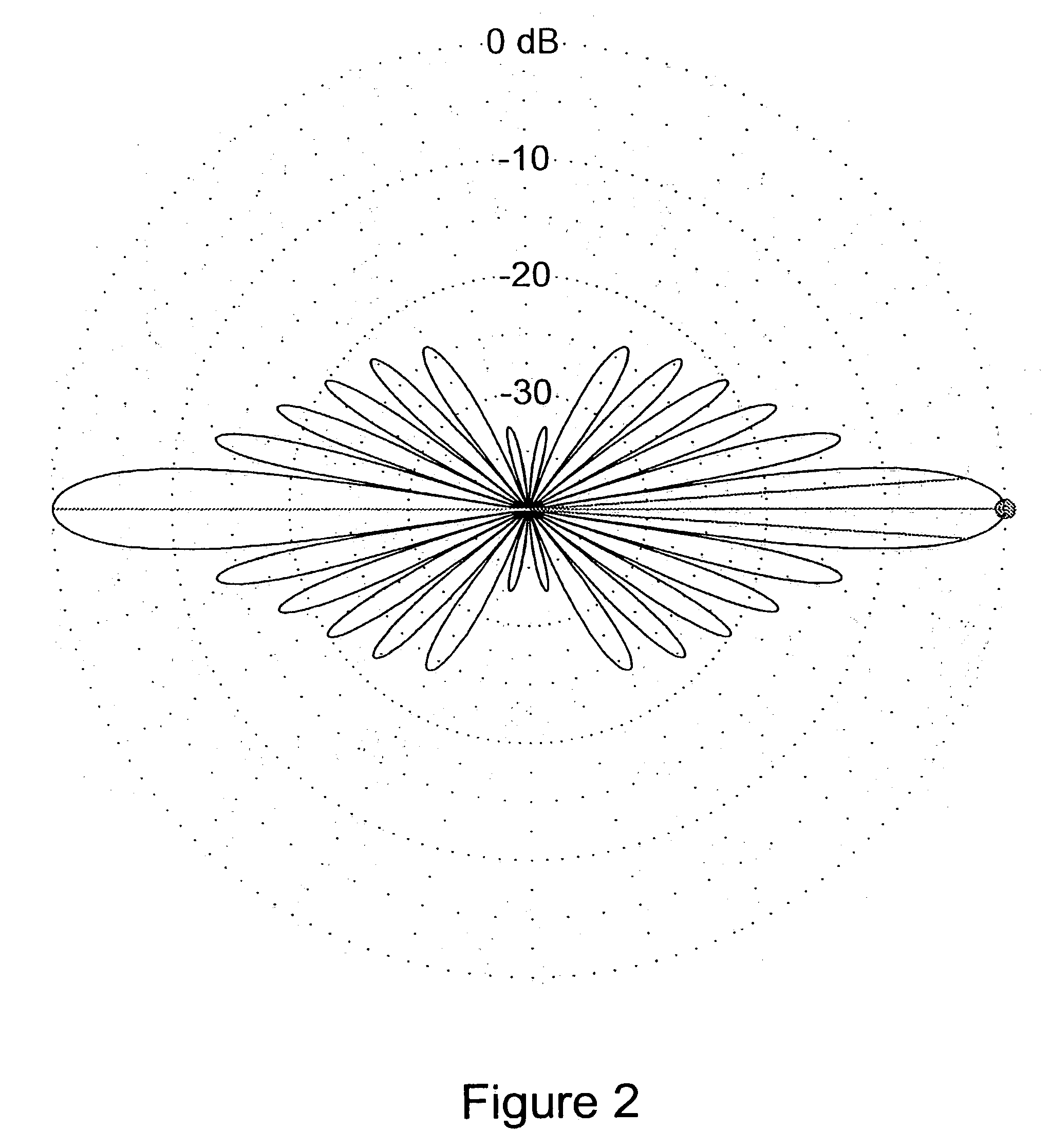

Antenna system

An antenna system including a coverage antenna (2) with a coverage beam pattern; and an auxiliary antenna (3) with an auxiliary beam pattern. The auxiliary beam pattern is arranged to perform sidelobe suppression, null steering, null addition, or null-fill. In the case where the auxiliary antenna is used to perform sidelobe suppression, the auxiliary beam pattern has a mainlobe with: an amplitude lower than an amplitude of a mainlobe of said coverage beam pattern; a width lower than a width of said mainlobe of said coverage beam pattern; a phase different to a phase of a sidelobe of said coverage beam pattern; and a direction which is selected so as to at least partially suppress said sidelobe.

Owner:ANDREW CORP

Phase-locked loop using multi-phase feedback signals

InactiveUS7496168B2Pulse automatic controlAngle demodulation by phase difference detectionPhase shiftedControl signal

A signal generator, such as a fractional-N PLL, has, in its feedback signal path, a divider, a phase circuit, and a fractional accumulator that generates control signals for the divider and the phase circuit. The divider control signal controls the divisor value applied by the divider. In one embodiment, a phase selector selects, based on the phase-circuit control signal, one of a plurality of phase-shifted output signals generated by the PLL's main signal path (e.g., by a multi-phase VCO) and the divider generates the feedback signal for the PLL from the selected signal. In another embodiment, the divider generates a divided signal from one of the phase-shifted output signals, and a phase mixer generates, from the divided signal, a plurality of phase-shifted divided signals and selects, based on the phase-circuit signal, one of the phase-shifted divided signals as the PLL's feedback signal.

Owner:AVAGO TECH INT SALES PTE LTD

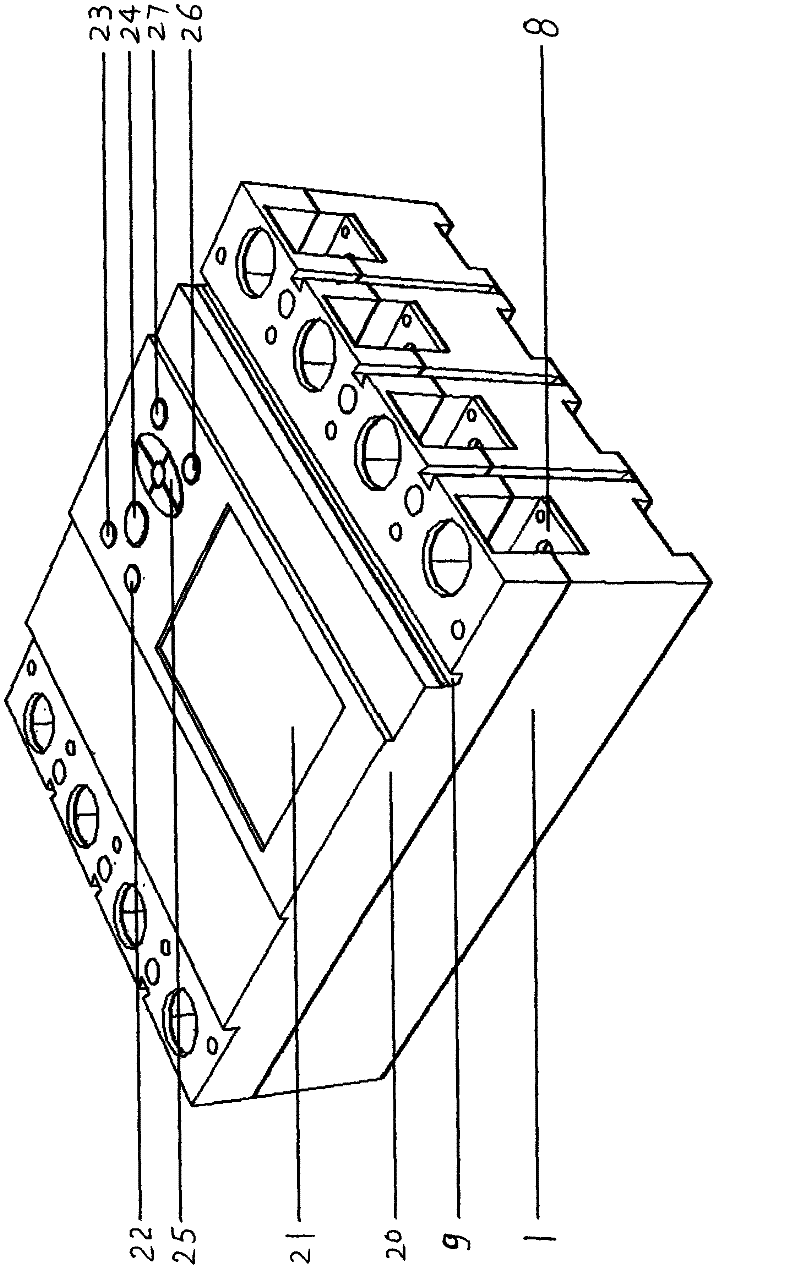

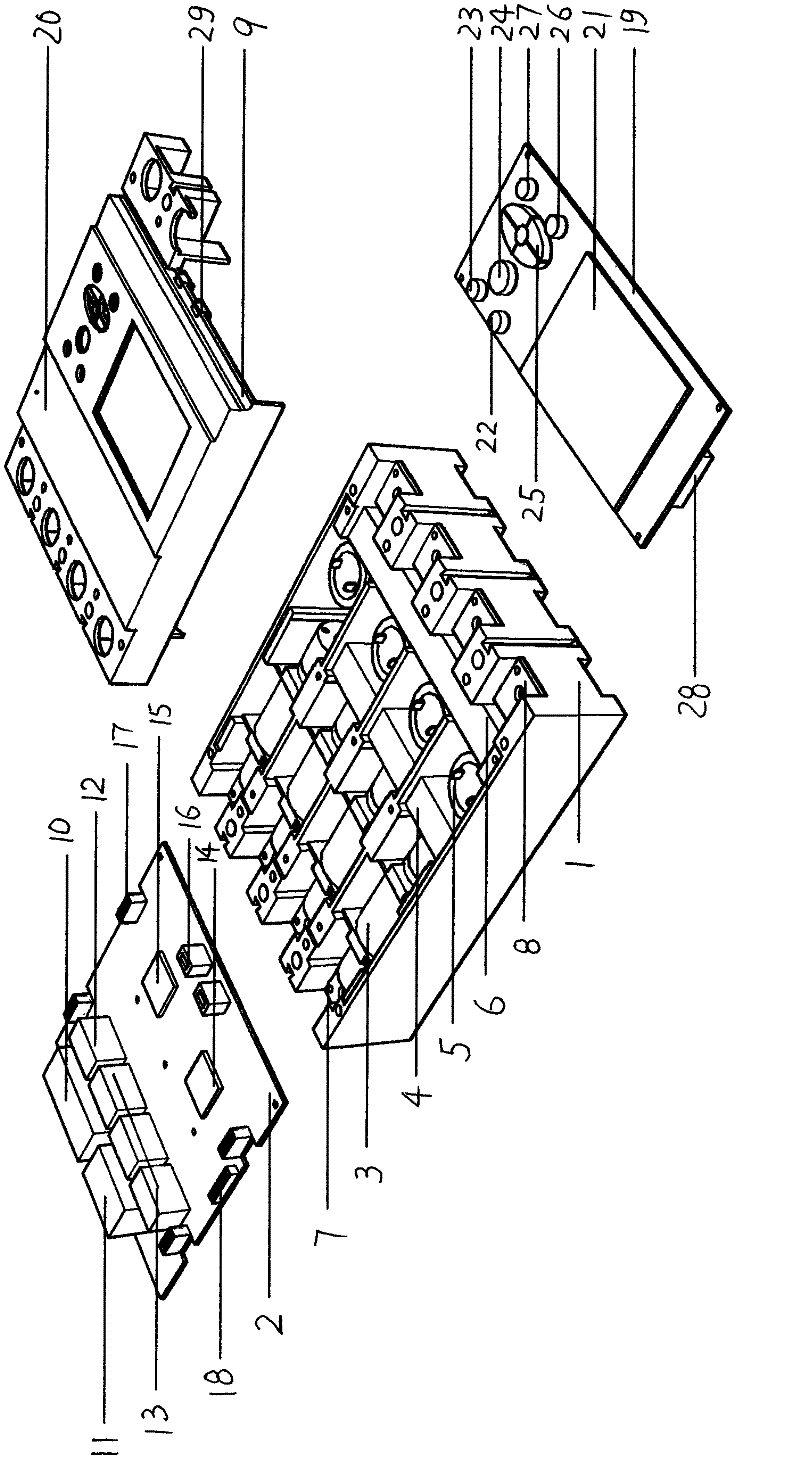

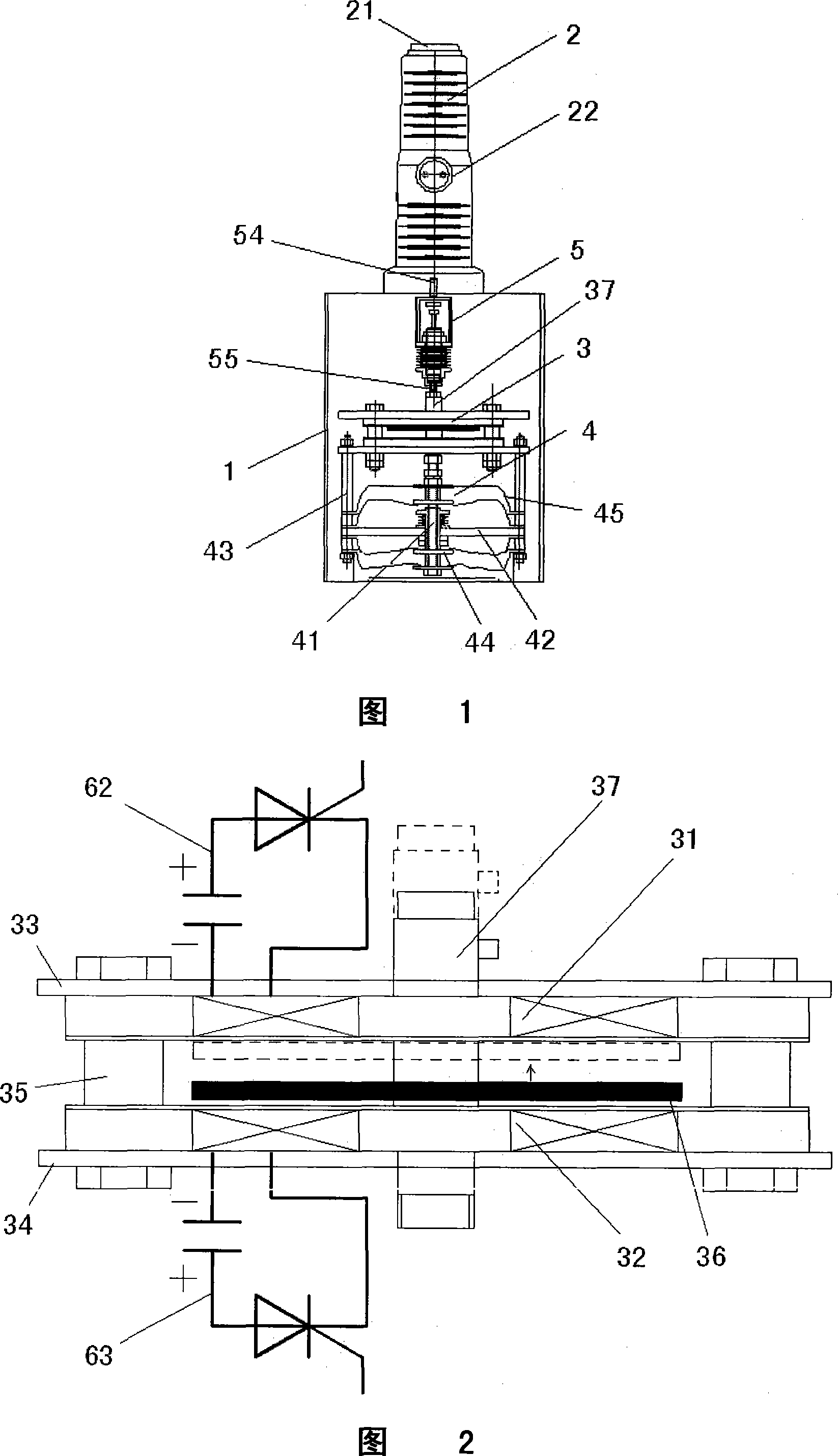

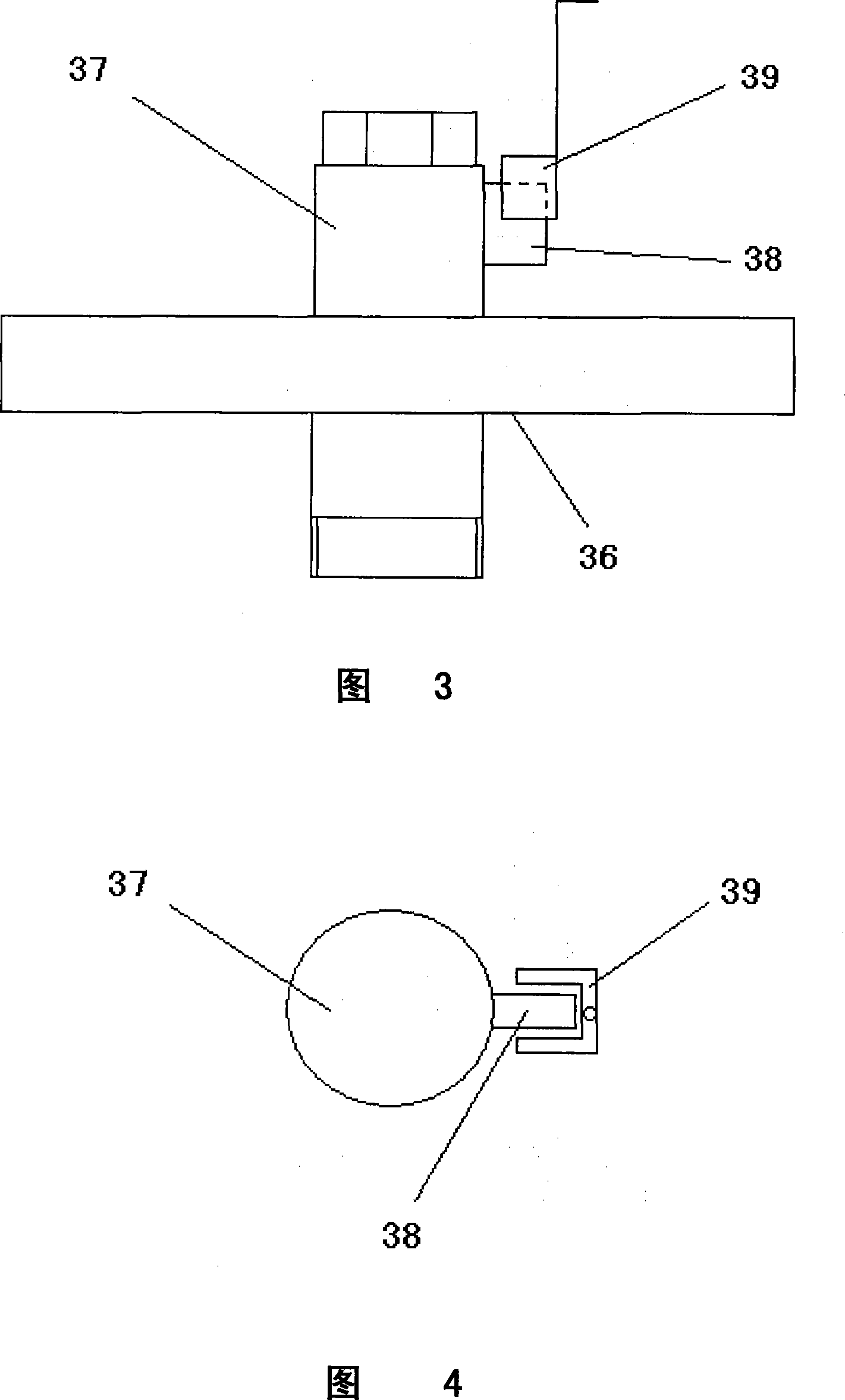

Low-voltage intelligent circuit breaker with plastic shell

ActiveCN102347168AConvenient queryPowerful and complete protection functionProtective switch detailsEmergency protective arrangements for automatic disconnectionCapacitanceAutomatic control

The invention relates to a low-voltage intelligent circuit breaker with a plastic shell. The low-voltage intelligent circuit breaker comprises a switch base and a switch cover, wherein the switch base is provided with four longitudinal through grooves and a transverse through groove penetrating through the longitudinal through grooves, a vacuum electromagnetic switch, a current transformer and a storage capacitor are sequentially installed in three longitudinal through grooves; another vacuum electromagnetic switch and another storage capacitor are sequentially installed in the other longitudinal through grooves, and a zero sequence transformer is installed in the transverse through groove; and a control circuit board is fixed at the upper middle of the switch base, a power module, a charging module, a phasing voltage transformer, three voltage transformer for phase selection, two main processors and two auxiliary processors, wherein the display circuit board is located in the upper middle of the control circuit board and embedded in the switch cover and provided with a display screen, a red indication lamp, a green indication lamp, a switching-in operation button, a switching-off operation button and the like. The invention has the advantages of small volume, compact structure, convenience for use and installation and capability of truly realizing comprehensive intelligence of digital protection, automatic control and communication function.

Owner:胡俊兵

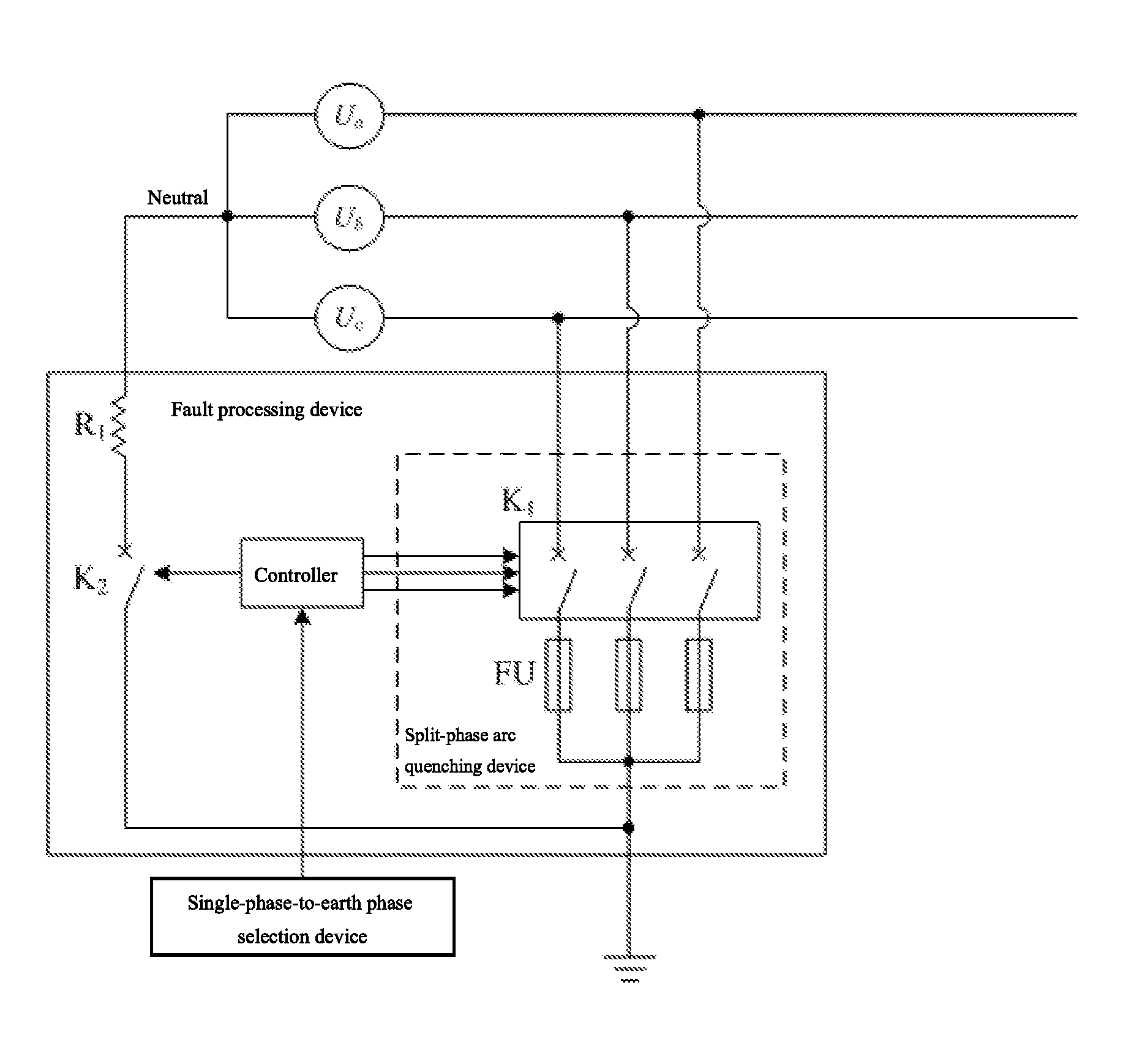

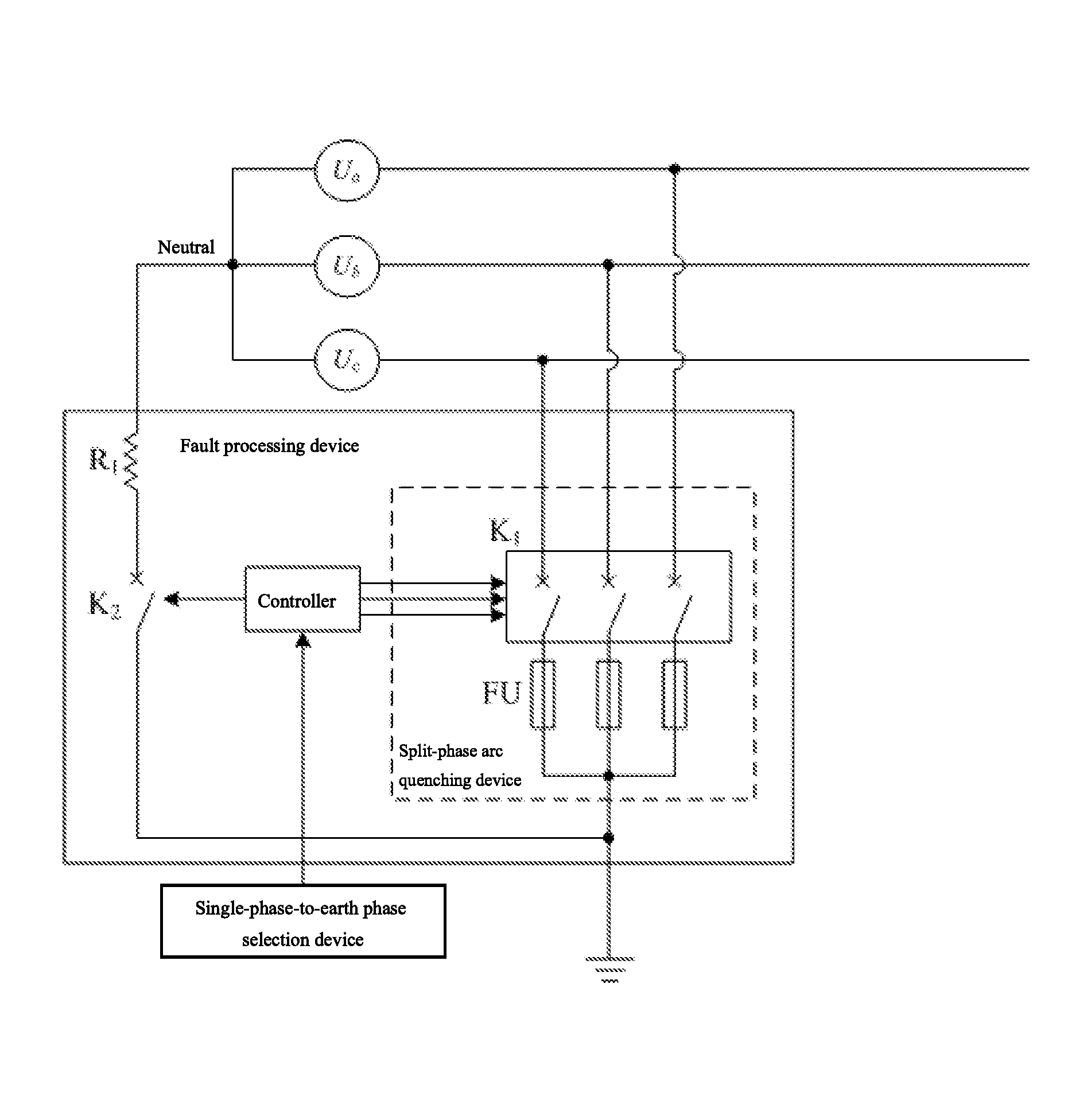

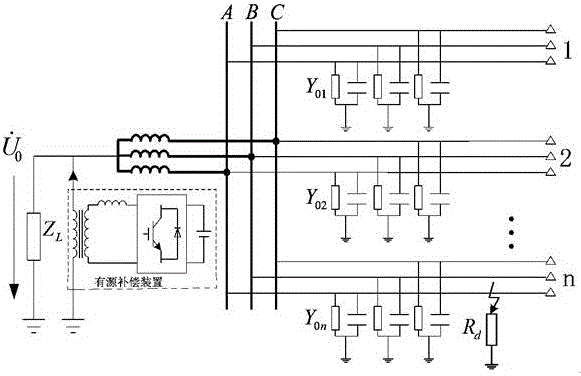

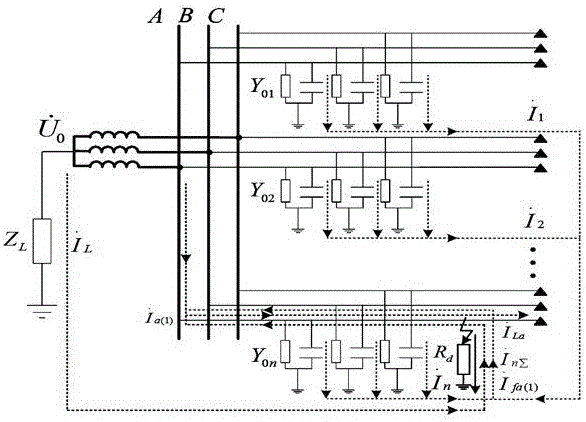

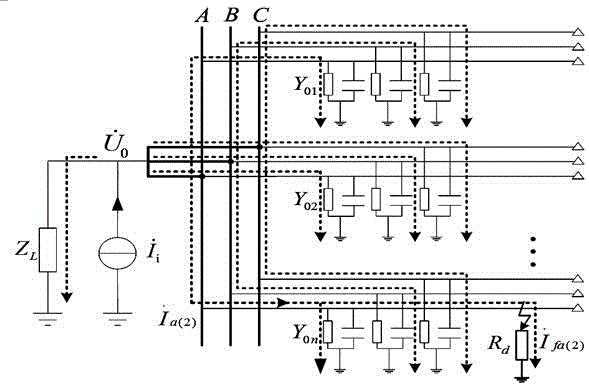

Single-phase-to-earth fault processing device and method for neutral non-effectively grounded distribution network

ActiveUS20160233661A1Rapid fault line selectionFast locationHigh-tension/heavy-dress switchesAir-break switchesThree-phaseEngineering

A single-phase-to-earth fault processing device for a neutral non-effectively grounded distribution network includes a split-phase arc quenching device connected between earth and a three-phase bus of the distribution network, and a controller with an input end connected with a single-phase-to-earth phase selection device of the distribution network. The split-phase arc quenching device includes a multiphase switching device which operates independently for each phase, and a fuse connected in series with the multiphase switching device. The controller is for controlling opening and closing of three single-phase switches, in the multiphase switching device. A single-phase-to-earth fault processing method firstly controls the split-phase arc quenching device to preprocess the fault. If the fault still exists, through a ground resistor a zero-sequence current is generated on a fault line. After delaying to wait for a line to isolate a fault section, a ground connection of the neutral is cut, to restore the distribution network.

Owner:STATE GRID CORP OF CHINA +1

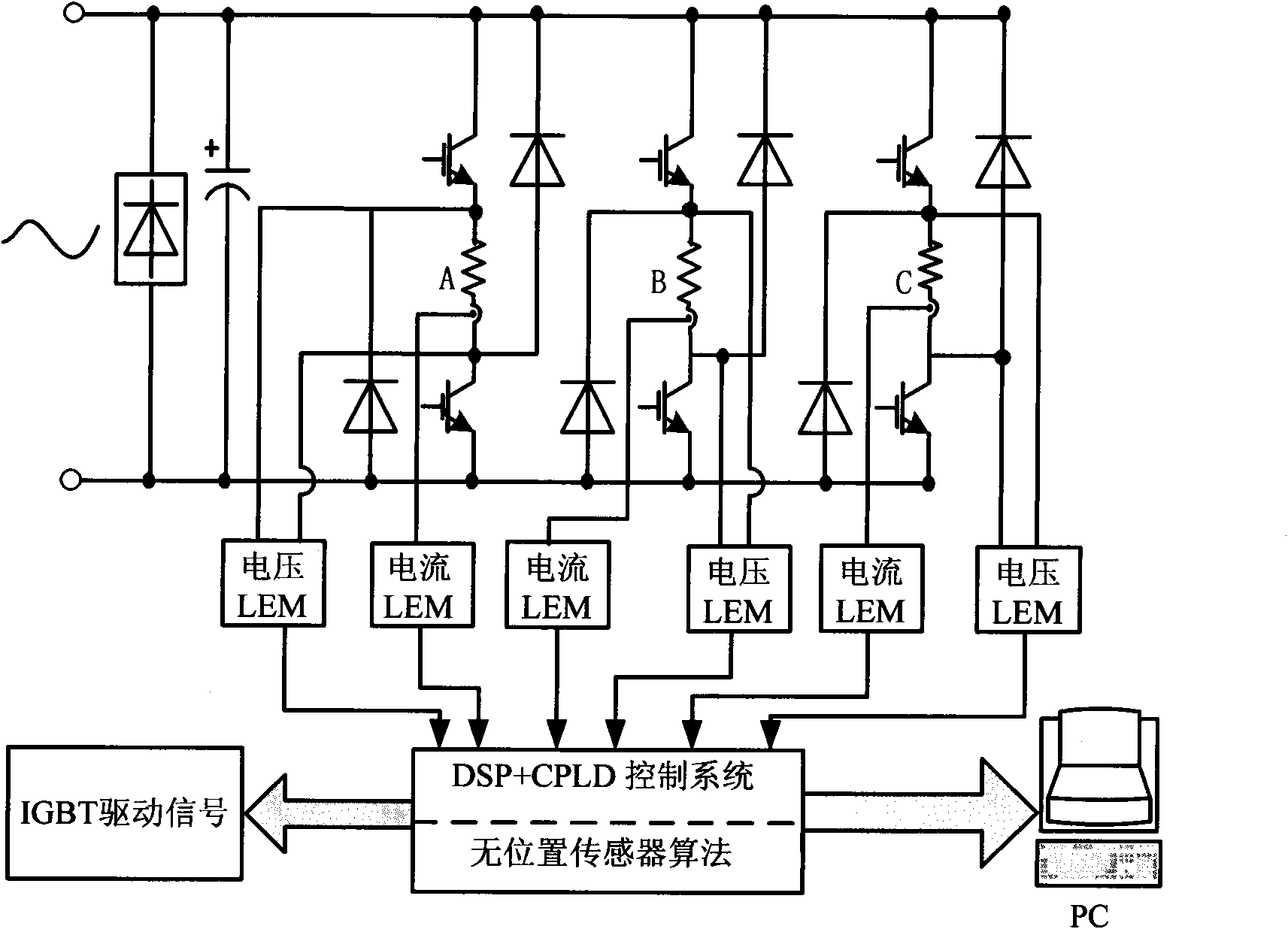

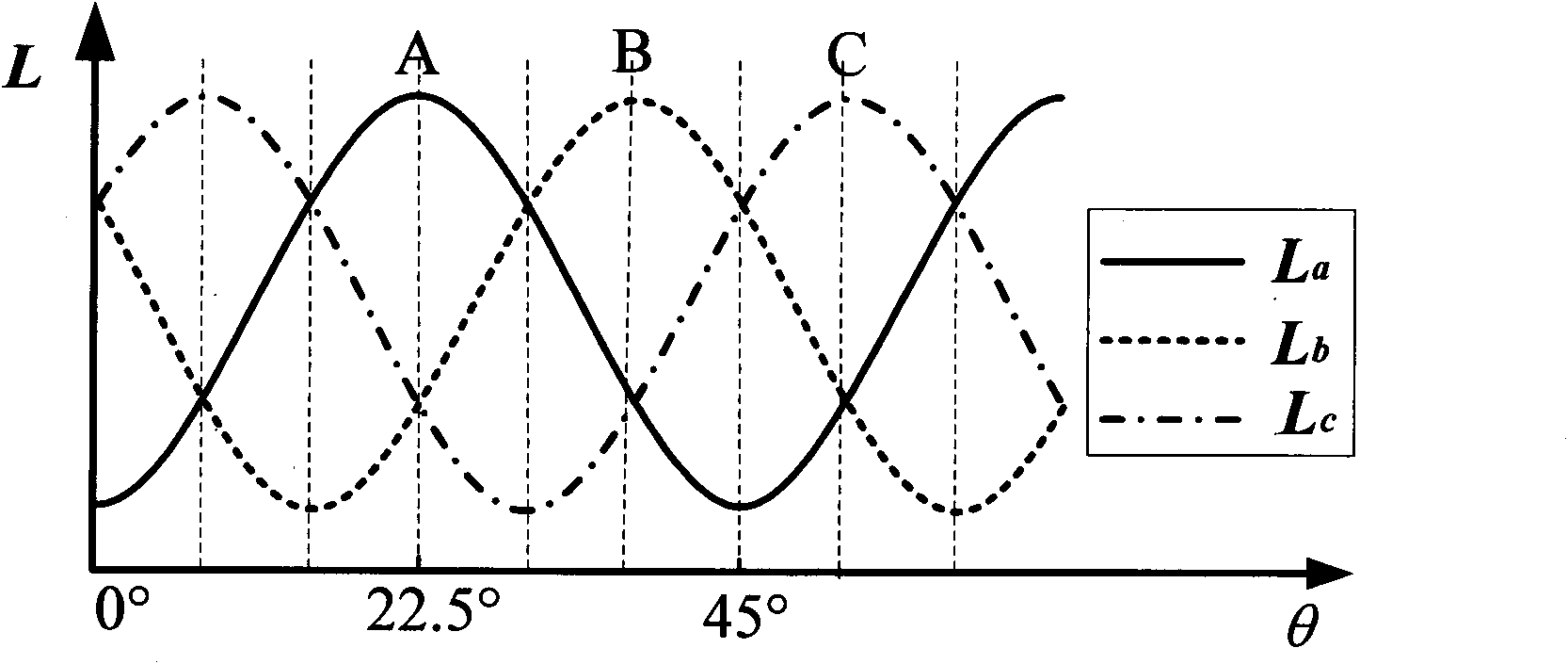

Method for initially positioning and starting switched reluctance motor without position sensor

InactiveCN101902189AAvoid wrong choiceEasy to implementAC motor controlElectronic commutatorsMathematical modelPosition angle

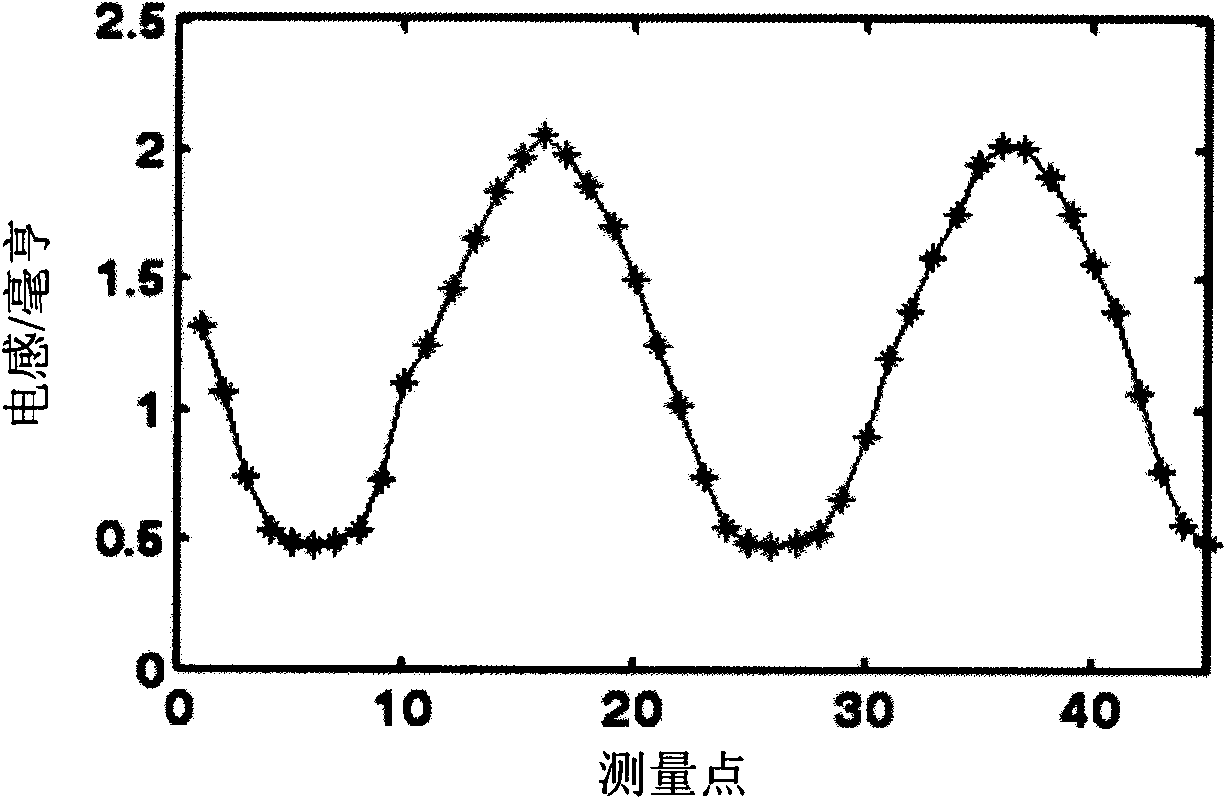

The invention discloses a method for initially positioning and starting a switched reluctance motor without a position sensor, and belongs to the technical field of control of the switched reluctance motor. The method comprises the following steps of: setting an inductance bottom threshold value LLow and an inductance top threshold value LHigh based on the basic characteristic that the inductance of the switched reluctance motor periodically changes with the position of a rotor; injecting short pulses into each phase winding and calculating inductance values according to a phase voltage equation; judging phases which can be currently switched on according to the relation among each phase inductance calculated value and LLow and LHigh and selecting estimated phases of an initial position angle at the same time; and establishing a phase inductance mathematical model to obtain angle information in the selected phases by using the relation between the inductance mathematical model and the inductance calculated values. Though the method, an initial switch-on phase selection signal can be accurately acquired and the initial position angle of the rotor can be calculated at the same time, so the switched reluctance motor can be started and initially positioned without the position sensor, an algorithm is simple and generality is high.

Owner:NANJING UNIV OF AERONAUTICS & ASTRONAUTICS

Oversampling data recovery apparatus and method

InactiveUS6611219B1Analogue/digital conversionElectric signal transmission systemsClock phaseComputer science

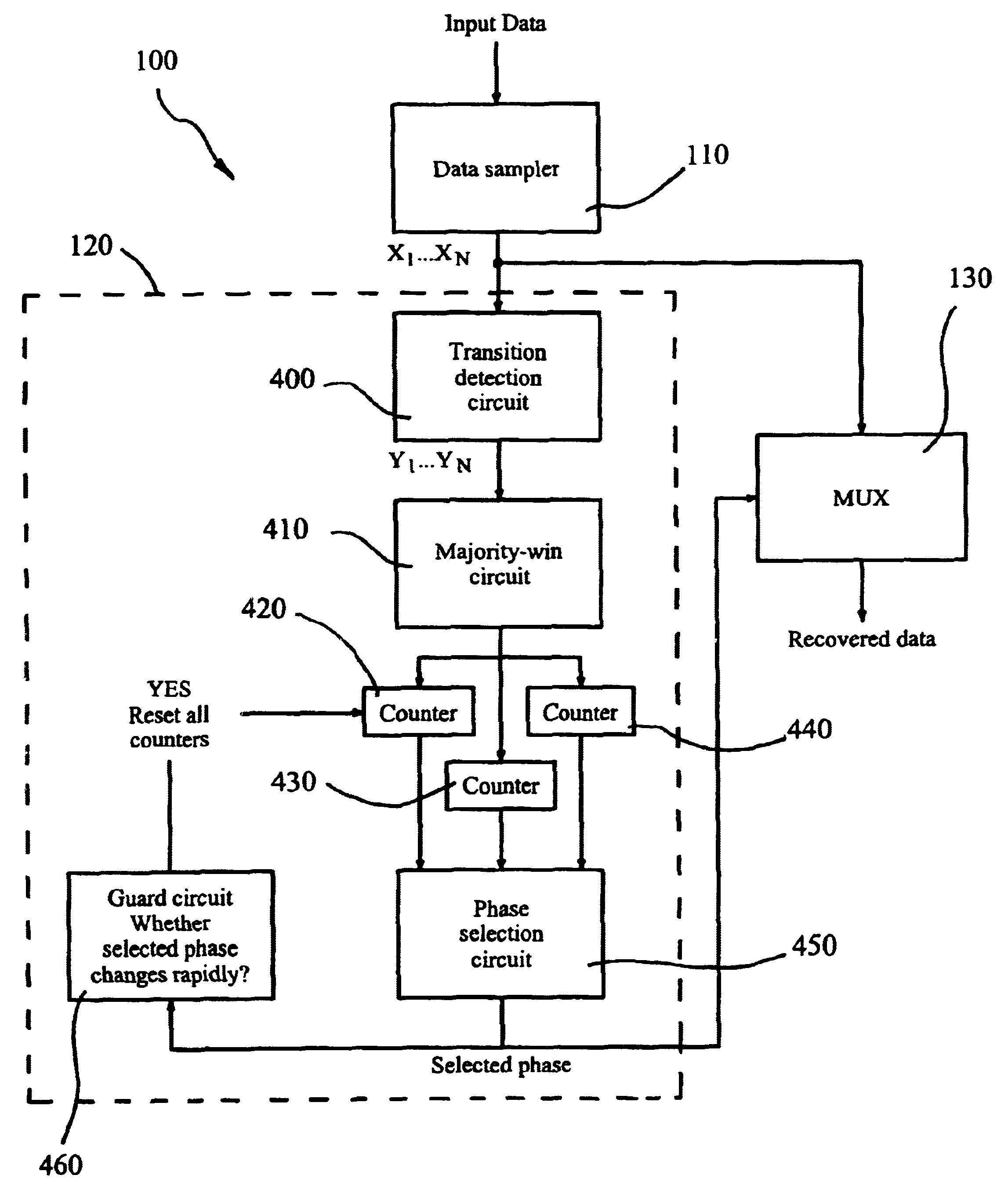

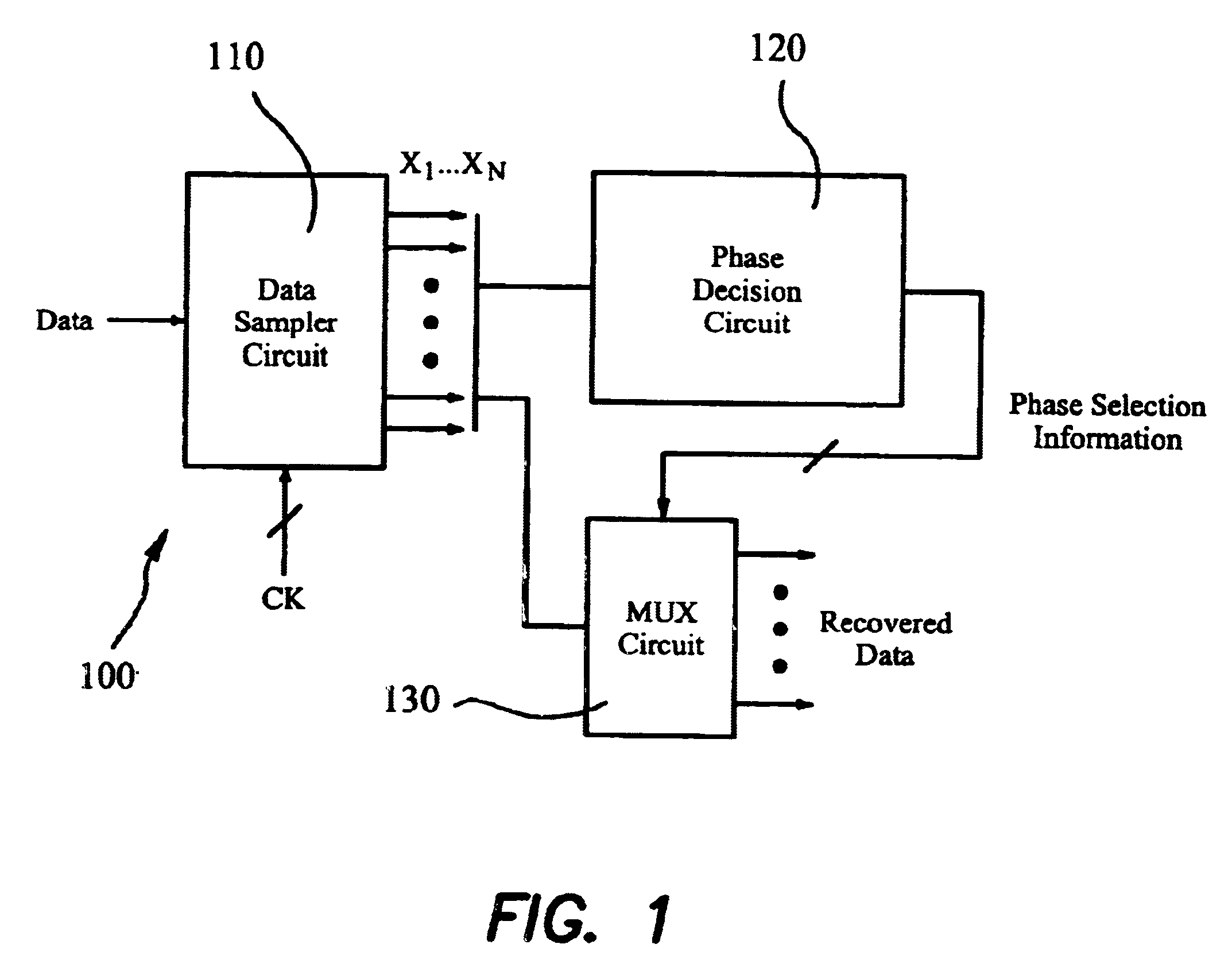

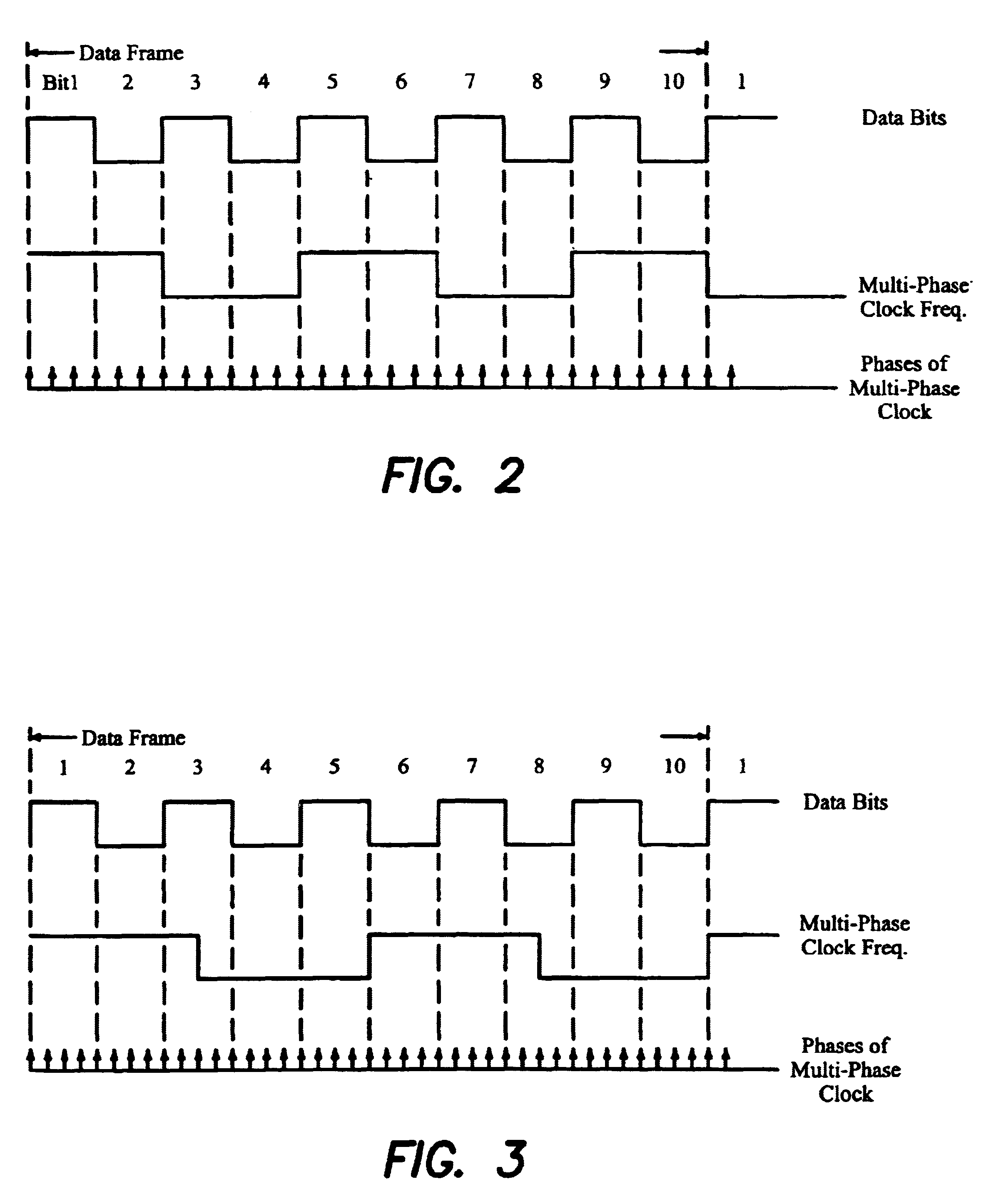

An open-loop data recovery apparatus and method utilizing an oversampling technique is provided, by which the occurrence of data transitions is counted and a proper sampling clock phase is decided. Counters with variable thresholds are used to monitor the occurrence of phase transitions for a phase selection circuit to determine a preferred phase for recovery of sampled data. The thresholds of the counters are further adjusted in reference with the preferred phase decided by the phase selection circuit.

Owner:MACRONIX INT CO LTD

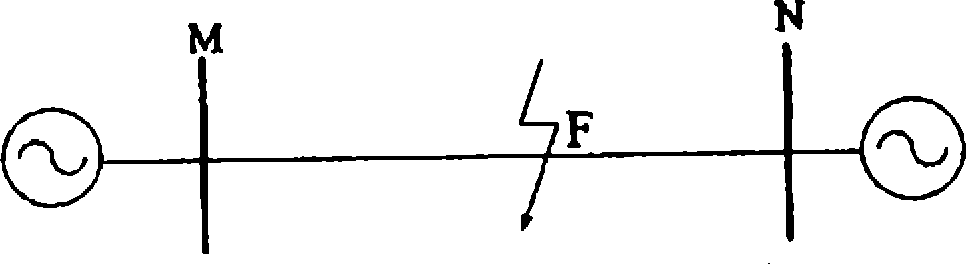

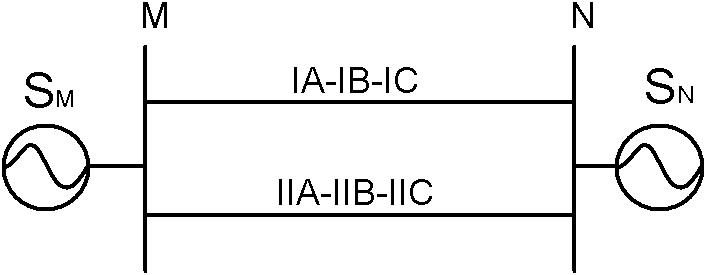

Fault positioning method for common-tower double-circuit line

A fault positioning method for a common-tower double-circuit line comprises the following steps: firstly, carrying out six-sequence decomposition for electrical quantity at two ends of the double-circuit line; next, calculating the fault distance by a long line equation of a transmission line of a same positive-sequence fault component of the six-sequence components, and obtaining six-sequence current of a fault point according to the electrical quantity at two ends of the double-circuit line, the fault distance and the long line equation; then converting the six-sequence current into six-phase current; and finally, judging a fault phase according to the amplitude value characteristic of the phase current of the fault point. According to the method provided by the invention, when fault phase-selection of the double-circuit line is carried out, the fault distance detection can be performed at the same time, and the advantages of clear principle, high distance detection accuracy, simple and reliable phase-selection logic and the like are provided. The method provided by the invention is free of the influence of fault point transitional resistance, circuit distributed capacitor current and load current, can automatically adapt to and regulate a definite value of the phase-selection criterion with the change of a system operation manner, and can provide effective phase-selection logic for distance protection of the common-tower double-circuit line.

Owner:NORTH CHINA ELECTRIC POWER UNIV (BAODING)

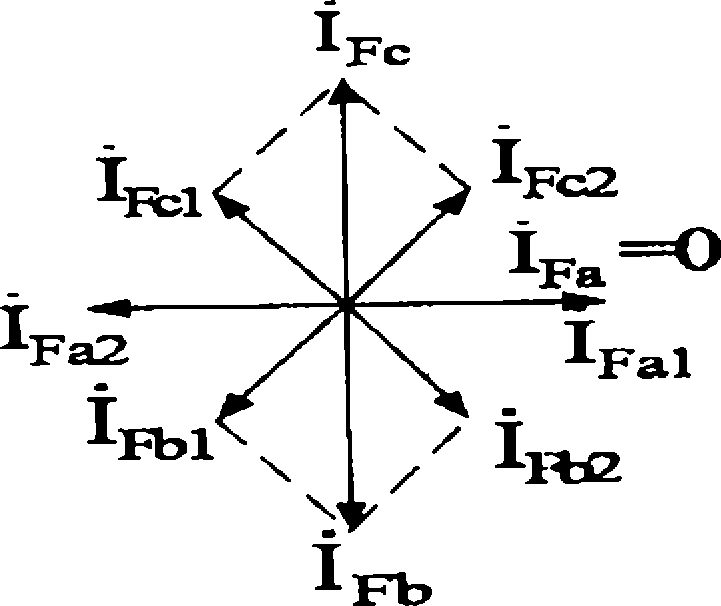

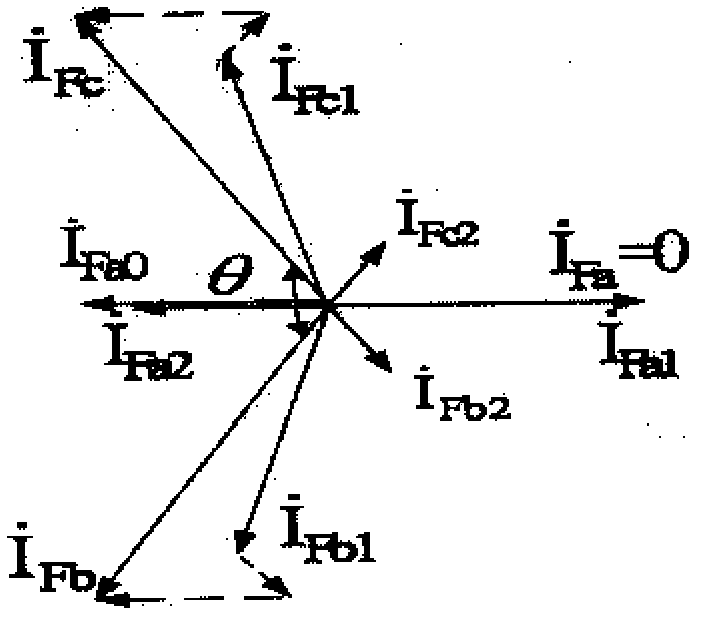

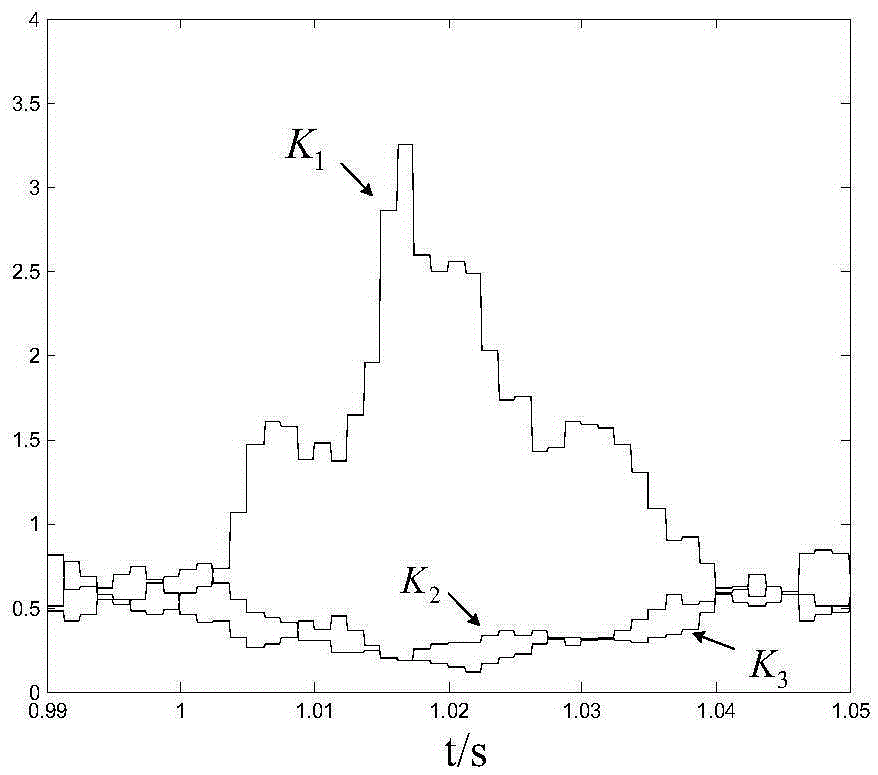

Fault phase selection method based on current break variable

ActiveCN102608495AAvoid shockShorten time to correct actionFault locationElectrical resistance and conductanceElectric power system

The invention relates to a fault phase selection method based on a current break variable, which belongs to the technical field of fault judgment of a power system and constructs a fault phase selection coefficient by use of the current break variable to realize selection of the fault type and fault phase. The method comprises the following steps of: constructing a fault phase selection coefficient by use of the proportional relationship between the fault current of one phase and the difference between the fault current of other two phases measured by a protection device of a high-voltage line; and then analyzing the different characteristics of the coefficient in various fault conditions to realize fault phase selection of the power system. The method can accurately identify the fault phase within a cyclic wave after the fault occurs, has relatively high sensitivity to various types of faults, is not influenced by the fault position, transition resistance and load current, and has relatively high reliability and good selectivity; and meanwhile, the method has enough sensitivity to the fault phase selection on the weak power side.

Owner:NORTH CHINA ELECTRIC POWER UNIV (BAODING)

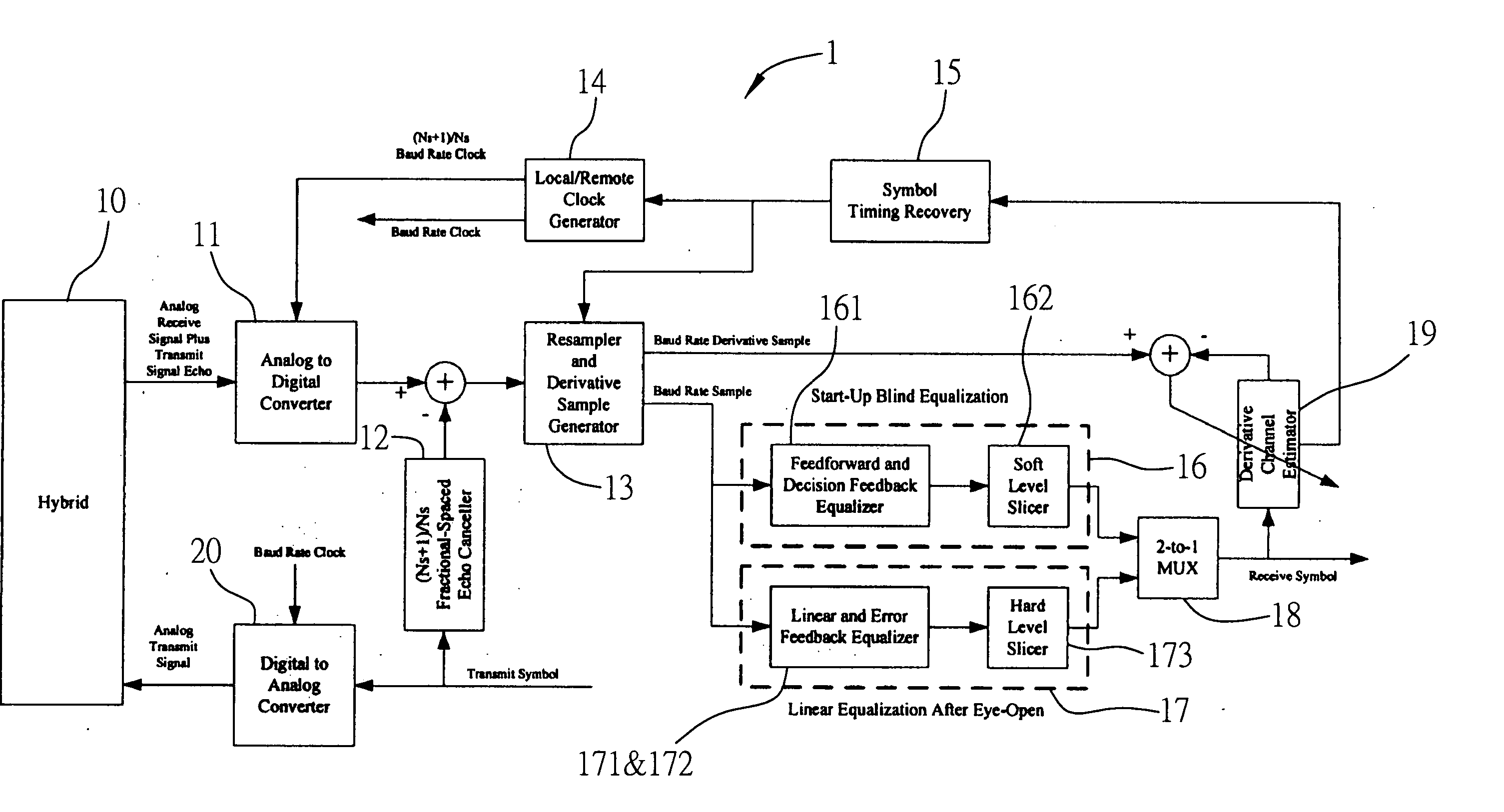

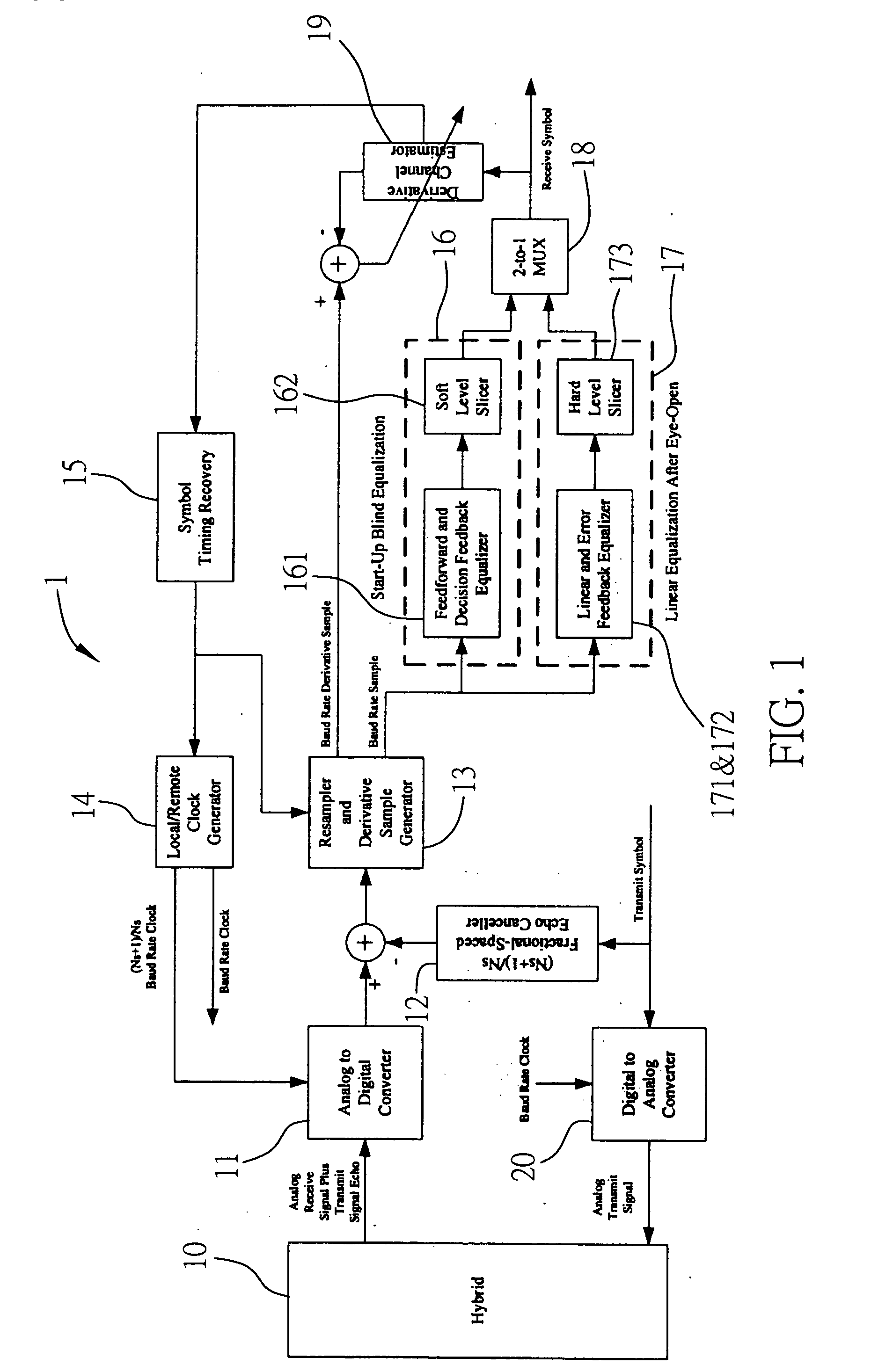

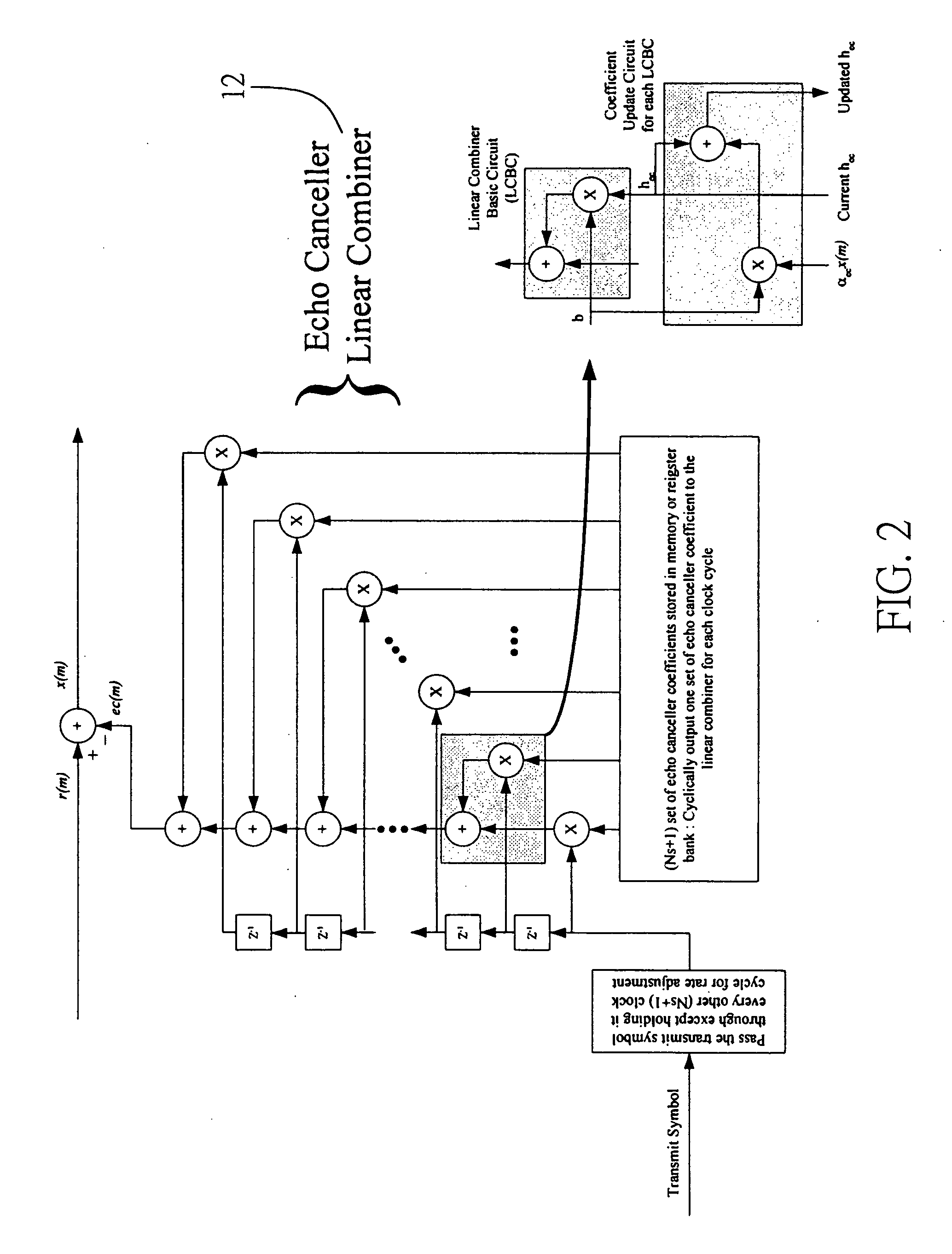

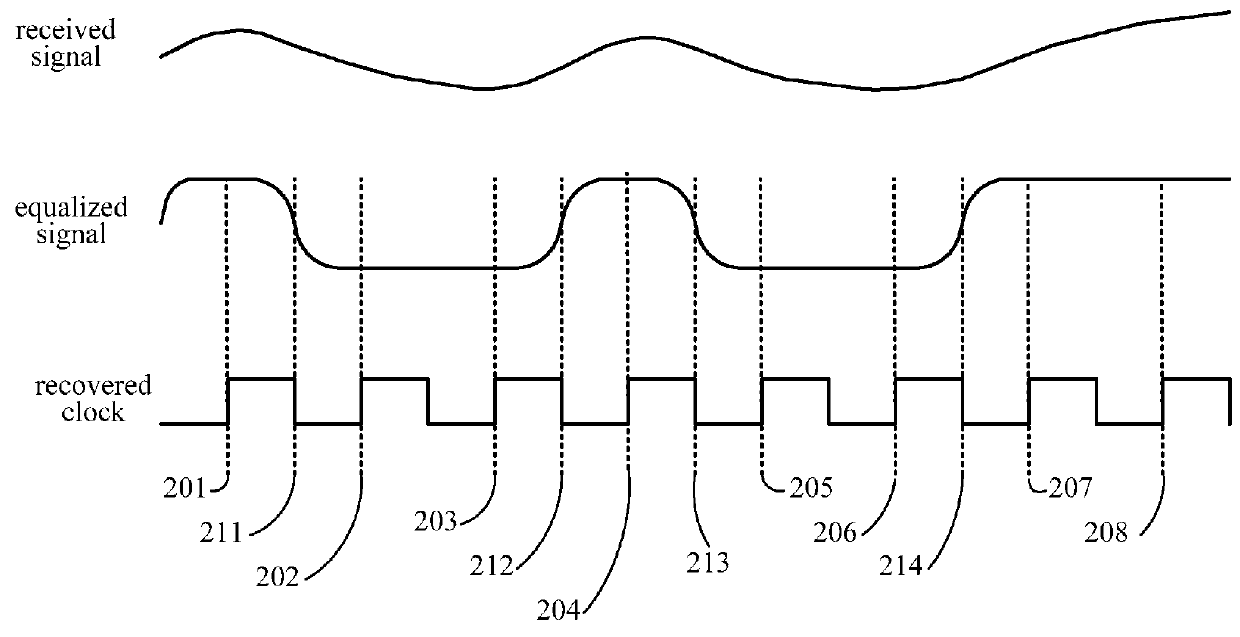

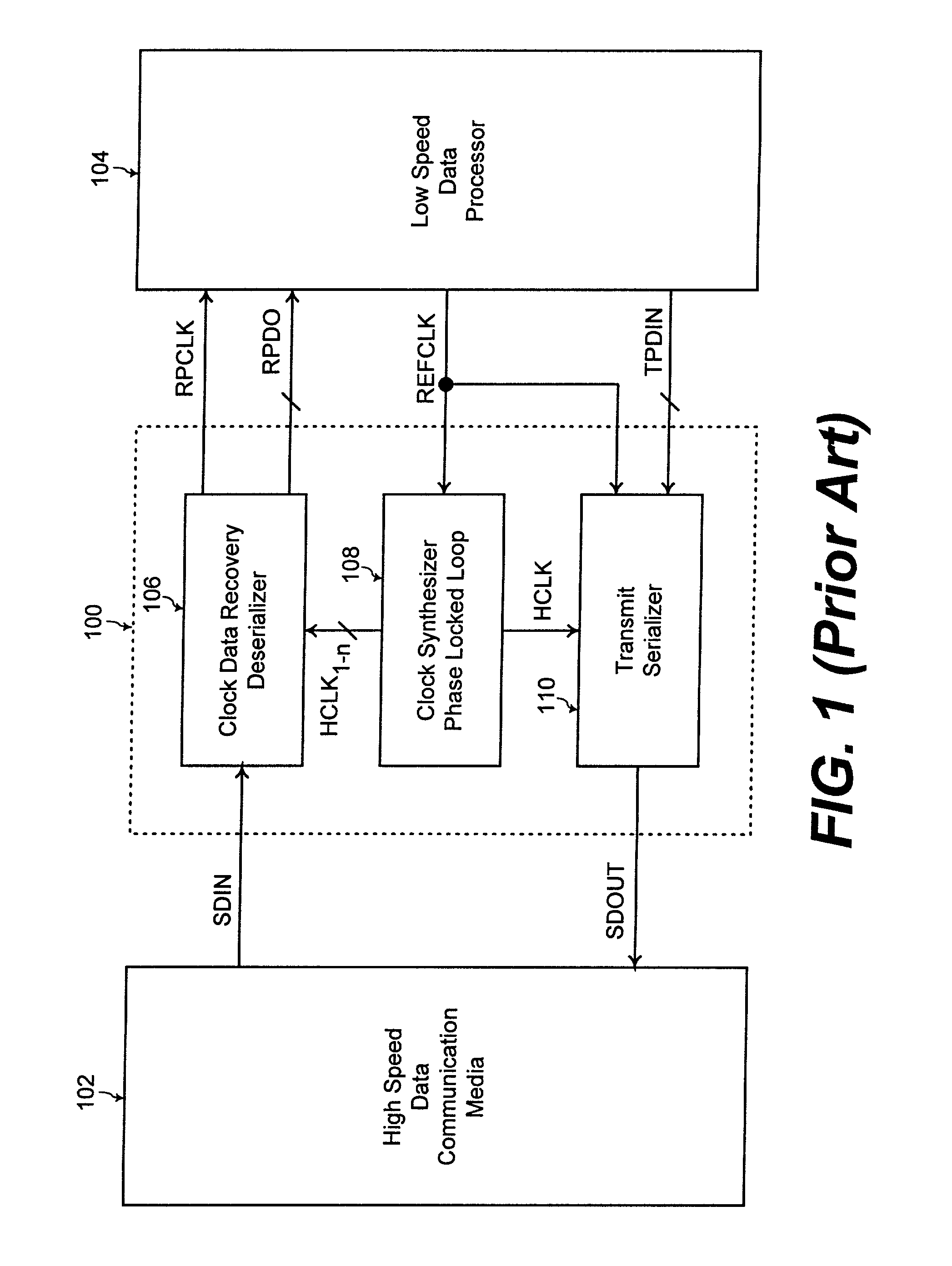

Adaptive blind start-up receiver architecture with fractional baud rate sampling for full-duplex multi-level PAM systems

ActiveUS20060256849A1Maximize signal to noise ratioEasy to useMultiple-port networksError preventionA d converterEqualization

This invention presents a novel receiver architecture for full-duplex multi-level PAM systems. The receiver employs an Analog-to-Digital Converter (ADC) that has a sample rate flexibly specified as (Ns+1) / Ns baud rate where Ns is an integer equal or greater than 1. A fractional-spaced echo canceller is used to cancel the echo at the ADC output. The use of a fractional sampling rate higher than the baud rate also enables the timing recovery function be implemented in the digital domain and hence eliminates the need of using the complex analog phase selection circuit. The receiver is also capable of fast, blind start-up by use of a decision feedback equalizer with unity main tap and a soft level slicer. The timing phase can be optimally located using a derivative channel estimator. Once the “eye-open” condition is achieved, the channel equalization is switched to the use of linear equalizer coupled with an error feedback equalizer to alleviate the error propagation problem associated with the decision feedback equalizer.

Owner:RDC SEMICON CO LTD

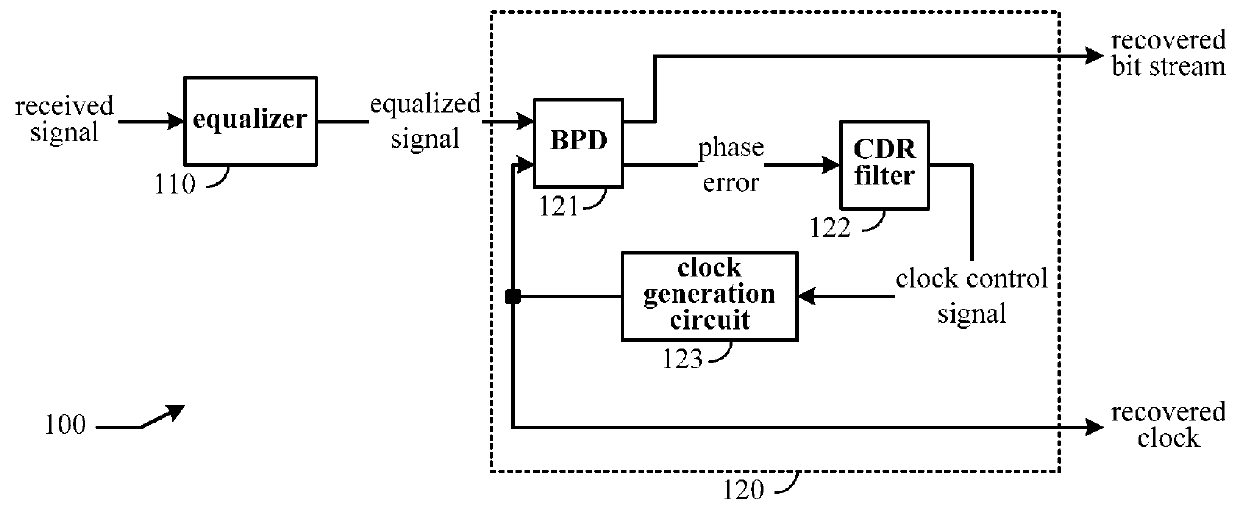

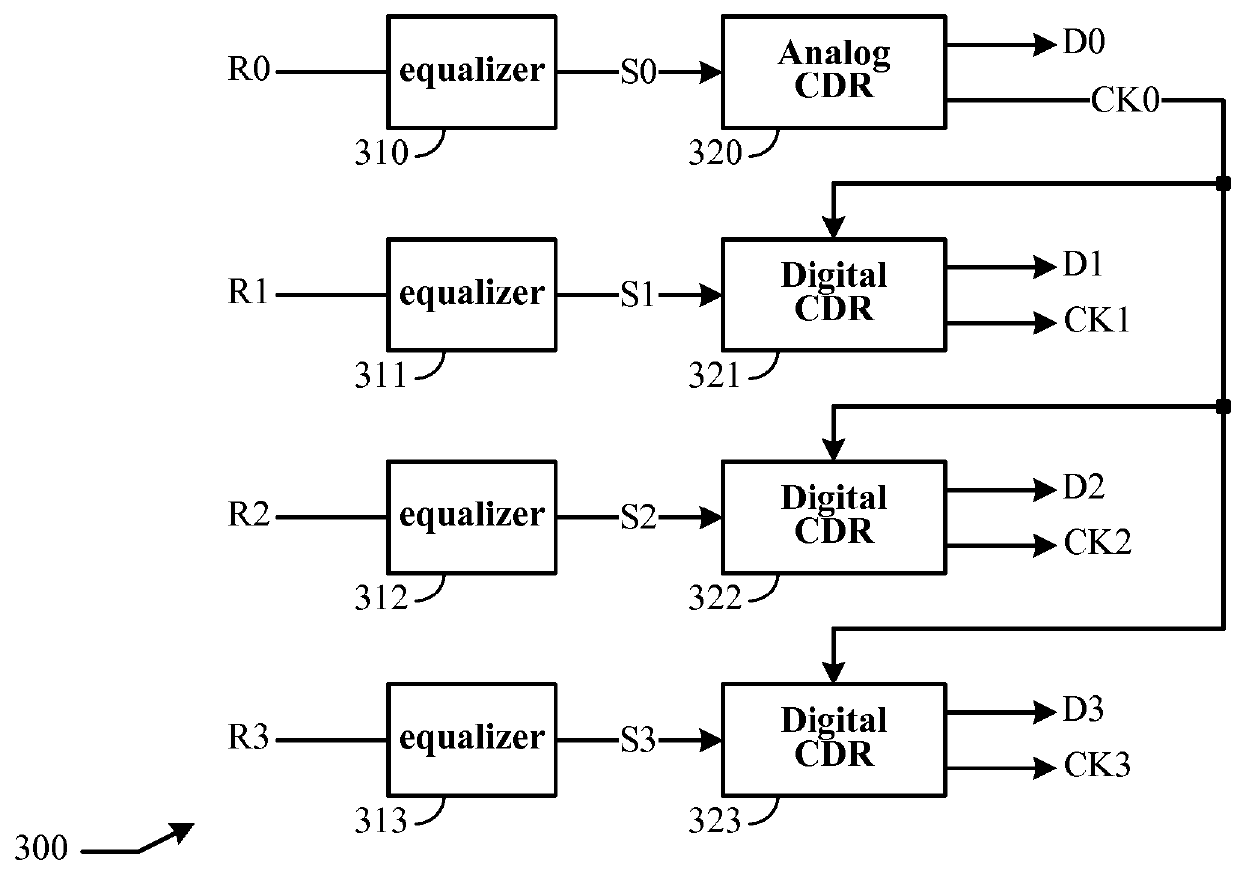

Multi-lane serial data link receiver and method thereof

A serial data link receiver and method are provided. In one implementation, the receiver includes a first equalizer for receiving a first received signal and outputting a first equalized signal, and a second equalizer for receiving a second received signal and outputting a second equalized signal. The receiver further includes an analog CDR (clock-data recovery) circuit for receiving the first equalized signal and outputting a first recovered bit stream and a first recovered clock generated in accordance with an analog control voltage, and a digital CDR circuit for receiving the second equalized signal and the first recovered clock and outputting a second recovered bit stream and a second recovered clock based on selecting a phase of the first recovered clock in accordance with a digital phase selection signal.

Owner:REALTEK SEMICON CORP

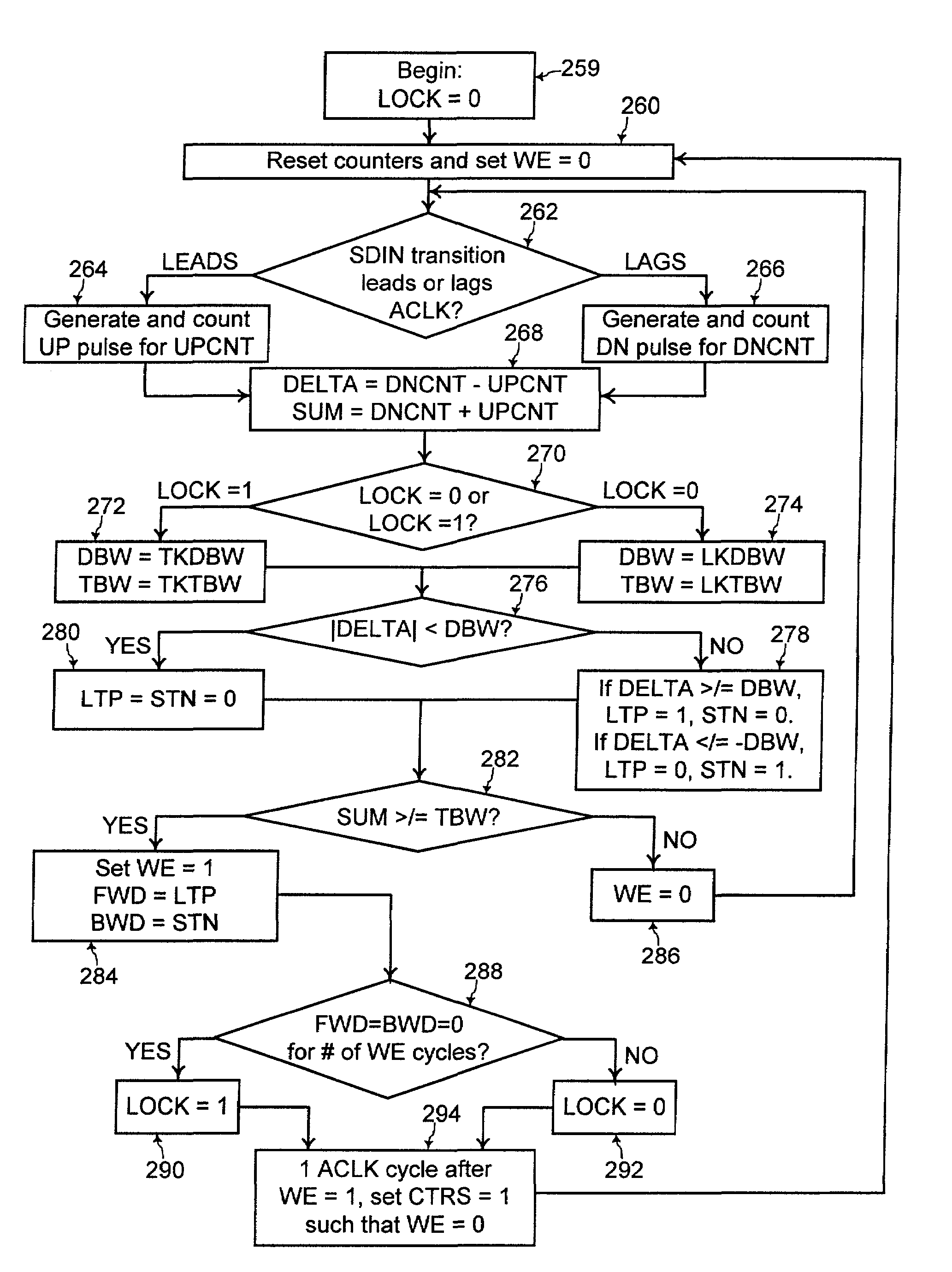

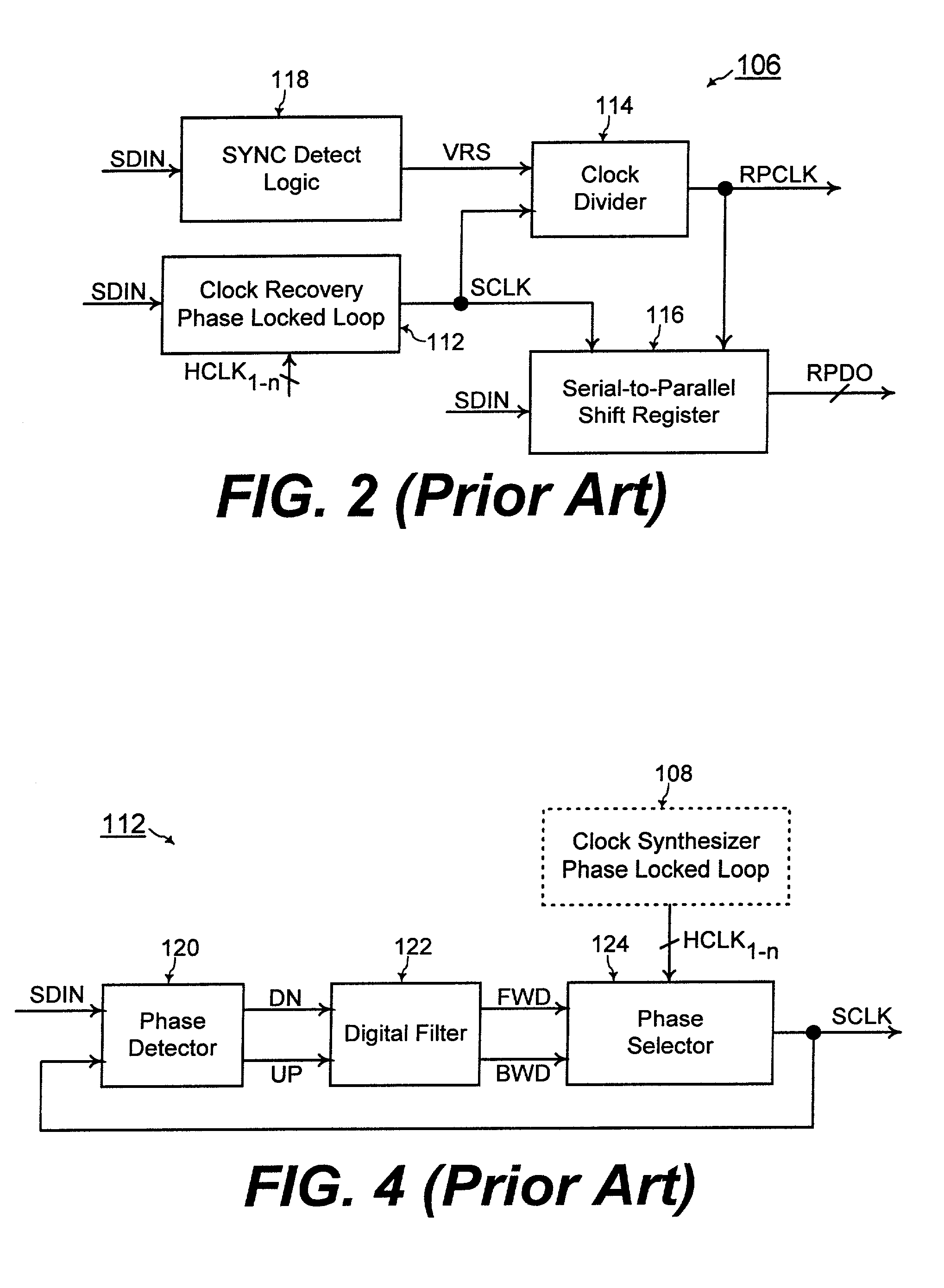

Digital phase locked loop with phase selector having minimized number of phase interpolators

ActiveUS7003066B1Minimize the numberPhase selectorPulse automatic controlAngle demodulation by phase difference detectionMultiplexerDigital filter

In one embodiment of the invention, a phase selection unit for generating a recovered clock signal (SCLK), a phase select signal generator generates a phase select signals in response to a FWD signal and a BWD signal from a digital filter. The digital filter asserts the FWD signal if the phase of a SDIN (serial digital input) signal leads the phase of the recovered clock signal, and asserts the BWD signal if the phase of the SDIN (serial digital input) signal lags the phase of the recovered clock signal. A multiplexer receives a number of given clock signals arranged in a predetermined phase order and outputs selected first and second output clock signals, each being one of the given clock signals. A phase interpolator receives the selected first and second output clock signals from the multiplexer to generate the recovered clock signal having a phase that is phase interpolated between the phases of the first and second output clock signals.

Owner:LATTICE SEMICON CORP

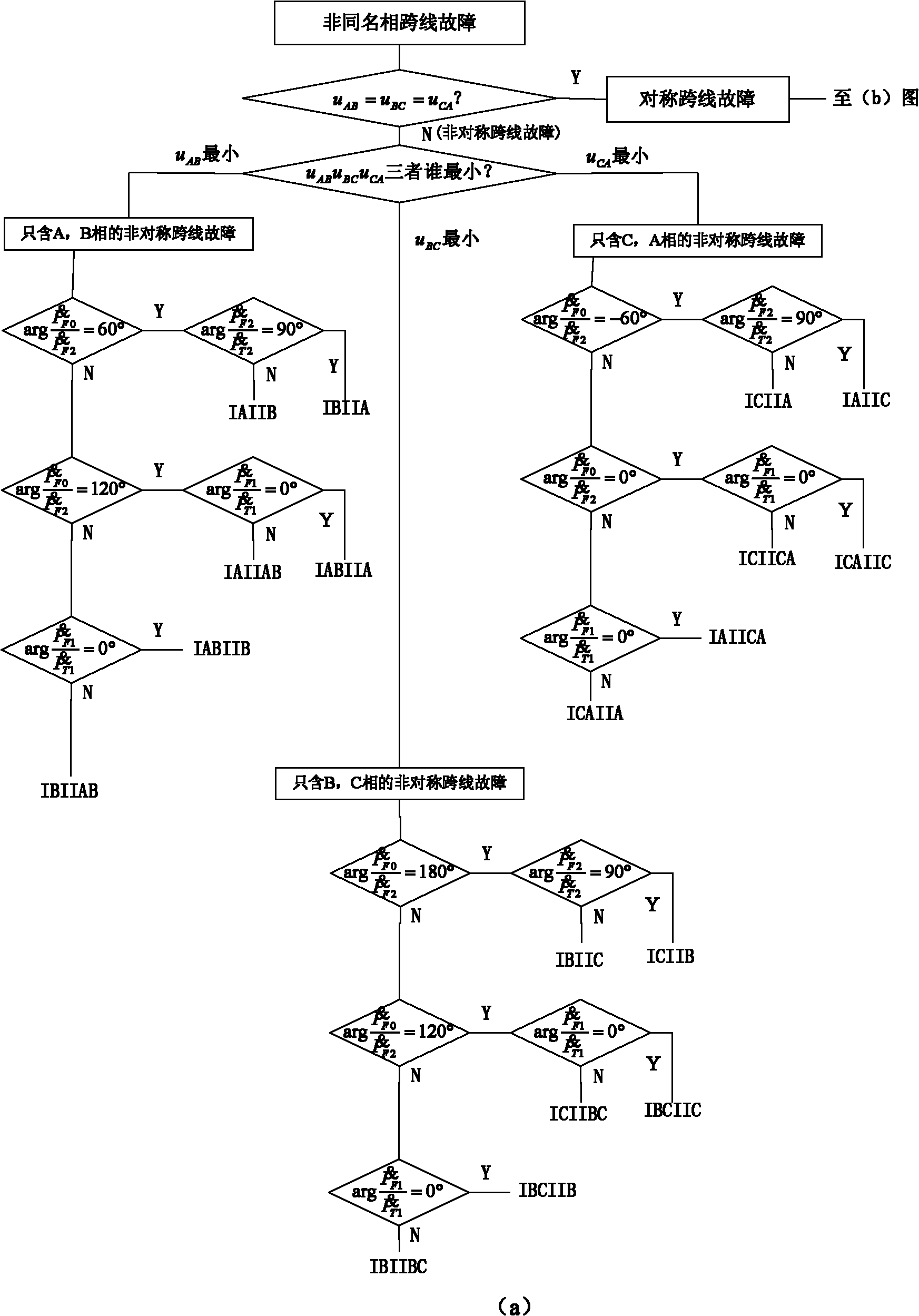

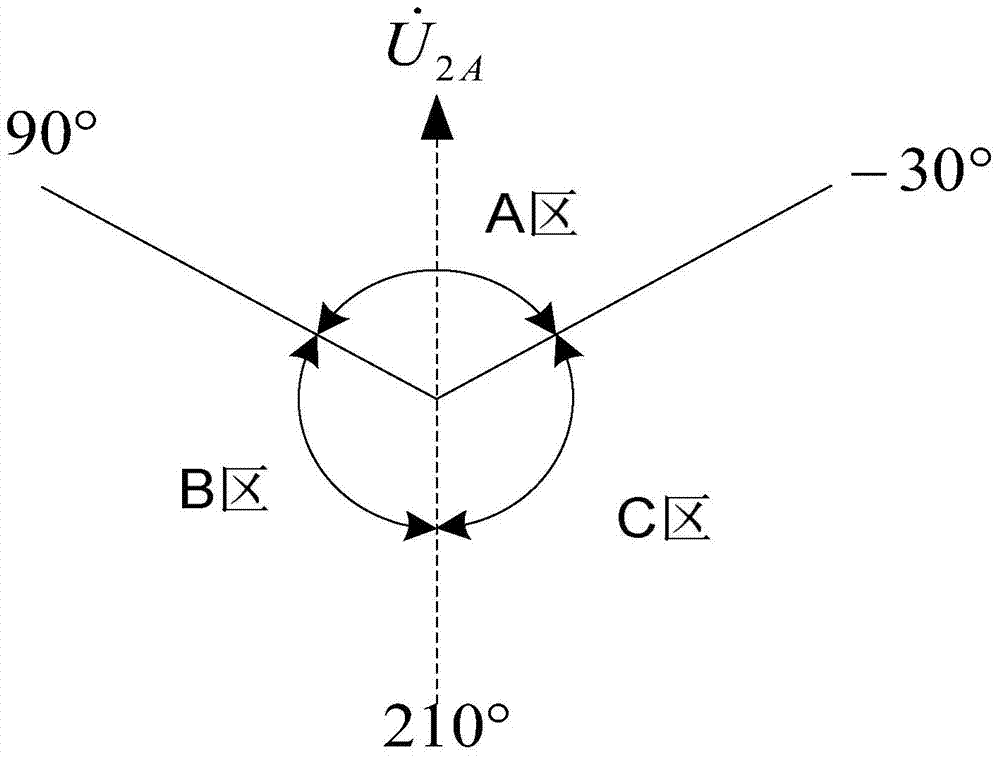

A comprehensive phase selection method for double-circuit lines paralleled on the same tower

The invention relates to the technical field of relay protection, and relates to a comprehensive phase selection method for double-circuit lines paralleled on the same tower: using the six-sequence component method to eliminate the mutual inductance current between the phases; according to the transformed six-sequence component, First distinguish the ground fault and non-ground fault, and then select the fault phase according to the following steps: According to the current amplitude characteristics of the single circuit fault, the non-identical phase cross-line fault and the same name phase cross-line fault, distinguish the non-identical phase span line fault, single circuit fault and phase line fault with the same name; for a single circuit fault, the phase angle of the positive and negative zero-sequence components in the same direction is 0° or 180° from the two The fault line is selected from three lines, and then the phase selection is carried out according to the negative sequence and zero sequence current phase selection principles; for the cross-line faults of the same name phase and non-same name phase, the fault type is judged respectively. The invention can make up for the disadvantages of incomplete phase selection function and even wrong phase selection of other phase selection methods currently used on double-circuit lines.

Owner:TIANJIN UNIV

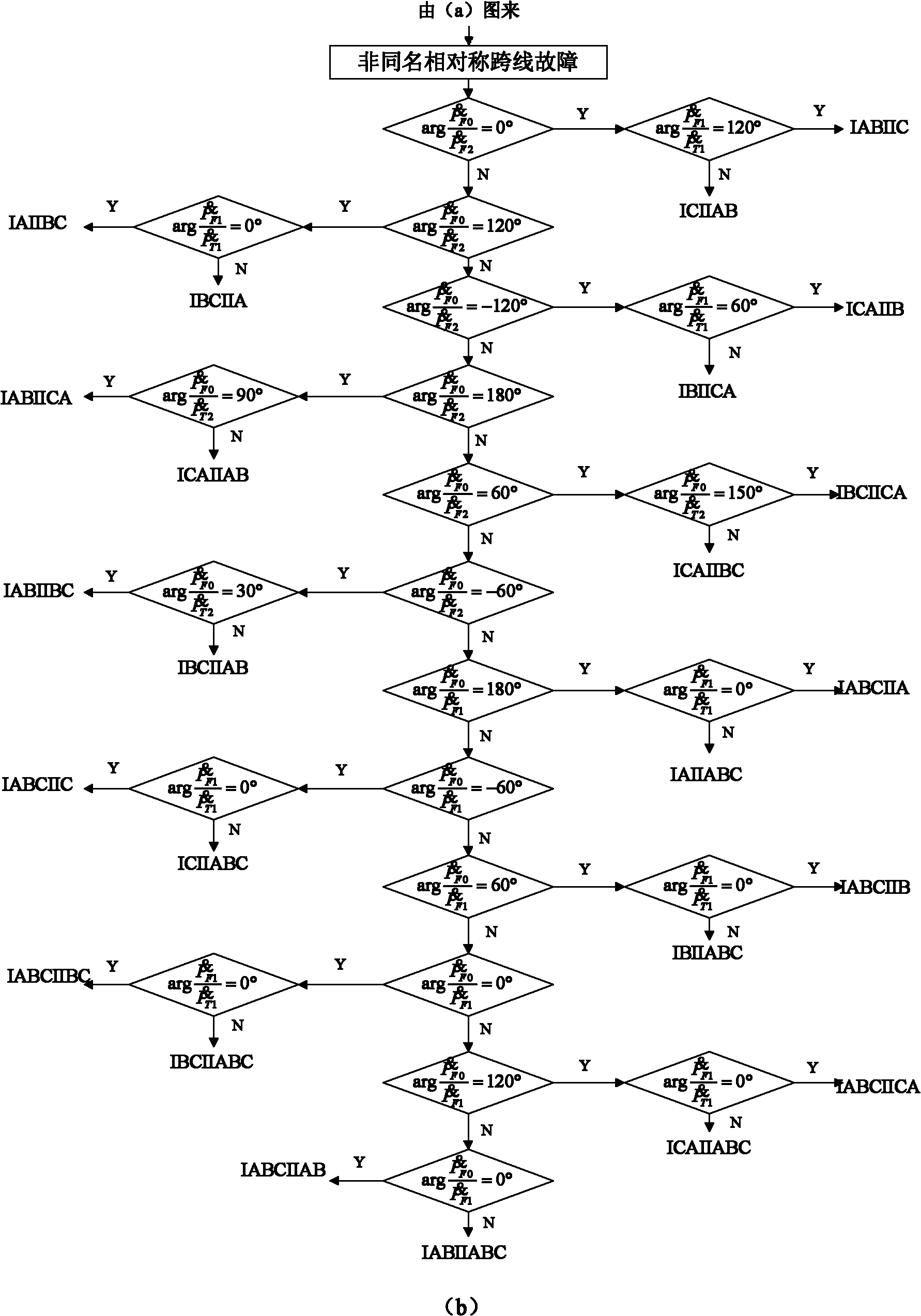

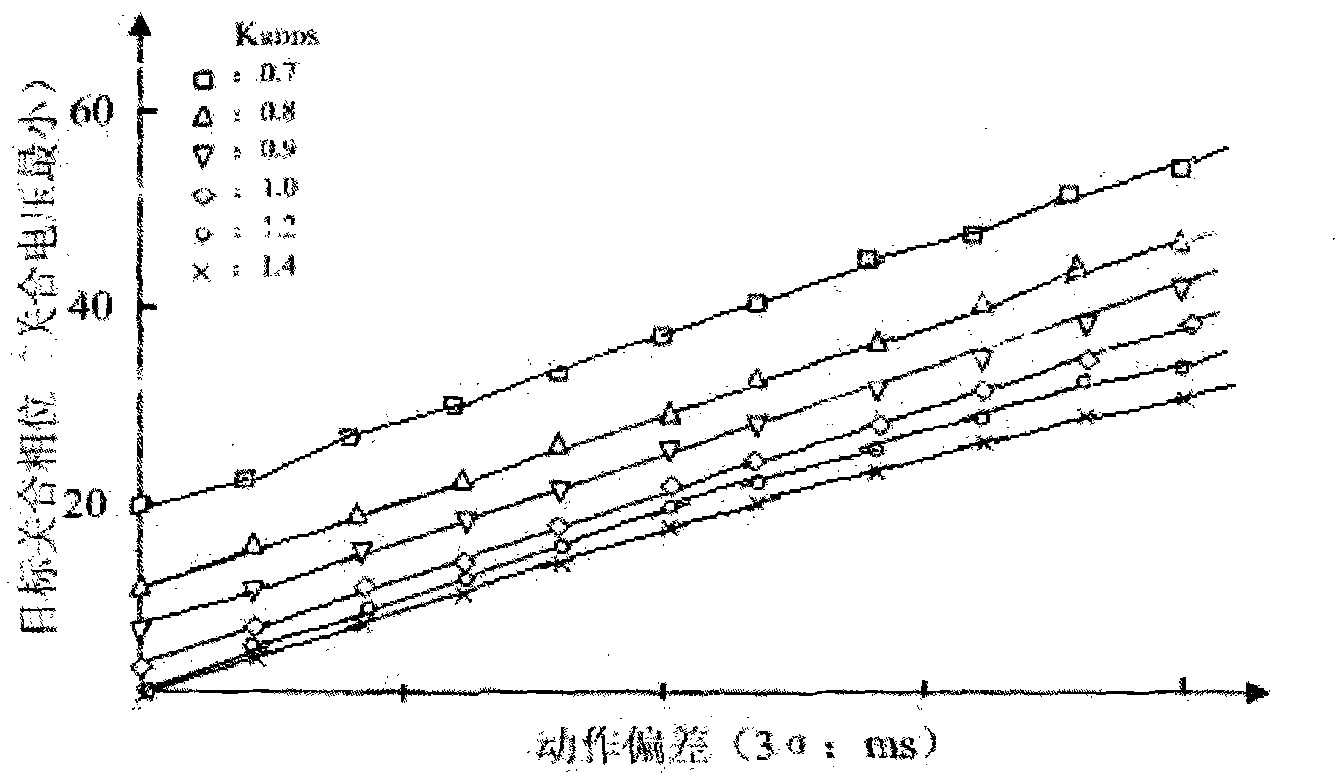

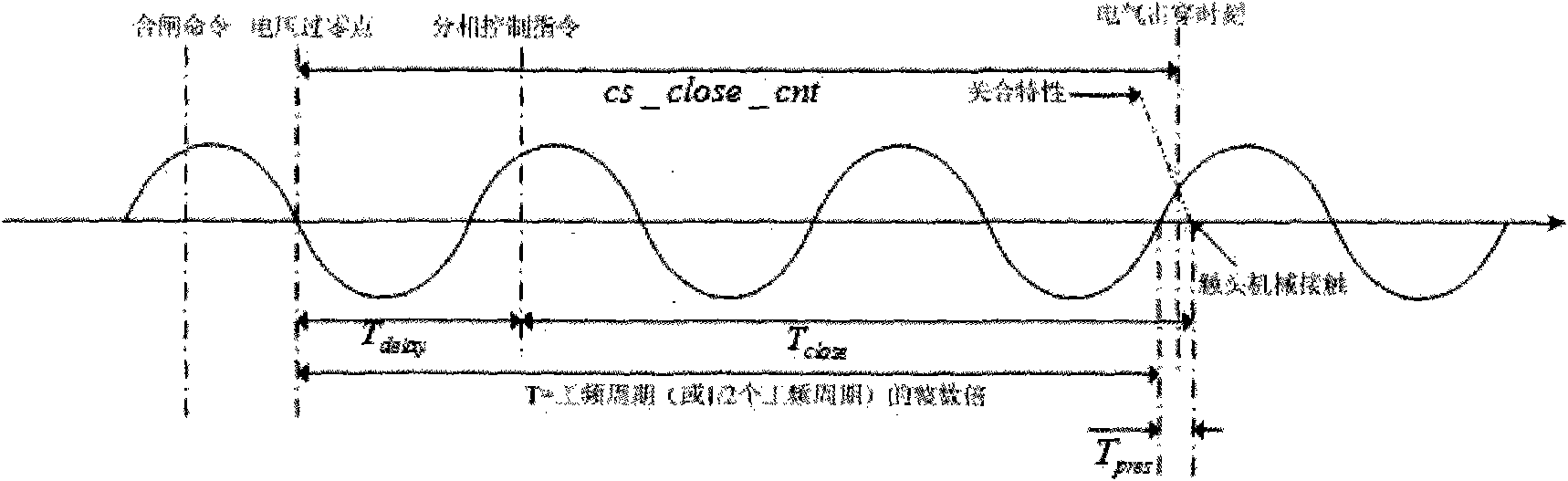

Self-learning switching-on phase control method

ActiveCN102315045AOvercome limitationsMake up for limitationsProtective switch detailsElectric switchesDigital dataPhase control

The invention discloses a self-learning switching-on phase control method adopted by a phase selection switching-on device, which is applied to the phase selection switching-on control of electric equipment in an alternating current station and a direct current converter station. The self-learning switching-on phase control method is characterized in that the self learning of an optimum object throw phase based on the circuit breaker mechanical action deviation and real-time digital data service (RDDS) function combination and the action record comparison correction is adopted. The strong switch characteristic self learning capability is realized, the switch characteristics can be accumulated according to the in-site operation, and the real-time correction is carried out. The intelligent correction is realized in the application, and the limitation of determining the optimum object phase by the artificial factors or the empirical values is avoided.

Owner:NR ELECTRIC CO LTD +1

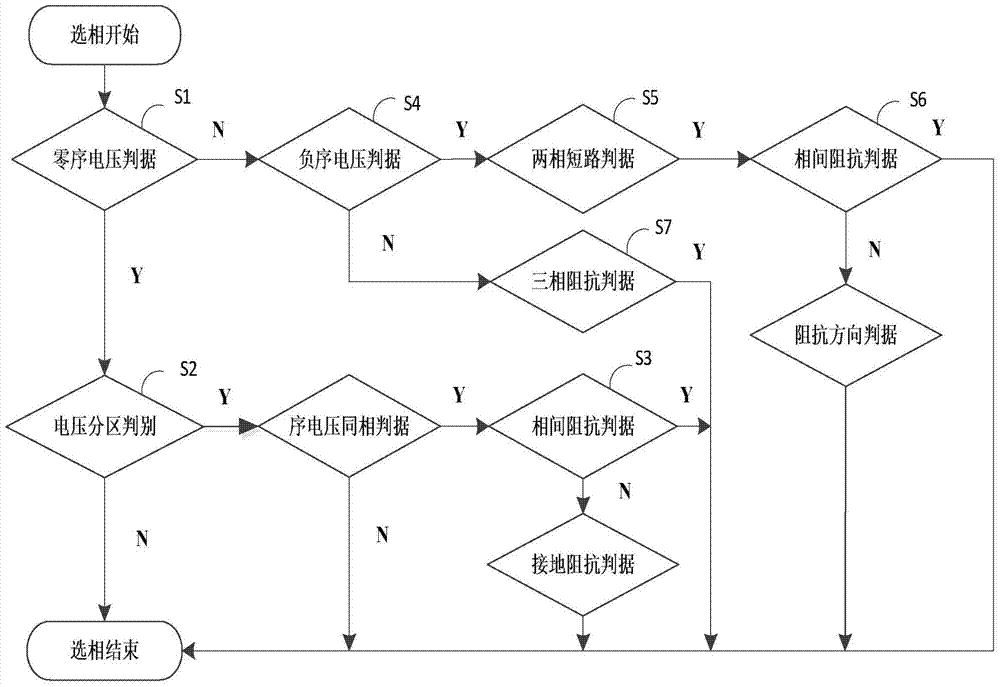

Phase selection method for faults of double-circuit lines on same tower

ActiveCN104267311AOvercome the problem of imperfect function or even wrong phase selectionImprove performanceFault locationGround impedanceThree-phase

The invention discloses a phase selection method for faults of double-circuit lines on the same tower. The method includes the steps that the fault types and the fault phases are judged according to sequence voltage and voltage between phases, and different criteria are adopted for judging the physical fault phase of the local lines according to the fault type; the interphase impedance criterion and the ground impedance criterion are adopted for the two-phase grounding faults; the interphase impedance criterion and the impedance direction criterion are adopted for the two-phase non-grounding faults; the three-phase impedance direction is adopted for the three-phase faults. The phase selection method is simple and reliable in principle, the phase can be selected correctly under the single-return-wire faults and the overline faults, and the practical and feasible phase selection method is provided for protecting the lines on the same tower.

Owner:ELECTRIC POWER RES INST OF GUANGDONG POWER GRID +1

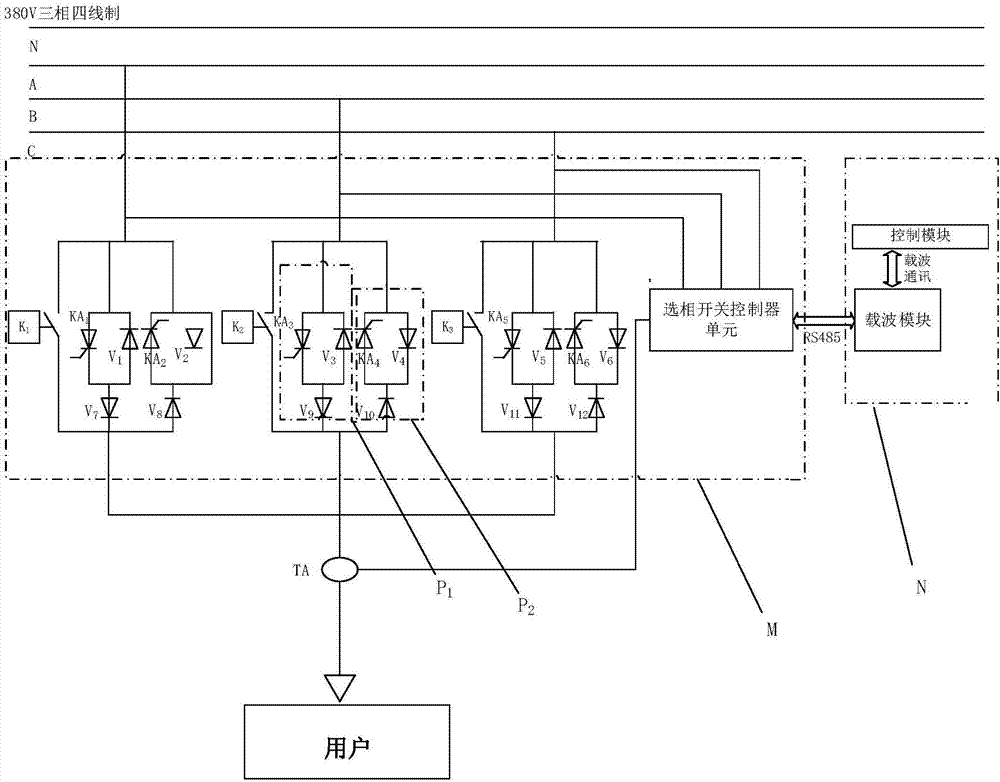

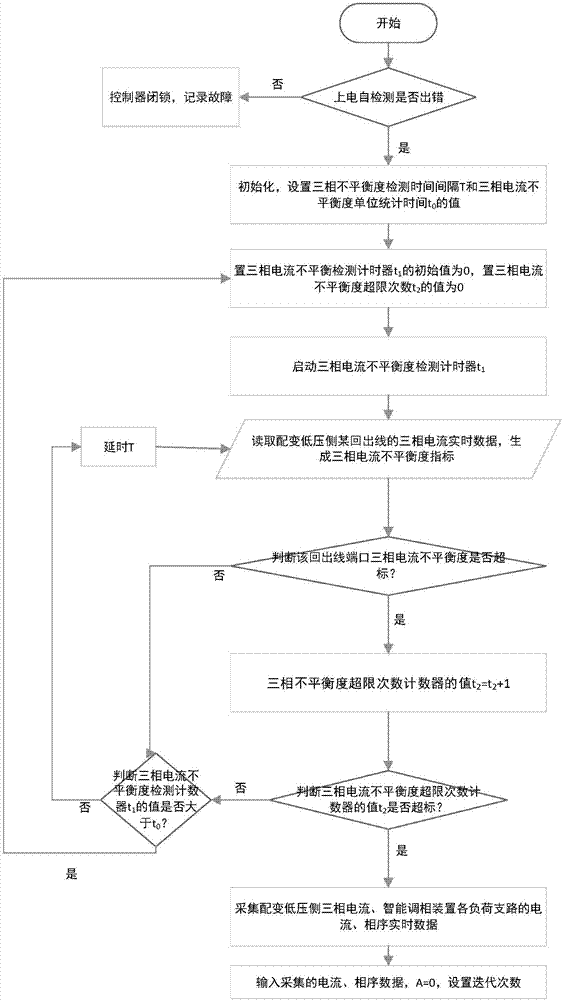

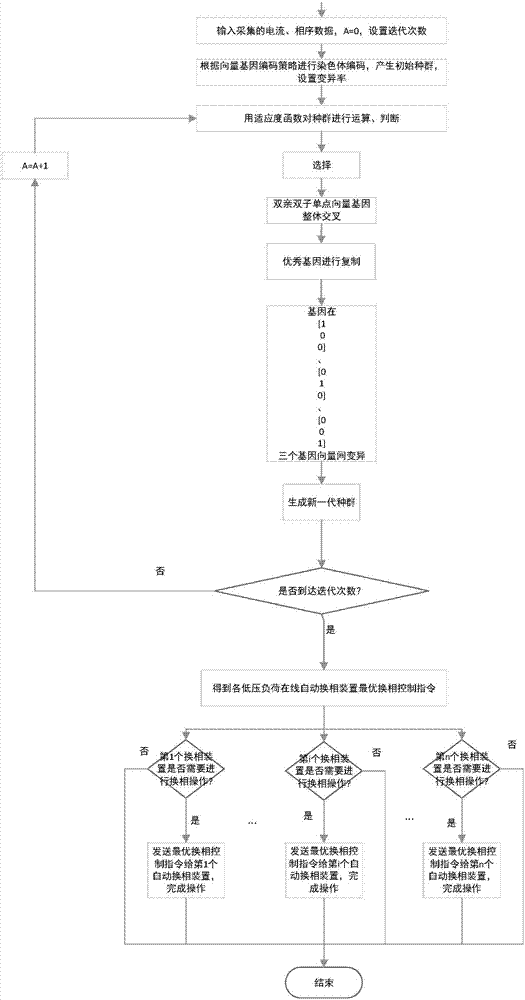

Three-phase load imbalance automatic adjusting method of power distribution network

InactiveCN106877366AReduce transmission consumptionLow costPolyphase network asymmetry elimination/reductionPolyphase network asymmetry reductionElectric power systemElectronic switch

The invention provides a three-phase load imbalance automatic adjusting method of a power distribution network. A phase change switch module and a central control region module are arranged. The central control region module comprises a control module and a carrier wave module. The phase change switch module comprises an electric power electronic switch unit and a phase selection switch controller unit. The three-phase load imbalance automatic adjusting process comprises steps of acquiring three-phase current data into the central control region module; calculating imbalance degree; adopting the genetic algorithm during over-limit; coding a vector gene for a three-phase switch switching state corresponding to each load branch; obtaining an optimal phase change control instruction according to corresponding target function of the phase change module; transmitting the optimal phase change instruction to a phase selection switch controller unit of a phase change switch module on each load branch through the carrier wave module; and controlling the electric power electronic switch unit to finish the phase change operation. According to the invention, the method is used for supporting automatic detection during operation of an electric power system, so large quantity of manpower and materials are saved, device safety is improved and power supply reliability is improved.

Owner:WUHAN UNIV

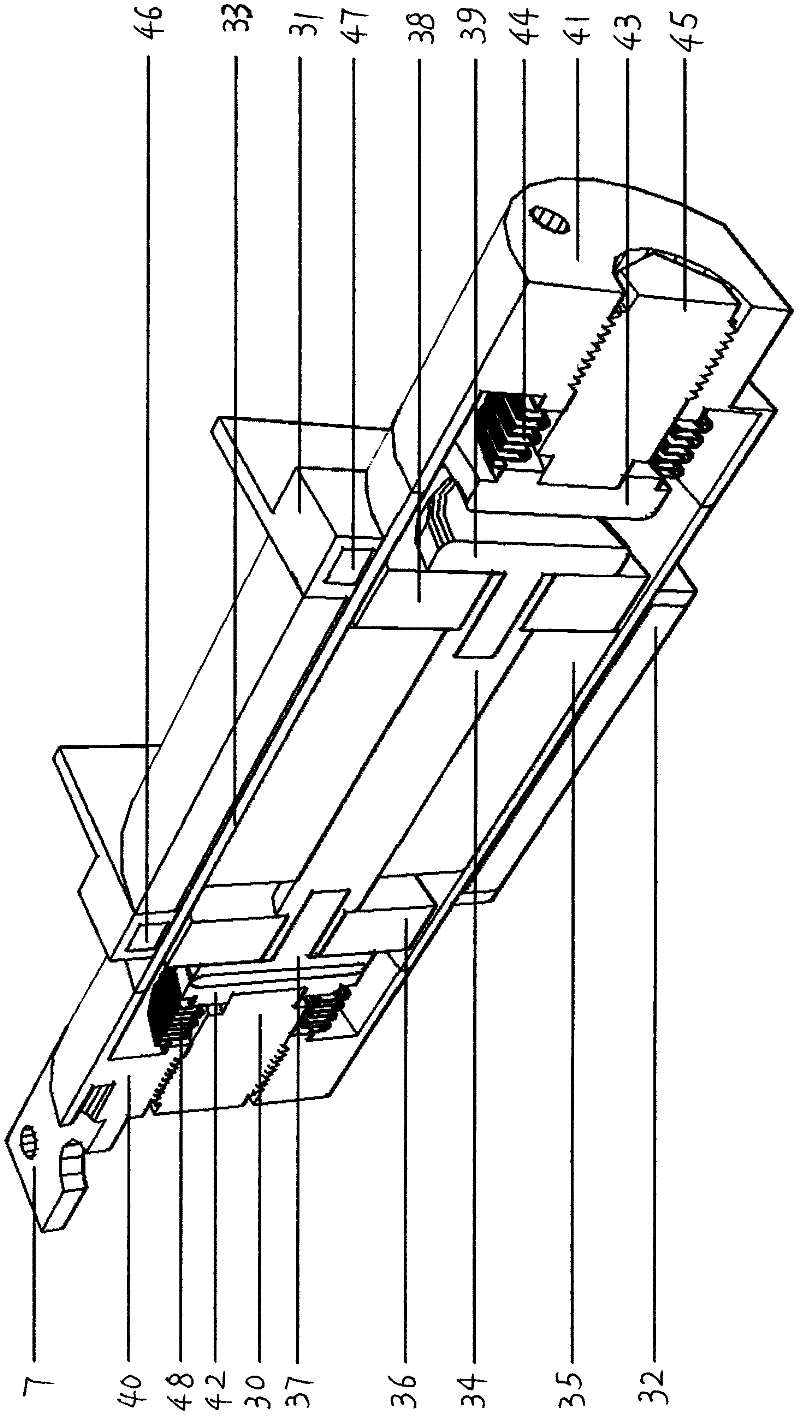

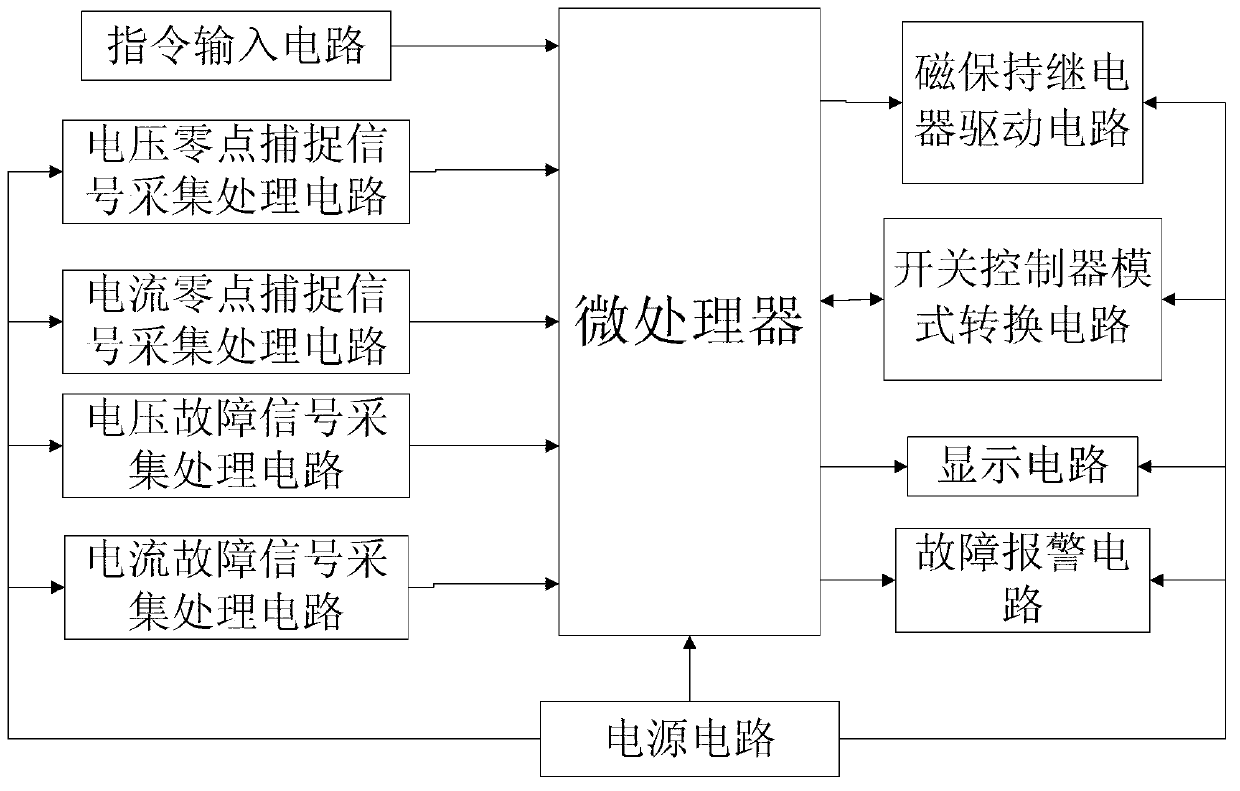

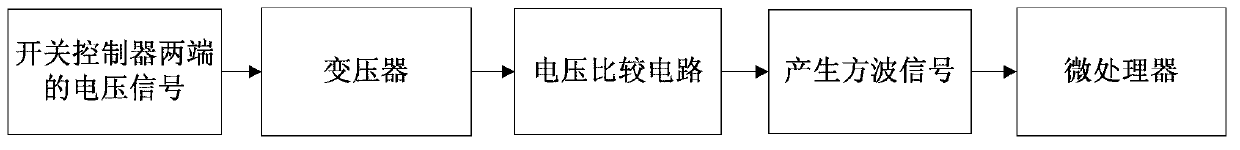

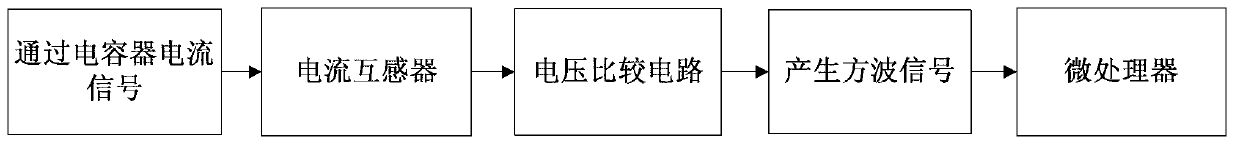

Intelligent phase selection switch controller

InactiveCN103346578ANo arc breakingPrecise closureReactive power adjustment/elimination/compensationReactive power compensationTime errorMode transformation

The invention discloses an intelligent phase selection switch controller, and belongs to the technical field of power electronics. The intelligent phase selection switch controller comprises a microprocessor, a power supply circuit, a displaying circuit, a failure alarming circuit, a voltage zero point capturing signal collecting processing circuit, a current zero point capturing signal collection processing circuit, a voltage failure detection signal collection processing circuit, a current failure detection signal collection processing circuit, a magnetic latching relay driving circuit and a switch controller mode conversion circuit. The microprocessor receives input commands and signals input by the four signal collection circuits, carries out processing on the input signals, and controls the magnetic latching relay to achieve zero passage switching. The intelligent phase selection switch controller can achieve flashy-flow-free input of a capacitor and electric-arc-free disjunction of relay contactors, can detect and automatically compensate action time error of zero switching, and can carry out detection on the performance of the relay, so that a user an replace different magnetic latching relays according to actual needs.

Owner:DALIAN JIAOTONG UNIVERSITY

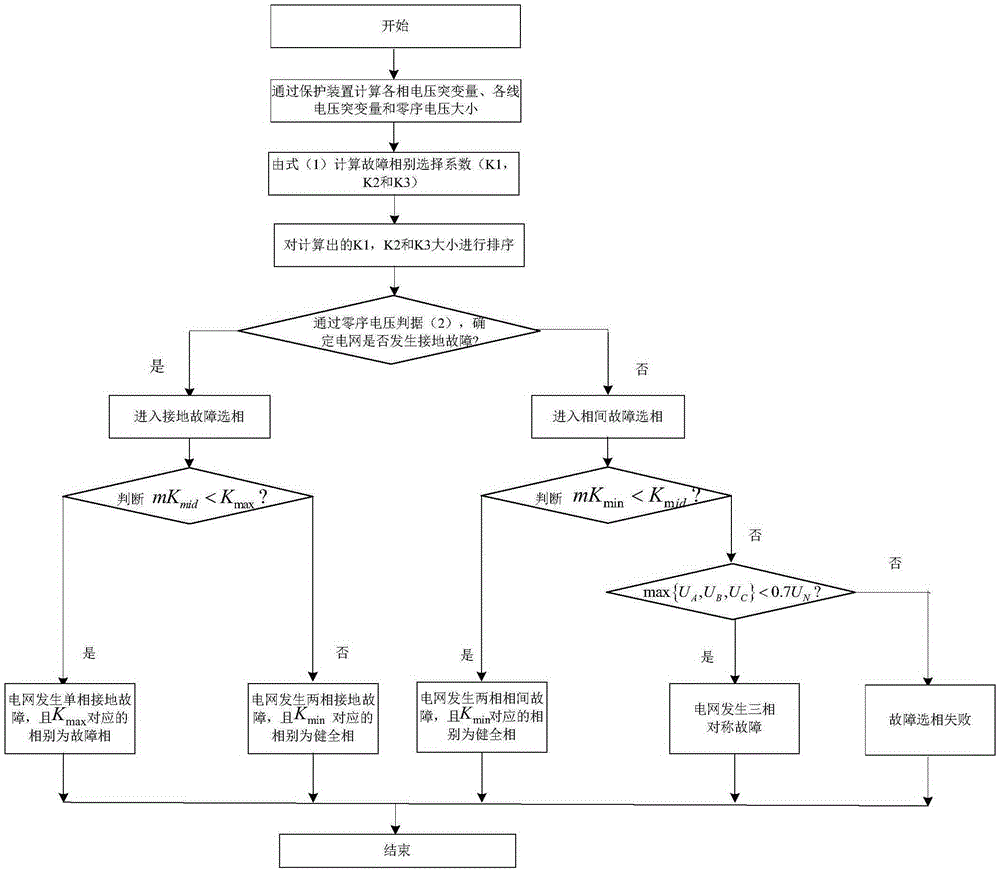

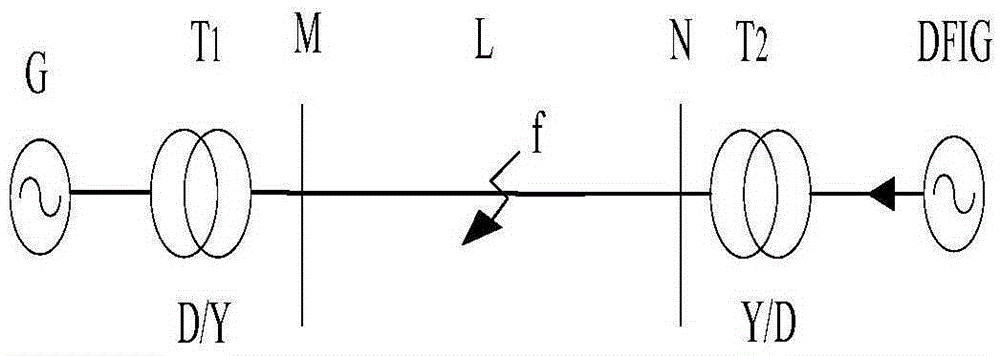

Fault phase selection method for double-fed wind power plant tie line

ActiveCN105375532ASolve the problem of incorrect phase selectionMeet the needs of phase selectionContigency dealing ac circuit arrangementsSingle network parallel feeding arrangementsStable statePower grid

The invention discloses a fault phase selection method for a double-fed wind power plant tie line. The fault phase selection method comprises the following steps: (1) obtaining the voltage of each phase, the break variable of voltage of each phase, the break variable of voltage of each line and a zero sequence voltage at the position where a line protector is mounted; (2) obtaining a fault phase selection coefficient according to the proportion of the break variable of voltage of single voltage to the difference between two phases in the break variable of voltage; (3) judging whether a power grid has an earth fault or not according to the value of the zero sequence voltage and a rated voltage; (4) according to the proportion of the maximum value to the intermediate value of the fault phase selection coefficient, determining the type of the earth fault of the power grid; (5) according to the proportion of the minimum value to the intermediate value of the fault phase selection coefficient, determining the type of the interphase fault of the power grid; and (6) according to the maximum stable-state value of a three-phase voltage and the rated voltage, judging whether the power grid has a three-phase symmetry fault. Based on the characteristic that the break variable of voltage of a fault phase and the break variable of interphase voltage related to a fault have high sensitivity to the fault, the fault phase selection method can be used for accurately judging a fault type and a fault phase.

Owner:HUAZHONG UNIV OF SCI & TECH

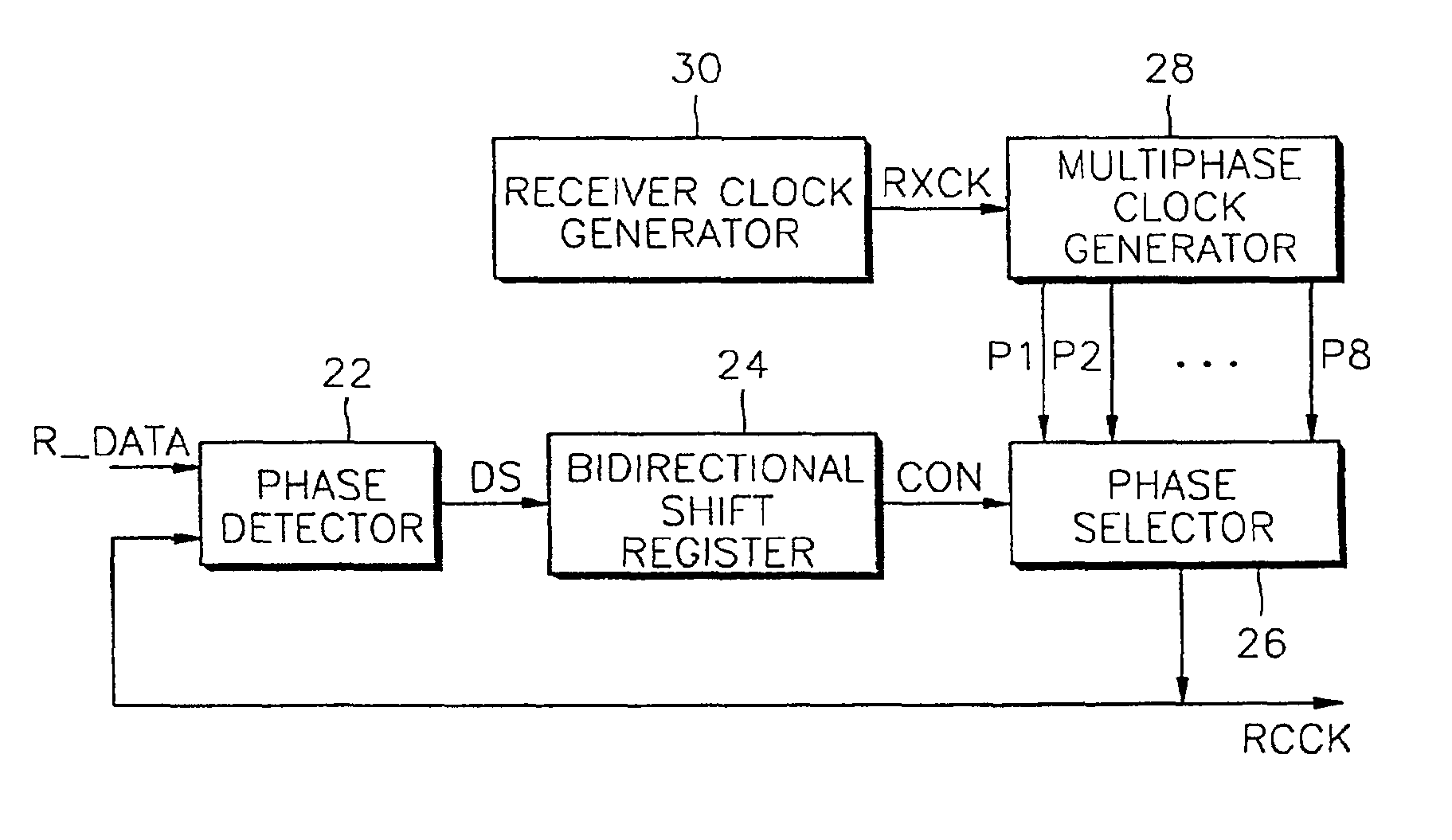

Clock signal recovery circuit used in receiver of universal serial bus and method of recovering clock signal

InactiveUS6954506B2Energy efficient ICTAmplitude demodulation by homodyne/synchrodyne circuitsPhase detectorShift register

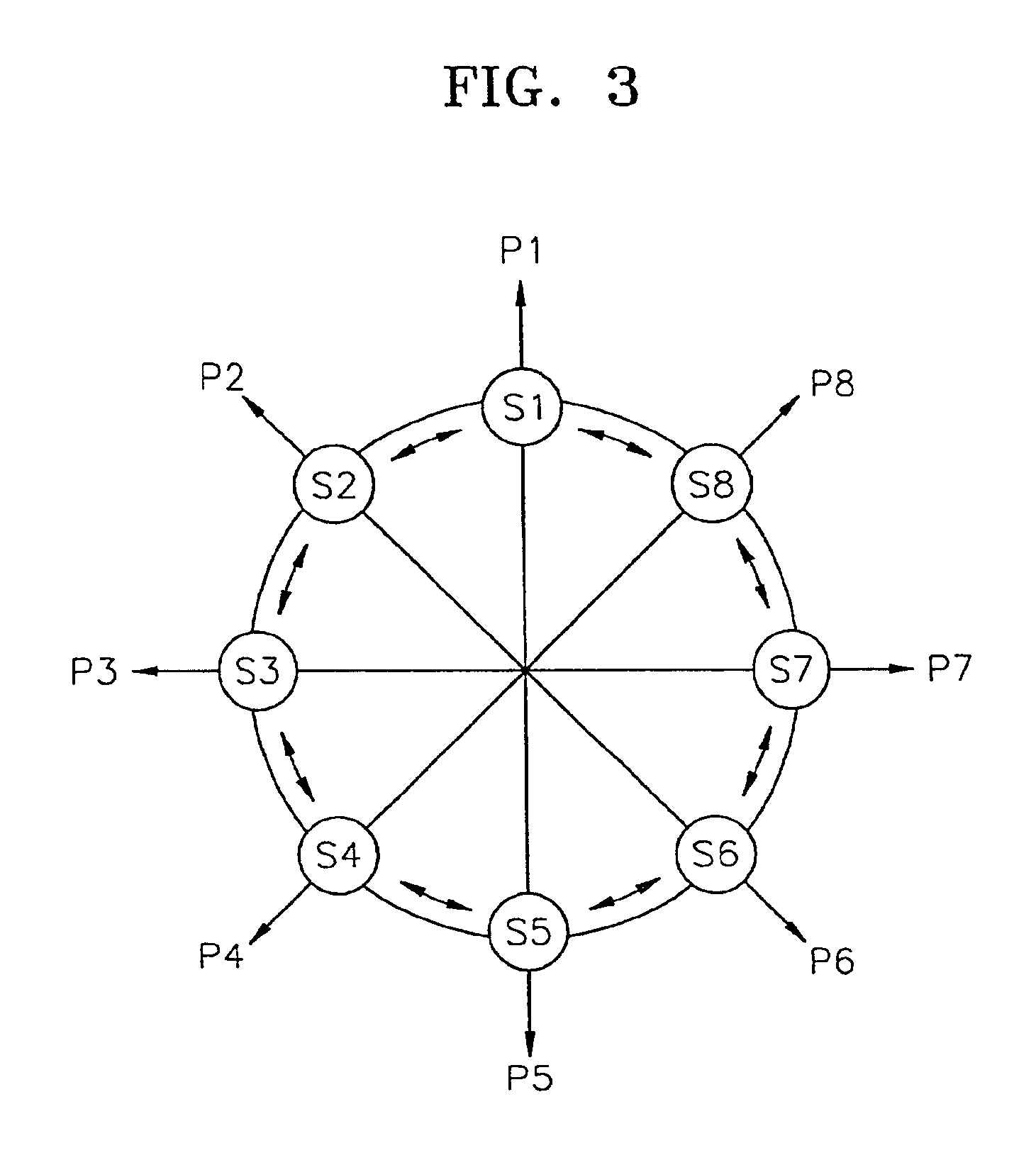

A clock signal recovery circuit that is implemented in a receiver of a universal serial bus (USB) and a method for recovering a clock signal. The clock signal recovery circuit comprises a phase detector, a bidirectional shift register, a multiphase clock signal generator, and a phase selector. The phase detector detects a difference in phases between received data and a predetermined recovery clock signal and generates a first control signal indicative of the detected phase difference. The shift register is shifted in response to the detected signal and outputs a second control signal. The multiphase clock signal generator receives a receiver clock signal having the same frequency as that of a clock signal used in a USB transmitter (from which the data is transmitted) and generates a plurality of phase clock signals, preferably, first through N-th phase clock signals having the same frequencies as that of the receiver clock signal and having differences of about (360 / N)*I degree (°) (where N is an integer, and I is an integer equal to or greater than 0 and equal to or less than N−1) from a phase of the receiver clock signal, respectively. The phase selector selects one of the first through N-th phase clock signals in response to the second control signal and outputs the selected phase clock signal as the recovery clock signal. Preferably, N is an integer equal to or greater than 2 and equal to or less than 8.

Owner:SAMSUNG ELECTRONICS CO LTD

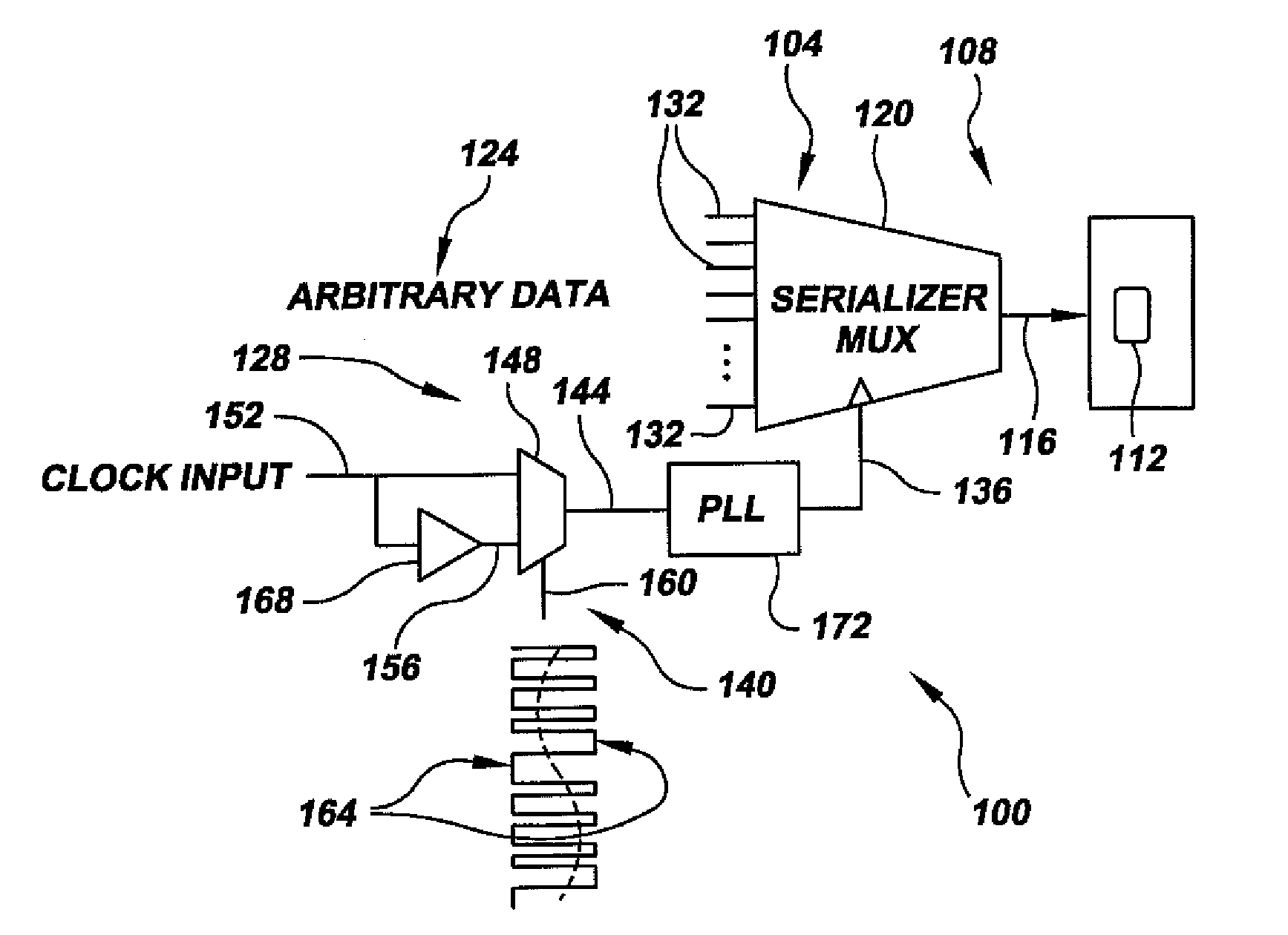

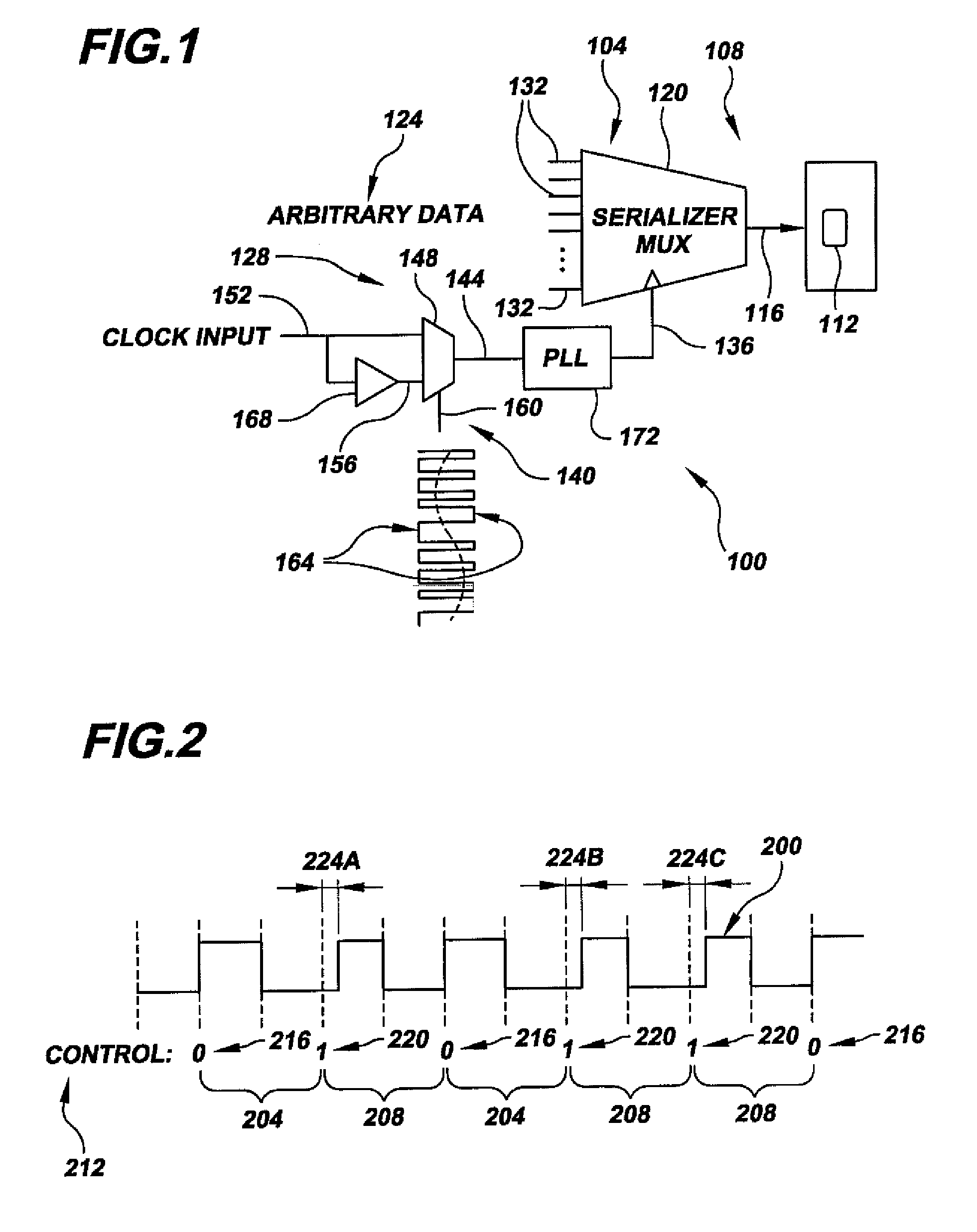

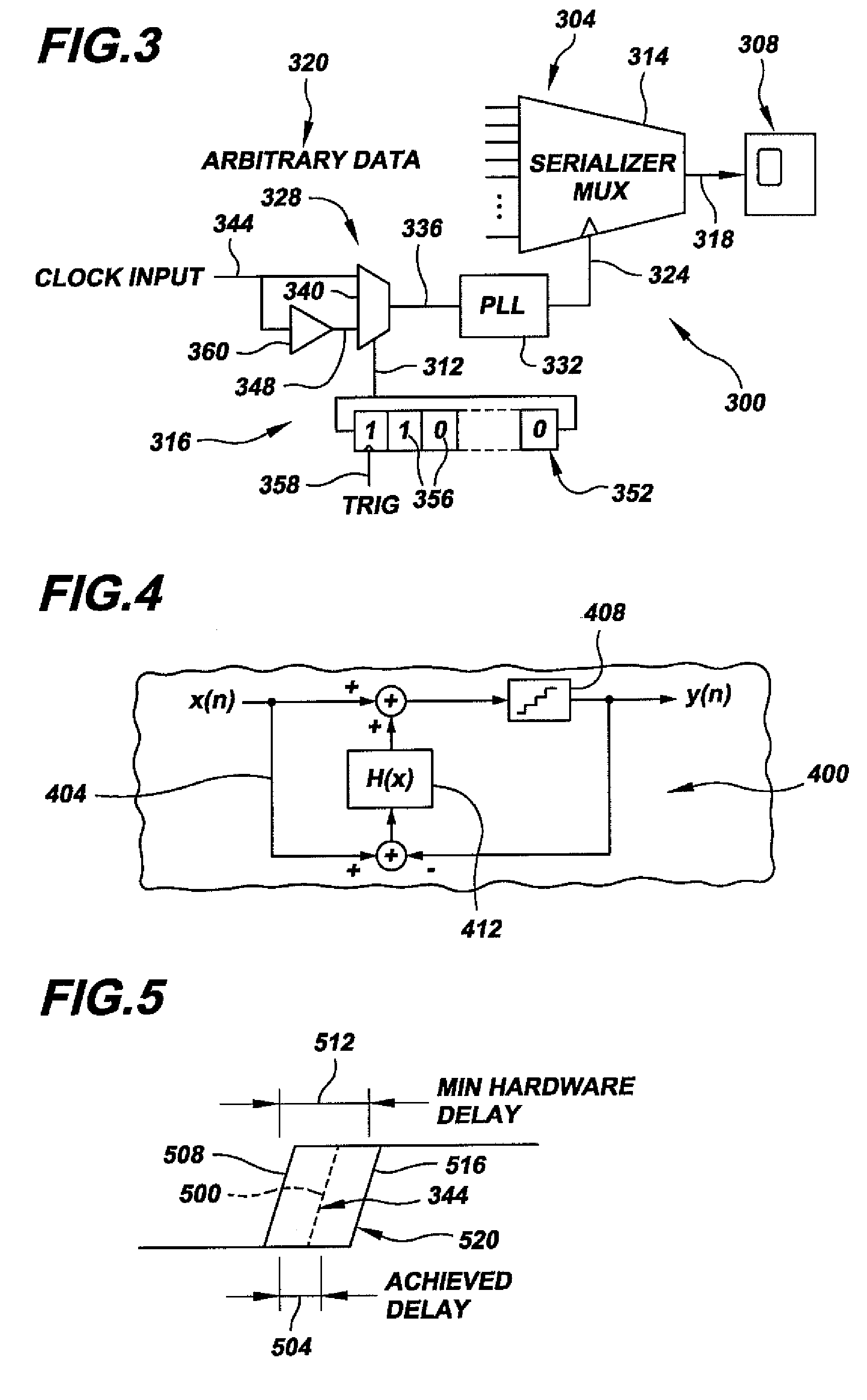

High-Speed Transceiver Tester Incorporating Jitter Injection

A tester for testing high-speed serial transceiver circuitry. The tester includes a jitter generator that uses a rapidly varying phase-selecting signal to select between two or more differently phased clock signals to generate a phase-modulated signal. The phase-selecting signal is designed to contain low-and high-frequency components. The phase-modulated signal is input into a phase filter to filter unwanted high-frequency components. The filtered output of the phase filter is input into a data-transmit serializer to serialize a low-speed parallel word into a high-speed jittered test pattern for input into the transceiver circuitry.

Owner:DFT MICROSYST

Active voltage arc-extinction method applicable to single-phase earth fault of medium voltage distribution network

InactiveCN106602540AImprove arc suppression performanceHigh engineering application valueEmergency protective arrangements for limiting excess voltage/currentPhase currentsNonlinear resistor

The invention discloses an active voltage arc-extinction method applicable to a single-phase earth fault of a medium voltage distribution network, and relates to the technical field of fault self-recovery of a medium voltage distribution network. The active voltage arc-extinction includes the following steps: a. continuously measuring bus three-phase voltage, zero sequence voltage and each outlet three-phase current, and when a single-phase earth fault is detected, conducting fault phase selection; b. designating a threshold Ires.g of a fault phase current magnitude and a threshold Ures.g of a fault phase voltage magnitude of a fault feeder; c. measuring the voltage and current of the fault phase, comparing the fault phase current magnitude of the fault feeder with Ires.g. According to the invention, the method can effectively increase the arc extinction of a low-resistance earth fault, and compensate current at a fault point as much as possible while excess voltage is effectively controlled, and ensures that arc at the fault point can be reliably extinct. According to the invention, for non-linear resistance earth, the method is also effective simply by changing program codes in current active compensating apparatuses, and has higher values when applied to engineering.

Owner:STATE GRID SHANDONG ELECTRIC POWER +1

AC high voltage vacuum breaker

ActiveCN101226847AUndisturbedMove quicklyHigh-tension/heavy-dress switchesAir-break switchesForce structureFault current limiter

The invention relates to an alternating current high-voltage vacuum circuit breaker, which is characterized in that the invention comprises a case body, a vacuum arc extinguish chamber is seated and connected to the case body, an electromagnetic repulsive force mechanism is disposed in the case body, the mechanism comprises an open coil and a close coil which form a fixed gap, a repulsion disk arranged in the gap, a repulsion rod which is fixedly penetrated by the equipped repulsion disk, a retention capacity rod of a composite disc spring retention force structure connected with the lower end of the repulsion rod, a catch spring fixed on the retention force rod and at least two pieces of disc springs top-arranged on the catch spring. The upper end of the electromagnetic repulsive force is connected with a closing buffer gear which comprises a spring frame structure and a hydraulic cylinder, further, the closing buffer gear comprises an intelligent pulse generator. Because the invention employs the electromagnetic repulsive force mechanism, employs bi-stable composite disc springs to retain, employs the closing hydraulic pressure buffer gear to inhibit closing bouncing, and employs a photoelectric sensor to realize position returning, thereby belonging to the advanced design at home and abroad, therefore, the invention can be widely applied to the field of fault current limiters, phase selection switches, solid change-over switches and the like.

Owner:CHINA ELECTRIC POWER RES INST +1