Symbol timing synchronizing apparatus for complete digital receiver

A symbol timing synchronization and all-digital receiver technology, which is applied in the direction of synchronization devices, digital transmission systems, electrical components, etc., can solve the problem of inability to ensure the best value, the degradation of receiver performance, and the selection of sample points that cannot be oversampled, etc. problem, achieve the effect of streamlining multiplier redundancy, reducing the number of multipliers, and removing single estimation errors

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0033] The embodiments of the present invention are described in detail below in conjunction with the accompanying drawings: this embodiment is implemented on the premise of the technical solution of the present invention, and detailed implementation methods and specific operating procedures are provided, but the protection scope of the present invention is not limited to the following the described embodiment.

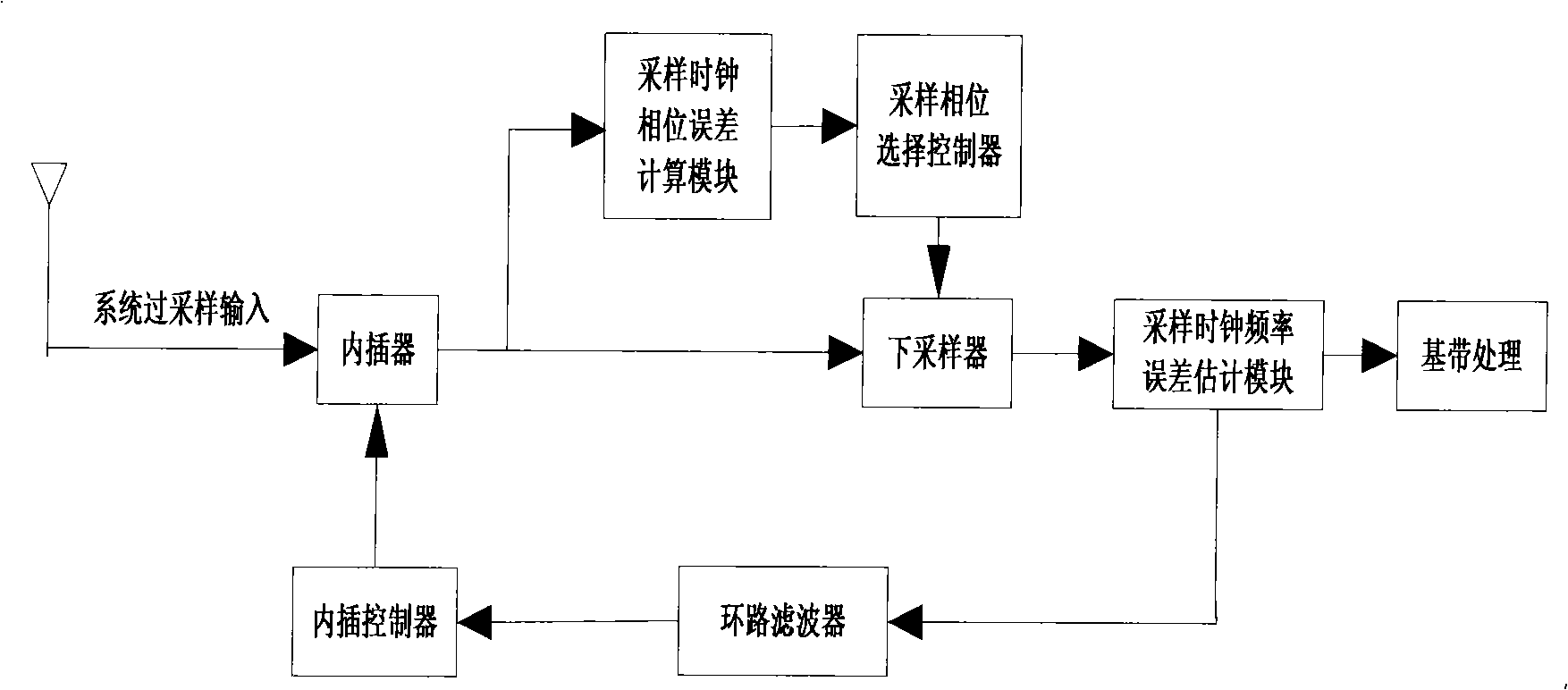

[0034] figure 1A general structural block diagram of the device for synchronizing the symbol timing of the all-digital receiver according to the preferred embodiment of the present invention is shown.

[0035] refer to figure 1 , the timing synchronization device includes: an interpolator 100, a sampling clock frequency error estimation module 200, a loop filter 300, an interpolation controller 400, a downsampler 500, a sampling clock phase error calculation module 600, and a sampling phase selection controller 700. The connection relationship between these compone...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More