Clock detection circuit and method

A clock detection, circuit technology, applied in electrical components, pulse processing, pulse technology, etc.

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment 1

[0074] At present, in the prior art, the burrs in the clock signal are generally eliminated by D flip-flops, and the characteristics of the D flip-flops being insensitive to burrs are used to eliminate them, but the existing methods are not thorough in eliminating burrs. A deburring unit 3 is provided;

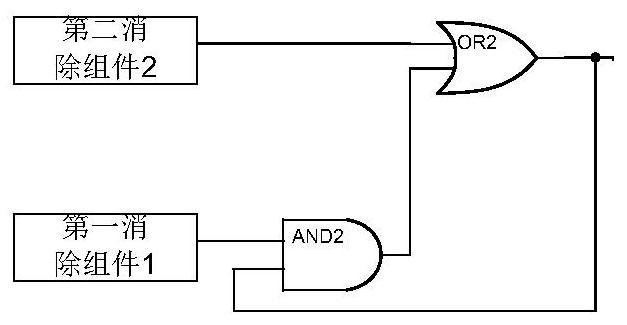

[0075] Such as figure 1 As shown, the burr elimination unit 3 includes a primary elimination unit and a secondary elimination unit, and the secondary elimination unit includes a first OR gate and a first AND gate, wherein,

[0076] The primary elimination unit includes a first elimination component 1 and a second elimination component 2;

[0077] The first elimination component 1 is used to eliminate low burrs in the clock signal to be tested;

[0078] The second elimination component 2 is used to eliminate high burrs in the clock signal to be tested;

[0079] One input end of the first AND gate is connected to the output end of the first elimination component 1, and the ot...

Embodiment 2

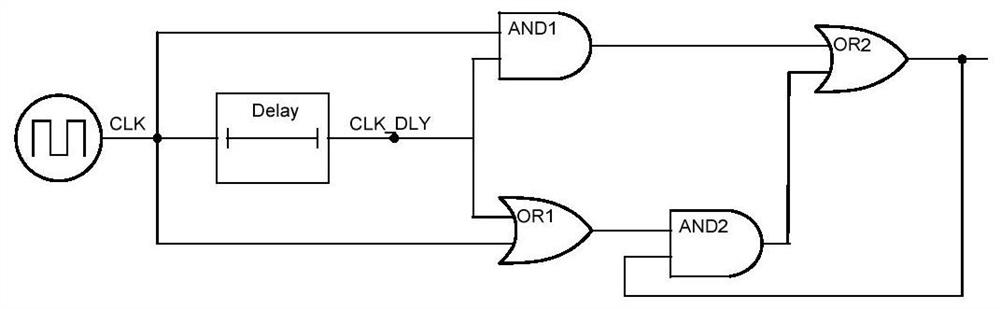

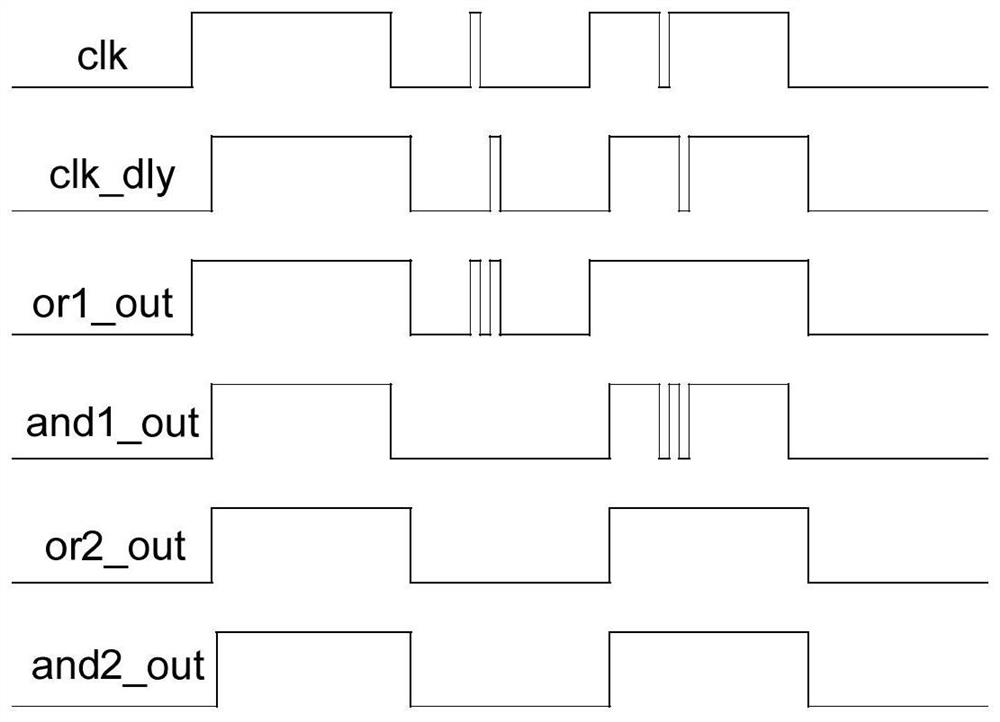

[0089] Embodiment 2 includes all the content in Embodiment 1, and will not be repeated here, wherein the first elimination component 1 includes a second OR gate and a delayer,

[0090] The input end of the delayer is connected to the clock 7 to be tested, and the output end of the delayer is connected to an input end of the second OR gate;

[0091] The other input end of the second OR gate is connected to the clock 7 to be tested;

[0092] An output end of the second OR gate is connected to an input end of the first AND gate.

[0093] In this embodiment, the two input terminals of the second OR gate respectively input the clock signal to be tested and the delayed signal, and low glitches can be eliminated by performing OR processing on the two input signals.

[0094] It should be noted that, in this embodiment, the first elimination component 1 may be a D flip-flop or other components capable of eliminating high glitches, which is not limited.

[0095] This embodiment realiz...

Embodiment 3

[0097] Embodiment 3 includes all the content in Embodiment 1, and will not be repeated here, wherein, the second elimination component 2 includes a second AND gate and a delayer;

[0098] The input end of the delayer is connected to the clock 7 to be tested, and the output end of the delayer is connected to an input end of the second AND gate;

[0099] The other input end of the second AND gate is connected to the clock 7 to be tested;

[0100] An output end of the second AND gate is connected to an input end of the first OR gate.

[0101] In this embodiment, the two input terminals of the second AND gate respectively input the clock signal to be tested and the delayed signal, and by performing AND processing on the two input signals, it is possible to eliminate the clock signal to be tested. High glitch.

[0102] It should be noted that, in this embodiment, the first elimination component 1 may be a D flip-flop or other components capable of achieving low glitch elimination...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More