Patents

Literature

526 results about "Delay calculation" patented technology

Efficacy Topic

Property

Owner

Technical Advancement

Application Domain

Technology Topic

Technology Field Word

Patent Country/Region

Patent Type

Patent Status

Application Year

Inventor

Delay calculation is the term used in integrated circuit design for the calculation of the gate delay of a single logic gate and the wires attached to it. By contrast, static timing analysis computes the delays of entire paths, using delay calculation to determine the delay of each gate and wire.

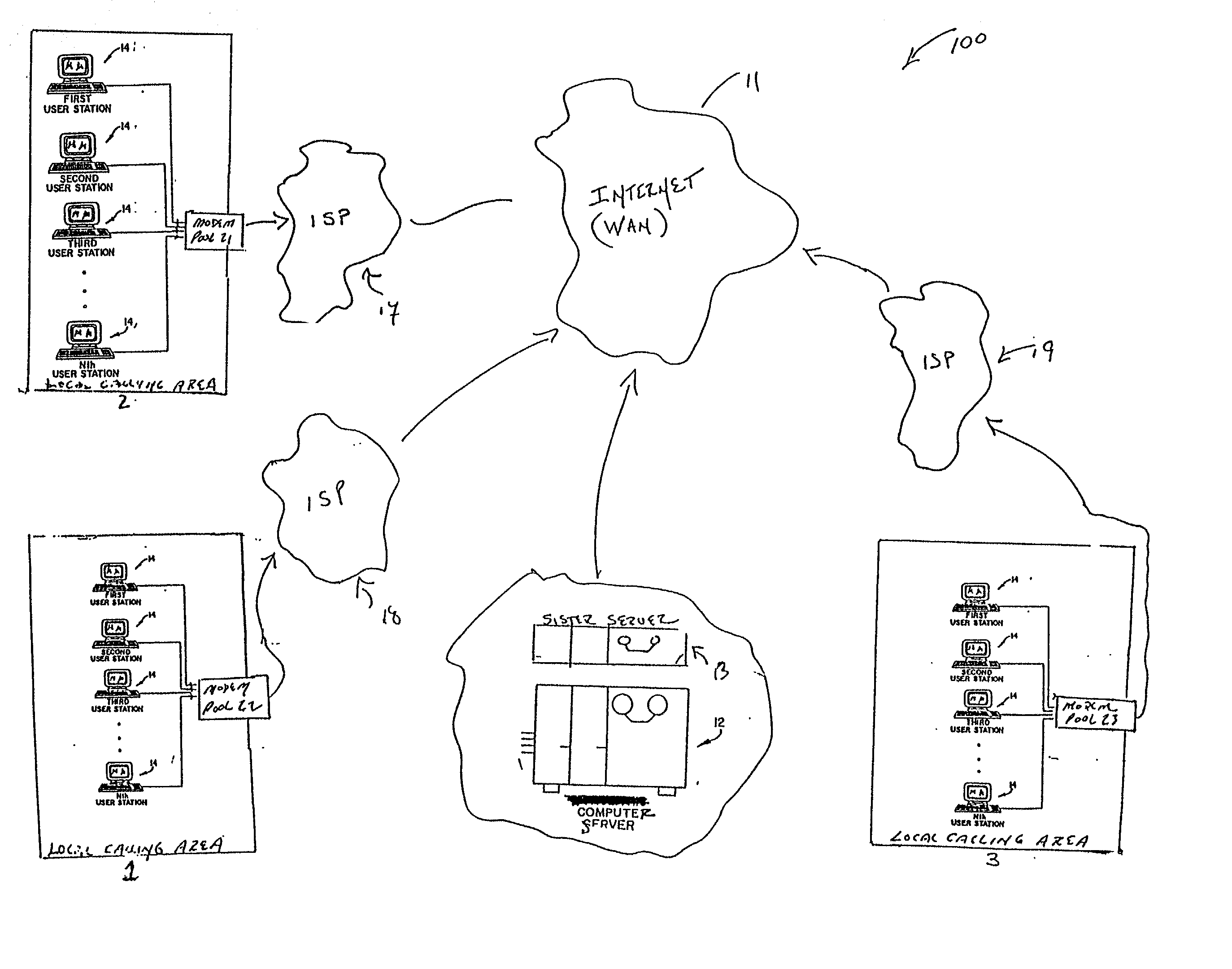

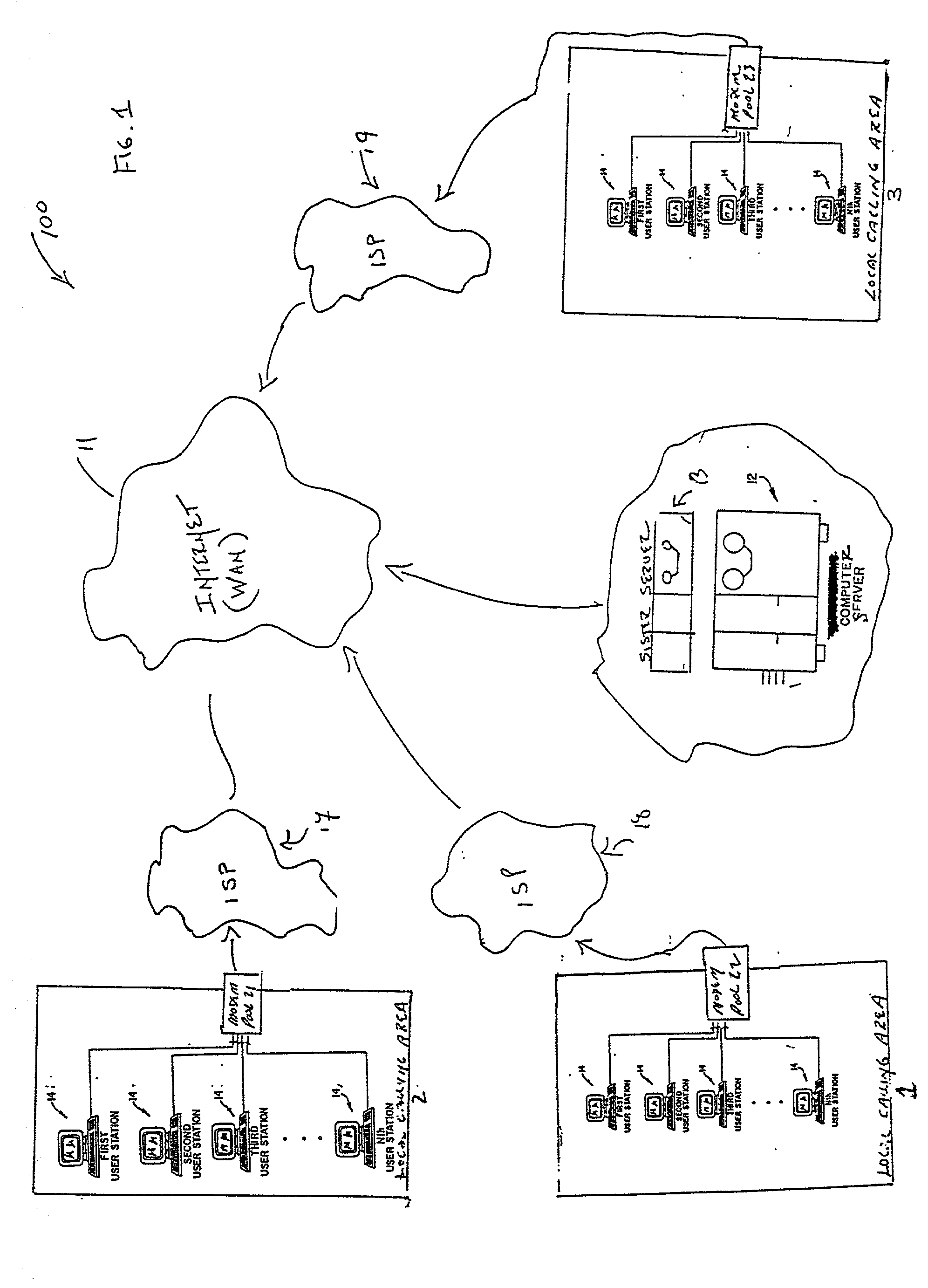

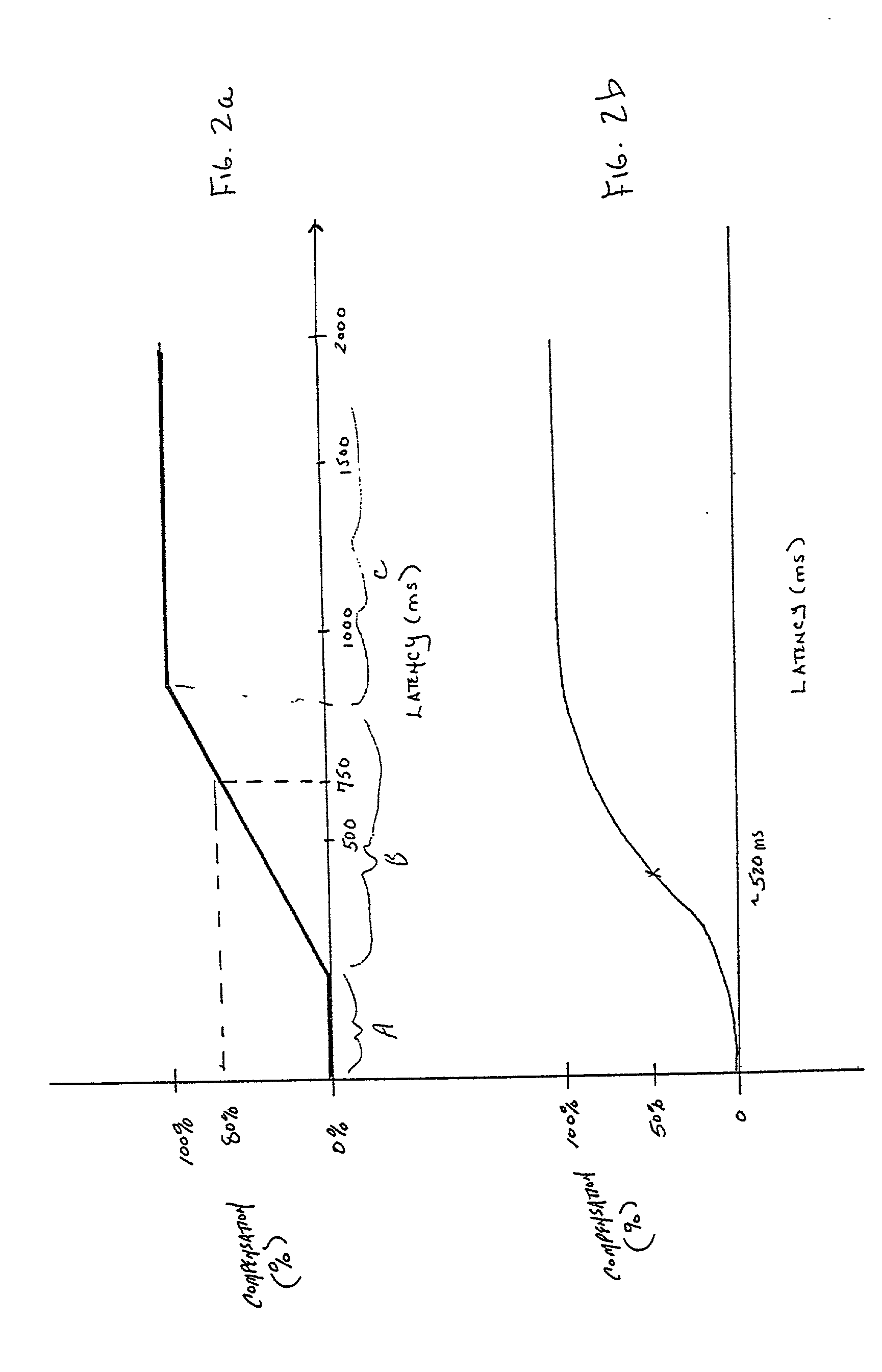

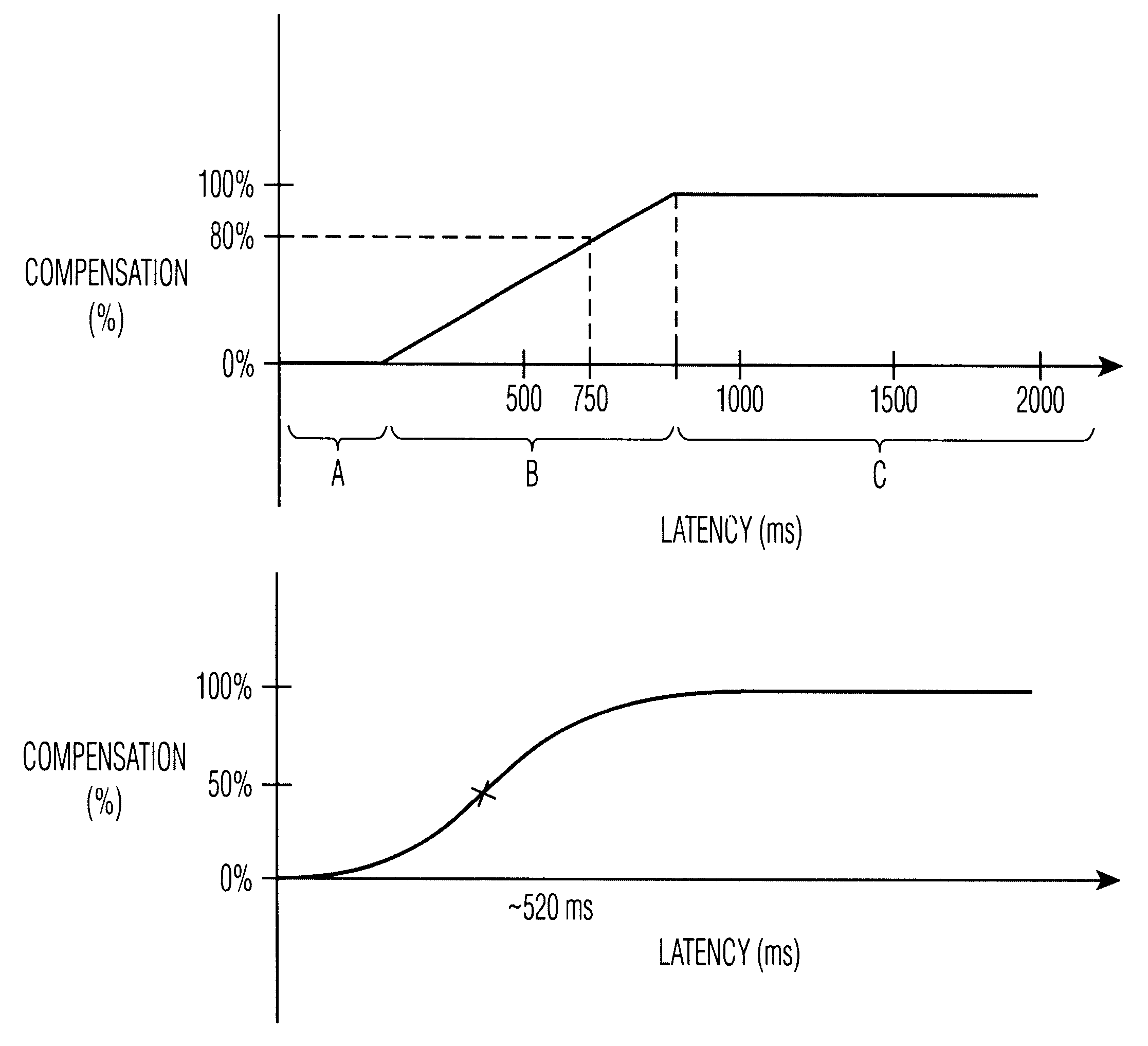

Compensating for network latency in a multi-player game

InactiveUS20020142843A1Effectively competeImprove invisibilityData processing applicationsVideo gamesComputer terminalGame play

Owner:KONINKLIJKE PHILIPS ELECTRONICS NV

Compensating for network latency in a multi-player game

InactiveUS6475090B2Effectively competeImprove invisibilityData processing applicationsVideo gamesComputer terminalClient machine

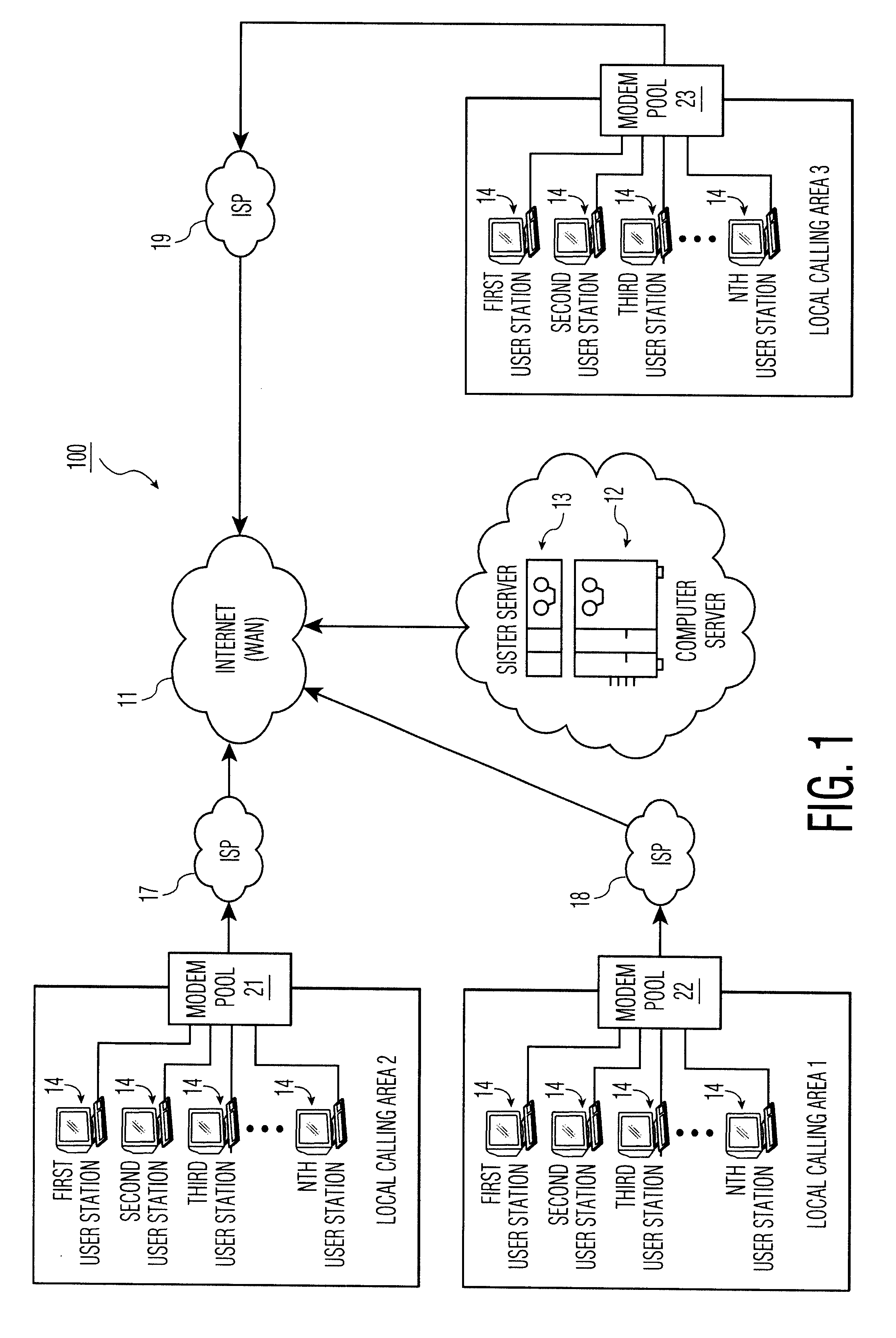

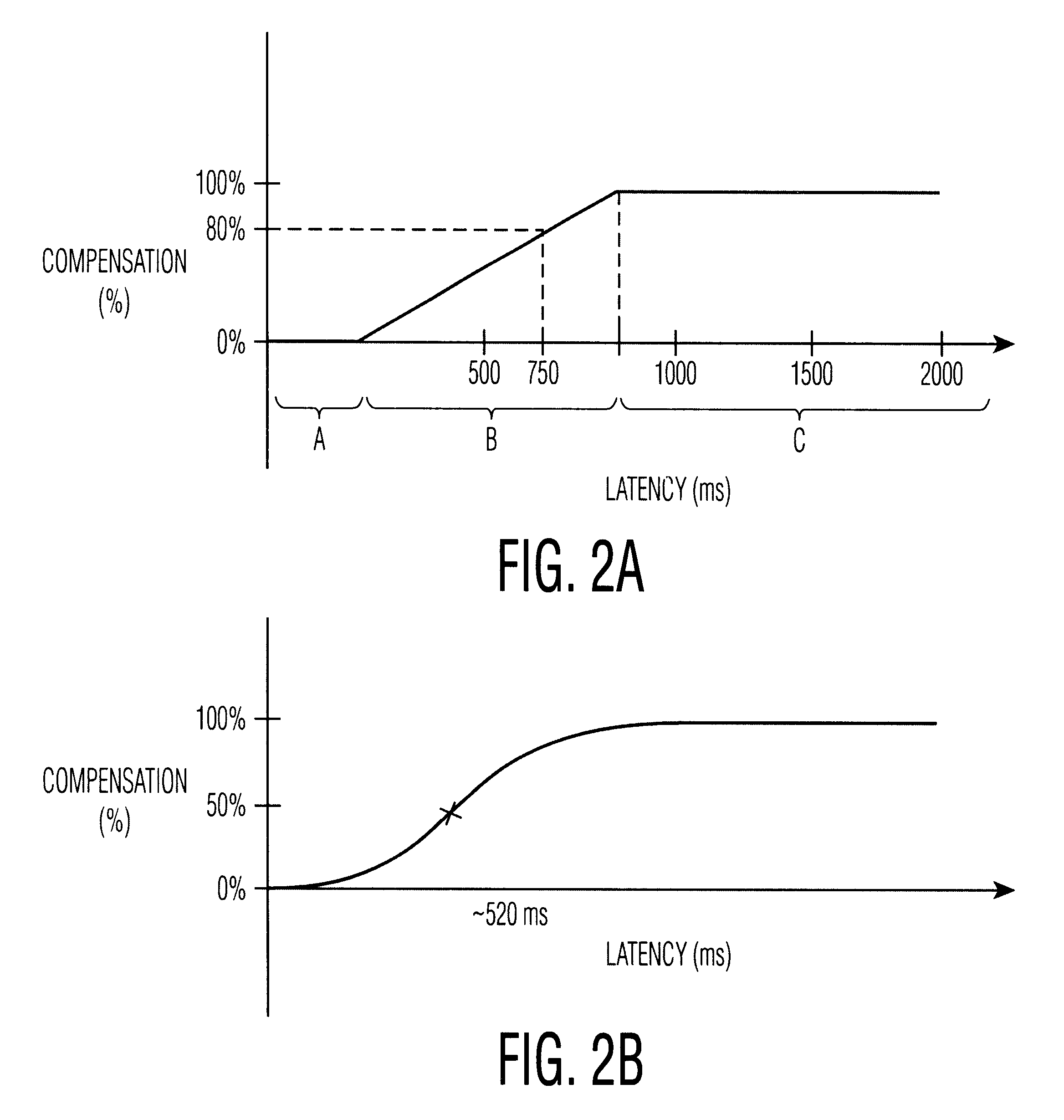

A method is provided for compensating for high-latency computer clients in a multi-player electronic game played on a plurality of terminals connected by a network. A latency value is determined for computer clients operating the terminals. Then a latency compensation factor is determined from the latency value for each client computer. The playing modality of a client computer can then be adjusted based on the latency compensation factor.

Owner:KONINKLIJKE PHILIPS ELECTRONICS NV

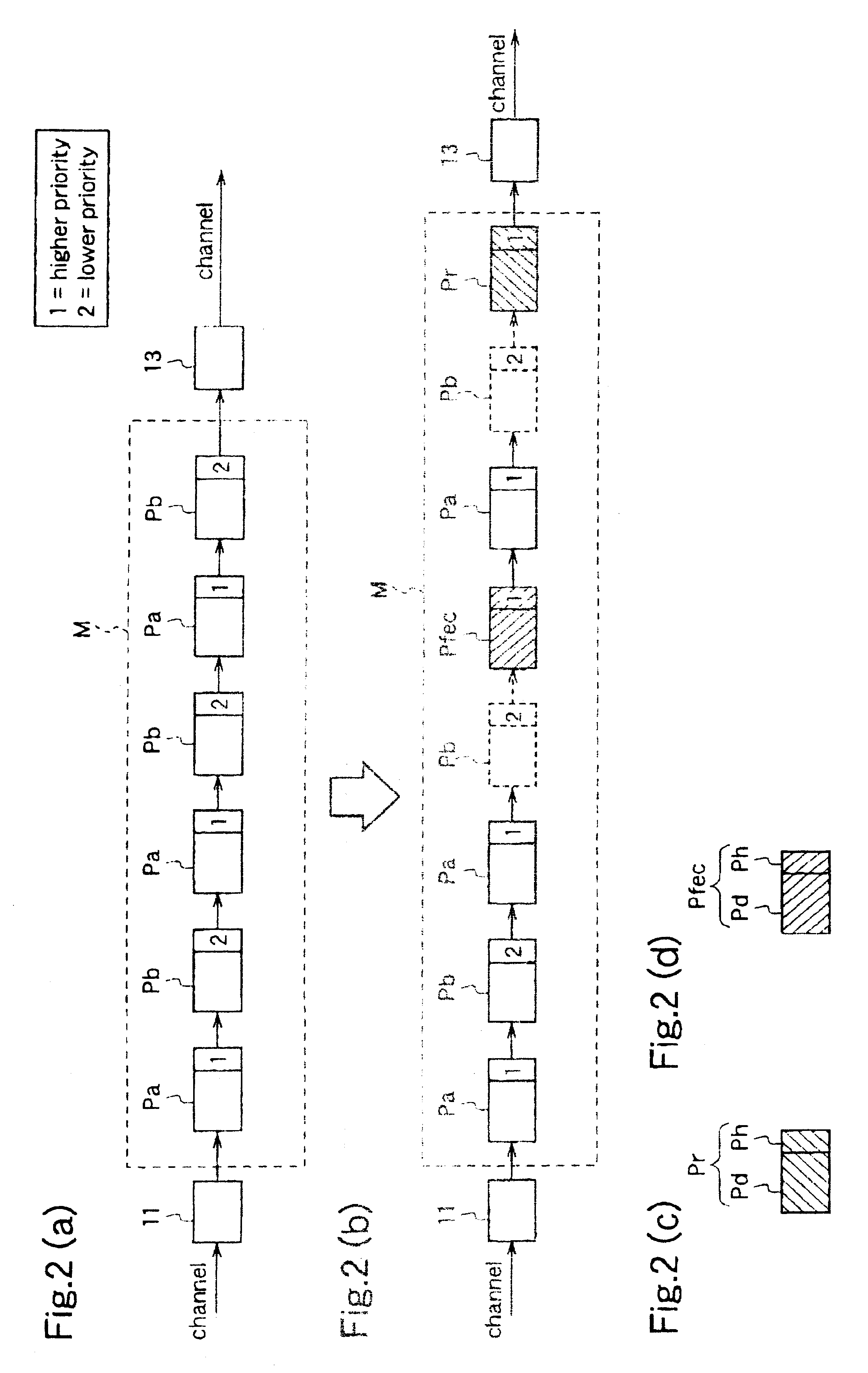

Data transmission method

InactiveUS6891799B1Guaranteed normal transmissionAvoid changeError prevention/detection by using return channelTransmission systemsDelayed timeData transmission

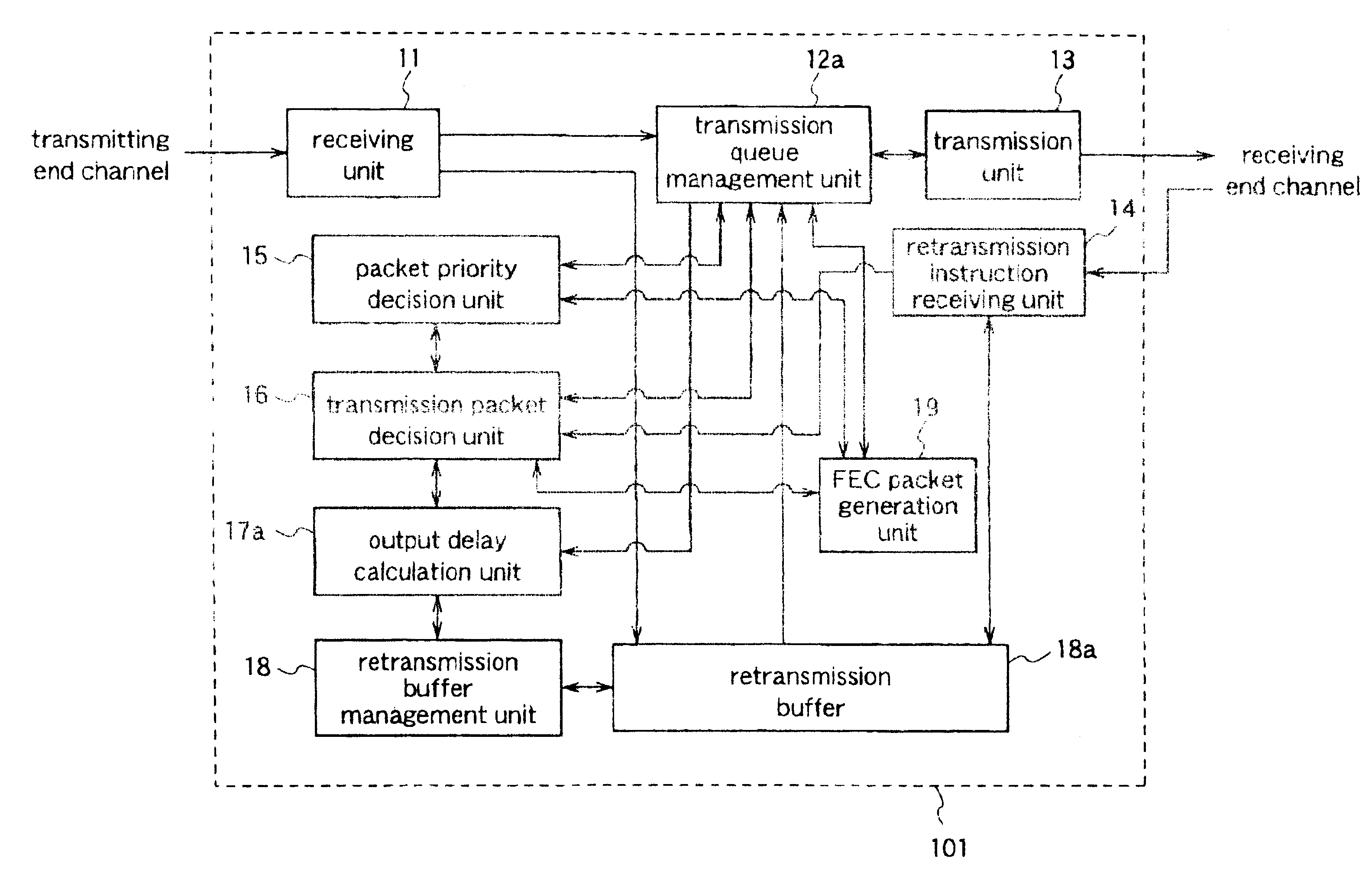

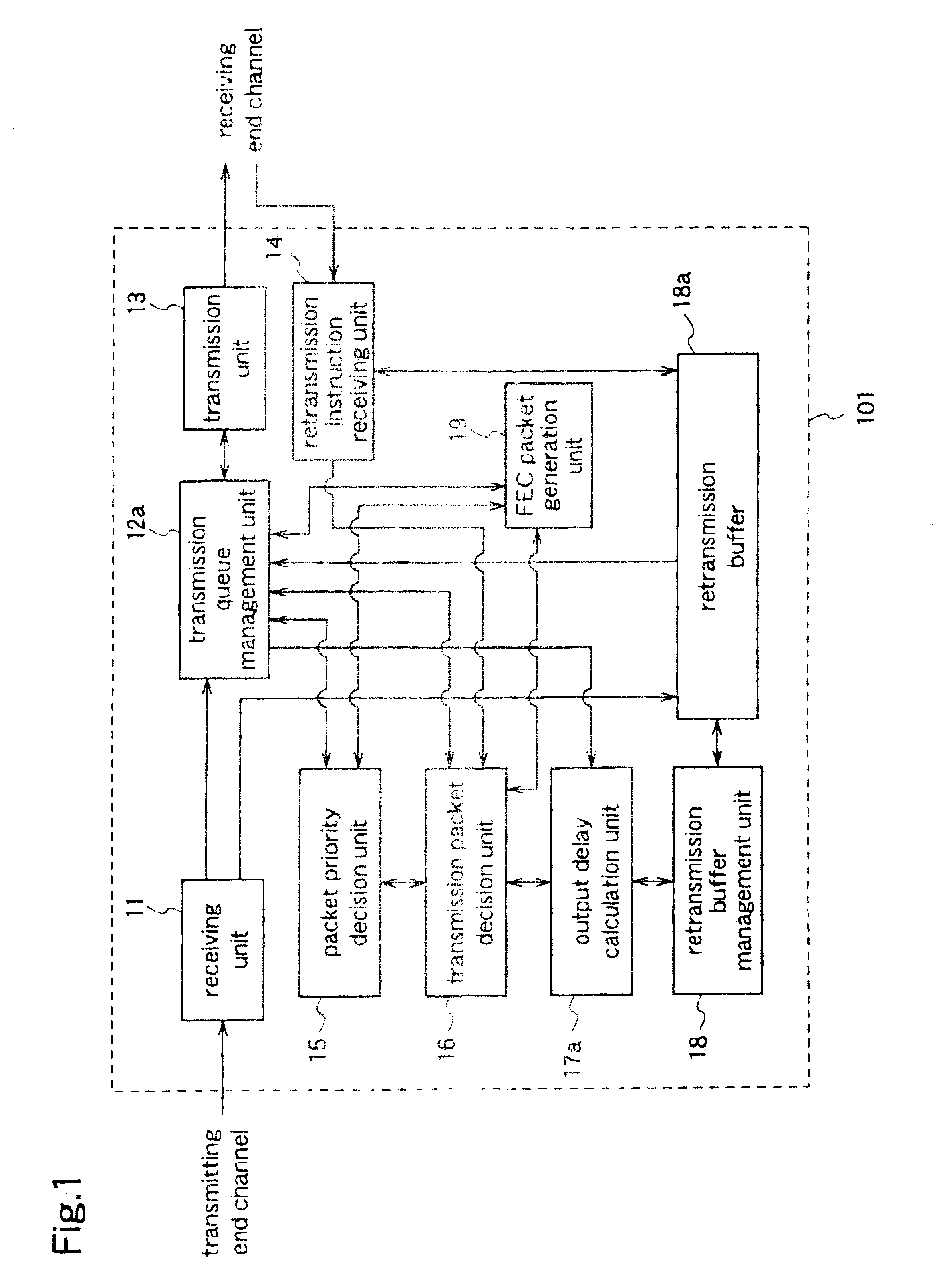

In a data transmission method of the present invention, not only when relay of input packets is performed but also transmission of a retransmission packet or a correction packet is performed, changes in an output rate due to output rate control is suppressed, and data transmission is efficiently performed according to a capacity of an output channel. A data transmission device comprises a packet priority decision unit 15 for deciding priorities of input packets, a retransmission packet, and an FEC packet, an output delay calculation unit 17 for calculating a delay time until data of the respective packets is reproduced by a receiving terminal, and an FEC packet generation unit 19 for generating an FEC packet containing an error correcting code which corresponds to a packet designated on the basis of the priorities of the respective packets. When transmission of the retransmission packet and the FEC packet together with the input packets is performed, lower priority packets corresponding to a size of packets which are additionally transmitted are thinned out.

Owner:PANASONIC CORP

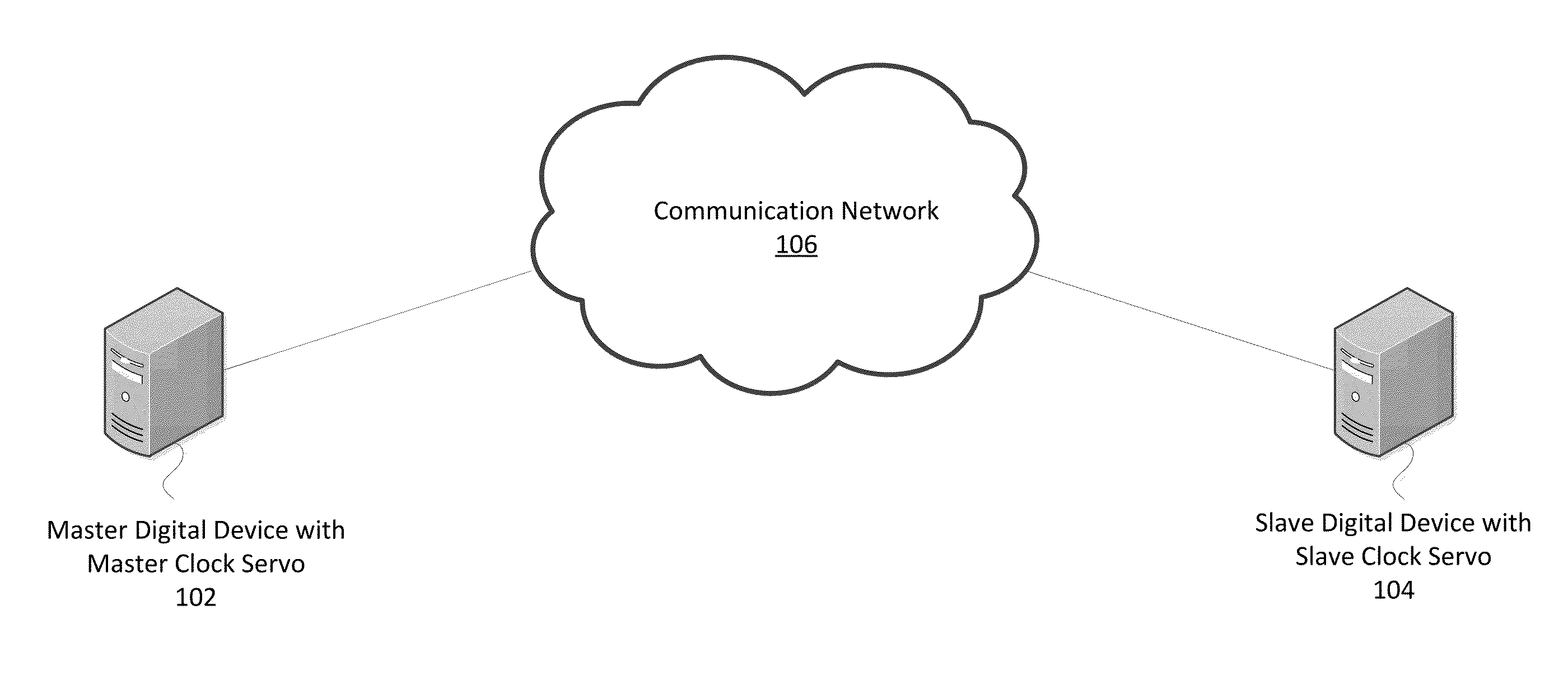

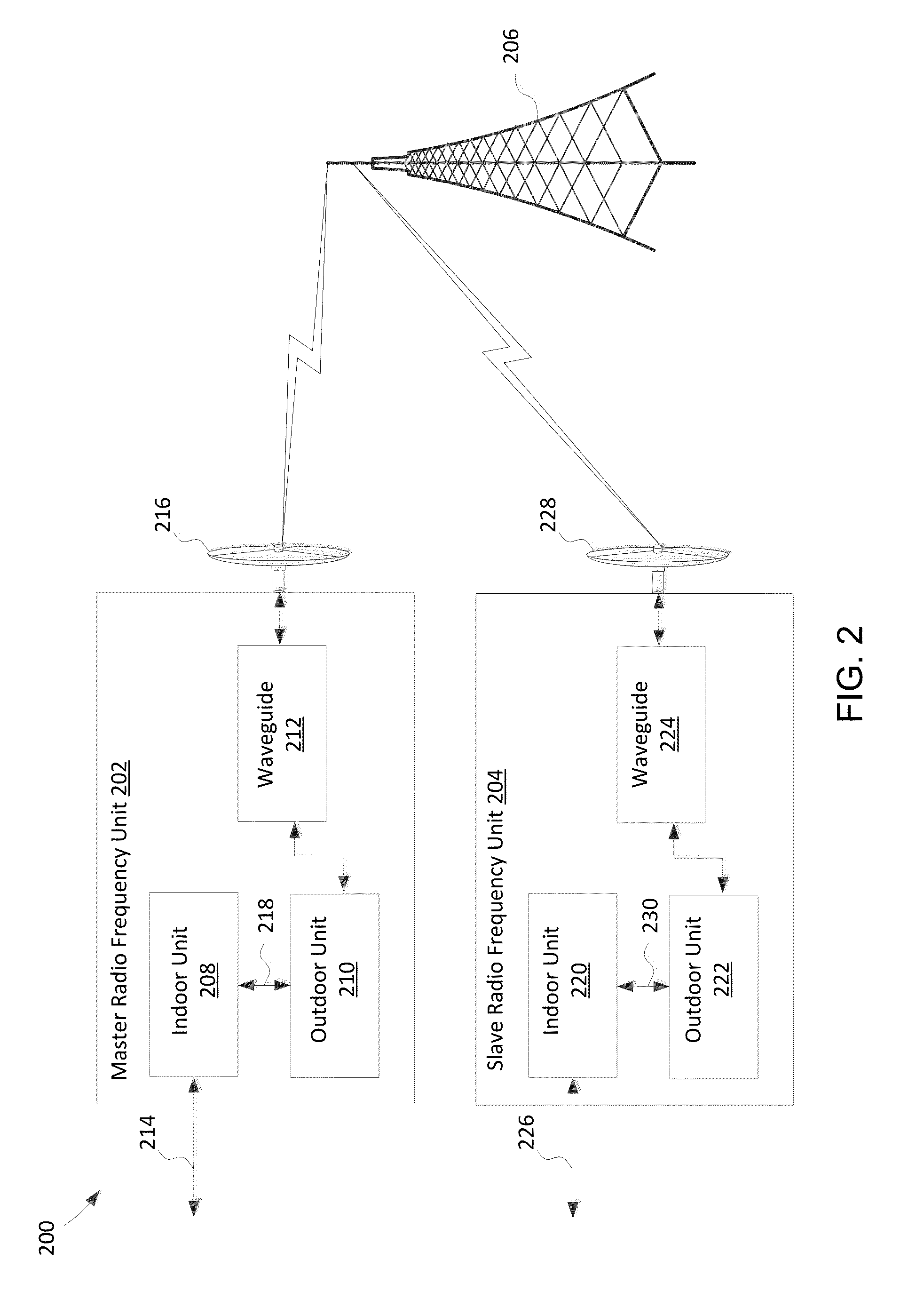

Systems and Methods of Network Synchronization

ActiveUS20130080817A1Time-division multiplexGenerating/distributing signalsSlave clockDelay calculation

An exemplary method of synchronizing a master clock and a slave clock comprises transmitting a plurality of packets between a master device and a slave device, calculating a first skew between a first pair of the plurality of packets at the slave device and a second skew between the first pair at the master device, calculating a ratio between the first skew and the second skew, providing a slave clock frequency correction to the slave device, calculating a first packet trip delay using a time that the master device initiates sending a packet to the slave device, a time the master device receives a response from the slave device, a corrected time the slave device receives the packet, and a corrected time the slave device initiates sending the response, calculating a first offset based on the first packet trip delay, and providing the first offset to the slave device.

Owner:AVIAT U S

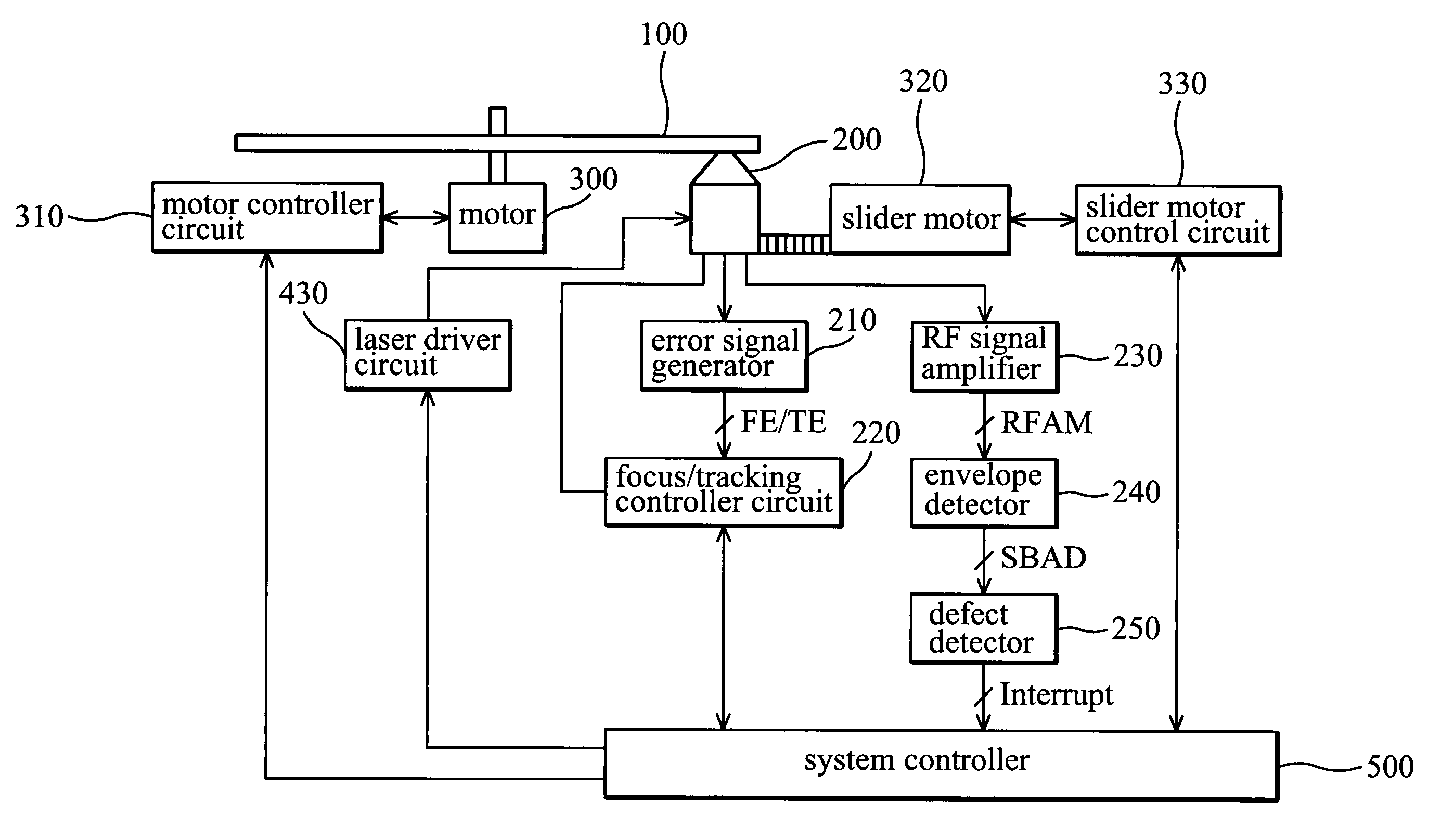

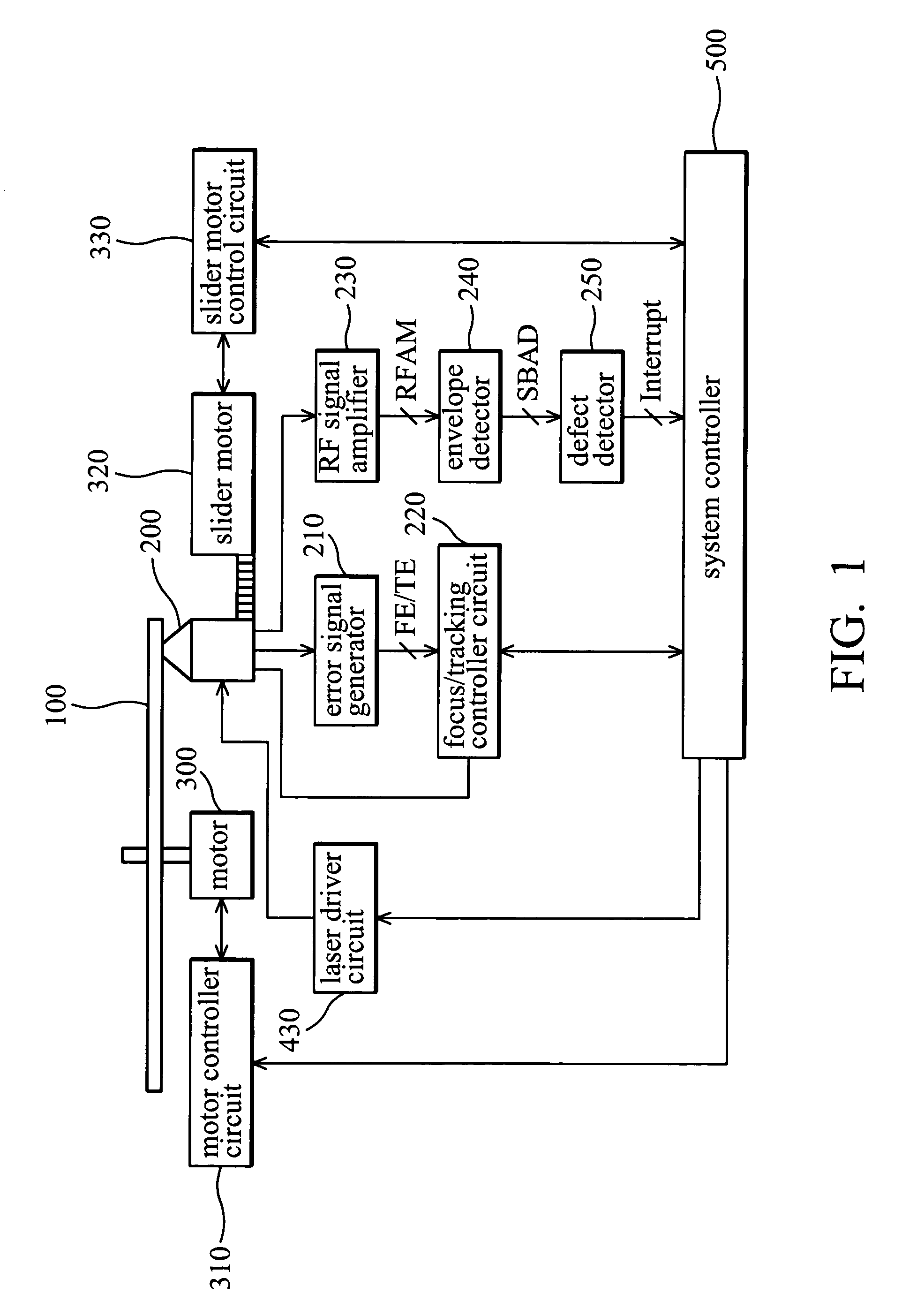

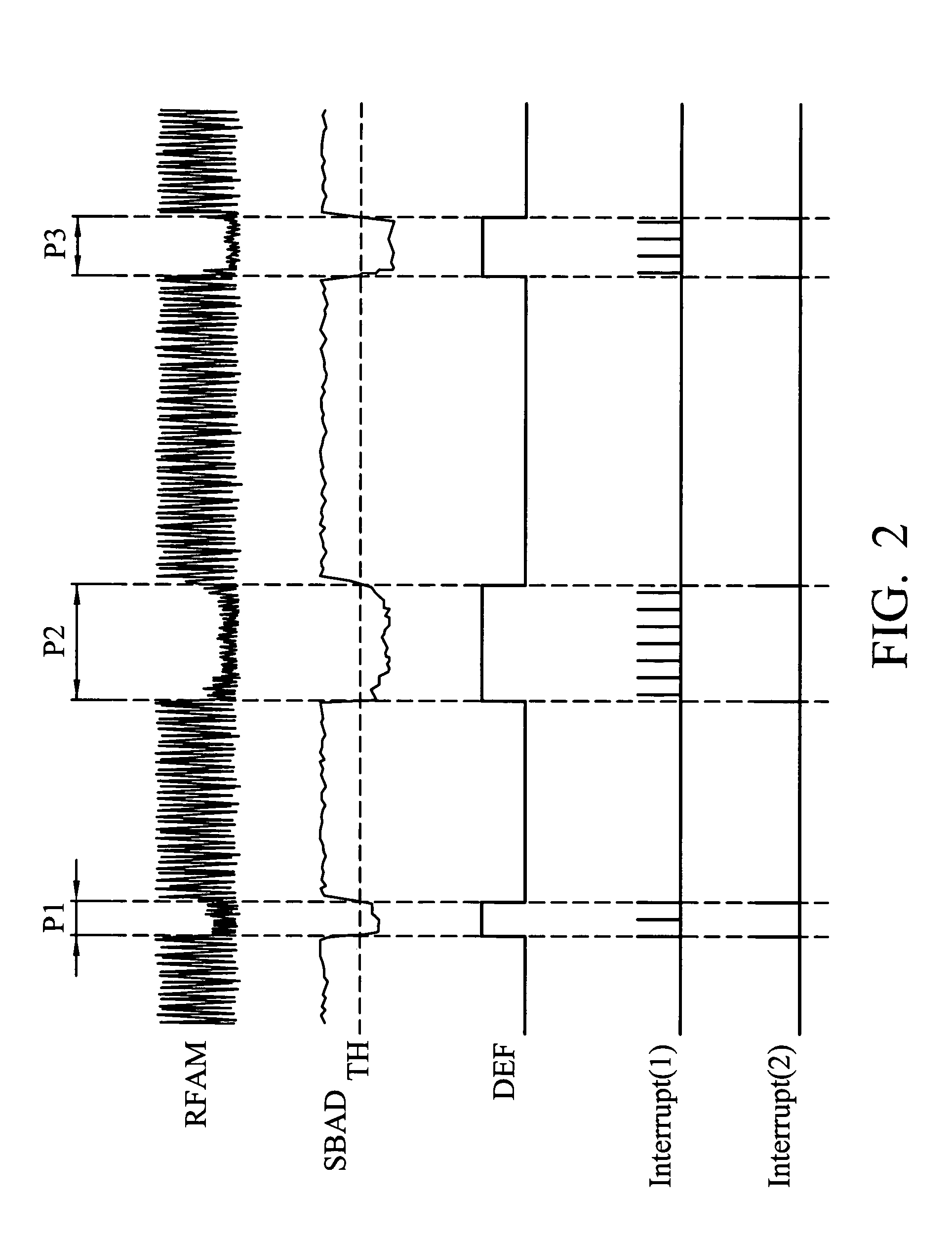

Method and apparatus for retry calculation in an optical disk device

A method for determining a maximum number of attempted retry operations when a read error occurs in an optical disk device. The method includes the steps of receiving an RF signal from a pickup of the optical disk device, detecting an envelope of the RF signal, asserting a defect signal when a level of the envelope is lower than a predetermined threshold, generating interrupt pulses during the assertion of the defect signal, and determining the maximum number of attempted retry operations using the interrupt pulses.

Owner:TIAN HLDG LLC

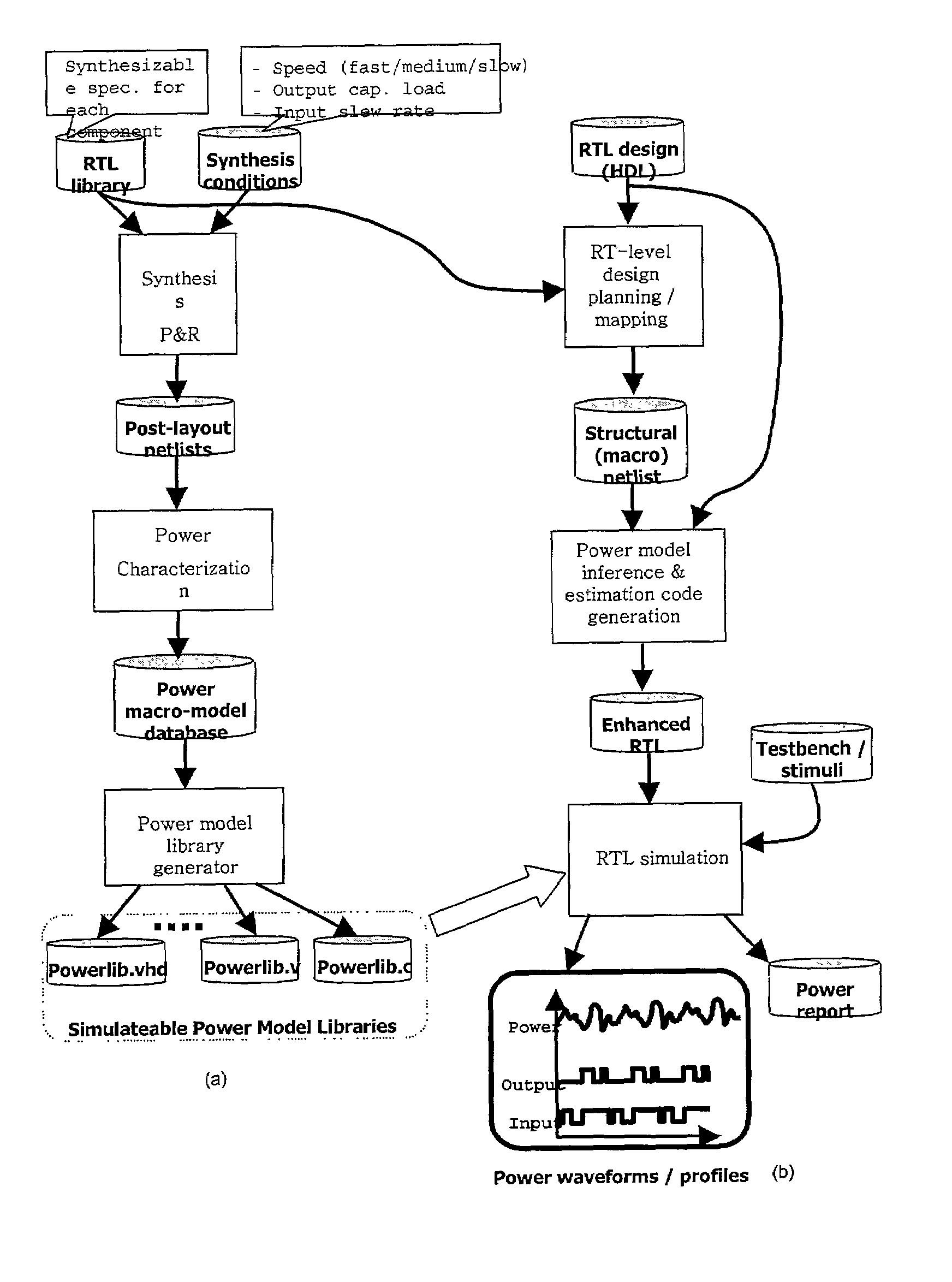

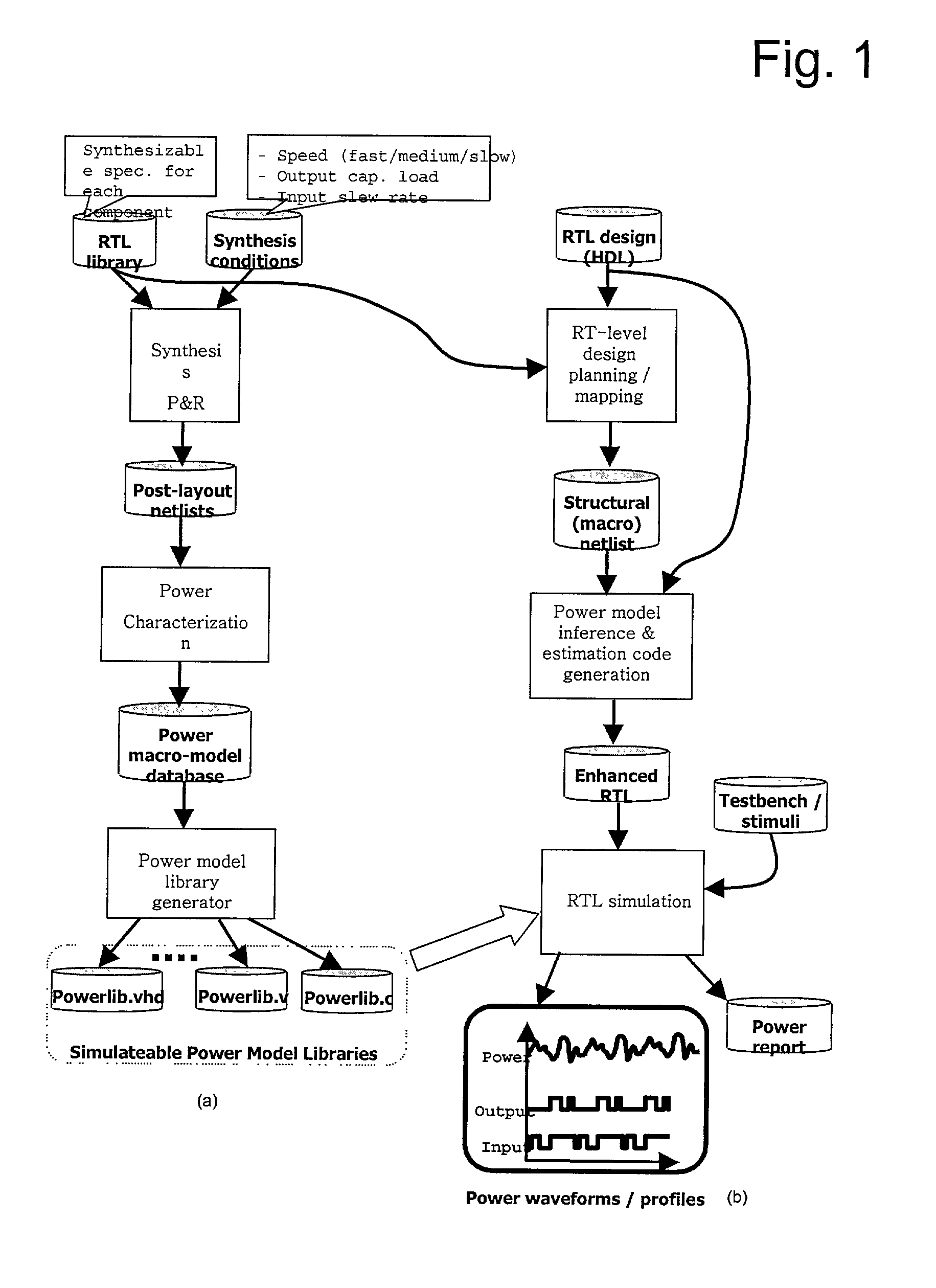

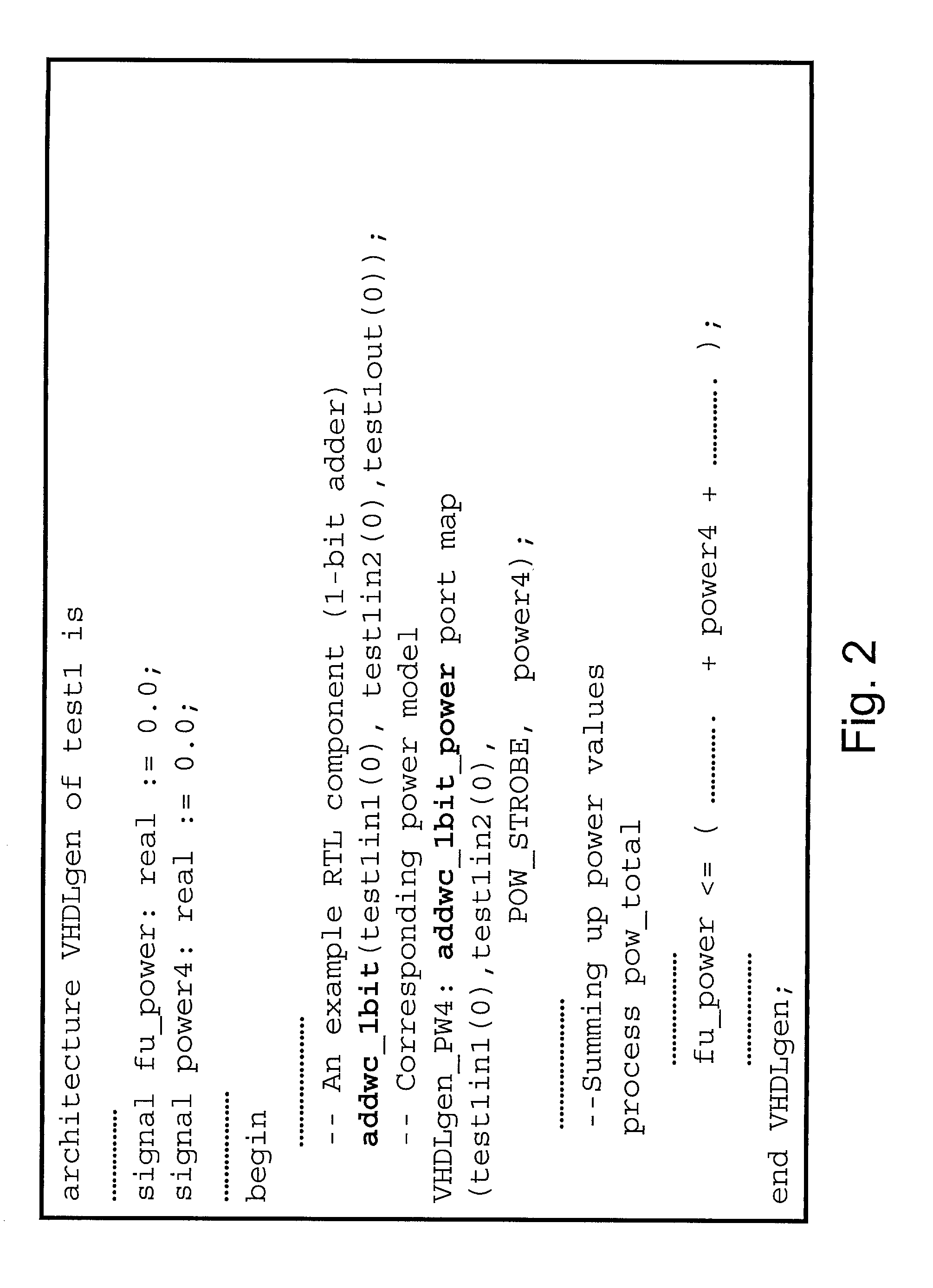

Method and apparatus for efficient register-transfer level (RTL) power estimation

InactiveUS7134100B2Accelerating power estimationEnhanced RTL descriptionCAD circuit designSoftware simulation/interpretation/emulationComputer scienceDelay calculation

Techniques for accelerating power estimation for a circuit comprising generating an RTL description of the circuit. A power model enhanced RTL description of the circuit is generated. A simulator is selected. The power model enhanced RTL description is modified to make it more friendly to the simulator. The simulator is run to estimate the power consumed by the circuit. Techniques using delayed computation and partitioned sampling are also provided. Power estimation systems using the above techniques area also provided.

Owner:NEC CORP

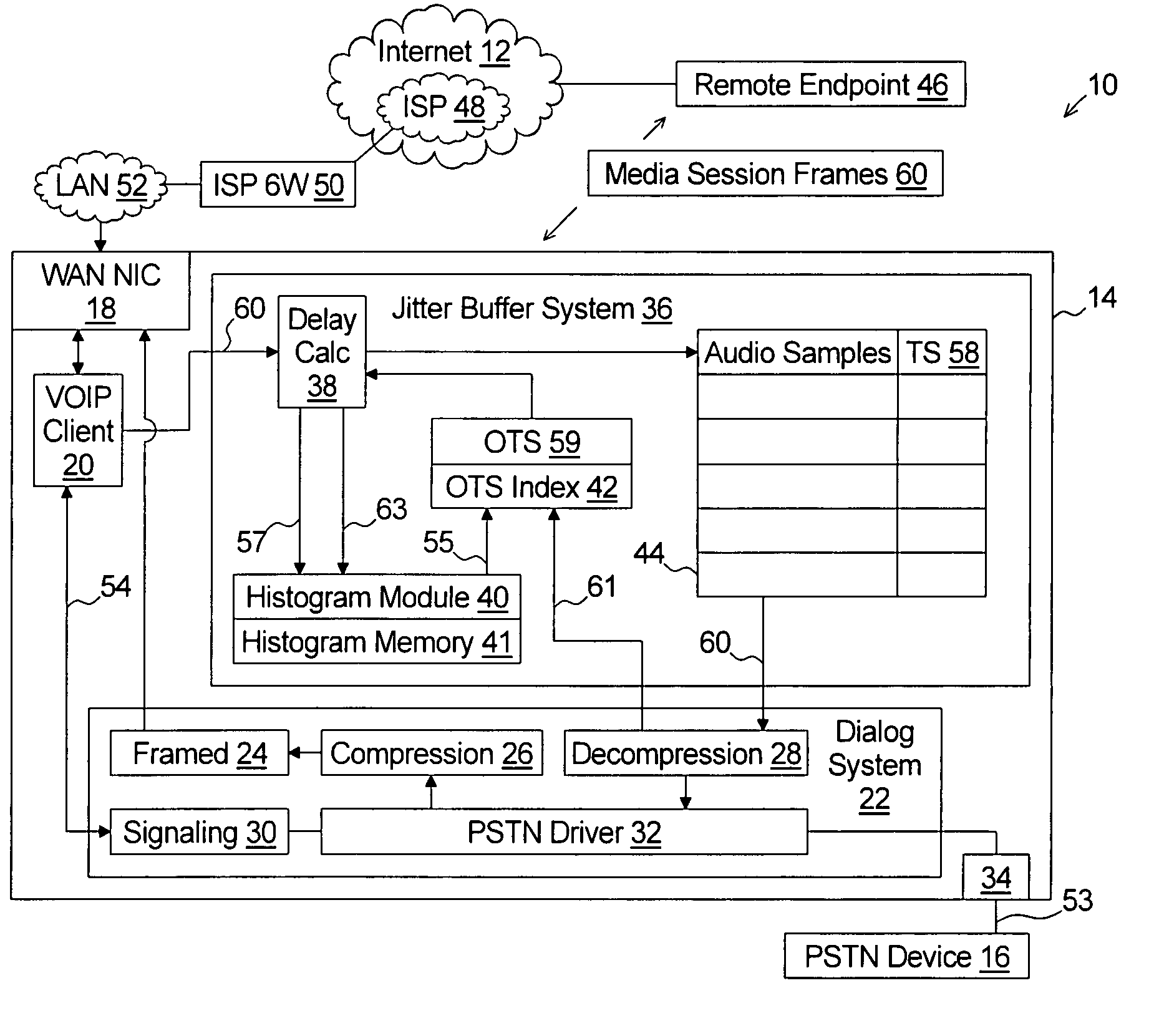

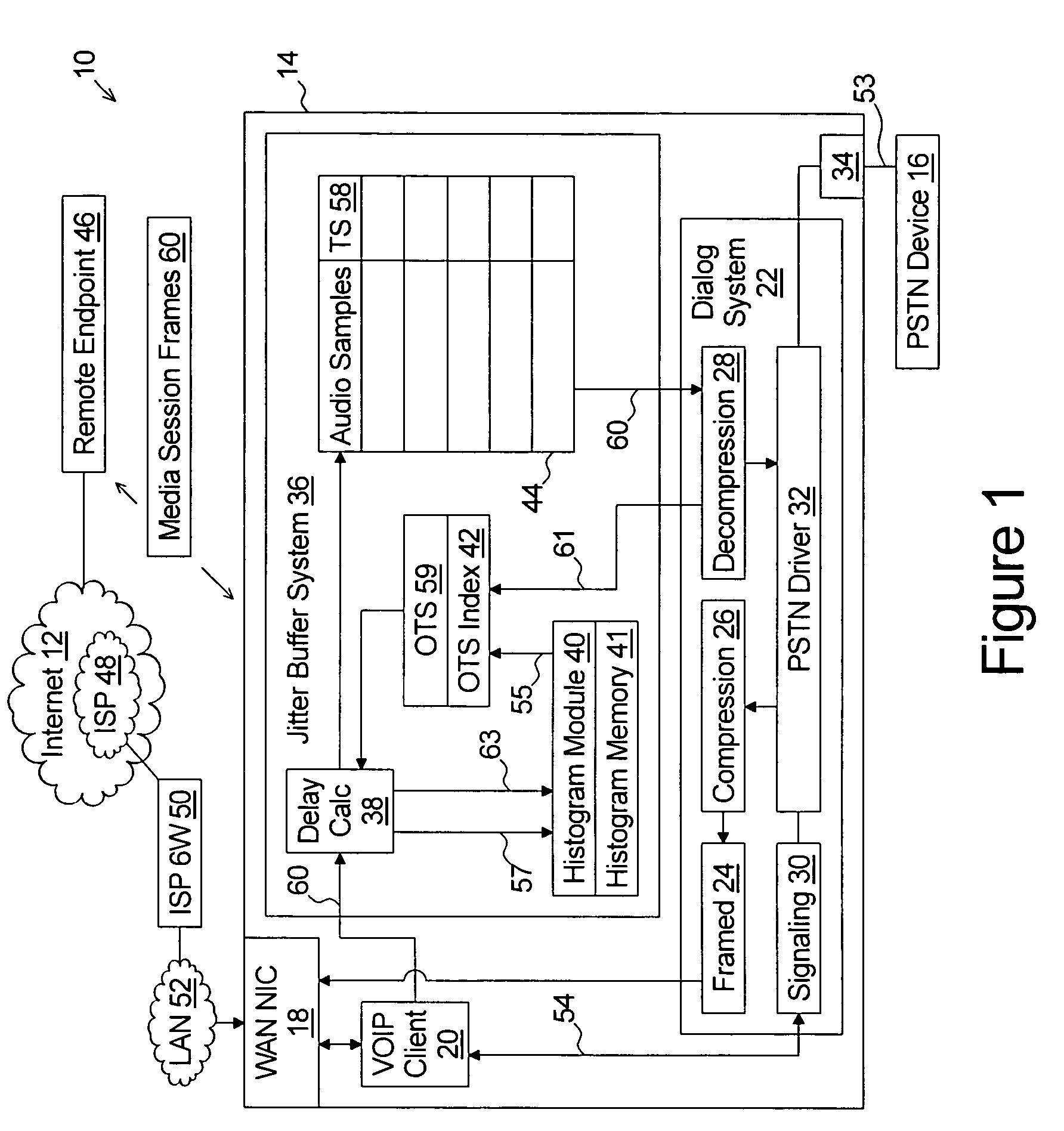

In band signal detection and presentation for IP phone

ActiveUS20050232309A1Reduce jitterTime-division multiplexData switching by path configurationAudio frequencyTime difference

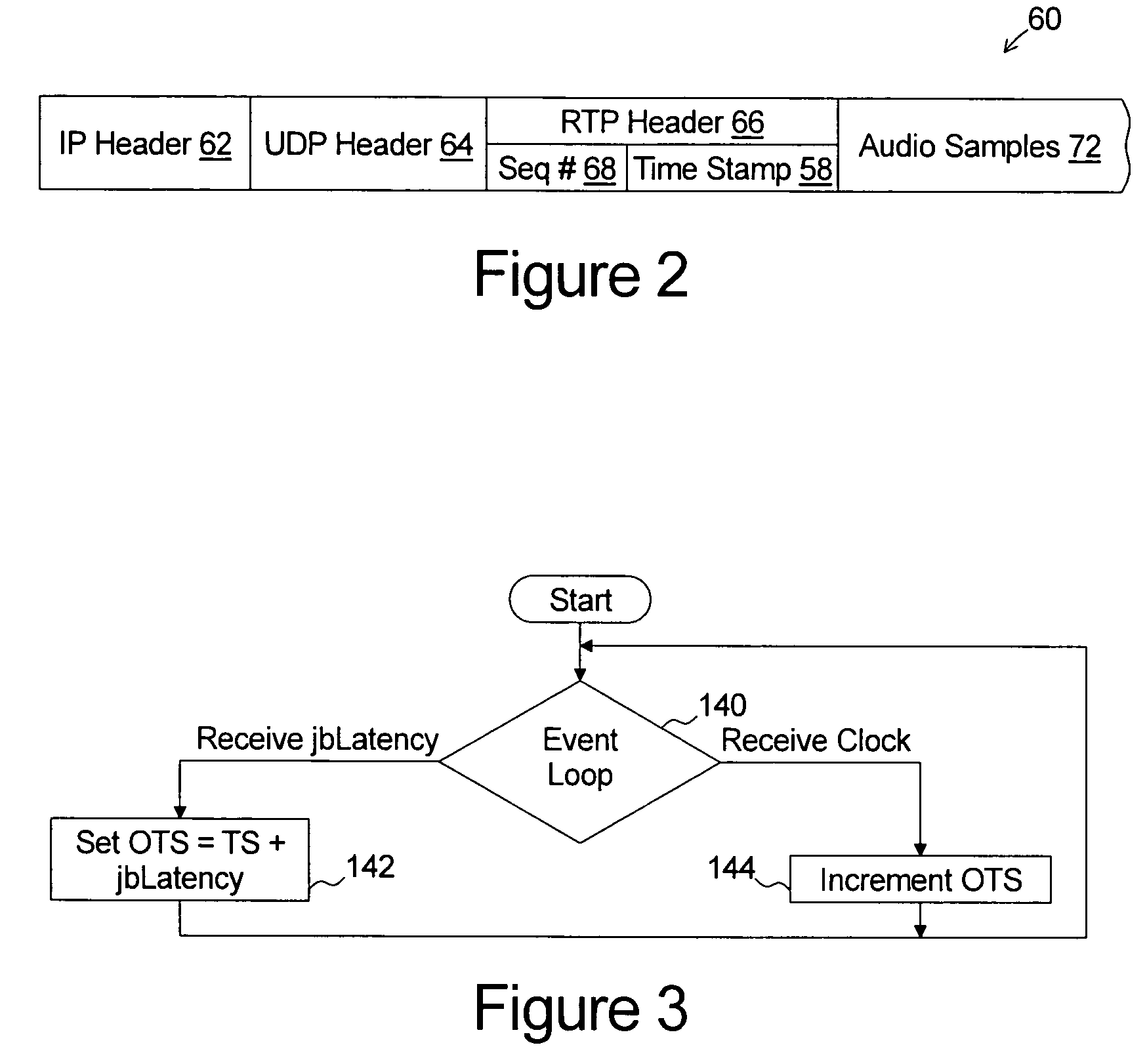

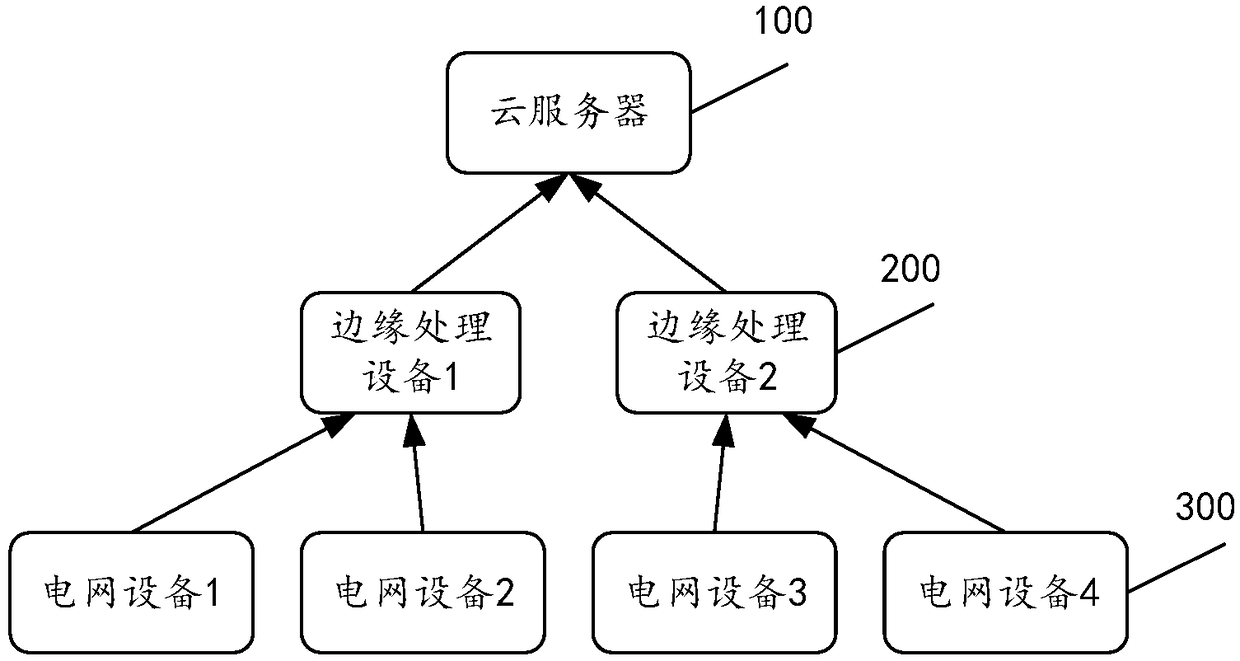

A jitter buffer system for reducing jitter in a packet audio reception device comprises an output time stamp index, a delay calculation module, and a histogram module. The output time stamp index determines an initial output time stamp value upon receipt of a jitter buffer latency value and increments the output time stamp upon release of each of the frames by a jitter buffer. The delay calculation module calculates a delay value for each of the sequence of received frames. The delay value is equal to the time difference between the output time stamp value and a transmission time stamp assigned to the frame by the transmitting system. The histogram module is coupled to each of the output time stamp index and the delay calculation module, the histogram module periodically calculates a target delay value which, based on a buffered history of values representing the delay value of each of a fixed quantity of the most recently received frames from the sequence of receive frames, would have resulted in a predetermined portion of the fixed quantity of frames being dropped, and adjusting the jitter buffer latency value to a value equal to the target value.

Owner:INNOMEDIA PTE

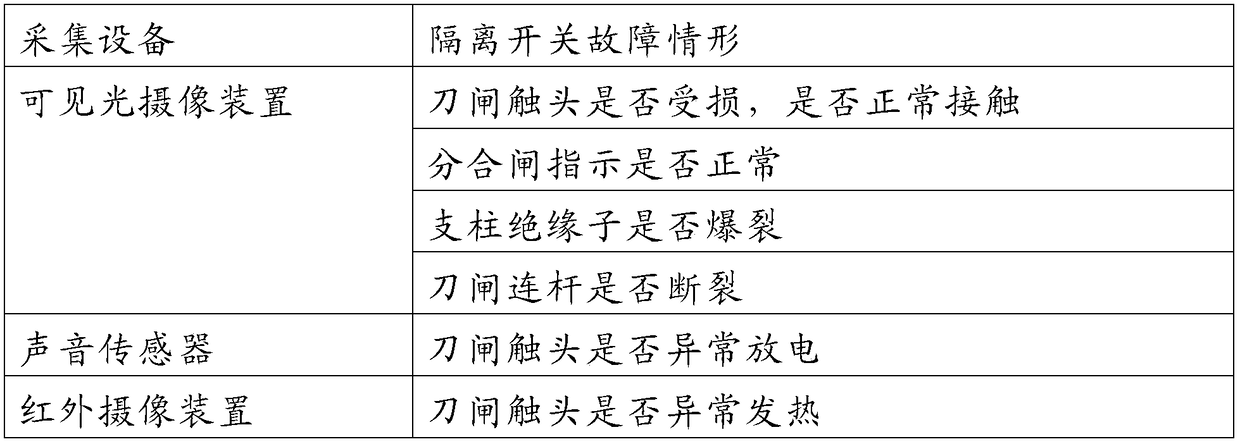

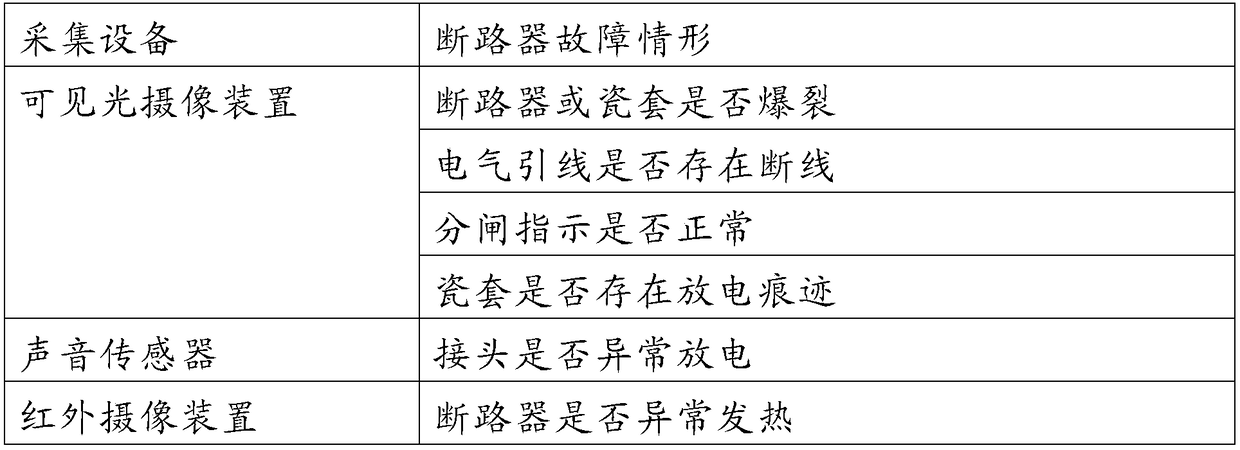

Fault detection system based on edge calculation

InactiveCN108828409AReduce computing pressureImprove fault detection efficiencyFault locationInformation technology support systemPower gridEdge based

The invention discloses a fault detection system based on edge calculation. The fault detection system comprises a cloud server, an edge processing device, and an acquisition device. The cloud serveris used for training a neural network in advance and downloading the trained neural network to the edge processing device. After acquiring the state data of a grid device in a grid system, the acquisition device transmits the state data to the edge processing device. The edge processing device uses the neural network to analyze the state data, and the cloud server determines whether the grid device generates a fault according to an analysis result. It can be seen that the system, by downloading the neural network to the edge processing device, and can analyze the state data first by using theedge processing device during fault detection, thereby reducing the computing pressure of the cloud server and improving the fault detection efficiency.

Owner:ELECTRIC POWER RESEARCH INSTITUTE, CHINA SOUTHERN POWER GRID CO LTD +1

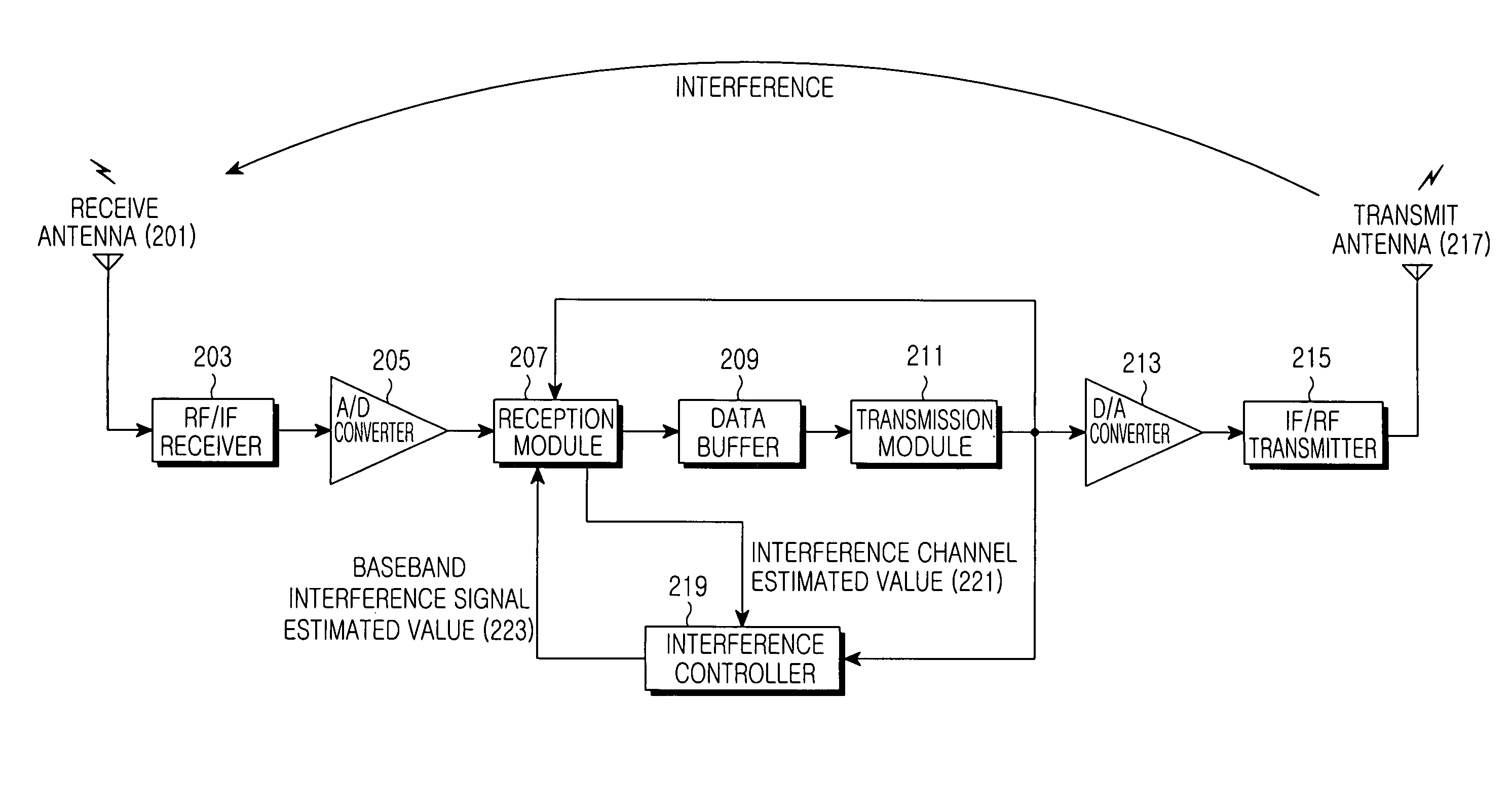

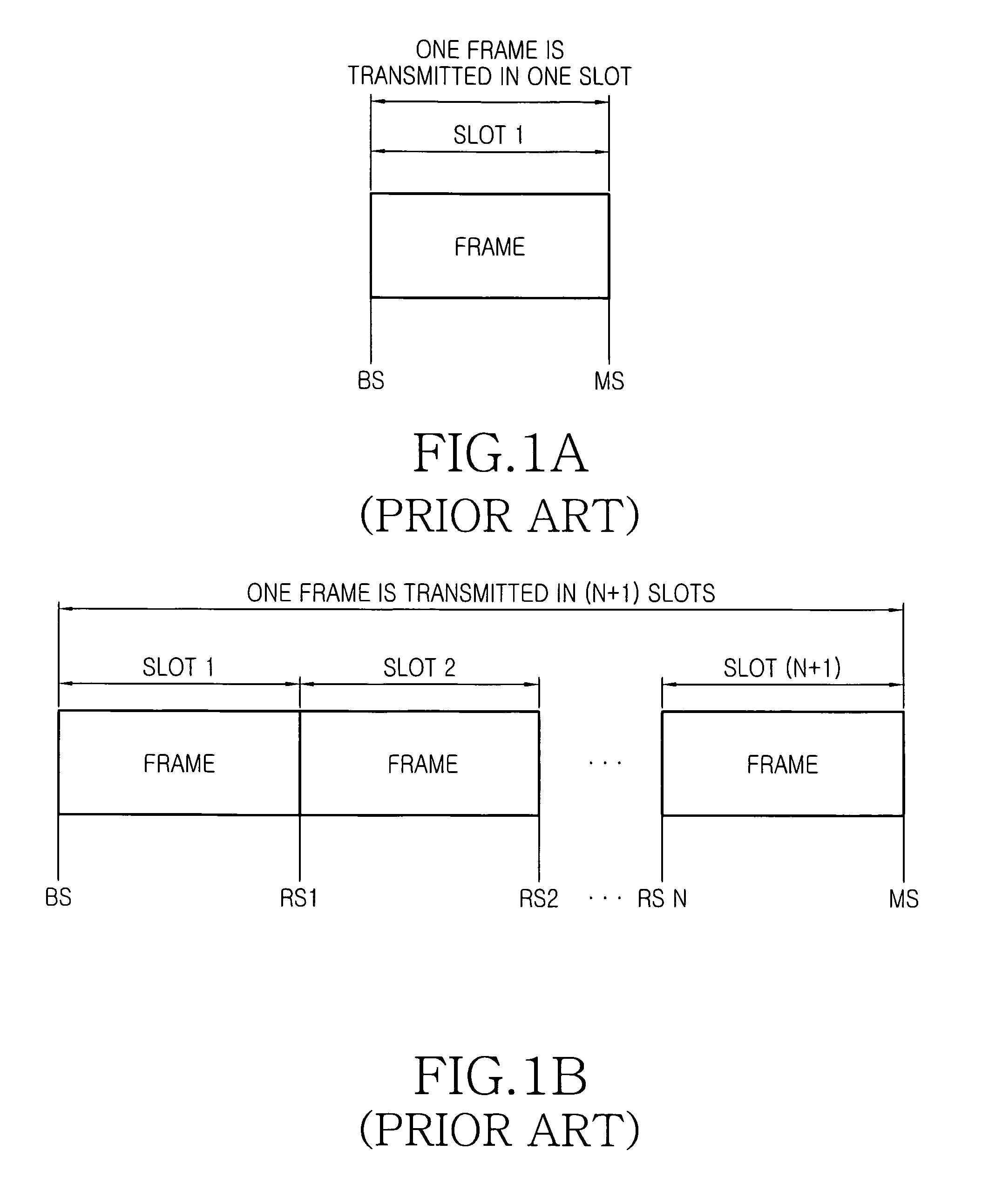

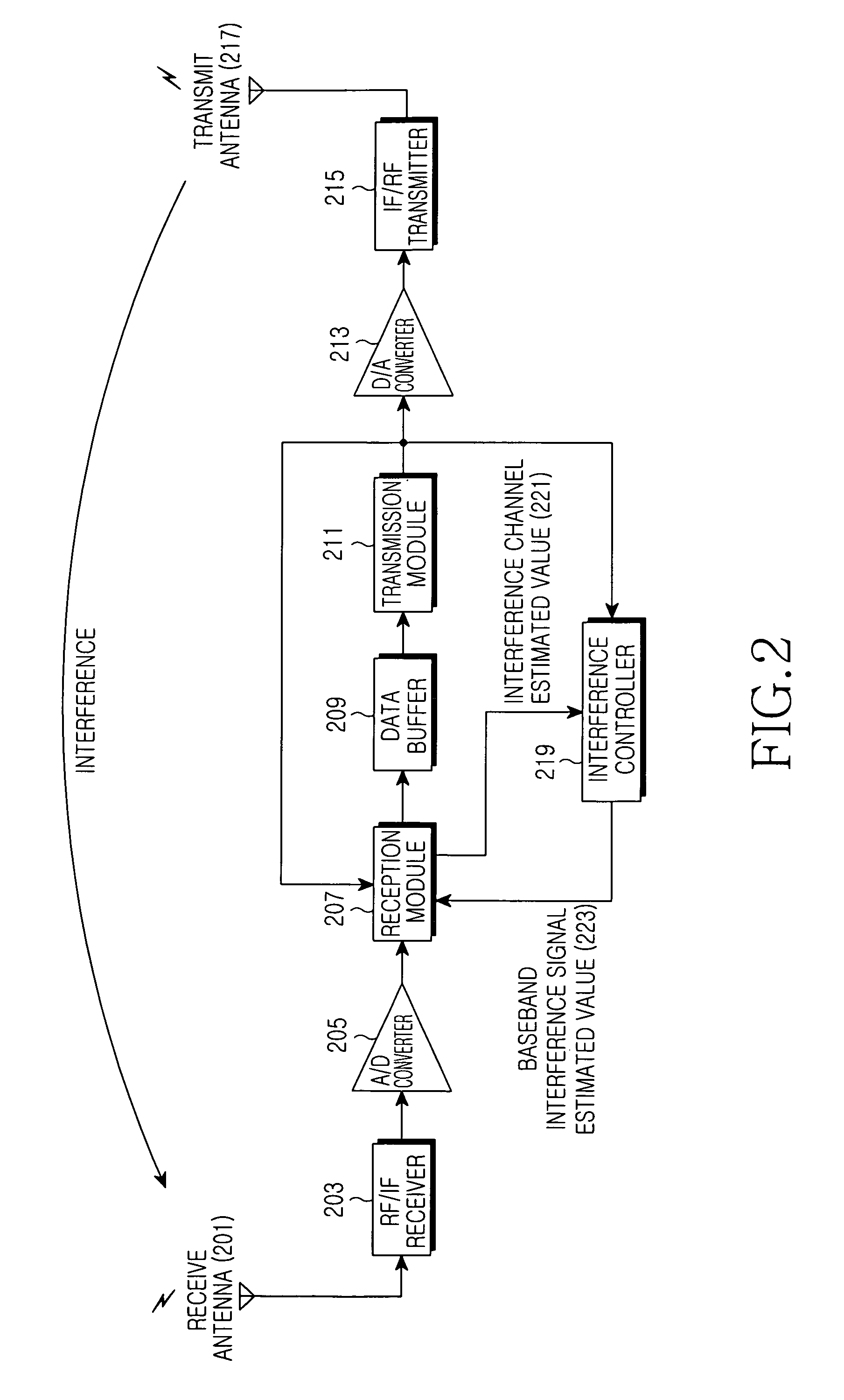

Apparatus and method for canceling interference in relay station in a communication system

InactiveUS7733813B2Eliminate distractionsError preventionModulated-carrier systemsCommunications systemEngineering

A method and apparatus for canceling interference between a transmission signal and a received signal in a full-duplex RS in a communication system are provided, in which an RF / IF signal received from a first node through an antenna is converted to a baseband received signal, demodulated and decoded, a baseband transmission signal is generated by encoding and decoding the decoded data, a baseband interference estimate is calculated using the baseband received signal and the baseband transmission signal, a baseband interference is eliminated from the baseband received signal according to the baseband interference estimate, the baseband transmission signal is converted to an RF / IF transmission signal for a second node, an RF / IF interference estimate is calculated by converting amplitude of the RF / IF transmission signal and delaying it, and an RF / IF interference is eliminated from the RF / IF received signal according to the RF / IF interference estimate.

Owner:SAMSUNG ELECTRONICS CO LTD

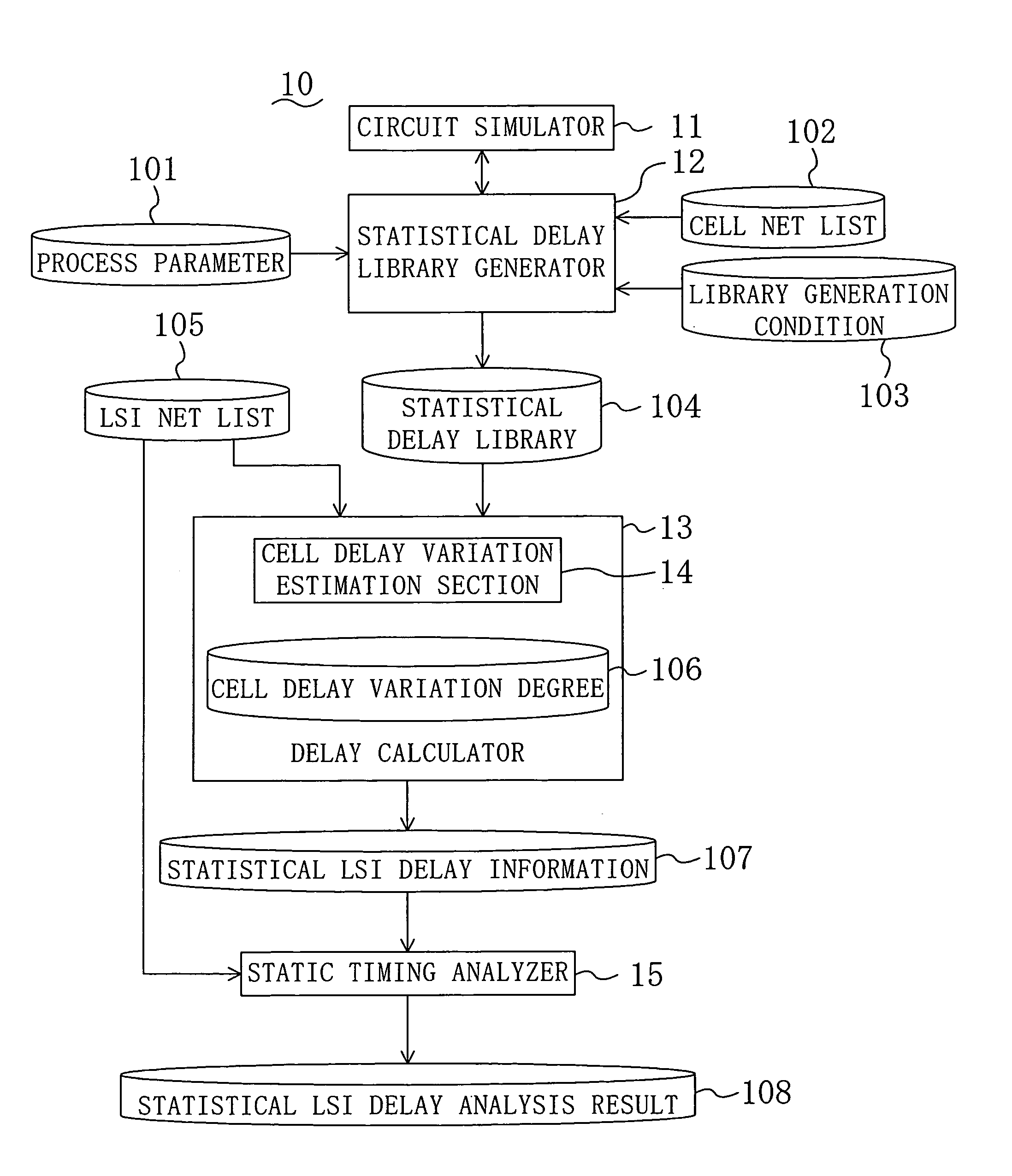

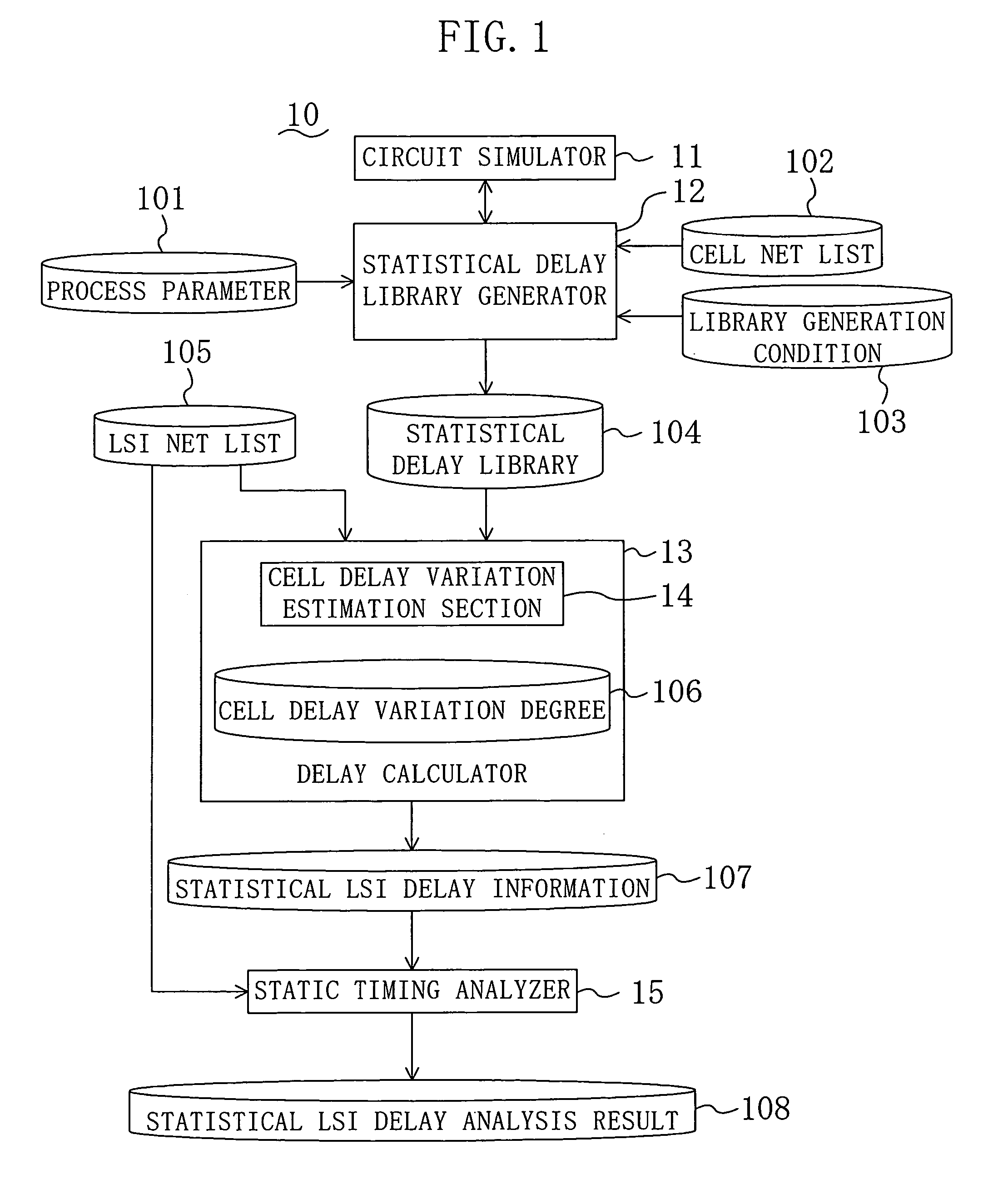

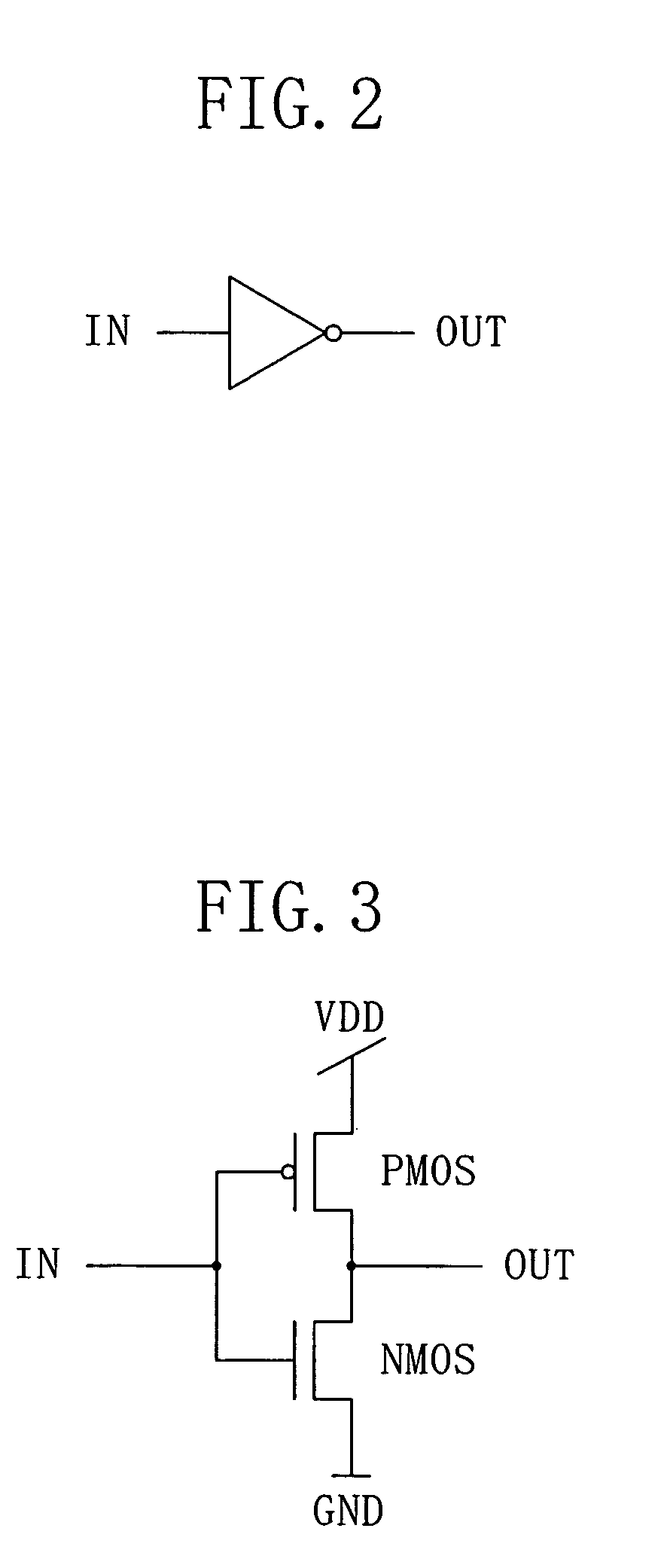

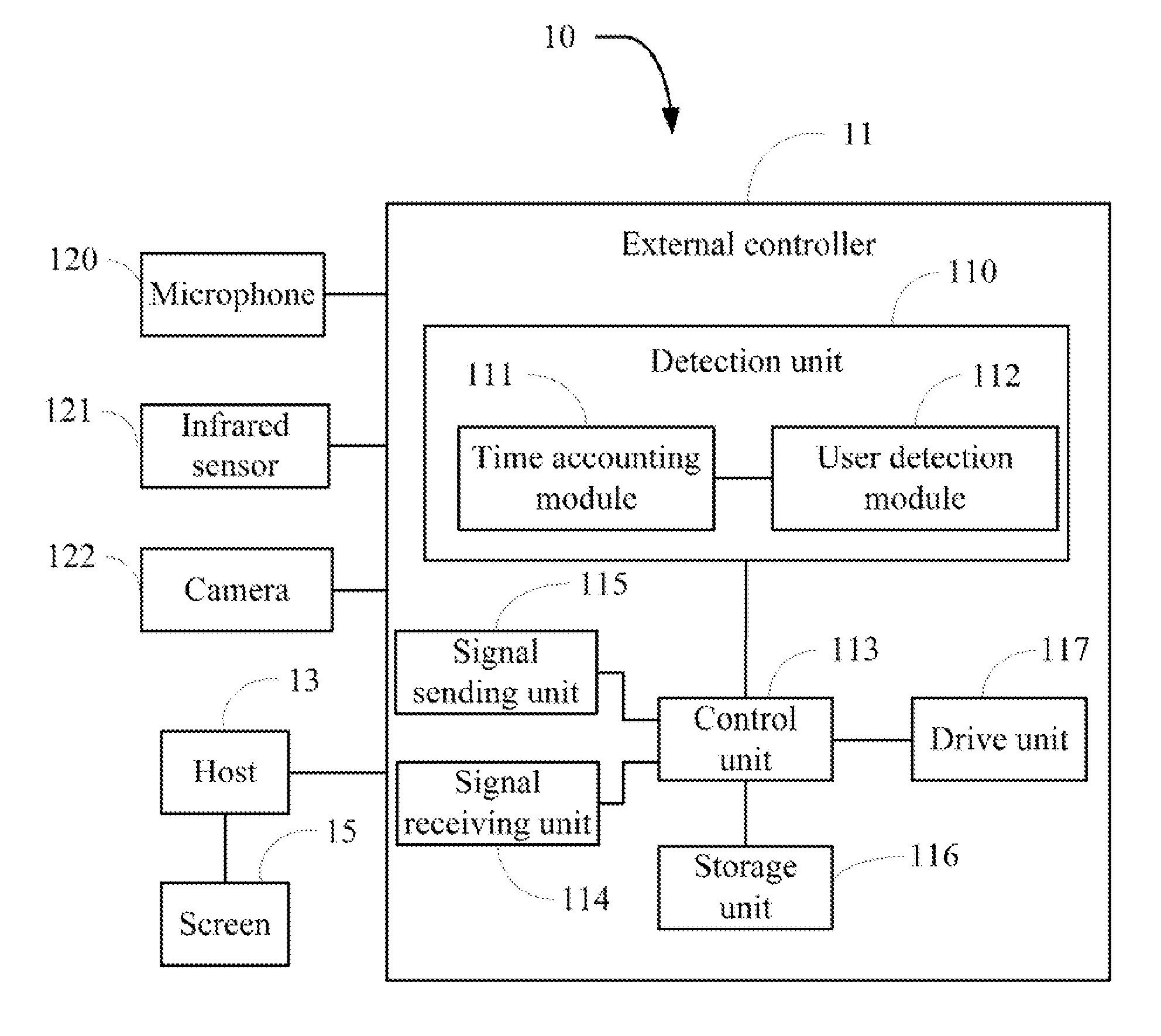

Apparatus for statistical LSI delay simulation

InactiveUS7239997B2Simple wayReliable resultsAnalogue computers for electric apparatusComputation using non-denominational number representationDriver circuitDelay analysis

A statistical delay simulation apparatus includes: a circuit simulator for simulating a circuit operation of a circuit cell constituting an LSI; a statistical delay library generator for driving the circuit simulator and generating, based on a process parameter and the like, a statistical delay library in which the dependency of a delay variation on a predetermined operation condition in each circuit cell is described; a delay calculator for calculating a delay amount of each circuit cell to generate a statistical LSI delay information file containing data on the calculated delay amount; and a static timing analyzer for simulating, based on data of the statistical LSI delay information file, an operation with a delay variation of the LSI to generate a statistical LSI delay analysis result file.

Owner:PANASONIC CORP

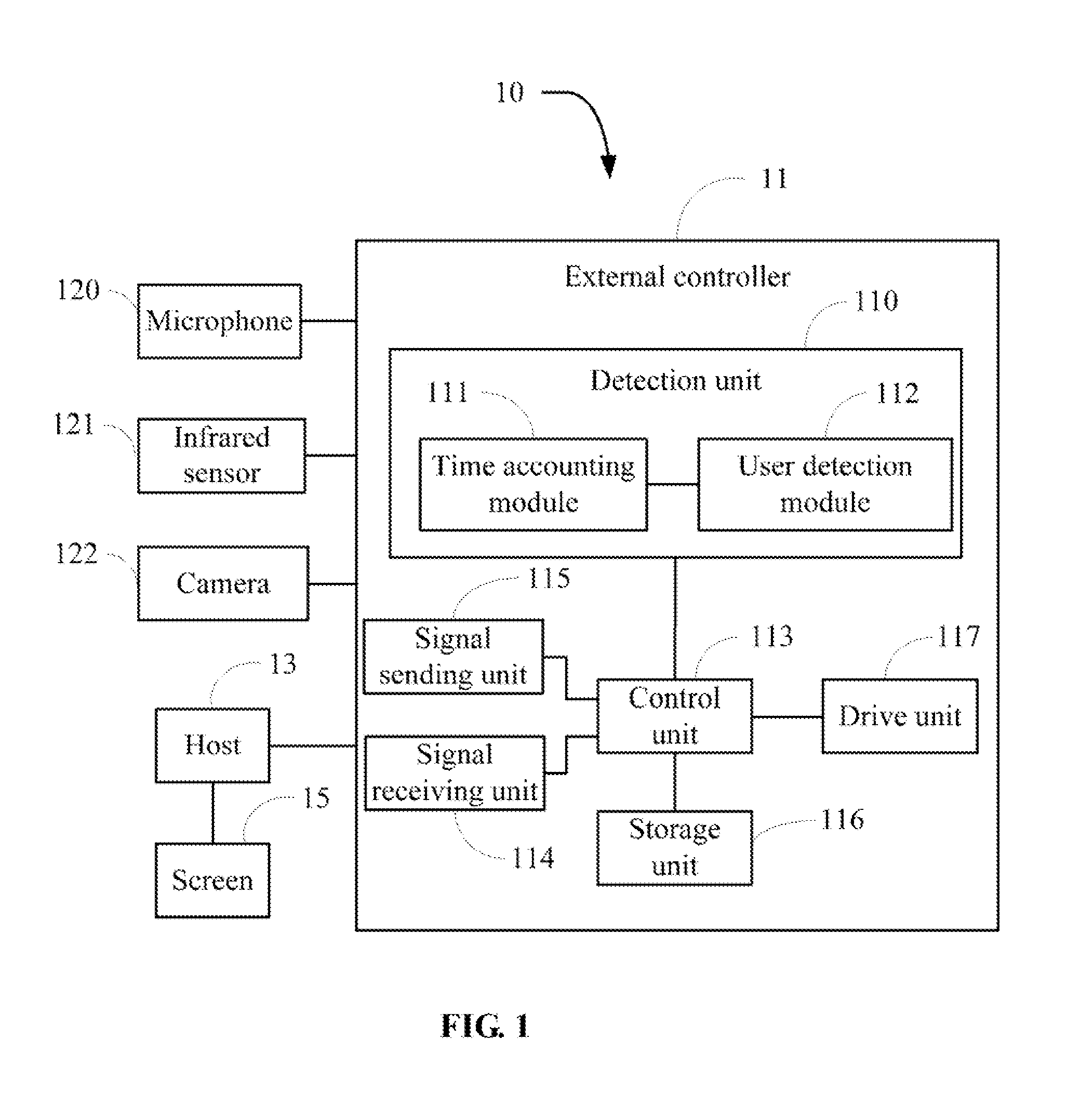

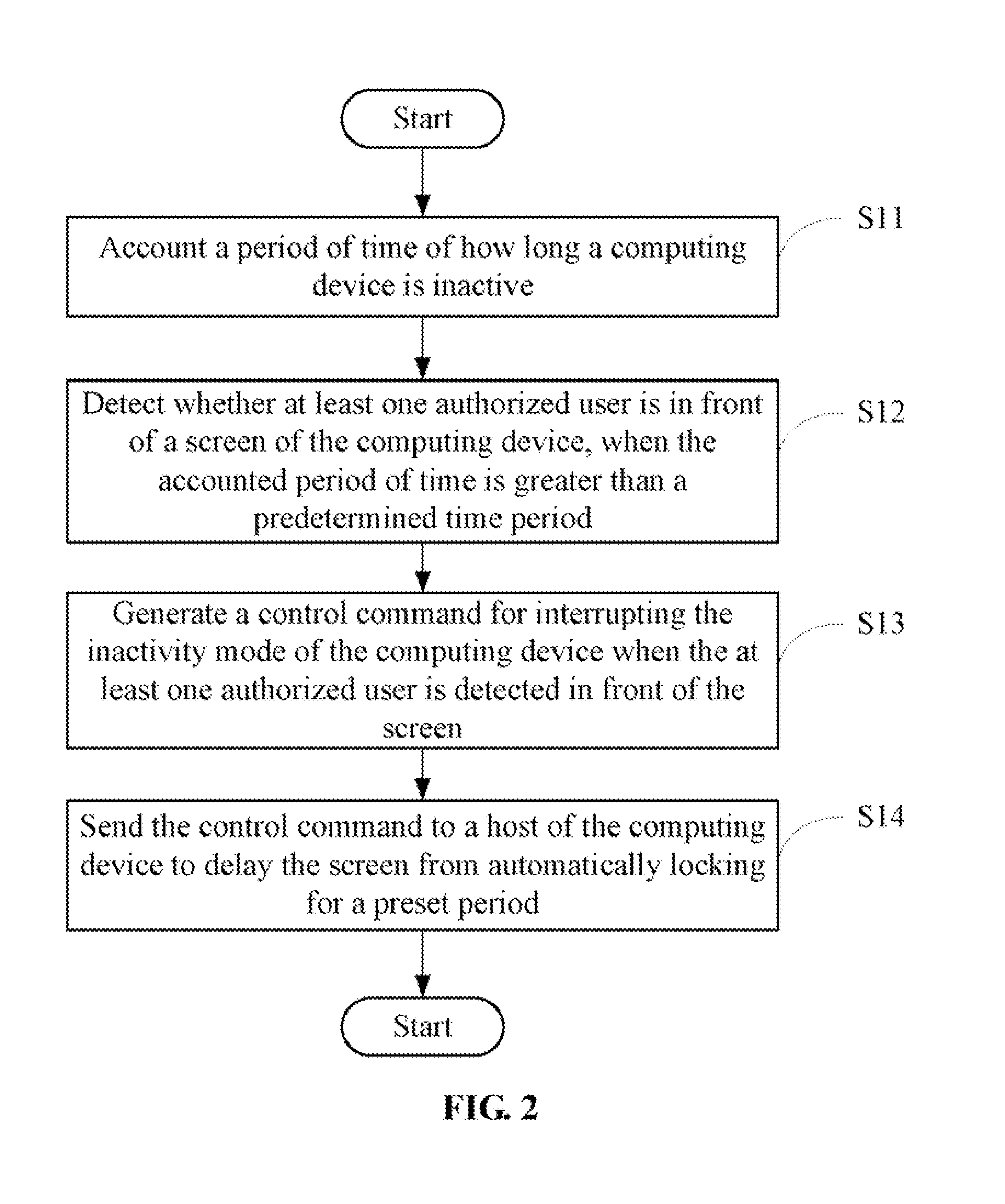

External controller and method for delaying screen locking of computing device

An external controller for delaying screen locking of a computing device, the screen of the computing device is automatically locked after a preset period of inactivity of the computing device. The external controller includes a detection unit and a control unit. The detection unit accounts a period of time of how long the computing device is inactive, and detects whether at least one authorized user is in front of the screen when the accounted period of time is greater than a predetermined time period. The control unit generates a control command for interrupting the inactivity mode of the computing device to delay the screen from automatically locking for the preset period, when the at least one authorized user is detected in front of the screen.

Owner:FU TAI HUA IND SHENZHEN +1

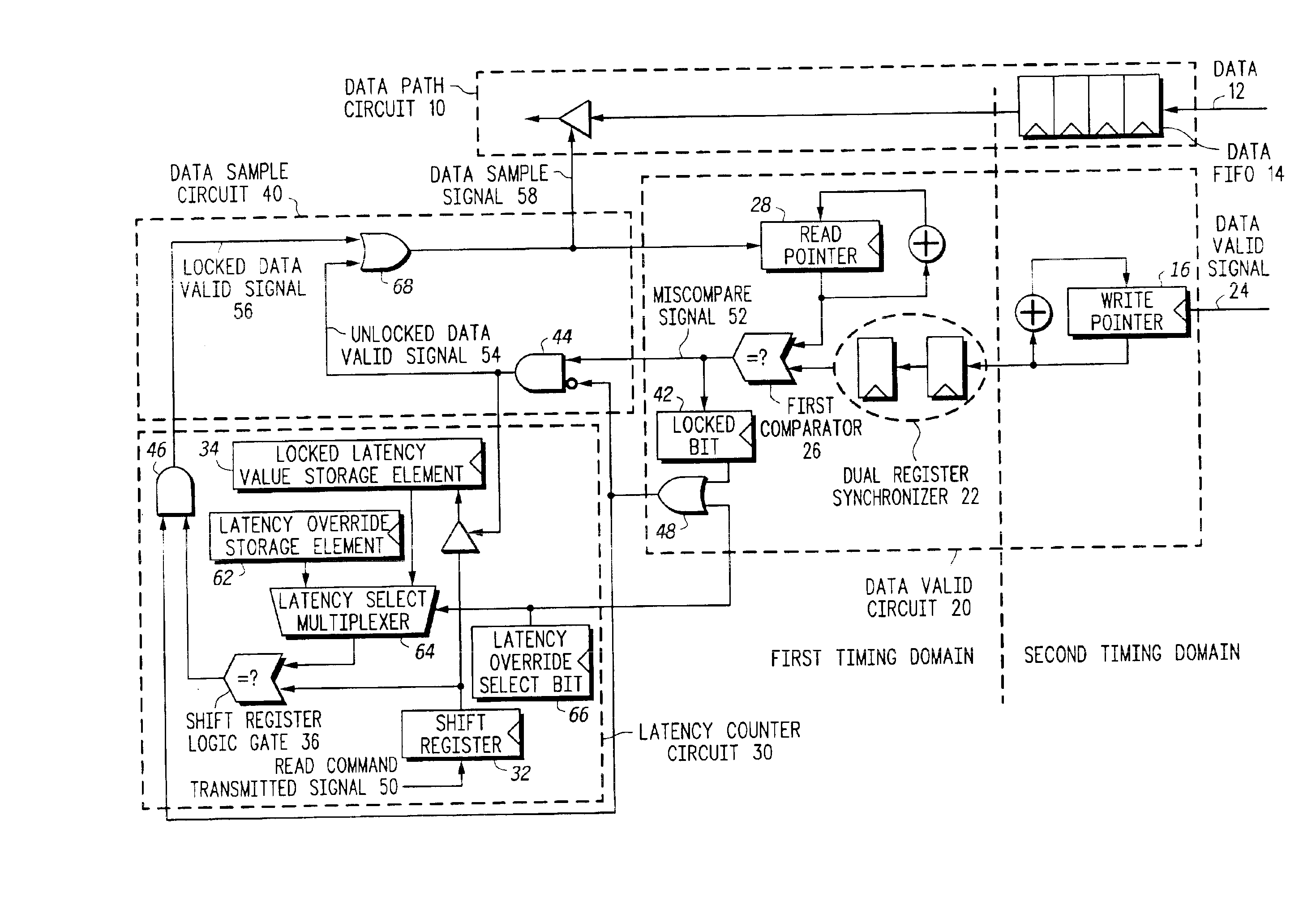

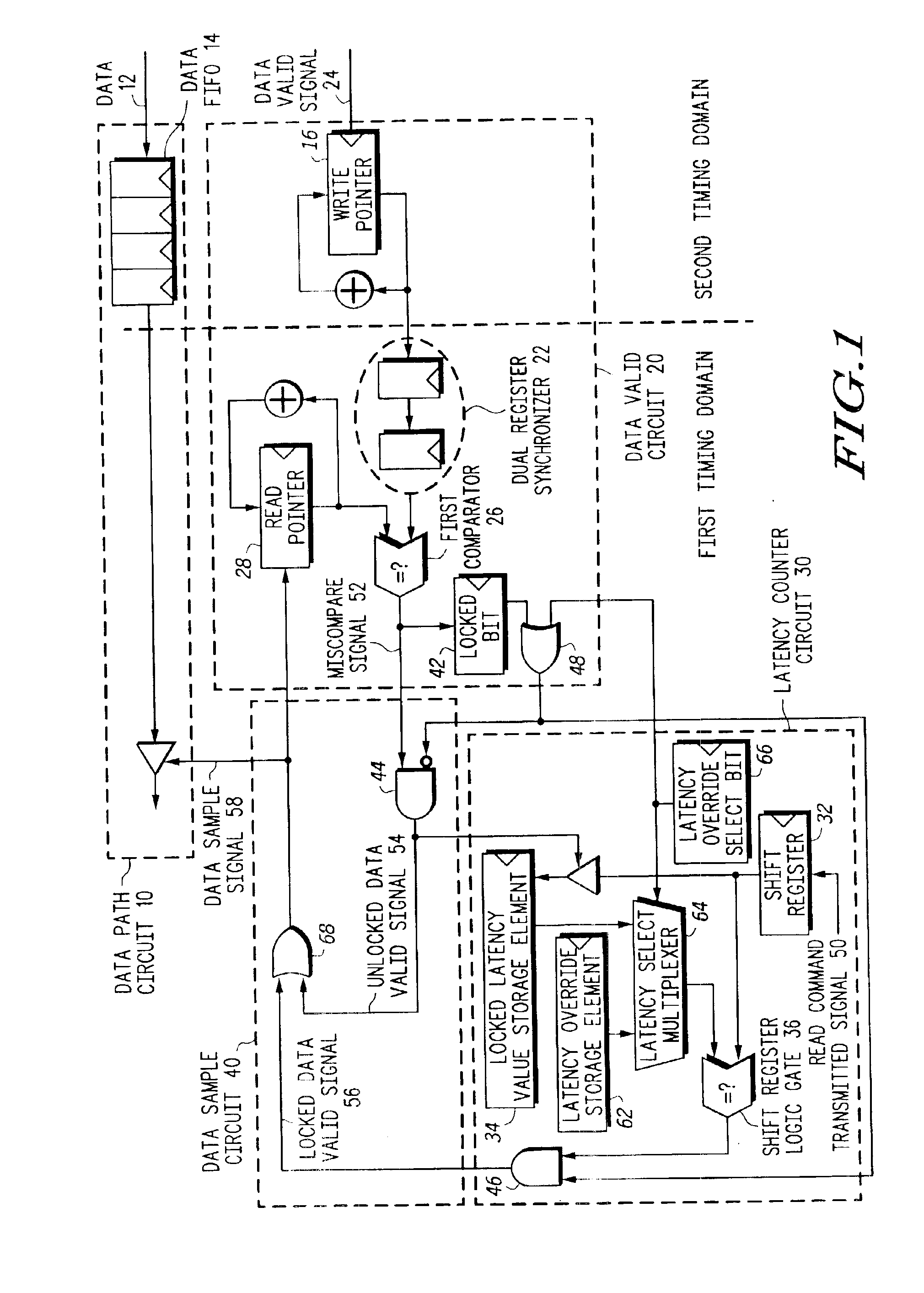

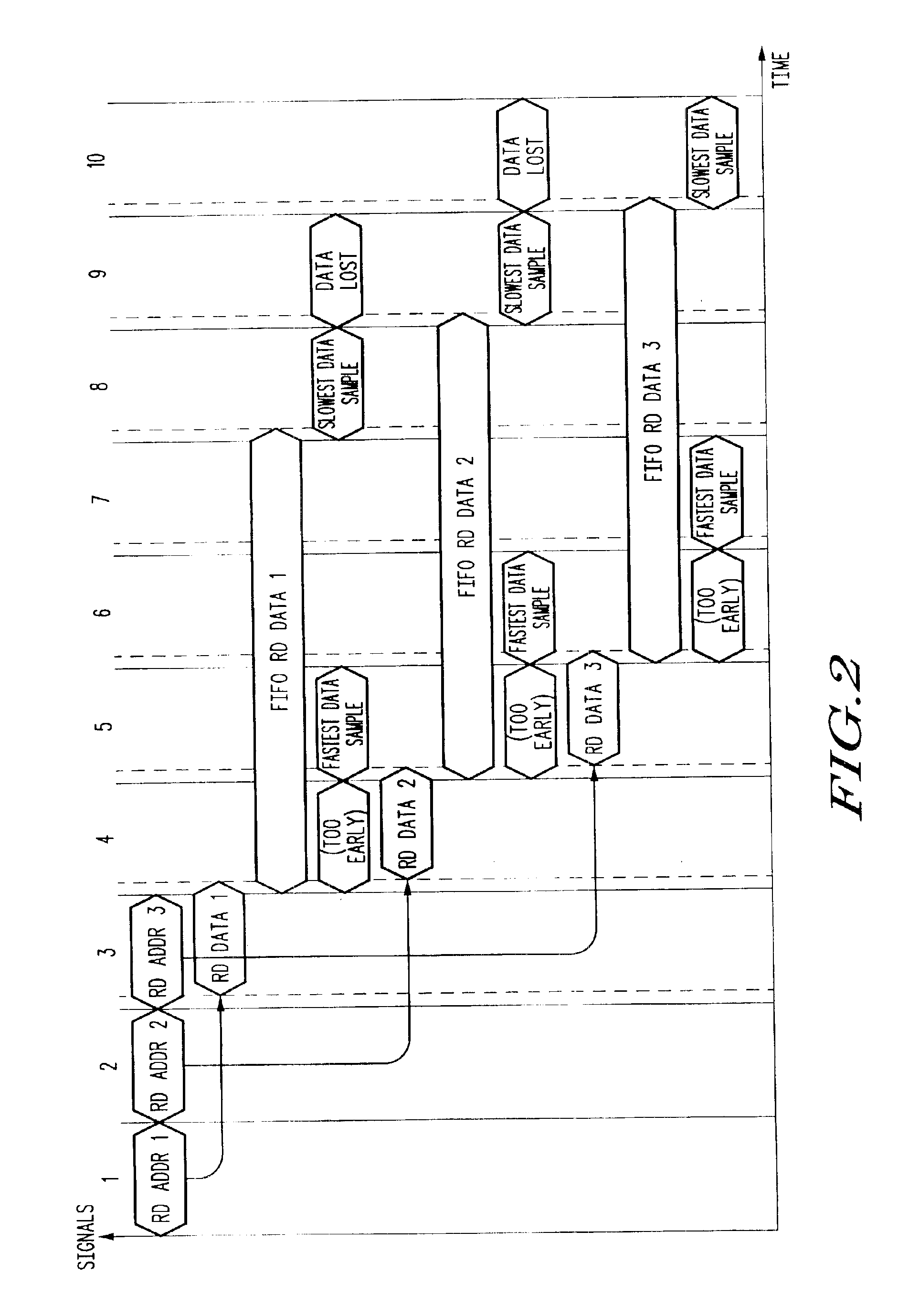

Automatic READ latency calculation without software intervention for a source-synchronous interface

InactiveUS6898682B2Unauthorized memory use protectionDigital storageMultiple deviceSource-synchronous

In response to a clock cycle and a pending READ command for data with a variably recurring access latency, a clock cycle count is adjusted. If a latency value has not been locked and if the READ command is a first READ command, the clock cycle count is stored as a locked latency value upon receiving a synchronized data available event (DQS for instance). Each subsequent READ command has an associated clock cycle count to enable pipelining wherein the clock cycle count for each READ starts incrementing when the individual READ command is issued. For subsequent READ commands, if the cycle count compares favorably with the locked latency value, data can be sampled safely from the interface at the identical latency for every READ request issued. The locked latency value can be read and / or written by software / hardware such that the read latency is consistent across multiple devices for reproducibility during debug.

Owner:NORTH STAR INNOVATIONS

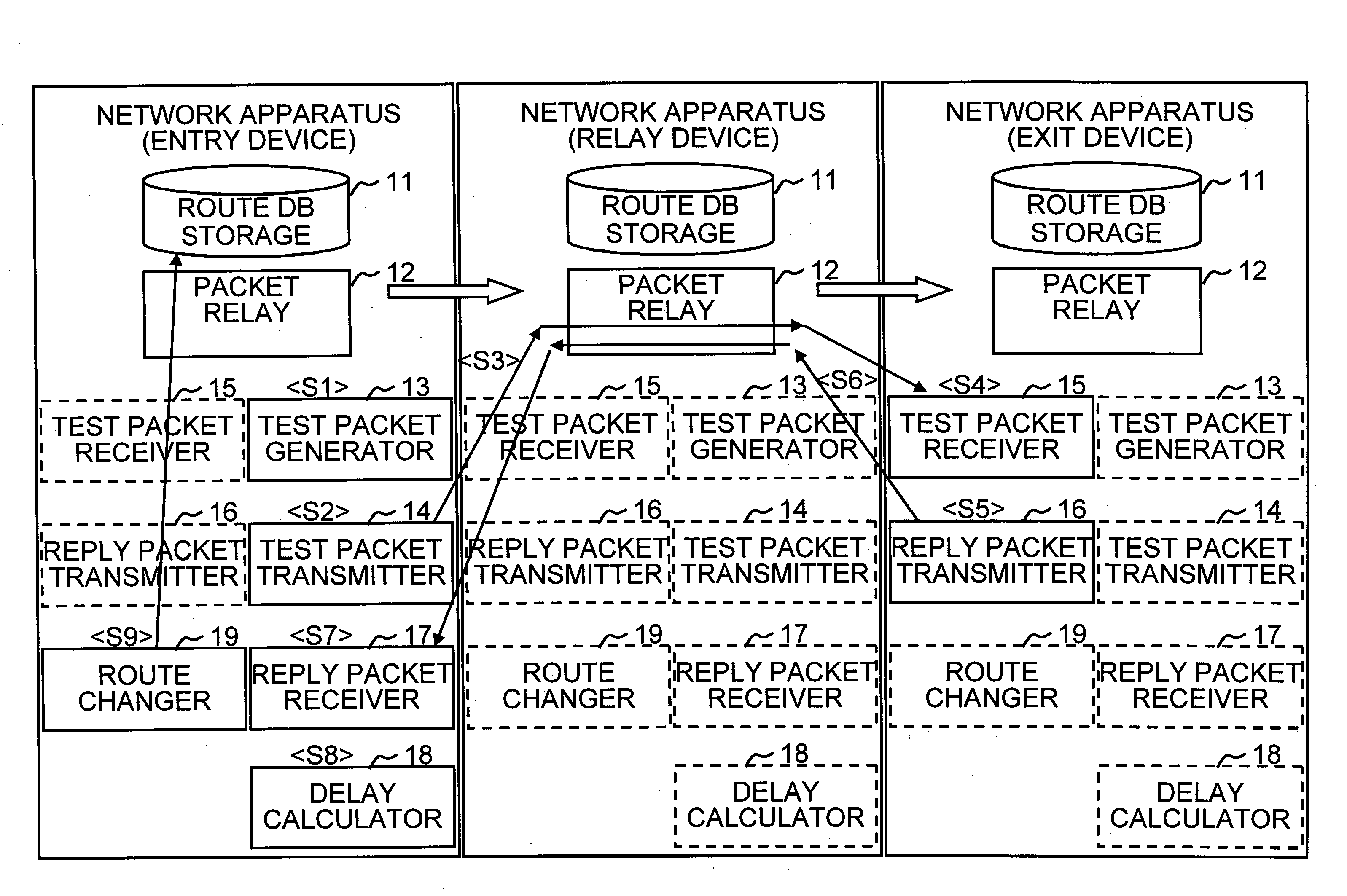

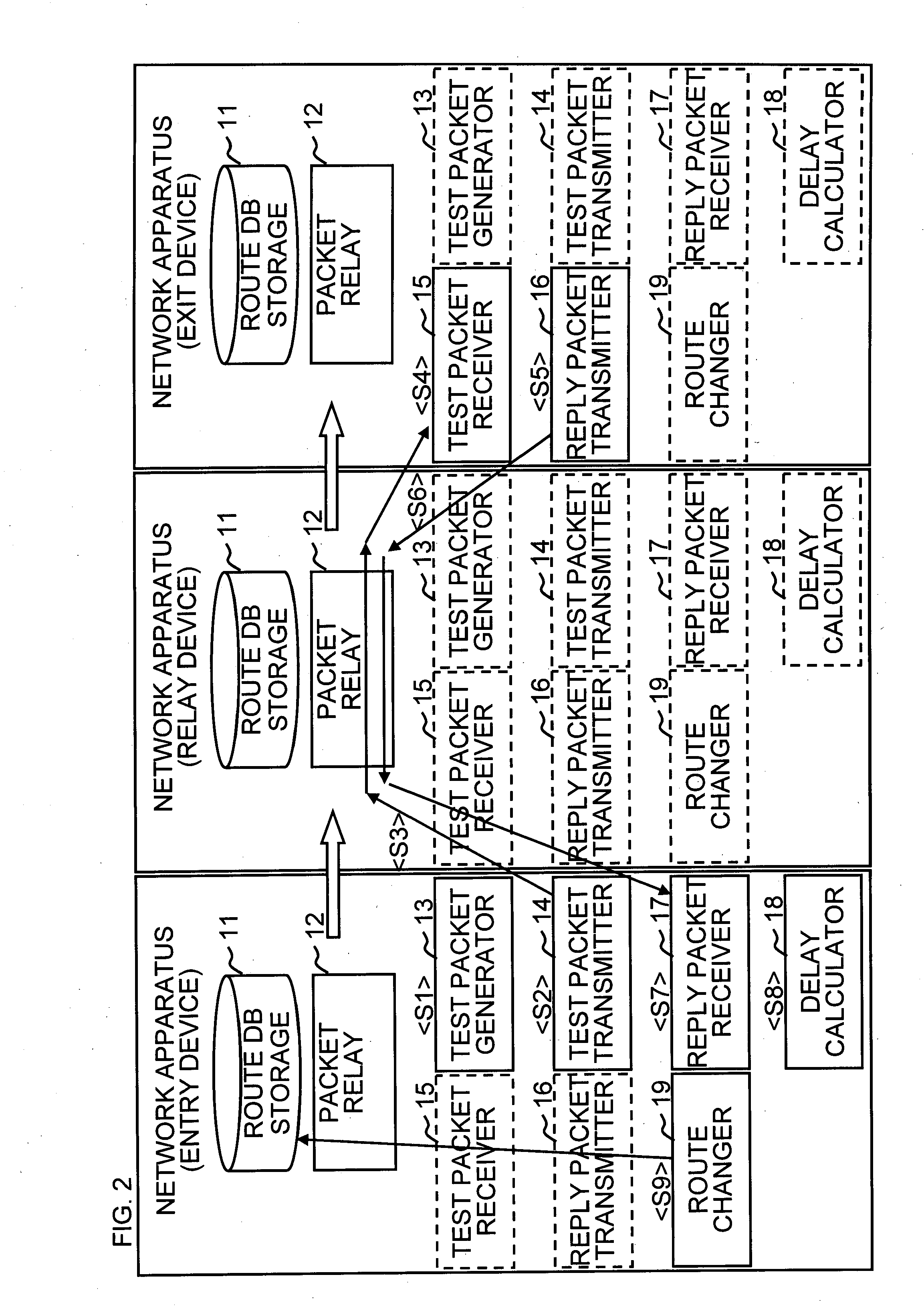

Network system, network apparatus, route change method, and program storage medium storing program thereof

InactiveUS20080117829A1Good serviceError preventionFrequency-division multiplex detailsPacket generatorNetworked system

A test packet generator of an entry device generates a delay test packet including priority information. A test packet transmitter of the entry device transmits the delay test packet to an exit device through a route corresponding to the priority information. A test packet receiver of the exit device receives the delay test packet. A reply packet transmitter of the exit device returns a reply-delay test packet toward the entry device through the same route in the counter direction. A reply packet receiver of the entry device receives the reply-delay test packet. A delay calculator of the entry device calculates a delay time on the basis of the time of transmitting the delay test packet and the time of receiving the reply-delay test packet. A route changer of the entry device changes routing appropriately on the basis of the delay time.

Owner:FUJITSU LTD

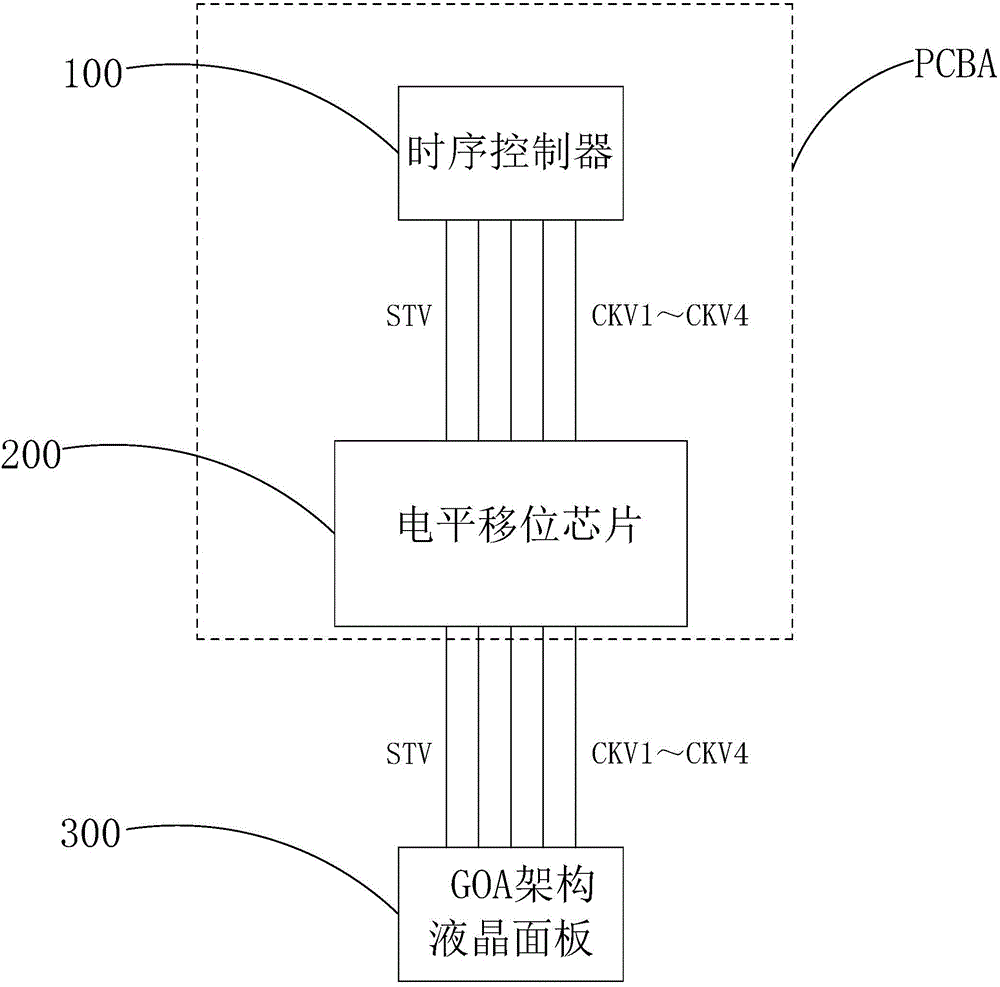

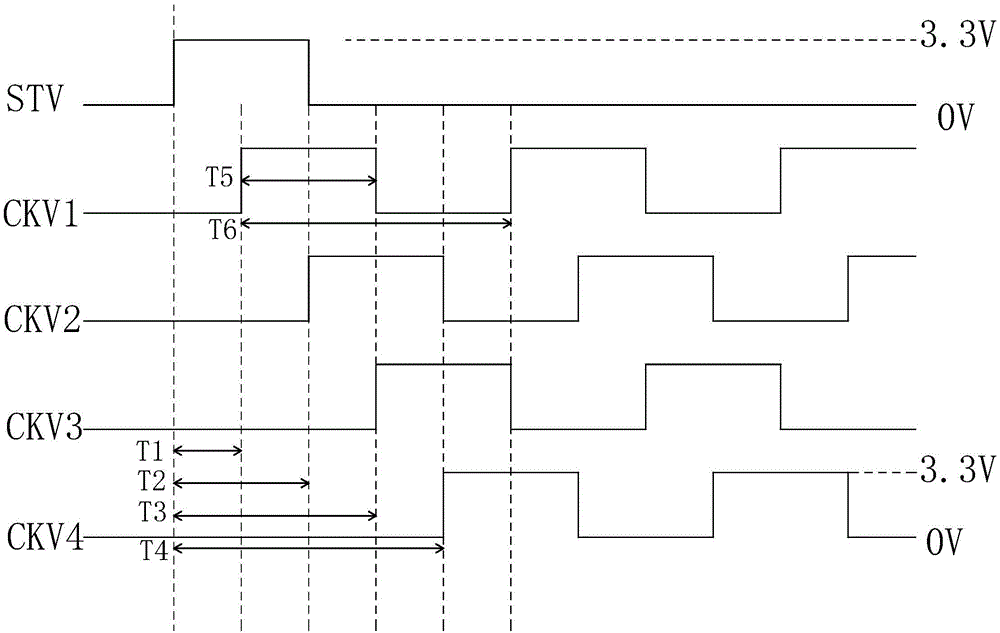

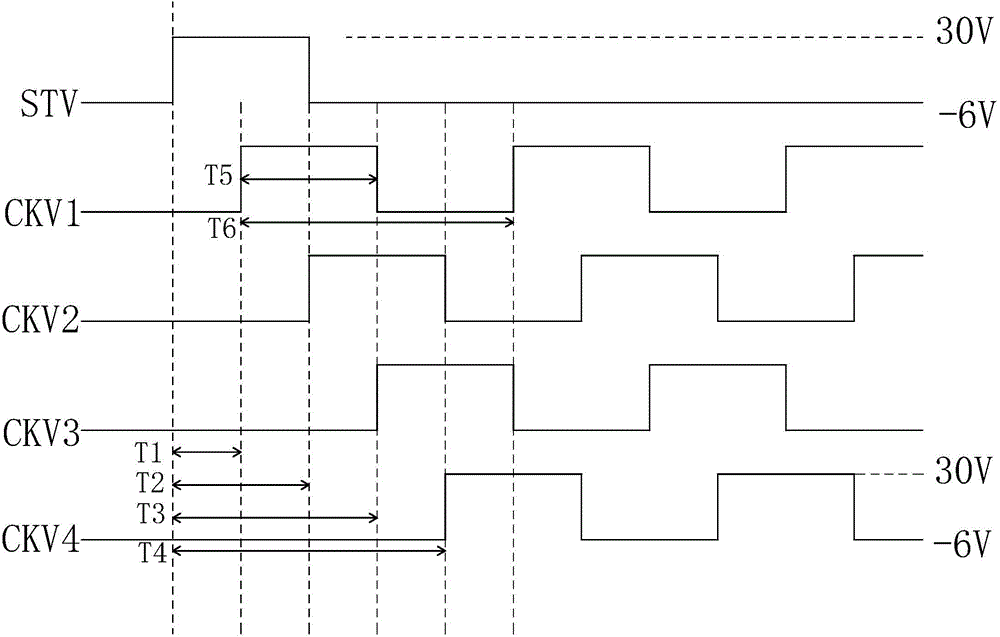

Level shifting circuit and method for GOA-framework liquid crystal panel

ActiveCN104680991AReduced package numberReduced pin countStatic indicating devicesLevel shiftingComputer module

The invention provides a level shifting circuit and method for a GOA-framework liquid crystal panel. A delay calculation and registration module (201) is arranged inside a level shifting chip (20); a time sequence controller (10) is in communication connection with the level shifting chip (20) through a start signal line (30) and an IIC bus (40); the time sequence controller (10) performs initialized assignment (T1-Tn) on the delay calculation and registration module (201) through the IIC bus (40), and sends a start signal (STV) to the level shifting chip (20) through the start signal line (30); with the start signal (STV) as a reference, the level shifting chip (20) triggers to output at least four groups of time sequence signals (CKV1-CKVn) according to the initialized assignment (T1-Tn) in the delay calculation and registration module, and boosts the start signal (STV) and the voltages of at least four groups of time sequence signals (CKV1-CKVn)) so as to drive the GOA-framework liquid crystal panel (50), so that more time sequence signals are generated at the relatively low cost.

Owner:TCL CHINA STAR OPTOELECTRONICS TECH CO LTD

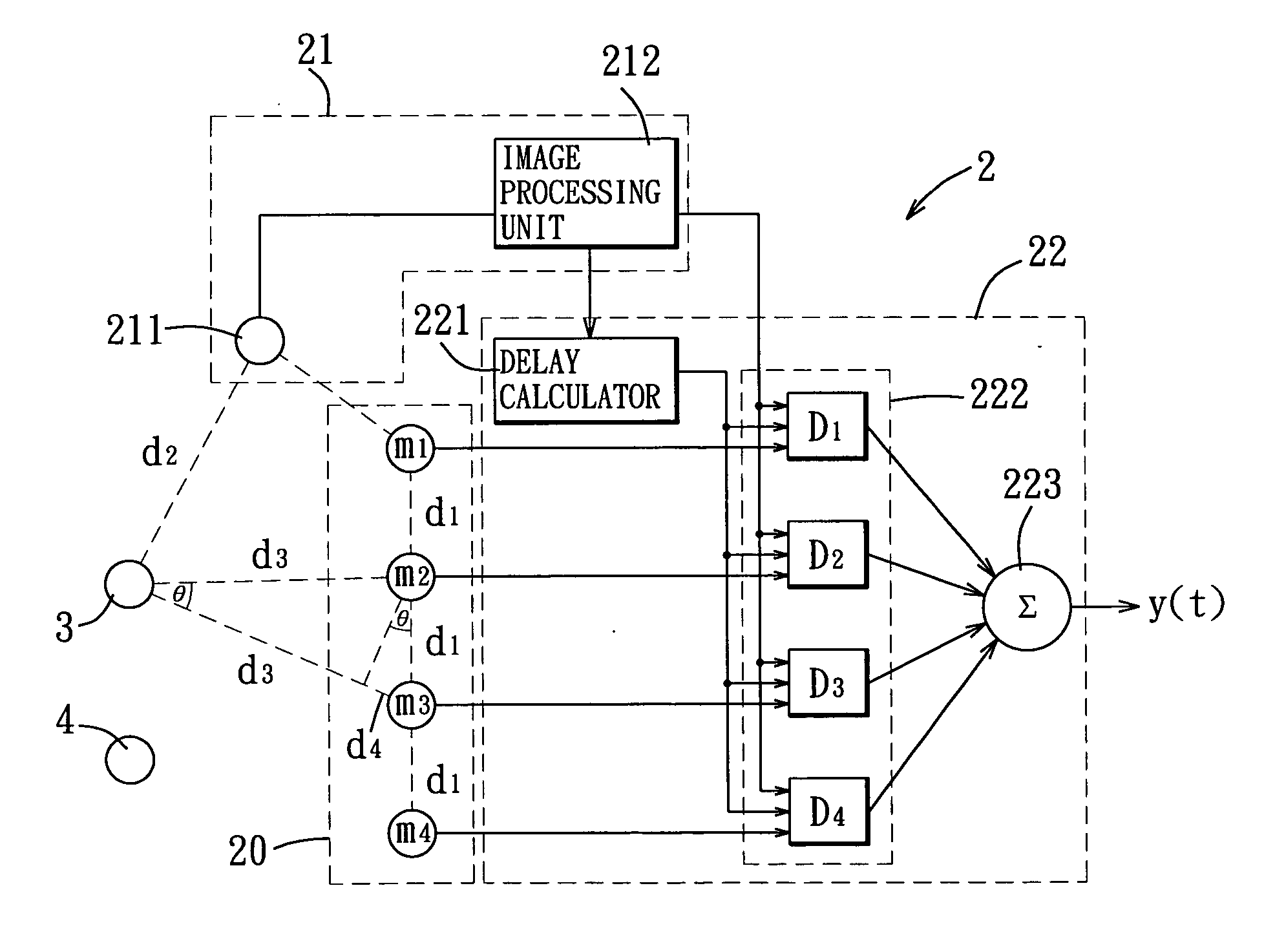

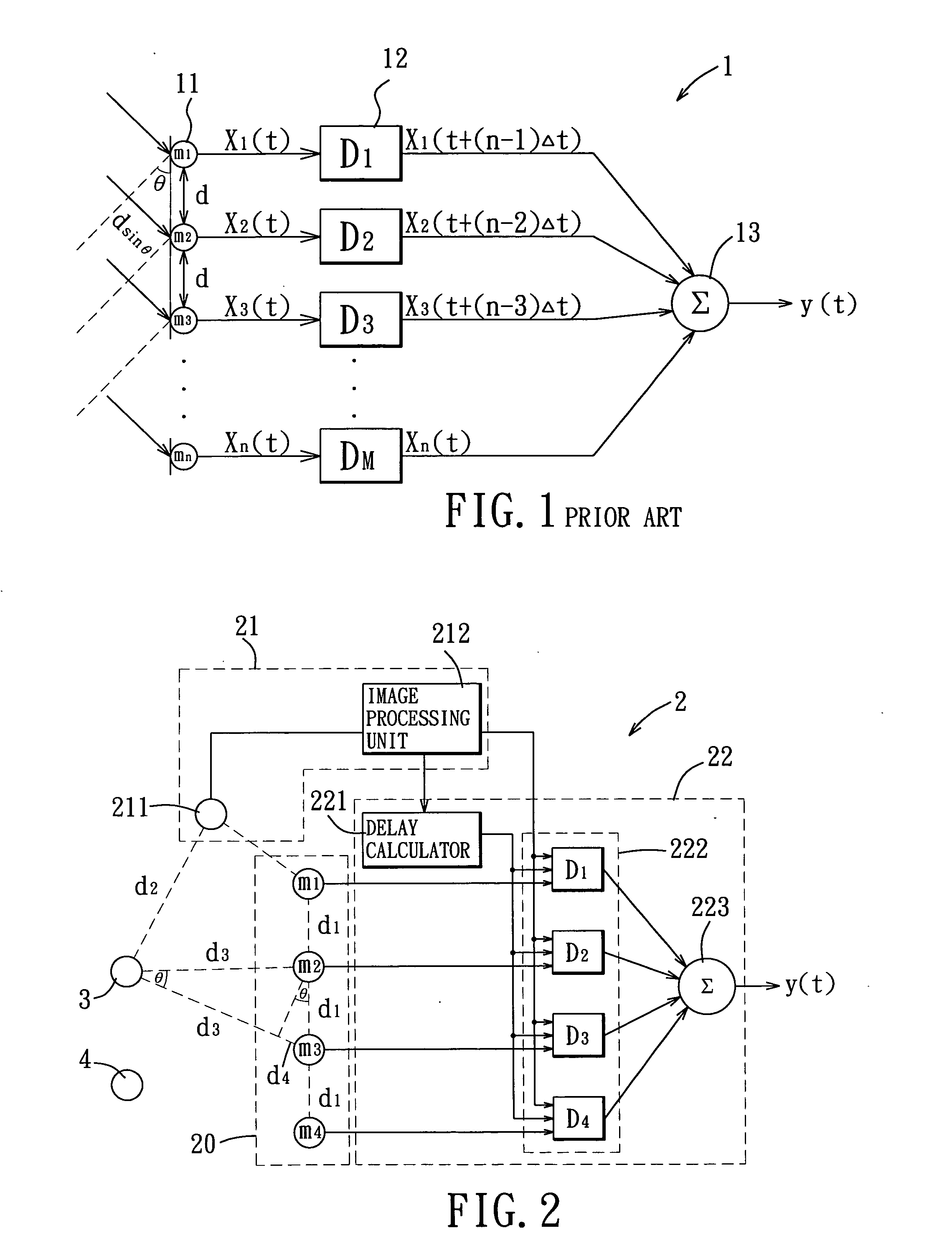

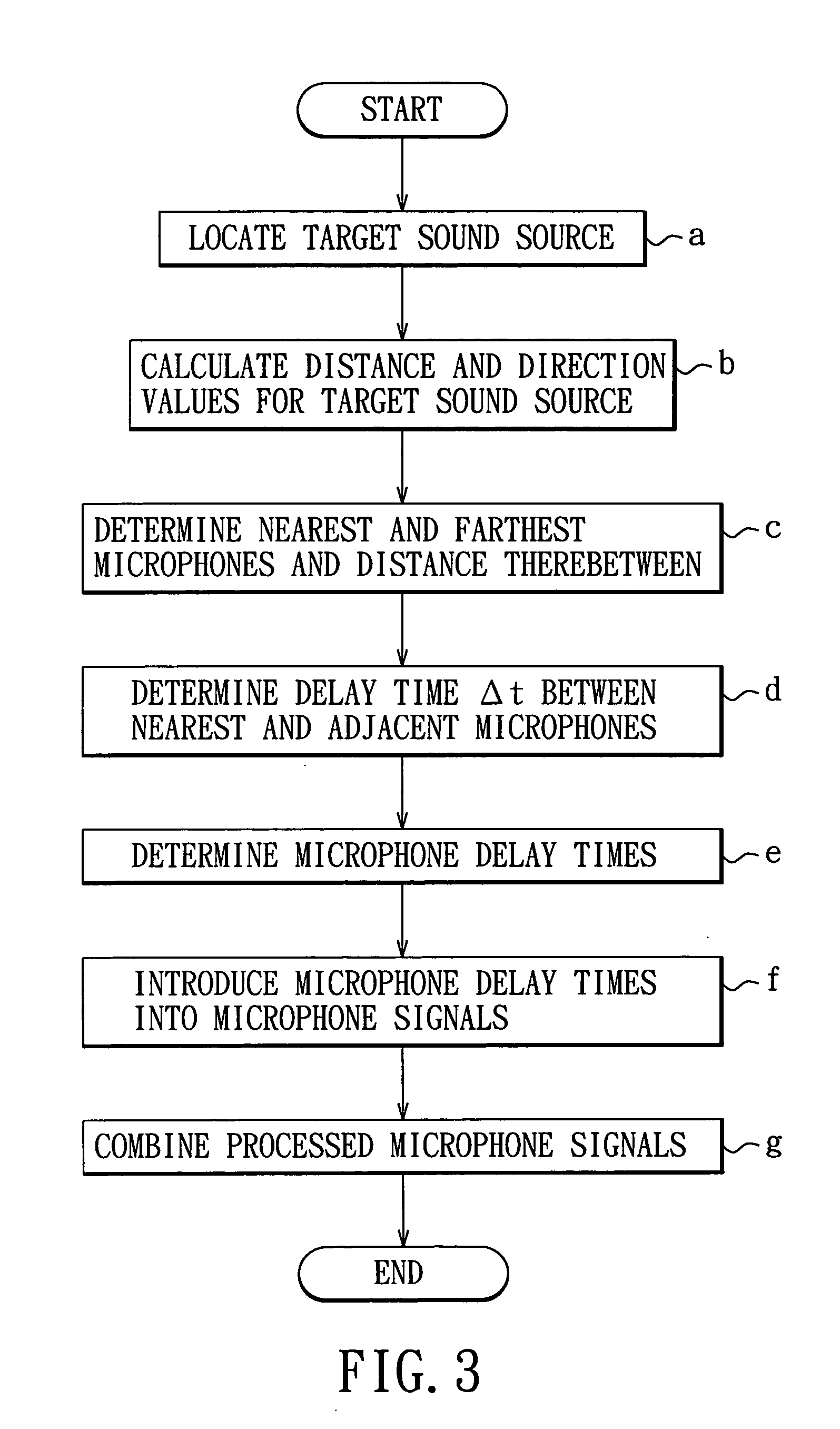

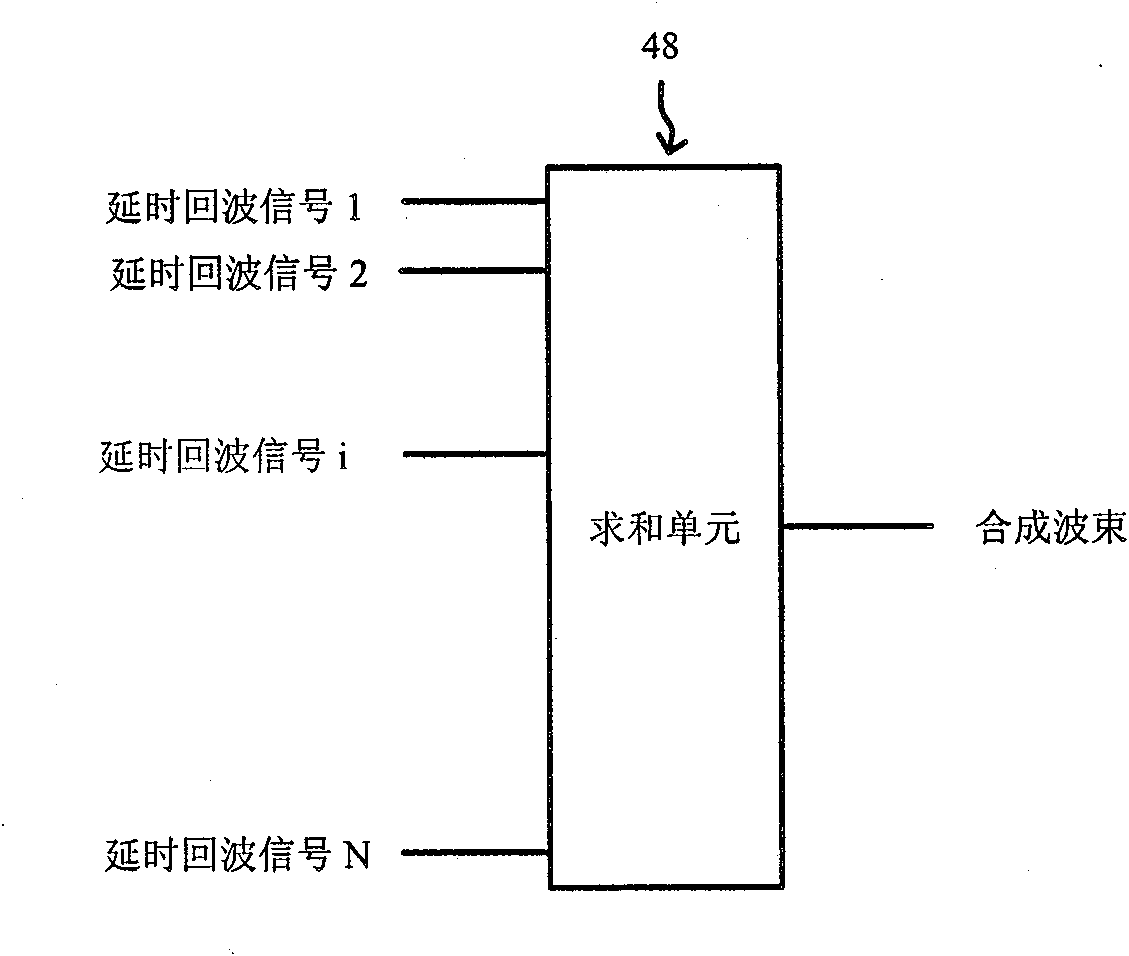

Sound pickup method and system with sound source tracking

A sound pickup system includes a sound source tracking device that is operable to obtain distance and direction values of a target sound source relative to the sound source tracking device, and that determines nearest and farthest ones of a plurality of microphones in a microphone array relative to the target sound source with reference to determined distances of the sound source tracking device from the microphones, and the distance and direction values obtained by the sound source tracking device. A signal processing unit includes a delay calculator for determining appropriate time delays for the microphones with reference to information from the sound source tracking device, and a delay processor for processing signals generated by the microphones in the microphone array by introducing the corresponding time delays determined by the delay calculator into the signals from the microphones.

Owner:ACER INC

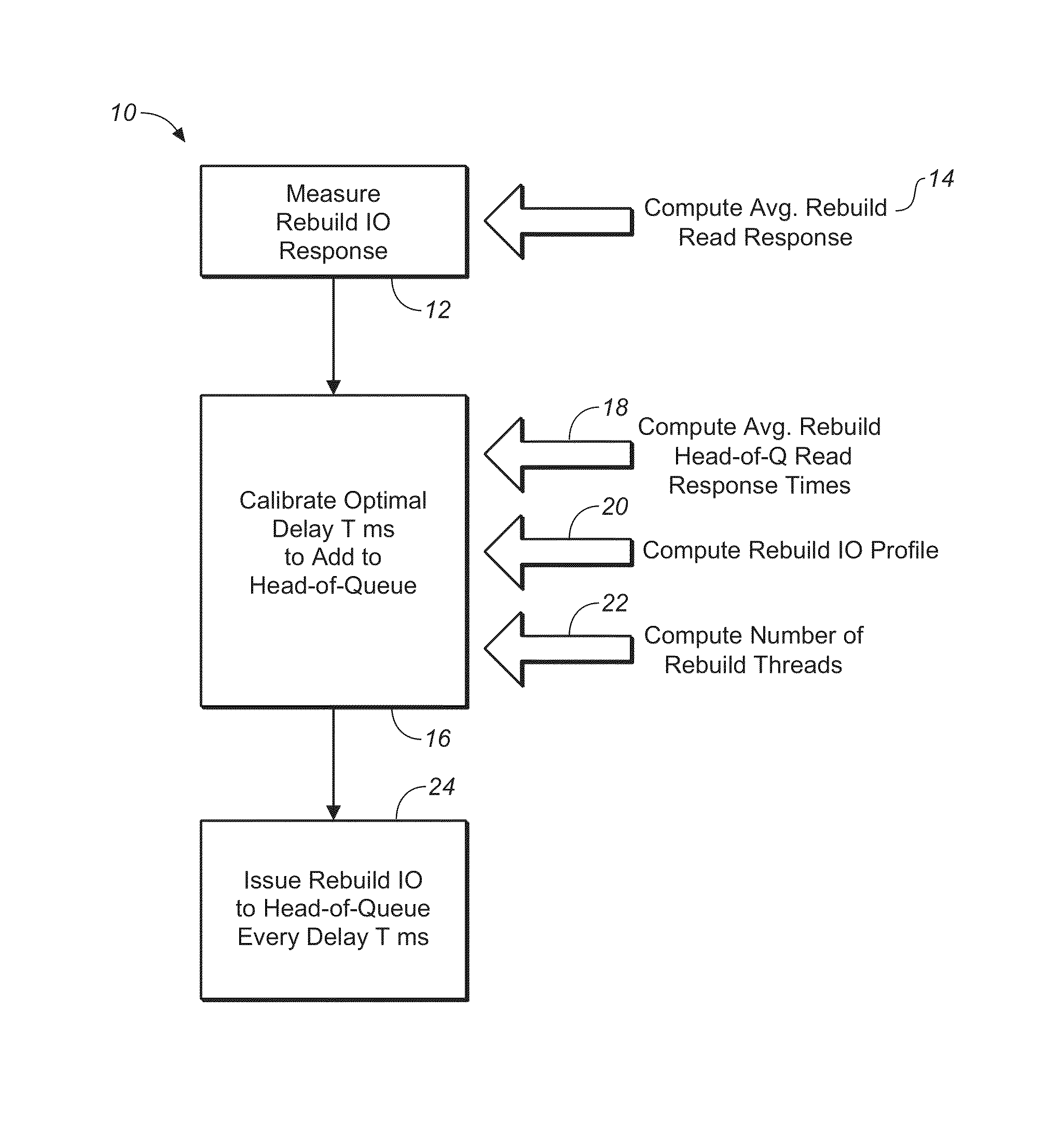

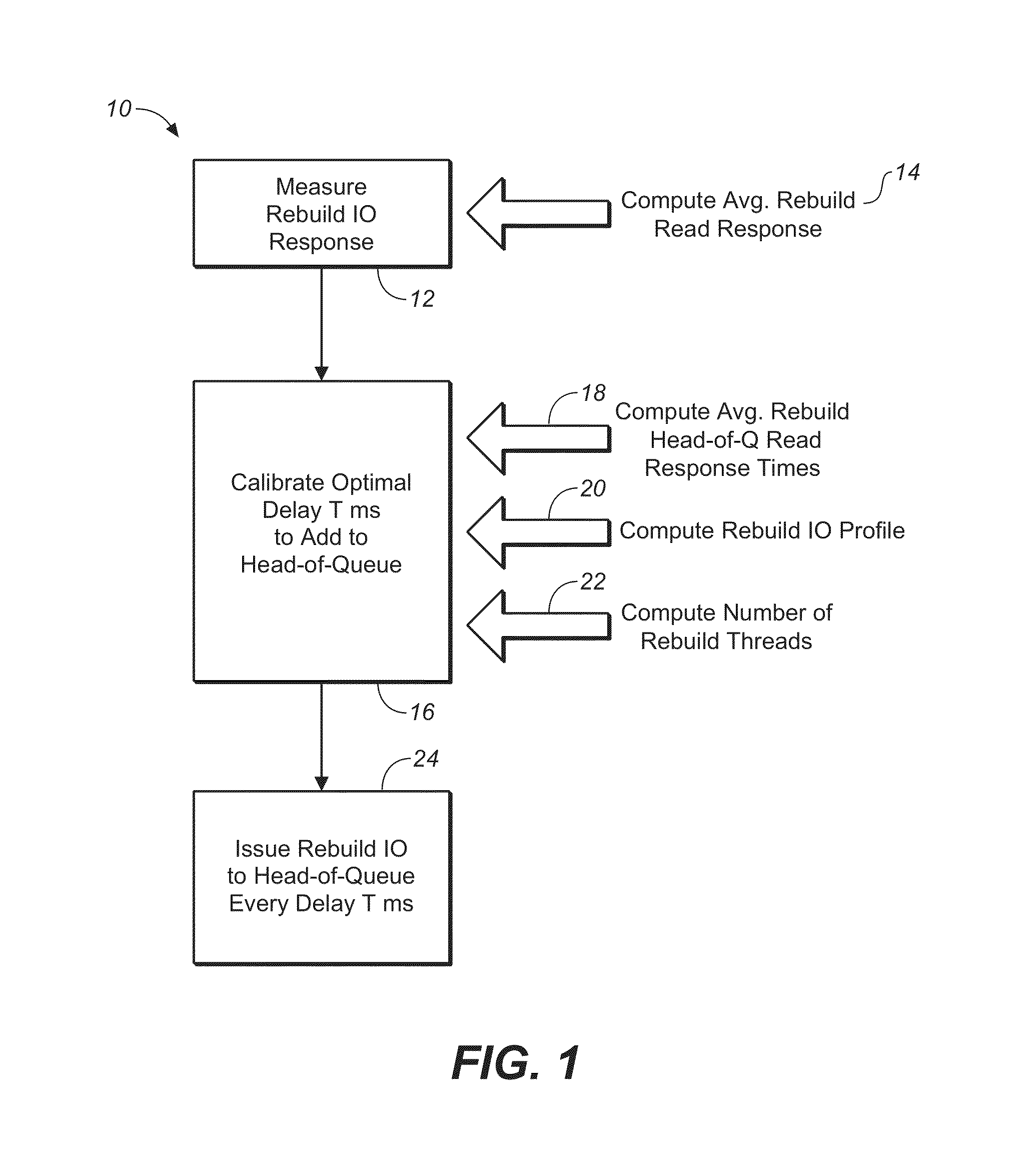

System and method for improved rebuild in RAID

ActiveUS8751861B2Extension of timeIncrease delayMemory loss protectionRedundant hardware error correctionRAIDHeuristic function

Owner:AVAGO TECH INT SALES PTE LTD

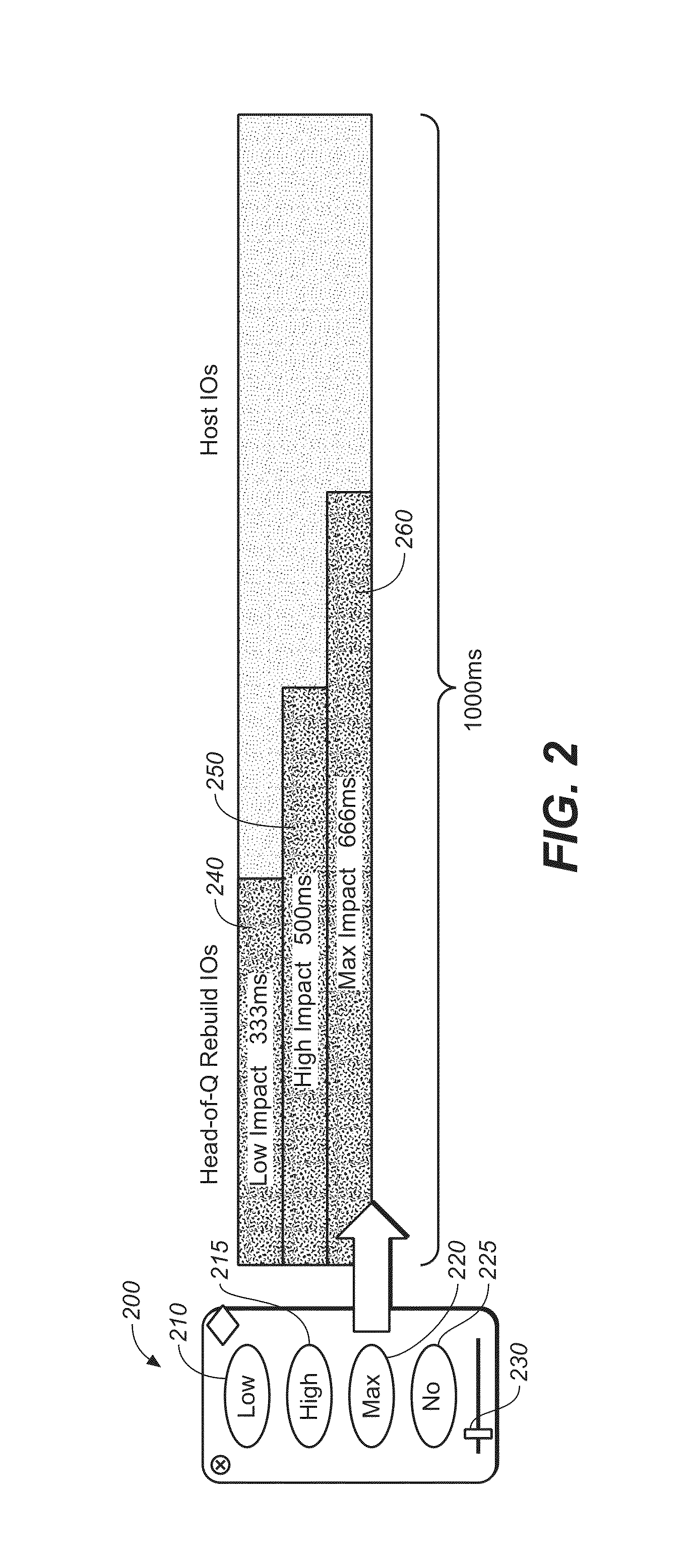

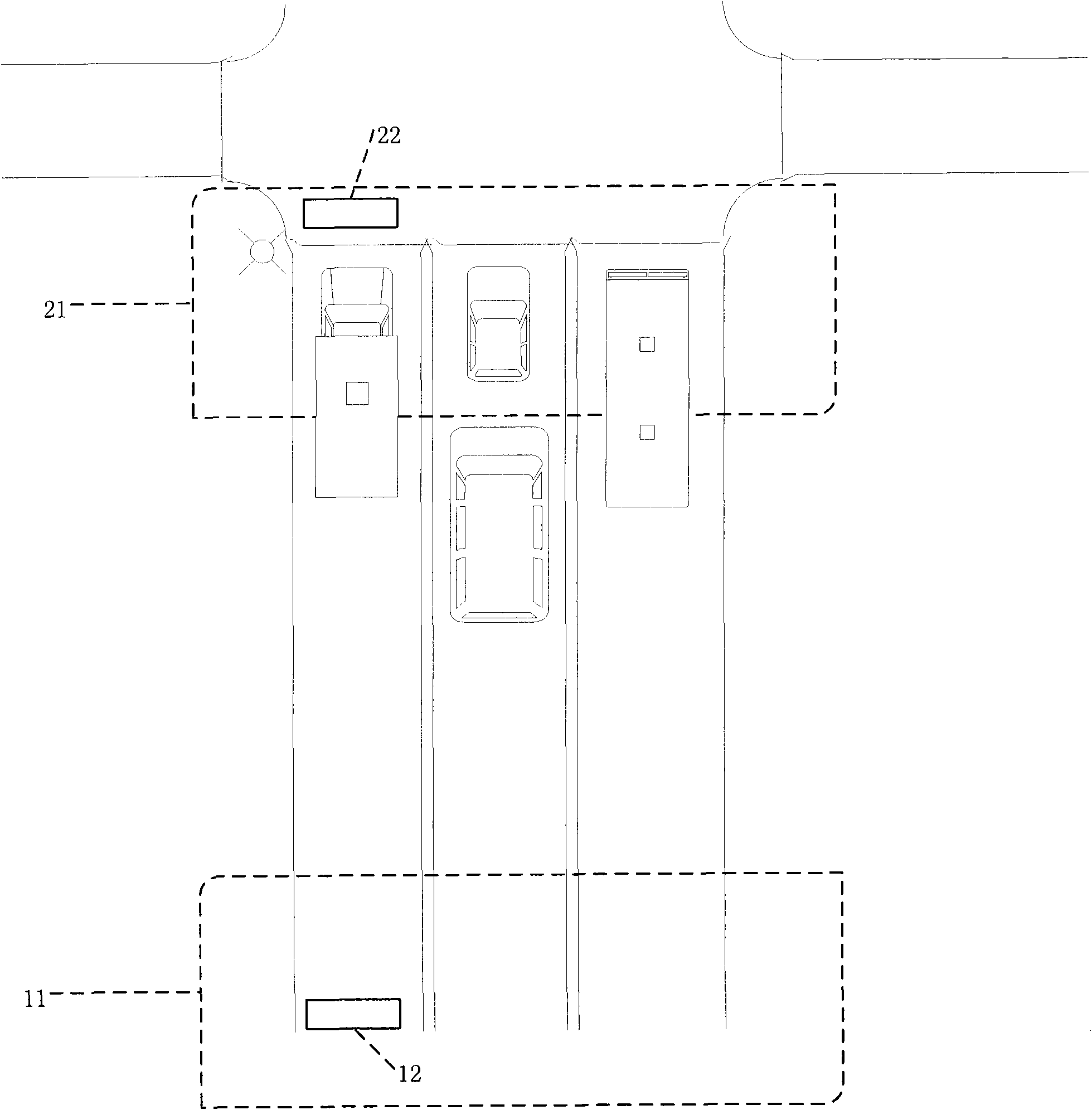

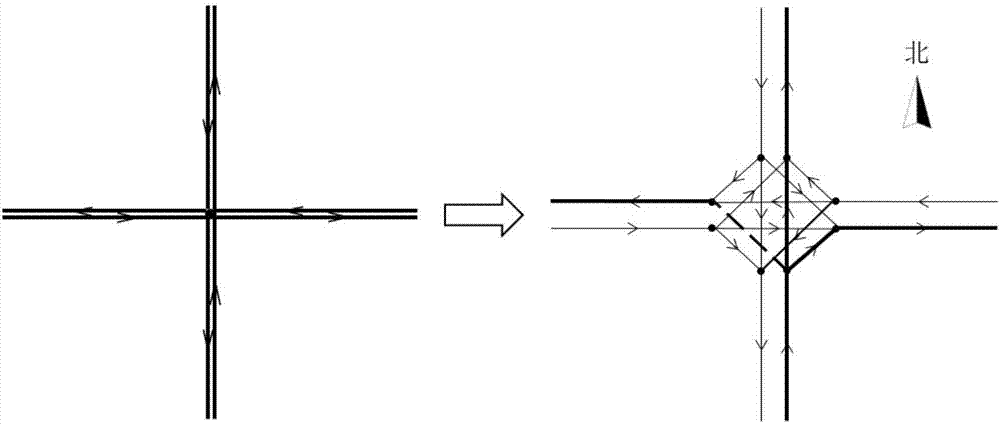

Method for acquiring mean delay of urban road junction

InactiveCN101777259AGet the average delay value accuratelyAvoid heavy dependenceDetection of traffic movementVehicle detectionTime headway

The invention relates to a method for acquiring the mean delay of an urban road junction. The method comprises the following steps of: (1) double section selection: firstly, respectively mounting a plurality of cameras at an inlet passage and an outlet passenger of a junction, and then drawing a virtual detection frame used for detecting vehicles; (2) vehicle detection and traffic flow counting: carrying out information acquisition by utilizing the virtual detection frame, and carrying out vehicle detection in each frame of an acquired video; (3) queue length calculation: detecting the changes of time headway by adopting the virtual detection frame so as to distinguish queue vehicles and non-queue vehicles; and (4) delay value calculation according to a one-to-one principle: calculating according to last data in a inlet passage detector recording list, adopting a calculation policy and eliminating an accumulated error so as to ensure that an error is controlled within the range of theperiod without influencing other periods. The invention has the advantages of simple and convenient calculation, high operation speed, good stability, high reliability, and the like.

Owner:TONGJI UNIV

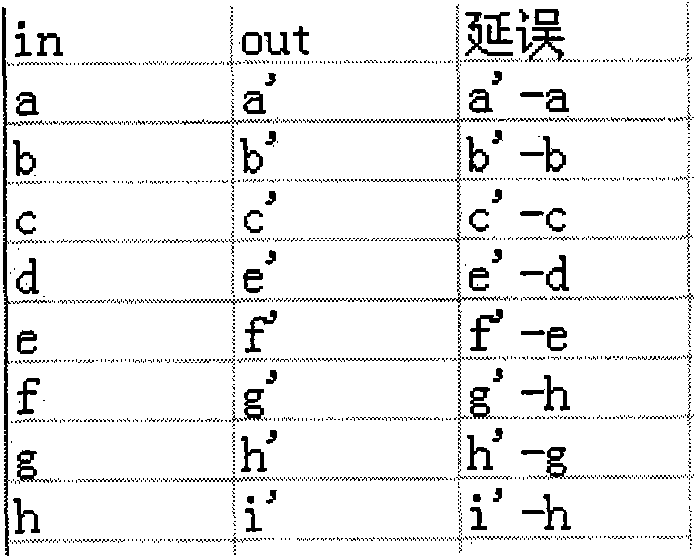

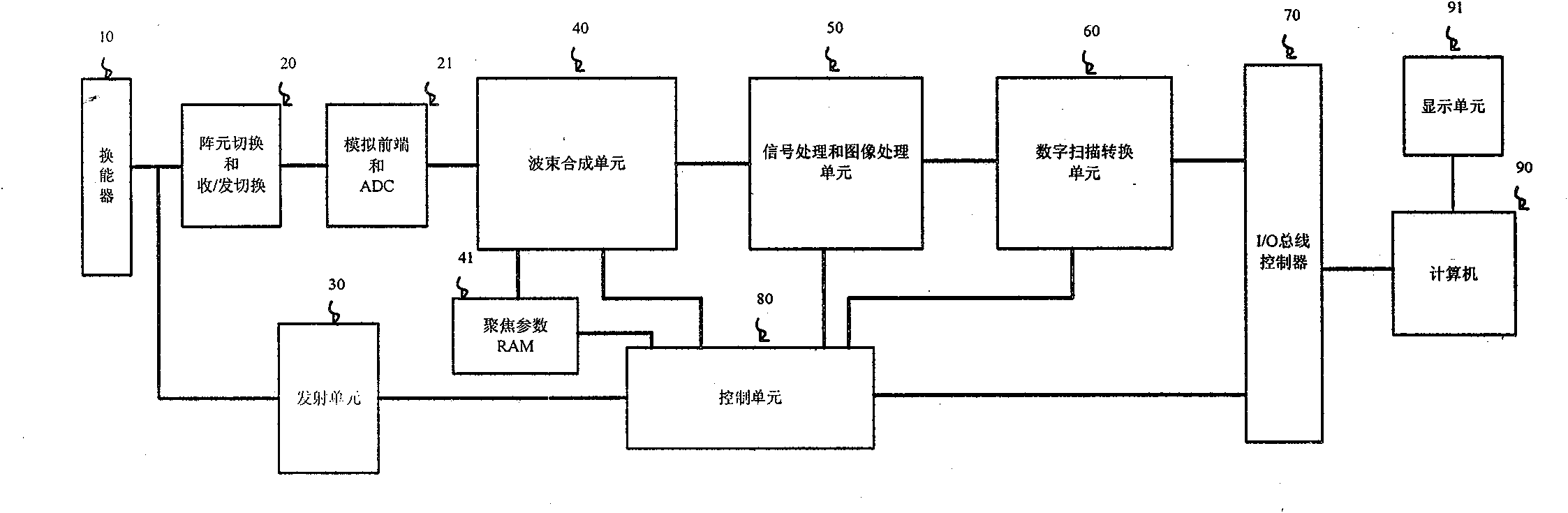

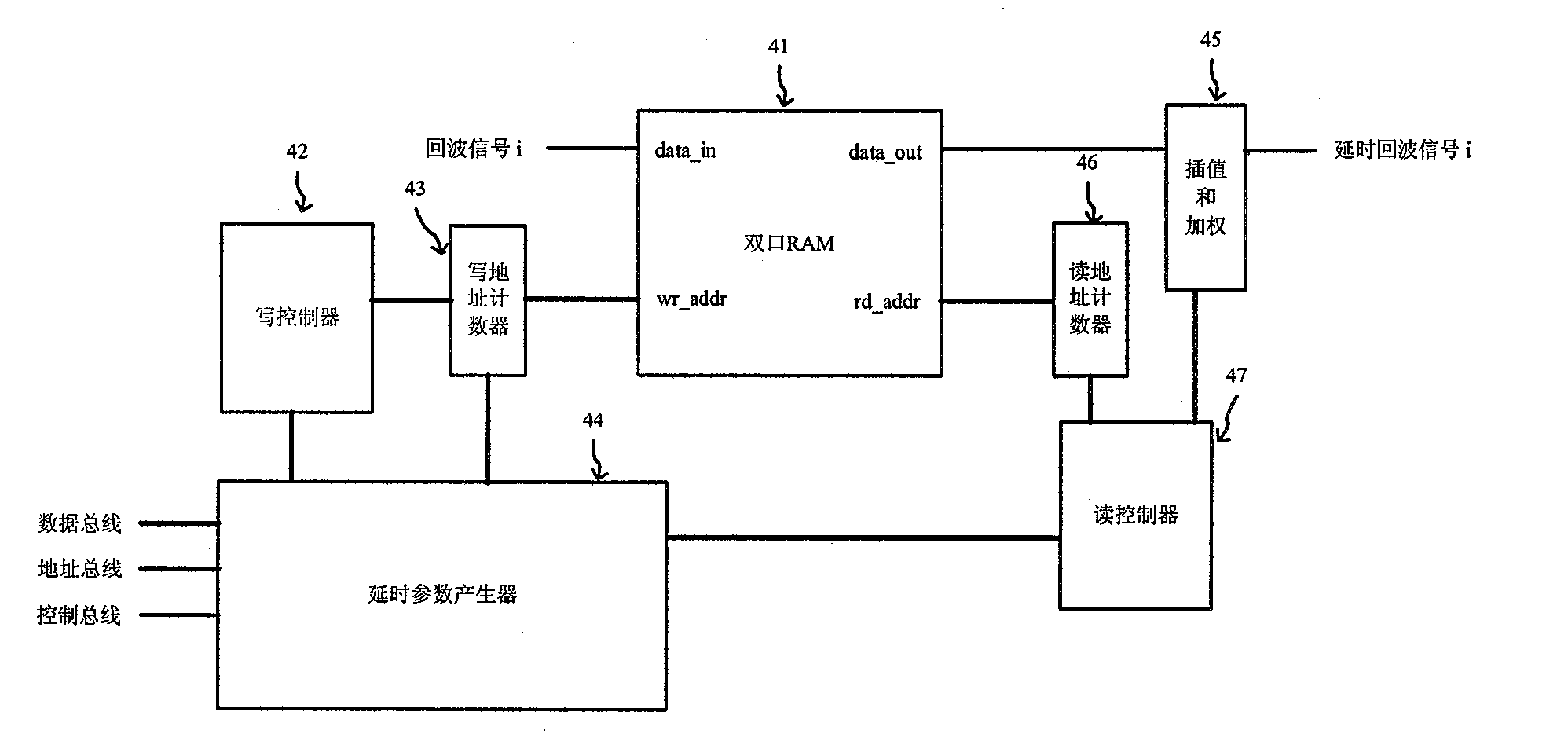

Multi-beam synthesis method and device based on delay parameter real-time calculation and assembly line

InactiveCN101858972AUltrasonic/sonic/infrasonic diagnosticsInfrasonic diagnosticsSynthesis methodsAssembly line

The invention relates to a multi-beam synthesis method and device based on delay parameter real-time calculation and assembly line. The device utilizes the separation of parameters requiring real-time calculation and parameters not requiring real-time calculation in delay calculation, the parameters related to the sequence number of beams and the separation of unrelated parameters to design the real-time delay calculation unit which only performs simple switching to adapt to different types of probes. The calculation unit adopts assembly line design, the delay parameters of M-numbered beams are calculated in the calculation unit in the assembly line mode and then the echo data storage units in the same path are read to realize delay of each beam. Therefore, the consumption of resources inFPGA is greatly reduced. The device of the invention uses direct calculation to obtain high delay precision. In order to solve the problem that too many hardware resources are occupied, the device ofthe invention adopts the assembly line design to ensure that M-numbered beams commonly use the delay parameter calculation unit, thus largely reducing the consumption of hardware resources.

Owner:SHENZHEN LANDWIND IND

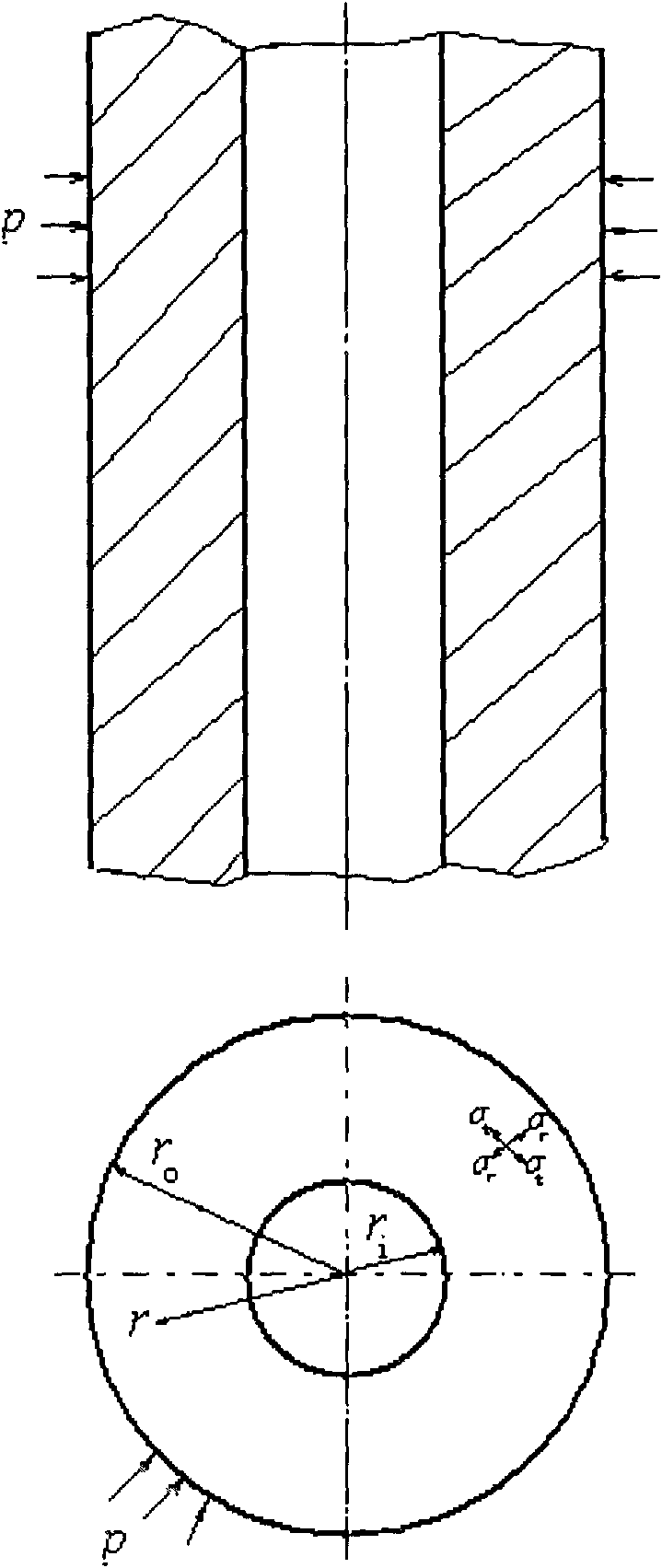

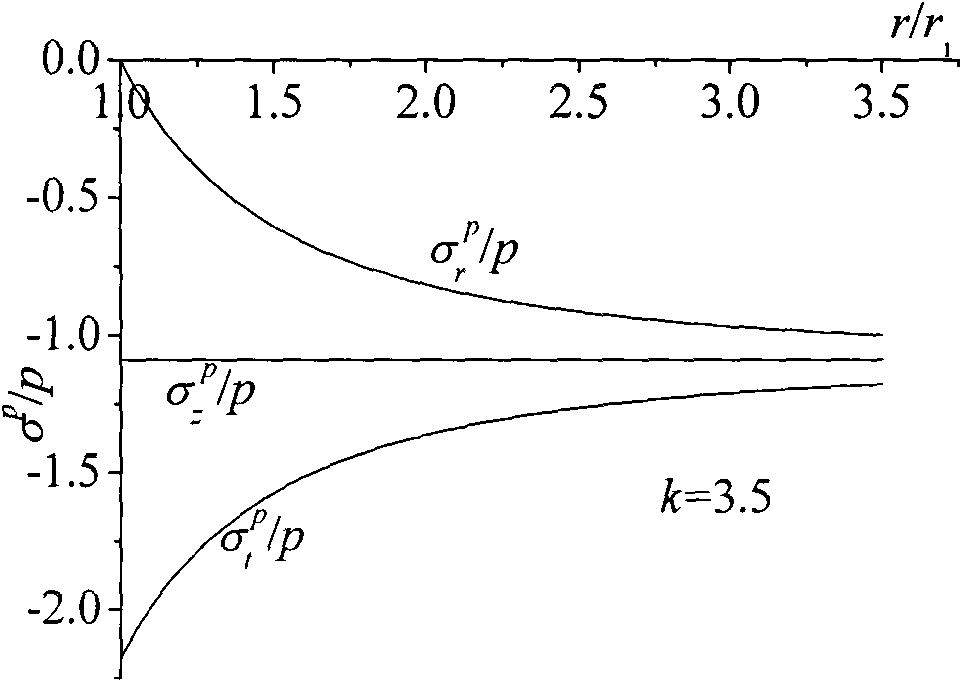

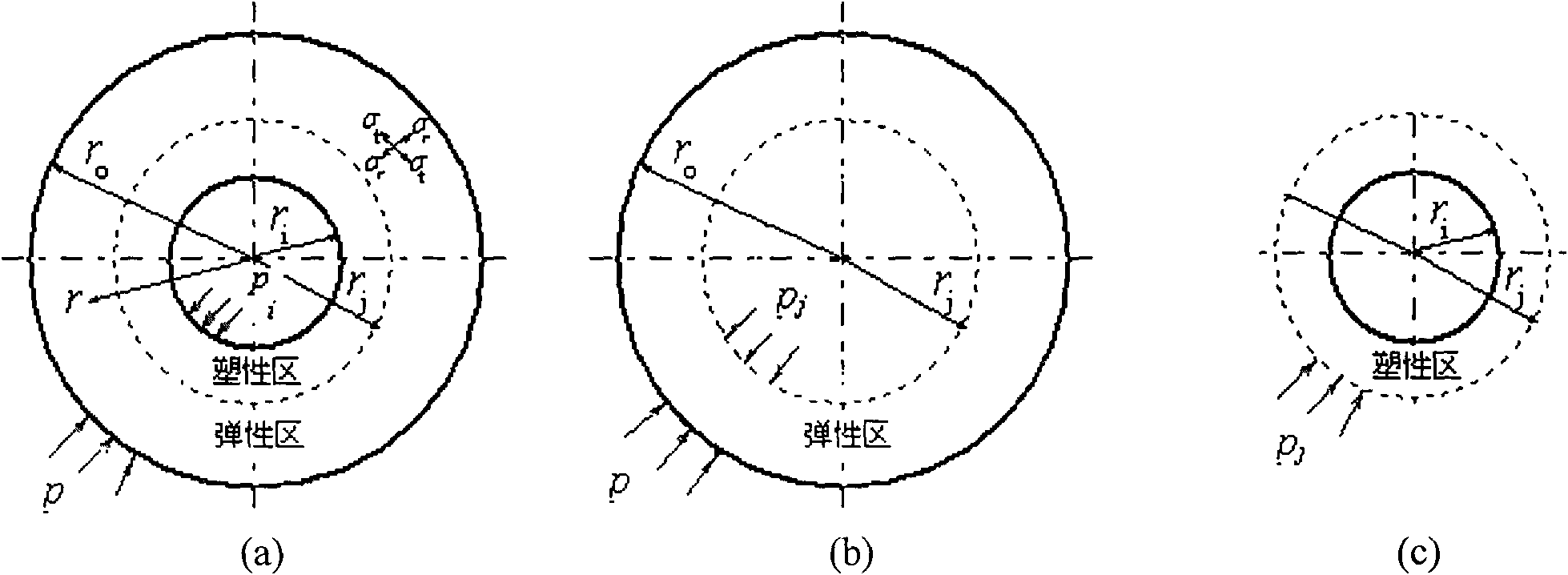

External pressure self-intensification cylinder and design calculation and manufacturing method thereof

InactiveCN101655829AFill vacancyPressure vesselsSpecial data processing applicationsInternal pressureMaximum diameter

The invention discloses an external pressure self-intensification cylinder and a design calculation and a manufacturing method thereof, which is used for improving the safety and the bearing capability of a pressure vessel and solving the phenomenon of lacking external pressure self-intensification vessel design calculation and manufacturing methods and the technical problems of unsafety and the like caused by complex or inaccurate design calculation of the existing internal pressure self-intensification technology. The invention has the following technical scheme key points: adopting a special bearing capability, plastic zone depth and cylinder wall thickness calculating formula to ensure that the equivalent stress of the total stress (the sum of stress caused by operation pressure and self-intensification residual stress) in the wall of the cylinder is not more than the yield strength sigma y of cylinder material; or ensuring that the equivalent stress of the residual stress in the whole cylinder wall of the self-intensification cylinder and the equivalent stress of the total stress are both not more than sigma y. The invention also provides a maximum diameter ratio which does not yield after the self-intensification pressure is removed no mater how deep the plastic zone is when the self-intensification technology is applied. The technical scheme of the invention is also suitable for an internal pressure self-intensification cylinder.

Owner:HUNAN NORMAL UNIVERSITY

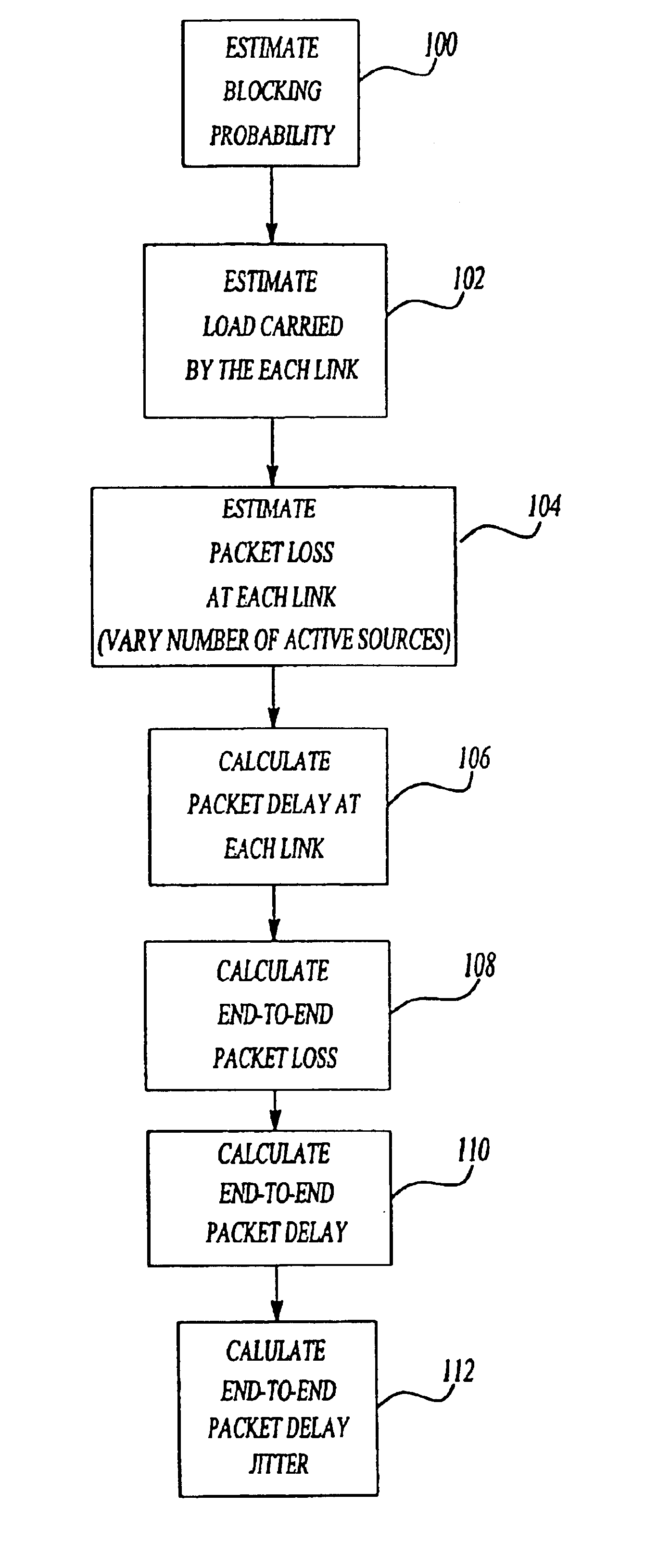

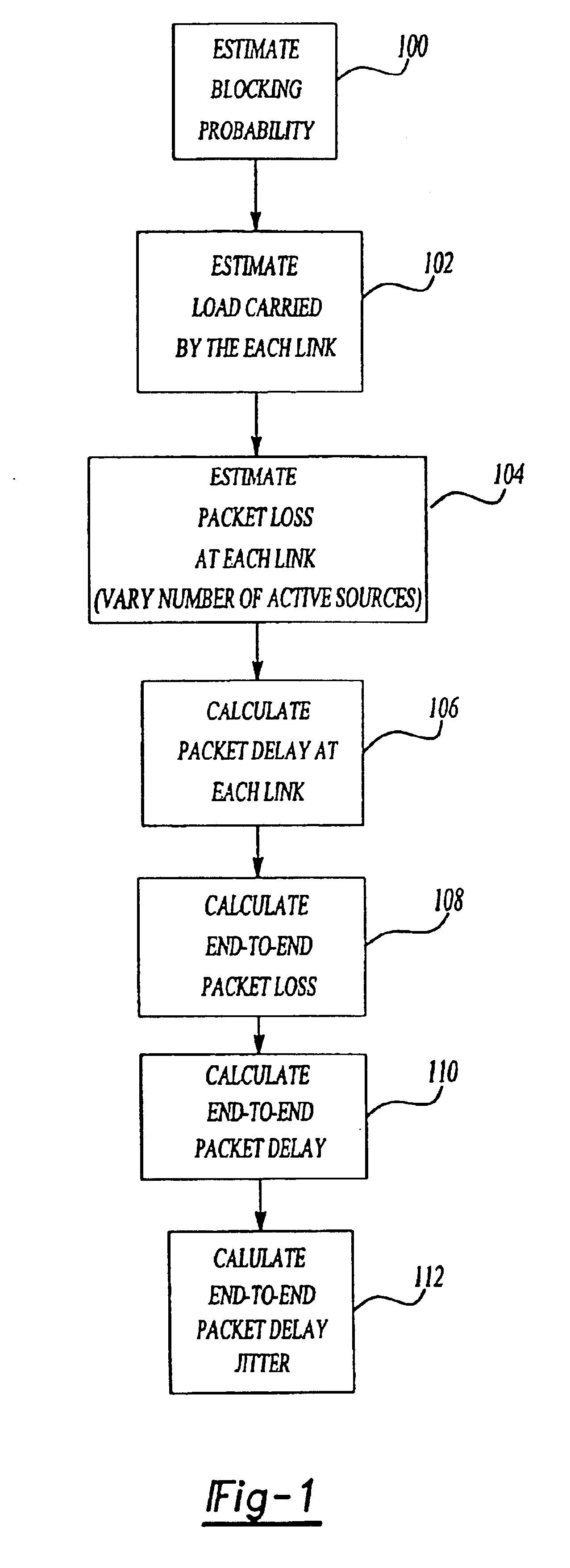

Method and system for estimating performance metrics in a packet-switched communication network

InactiveUS6912216B1Enhances network planningOptimize networkError preventionTransmission systemsQuality of servicePacket loss

A method for estimating end-to-end quality of service (QOS), such as packet loss, delay, and delay jitter, in a packet-switched communications network includes steps for calculating packet loss and packet delay each router output link in a network path and using the packet loss and packet delay calculations for each individual router output link to estimate end-to-end QOS. The method includes calculating the loss probability for all possible numbers of active sources to take into account changes in the number of active sources as active sources connect to and disconnect from the network. As a result, the inventive method allows the number of active sources to vary in its estimation of end-to-end packet loss, delay, and delay jitter for enhanced Internet Protocol network planning.

Owner:VERIZON LAB

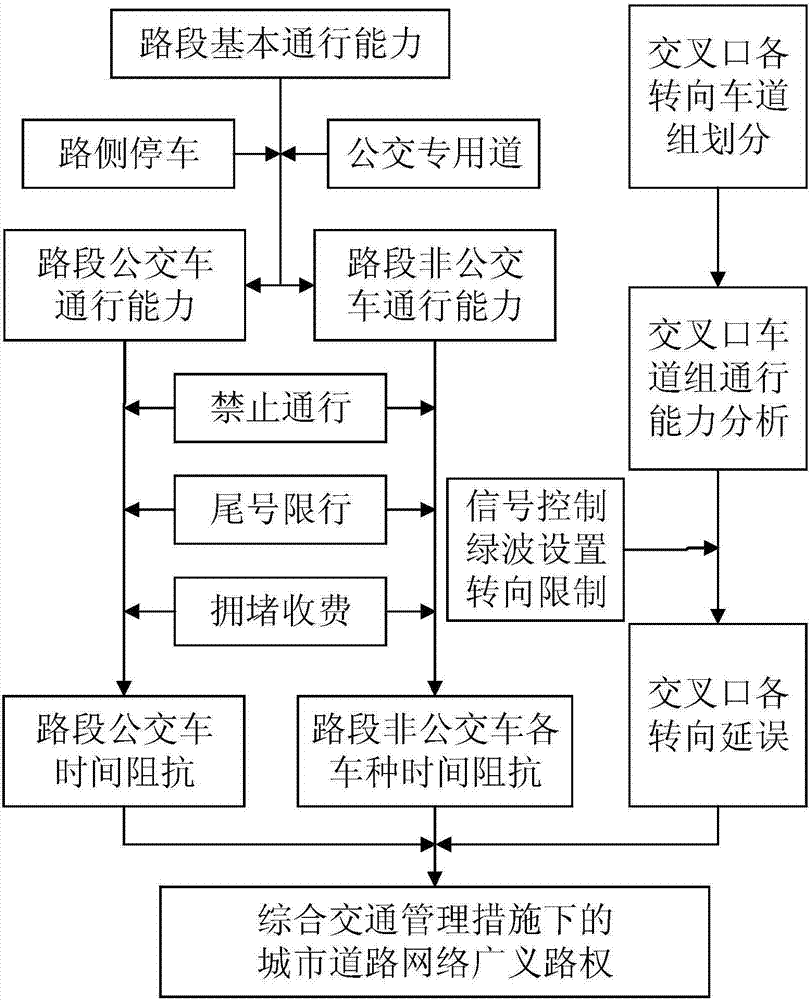

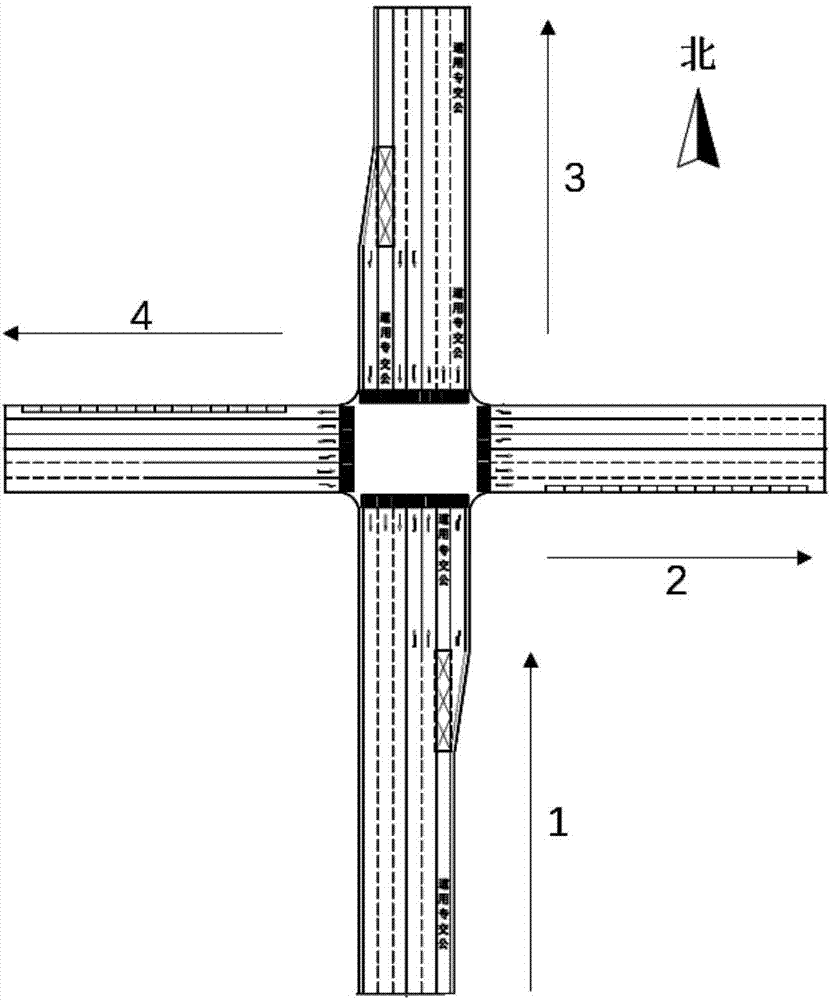

An urban road network generalized road right calculating method considering comprehensive traffic management measures

ActiveCN107038863ASimulation is accuratePrediction is accurateDetection of traffic movementTraffic capacityUrban Traffic Management and Control

The invention discloses an urban road network generalized road right calculating method considering comprehensive traffic management measures. The method comprises road section time impedance calculation with traffic management measures being taken into consideration and intersection delay calculation under a traffic control strategy, and specifically comprises road section basic traffic capacity analysis, influence correction of the traffic management measures on road section traffic capacity, road section time impedance analysis and correction of the traffic management measures on road section time impedance; and intersection entrance road lane group division based on turning relation, lane group motor basic traffic capacity analysis, influence correction of the traffic management measures on lane group traffic capacity and intersection delay analysis for traffic assignment. The method can reflect independent road rights of different types of vehicles in an urban road network, can enable simulation and prediction results to be more accurate, quantifies difference of different traffic management strategy combination schemes and provides powerful support for planning of current urban traffic management and control and formulation of traffic policies.

Owner:SOUTHEAST UNIV

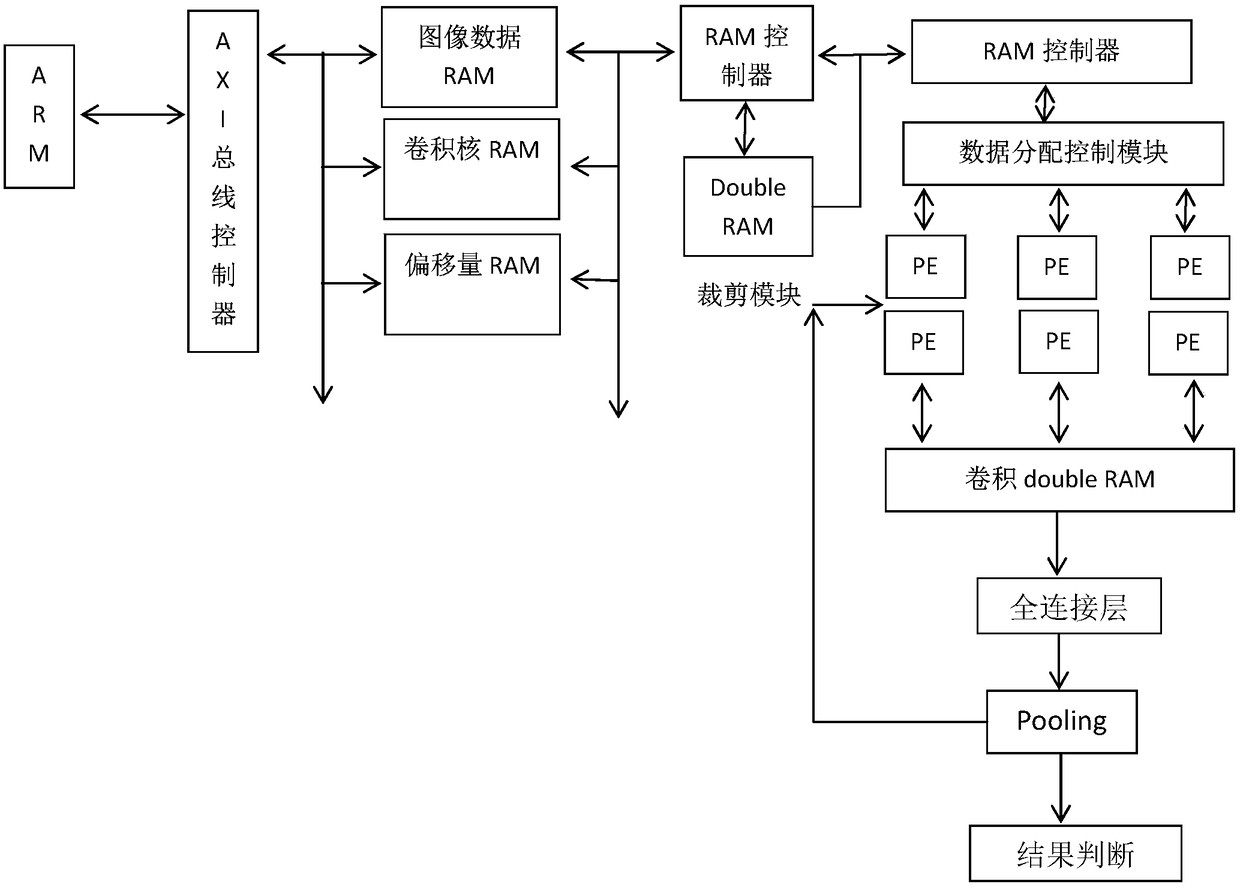

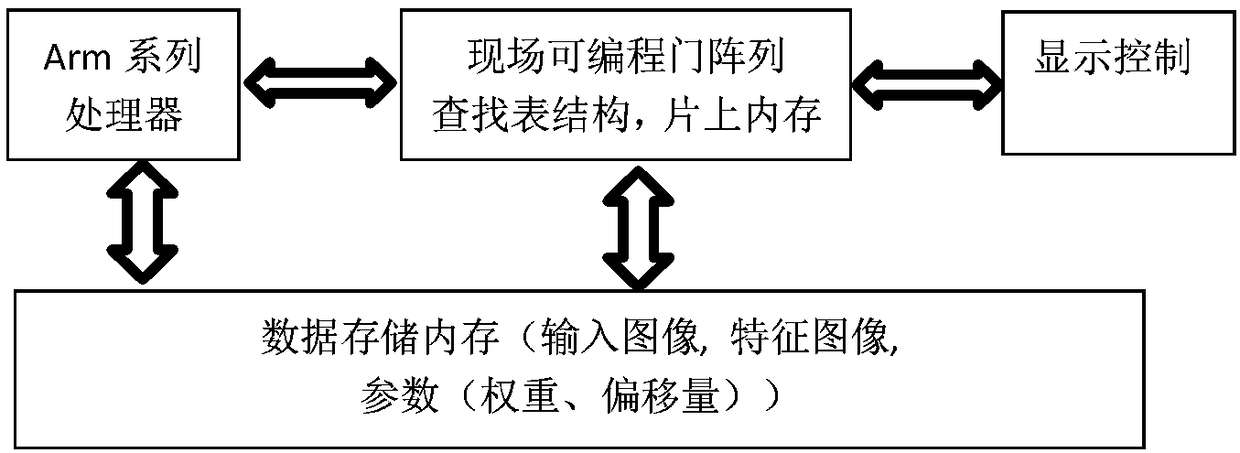

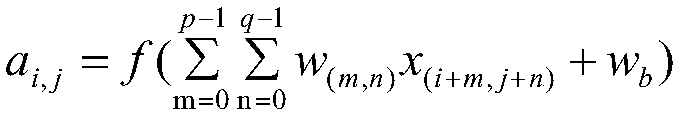

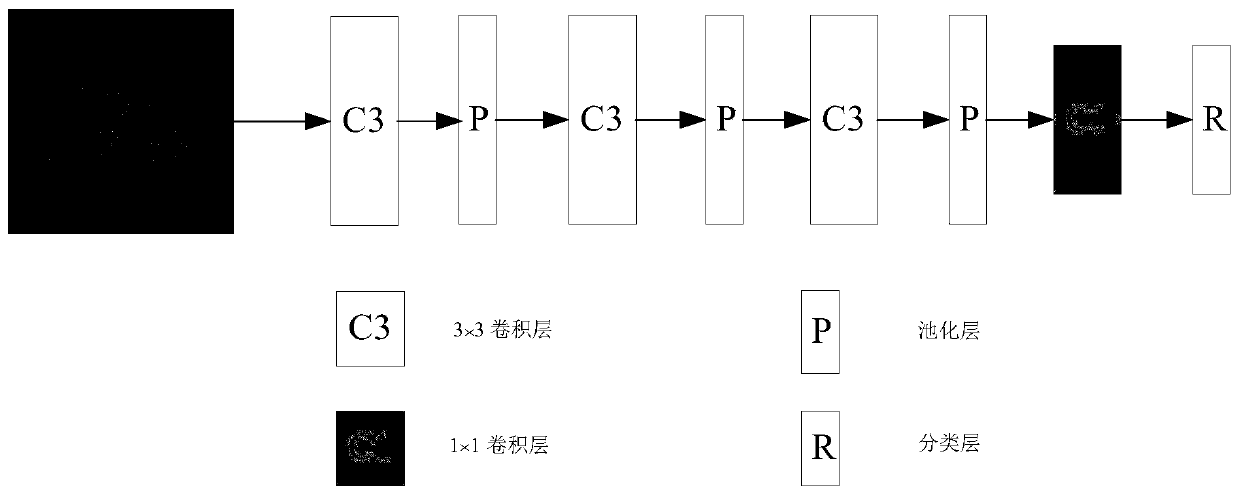

Hardware framework for carrying out reasoning acceleration by aiming at convolution neural network, and working method thereof

ActiveCN108108809AIncrease bus transferImplement recursive utilizationNeural architecturesPhysical realisationComputer hardwareNeuron network

The invention relates to a hardware framework for carrying out reasoning acceleration by aiming at a convolution neural network, and a working method thereof. The hardware framework comprises a preprocessing unit, a hardware acceleration unit and a storage unit, wherein the preprocessing unit is used for preprocessing an original image frame which is originally input; the hardware acceleration unit is used for reading the preprocessed original image frame to be convoluted, a convolution kernel coefficient and an offset parameter for convolution, executing fully connected layer calculation after convolution is finished, and outputting a calculation characteristic judgment result after the fully connected layer calculation is finished; the storage unit is used for storing the original imageframe which is originally input, the convolution kernel coefficient, the offset parameter, output data obtained by each convolution and the output data of the fully connected layer. According to the hardware framework, the problems that a traditional processor is low in speed and high in time delay, real-time reasoning can not be realized and the like are solved, and a new solution is provided fordesigning the processor which carries out the reasoning calculation by aiming at the CNN (Convolution Neural Network).

Owner:SHANDONG LINGNENG ELECTRONIC TECH CO LTD

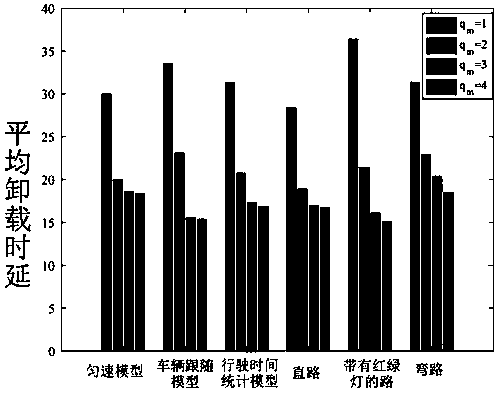

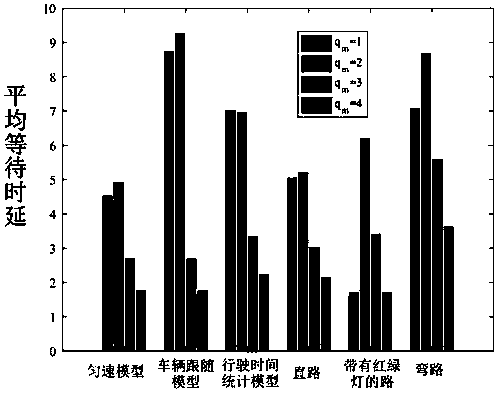

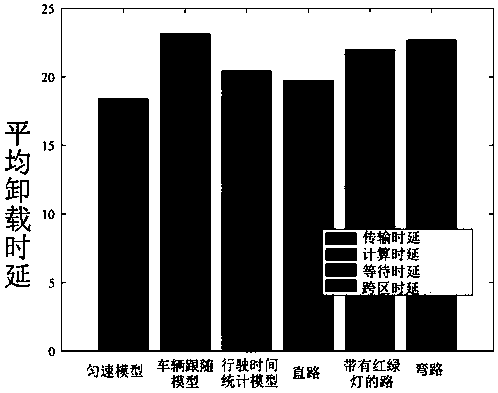

A task allocation strategy based on a matching algorithm in vehicle-mounted edge calculation

ActiveCN109862086AParticular environment based servicesCharacter and pattern recognitionEdge serverIn vehicle

The invention relates to a task allocation strategy based on a matching algorithm in vehicle-mounted edge calculation, and the optimization of the overall delay of a system under resource constraint and delay constraint conditions is realized through the selection of an edge server by a vehicle and the task unloading. According to the optimization problem provided by the invention, a task unloading delay model is derived from a constant-speed model, a vehicle following model and a driving time statistical model, and a price-based one-to-one and one-to-many matching algorithm is further used for solving, so that an optimal task distribution scheme under the constraint condition is obtained. According to the algorithm, information of vehicles, roadside units and roads is effectively integrated, and the time delay of the system is remarkably reduced under the condition that QoS requirements are met.

Owner:NORTH CHINA ELECTRIC POWER UNIV (BAODING)

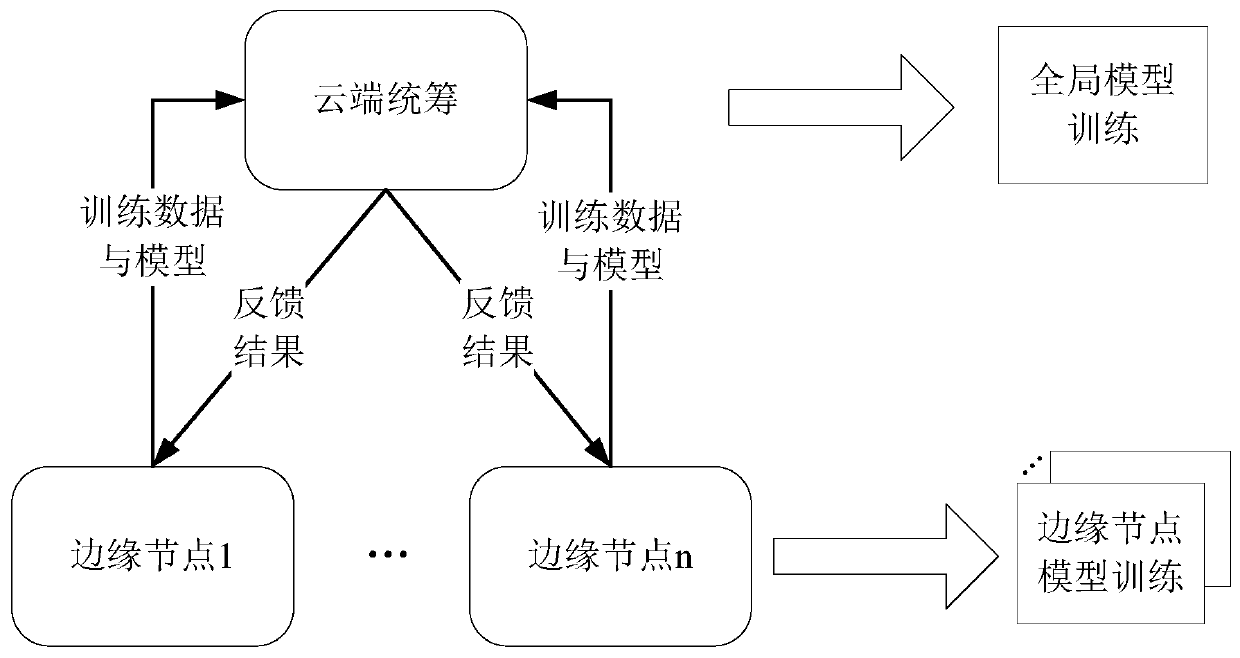

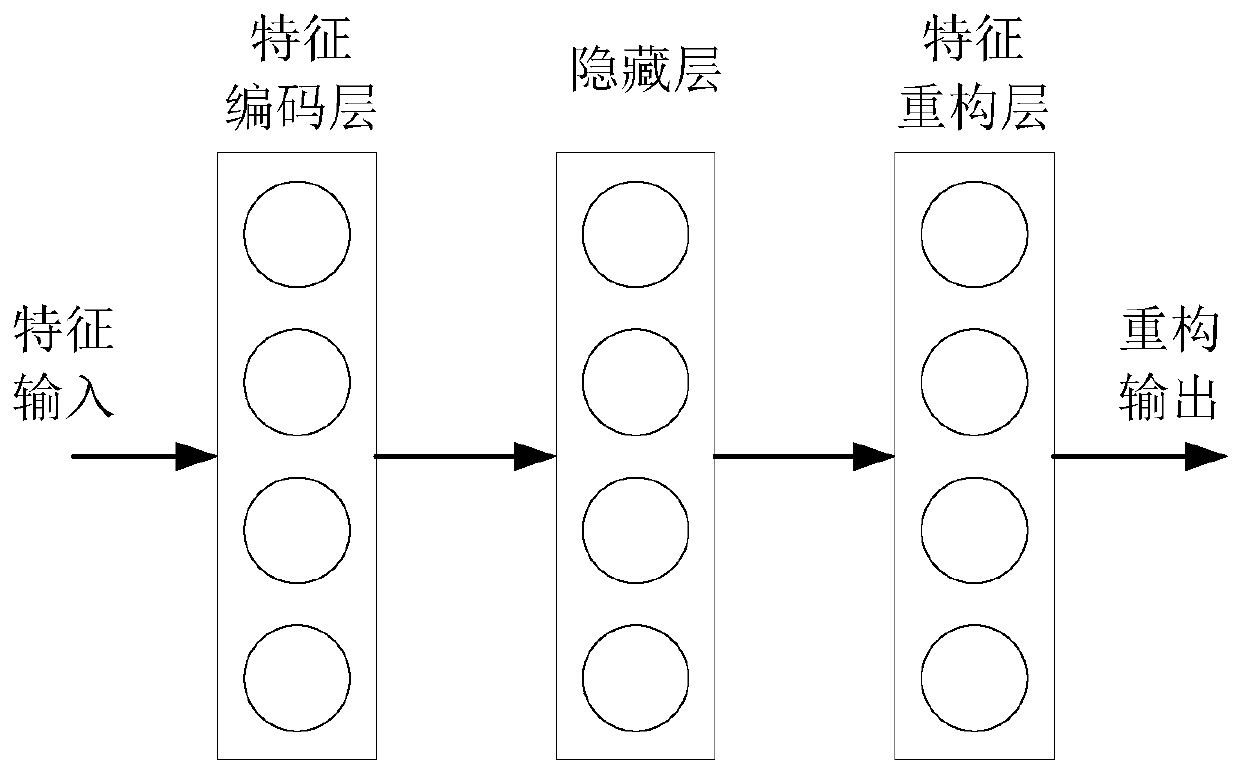

Face recognition architecture design method based on edge calculation and cloud overall planning

InactiveCN110197128AImprove accuracyShort response timeCharacter and pattern recognitionNeural learning methodsPattern recognitionEdge computing

The invention discloses a face recognition architecture design method based on edge calculation and cloud overall planning. The method comprises an edge node model training step of designing the corresponding lightweight deep learning networks in different region points according to the concept of edge calculation, and carrying out local model training; a data and model transmission step of uploading a corresponding model result according to a calculation result of the multi-stage edge node; a cloud model training step of performing training learning on the uploaded data and the model in a cloud overall planning mode to obtain a global face recognition model; and a task final feedback step. According to the invention, the edge computing technology and the cloud overall planning form are applied to the face recognition task under the big data to construct the face recognition architecture with fast response time and high accuracy, and the basic task is placed at the front end of the data to be processed, so that the response delay caused by data transmission is reduced; and the local model of each edge node is integrated, so that the overall face recognition accuracy is improved.

Owner:SOUTH CHINA UNIV OF TECH

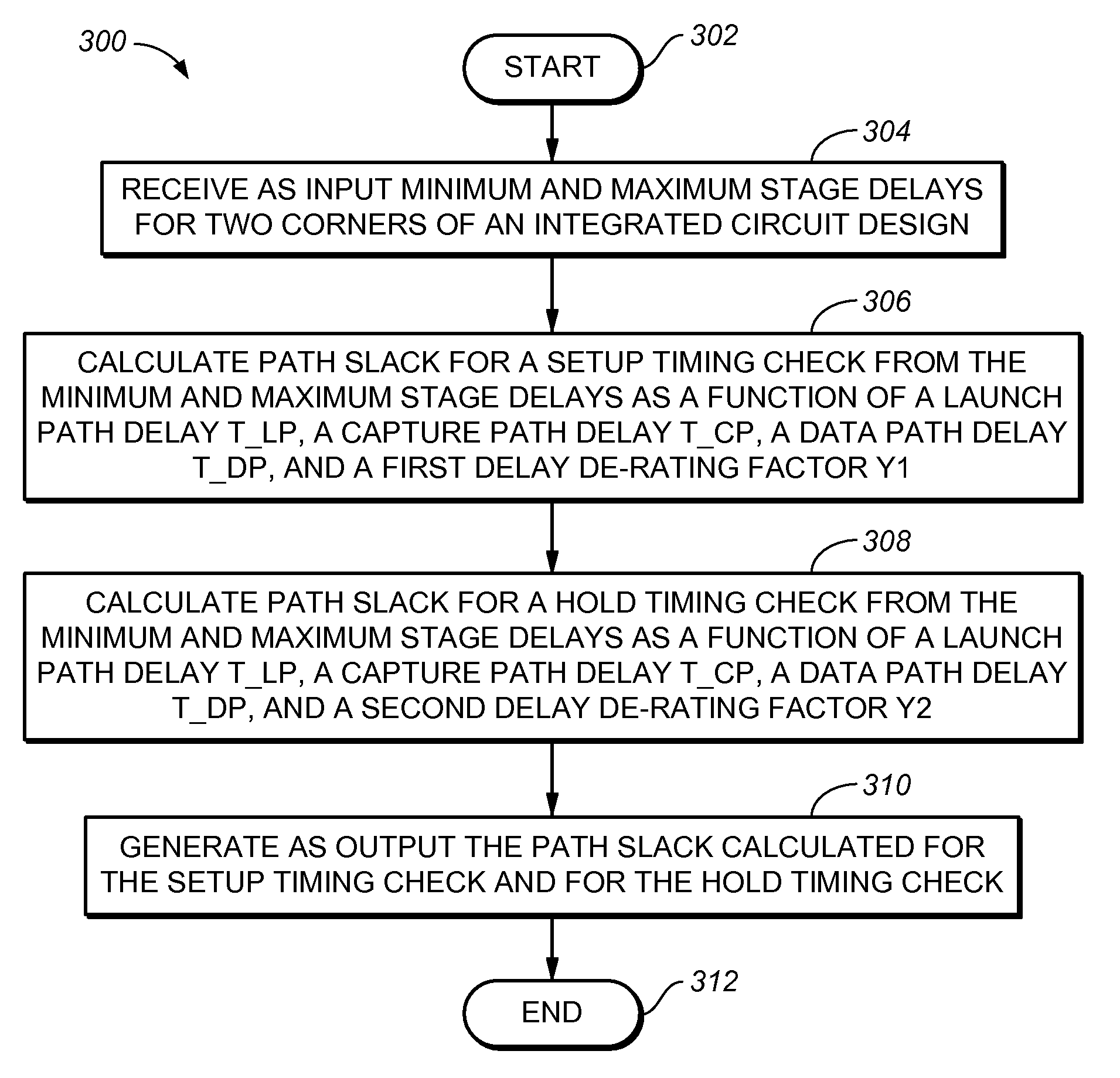

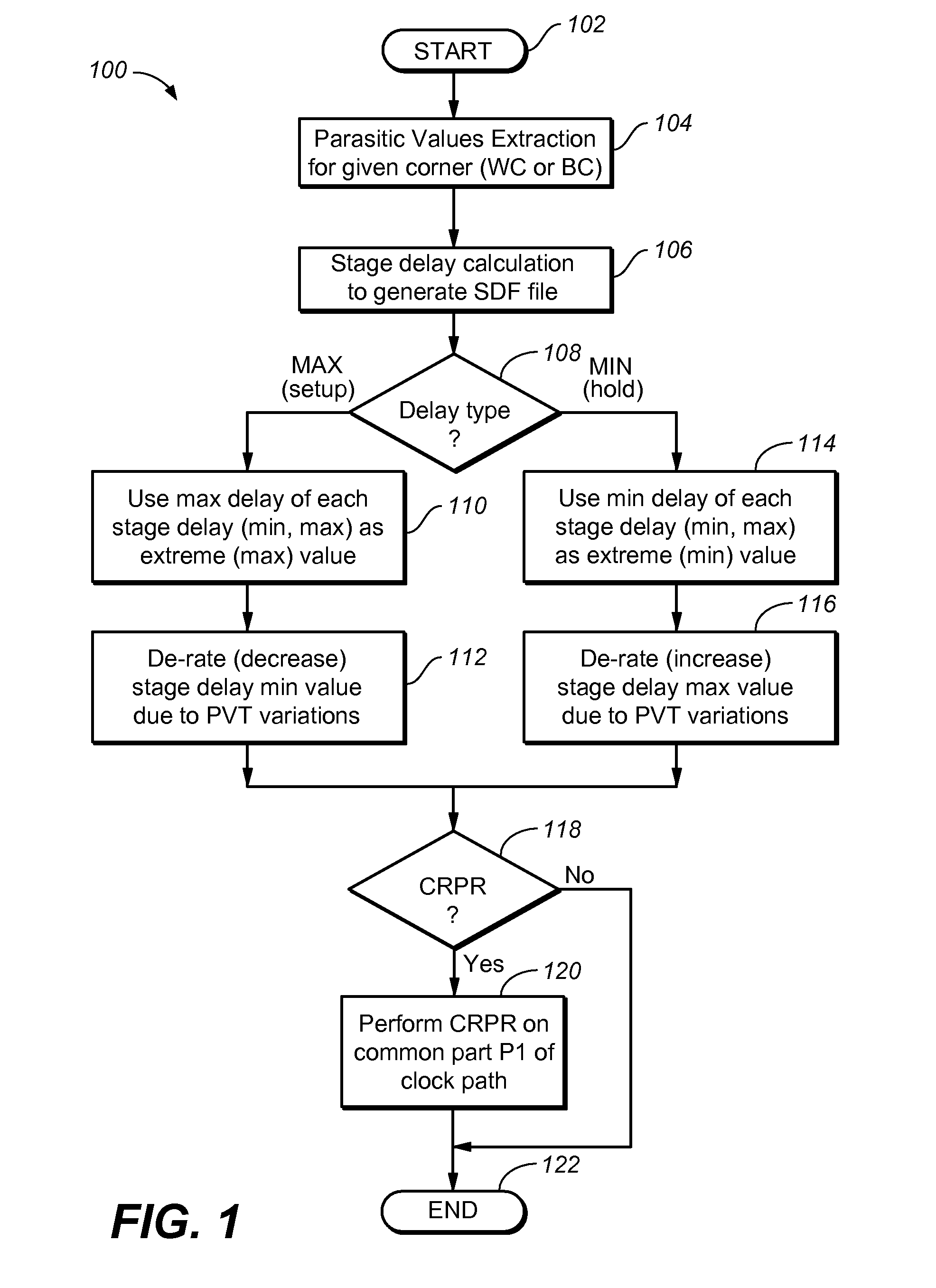

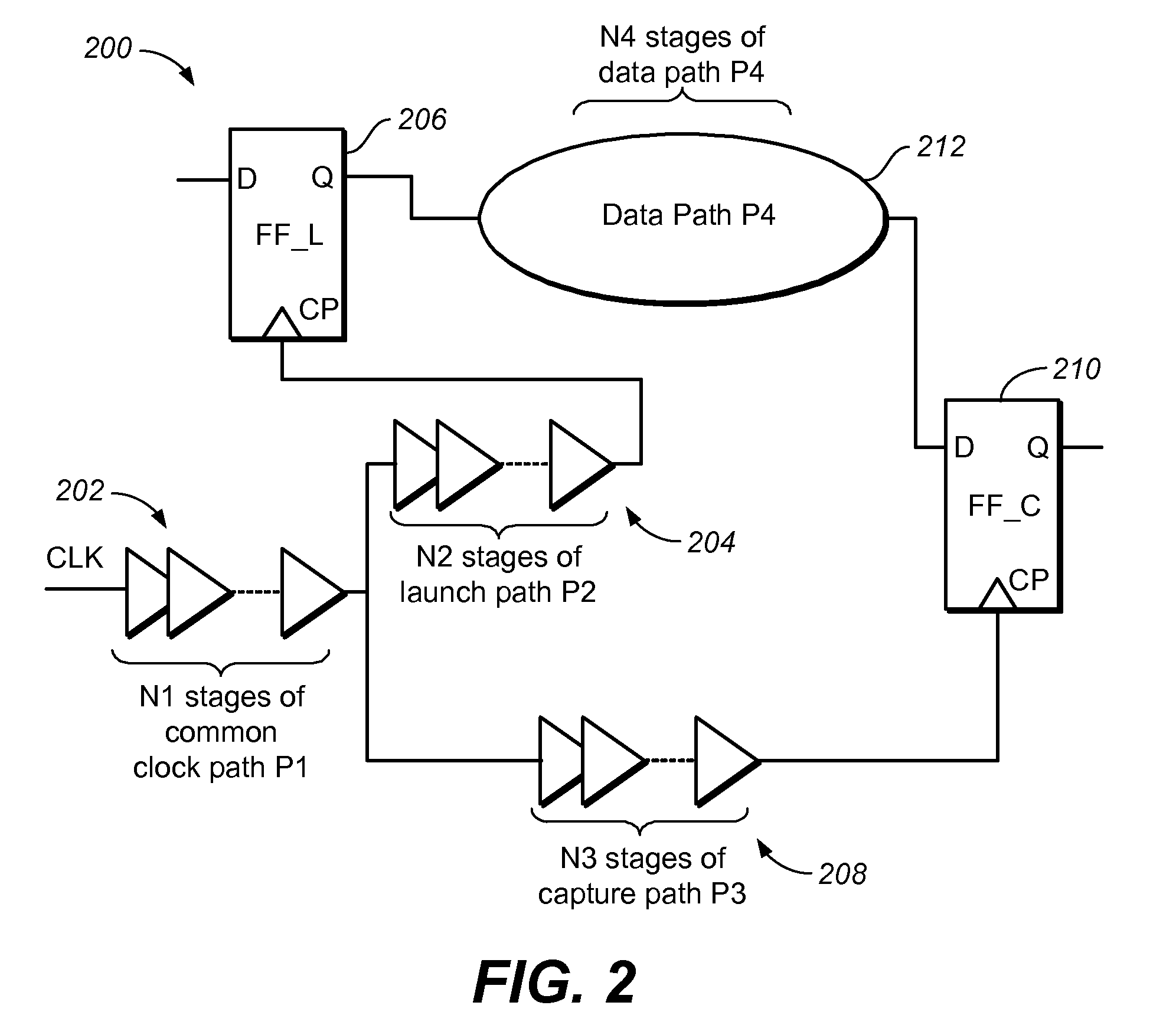

Method and computer program for static timing analysis with delay de-rating and clock conservatism reduction

InactiveUS7480881B2Computer aided designSoftware simulation/interpretation/emulationStatic timing analysisDatapath

A method and computer program for static timing analysis includes receiving as input minimum and maximum stage delays for two corners of an integrated circuit design. A path slack for a setup timing check is calculated from the minimum and maximum stage delays as a function of net clock cycle interval T_clk, launch path delay T_LP, capture path delay T_CP, data path delay T_DP, and a first delay de-rating factor Y1. A path slack for a hold timing check is calculated from the minimum and maximum stage delays as a function of the launch path delay T_LP, the capture path delay T_CP, the data path delay T_DP, and a second delay de-rating factor Y2. The path slack calculated for the setup timing check and for the hold timing check is generated as output.

Owner:BELL SEMICON LLC

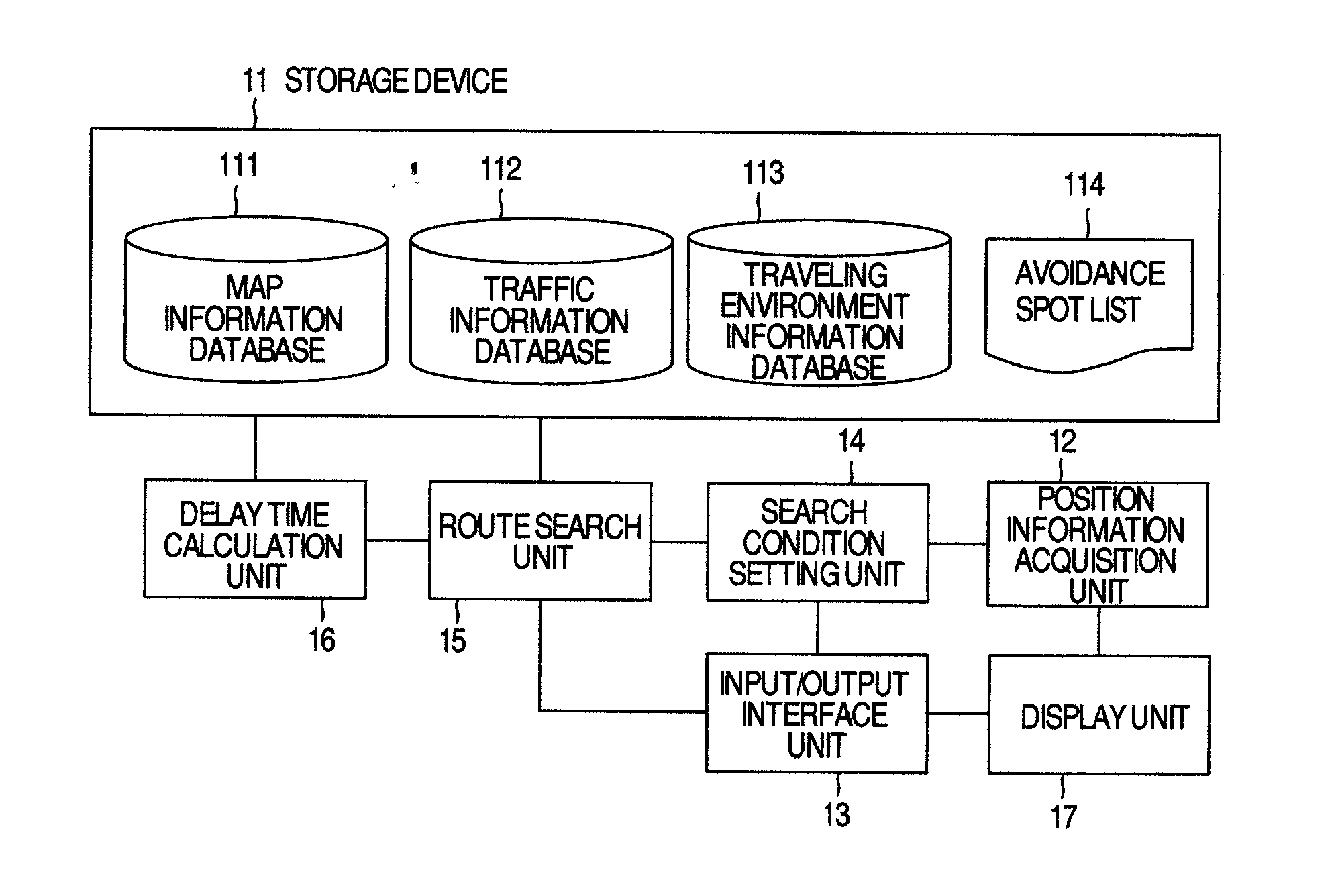

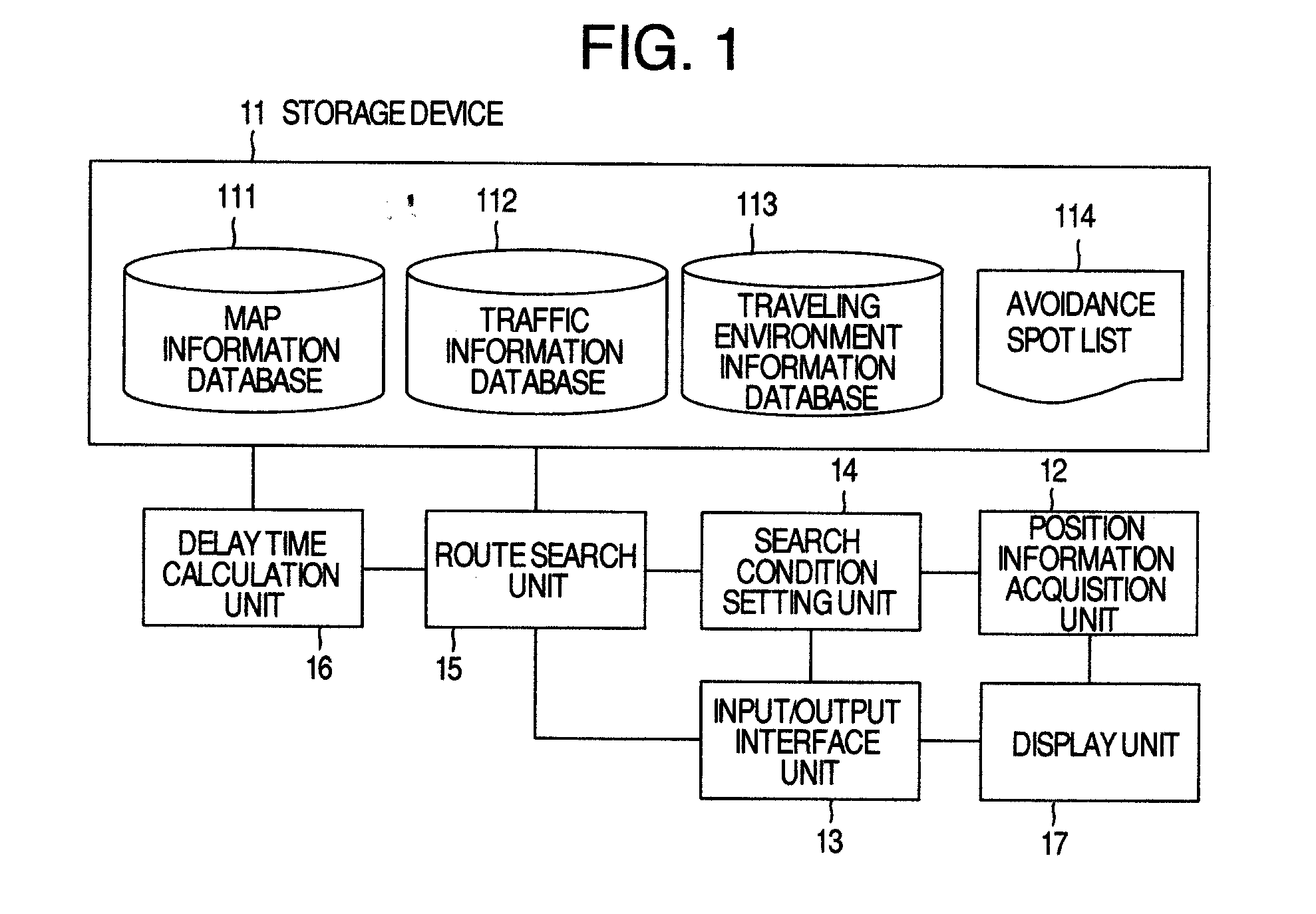

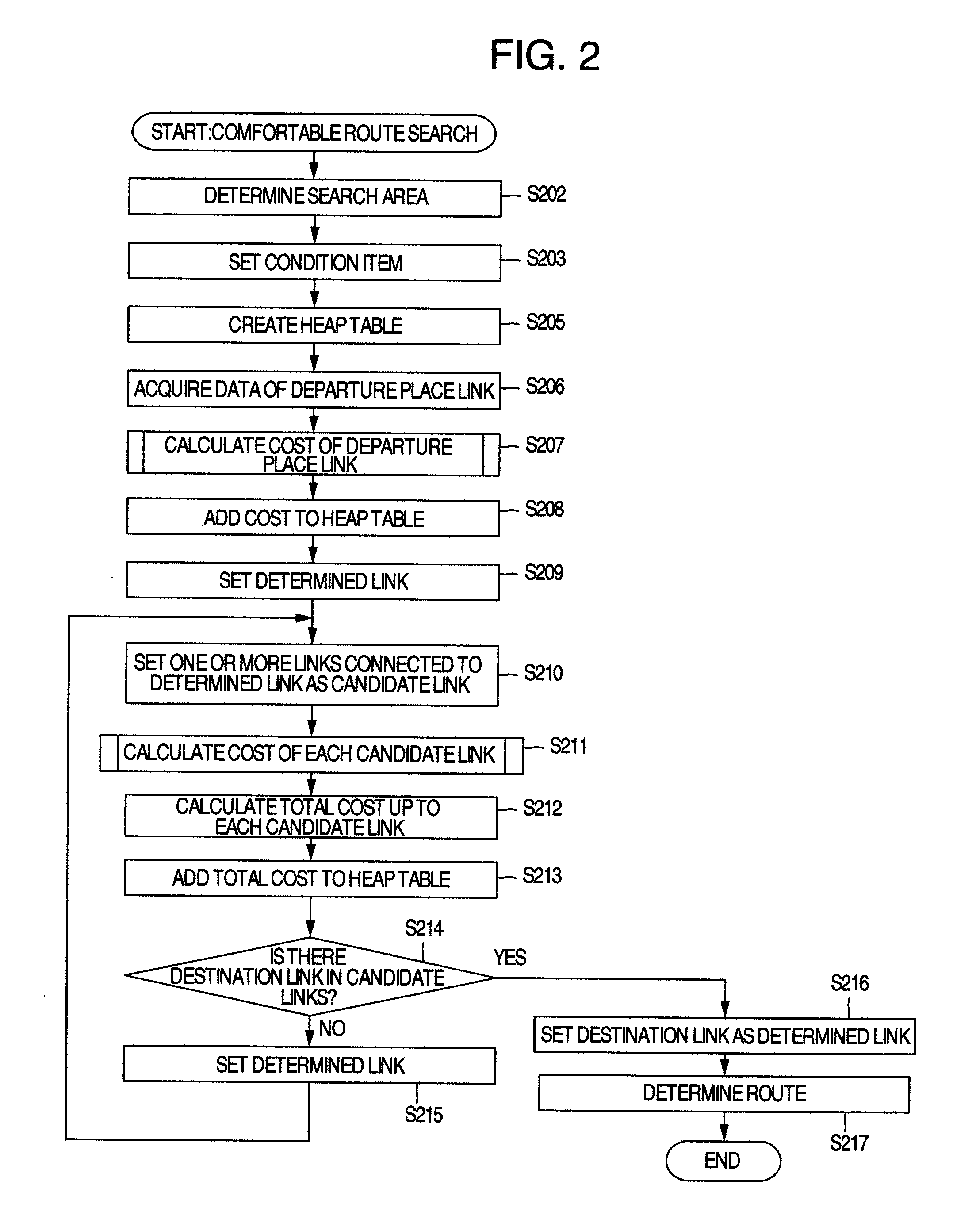

Method and Apparatus for Route Searching

InactiveUS20120158285A1Comfortable travelReduce delaysInstruments for road network navigationRoad vehicles traffic controlUser inputRoute search

Provided is a route through which a user can smoothly travel and on which an evaluation of traveling environment is reflected. A route search system includes a user input receiving unit which uses a delay time from an expected travel time as an index indicating comfort of a route and selects a factor such as traffic conditions and pedestrians set as a condition that a user desires avoidance, a delay time calculation unit which calculates a delay time from an expected arrival prediction time according to map information, traffic information, and traveling environment information so as to reduce a delay as far as possible due to the selected factor, and calculates a cost based on the delay time, and a route search unit which calculates a cost of a link used for a route search from the delay time, and searches a route by using the calculated cost.

Owner:CLARION CO LTD

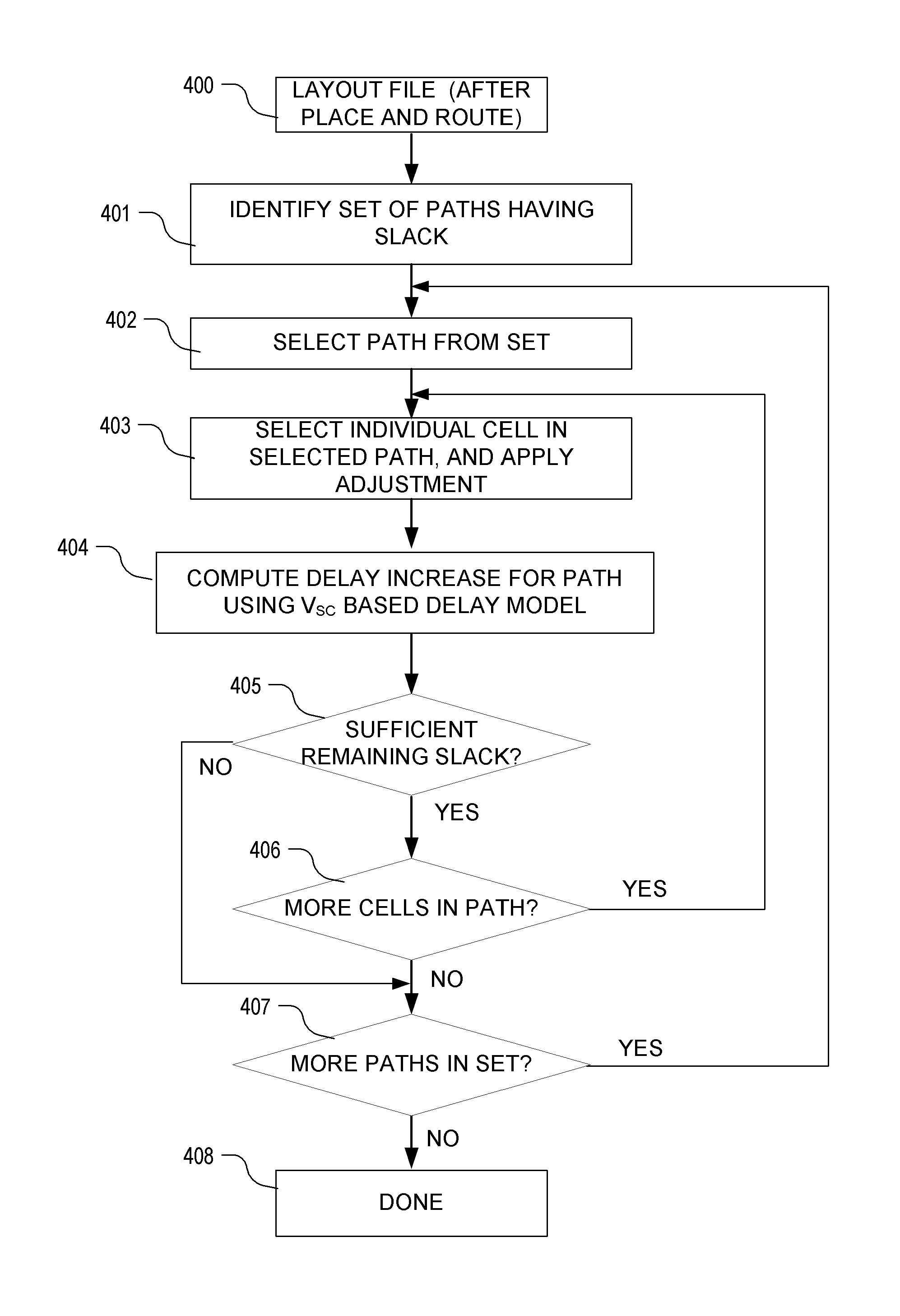

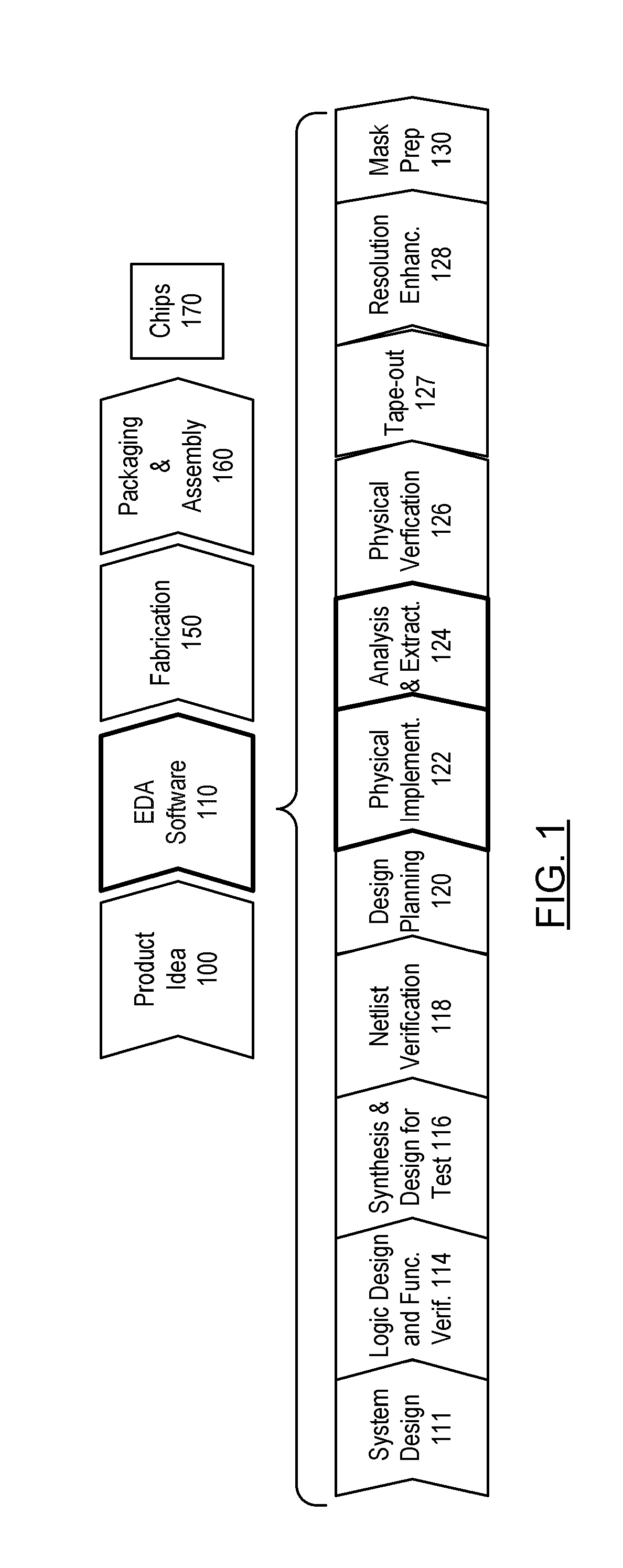

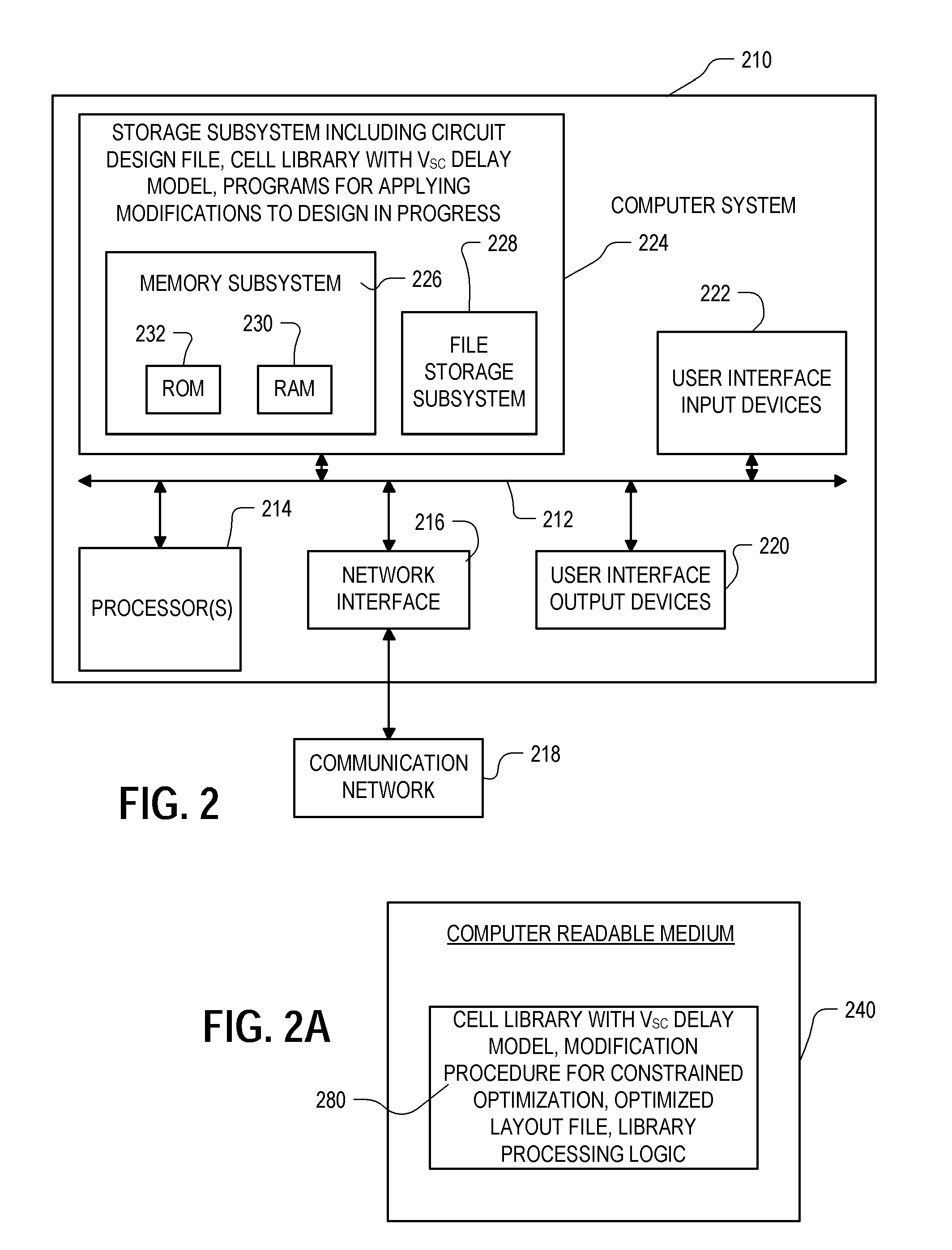

Modeling of cell delay change for electronic design automation

ActiveUS20110231811A1Reduce the required powerDesign optimisation/simulationCAD circuit designCell featureLeakage power

An integrated circuit design optimization procedure to modify a cell feature, such as gate length, models changes in delay as a result of the modification. In the delay change calculation, a characteristic of an event in cell switching behavior, such as the output short-circuit voltage VSC, is determined for the modified cell, where changes in the determined characteristic correlate with changes in delay of the cell due to the modification. Next, a value for delay of the modified cell is determined as a function of the determined characteristic of the event. The procedure can be applied after placement and routing. A timing-constrained, leakage power reduction is described using the delay change model.

Owner:SYNOPSYS INC

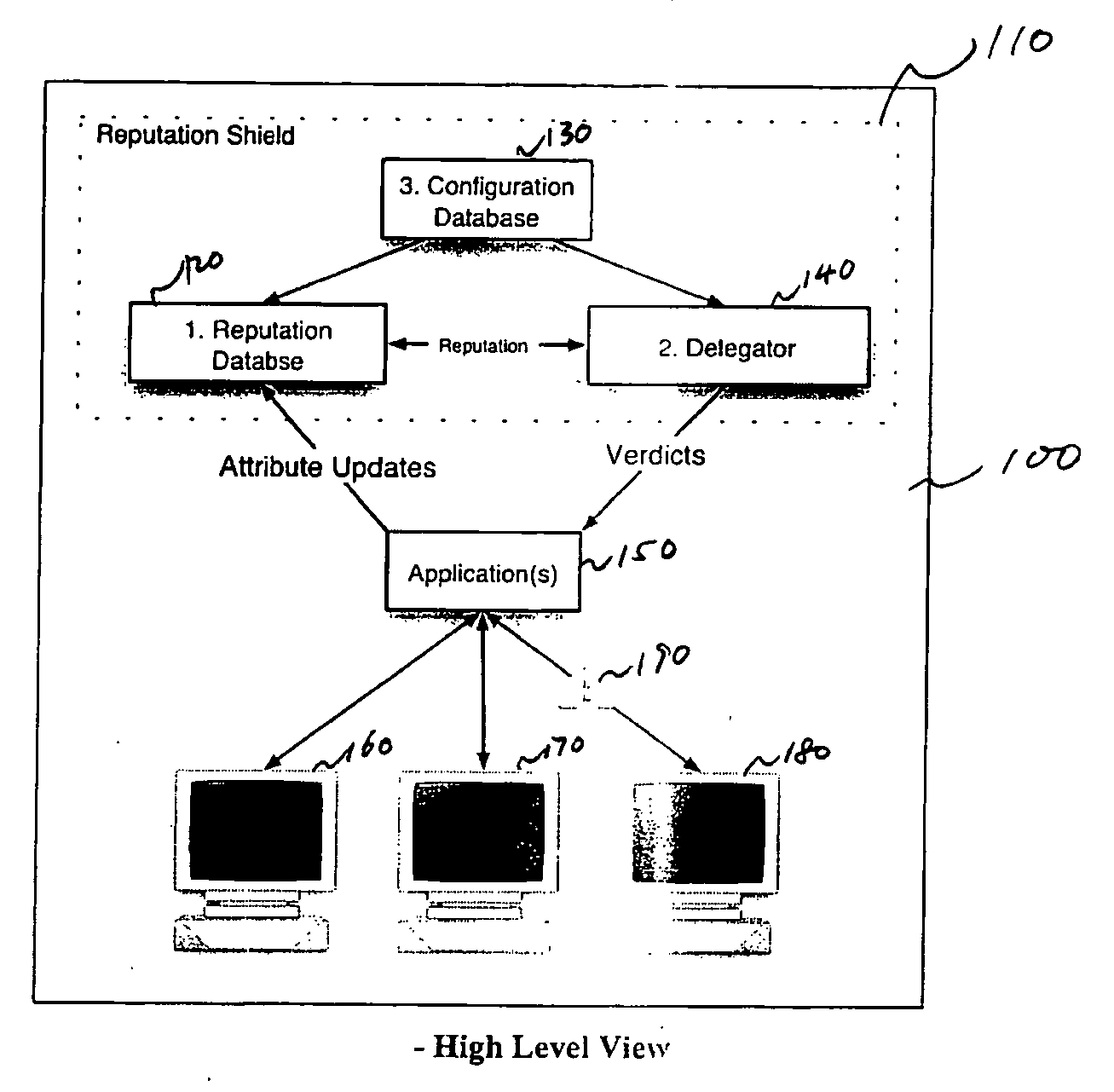

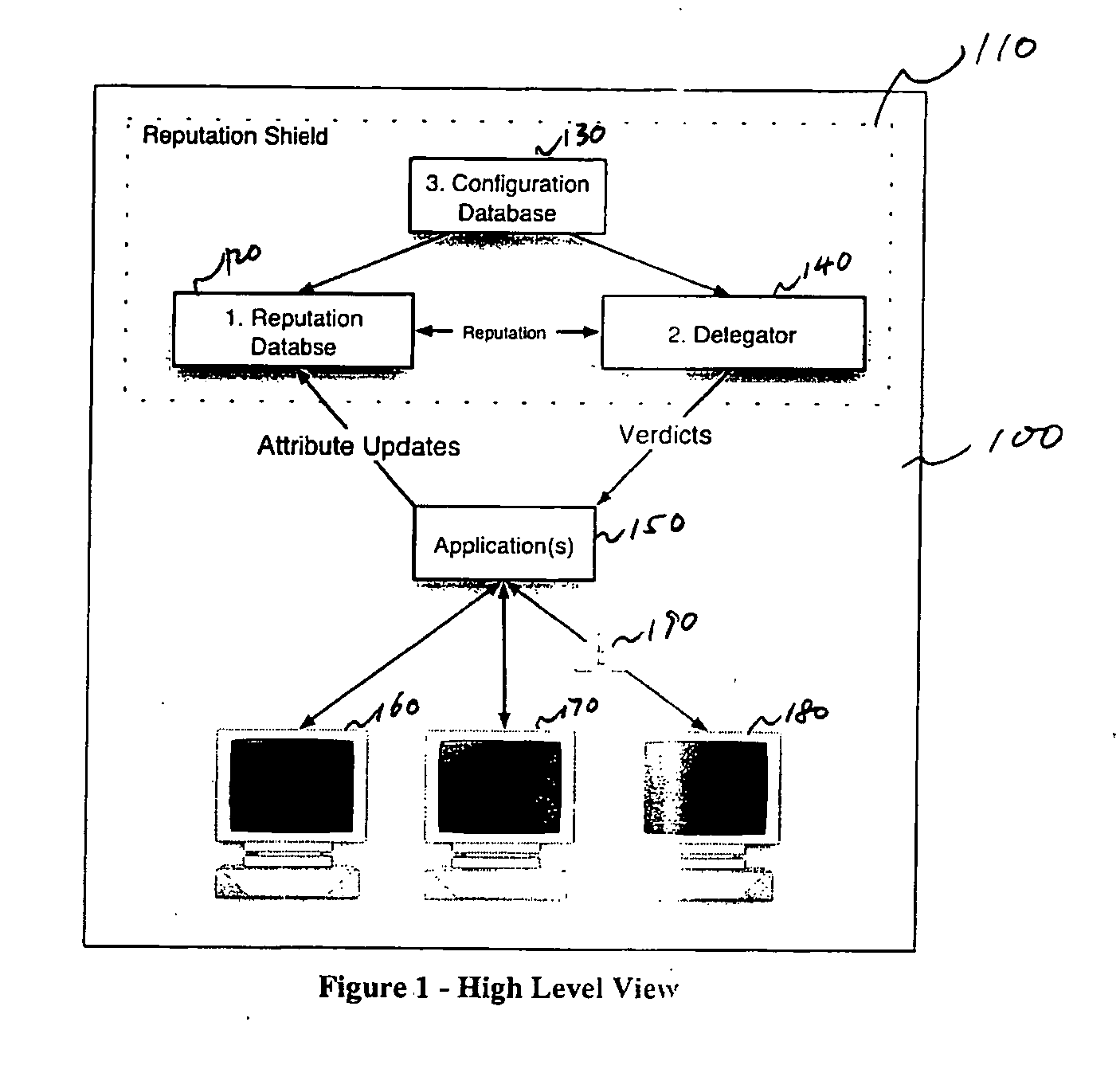

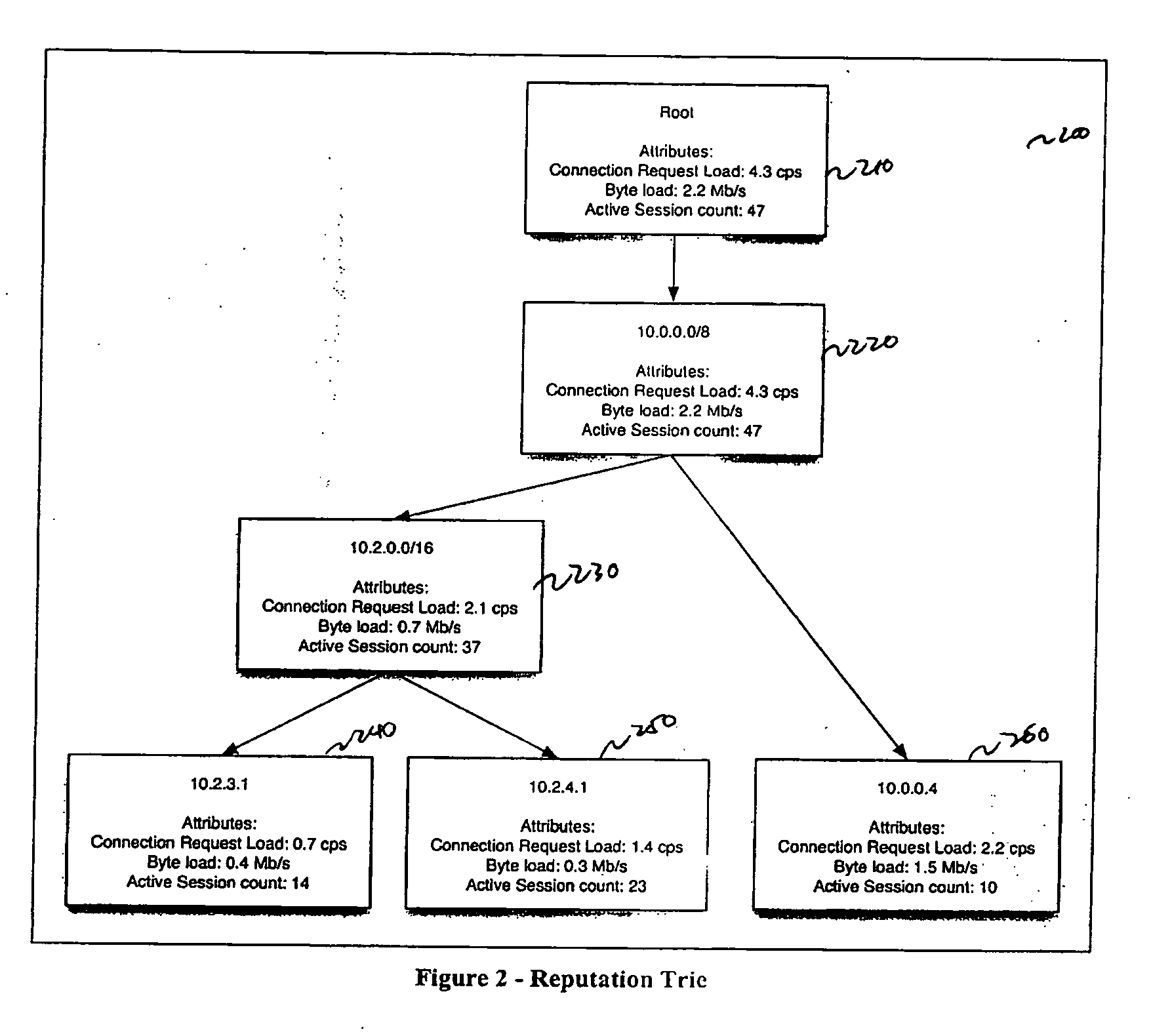

Methods and systems for reputation based resource allocation for networking

InactiveUS20070043738A1Effective distributionResource allocationTransmissionComputer resourcesTerm memory

A method and system for reputation-based resource allocation for networking. The present invention provides a method for determining an allocation of a plurality of computer resources based on a reputation factor for each of the one ore more clients. Clients associated with bad reputation factors may be denied or delayed from computer resources. According to an embodiment, the method is used in a computer network environment wherein one or more clients share a plurality of computer resources. The method includes a step of providing a network appliance. The network appliance includes one or more memories and a central processing unit. The networking appliance has at least a first port and a second port. The first port and the second port exchanges a stream of information. The network appliance is characterized by a limited quantity of system resources. The method also includes a step for processing the stream of network traffic.

Owner:UNTANGLE HLDG INC

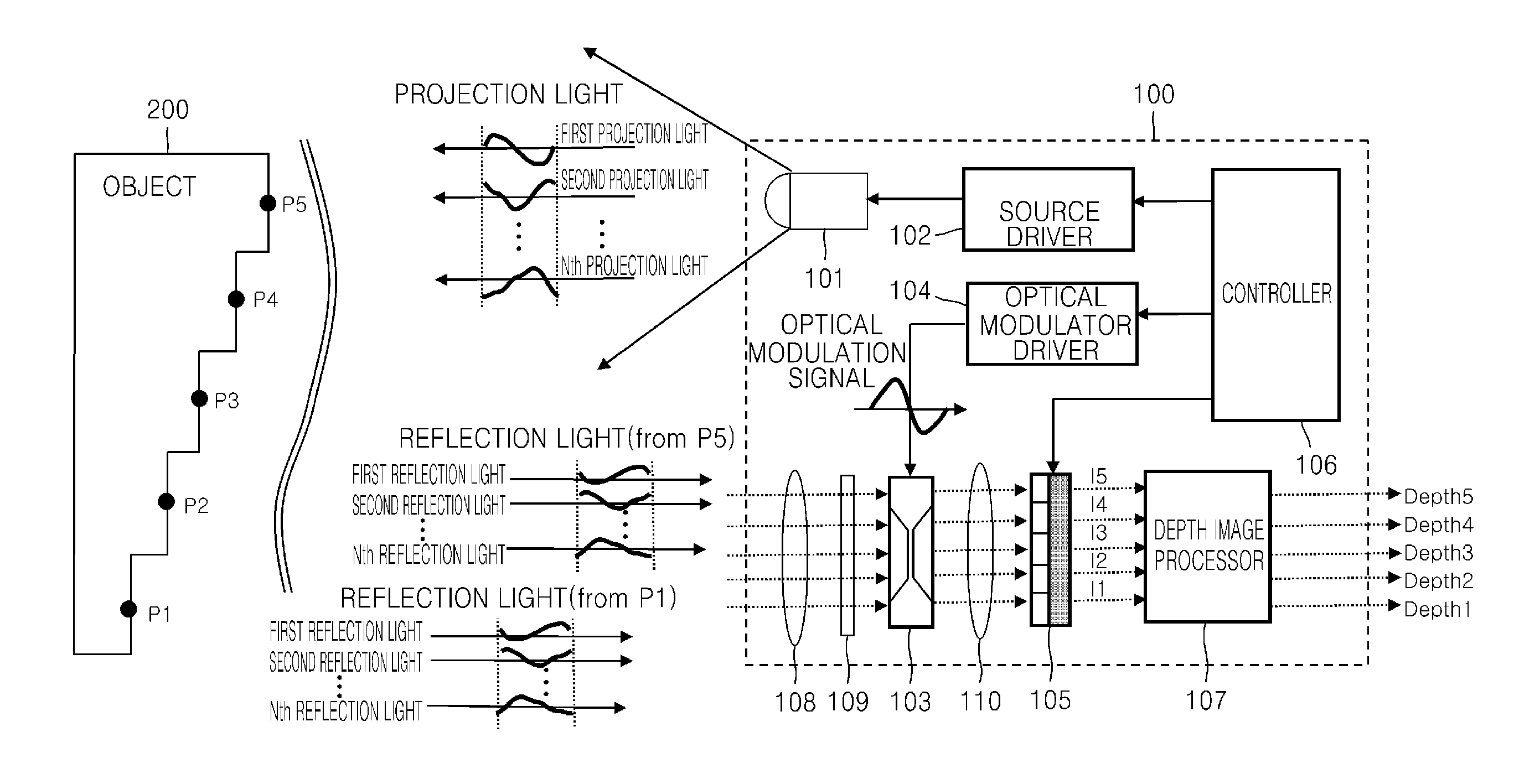

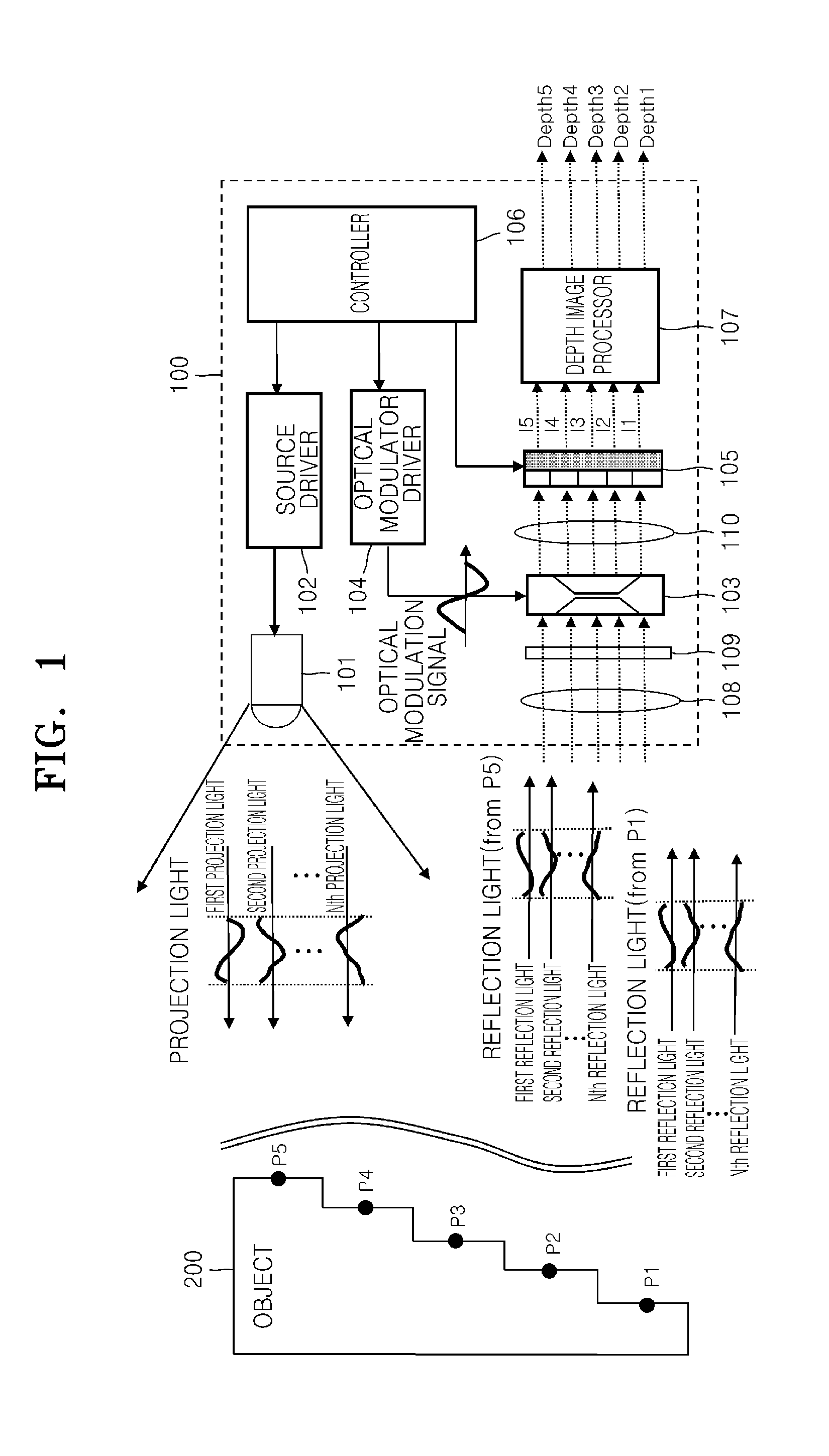

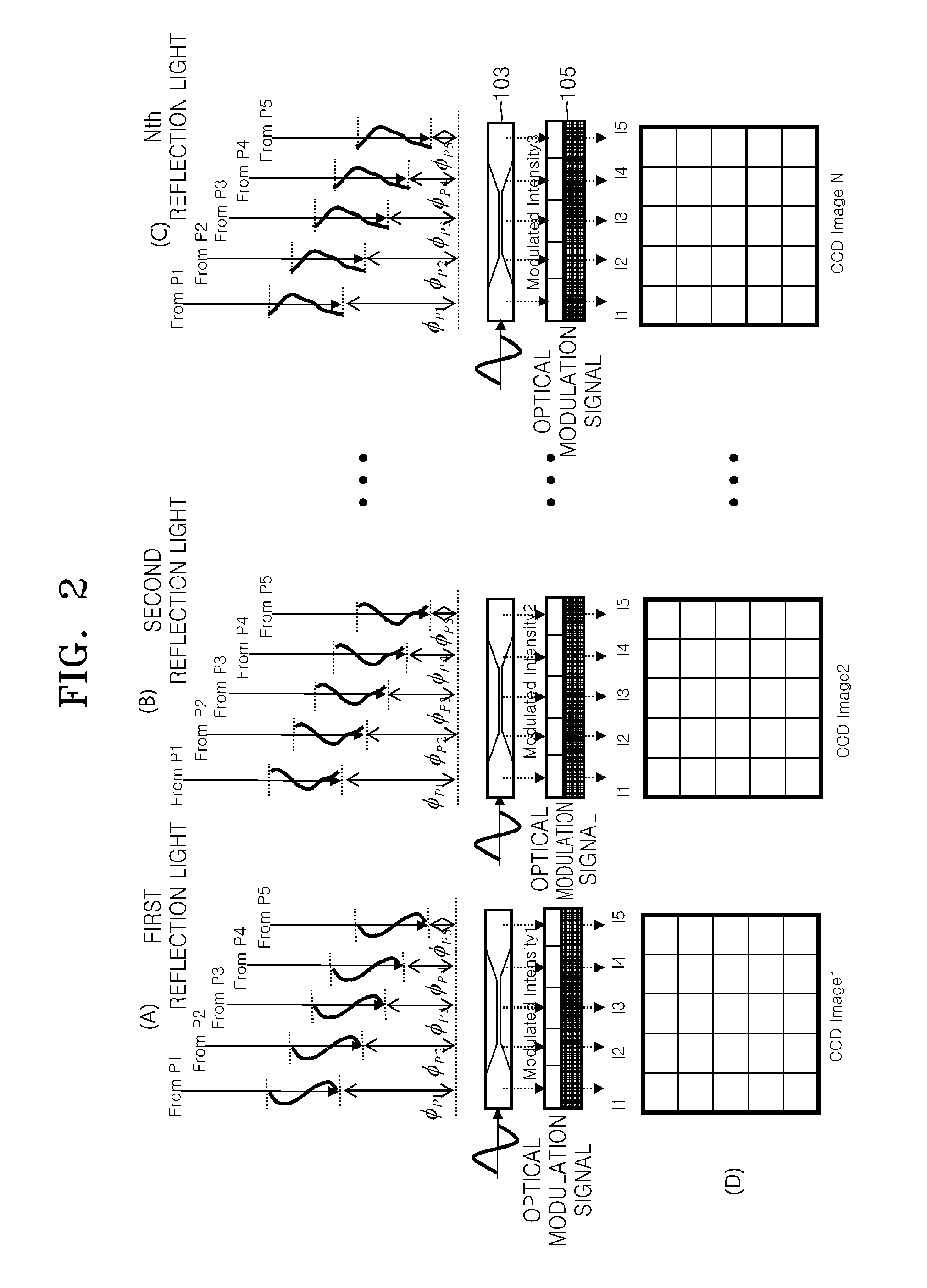

3-dimensional image acquisition apparatus and method of extracting depth information in the 3D image acquisition apparatus

ActiveUS20120162197A1Efficient removalElectromagnetic wave reradiationSteroscopic systemsAcquisition apparatus3d image

A 3 dimensional (3D) image acquisition apparatus and a method of extracting depth information in the 3D image acquisition apparatus are provided. The method of extracting depth information includes sequentially projecting N (N is a natural number equal to or greater than 3) different pieces of projection light onto a object; modulating N pieces of reflection light reflected from the object with an optical modulation signal having a gain waveform; generating N images by capturing the N pieces of modulated reflection light; generating a first averaged image by multiplying the N images by primary weights and generating a second averaged image by multiplying the N images by secondary weights; acquiring an average phase delay from the first and second averaged images; and calculating a distance to the object from the average phase delay.

Owner:SAMSUNG ELECTRONICS CO LTD

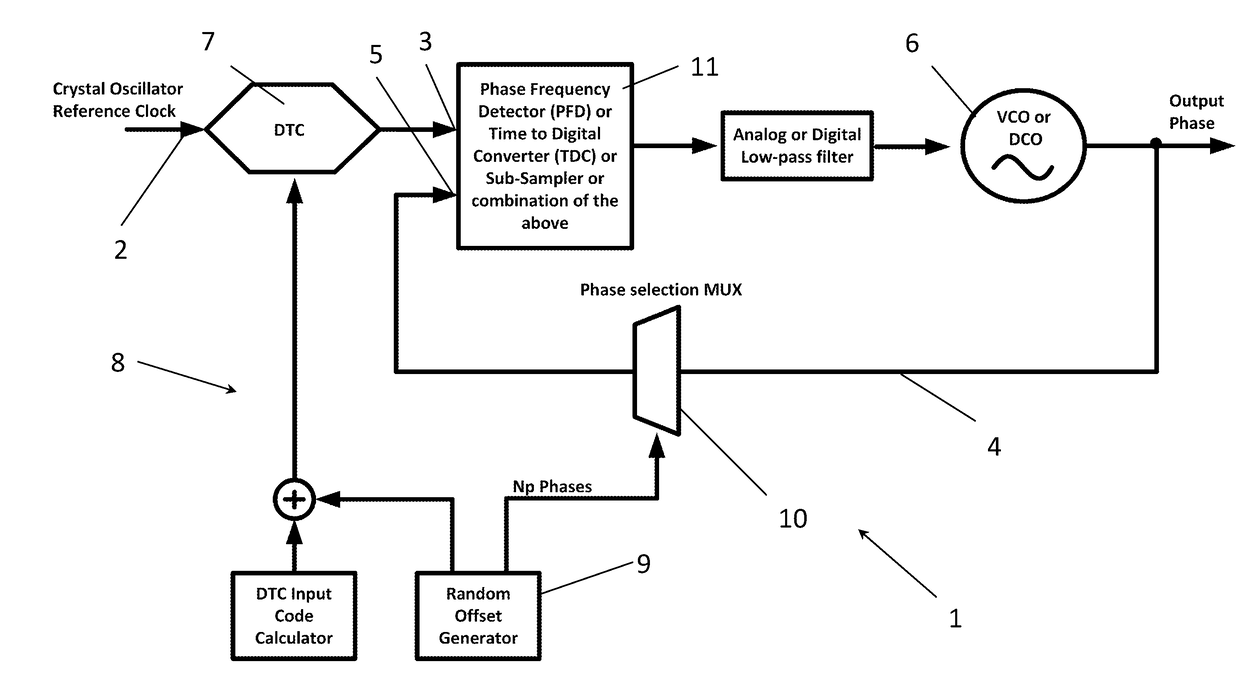

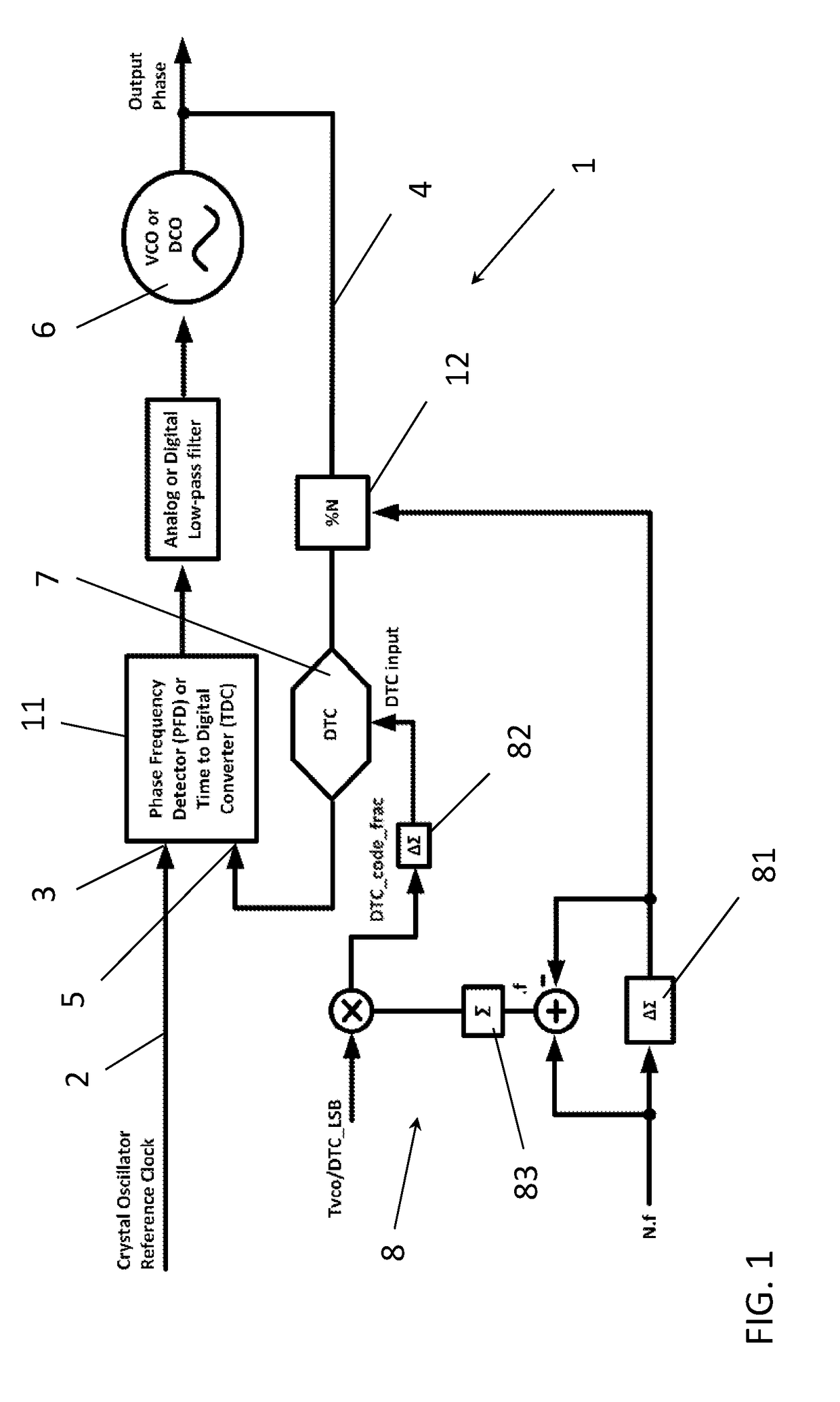

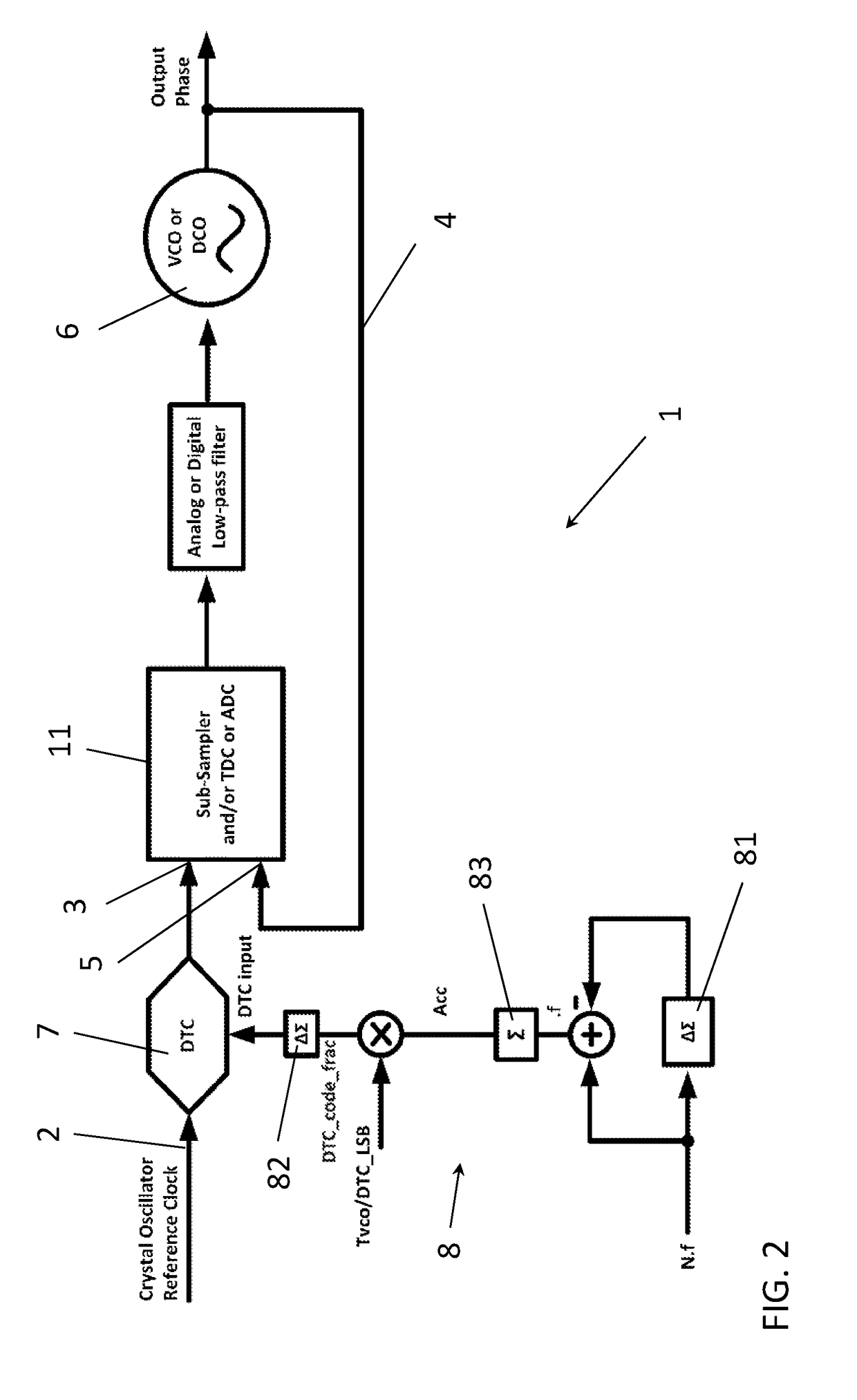

DTC-Based PLL and Method for Operating the DTC-Based PLL

ActiveUS20170346493A1Increase productionInfluence of errorsPulse automatic controlDelay line applicationsPhase detectorPhase difference

The disclosure provides a phase locked loop, PLL, for phase locking an output signal to a reference signal. The PLL comprises a reference path providing the reference signal to a first input of a phase detector, a feedback loop providing the output signal of the PLL as a feedback signal to a second input of the phase detector, a controllable oscillator generating the output signal based on at least a phase difference between reference and feedback signal, a digital-to-time converter, DTC, delaying a signal that is provided at one of the first and second input, a delay calculation path for calculating a DTC delay value. The PLL further comprises a randomization unit for generating and adding a random offset, i.e. a pseudo-random integer, to the delay value. The offset is such that a target output of the phase detector remains substantially unchanged.

Owner:INTERUNIVERSITAIR MICRO ELECTRONICS CENT (IMEC VZW) +2