Multi-level collaborative low-power design method

A design method, low-power technology, applied in computing, special data processing applications, data processing power supply, etc., can solve problems such as stability and performance degradation, affecting processor stability, processor restriction and impact, etc., to achieve dynamic Power consumption reduction, optimization of good power consumption, effect of avoiding invalid flips

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

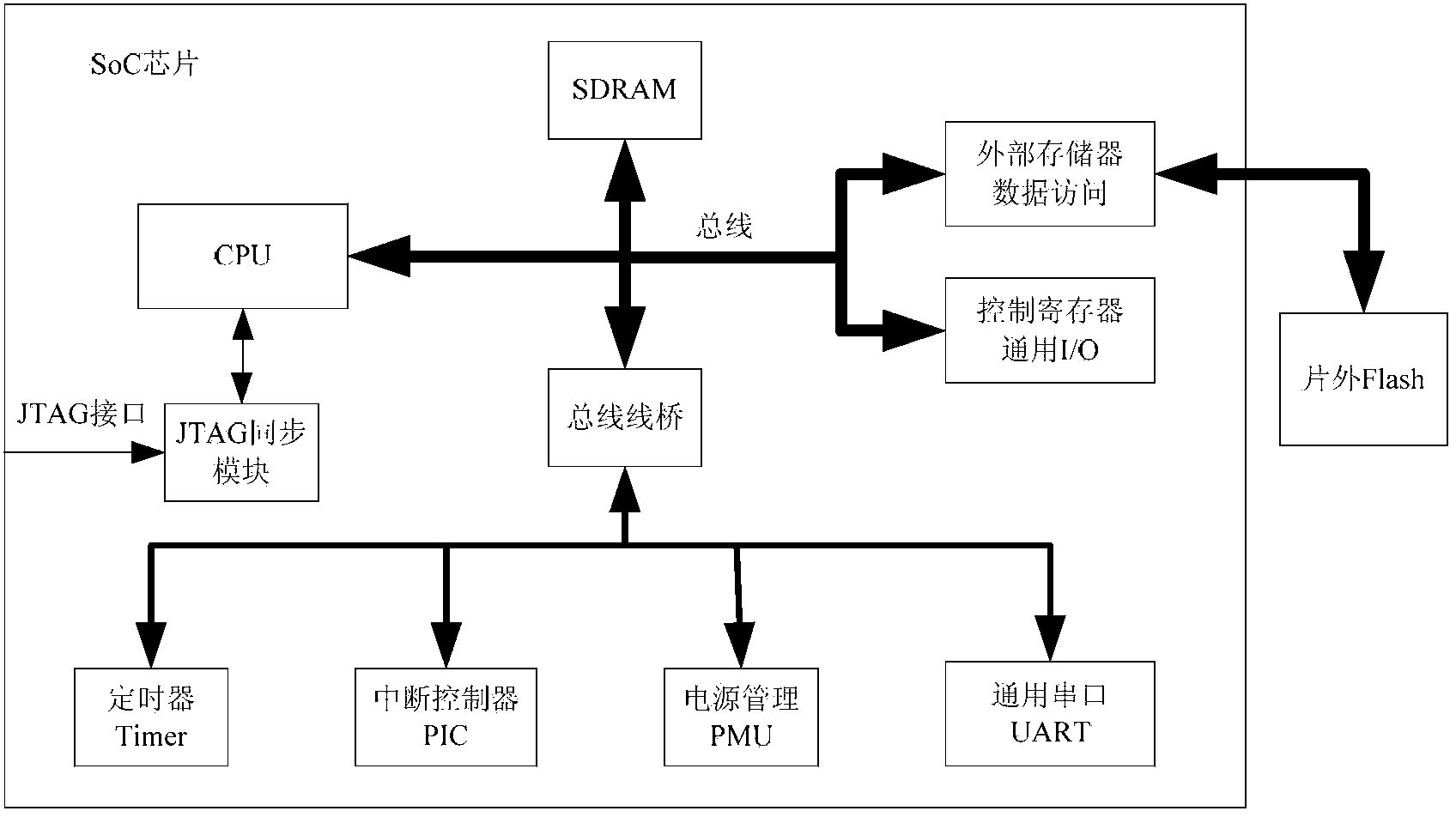

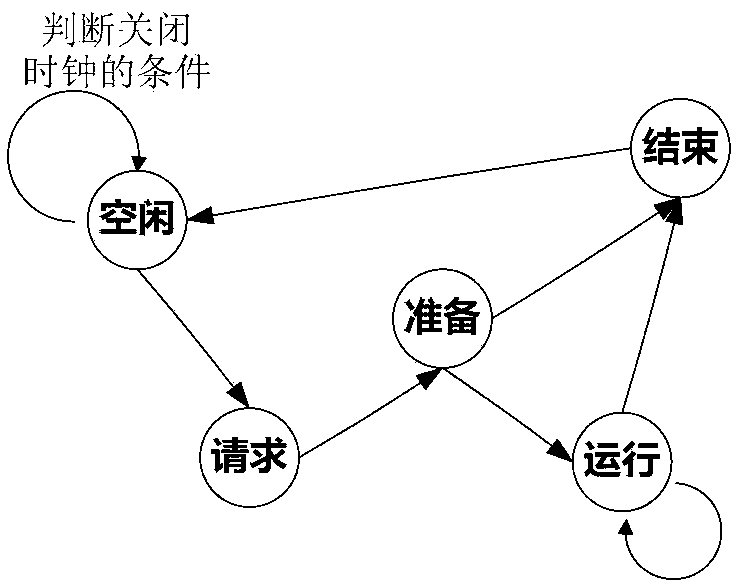

[0041] The core part of the present invention is as Figure 4 As shown, this part needs to complete the multi-level low-power co-optimization functions of system level, register transfer level and gate level. The overall structure mainly includes four parts, JTAG module, programmable interrupt controller (PIC) module, power management module (power management) module and gated clock module. The gated clock module mainly includes two sub-modules, namely the gated clock module controlling the processor (cpu) and the gated clock module controlling the tick timer (Tick Timer).

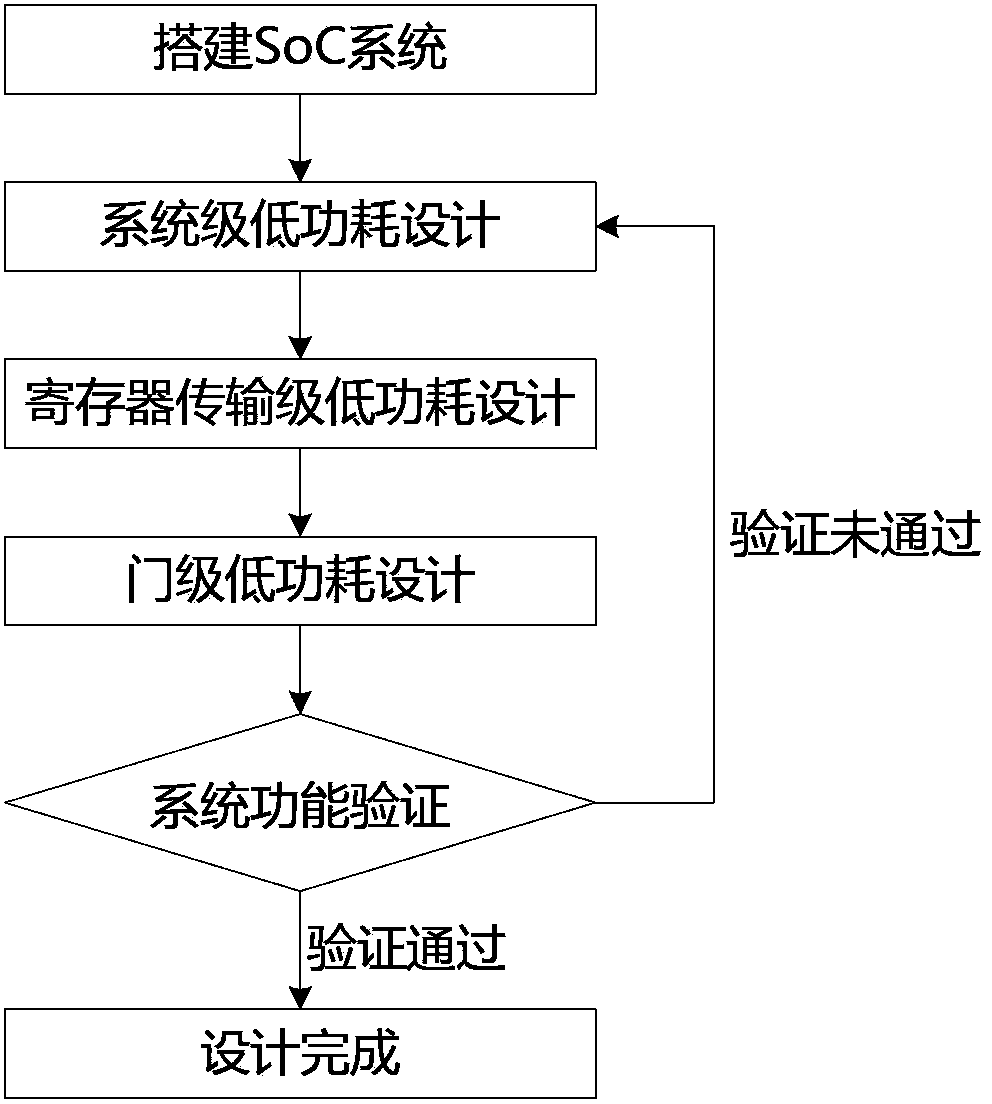

[0042] In the specific implementation process, we need to test all modules to ensure that all modules can work normally, and debug them as a whole to ensure that their online debugging interface with the host computer is normal and their functions are normal. Collaborative low-power design at different levels, low-power design for the system level, register transfer level and gate level respectively to re...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More