Noise adding signal synchronization clock extraction device based on FPGA (field programmable gate array)

A technology of clock extraction and signal synchronization, applied in the direction of automatic power control, electrical components, etc., can solve the problem that the self-synchronization method cannot be used, and achieve the effect of good noise immunity

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0049] The content of the present invention will be further described below in conjunction with the accompanying drawings.

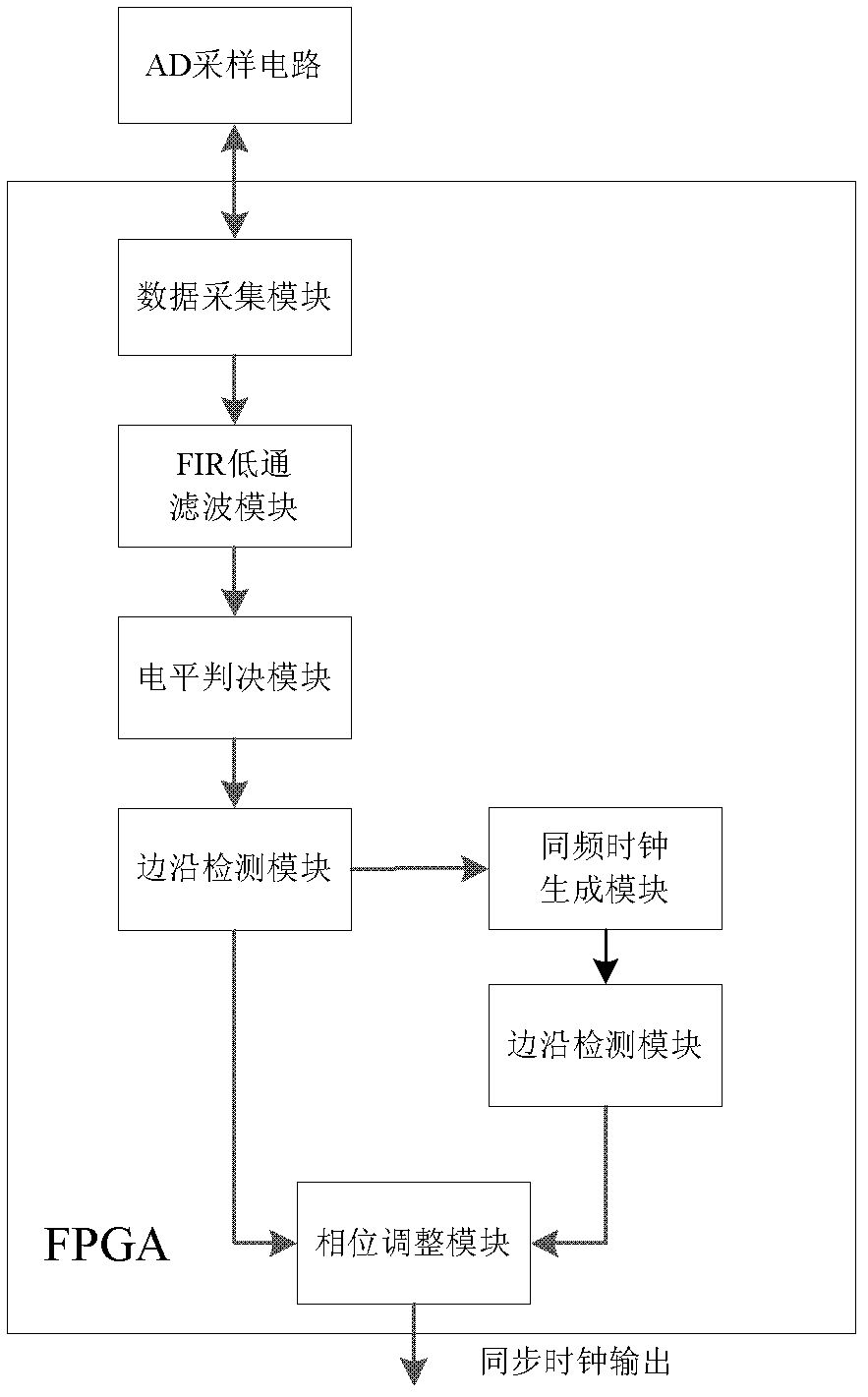

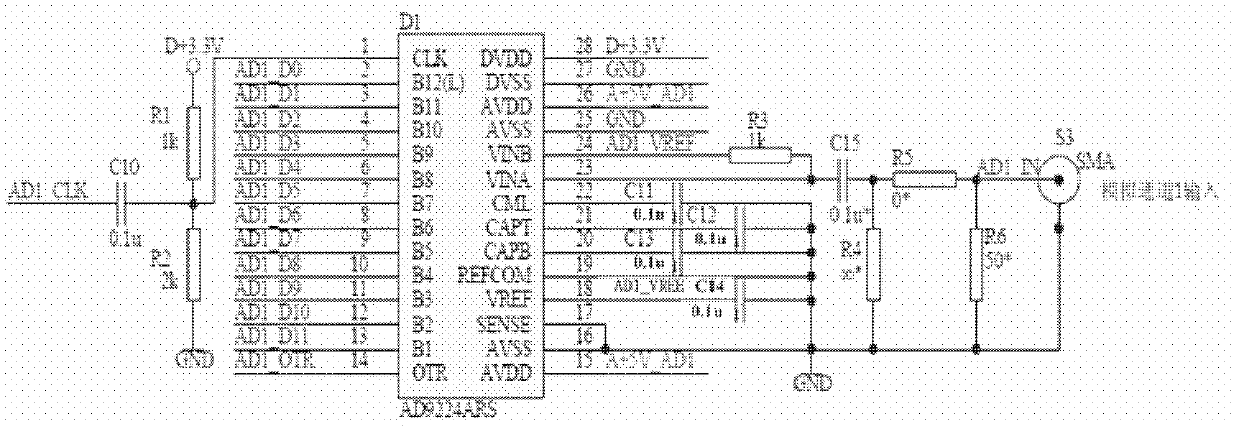

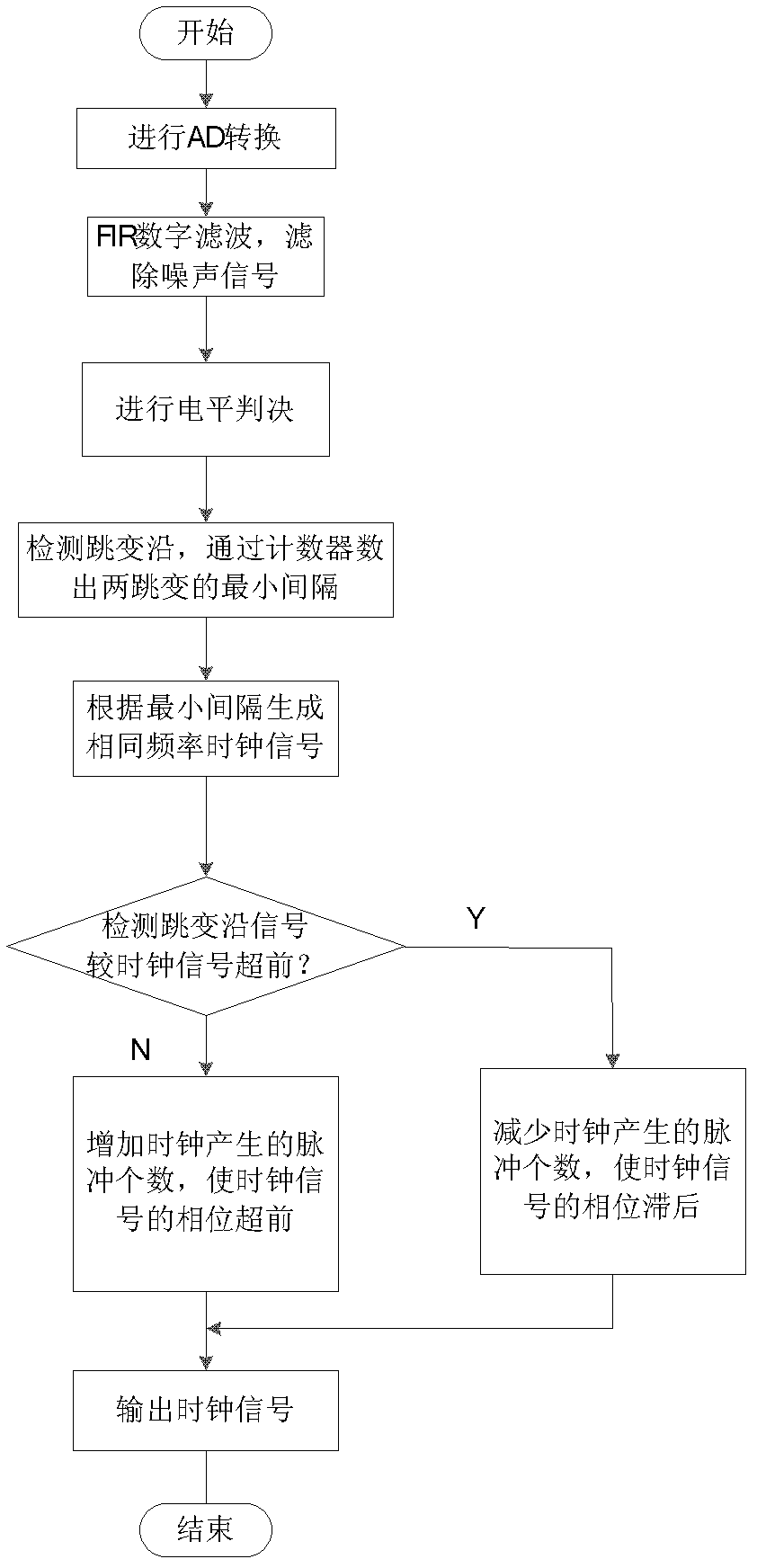

[0050] The overall structure diagram of the system is shown in the figure 1 Shown, including AD sampling circuit and FPGA. The FPGA chip that the embodiment of the present invention adopts is the EP1C12Q240C6 of the Cyclone series of Altera Company, and described FPGA comprises the data acquisition module of realization, FIR low-pass filter module, level judgment module, edge detection module, same frequency clock generation module and Phase adjustment module. The data output pin of the AD sampling circuit is connected to the I / O port of the FPGA, and the modules inside the FPGA are generated by the Verilog HDL hardware description language in the Quartus II environment, and the data connection between the modules is realized. The signal transmission process is: AD The data collected by the sampling circuit is output to the FPGA, and the data acquisiti...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More