Izhikevich neural network synchronous discharging simulation platform based on FPGA

A neuron network and simulation platform technology, applied in the direction of electrical digital data processing, special data processing applications, instruments, etc., can solve the difficulty of FPGA simulation analysis, poor network connection flexibility, and no synchronous simulation FPGA experiment platform for neuron network, etc. problems, to achieve the effect of improving operability, improving flexibility, and portable hardware experiment platform

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

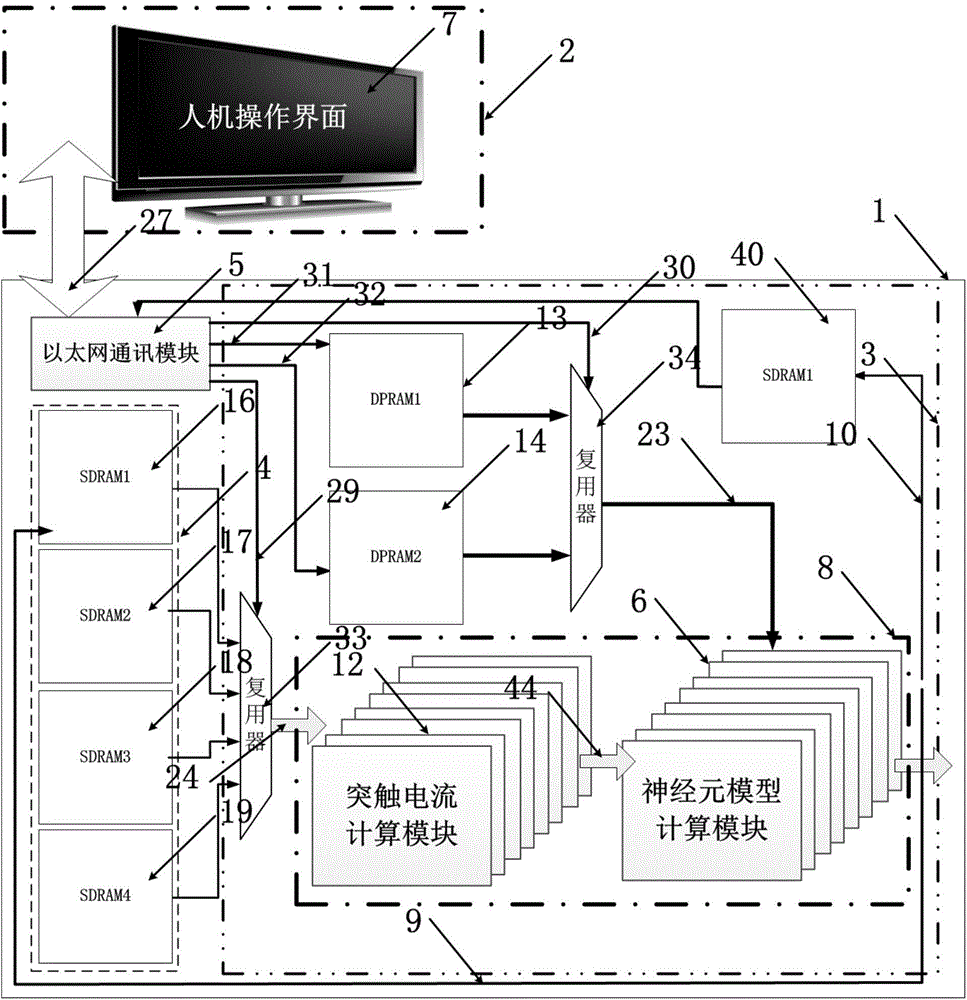

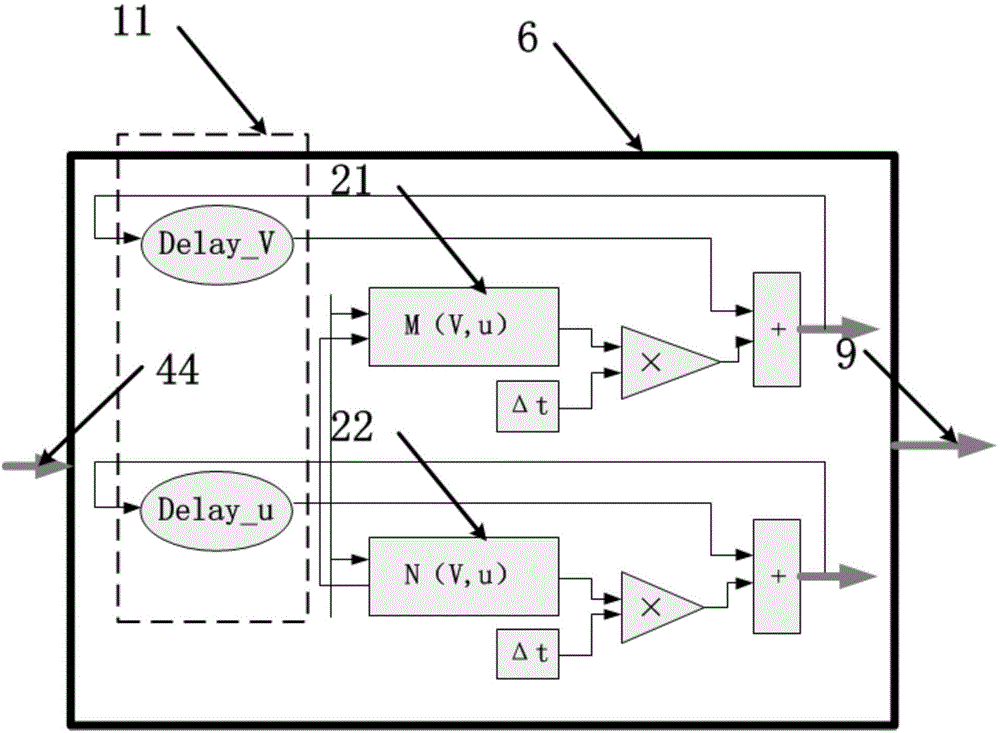

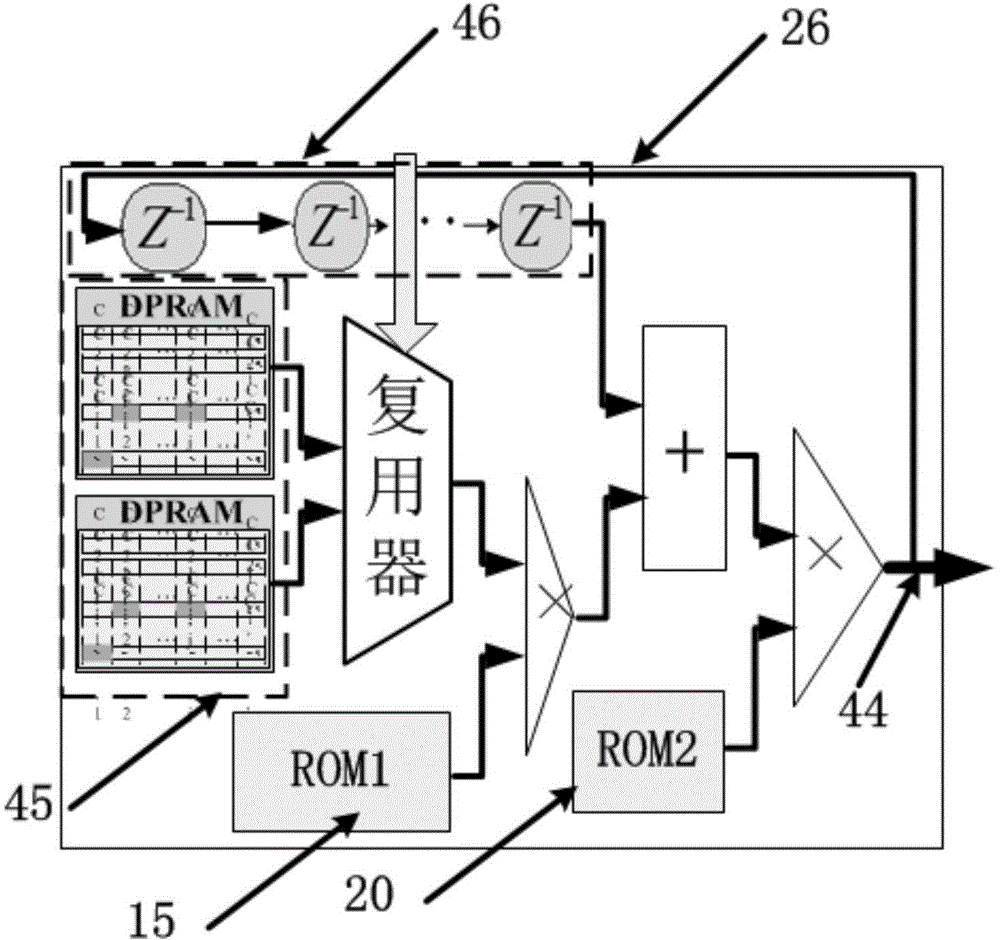

[0020] The structure of the FPGA-based Izhikevich neuron network synchronous discharge simulation platform of the present invention will be described below in conjunction with the accompanying drawings.

[0021] The design idea of the FPGA-based Izhikevich neuron network synchronous discharge simulation platform of the present invention is to first build a parallel computing neuron network model on the FPGA chip; then design the off-chip memory of different storage spaces independently of the neuron network model on the FPGA , for the storage and transfer of intermediate data of neuron network information of different scales; the Ethernet communication module is used for data transmission between the upper computer and the lower computer, and performs corresponding control operations on data transmission and selection according to the instructions input from the upper computer software interface; finally Design the software interface of the host computer. The software interfa...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More