AT96 bus controller IP (internet protocol) core based on FPGA (field programmable gate array) and construction method thereof

A technology of a bus controller and a construction method, applied in the fields of instruments, electrical digital data processing, etc., can solve the problems of cumbersome configuration operations, low application efficiency, poor portability, etc., and achieve simple configuration operations, reduce application costs, and reduce CPU. the effect of the load

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment

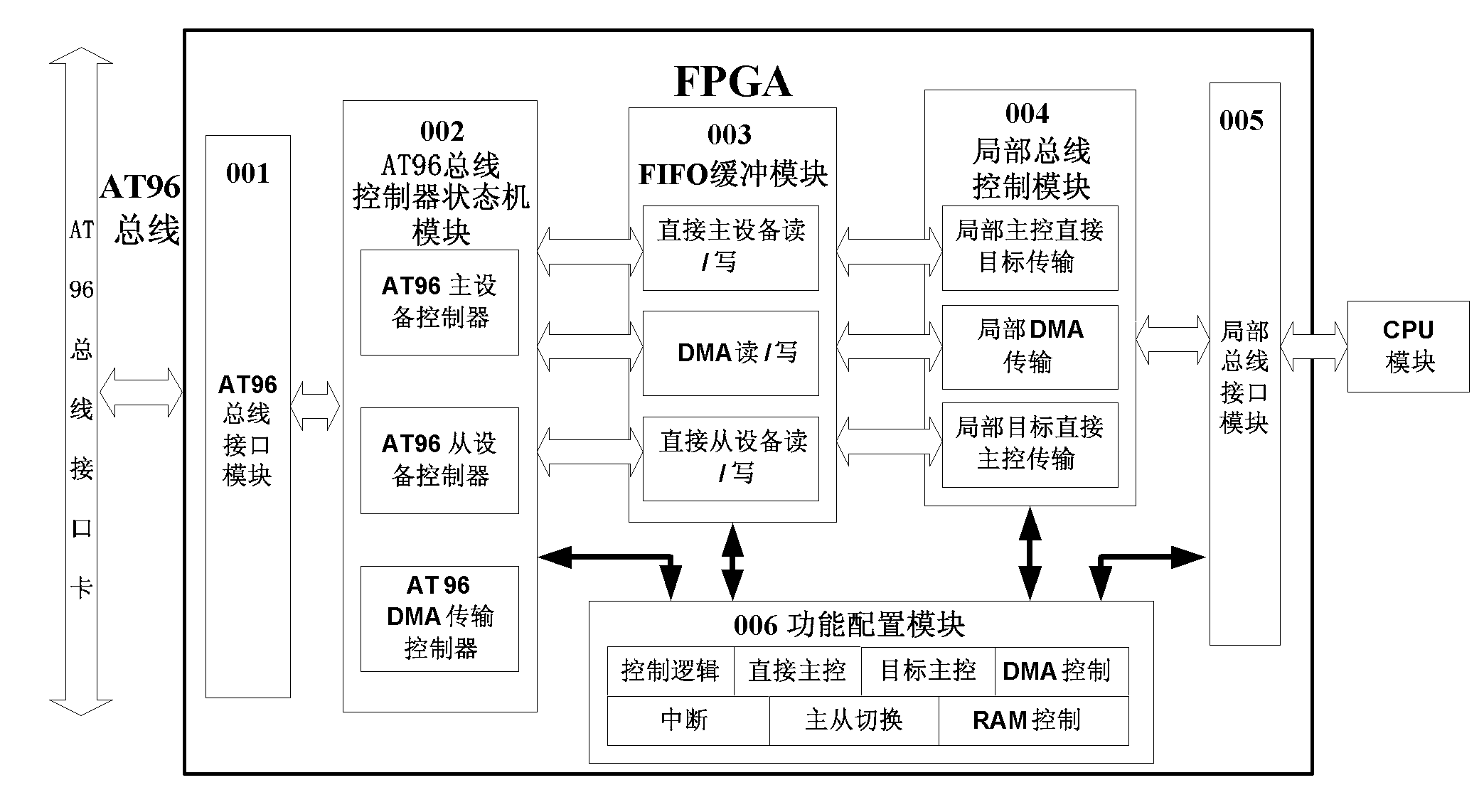

[0048] figure 2 Shown is the functional block diagram of the IP core of the AT96 bus controller based on FPGA. Taking a bus read and write access through an AT96 bus controller as an example, an embodiment of the present invention will be described.

[0049] 1. The present invention is an FPGA-based AT96 bus controller IP core, such as figure 2 As shown, it is composed of AT96 bus interface module (001), AT96 bus controller state machine module (002), FIFO buffer module (003), local bus control module (004), local bus interface module (005) and functional configuration Module (006) composition, such as figure 2 As shown, the positional connection relationship and signal flow between them are as follows. a) One end of the AT96 bus interface module (001) is connected to the AT96 bus interface card, and the other end is connected to the AT96 bus controller state machine module (002), which receives data and control signals from the AT96 bus or sends data and control signals On the ...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More