Patents

Literature

59 results about "Clos network" patented technology

Efficacy Topic

Property

Owner

Technical Advancement

Application Domain

Technology Topic

Technology Field Word

Patent Country/Region

Patent Type

Patent Status

Application Year

Inventor

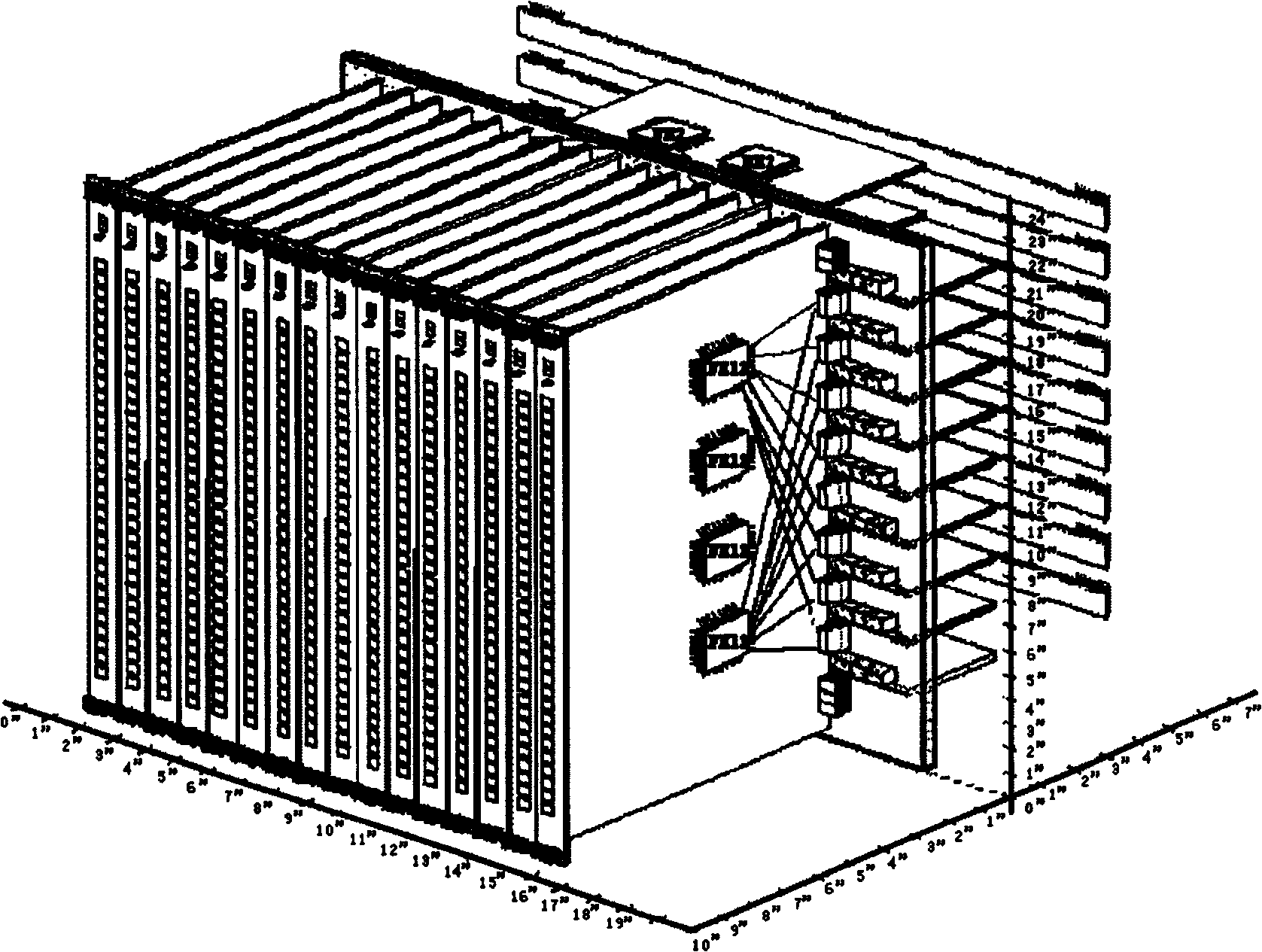

In the field of telecommunications, a Clos network is a kind of multistage circuit-switching network which represents a theoretical idealization of practical, multistage switching systems. It was invented by Edson Erwin in 1938 and first formalized by Charles Clos ([ʃaʁl klo])in 1952.

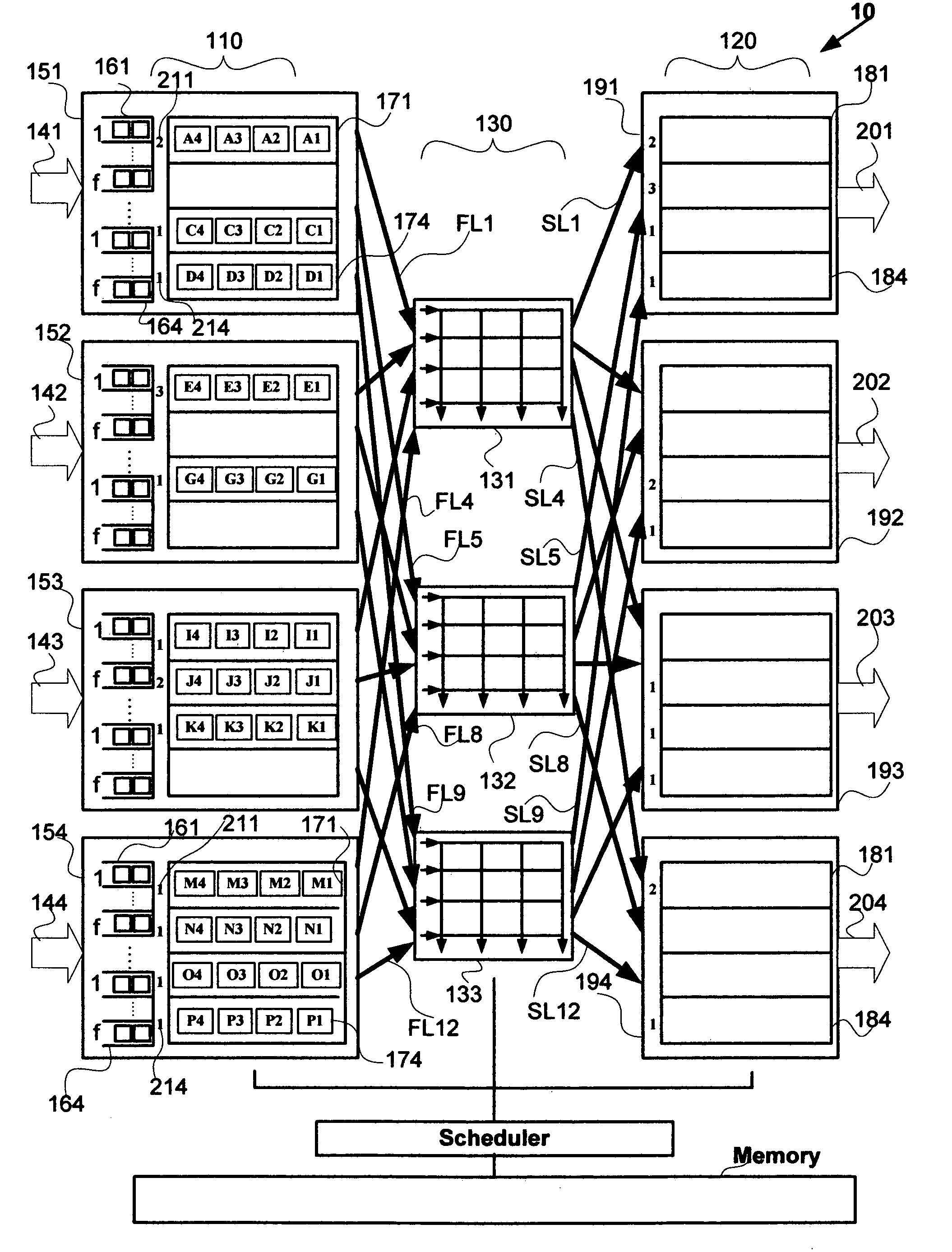

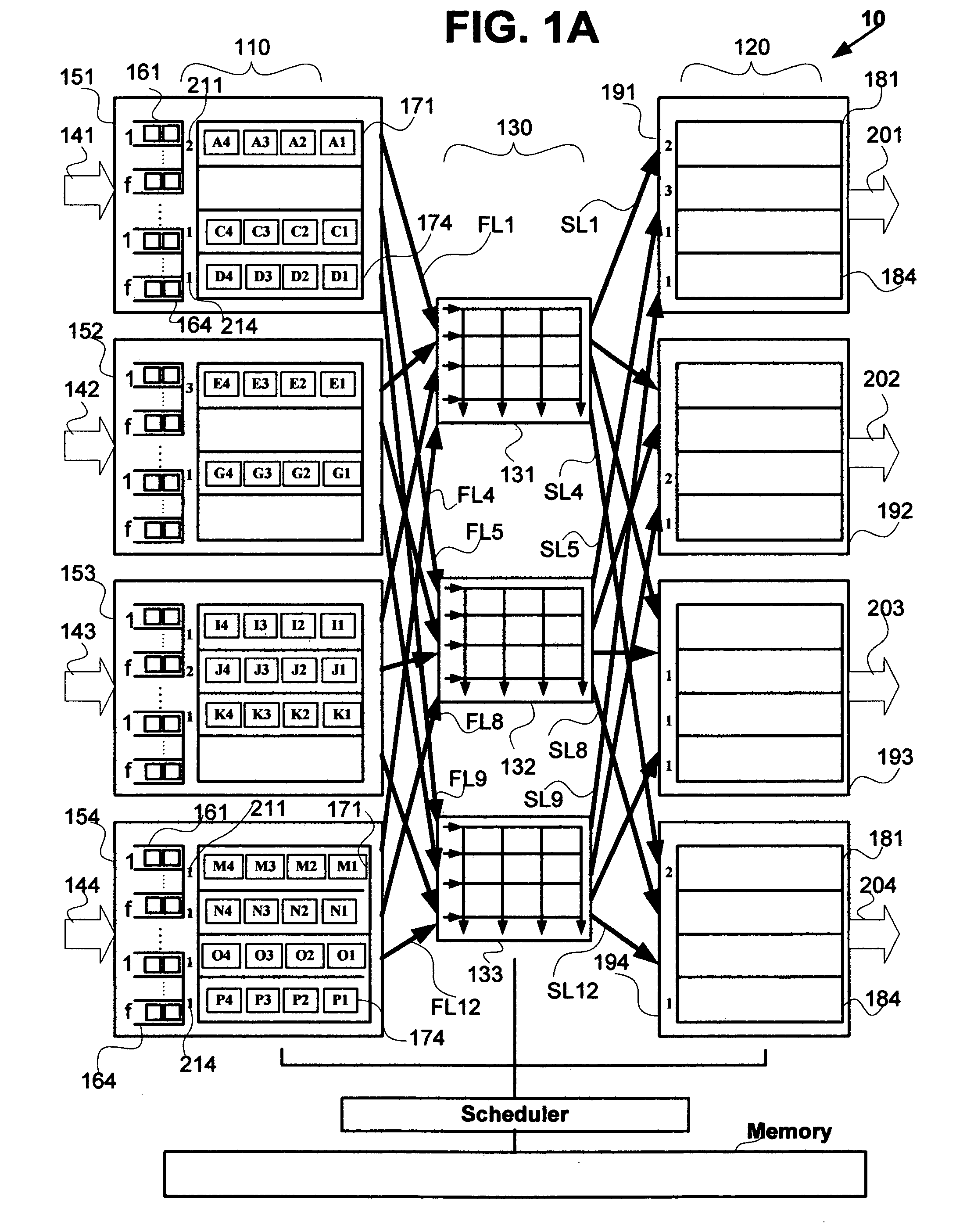

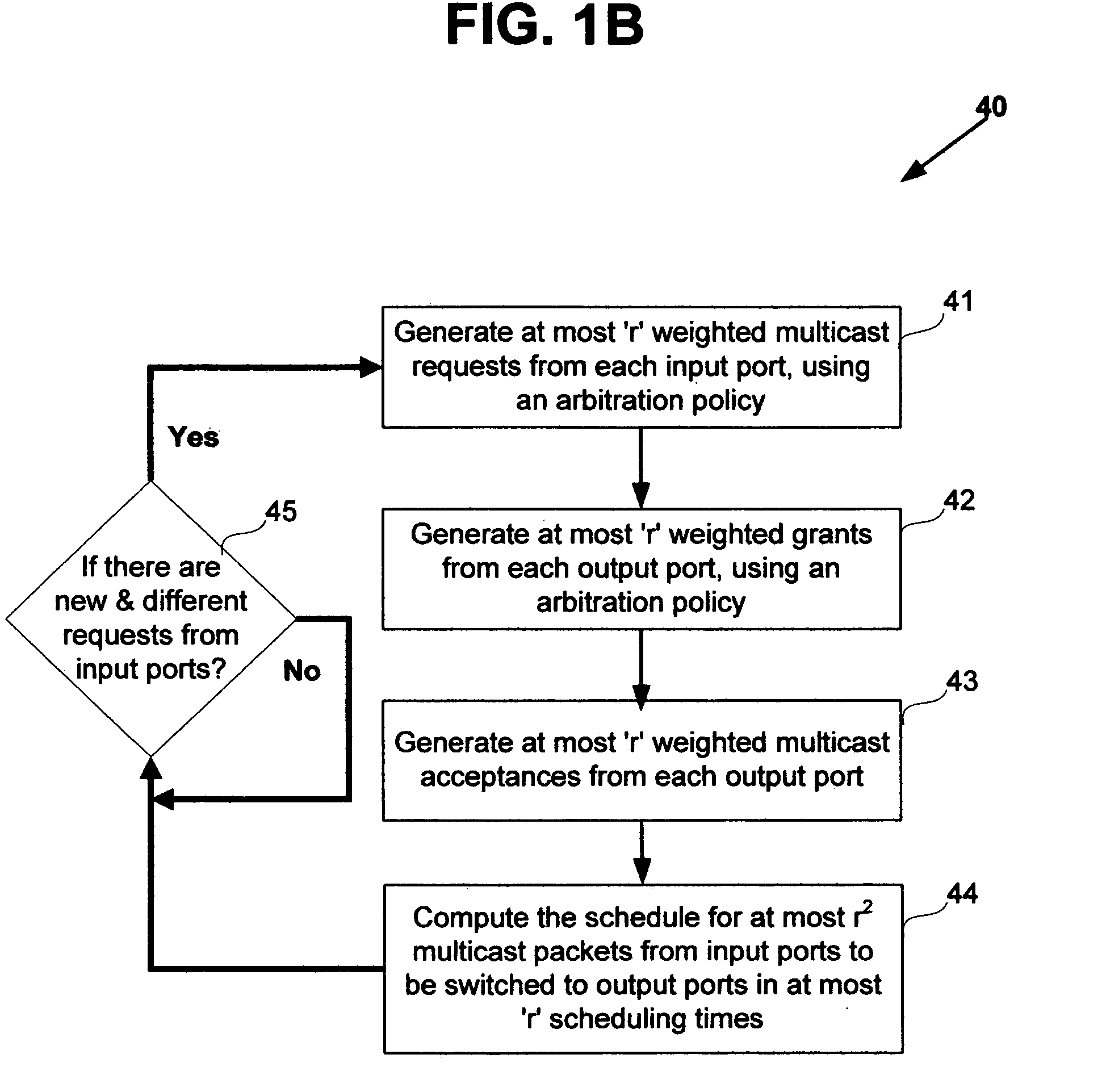

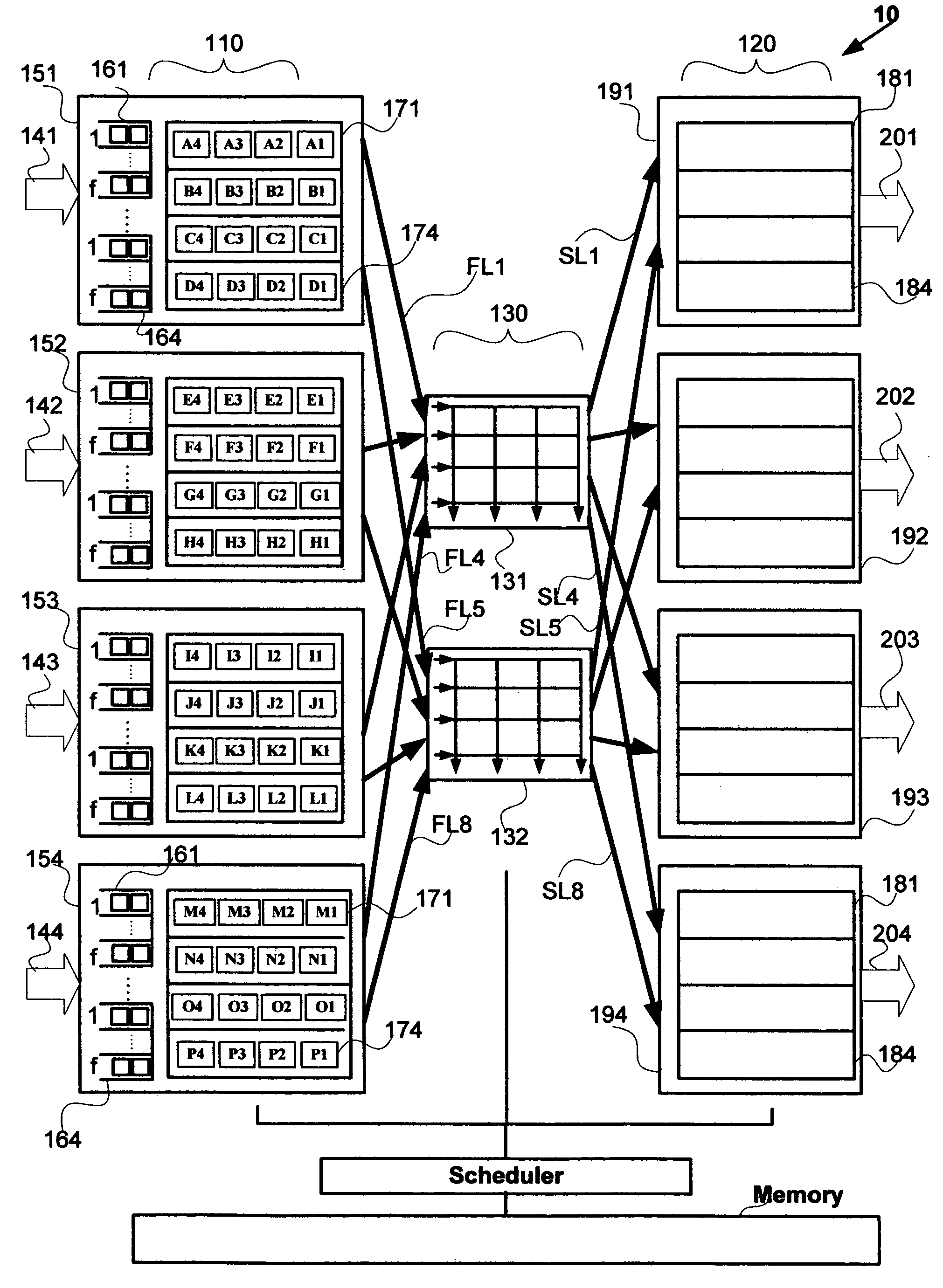

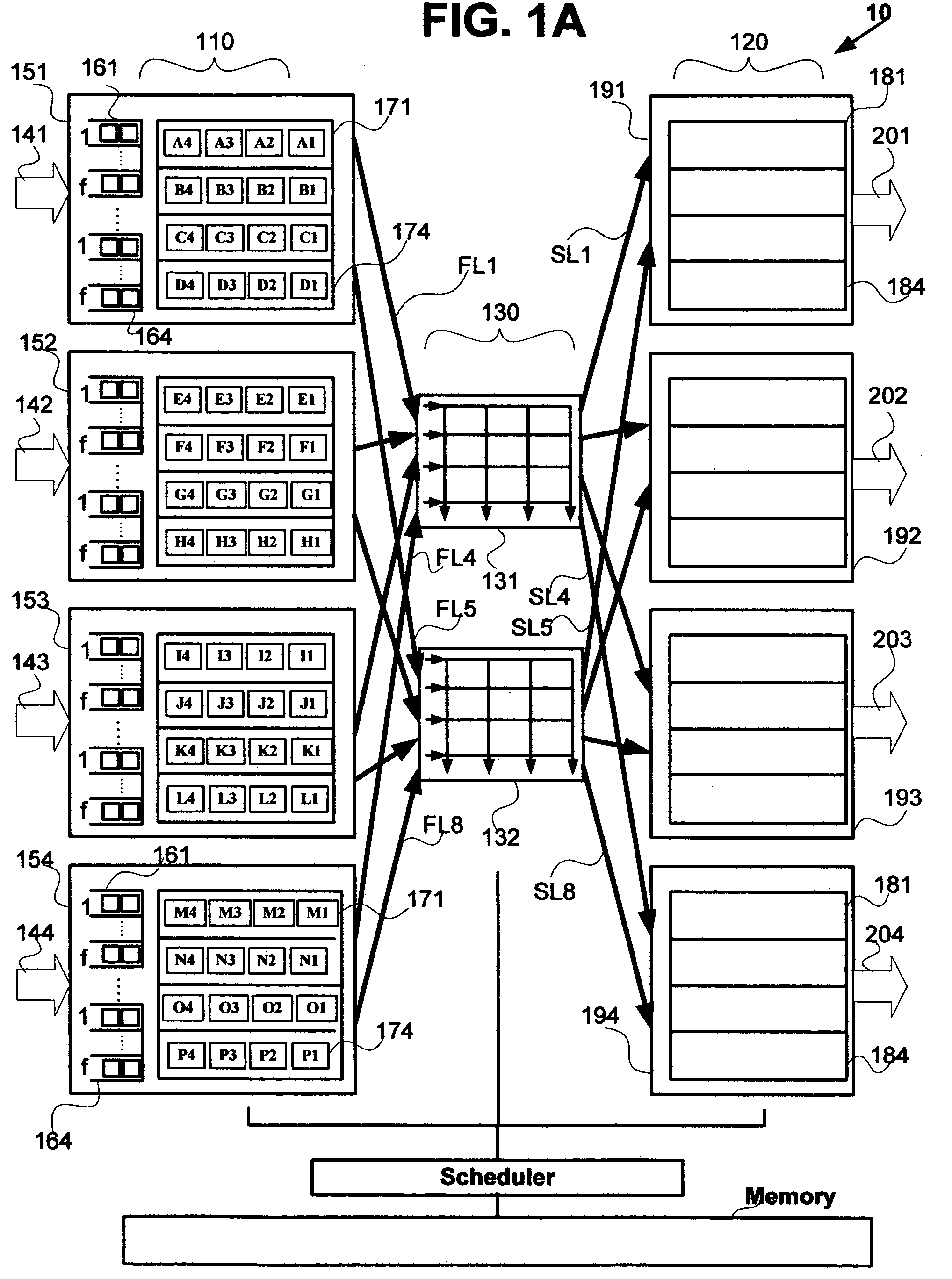

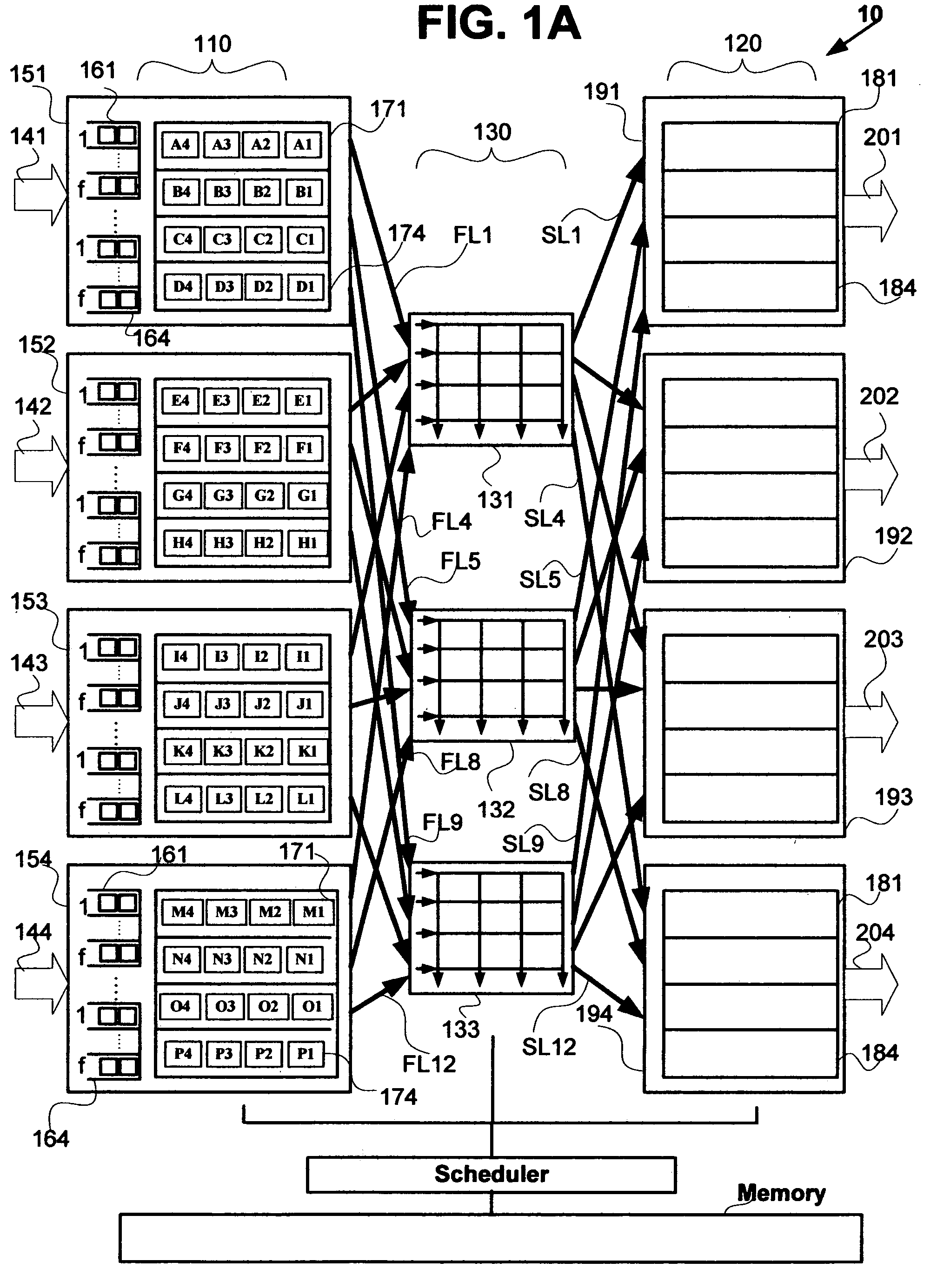

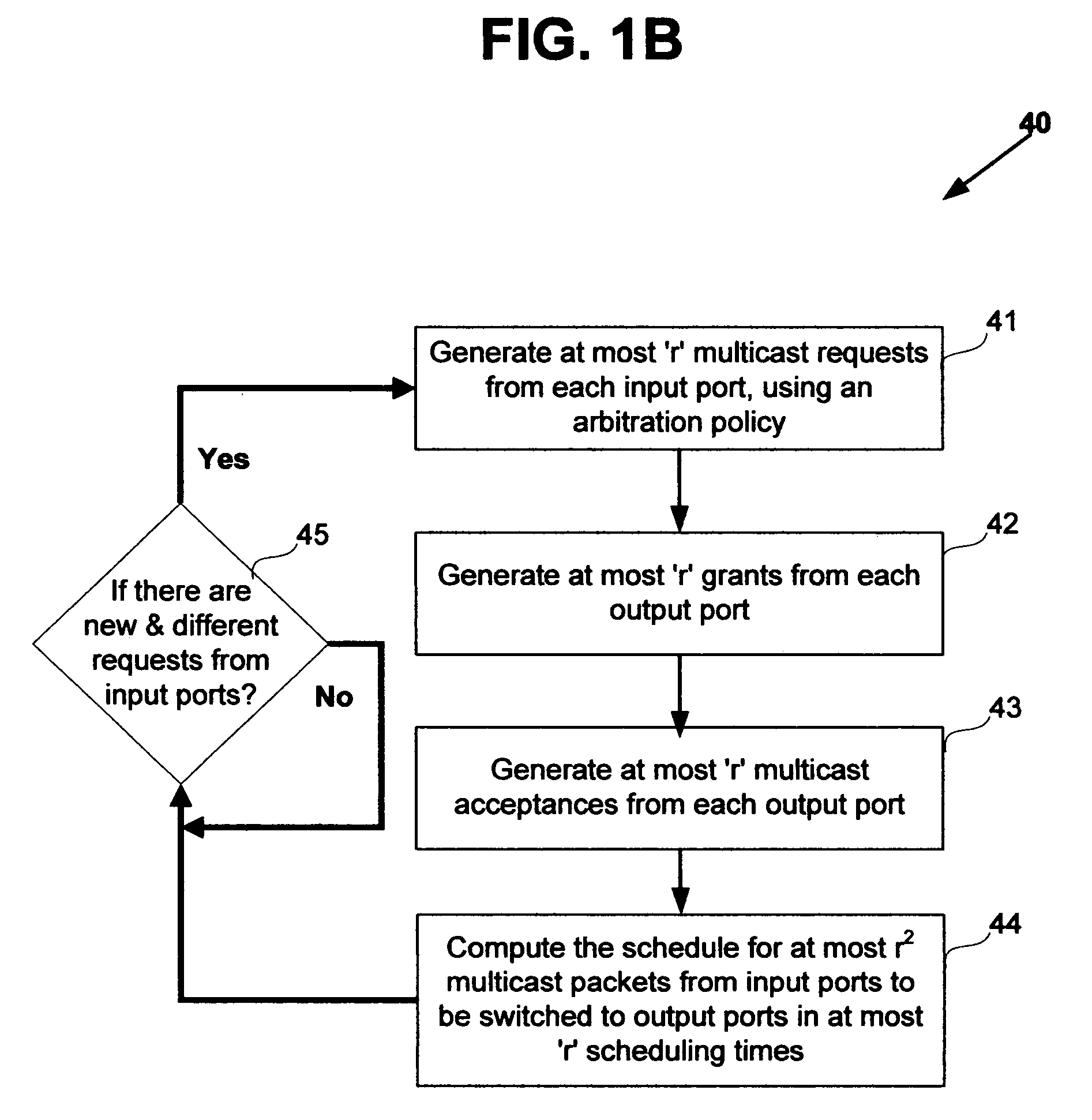

Nonblocking and deterministic multirate multicast packet scheduling

InactiveUS20070053356A1Guaranteed bandwidthGuaranteed LatencyData switching by path configurationSwitching timeMulti rate

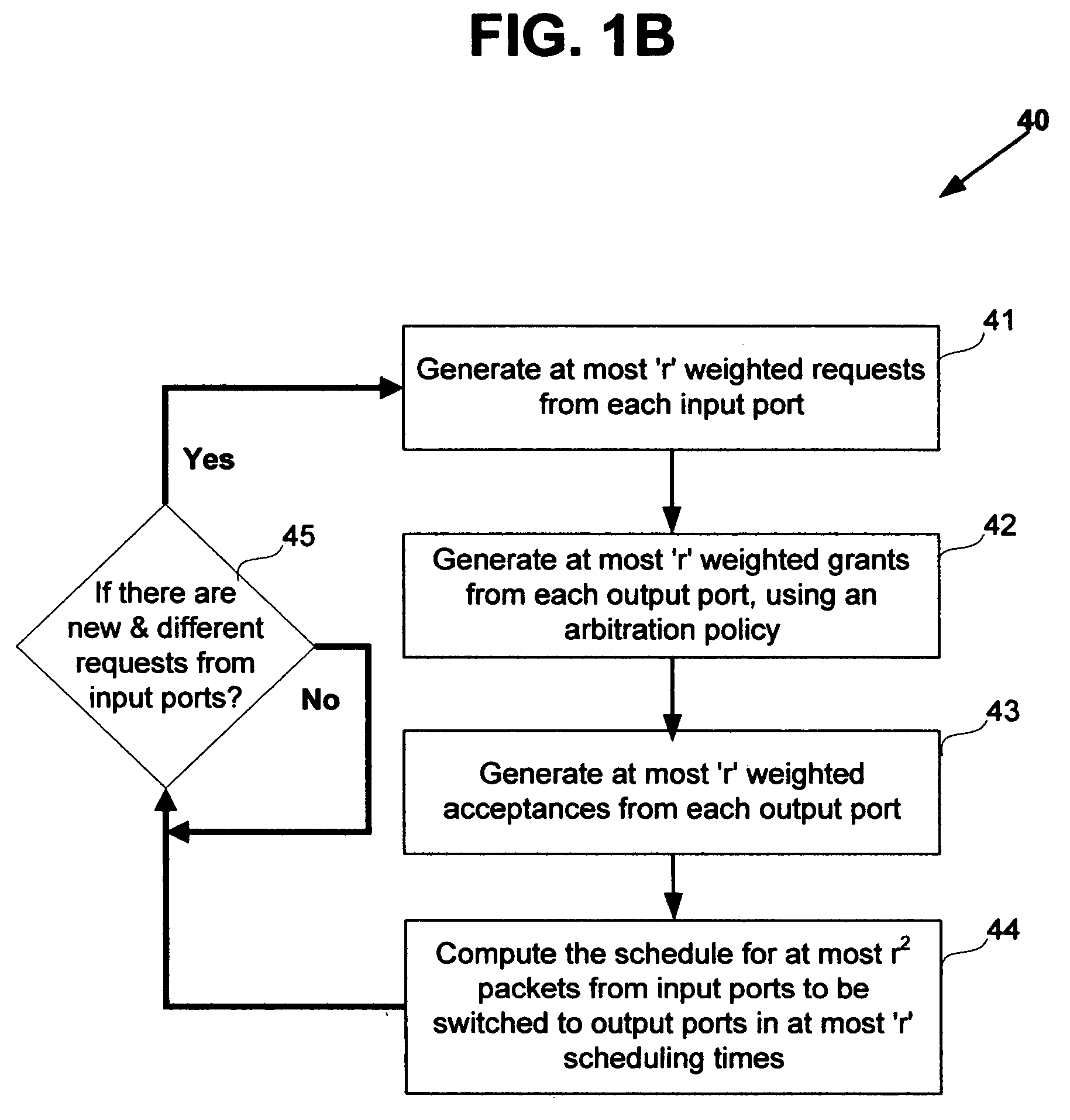

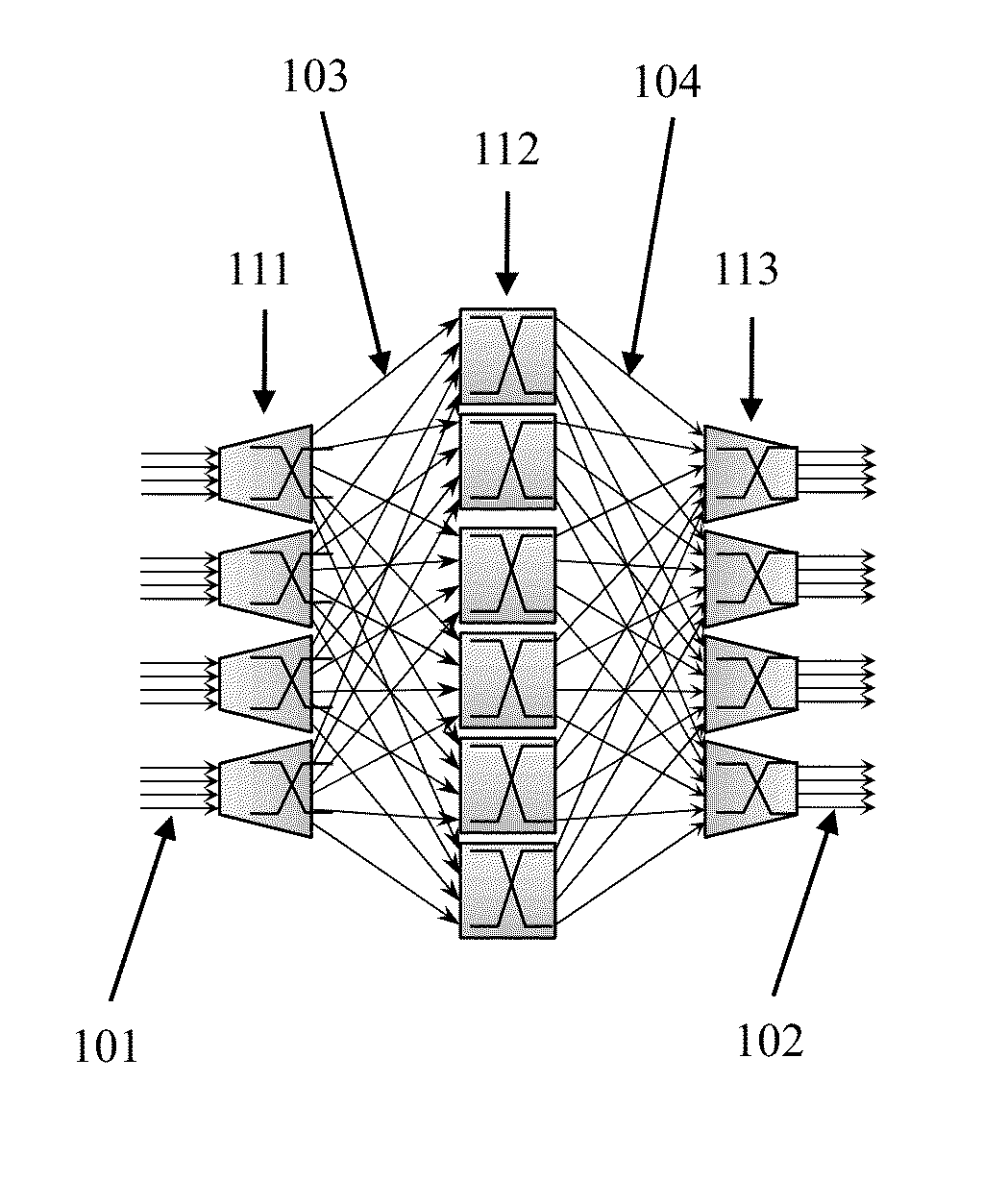

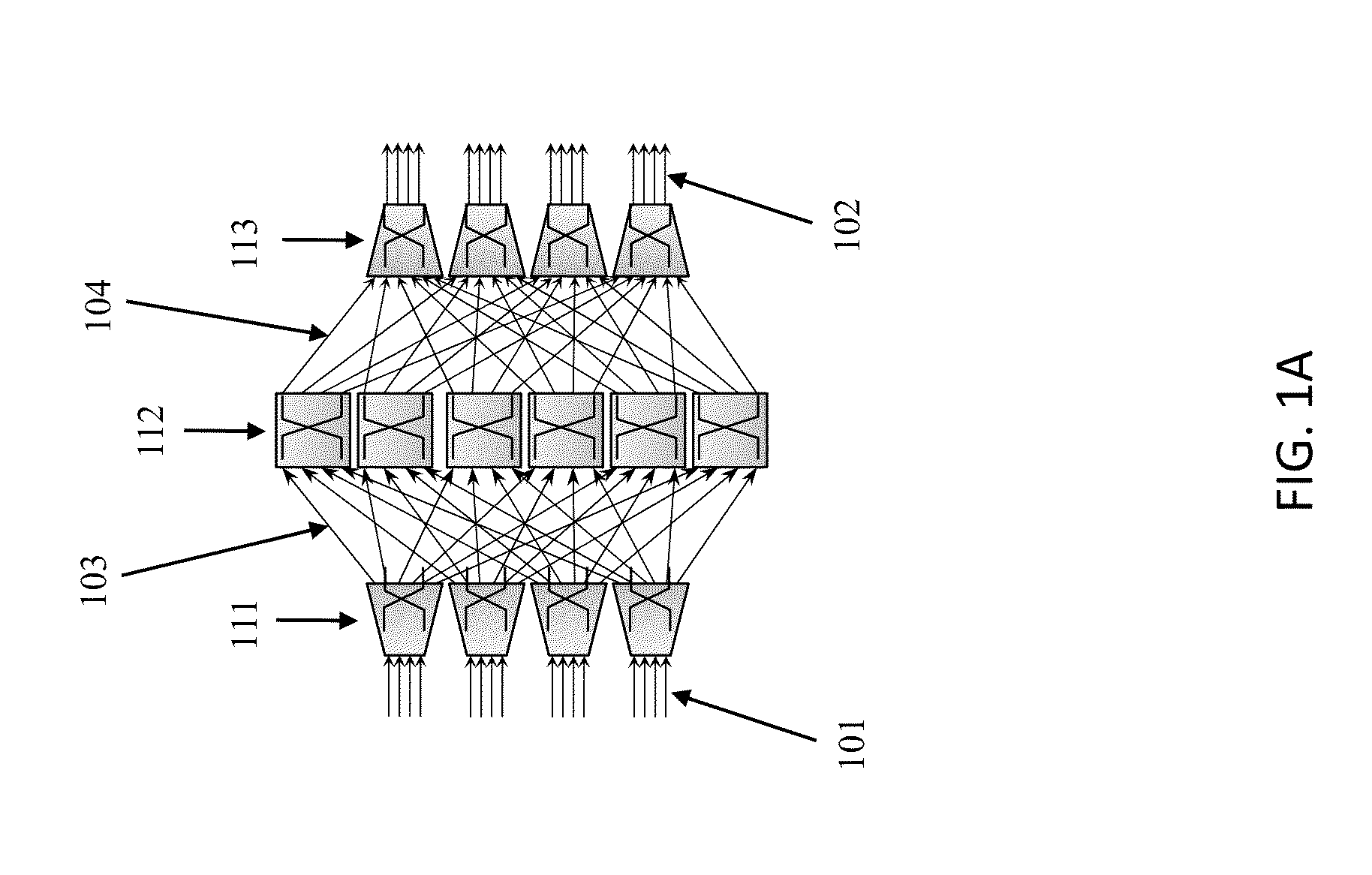

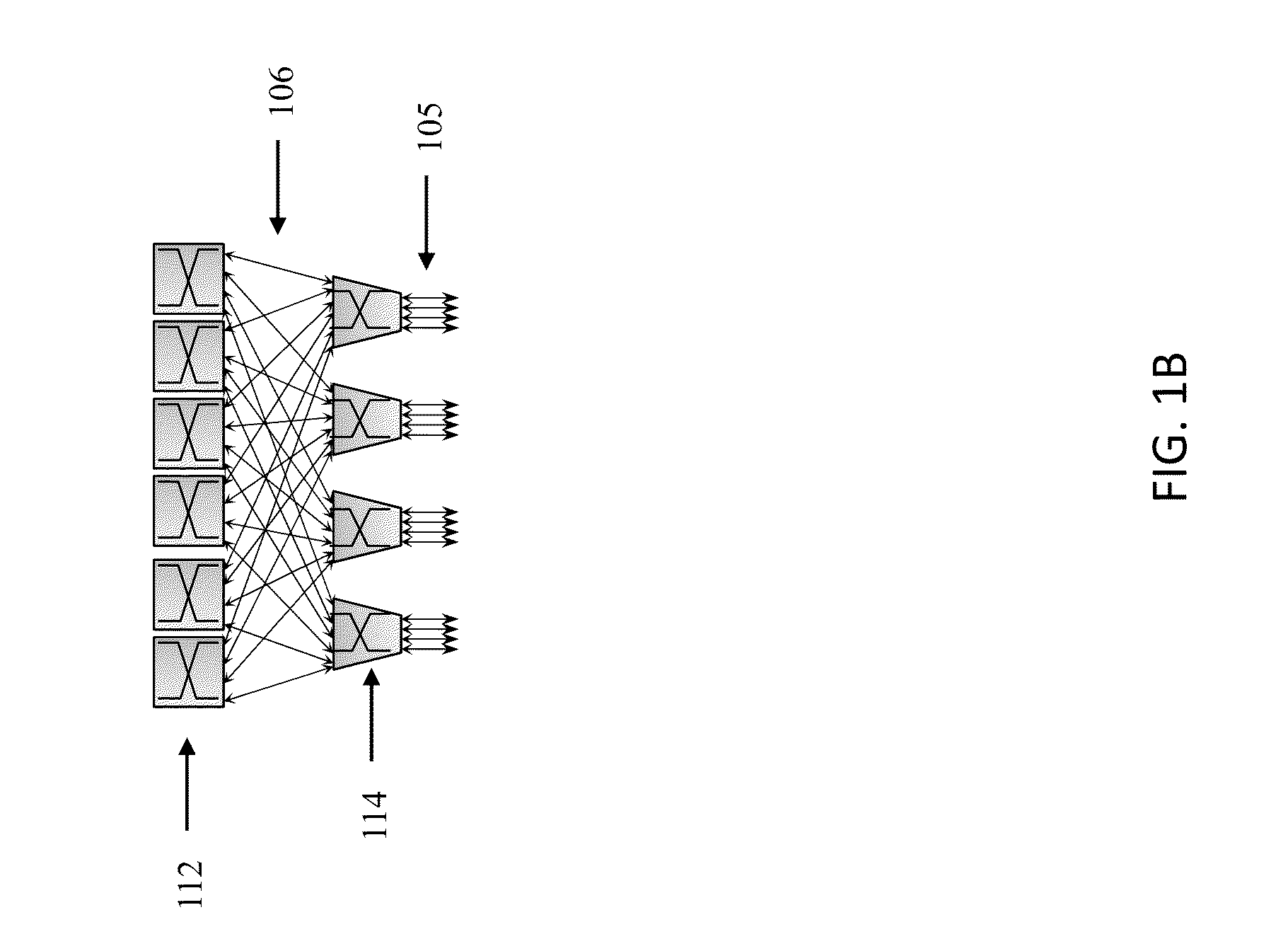

A system for scheduling multirate multicast packets through an interconnection network having a plurality of input ports, a plurality of output ports, and a plurality of input queues, comprising multirate multicast packets with rate weight, at each input port is operated in nonblocking manner in accordance with the invention by scheduling corresponding to the packet rate weight, at most as many packets equal to the number of input queues from each input port to each output port. The scheduling is performed so that each multicast packet is fan-out split through not more than two interconnection networks and not more than two switching times. The system is operated at 100% throughput, work conserving, fair, and yet deterministically thereby never congesting the output ports. The system performs arbitration in only one iteration, with mathematical minimum speedup in the interconnection network. The system operates with absolutely no packet reordering issues, no internal buffering of packets in the interconnection network, and hence in a truly cut-through and distributed manner. In another embodiment each output port also comprises a plurality of output queues and each packet is transferred corresponding to the packet rate weight, to an output queue in the destined output port in deterministic manner and without the requirement of segmentation and reassembly of packets even when the packets are of variable size. In one embodiment the scheduling is performed in strictly nonblocking manner with a speedup of at least three in the interconnection network. In another embodiment the scheduling is performed in rearrangeably nonblocking manner with a speedup of at least two in the interconnection network. The system also offers end to end guaranteed bandwidth and latency for multirate multicast packets from input ports to output ports. In all the embodiments, the interconnection network may be a crossbar network, shared memory network, clos network, hypercube network, or any internally nonblocking interconnection network or network of networks.

Owner:TEAK TECH

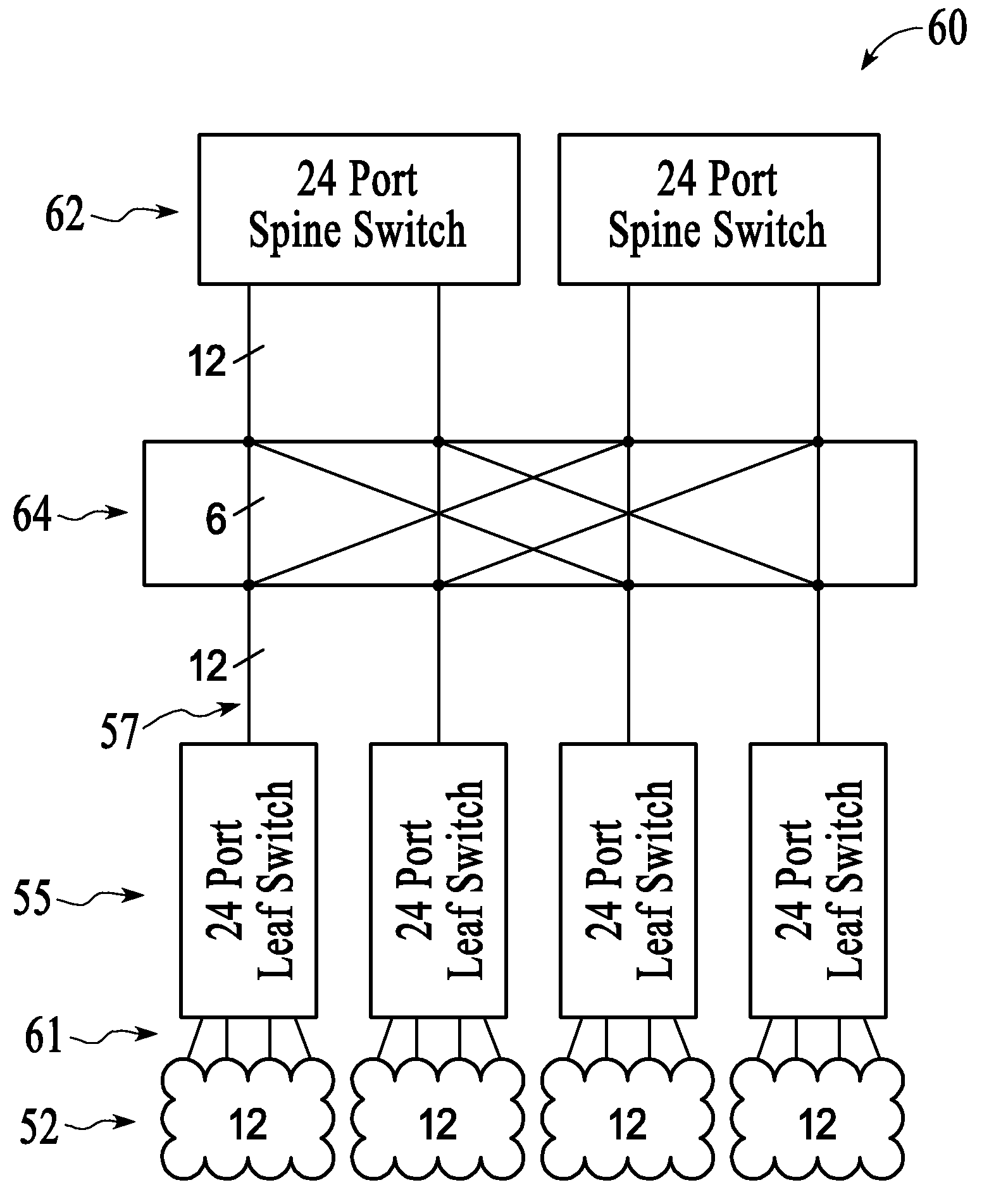

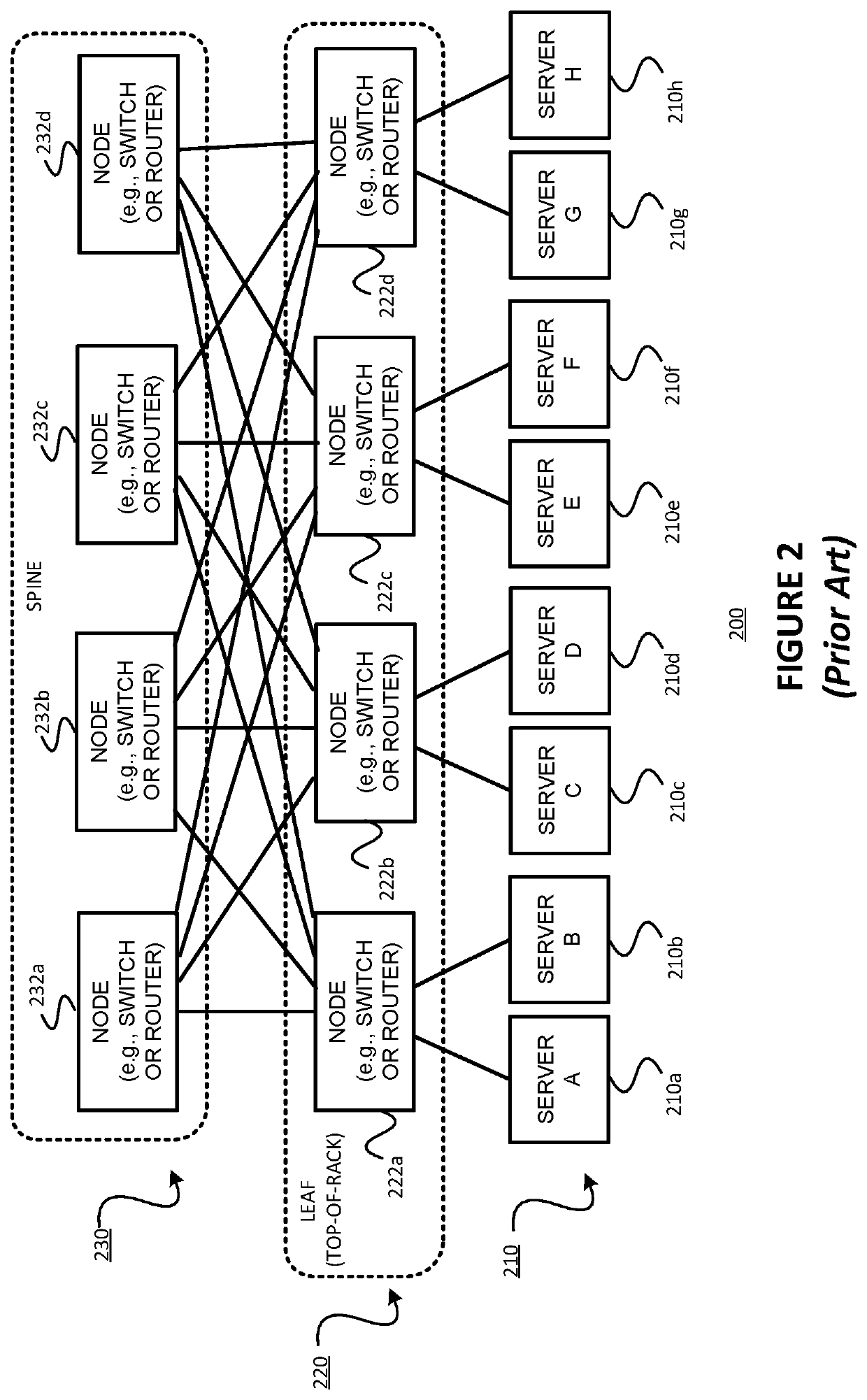

Optical Network for Cluster Computing

ActiveUS20100254652A1Multiplex system selection arrangementsCoupling light guidesDistributed computingPower consumption

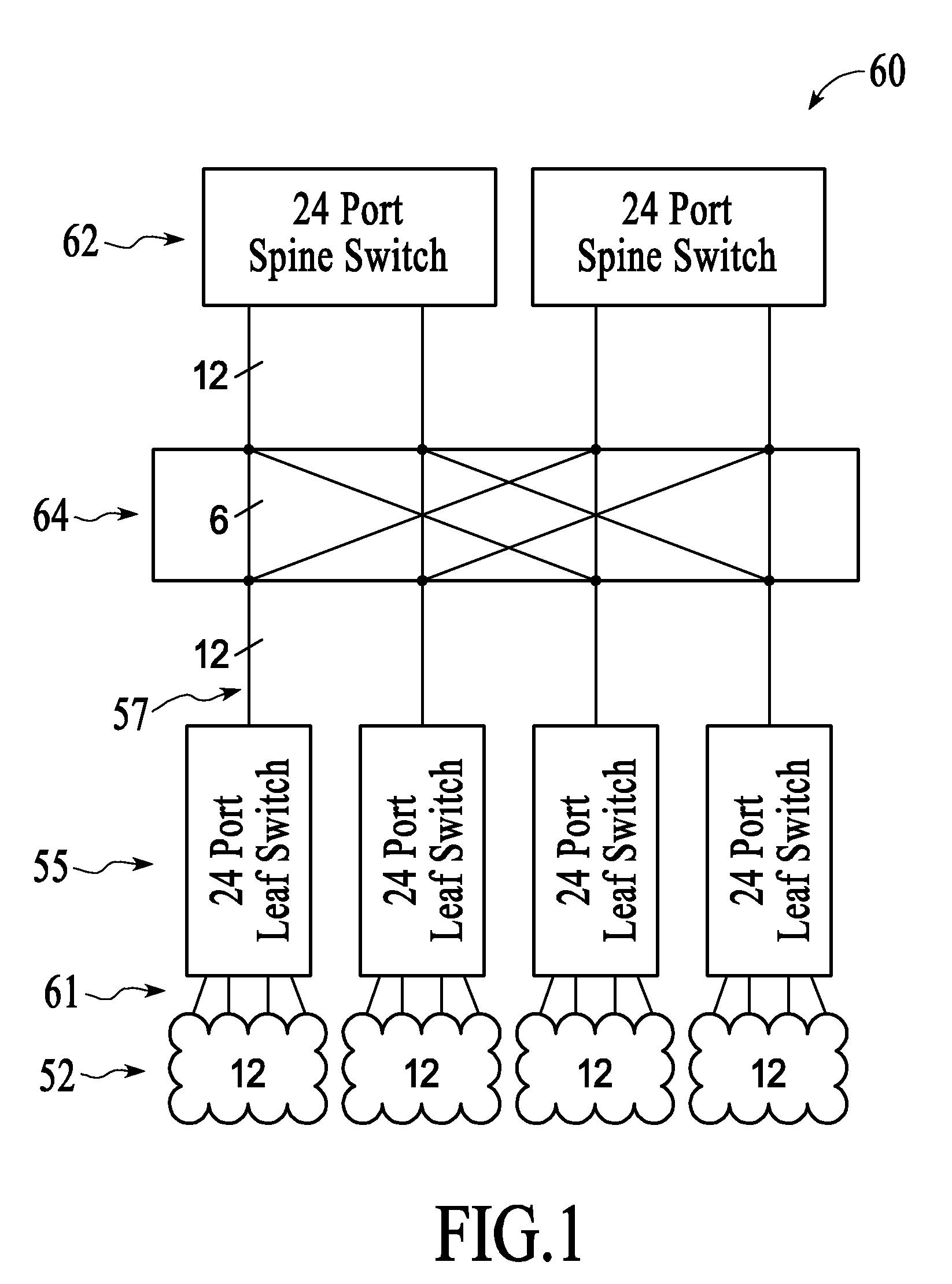

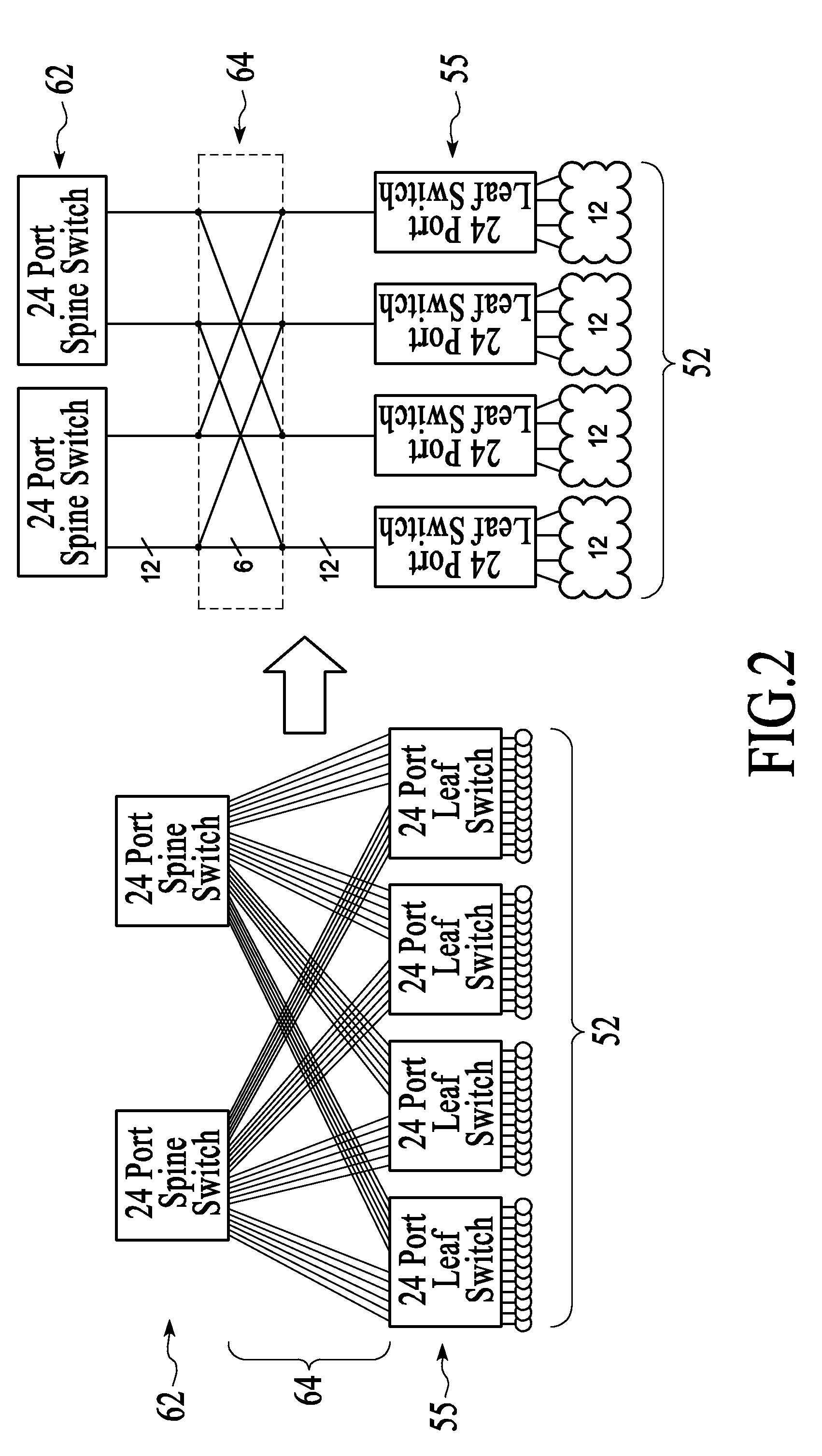

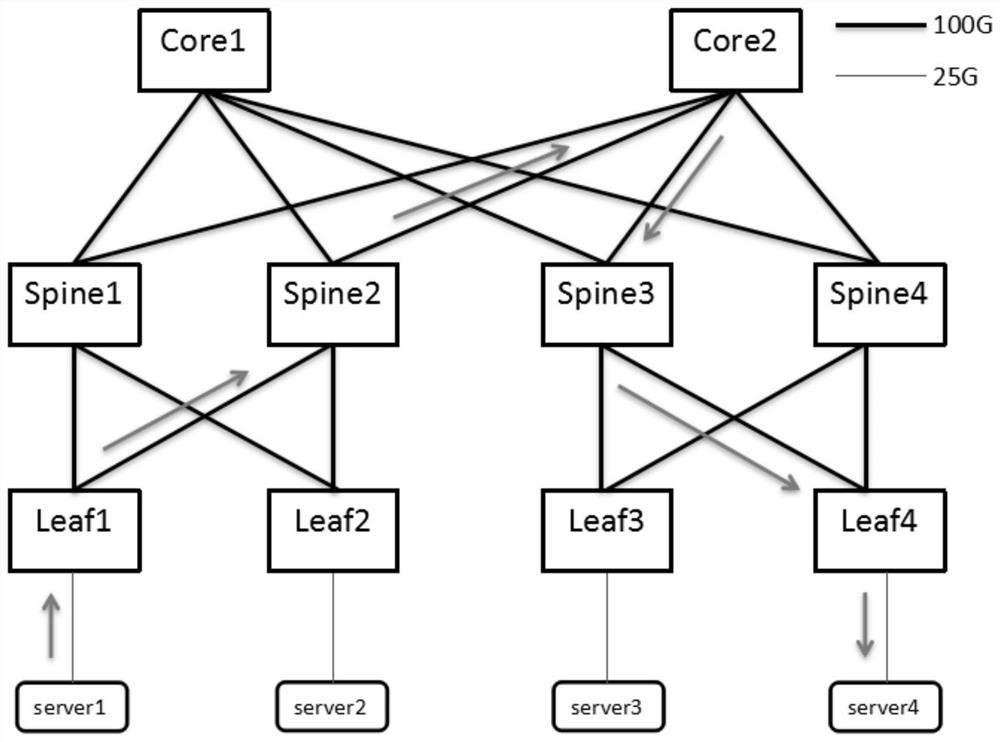

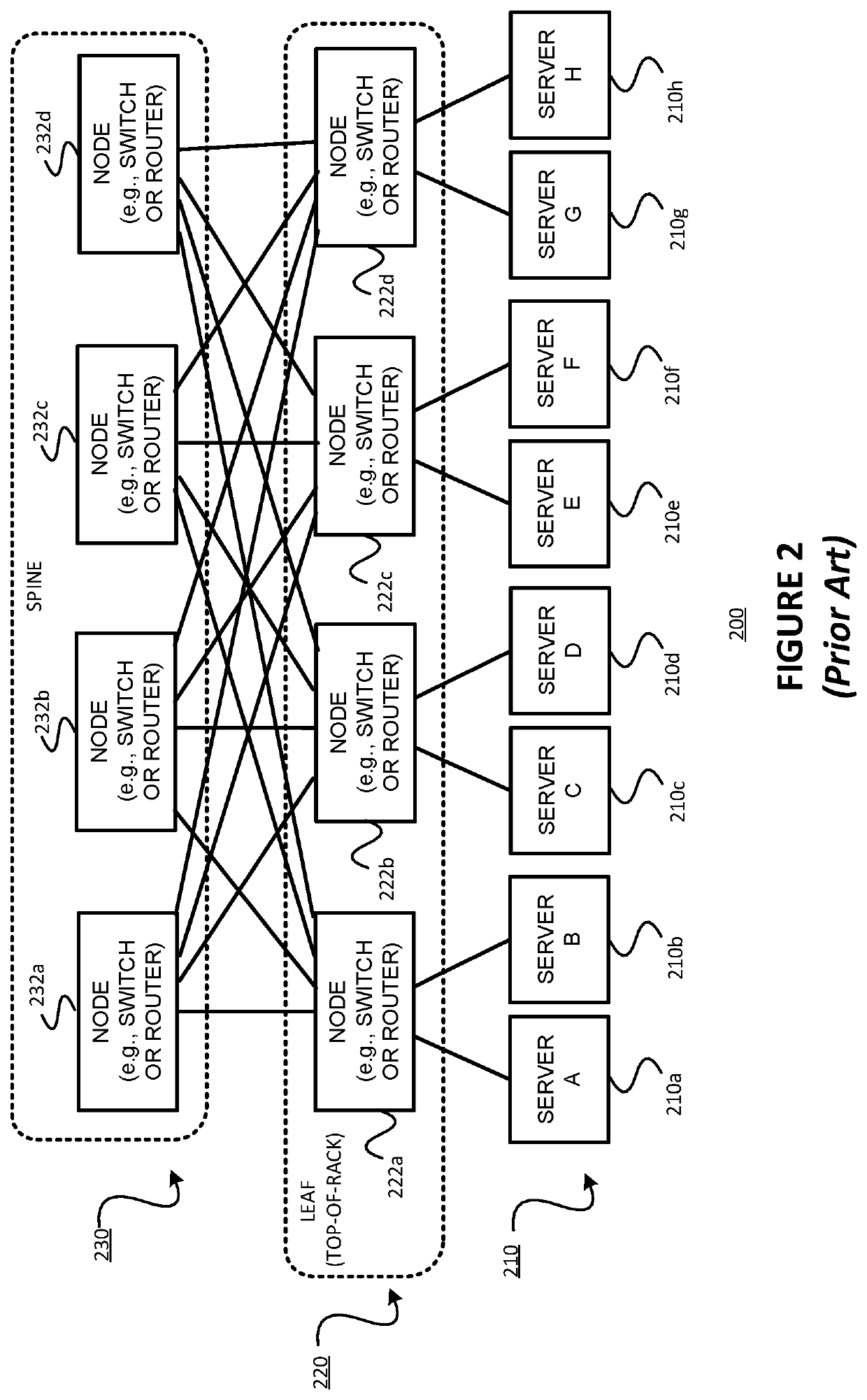

Leaf switches and spine switches in a Clos network are interconnected by optical fibers. The network enables large numbers of servers or other apparatus to communicate with each other with minimal delay and minimal power consumption.

Owner:SANDISK TECH LLC

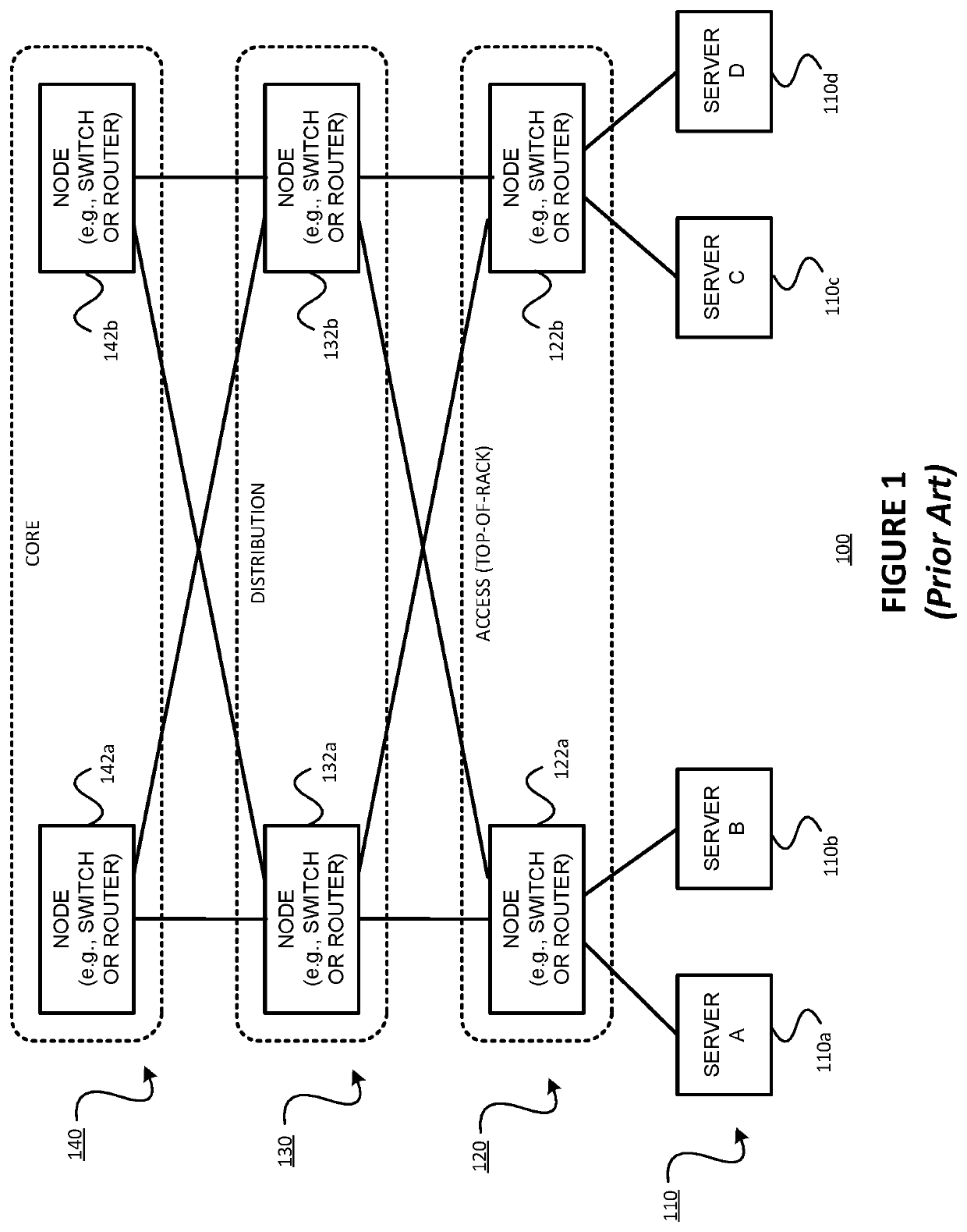

Reducing or eliminating routing microloops in networks having a clos topology, such as data center clos networks employing the exterior border gateway protocol (EBGP) for example

ActiveUS20190363975A1Avoid discardingAvoids otherwise droppingData switching networksBorder Gateway ProtocolEngineering

The problem of routing micro-loops in networks having a CLOS topology, such as data center CLOS networks employing the exterior border gateway protocol (eBGP) for example, is solved by: (a) receiving, on an interface of one of the nodes, a datagram, the datagram including destination information; (b) determining a next hop and an egress interface using (1) an identifier of the interface on which the datagram was received, (2) the destination information of the received datagram, and (3) stored forwarding information such that a routing micro-loop is avoided without discarding the datagram; and (c) forwarding the datagram via the egress interface. For example, this problem may be solved by (a) receiving, on an interface a node of the CLOS network, a datagram, the datagram including destination information; (b) looking up, using the destination information of the received datagram and stored forwarding information, a next hop egress interface on the node; (c) determining whether or not the next hop egress interface on the node is the same as the interface on which the datagram was received; and (d) responsive to a determination that the next hop egress interface on the node is the same as the interface on which the datagram was received, (1) replacing the next hop egress interface with a safe multipath next hop egress interface, and (2) forwarding the datagram via the safe multipath next hop egress interface, and otherwise, responsive to a determination that the next hop egress interface on the node is not the same at the interface on which the datagram was received, simply forwarding the datagram via the next hop egress interface.

Owner:JUMIPER NETWORKS INC

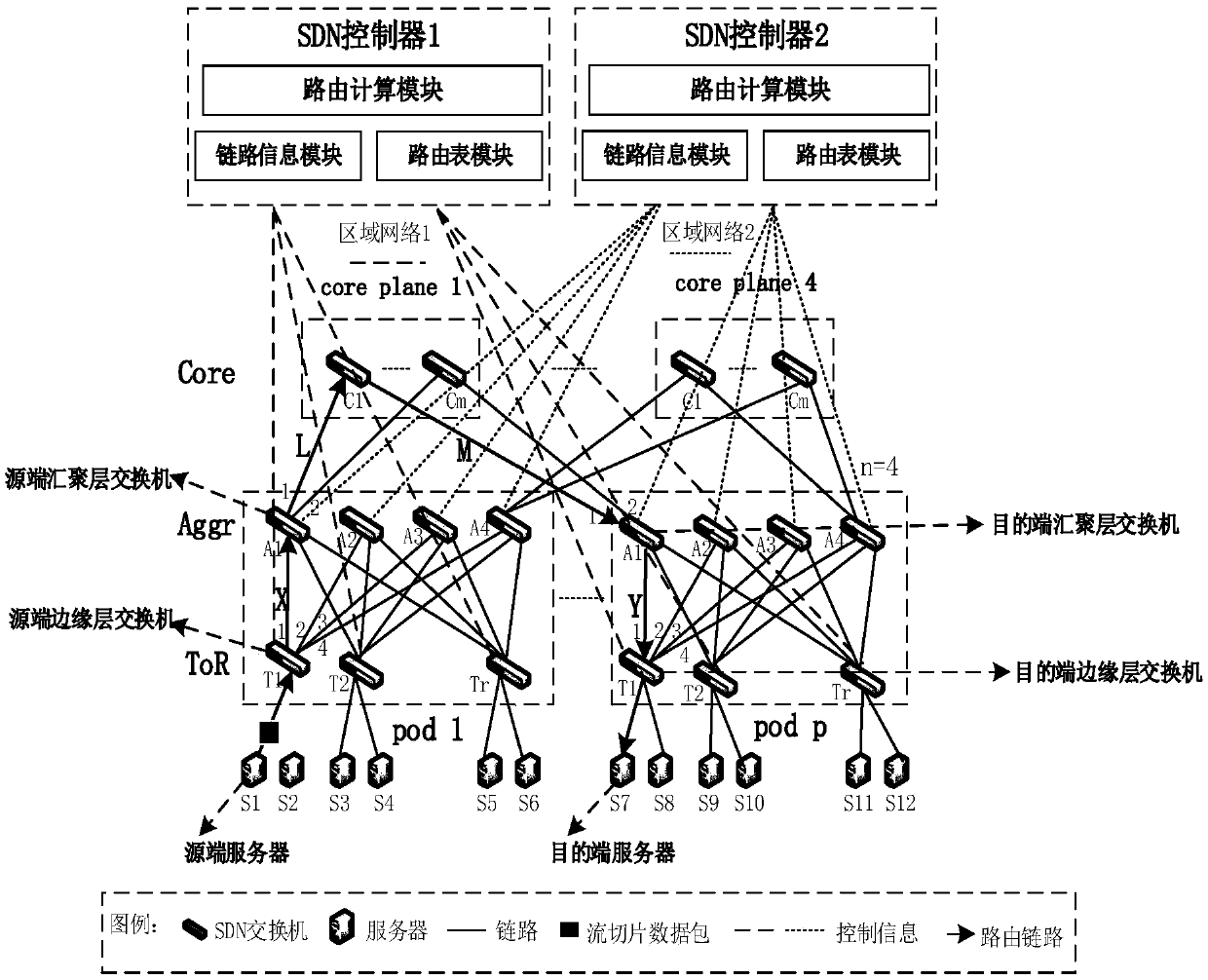

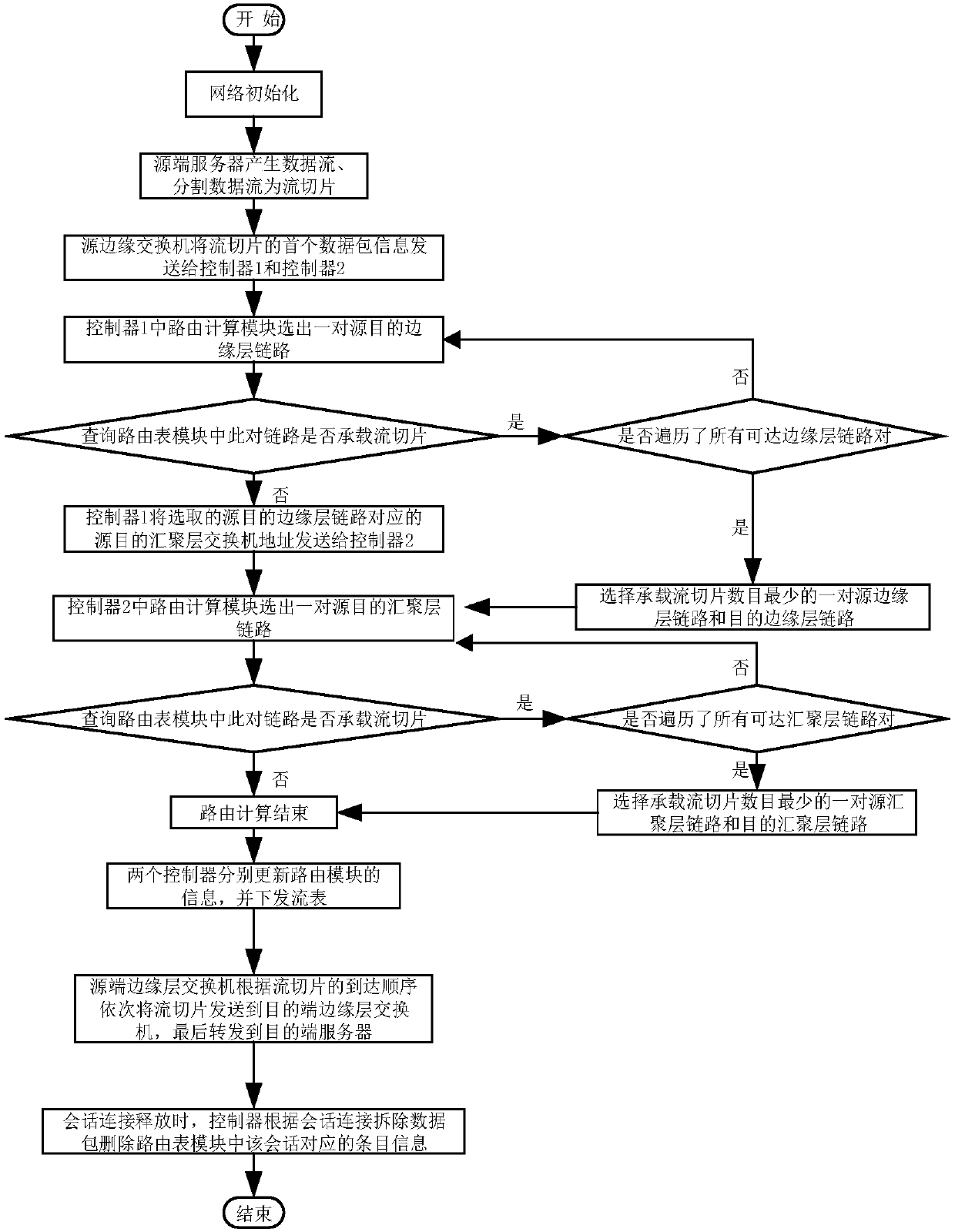

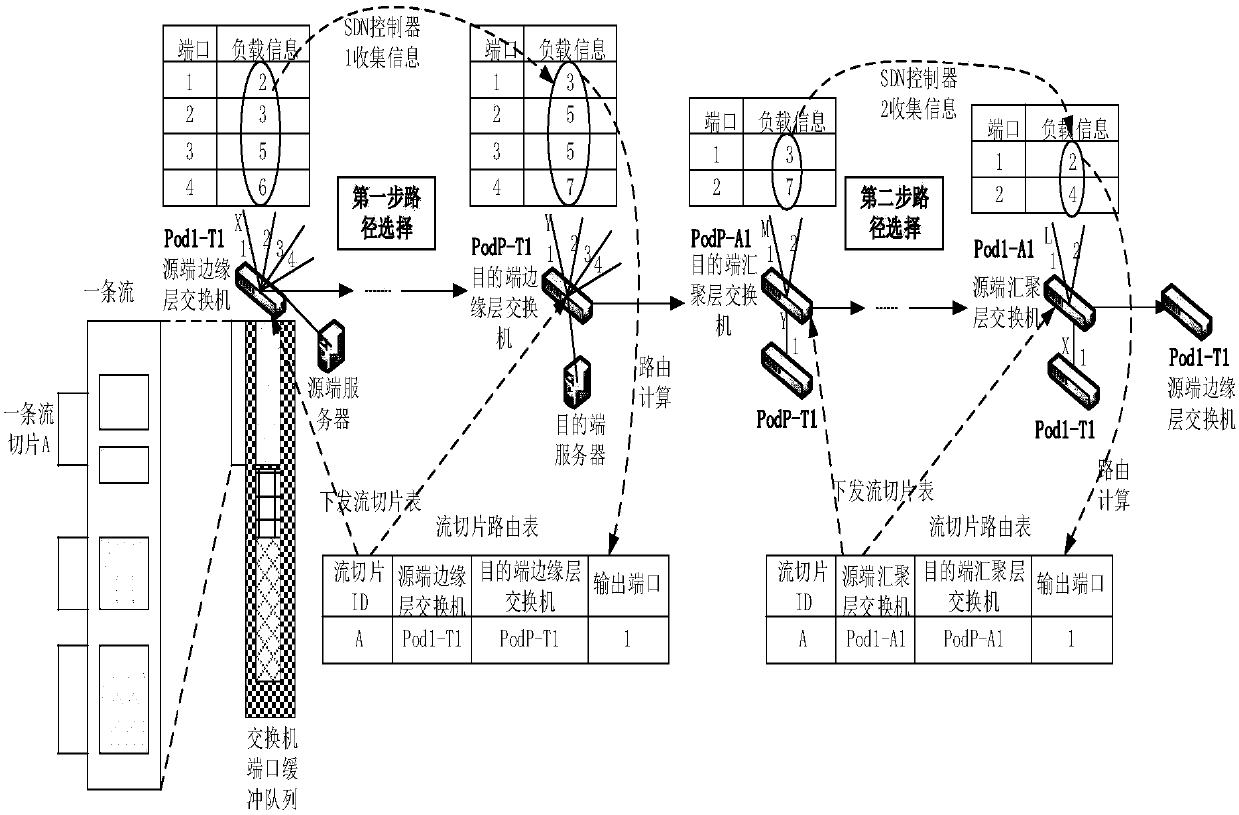

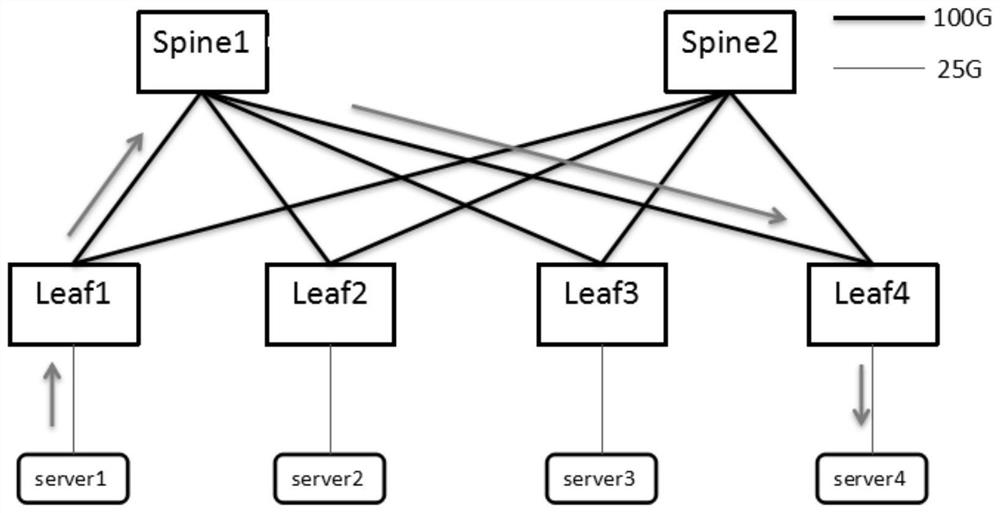

SDN based distributed control load balancing system and method

ActiveCN107819695AOvercoming the Distributed Scaling ProblemOvercome overheadData switching networksData streamRouting table

The invention discloses an SDN based distributed control load balancing system and method, aiming at mainly solving the problems of distributed extension, network overheads, uneven load and link congestion in existing small-scale single data center networks. The system disclosed by the invention comprises a three-layer Clos underlying network and two SDN controllers, wherein the SDN controller isadditionally provided with link information, a routing table and a routing calculation module, and the above modules act together to calculate a path for a data stream. The load balancing method includes the following steps: adopting two-step path selection, partitioning the data stream into stream slices in a buffer area of an end host, separately monitoring and collecting local link informationof two local area networks by using the two controllers, and taking a queuing delay of each port of a switch as the link information to optimize the selection of routing links. According to the schemeof the invention, the distributed multi-controller and two-step path selection are adopted in the three-layer Clos network, and a significant network balancing effect can be achieved; and the schemecan be used for load balancing control of large-scale single data center networks.

Owner:XIDIAN UNIV +1

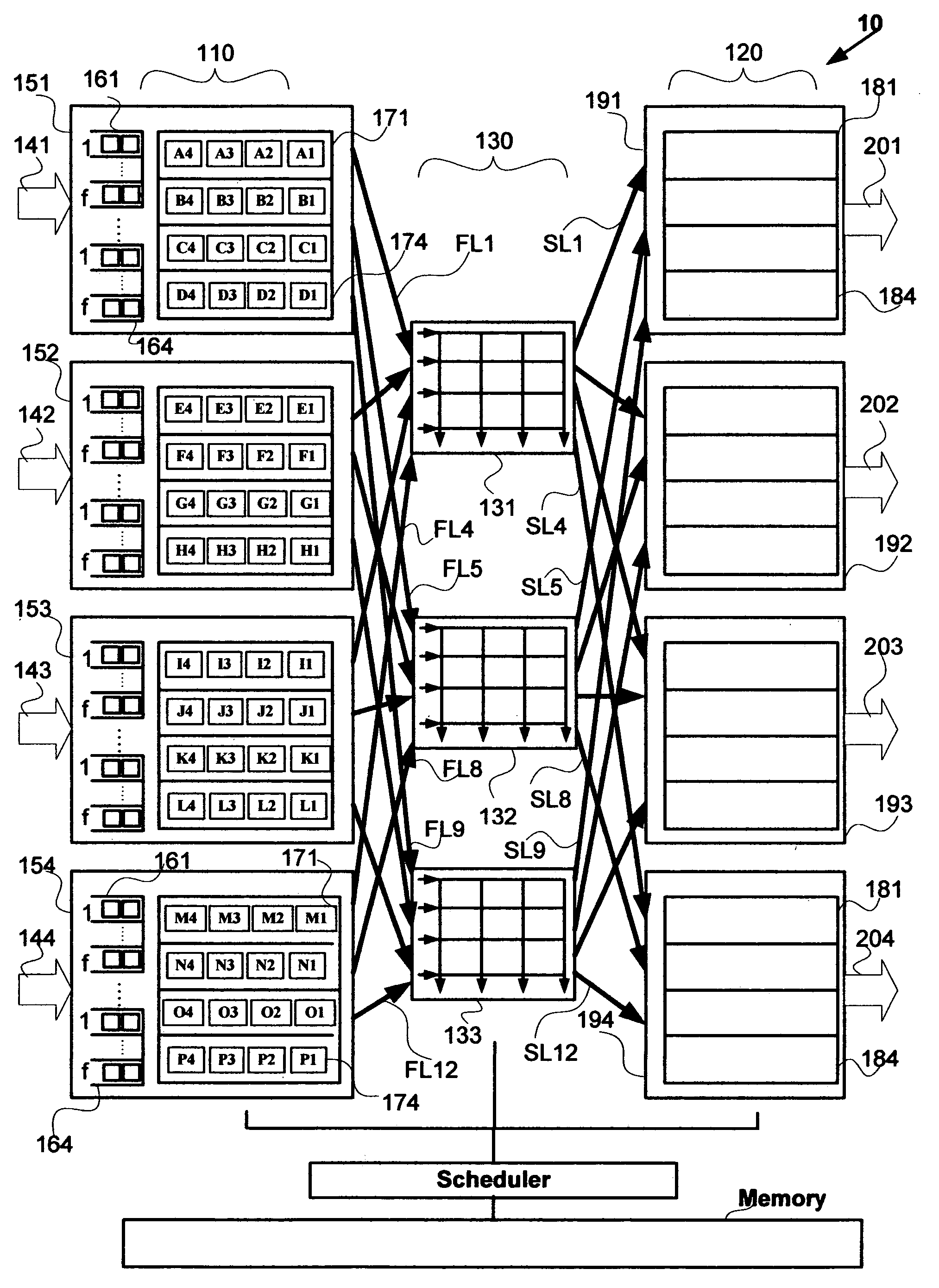

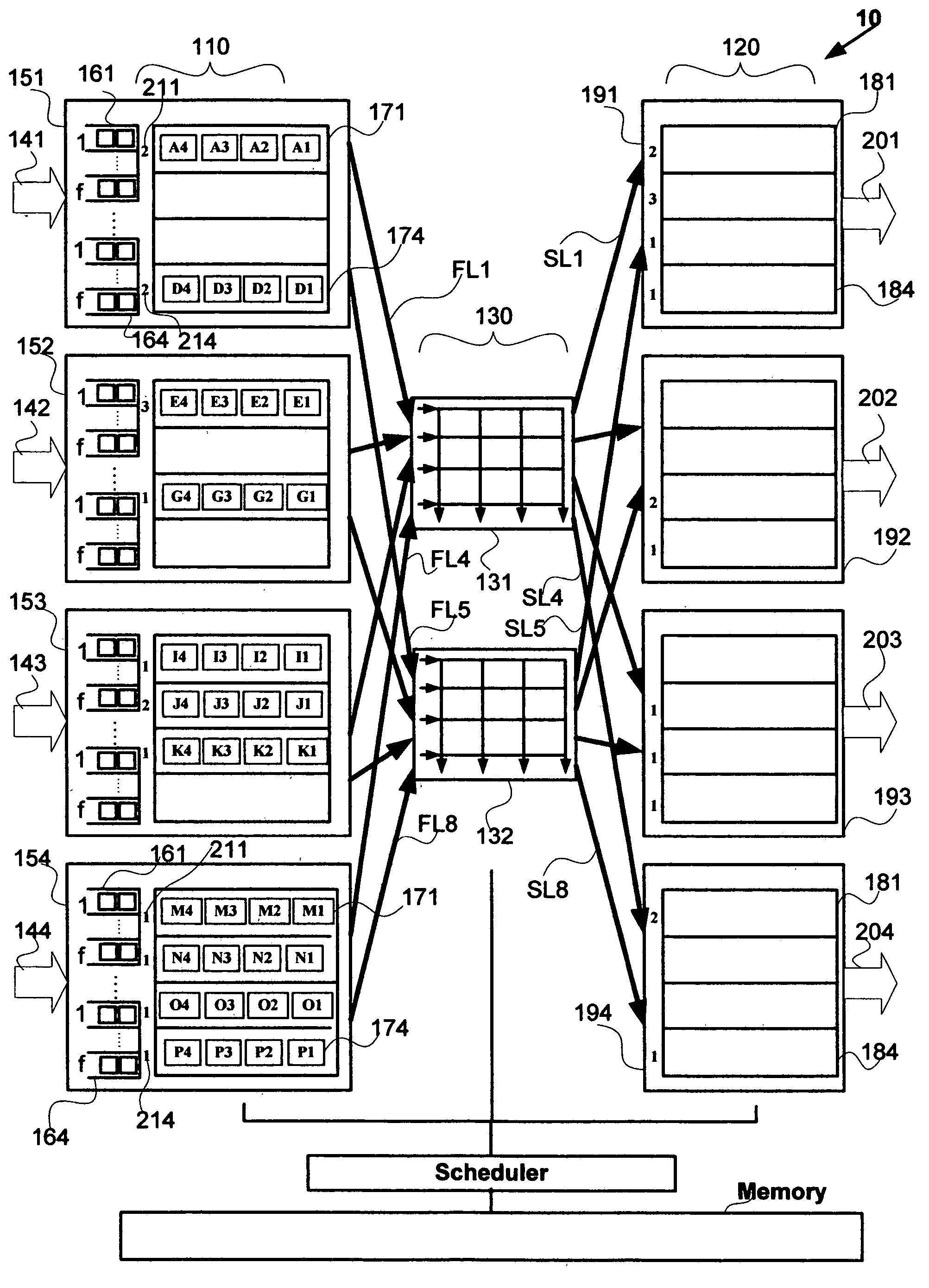

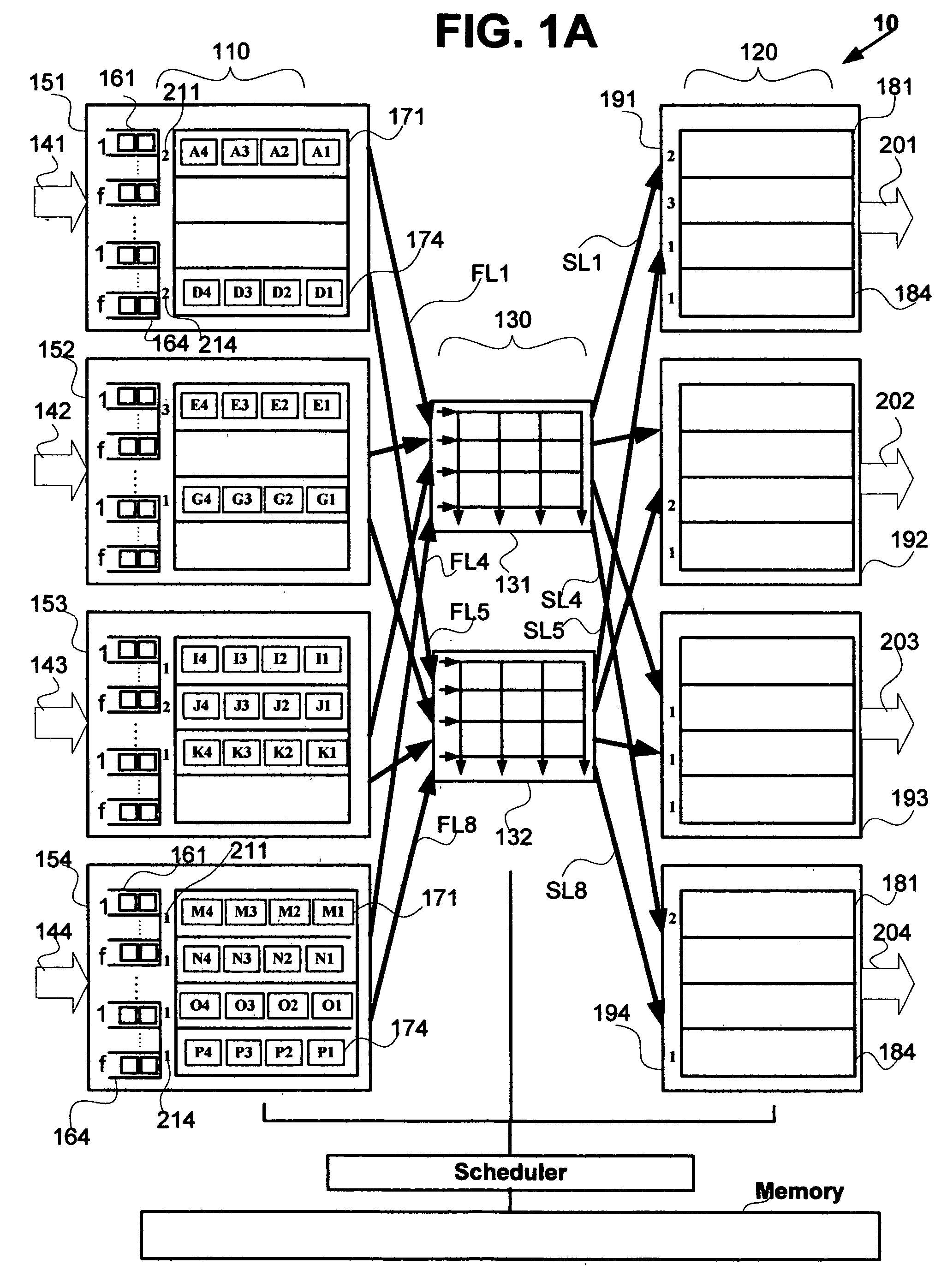

Nonblocking and deterministic unicast packet scheduling

InactiveUS20050117575A1Guaranteed bandwidthElectronic switchingData switching by path configurationCrossbar switchPacket scheduling

A system for scheduling unicast packets through an interconnection network having a plurality of input ports, a plurality of output ports, and a plurality of input queues, comprising unicast packets, at each input port is operated in nonblocking manner in accordance with the invention by scheduling at most as many packets equal to the number of input queues from each input port to each output port. The system is operated at 100% throughput, work conserving, fair, and yet deterministically thereby never congesting the output ports. The system performs arbitration in only one iteration, with mathematical minimum speedup in the interconnection network. The system operates with absolutely no packet reordering issues, no internal buffering of packets in the interconnection network, and hence in a truly cut-through and distributed manner. In another embodiment each output port also comprises a plurality of output queues and each packet is transferred to an output queue in the destined output port in nonblocking and deterministic manner and without the requirement of segmentation and reassembly of packets even when the packets are of variable size. In one embodiment the scheduling is performed in strictly nonblocking manner with a speedup of at least two in the interconnection network. In another embodiment the scheduling is performed in rearrangeably nonblocking manner with a speedup of at least one in the interconnection network. The system also offers end to end guaranteed bandwidth and latency for packets from input ports to output ports. In all the embodiments, the interconnection network may be a crossbar network, shared memory network, clos network, hypercube network, or any internally nonblocking interconnection network or network of networks.

Owner:TEAK TECH

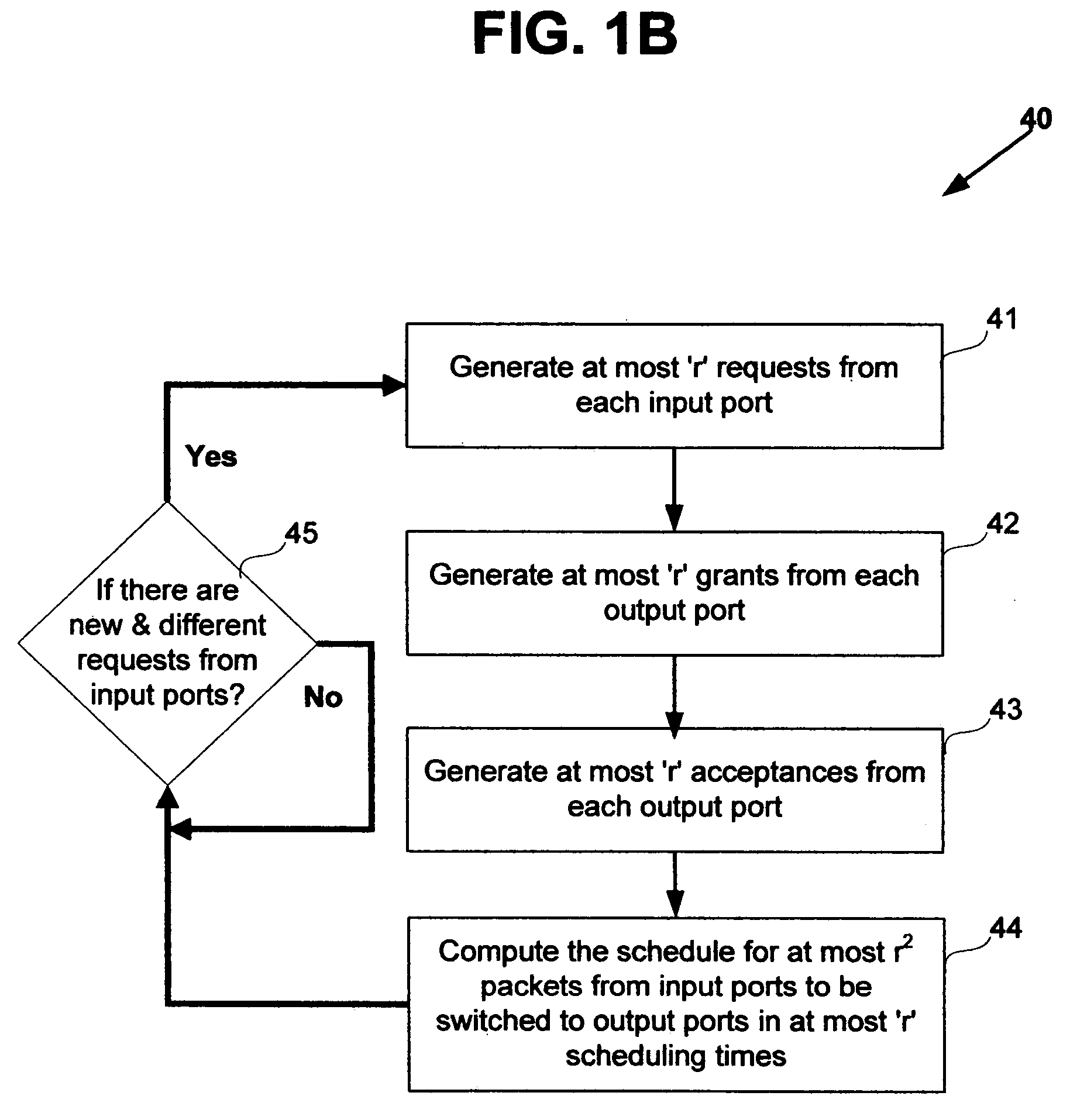

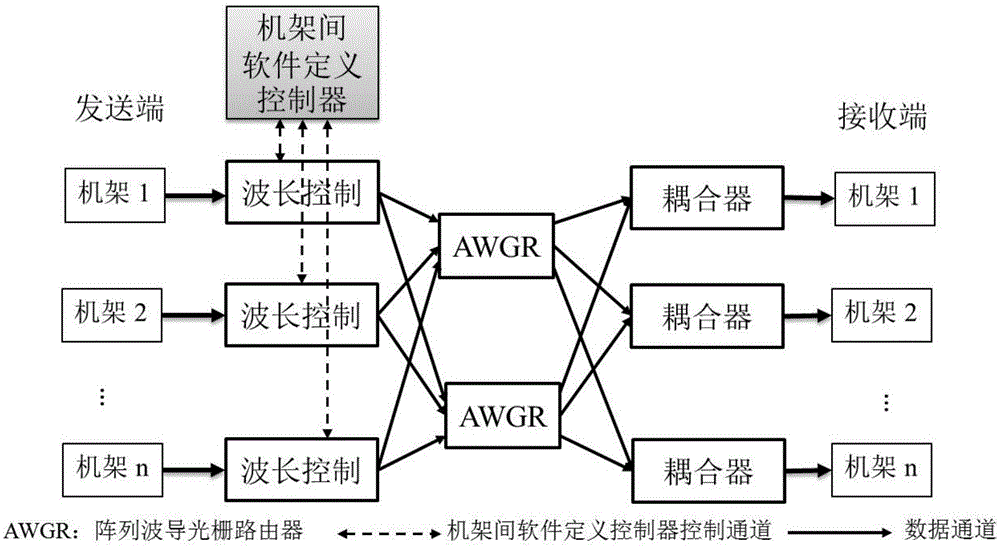

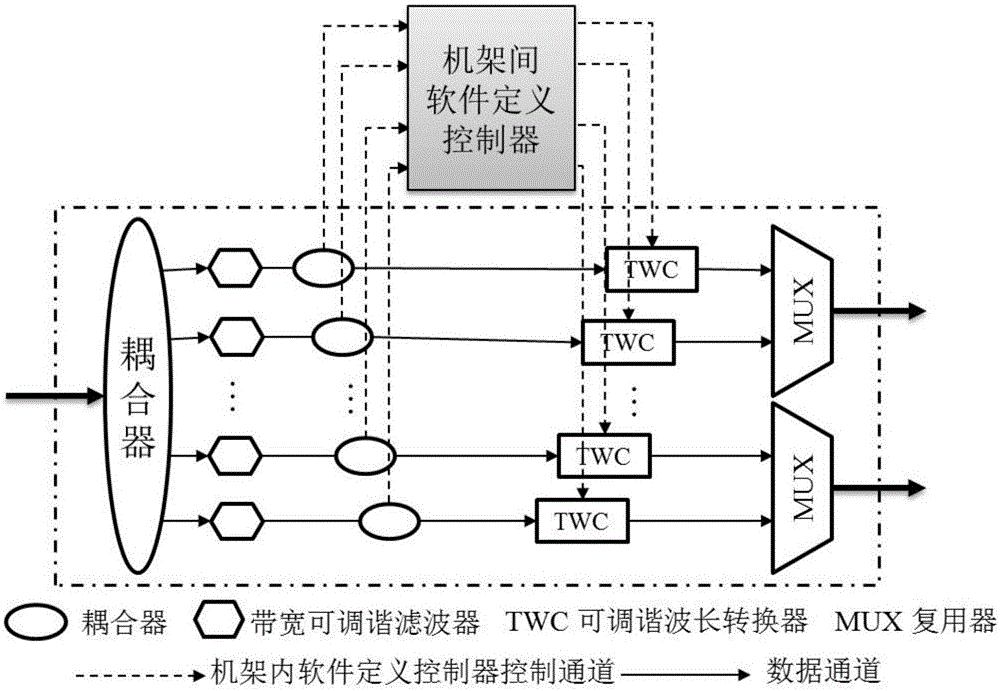

All-optical interconnection data center network system based on software defined network and data communication method

ActiveCN105162721AReduce energy consumptionMeeting Communication NeedsMultiplex system selection arrangementsData switching networksData centerStructure of Management Information

The invention relates to an all-optical interconnection data center network system based on a software-defined network and a data communication method, and relates to the technical field of cloud computing and communication. A passive optical network interconnection server constructed rack of the system replaces a traditional top-of-rack switch. An optical Clos network interconnects the racks to construct an all-optical interconnection data center network. An in-rack passive optical network is composed of a coupler module. The optical Clos network is composed of a wavelength control module, an array waveguide grating router, and a coupler. In-rack software defined controllers and inter-rack software defined controllers are interconnected in a hierarchical structure, and respectively control data communication of in-rack servers and inter-rack servers in a centralized mode so as to separate control and forwarding. The all-optical interconnection data center network system of the invention is highly energy-saving and cost-effective, and can improve the management efficiency and network performance of the data center network.

Owner:CHONGQING UNIV

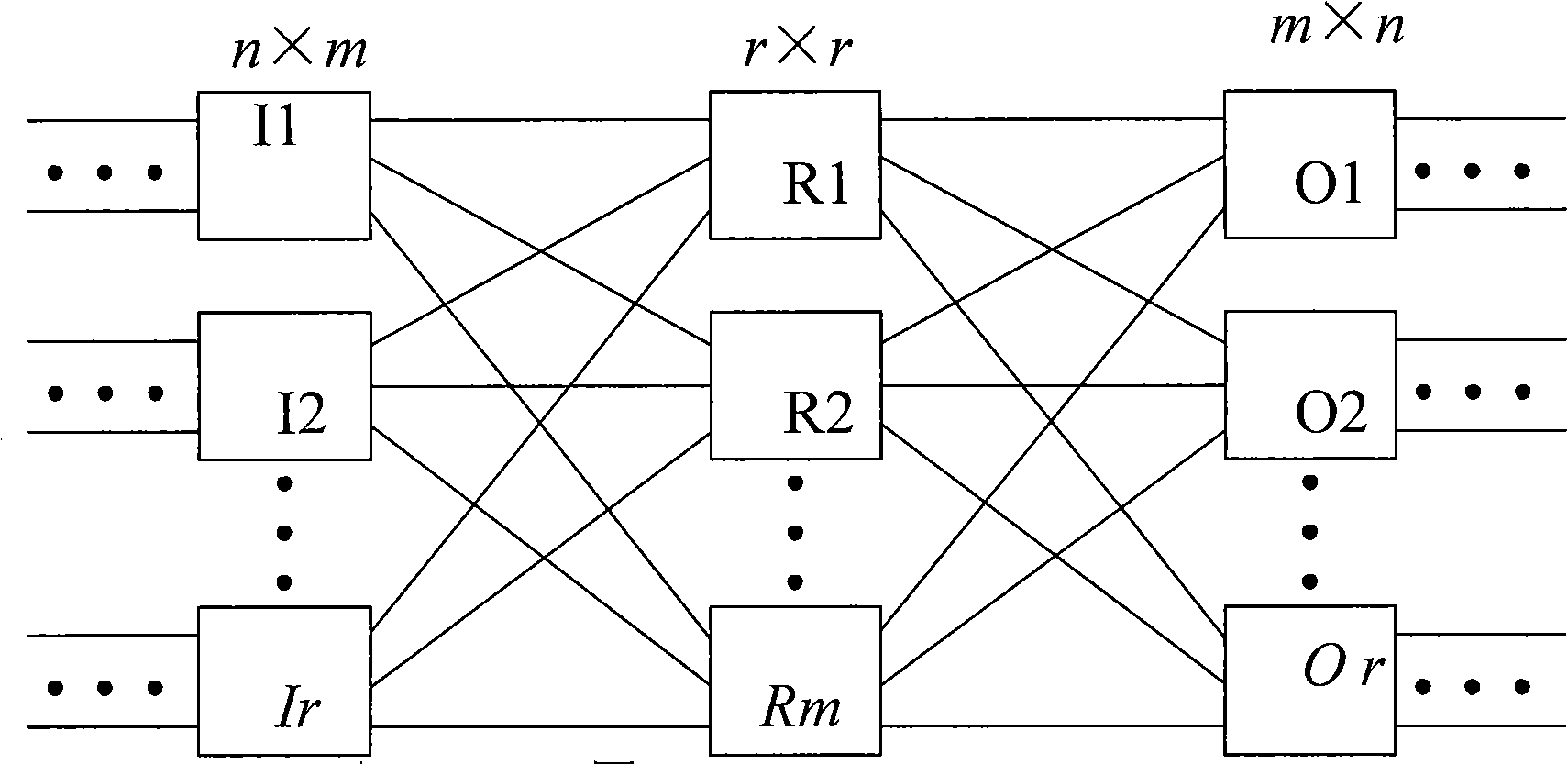

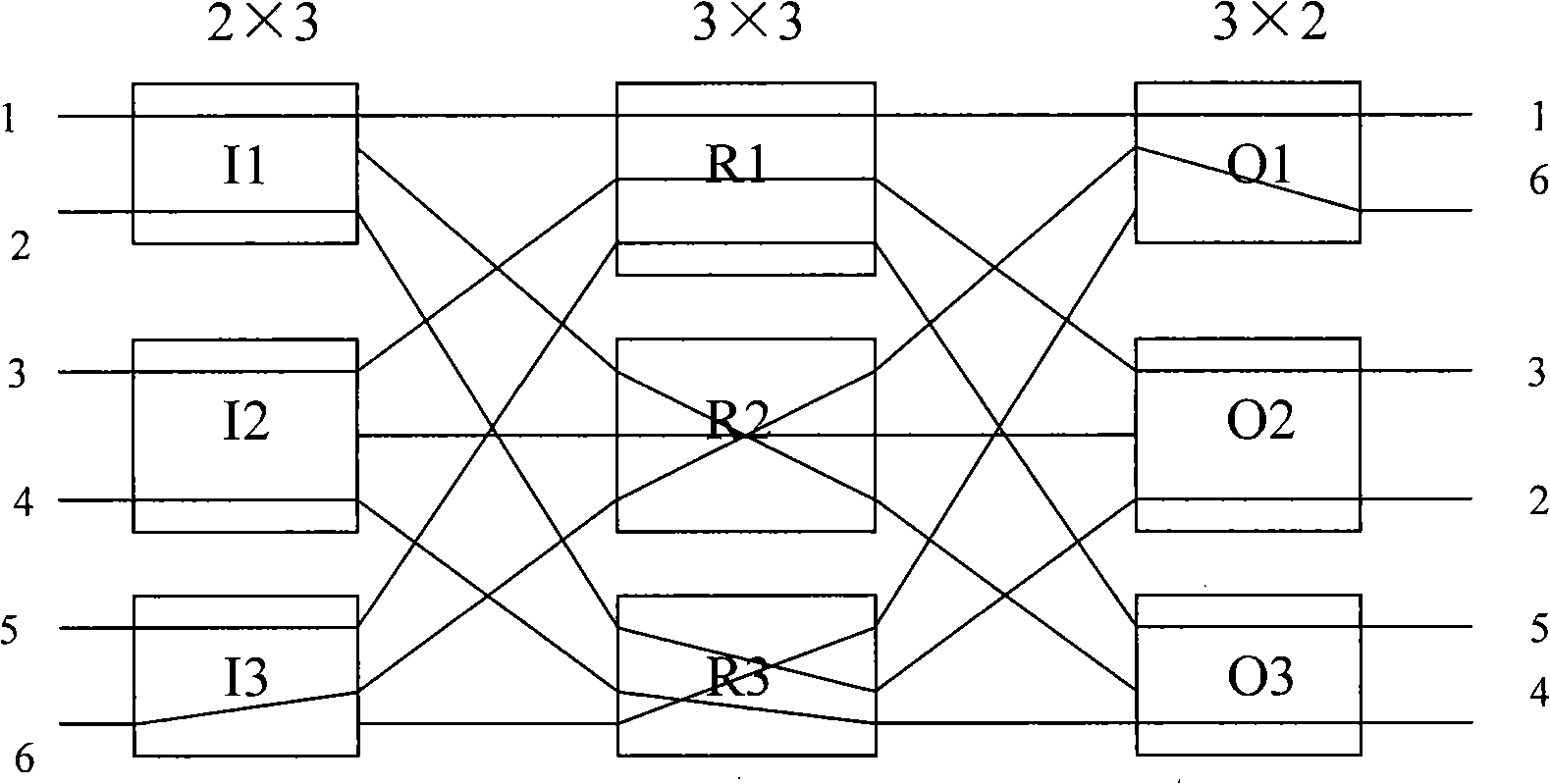

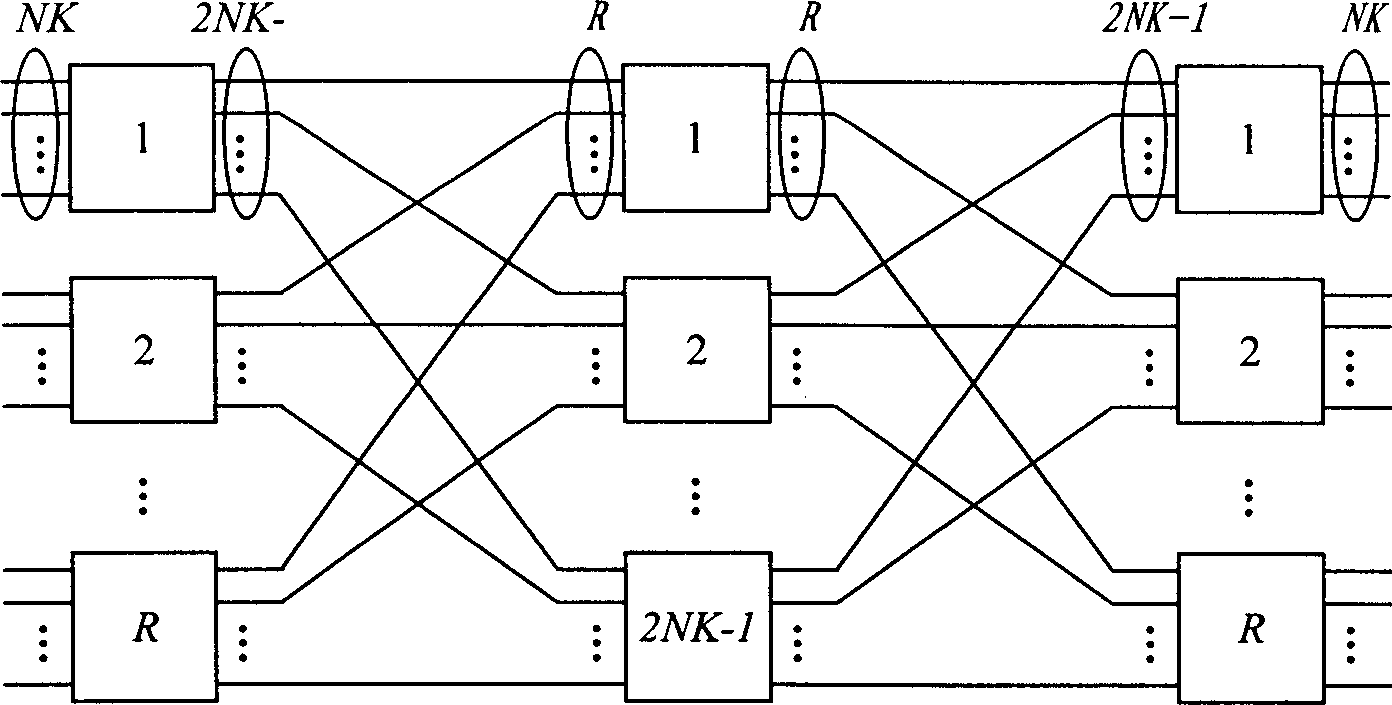

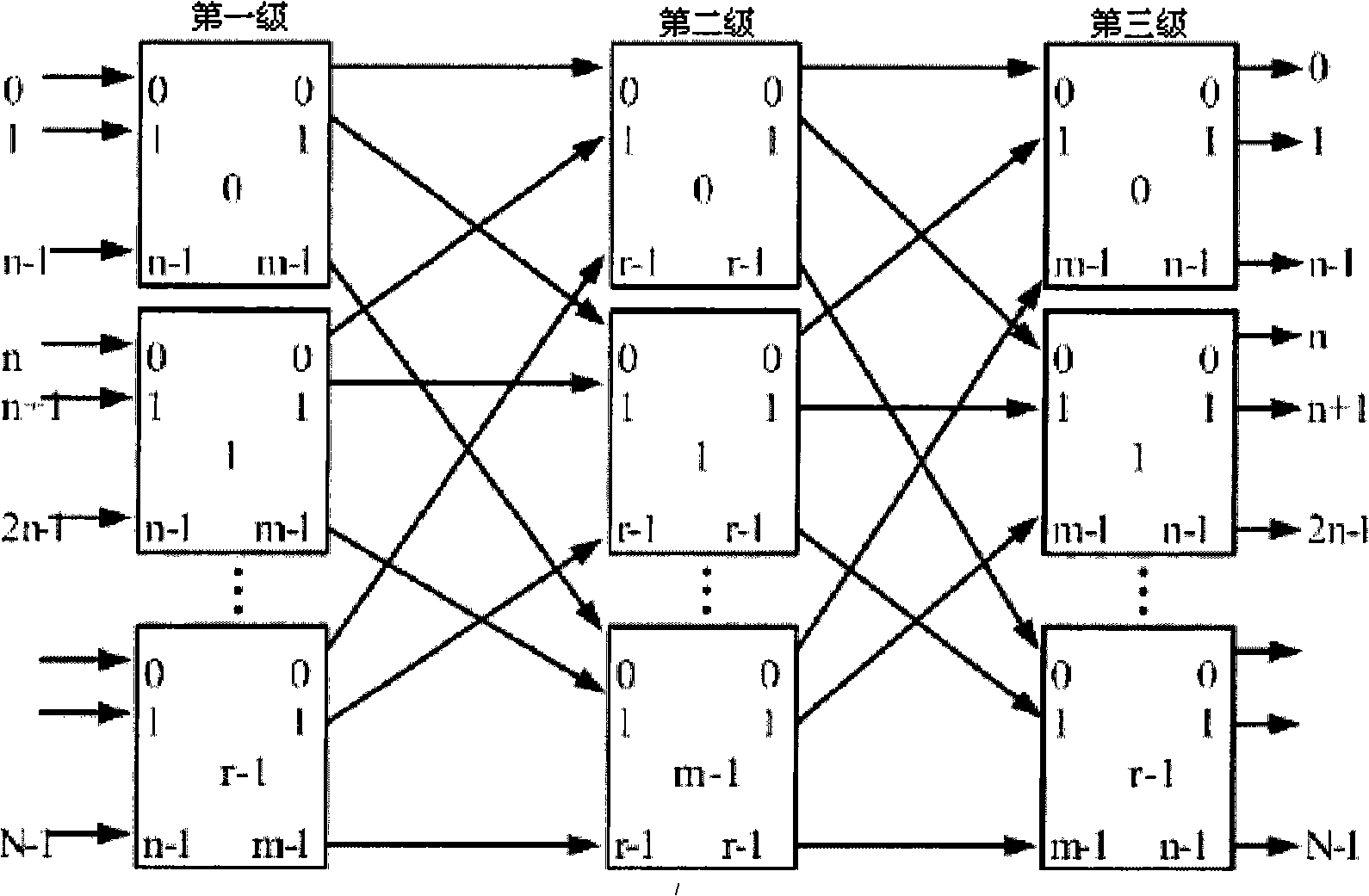

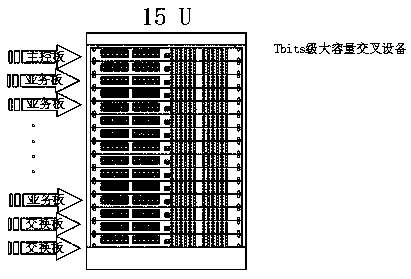

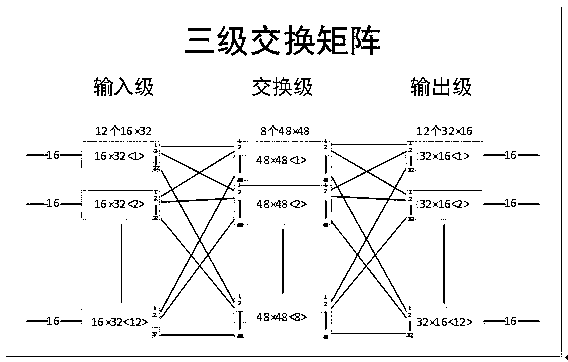

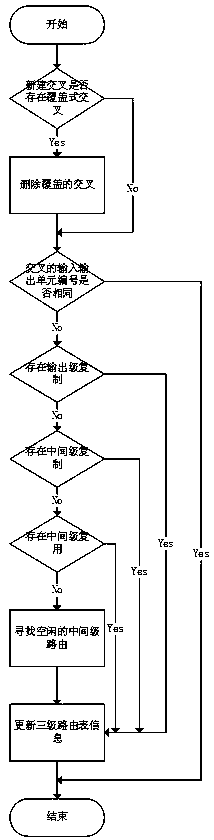

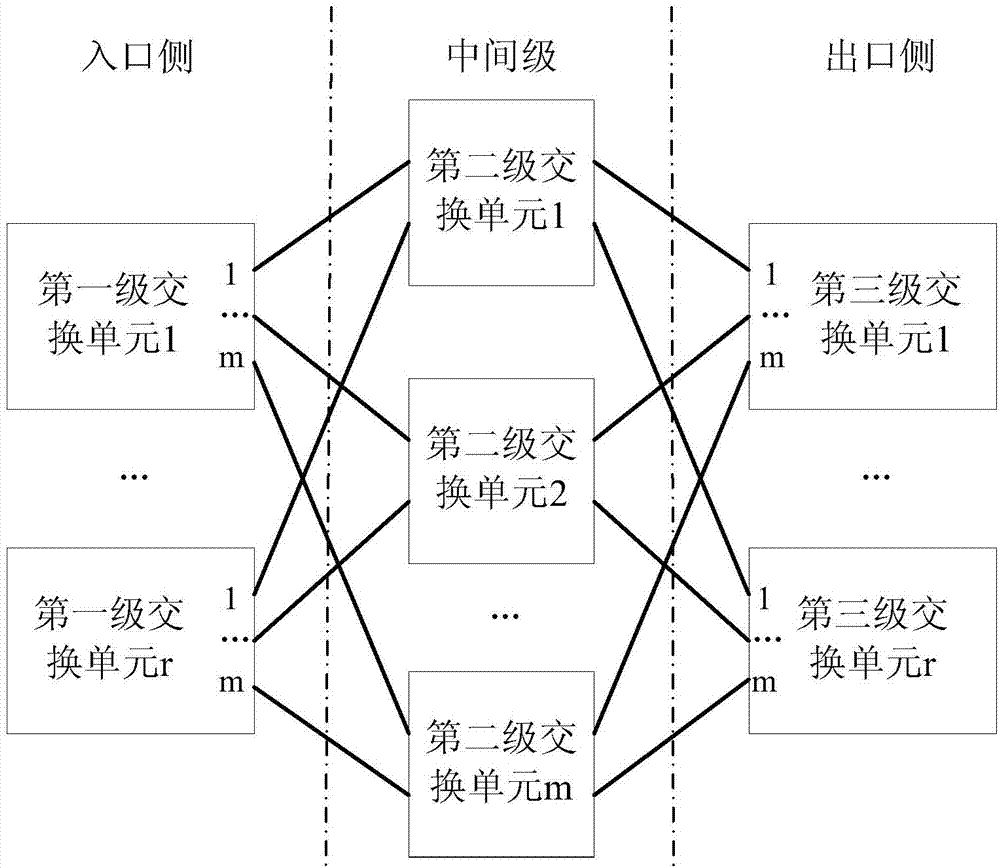

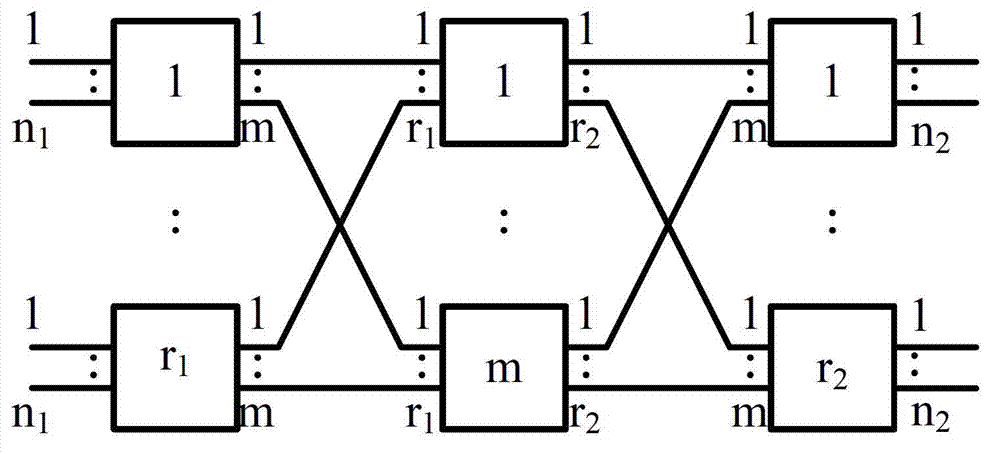

Large-scale strict non-blockage light-crossing connection matrix structure and control method thereof

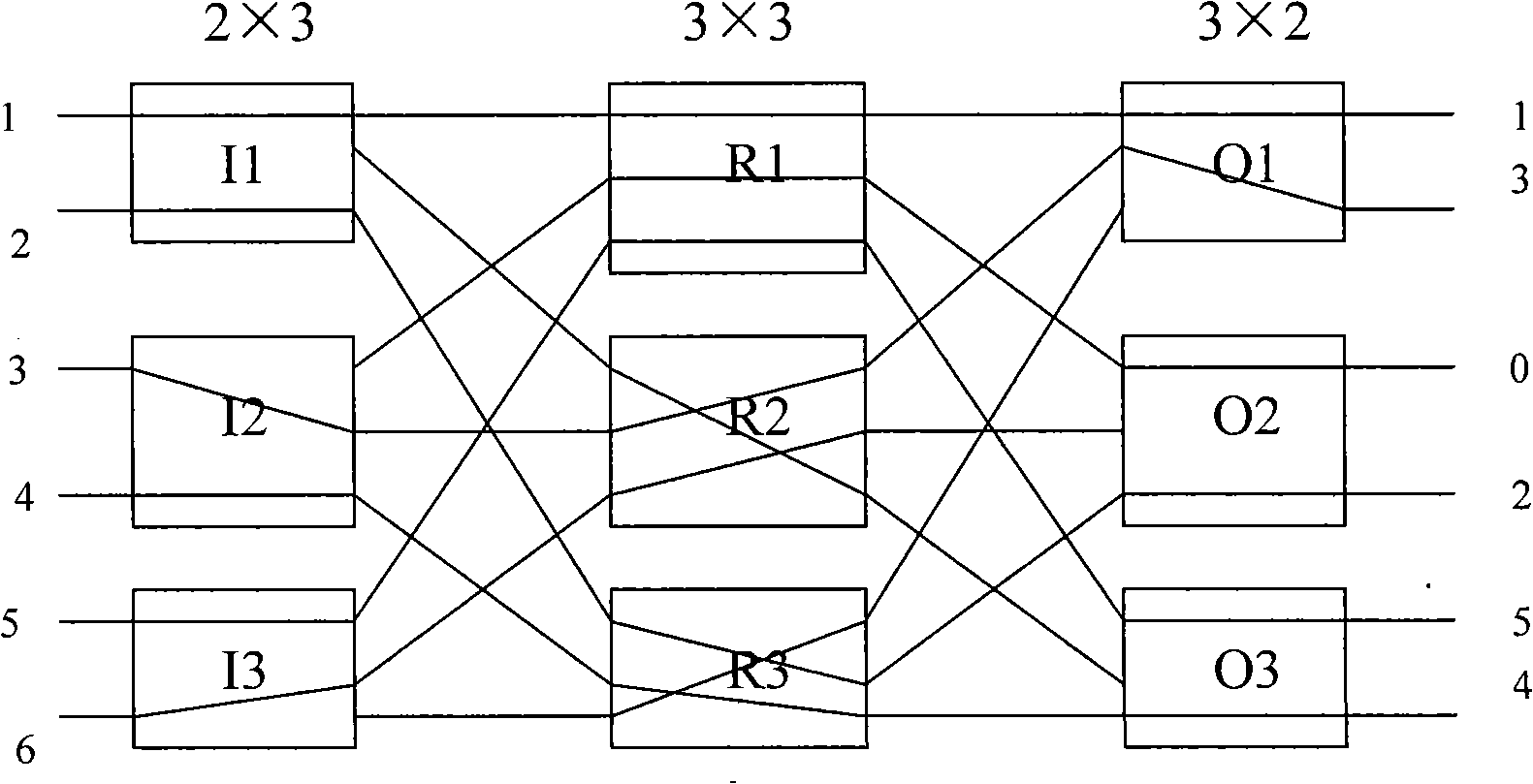

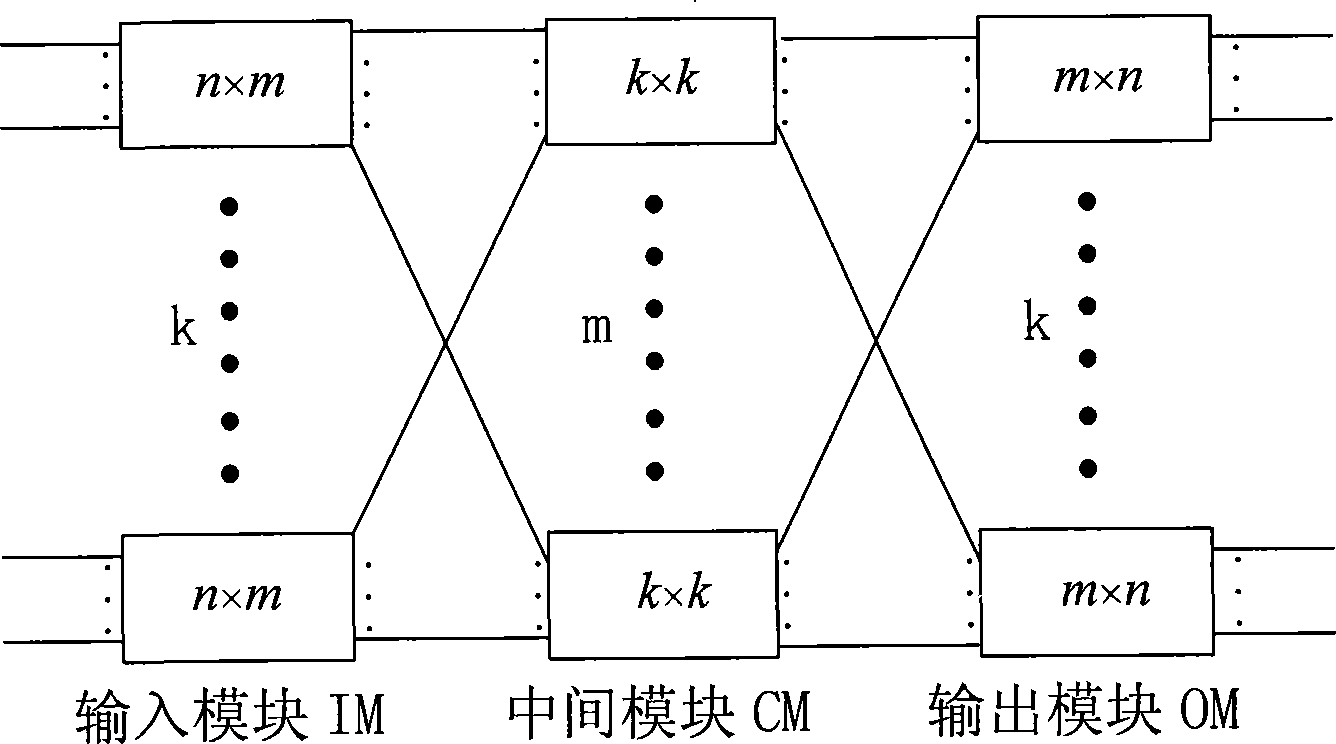

InactiveCN101277547ASwitching does not affectDoes not affect configurationMultiplex system selection arrangementsThree levelCross connection

The present invention provides a large-scale strictly nonblocking optical switching matrix structure and its control method. The optical switching matrix structure is a three-level symmetrical CLOS network, including an input level composed of r n*m optical switch module; a middle level composed of m r*r optical switch module; an output level composed of r m*n optical switch module, a symmetrical switching connection is between the three-level optical switching modules. The invention has advantages that the switching connection is routed configuration by large capacity connection fit for large scale optical switching; the matrix realizes the switching of N*N optical route, and when m>=2n-1, the matrix has strictly nonblocking ability, that is meeting the requirement of non error code produced by the non switching route when selecting the route, ensuring less optical switch generation switching as possible in each configuration; the invention has high efficient algorithm, accuracy and credibility, if the aim output state has N different states with the initial output states, only counting N times.

Owner:TOEC TECH

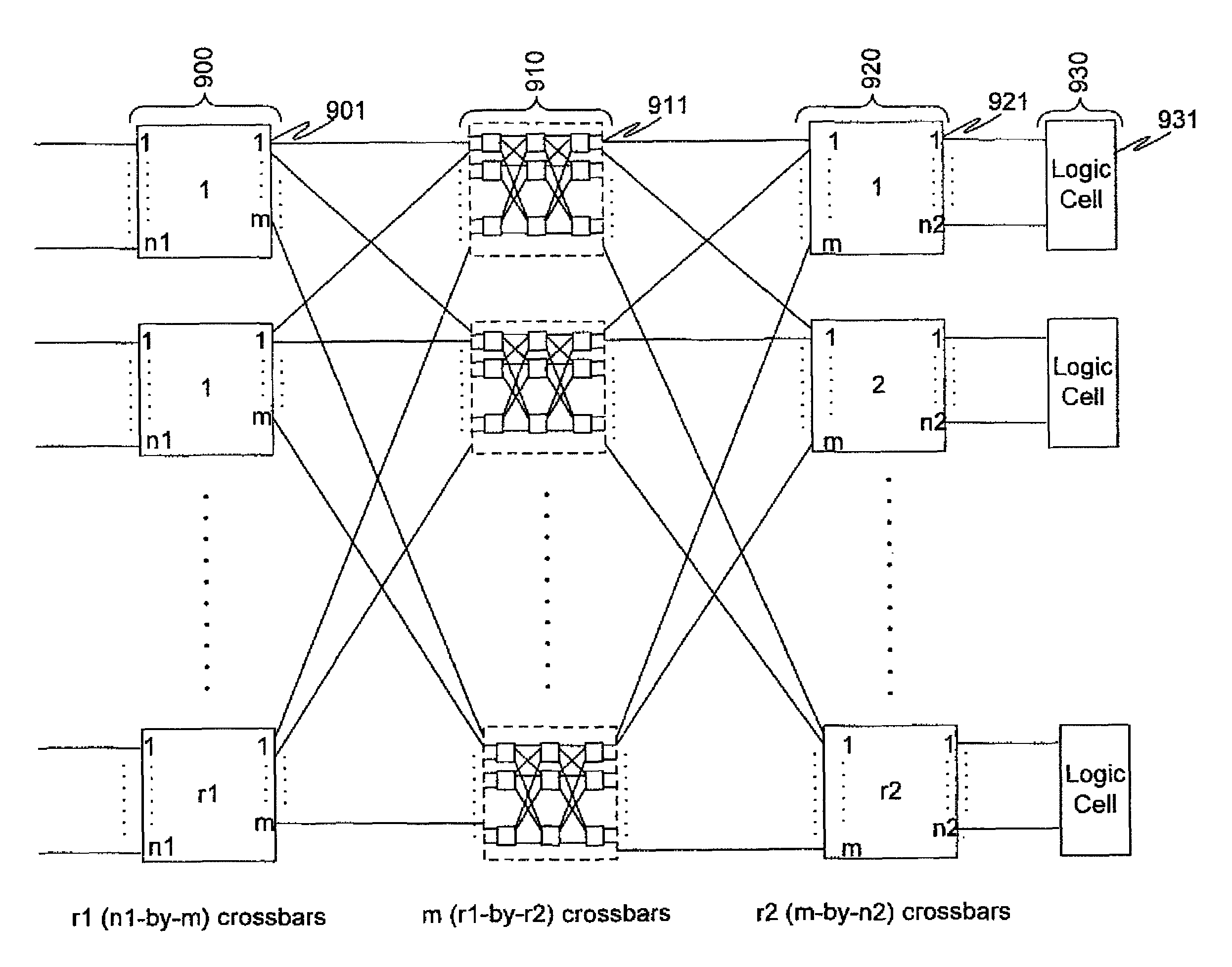

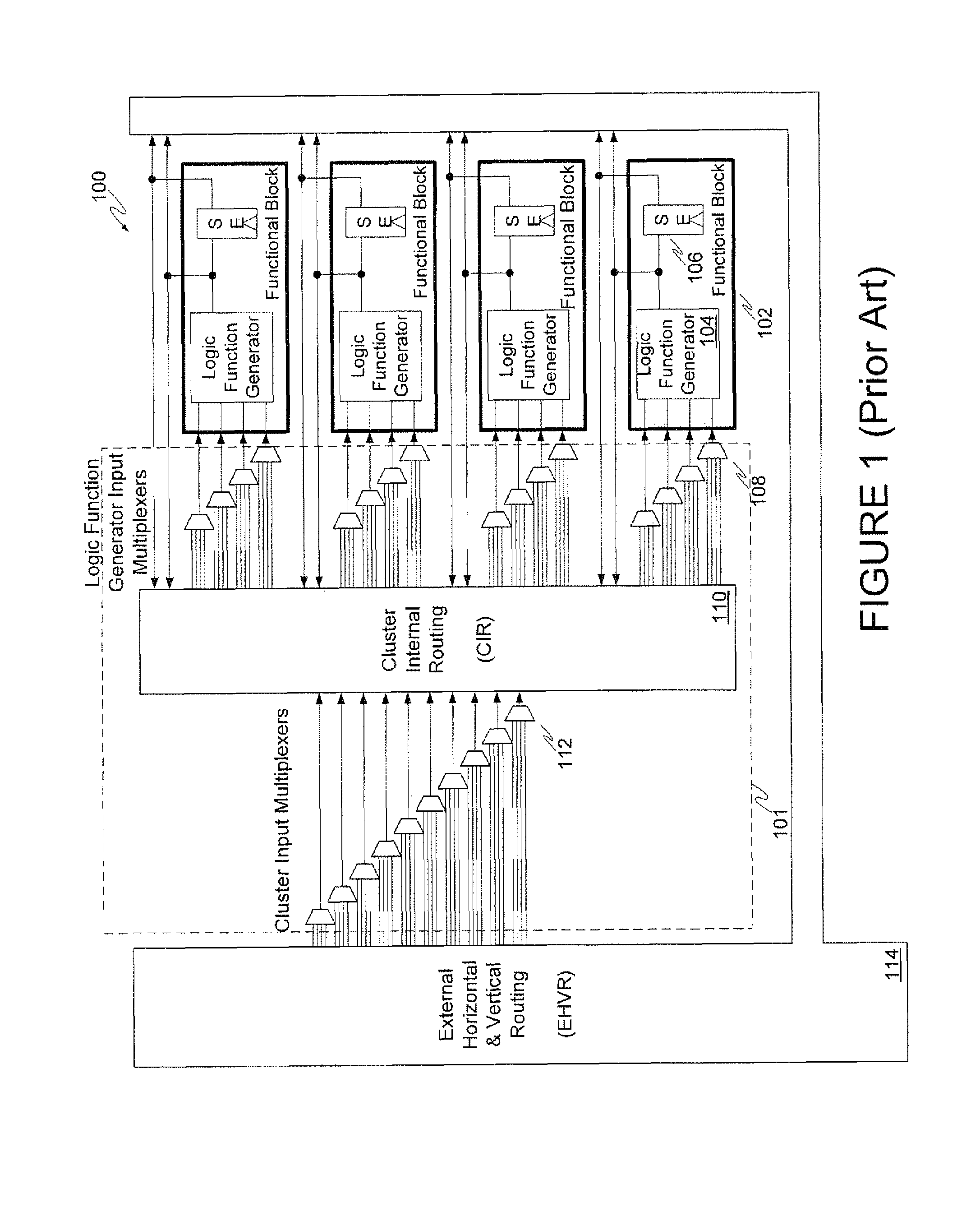

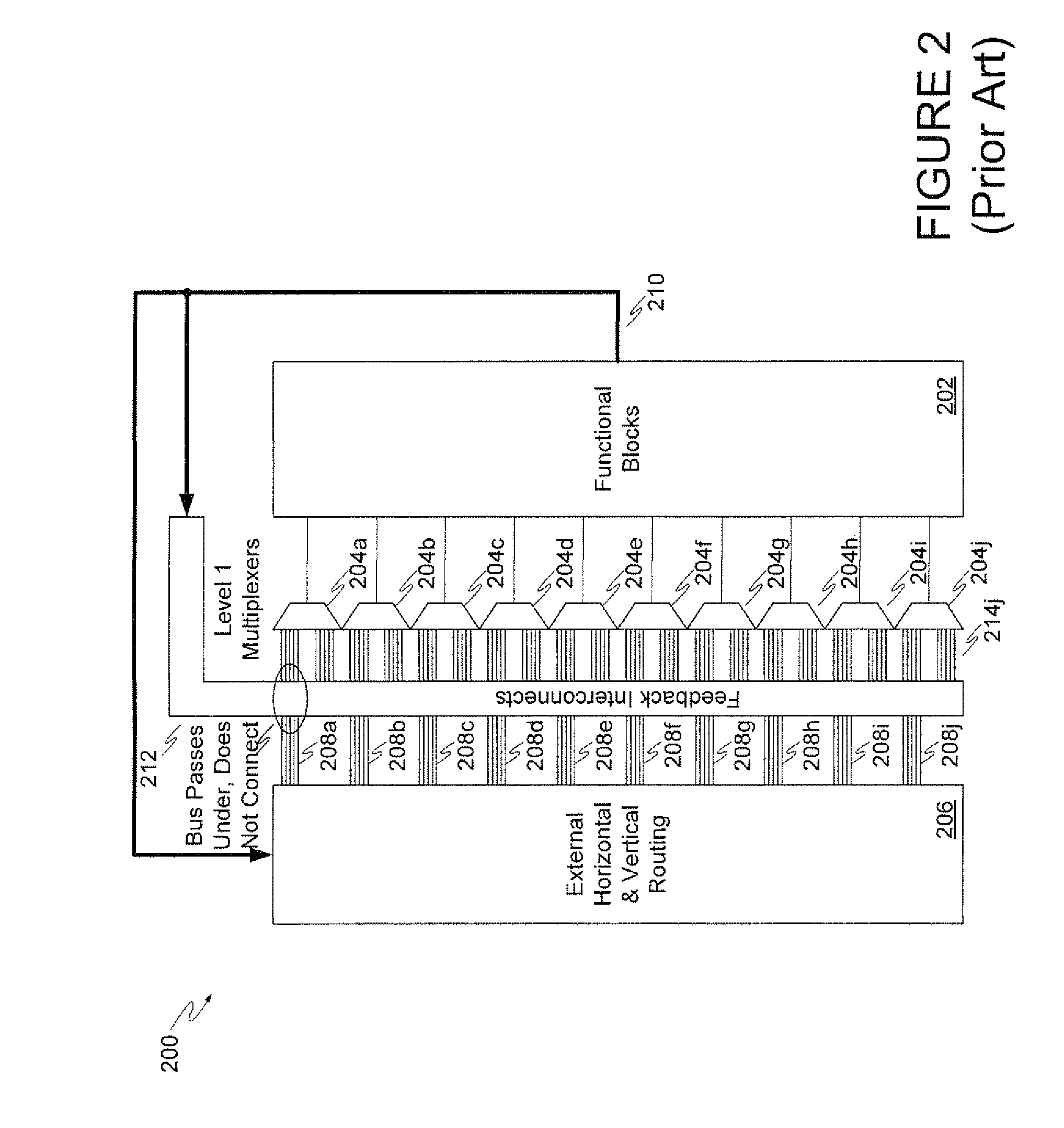

Field programmable gate array architecture having Clos network-based input interconnect

ActiveUS7924052B1Multiplex system selection arrangementsSolid-state devicesProgrammable logic deviceCluster based

A cluster internal routing network for use in a programmable logic device with a cluster-based architecture employs a Clos network-based routing architecture. The routing architecture is a multi-stage blocking architecture, where the number of inputs to the first stage exceeds the number of outputs from the first stage.

Owner:MICROSEMI SOC

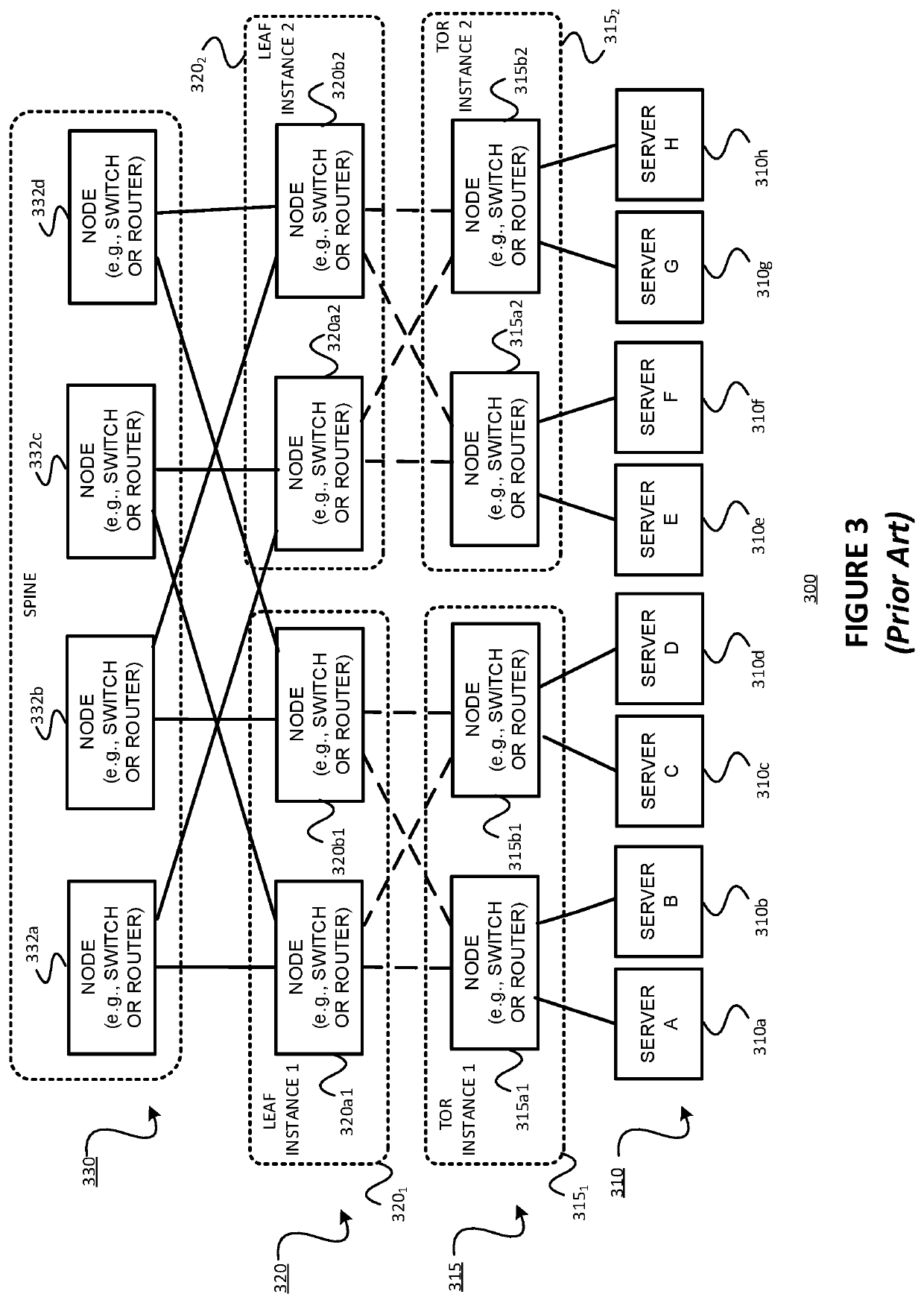

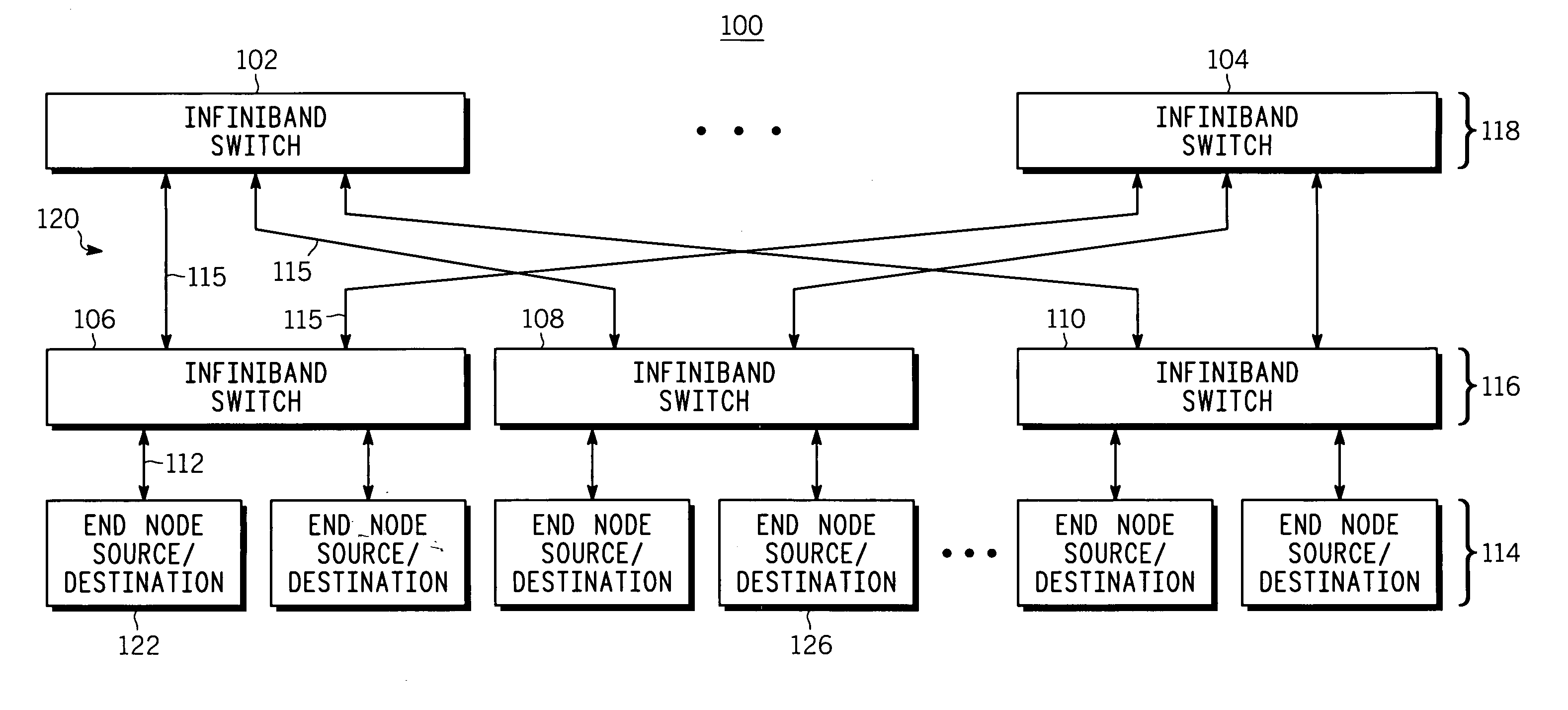

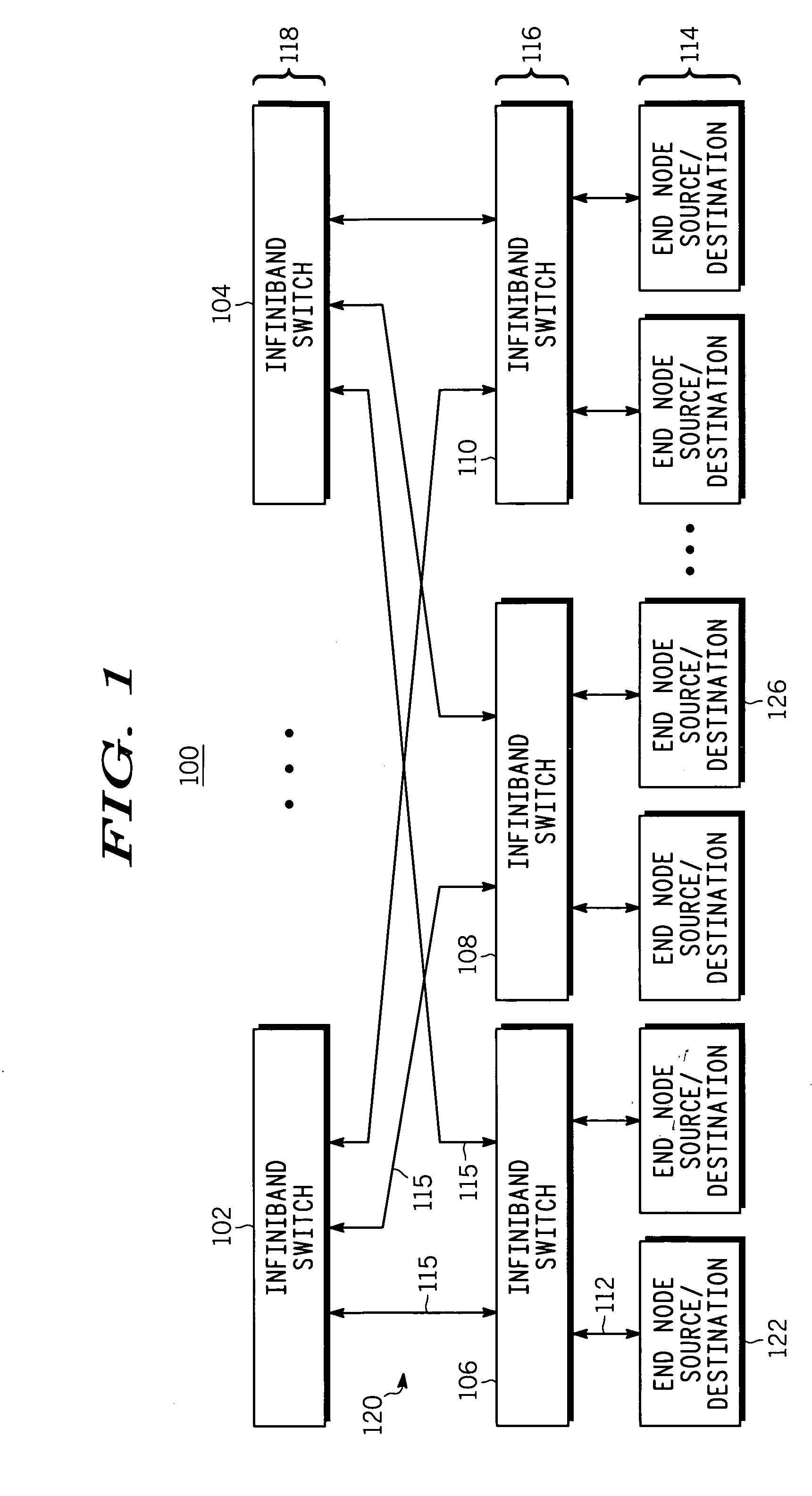

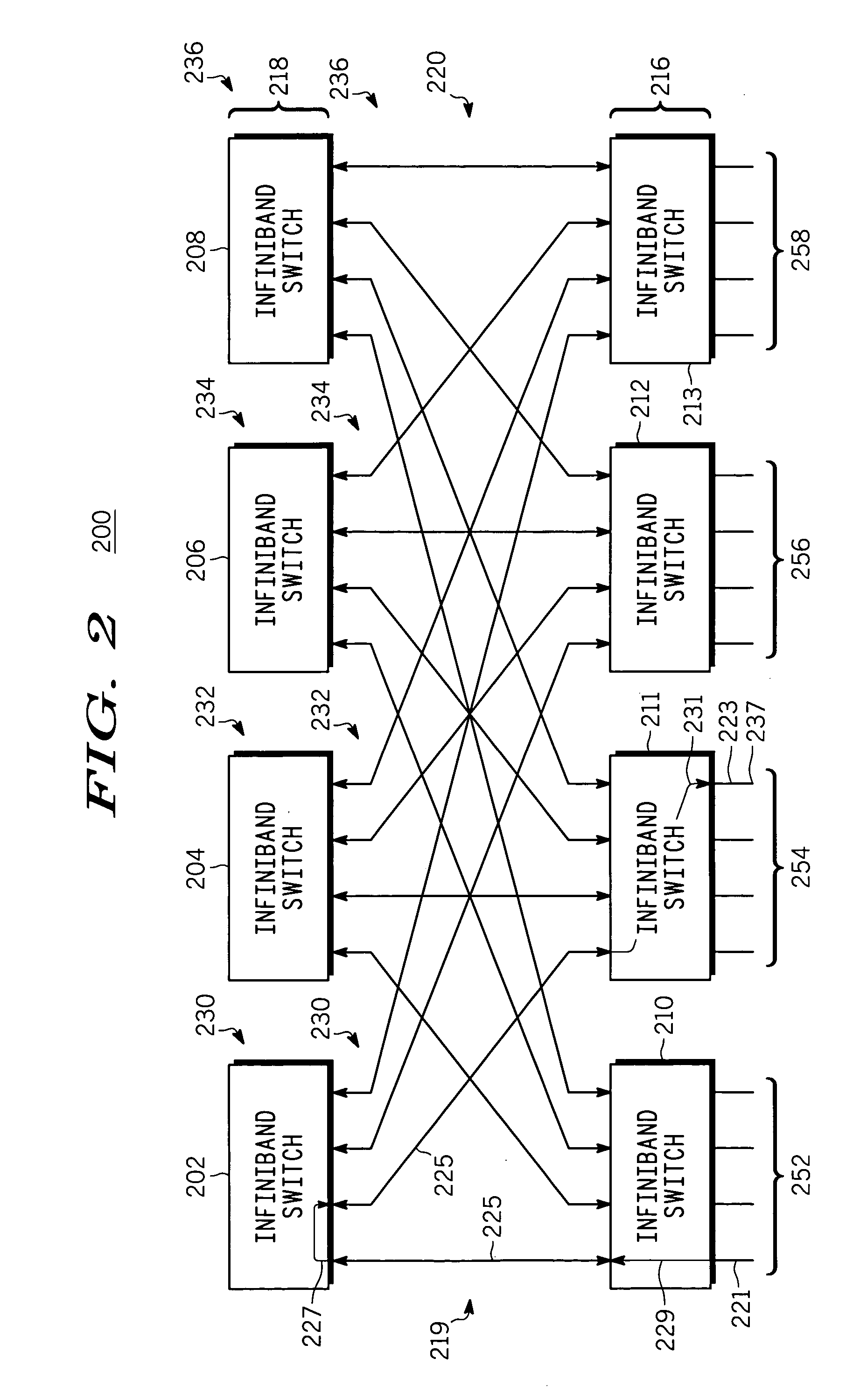

Method of operating a Clos network

A method includes providing a plurality of InfiniBand switches (350, 318), wherein the plurality of InfiniBand switches are coupled to form a Clos network (320), providing a plurality of sources coupled to the Clos network, and providing a plurality of destinations coupled to the Clos network. Calculating a plurality of routing trees (330, 332, 334, 336) for the plurality of InfiniBand switches, and calculating a plurality of DLIDs (410) and a set of forwarding instructions (413) for each of the plurality of InfiniBand switches, where each of the plurality of DLIDs corresponds to one of the plurality of routing trees and one of the plurality of destinations. Populating a forwarding table (415) of each of the plurality of InfiniBand switches in the Clos network with the plurality of DLIDs and the set of forwarding instructions.

Owner:EMERSON NETWORK POWER EMBEDDED COMPUTING

Nonblocking and deterministic multicast packet scheduling

InactiveUS20050129043A1Guaranteed bandwidthNetwork traffic/resource managementNetwork topologiesInterconnectionSwitching time

A system for scheduling multicast packets through an interconnection network having a plurality of input ports, a plurality of output ports, and a plurality of input queues, comprising multicast packets, at each input port is operated in nonblocking manner in accordance with the invention by scheduling at most as many packets equal to the number of input queues from each input port to each output port. The scheduling is performed so that each multicast packet is fan-out split through not more than two interconnection networks and not more than two switching times. The system is operated at 100% throughput, work conserving, fair, and yet deterministically thereby never congesting the output ports. The system performs arbitration in only one iteration, with mathematical minimum speedup in the interconnection network. The system operates with absolutely no packet reordering issues, no internal buffering of packets in the interconnection network, and hence in a truly cut-through and distributed manner. In another embodiment each output port also comprises a plurality of output queues and each packet is transferred to an output queue in the destined output port in nonblocking and deterministic manner and without the requirement of segmentation and reassembly of packets even when the packets are of variable size. In one embodiment the scheduling is performed in strictly nonblocking manner with a speedup of at least three in the interconnection network. In another embodiment the scheduling is performed in rearrangeably nonblocking manner with a speedup of at least two in the interconnection network. The system also offers end to end guaranteed bandwidth and latency for multicast packets from input ports to output ports. In all the embodiments, the interconnection network may be a crossbar network, shared memory network, clos network, hypercube network, or any internally nonblocking interconnection network or network of networks.

Owner:TEAK TECH

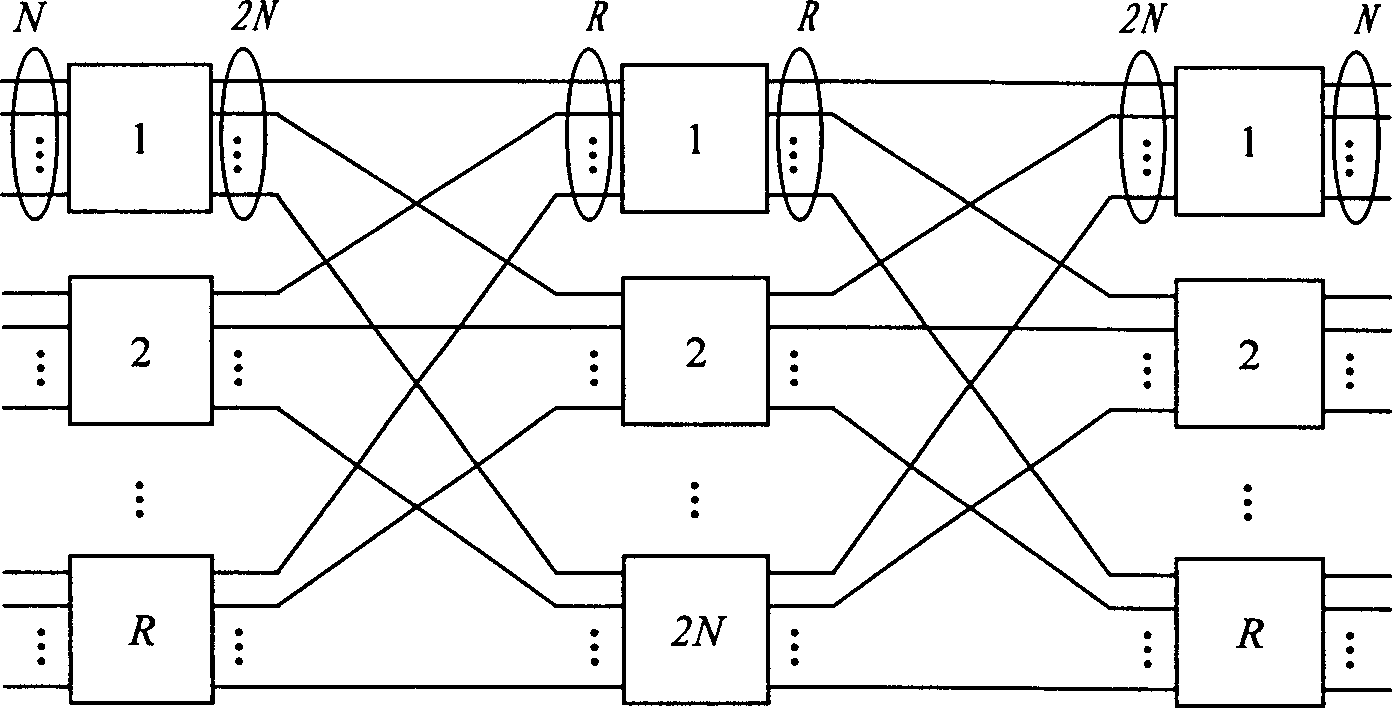

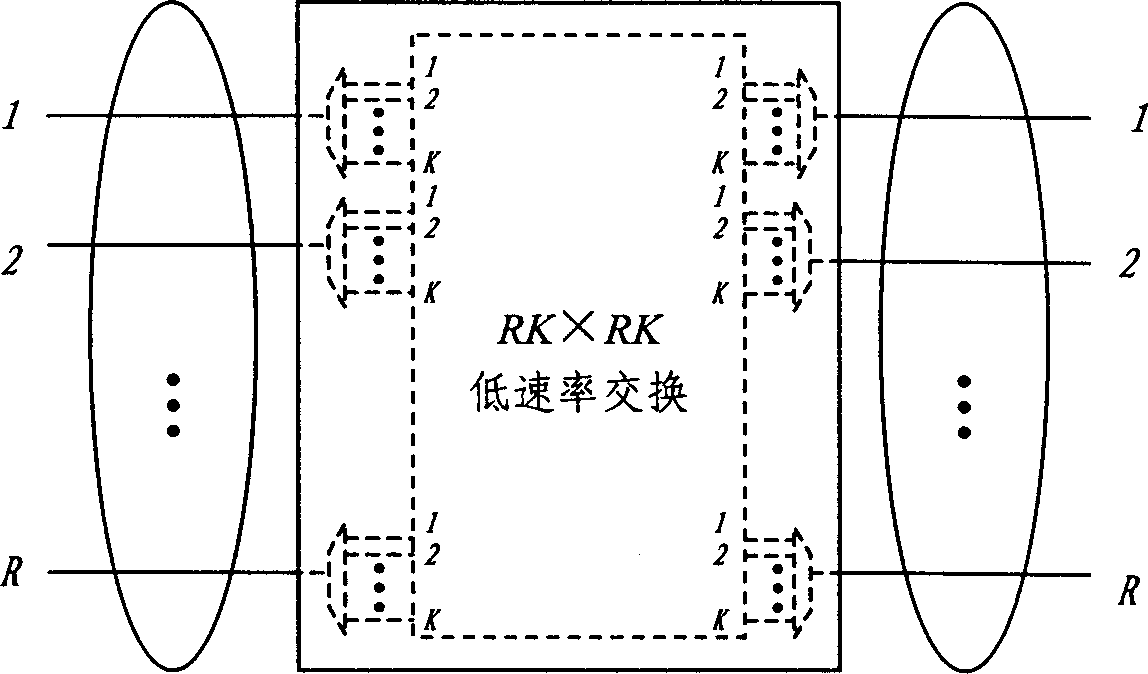

Three levels exchange structure with characters of high and low dual speeds, strict ranking and without blocking expansion

InactiveCN1431832AAvoid disadvantagesGuaranteed strictly non-blockingMultiplex system selection arrangementsAutomatic exchangesThree levelRanking

The three levels exchange structure is suitable to the strict expansion without blocking of the exchange structure in the network node devices and the implement of the interlinkage without blocking in large scale of network. The main character is that the structure is composed of the optical fiber and the matrix switches with high and low dual speeds. Based on the general three levels CLOS network interconnection mode and the general CLOS strict condition without blocking, with a small quantity of matrix switches being added, according to the specified connection mode and the specified quantitative conditions being met, the strict non-blocking expansion of the exchange structure with the high and low dual speeds can be realized to construct the non-blocking exchange structure with super large scale and super large capability.

Owner:SHANGHAI JIAO TONG UNIV

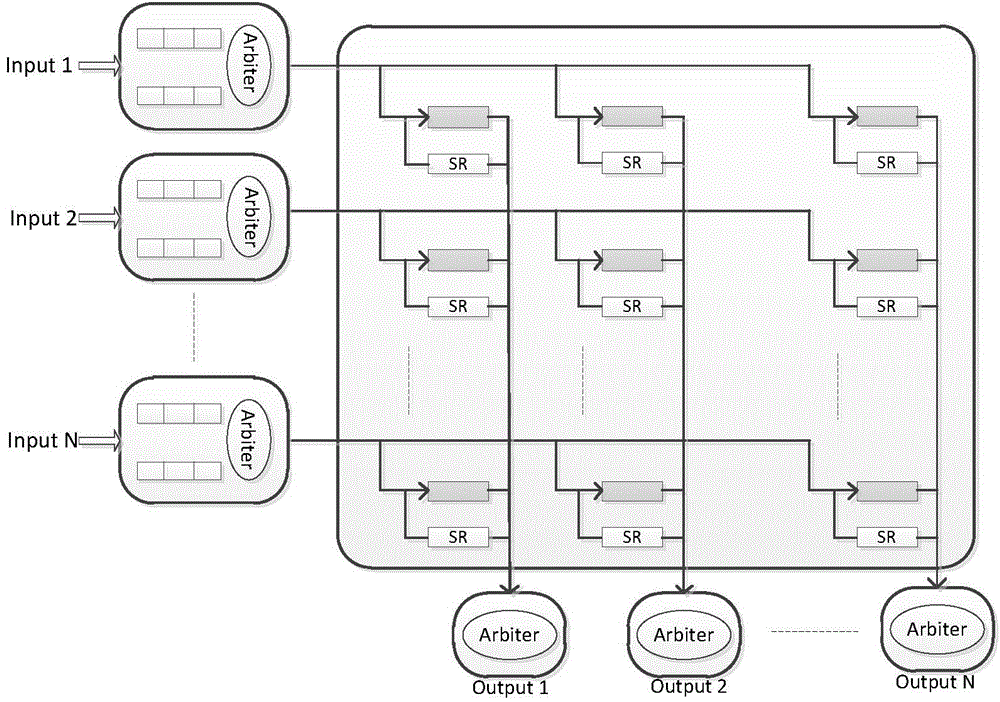

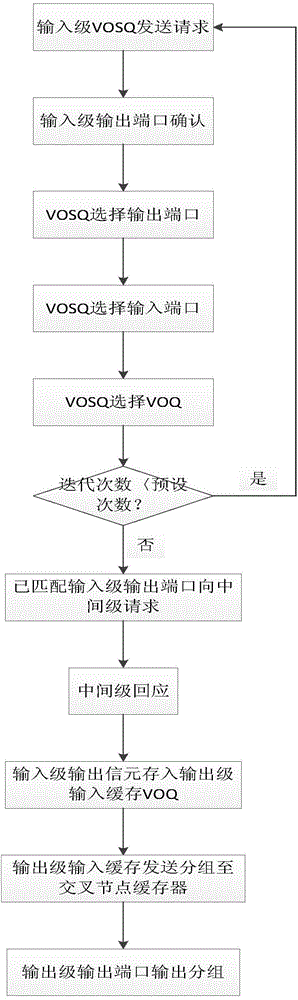

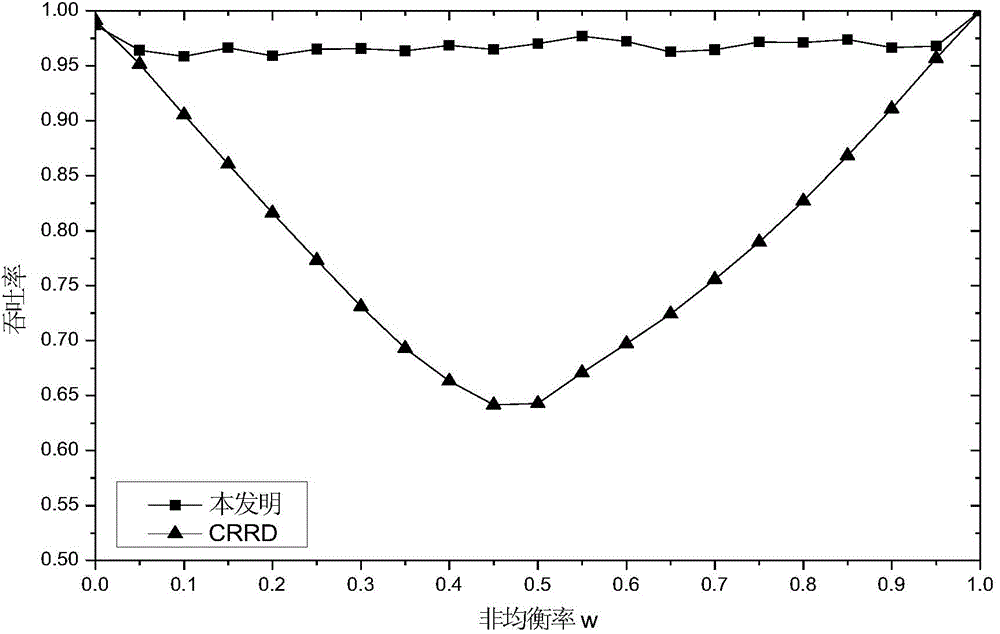

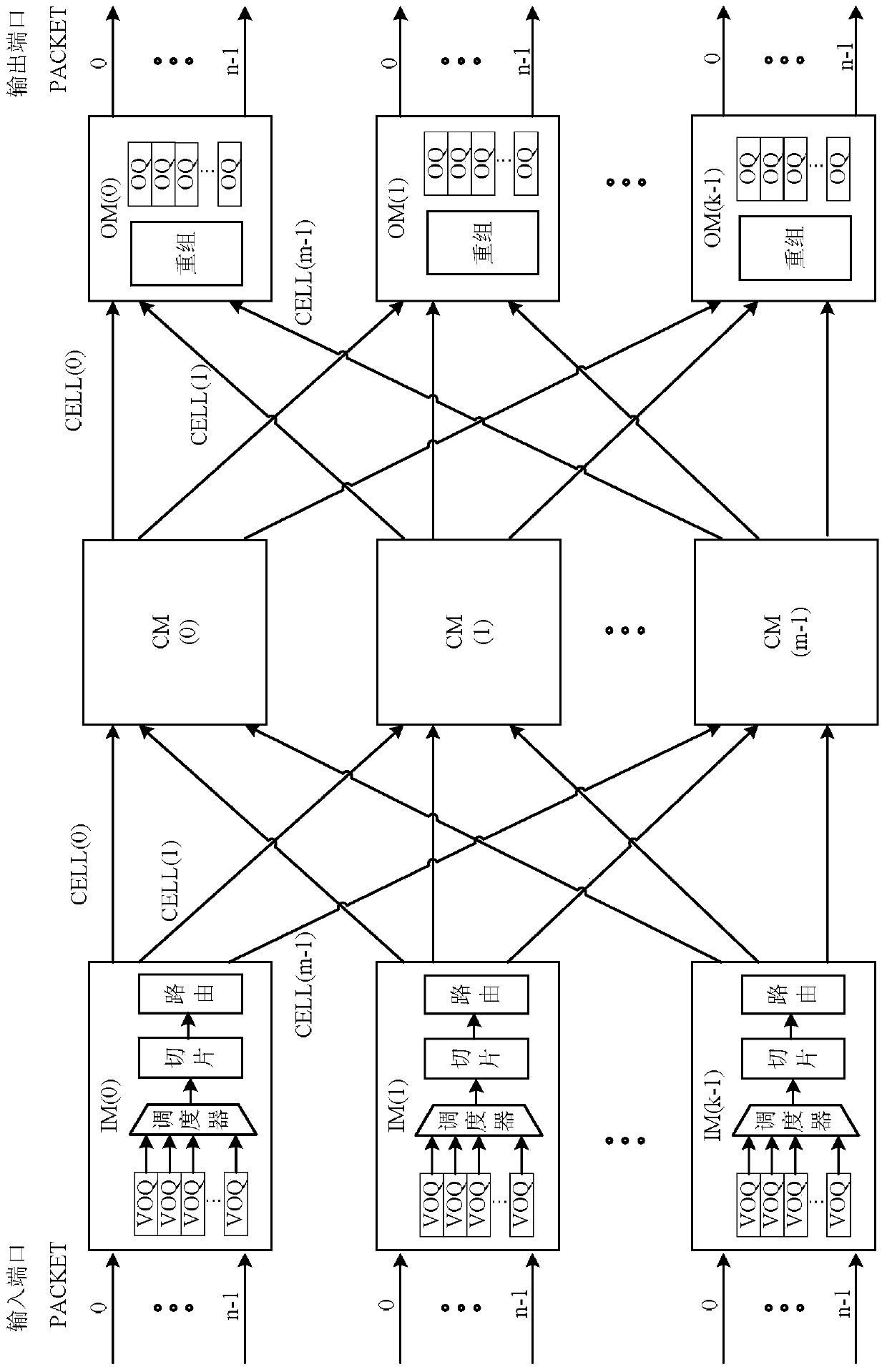

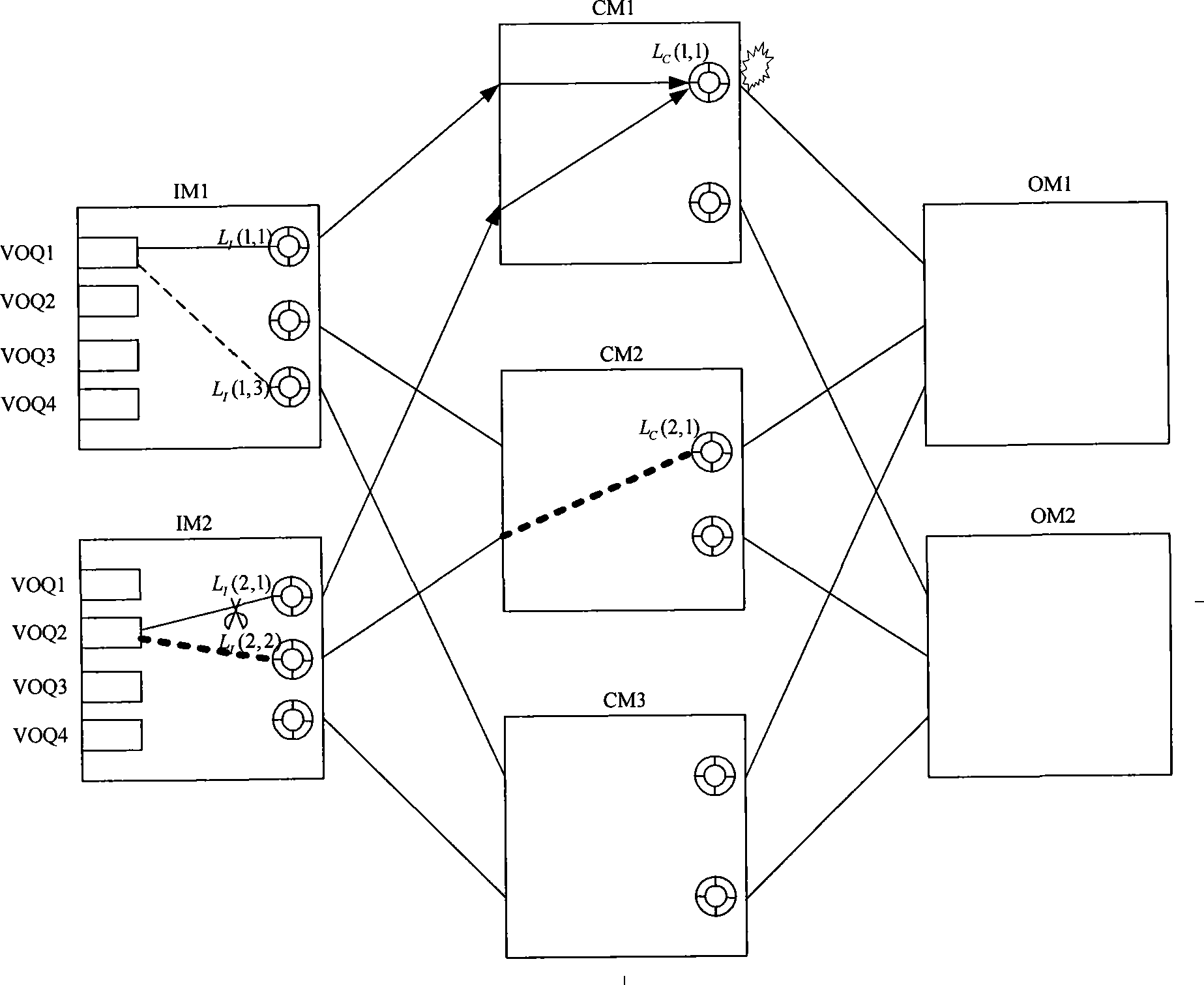

Orderly packet routing and scheduling method in clos network

ActiveCN104486237ASolve group disorderSolve the problem of not being able to exchange at high speedData switching networksIntermediate stageDistributed computing

The invention discloses an orderly packet routing and scheduling method in a Clos network, and mainly aims to solve the problem that pockets cannot be exchanged at high speed and are exchanged with disorders in the prior art. The technical scheme adopted by the invention is that the orderly packet routing and scheduling method comprises the following steps: 1, a first-stage virtual output queue group is used for sending a request to a first-stage output port, and the output port is used for selecting a request approval with a maximum weight; 2, the first-stage virtual output queue group is selected to be matched with one output port; 3, the first-stage virtual output queue group is used for selecting a virtual output queue in an input port to be matched with the output port; 4, a first-stage matched output port is used for sending a request to an intermediate stage; 5, a first stage is used for sending packets to a third-stage input cache by passing through the intermediate stage after the intermediate stage responds; 6, the third-stage input cache is used for sending the packets to a cross node cache; 7, the pockets are taken out of the cross node cache and are output. The orderly packet routing and scheduling method is capable of ensuring that the packets are exchanged at high speed and are orderly exchanged; the high throughput can be realized; the orderly packet routing and scheduling method is suitable for high-speed and large-capacity exchangers and routers.

Owner:XIDIAN UNIV

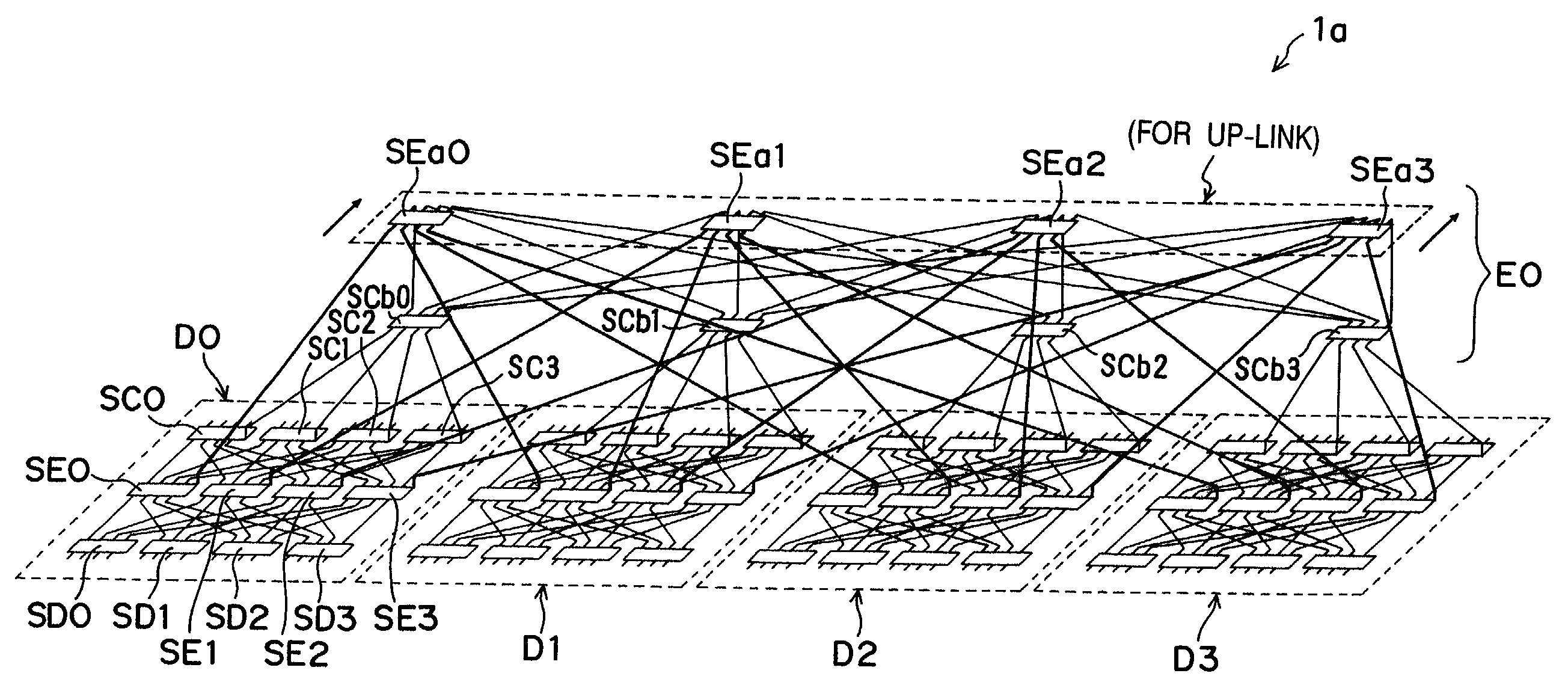

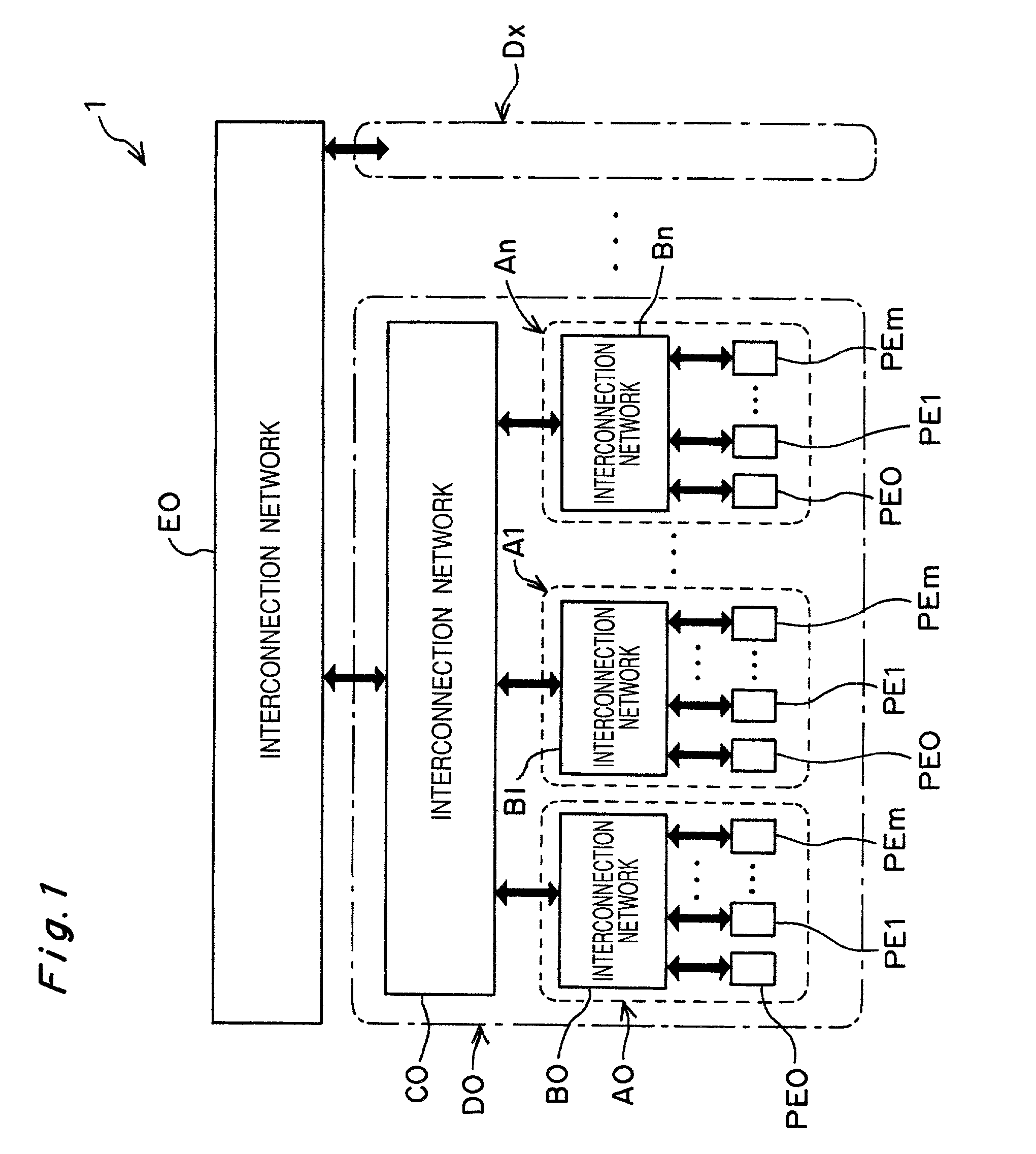

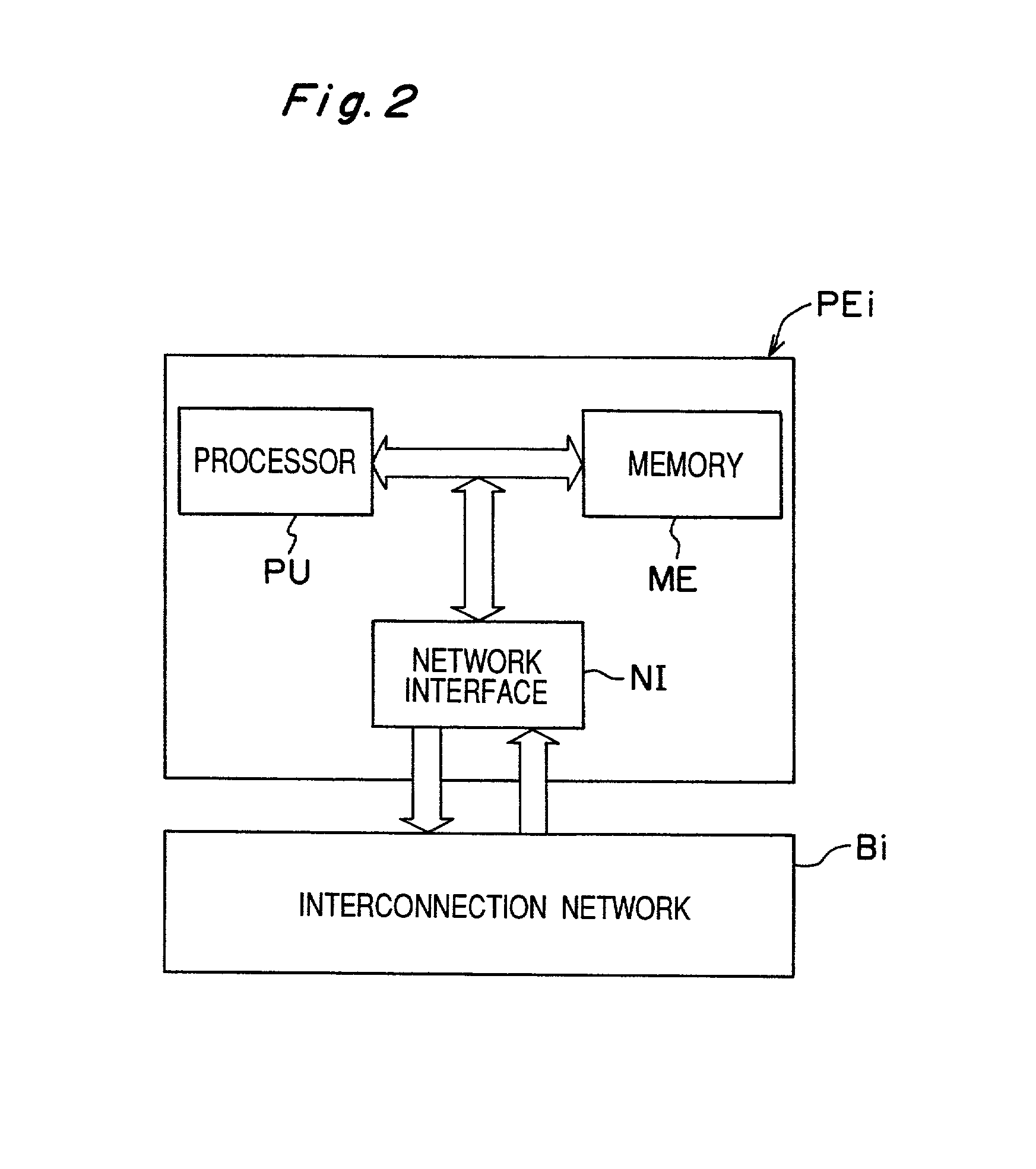

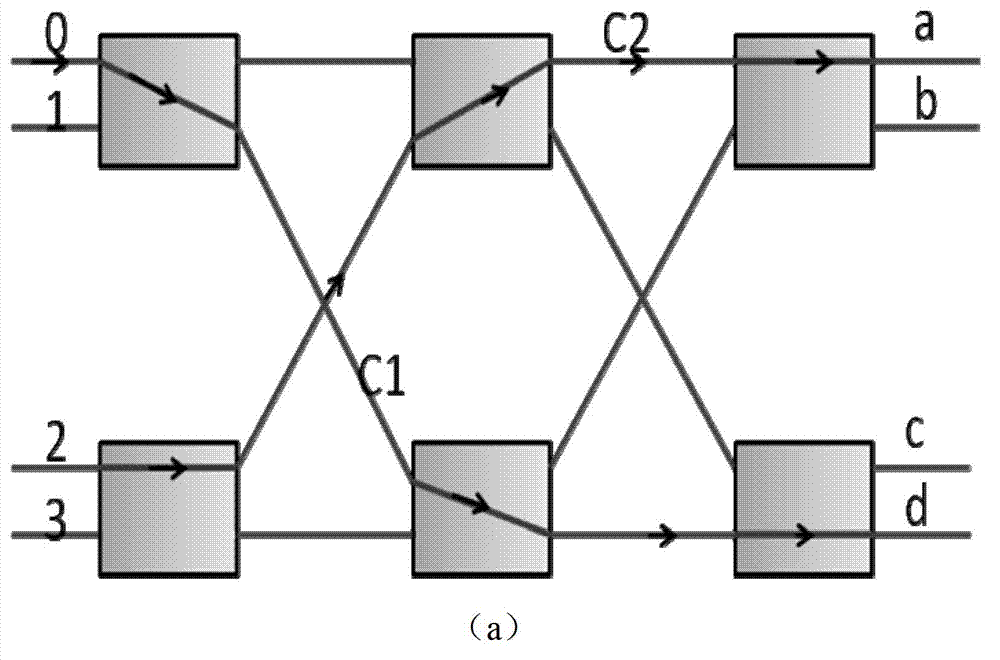

Multi-processor system apparatus allowing a compiler to conduct a static scheduling process over a large scale system of processors and memory modules

InactiveUS7203816B2Reduce overheadParallel operation be in efficiencyGeneral purpose stored program computerMultiple digital computer combinationsProcessor elementMulti processor

A multi-processor system apparatus allows a compiler to perform a static scheduling action easily and can conduct the transfer of data packets without collision in response to a common pattern of simultaneous access demands. Processor elements are interconnected by a multi-stage interconnection network having multiple stages. As each of switching elements in the multi-stage interconnection network is preliminarily subjected to the static scheduling action of a compiler. The multi-stage interconnection network is emulated without producing collision of data. When the transfer of packets is carried out in one clos network arrangement of the multi-stage interconnection network, the scheduling of switching elements SE0 to SE3 in the exchanger at Level 1 is determined so that a packet lost in the arbitration is transferred through the free port of any applicable one of the switching elements.

Owner:SEMICON TECH ACADEMIC RES CENT

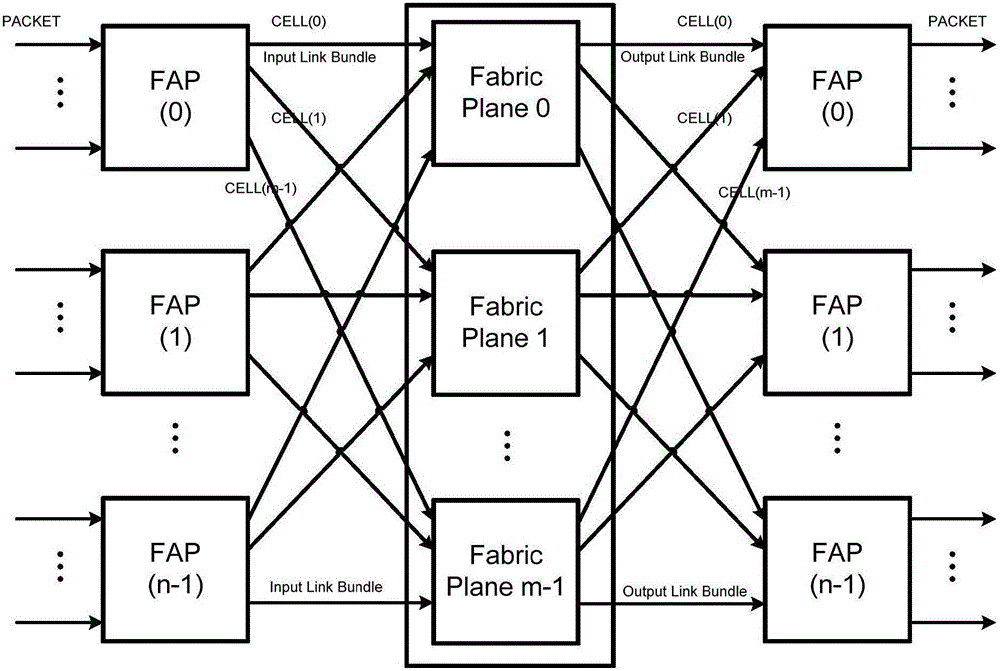

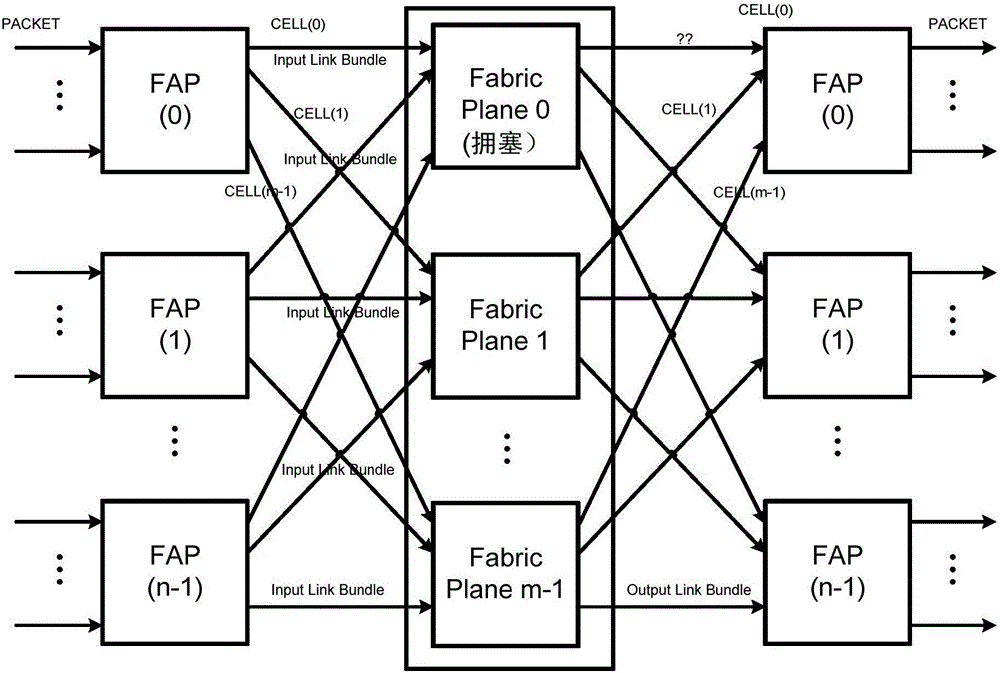

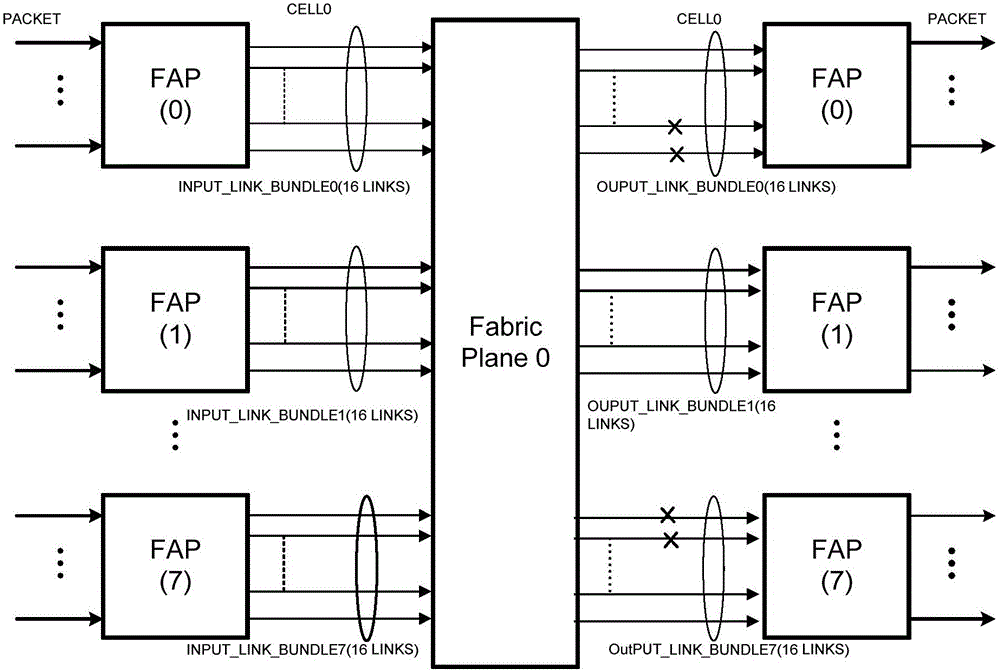

Method and system for link congestion detection and bandwidth control in three-level Clos network architecture

The invention discloses a method and a system for link congestion detection and bandwidth control in a three-level Clos network architecture. The congestion detection method comprises the following steps: each fabric plane regularly detects effectiveness of bidirectional link interconnection between an input link and an output link through a heartbeat signal; the remaining cache capacity of each output link is calculated in real time, and thus, the output cache congestion condition of each output link bundle and the output link bundle cache state are acquired; according to a bandwidth ratio of all effective input links from a source FAP to the fabric plane to all effective output links from a destination FAP to the fabric plane, whether the output link bundle congestion happens or not is judged, and if congestion happens, a control notification message for cancelling the congestion or enabling the congestion is sent to a corresponding source FAP according to the output cache congestion condition of each output link bundle and the output link bundle cache state.

Owner:FENGHUO COMM SCI & TECH CO LTD

Nonblocking and deterministic multirate unicast packet scheduling

InactiveUS20050094644A1Guaranteed bandwidthGuaranteed LatencyData switching by path configurationPacket schedulingInterconnection

A system for scheduling multirate unicast packets through an interconnection network having a plurality of input ports, a plurality of output ports, and a plurality of input queues, comprising multirate unicast packets with rate weight, at each input port is operated in nonblocking manner in accordance with the invention by scheduling corresponding to the packet rate weight, at most as many packets equal to the number of input queues from each input port to each output port. The system is operated at 100% throughput, work conserving, fair, and yet deterministically thereby never congesting the output ports. The system performs arbitration in only one iteration, with mathematical minimum speedup in the interconnection network. The system operates with absolutely no packet reordering issues, no internal buffering of packets in the interconnection network, and hence in a truly cut-through and distributed manner. In another embodiment each output port also comprises a plurality of output queues and each packet is transferred corresponding to the packet rate weight, to an output queue in the destined output port in deterministic manner and without the requirement of segmentation and reassembly of packets even when the packets are of variable size. In one embodiment the scheduling is performed in strictly nonblocking manner with a speedup of at least two in the interconnection network. In another embodiment the scheduling is performed in rearrangeably nonblocking manner with a speedup of at least one in the interconnection network. The system also offers end to end guaranteed bandwidth and latency for multirate packets from input ports to output ports. In all the embodiments, the interconnection network may be a crossbar network, shared memory network, clos network, hypercube network, or any internally nonblocking interconnection network or network of networks.

Owner:TEAK TECH

Switching clos network universal element

ActiveUS20140133851A1Multiplex system selection arrangementsCoupling light guidesPhotodiodeComputer science

A switching Clos network universal element that can dynamically change its role is disclosed. The universal element contains a matrix of VCSELs and a matrix of photodiodes on top of an electro-optical chip. The matrix of VCSELs sends data via a first set of optical links, and the matrix of photodiodes receives data a second set of optical links. The universal element also receives and sends data through electronic links. The universal element can function as an expander, aggregator or transitive switch in a folded Clos network. As an expander or an aggregator, the universal element uses its optical links as ingress links and its electronic links as egress links. Using this universal element, a network can be constructed without separate switching elements. Multiple universal elements can be positioned on a PCB, and the multiple universal elements can function as one switch.

Owner:RUSNANO

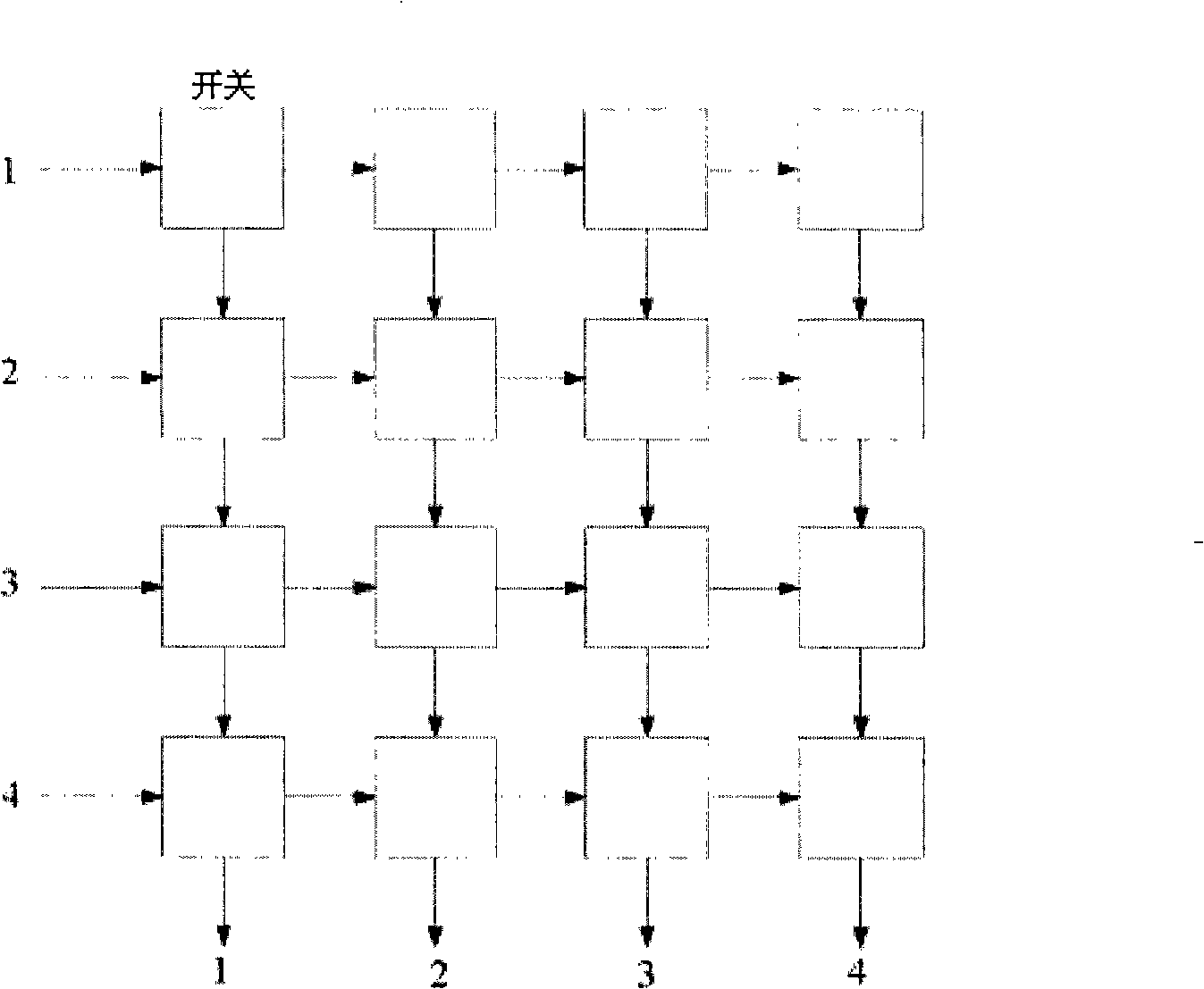

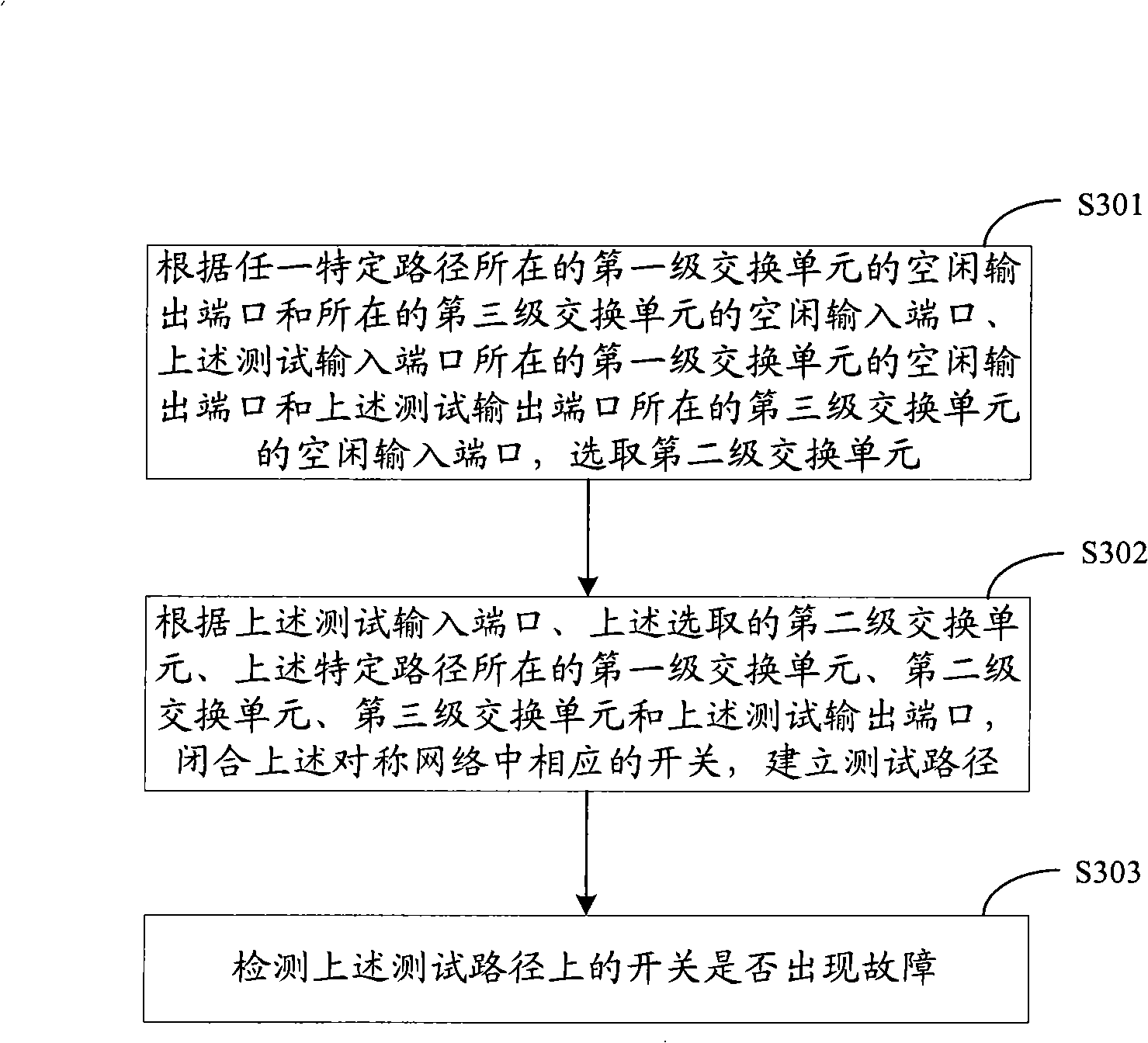

Network fault detection method, apparatus and system

InactiveCN101360018AImplement fault detectionCorrect operation testingData switching networksTest inputLevel iii

An embodiment of the invention discloses a detection method of network failure, comprising: selecting a Level II exchange unit according to an idle output port of a Level I exchange unit that is the site of any specific path and an idle input port of a Level III exchange unit that is the site of any specific path, the idle output port of the Level I exchange unit that is the site of a test input port and the idle input port of the Level III exchange unit that is the site of a test output port; closing the corresponding switches in symmetrical network and building a test path according to the test input port, the selected Level II exchange unit, the Level I exchange unit that is the site of the specific path, the Level II exchange unit, the Level III exchange unit and the test output port; and detecting the switches on the test path to see whether fault exists. The invention also provides a device and a system for detecting network failure, realizing the fault detection to all switches in the whole CLOS network, and overcoming the defects of great time and labor input when switching test interfaces manually and costly undertaking.

Owner:HUAWEI TECH CO LTD

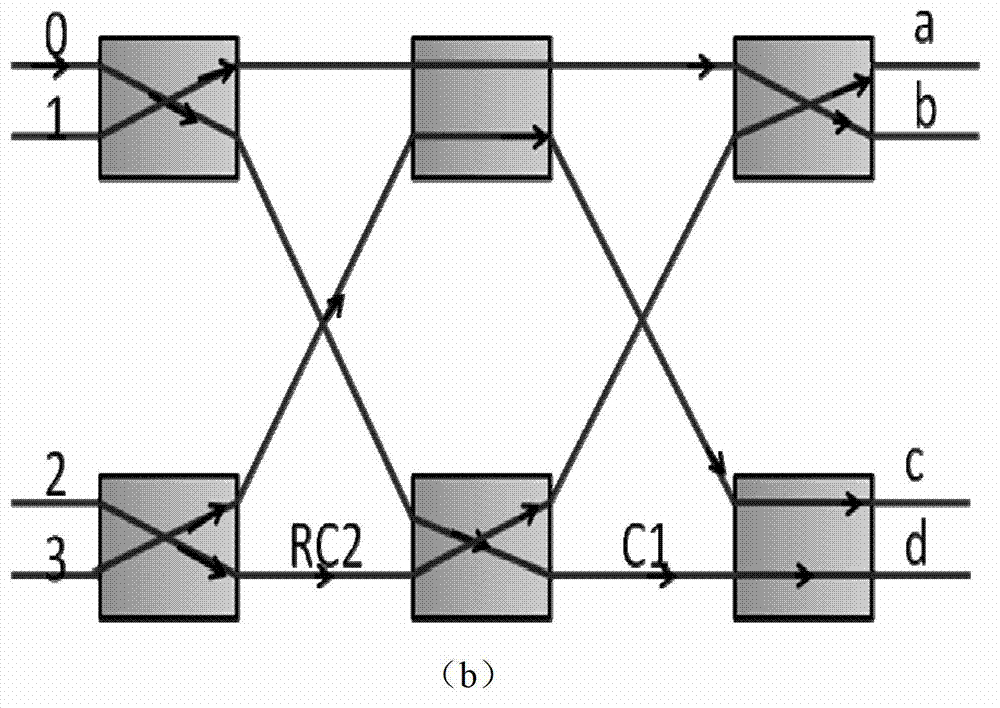

Improved three-level CLOS routing algorithm based on FPGA crossover

ActiveCN109327410ALarge Routing Cross CapabilityMeeting large-capacity crossover requirementsMultiplex system selection arrangementsData switching networksThree levelIntermediate level

Owner:TOEC TECH

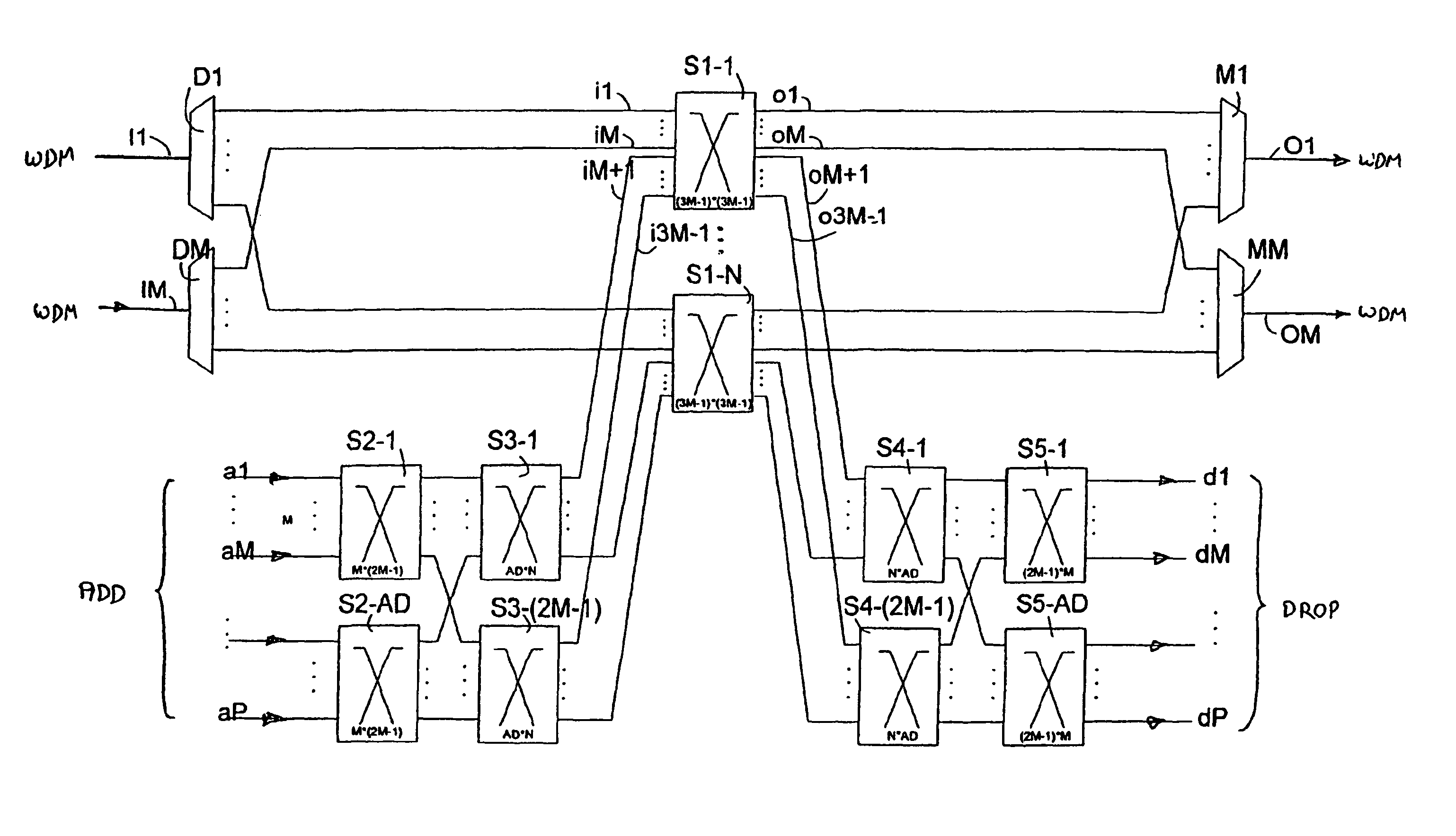

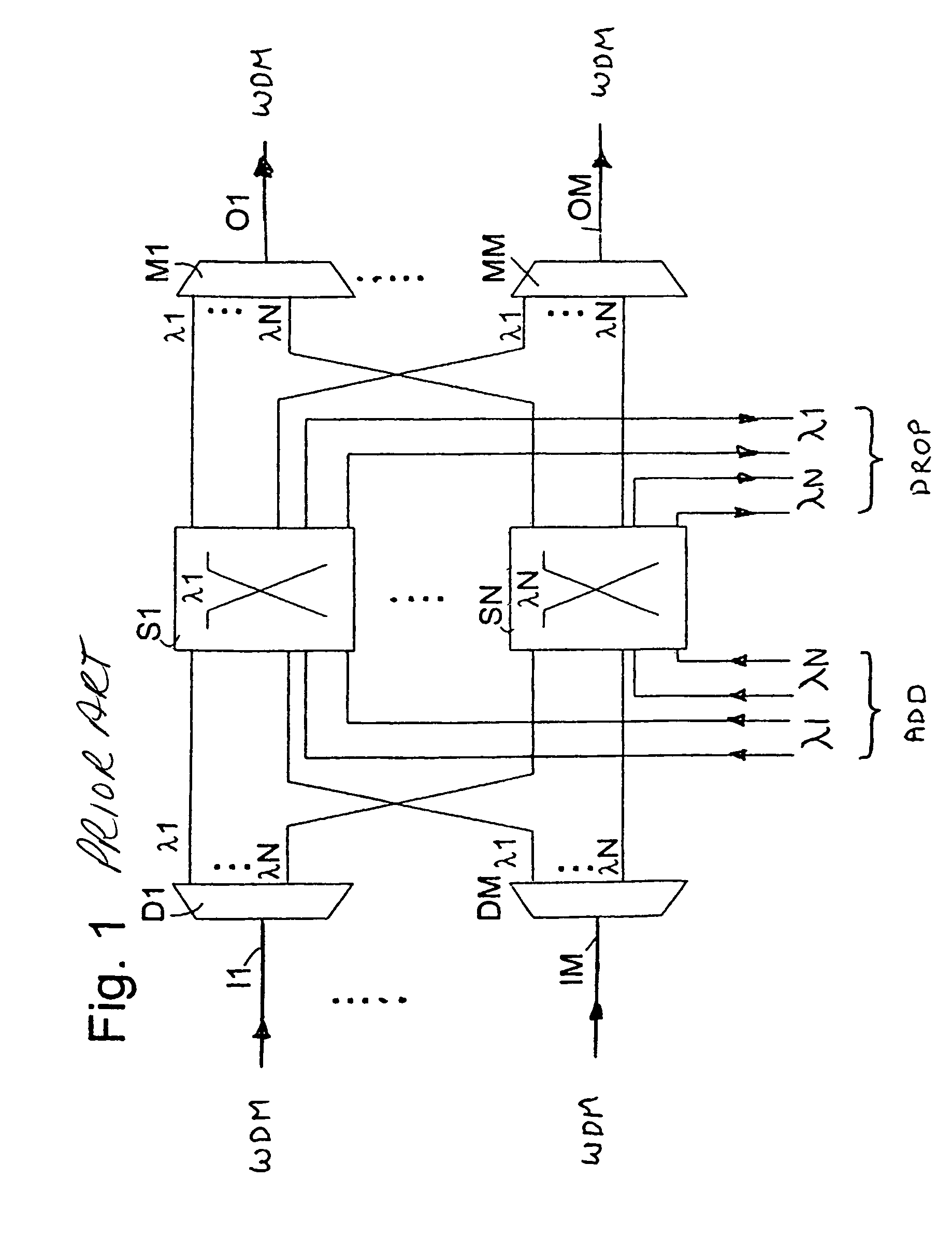

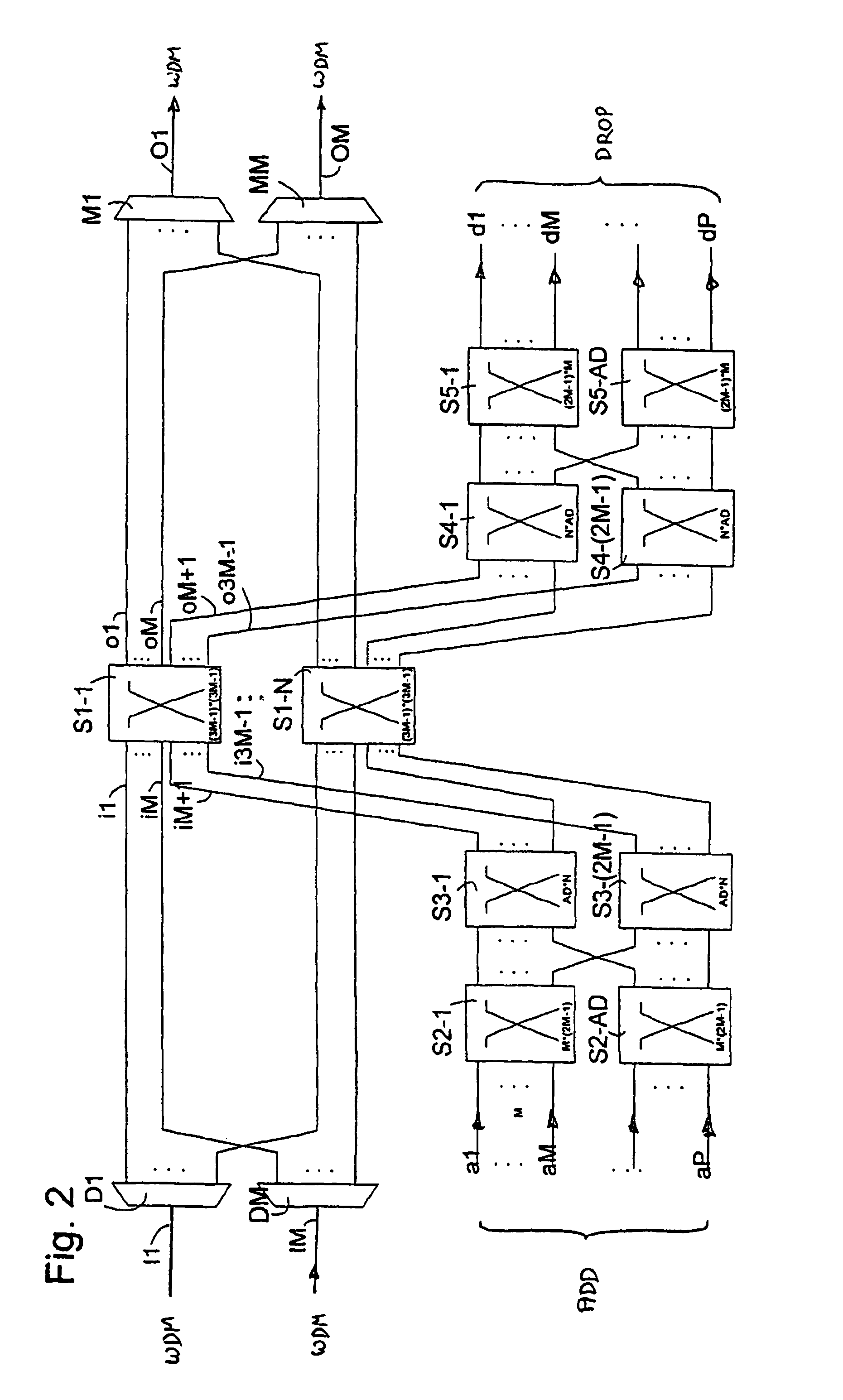

Optical cross-connector containing multi-stage Clos network in which a single-stage matrix comprises one stage of the Clos network

InactiveUS7787768B2Multiplex system selection arrangementsRing-type electromagnetic networksSingle stageCross connection

A WDM optical cross-connect has input and output channels for through traffic. A first group of matrices connects the input channels to the output channels. Each input channel is connected to an input of a matrix of the first group and each output channel is connected to an output of the matrix. Input / output channels are provided for adding / dropping traffic. Each add / drop channel is connected to an input / output of a second group of matrices. The outputs / inputs of the second group of matrices are connected to inputs of a third group of matrices or outputs of a fourth group of matrices and the outputs / inputs of the third / fourth group of matrices are connected to inputs / outputs of the first group of matrices such that the matrices of the second, third and first groups of the first, fourth and second groups each form a Clos network.

Owner:TELEFON AB LM ERICSSON (PUBL)

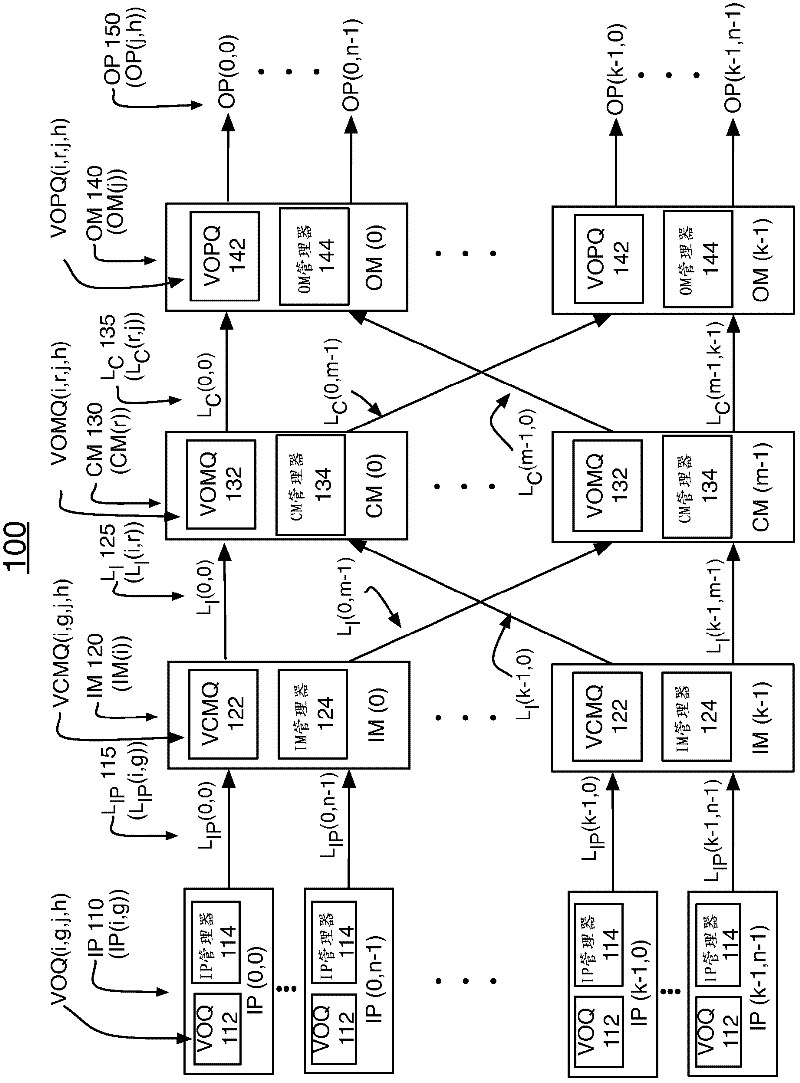

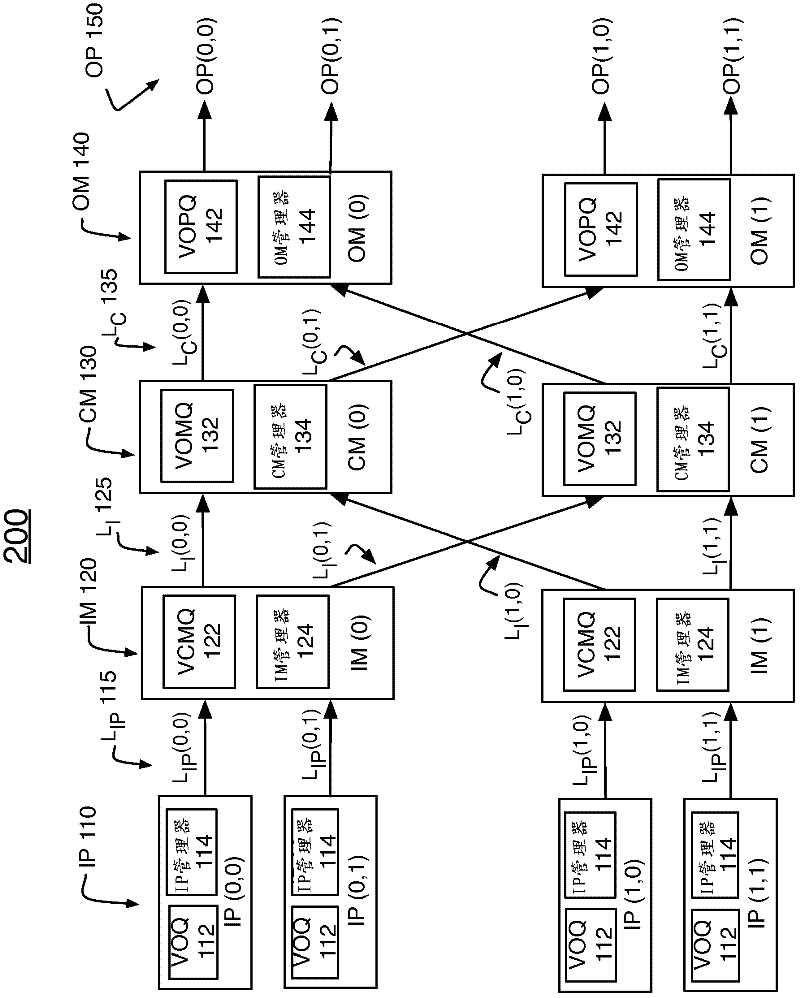

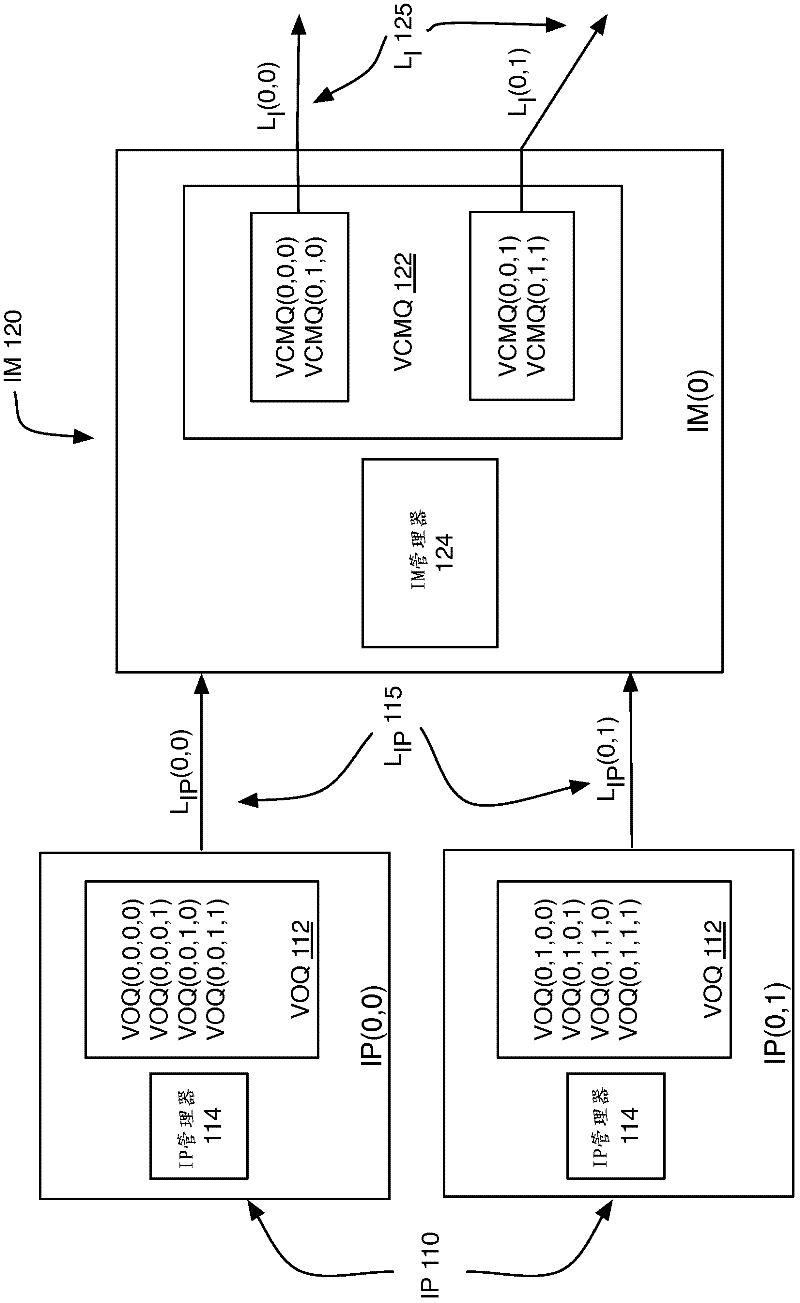

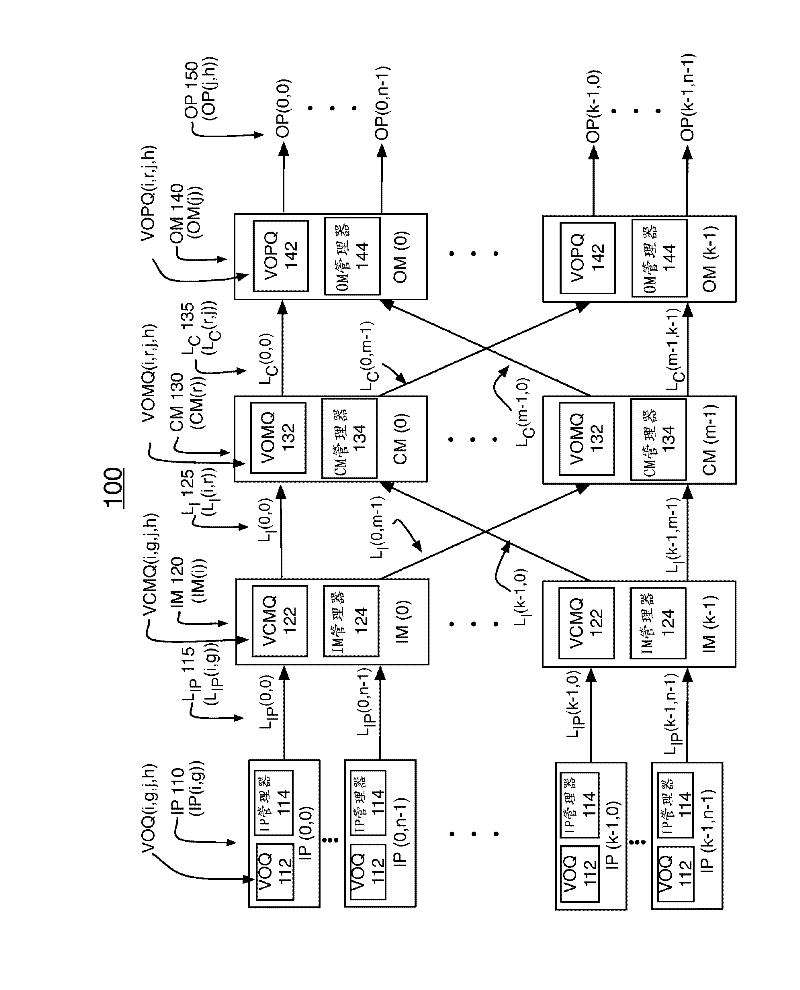

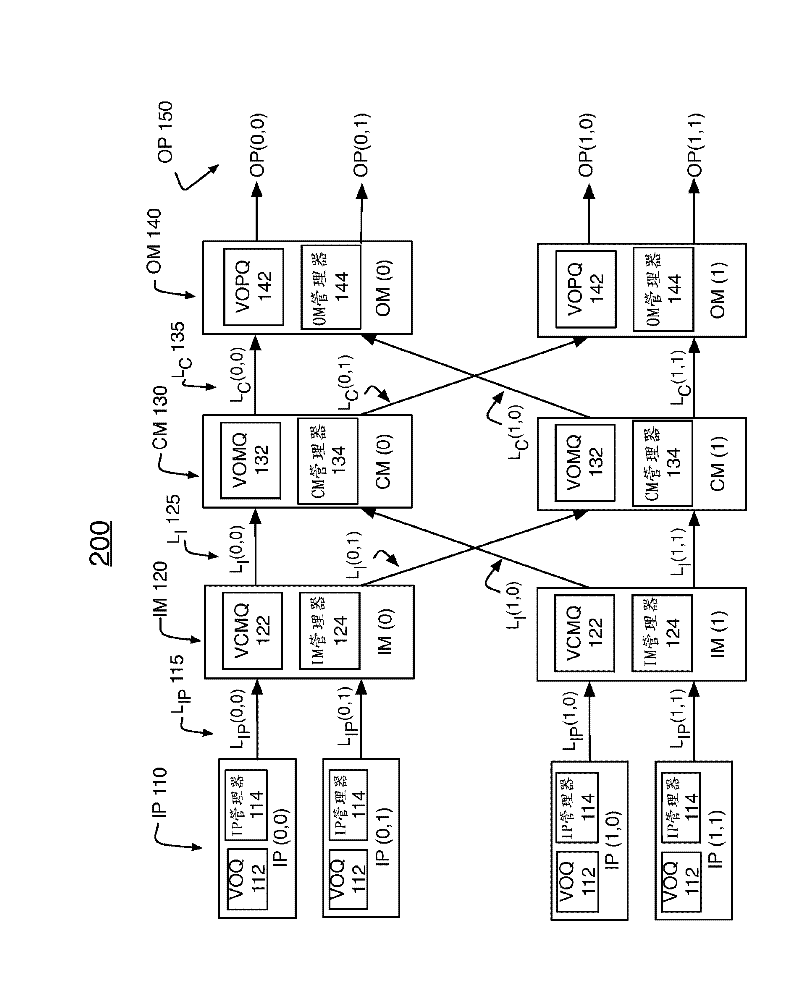

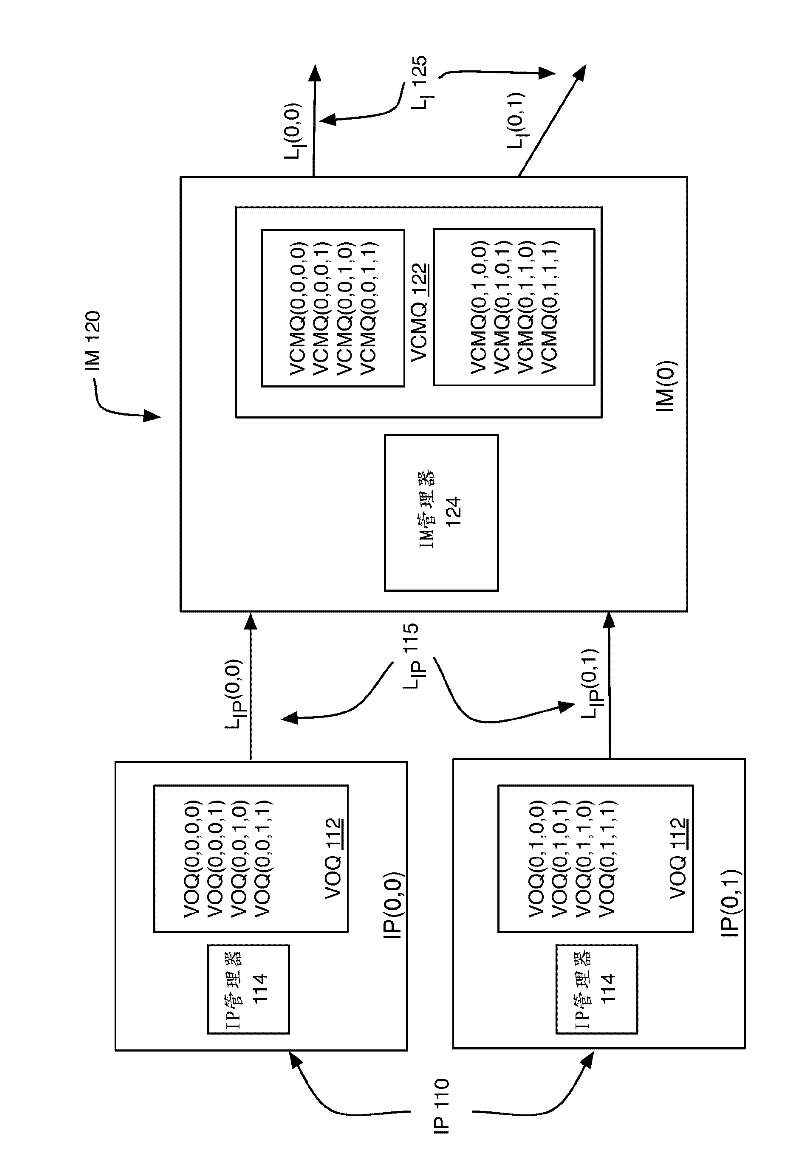

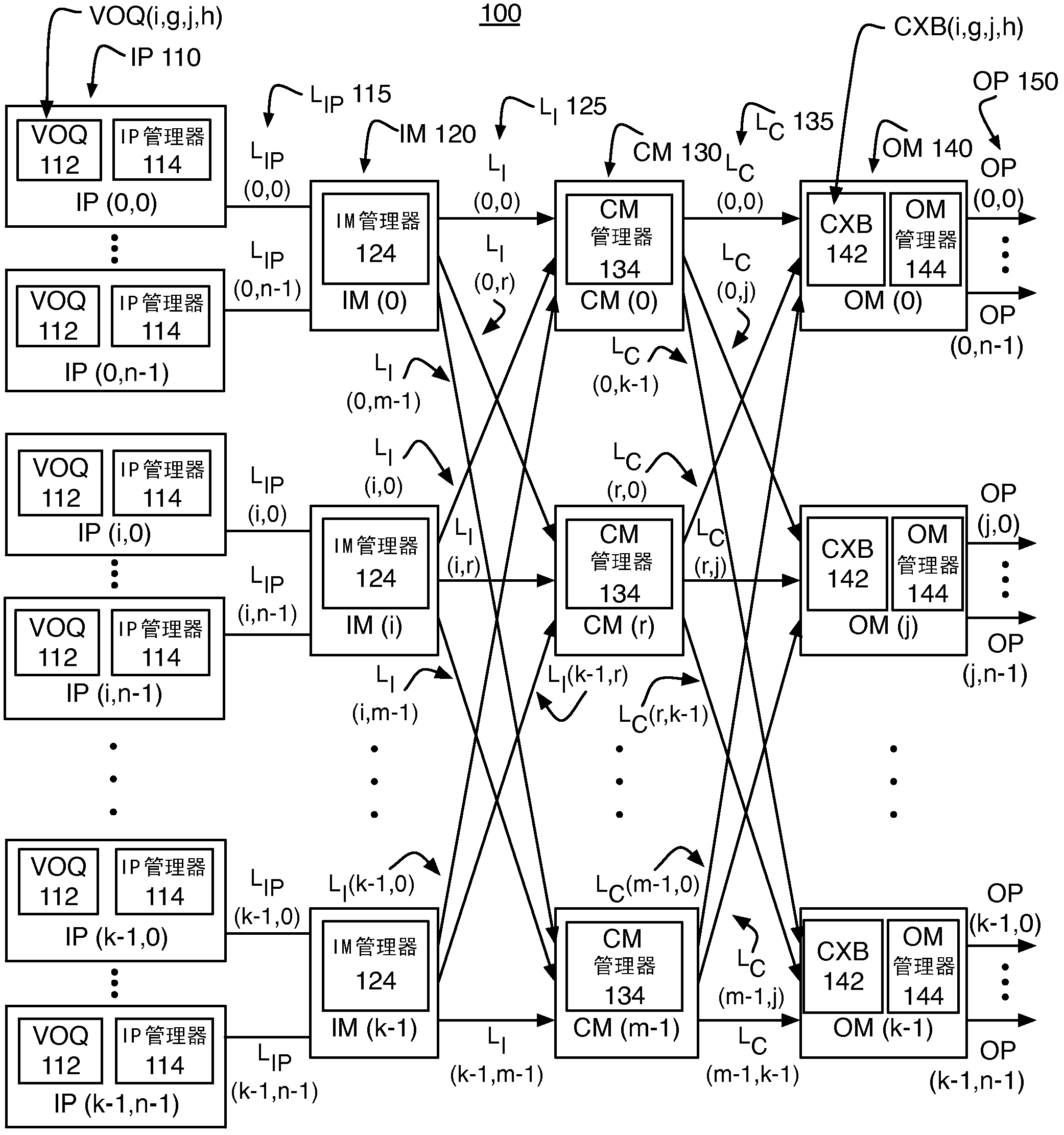

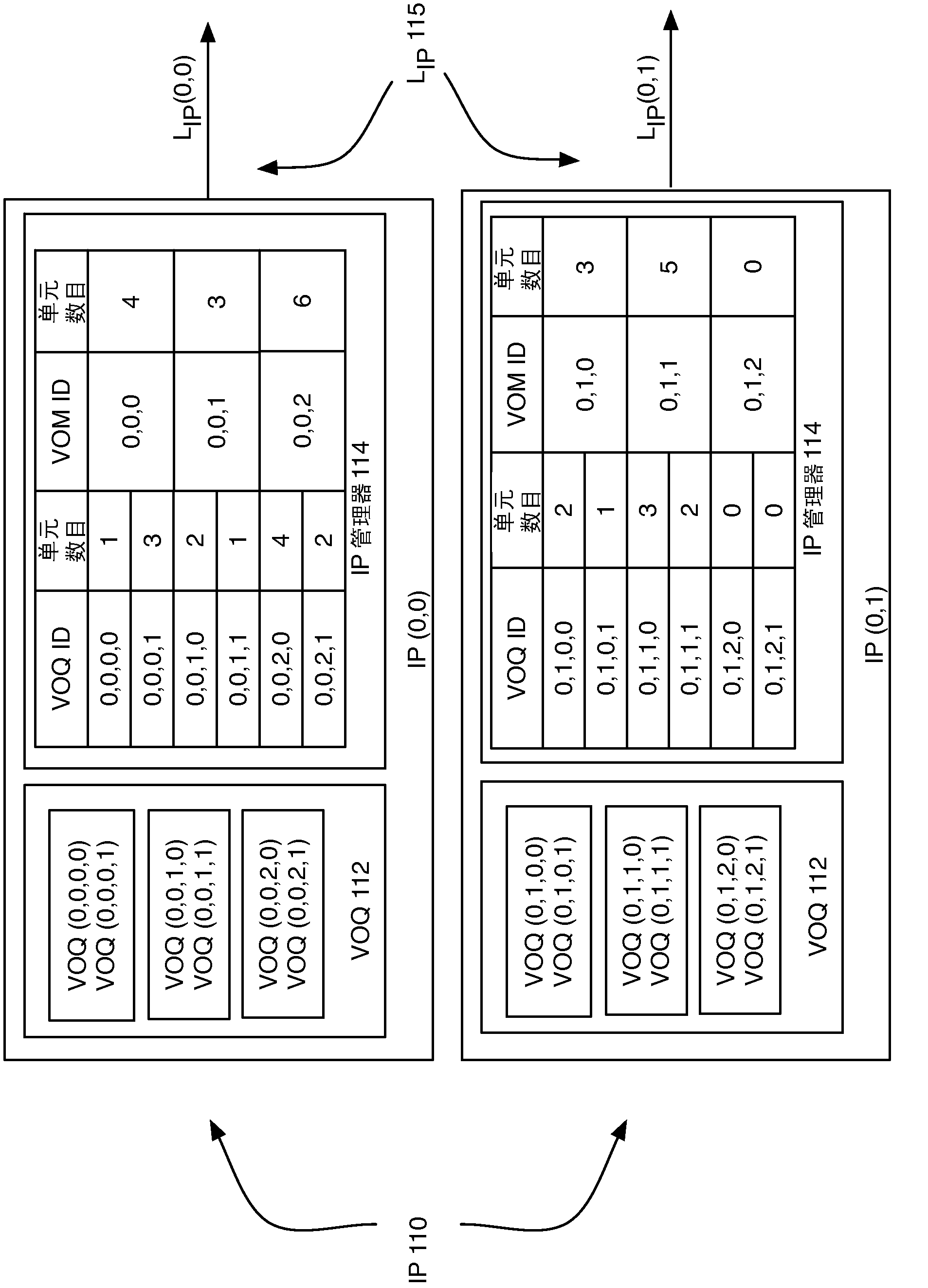

Forwarding data through a three-stage clos-network packet switch with memory at each stage

InactiveCN102474460AMultiplex system selection arrangementsData switching networksThree stageComputer module

Examples are disclosed for forwarding data partitioned into one or more cells through at least a portion of a three-stage memory-memory-memory (MMM) input-queued Clos-network (IQC) packet switch. In some examples, each module of the three-stage MMM IQC packet switch includes a virtual queue and a manager that are configured in cooperation with one another to forward cells through at least a portion of the switch. The cells may have been partitioned and stored at an input port for the switch and destined for an output port for the switch.

Owner:NEW JERSEY INSTITUTE OF TECHNOLOGY

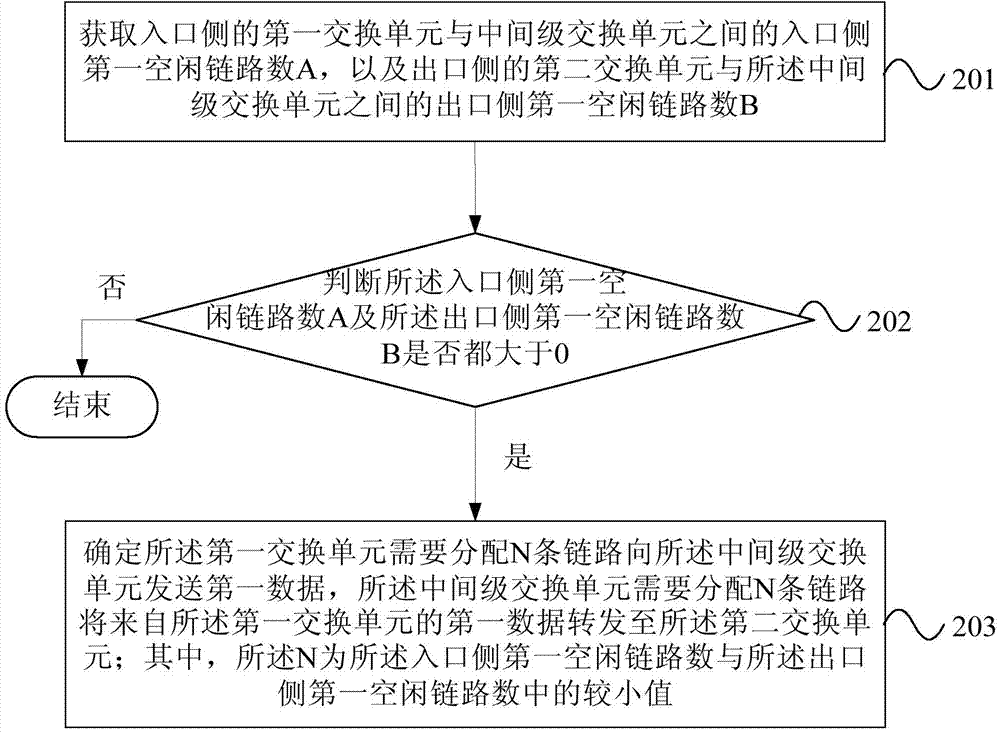

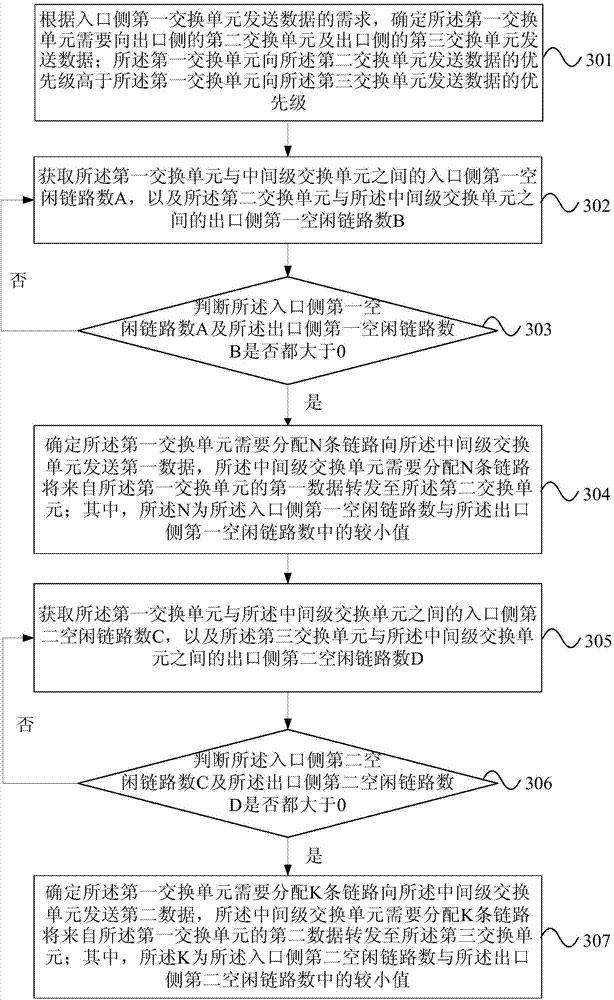

CLOS network link distribution method and device

InactiveCN104243354AAvoid swap blocking problemsData switching networksNetwork linkDistribution method

The invention provides a CLOS network link distribution method and device. The method includes: acquiring a number A of entry-side first idle links between first exchange units and intermediate-stage exchange units on an entry side and a number B of exit-side first idle links between second exchange units and the intermediate-stage exchange units on an exit side; judging whether both the number A of the entry-side first idle links and the number B of the exit-side first idle links are lager than zero or not; if yes, determining that N links need to be distributed to the first exchange units to send first data to the intermediate-stage exchange units and N links need to be distributed to the intermediate-stage exchange units to forward the first data from the first exchange units to the second exchange units, wherein N is a minimum value in the number of the entry-side first idle links and the number of the number of the exit-side first idle links.

Owner:RUIJIE NETWORKS CO LTD

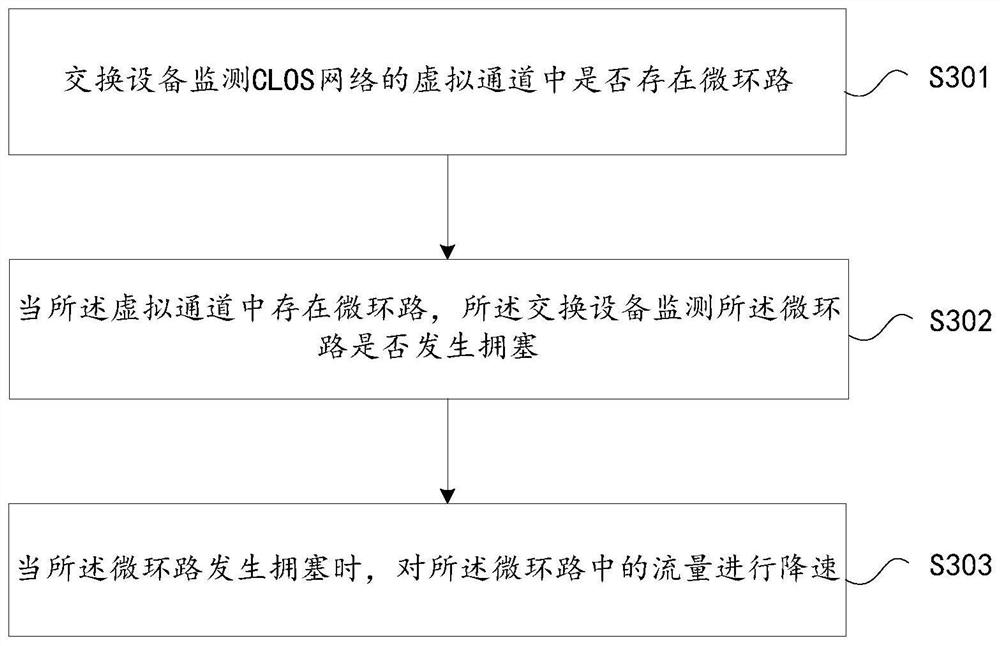

Flow control anti-deadlock method and device based on priority

The embodiment of the invention provides a flow control anti-deadlock method and device based on priority. The method comprises the following steps: switching equipment monitors whether a micro loop exists in a virtual channel of a CLOS network or not; when the micro-loop exists in the virtual channel, the switching equipment monitors whether the micro-loop is congested or not; and when the micro loop is congested, the speed of the flow in the micro loop is reduced. According to the invention, when the micro-loop in the network is congested, PFC deadlock can be avoided by reducing the speed of the flow in the micro-loop, so that the problem of PFC deadlock in the network for generating the micro-loop in the related technology is solved, and the effects of avoiding PFC deadlock and avoiding message loss caused by deadlock are achieved.

Owner:ZTE CORP

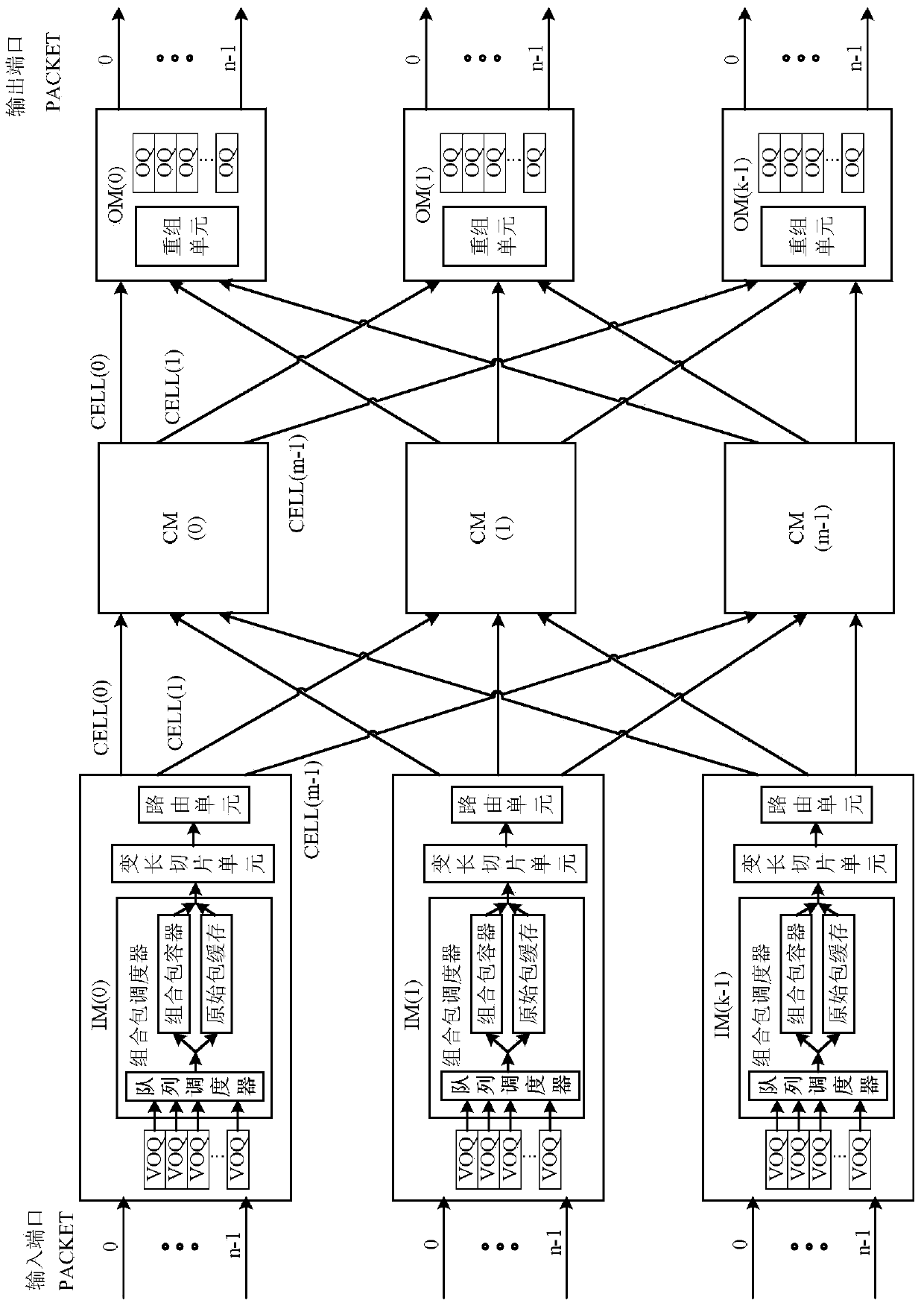

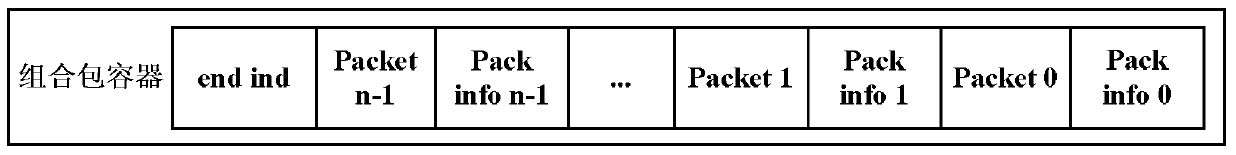

System and method for data packet segmentation and reassembly based on clos switching network

ActiveCN104954292BImprove throughputAvoid the case of short packetsData switching networksNetwork packetVariable length

Owner:FENGHUO COMM SCI & TECH CO LTD +1

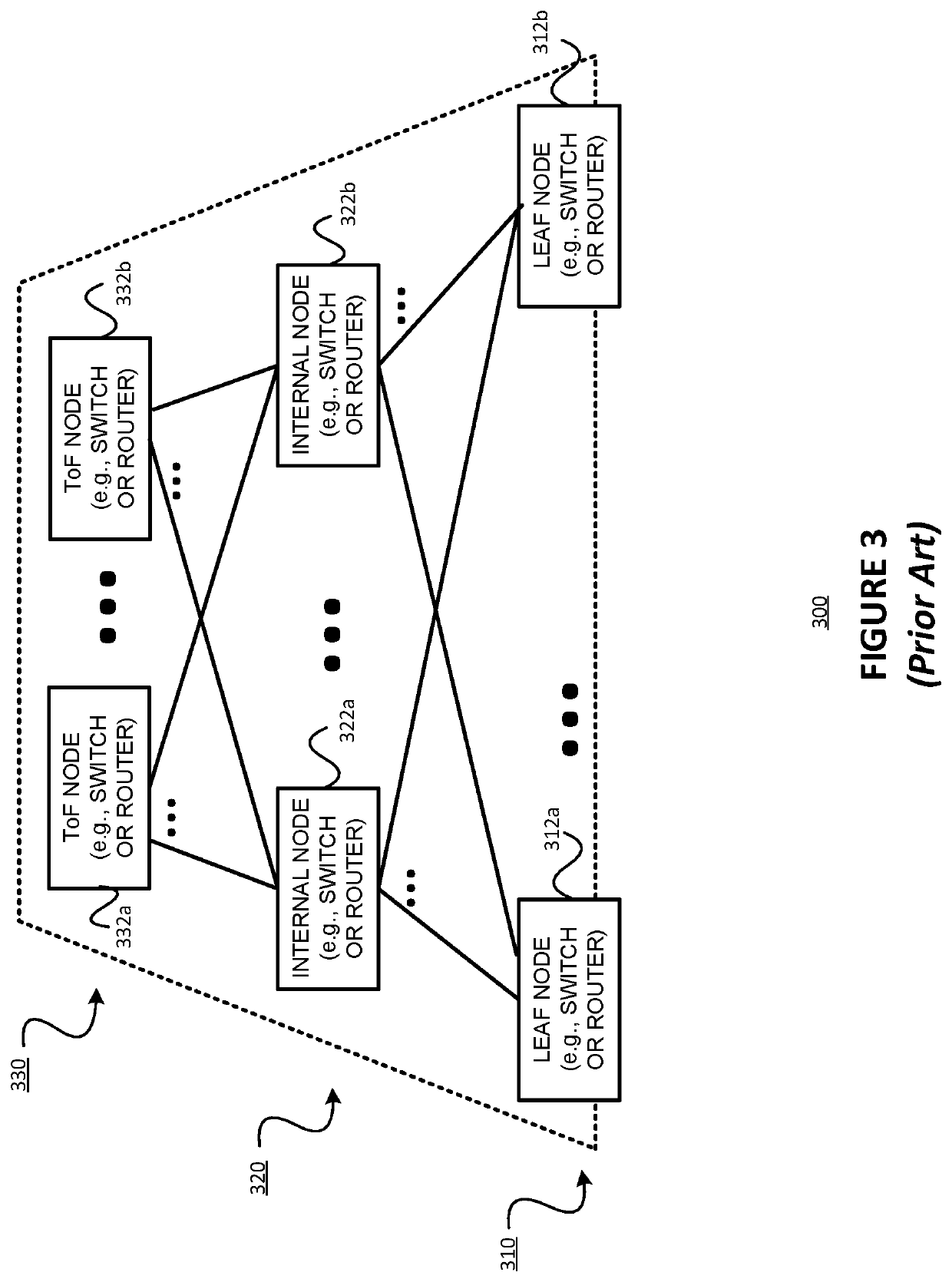

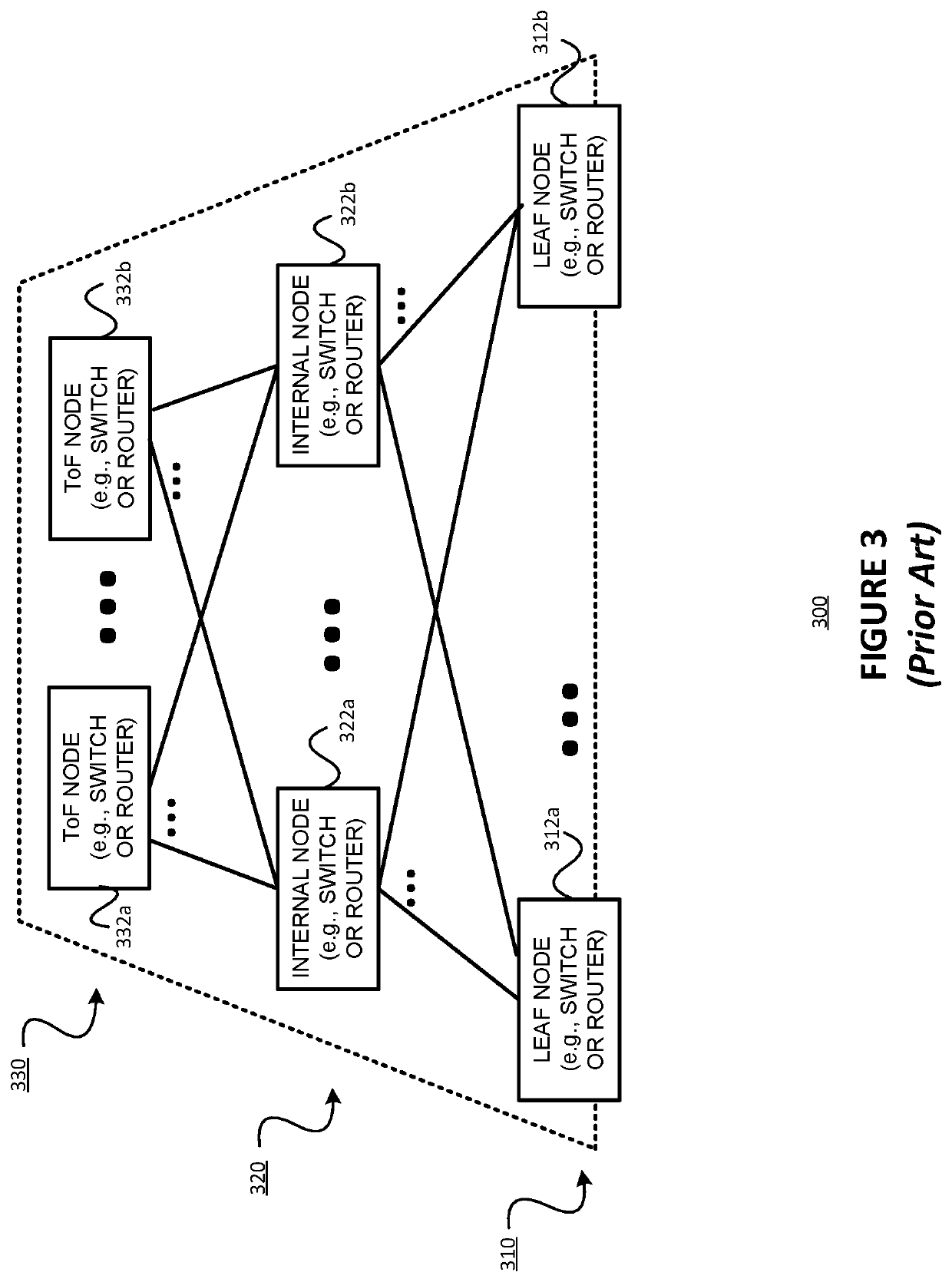

Defining non-forwarding adjacencies in bipartite networks, such as Clos networks, having a level 2 backbone and level 1 nodes

Problems associated with providing a large Clos network having at least one top of fabric (ToF) node, a plurality of internal nodes, and a plurality of leaf nodes may be solved by: (a) providing L2 tunnels between each of the leaf nodes of the Clos and one or more of the at least one ToF node to ensure a non-partitioned IGP L2 backbone, and (b) identifying the L2 tunnels as non-forwarding adjacencies in link state topology information stored in ToF node(s) and leaf node(s) such that the L2 tunnels are not used for forwarding traffic. Tunnel formation is prevented over L2.

Owner:JUMIPER NETWORKS INC

Defining non-forwarding adjacencies in bipartite networks, such as Clos newtorks, having a level 2 backbone and level 1 nodes

ActiveUS11050679B1Minimize and avoid useGuaranteed connectivityData switching networksTopology informationEngineering

Problems associated with providing a large Clos network having at least one top of fabric (ToF) node, a plurality of internal nodes, and a plurality of leaf nodes may be solved by: (a) providing L2 tunnels between each of the leaf nodes of the Clos and one or more of the at least one ToF node to ensure a non-partitioned IGP L2 backbone, and (b) identifying the L2 tunnels as non-forwarding adjacencies in link state topology information stored in ToF node(s) and leaf node(s) such that the L2 tunnels are not used for forwarding traffic. In some example implementations consistent with the present disclosure, the L2 tunnels are not used to compute routes from the link state topology information. Alternatively, in some other example implementations consistent with the present disclosure, the L2 tunnels are used to compute routes, but such routes are not used, or only used if no routes using only L1 (or L1-down adjacencies) are available. In some example implementations consistent with the present disclosure, L2 prefix information is leaked down to L1 of the IGP.

Owner:JUMIPER NETWORKS INC

Forwarding cells of partitioned data through a three-stage CLOS-network packet switch with memory at each stage

Examples are disclosed for forwarding cells of partitioned data through a three-stage memory-memory-memory (MMM) input-queued Clos-network (IQC) packet switch. In some examples, each module of the three-stage MMM IQC packet switch includes a virtual queue and a manager that are configured in cooperation with one another to forward a cell from among cells of partitioned data through at least a portion of the switch. The cells of partitioned data may have been partitioned and stored at an input port for the switch and have a destination of an output port for the switch.

Owner:NEW JERSEY INSTITUTE OF TECHNOLOGY

Configuring a three-stage CLOS-network packet switch

The present invention generally relates to configuring one or more routes through a three stage Clos network packet switch to forward data received at an input port for the three stage Clos network packet switch. The received data is partitioned into one o more cells stored at one or more virtual output queues maintained at the input port coupled to an input module for the three stag Clos network packet switch. The one or more cells is / are stored at the one or more virtual output queues separately destined for an output port coupled to an output module from among the one or more output modules for the three stage Clos network packet switch.

Owner:NEW JERSEY INSTITUTE OF TECHNOLOGY

Sequence matching scheduling algorithm based on Clos network switching structure

A sequential match scheduling algorithm based on a Clos network switching structure relates to the field of network crossbar scheduling algorithm, which comprises the following steps: step 1, output ports (the number being m) of an input module send request information to a corresponding output port of each middle module; step 2, the output port of each middle module selects one virtual output group of one sent request information and sends the allowed message to the virtual output group; step 3, the output port of each middle module selects an output port of the middle module and discharges the allowed message sent from the output port; step 4, the establishing process of the channel from a virtual output queue to the output port is finished; step 5, information cells are sent out and a pointer is updated; the fourth step and the fifth step are repeated until all the information cells are sent out or all the allowed message are accepted. The scheduling algorithm of the invention adopts a straight-through type match, the whole match is finished at one time and a many-to-many 'request-allow-accept' mode is adopted, which uses the scheduling opportunity to a maximum extent.

Owner:WUHAN POST & TELECOMM RES INST CO LTD

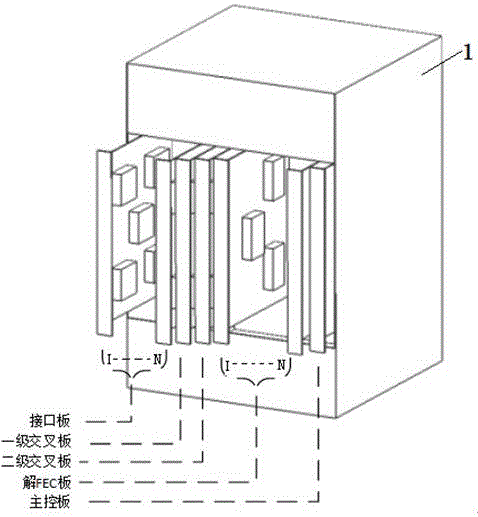

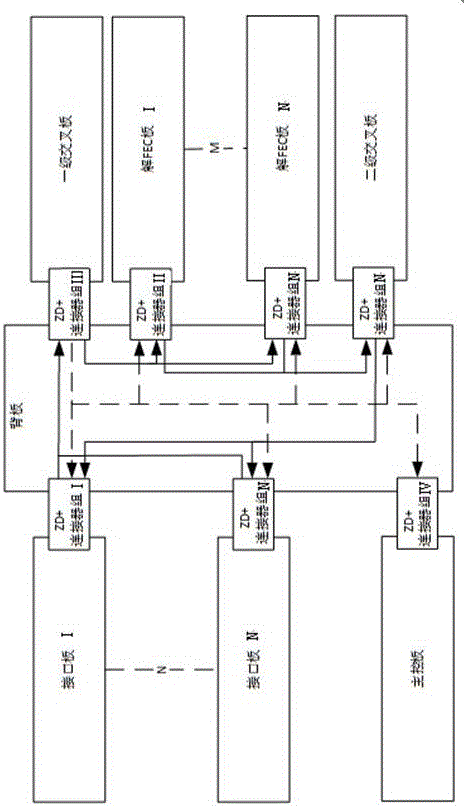

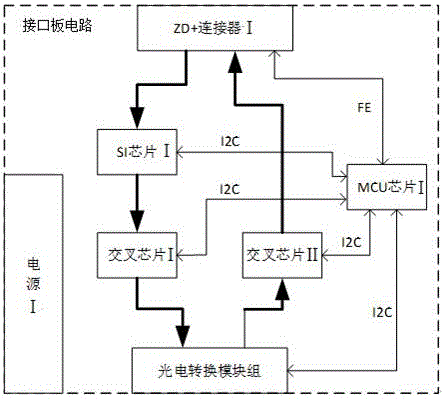

FEC decoding system with optical line crossing function realized based on electric domain and method

InactiveCN106487483AImplement cross-functionalityRealize the function of solving FECError preventionDistortion/dispersion eliminationThree levelLevel crossing

The invention relates to an FEC decoding system with an optical line crossing function realized based on an electric domain and a method. The system adopts a structure in which cards are plugged into a backboard. The plug-in cards comprise an interface board, an FEC decoding board, a first-level cross board, a second-level cross board, and a master control board. The system is based on a three-level rigorous obstruction-free CLOS network. Input-level crossing and output-level crossing are completed by high-speed cross chips distributed on the cross boards. Intermediate-level crossing is completed by an FPGA on the FEC decoding board. Three kinds of board cards form a rigorous obstruction-free cross network. The FPGA chip on the FEC decoding board also completes an FEC decoding function. The interface board is responsible for accessing and outputting optical signals and achieving an O / E / O function. The master control board is responsible for receiving an instruction from a principal computer and communicating with other board cards. With the system, the function of FEC decoding at multiple rates can be achieved, and optical channels can be crossed by means of O / E / O. Moreover, the system has broadcast and replication functions.

Owner:TOEC TECH

Path distribution method in Clos network based on device constraint

InactiveCN102904805AReduce running timeImprove the efficiency of exchange schedulingData switching networksIdle timeDistribution method

The invention discloses a path distribution method in a Clos network based on device constraint. An idling time slot is filled by an ineffective service by introducing the ineffective service, so that the idling time slot can emit light by virtue of wavelengths of other effective services different from the current time slot instead of emitting light by virtue of the wavelength of a service of more than one time slot under the action of the device constraint of a flash translation layer (FTL); and therefore, interference to the effective service of the current time slot is eliminated. When the ineffective service is distributed, the ineffective service can be generated by adopting a sequential distribution strategy; compared with a random distribution strategy, algorithm optimization is executed; and running efficiency is improved.

Owner:UNIV OF ELECTRONICS SCI & TECH OF CHINA