CMOS circuit based on semi-conductor nano material and preparation therefor

A technology of nanomaterials and semiconductors, applied in the field of nanoelectronics, can solve the problems that the performance of p-type and n-type devices is not very matched, the performance of n-type and p-type field effect transistors is low, and it is not suitable for scale integration, etc., to achieve overall performance Best, improve carrier mobility, reduce scattering effect

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment 1

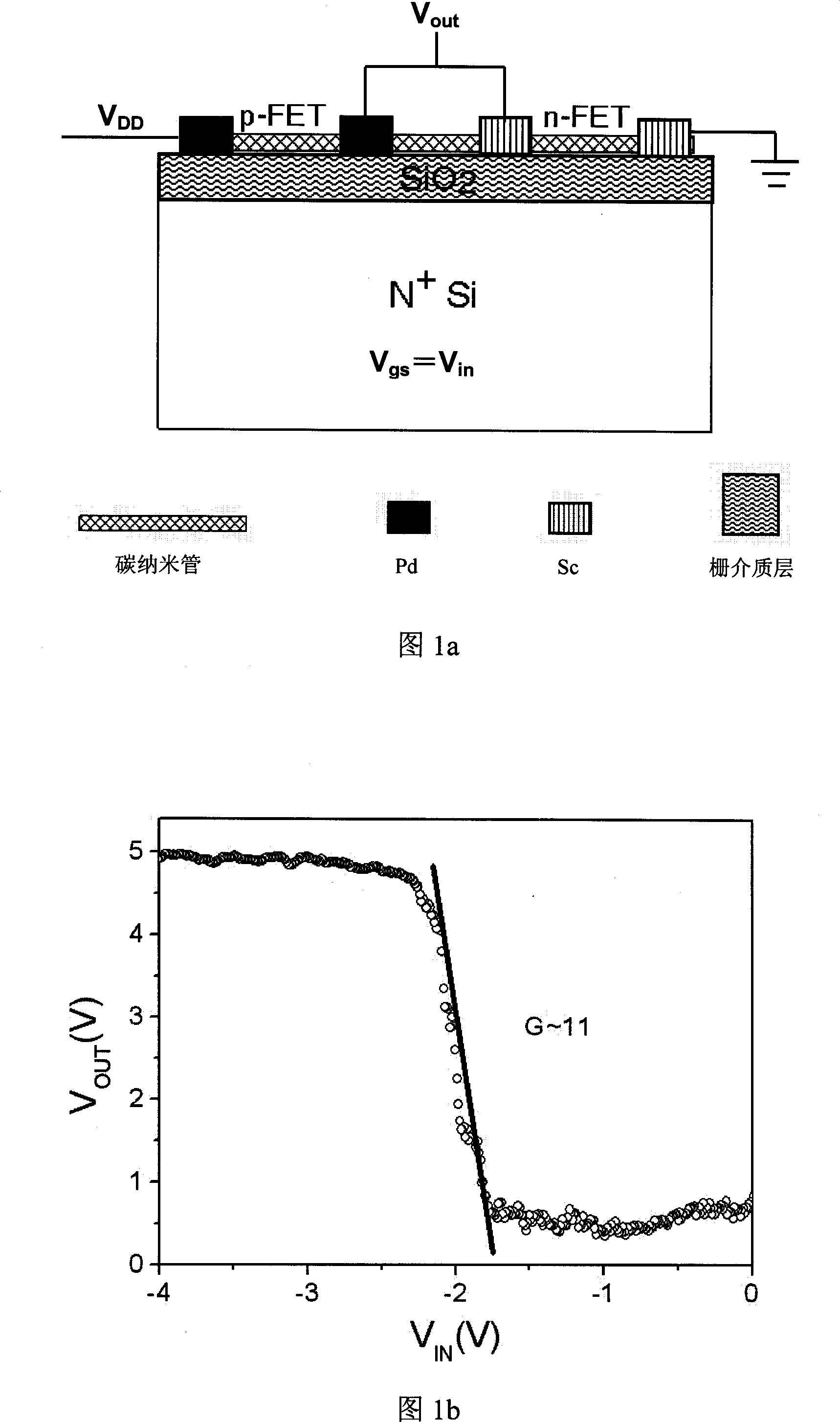

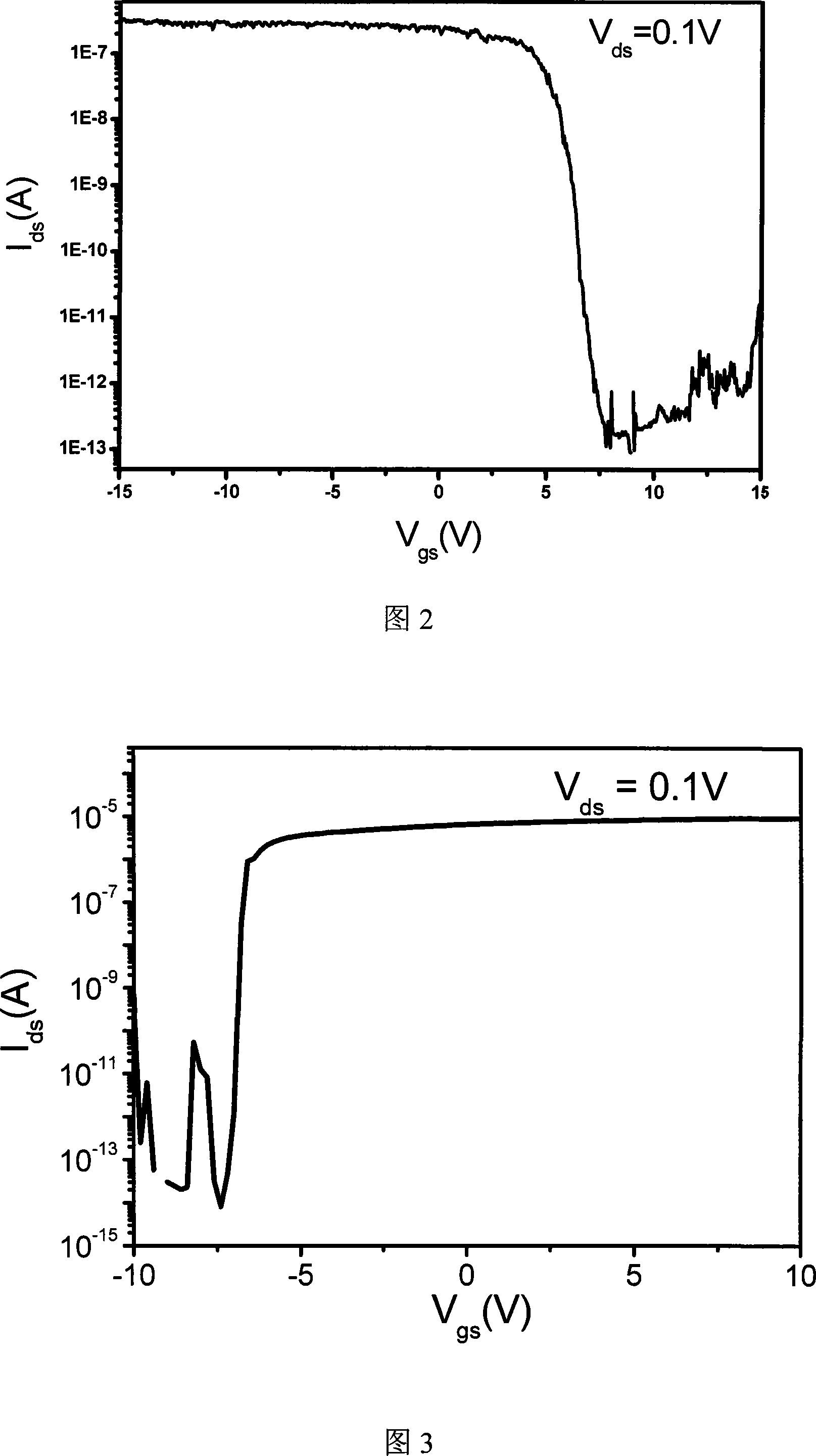

[0036] Example 1: Single-walled carbon nanotube CMOS inverter with bottom gate structure using Pd and Sc as source and drain electrodes and its preparation

[0037] SiO as shown in Figure 1a 2 Single-walled carbon nanotube CMOS inverter with Si as the gate dielectric and Si as the back gate. On the left, Pd is used as the source (left) and drain (right) electrode material, plus carbon nanotubes between the two electrodes, forming a p-type FET. On the right, Sc is used as the source (right) and drain (left) electrode material, plus carbon nanotubes between the two electrodes, forming an n-type FET. As shown in the figure, connect the drain electrode of the p-type FET to the drain electrode of the n-type FET, and its potential is the output voltage of the inverter. The common bottom gate voltage of the p-type FET and the n-type FET is used as the input voltage Vin, thus forming a CMOS inverter circuit. Concrete preparation steps are as follows:

[0038] 1. By positioning gro...

Embodiment 2

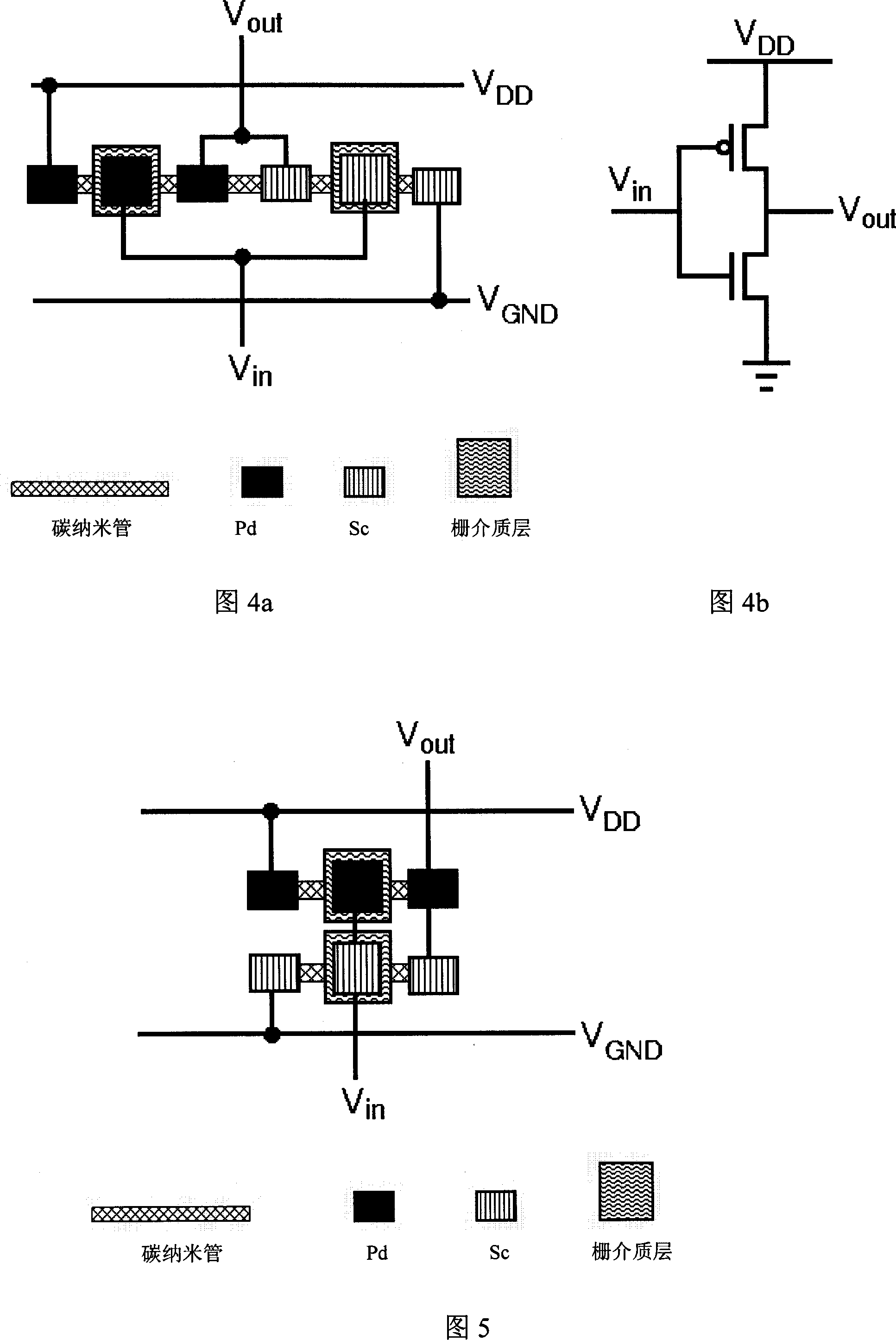

[0046] Example 2: Carbon nanotube CMOS inverter with top gate structure

[0047] As shown in FIG. 4 a and FIG. 5 , a CMOS inverter with a top-gate structure can be fabricated by using steps similar to those in Embodiment 1. Concrete preparation comprises the following steps:

[0048] 1. By positioning growth, or dropping the dispersed carbon tube solution onto the marked substrate to obtain the Si / SiO 2 One or more parallel carbon nanotubes on a substrate;

[0049] 2. Observe and record the specific position of carbon nanotubes through scanning electron microscope or atomic force microscope;

[0050] 3. Apply photoresist on the substrate and form the shape of the gate by optical exposure or electron beam lithography;

[0051] 4. Put the sample into the atomic layer deposition system to grow a gate dielectric layer (ZrO 2 , Al 2 o 3 or HfO 2 ), the growth temperature should not be higher than 170 degrees Celsius;

[0052] 5. Put the sample into acetone to peel off, or u...

Embodiment 3

[0058] Example 3: Carbon nanotube CMOS NAND gate circuit with top gate structure

[0059] As shown in Figure 6a and Figure 7, a carbon nanotube n-type FET and a p-type FET with a top-gate structure can be prepared respectively by steps similar to those in Example 2, and the source, drain electrode and p-type FET are respectively shown in Figure 6a and Figure 7 The gate electrodes are connected as shown in the figure to obtain CMOS NAND gate circuits based on 2 and 1 carbon nanotubes.

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More