Circuit capable of realizing multiplexing of exclusive-OR gate or XNOR gate

A circuit and gating circuit technology, applied in the direction of logic circuits with logic functions, etc., can solve the problem of reducing the scale of the circuit, and achieve the effect of reducing the number of transistors, reducing the power consumption of the circuit, and reducing the number of tubes

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0032] The technical solution of the invention will be described in detail below in conjunction with the accompanying drawings.

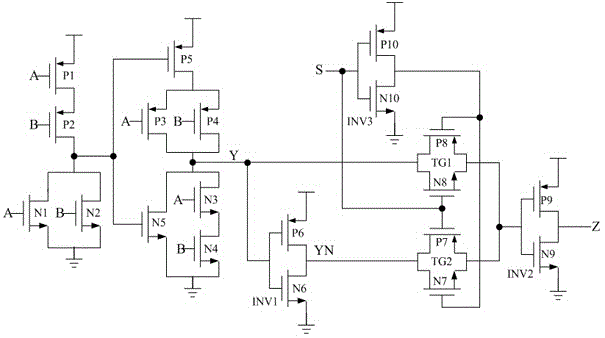

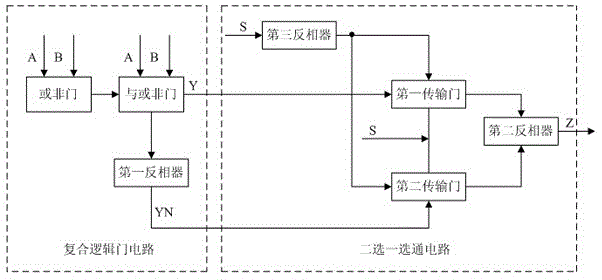

[0033] The present invention provides a figure 1 , figure 2 The shown logic gate circuit based on the two-stage circuit connection realizes the multiplexing of the XOR gate and the NOR gate. The first-stage circuit is a composite logic gate circuit of an XOR gate / XOR gate, including: a NOR gate composed of a first PMOS transistor P1, a second PMOS transistor P2, a first NMOS transistor N1, and a second NMOS transistor N2 A unit, an NOR gate unit composed of the third PMOS transistor P3, the fourth PMOS transistor P4, the fifth PMOS transistor P5, the third NMOS transistor N3, the fourth NMOS transistor N4, and the fifth NMOS transistor N5, and the sixth The first inverter INV1 composed of the PMOS transistor P6 and the sixth NMOS transistor N6; the second stage circuit is a two-to-one selection circuit, including: the first transmission gate comp...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More