Ultra-low power consumption comparer based on time domain

An ultra-low power, comparator technology, applied in instruments, signal transmission systems, electrical components, etc., can solve problems such as wasting energy, and achieve the effect of saving energy and improving working speed

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

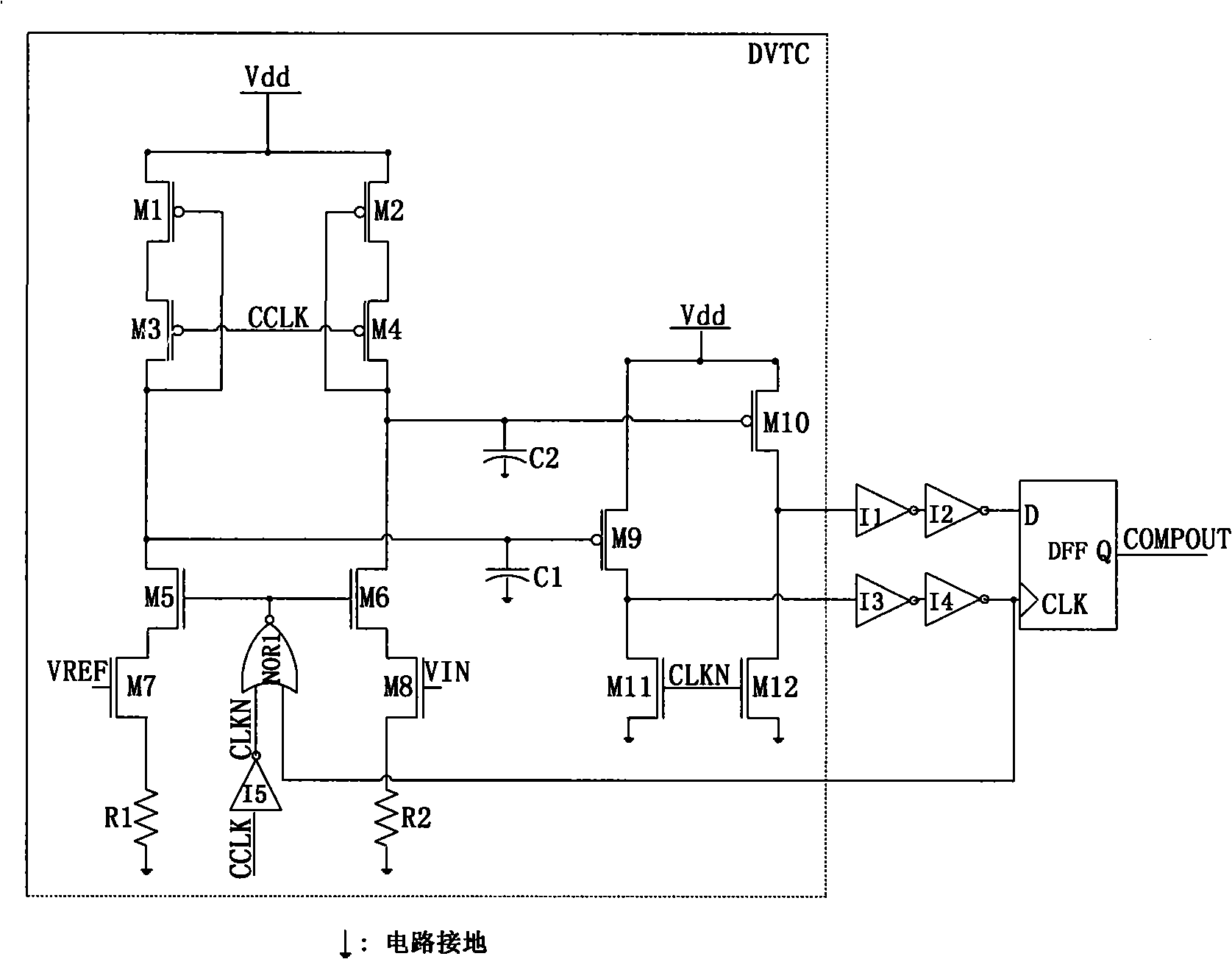

[0030] The technical scheme that the present invention solves its technical problem is: the TDC based on the dynamic voltage-time conversion circuit DVTC that the present invention proposes, such as image 3 shown. The TDC of the present invention adopts DVTC technology to reduce the energy consumed by the voltage change on the capacitor, and at the same time increases the maximum speed of the comparator.

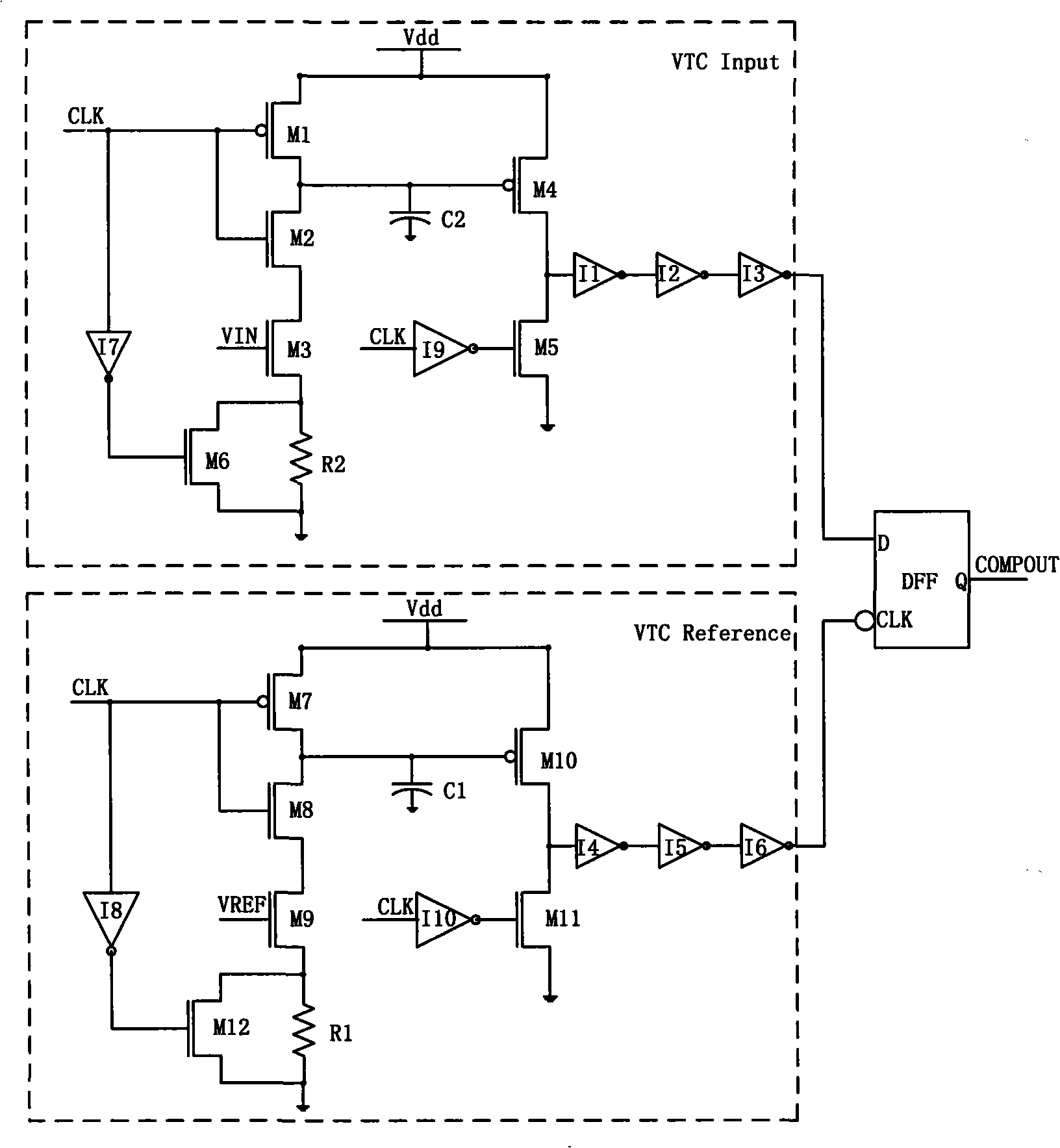

[0031] figure 2 is a comparator circuit proposed by Andrea Agnes. It is mainly composed of two parts: voltage-time converter VTC and output D flip-flop. The voltage-time converter consists of two branches: VTC Input and VTC Reference. The output of VTC Input is connected to the data terminal D of DFF through three inverters I1, I2 and I3, and the output of VTC Reference is also passed through three inverters. Phasers I4, I5, and I6 are connected to the trigger terminal of the DFF. The operation of the comparator includes two modes. First in the reset mode, CCLK is low...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More