Digital self-adaptive dead-time control circuit

A dead-time control and self-adaptive technology, applied in the field of electronics, can solve problems such as efficiency, accuracy, response time that cannot meet the expected requirements of dead-time design, large delay time, and accuracy impact.

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

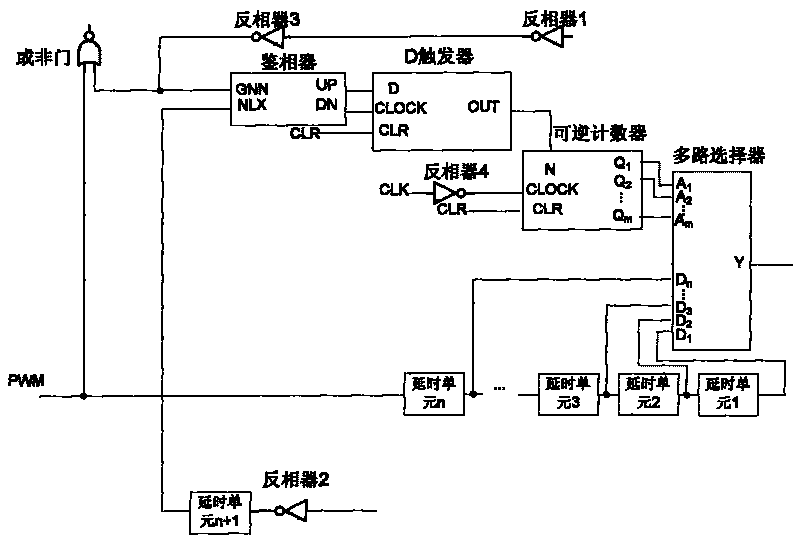

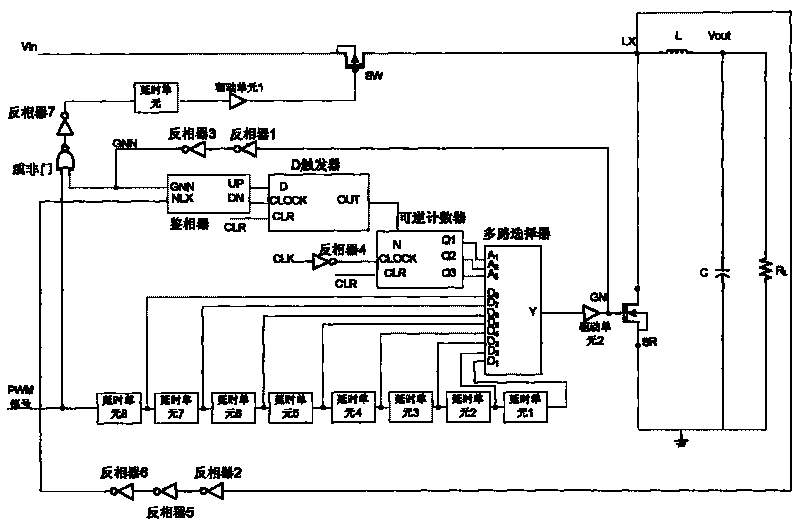

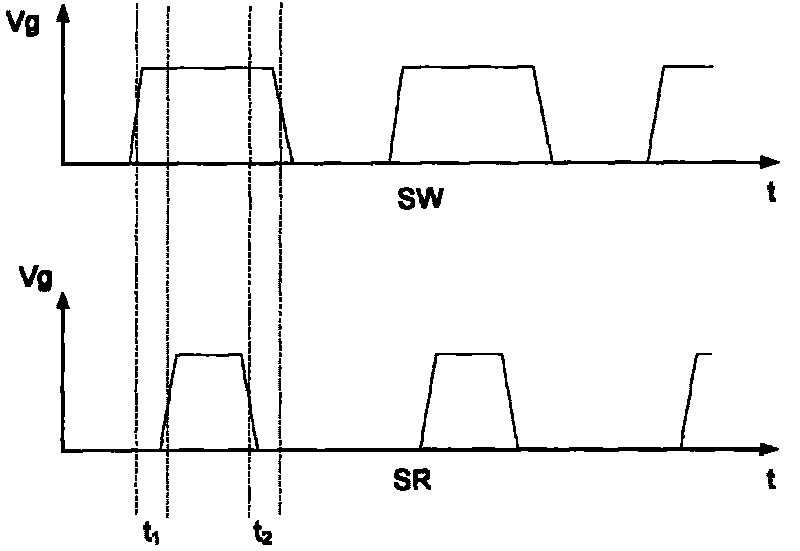

[0036] A digital adaptive dead time control circuit, such as figure 1 As shown, it is composed of a phase detector, a D flip-flop, a reversible counter, an n-to-1 multiplexer, (n+1) delay units, two low flip-level inverters, and two ordinary inverters. A NOR gate is formed. The inverting output terminal of the low inversion level inverter 2 is connected to the NLX input terminal of the phase detector through the (n+1)th delay unit, and the inverting output terminal of the low inversion level inverter 1 is connected to the common inverter 3 The GNN input terminal of the phase detector; the UP output terminal of the phase detector is connected to the D input terminal of the D flip-flop, and the DN output terminal of the phase detector is connected to the CLOCK input terminal of the D flip-flop; the clearing terminal CLR of the D flip-flop is connected to External clearing signal, the OUT output terminal of the D flip-flop is connected to the N input terminal of the reversible c...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More