Patents

Literature

30results about How to "Correction of phase difference" patented technology

Efficacy Topic

Property

Owner

Technical Advancement

Application Domain

Technology Topic

Technology Field Word

Patent Country/Region

Patent Type

Patent Status

Application Year

Inventor

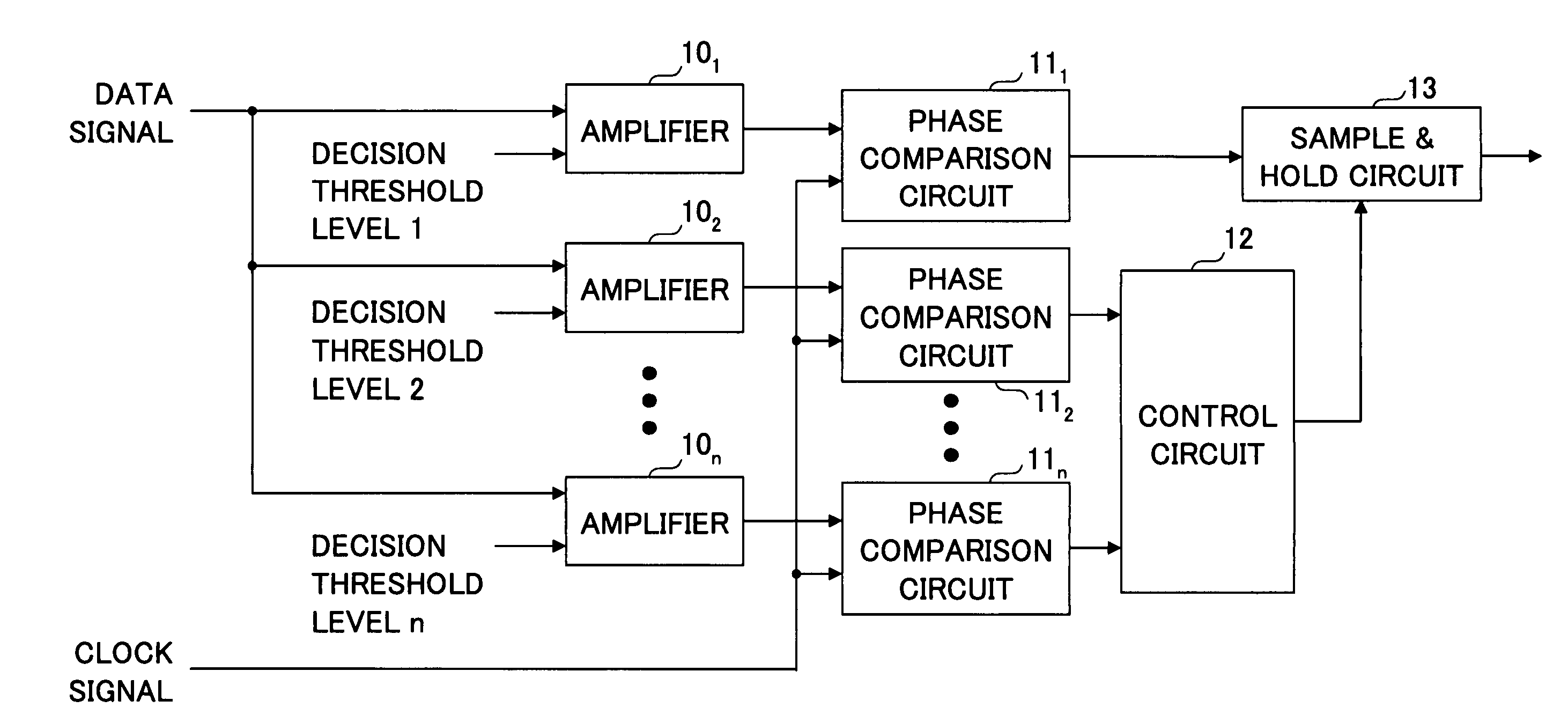

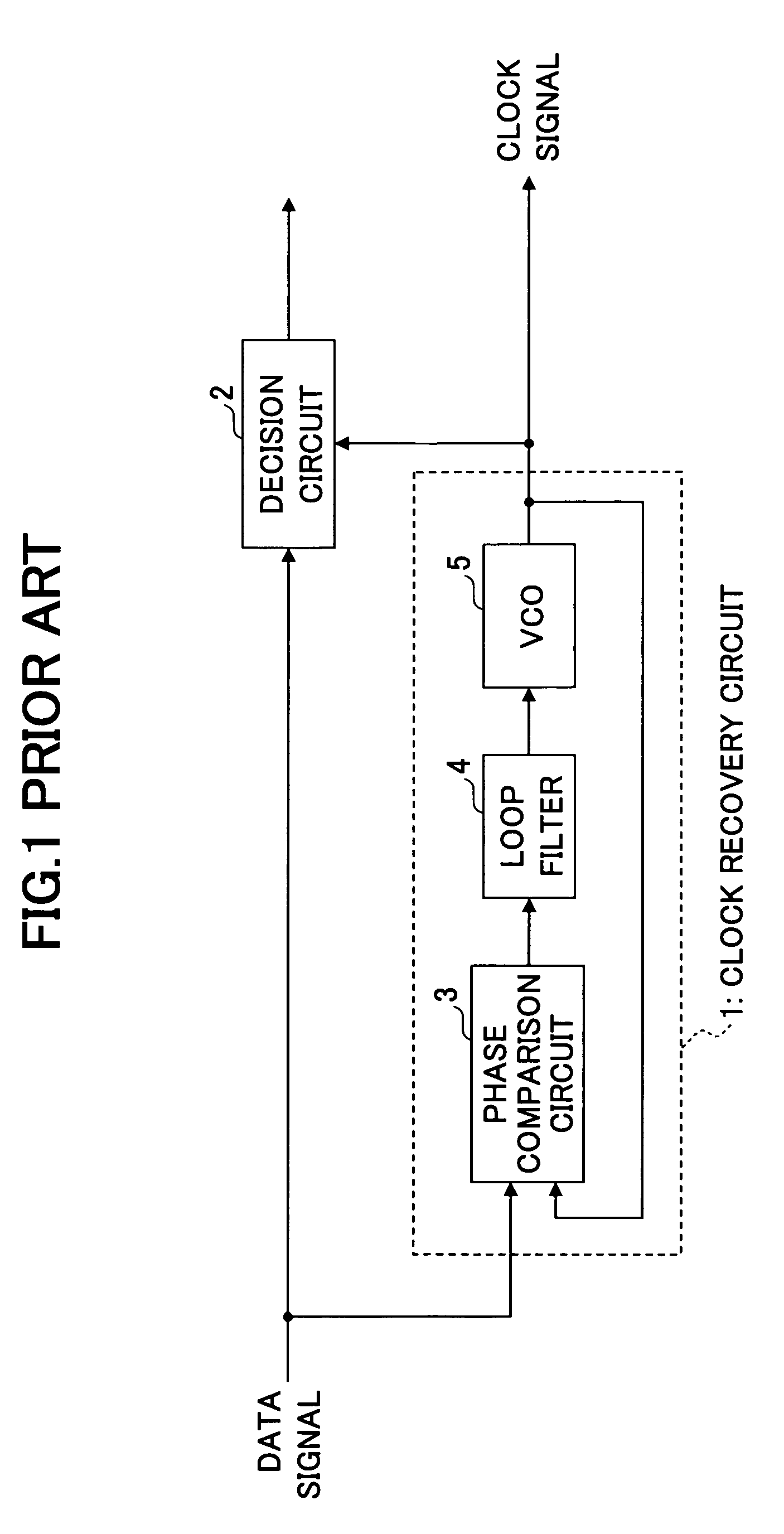

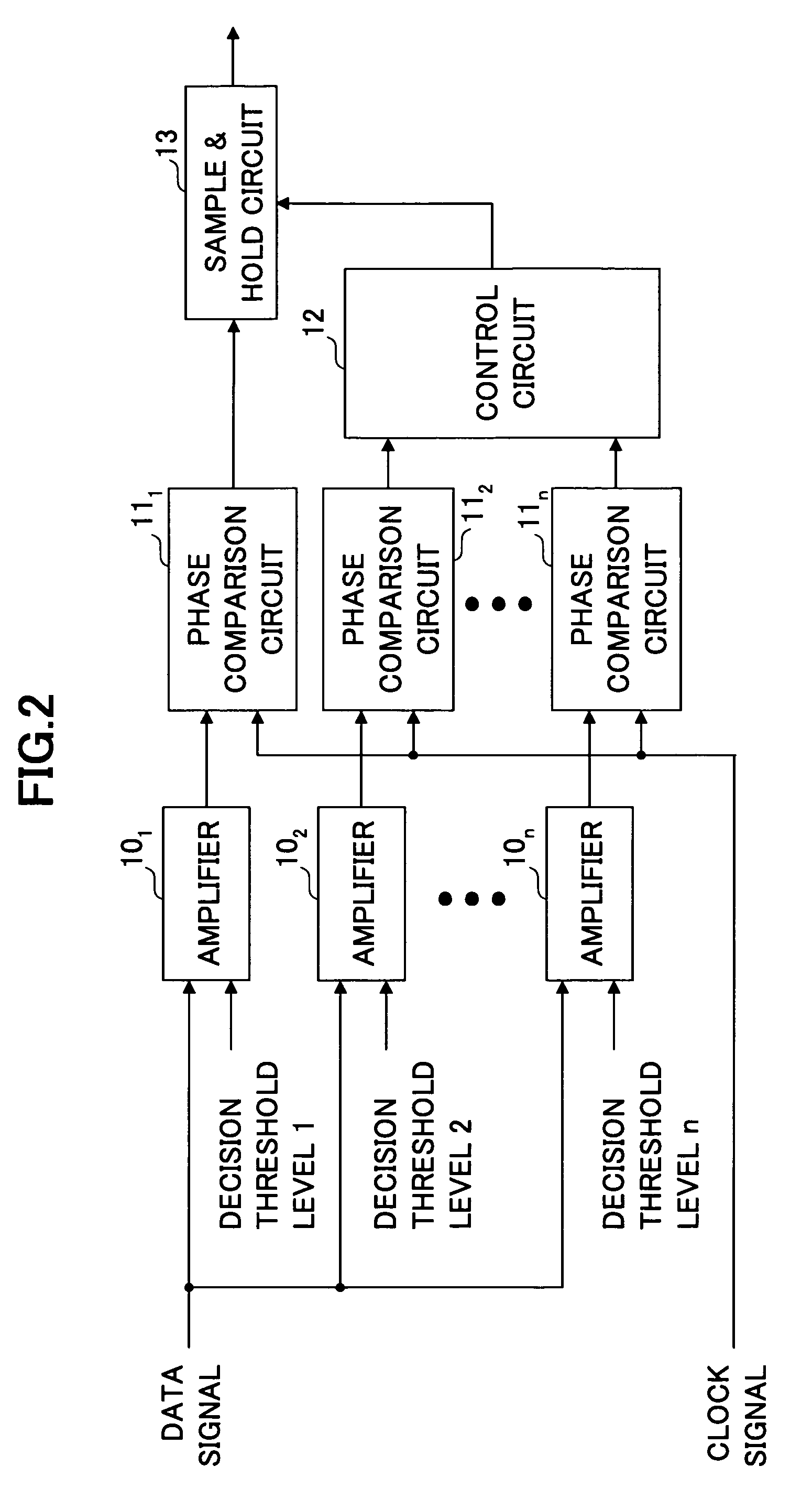

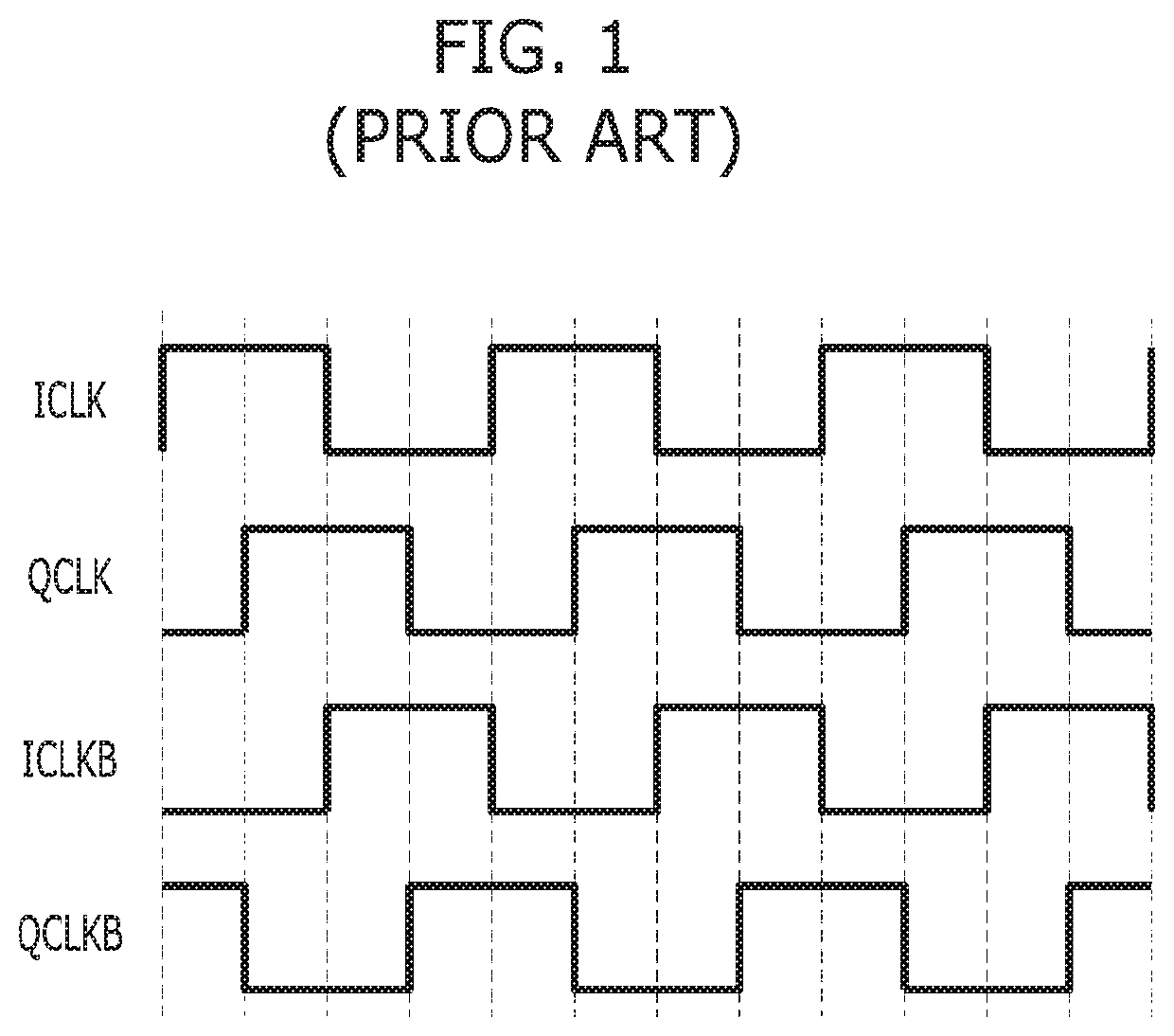

Phase comparison circuit and clock recovery circuit

InactiveUS20050220182A1Correction of phase differenceCancel noiseMultiple input and output pulse circuitsPulse automatic controlPhase differenceClock recovery

A phase comparison circuit for outputting a phase difference signal indicating a phase difference between a data signal and a clock signal is disclosed. The disclosed phase comparison circuit includes: a detection part for outputting a plurality of signals indicating phases of the data signal according to different decision threshold levels; a phase comparison part for outputting phase difference signals each indicating a phase difference between a signal in the plurality of signals output from the detection part and the clock signal; and a control part for determining whether to output a particular phase difference signal in the phase difference signals by using the whole or a part of the phase deference signals.

Owner:FUJITSU LTD

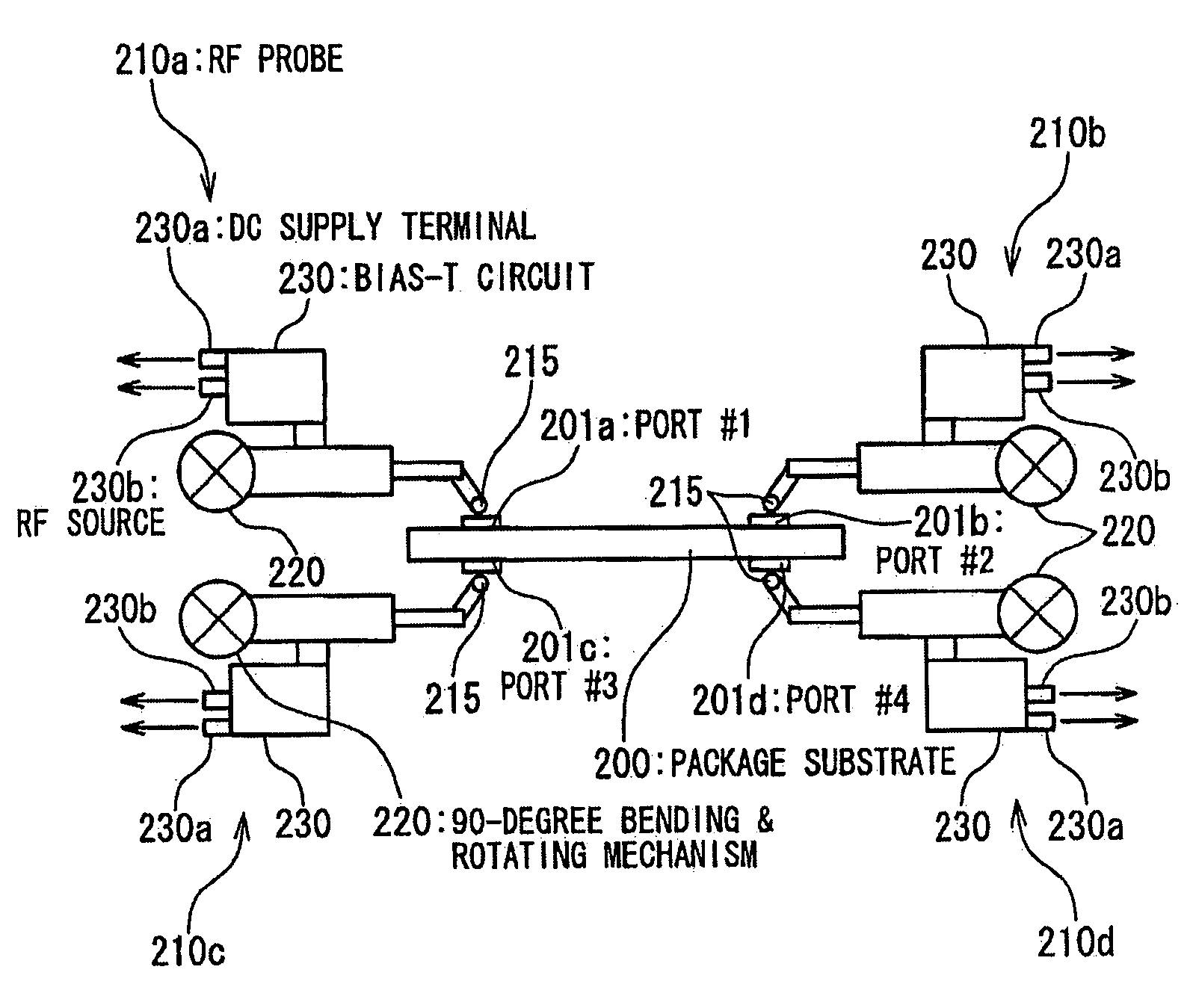

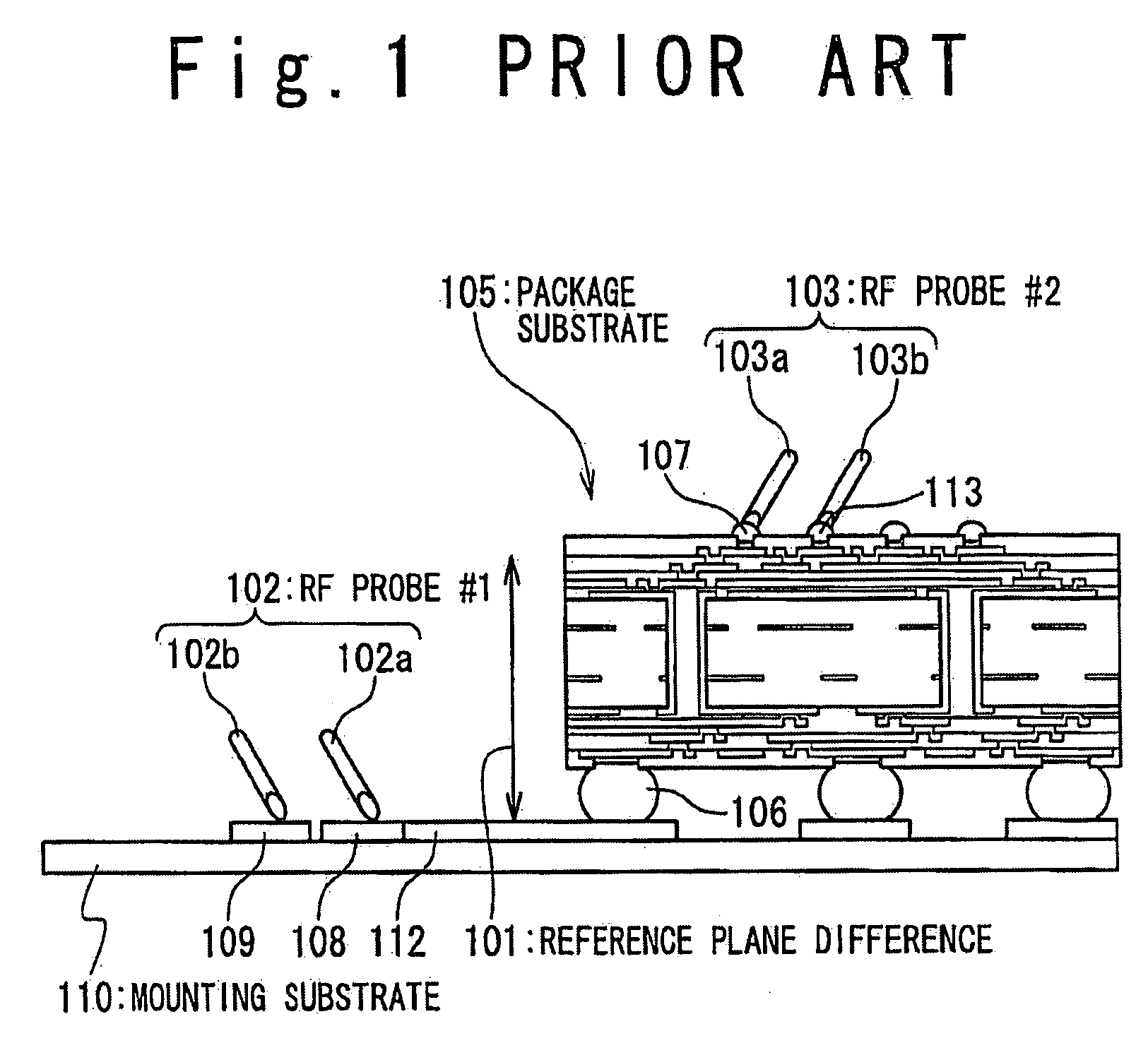

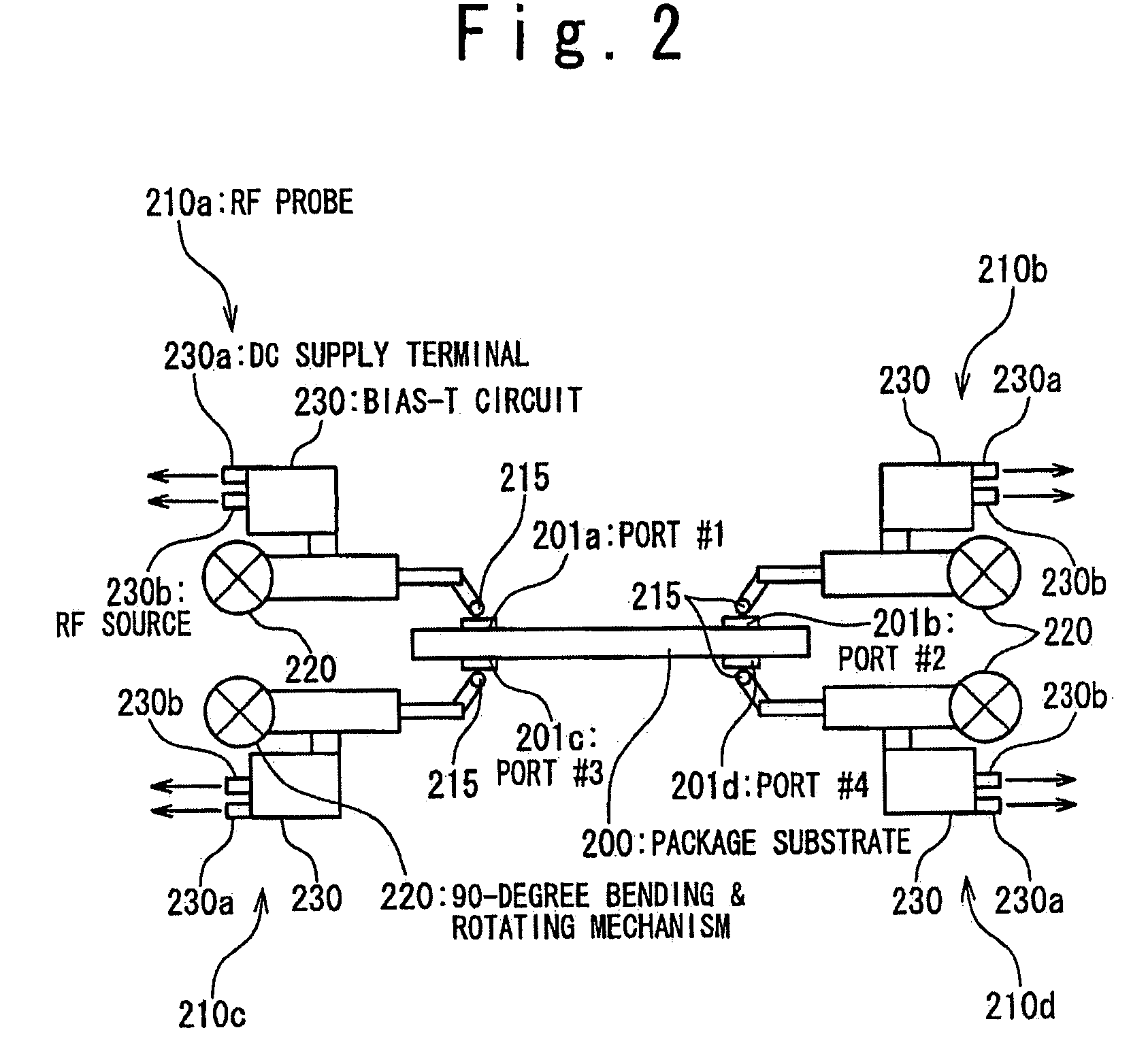

Impedance measuring apparatus of package substrate and method for the same

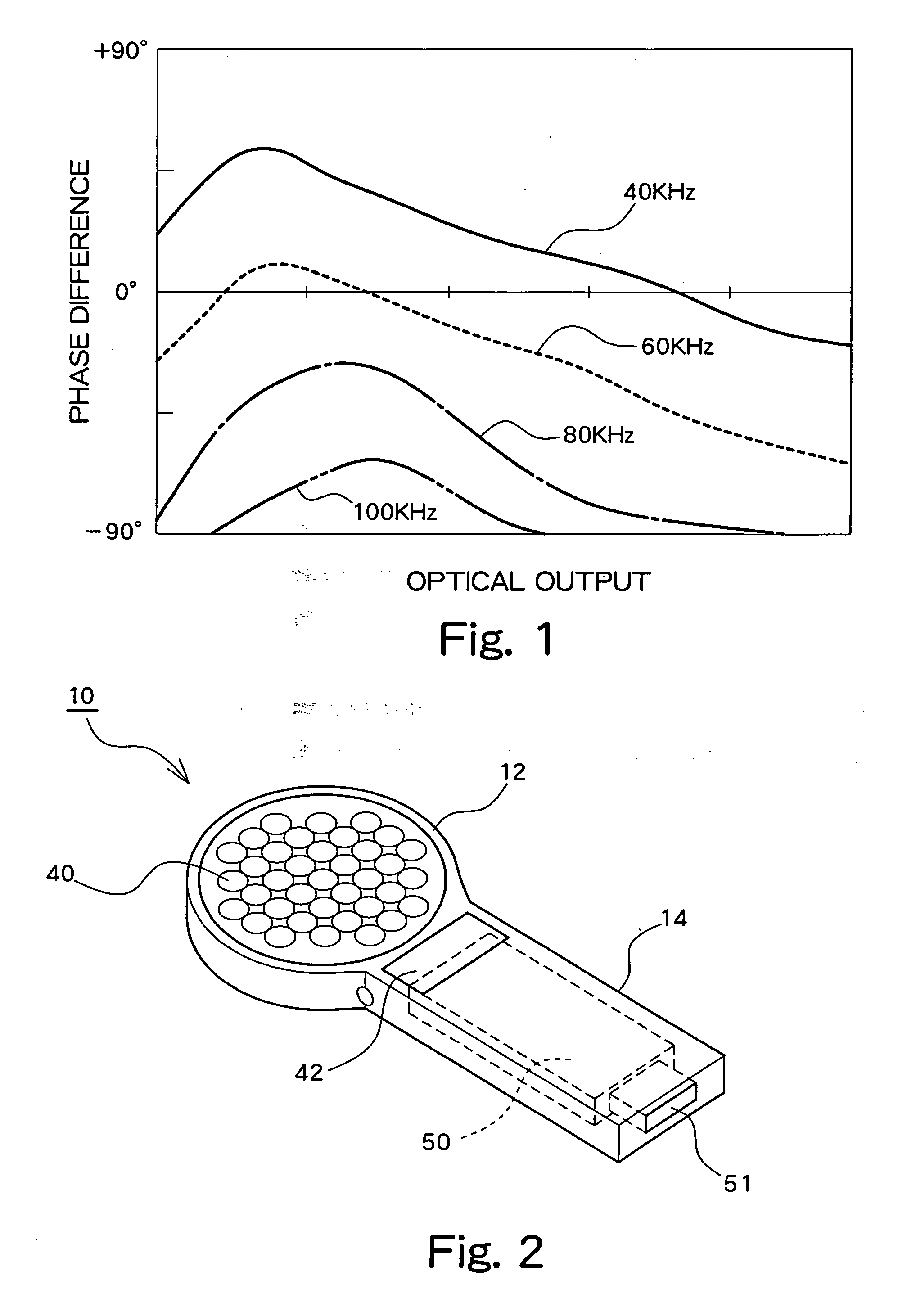

InactiveUS20060220663A1Improve accuracyCorrection of phase differenceResistance/reactance/impedenceElectrical testingRF probePhase difference

An impedance measuring apparatus includes a plurality of RF (radio frequency) probes; a plurality of rotation mechanisms coupled to the plurality of RF probes, respectively; a processing unit, and a mechanical controller. The mechanical controller controls the plurality of rotation mechanisms and the plurality of RF probes to measure package RF signals between terminals formed on a package substrate. The processing unit measures calibration RF signals between terminals formed on at least one calibration substrate; determines RF impedances of the package substrate from the package RF signals and phase differences corresponding to a thickness of the package substrate and distances between the terminals on the package substrate from the calibration RF signals, and calibrates the RF impedances based on the phase differences.

Owner:RENESAS ELECTRONICS CORP

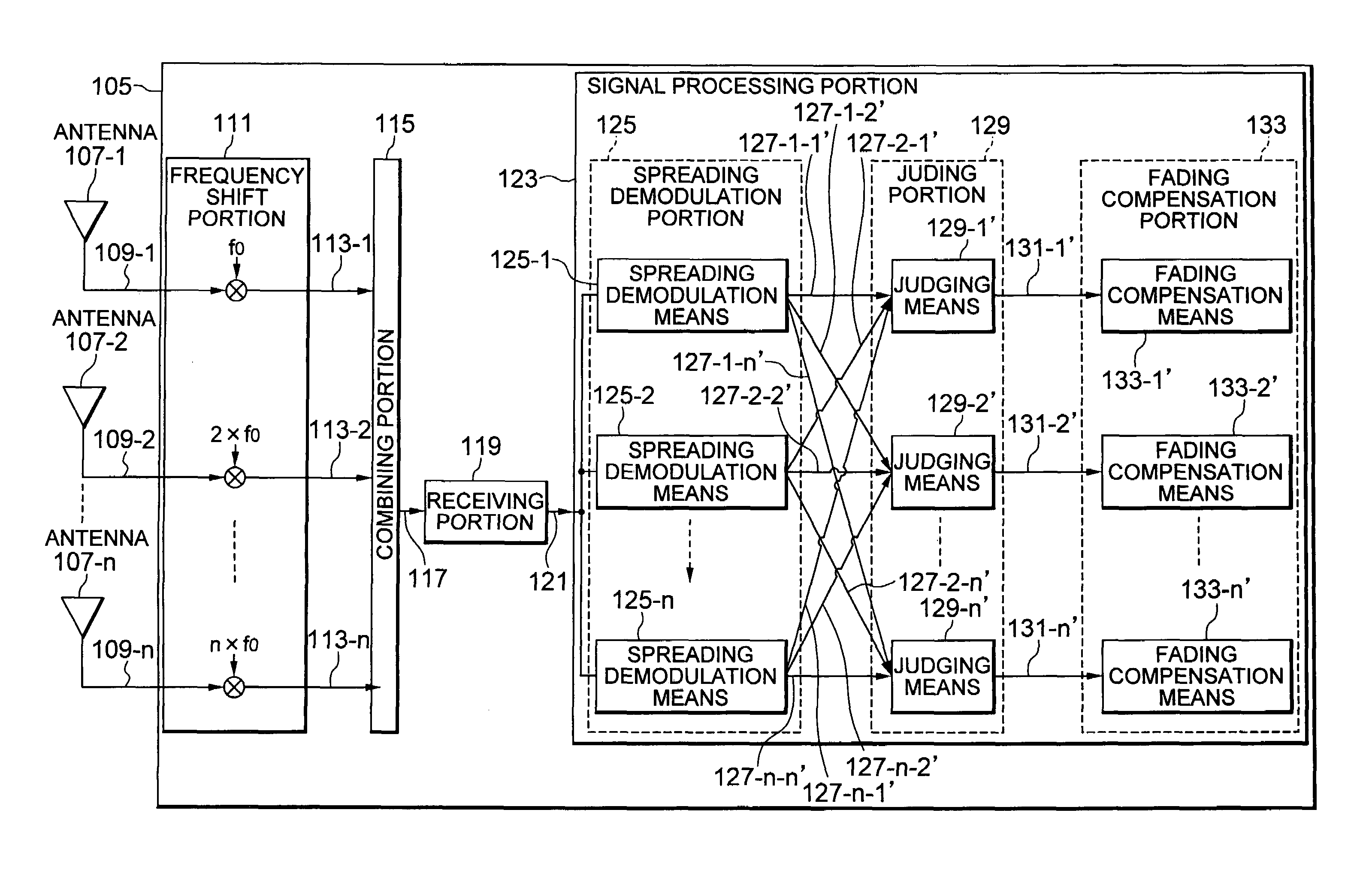

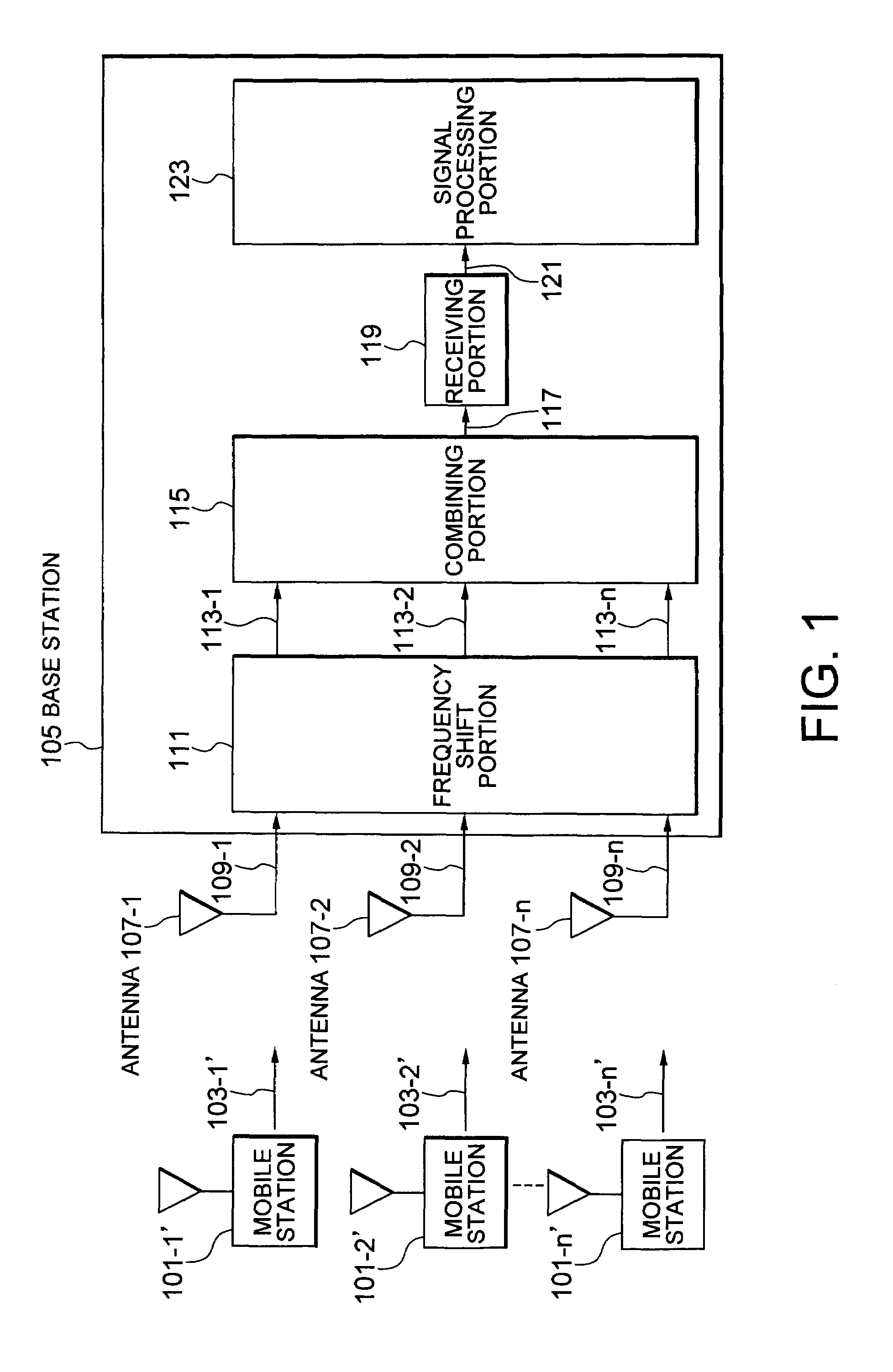

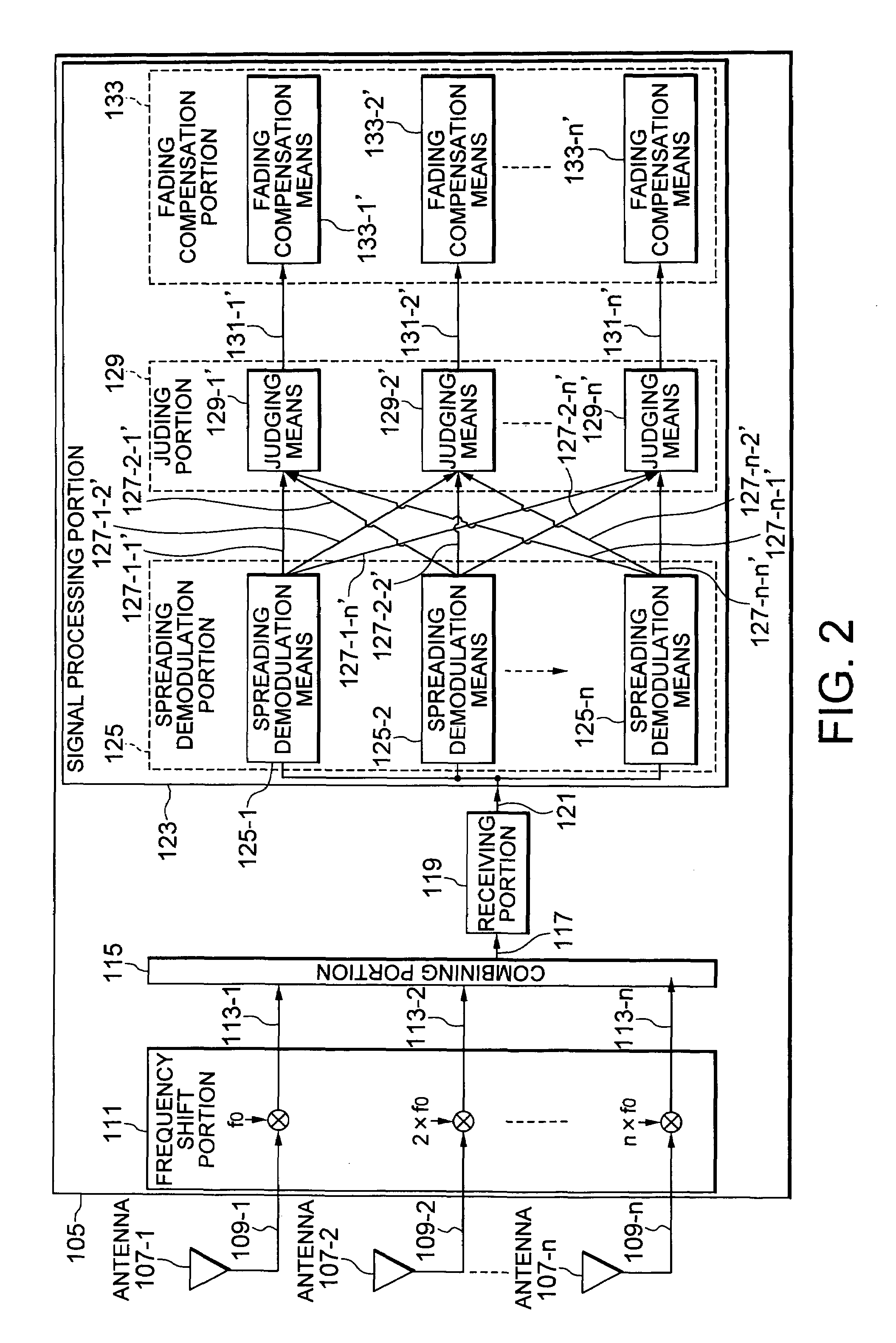

Mobile communication system having mobile stations and a base station

InactiveUS7054397B1Small sizeLow costSpatial transmit diversityPolarisation/directional diversityIntermediate frequencyMobile communication systems

A mobile communication system has a plurality of mobile stations and a base station which includes a plurality of antennas, a frequency shift portion, a combining portion, a receiving portion and a signal processing portion. The antenna receives radio waves transmitted by the mobile stations. The frequency shift portion shifts the received signal with a frequency corresponding to each of the antennas. The combining portion determines the shifted signal as a combining signal. The receiving portion converts the combining signal in frequency to make an intermediate frequency signal, and converts the intermediate frequency signal into a digital signal. The signal processing portion includes spreading demodulation means judging means, and fading compensation means.

Owner:NEC CORP

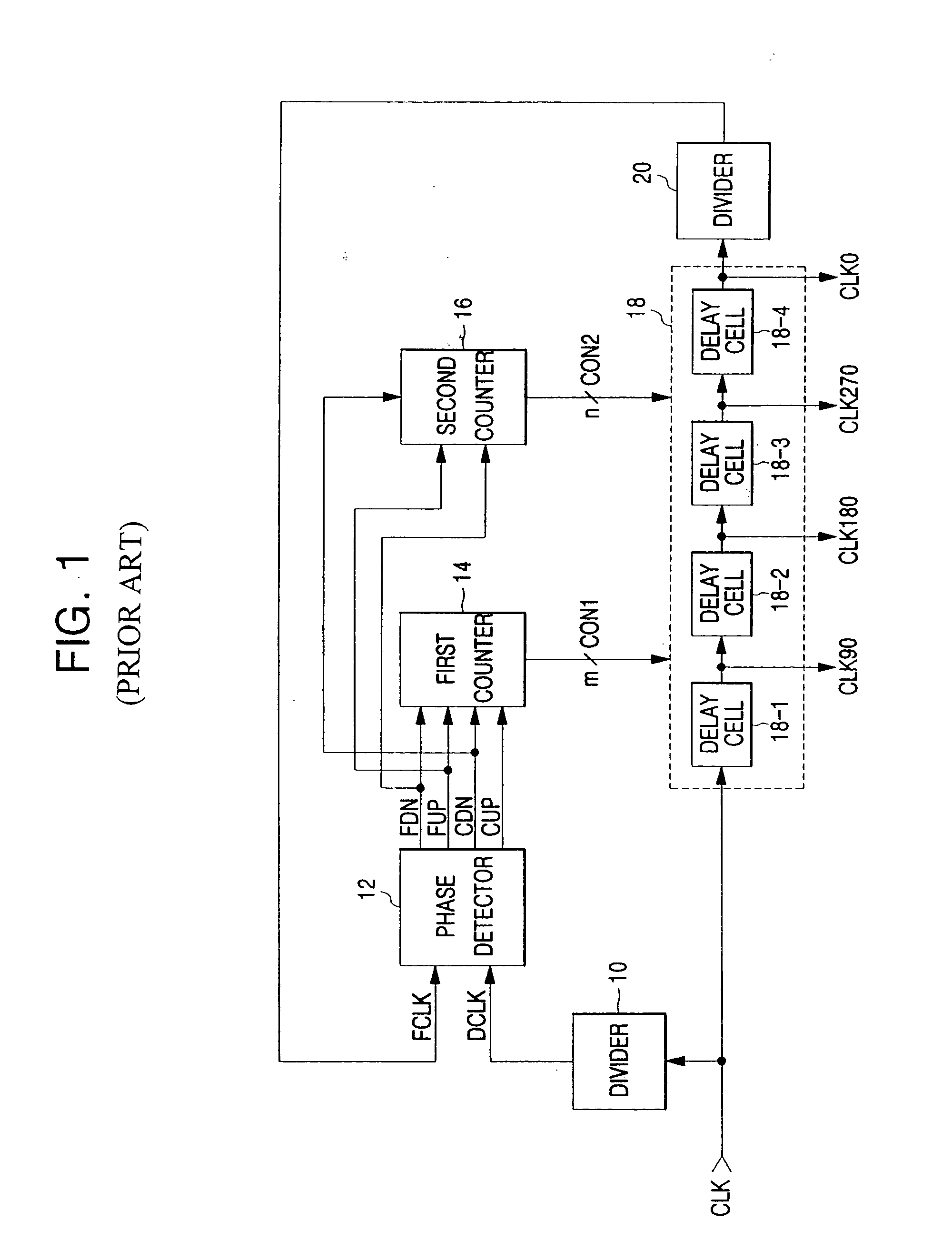

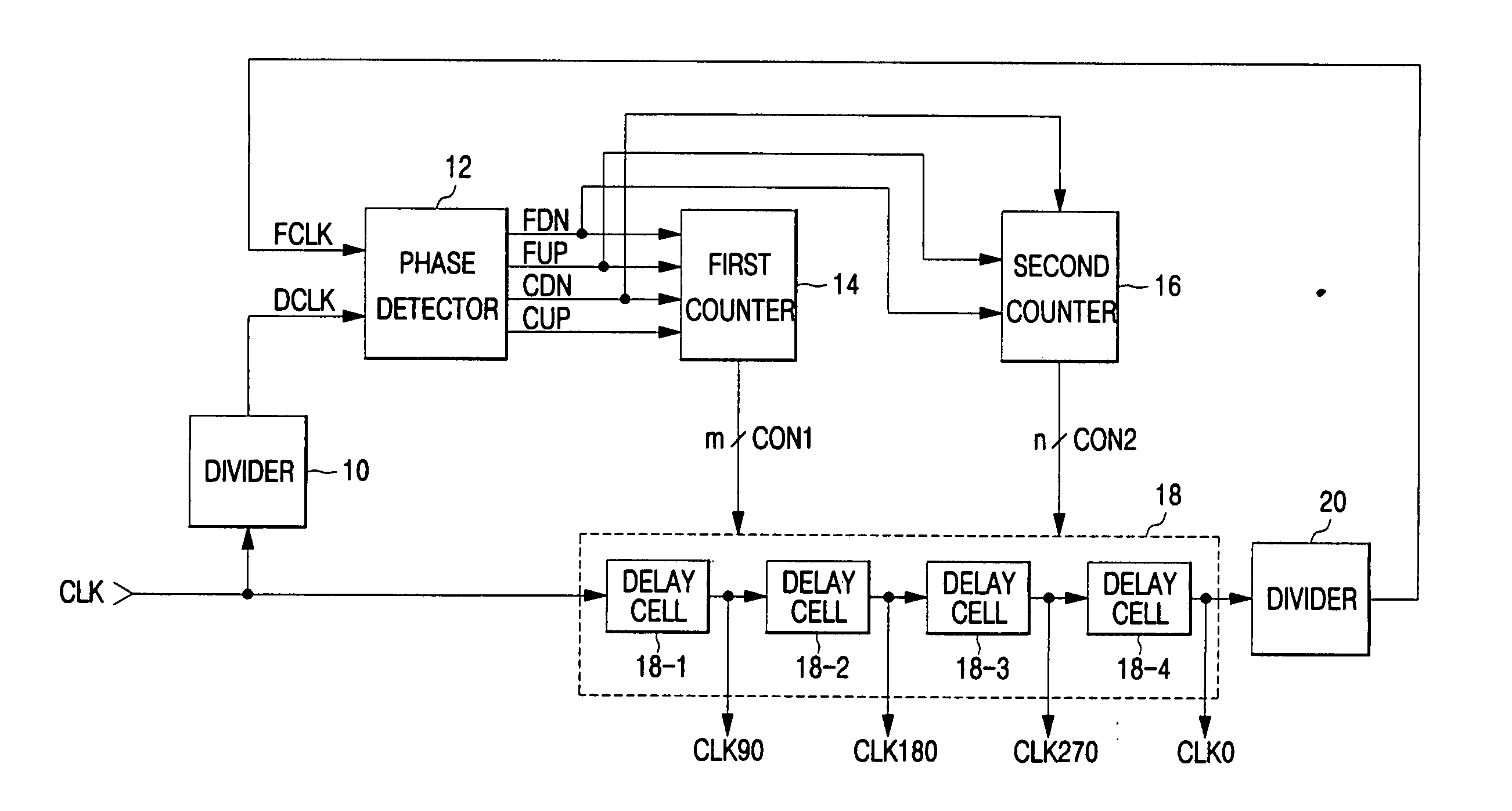

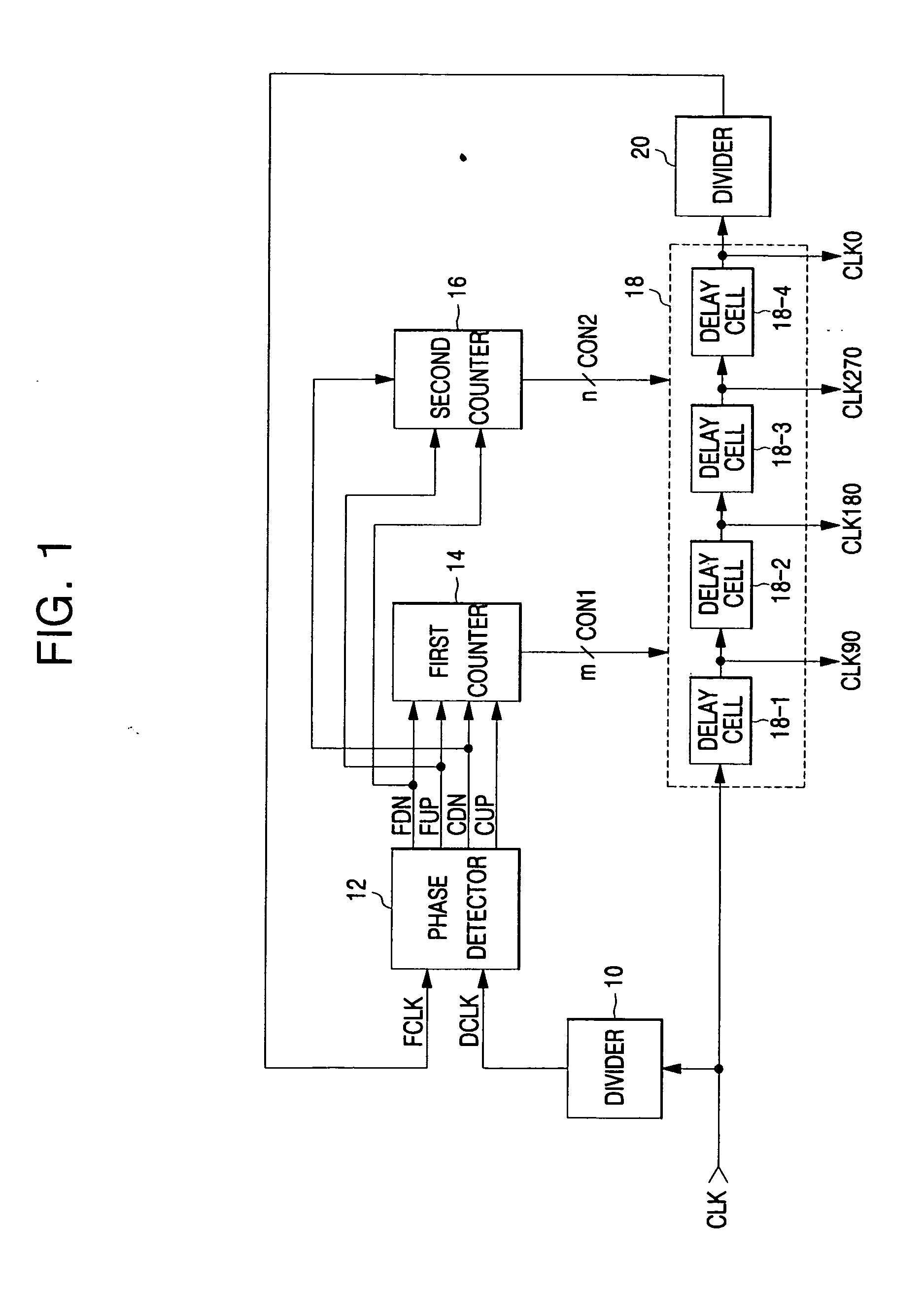

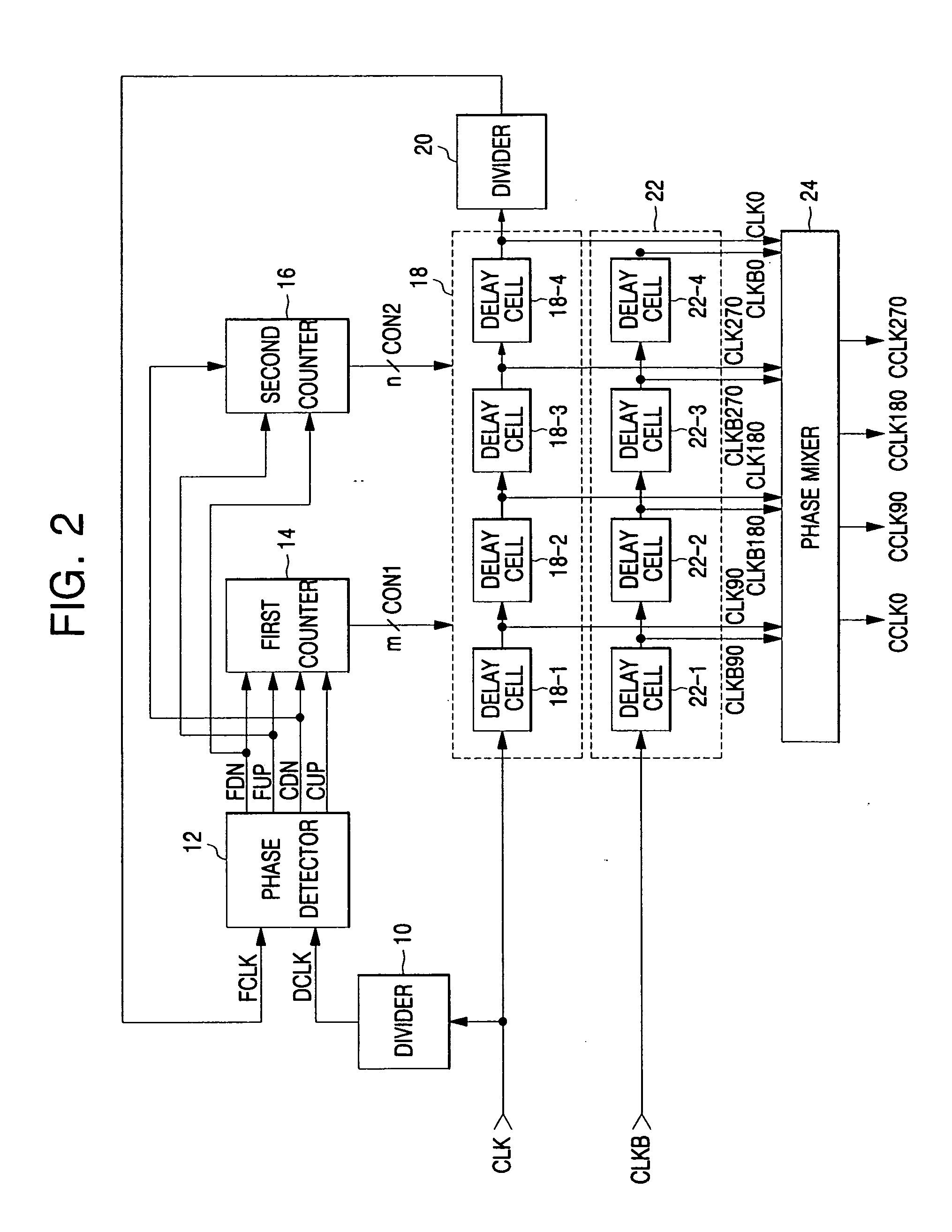

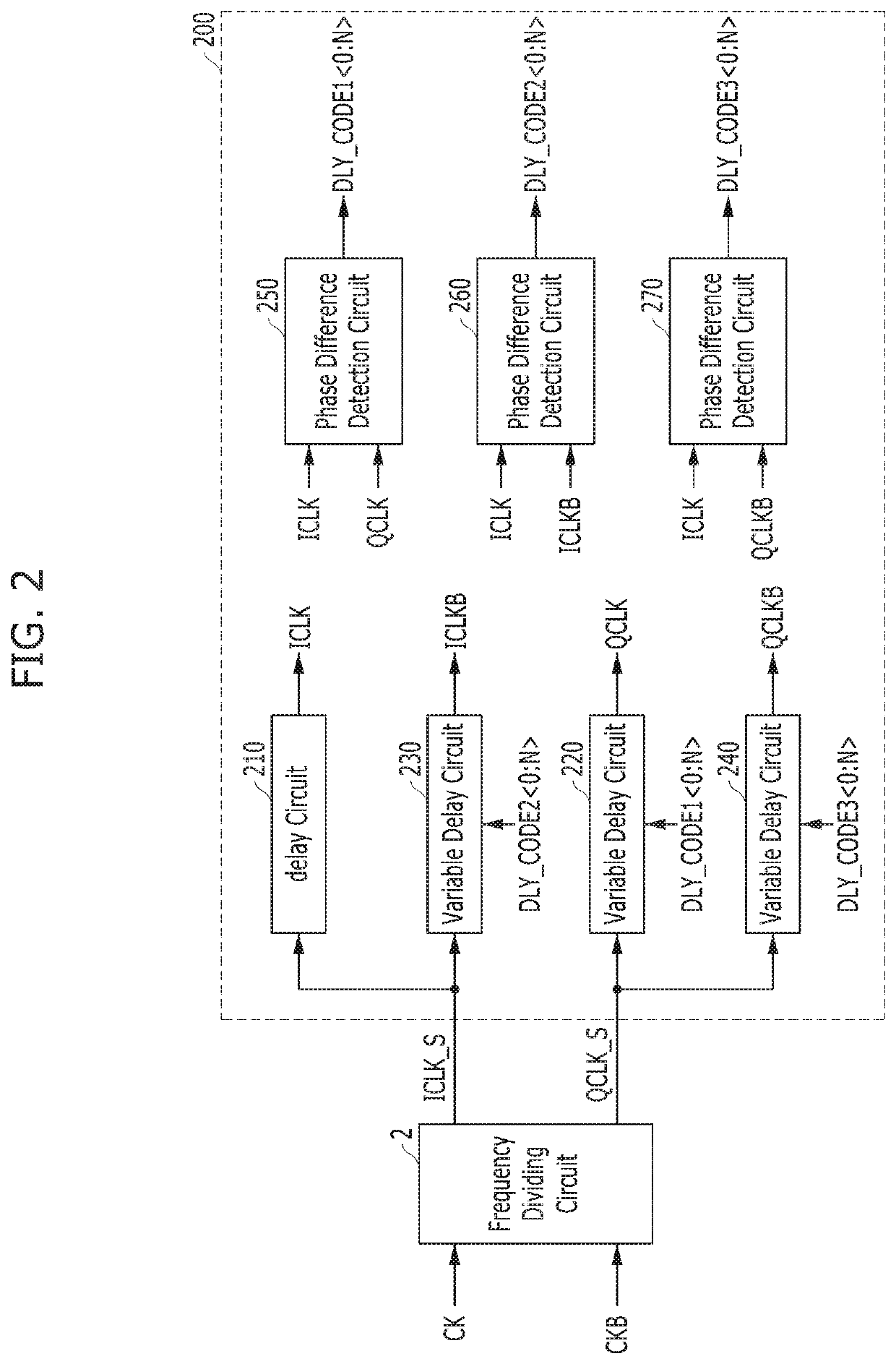

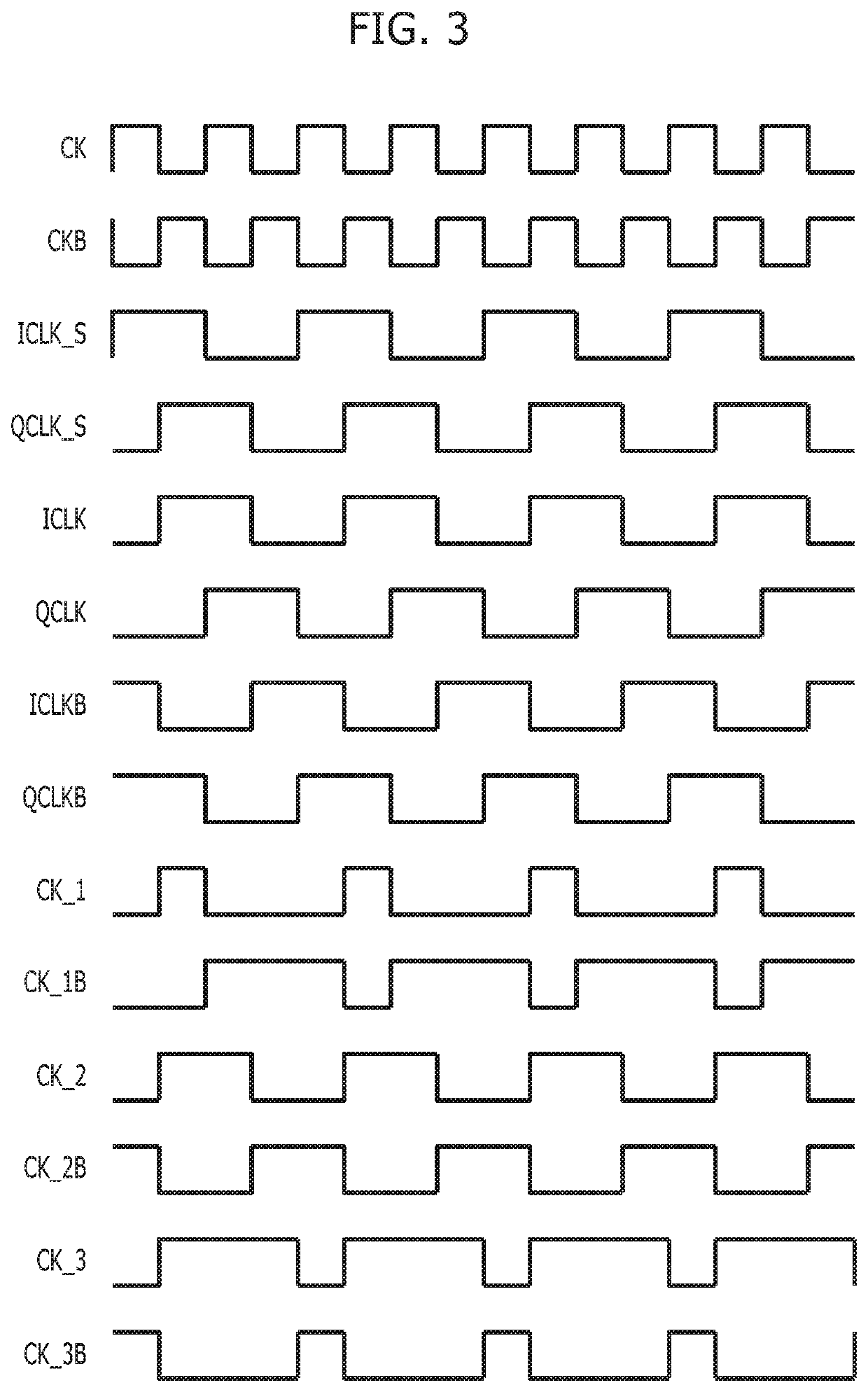

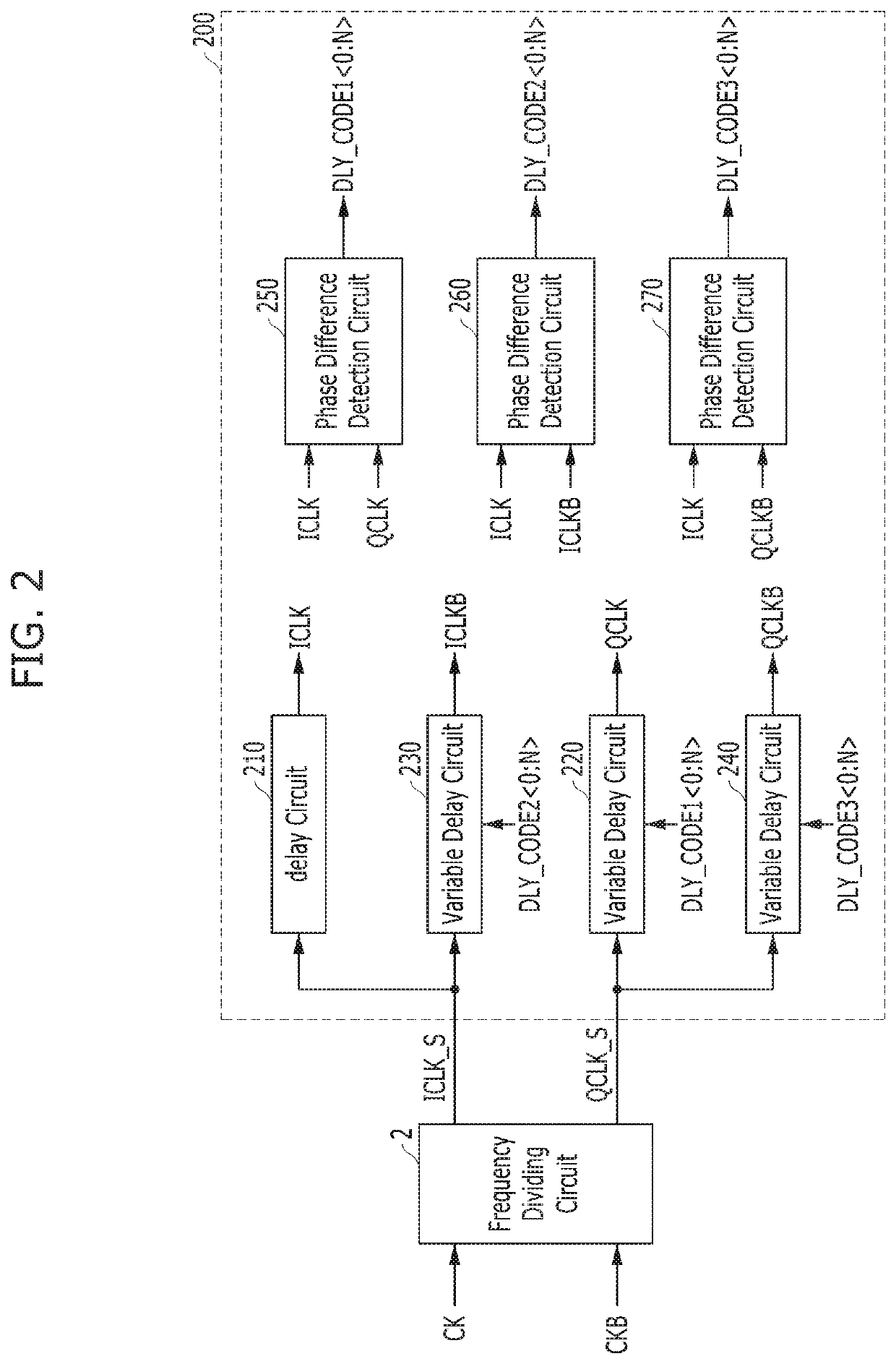

Delay locked loop and semiconductor memory device having the same

InactiveUS7202721B2Correction of phase differencePulse automatic controlPulse modulationPhase mixingPhase difference

Owner:SAMSUNG ELECTRONICS CO LTD

Short and ultra-short baseline phase maps

ActiveUS20110090113A1Correction of phase differenceImprove accuracySatellite radio beaconingAngle of incidenceError map

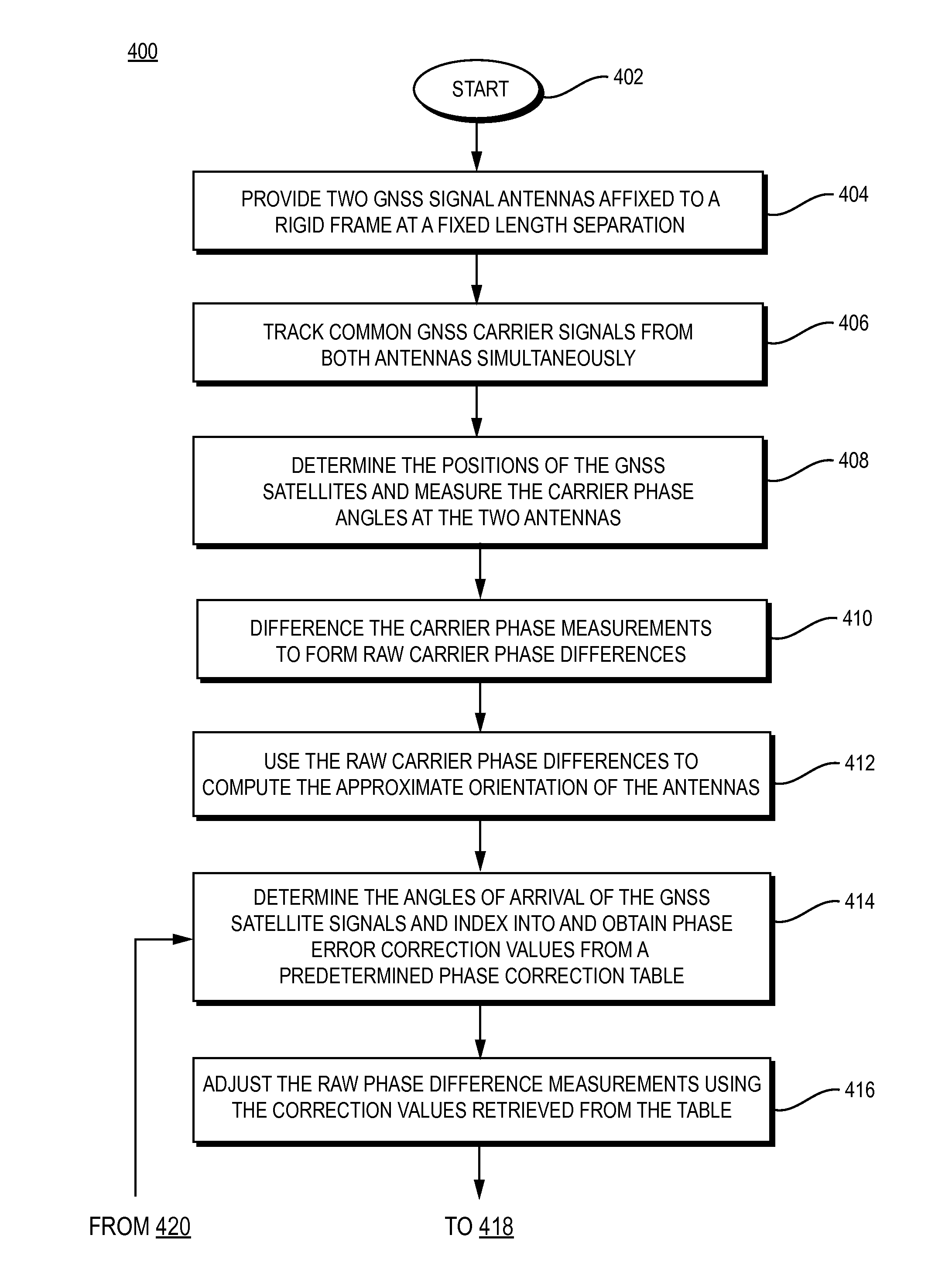

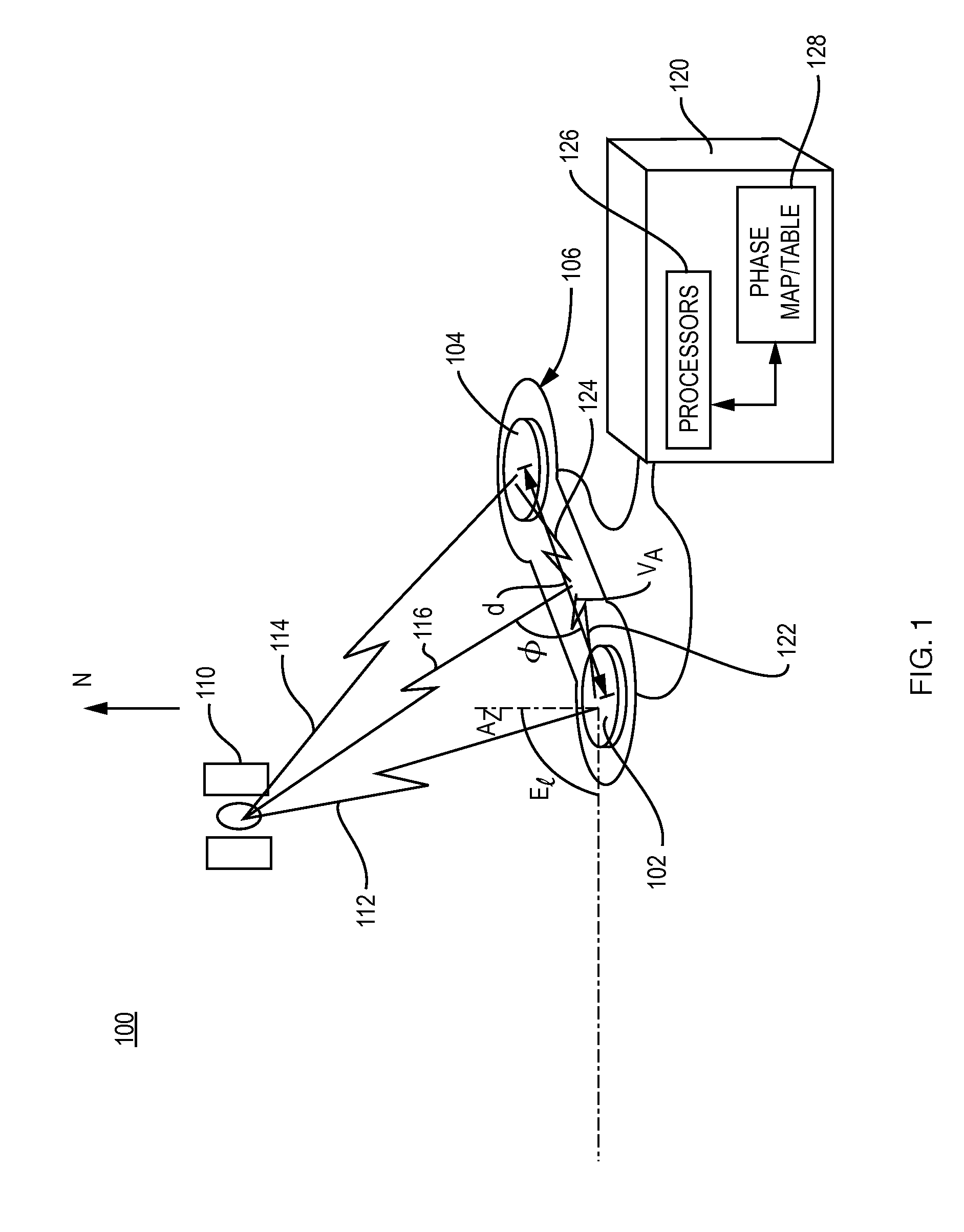

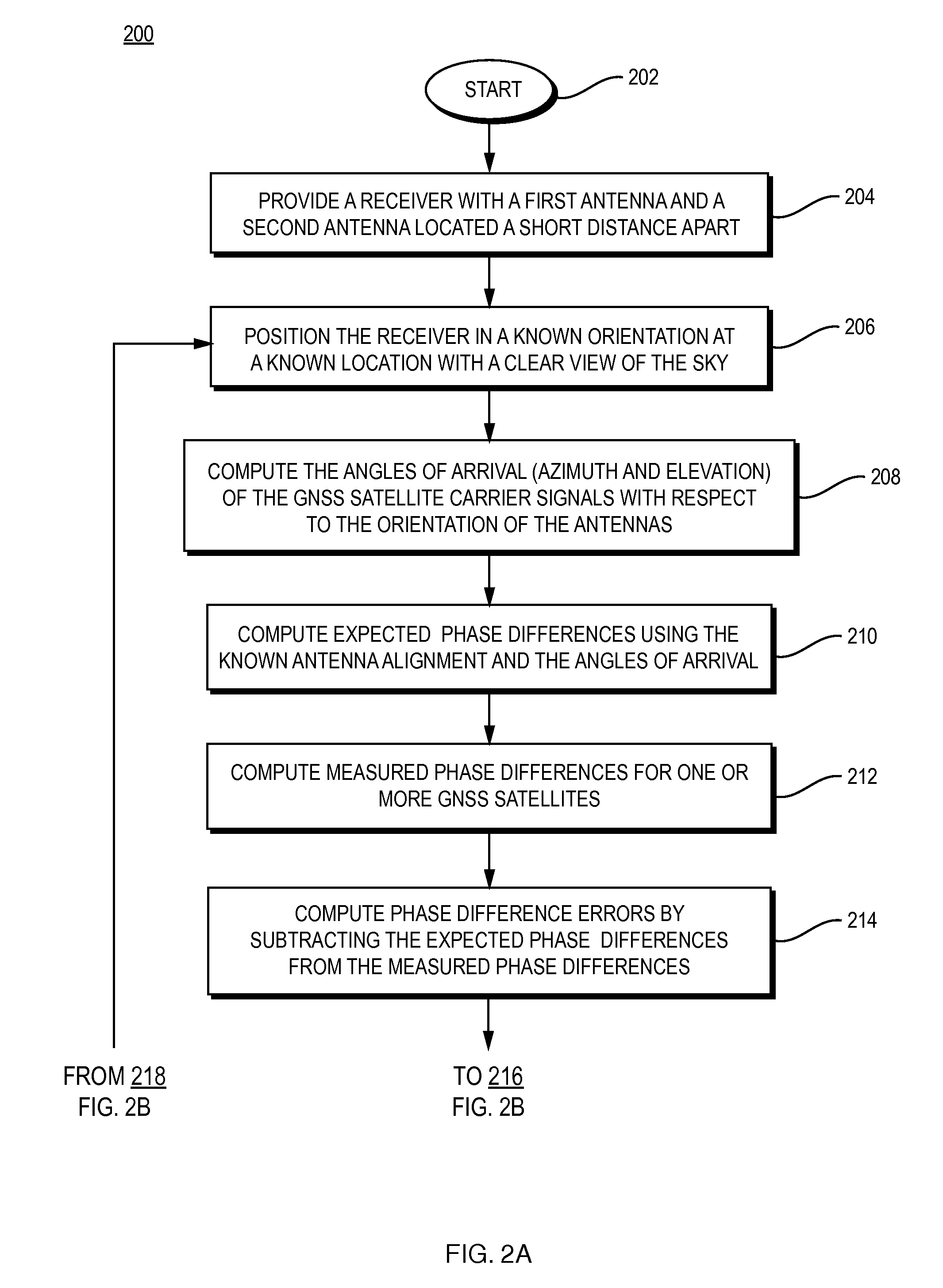

A system for generating and utilizing a look-up mechanism consisting of one or more phase difference error maps, tables and / or mathematical models calculates the respective maps, tables and / or models by placing a short baseline or ultra-short baseline antenna array in a known location and known orientation, determining angles of incidence of incoming GNSS satellite signals with respect the antenna array and calculating expected carrier phase differences between respective pairs of antennas, calculating measured carrier phase differences between the respective pairs of antennas, and determining carrier phase difference errors using the expected and measured carrier phase differences. The carrier phase difference errors are then recorded in the look-up mechanism, with the maps and, as appropriate, look-up tables for the respective pairs of antennas being indexed by angles of incidence. Thereafter, the system utilizes the look-up mechanism when determining the unknown orientation of the antenna structure. For respective pairs of antennas, the system enters the look-up mechanism based on angles of incidence determined from a calculated orientation, and uses the retrieved values in the calculation of a corrected orientation, to compensate for phase distortion.

Owner:NOVATEL INC

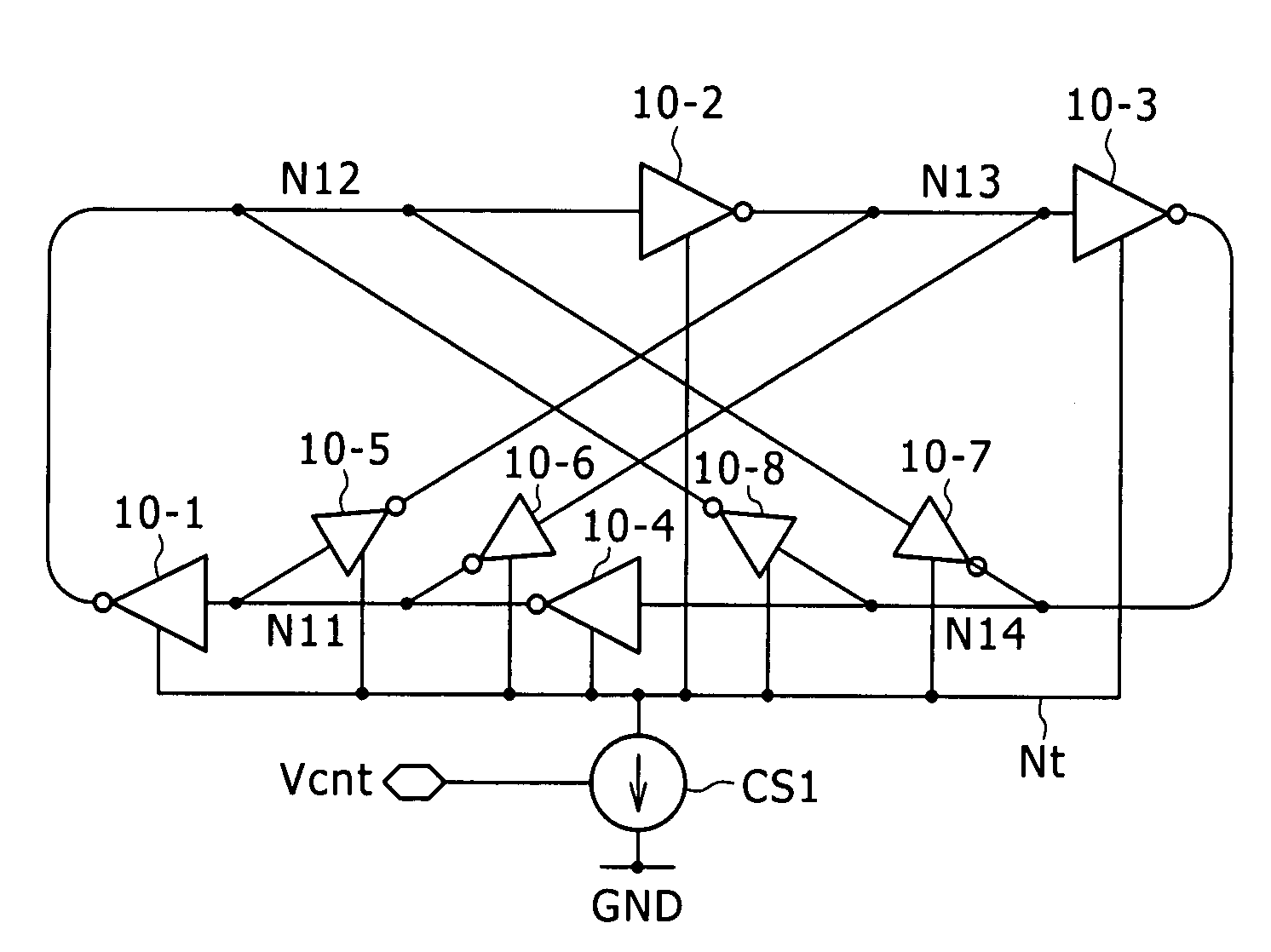

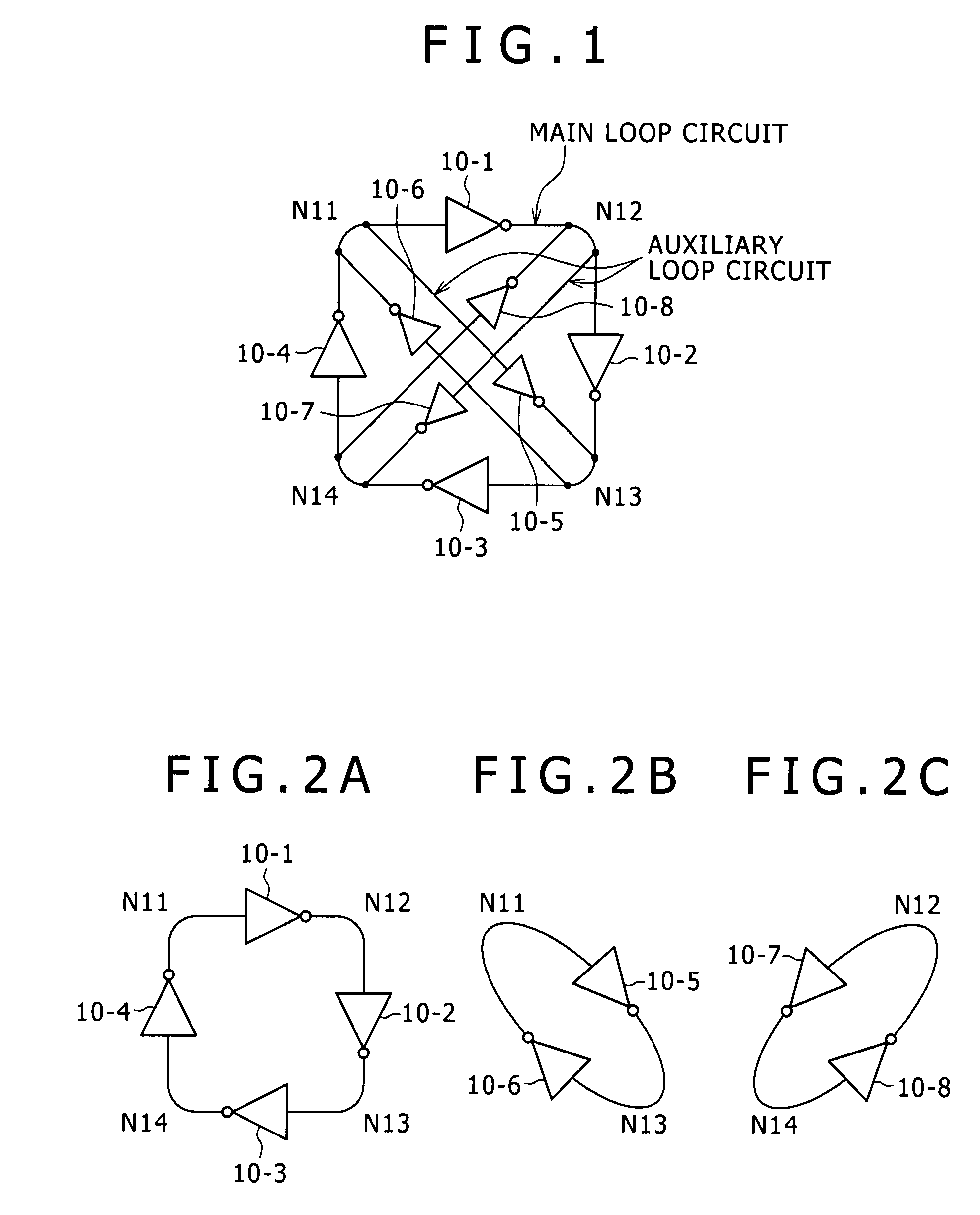

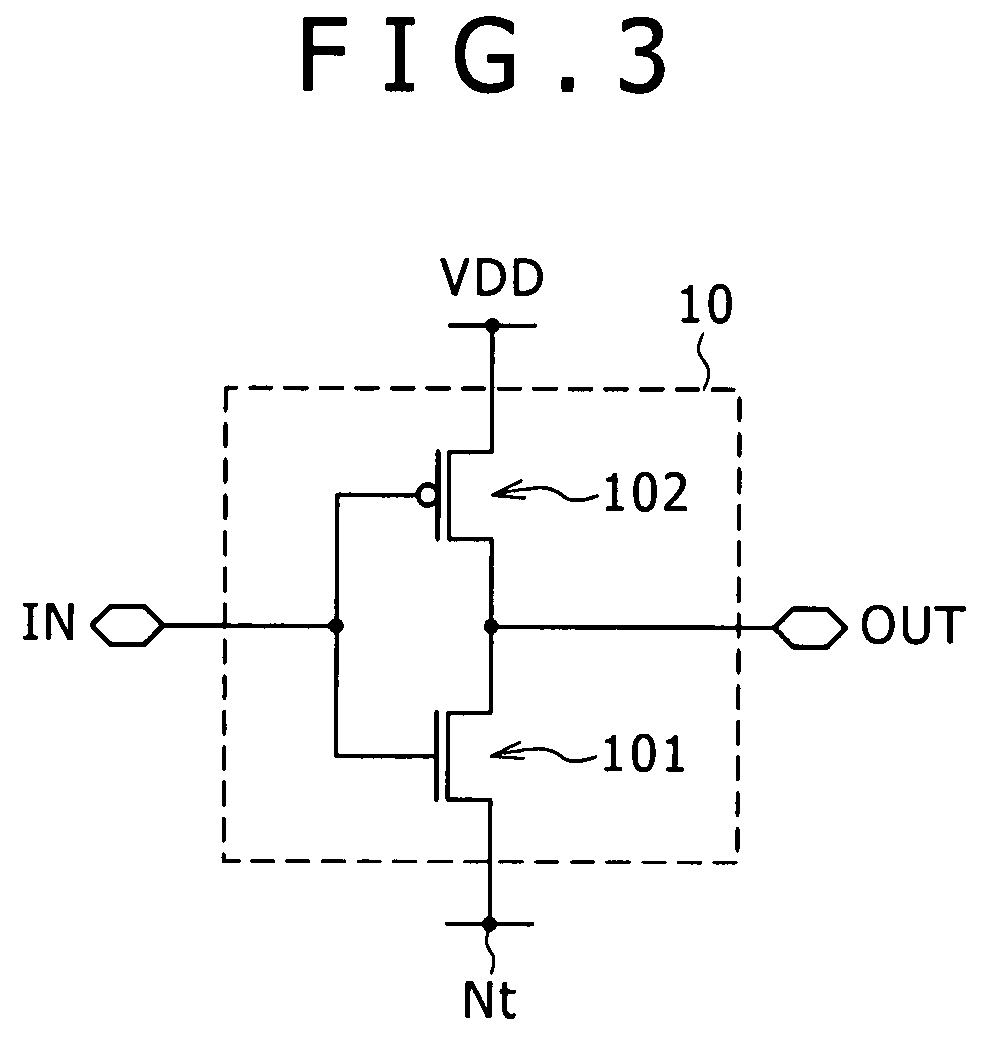

Oscillating circuit

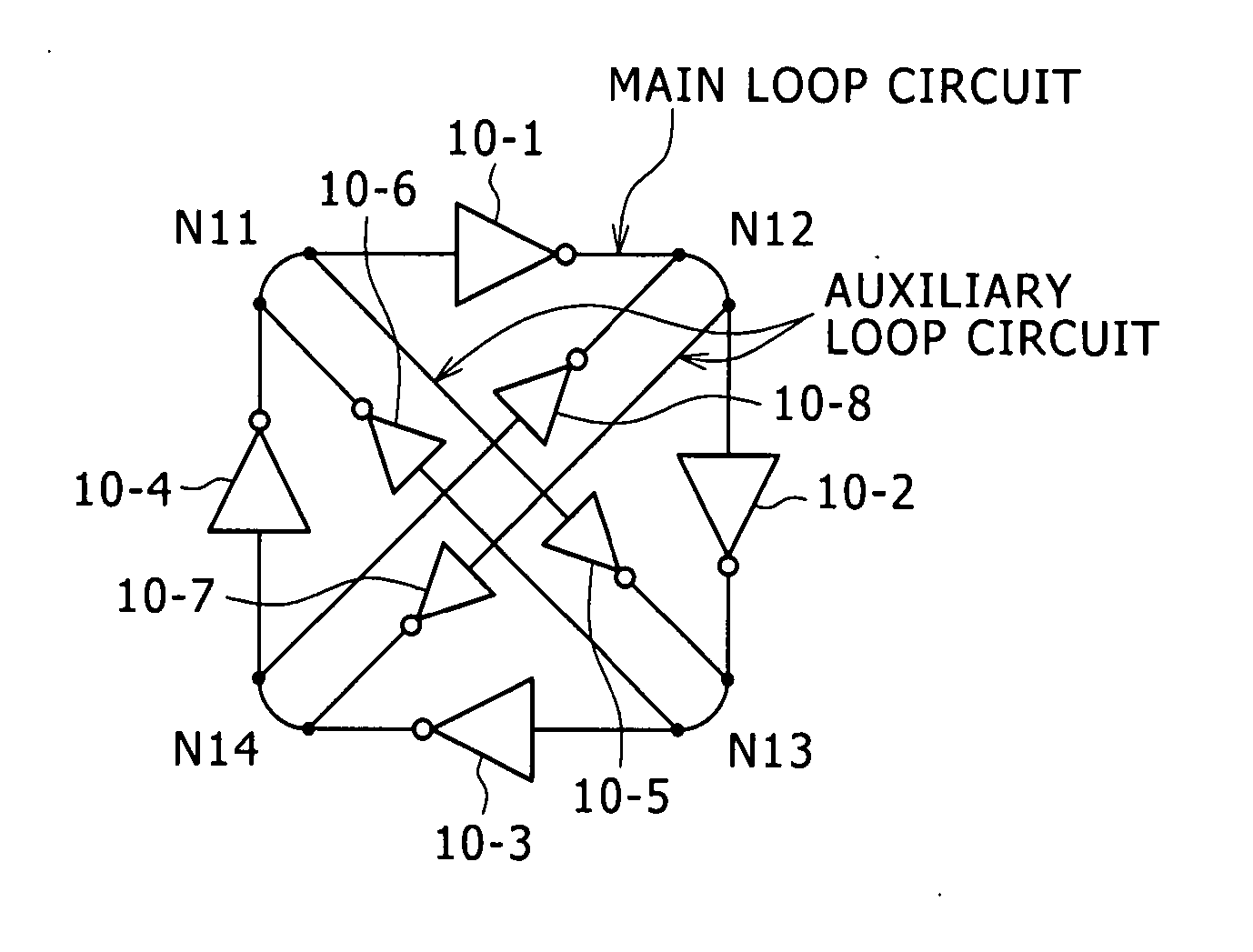

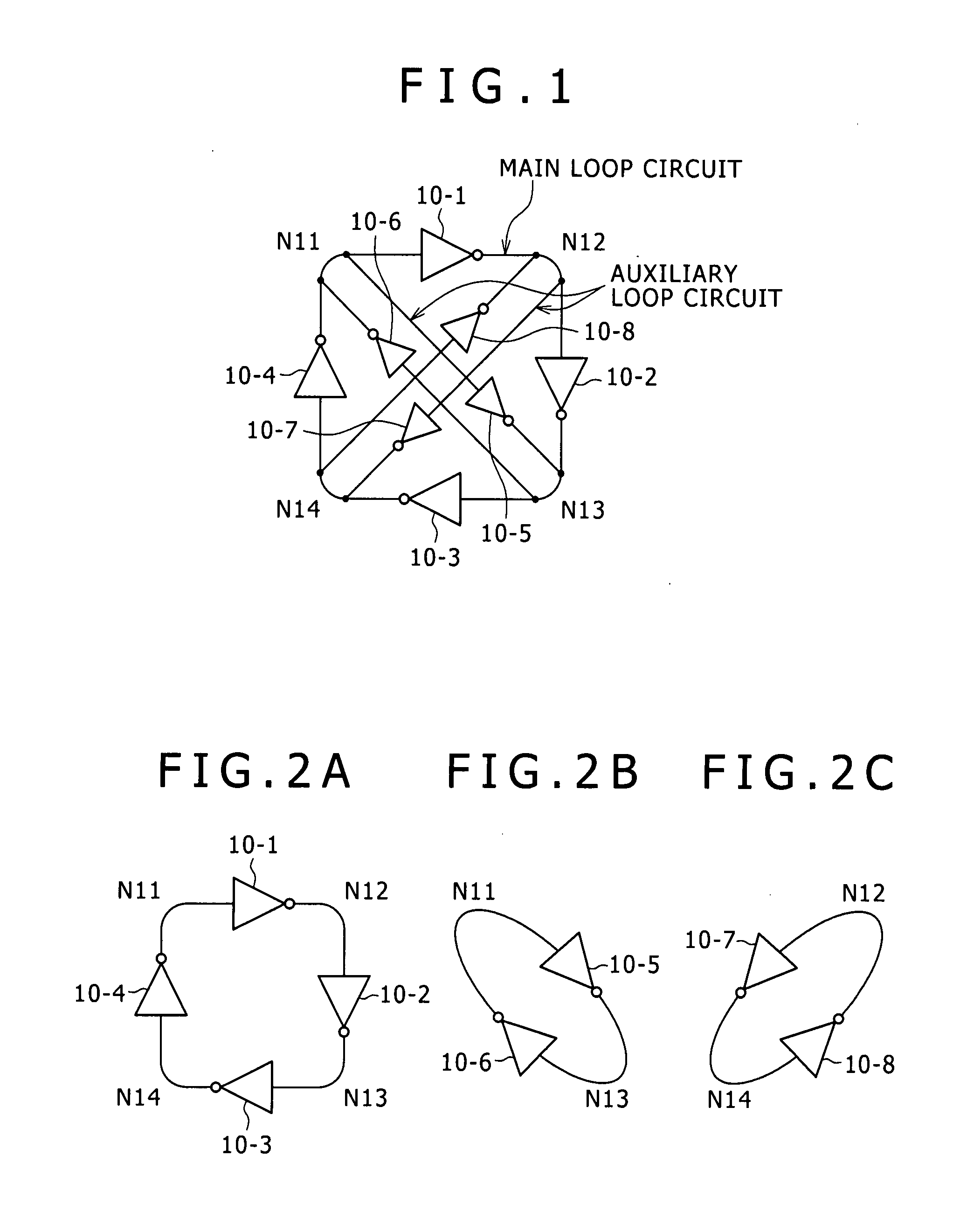

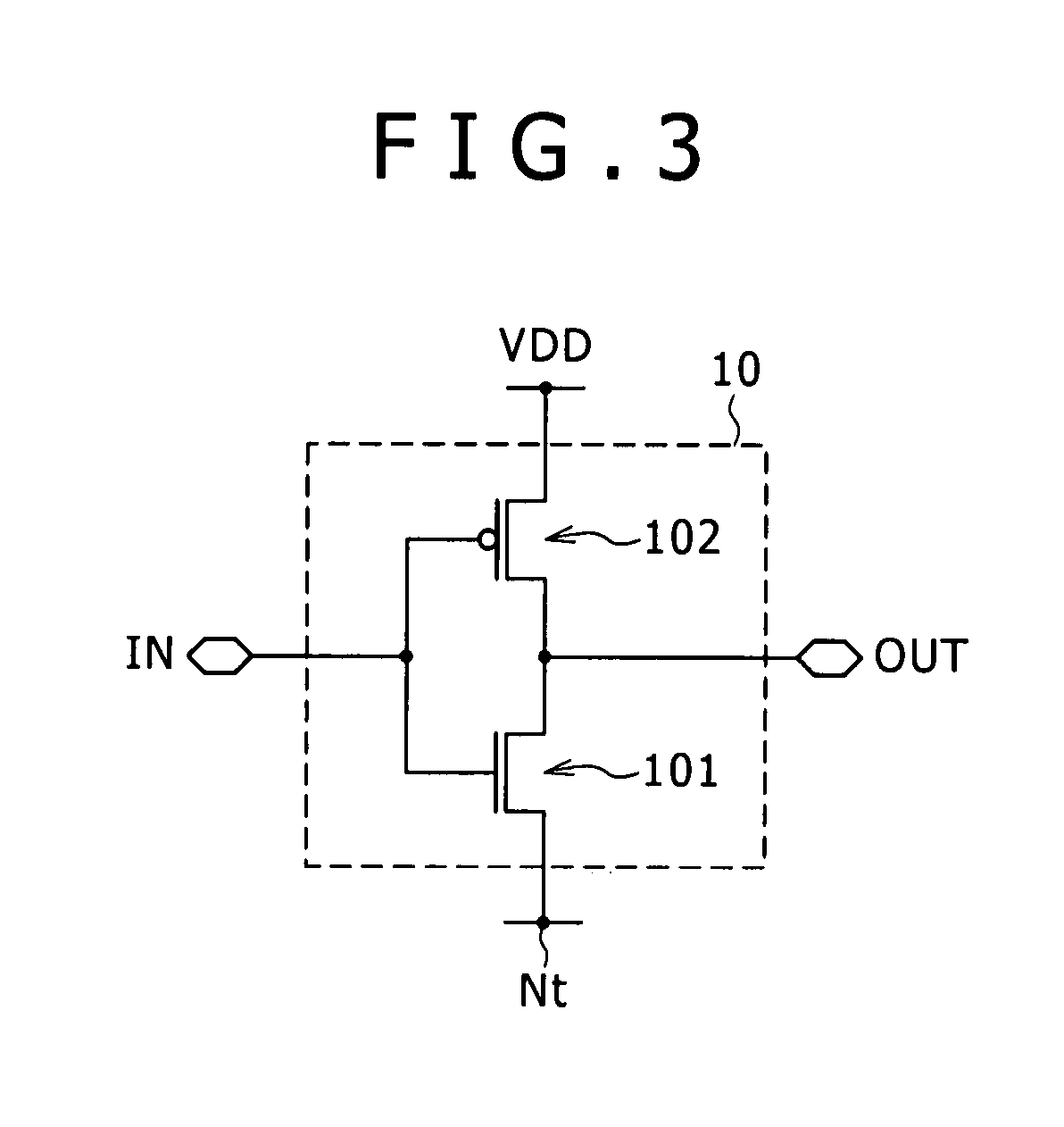

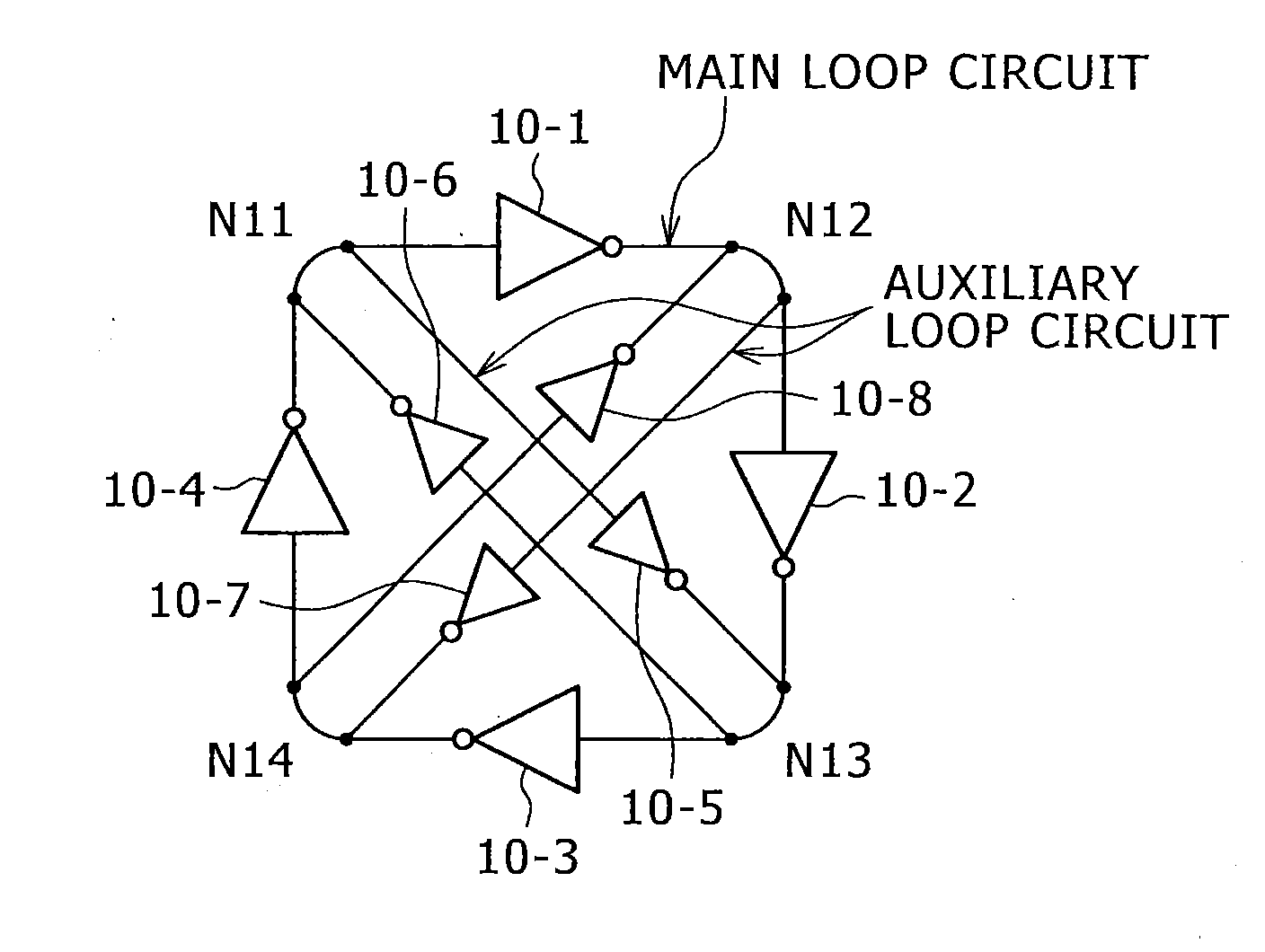

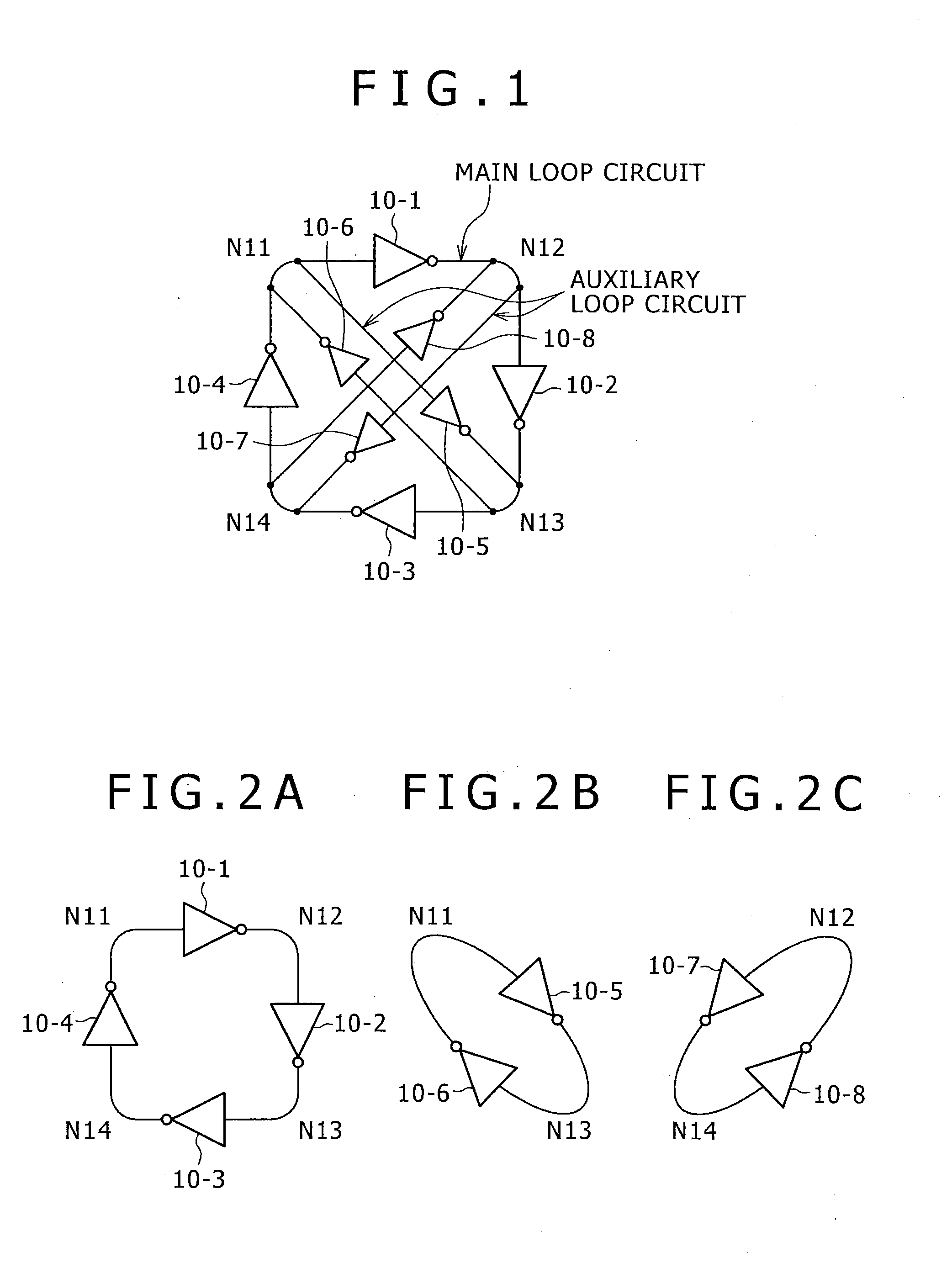

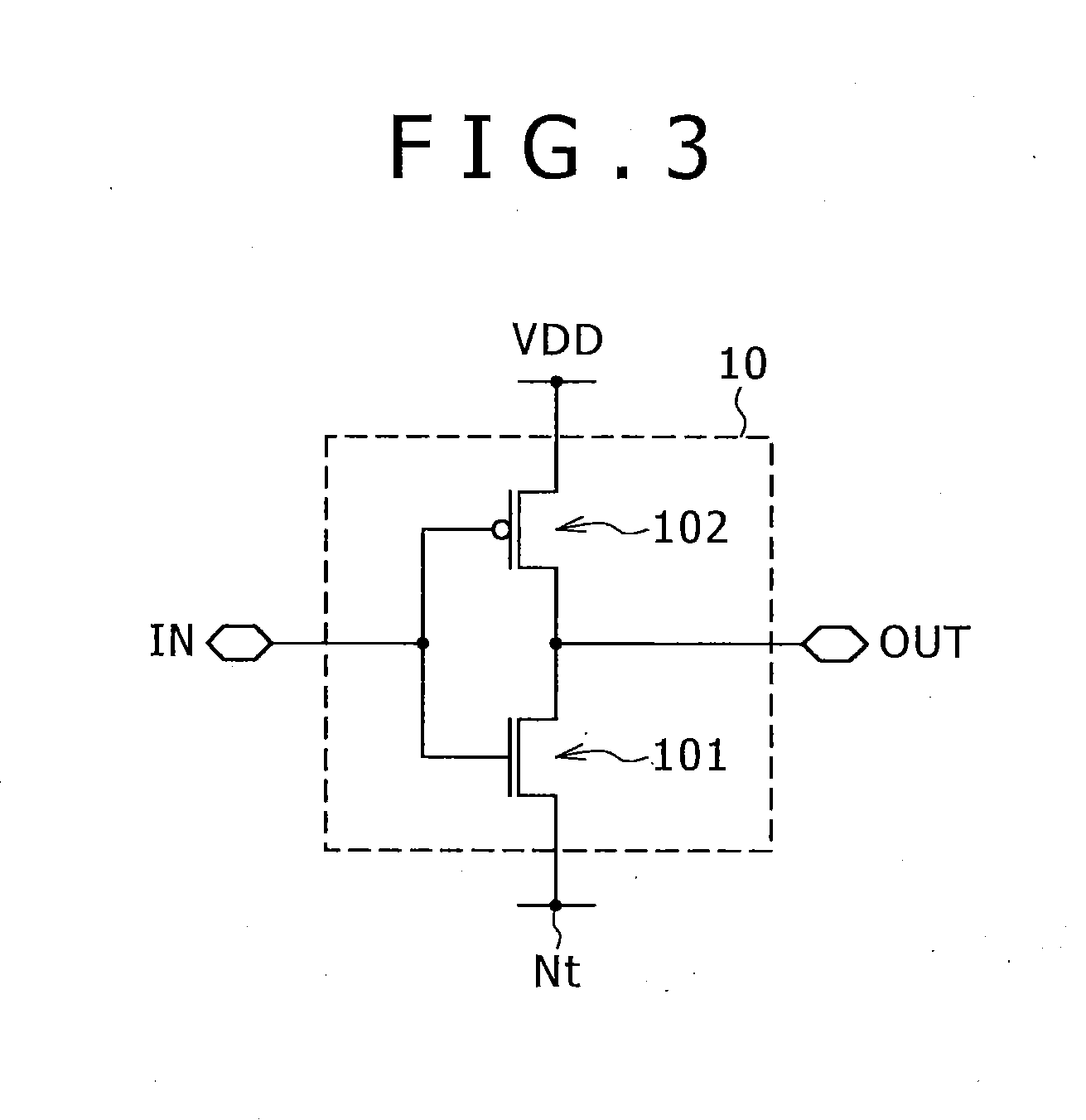

ActiveUS20070241826A1Correction of phase differenceHigh sensitivityPulse automatic controlPulse generation by logic circuitsEngineeringOutput feedback

An oscillating circuit includes N nodes outputting oscillating signals, a main loop circuit including N inverting circuits, and a plurality of auxiliary loop circuits. Each inverting circuit in the auxiliary loop circuits is connected in parallel with even numbers of inverting circuits cascaded in the main loop circuit. The circuits for feeding back signals from outputs to inputs of the respective inverters of the main loop circuit have circuit configurations equivalent to each other. Each inverting circuit in the main loop circuit and the auxiliary loop circuits drives an output line such that a phase of an output signal is inverted with respect to a phase of an input signal and has driving power that becomes lower when the phases of the output signal and the input signal are inverted with respect to each other than when the output signal and the input signal are in phase with each other.

Owner:SONY SEMICON SOLUTIONS CORP

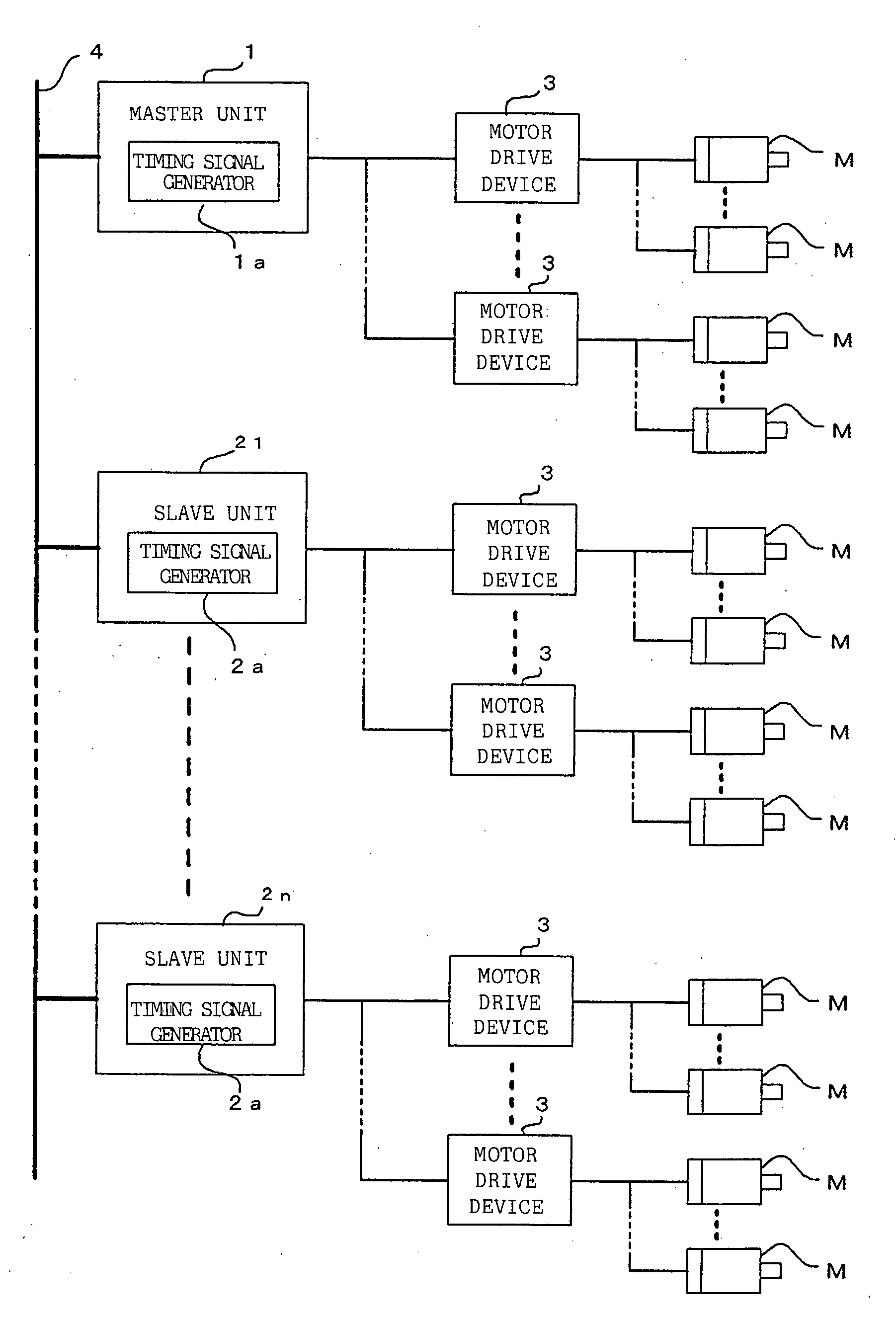

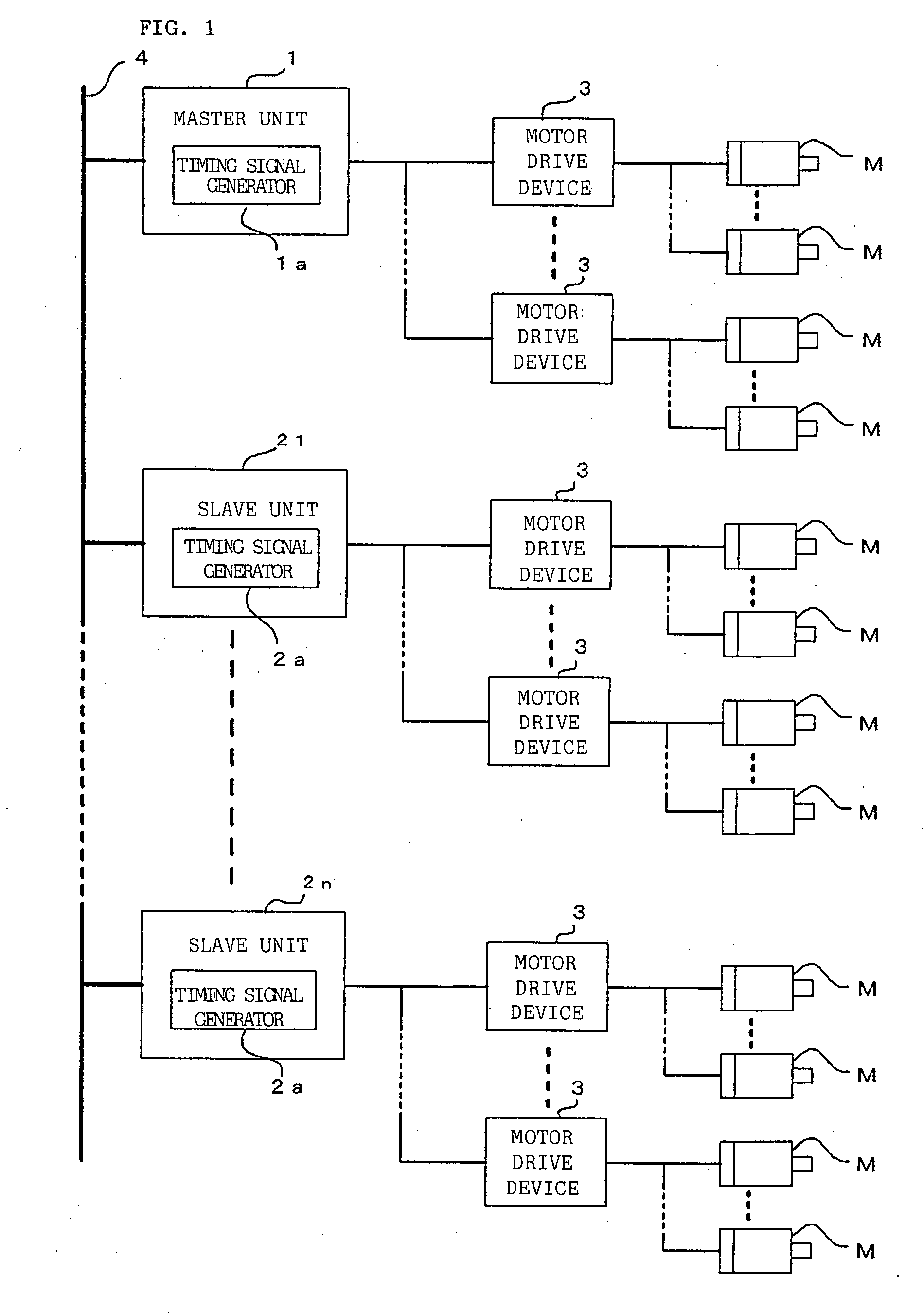

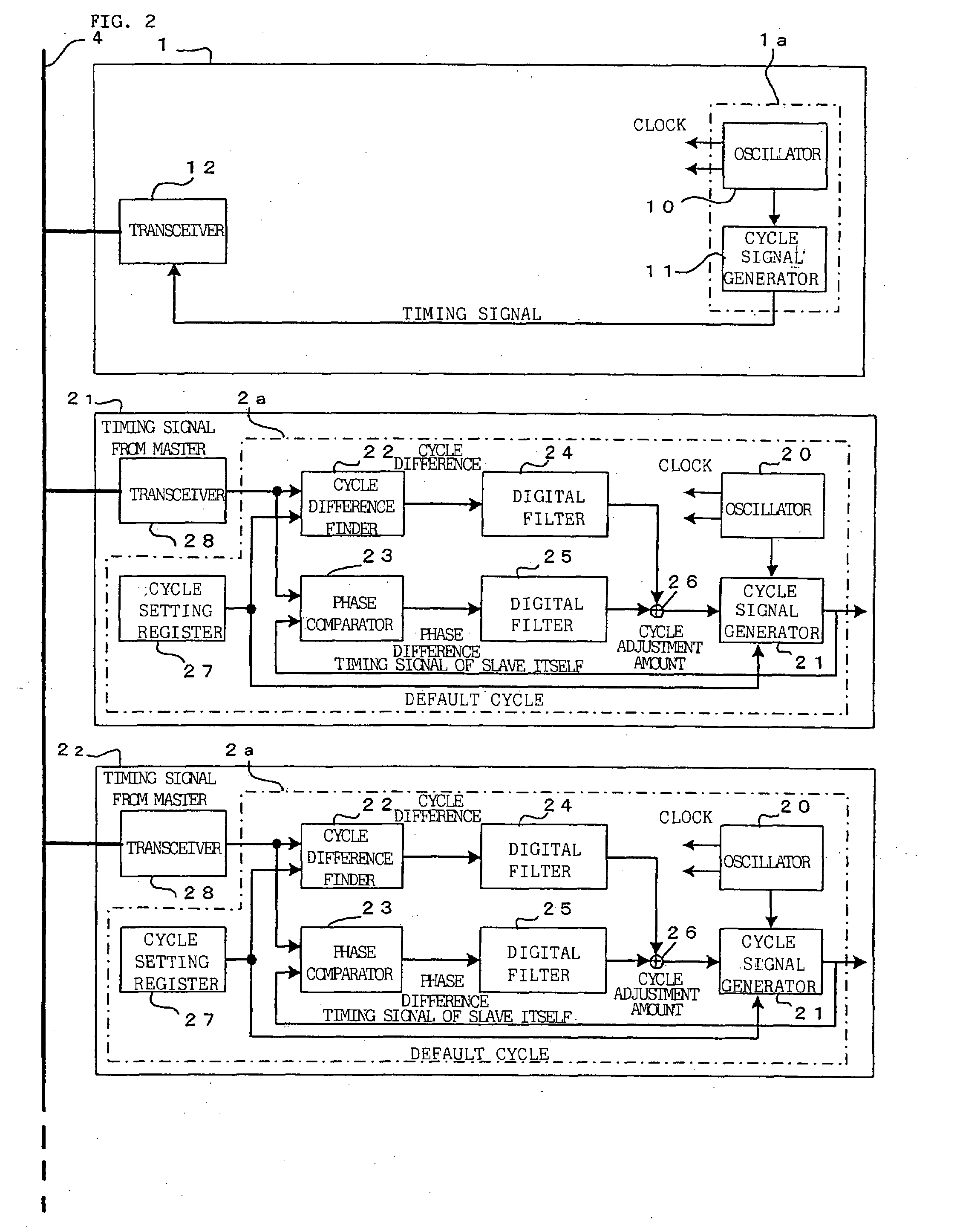

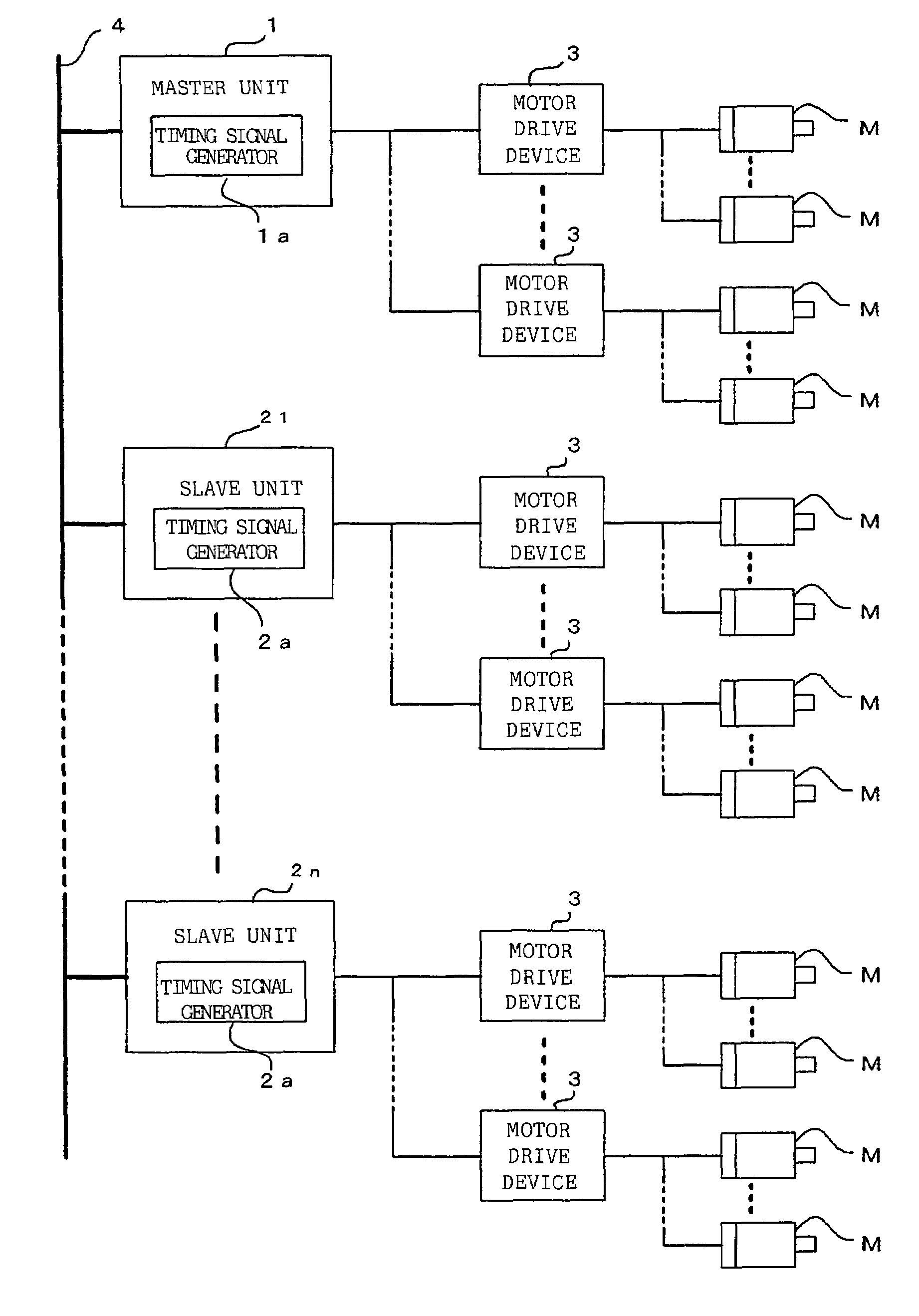

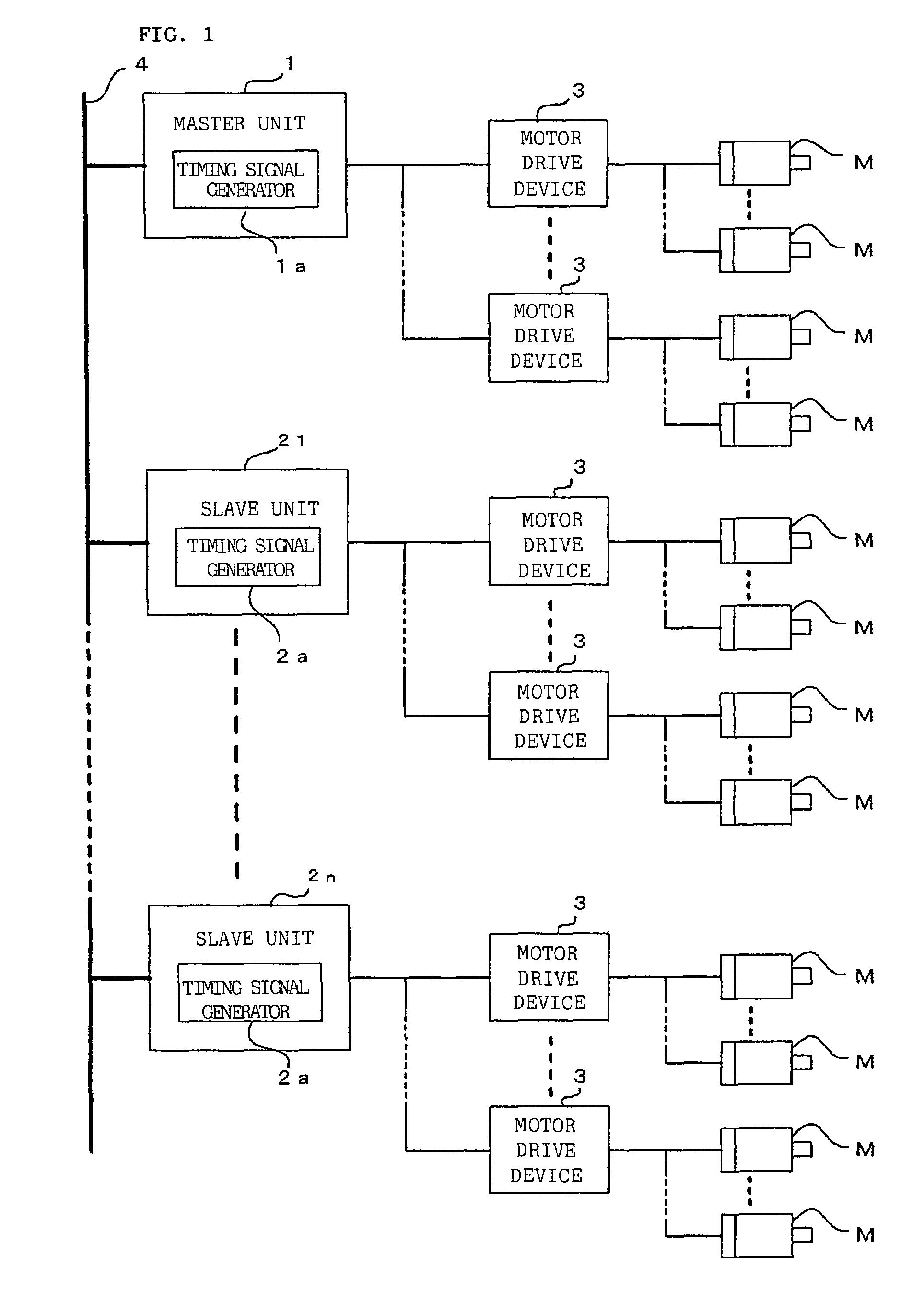

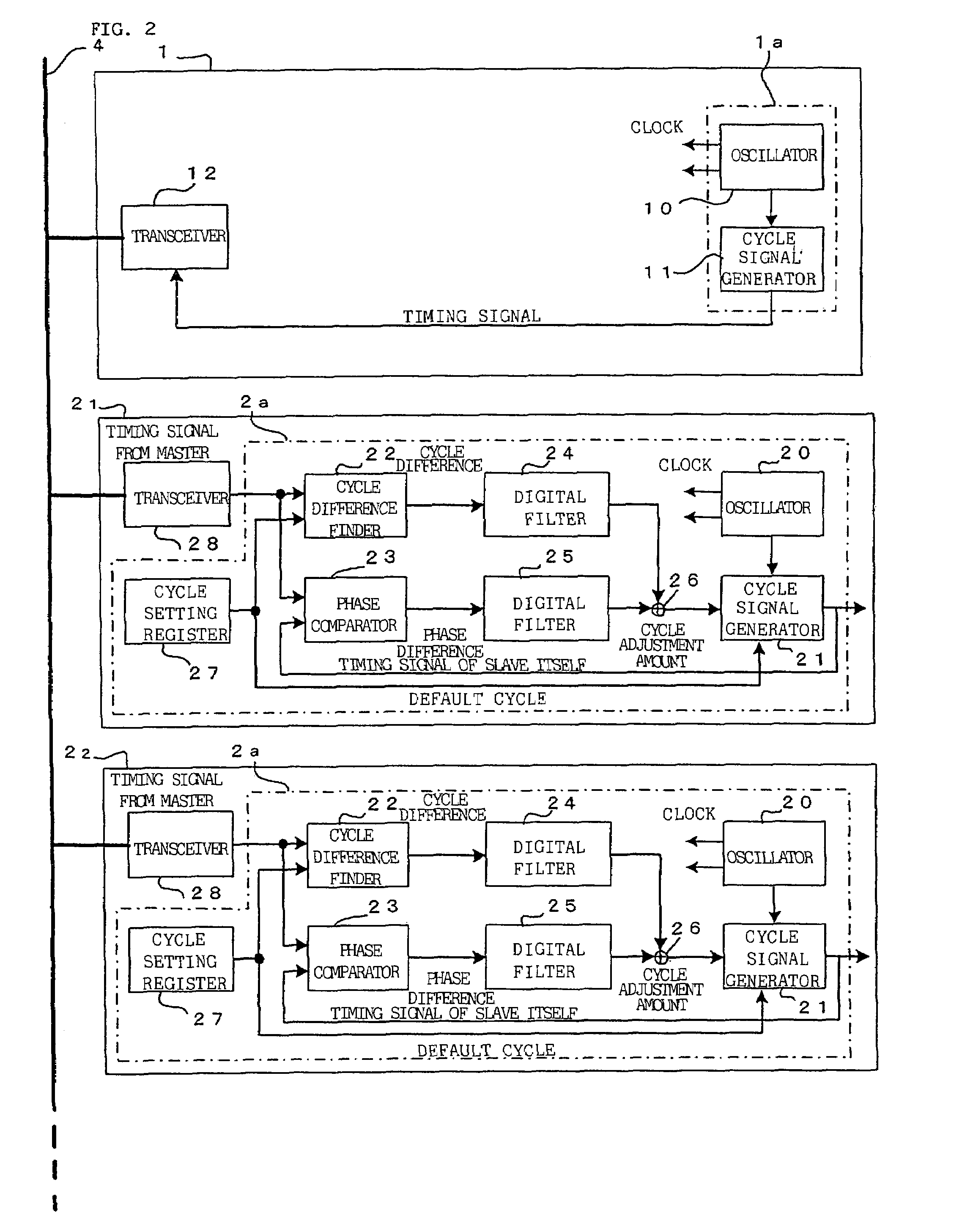

Control system

InactiveUS20070188116A1Improve accuracyCorrection of phase differenceProgramme controlPulse automatic controlPhase differenceControl system

A master unit and a plurality of slave units are connected by way of a communication path. The master unit sends to the slave units timing signals generated by its own cycle signal generator by way of a communication path. The slave units determine the cycle difference and the phase difference between a timing signal generated by its own cycle signal generator and the timing signal sent from the master unit and, in accordance therewith, determine a cycle adjustment amount. The cycle signal generators of the slave units adjust the timing signal cycle based on the cycle adjustment amount.

Owner:FANUC LTD

Oscillating circuit

ActiveUS8154352B2High sensitivityImprove featuresPulse automatic controlPulse generation by logic circuitsEngineeringOutput feedback

An oscillating circuit includes N nodes outputting oscillating signals, a main loop circuit including N inverting circuits, and a plurality of auxiliary loop circuits. Each inverting circuit in the auxiliary loop circuits is connected in parallel with even numbers of inverting circuits cascaded in the main loop circuit. The circuits for feeding back signals from outputs to inputs of the respective inverters of the main loop circuit have circuit configurations equivalent to each other. Each inverting circuit in the main loop circuit and the auxiliary loop circuits drives an output line such that a phase of an output signal is inverted with respect to a phase of an input signal and has driving power that becomes lower when the phases of the output signal and the input signal are inverted with respect to each other than when the output signal and the input signal are in phase with each other.

Owner:SONY SEMICON SOLUTIONS CORP

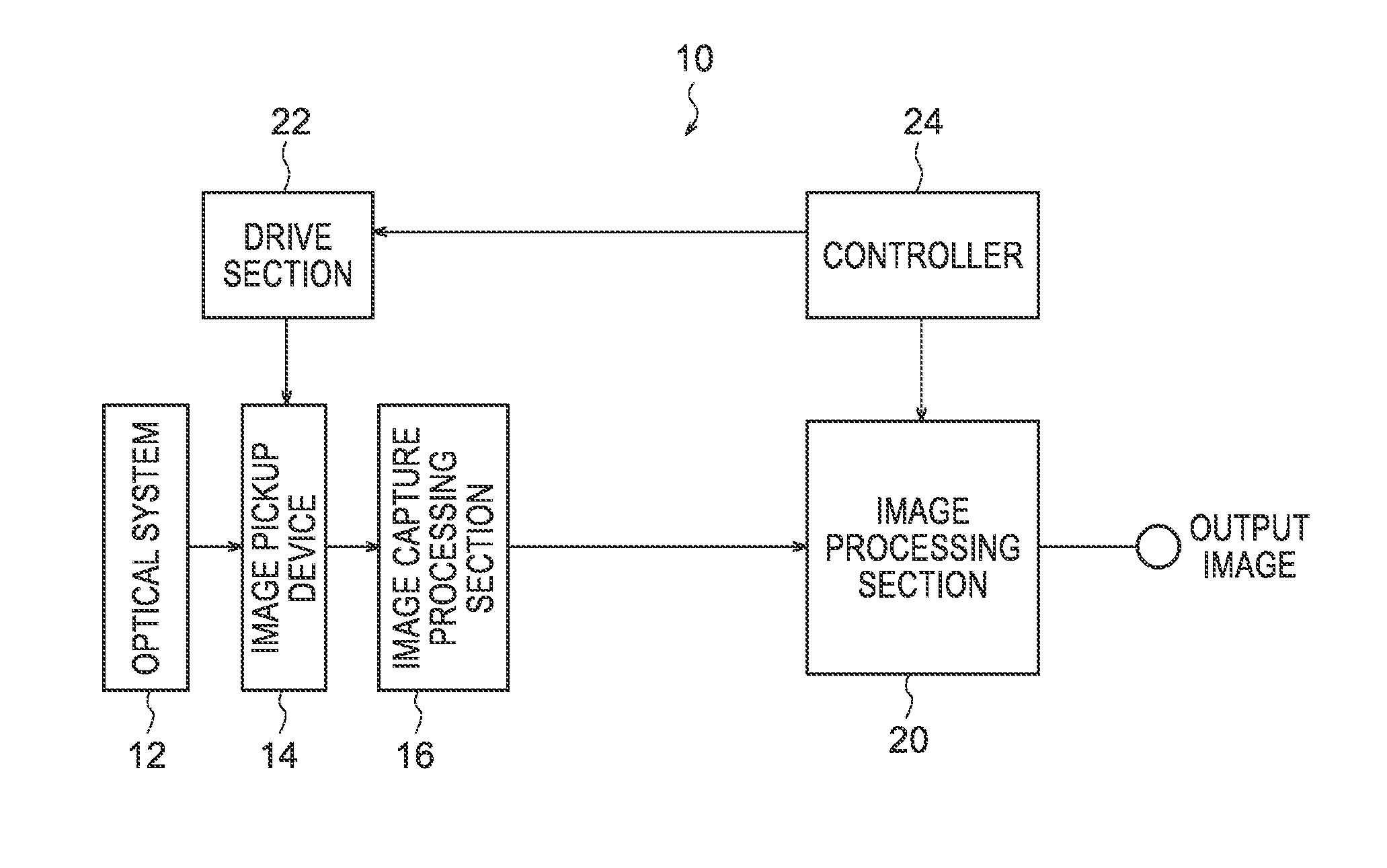

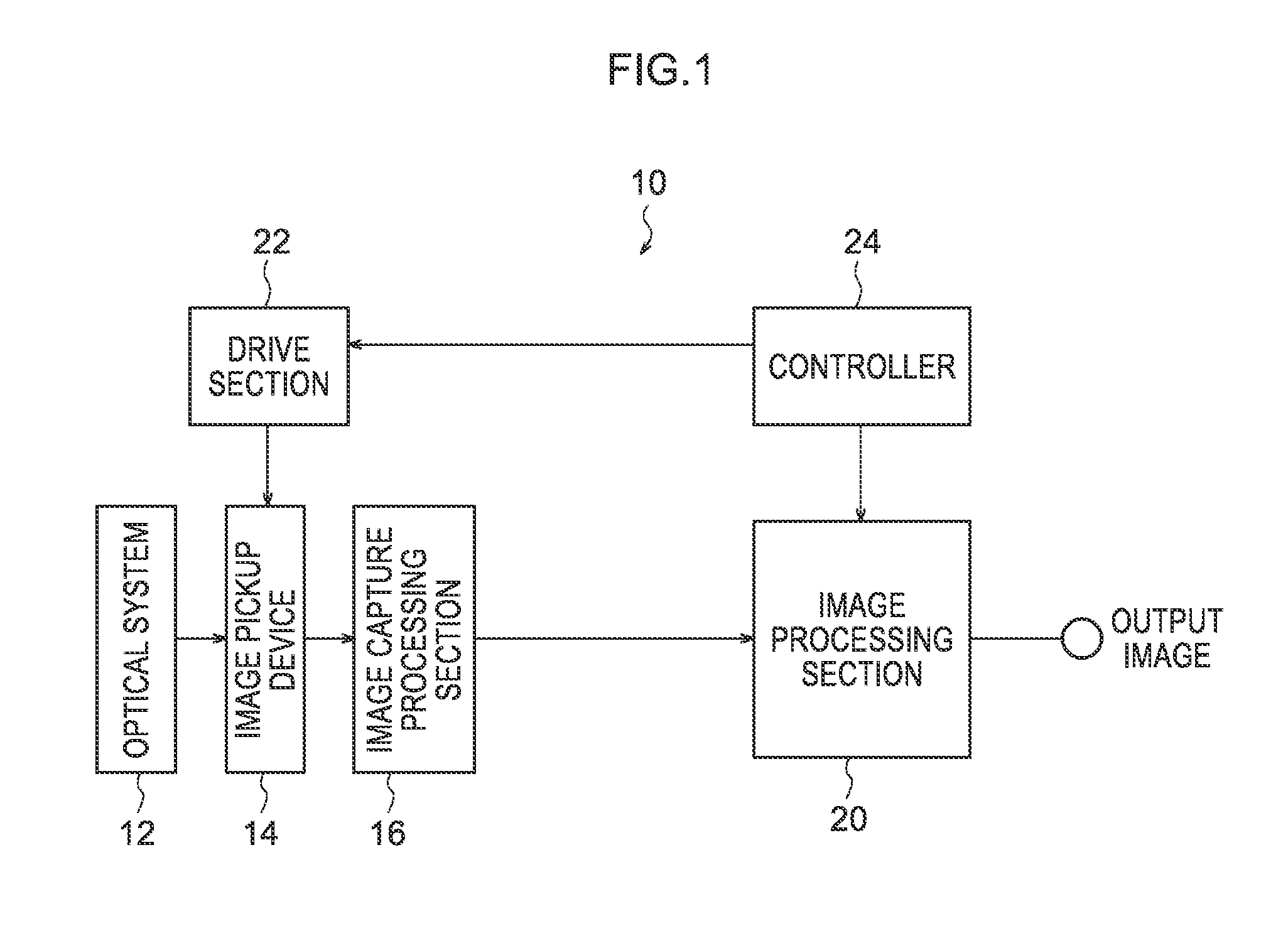

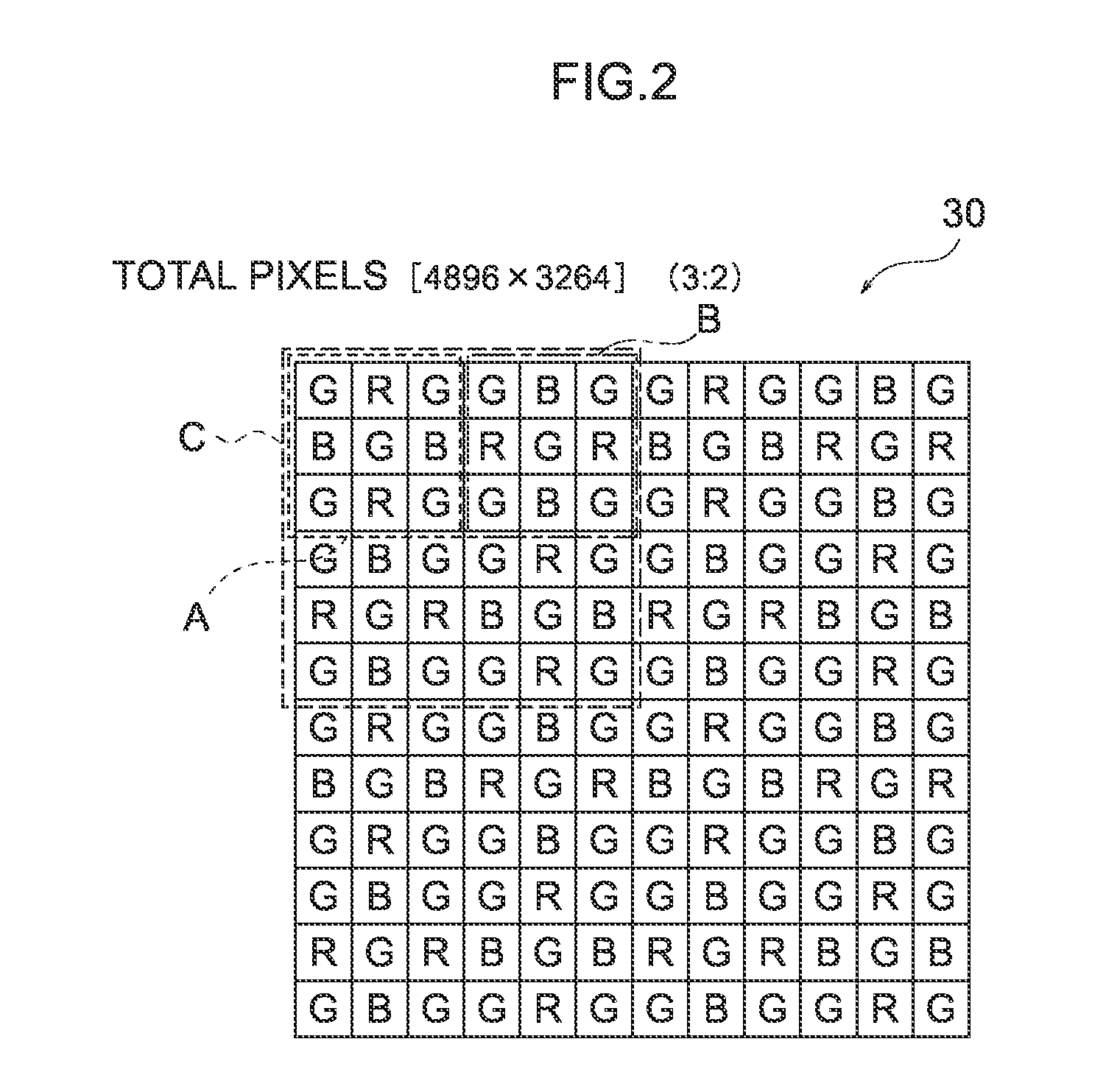

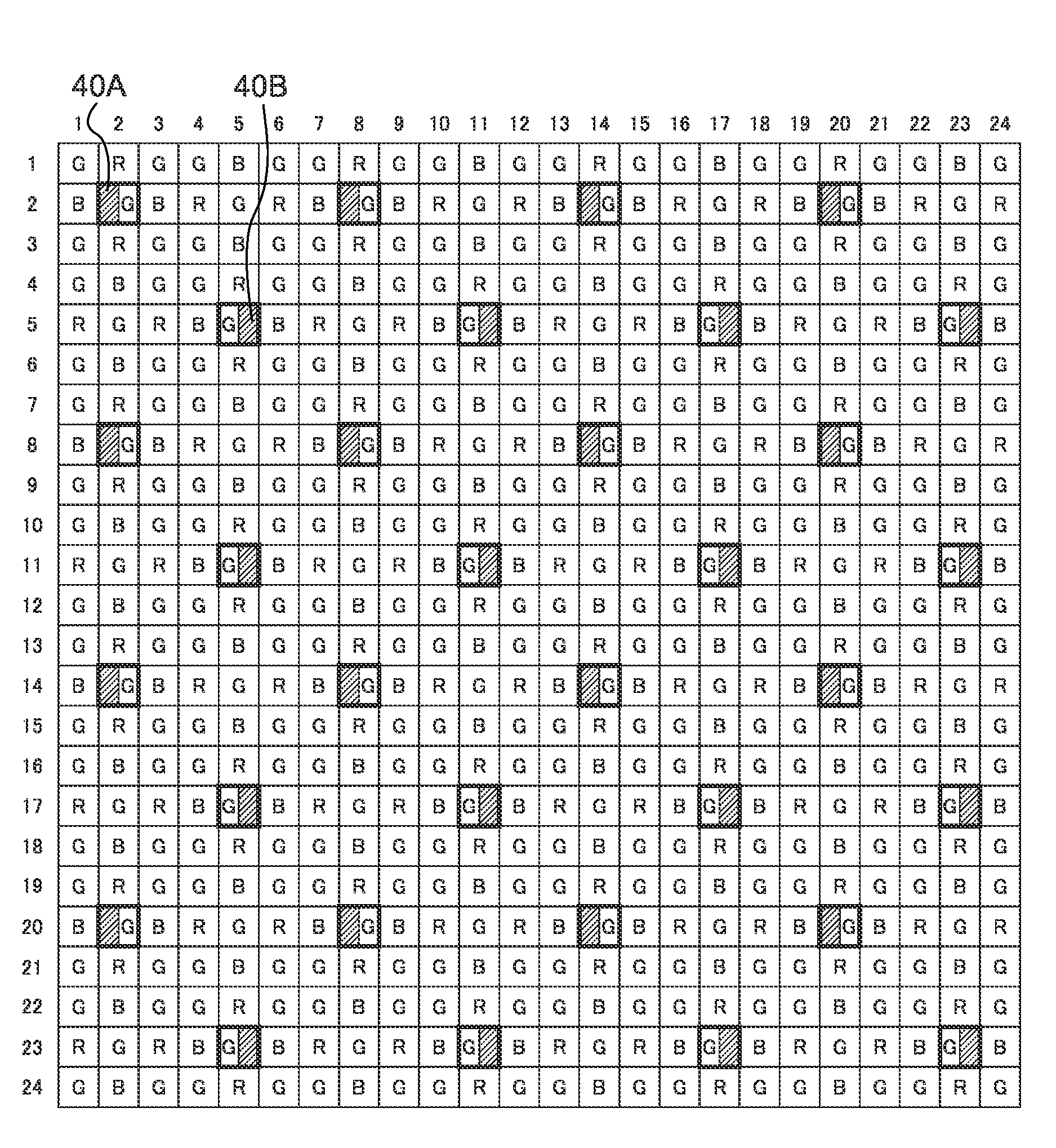

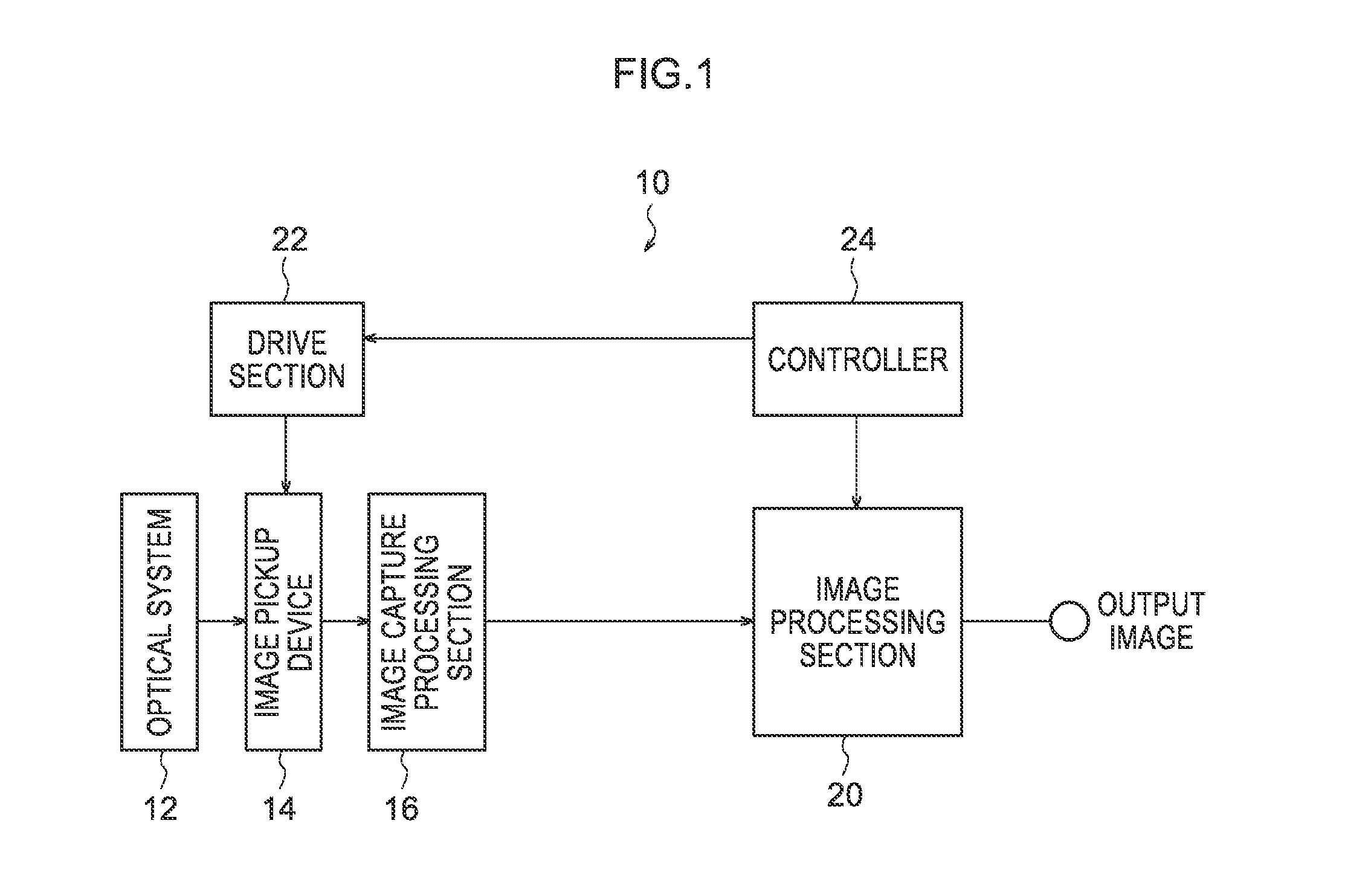

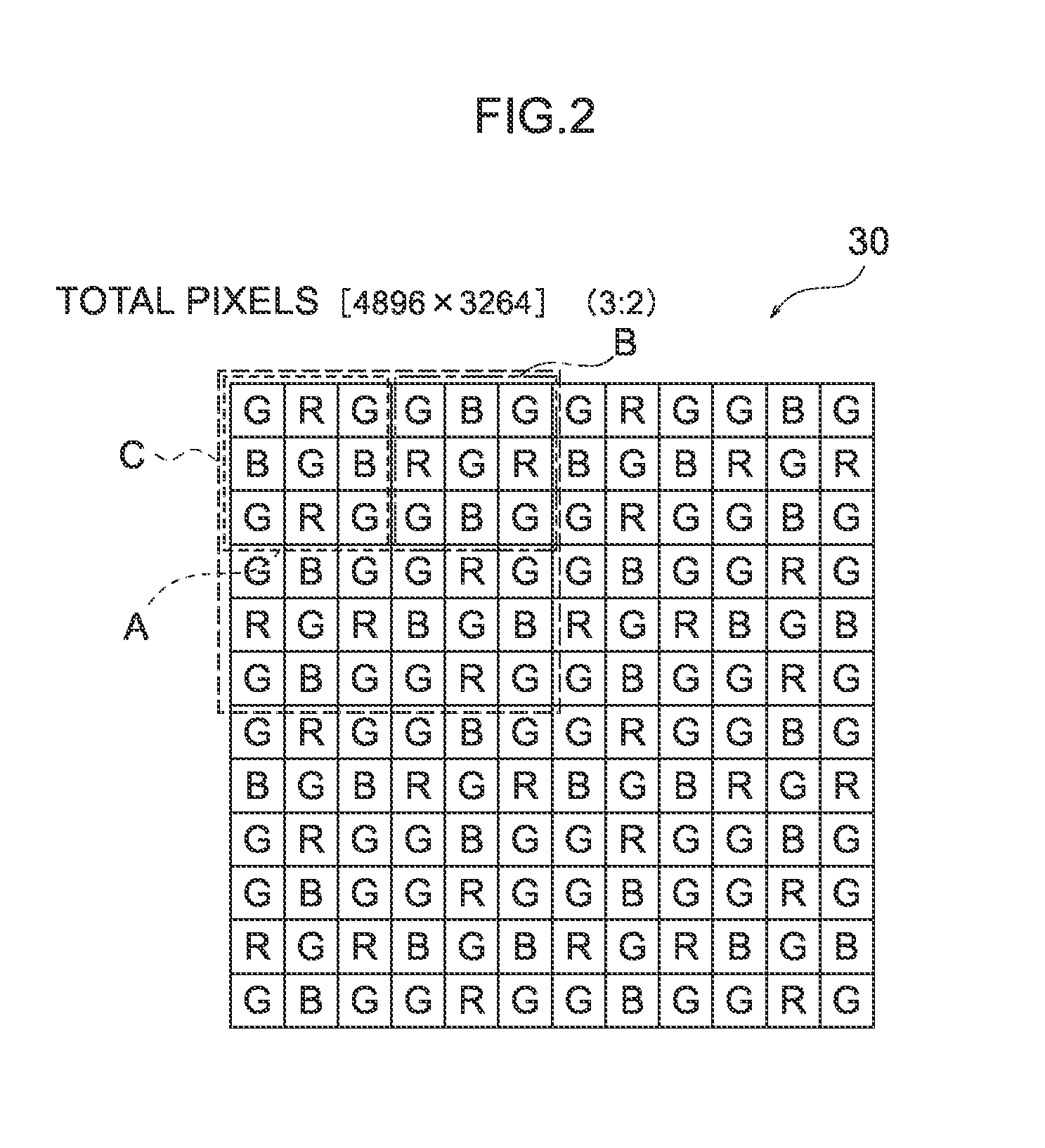

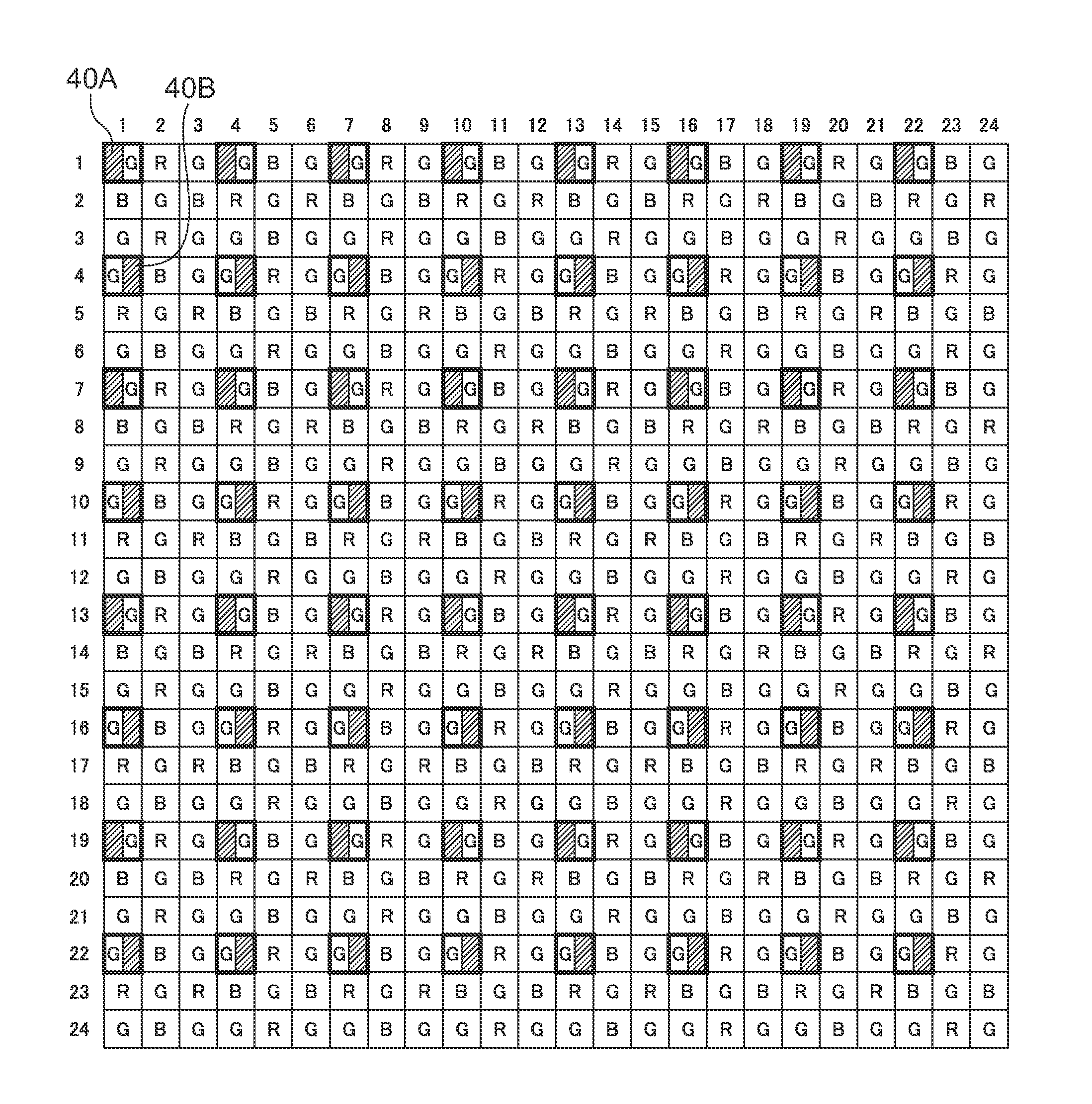

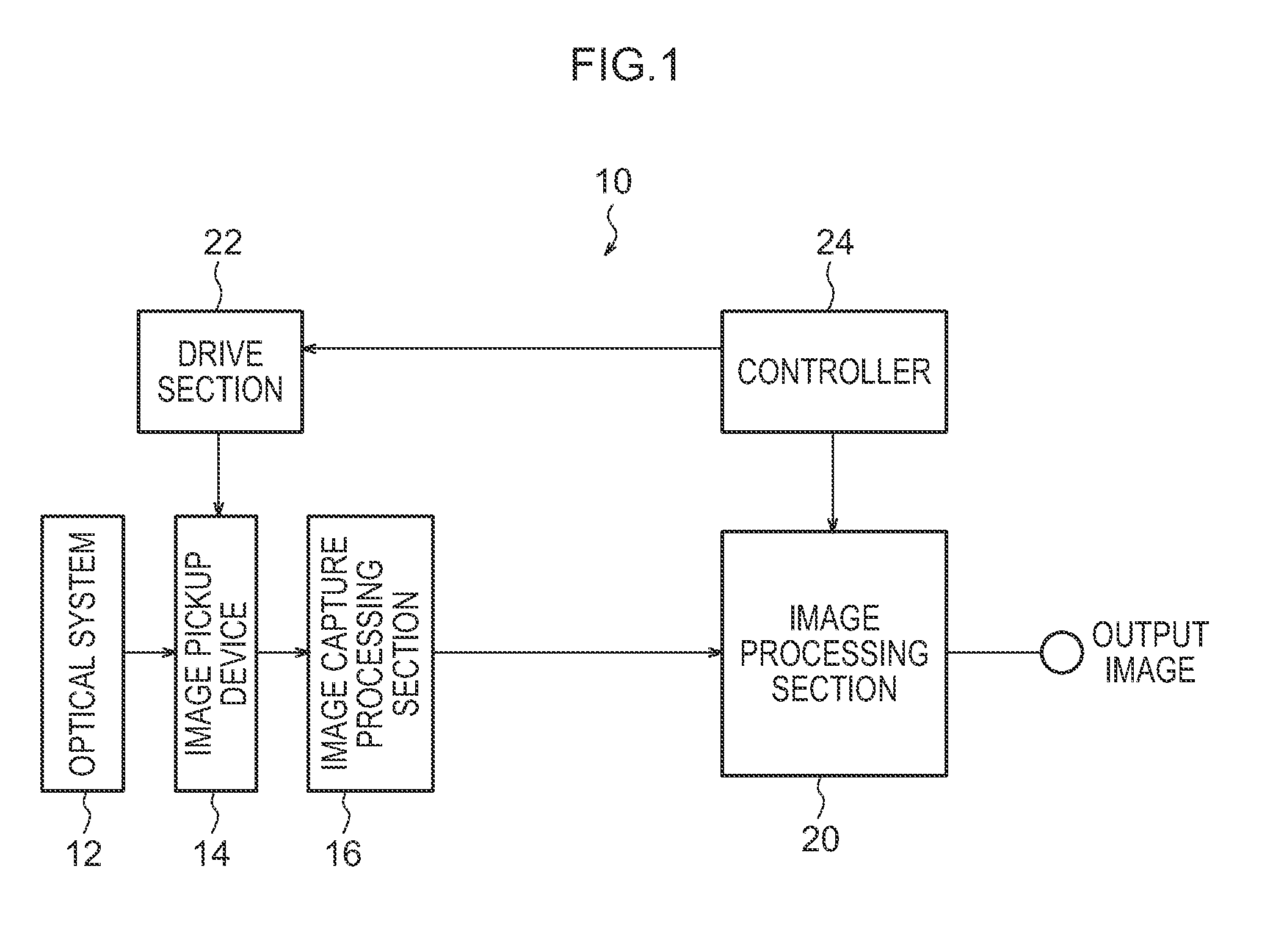

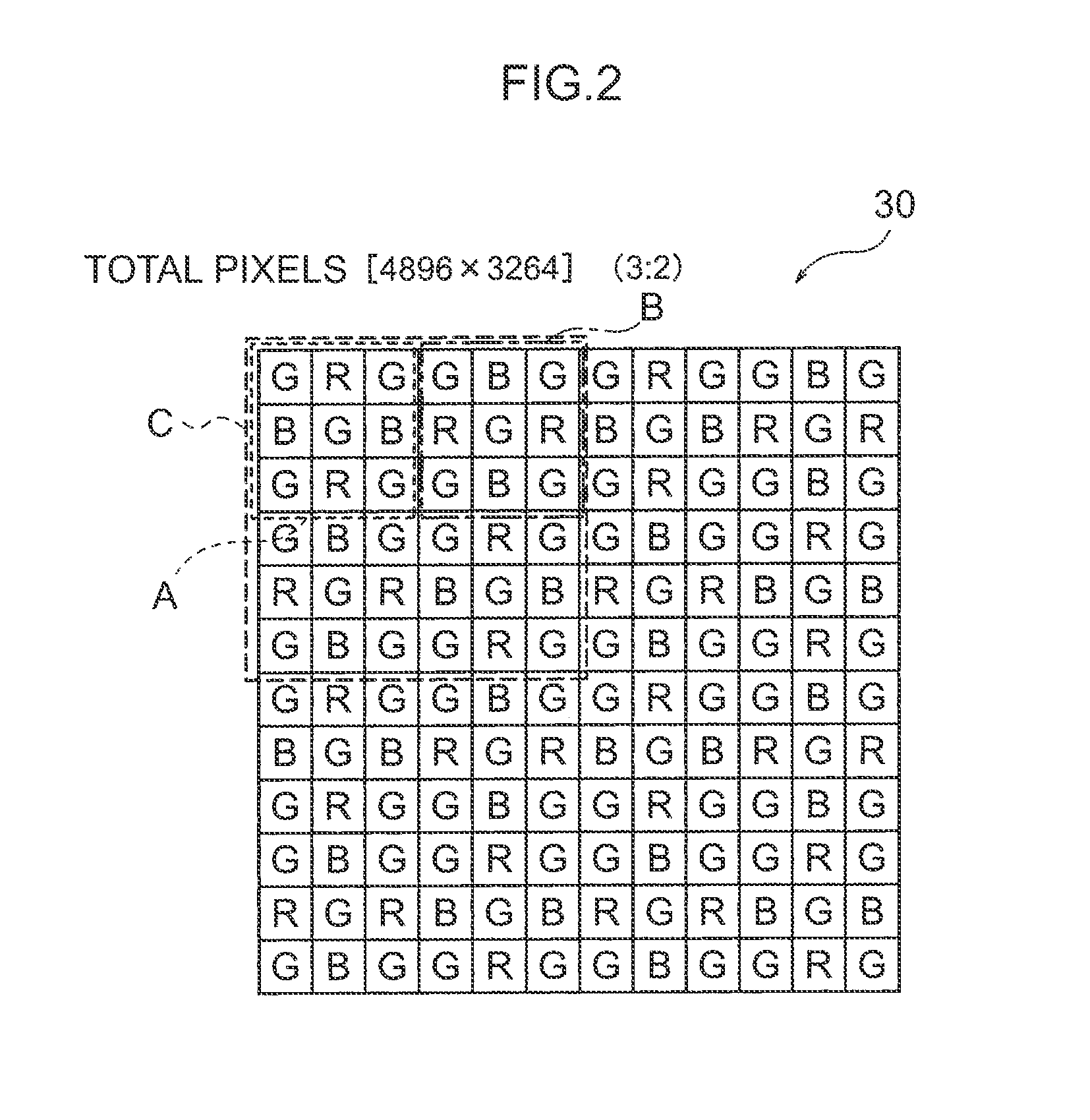

Color imaging element, imaging device, and storage medium storing an imaging program

InactiveUS20140043508A1Correction of phase differenceHigh precisionTelevision system detailsTelevision system scanning detailsSquare arrayColor imaging

An image pickup device includes: a color filter having basic array patterns with first and second array patterns disposed symmetrically, wherein the first array pattern has a first filter at the 4 corner and center pixels of a 3×3 pixel square array, a second filter in a line at the horizontal direction center of the square array, and a third filter placed in a line at the vertical direction center of the square array, and the second array pattern has the same placement of the first filter as the first array pattern and has placement of the second filter and placement of the third filter swapped to that of the first array pattern; and phase difference detection pixels placed on pixels corresponding to positions of centers of at least 1 pair of patterns out of 2 pairs of the first array pattern and the second array pattern.

Owner:FUJIFILM CORP

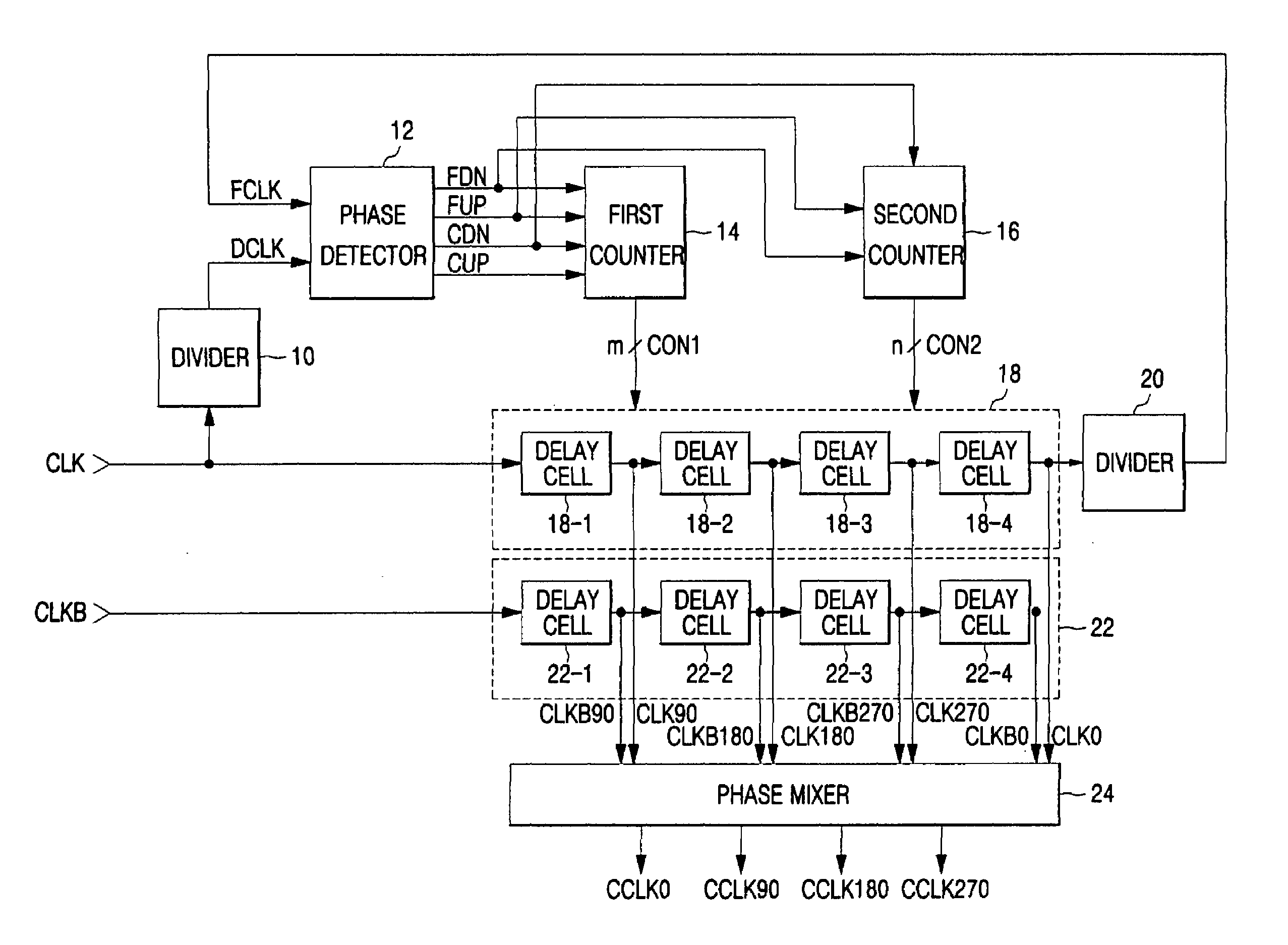

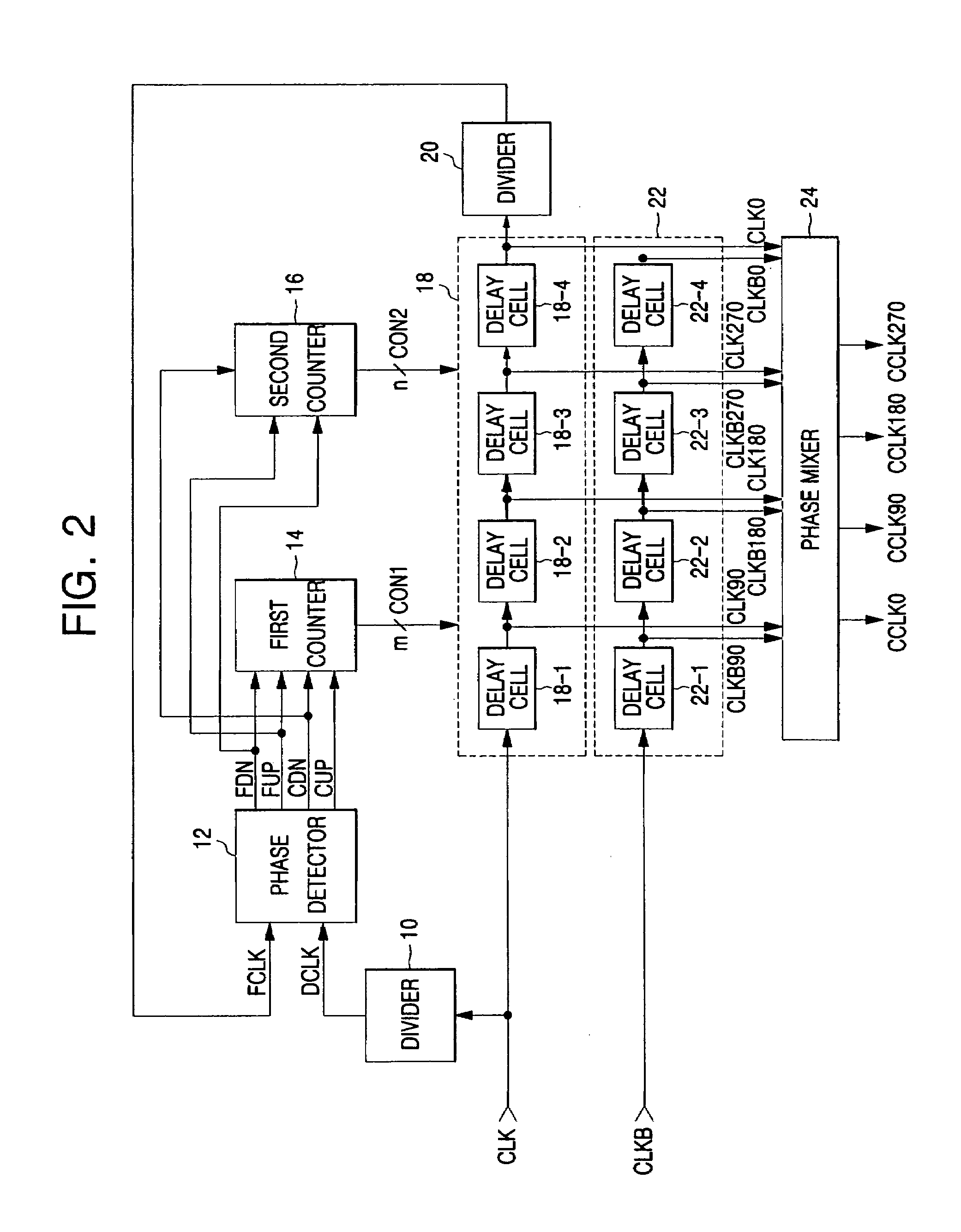

Delay locked loop and semiconductor memory device having the same

InactiveUS20060097762A1Correction of phase differencePulse automatic controlDigital storagePhase mixingControl signal

In a delay locked loop and a semiconductor memory device having the same, the delay locked loop includes a phase detecting and control signal generator for detecting a phase difference between a clock signal and a feedback clock signal and generating a plural-bit delay control signal which varies according to the phase difference; a first delay having a predetermined number of first delay cells which are cascade-connected for delaying the clock signal to generate a plurality of output clock signals and the feedback clock signal in response to the plural-bit delay control signal; a second delay having a predetermined number of second delay cells which are cascade-connected for delaying an inverted clock signal to generate a plurality of inverted output clock signals in response to the plural-bit delay control signal; and a phase mixer for phase-mixing corresponding clock signals among the plurality of output clock signals and the plurality of inverted output clock signals to output a plurality of corrected output clock signals.

Owner:SAMSUNG ELECTRONICS CO LTD

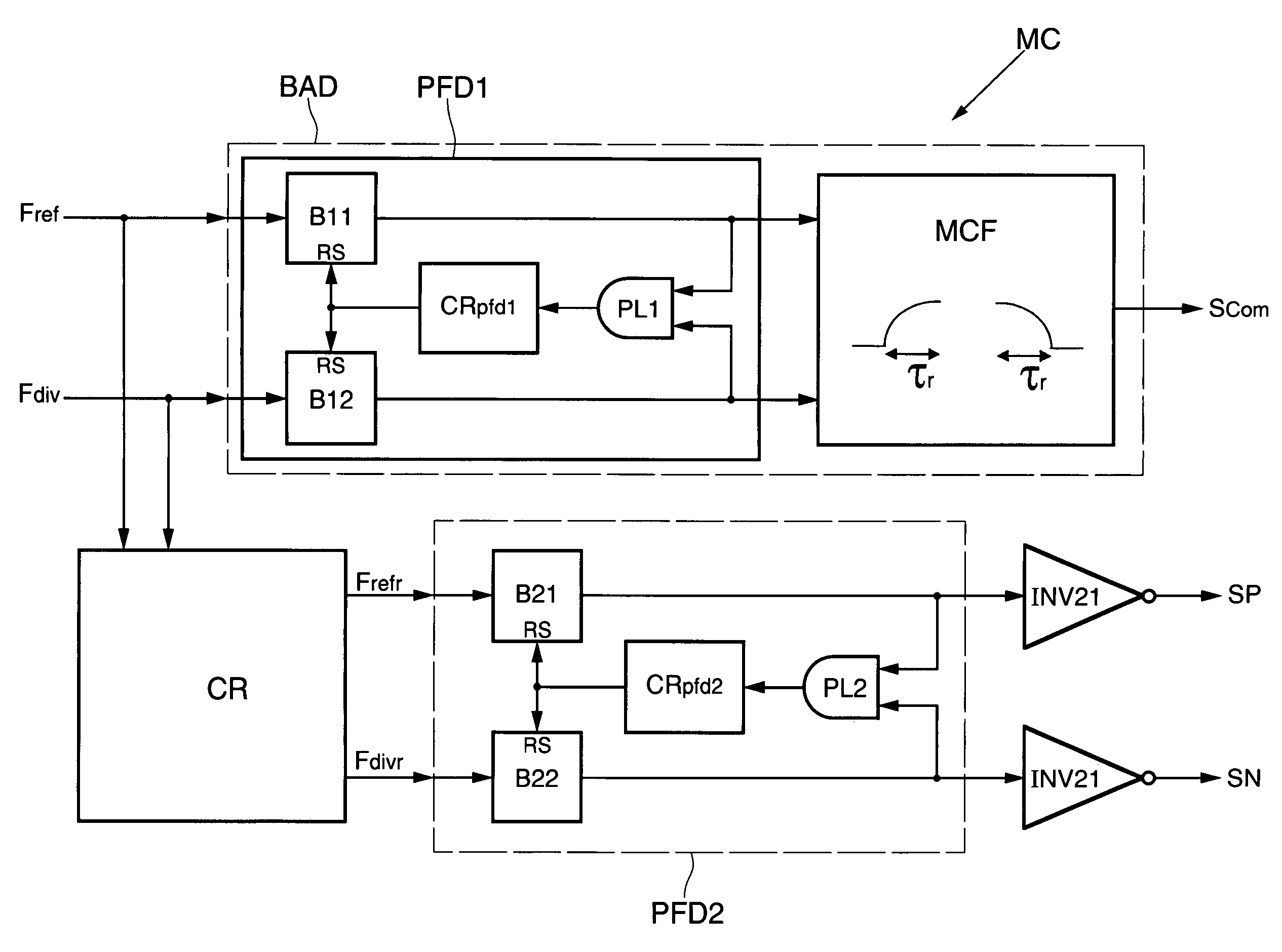

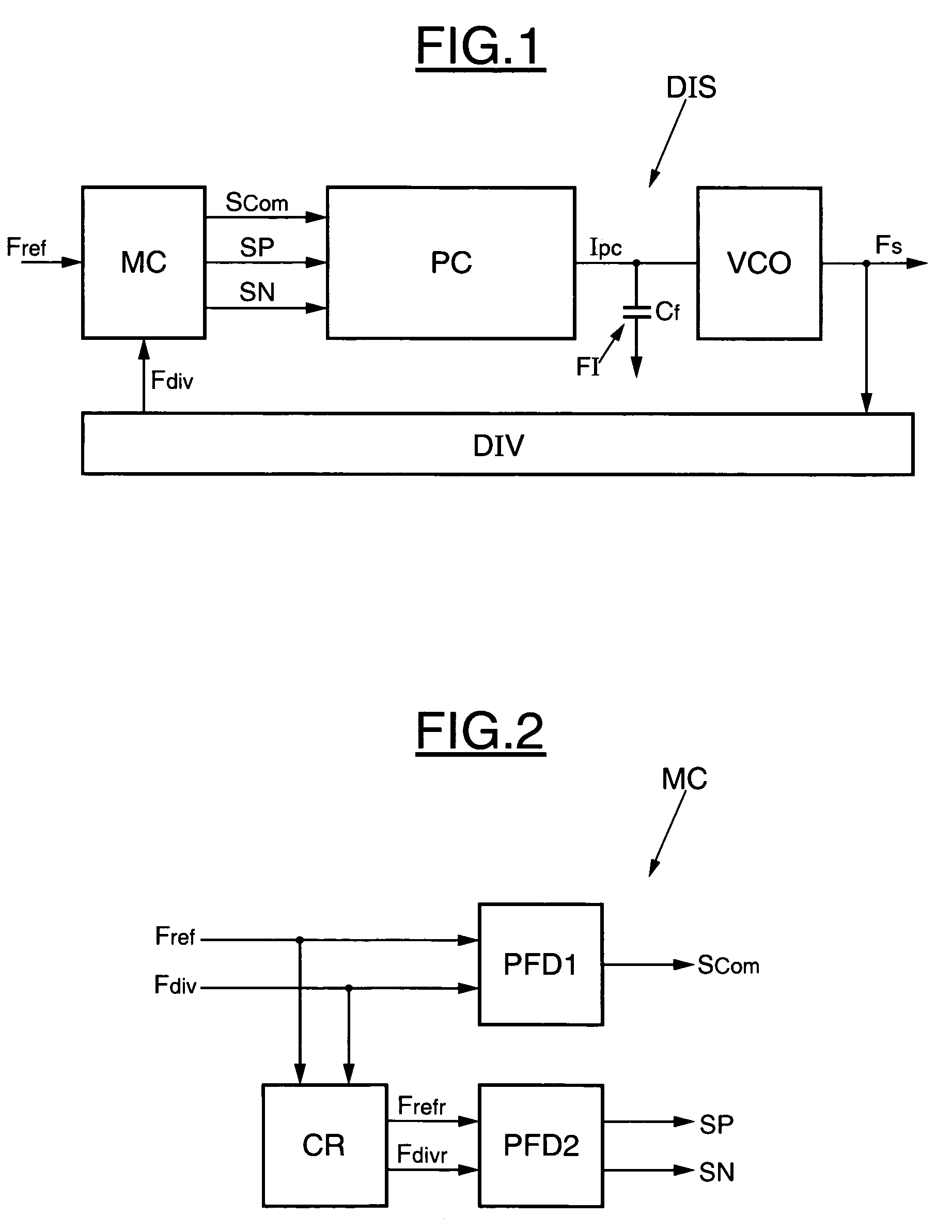

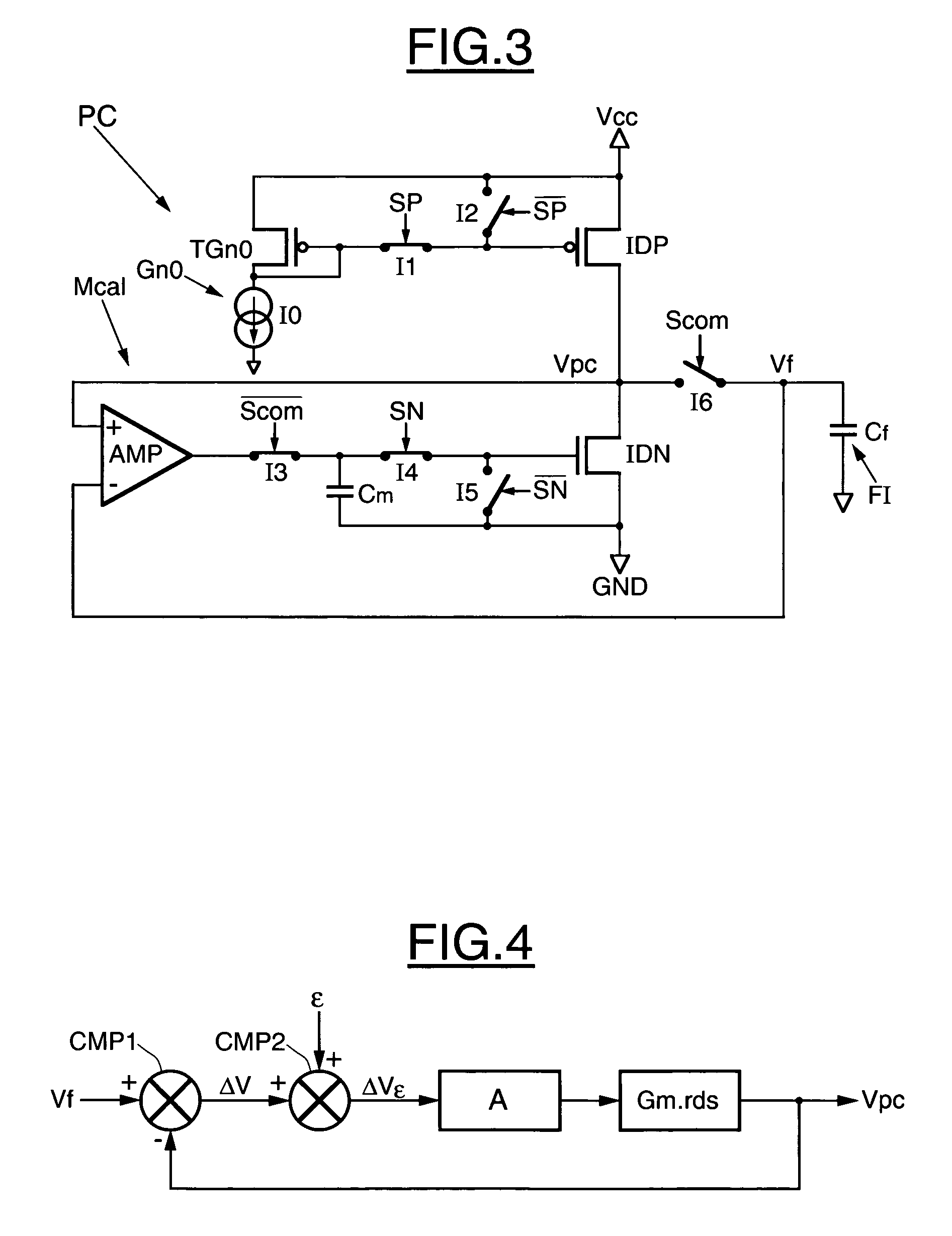

Method of correcting the phase difference between two input signals of a phase-locked loop and associated device

A method for correcting the phase difference between two input signals of a phase-locked loop may include a charge pump connected to a filter. Prior to the occurrence of the first of the two input signals, a calibration phase may be carried out in which the input of the filter is disconnected from the output of the charge pump, the output voltage from the charge pump is equalized, to within a given error, with the input voltage of the filter, the amplitudes of the opposing currents flowing in the charge pump being equalized. Then, during the two respective occurrences of the two input signals, the input of the filter is reconnected to the output of the charge pump, and two phase-shifted signals that are delayed with respect to the input signals are respectively generated, in response to which the two opposing currents are, respectively and successively, interrupted, before the calibration phase is recommenced.

Owner:STMICROELECTRONICS INT NV

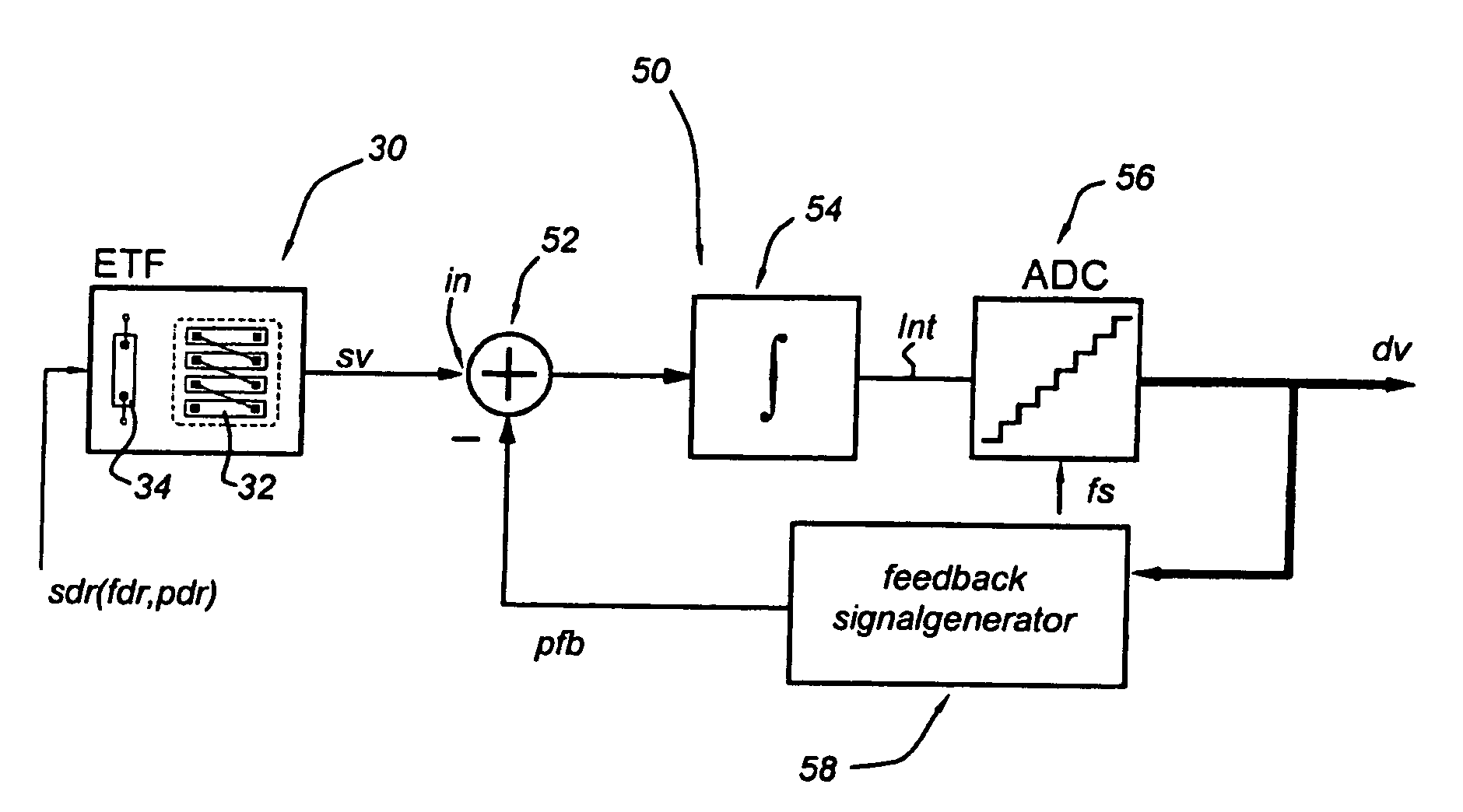

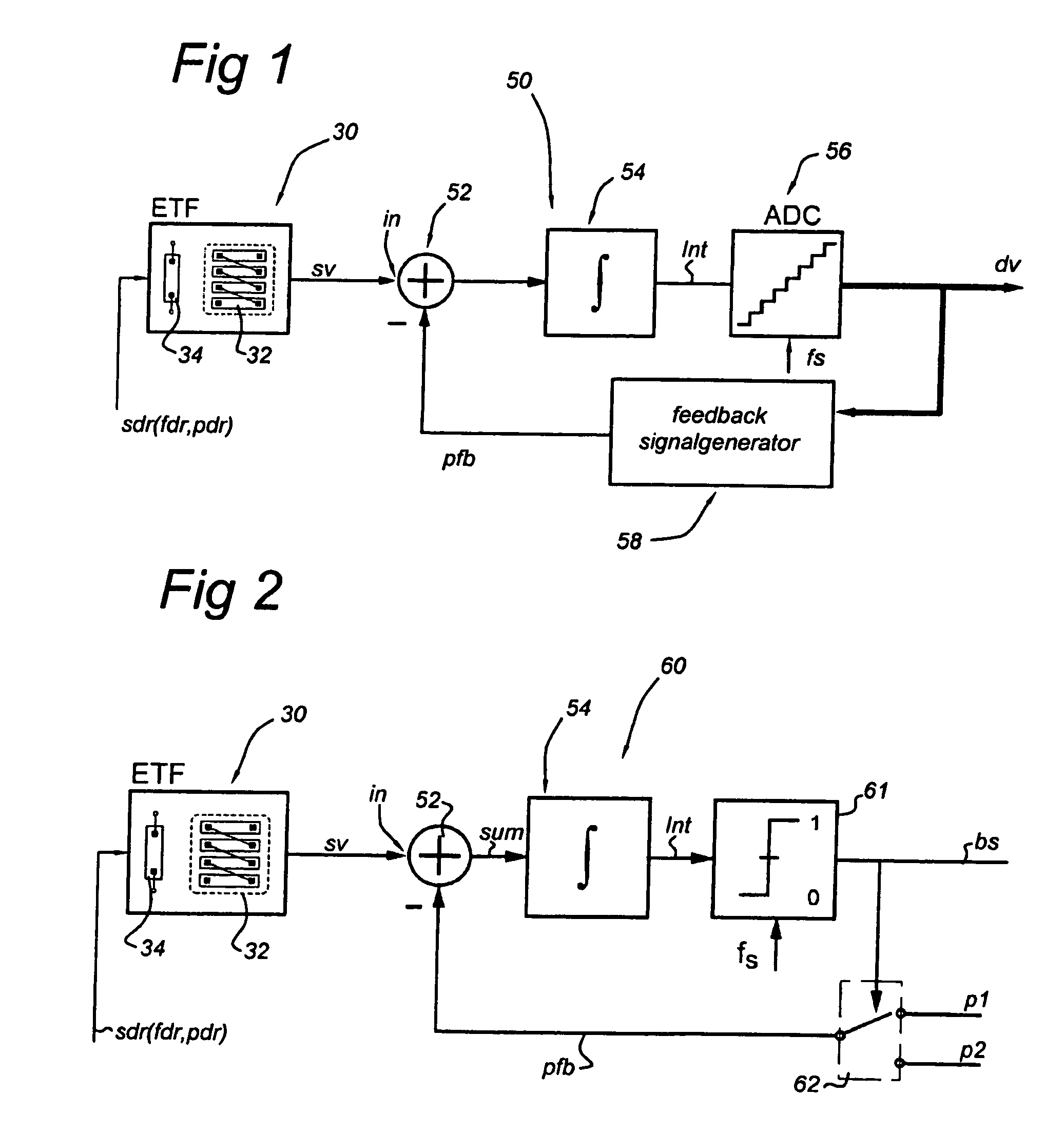

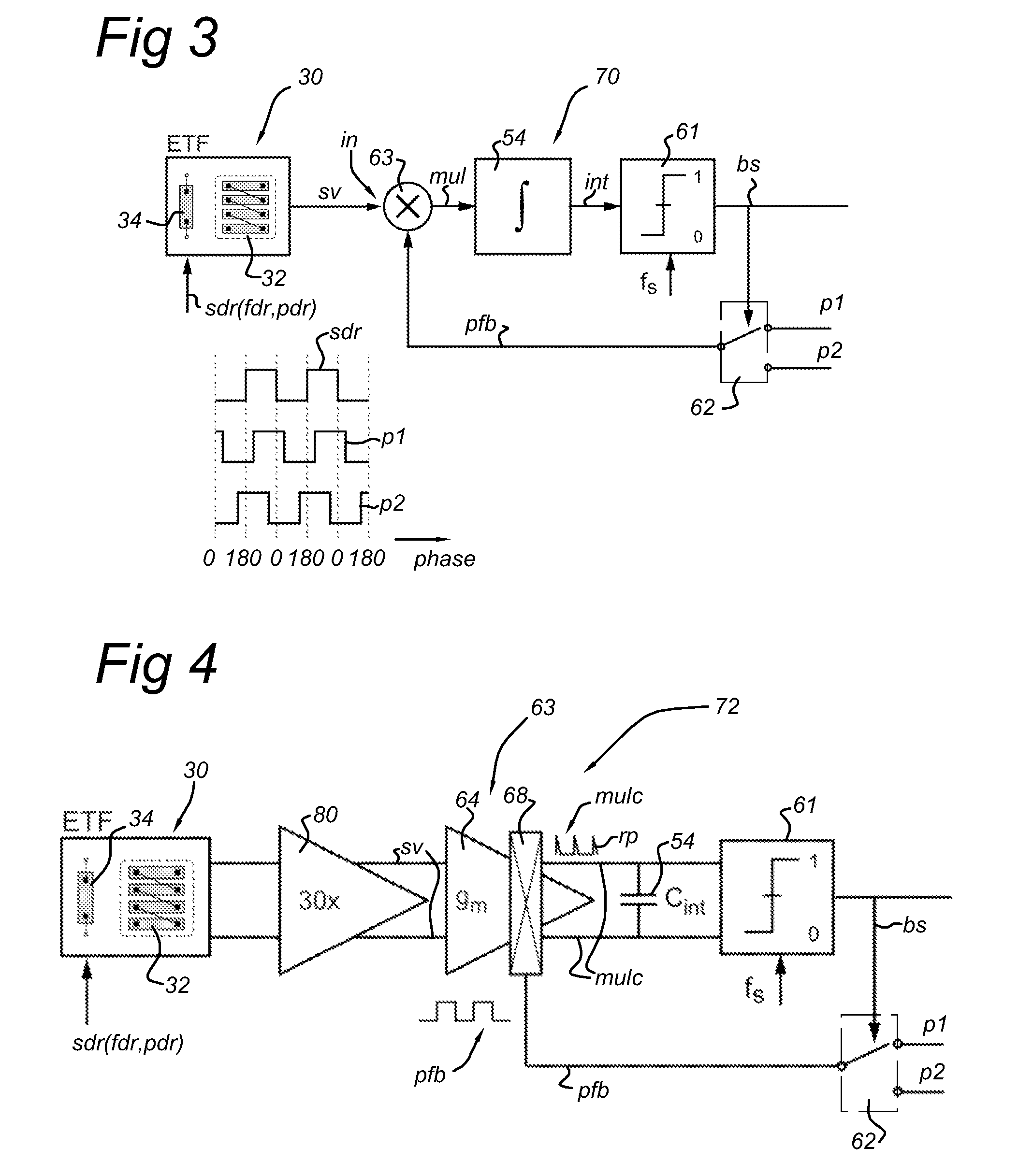

Synchronous phase detection circuit

ActiveUS8013636B2Correction of phase differenceAccurate measurementPulse automatic controlAnalogue conversionStationary phaseIntegrator

A phase detection circuit determines phase difference between a periodic signal and a reference signal of substantially equal frequency. The circuit includes: a source input receiving the periodic signal; a feedback signal generator providing a feedback signal (PFB) with substantially the same frequency as the reference signal; a phase difference circuit coupled to the source input node and a second signal input node coupled to the feedback signal generator, determining an error signal from phase difference between the periodic signal and PFB; an integrator circuit integrating the error signal into an integration signal; and a digitizing circuit digitizing the integration signal. The feedback signal generator is coupled to the digitizing circuit, providing PFB based on the digitized integration signal, and selecting the phase of PFB from a number of fixed phases. The phase detection circuit generates a time-average of the phase of PFB selected from the plurality of fixed phases.

Owner:STICHTING VOOR DE TECH WETENSCHAPPEN

Color imaging element, imaging device, and storage medium storing an imaging program

InactiveUS8723991B2Correction of phase differenceHigh precisionTelevision system detailsTelevision system scanning detailsSquare arrayPhase difference

An image pickup device includes: a color filter having basic array patterns with first and second array patterns disposed symmetrically, wherein the first array pattern has a first filter at the 4 corner and center pixels of a 3×3 pixel square array, a second filter in a line at the horizontal direction center of the square array, and a third filter placed in a line at the vertical direction center of the square array, and the second array pattern has the same placement of the first filter as the first array pattern and has placement of the second filter and placement of the third filter swapped to that of the first array pattern; and phase difference detection pixels placed on pixels corresponding to positions of centers of at least 1 pair of patterns out of 2 pairs of the first array pattern and the second array pattern.

Owner:FUJIFILM CORP

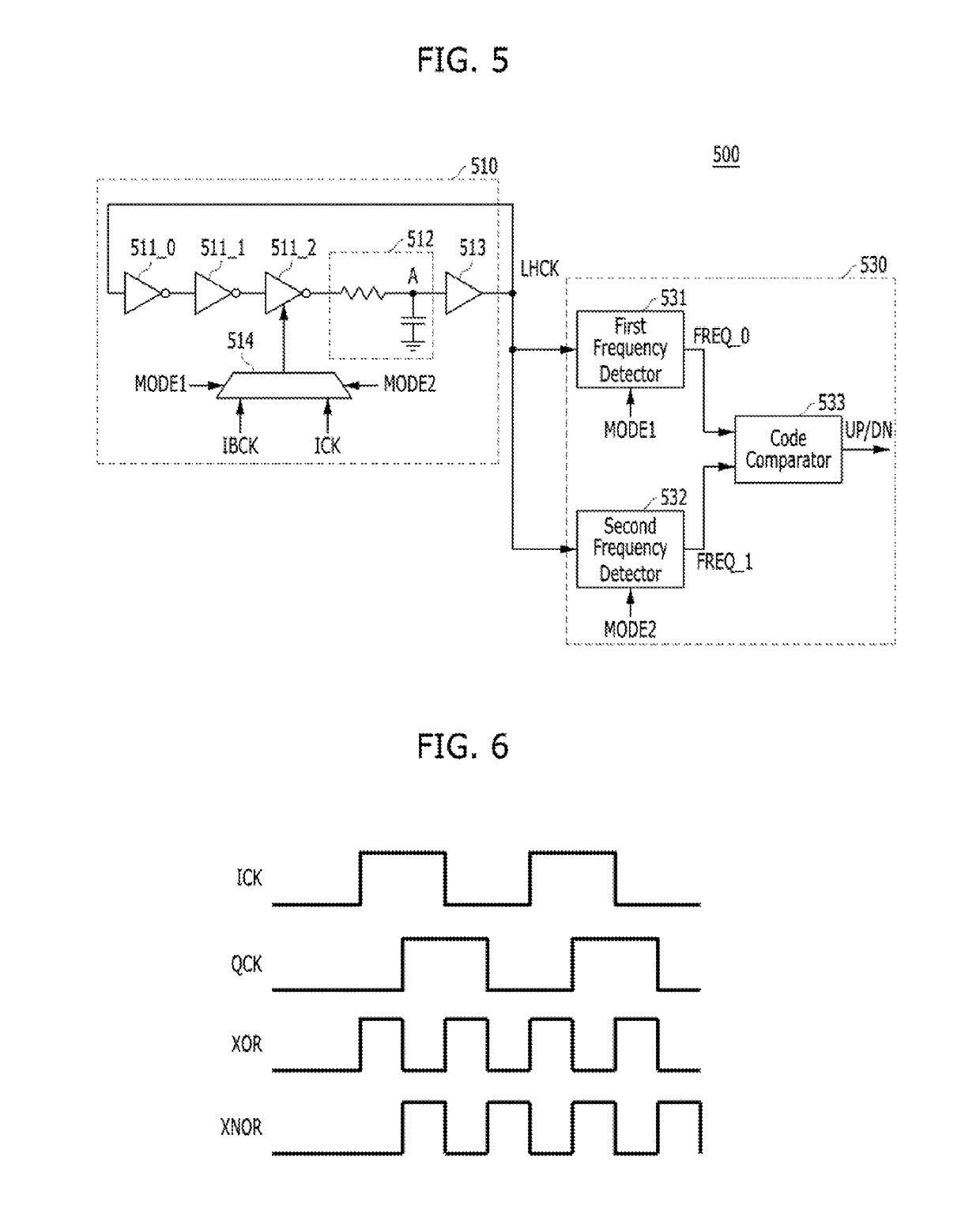

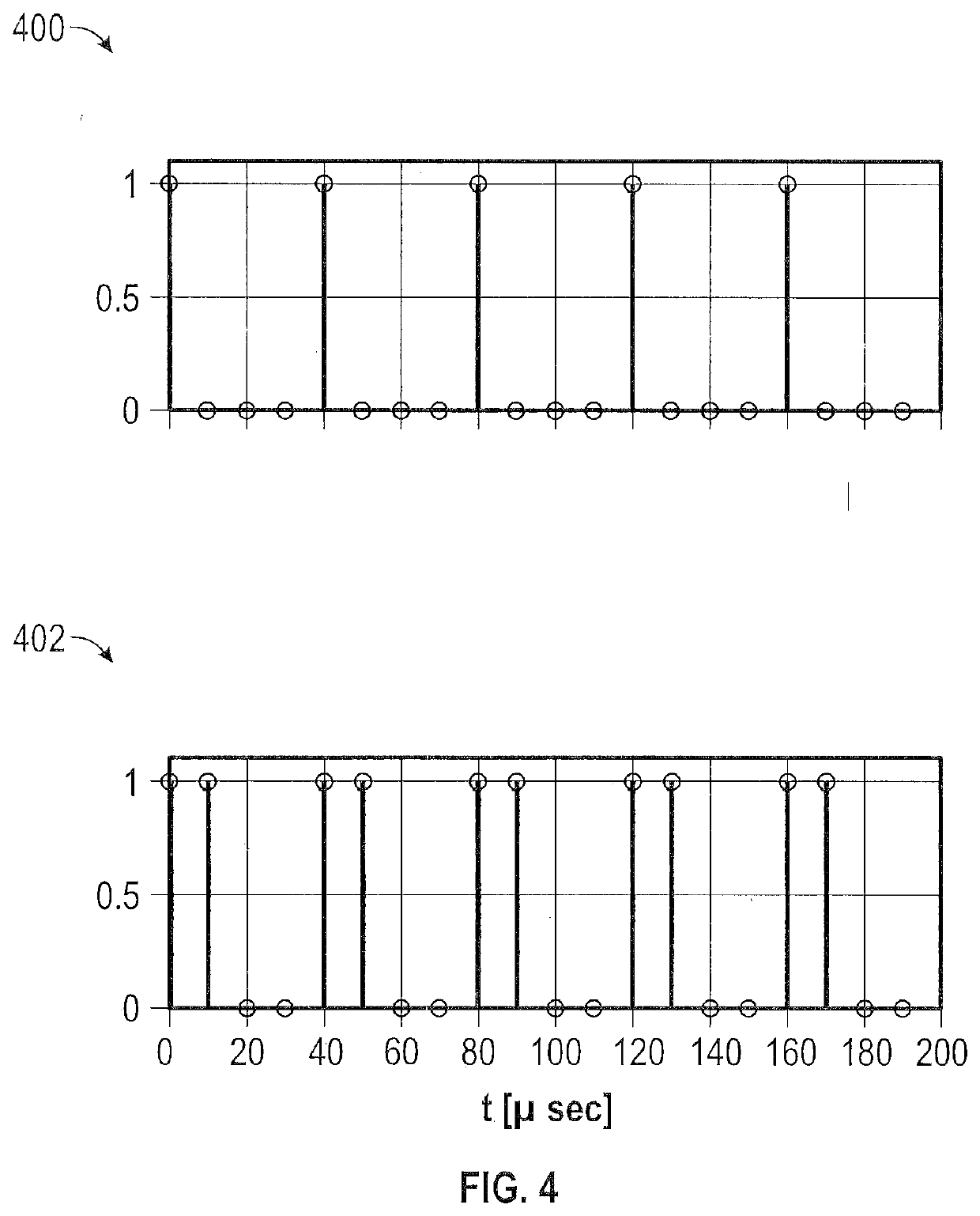

Asymmetric pulse width comparator circuit and clock phase correction circuit including the same

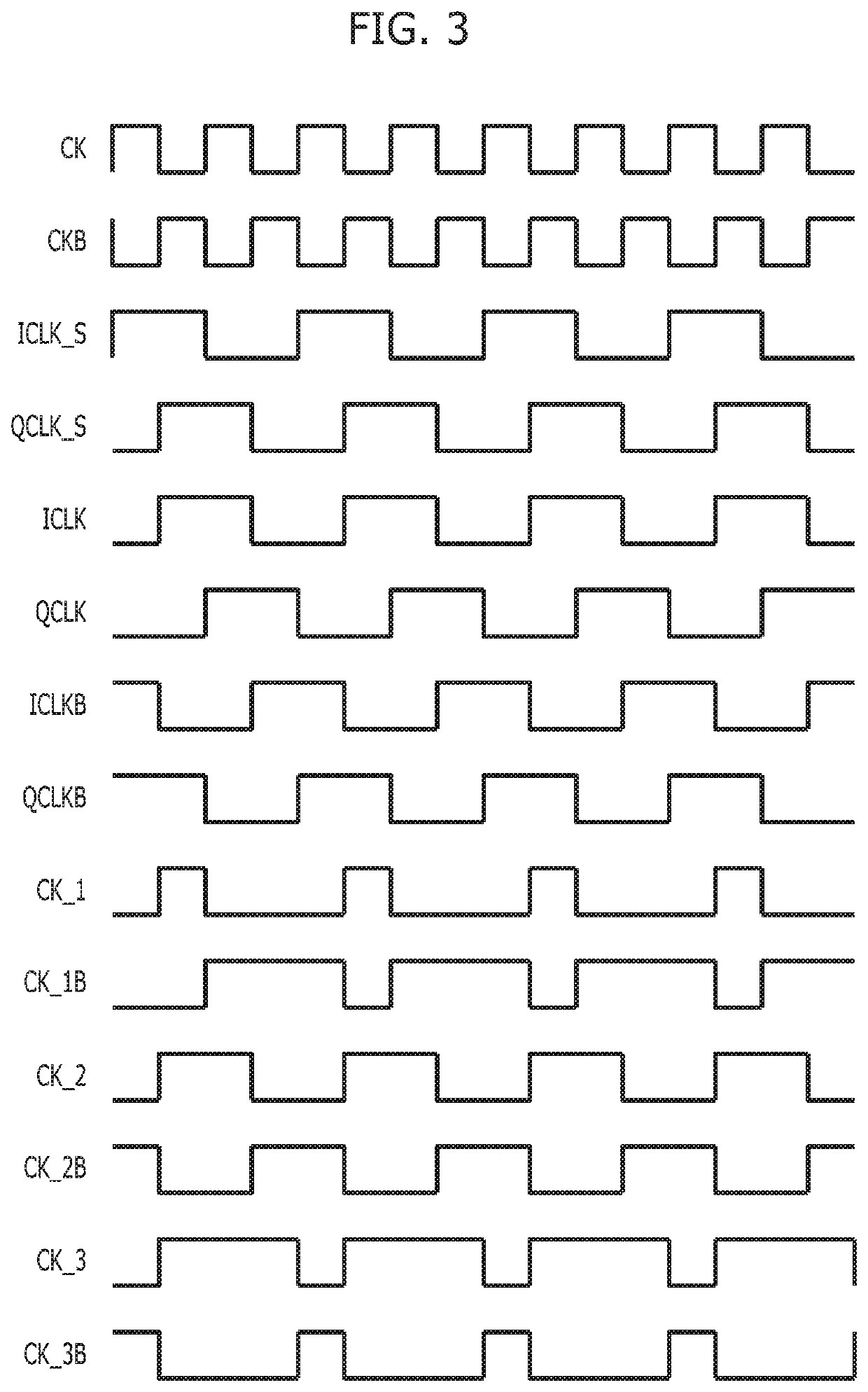

ActiveUS20190379369A1Accurate correctionCorrection of phase differencePulse train pattern monitoringContinuous to patterned pulse manipulationComparators circuitsEngineering

A clock phase correction circuit includes: a first variable delay circuit suitable for delaying a second source clock to generate a third clock; a first pulse generation circuit suitable for generating a first pulse signal that is activated from an edge of a first clock to an edge of the third clock and generating a second pulse signal that is activated from the edge of the third clock to the edge of the first clock; and a first delay value adjustment circuit suitable for detecting whether a ratio of a pulse width of the first pulse signal to a pulse width of the second pulse signal is greater or less than 1:3 to produce a detection result and adjusting a delay value of the first variable delay circuit based on the detection result.

Owner:SK HYNIX INC

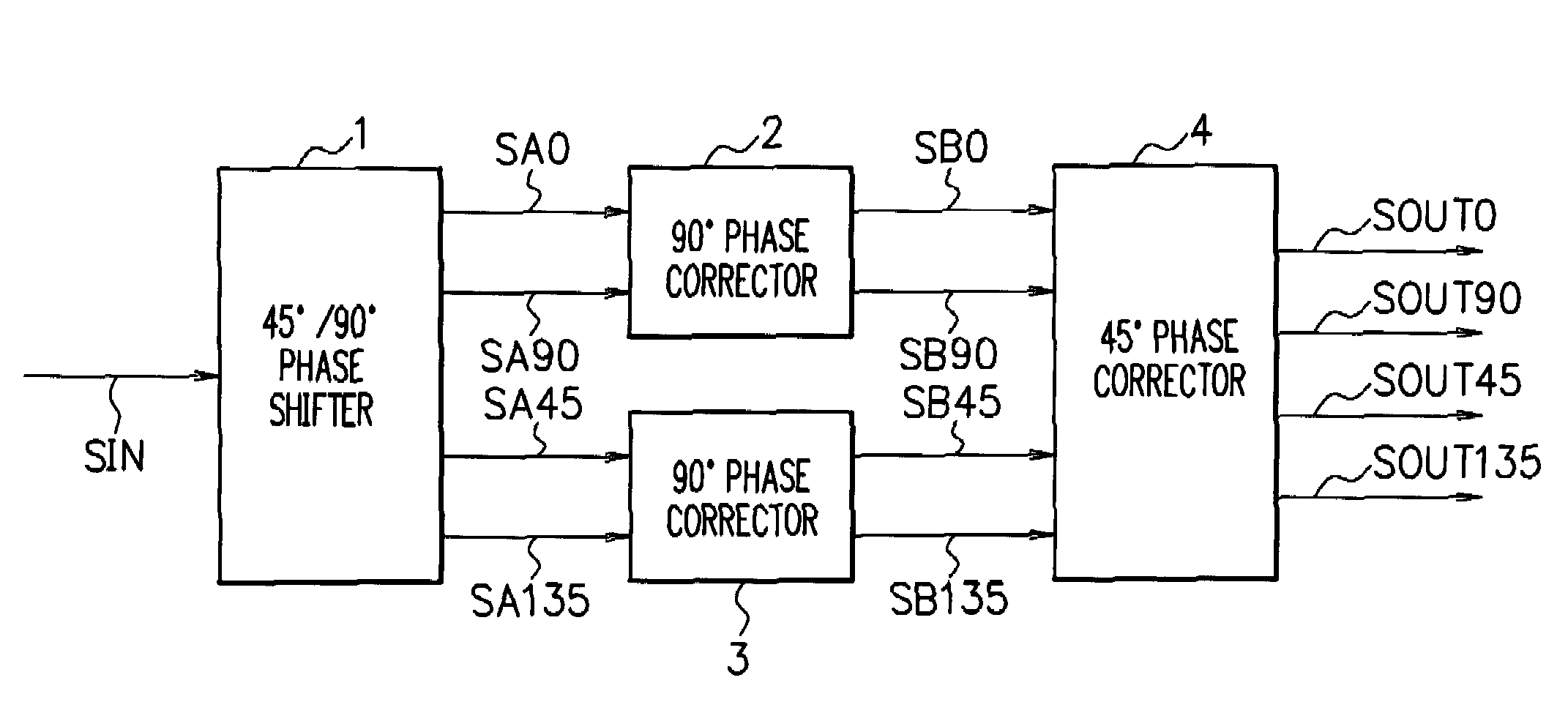

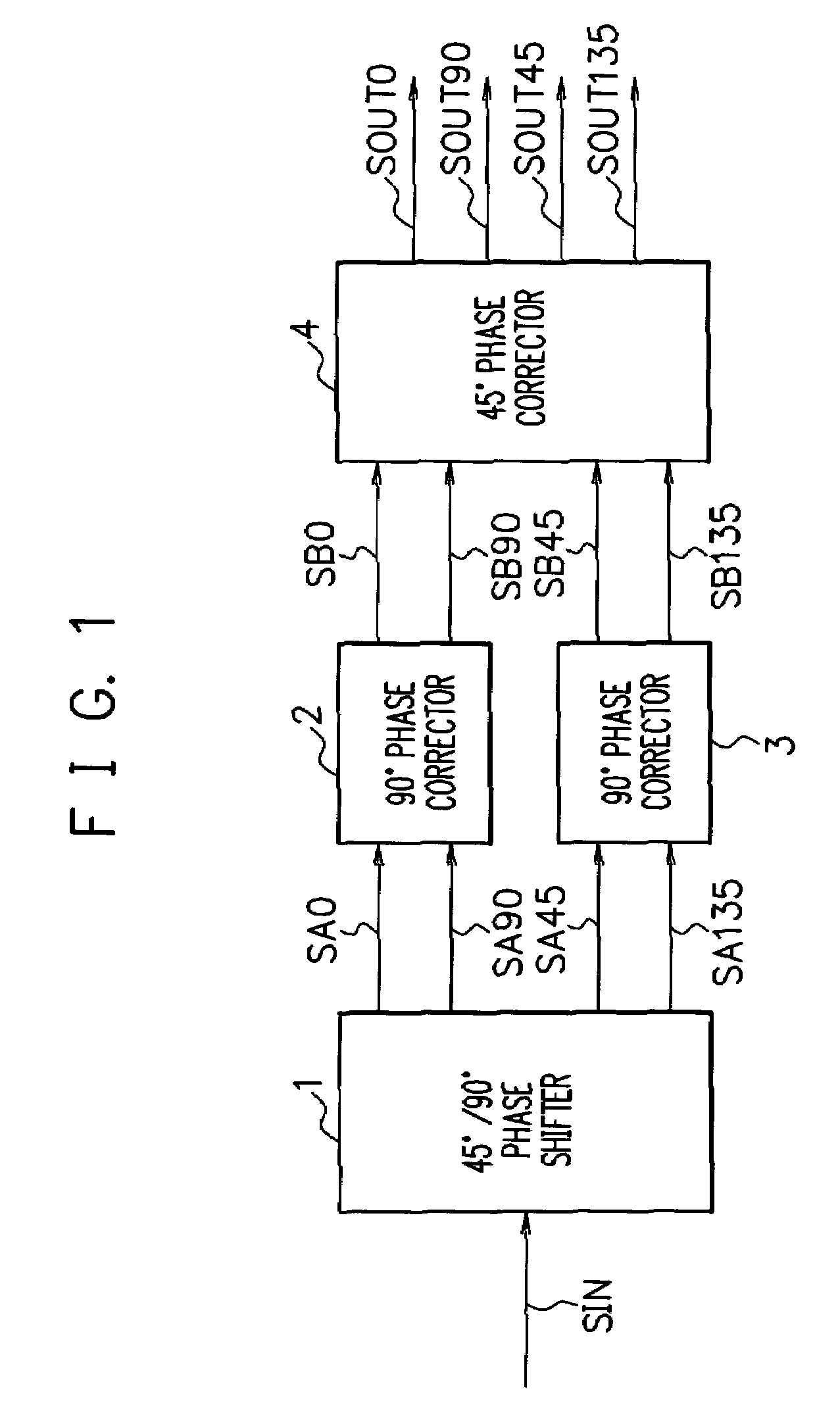

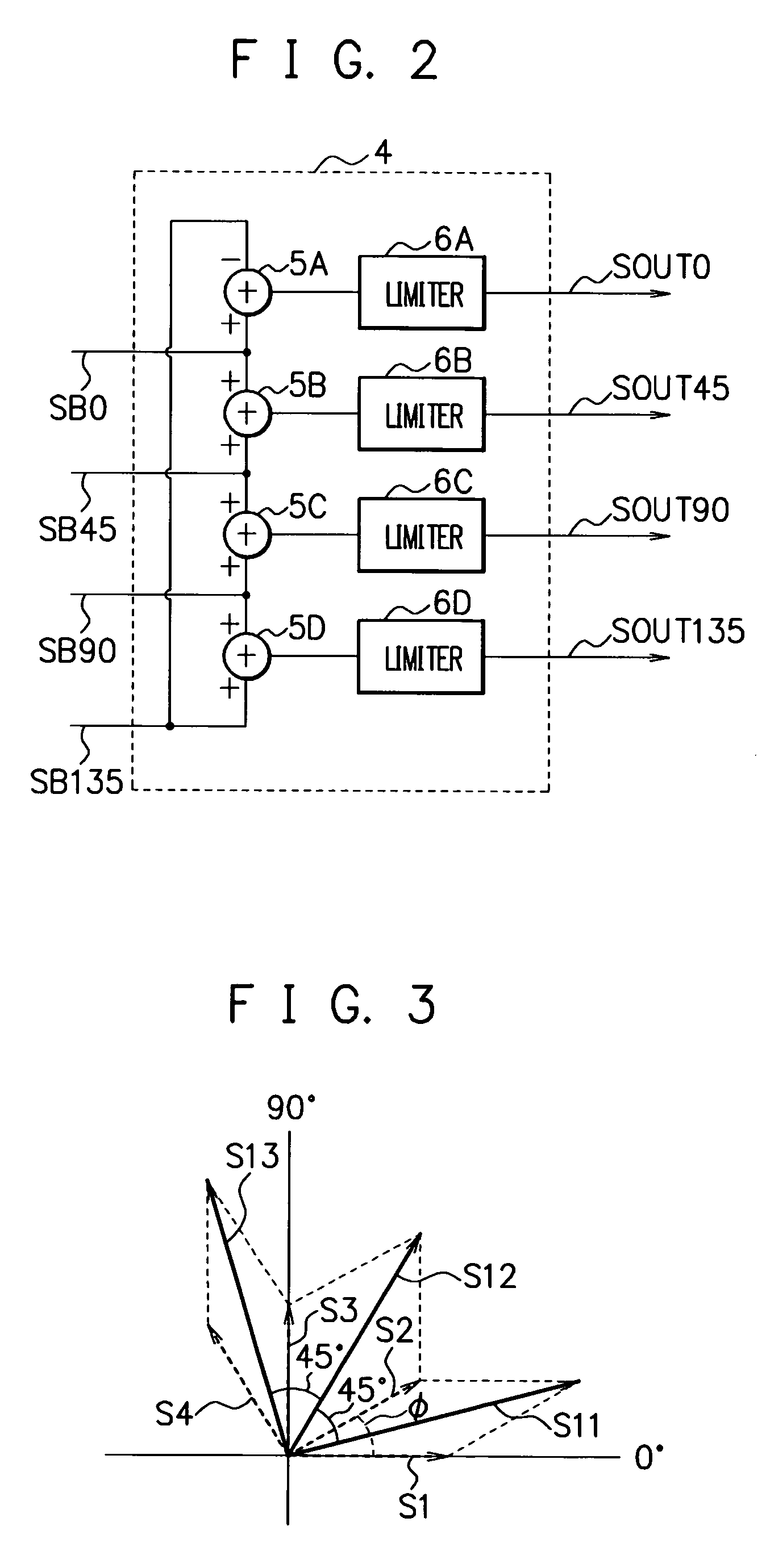

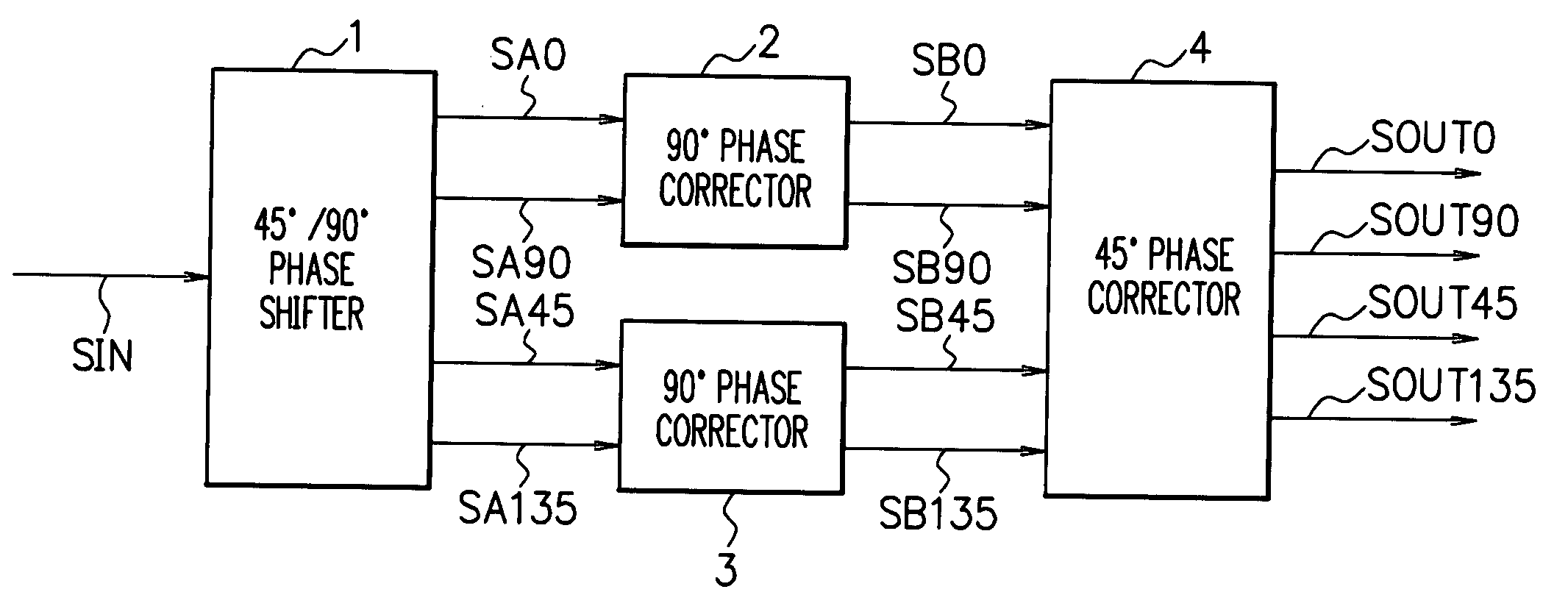

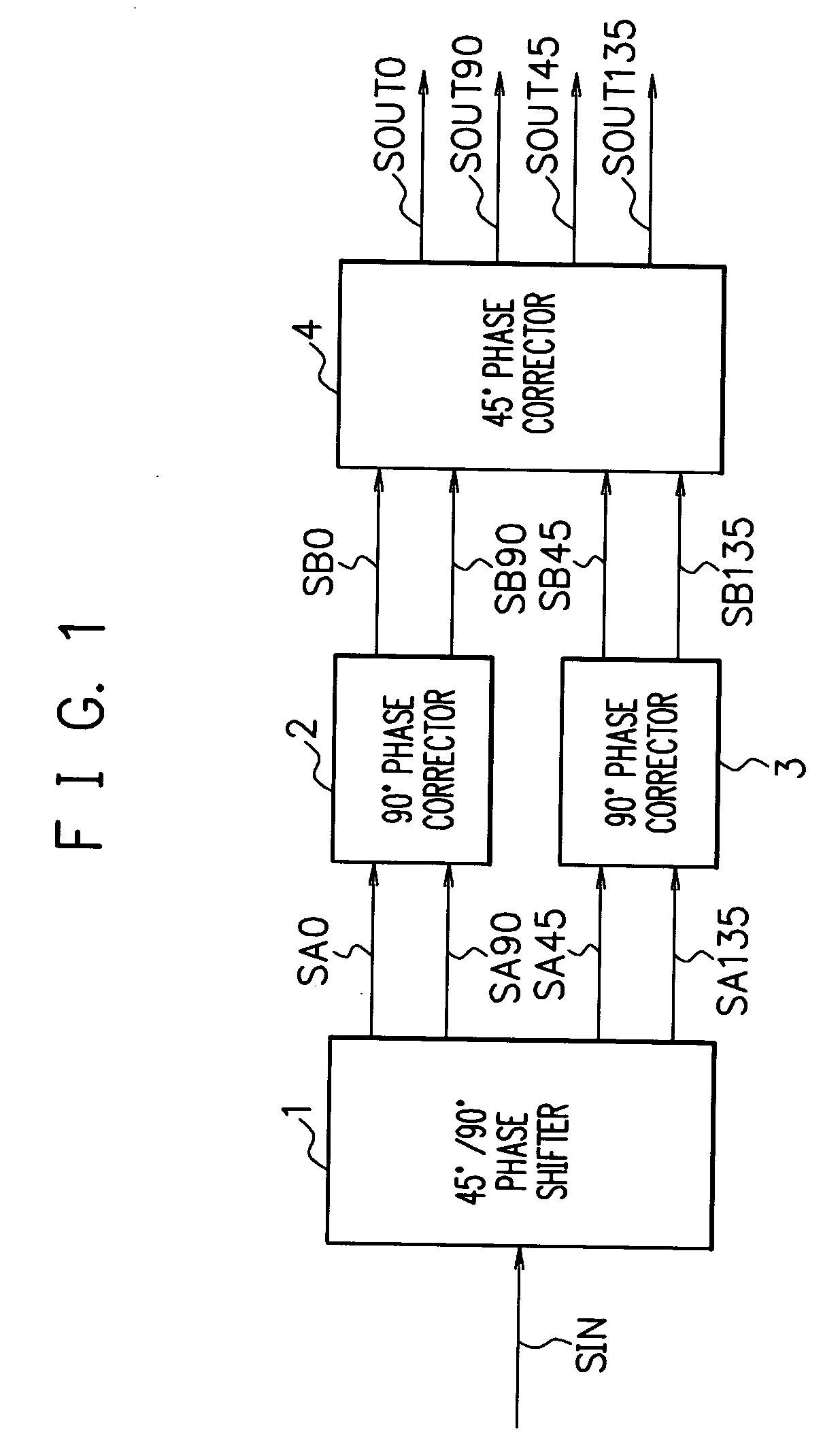

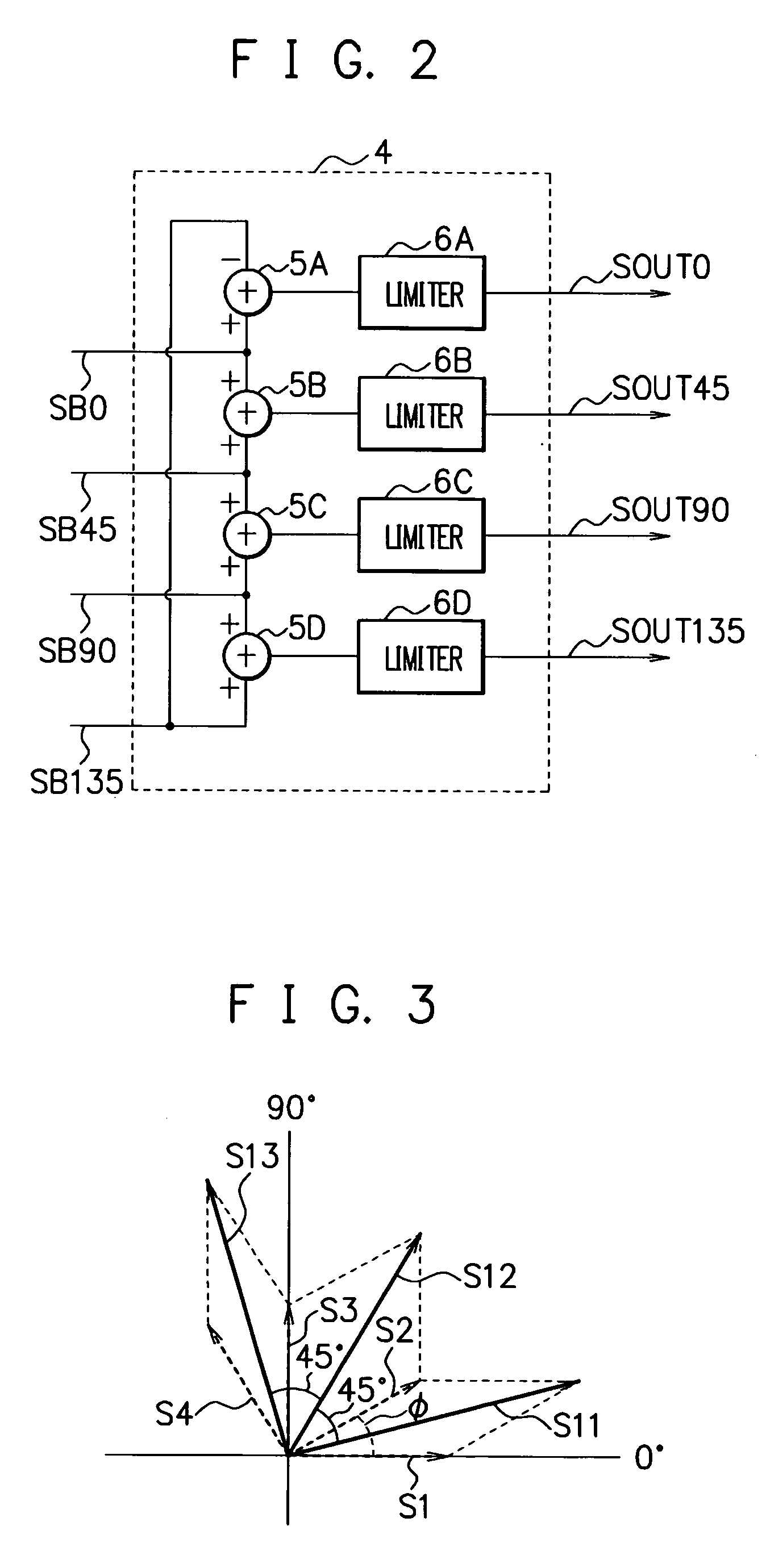

Phase shift circuit and phase correcting method

ActiveUS7443220B2Correction of phase differenceEliminate errorsMultiple-port networksSingle output arrangementsPhase correctionPhase shifted

A phase shift circuit includes a 45° phase corrector that performs vector synthesis of signals supposed to have a 45° phase difference, out of a plurality of sets of orthogonal phase signals having an about 45° phase difference and an equal amplitude, the orthogonal phase signals in each set having undergone 90° phase correction, and outputs signals resulting from the vector synthesis, whereby a phase error between the orthogonal phase signals in the different sets is eliminated by the vector synthesis to make it possible to correct their phase difference to accurately 45°.

Owner:SOCIONEXT INC

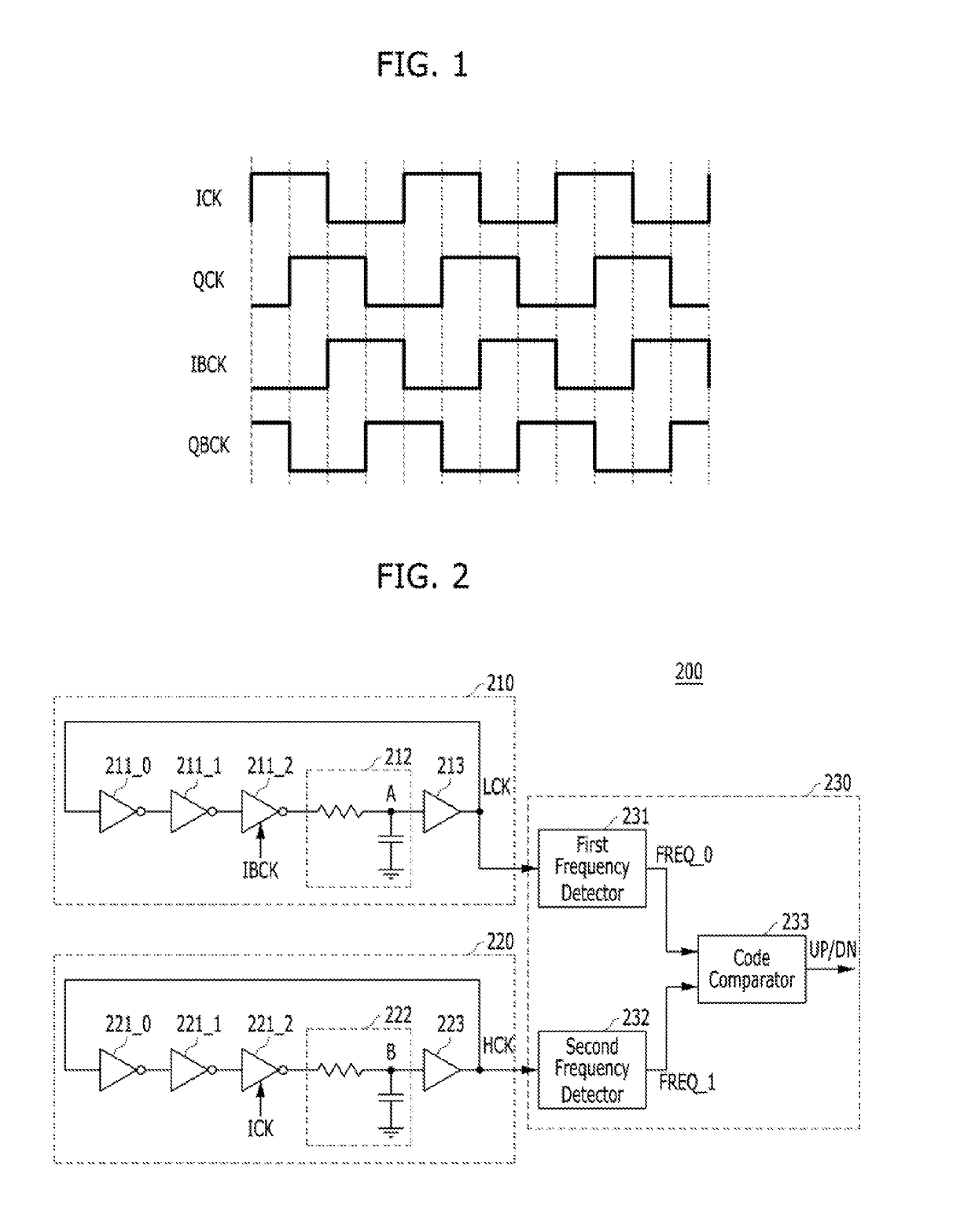

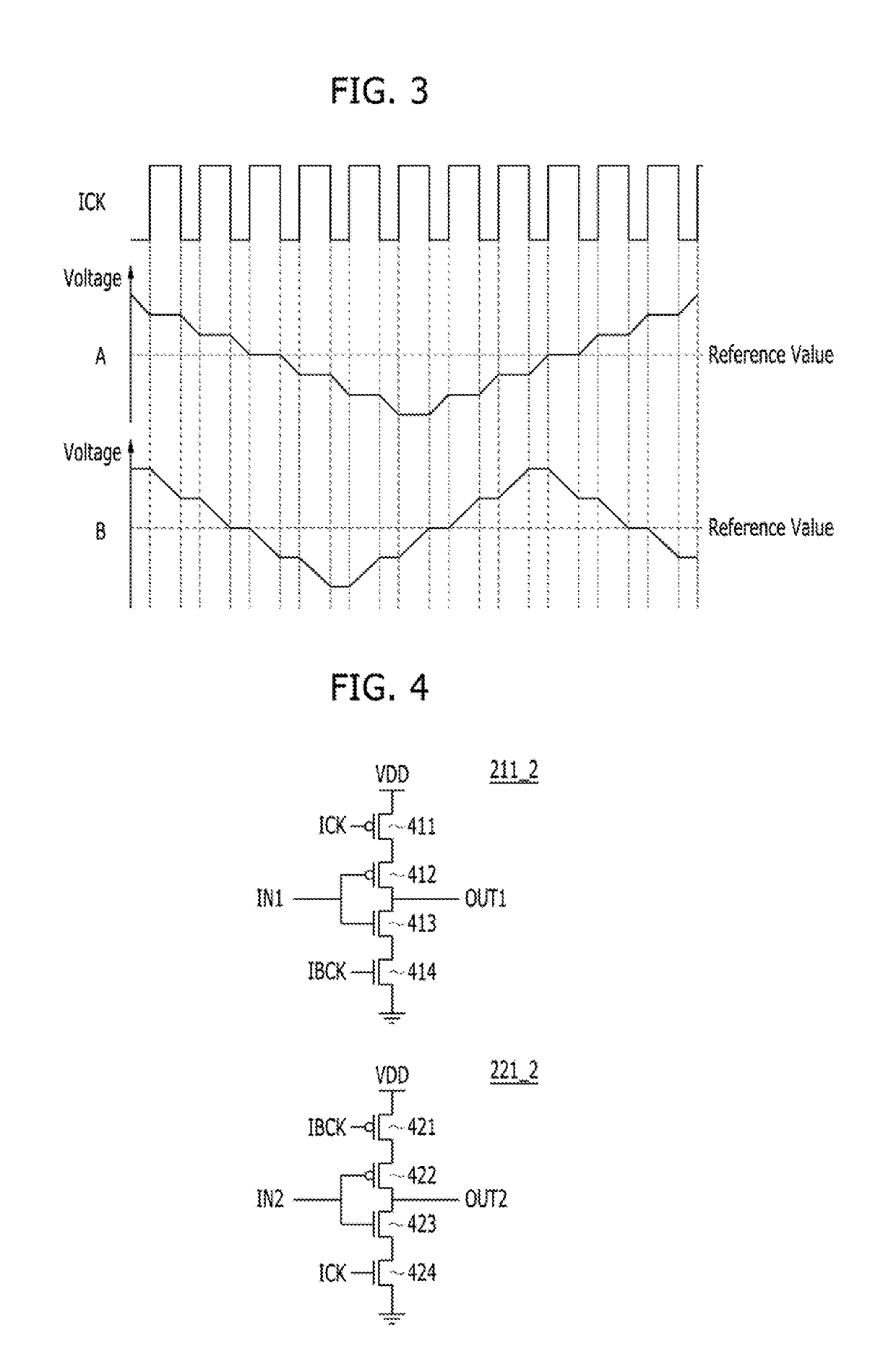

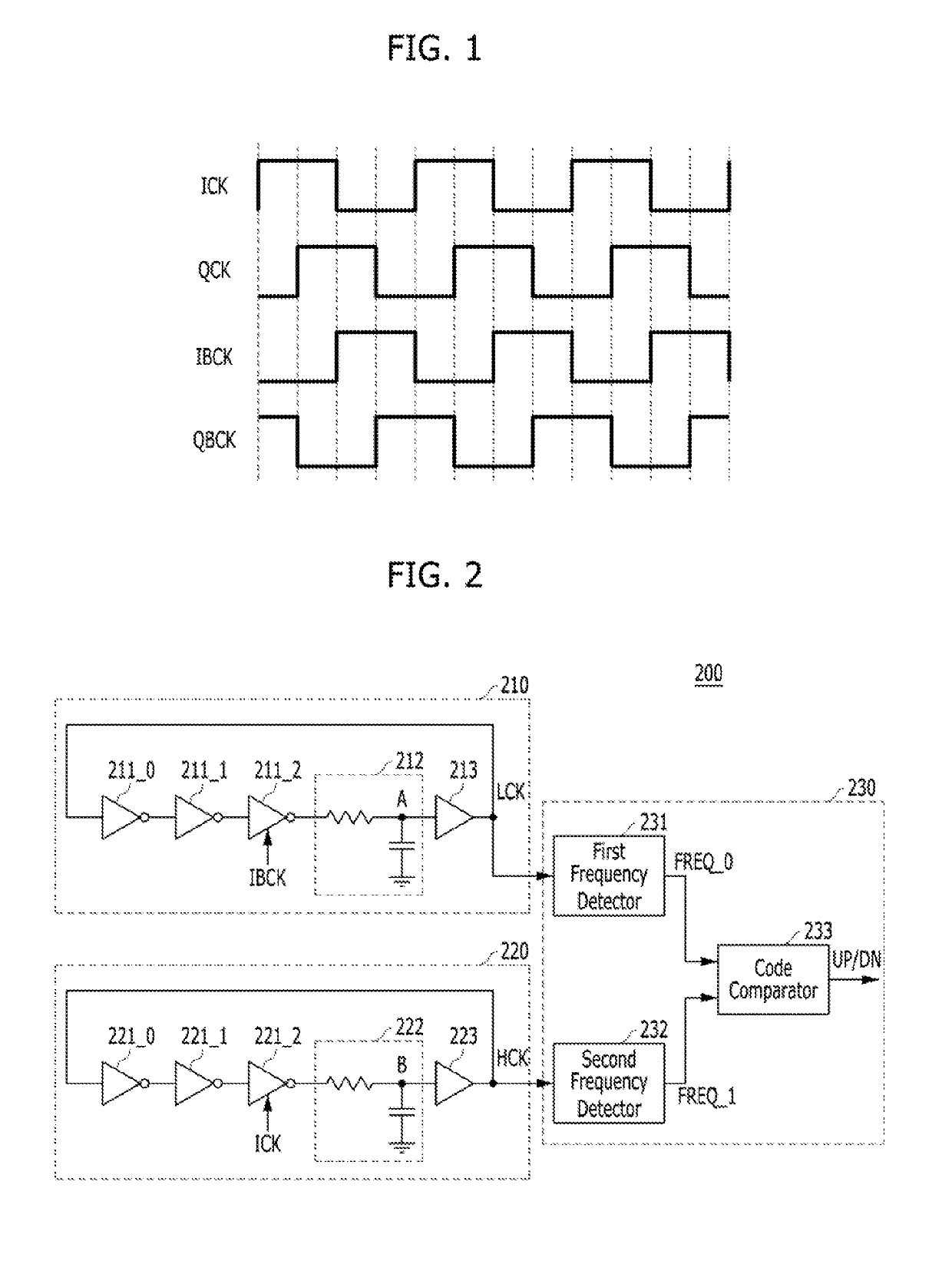

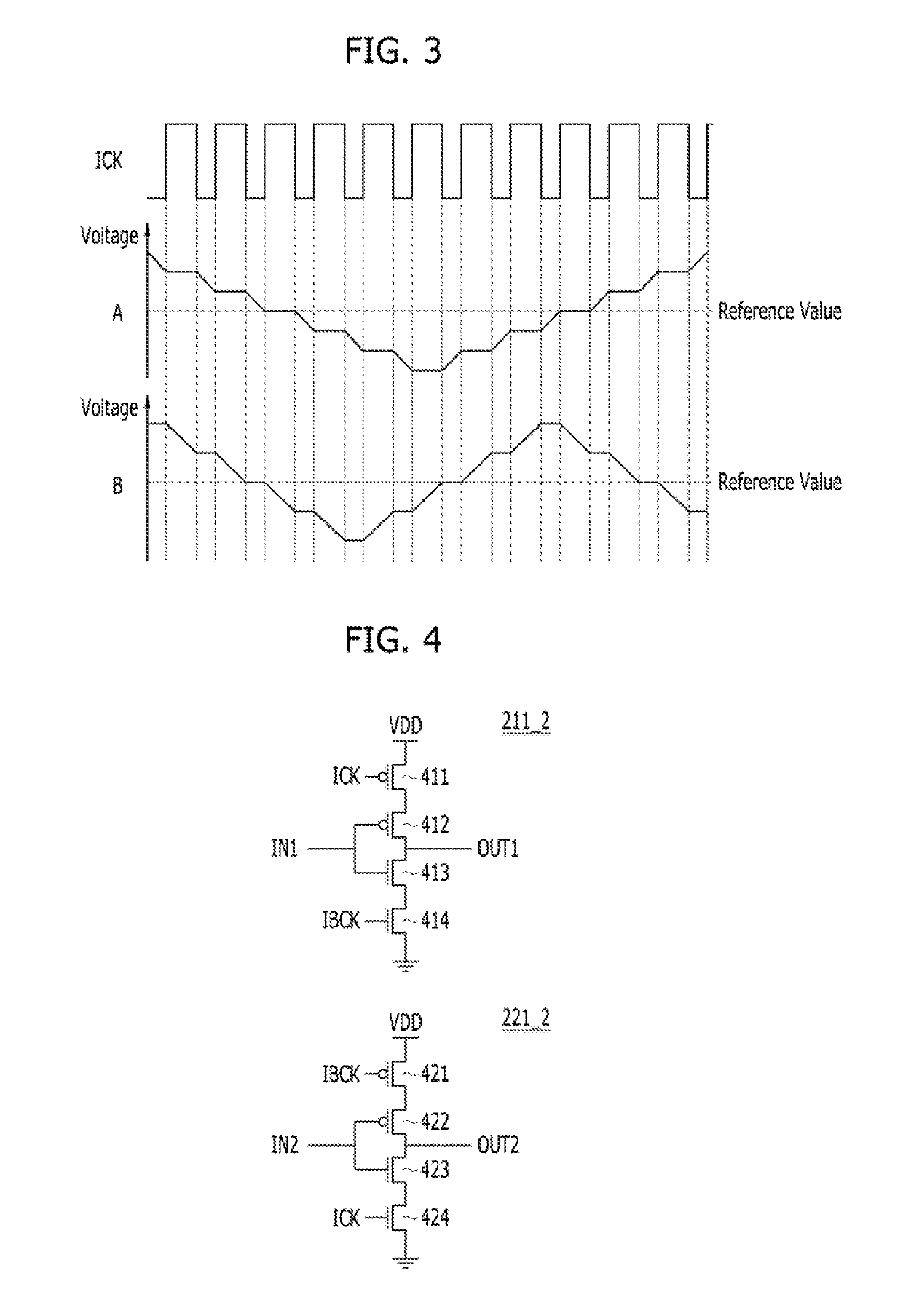

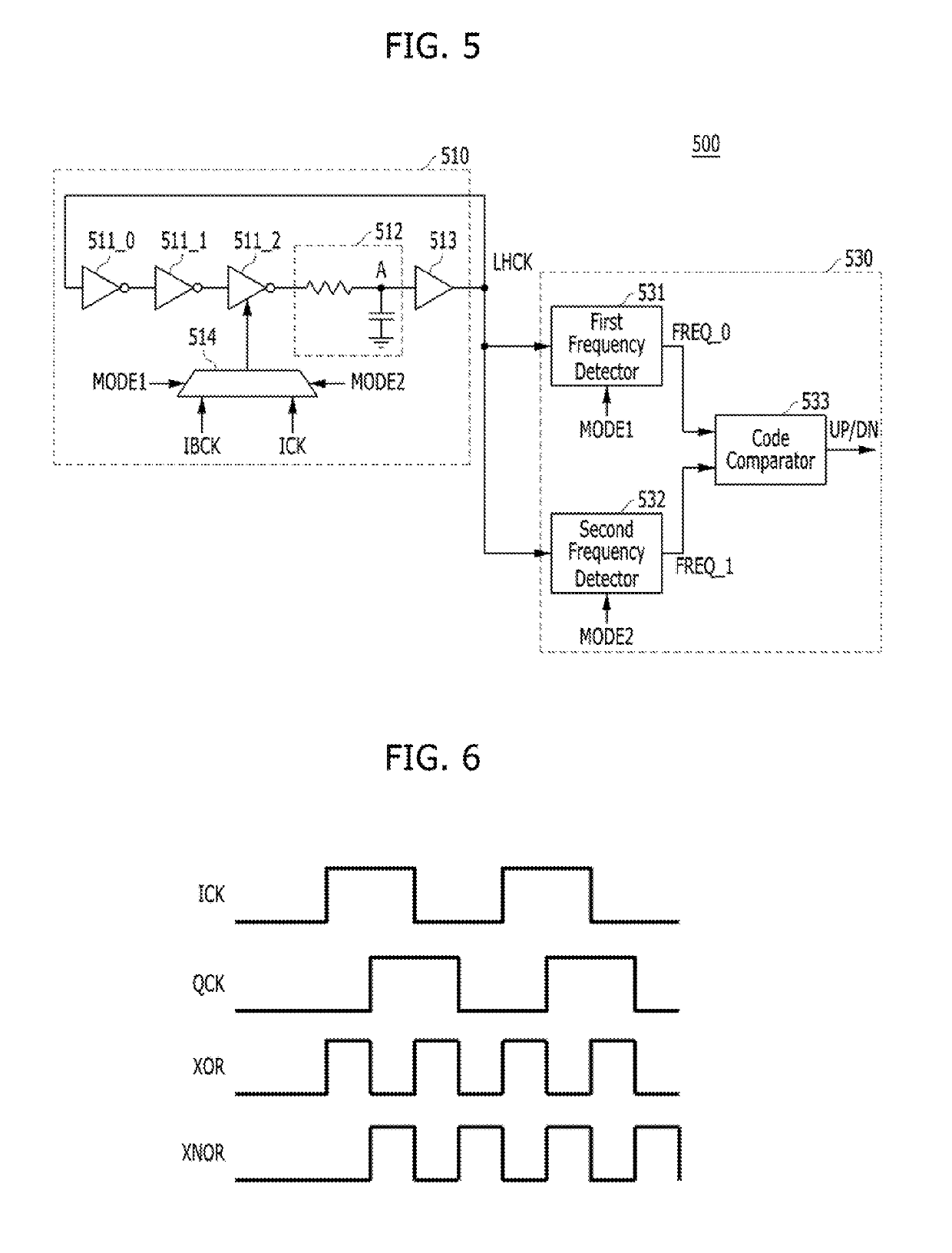

Duty cycle detector and phase difference detector

ActiveUS20190131962A1Precise ratioCorrection of phase differenceMultiple-port networksMultiple input and output pulse circuitsPhase differenceComparator

A duty cycle detector includes a first ring oscillator suitable for including an odd number of first inverters and generating a first periodic signal by using the first inverters, at least one inverter among the first inverters being enabled during a time interval when a clock has a first value, a second ring oscillator including an odd number of second inverters and suitable for generating a second periodic signal using the second inverters, at least one inverter among the second inverters being enabled during a time interval when the clock has a second value. The duty cycle detector further includes a frequency comparator suitable for comparing a frequency of the first periodic signal with a frequency of the second periodic signal and generating a duty cycle detection signal of the clock.

Owner:SK HYNIX INC +1

Oscillating circuit

InactiveUS20120075025A1High sensitivityImprove featuresPulse generation by logic circuitsEngineeringOutput feedback

An oscillating circuit includes N nodes outputting oscillating signals, a main loop circuit including N inverting circuits, and a plurality of auxiliary loop circuits. Each inverting circuit in the auxiliary loop circuits is connected in parallel with even numbers of inverting circuits cascaded in the main loop circuit. The circuits for feeding back signals from outputs to inputs of the respective inverters of the main loop circuit have circuit configurations equivalent to each other. Each inverting circuit in the main loop circuit and the auxiliary loop circuits drives an output line such that a phase of an output signal is inverted with respect to a phase of an input signal and has driving power that becomes lower when the phases of the output signal and the input signal are inverted with respect to each other than when the output signal and the input signal are in phase with each other.

Owner:SONY CORP

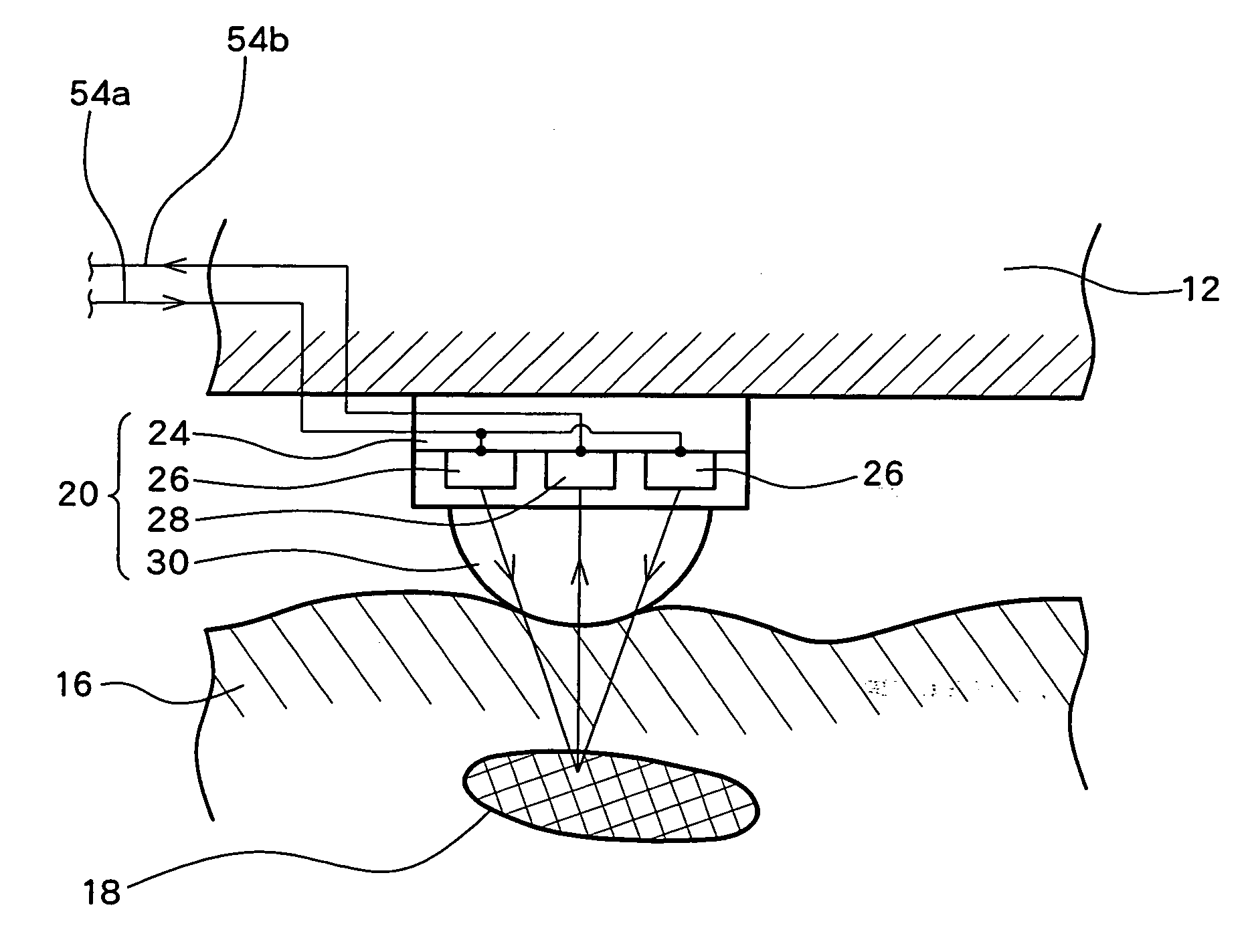

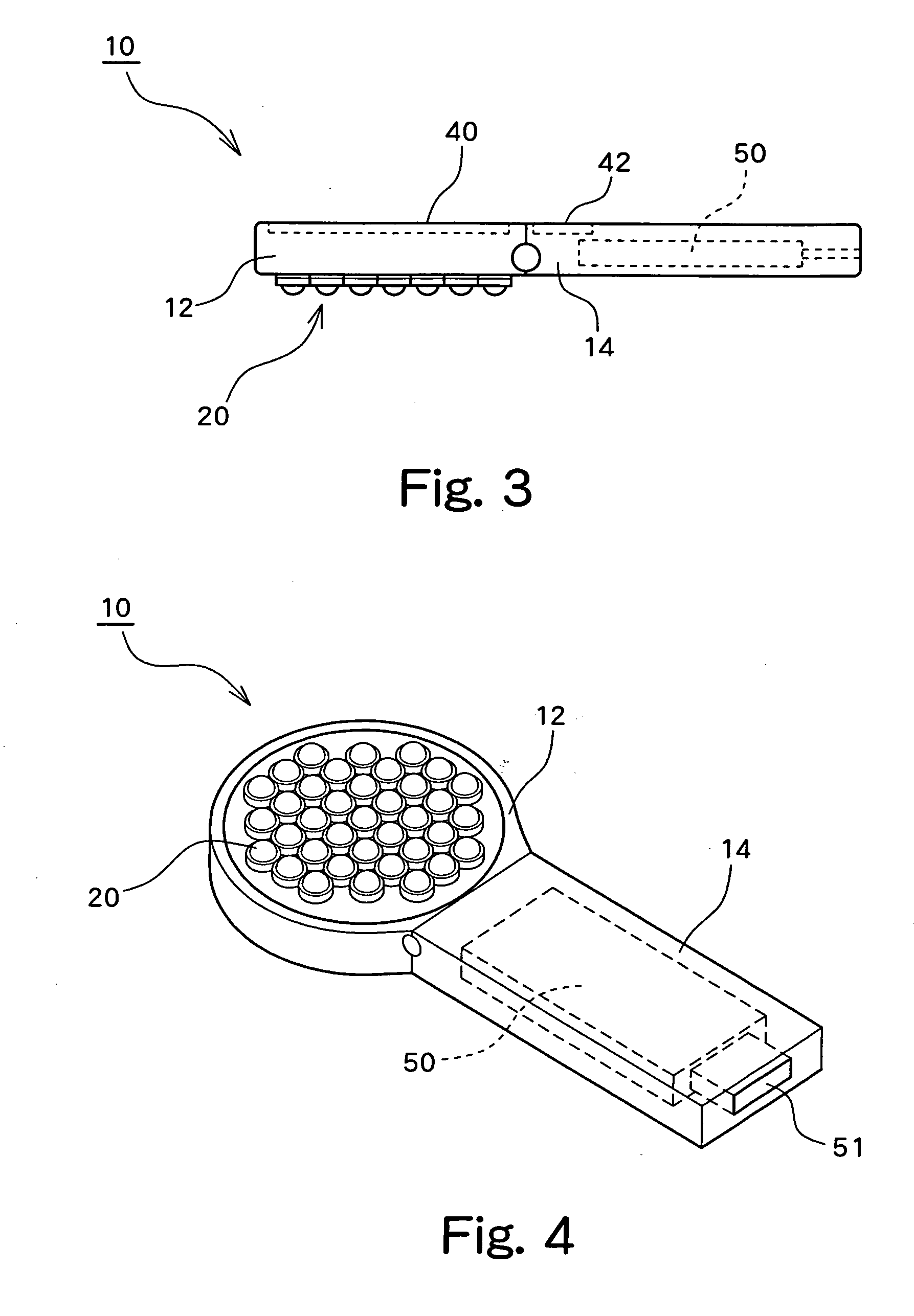

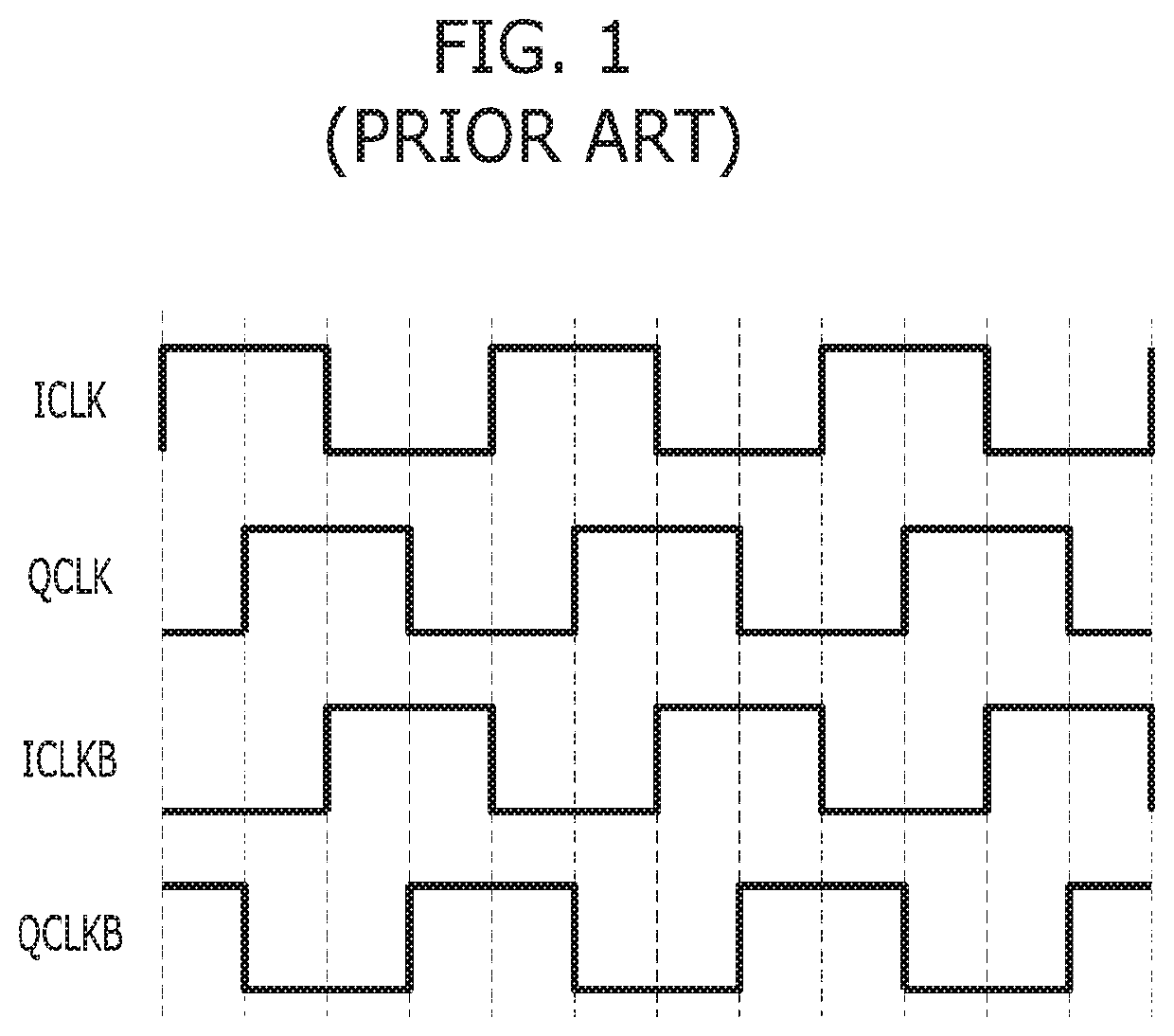

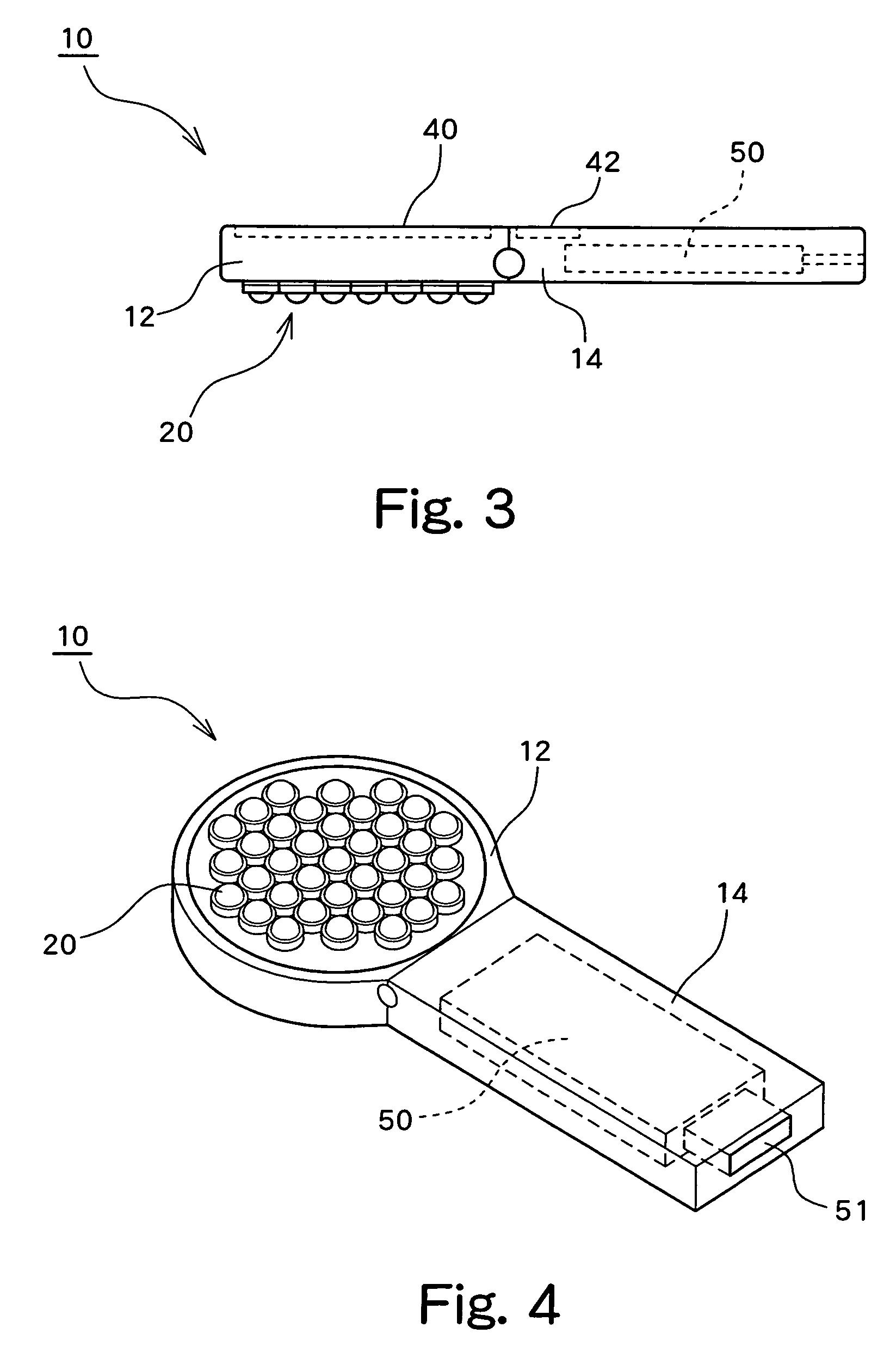

Biological Property Check Device Using Light

InactiveUS20080037021A1Accurately determineCorrection of phase differenceDiagnostics using lightSurgeryDisplay processingPhase shifted

A biological property check device includes a plurality of probes (20) each having a light emitting element (26) for applying light to a biological tissue and a light reception element (28) for detecting the reflected light. Each probe (20) is successively selected by a switch circuit (60) under control of a control section (76) and connected to a property calculation section (64). The property calculation section (64) includes a phase shift circuit for changing the frequency according to the phase difference between the input waveform to the light emitting element (26) and the output waveform from the light reception element (28). According to the frequency change, the property of the biological tissue is calculated. The property calculated is displayed on a display section (74) via a data collection section (70) and a display processing section (72).

Owner:NIHON UNIVERSITY

Asymmetric pulse width comparator circuit and clock phase correction circuit including the same

ActiveUS10686435B2Correction of phase differencePulse train pattern monitoringContinuous to patterned pulse manipulationPhase correctionSoftware engineering

A clock phase correction circuit includes: a first variable delay circuit suitable for delaying a second source clock to generate a third clock; a first pulse generation circuit suitable for generating a first pulse signal that is activated from an edge of a first clock to an edge of the third clock and generating a second pulse signal that is activated from the edge of the third clock to the edge of the first clock; and a first delay value adjustment circuit suitable for detecting whether a ratio of a pulse width of the first pulse signal to a pulse width of the second pulse signal is greater or less than 1:3 to produce a detection result and adjusting a delay value of the first variable delay circuit based on the detection result.

Owner:SK HYNIX INC

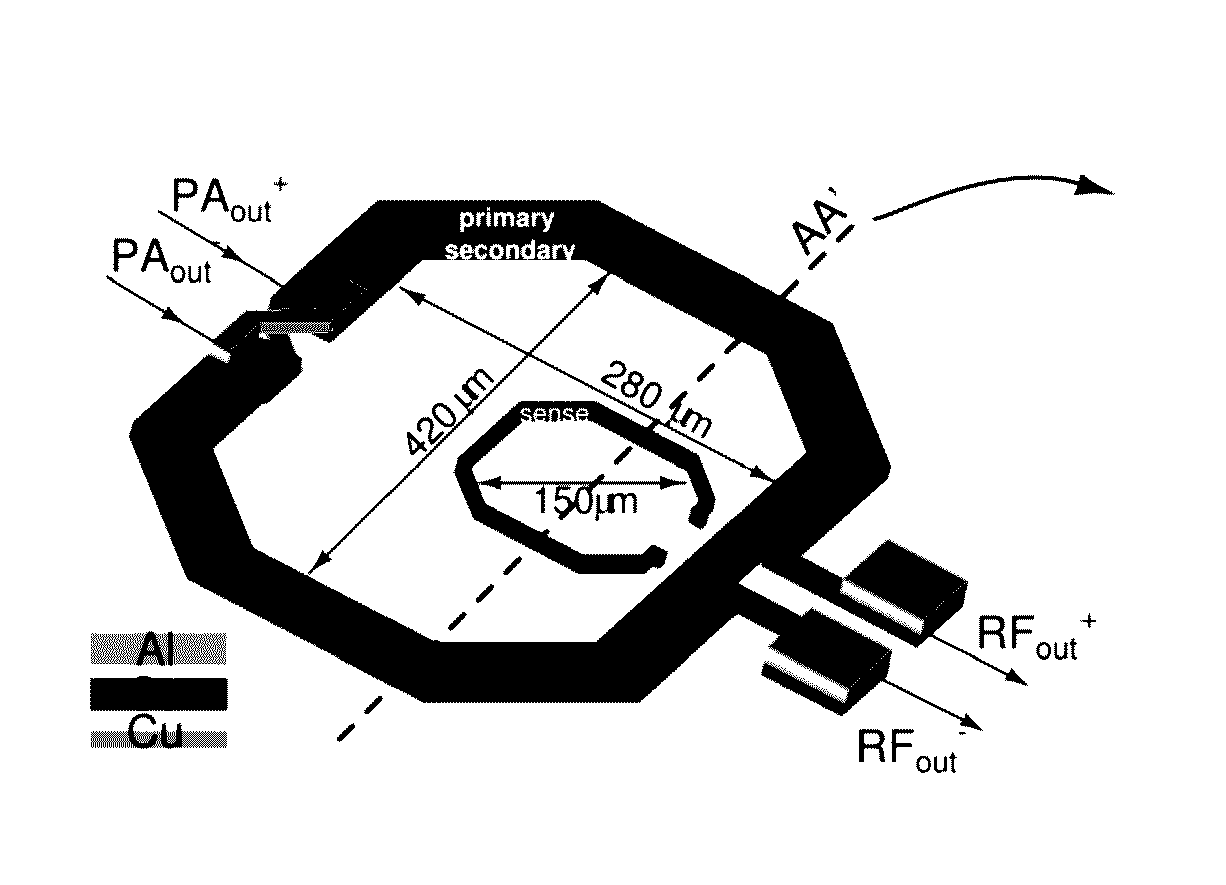

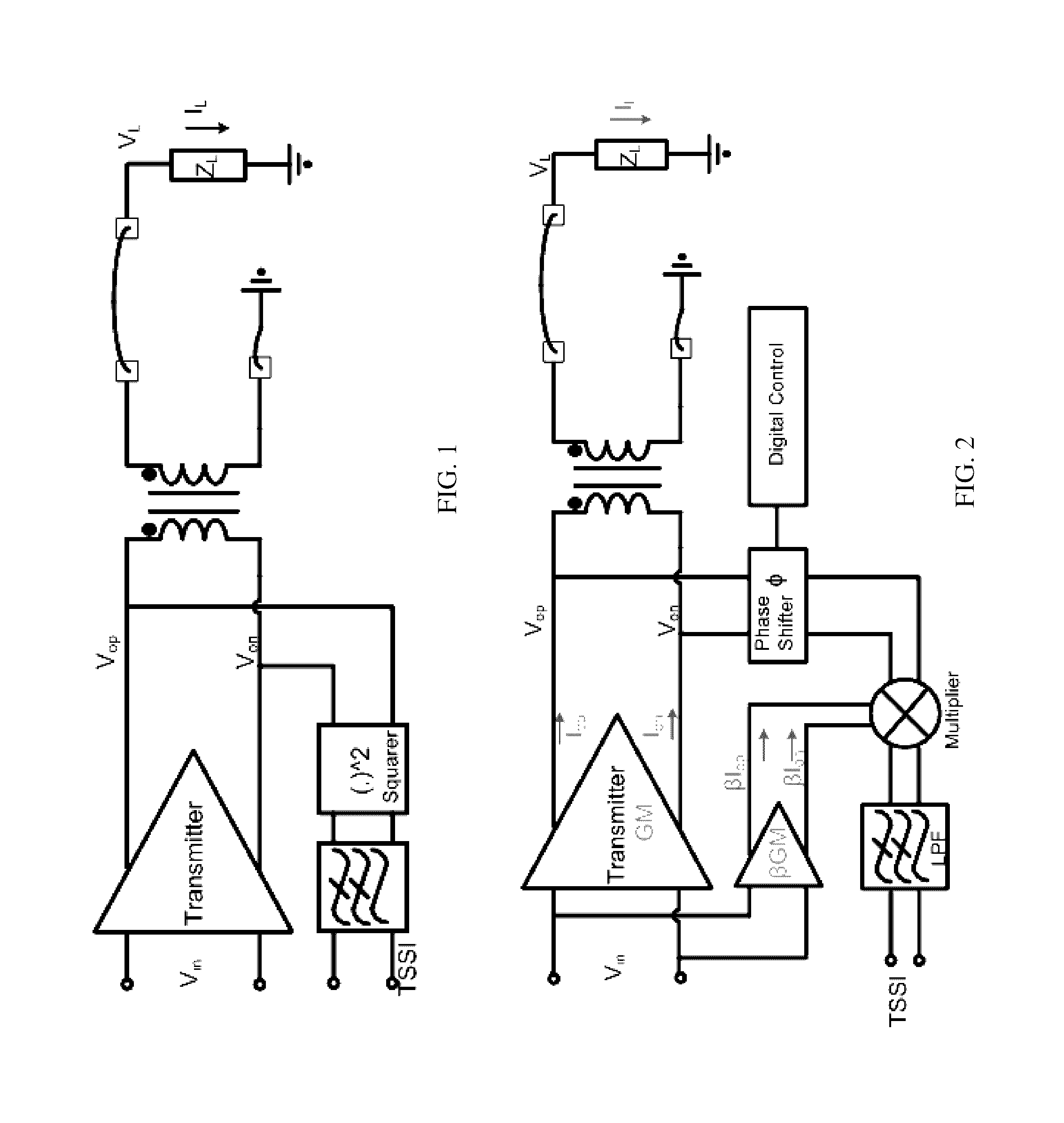

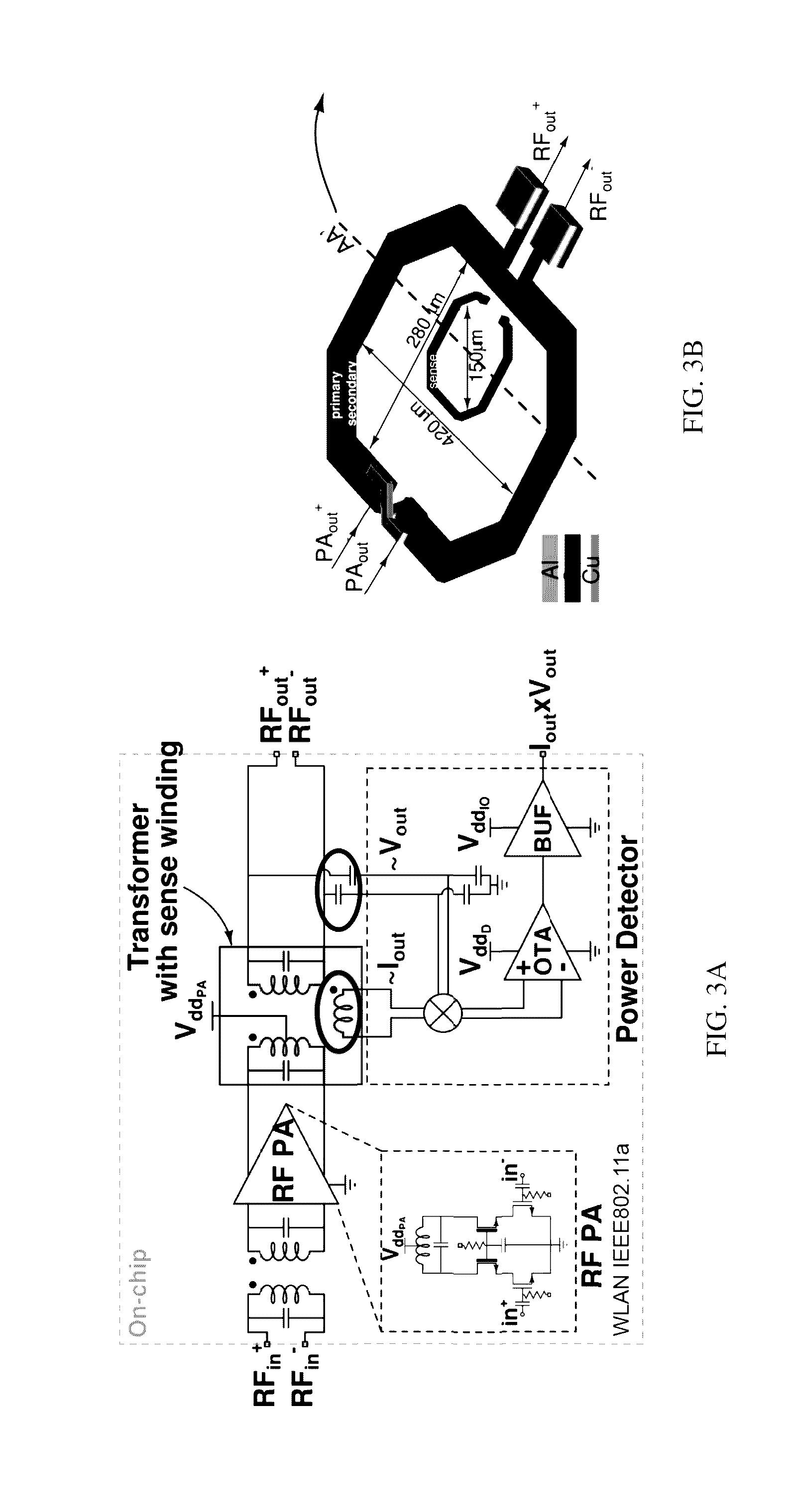

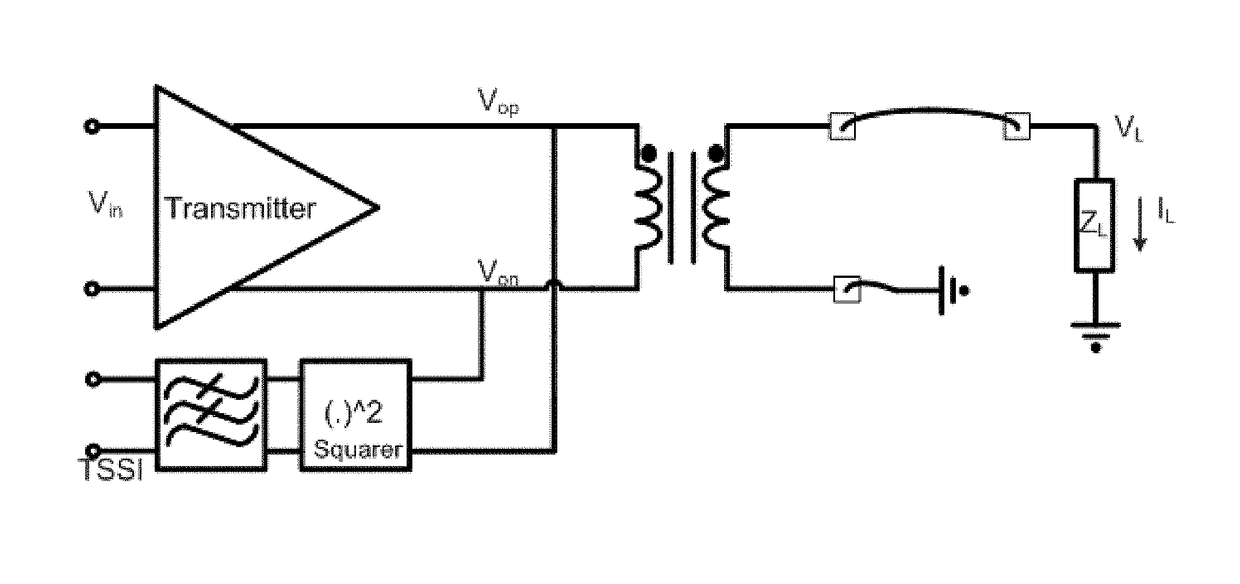

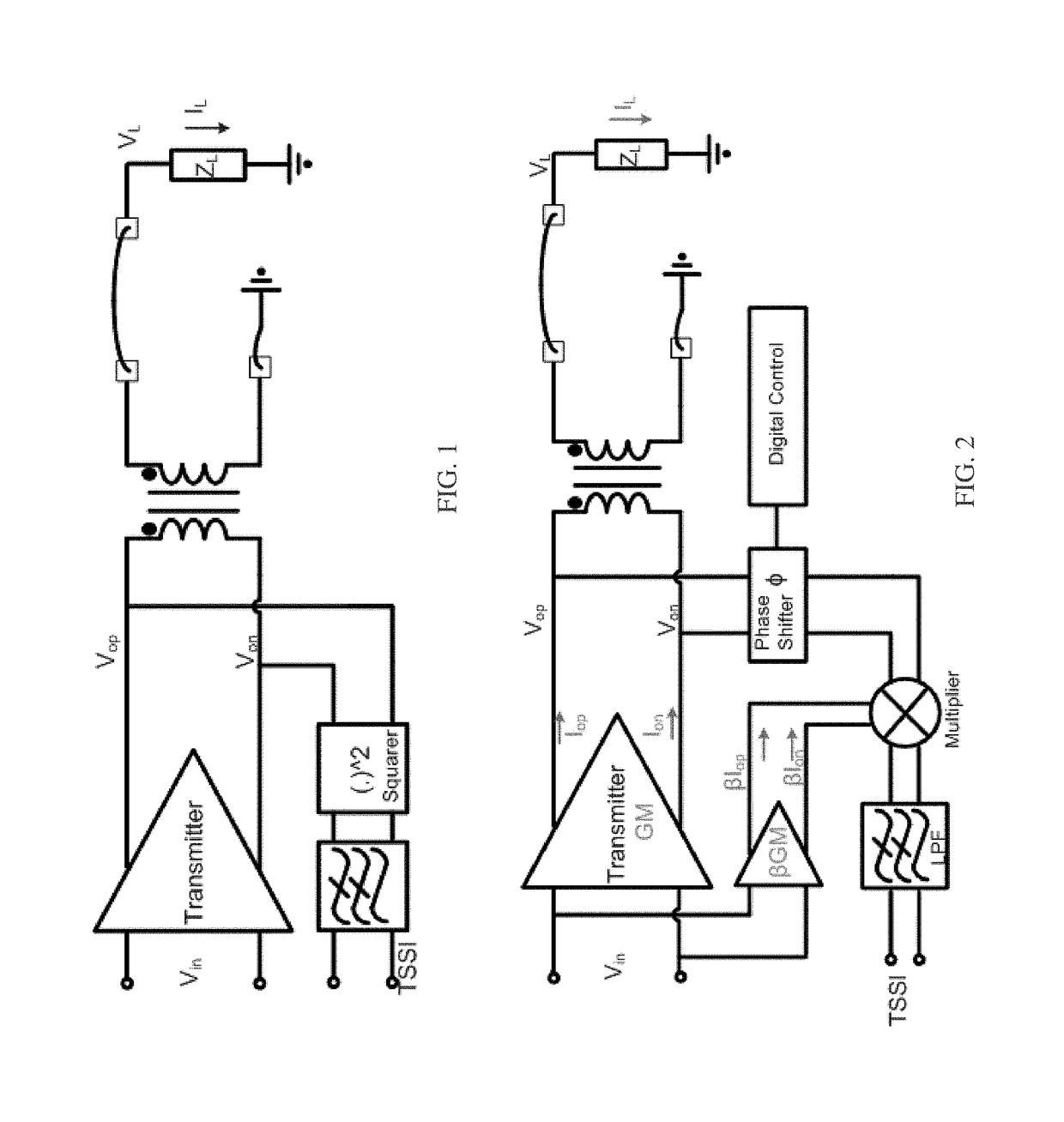

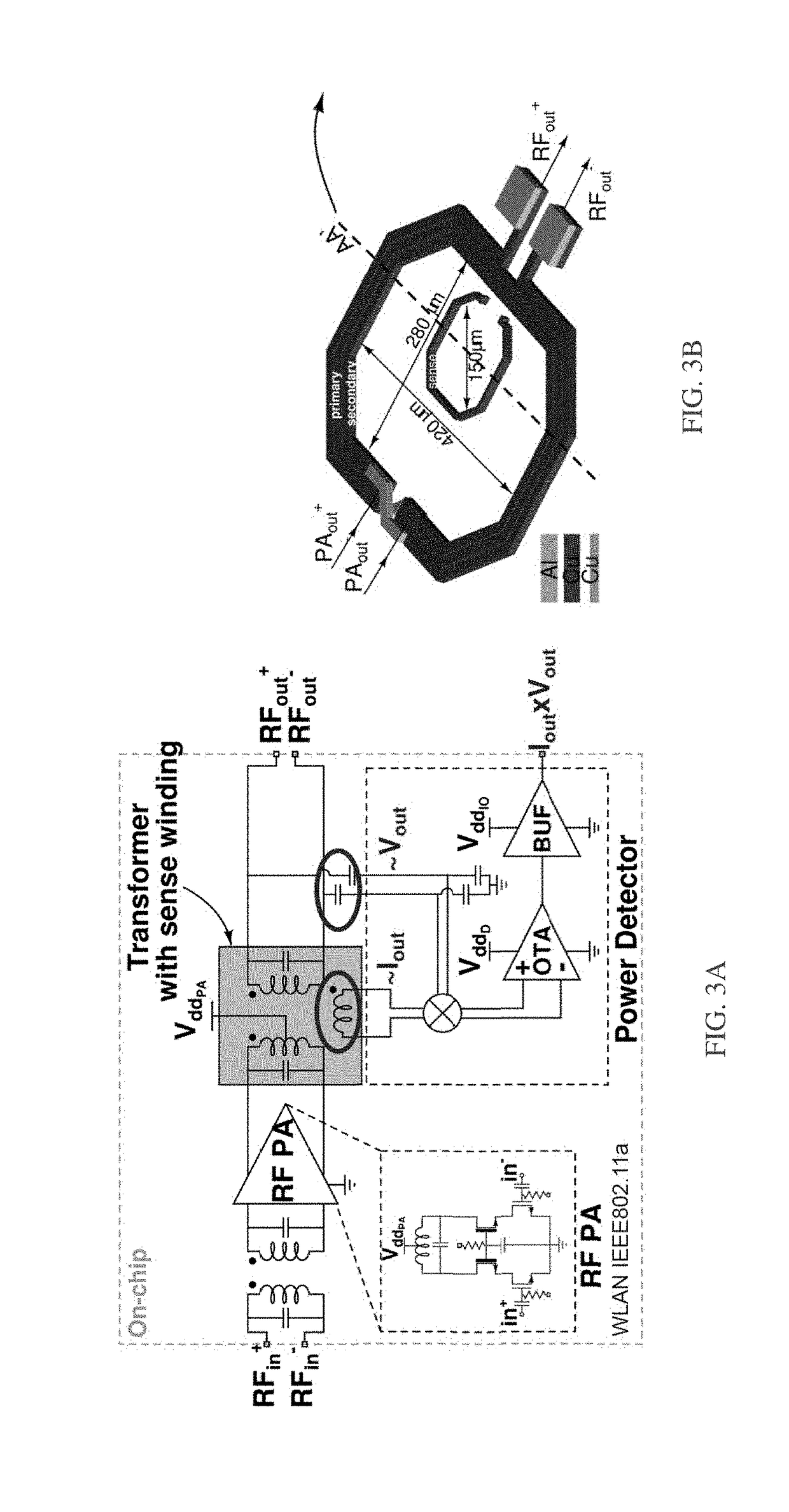

Power detector

ActiveUS20160334444A1Correction of phase differencePower measurement by current/voltagePower detectorEngineering

Some embodiments relate to power detector including a voltage sensor configured to detect a voltage of a load and a current sensor configured to detect a current of the load. The power detector also includes circuitry configured to introduce a phase delay between the detected voltage of the load and the detected current of the load, thereby producing a voltage measurement and a current measurement. The circuitry is also configured to multiply the voltage measurement and the current measurement.

Owner:MEDIATEK INC

Phase shift circuit and phase correcting method

ActiveUS20070075805A1Eliminate errorCorrection of phase differenceMultiple-port networksSingle output arrangementsPhysicsPhase shifted

A phase shift circuit includes a 45° phase corrector that performs vector synthesis of signals supposed to have a 45° phase difference, out of a plurality of sets of orthogonal phase signals having an about 45° phase difference and an equal amplitude, the orthogonal phase signals in each set having undergone 90° phase correction, and outputs signals resulting from the vector synthesis, whereby a phase error between the orthogonal phase signals in the different sets is eliminated by the vector synthesis to make it possible to correct their phase difference to accurately 45°.

Owner:SOCIONEXT INC

Control system

InactiveUS7525263B2Improve accuracyCorrection of phase differenceProgramme controlMultiple dynamo-motor startersPhase differenceControl system

A master unit and a plurality of slave units are connected by way of a communication path. The master unit sends to the slave units timing signals generated by its own cycle signal generator by way of a communication path. The slave units determine the cycle difference and the phase difference between a timing signal generated by its own cycle signal generator and the timing signal sent from the master unit and, in accordance therewith, determine a cycle adjustment amount. The cycle signal generators of the slave units adjust the timing signal cycle based on the cycle adjustment amount.

Owner:FANUC LTD

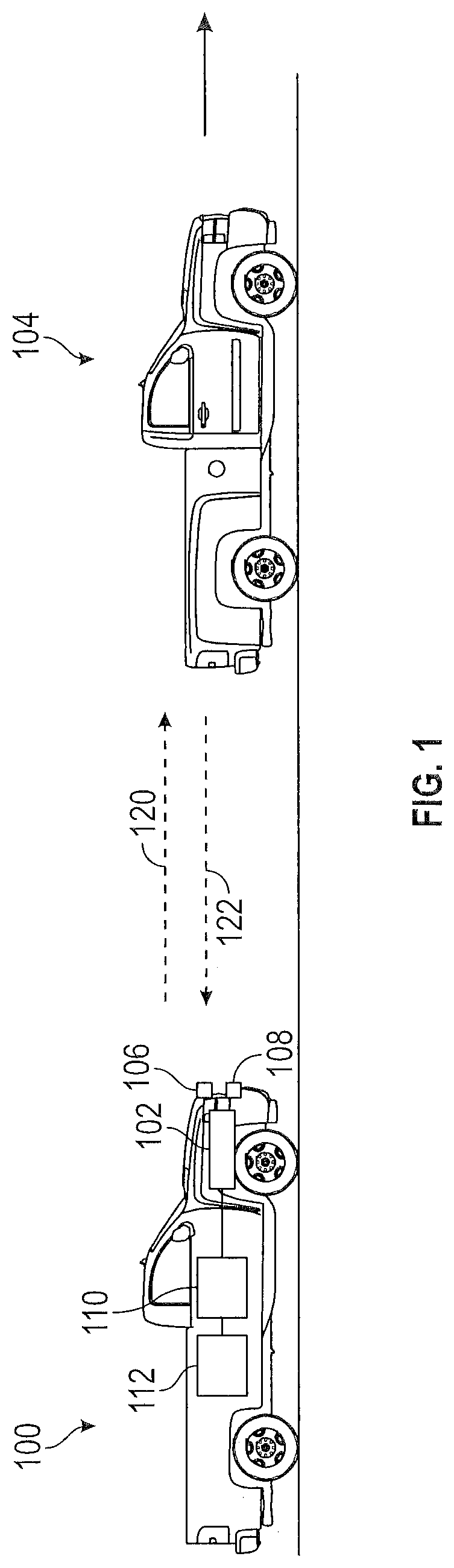

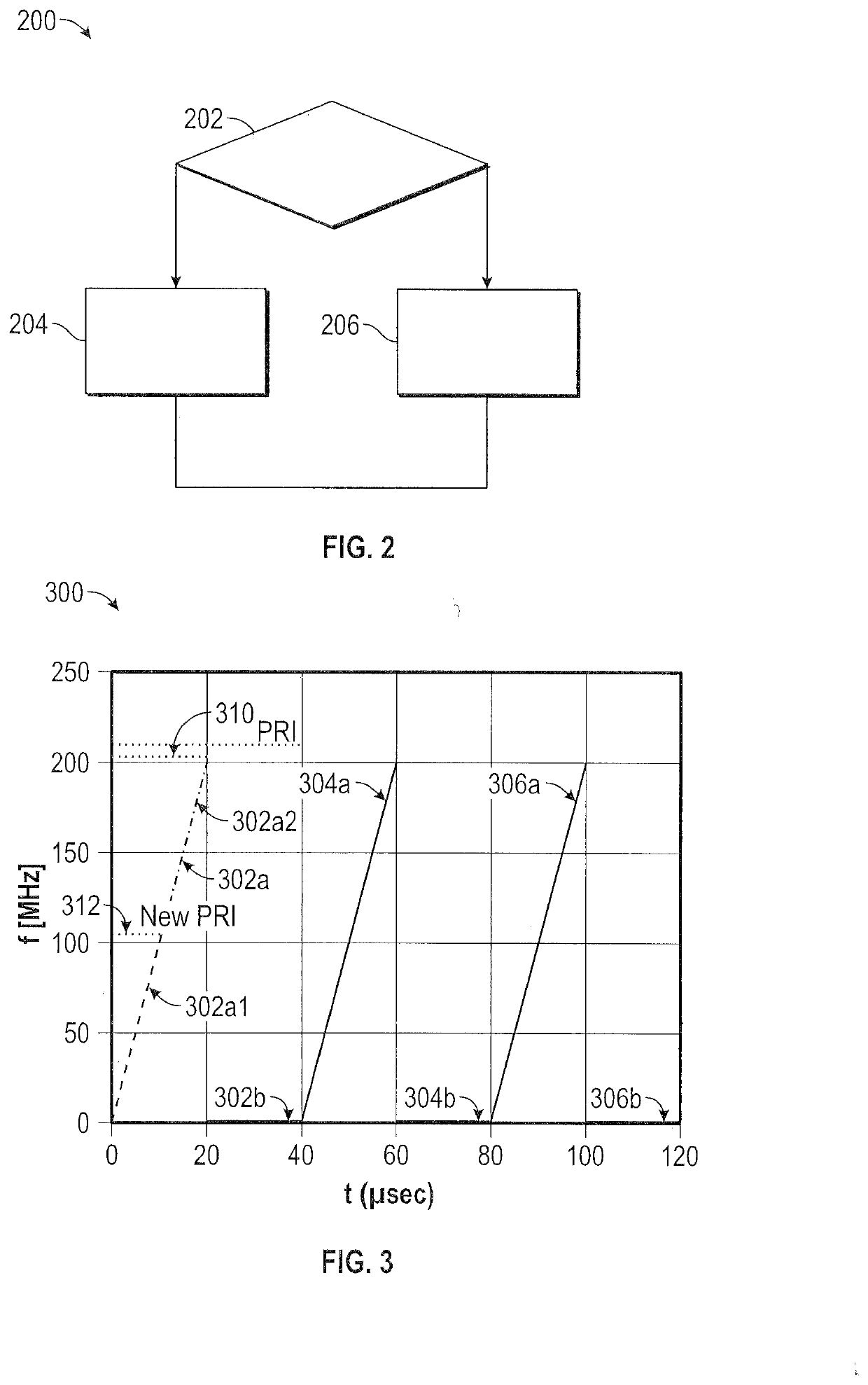

Maximum doppler extension via recursive chirp decimation

ActiveUS20190346551A1Correction of phase differenceRadio wave reradiation/reflectionDoppler spreadRadar systems

A vehicle, system for navigating the vehicle and method of operating the vehicle. The system includes a radar system and a processor. The radar system transmits a linear frequency modulated signal into an environment of the vehicle and receives a reflection of the linear frequency modulated signal from an object in the environment. The processor partitions the reflection into a plurality of streams to obtain a Doppler frequency that exceeds a maximum Doppler frequency of the radar.

Owner:GM GLOBAL TECH OPERATIONS LLC

Color imaging element, imaging device, and storage medium storing an imaging program

InactiveUS8723992B2Correction of phase differenceHigh precisionTelevision system detailsTelevision system scanning detailsPattern recognitionSquare array

Owner:FUJIFILM CORP

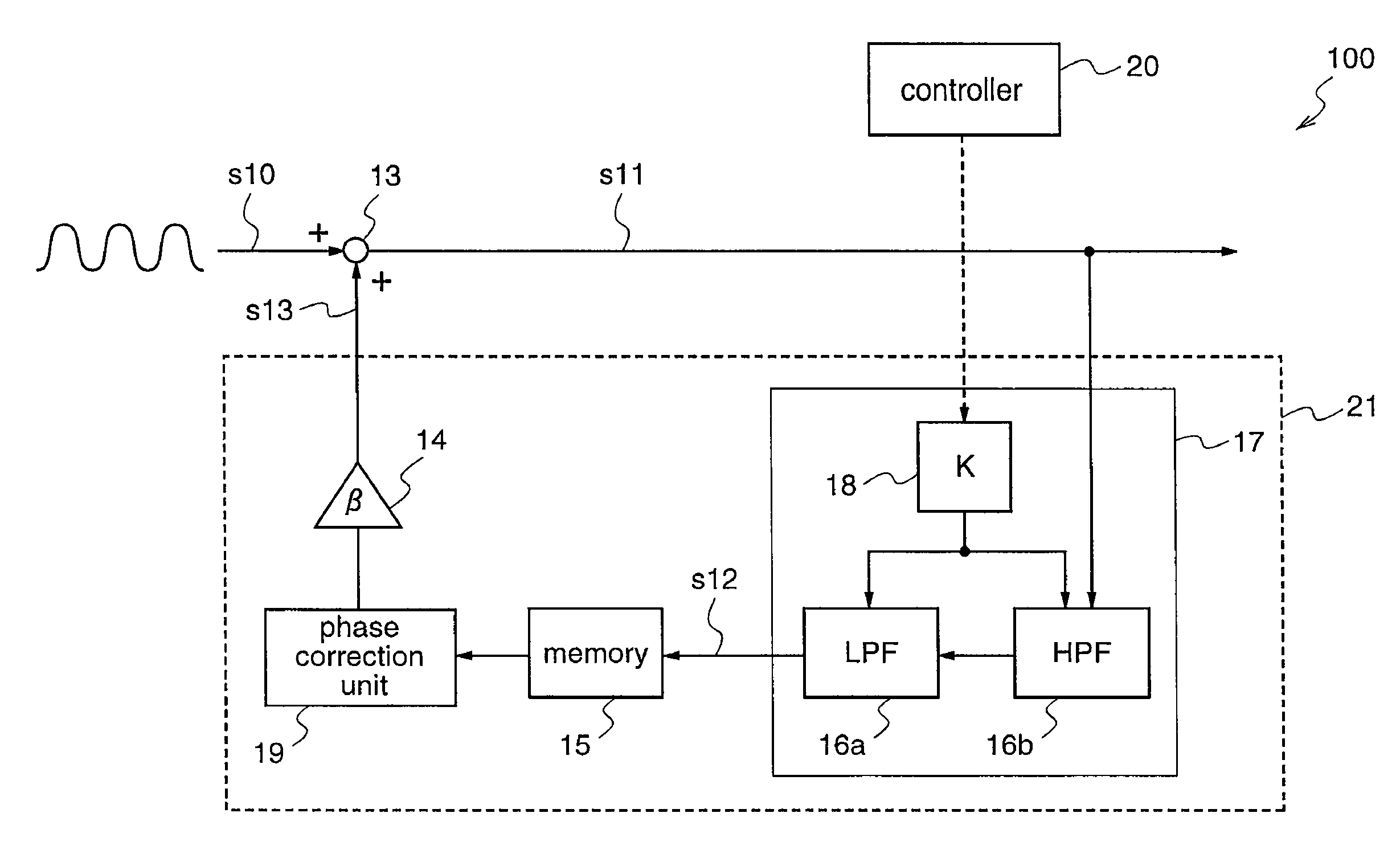

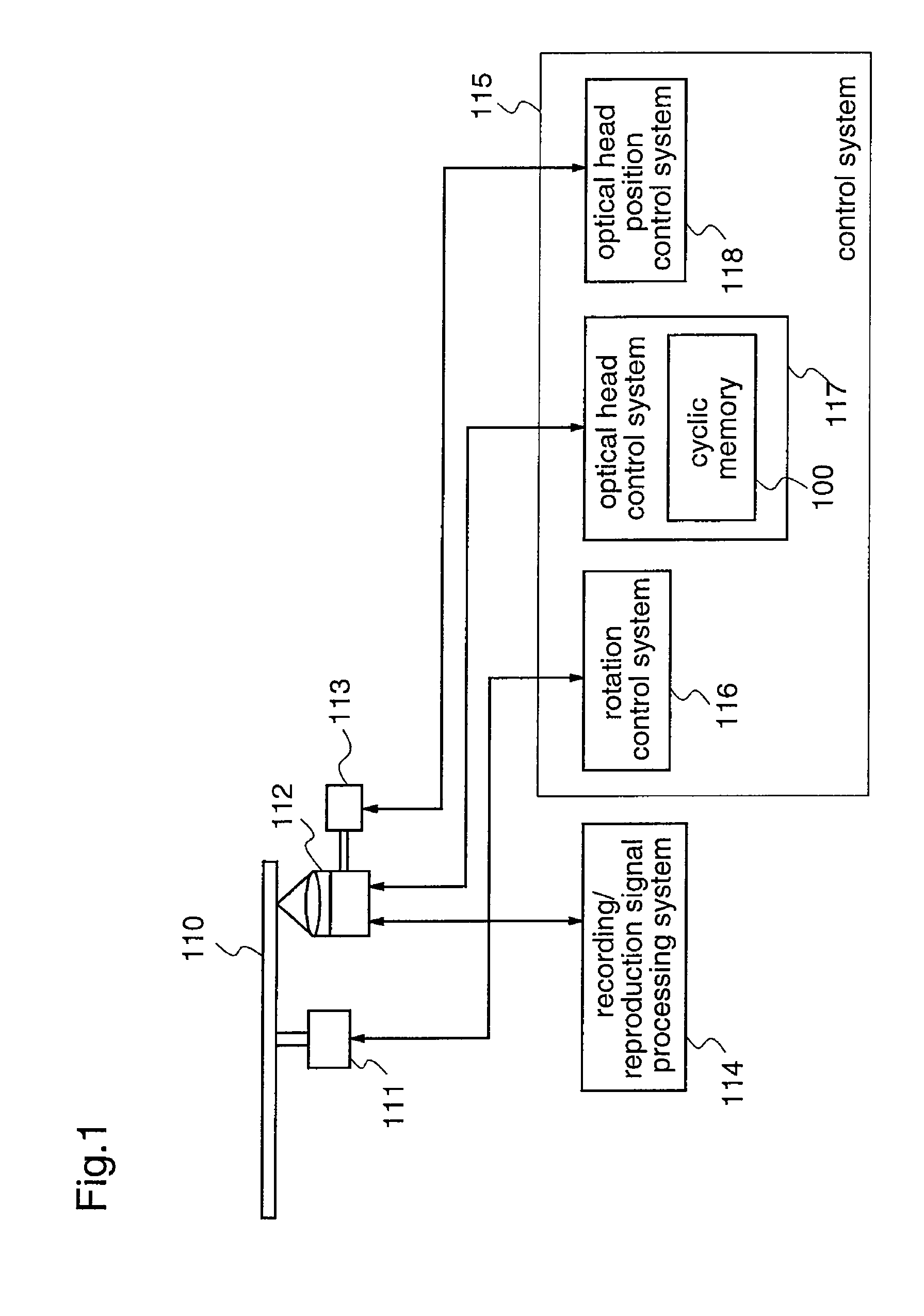

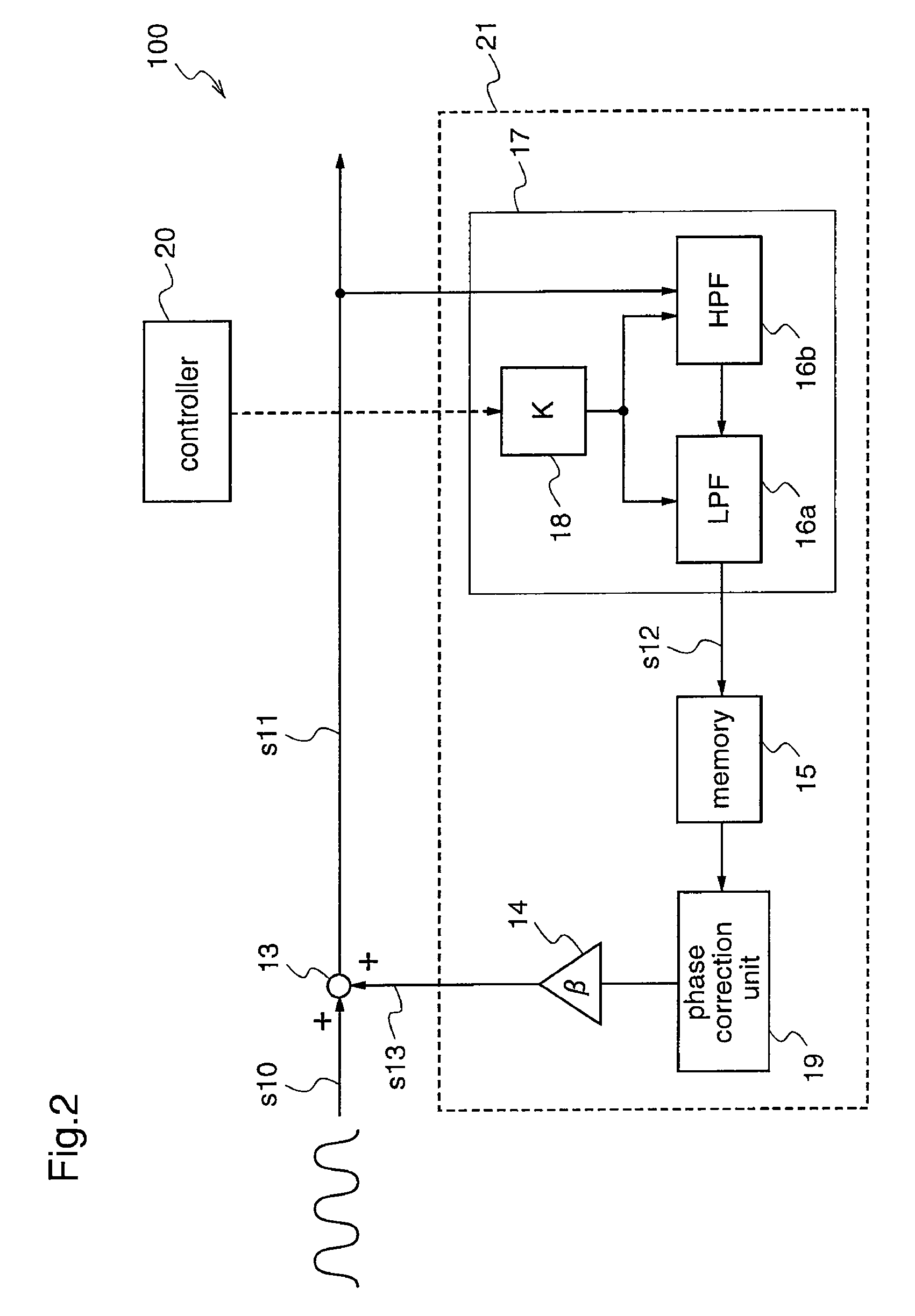

Cyclic memory and disc device

InactiveUS8284645B2Followability would not be deterioratedCorrection of phase differenceModification of read/write signalsFilamentary/web record carriersPhase correctionPhase difference

Provided is an orbiting memory capable of suppressing residual deviation even when a phase difference is caused between a signal to be compensated and information stored in a memory to be fed back and a disc device using the orbiting memory. The disc device includes: an adder to which a signal (s10) to be compensated and having a cyclic frequency component such as a control system error signal is inputted; and a feed back signal system for successively updating and storing an output signal of the adder for each cycle in a memory and inputting one-cycle information stored in the memory to the adder. The feed back signal system includes: a filter unit for outputting a signal contained in a learning band which is arbitrarily set among output signals from the adder; the memory for successively updating and storing the output signal of the filter unit; a phase correction unit capable of arbitrarily setting a phase amount when inputting the output of the memory to the adder; and a gain element for multiplying the one-cycle information subjected to the phase correction by the phase correction unit by a value not smaller than 0 and not greater than 1 and inputting the obtained value to the adder.

Owner:PANASONIC CORP

Power detector

ActiveUS10082528B2Correction of phase differencePower measurement by current/voltagePower detectorEngineering

Some embodiments relate to power detector including a voltage sensor configured to detect a voltage of a load and a current sensor configured to detect a current of the load. The power detector also includes circuitry configured to introduce a phase delay between the detected voltage of the load and the detected current of the load, thereby producing a voltage measurement and a current measurement. The circuitry is also configured to multiply the voltage measurement and the current measurement.

Owner:MEDIATEK INC

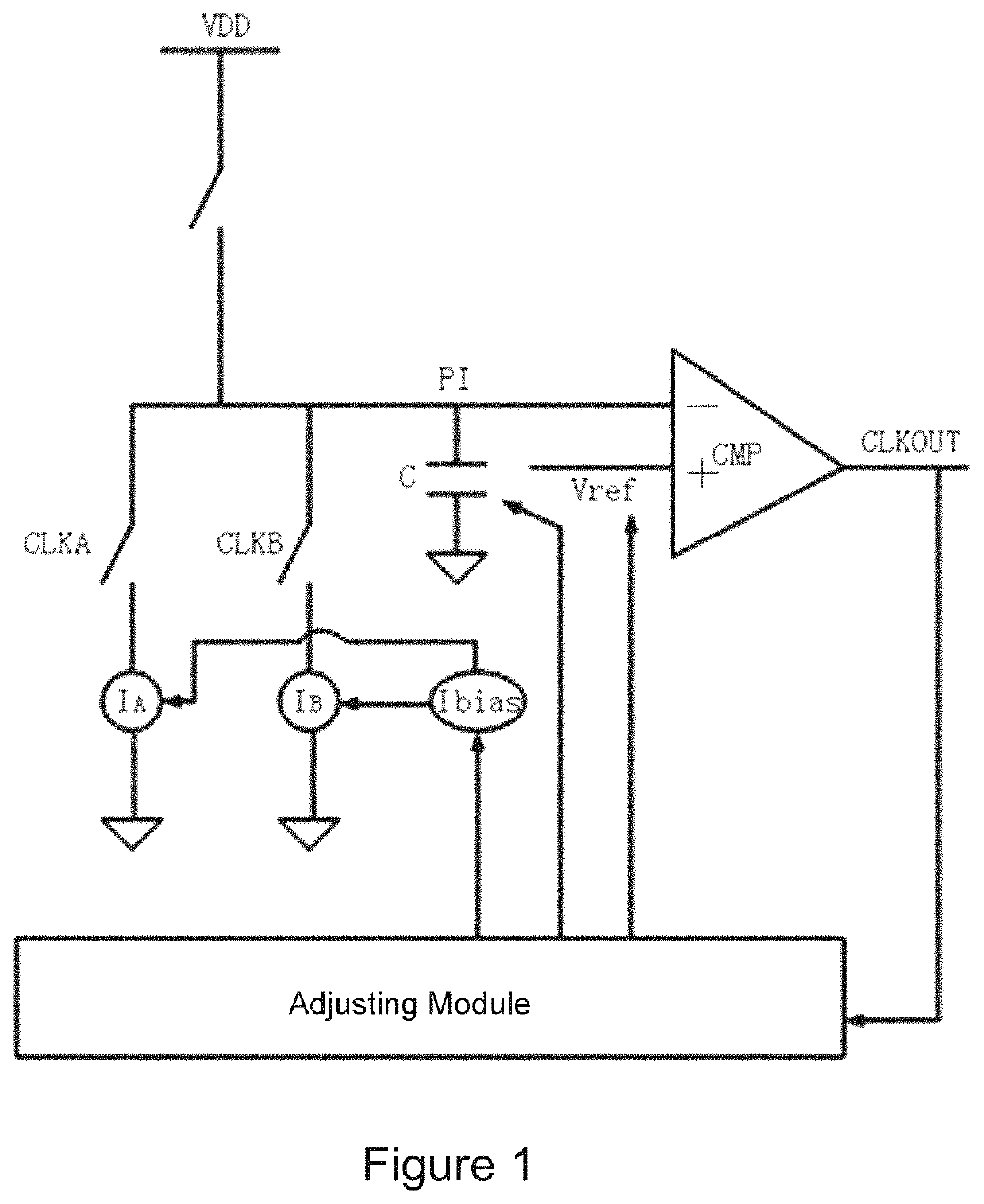

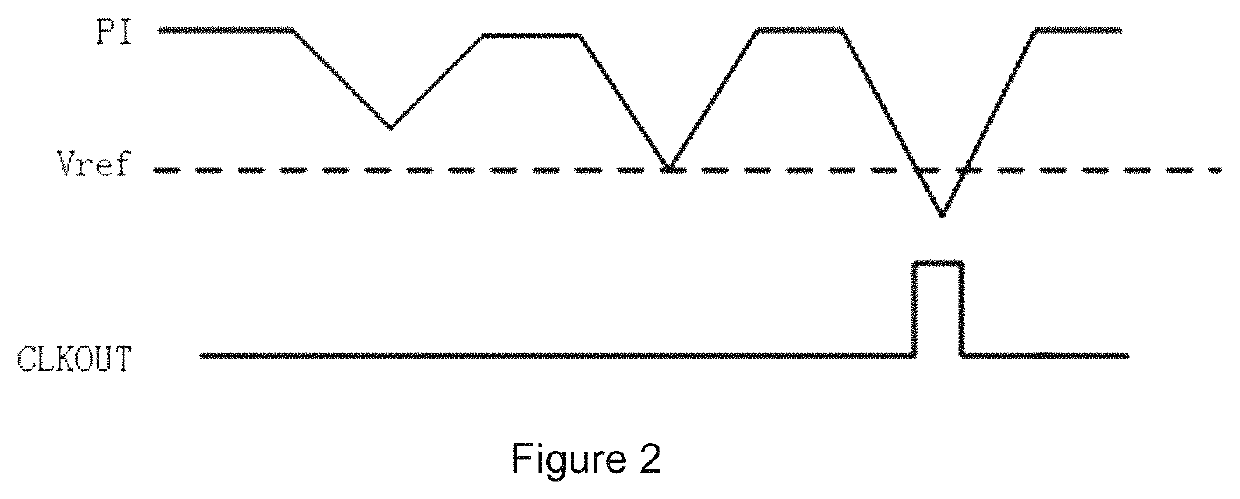

Phase difference generator error compensation method of digital frequency generator

ActiveUS10866611B2Correction of phase differenceImprove product qualityMultiple input and output pulse circuitsPulse automatic controlPhase differenceSoftware engineering

The invention provides a phase difference generator error compensation method of a digital frequency generator, wherein the digital frequency generator comprises a phase difference generator, the phase difference generator comprises a phase compensation module and an adjusting module, the phase compensation module provides at least two clock signals, the at least two clock signals comprise a first clock signal and a second clock signal, and a phase difference exists between the first clock signal and the second clock signal; the phase compensation module outputs a third clock signal according to the first clock signal and the second clock signal, and the third clock signal is a difference signal of the first clock signal and the second clock signal; the adjusting module compensates the error of the third clock signal according to the clock phase difference. The method has the benefits that process errors in the phase difference generator are compensated.

Owner:AMOLOGIC (SHANGHAI) CO LTD

Duty cycle detector and phase difference detector

ActiveUS10361692B2Precise ratioCorrection of phase differenceMultiple-port networksMultiple input and output pulse circuitsPhase differenceComparator

A duty cycle detector includes a first ring oscillator suitable for including an odd number of first inverters and generating a first periodic signal by using the first inverters, at least one inverter among the first inverters being enabled during a time interval when a clock has a first value, a second ring oscillator including an odd number of second inverters and suitable for generating a second periodic signal using the second inverters, at least one inverter among the second inverters being enabled during a time interval when the clock has a second value. The duty cycle detector further includes a frequency comparator suitable for comparing a frequency of the first periodic signal with a frequency of the second periodic signal and generating a duty cycle detection signal of the clock.

Owner:SK HYNIX INC +1

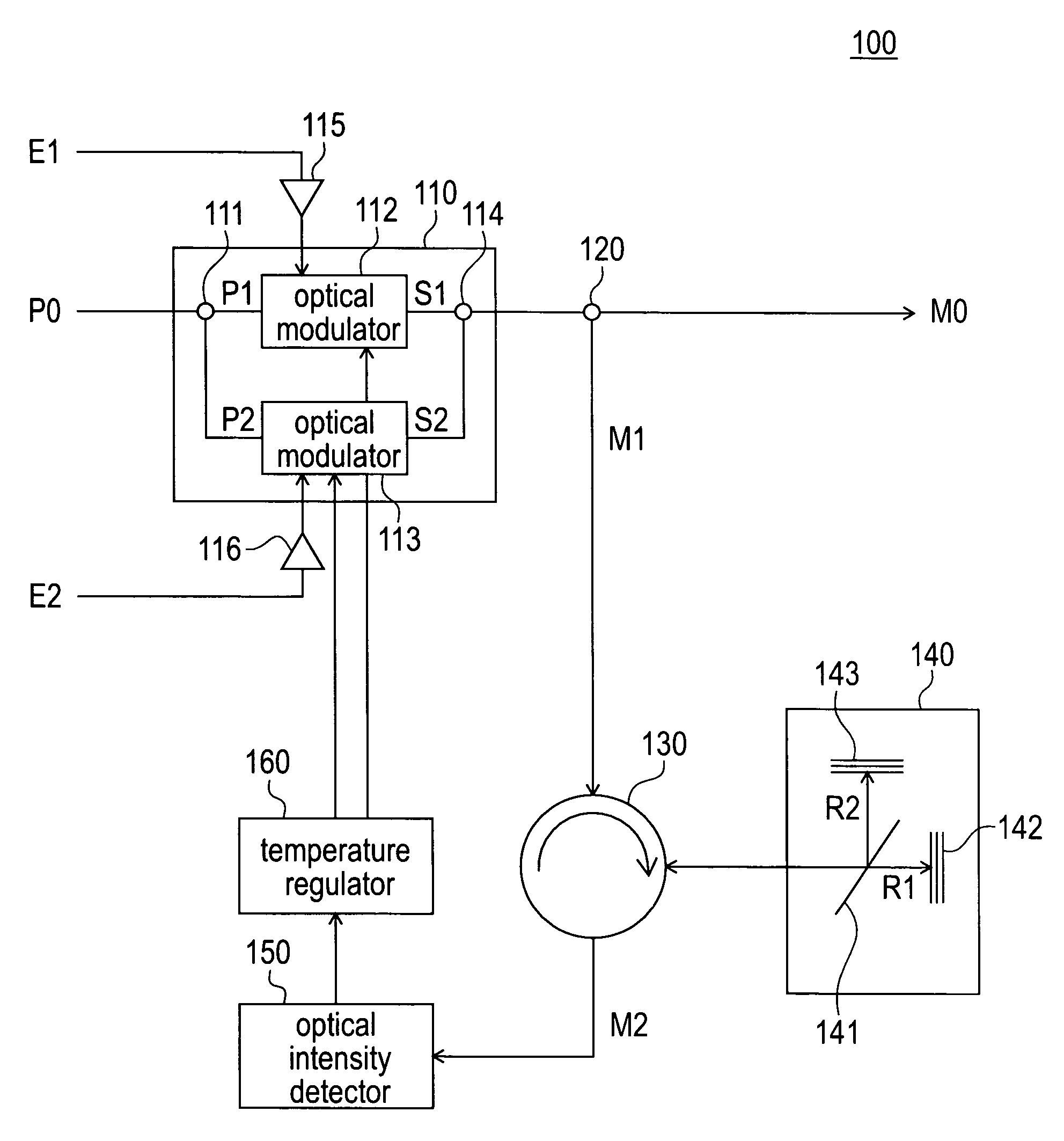

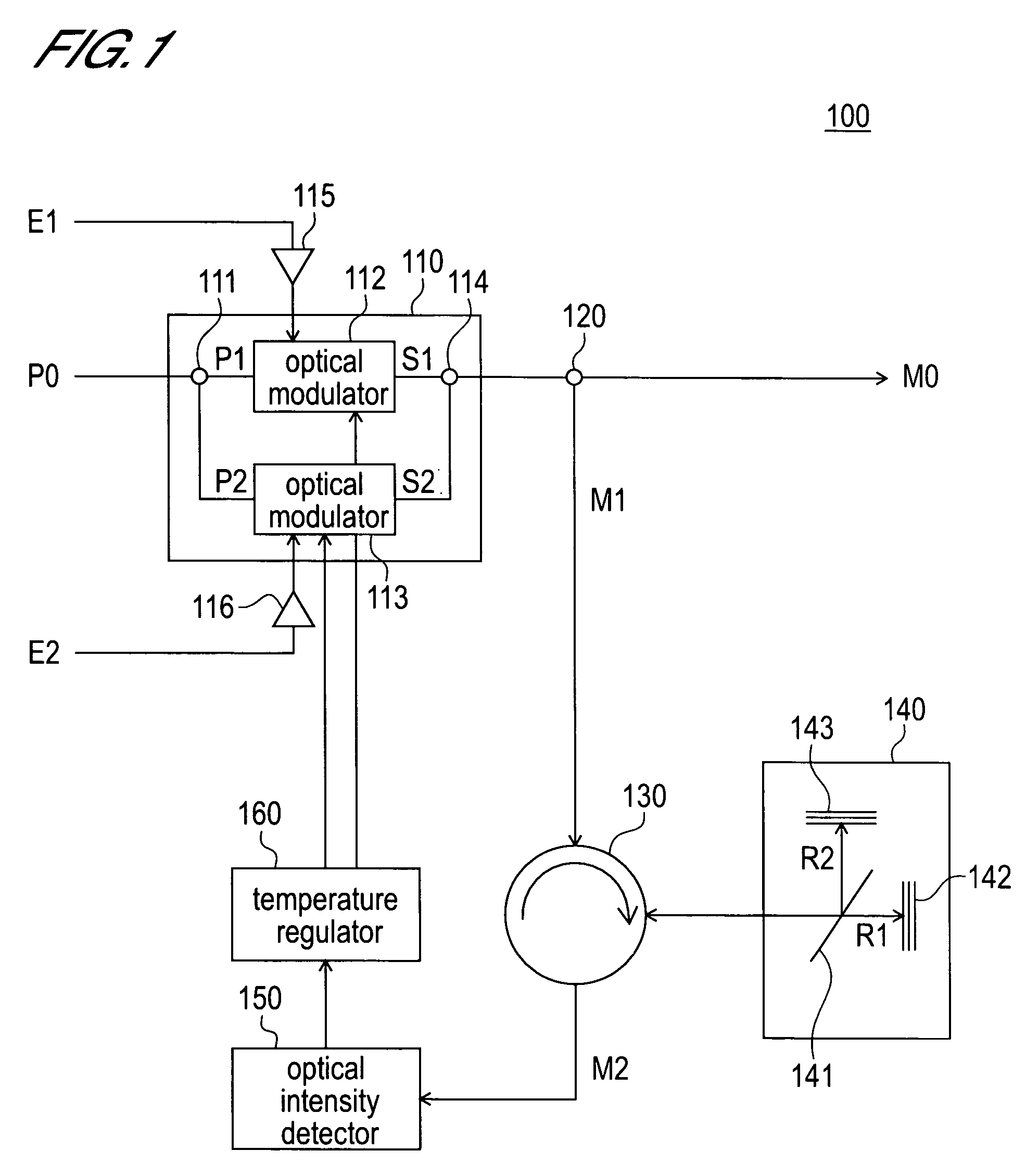

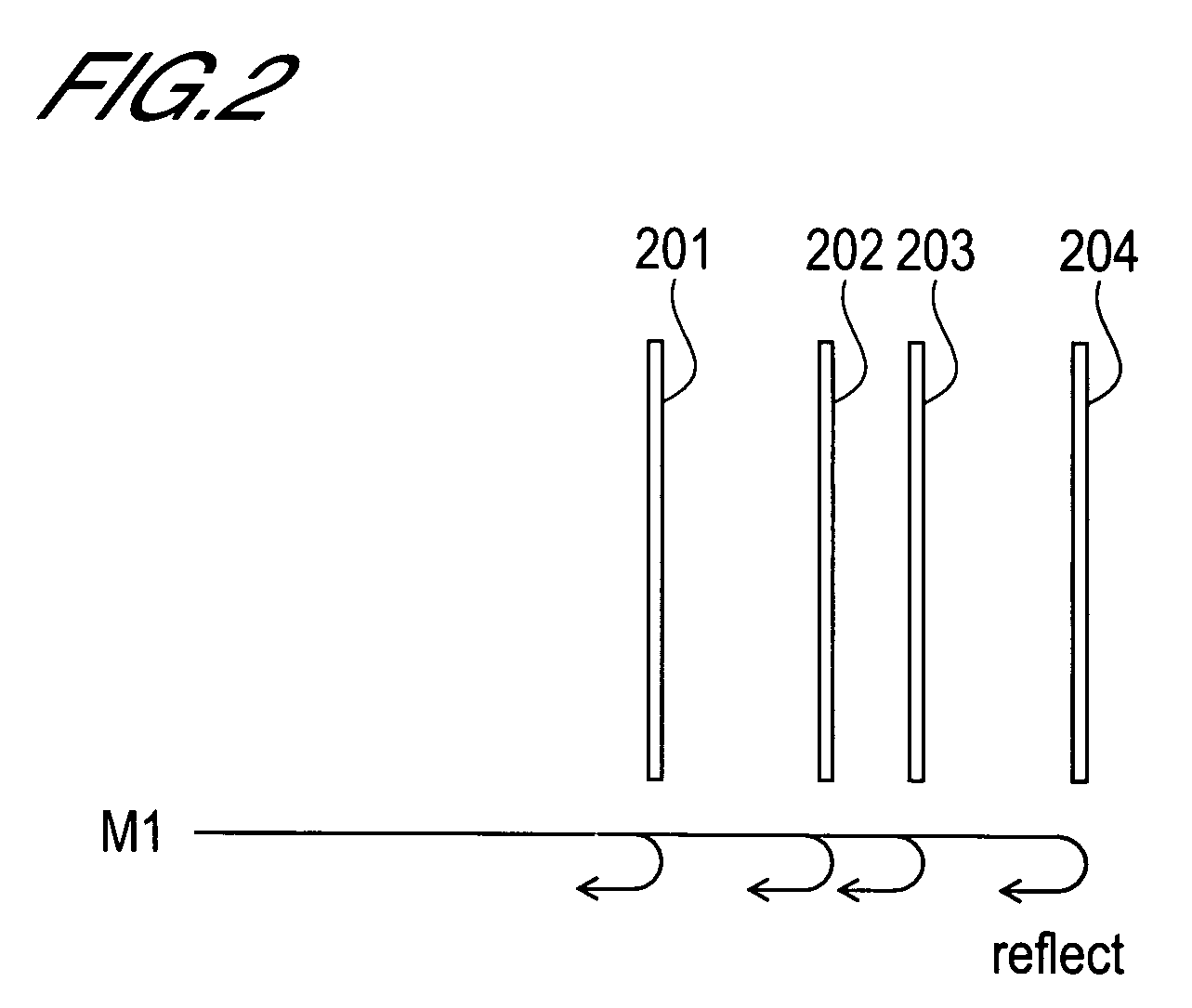

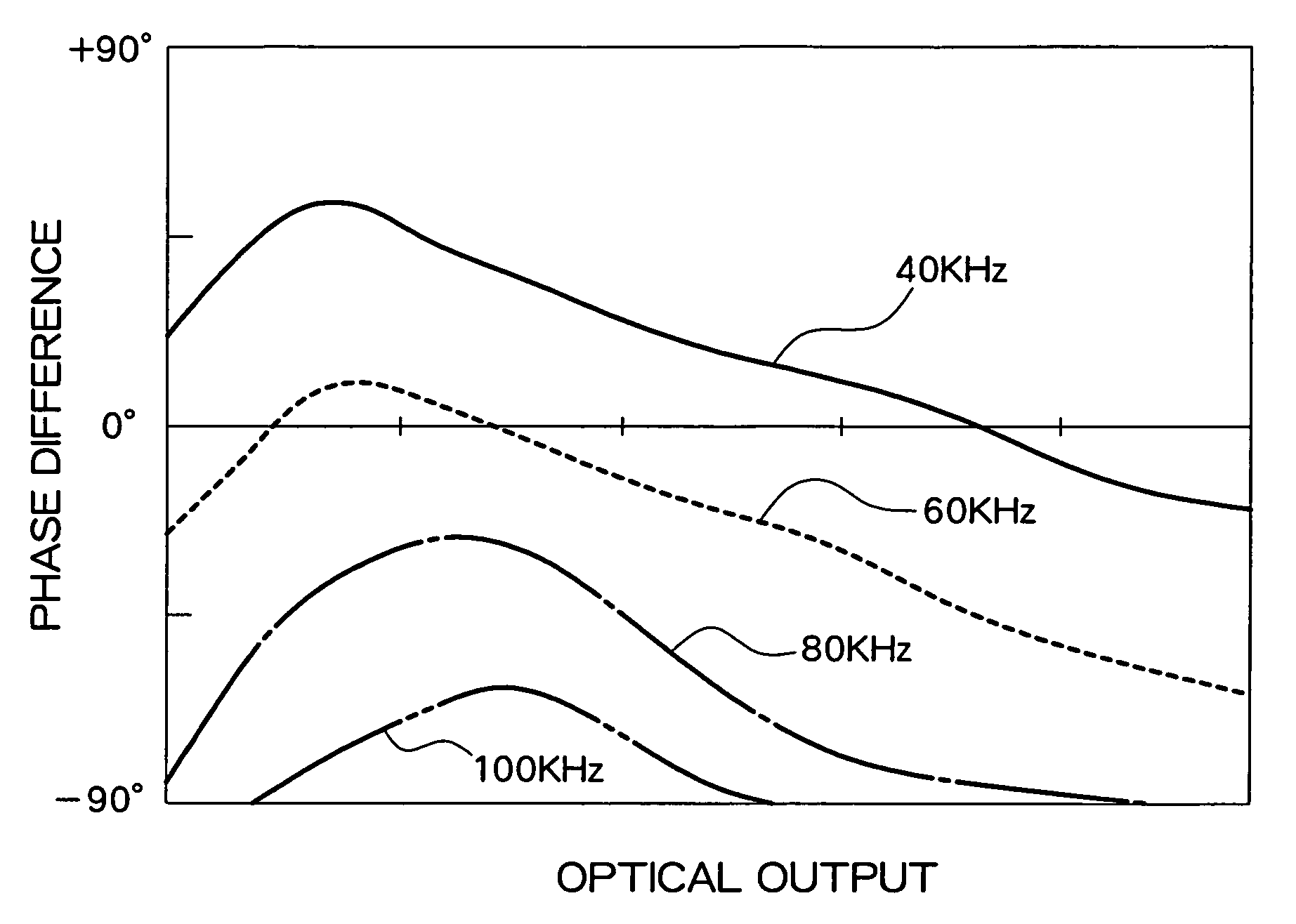

Optical time division multiplexing transmitter

ActiveUS7957646B2Correction of phase differenceAccurate detectionTime-division optical multiplex systemsElectromagnetic transmittersPhase differenceMultiplexer

The optical time division multiplexer generates a time-division-multiplexed optical signal by time-division-multiplexing optical signals of a plurality of channels, the carrier-wave phases of which are shifted with respect to one another. The circulator guides the multiplexed optical signals split by the optical splitter to the optical interference device and the superimposed light outputted from the optical interference device is guided to the optical intensity detector. The optical interference device extends the pulse width of the multiplexed optical signal to a width equal to or more than the bit interval and superimposes the extended light of an adjacent bit onto the extended light. The optical intensity detector detects the intensity of the superimposed light outputted by the optical interference device. The temperature regulator controls the temperature of the modulator so that the phase difference of the carrier waves constituting the optical signal trains is to be a half wavelength.

Owner:OKI ELECTRIC IND CO LTD

Biological property check device using light

InactiveUS7583383B2Accurately determineCorrection of phase differenceDiagnostics using lightSurgeryPhase shiftedBiological property

Owner:NIHON UNIVERSITY