Patents

Literature

36 results about "Bus encoding" patented technology

Efficacy Topic

Property

Owner

Technical Advancement

Application Domain

Technology Topic

Technology Field Word

Patent Country/Region

Patent Type

Patent Status

Application Year

Inventor

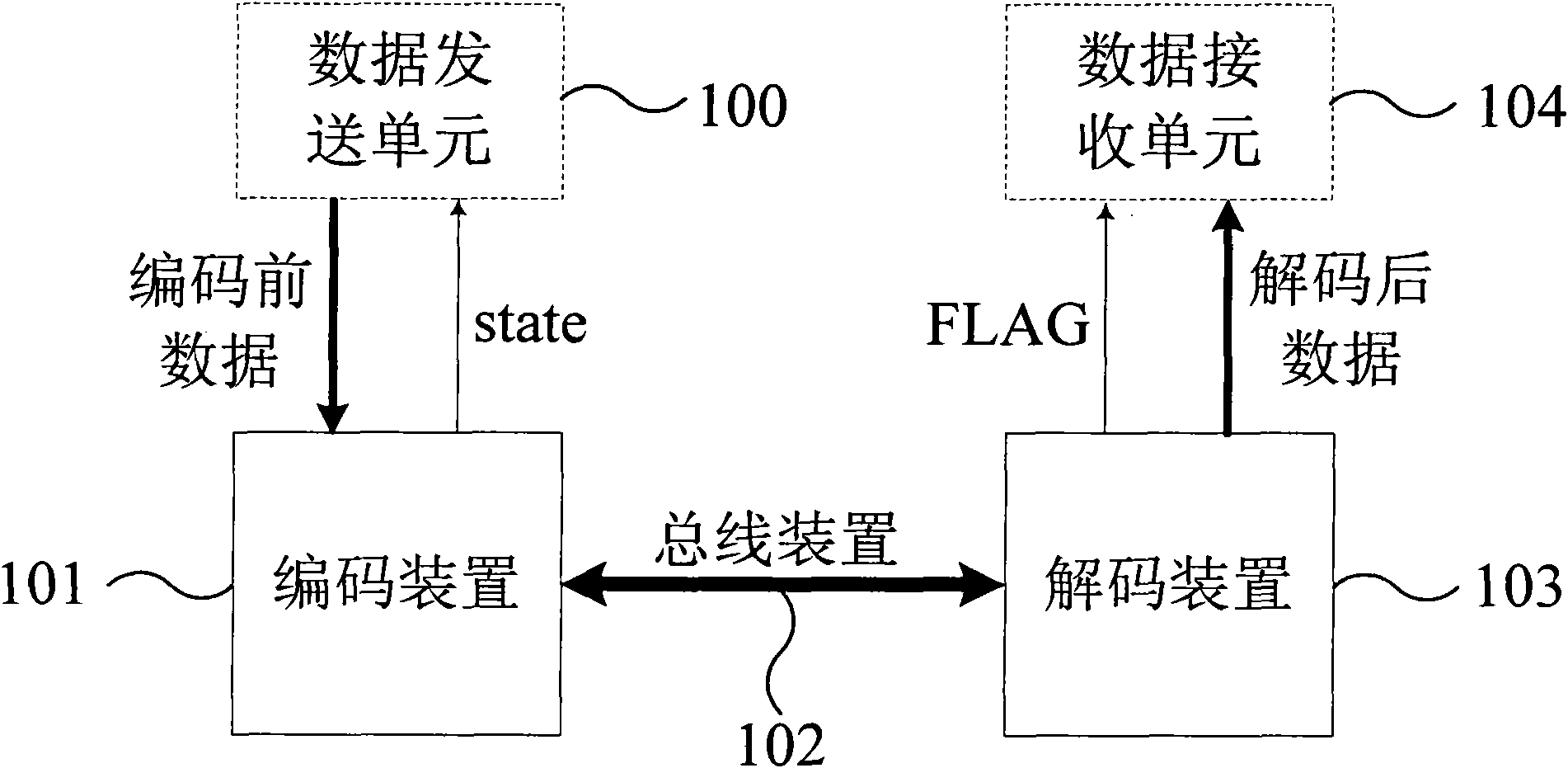

Bus encoding refers to converting/encoding a piece of data to another form before launching on the bus. While bus encoding can be used to serve various purposes like reducing the number of pins, compressing the data to be transmitted, reducing cross-talk between bit lines, etc., it is one of the popular techniques used in system design to reduce dynamic power consumed by the system bus. Bus encoding aims to reduce the Hamming distance between 2 consecutive values on the bus. Since the activity is directly proportional to the Hamming distance, bus encoding proves to be effective in reducing the overall activity factor thereby reducing the dynamic power consumption in the system.

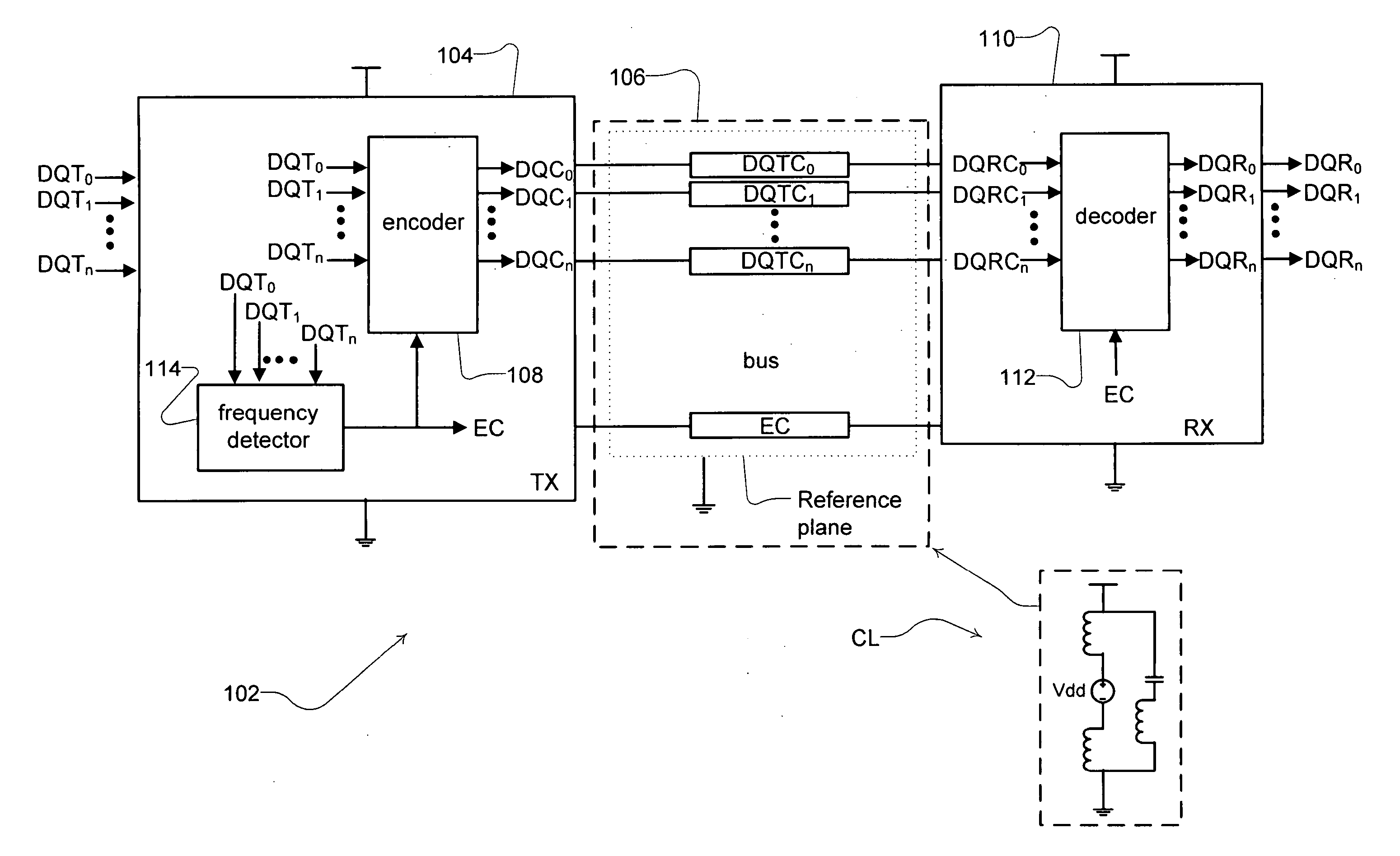

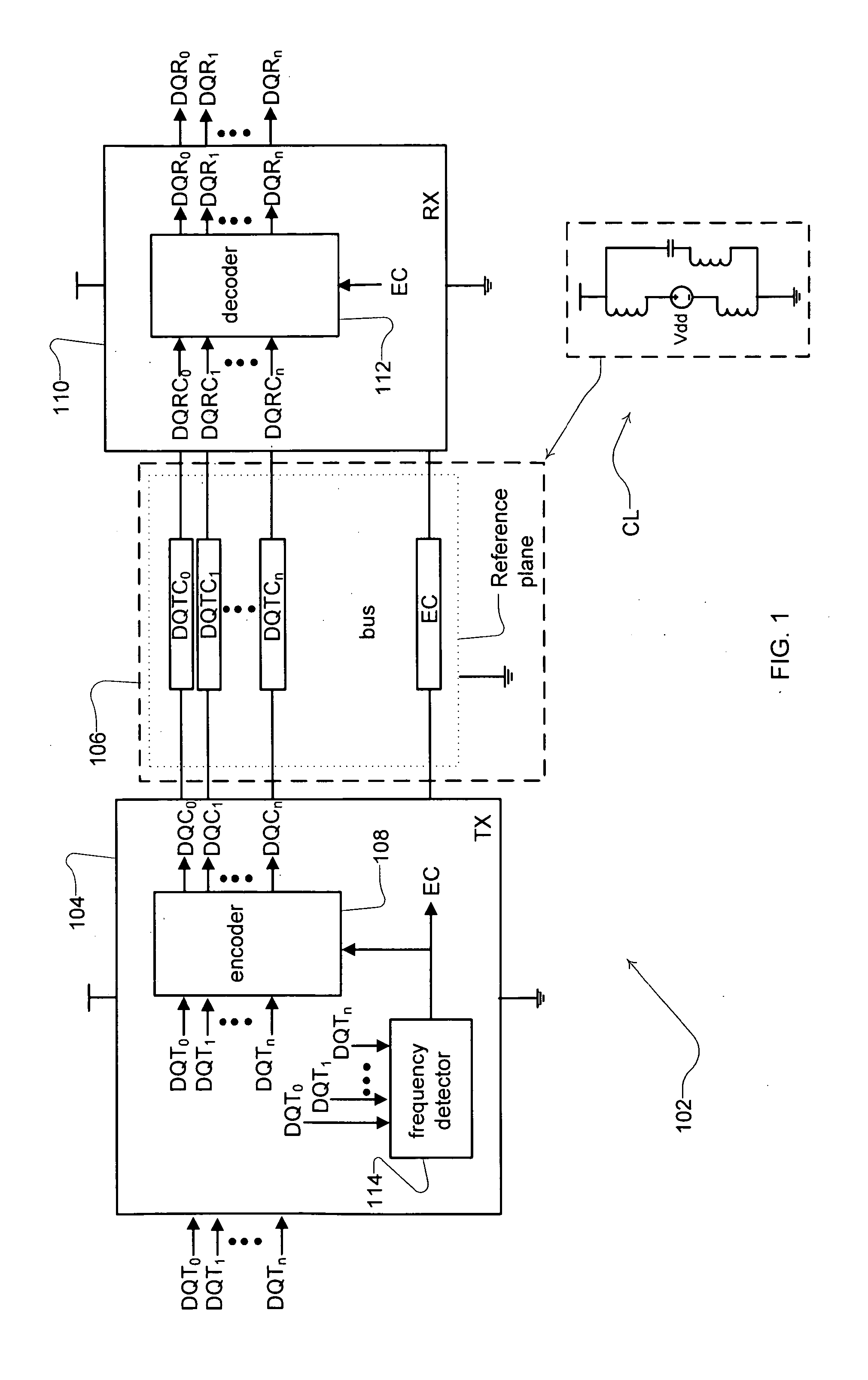

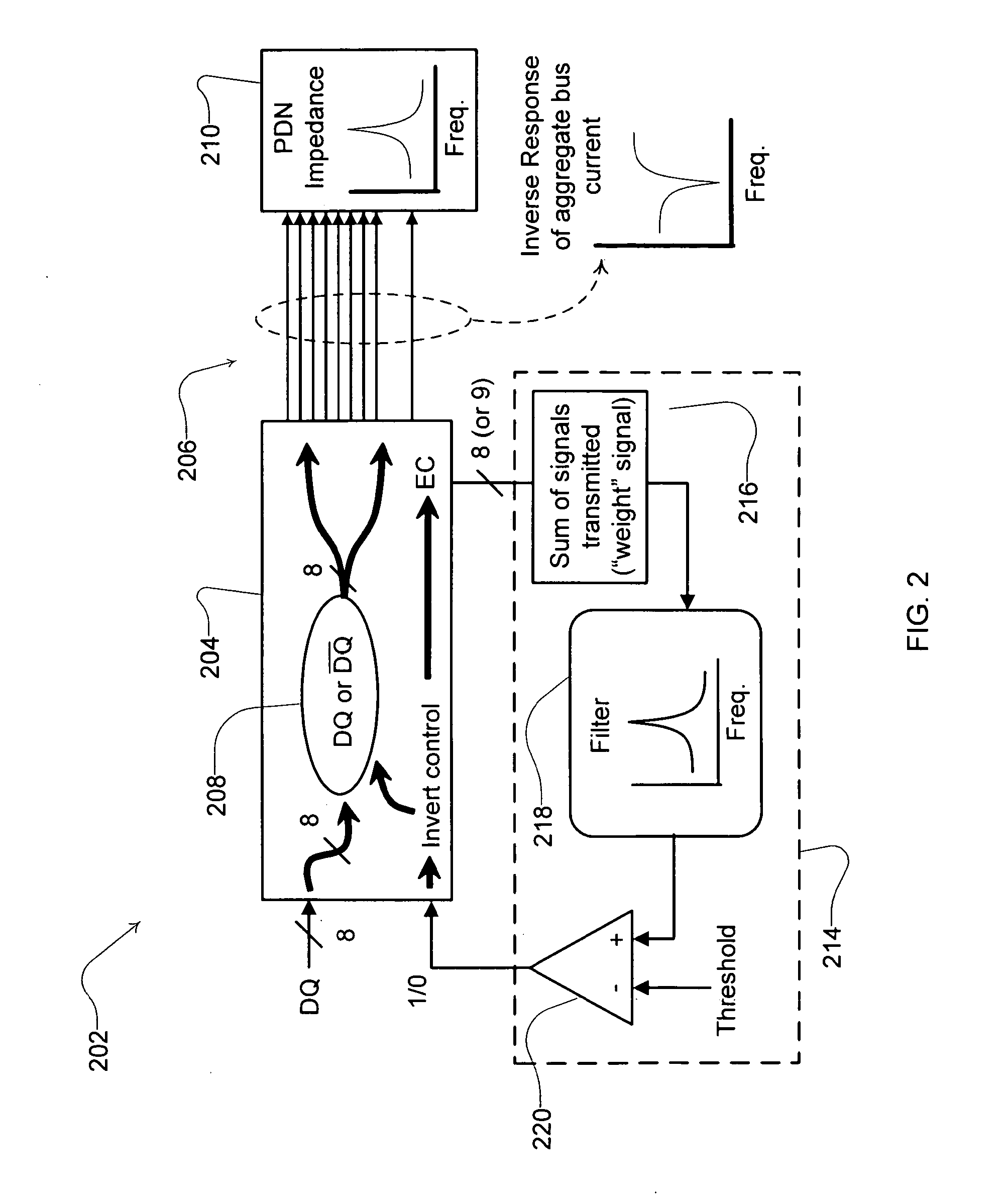

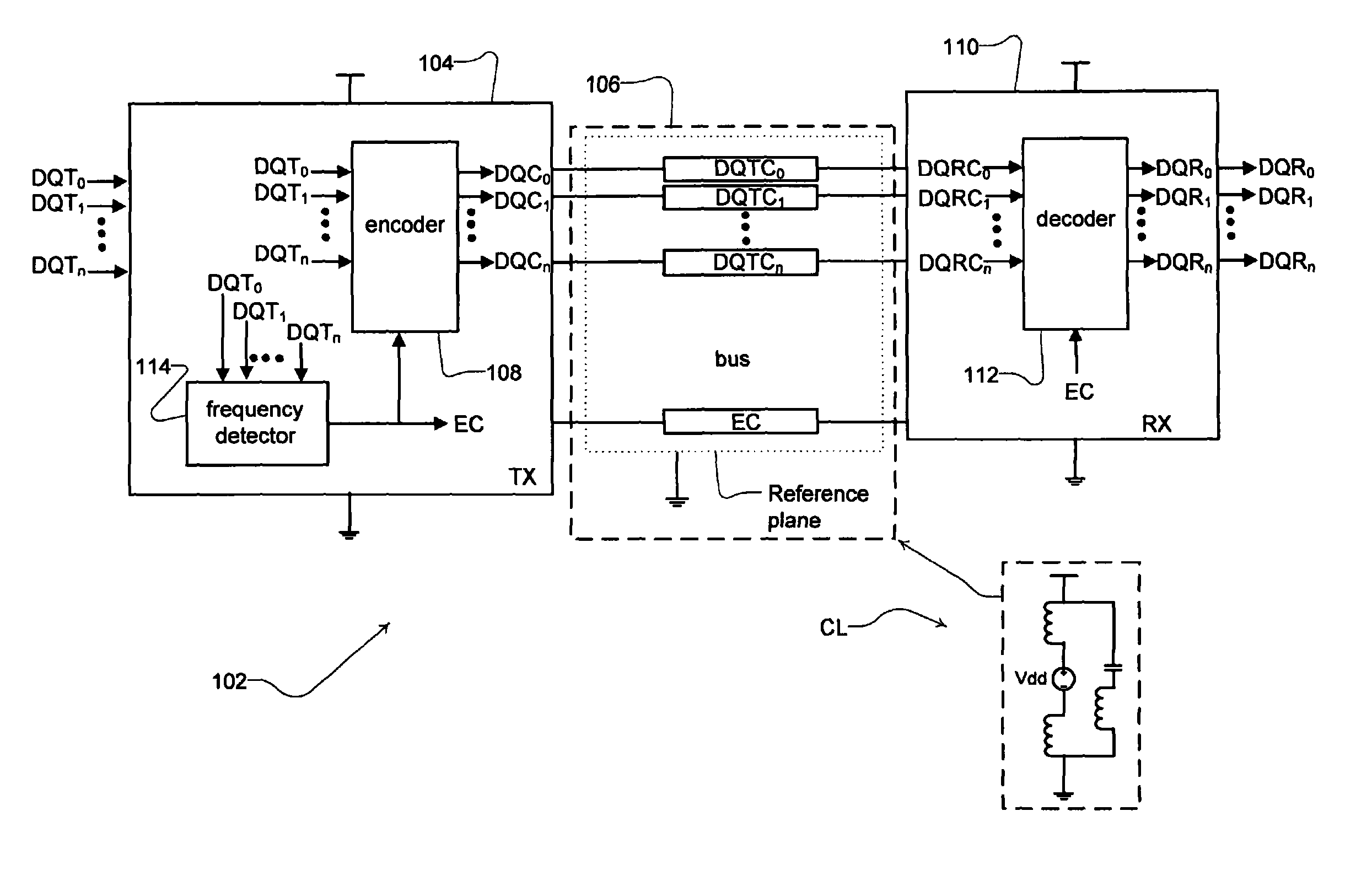

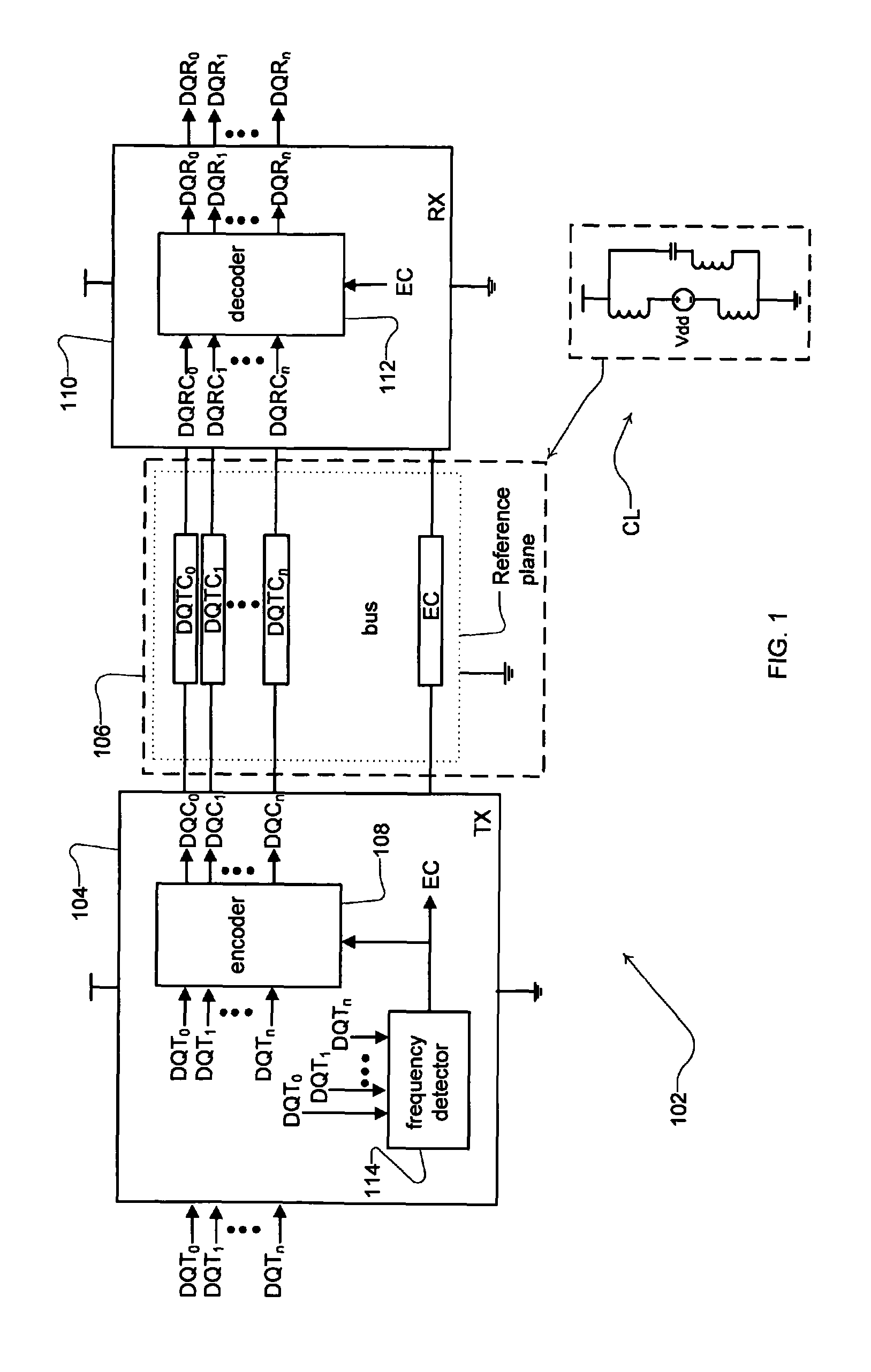

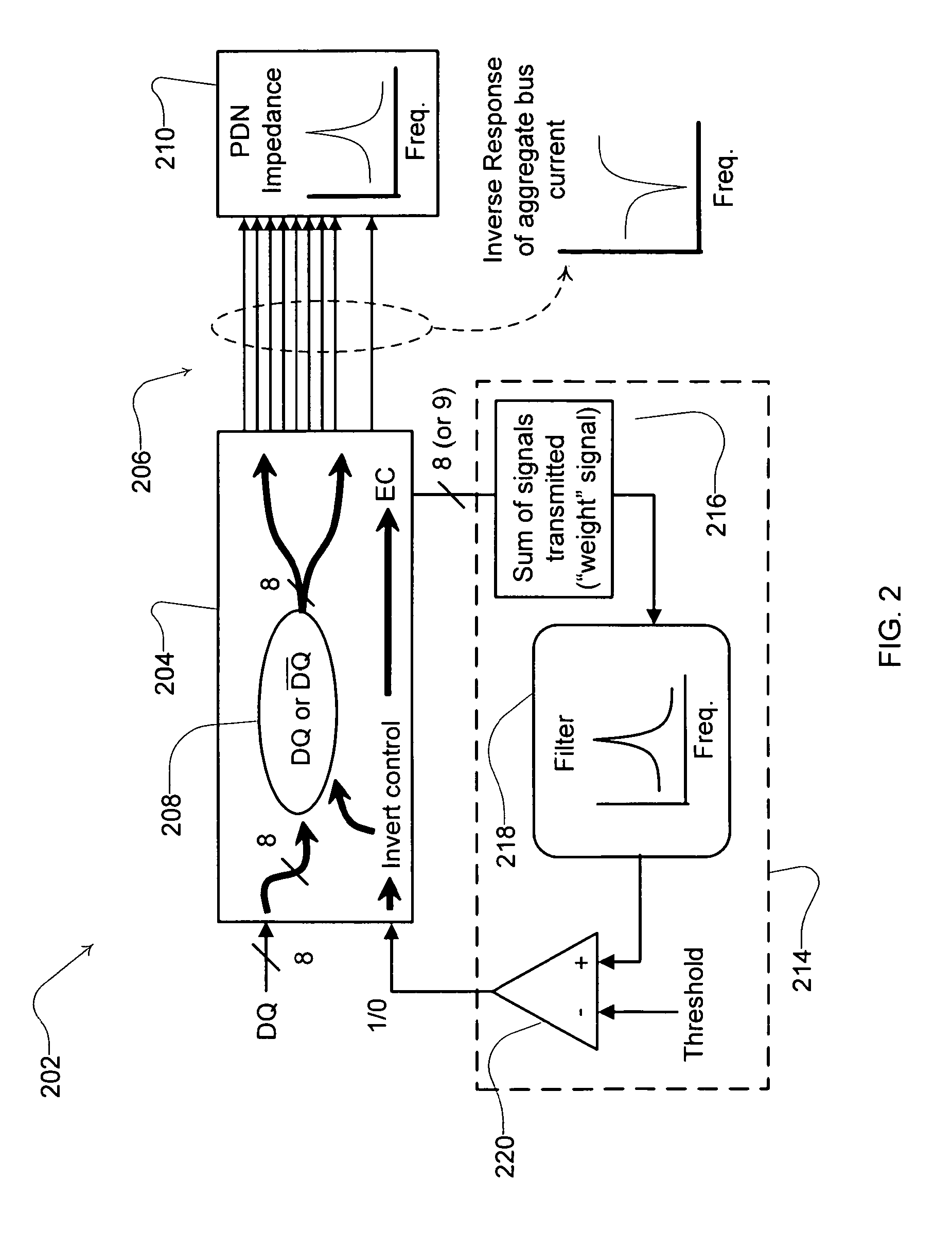

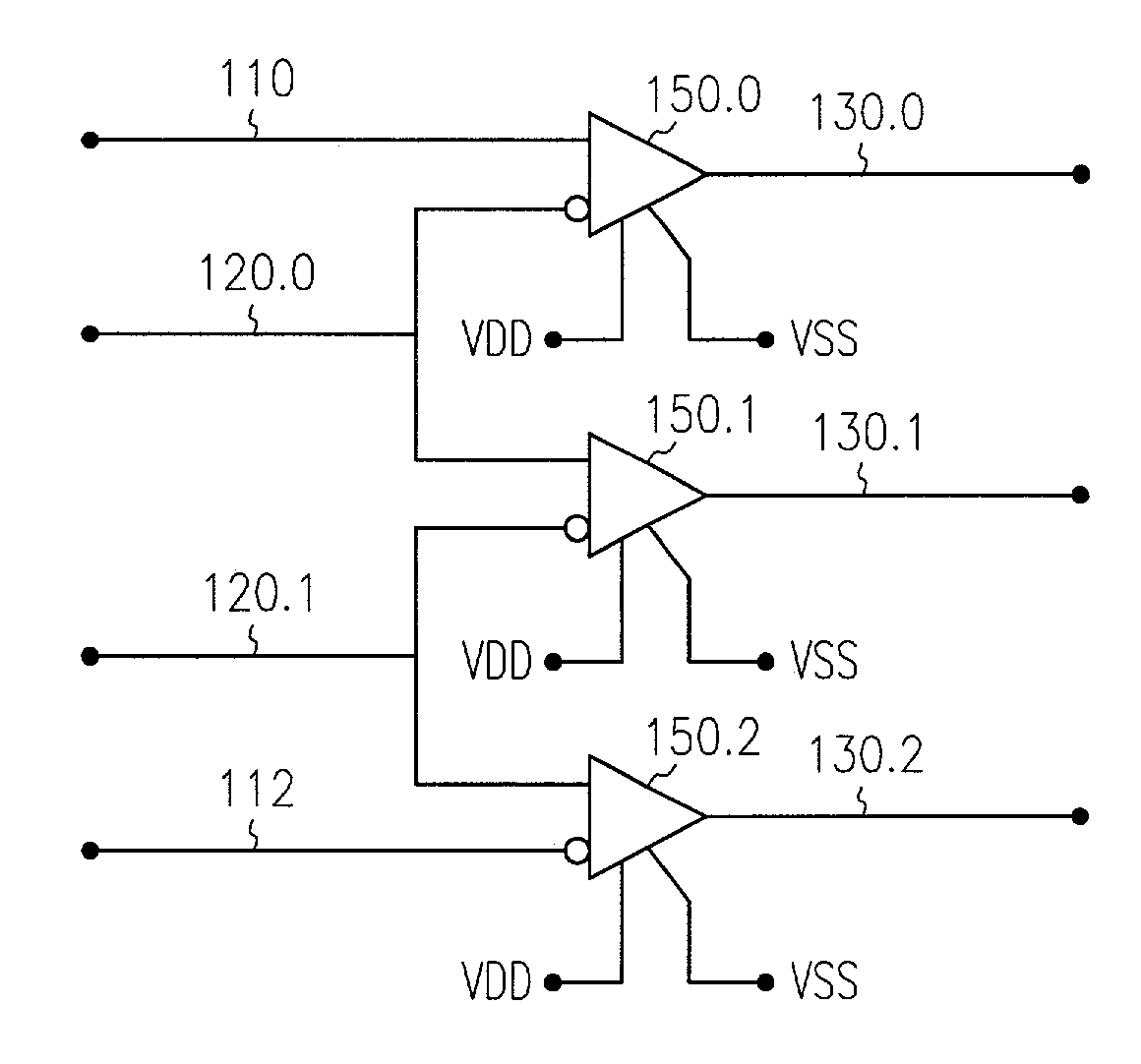

Frequency responsive bus coding

A data system 102 permits bus encoding based on frequency of the bus; an encoding scheme may be implemented to avoid undesirable frequency conditions such as a resonant condition that may lead to degradation in system performance. The device or integrated circuit will typically include an encoder; in one embodiment, the encoder is a data bus inversion (DBI) circuit that selectively inverts all lines of a data bus. A detector that may include a band-pass or stop-band filter that, for example, evaluates data for transmission on the bus to detect frequency, for example, a predetermined frequency or a frequency range. The detector provides a control signal for the encoder to selectively apply an encoding scheme as a function of frequency.

Owner:RAMBUS INC

Frequency responsive bus coding

A data system 102 permits bus encoding based on frequency of the bus; an encoding scheme may be implemented to avoid undesirable frequency conditions such as a resonant condition that may lead to degradation in system performance. The device or integrated circuit will typically include an encoder; in one embodiment, the encoder is a data bus inversion (DBI) circuit that selectively inverts all lines of a data bus. A detector that may include a band-pass or stop-band filter that, for example, evaluates data for transmission on the bus to detect frequency, for example, a predetermined frequency or a frequency range. The detector provides a control signal for the encoder to selectively apply an encoding scheme as a function of frequency.

Owner:RAMBUS INC

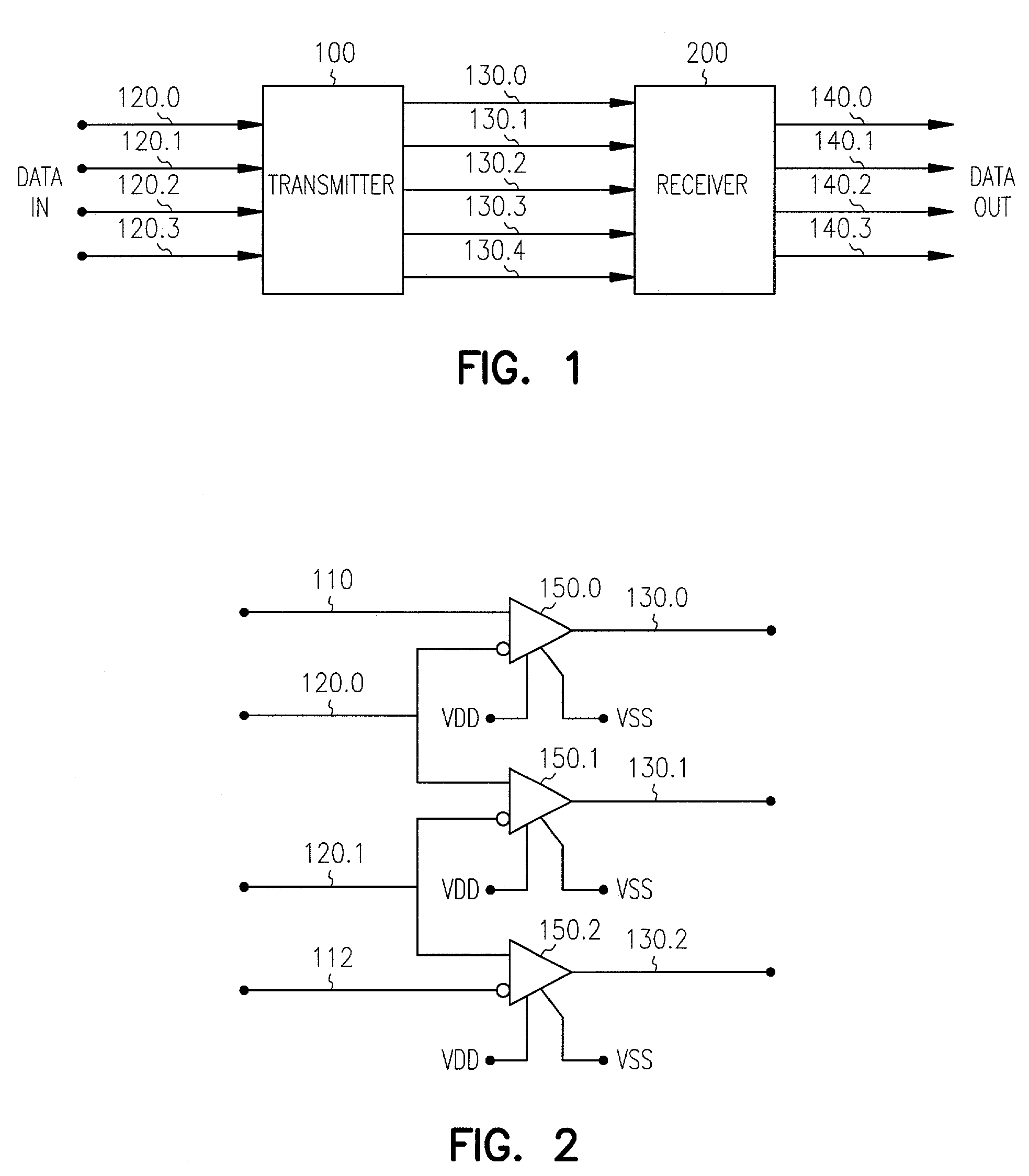

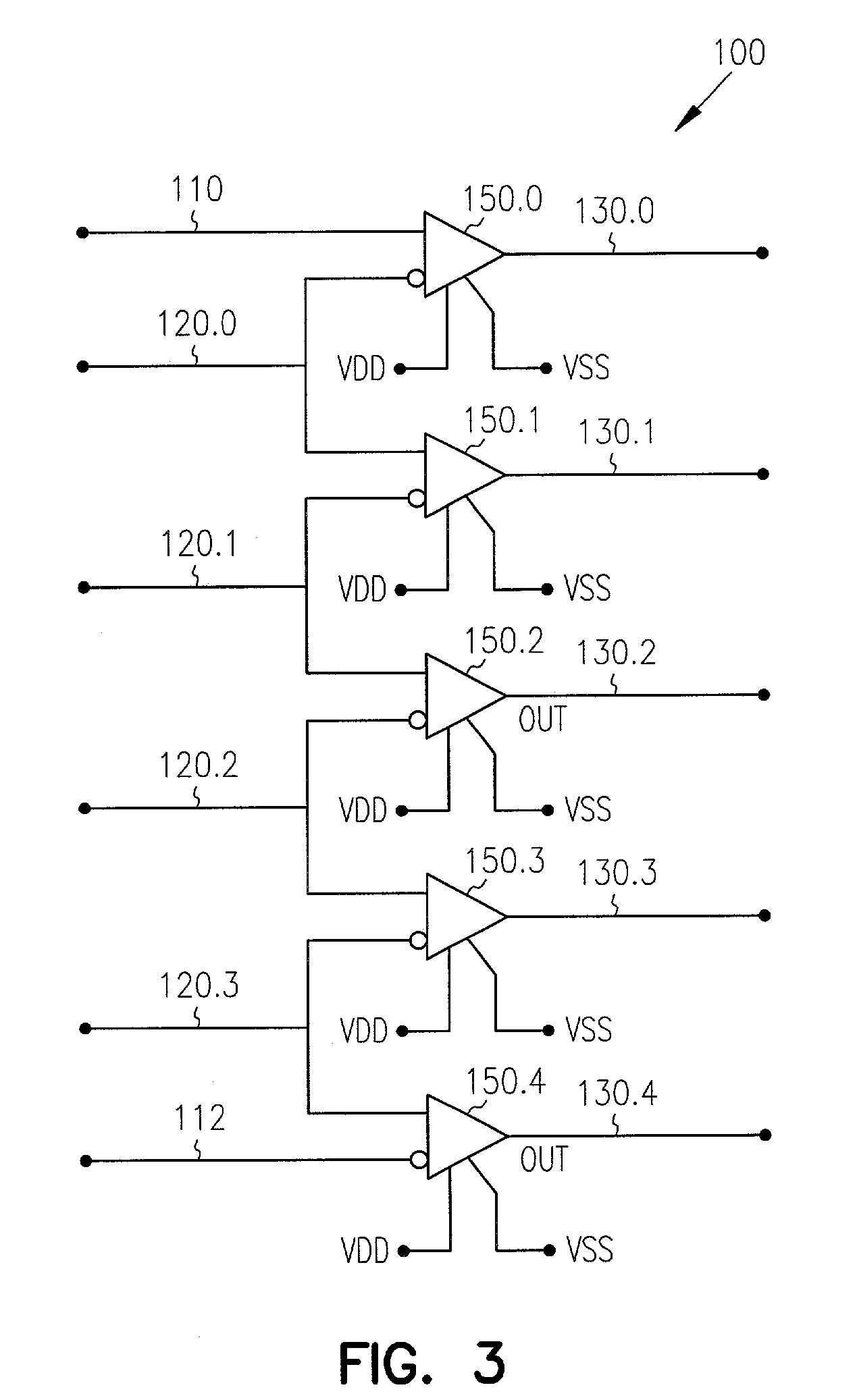

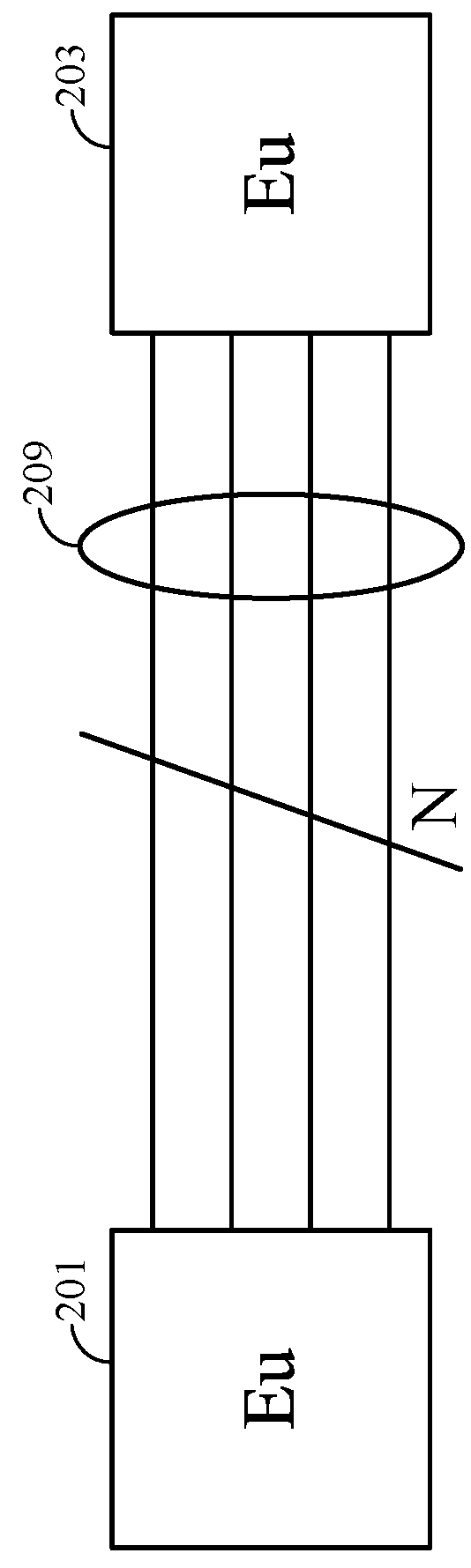

Spacial derivative bus encoder and decoder

InactiveUS7167523B2Reduce noiseReduce power consumptionMultiple input and output pulse circuitsChannel dividing arrangementsData signalBus encoding

A method and apparatus for providing efficient and accurate electronic data transmission of information on a data bus in the presence of noise. Data signals are received on a plurality of input lines by a spacial derivative encoder. The spacial derivative encoder encodes the signals and transmits them to a receiver having a spacial derivative decoder. The spacial derivative decoder then decodes the signals. Minimal overhead is required as for n input lines only n+1 lines are needed to transmit each of the encoded signals.

Owner:MORGAN STANLEY +1

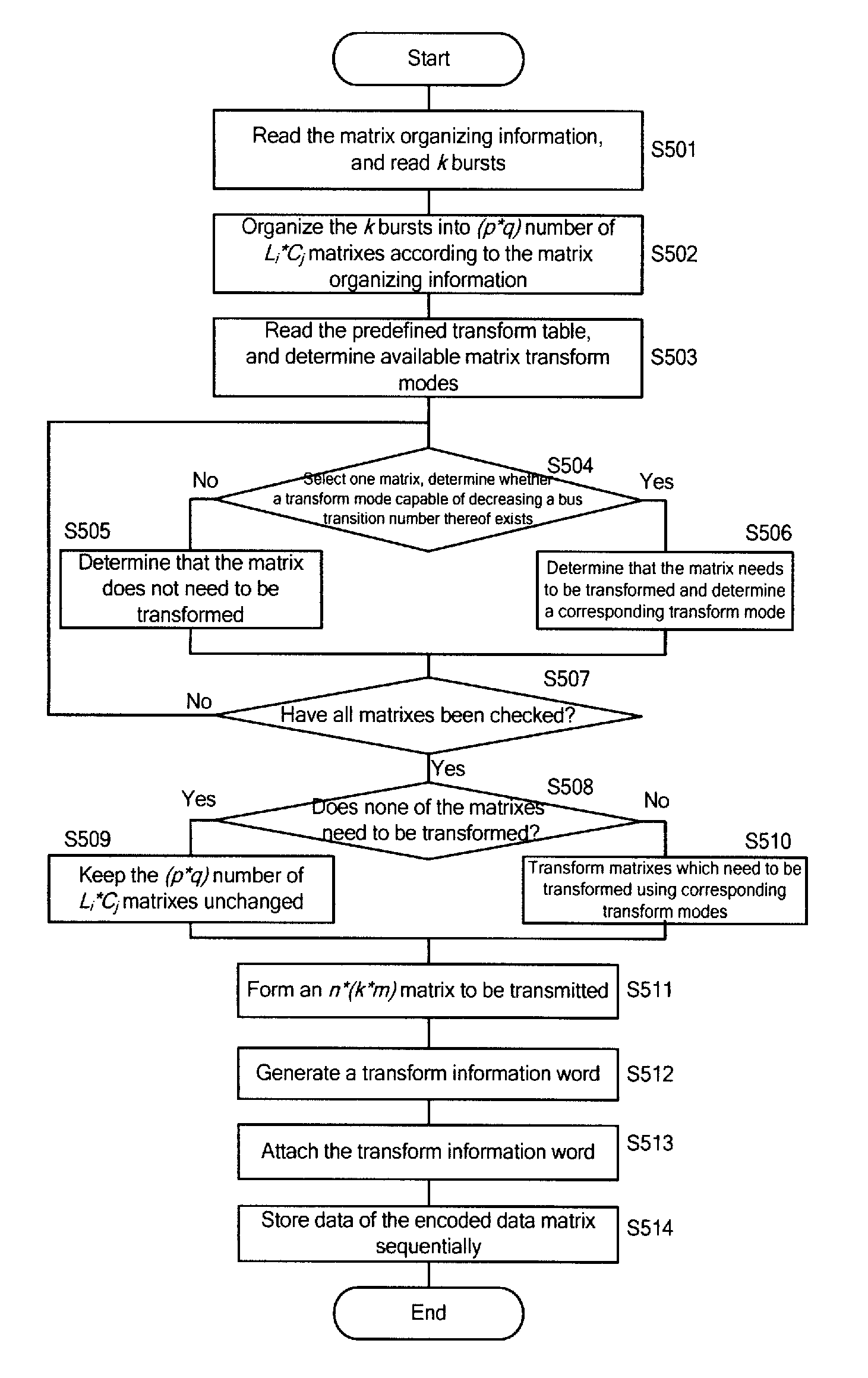

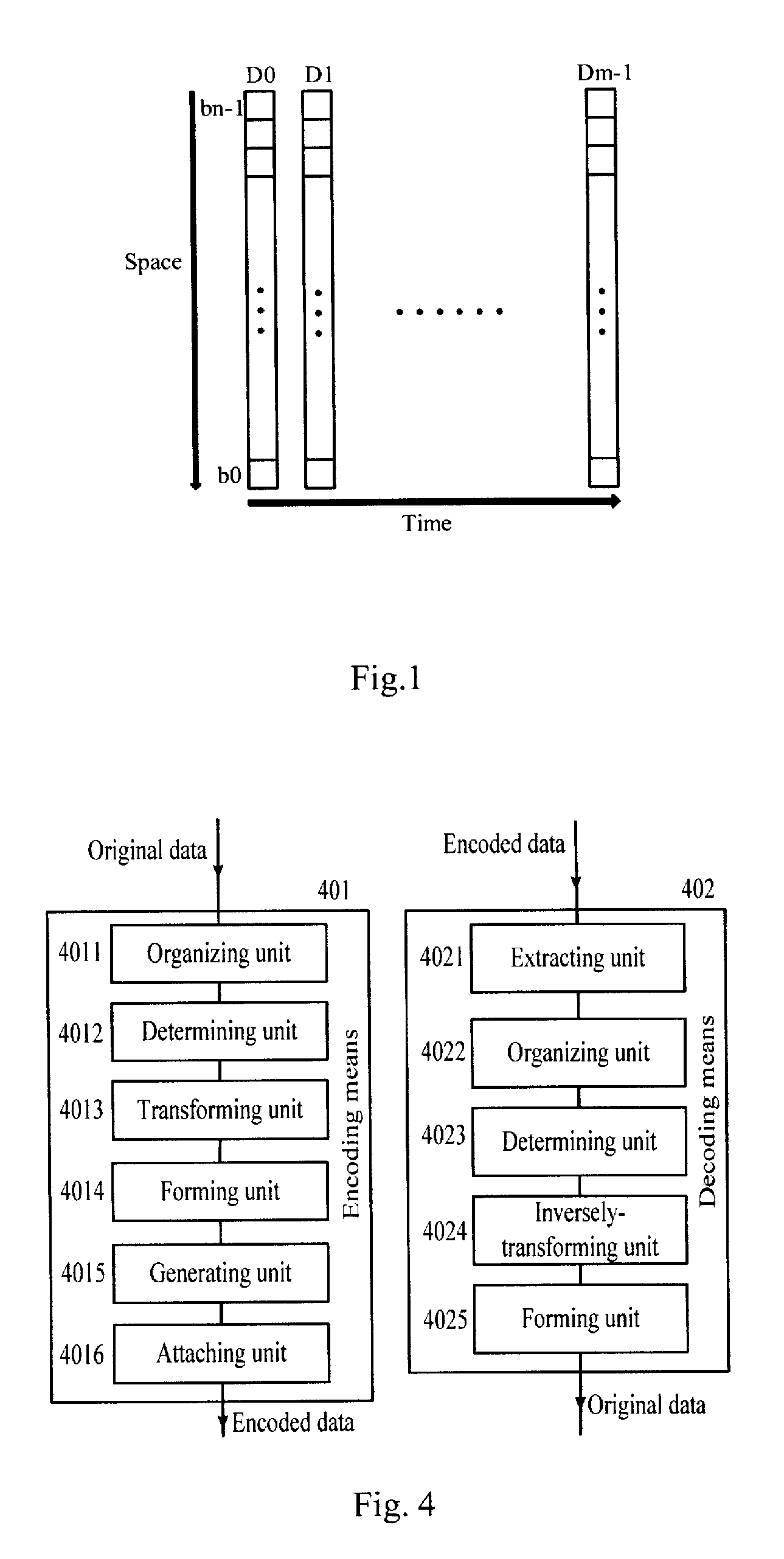

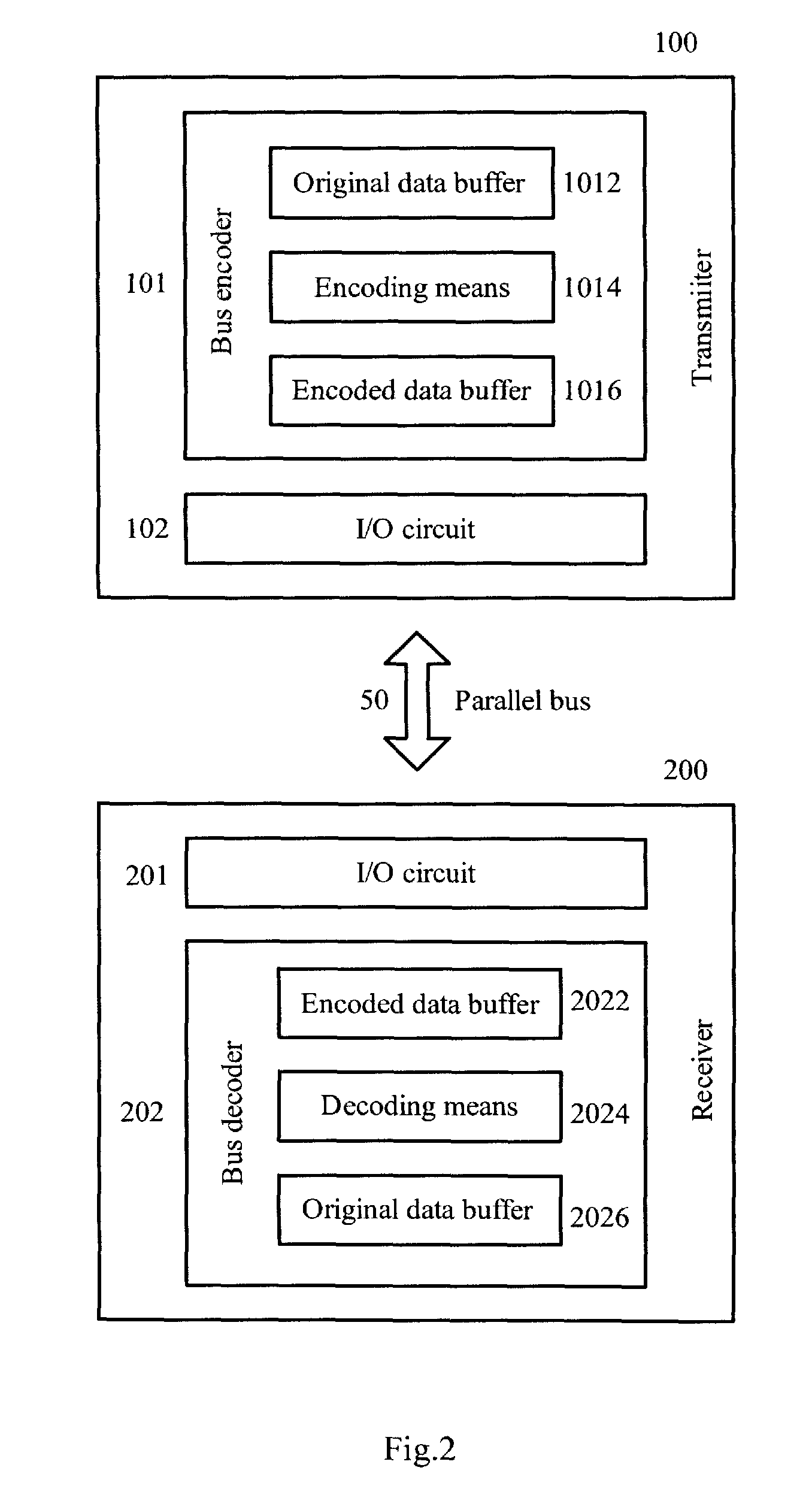

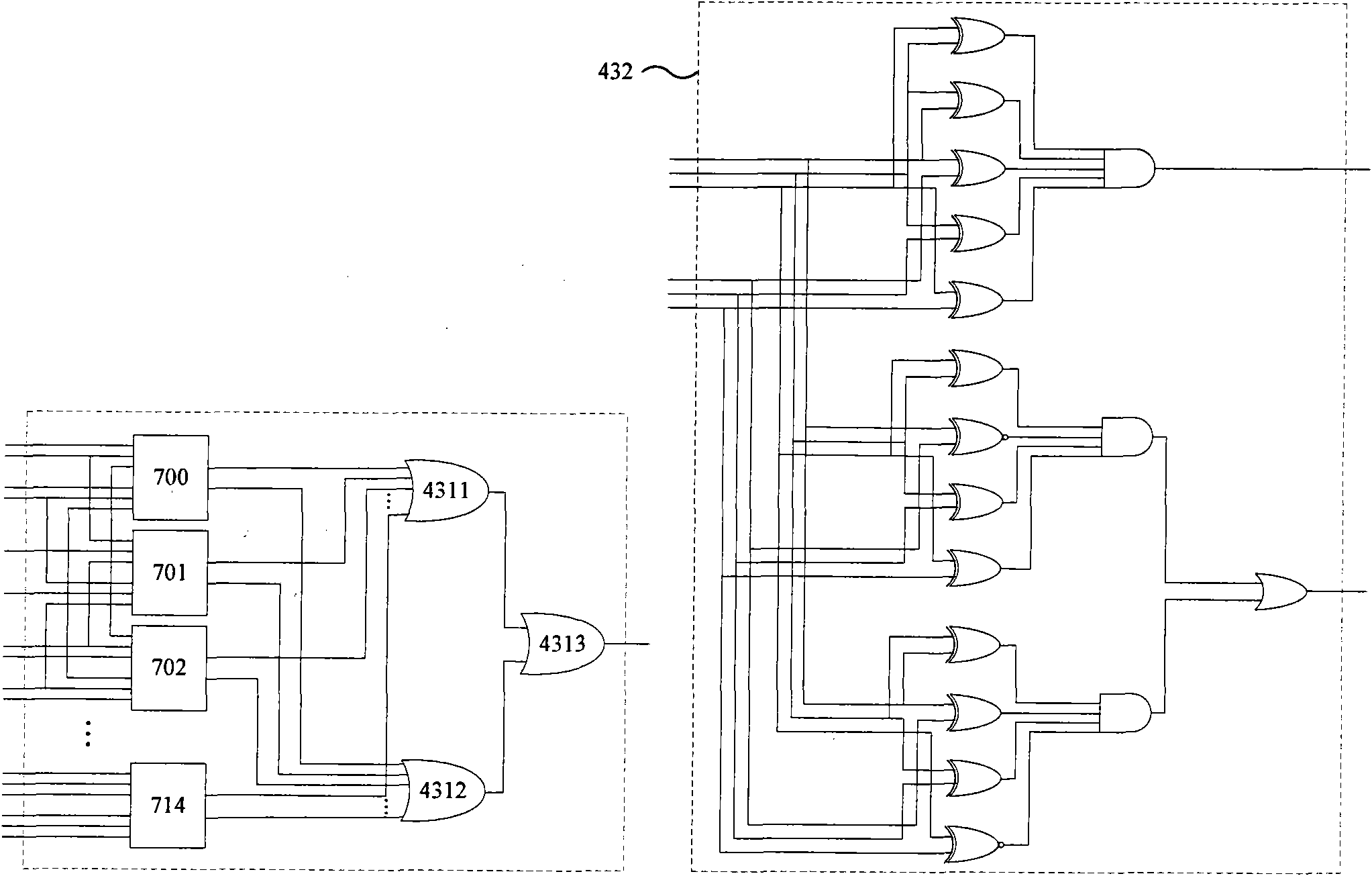

Bus encoding/decoding method and bus encoder/decoder

InactiveUS8085172B2Decreasing bus transition numberReduce I/O power and powerEnergy efficient ICTDigital data processing detailsDecoding methodsTransmission matrix

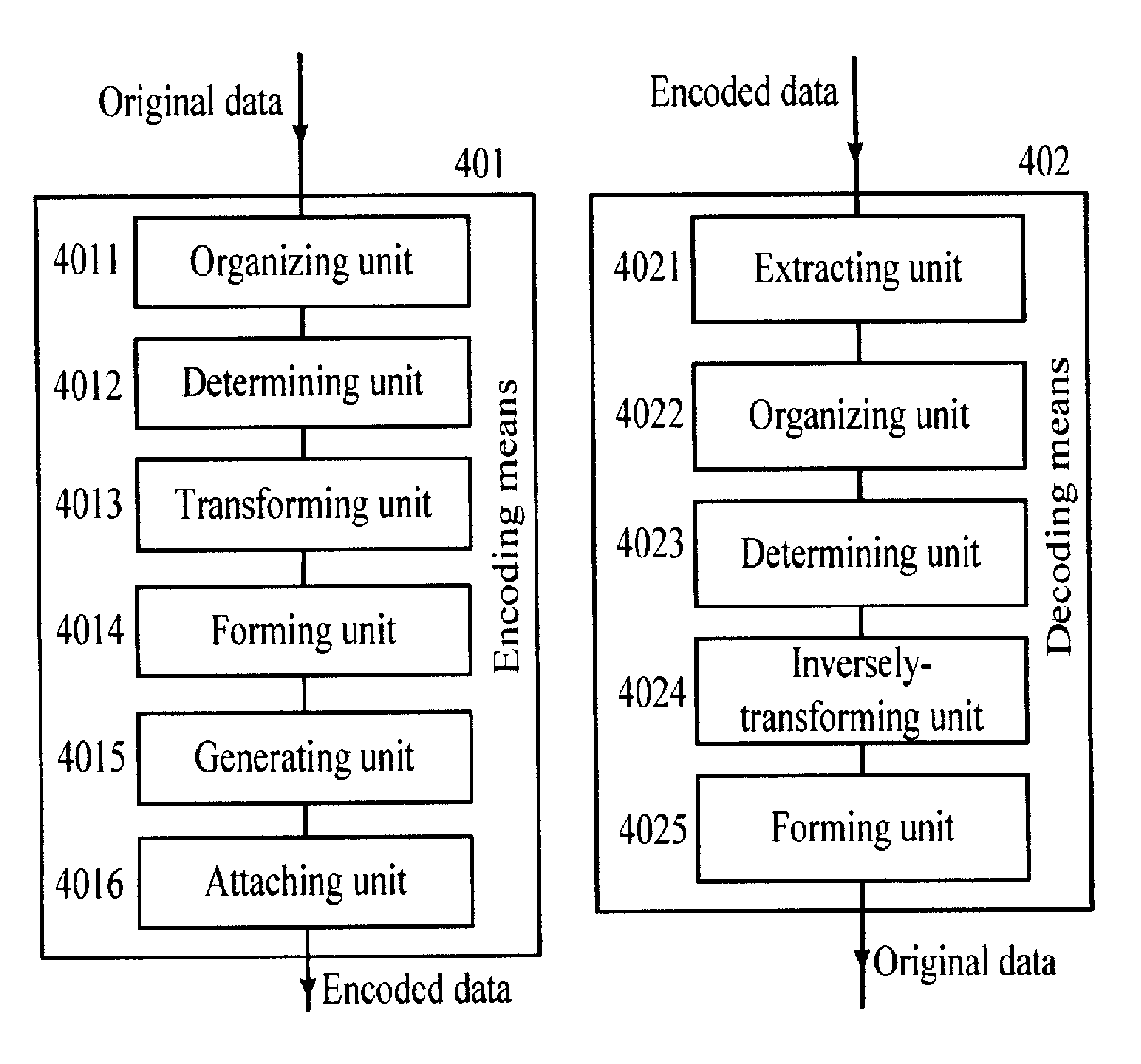

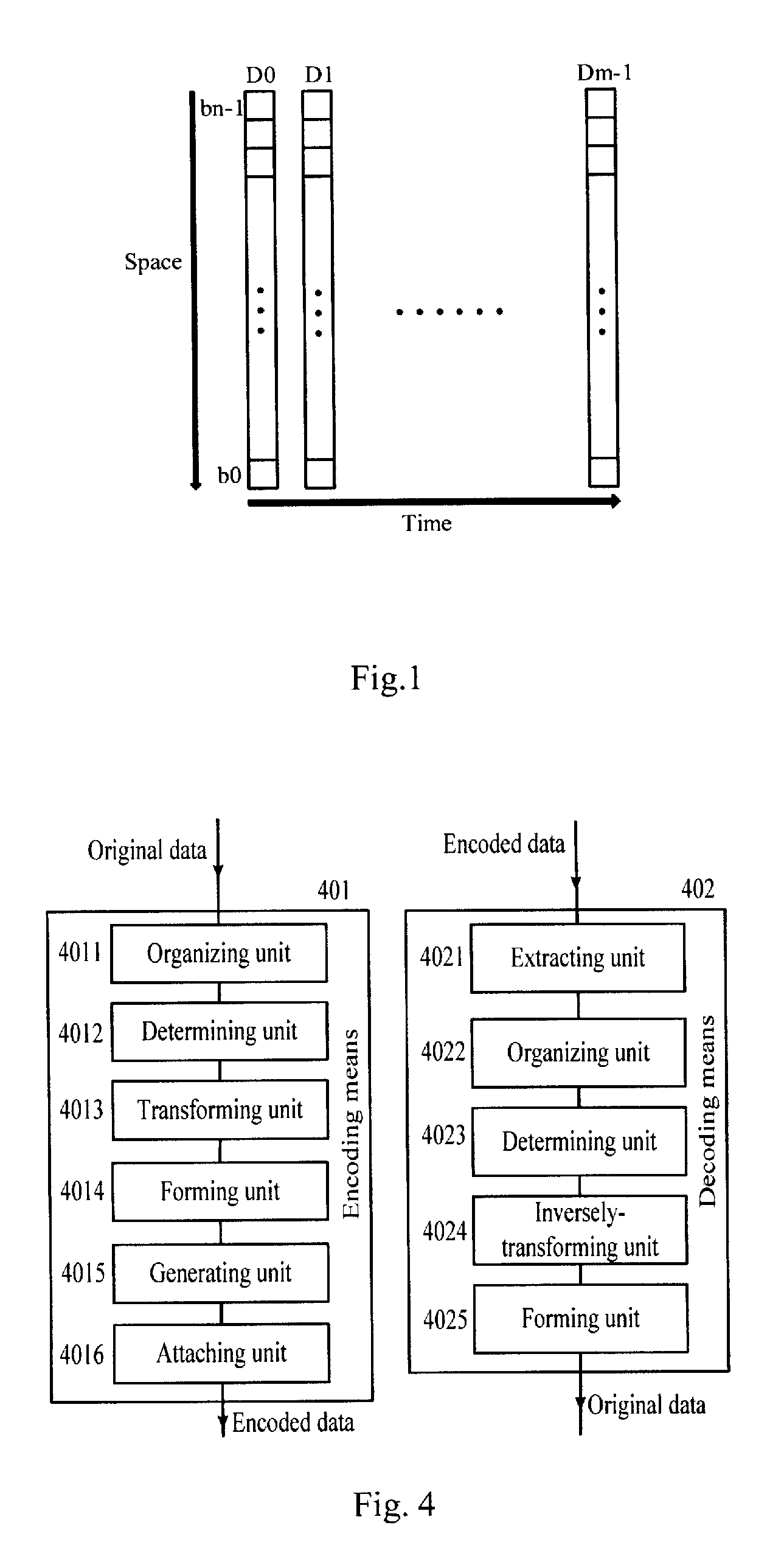

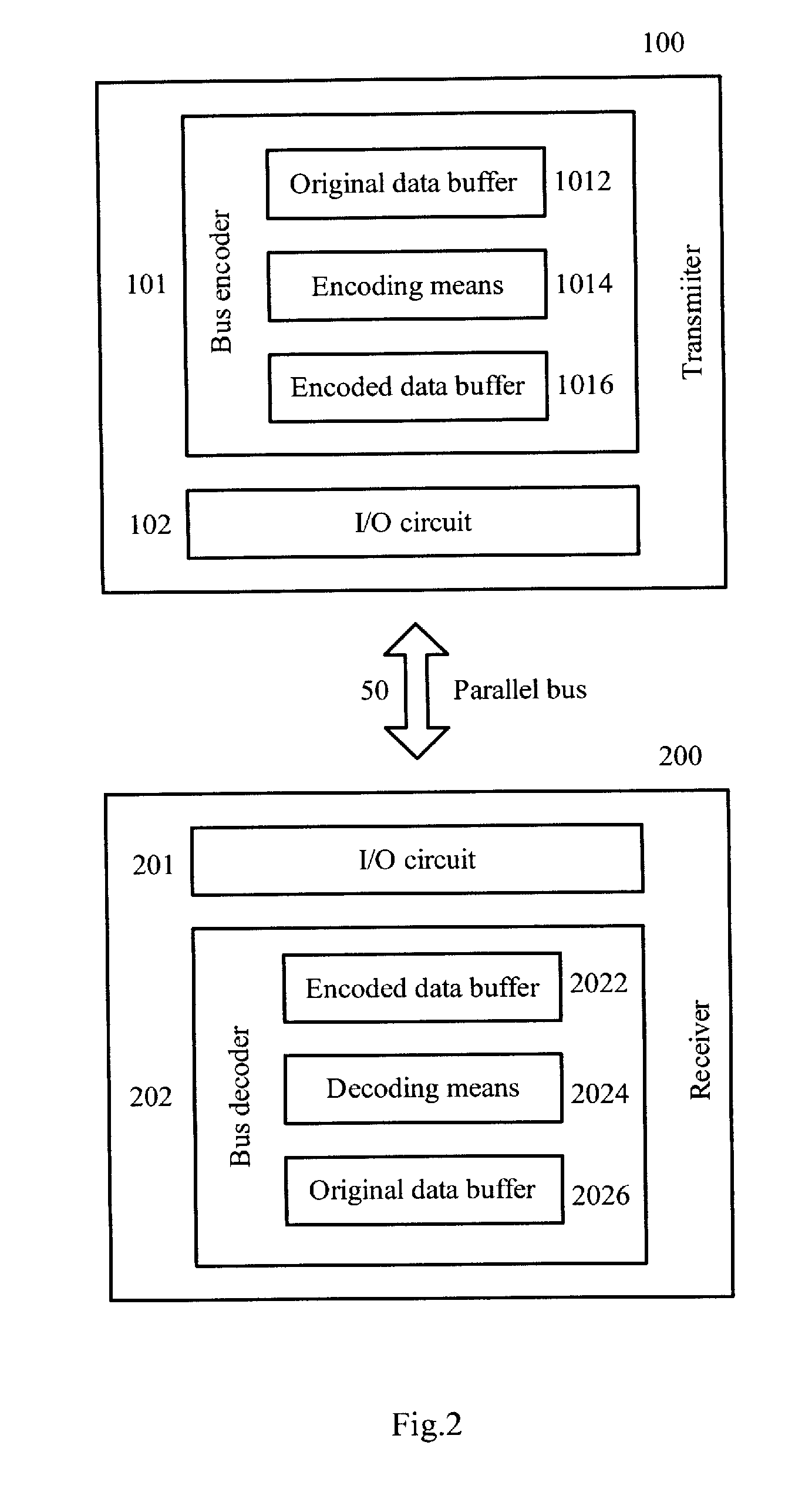

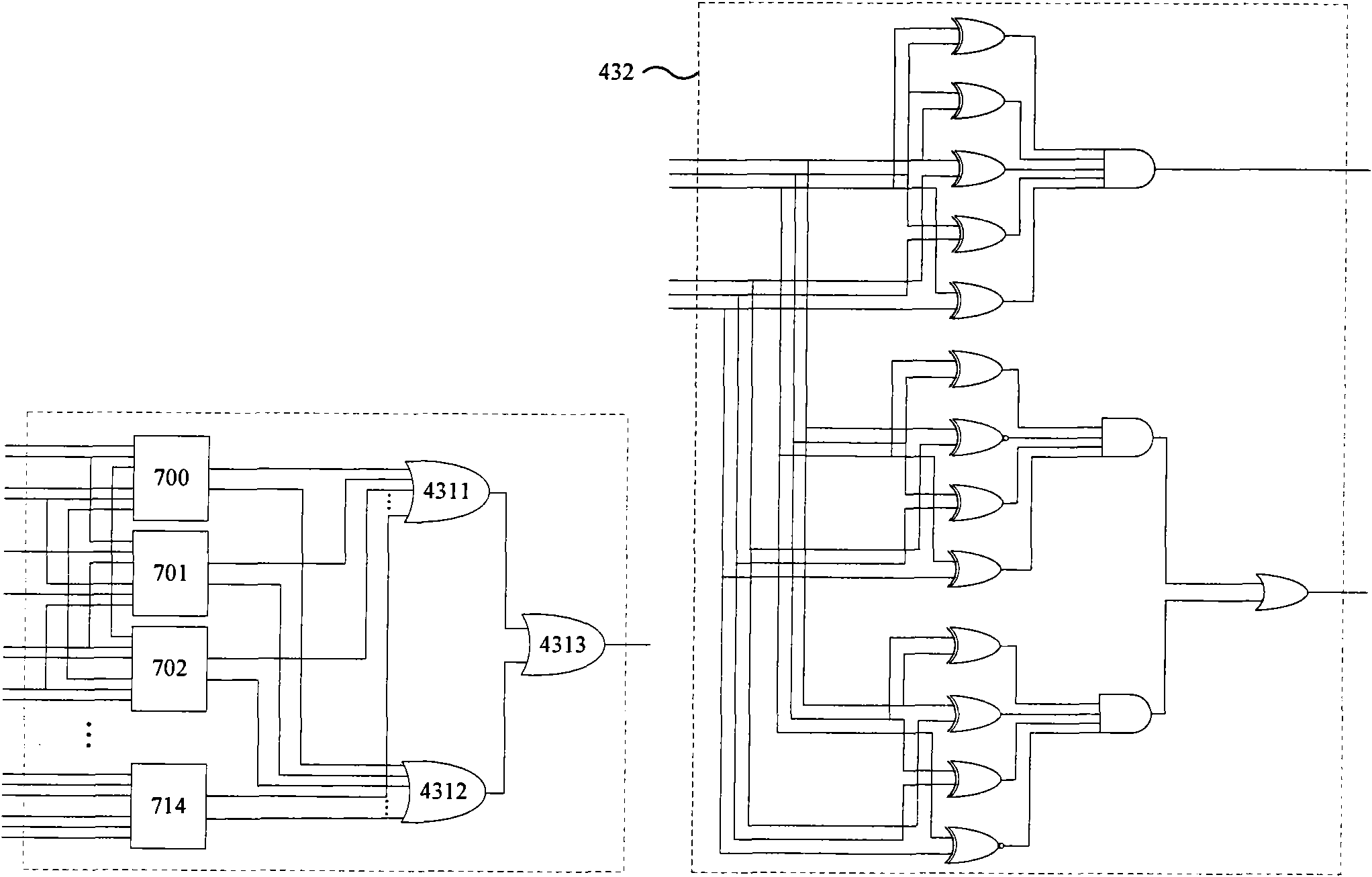

An encoding method and an encoder for encoding data transmitted in a manner of bursts via a parallel bus and a decoding method and a decoder. The encoding method includes organizing data of the bursts into matrixes, determining for each of the matrixes whether a transform mode capable of decreasing the bus transition number exists, determining that the matrix needs to be transformed, determining a transform mode for transforming the matrix, and replacing the initial matrix with the transformed matrix. Then, forming a new matrix to be transmitted from matrixes which do not need to be transformed and matrixes which have been transformed. Thereafter, first generating a transform information word indicating transform states of the respective matrixes and then attaching the transform information word to the matrix to be transmitted to form an encoded matrix for actual transmission.

Owner:IBM CORP

Bus encoding/decoding method and bus encoder/decoder

InactiveUS20090193159A1Reduce in quantityImprove compatibilityEnergy efficient ICTDigital data processing detailsComputer hardwareDecoding methods

An encoding method and an encoder for encoding data transmitted in a manner of bursts via a parallel bus and a decoding method and a decoder. The encoding method includes organizing data of the bursts into matrixes, determining for each of the matrixes whether a transform mode capable of decreasing the bus transition number exists, determining that the matrix needs to be transformed, determining a transform mode for transforming the matrix, and replacing the initial matrix with the transformed matrix. Then, forming a new matrix to be transmitted from matrixes which do not need to be transformed and matrixes which have been transformed. Thereafter, first generating a transform information word indicating transform states of the respective matrixes and then attaching the transform information word to the matrix to be transmitted to form an encoded matrix for actual transmission.

Owner:IBM CORP

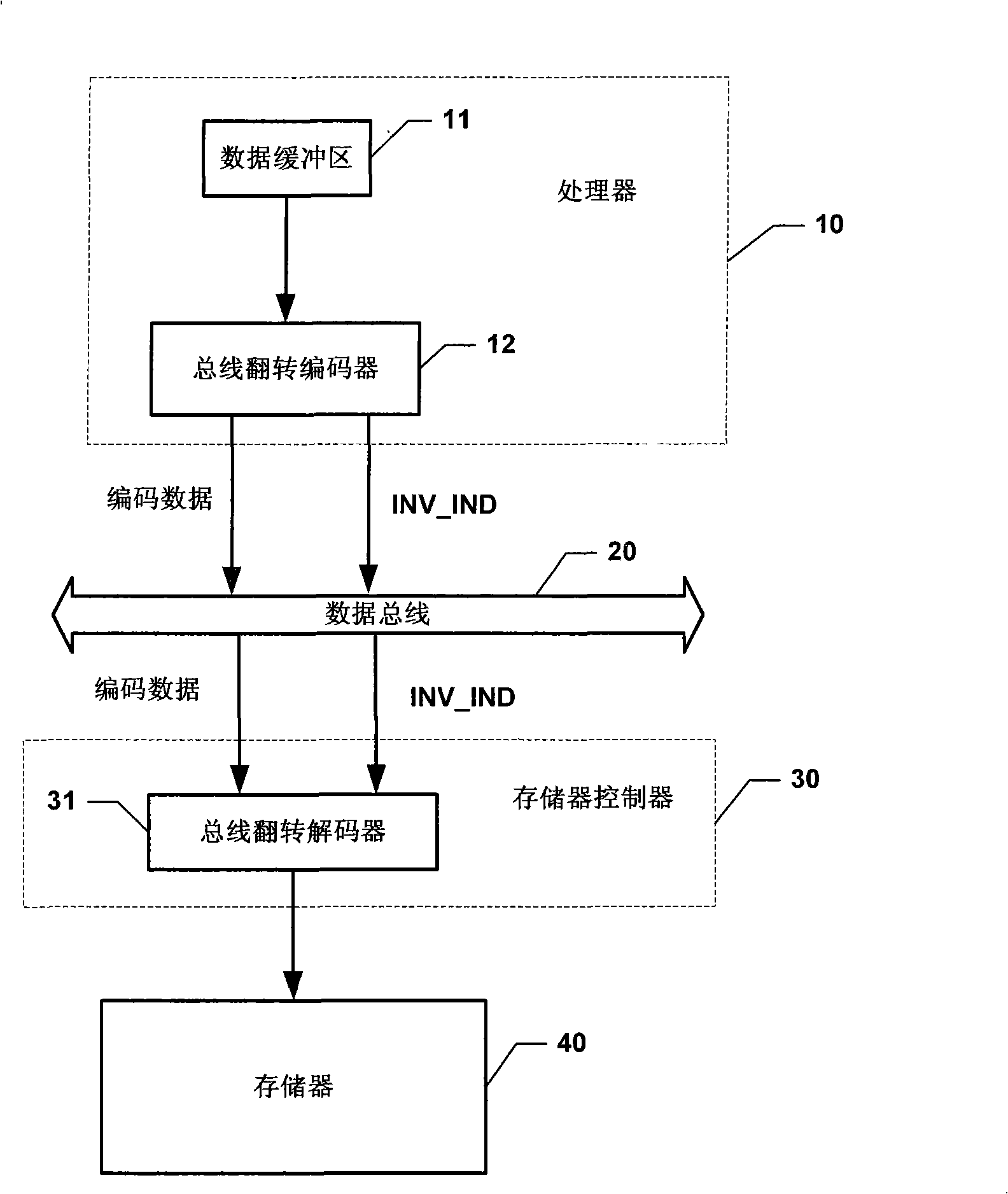

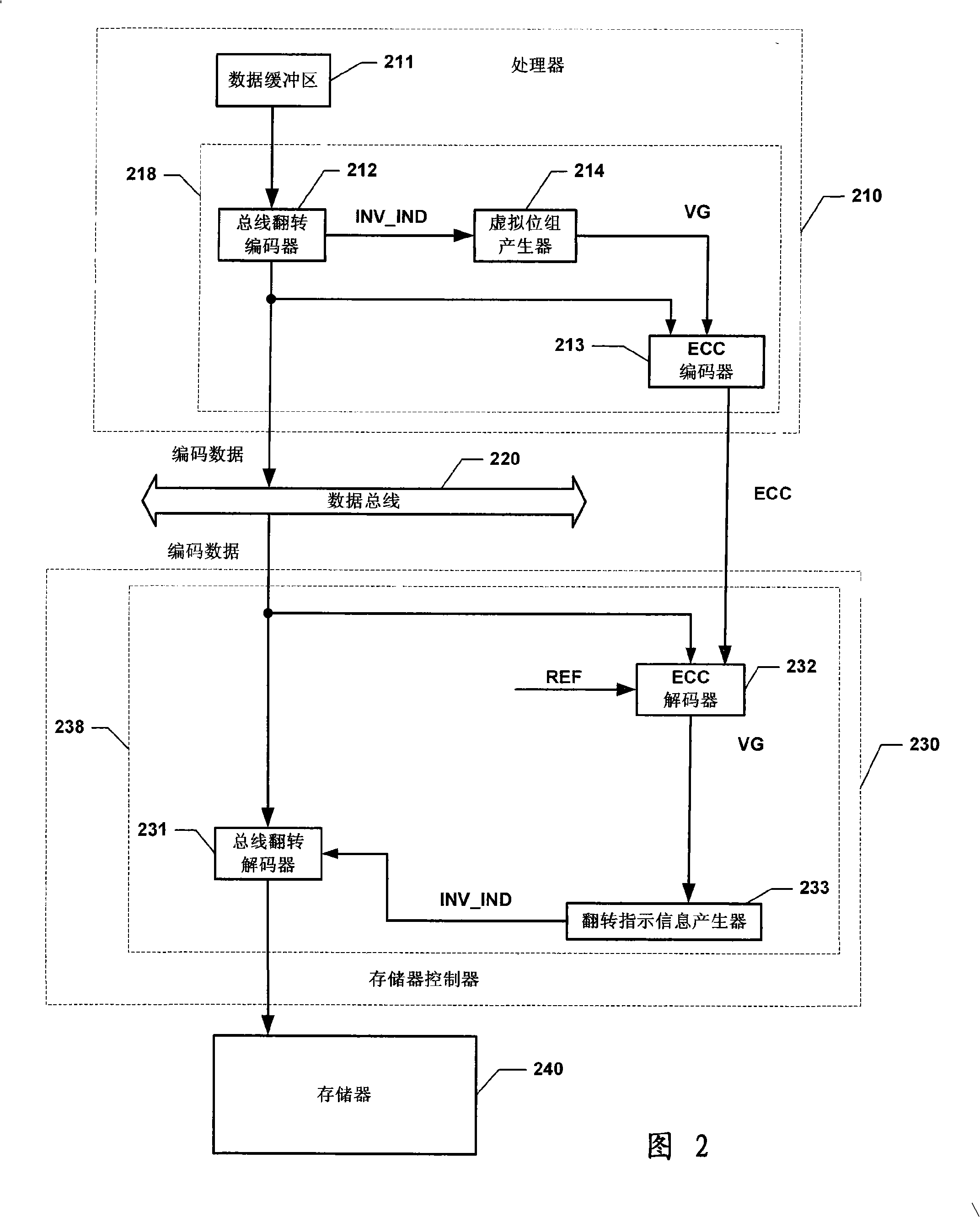

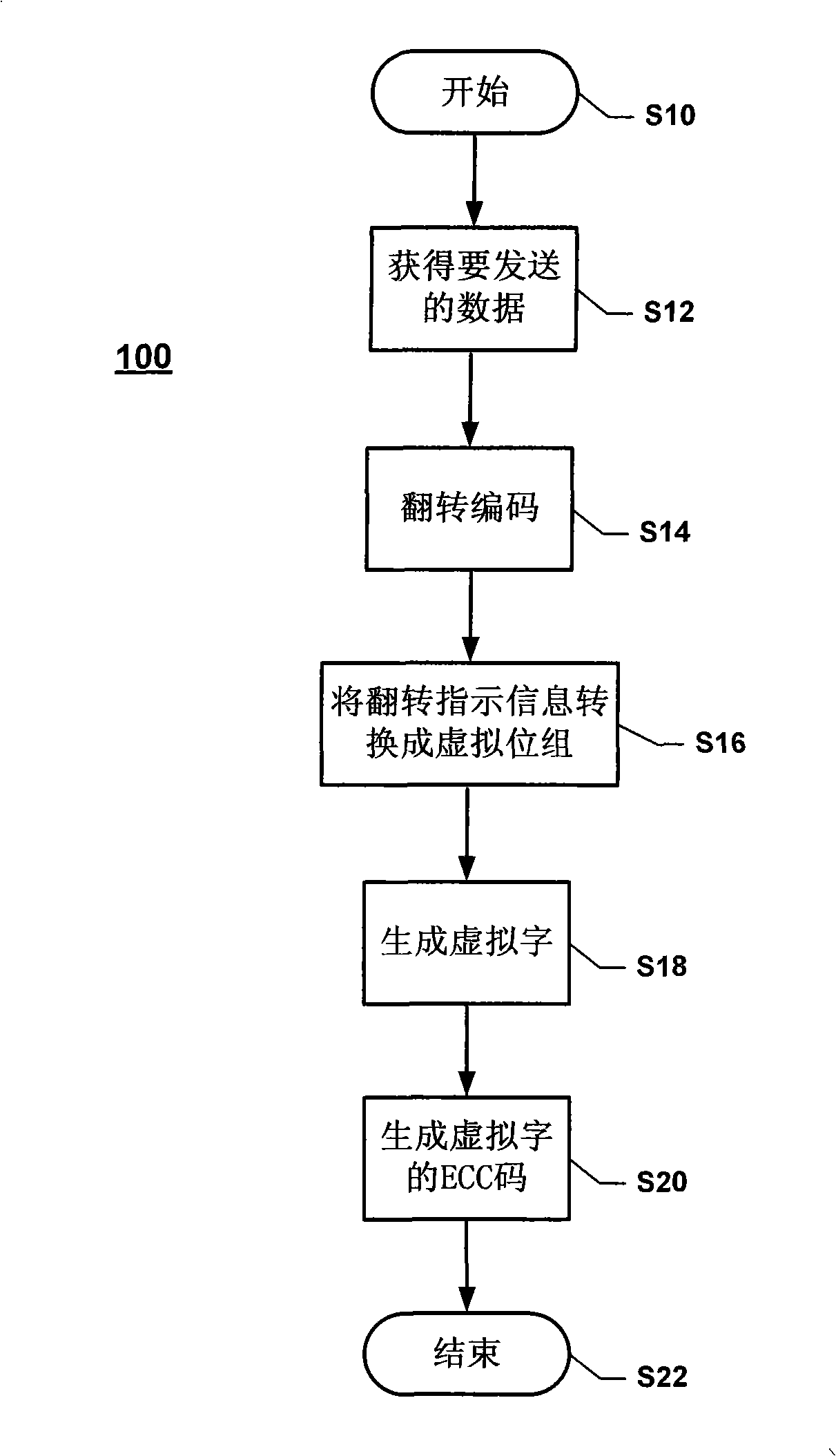

Data bus system, coder/decoder thereof and coding/decoding method

The invention relates to a data bus system and a coder / decoder and a method thereof. The data bus coder comprises: a bus transition coder for carrying out bus transition coding to data according to a preset bus transition coding scheme so as to generate encoding data and transition indicting information; a virtual byte generator for converting the transition indicting information into virtual bytes according to a preset coding mapping; and an error correcting and detecting encoder for generating the error correcting and detecting codes of a virtual character according to a preset error correction and detection coding scheme, wherein the detecting bit number of the preset error correcting and detecting coding scheme is at least one bit more than the error correcting bit number; the mapping leads the hamming distance between all the possible values of the virtual bytes and the referential virtual bytes beyond the conversion of the mapping to be a fixed value and not more than the correcting bit number of the error correcting and detecting coding scheme; and the virtual character contains data to be output, virtual bytes corresponding to the data and stuff bits needing to be allocated with fixed values according to the requirements of the error correcting and detecting coding scheme.

Owner:IBM CORP

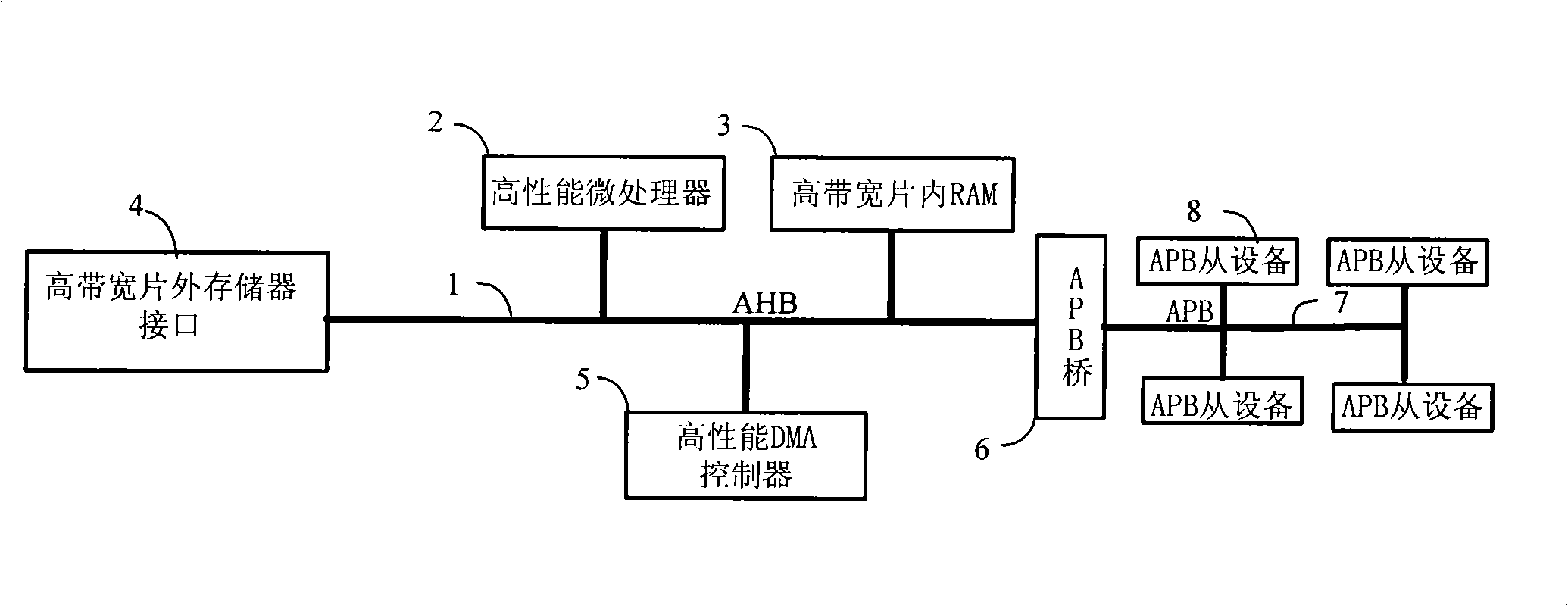

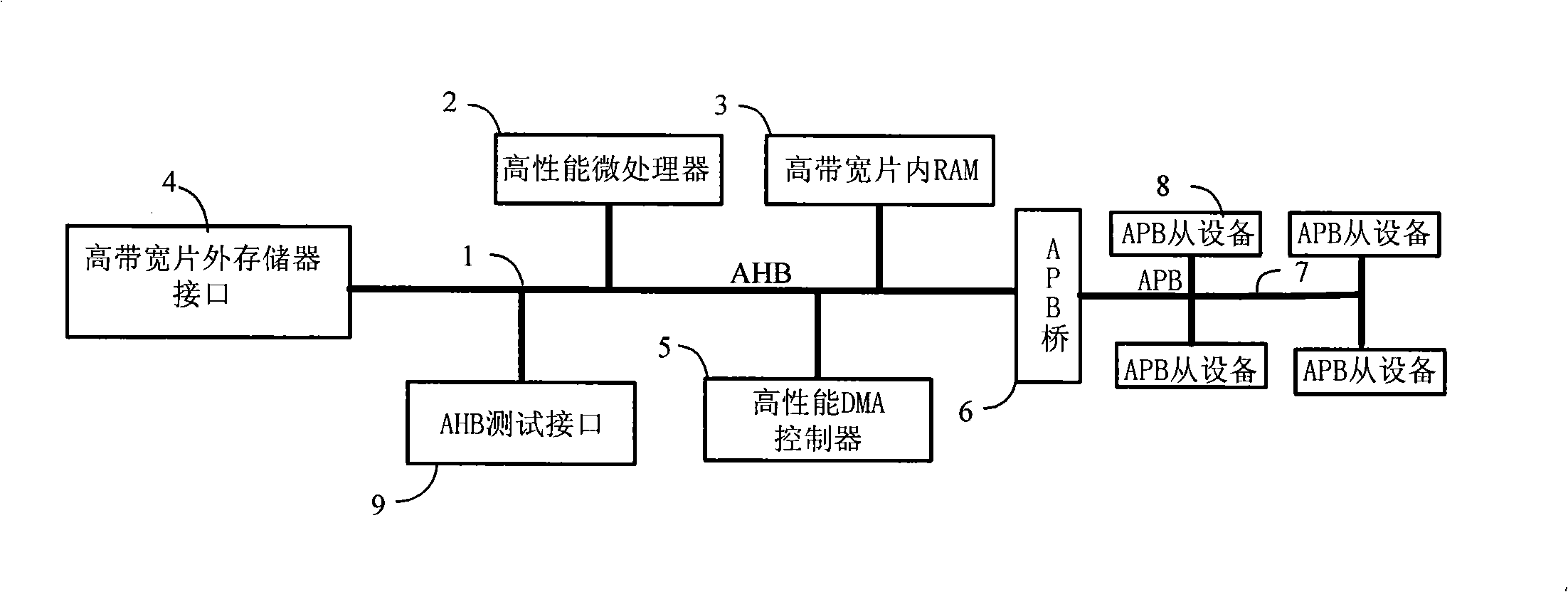

AHB bus test method and system

The present invention discloses an AHB bus test method and system, applied in the test to the AHB bus in the system-on-chip (SOC), which is provided with AHB test interfaces. The method includes: producing first AHB bus signals at the exterior of the SOC; converting the first AHB bus signals into the test signals, and then transmits to the AHB test interface; the AHB test interface converting the received test signals into AHB bus transmission signals to execute AHB bus test. The AHB bus test system provided by the present invention at least includes a microprocessor for producing the first AHB bus transmission signals, as well as a test interface bus encoder for receiving the first AHB bus transmission signals and converting the signals into the test signals. The present invention can simply and exactly produce the test signals with high-efficiency, and can effectively realize the test to the AHB bus in the SOC.

Owner:ACTIONS ZHUHAI TECH CO

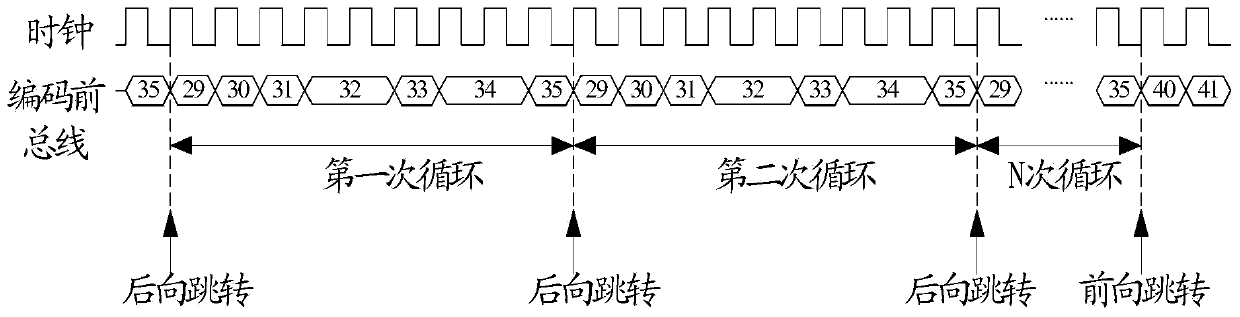

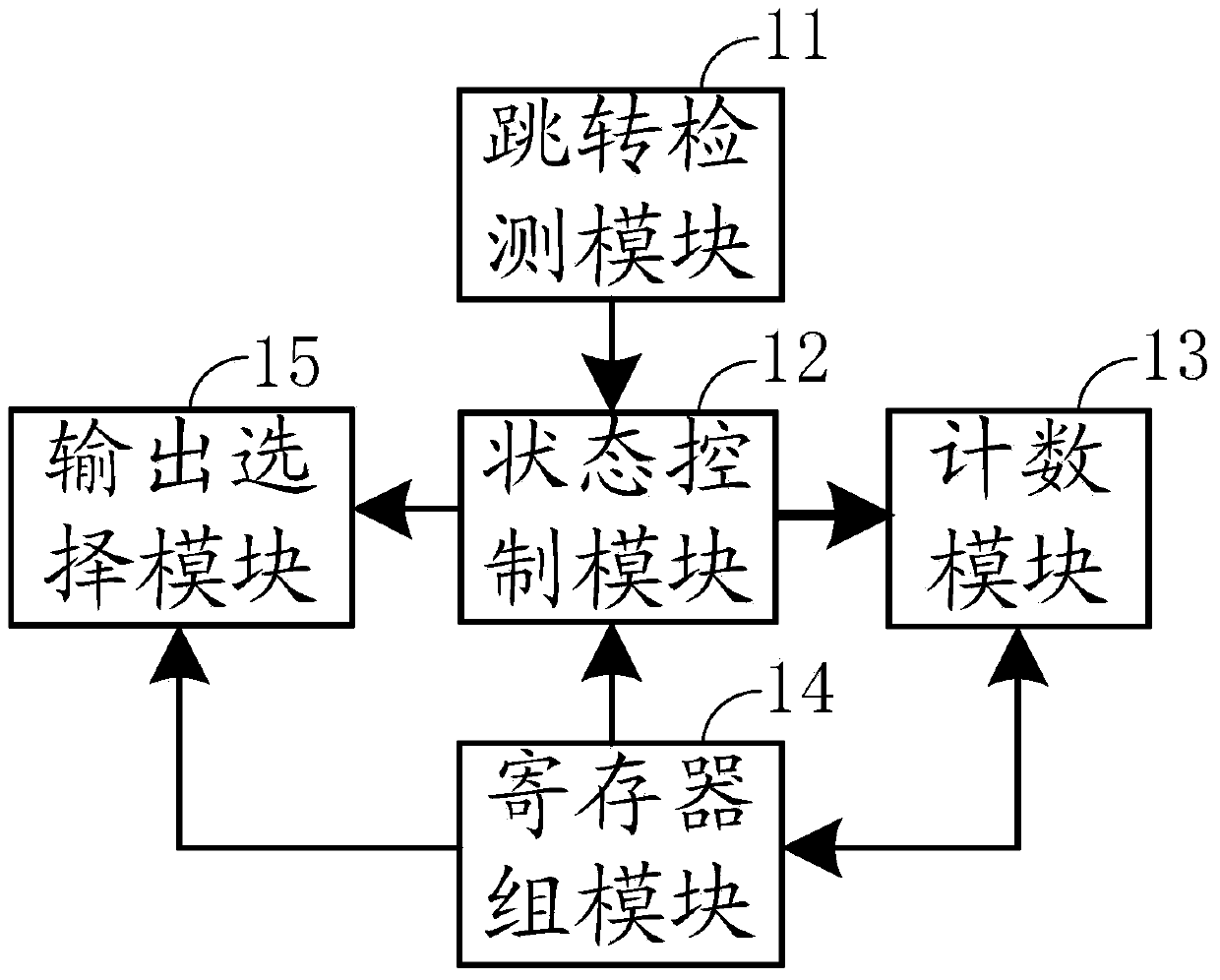

Bus encoding and decoding device and method thereof

ActiveCN103885913AReduce power consumptionReduce areaEnergy efficient computingElectric digital data processingBus encodingAddress bus

The invention relates to a bus encoding and decoding device and a method thereof. The bus encoding and decoding device forecasts and hits an instruction address bus, an encoding rear bus output by the encoding and decoding device can keep unchanged during a lot of execution time, meanwhile, the power consumption for sequential instruction executing, unchanged instruction keeping and instruction jumping on the instruction address bus can be effectively reduced, and therefore the bus power consumption of a cycle program can be reduced.

Owner:INST OF ACOUSTICS CHINESE ACAD OF SCI

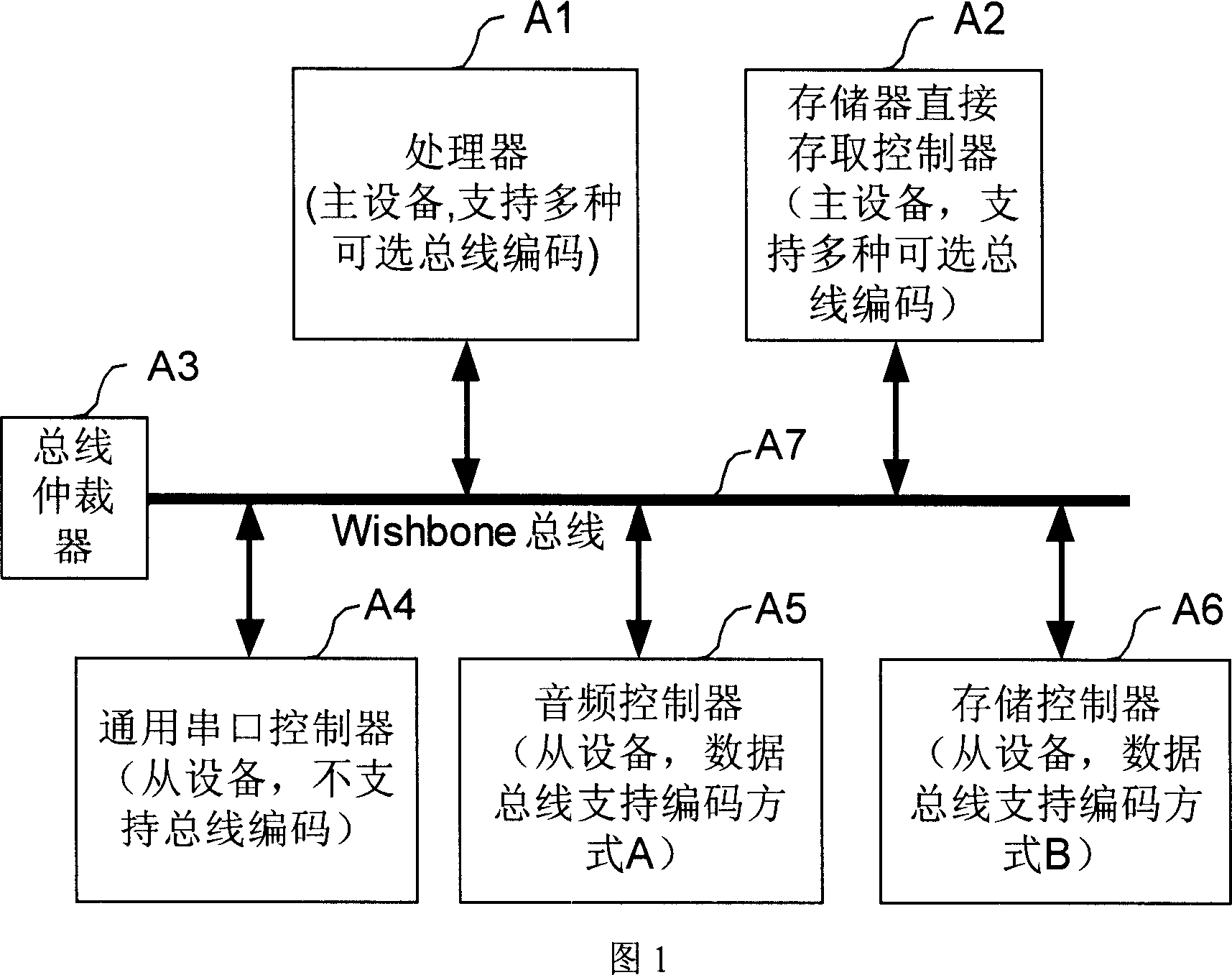

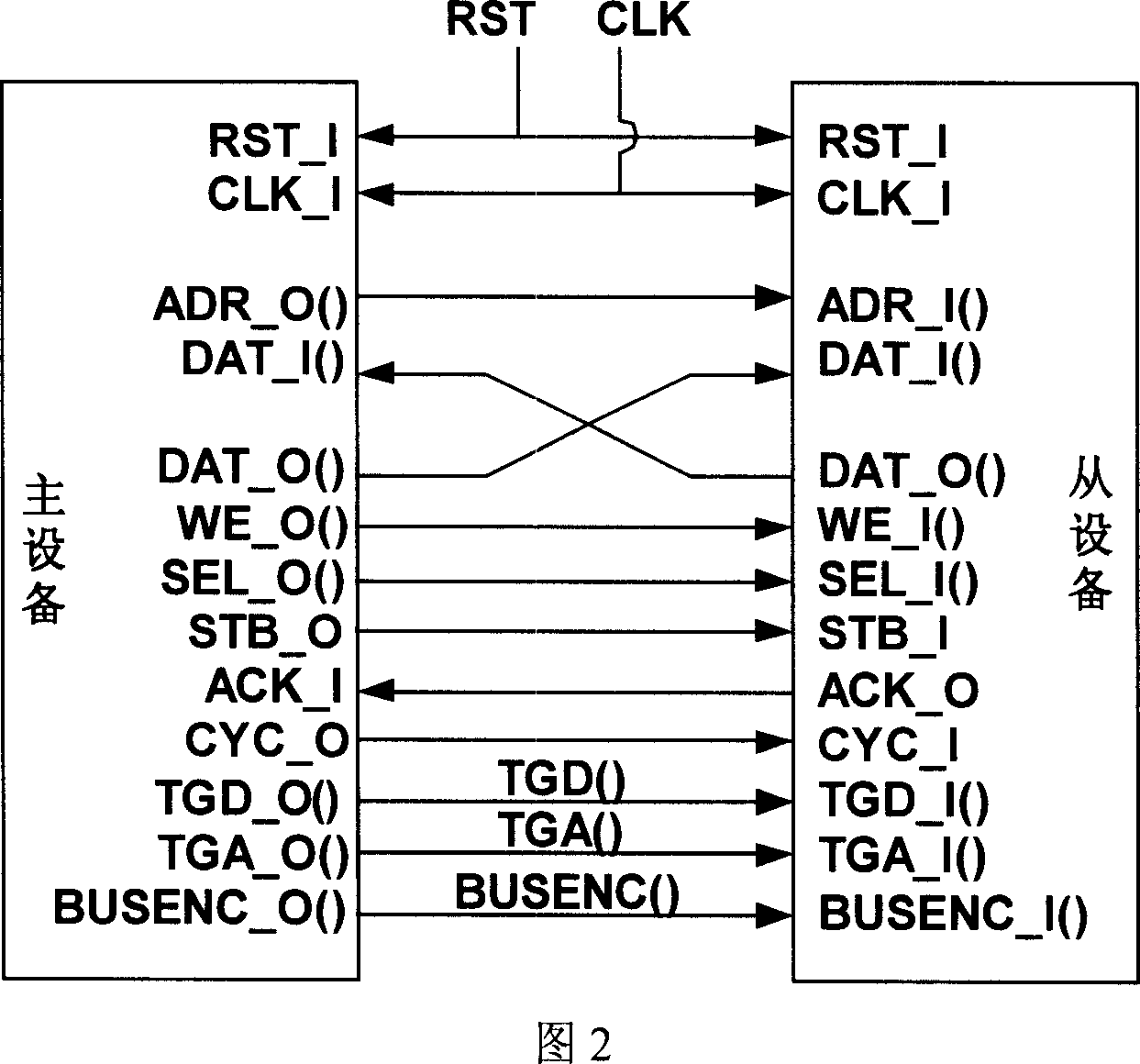

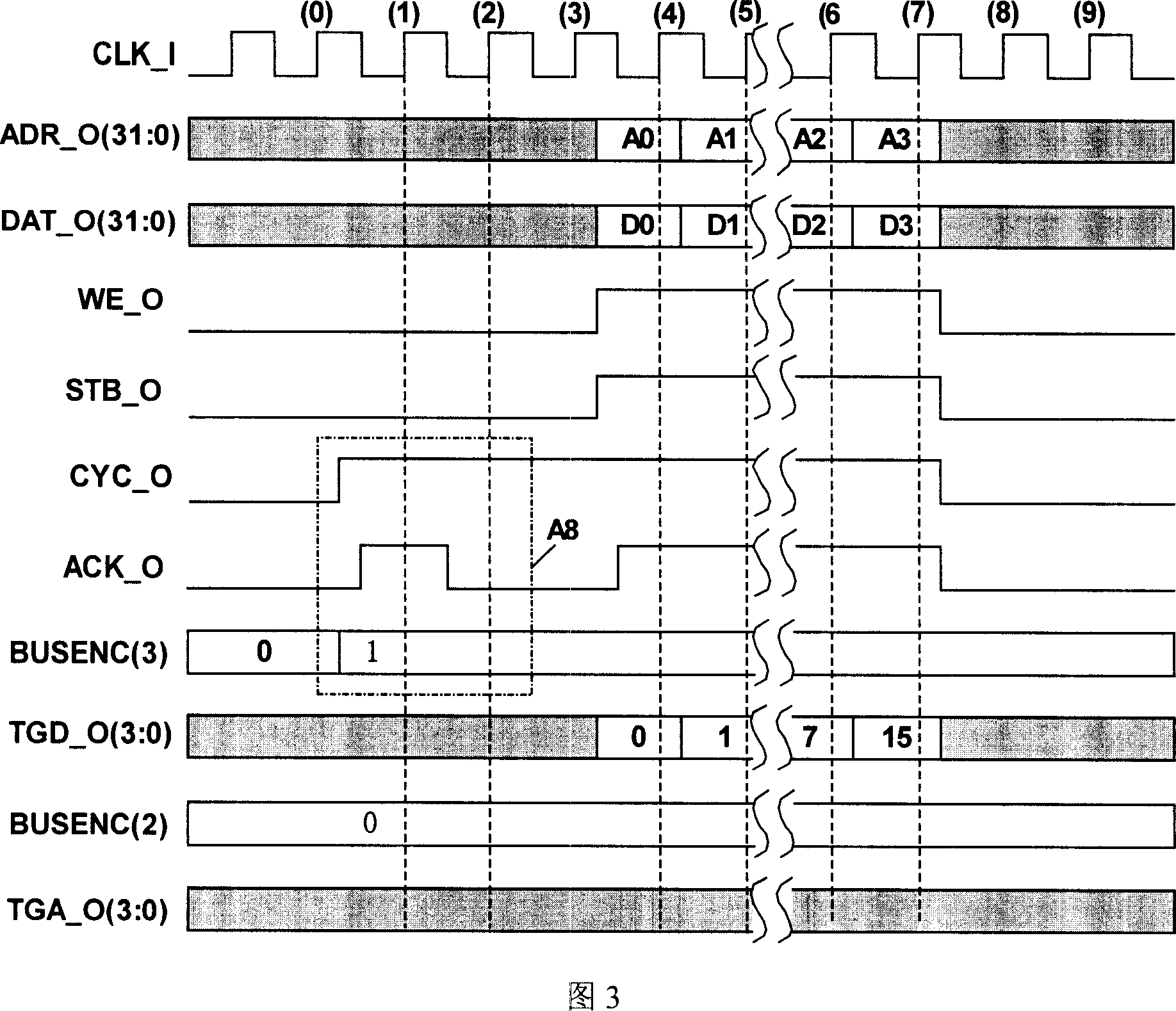

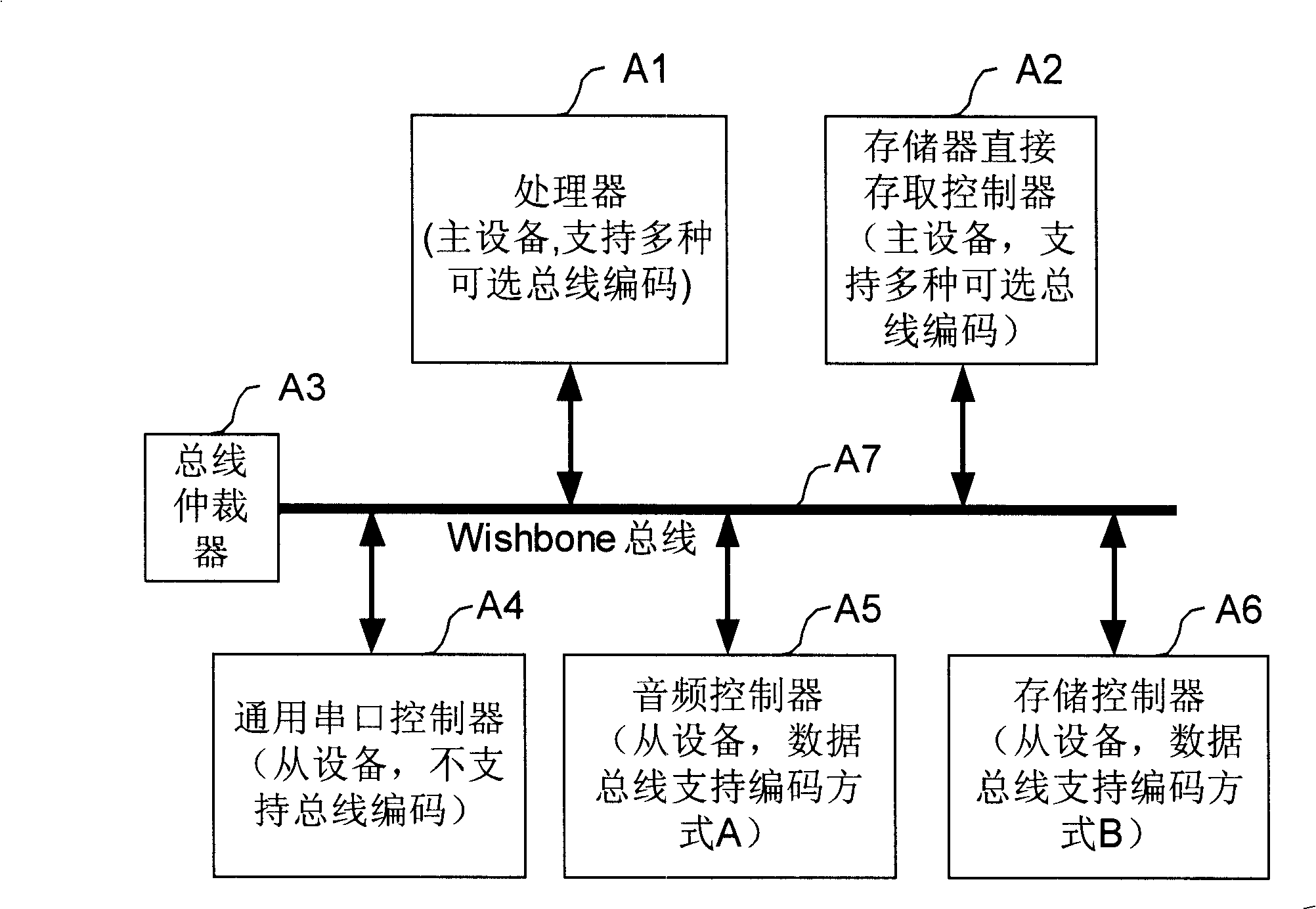

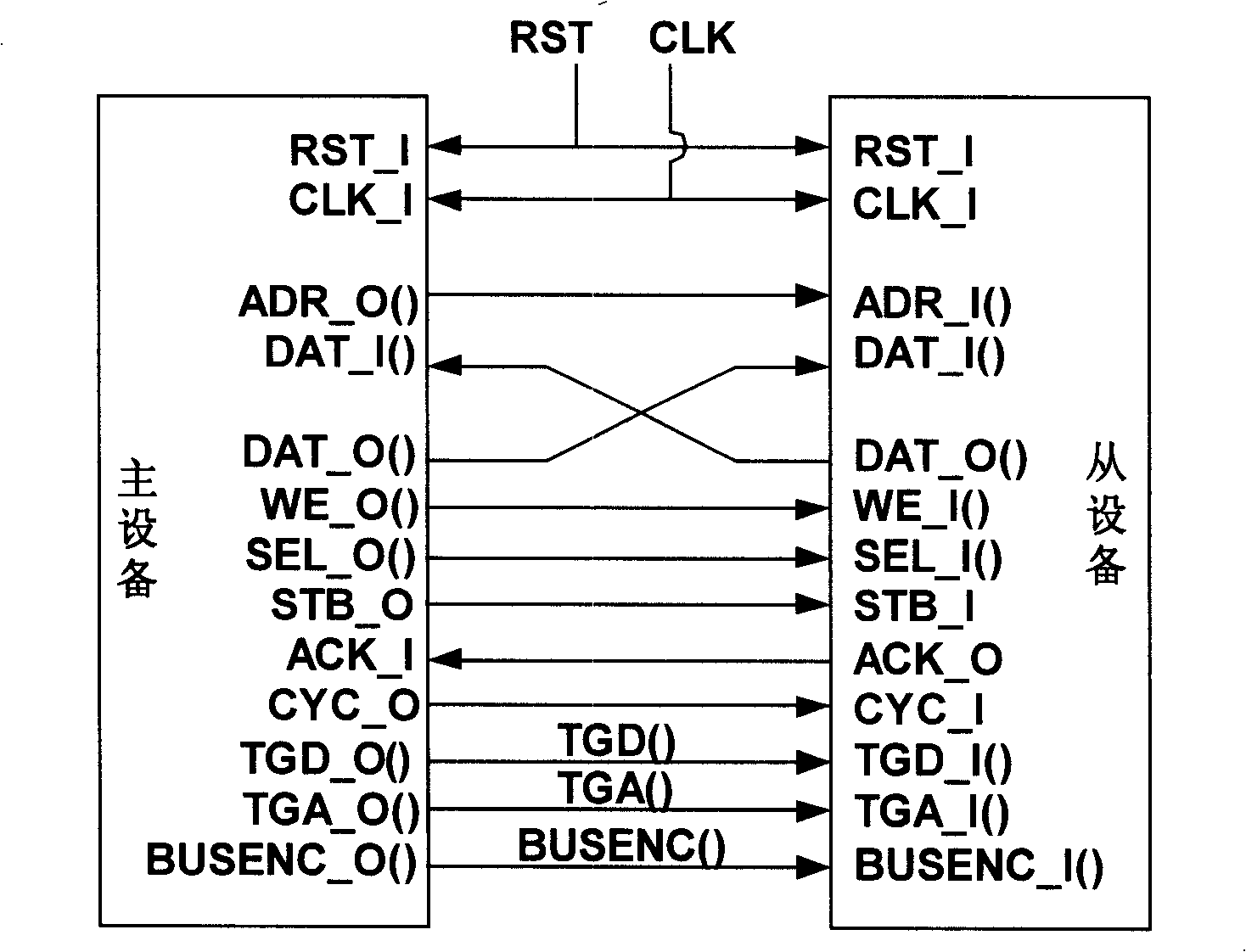

Enhanced wishbone on-chip bus for leading-in bus code

InactiveCN1975635AReduce the number of bit flipsReduce power consumptionEnergy efficient ICTPower supply for data processingControl signalAddress bus

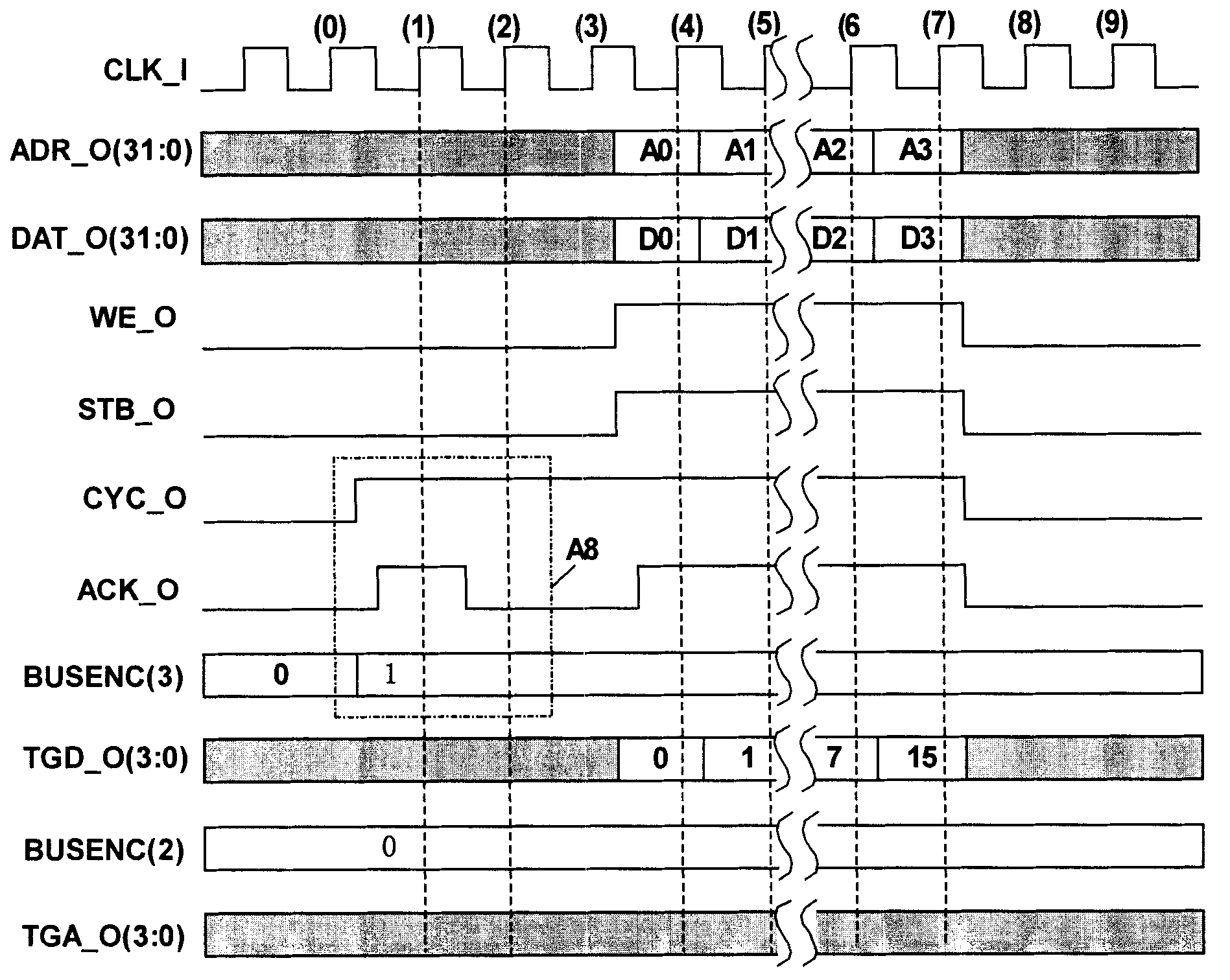

The invention relates to a bus on the strengthen Wishbone sheet which leads the bus coding to decrease the bus power consumption. The method in the invention is: first to add the controlling signal BUSENC_O () on the bus main device in Wishbone sheet, as the same, adding the controlling signal BUSENC__I() on the slave device; then to define the meaning in every using bus coding mode of every value from the Wishbone bus data label TGD() and / or address label TGA(); next the main and slave devices arranges the coding mode of the data bus and the address bus used by the communication; last to communicate by the arranging mode. The invention can decrease the bit reversal times of the Wishbone bus to decrease the power consumption in sheet system.

Owner:朱海鸿

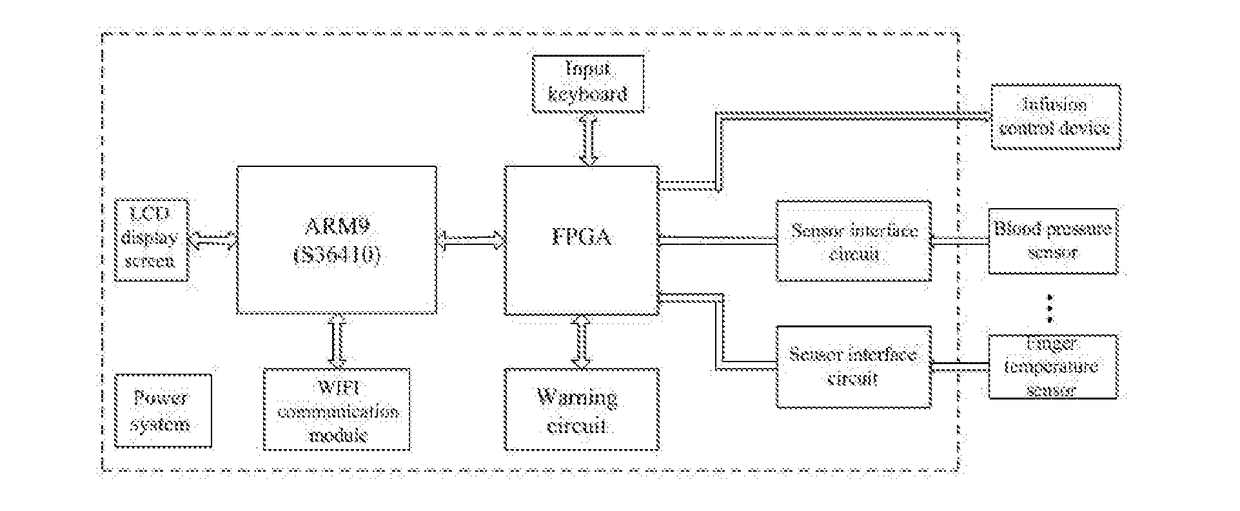

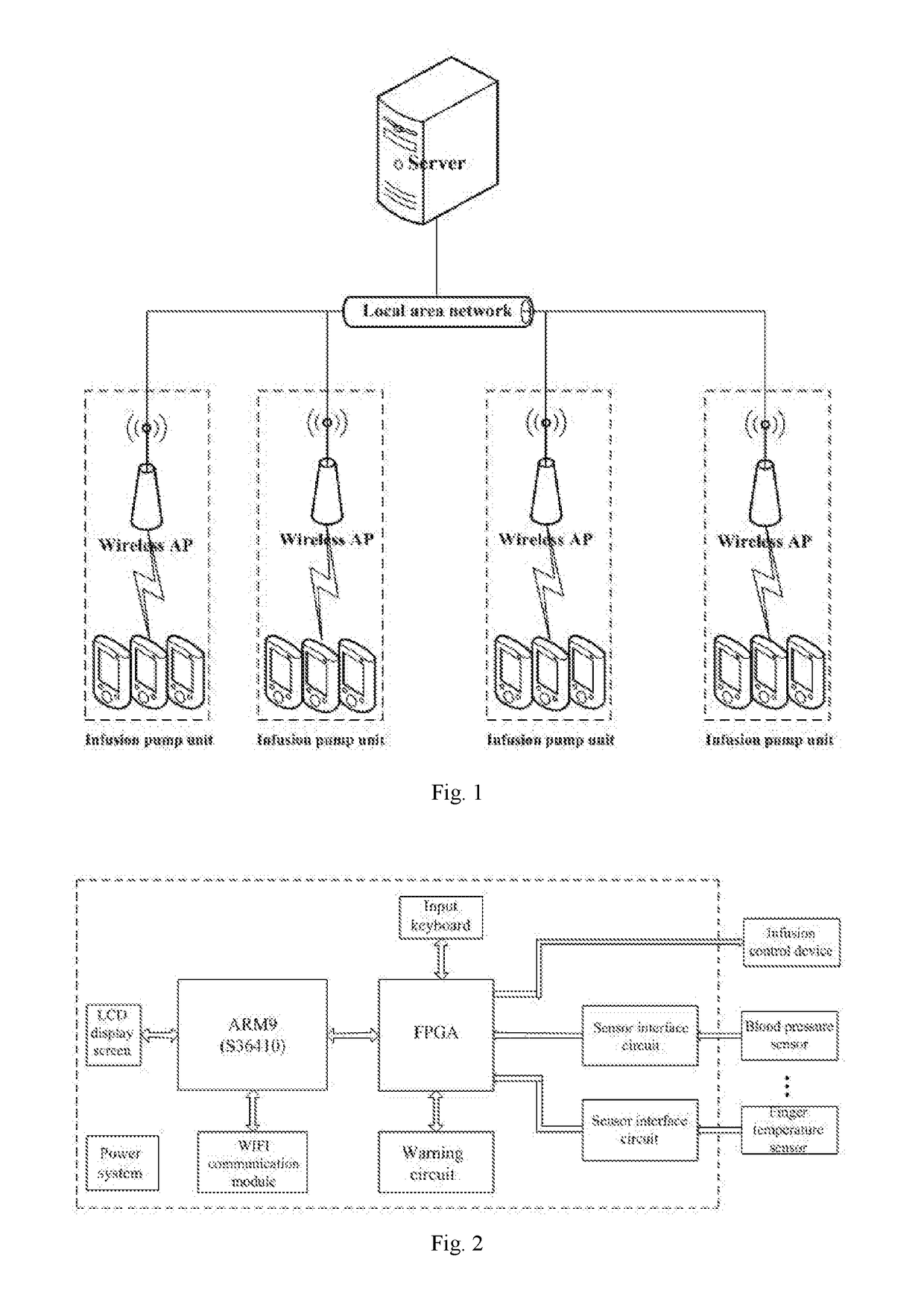

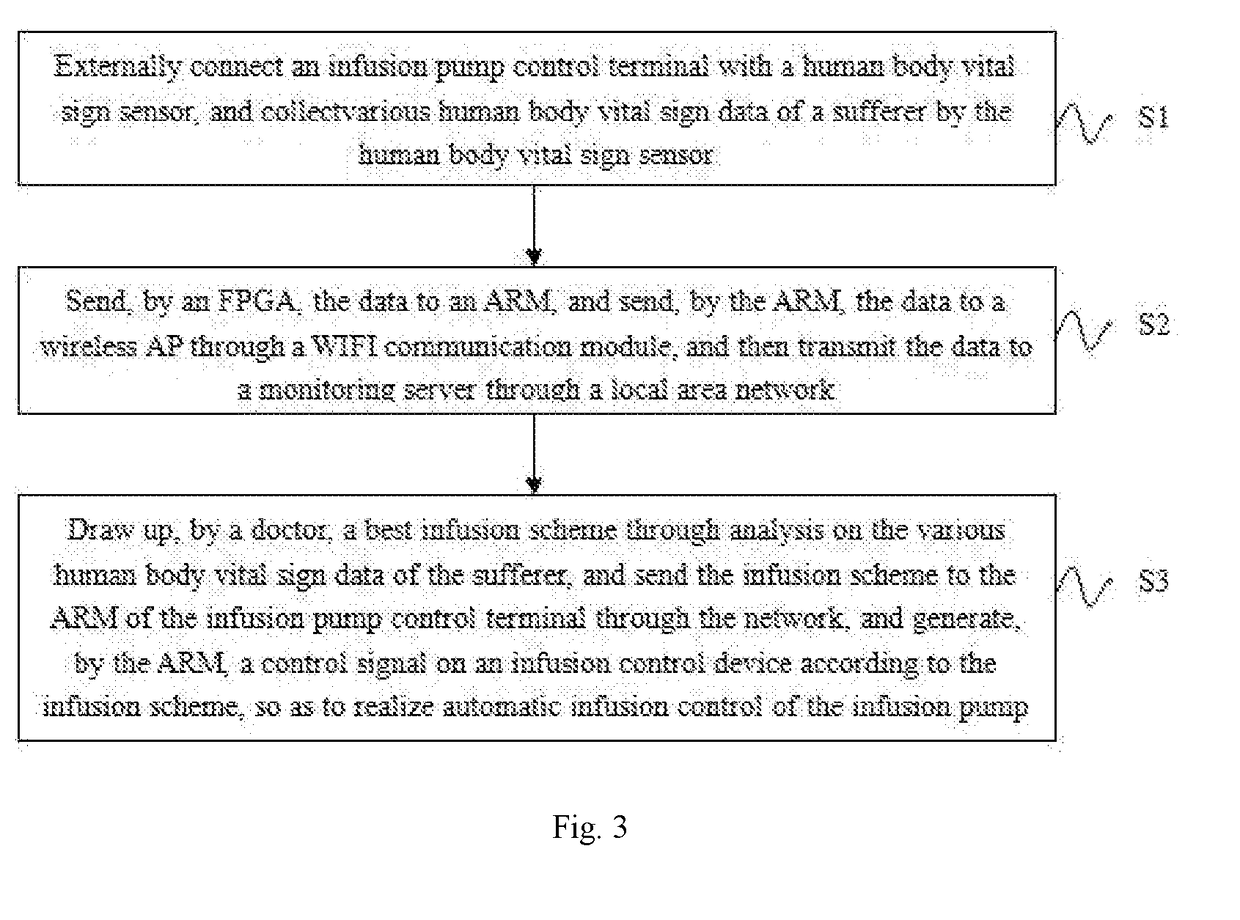

Intelligently-analgesic infusion pump monitoring system and method

InactiveUS20170185747A1Improve infusion safetyImprove securityDrug and medicationsCatheterControl signalMonitoring system

The present invention discloses a system and method for monitoring an infusion pump capable of intelligently easing pain. Each infusion pump control terminal is connected with a monitoring server through a wireless AP and a local area network respectively; each human body vital sign sensor is connected with the signal input end of a field programmable gate array FPGA through a sensor interface circuit respectively, an infusion control device is connected with the control signal output end of the field programmable gate array FPGA, the field programmable gate array FPGA is in communication with an ARM processor in a bus coding mode, and the ARM processor is in communication connection with the wireless AP through a WIFI communication module. By means of the system and method for monitoring infusion pump capable of intelligently easing pain, a plurality of basic vital sign data of a patient is collected in real time, corresponding infusion schemes are generated through analysis of the data, the infusion pump is controlled to achieve automatic infusion, monitoring and pain-easing infusion are combined together for coordinative work, and infusion control is more scientific and reliable; patient online perception and feedback is supported, self-improvement of a system is facilitated, and more accurate and reliable infusion schemes can be acquired.

Owner:YU WEIZHONG

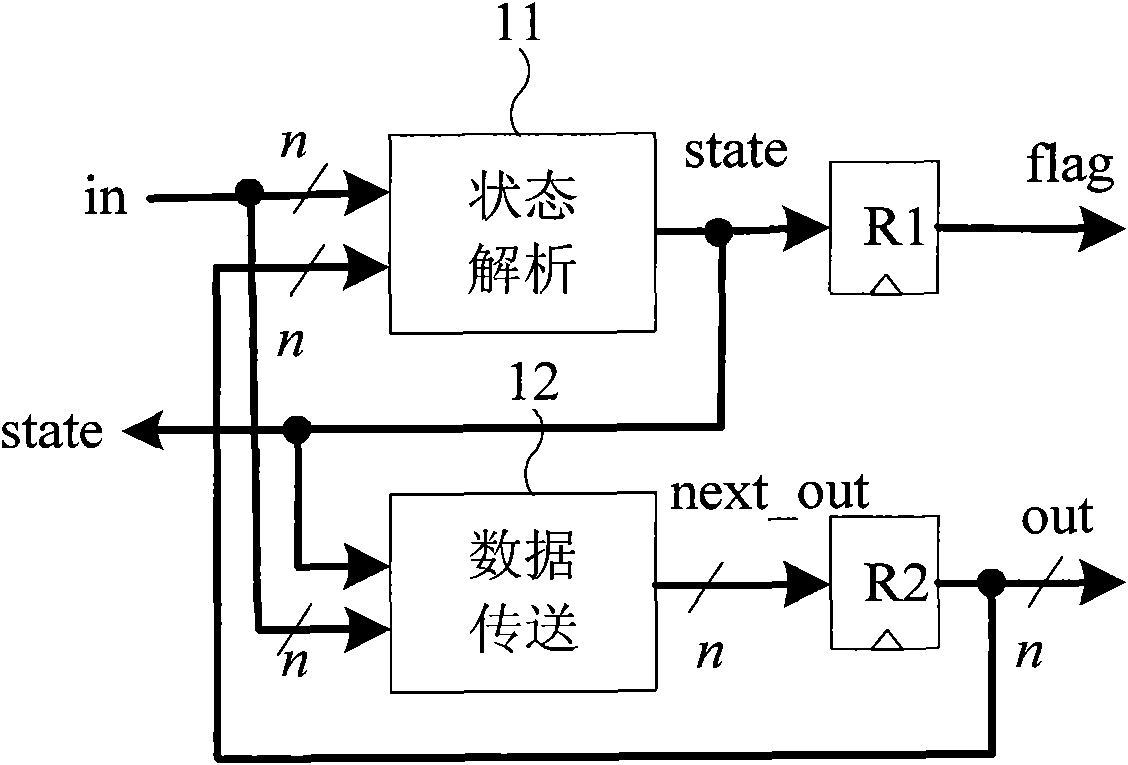

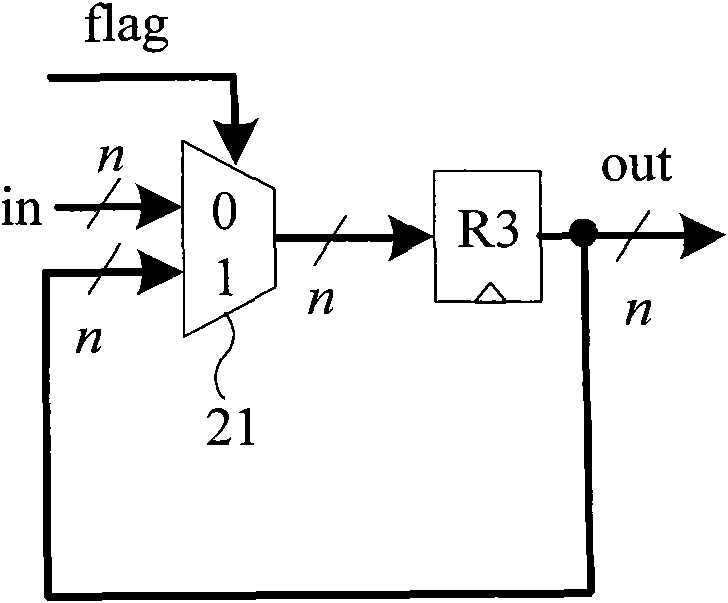

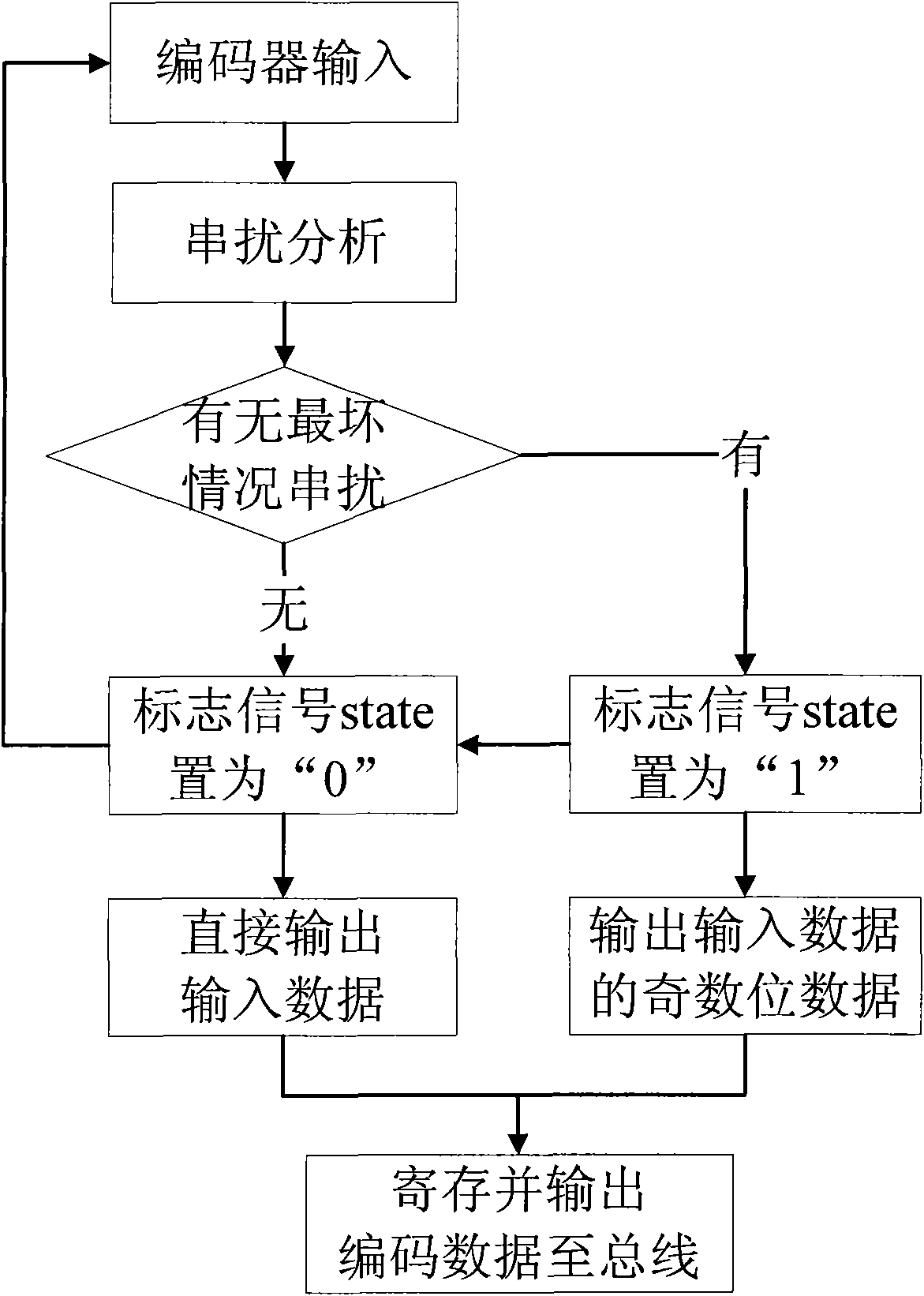

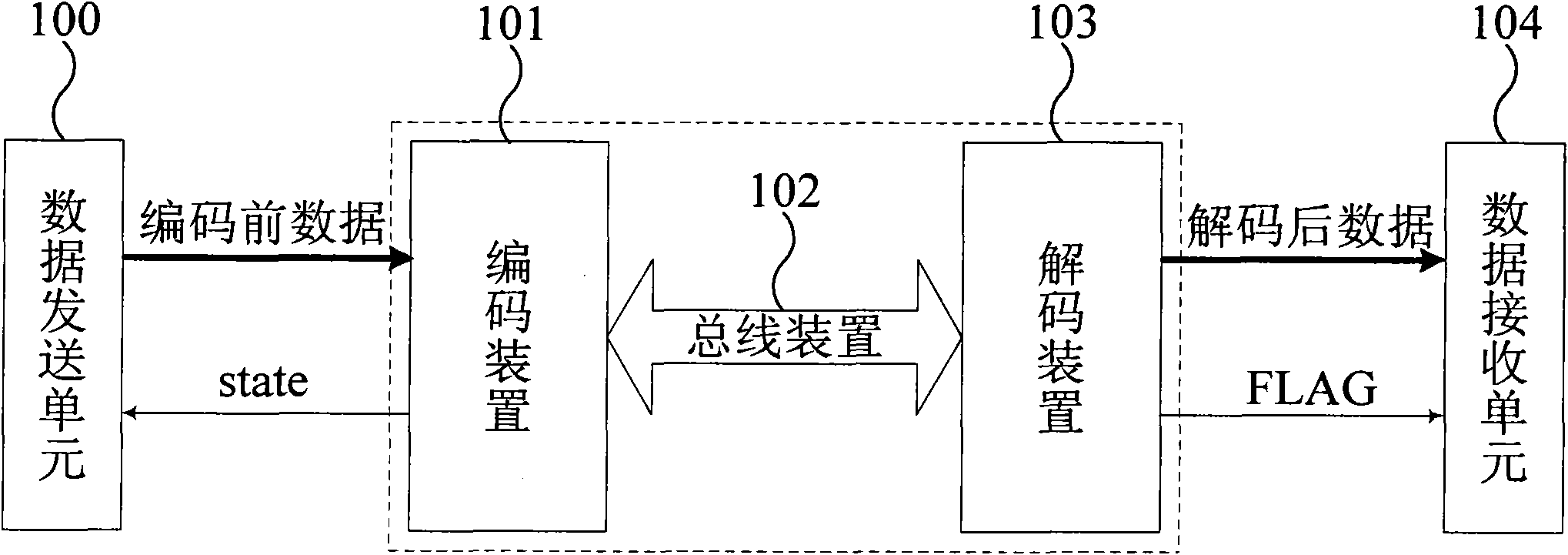

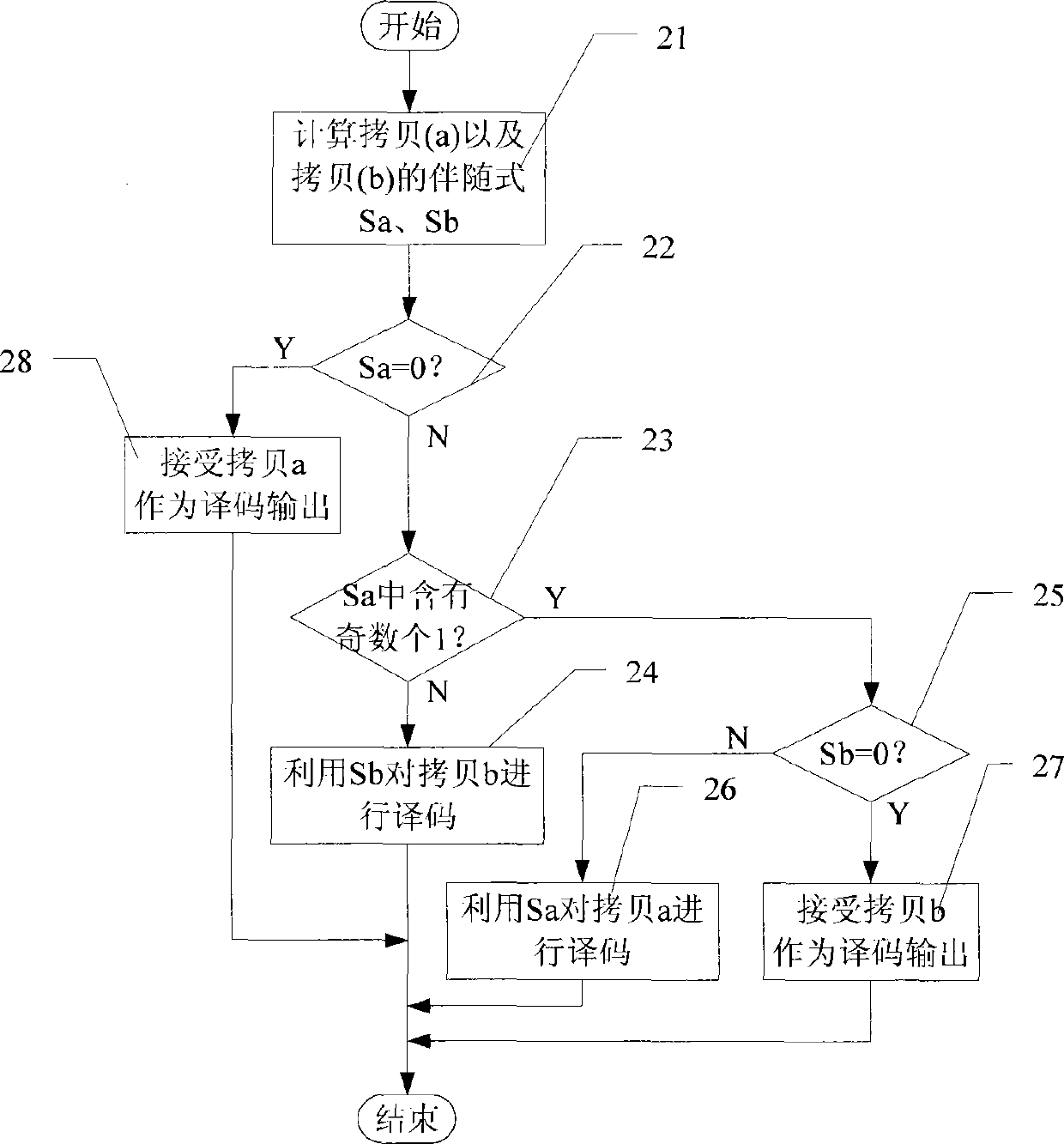

Adaptive time coding/decoding device for inhibiting bus interference and coding/decoding method thereof

ActiveCN101848059AIncrease working frequencyImprove data transfer efficiencyError preventionDecoding methodsVery large scale integrated circuits

The invention discloses an adaptive time coding / decoding device for inhibiting bus interference and a coding / decoding method thereof, which mainly solve the problems of low data transmission efficiency and high bus power consumption of the conventional time bus coding method. The coding process comprises the following steps of: (1) judging whether to-be-transmitted data of a bus cause interference of worst condition, and generating a mark signal; (2) directly transmitting the data without the interference of the worst condition according to the state of the mark signal, and transmitting even data of the data with the interference of the worst condition; and (3) indicating an input state of a next period according to the mark signal. The device and the method thoroughly eliminate the interference of the worst condition, have the advantages of high data transmission efficiency and low bus power consumption, and can be used for designing super-large scale integrated circuits.

Owner:陕西光电子先导院科技有限公司

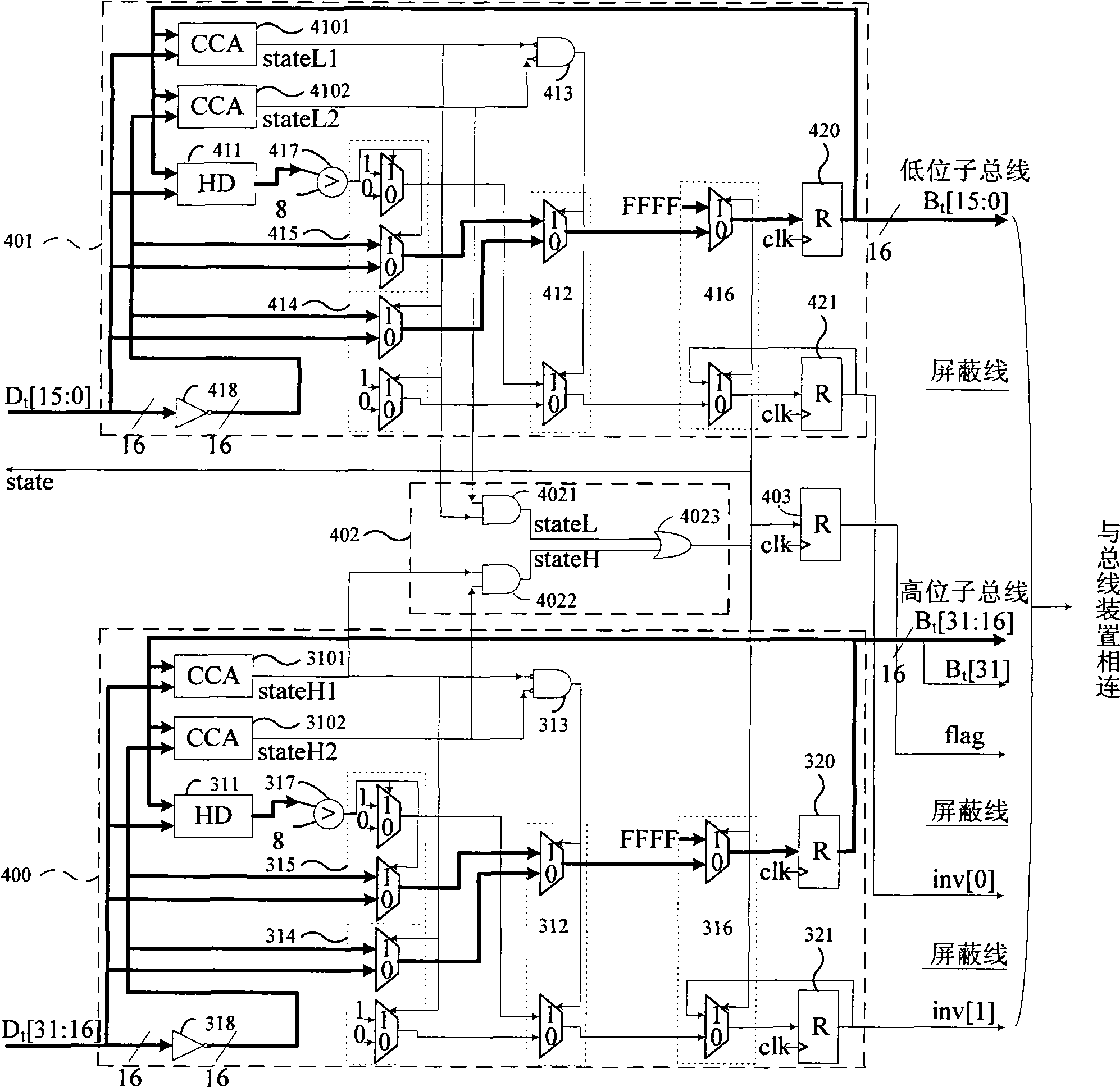

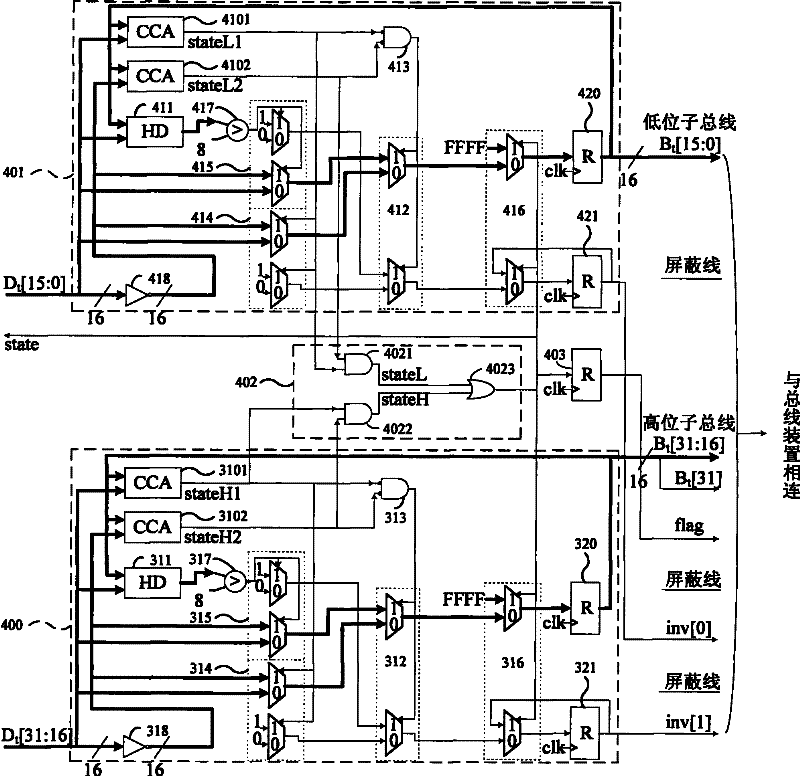

Encoding and decoding method for crosstalk resistant on-chip bus and encoding and decoding device thereof

ActiveCN101788967AEliminate crosstalkIncrease working frequencyEnergy efficient ICTEnergy efficient computingVery large scale integrated circuitsDecoding methods

The invention discloses an encoding and decoding method for a crosstalk resistant on-chip bus and an encoding and decoding device thereof, which mainly solve the problems of low data transmission efficiency and high power consumption in the conventional bus encoding method. The method comprises the following steps of: firstly, partitioning an N-position bus into a low-position sub-bus and a high-position sub-bus by inserting a shielded wire; secondly, judging whether a true code and a counter code of data to be transmitted of the two sub-buses can cause worst-case-crosstalk or not and generating a mark signal; and finally, obtaining whether the worst-case-crosstalk exists in the sub-buses or not according to the mark signal, if the worst-case-crosstalk exists in one or both sub-buses, inserting an N-position shielded word to eliminate the worst-case-crosstalk, and if the worst-case-crosstalk does not exist in both sub-buses, optimizing the power consumption of the encoding method, namely, if the true code and the counter code do not cause the worst-case-crosstalk, selecting one with lower power consumption to transmit, and if one code causes the worst-case-crosstalk, selecting the data not causing the worst-case-crosstalk to transmit. The method and the device have the advantages of high data transmission efficiency and low power consumption and can be applied to the design of a super-large scale integrated circuit.

Owner:陕西光电子先导院科技有限公司

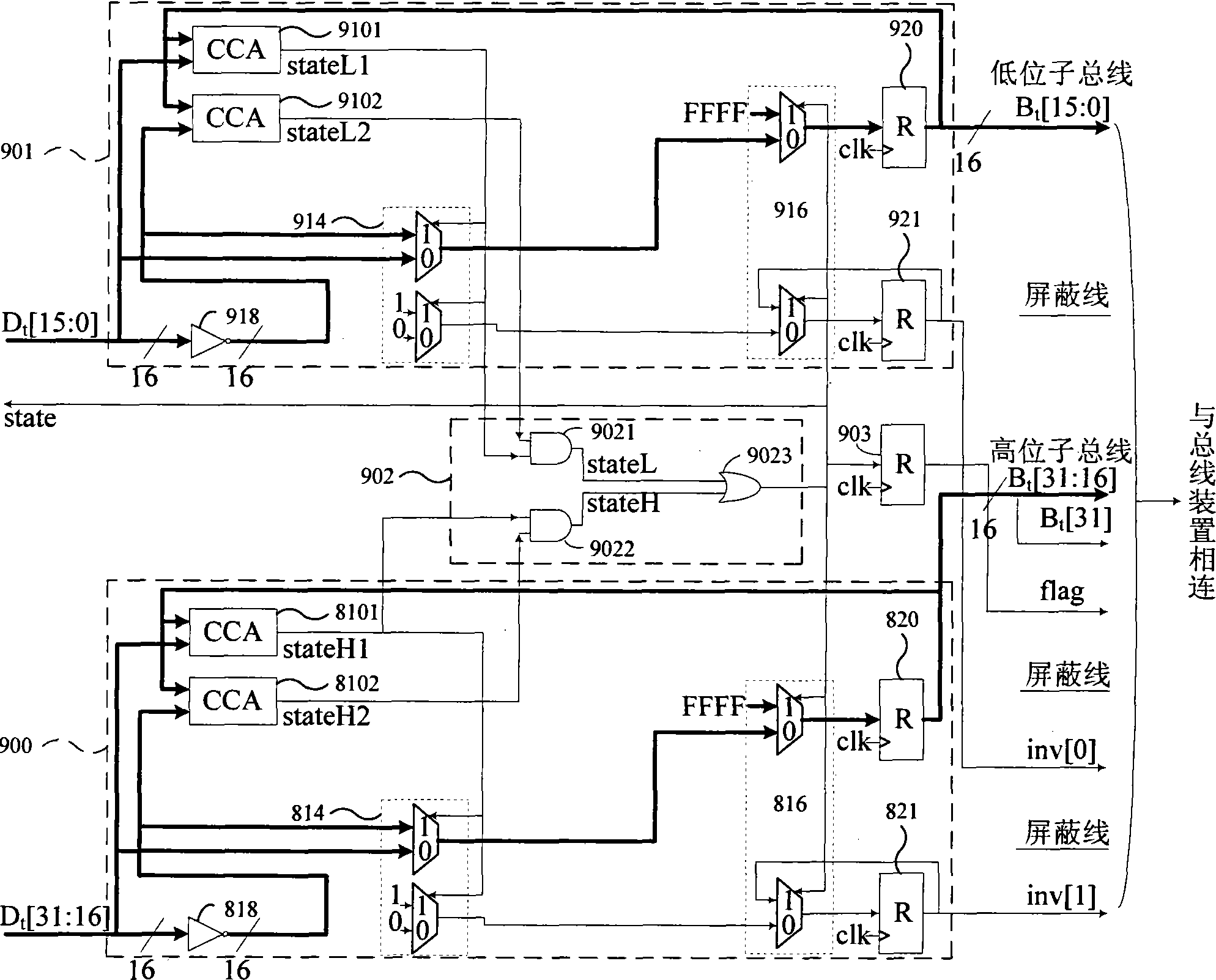

High performance anti-crosstalk space-time bus coding and decoding method and coding and decoding device thereof

ActiveCN101834704AEliminate crosstalkIncrease working frequencyError prevention/detection by diversity receptionVery large scale integrated circuitsDecoding methods

The invention discloses a high performance anti-crosstalk space-time bus coding and decoding method and a coding and decoding device thereof, mainly solving the problem that the existing space-time bus coding method has low data transfer efficiency and large bus power consumption. The coding process comprises the following steps: (1) patching a shielding line to divide the N-bit bus to a low bit bus and a high bit bus; (2) separately judging whether the true code and complement code of to-be transmitted data of the two sub-buses to cause worst-case crosstalk or not, generating a marking signal; (3) reaching a conclusion according to the marking signal, if so, inserting N-bit mask words to eliminate the worst-case crosstalk; if worst-case crosstalk does not exists in either of the two sub-buses, selecting a data item which can not cause the worst-case crosstalk in the true code and complement code of to-be transmitted data of the two sub-buses for transmission by the two sub-buses. Themethod of the invention has the advantages of high data transfer efficiency and low power consumption and can be used for the design of the ultra-large scale integrated circuit.

Owner:陕西光电子先导院科技有限公司

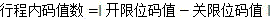

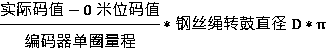

Method for quickly correcting code value of blast furnace top bus-based encoder

ActiveCN106086268ARealize one-button quick correction intelligent control functionReduce the impactBell-and-hopper arrangementChecking devicesAutomatic controlComputer module

The invention belongs to the technical field of blast furnace automatic control and particularly relates to a method for quickly correcting the code value of a blast furnace top bus-based encoder. According to the method, the means that the actual angle of a distributing device distributing angle alpha angle motor and the actual angle of a material flow speed throttling gamma angle motor at the top of a blast furnace are worked out, a calculation formula is modified according to the actual working condition, the operation counting range limit of an detection device is determined, and the function of achieving angle one-key correcting is established through a one-key quick correcting button is adopted, so that the one-key quick correcting intelligent control function of the blast furnace top bus-based encoder is achieved, the production efficiency and reliability of a blast furnace are improved, and the time for processing the fault of winding PLC system bus hardware and related modules, the fault of the encoder and the fault of bus communication is shortened; and accordingly, the influence on blast furnace production is reduced, damping down and blast reducing of the blast furnace are reduced, and normal smelting and production of the blast furnace are ensured.

Owner:GANSU JIU STEEL GRP HONGXING IRON & STEEL CO LTD

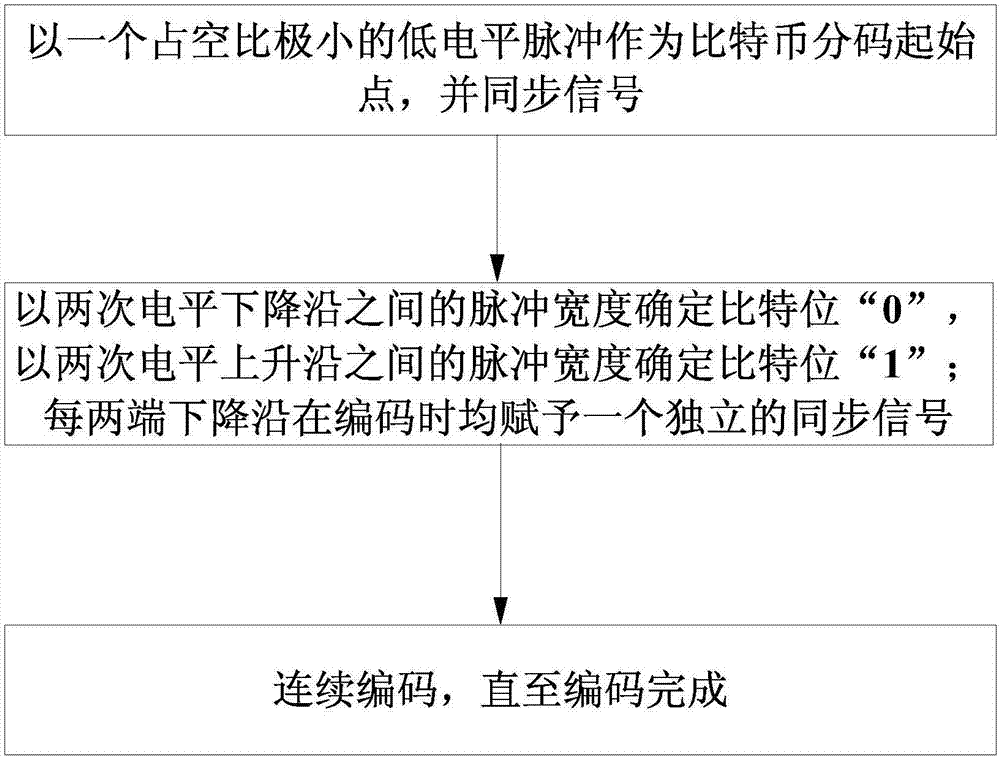

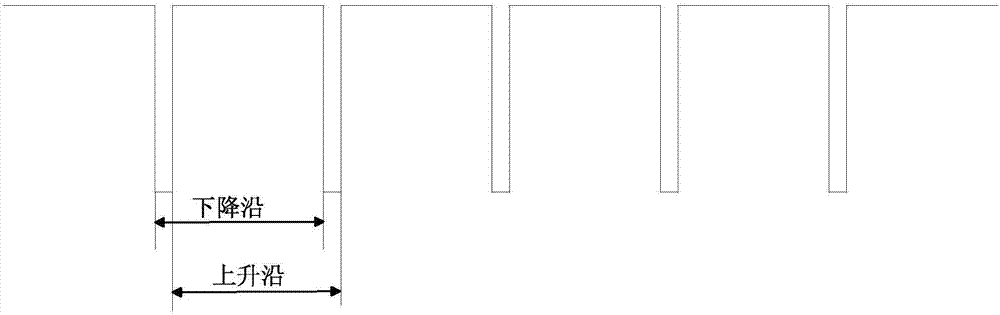

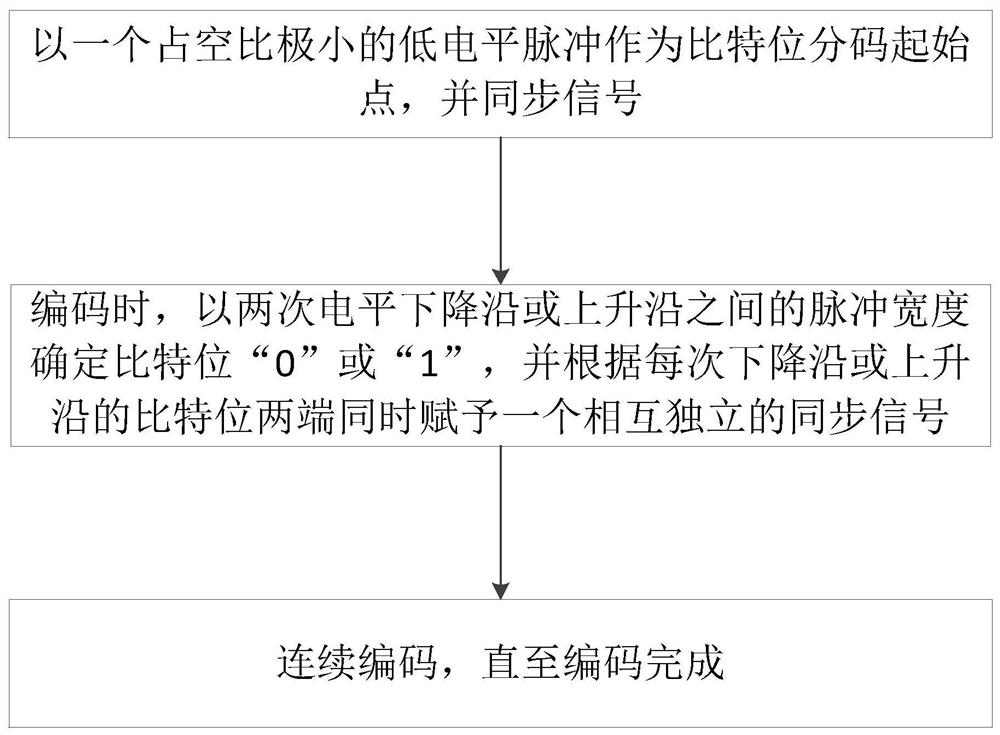

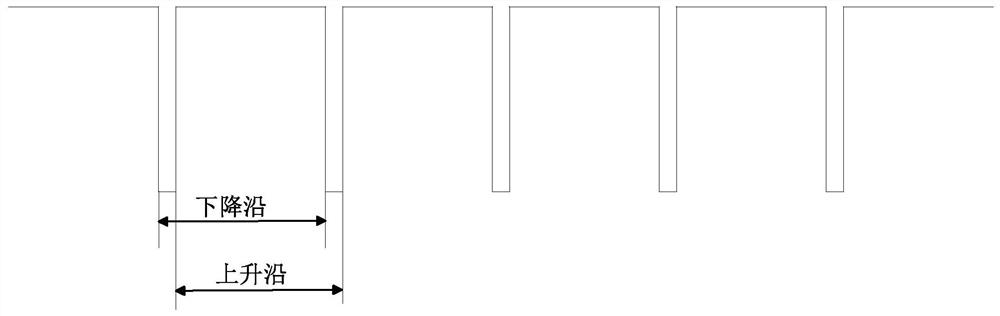

Fire-fighting industrial bus encoding method

ActiveCN106911334AReduce Capacitance RequirementsEnsure power supplyIndividual digits conversionBus encodingData transmission

The invention discloses a fire-fighting industrial bus encoding method comprising the following steps: a fire alarm controller carries out encoding with a low-level pulse of which the duty ratio is below 0.3 as the starting point of bit code division, and synchronizes the signal; (2) during encoding, the bit '0' is determined according to the pulse width between two level falling edges, and the bit '1' is determined according to the pulse width between two level rising edges; and every two falling edges are given a separate synchronization signal during encoding; and (3), the step (2) is repeated, continuous encoding is carried out until encoding is completed, and a code is sent to an intelligent component through a bus. The process is simple. The mode of encoding is easy. The problem that a bus is idle for a long time is avoided while the accuracy of data transmission is ensured. Therefore, the method is suitable for popularization and application.

Owner:光和电科技(广东)有限公司

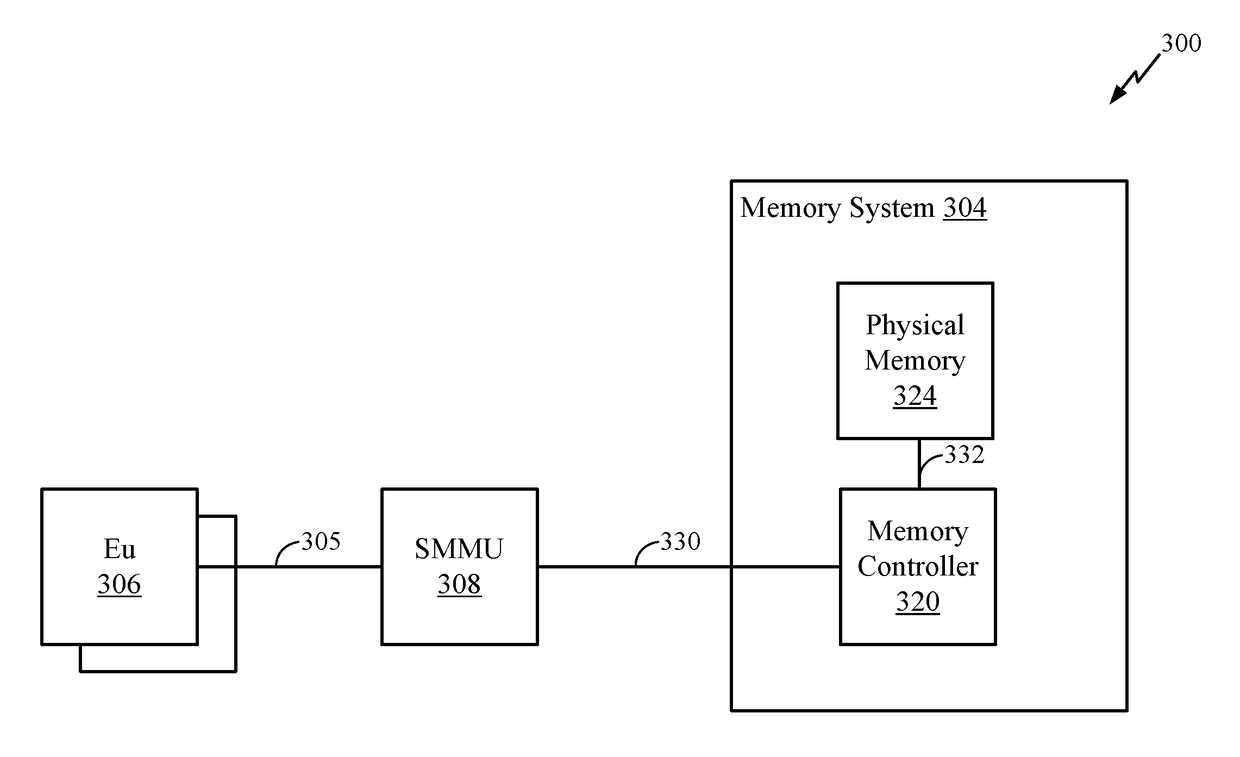

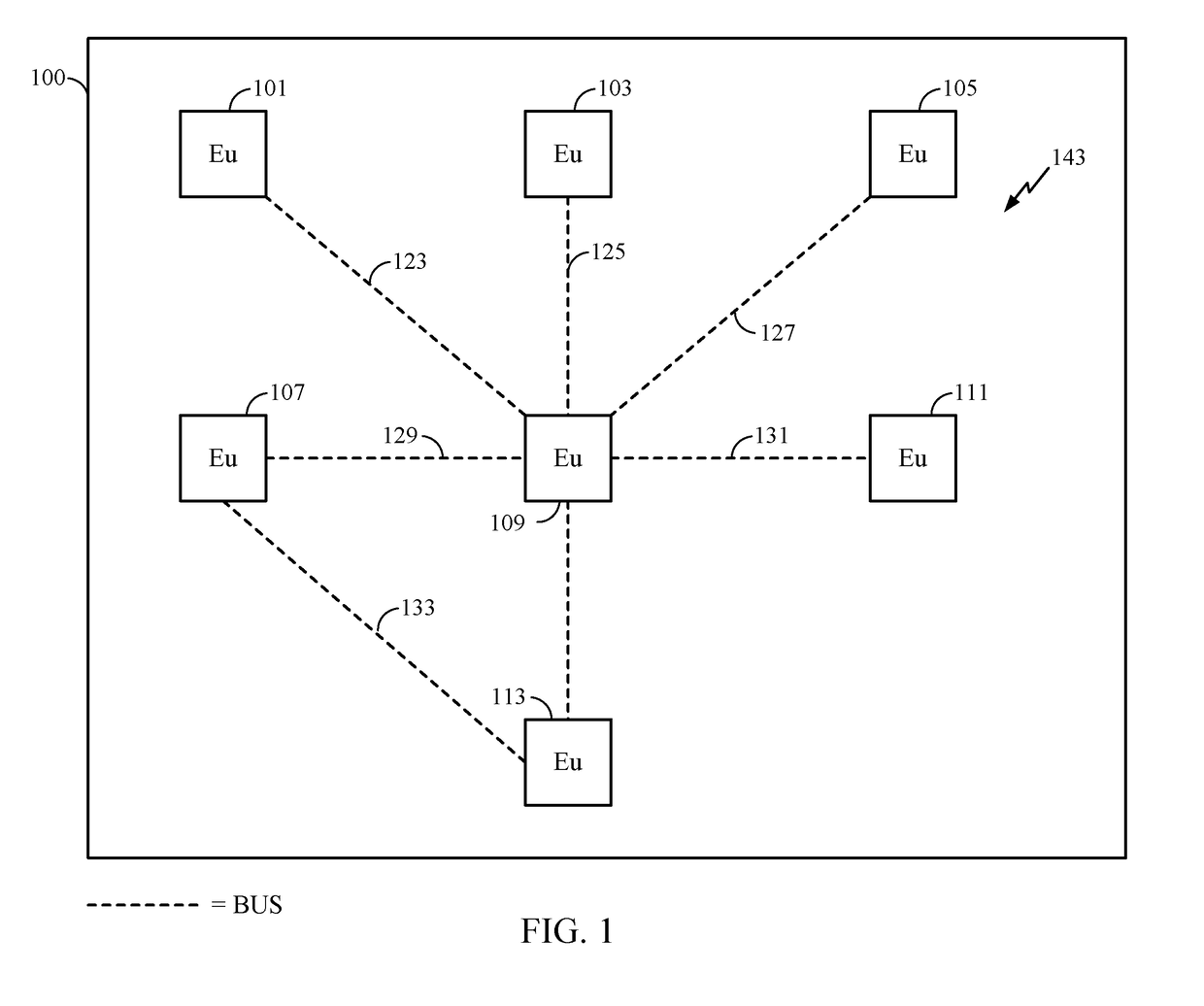

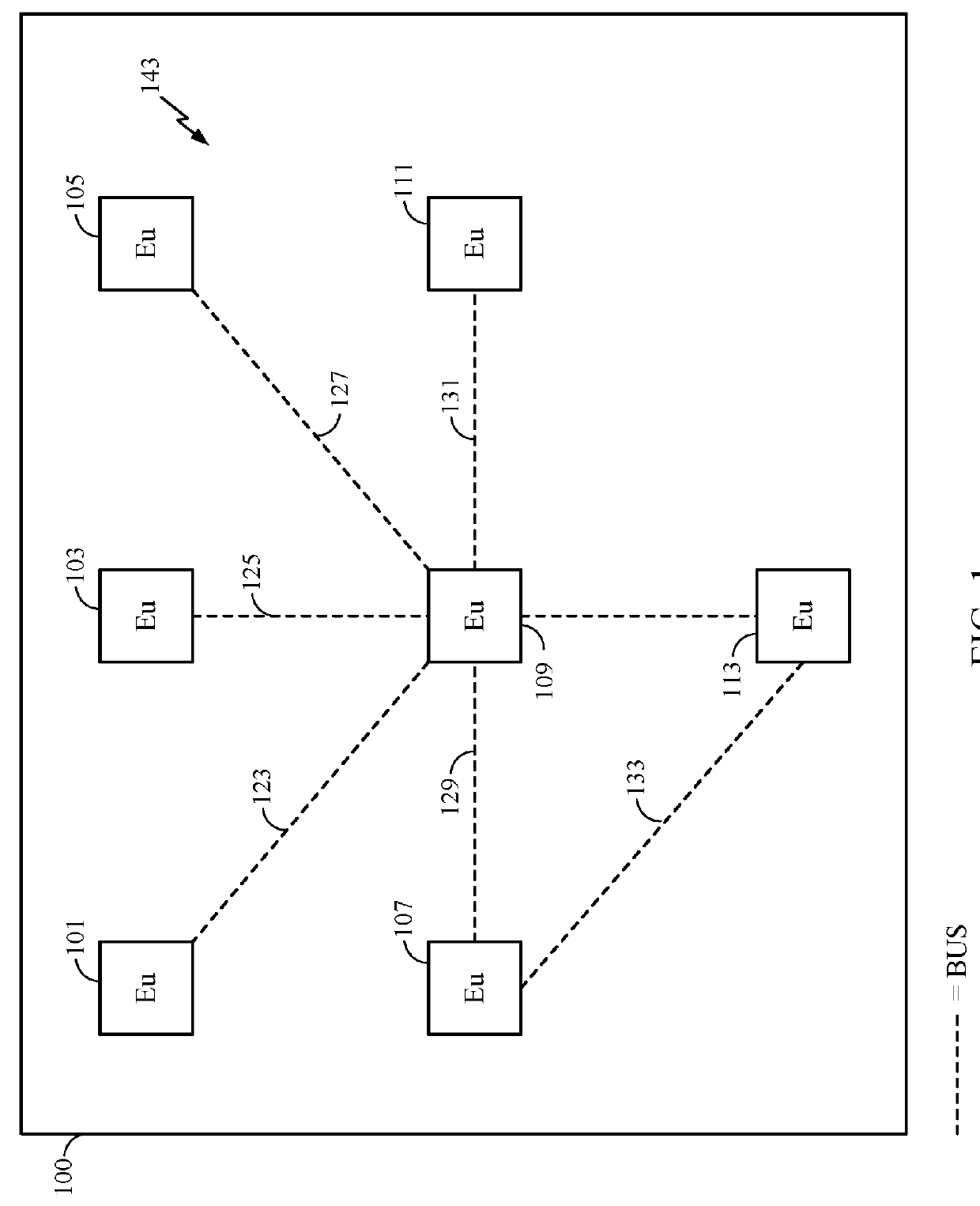

Bus encoding using on-chip memory

ActiveUS20180210858A1Well formedDigital data processing detailsDigital storageControl dataBus encoding

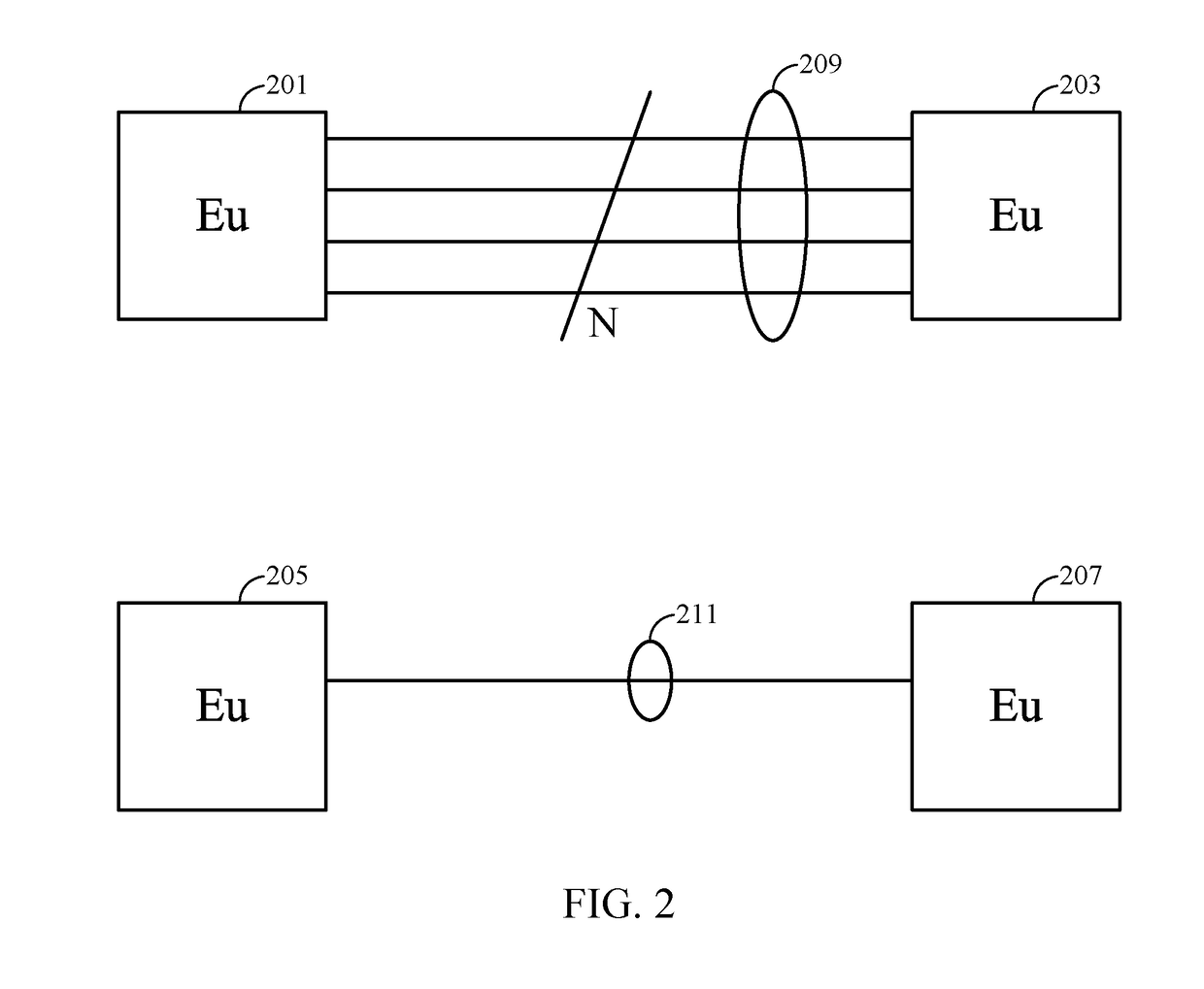

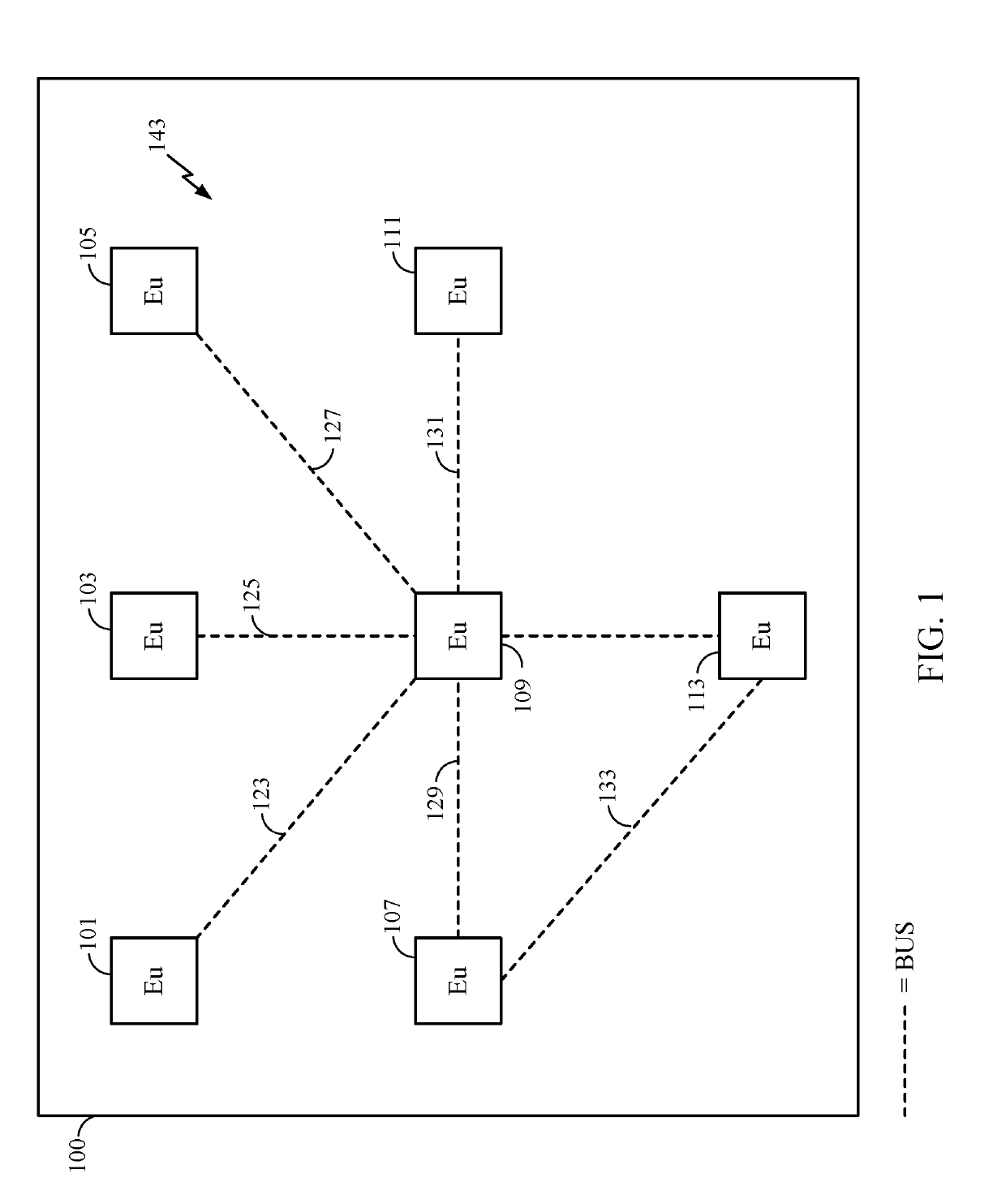

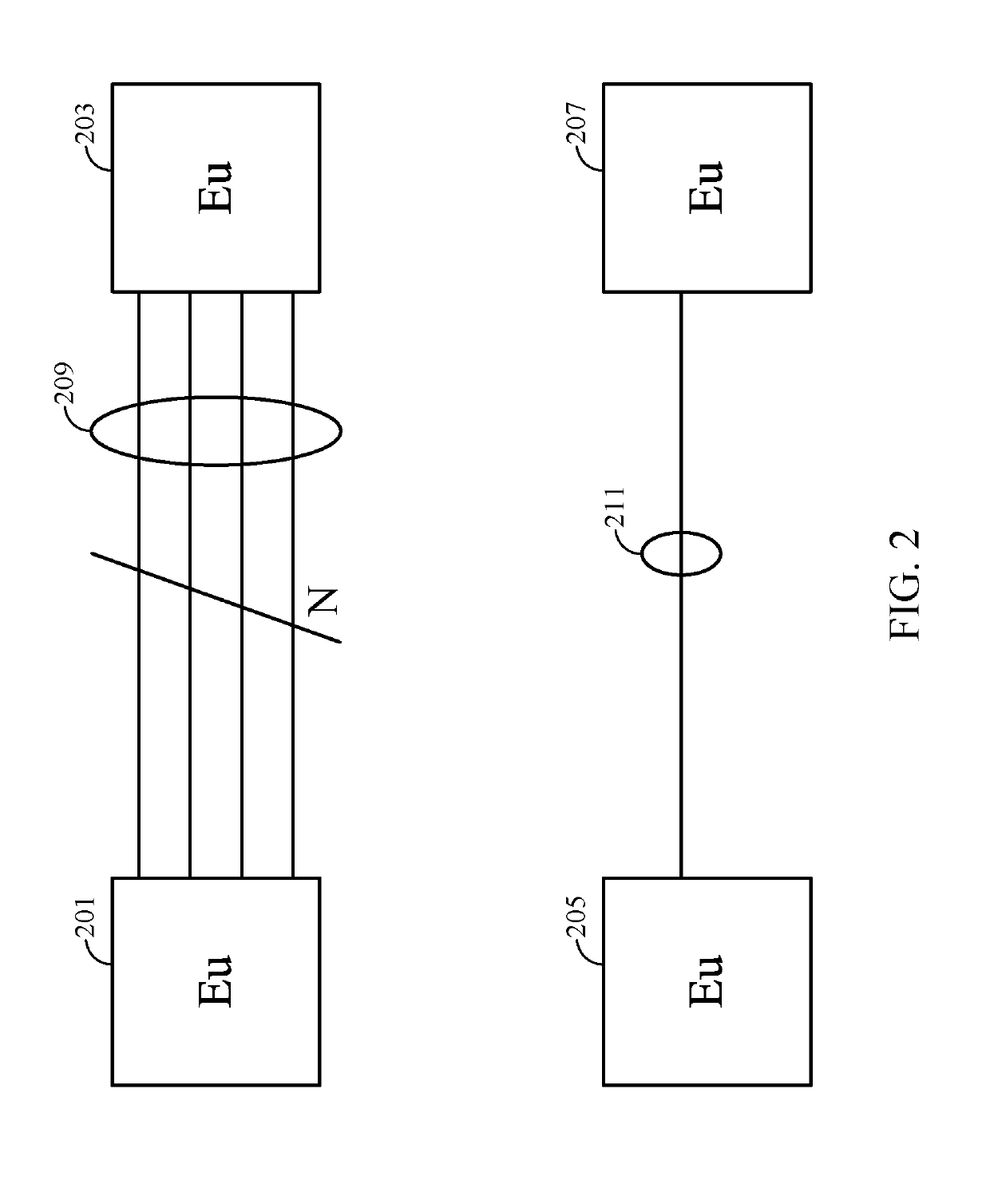

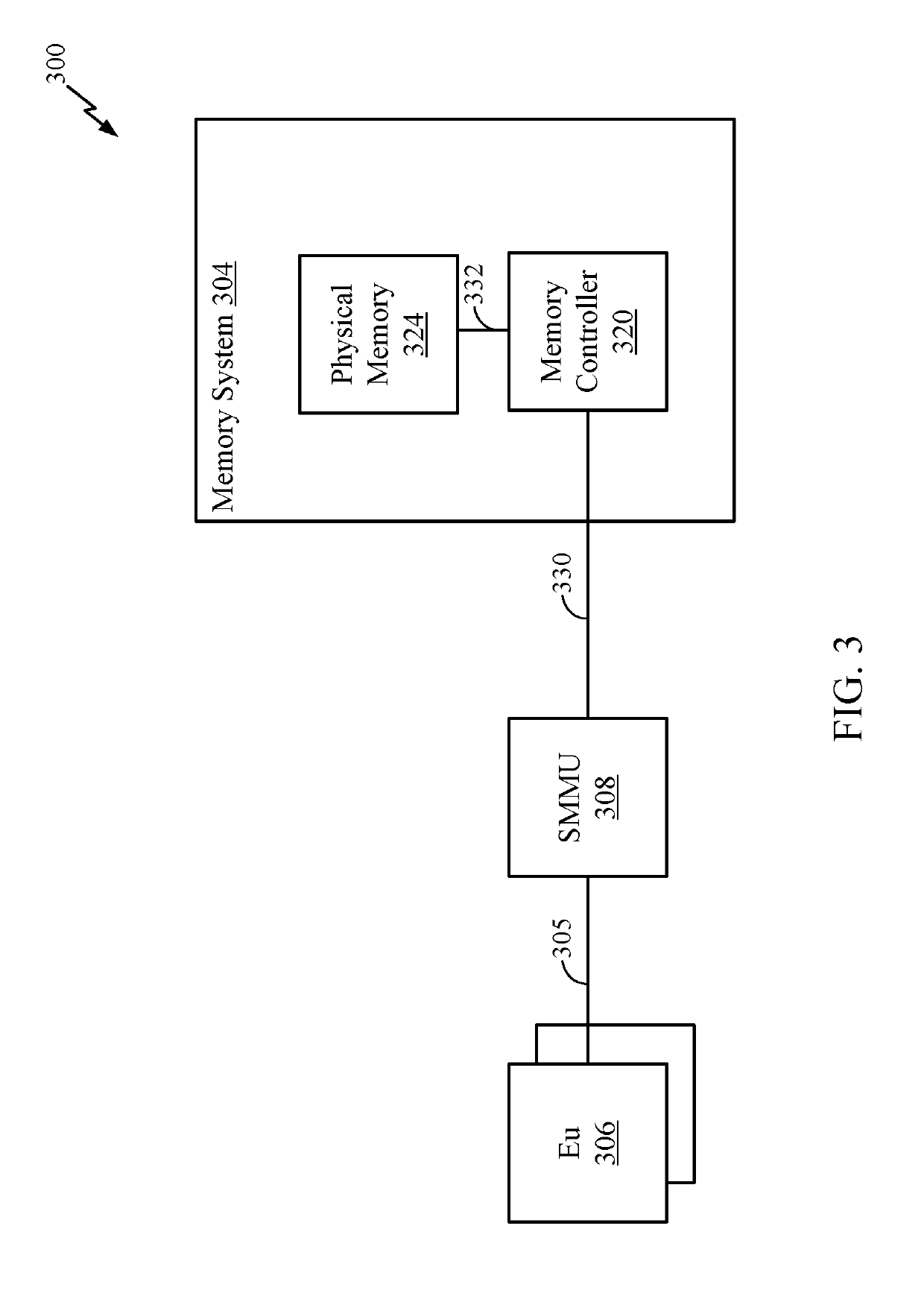

Various additional and alternative aspects are described herein. In some aspects, the present disclosure provides a method of communicating data between an electronic unit (EU) of a system-on-chip (SoC) and a dynamic random access memory (DRAM). The method includes encoding data at the EU. The method includes generating control data for decoding the encoded data at the EU. The method includes directing storage of the encoded data in the DRAM. The method includes directing storage of the control data in an on-chip memory separate from the DRAM, wherein the on-chip memory is on a same chip as the EU.

Owner:QUALCOMM INC

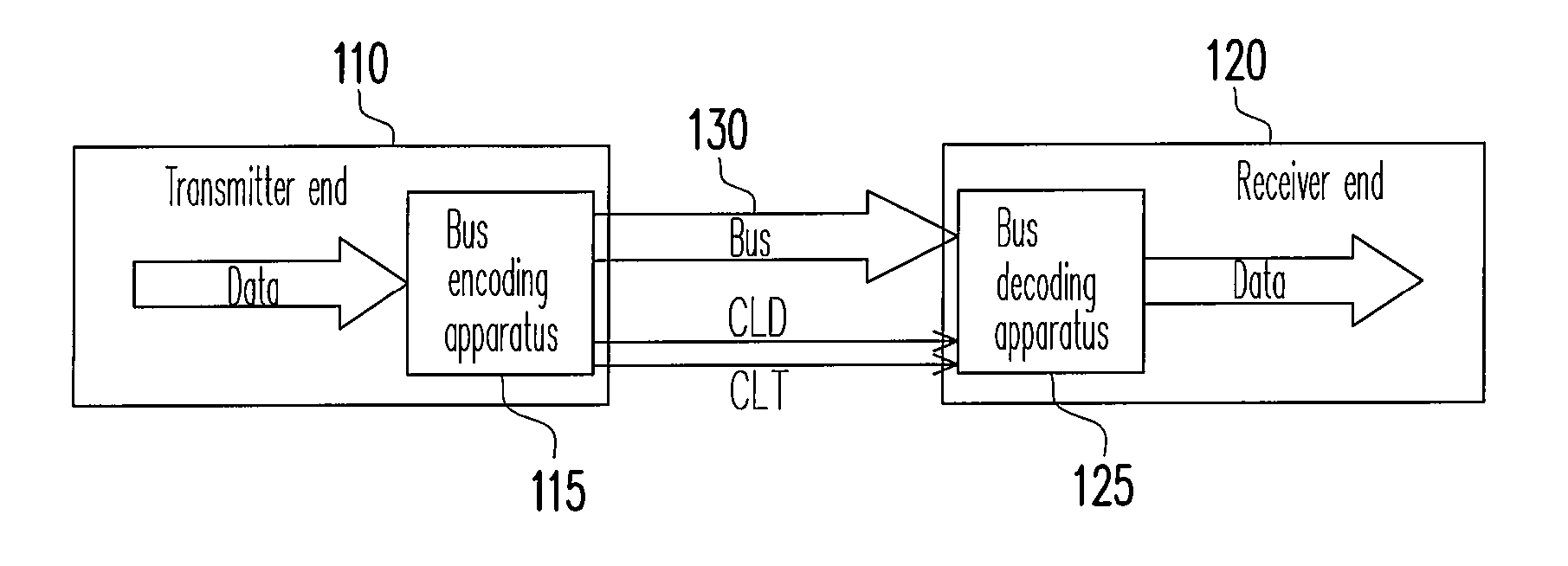

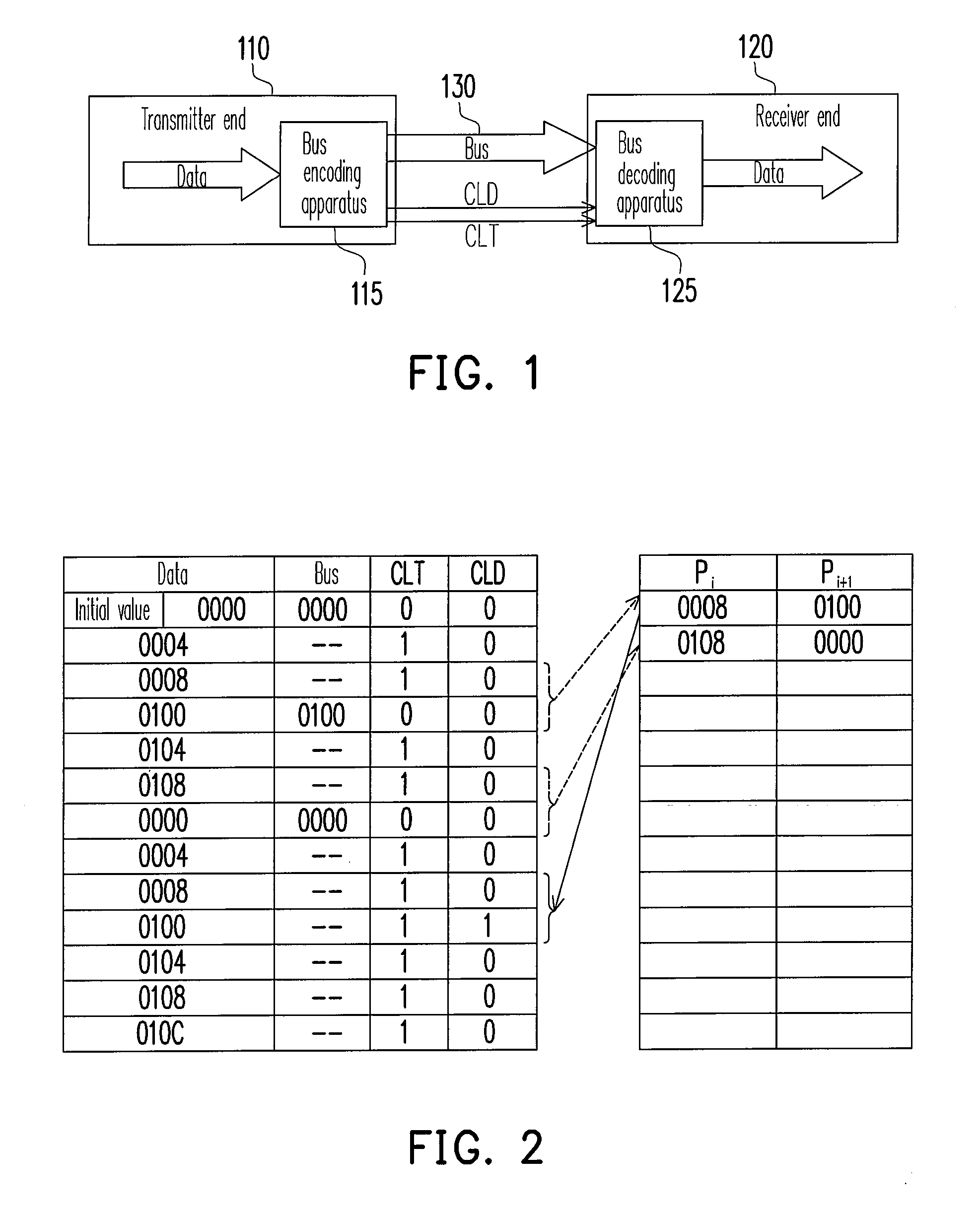

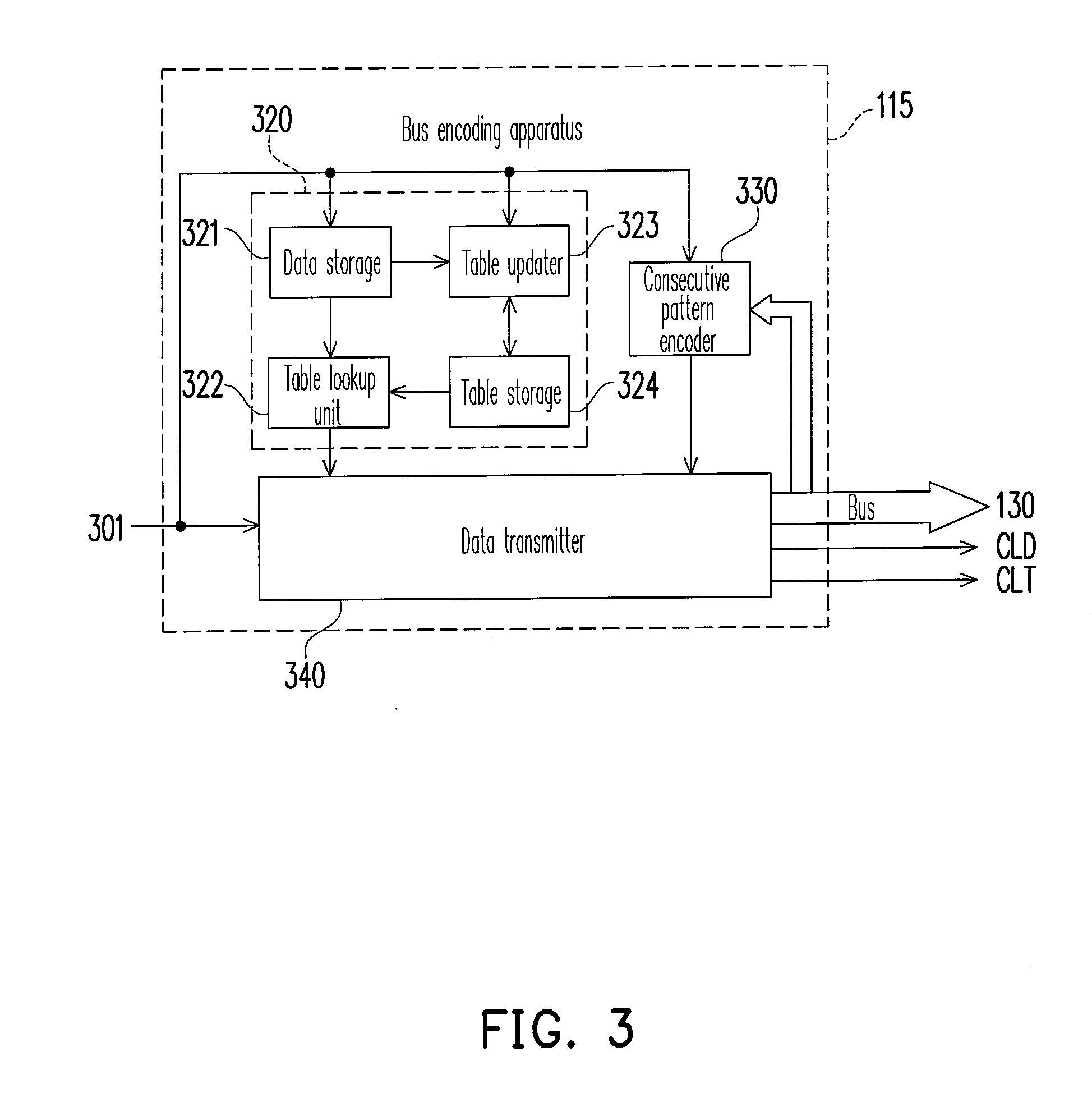

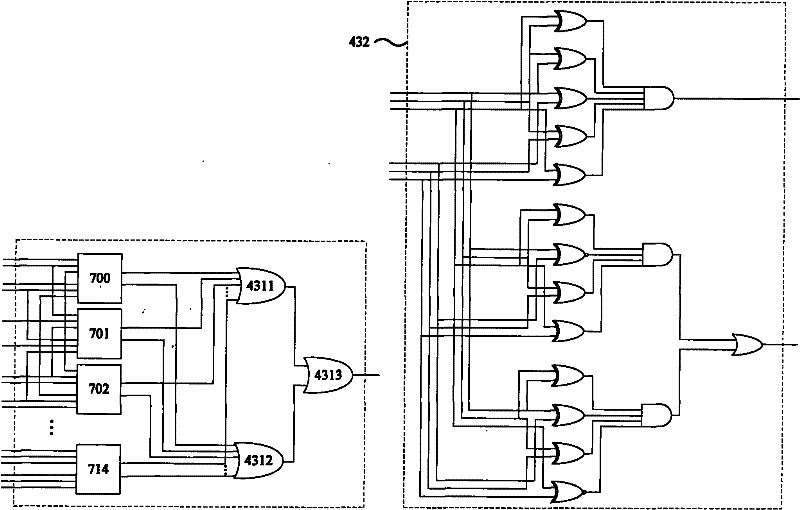

Method and apparatus for bus encoding and decoding

ActiveUS20080235417A1Reduce in quantityReduce the numberPulse conversionElectric digital data processingControl lineBus encoding

A method and an apparatus for bus encoding and a method and an apparatus for bus decoding are provided. The methods and apparatuses for bus encoding / decoding use a discontinuous pattern table (DPT) to store discontinuous pattern pairs. The tables are kept synchronous in both transmitter and receiver ends. After transmitting the first data in a discontinuous pattern pair, the second data may be transmitted by merely informing the receiver end through a control line instead of transmitting the second data by the bus.

Owner:IND TECH RES INST

Bus encoding using on-chip memory

ActiveUS10445288B2Digital data processing detailsDigital storageStatic random-access memoryRandom access memory

Various additional and alternative aspects are described herein. In some aspects, the present disclosure provides a method of communicating data between an electronic unit (EU) of a system-on-chip (SoC) and a dynamic random access memory (DRAM). The method includes encoding data at the EU. The method includes generating control data for decoding the encoded data at the EU. The method includes directing storage of the encoded data in the DRAM. The method includes directing storage of the control data in an on-chip memory separate from the DRAM, wherein the on-chip memory is on a same chip as the EU.

Owner:QUALCOMM INC

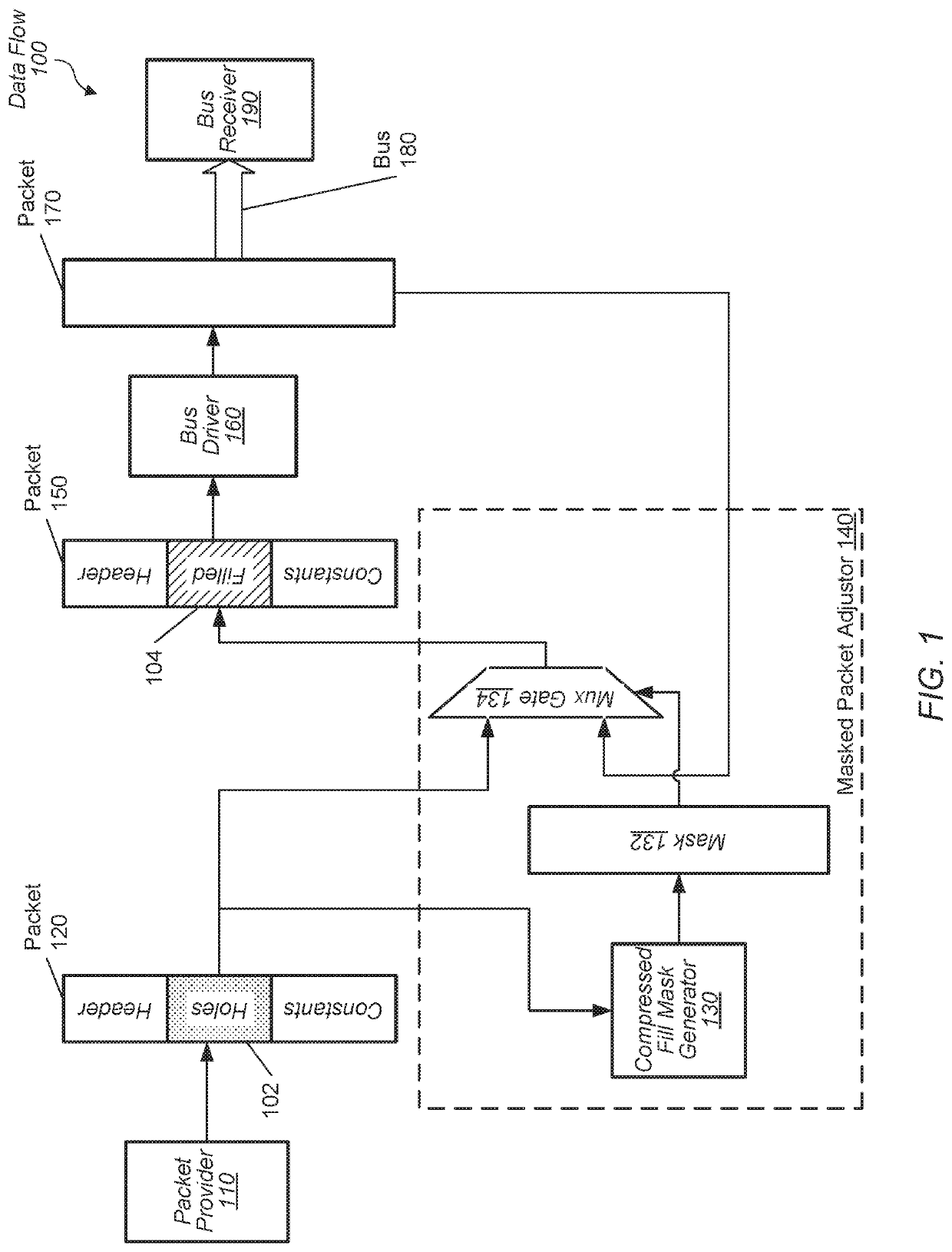

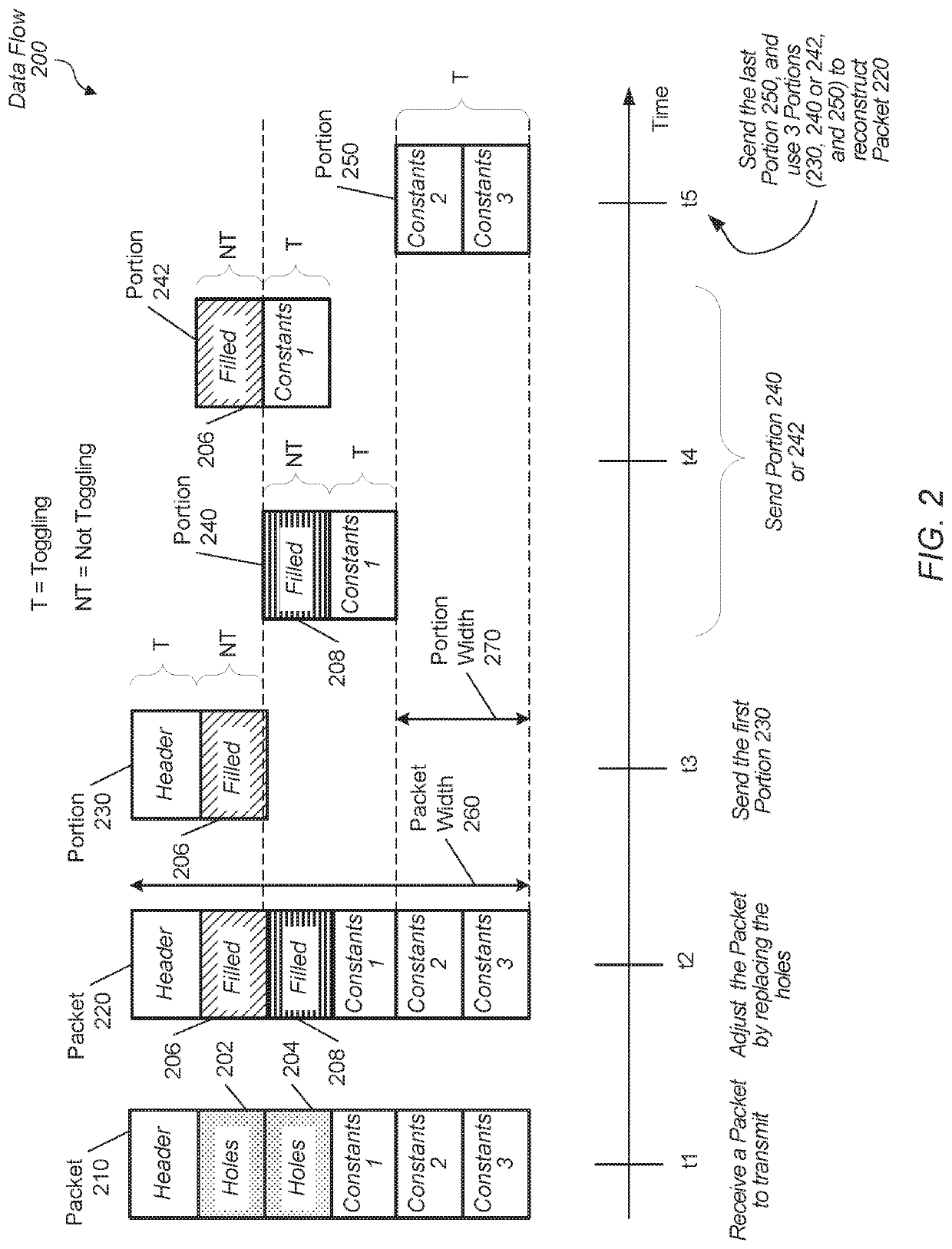

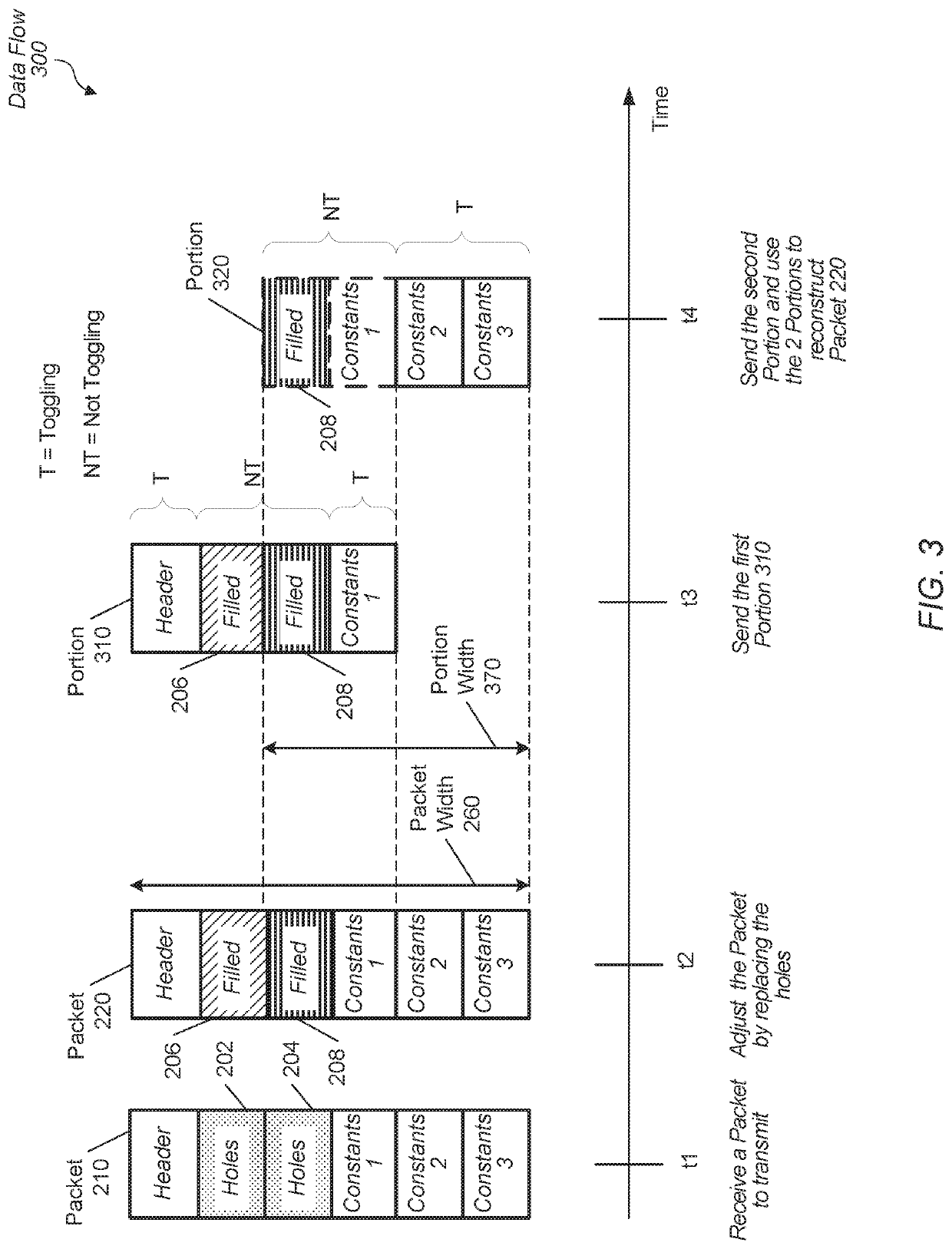

Power-oriented bus encoding for data transmission

Systems, apparatuses, and methods for reducing the toggle rates on buses are disclosed. A computing system includes a source which provides packets for transmission on a bus. The packet is compressed by a compression engine. The compressed data format of the packet includes locations (bit positions) referred to as holes which do not include valid data. A bus configuration module identifies the locations of the holes and replaces the holes with information from a previous packet transmitted earlier on the bus. The bus configuration module also determines a new transmission bus width for the packet for lowering the bus toggle rate on the bus during transmission.

Owner:ADVANCED MICRO DEVICES INC

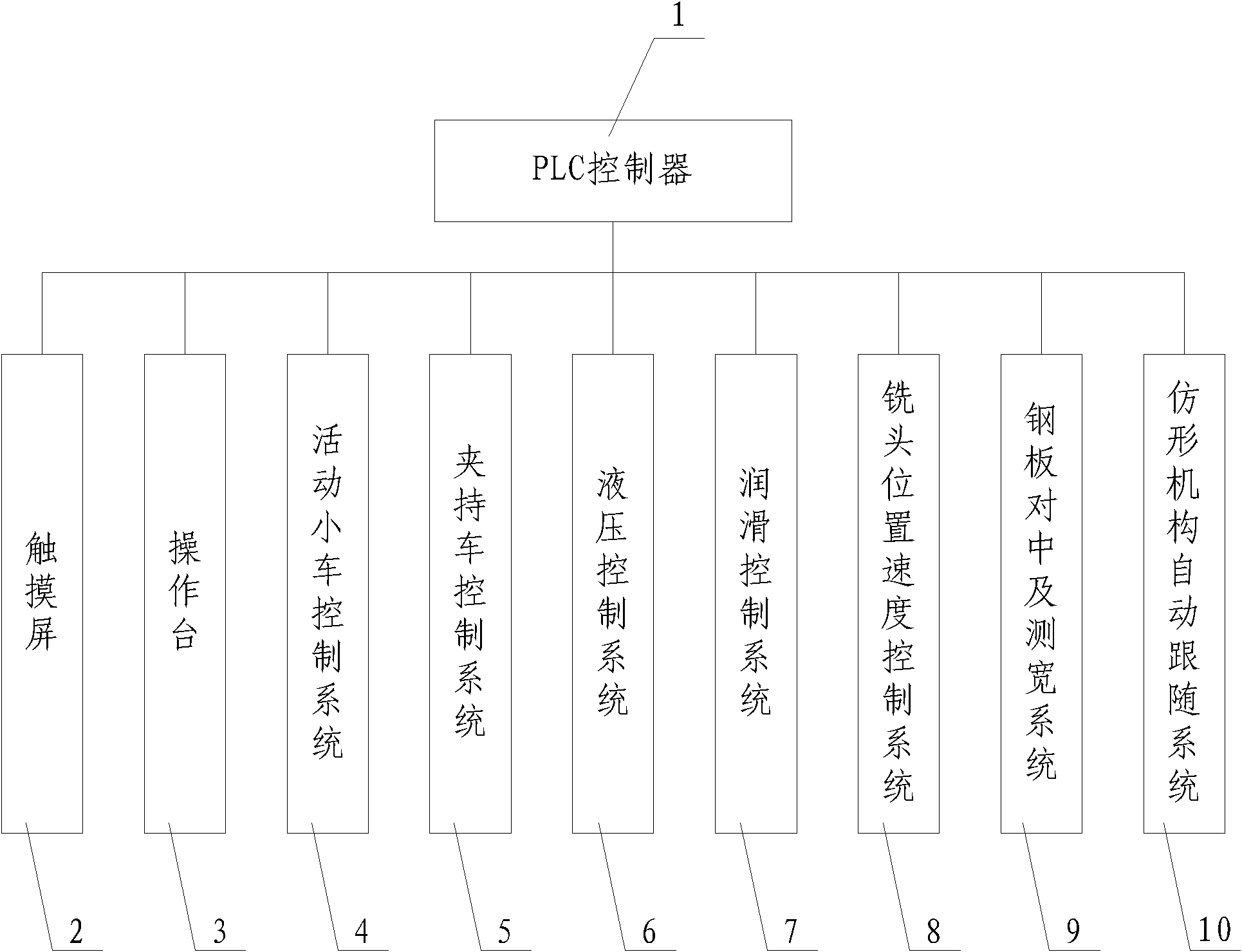

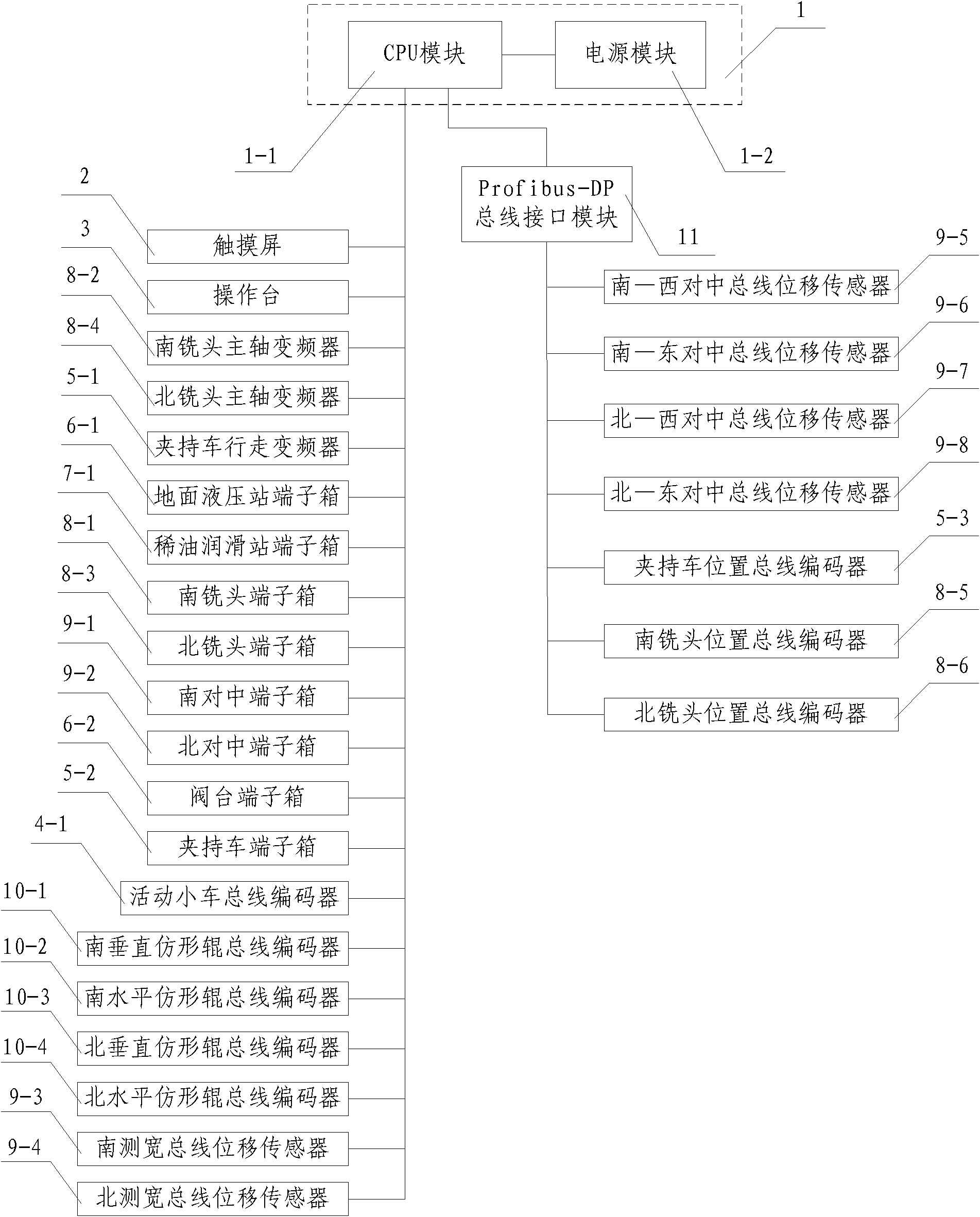

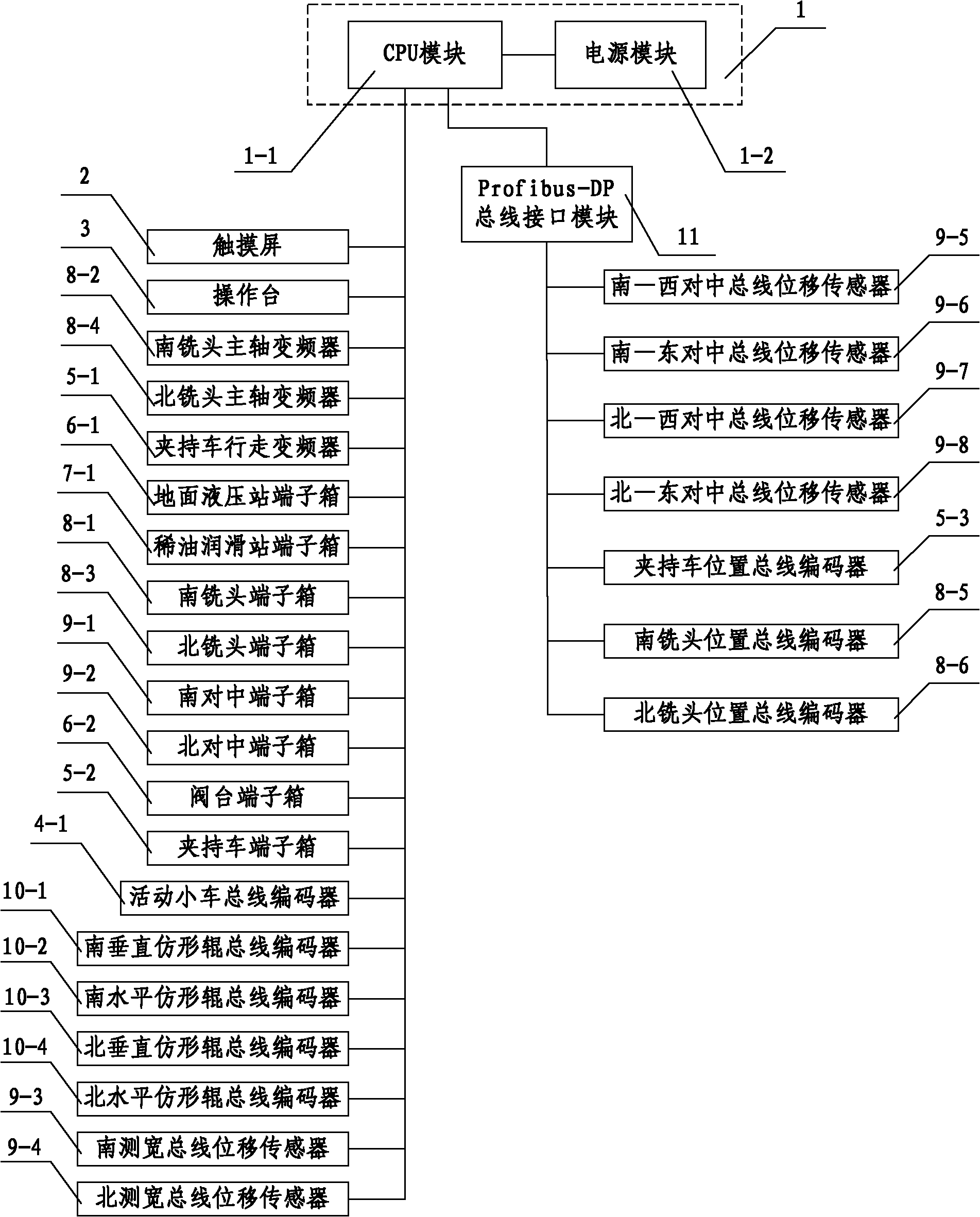

Electrical control system of steel plate edge milling machine

InactiveCN102467125AImprove machining accuracyReasonable designTotal factory controlProgramme total factory controlFailure rateBus encoding

The invention discloses an electrical control system of a steel plate edge milling machine, and the system comprises a PLC (programmable logic controller), a touch screen, an operating console, a movable trolley control system, a clamping trolley control system, a hydraulic control system, a lubrication control system, a milling head position and speed control system, a steel plate centering and width measuring system and a profiling mechanism automatic following system. The touch screen is connected with the PLC through a Profibus-DP bus. The steel plate centering and width measuring system comprises a southern centering terminal box, a northern centering terminal box, a southern width measuring bus displacement sensor, a northern width measuring bus displacement sensor, a south-west centering bus displacement sensor, a south-east centering bus displacement sensor, a north-west centering bus displacement sensor and a north-east centering bus displacement sensor, and the profiling mechanism automatic following system comprises a southern vertical profiling roller bus encoder, a northern vertical profiling roller bus encoder, a southern horizontal profiling roller bus encoder and a northern horizontal profiling roller bus encoder. The electrical control system of the steel plate edge milling machine has a reasonable design, advanced technology, high processing accuracy of control equipment, high processing quality, high production efficiency and low failure rate, the cost and energy can be saved, the use effects are good, and the promotion and application can be facilitated.

Owner:THE NORTHWEST MACHINE

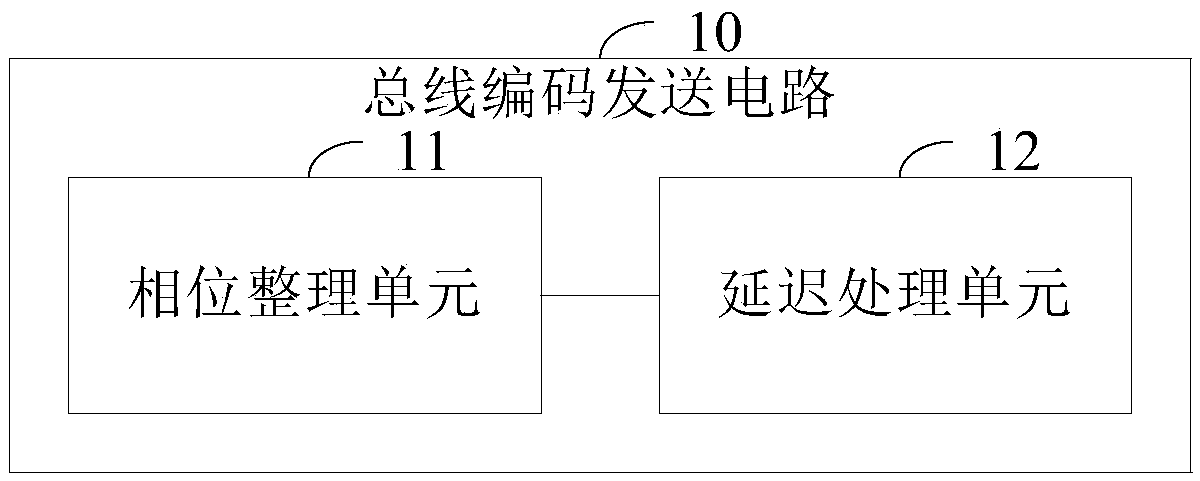

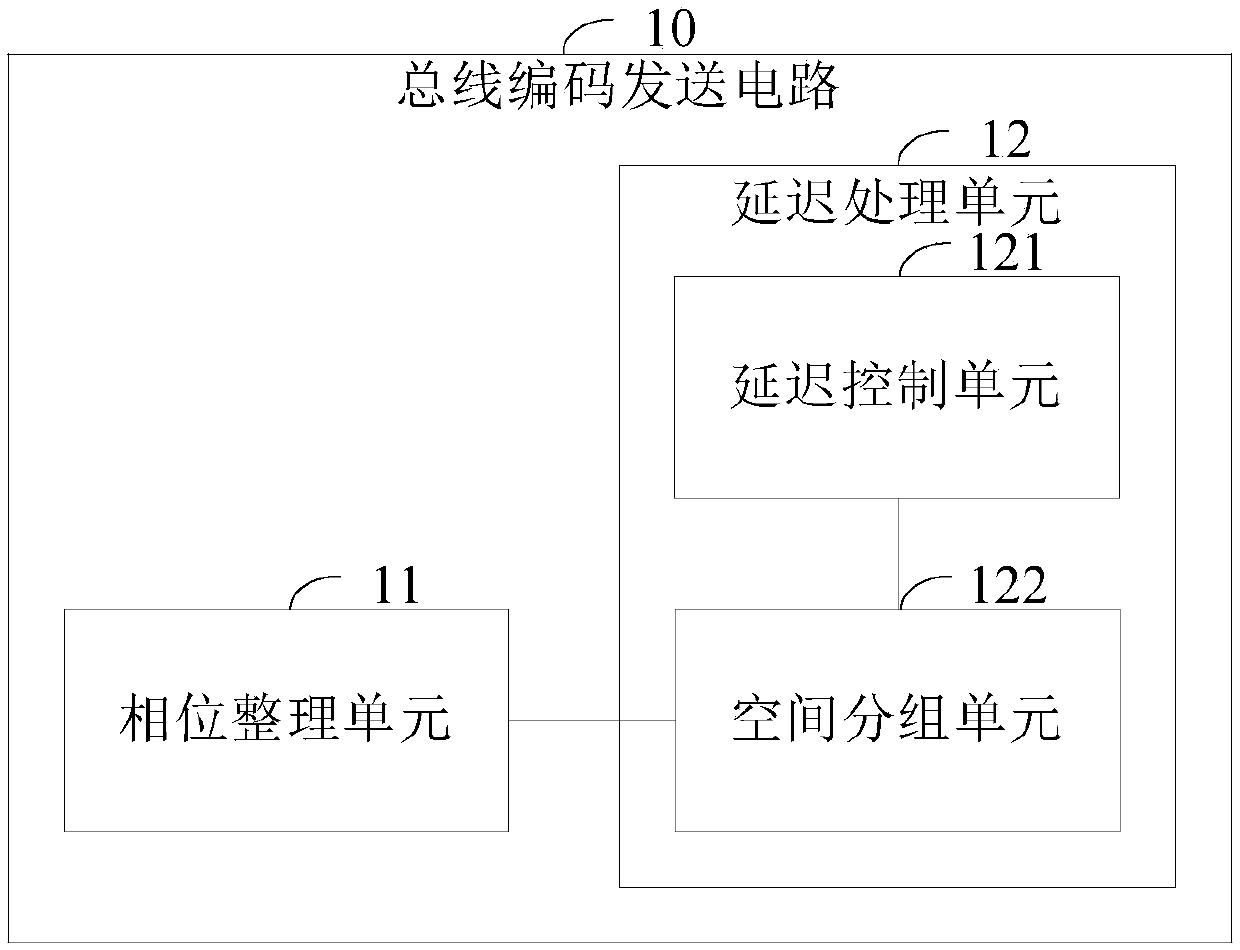

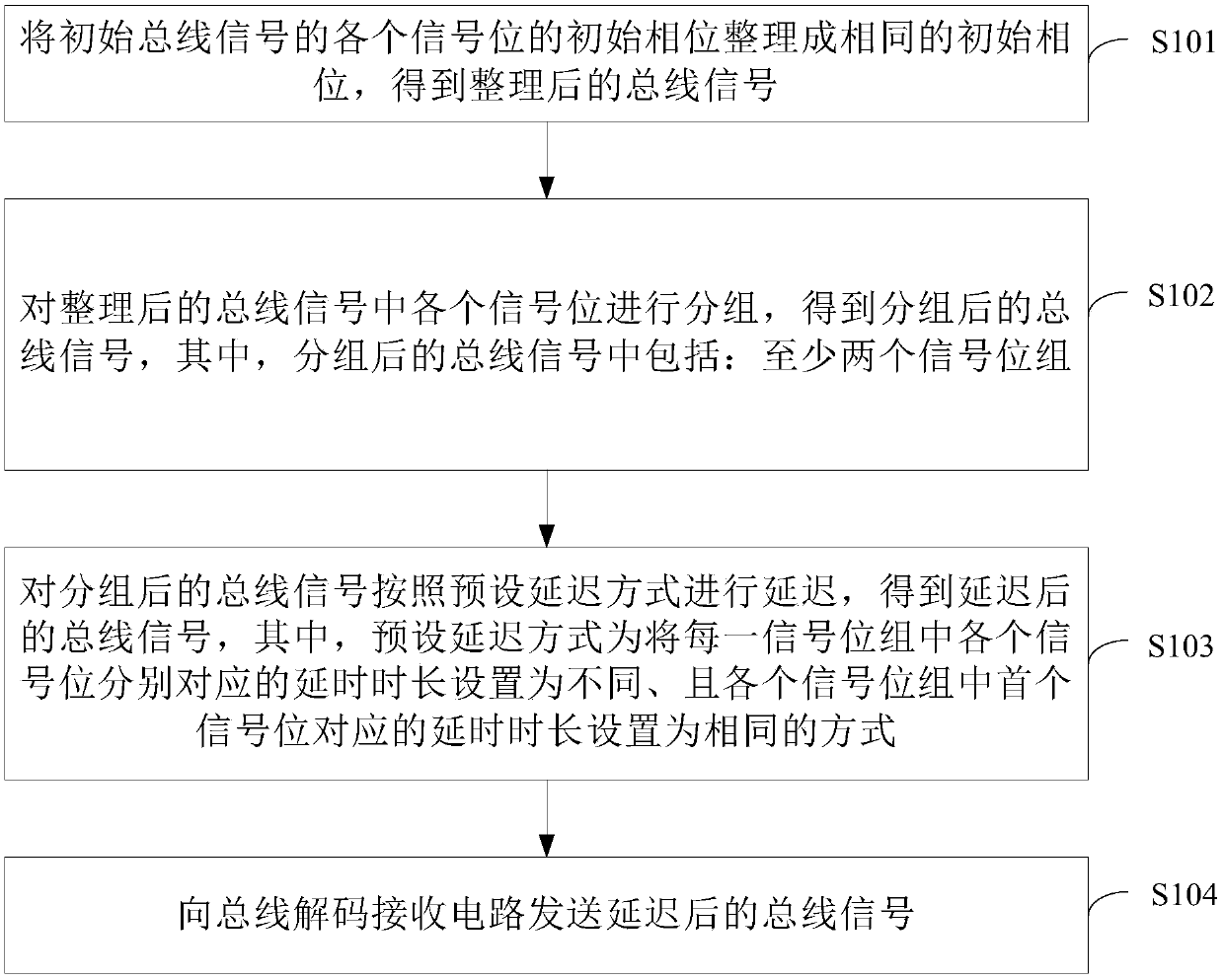

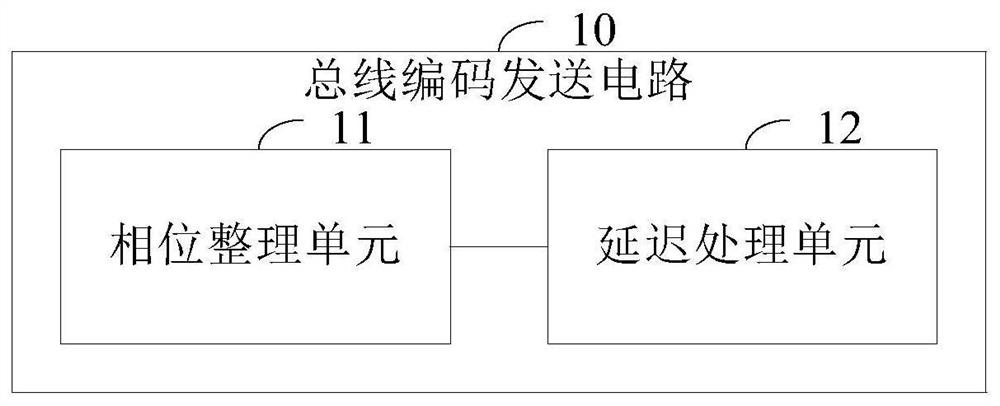

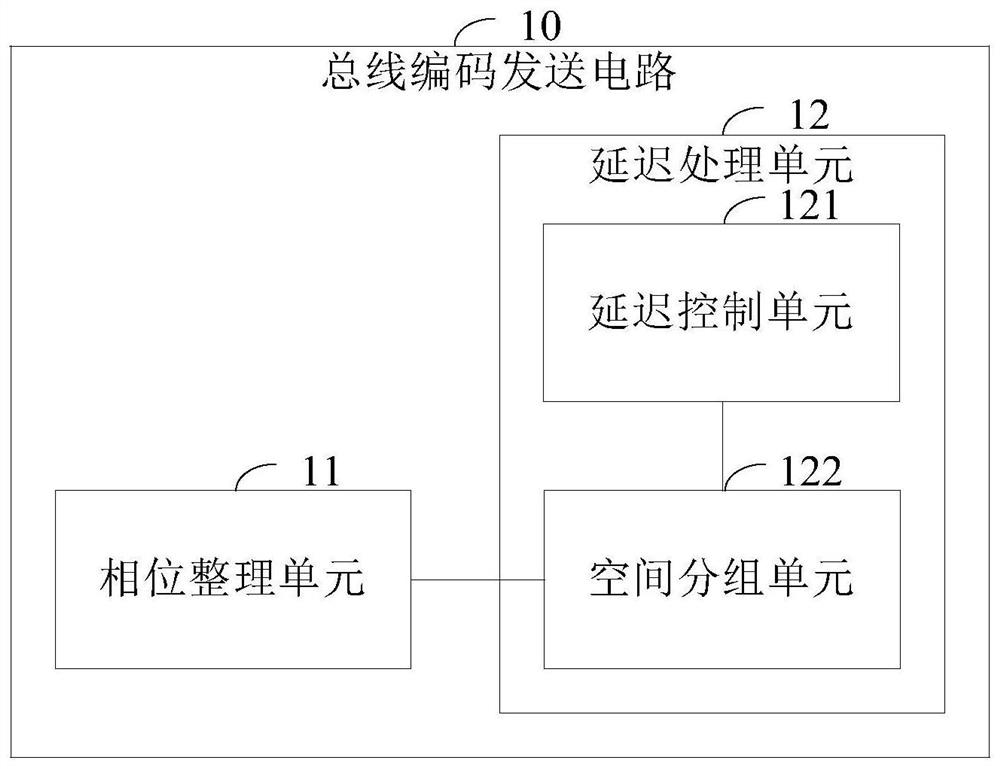

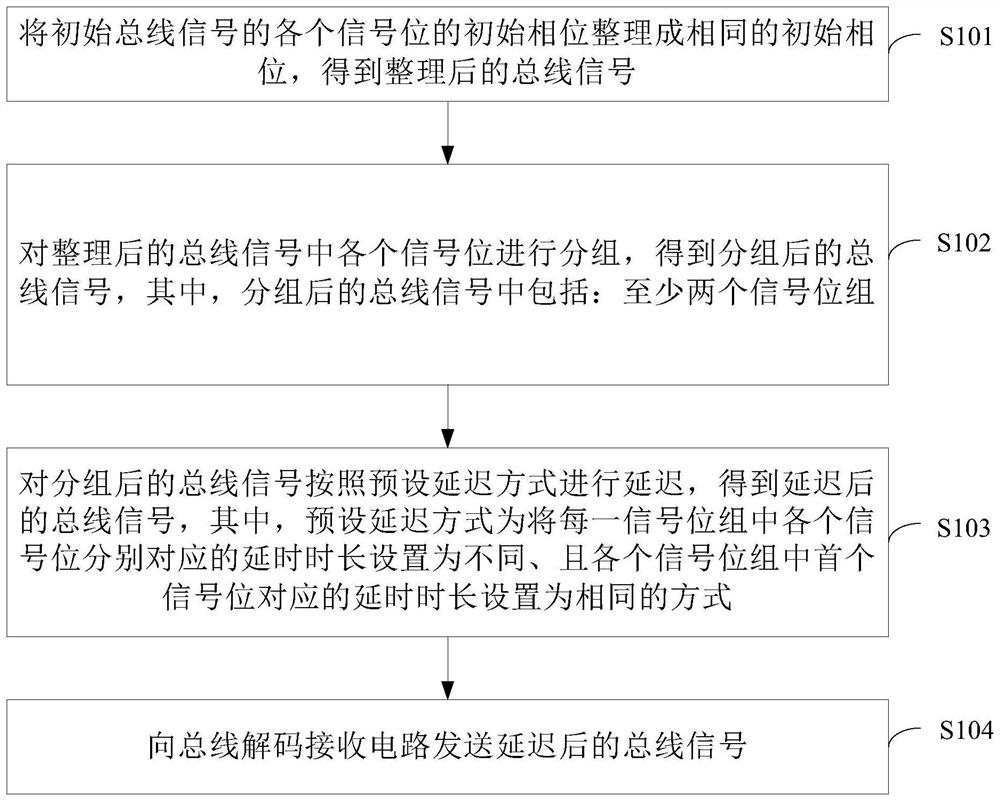

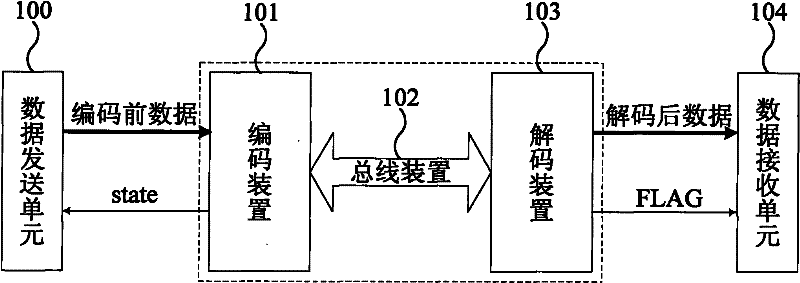

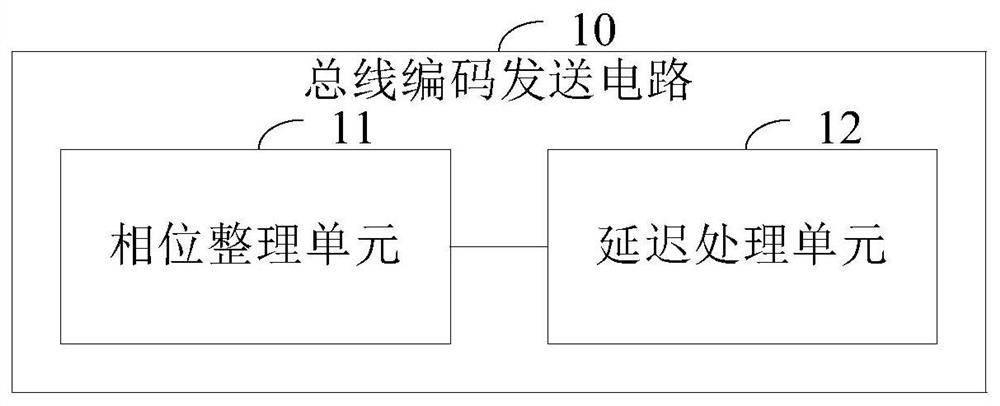

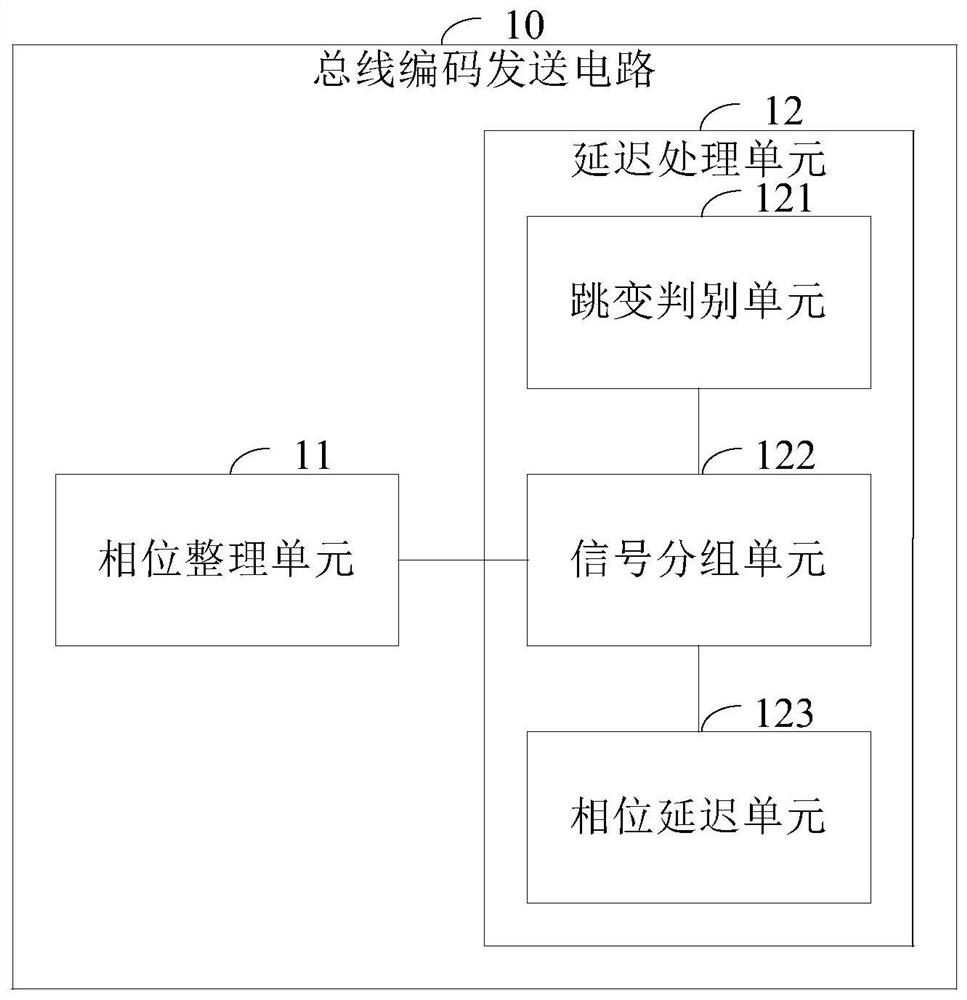

Bus code sending circuit and method and bus transmission system

ActiveCN111177038AReduce crosstalk effectsEliminate crosstalkElectric digital data processingBus networksTransport delayEngineering

The invention provides a bus code sending circuit, a bus code sending method and a bus transmission system. The circuit comprises a phase arrangement unit and a delay processing unit which are connected in sequence, wherein the phase arrangement unit is used for arranging the initial phase of each signal bit in an initial bus signal into the same initial phase, sending the arranged bus signal to the delay processing unit; the delay processing unit is used for grouping each signal bit in the arranged bus signals, delaying each group of signal bits in the grouped bus signals according to a preset delay mode that the delay durations corresponding to the signal bits in each signal bit group are set to be different and the delay duration corresponding to the first signal bit in each signal bitgroup is set to be the same, and sending the delayed bus signal to a bus decoding receiving circuit. According to the invention, on the premise that the wiring resource demand is not changed, the worst crosstalk condition is avoided, and the transmission delay caused by crosstalk is reduced.

Owner:LOONGSON TECH CORP

Bus encoding sending circuit and method, bus transmission system

ActiveCN111177038BReduce crosstalk effectsEliminate crosstalkElectric digital data processingBus networksTransport delayBus encoding

The invention provides a bus coding sending circuit and method, and a bus transmission system. The circuit includes: a phase sorting unit and a delay processing unit connected in sequence; wherein, the phase sorting unit is used to sort the initial phases of each signal bit in the initial bus signal into the same initial phase; and send the sorted initial phase to the delay processing unit The bus signal; the delay processing unit is used to group each signal bit in the sorted bus signal; and each group of signal bits in the grouped bus signal according to the corresponding delay time The duration is set to be different, and the delay duration corresponding to the first signal bit in each signal bit group is set to the same preset delay mode for delay; and the delayed bus signal is sent to the bus decoding receiving circuit. The present invention avoids the occurrence of the worst crosstalk situation and reduces the transmission delay caused by the crosstalk under the premise that the wiring resource requirement remains unchanged.

Owner:LOONGSON TECH CORP

Anti-crosstalk on-chip bus encoding and decoding method and encoding and decoding device

ActiveCN101788967BEliminate crosstalkIncrease working frequencyEnergy efficient ICTEnergy efficient computingDecoding methodsVery large scale integrated circuits

The invention discloses an encoding and decoding method for a crosstalk resistant on-chip bus and an encoding and decoding device thereof, which mainly solve the problems of low data transmission efficiency and high power consumption in the conventional bus encoding method. The method comprises the following steps of: firstly, partitioning an N-position bus into a low-position sub-bus and a high-position sub-bus by inserting a shielded wire; secondly, judging whether a true code and a counter code of data to be transmitted of the two sub-buses can cause worst-case-crosstalk or not and generating a mark signal; and finally, obtaining whether the worst-case-crosstalk exists in the sub-buses or not according to the mark signal, if the worst-case-crosstalk exists in one or both sub-buses, inserting an N-position shielded word to eliminate the worst-case-crosstalk, and if the worst-case-crosstalk does not exist in both sub-buses, optimizing the power consumption of the encoding method, namely, if the true code and the counter code do not cause the worst-case-crosstalk, selecting one with lower power consumption to transmit, and if one code causes the worst-case-crosstalk, selecting the data not causing the worst-case-crosstalk to transmit. The method and the device have the advantages of high data transmission efficiency and low power consumption and can be applied to the design of a super-large scale integrated circuit.

Owner:陕西光电子先导院科技有限公司

A Method of Quickly Correcting the Code Value of Blast Furnace Roof Bus Type Encoder

ActiveCN106086268BRealize one-button quick correction intelligent control functionImprove efficiencyBell-and-hopper arrangementChecking devicesAutomatic controlComputer module

The invention belongs to the technical field of blast furnace automatic control and particularly relates to a method for quickly correcting the code value of a blast furnace top bus-based encoder. According to the method, the means that the actual angle of a distributing device distributing angle alpha angle motor and the actual angle of a material flow speed throttling gamma angle motor at the top of a blast furnace are worked out, a calculation formula is modified according to the actual working condition, the operation counting range limit of an detection device is determined, and the function of achieving angle one-key correcting is established through a one-key quick correcting button is adopted, so that the one-key quick correcting intelligent control function of the blast furnace top bus-based encoder is achieved, the production efficiency and reliability of a blast furnace are improved, and the time for processing the fault of winding PLC system bus hardware and related modules, the fault of the encoder and the fault of bus communication is shortened; and accordingly, the influence on blast furnace production is reduced, damping down and blast reducing of the blast furnace are reduced, and normal smelting and production of the blast furnace are ensured.

Owner:GANSU JIU STEEL GRP HONGXING IRON & STEEL CO LTD

A fire industry bus coding method

ActiveCN106911334BReduce Capacitance RequirementsLow costIndividual digits conversionIdle timeAgricultural engineering

The invention discloses a fire-fighting industrial bus coding method, which includes: (1) a fire alarm controller uses a low-level pulse with a duty ratio of 0.3 or less as the starting point of bit code division to perform coding, and synchronizes the signal; (2) When encoding, the bit "0" is determined by the pulse width between two level falling edges, and the bit "1" is determined by the pulse width between two level rising edges; Give an independent synchronous signal; (3) Repeat step (2) for continuous encoding until the encoding is completed, and then send codes to the smart components through the bus. The invention has a simple process and a simple and convenient coding method, and can avoid the problem of long idle time of the bus while ensuring the accuracy of data transmission. Therefore, the invention is suitable for popularization and application.

Owner:光和电科技(广东)有限公司

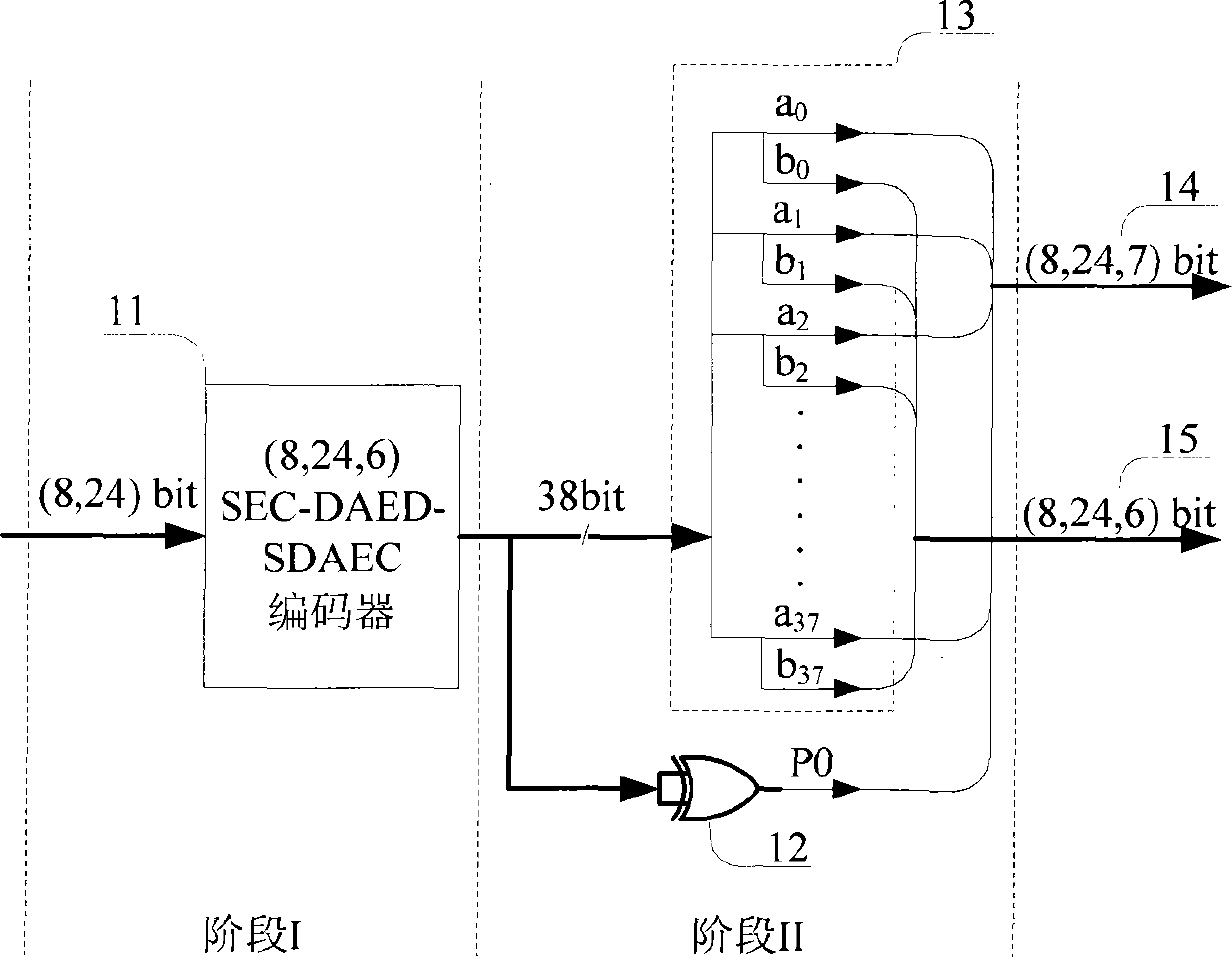

On-chip bus encoding based on combined unequal error protection (UEP) with crosstalk avoidance coding (CAC)

InactiveCN102130691BError correction/detection using multiple parity bitsStore and forwardTime delays

Owner:UNIV OF ELECTRONICS SCI & TECH OF CHINA

Bus encoding using metadata

ActiveUS20180095697A1Well formedInput/output to record carriersDigital video signal modificationControl dataBus encoding

Various additional and alternative aspects are described herein. In some aspects, the present disclosure provides a method of communicating data between an electronic unit (EU) of a system-on-chip (SoC) and a dynamic random access memory (DRAM). The method includes compressing data at the EU. The method further includes encoding the compressed data at the EU. The method further includes generating control data for decoding the encoded data at the EU. The method further includes generating metadata corresponding to the compressed data at the EU. The metadata further includes the control data. The method further includes directing storage of the encoded data and the metadata in the DRAM.

Owner:QUALCOMM INC

Multiplier, data processing method and chip

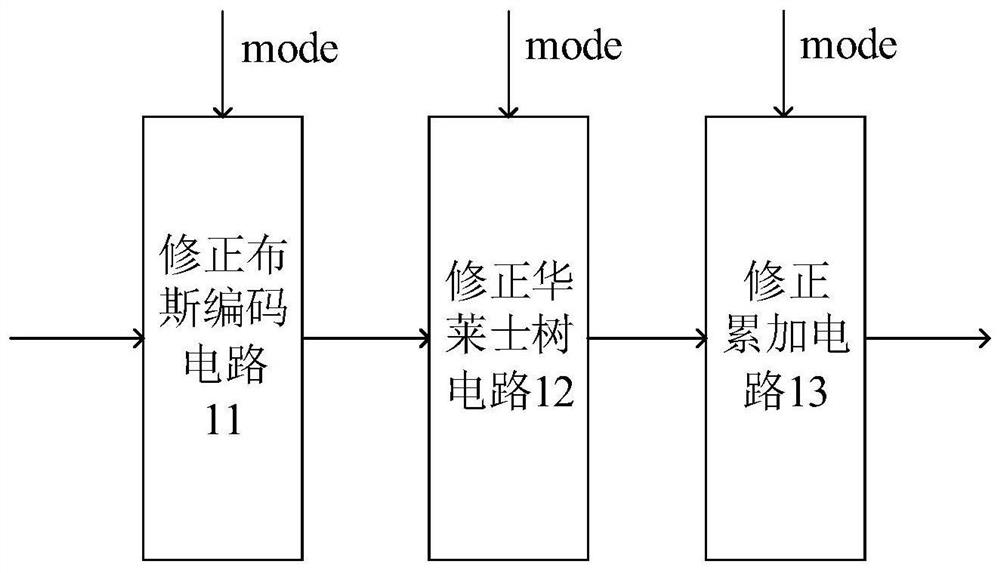

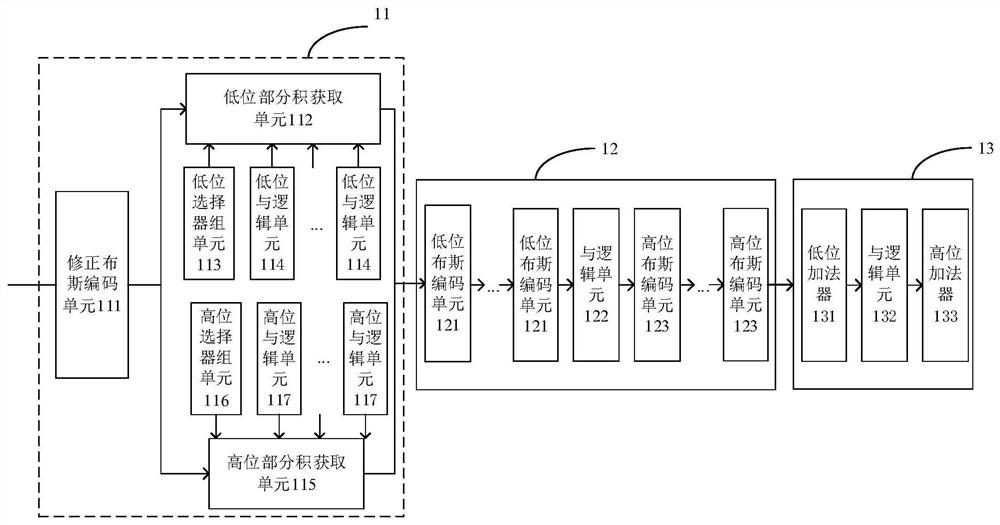

The application provides a multiplier, a data processing method and a chip, the multiplier includes: a modified Booth coding circuit, a modified Wallace tree circuit and a modified accumulation circuit, the output terminal of the modified Booth coding circuit is connected to the The input end of the modified Wallace tree circuit is connected, the output end of the modified Wallace tree circuit is connected with the input end of the modified accumulation circuit, and the multiplier can perform multiplication operations on data with different bit widths, thereby improving the versatility of the multiplier.

Owner:SHANGHAI CAMBRICON INFORMATION TECH CO LTD

Enhanced wishbone on-chip bus for leading-in bus code

InactiveCN1975635BReduce the number of bit flipsReduce power consumptionEnergy efficient ICTPower supply for data processingControl signalWishbone

Owner:朱海鸿

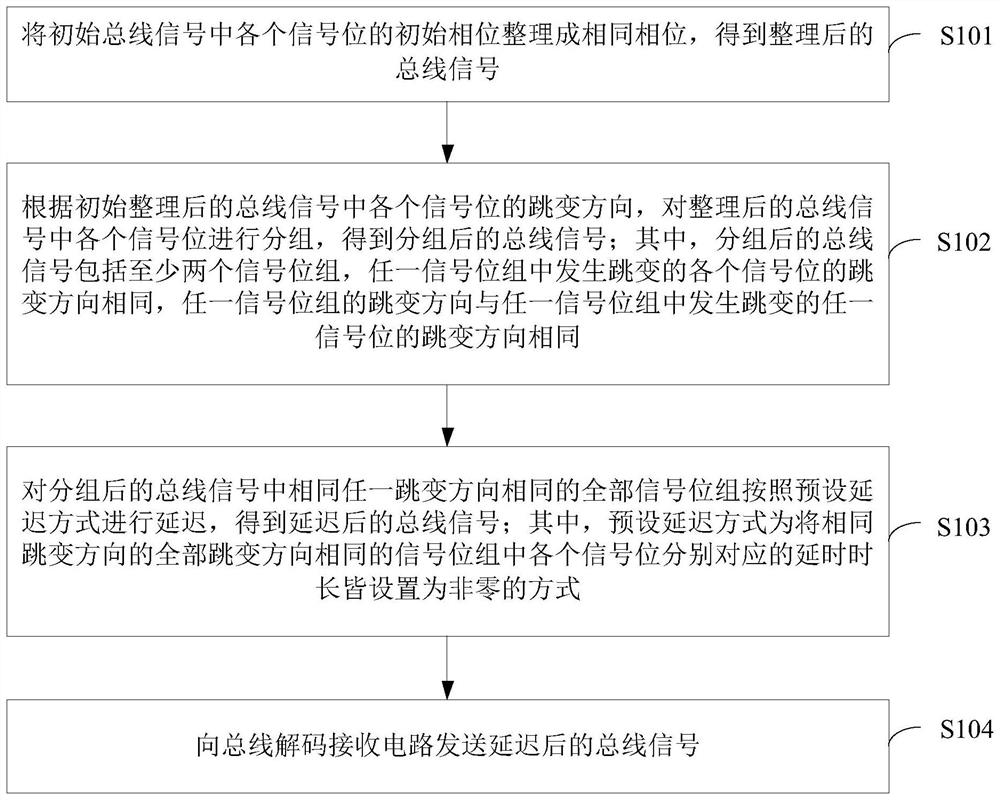

Bus encoding sending circuit and method, bus transmission system

ActiveCN111177057BMitigate the effect of transmission delayEasy to operateElectric digital data processingTransport delayBus encoding

The invention provides a bus coding sending circuit and method, and a bus transmission system. The circuit includes: a sequentially connected phase arrangement unit and a delay processing unit. The phase sorting unit can sort the initial phases of each signal bit in the initial bus signal into the same phase. The delay processing unit groups each signal bit in the sorted bus signal according to the transition direction of each signal bit in the initial bus signal, and obtains at least two signal bit groups and the transition of each signal bit in any signal bit group Grouped bus signals with the same direction, and then perform non-zero delay on all signal bit groups with the same jump direction in the grouped bus signals according to the preset delay method to obtain the delayed bus signal, and send it to the bus decoding receiving circuit Delayed bus signal. The invention eliminates the occurrence of the worst crosstalk and reduces the transmission delay caused by the crosstalk under the premise that the wiring resource requirement remains unchanged.

Owner:LOONGSON TECH CORP