Enhanced wishbone on-chip bus for leading-in bus code

A bus encoding and bus technology, which is applied in the fields of instruments, electrical digital data processing, sustainable buildings, etc., can solve the problems of unsupported bus specifications and power consumption difficulties, and achieve the reduction of the number of bit inversions, power consumption, and low power consumption. The effect of consuming requirements

Inactive Publication Date: 2011-01-05

朱海鸿

View PDF1 Cites 0 Cited by

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

In the existing bus standards such as AMBA and Wishbone, they only focus on data transmission and redundancy, and none of them introduces bus coding. The main difficulties include: a. The on-chip bus is connected to a variety of IP cores, not all IP cores can be applied The same bus encoding; b. Now on-chip buses use additional hard wiring to implement control and management functions. As far as the author knows, no bus introduces additional protocols to transmit additional bytes for management; c. Must be backward compatible , to ensure that a module that uses bus encoding and does not use bus encoding can achieve normal intercommunication, so that existing intellectual property cores can be reused

For the widely used Wishbone bus, not only the bus specification itself does not support the traditional bus encoding that can reduce power consumption, but also includes two high-speed and low-speed buses to improve support for different peripherals, which further reduces its performance. Consumption brings difficulties

Method used

the structure of the environmentally friendly knitted fabric provided by the present invention; figure 2 Flow chart of the yarn wrapping machine for environmentally friendly knitted fabrics and storage devices; image 3 Is the parameter map of the yarn covering machine

View moreImage

Smart Image Click on the blue labels to locate them in the text.

Smart ImageViewing Examples

Examples

Experimental program

Comparison scheme

Effect test

Embodiment Construction

the structure of the environmentally friendly knitted fabric provided by the present invention; figure 2 Flow chart of the yarn wrapping machine for environmentally friendly knitted fabrics and storage devices; image 3 Is the parameter map of the yarn covering machine

Login to View More PUM

Login to View More

Login to View More Abstract

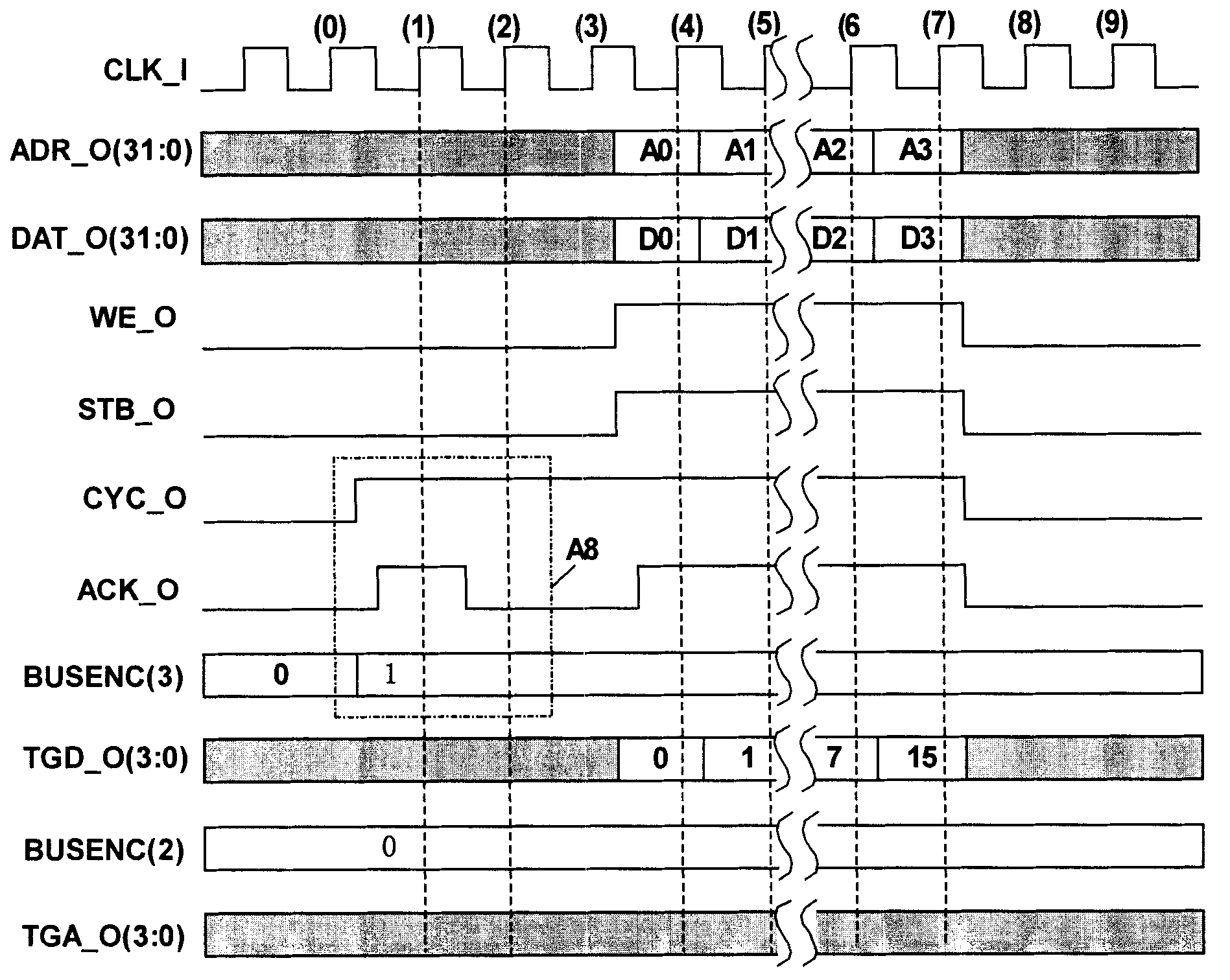

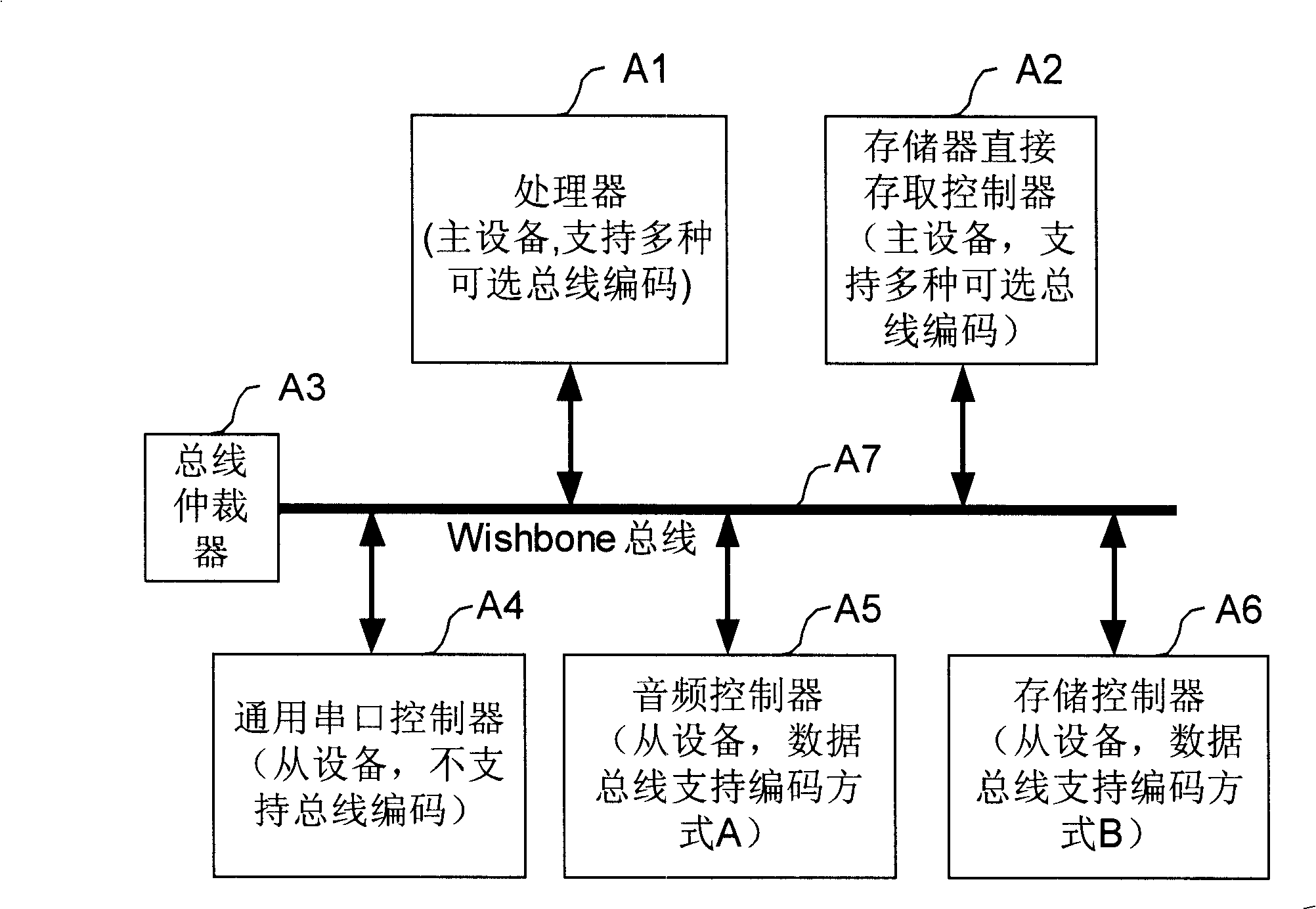

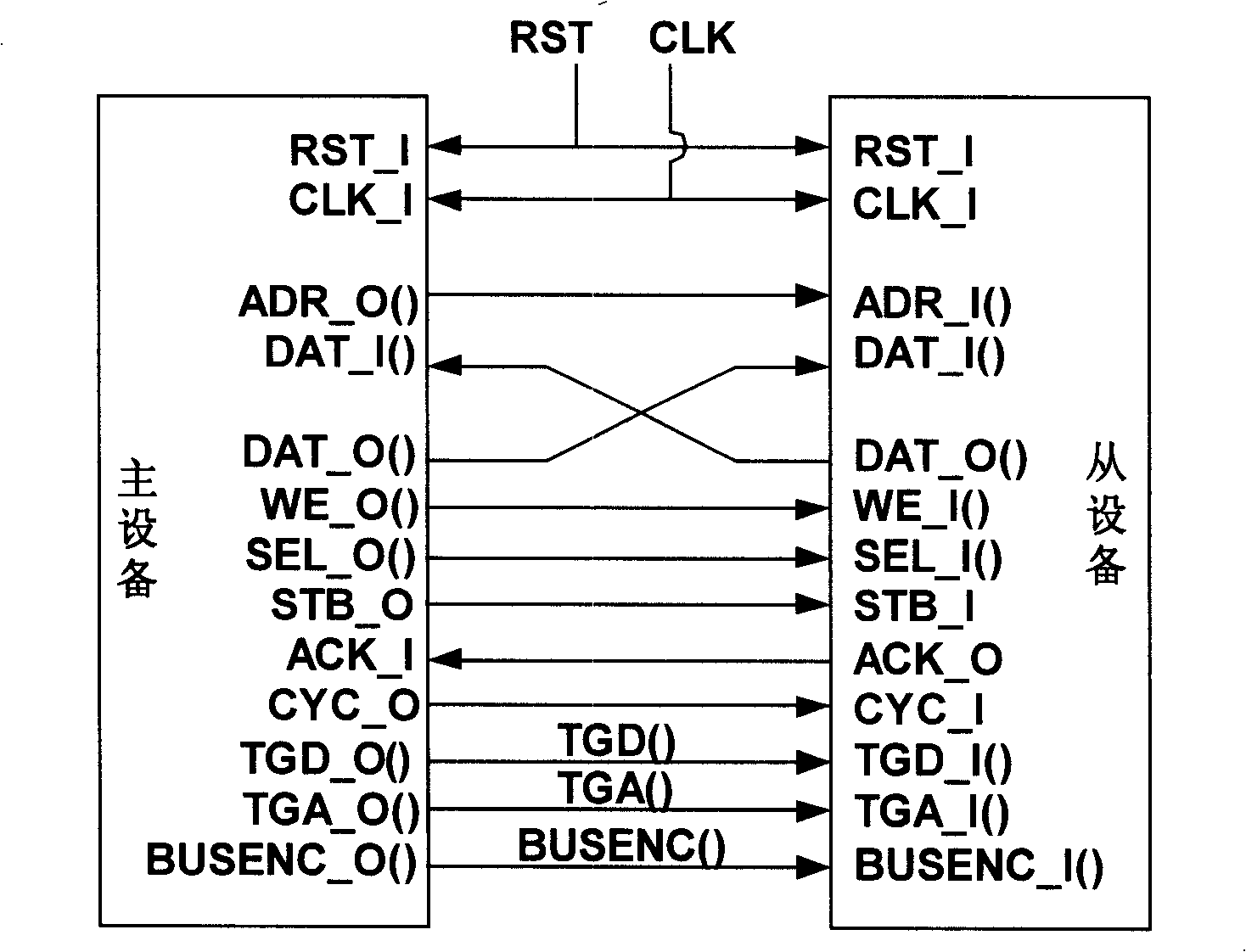

The invention relates to a bus on the strengthen Wishbone sheet which leads the bus coding to decrease the bus power consumption. The method in the invention is: first to add the controlling signal BUSENC_O () on the bus main device in Wishbone sheet, as the same, adding the controlling signal BUSENC__I() on the slave device; then to define the meaning in every using bus coding mode of every value from the Wishbone bus data label TGD() and / or address label TGA(); next the main and slave devices arranges the coding mode of the data bus and the address bus used by the communication; last to communicate by the arranging mode. The invention can decrease the bit reversal times of the Wishbone bus to decrease the power consumption in sheet system.

Description

Enhanced Wishbone on-chip bus introducing bus encoding technical field The invention relates to an integrated circuit on-chip bus, in particular to a method for introducing bus coding into the Wishbone on-chip bus to reduce bus power consumption. Background technique With the rapid development of VLSI, people can integrate millions to hundreds of millions of transistors on a single chip. Such dense integration makes it possible to integrate the functions previously realized by several chips such as processors and peripherals on a small chip, and form a powerful and complete system from a single integrated circuit, which is what is usually called So-called system-on-a-chip. Intellectual property core (IP) multiplexing is one of the core technologies in the SoC era. Because the designs of IP cores vary greatly, they must abide by the same interface standard if they want to be able to connect directly. In a system-on-chip, the processor core and all peripherals are interco...

Claims

the structure of the environmentally friendly knitted fabric provided by the present invention; figure 2 Flow chart of the yarn wrapping machine for environmentally friendly knitted fabrics and storage devices; image 3 Is the parameter map of the yarn covering machine

Login to View More Application Information

Patent Timeline

Login to View More

Login to View More Patent Type & Authority Patents(China)

IPC IPC(8): G06F1/32G06F13/42

CPCY02B60/1228Y02B60/1235Y02D10/00

Inventor 陈曦辛晓刚陈铮

Owner 朱海鸿