AHB bus test method and system

A technology of bus testing and bus transmission, applied in error detection/correction, detection of faulty computer hardware, instruments, etc., can solve problems such as heavy workload, low efficiency, and many SOC pins, and achieve simple effects

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

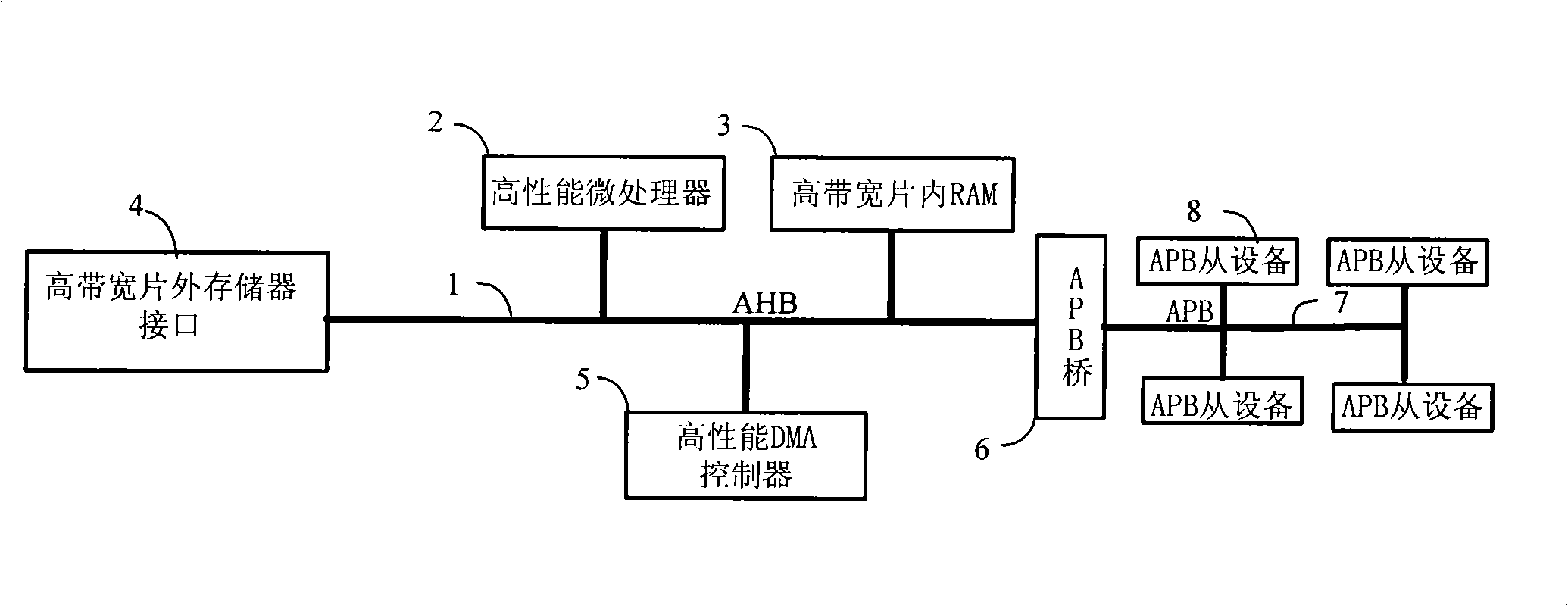

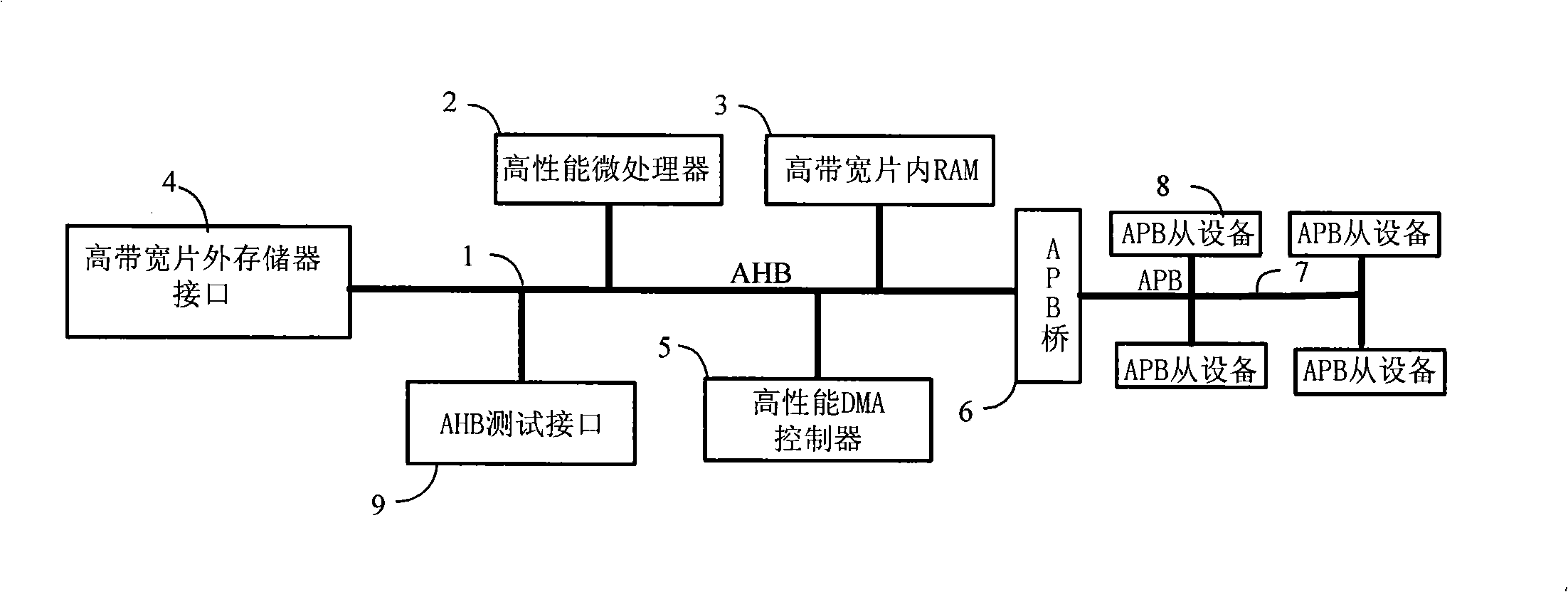

[0063] The AHB bus testing method and system provided by the present invention will be described in detail below in conjunction with the accompanying drawings.

[0064] The AHB bus test method provided by the present invention is applied to the AHB bus test in the SOC, the AHB test interface is provided in the SOC, and the structure of the AHB test interface is shown in figure 2 and image 3 , the same as the prior art, the function and state transition of the AHB test interface refer to Figure 4 , used to convert the received test signal into AHB bus transmission signal for AHB bus test.

[0065] The method of the invention utilizes the AHB test interface in the prior art to complete the AHB bus test in the SOC.

[0066] see Figure 5 , AHB bus test method flowchart provided by the present invention, specifically includes:

[0067] Step S101, generating a first AHB bus transmission signal outside the SOC.

[0068] Since the AHB bus transmission signal is a bus transmis...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More