On-chip bus encoding based on combined unequal error protection (UEP) with crosstalk avoidance coding (CAC)

A protection code and capability technology, applied in error detection coding using multi-bit parity bits, error correction/detection using block codes, data representation error detection/correction, etc., can solve the problem of SEC-DAED-SDAEC code With crosstalk avoidance characteristics and other issues

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0014] specific implementation plan

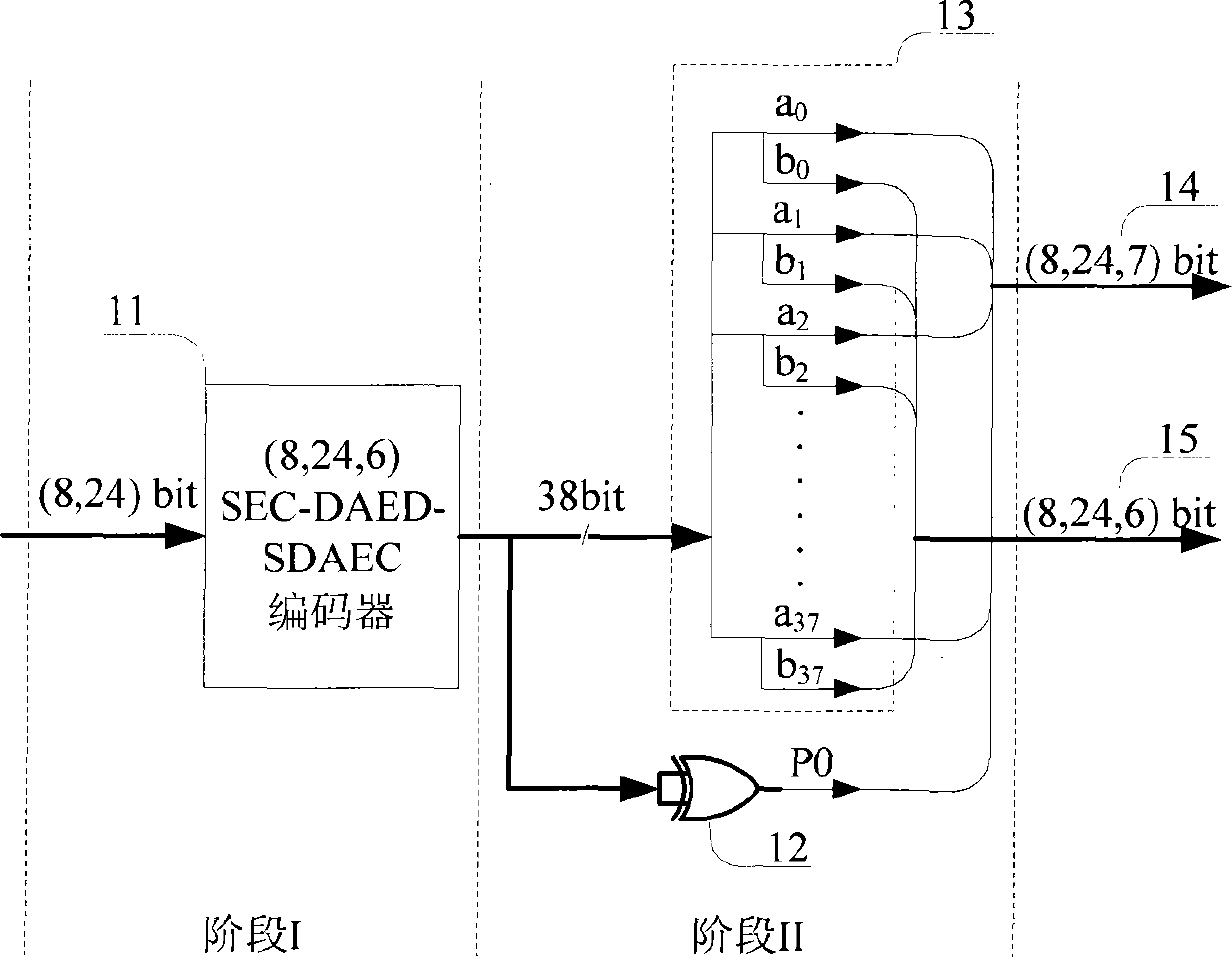

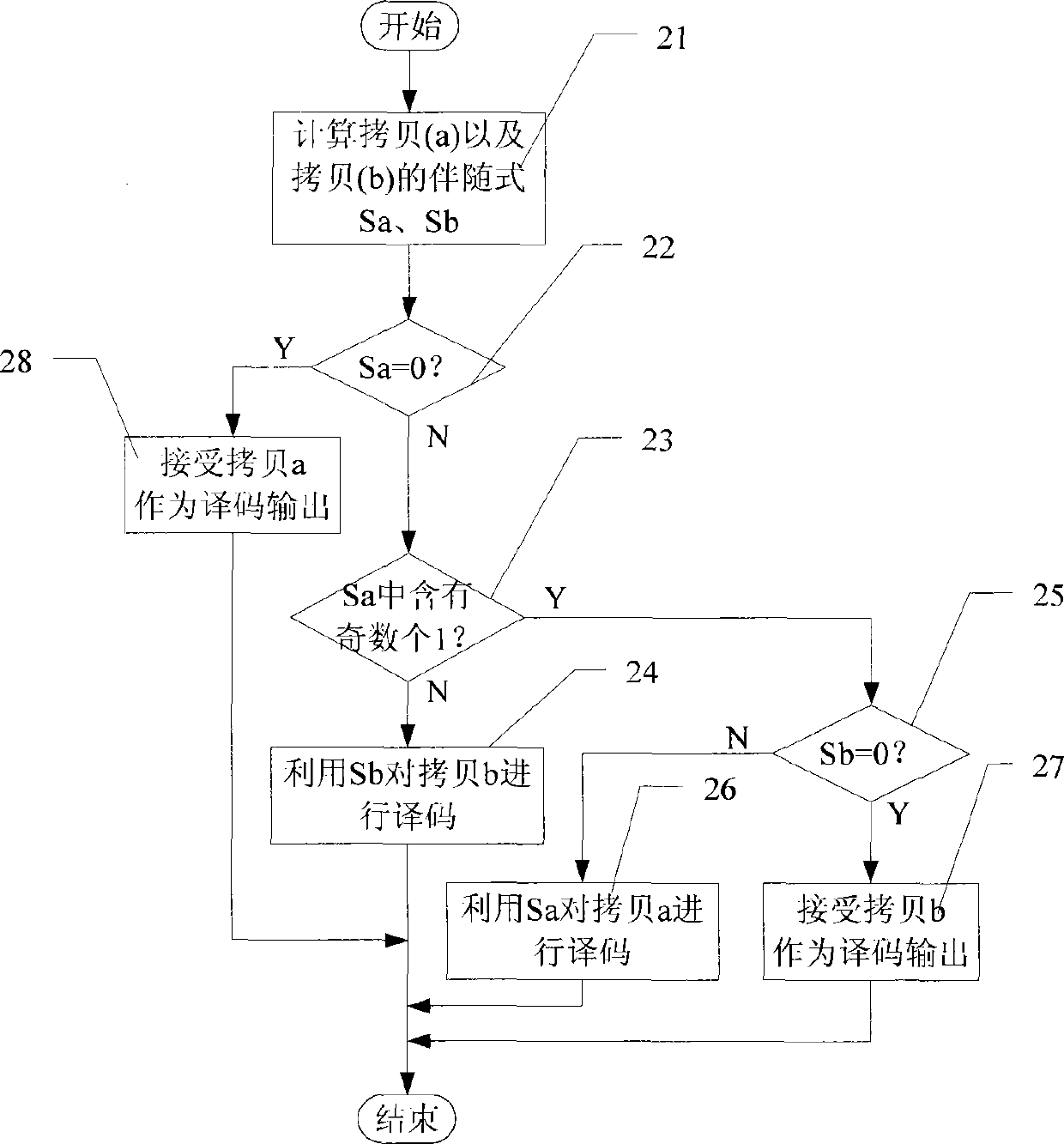

[0015] figure 1The coding block diagram of SEC-DAED-SDAEC+DAP joint code is given. Be 8-bit for the head, the (8, 24) information that data is 24-bit, encoding is divided into two stages, and stage I carries out (8, 24, 6) SEC-DAED-SDAEC encoding in encoding module 11, obtains 38-bit codeword with CAC properties. In order to reduce the bus delay of the codeword, phase II encoding, that is, DAP encoding, is performed. Wherein, in module 13, each information bit is copied to obtain copy a (by a 0 …a 37 Composed of) and copy b15 (consisting of b 0 …b 37 Composition); and the parity bit P0 of the 38-bit code word is appended to the copy a, thereby obtaining the copy a14 of the (8, 24, 7) SEC-DAED-SDAEC code, which is more than the ordinary SEC-DAED-SDAEC 1bit parity bit. Since SEC-DAED-SDAEC has 2-bit error correction capability for the header part of the packet and 1-bit error correction capability for the data part, the Hamming dista...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More