Patents

Literature

197results about How to "Increase system cost" patented technology

Efficacy Topic

Property

Owner

Technical Advancement

Application Domain

Technology Topic

Technology Field Word

Patent Country/Region

Patent Type

Patent Status

Application Year

Inventor

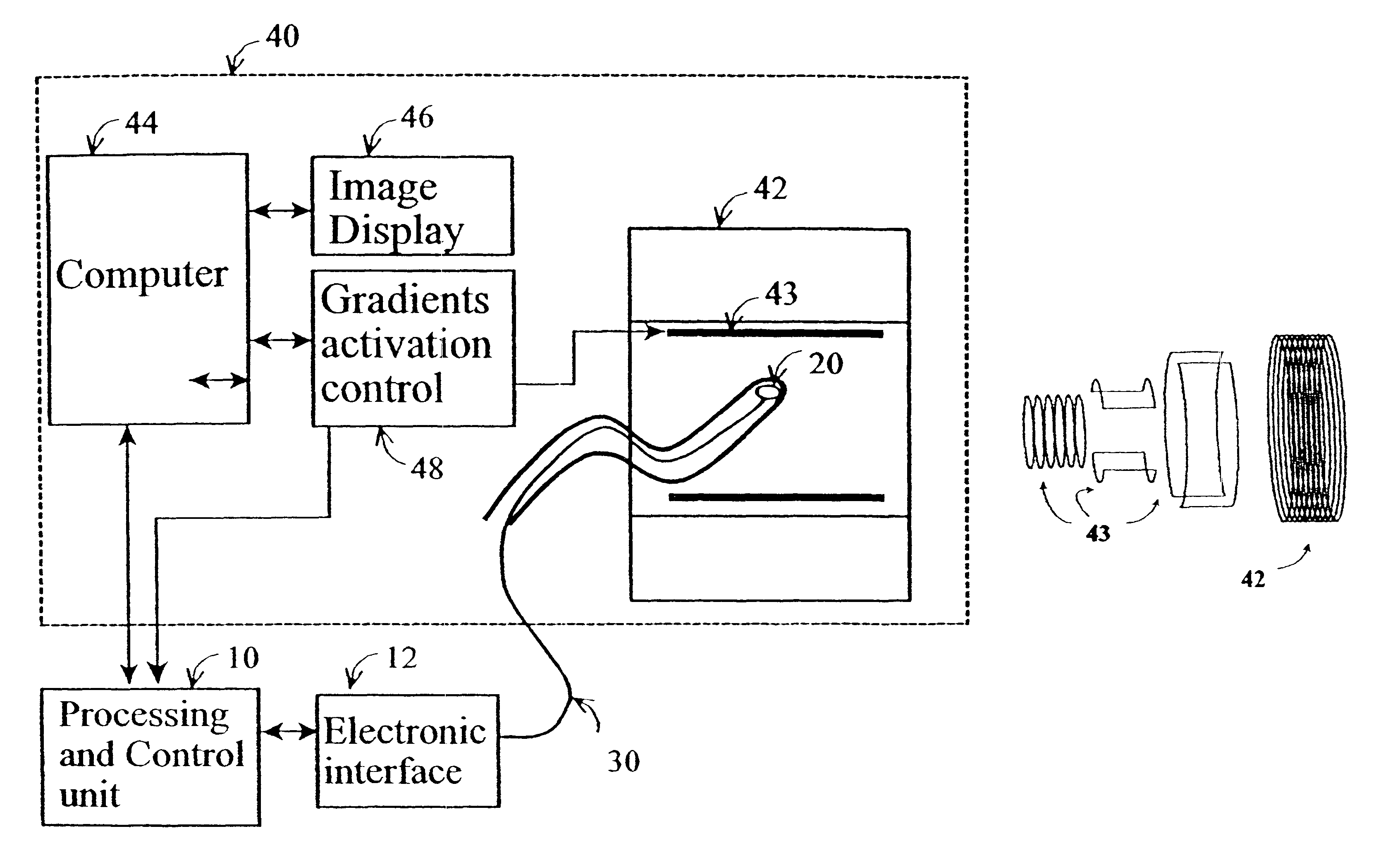

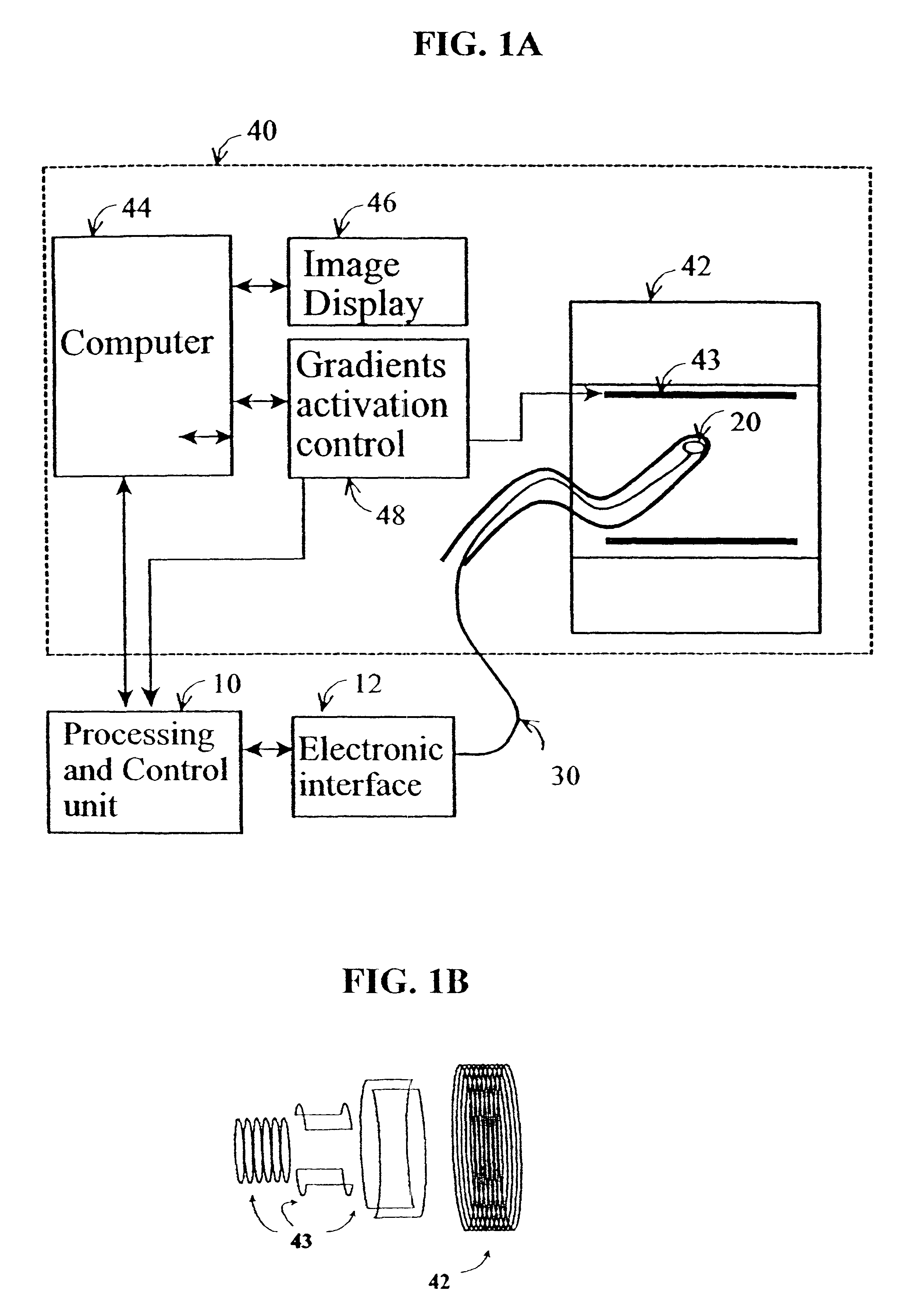

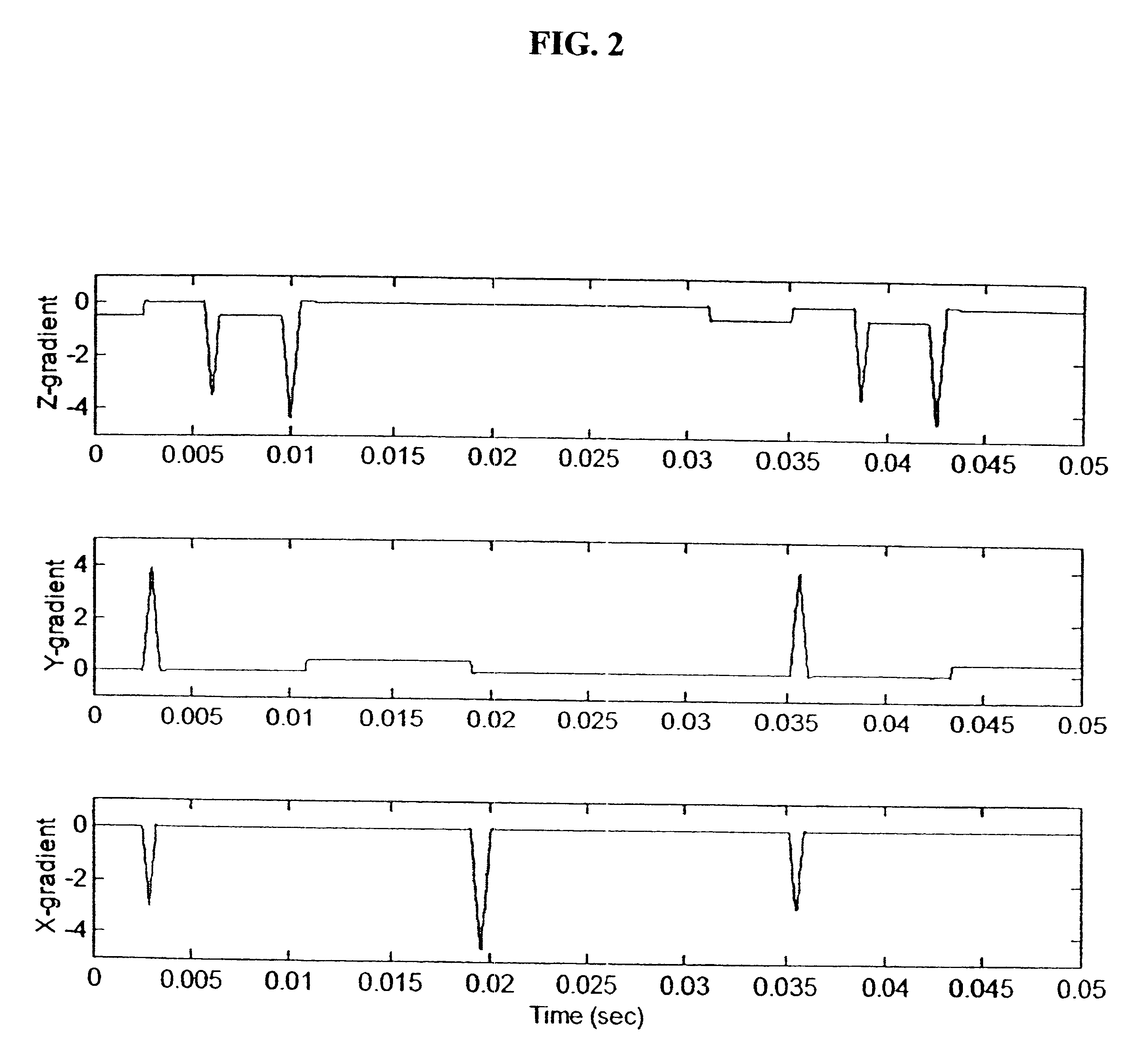

Method and apparatus to estimate location and orientation of objects during magnetic resonance imaging

InactiveUS6516213B1Limited accuracy of orientationSatisfies requirementDiagnostic recording/measuringSensorsMagnetic field gradientThree-dimensional space

Method and apparatus for determining the instantaneous location, the orientation of an object moving through a three-dimensional space by applying to the object a coil assembly including a plurality of sensor coils (20) having axes of known orientation with respect to each other including components in the three orthogonal planes; generating a time-varying, three-dimensional magnetic field gradient having known instantaneous values of magnitude and direction; applying the magnetic field gradient to the space, and object moving therethrough to induce electrical potentials in the sensor coils; measuring the instantaneous values of the induced electrical potentials generated in the sensor coils; processing the measured instantaneous values generated in the sensor coils together with the known magnitude, direction of the generated magnetic field gradient, the known relative orientation of the sensor coils in the coil assembly to compute the instantaneous location, orientation of the object within the space.

Owner:ROBIN MEDICAL

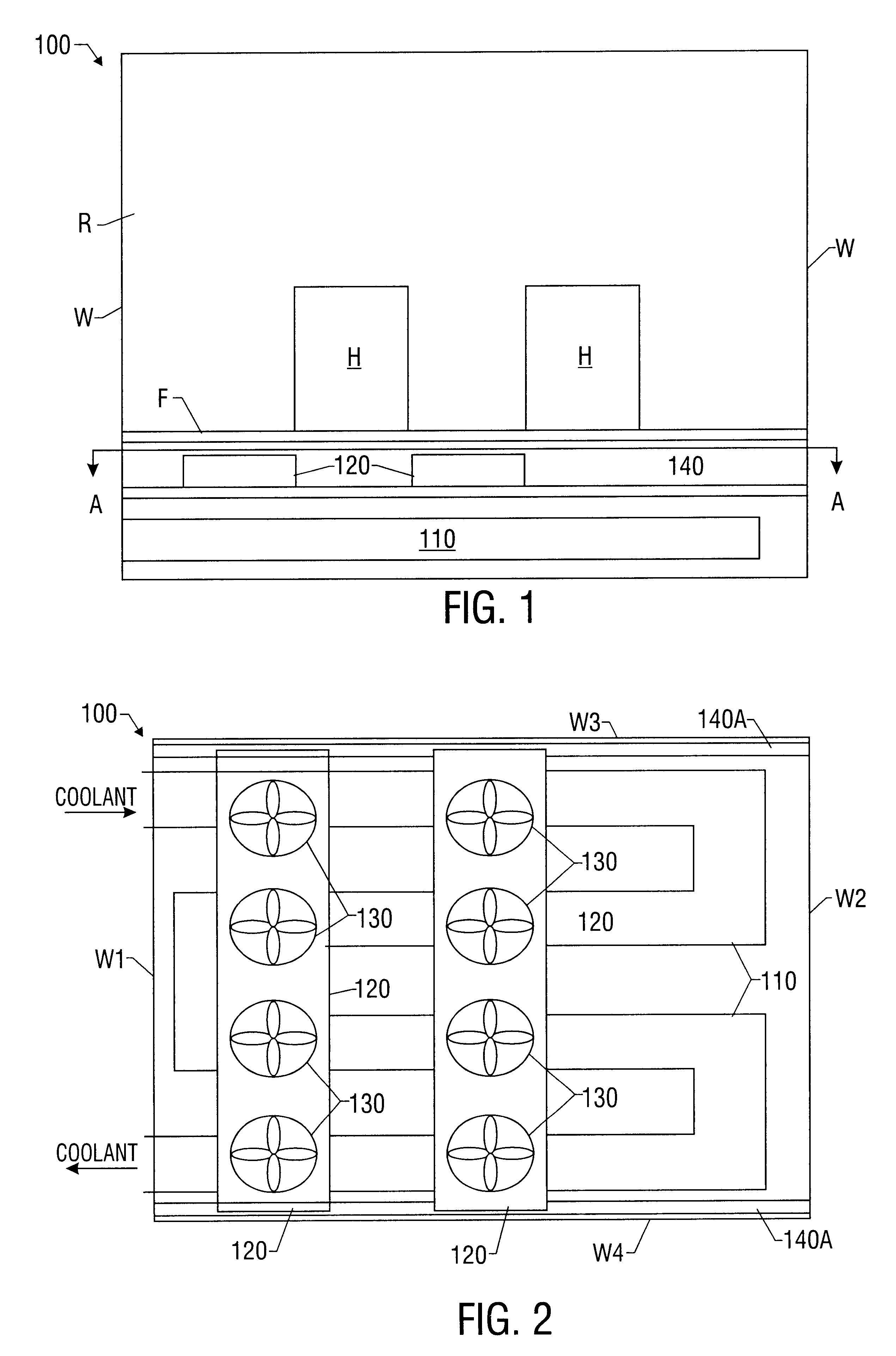

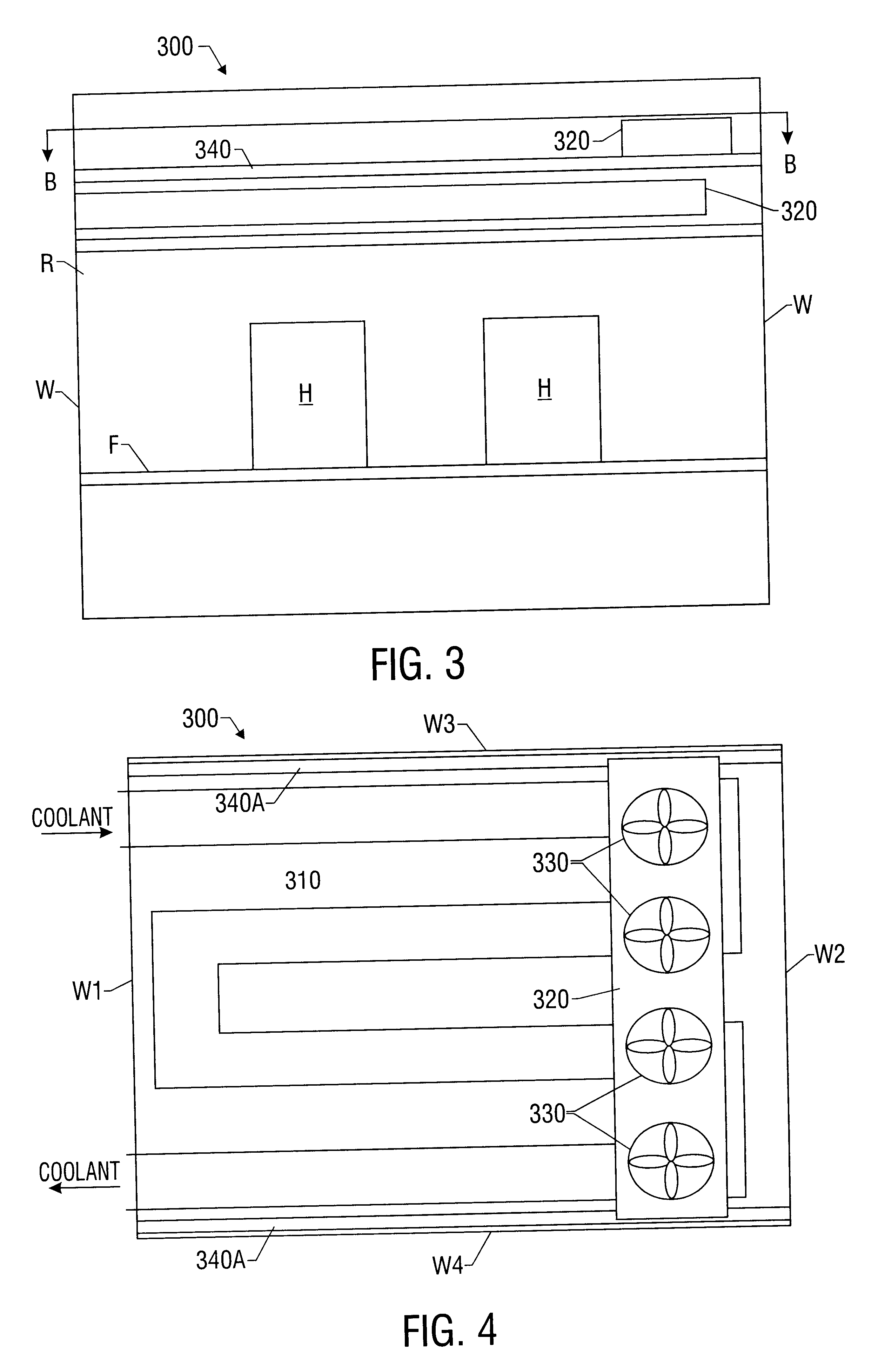

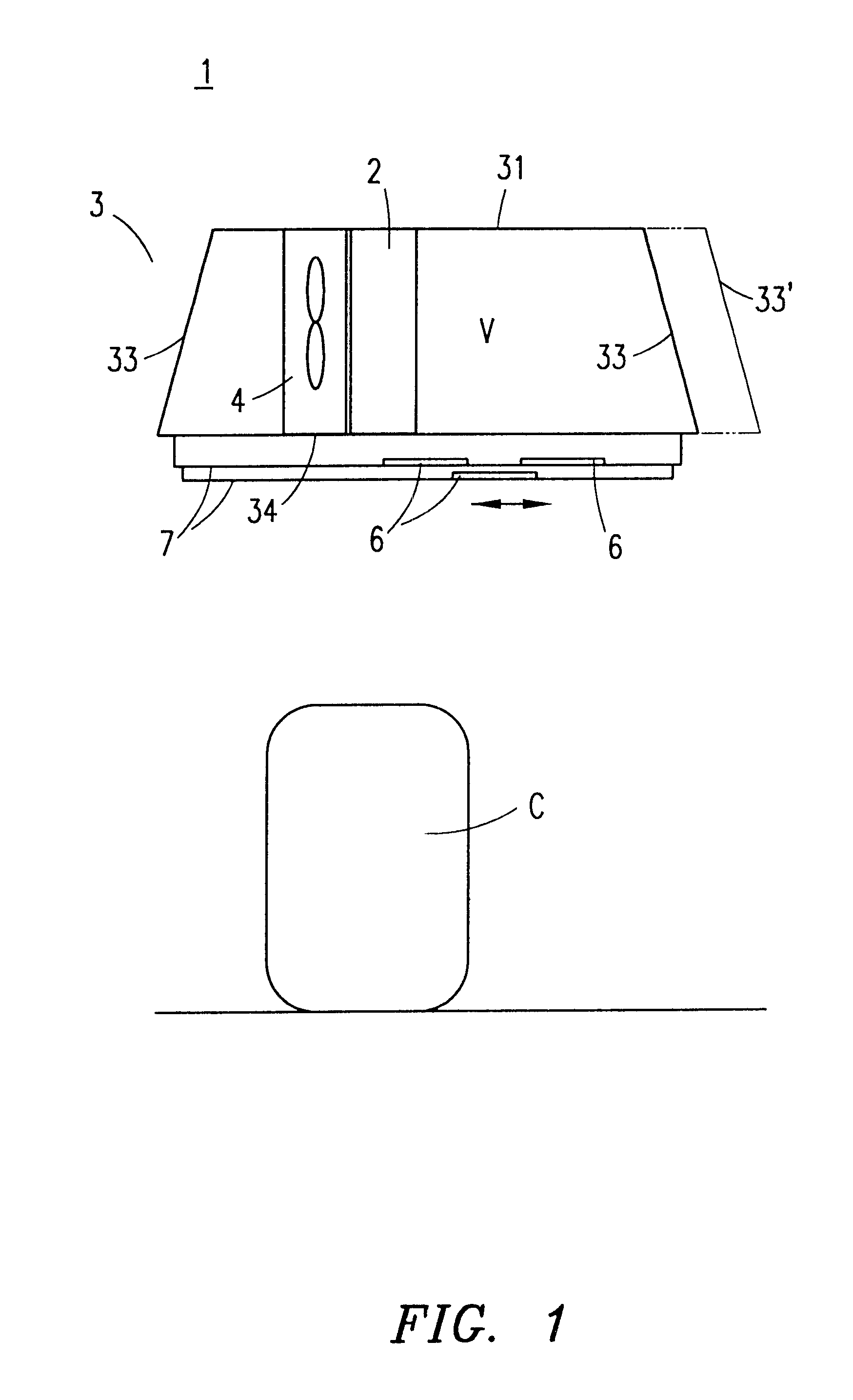

Configurable system and method for cooling a room

InactiveUS6557624B1Improve efficiencyReduce air pressureMechanical apparatusHot-air central heatingNuclear engineeringConfigurable systems

A method and system are disclosed for cooling a room having one or more heat generating objects. A number of heat exchangers are disposed adjacent a floor or ceiling and extends substantially entirely or partially between the walls of the room. A fan unit is disposed adjacent the heat exchanger and draws or blows cooled air from the heat exchanger and directs the drawn air into the room. The fan unit is capable of being repositioned along a different portion of the heat exchanger so as to redefine the flow of cooled air into the room. The cooling system components are modularized enabling configuration of a number of components to cool a room.

Owner:VERTIV CORP

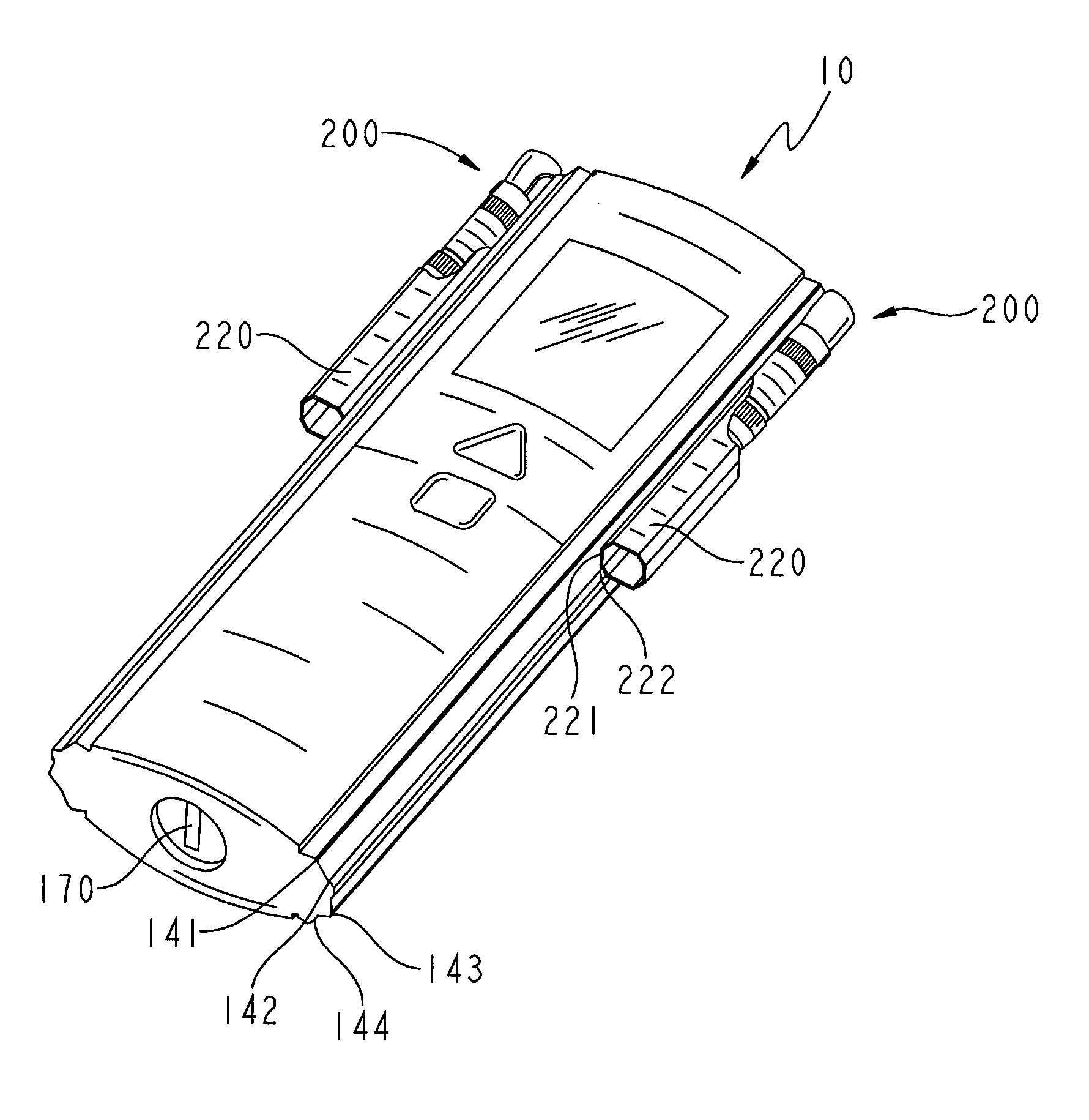

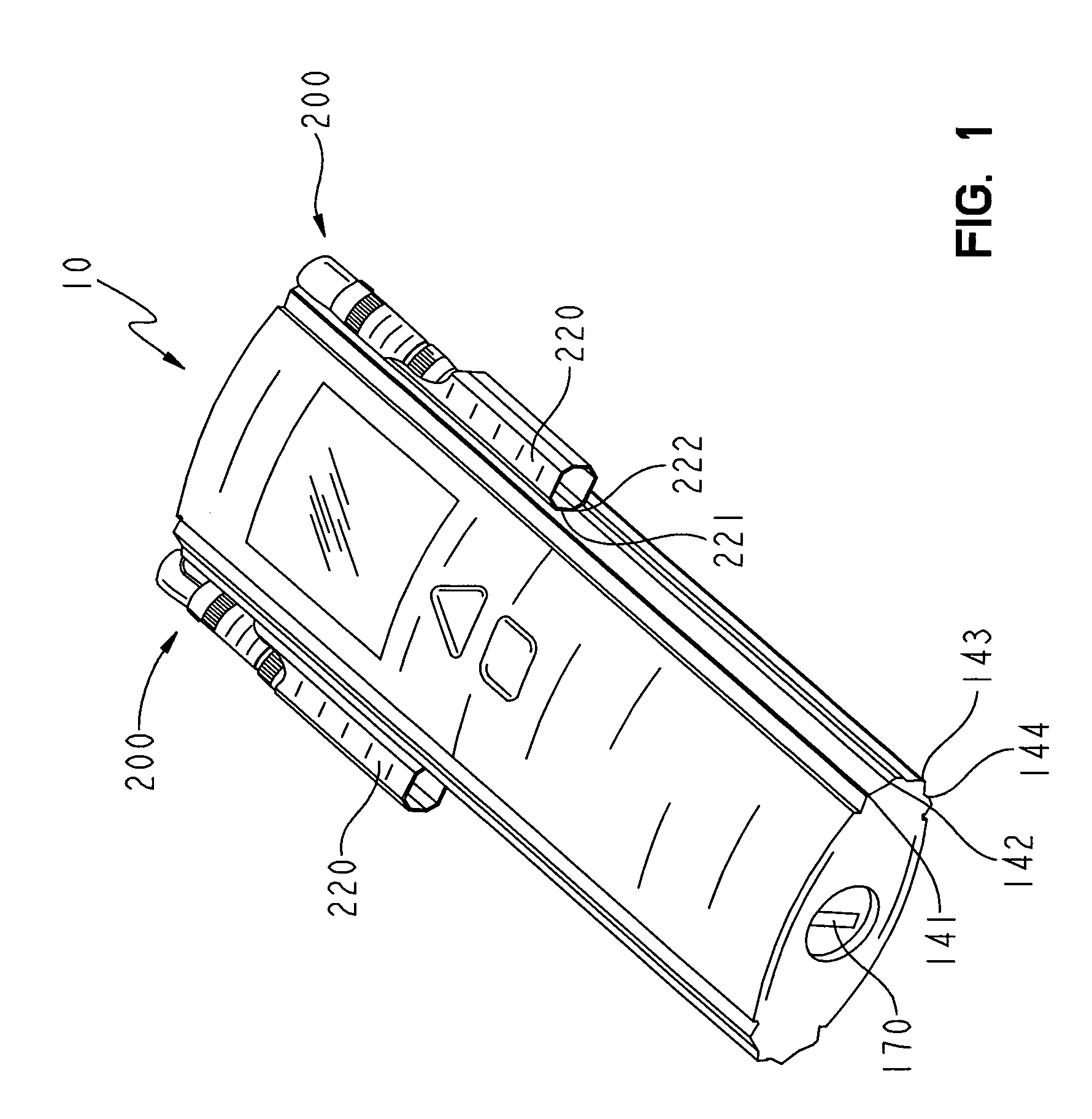

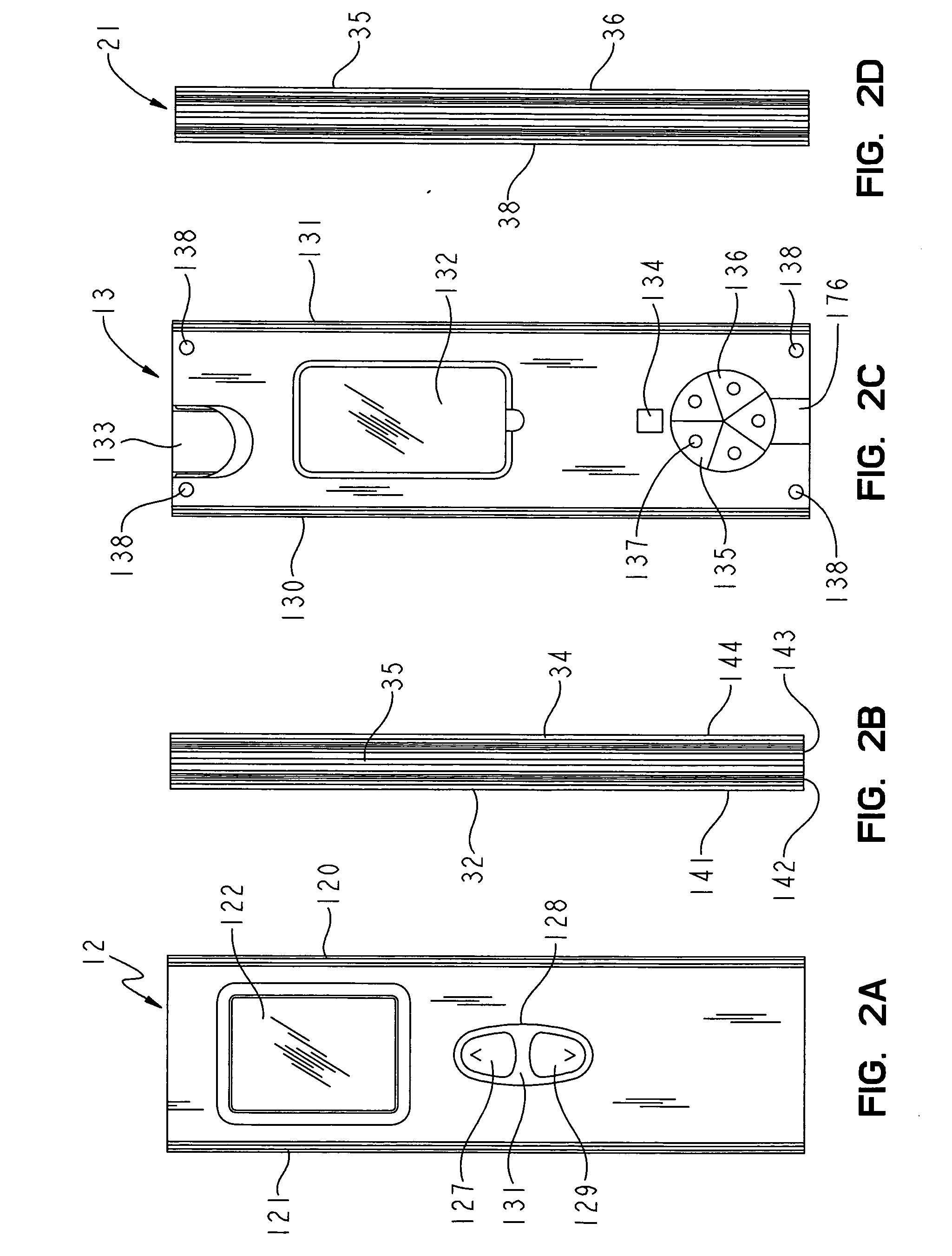

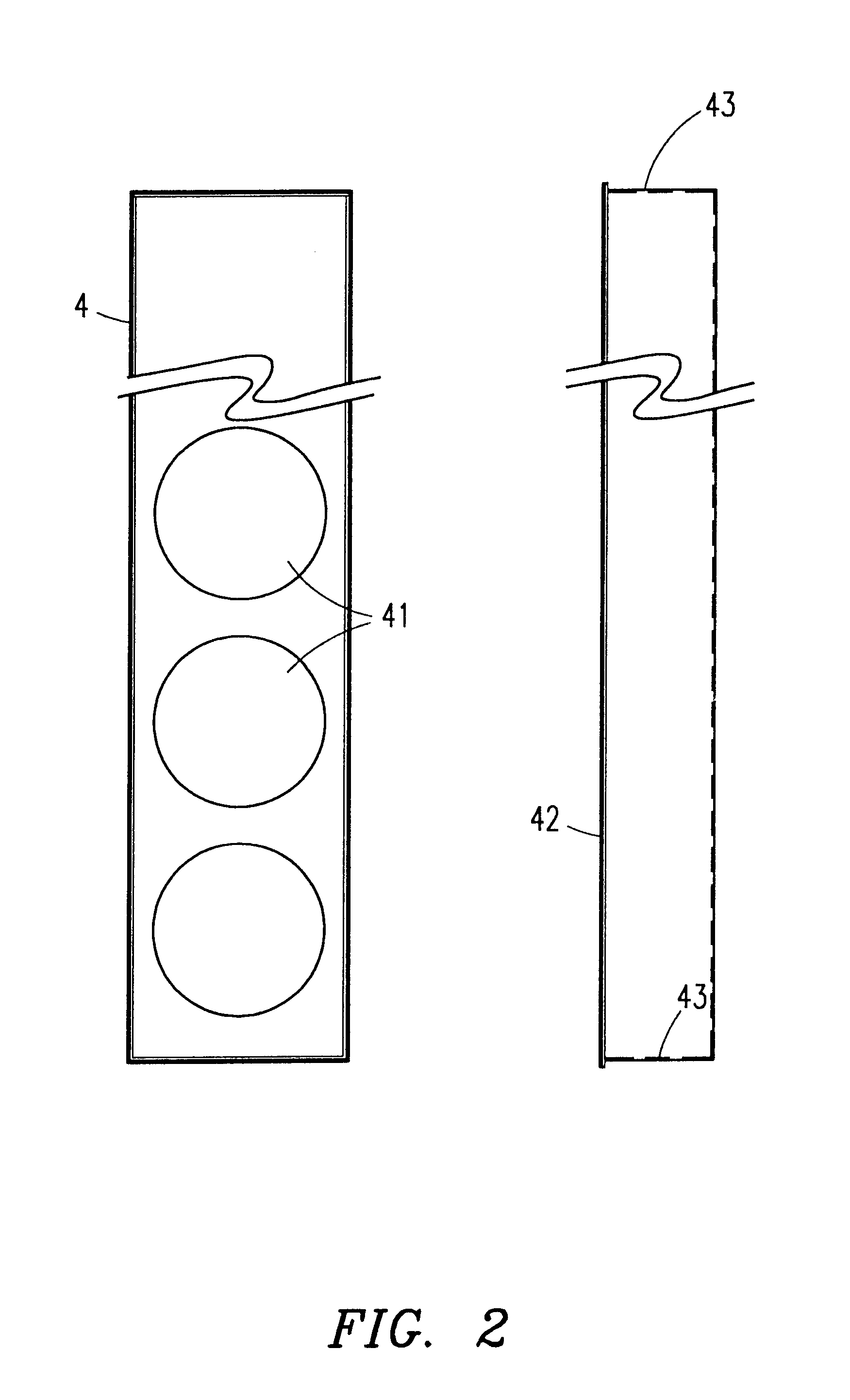

Methods and apparatus for analyzing an analysis fluid

InactiveUS20060034728A1Minimal surface areaIncreased background noiseAnalysis using chemical indicatorsMicrobiological testing/measurementEngineeringMechanical engineering

A meter and test wand system is capable of cooperatively processing an analysis fluid and communicating results to a user. The system includes a meter case including a case front, a case back, a case top, a case bottom, a first case side member, and a second case side member. The first and second case side members connect the case front to case back. The first case side member has a longitudinal dimension between said case top and said case bottom and a latitudinal dimension between said case front and said case back. The first case side member includes a first case ridge; A test wand is capable of receiving an analysis fluid, and includes a cartridge including a cartridge ridge. The cartridge ridge is sized and shaped to matingly engage with said first case ridge to connect said test wand to said meter case.

Owner:KLOEPFER DR HANS

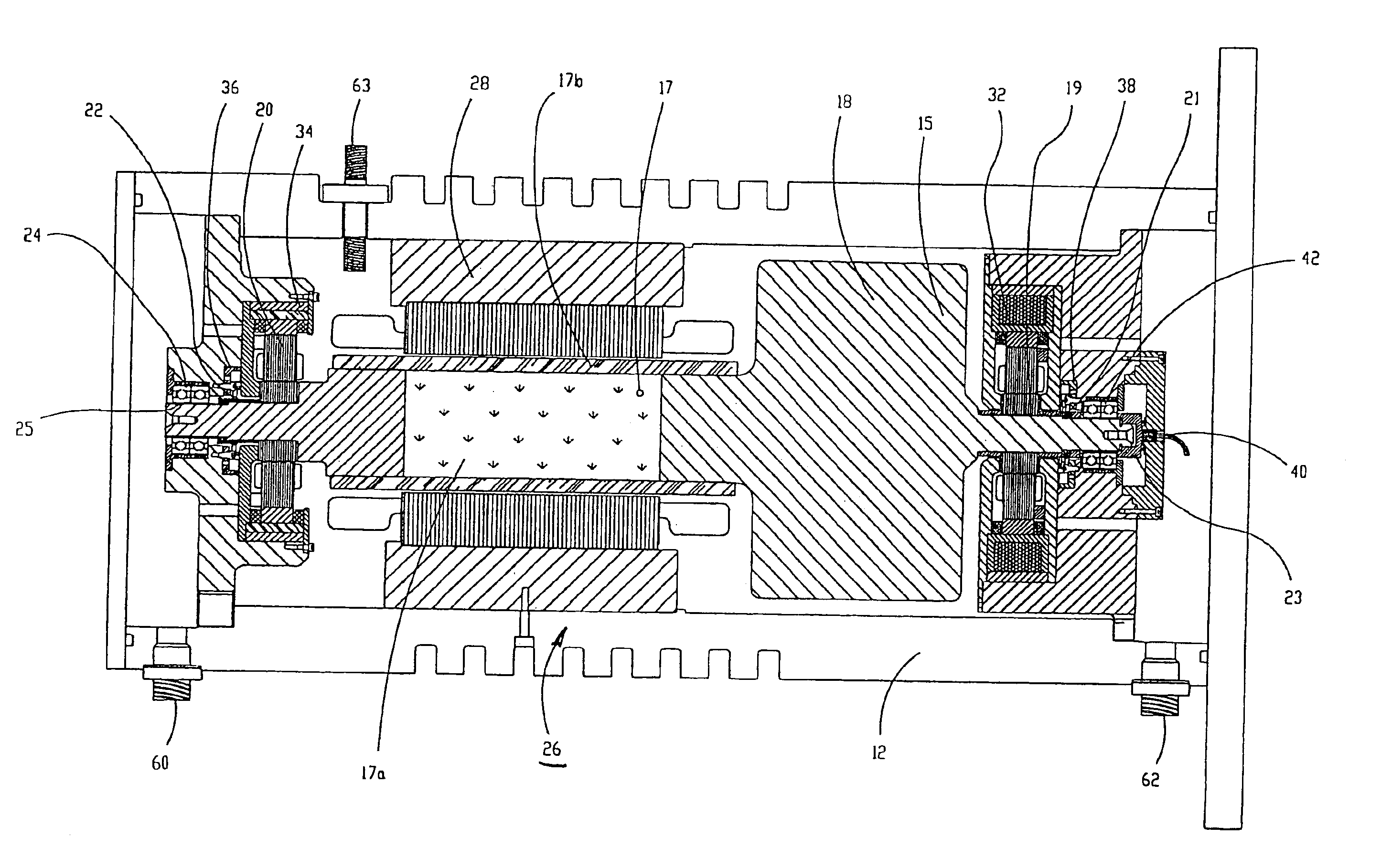

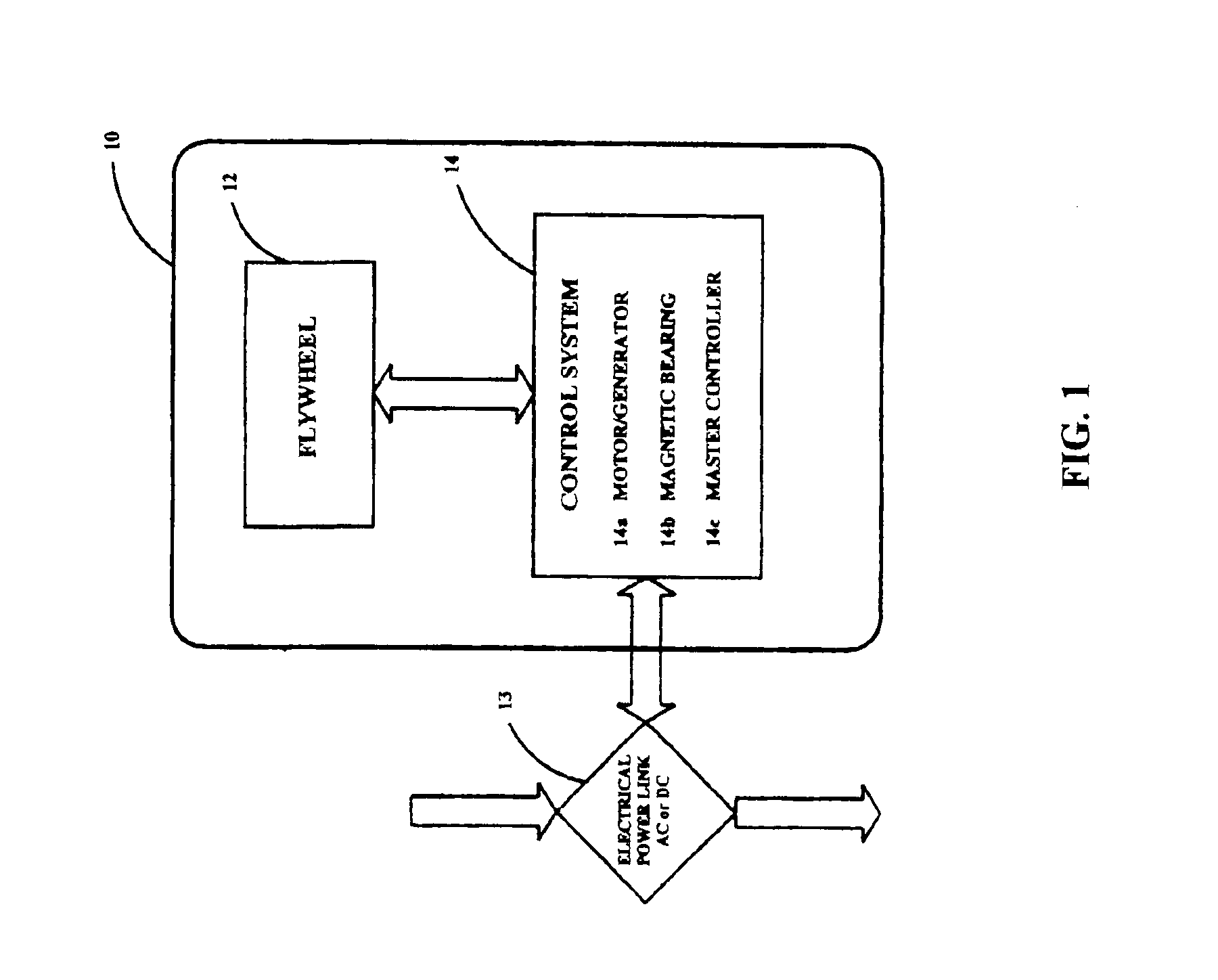

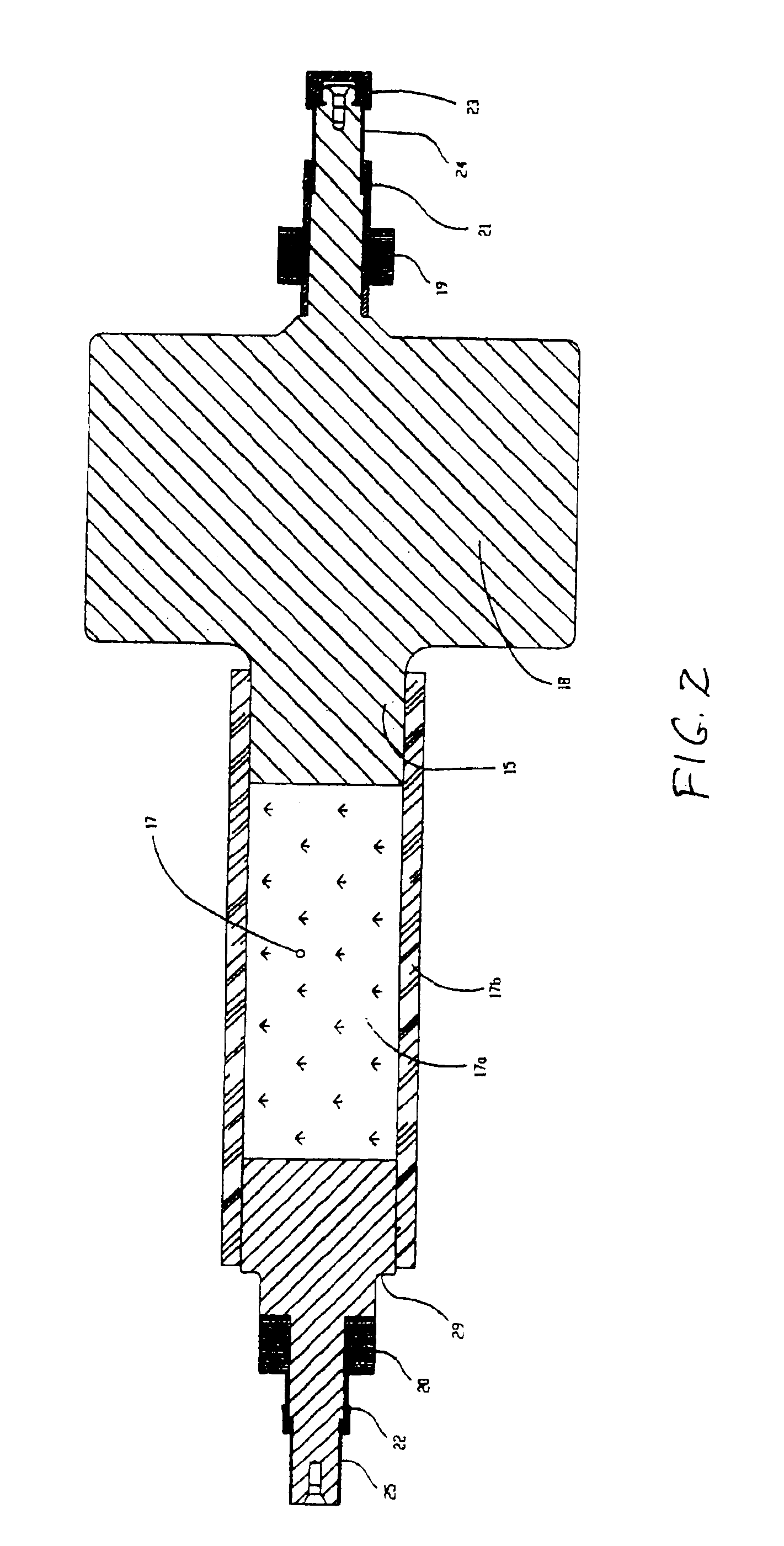

Energy storage flywheel with minimum power magnetic bearings and motor/generator

InactiveUS6897587B1Minimum rotor lossLow maintenanceMagnetic circuit rotating partsEngine componentsFlywheel energy storage systemAutomotive engineering

An optimized flywheel energy storage system utilizing magnetic bearings, a high speed permanent magnet motor / generator, and a flywheel member. The flywheel system is constructed using a high strength steel wheel for kinetic energy storage, high efficiency magnetic bearings configured with dual thrust acting permanent magnet combination bearings, and a high efficiency permanent magnet motor generator. The steel wheel provides a cost effective, high speed construction for the energy storage rotor.

Owner:VYCON ENERGY INC

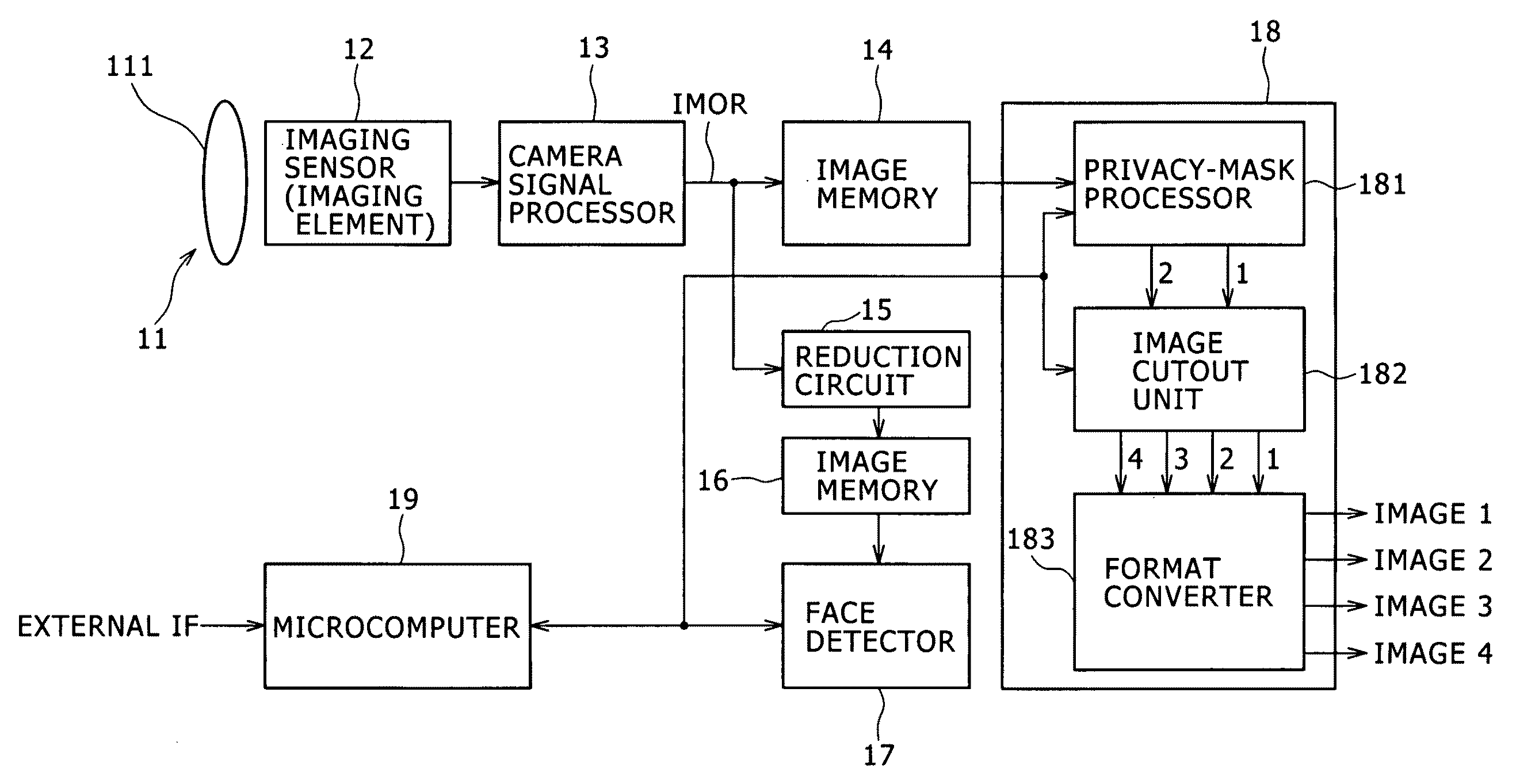

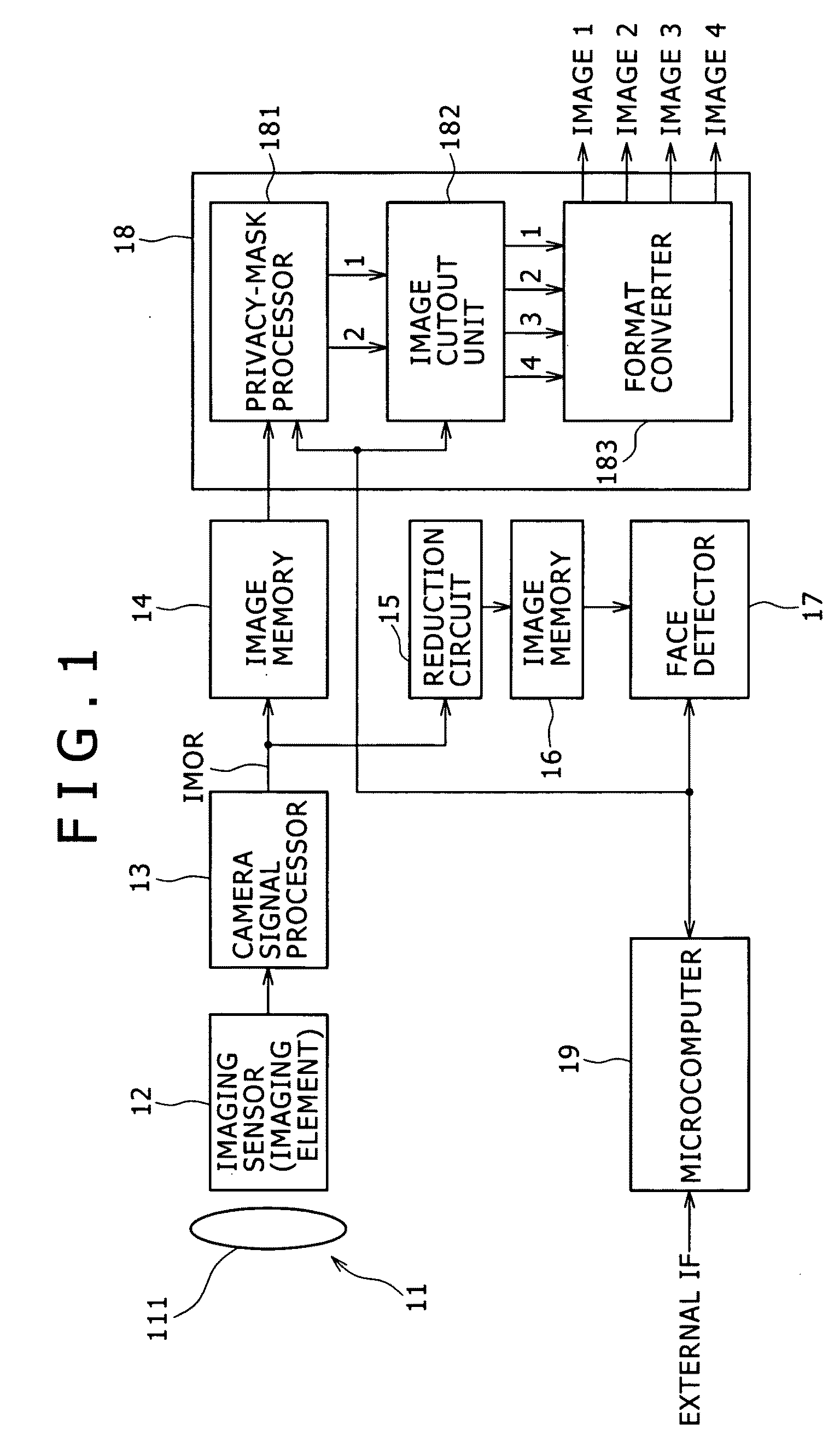

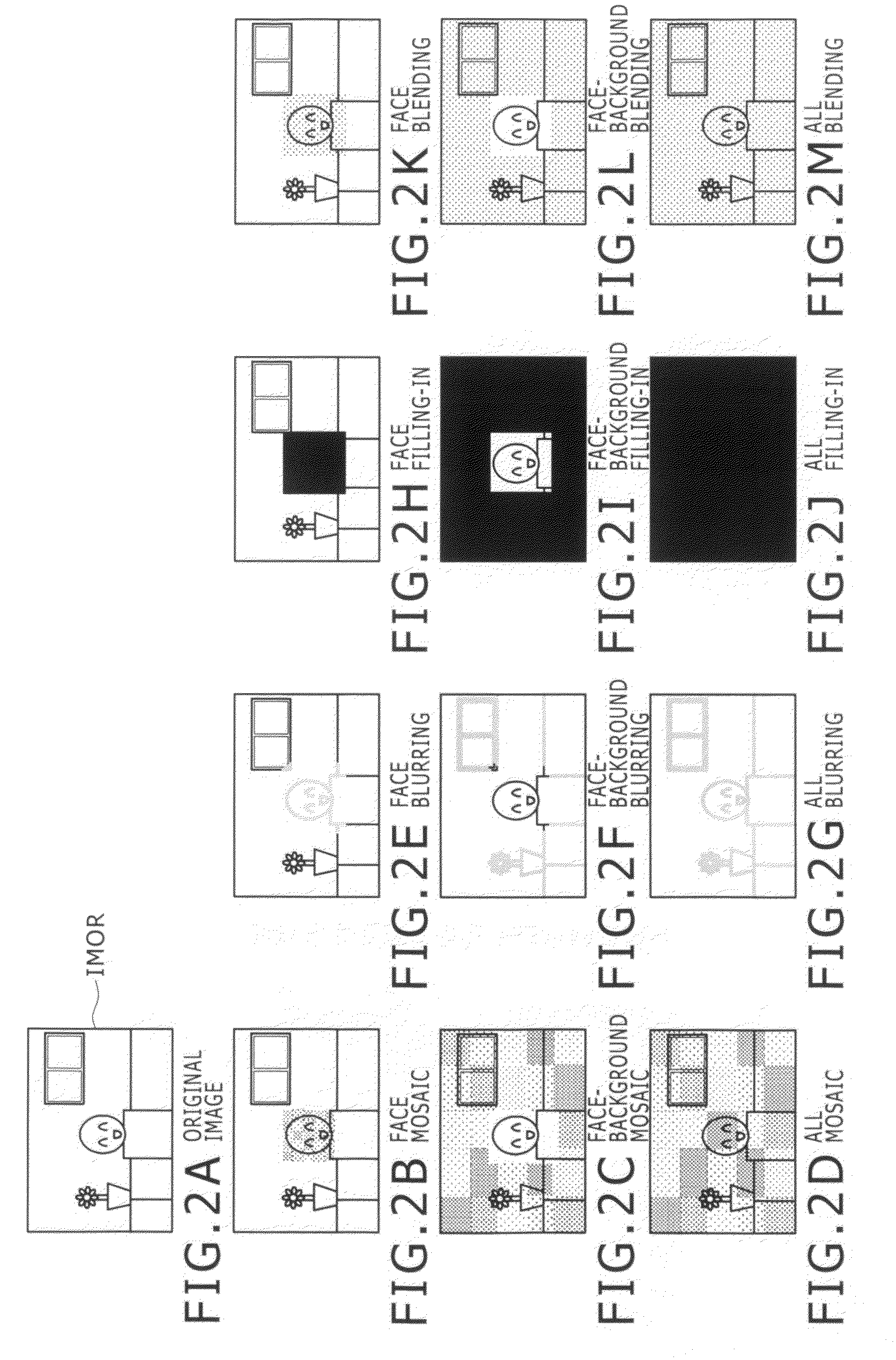

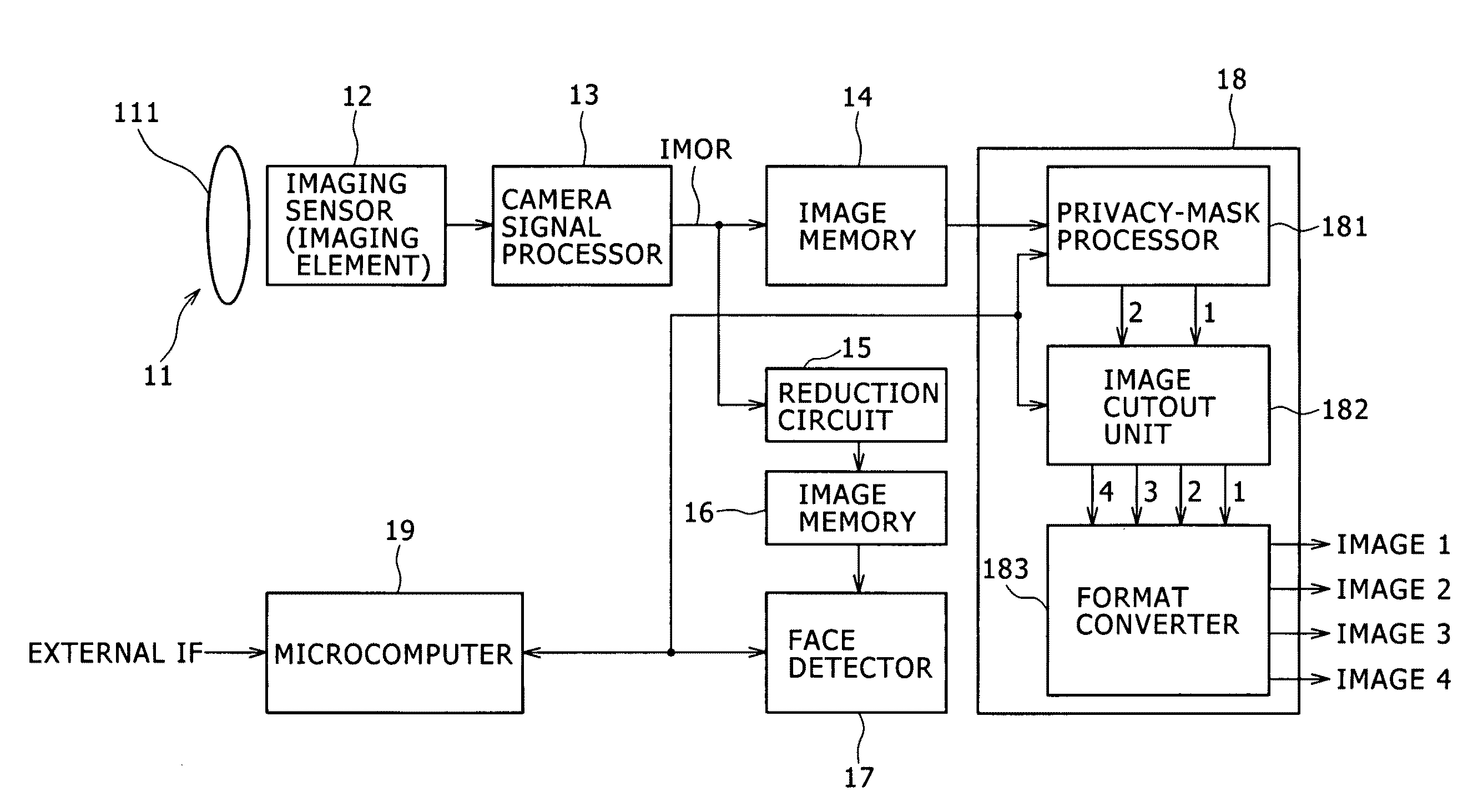

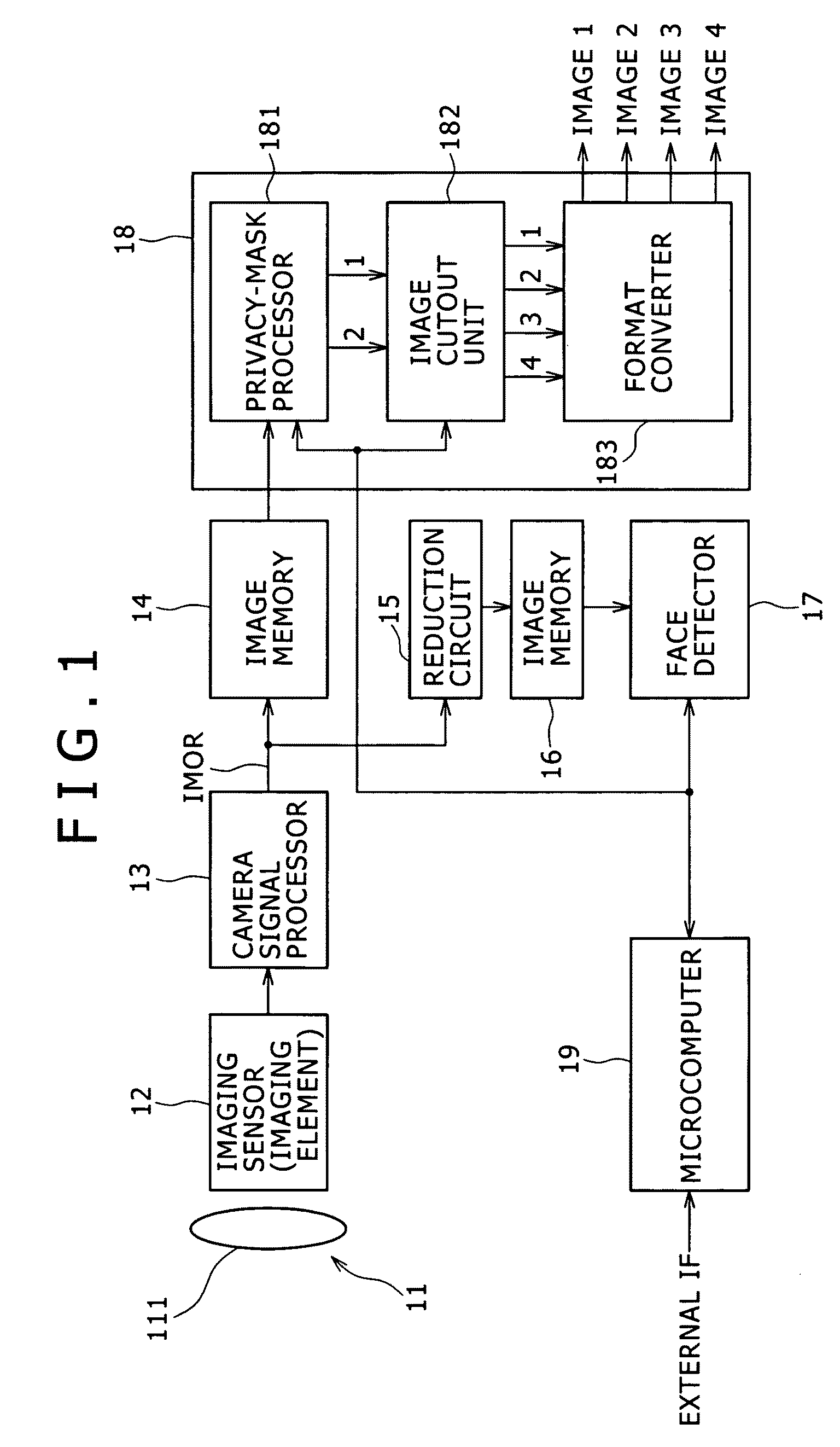

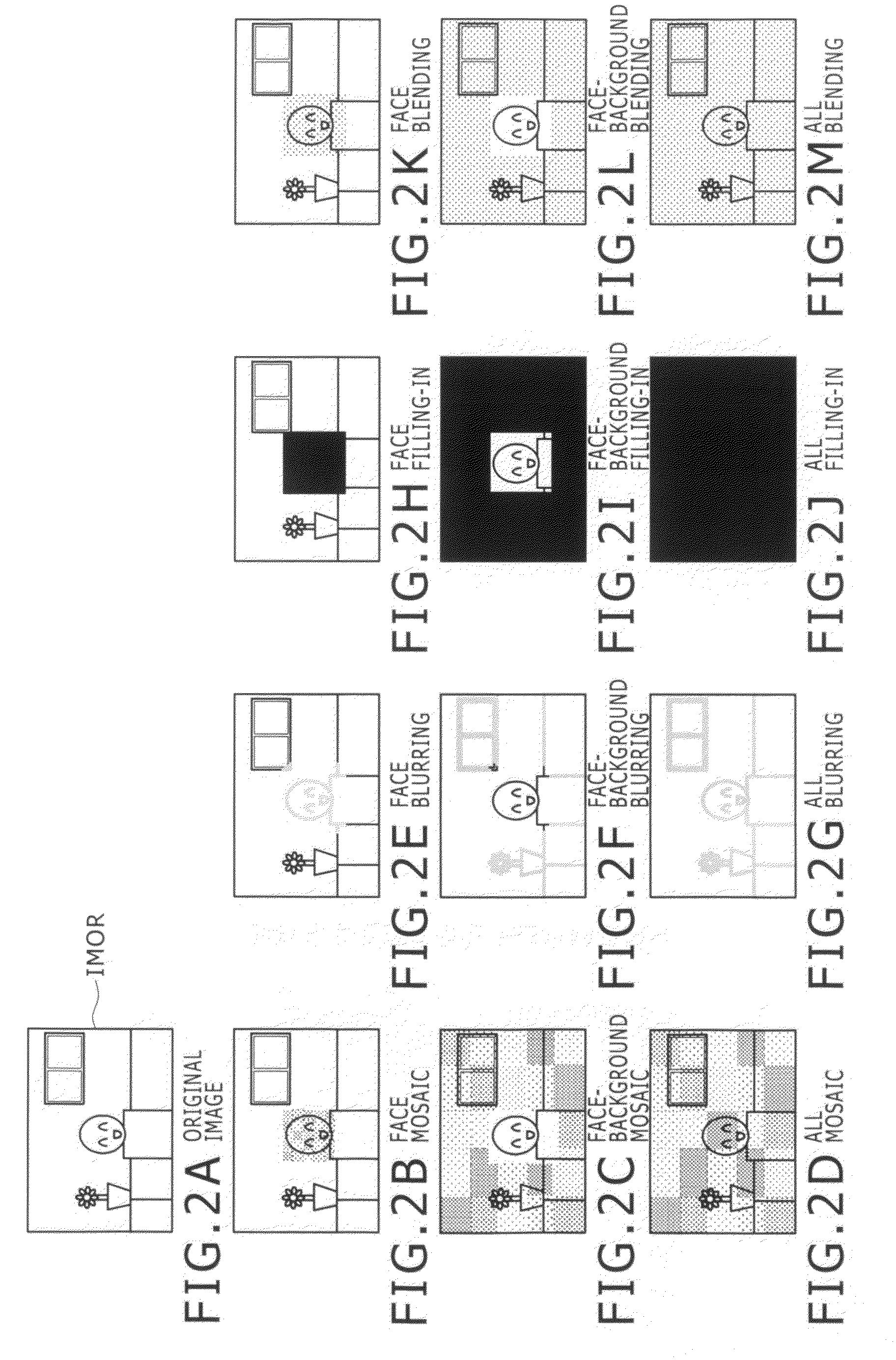

Image processing device, camera device, communication system, image processing method, and program

ActiveUS20090207269A1Reduce latencyReduce loadTelevision system detailsCharacter and pattern recognitionPattern recognitionCommunications system

An image processing device includes a face detector configured to detect a face based on a taken image, and an output processor configured to have a function to execute privacy-mask processing for privacy protection for an image of a face detected by the face detector or an image of a background of the face. The output processor includes a function to separately output an image of a face detected by the face detector and an image of a background of the face which are each subjected to or not subjected to the privacy-mask processing.

Owner:SONY SEMICON SOLUTIONS CORP

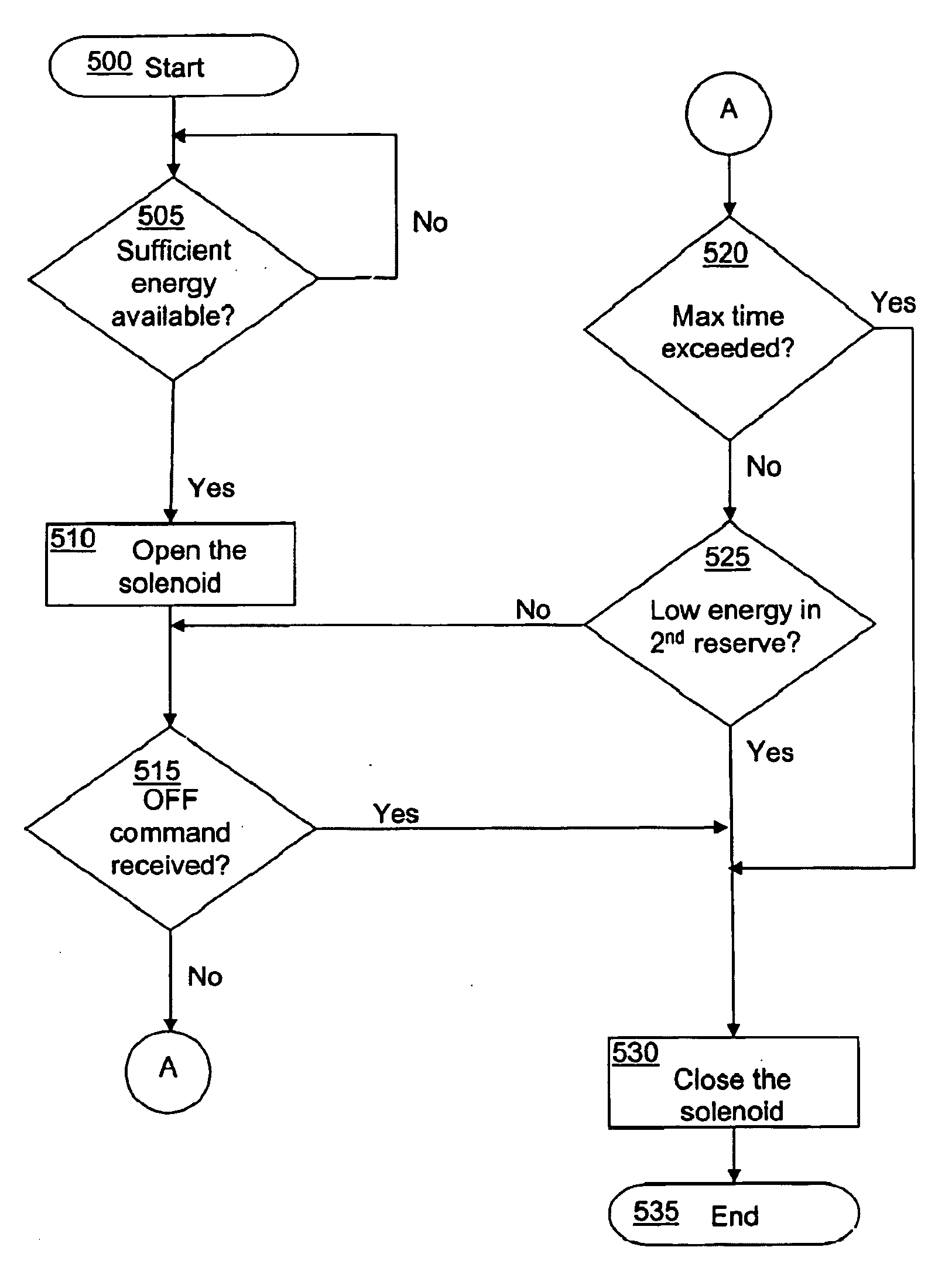

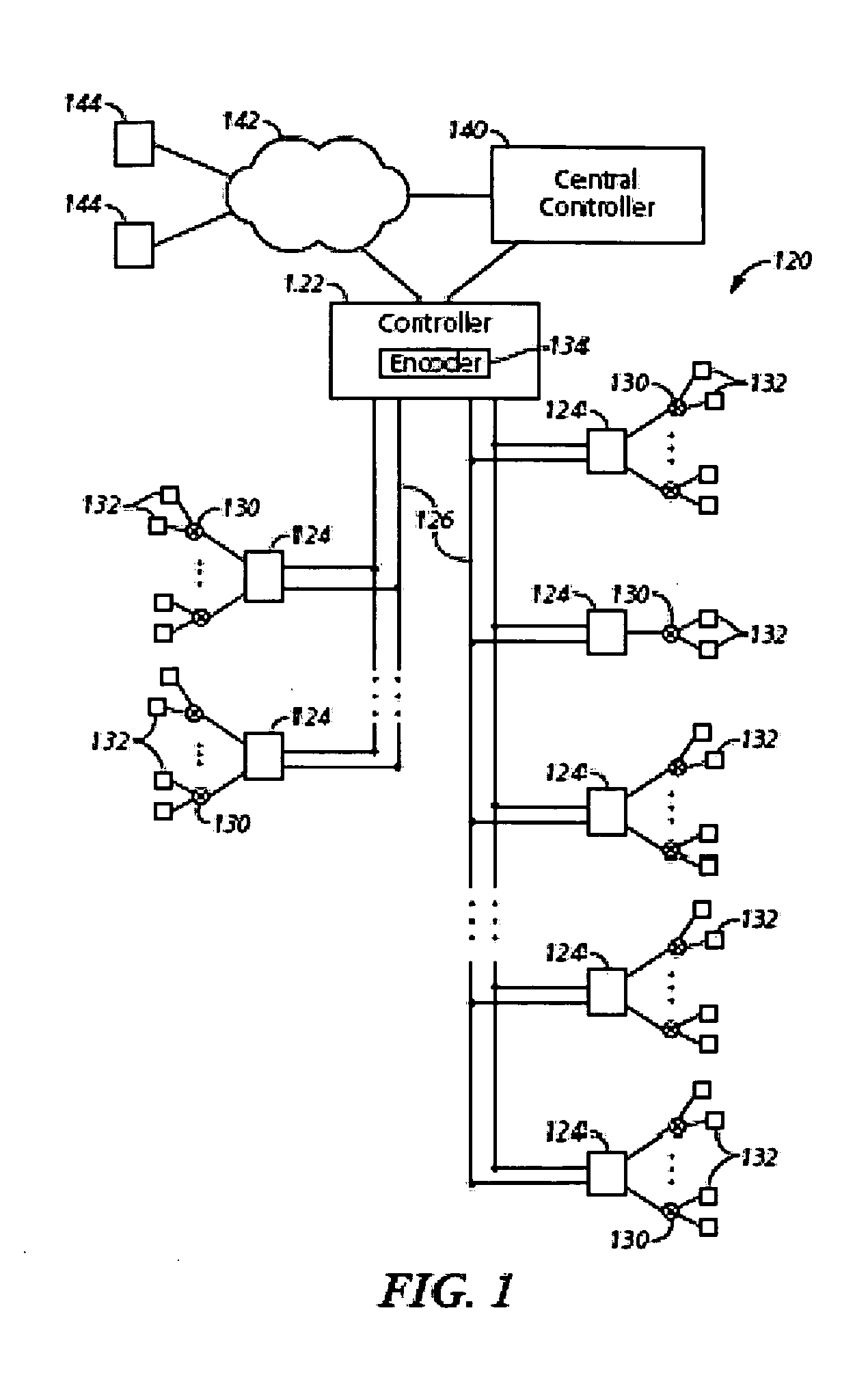

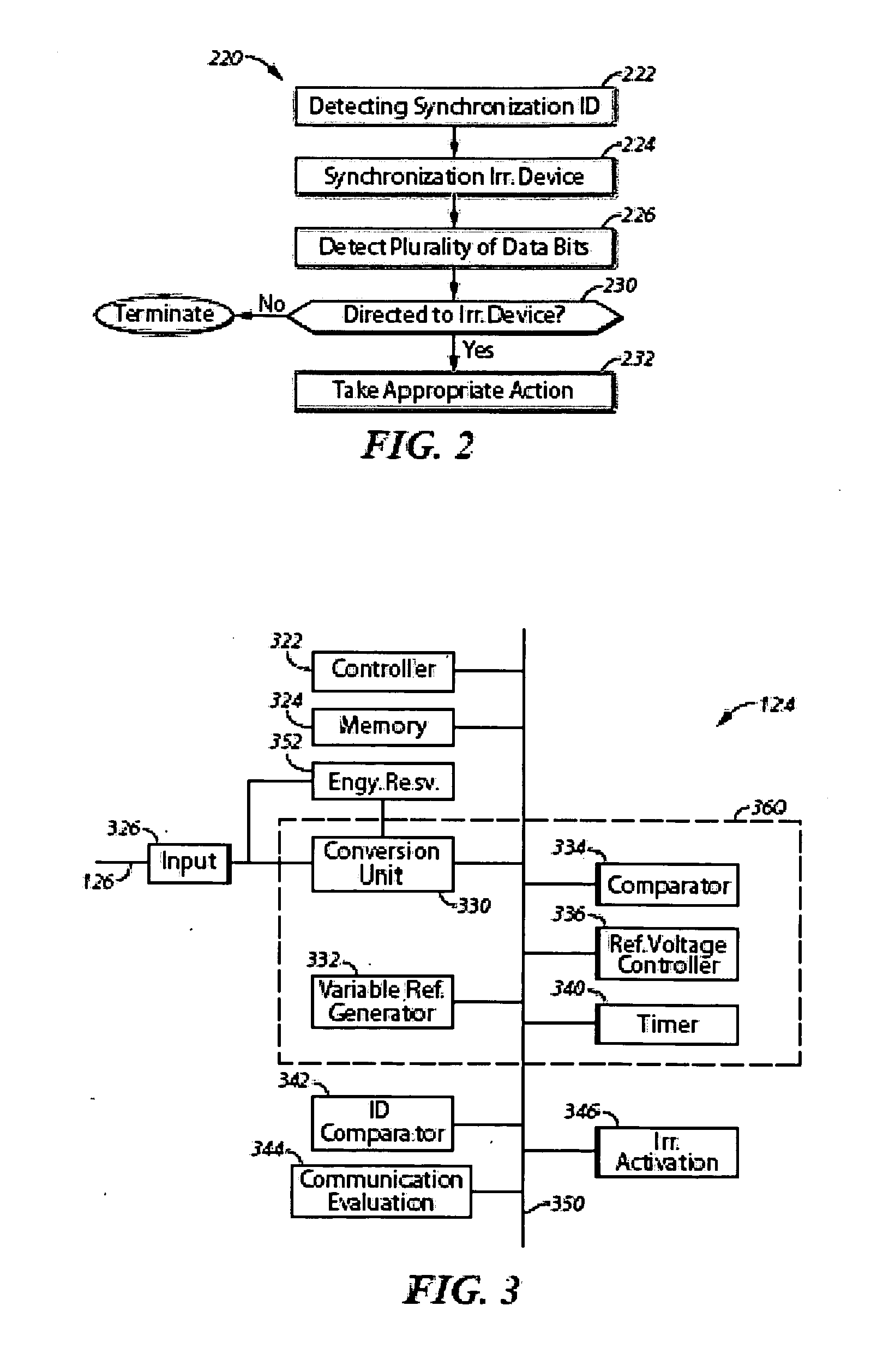

Latching solenoid energy reserve

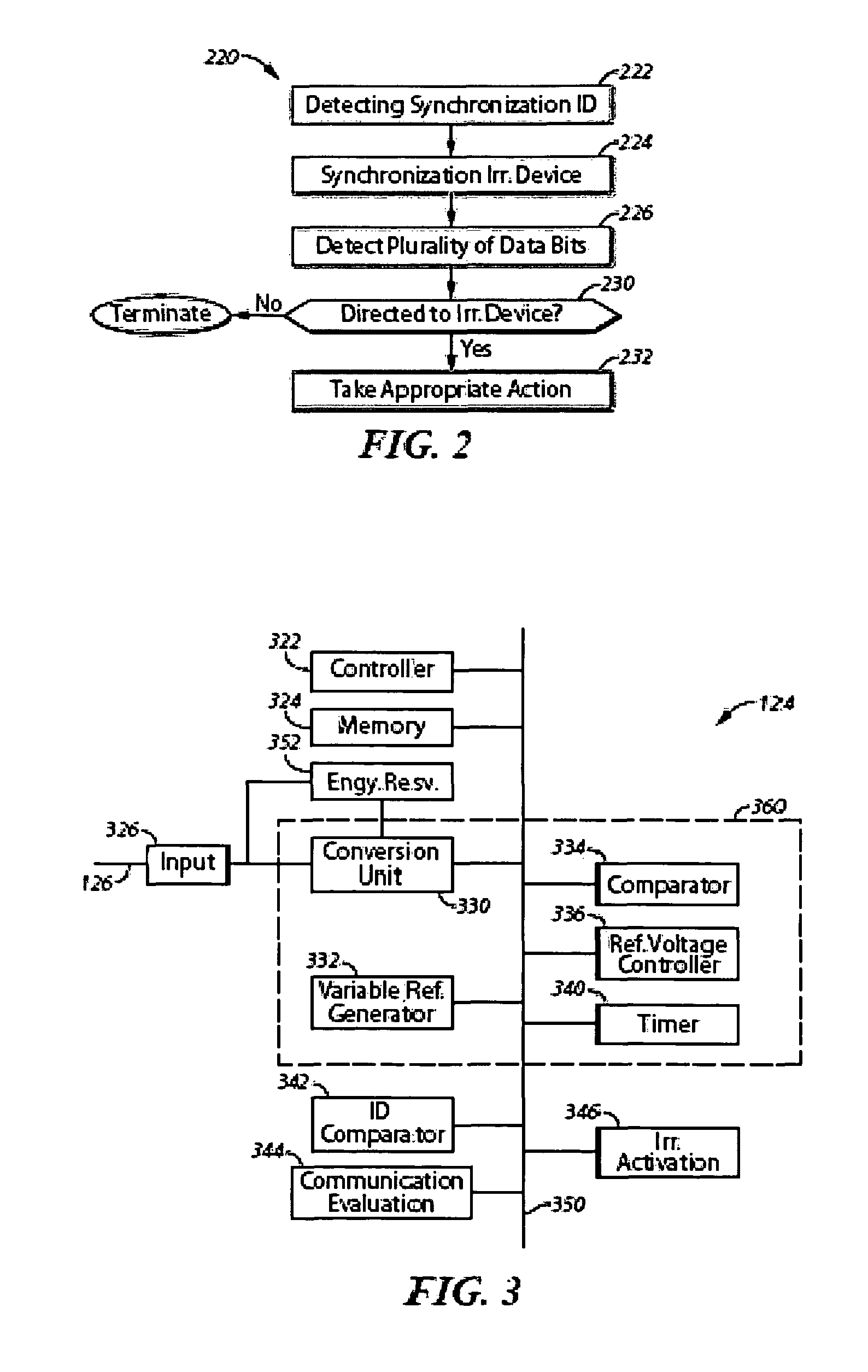

ActiveUS20100161144A1Increase system costSmall power demandOperating means/releasing devices for valvesWatering devicesStored energySolenoid valve

An irrigation device including an actuator configured to control water flow to at least one water delivery device, a first stored energy source configured to power the actuator to effect irrigation via the at least one water delivery device, and a second stored energy source which is separate from the first stored energy source, wherein the second stored energy source is configured to power the actuator to terminate the irrigation via the at least one water delivery device. The irrigation devices further includes a controller configured to cause the first stored energy source to power the actuator to effect the irrigation, responsive to an instruction to provide irrigation, and to cause the second stored energy source to power the actuator to terminate the irrigation responsive to a termination condition.

Owner:RAIN BIRD CORP

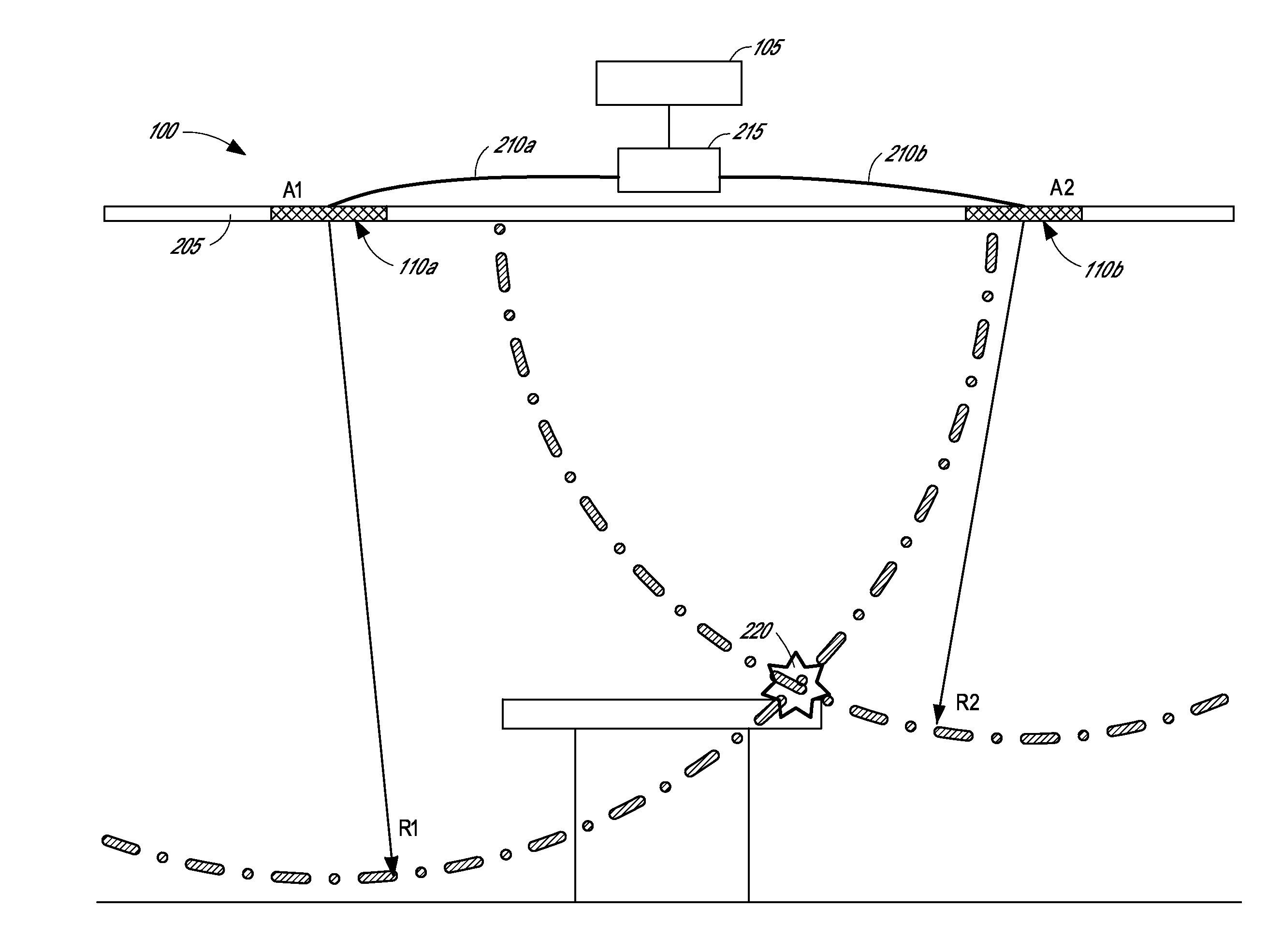

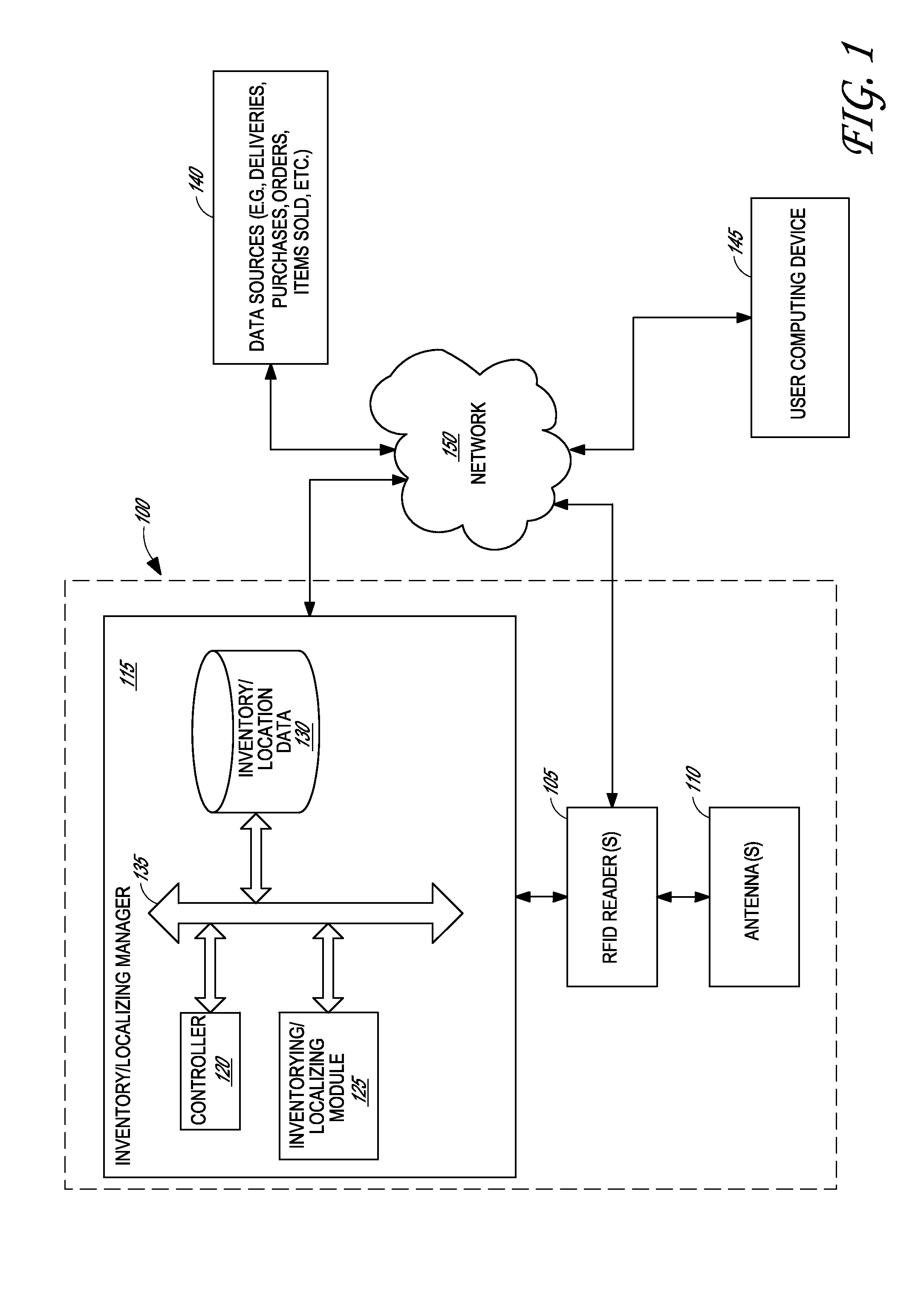

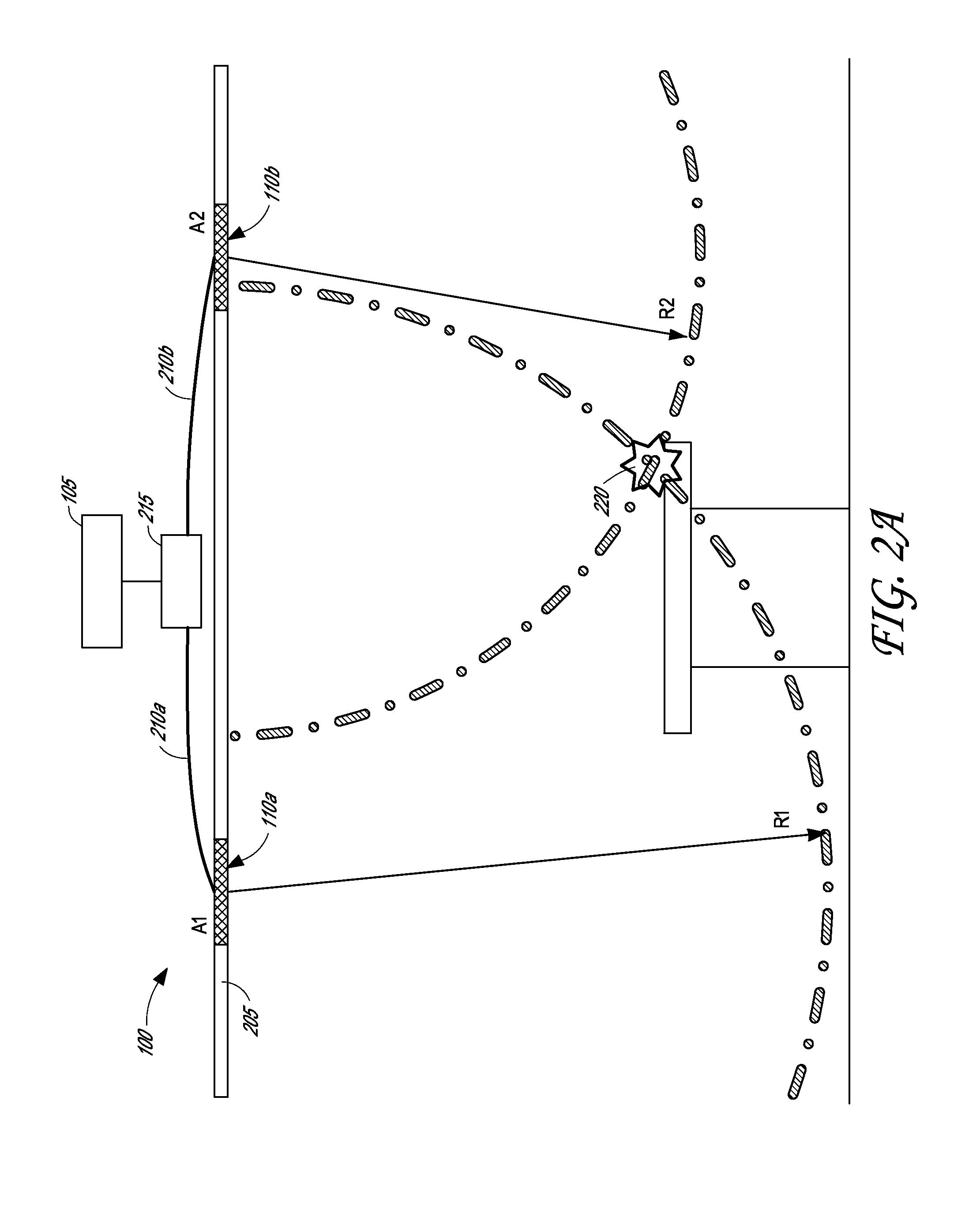

Overhead antenna live inventory locating system

InactiveUS20140361078A1Reduce stepsReduce distanceLogisticsCommerceEmbedded systemPositioning system

Overhead antenna live inventory locating systems and methods are provided. The overhead antenna inventory / locating system can include a plurality of antennas mounted in an elevated support structure. The antennas can be coupled to RFID readers that interrogate electronic tags. The inventory system can analyze the information received from the detected electronic tags and produce inventory data and location information for the tags. The antennas can be patch antennas mounted to ceiling tiles such that they can be positioned in the ceiling of a facility. The antennas can be configured to provide broad coverage from a relatively low ceiling height. The low-cost antennas can be configured in such a way as to provide accurate location information for detected tags. The inventory system can be configured to provide near real-time inventory and location information.

Owner:RFID RESOLUTION TEAM

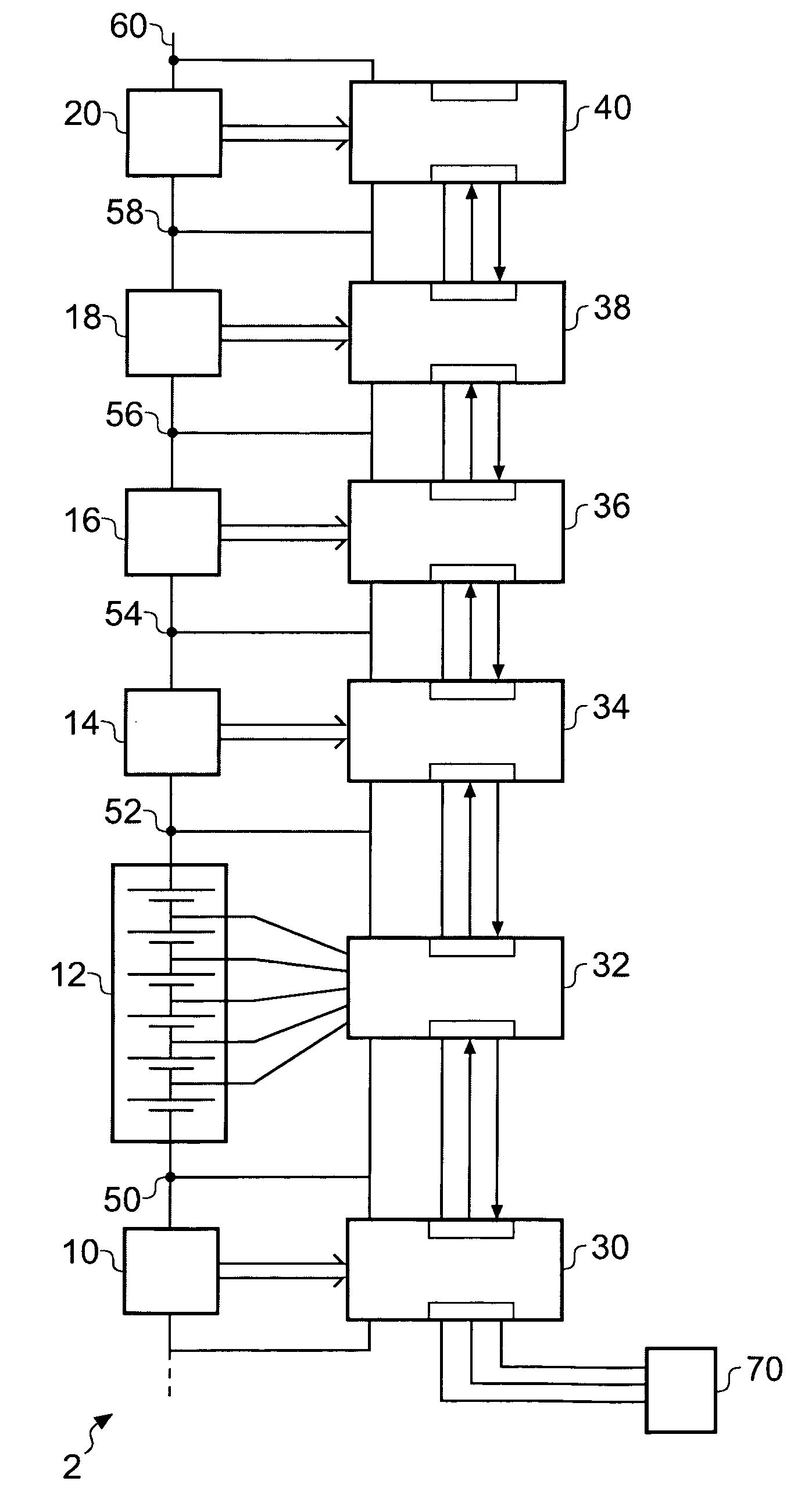

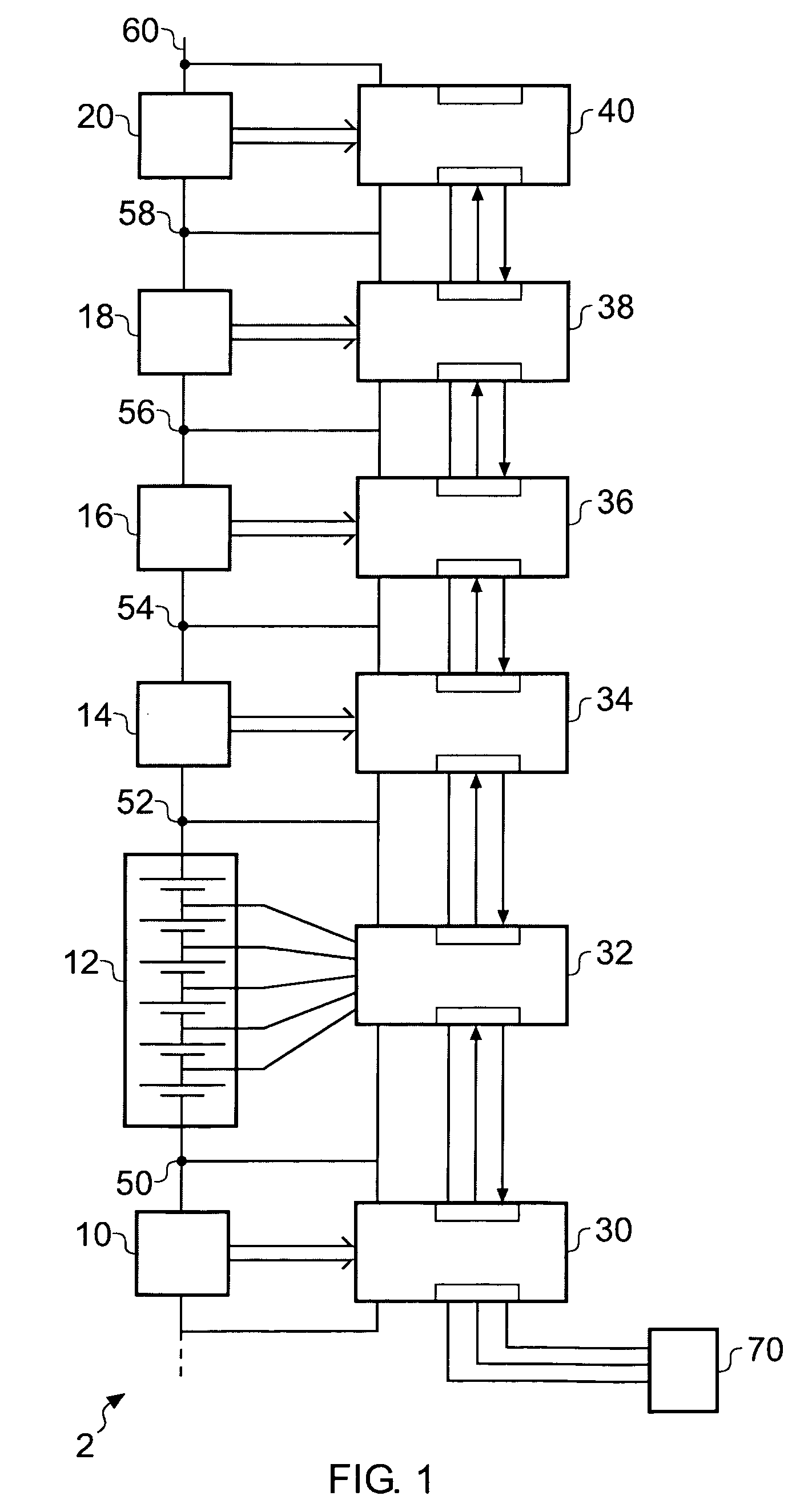

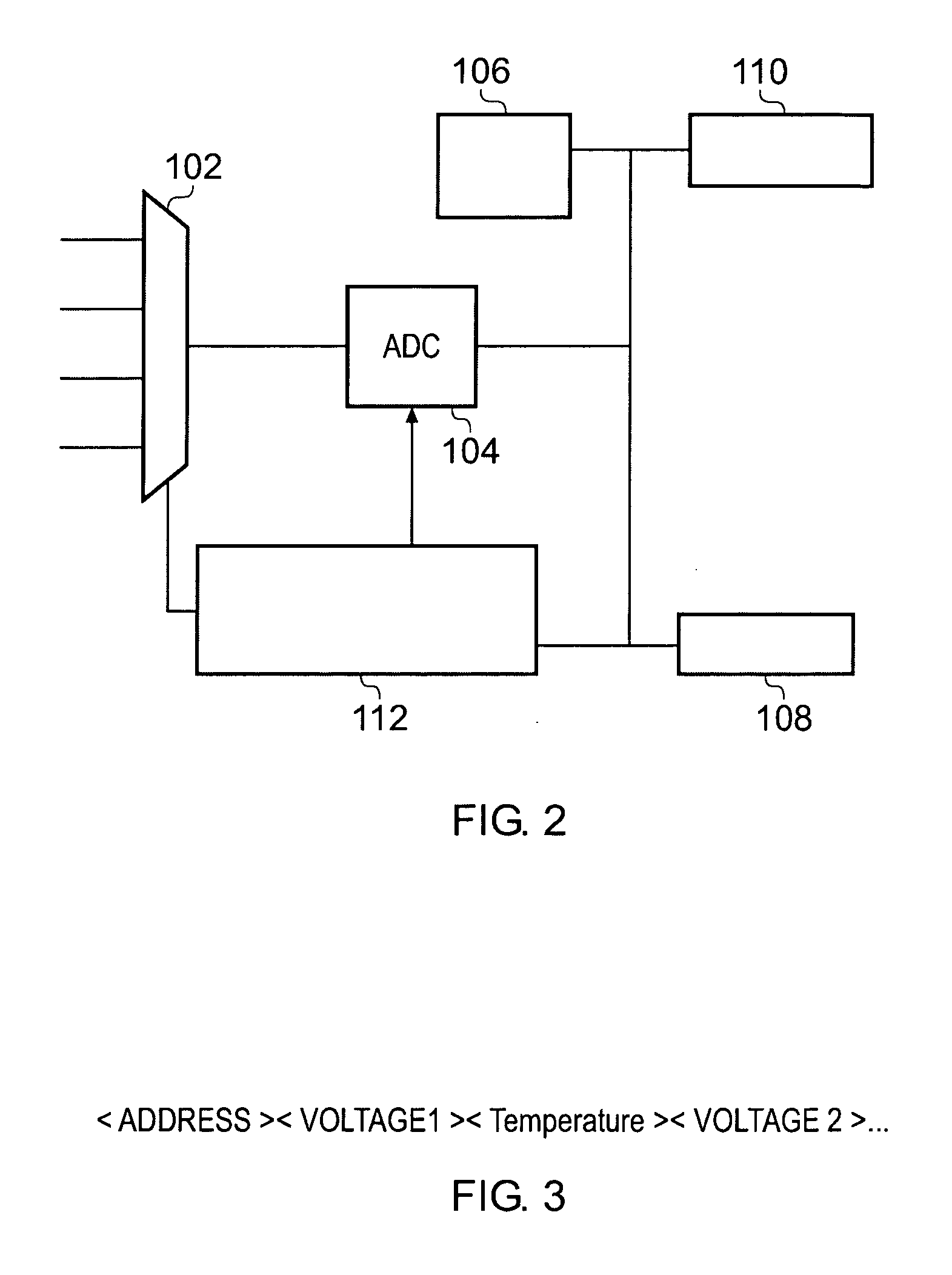

Battery montoring apparatus and daisy chain interface suitable for use in a battery monitoring apparatus

ActiveUS20080180106A1Reduce potential differenceCost reductionBatteries circuit arrangementsMaterial analysis by electric/magnetic meansEmbedded systemElectrical battery

A battery monitor for monitoring the performance of at least one battery within an array of batteries, comprising: a data acquisition device for measuring at least one parameter of the at least one battery associated with the battery monitor, a first data interface operable to exchange data with a first device, and a second data interface operable to exchange data with a second device.

Owner:ANALOG DEVICES INC

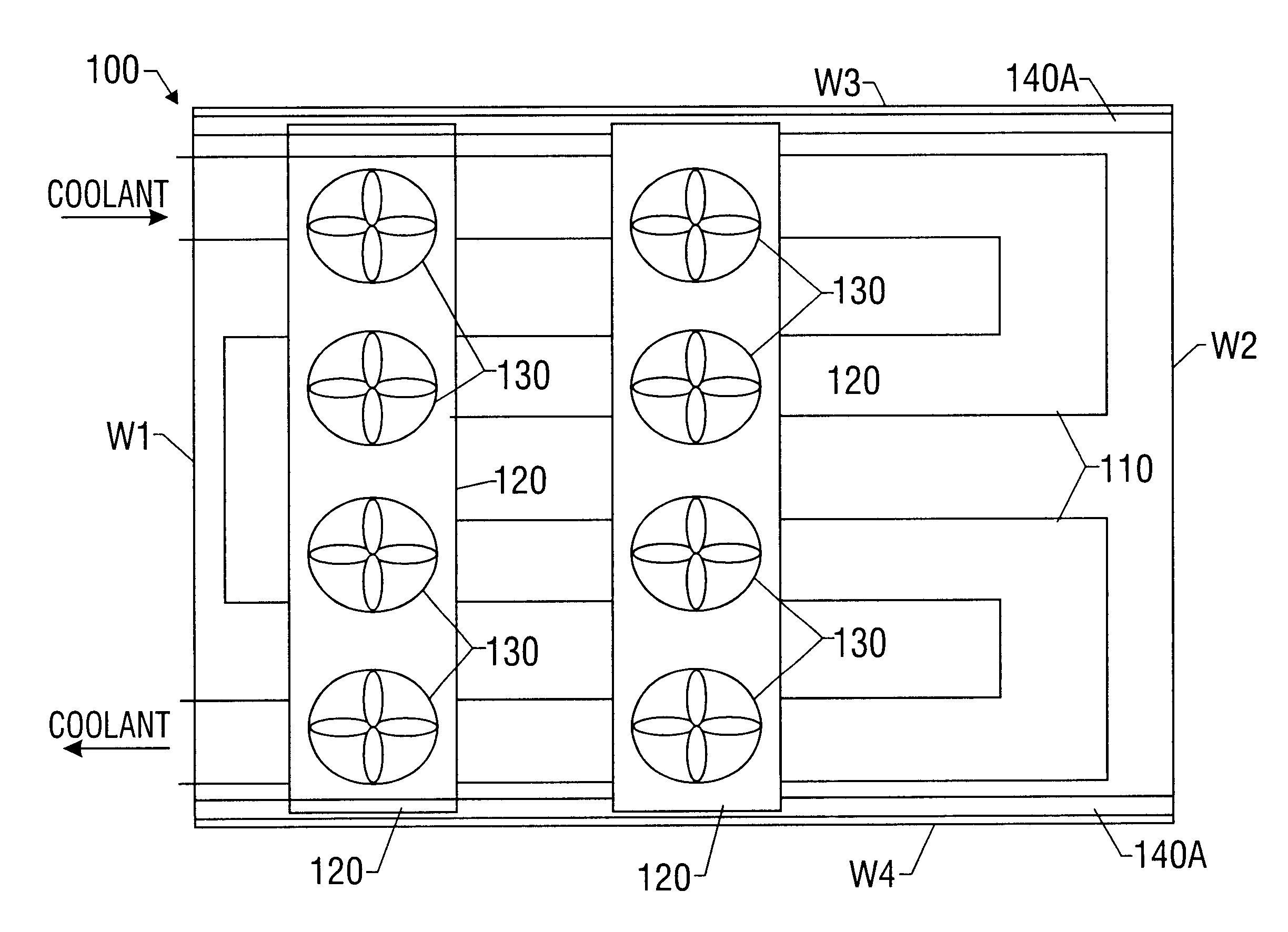

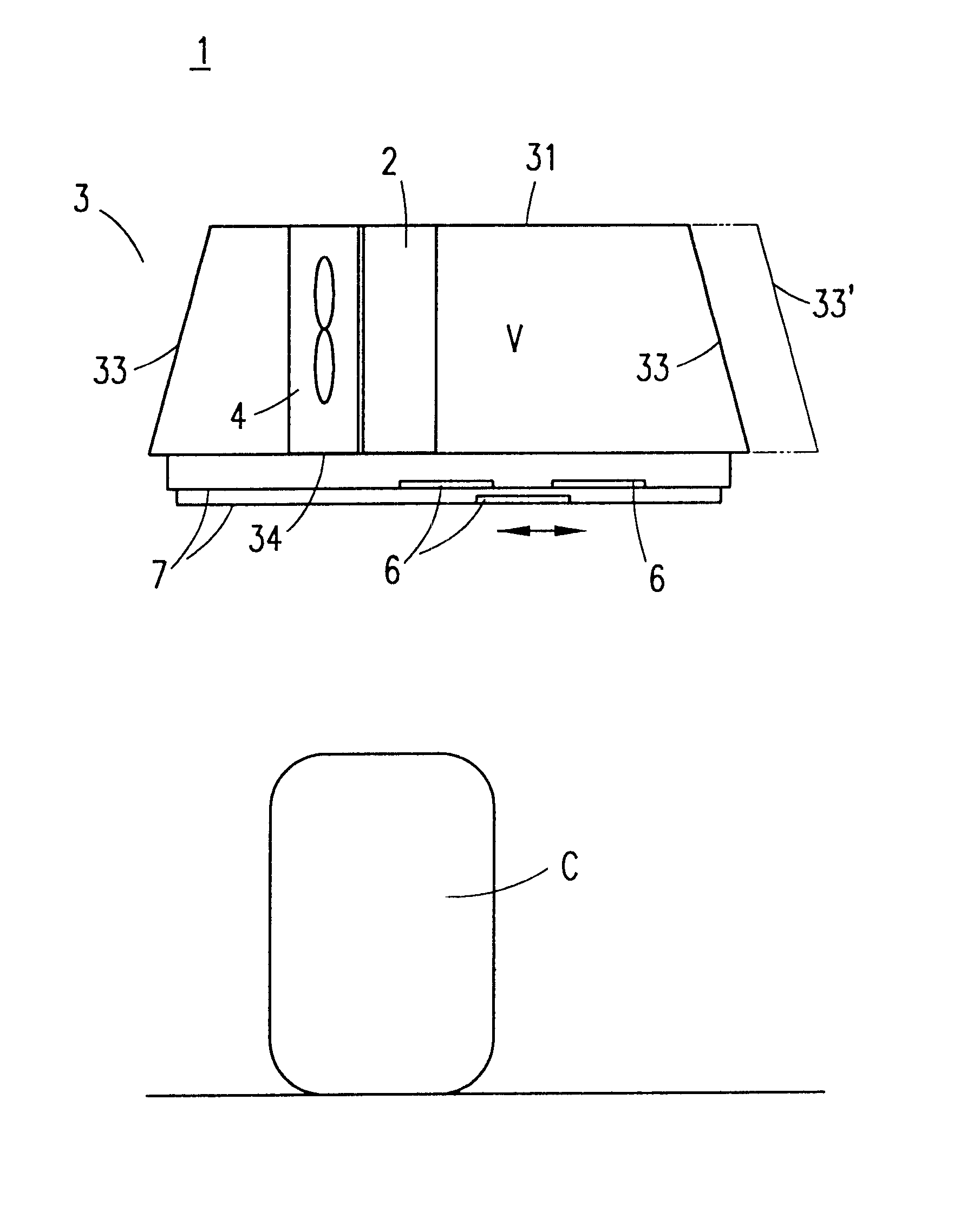

Overhead cooling system with selectively positioned paths of airflow

InactiveUS6564858B1Great and great efficiencyImprove efficiencyAir heatersModifications for standard racks/cabinetsNuclear engineeringCoolant

A method and system are disclosed for cooling a heat generating object. A coolant is passed through a heat exchanger so that heated air passing through the heat exchanger is cooled. A fan unit is selectively positioned adjacent to a first side of the heat exchanger. When activated, the fan unit draws the cooled air through the heat exchanger and directs the cooled air towards the heat generating object. The fan unit may be repositioned along a second side of the heat exchanger so as to redefine the flow of air drawn from and directed towards the heat generating object.

Owner:VERTIV CORP

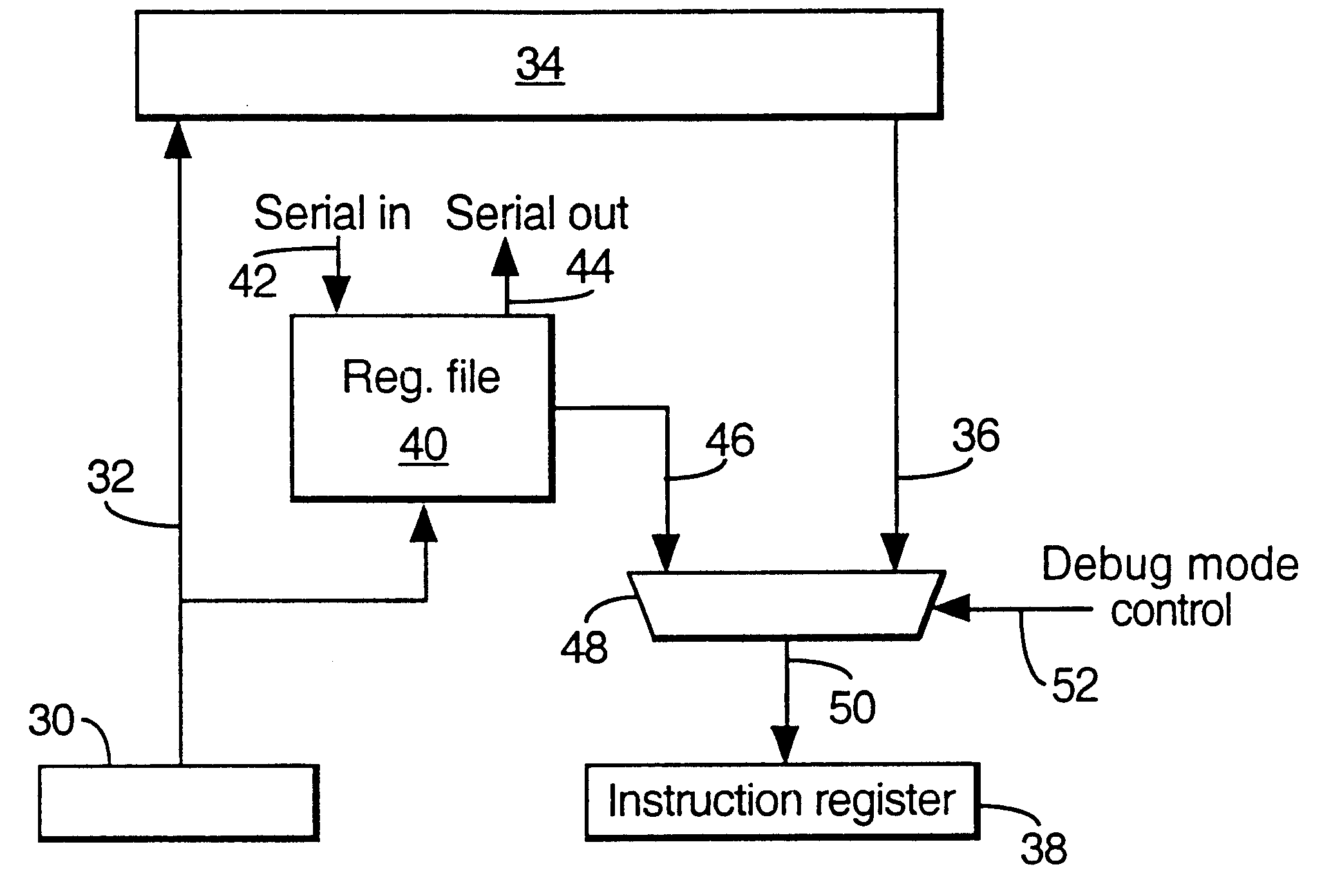

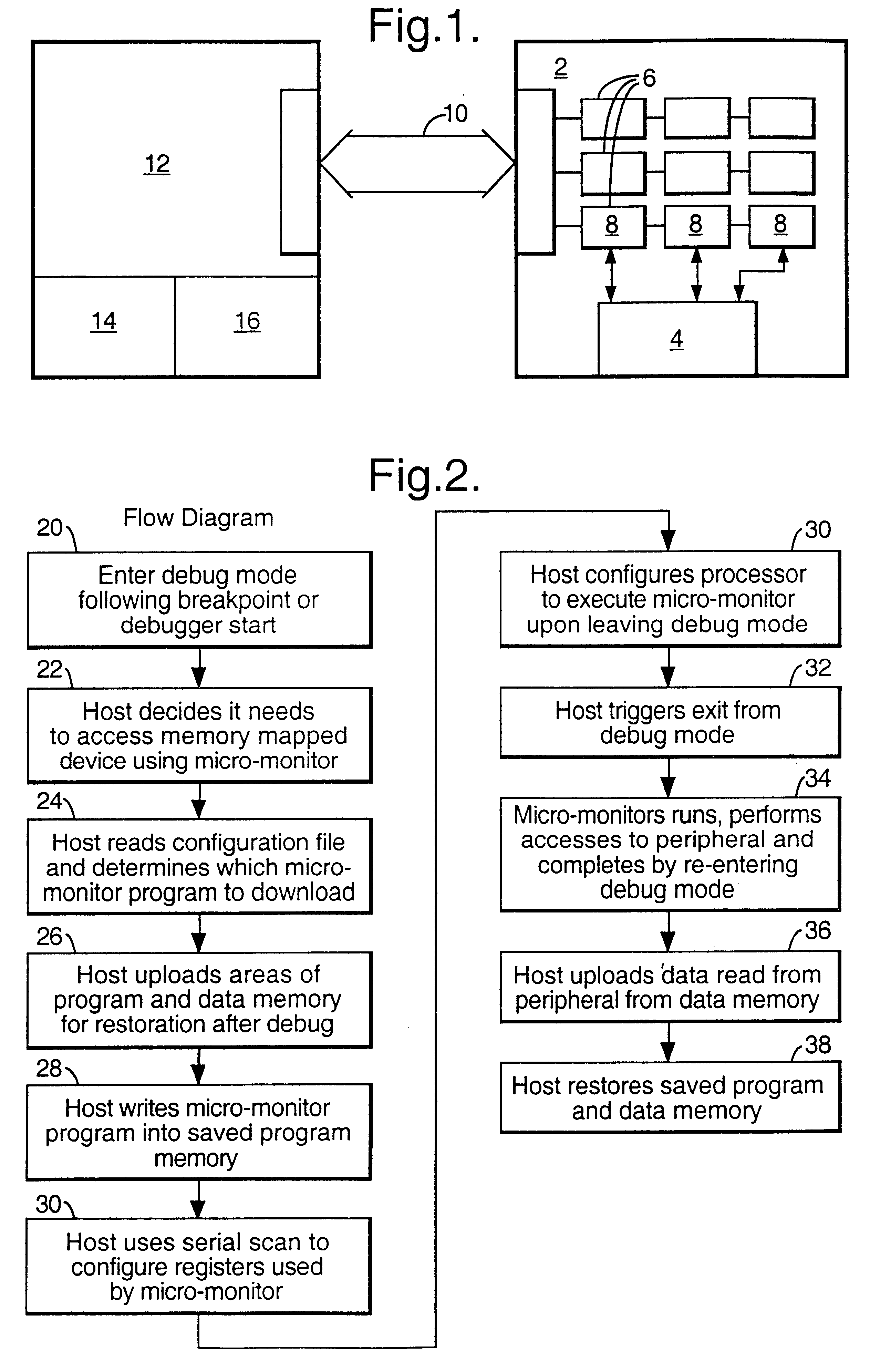

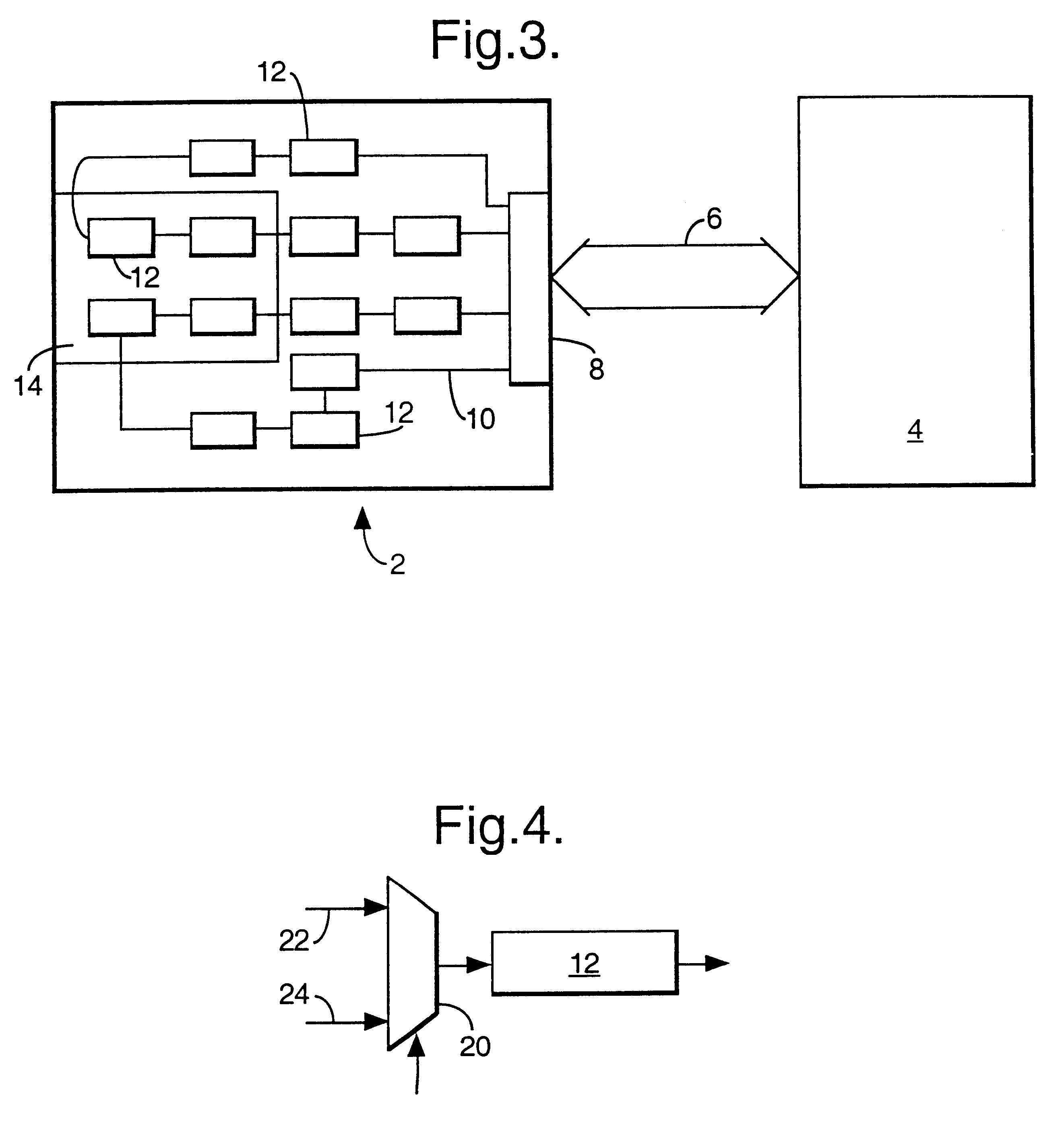

Microprocessor development systems

InactiveUS6574590B1Difficult to useSimple memory accessElectronic circuit testingDigital computer detailsEmbedded applicationsTime delays

A procedure and processor are disclosed for avoiding lengthy delays in debug procedures during access by a memory mapped peripheral device. The processor includes in-circuit emulation means comprising one or more scan chains or serially connected registers for access by an external host computer system. The procedure comprises:a) the host computer system carrying out a debug procedure via said scan chains, and selectively interrupting such debug procedure for access to a peripheral memory mapped device;b) the host computer system writing into an area or memory of the processor a program for reading and / or writing data at a specified memory location; andc) the host computer system causing said processor to run said program, and then to return to said debug procedure.In another aspect, in order to permit small debugging programs to run, in serial scan in circuit emulation processes, on a processor in a deeply embedded application where no program RAM is provided, the processor includes one or more chains of serially connected registers coupled to interface means for access by an external host to enable a serial scan procedure to be carried out, one such chain including a set of serially coupled registers for storing one or more processor instructions read into a set of registers through the interface means, and the processor including address means, for addressing program memory, coupled to said set of registers for addressing the set of registers, and means for reading the processor instructions in the set of registers to an instruction resister of the processor.

Owner:AVAGO TECH WIRELESS IP SINGAPORE PTE

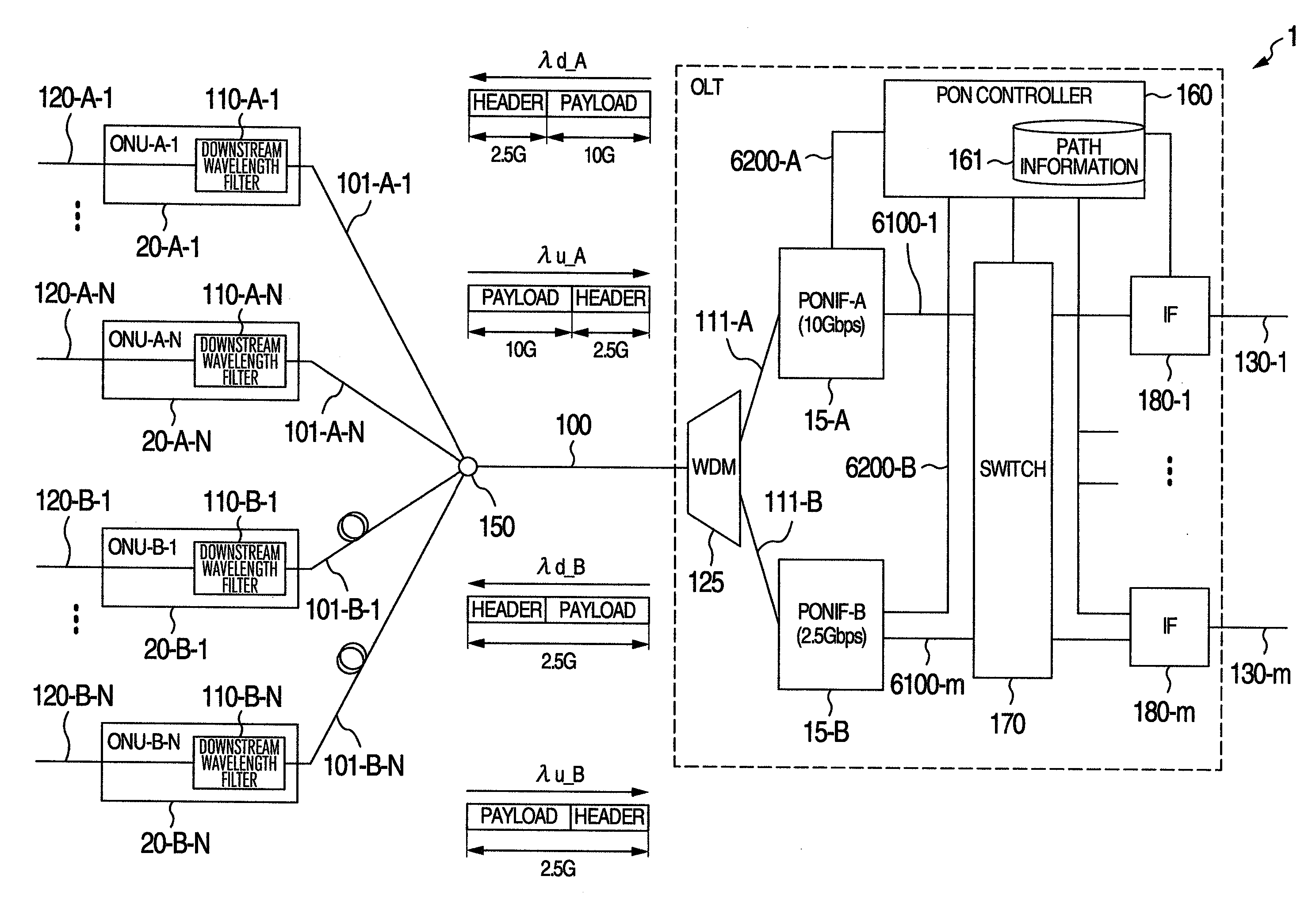

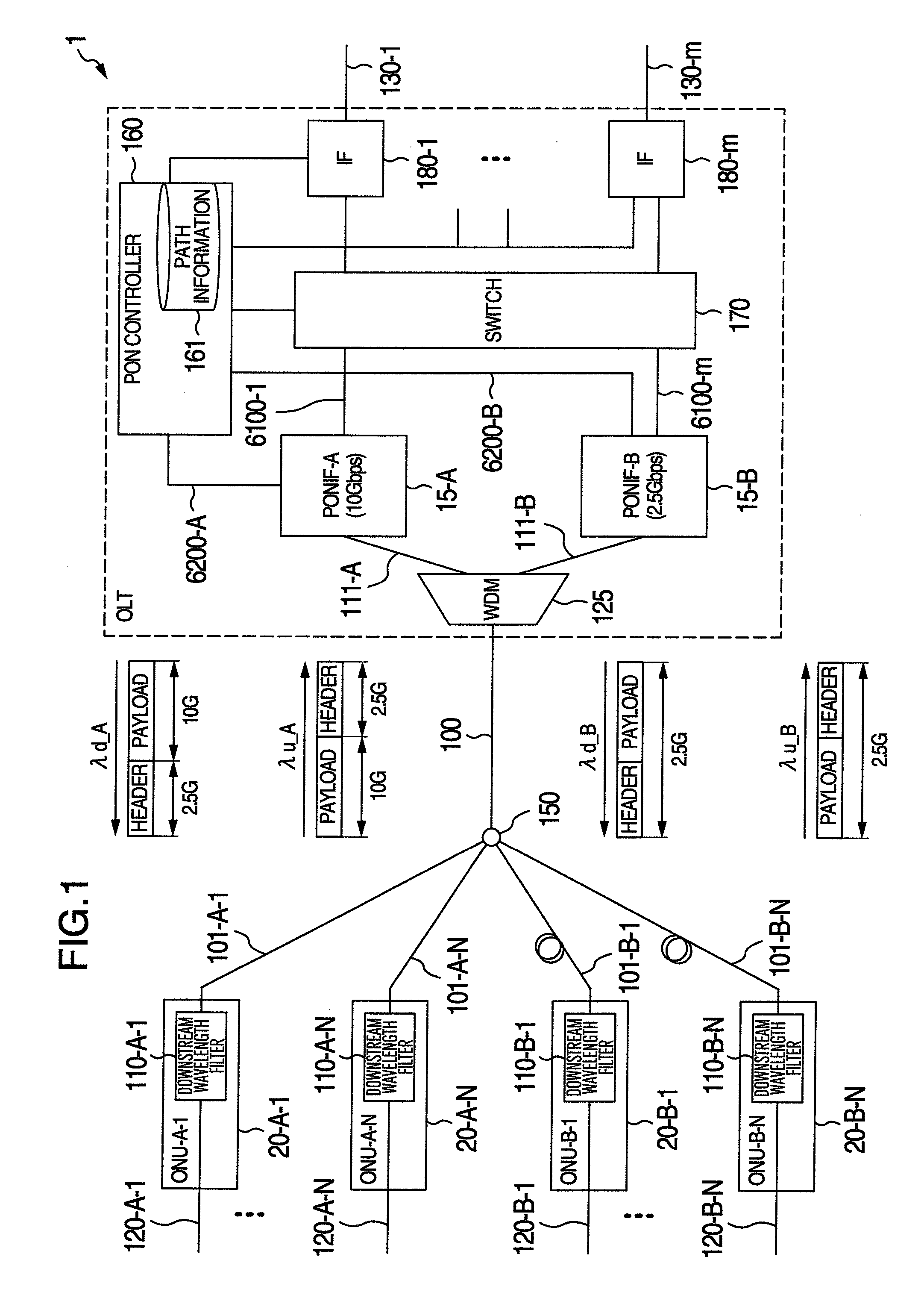

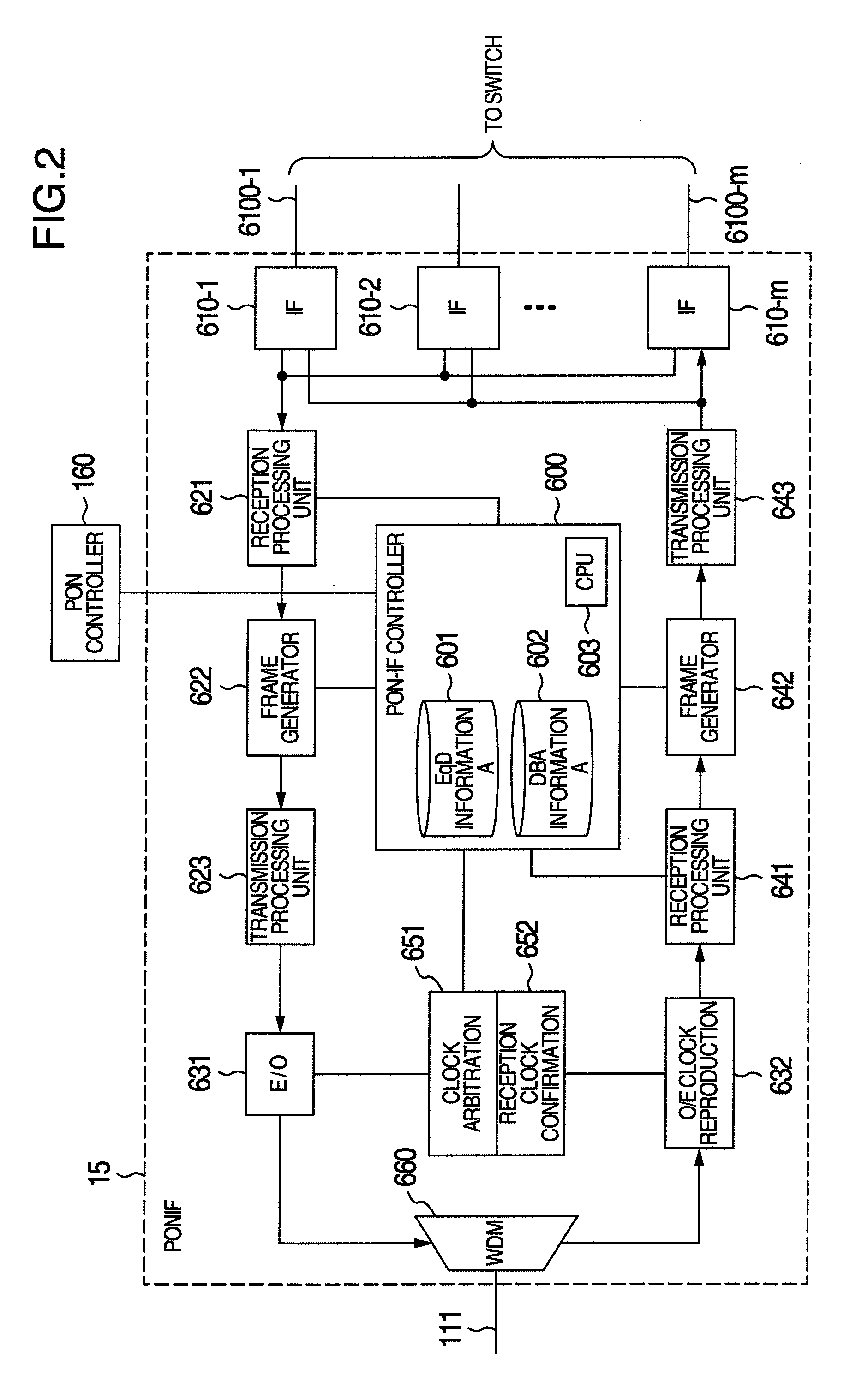

Passive optical network system and operation method of the same

InactiveUS20090245790A1Increase transfer speedIncrease the stationTime-division multiplexStar/tree networksPrimary stationEngineering

In a passive optical network system, in order that by measuring a transmission distance and a transmission time between an OLT and an ONU in operation of the system, if the distance or the time is short, communication is conducted at a high transmission speed to increase a capacity of user; if the distance or the time is long, communication is conducted at a low transmission speed to increase the capacity of user communicating in a state in which a predetermined quality is secured, a main station includes a signal communication circuit to communicate with subsidiary stations at a first or second transmission speed and a controller to measure a transmission distance or a transmission time between the main station and each subsidiary station. Based on a result of the measurement, the controller selects a transmission speed for communication with the subsidiary station.

Owner:HITACHI LTD

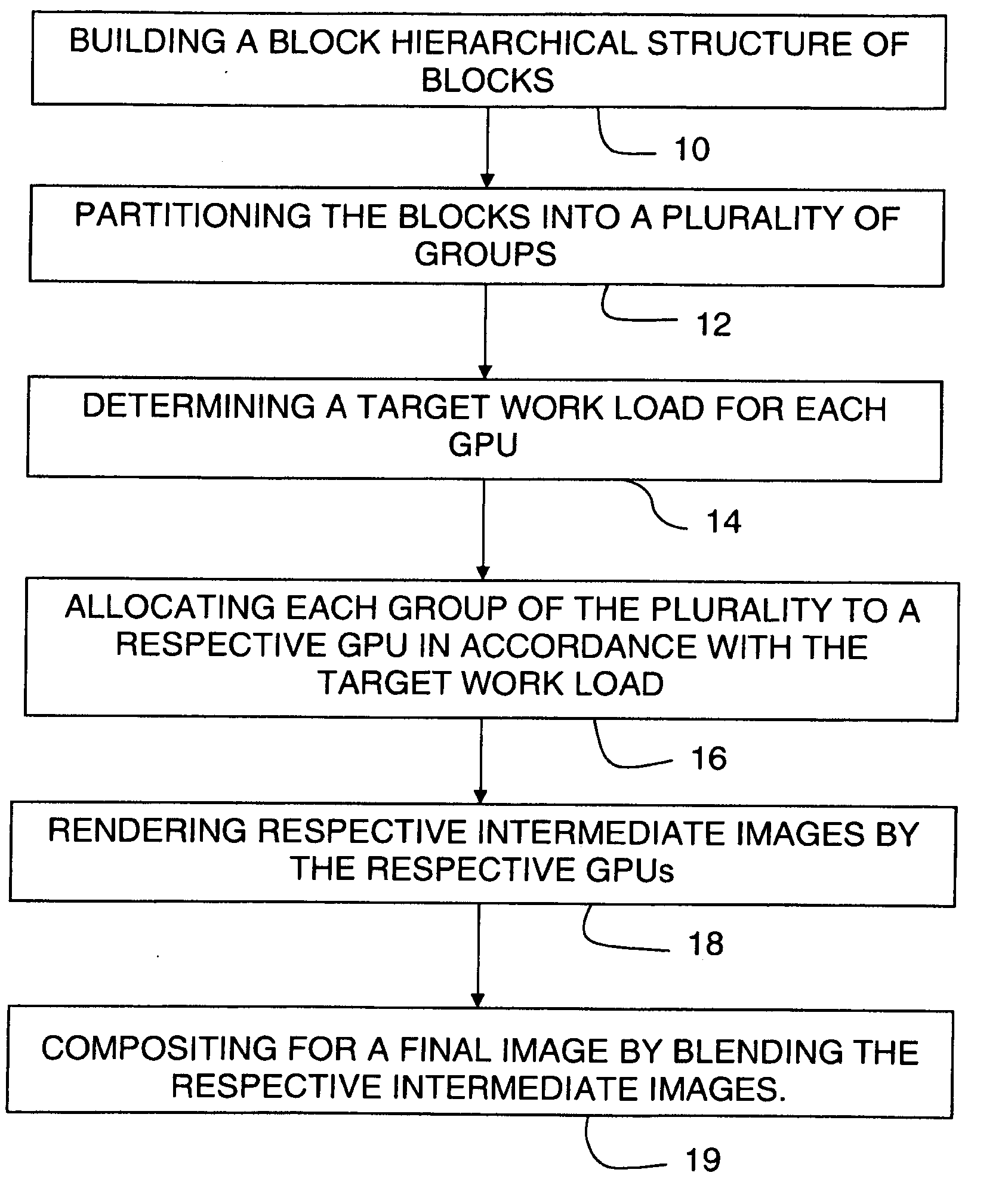

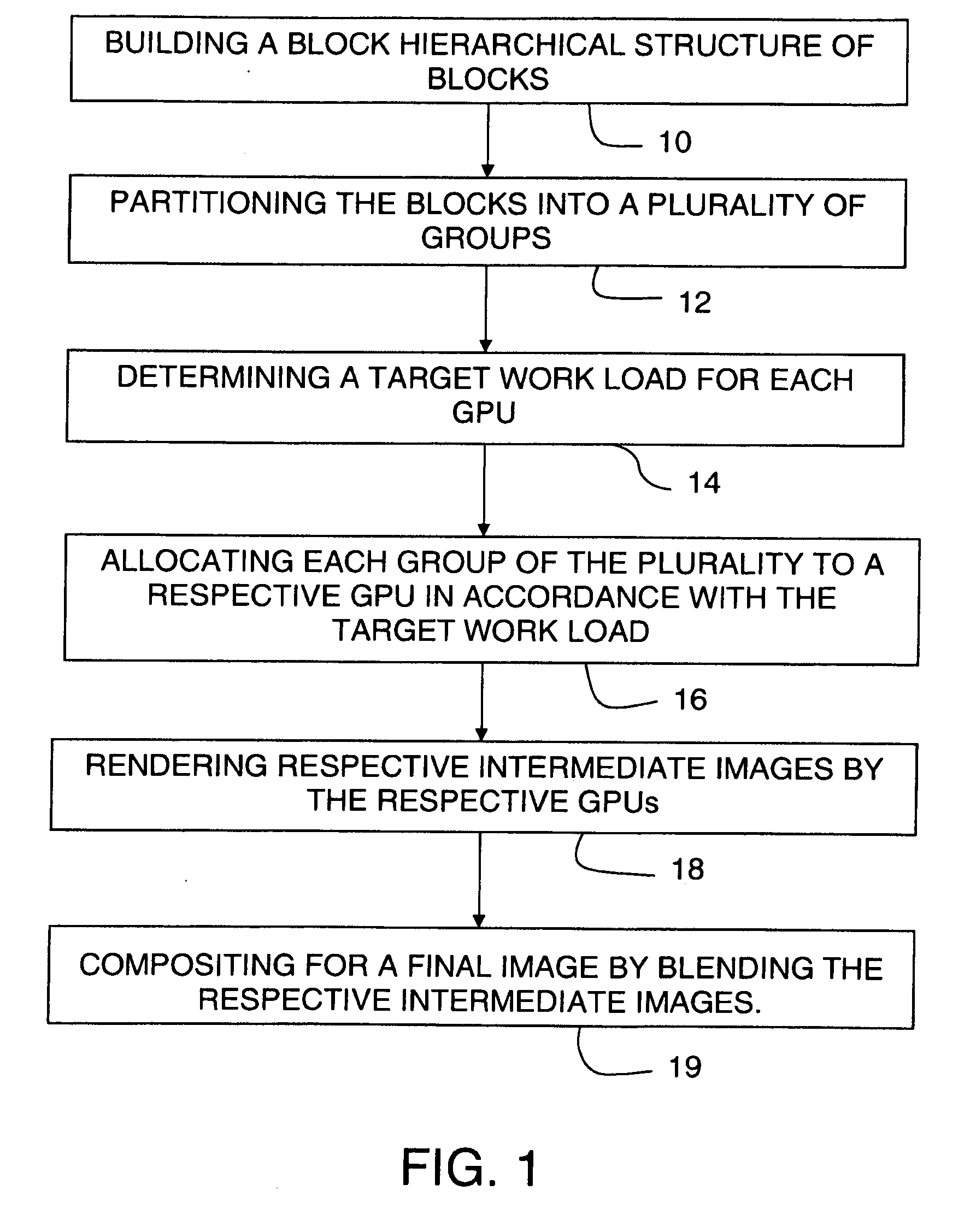

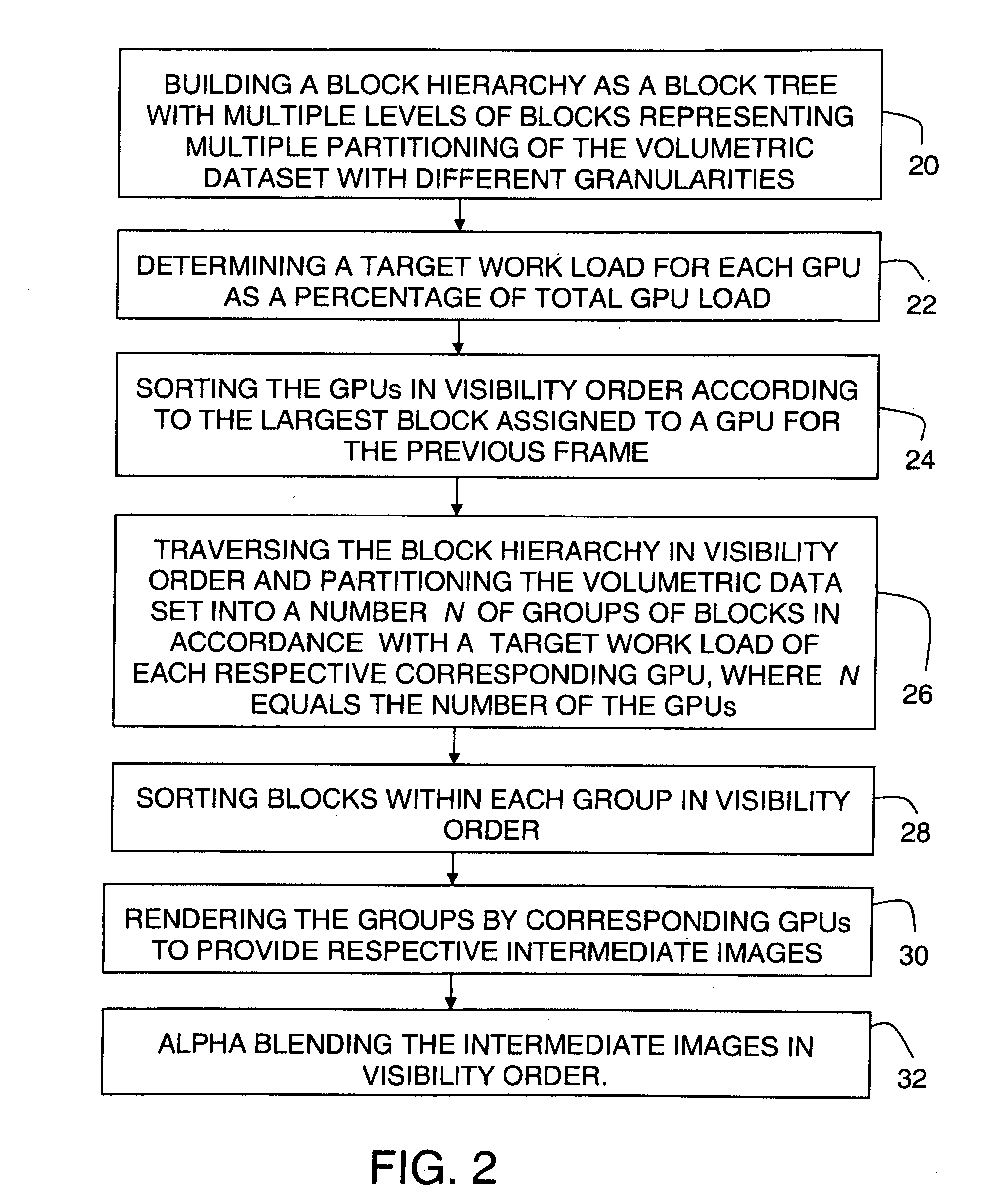

APPARATUS AND METHOD FOR VOLUME RENDERING ON MULTIPLE GRAPHICS PROCESSING UNITS (GPUs)

ActiveUS20090135180A1Significant speed advantageIncreases cost of systemCathode-ray tube indicatorsMultiple digital computer combinationsVolume renderingLayered structure

A method for volume rendering a volumetric dataset with multiple graphics processing units (GPUs) coupled to a computer system, comprises building a block hierarchical structure of blocks for the volumetric dataset, the block hierarchy comprising a block sequence; partitioning the block sequence into a plurality of groups; determining a target work load for each GPU; allocating each group of the plurality to a respective GPU in accordance with the target load; rendering respective intermediate images by the respective GPUs; and compositing for a final image by blending the respective intermediate images.

Owner:SIEMENS HEALTHCARE GMBH

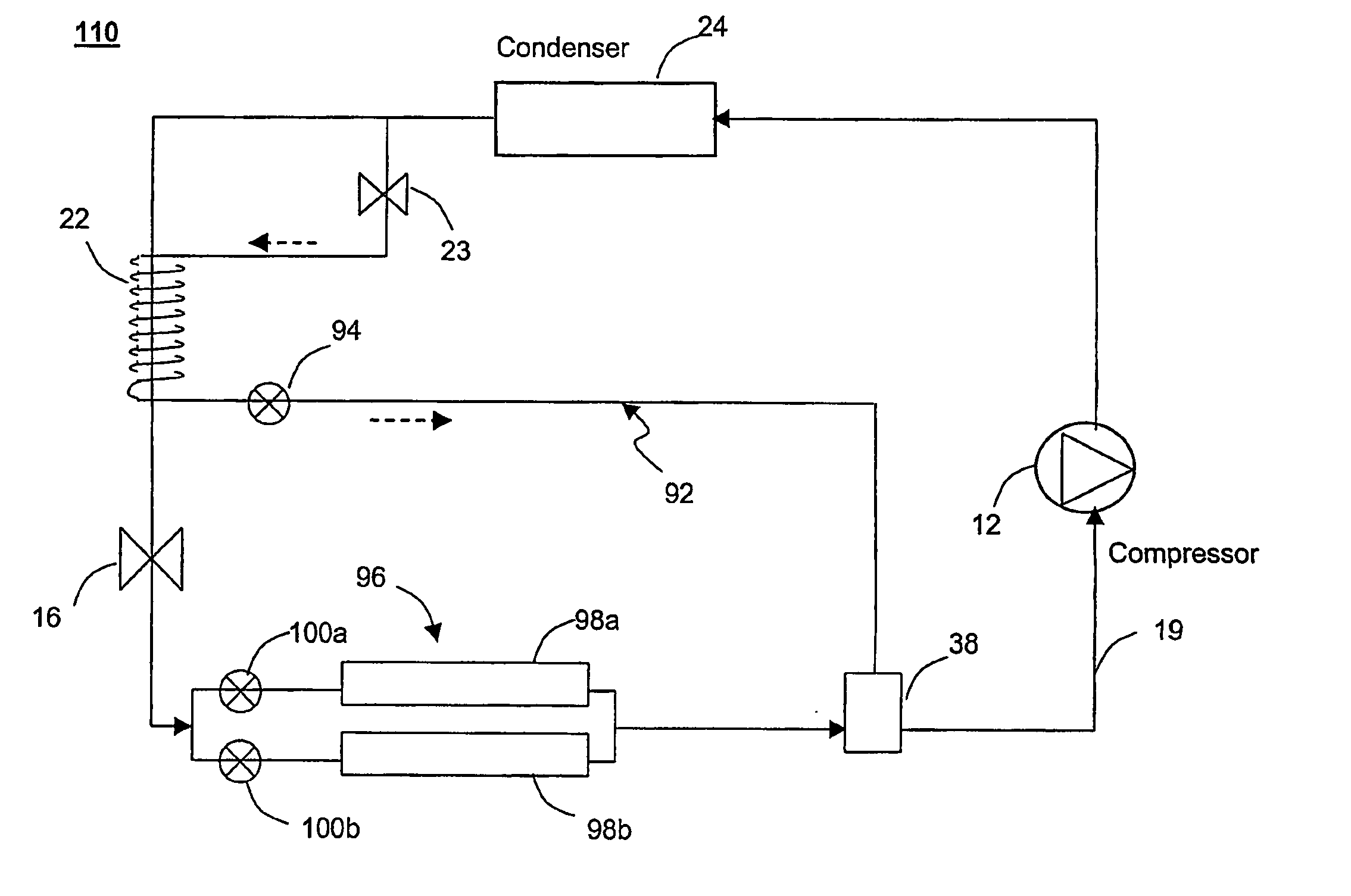

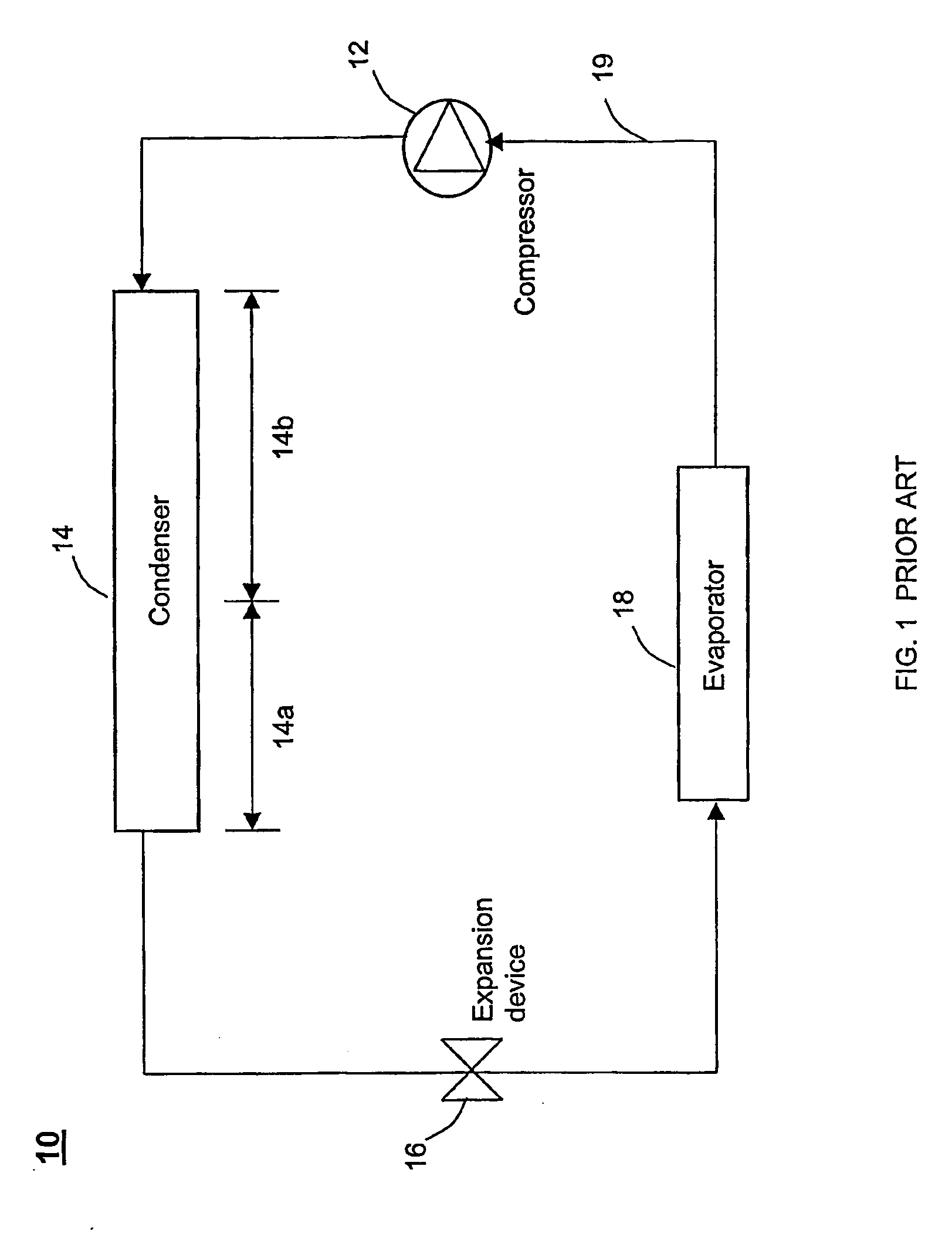

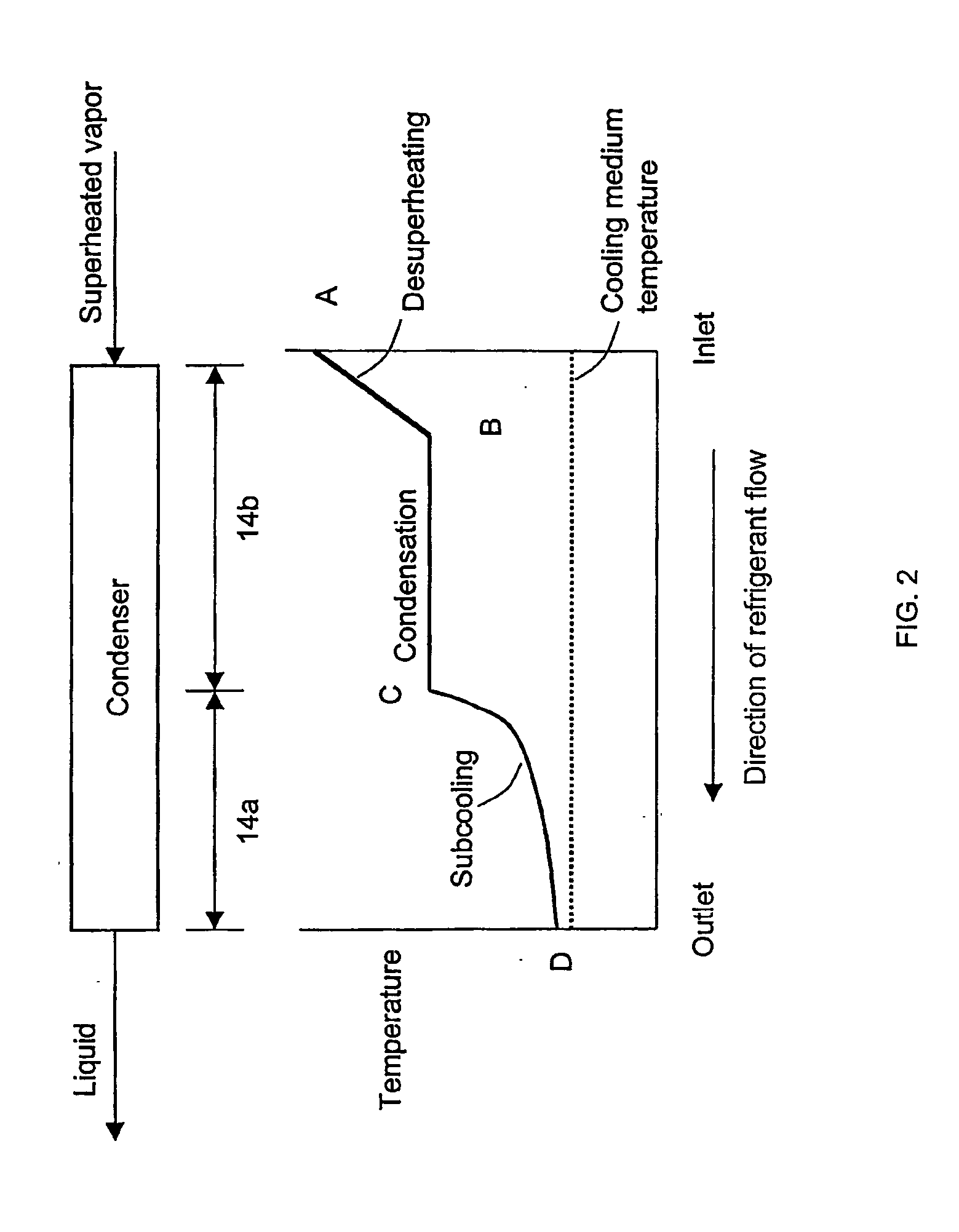

Refrigeration system with bypass subcooling and component size de-optimization

InactiveUS20070074536A1Boost capacityLower pressureCompression machines with several condensersCompression machines with several evaporatorsRefrigerantSubcooling

A refrigeration system having a primary refrigerant path including a compressor, a condenser, a primary expansion device, and an evaporator connected together to form a closed loop system with a refrigerant circulating therein; and a bypass path coupled to an outlet of the condenser. The bypass path includes a secondary expansion device; and a heat exchanger thermally coupled to the primary refrigerant path between the condenser outlet and the primary expansion device inlet to remove heat from the refrigerant discharged from the condenser. The condenser is downsized such that lacks the heat transfer capacity to provide some or all of the required subcooling as provided according to conventional practice, and the heat exchanger provides some or all the required subcooling according to the capacity of the condenser. A pressure differential accommodating device operative to mix two vapors at different pressures may also be provided to connect the outlets of the evaporator and the heat exchanger to an inlet of the compressor. A method of operating a refrigeration system with a downsized condenser and an a bypass path including a heat exchanger to provide subcooling is also described.

Owner:VORTEX AIRCON

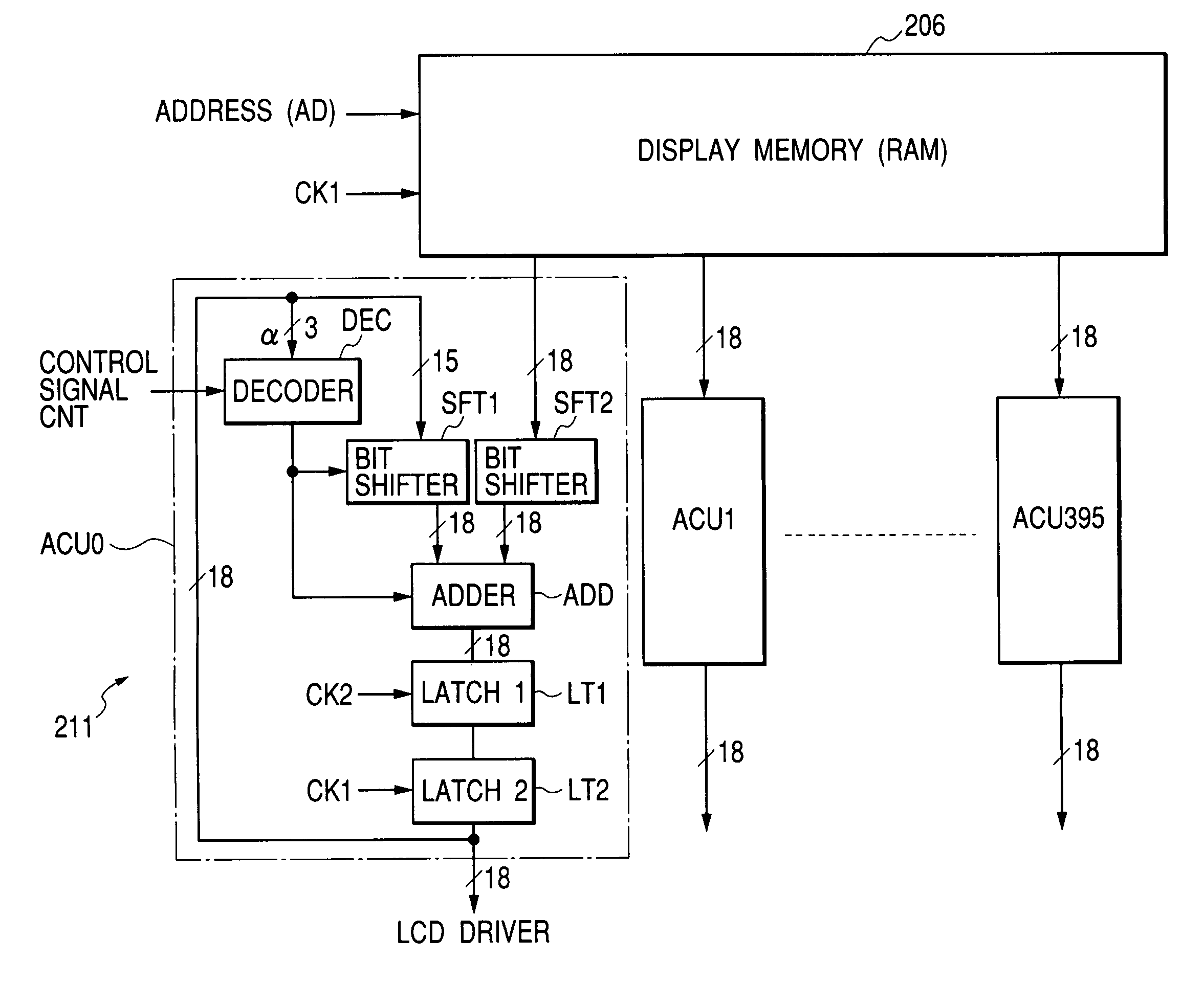

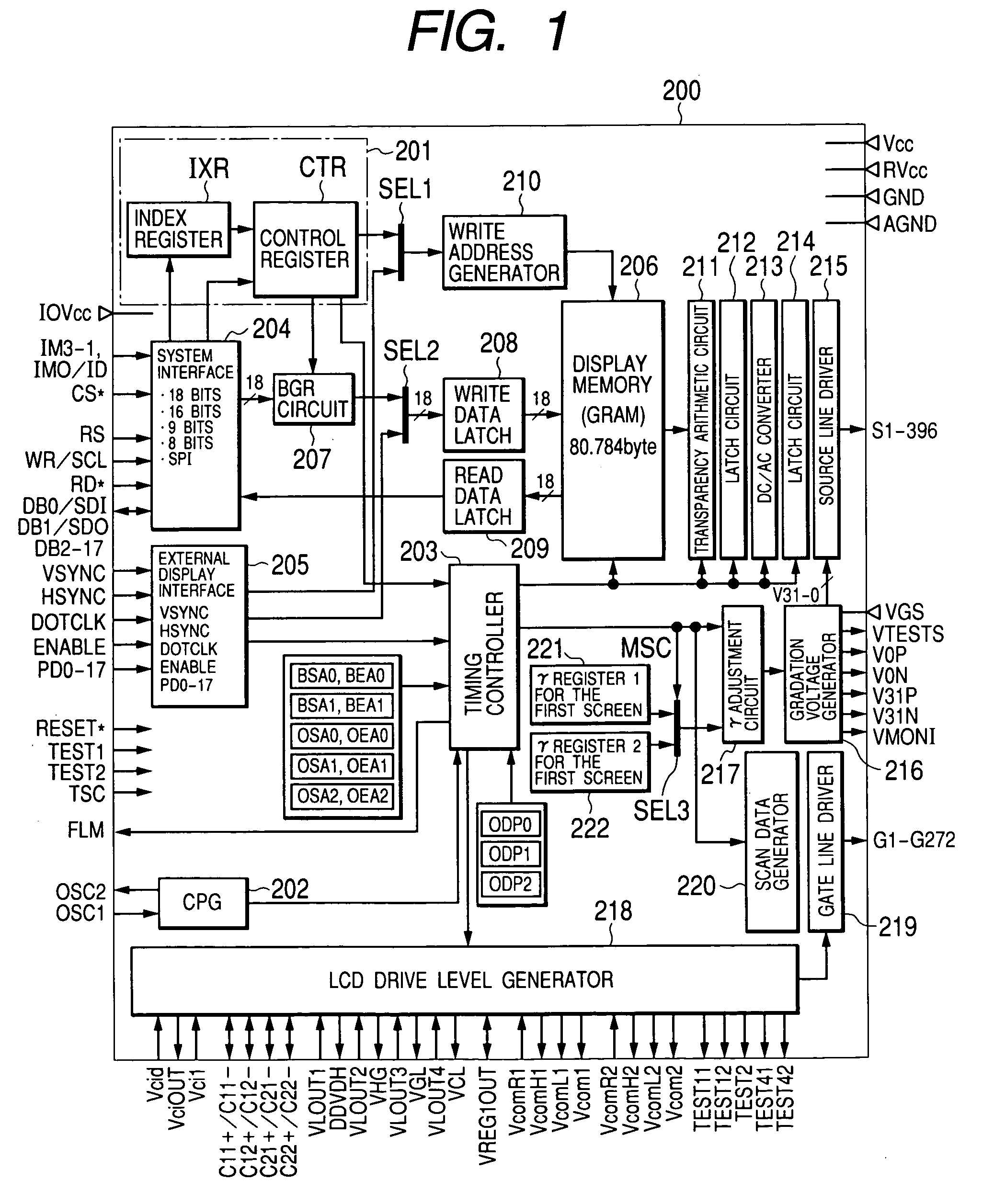

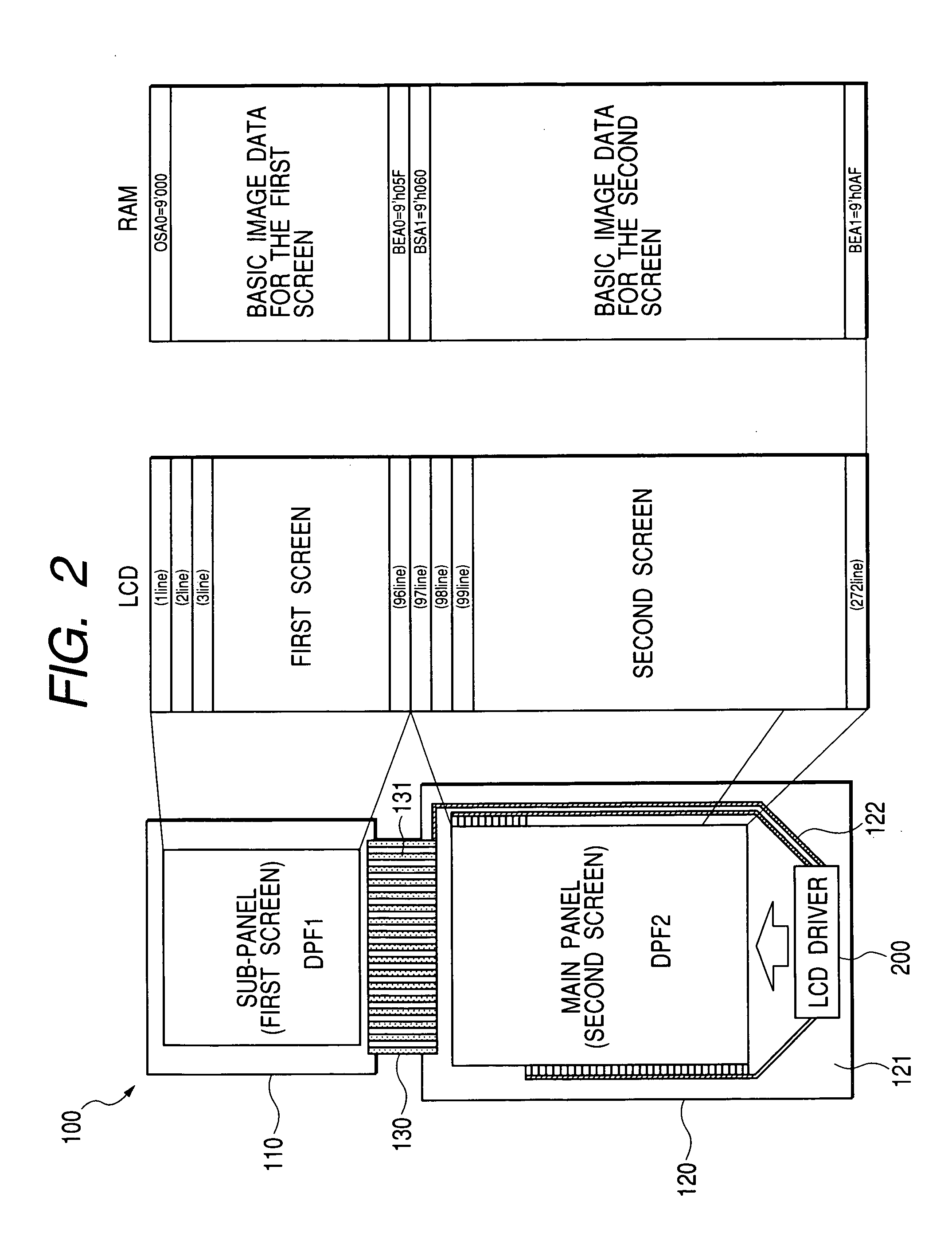

Display drive control device and electric device including display device

InactiveUS7142221B2Enhance the imageFunction increaseCathode-ray tube indicatorsDisplay deviceImaging data

In a system including a color liquid crystal panel, a drive control device for driving the panel, and a microprocessor, the drive control device reduces the burden on the microprocessor as well as power consumption. In a liquid crystal display drive control device that incorporates a memory for storing image data displayed on a color liquid crystal panel, reads out the image data sequentially from the memory, generates image signals of the three primary colors for each pixel of the panel, and outputs the image signals from external output terminals, the drive control device includes a transparency arithmetic circuit that applies calculation processing to two image data read out from built-in memory and generates data for a transparent display, supplies display data generated by the transparency arithmetic circuit to a driver, and makes the driver generate and output drive signals to the liquid crystal panel.

Owner:SYNAPTICS JAPAN GK

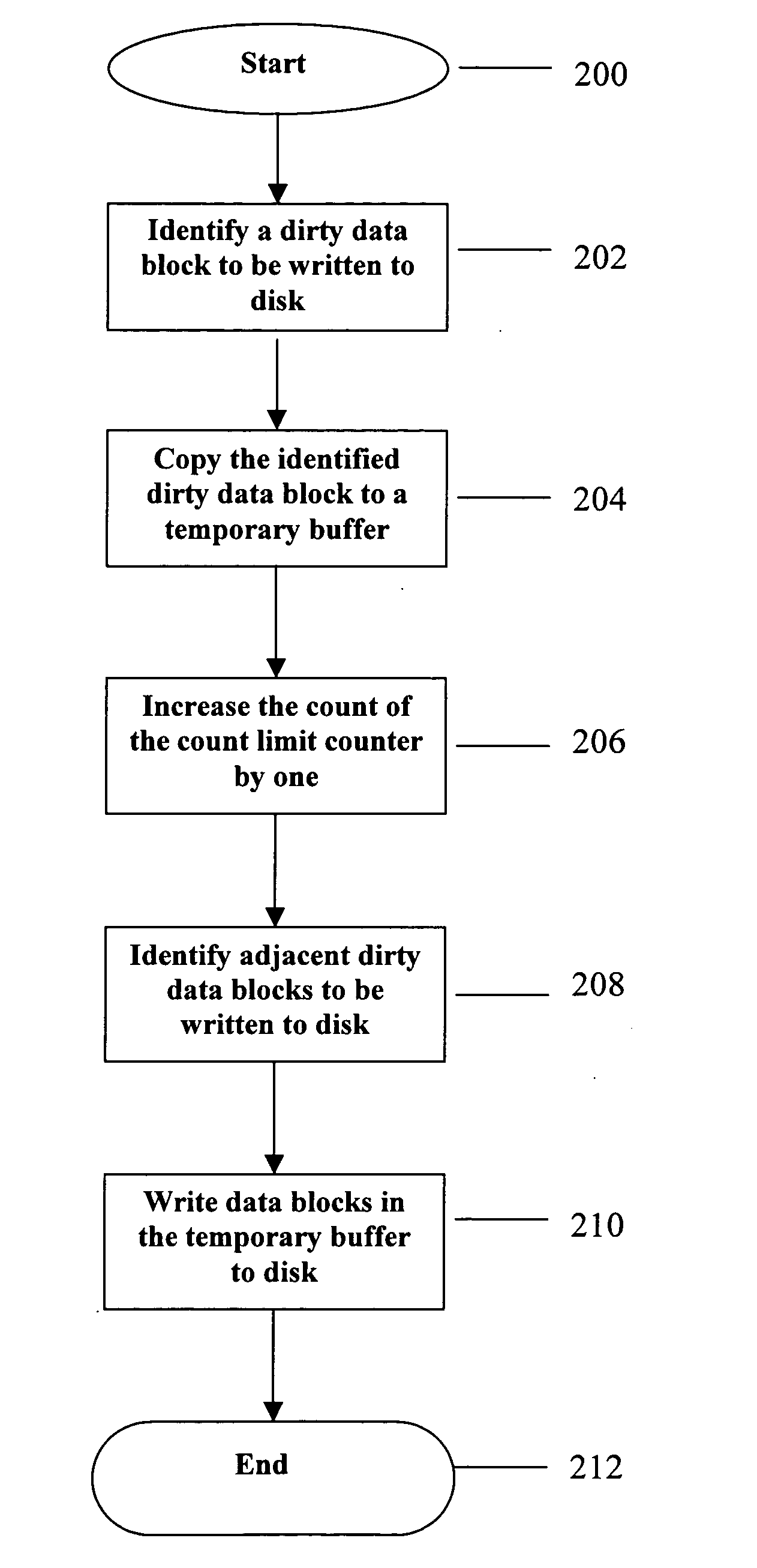

Reducing disk IO by full-cache write-merging

ActiveUS20050044311A1Reduced head movementImprove performanceMemory adressing/allocation/relocationHead movementsDirty data

A method and system for implementing coalescing write IOs for an electronic and computerized system is disclosed. The electronic and computerized system has a buffer cache storing data blocks waiting for being written into a disk of the electronic and computerized system. Dirty data blocks with consecutive data block addresses in the buffer cache are coalesced and written to the disk together. Thus, the disk head movements for performing the write IOs are significantly reduced, thereby allowing the electronic and computerized system to maintain a high IO throughput and high peak performance with fewer disks.

Owner:ORACLE INT CORP

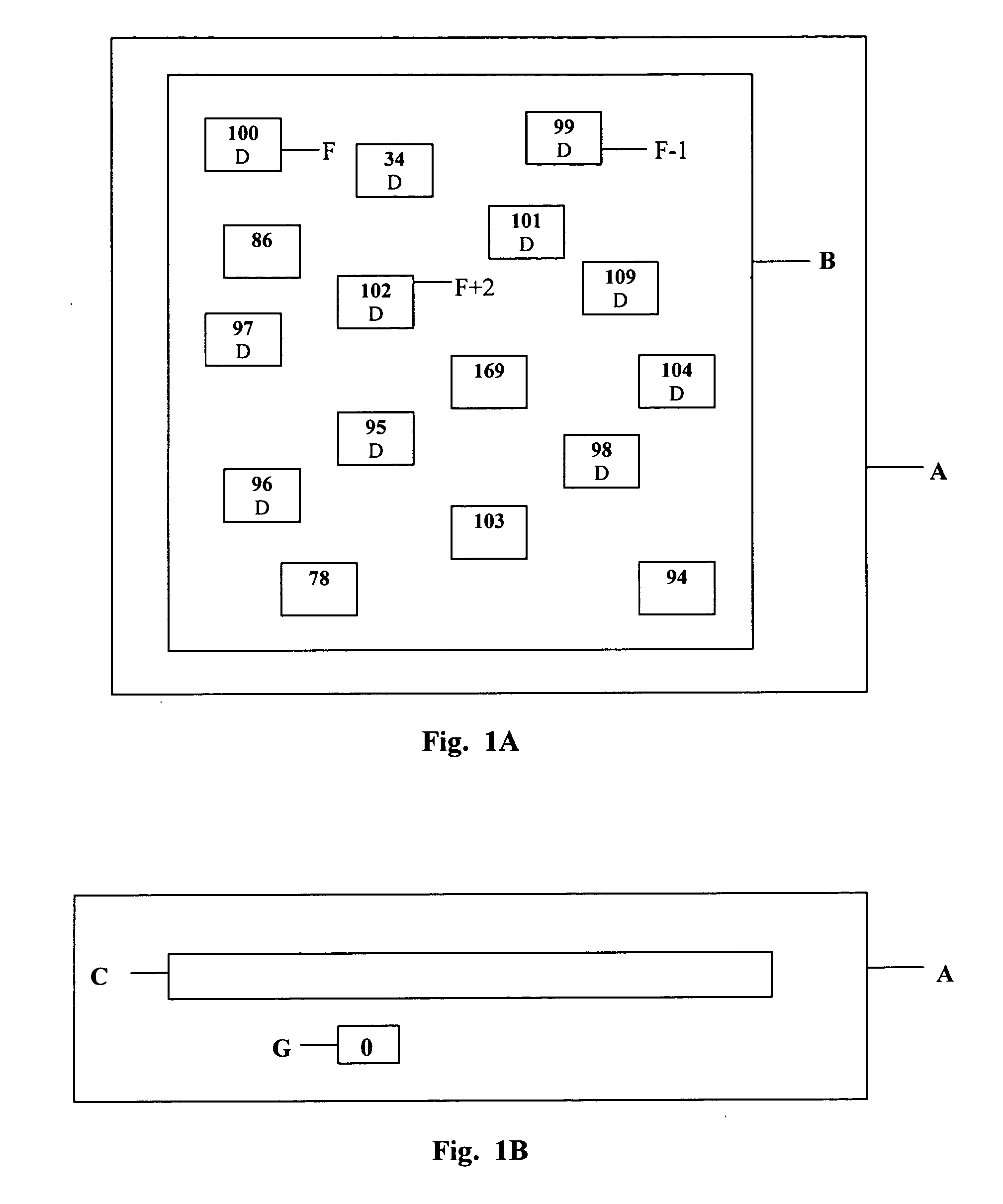

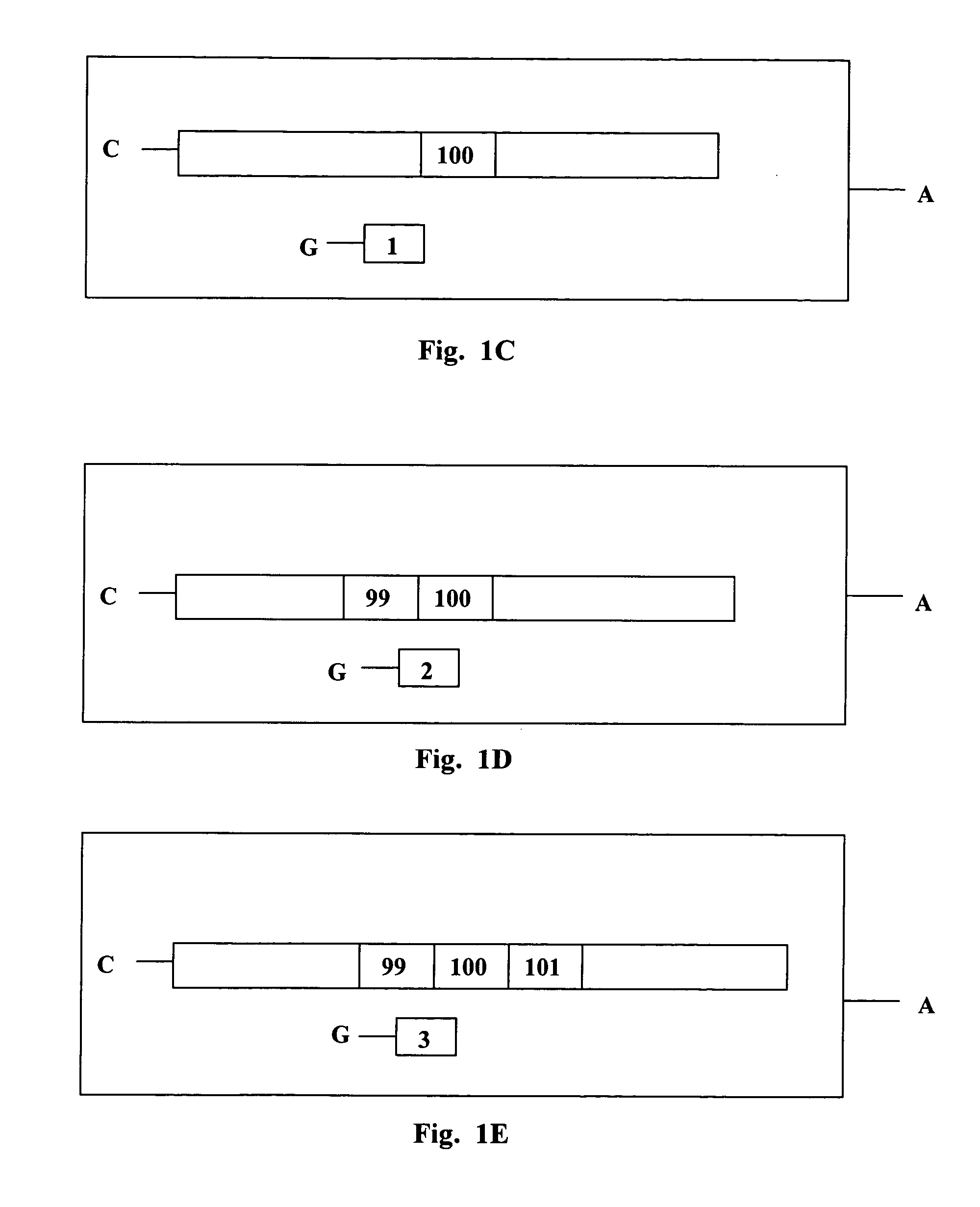

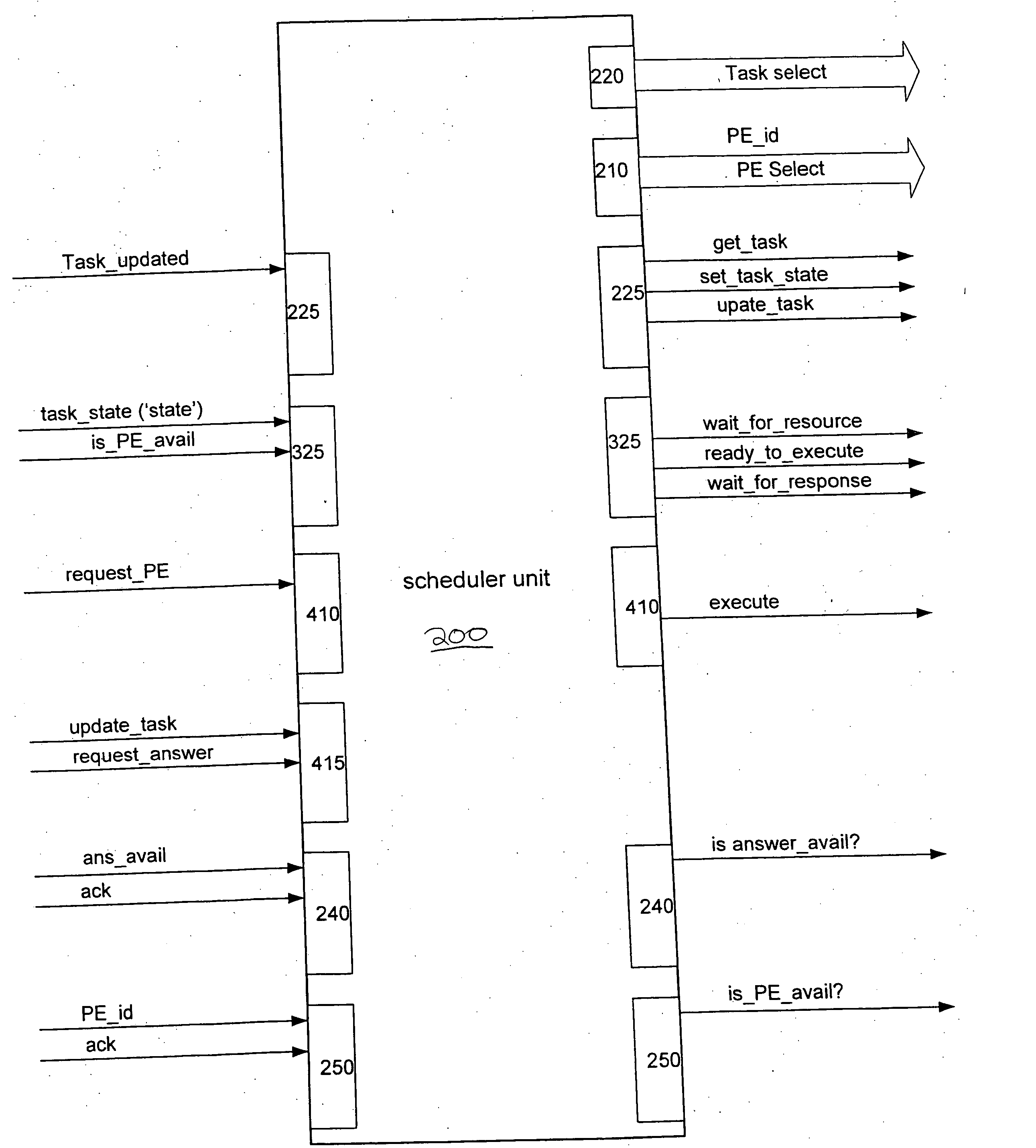

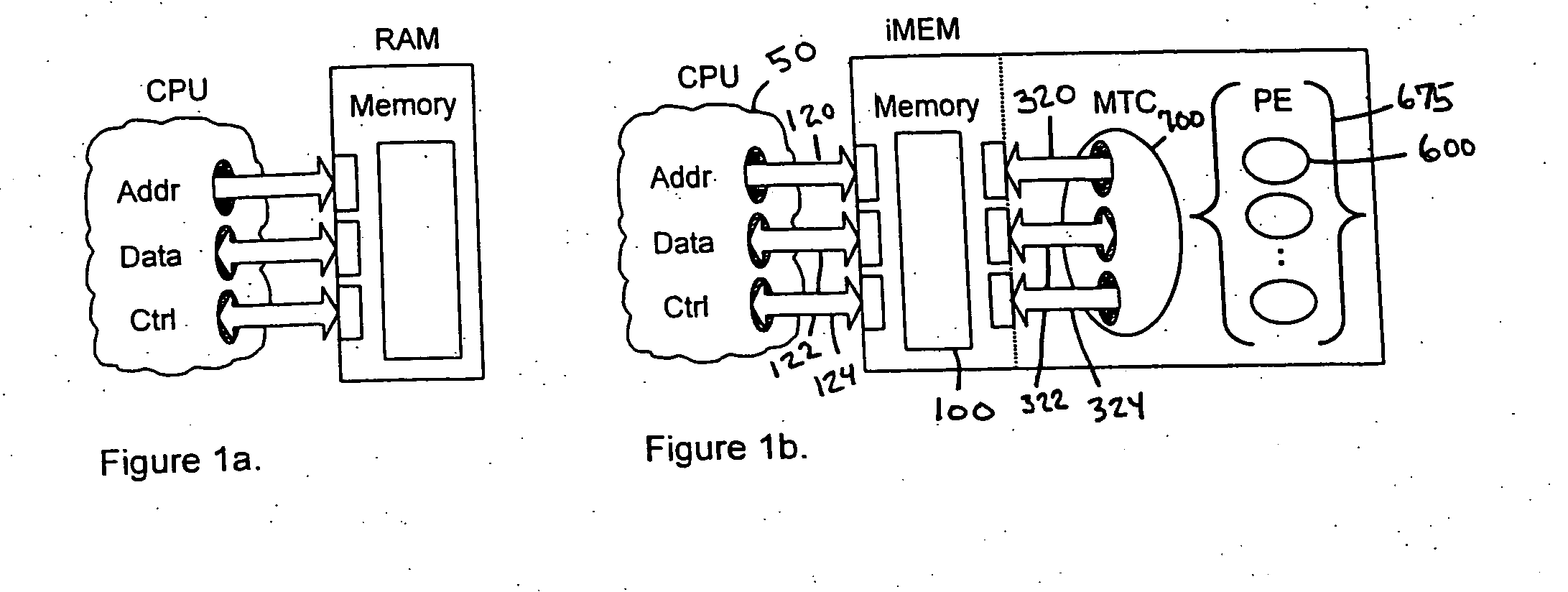

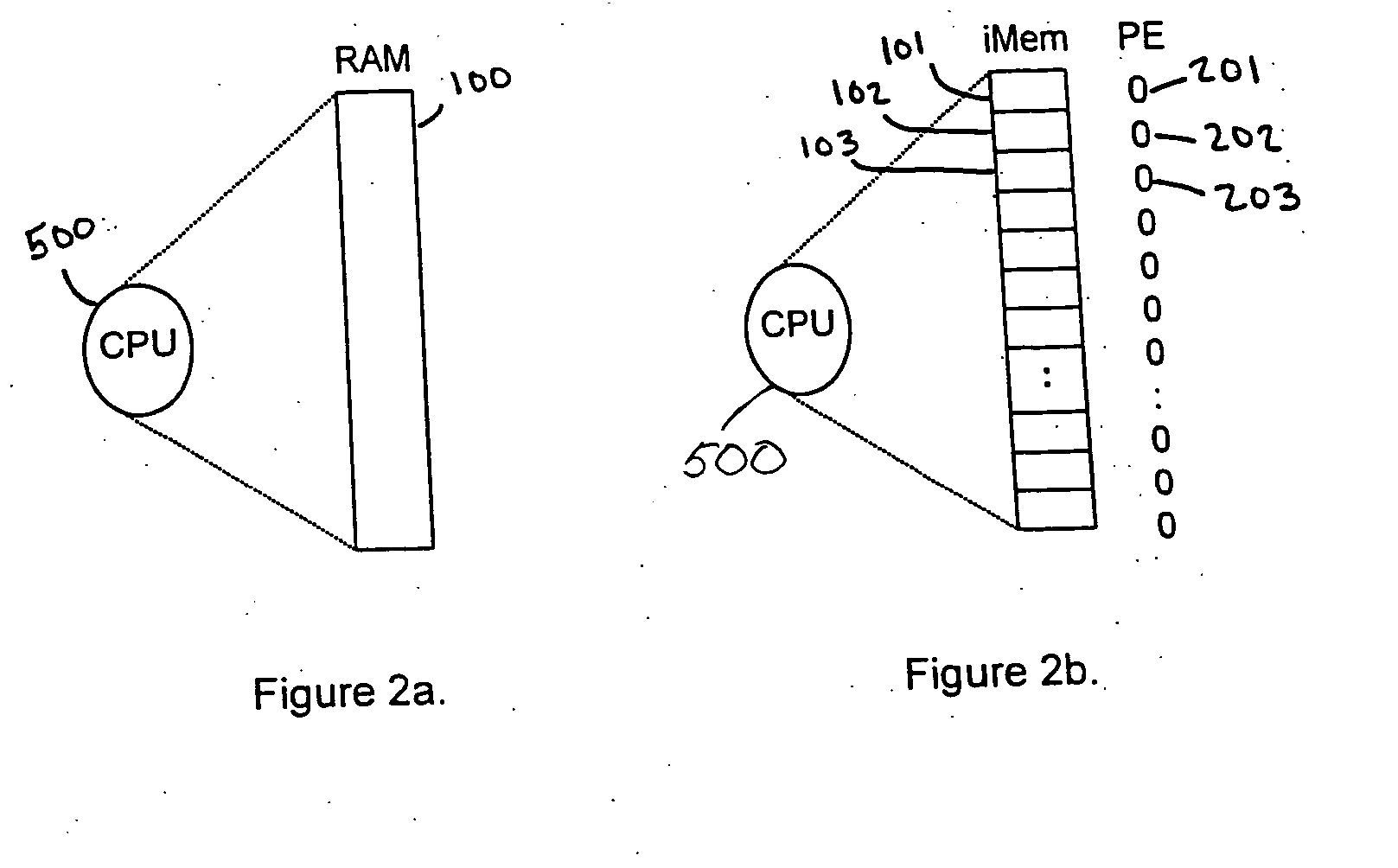

Intelligent memory device with ASCII registers

InactiveUS20050172087A1Extraordinary capabilityEconomic benefitMultiprogramming arrangementsSoftware simulation/interpretation/emulationMemory addressData stream

An ASCII-based processing system is disclosed. A memory is divided into a plurality of logical partitions. Each partition has a range of memory addresses and includes information associated with a particular task. Task information includes contents of task state register and one or more task data registers, with each task data register having an ASCII name. Each task data register is successively labeled with a unique alphabetic character label starting with the character ‘A.’ A dataflow unit within the processing system is configured to manage a mapping between registers with ASCII names and the memory addresses of a particular task. Task instructions can include ASCII characters that indicate a request for resources and indicate the ASCII-character designated names of task data registers on which the task instruction operates. A processing element receiving the task instruction performs the operation indicated by the ASCII operator code on the indicated task data registers.

Owner:KLINGMAN REVOCABLE TRUST

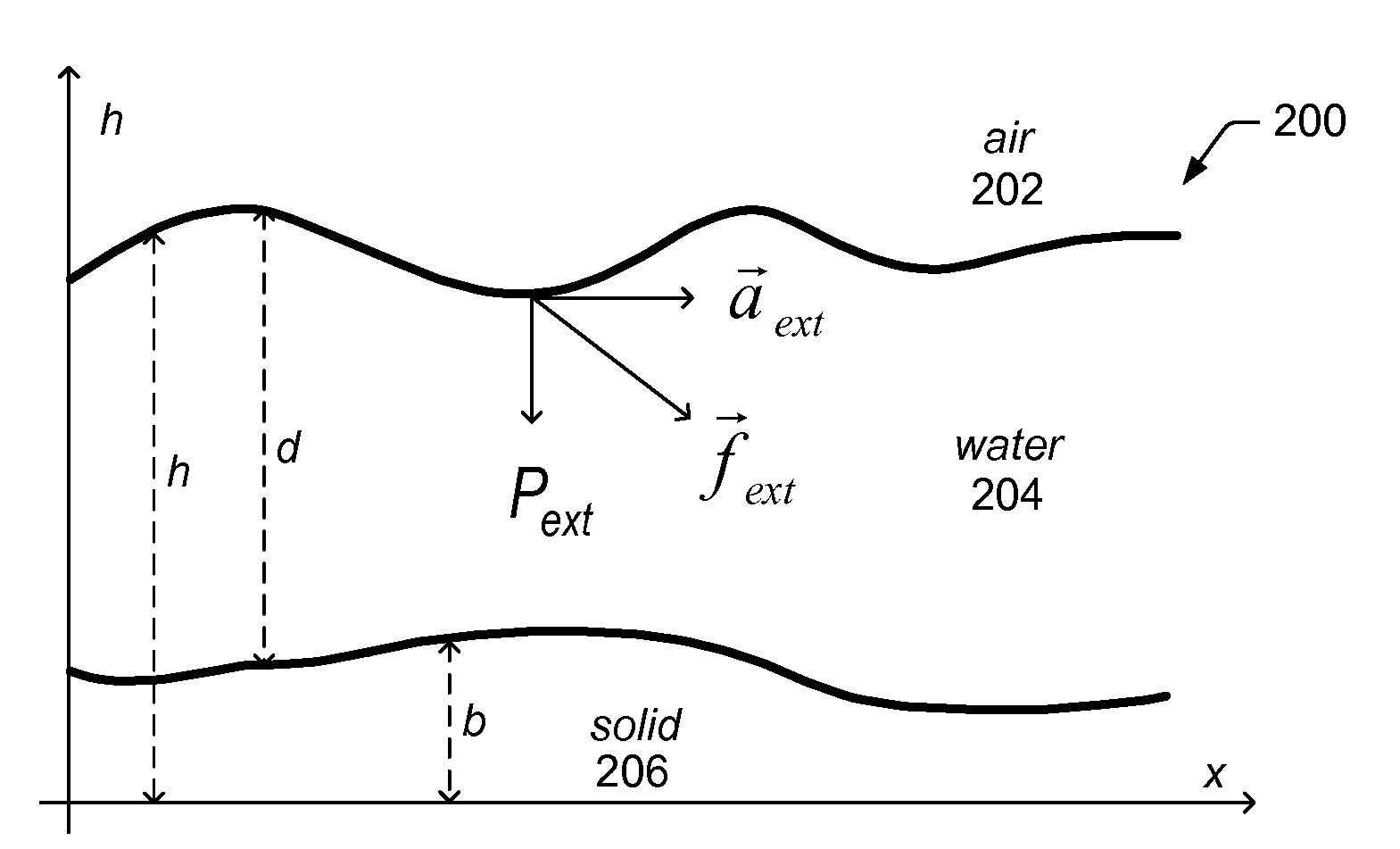

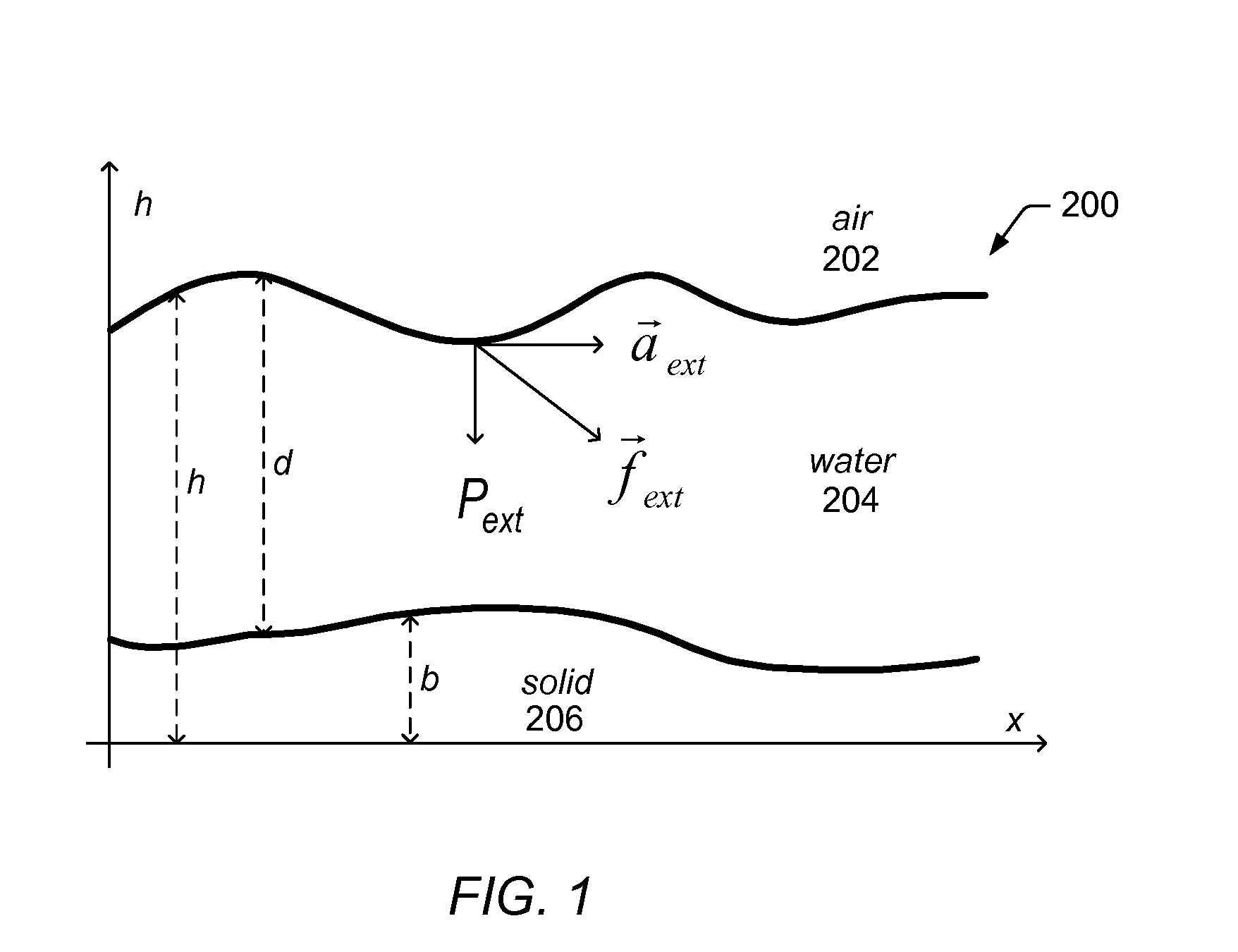

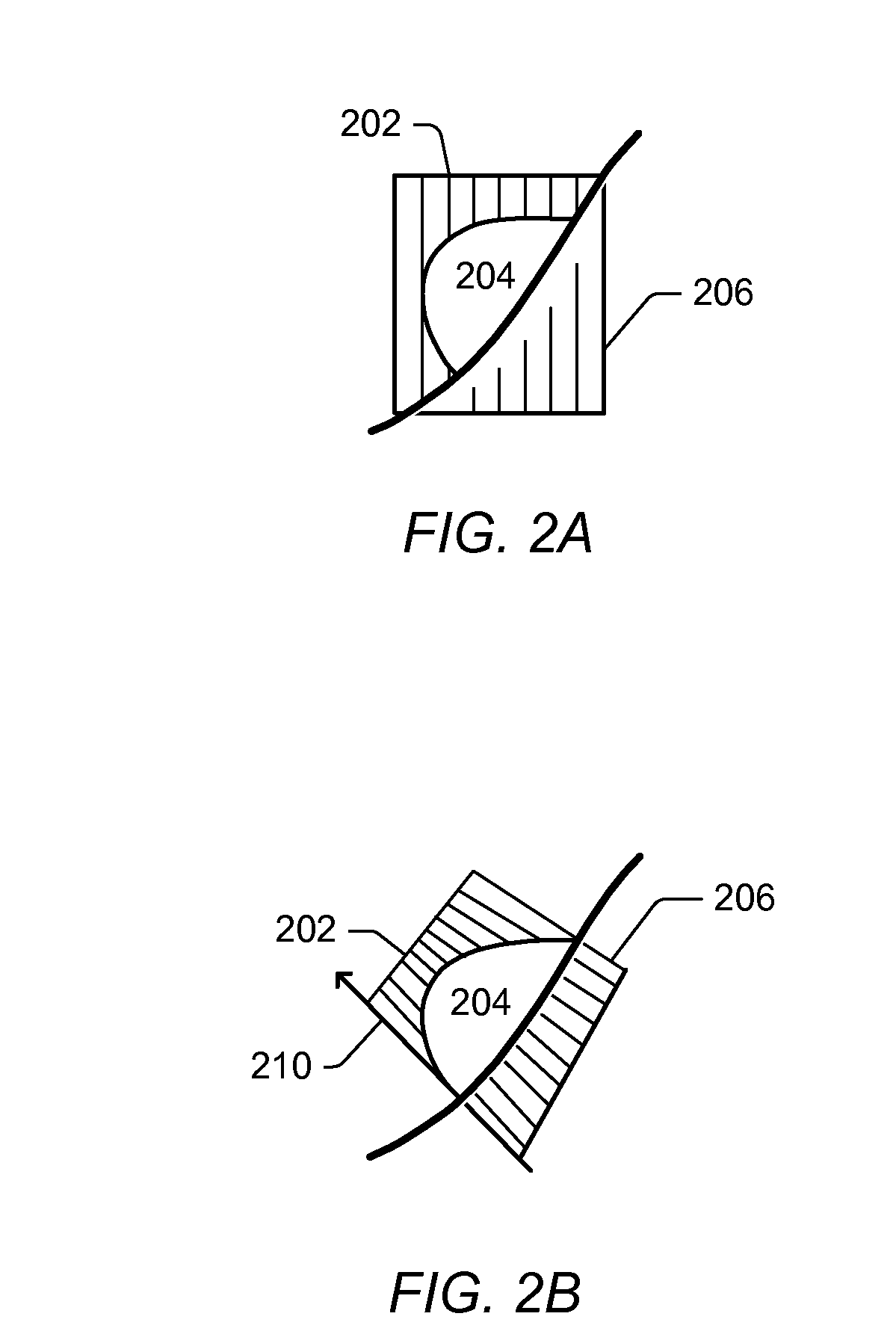

System and Method for Simulating Shallow Water Effects on Arbitrary Surfaces

ActiveUS20080177519A1Effective simulationFacilitate real-time fluid controlAnimationImage generationFluid controlWave equation

A system and method for shallow water simulation may provide a framework for solving General Shallow Wave Equations (GSWE) to efficiently simulate 3D fluid effects on arbitrary surfaces using a height field representation. The height field representation may include height columns constructed along surface normals, which may be dependent on a condition of boundary cells adjacent to fluid cells and / or artificial viscosity effects. The framework may provide implicit schemes for solving for the effects of external forces applied to the fluid, including gravity and surface tension, and explicit schemes for solving for advection effects. The system and method may be implemented on general-purpose CPU(s) and / or GPU(s) and may be capable of simulating a variety of fluid effects including: waves, rivulets and streams, drops, and capillary events. In some embodiments, the system and method may achieve real-time fluid control and fluid shape design through user-interaction (e.g., in a graphical painting application).

Owner:ADOBE INC

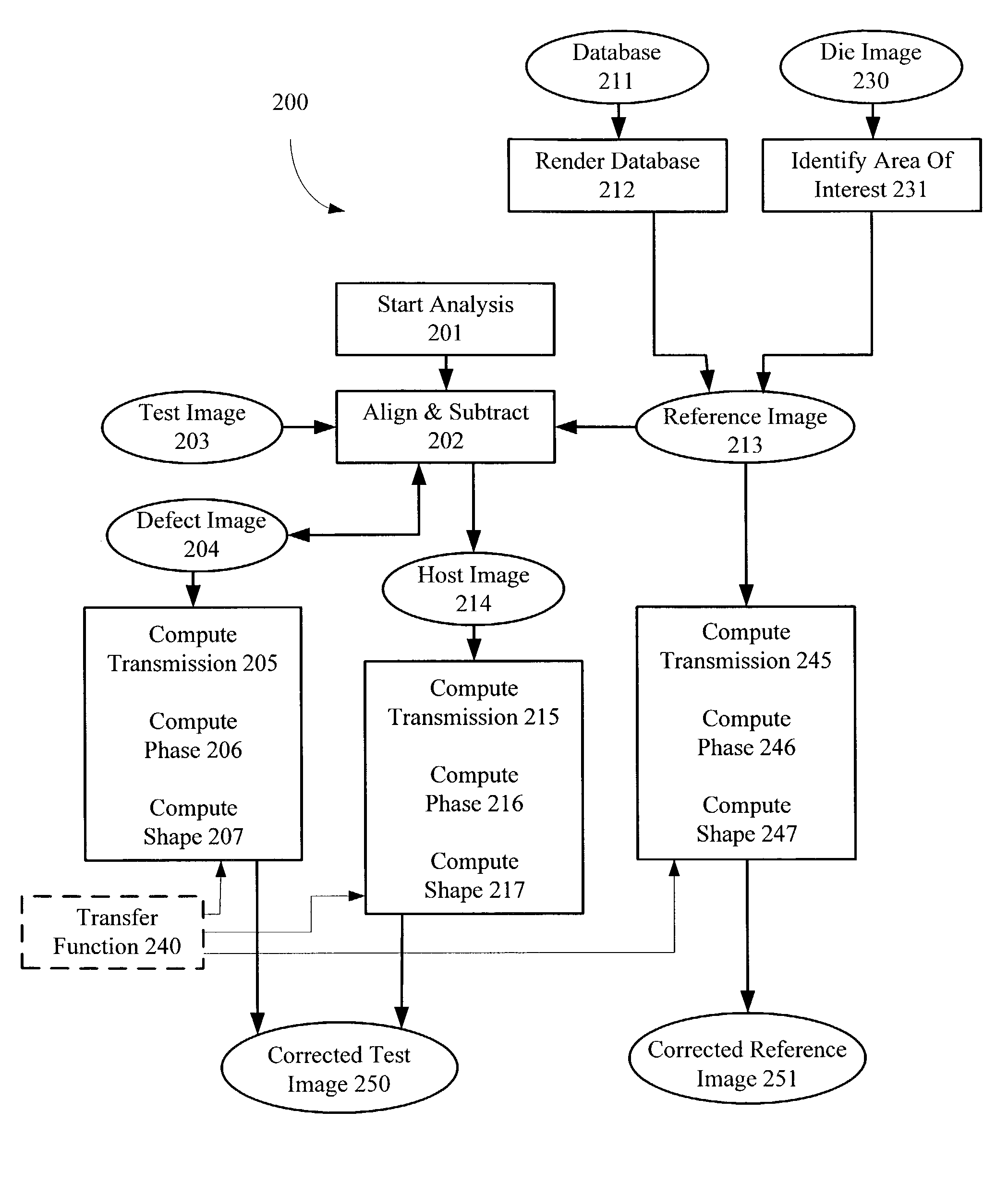

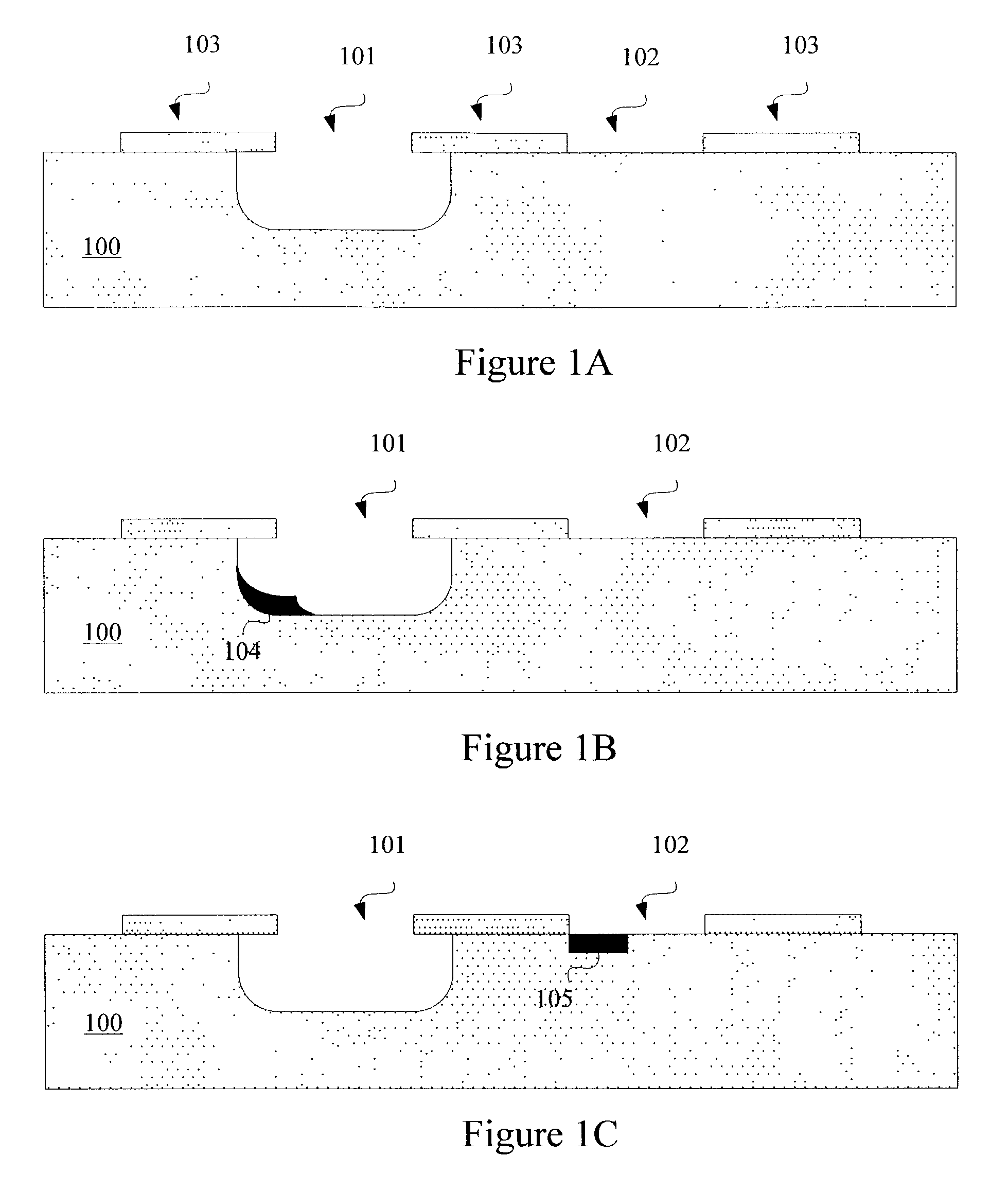

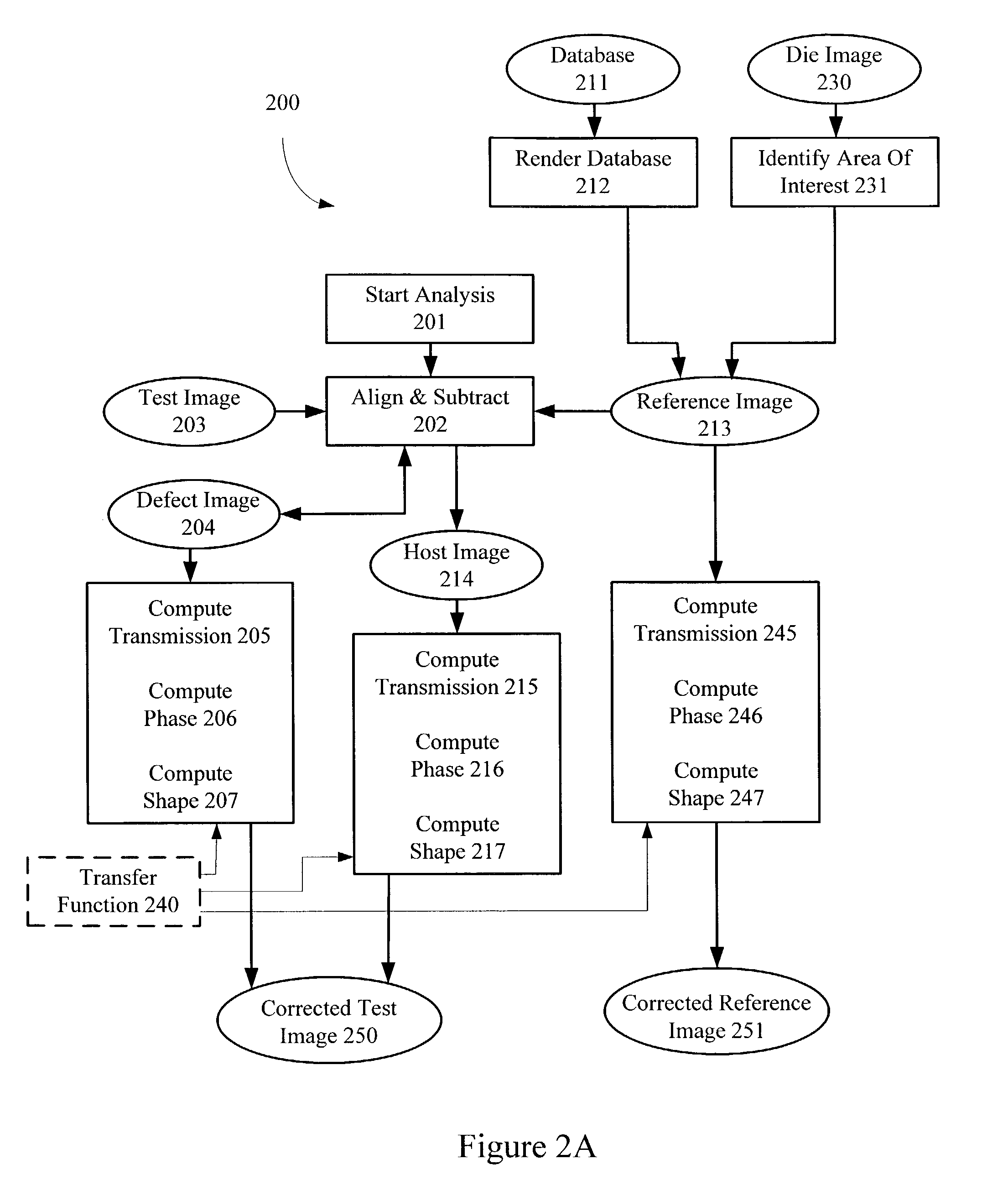

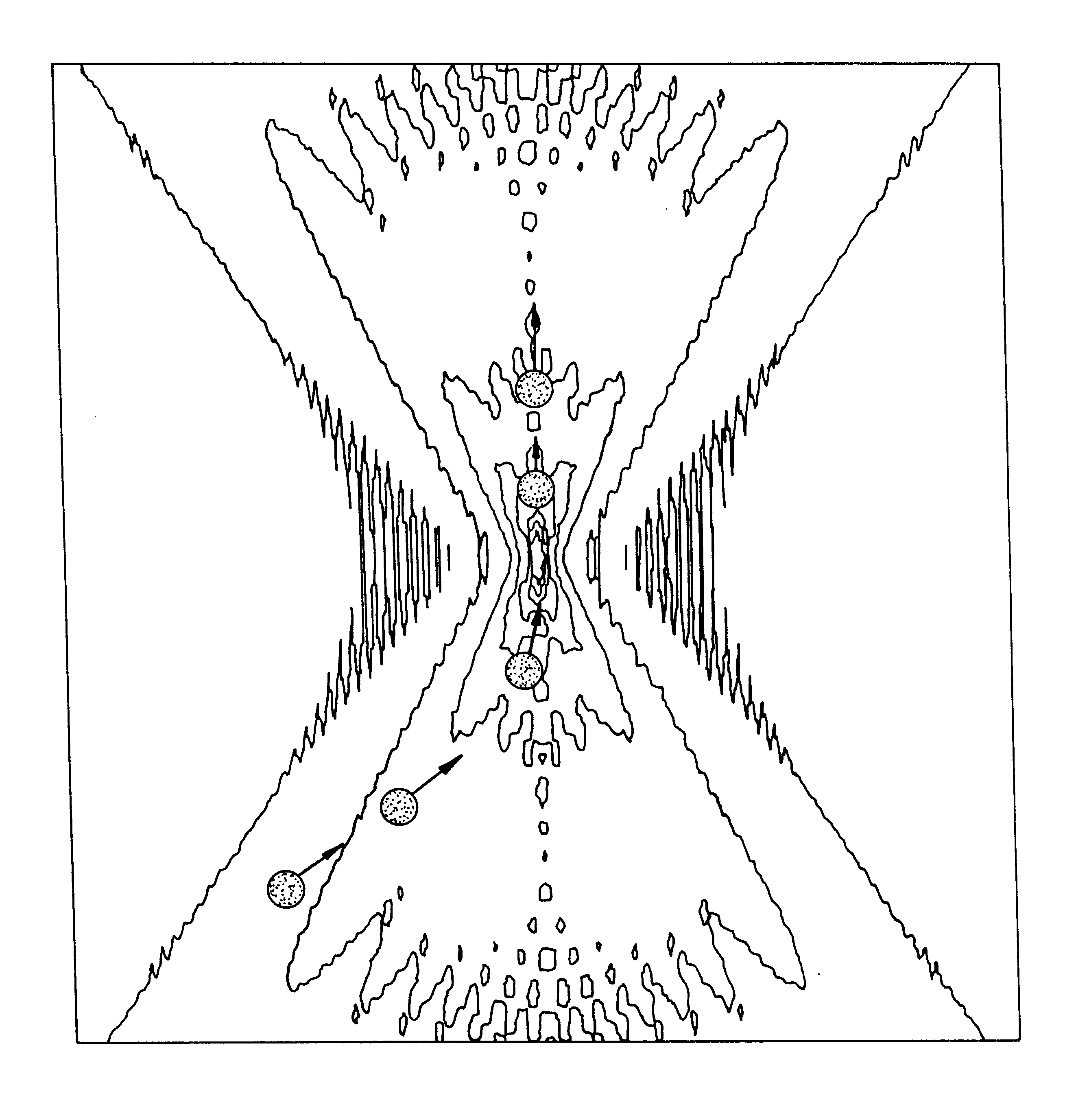

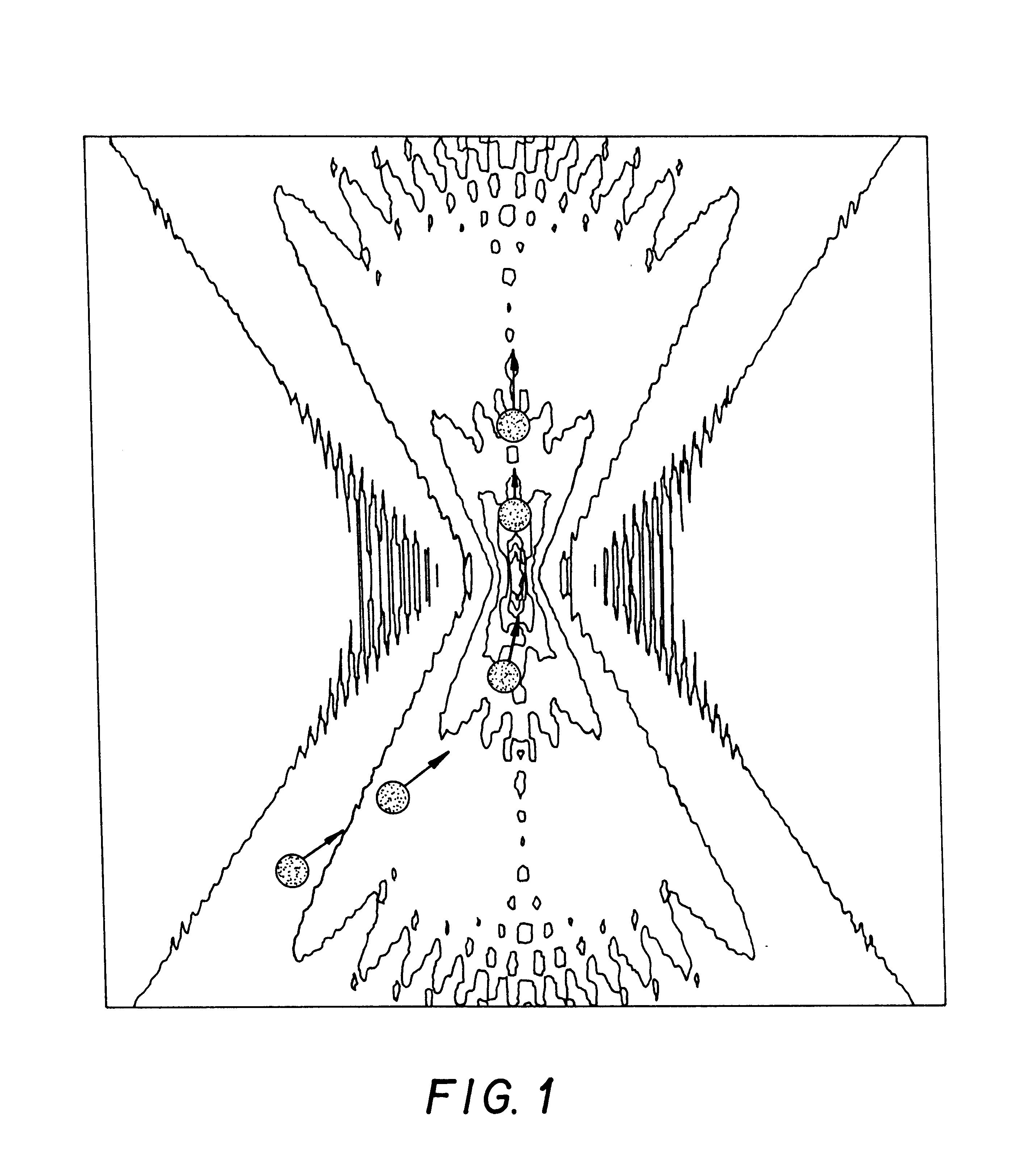

Soft defect printability simulation and analysis for masks

ActiveUS7043071B2Spread the wordGood decisionImage enhancementImage analysisEngineeringStandard test image

Masks that include optical proximity correction or phase shifting regions are increasingly being used in the manufacturing process. These masks, either initially or after repair, can have “soft” defects, e.g. phase and / or transmission defects. In accordance with one feature of the invention, soft defect information can be computed from standard test images of a mask. This soft defect information can be used to generate an accurate simulated wafer image, thereby providing valuable defect impact information to a user. Knowing the impact of the soft defect can enable a user to make better decisions regarding the mask. Specifically, a user can now with confidence accept the mask for the desired lithographic process, repair the mask at certain critical locations, or reject the mask, all without exposing a wafer.

Owner:SYNOPSYS INC

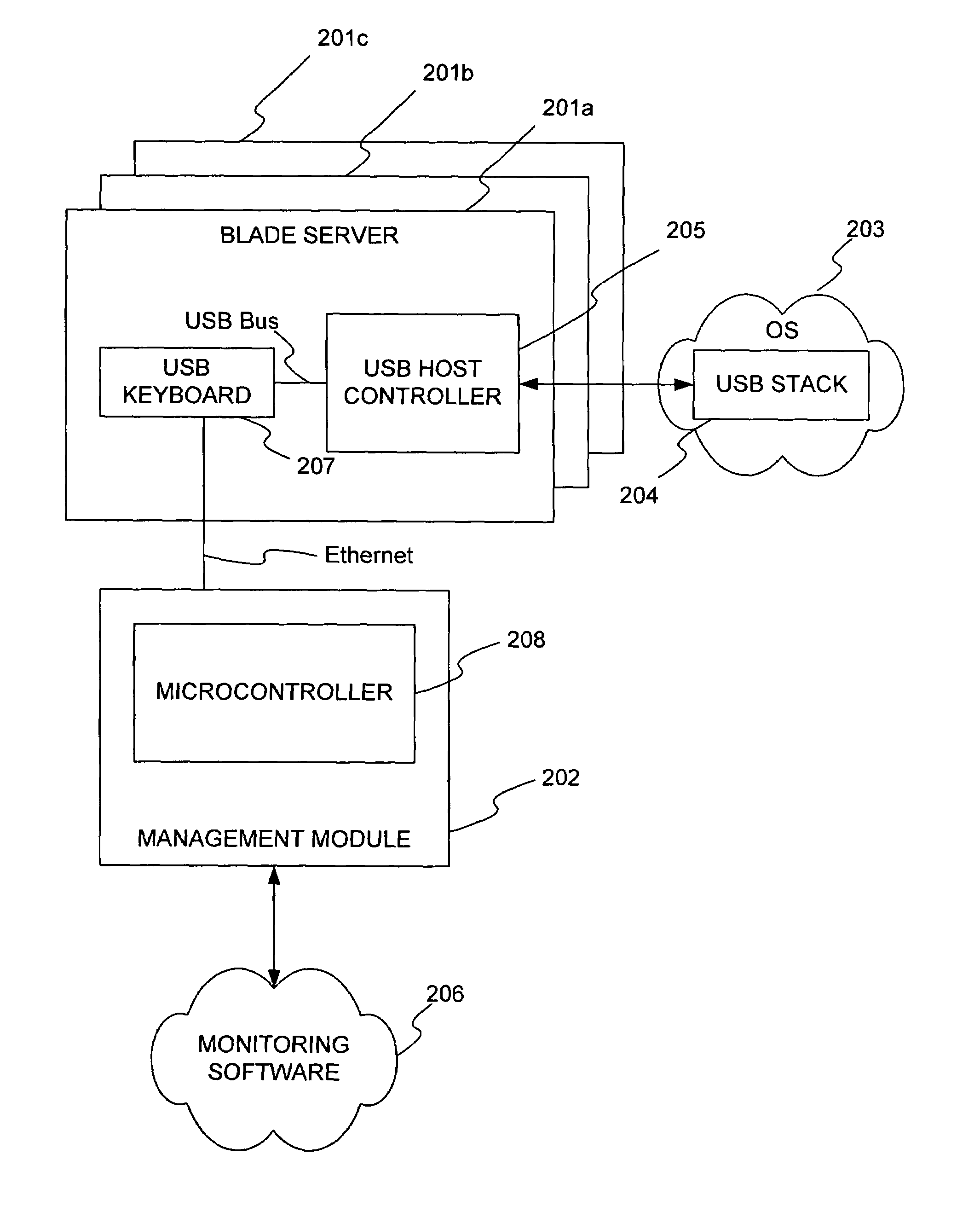

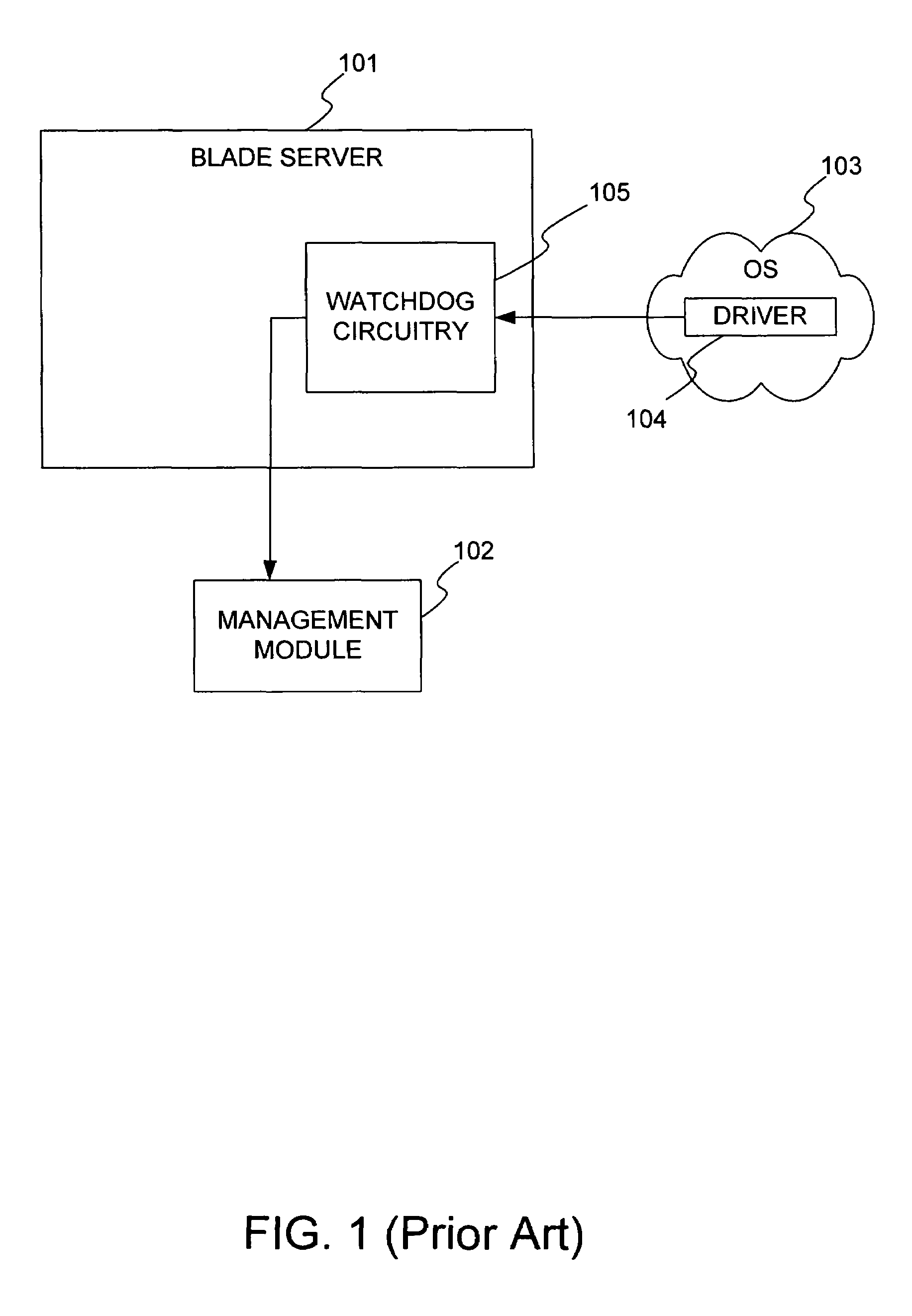

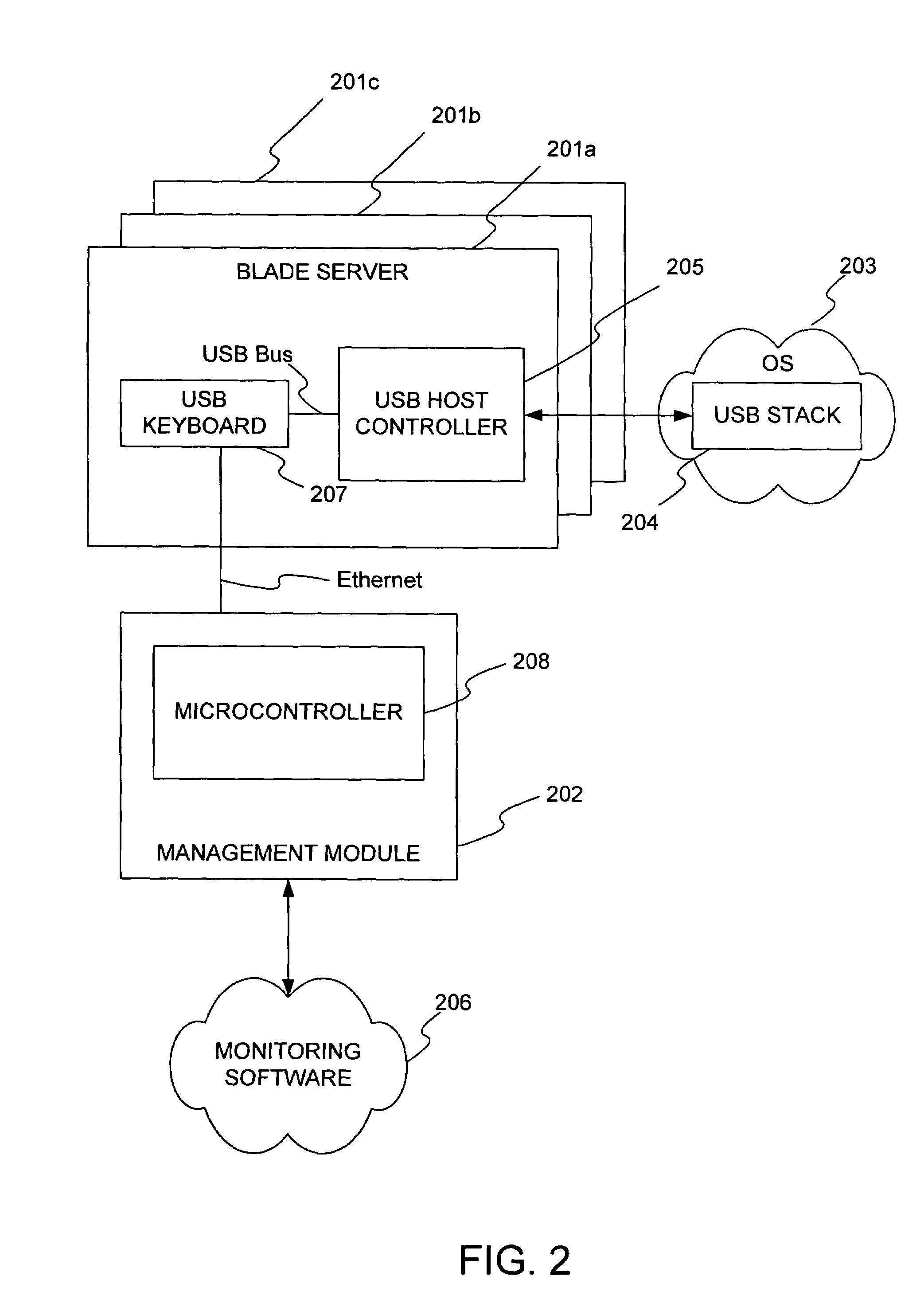

Software independent watchdogging scheme for monitoring operating system

InactiveUS7216265B2Increase system costState can be quickly and efficientlyNon-redundant fault processingOperational systemEngineering

An improved method and system for determining the state of an operating system includes an operating system, a USB host controller that is driven by the operating system to send a polling signal to a USB device, and a management module that monitors the polling signal. If the polling signal has stopped, then the management module takes corrective action to restore the operating system. No specialized software or specialized hardware is required to determine the state of the operating system. The state of the operating system can be determined quickly and efficiently without adding to the costs of the system.

Owner:INT BUSINESS MASCH CORP

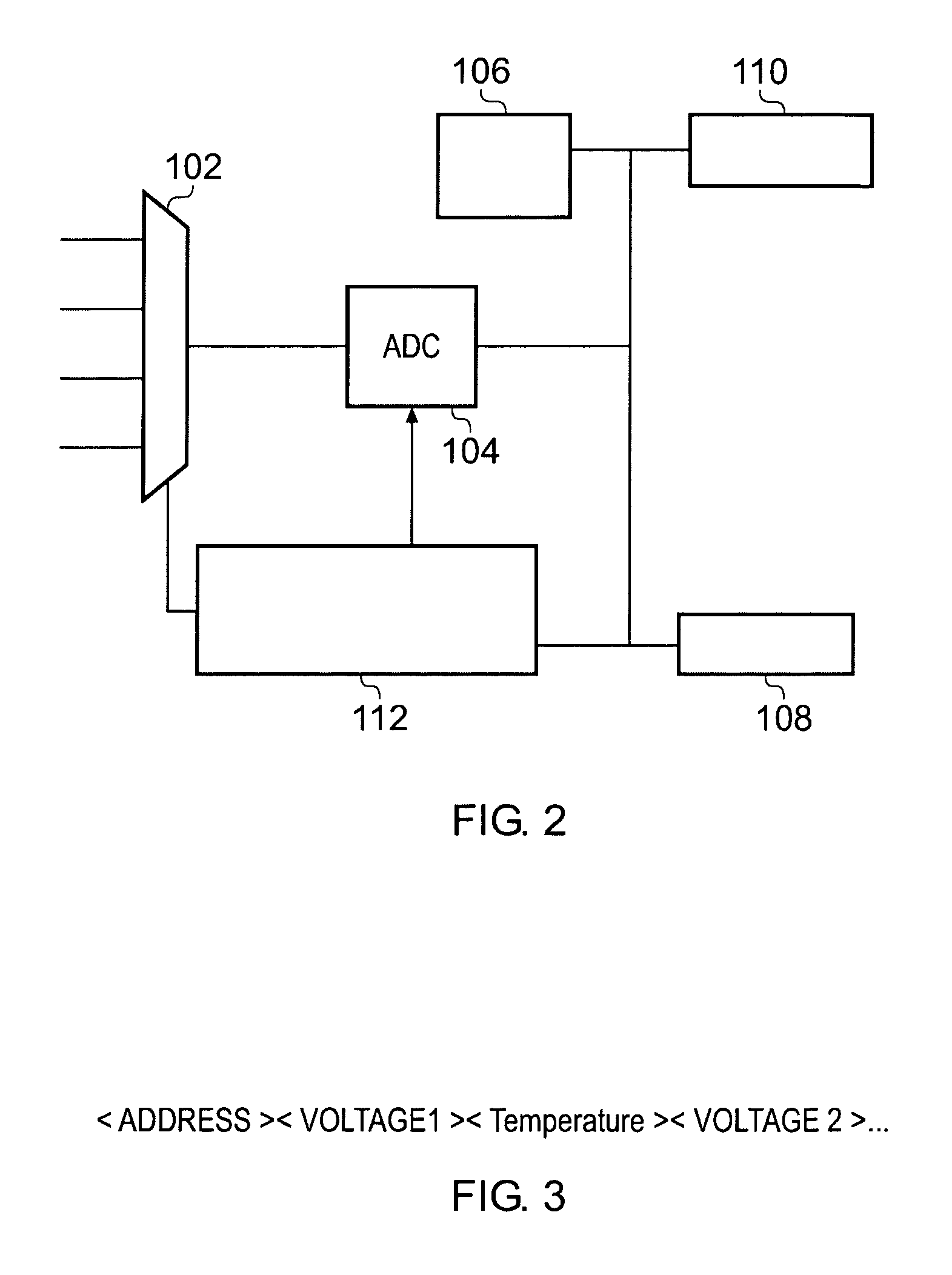

Battery monitoring apparatus and daisy chain interface suitable for use in a battery monitoring apparatus

ActiveUS7859223B2Reduce potential differenceReduce the voltage rangeBatteries circuit arrangementsMaterial analysis by electric/magnetic meansElectrical batteryData acquisition

A battery monitor for monitoring the performance of at least one battery within an array of batteries, comprising: a data acquisition device for measuring at least one parameter of the at least one battery associated with the battery monitor, a first data interface operable to exchange data with a first device, and a second data interface operable to exchange data with a second device.

Owner:ANALOG DEVICES INC

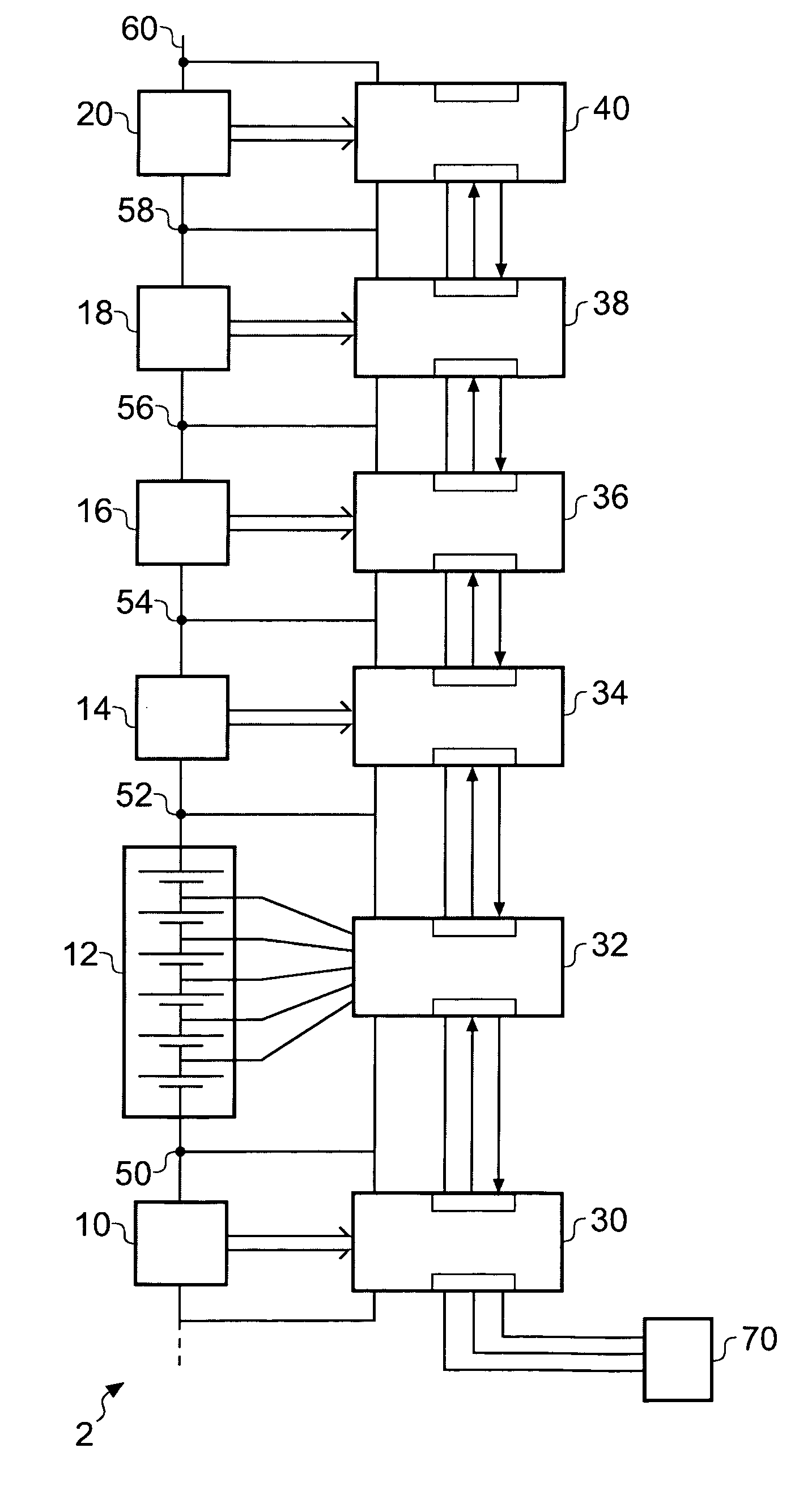

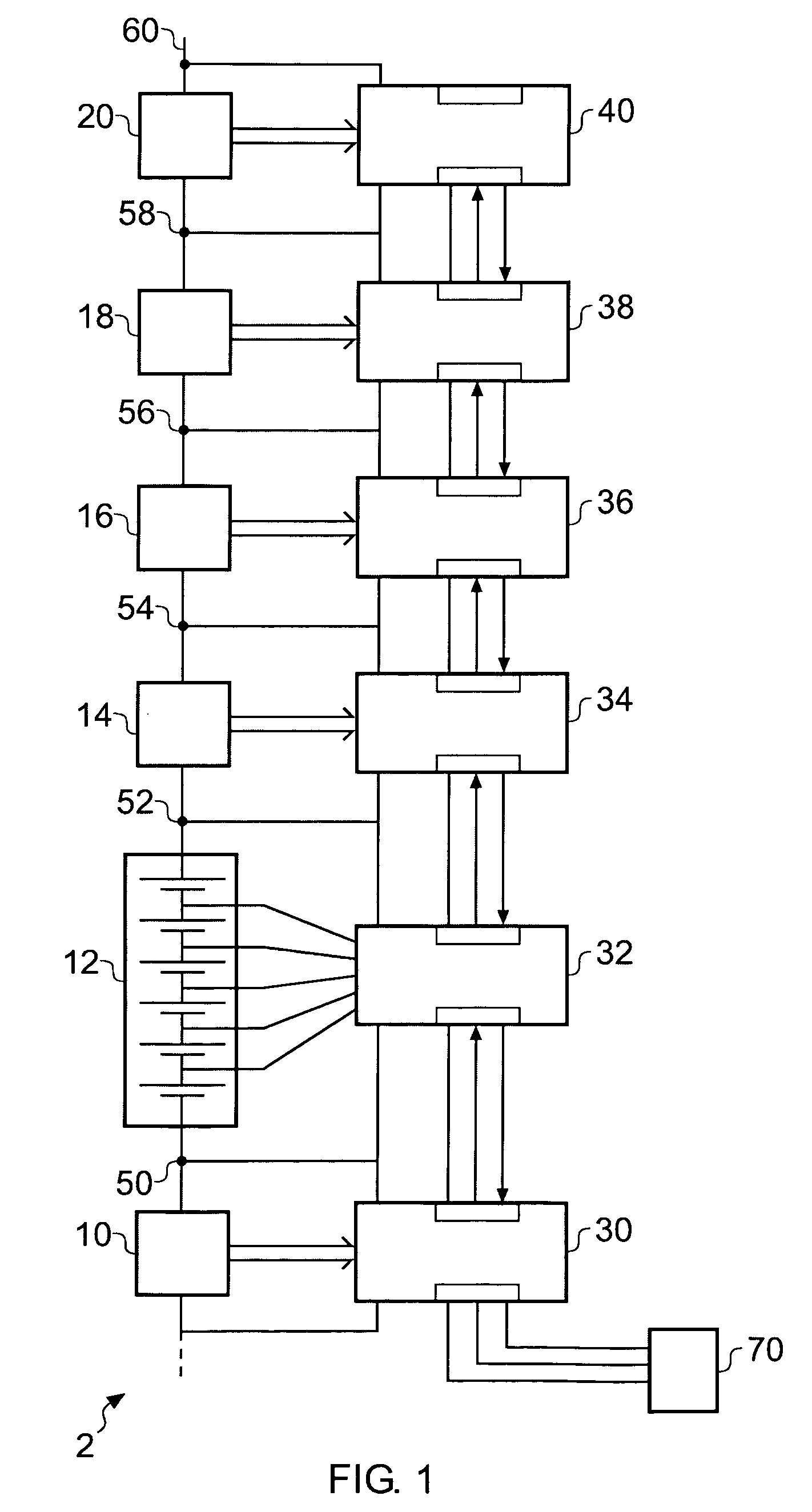

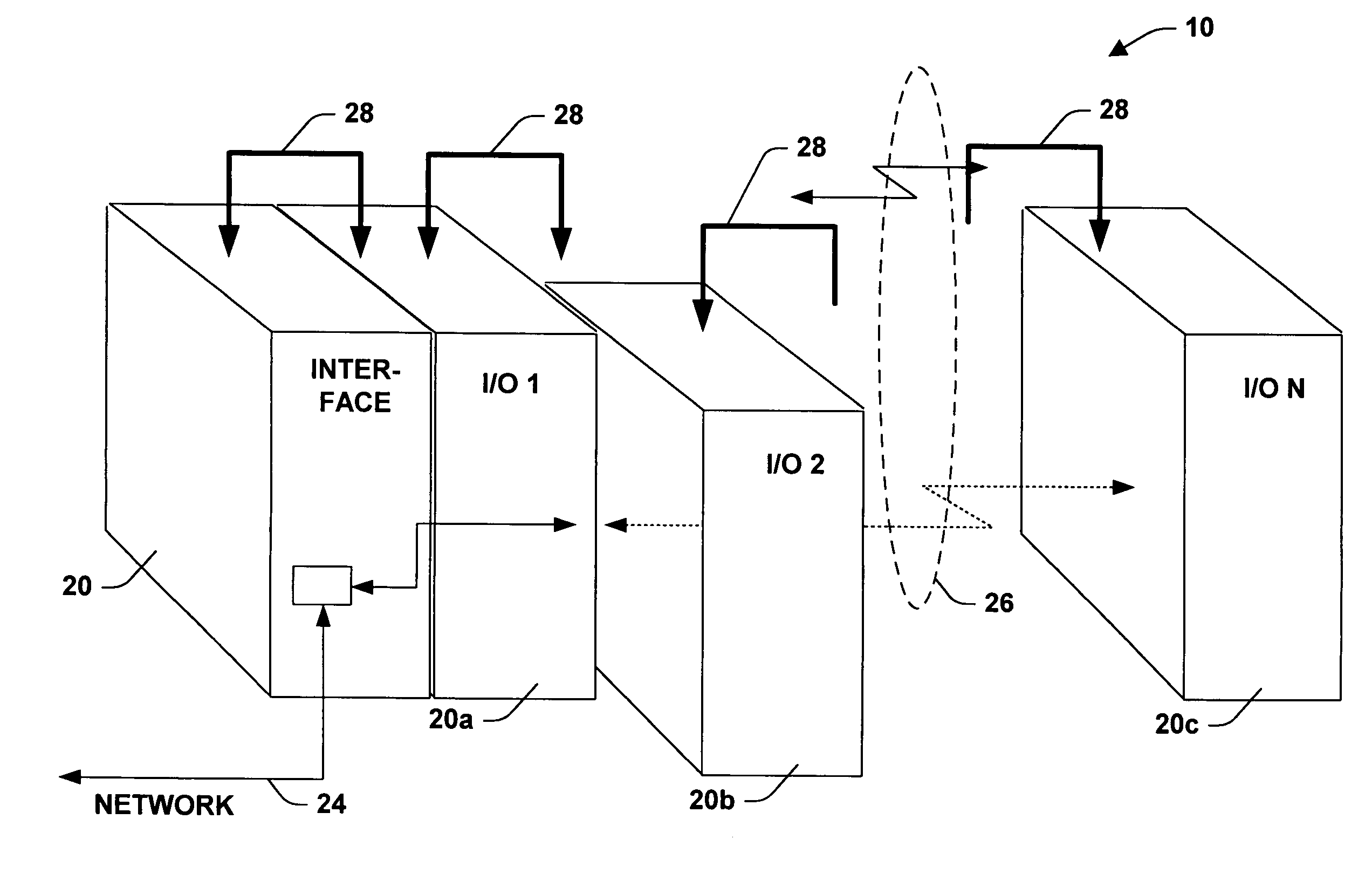

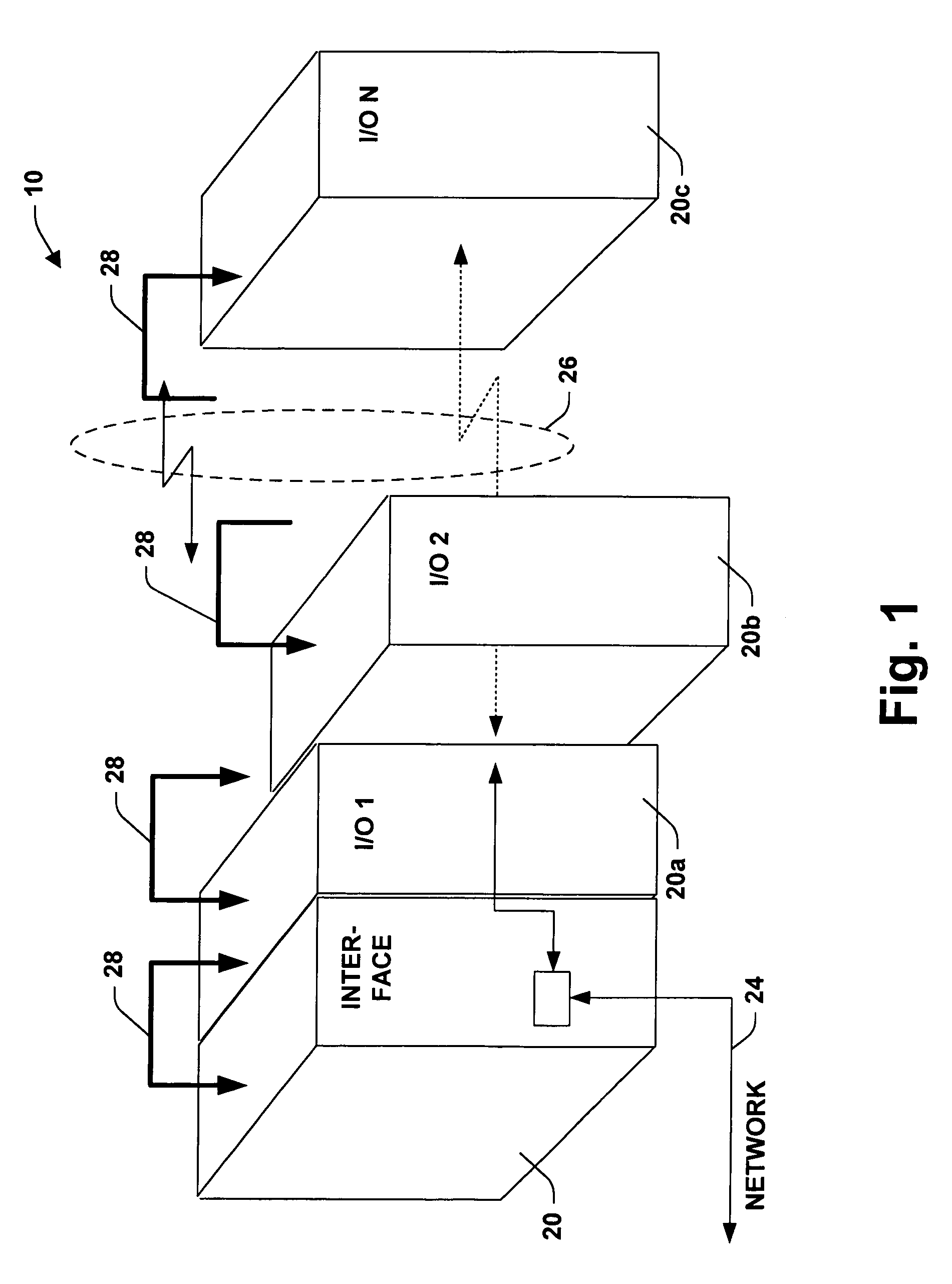

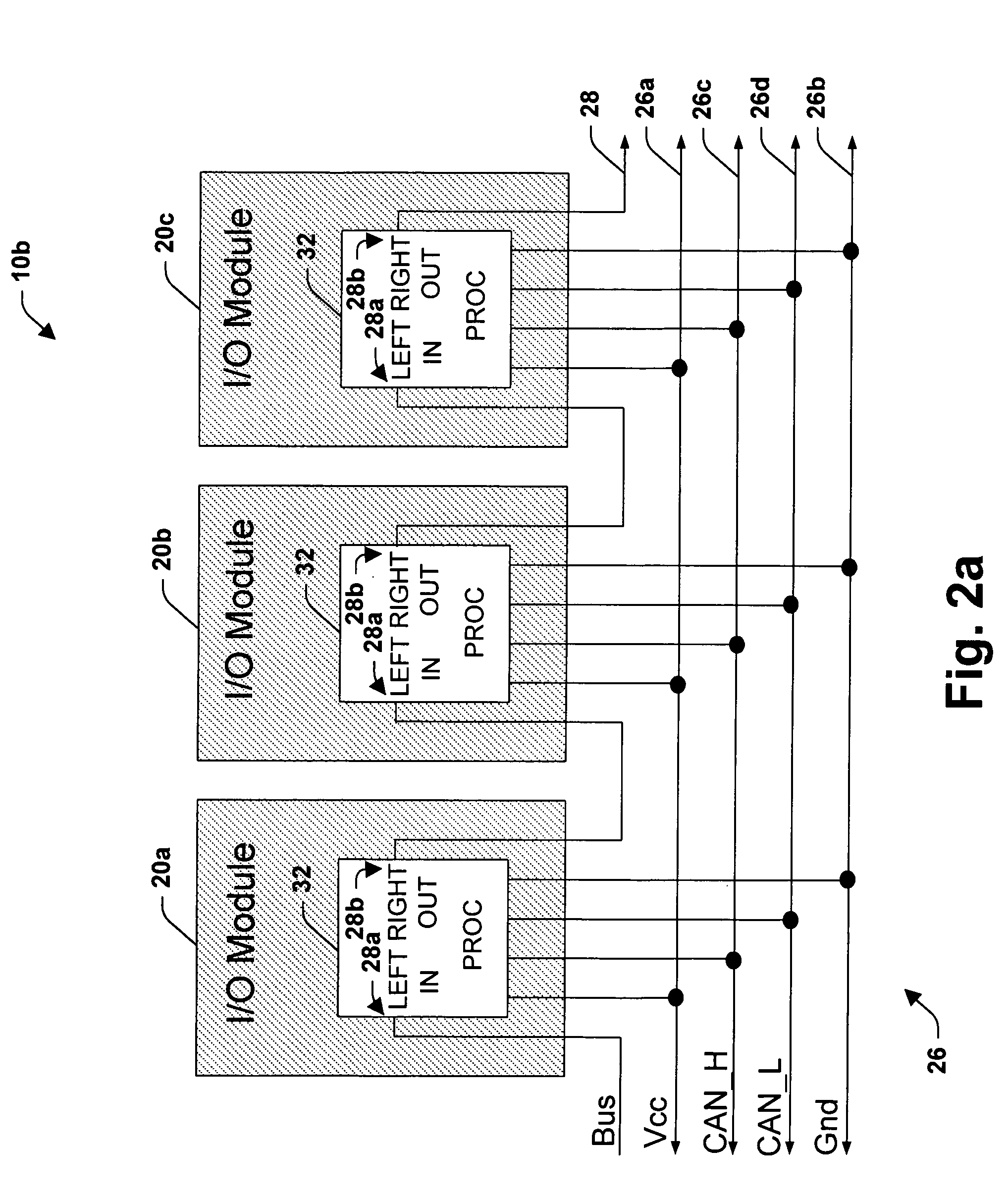

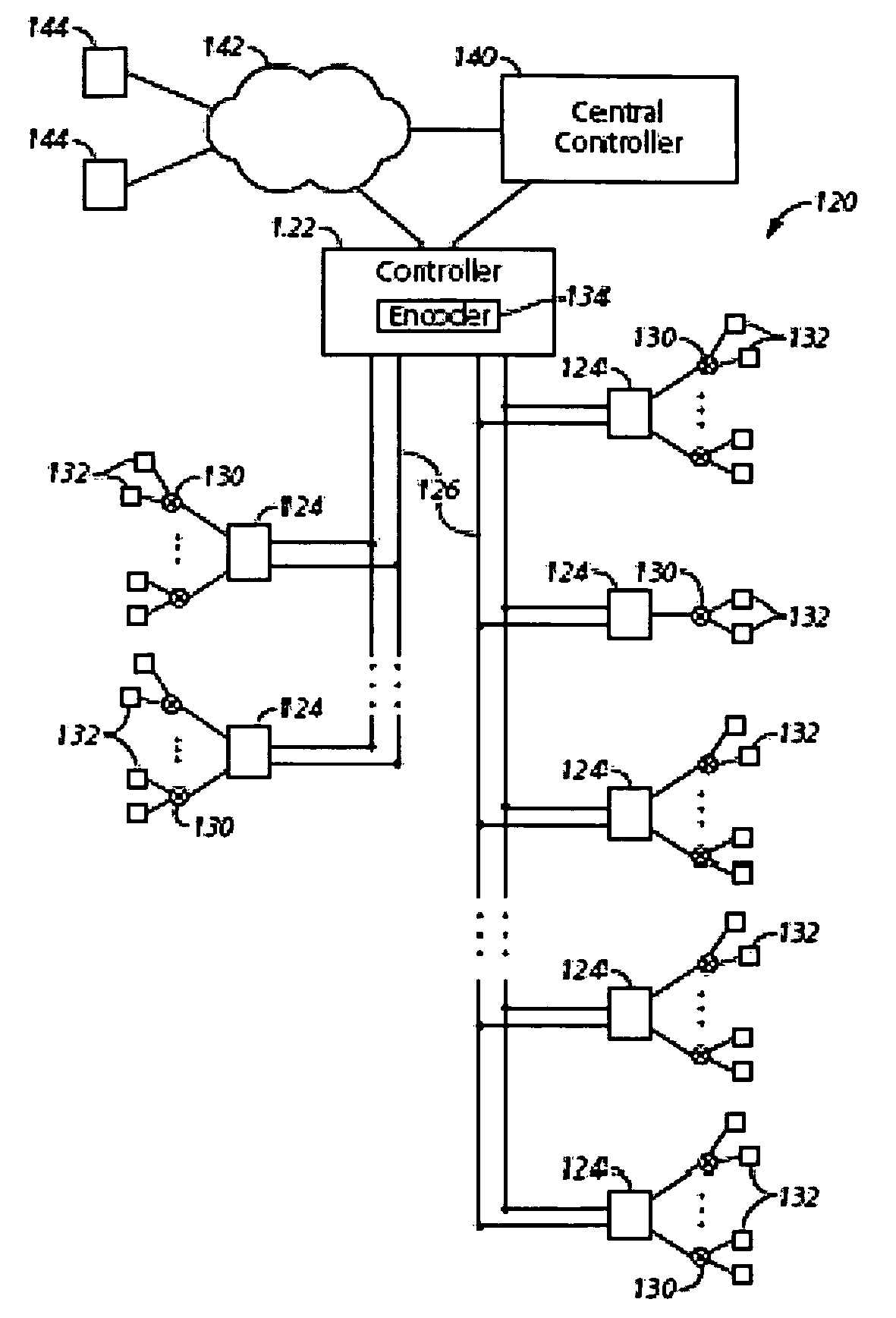

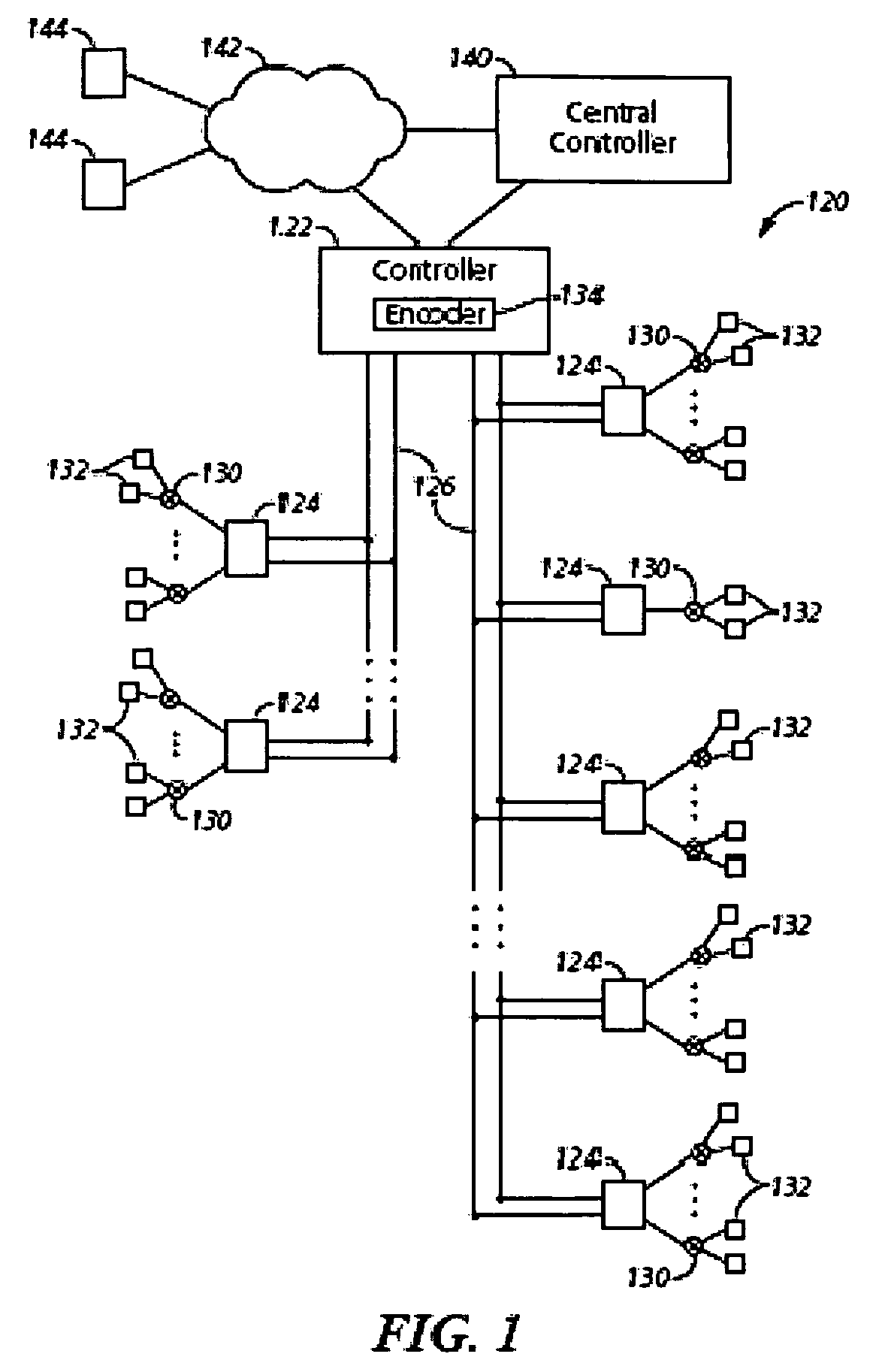

Pointbus architecture and automatic sequential addressing

InactiveUS7228363B1Low costReduce system costEnergy efficient ICTError preventionComputer architecture

A system for automatically configuring I / O devices is provided in accordance with the present invention. The system includes a plurality of I / O devices operatively coupled to each other and a sub-system for determining physical locations of the I / O devices with respect to one another. The sub-system assigns node addresses to each I / O device—each assigned node address corresponds to the physical location of the respective I / O devices.

Owner:ROCKWELL AUTOMATION TECH

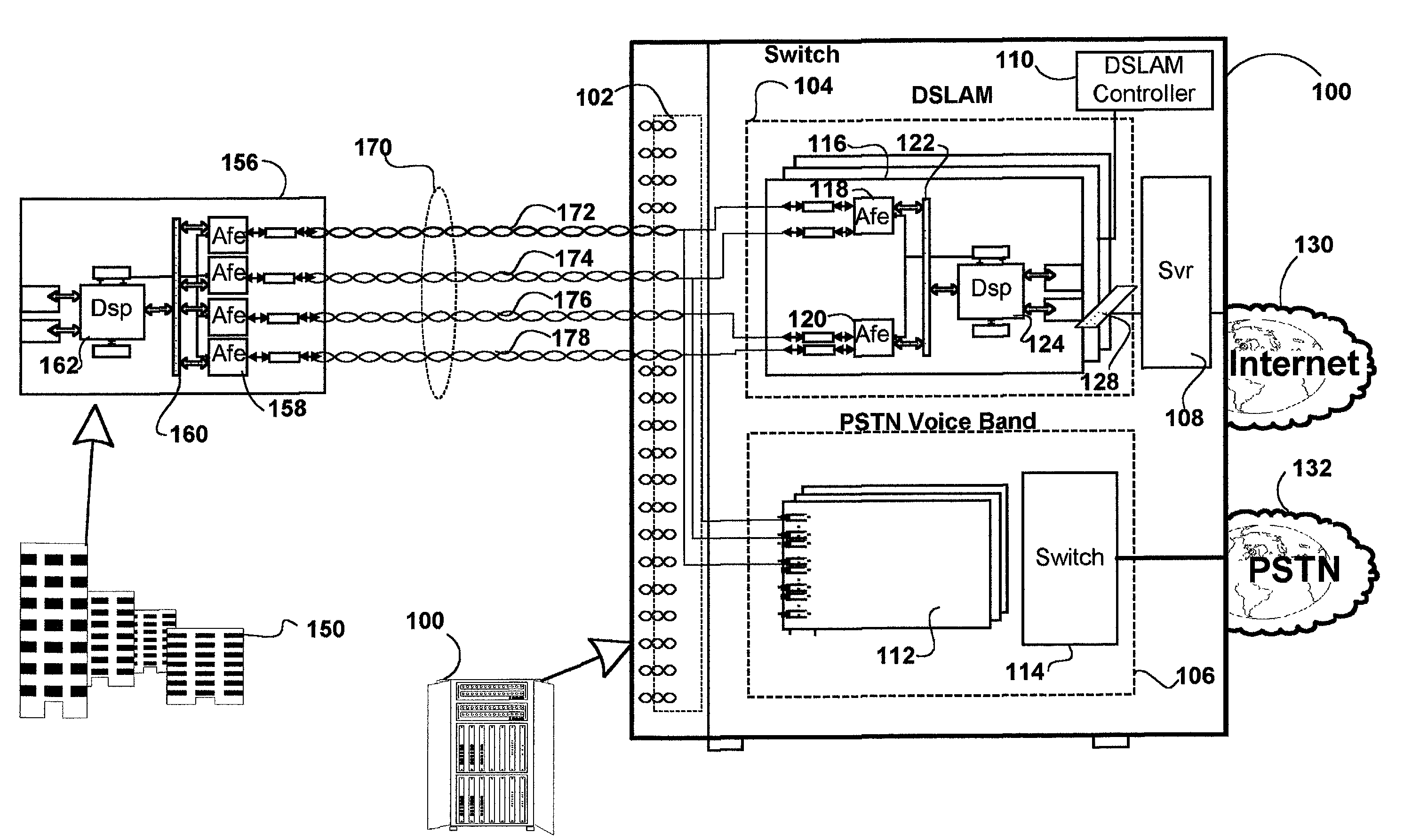

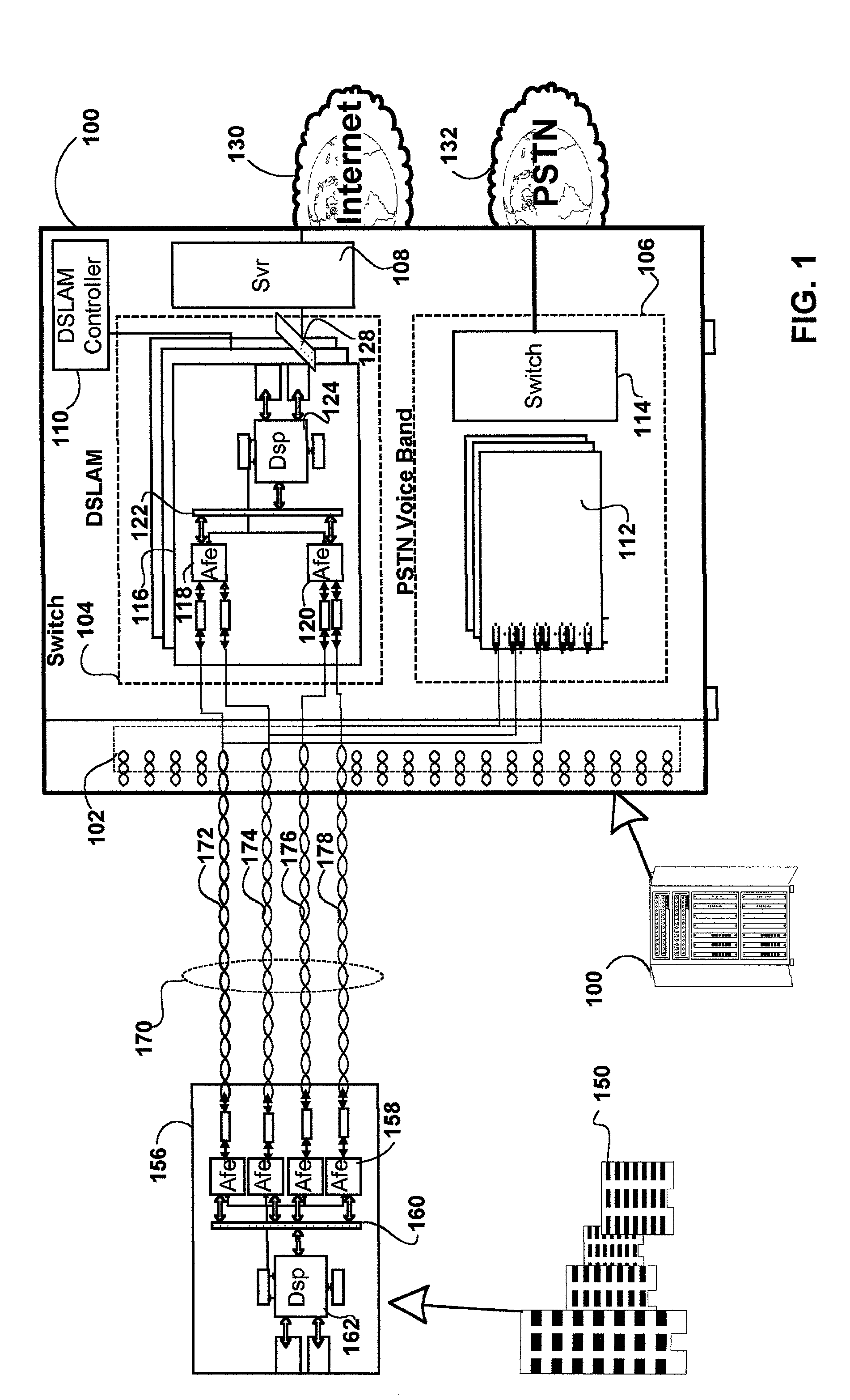

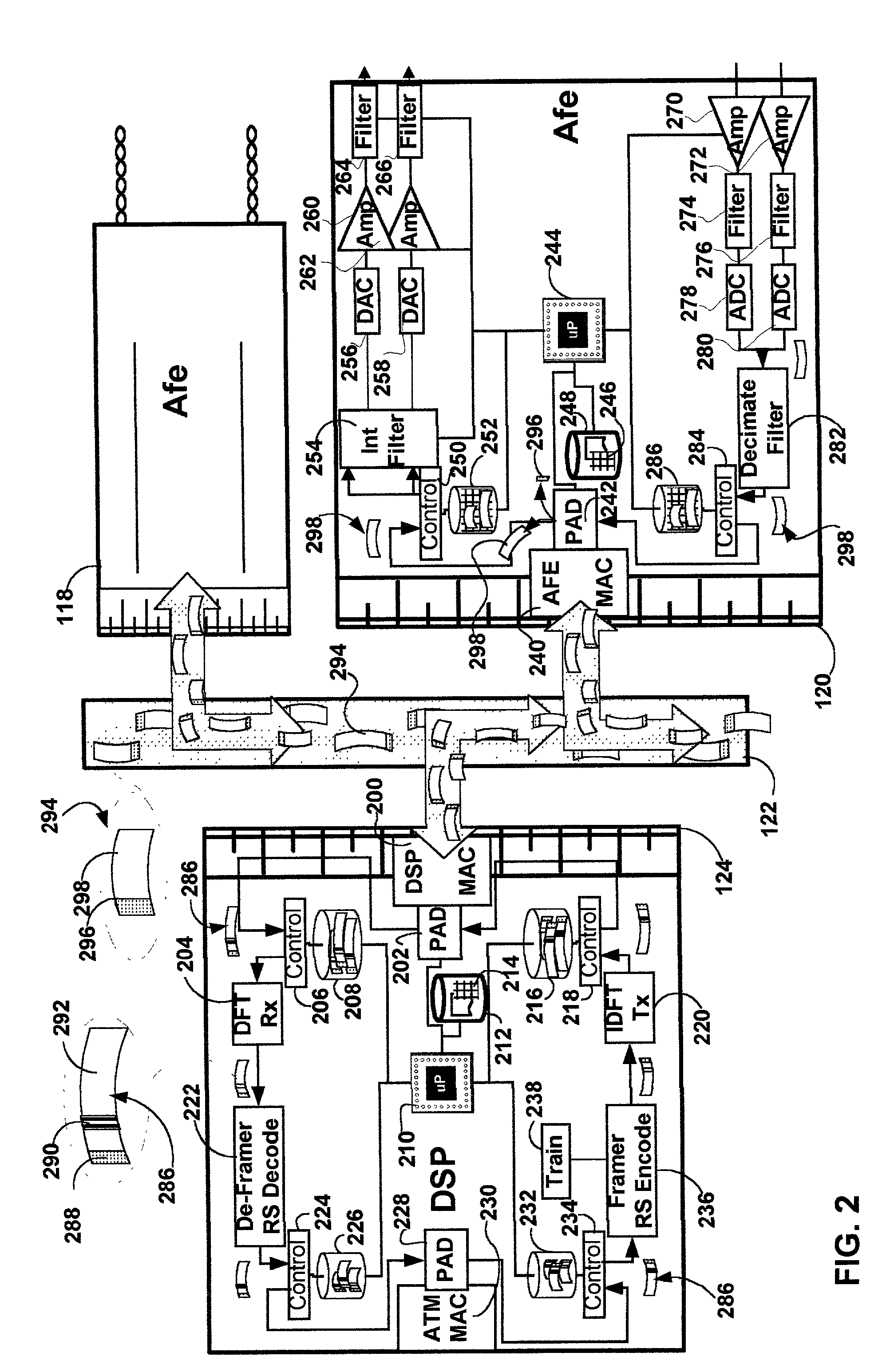

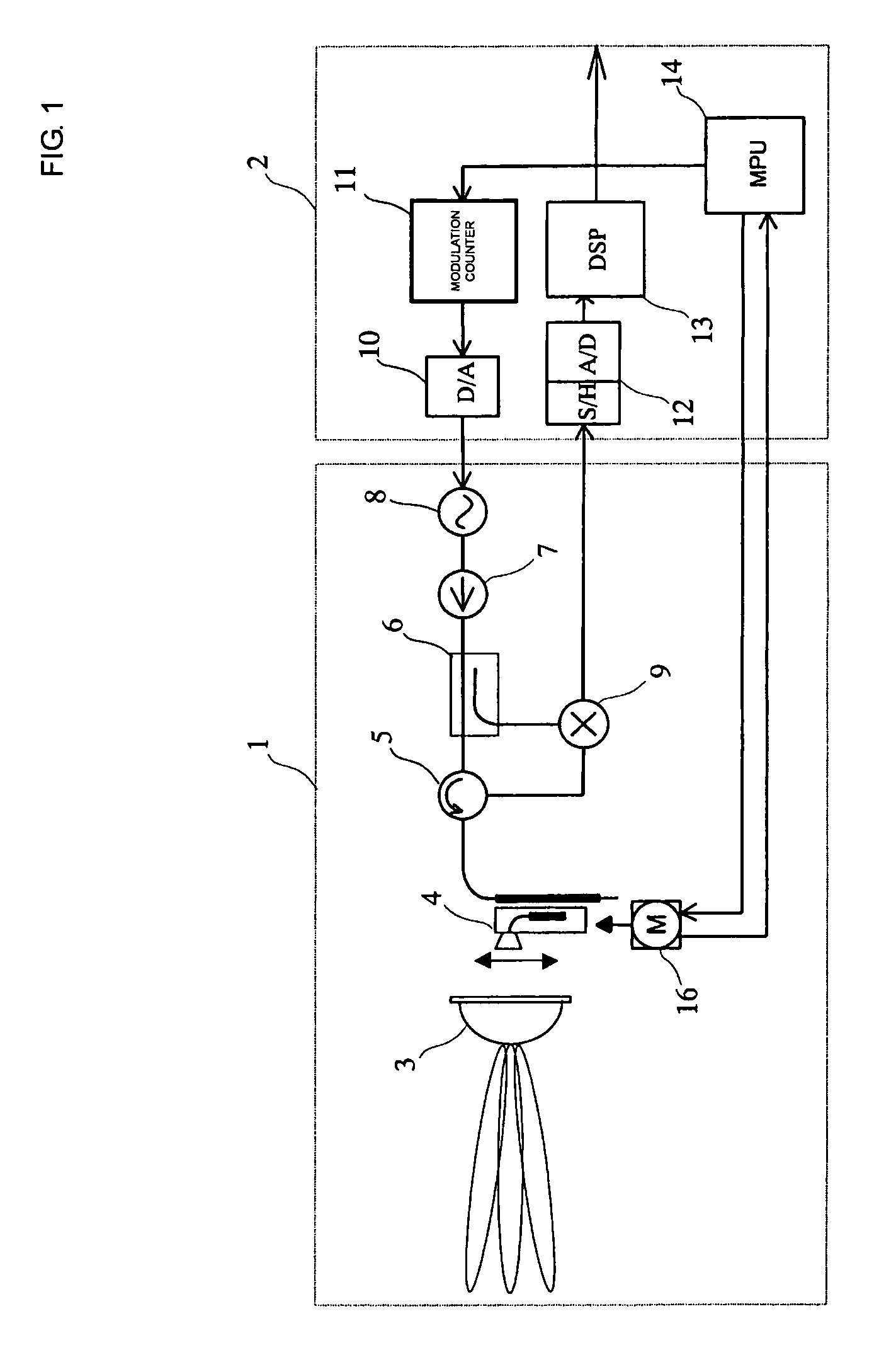

Method and apparatus for a variable bandwidth multi-protocol X-DSL transceiver

InactiveUS7315571B1Low costReduce complexityTelephonic communicationTime-division multiplexTransceiverMulti protocol

A transceiver for communicating a multi-tone modulated communication channel on a subscriber line. The transceiver includes: a digital signal processor (DSP) with a Fourier transform module and an analog front end (AFE). The DSP determines an available range of frequencies on the subscriber line and expands or contracts the tone spacing of each of a fixed number “N” of tones accordingly by decreasing or increasing the processing interval associated with the Fourier transform of each tone set. The AFE performs digital-to-analog conversion of the multi-tone modulated communication channel at rates compatible with the processing interval of the Fourier transform module; whereby the range of frequencies spanned by the modulated tones on the subscriber line conforms to the available of frequencies on the subscriber line.

Owner:IKANOS COMMUNICATIONS

Latching solenoid energy reserve

ActiveUS8295985B2Increase system costSmall power demandOperating means/releasing devices for valvesWatering devicesStored energySolenoid valve

An irrigation device including an actuator configured to control water flow to at least one water delivery device, a first stored energy source configured to power the actuator to effect irrigation via the at least one water delivery device, and a second stored energy source which is separate from the first stored energy source, wherein the second stored energy source is configured to power the actuator to terminate the irrigation via the at least one water delivery device. The irrigation devices further includes a controller configured to cause the first stored energy source to power the actuator to effect the irrigation, responsive to an instruction to provide irrigation, and to cause the second stored energy source to power the actuator to terminate the irrigation responsive to a termination condition.

Owner:RAIN BIRD CORP

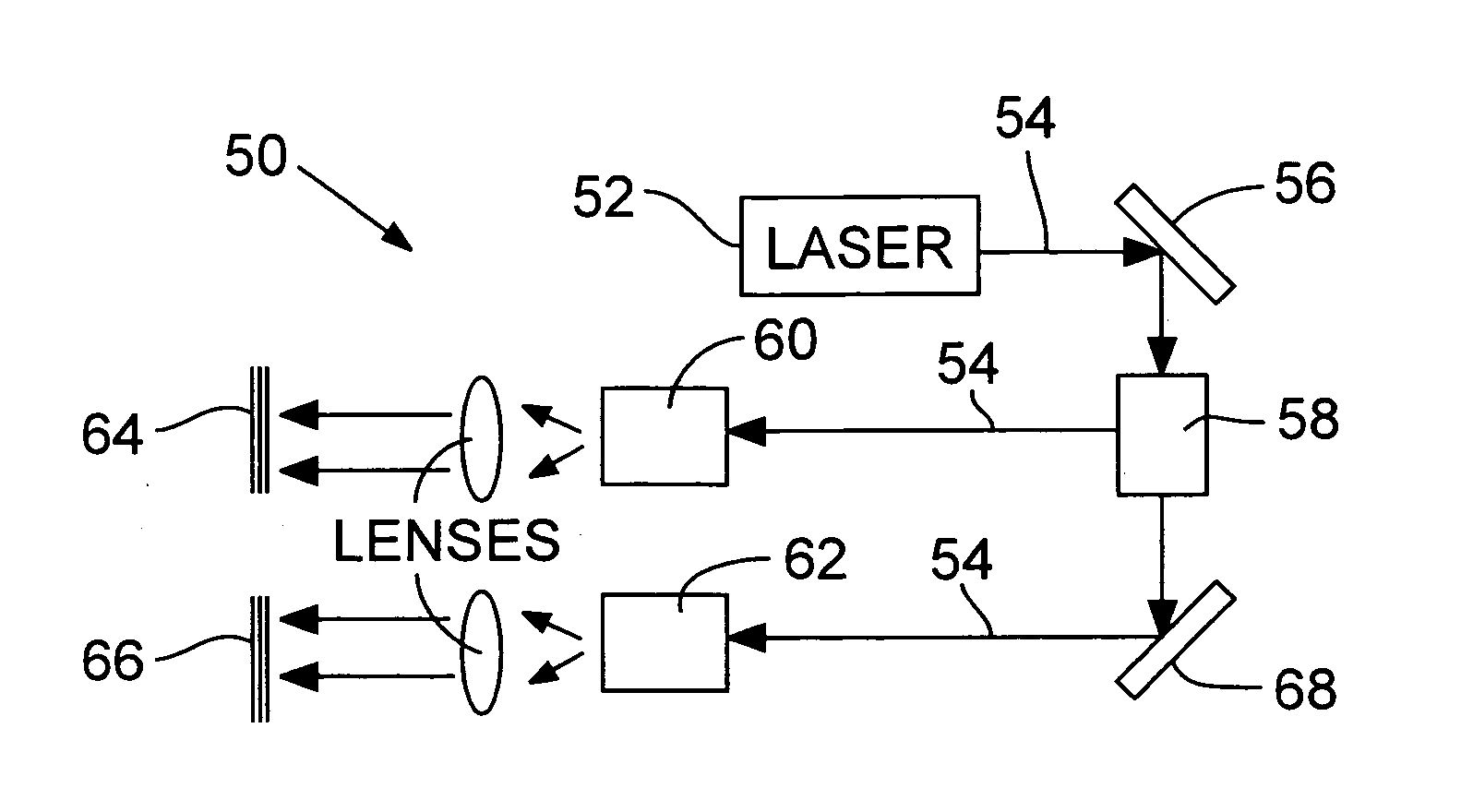

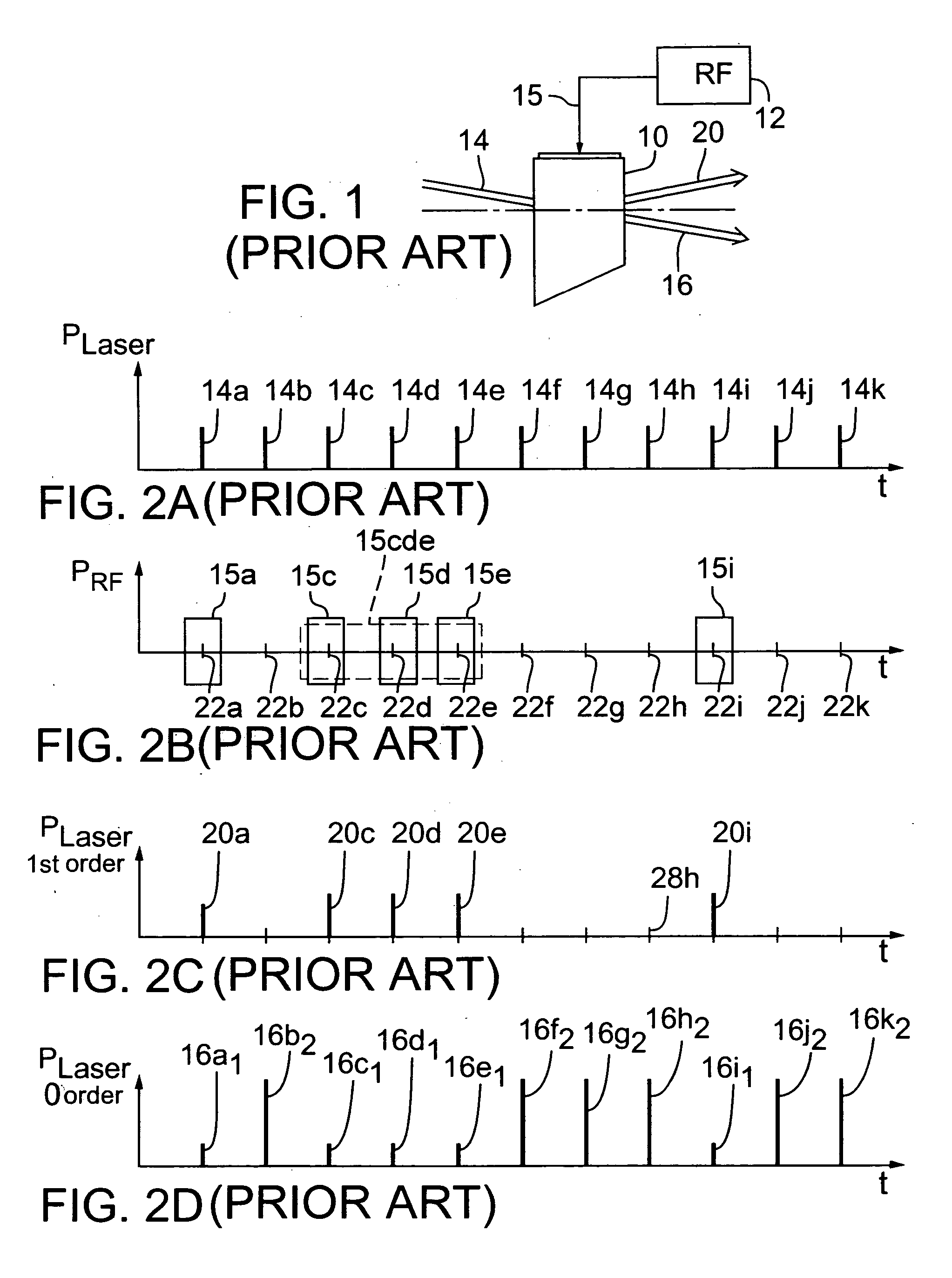

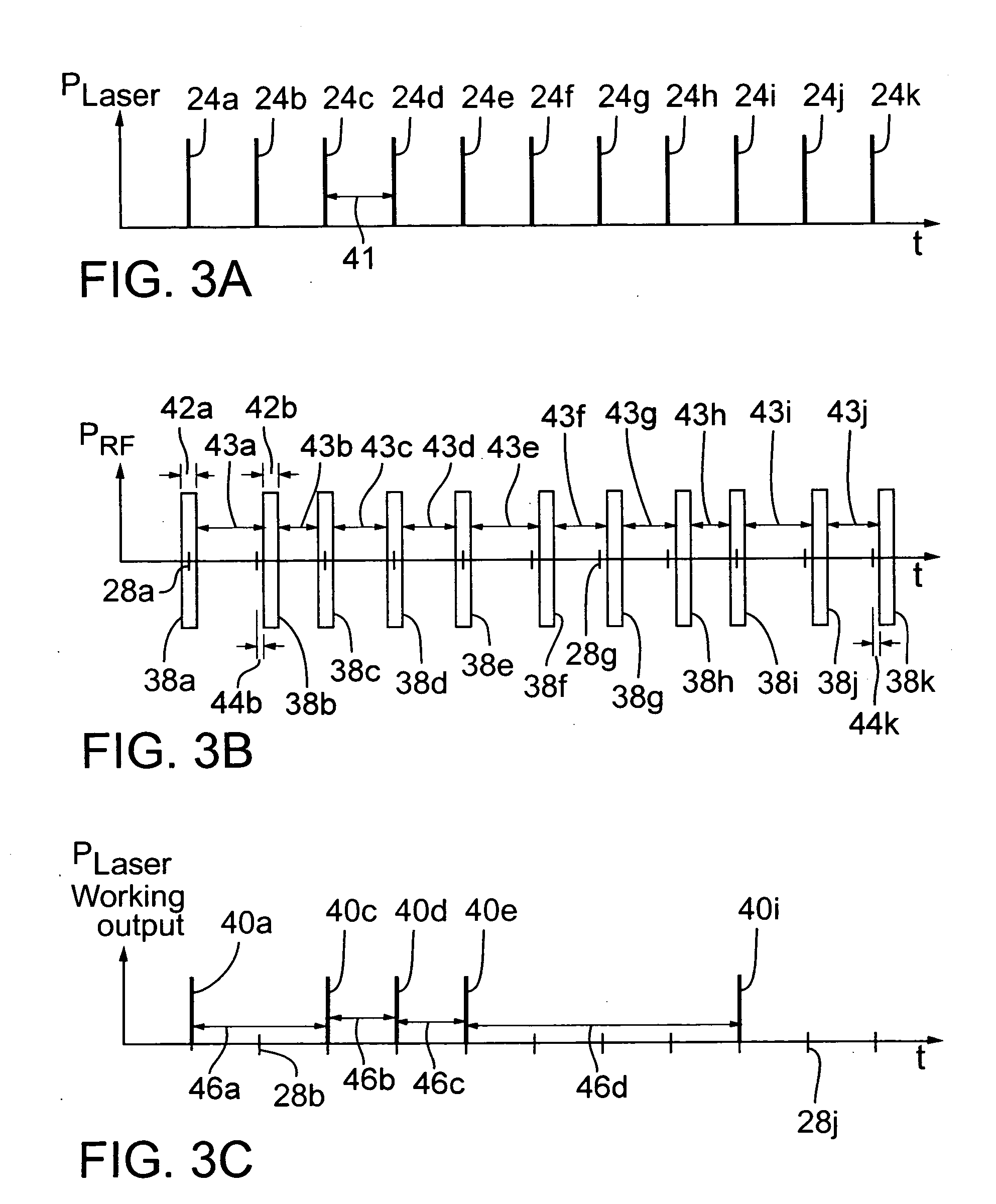

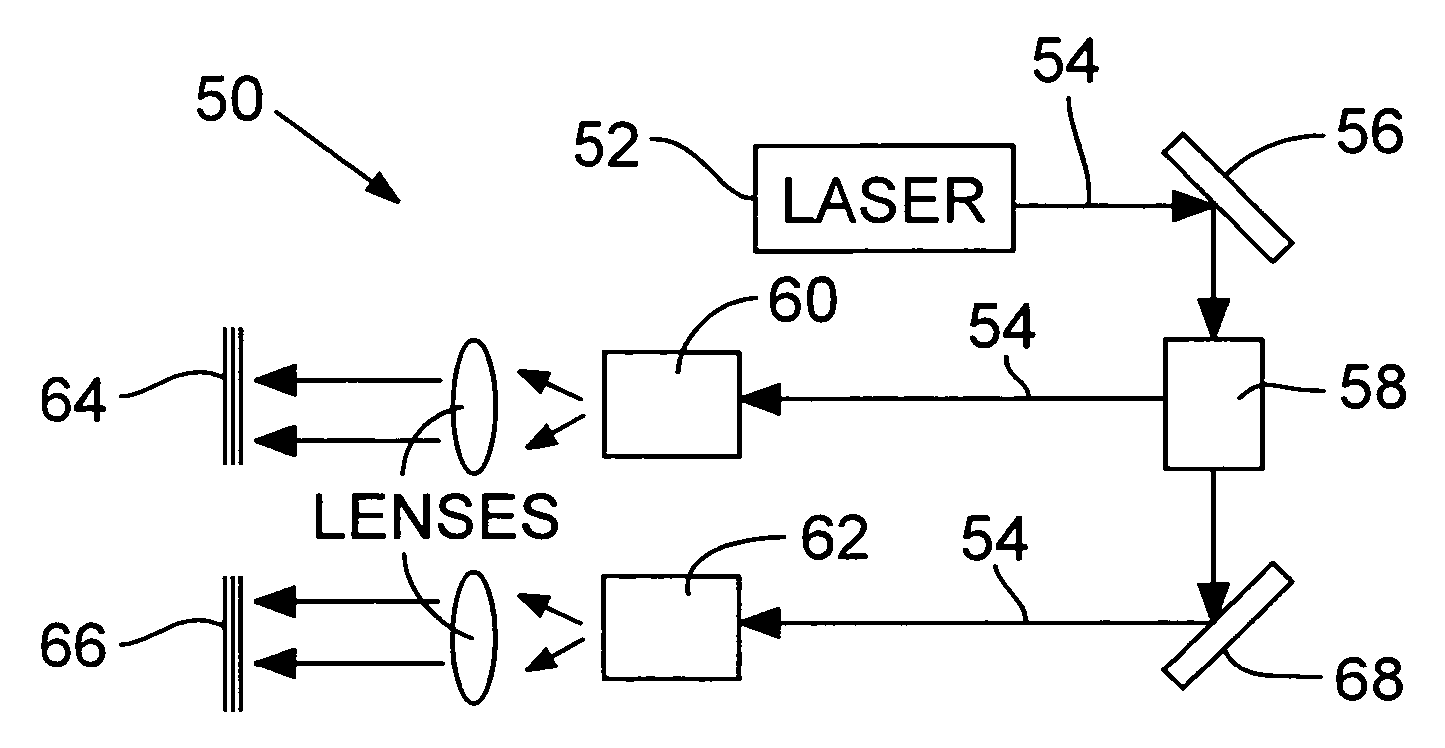

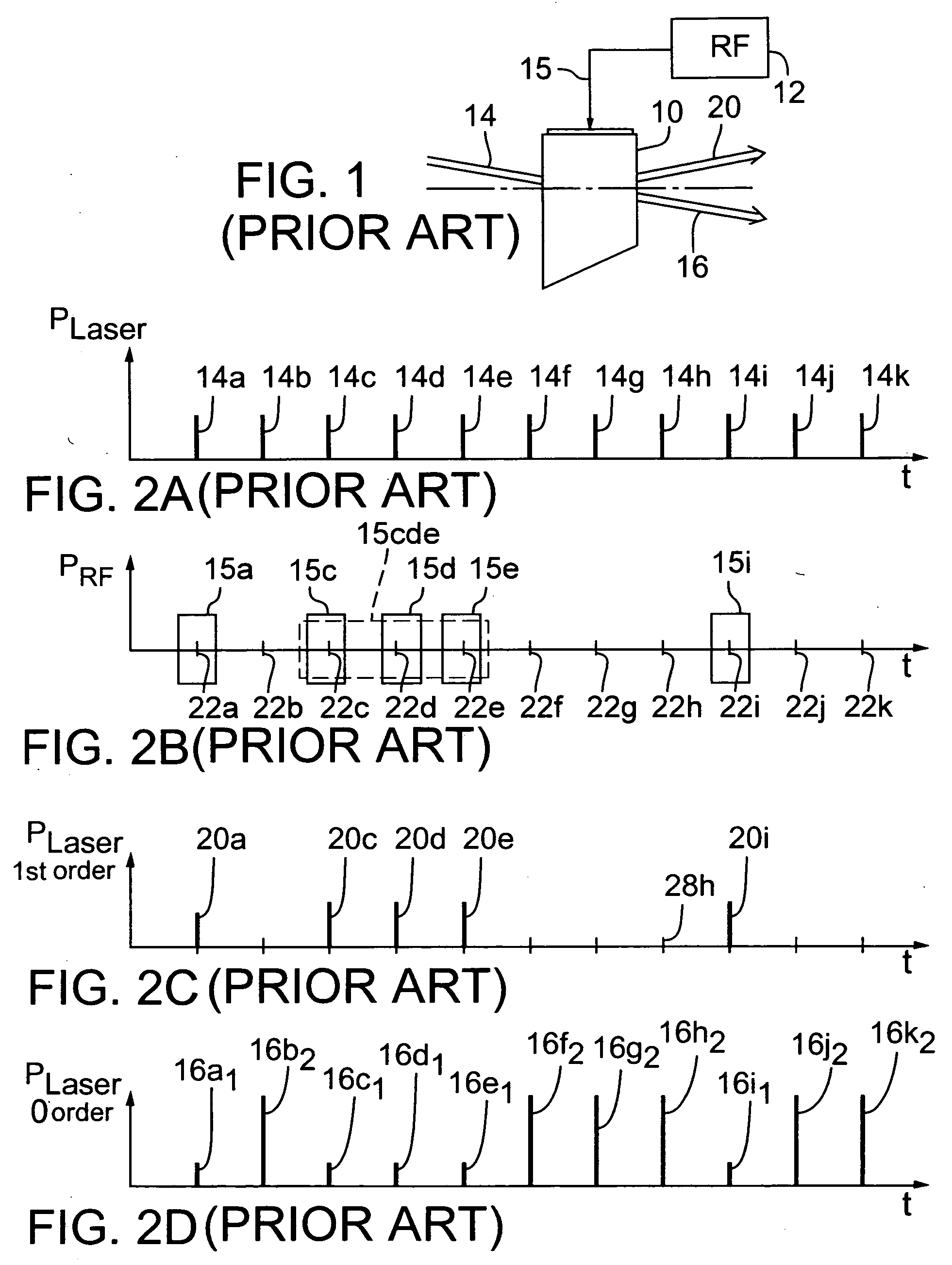

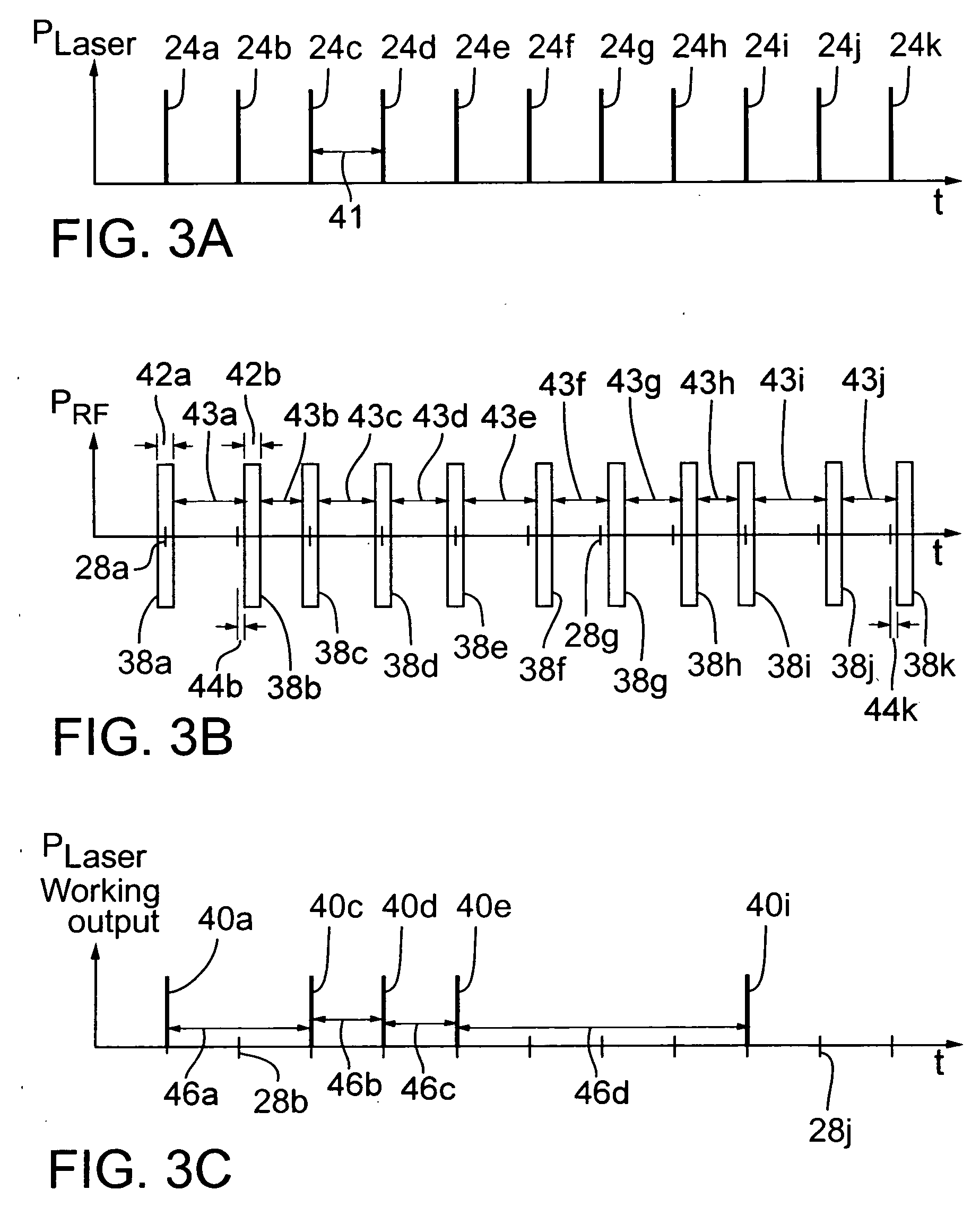

Efficient micro-machining apparatus and method employing multiple laser beams

InactiveUS20050224469A1Minimize distortionEnergy stabilitySemiconductor/solid-state device manufacturingOptical devices for laserLight beamOptoelectronics

Owner:ELECTRO SCI IND INC

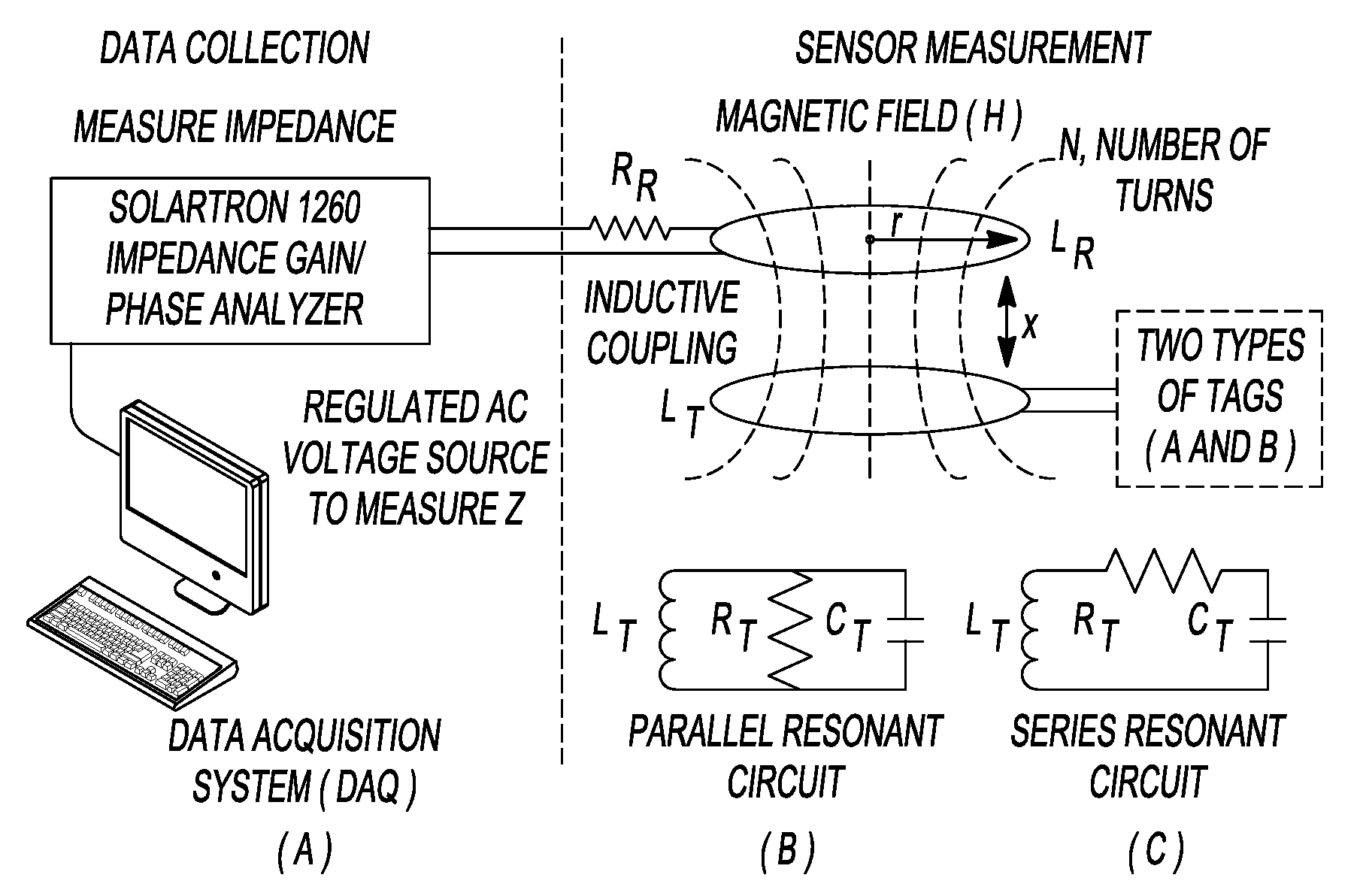

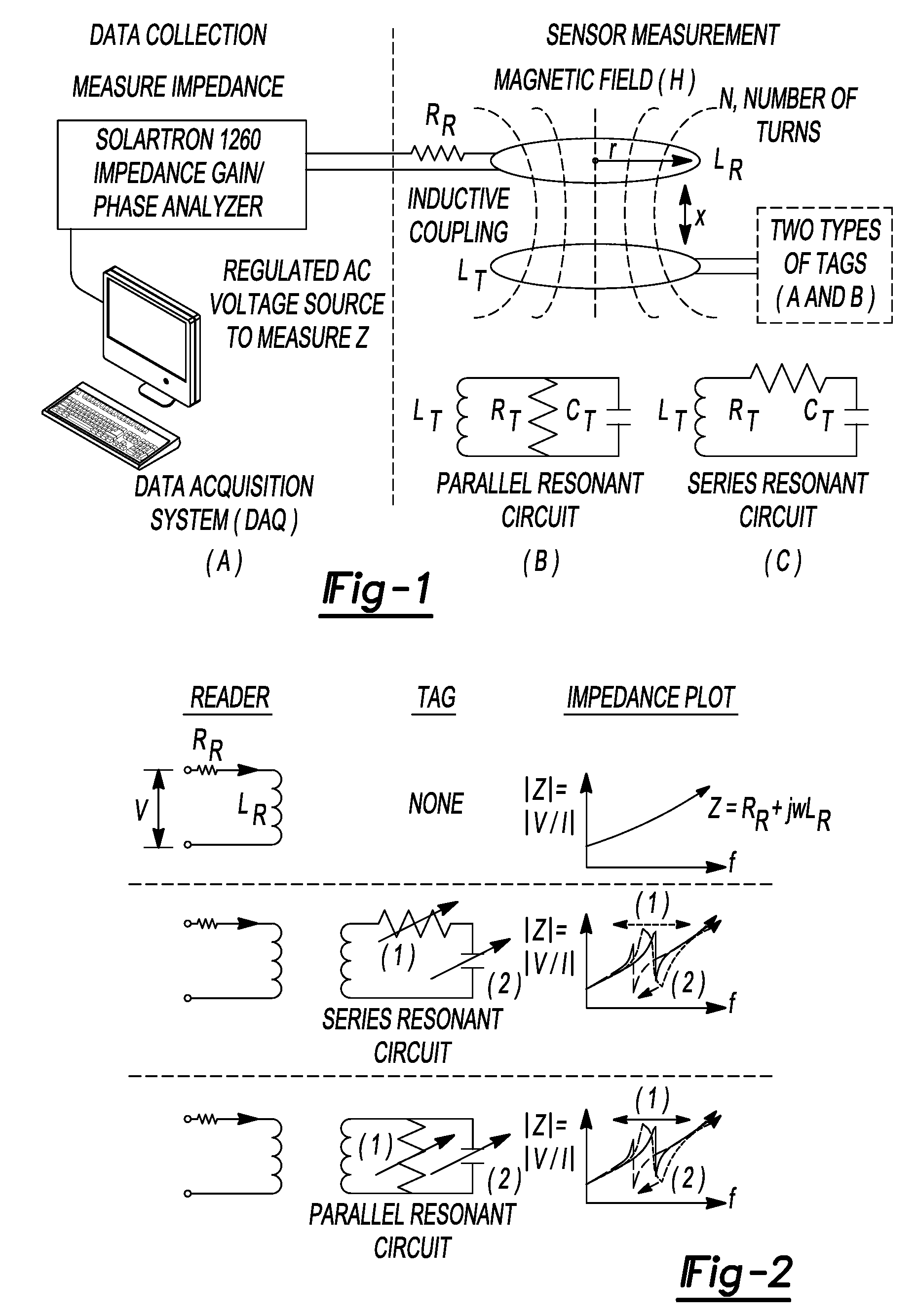

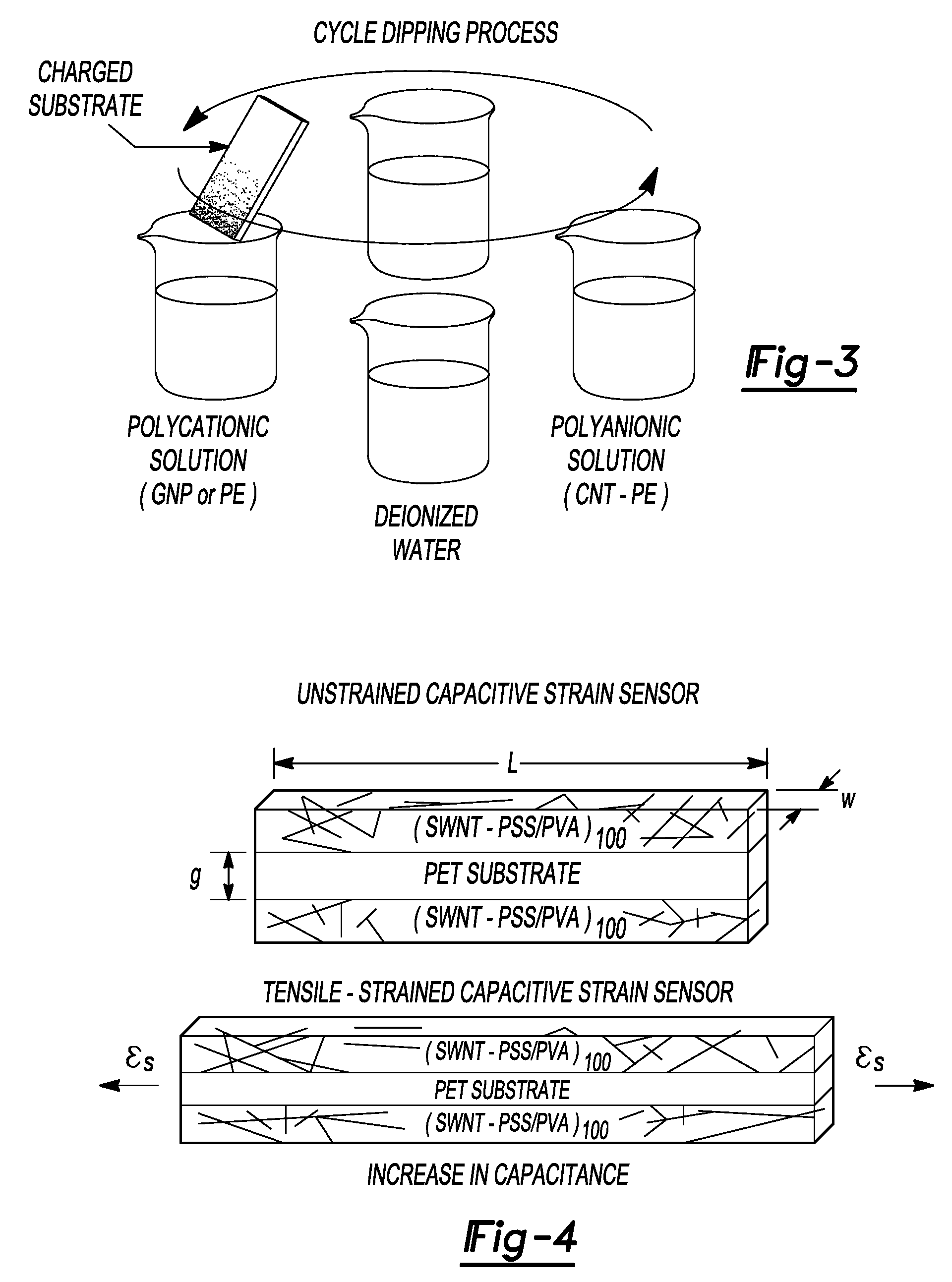

Passive wireless readout mechanisms for nanocomposite thin film sensors

ActiveUS20090121872A1Increase in bulk film conductivityImprove conductivityMemory record carrier reading problemsRecord carriers used with machinesNanocomposite thin filmsElectrical and Electronics engineering

A method for sensing a stimulus comprising providing a sensing assembly having a first structure and a second structure, wherein the first structure is made of a material different than the second structure and each of the first structure and the second structure is nanoscale. The method further includes providing an inductive antenna operably coupled to the sensing assembly, disposing the sensing assembly upon a spatial area, exposing the sensing assembly to the stimulus thereby producing a detectable change in the sensing assembly, and wirelessly coupling a reader with the inductive antenna to obtain a signal representative of the detectable change in the sensing assembly.

Owner:RGT UNIV OF MICHIGAN

Selective privacy protection for imaged matter

ActiveUS8305448B2Reduce loadIncrease system costTelevision system detailsCharacter and pattern recognitionPattern recognitionImaging processing

Owner:SONY SEMICON SOLUTIONS CORP

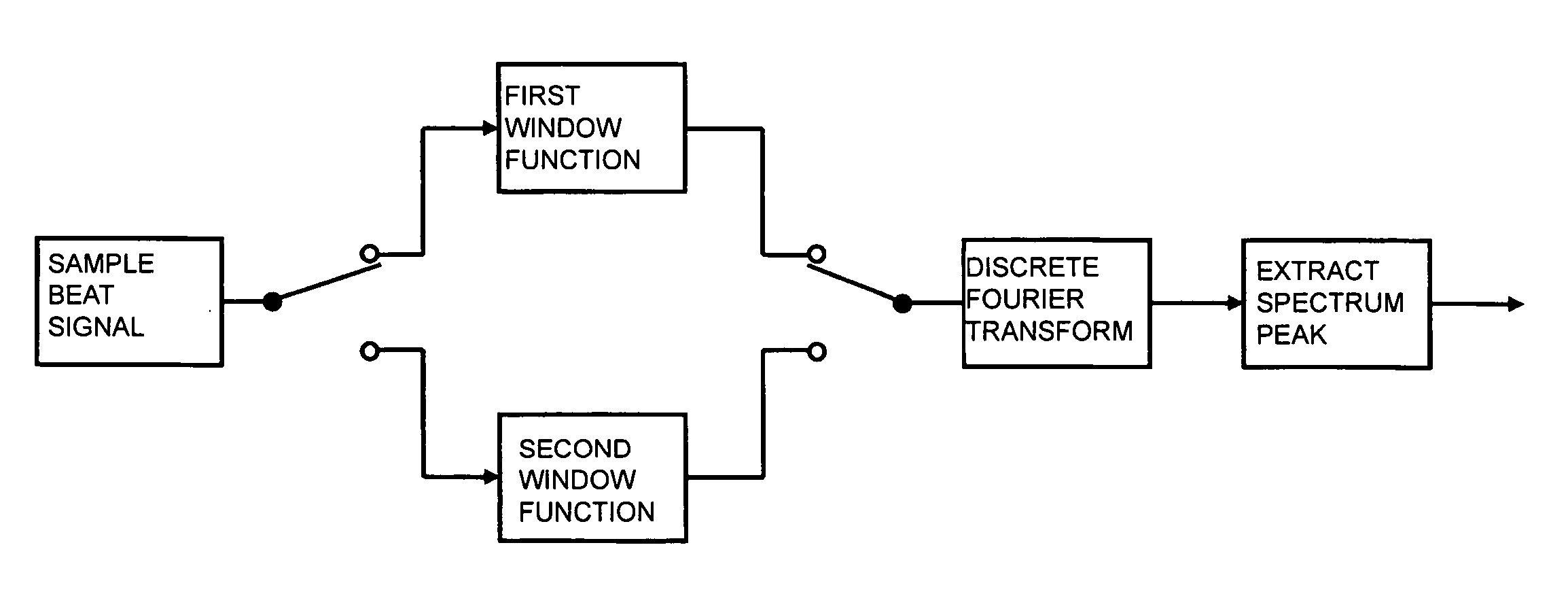

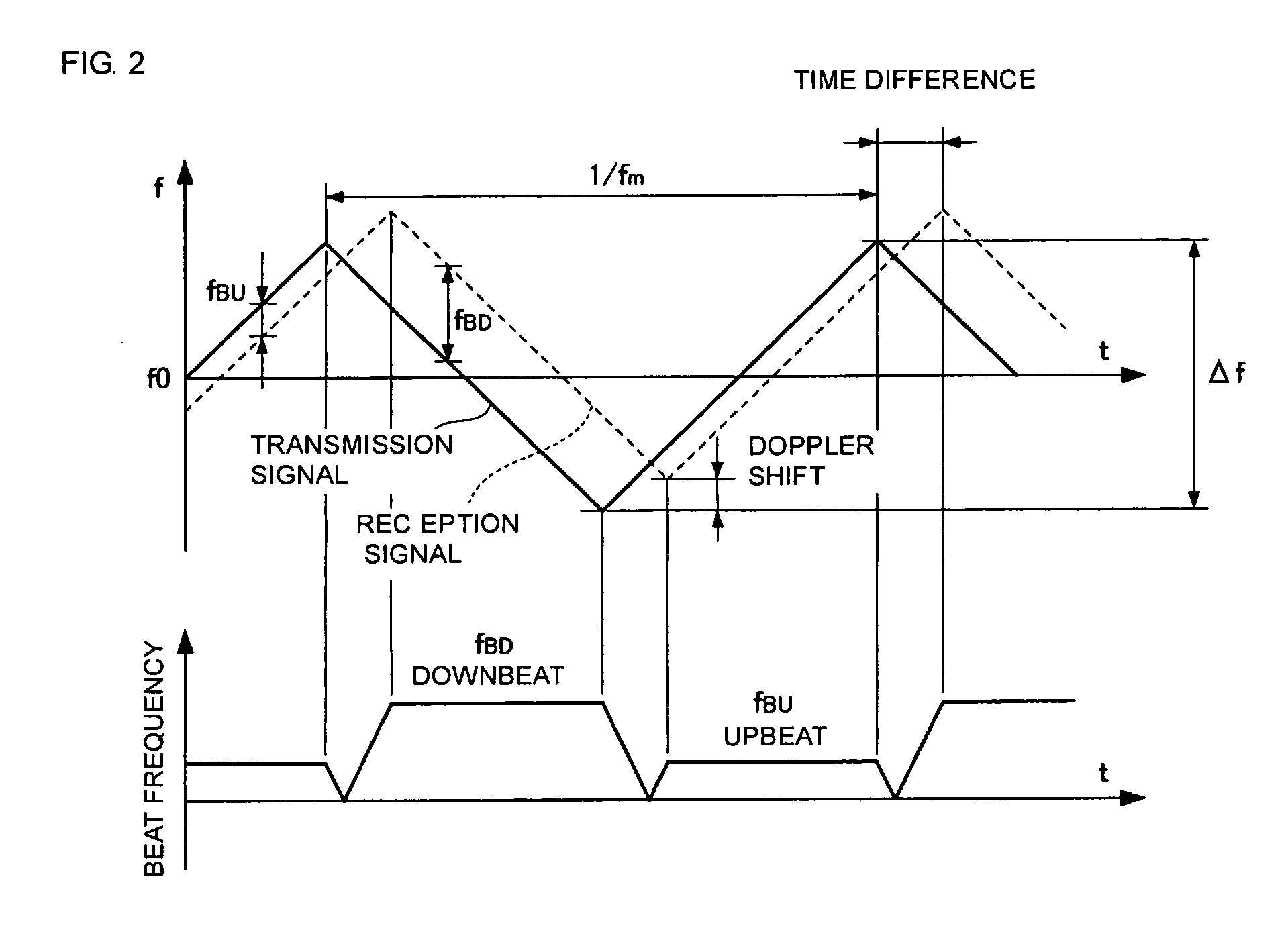

Radar system

InactiveUS20070040728A1Increase system costEasy to detectRadio wave reradiation/reflectionFrequency spectrumRadar systems

A radar system in which a beat signal is generated by transmitting a transmission signal that is subjected to frequency modulation into a triangular wave and receiving a reflection signal from a target, the beat signal is sampled, and a window function is applied to yield a discrete frequency spectrum. When the window function is applied, a first window function having an amplitude that is gently attenuated from the center of the sampling period toward both sides thereof is applied in a lower frequency band in the frequency spectrum (at close range), and a second window function having an amplitude that is sharply attenuated from the center of the sampling period toward both sides thereof is applied in a higher frequency band in the frequency spectrum (at far range).

Owner:MURATA MFG CO LTD

Workpiece processing system using a common imaged optical assembly to shape the spatial distributions of light energy of multiple laser beams

InactiveUS20060114948A1Eliminates thermal drifting of laser outputIncreasing laser beam positioning accuracyOptical resonator shape and constructionLaser beam welding apparatusBeam expanderLight energy

A workpiece processing system employs a common modular imaged optics assembly and an optional variable beam expander for optically processing multiple laser beams. In one embodiment, a laser and a fixed beam expander cooperate to produce a laser beam that propagates through a beam switching device to produce multiple laser beams that propagate along separate propagation path portions and subsequently merge into a common path portion through an imaged optics assembly and optional variable expander. The beam expander sets the shape of the laser beams in the form of a Gaussian spatial distribution of light energy. The imaged optics assembly shapes the Gaussian spatial distribution of the laser beams to form output beams of uniform spatial distribution. In an alternative embodiment, the beam switching device is removed and the laser beams propagate from separate laser sources associated with separate optional beam expanders.

Owner:ELECTRO SCI IND INC

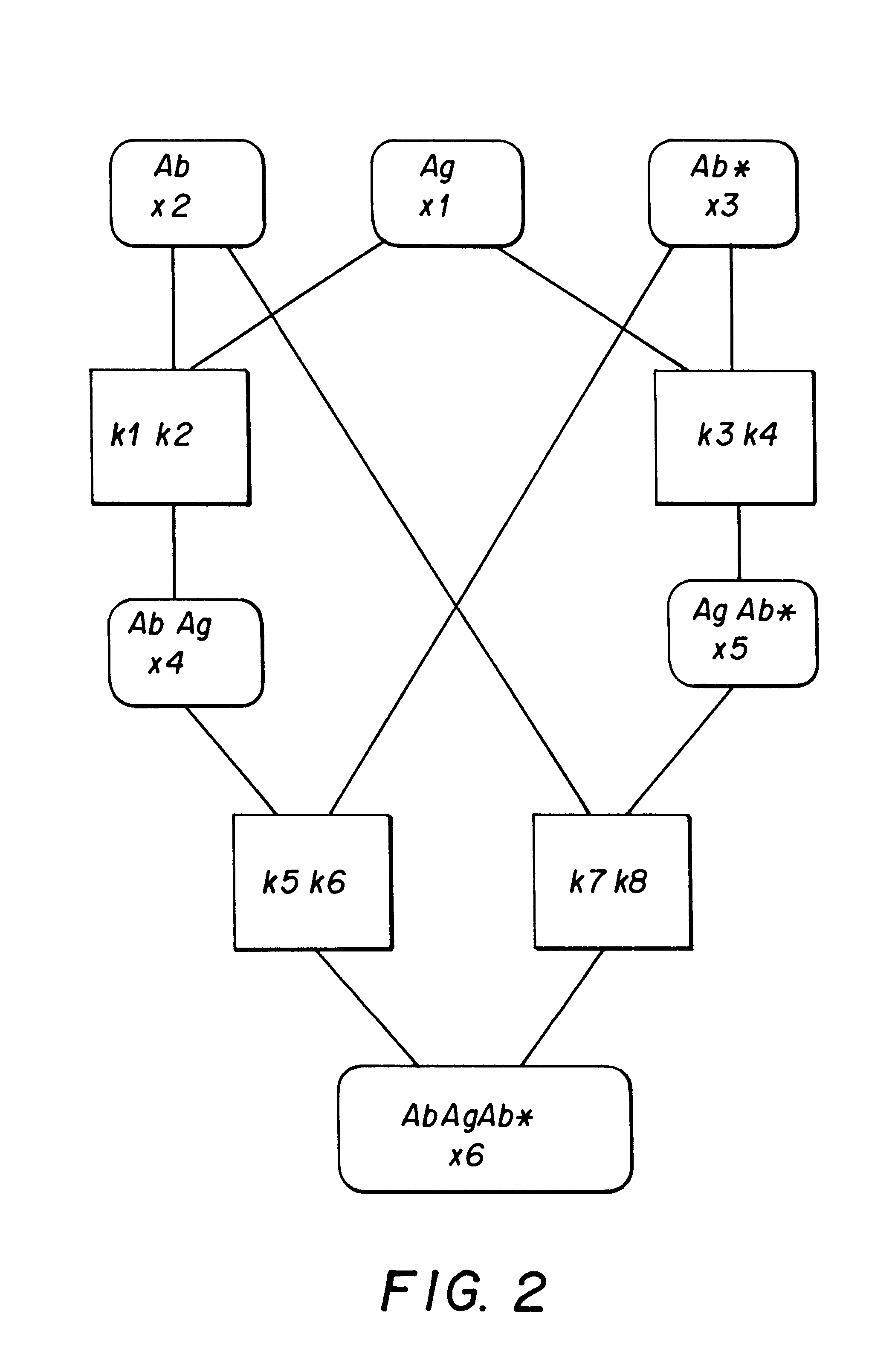

Biospecific, two photon excitation, fluorescence detection and device

InactiveUS6361956B1Avoid separationIncrease system costOptical radiation measurementParticle separator tubesMicroparticleLaser beams

A method for measuring the end point and for monitoring the real time kinetics of a bioaffinity reaction in biological fluids and suspensions, employing microparticles as bioaffinity binding solid phase, biospecific reagent labelled with a fluorescent label and a fluorescence detection system which is based on two-photon fluorescence excitation, contacting the analyte, the labelled reagent and the solid phase simultaneously, focusing a two-photon exciting laser beam into the reaction suspension and measuring the fluorescence signal emitted by the microparticles from one particle at a time when they randomly float through the focal volume of the laser beam. In this method the signal is monitored kinetically to obtain information about the analyte concentration before the reaction approaches the highest point of the response. Since the growth rate of the signal intensity is directly proportional to the analyte concentration, the analyte concentration can be predicted in the initial phase of the reaction. The growth rate monitoring also predicts whether the analyte concentration is higher than the binding capacity of the reagent and whether the reaction will be continued over the highest point of the response curve.

Owner:ERKKI SOINI

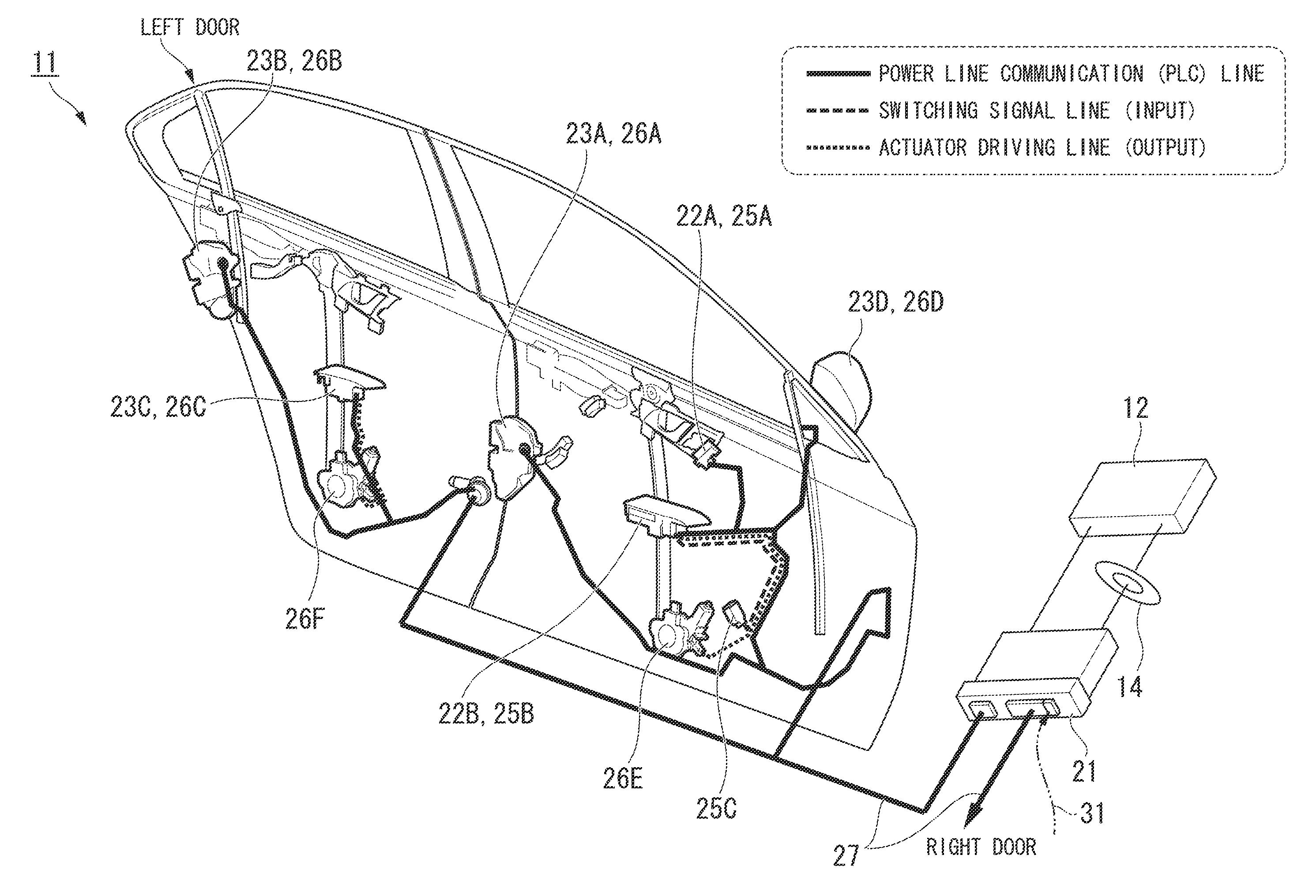

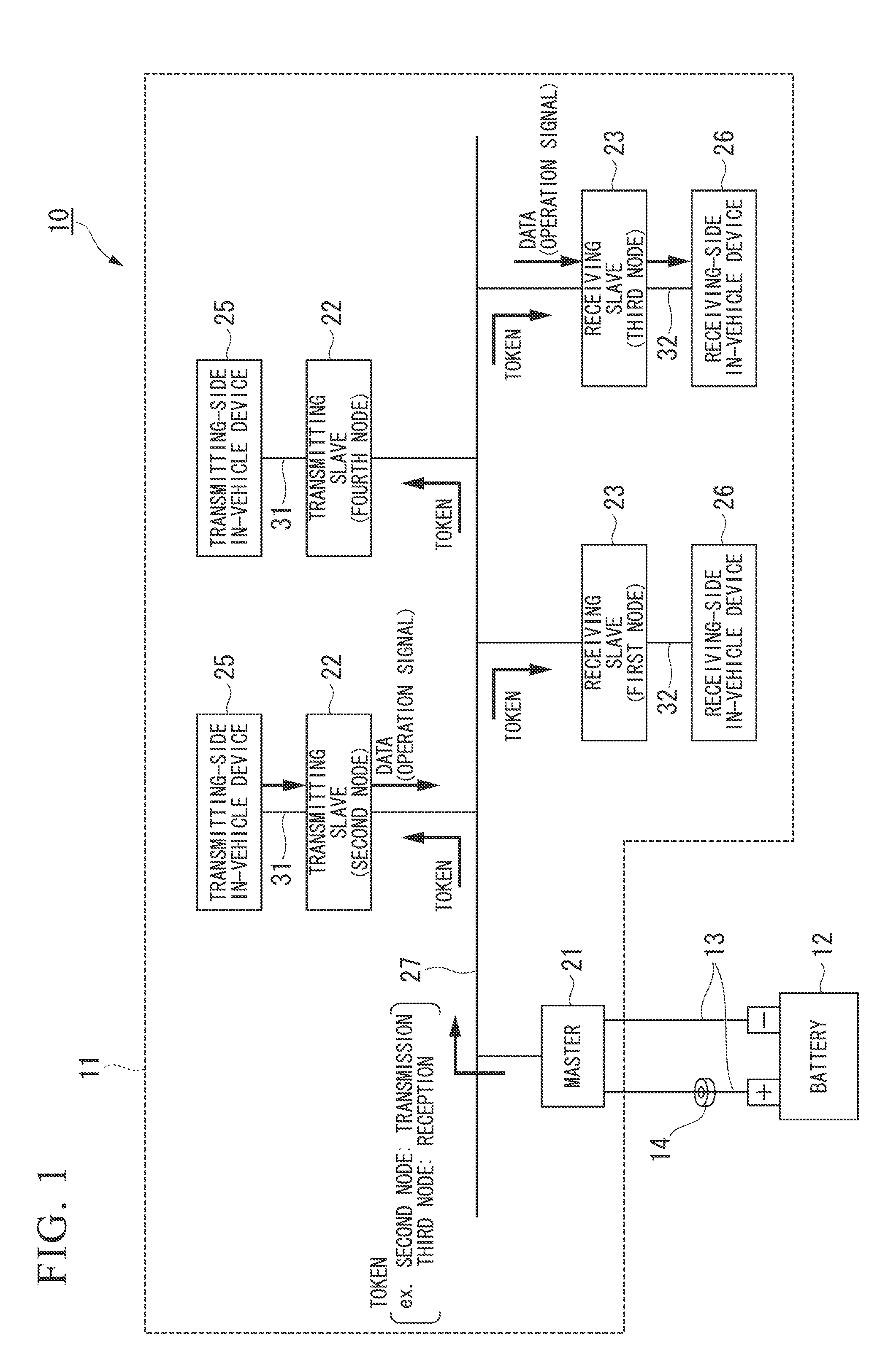

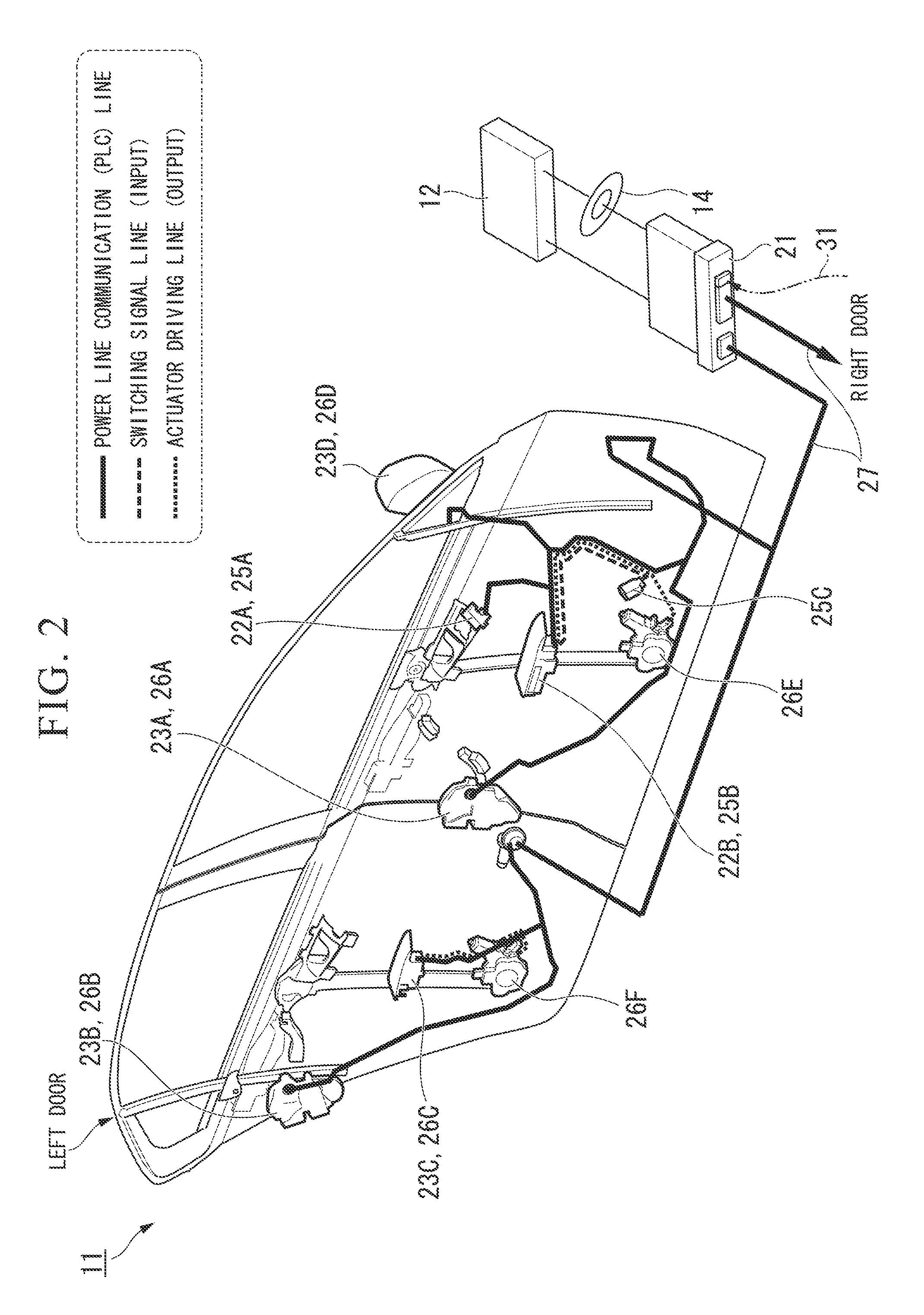

In-vehicle power line communication system

ActiveUS20120146776A1Low costAvoid noiseElectric signal transmission systemsElectric controllersIn vehicleEngineering

In an in-vehicle power line communication system in which a power line communication network and a battery are connected to each other via a first power line, the power line communication network includes a master power line communication node connected to the battery via the first power line, a second power line, slave power line communication nodes including at least a transmitting slave power line communication node and a receiving slave power line communication node, a transmitting-side in-vehicle device, and a receiving-side in-vehicle device. The master power line communication node and the slave power line communication nodes communicate with each other using a time-triggered communication protocol. The mutual communicating of the slave power line communication nodes are controlled by a token signal output from the master power line communication node. Only the master power line communication node and the slave power line communication nodes are connected to the second power line.

Owner:HONDA MOTOR CO LTD