Patents

Literature

132 results about "Configurable systems" patented technology

Efficacy Topic

Property

Owner

Technical Advancement

Application Domain

Technology Topic

Technology Field Word

Patent Country/Region

Patent Type

Patent Status

Application Year

Inventor

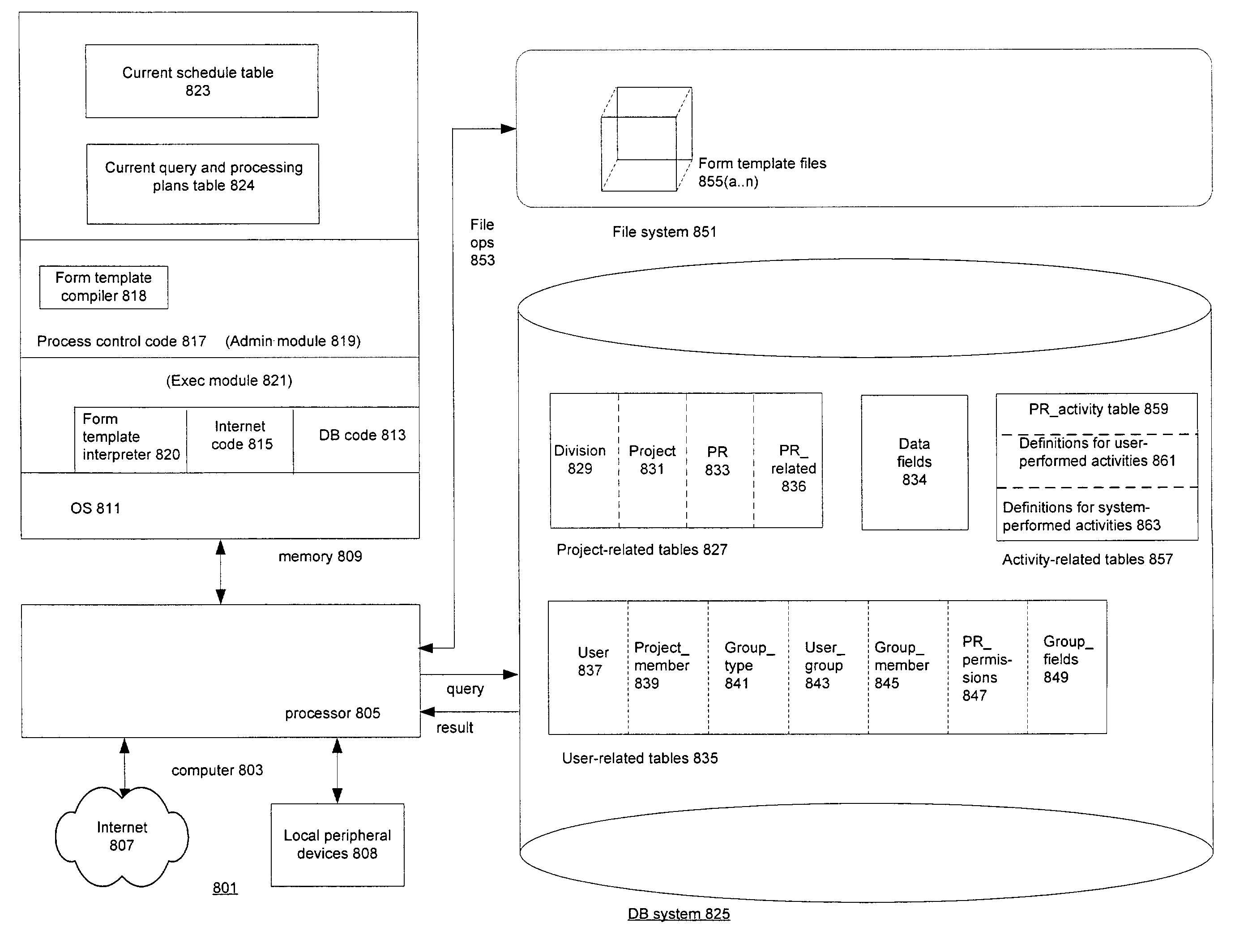

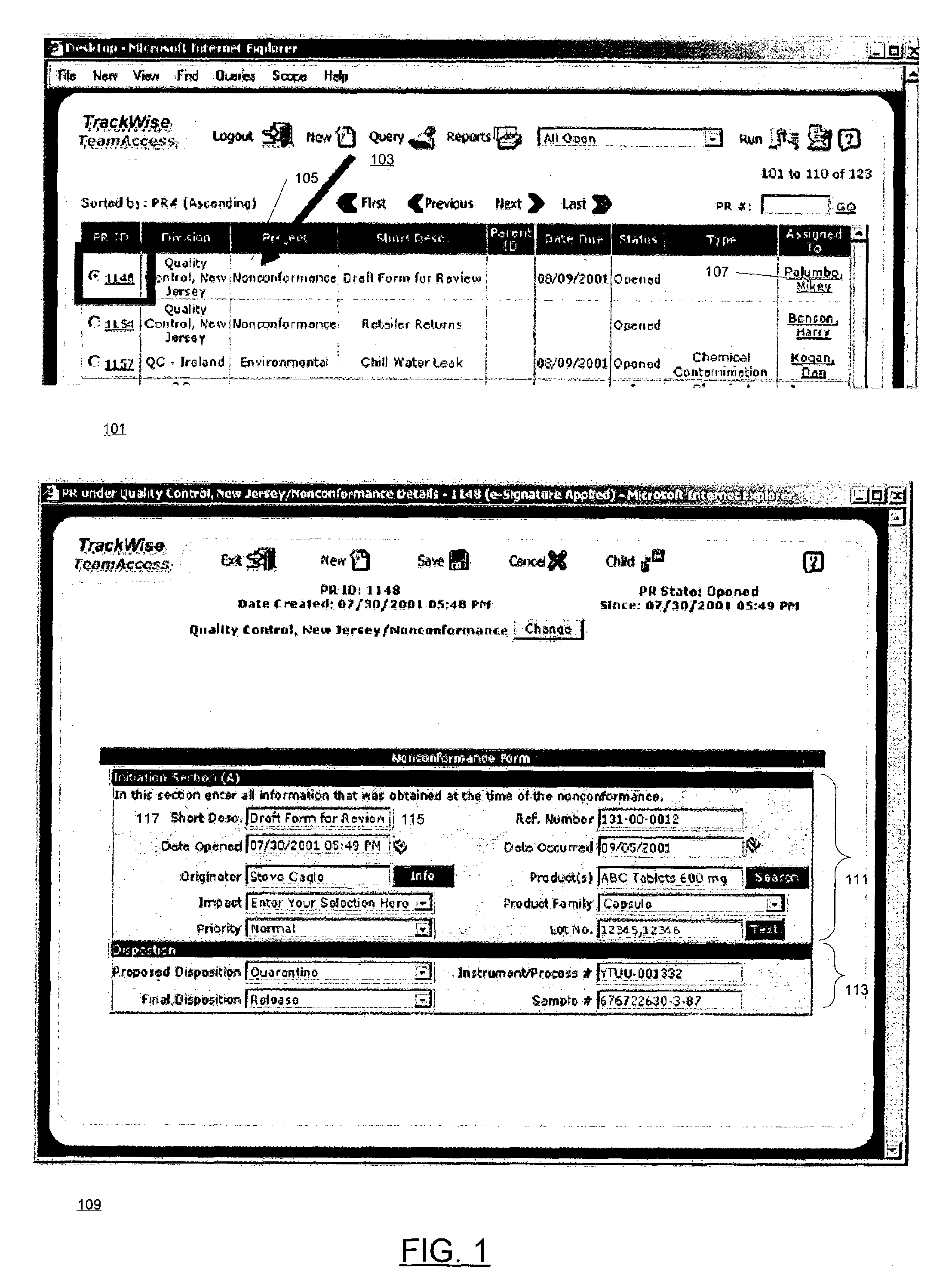

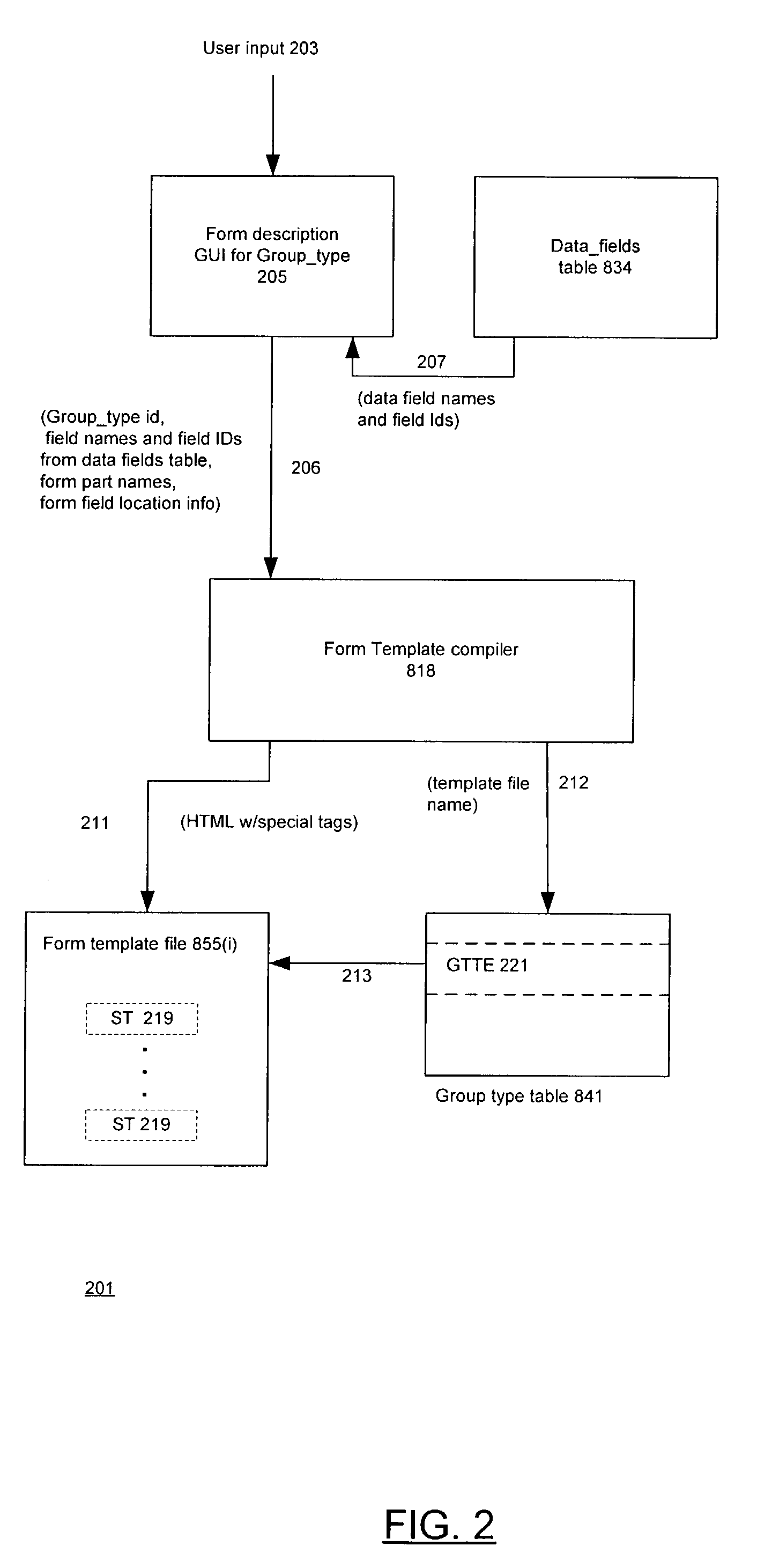

Defining user access in highly-configurable systems

ActiveUS7703021B1Computer security arrangementsInput/output processes for data processingConfigurable systemsDatabase

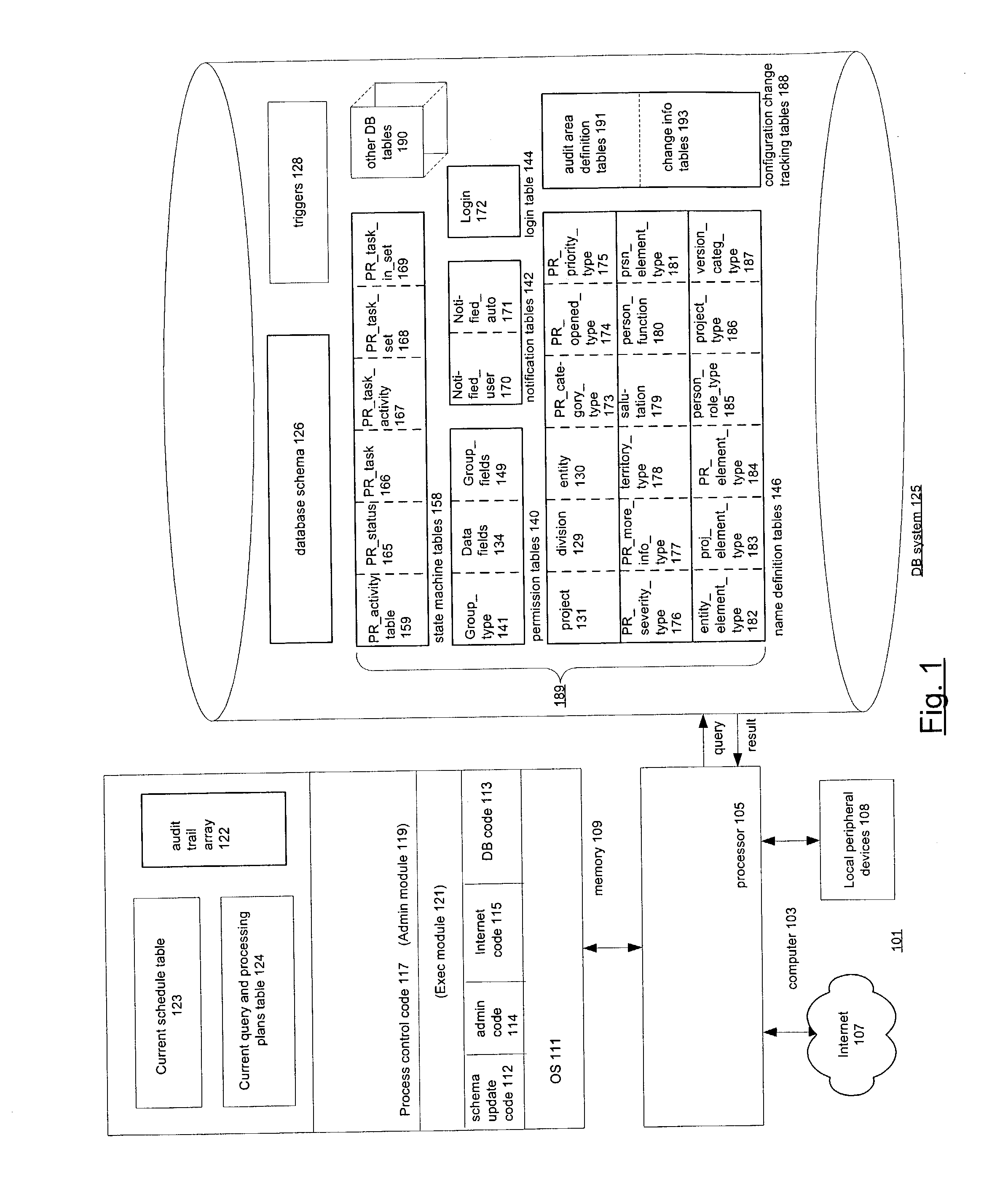

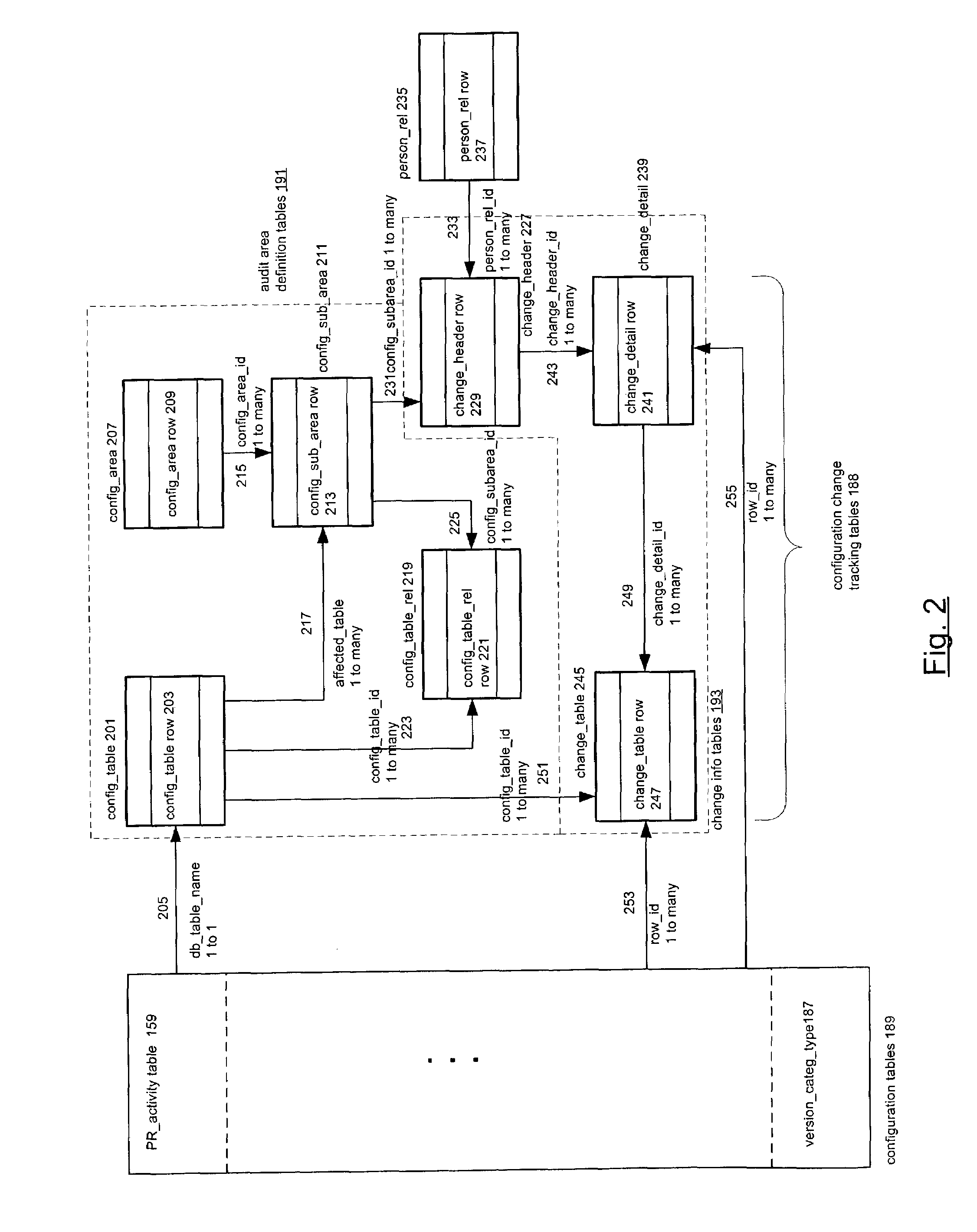

A highly-configurable process control system that uses process records in a database system to track a process. The database system relates process records, users, and projects. User permissions to view the process records include permissions for all process records related to a project to which the user is related, all such records that the user has created, all such records that a group the user belongs to have created, all such records that have been assigned to the user, and all such records that belong to an entity to which the user is related.The process records further include user-configurable fields. User permissions for the fields are provided according to group types which are related to groups to which the users belong. Included are permissions for inserting and deleting values in the user-configurable fields which are separate from the permission to edit the values.

Owner:SPARTA SYST INC

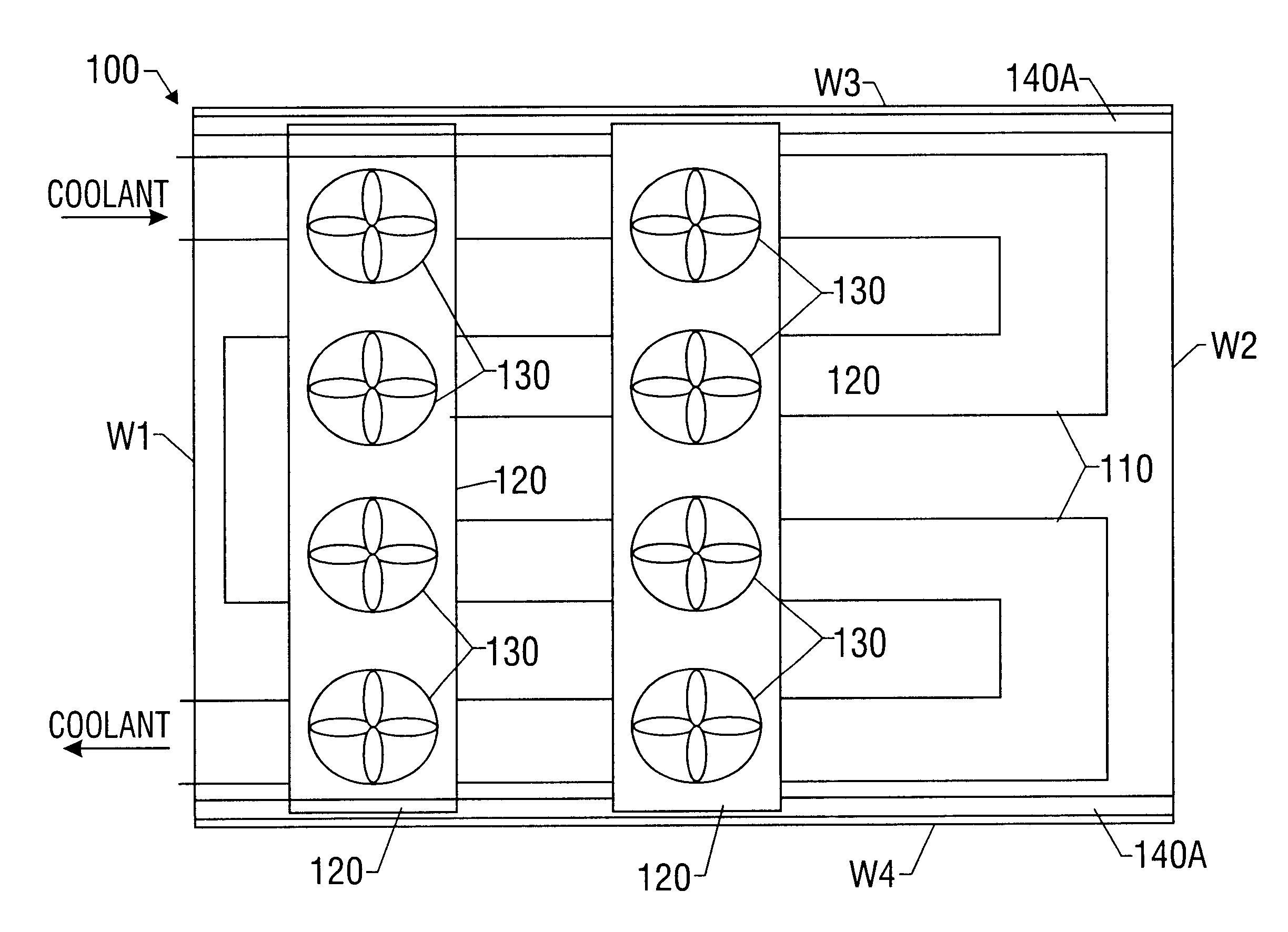

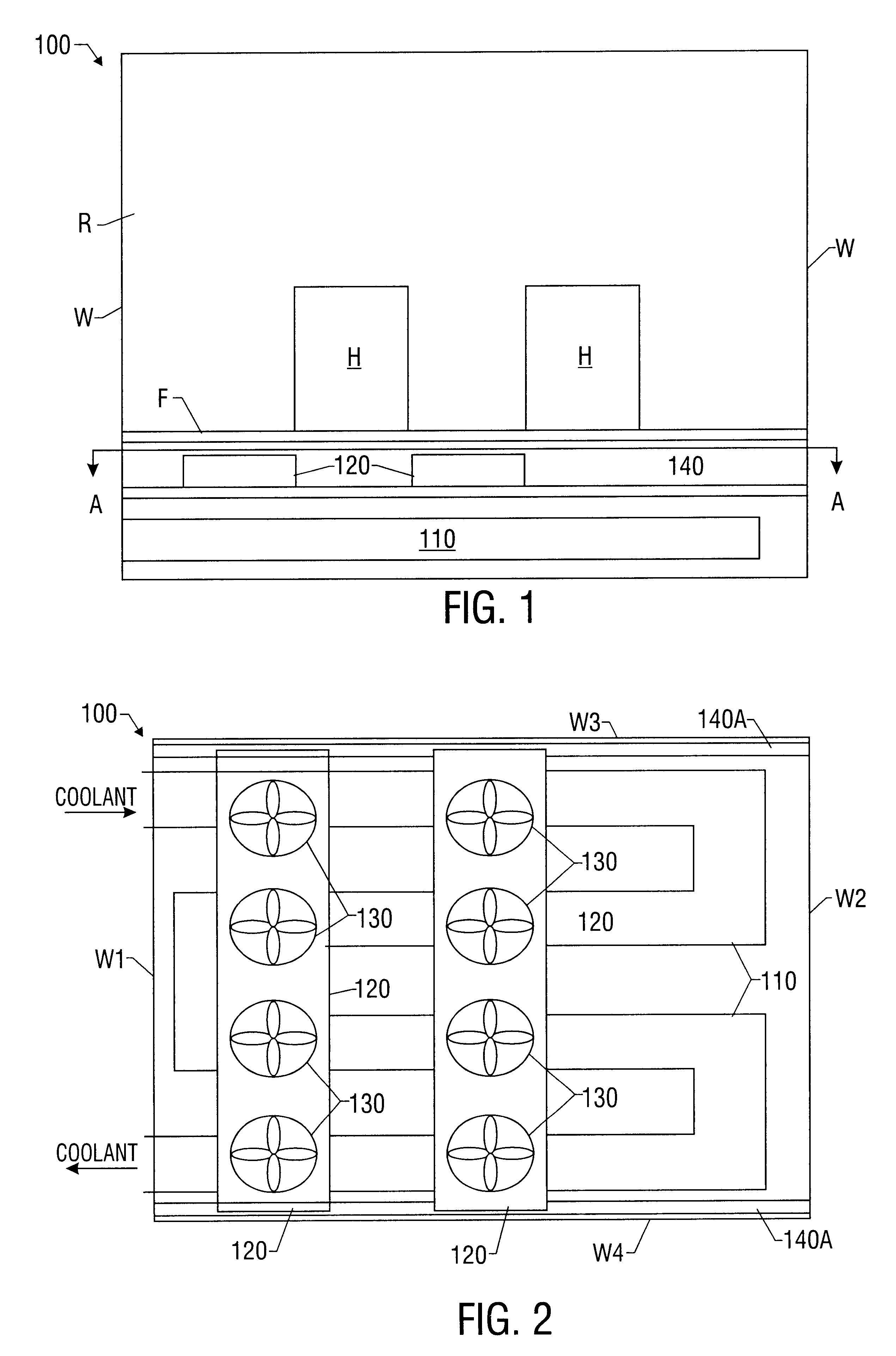

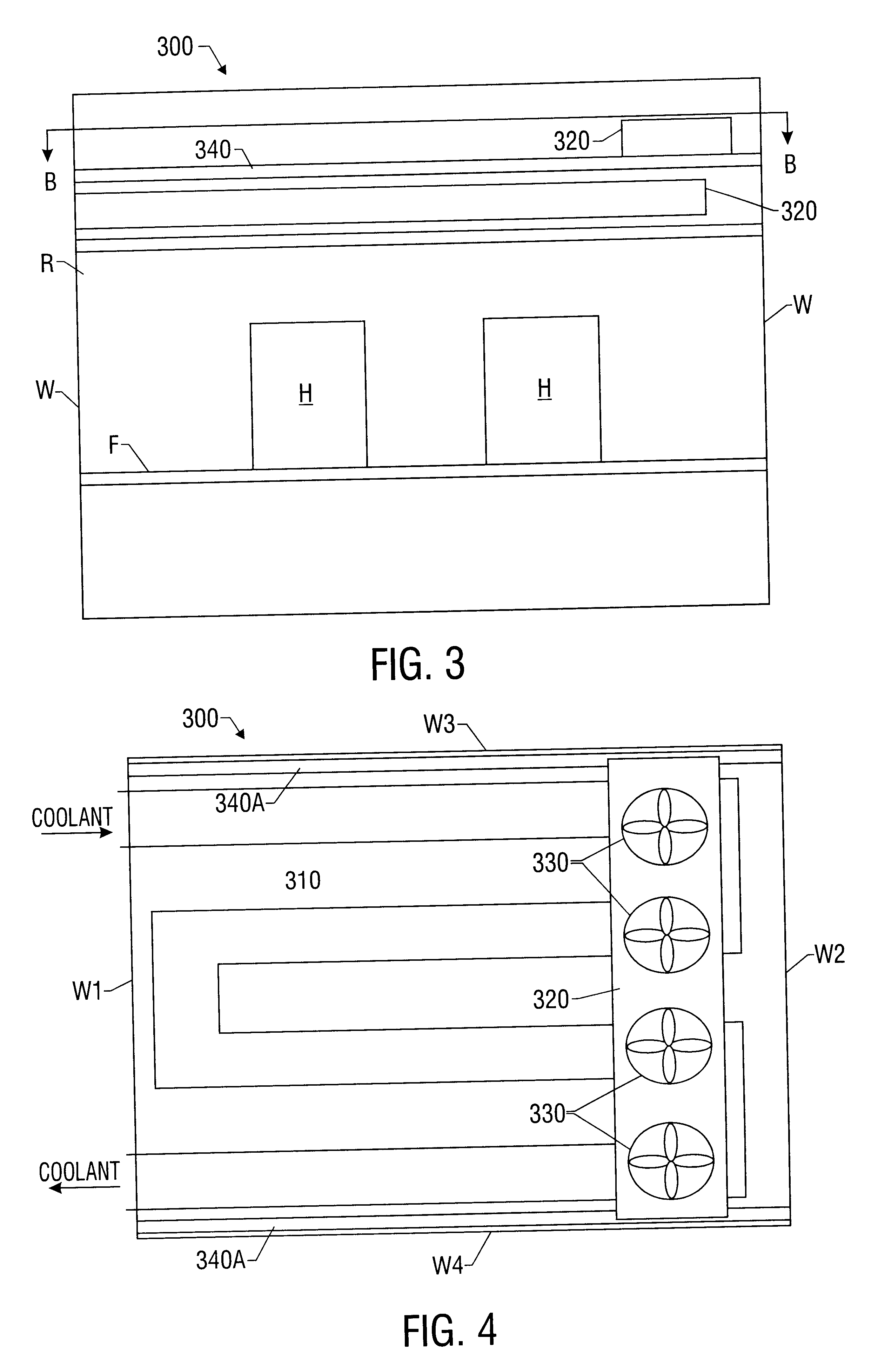

Configurable system and method for cooling a room

InactiveUS6557624B1Improve efficiencyReduce air pressureMechanical apparatusHot-air central heatingNuclear engineeringConfigurable systems

A method and system are disclosed for cooling a room having one or more heat generating objects. A number of heat exchangers are disposed adjacent a floor or ceiling and extends substantially entirely or partially between the walls of the room. A fan unit is disposed adjacent the heat exchanger and draws or blows cooled air from the heat exchanger and directs the drawn air into the room. The fan unit is capable of being repositioned along a different portion of the heat exchanger so as to redefine the flow of cooled air into the room. The cooling system components are modularized enabling configuration of a number of components to cool a room.

Owner:VERTIV CORP

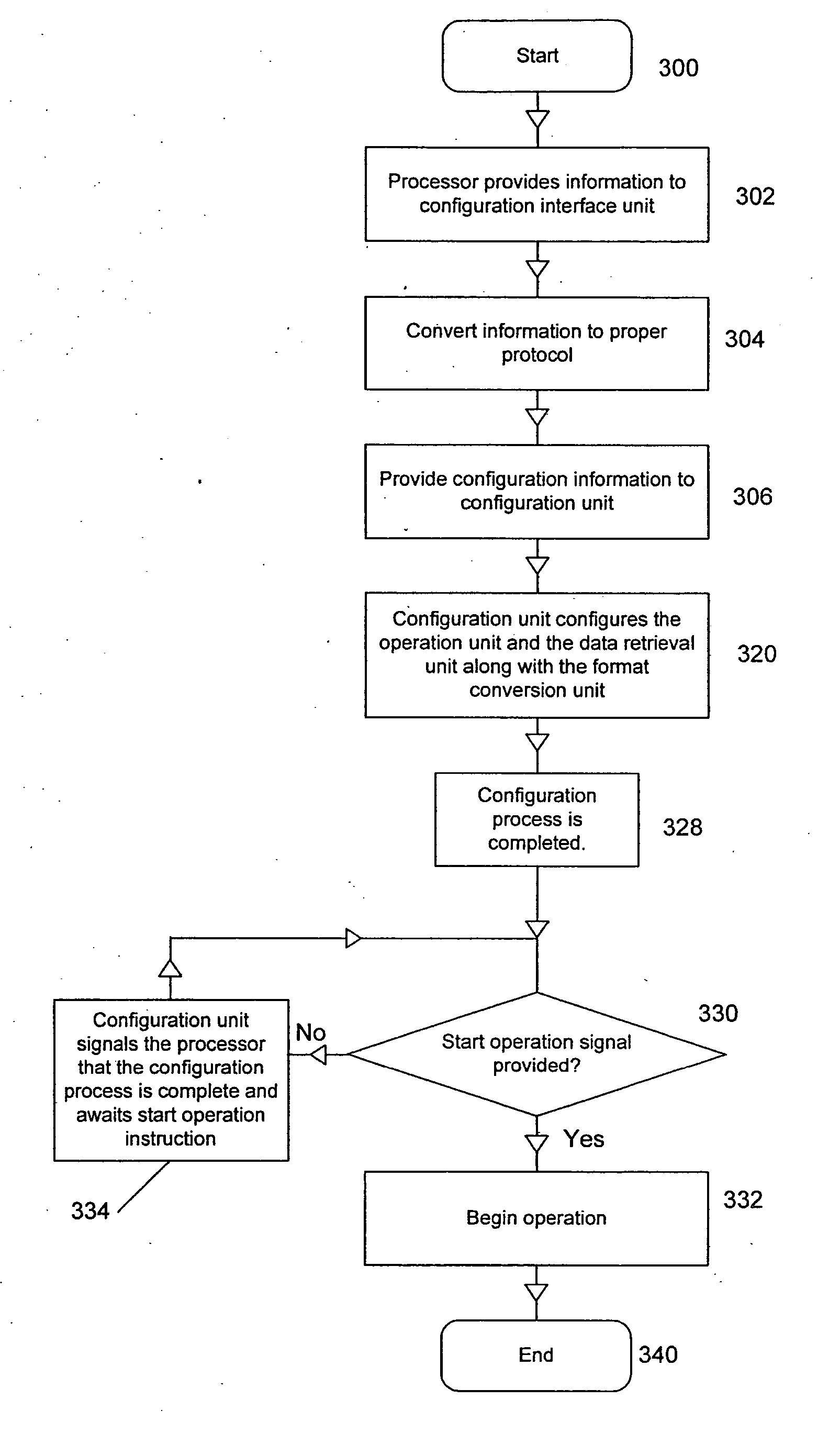

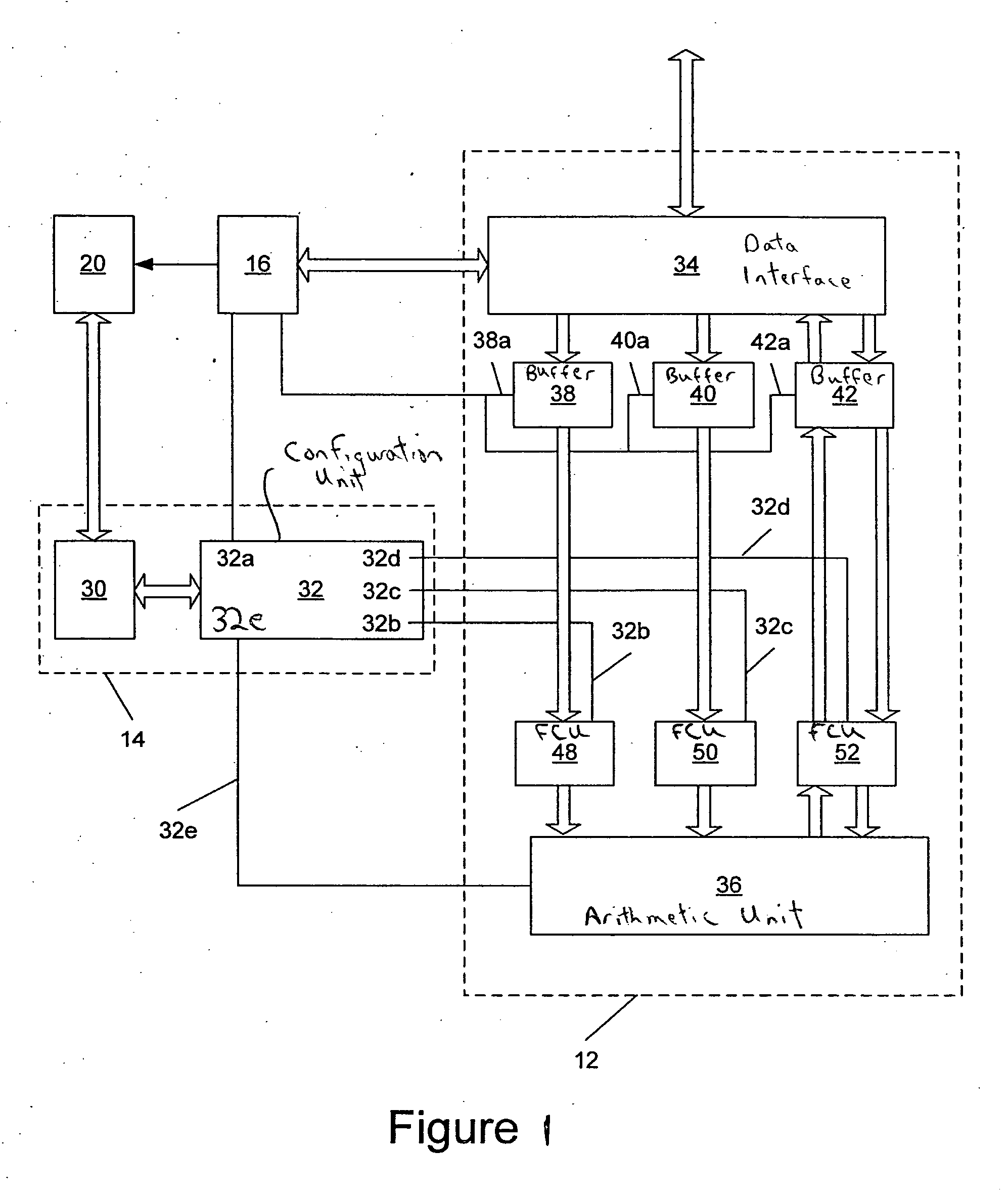

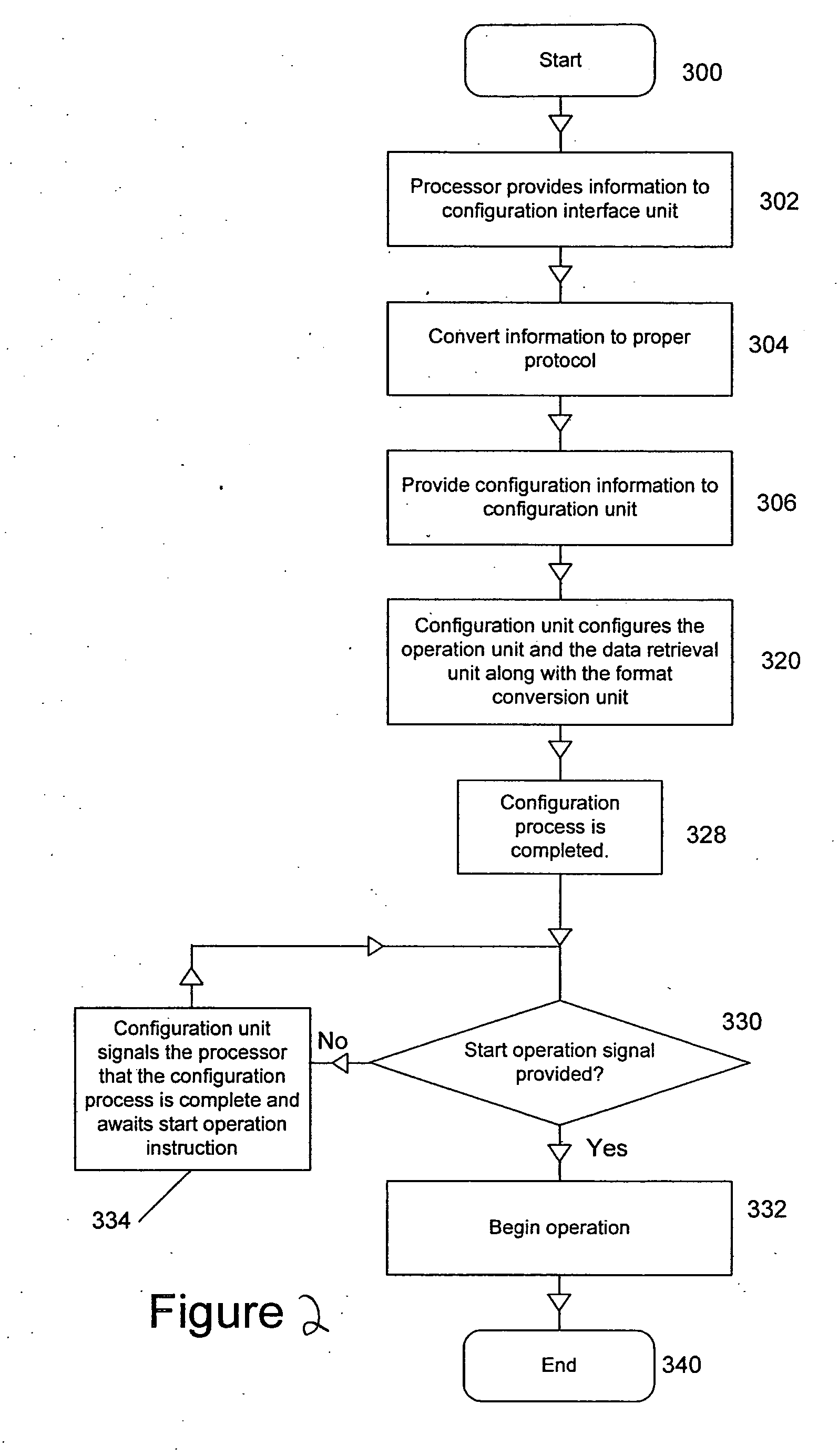

Configurable system for performing repetitive actions and method for configuring and operating same

ActiveUS20070078661A1Efficient executionHigh power consumptionSpeech analysisSpecial data processing applicationsData processing systemOperand

In some embodiments, a data processing system including an operation unit including circuitry configurable to perform any selected one of a number of operations on data (e.g., audio data) and a configuration unit configured to assert configuration information to configure the operation unit to perform the selected operation. When the operation includes matrix multiplication of a data vector and a matrix whose coefficients exhibit symmetry, the configuration information preferably includes bits that determine signs of all but magnitudes of only a subset of the coefficients. When the operation includes successive addition and subtraction operations on operand pairs, the configuration information preferably includes bits that configure the operation unit to operate in an alternating addition / subtraction mode to perform successive addition and subtraction operations on each pair of data values of a sequence of data value pairs. In some embodiments, the configuration information includes bits that configure the operation unit to operate in a non-consecutive (e.g., butterfly or bit-reversed) addressing mode to access memory locations having consecutive addresses in a predetermined non-consecutive sequence. Other aspects are audio encoders and decoders including any embodiment of, and configuration units and operation units for use in, any embodiment of the system, and methods performed during operation of any embodiment of the system or configuration or operation unit thereof.

Owner:NVIDIA CORP

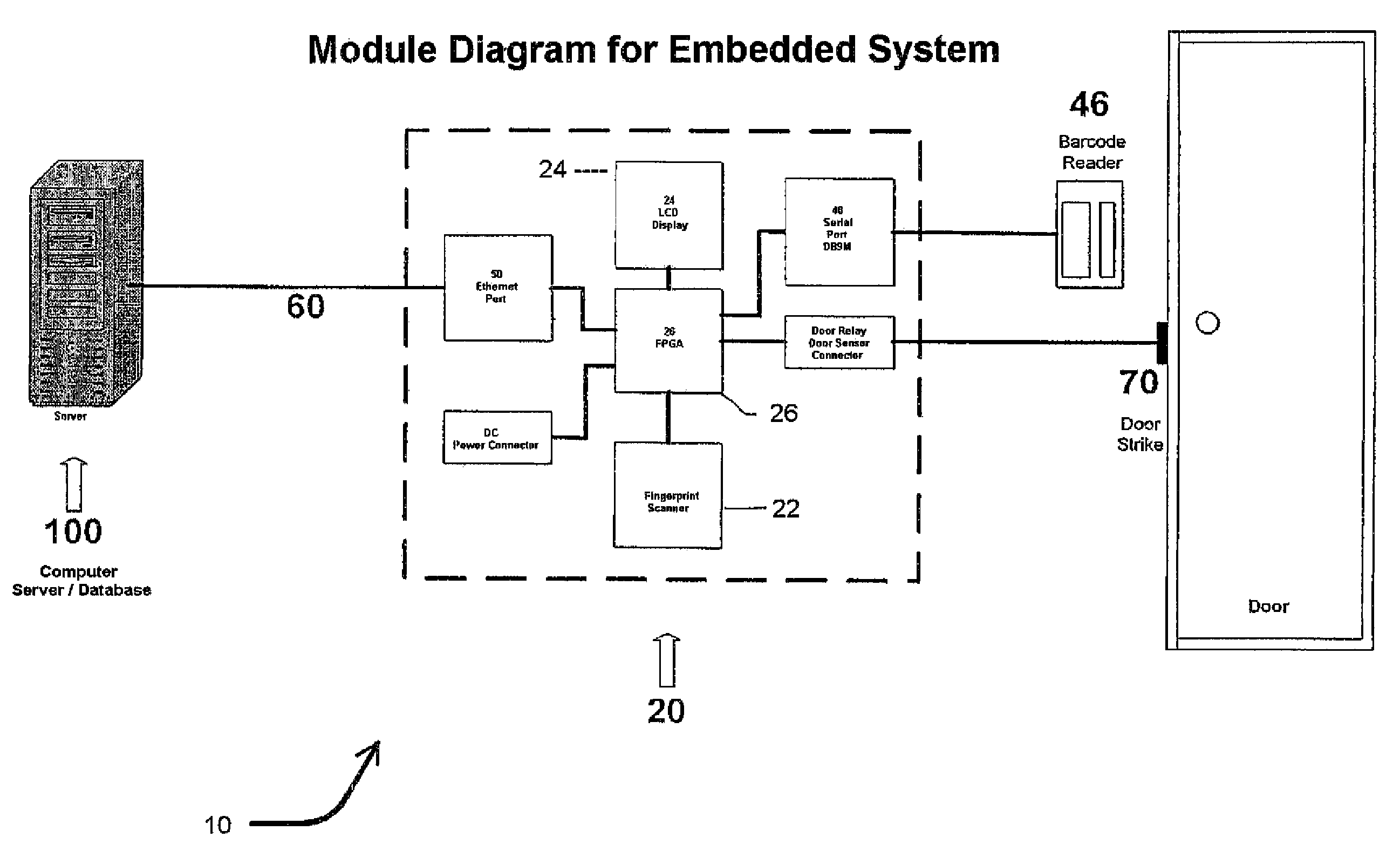

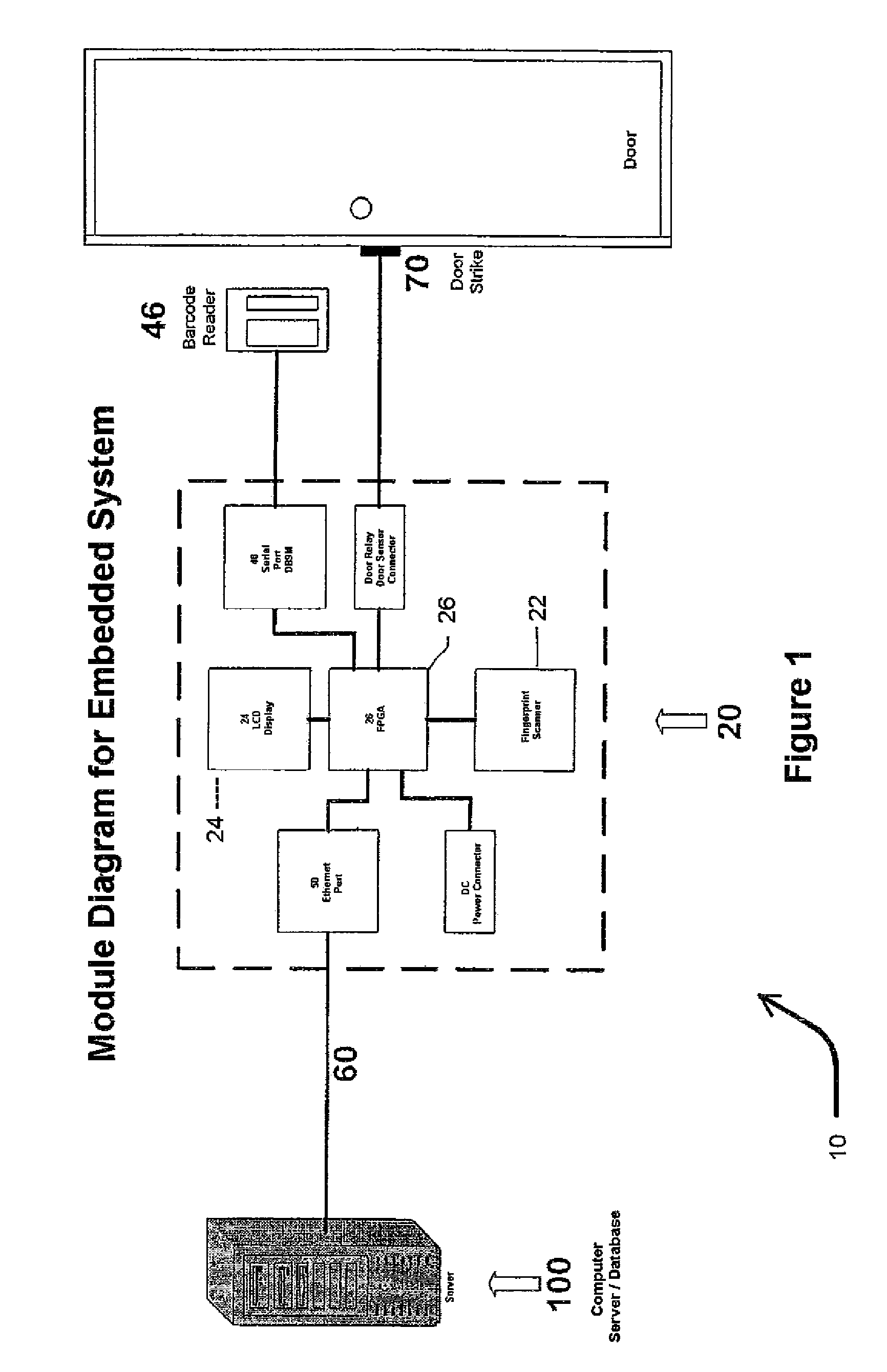

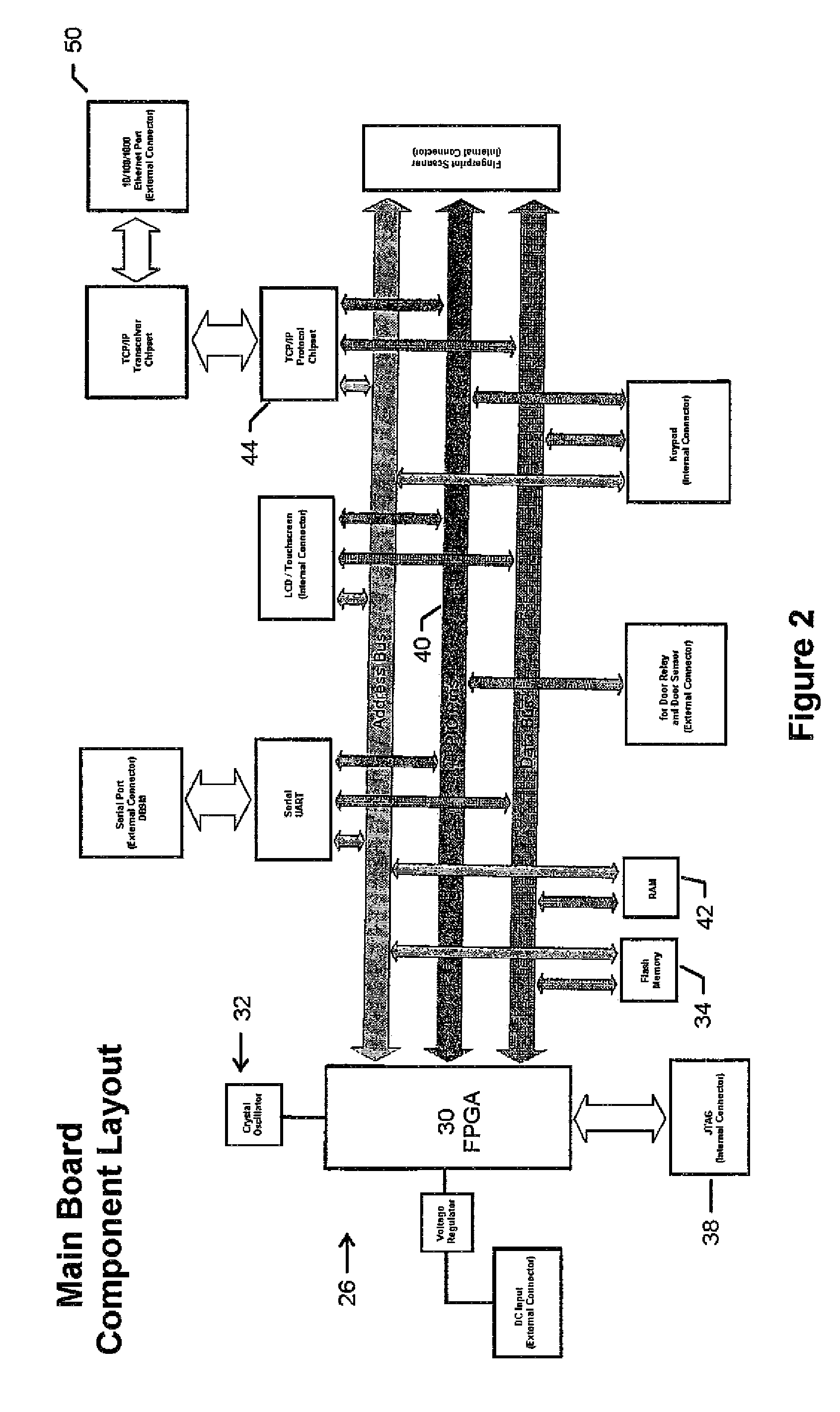

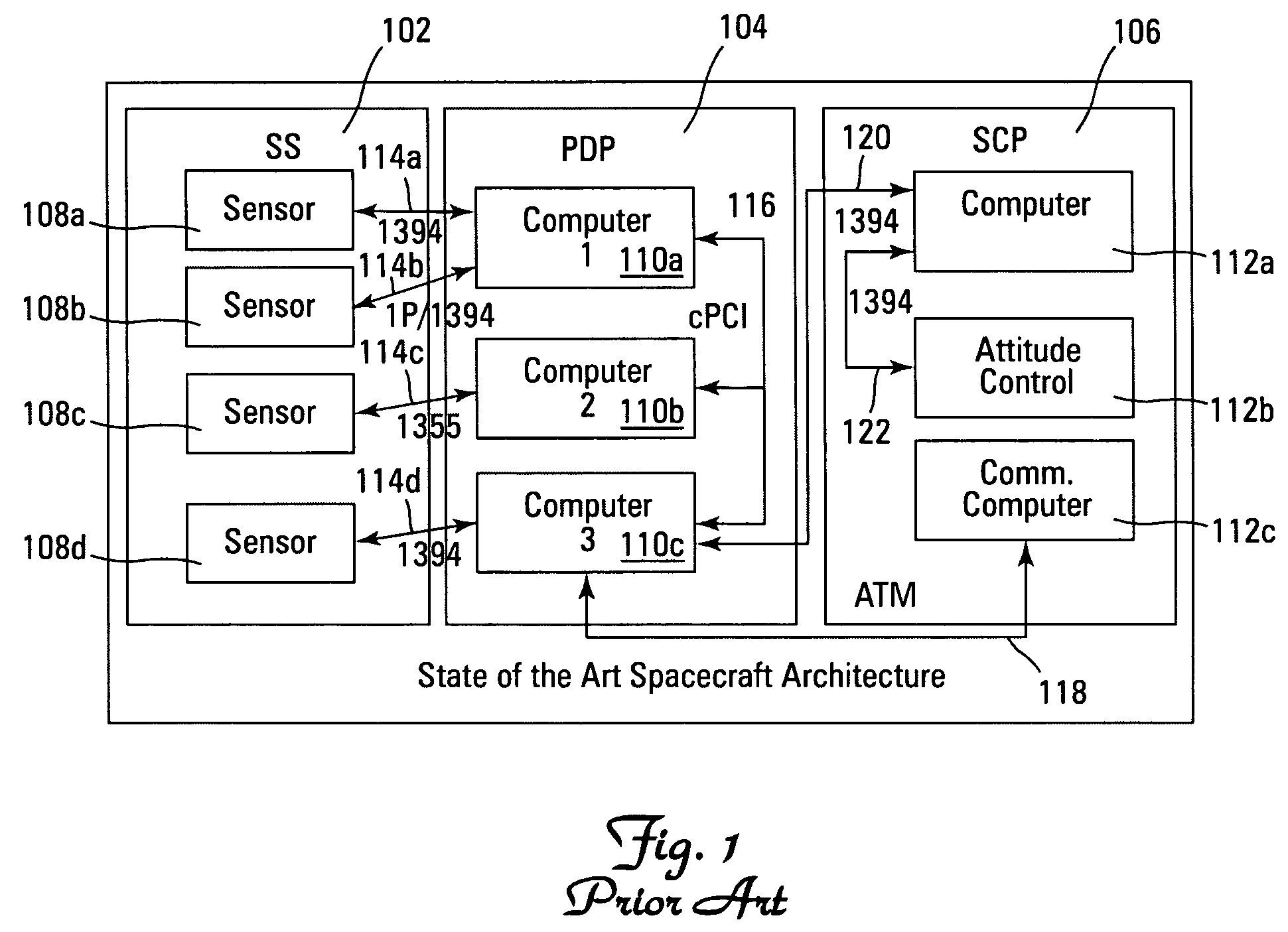

Biometric access control and time and attendance network including configurable system-on-chip (CSOC) processors with embedded programmable logic

ActiveUS7424618B2Compact efficient designCost efficient designElectric signal transmission systemsDigital data processing detailsHard disc driveHuman interaction

A biometric access control and time and attendance system comprises an integrated network including one or more remote access devices in electronic communication with a computer database. Each remote access device comprises a silicon chip based system and preferably includes a biometric input device, a liquid crystal display (LCD), computer processing capabilities based on embedded system architecture with configurable system-on-chip (CSOC) technology, and an electrical output for controlling a door lock or the like. The use of CSOC architecture in lieu of conventional personal computer technology (e.g. mother boards, hard drives, video controllers and the like) allows for a more compact and cost efficient design. A plurality of remote access devices is configured for communication with a primary computer database wherein data corresponding to biometric samples for all authorized users is stored. In an embodiment wherein the biometric input devices comprise fingerprint scanners, the devices are configured to facilitate fingerprint identification by incorporating an auto-targeting capability that enables the user to simply place his or her finger on the fingerprint scanner whereafter the system adjusts the scanned image by automatically shifting the scanned image data to a properly targeted position thereby enabling the system compare the scanned print to the biometric samples in the system's data storage memory. Auto-targeting capability eliminates the requirement for manual targeting present in systems of the background art thereby improving system performance and minimizing reliance on human interaction. The present invention contemplates the use of auto-targeting with other biometric systems, such as facial recognition and / or retinal scanning systems, or any other biometric identification technology.

Owner:PROFILE SOLUTIONS

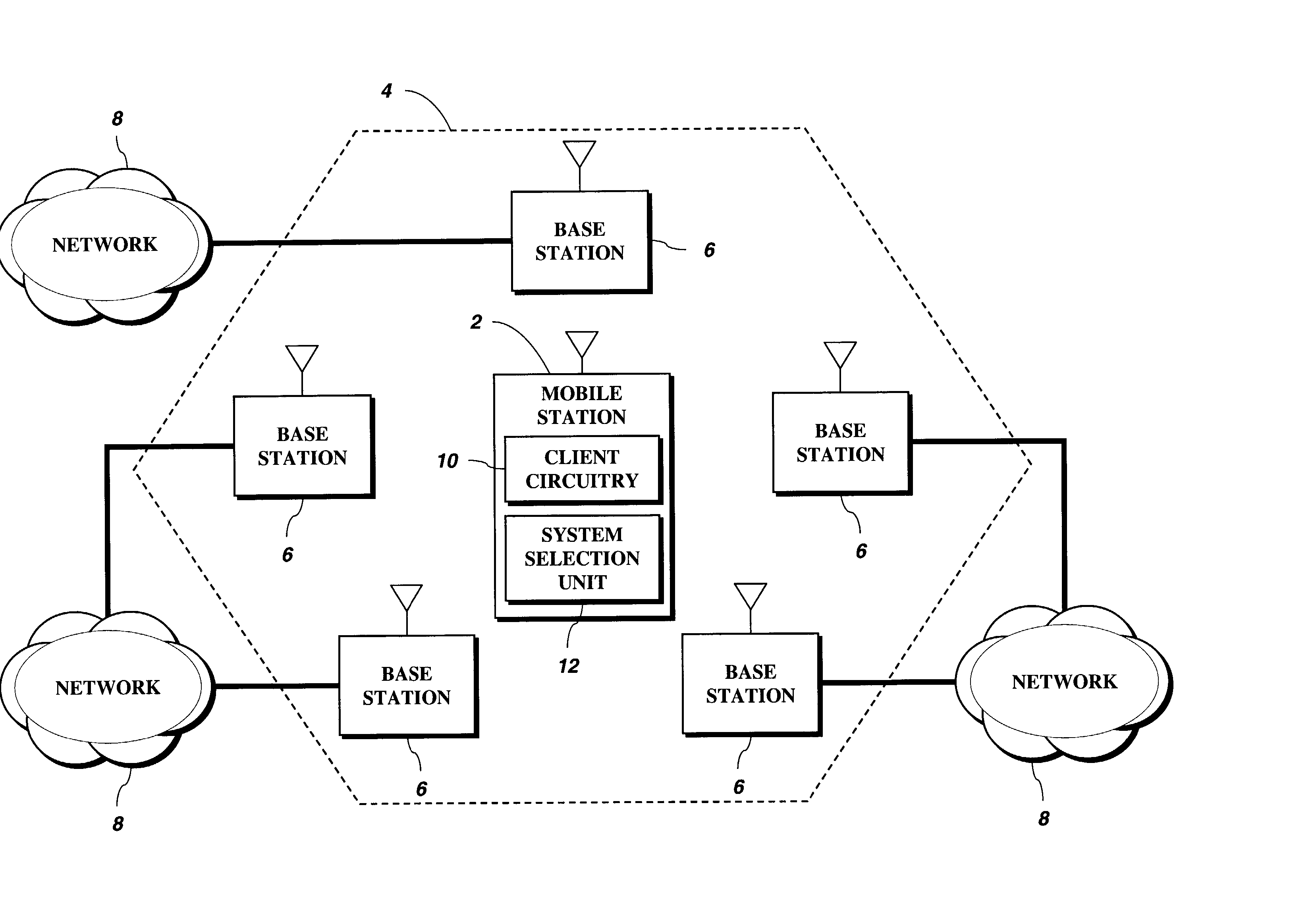

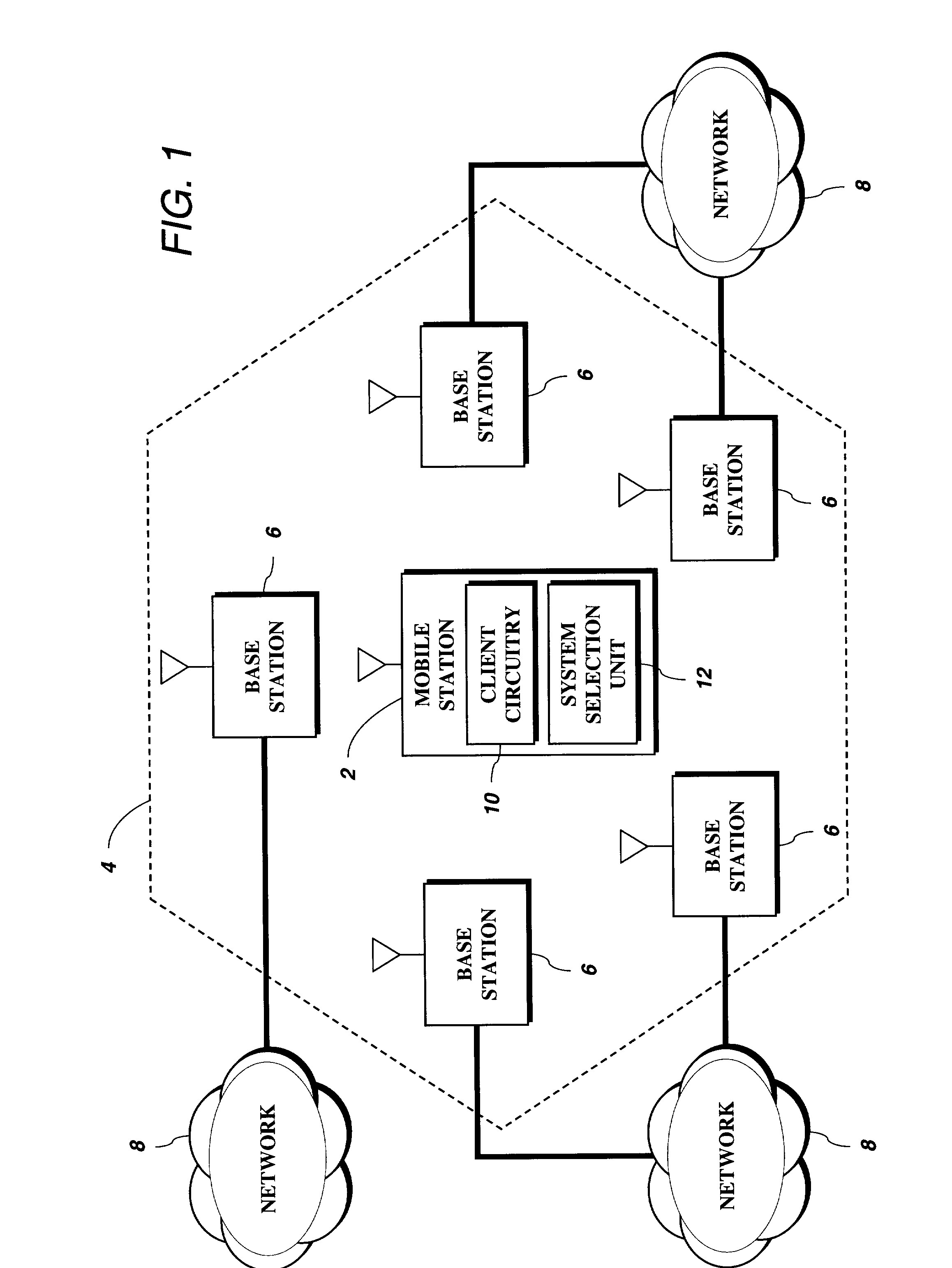

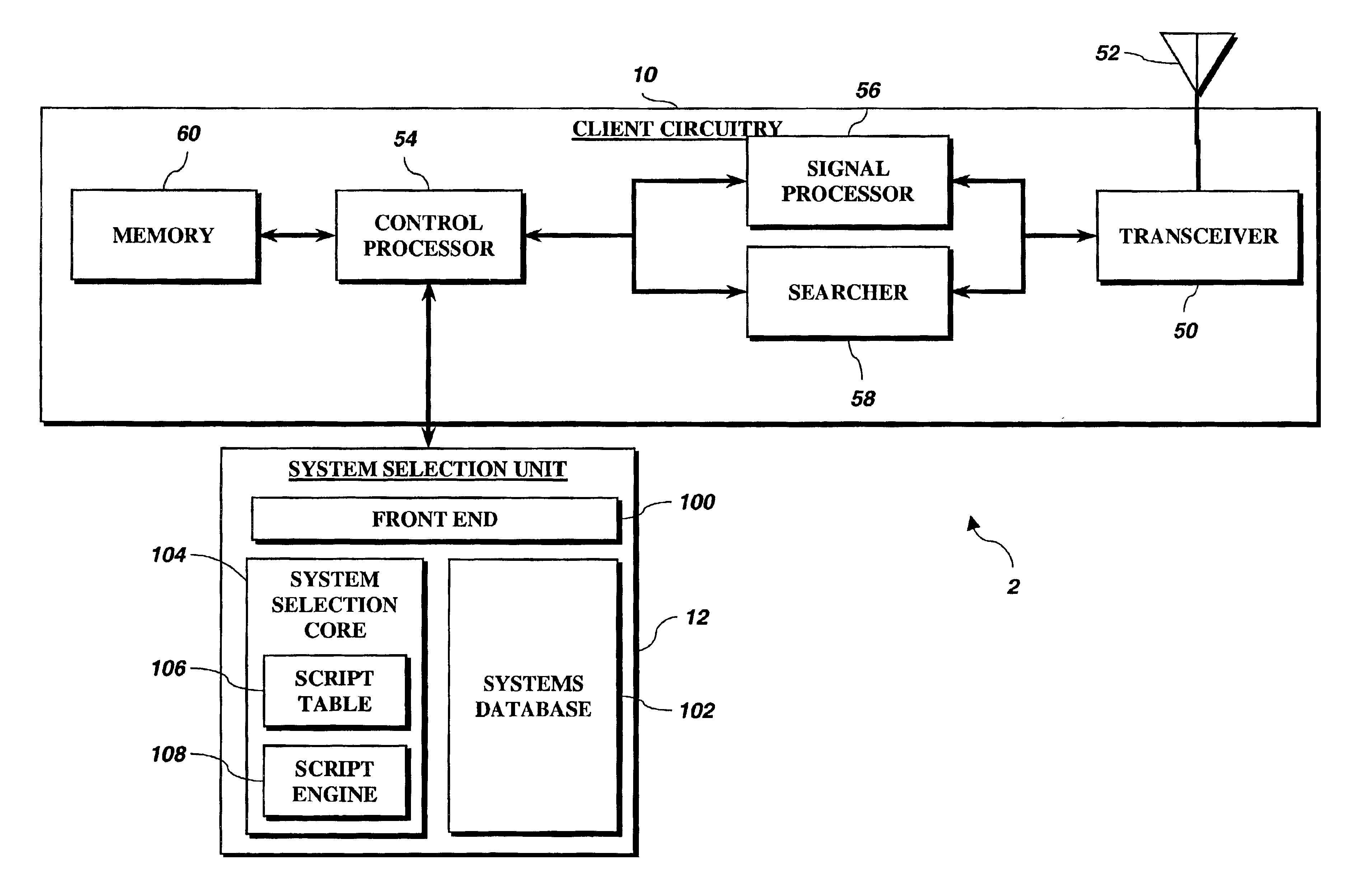

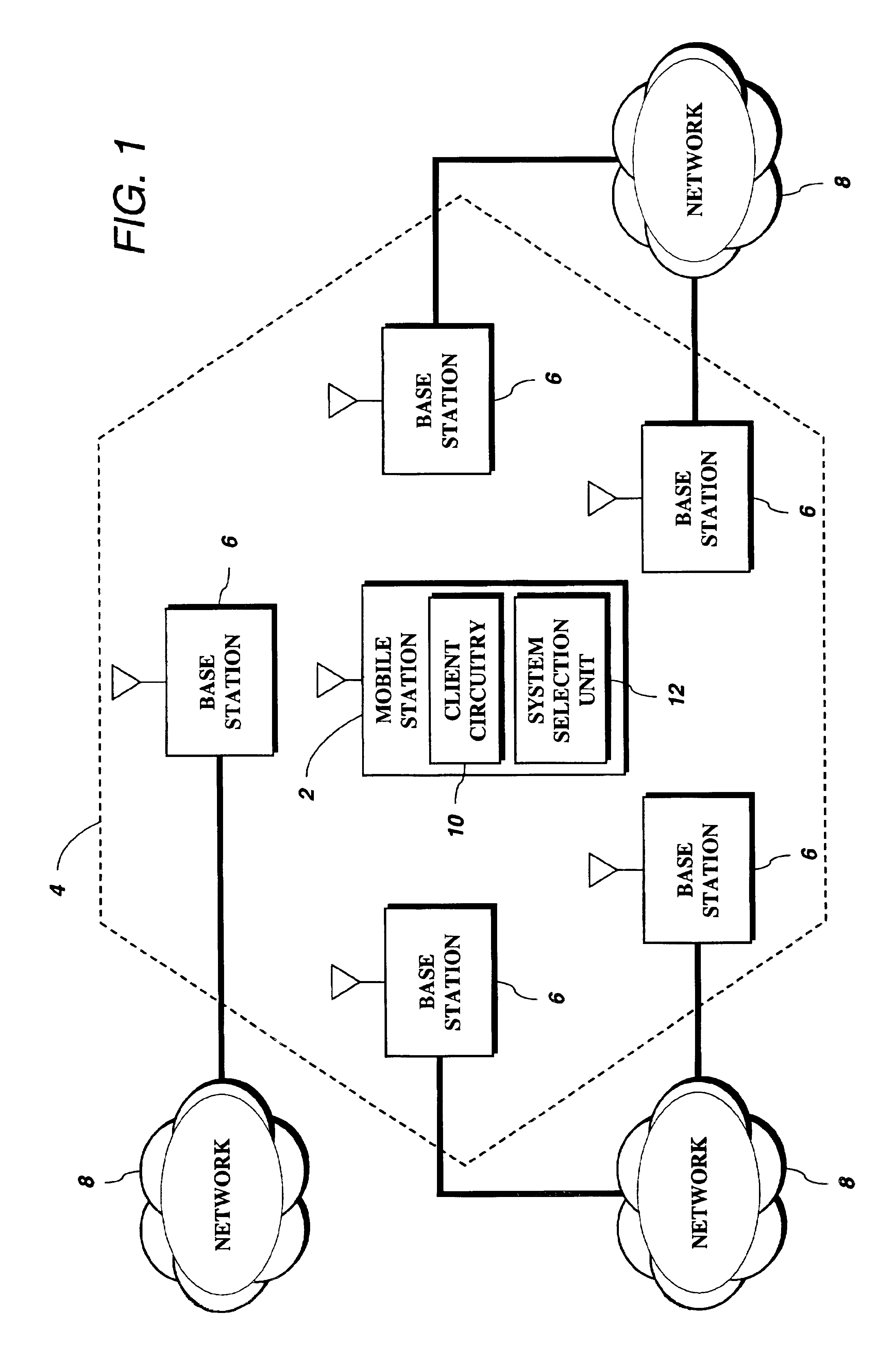

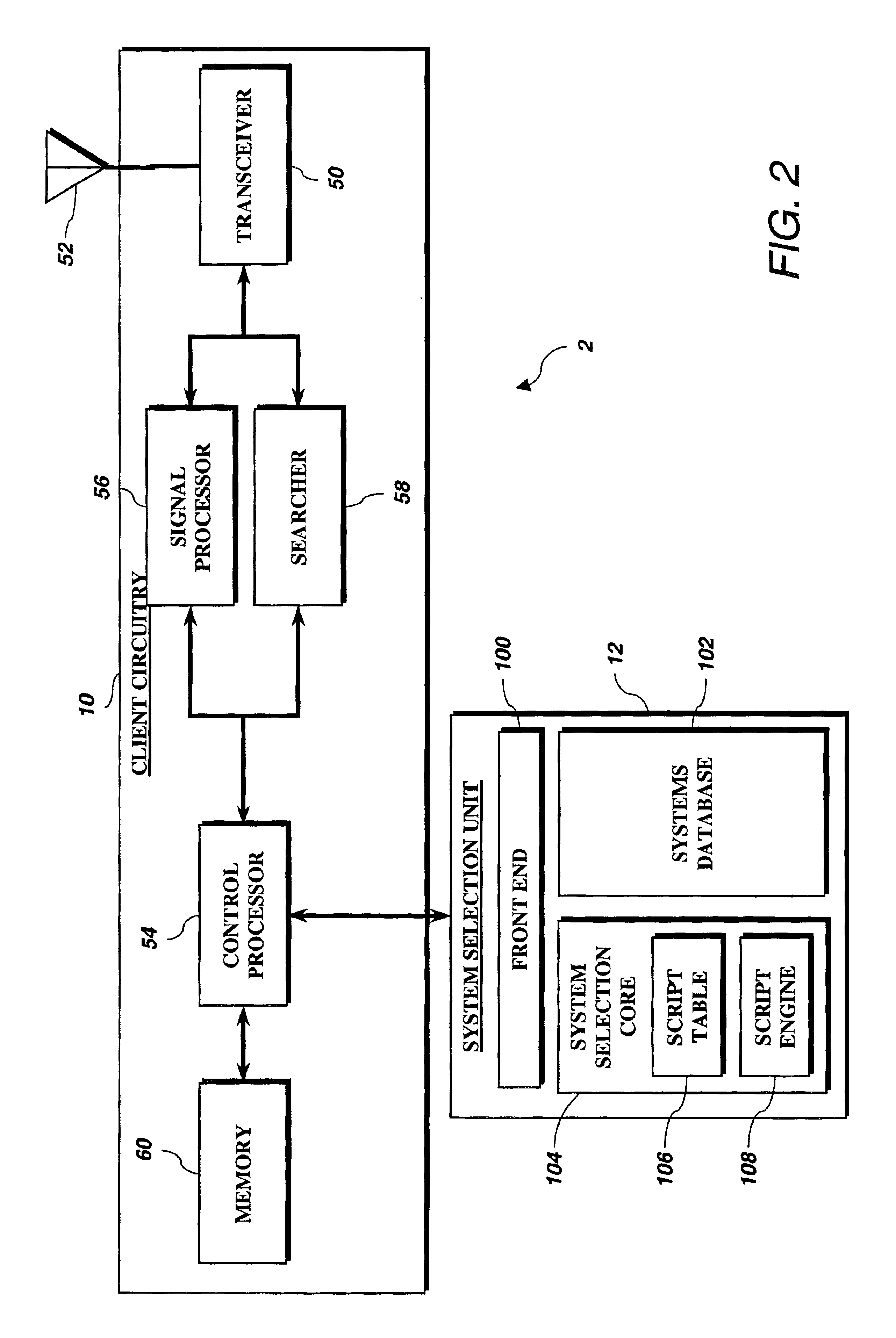

Method and apparatus for configurable selection and acquisition of a wireless communications system

InactiveUS20030148786A1Network traffic/resource managementAssess restrictionCommunications systemClient-side

A mobile station includes client circuitry for facilitating wireless communications with a wireless communications system, and a configurable system selection unit that executes a system selection and acquisition procedure. The configurable system selection unit includes a front end and a system selection core. The front end facilitates communications between the configurable system selection unit and the client circuitry. The system selection core is coupled to the front end and includes a script engine and a nonvolatile memory storing at least one script table. The script table includes a plurality of system selection event conditions and corresponding scripts that define a system selection and acquisition procedure. The script engine is adapted to detect an event condition and execute the corresponding script. The system selection core is adapted to receive a system selection script and store the received script in the script table, thereby altering the system selection and acquisition procedure.

Owner:QUALCOMM INC

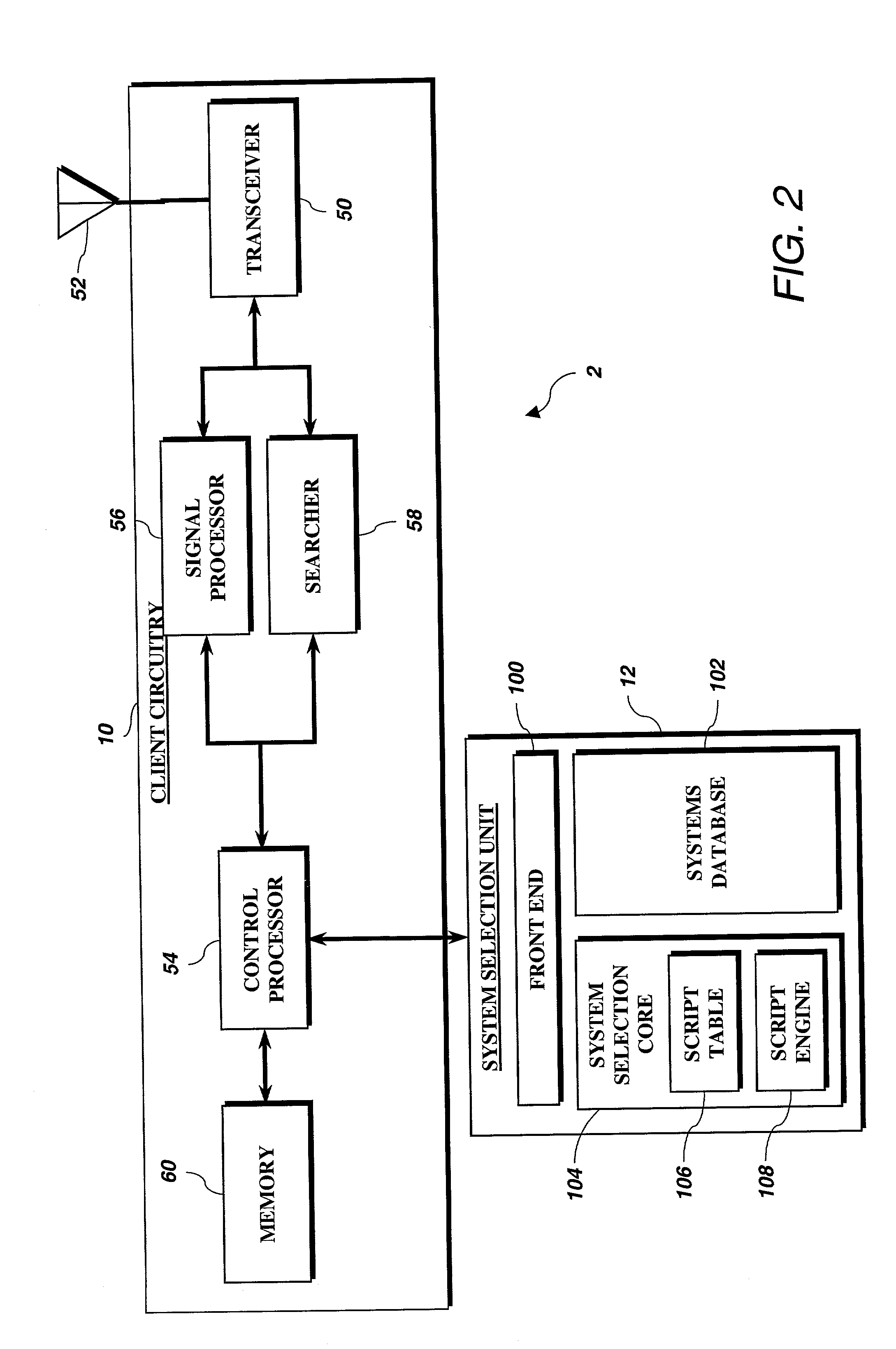

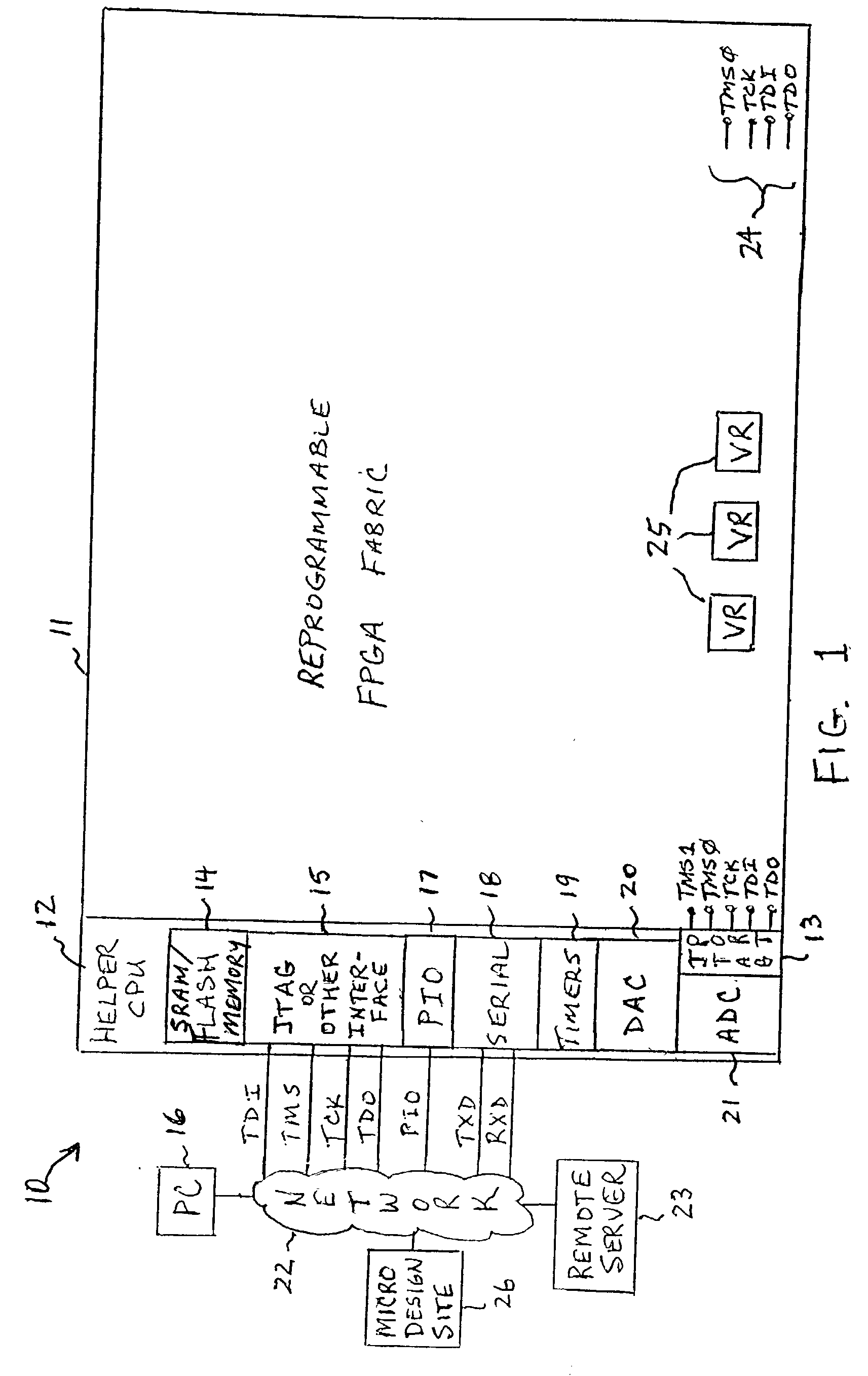

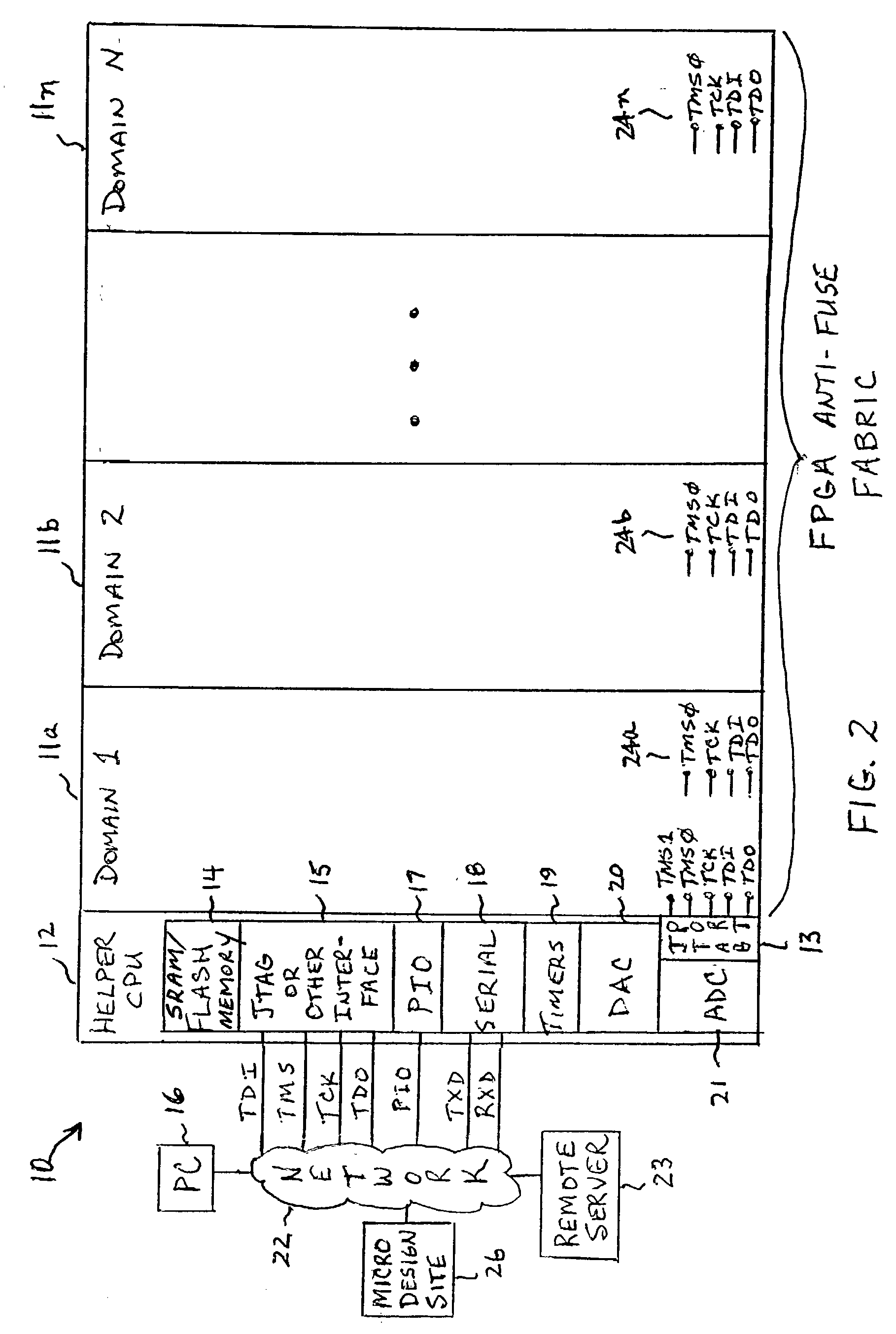

Self-programmable microcomputer and method of remotely programming same

InactiveUS20030217306A1Error preventionDetecting faulty hardware by remote testMicrocontrollerMicrocomputer

A user-configurable and / or self-configurable System on a Chip (SoC) device and corresponding remote programming method enabling the SoC to be reprogrammed multiple times from a remote chip file server. Once programmed with the desired SoC design, the device can be debugged remotely in real-time by one or more users. The device includes a helper microcontroller / programmer, and a Field Programmable Gate Array (FPGA) fabric which is divided into a plurality of programmable logic and clock driver domains that may be independently programmed by way of the helper microcontroller. Once programmed, the helper microcontroller can serve as a real-time monitor / data exchange sub-controller and / or may be used by the end application.

Owner:HARTHCOCK JERRY D +1

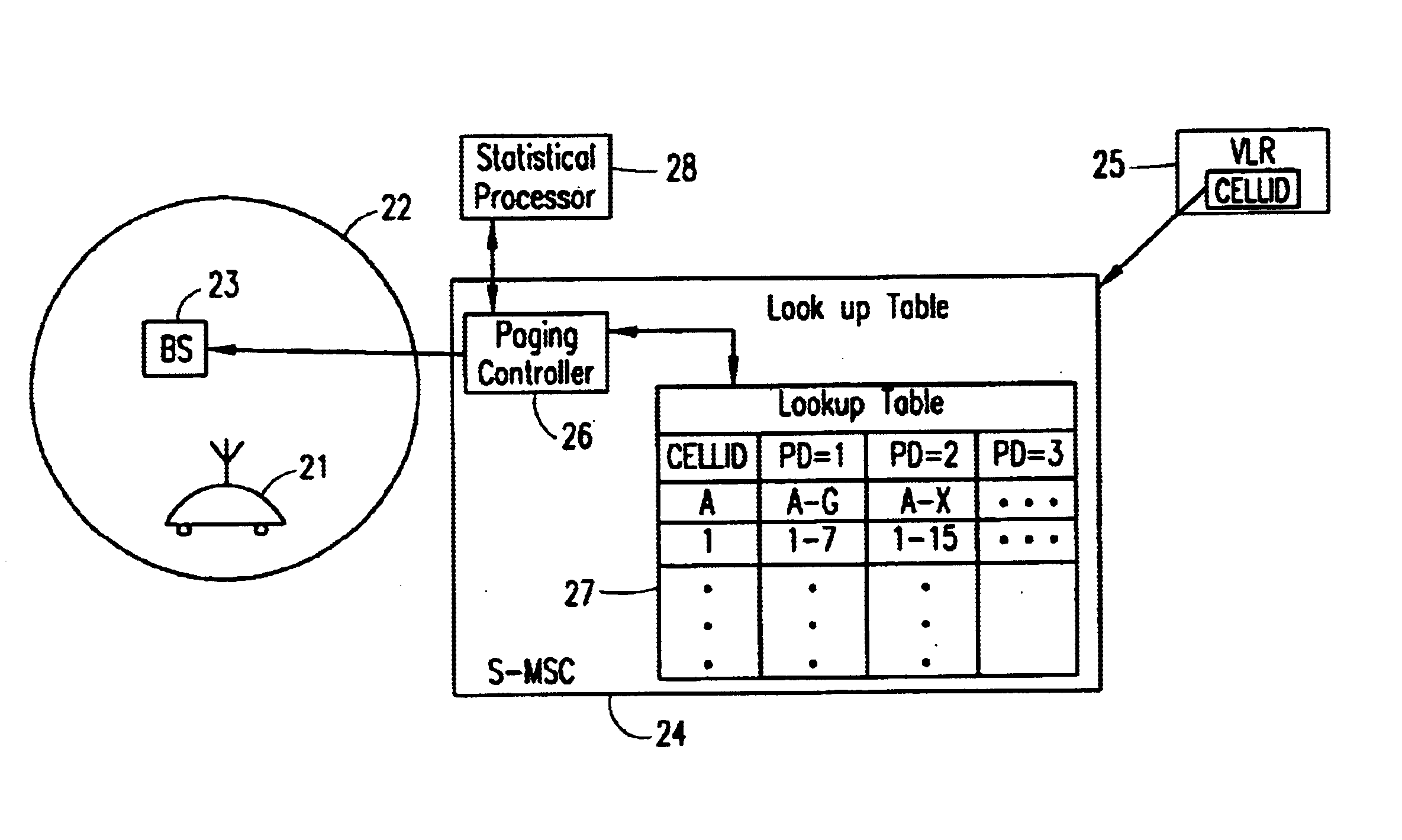

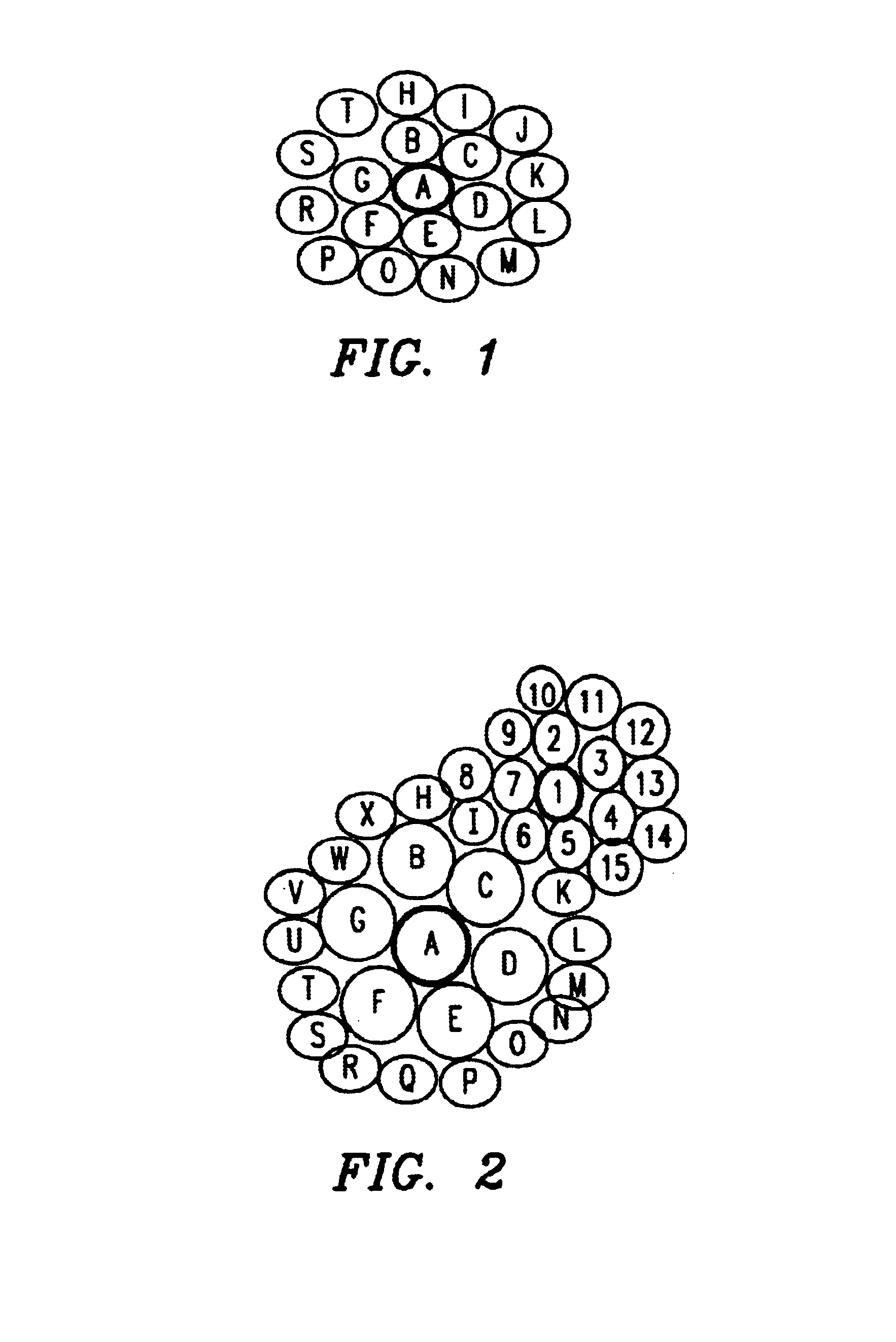

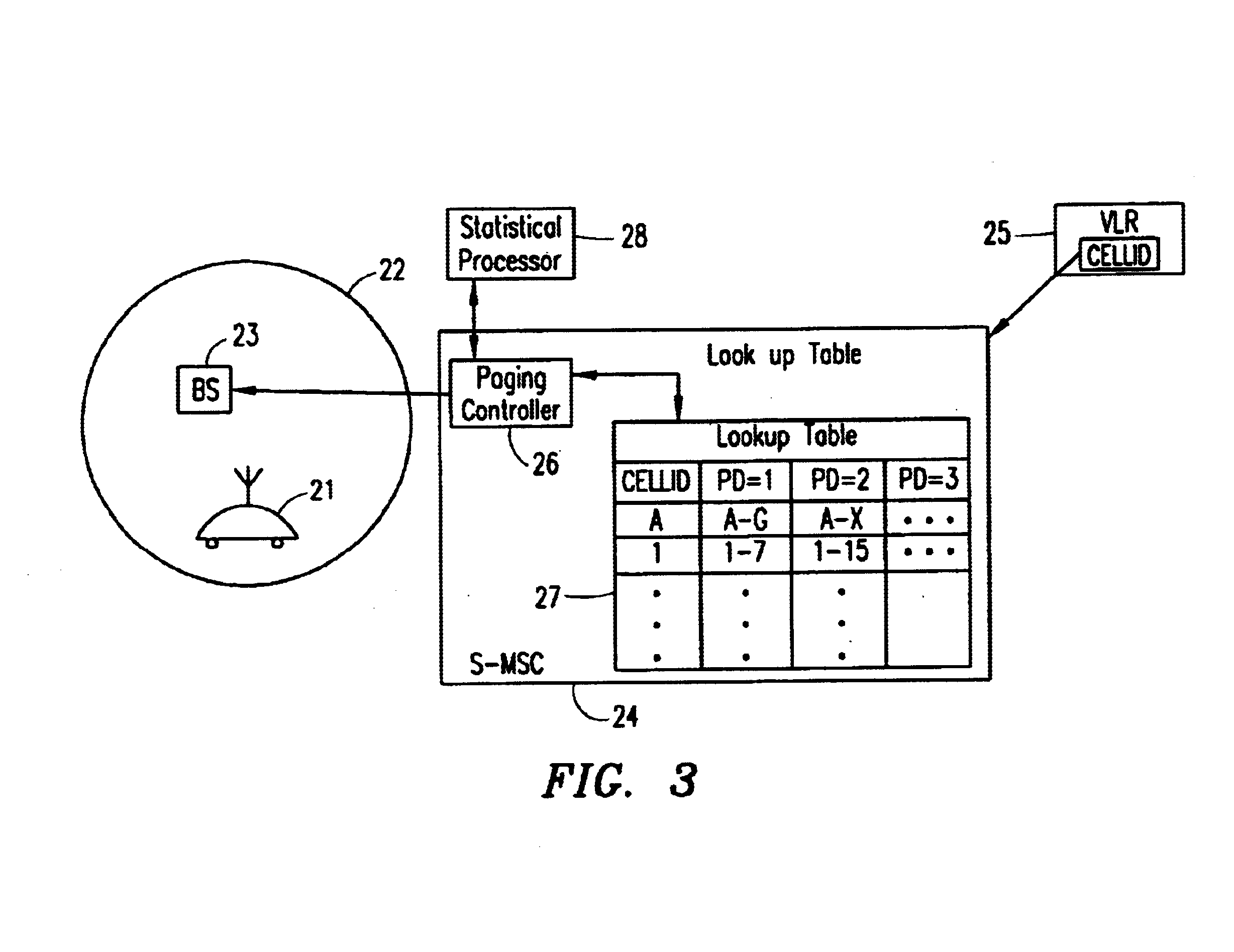

Self-configurable paging system for a cellular telecommunications network

InactiveUS6745039B1Radio/inductive link selection arrangementsWireless commuication servicesTelecommunications networkConfigurable systems

A self-configurable system and method in a cellular telecommunications network for efficiently paging for mobile stations that last registered in a particular cell by automatically adjusting the size of an initial paging area on a per-cell basis. A plurality of sets of cells surrounding the particular cell are identified as Paging Depths (PDs) and are stored in a lookup table in a serving Mobile Switching Center (MSC). The PDs contain varying numbers of cells, and a first PD is selected to utilize for the particular cell's initial paging area. A plurality of paging attempts are then performed for mobile stations that last registered in the particular cell, and a statistical processor compiles statistics regarding the paging efficiency (percentage of mobile stations found versus total system resources used) and the success rate (percentage of paging attempts that were successful at locating mobile stations within the first PD). If the statistics indicate that the success rate was below a first threshold, the method increases the PD so as to select a set of cells having a greater number of cells than the first set of cells for the particular cell's initial paging area. If the statistics indicate that the success rate was above a first threshold, and the paging efficiency was above a second threshold, the method decreases the PD so as to select a set of cells having a lesser number of cells than the first set of cells.

Owner:UNWIRED PLANET

Configurable clinical information system and method of use

InactiveUS20070168223A1Easy diagnosisIncrease flexibilityMedical automated diagnosisMedical report generationClinical informationUsability

Certain embodiments of the present invention provide a user-configurable clinical information system. Certain embodiments provide for a user-configurable data and functionality entry and retrieval system. Certain embodiments provide a system and method for configuration and / or customization of patient and practice data entry, analysis and manipulation. Certain embodiments provide a configurable system that allows easy update of components and rules transparently to a user. In an embodiment, a user may dynamically make changes to the system. Certain embodiments of the present invention provide a configurable system that provides greater flexibility, greater usability, greater diagnosis and support, and greater functionality for healthcare practitioners.

Owner:GENERAL ELECTRIC CO

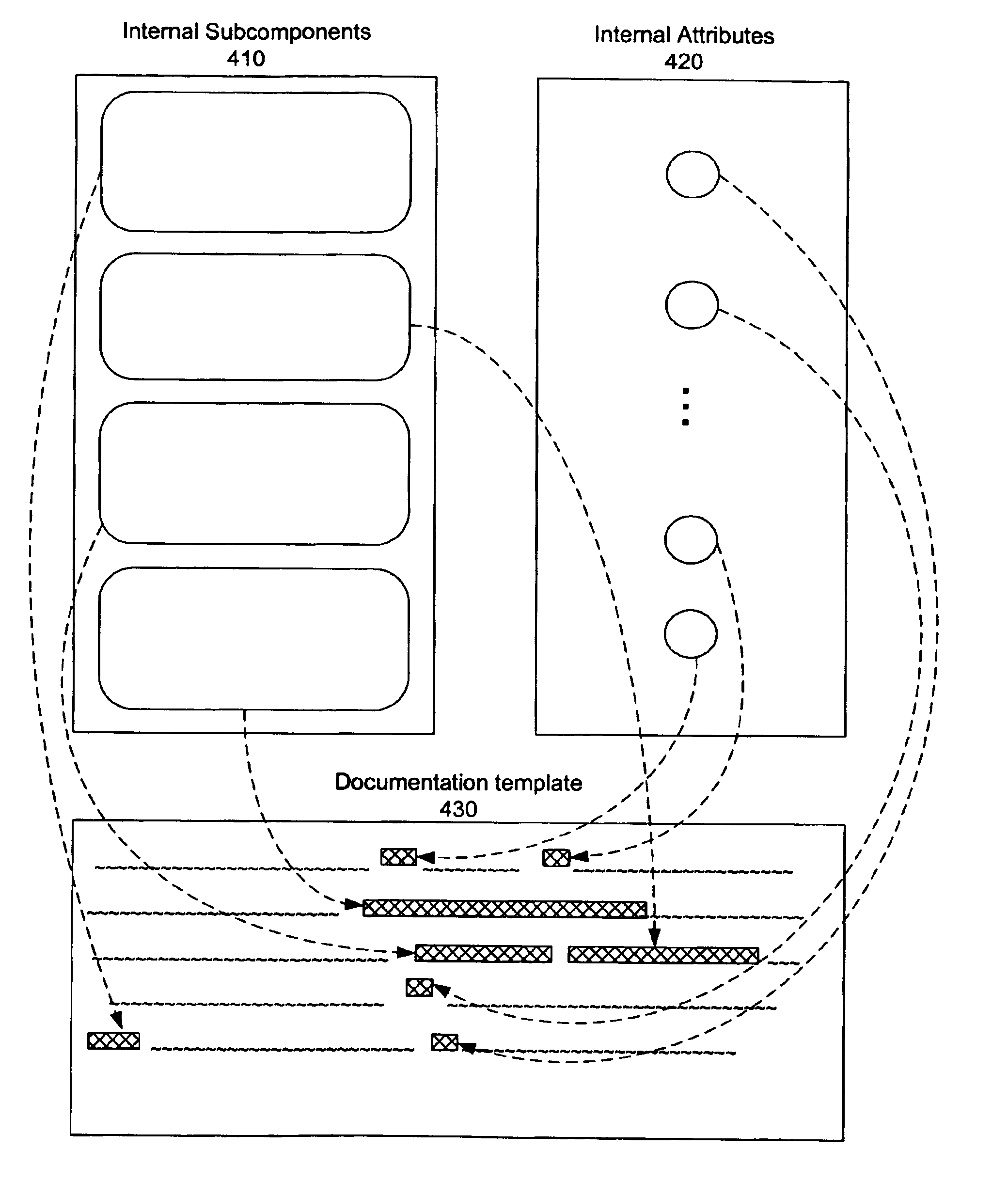

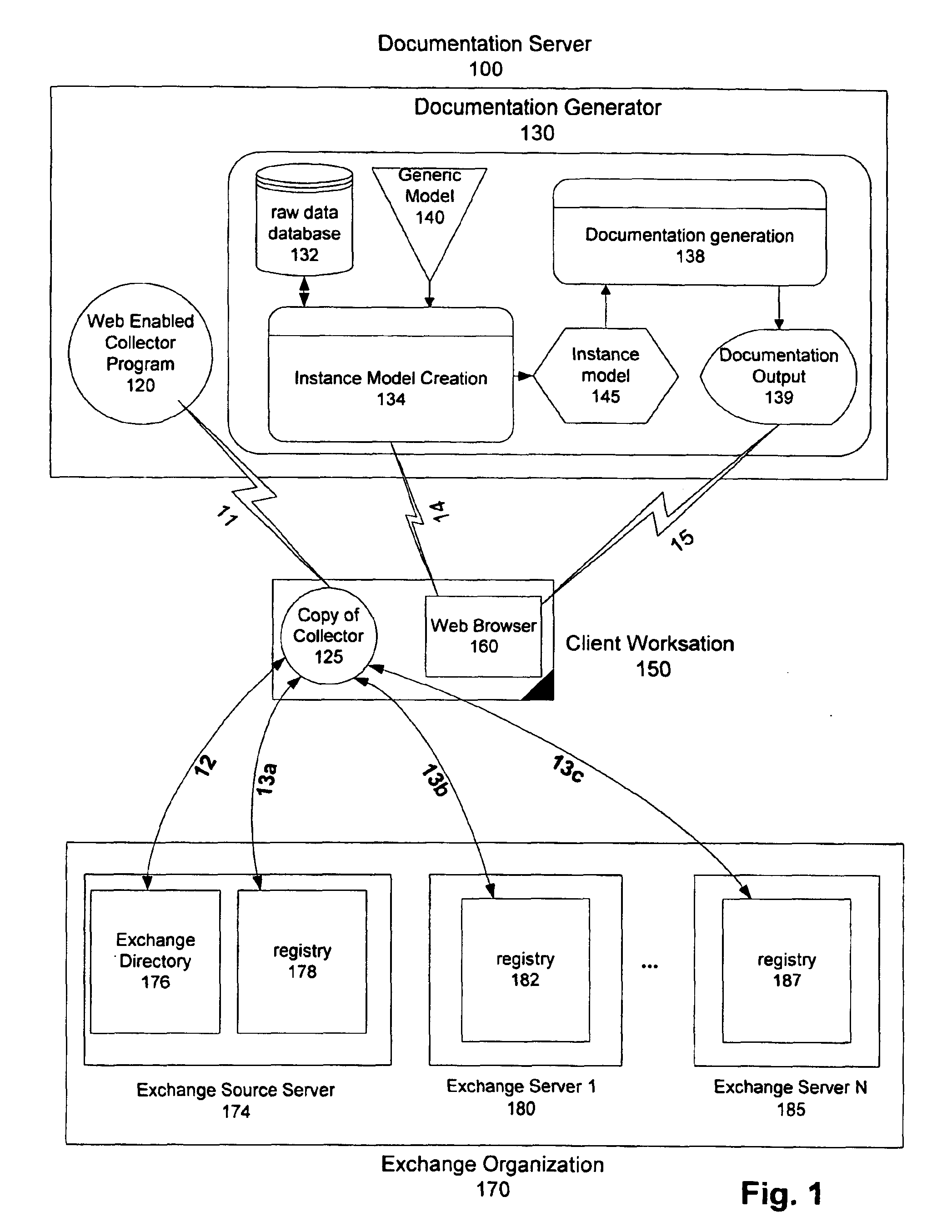

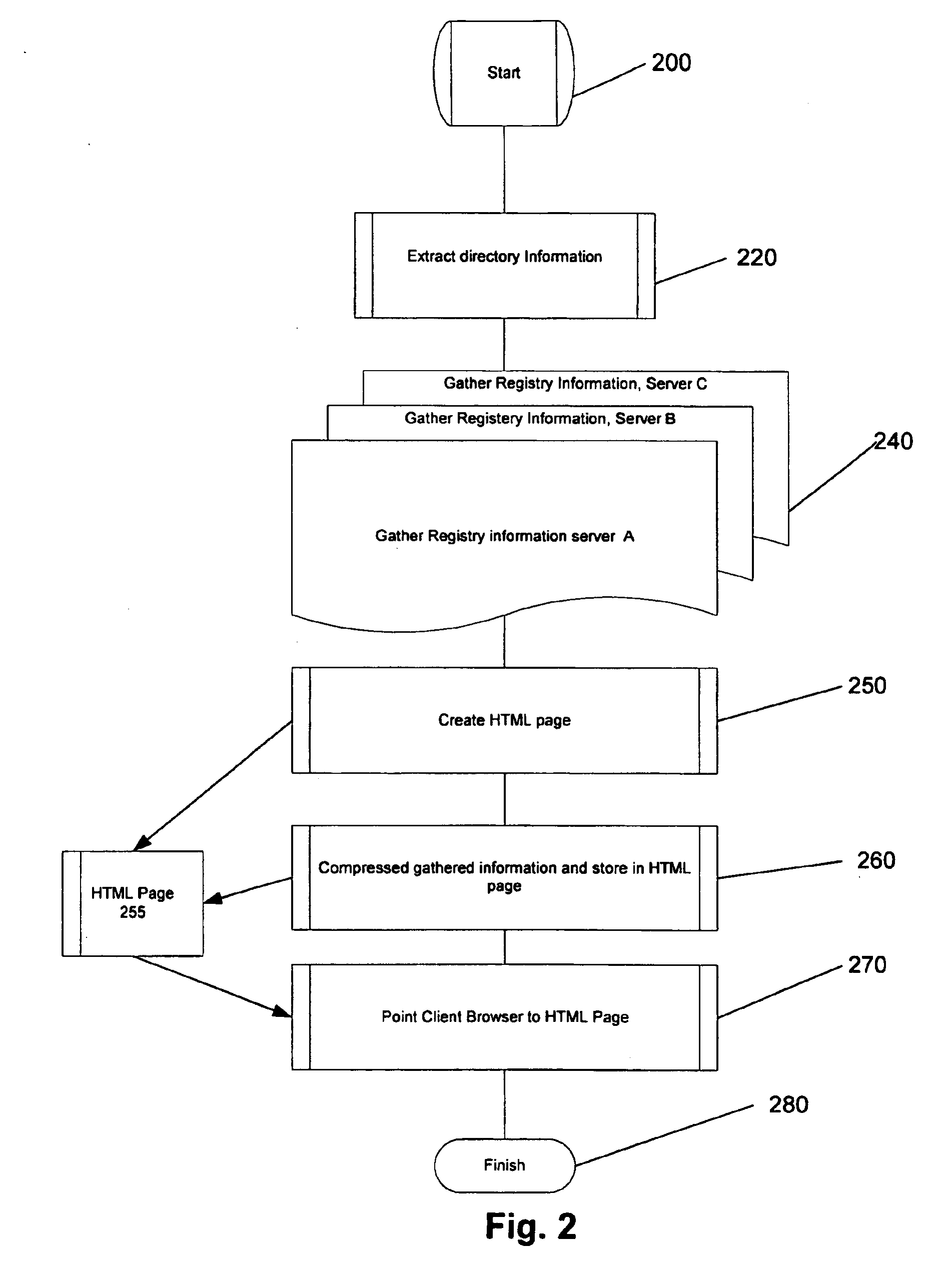

Automatic documentation of configurable systems by outputting explanatory information of configuration parameters in a narrative format and configuration parameters differences

InactiveUS6981207B1Fast and efficient checkingEasy flagging of error conditionDigital data processing detailsLogical operation testingDocumentation procedureApplication software

An automatic documentation generation and management system and method, for documenting configurable systems such as complex software applications and hardware systems is disclosed. The method retrieves configuration parameters from the configurable system and utilizes them to automatically generate an explanatory document specific to the configured system. The invention also discloses a documentation appliance system, which is a dedicated documentation server coupled to the configurable system via a communication network, preferably via an Intranet. In yet another alternative, the invention may be practiced by integrating code for automatic documentation generation within the configurable system program.

Owner:VERSATA

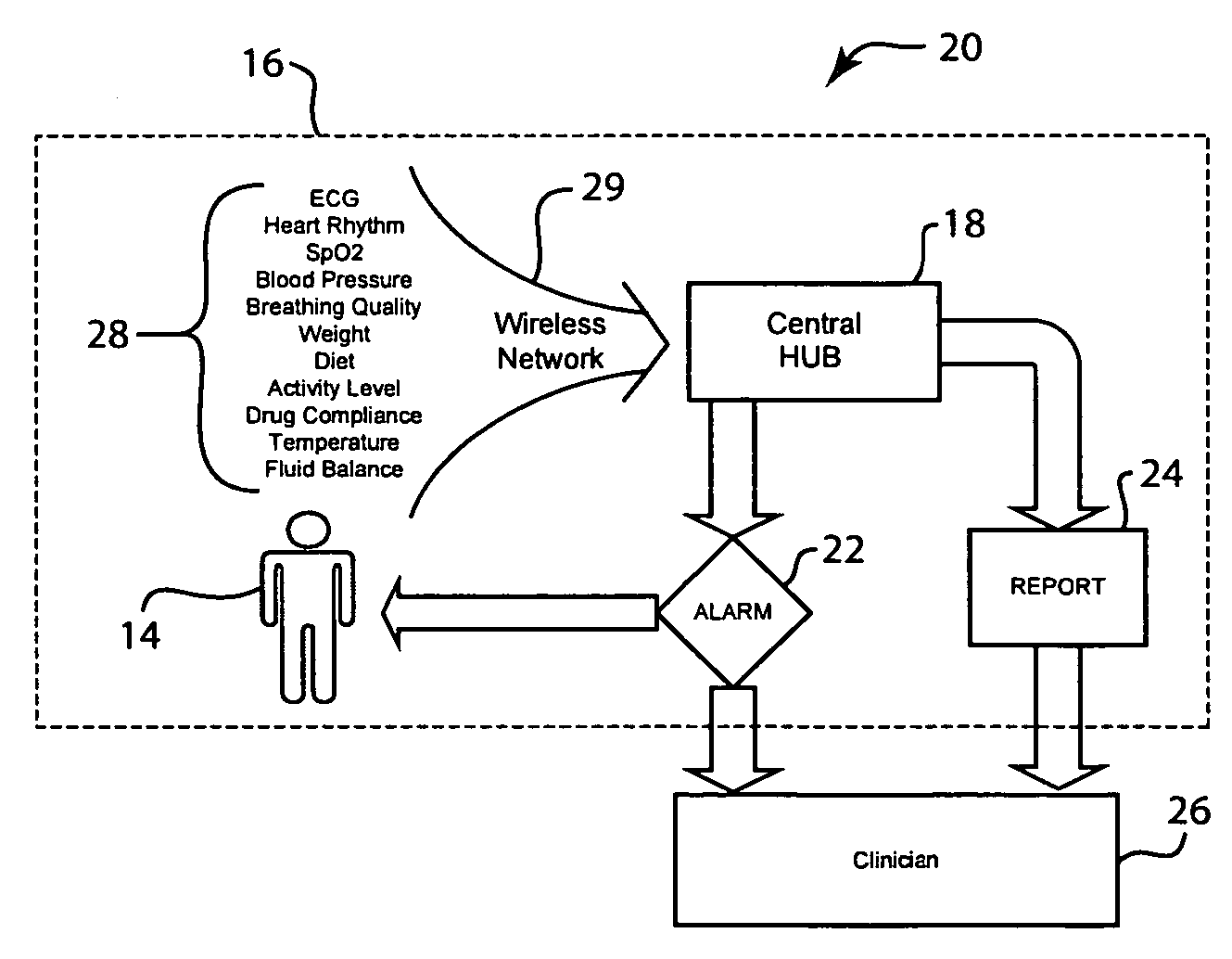

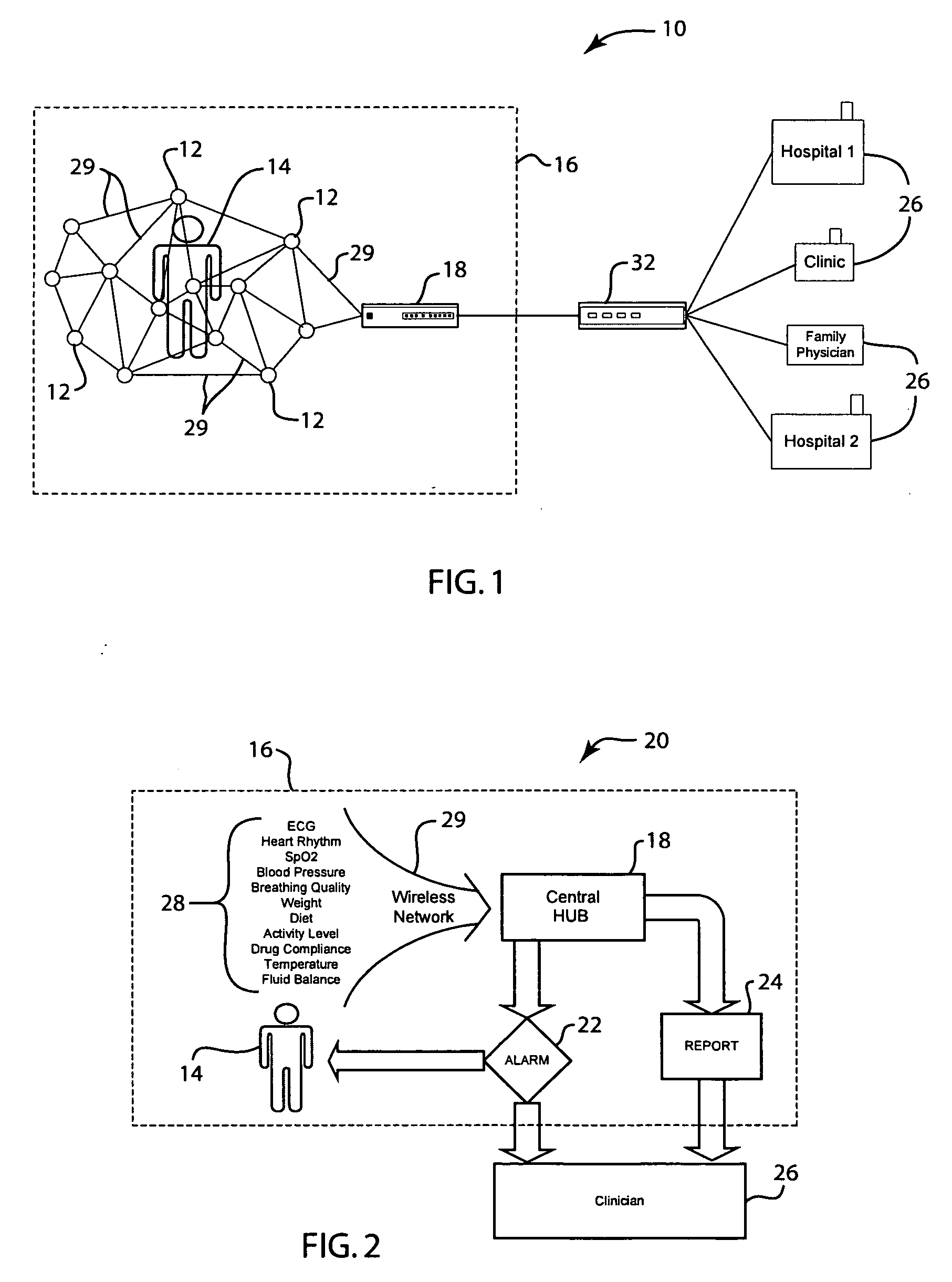

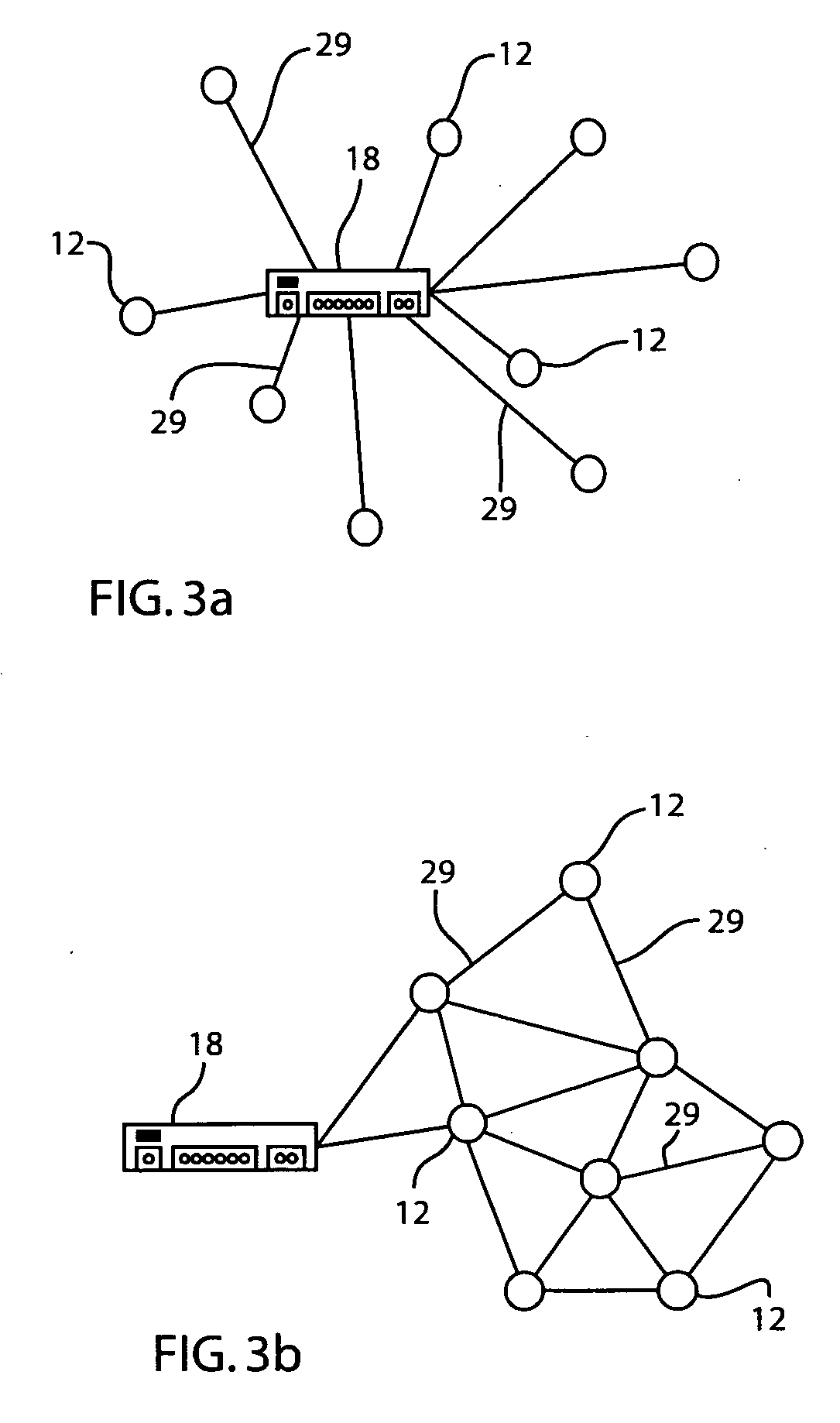

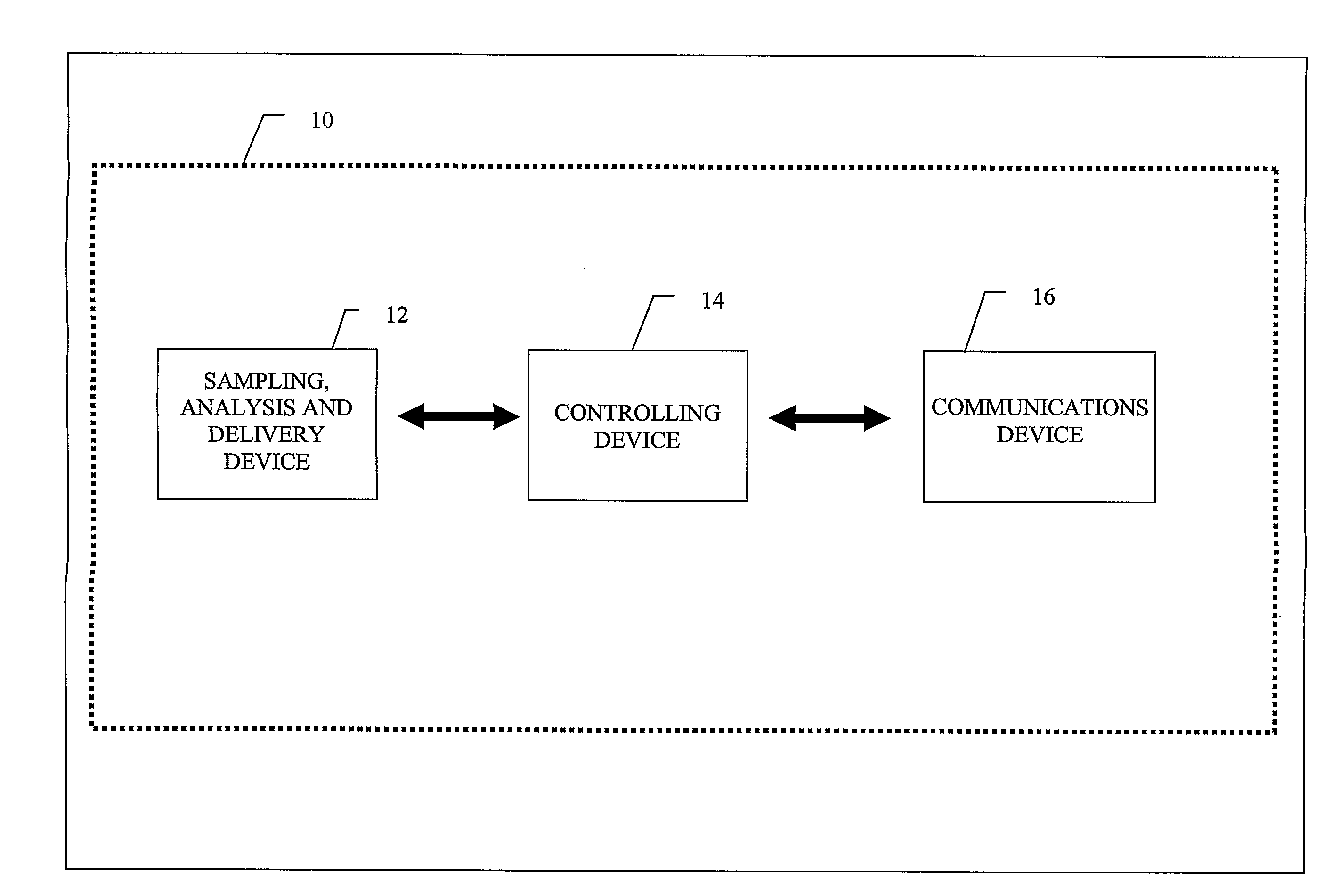

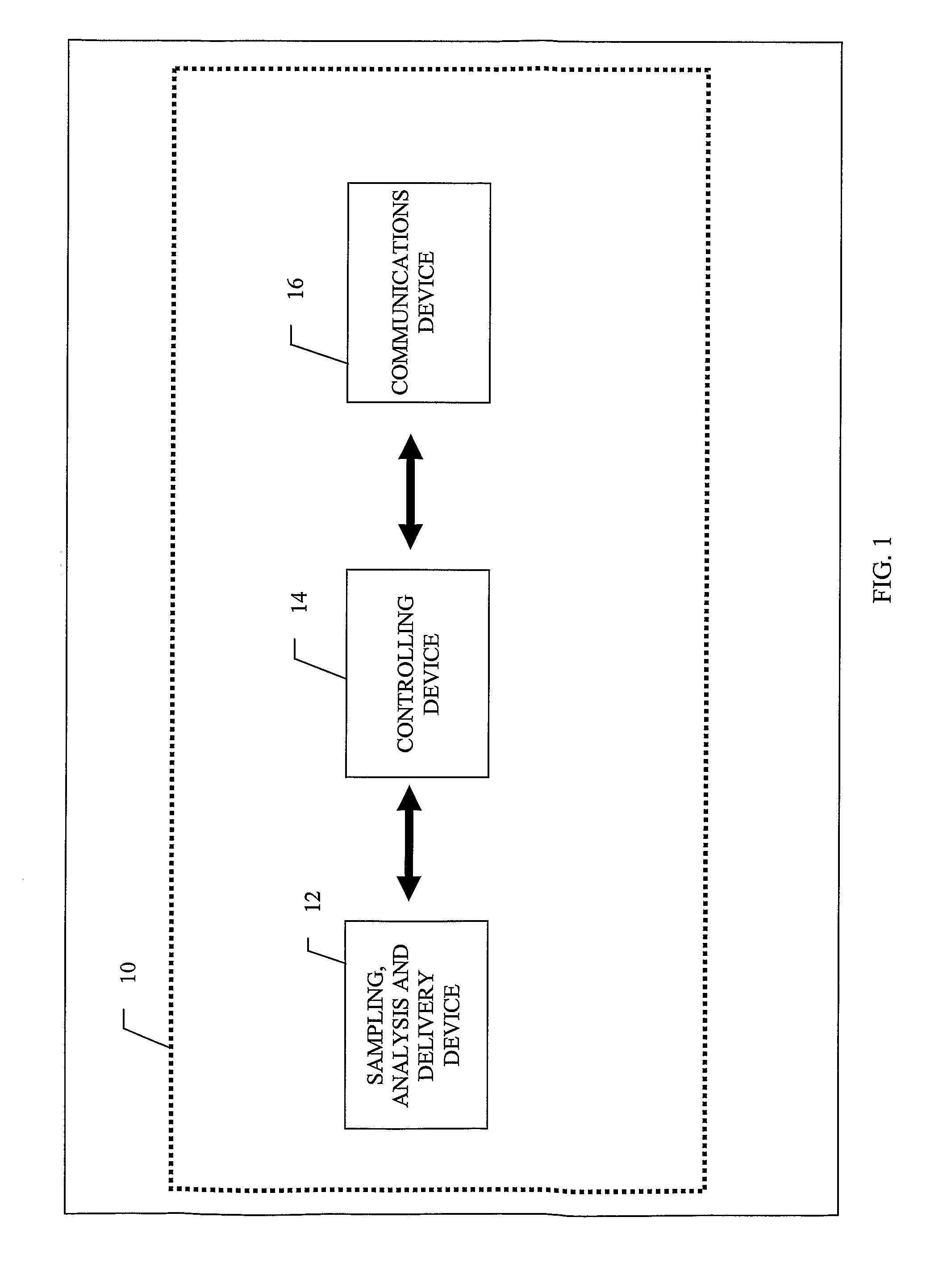

Networked modular and remotely configurable system and method of remotely monitoring patient healthcare characteristics

The present invention is a system and method of remotely monitoring patient health care characteristics. The system utilizes at least two micro-scale to millimeter-scale sensors, a wireless network, a central hub and pre-processing center and a means for notifying a clinician of the remote patient's condition. The system and method includes sensor to sensor coordination, modular-based sensors and processing, and allows a clinician to remotely configure the system.

Owner:GENERAL ELECTRIC CO

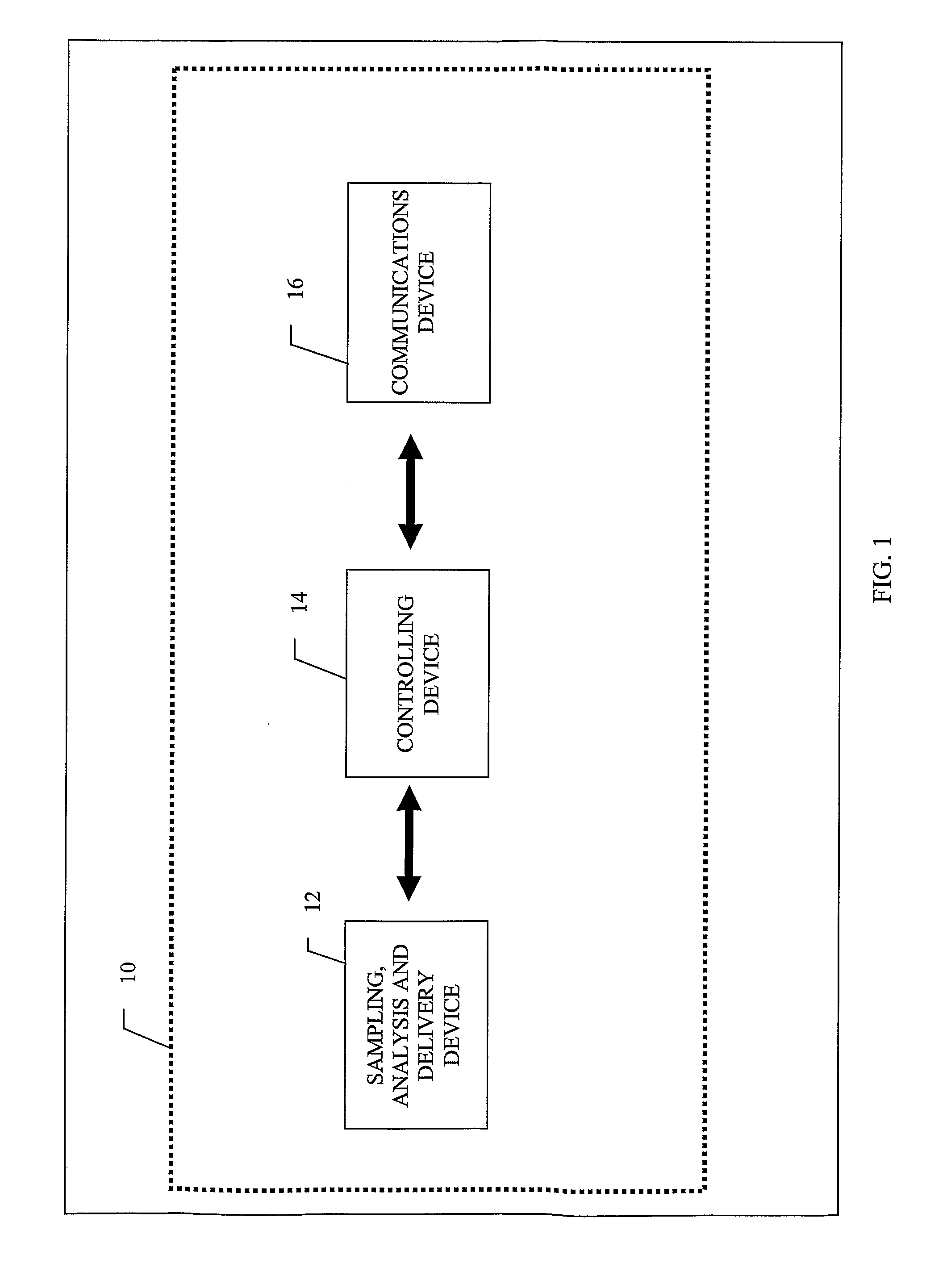

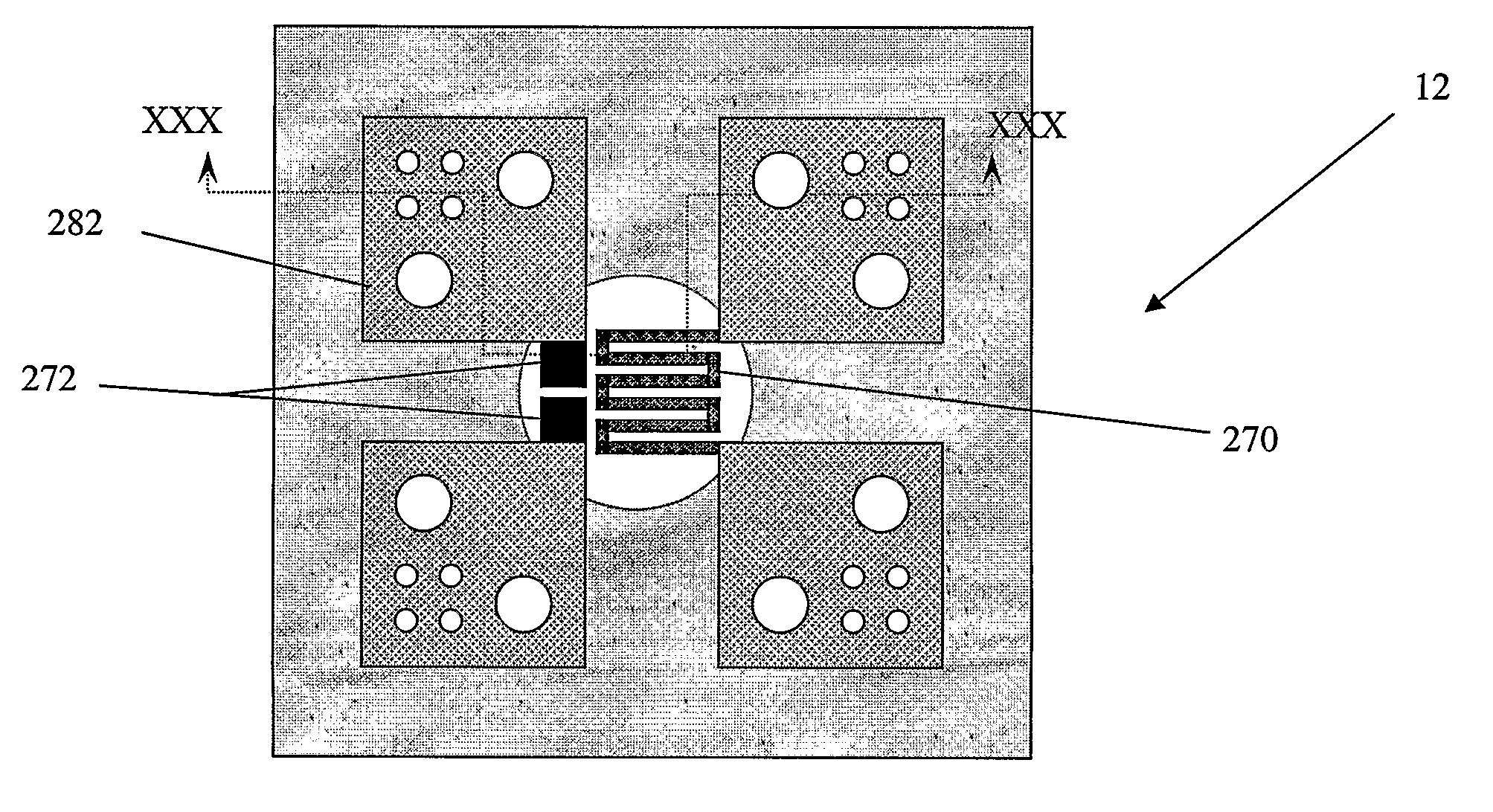

Flexible Apparatus and Method for Monitoring and Delivery

The present invention generally relates to a system and method that co-locates in a small flexible, configurable system and multi-level substrate sampling, rapid analysis, bio-sample storage and delivery functions to be performed on living tissues or matter obtained from living organisms. The types of the sampling may include chemical, biochemical, biological, thermal, mechanical, electrical, magnetic and optical sampling. In general, the analysis performed at the point of sampling measures the sample taken and records its value. The bio-sample storage function encapsulates a small sample of analyte and preserves it for subsequent examination or analysis, either on the organism by the system or at a remote location by an independent analysis system. Once stored, the sample can provide a record of a biological state at the precise time of sampling. The delivery at the point of sampling can include chemical, biochemical, thermal, mechanical, electrical, magnetic and optical stimuli.

Owner:FISH & RICHARDSON P C

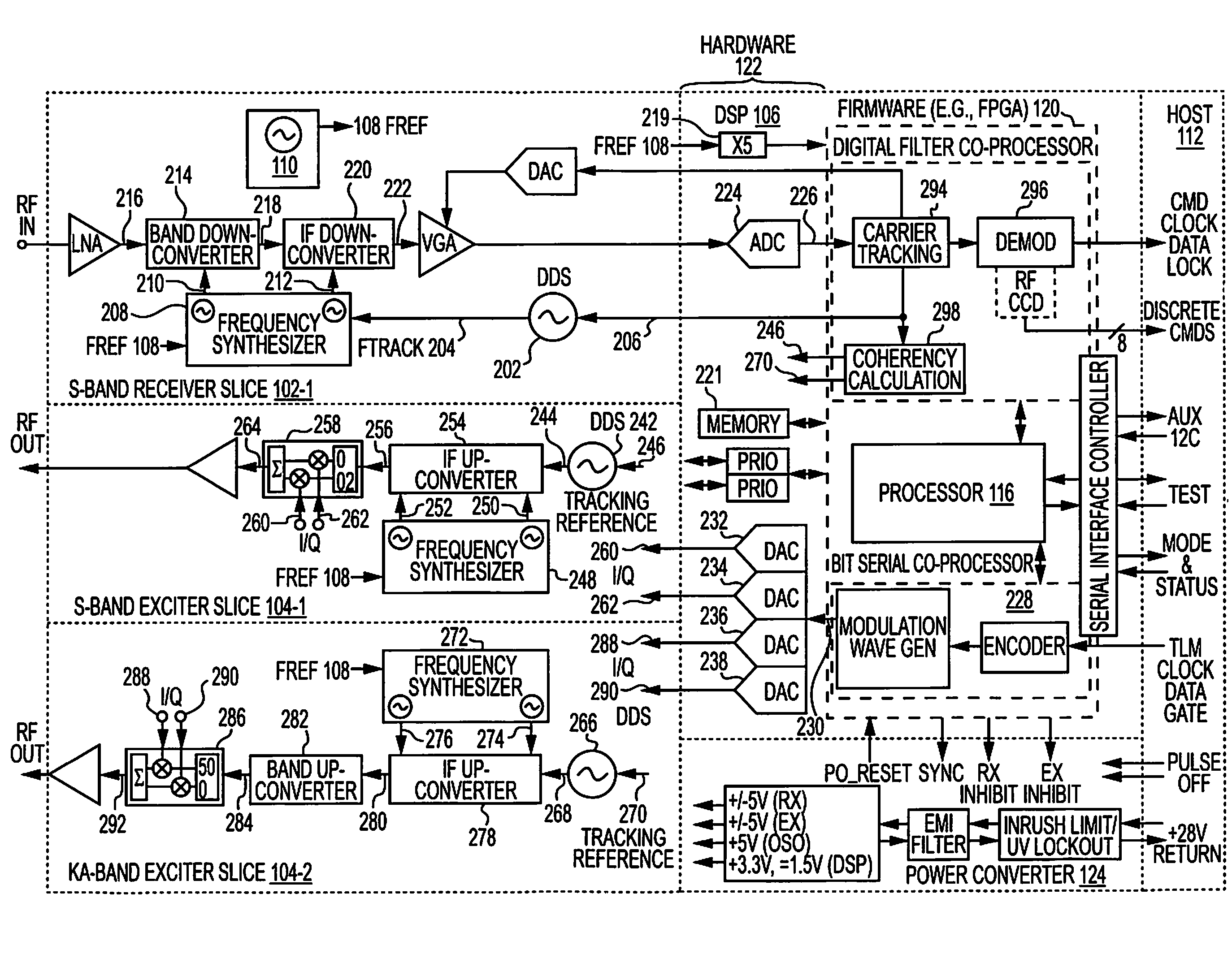

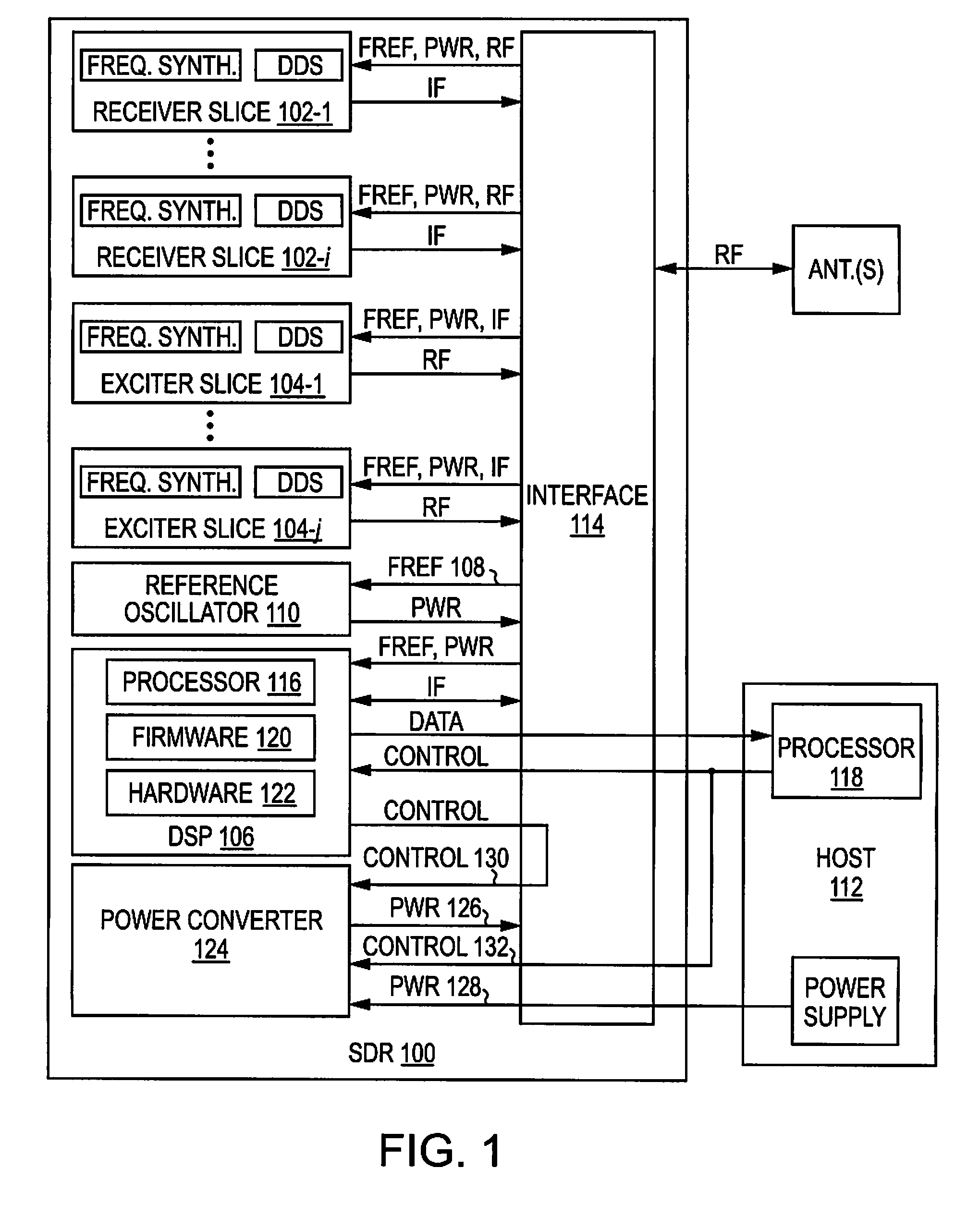

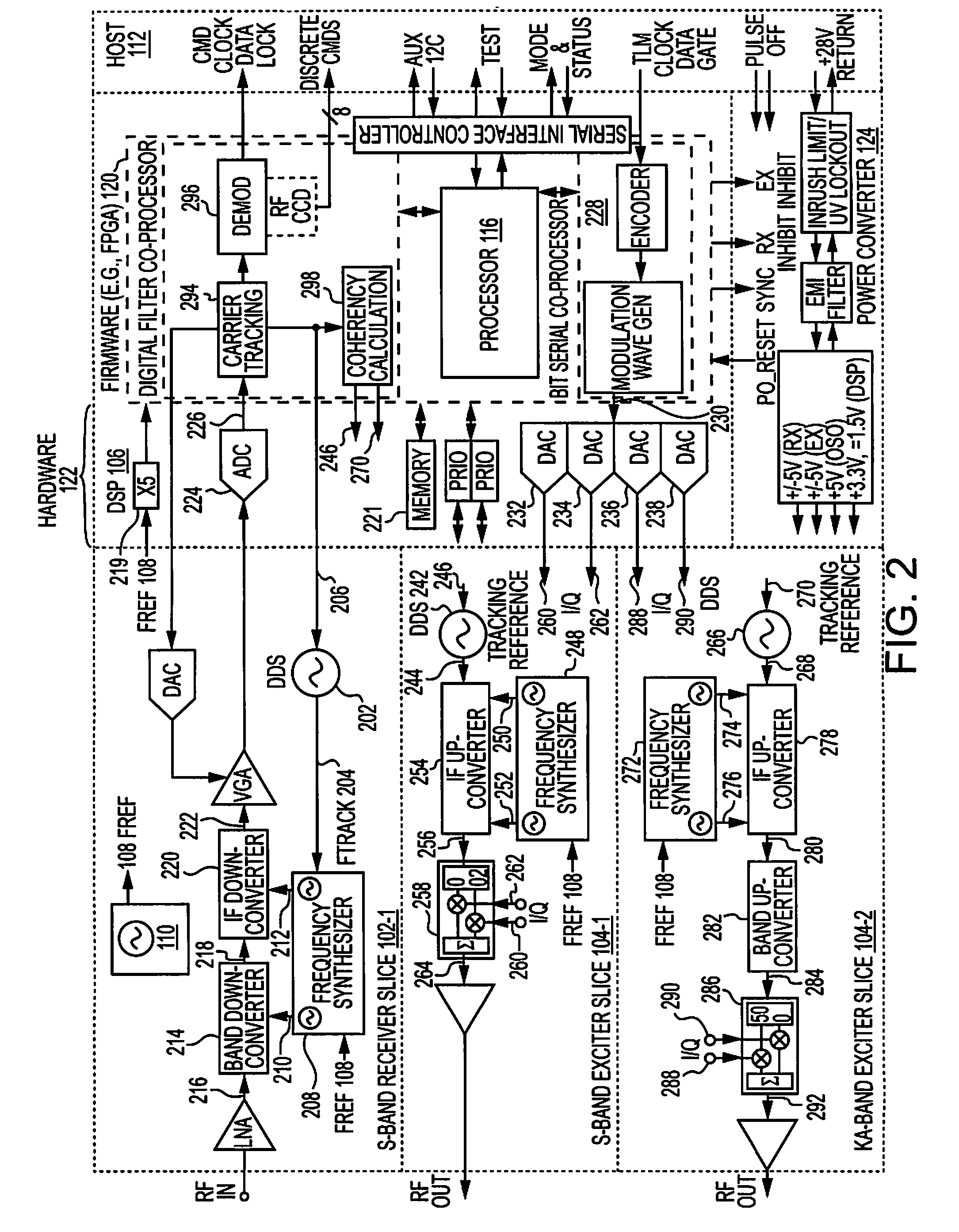

Low Power, Low Mass, Modular, Multi-Band Software-Defined Radios

ActiveUS20120252387A1Low spuriousHigh precisionPulse automatic controlRadio transmissionMulti bandLow noise

Methods and systems to implement and operate software-defined radios (SDRs). An SDR may be configured to perform a combination of fractional and integer frequency synthesis and direct digital synthesis under control of a digital signal processor, which may provide a set of relatively agile, flexible, low-noise, and low spurious, timing and frequency conversion signals, and which may be used to maintain a transmit path coherent with a receive path. Frequency synthesis may include dithering to provide additional precision. The SDR may include task-specific software-configurable systems to perform tasks in accordance with software-defined parameters or personalities. The SDR may include a hardware interface system to control hardware components, and a host interface system to provide an interface to the SDR with respect to a host system. The SDR may be configured for one or more of communications, navigation, radio science, and sensors.

Owner:THE JOHN HOPKINS UNIV SCHOOL OF MEDICINE

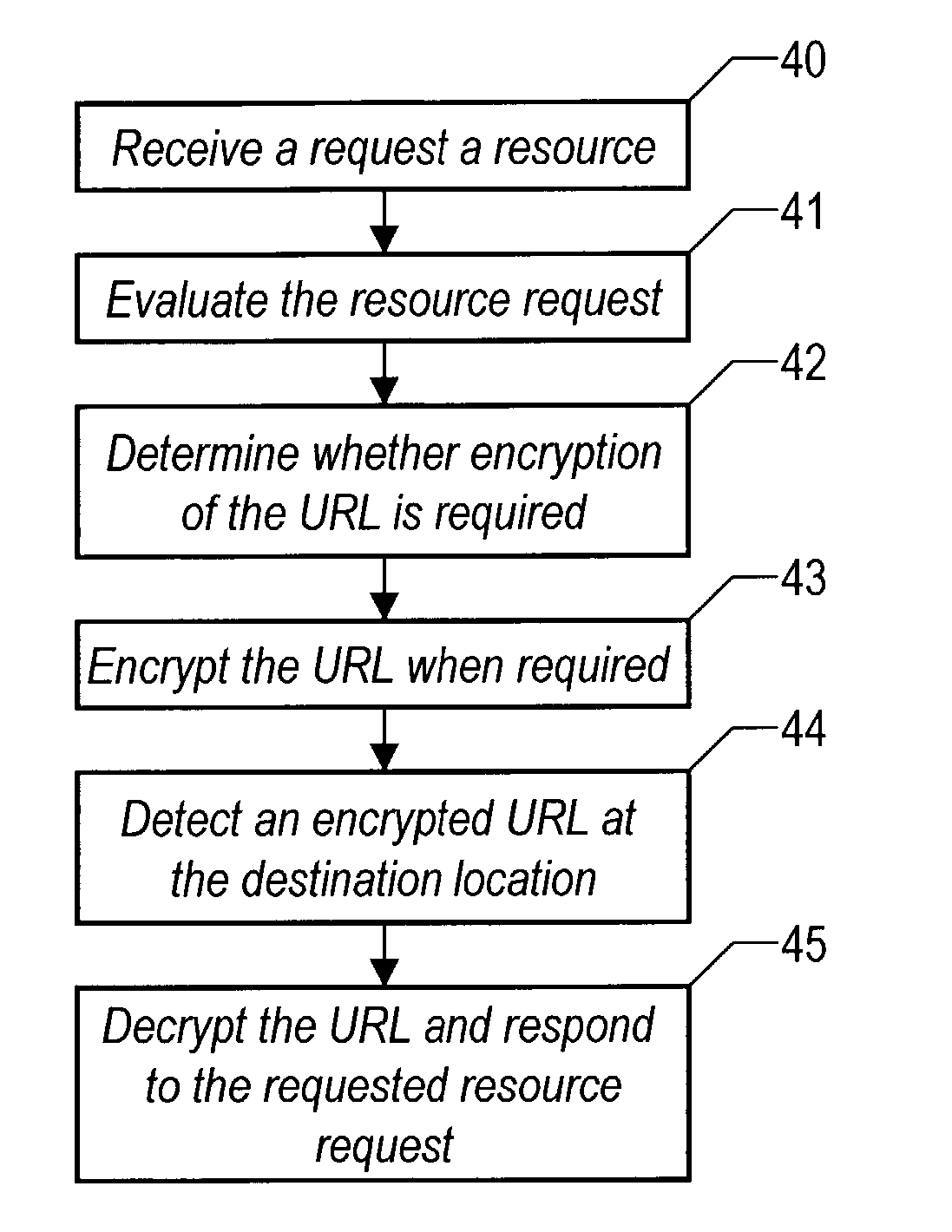

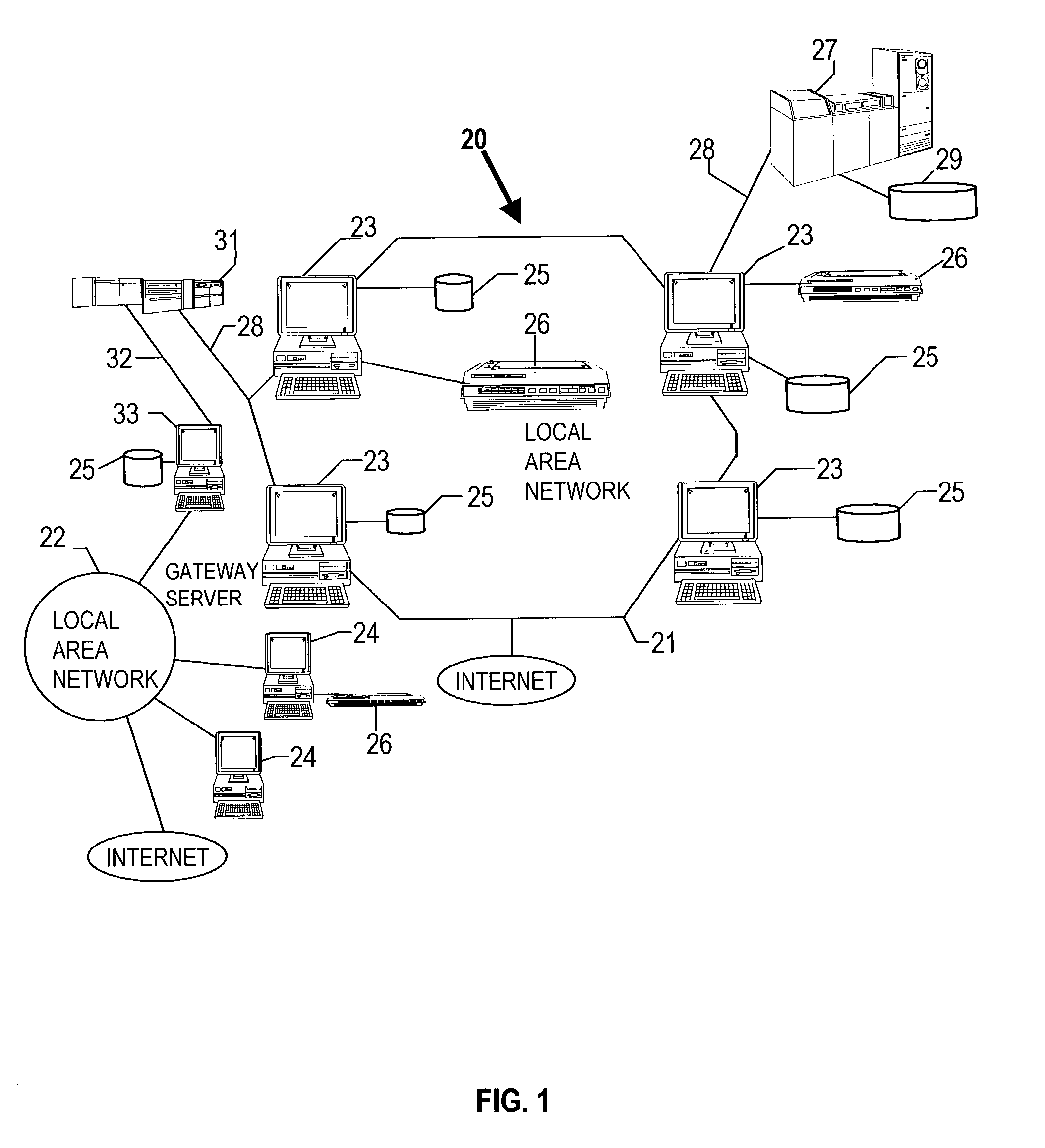

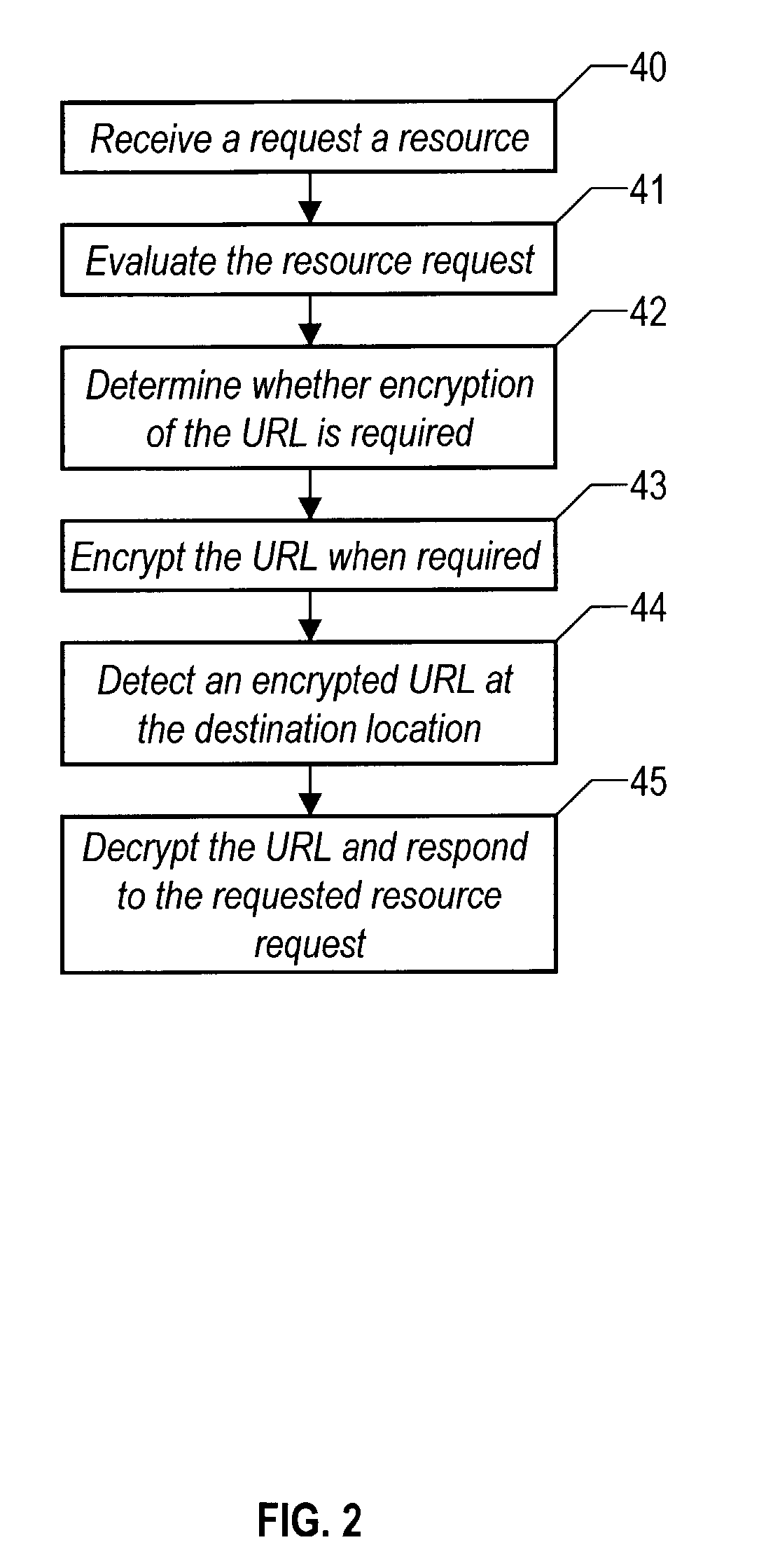

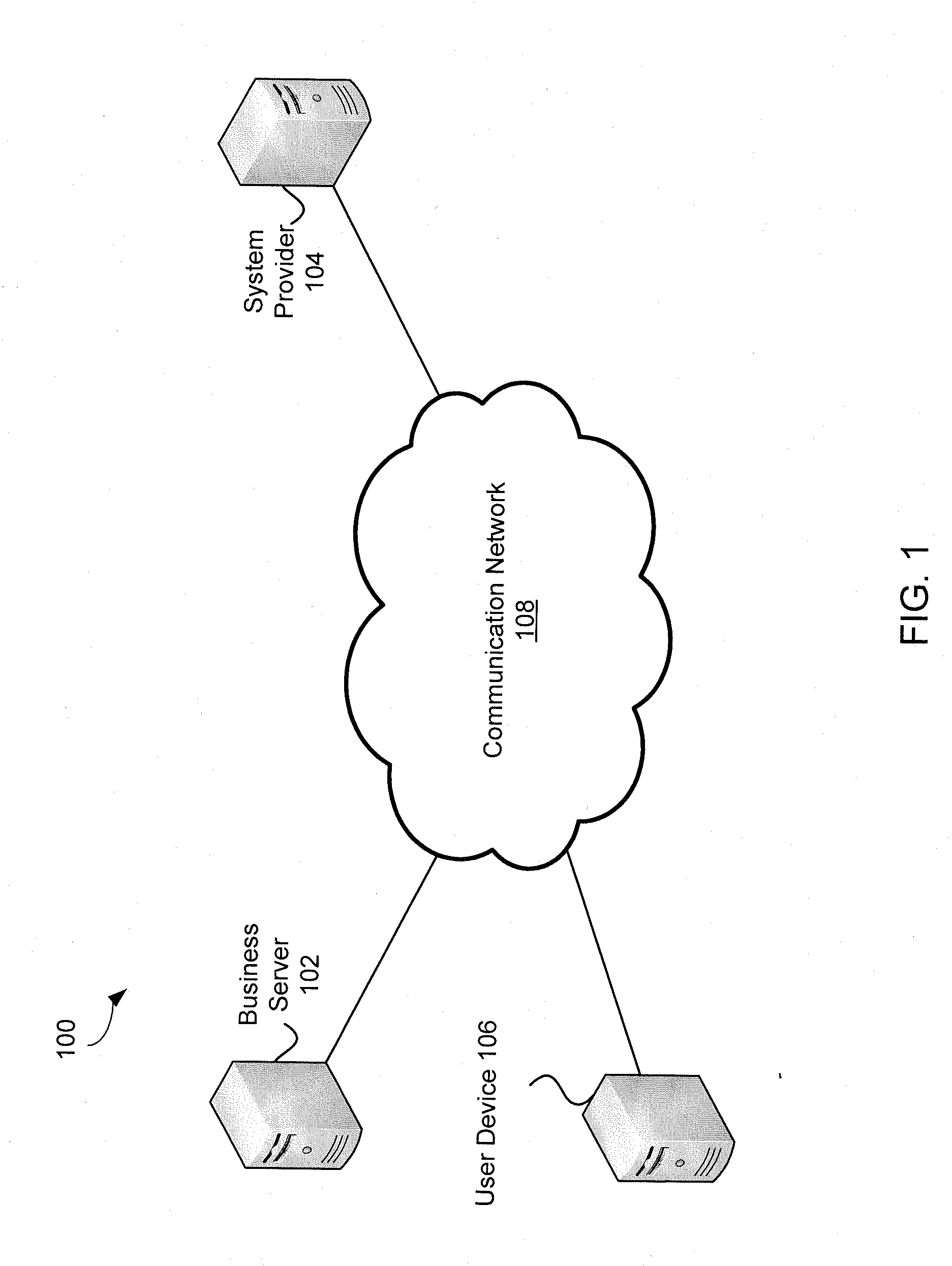

Method and system for dynamic encryption of a URL

ActiveUS8819419B2OptimizationSpecial data processing applicationsSecuring communicationUniform resource locatorConfigurable systems

The present invention provides a dynamic, easily configurable system, which can be used to encrypt or otherwise hide the internal structure of a network. The present invention protects access to computing systems via a URL by encrypting all or a portion of the URL during the transmission of information over a network. Prior to the actual transmission of the information, fields in the URL can be encrypted using conventional encryption techniques. The encryption will occur after the destination has been determined such that the encryption will not cause the information to be misdirected to a wrong destination. At the destination location, there is first a determination that this URL is an encrypted URL. At this point, a decryption technique is employed based on the predetermined encryption scheme to decrypt the URL. The full URL is now accessed only by the destination location and is not accessible during travel over the network between the originating and destination locations.

Owner:TAASERA LICENSING LLC

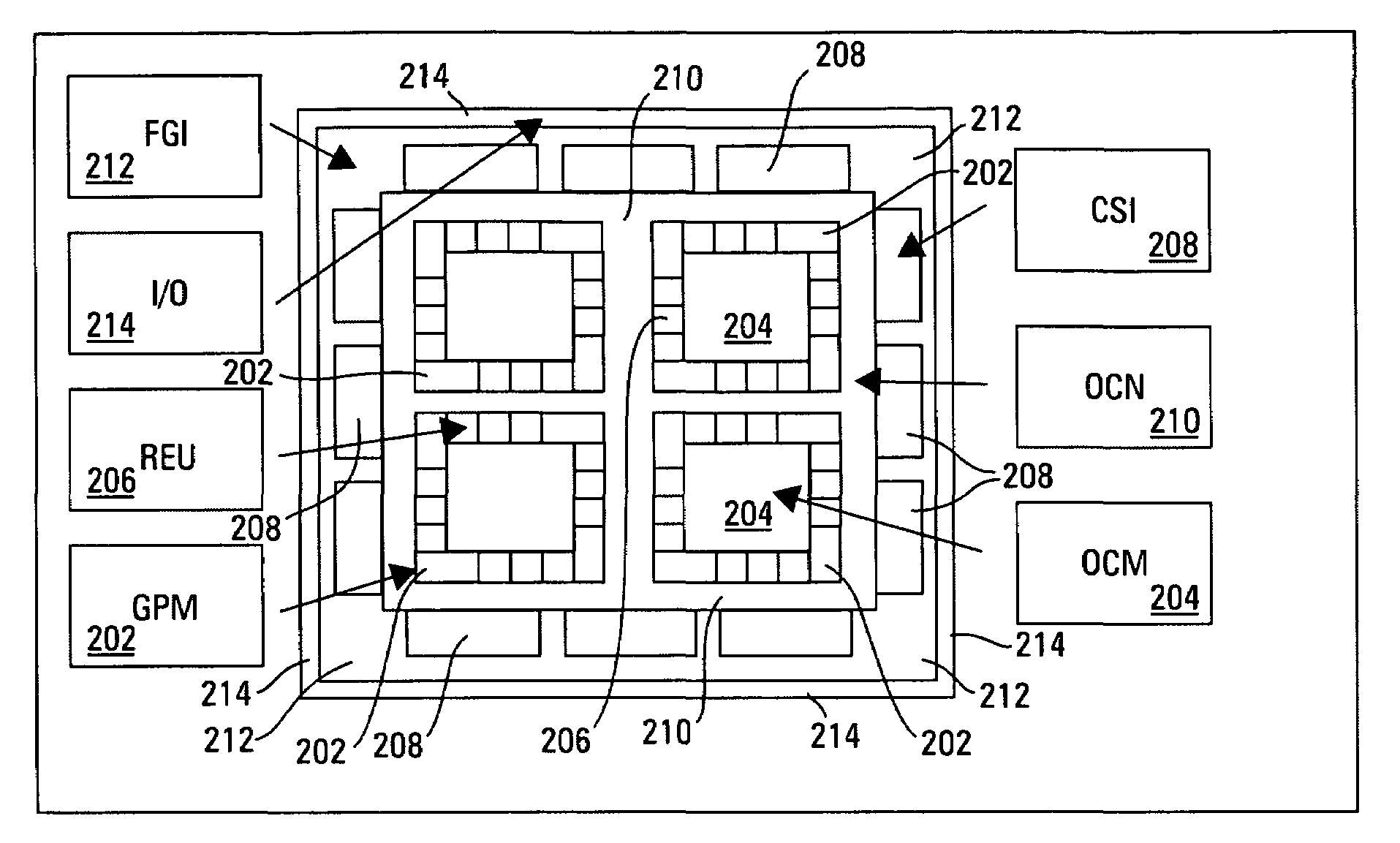

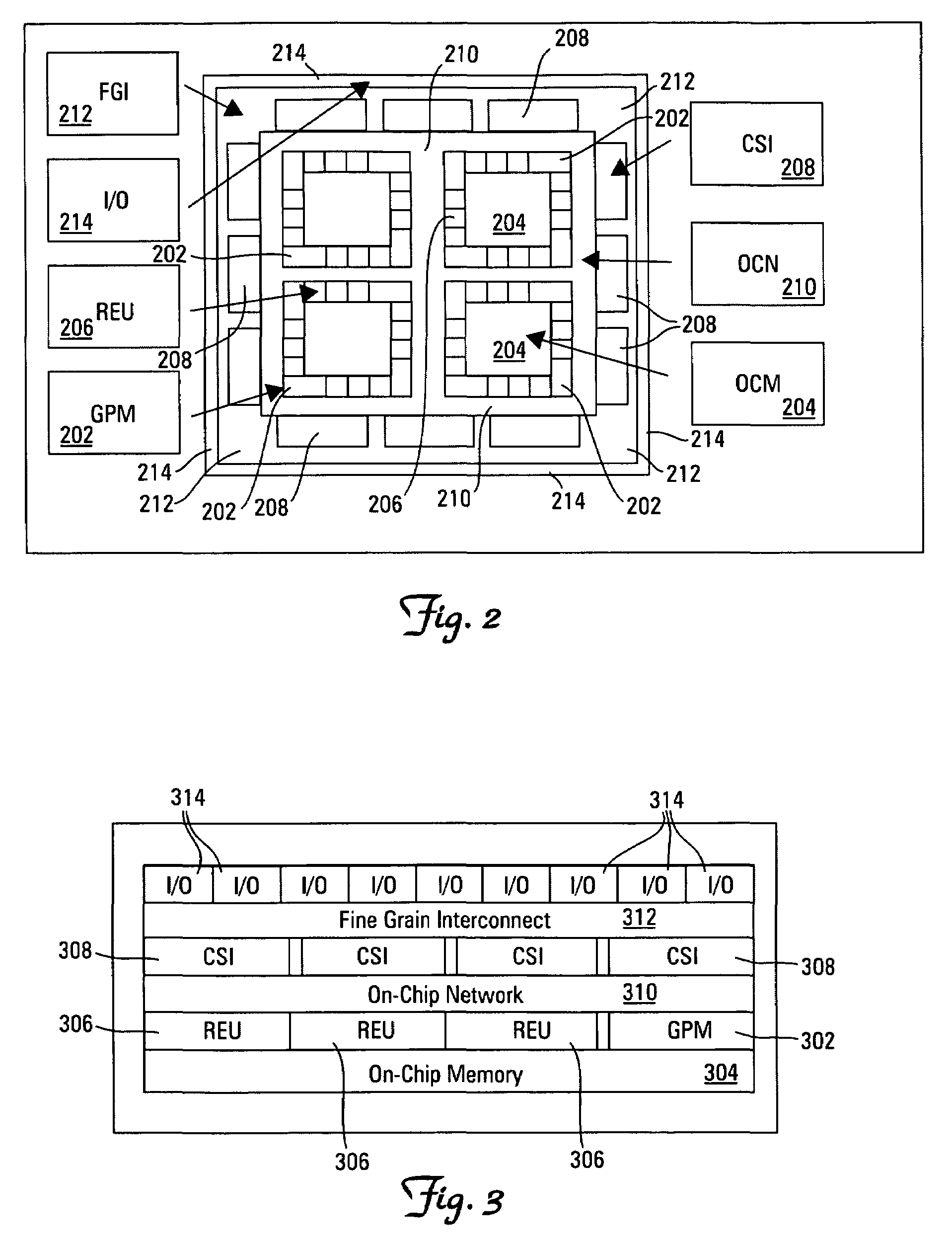

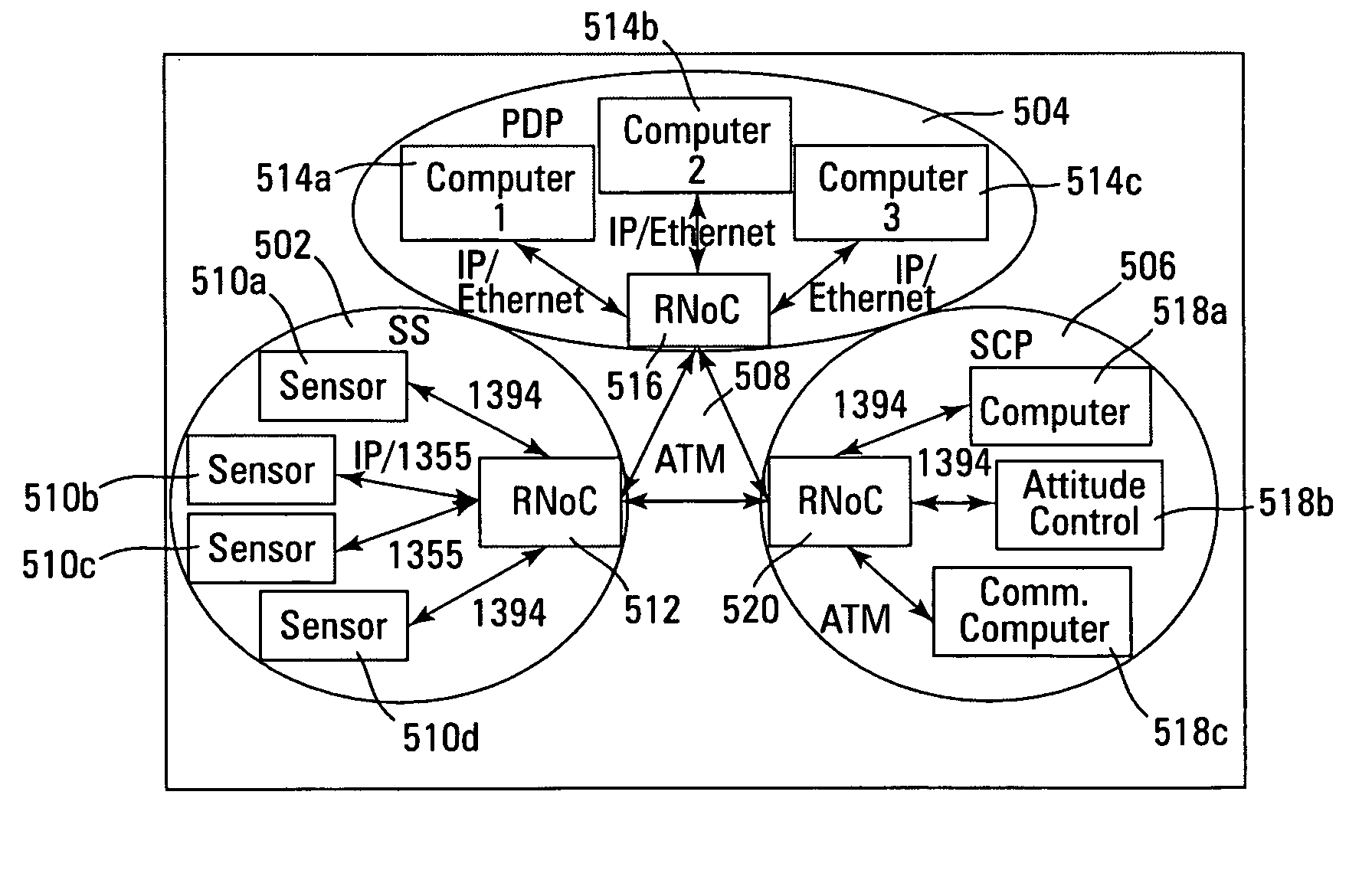

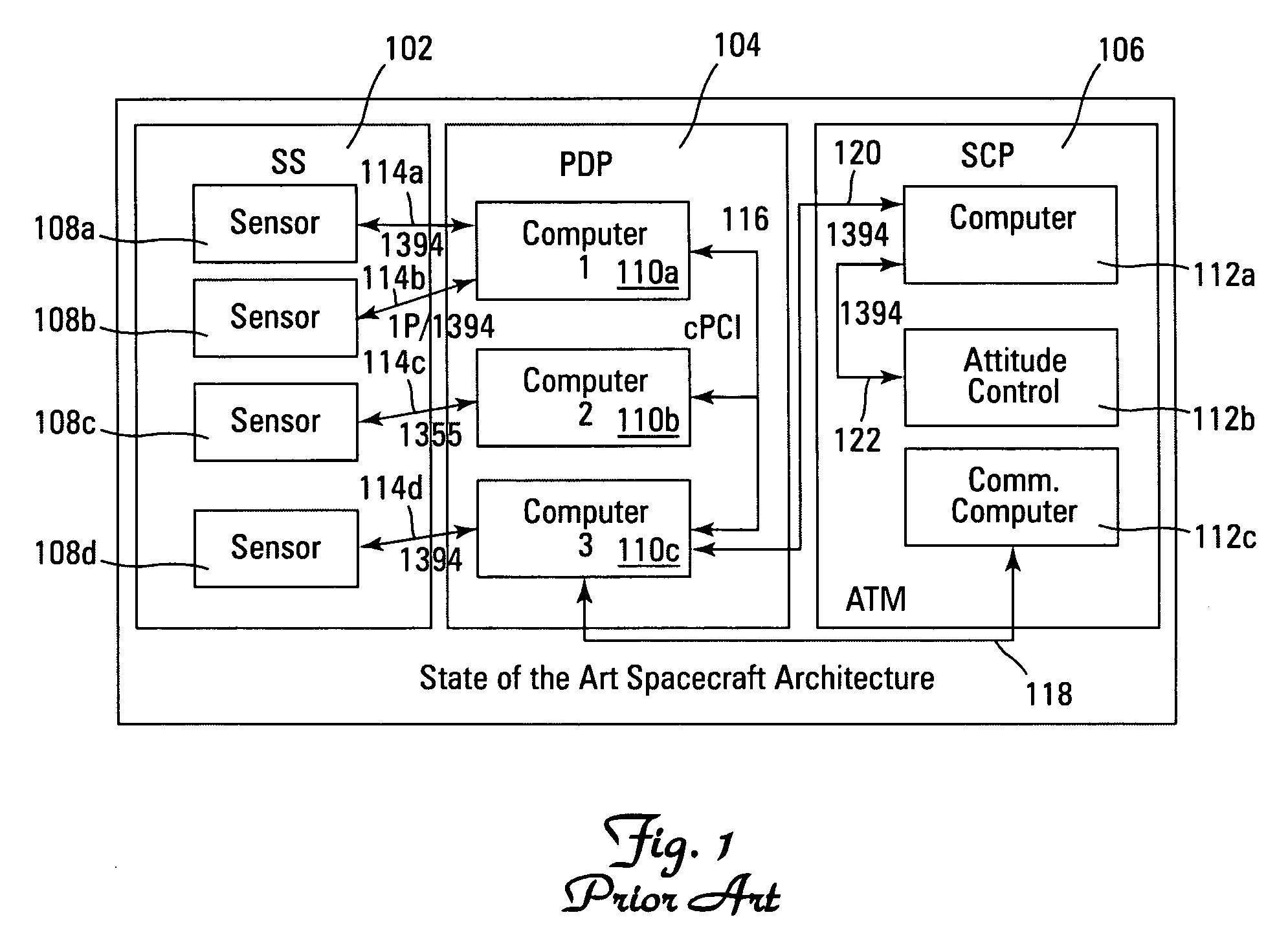

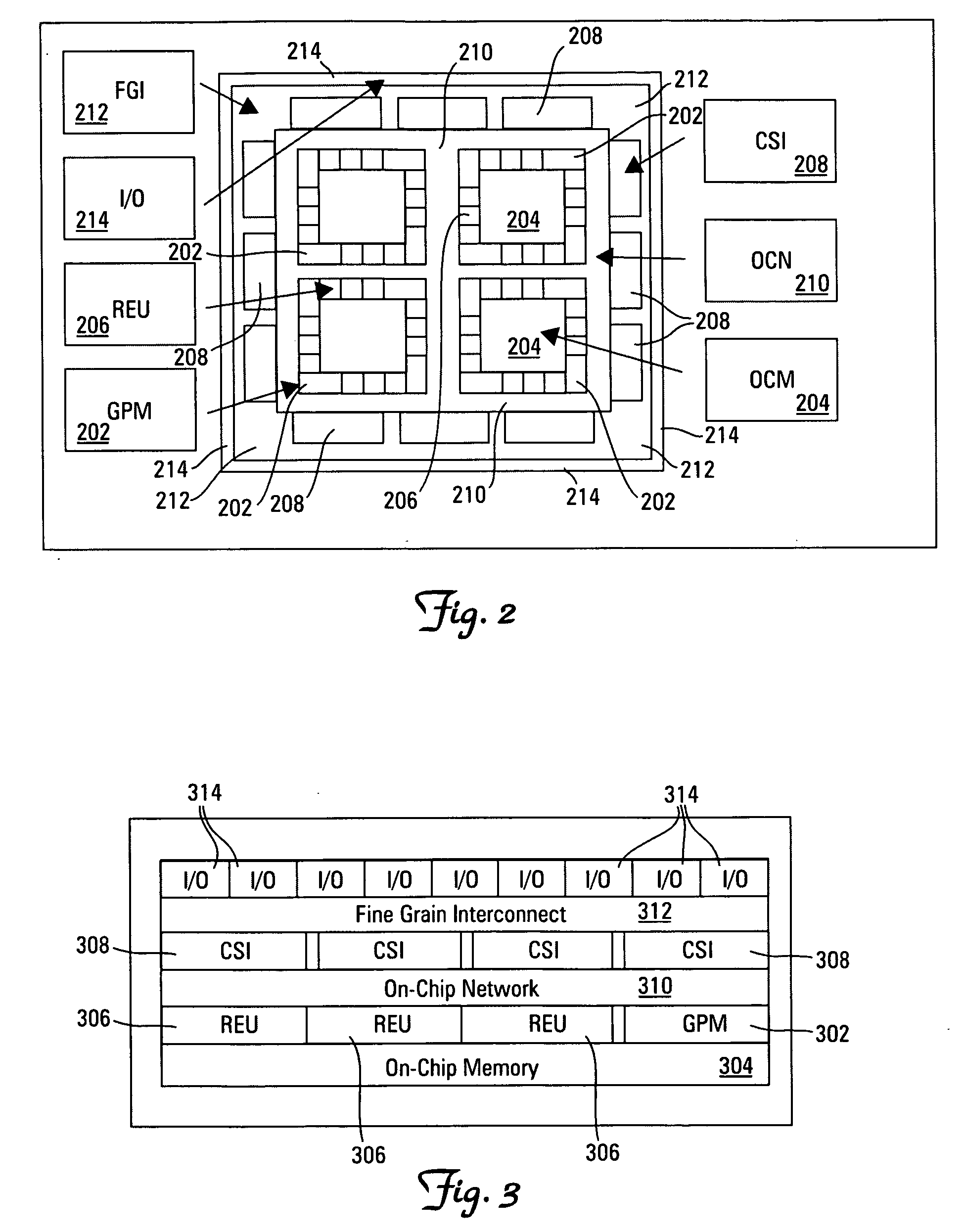

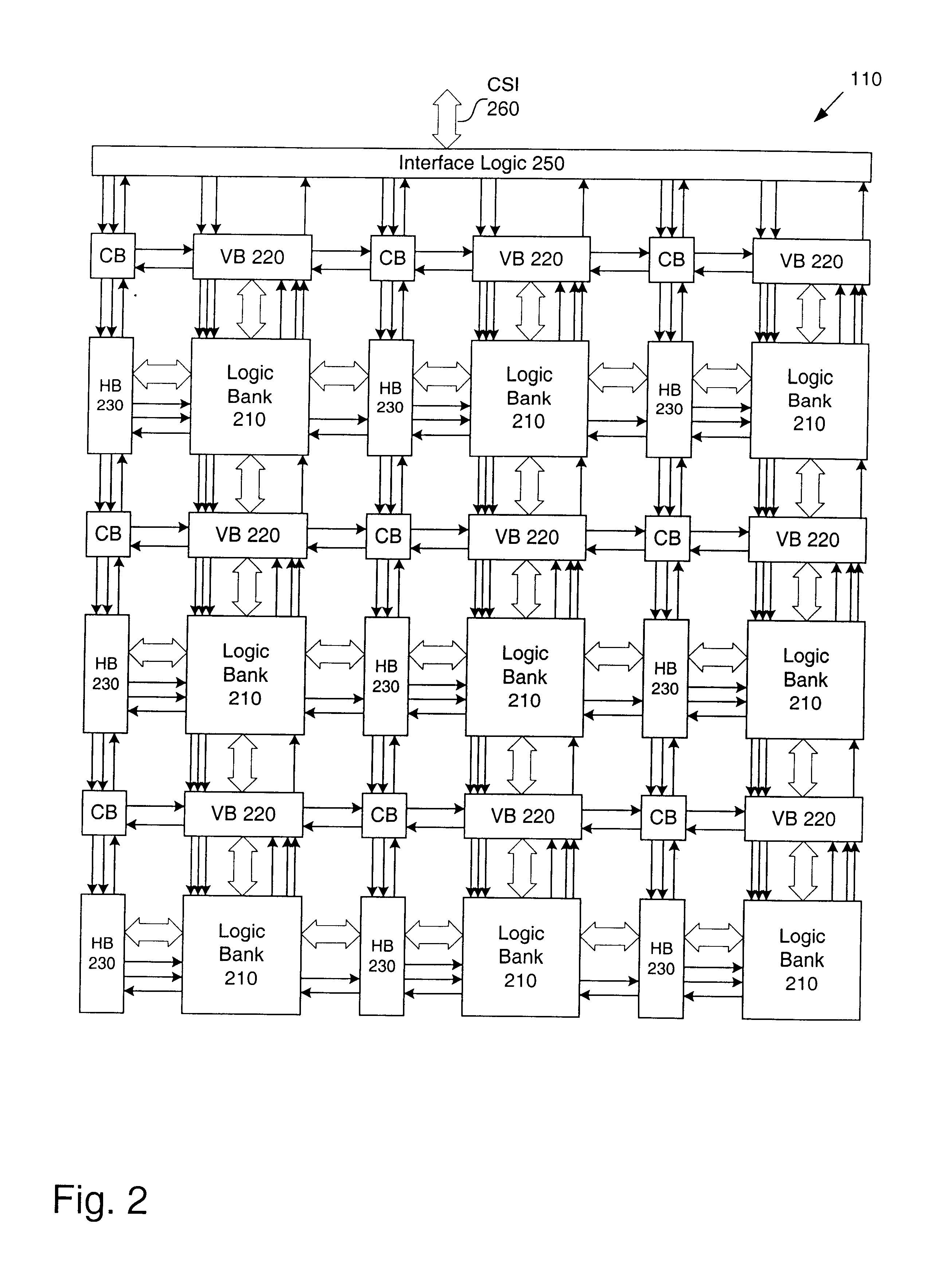

Reconfigurable network on a chip

ActiveUS7382154B2Easy programmingIncrease flexibilitySolid-state devicesDigital computer detailsSemiconductor chipProgrammable logic array

An architecture for a reconfigurable network that can be implemented on a semiconductor chip is disclosed, which includes a hierarchical organization of network components and functions that are readily programmable and highly flexible. Essentially, a reconfigurable network on a chip is disclosed, which includes aspects of reconfigurable computing, system on a chip, and network on a chip designs. More precisely, a reconfigurable network on a chip includes a general purpose microprocessor for implementing software tasks, a plurality of on-chip memories for facilitating the processing of large data structures as well as processor collaboration, a plurality of reconfigurable execution units including self-contained, individually reconfigurable programmable logic arrays, a plurality of configurable system interface units that provide interconnections between on-chip memories, networks or buses, an on-chip network including a network interconnection interface that enables communication between all reconfigurable execution units, configurable system interface units and general purpose microprocessors, a fine grain interconnect unit that gathers associated input / output signals for a particular interface and attaches them to a designated system interface resource, and a plurality of input / output blocks that supply the link between an on-chip interface resource and a particular external network or device interface. Advantageously, the network minimizes the configuration latency of the reconfigurable execution units and also enables reconfiguration on-the-fly.

Owner:HONEYWELL INT INC

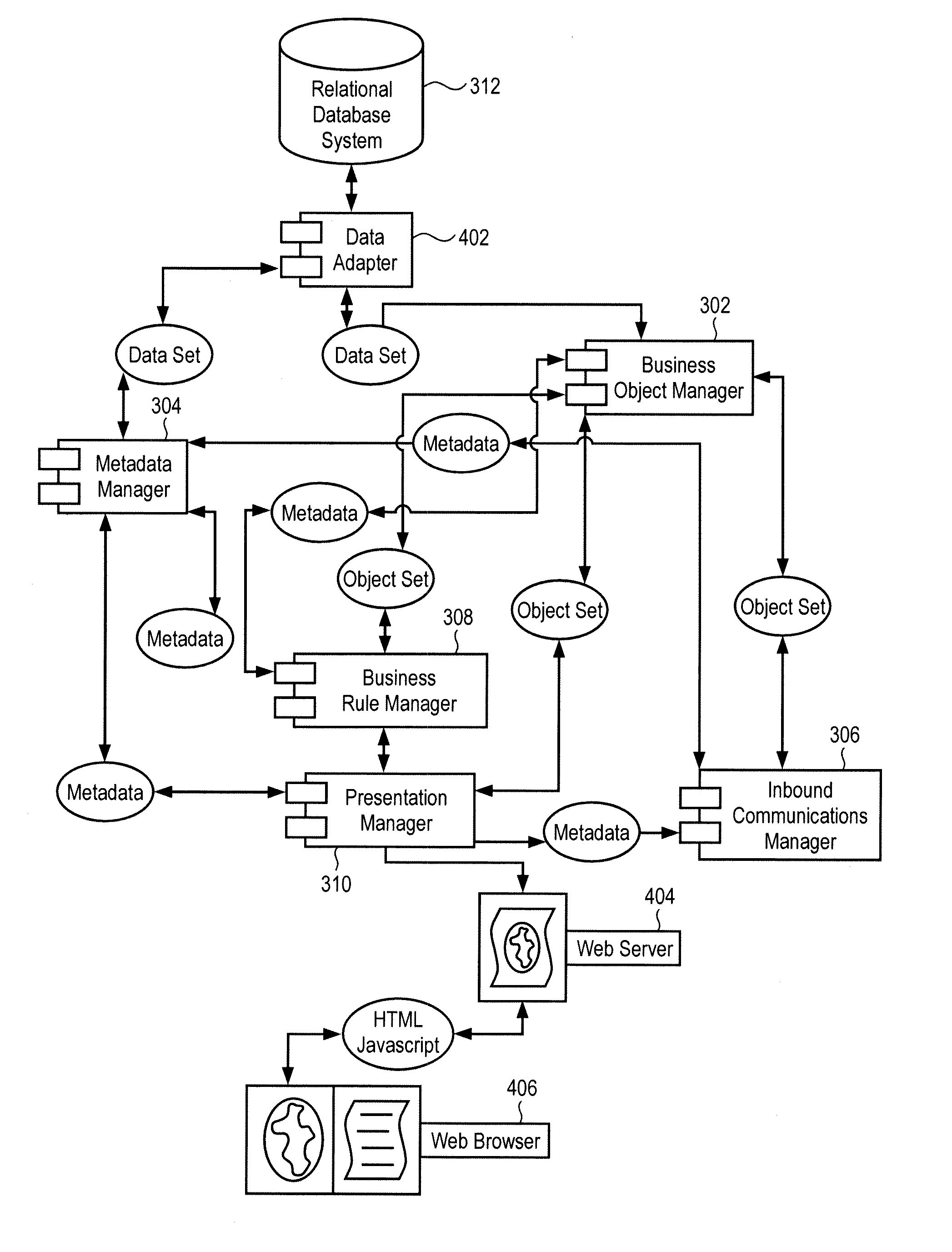

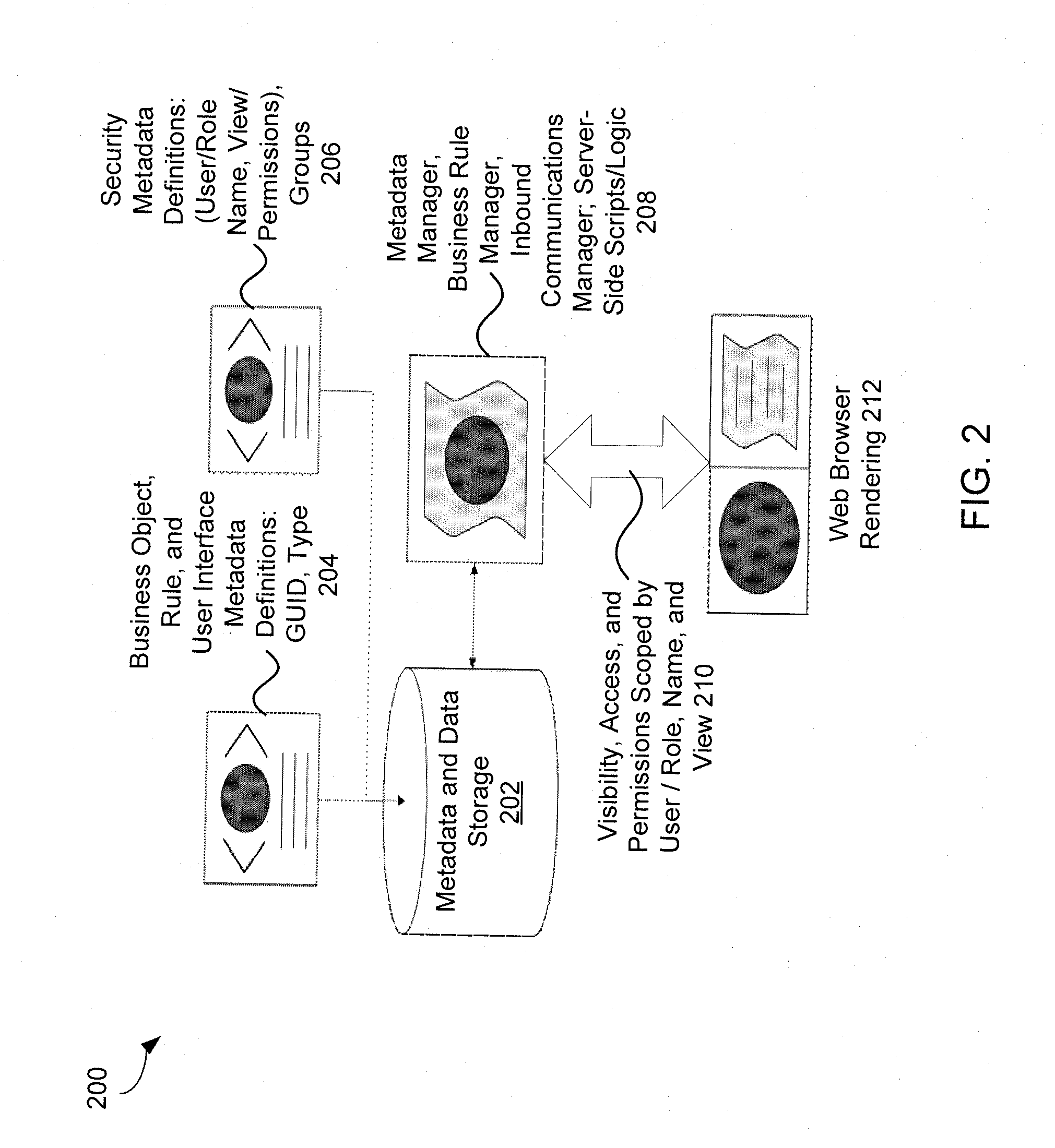

Metadata-configurable systems and methods for network services

ActiveUS20110179110A1Digital data information retrievalMultiple digital computer combinationsMetadata managementPresentation Manager

In some embodiments, the presentation manager is configured to provide an interface requesting information regarding a proposal from a digital device over a network and receive the information from the digital device. The business object manager is configured to instantiate a business object based on the received information and store the instantiated business object within a data structure residing in a computer readable medium. The business rule manager is configured to generate a business rule associated with the business object, the business rule comprising instructions to perform an operation, the instructions being conditional based on the instantiated business object. The metadata manager is configured to generate metadata associated with the instantiated business object, store the generated metadata in the computer readable medium, perform the operation based on the business rule and the generated metadata, and instruct the presentation manager to provide a second interface indicating a status of the proposal.

Owner:VERSAIC

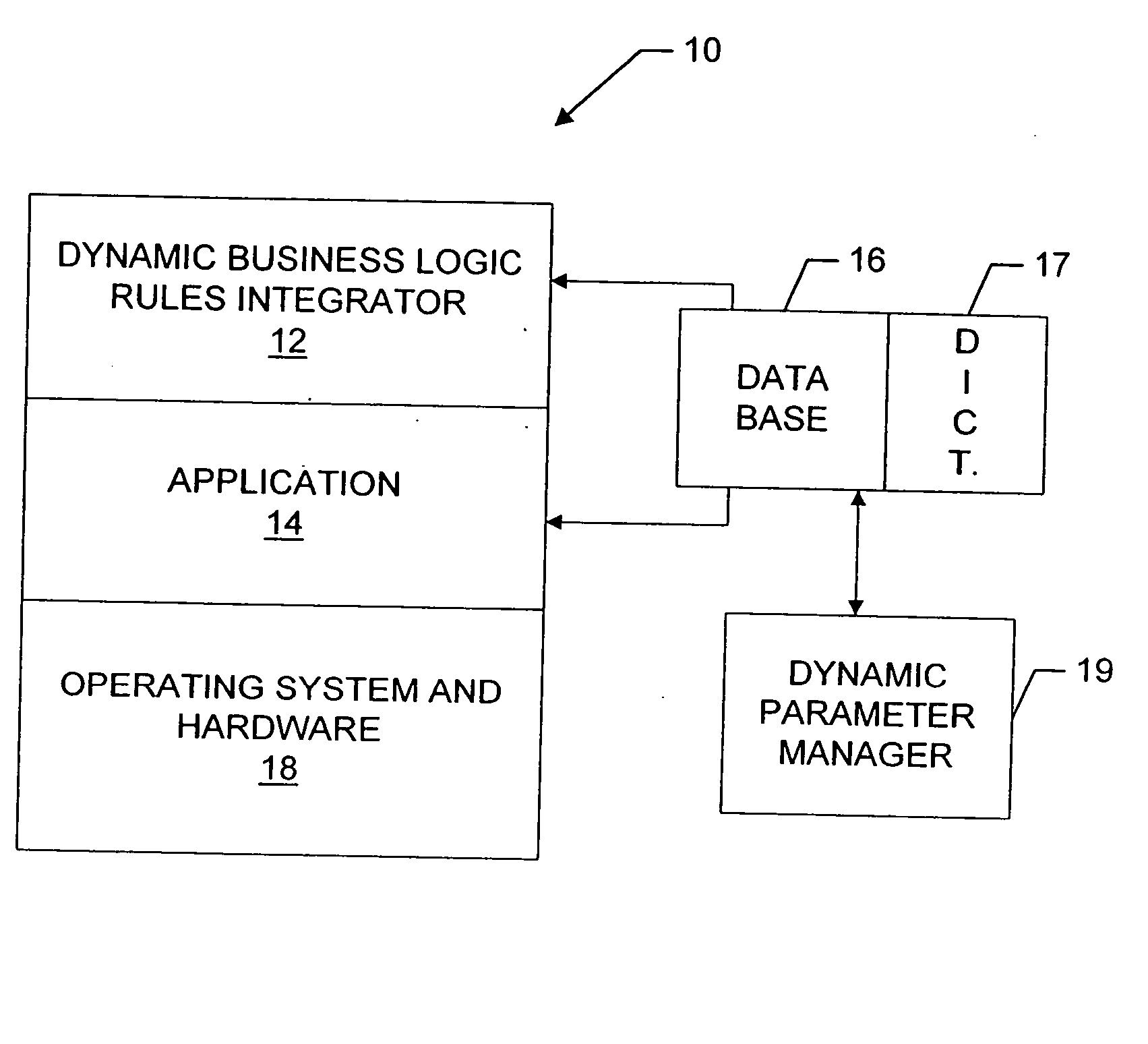

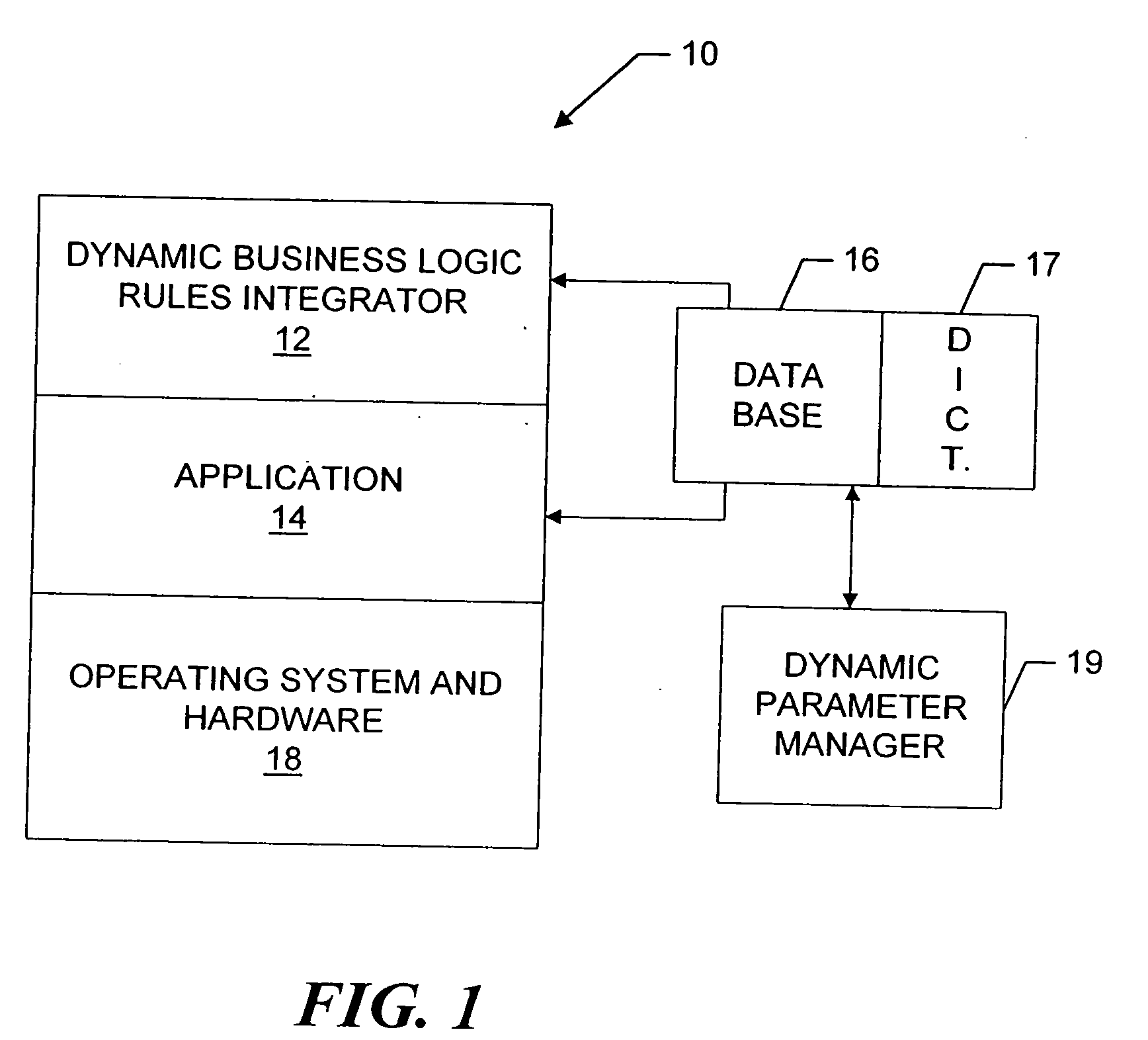

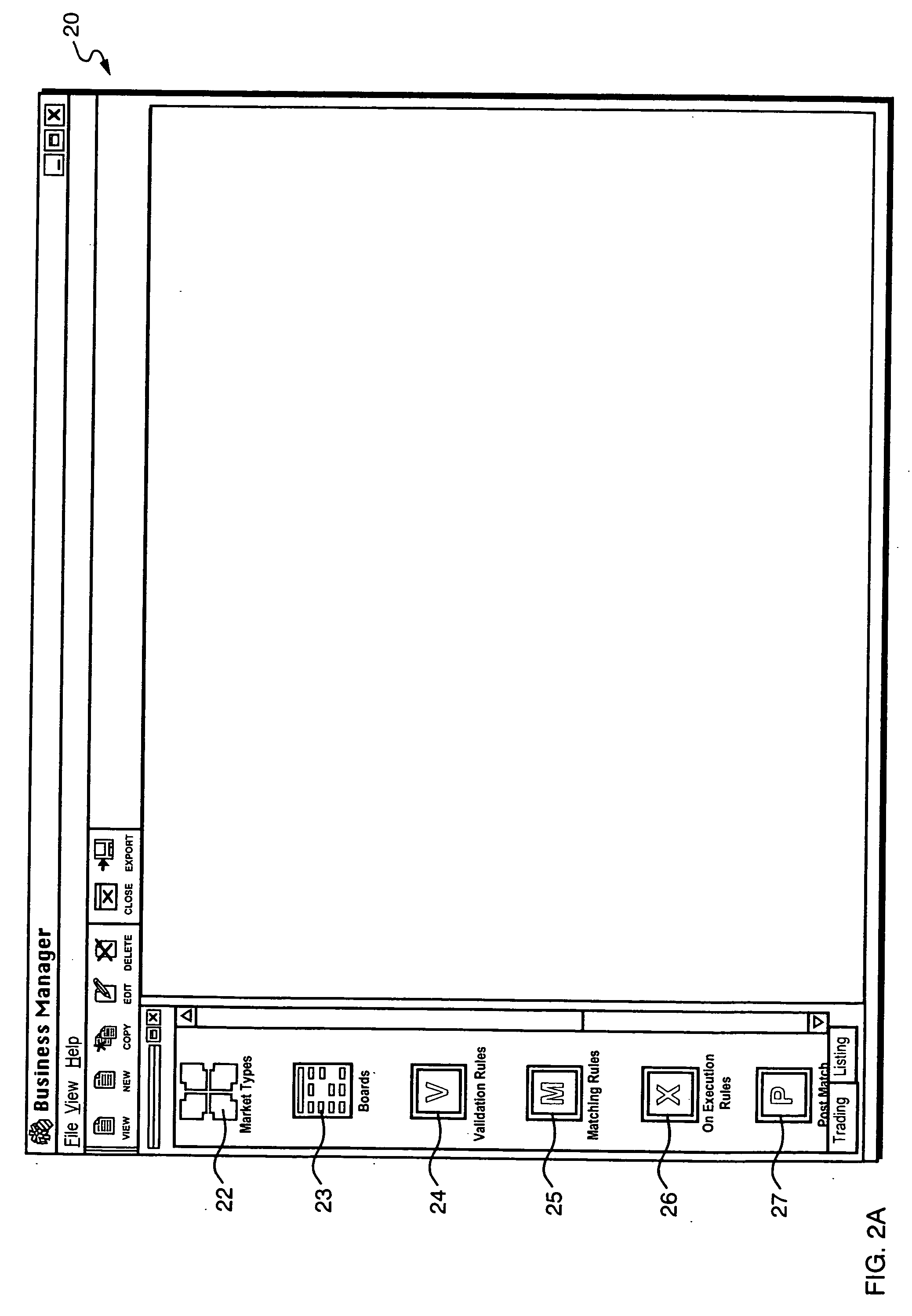

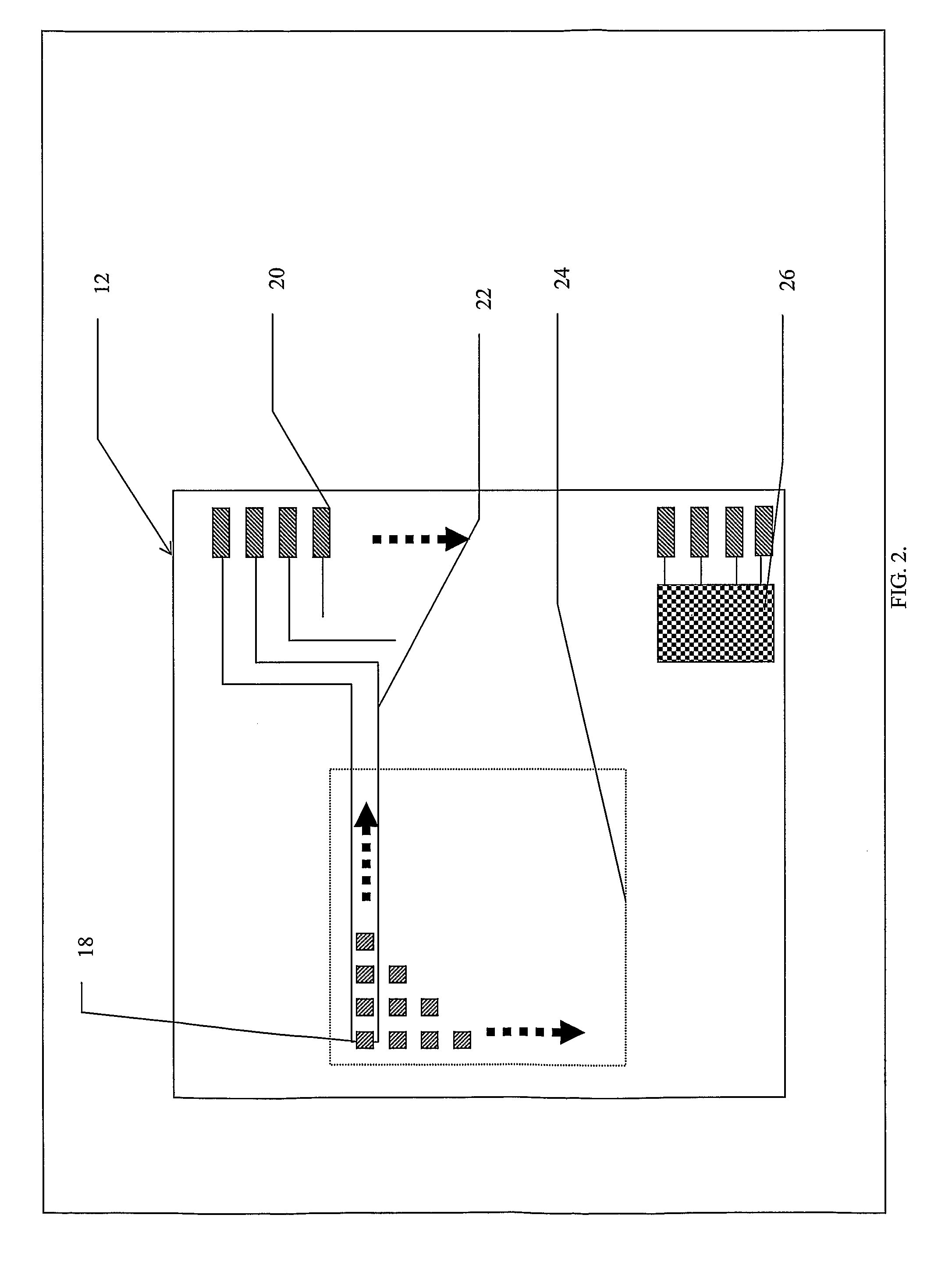

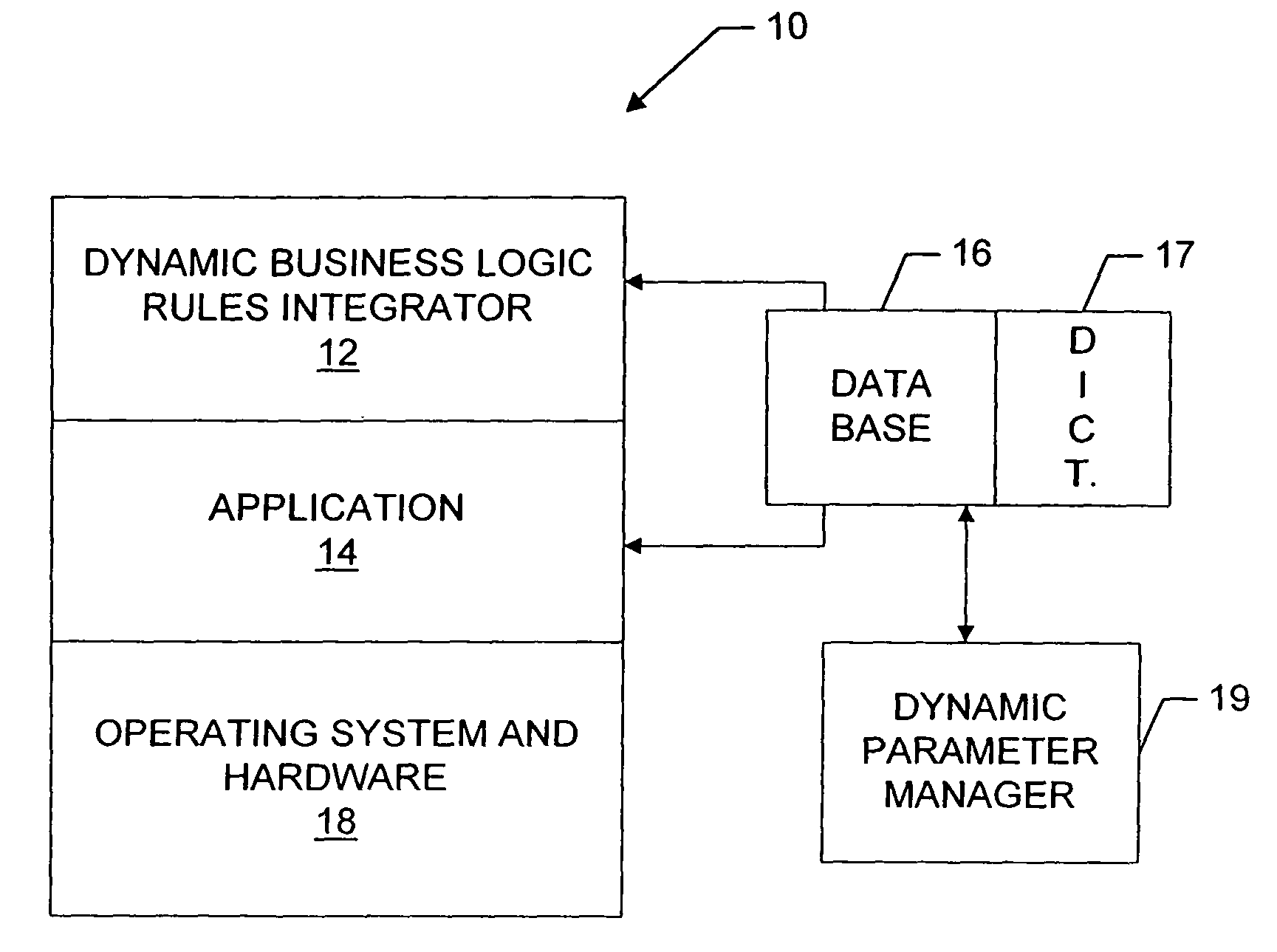

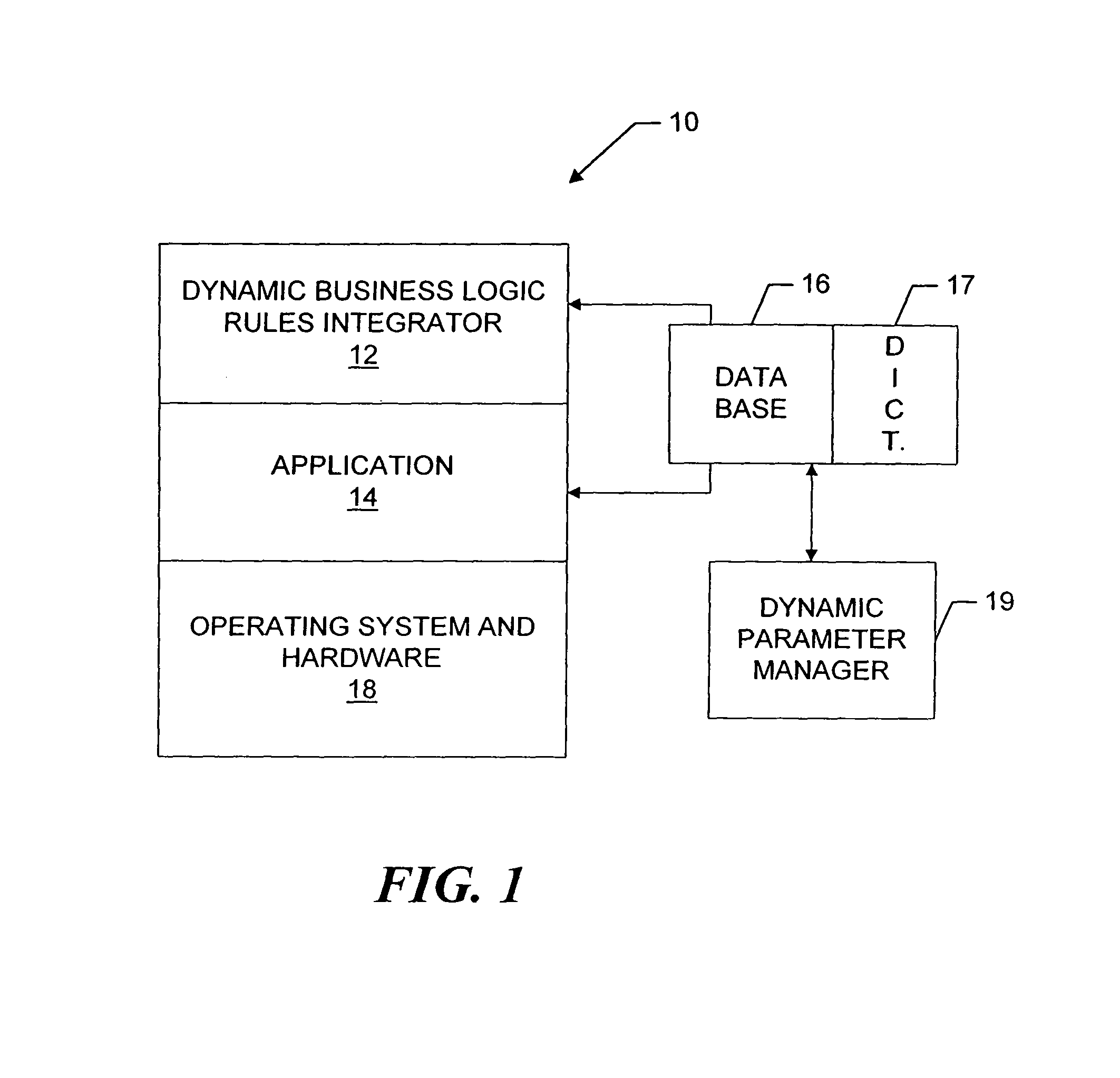

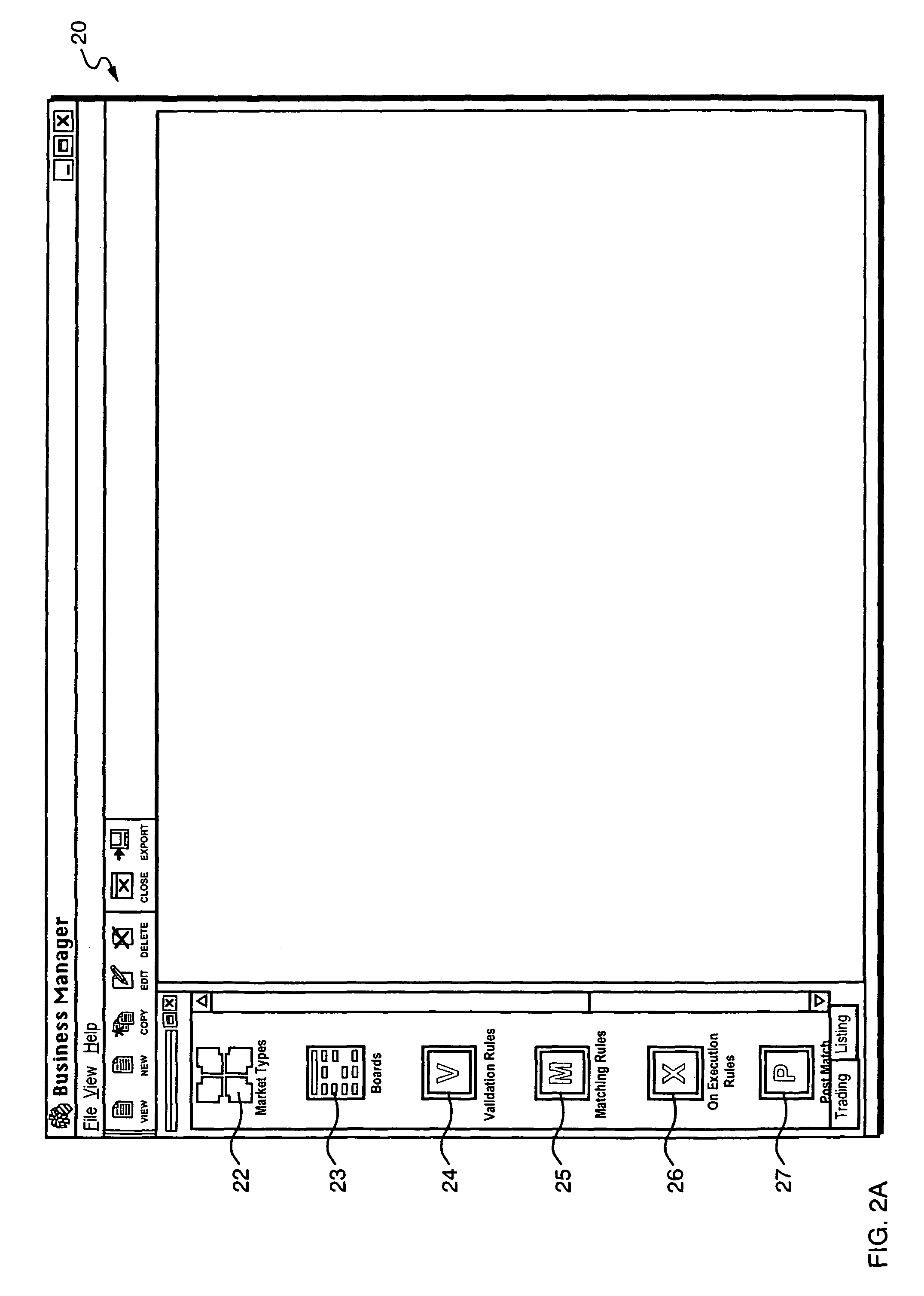

System and method for configurable trading system

A system dynamically integrates into an application program that implements rules for controlling business operations changes in the parameters and parameter groupings that are used by or in conjunction with the rules. The system includes a dynamic business logic rule integrator that provides business logic rules to the application software as executable routines, and a dynamic parameter manager that organizes and manages the parameters. The manager integrates changes to the parameters, groups and / or links the parameters, and makes the parameters available to the rules through a dynamically configurable system database—using a set of static database tables and related dynamically configurable database tables, in which certain database fields or sub-fields correspond to parameters that are used in the rules. The respective database tables and the various fields and sub-fields are established and linked together in accordance with user-defined categories and sub-categories, or “instances.” When parameters are added, edited, grouped, re-grouped, or deleted, the dynamic parameter manager updates, creates and / or removes database tables. The revised set of tables is then made available to the rules, and rules utilize the information in the various fields and sub-fields of the tables to control appropriate trading and associated reporting activities.

Owner:MILLENNIUM IT USA

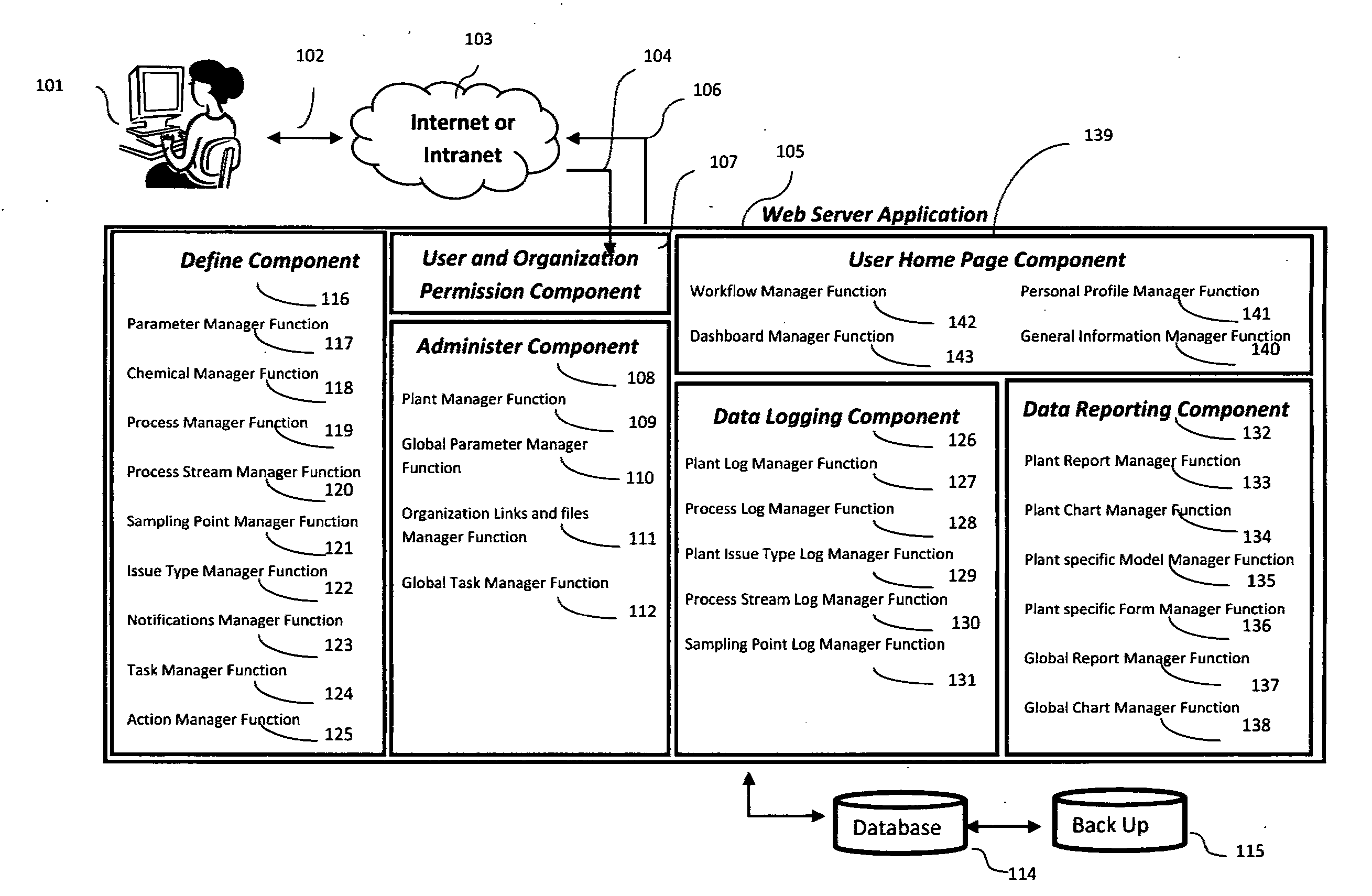

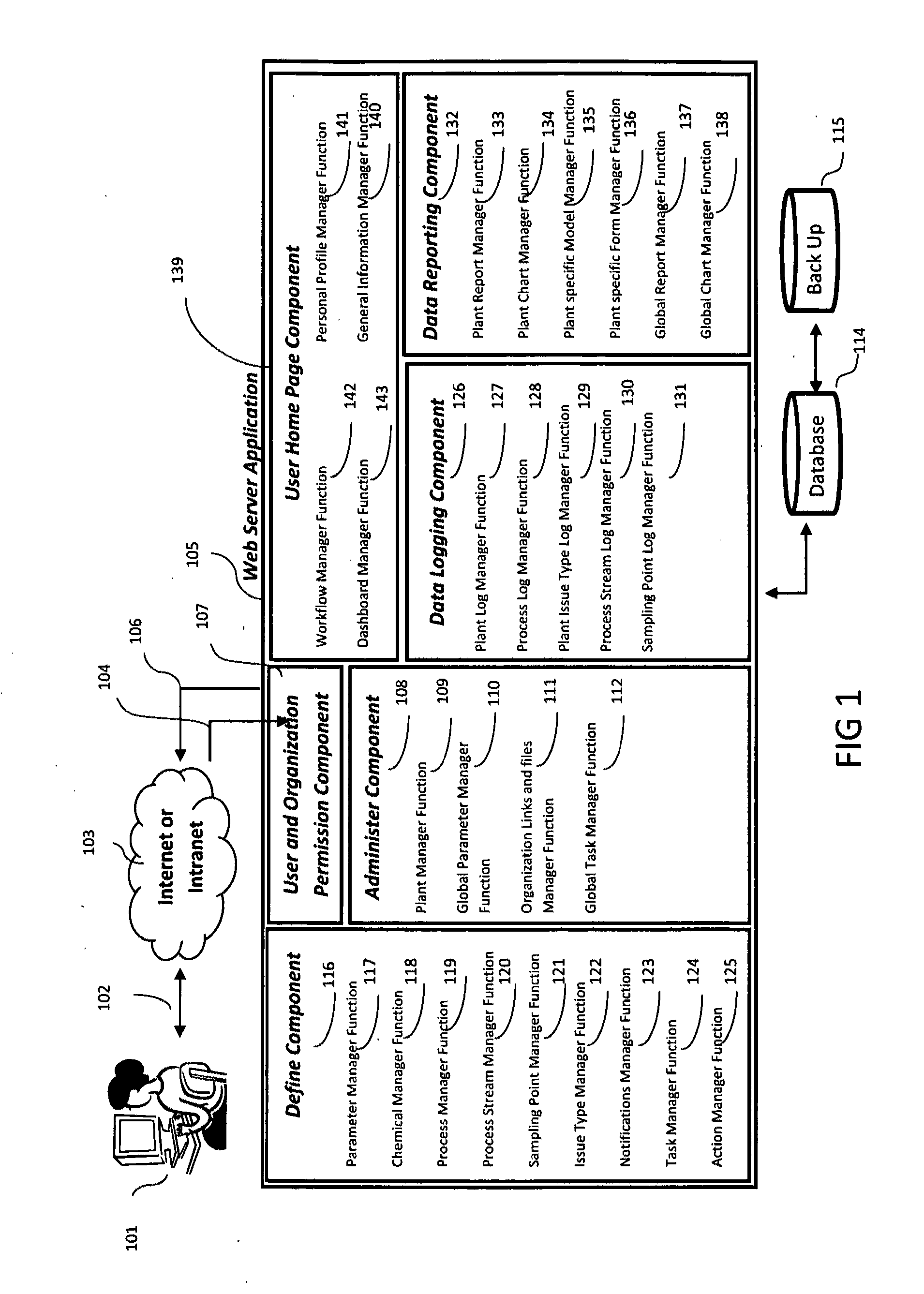

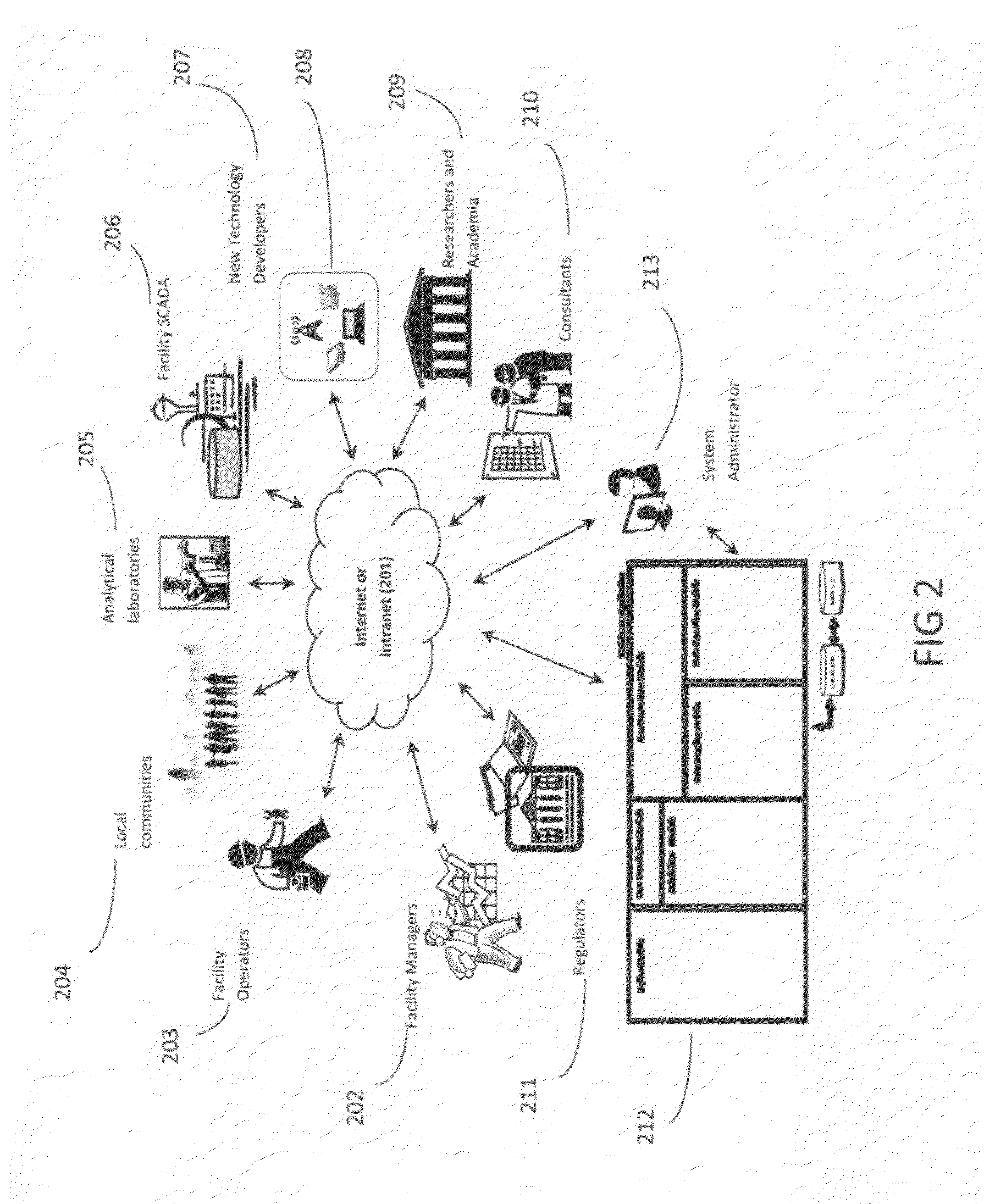

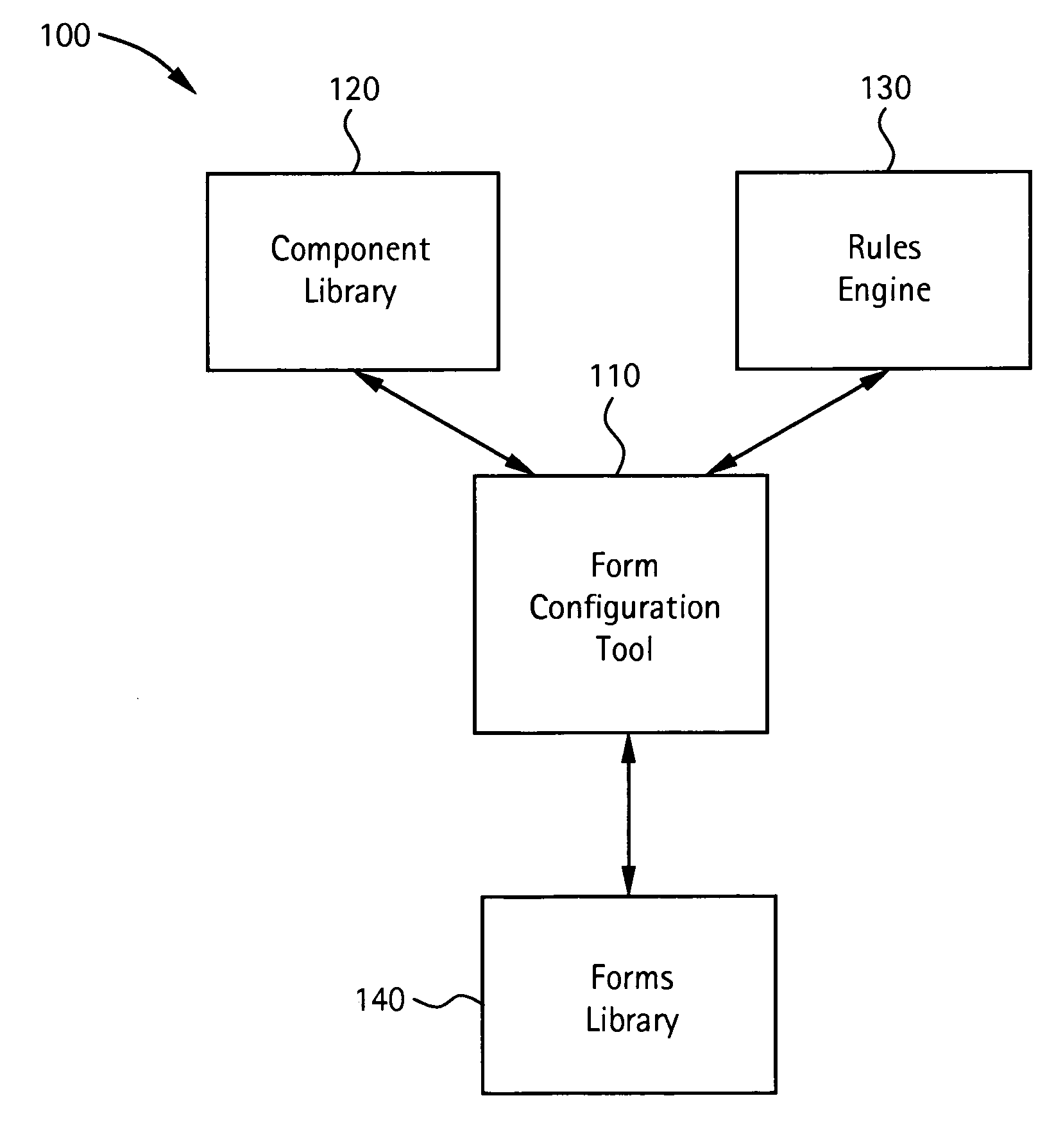

Form-based user-configurable processing plant management system and method

A computer-implemented system and method for defining the processes in a processing plant are disclosed. In one embodiment, the system uses input forms to allow a user to define the processes, chemicals, process streams, and sampling points in the plant in a way that requires no programming code to be written by the person defining the plant. In one embodiment, the electronic form-based user-configurable system can be used to configure and manage multiple plants belonging to one organization. The plant definition can be used to log information about the plant. The logged information can be used to generate reports or charts. Logging, reporting, and charting can be managed using input forms and without the user needing to write any computer code.

Owner:FLOWATCH

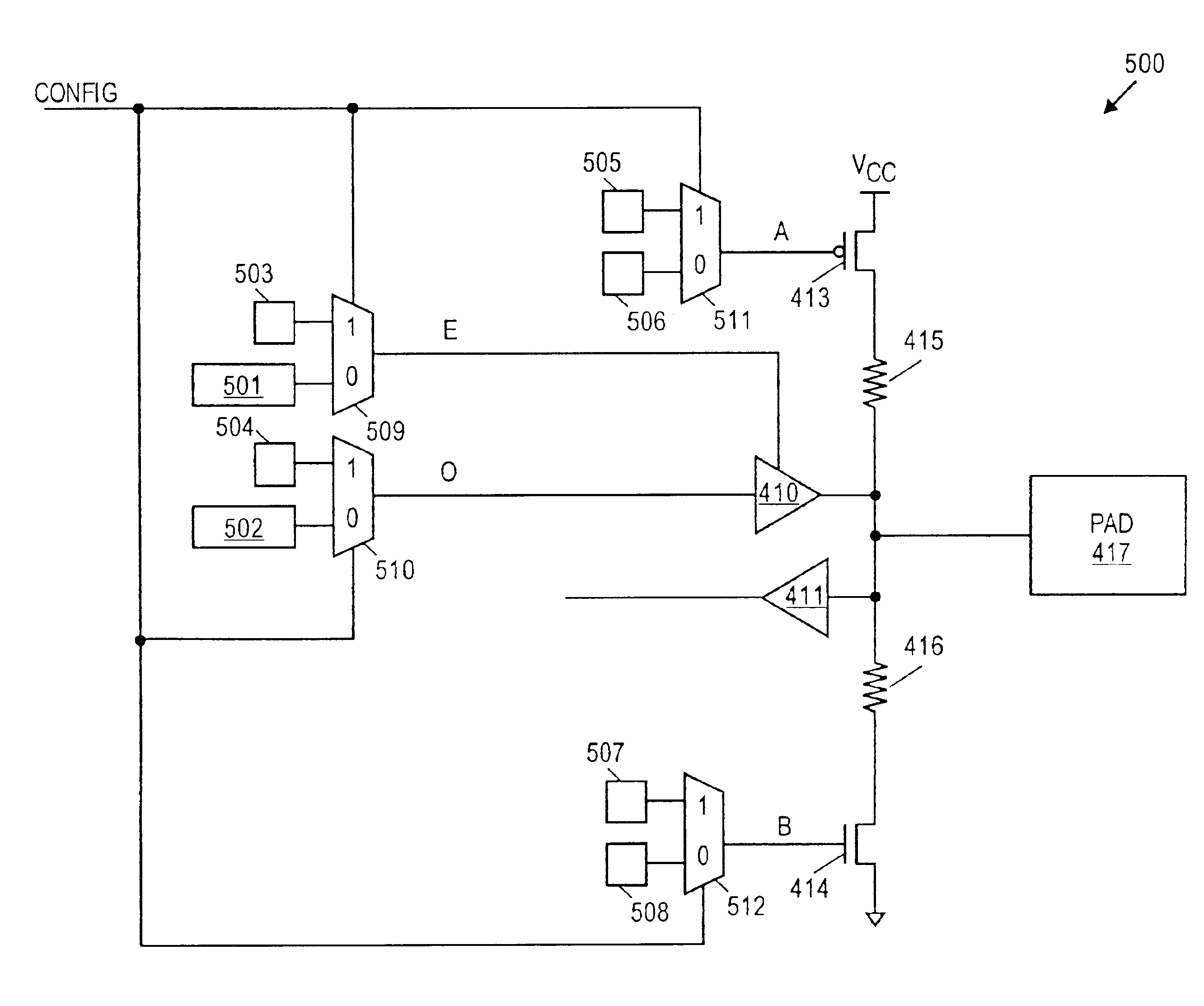

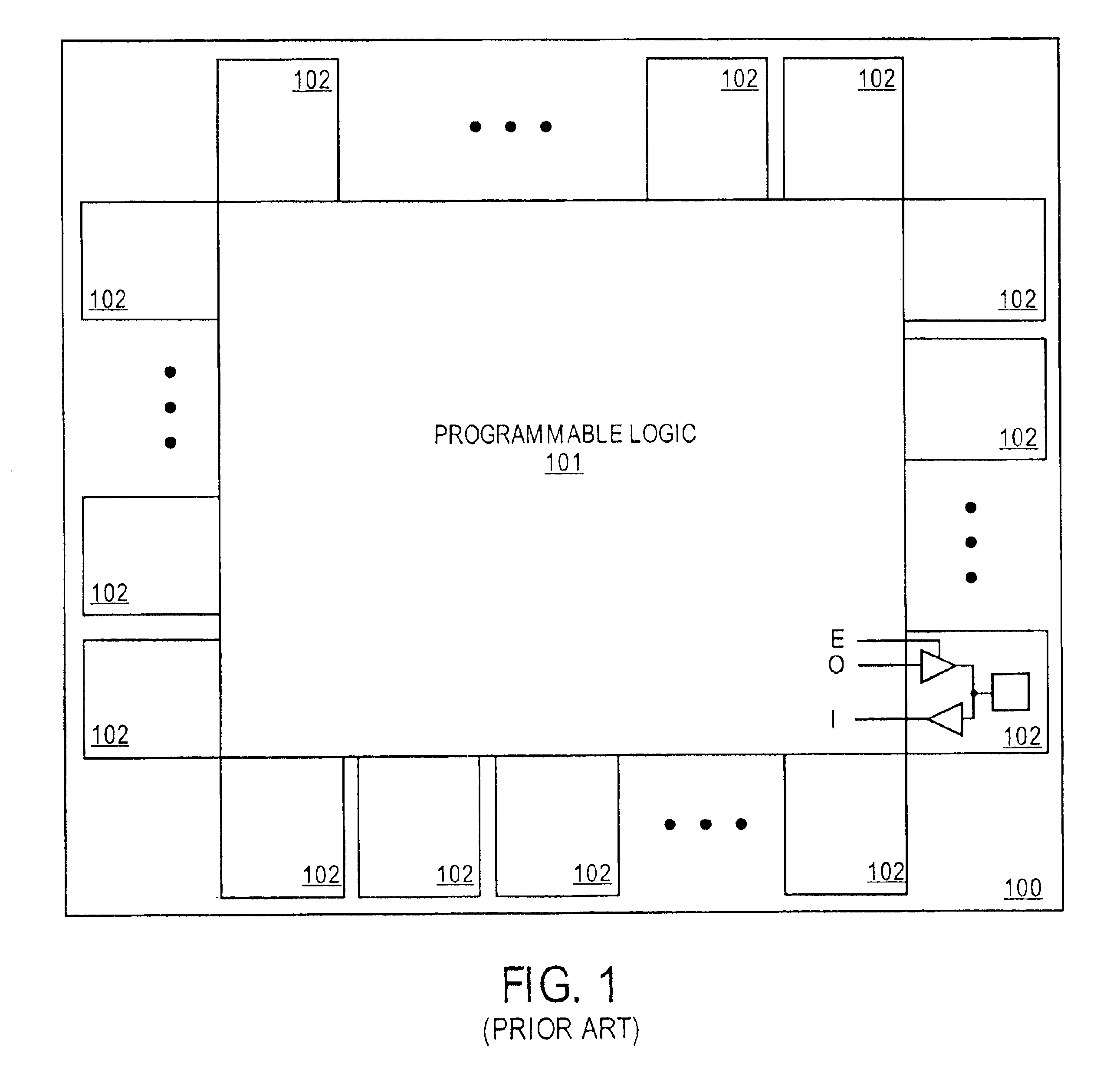

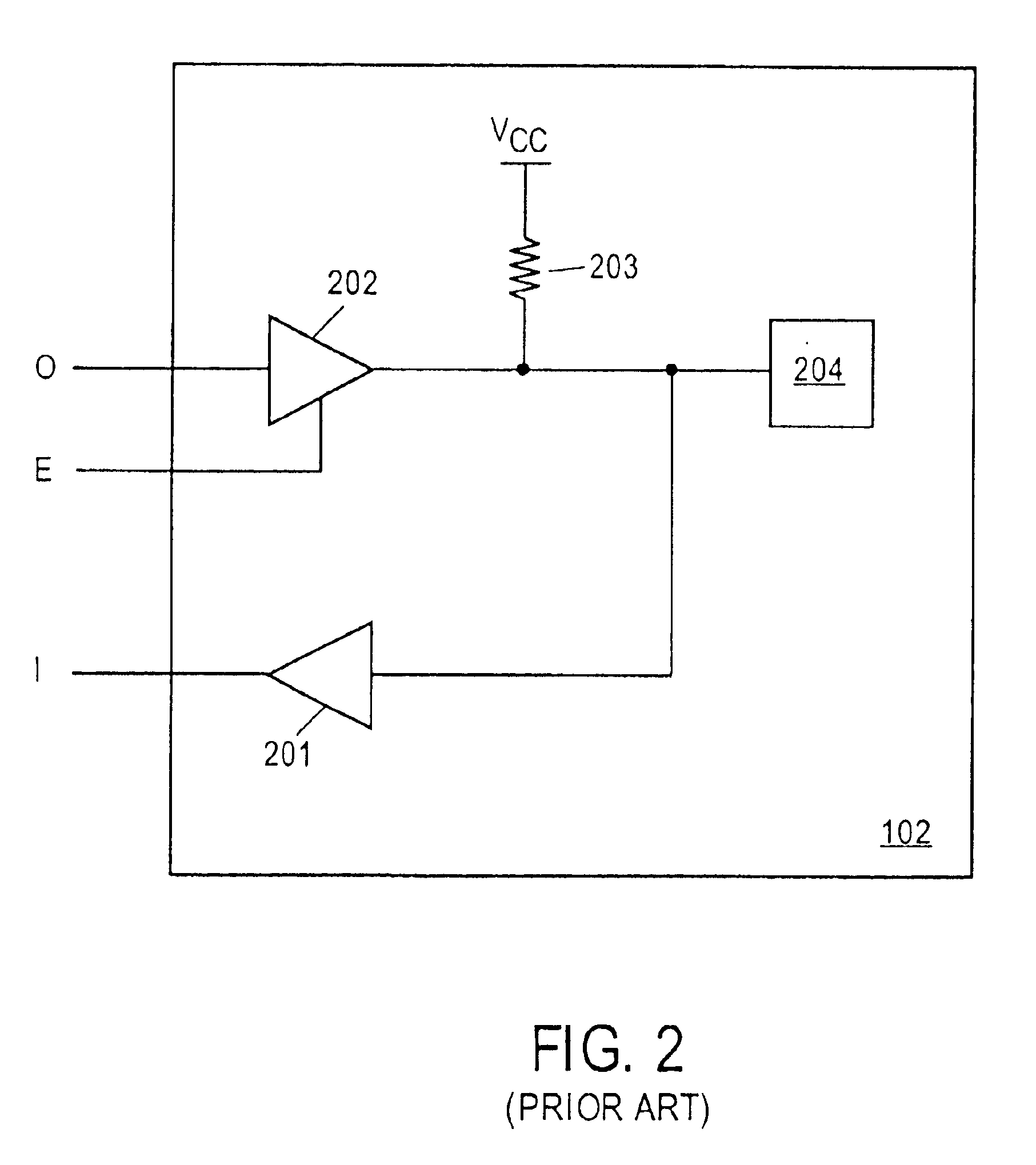

Input/output circuit with user programmable functions

InactiveUS6870397B1Increase flexibilityImprove performanceSolid-state devicesLogic circuits using elementary logic circuit componentsPropagation delayFir system

The I / O circuit of the present invention provides optimal flexibility and performance using a number of different structures and methods. The present invention provides a signal follower circuit for an input pad. In one embodiment, the output buffer is capable of injecting a constant onto a pad during reconfiguration of a configurable system logic circuit. The present invention also provides a circuit for generating a programmable data propagation delay, thereby guaranteeing zero hold time for an arbitrary input register. Zero hold time is accomplished by allowing the user to optimally characterize clock delay to a given input / output circuit. The present invention also provides fast switching between input pads, thereby minimizing data propagation delay between the input pads. Additionally, the present invention reduces time spent in production product test by facilitating the testing of multiple routes with one test configuration. A circuit expanding the number of data input channels available to system routing is provided. Lastly, a plurality of identical input / output block tiles (IOBTs) is disclosed, thereby enabling each I / O circuit to provide the same signals regardless of the IOBTs location in the I / O circuit.

Owner:XILINX INC

Method and apparatus for configurable selection and acquisition of a wireless communications system

InactiveUS6934544B2Network traffic/resource managementAssess restrictionCommunications systemMobile station

A mobile station includes client circuitry for facilitating wireless communications with a wireless communications system, and a configurable system selection unit that executes a system selection and acquisition procedure. The configurable system selection unit includes a front end and a system selection core. The front end facilitates communications between the configurable system selection unit and the client circuitry. The system selection core is coupled to the front end and includes a script engine and a nonvolatile memory storing at least one script table. The script table includes a plurality of system selection event conditions and corresponding scripts that define a system selection and acquisition procedure. The script engine is adapted to detect an event condition and execute the corresponding script. The system selection core is adapted to receive a system selection script and store the received script in the script table, thereby altering the system selection and acquisition procedure.

Owner:QUALCOMM INC

Reconfigurable network on a chip

ActiveUS20070075734A1Easy programmingIncrease flexibilitySolid-state devicesDigital computer detailsSemiconductor chipProgrammable logic array

An architecture for a reconfigurable network that can be implemented on a semiconductor chip is disclosed, which includes a hierarchical organization of network components and functions that are readily programmable and highly flexible. Essentially, a reconfigurable network on a chip is disclosed, which includes aspects of reconfigurable computing, system on a chip, and network on a chip designs. More precisely, a reconfigurable network on a chip includes a general purpose microprocessor for implementing software tasks, a plurality of on-chip memories for facilitating the processing of large data structures as well as processor collaboration, a plurality of reconfigurable execution units including self-contained, individually reconfigurable programmable logic arrays, a plurality of configurable system interface units that provide interconnections between on-chip memories, networks or buses, an on-chip network including a network interconnection interface that enables communication between all reconfigurable execution units, configurable system interface units and general purpose microprocessors, a fine grain interconnect unit that gathers associated input / output signals for a particular interface and attaches them to a designated system interface resource, and a plurality of input / output blocks that supply the link between an on-chip interface resource and a particular external network or device interface. Advantageously, the network minimizes the configuration latency of the reconfigurable execution units and also enables reconfiguration on-the-fly.

Owner:HONEYWELL INT INC

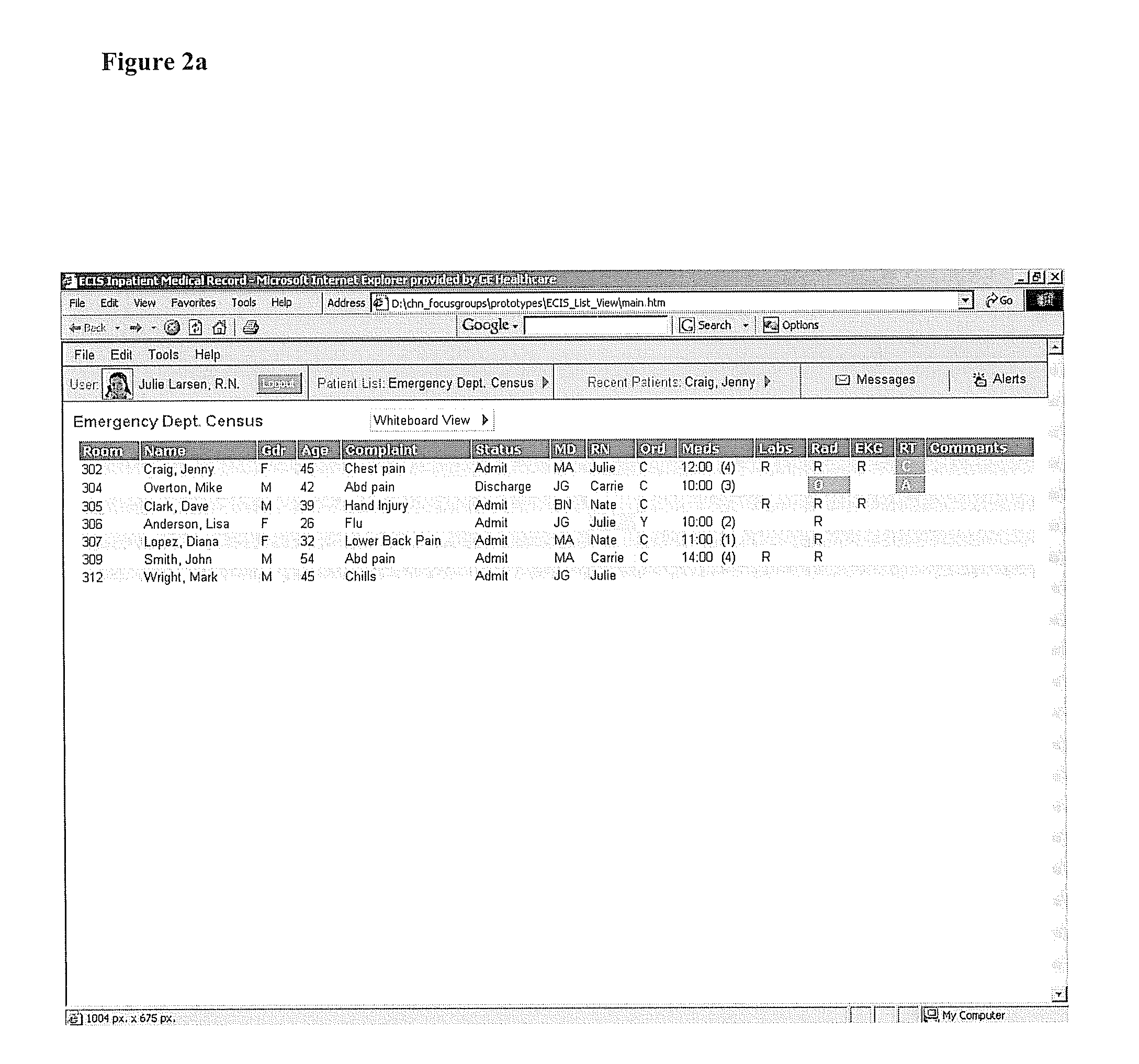

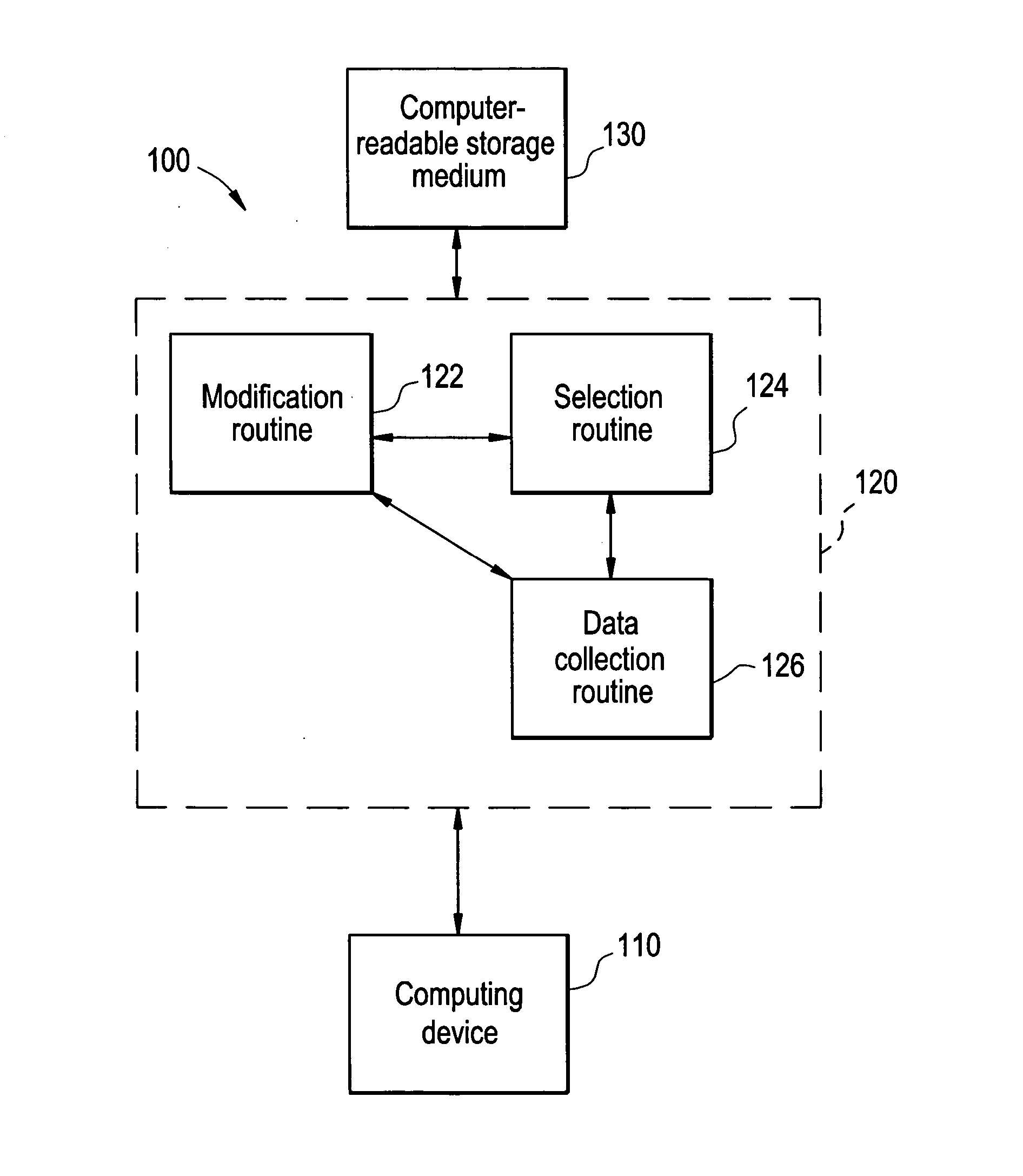

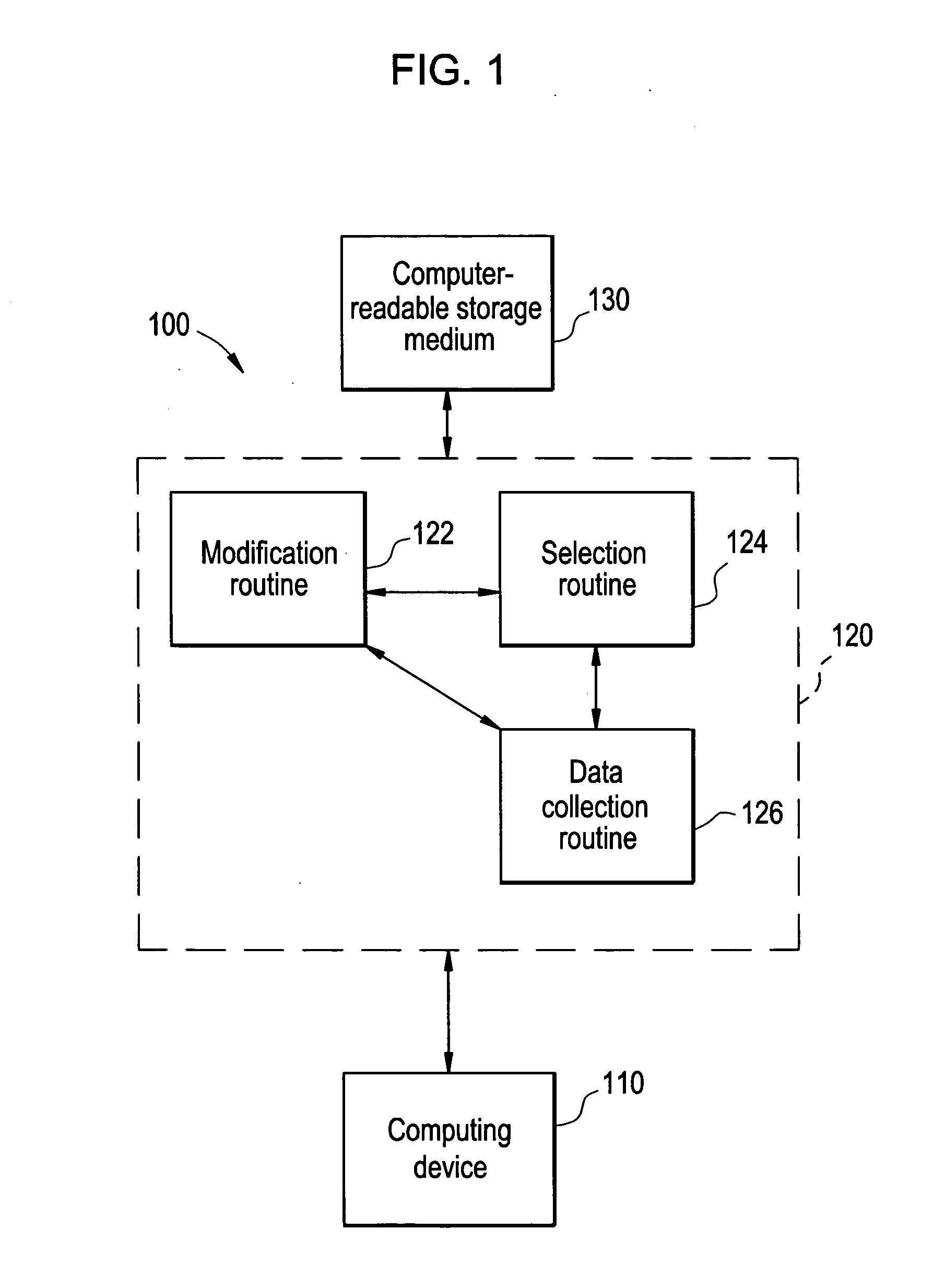

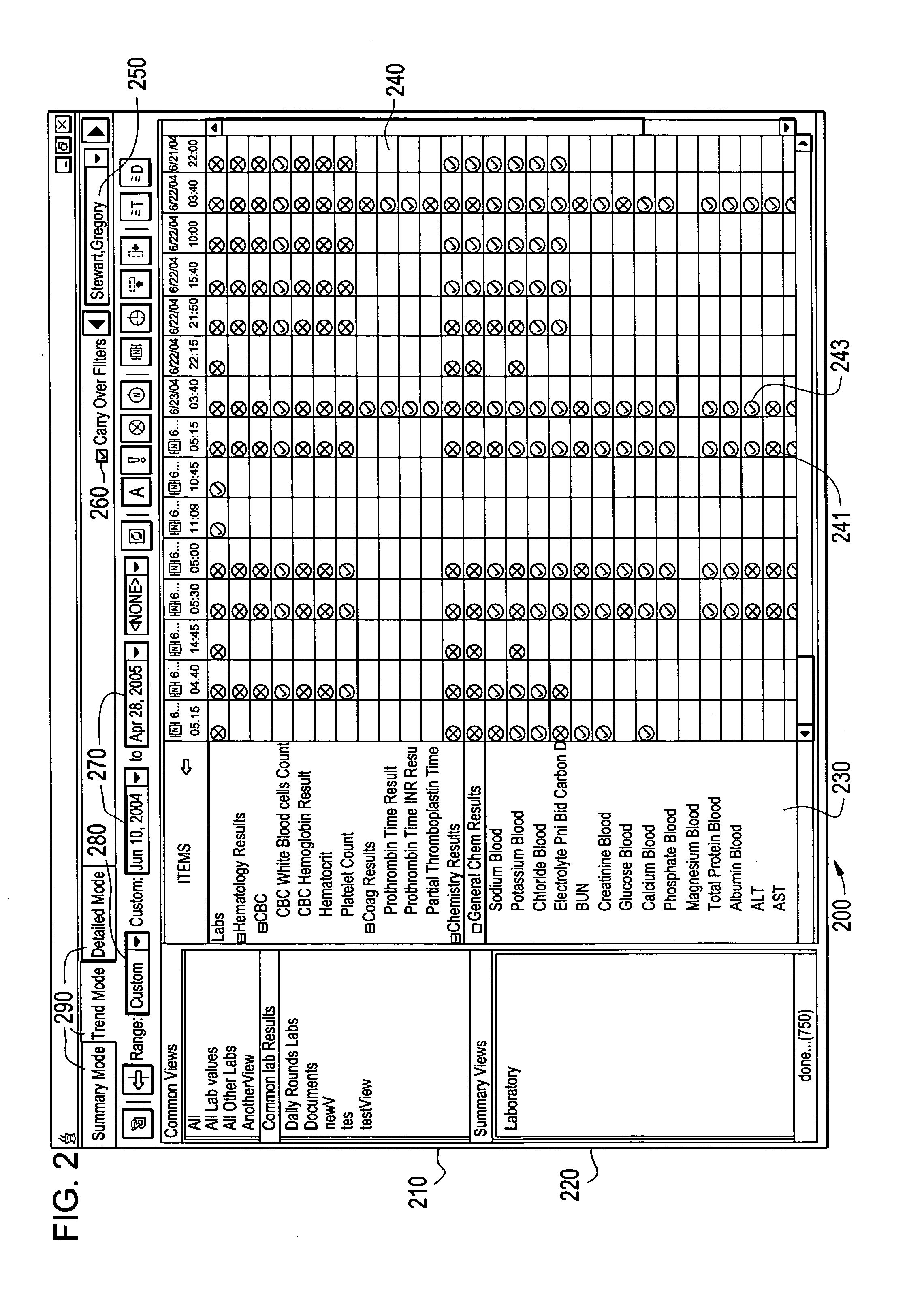

Configurable system and method for results review

InactiveUS20070165049A1Drawing from basic elementsData processing applicationsView basedInput selection

The system includes a remote computer-readable storage medium including a set of medical results for a plurality of patients and a computing device including a computer-readable storage medium, where the computer-readable storage medium includes a set of instructions for the computing device. The set of instructions includes a selection routine configured to select at least one of a plurality of views based on input from a user, where each of the plurality of views includes a template for presentation of a subset of the set of medical results to the user and a modification routine configured to dynamically modify the template of one or more of the views based on input from the user.

Owner:GENERAL ELECTRIC CO

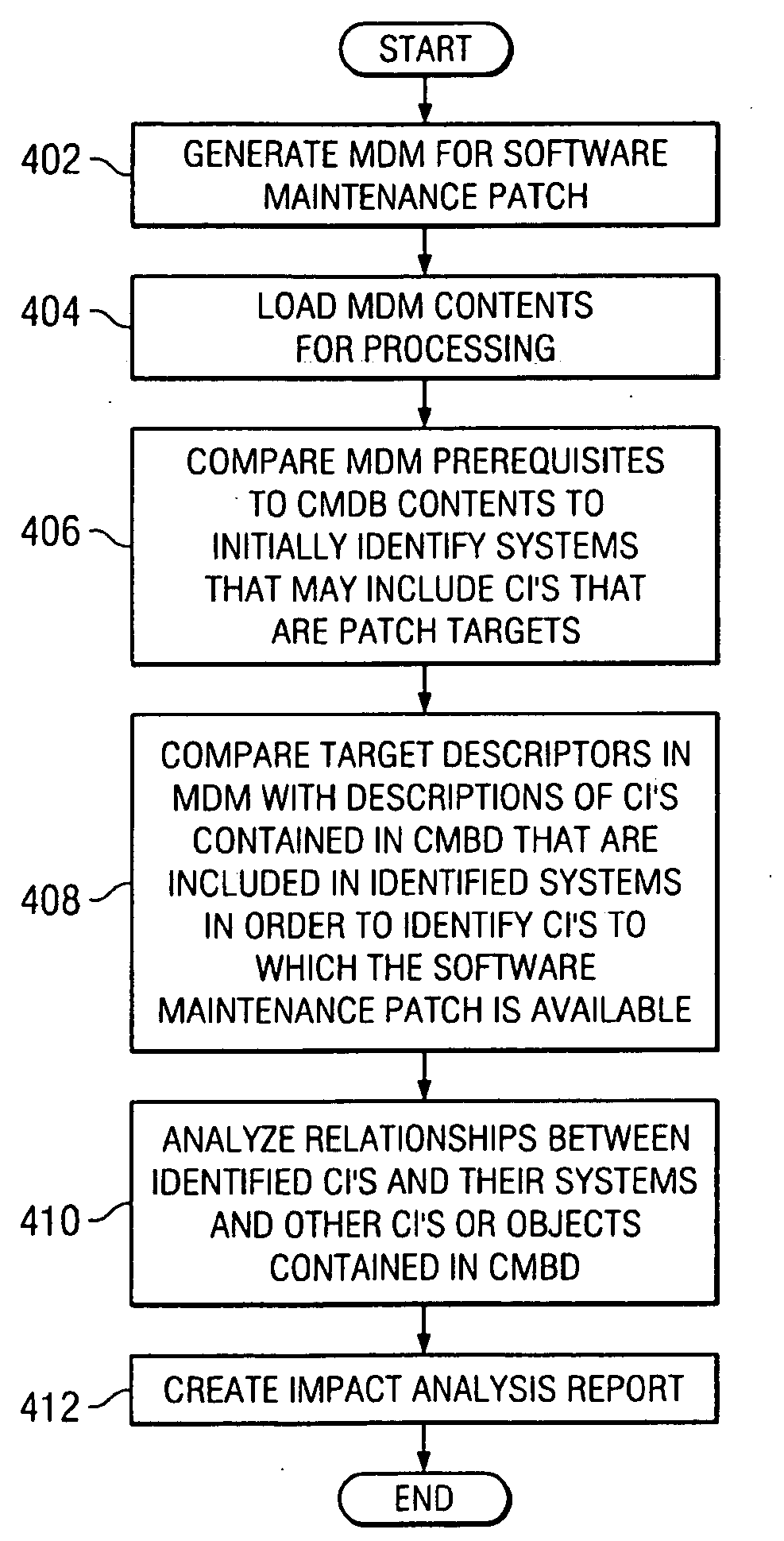

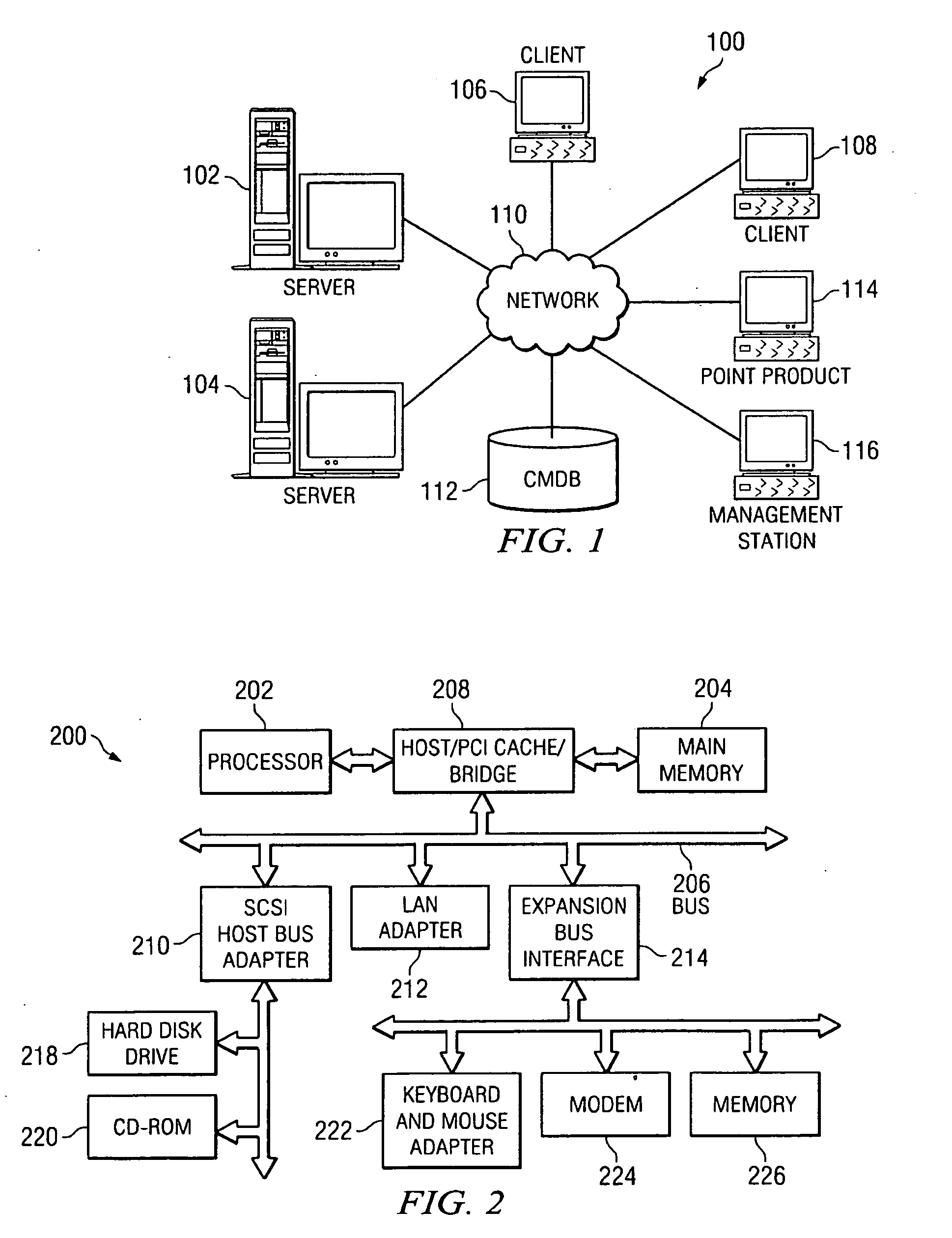

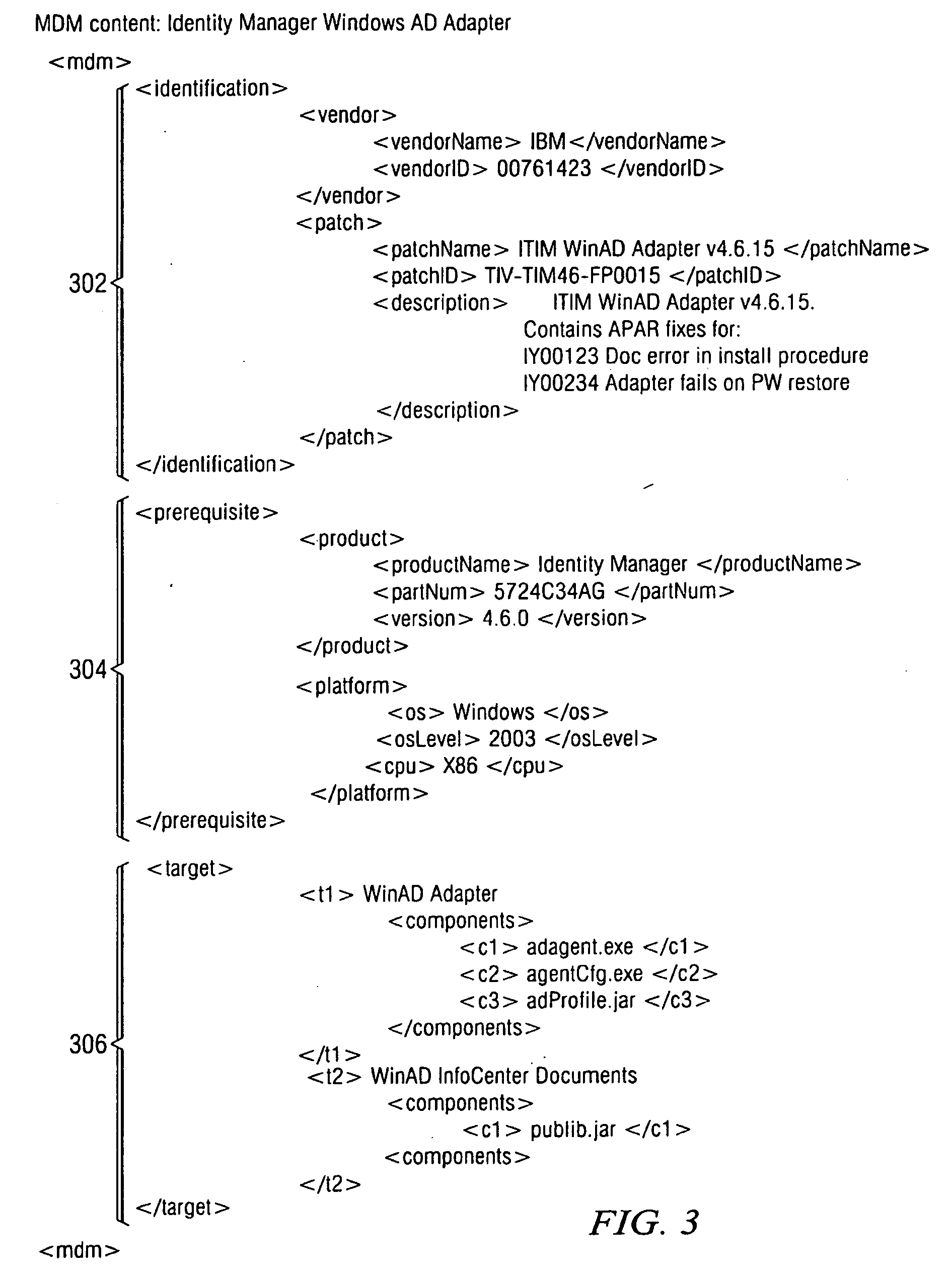

Analysis of effects of a software maintenance patch on configuration items of a cmdb

Embodiments of the invention provide a method, a system and a computer program product for analyzing the effect of a software maintenance patch on configuration items of a CMDB. One embodiment, directed to a method, is associated with a CMDB containing information that relates to configuration items (CIs) included in one or more managed configurable systems. The method includes the step of generating a manifest that defines a target system, and contains a description of a maintenance patch disposed to update one or more specified software components. The method further includes using information contained in the manifest to search the CMDB, in order to detect each configurable system in the CMDB that corresponds to the definition of the target system, and contains at least one CI that includes at least one of the specified software components. For a given CI that includes at least one of the specified software components, an identification is made of every other CI in the CMDB that would be affected, if the maintenance patch was used to update each specified software component of the given CI.

Owner:IBM CORP

Flexible apparatus and method for monitoring and delivery

The present invention generally relates to a system and method that co-locates in a small flexible, configurable system and multi-level substrate sampling, rapid analysis, bio-sample storage and delivery functions to be performed on living tissues or matter obtained from living organisms. The types of the sampling may include chemical, biochemical, biological, thermal, mechanical, electrical, magnetic and optical sampling. In general, the analysis performed at the point of sampling measures the sample taken and records its value. The bio-sample storage function encapsulates a small sample of analyte and preserves it for subsequent examination or analysis, either on the organism by the system or at a remote location by an independent analysis system. Once stored, the sample can provide a record of a biological state at the precise time of sampling. The delivery at the point of sampling can include chemical, biochemical, biological, thermal, mechanical, electrical, magnetic and optical stimuli.

Owner:FISH & RICHARDSON P C

System and method for configurable trading system

A system dynamically integrates into an application program that implements rules for controlling business operations changes in the parameters and parameter groupings that are used by or in conjunction with the rules. The system includes a dynamic business logic rule integrator that provides business logic rules to the application software as executable routines, and a dynamic parameter manager that organizes and manages the parameters. The manager integrates changes to the parameters, groups and / or links the parameters, and makes the parameters available to the rules through a dynamically configurable system database—using a set of static database tables and related dynamically configurable database tables, in which certain database fields or sub-fields correspond to parameters that are used in the rules. The respective database tables and the various fields and sub-fields are established and linked together in accordance with user-defined categories and sub-categories, or “instances.” When parameters are added, edited, grouped, re-grouped, or deleted, the dynamic parameter manager updates, creates and / or removes database tables. The revised set of tables is then made available to the rules, and rules utilize the information in the various fields and sub-fields of the tables to control appropriate trading and associated reporting activities.

Owner:MILLENNIUM IT USA

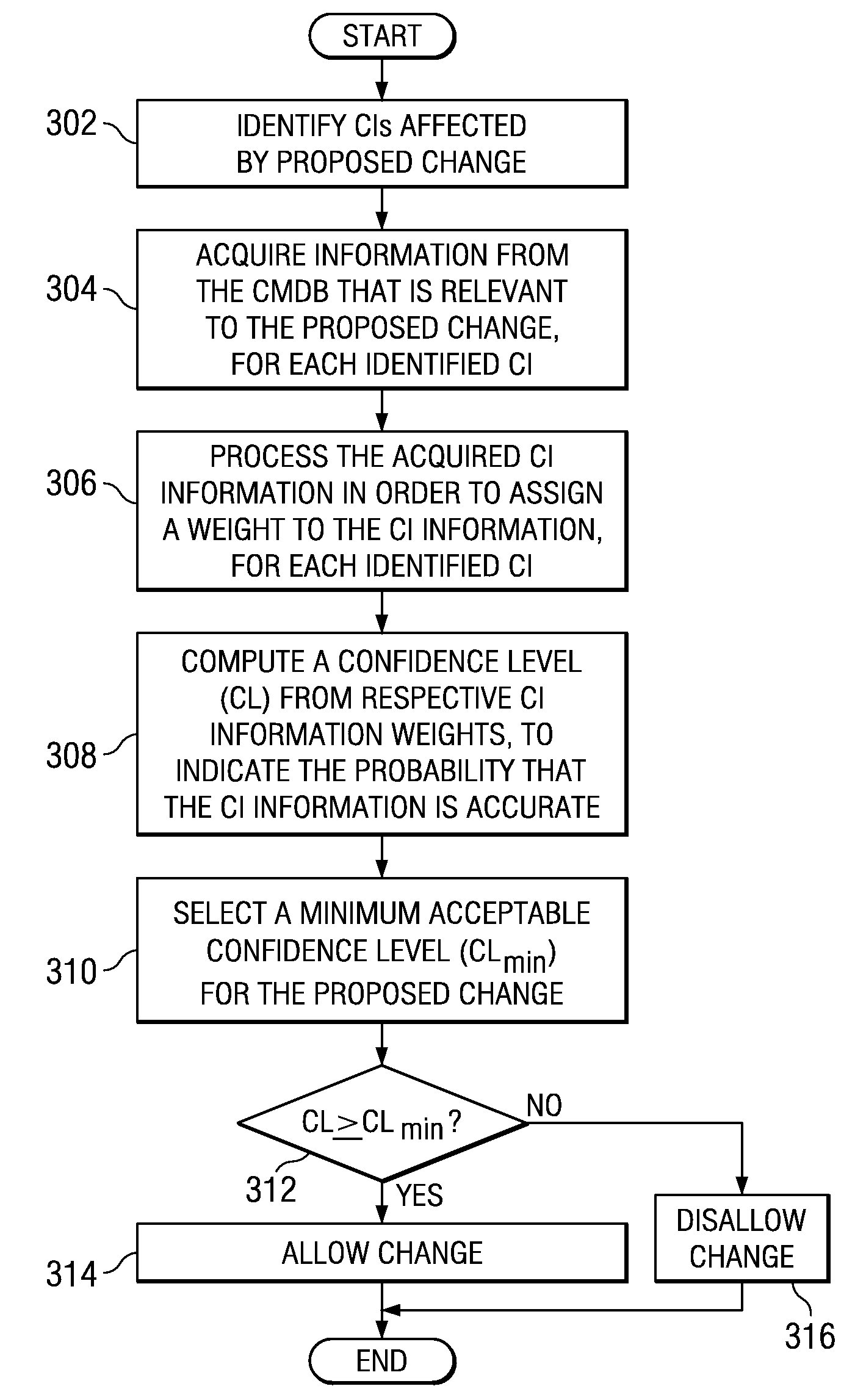

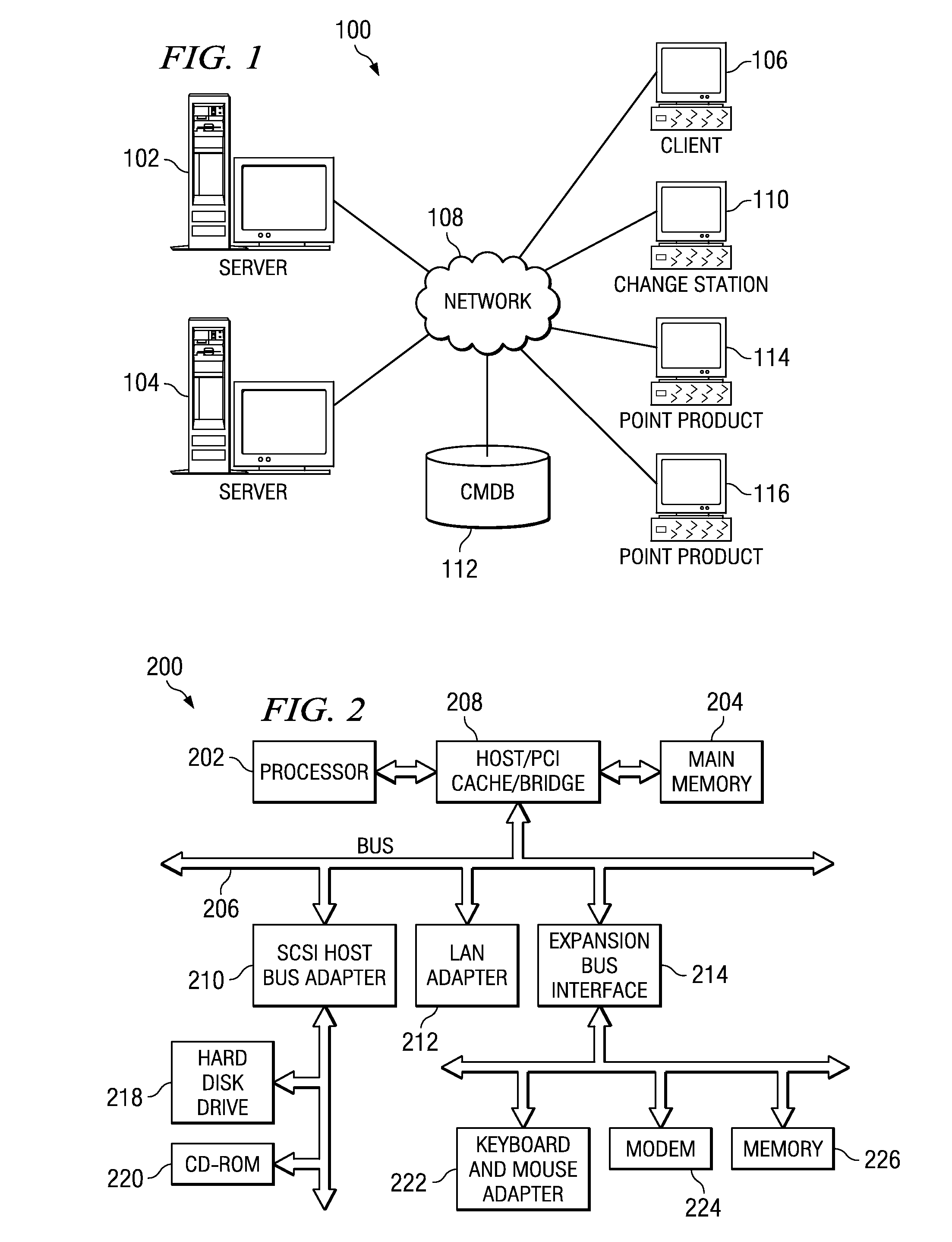

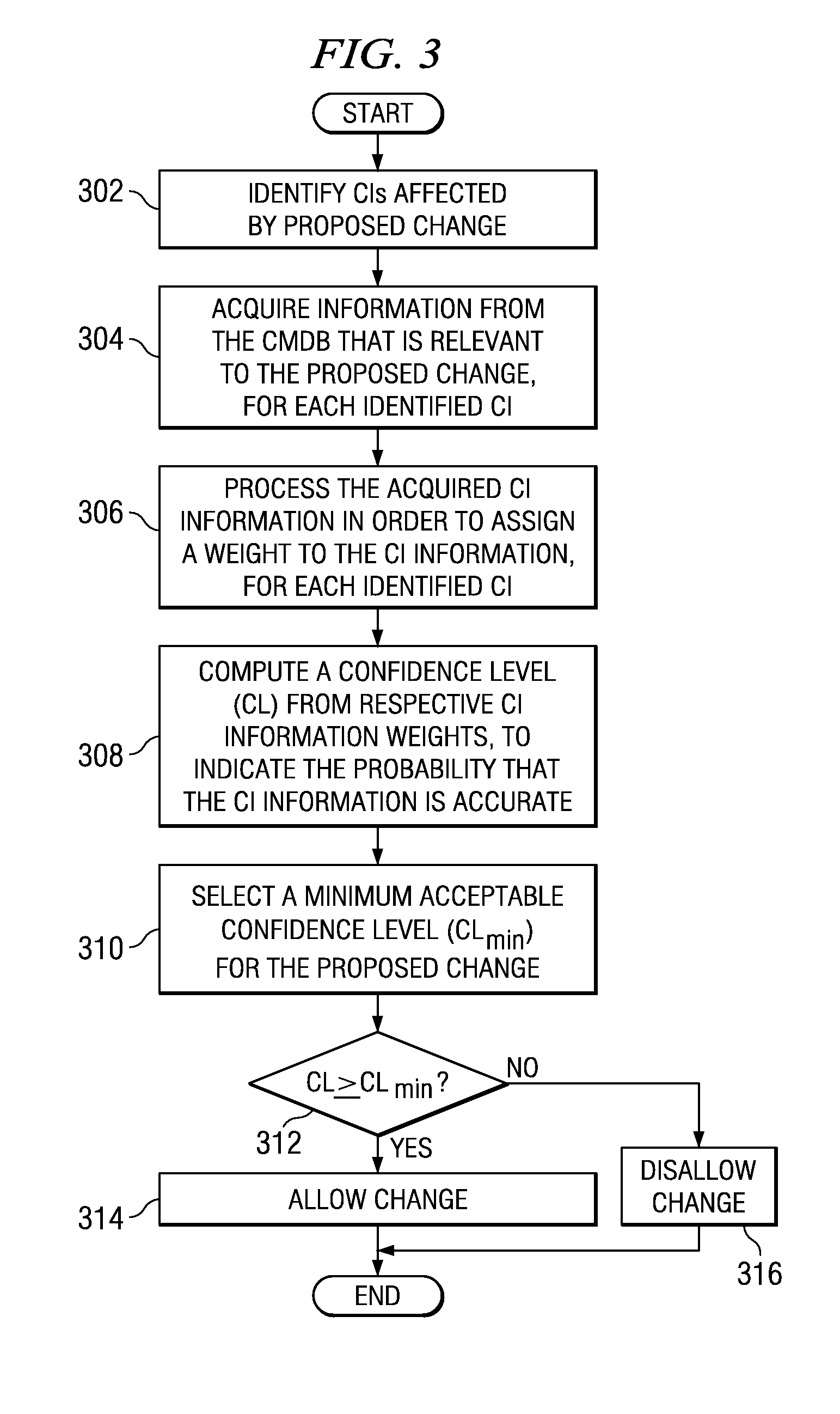

Method for providing assistance in making change decisions in a configurable managed environment

InactiveUS20080183690A1Digital data information retrievalVersion controlData integrityConfidence metric

A method is provided for assigning weights to CIs in a configurable managed system, wherein respective weights are derived from information contained in an associated CMDB. The information could include without limitation the relationships that a CI has with other CIs and the number of reads and writes that are made between the CI and other CIs. A Change Manager in the configurable system makes changes affecting CIs, wherein different types of changes require different levels of confidence in the integrity of data in the CMDB. Accordingly, the weights of respective CIs are used to provide a confidence level regarding the accuracy of CMDB data, pertinent to a proposed change. The confidence level is then used by the Change Manager in deciding whether or not to make the change. One embodiment comprises acquiring information from the CMDB pertaining to CIs that would be affected by a particular change, and processing the acquired information to compute a confidence level indicating the probability that the acquired information is correct. The particular change is then allowed only if the confidence level is no less than a pre-specified minimum value.

Owner:SERVICENOW INC

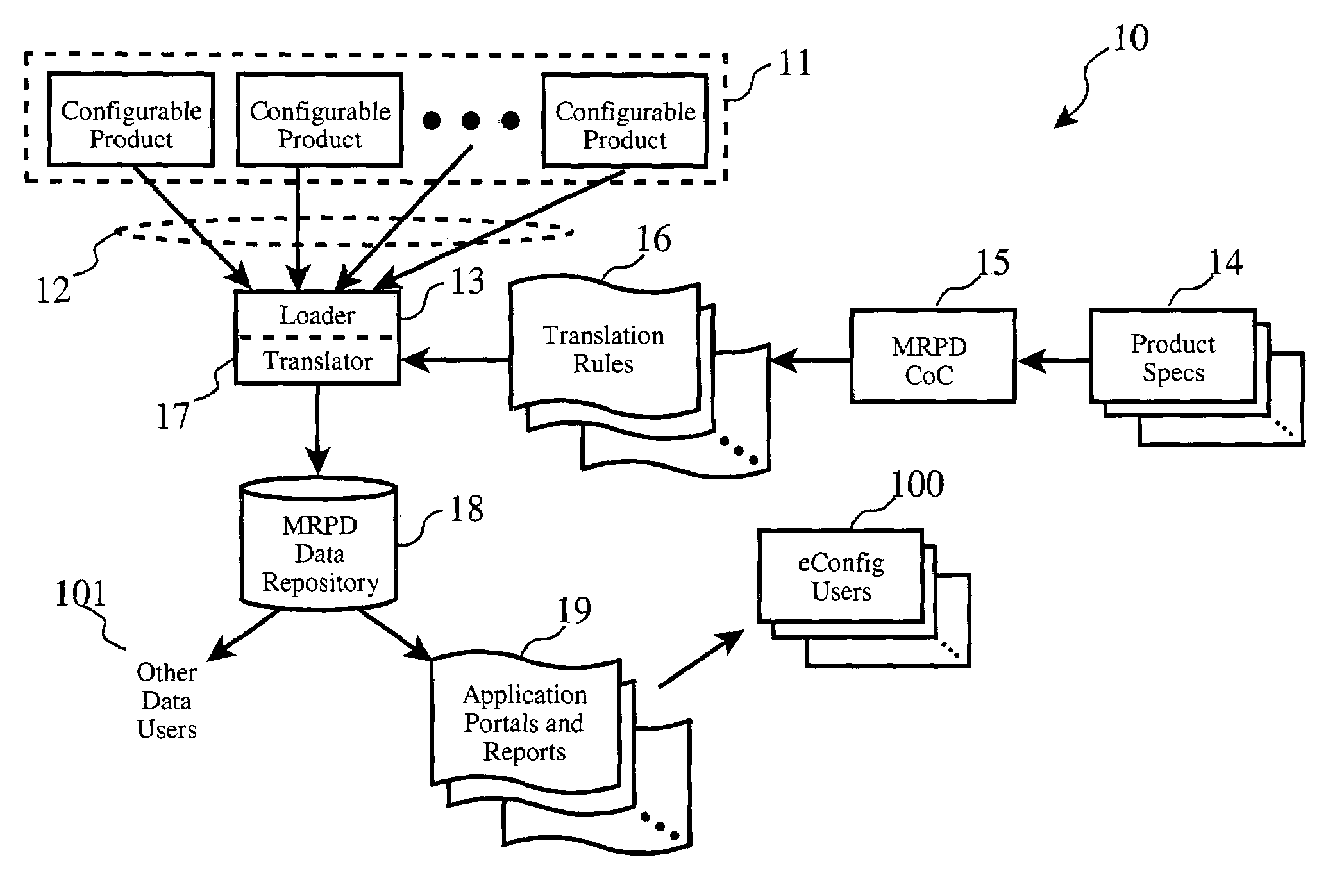

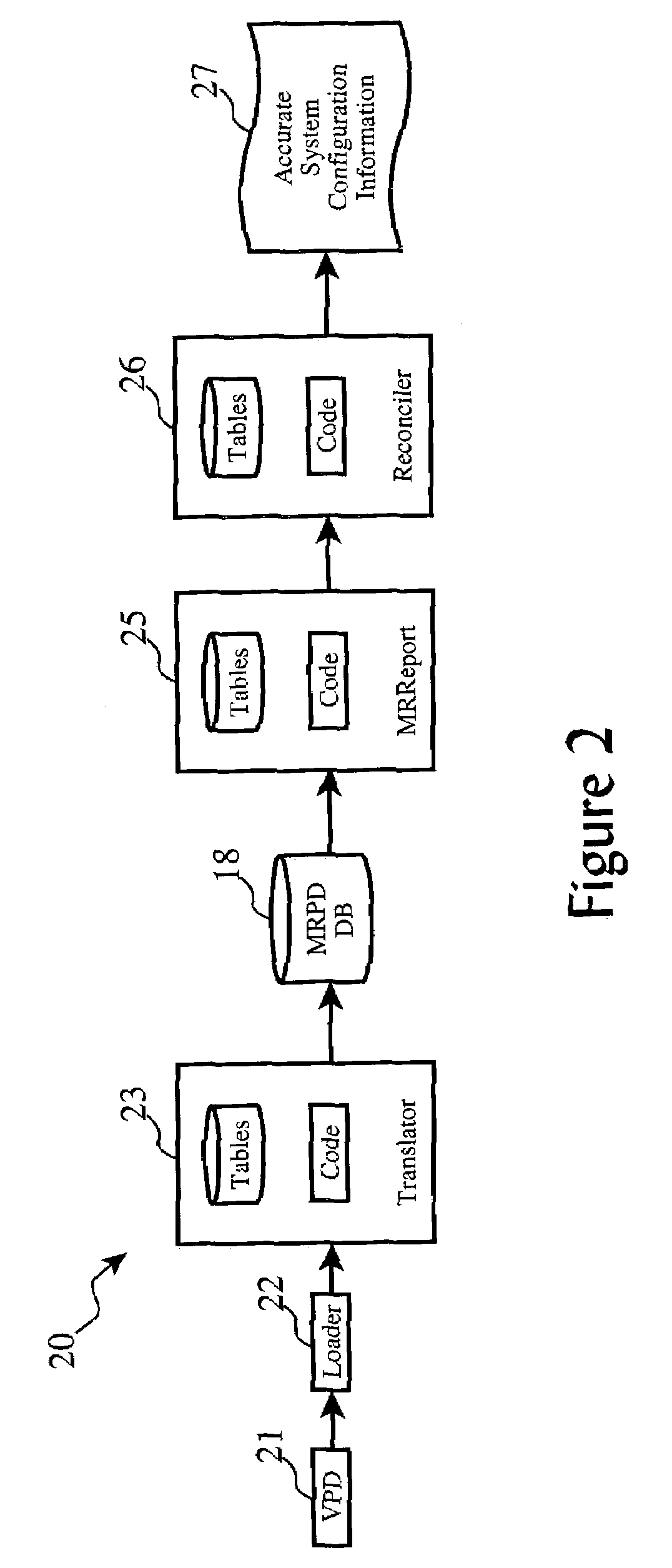

Method and system for reporting configuration data for queriable and non-queriable installed components

InactiveUS7073050B2Improve data accuracyAdvantageously effectiveError detection/correctionDigital computer detailsData setConfigurable systems

The machine-native format of a machine reported configuration data set is identifying, and a set of rules is employed to translate the data set from machine-native format into a common format such as sales nomenclature. The common format configuration information is stored in a globally accessible repository, and retrieved to produce accurate and comprehensive configuration reports for complex configurable systems such as computer servers. These configuration reports may be utilized in order and need fulfillment, such as ordering system upgrades and repair components, scheduling manufacturing, assembly and shipping.

Owner:INT BUSINESS MASCH CORP

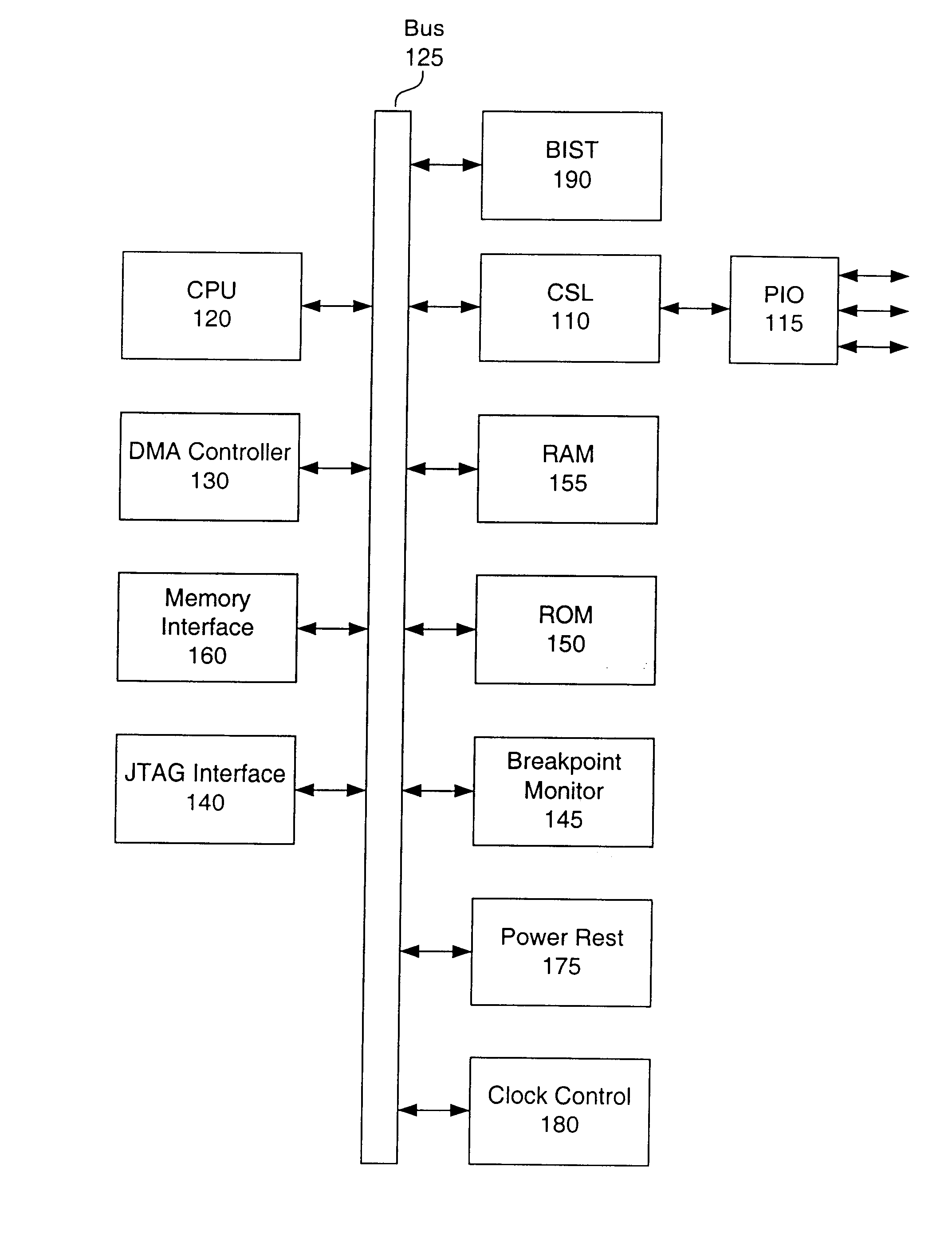

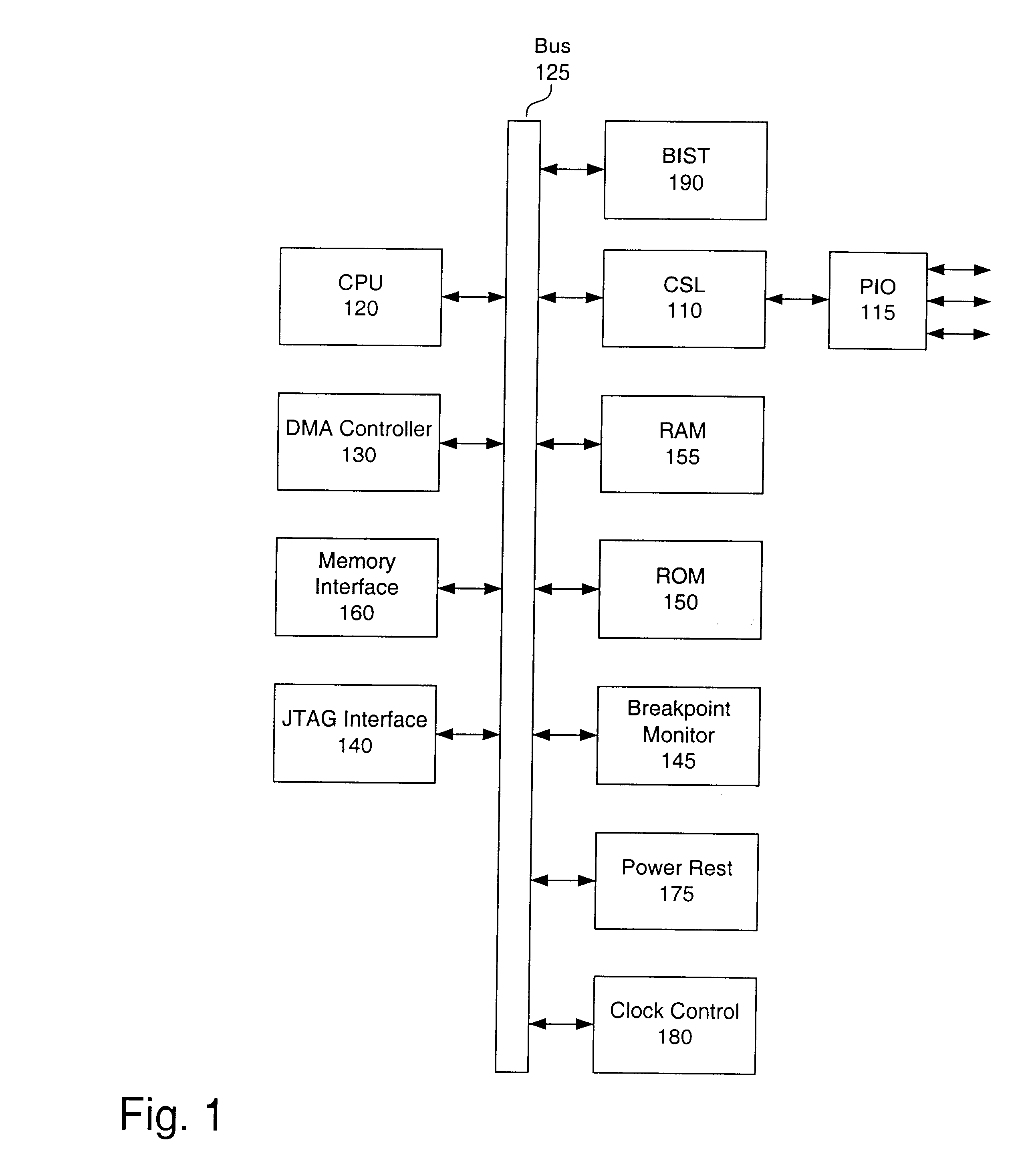

Method and apparatus to facilitate self-testing of a system on a chip

InactiveUS6857092B1Electronic circuit testingError detection/correctionInterconnectionConfigurable systems

A method and apparatus for providing a system-on-a-chip comprising a processor and a configurable system logic (CSL) including a plurality of banks arranged in an array coupled to the processor. The system on a chip further includes a built-in self test (BIST) mechanism coupled to the CSL to perform tests on the CSL to verify that the banks and interconnections between the banks are functioning properly.

Owner:XILINX INC

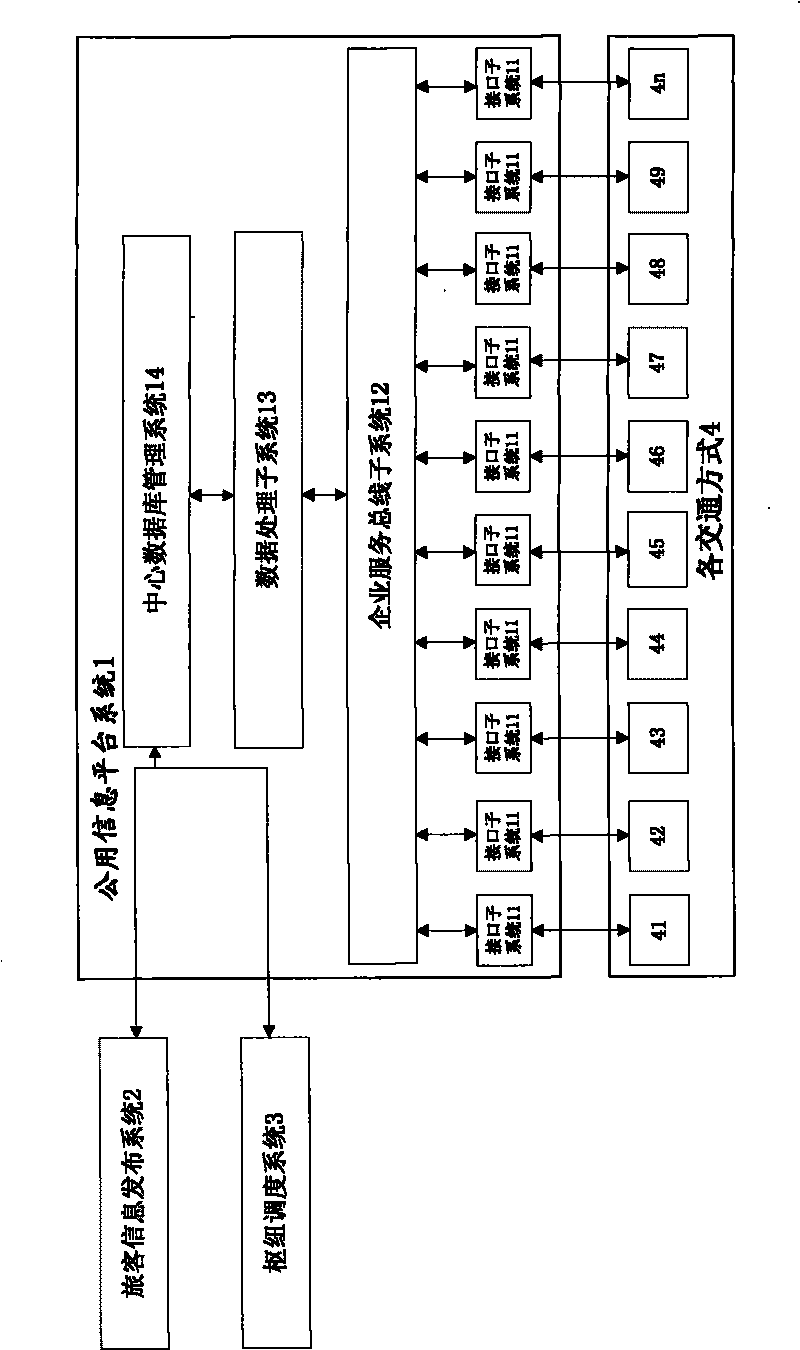

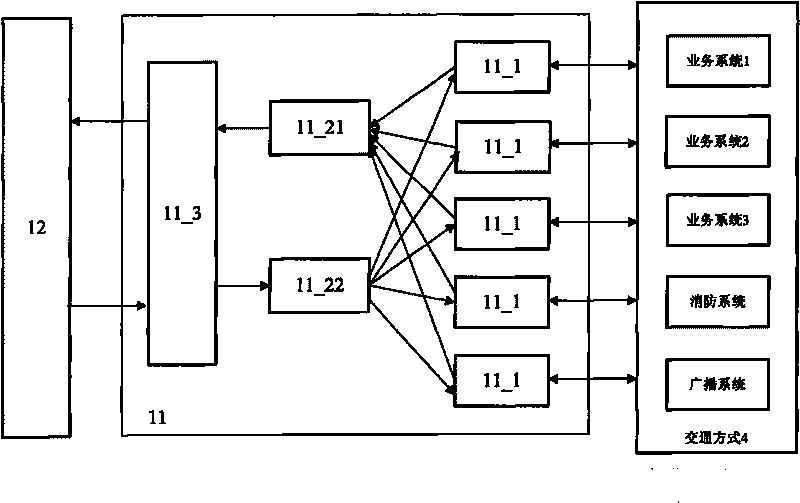

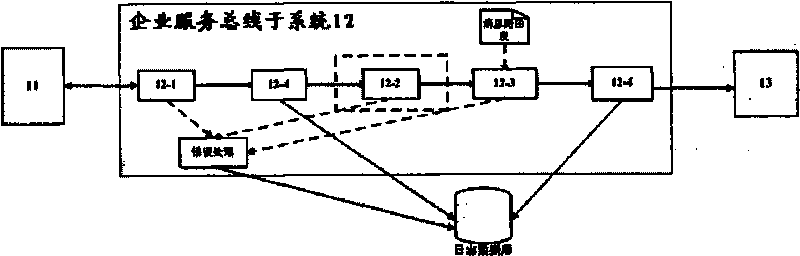

Passenger flow management system for comprehensive transportation hub

InactiveCN101697223ASimplify the integration processSimplified wayData processing applicationsTransmissionComputer modulePersonal computer

The invention relates to a passenger flow management system for a comprehensive transportation hub, which comprises a common information platform system, at least one passenger guidance display sub-system, at least one route inquiry sub-system and a hub dispatching system, wherein the common information platform system comprises an interface sub-system, a data processing sub-system and a central database management system; the central database management system is used for storing correct data processed by a data cleaning module; the passenger guidance display sub-system comprises a display page generator industrial personal computer and a display terminal for realizing the display of passenger guidance information; the route inquiry sub-system comprises an inquiry terminal and an inquiry server; and the hub dispatching system is connected to the central database management system. The passenger flow management system for the comprehensive transportation hub can communicate and cooperate with various heterogeneous systems, provide flexible and configurable systems, cut out and expand the systems easily, process various data of various modes of transportation and ensure correctness of the stored date.

Owner:EASYWAY

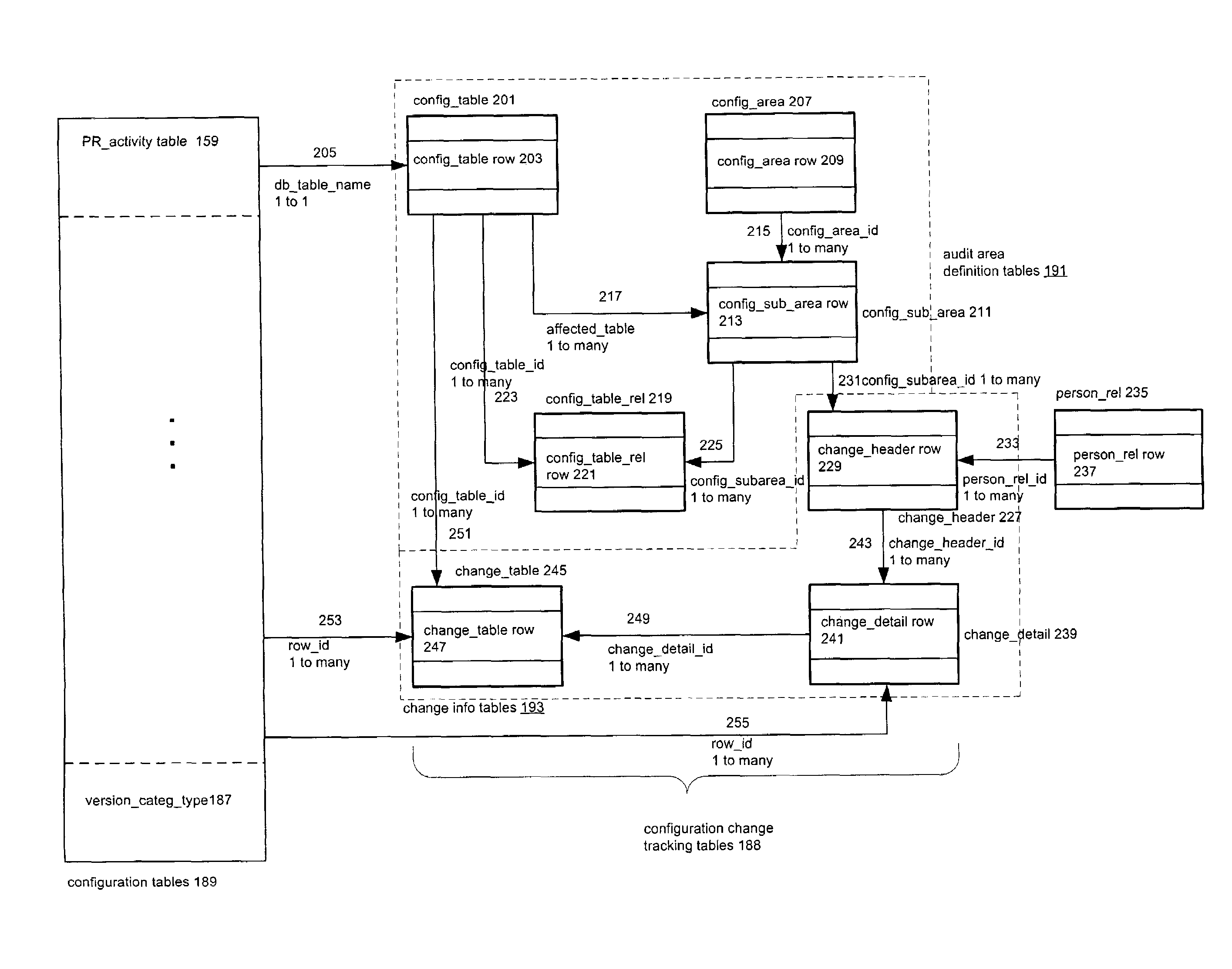

Techniques for providing audit trails of configuration changes

Owner:SPARTA SYST INC

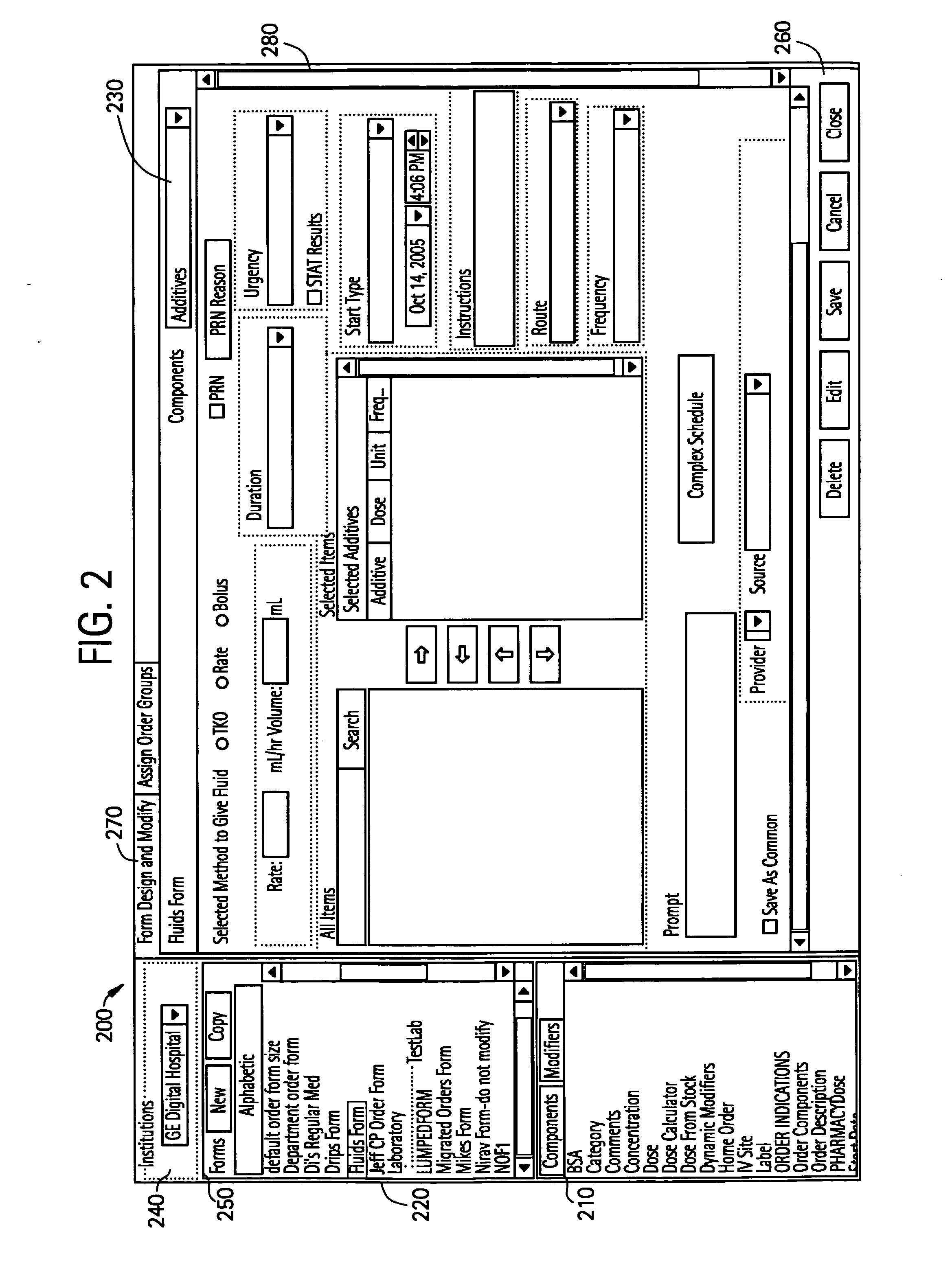

Configurable system and method for order entry

InactiveUS20070083805A1Natural language data processingSpecial data processing applicationsOrder formConfigurable systems

Certain embodiments of the present invention provide for a configurable order entry form. In certain embodiments, the form may be configured by a user. In certain embodiments, the form may mimic a paper form to encourage doctors to use the computer to complete an order form. In certain embodiments, a user may create and / or customize a form. In certain embodiments, a user may specify rules and / or defaults for filling out or completing a form. In certain embodiments, a configurable order form is built in a validation tool. In certain embodiments, a configurable order entry system allows automatic updates of components and / or rules. In certain embodiments, the update of components and / or rules is transparent to a user. Certain embodiments include a component list including a plurality of components and a form configuration tool configured to automatically construct an electronic order entry form using selected components.

Owner:GENERAL ELECTRIC CO