Hardware architecture of binary weight convolution neural network accelerator and calculation process thereof

A binary weight convolution and neural network technology, applied to the hardware architecture and calculation process of the binary weight convolutional neural network dedicated accelerator, to achieve the effect of reducing access, reducing access, and reducing power consumption requirements

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

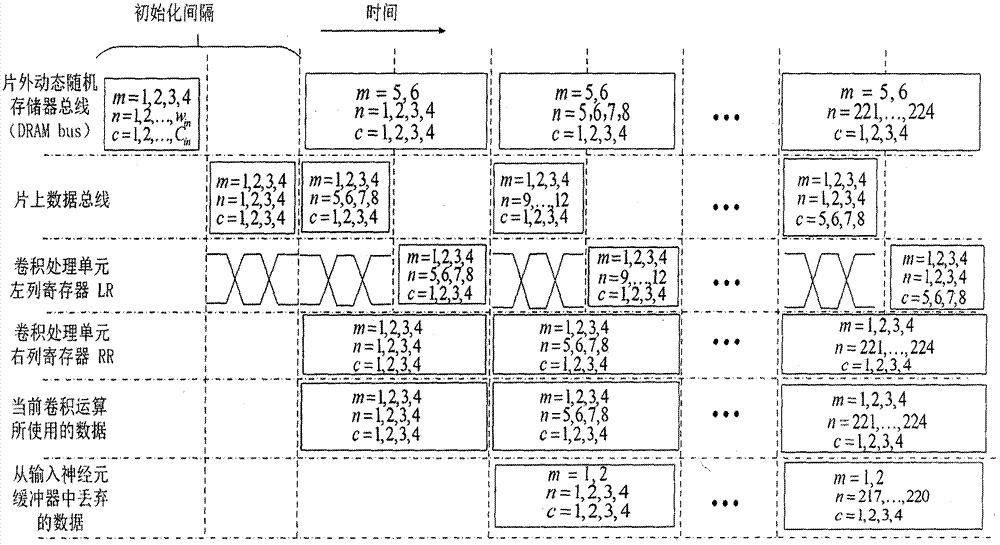

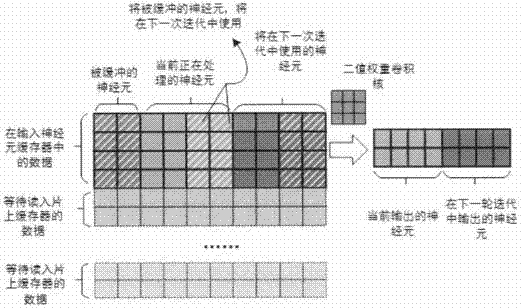

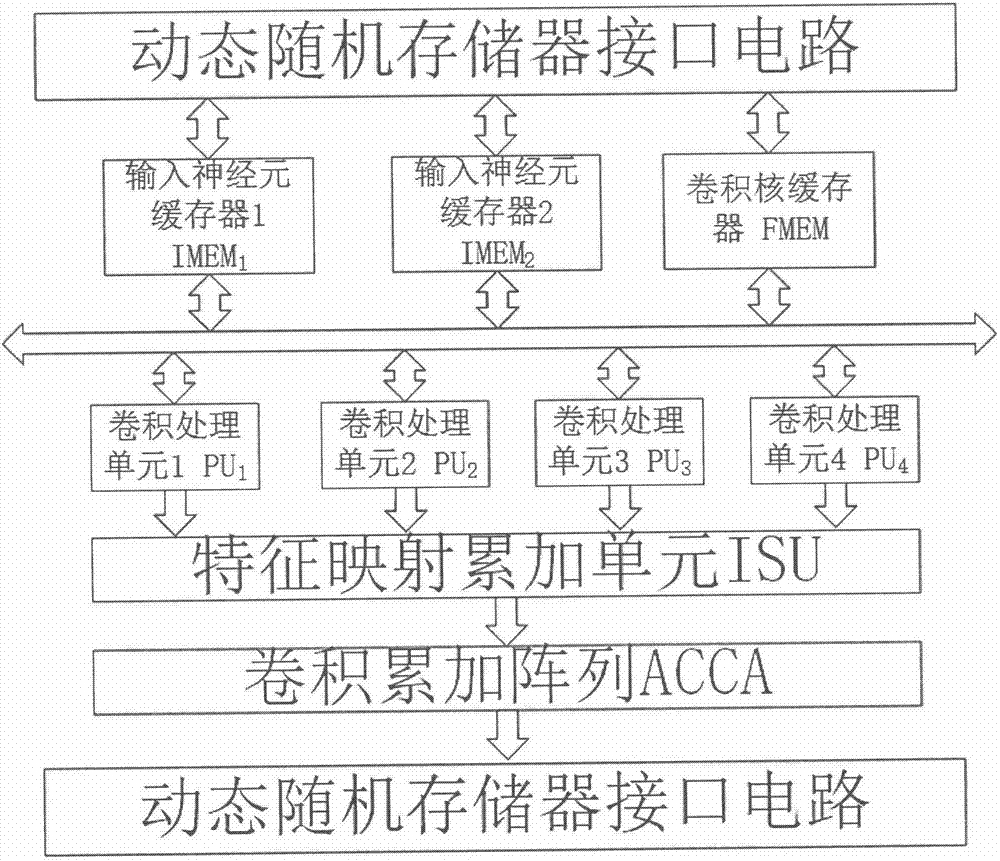

[0039] The embodiments of the present invention are detailed below, and examples of the embodiments are shown in the accompanying drawings. First introduce the necessary hardware overall architecture, and then introduce the optimized calculation process based on this hardware architecture. The following implementations described with reference to the accompanying drawings are exemplary, and are intended to explain the present invention, but should not be construed as limiting the present invention.

[0040] In the description of the present invention, it should be understood that the orientation or positional relationship indicated by the terms "upper", "lower", "left", "right", "vertical", "horizontal", etc. are based on the drawings shown The orientation or positional relationship of is only a simplified description for the convenience of describing the present invention, rather than indicating or implying that the device or element referred to must have a specific orientation,...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More