Efficient interrupt system for system on chip design

A technology for managing systems and external equipment, applied in a variety of digital computer combinations, instruments, multi-programming devices, etc., can solve the problems of complexity, increase in integrated circuit time, and inflexibility, and achieve the effect of improving efficiency

Inactive Publication Date: 2004-10-06

KONINKLIJKE PHILIPS ELECTRONICS NV

View PDF0 Cites 14 Cited by

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

State-of-the-art interrupt management techniques may require complex and inefficient multi-bus designs

Additionally, existing techniques may not allow processors to communicate with each other regarding the handling of interrupt requests

In addition, the existing technology may assign certain interrupt requests to specific CPUs in the hardware, so the existing technology appears to be relatively fixed and inflexible

Moreover, existing technologies may force IC designers to face difficult timing and placement constraints, thereby significantly increasing the time to design and produce ICs

Method used

the structure of the environmentally friendly knitted fabric provided by the present invention; figure 2 Flow chart of the yarn wrapping machine for environmentally friendly knitted fabrics and storage devices; image 3 Is the parameter map of the yarn covering machine

View moreImage

Smart Image Click on the blue labels to locate them in the text.

Smart ImageViewing Examples

Examples

Experimental program

Comparison scheme

Effect test

Embodiment approach

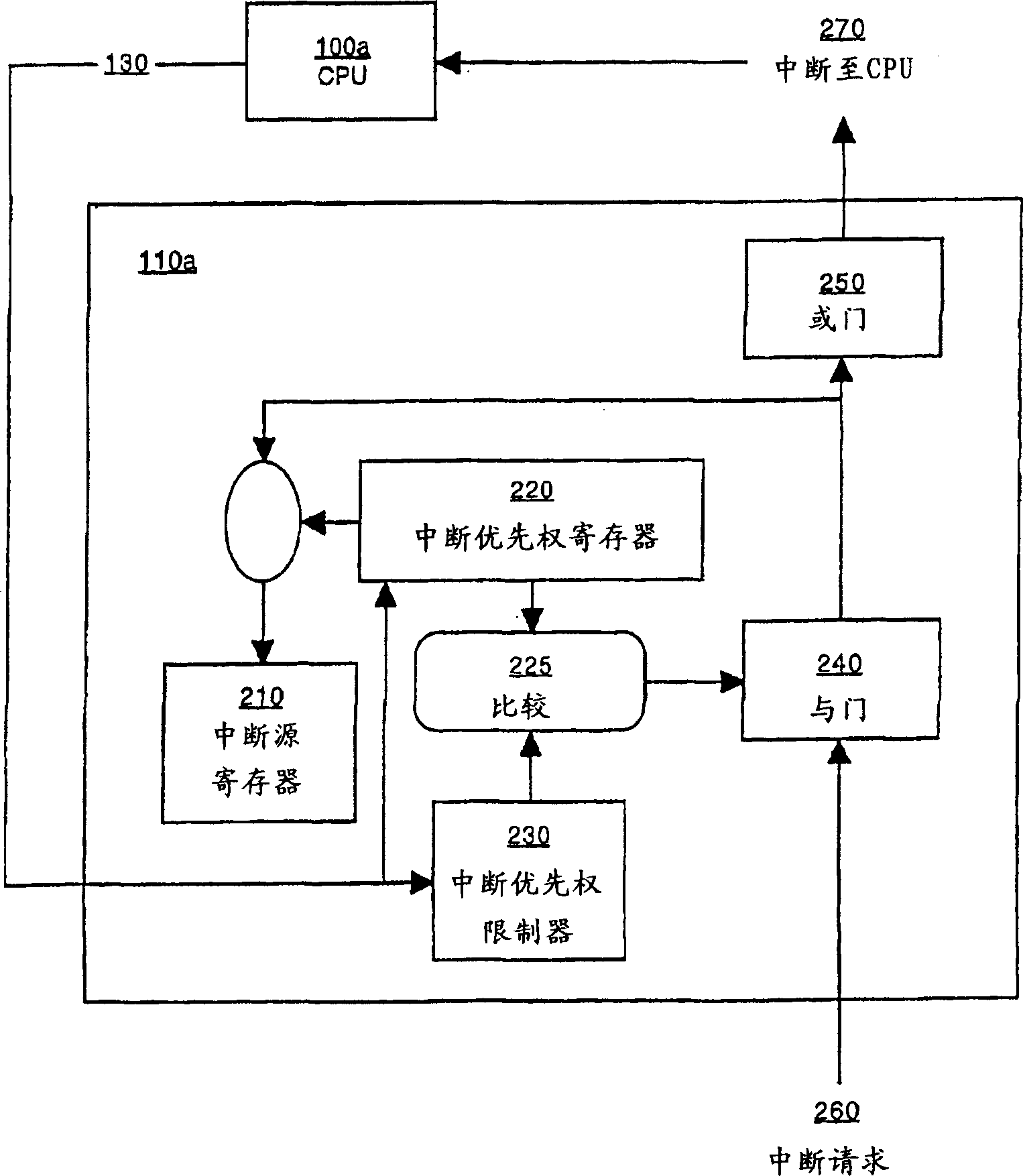

[0018] figure 2 is a block diagram of an embodiment of an interrupt controller according to the present invention.

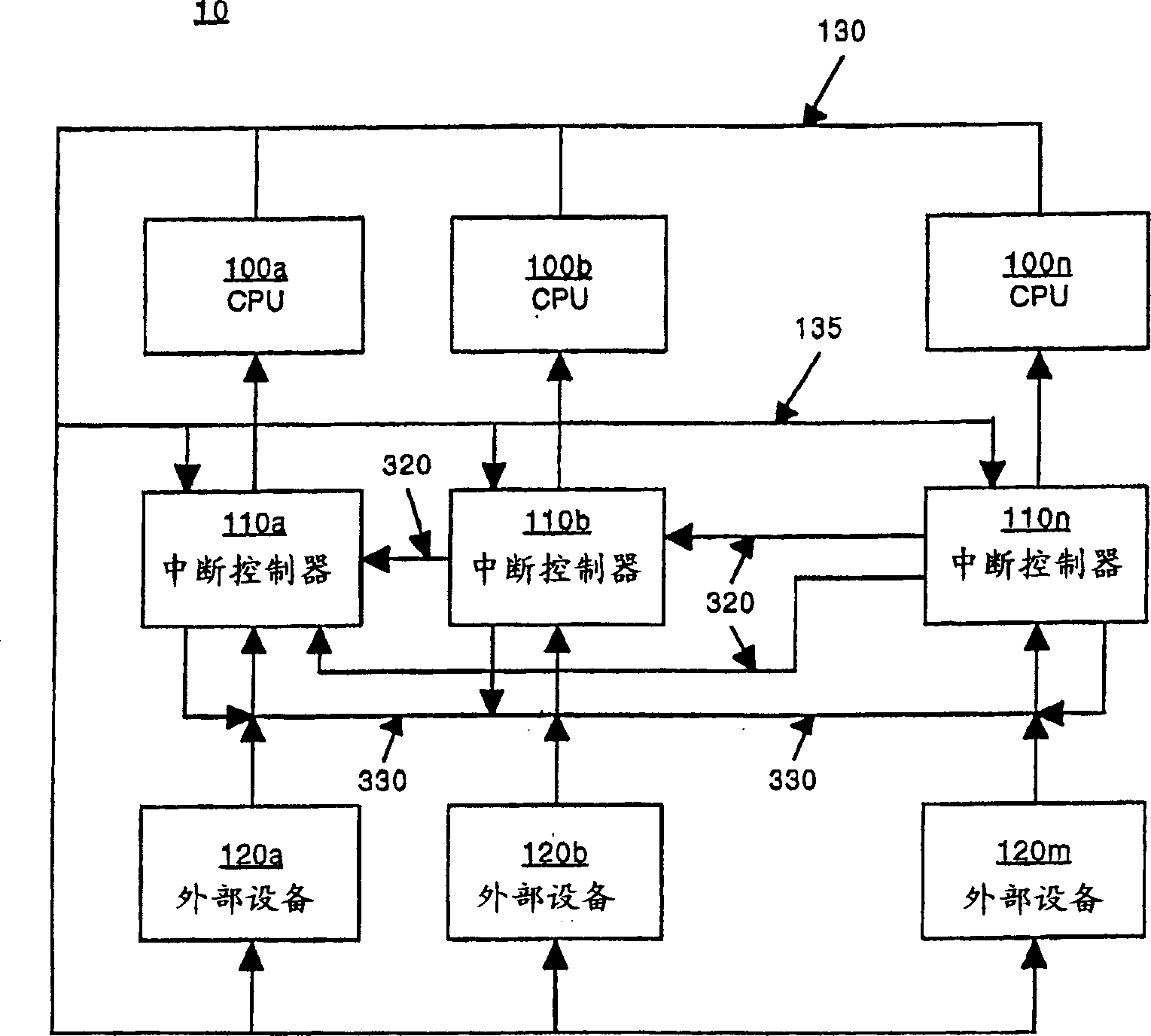

[0019] image 3 yes figure 1 Detailed block diagram of the interconnection between the blocks in the shown interrupt management system.

[0020] Figure 4 It is a flow chart of the steps of the interrupt management process given according to an embodiment of the present invention.

[0021] Figure 5A is a data flow diagram showing inter-processor communication through an interrupt controller according to an embodiment of the present invention.

[0022] Figure 5B is like Figure 5A Timing diagram of interprocessor communication shown.

the structure of the environmentally friendly knitted fabric provided by the present invention; figure 2 Flow chart of the yarn wrapping machine for environmentally friendly knitted fabrics and storage devices; image 3 Is the parameter map of the yarn covering machine

Login to View More PUM

Login to View More

Login to View More Abstract

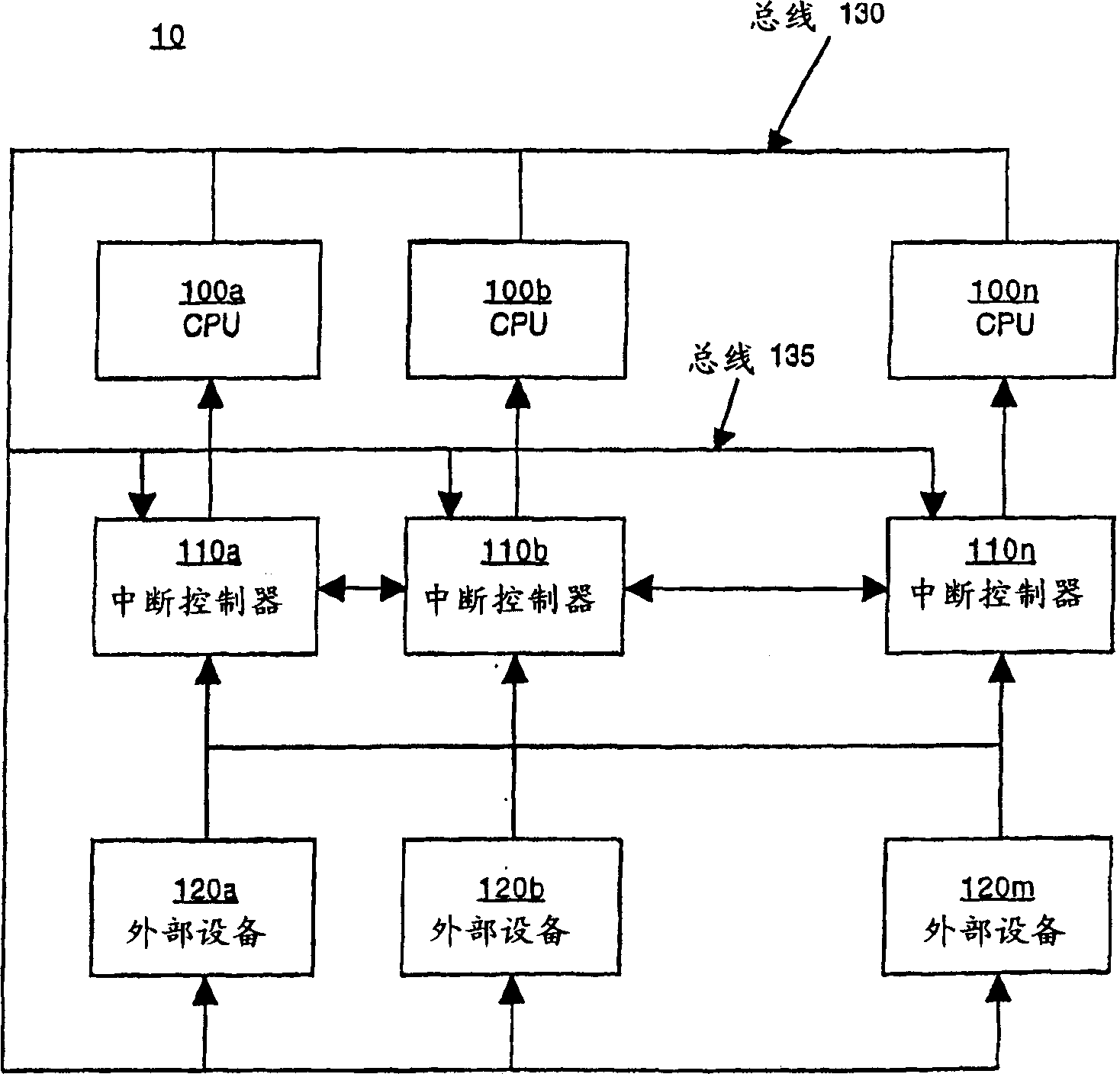

A method (400) and system (10) for managing interrupts in a system on a chip design that includes multiple processors (100a, 100b, ..., 100n) coupled to multiple peripheral devices (120a, 120b, ..., 120m). A plurality of interconnected interrupt controllers (110a, 110b, ..., 110n) are coupled between the processors and the peripheral devices. Interrupts generated by the peripheral devices are received by all of the interrupt controllers. In one embodiment, an interrupt controller is paired with a processor. Each interrupt controller can identify which interrupts will be passed to its respective processor. The interrupt controllers work in concert to pass each interrupt to a particular processor.

Description

technical field [0001] The present invention relates generally to the field of integrated circuits ("chips") and, more particularly, to implementing interrupt management in "system-on-chip designs" that include multiple processors and multiple peripherals. technical background [0002] "System-on-a-chip" architectures such as microcontrollers or microprocessors are commonly used in applications including audio, radio, portable devices, data communications, Internet control, and industrial and consumer systems. System-on-a-chip architectures provide design and manufacturing efficiencies in chip production and the integration of chips in specific applications. [0003] To improve performance, some system-on-chip architectures utilize multiple central processing units (CPUs). In addition, system-on-chip architectures may utilize multiple buses, typically arranged in some type of hierarchy. [0004] As the complexity of chips increases, some problems arise with system-on-chip ...

Claims

the structure of the environmentally friendly knitted fabric provided by the present invention; figure 2 Flow chart of the yarn wrapping machine for environmentally friendly knitted fabrics and storage devices; image 3 Is the parameter map of the yarn covering machine

Login to View More Application Information

Patent Timeline

Login to View More

Login to View More IPC IPC(8): G06F15/16G06F9/46G06F13/24G06F13/26

CPCG06F13/26

Inventor R·詹森A·德奥利维拉T·奥德维尔

Owner KONINKLIJKE PHILIPS ELECTRONICS NV