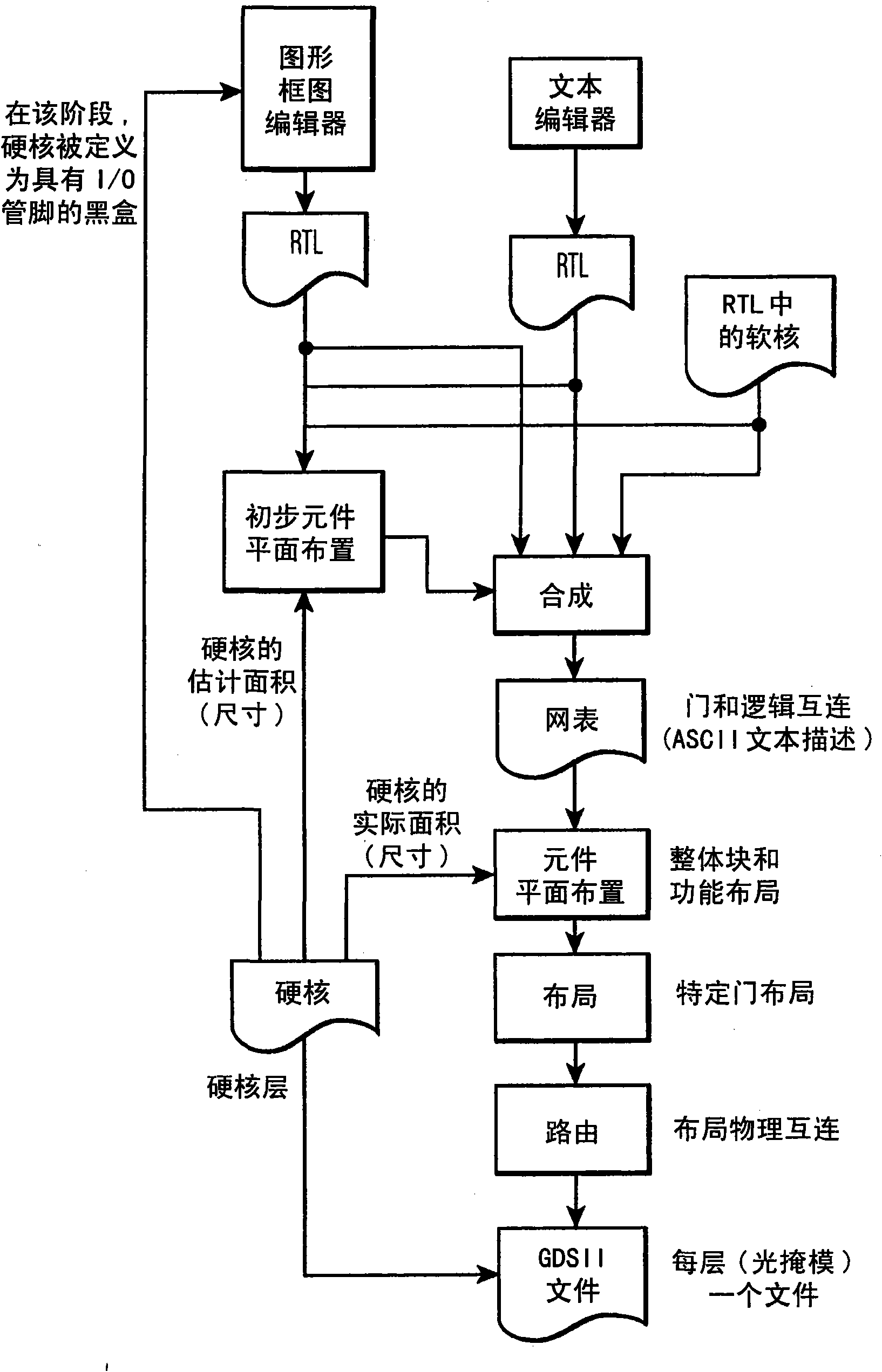

Source-synchronous data link for system-on-chip design

A system-level chip and data link technology, applied in the field of IC products, can solve problems such as performance changes and soft-core performance not being "solid-state"

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0019] In the following detailed description, for purposes of illustration and not limitation, example embodiments disclosing specific details are set forth in order to provide a more complete understanding of embodiments in accordance with the present teachings. However, it will be apparent to those skilled in the art having the benefit of this disclosure that other embodiments in accordance with the teachings of the invention than the specific details disclosed herein are within the scope of the appended claims. Moreover, descriptions of well-known devices and methods may be omitted so as not to obscure the description of the example embodiments. Such methods and devices are clearly within the scope of the teachings.

[0020] One type of communication link that does not require a globally synchronous clock is an asynchronous data link.

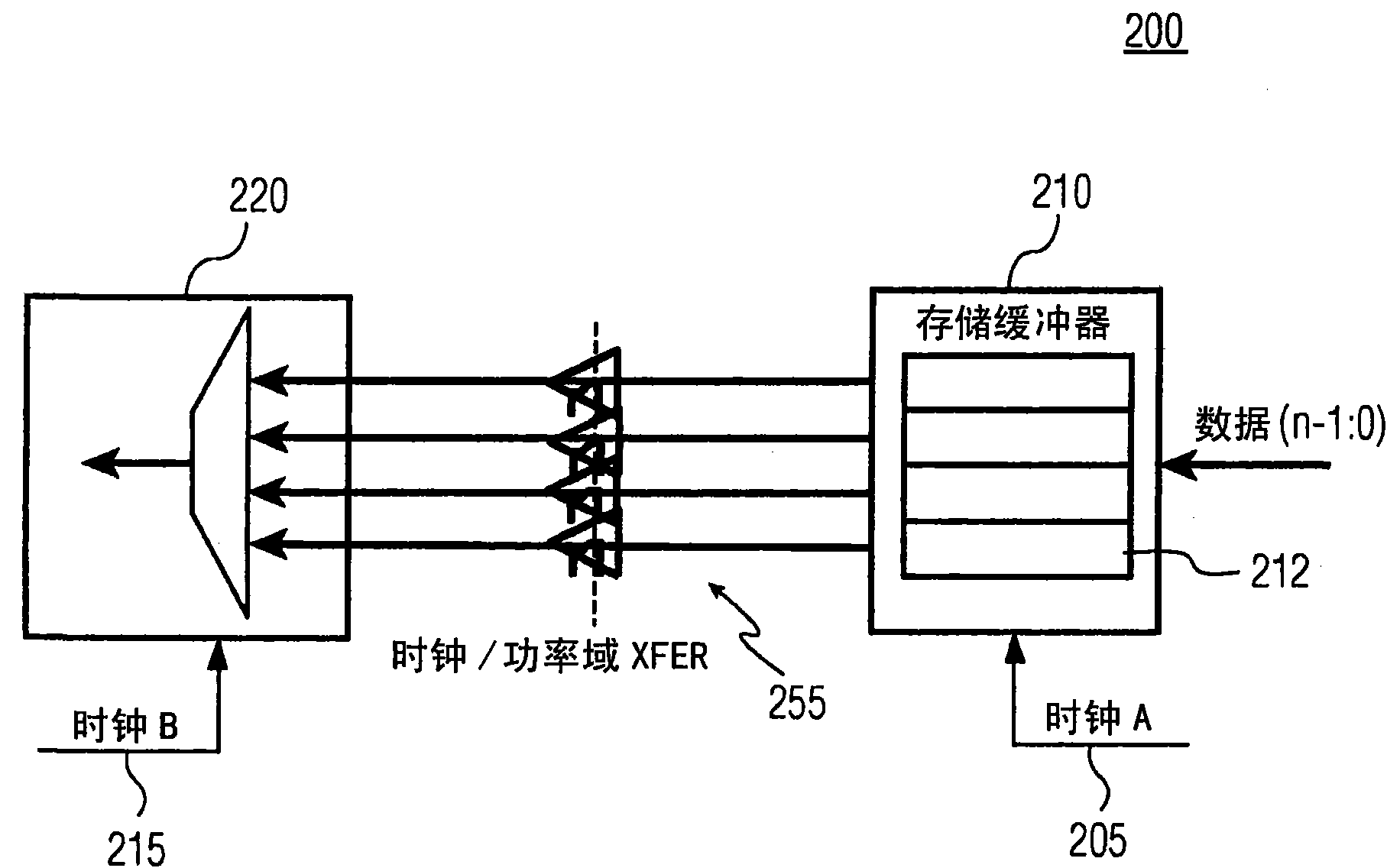

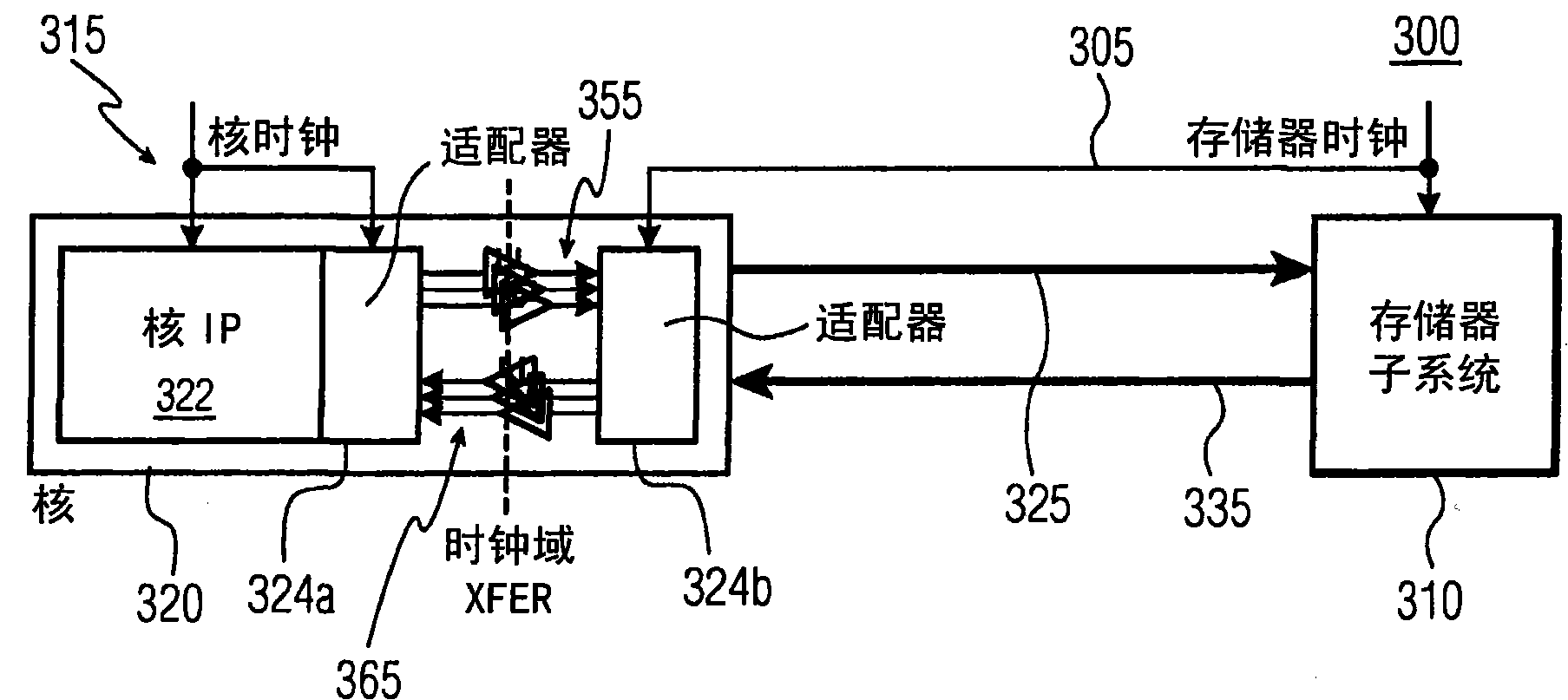

[0021] figure 2 An example embodiment of a device 200 with an asynchronous data link 255 is shown. figure 2 The flow of data between t...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More