Patents

Literature

82 results about "Voltage islands" patented technology

Efficacy Topic

Property

Owner

Technical Advancement

Application Domain

Technology Topic

Technology Field Word

Patent Country/Region

Patent Type

Patent Status

Application Year

Inventor

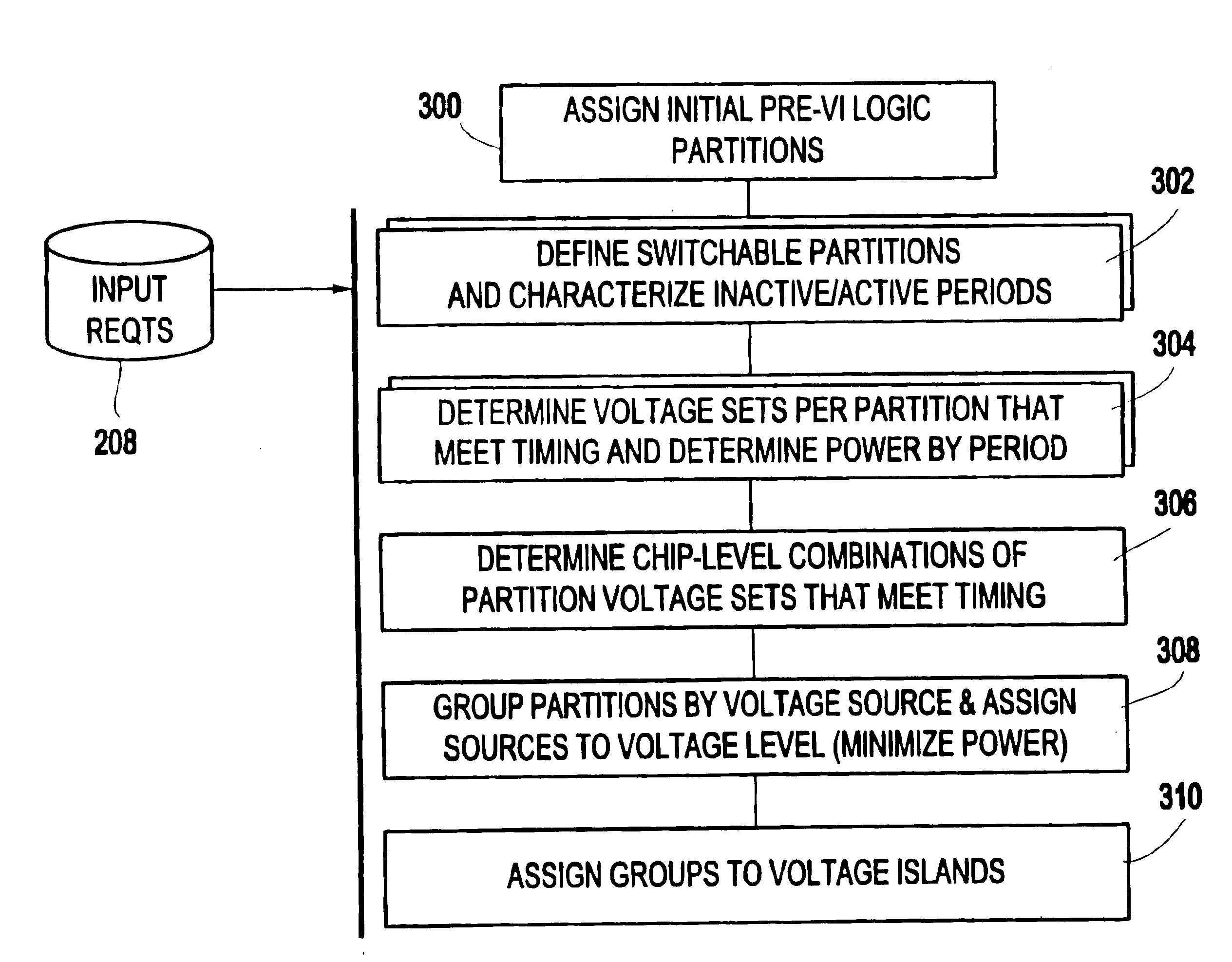

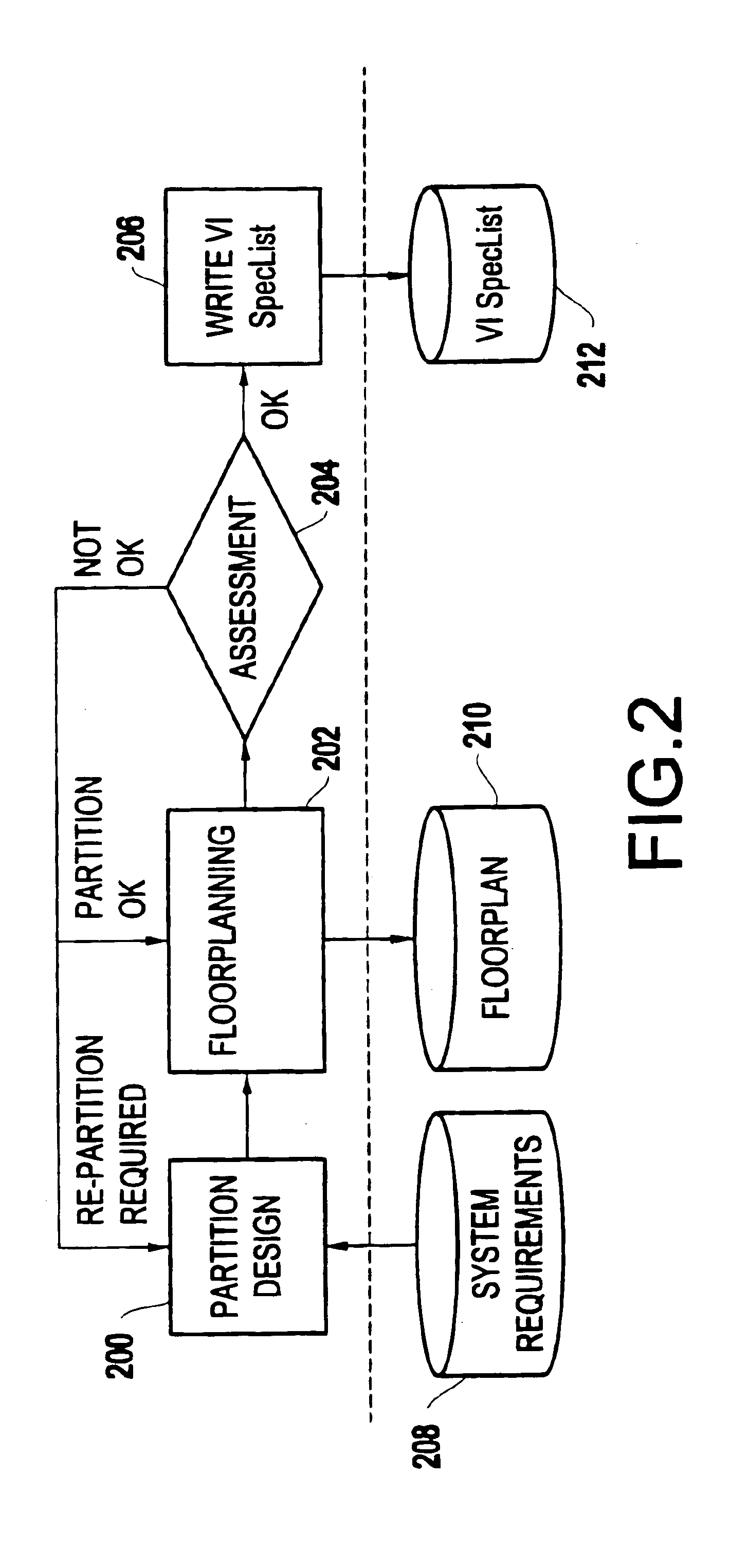

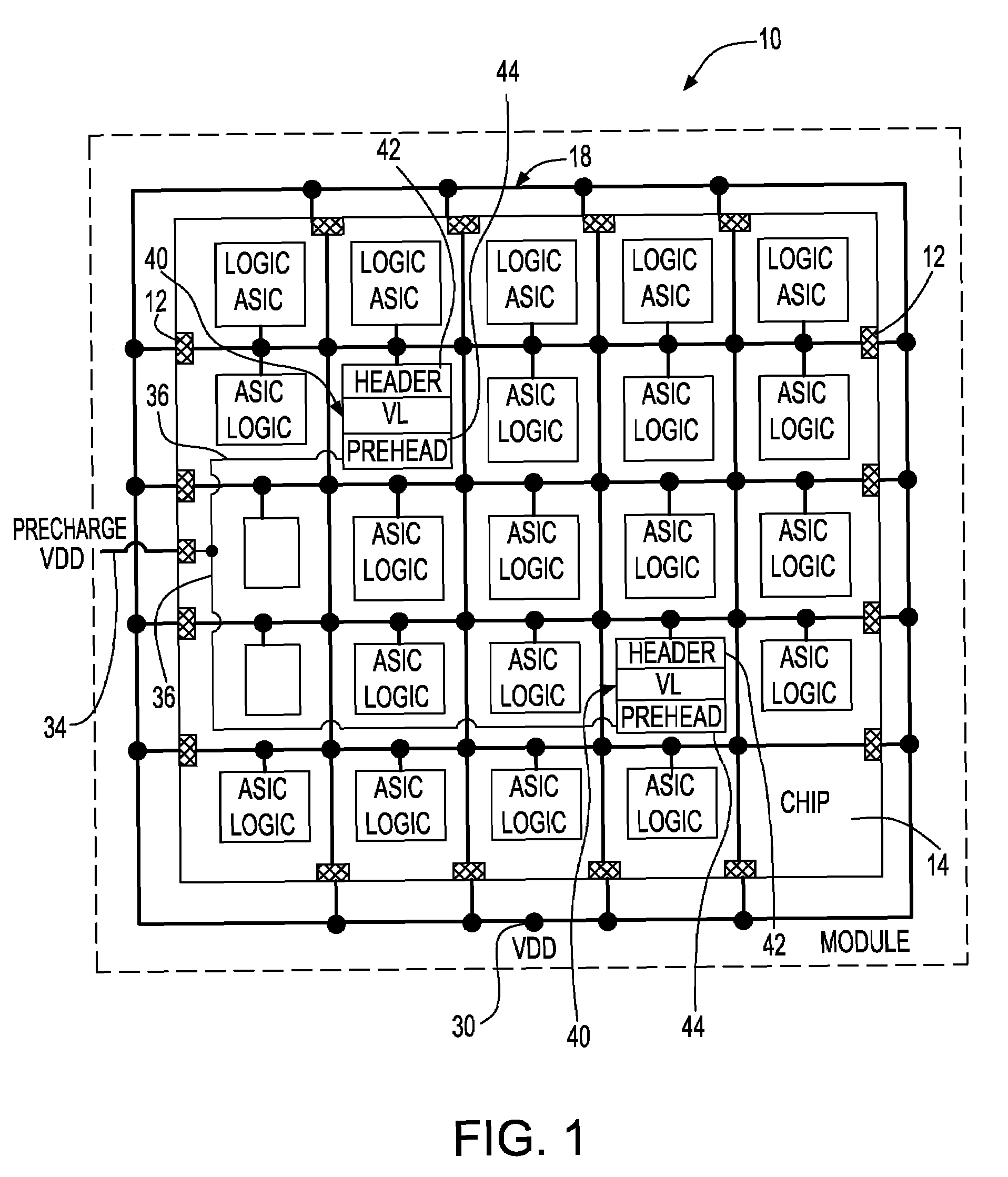

Voltage island chip implementation

InactiveUS6883152B2CAD circuit designSoftware simulation/interpretation/emulationEngineeringIntegrated circuit

A method and structure for designing an integrated circuit chip supplies a chip design and partitions elements of the chip design according to similarities in voltage requirements and timing of power states of the elements to create voltage islands. The invention outputs a voltage island specification list comprising power and timing information of each voltage island; and automatically, and without user intervention, synthesizes power supply networks for the voltage islands.

Owner:GLOBALFOUNDRIES INC

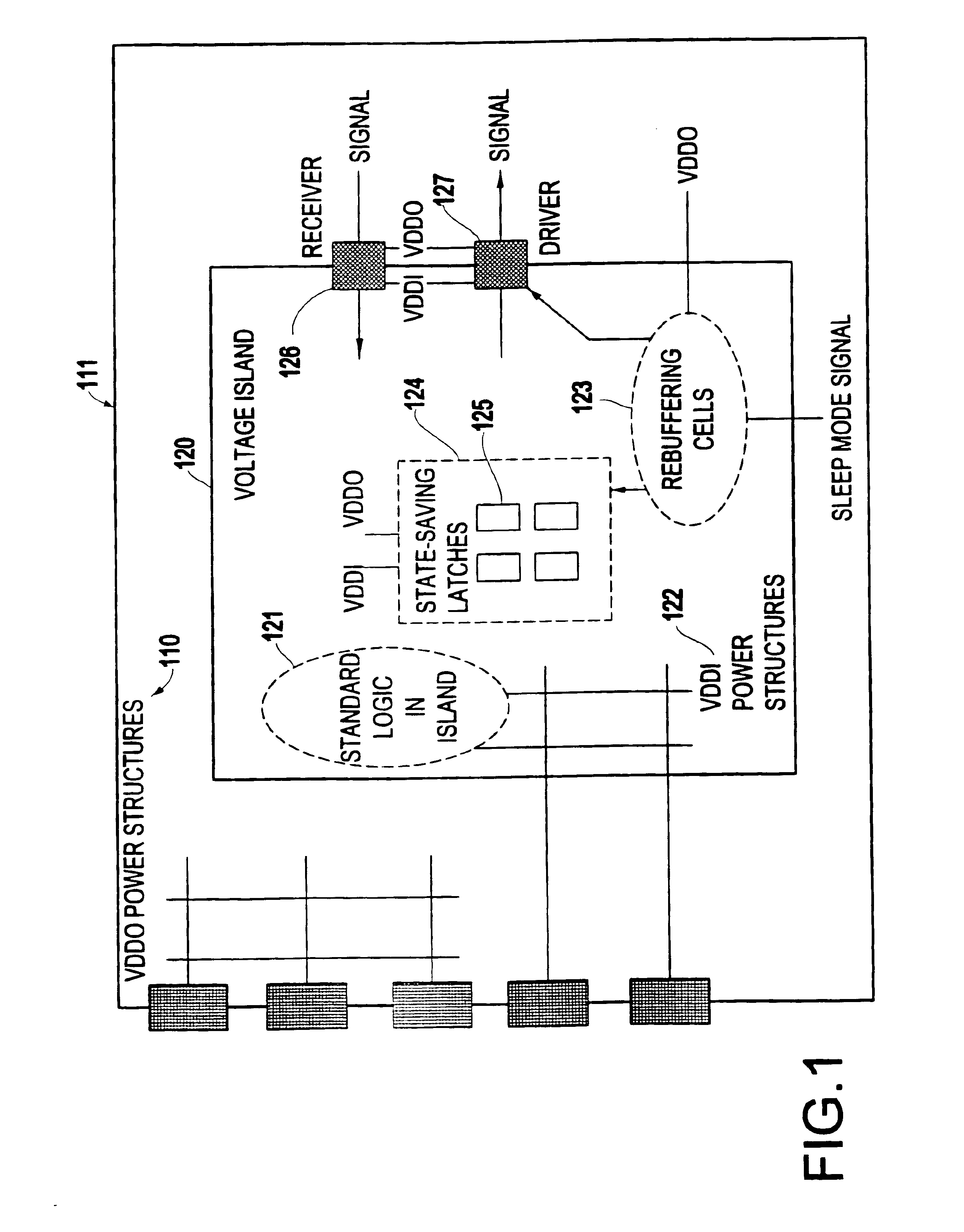

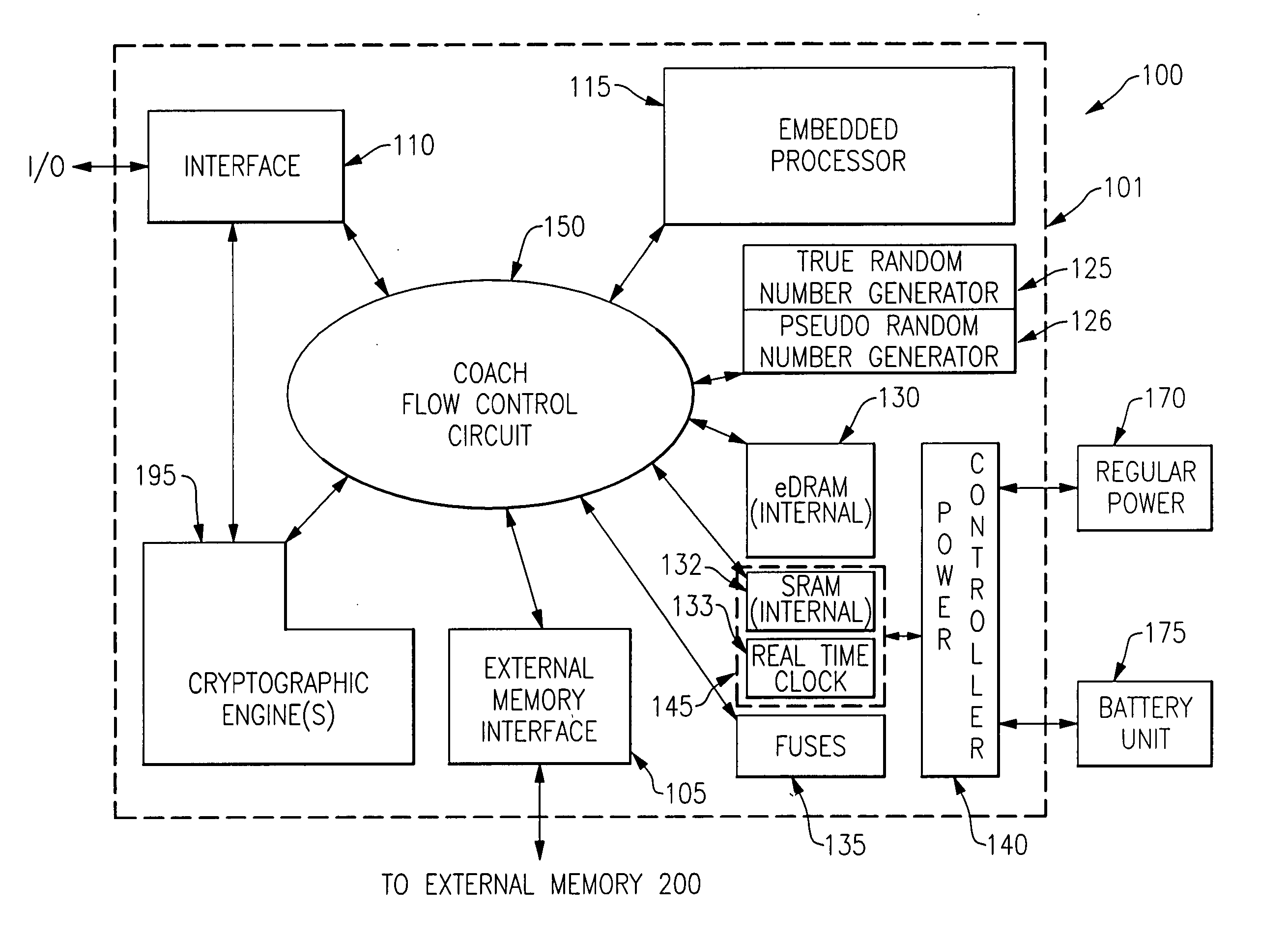

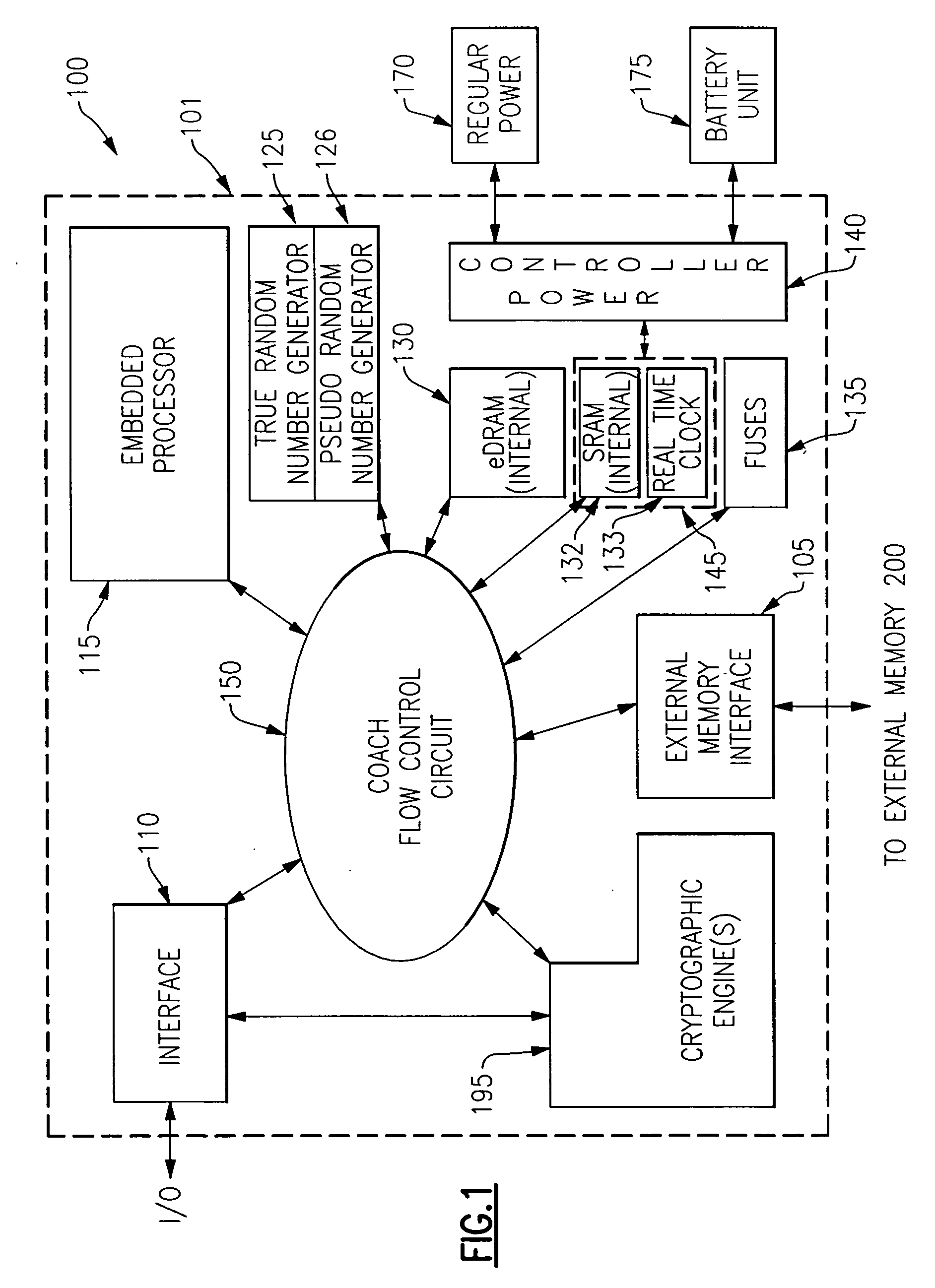

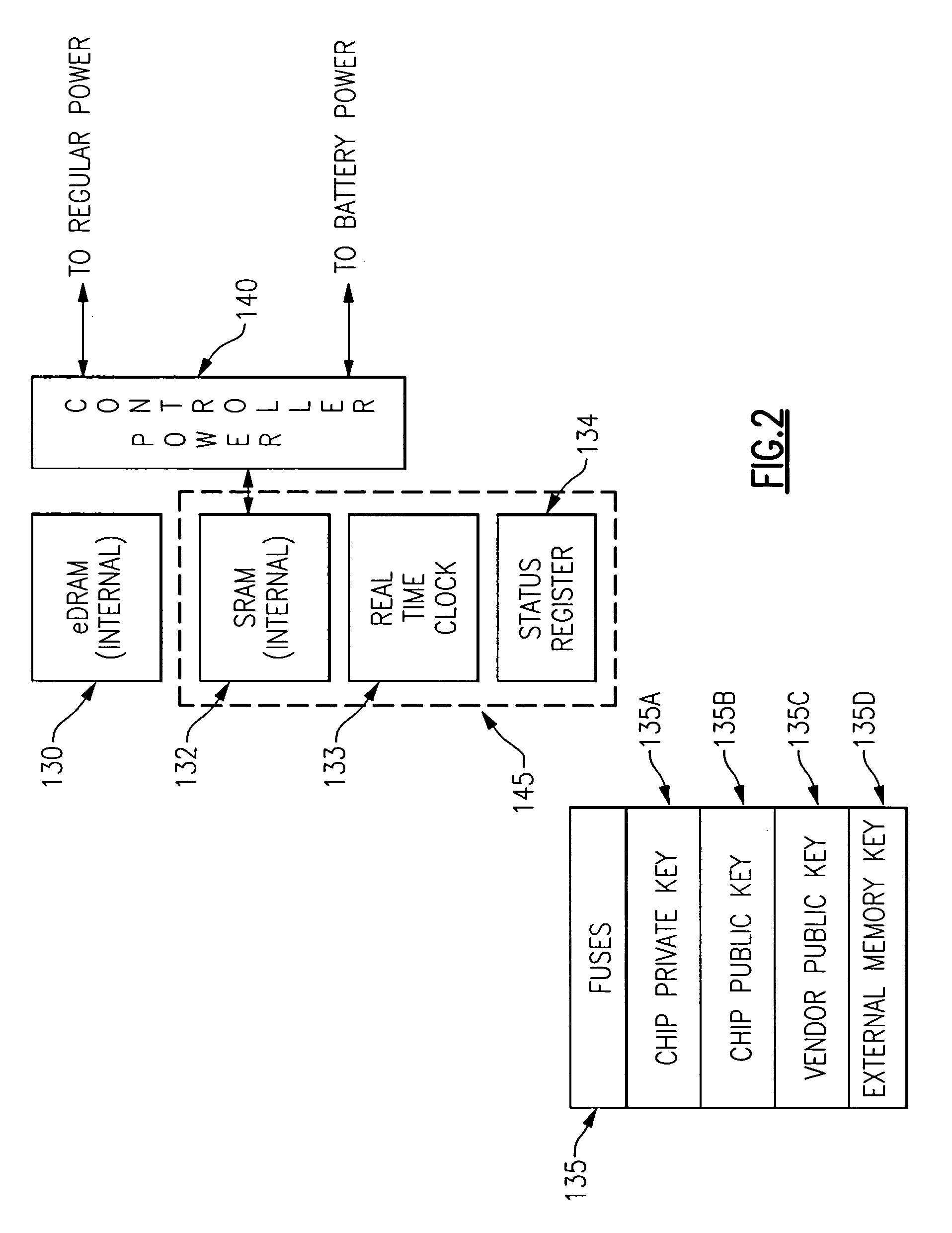

Integrated circuit chip for encryption and decryption having a secure mechanism for programming on-chip hardware

InactiveUS20060059372A1Improve process capabilityInhibit involvementUnauthorized memory use protectionHardware monitoringHard codingChip architecture

An integrated circuit chip is provided which contains one or more processors and one or more cryptographic engines. A flow control circuit having a command processor accepts requests and data via a secure external interface through which only encrypted information is passed. The flow control circuit mediates decryption of this information using cryptographic keys that are present in hard coded form on the chip. In particular the flow control circuit includes a programmable hardware portion which is configurable in a secure manner to create a flexible internal chip architecture. The chip also includes a volatile memory disposed on a voltage island on which is maintained either through a battery backup or from a fixed power source (mains). The chip is thus enabled to securely perform cryptographic operations with the processors controlling the cryptographic engines through the flow control circuit.

Owner:IBM CORP

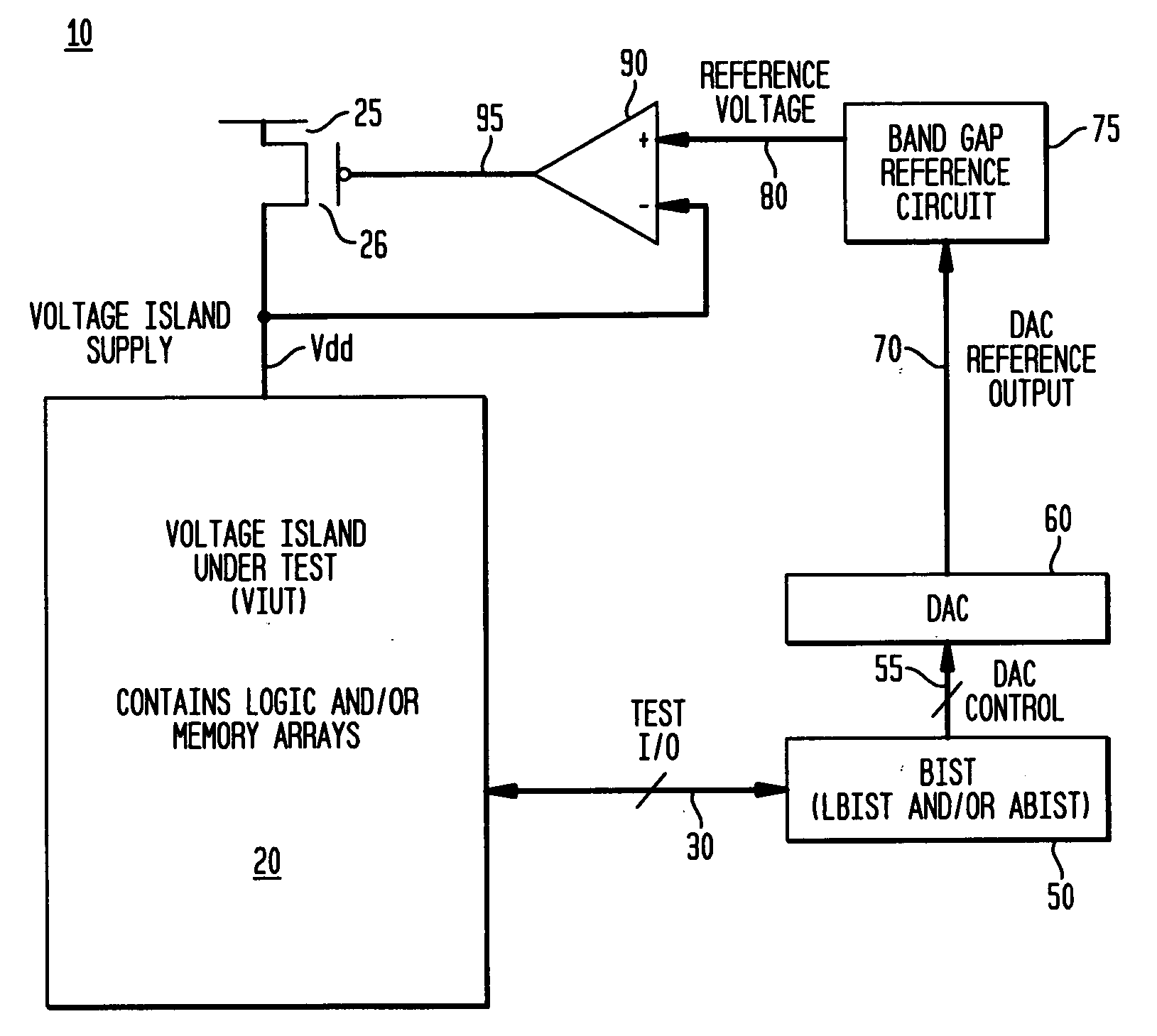

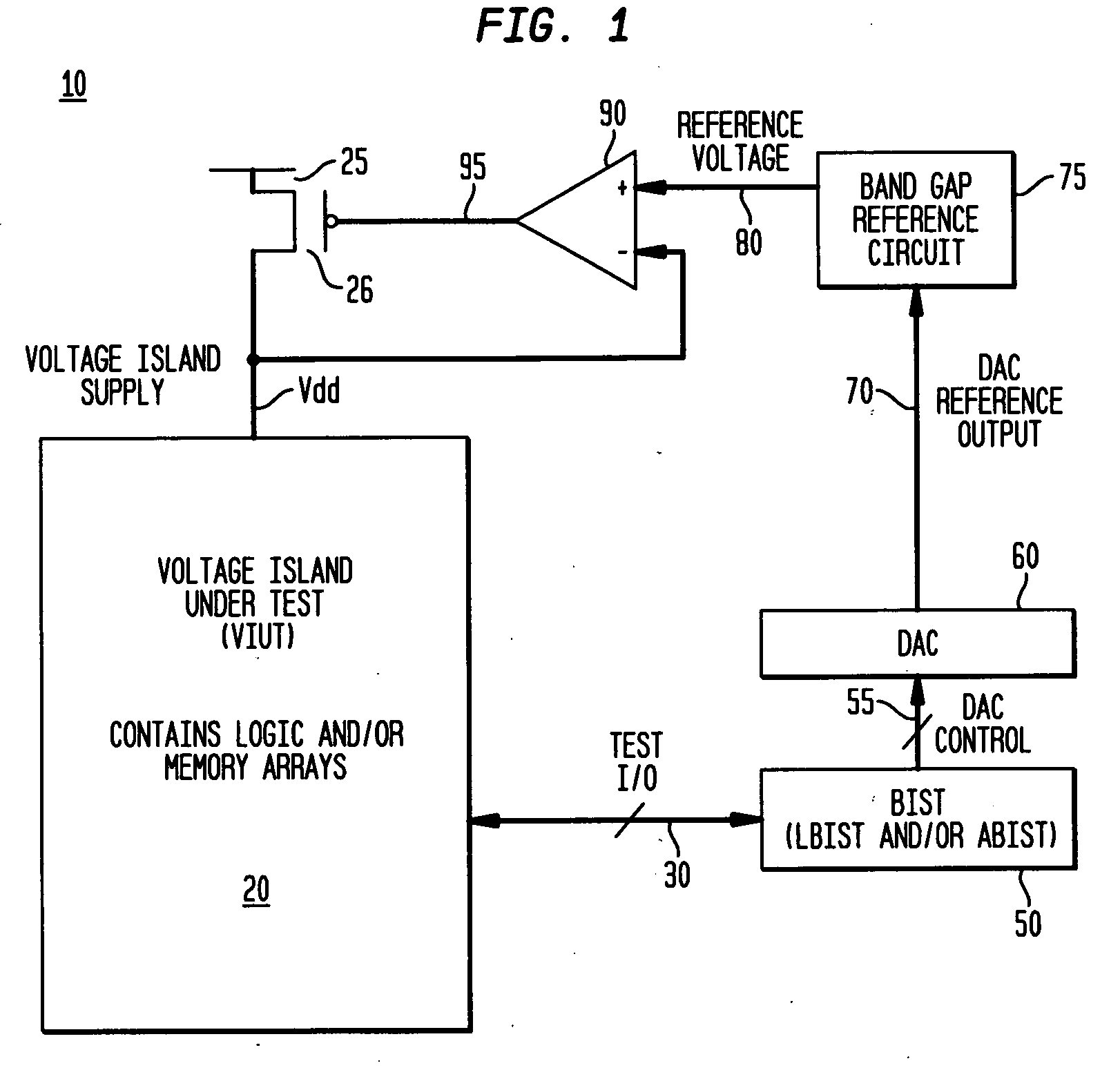

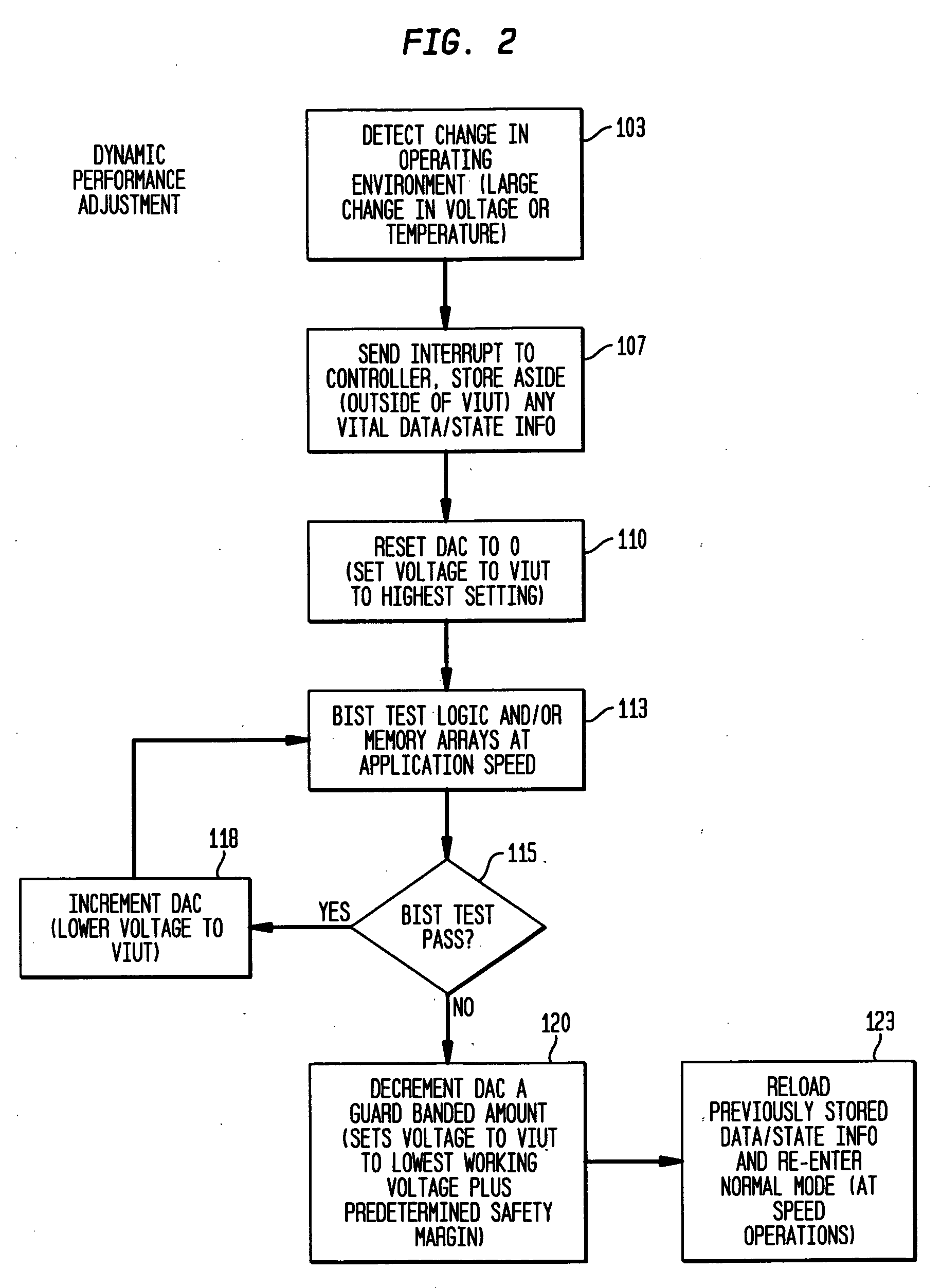

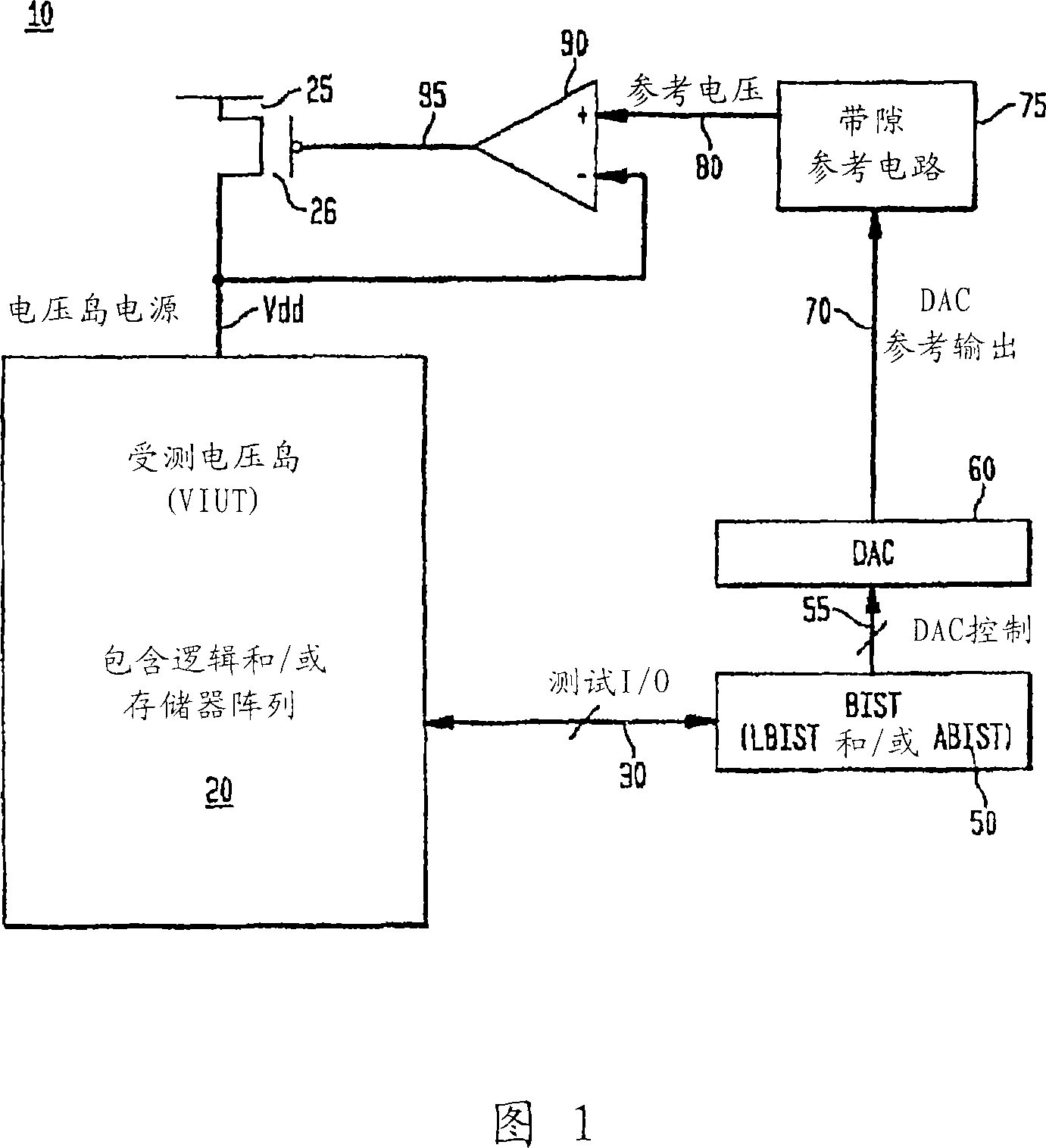

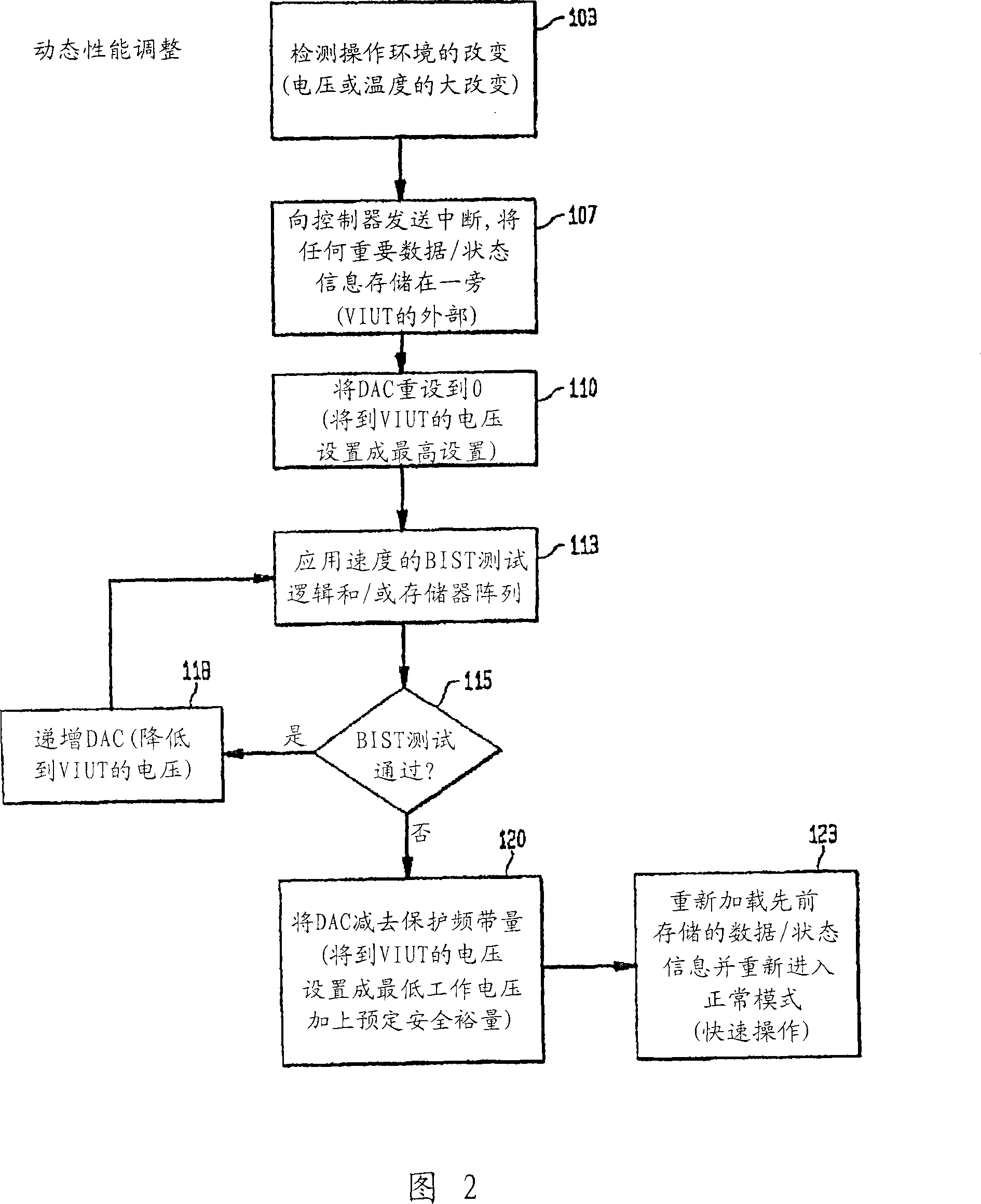

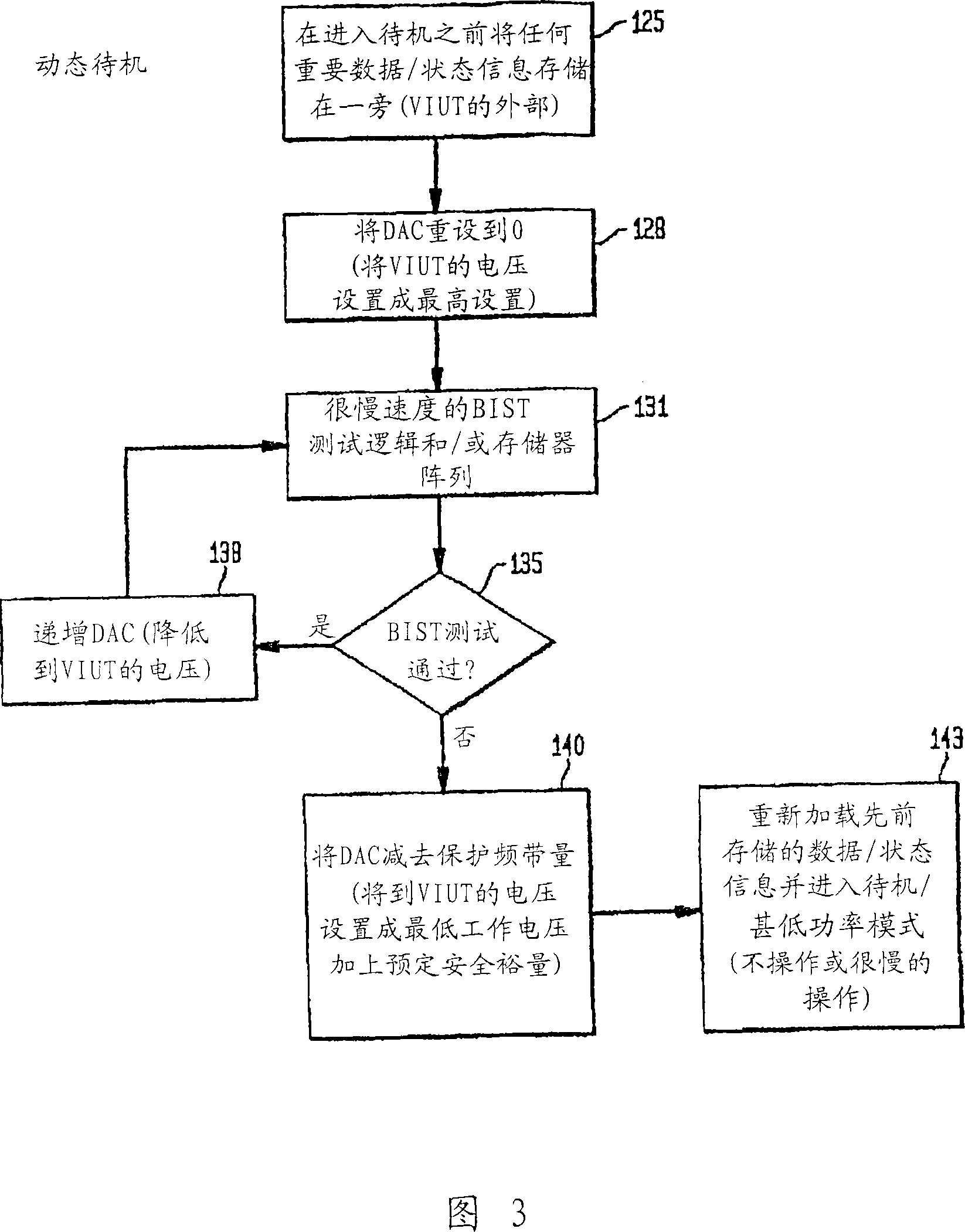

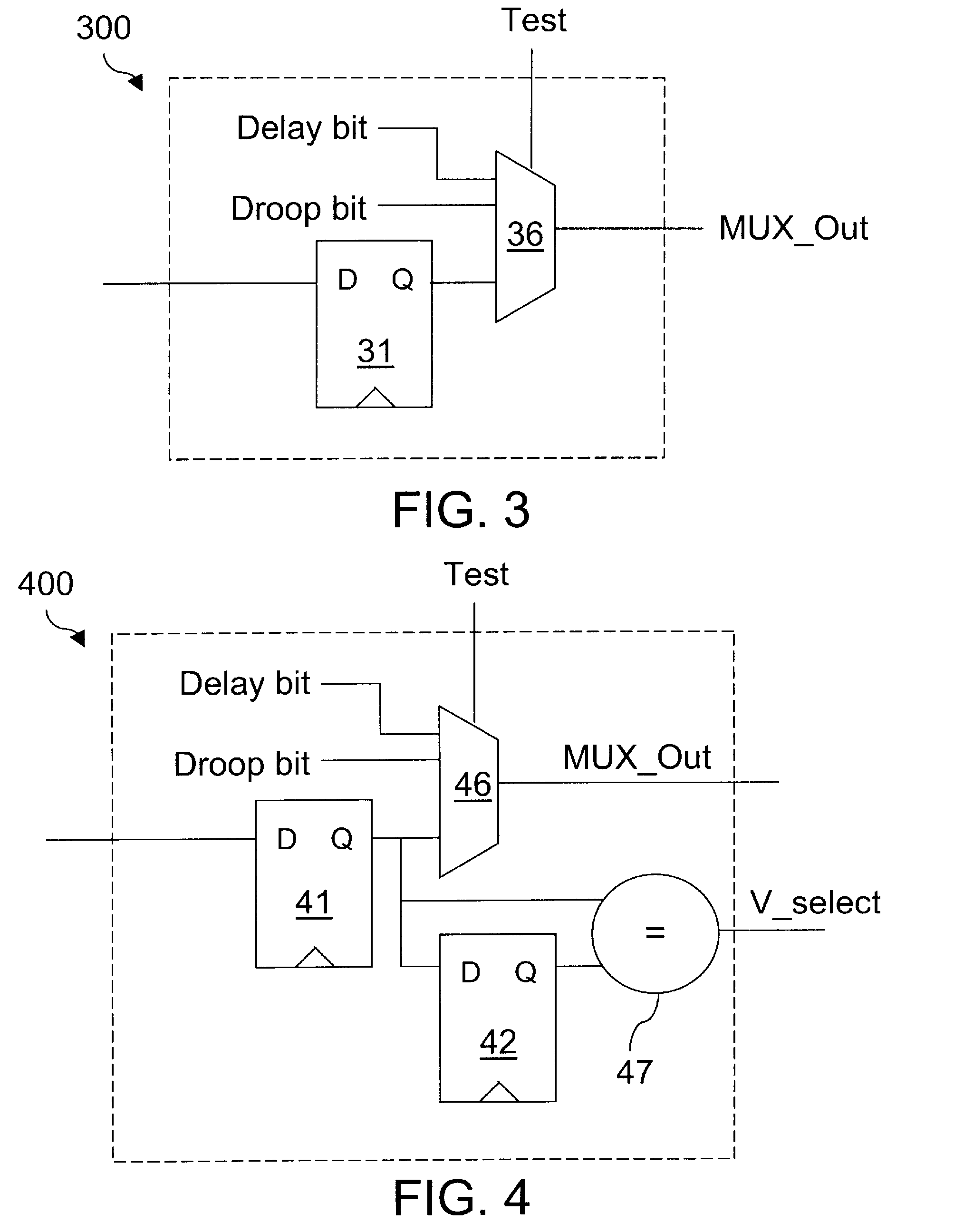

Self-test circuitry to determine minimum operating voltage

InactiveUS20060259840A1Reduce power consumptionMaintaining at-application speed performanceMarginal circuit testingTest flowVoltage source

A solution for determining minimum operating voltages due to performance / power requirements would be valid for a wide range of actual uses. The solution includes a test flow methodology for dynamically reducing power consumption under applied conditions while maintaining application performance via a BIST circuit. There is additionally provided a test flow method for dynamically reducing power consumption to the lowest possible stand-by / very low power level under applied conditions that will still be sufficient to maintain data / state information. One possible application would be for controlling the voltage supply to a group of particular circuits on an ASIC (Application Specific Integrated Circuit). These circuits are grouped together in a voltage island where they would receive a voltage supply that can be different from the voltage supply other circuits on the same chip are receiving. The same solution could be applied to a portion of a microprocessor (the cache logic control, for example).

Owner:IBM CORP

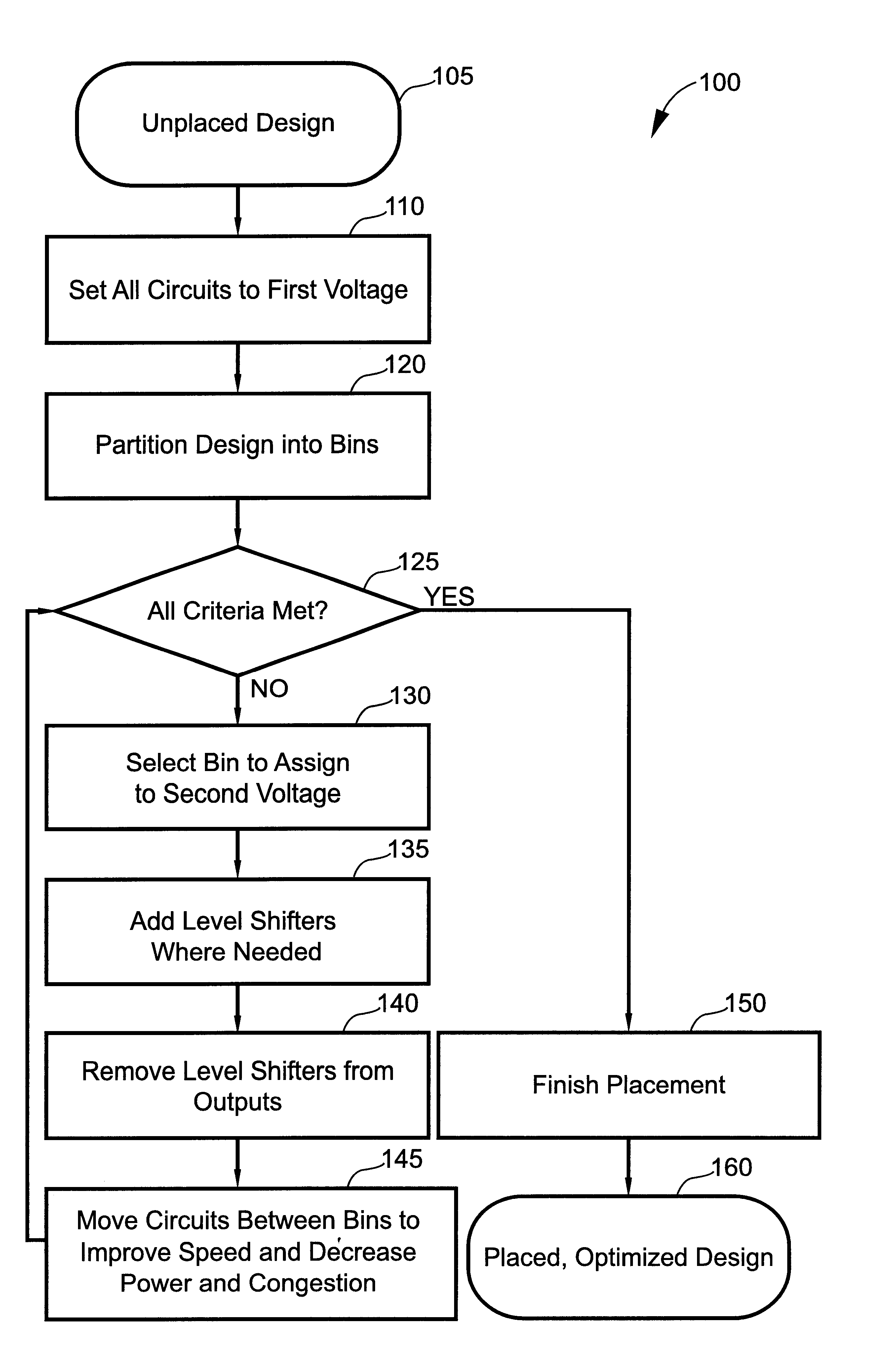

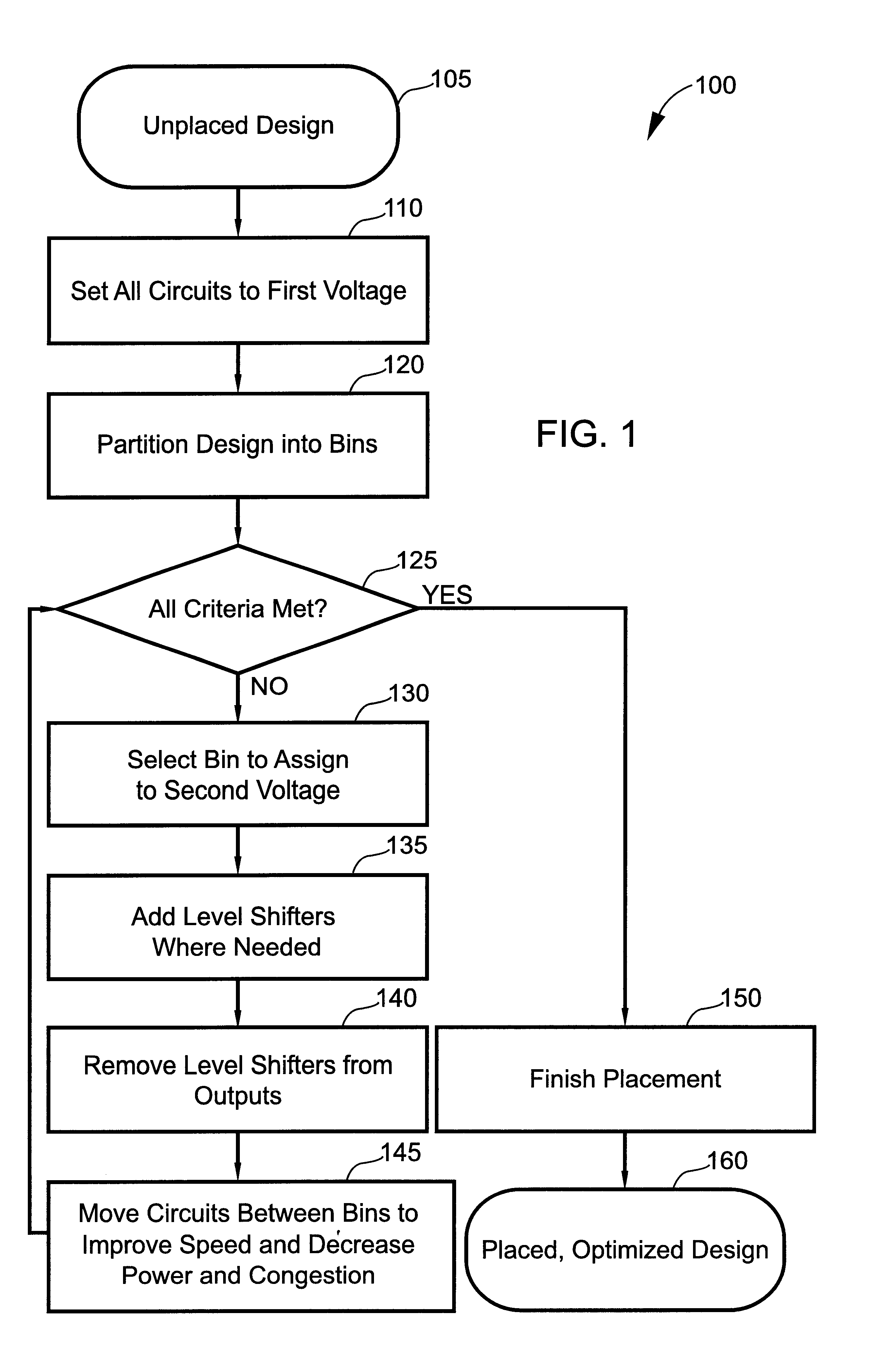

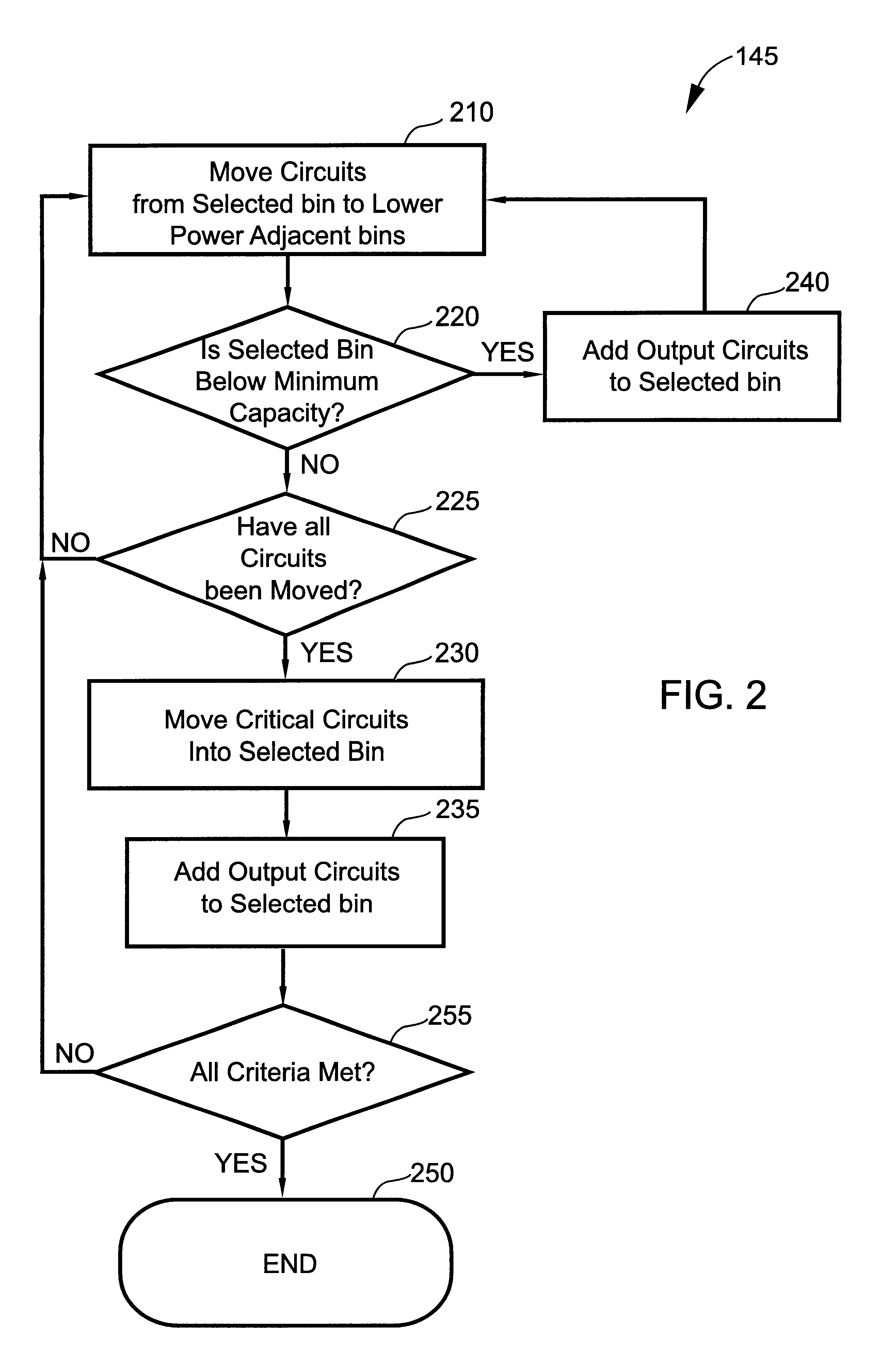

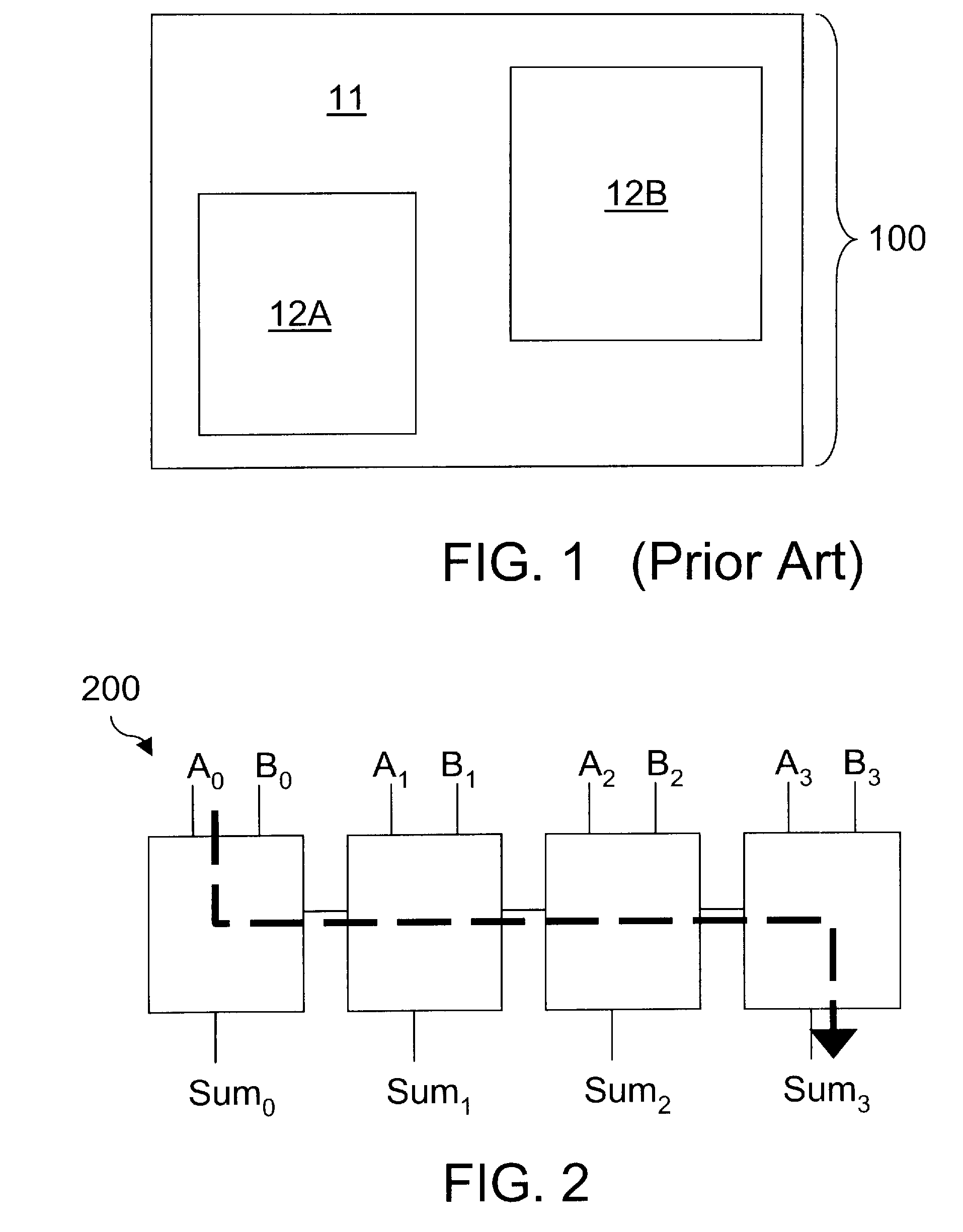

Concurrent logical and physical construction of voltage islands for mixed supply voltage designs

InactiveUS6792582B1Minimize the numberReduce distribution costsSemiconductor/solid-state device manufacturingCAD circuit designLow voltageSemiconductor chip

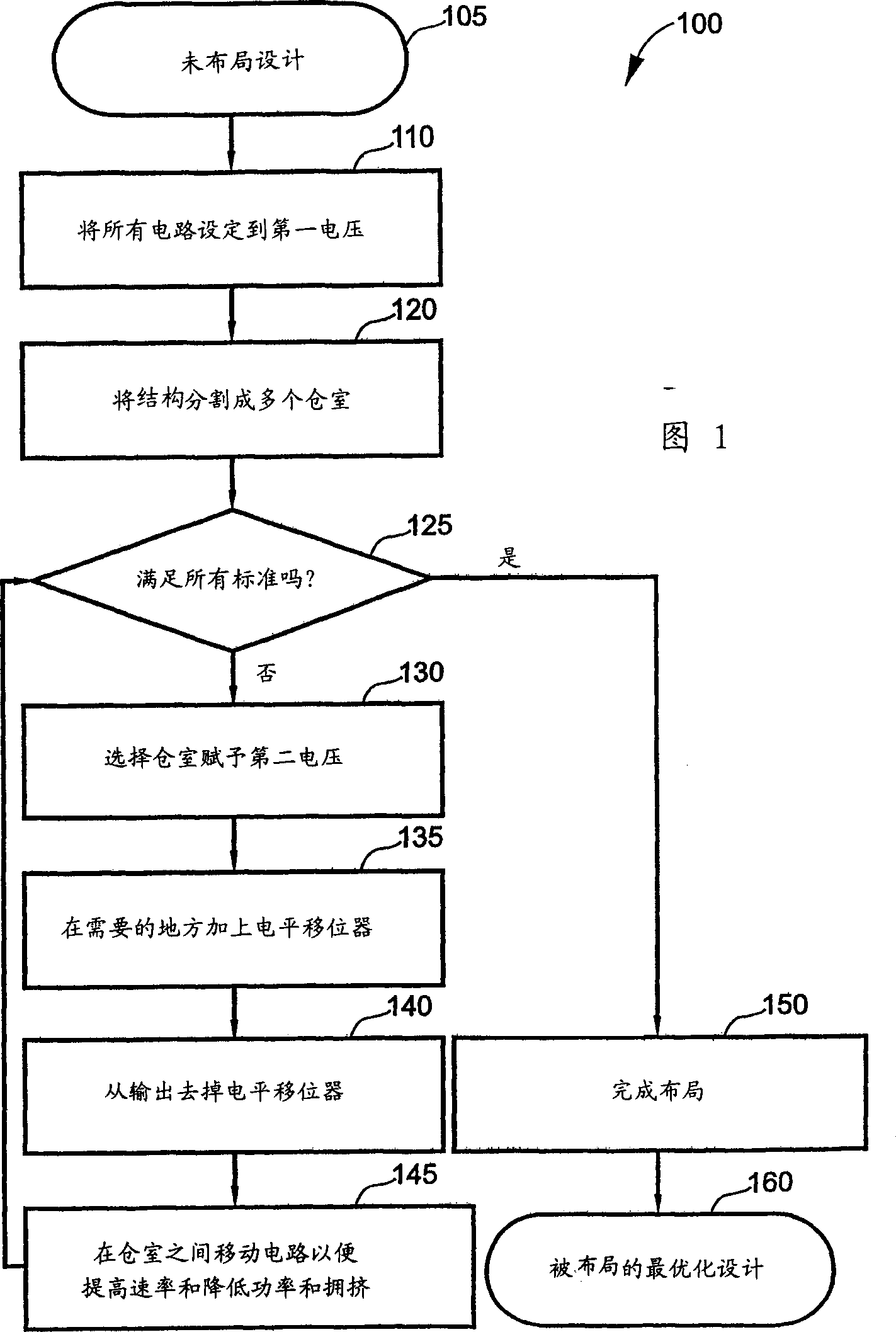

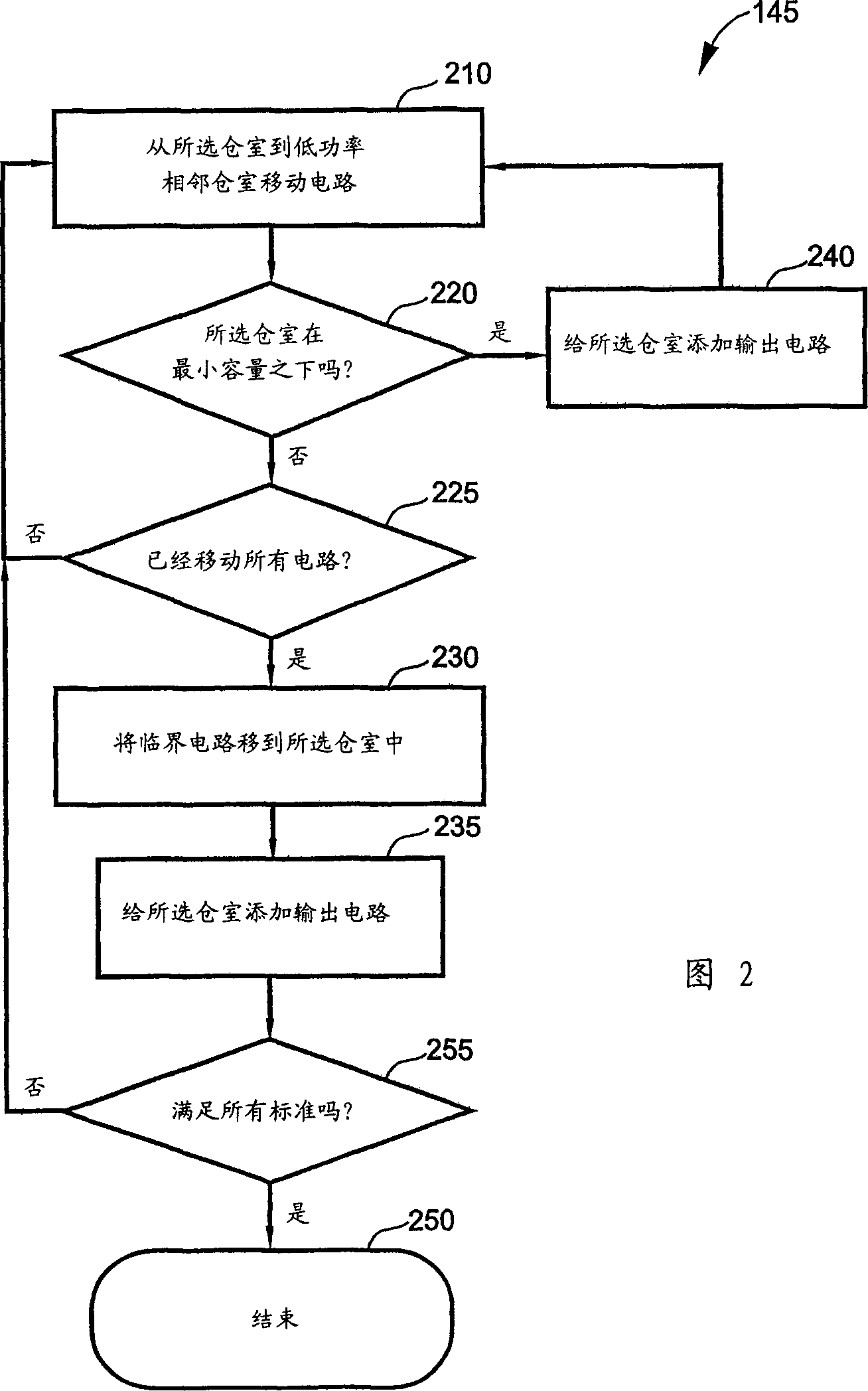

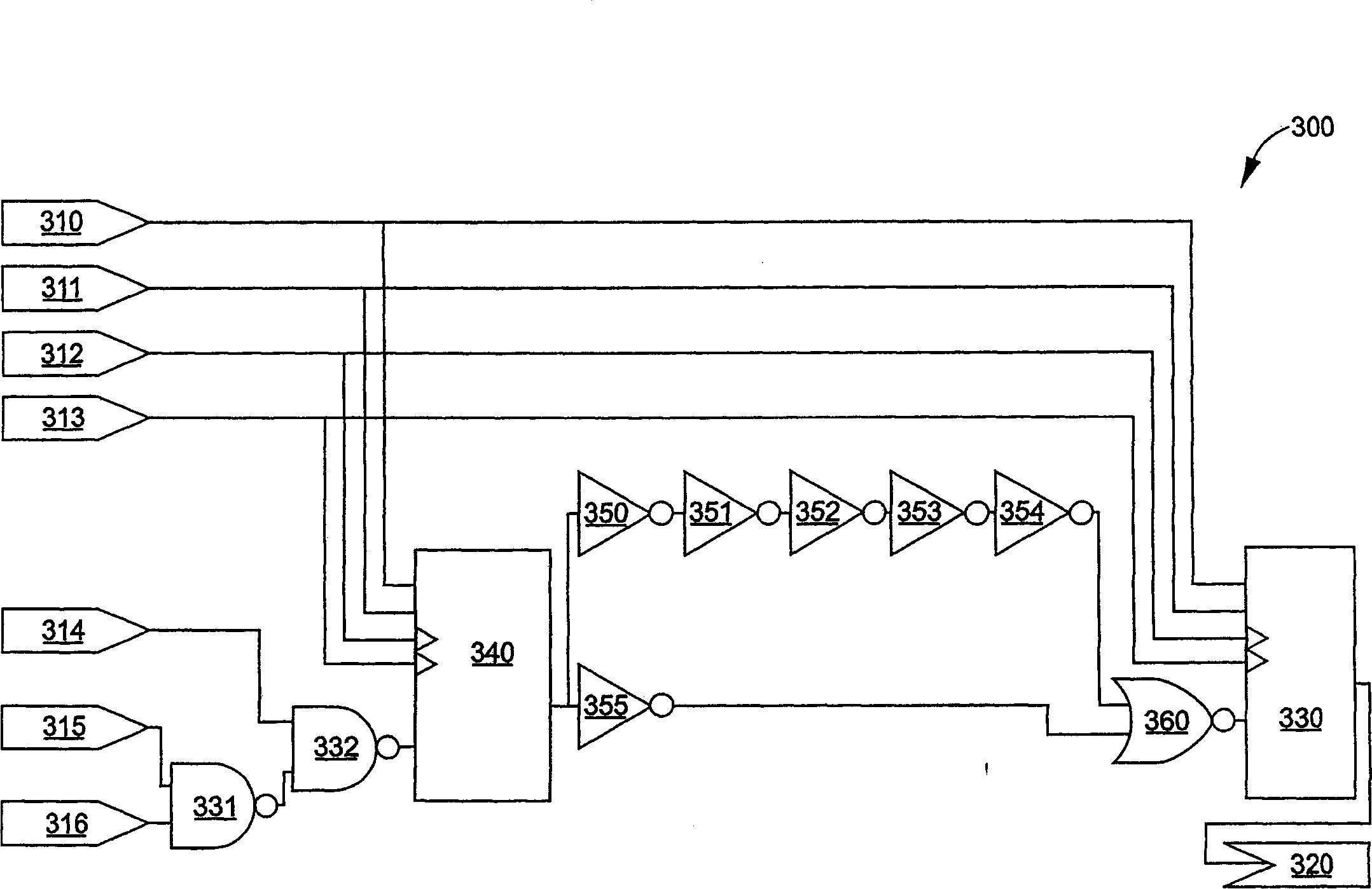

Both logical and physical construction of voltage islands is disclosed. A semiconductor chip design is partitioned into "bins", which are areas of the design. In this way, a semiconductor chip design may be "sliced" into various areas and the areas may then be assigned to various voltage levels. Each bin may be thought of as a voltage island. Circuits in the design can be added to or removed from the various bins, thereby increasing or decreasing the speed and power of the circuits: the speed and power increase if a circuit is placed into a bin assigned a higher voltage, and the speed and power decrease if a circuit is placed into a bin having a lower voltage. The size and location of the bins may also be changed. By iterating these steps, the optimum power consumption may be met while still meeting speed constraints and other criteria. The present invention is applicable to any placement environment, such as an annealing placement tool, that proceeds through successive refinement of the locations of the circuits on the design and in which the placement process may be interrupted to make changes in placement of the logic.

Owner:IBM CORP

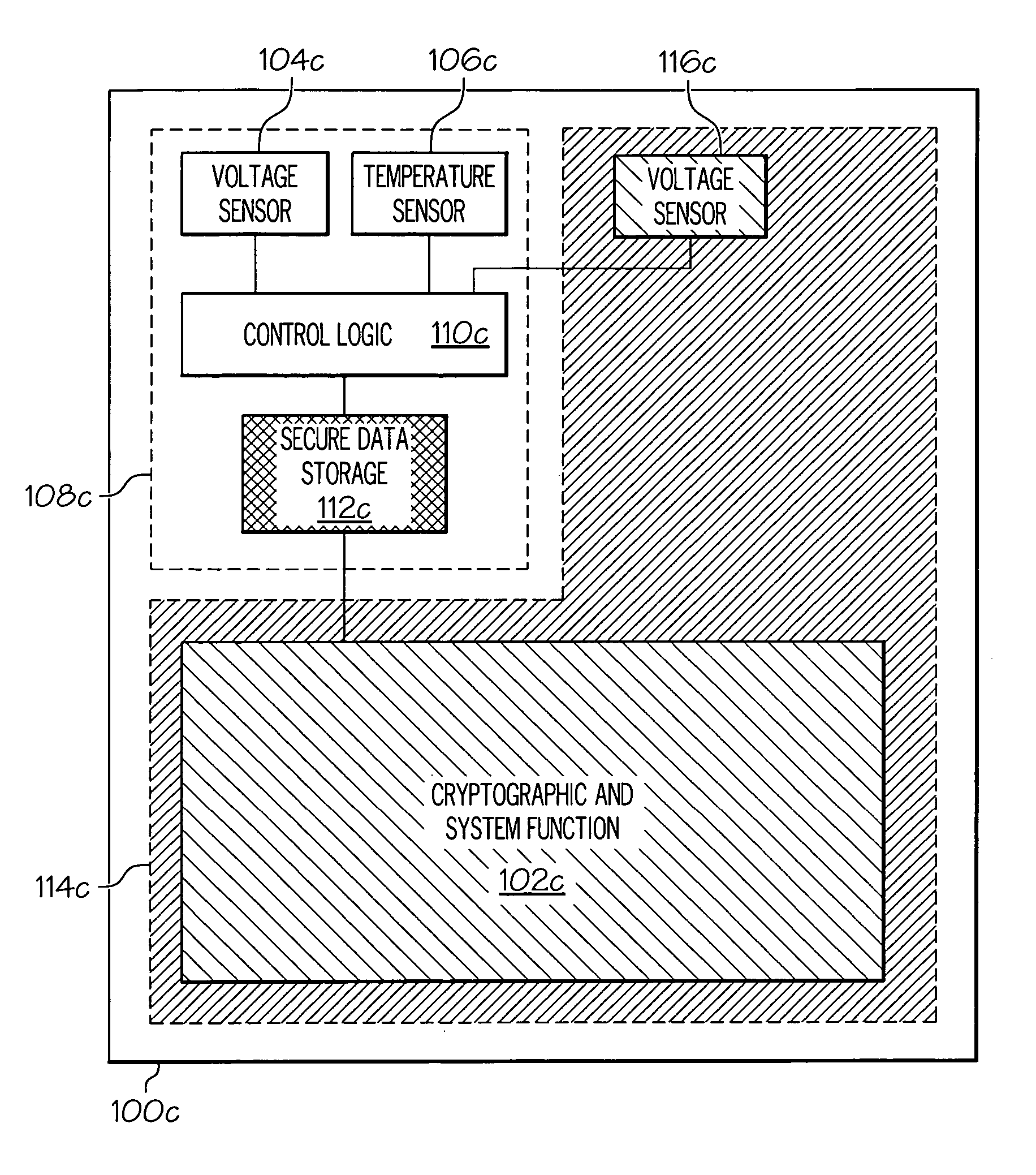

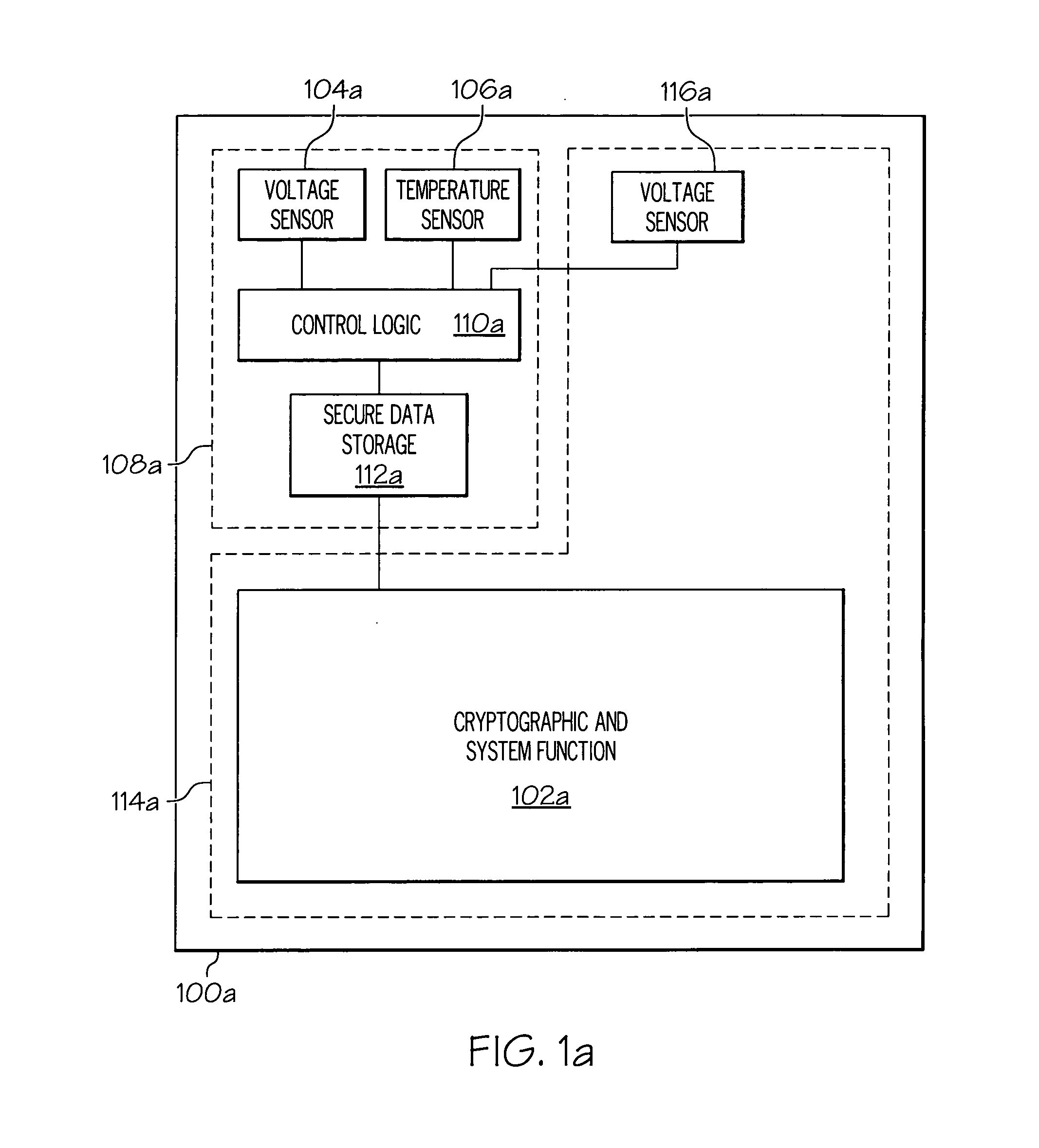

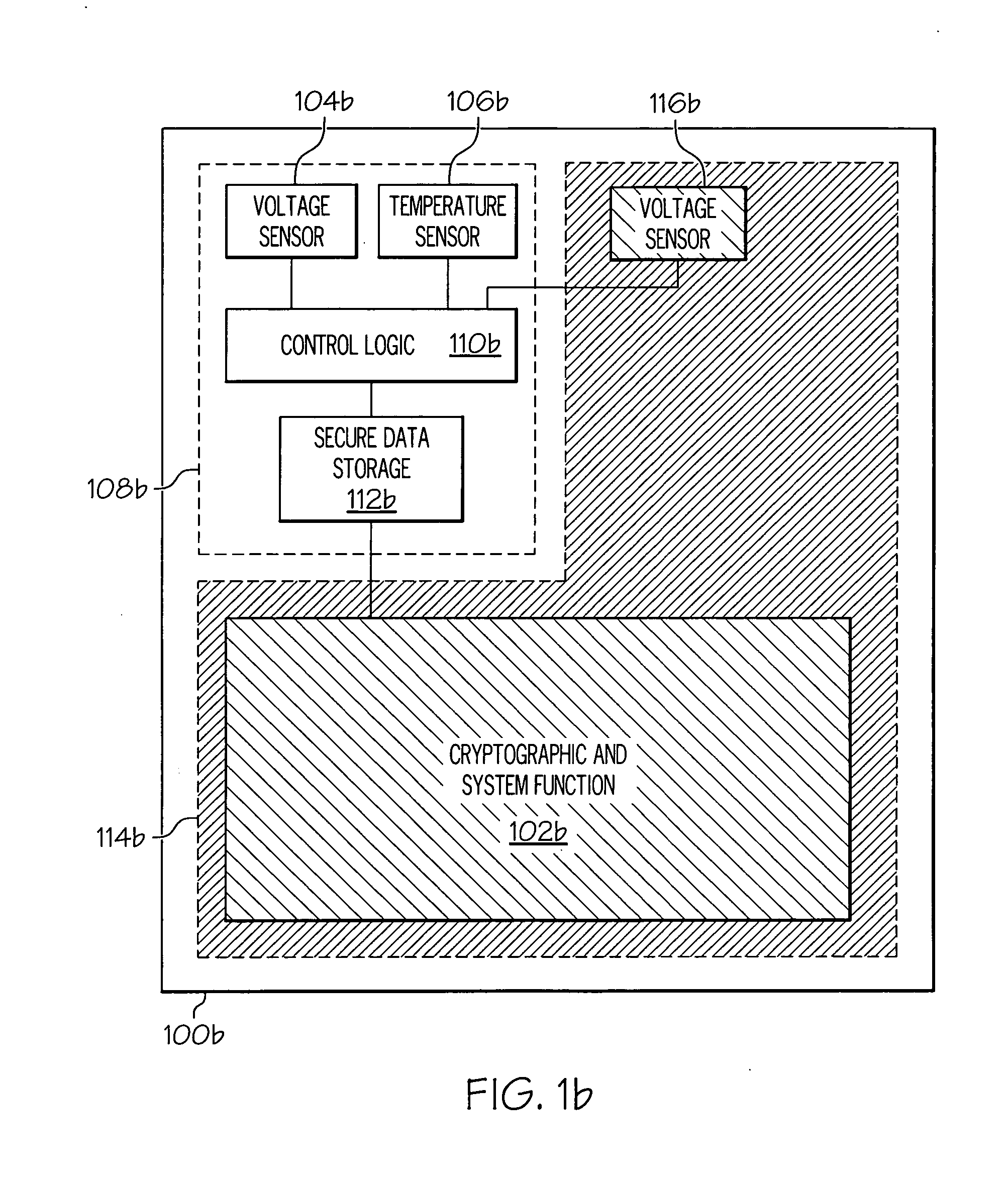

Cryptographic circuit with voltage-based tamper detection and response circuitry

InactiveUS20070255966A1Reduce power consumptionExtends the battery “shelf-life”Unauthorized memory use protectionHardware monitoringSecurity parameterKey storage

A cryptographic circuit with voltage island-based tamper detection and response is disclosed. The circuit includes a voltage island having at least one monitoring circuit and a first storage area for security parameters. The circuit also includes a second storage area for key storage and management logic to tamper the security parameters upon detection of an environmental failure.

Owner:IBM CORP

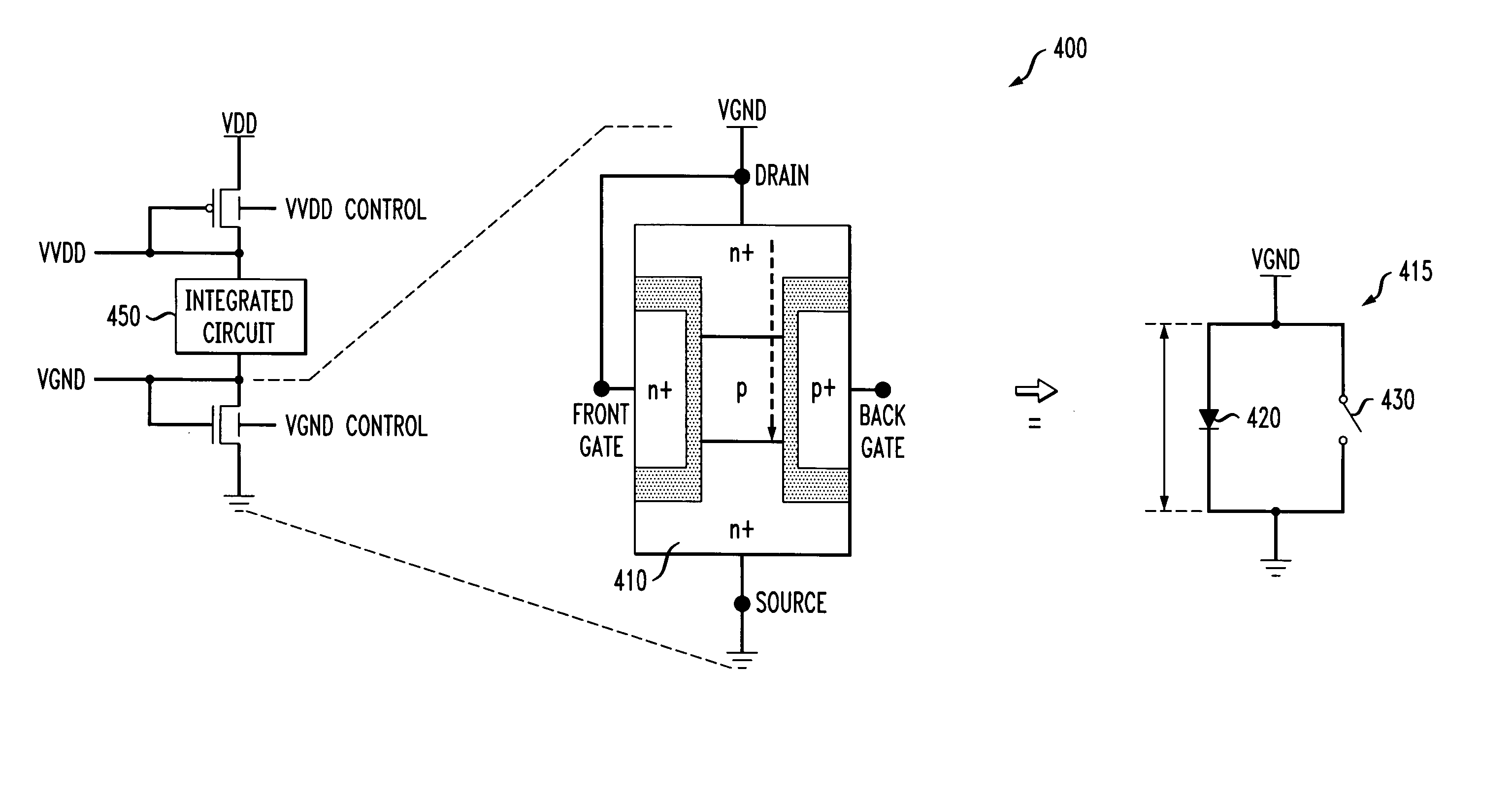

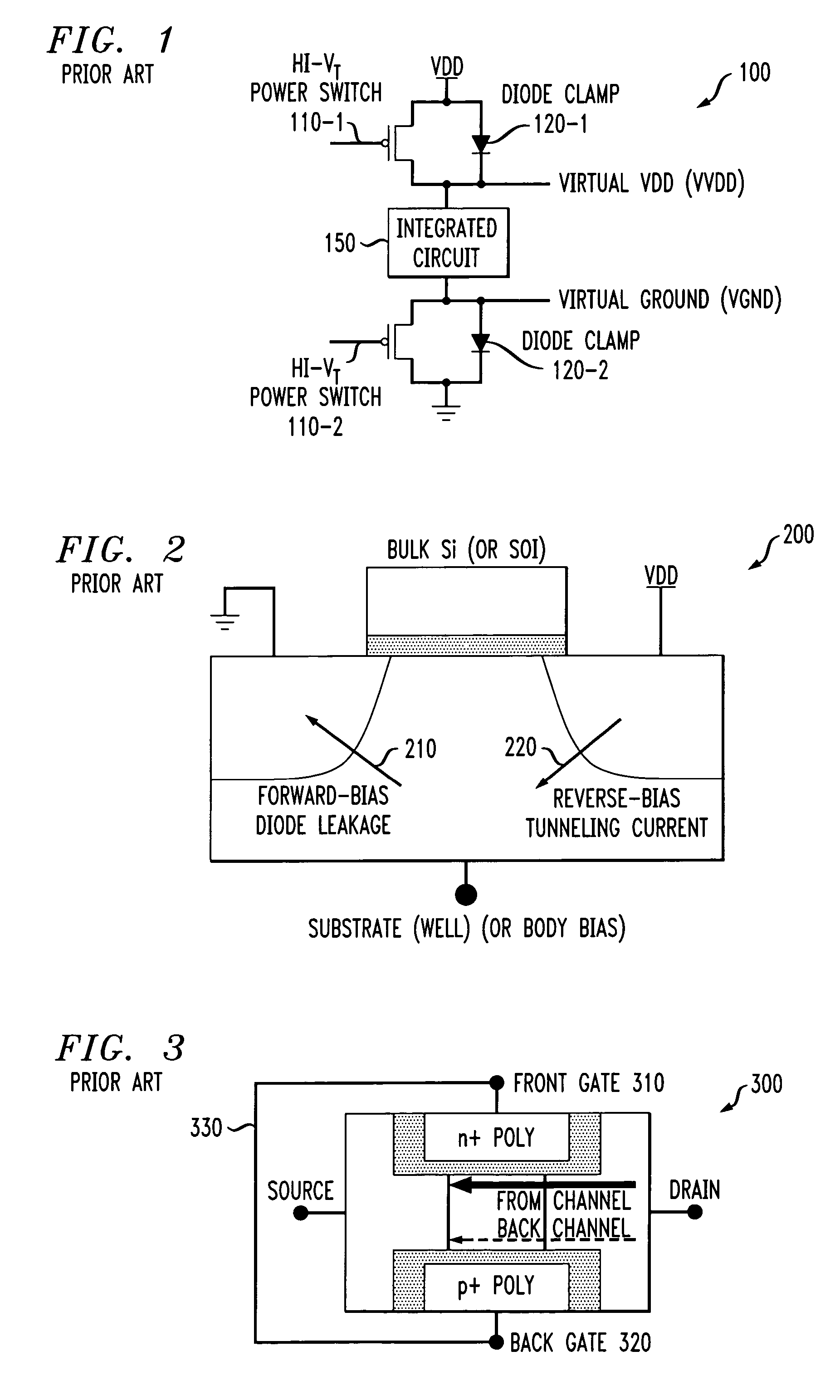

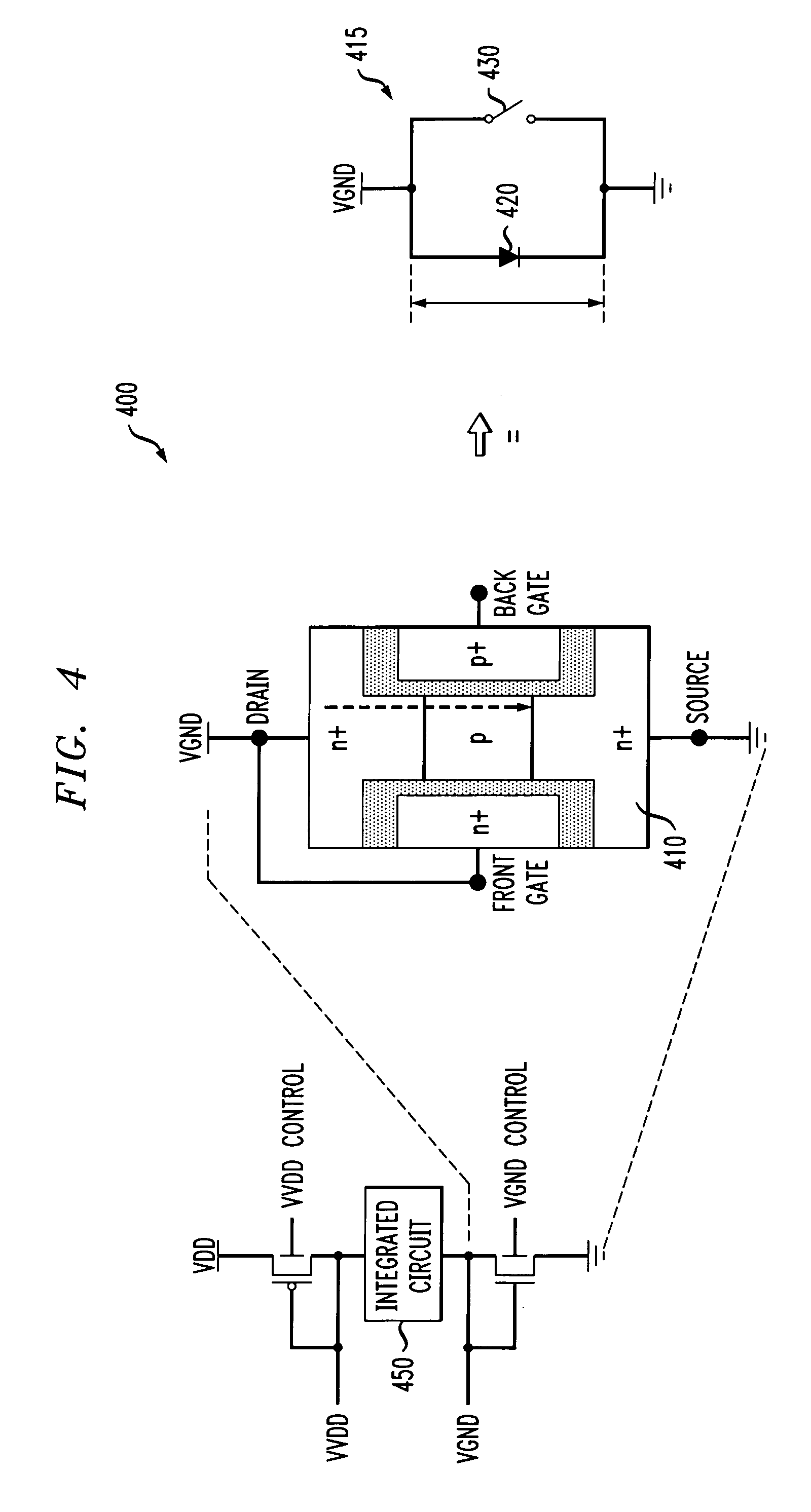

Methods and apparatus for varying a supply voltage or reference voltage using independent control of diode voltage in asymmetrical double-gate devices

Methods and apparatus are provided for varying one or more of a supply voltage and reference voltage in an integrated circuit, using independent control of a diode voltage in an asymmetrical double-gate device. An integrated circuit is provided that is controlled by one or more of a supply voltage and a reference voltage. The integrated circuit comprises an independently controlled asymmetrical double-gate device to adjust one or more of the supply voltage and the reference voltage. The independent control may comprise, for example, a back gate bias. The independently controlled asymmetrical double-gate device may be employed in a number of applications, including voltage islands, static RAM, and to improve the power and performance of a processing unit.

Owner:IBM CORP

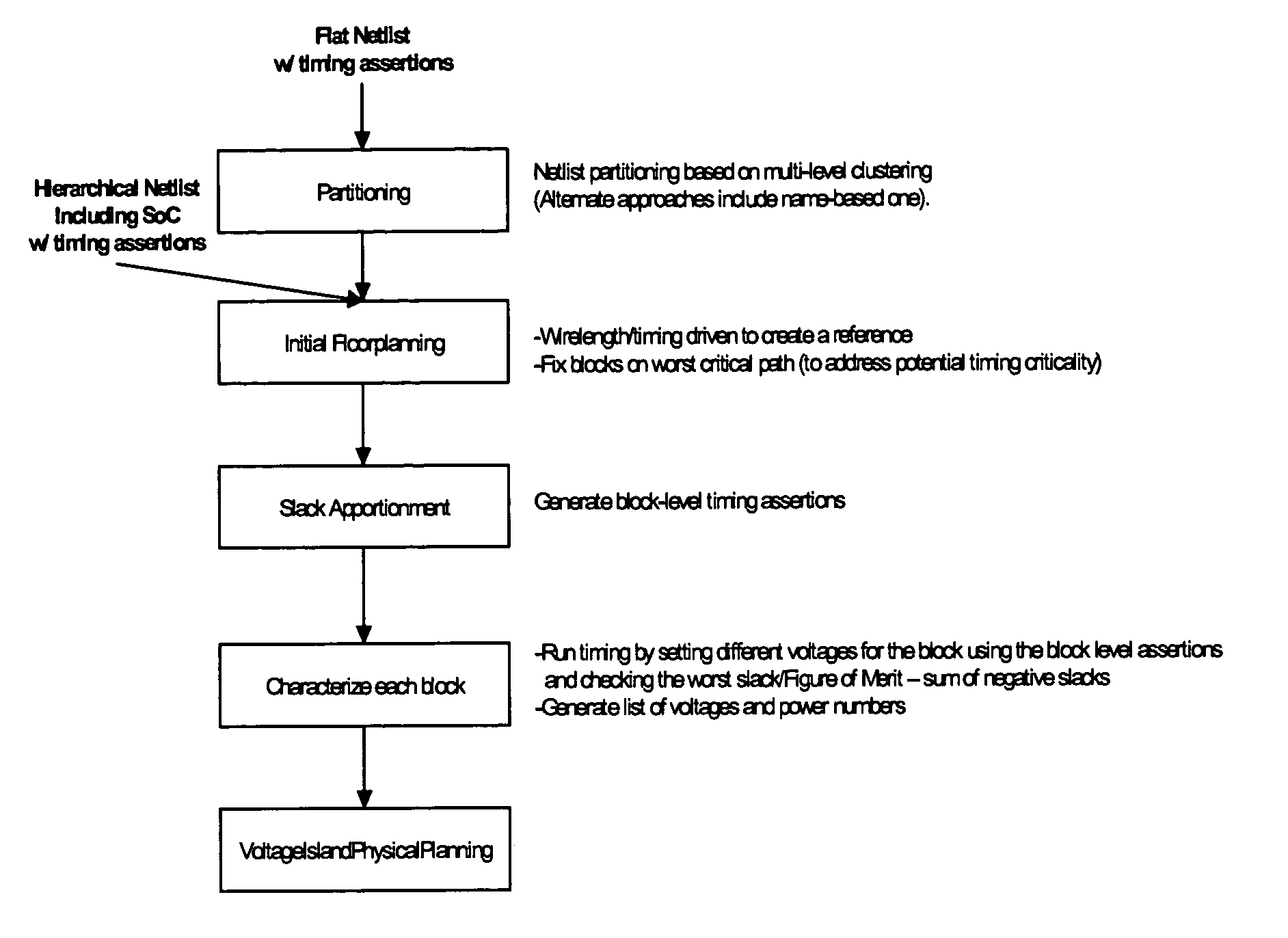

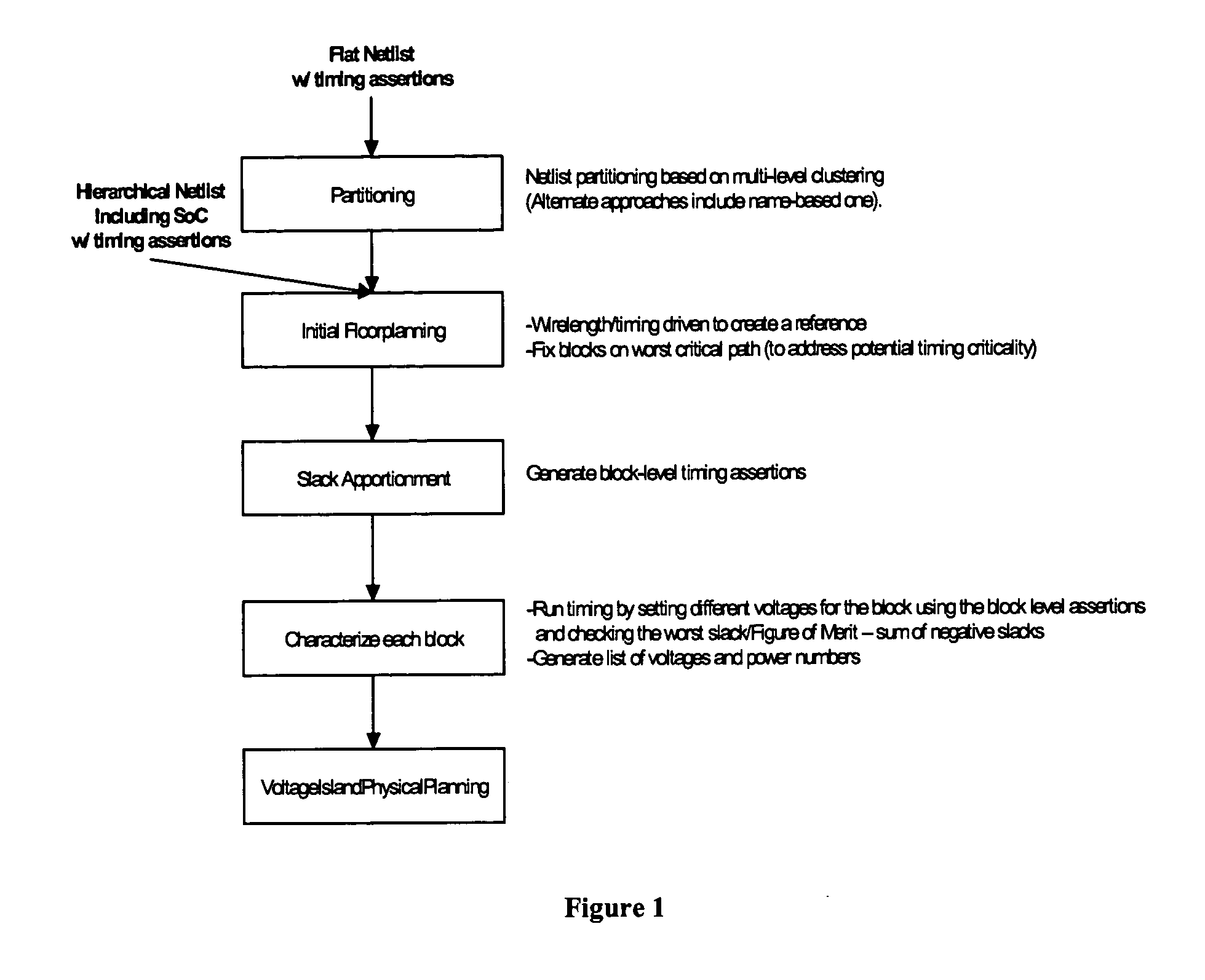

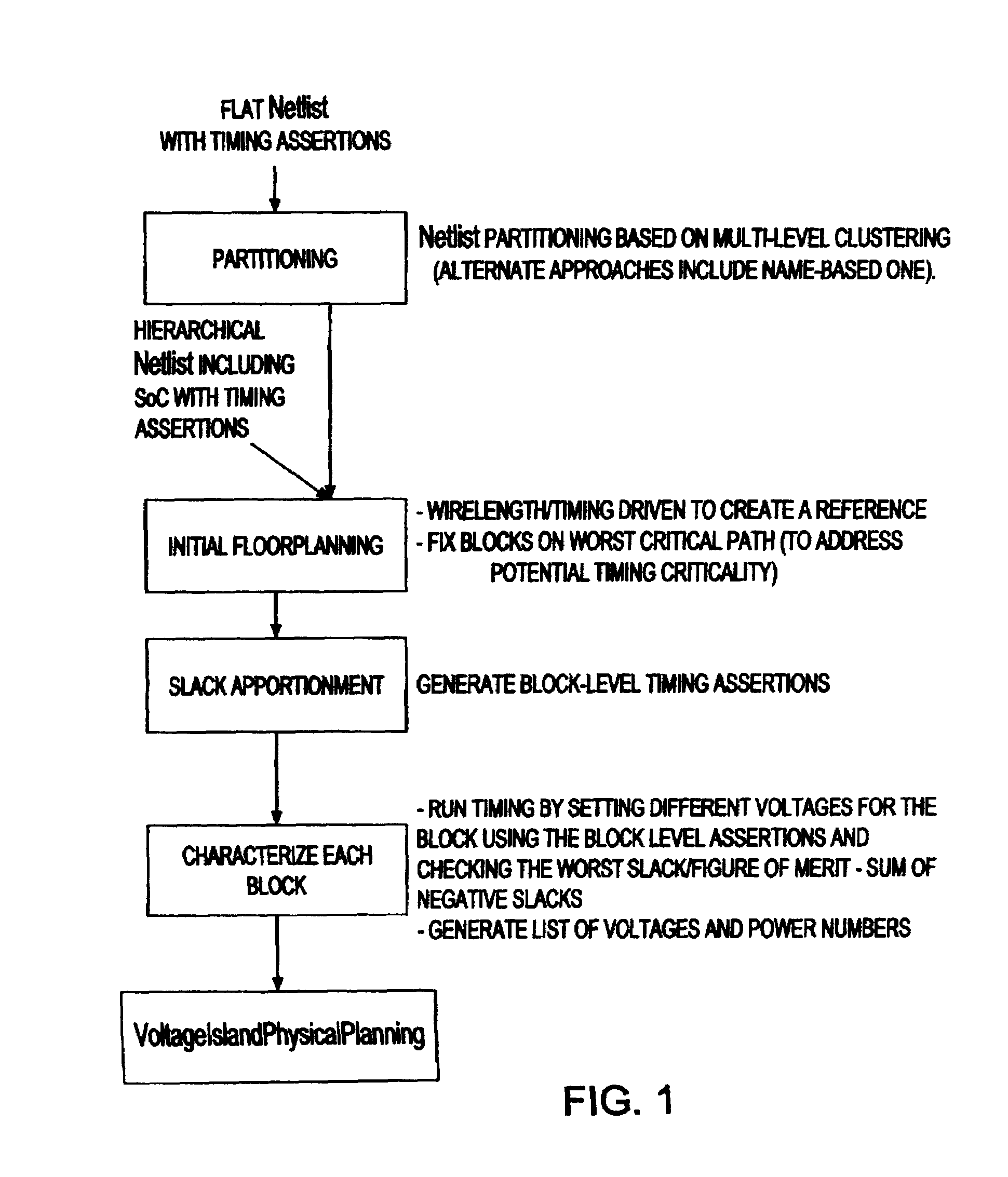

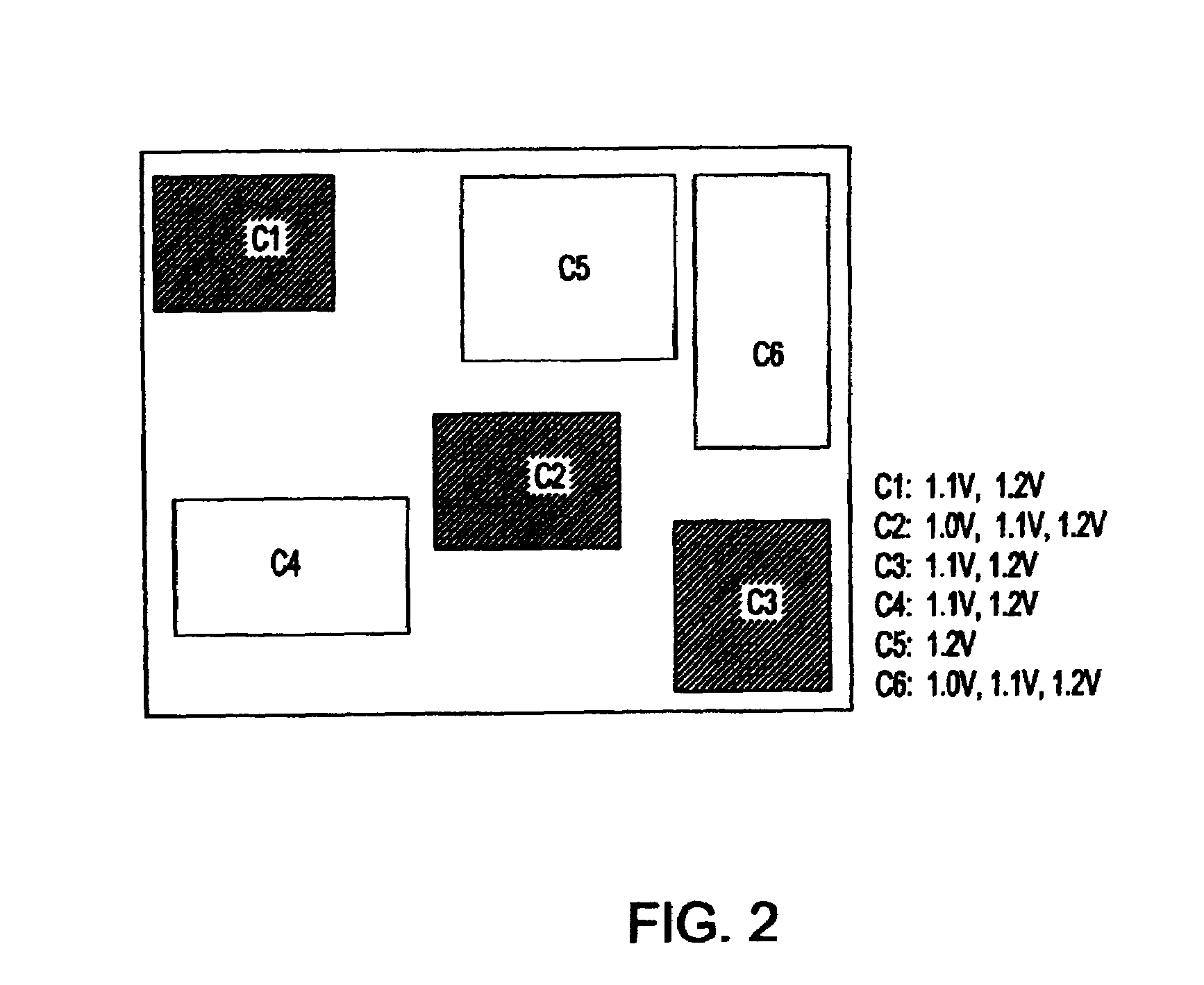

Method of physical planning voltage islands for ASICs and system-on-chip designs

InactiveUS20050278676A1Minimize power consumptionCAD circuit designSoftware simulation/interpretation/emulationPhysical planningIslanding

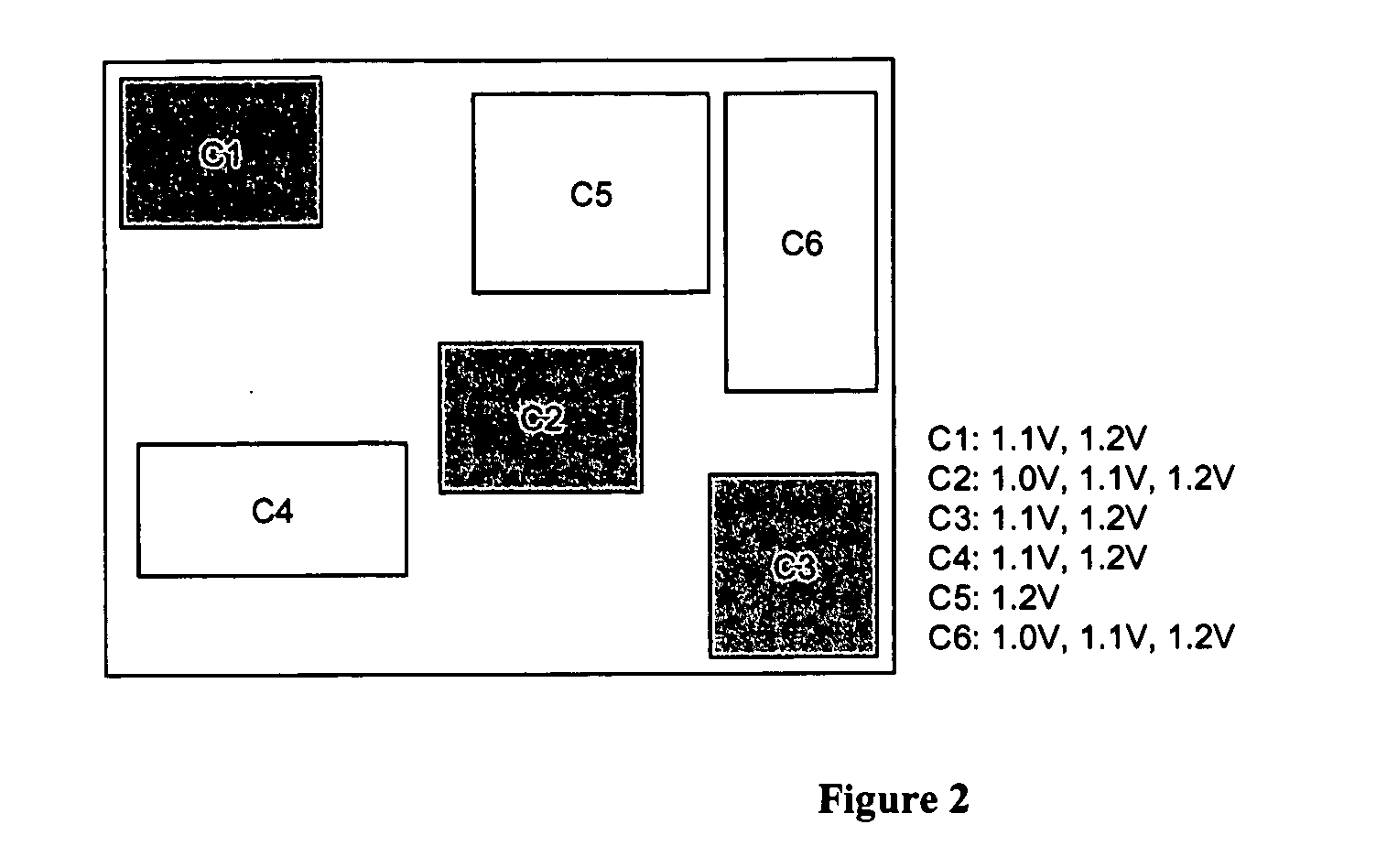

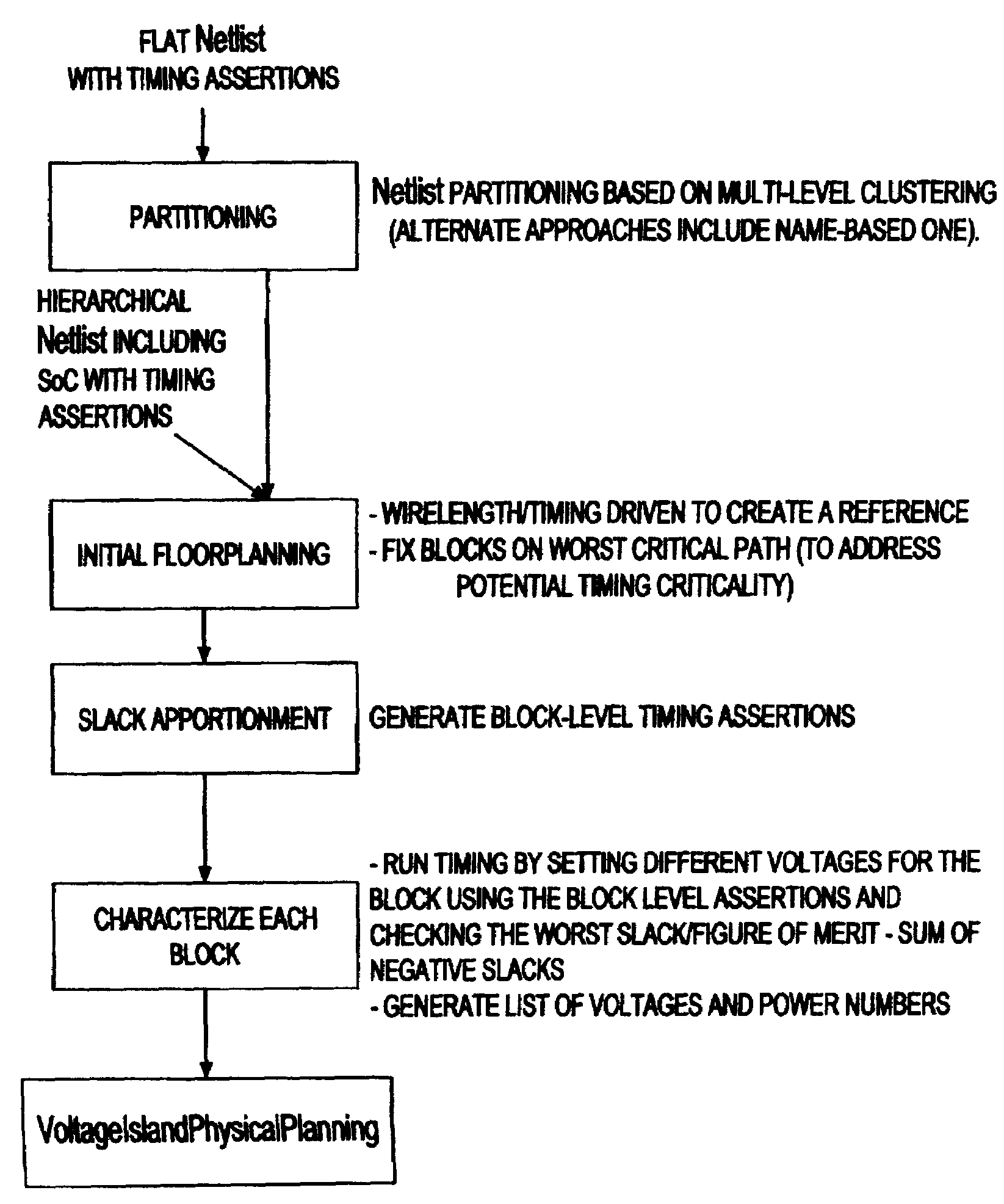

Voltage islands enable a core-level power optimization of ASIC / SoC designs by utilizing a unique supply voltage for each cluster of the design. Creating voltage islands in a chip design for optimizing the overall power consumption consists of generating voltage island partitions, assigning voltage levels and floorplanning. The generation of voltage island partitions and the voltage level assignment are performed simultaneously in a floorplanning context due to the physical constraints involved. This leads to a floorplanning formulation that differs from the conventional floorplanning for ASIC designs. Such a formulation of a physically aware voltage island partitioning and method for performing simultaneous voltage island partitioning, level assignment and floorplanning are described, as are the definition and the solution of floorplanning for voltage island based designs executed under area, power, timing and physical constraints. The physical planning of voltage islands includes: a) characterizing cell clusters in terms of voltages and power consumption values; b) providing a set of cell clusters that belong to a single voltage island Random Logic Macro (RLM); and c) assigning voltages for the voltage island RLMs, all within the context of generating a physically realizable floorplan for the design.

Owner:GOOGLE LLC

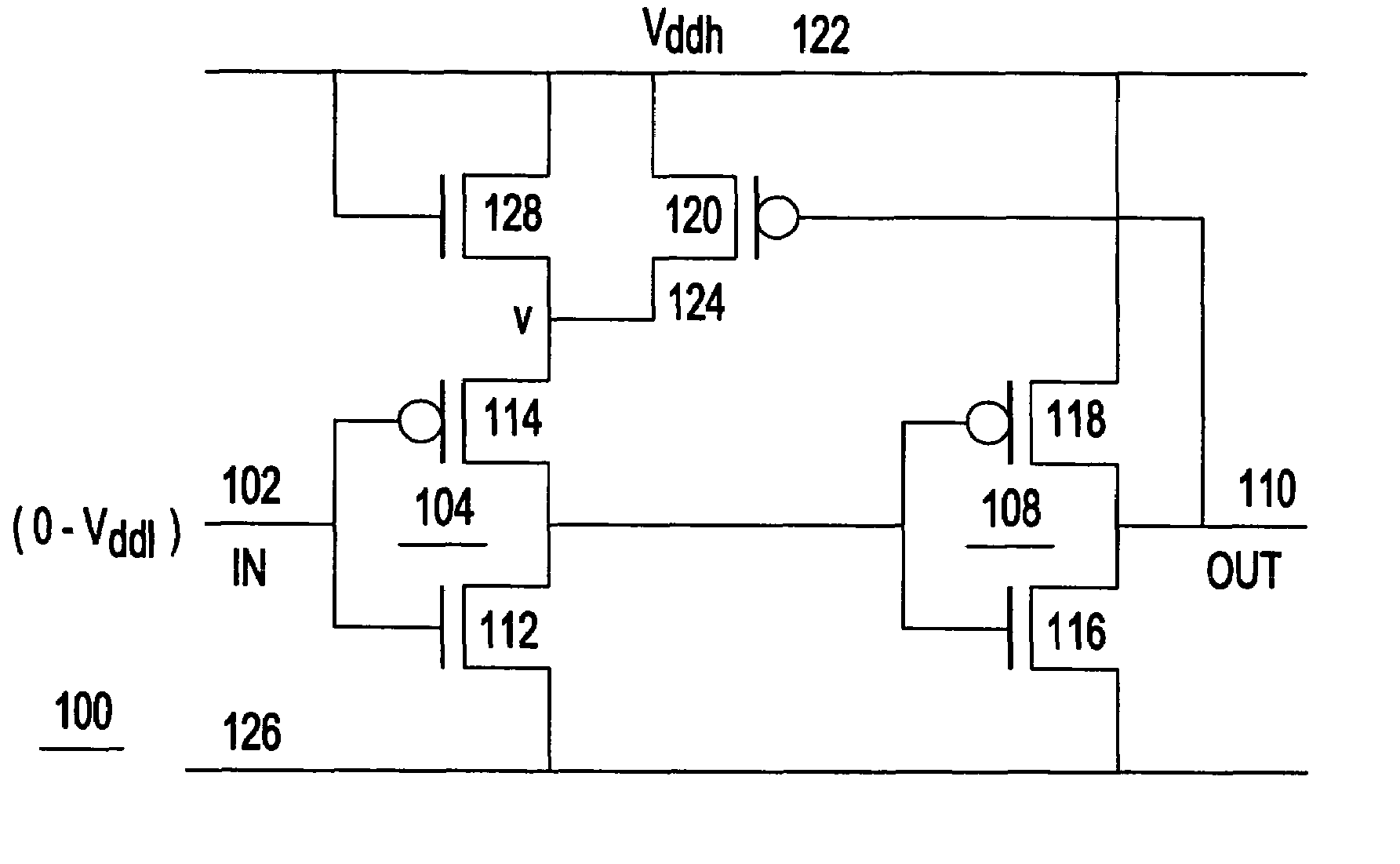

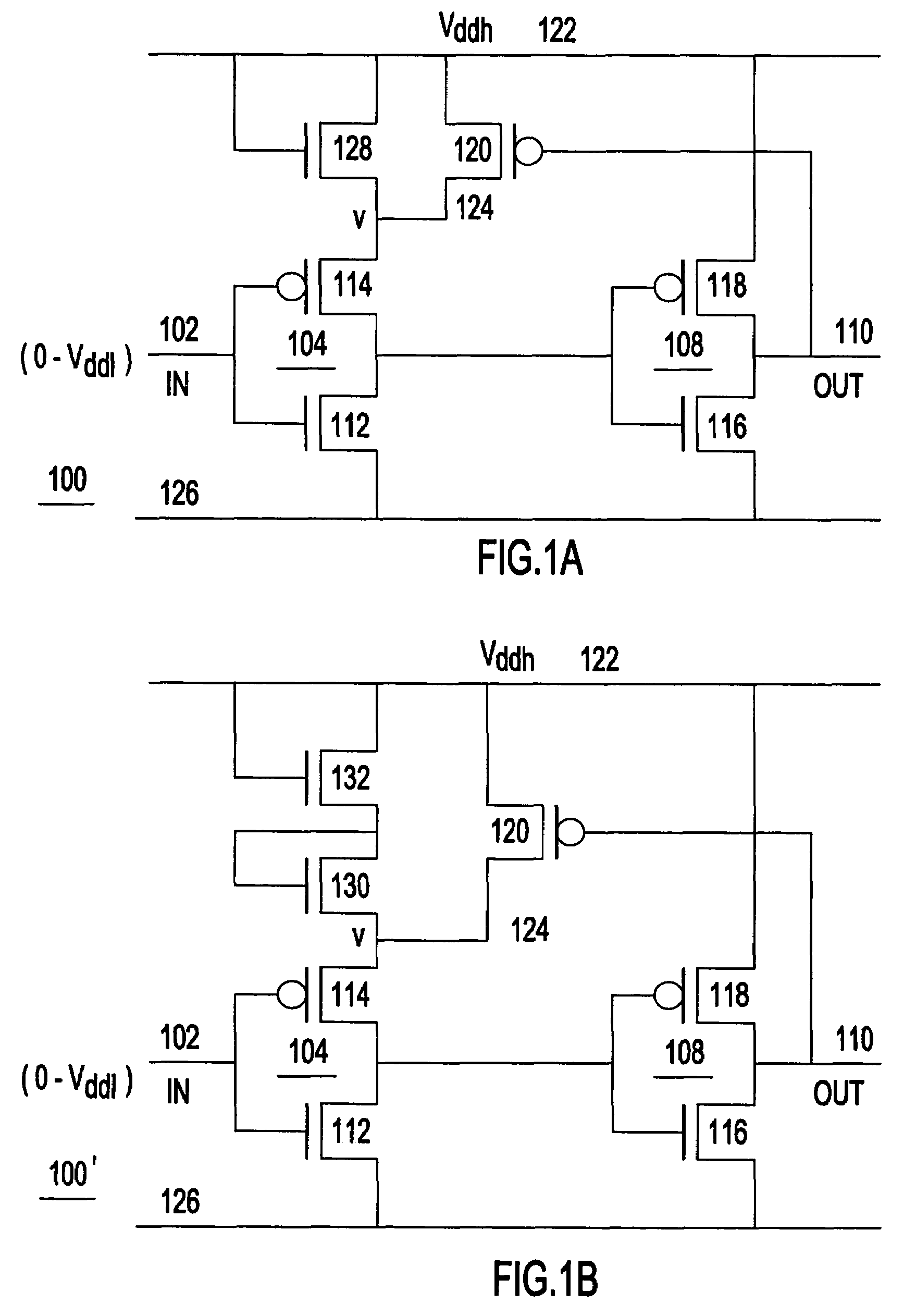

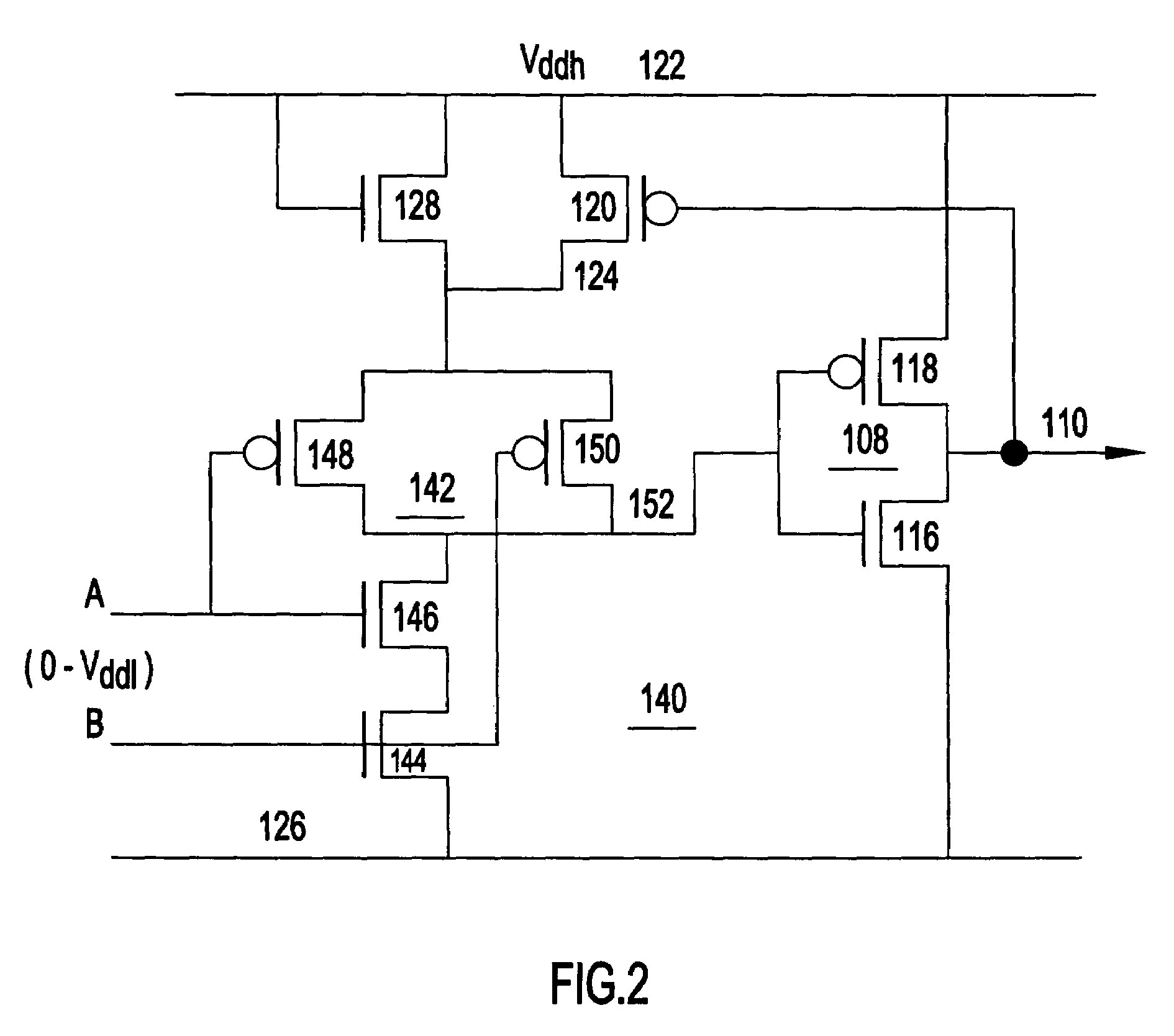

Single supply level converter

ActiveUS7119578B2Pulse automatic controlLogic circuits coupling/interface using field-effect transistorsLow voltage circuitsEngineering

A level converter for interfacing two circuits supplied by different supply voltages, and integrated circuit including the level converter interfacing circuit in two different voltage islands. A first buffer is supplied by a virtual supply and receives an input signal from a lower voltage circuit. The first buffer drives a second buffer, which is supplied by a higher supply voltage. An output from the second buffer switches a supply select to selectively pass the higher supply voltage or a reduced supply voltage to the first buffer.

Owner:MEDIATEK INC

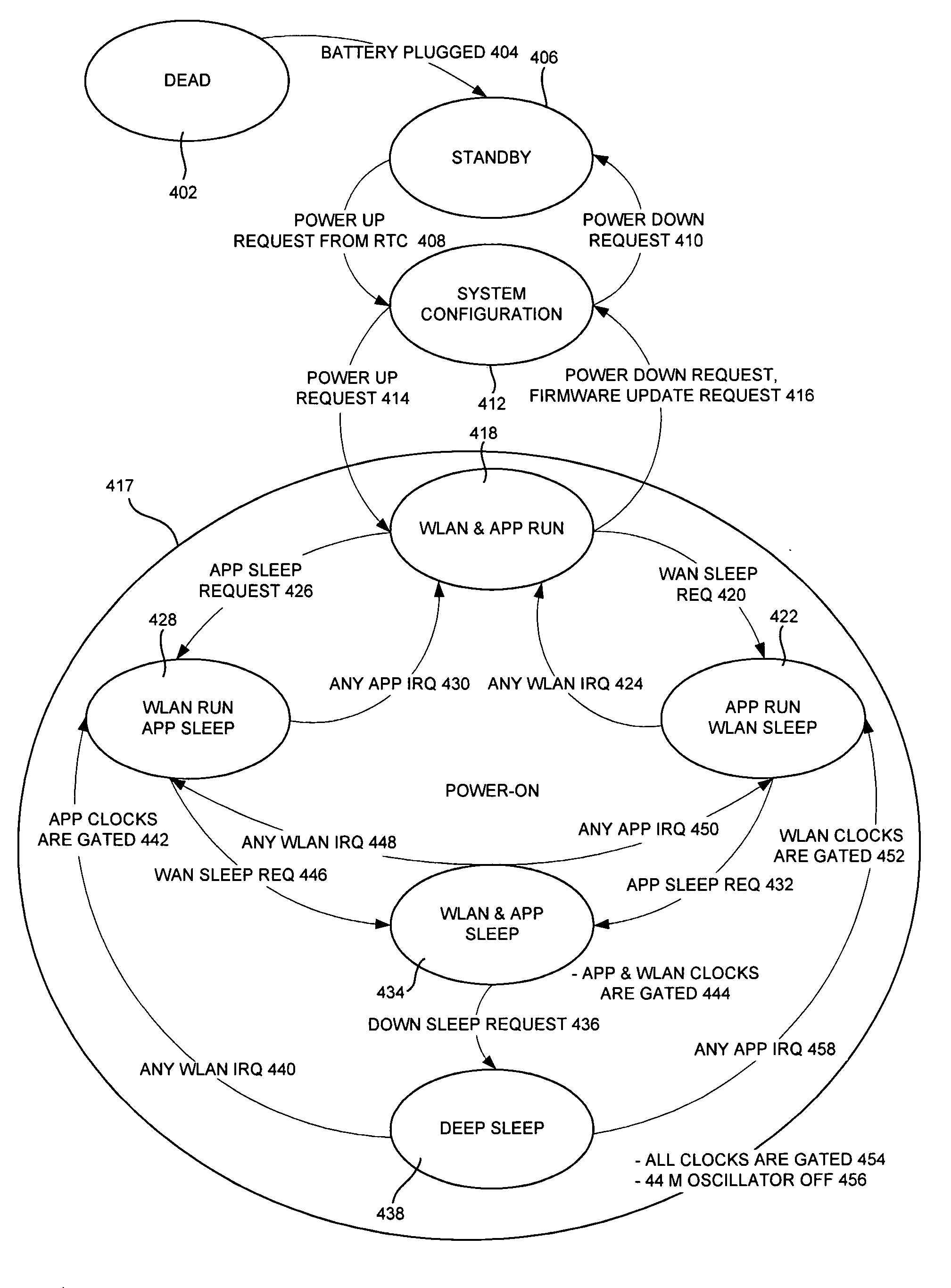

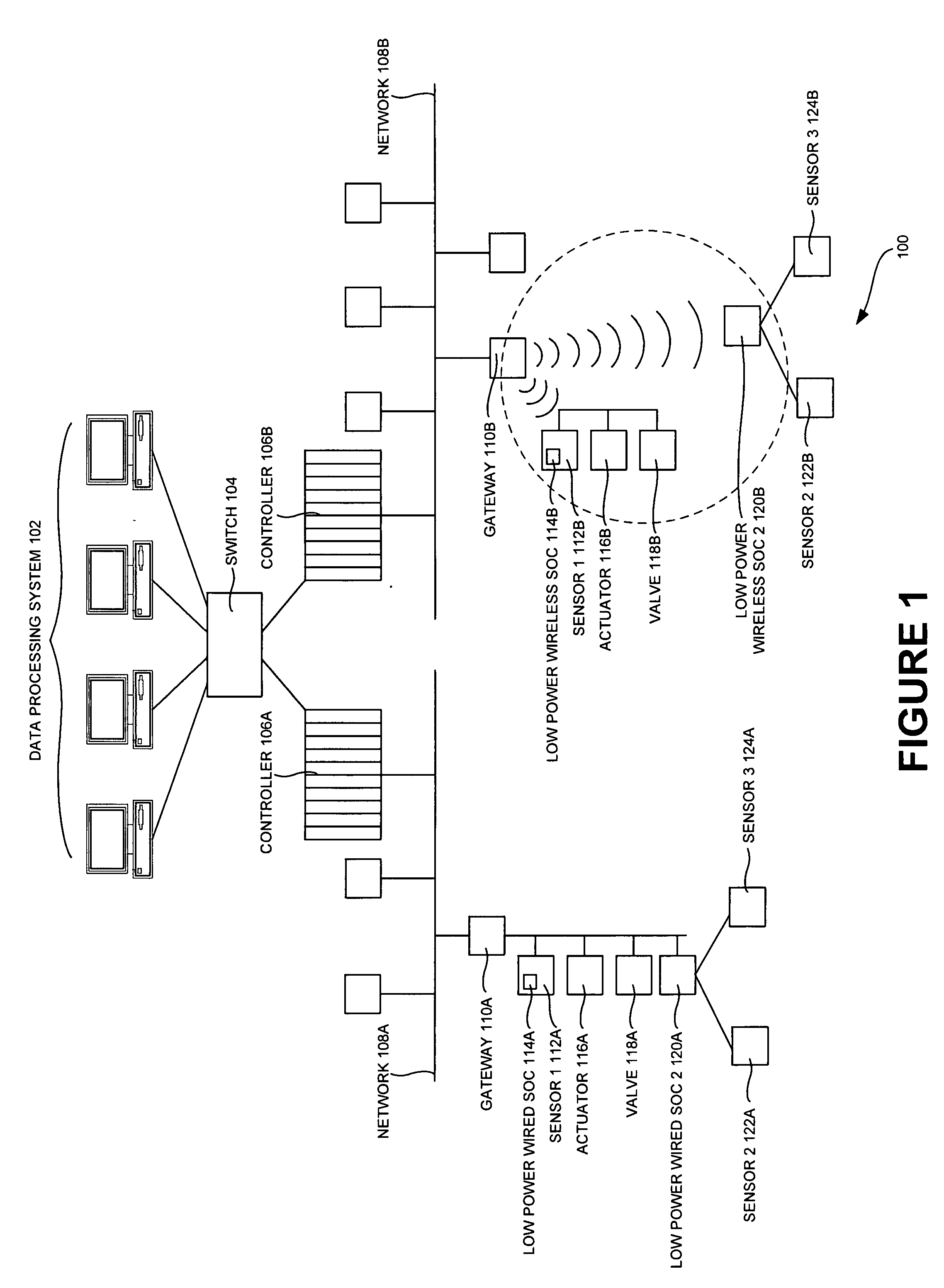

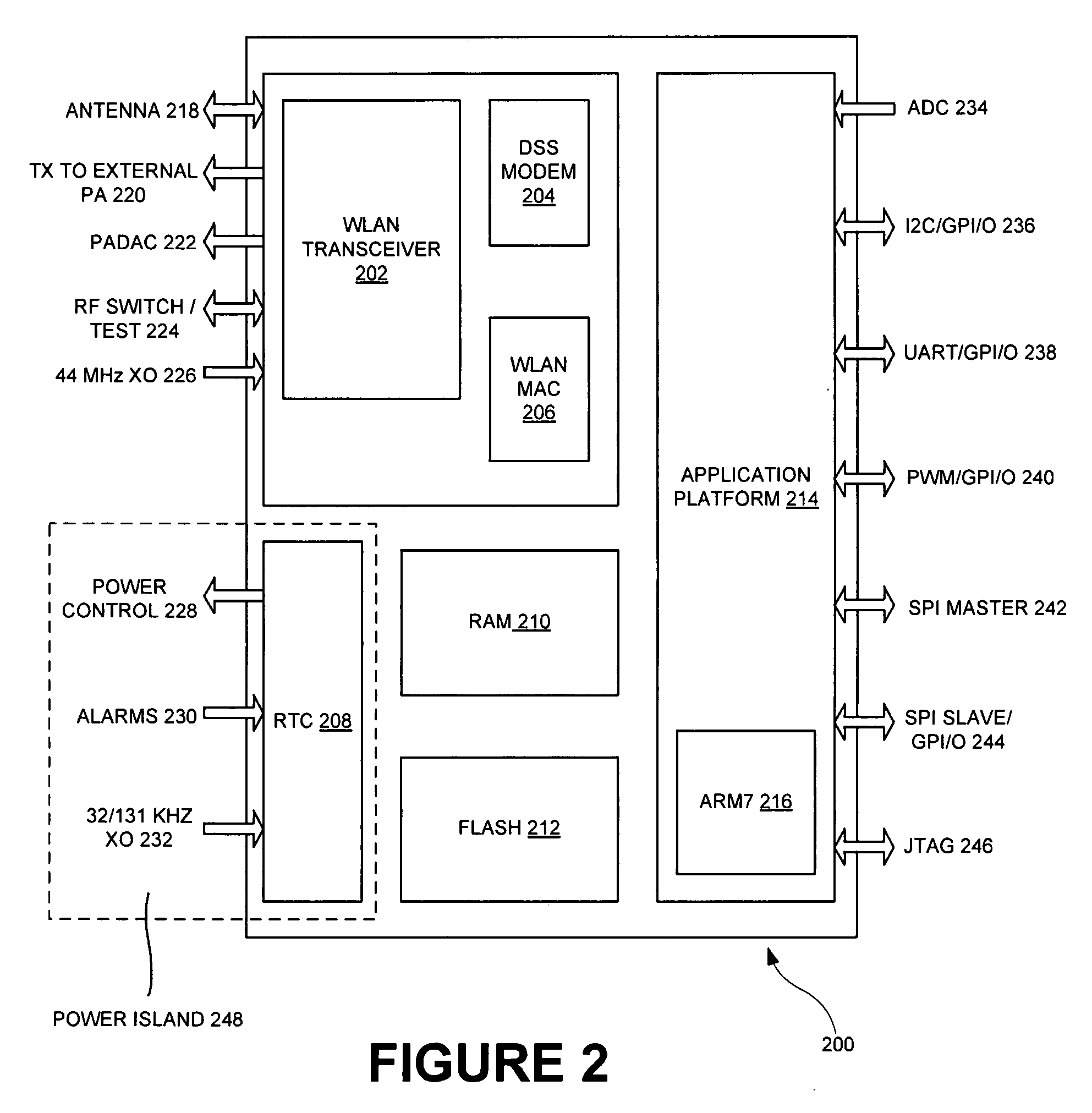

Optimum power management of system on chip based on tiered states of operation

ActiveUS20080282101A1Reduce power consumptionPrevent leakageEnergy efficient ICTVolume/mass flow measurementVoltage islandsLevel shifting

Optimum power management of system on chip based on tiered states of operation is disclosed. In one embodiment, a system on chip includes a hardware module including one or more of a microcontroller, a microprocessor, a DSP core, a memory, a timing source, a peripheral, and an external interface to have a real time counter module of the peripheral isolated from a rest of the hardware module using a plurality of voltage level shifting cells and / or a plurality of voltage island cells. Also, the system on chip includes a software module associated with the real time counter module to generate one or more control signals to one or more devices external to the system on chip during a sleep mode of the system on chip.

Owner:GAINSPAN

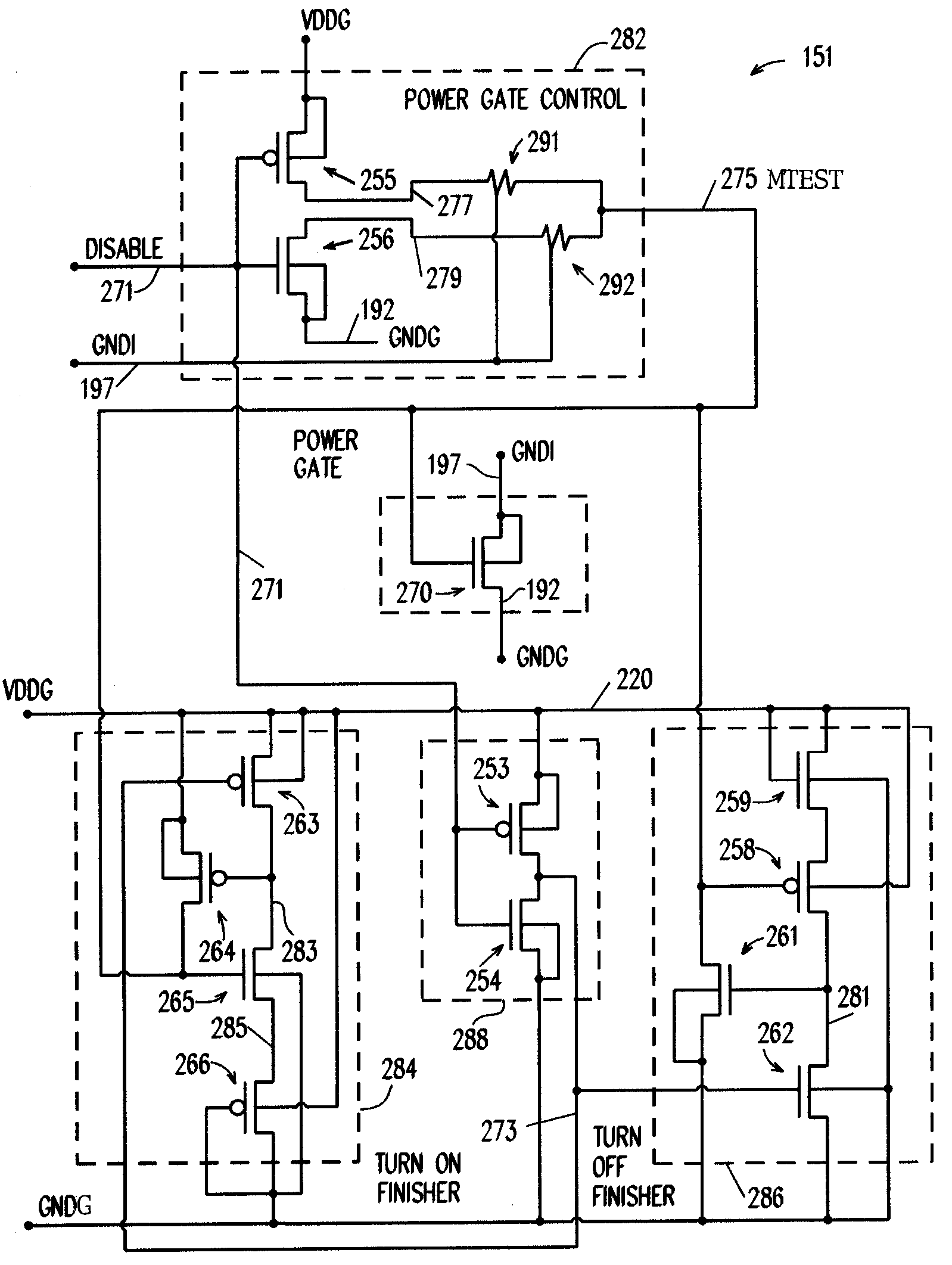

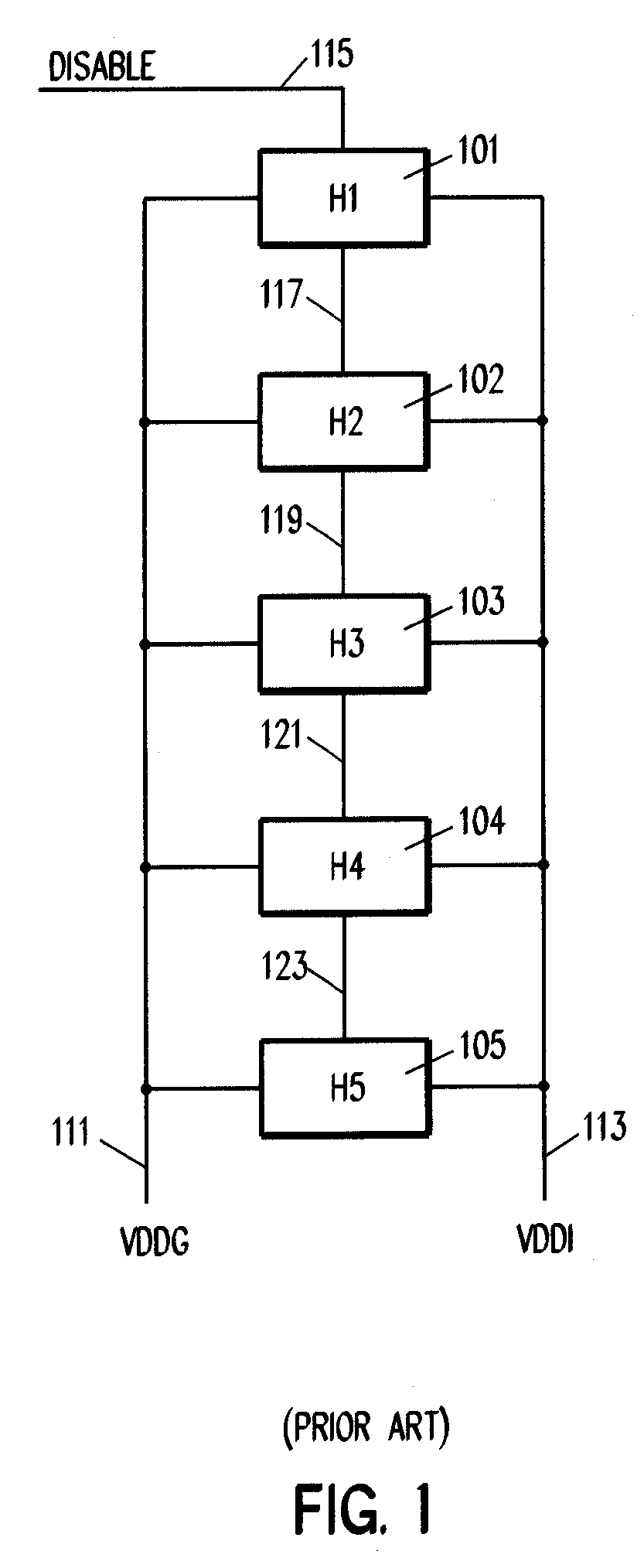

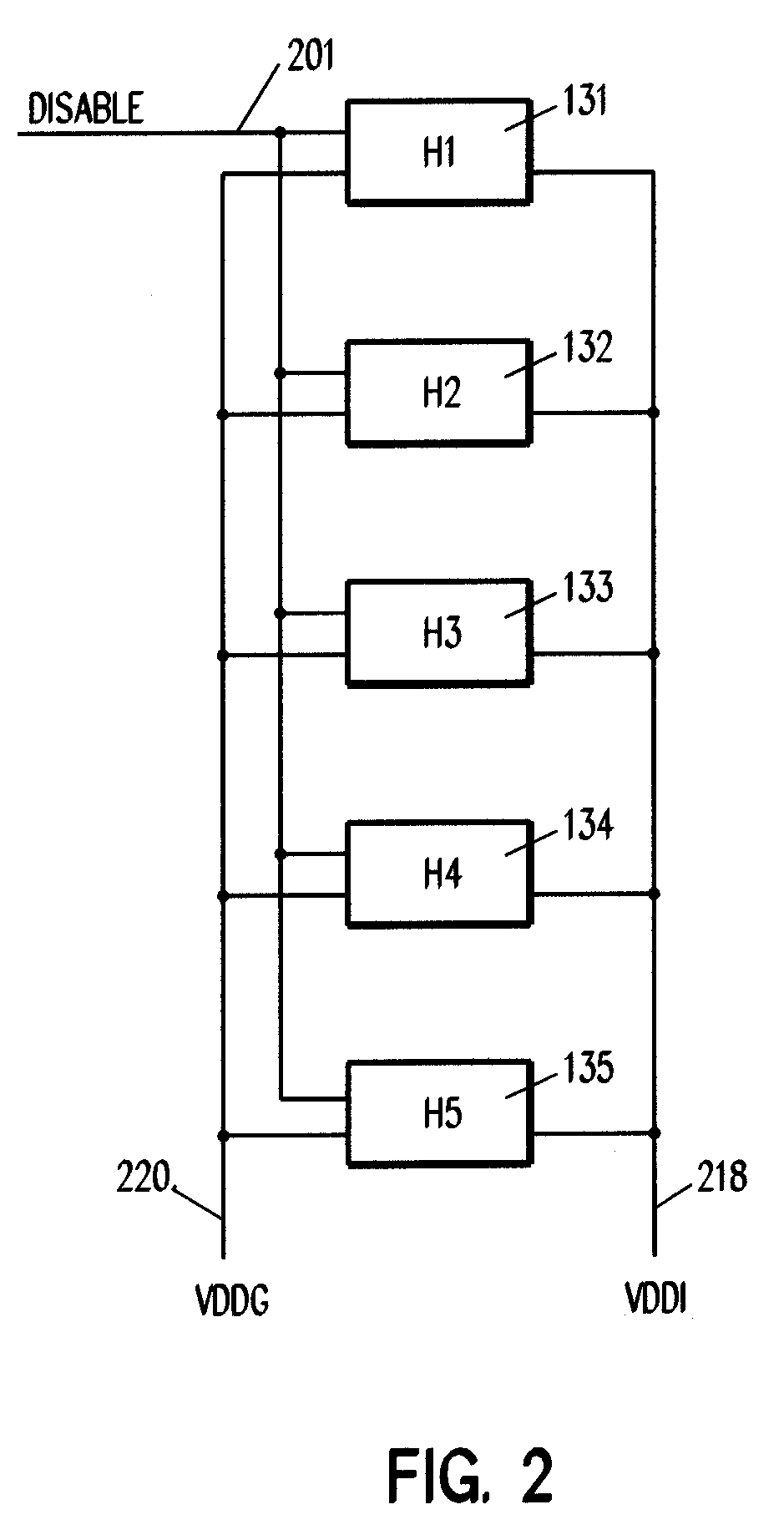

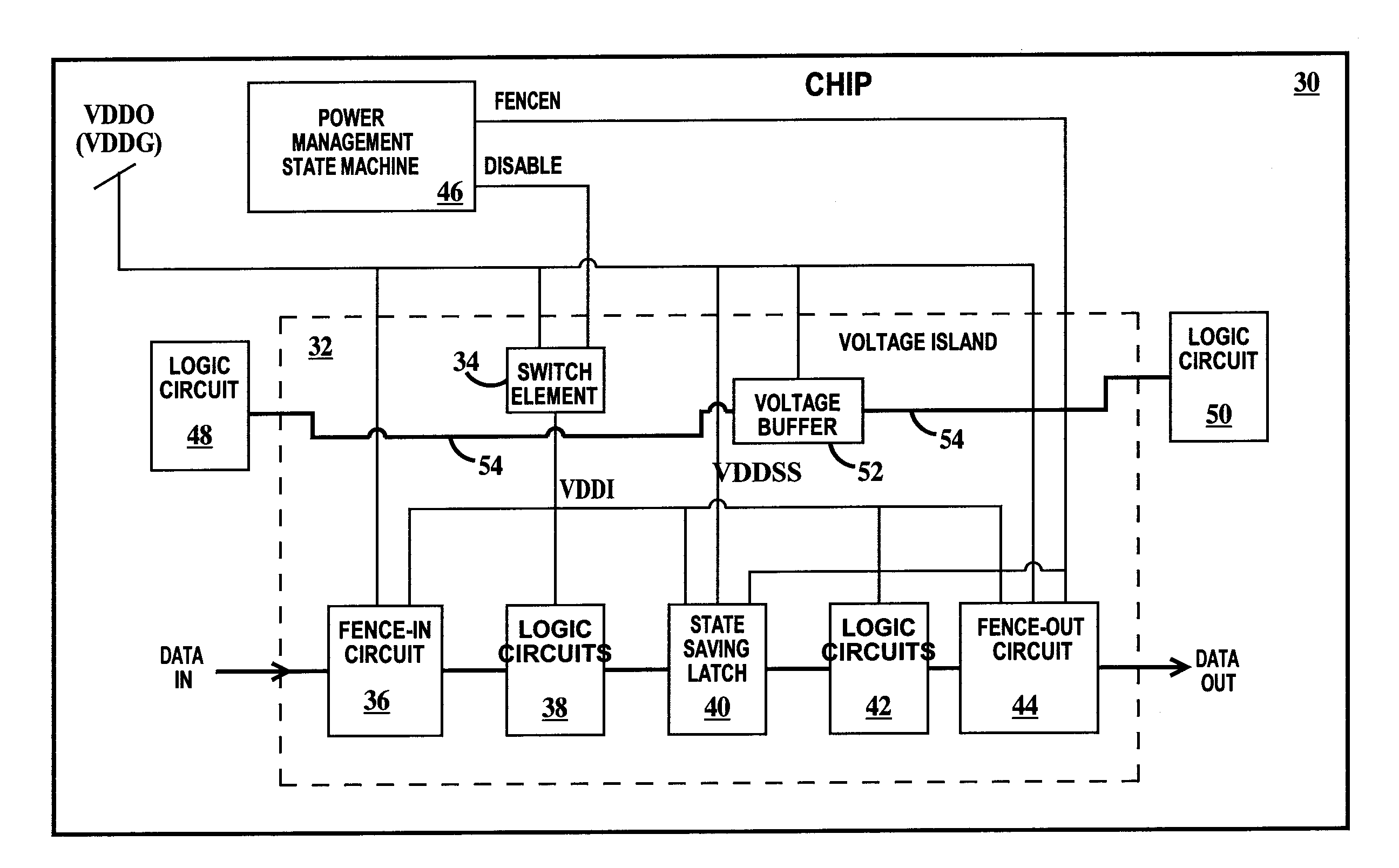

System and method for power gating

InactiveUS7088131B1Control leakagePower reduction in field effect transistorsPower reduction by control/clock signalTerrainEngineering

Owner:IBM CORP

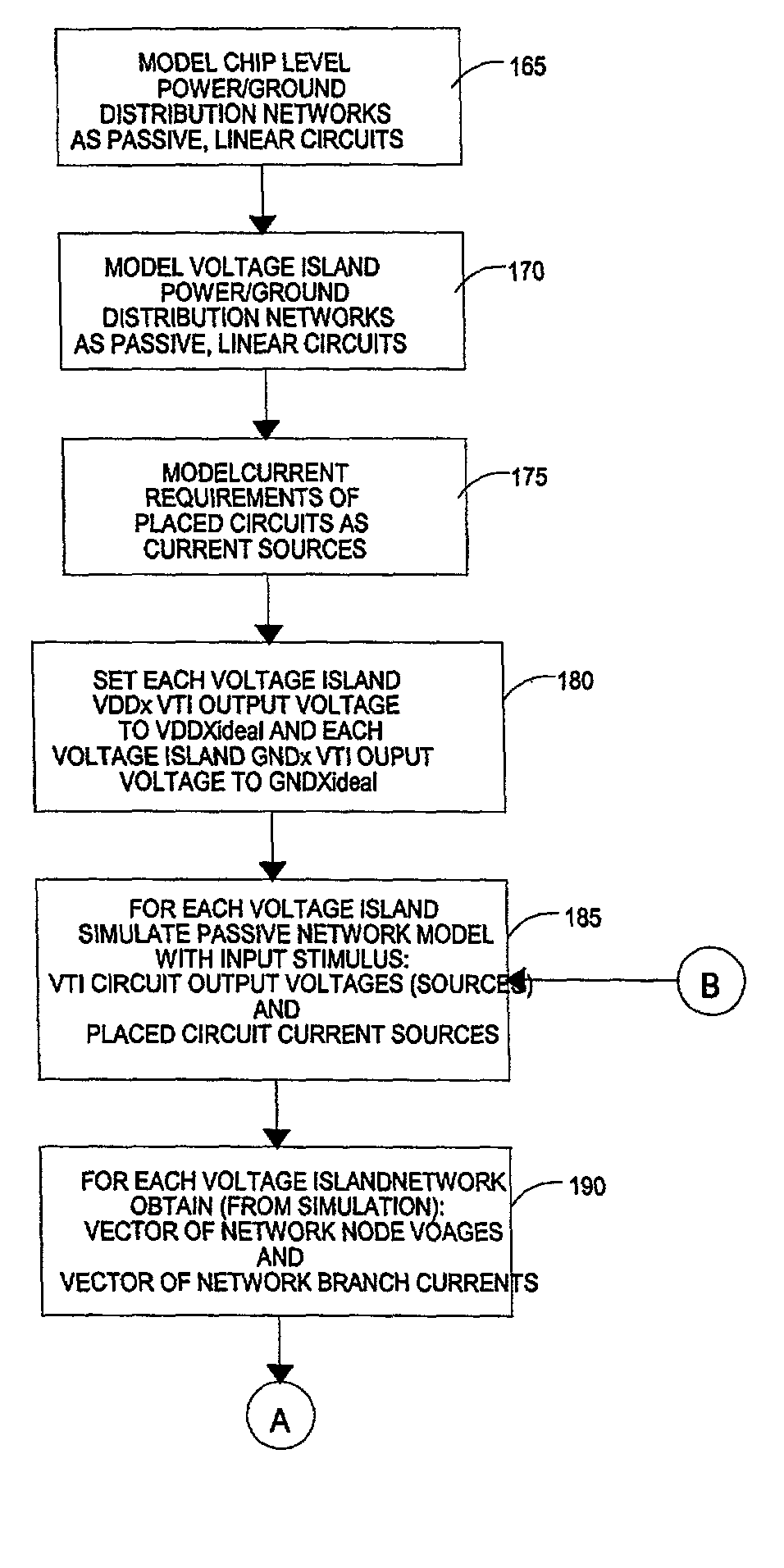

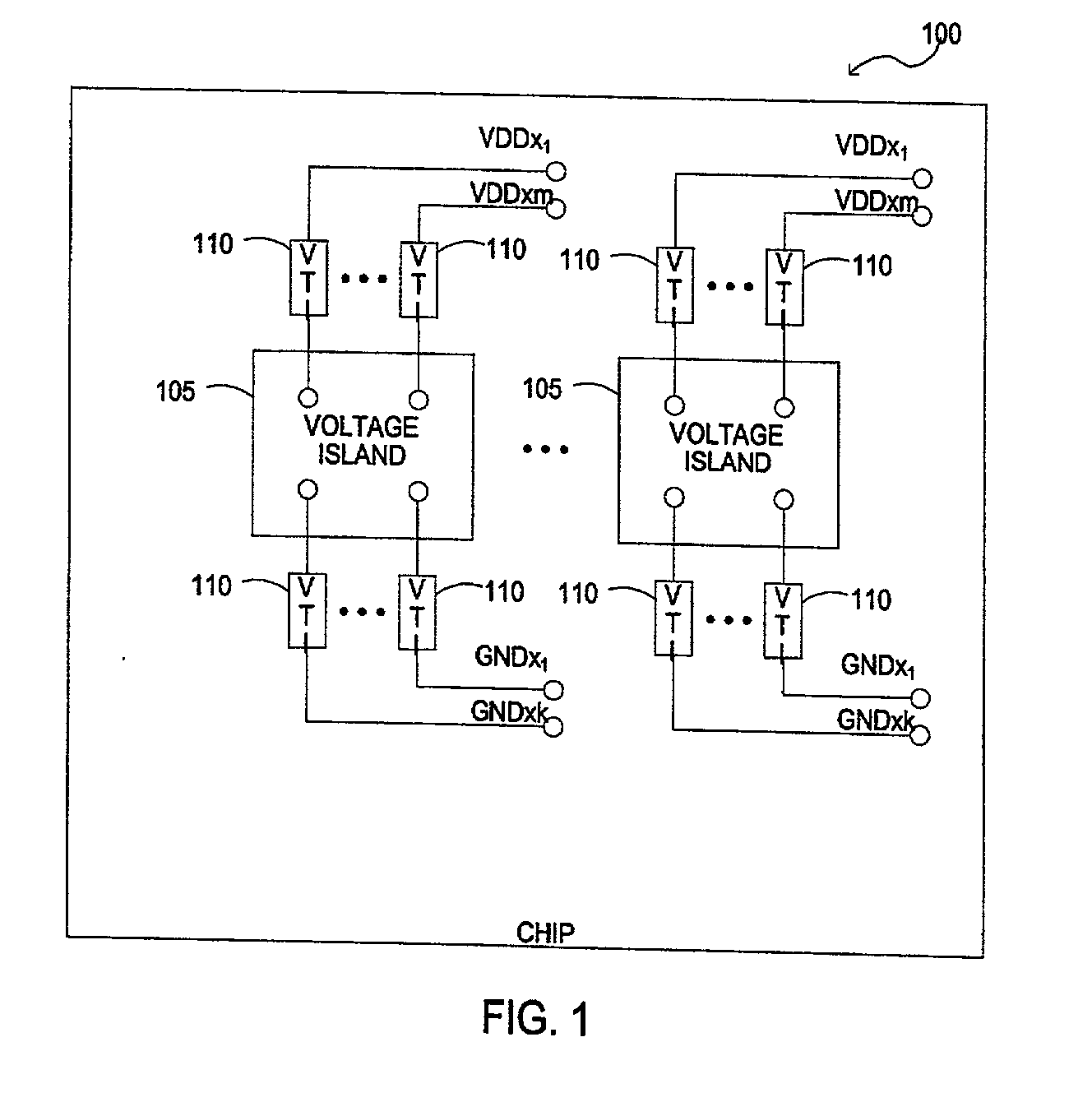

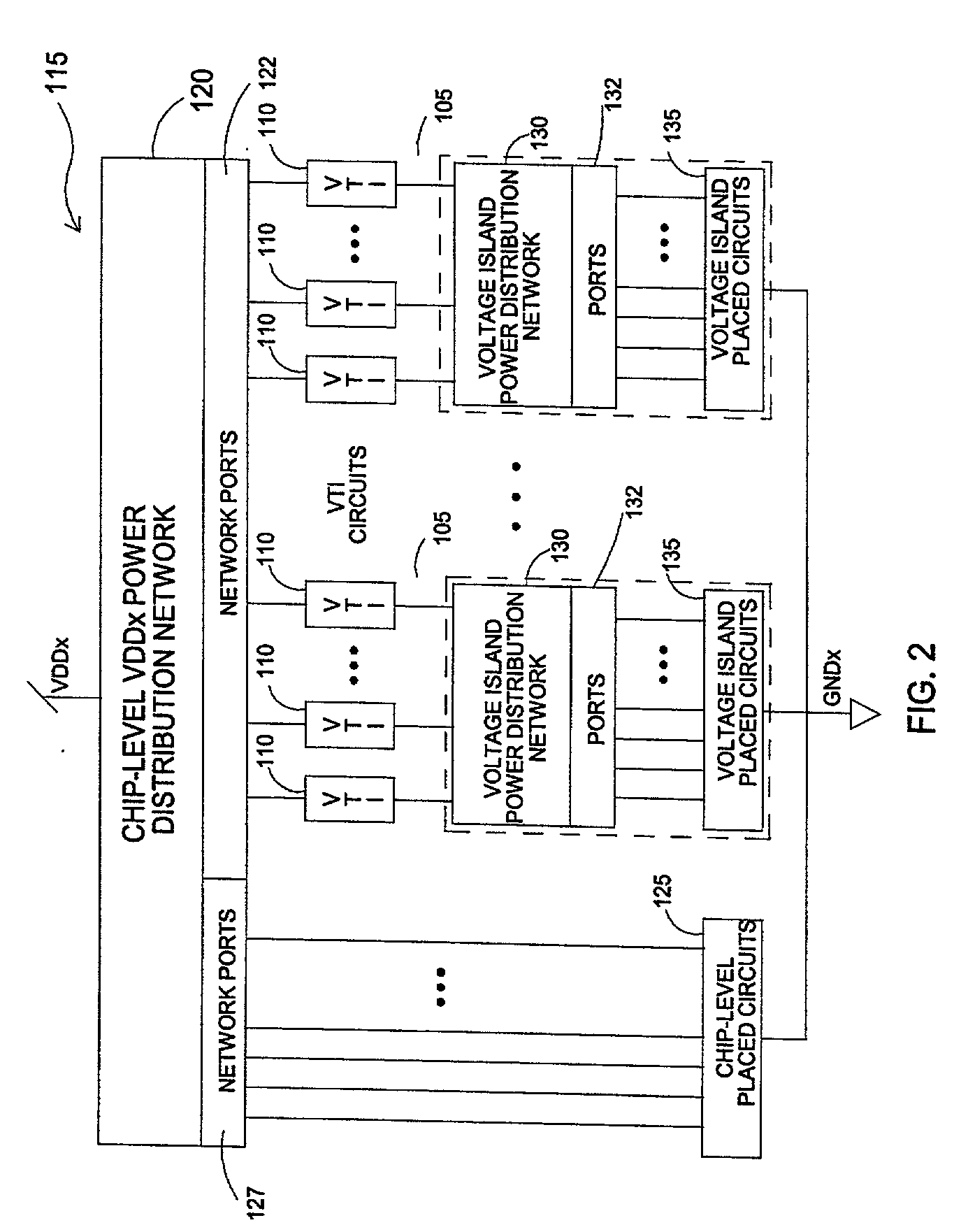

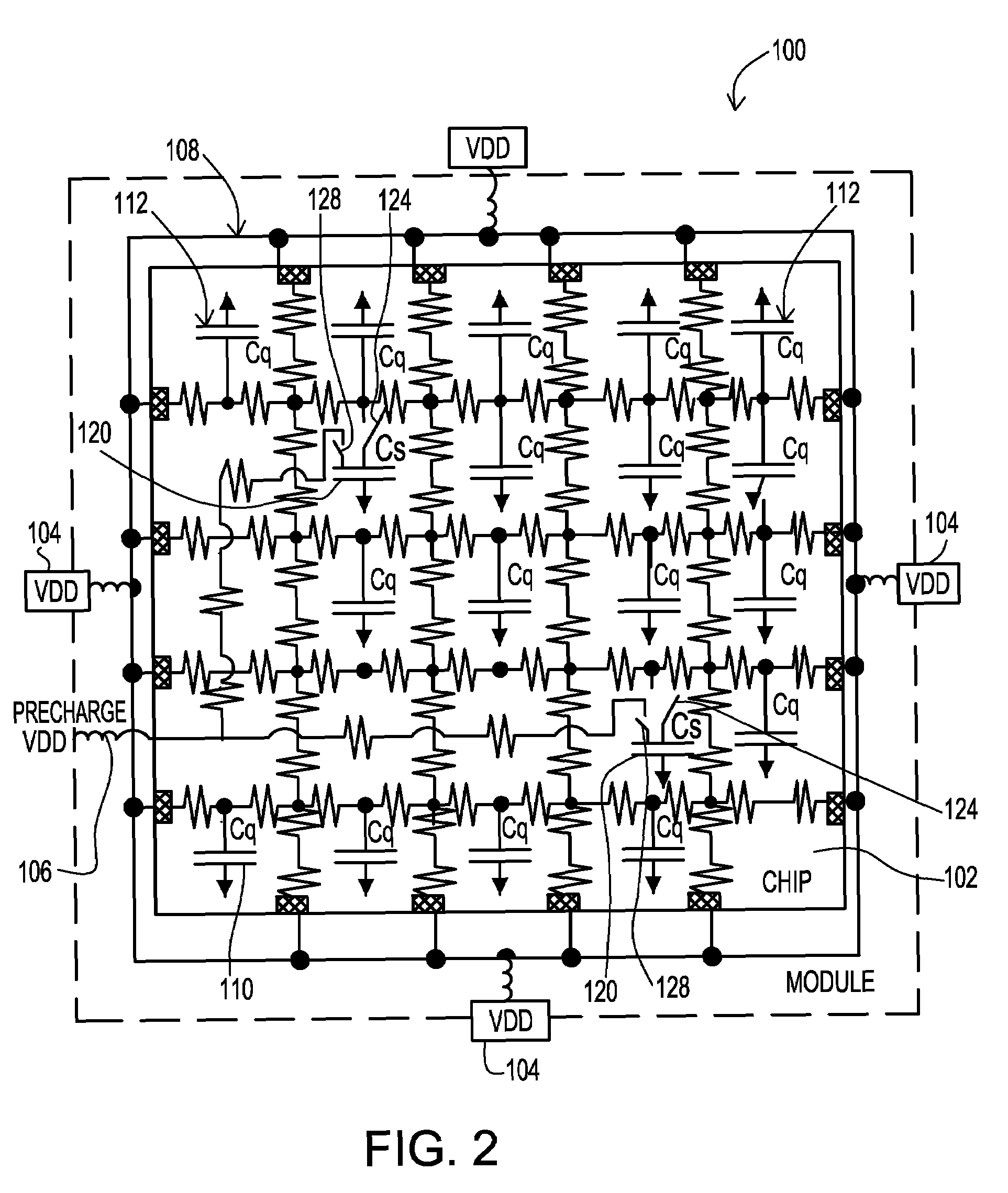

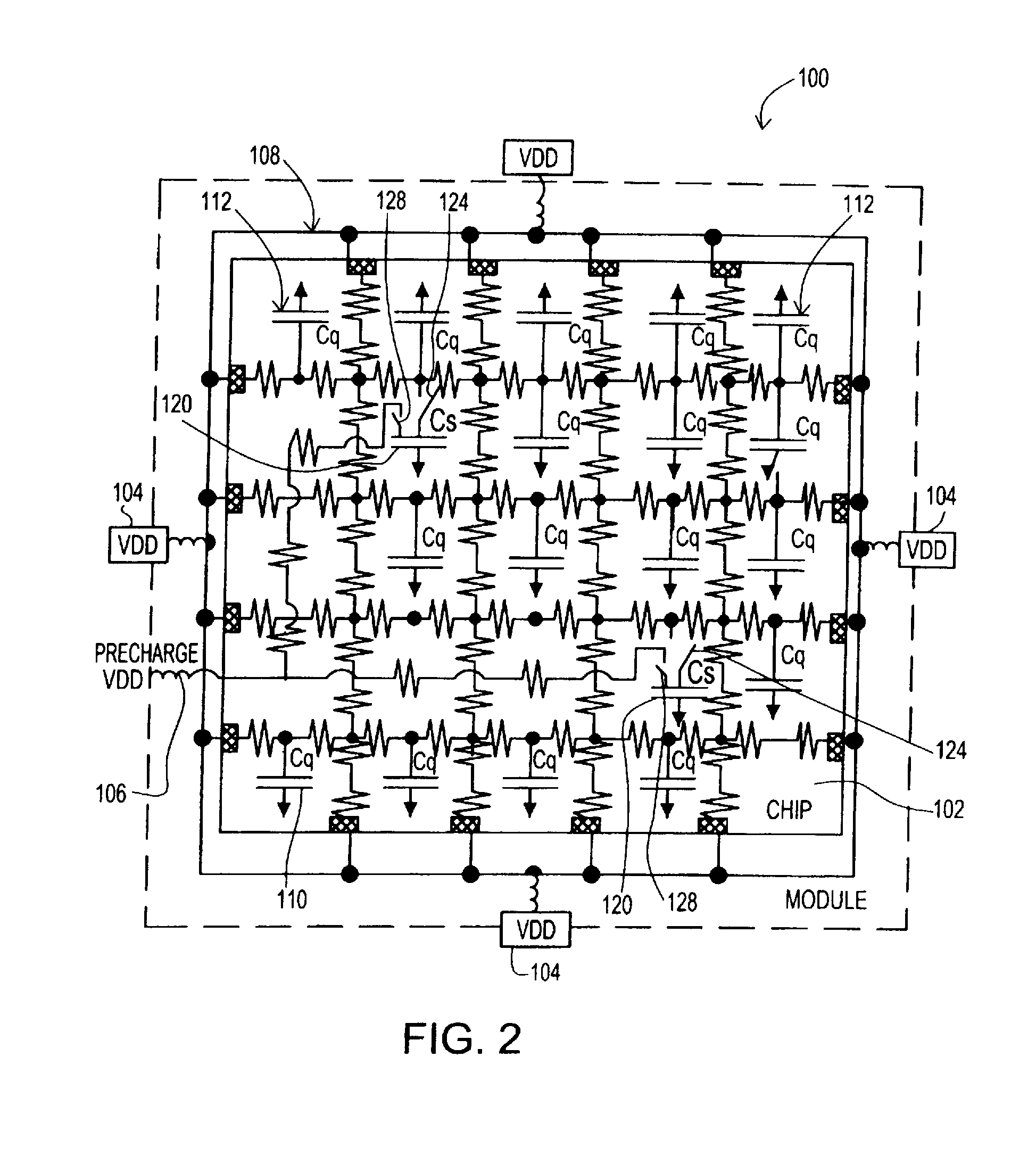

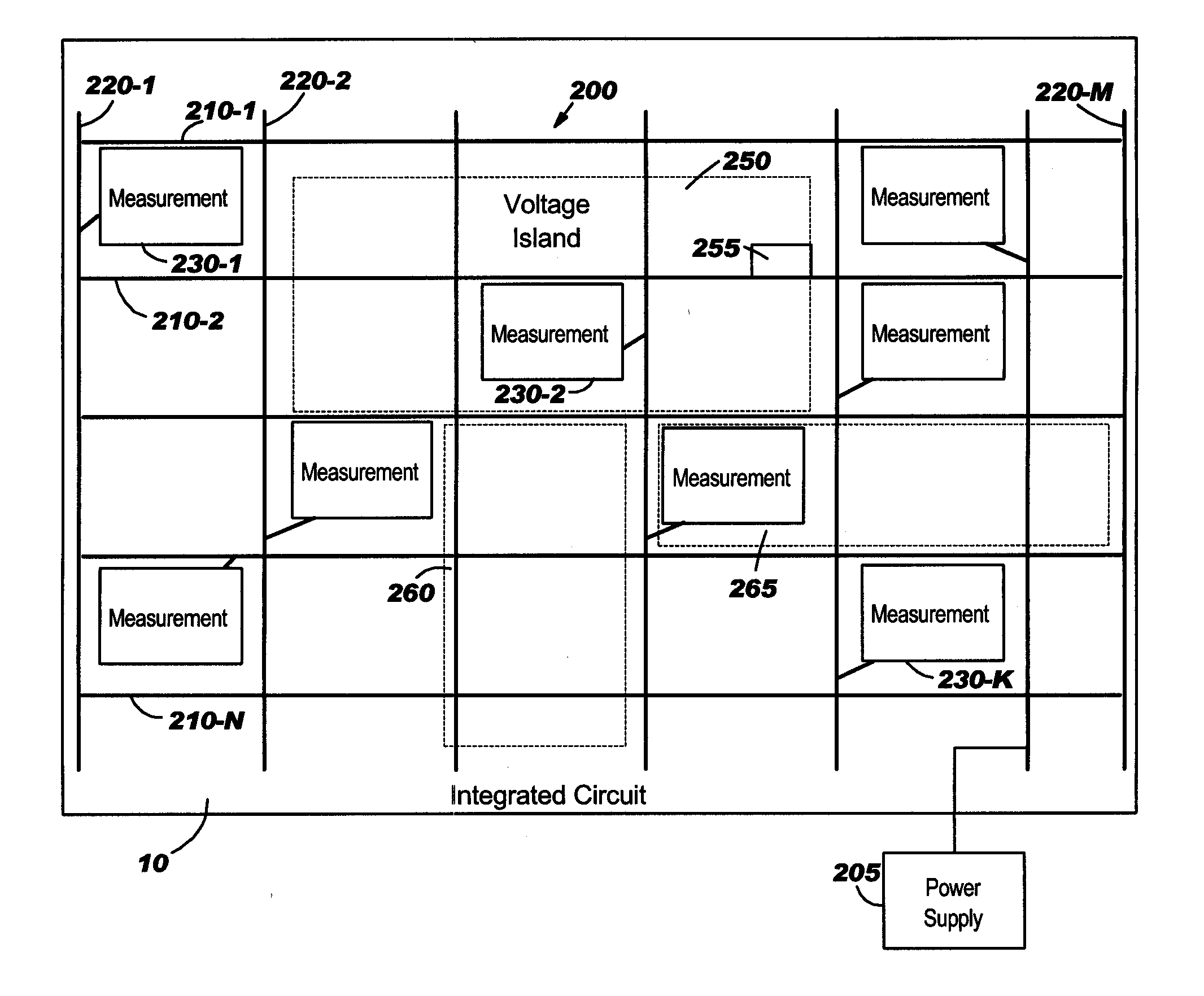

Method of analyzing integrated circuit power distribution in chips containing voltage islands

InactiveUS20030135830A1Detecting faulty computer hardwareComputer aided designHemt circuitsElectric distribution network

A method of analyzing the power distribution in a chip containing one or more voltage islands, each voltage island having a power distribution network connected to a chip-level power distribution network by one or more voltage translation interface circuits. The method comprising: analyzing the voltage-island power distribution networks independently of the chip-level power distribution network to obtain voltage translation interface circuit currents; using the voltage translation interface circuit currents as input to a model of the chip-level power distribution network to obtain voltage translation interface circuit input voltages; and calculating voltage translation interface circuit output voltages based on the voltage translation interface circuit input voltages, the voltage translation interface circuit currents, and current-voltage characteristics of the voltage translation interface circuits.

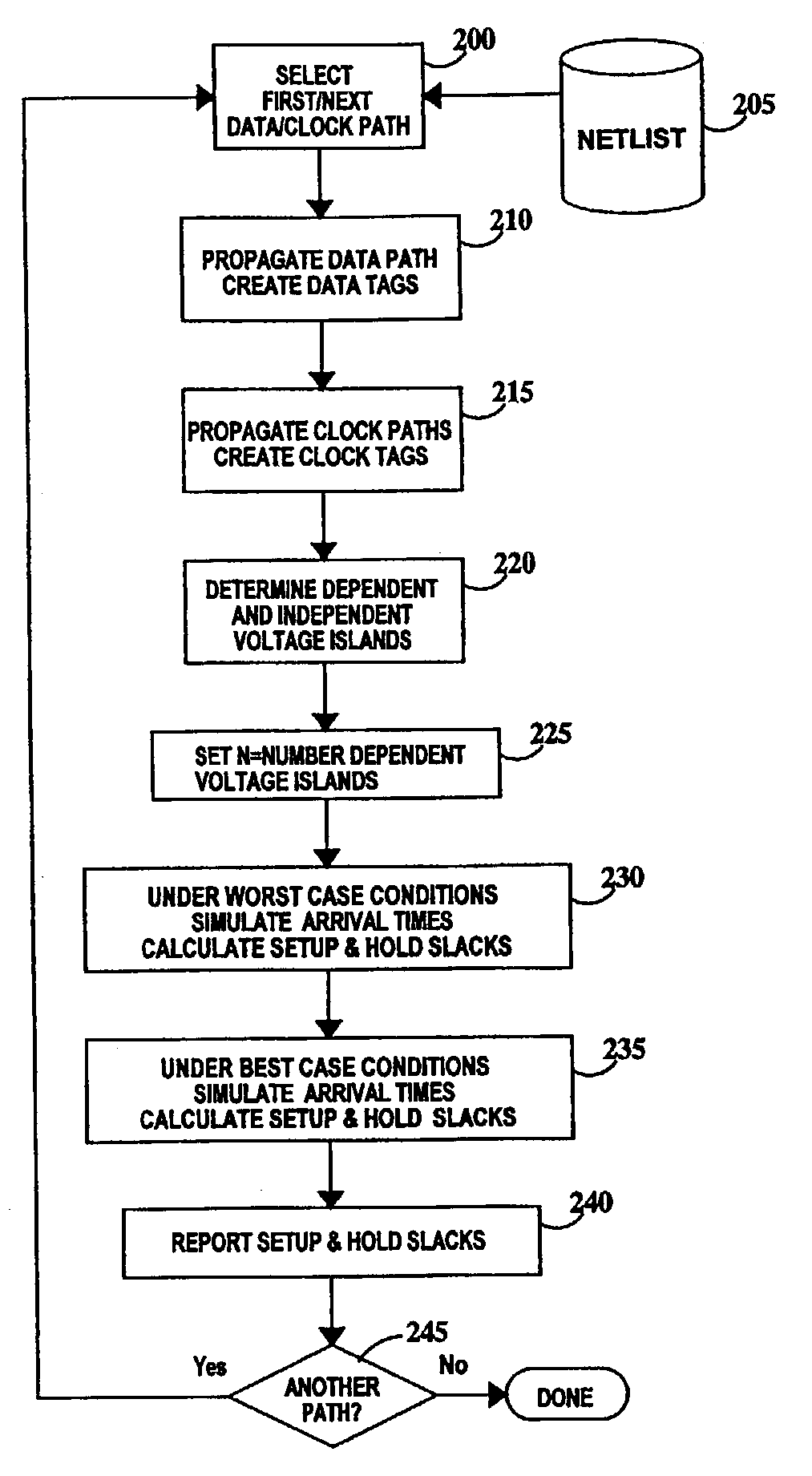

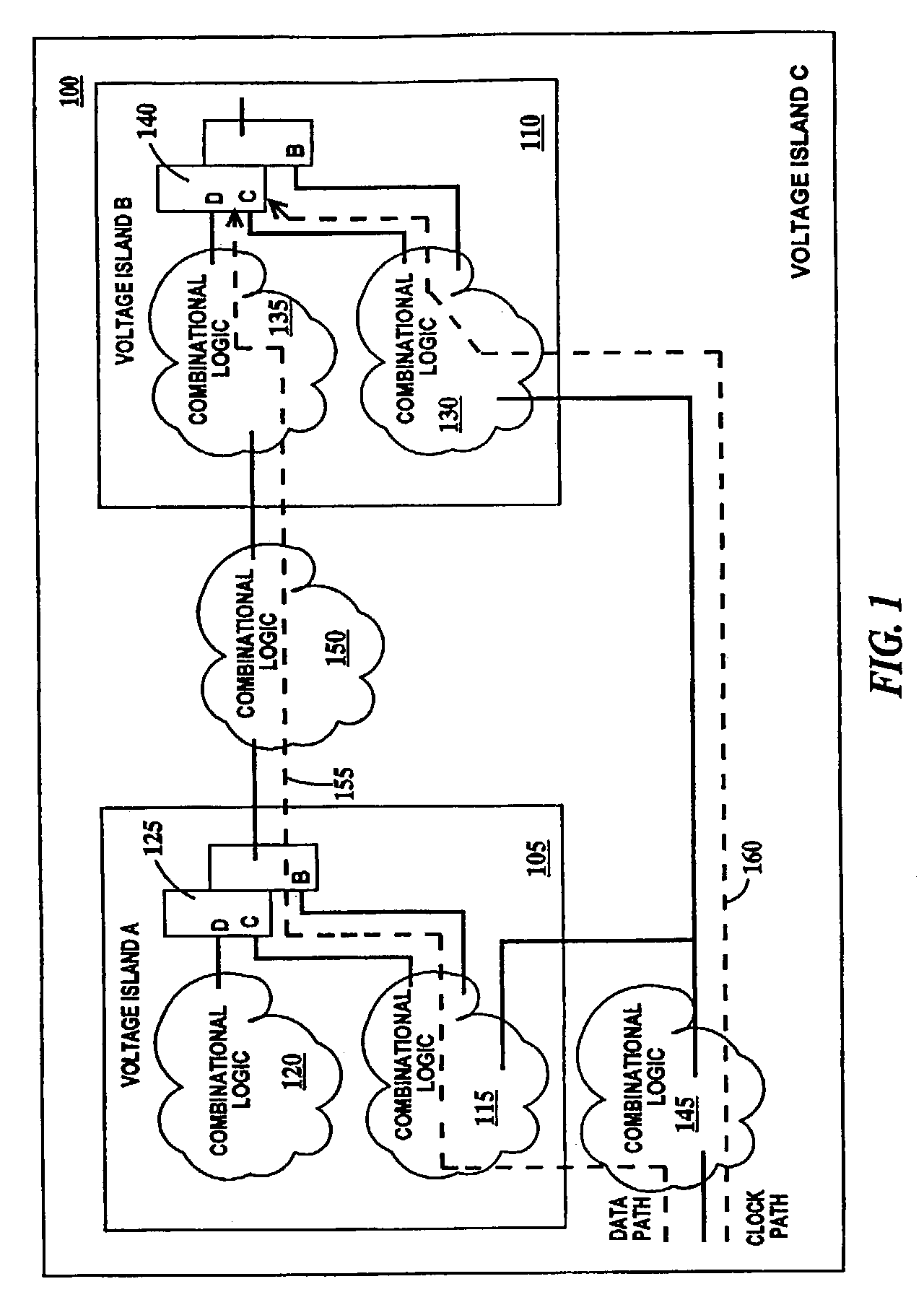

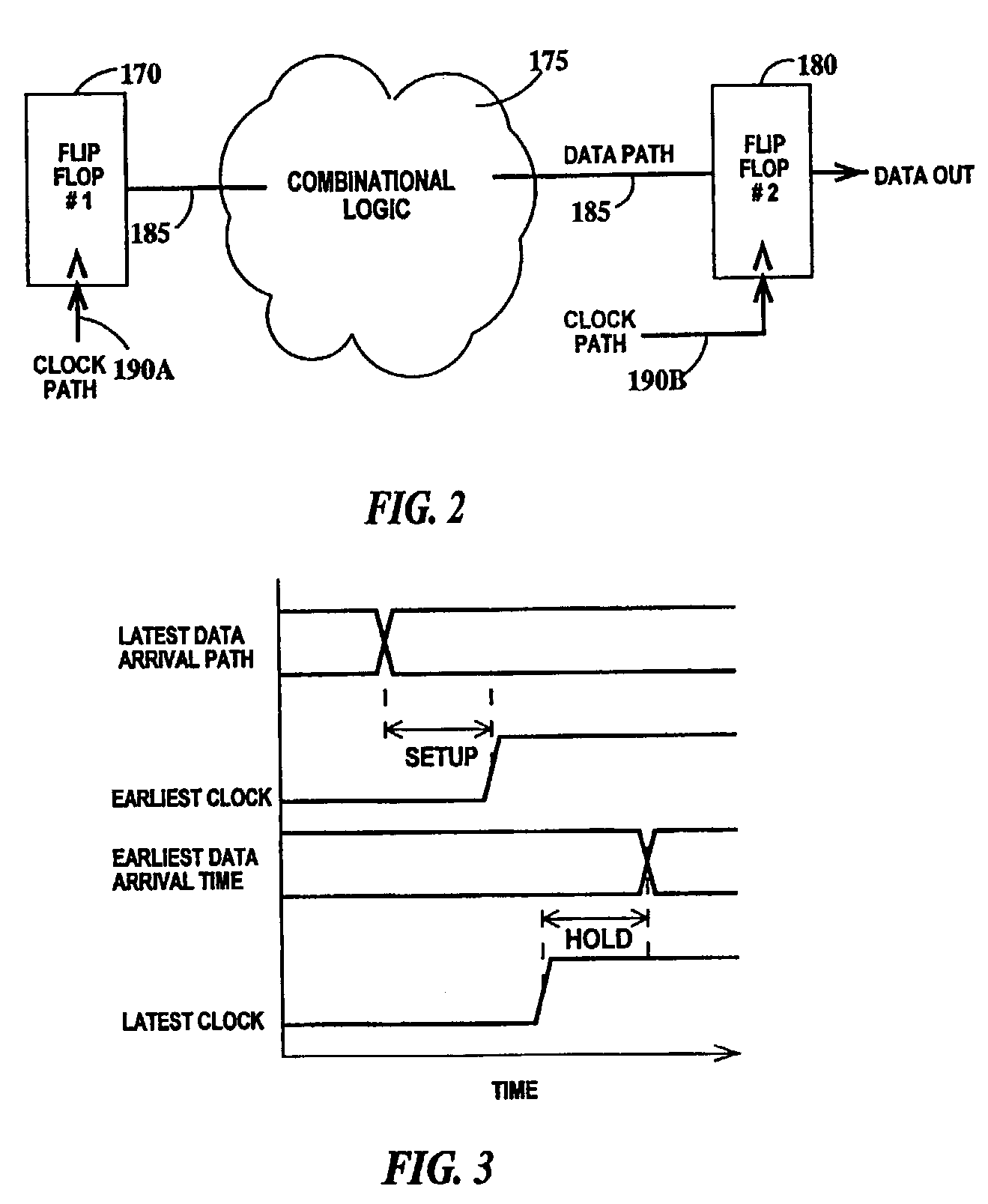

Method for static timing verification of integrated circuits having voltage islands

InactiveUS6990645B2Computer aided designSoftware simulation/interpretation/emulationStatic timing analysisEngineering

A method of analysis of an integrated circuit design having multiple voltage islands, including: (a) determining a clock path through the voltage islands; (b) determining a data path through the voltage islands; (c) determining which voltage islands are independent voltage islands; (d) determining which voltage islands are dependent voltage islands; (e) for the data path and the clock path, performing a worst case static timing analysis based on minimum and maximum operating voltages of each independent and dependent voltage island in the data and clock paths; and (f) for the data path and the clock path, performing a best case static timing analysis based on minimum and maximum operating voltages of each independent and dependent voltage island in the data and clock paths.

Owner:IBM CORP

Design method of semiconductor chip

InactiveCN1353454AMeet predetermined criteriaSolid-state devicesSemiconductor/solid-state device manufacturingRate limitingLow voltage

Both logical and physical construction of voltage islands is disclosed. A semiconductor chip design is partitioned into 'bins', which are areas of the design. In this way, a semiconductor chip design may be 'sliced' into various areas and the areas may then be assigned to various voltage levels. Each bin may be thought of as a voltage island. Circuits in the design can be added to or removed from the various bins, thereby increasing or decreasing the speed and power of the circuits: the speed and power increase if a circuit is placed into a bin assigned a higher voltage, and the speed and power decrease if a circuit is placed into a bin having a lower voltage. The size and location of the bins may also be changed. By iterating these steps, the optimum power consumption may be met while still meeting speed constraints and other criteria. The present invention is applicable to any placement environment, such as an annealing placement tool, that proceeds through successive refinement of the locations of the circuits on the design and in which the placement process may be interrupted to make changes in placement of the logic.

Owner:IBM CORP

Method of physical planning voltage islands for ASICs and system-on-chip designs

InactiveUS7296251B2Minimize power consumptionCAD circuit designSoftware simulation/interpretation/emulationPhysical planningCore level

Owner:GOOGLE LLC

Self-test circuitry to determine minimum operating voltage

A solution for determining minimum operating voltages due to performance / power requirements would be valid for a wide range of actual uses. The solution includes a test flow methodology for dynamically reducing power consumption under applied conditions while maintaining application performance via a BIST circuit. There is additionally provided a test flow method for dynamically reducing power consumption to the lowest possible stand-by / very low power level under applied conditions that will still be sufficient to maintain data / state information. One possible application would be for controlling the voltage supply to a group of particular circuits on an ASIC (Application Specific Integrated Circuit). These circuits are grouped together in a voltage island where they would receive a voltage supply that can be different from the voltage supply other circuits on the same chip are receiving. The same solution could be applied to a portion of a microprocessor (the cache logic control, for example).

Owner:INT BUSINESS MASCH CORP

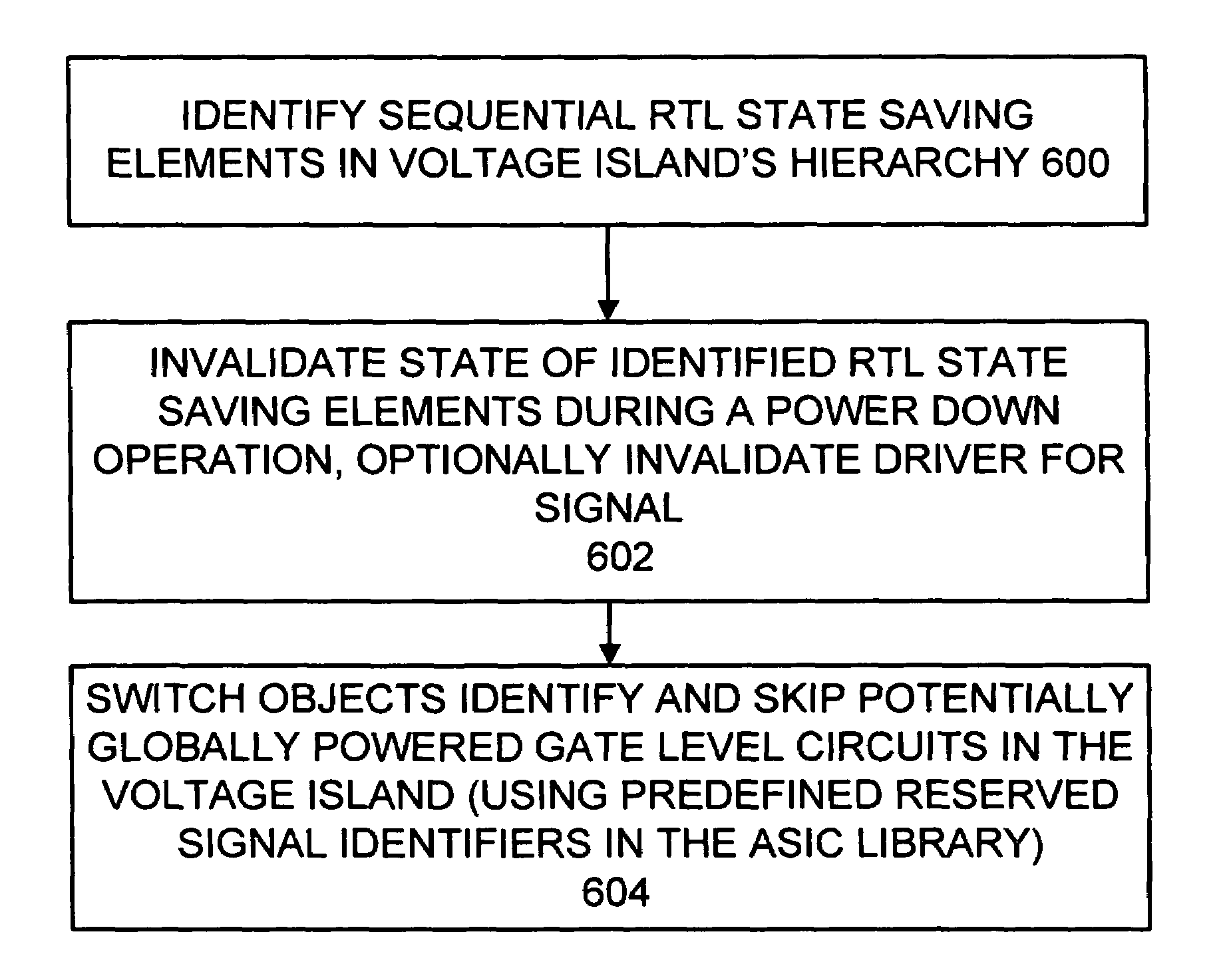

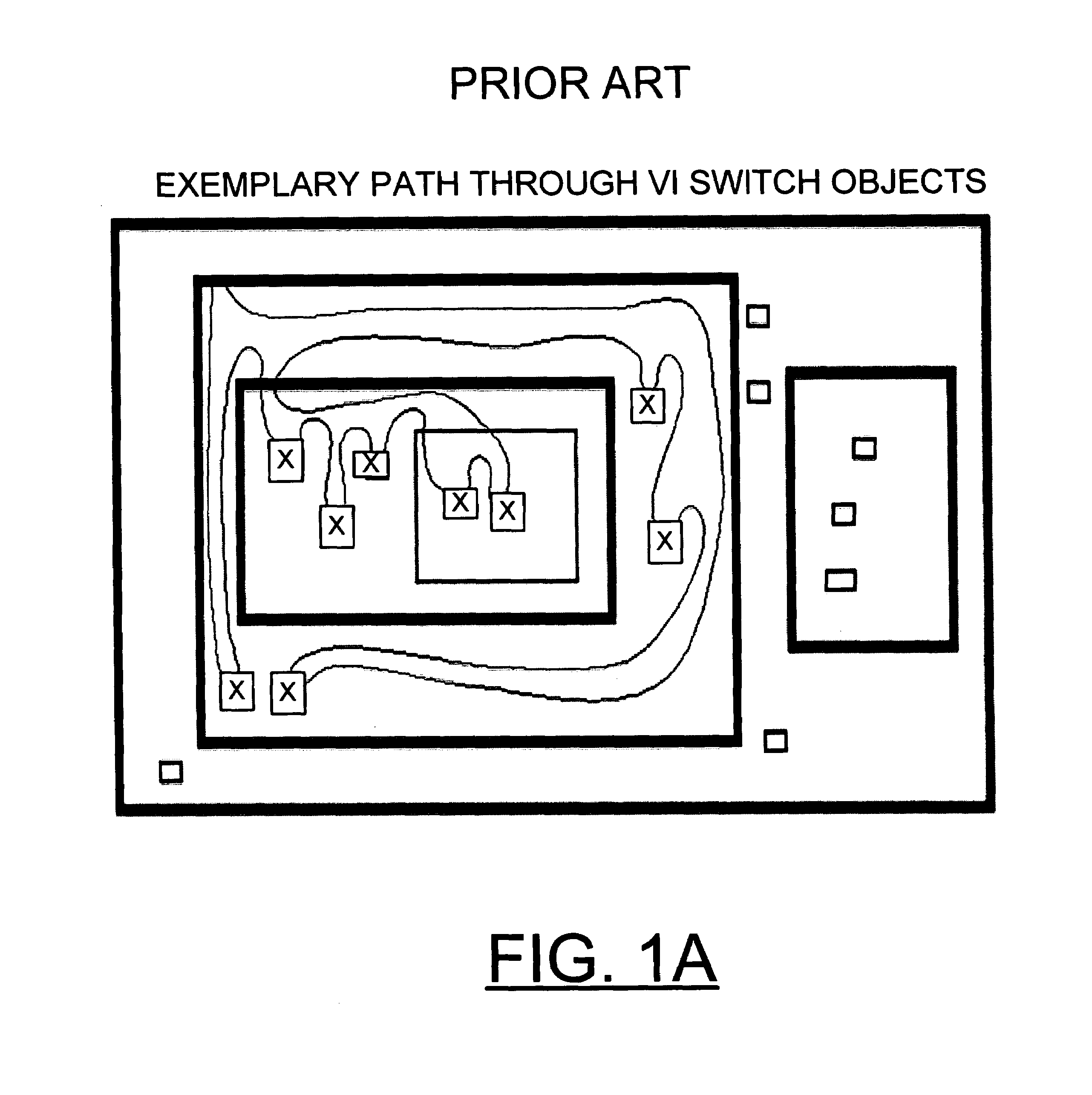

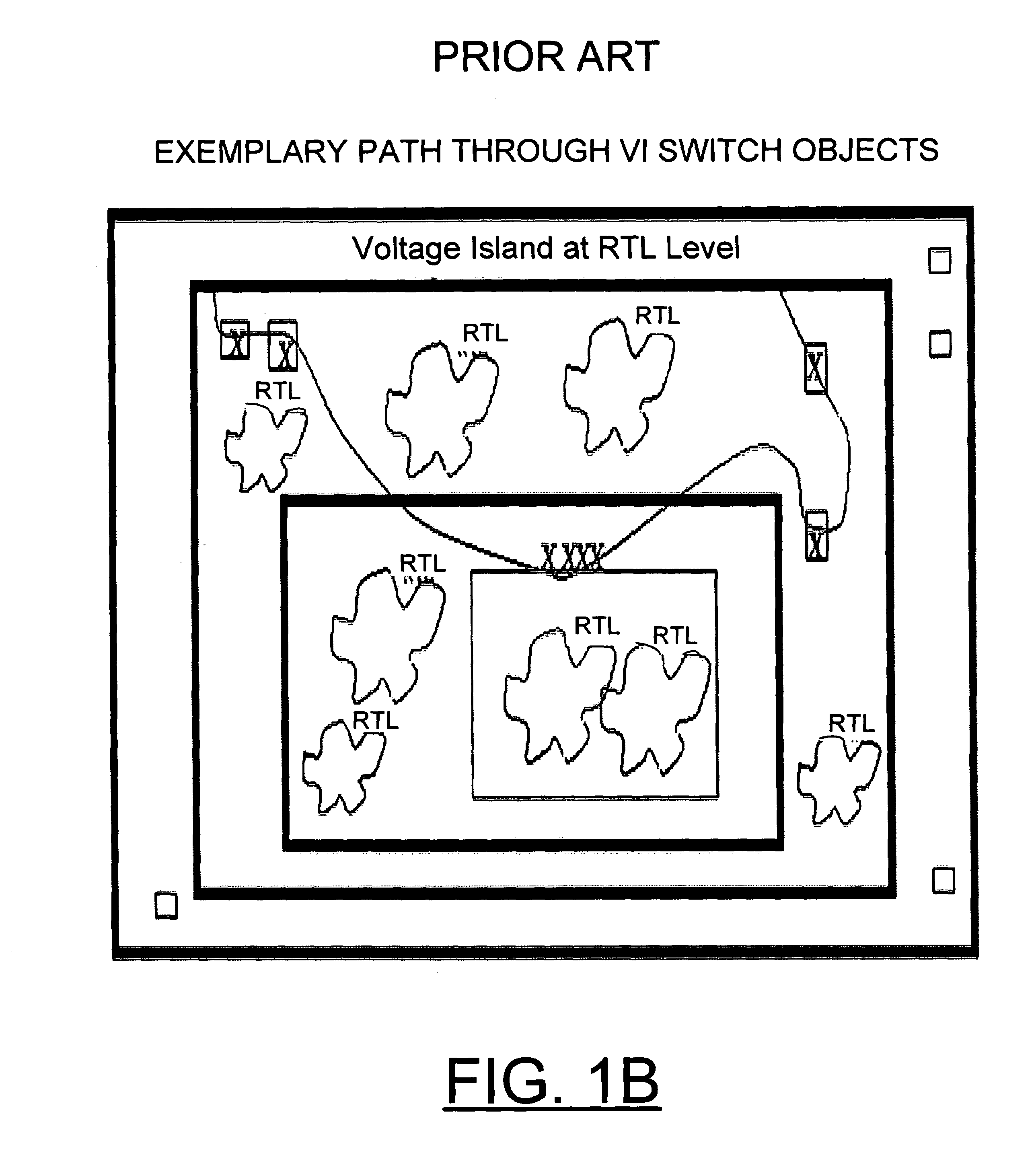

Method, apparatus, and computer program product for RTL power sequencing simulation of voltage islands

InactiveUS7131099B2Detecting faulty computer hardwareAnalogue computers for electric apparatusEngineeringApplication-specific integrated circuit

A method, apparatus and computer program product are provided for implementing RTL power sequencing simulation of voltage islands for application specific integrated circuit (ASIC) designs. RTL sequential state saving elements in a voltage island hierarchy are identified. A state is invalidated for each identified RTL sequential state saving element during a power down operation. Switch objects are used to identify and skip globally powered gate level circuits in the voltage island. RTL sequential state saving elements and VI switch objects can be identified using predefined reserved signal identifiers in the ASIC library.

Owner:INT BUSINESS MASCH CORP

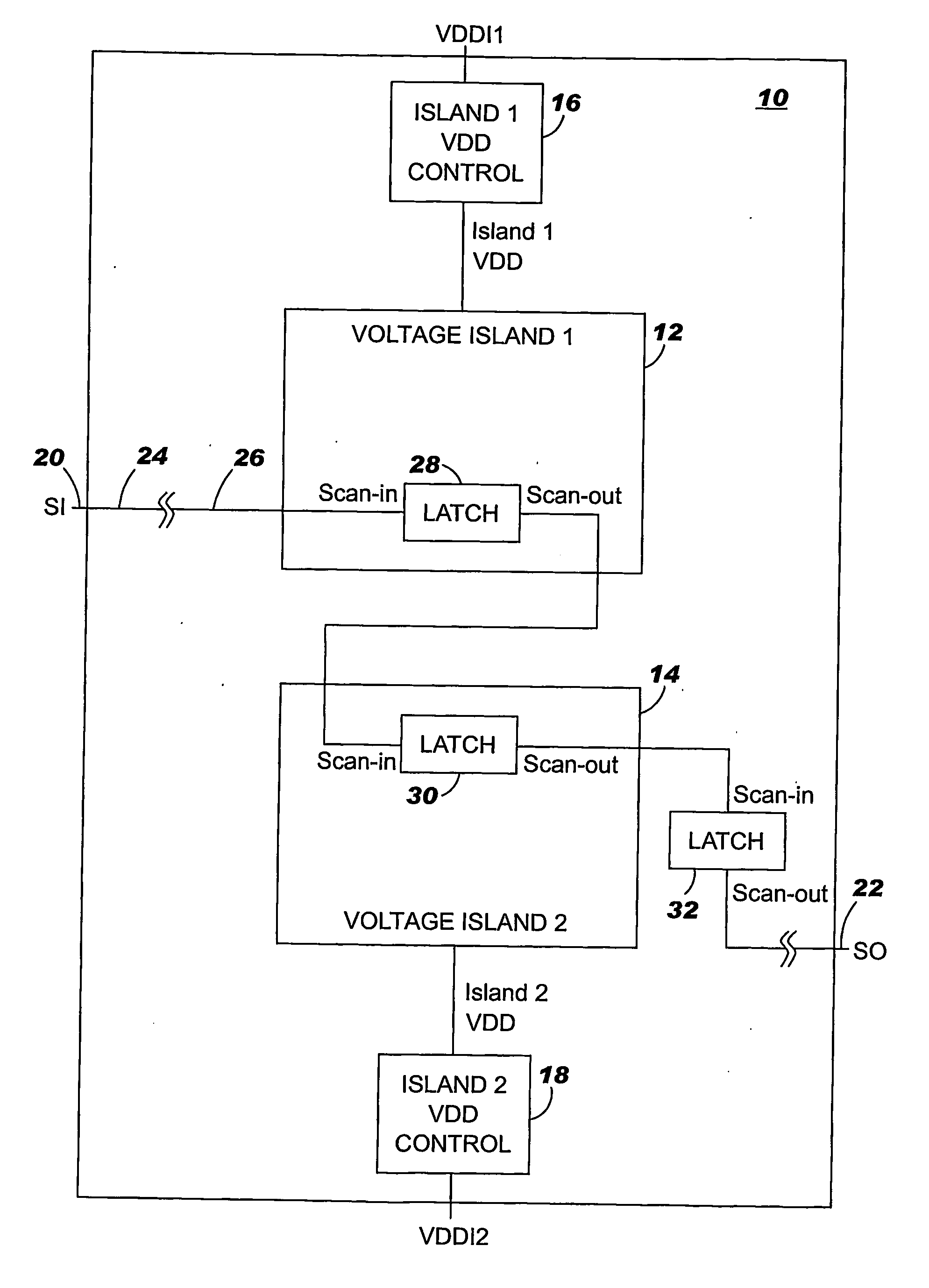

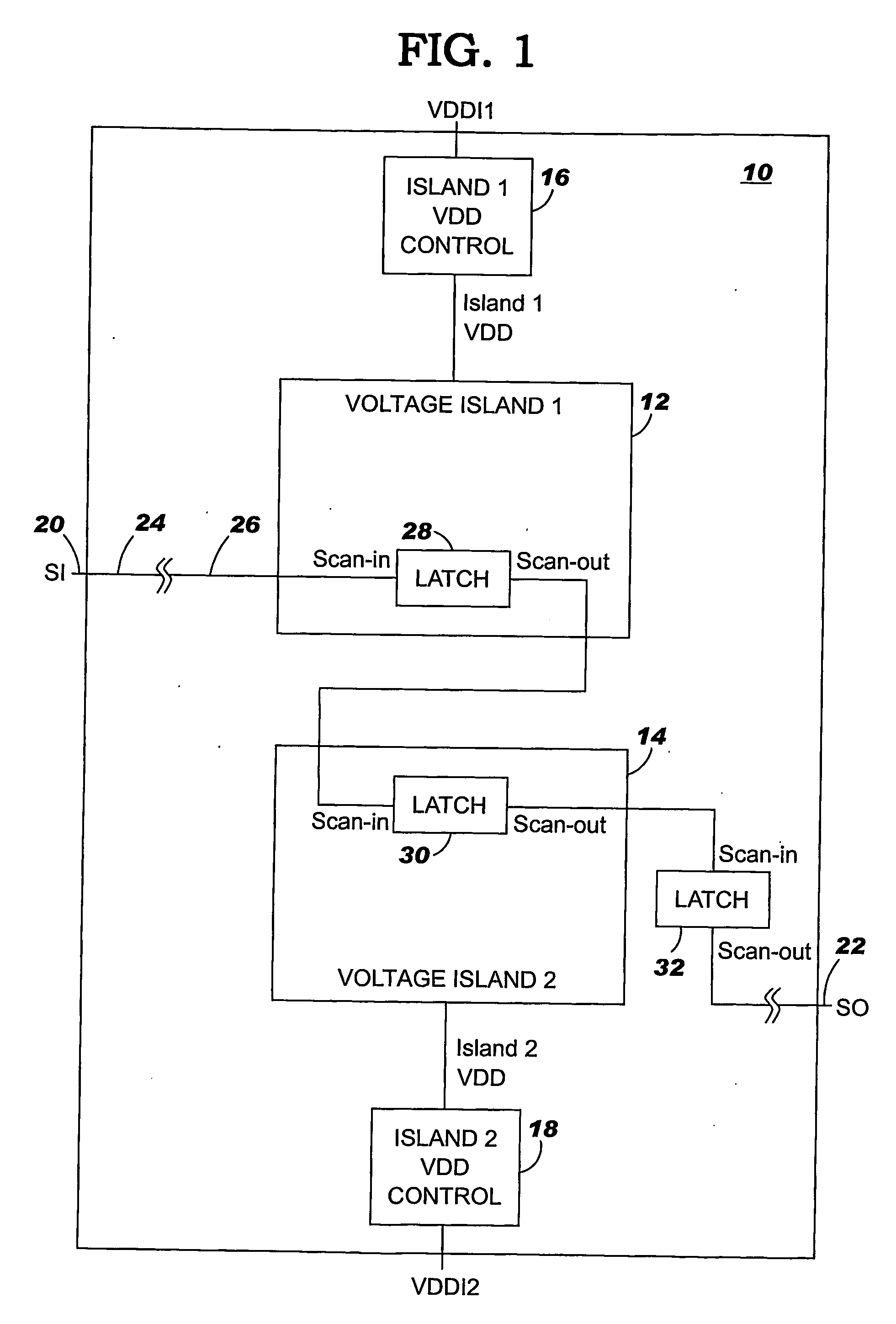

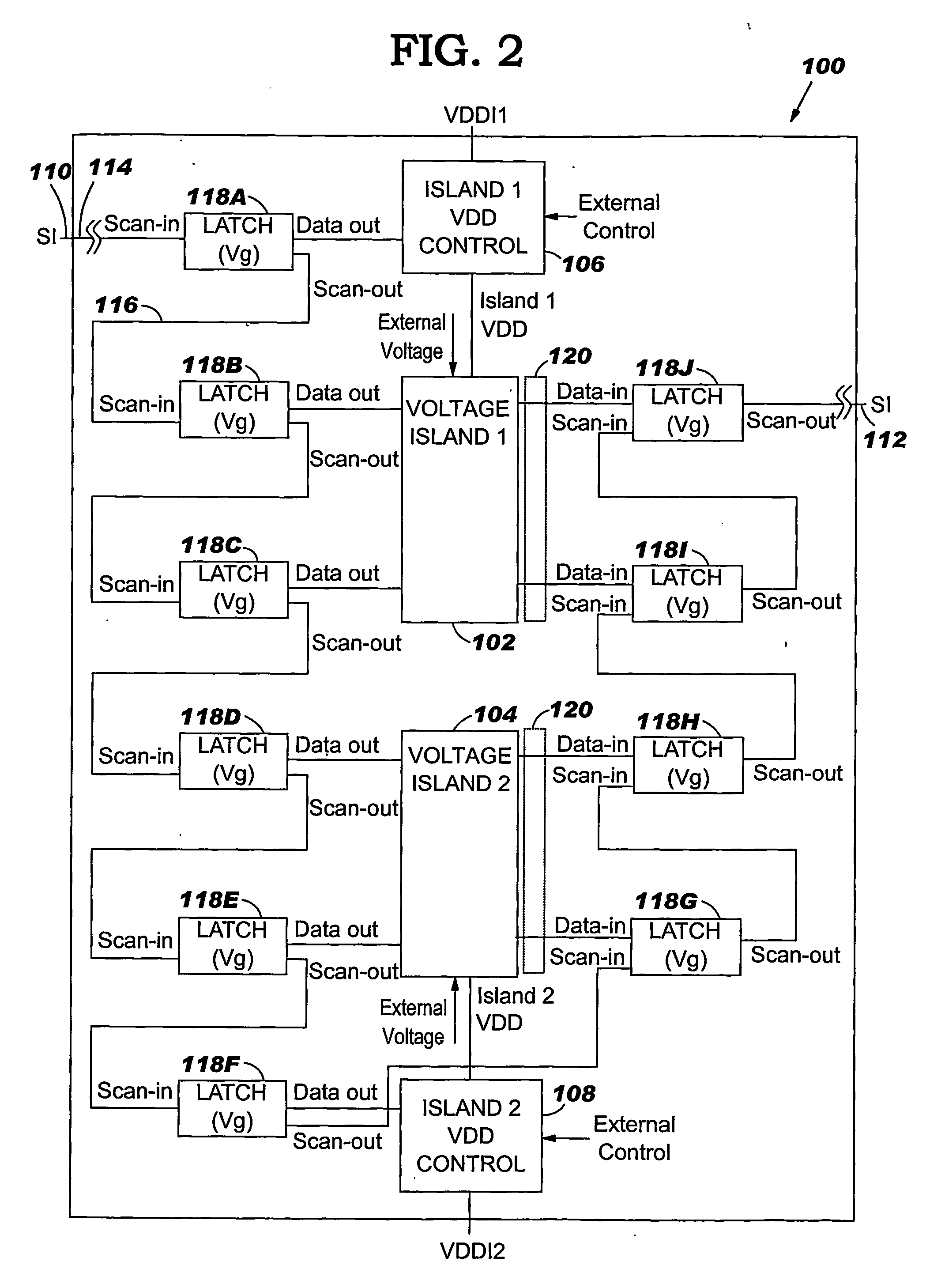

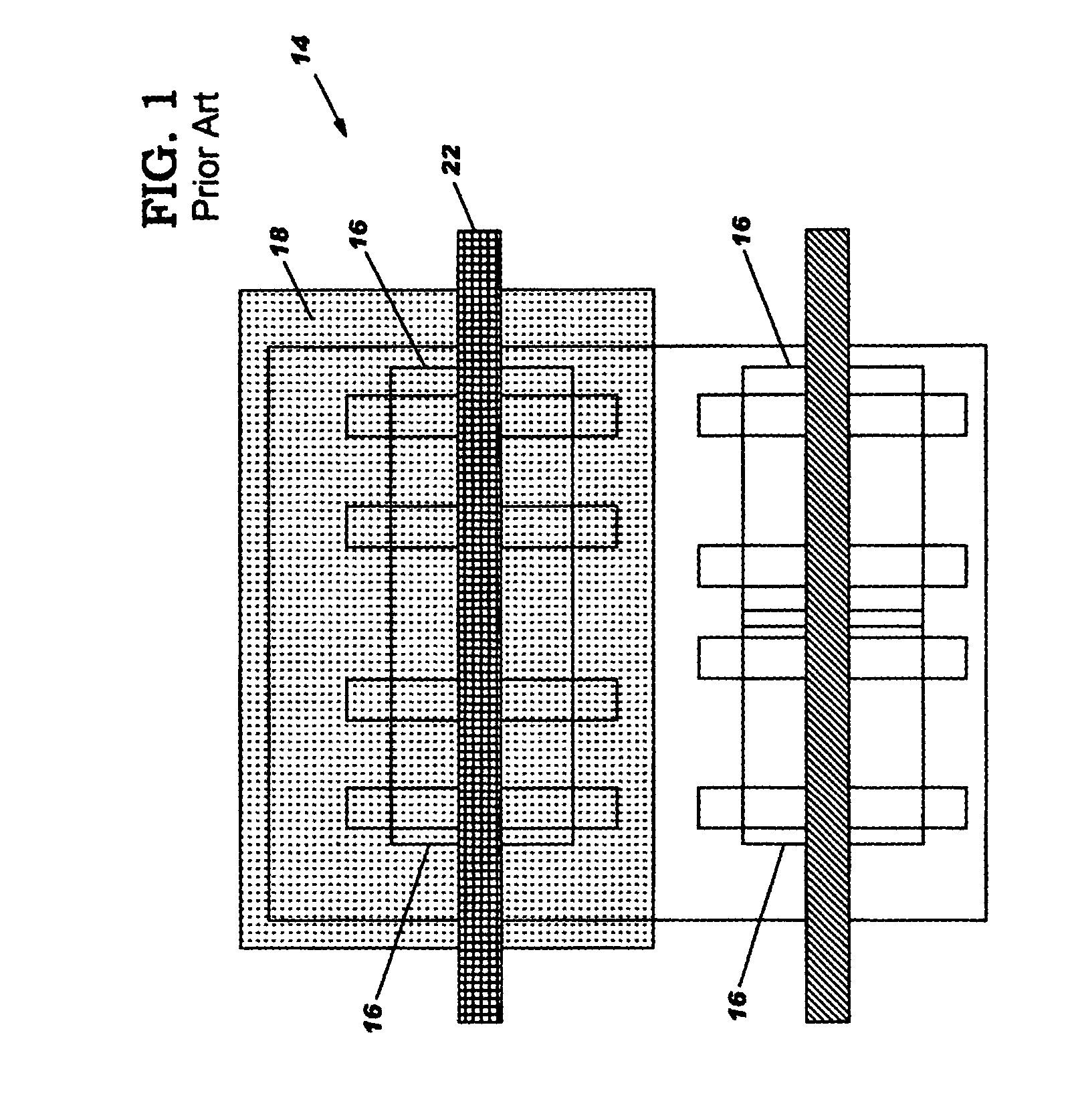

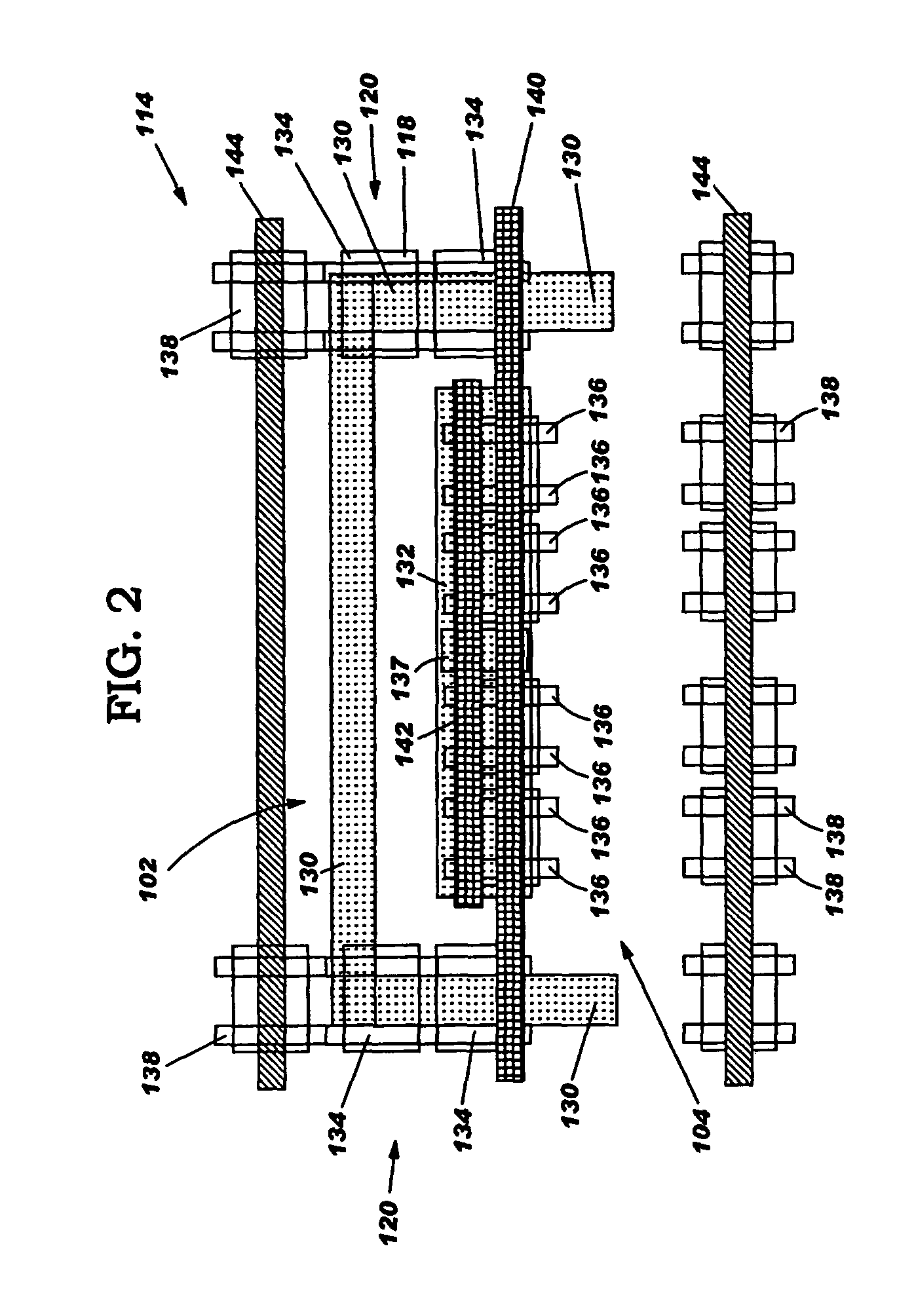

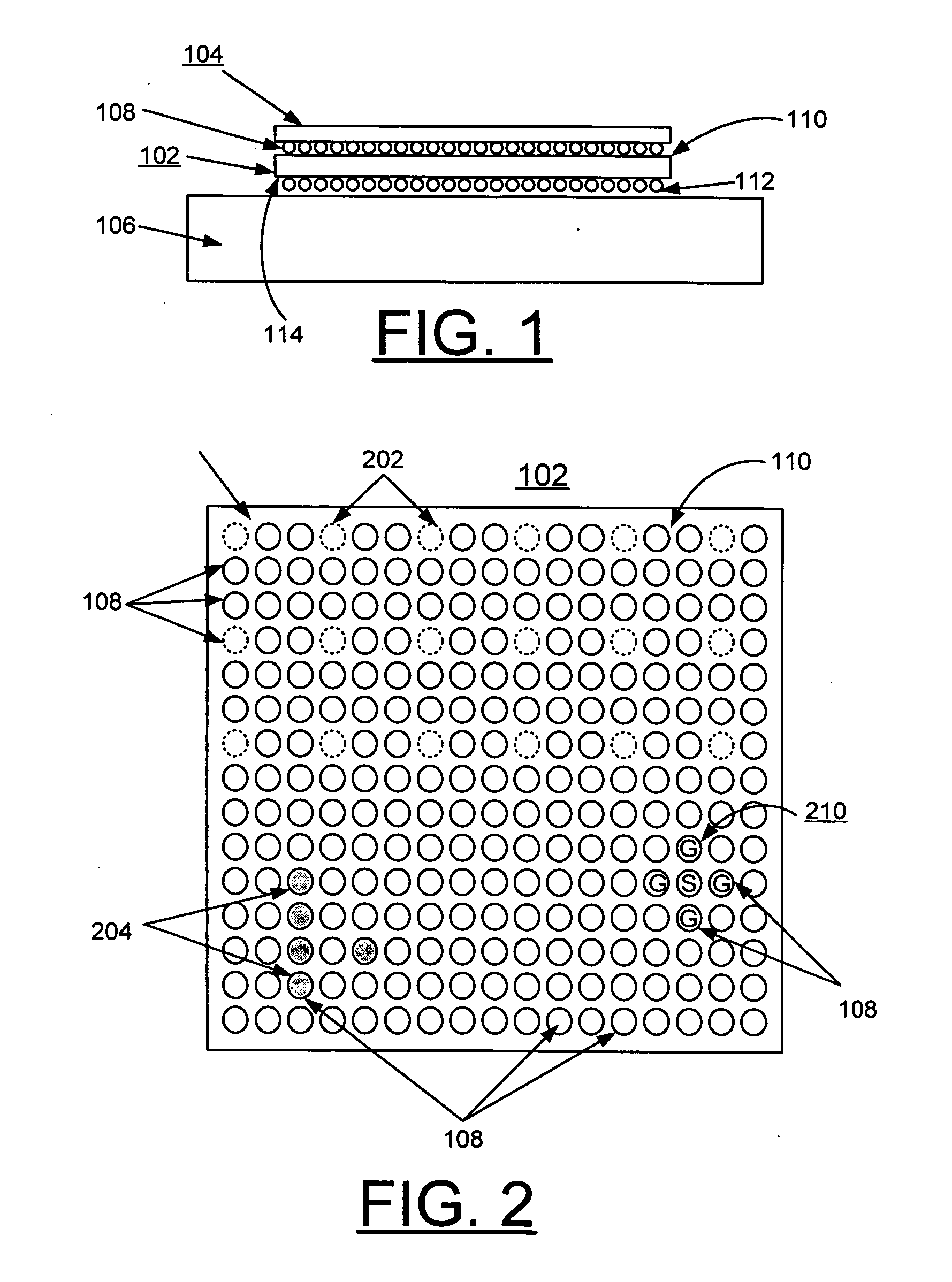

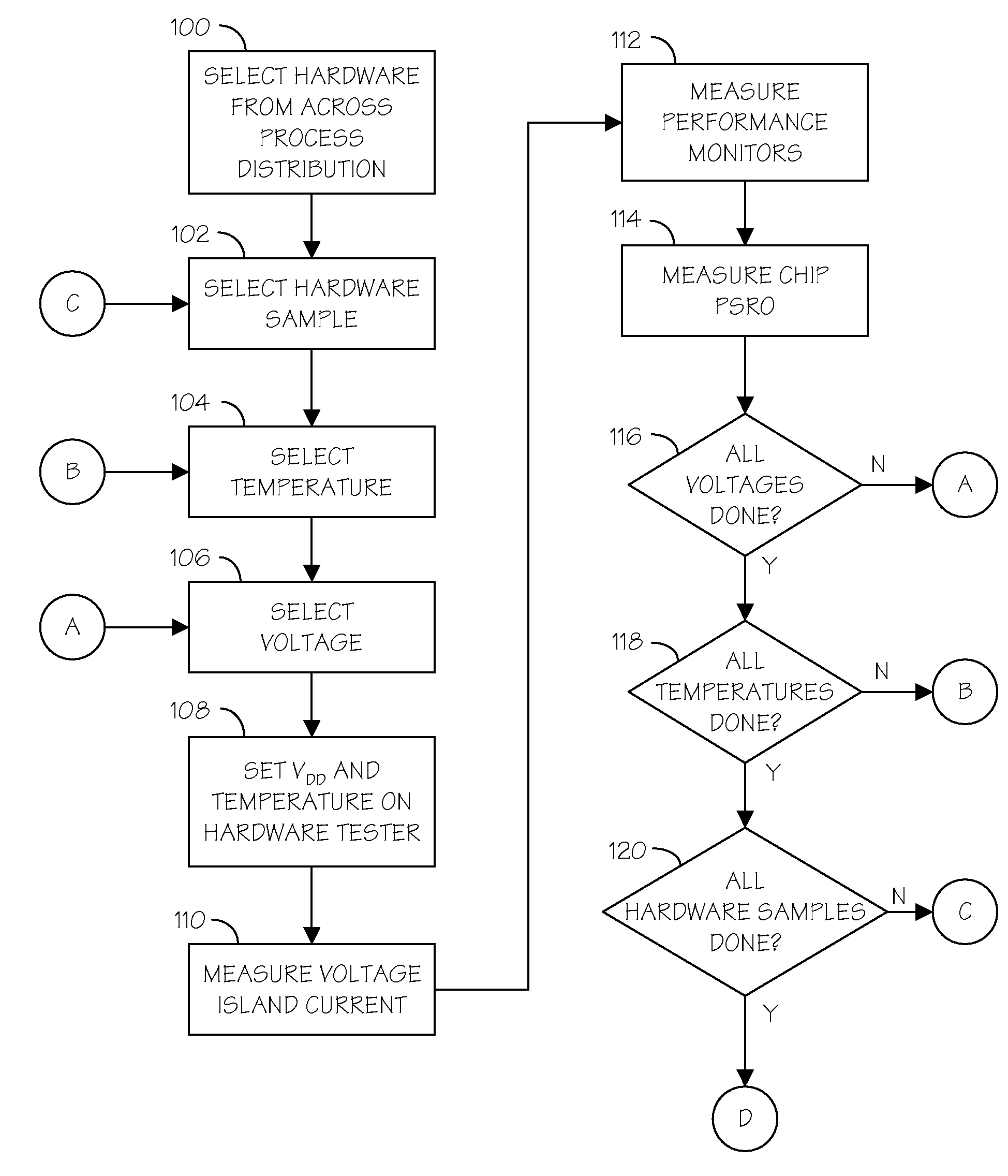

Testing using independently controllable voltage islands

InactiveUS20060158222A1Semiconductor/solid-state device testing/measurementElectronic circuit testingVoltage islandsEngineering

A voltage island architecture wherein the source voltage of each voltage island can be independently turned on / off or adjusted during a scan-based test. The architecture includes a plurality of voltage islands (102, 104), each powered by a respective island source voltage (VDDI1, VDDI2), and a testing circuit (116), coupled to the voltage islands, and powered by a global source voltage (Vg) that is always on during test, wherein each island source voltage may be independently controlled (106, 108) during test.

Owner:IBM CORP

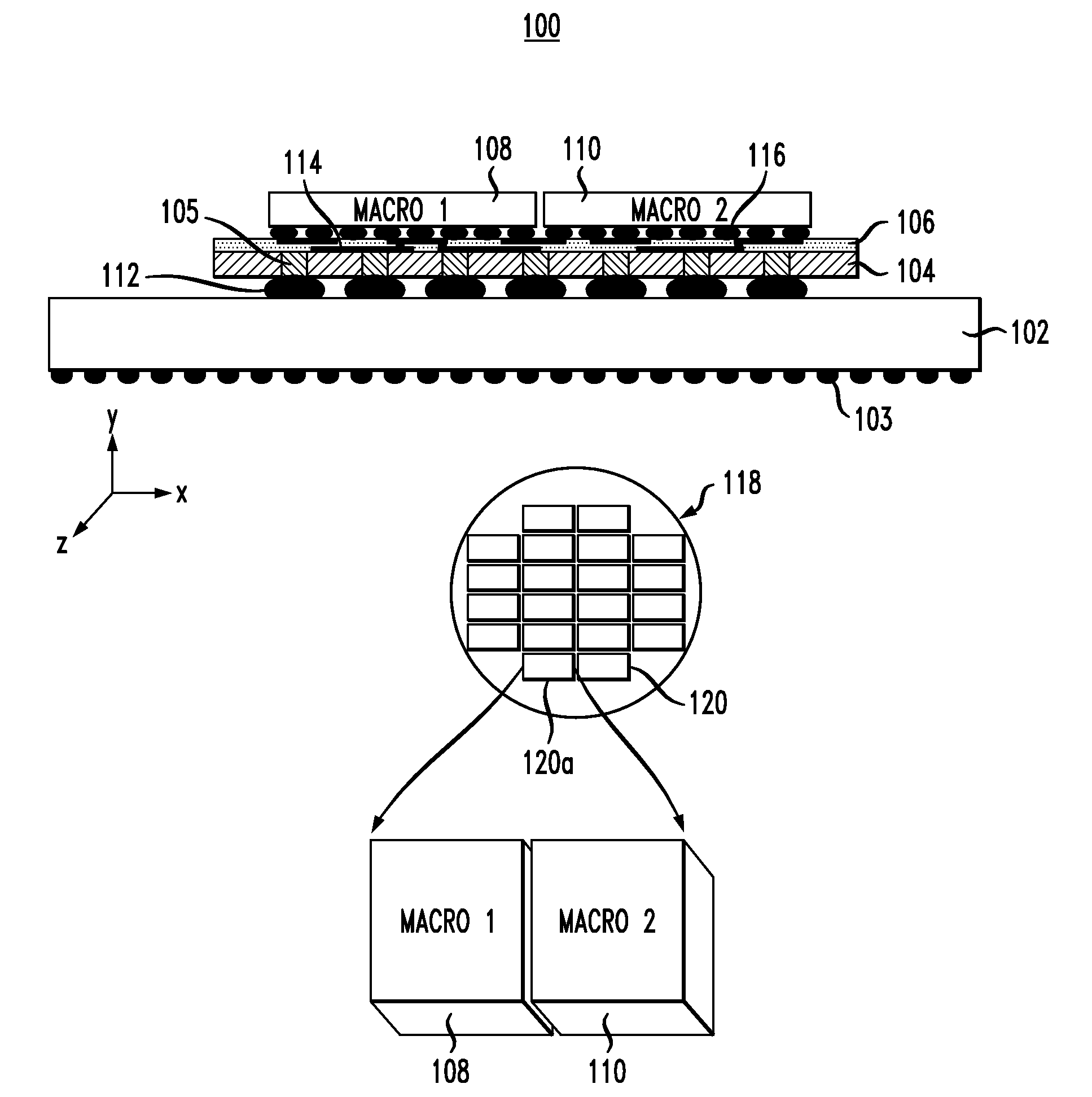

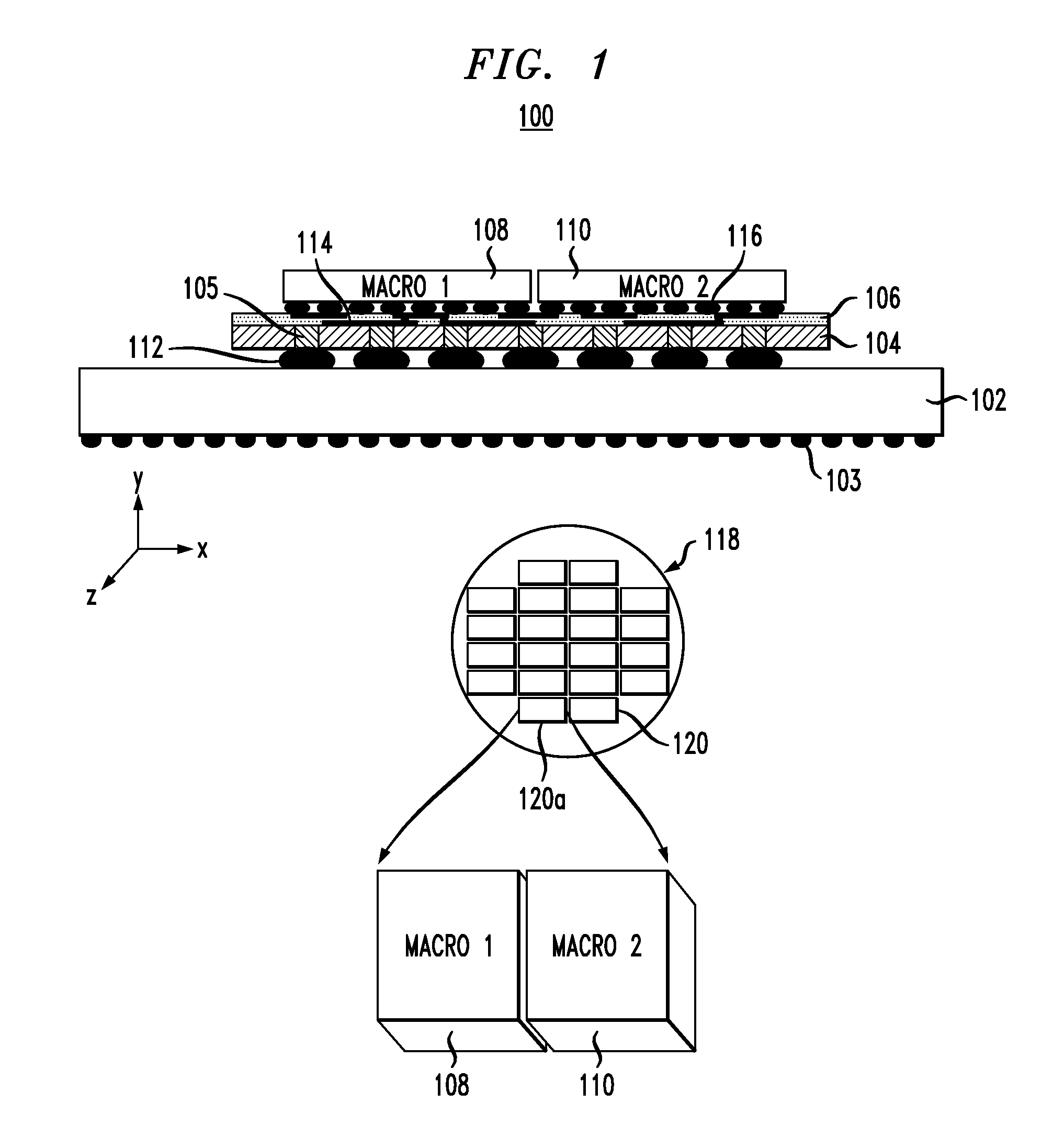

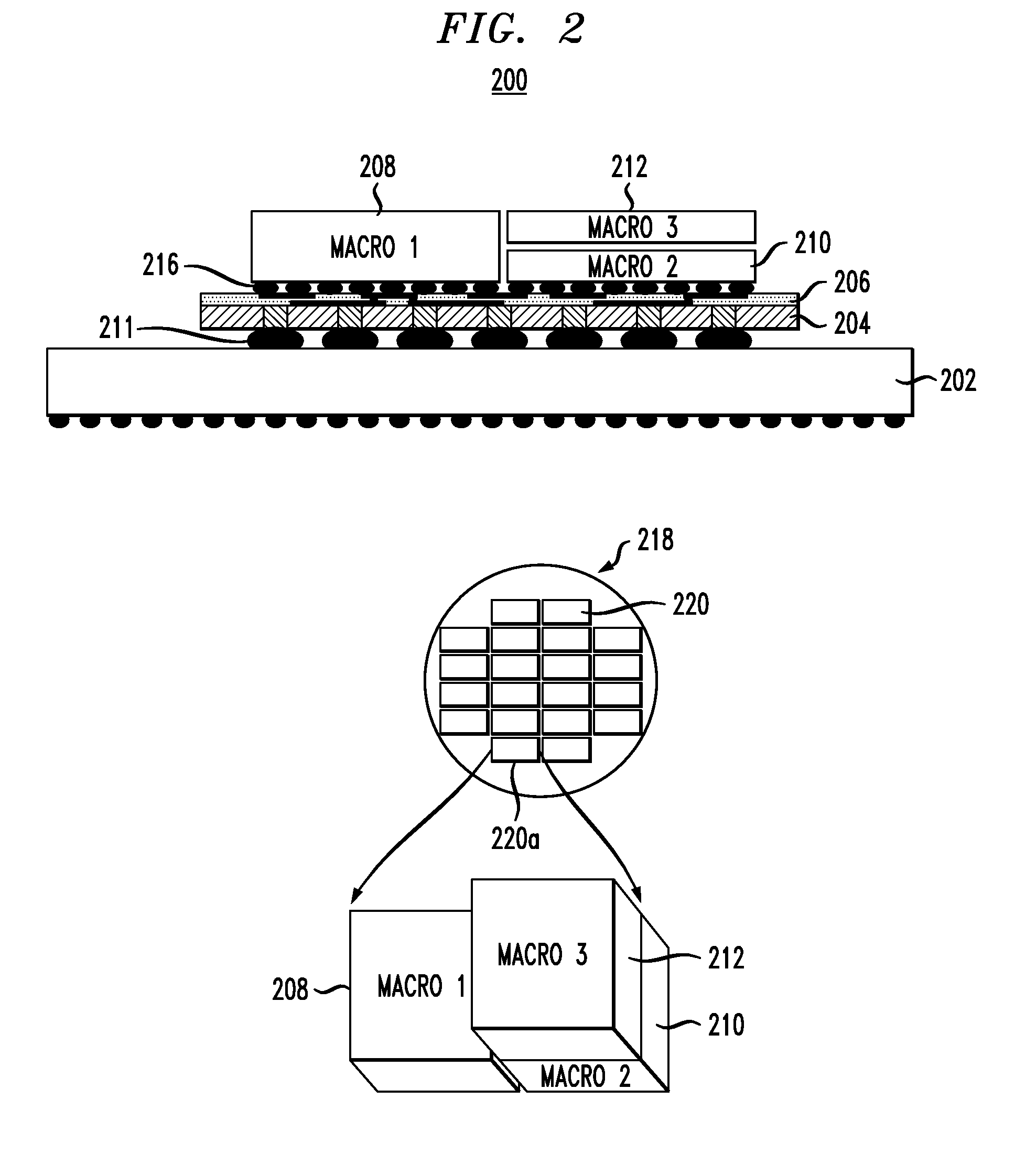

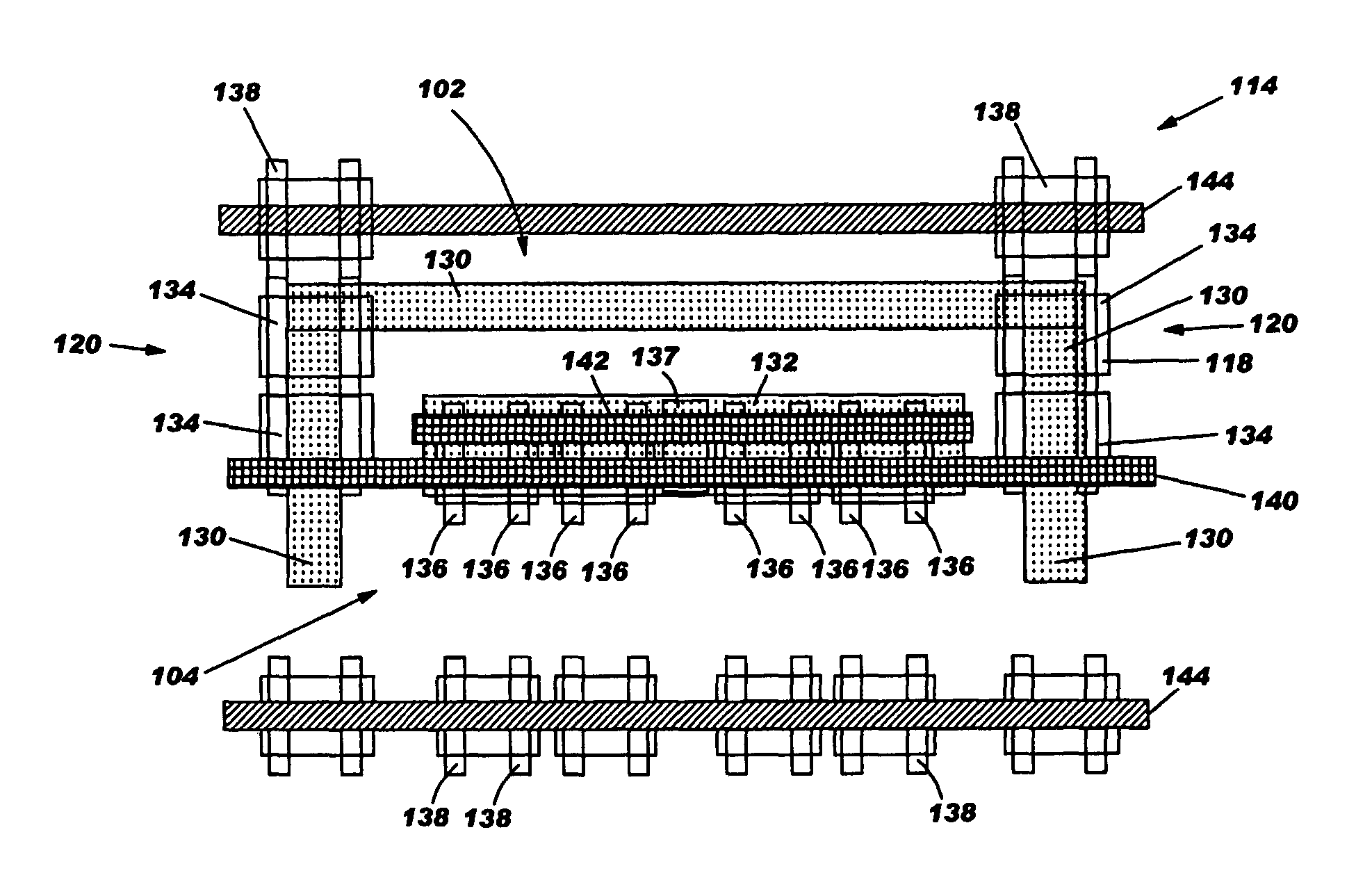

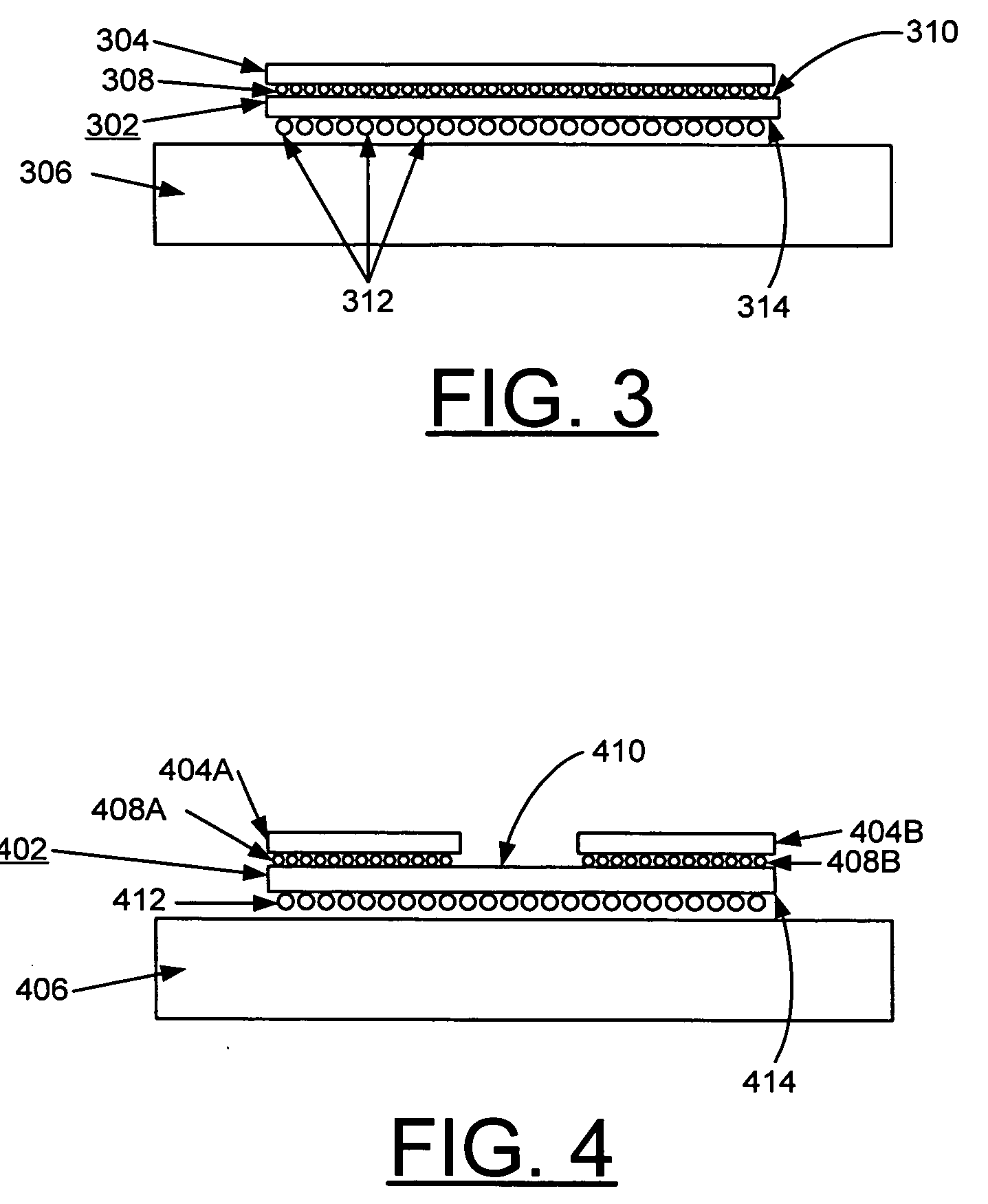

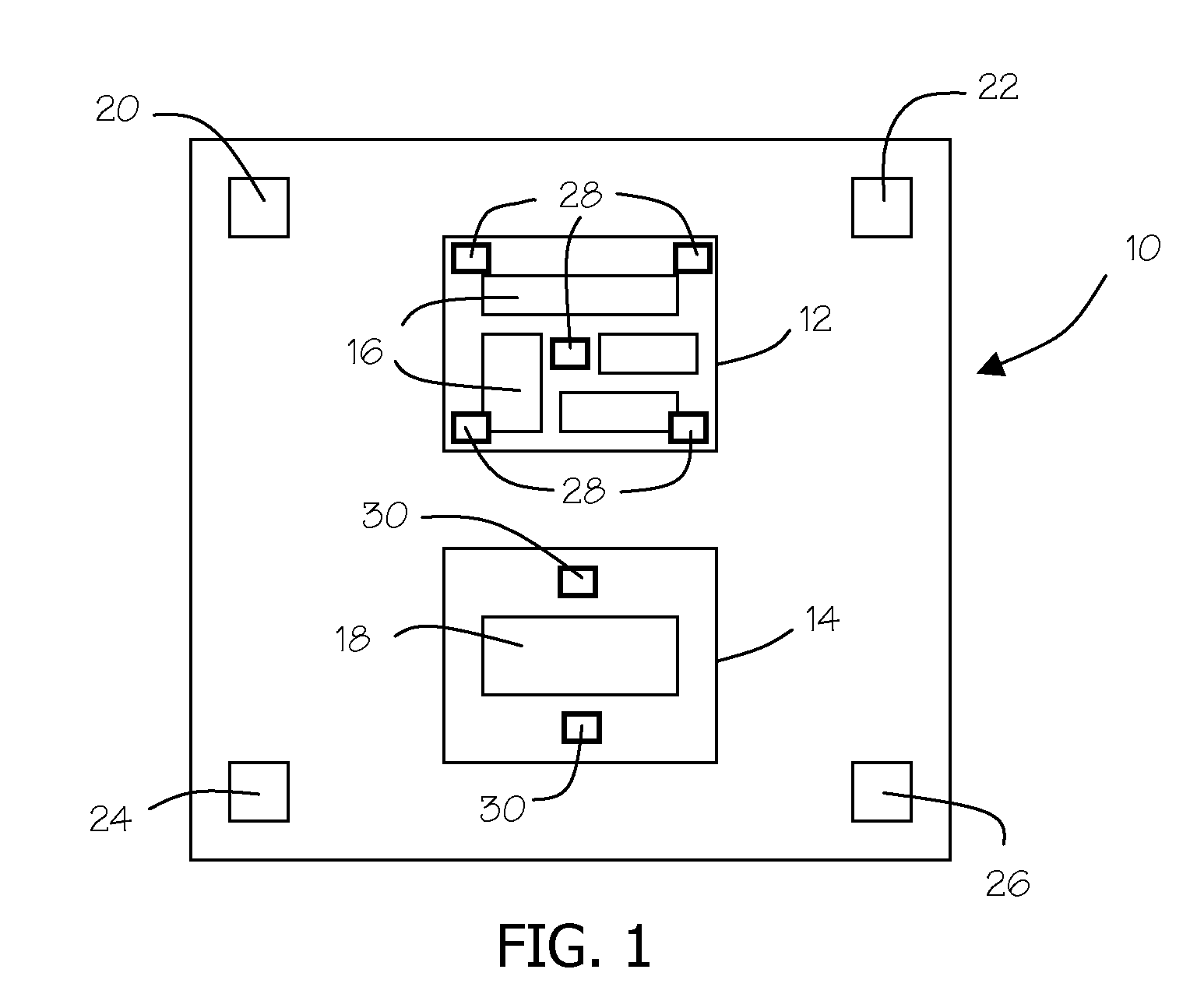

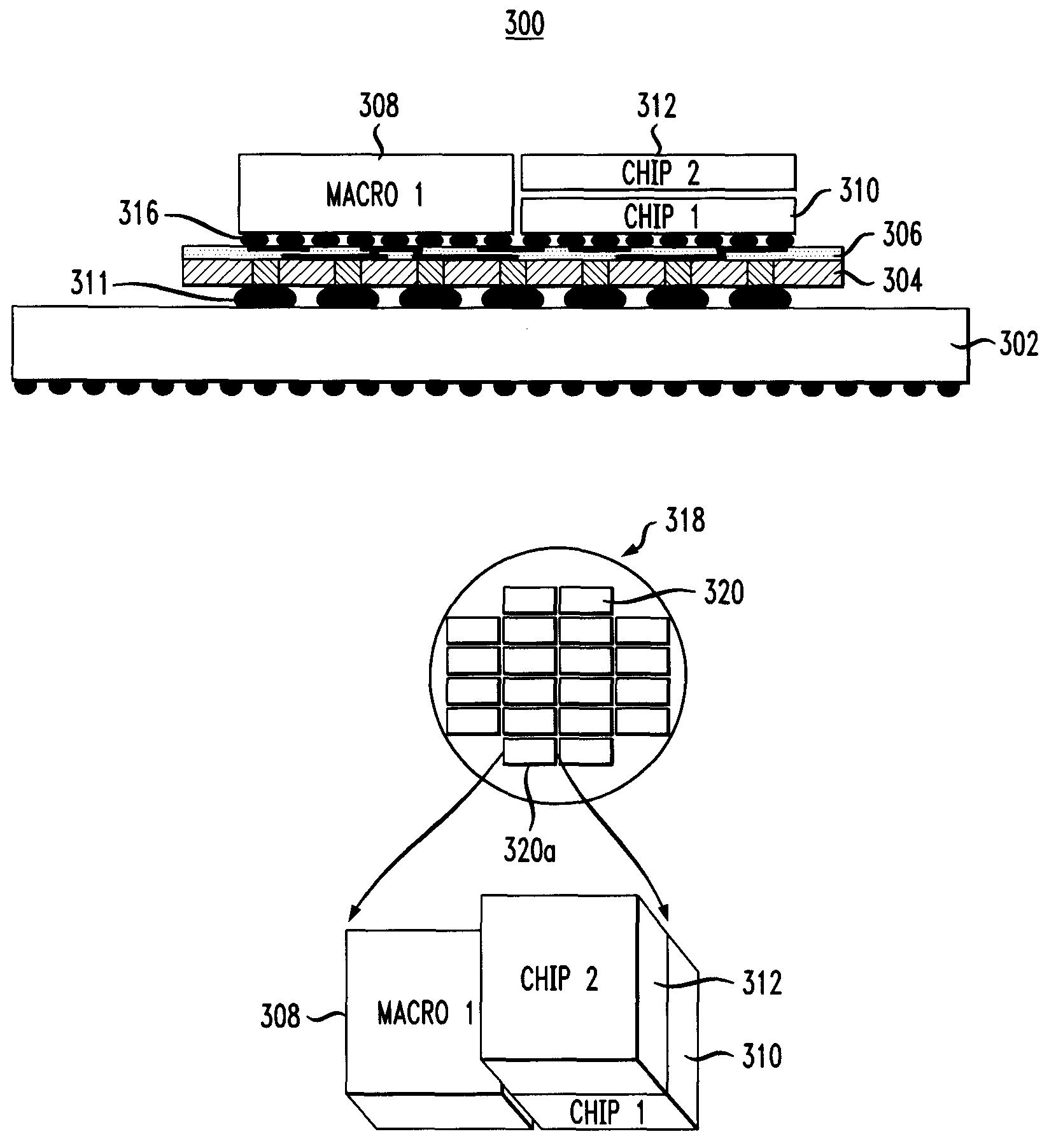

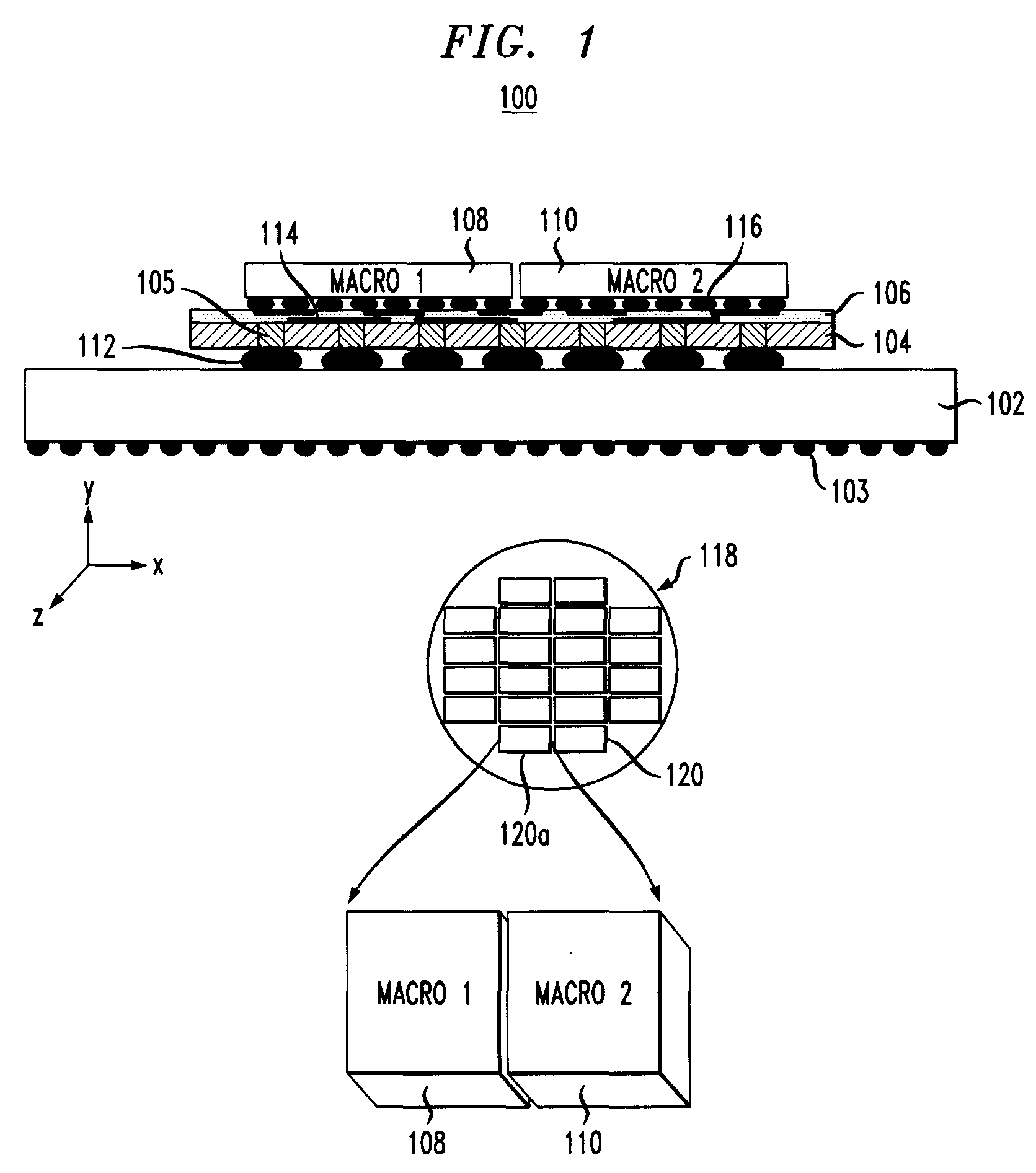

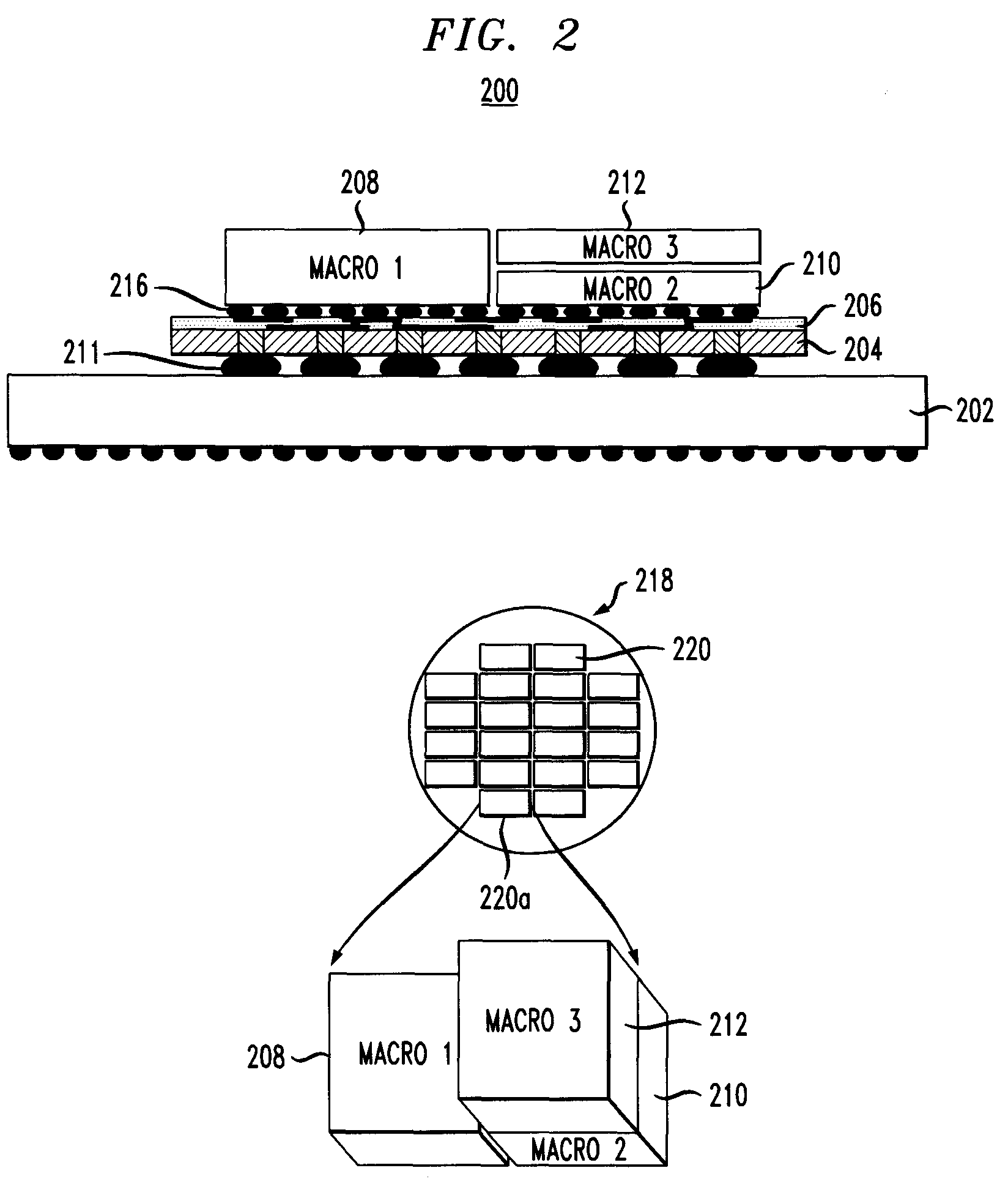

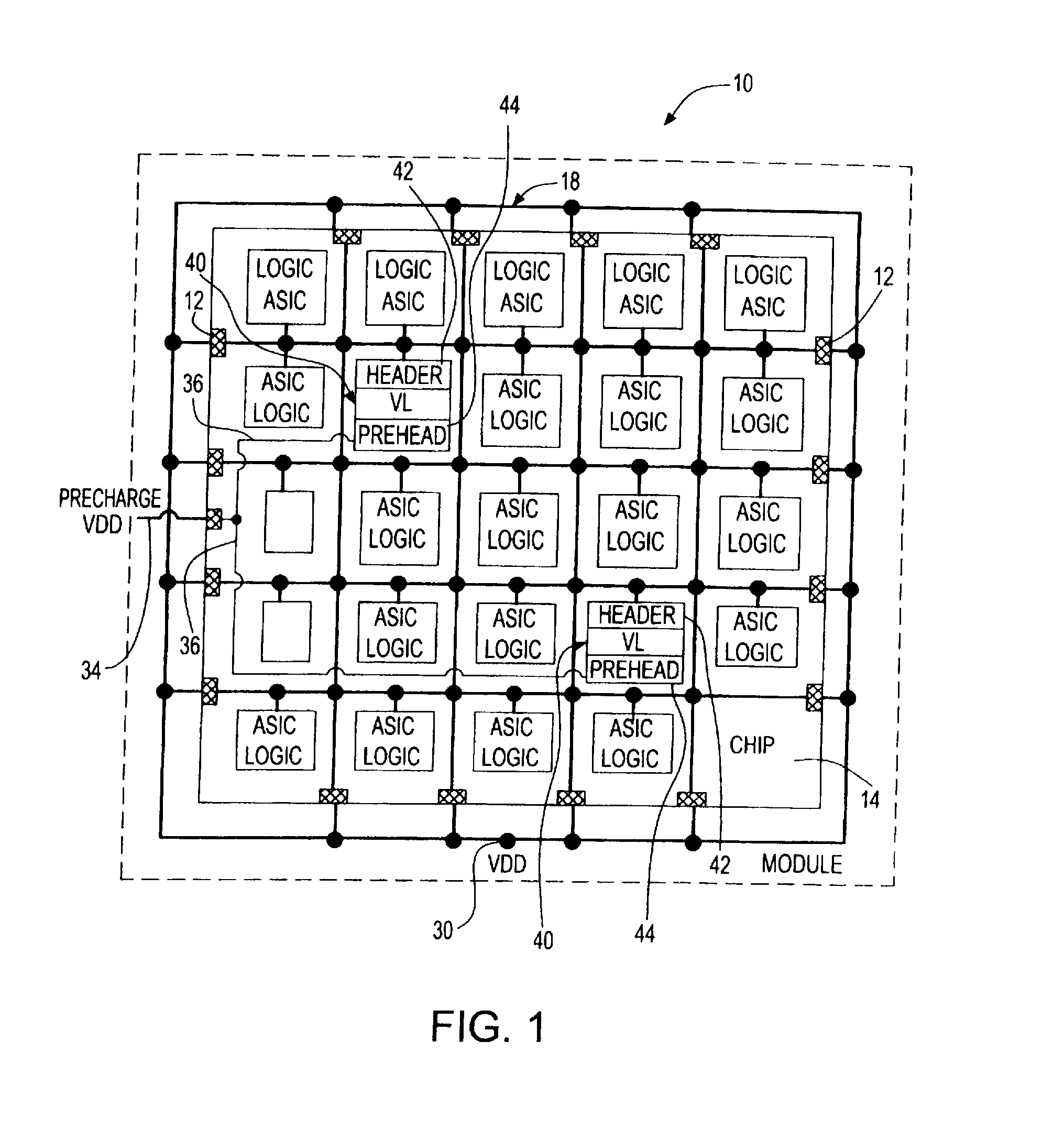

Techniques for Modular Chip Fabrication

ActiveUS20090108427A1Semiconductor/solid-state device detailsSolid-state devicesModularityVoltage islands

Techniques for modular chip fabrication are provided. In one aspect, a modular chip structure is provided. The modular chip structure comprises a substrate; a carrier platform attached to the substrate, the carrier platform comprising a plurality of conductive vias extending through the carrier platform; and a wiring layer on the carrier platform in contact with one or more of the conductive vias, wherein the wiring layer comprises one or more wiring levels and is configured to divide the carrier platform into a plurality of voltage islands; and chips, chip macros or at least one chip in combination with at least one chip macro assembled on the carrier platform.

Owner:IBM CORP

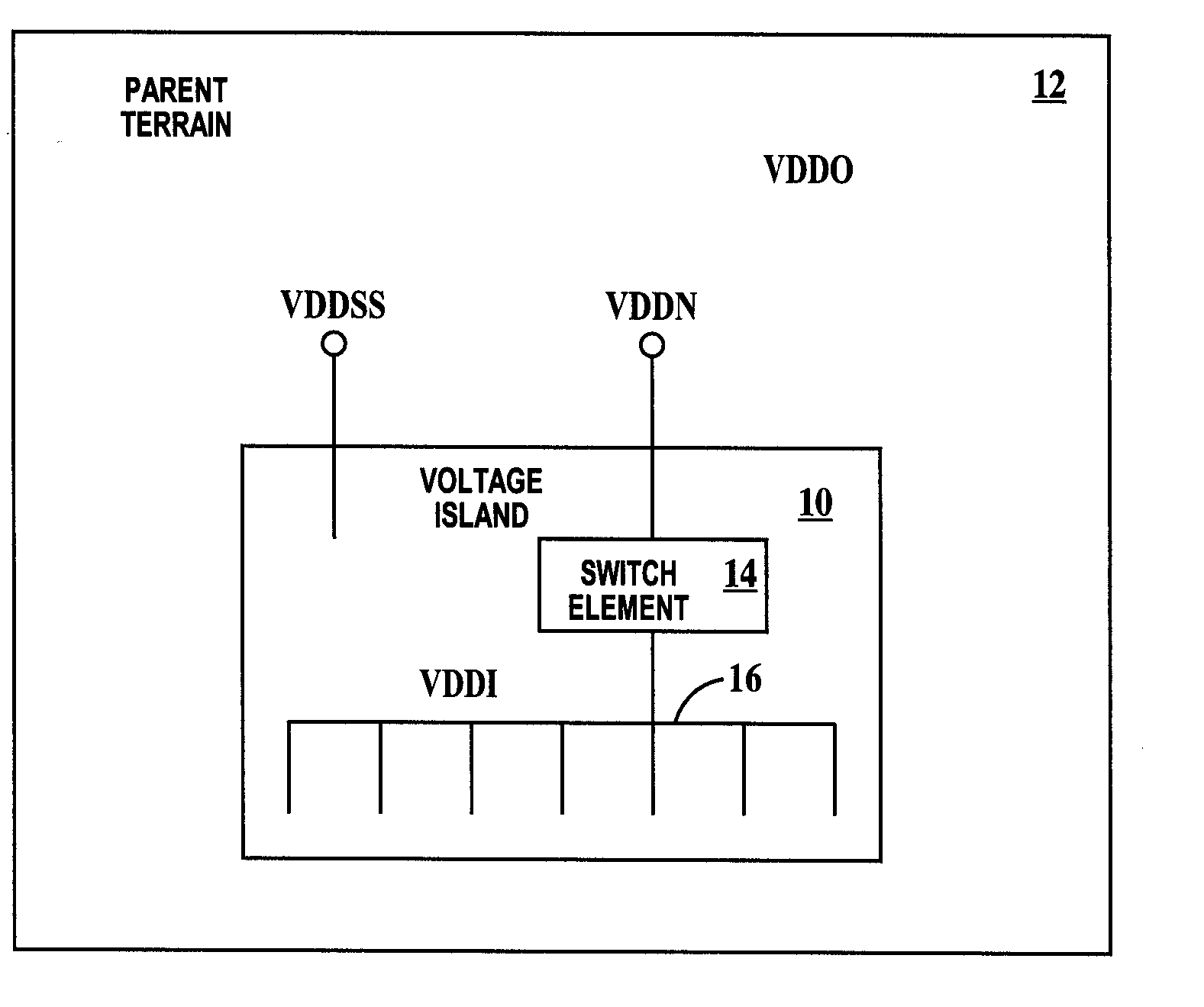

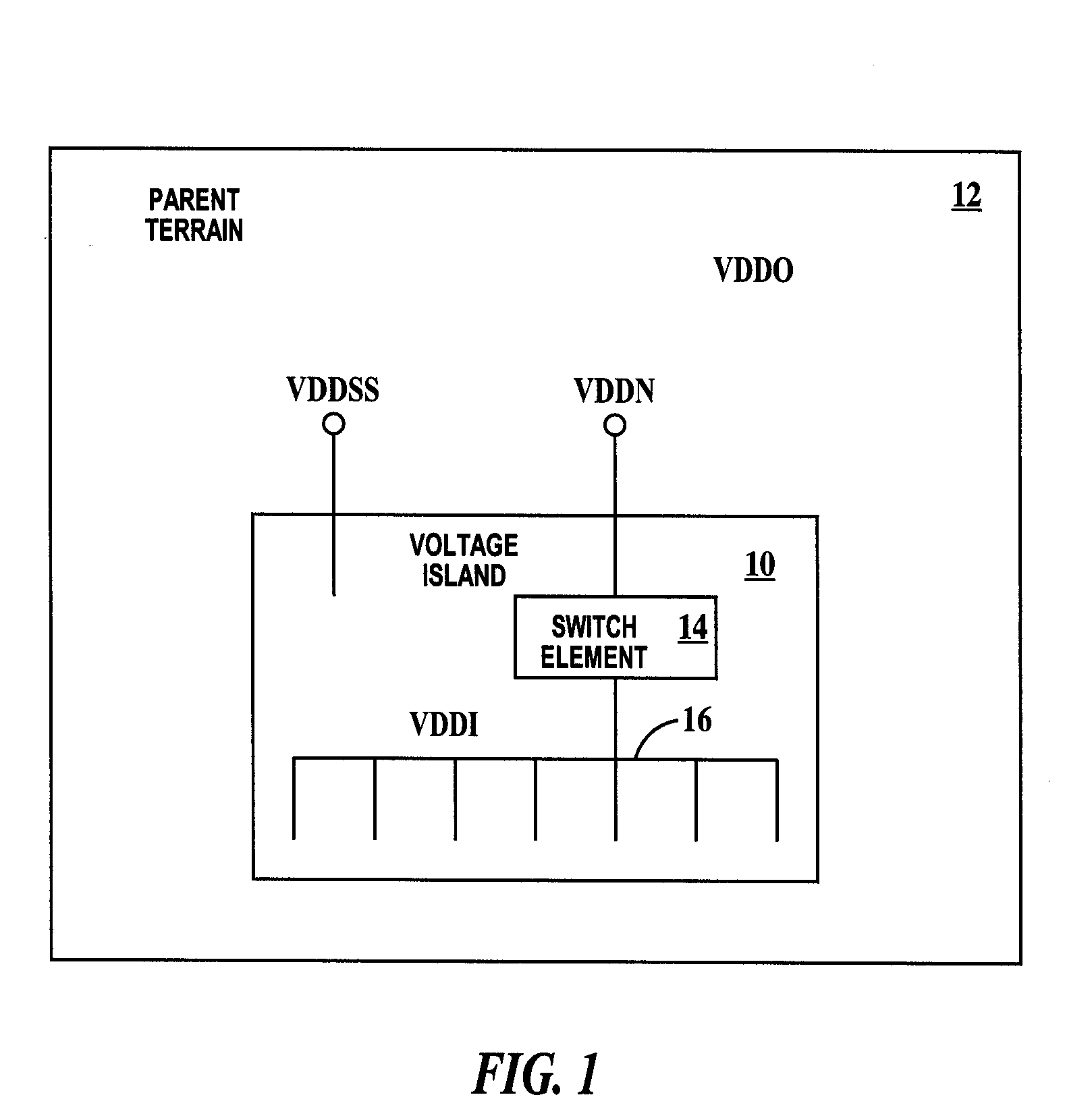

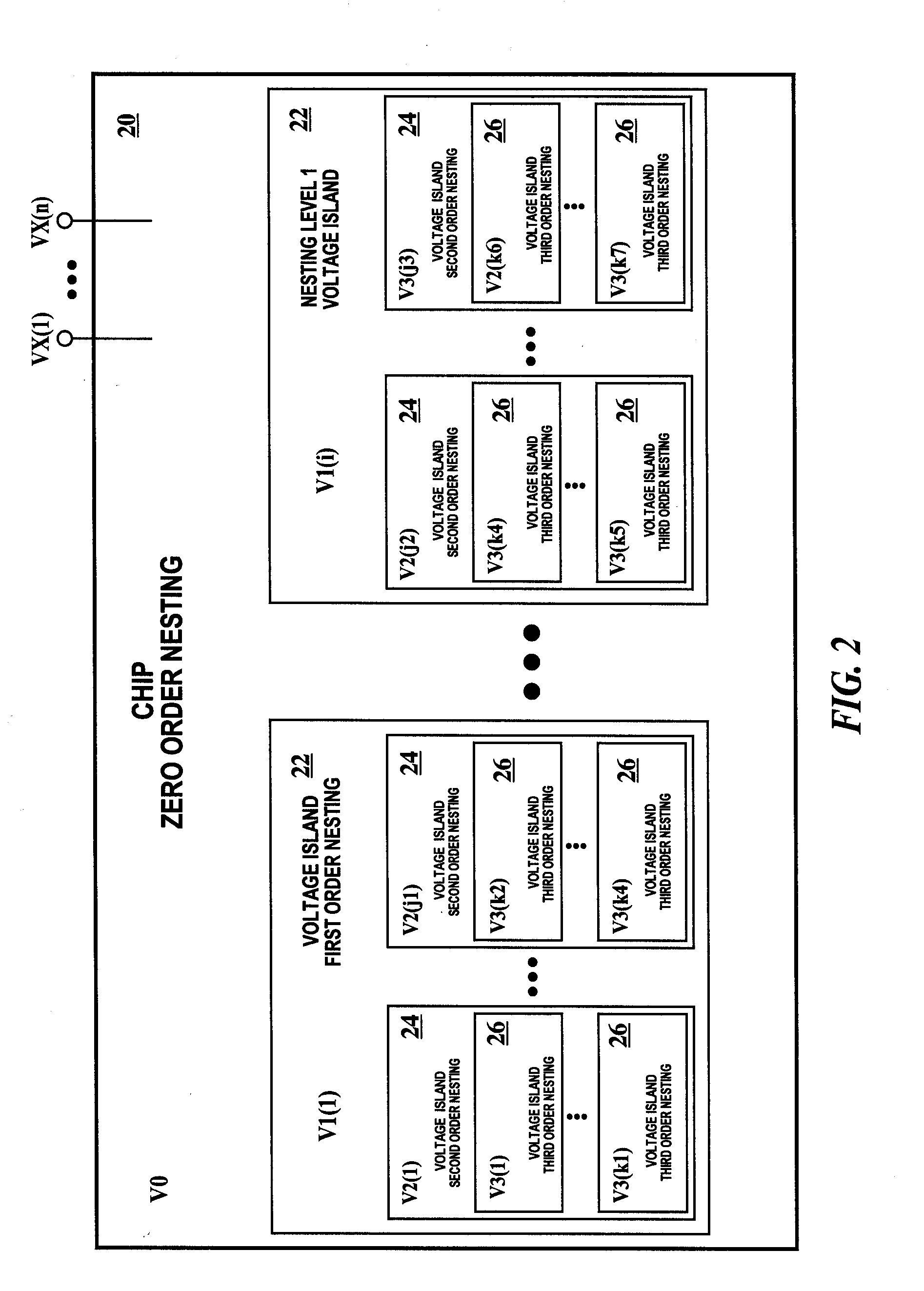

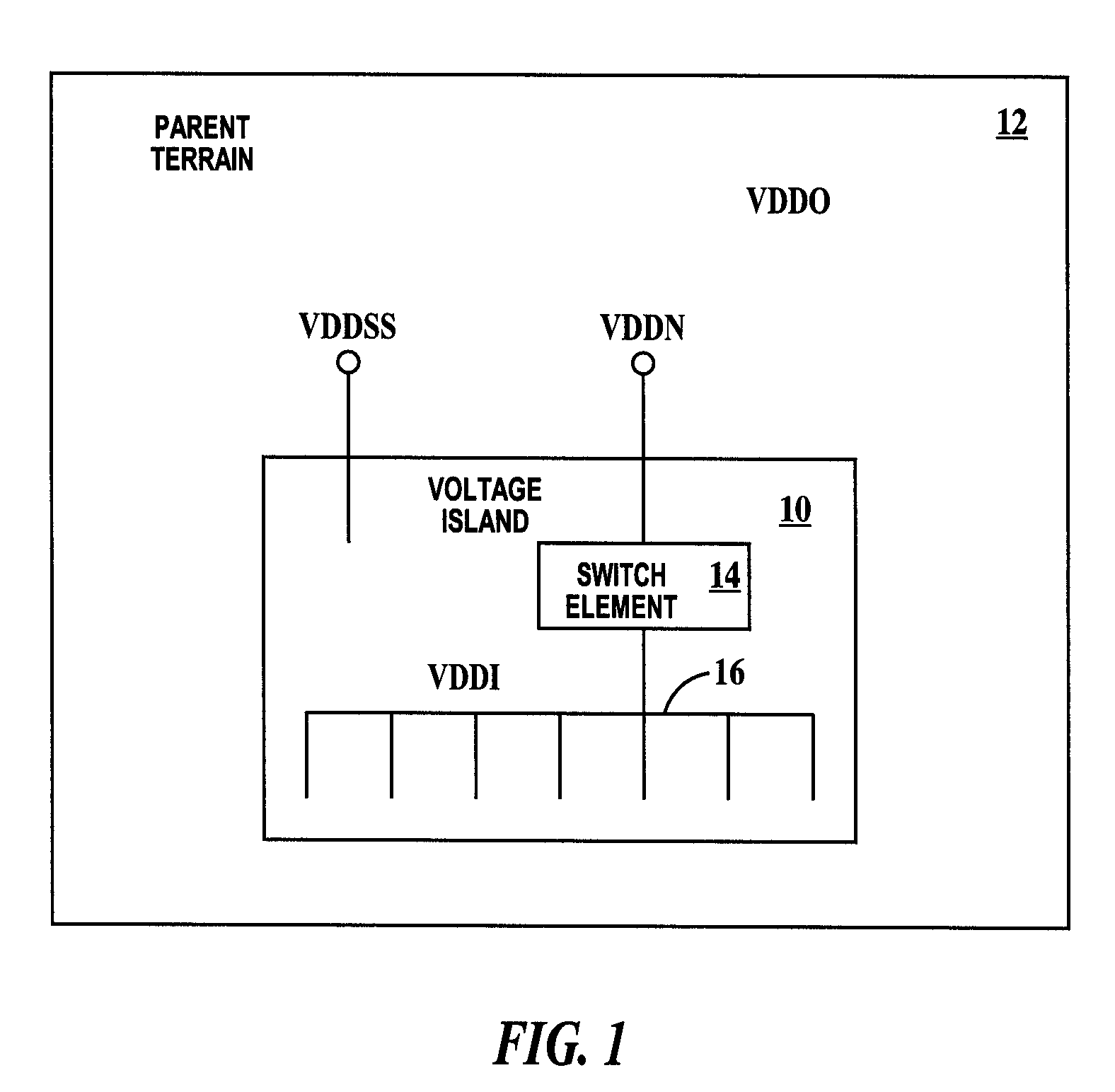

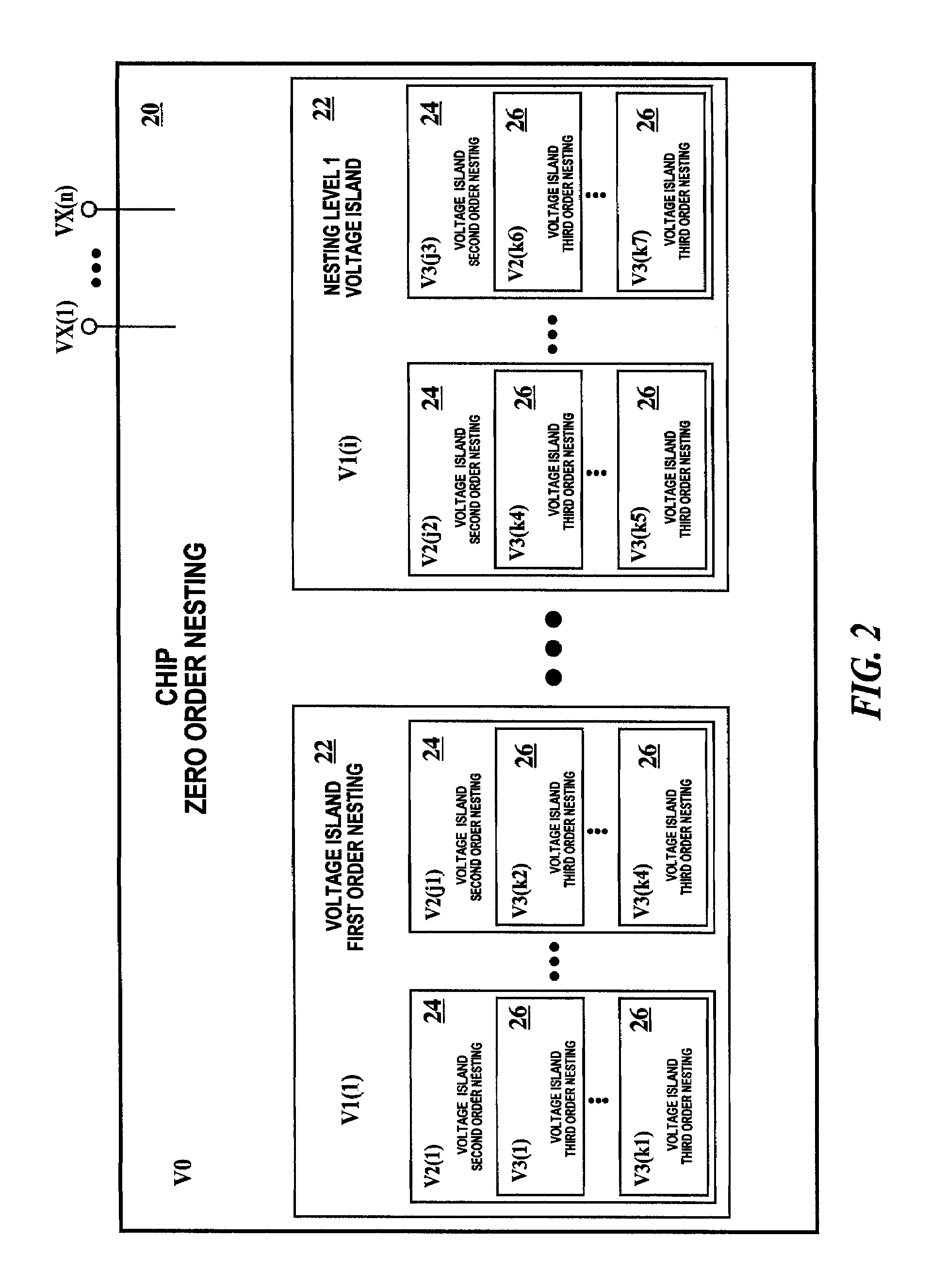

Nested voltage island architecture

InactiveUS20050010887A1Semiconductor/solid-state device detailsSolid-state devicesTerrainEngineering

Owner:MARVELL ASIA PTE LTD

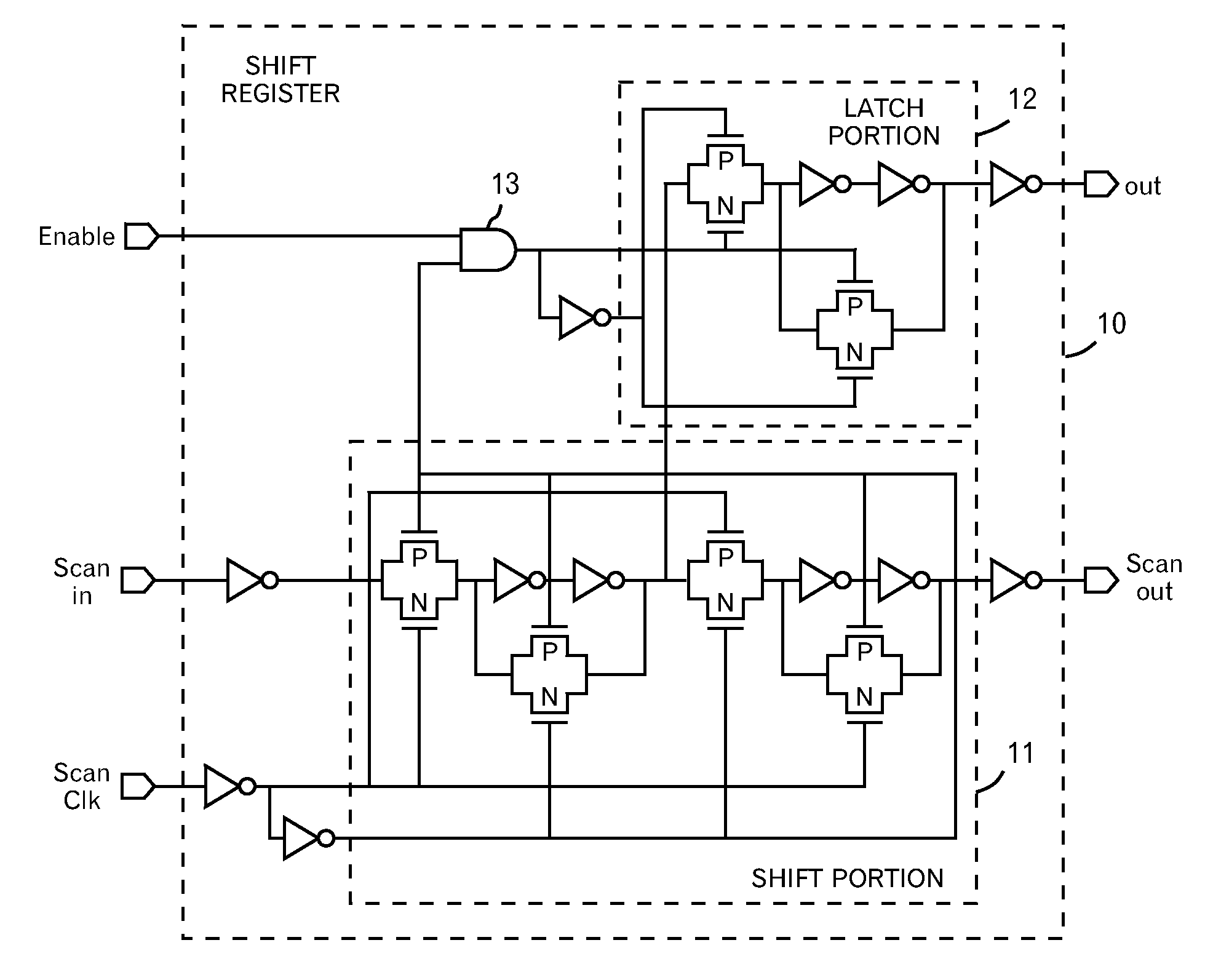

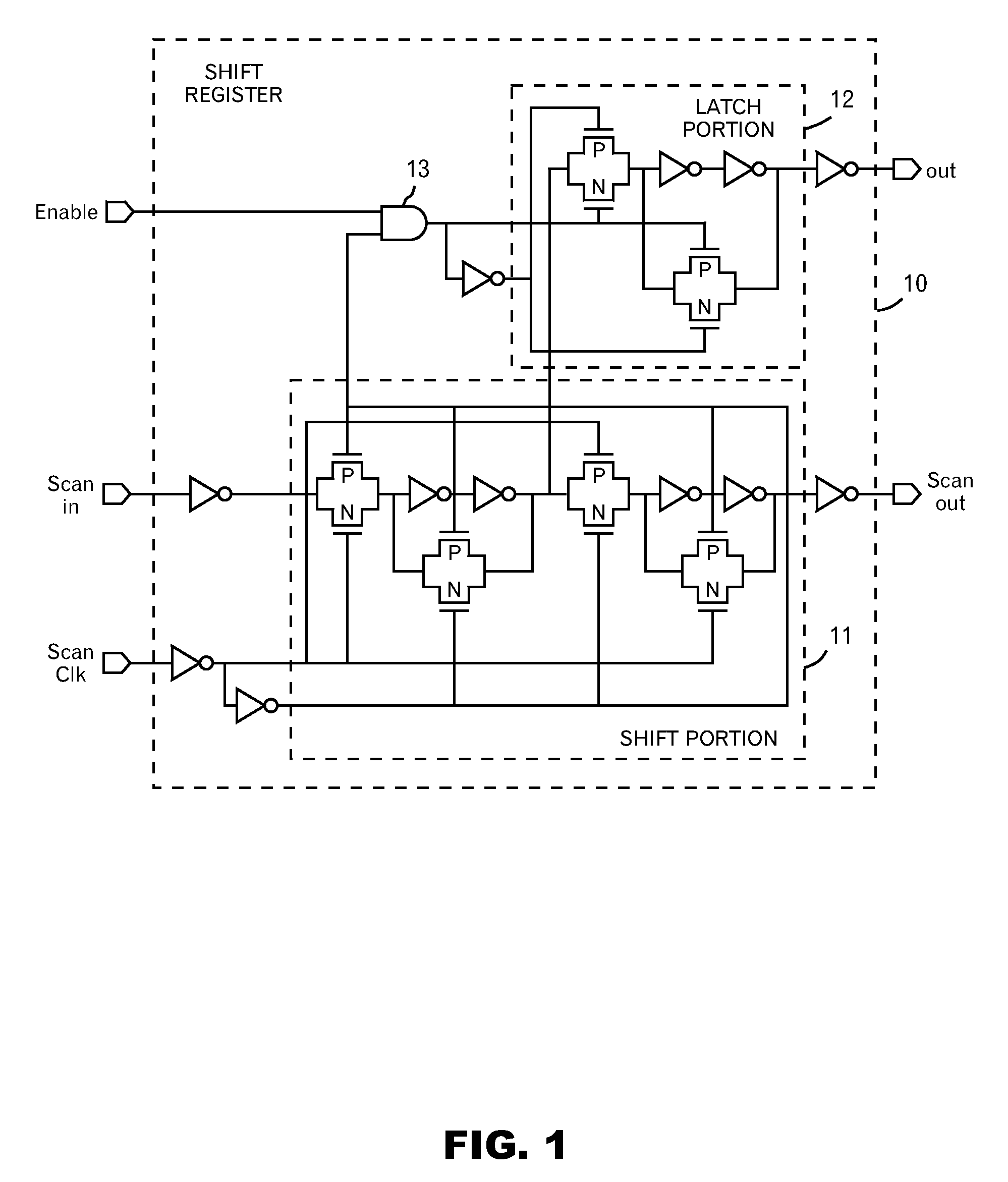

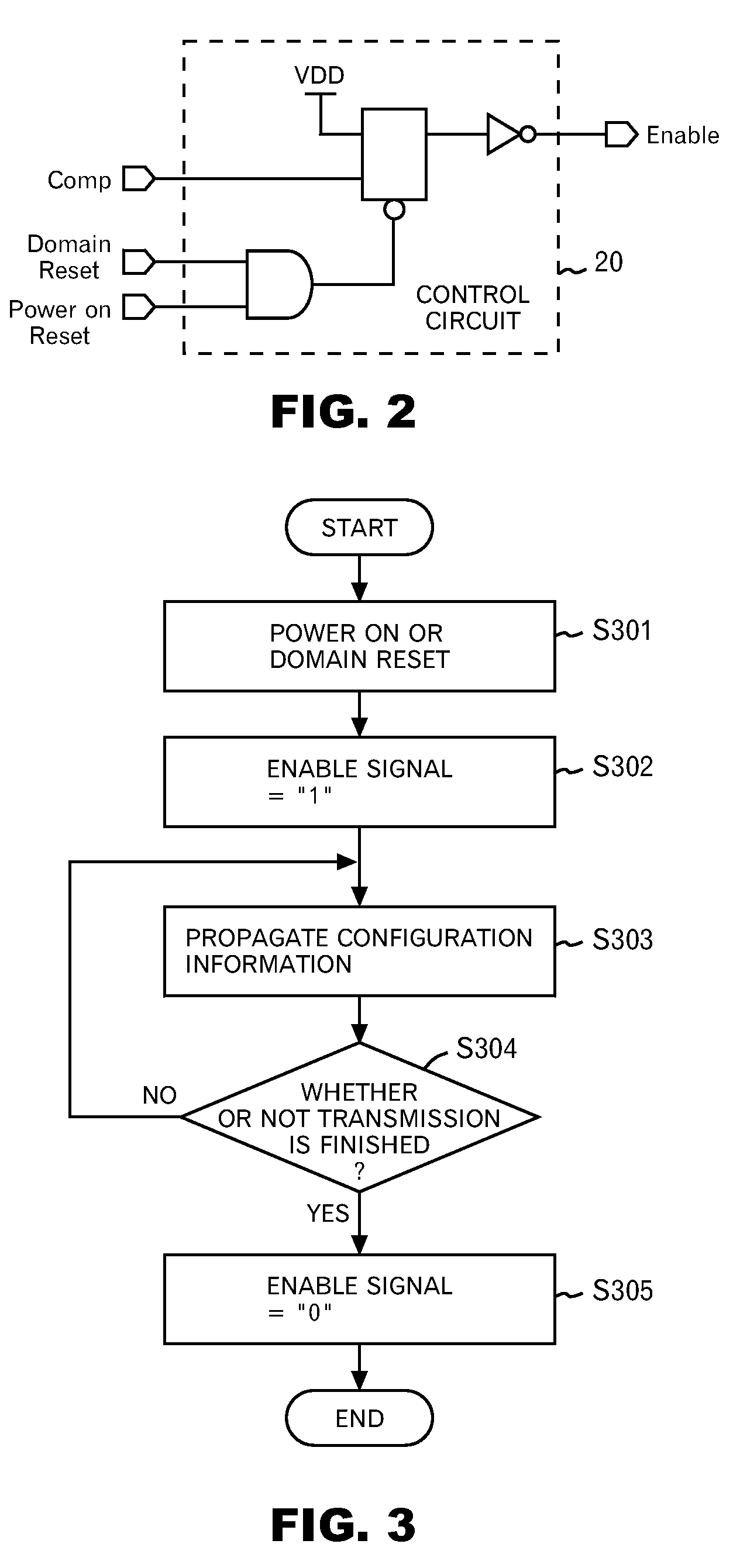

Method and apparatus for redundant memory configuration in voltage island

A method and apparatus to configure redundant memory elements in a system on a chip (SoC) having discrete voltage domains (islands). A plurality of memories are provided for each voltage island, each containing redundancy elements or having the capability to access redundant memory elements in a neighboring voltage domain; a fuse cell stores configuration information for controlling the switching of memory elements of the plurality of memories; a shift register receives and retains configuration information on a memory array from the fuse cell corresponding to each memory; and a control circuit directs operation of the shift register. The shift register includes a shift portion for receiving the data of the configuration information and transferring the data to another shift register, and a latch portion for retaining the data inputted to the shift portion. The control circuit controls whether or not the data of the shift register, which is inputted to the shift portion, is to be retained in the latch portion.

Owner:IBM CORP

Multiple supply gate array backfill structure

A multiple supply gate array structure facilitated by the provision of a shared n-well and an isolated n-well is described. The gate array structure allows implementation of a single voltage circuit or a multiple voltage circuit. In addition, the gate array structure allows metal reprogram to provide standard logic functions, or special logic functions such as a buffer function for a signal crossing a voltage island boundary. Other special logic functions may include, for example, a level-shifter function or a fence-hold function.

Owner:IBM CORP

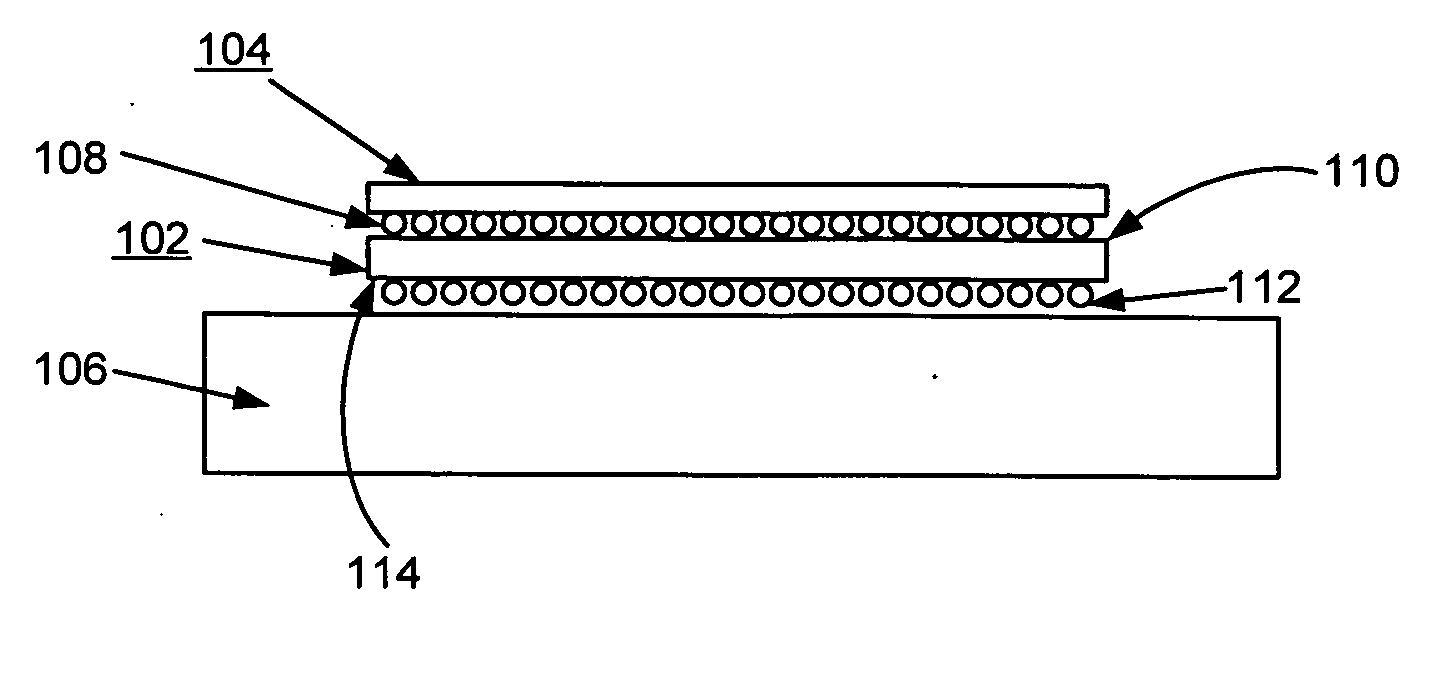

Method and power control structure for managing plurality of voltage islands

InactiveUS20070138653A1Overcome disadvantagesSemiconductor/solid-state device detailsCross-talk/noise/interference reductionElectricityElectrical connection

A power control method and power control structures are provided for managing a plurality of voltage islands of a functional chip. The power control structure includes a supply control and partition chip positioned between a substrate carrier and a functional chip including a plurality of voltage islands. The supply control and partition chip includes a plurality of first electrical connections to the functional chip including the plurality of voltage islands. The supply control and partition chip includes a plurality of second electrical connections to the substrate carrier. Power applied to predefined ones of the first electrical connections to the functional chip are selectively switched on and off by the supply control and partition chip.

Owner:IBM CORP

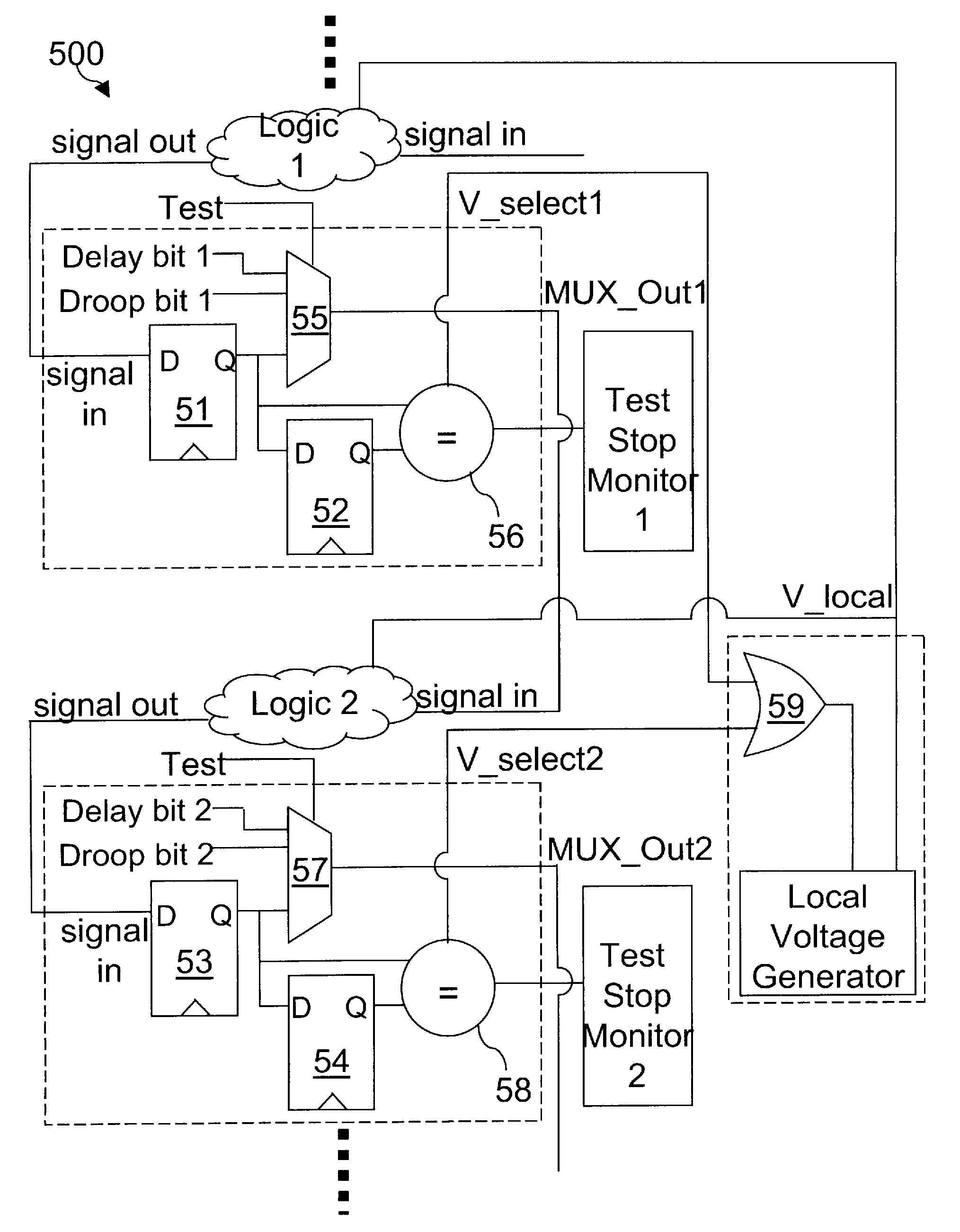

Optimal local supply voltage determination circuit

InactiveUS7898285B2Logic circuit coupling/interface arrangementsElectric variable regulationProcessor registerCritical test

A test circuit that compares test results between two tests with different local supply voltages is provided. The output of each stage of the logic circuits is stored in a first register of each test circuit. Each test is performed with a critical test vector and a local supply voltage that decreases from test to test. The outputs of successive tests are compared in each test circuit. The tests are performed iteratively with successive reduction in the value of the local supply voltage until at least one stage of the logic circuits produces non-matching results between the first and second register. The voltage immediately before producing such non-matching results is the minimum operational voltage for the local voltage island.

Owner:INT BUSINESS MASCH CORP

Device and method to eliminate step response power supply perturbation

InactiveUS7511528B2Electronic switchingVoltage/current interference eliminationElectricityStep response

Owner:GLOBALFOUNDRIES INC

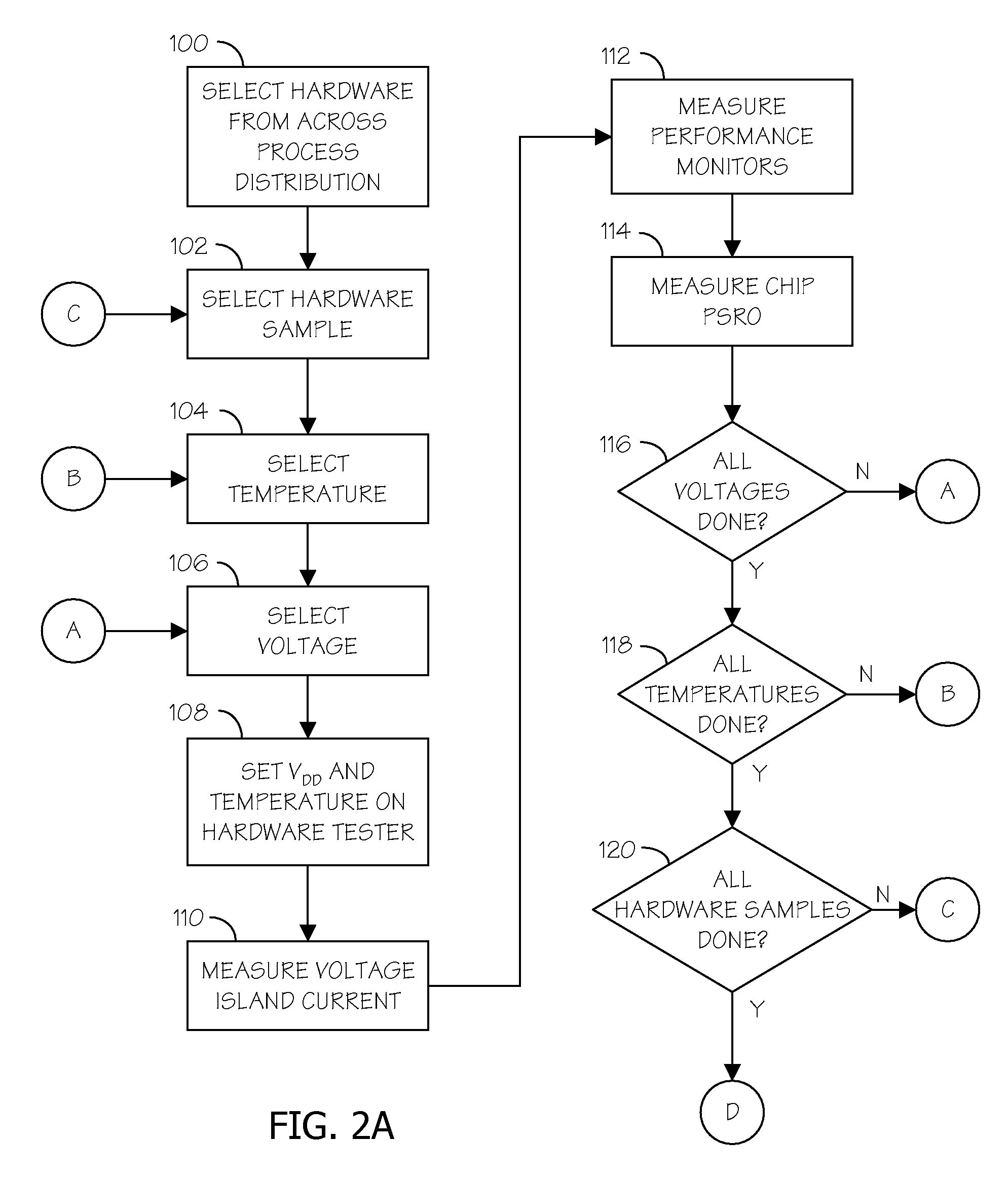

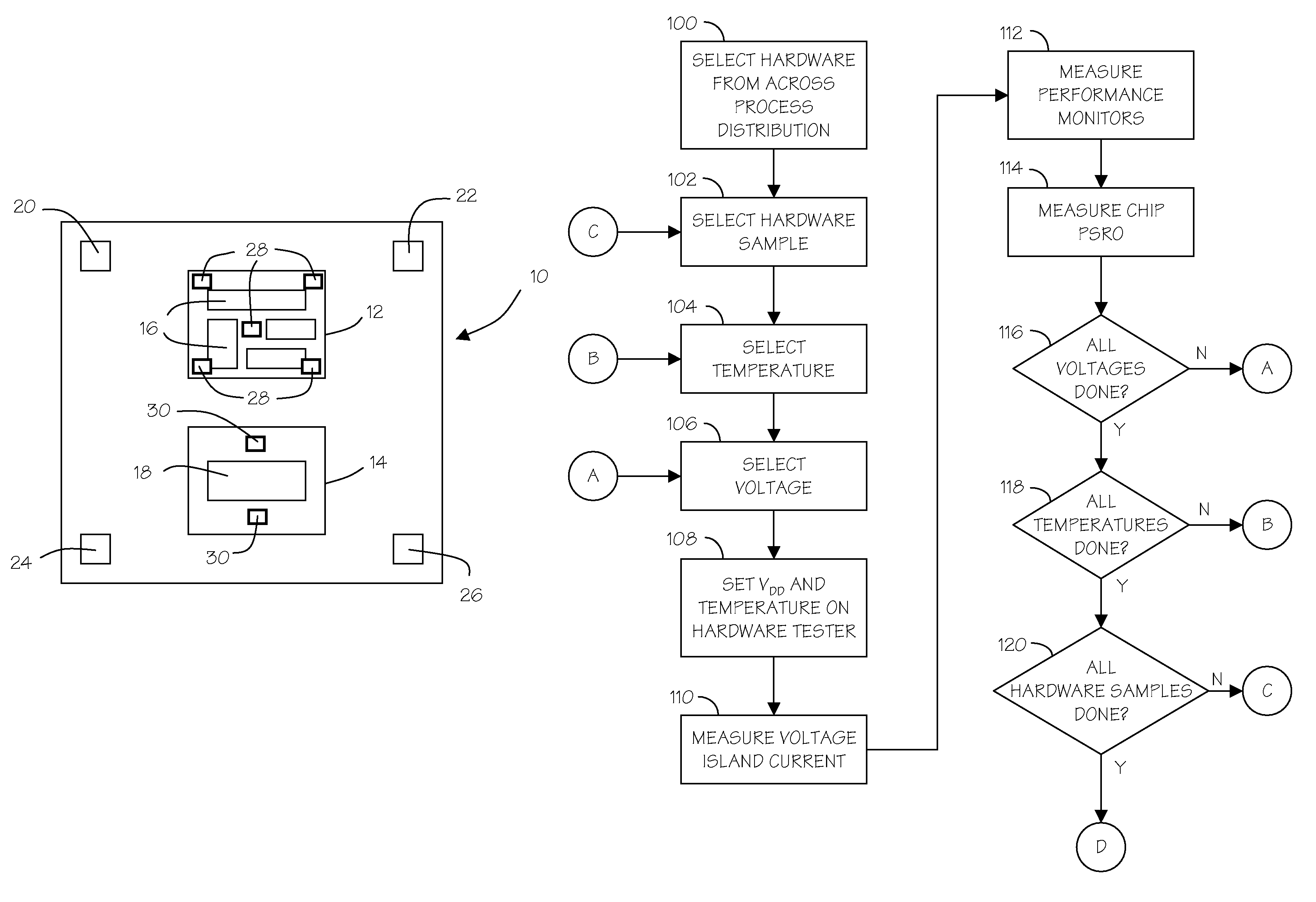

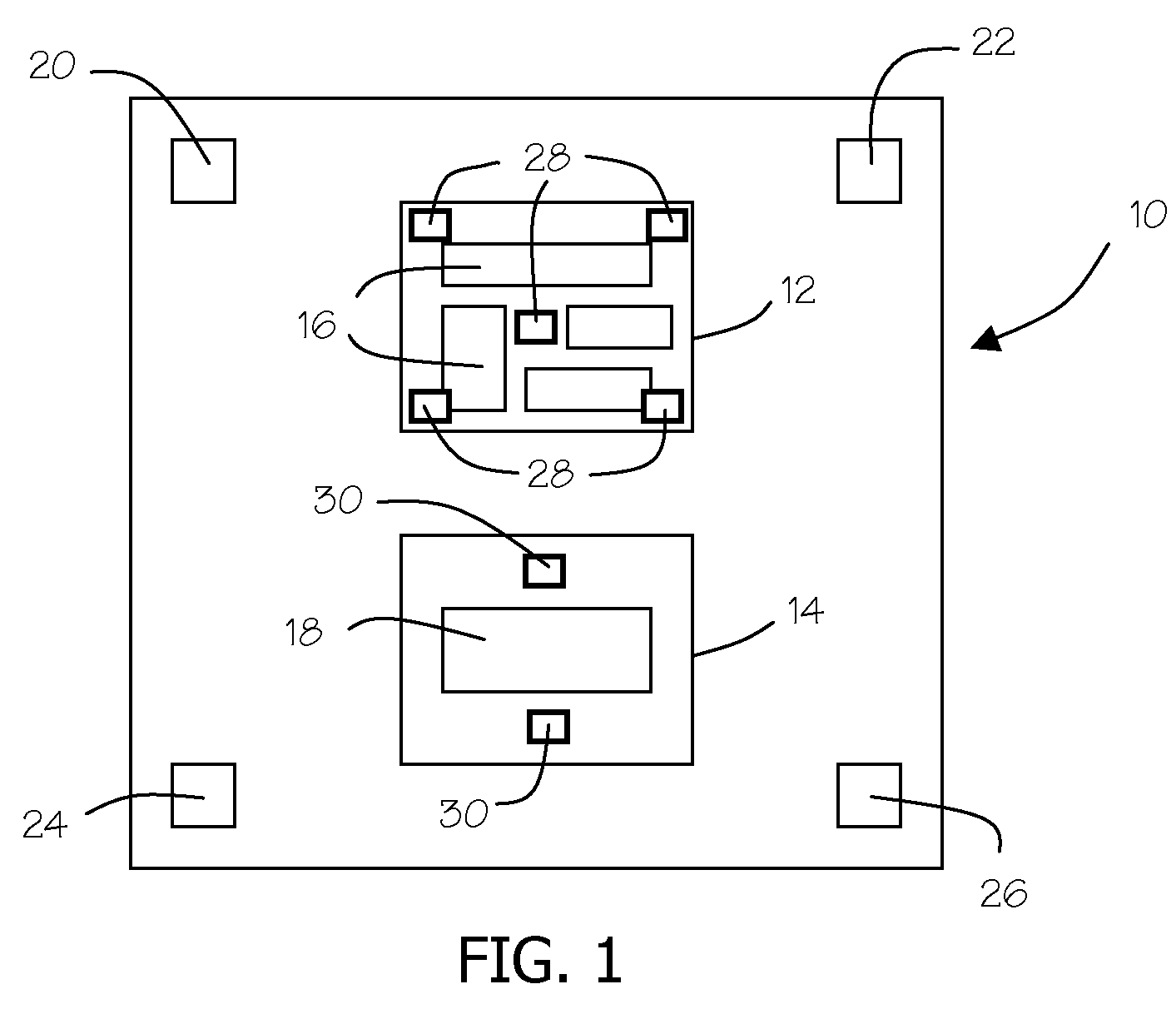

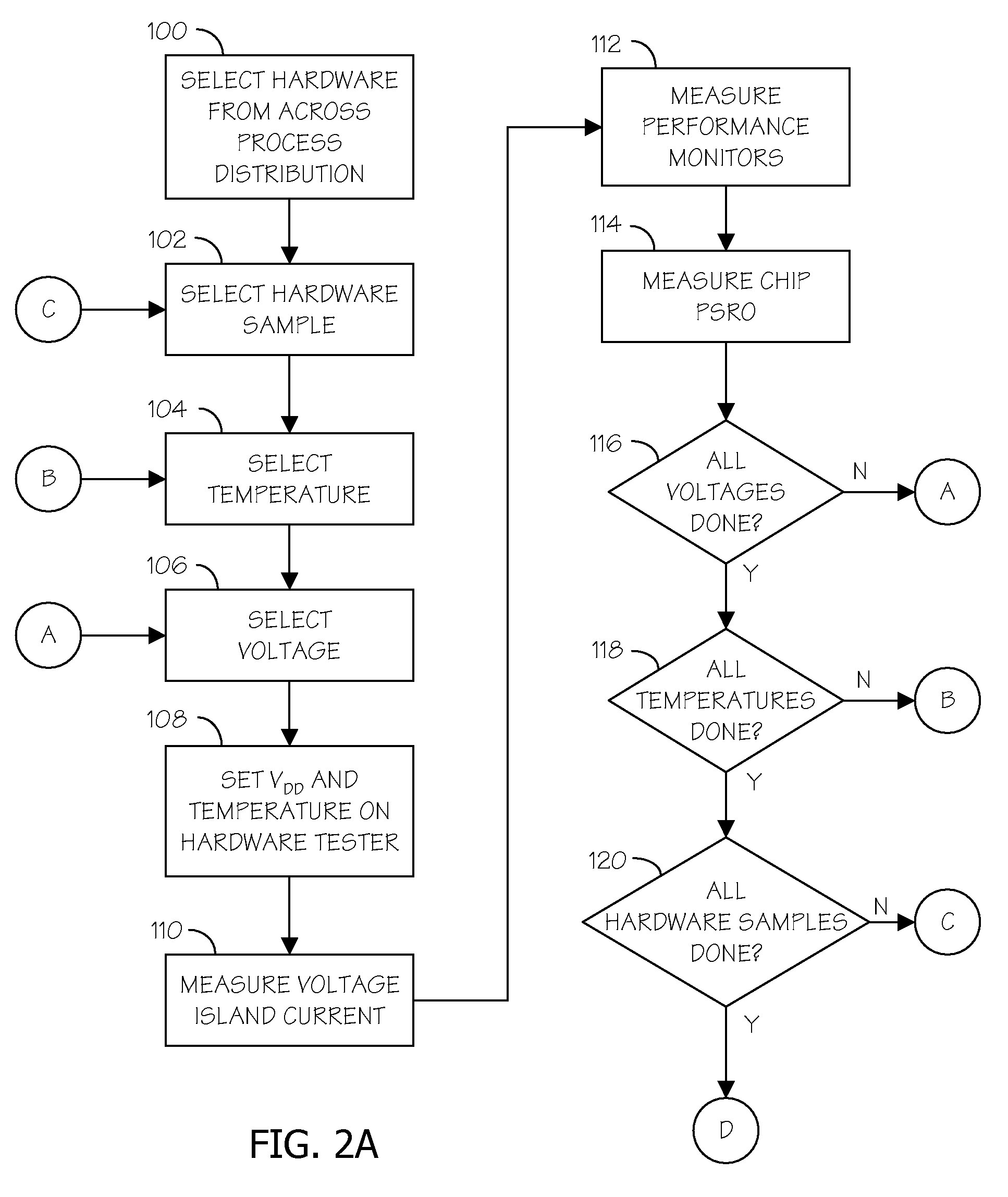

Voltage island performance/leakage screen monitor for IP characterization

InactiveUS20090295402A1Detecting faulty computer hardwareElectrical testingPerformance modelRing oscillator

A method is provided for characterizing performance of a chip having at least one voltage island and at least one performance screen ring oscillator (PSRO). An on-chip performance monitor (OCPM) is incorporated on the voltage island. Performance measurements of the voltage island are generated with only the voltage island under power. Performance measurements of the performance screen ring oscillator (PSRO) are generated with only the voltage island under power. Performance measurements of the performance screen ring oscillator (PSRO) is compared to the performance measurements of the on-chip performance monitor (OCPM) to determine a systematic offset due to the voltage island. Performance models are adjusted using the systematic offset due to the voltage island.

Owner:GLOBALFOUNDRIES INC

Modular Chip Integration Techniques

ActiveUS20090111215A1Semiconductor/solid-state device detailsSolid-state devicesModularityEngineering

Modular chip integration and operation techniques are provided. In one aspect, a method of integrating chips, chip macros or at least one chip in combination with at least one chip macro is provided. The method comprises the following steps. The chips, chip macros or at least one chip in combination with at least one chip macro are assembled on a single carrier platform. One or more signal inputs and outputs are provided to each of the chips, chip macros or at least one chip in combination with at least one chip macro. One or more power and ground inputs and outputs are provided to each of the chips, chip macros or at least one chip in combination with at least one chip macro. The power and ground inputs and outputs to one or more of the chips, chip macros or at least one chip in combination with at least one chip macro are segmented from the power and ground inputs and outputs to at least one other of the chips, chip macros or at least one chip in combination with at least one chip macro so as to form a plurality of voltage islands.

Owner:IBM CORP

Voltage island performance/leakage screen monitor for IP characterization

Owner:GLOBALFOUNDRIES INC

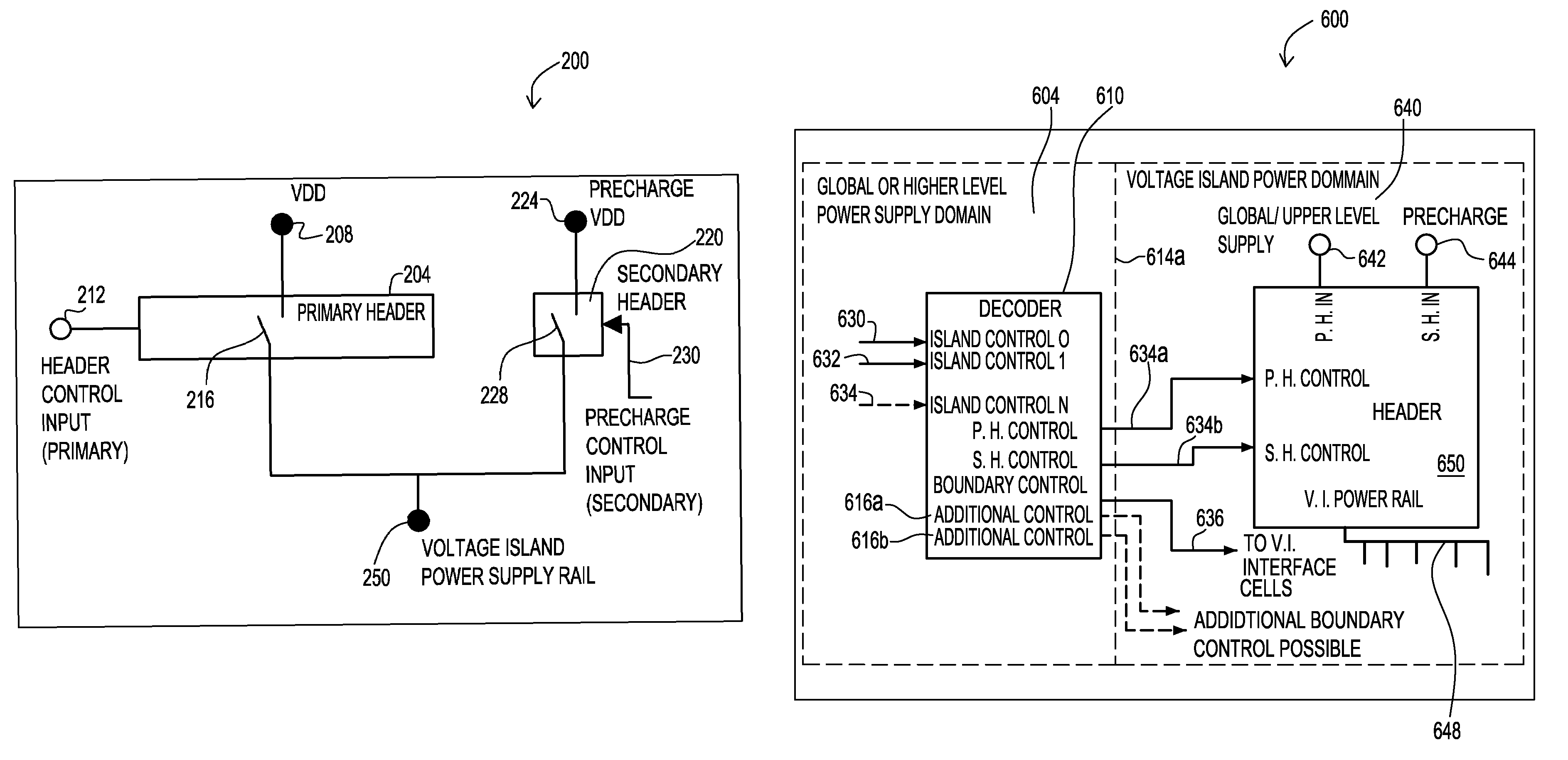

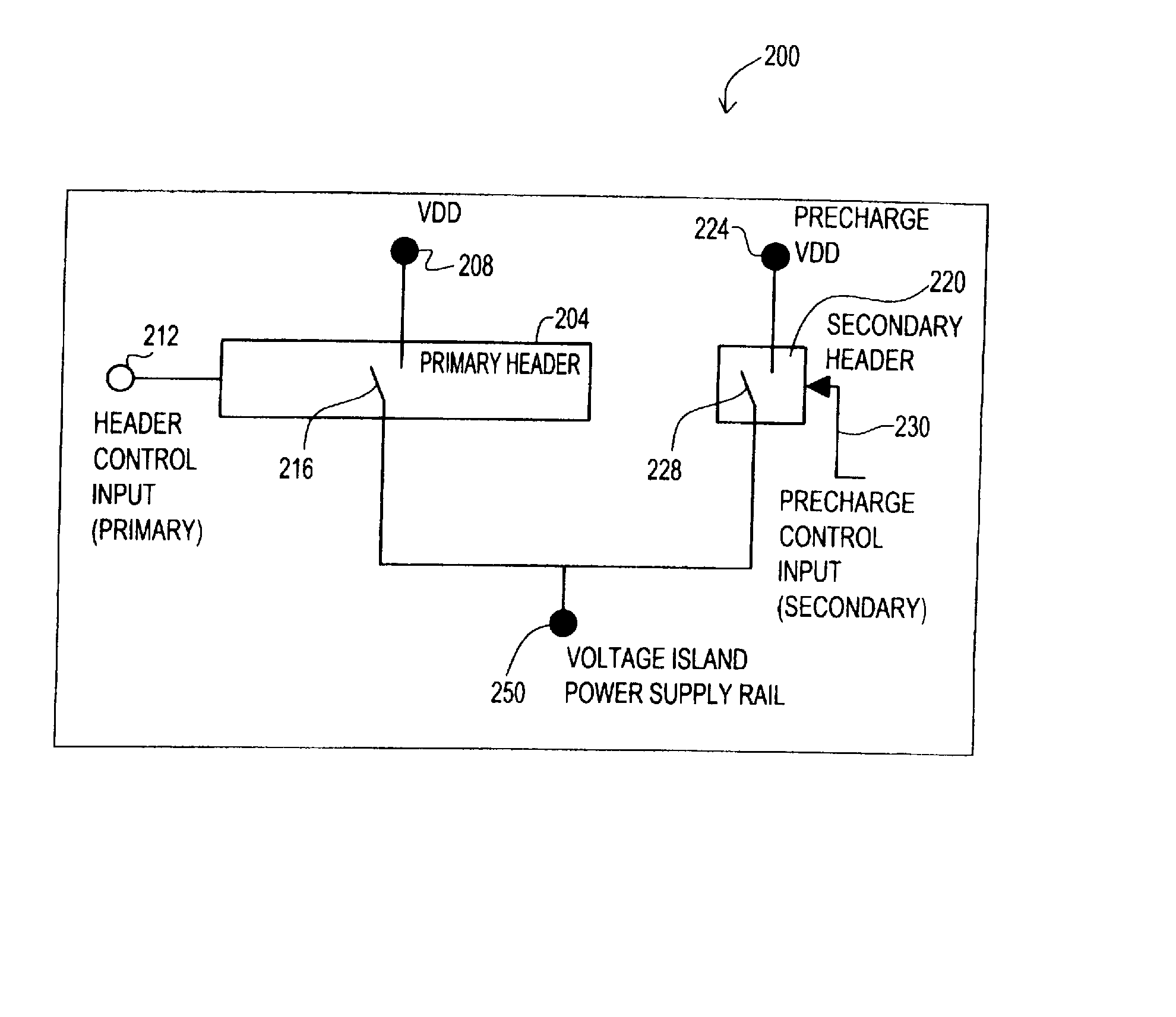

Design structure to eliminate step response power supply perturbation

InactiveUS20080030254A1Detecting faulty computer hardwareElectronic switchingStep responseIntegrated circuit

A design structure for eliminating step response power supply perturbation during voltage island power-up / power-down on an integrated circuit is disclosed. An IC chip communicates with a primary power supply and includes at least one voltage island. A primary header on the voltage island of the chip communicates with the primary power supply via a primary header power path. A secondary header on the voltage island of the chip communicates with a secondary power supply via a secondary header power path. A control decoder communicating with the IC chip and the voltage island regulates the state of the primary and secondary headers.

Owner:GLOBALFOUNDRIES INC

Nested voltage island architecture

An integrated circuit. The integrated circuit includes a parent terrain; and a hierarchical order of nested voltage islands within the parent terrain, each higher-order voltage island nested within a lower-order voltage island, each nested voltage island having the same hierarchical structure.

Owner:MARVELL ASIA PTE LTD

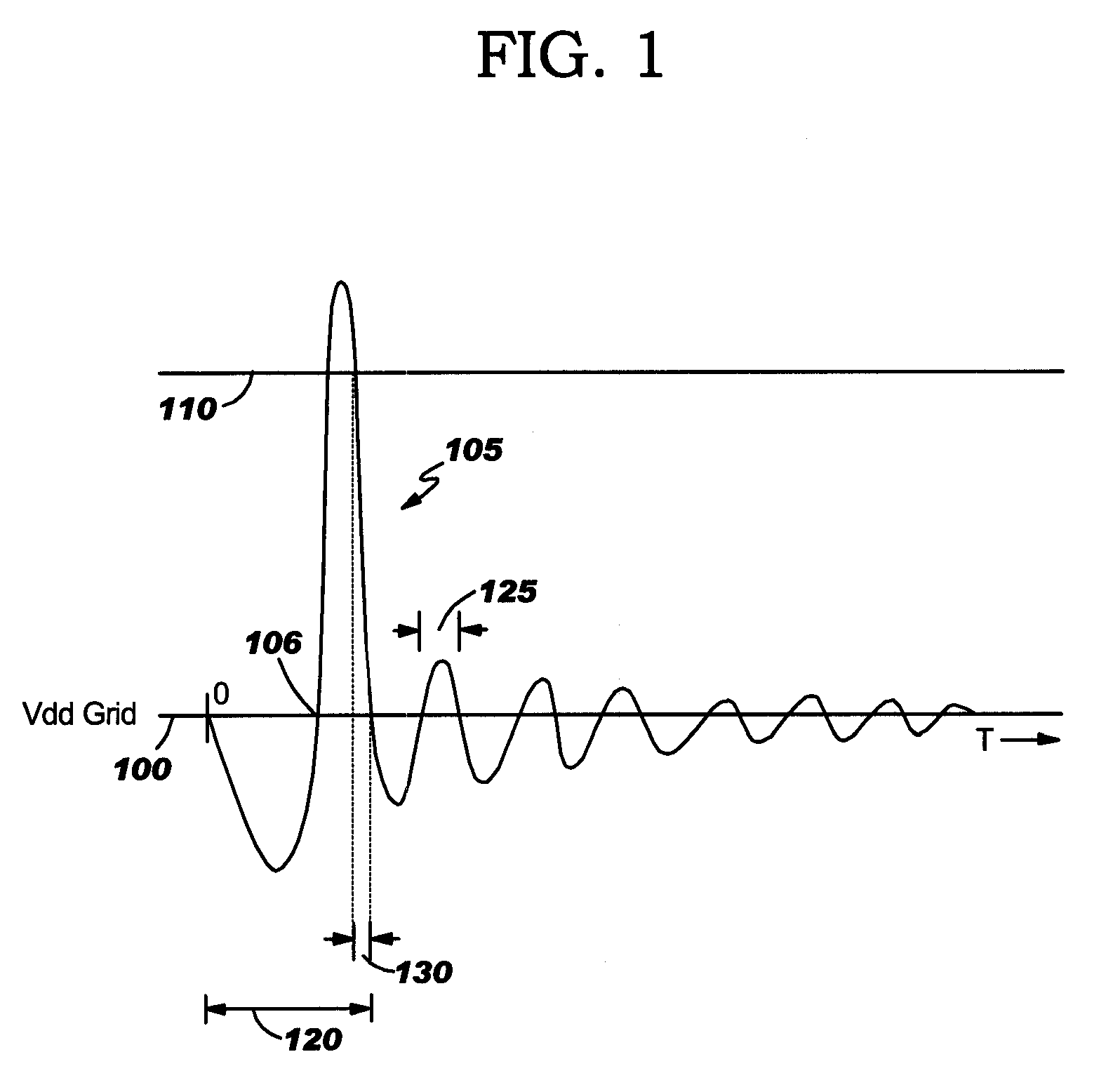

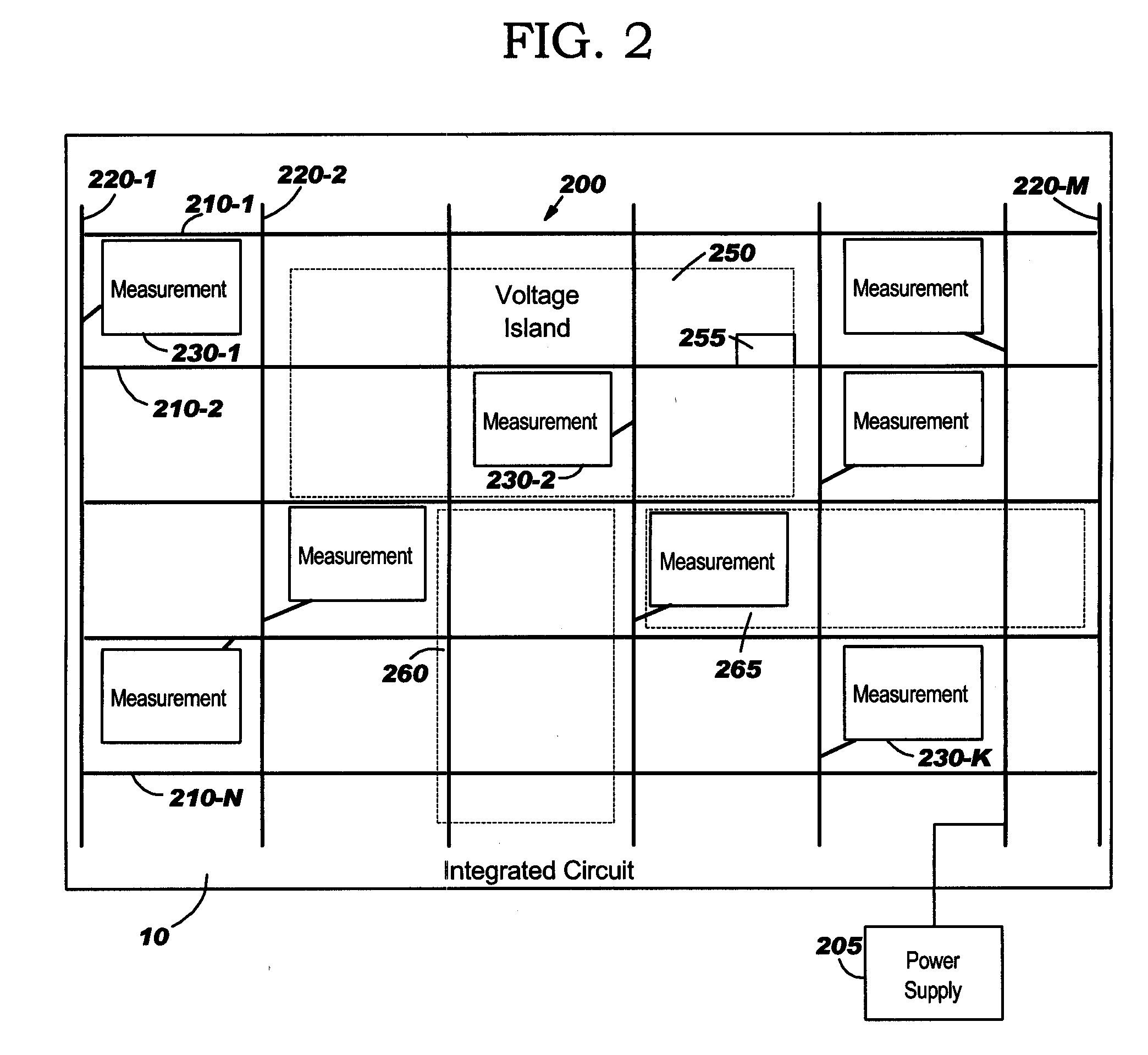

Method of switching voltage islands in integrated circuits

ActiveUS20060190744A1Reduce the impactReduce impactEnergy efficient ICTVolume/mass flow measurementPower gridEngineering

An integrated circuit has a power grid and a set of independently switchable voltage islands, together with a system and method for measuring the voltage and history of the voltage on the power grid to determine the correct time to allow a large capacitive load (such as a voltage island) to be switched on to or off the power grid.

Owner:GOOGLE LLC