SM4 algorithm encryption unit based on FPGA chip and USB interface chip

A USB interface and encryption device technology, applied in the field of information security, can solve the problems of poor security and slow operation speed, and achieve the effects of high security, convenient use, and fast data encryption and decryption speed.

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

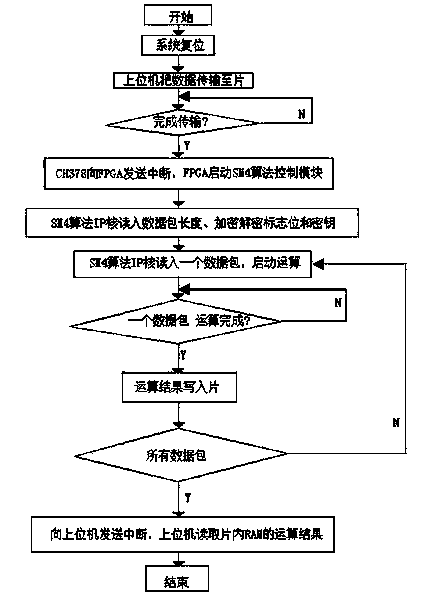

[0024] Below with reference to accompanying drawing, the present invention is further described by specific embodiment:

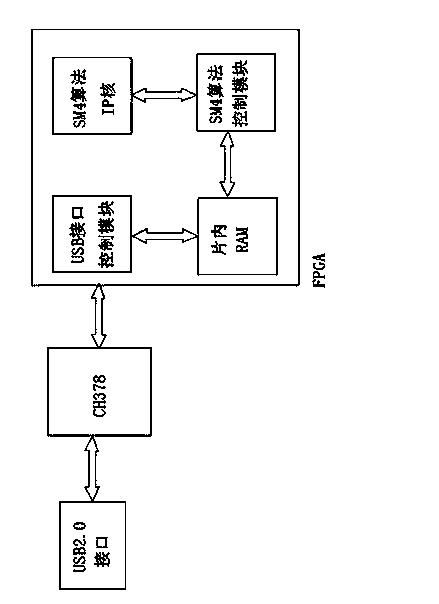

[0025] An SM4 algorithm encryption device based on FPGA and USB interface chip, including USB interface chip, field programmable gate array (FPGA) chip, USB interface control module realized by FPGA, SM4 algorithm IP core, SM4 algorithm control module and chip Internal RAM,

[0026] Among them, the USB interface chip implements the USB2.0 bus protocol and interacts with the FPGA local side;

[0027] FPGA chip, as the core unit of the device, controls and schedules each module of the system;

[0028] The USB interface control module, a sub-module of the FPGA, realizes the control of the USB interface chip;

[0029] SM4 algorithm IP core, FPGA sub-module, realizes domestic SM4 symmetric encryption algorithm;

[0030] SM4 algorithm control module, a sub-module of FPGA, realizes the control of SM4 algorithm IP core;

[0031] On-chip RAM, a sub-module of FPG...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More