CMOS (Complementary Metal-Oxide-Semiconductor) transistor and stress memory treatment method thereof

A technology of stress memory and processing method, which is applied in the direction of transistor, semiconductor/solid-state device manufacturing, electrical components, etc., can solve the problems of not adapting to the development trend of integrated circuit miniaturization, unsatisfactory effect, product stability and yield impact, etc. Achieve the effects of improving stability and yield, saving costs, and reducing the probability of occurrence

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment 1

[0037] This embodiment provides a stress memory processing method for CMOS transistors, such as Figure 7 shown, including:

[0038] S101, providing a substrate formed with CMOS transistors.

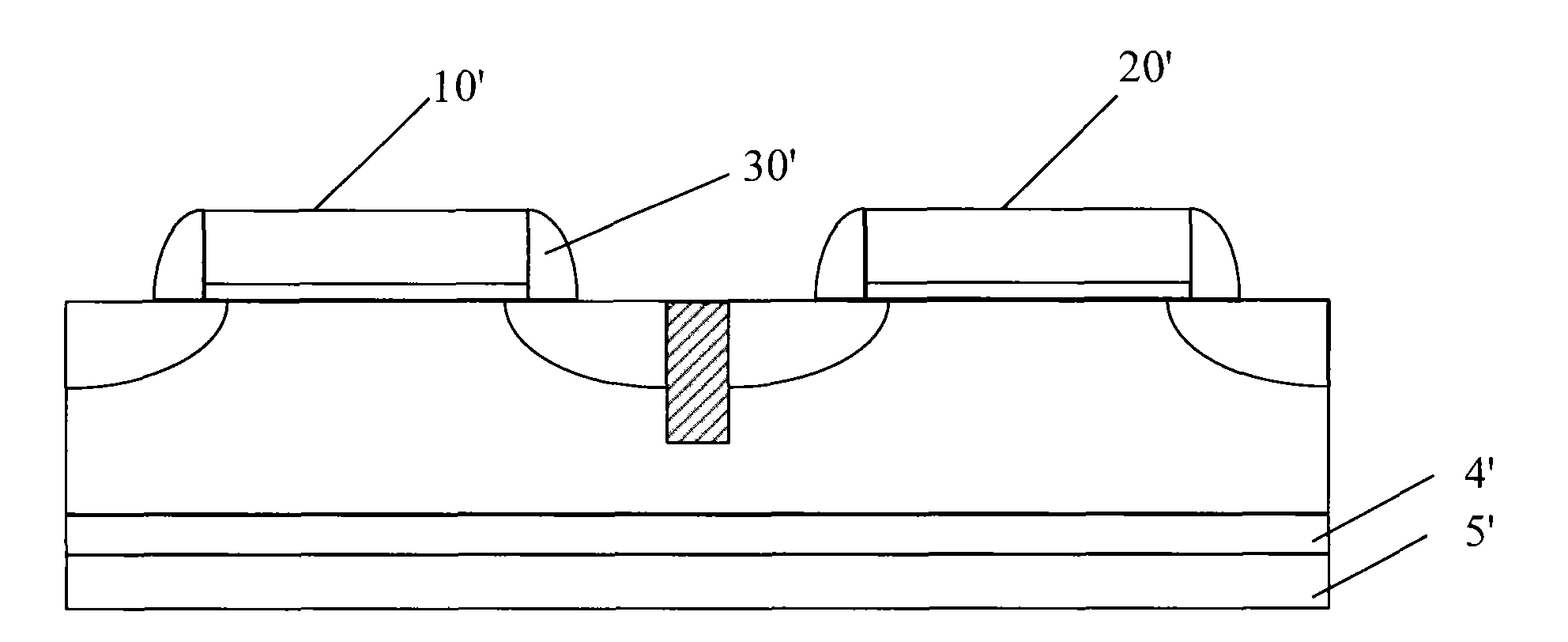

[0039] Each CMOS transistor includes a gate, a source, a drain, a conductive channel, a gate oxide layer and a gate sidewall, the inner layer of the gate sidewall is a silicon oxide layer, and the outer layer is a silicon nitride layer. Wherein, the source, the drain and the conductive channel are located in the well of the reverse type of the source / drain in the substrate (the technical solution of the present invention is not involved, and are simplified and not shown in the accompanying drawings) and are located in the source Between the electrode and the drain, the gate oxide layer is located on the upper surface of the substrate corresponding to the position of the conductive channel, the gate (usually polysilicon) is located on the upper surface of the gate oxide layer, and the si...

Embodiment 2

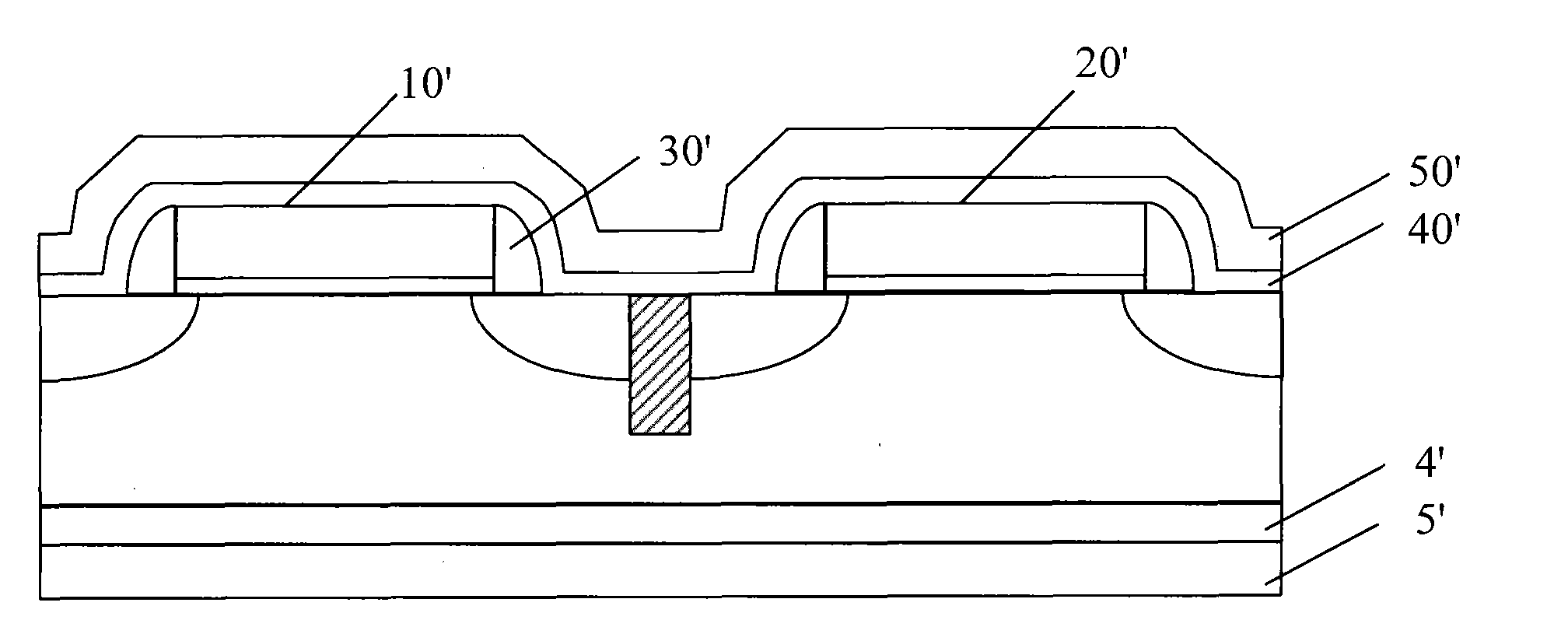

[0073] The present invention also provides a CMOS transistor, such as Figure 21 shown.

[0074] The CMOS transistor includes a gate, a source, a drain, a conductive channel (not shown in the figure), a gate oxide layer 22 and a gate sidewall 33, and the inner layer of the gate sidewall 33 is a silicon oxide layer , the outer layer is a silicon nitride layer, and the lower surface of the substrate 11 where the CMOS transistor is located has a silicon oxide layer 44 and a silicon nitride layer 55 corresponding to the gate sidewall 33;

[0075] Among the CMOS transistors, the conduction channel of the NMOS transistor 66 has compressive stress, and the conduction channel of the PMOS transistor 77 has no stress.

[0076] The CMOS transistor of the present invention increases the thickness T of the insulating layer by retaining the silicon oxide layer and the silicon nitride layer on the lower surface of the substrate, thereby reducing the electric field E formed on the substrate ...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More