LDMOS (laterally diffused metal oxide semiconductor) and manufacturing method thereof

A doping type and heavy doping technology, which is applied in semiconductor/solid-state device manufacturing, electrical components, circuits, etc., can solve the problems of LDMOS device threshold voltage drift, transconductance reduction, and driving ability decline

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

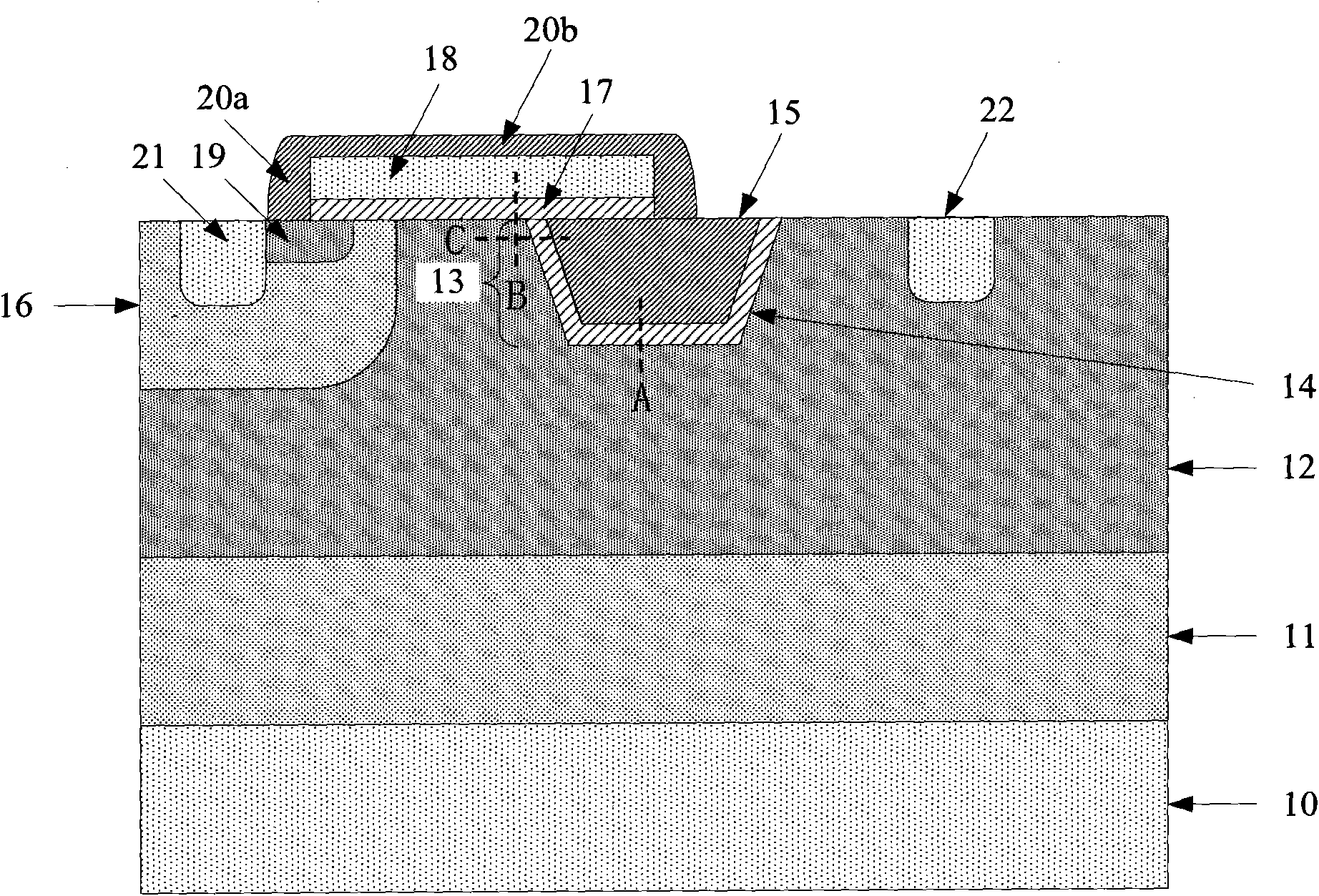

[0041] The structure of the LDMOS device of the present invention will be described below by taking an n-type LDMOS as an example.

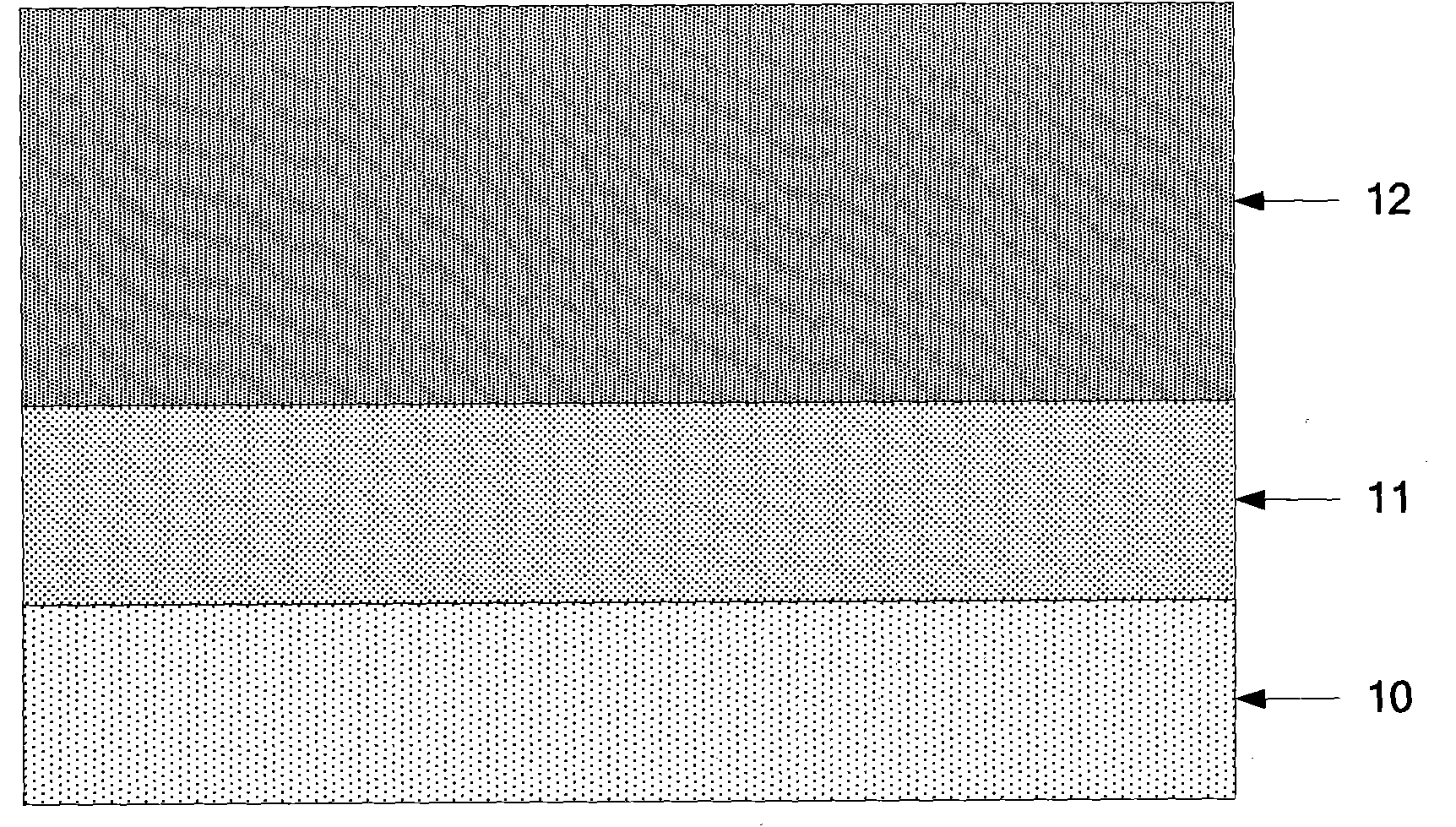

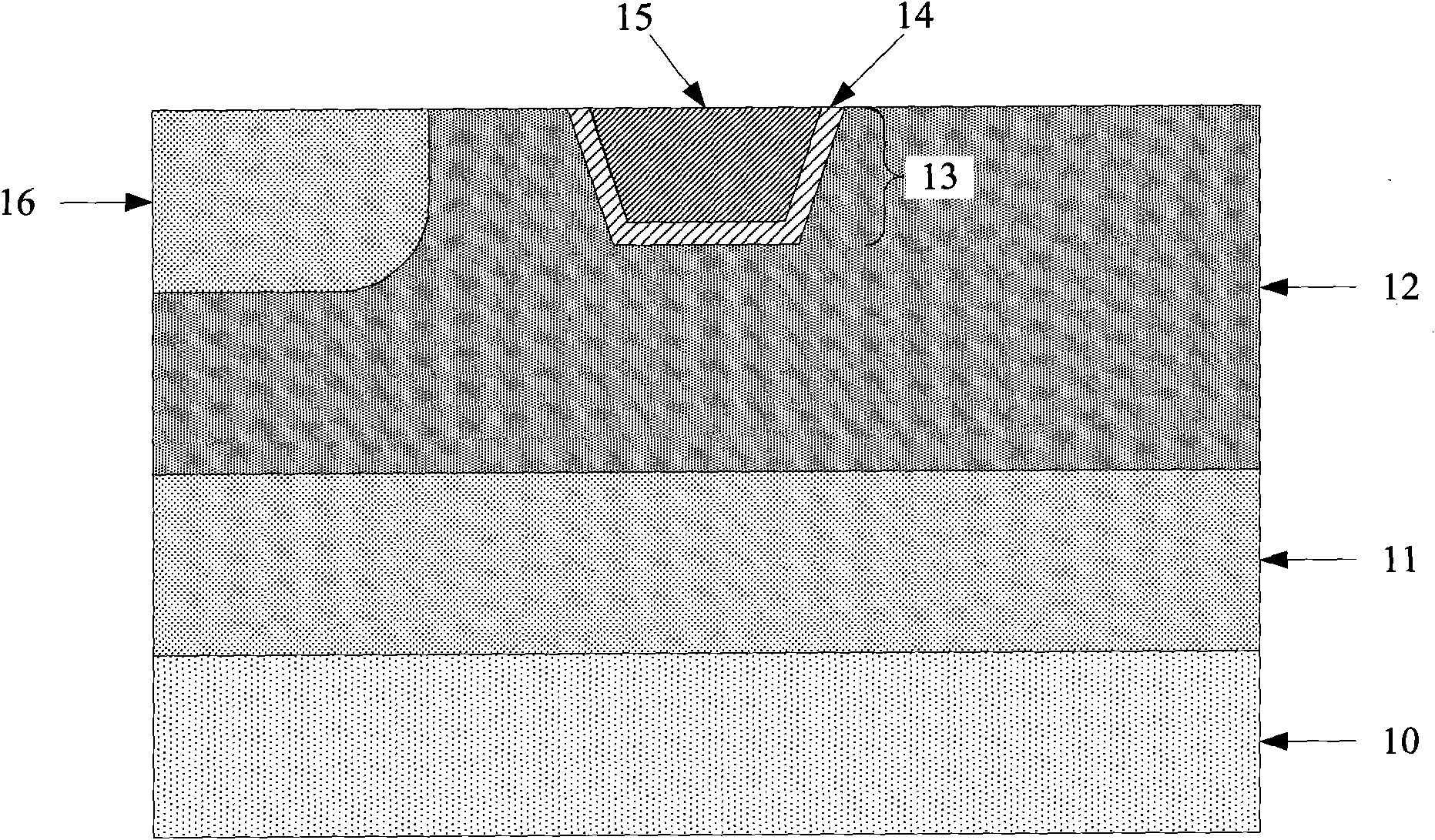

[0042] see image 3 , The n-type LDMOS of the present invention respectively includes a p-type substrate 10, a p-type epitaxial layer 11 and an n-well 12 from bottom to top. The thickness of the n well 12 is usually 4-5 μm, and it is sometimes called "deep n well". The n well 12 has a trench 13, a p well 16, and an n-type heavily doped drain region 22, and the p well 16 and the n-type heavily doped drain region 22 are respectively on both sides of the trench 13 and are not in phase with the trench 13. coincident (that is, they are all at a certain distance from the groove 13). A pad oxide layer 14 is formed on the sidewall and bottom of the trench 13 , and the trench 13 is filled with a shallow trench isolation structure 15 (usually a dielectric material such as silicon oxide, silicon nitride, silicon oxynitride, etc.). There is an n-type ligh...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More