Patents

Literature

30results about How to "Low leakage current" patented technology

Efficacy Topic

Property

Owner

Technical Advancement

Application Domain

Technology Topic

Technology Field Word

Patent Country/Region

Patent Type

Patent Status

Application Year

Inventor

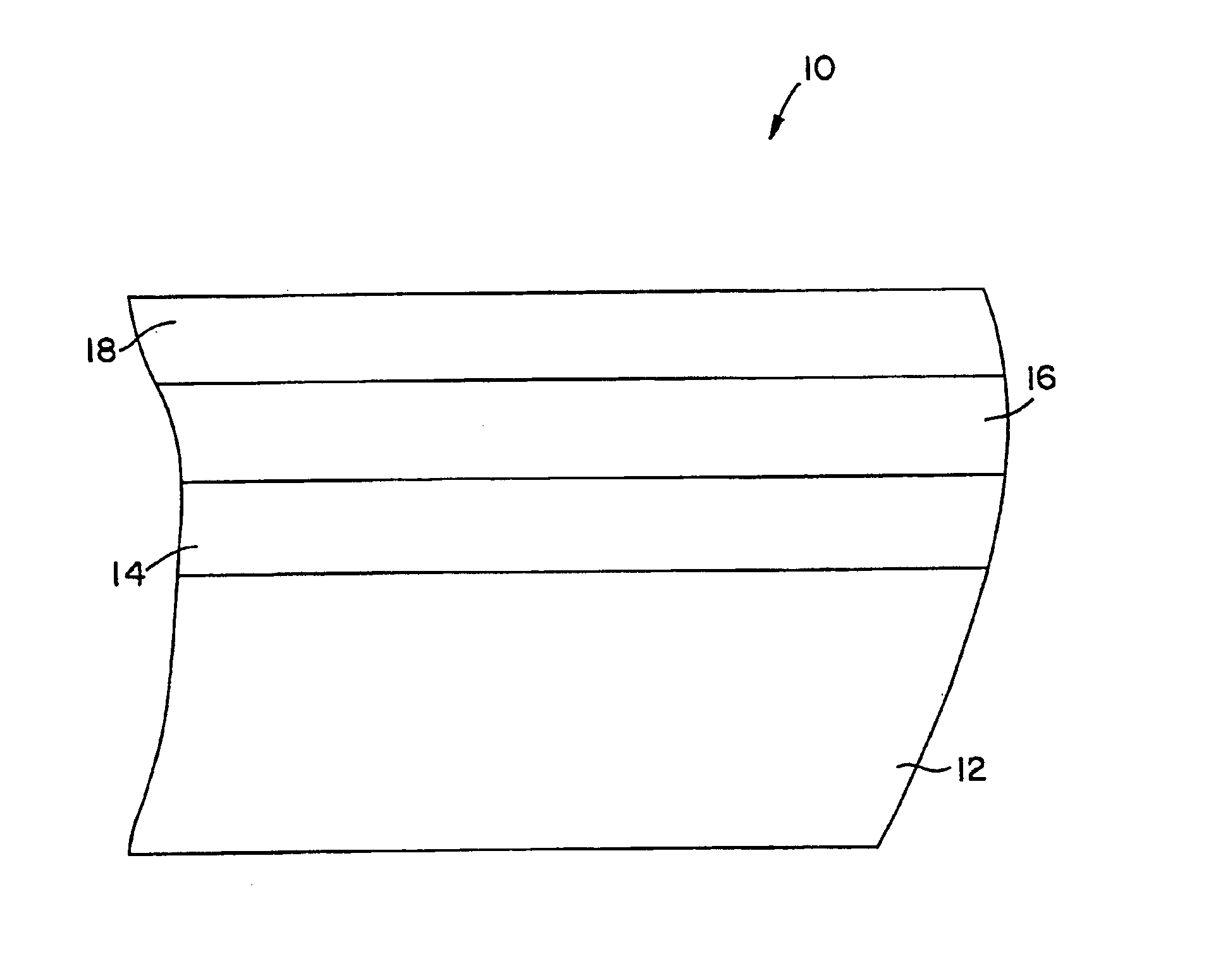

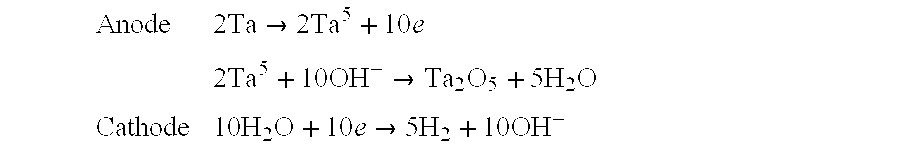

Protective coating for electrolytic capacitors

InactiveUS6864147B1Low dissipation factorLow leakage currentSolid electrolytic capacitorsSemiconductor/solid-state device manufacturingShellacElectrolysis

A solid electrolytic capacitor that comprises an anode that contains a valve-action metal (e.g., tantalum, niobium, and the like) and a dielectric film overlying the anode is provided. The capacitor also comprises a protective coating overlying the dielectric film, wherein the protective coating contains a relatively insulative, resinous material. For example, in one embodiment, the resinous material can be a drying oil, such as olive oil, linseed oil, tung oil, castor oil, soybean oil, shellac, and derivatives thereof. The capacitor also comprises a conductive polymer coating overlying the protective coating. As a result of the present invention, it has been discovered that a capacitor can be formed that can have a relatively low leakage current, dissipation factor, and equivalents series resistance.

Owner:KYOCERA AVX COMPONENTS CORP

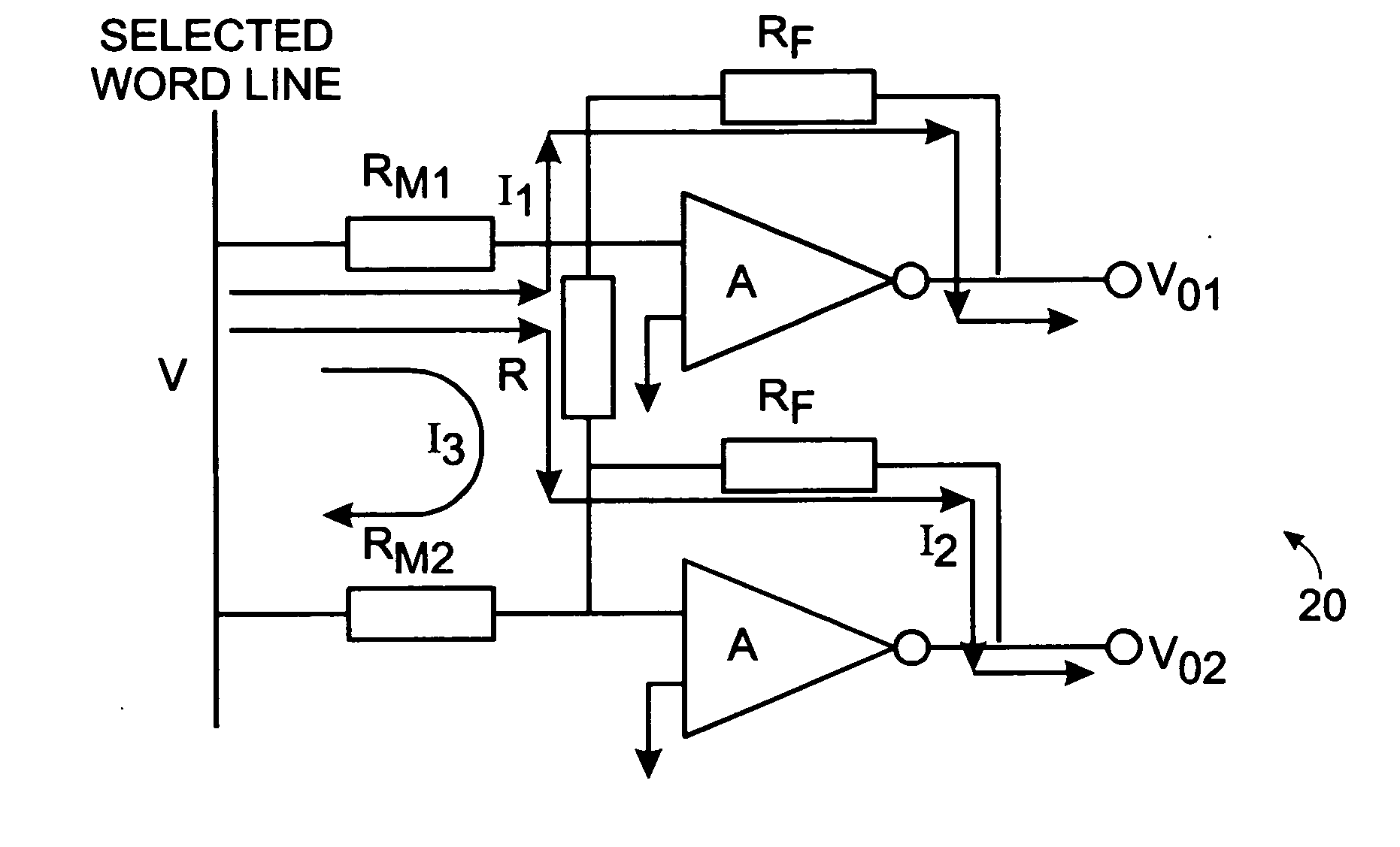

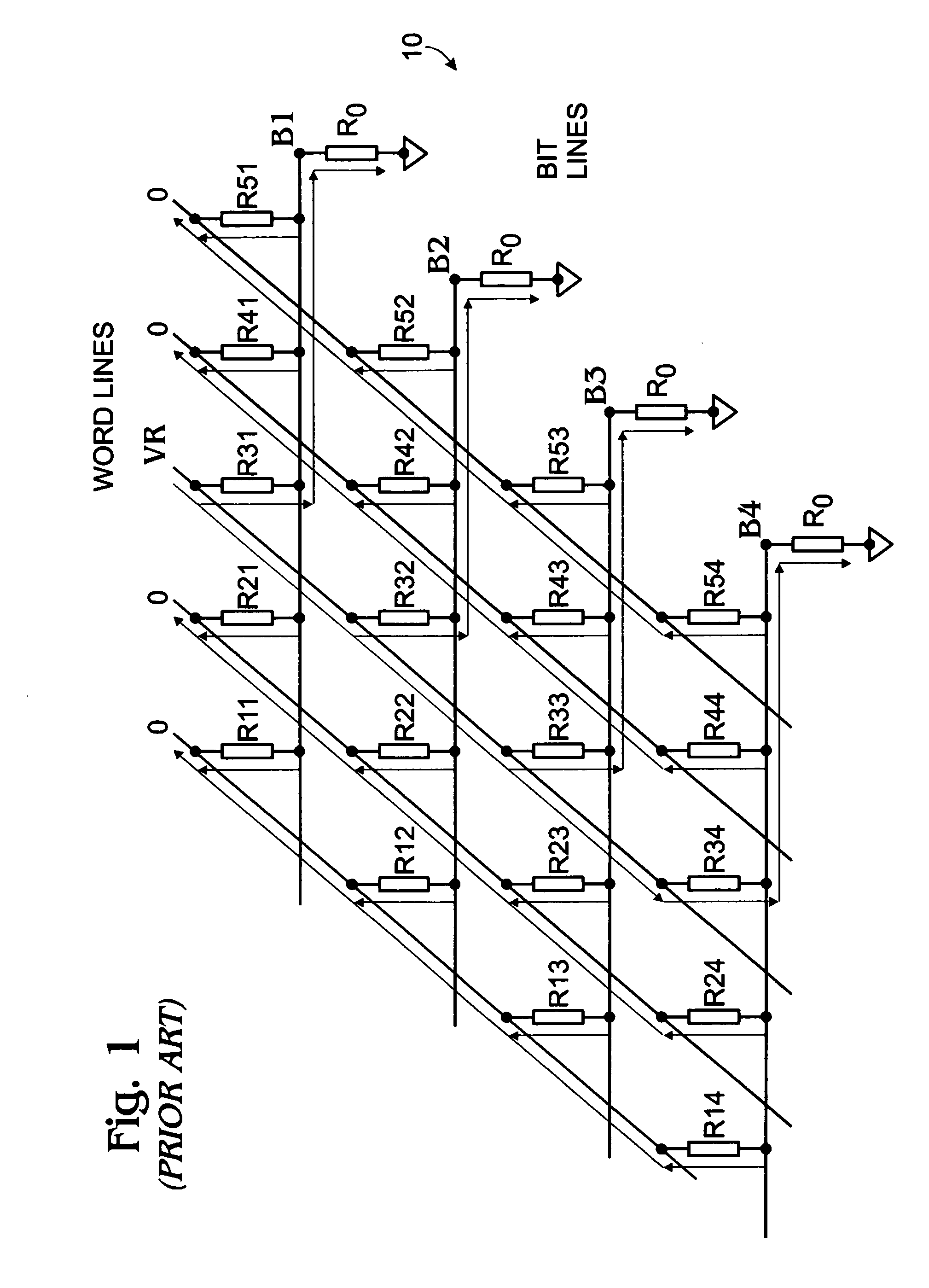

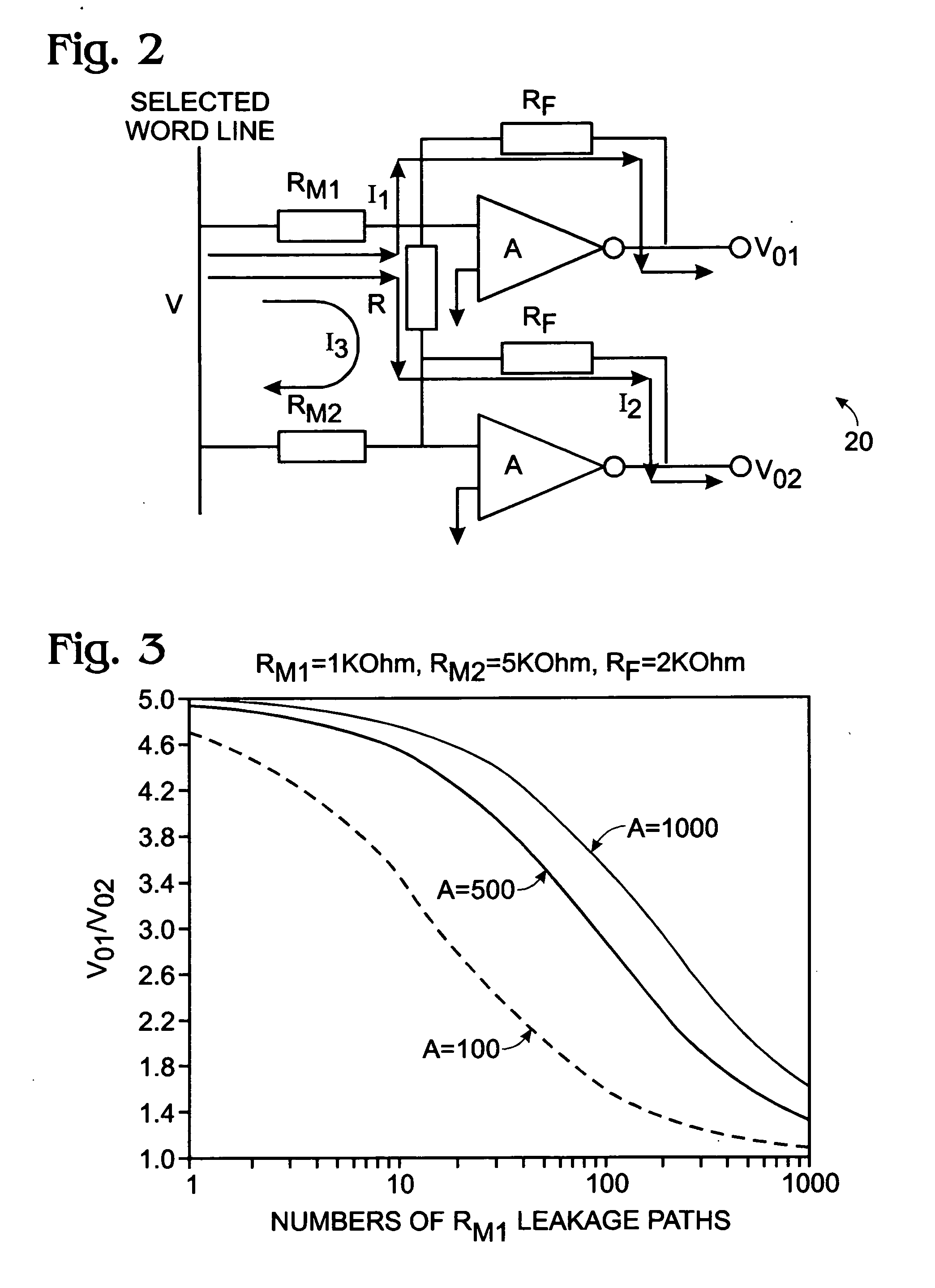

Cross-point RRAM memory array having low bit line crosstalk

ActiveUS20070109835A1Low leakage currentReduce leakage currentDigital storageDifferential amplifierAudio power amplifier

A cross-point RRAM memory array includes a word line array having an array of substantially parallel word lines therein and a bit line array having an array of substantially parallel bit lines therein, wherein said bit lines are substantially perpendicular to said word lines, and wherein a cross-point is formed between said word lines and said bit lines. A memory resistor located between said word lines and said bit lines at each cross-point. A high-open-circuit-voltage gain, bit line sensing differential amplifier circuit located on each bit line, including a feedback resistor and a high-open-circuit-voltage gain amplifier, arranged in parallel, wherein a resistance of the feedback resistors is greater than a resistance of any of the memory resistors programmed at a low resistance state.

Owner:XENOGENIC DEV LLC

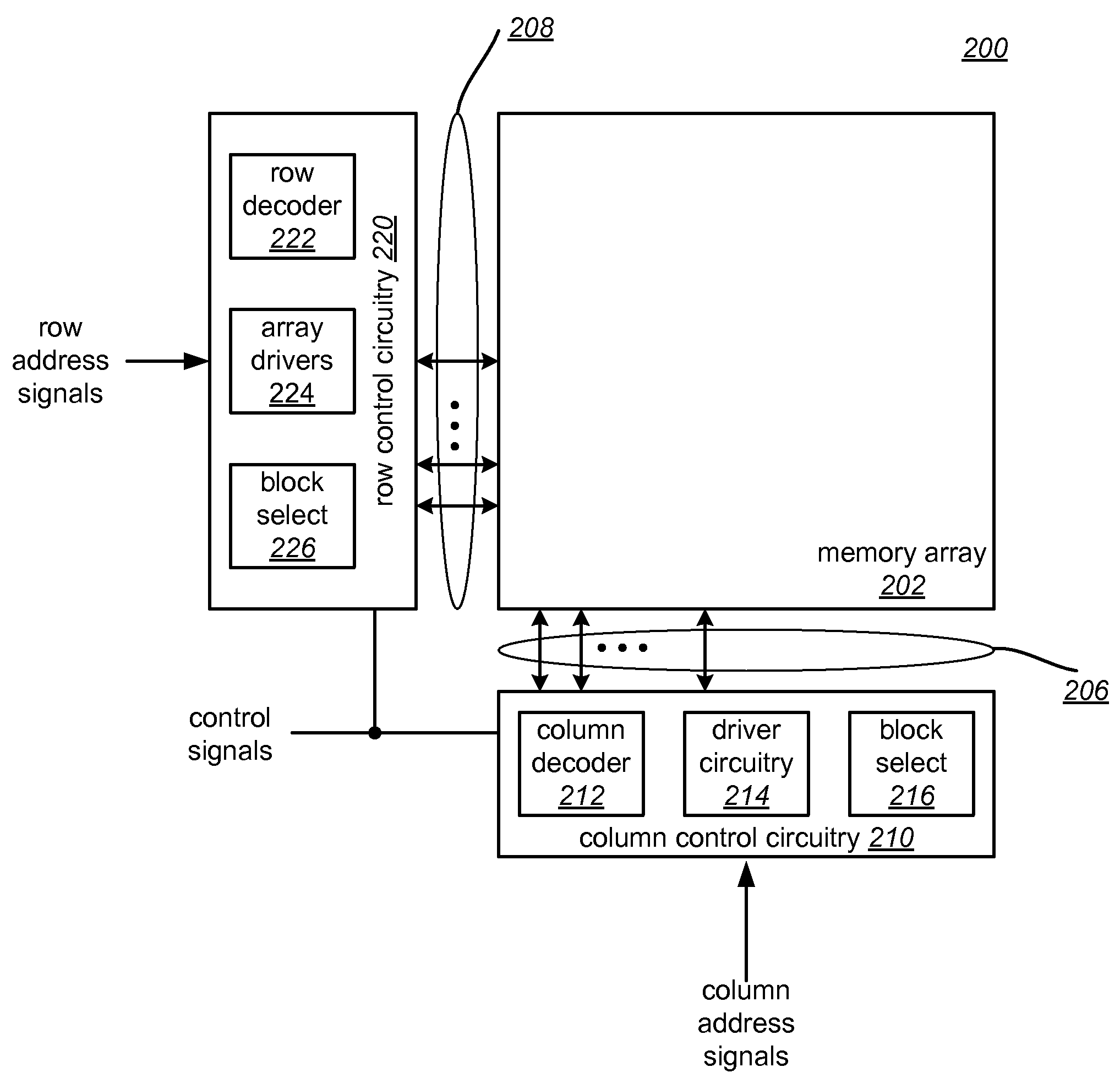

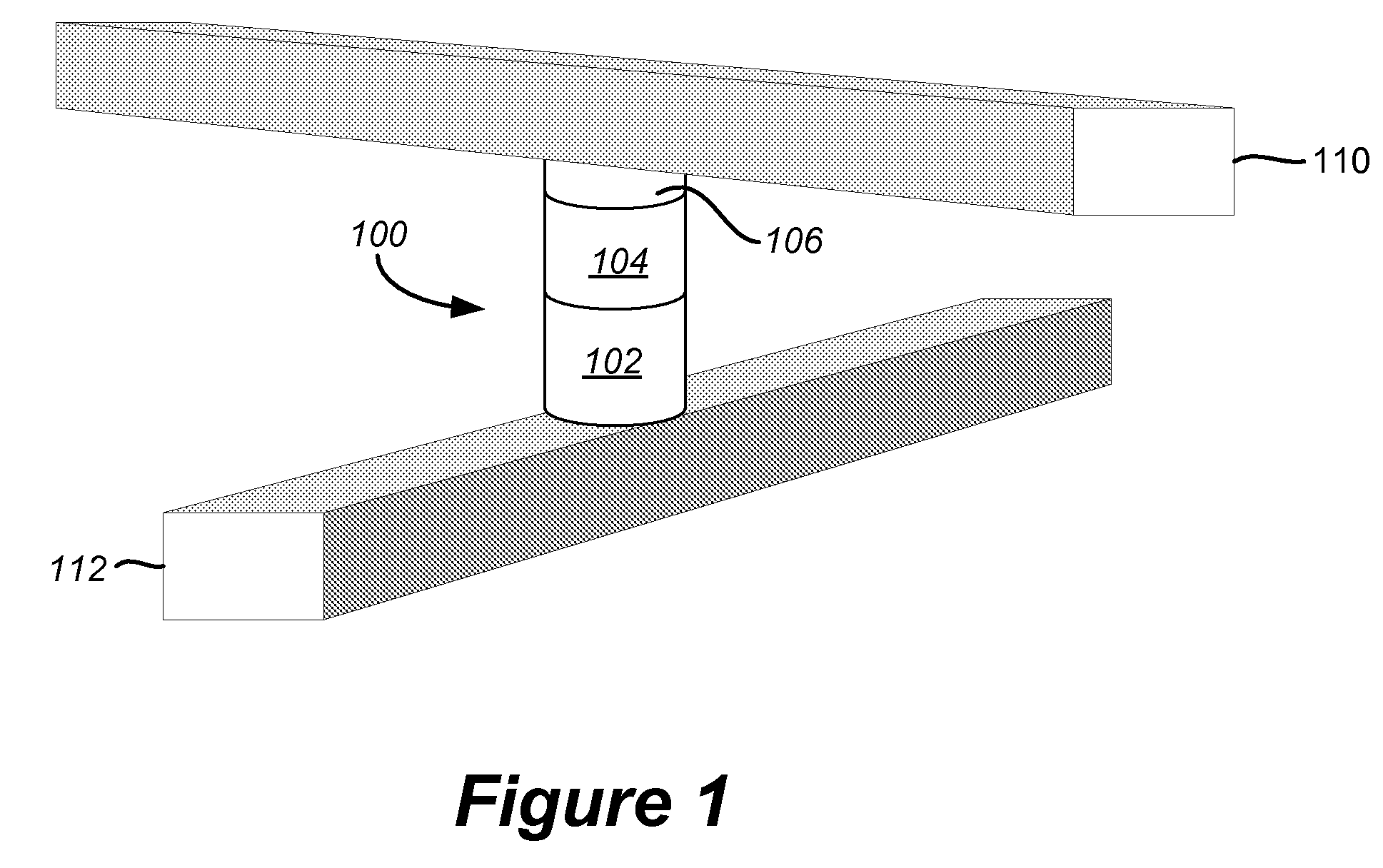

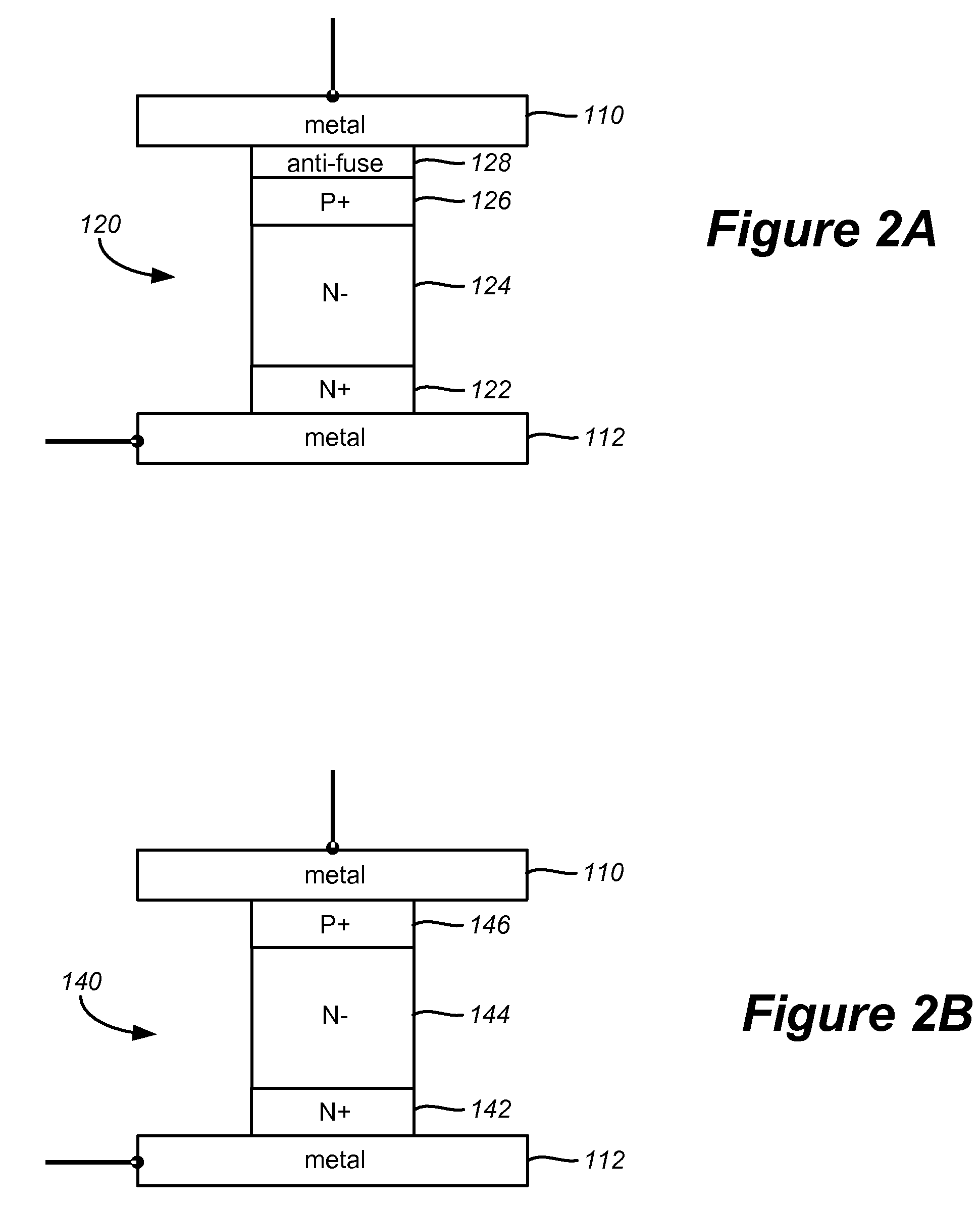

Controlled pulse operations in non-volatile memory

InactiveUS20080025076A1Low leakage currentIncrease bandwidthRead-only memoriesDigital storageVoltage pulseDrain current

A passive element memory device is provided that includes memory cells comprised of a state change element in series with a steering element. Controlled pulse operations are used to perform resistance changes associated with set and reset operations in an array of memory cells. Selected memory cells in an array are switched to a target resistance state in one embodiment by applying a positive voltage pulse to selected first array lines while applying a negative voltage pulse to selected second array lines. An amplitude of voltage pulses can be increased while being applied to efficiently and safely switch the resistance of cells having different operating characteristics. The cells are subjected to reverse biases in embodiments to lower leakage currents and increase bandwidth. The amplitude and duration of voltage pulses are controlled, along with the current applied to selected memory cells in some embodiments. These controlled pulse-based operations can be used to set memory cells to a lower resistance state or reset memory cells to a higher resistance state in various embodiments.

Owner:SANDISK TECH LLC

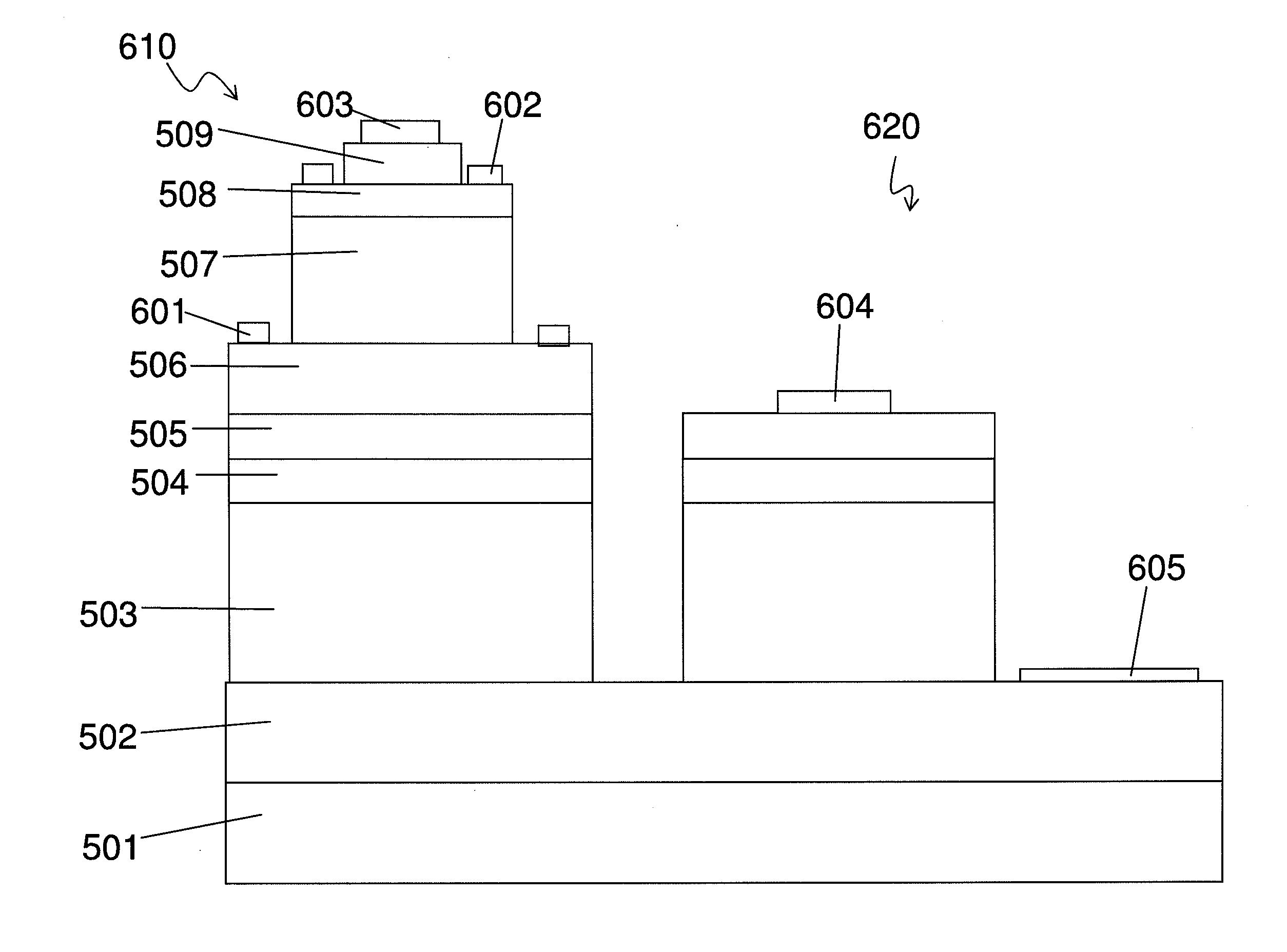

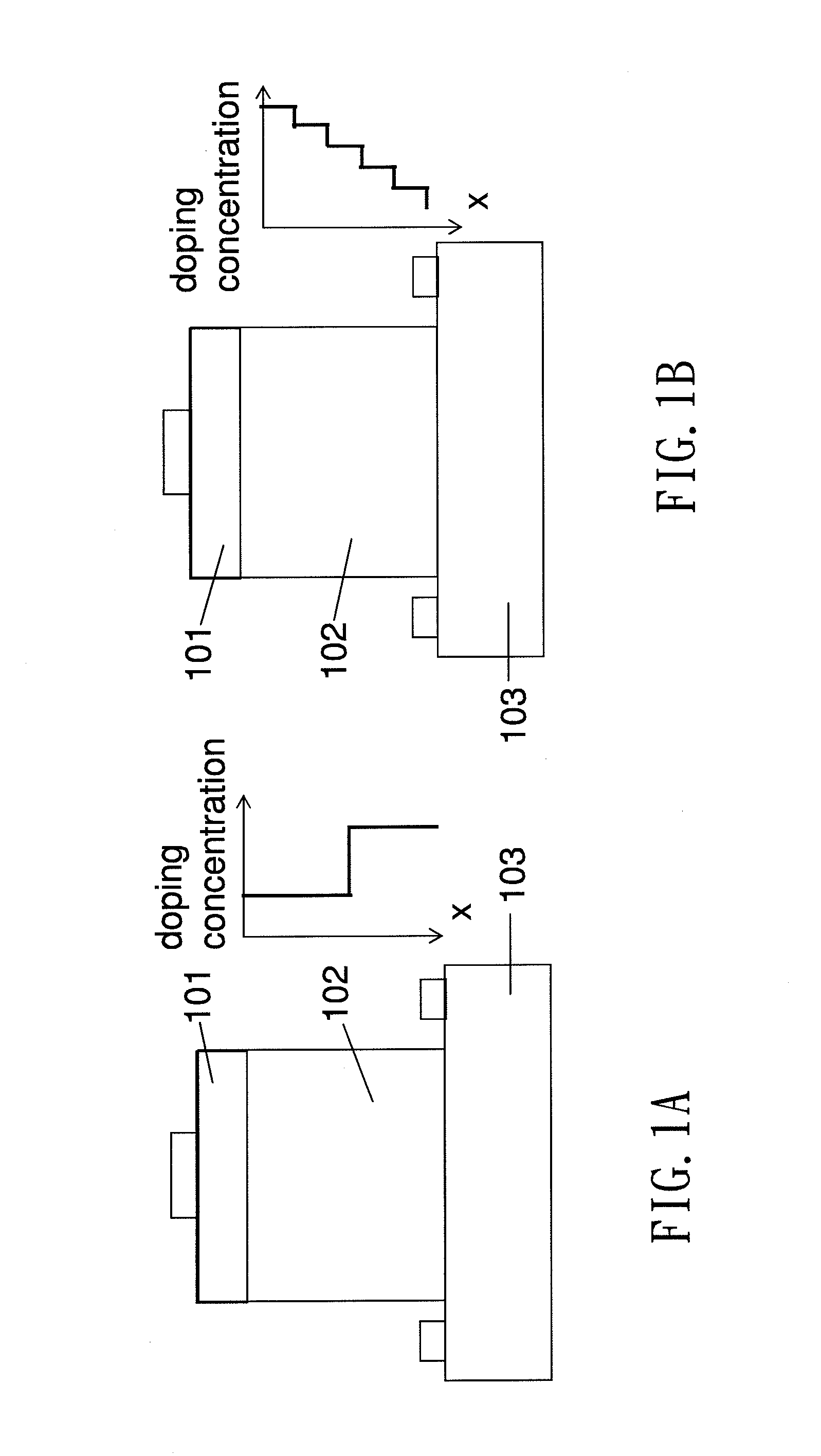

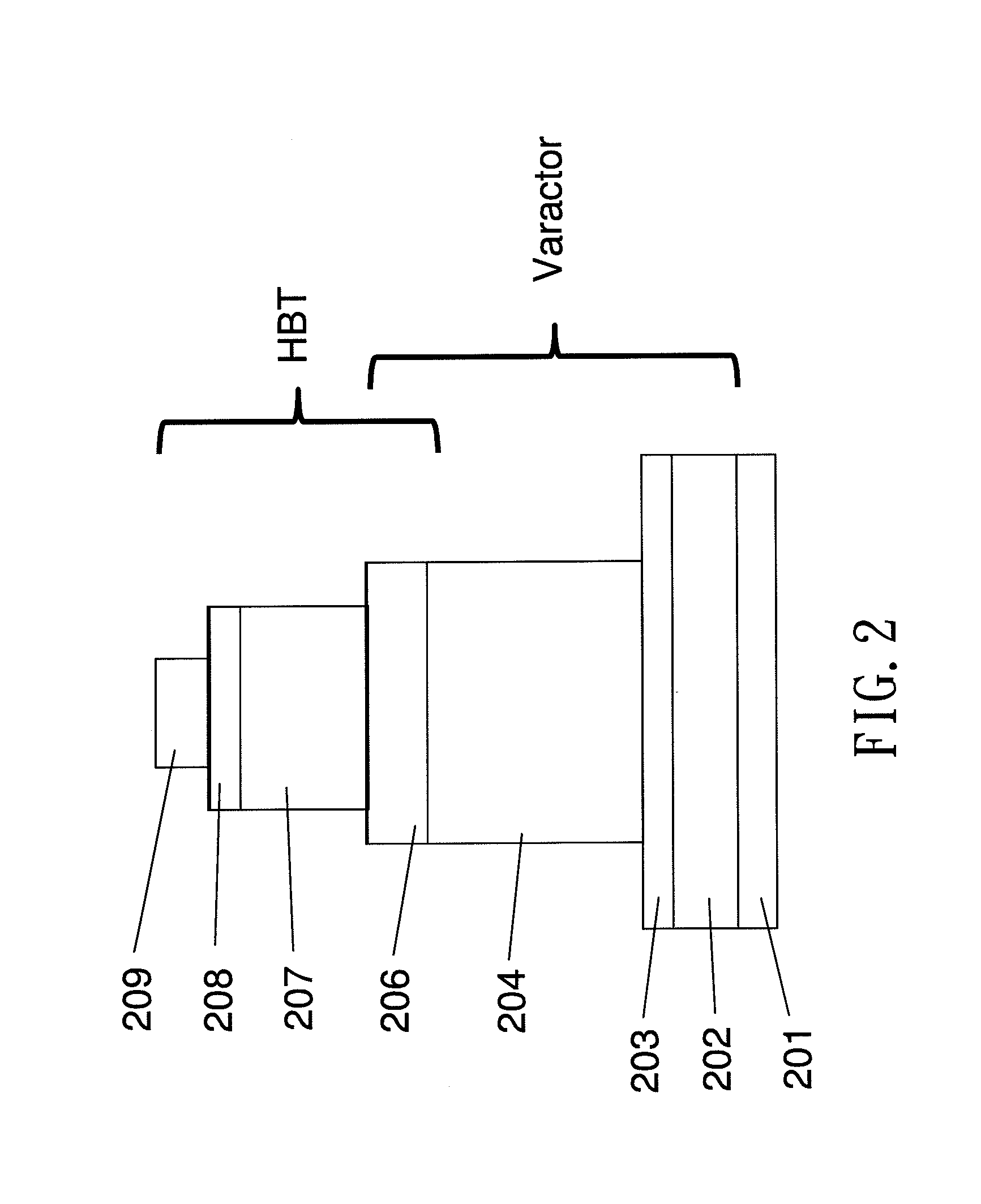

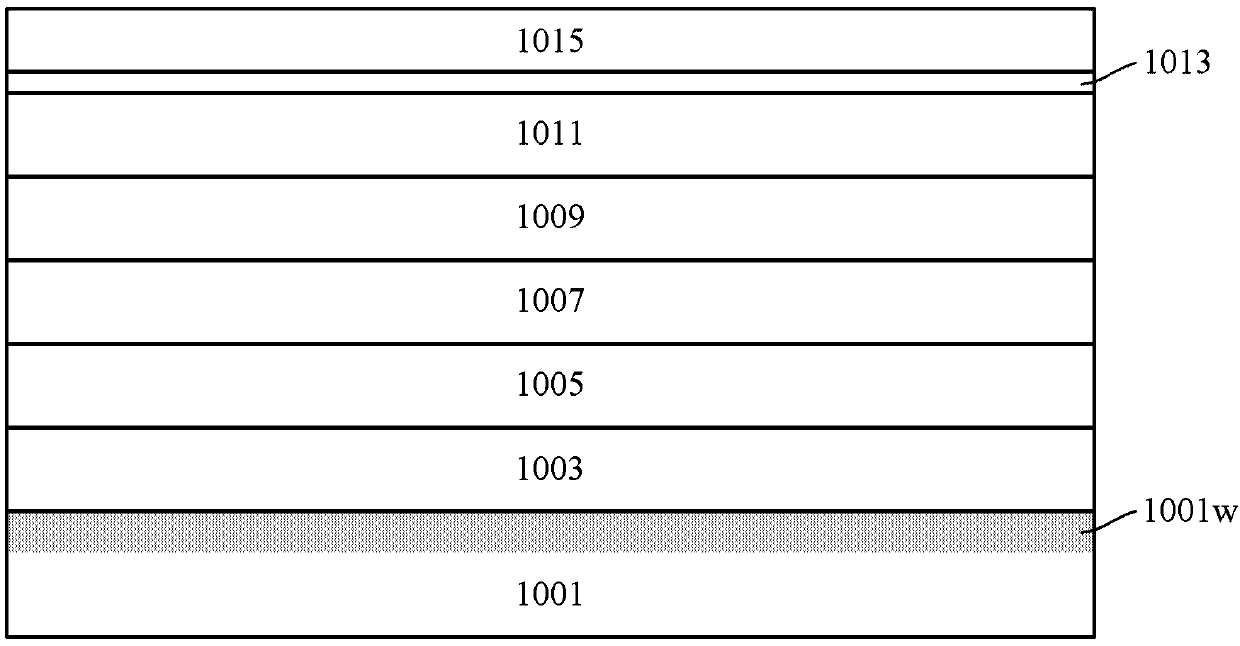

Integrated structure of compound semiconductor devices

ActiveUS20130334570A1High breakdown voltageLow leakage currentSolid-state devicesSemiconductor devicesVaricapPower semiconductor device

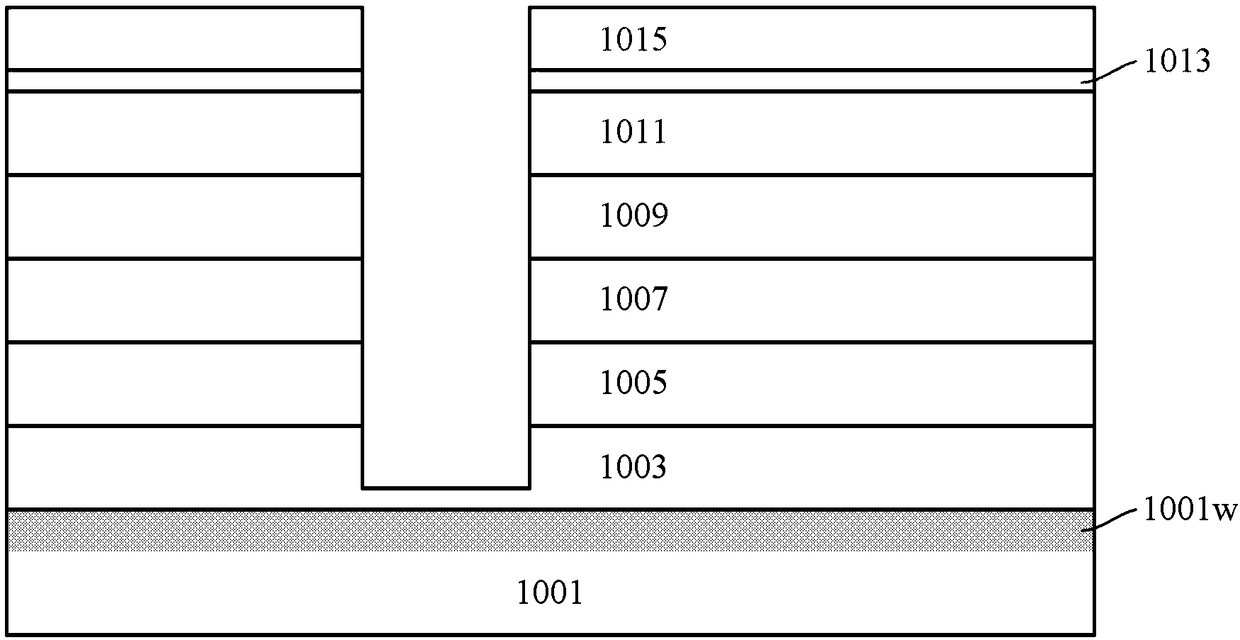

An integrated structure of compound semiconductor devices is disclosed. The integrated structure comprises from bottom to top a substrate, a first epitaxial layer, an etching-stop layer, a second epitaxial layer, a sub-collector layer, a collector layer, a base layer, and an emitter layer, in which the first epitaxial layer is a p-type doped layer, the second epitaxial layer is an n-type graded doping layer with a gradually increased or decreased doping concentration, and the sub-collector layer is an n-type doped layer. The integrated structure can be used to form an HBT, a varactor, or an MESFET.

Owner:WIN SEMICON

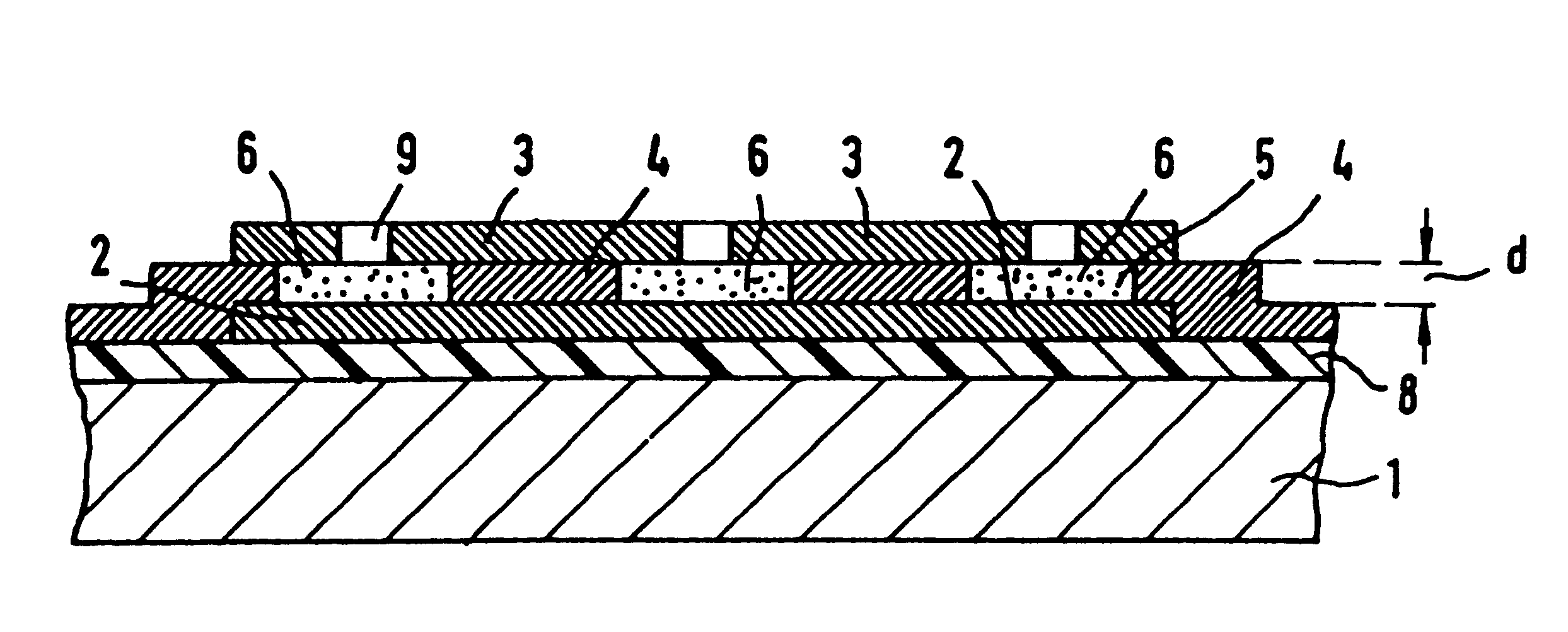

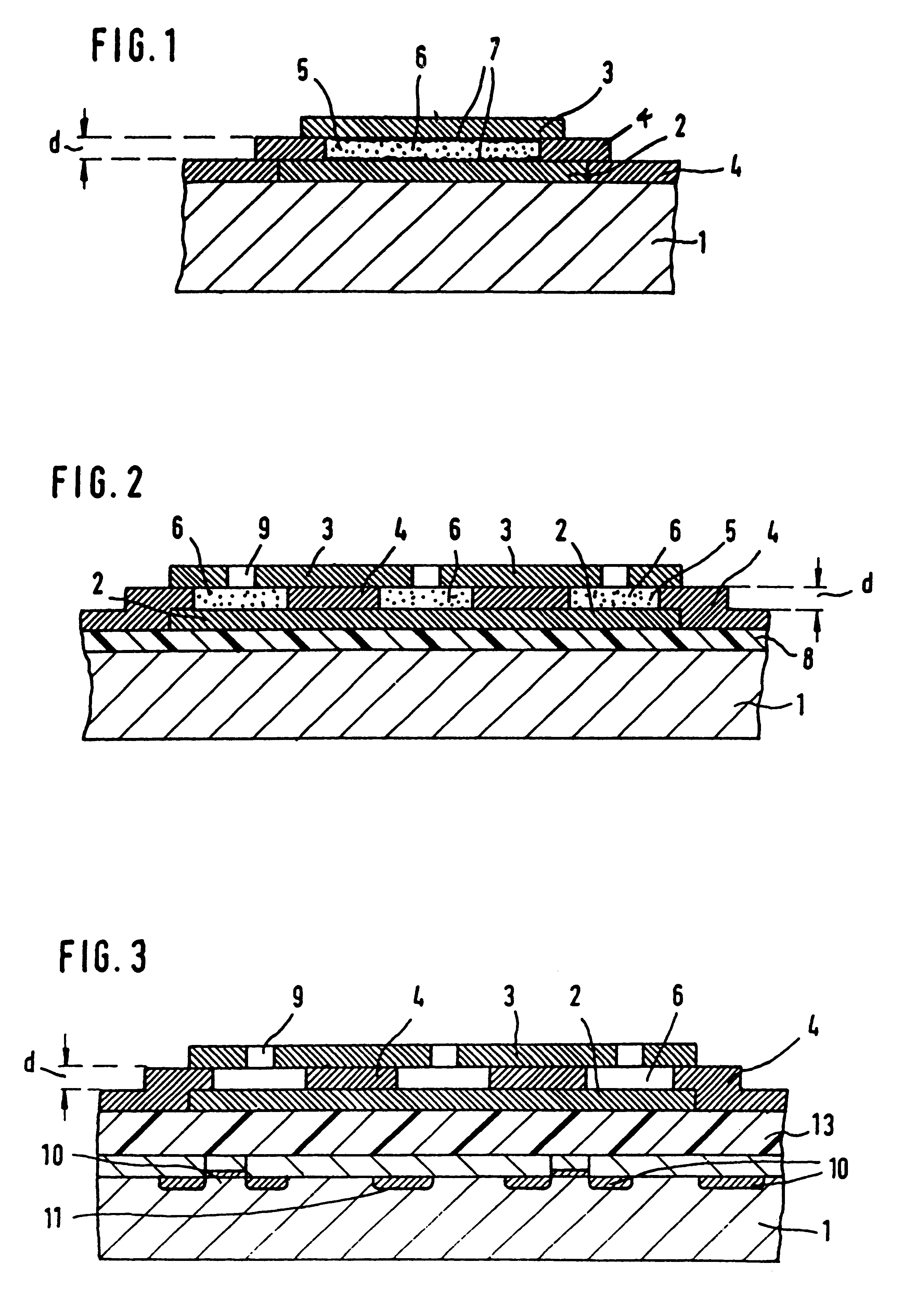

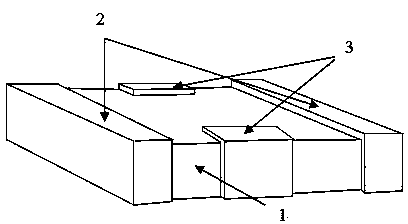

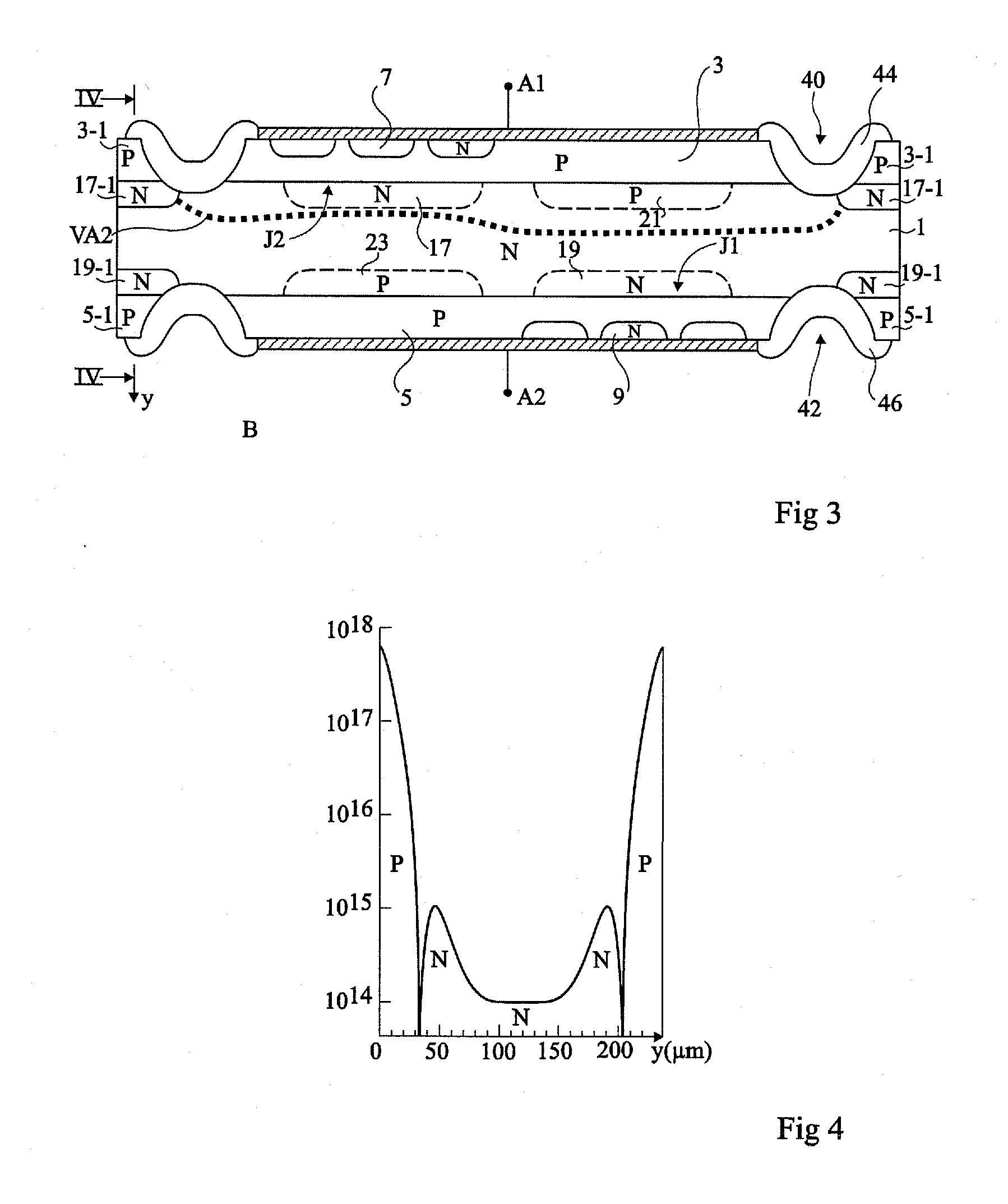

Overvoltage protection device

InactiveUS6204549B1Low leakage currentLow power lossThyristorSemiconductor/solid-state device detailsOptoelectronicsOvervoltage

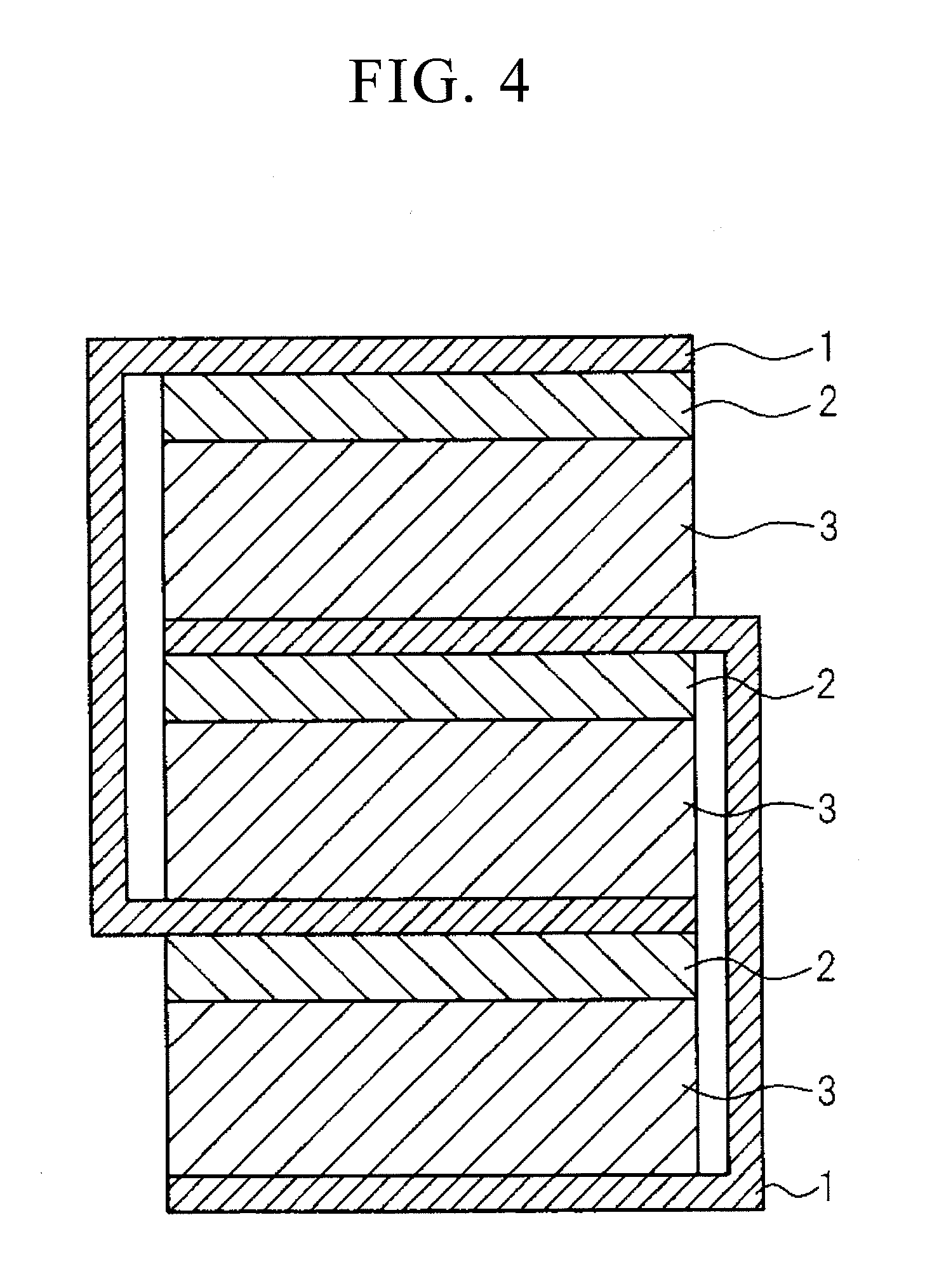

The invention relates to an overvoltage protection device and to a method for fabricating such a device. A substrate (1) is provided with a first electrode layer (2), above which extends a second electrode layer (3) which is separated from the first electrode layer (2) by a distance (d) determined by the thickness of a spacing layer (4). The spacing layer (4) has an opening (5) which forms a cavity (6) between the electrode layers (2, 3).

Owner:MICRONAS INTERMETTAL GMBH

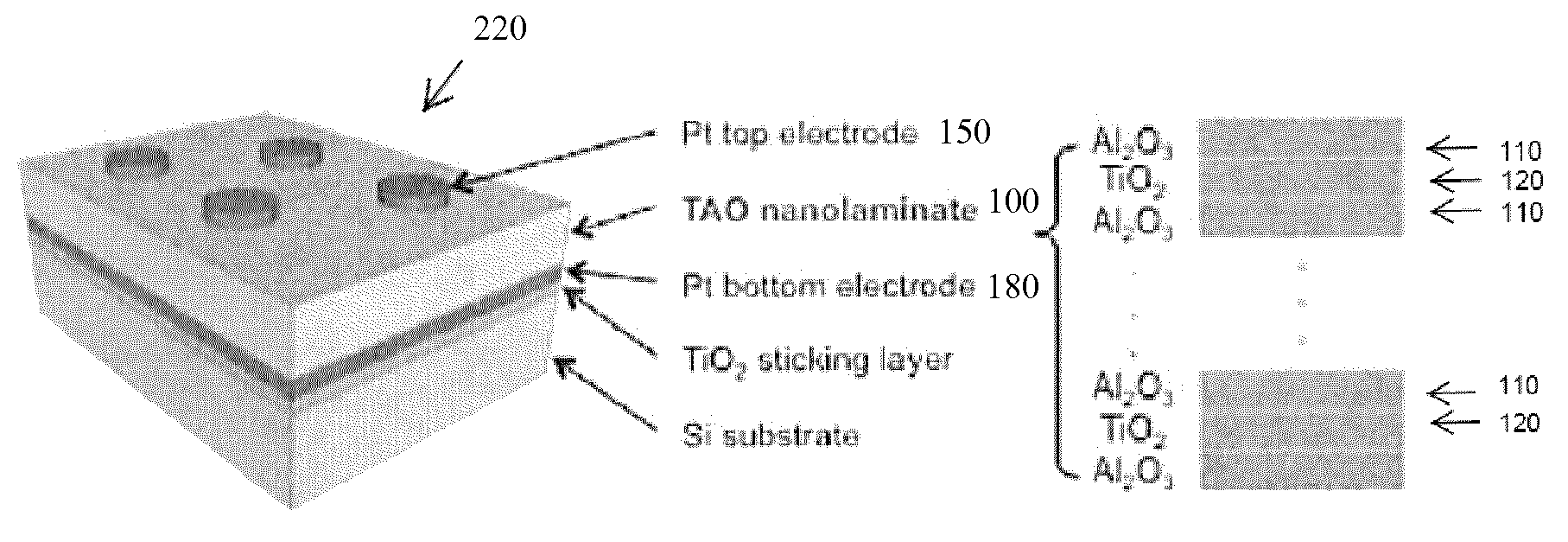

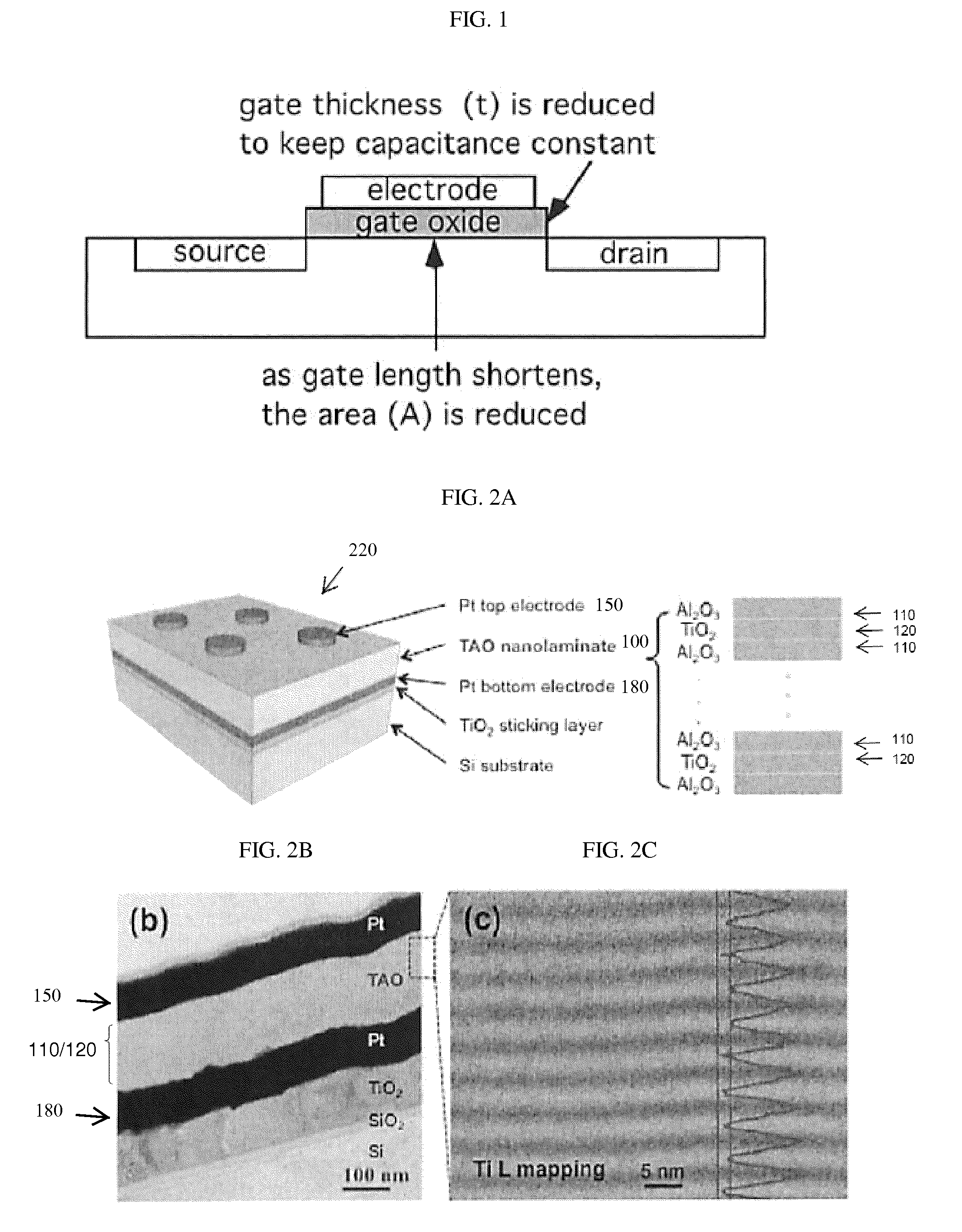

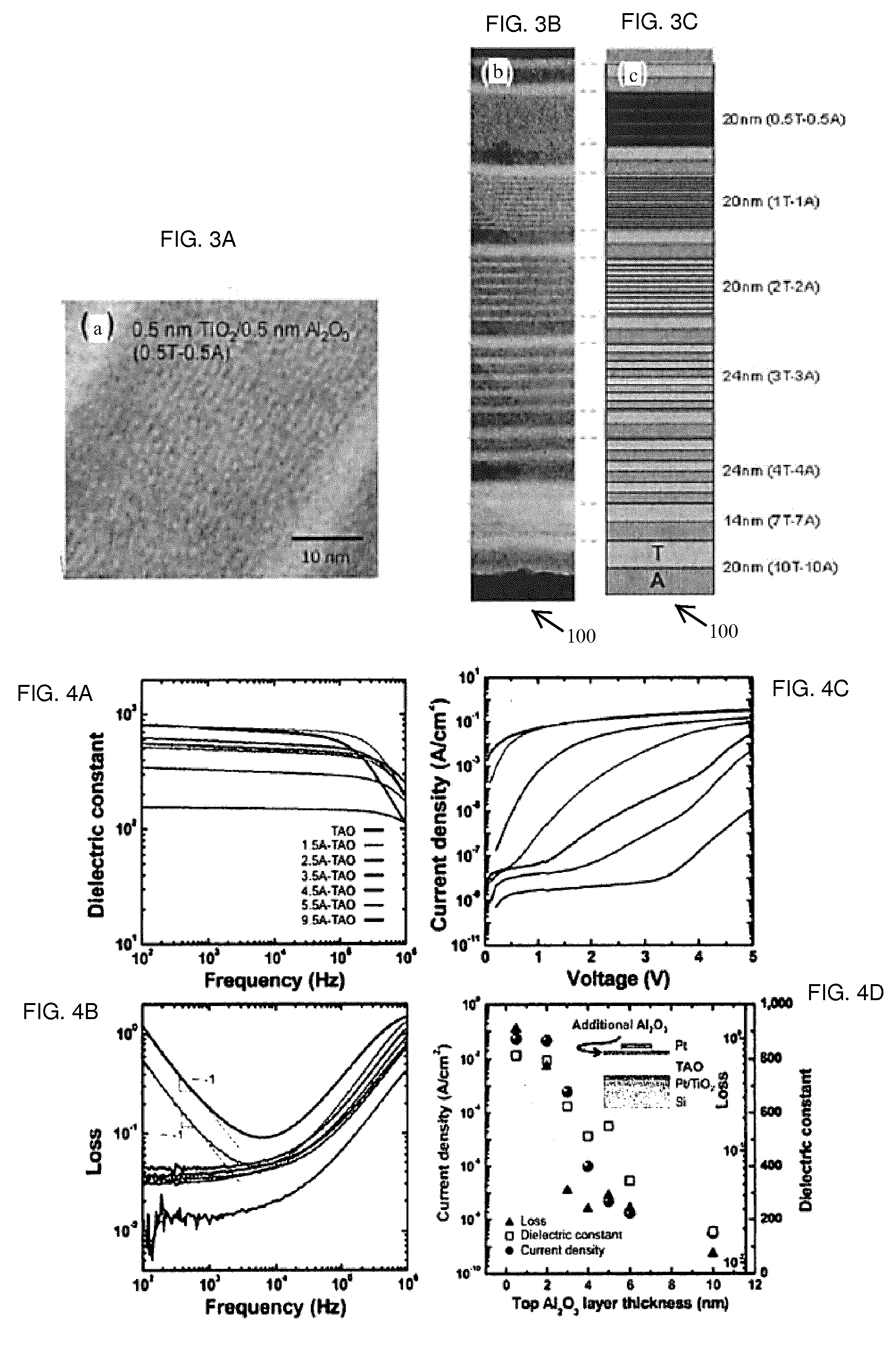

NANOLAMINATES OF Al2O3/TiO2 WITH GIANT DIELECTRIC CONSTANT LOW-LEAKAGE-LOW LOSS-EXTENDED FREQUENCY OPERATION FOR NEW-GENERATION NANOELECTRONICS AND ENERGY STORAGE DEVICES

InactiveUS20130264680A1Low leakage currentLow lossMaterial nanotechnologyLayered productsLow leakageEngineering

Owner:UCHICAGO ARGONNE LLC

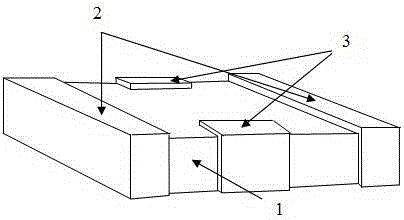

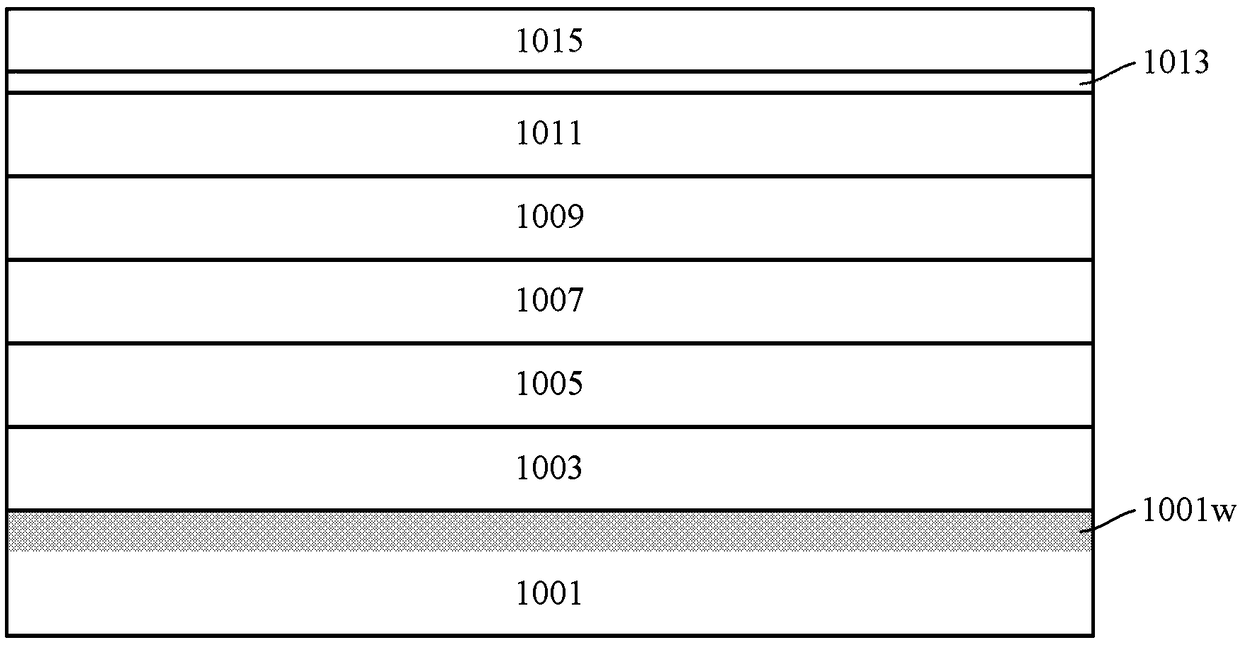

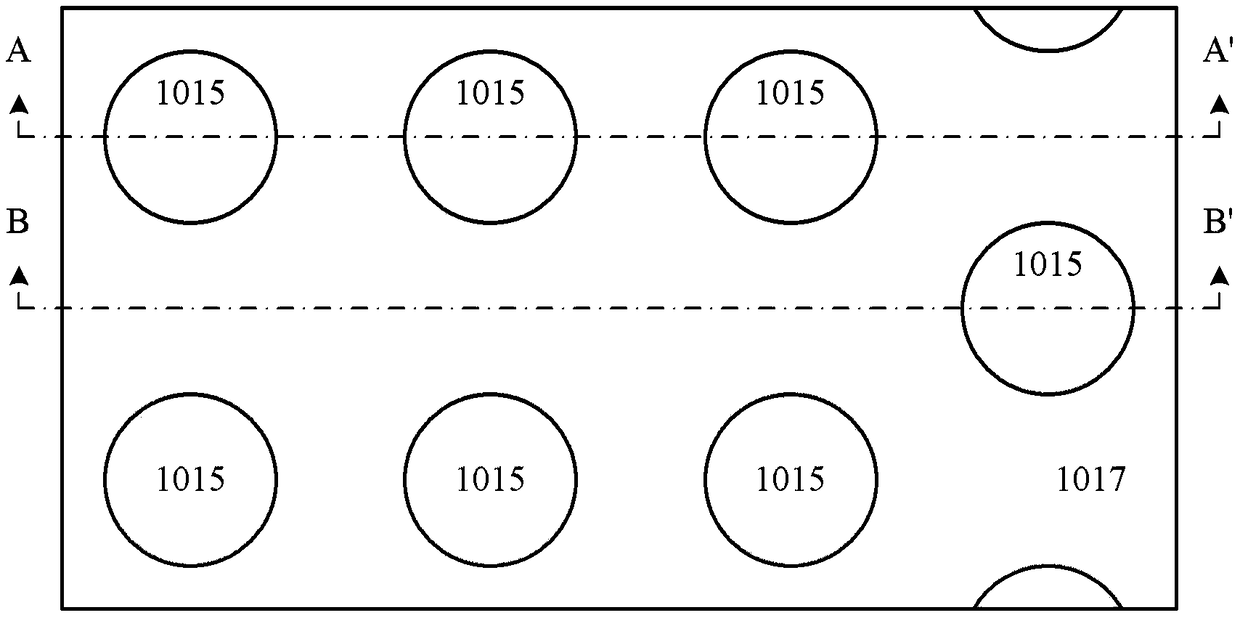

Surface mounting type overvoltage and overcurrent protection device and manufacturing method thereof

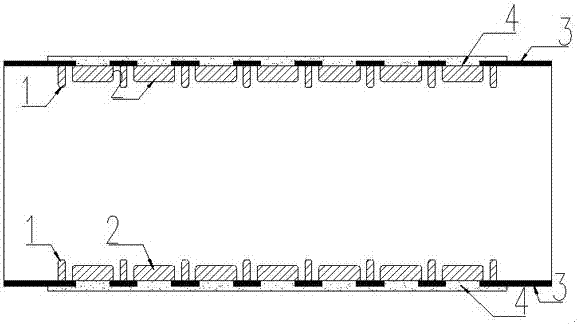

ActiveCN103745898AReduce capacitanceLow leakage currentFuse device manufactureResistor manufactureOvervoltageElectric capacity

The invention provides a surface mounting type overvoltage and overcurrent protection device and a manufacturing method thereof. The surface mounting type overvoltage and overcurrent protection device comprises a protection device body, wherein the left end and the right end of the protection device body are provided with end electrodes; the front side and the rear side of the protection device body are provided with side electrodes; at least one melt layer electrode, at least two first electrode layers and at least two second electrode layers are arranged inside the protection device body; the melt layer electrode is covered by an arc extinction material coating; through holes are formed between the first electrode layers and the second electrode layers; piezoresistor function phases are filled in the through holes. The surface mounting type overvoltage and overcurrent protection device is manufactured by the steps of molding LTCC (Low Temperature Co-Fired Ceramic) membranes, printing the melt layer electrode, printing electrode layer electrodes, printing the arc extinction material coating, forming the through holes in the LTCC stacked membranes, filling the piezoresistor function phases in the through holes, stacking according to the design, cutting to form a single product, sintering the product, forming the end electrodes and the side electrodes and the like. The surface mounting type overvoltage and overcurrent protection device has the advantages of low electric capacity, low leakage conductance current, rapid response speed, and high reliability and stability.

Owner:NANJING SART SCI & TECH DEV

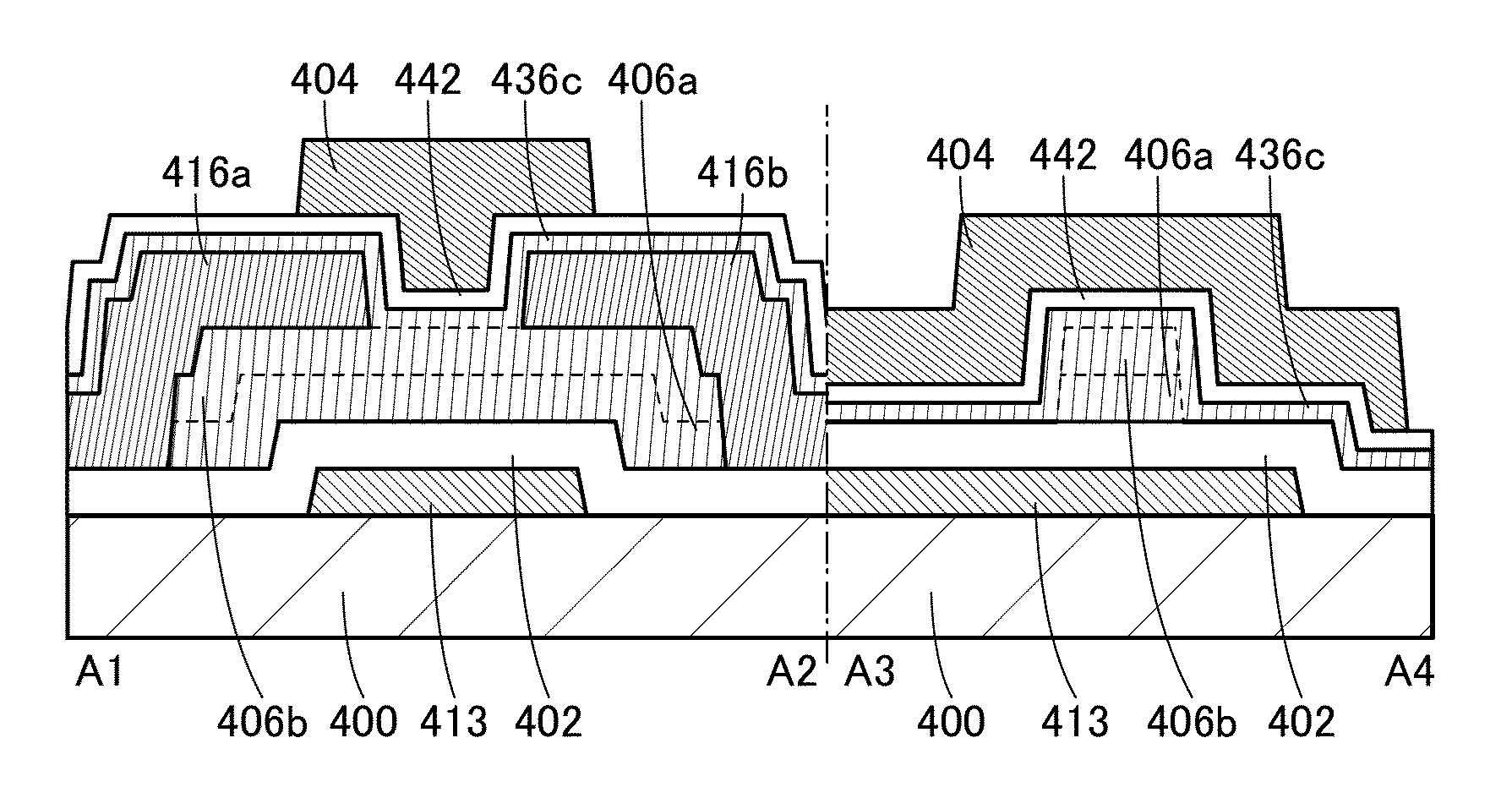

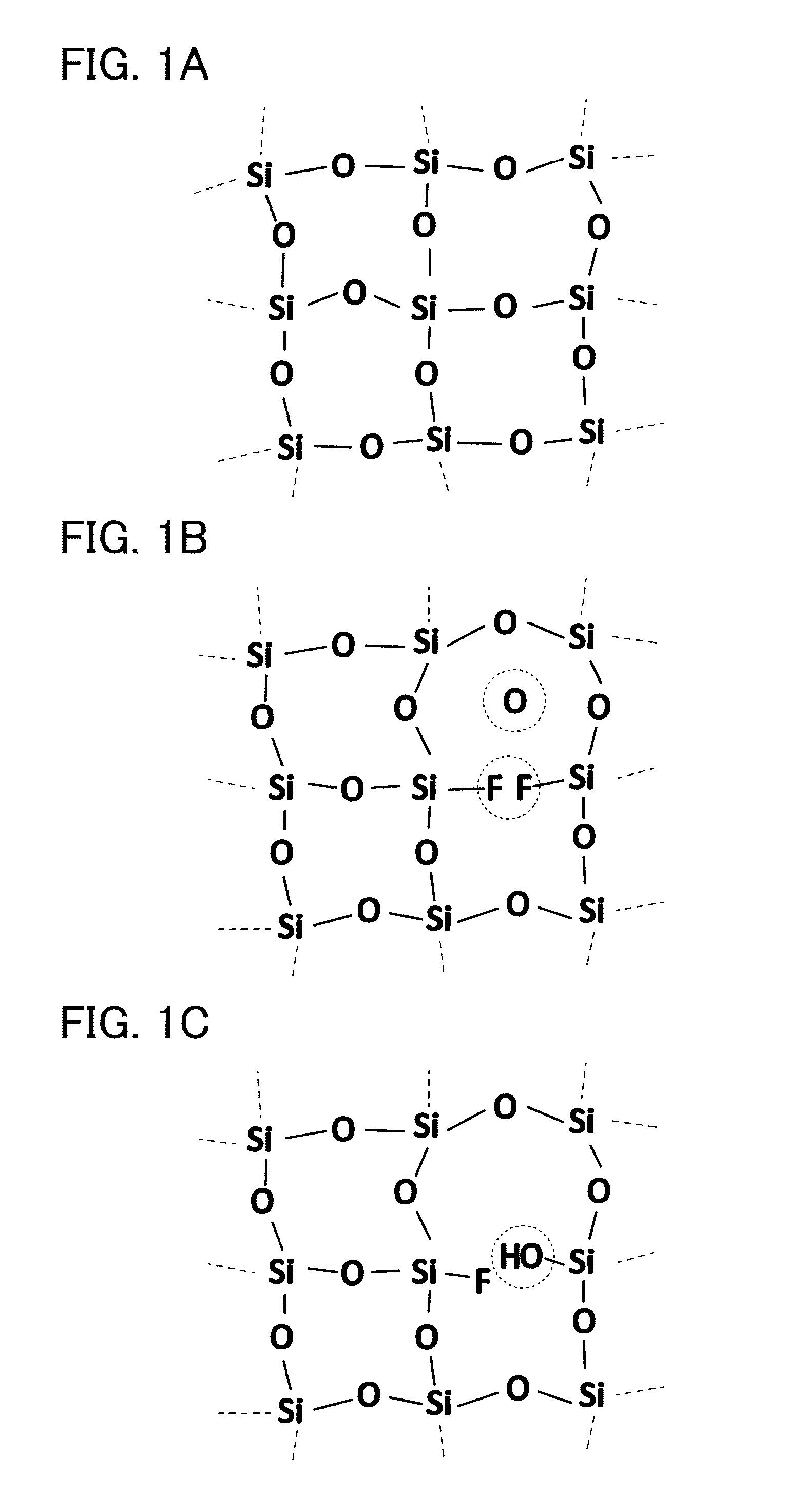

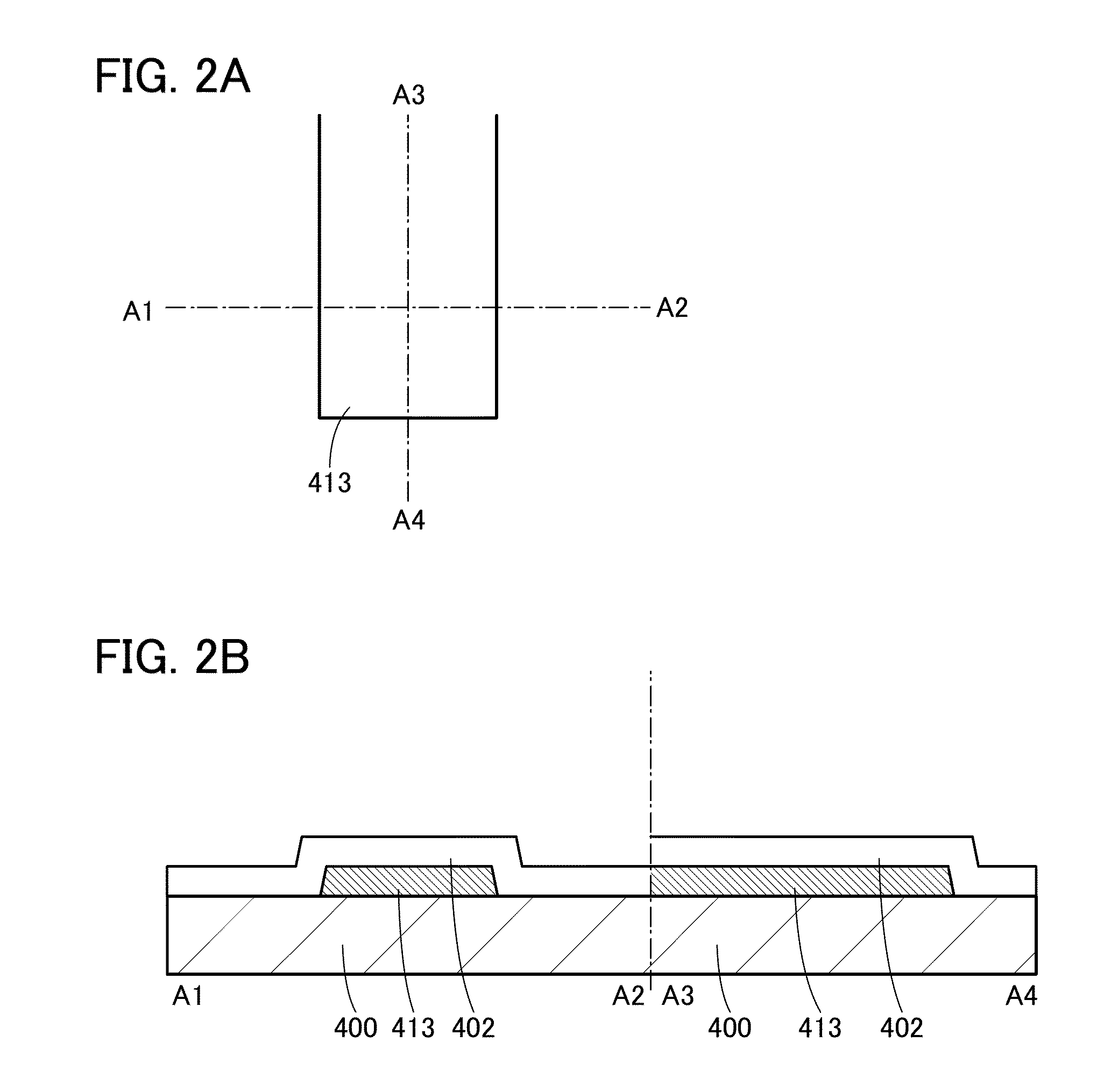

Semiconductor device and manufacturing method thereof, module, and electronic device

InactiveUS20160111547A1Stable electrical characteristicLow leakage currentTransistorSolid-state devicesHydrogen concentrationPower semiconductor device

A transistor with stable electrical characteristics or a transistor with normally-off electrical characteristics. The transistor is a semiconductor device including a conductor, a semiconductor, a first insulator, and a second insulator. The semiconductor is over the first insulator. The conductor is over the semiconductor. The second insulator is between the conductor and the semiconductor. The first insulator includes fluorine and hydrogen. The fluorine concentration of the first insulator is higher than the hydrogen concentration of the first insulator.

Owner:SEMICON ENERGY LAB CO LTD

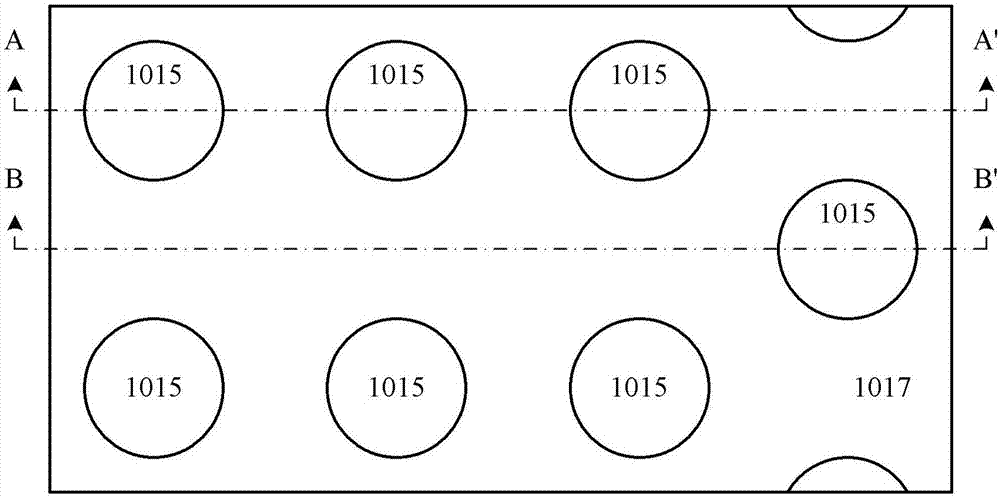

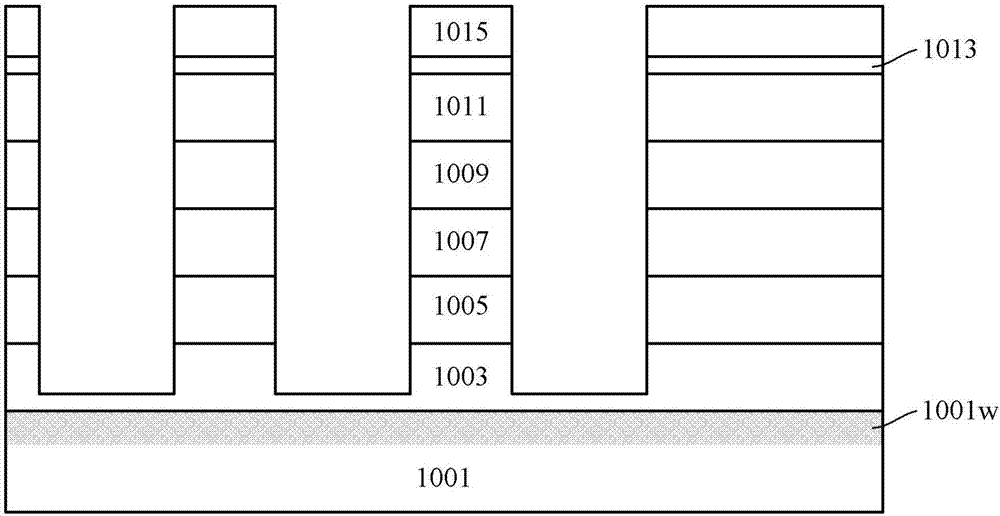

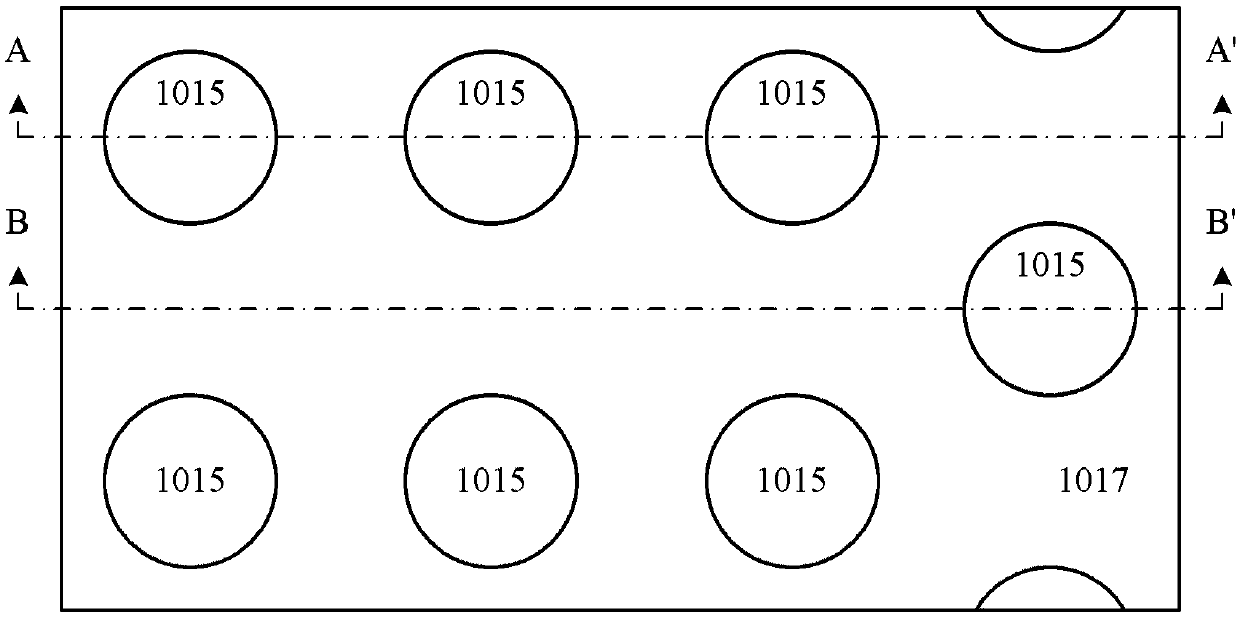

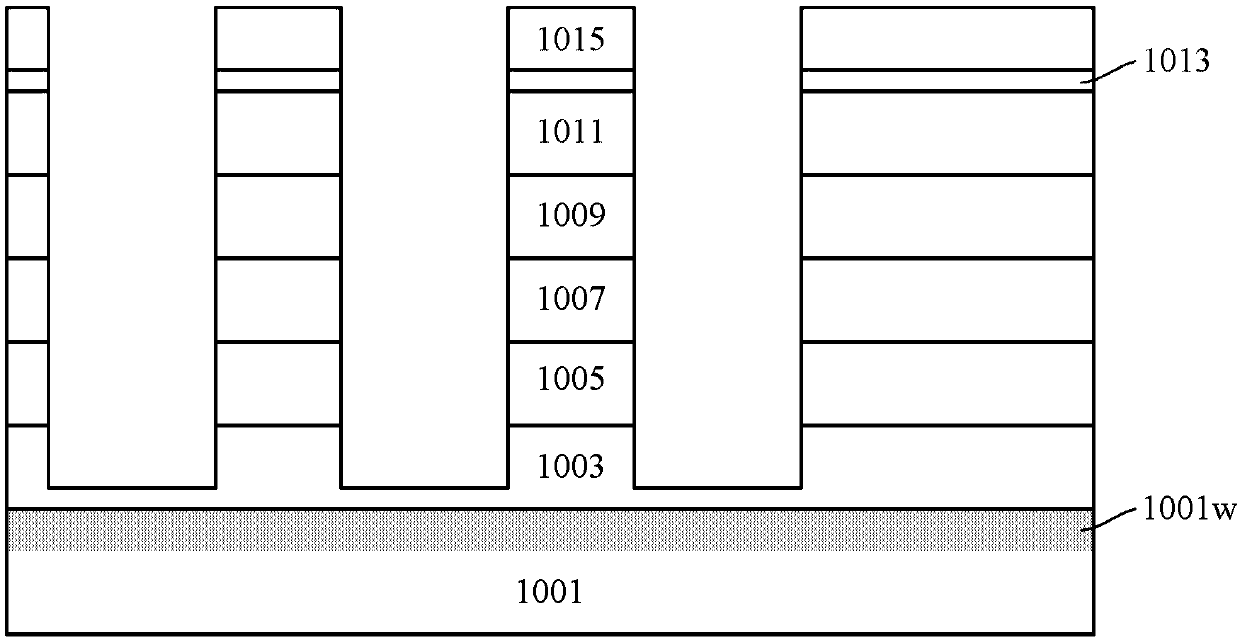

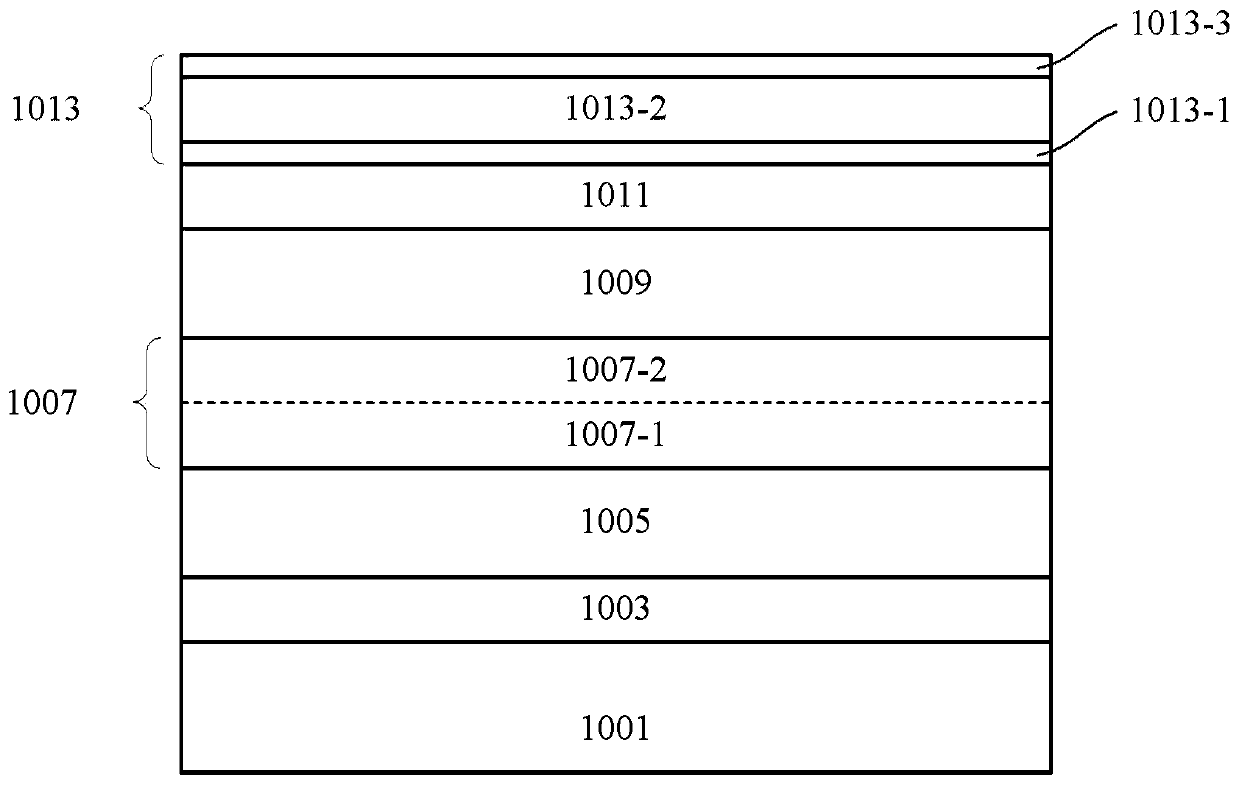

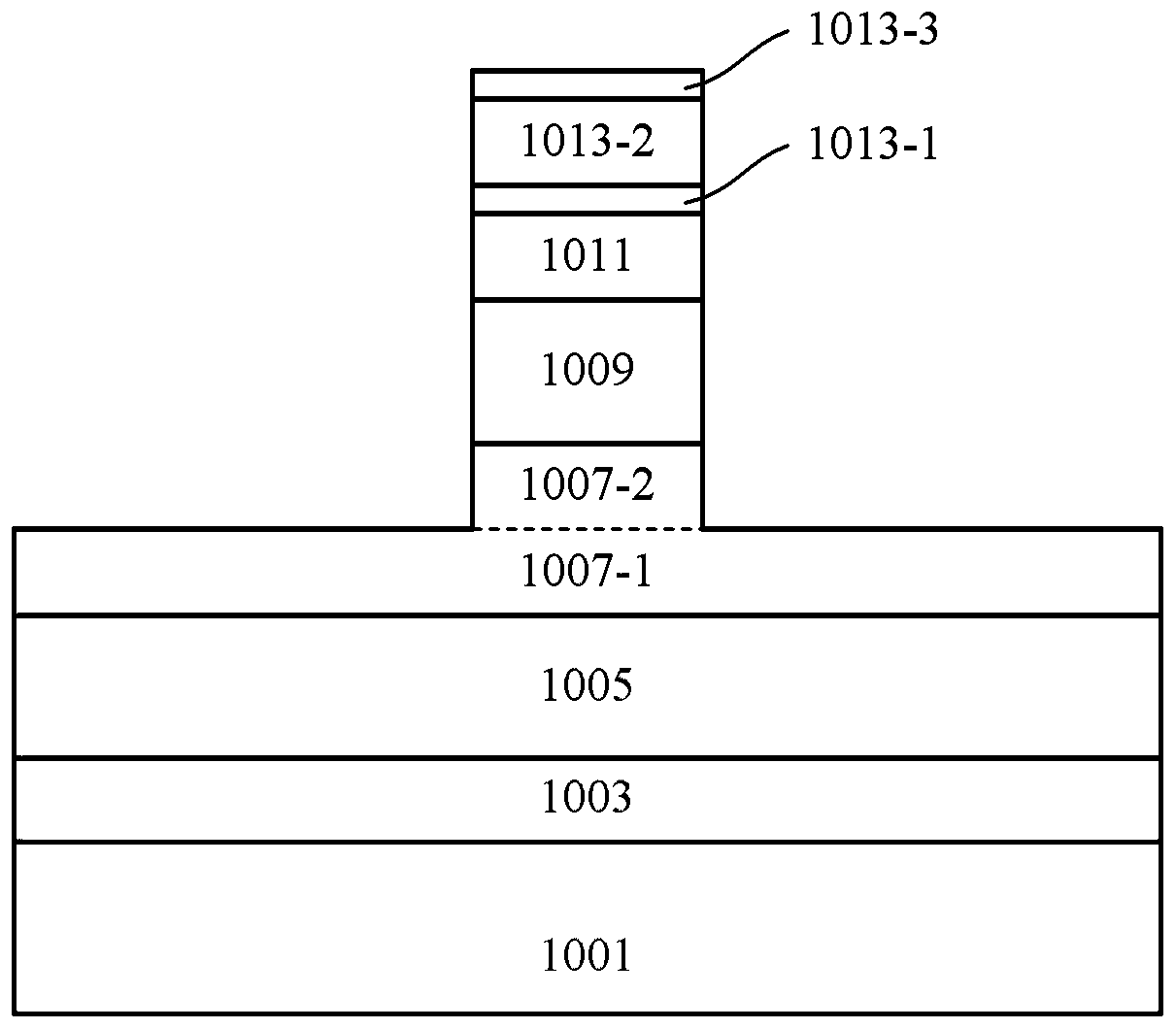

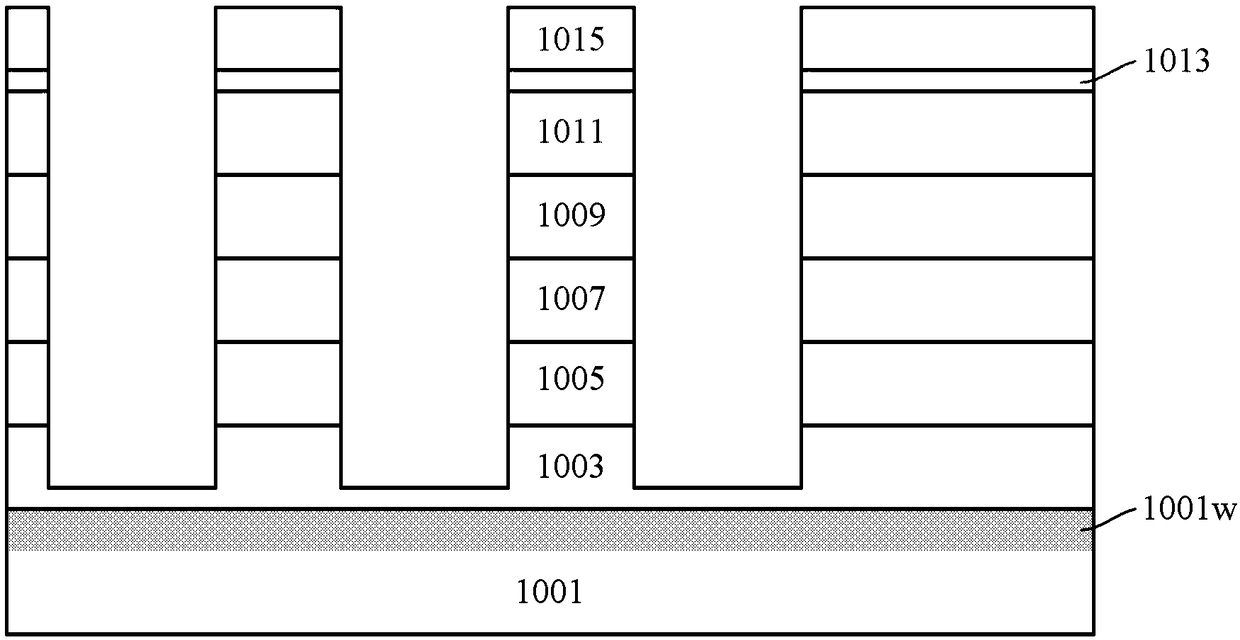

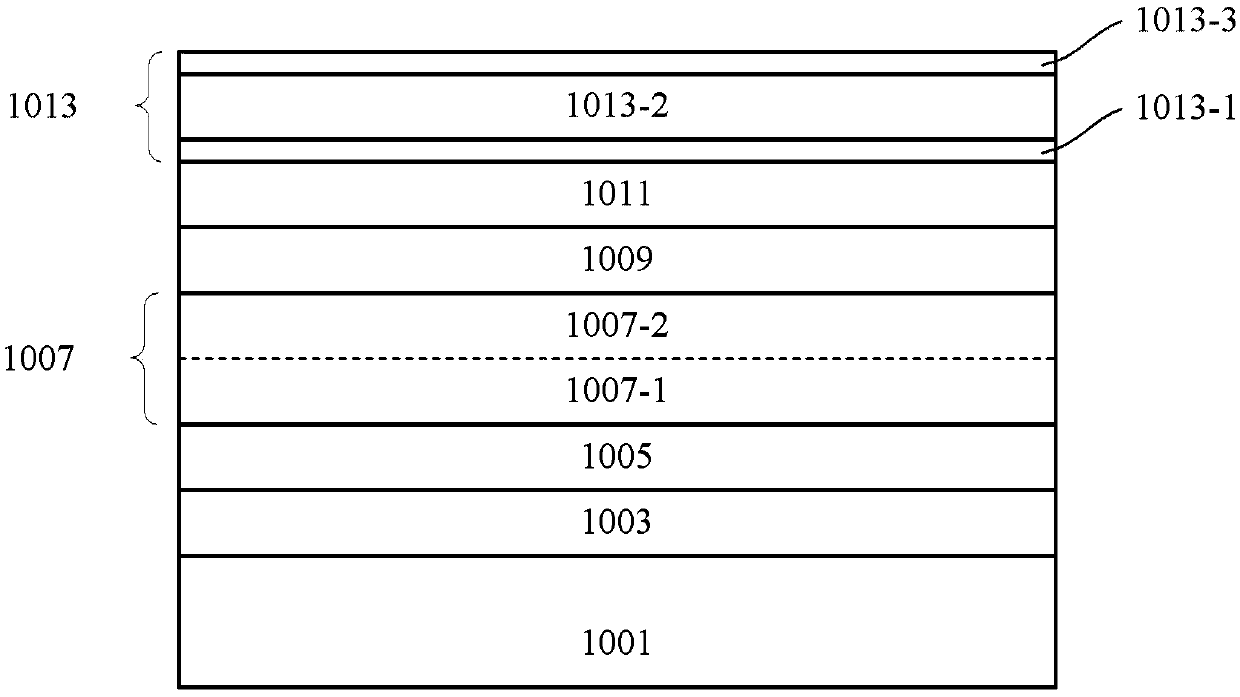

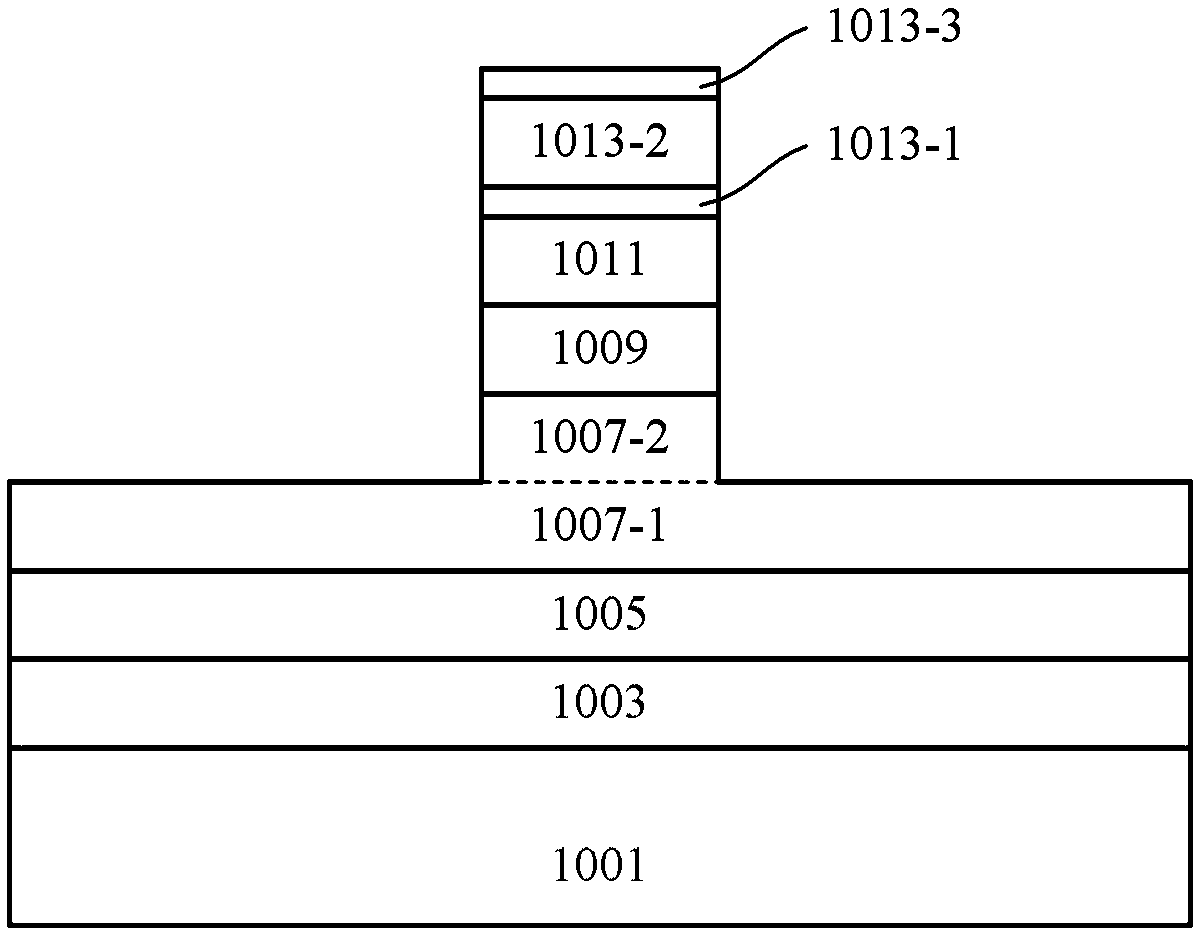

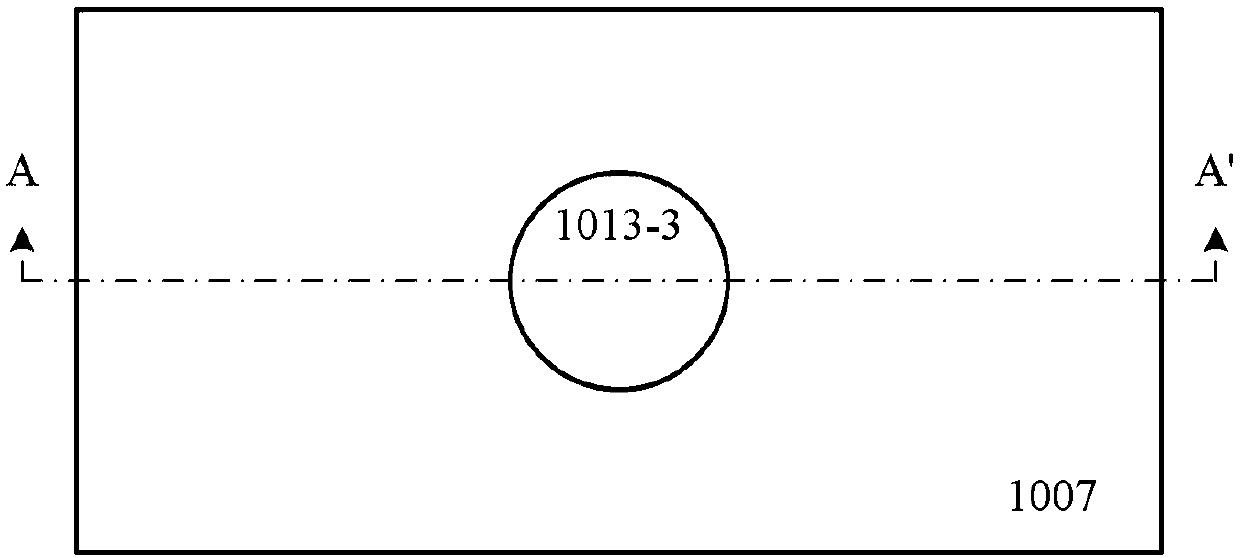

Memory device, manufacturing method thereof and electronic device comprising memory device

ActiveCN107887391AImprove performanceReduce areaSolid-state devicesSemiconductor devicesGate stackComputer science

Owner:INST OF MICROELECTRONICS CHINESE ACAD OF SCI

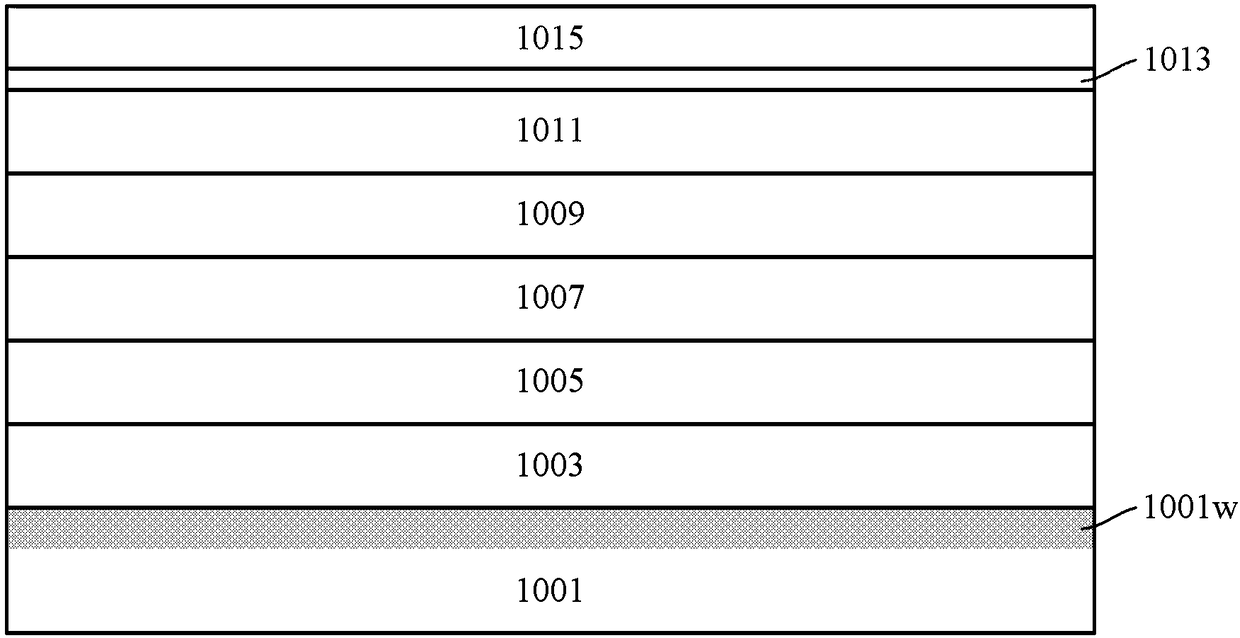

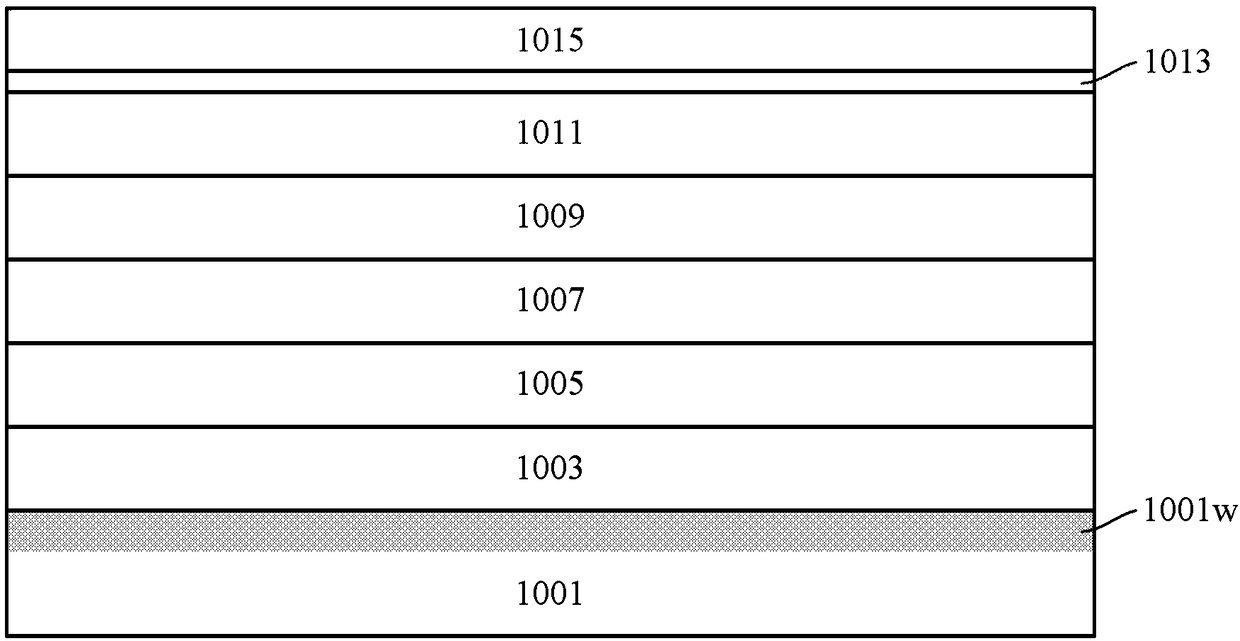

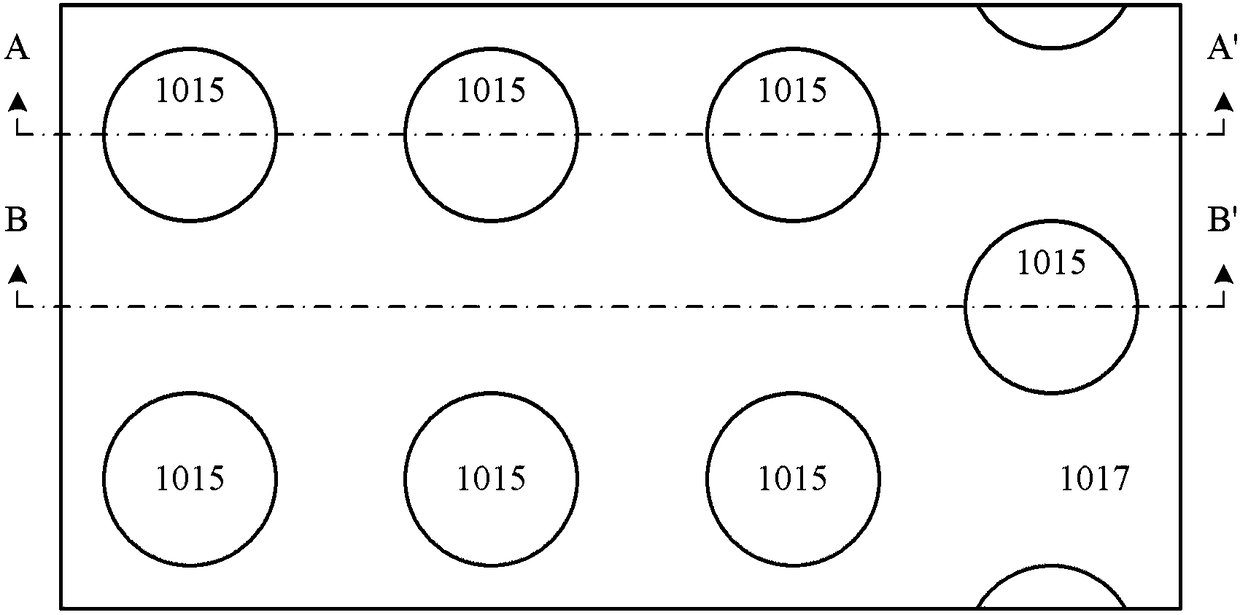

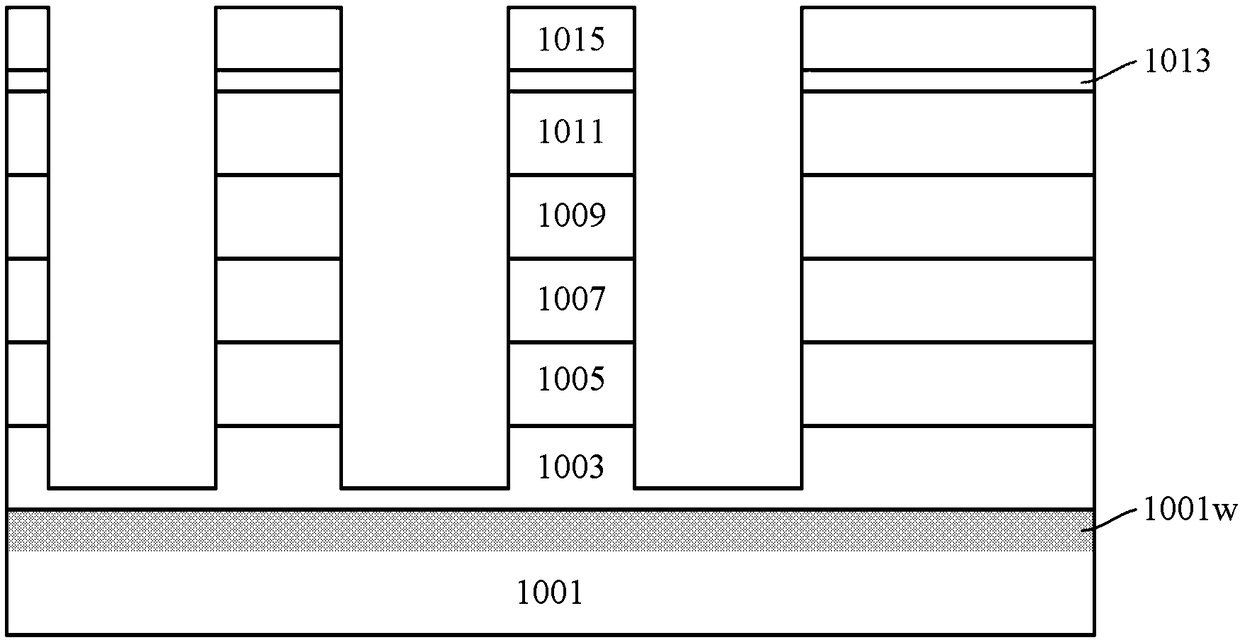

Storage device, manufacturing method thereof and electronic equipment comprises same

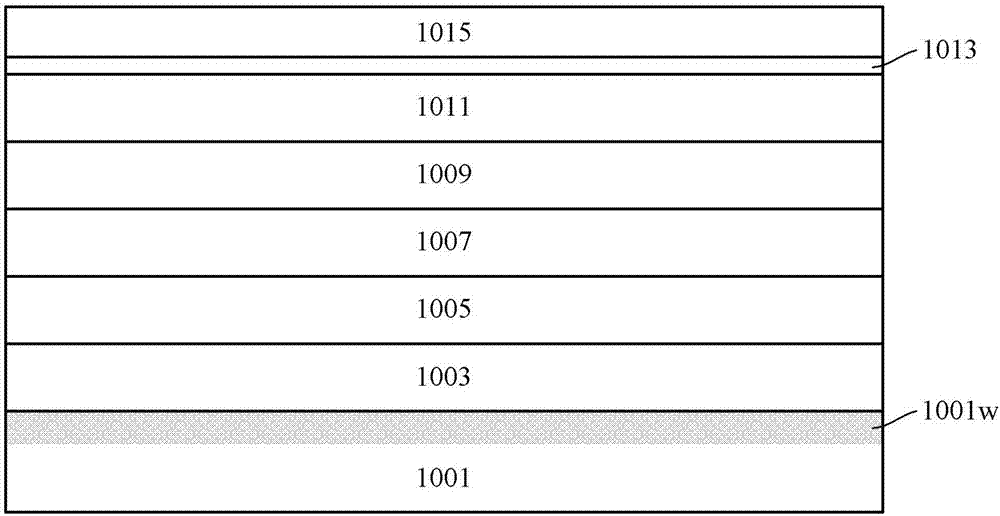

ActiveCN108962905AReduce overall stack thicknessReduce thicknessSolid-state devicesSemiconductor devicesElectric equipmentElectronic equipment

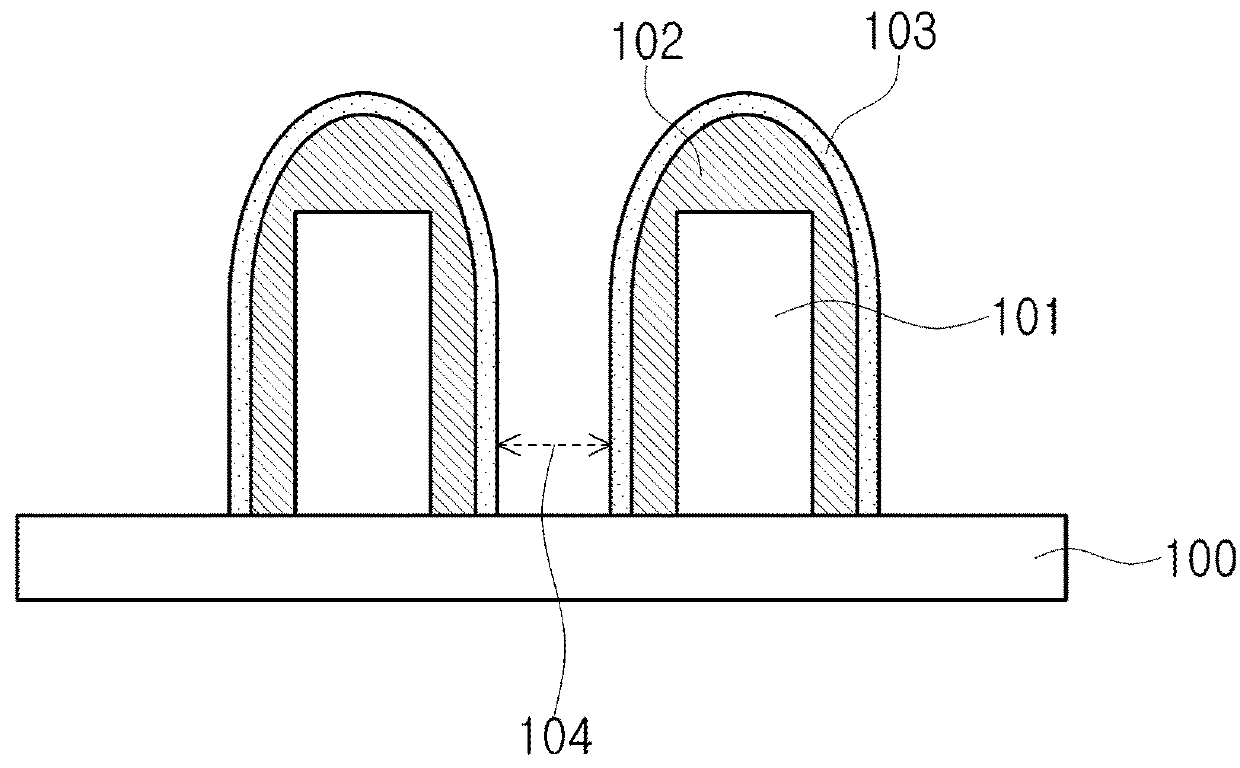

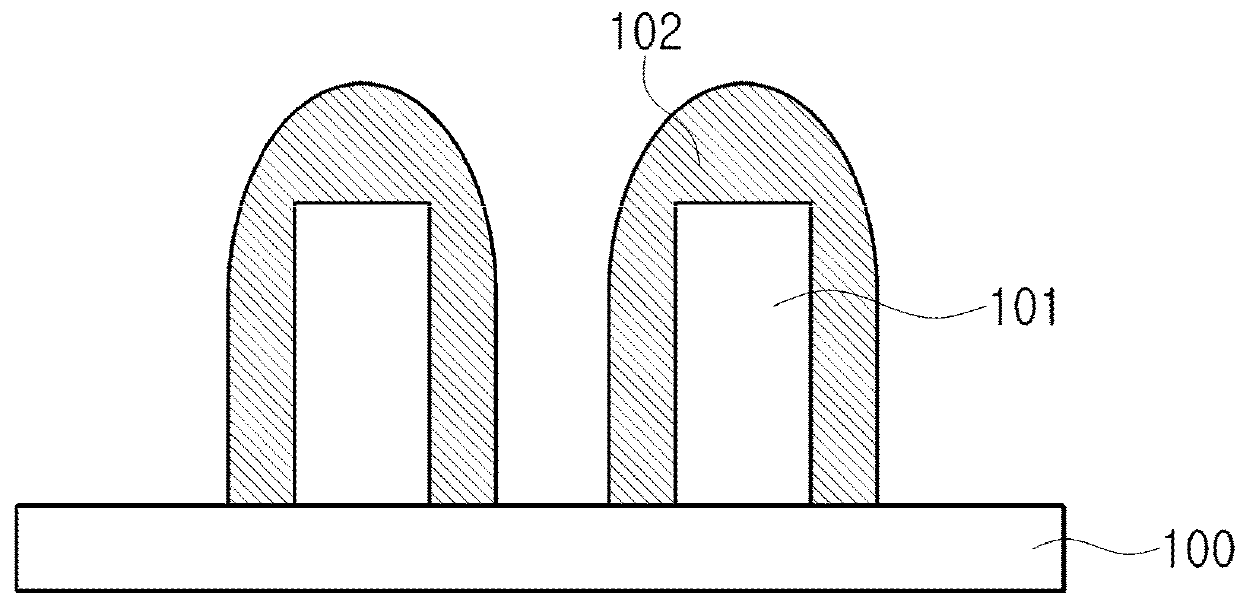

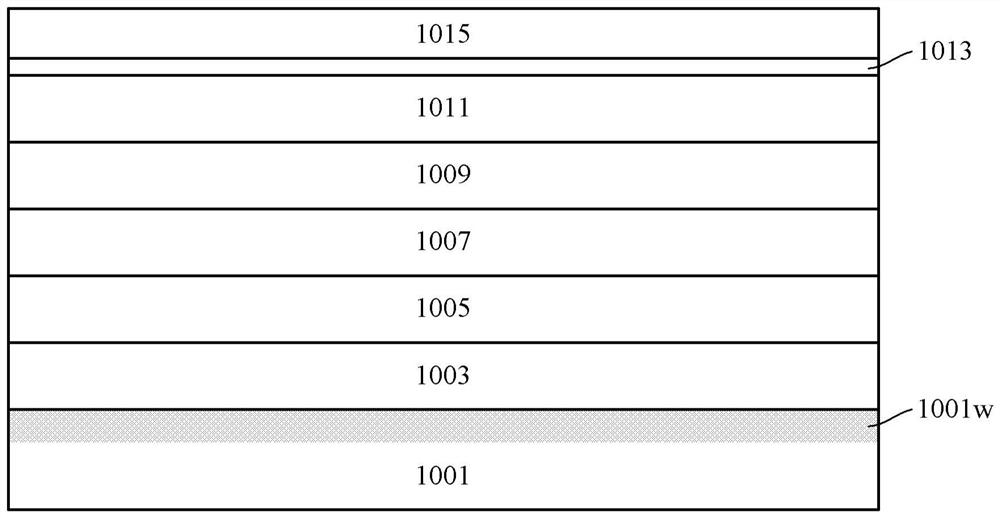

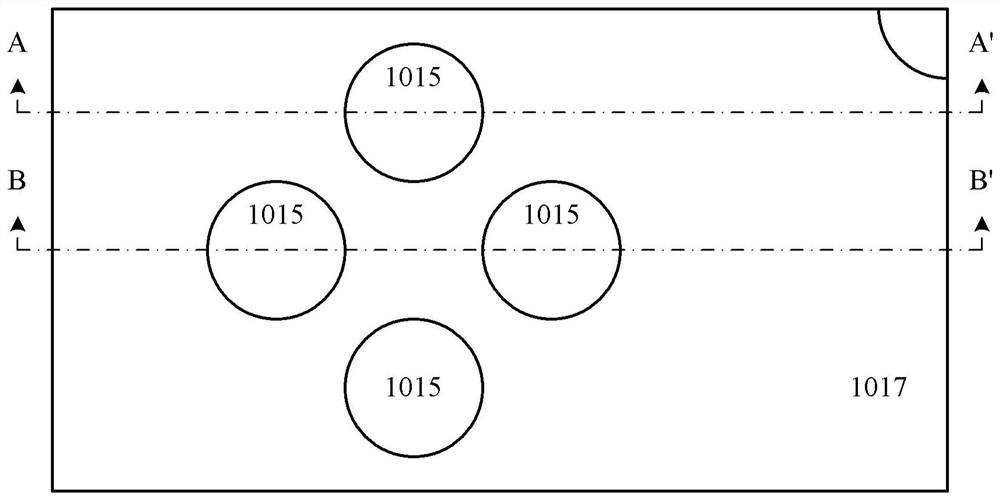

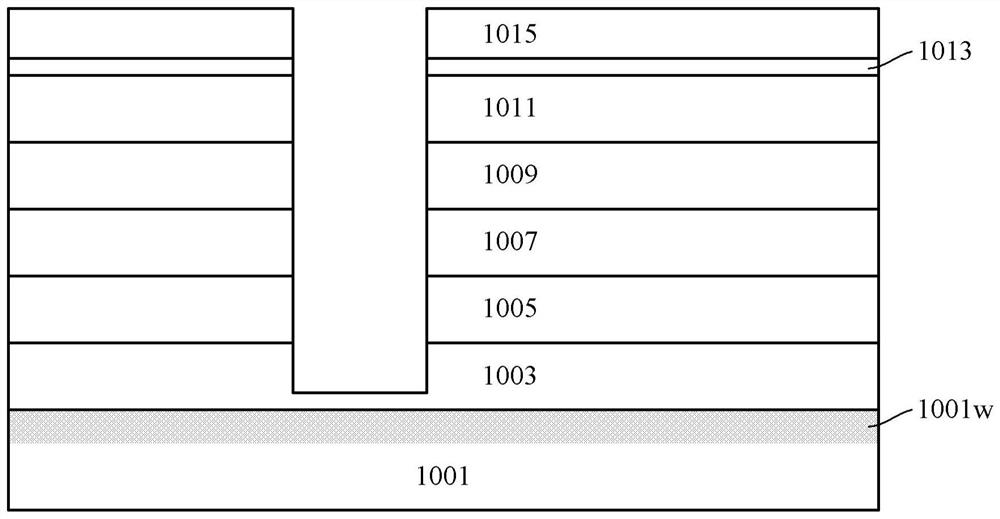

The invention discloses a storage device, a manufacturing method thereof, and electronic equipment comprises the storage device. According to an embodiment, the storage device can comprise a pluralityof first columnar active regions formed on a substrate and extending upwards from the substrate, first storage gates formed in the inner side walls of the first columnar active regions, and a multi-layer control gate formed on the outer side wall surrounding the first columnar active regions, wherein each of the first columnar active regions has an annular cross section.

Owner:INST OF MICROELECTRONICS CHINESE ACAD OF SCI

Semiconductor device

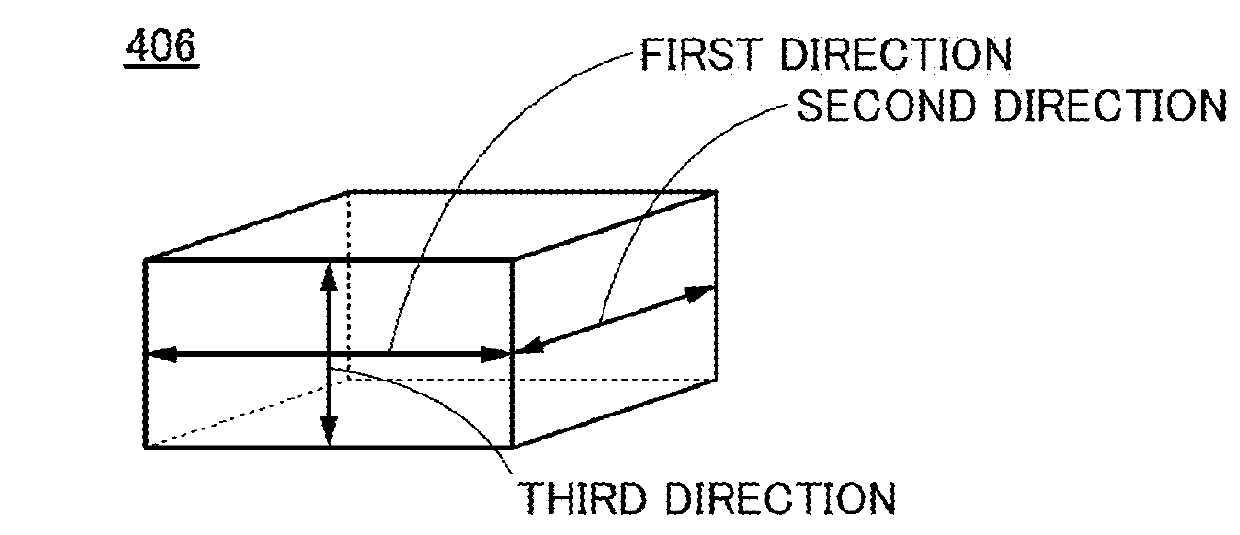

ActiveUS20160035897A1Low leakage currentExcellent electrical characteristicTransistorSolid-state devicesDielectric anisotropyLow leakage

A transistor whose channel is formed in a semiconductor having dielectric anisotropy is provided. A transistor having a small subthreshold swing value is provided. A transistor having normally-off electrical characteristics is provided. A transistor having a low leakage current in an off state is provided. A semiconductor device includes an insulator, a semiconductor, and a conductor. In the semiconductor device, the semiconductor includes a region overlapping with the conductor with the insulator positioned therebetween, and a dielectric constant of the region in a direction perpendicular to a top surface of the region is higher than a dielectric constant of the region in a direction parallel to the top surface.

Owner:SEMICON ENERGY LAB CO LTD

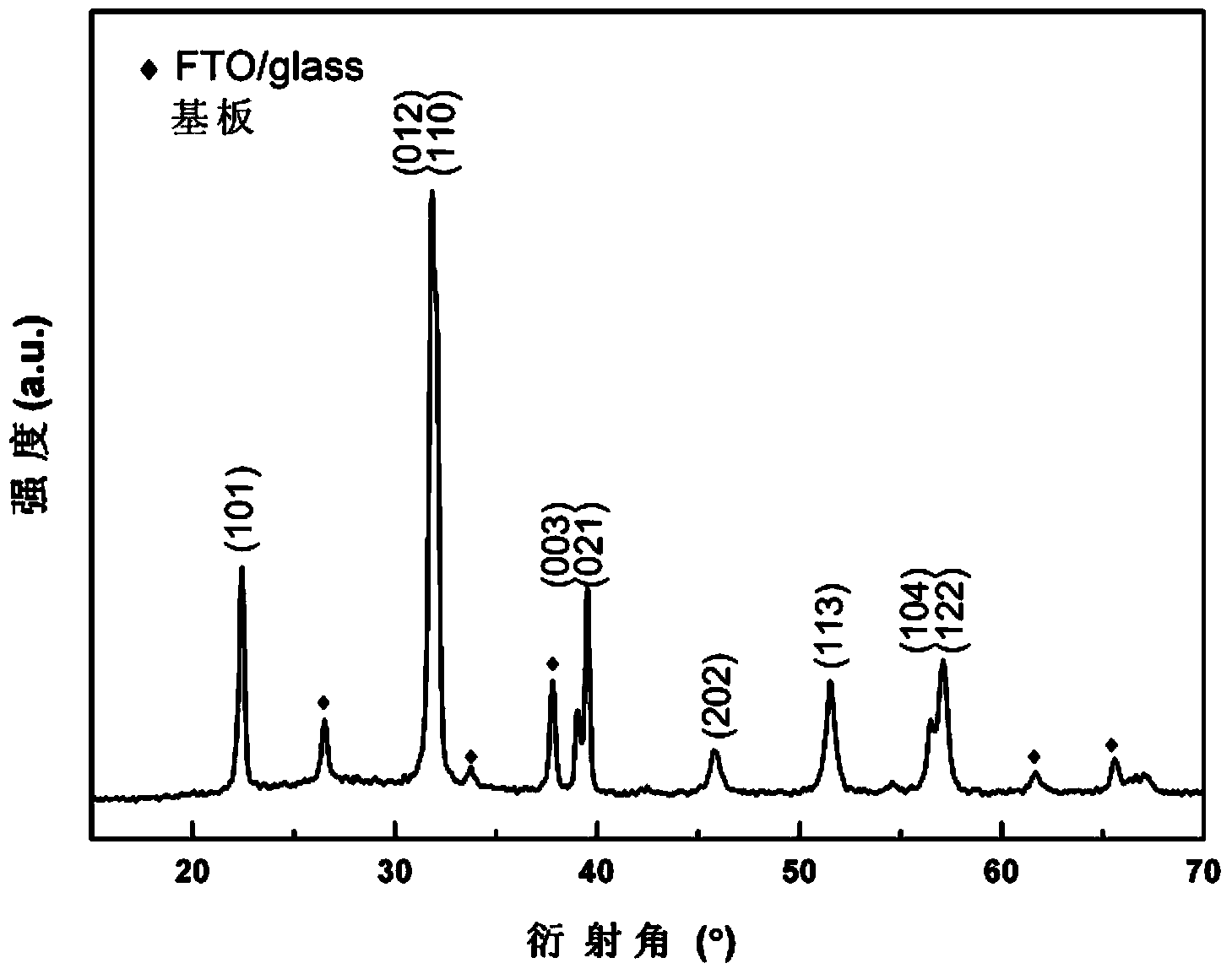

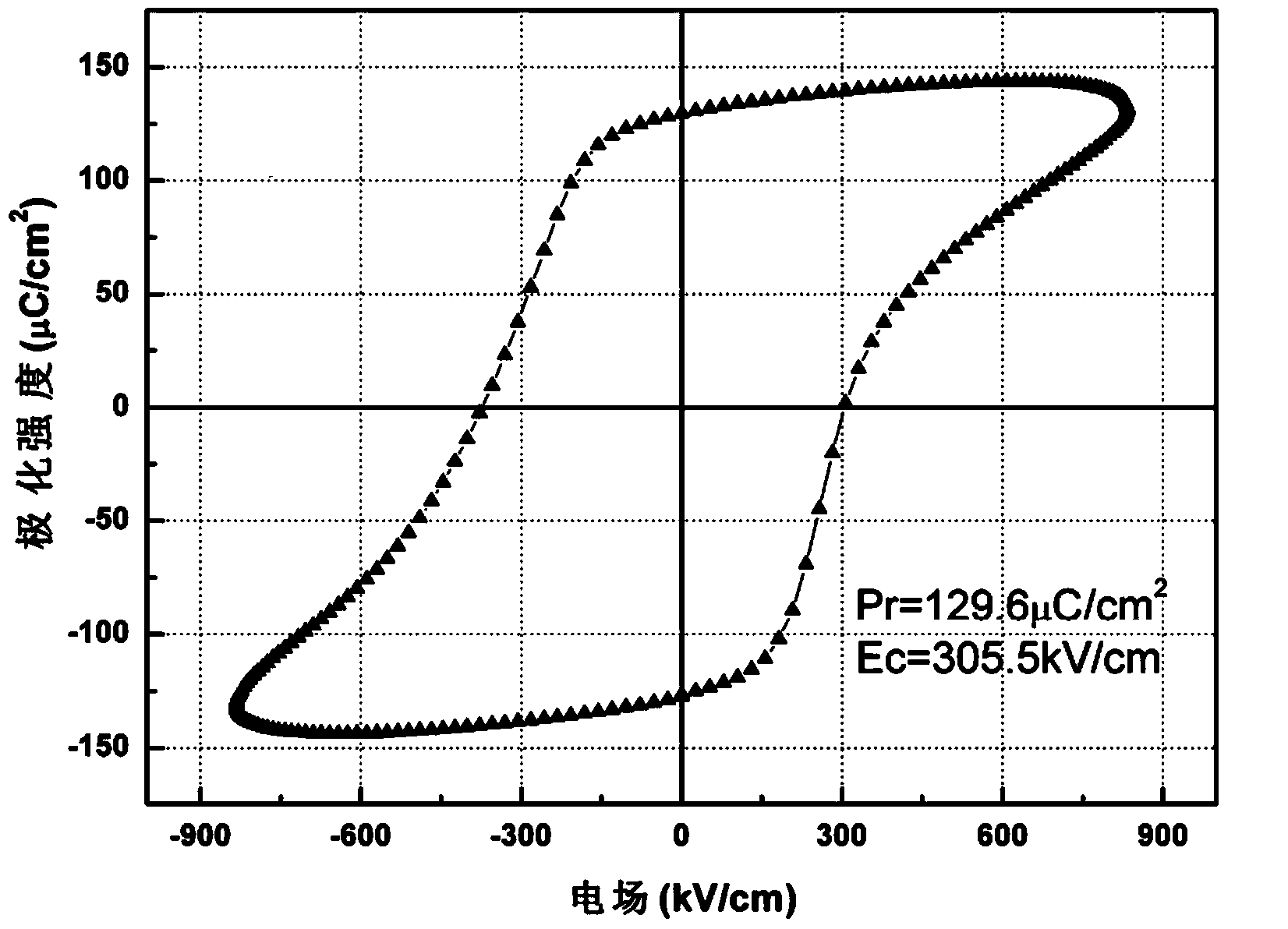

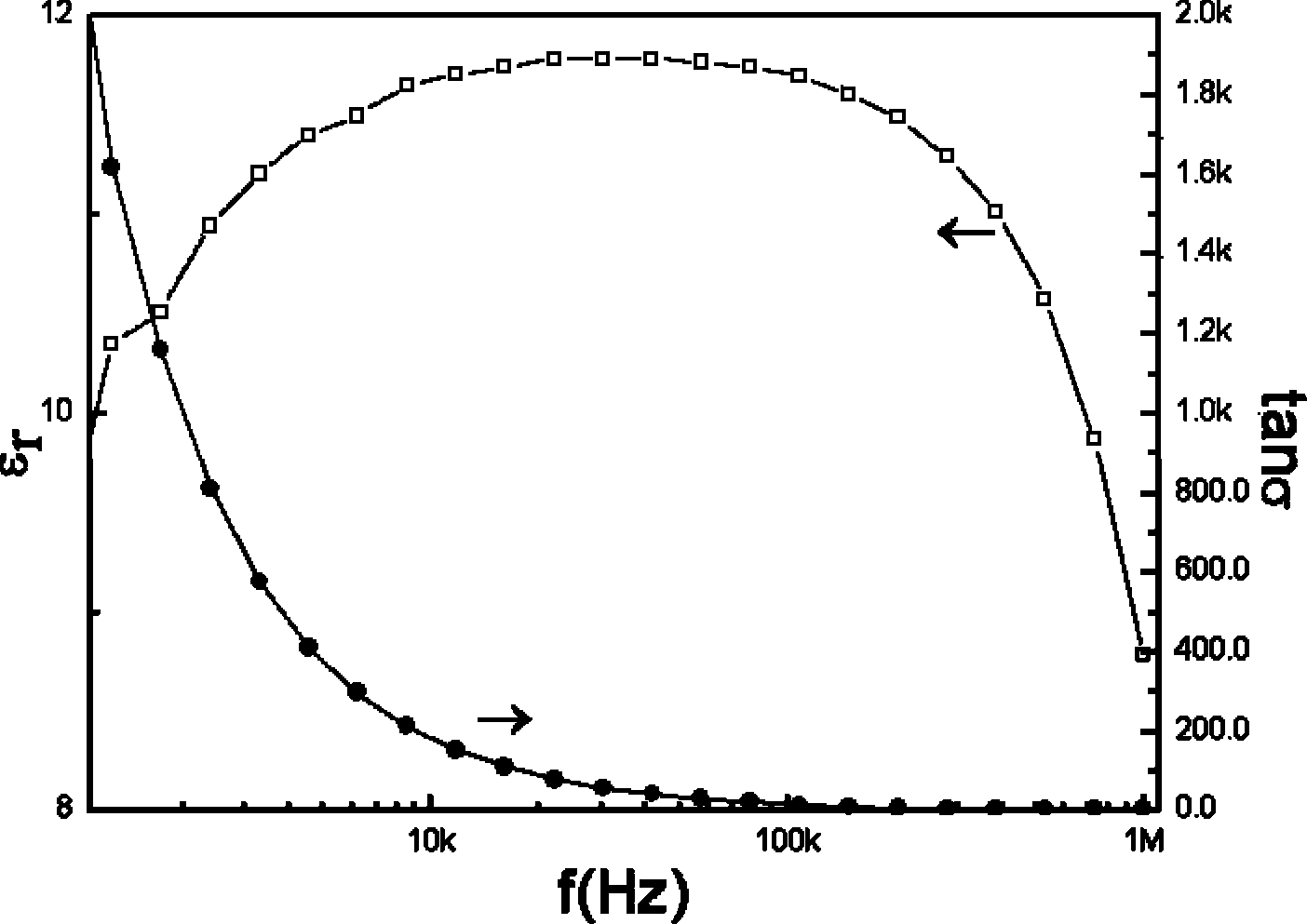

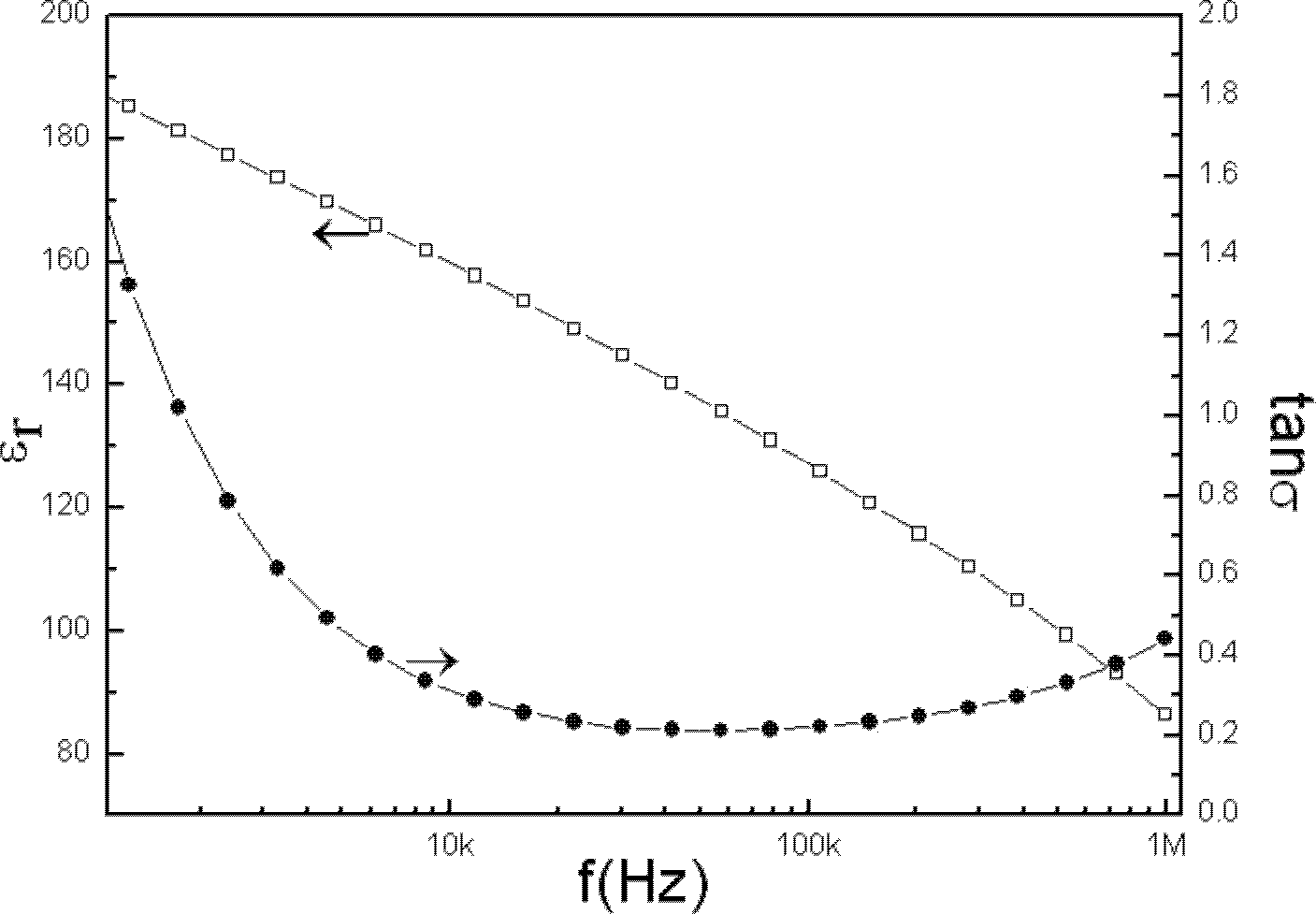

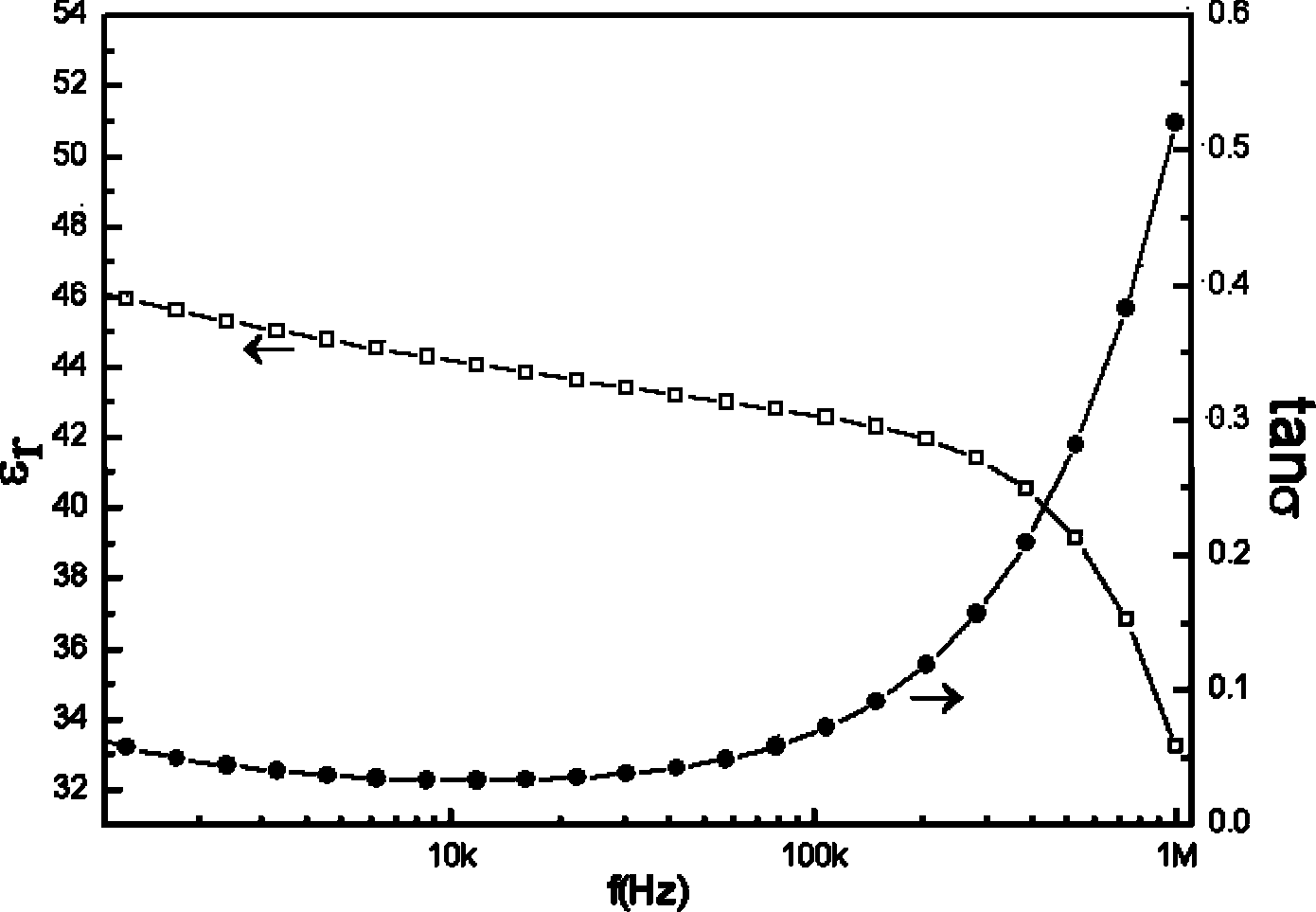

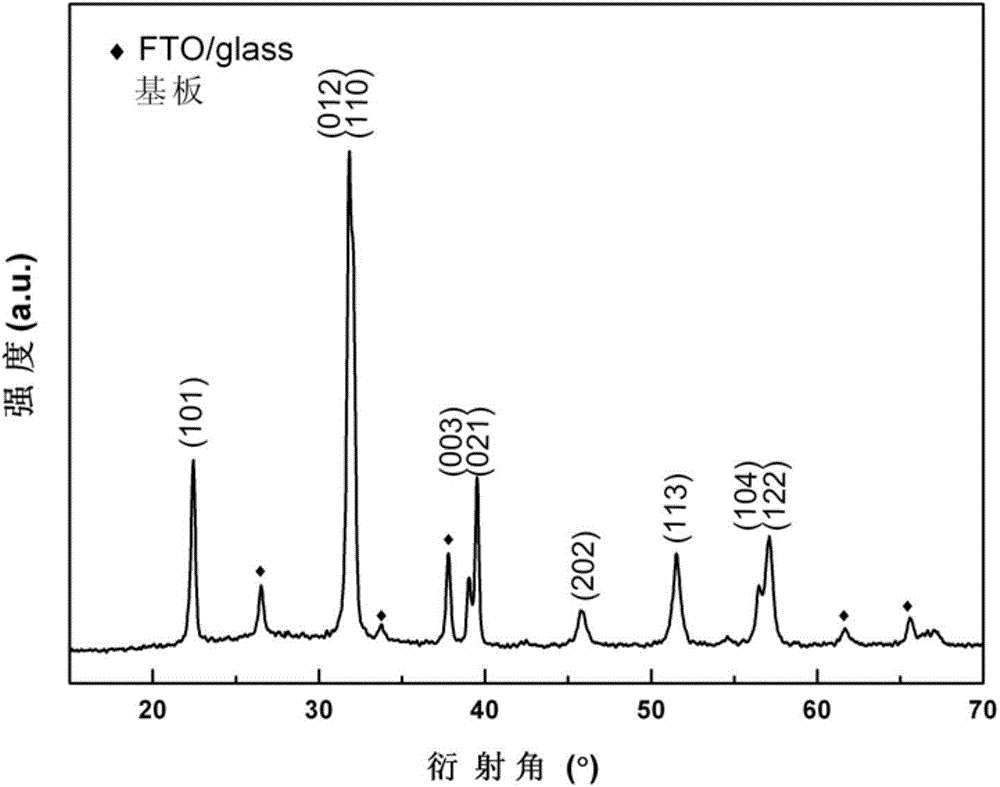

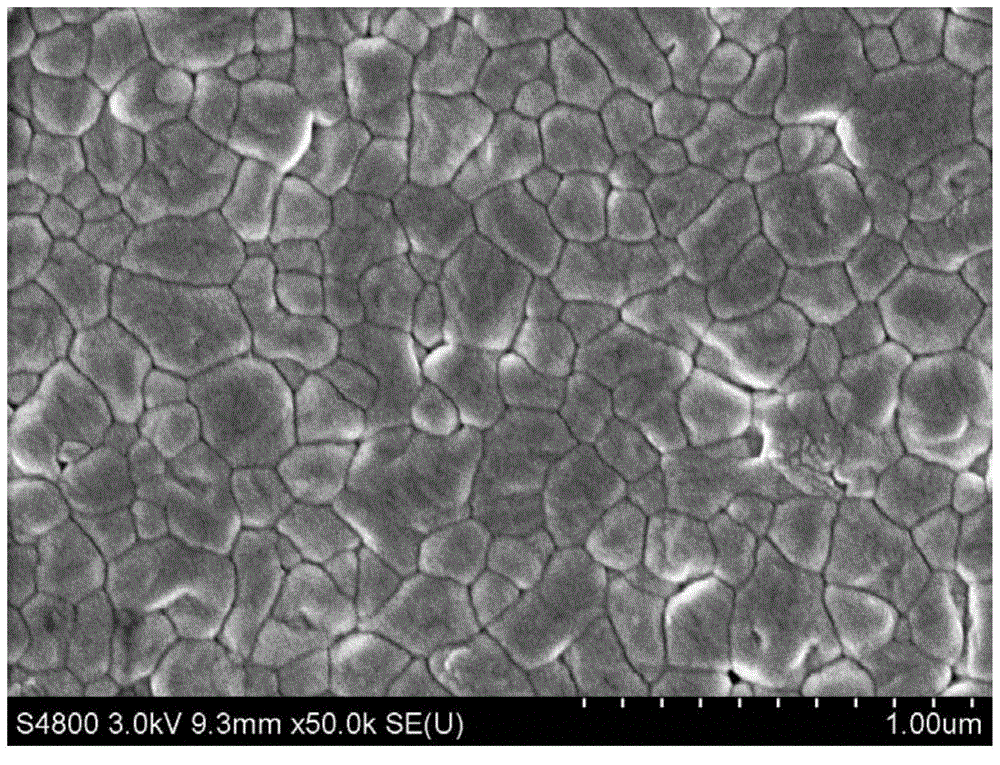

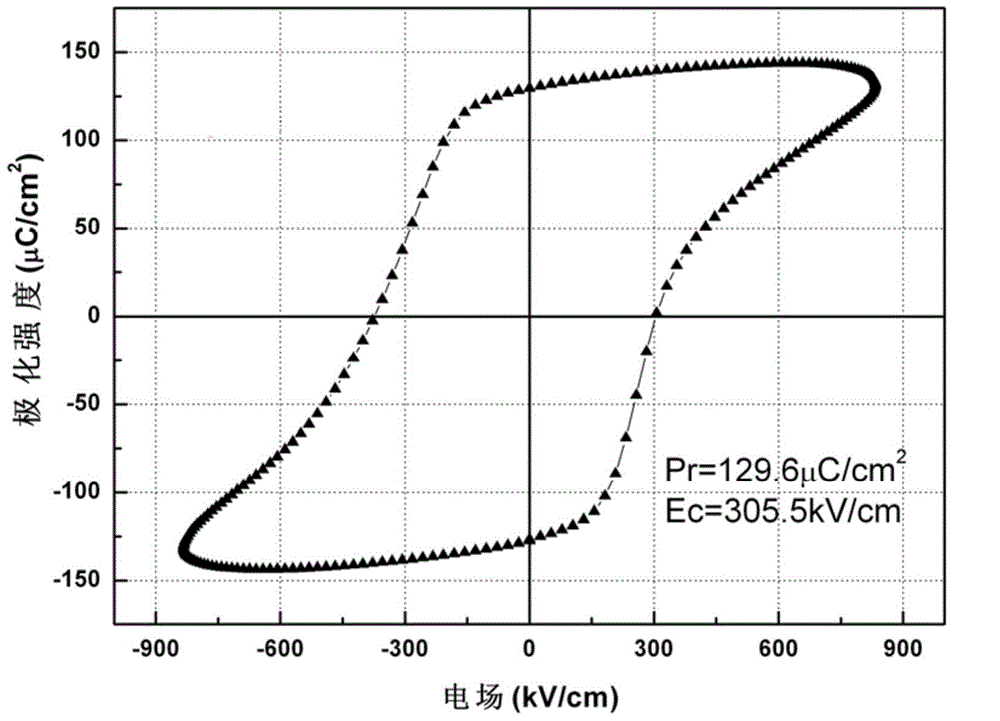

B-site Mn and Cu codoped high remanent polarization BiFeO3 film and preparation method

ActiveCN103613144AImprove multiferroic propertiesDistortionIron compoundsIonEthylene glycol monomethyl ether

The invention relates to a B-site Mn and Cu codoped high remanent polarization BiFeO3 film and a preparation method, the method comprises the following steps: dissolving bismuth nitrate, ferric nitrate, manganese acetate and cupric nitrate according to mol ratio of 1.05: [(0.92-0.98)-x]: (0.02-0.08):x in a mixed liquor of ethylene glycol monomethyl ether and acetic anhydride, then uniformly stirring to obtain a BiFeO3 precursor; wherein total metal ion concentration of the BiFeO3 precursor is 0.1-0.5mol / L, X is 0.01-0.03; performing spin coating of the BiFeO3 precursor on a FTO / glass substrate to prepare a wet membrane, baking the wet membrane to obtain a dry membrane, then annealing at 550 DEG C to obtain the crystalline state BiFeO3 film; cooling the crystalline state BiFeO3 film, and repeatedly making the crystalline state BiFeO3 film to reach a required thickness to obtain the B-site Mn and Cu codoped high remanent polarization BiFeO3 film. According to the invention, a sol gel technology is employed, the equipment requirement is simple, the film is prepared on large surface and surfaces with irregular shapes, the chemical component is accurate and controllable, and the regulation and control to its crystal structure can be carried out by codoping thereby the ferroelectric performance of the film is greatly increased.

Owner:盐城梦心缘鞋服有限公司

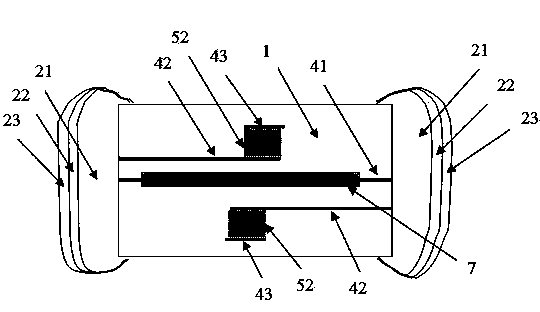

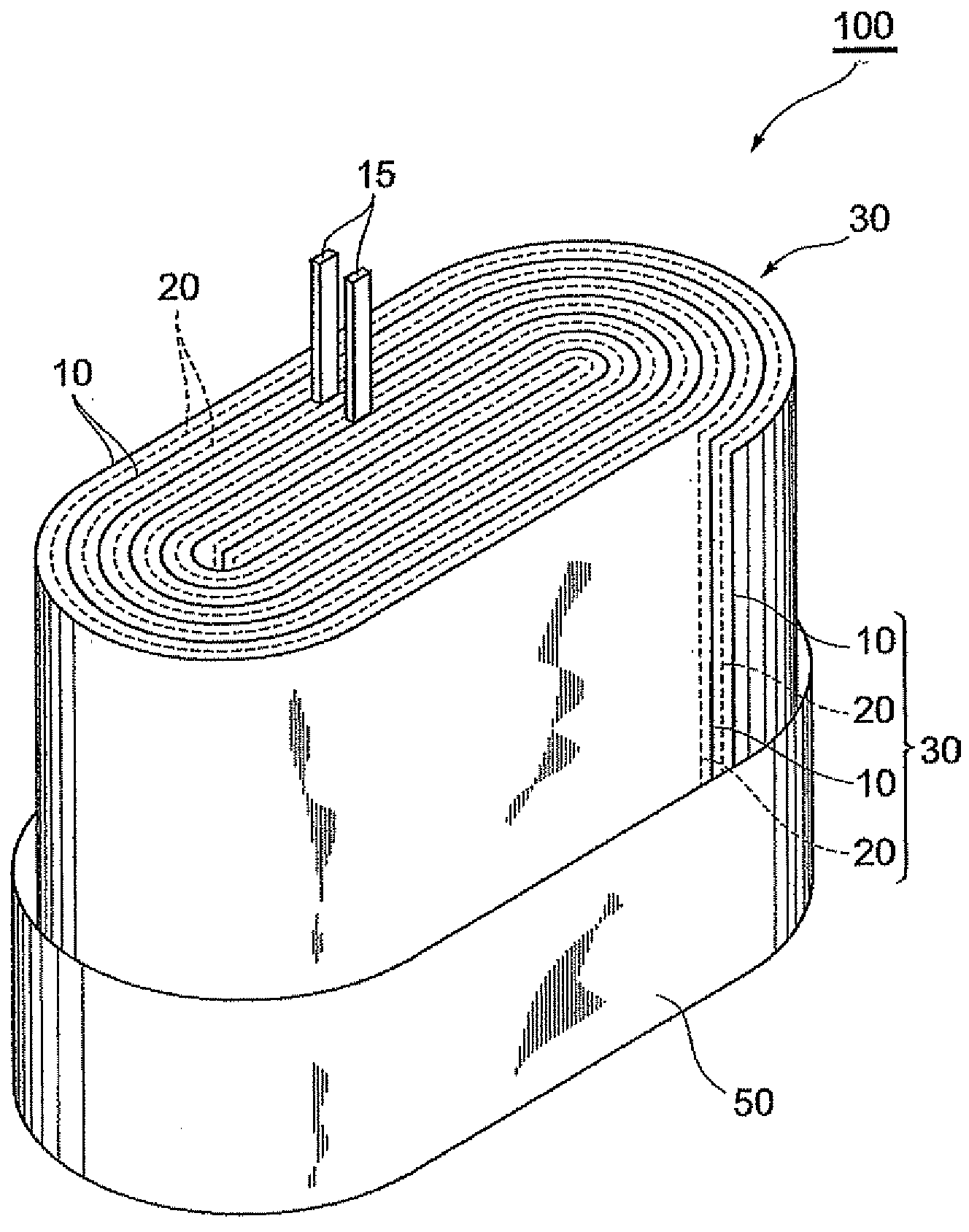

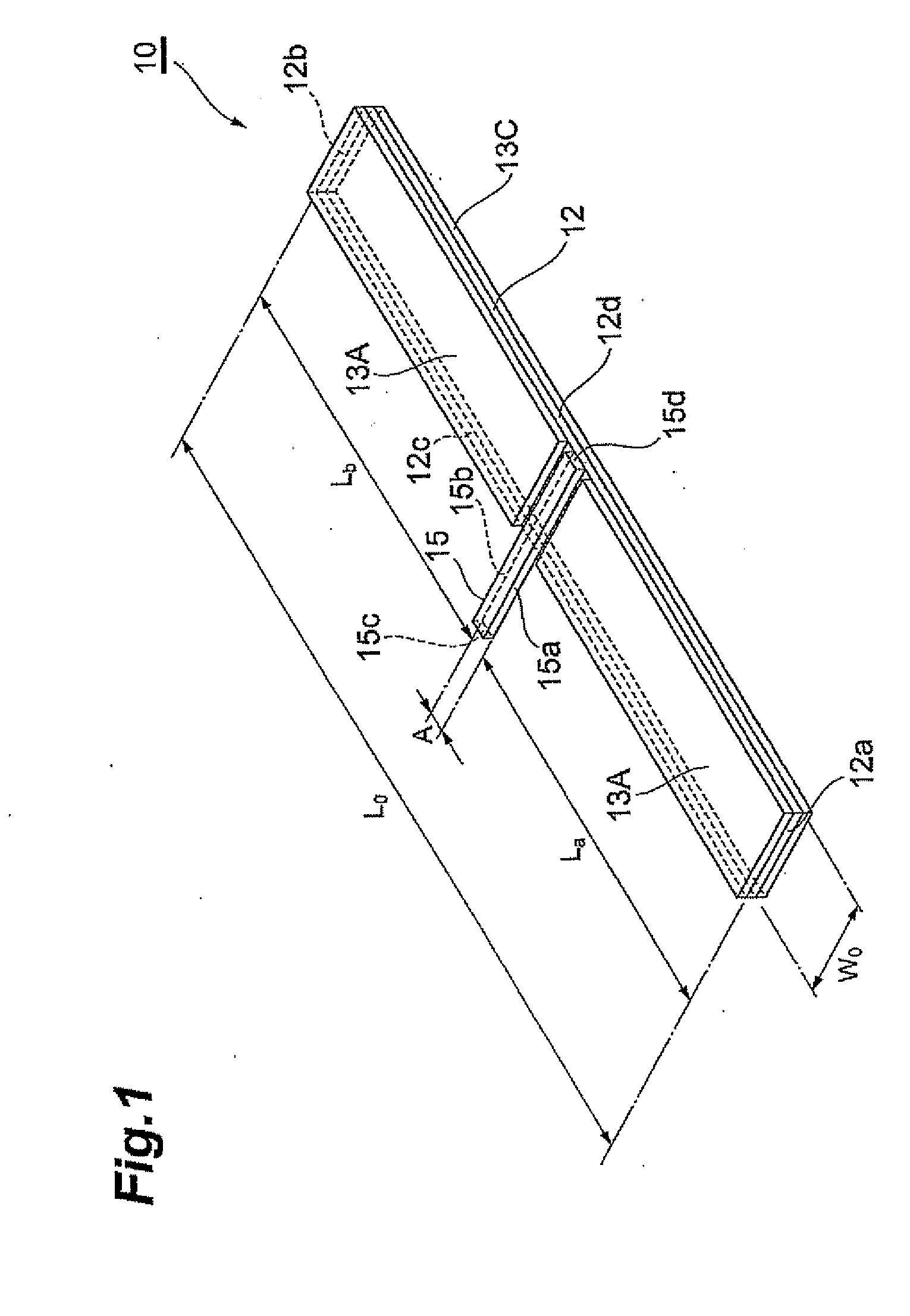

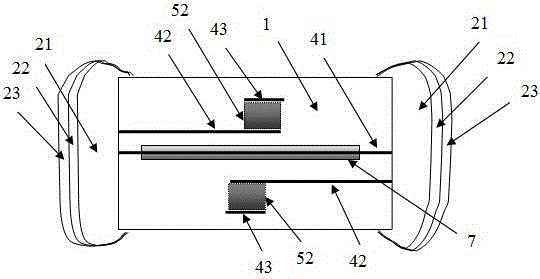

Electrode for electrochemical device and electrochemical device

InactiveUS20090166192A1Low impedanceLow leakage currentSolid electrolytic capacitorsFinal product manufactureEngineeringElectrochemical cell

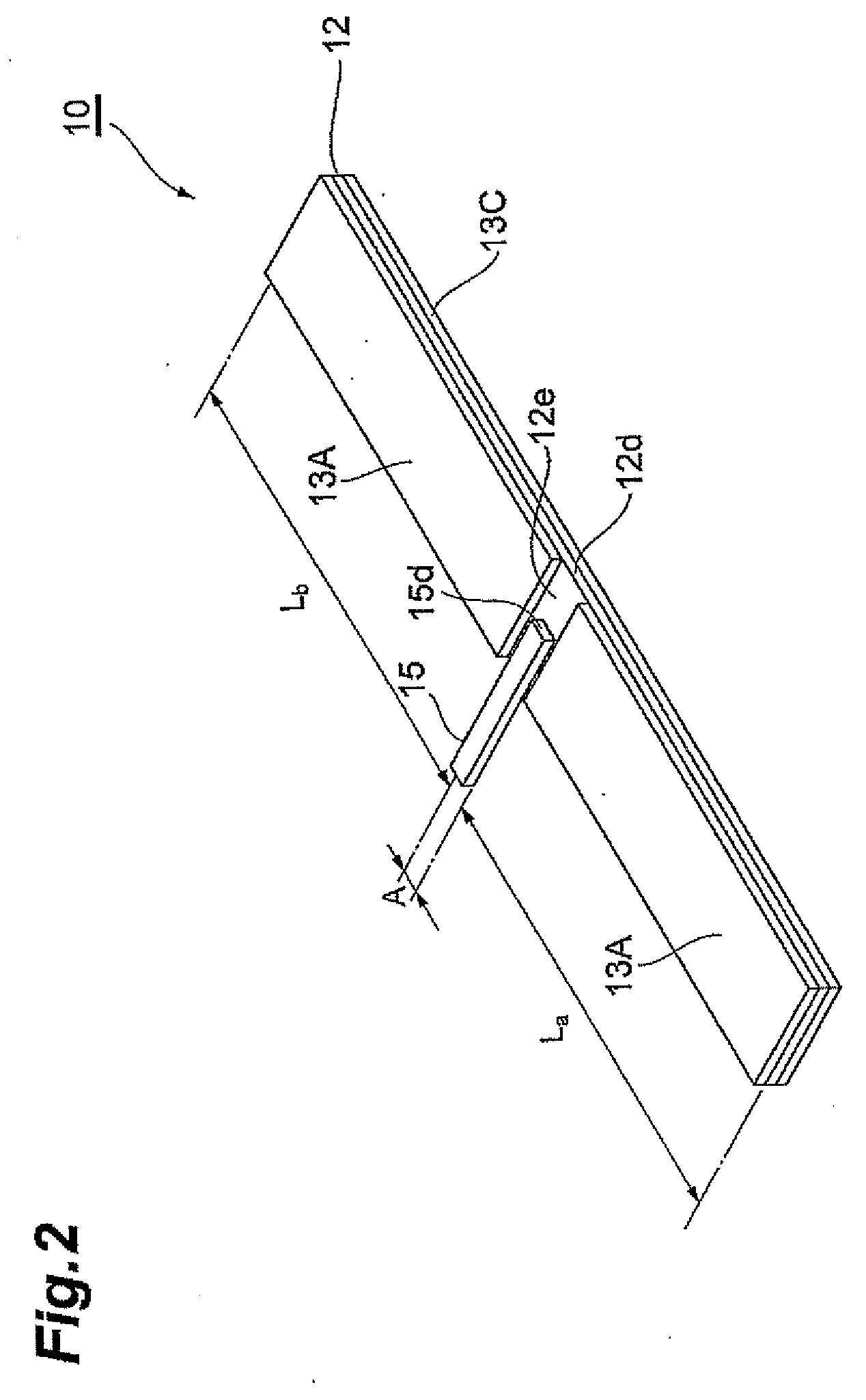

An electrode for an electrochemical device, including an elongated collector, a lead provided halfway along a longitudinal direction of the collector, and active material layers provided on the collector, wherein when La (m) is a distance from one end of the collector, in the longitudinal direction, up to the lead, and Lb (m) is a distance from the other end of the collector, in the longitudinal direction, up to the lead, and ρ (Ωm) is a resistivity of the collector at 25°, where Lopt (m) being 1.9×106ρ, the La (m) and Lb (m) are from 0.95 Lopt to 1.05 Lopt respectively.

Owner:TDK CORPARATION

Low-voltage punch-through bi-directional transient-voltage suppression devices having surface breakdown protection and methods of making the same

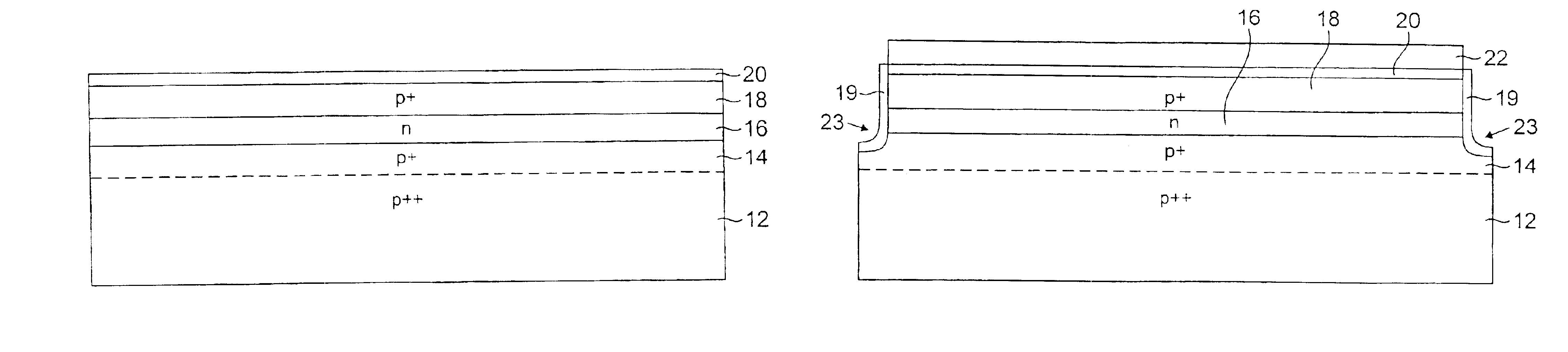

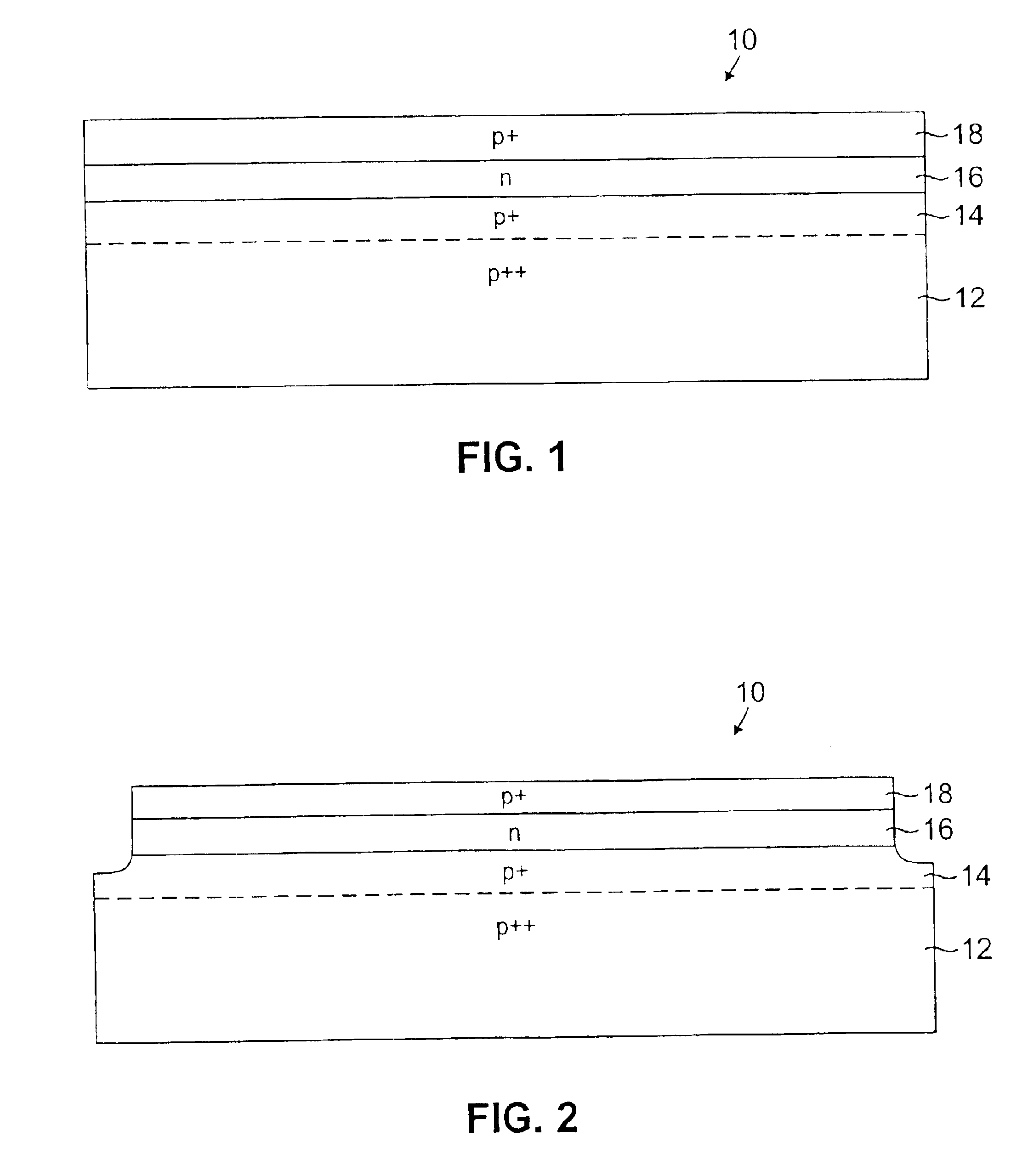

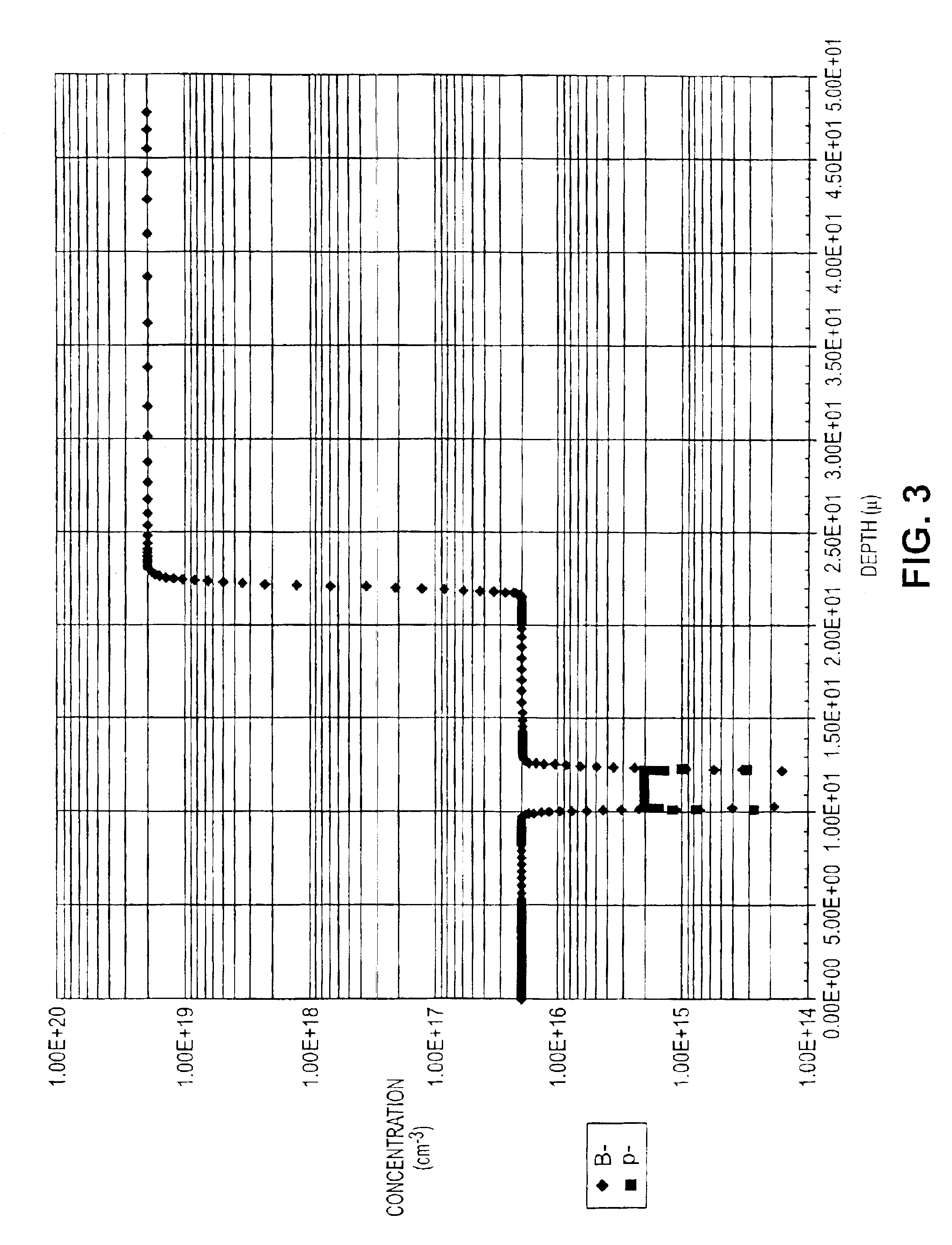

InactiveUS6858510B2Low leakage currentLower capacitanceTransistorSolid-state devicesN type conductivityEngineering

A method of making a bi-directional transient voltage suppression device is provided, which comprises: (a) providing a p-type semiconductor substrate; (b) epitaxially depositing a lower semiconductor layer of p-type conductivity; (c) epitaxially depositing a middle semiconductor layer of n-type conductivity over the lower layer; (d) epitaxially depositing an upper semiconductor layer of p-type conductivity over the middle layer; (e) heating the substrate, the lower epitaxial layer, the middle epitaxial layer and the upper epitaxial layer; (f) etching a mesa trench that extends through the upper layer, through the middle layer and through at least a portion of the lower layer, such that the mesa trench defines an active area for the device; and (g) thermally growing an oxide layer on at least those portions of the walls of the mesa trench that correspond to the upper and lower junctions of the device.

Owner:GEN SEMICON

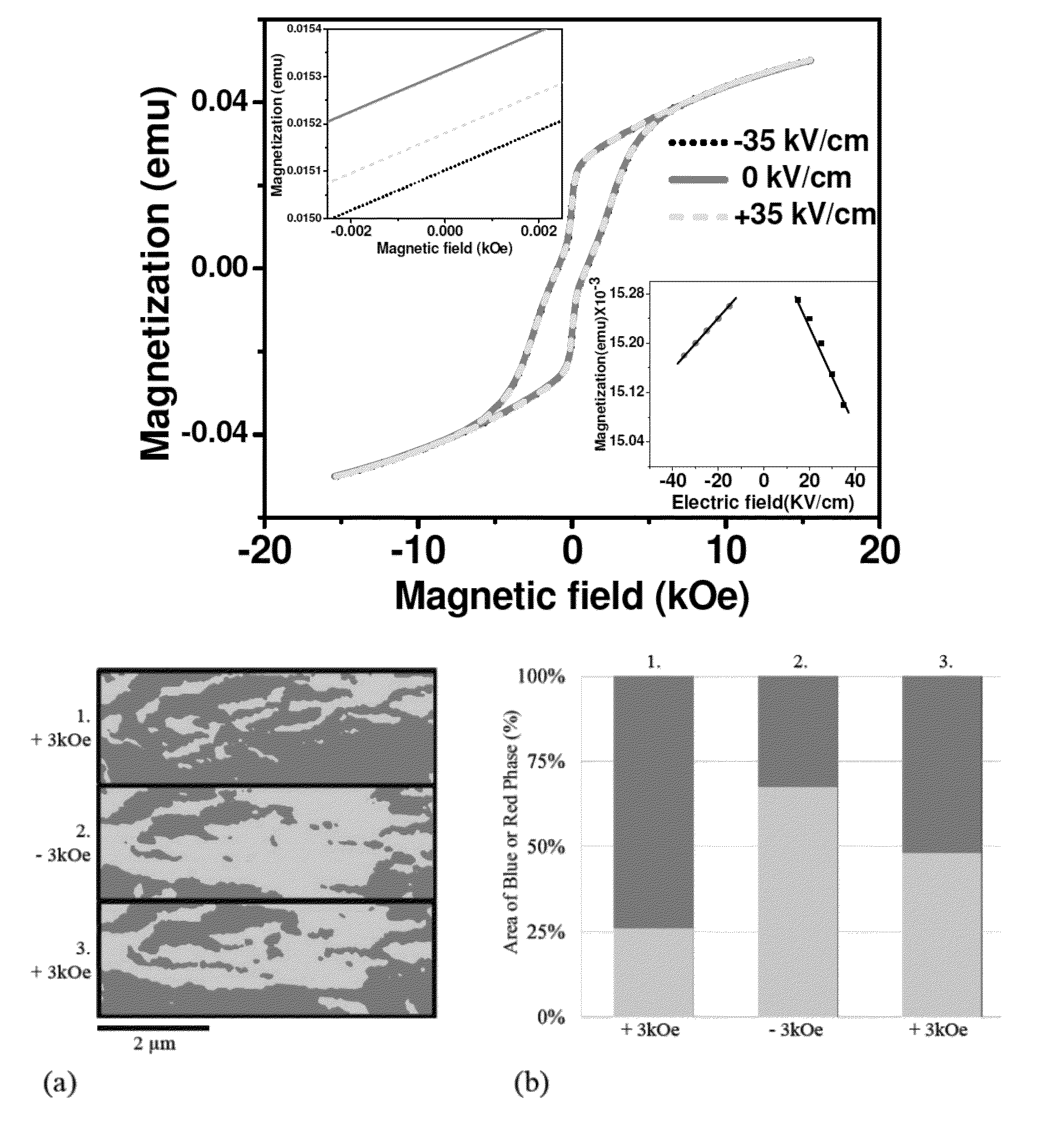

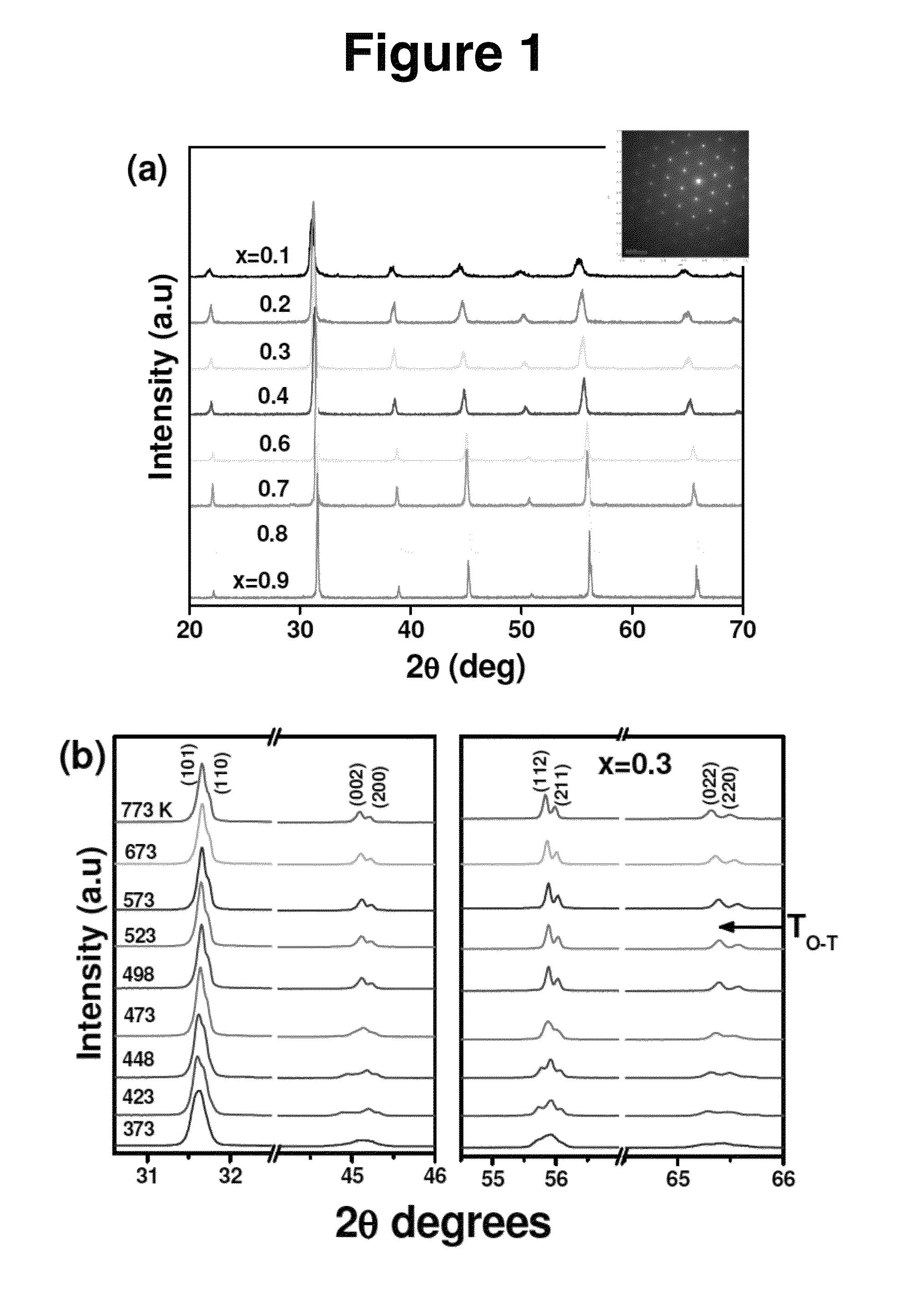

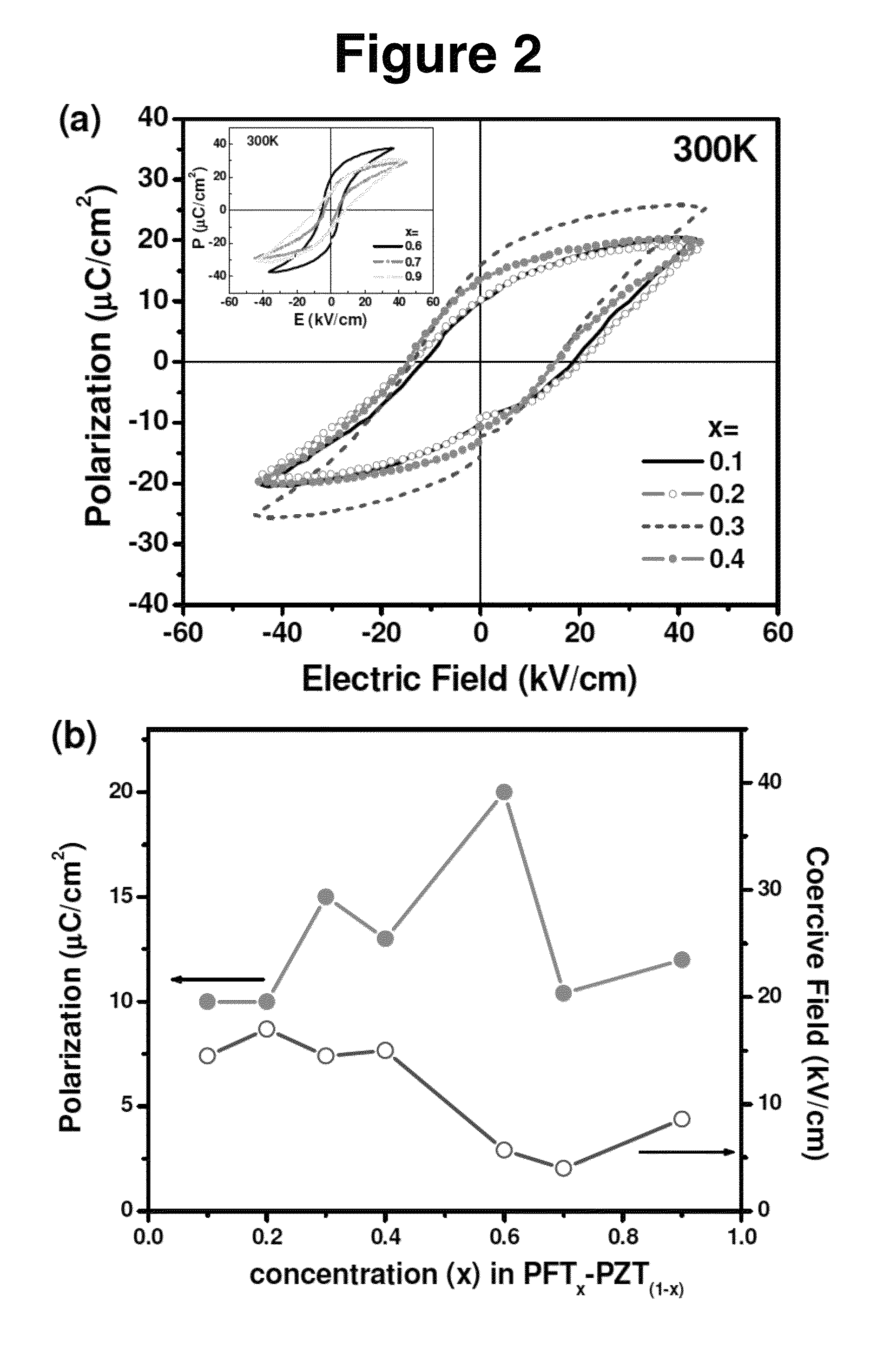

Micro and nanoscale magnetoelectric multiferroic lead iron tantalate-lead zirconate titanate

ActiveUS9299485B1High dielectric constantLow leakage currentVacuum evaporation coatingSputtering coatingMultiferroicsLead zirconate titanate

The invention is a novel class of materials made by combining the best qualities of both lead iron tantalate (PFT) and lead iron titanate (PZT) to synthesize (PbZr0.53Ti0.47O3)(1-x)—(PbFe0.5Ta0.5O3)x (PZTFT) (0.1≦x≦0.9) compositions that have multiferroic (ferroelectric and ferromagnetic) and magnetoelectric properties.

Owner:UNIVERSITY OF PUERTO RICO

Semiconductor device

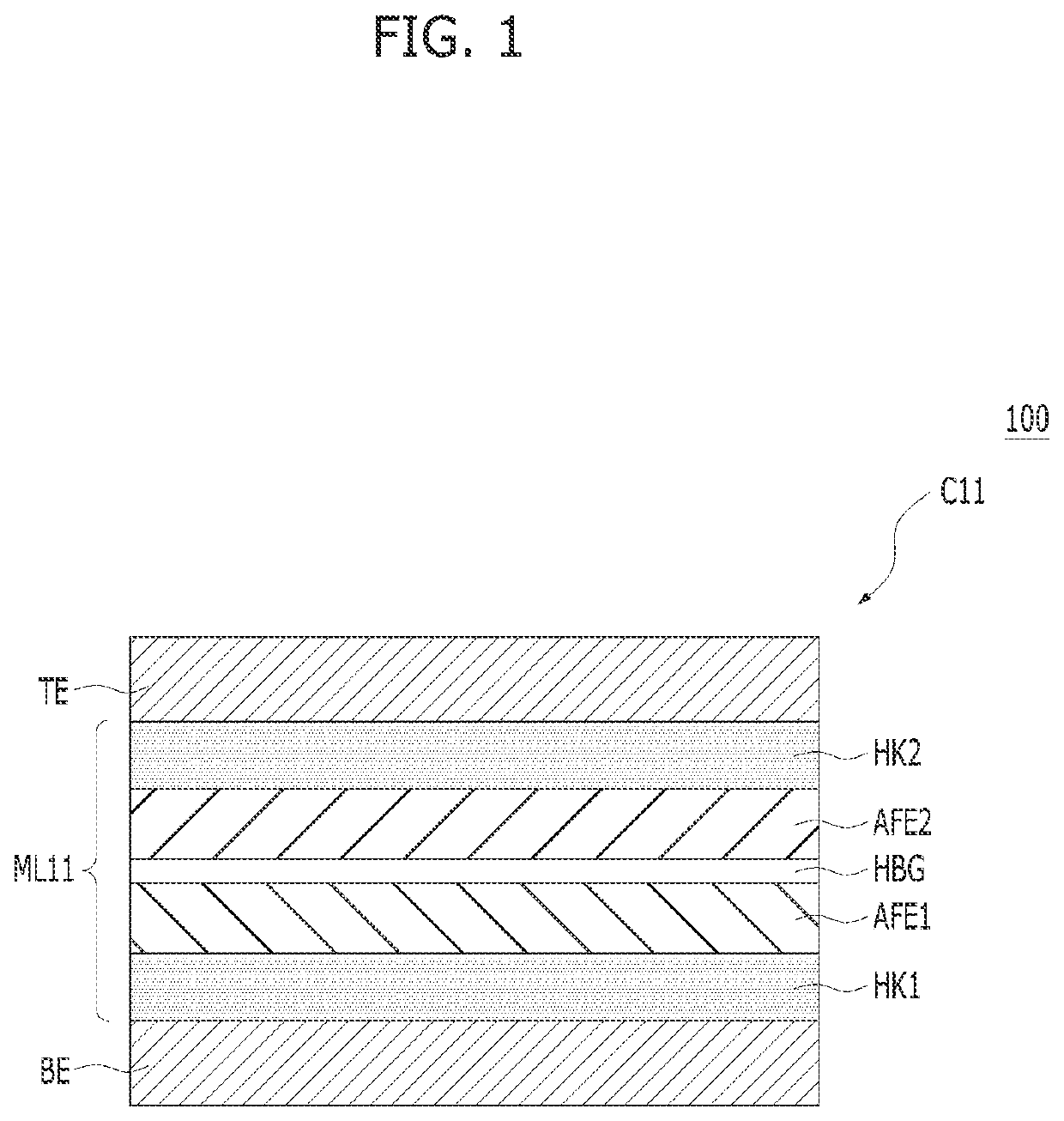

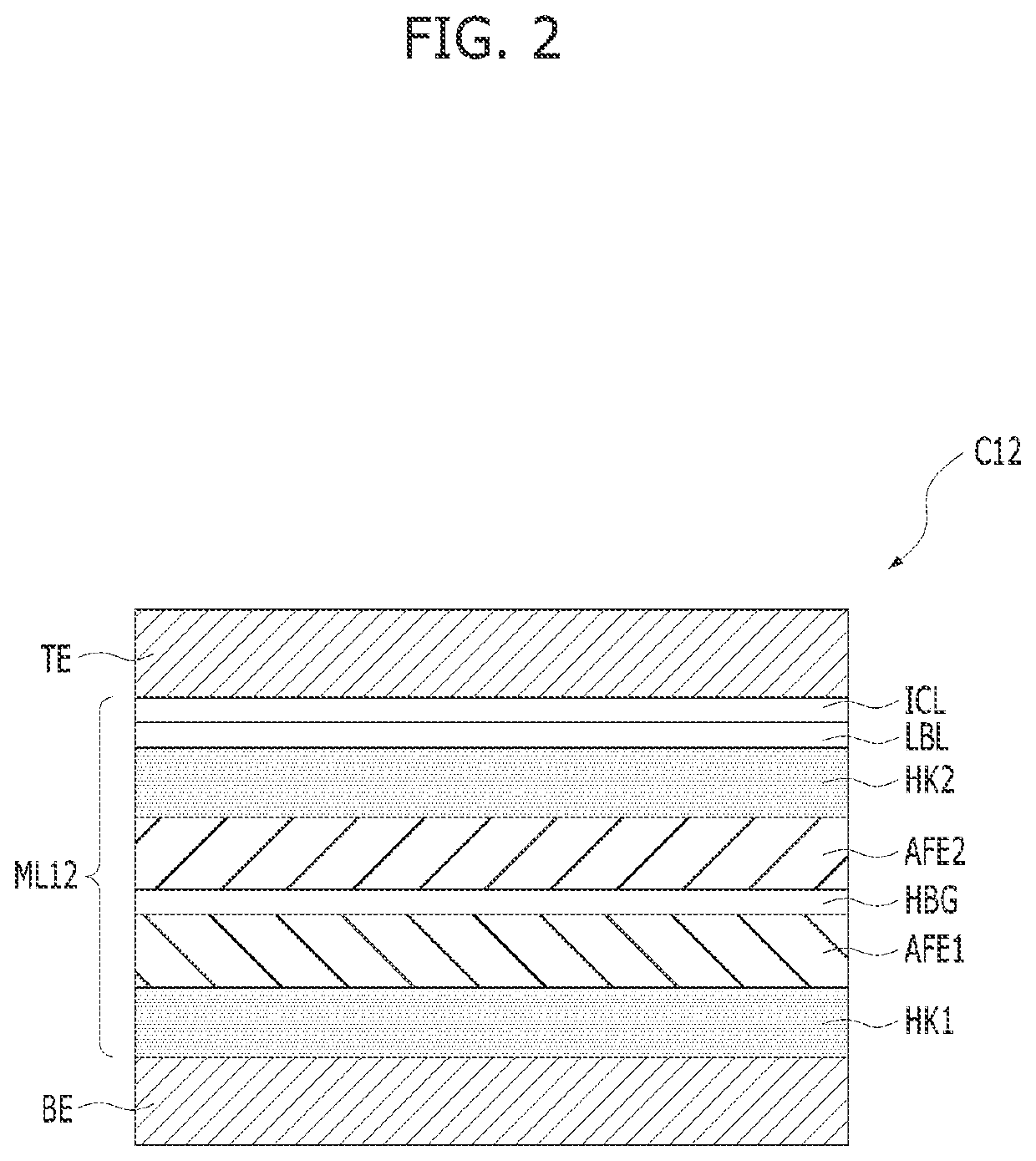

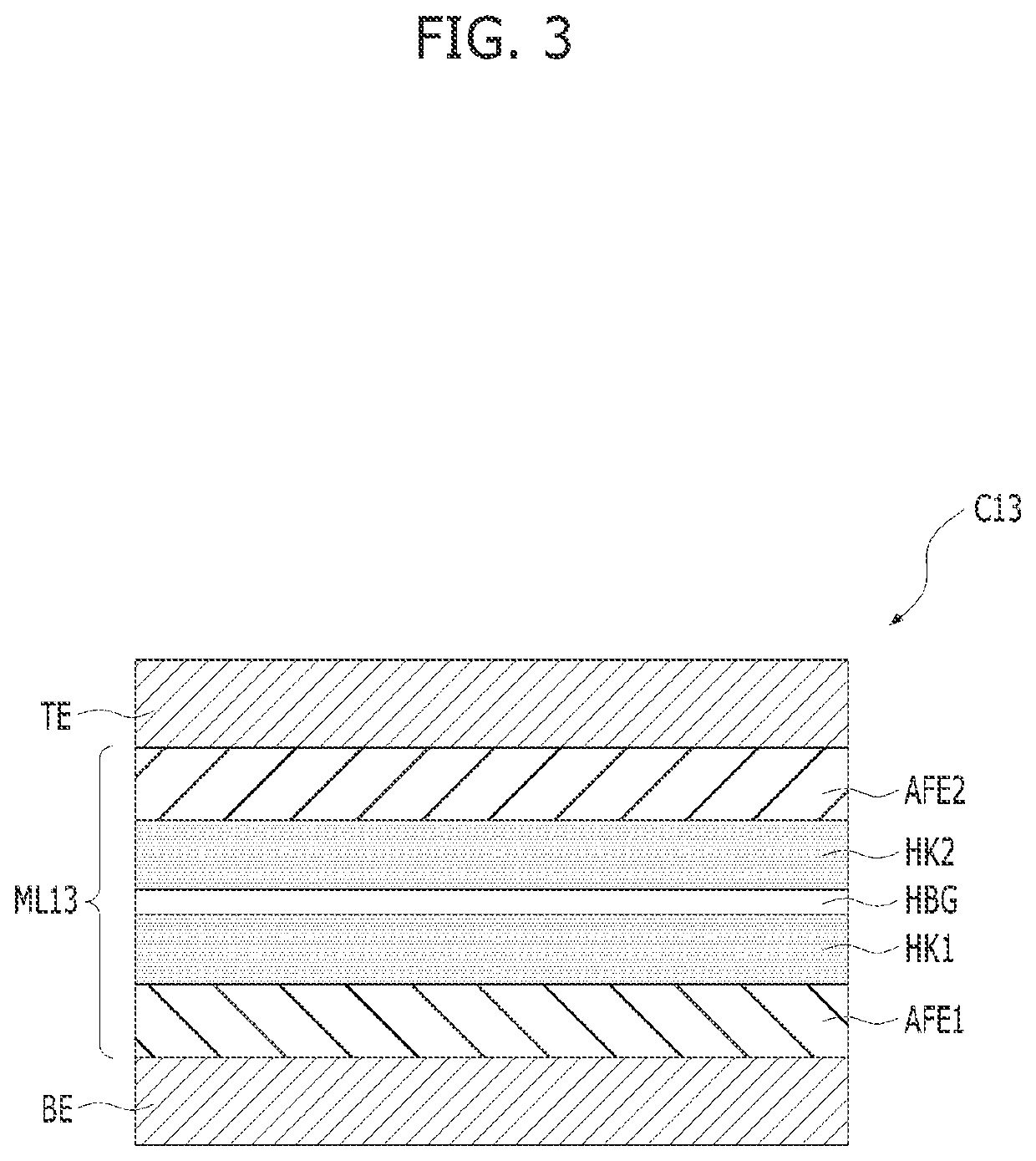

PendingUS20210359082A1High dielectric constantLow leakage currentFixed capacitor dielectricStacked capacitorsPhysicsEngineering

A semiconductor device includes a first electrode, a second electrode, and a multi-layer stack positioned between the first electrode and the second electrode, the multi-layer stack including at least one anti-ferroelectric layer and at least one high-k dielectric layer.

Owner:SK HYNIX INC

Method of manufacturing semiconductor device

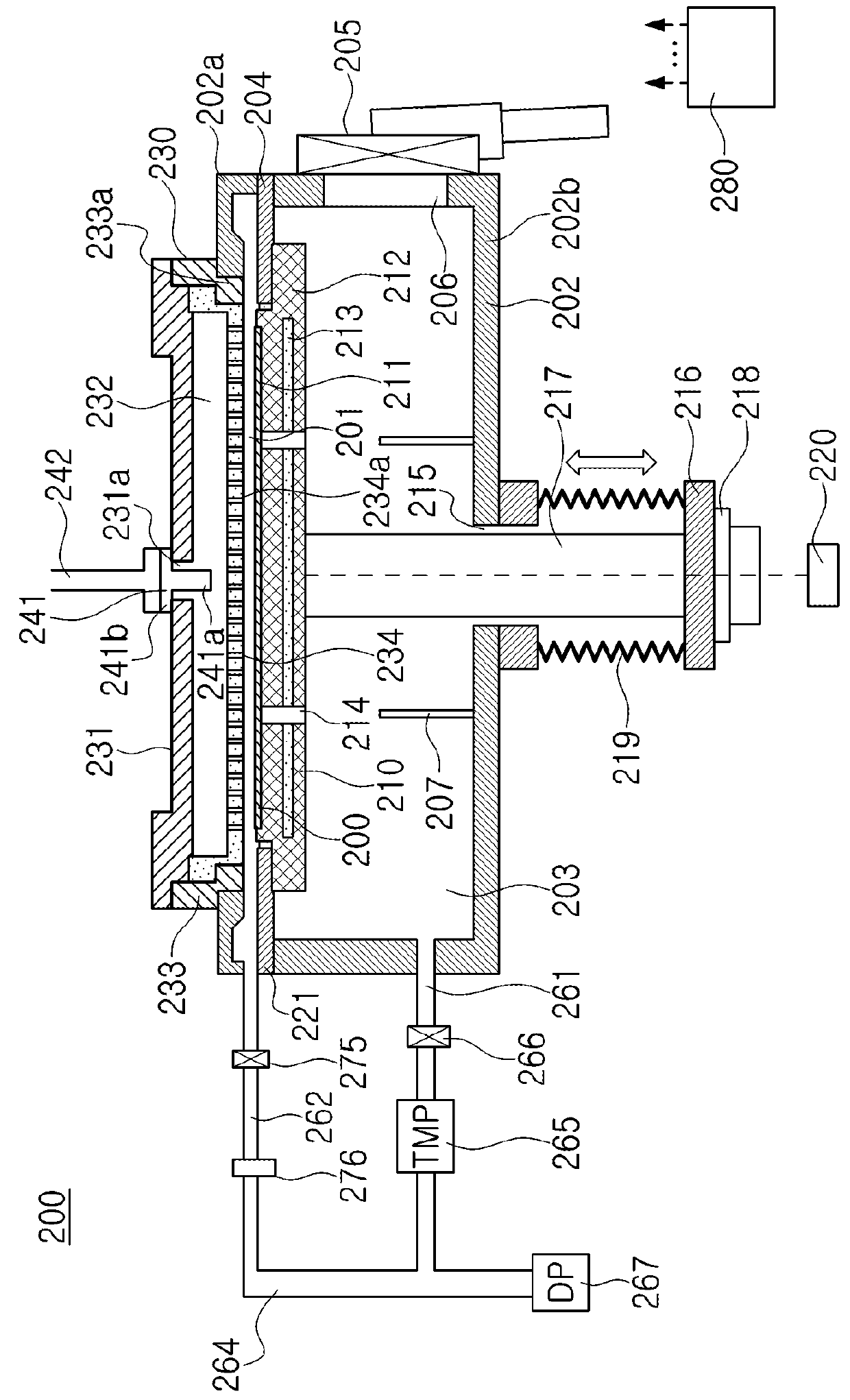

ActiveUS20180182619A1Low leakage currentIncreased etch resistanceElectric discharge tubesSemiconductor/solid-state device manufacturingLow leakageEngineering

A technique capable of forming a side wall of a gate electrode having high resistance-to-etching and low leakage current is provided. A method of manufacturing a semiconductor device according to the technique includes: (a) loading a substrate into a processing space in a process vessel, the substrate having thereon a gate electrode and an insulating film formed on a side surface of the gate electrode as a side wall; and (b) forming an etching-resistant film containing carbon and nitrogen on a surface of the insulating film by supplying a carbon-containing gas into the processing space.

Owner:NTT MOBILE COMM NETWORK INC

Memory device, manufacturing method thereof, and electronic equipment including the same

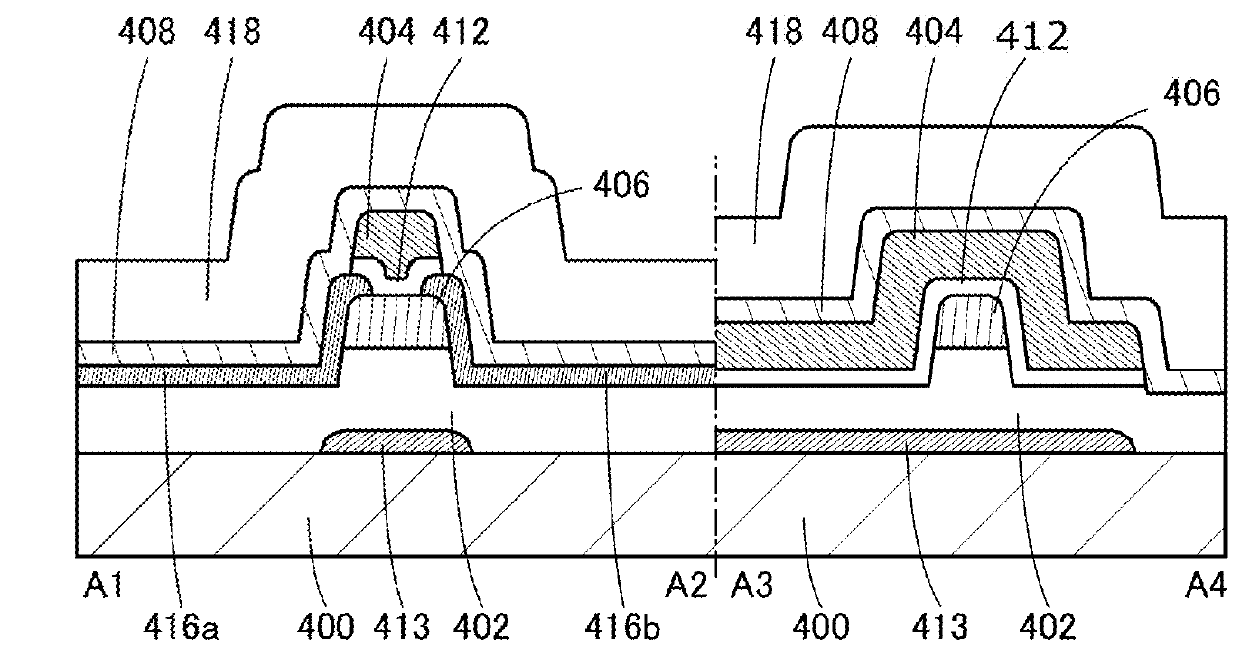

ActiveCN106340521BImprove performanceReduce areaSolid-state devicesSemiconductor/solid-state device manufacturingElectrical conductorGate stack

Disclosed are a storage device, a manufacturing method thereof, and electronic equipment including the storage device. According to an embodiment, a memory device may include a plurality of memory cell layers sequentially stacked on a substrate, each memory cell layer including a first array of first memory cells and a second array of second memory cells, the first array and The second arrays are nested within each other. The first and second memory cells in each memory cell layer are substantially substantially to each other along the stacking direction of the memory cell layers. Each first memory cell is a vertical device based on sequentially stacked first source / drain layers, channel layers and second source / drain layers. Each second memory cell is a vertical device based on an active semiconductor layer extending in the stacking direction. Each of the first memory cells and each of the second memory cells includes respective memory gate stacks, and they share a gate conductor layer. The gate conductor layers in the same memory cell layer are integrated.

Owner:INST OF MICROELECTRONICS CHINESE ACAD OF SCI

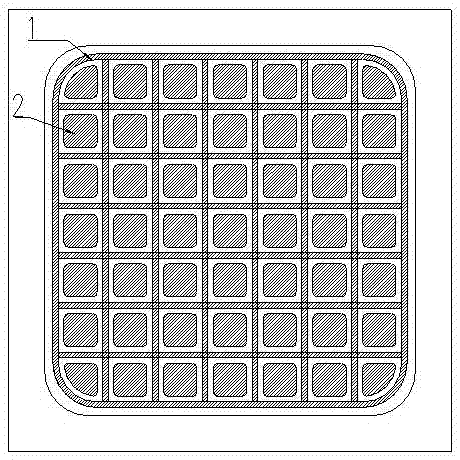

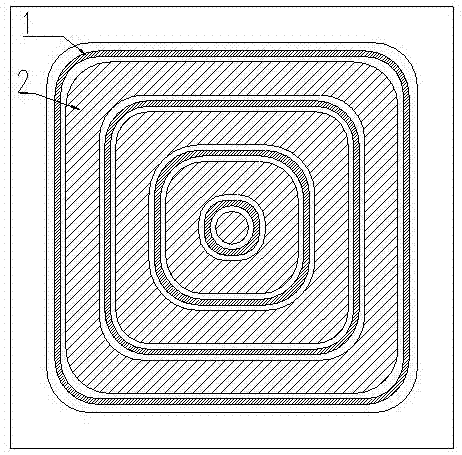

Low-voltage TVS device with an ultralow electric leakage level and manufacturing method thereof

ActiveCN107331711ASimple processLow leakage currentFinal product manufactureSemiconductor/solid-state device manufacturingPhysical chemistryEngineering

The invention discloses a low-voltage TVS device with an ultralow electric leakage level and a manufacturing method thereof. The N+ breakdown region (1) and the N+ gettering region (2) of the longitudinal structure can use a vertical crossed structure or a circular annluar structure. The N+ gettering region (1) has a junction depth of 15 to 25 [mu]m and a width range of 20 to 50 [mu]m. The N+ breakdown region (2) has a junction depth of 8 to 15 [mu]m and a width range customized according to different IPP requirements. The N+ gettering region and the N+ breakdown region have gap design requirements of 5 to 50 [mu]m. The main purpose of the N+ gettering region is to absorb oxidation-induced defects generated in the high temperature process of silicon single crystal, and generate a severe defect region. The N + breakdown region is actually the effective working region of the device. The low-voltage TVS device achieves alow electric leakage level and satisfies a requirement for a high IPP current-through capability.

Owner:捷捷半导体有限公司

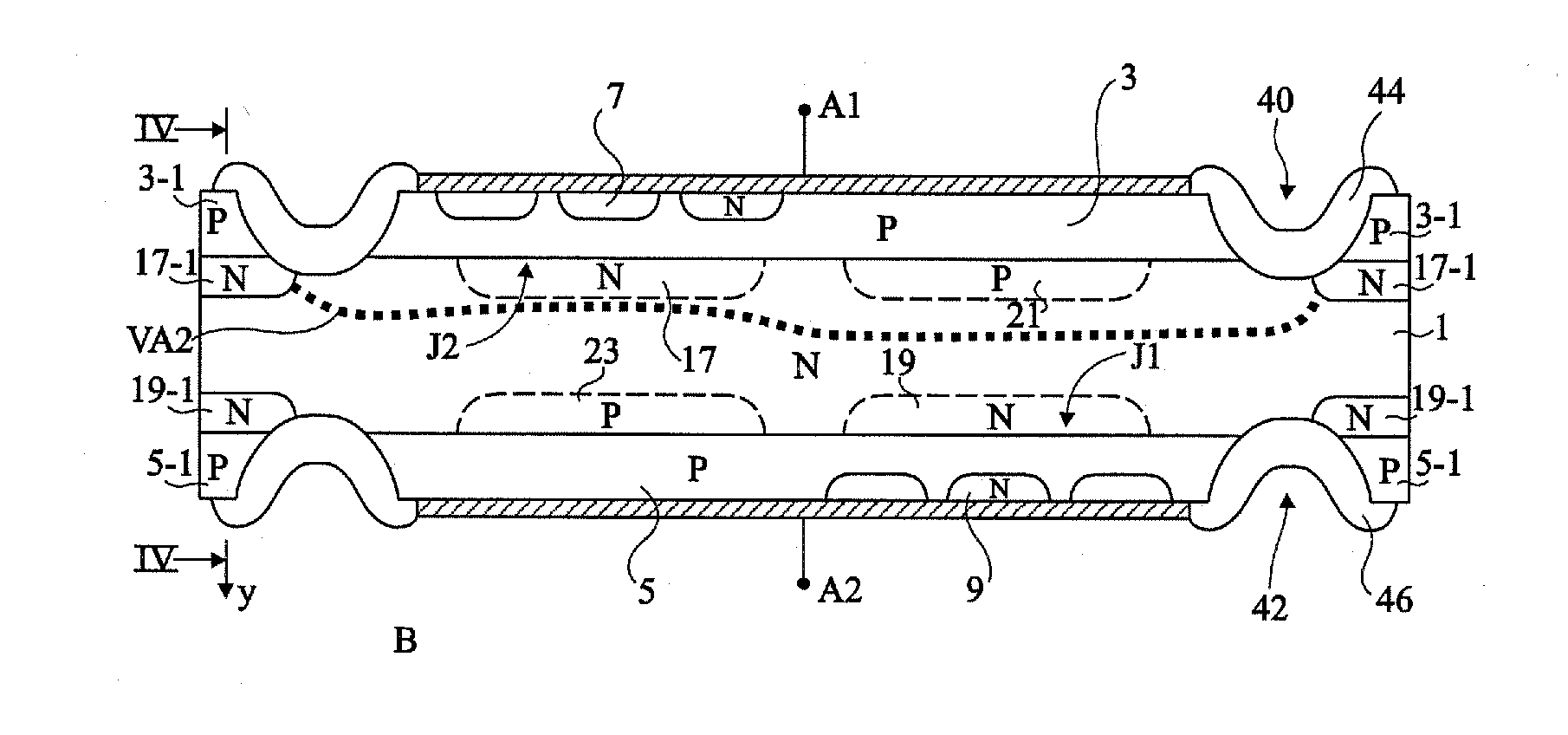

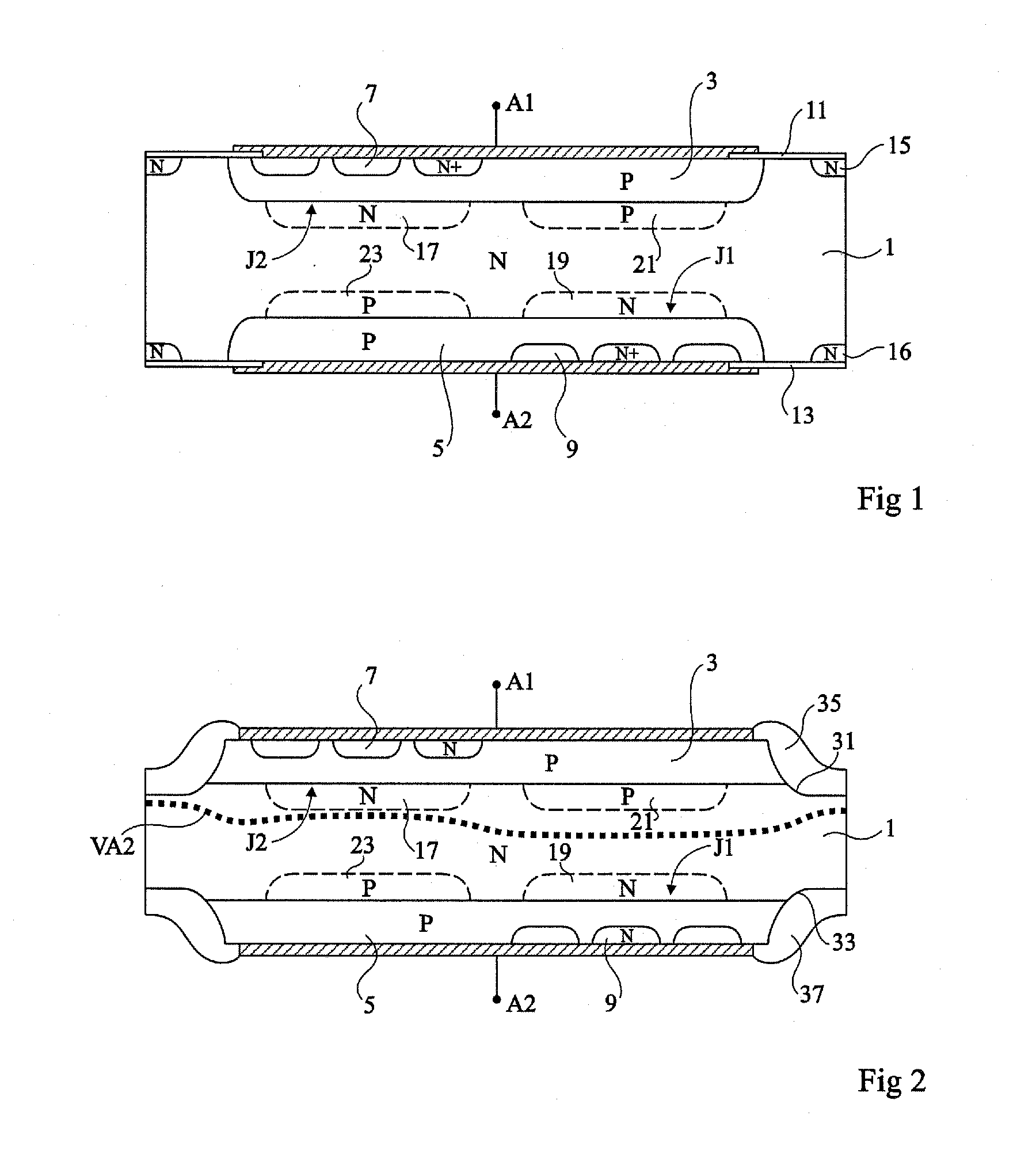

Bidirectional shockley diode with extended mesa

A mesa-type bidirectional Shockley diode including a substrate of a first conductivity type; a layer of the second conductivity type on each side of the substrate; a region of the first conductivity type in each of the layers of the second conductivity type; a buried region of the first conductivity type under each of said regions of the first conductivity type, each buried region being complementary in projection with the other; and a groove arranged in the vicinity of the periphery of the component on each of its surfaces, the component portion external to the groove comprising, under the external portion of the upper and lower regions of the second conductivity type, regions of the first conductivity type of same doping profile as said buried regions.

Owner:STMICROELECTRONICS (TOURS) SAS

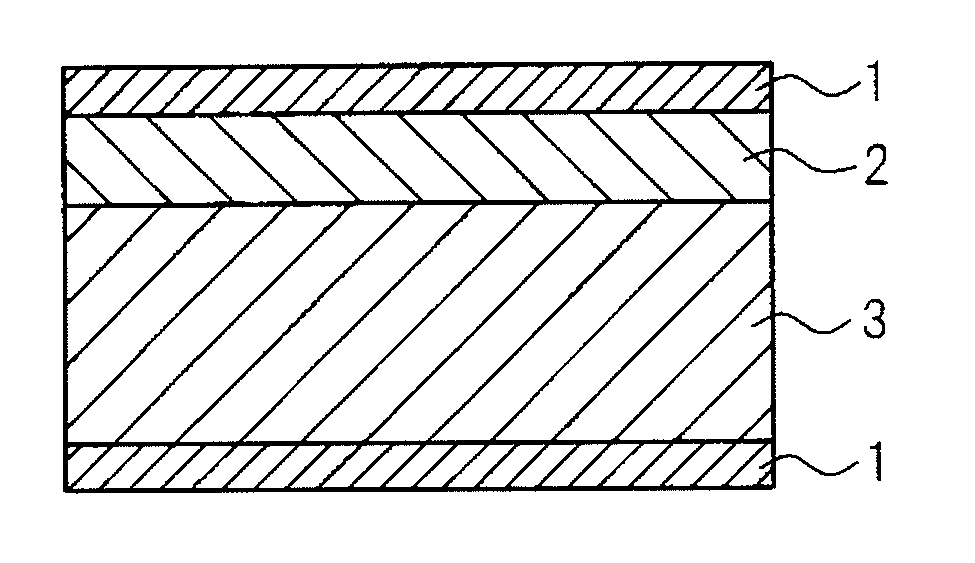

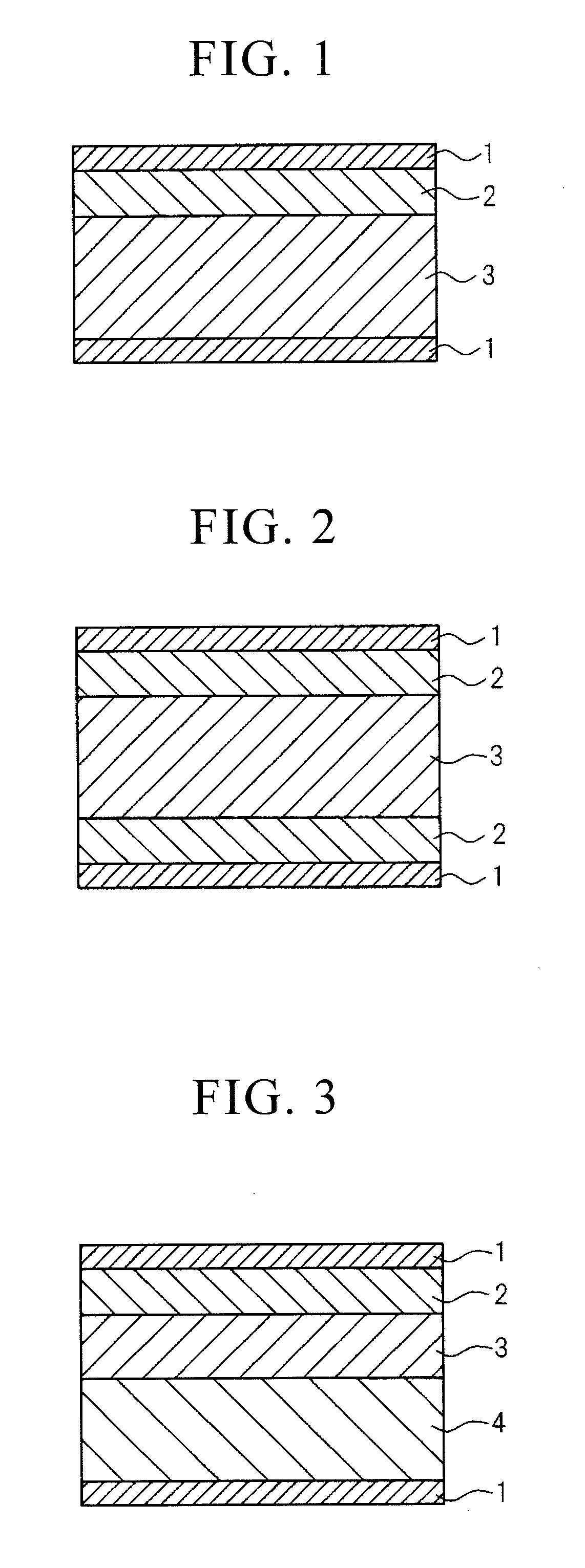

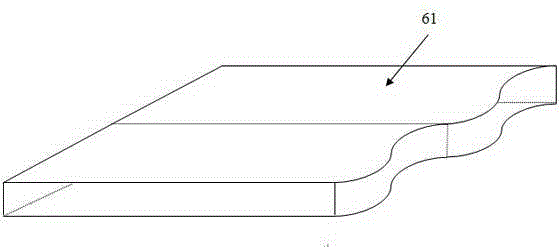

Capacitor material, production method of the same, and capacitor, wiring board and electronic device containing that material

InactiveUS20100014271A1High withstand voltageLow leakage currentElectrolytic capacitorsDigital data processing detailsDioxide titaniumPerovskite

The capacitor material of the present invention is comprised by laminating a titanium dioxide layer and a titanate compound layer having perovskite crystals.

Owner:SHOWA DENKO KK

Memory device, manufacturing method thereof, and electronic equipment including the same

ActiveCN108962905BReduce overall stack thicknessReduce thicknessSolid-state devicesSemiconductor devicesEngineering physicsMaterials science

Owner:INST OF MICROELECTRONICS CHINESE ACAD OF SCI

Surface-mounted overvoltage and overcurrent protection device and manufacturing method thereof

ActiveCN103745898BReduce capacitanceLow leakage currentFuse device manufactureResistor manufactureOvervoltageEngineering

The invention provides a surface-mounted overvoltage and overcurrent protection device and a manufacturing method thereof, comprising a protection device body, end electrodes are provided at the left and right ends of the protection device body, and side electrodes are provided at the front and rear sides to protect the device body. The device body is provided with at least one melt layer electrode, at least two first electrode layers, and at least two second electrode layers, and the melt layer electrode is covered by an arc-extinguishing material coating, the first electrode layer and the second electrode layer There are through holes between the electrode layers and they are filled with piezoresistive functional phases. Forming through LTCC ceramic diaphragm --> melt layer electrode printing --> electrode layer electrode printing --> arc extinguishing material coating printing --> forming a through hole in the LTCC ceramic stack diaphragm --> filling pressure in the through hole Functional phase of the sensitive resistor --> stacked according to the design --> cut into a single product --> product sintering --> forming end electrodes and side electrodes and other steps. It has the advantages of low capacitance, low leakage current, fast response, high reliability and stability.

Owner:NANJING SART SCI & TECH DEV

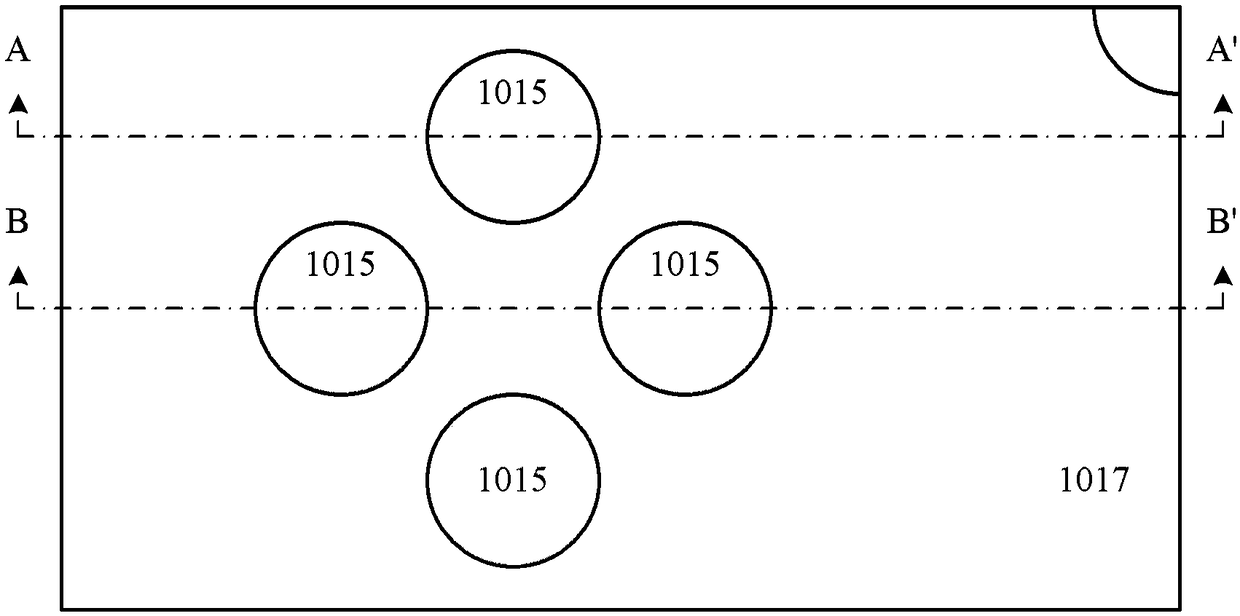

Memory device, manufacturing method thereof, and electronic equipment including the same

ActiveCN106158877BImprove performanceIncrease the areaSolid-state devicesSemiconductor devicesGate stackSemiconductor

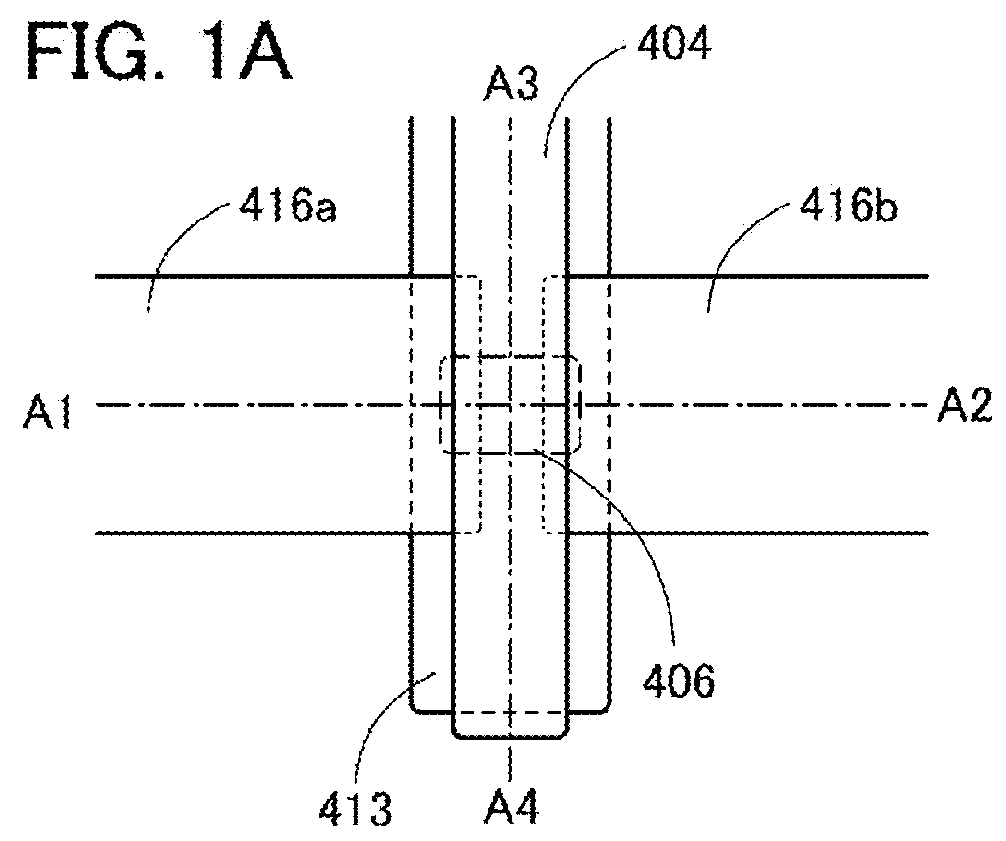

Disclosed are a storage device, a manufacturing method thereof, and electronic equipment including the storage device. The storage device may include: a plurality of first columnar active regions and a plurality of second columnar active regions extending upward on the substrate, arranged in first and second arrays respectively, and each first columnar active region includes a source / Drain layers and channel layers are alternately stacked, the corresponding channel layers in each first columnar active region are on substantially the same plane, and the corresponding source / drain layers are on substantially the same plane, and each second The columnar active region includes an integrally extended active semiconductor layer; a columnar conductive contact part located at the lower part of each second columnar active region; an insulating layer formed around the periphery of each columnar conductive contact part; Multi-layer first storage gate stacks in substantially the same plane and respectively surrounding the periphery of each channel layer on the corresponding plane; multi-layer second storage gate stacks surrounding the periphery of each second columnar active region.

Owner:INST OF MICROELECTRONICS CHINESE ACAD OF SCI

Memory device, manufacturing method thereof, and electronic equipment including the same

ActiveCN106298792BReduce parasitic capacitanceImprove performanceSolid-state devicesSemiconductor devicesSemiconductor materialsMemory cell

Disclosed are a storage device, a manufacturing method thereof, and electronic equipment including the storage device. According to an embodiment, the memory device may include a memory cell and a selection device sequentially stacked on a substrate. Each of the memory unit and the selection device may include: a first source / drain layer, a channel layer, and a second source / drain layer stacked in sequence, wherein the channel layer includes a layer different from the first and second source / drain layers a semiconductor material; and a gate stack formed around the periphery of the channel layer. The gate stack of the memory cell is a memory gate stack.

Owner:INST OF MICROELECTRONICS CHINESE ACAD OF SCI

Non-fullerene acceptor compound containing benzoselenadiazole and organic optoelectronic device including the same

PendingUS20210230130A1Reduce energy gapLow leakage currentOrganic chemistrySolid-state devicesPolymer chemistryPhotochemistry

Owner:RAYNERGY TEK INC

Method for preparing bismuth ferrite film with dielectric property by adopting liquid-phase self-assembly technology

Owner:SHAANXI UNIV OF SCI & TECH

B-site Mn and Cu codoped high remanent polarization BiFeO3 film and preparation method

ActiveCN103613144BImprove multiferroic propertiesPromote productionFrom gel stateMANGANESE ACETATEAcetic anhydride

The invention relates to a B-site Mn and Cu codoped high remanent polarization BiFeO3 film and a preparation method, the method comprises the following steps: dissolving bismuth nitrate, ferric nitrate, manganese acetate and cupric nitrate according to mol ratio of 1.05: [(0.92-0.98)-x]: (0.02-0.08):x in a mixed liquor of ethylene glycol monomethyl ether and acetic anhydride, then uniformly stirring to obtain a BiFeO3 precursor; wherein total metal ion concentration of the BiFeO3 precursor is 0.1-0.5mol / L, X is 0.01-0.03; performing spin coating of the BiFeO3 precursor on a FTO / glass substrate to prepare a wet membrane, baking the wet membrane to obtain a dry membrane, then annealing at 550 DEG C to obtain the crystalline state BiFeO3 film; cooling the crystalline state BiFeO3 film, and repeatedly making the crystalline state BiFeO3 film to reach a required thickness to obtain the B-site Mn and Cu codoped high remanent polarization BiFeO3 film. According to the invention, a sol gel technology is employed, the equipment requirement is simple, the film is prepared on large surface and surfaces with irregular shapes, the chemical component is accurate and controllable, and the regulation and control to its crystal structure can be carried out by codoping thereby the ferroelectric performance of the film is greatly increased.

Owner:盐城梦心缘鞋服有限公司

Memory device, manufacturing method thereof, and electronic equipment including the same

ActiveCN106206600BHigh carrier mobilityLow leakage currentSolid-state devicesSemiconductor devicesPhysicsStorage cell

Disclosed are a storage device, a manufacturing method thereof, and electronic equipment including the storage device. According to an embodiment, a memory device may include a plurality of memory cell layers sequentially stacked on a substrate, each memory cell layer includes an array of memory cells, and the memory cells in each memory cell layer are along the stacking direction of the memory cell layers are substantially aligned with each other. Each memory cell includes: a first source / drain layer, a channel layer, and a second source / drain layer stacked in sequence, wherein the channel layer includes a semiconductor material different from that of the first and second source / drain layers; and A memory gate stack is formed around the periphery of the channel layer. The memory gates of the memory cells in the same memory cell layer are stacked into one body. For each storage unit, its first source / drain layer is integrated with the second source / drain layer of the corresponding storage unit in the lower layer, and its second source / drain layer is integrated with the first source / drain layer of the corresponding storage unit in the upper layer.

Owner:INST OF MICROELECTRONICS CHINESE ACAD OF SCI

Semiconductor device, manufacturing method thereof, and electronic device including same

ActiveCN106252352BReduce parasitic capacitanceImprove performanceTransistorSolid-state devicesElectrical conductorSemiconductor materials

Disclosed are a semiconductor arrangement, a method of manufacturing the same, and an electronic device including the same. According to an embodiment, a semiconductor arrangement may include a first semiconductor device and a second semiconductor device sequentially stacked on a substrate. Each of the first semiconductor device and the second semiconductor device may include: a first source / drain layer, a channel layer, and a second source / drain layer stacked in sequence, wherein the channel layer includes the first and second source / drain layers. a different semiconductor material for the drain layer; and a gate stack formed around the periphery of the channel layer.

Owner:INST OF MICROELECTRONICS CHINESE ACAD OF SCI