Patents

Literature

30 results about "Serial processor" patented technology

Efficacy Topic

Property

Owner

Technical Advancement

Application Domain

Technology Topic

Technology Field Word

Patent Country/Region

Patent Type

Patent Status

Application Year

Inventor

A serial processor is a processor type used by systems where the central processing unit (CPU) carries out just one machine-level operation at a time. The term is often used in contrast to a parallel processor, which features more than one CPU to perform parallel processing.

Method and apparatus to schedule packets through a crossbar switch with delay guarantees

ActiveUS20070280261A1Minimize delay jitterMeet bandwidth requirementsMultiplex system selection arrangementsData switching by path configurationCrossbar switchDifferentiated services

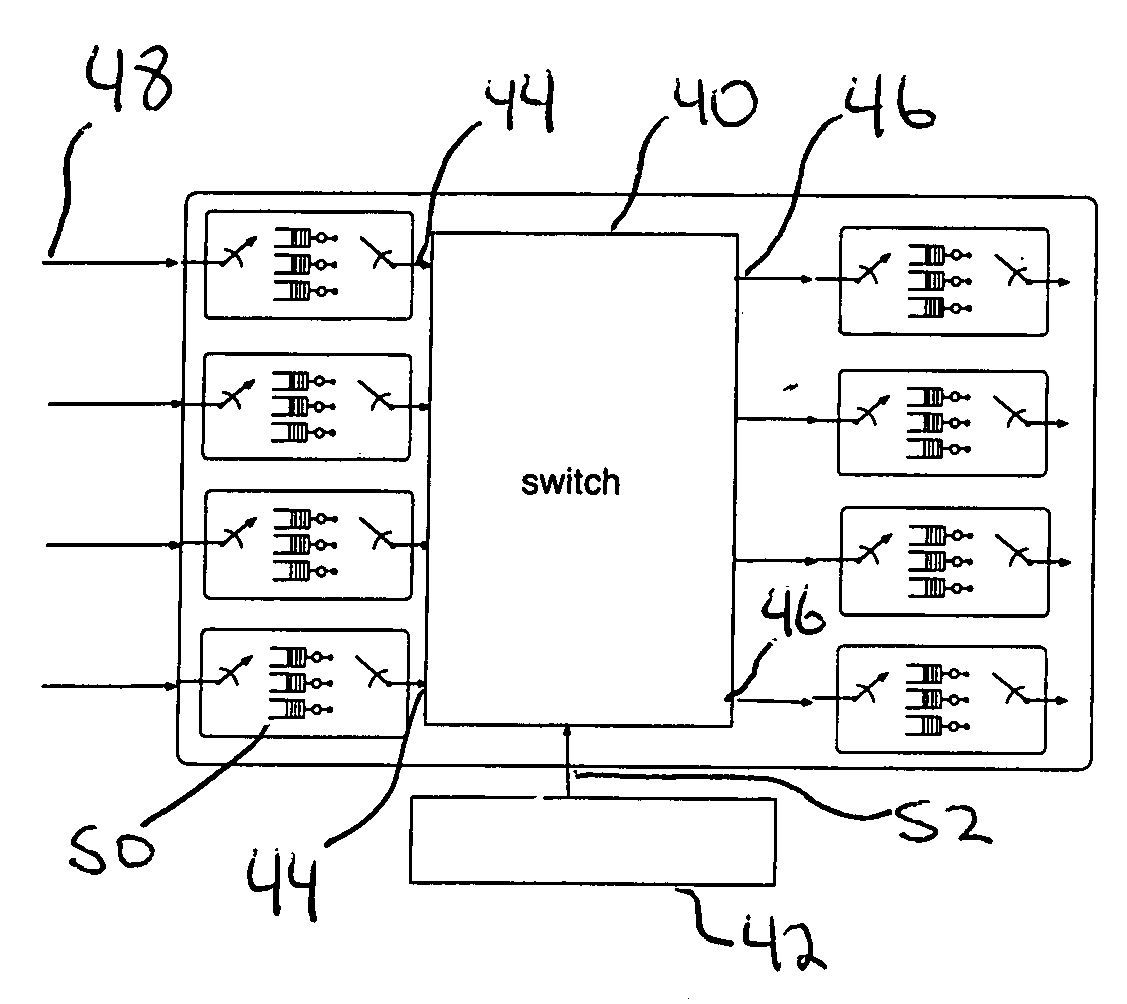

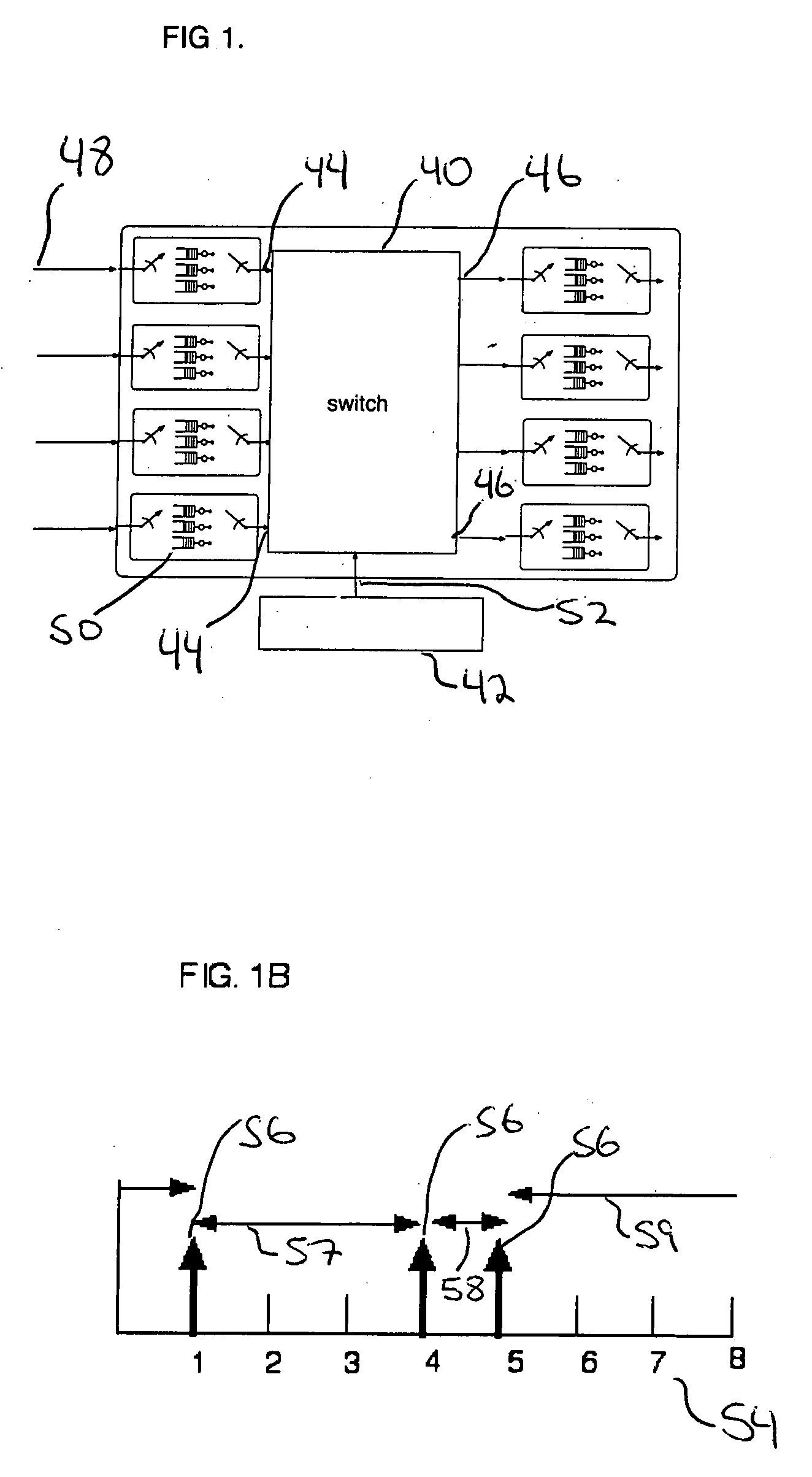

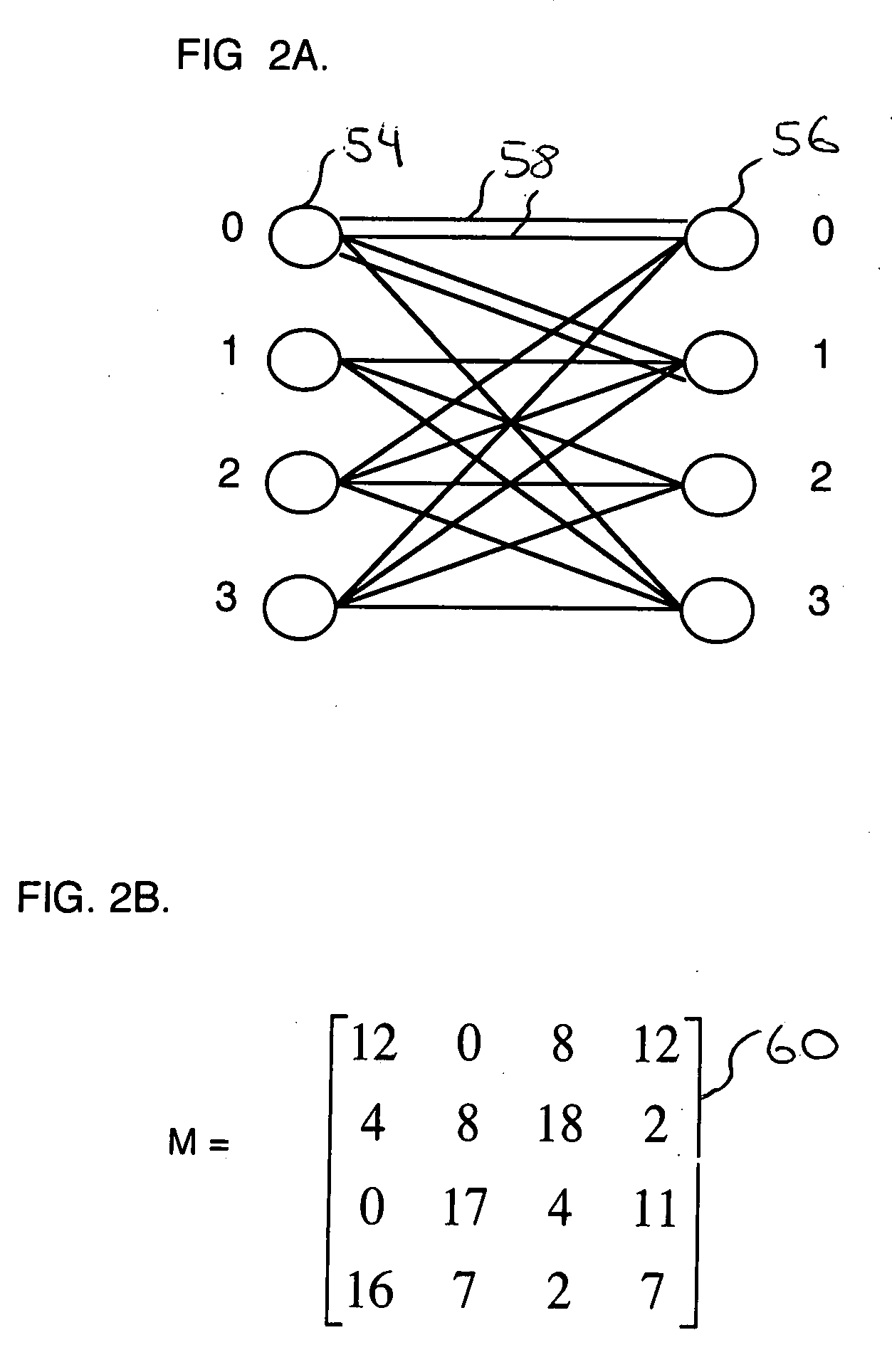

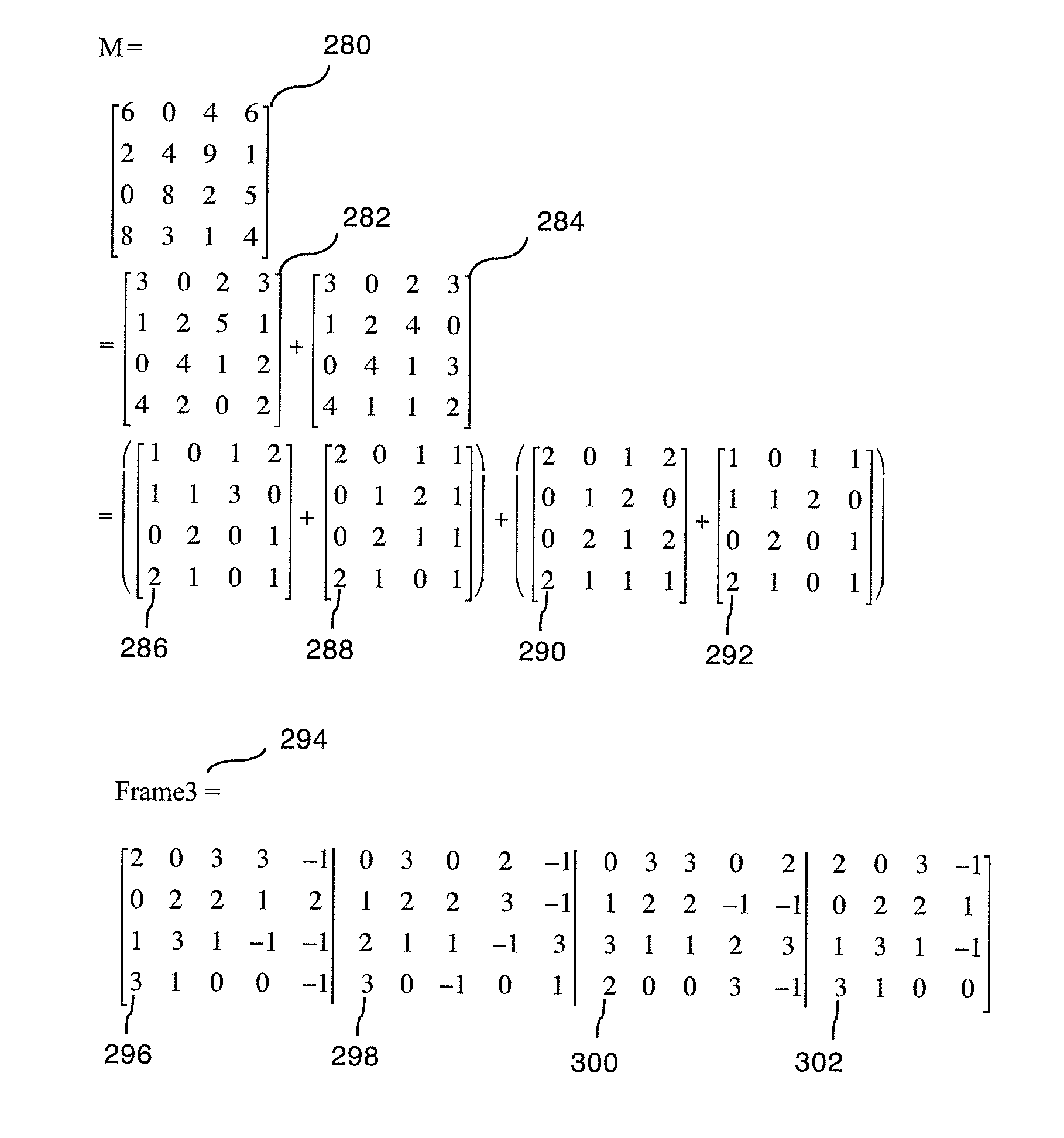

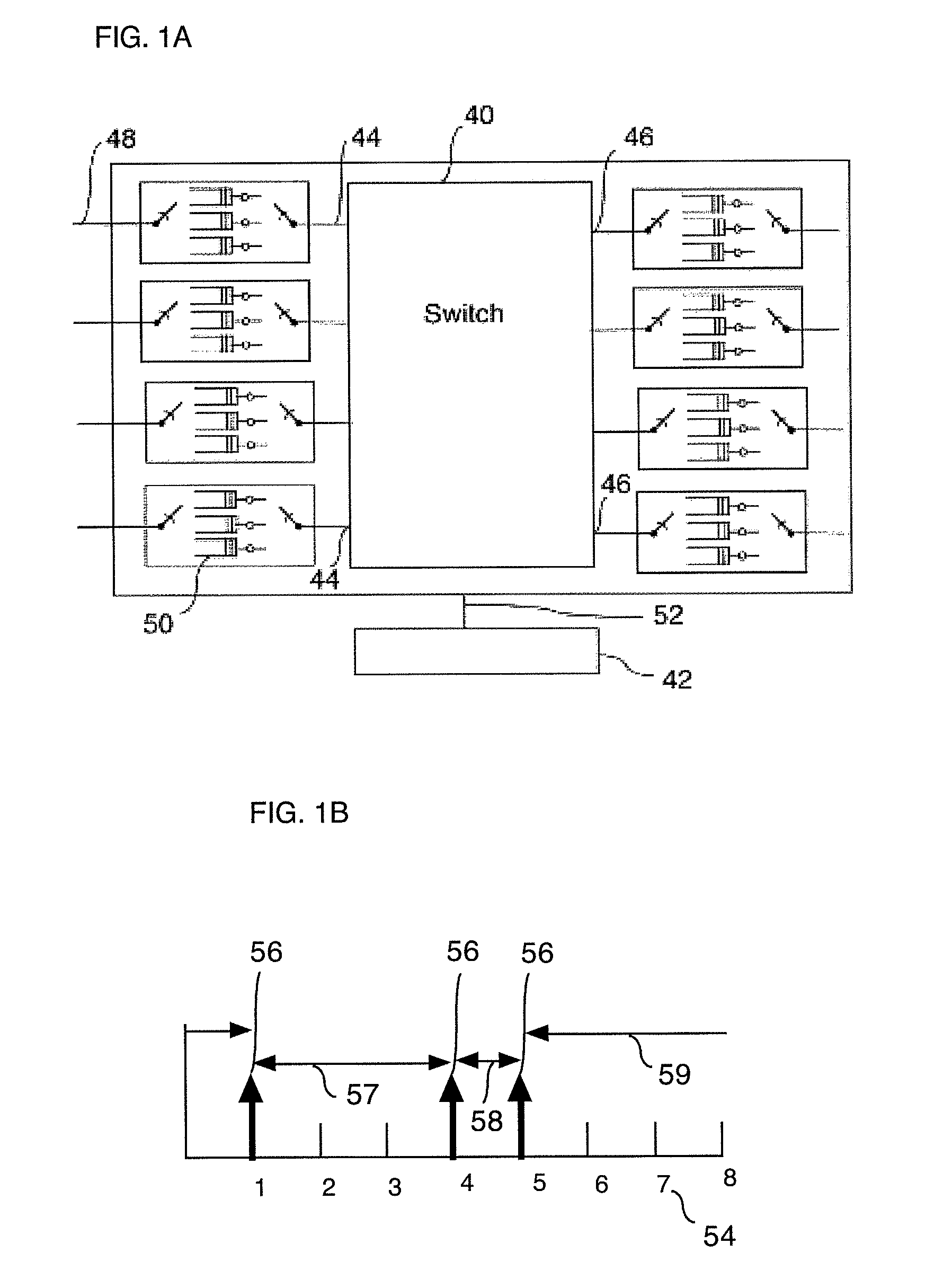

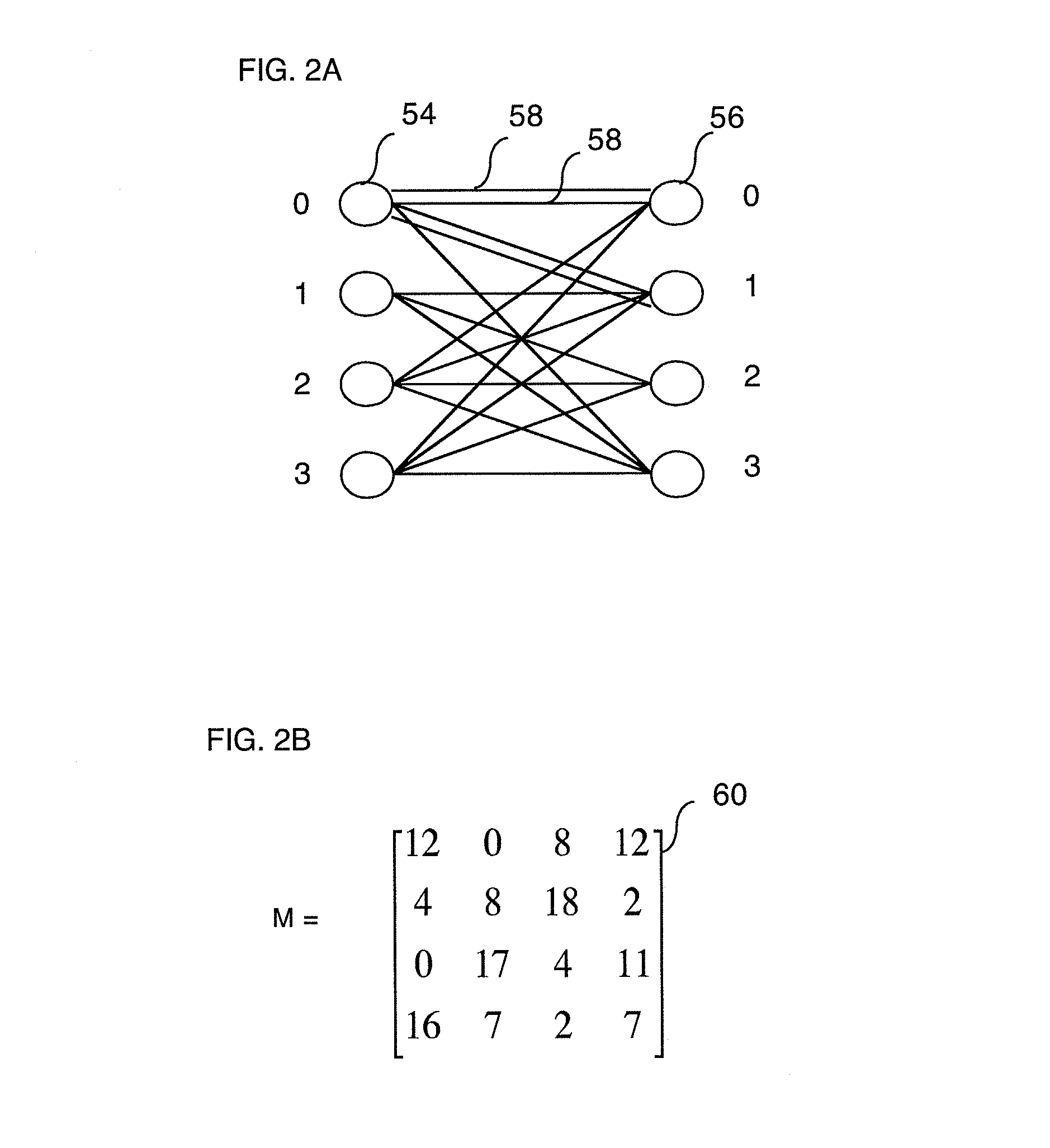

A method for scheduling cell transmissions through a switch with rate and delay guarantees and with low jitter is proposed. The method applies to a classic input-buffered N×N crossbar switch without speedup. The time axis is divided into frames each containing F time-slots. An N×N traffic rate matrix specifies a quantized guaranteed traffic rate from each input port to each output port. The traffic rate matrix is transformed into a permutation with NF elements which is decomposed into F permutations of N elements using a recursive and fair decomposition method. Each permutation is used to configure the crossbar switch for one time-slot within a frame of size F time-slots, and all F permutations result in a Frame Schedule. In the frame schedule, the expected Inter-Departure Time (IDT) between cells in a flow equals the Ideal IDT and the delay jitter is bounded and small. For fixed frame size F, an individual flow can often be scheduled in O(logN) steps, while a complete reconfiguration requires O(NlogN) steps when implemented in a serial processor. An RSVP or Differentiated Services-like algorithm can be used to reserve bandwidth and buffer space in an IP-router, an ATM switch or MPLS switch during a connection setup phase, and the proposed method can be used to schedule traffic in each router or switch. Best-effort traffic can be scheduled using any existing dynamic scheduling algorithm to fill the remaining unused switch capacity within each Frame. The scheduling algorithm also supports multicast traffic.

Owner:SZYMANSKI TED HENRYK

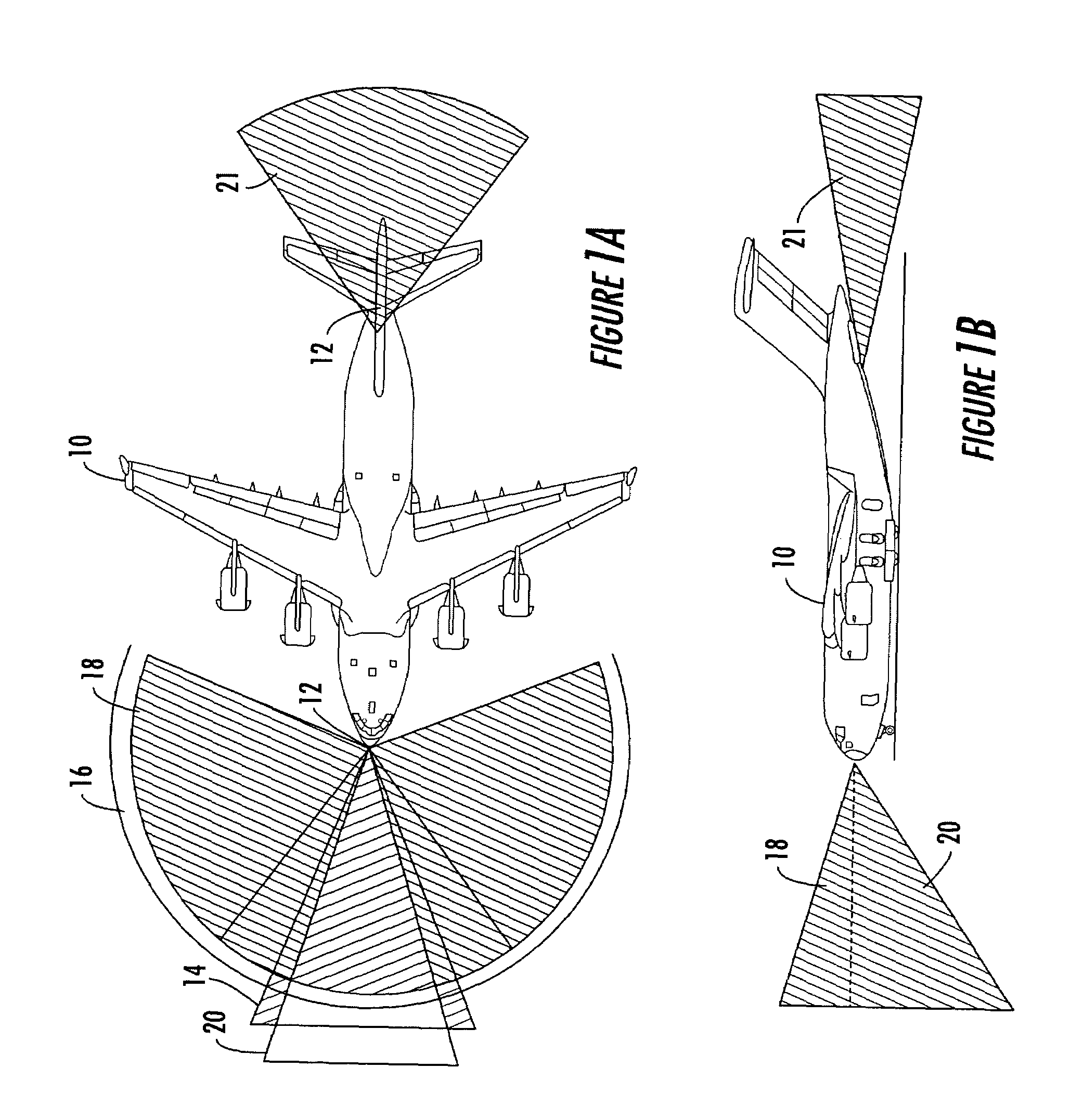

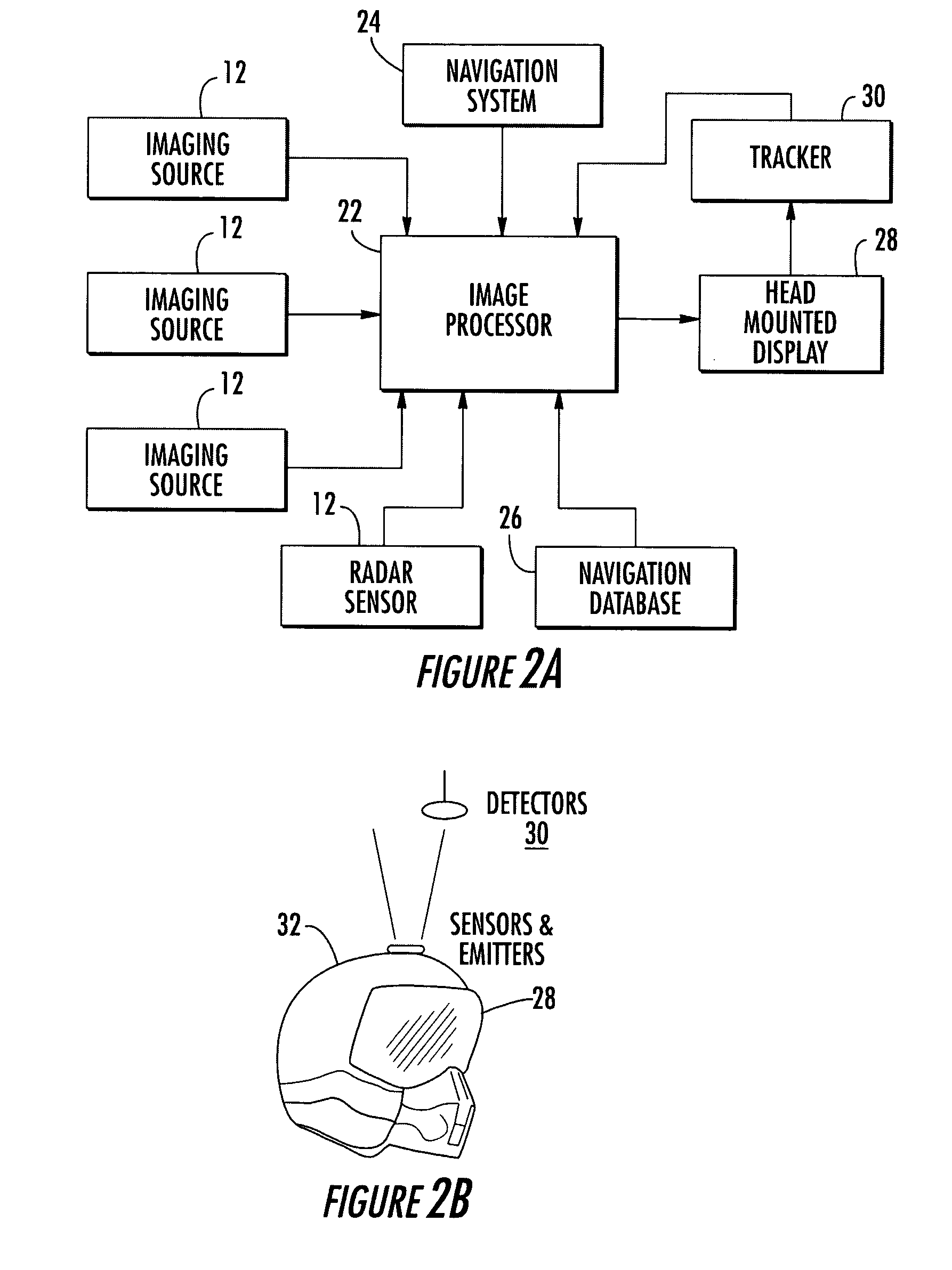

Systems and methods for providing enhanced vision imaging with decreased latency

ActiveUS7148861B2Mitigate issueReduce decreaseWater treatment parameter controlGeometric image transformationParallaxDisplay device

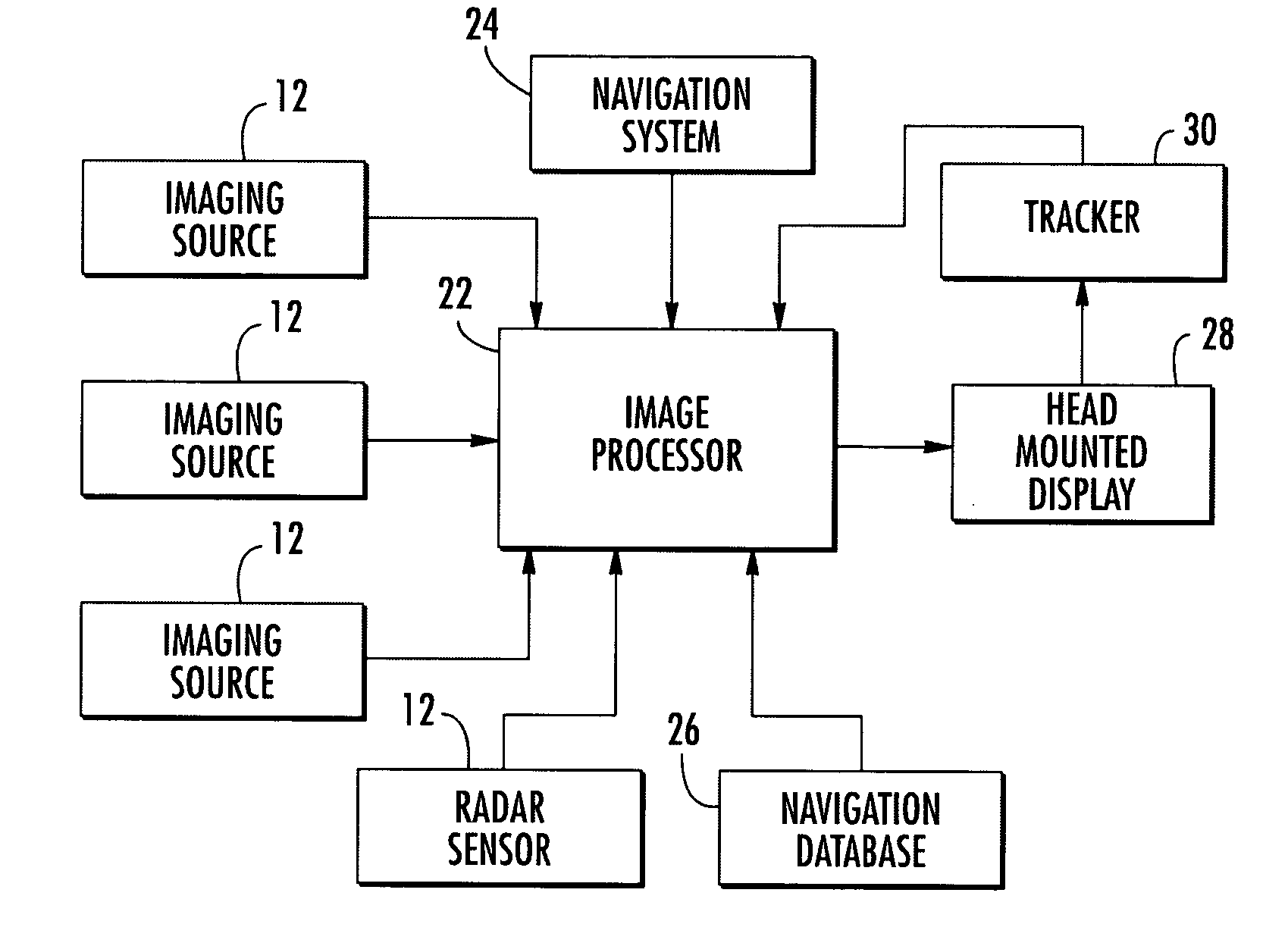

The systems and methods of the present invention provide an image processor that displays enhanced vision images based on a plurality images sources. The image processor comprises both serial and parallel processors. The serial processor performs low data volume calculations needed by the parallel processor for image display. The serial processor precalculates transformations needed to convert source data from each source to a primary coordinate system. The parallel processor uses these transforms and correlates source data with the display on a pixel by pixel basis as each frame from the sources is received to thereby provide display data with decreased latency. The image processor reduces parallax effect and is capable of: 1) stitching images of different fields of view to provide a mosaic image; 2) fusing images taken of the same field of view by different types of sources into a fused image; and 3) correcting anomalies in the displayed image.

Owner:THE BOEING CO

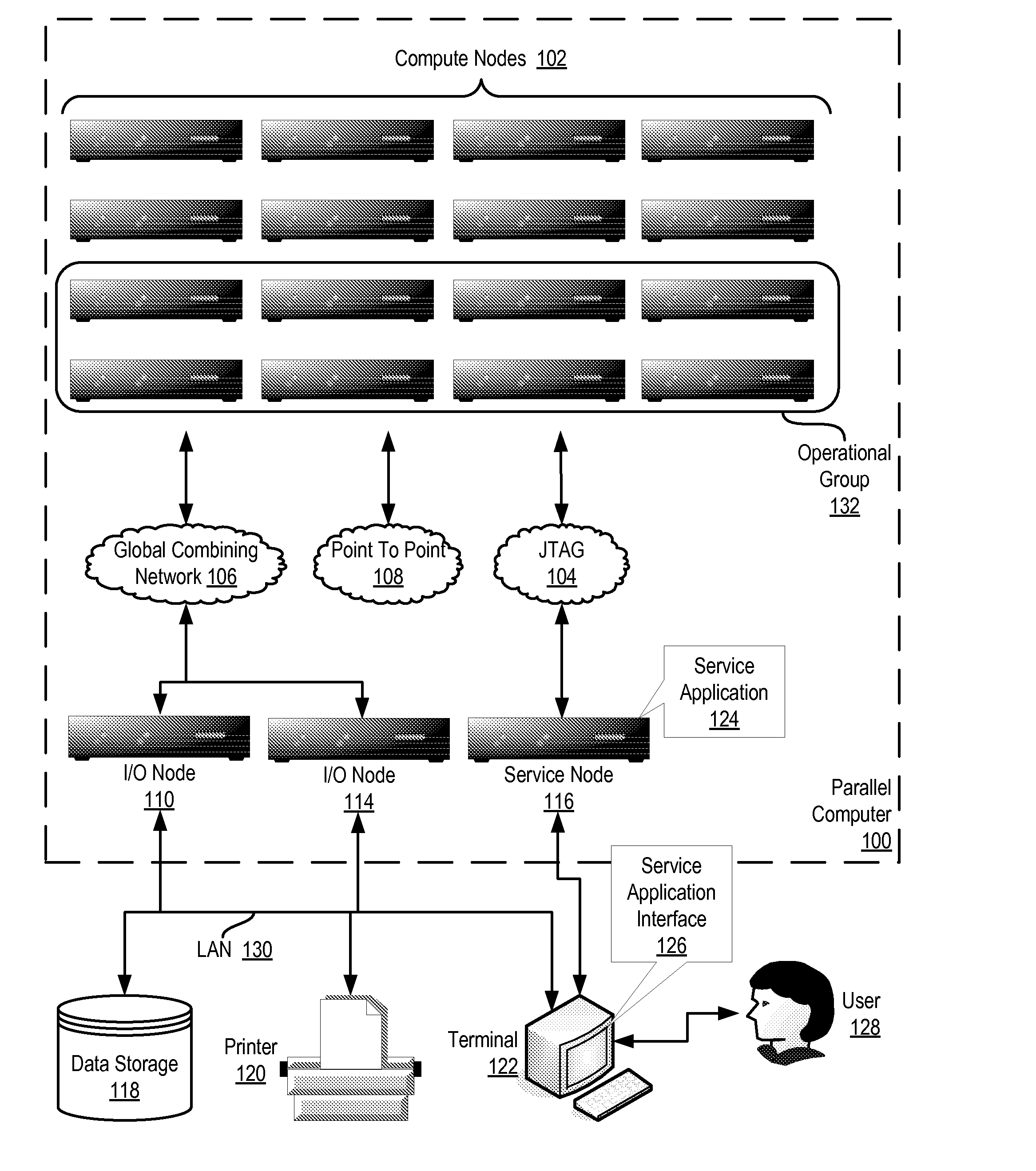

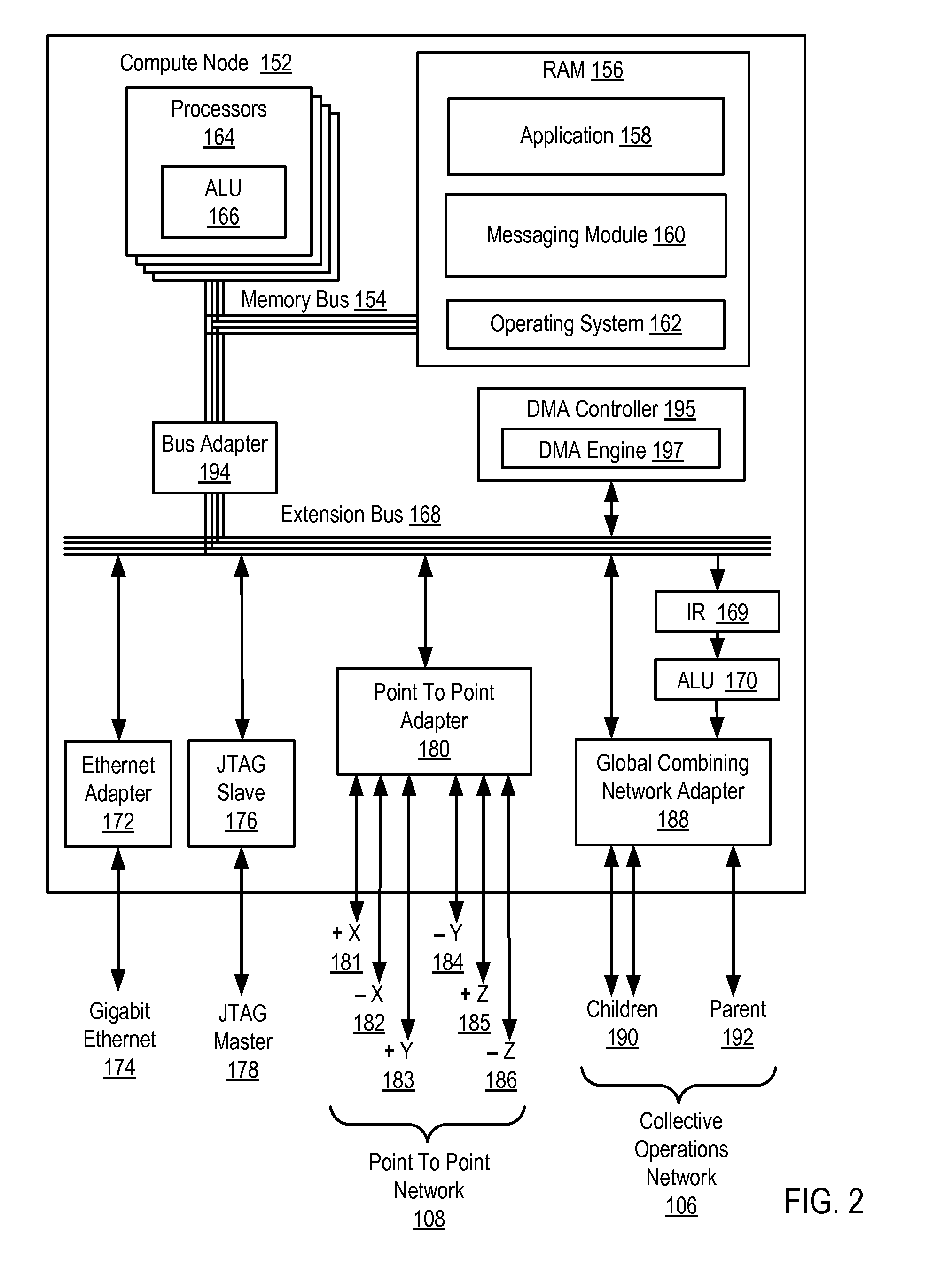

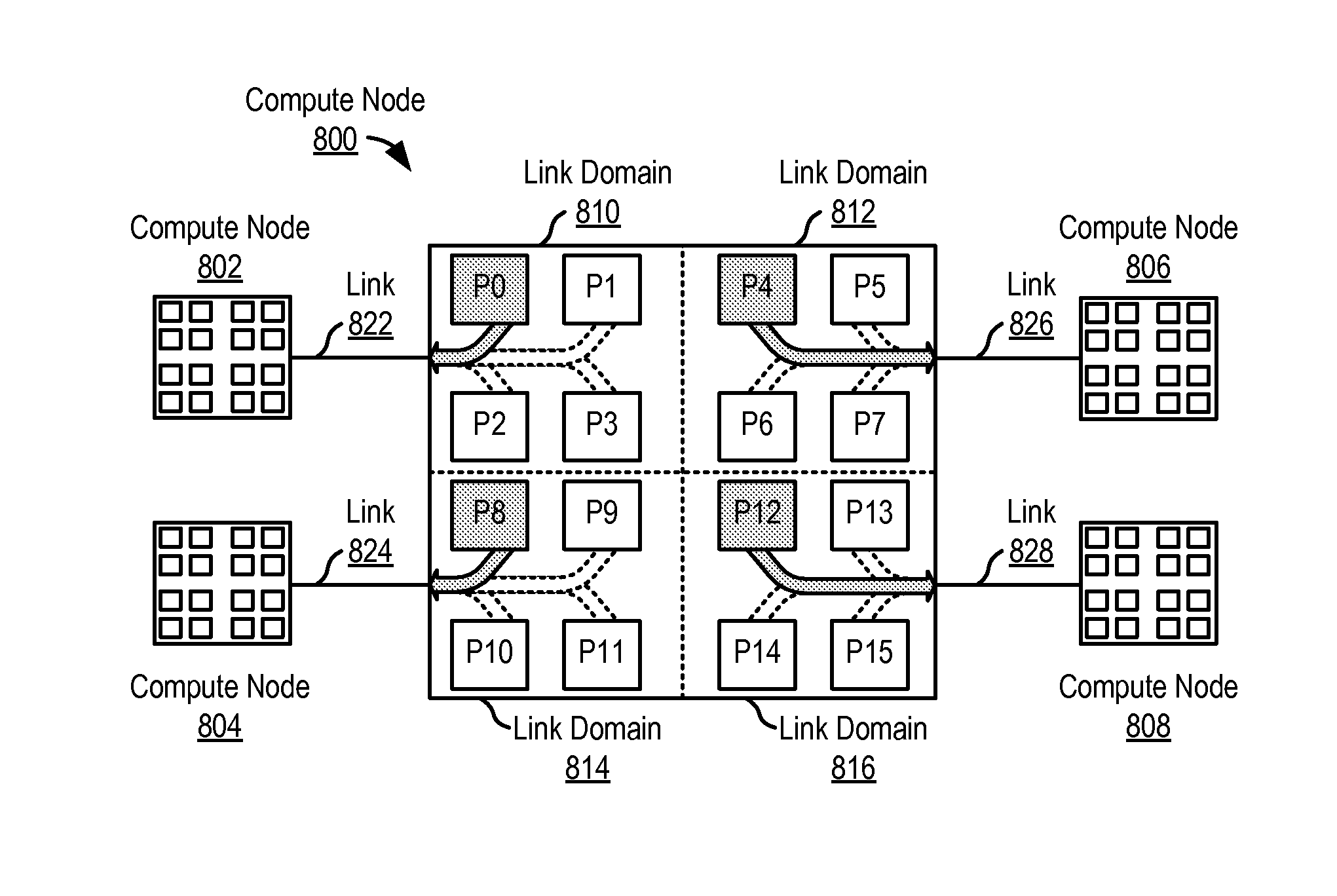

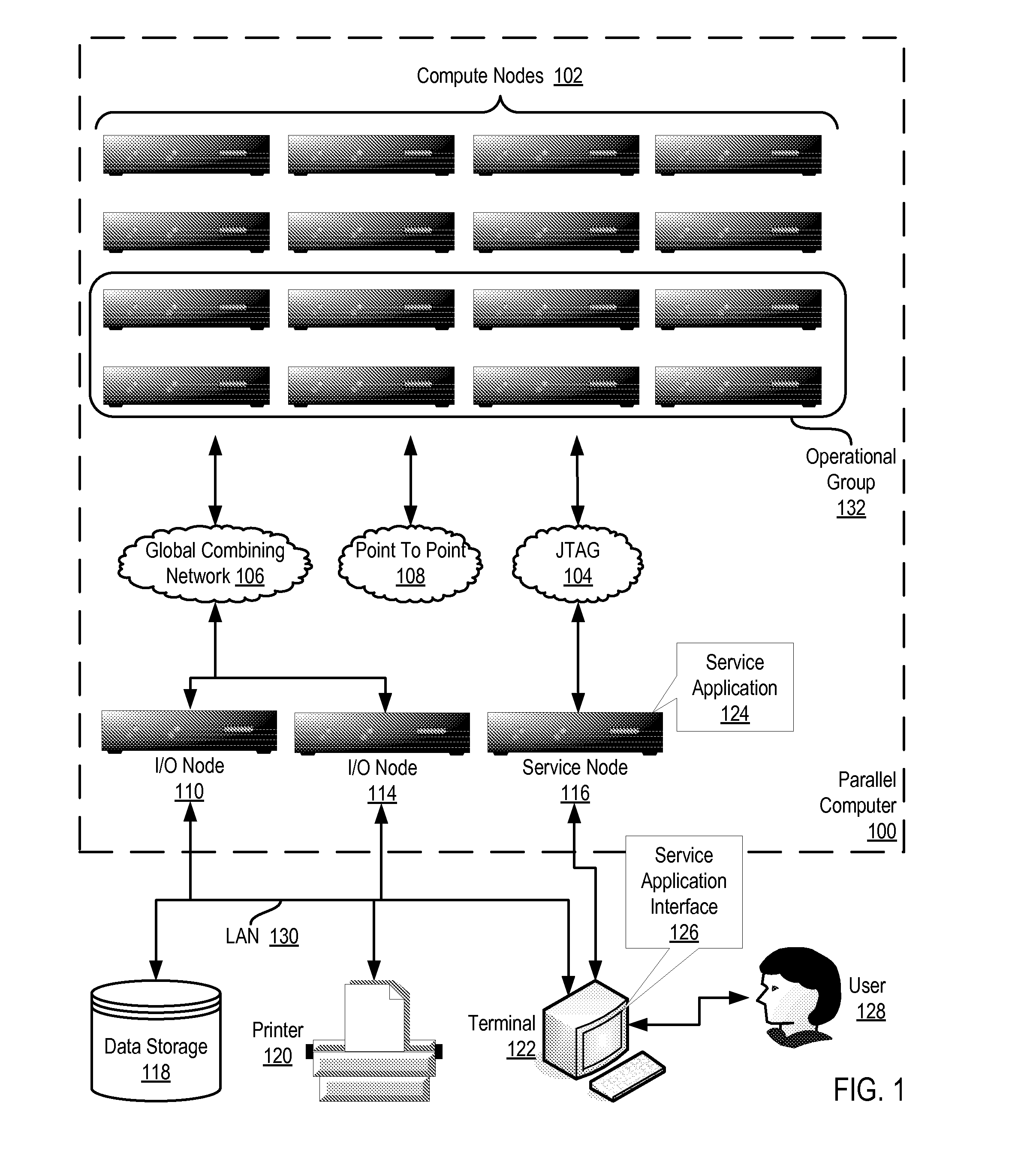

Broadcasting Collective Operation Contributions Throughout A Parallel Computer

InactiveUS20090240915A1Operational speed enhancementGeneral purpose stored program computerNetwork linkCollective operation

Owner:IBM CORP

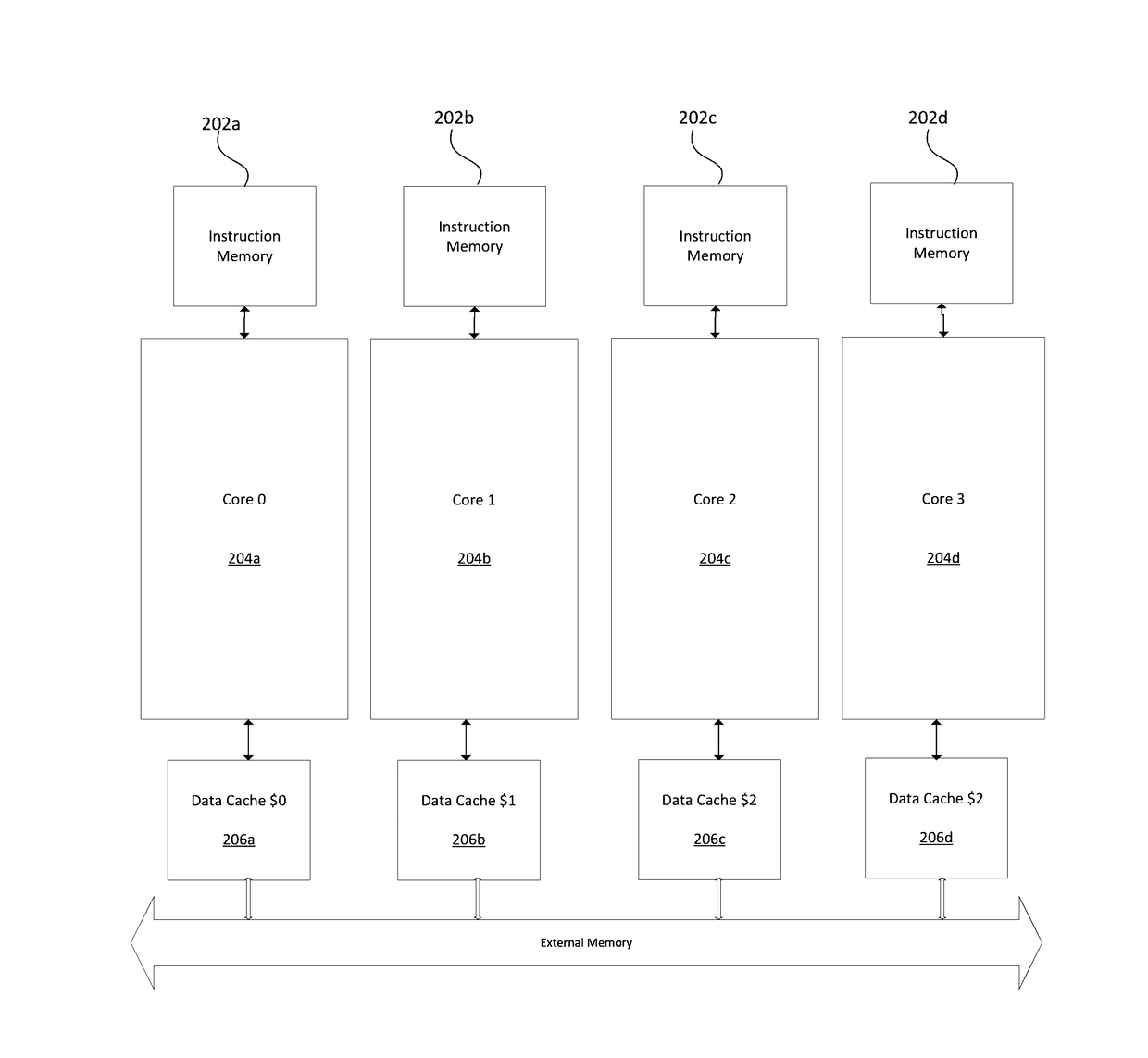

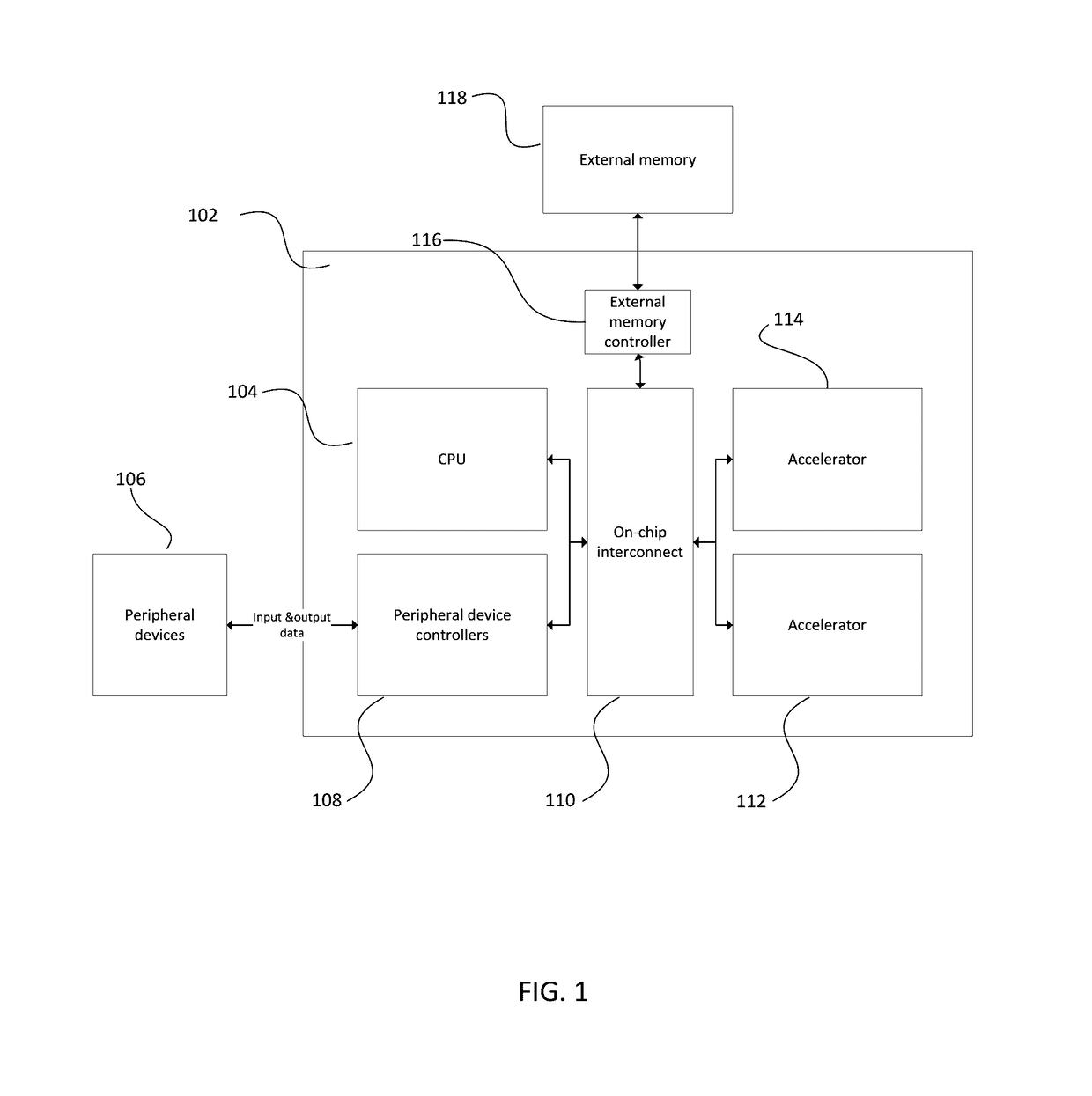

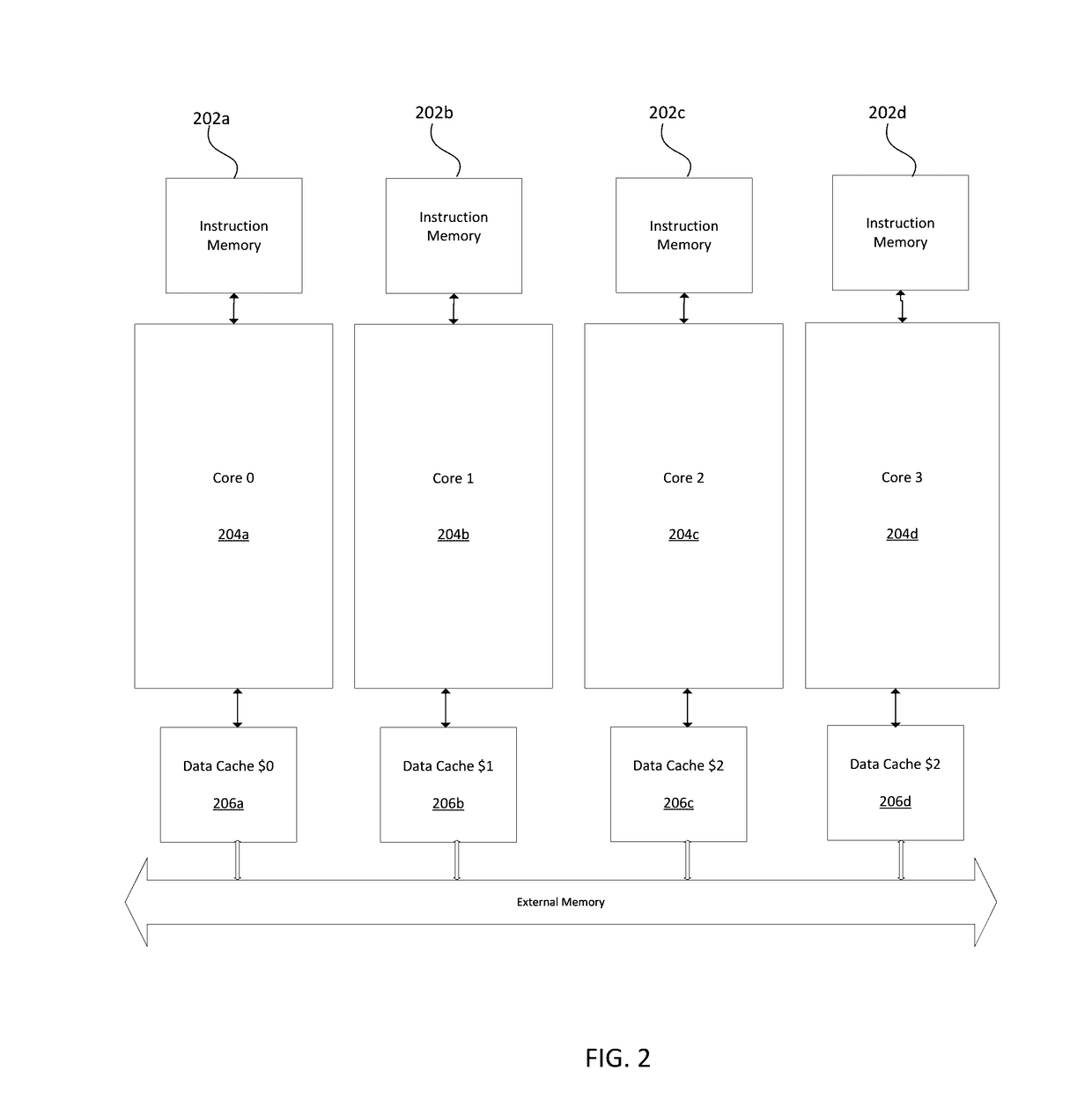

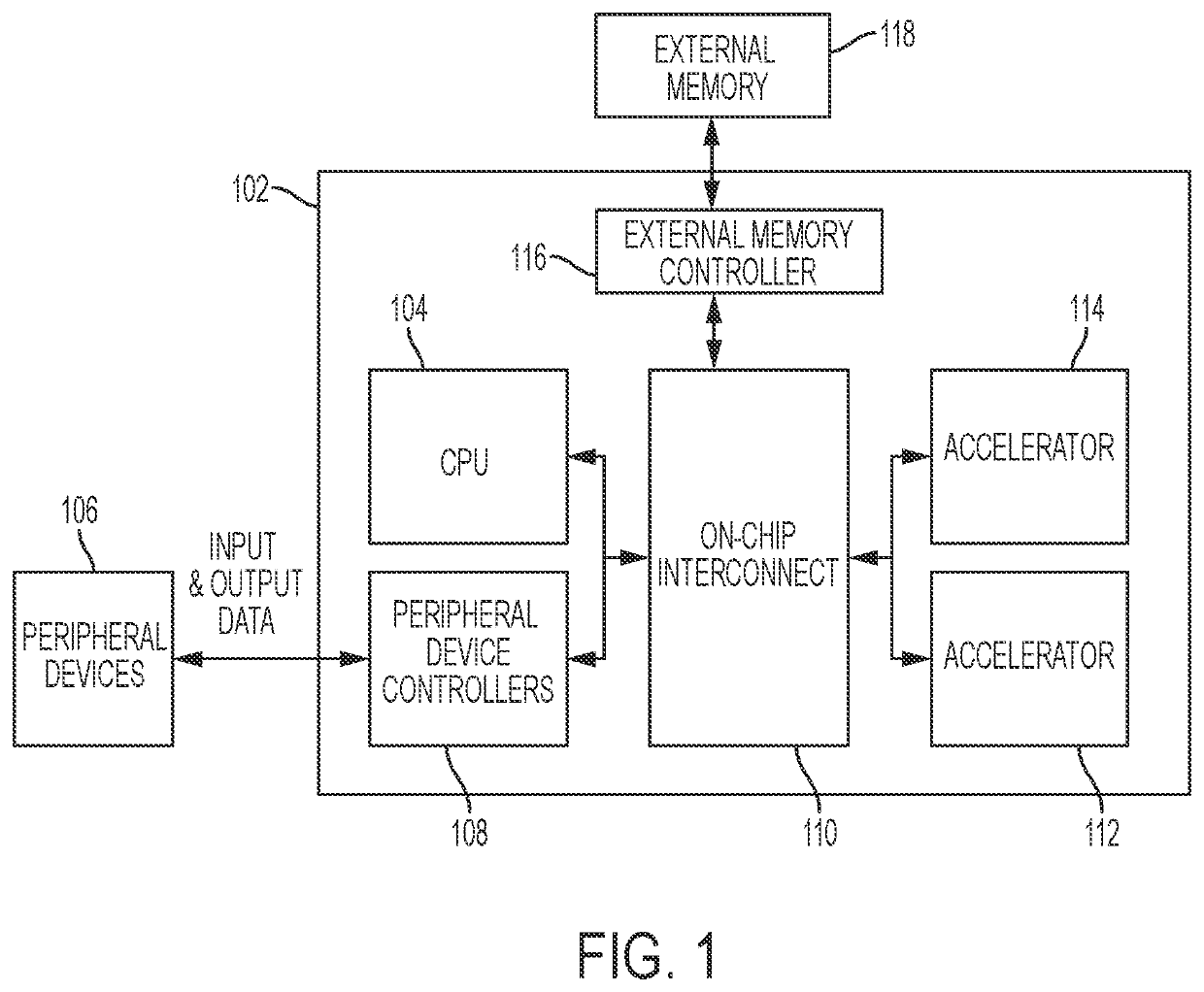

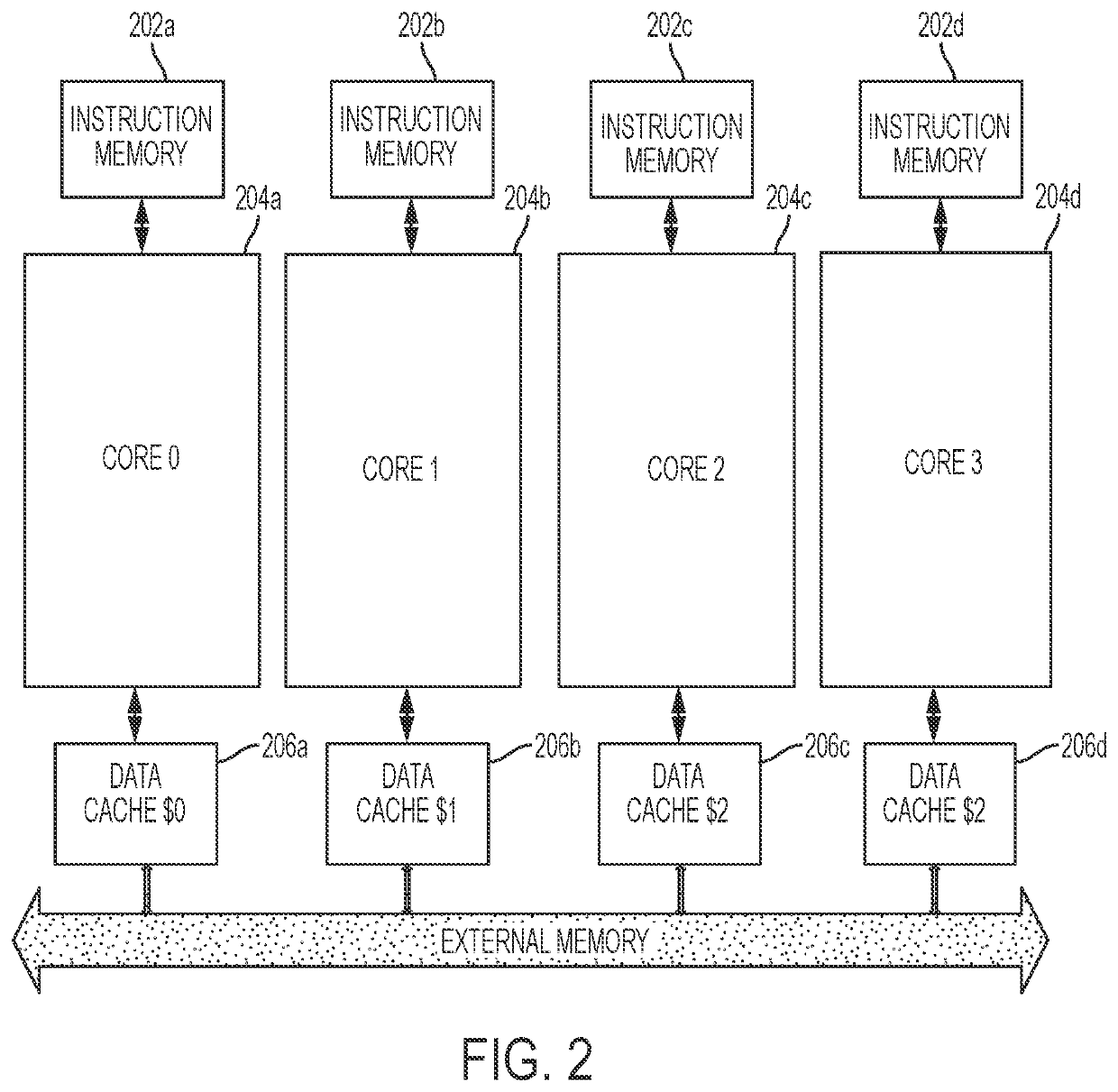

System on chip with image processing capabilities

ActiveUS20170103022A1Faster processing timeReduce in quantityMemory architecture accessing/allocationRegister arrangementsProcessing coreImaging processing

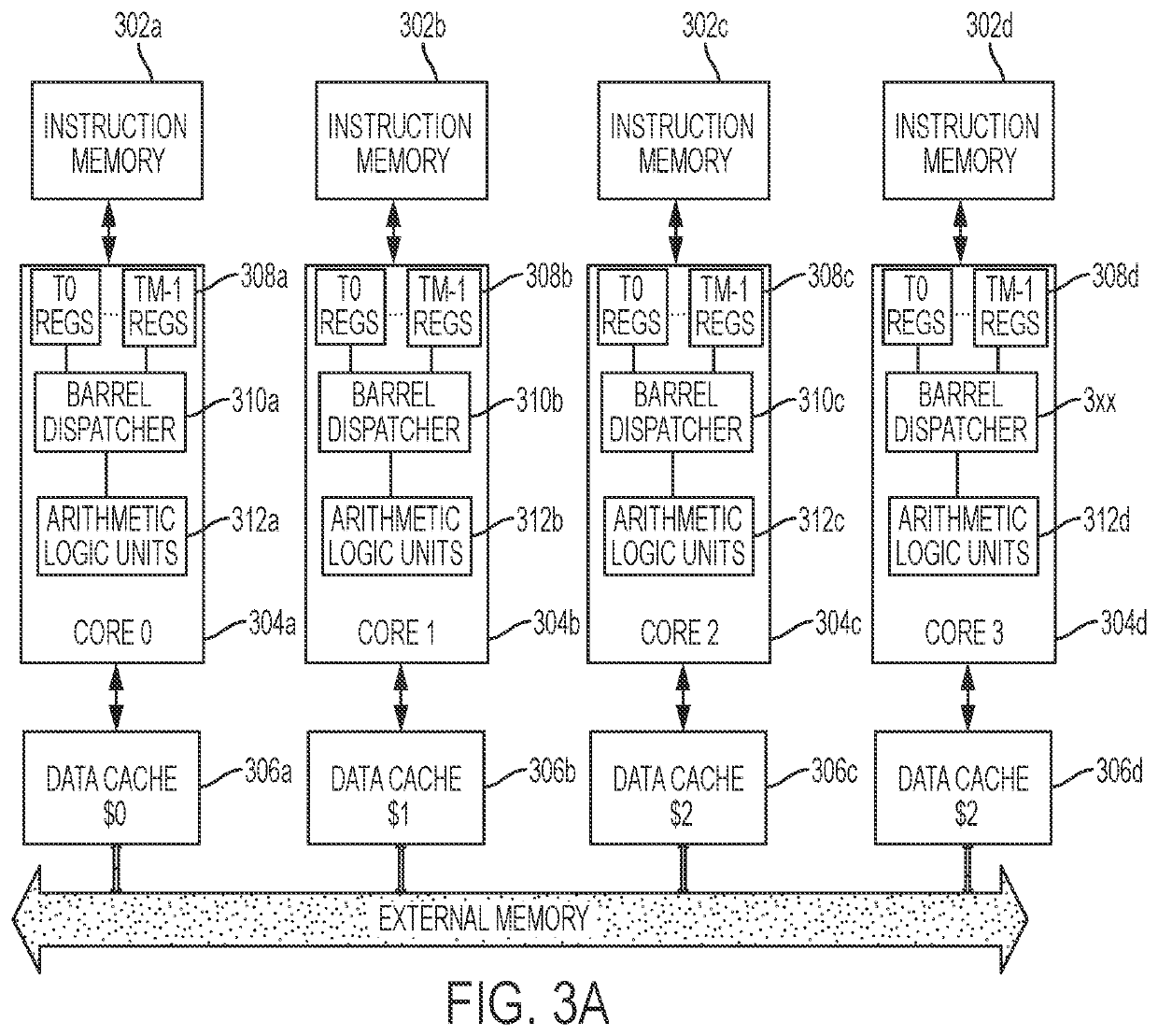

A multi-core processor configured to improve processing performance in certain computing contexts is provided. The multi-core processor includes multiple processing cores that implement barrel threading to execute multiple instruction threads in parallel while ensuring that the effects of an idle instruction or thread upon the performance of the processor is minimized. The multiple cores can also share a common data cache, thereby minimizing the need for expensive and complex mechanisms to mitigate inter-cache coherency issues. The barrel-threading can minimize the latency impacts associated with a shared data cache. In some examples, the multi-core processor can also include a serial processor configured to execute single threaded programming code that may not yield satisfactory performance in a processing environment that employs barrel threading.

Owner:MOBILEYE VISION TECH LTD

Method and apparatus to schedule packets through a crossbar switch with delay guarantees

ActiveUS8089959B2Multiplex system selection arrangementsData switching by path configurationDifferentiated servicesCrossbar switch

A method for scheduling cell transmissions through a switch with rate and delay guarantees and with low jitter is proposed. The method applies to a classic input-buffered N×N crossbar switch without speedup. The time axis is divided into frames each containing F time-slots. An N×N traffic rate matrix specifies a quantized guaranteed traffic rate from each input port to each output port. The traffic rate matrix is transformed into a permutation with NF elements which is decomposed into F permutations of N elements using a recursive and fair decomposition method. Each permutation is used to configure the crossbar switch for one time-slot within a frame of size F time-slots, and all F permutations result in a Frame Schedule. In the frame schedule, the expected Inter-Departure Time (IDT) between cells in a flow equals the Ideal IDT and the delay jitter is bounded and small. For fixed frame size F, an individual flow can often be scheduled in O(log N) steps, while a complete reconfiguration requires O(N log N) steps when implemented in a serial processor. An RSVP or Differentiated Services-like algorithm can be used to reserve bandwidth and buffer space in an IP-router, an ATM switch or MPLS switch during a connection setup phase, and the proposed method can be used to schedule traffic in each router or switch. Best-effort traffic can be scheduled using any existing dynamic scheduling algorithm to fill the remaining unused switch capacity within each Frame. The scheduling algorithm also supports multicast traffic.

Owner:SZYMANSKI TED HENRYK

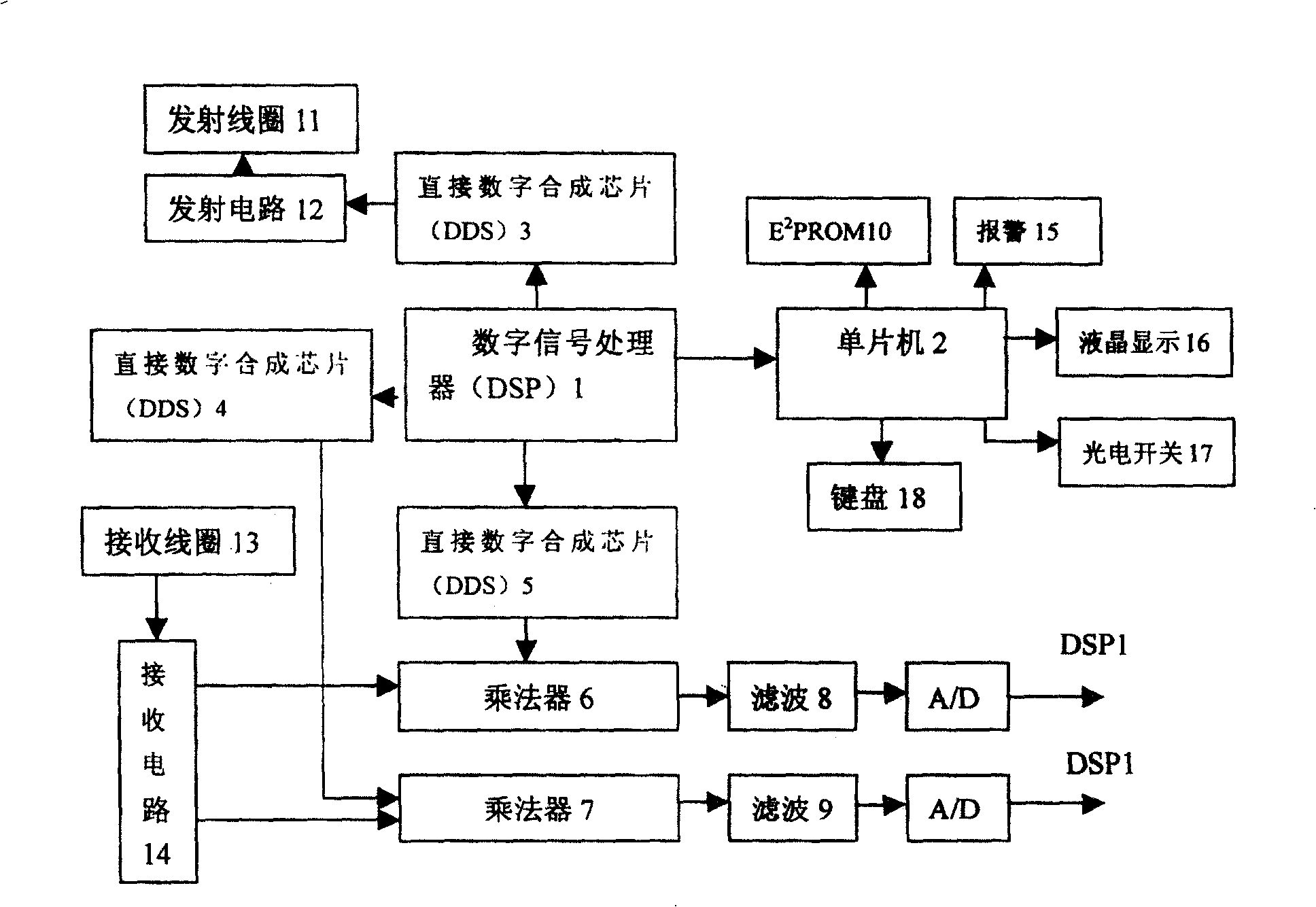

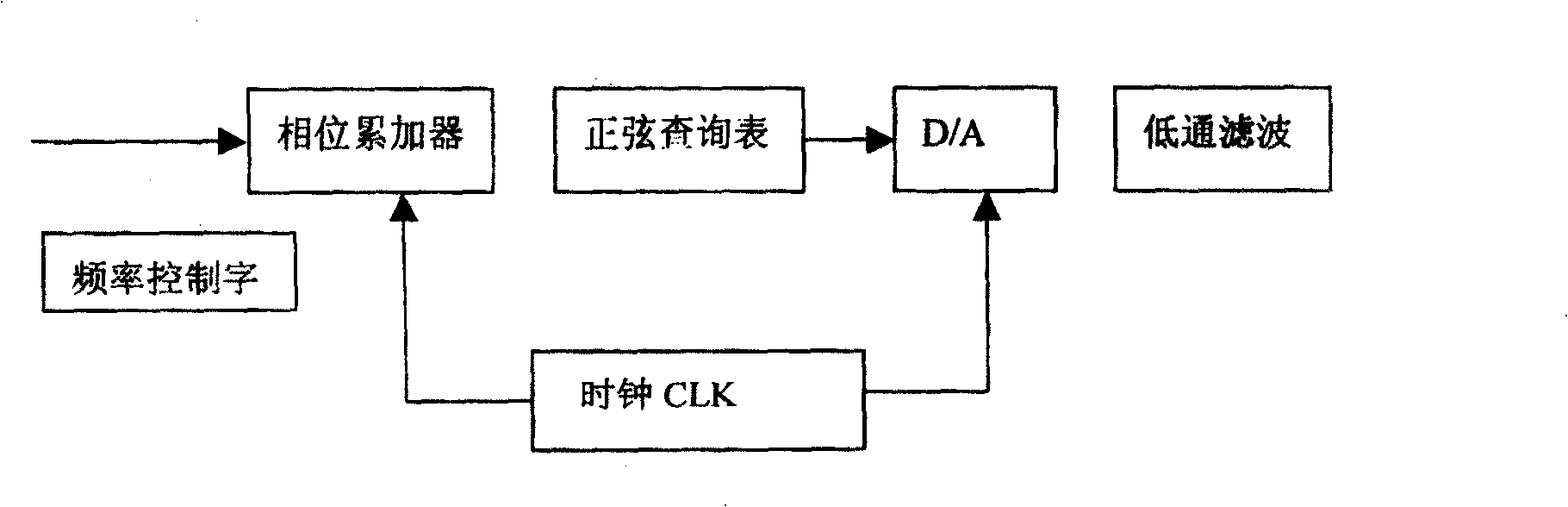

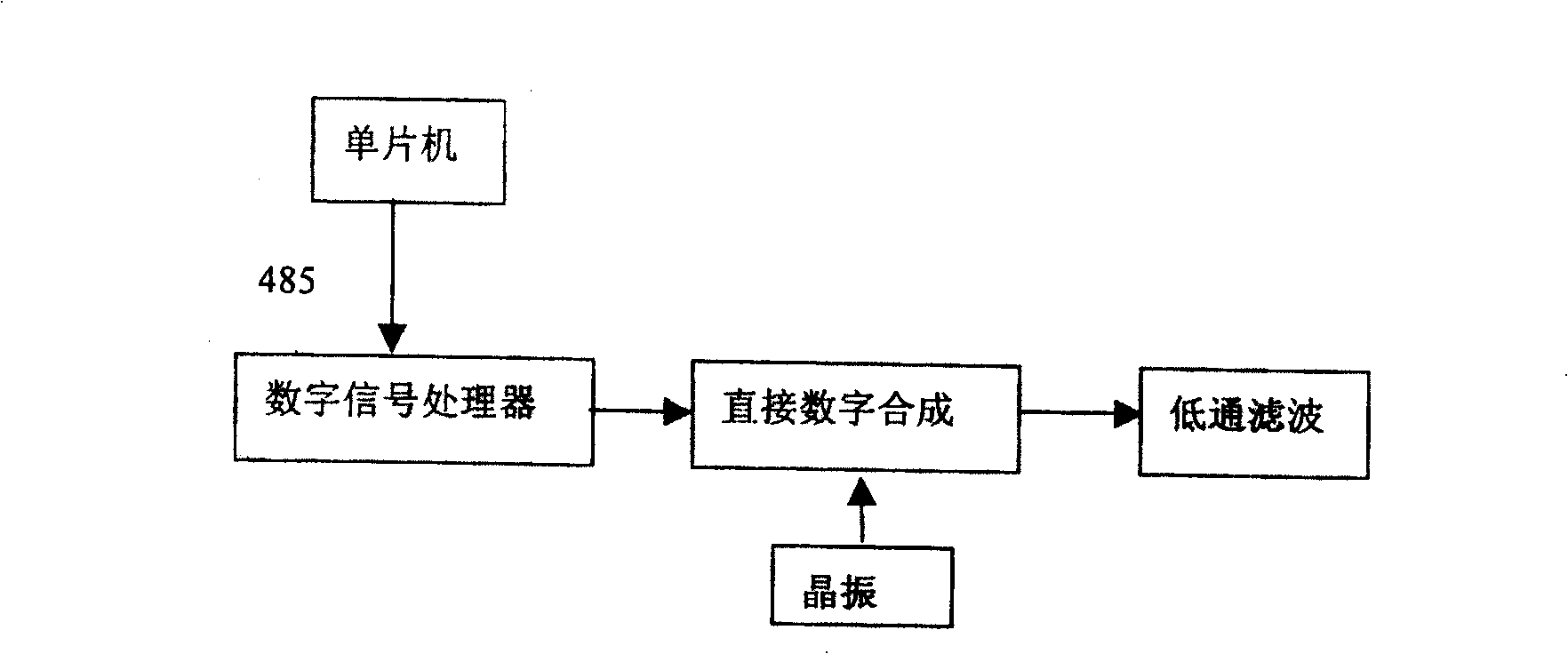

Intelligent metal detector

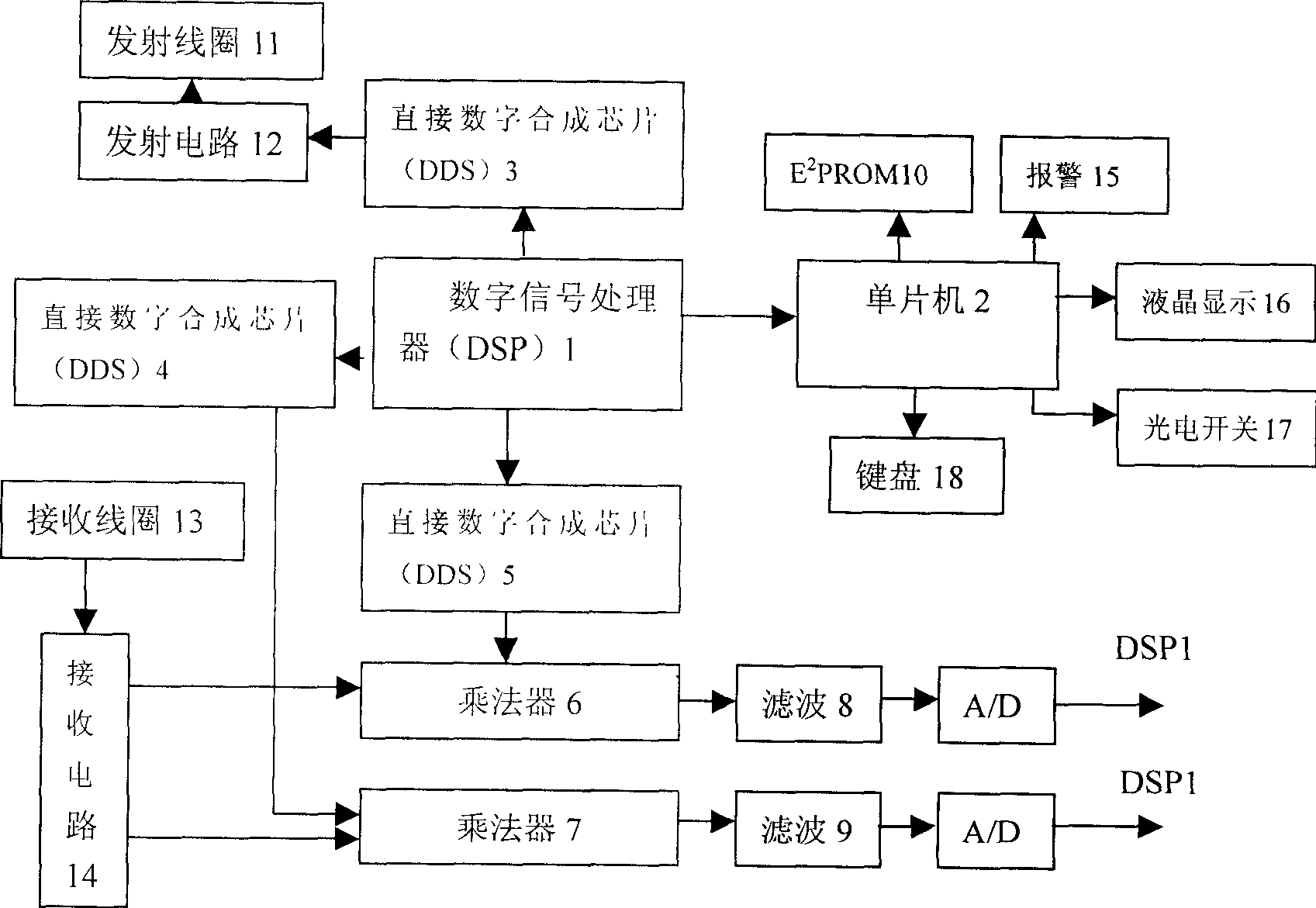

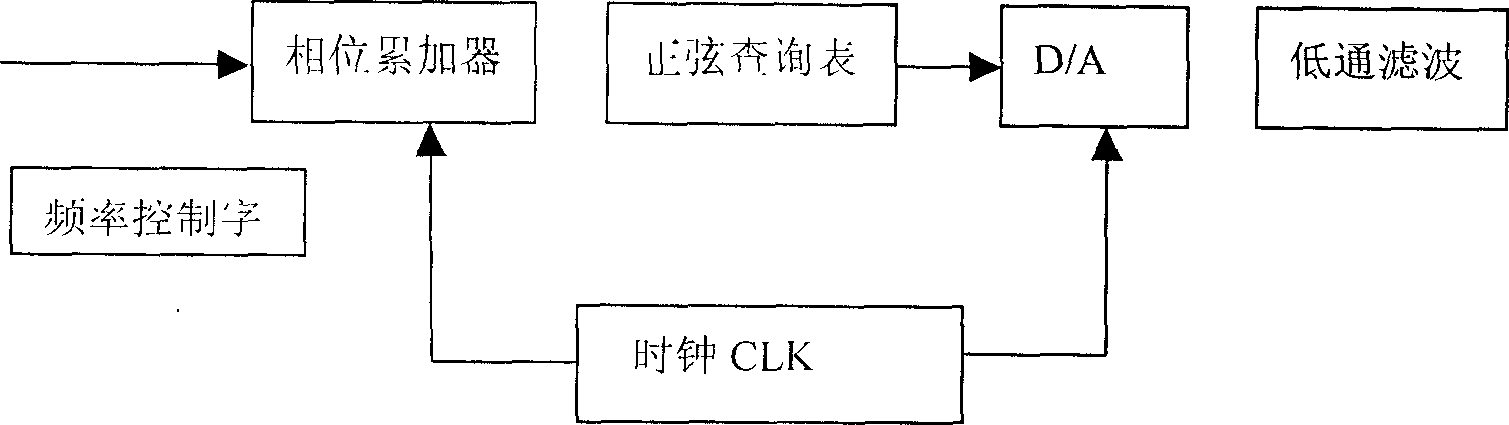

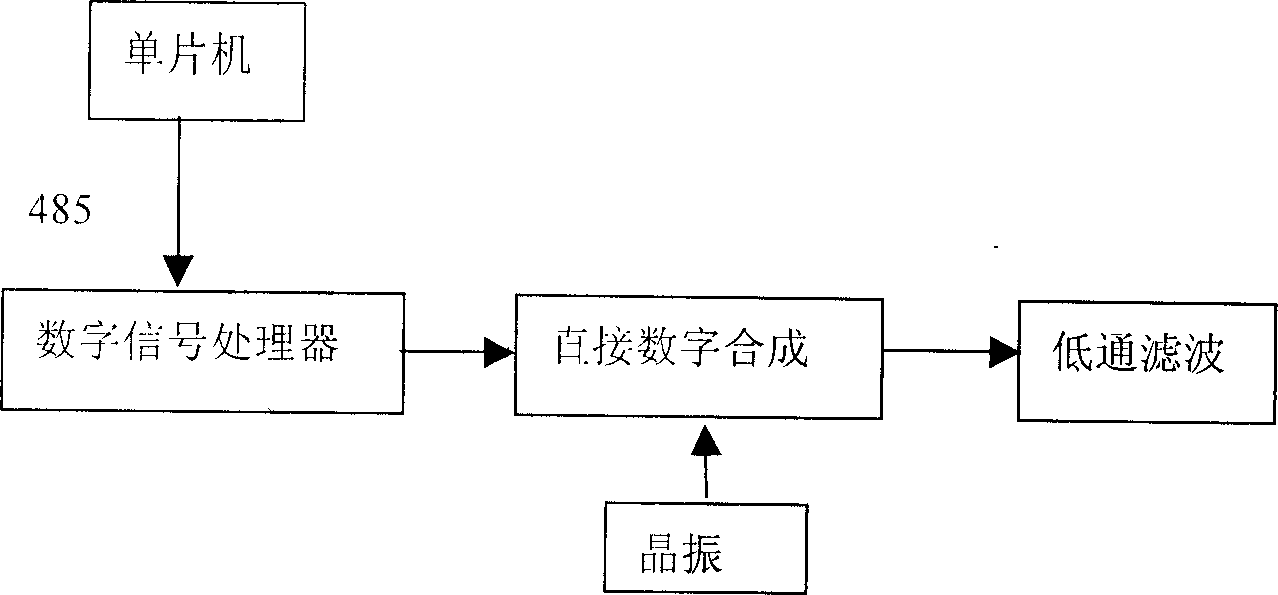

InactiveCN1603802AEasy to set upIntelligentMaterial analysis using microwave meansDigital signal processingMicrocontroller

It is a metal probe in lossless electromagnetism measurement technique field. The digital signal processor generates two paths of signals through two direct digital systemization chips into two multipliers that get two paths of separation signals through two low-pass filters. The data through the A / D conversion is sent to the digital signal processor for analysis and judgments. The human and machine dialogue system comprises single machines communicated with digital signal serial processors.

Owner:SHANGHAI JIAO TONG UNIV +1

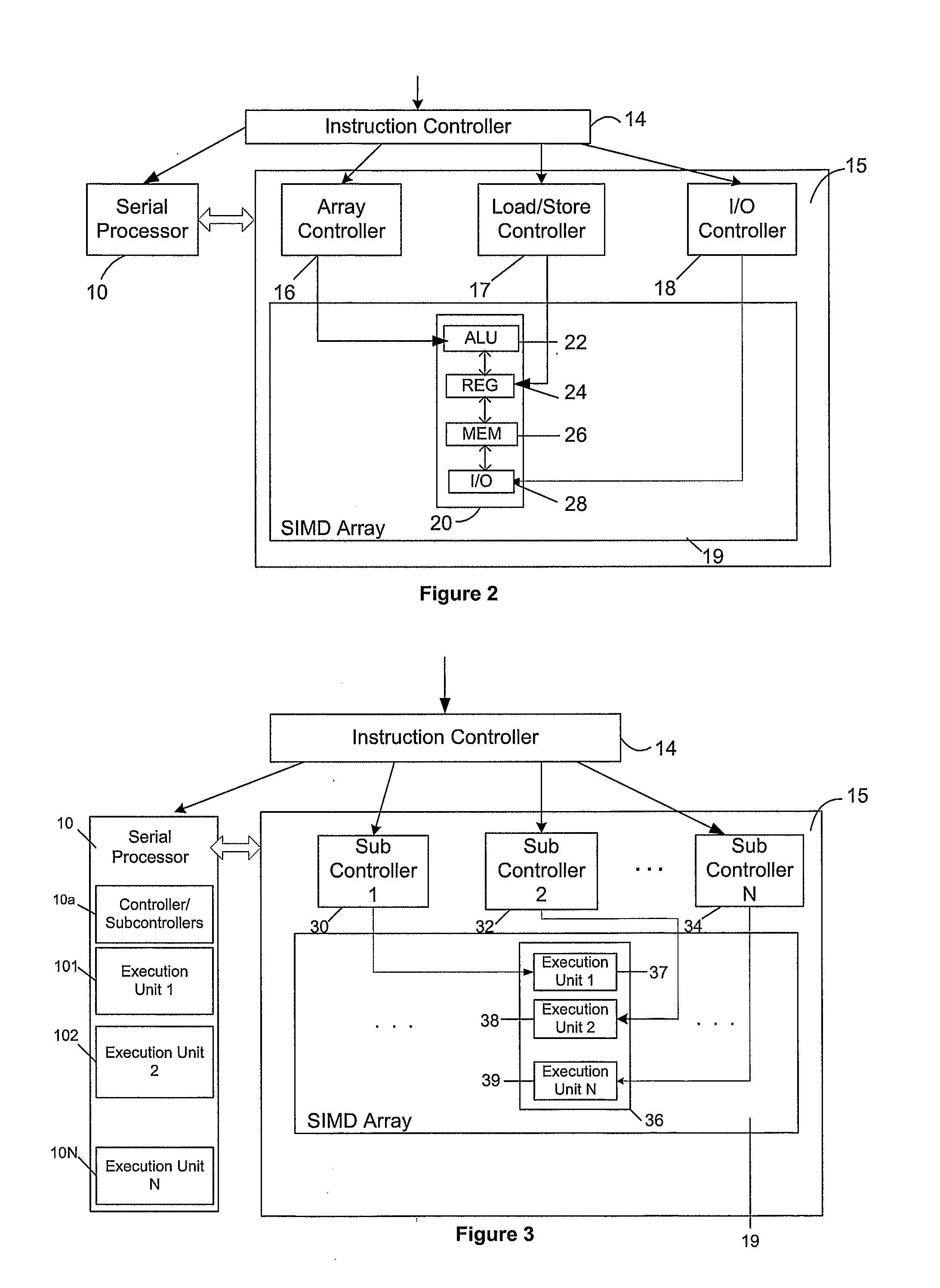

Microprocessor Architectures

InactiveUS20080209164A1Single instruction multiple data multiprocessorsProgram control using wired connectionsExecution unitProcessing element

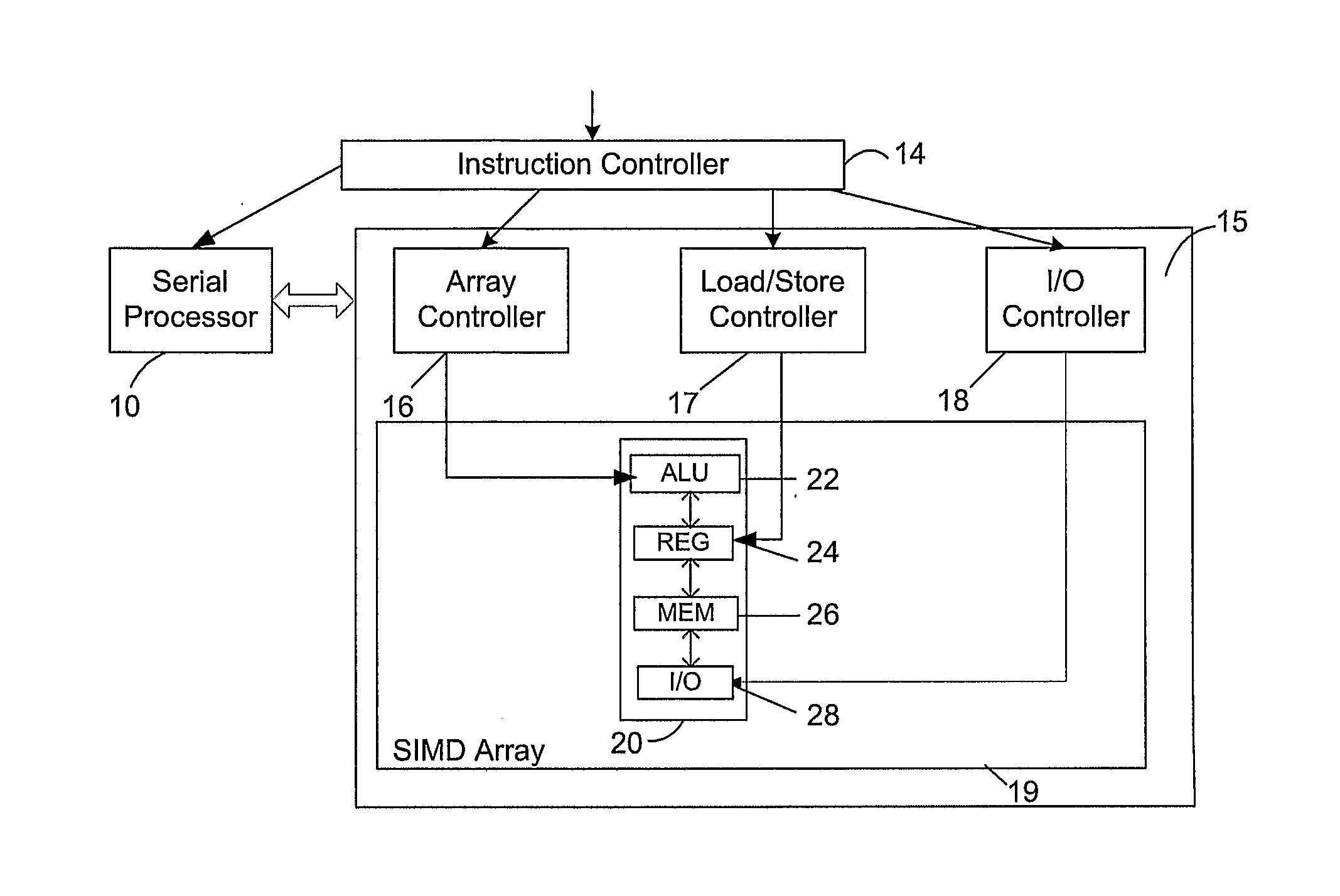

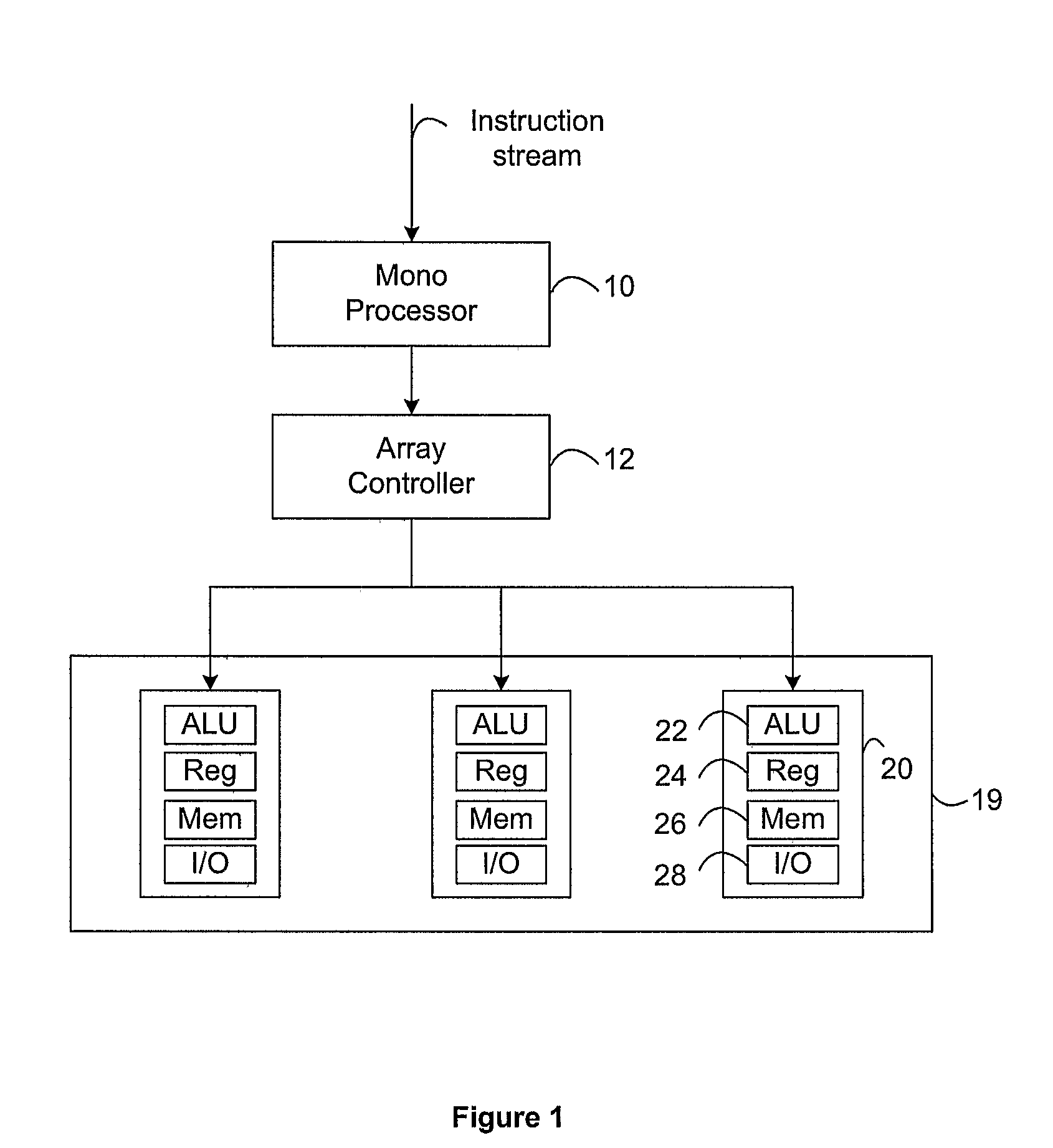

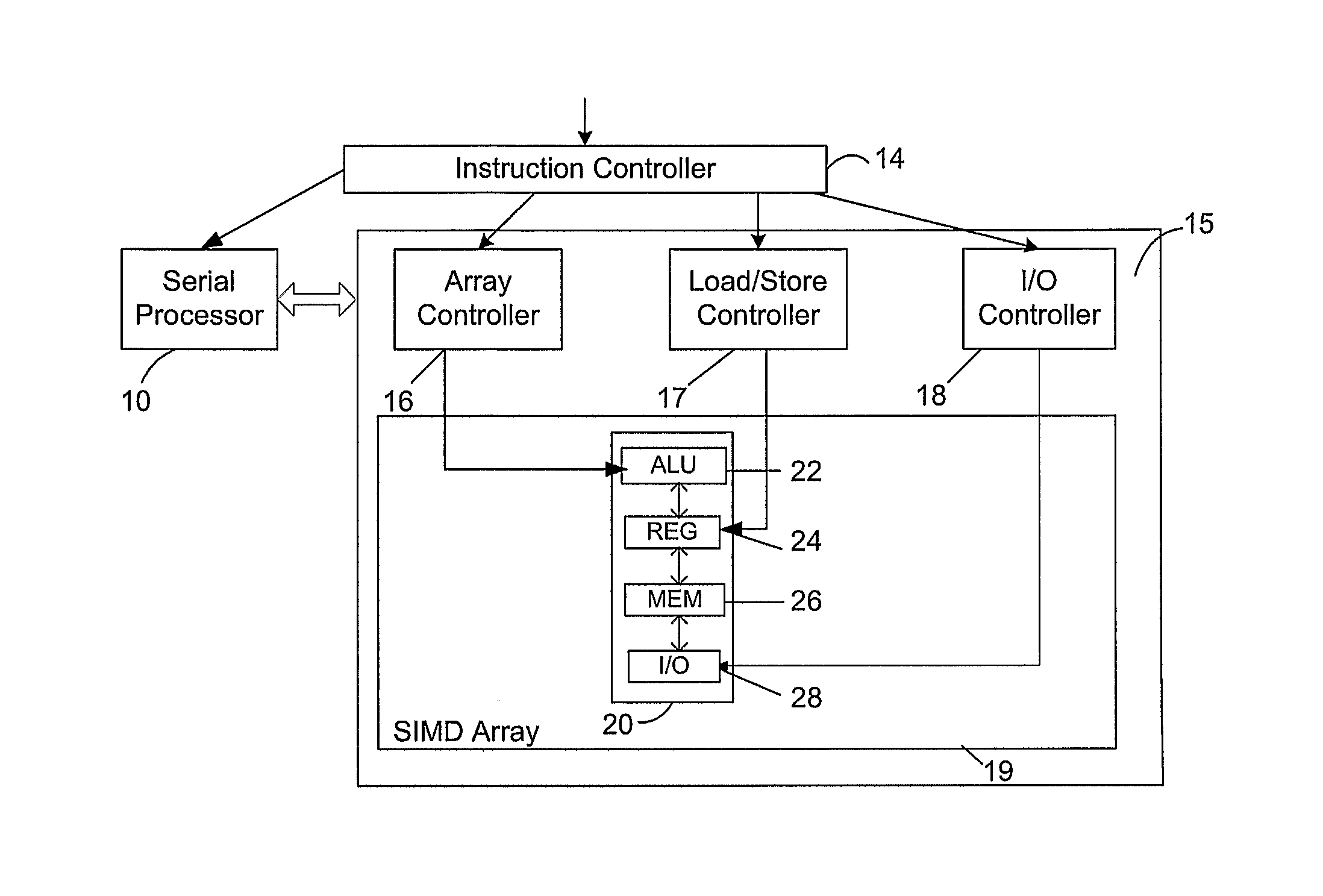

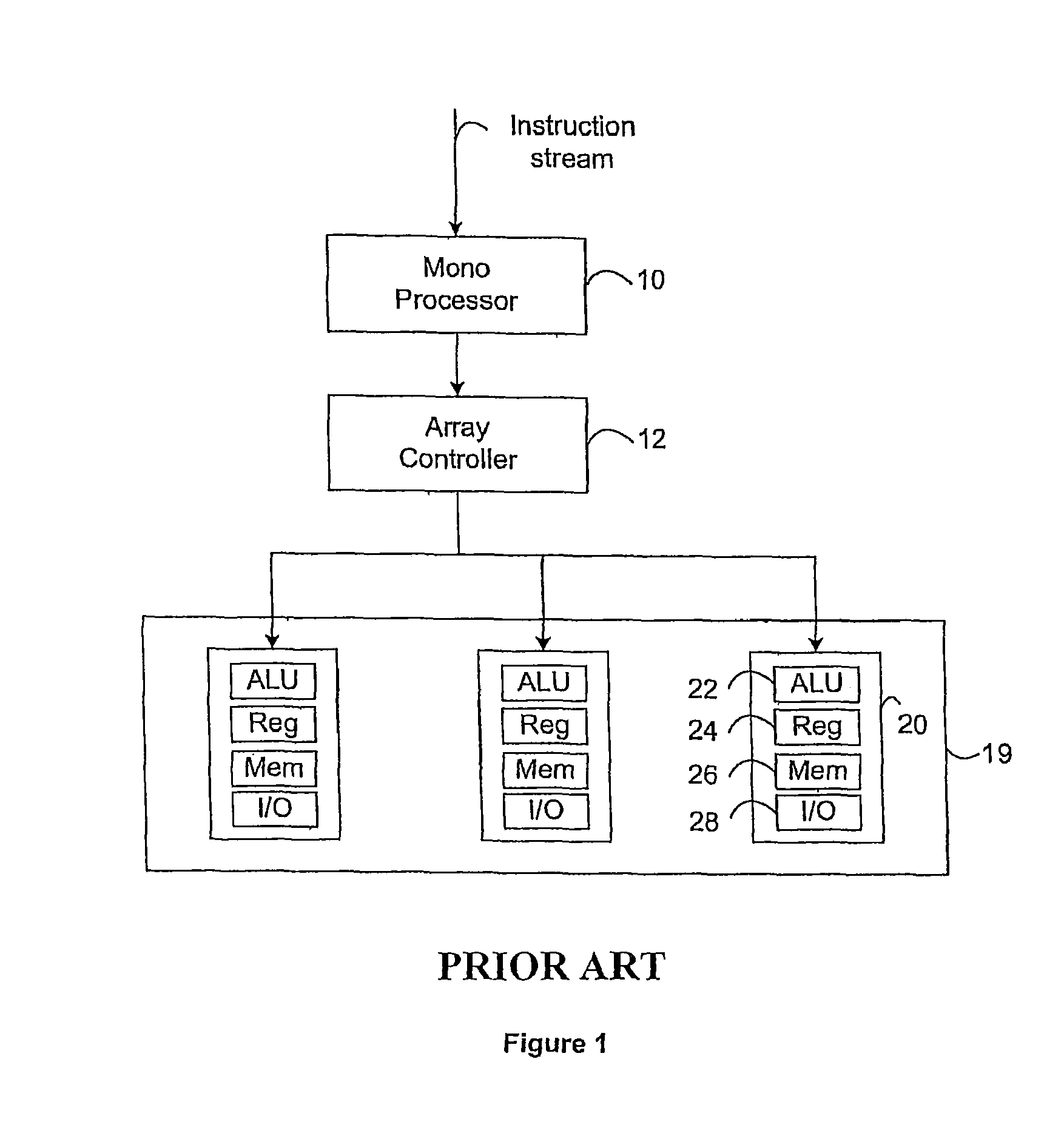

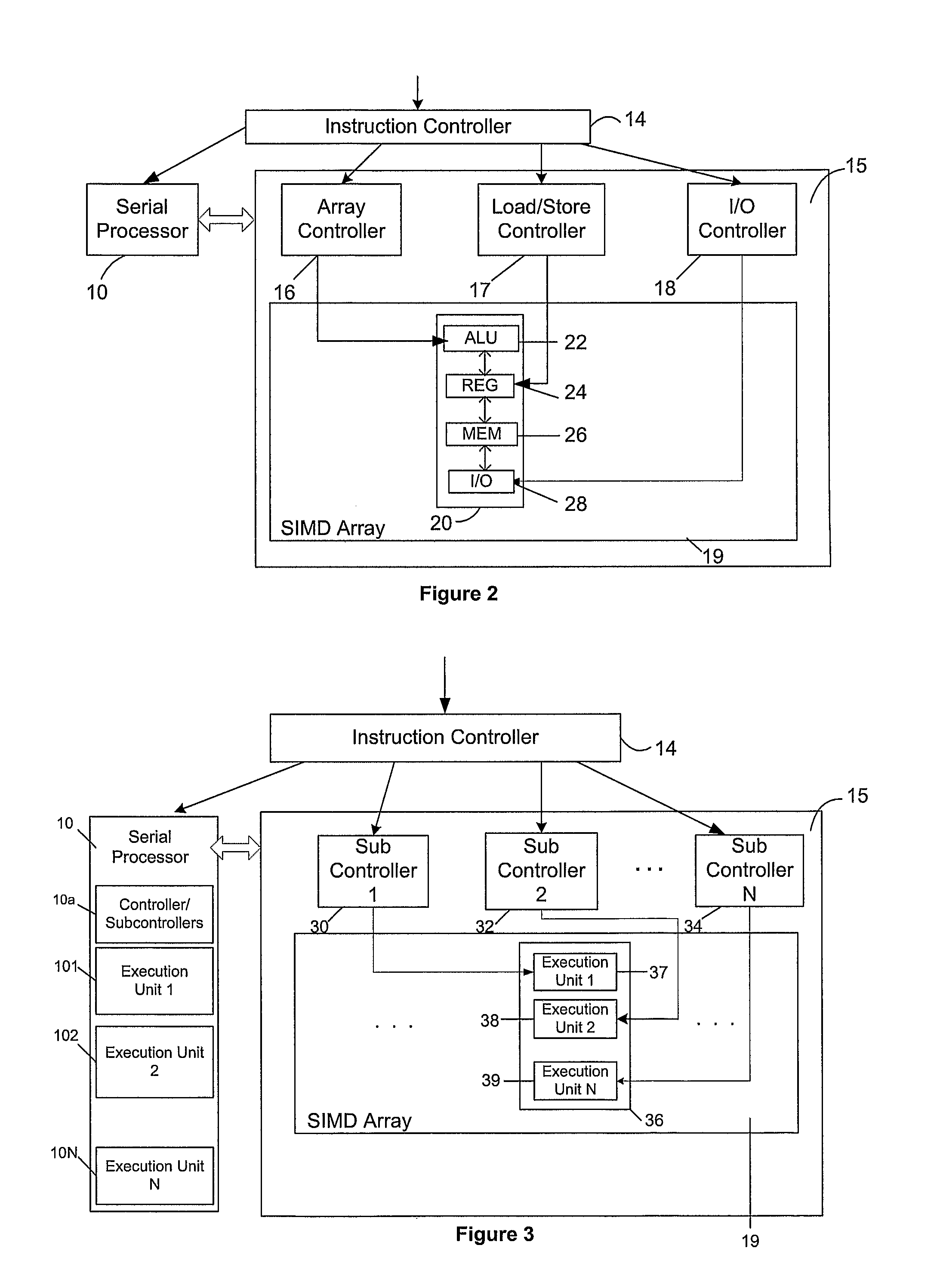

A microprocessor architecture comprises a plurality of processing elements arranged in a single instruction multiple data SIMD array, wherein each processing element includes a plurality of execution units, each of which is operable to process an instruction of a particular instruction type, a serial processor which includes a plurality of execution units, each of which is operable to process an instruction of a particular instruction type, and an instruction controller operable to receive a plurality of instructions, and to distribute received instructions to the execution units in dependence upon the instruction types of the received instruction. The execution units of the serial processor are operable to process respective instructions in parallel.

Owner:RAMBUS INC

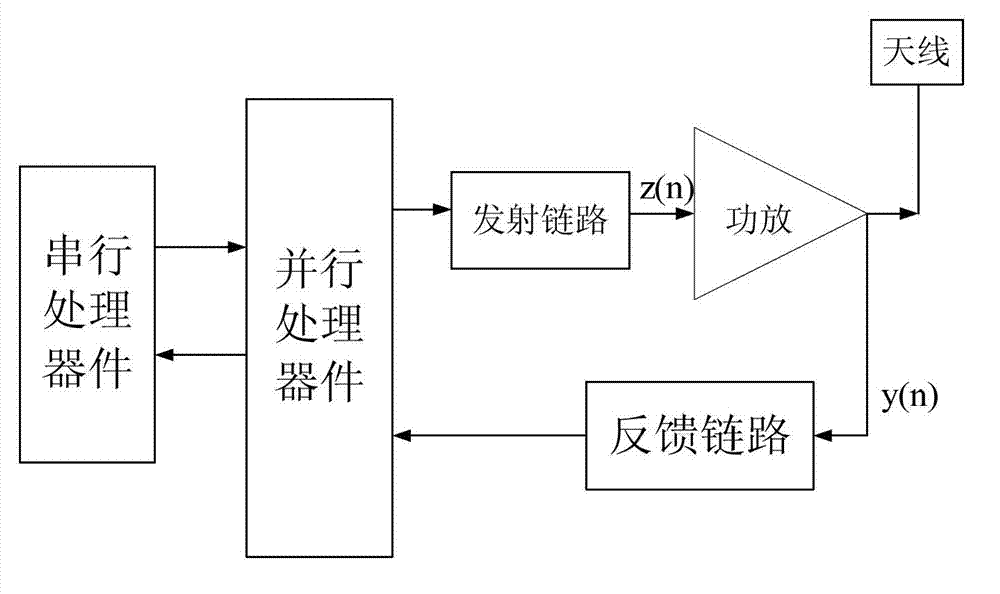

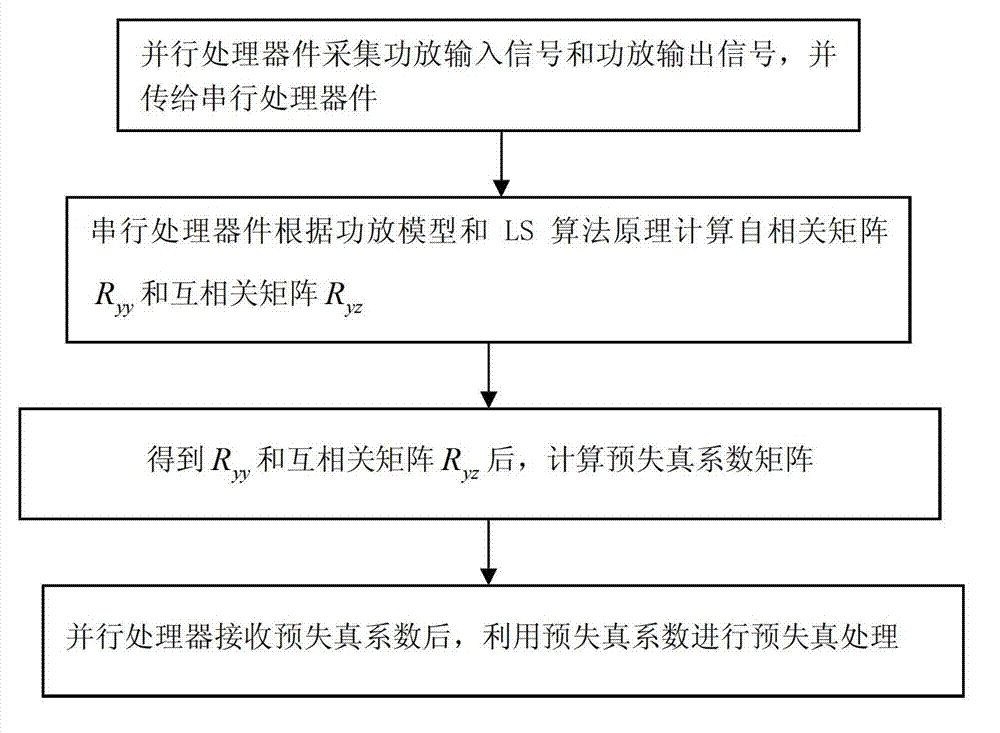

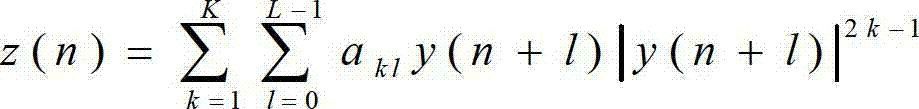

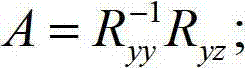

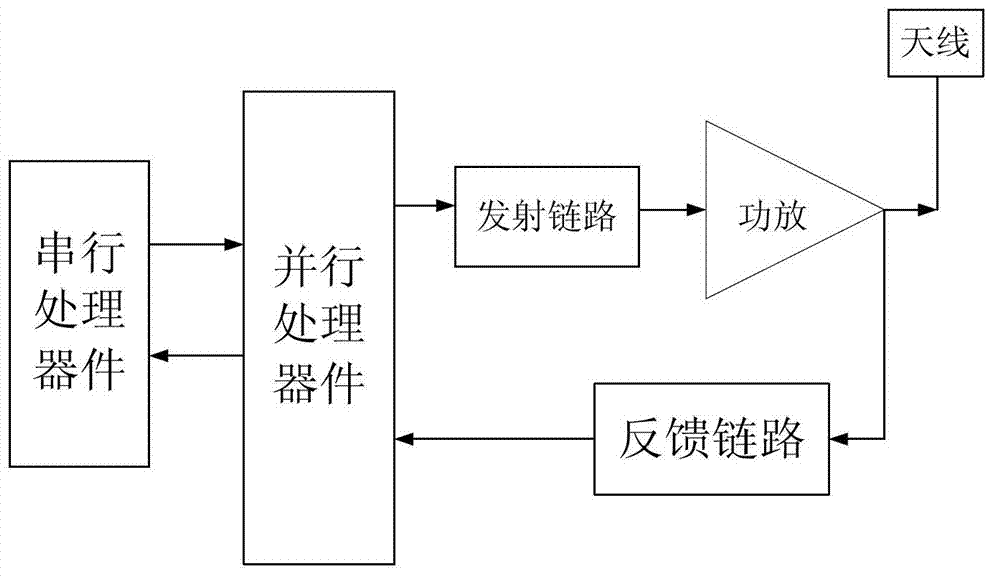

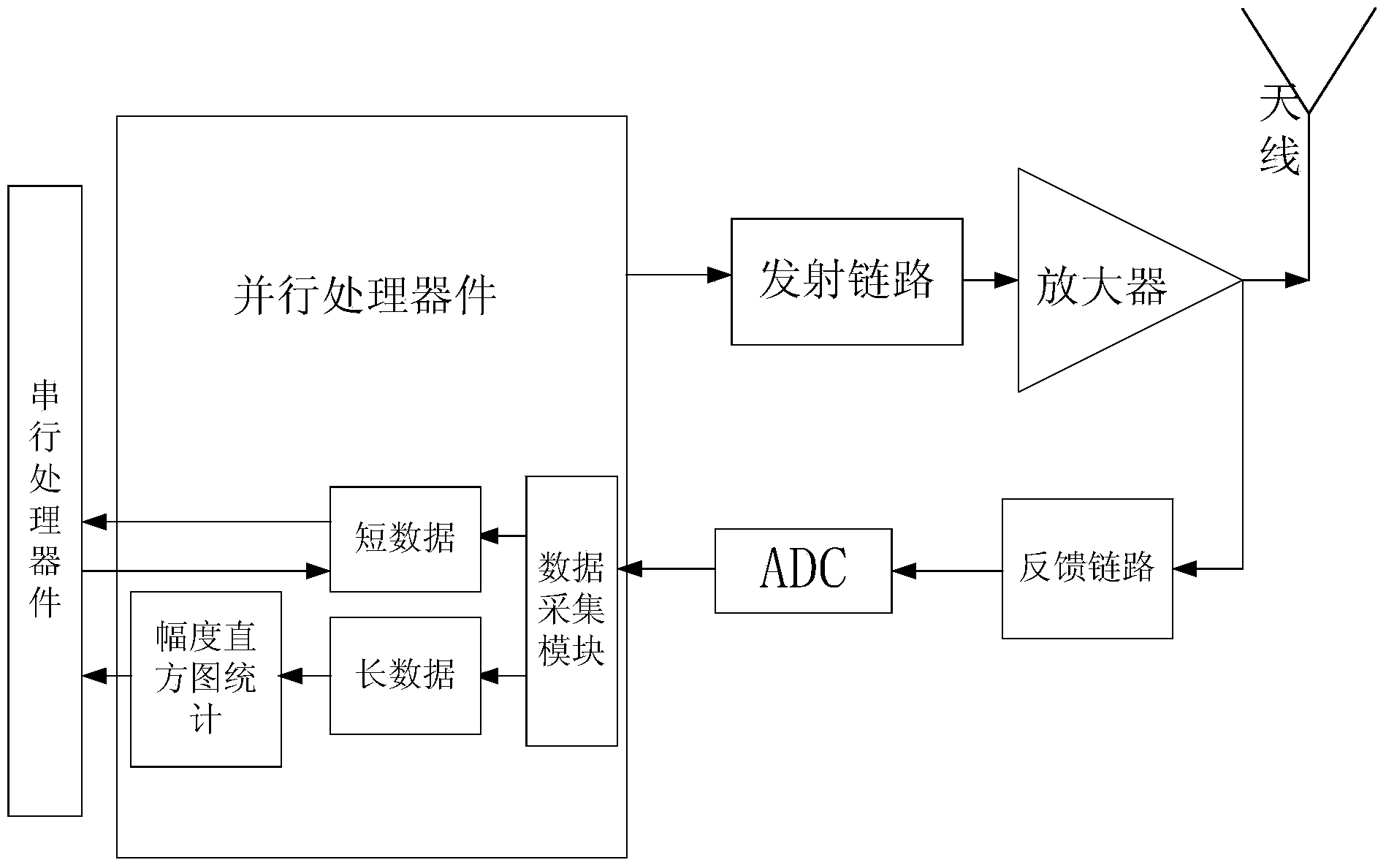

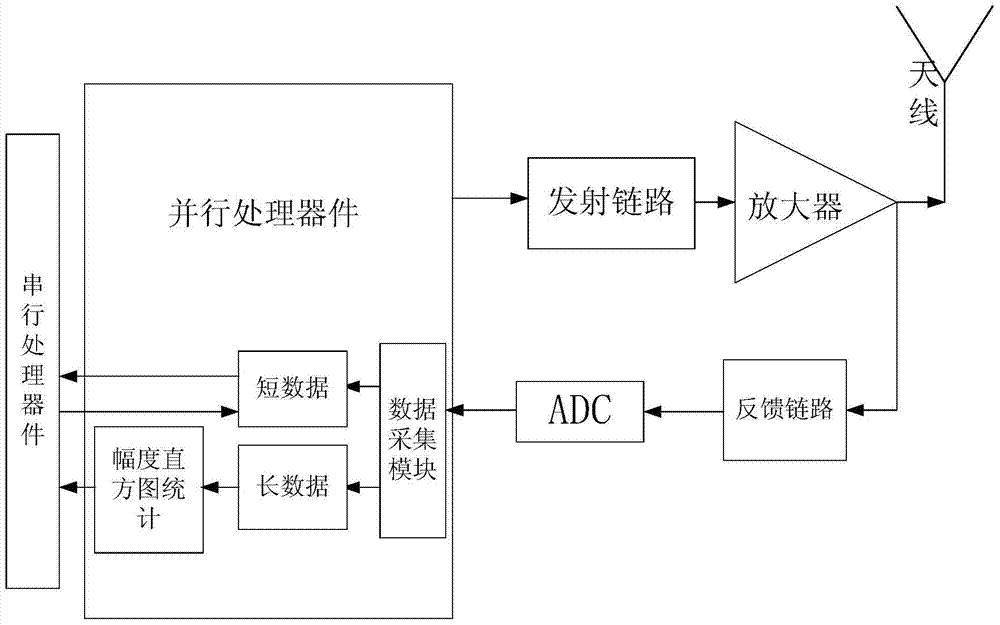

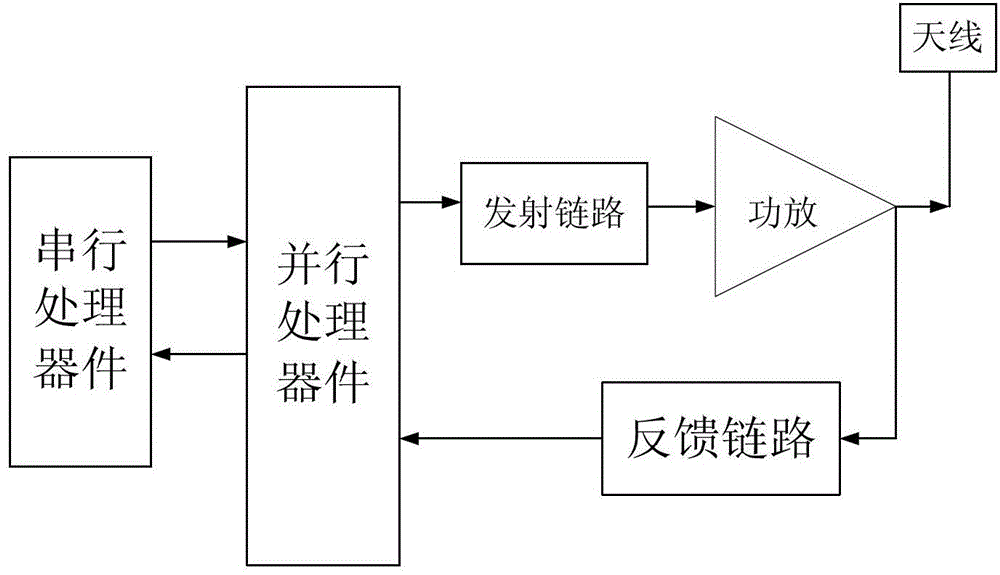

Method for improving digital pre-distortion processing speed

InactiveCN102970261AReduce power consumptionFast updateSynchronous/start-stop systemsCross correlation matrixOut of band interference

The invention discloses a method for improving the digital pre-distortion processing speed. The method comprises steps of continuously capturing amplifier input signals and amplifier output signals by using a parallel processing device and transmitting amplifier input signals and amplifier output signals to a series processing device; calculating an autocorrelation matrix Ryy and a cross-correlation matrix Ryz in accordance with an amplifier model and a Least Square (LS) algorithm principle by using the series processing device; calculating a pre-distortion coefficient matrix after obtaining the Ryy and the cross-correlation matrix Ryz; and receiving the pre-distortion coefficient matrix by using the parallel processing device, conducting the pre-distortion treatment for input signals, and transmitting the input signals to a transmitting chain. By the aid of the method, the change of signals can be tracked quickly during the actual application, and the out-of-band interference can be reduced.

Owner:SOUTH CHINA UNIV OF TECH

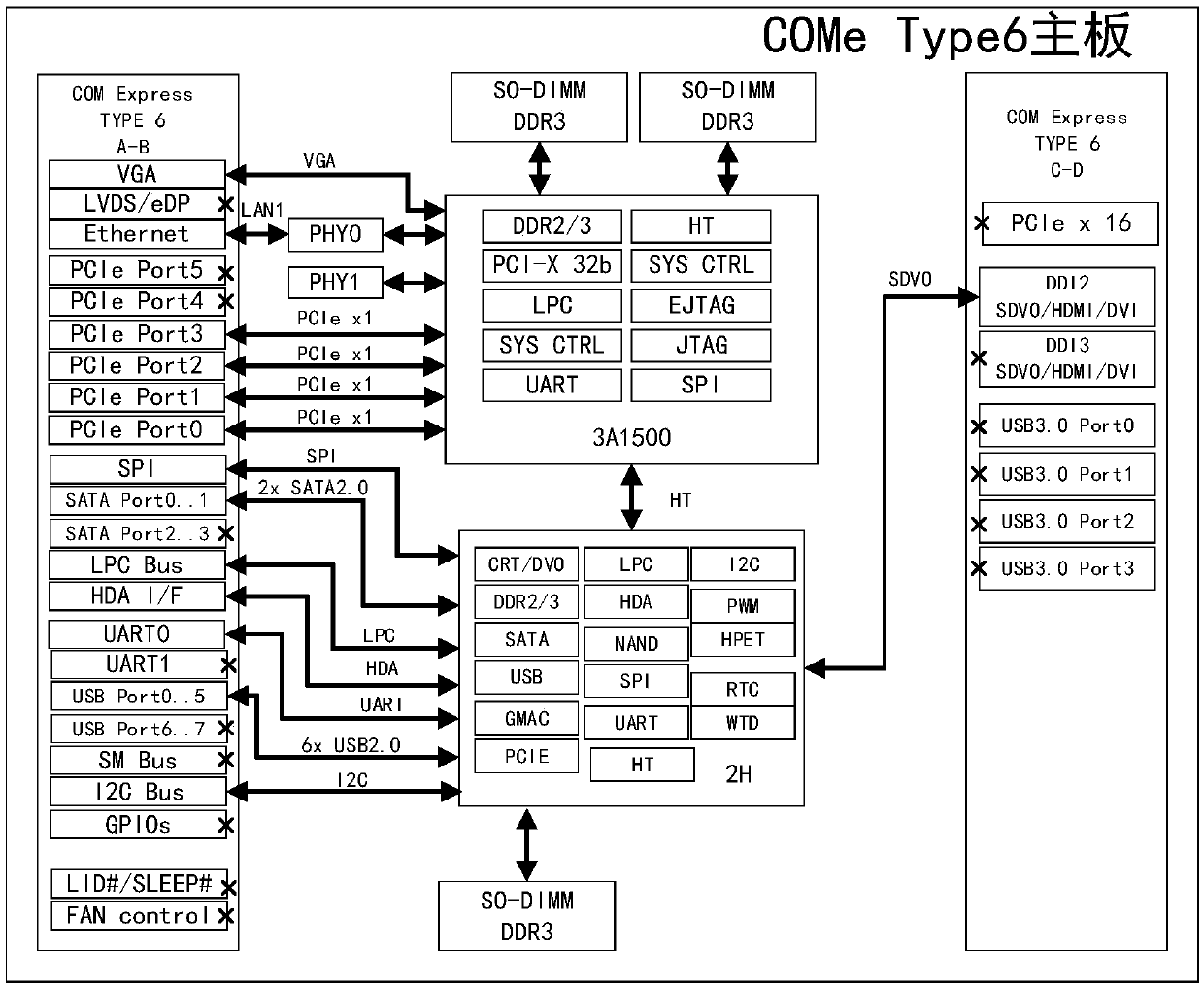

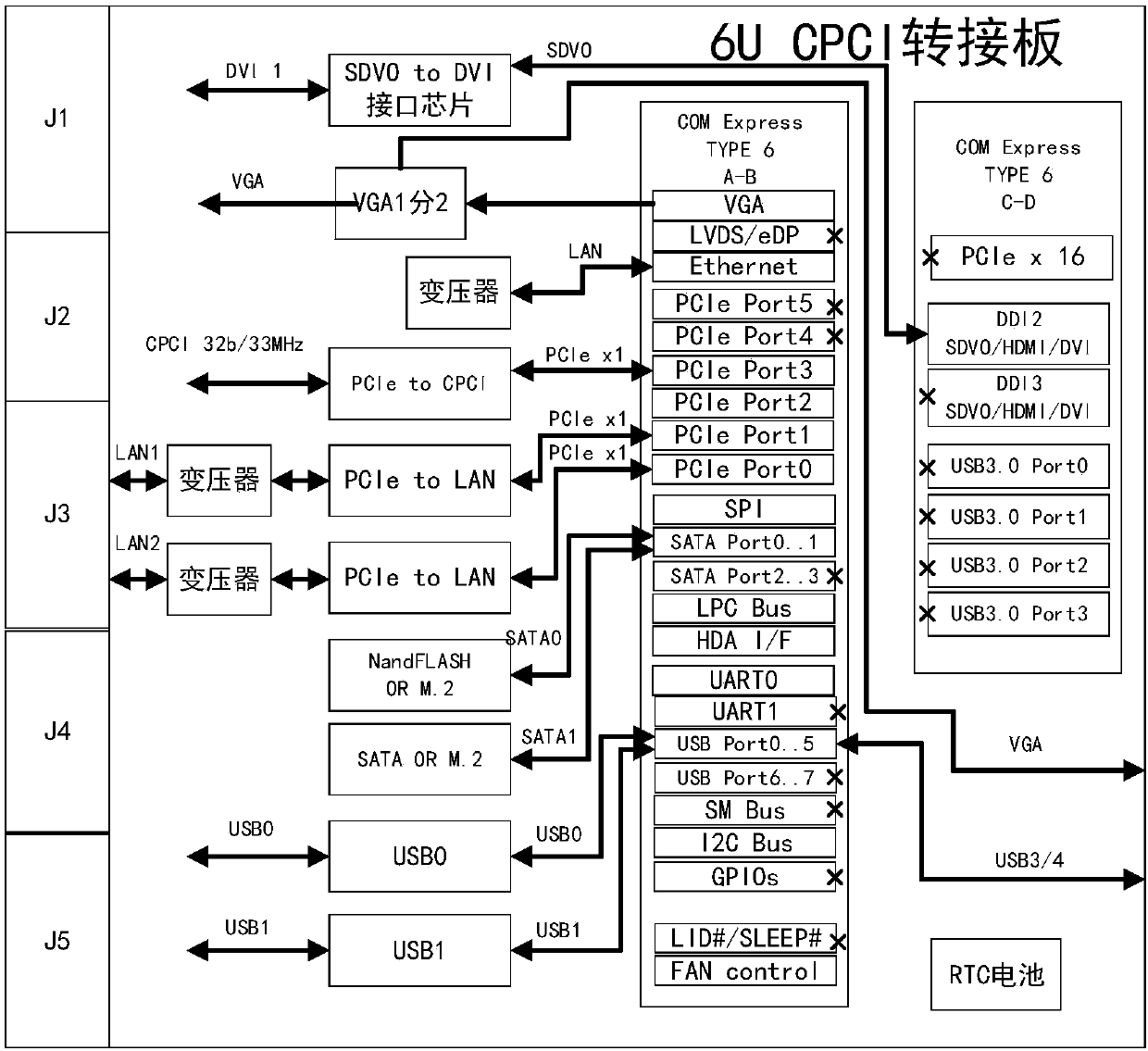

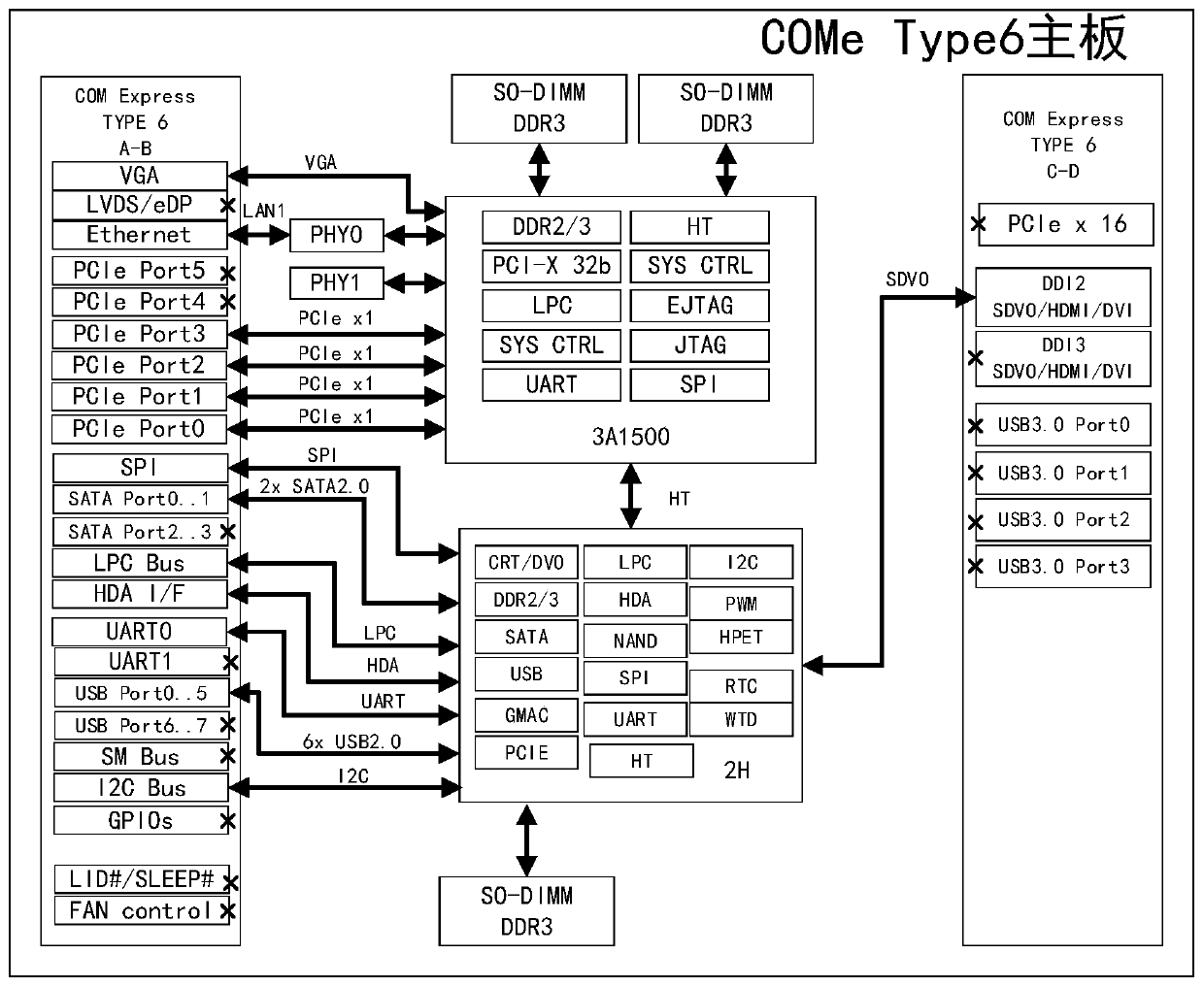

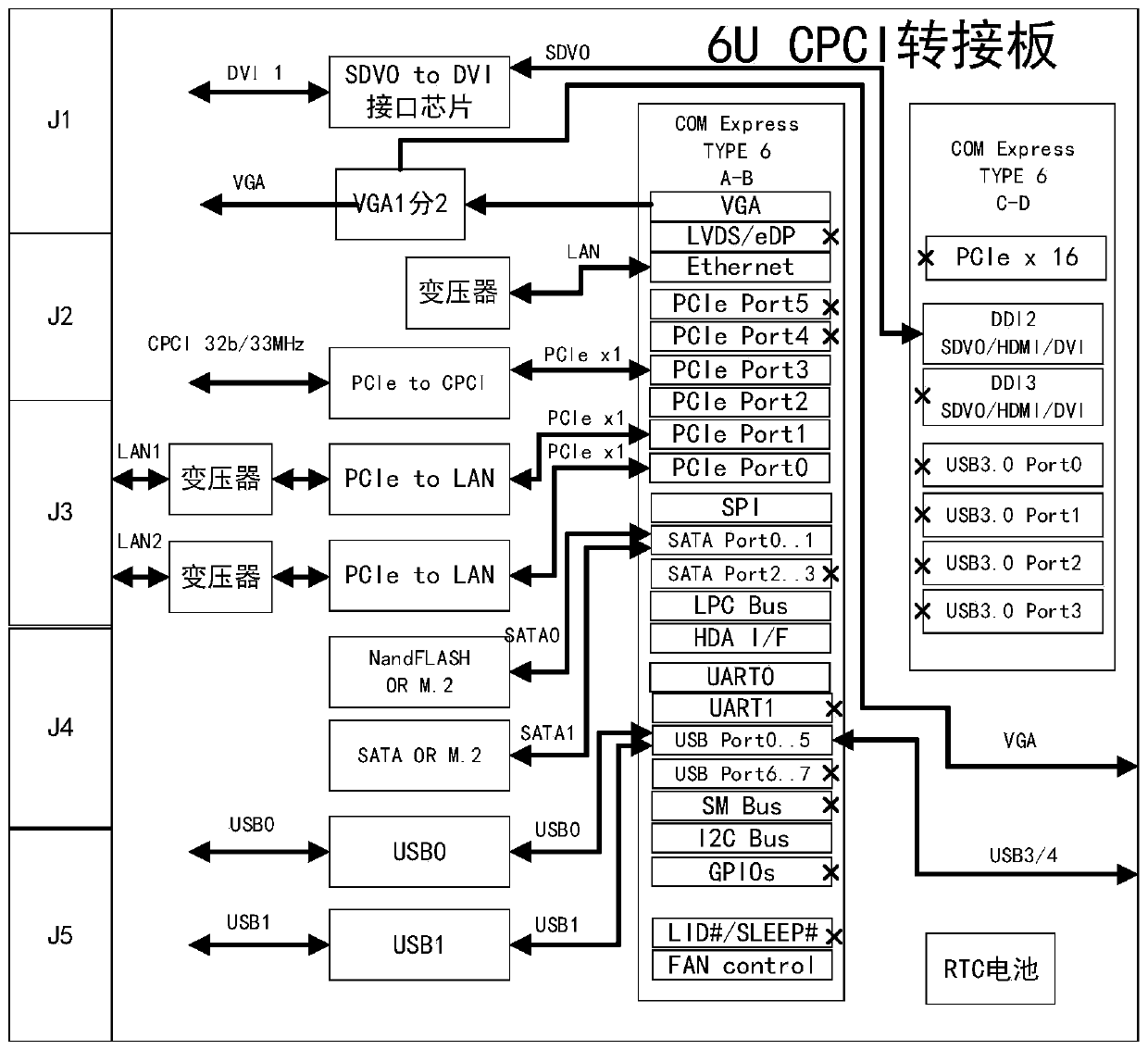

Self-controlled computer mainboard

ActiveCN107728712ASatisfy securityMeet needsDigital data processing detailsIntellectual propertyControllability

The invention discloses a self-controlled computer mainboard, which comprises a COMe mainboard, a CPCI pinboard, and a power module for supplying power for the COMe mainboard and the CPCI pinboard. The COMe mainboard comprises a processor, a bridge ribbon and a memory; the CPCI pinboard comprises a PCIe to PCI bridge chip; the processor adopts a Loongson 3A serial processor; the bridge ribbon adopts a Loongson 2H chip; the memory adopts a DDR3 memory grain chip; the Loongson 3A serial processor is connected with the Loongson 2H chip through an HT bus; the Loongson 3A serial processor and the Loongson 2H chip are connected with the DDR3 memory grain chip through memory channels; an EJTAG debugging interface used for carrying out reliability testing on the Loongson 3A serial processor and the Loongson 2H chip is also arranged on the COMe mainboard. According to the self-controlled computer mainboard provided by the invention, the Loongson 3A serial processor and the Loongson 2H matched bridge chip with full autonomy proprietary intellectual property rights are adopted, and the hardware interface of a mainboard platform is arranged, so that higher product domestication rate can be realized, the demands on information safety and self-controllability are met, and the technical risks and the uncontrollable hidden dangers in product use and maintenance are eliminated.

Owner:HUBEI SANJIANG AEROSPACE WANFENG TECH DEV

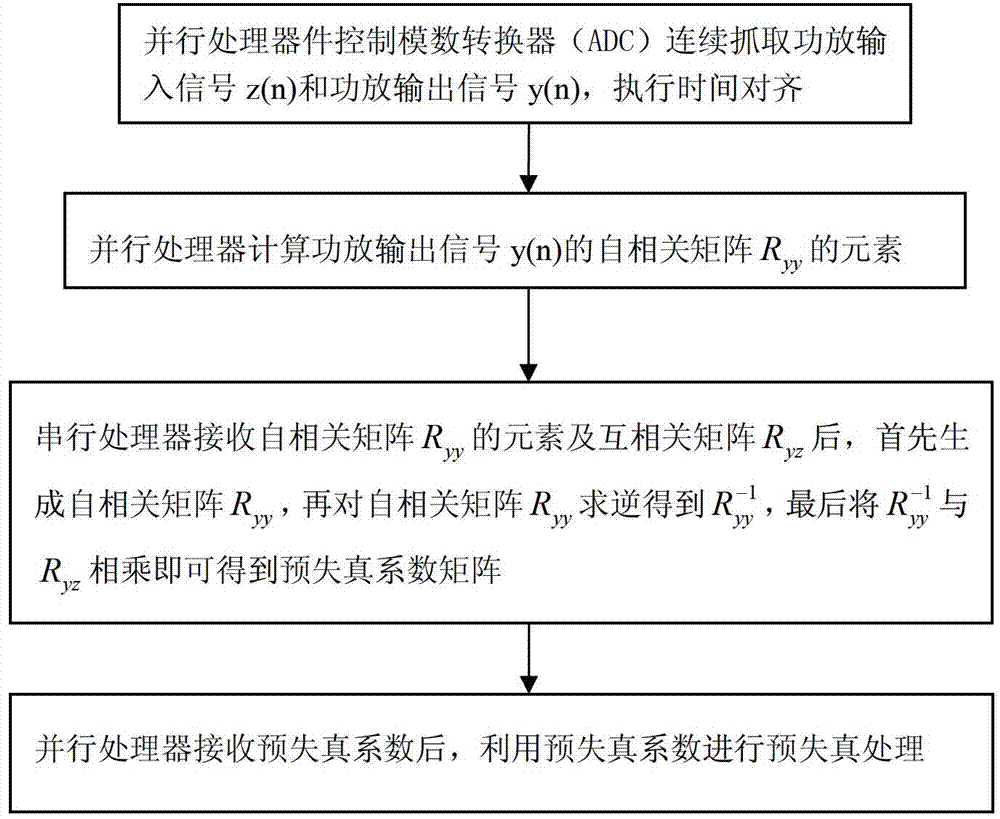

Digital predistortion processing method

InactiveCN102780665ARealize continuous computingThe coefficient calculation is accurateSynchronous/start-stop systemsCross correlation matrixEngineering

The invention discloses a digital predistortion processing method which comprises the following steps: (1) a parallel processor controls an analog-to-digital converter (ADC) to grab power amplifier input signals z(n) and amplifier output signals y(n) continuously, and time alignment is executed; (2) the parallel processor calculates elements of an autocorrelation matrix Ryy of the amplifier output signals y(n), calculates elements of a cross-correlation matrix Ryz of the amplifier input signals z(n) and the amplifier output signals y(n), and transmits the elements Ryz of the Ryy to a serial processor; (3) the serial processor receives the elements Ryz of the Ryy, generates the Ryy first and obtains inversion of the autocorrelation matrix Ryy, and finally times the Ryz to calculate predistortion coefficient; and (4) the parallel processor receives the predistortion coefficient and conducts predistortion processing. By means of the digital predistortion processing method, a simplifying method of the parallel processor for calculating the elements of the autocorrelation matrix is provided, data length of predistortion coefficient calculation is increased, and a predistortion processing effect is improved.

Owner:SOUTH CHINA UNIV OF TECH

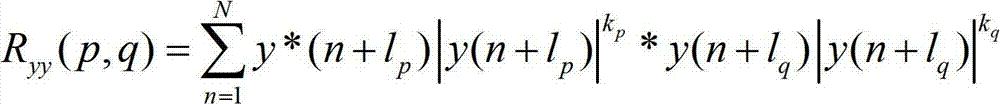

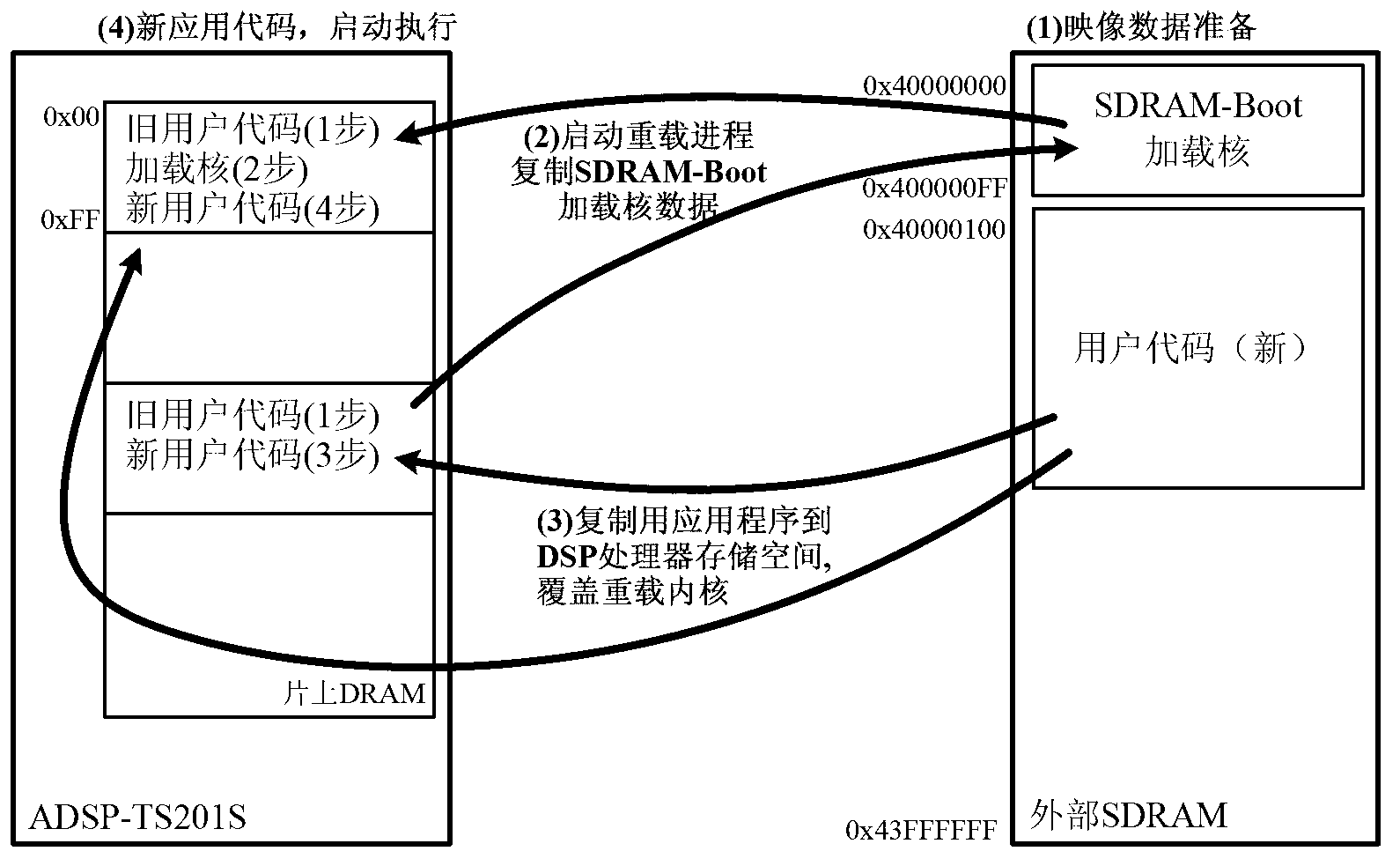

Dynamic overloading method for DSP (Digital Signal Processor)

InactiveCN103019774AEasy to debugEasy to upgradeProgram loading/initiatingInternal memoryExternal storage

The invention relates to a dynamic overloading method for a DSP (Digital Signal Processor). The method comprises the following steps: 1, generating mapping files; 2, initializing the DSP; 3, guiding and copying overloading kernels in the mapping files into an internal storage of the DSP so as to cover primary application programs through overloading interface functions; 4, guiding and copying application programs in the mapping files which are stored in an external storage space into the internal storage of the DSP so as to cover the overloading kernels through the overloading kernels in the internal storage, and generating application programs to be operated; and 5, executing the application programs to be operated so as to finish dynamic overloading. As the traditional boot loading mode of an embedded type signal processing ADSP-TS20xS serial processor hardware platform cannot satisfy requirements of system functional reconstruction, the dynamic overloading method is additionally provided with the overloading kernels, and can use the overloading kernels to realize the real-time dynamic overloading operation for program mapping, so that the reconstruction ability of an embedded system is improved.

Owner:AVIC NO 631 RES INST

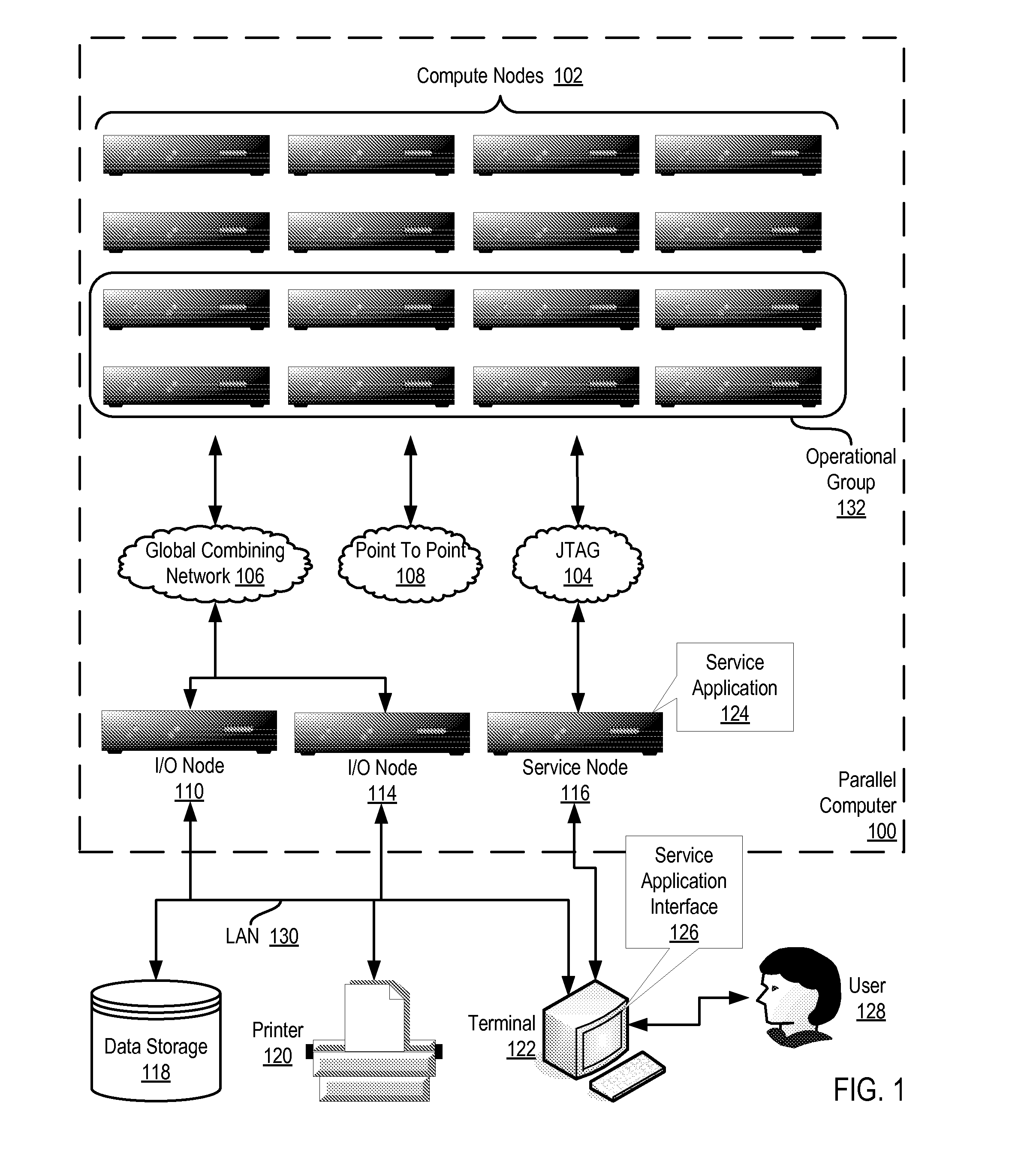

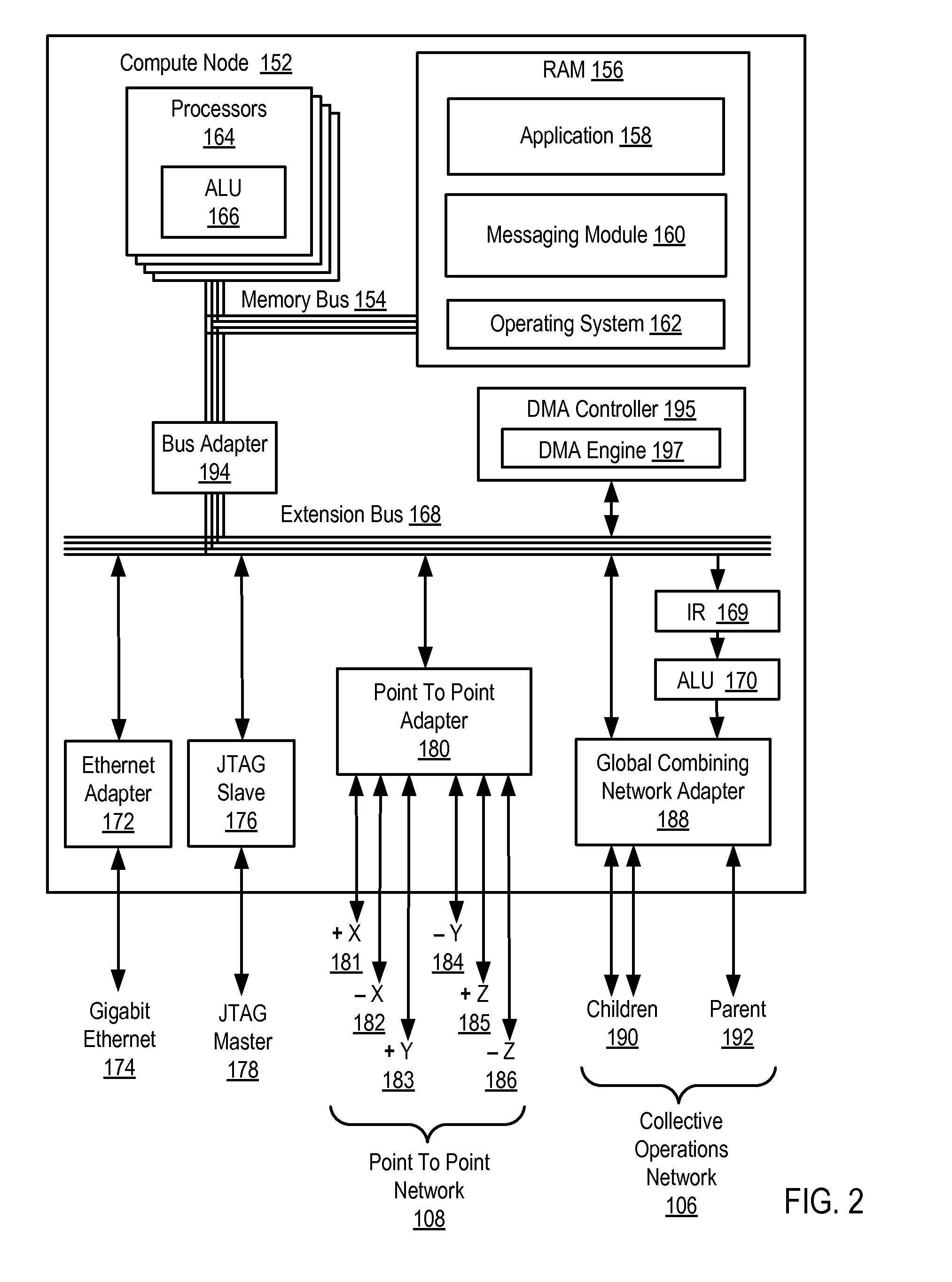

Broadcasting collective operation contributions throughout a parallel computer

InactiveUS8122228B2General purpose stored program computerProgram controlNetwork linkComputer methods

Methods, systems, and products are disclosed for broadcasting collective operation contributions throughout a parallel computer. The parallel computer includes a plurality of compute nodes connected together through a data communications network. Each compute node has a plurality of processors for use in collective parallel operations on the parallel computer. Broadcasting collective operation contributions throughout a parallel computer according to embodiments of the present invention includes: transmitting, by each processor on each compute node, that processor's collective operation contribution to the other processors on that compute node using intra-node communications; and transmitting on a designated network link, by each processor on each compute node according to a serial processor transmission sequence, that processor's collective operation contribution to the other processors on the other compute nodes using inter-node communications.

Owner:INT BUSINESS MASCH CORP

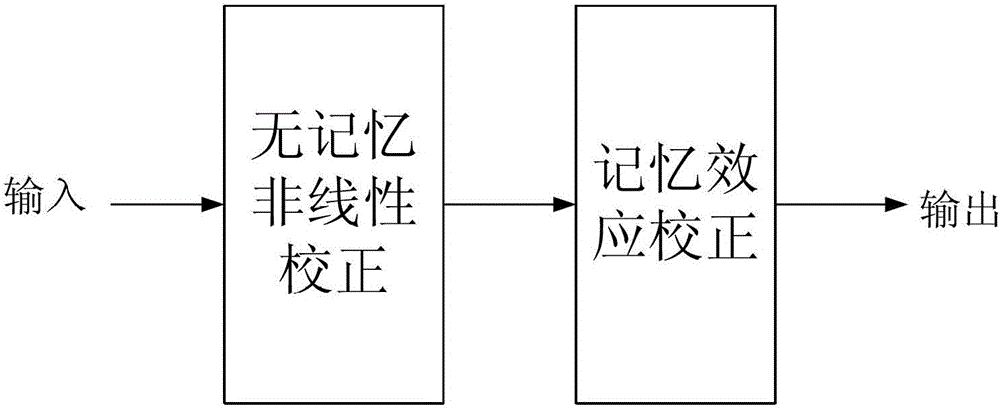

Digital pre-distortion processing method adaptive to quick-change signal

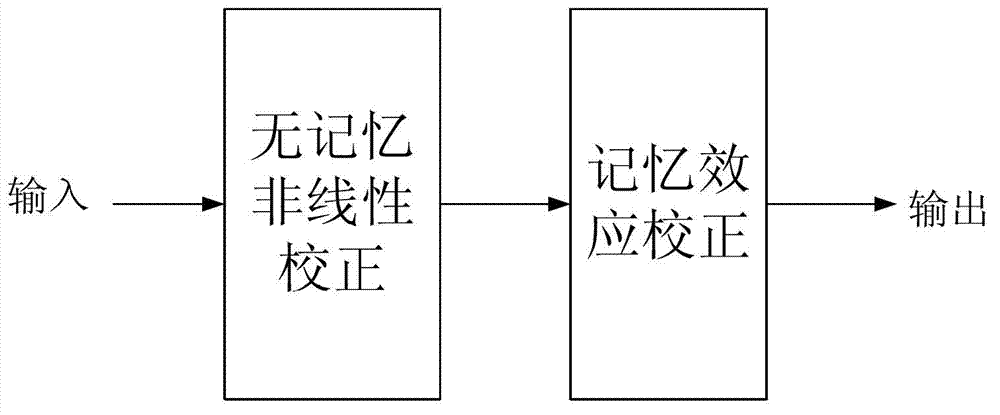

ActiveCN102904846AFast updateReduce memory effectAmplifier modifications to reduce non-linear distortionSynchronous/start-stop systemsSystem capacityFrequency spectrum

The invention discloses a digital pre-distortion processing method adaptive to a quick-change signal. The digital pre-distortion processing method comprises the following steps of: storing one group of training signals in a concurrent processor, when a system is started, sending the training signals to a power amplifier by the concurrent processor, acquiring an input signal and an output signal of the power amplifier to be provided to a serial processor, calculating a filter coefficient of eliminating a memory effect, after the serial processor eliminates time delay, calculating a passband ripple of the system, calculating a coefficient of reversely correcting the filter, providing the coefficient to the concurrent processor for correcting the memory effect; after the system is started, continuously acquiring the input signal and the output signal of the power amplifier by the concurrent processor, updating and correcting a memoryless and nonlinear search table in real time after eliminating time delay and gain difference; and when the system normally works, carrying out memoryless and nonlinear correction on the input signal by the concurrent processor, eliminating the memory effect, and outputting the memory effect to an emitting link. The invention is suitable for the quick-changing modern communication signal, and has the advantages of reducing out-of-band leakage and increasing frequency spectrum utilization rate and system capacity.

Owner:SOUTH CHINA UNIV OF TECH

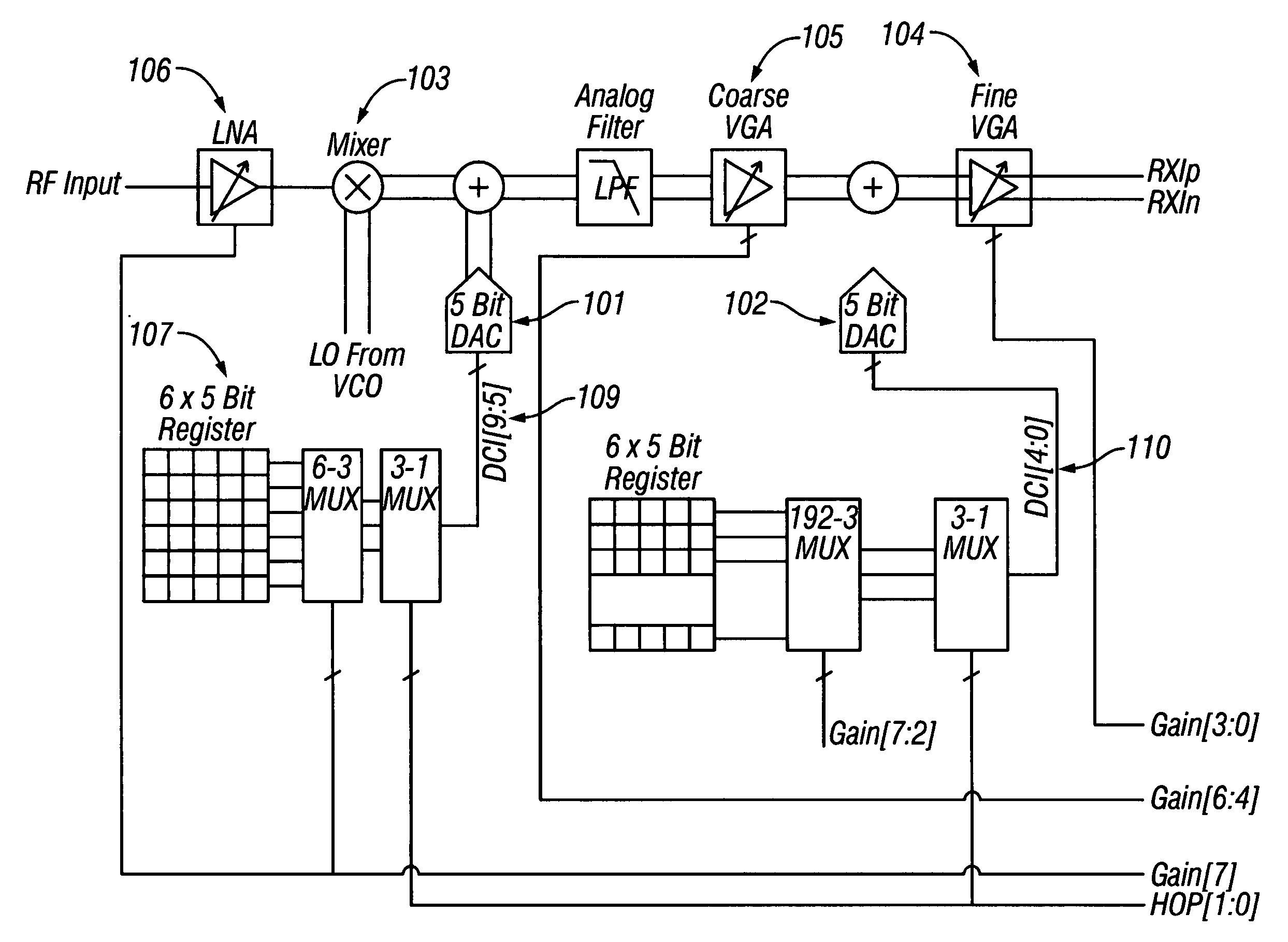

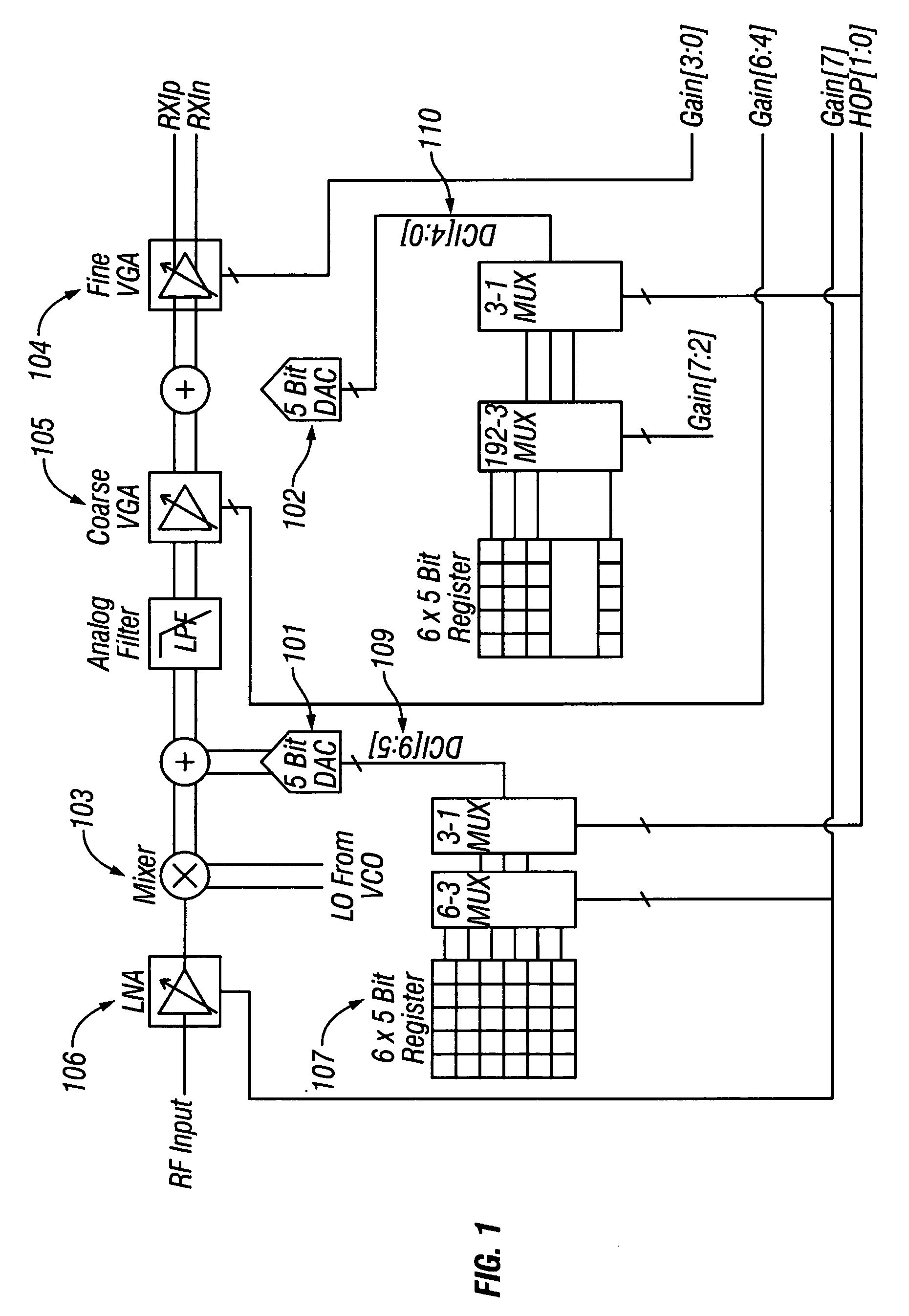

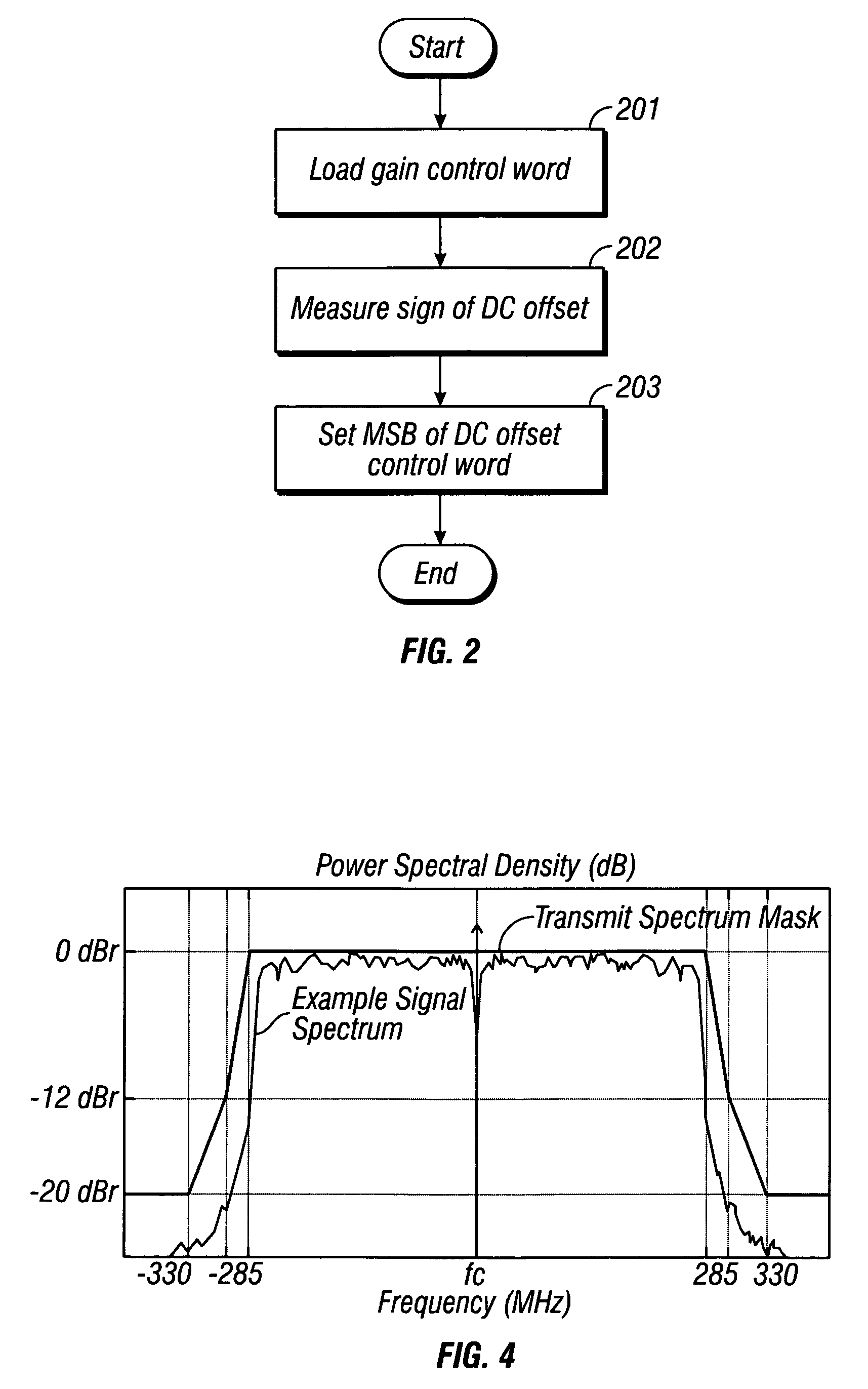

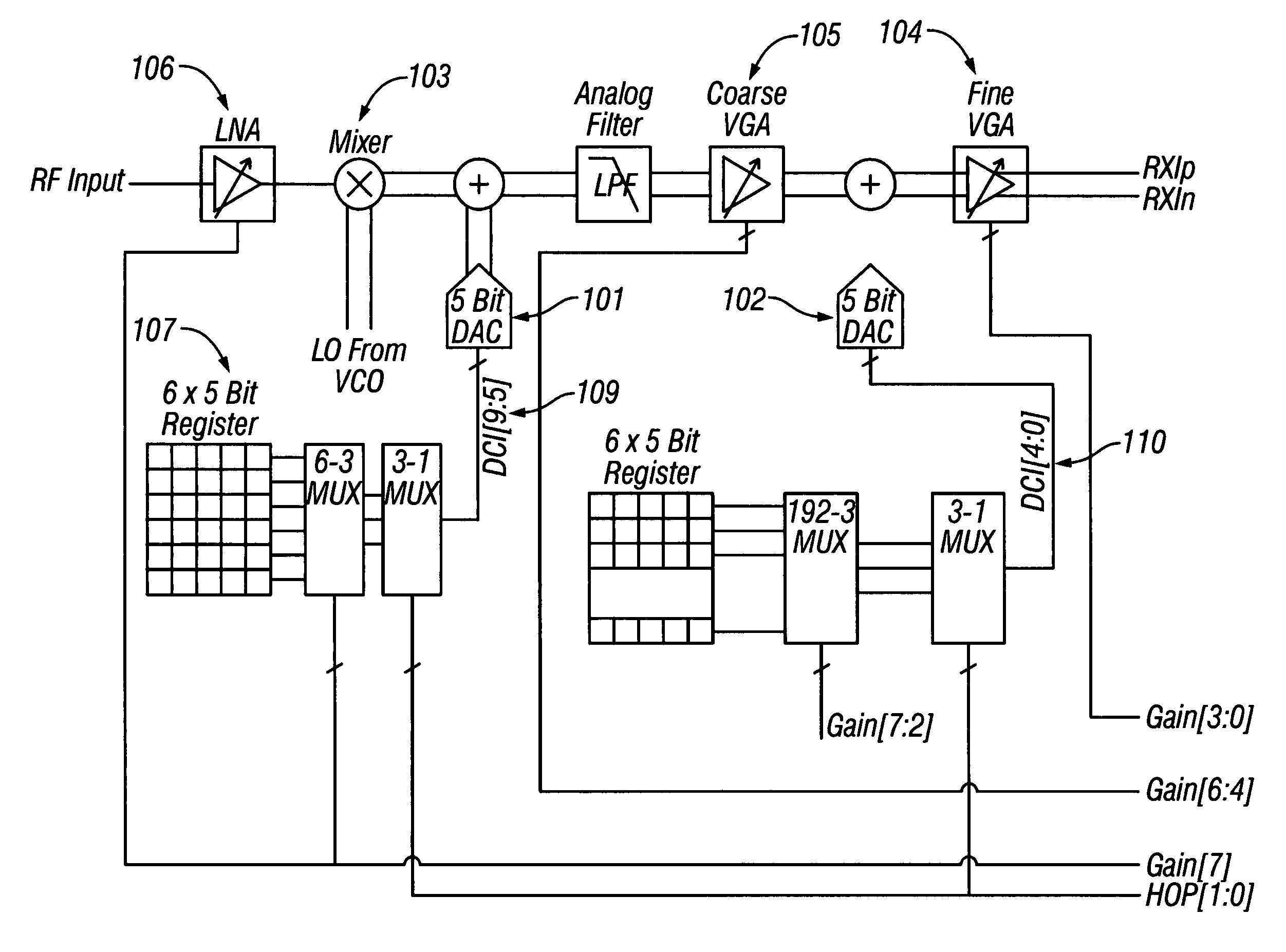

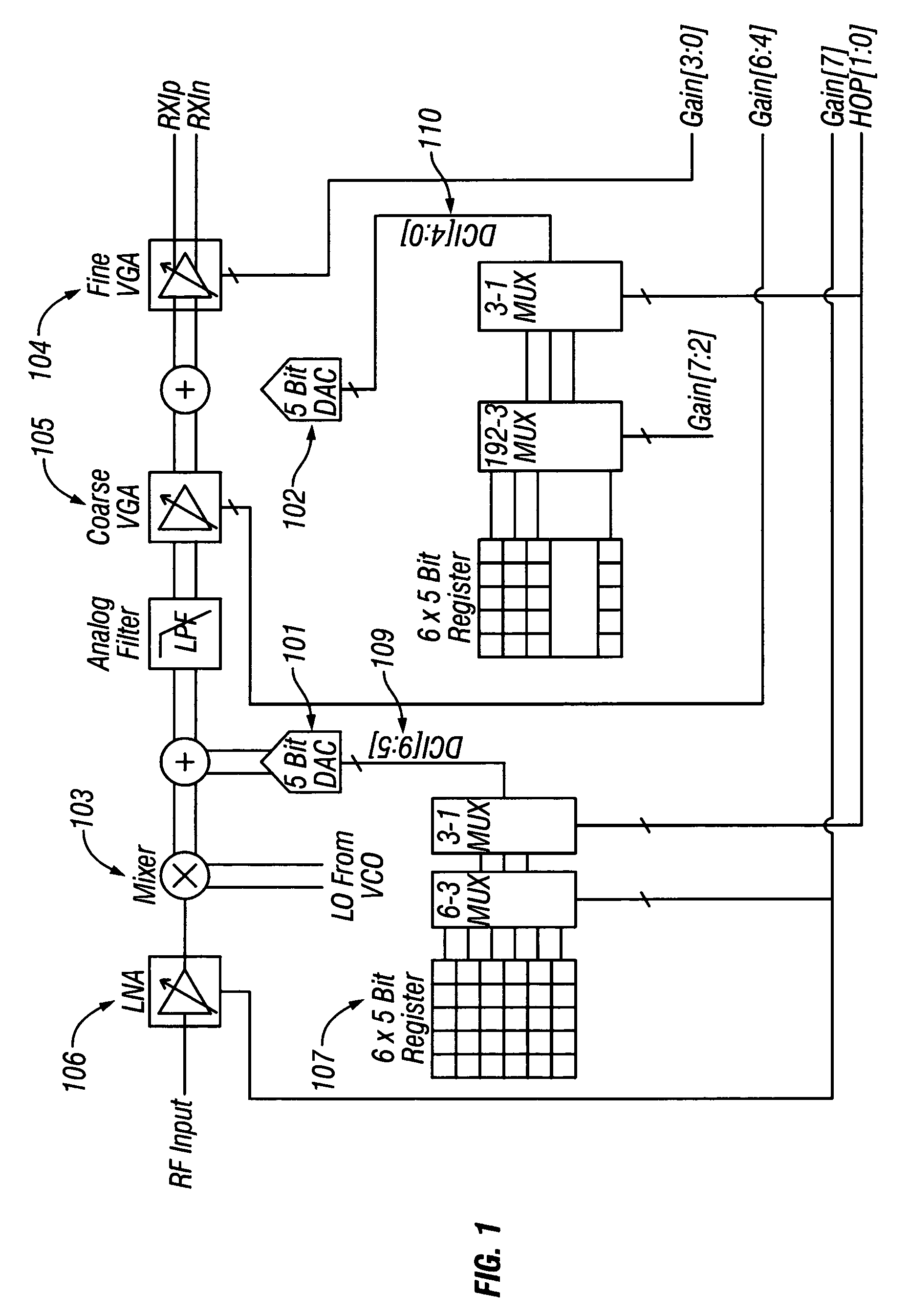

UWB radio interface with DC offset

InactiveUS20070230622A1Dc level restoring means or bias distort correctionLine balance variation compensationRadio receptionAnalog signal

The present invention provides a method and apparatus for correcting direct current (DC) offsets in radio output signals. The invention comprises a radio processor and a baseband processor. During a calibration routine, the baseband processor measures DC offset produced by the radio processor, generates a corresponding DC offset correction value, and writes the correction value to a discrete memory in the radio processor via a serial processor interface. During a subsequent normal receive operation, the radio processor reads the DC offset correction value from memory and feeds it into a into a digital to analog converter to produce an analog signal that in turn is fed into a radio receive path to nullify undesired DC offset.

Owner:WIQUEST COMMUNICATIONS +1

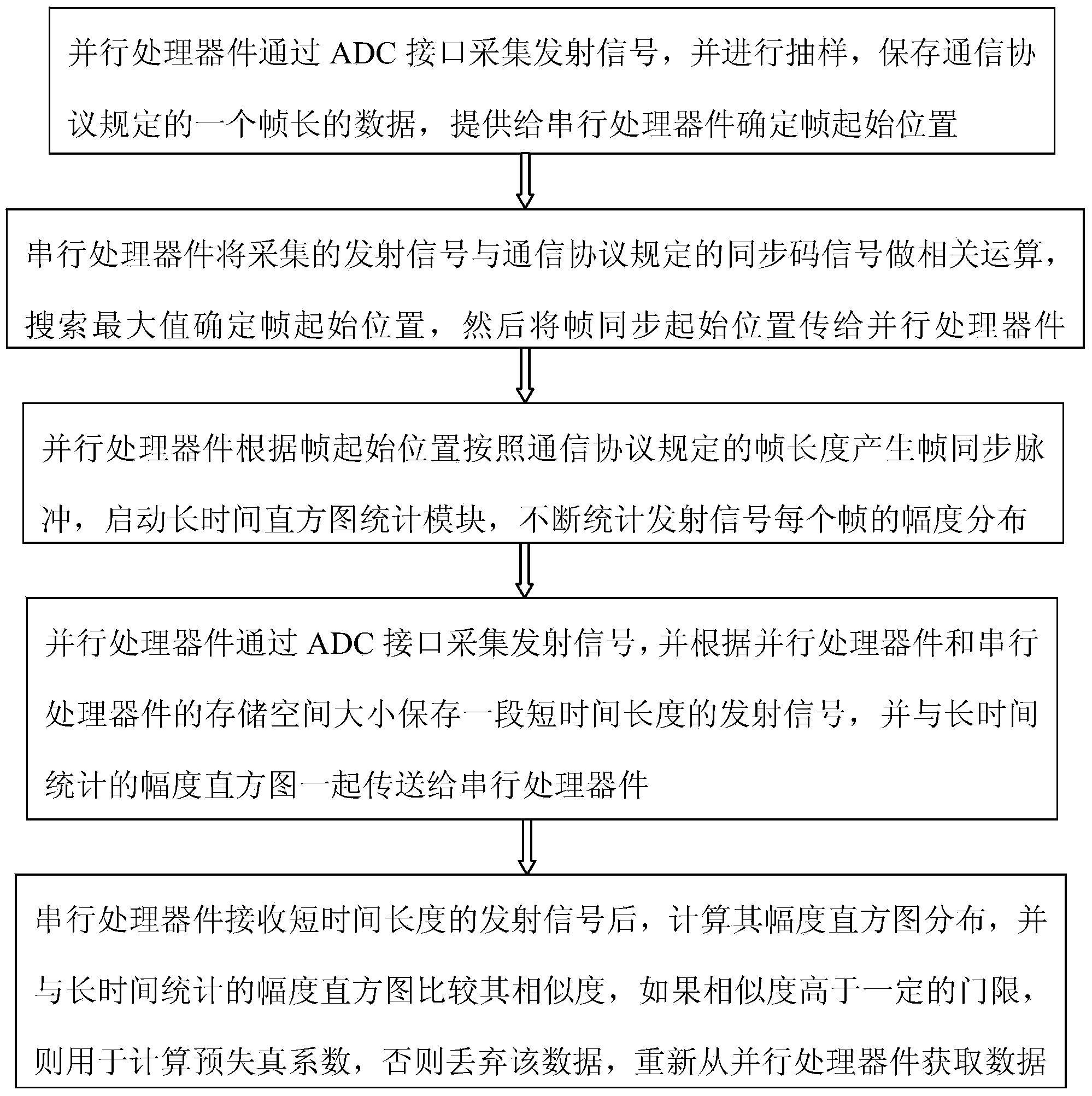

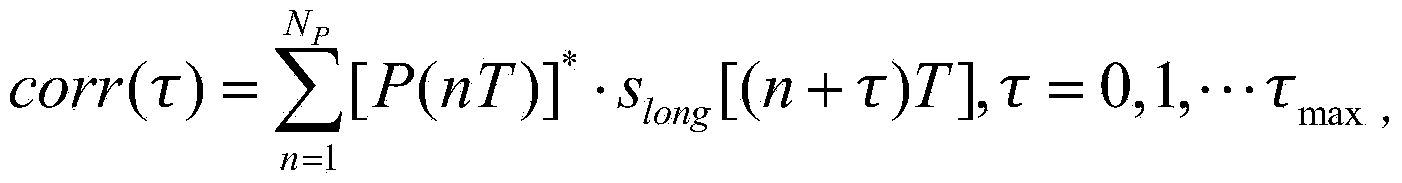

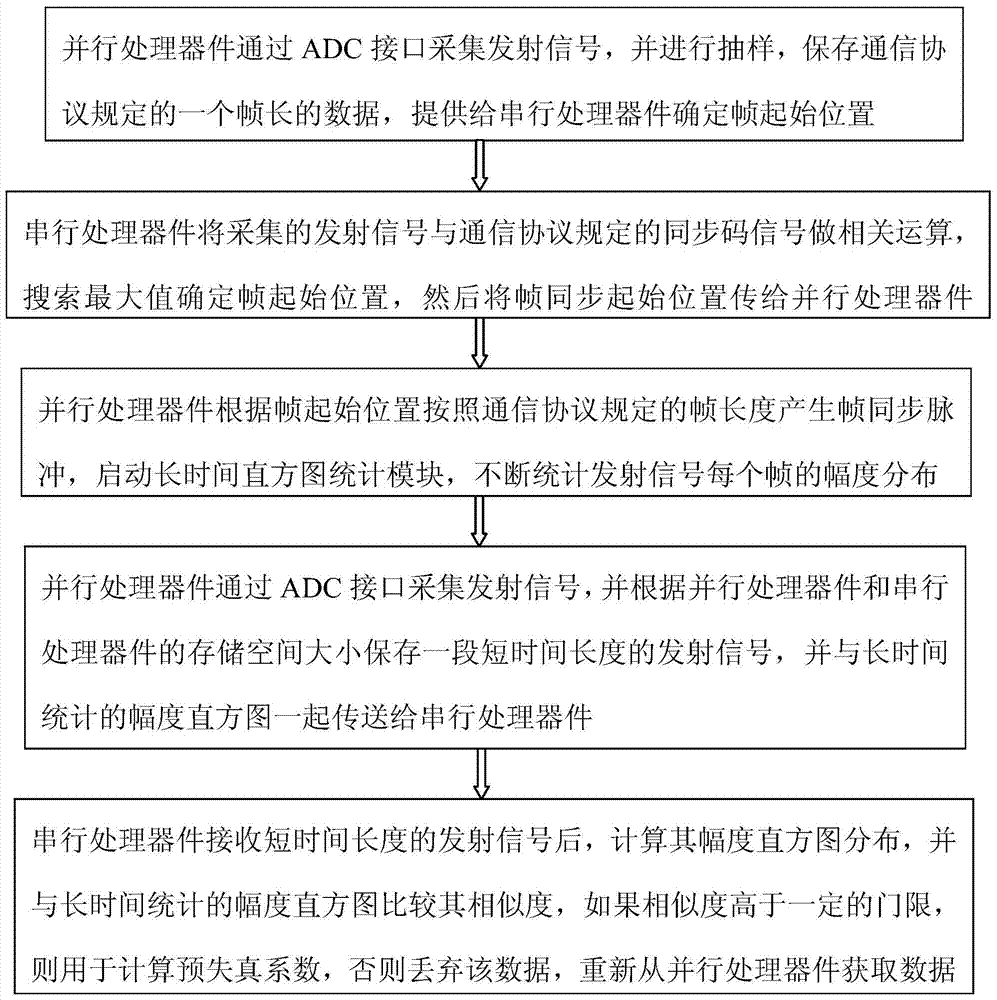

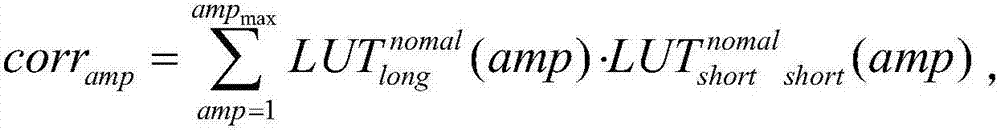

Method for collecting data in digital pre-distortion system

ActiveCN104270330AReduce performanceImprove performanceSynchronous/start-stop systemsData acquisitionAmplitude histogram

The invention discloses a method for collecting data in a digital pre-distortion system. The method comprises the following steps that (1) a parallel processing device collects emitting signals and samples the collected emitting signals, and a serial processing device determines the start position of frames; (2) the serial processing device searches for the largest value to determine the start position of the frames and transmits the synchronous start position of the frames to the parallel processing device; (3) the parallel processing device starts a long-time histogram statistic module to count amplitude distributions of all frames of the emitting signals; (4) the parallel processing device collects the emitting signals, stores the emitting signals in short time duration, transmits the collected emitting signals and amplitude histograms counted in a long time period to the serial processing device; (5) the serial processing device receives the emitting signals in short time duration, calculates the distributions of the amplitude histograms, and compares the similarity of the distributions of the amplitude histograms and the amplitude histograms calculated in a long time period, if the similarity is higher than the threshold, a pre-distortion factor is calculated, and if the similarity is not higher than the threshold, the similarity is abandoned, and data are obtained from the parallel processing device again. The method has the advantages of being high in adaptability, and the like.

Owner:SOUTH CHINA UNIV OF TECH

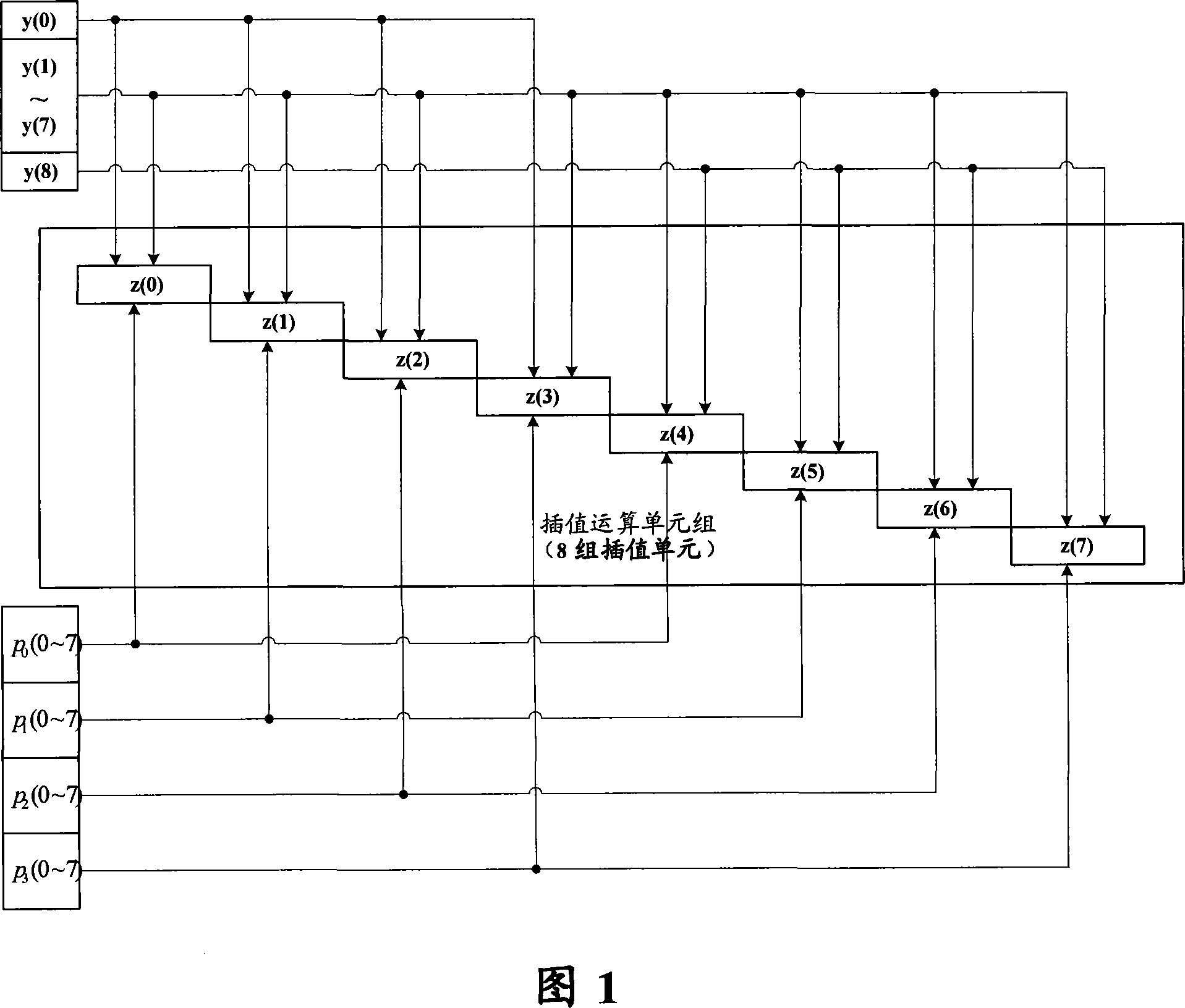

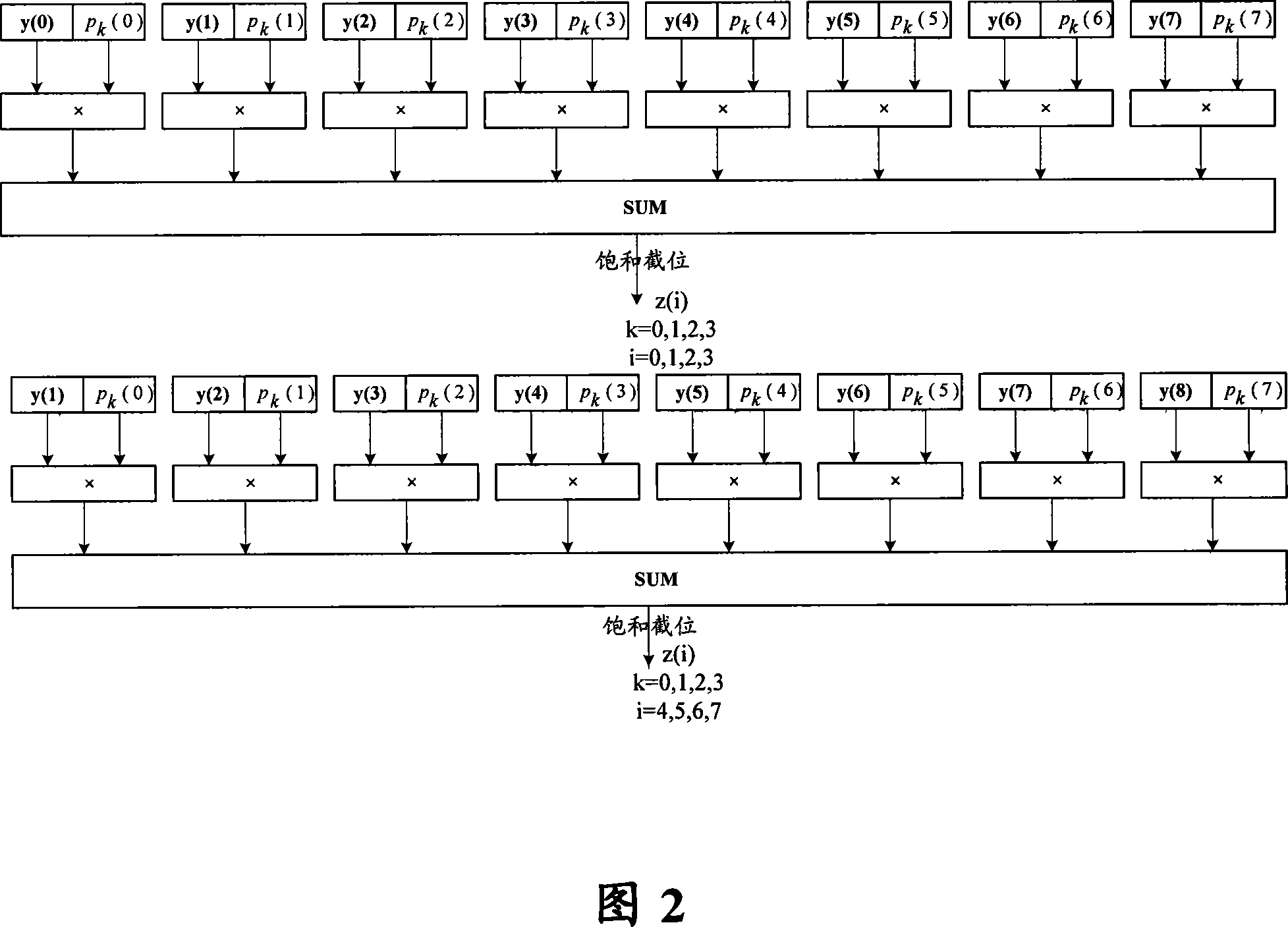

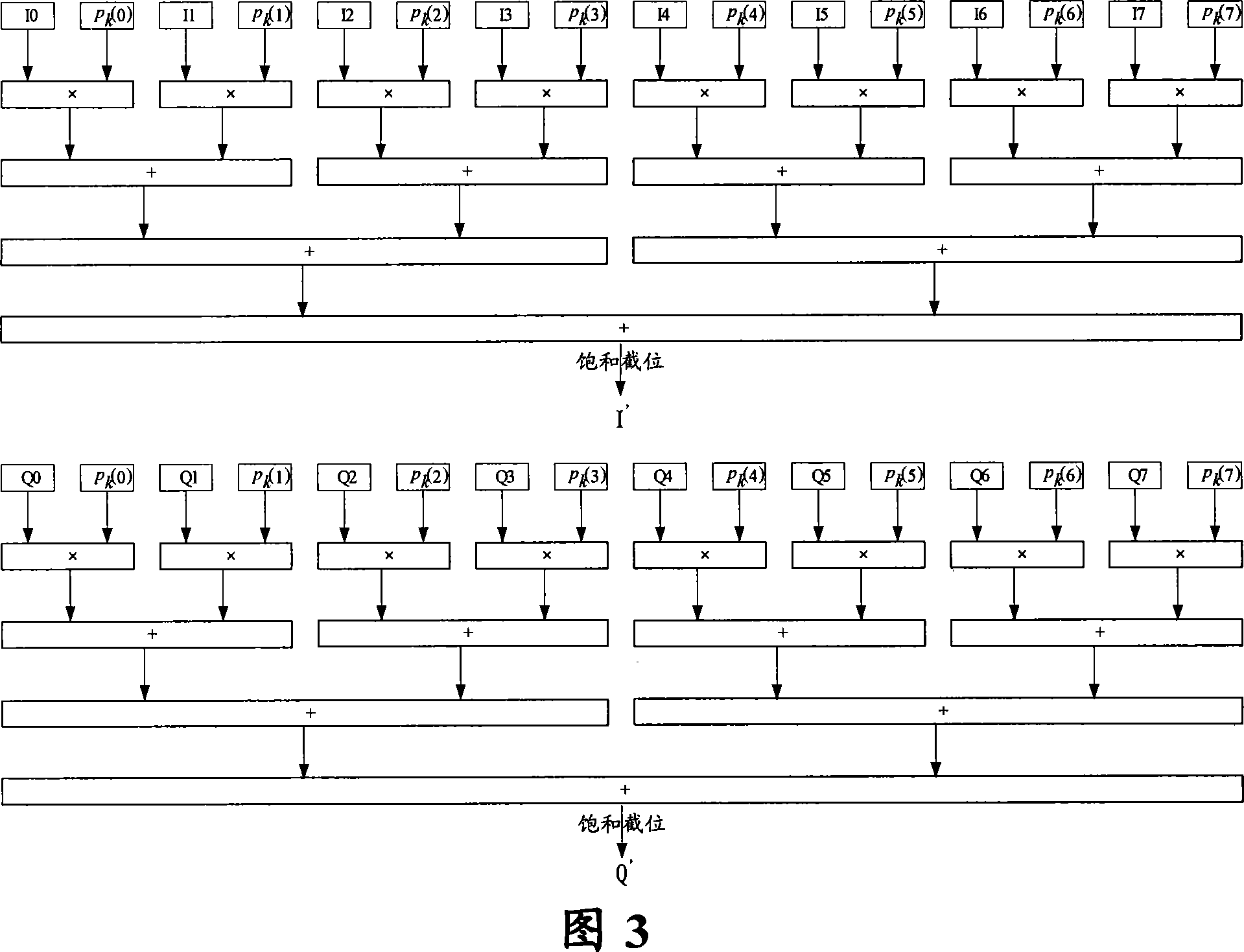

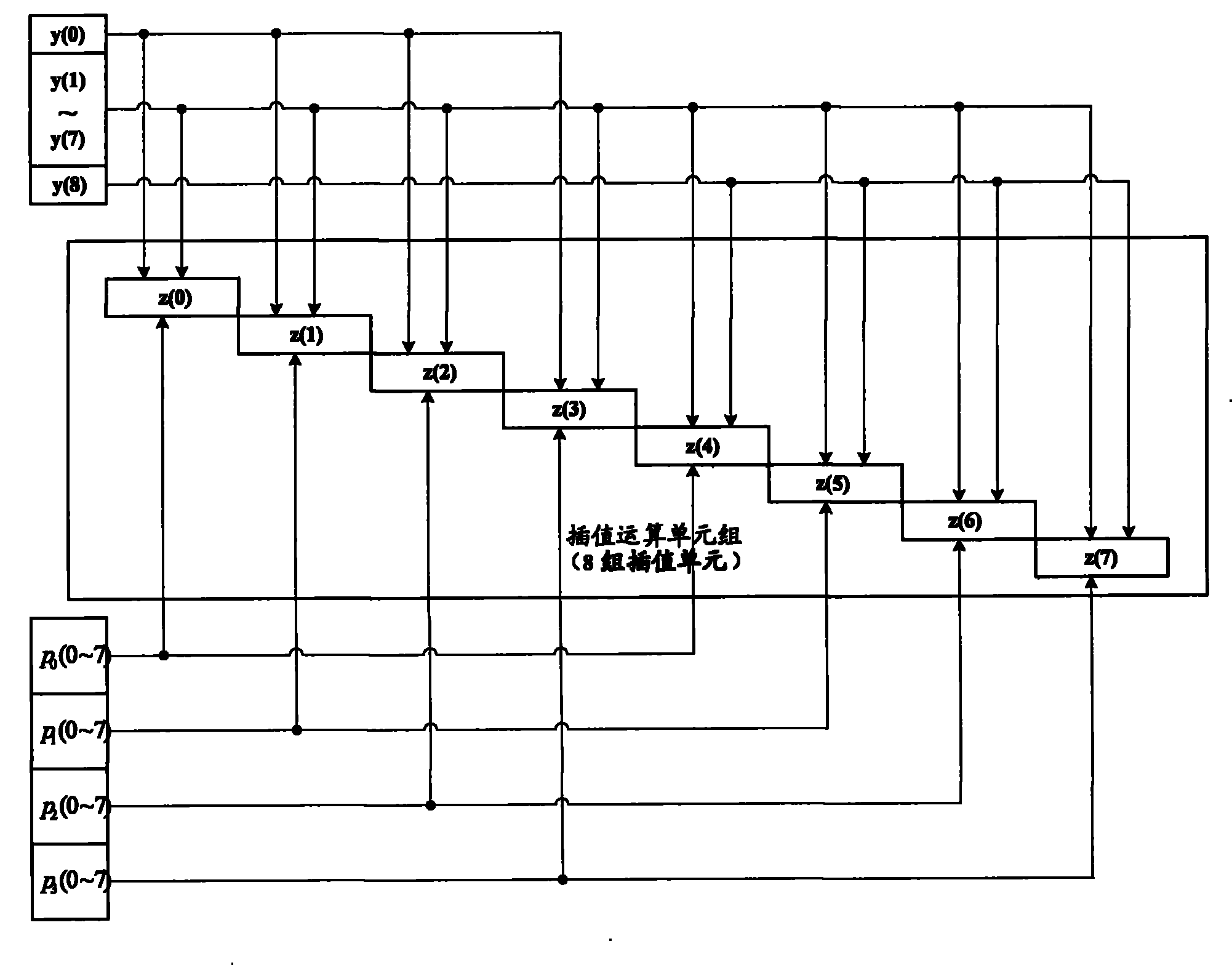

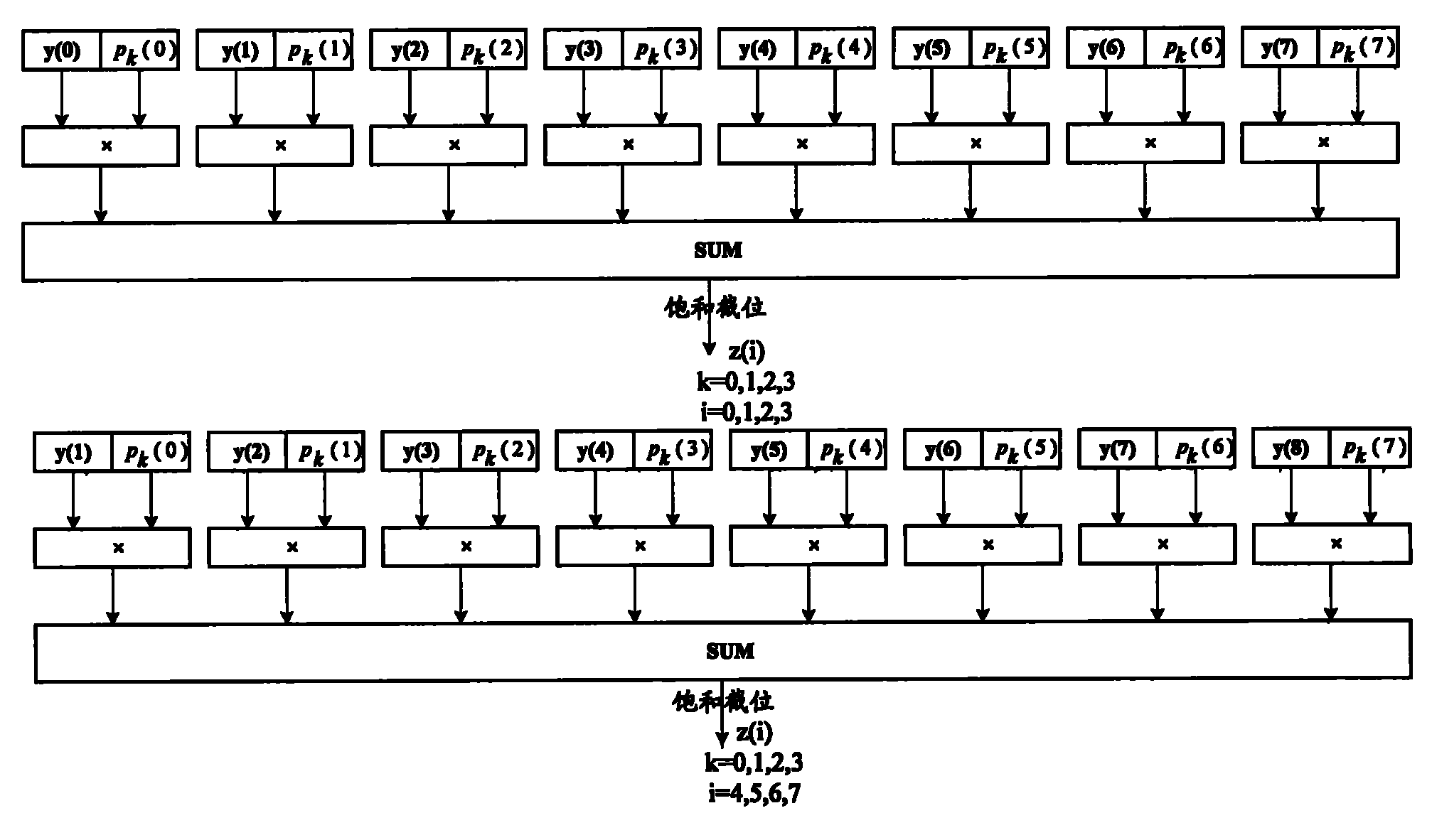

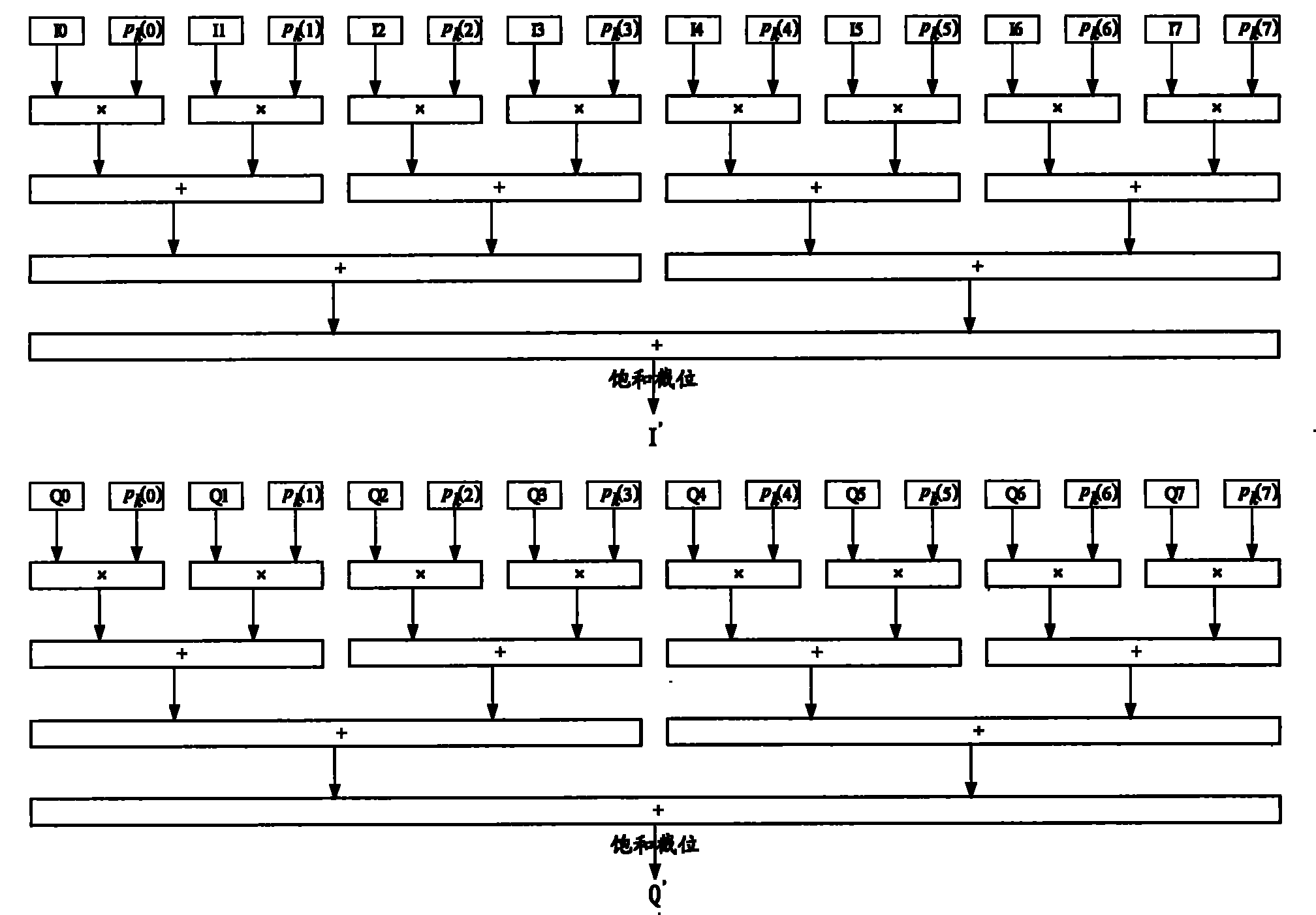

Serial processor and processing method for interpolation device

InactiveCN101076011ASave logic resourcesCode division multiplexTransmissionControl signalData transmission

The apparatus comprises: a control unit used for controlling the interpolation processing unit and generating the sample data, interpolation factor and control signal required by the interpolation processing unit; and an interpolation processing unit used for, under the control of the control unit, using the sample data, interpolation factor and control signal to make the multiply and summation calculation for the sample data, and transmitting the processed sample data to the control unit in order to output it.

Owner:ZTE CORP

Multiple multithreaded processors with shared data cache

ActiveUS11294815B2Improve processor performanceRealize performanceMemory architecture accessing/allocationSingle instruction multiple data multiprocessorsComputer architectureProcessing core

A multi-core processor configured to improve processing performance in certain computing contexts is provided. The multi-core processor includes multiple processing cores that implement barrel threading to execute multiple instruction threads in parallel while ensuring that the effects of an idle instruction or thread upon the performance of the processor is minimized. The multiple cores can also share a common data cache, thereby minimizing the need for expensive and complex mechanisms to mitigate inter-cache coherency issues. The barrel-threading can minimize the latency impacts associated with a shared data cache. In some examples, the multi-core processor can also include a serial processor configured to execute single threaded programming code that may not yield satisfactory performance in a processing environment that employs barrel threading.

Owner:MOBILEYE VISION TECH LTD

Instruction controller to distribute serial and SIMD instructions to serial and SIMD processors

InactiveUS8447953B2Single instruction multiple data multiprocessorsArchitecture with single central processing unitInstruction unitExecution unit

A microprocessor architecture comprises a plurality of processing elements arranged in a single instruction multiple data SIMD array, wherein each processing element includes a plurality of execution units, each of which is operable to process an instruction of a particular instruction type, a serial processor which includes a plurality of execution units, each of which is operable to process an instruction of a particular instruction type, and an instruction controller operable to receive a plurality of instructions, and to distribute received instructions to the execution units in dependence upon the instruction types of the received instruction. The execution units of the serial processor are operable to process respective instructions in parallel.

Owner:RAMBUS INC

A data acquisition method in a digital predistortion system

ActiveCN104270330BReduce performanceImprove performanceSynchronous/start-stop systemsStart timeData acquisition

The invention discloses a data acquisition method in a digital predistortion system, which comprises the following steps: 1. A parallel processing device collects and samples a transmission signal, and a serial processing device determines the starting position of a frame; 2. The serial processing device searches for the maximum The value determines the frame start position and transmits the frame synchronization start position to the parallel processing device; 3. The parallel processing device starts the long-time histogram statistical module to count the amplitude distribution of each frame of the transmitted signal; 4. The parallel processing device collects the transmitted signal And save the transmission signal of short time length and transmit it to the serial processing device with the amplitude histogram of long-term statistics; The similarity of the amplitude histogram that has been counted for a long time, if the similarity is higher than the threshold, the pre-distortion coefficient is calculated, otherwise, the similarity is discarded and the data is reacquired from the parallel processing device. It has the advantages of strong adaptability and so on.

Owner:SOUTH CHINA UNIV OF TECH

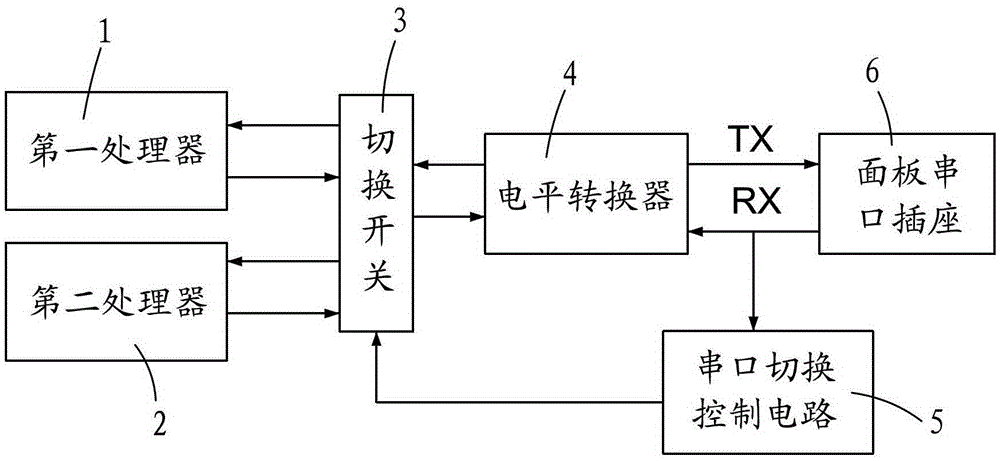

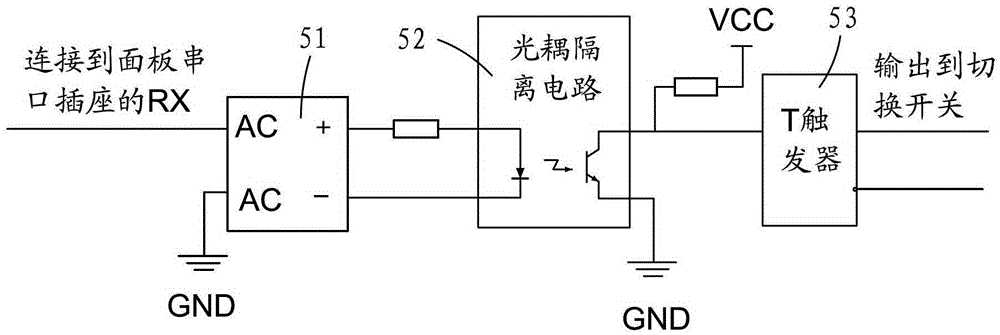

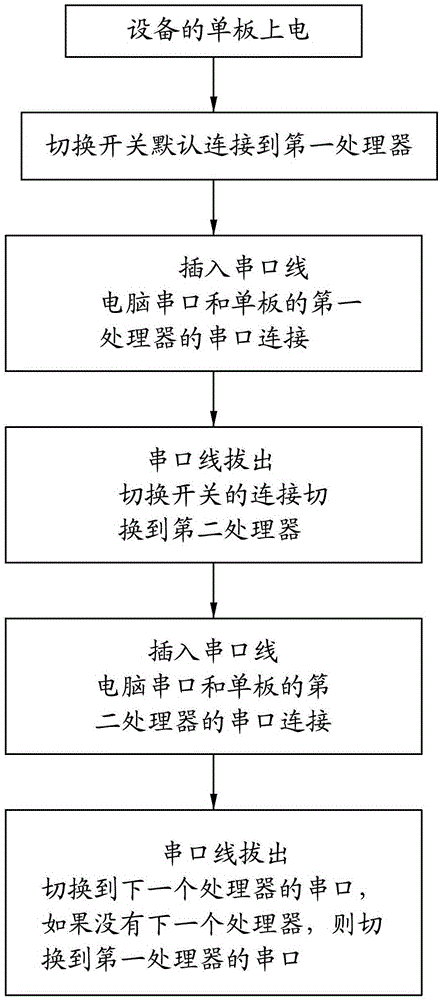

Switching method and switching circuit based on serial port multiplexing of multiple processors on single board

The invention provides a switching circuit based on multiplexing of multiple-processor serial ports on a single board. The switching circuit is arranged on the single board and comprises at least two processors, one selector switch, one electrical level shifter, a control circuit for serial port switching and a panel serial port socket, wherein the panel serial port socket is respectively connected with the electrical level shifter and the control circuit for serial port switching, the electrical level shifter is respectively connected with the first processor and the second processor through the selector switch, and a signal controlling pin of the serial port switching circuit is connected with the selector switch. The invention further provides a switching method based on multiplexing of the multiple-processor serial ports on the single board. Thus, the serial ports of the processors can share one panel serial port socket, through plugging-in and plugging-out, the panel serial port socket can be connected to different processor serial ports, and panel space of the single board is saved.

Owner:FUJIAN STAR NET COMM

Serial processor and processing method for interpolation device

InactiveCN101076011BSave logic resourcesCode division multiplexTransmissionControl signalData transmission

The apparatus comprises: a control unit used for controlling the interpolation processing unit and generating the sample data, interpolation factor and control signal required by the interpolation processing unit; and an interpolation processing unit used for, under the control of the control unit, using the sample data, interpolation factor and control signal to make the multiply and summation calculation for the sample data, and transmitting the processed sample data to the control unit in order to output it.

Owner:ZTE CORP

A Digital Predistortion Processing Method Adapting to Rapidly Changing Signals

ActiveCN102904846BFast updateReduce memory effectAmplifier modifications to reduce non-linear distortionSynchronous/start-stop systemsSystem capacityFrequency spectrum

The invention discloses a digital pre-distortion processing method adaptive to a quick-change signal. The digital pre-distortion processing method comprises the following steps of: storing one group of training signals in a concurrent processor, when a system is started, sending the training signals to a power amplifier by the concurrent processor, acquiring an input signal and an output signal of the power amplifier to be provided to a serial processor, calculating a filter coefficient of eliminating a memory effect, after the serial processor eliminates time delay, calculating a passband ripple of the system, calculating a coefficient of reversely correcting the filter, providing the coefficient to the concurrent processor for correcting the memory effect; after the system is started, continuously acquiring the input signal and the output signal of the power amplifier by the concurrent processor, updating and correcting a memoryless and nonlinear search table in real time after eliminating time delay and gain difference; and when the system normally works, carrying out memoryless and nonlinear correction on the input signal by the concurrent processor, eliminating the memory effect, and outputting the memory effect to an emitting link. The invention is suitable for the quick-changing modern communication signal, and has the advantages of reducing out-of-band leakage and increasing frequency spectrum utilization rate and system capacity.

Owner:SOUTH CHINA UNIV OF TECH

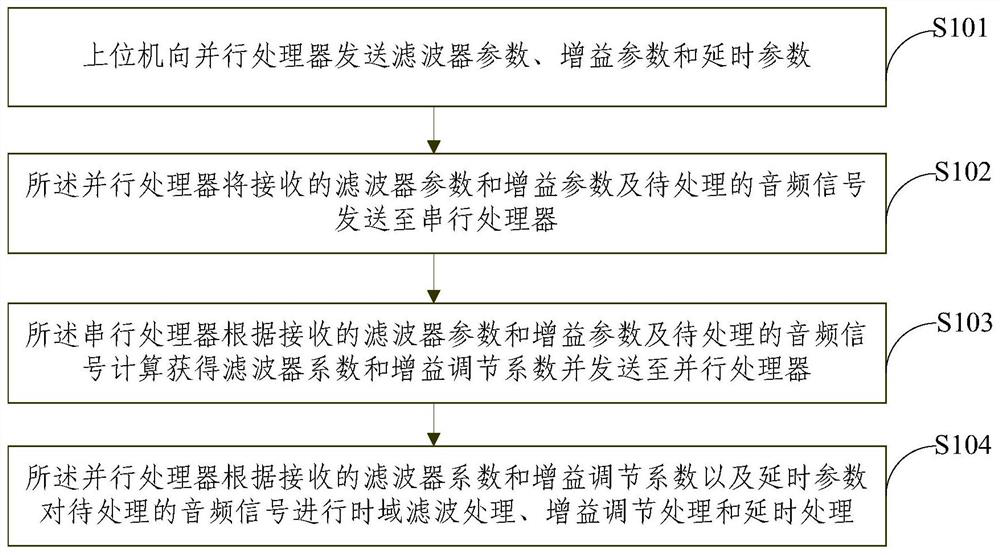

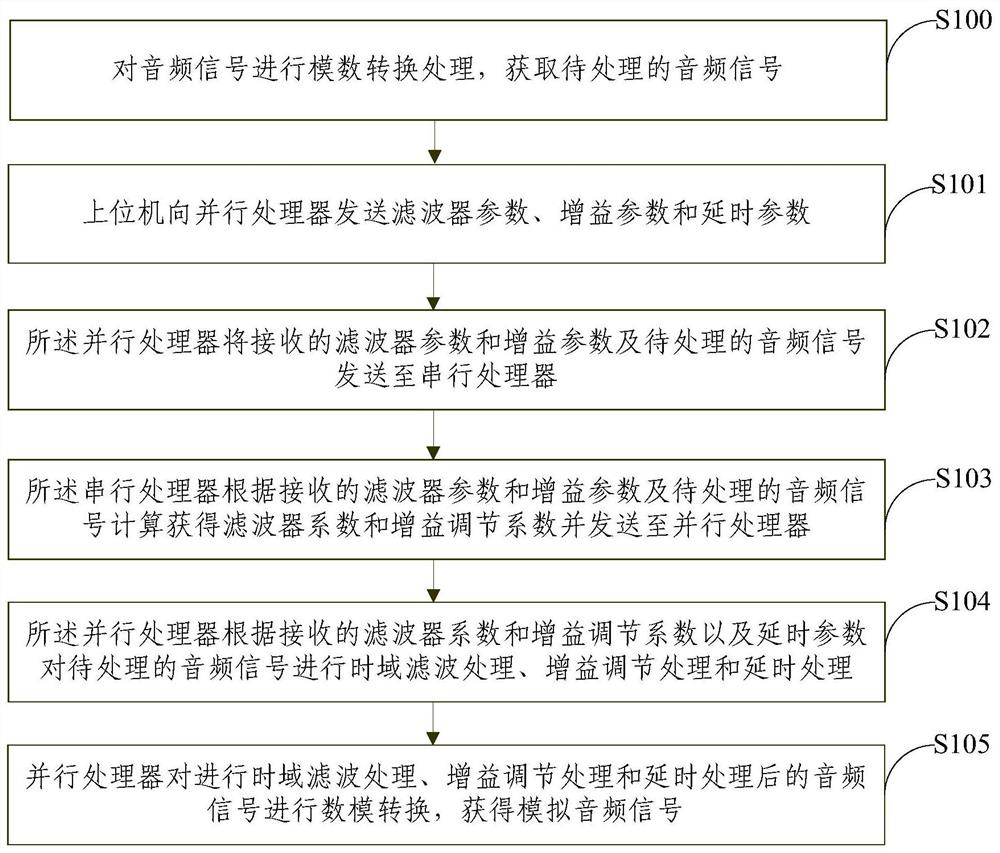

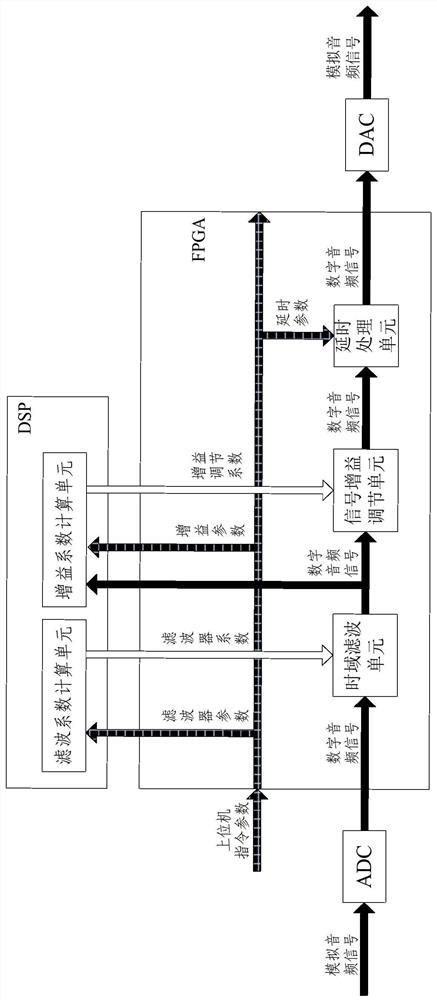

A method and system for real-time audio processing of multi-channel digital audio signals

ActiveCN106569780BImplement parallel processingLower latencySpeech analysisConcurrent instruction executionComputer hardwareTime domain

The invention provides a multi-channel digital audio signal real-time sound effect processing method and system, comprising: a host computer sends filter parameters, gain parameters and delay parameters to a parallel processor; the parallel processor receives the filter parameters and gain parameters And the audio signal to be processed is sent to the serial processor; the serial processor calculates and obtains the filter coefficient and gain adjustment coefficient according to the received filter parameter and gain parameter and the audio signal to be processed and sends it to the parallel processor; parallel processing The filter performs time domain filtering, gain adjustment and delay processing on the audio signal to be processed according to the received filter coefficients, gain adjustment coefficients and delay parameters. The present invention uses serial architecture processors and parallel architecture processors to jointly process sound effect data, reduces the delay in the sound effect processing process, realizes parallel processing of multi-channel audio data, and makes the sound effect processing have higher real-time performance.

Owner:北京飞利信电子技术有限公司

Intelligent metal detector

InactiveCN100439904CEasy to set upIntelligentMaterial analysis using microwave meansDigital signal processingMicrocontroller

It is a metal probe in lossless electromagnetism measurement technique field. The digital signal processor generates two paths of signals through two direct digital systemization chips into two multipliers that get two paths of separation signals through two low-pass filters. The data through the A / D conversion is sent to the digital signal processor for analysis and judgments. The human and machine dialogue system comprises single machines communicated with digital signal serial processors.

Owner:SHANGHAI JIAOTONG UNIV +1

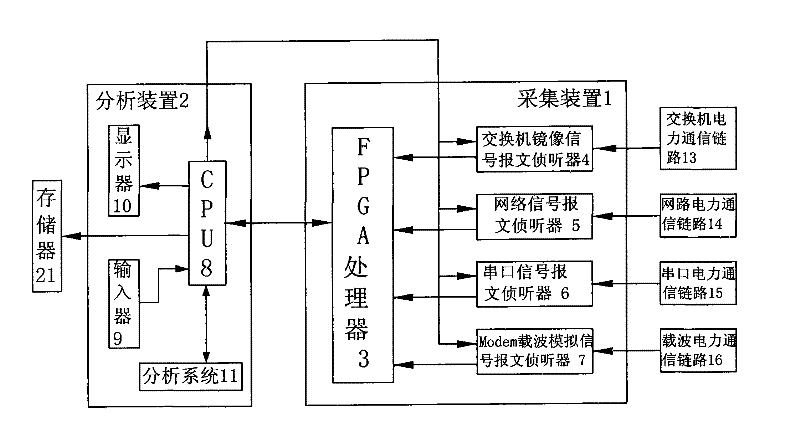

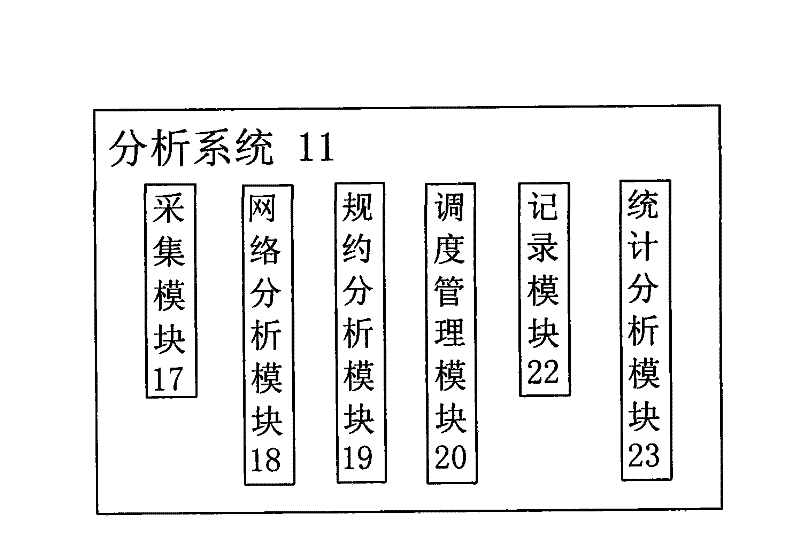

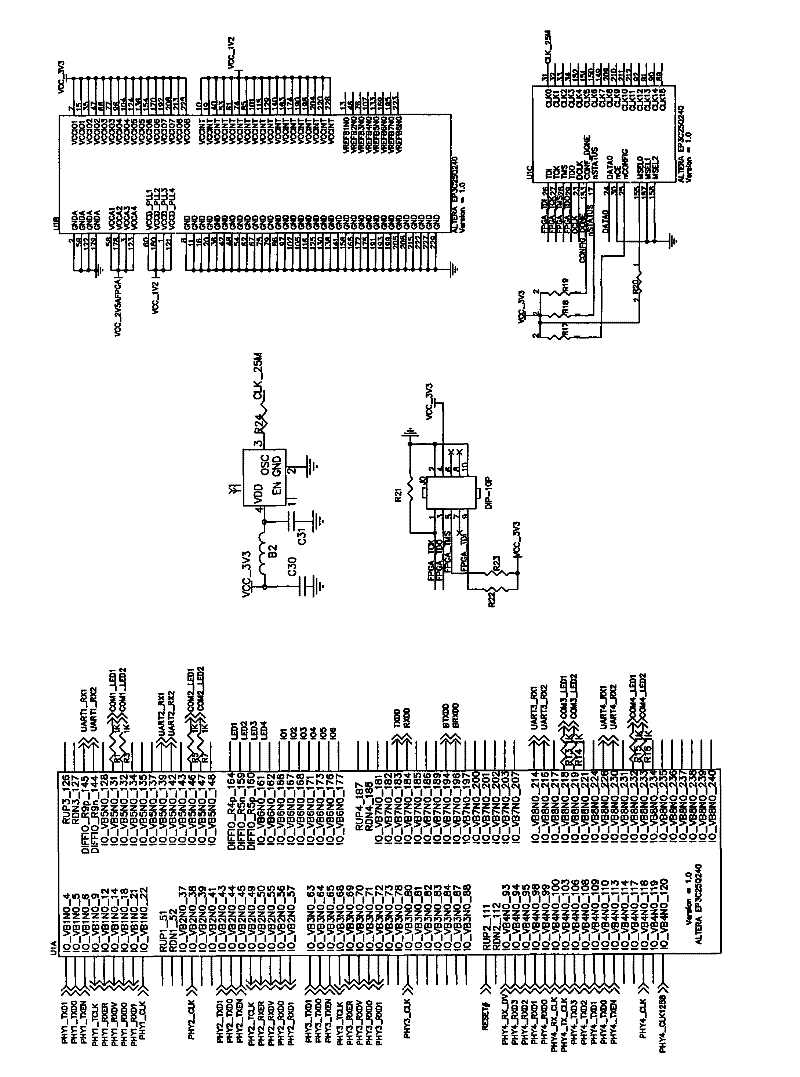

Portable electric power communication protocol detector and detection method thereof

The invention relates to a portable electric power communication protocol detector, simultaneously relates to a detection method of the detector and belongs to the technical field of communication detection in electric power systems. The detector comprises an acquisition device positioned in a portable machine case and in which includes a massage listener and a parallel to serial processor, and an analytic device containing a CPU, an analytic system, an input unit and a display, wherein the input unit and the display are respectively connected with the CPU. The input end of the massage listener is accessed into an electric power communication chain, and the output end of the massage listener is connected to the input end of the parallel to serial processor in parallel; the output end of the parallel to serial processor is connected with the CPU in series; and the control ends of the massage listener and the parallel to serial processor are respectively connected with the CPU. The detection method comprises the following steps: initializing the analytic system after parameters and system files of the detector are configured and then obtaining and displaying analysis results after the listened massage of the electric power communication chain is subjected to real-time network analysis and protocol analysis. The invention can eliminate the massage loss caused during the detectionof electric power communication, thereby truly and effectively detecting the electric power communication.

Owner:南京拓为电力科技发展有限公司 +3

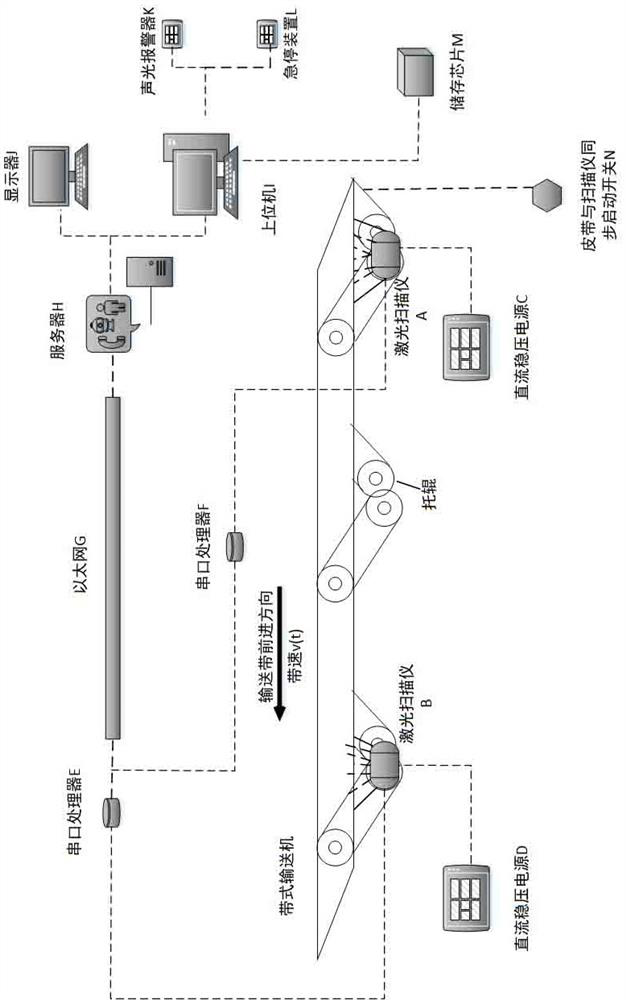

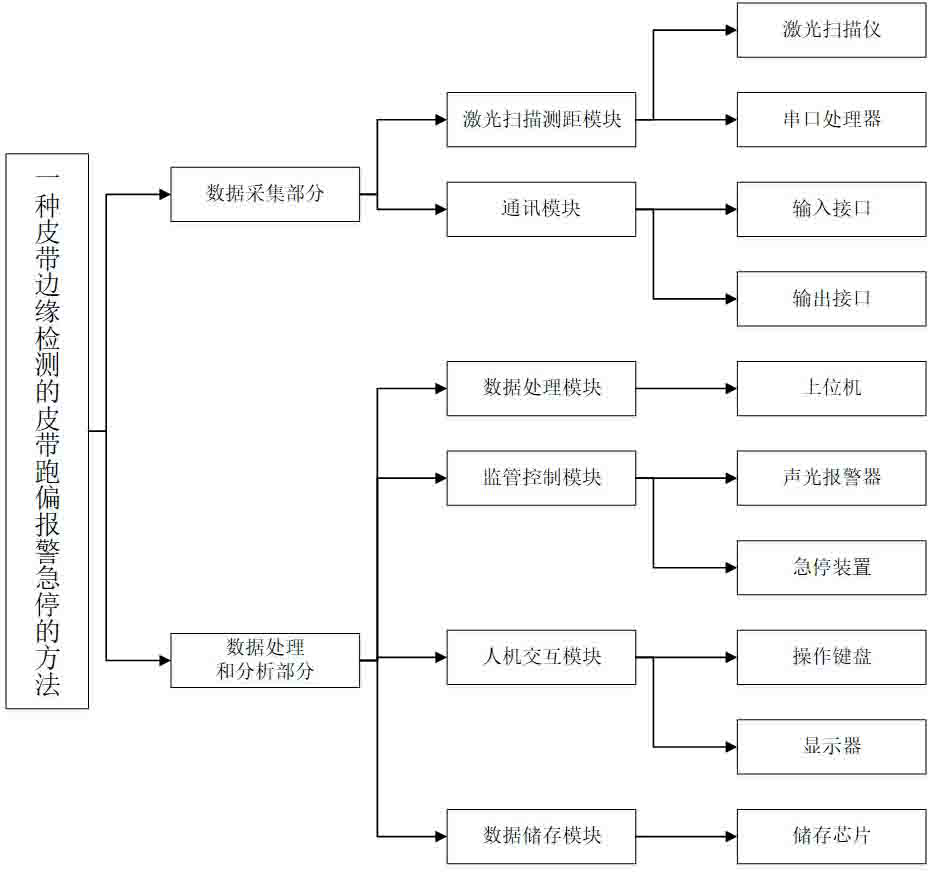

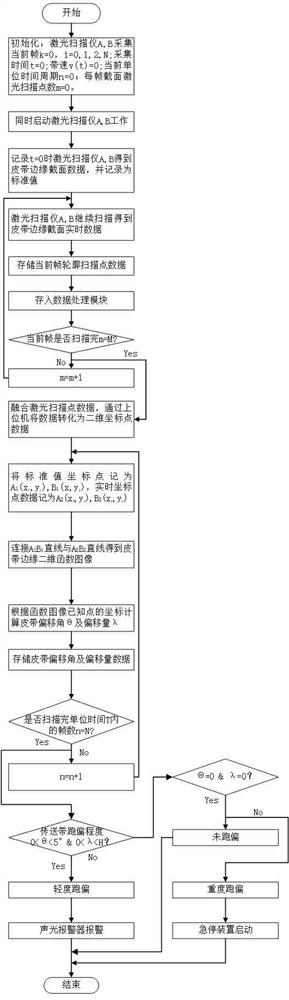

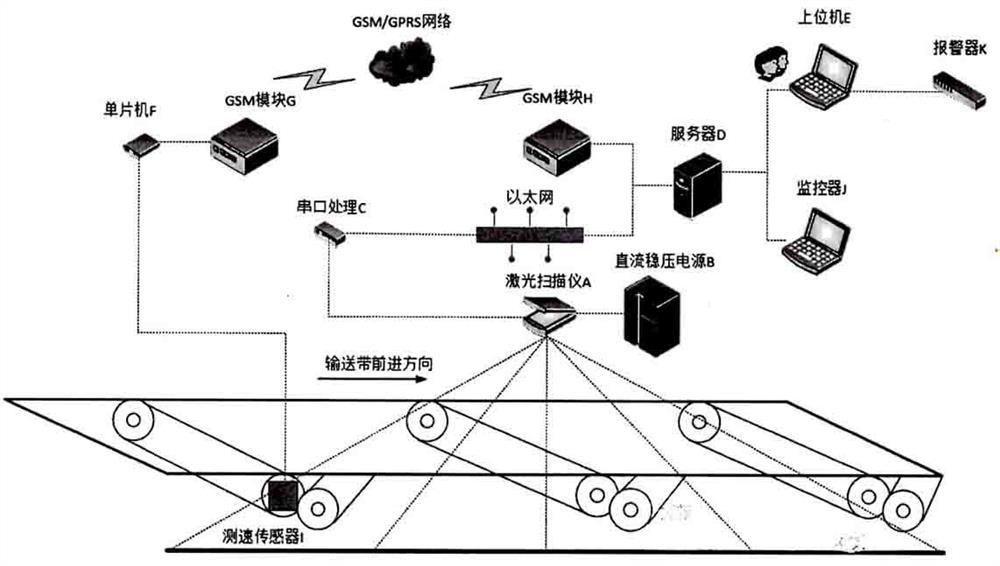

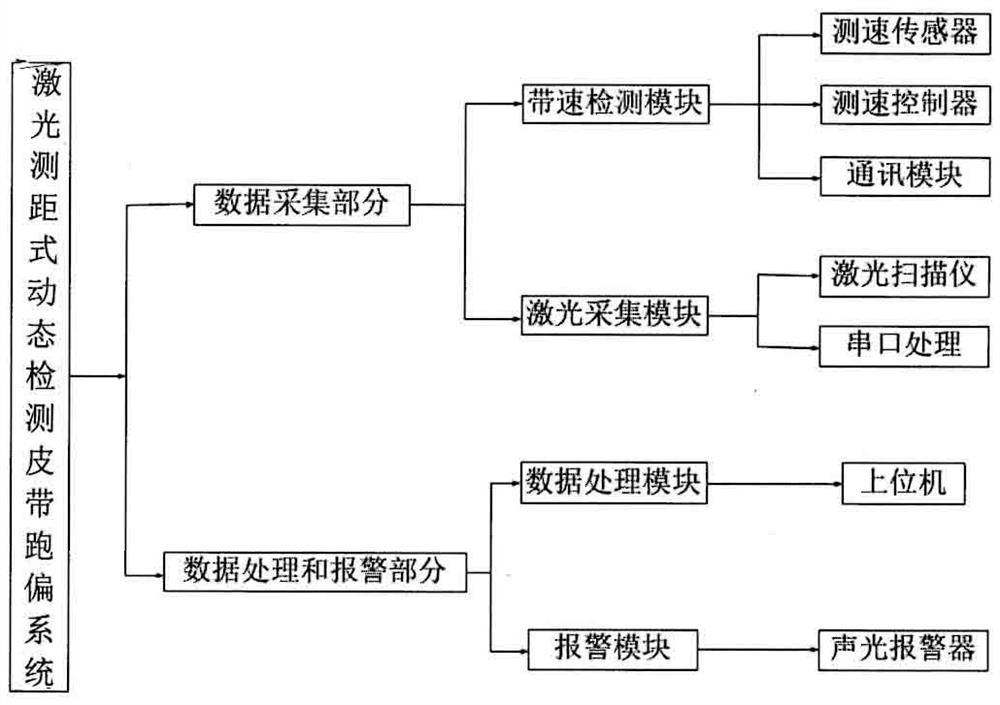

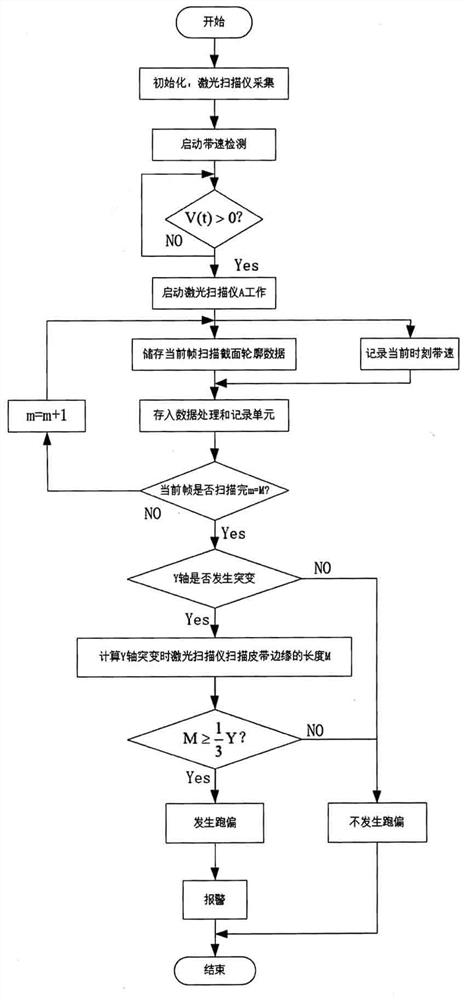

A method for belt deviation alarm emergency stop with belt edge detection

ActiveCN112027565BNot affected by distribution determinationImprove detection accuracyConveyorsControl devices for conveyorsAnti jammingLaser scanning

The invention discloses a belt deviation alarm and emergency stop method for belt edge detection, which adopts a conveyor belt deviation detection system based on laser lateral scanning belt edge distance measurement, including laser scanner A, laser scanner B and the conveyor belt. In the same plane, it is used to obtain the lateral distance between the edge of the belt and the edge support of the belt pulley; the laser scanning data can be sent to the Ethernet by the serial port processor for remote transmission; the upper computer realizes the online belt running according to the measurement data of the laser scanner A and B Real-time calculation of the offset angle and offset during the deviation process; the sound and light alarm and emergency stop device make corresponding judgments after data processing by the host computer, and control the operation of the sound and light alarm and emergency stop device. The invention makes up for the current situation that there is no high-precision non-contact belt conveyor real-time deviation detection system in the field. The invention has the advantages of simple and convenient measurement, strong anti-interference ability, high detection precision and strong real-time performance, and is not affected by the external environment on the determination of material distribution.

Owner:WUHAN UNIV OF SCI & TECH

An autonomous controllable computer motherboard

ActiveCN107728712BHigh localization rateFlexible modificationDigital data processing detailsTerm memoryBus

The invention discloses a self-controlled computer mainboard, which comprises a COMe mainboard, a CPCI pinboard, and a power module for supplying power for the COMe mainboard and the CPCI pinboard. The COMe mainboard comprises a processor, a bridge ribbon and a memory; the CPCI pinboard comprises a PCIe to PCI bridge chip; the processor adopts a Loongson 3A serial processor; the bridge ribbon adopts a Loongson 2H chip; the memory adopts a DDR3 memory grain chip; the Loongson 3A serial processor is connected with the Loongson 2H chip through an HT bus; the Loongson 3A serial processor and the Loongson 2H chip are connected with the DDR3 memory grain chip through memory channels; an EJTAG debugging interface used for carrying out reliability testing on the Loongson 3A serial processor and the Loongson 2H chip is also arranged on the COMe mainboard. According to the self-controlled computer mainboard provided by the invention, the Loongson 3A serial processor and the Loongson 2H matched bridge chip with full autonomy proprietary intellectual property rights are adopted, and the hardware interface of a mainboard platform is arranged, so that higher product domestication rate can be realized, the demands on information safety and self-controllability are met, and the technical risks and the uncontrollable hidden dangers in product use and maintenance are eliminated.

Owner:HUBEI SANJIANG AEROSPACE WANFENG TECH DEV

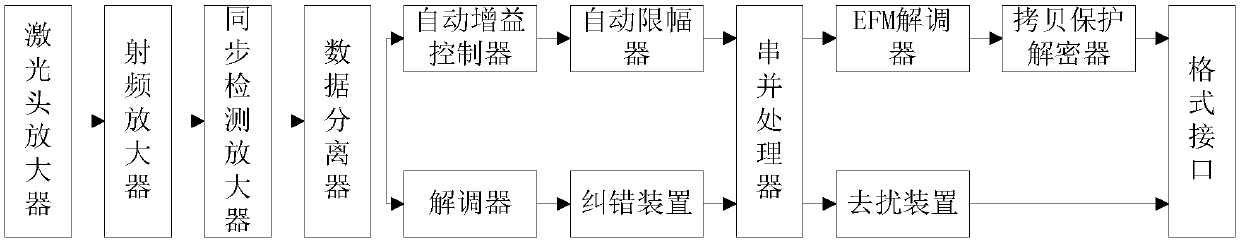

RF amplification and digital signal processing equipment

InactiveCN107657971AData decryption performance is stableRecord information storageDigital signal error detection/correctionDigital signal processingAutomatic control

The invention discloses RF amplification and digital signal processing equipment, including laser head amplifier, radio frequency amplifier, synchronous detection amplifier, data separator, automatic gain controller, automatic amplitude limiter, demodulator, error correction device and serial-parallel processor , EFM demodulator, copy protection decryptor, descrambling device, format interface, the laser head amplifier, radio frequency amplifier, synchronous detection amplifier, data separator are connected in turn, and the automatic gain controller is connected with the automatic limiter, The demodulator is connected to the error correction device, and the automatic gain controller and the demodulator are respectively connected to the data separator. The invention enhances DVD data through laser head amplifier, radio frequency amplifier, synchronous detection amplifier, data separator, automatic gain controller, automatic limiter, demodulator, error correction device, serial-parallel processor and EFM demodulator processing, and then improve the stability of the data decryption performance of the DVD player through the copy protection decryptor.

Owner:王梅

UWB radio interface with DC offset

InactiveUS7903761B2Dc level restoring means or bias distort correctionLine balance variation compensationDigital analog converterRadio reception

The present invention provides a method and apparatus for correcting direct current (DC) offsets in radio output signals. The invention comprises a radio processor and a baseband processor. During a calibration routine, the baseband processor measures DC offset produced by the radio processor, generates a corresponding DC offset correction value, and writes the correction value to a discrete memory in the radio processor via a serial processor interface. During a subsequent normal receive operation, the radio processor reads the DC offset correction value from memory and feeds it into a into a digital to analog converter to produce an analog signal that in turn is fed into a radio receive path to nullify undesired DC offset.

Owner:WIQUEST COMMUNICATIONS +1

Laser ranging dynamic detection belt deviation system

ActiveCN112254650BEasy to find the initial positionNot affected by distribution determinationUsing optical meansLaser rangingEngineering

The invention discloses a laser range-measuring type dynamic belt deviation detection system, which includes a belt conveyor, a laser scanner, a serial port processor, a speed sensor, a single-chip computer, and a host computer; the laser scanner is fixedly installed on the side of the edge of the transport belt side, the installation distance meets the error range of the belt deviation, and the scanning surface of the laser scanning distance measuring device is perpendicular to the horizontal plane of the belt and the ground; the laser scanning data is sent to the Ethernet by the serial port processor for remote transmission; the speed sensor is fixed on the belt The conveyor is on the central axis of the idler roller and rotates coaxially with the idler roller; the belt speed data is collected by the single chip microcomputer and transmitted to the remote host computer through the GSM / GPRS module; the host computer calculates in real time according to the measurement data of the detection system. The invention can dynamically detect the deviation of the belt, facilitates the discovery of the initial position of the deviation of the belt, has simple system structure, high degree of automation, strong real-time performance, and is not affected by the external environment on the determination of material distribution.

Owner:WUHAN UNIV OF SCI & TECH