Patents

Literature

1062 results about "Instruction unit" patented technology

Efficacy Topic

Property

Owner

Technical Advancement

Application Domain

Technology Topic

Technology Field Word

Patent Country/Region

Patent Type

Patent Status

Application Year

Inventor

The instruction unit (IU), also called instruction fetch unit (IFU) or instruction issue unit (ISU), in a central processing unit (CPU) is responsible for organising program instructions to be fetched from memory, and executed, in an appropriate order. It is a part of the control unit, which in turn is part of the CPU.

Microprocessors

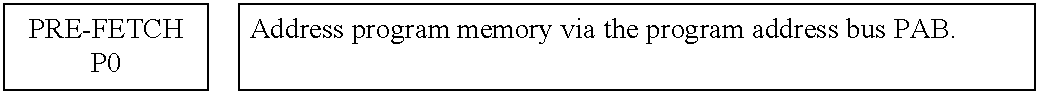

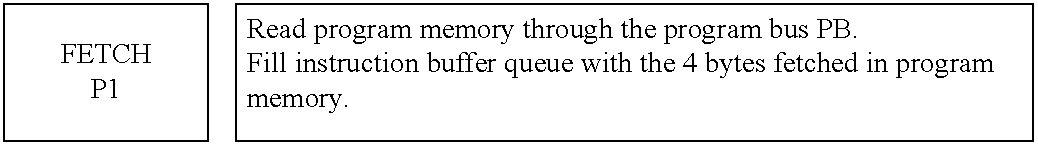

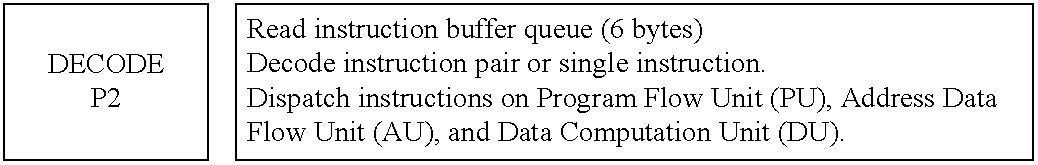

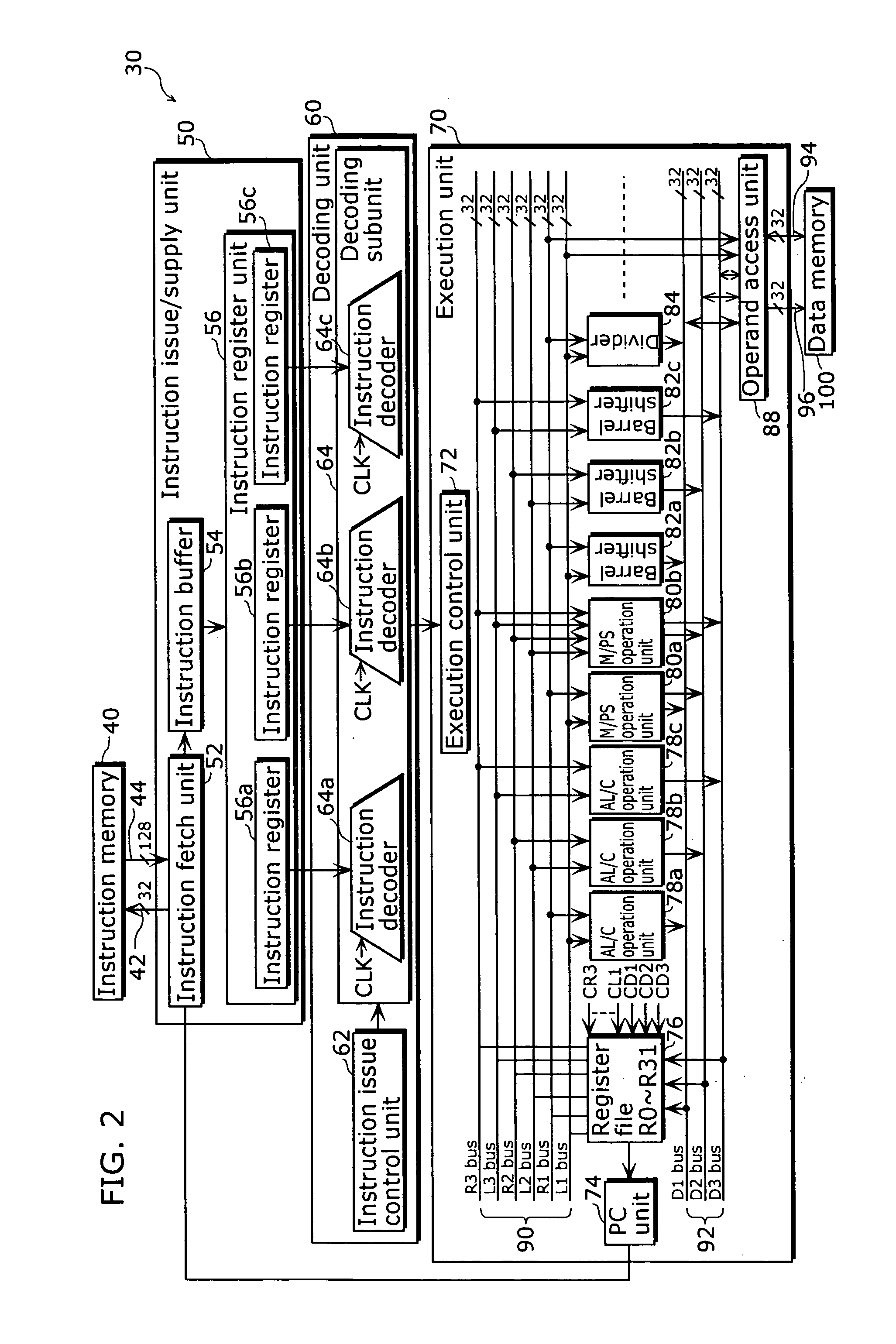

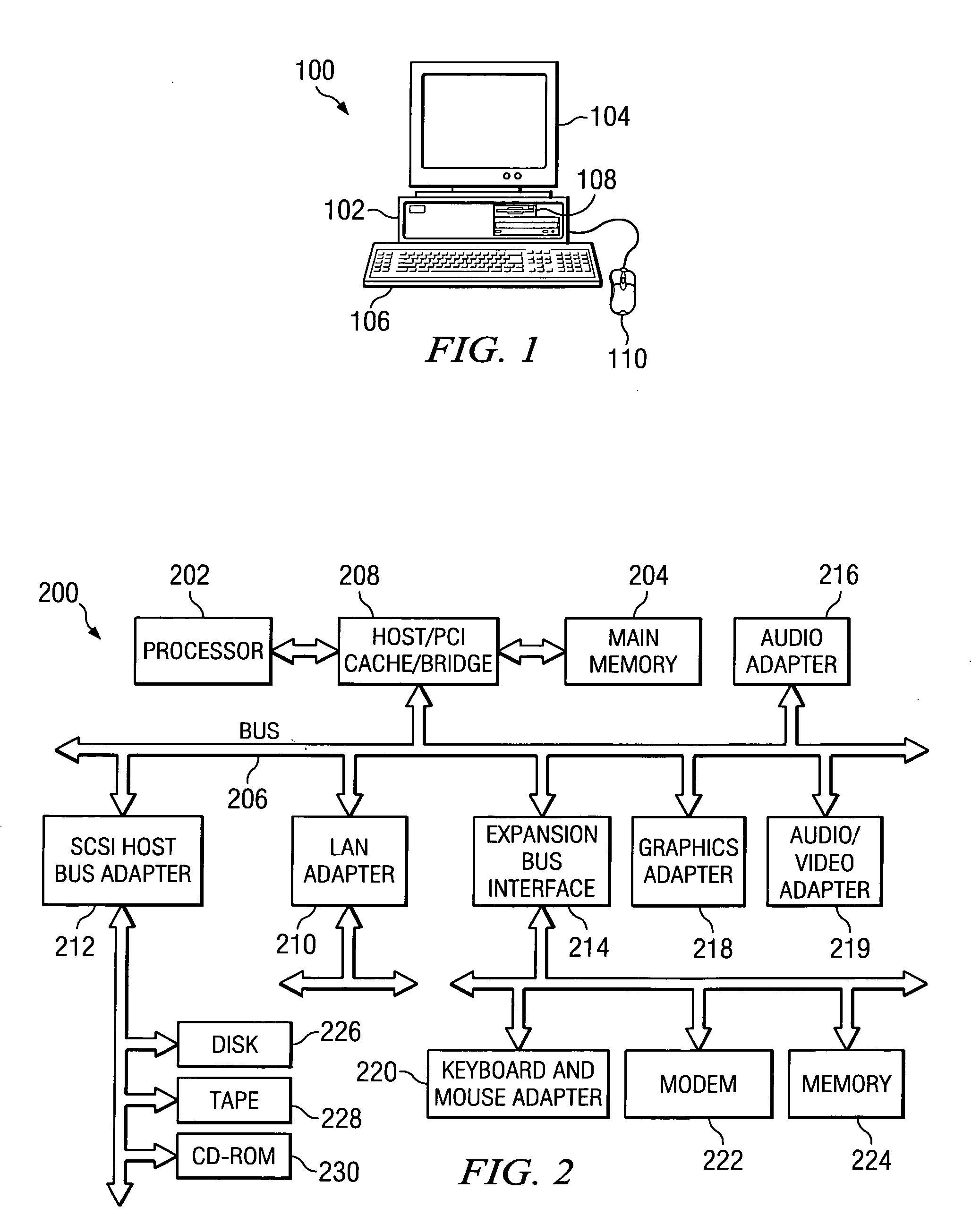

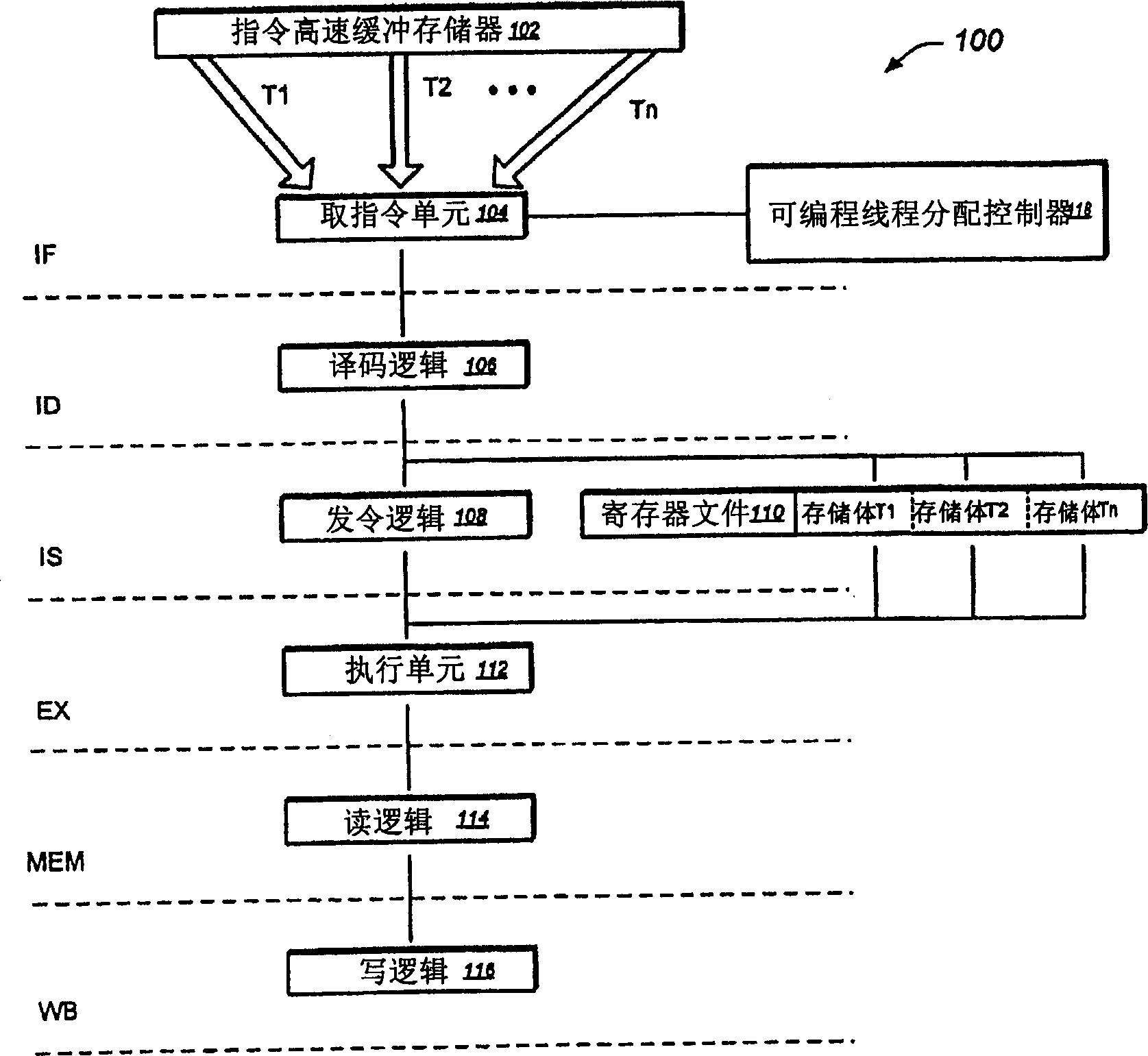

A processor (100) is provided that is a programmable fixed point digital signal processor (DSP) with variable instruction length, offering both high code density and easy programming. Architecture and instruction set are optimized for low power consumption and high efficiency execution of DSP algorithms, such as for wireless telephones, as well as pure control tasks. The processor includes an instruction buffer unit (106), a program flow control unit (108), an address / data flow unit (110), a data computation unit (112), and multiple interconnecting busses. Dual multiply-accumulate blocks improve processing performance. A memory interface unit (104) provides parallel access to data and instruction memories. The instruction buffer is operable to buffer single and compound instructions pending execution thereof. A decode mechanism is configured to decode instructions from the instruction buffer. The use of compound instructions enables effective use of the bandwidth available within the processor. A soft dual memory instruction can be compiled from separate first and second programmed memory instructions. Instructions can be conditionally executed or repeatedly executed. Bit field processing and various addressing modes, such as circular buffer addressing, further support execution of DSP algorithms. The processor includes a multistage execution pipeline with pipeline protection features. Various functional modules can be separately powered down to conserve power. The processor includes emulation and code debugging facilities with support for cache analysis.

Owner:TEXAS INSTR INC

Radio communication apparatus and radio communication method

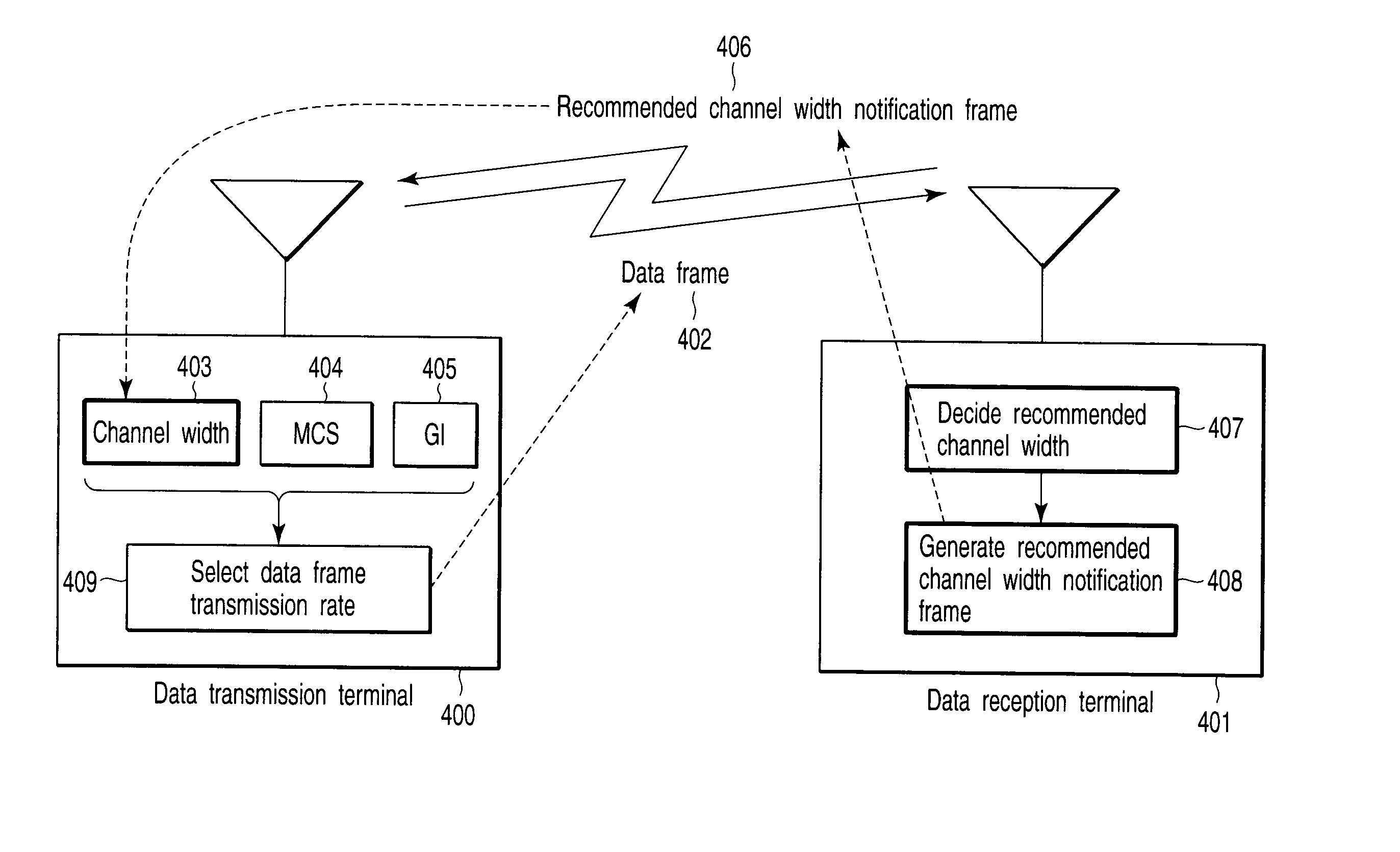

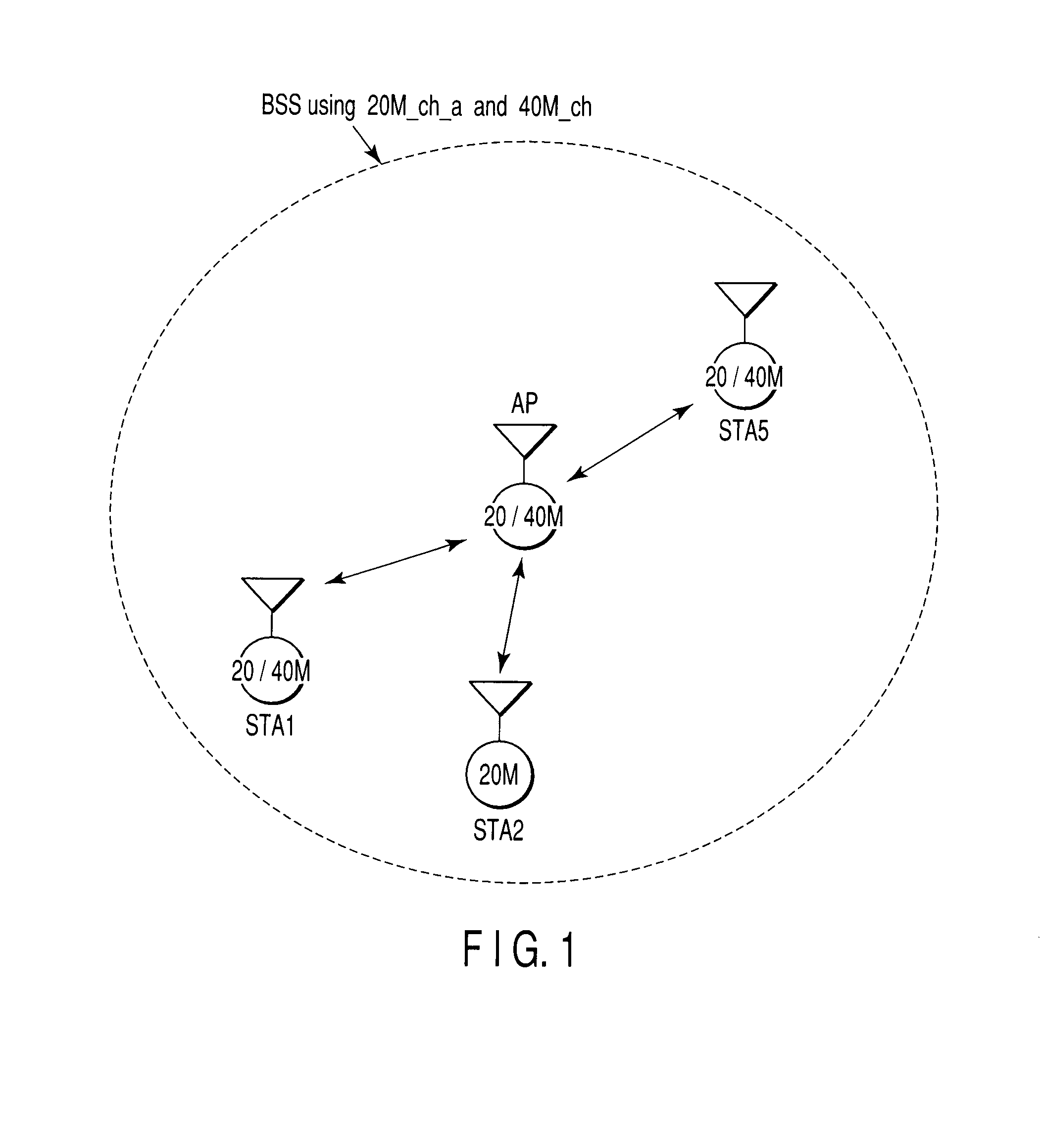

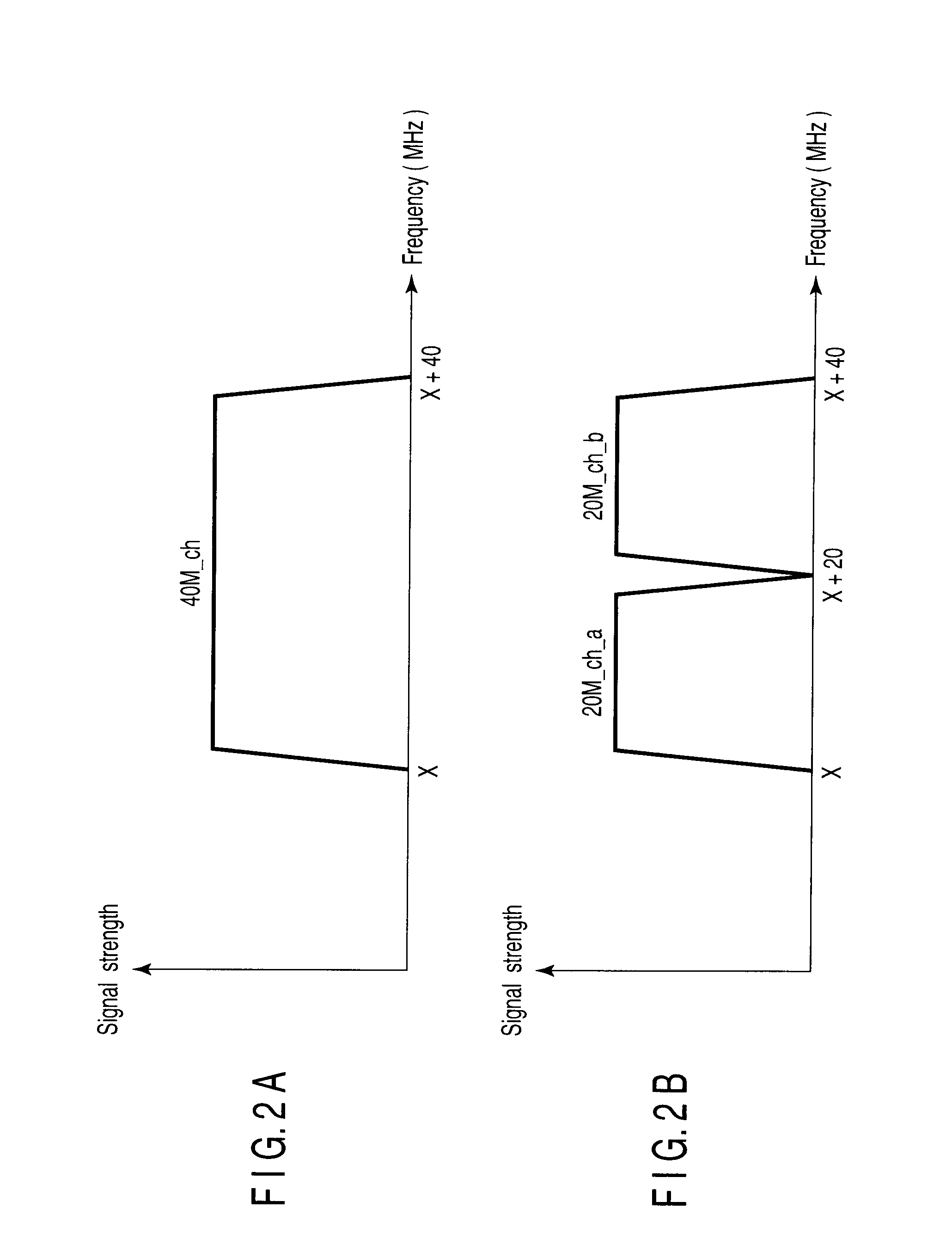

A radio communication apparatus that performs first radio communication using a first channel among two first channels each having a first channel width, and second radio communication using a second channel having a second channel width that is wider than the first channel width and also having a channel width overlapping with the two first channels. The apparatus includes an interference detection device which detects that interference occurs in the first channel among the two first channels, and a frame generation unit which generates a notification frame that recommends the use of only the first channel width. An instruction unit instructs the frame generation unit to generate the notification frame when the occurrence of interference is detected by the interference detection device. A frame transmission unit transmits the notification frame generated from the frame generation unit in response to the instruction from the instruction unit.

Owner:PALMIRA WIRELESS AG

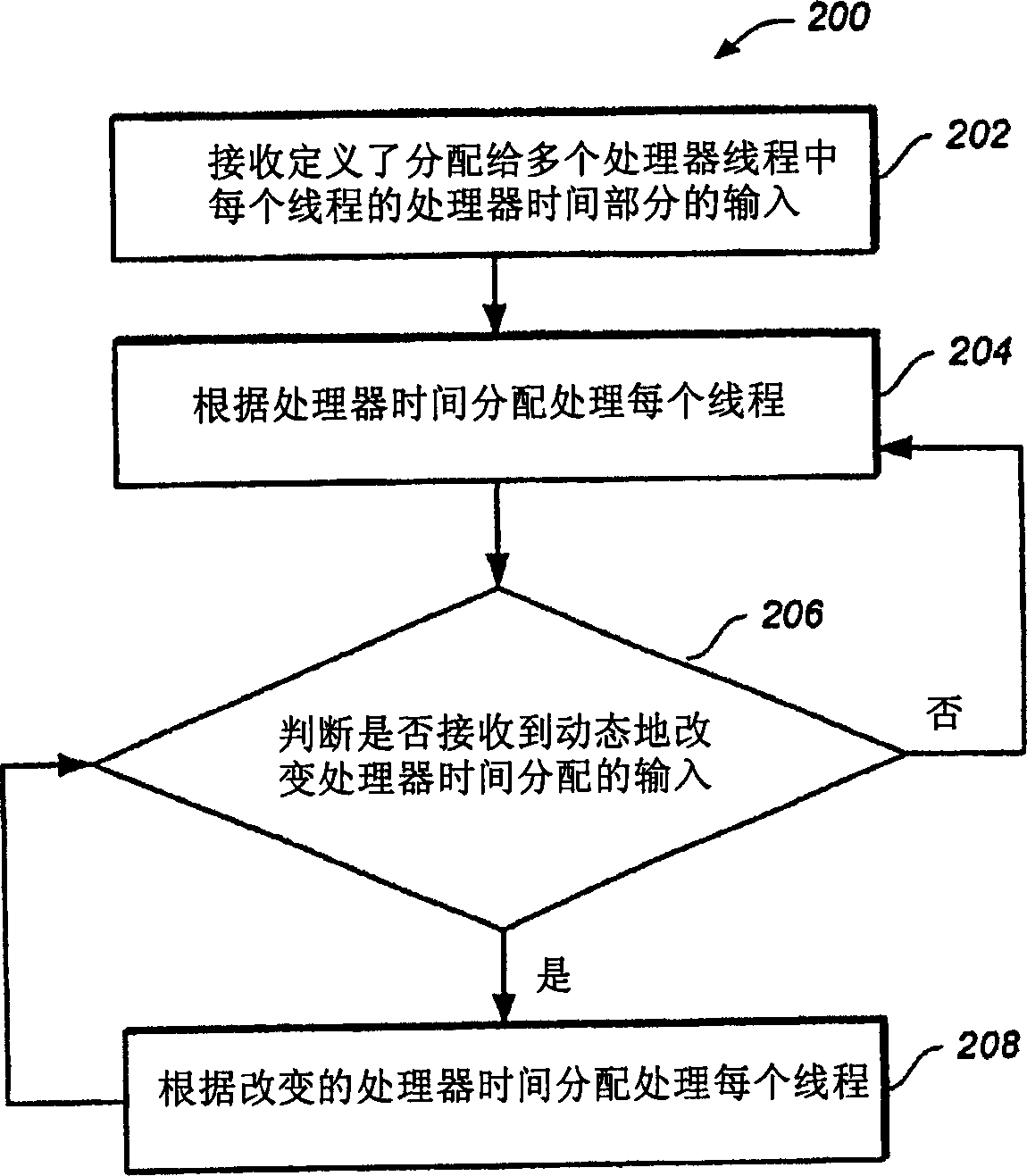

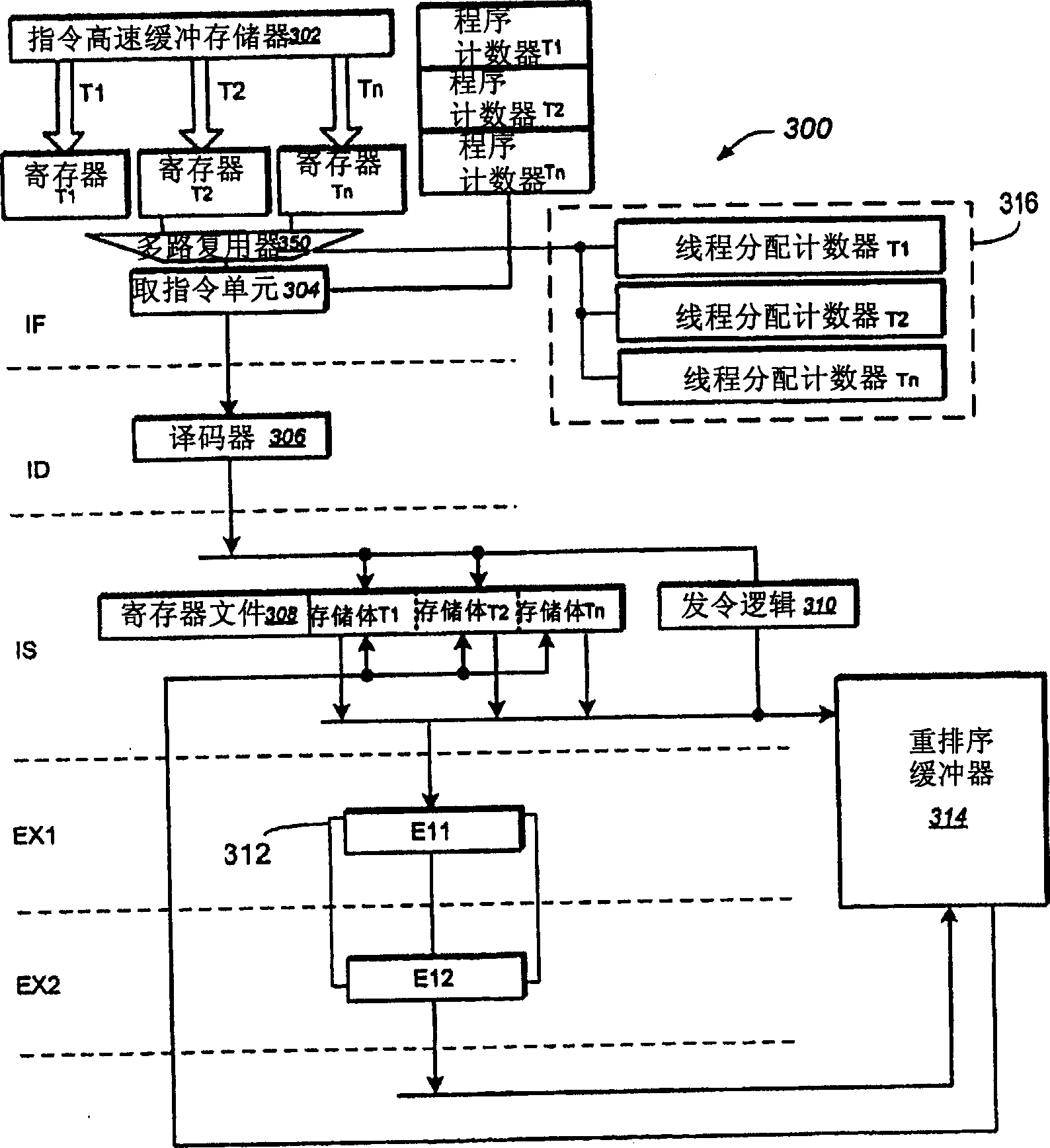

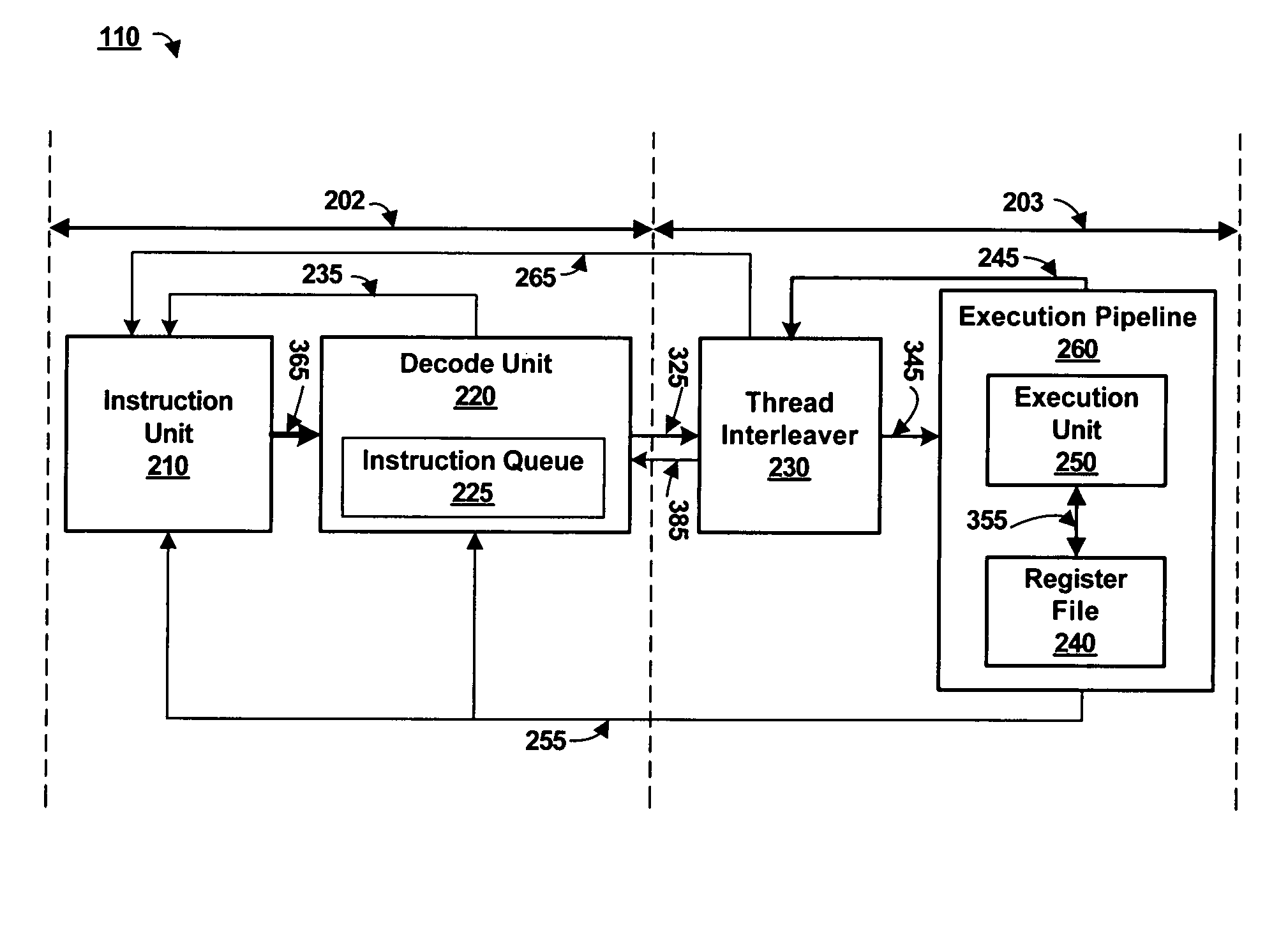

Thread interleaving in a multithreaded embedded processor

InactiveUS7360064B1Improves processor utilizationImprove performanceDigital computer detailsConcurrent instruction executionTime conditionInstruction unit

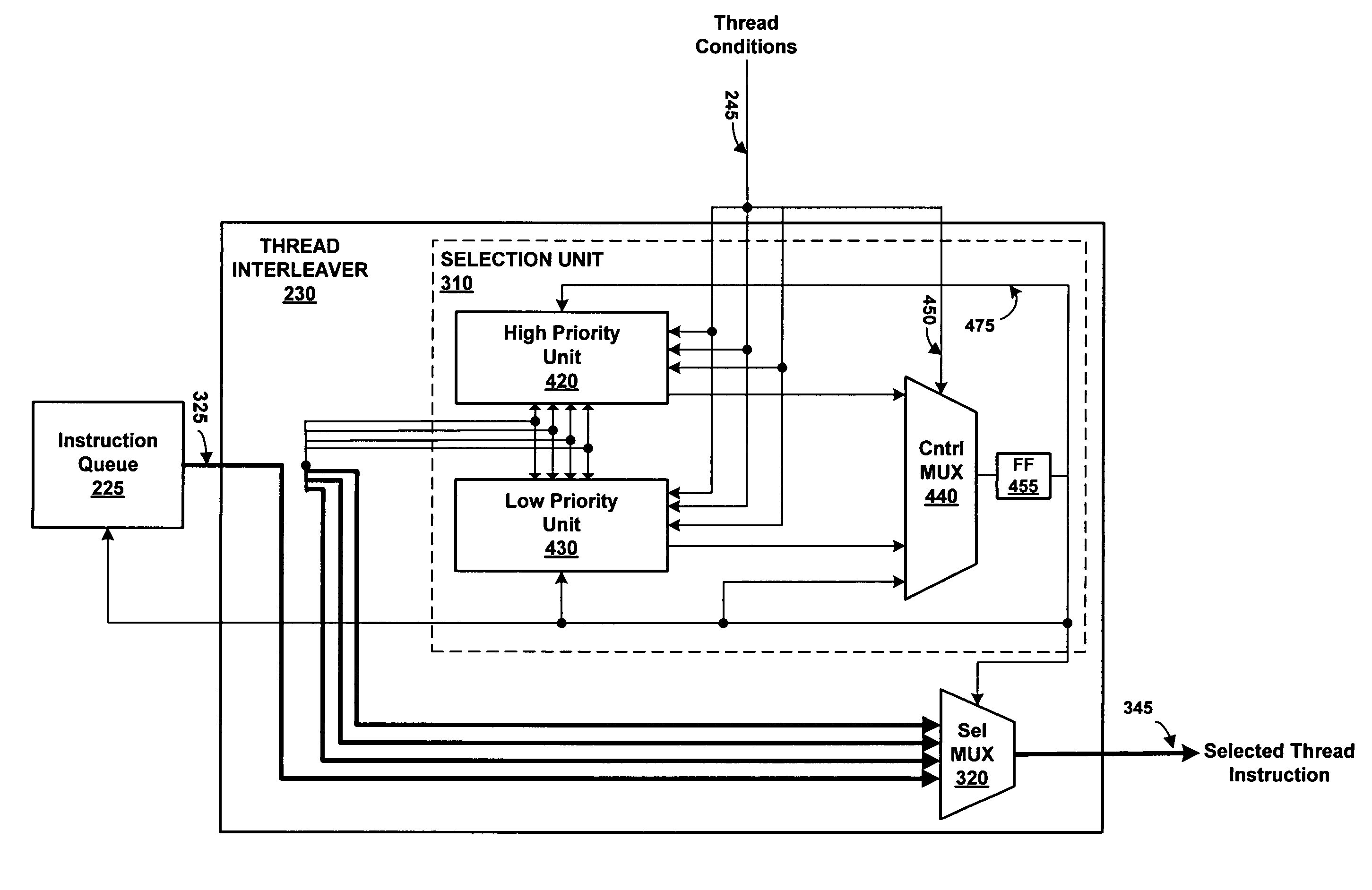

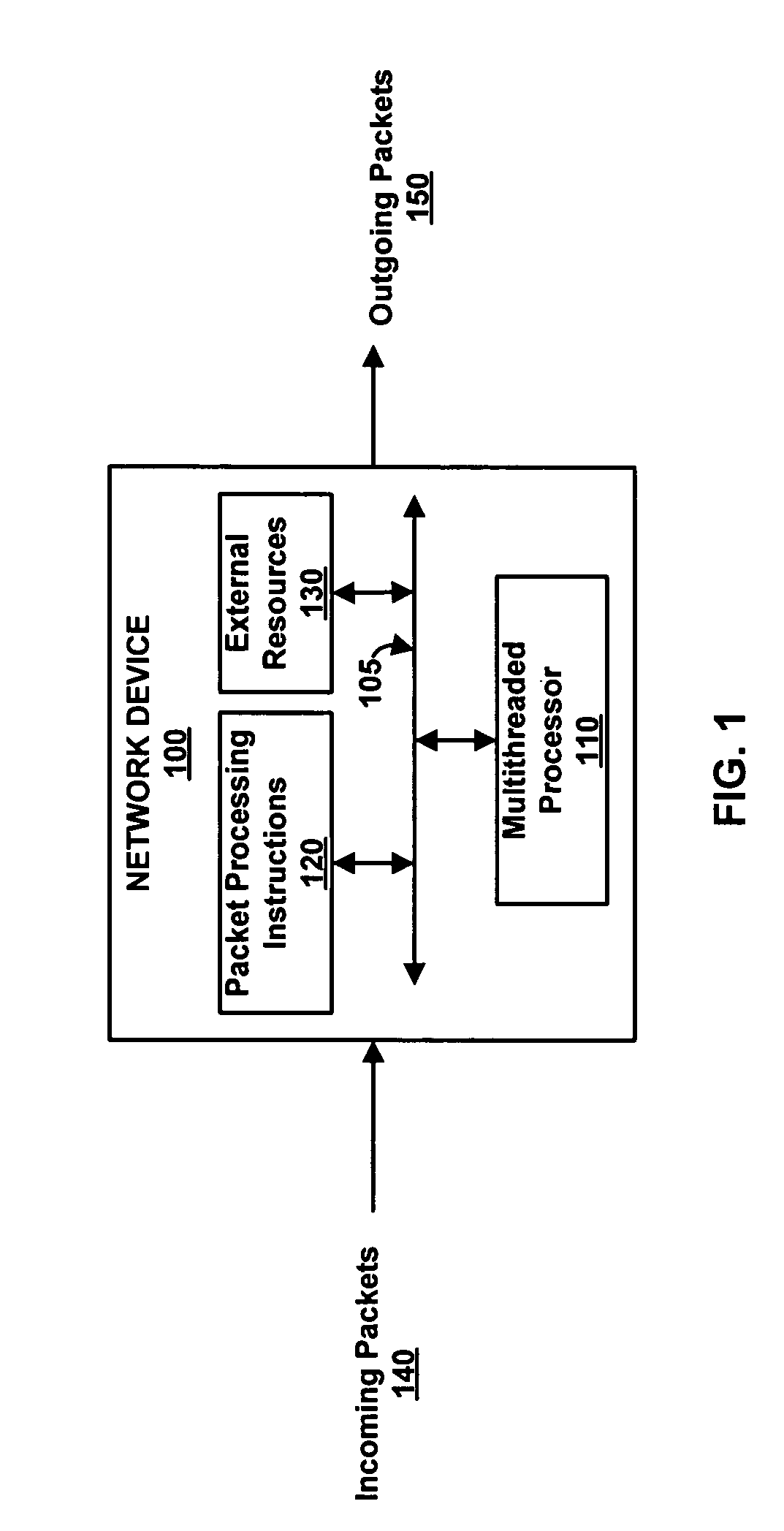

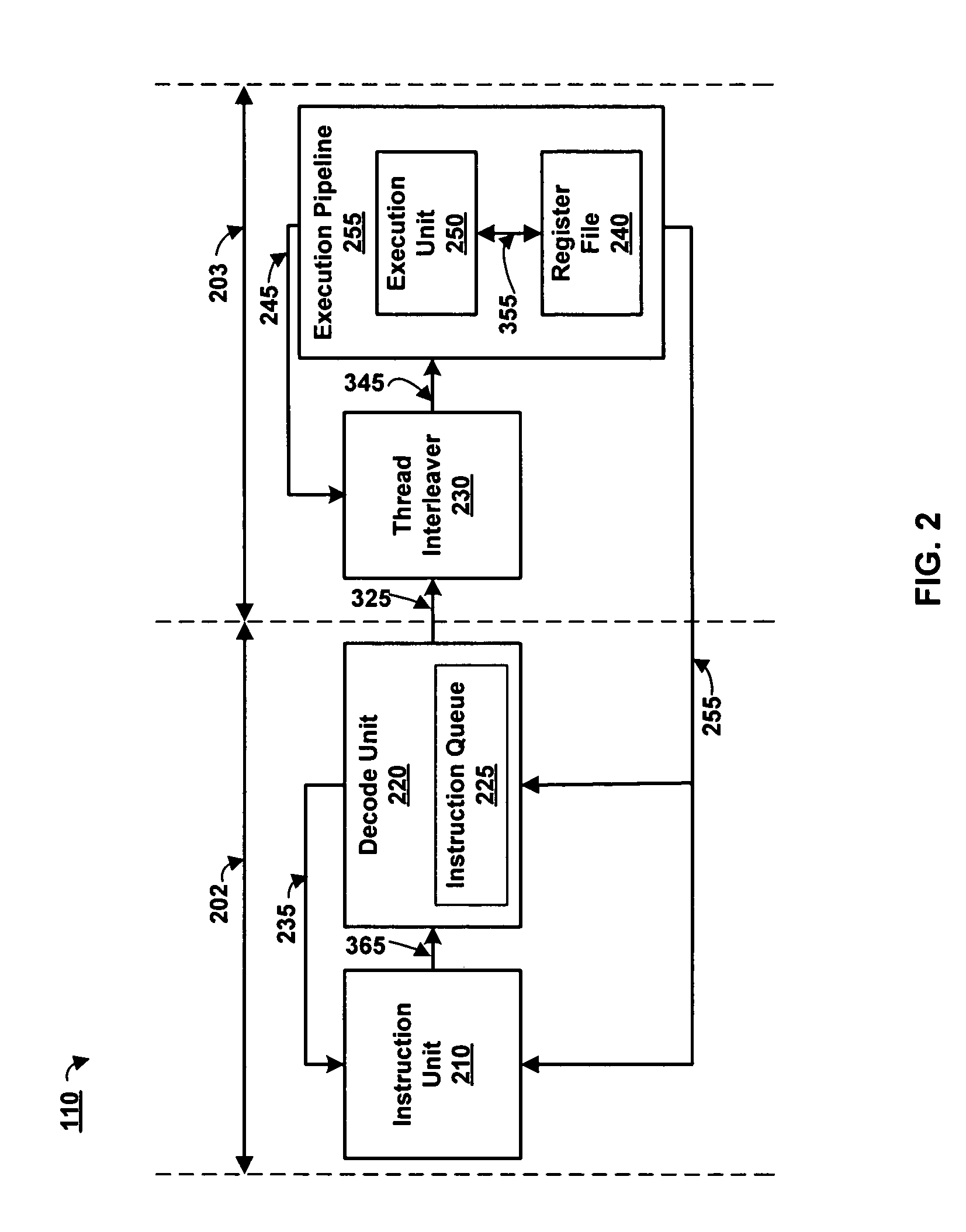

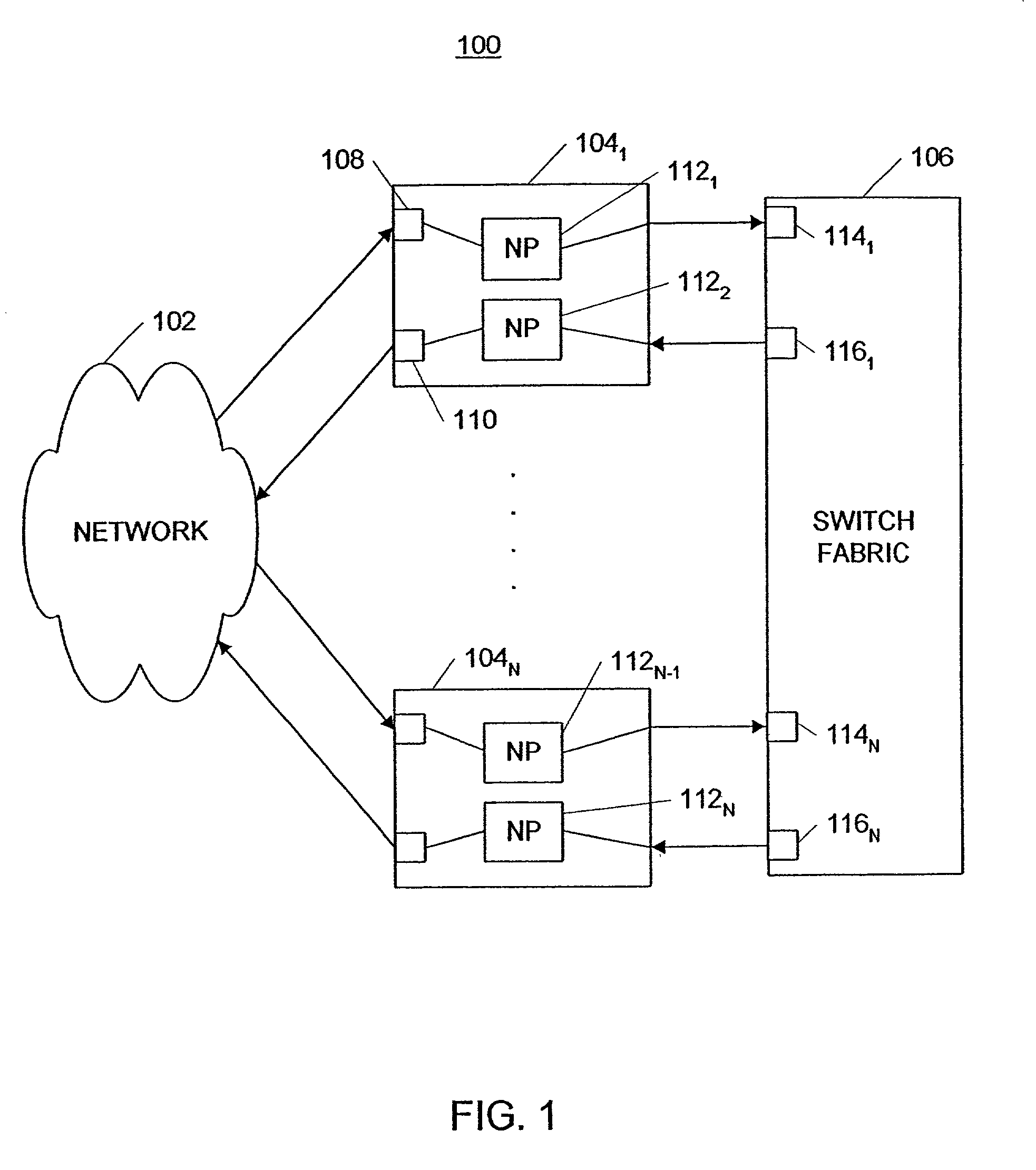

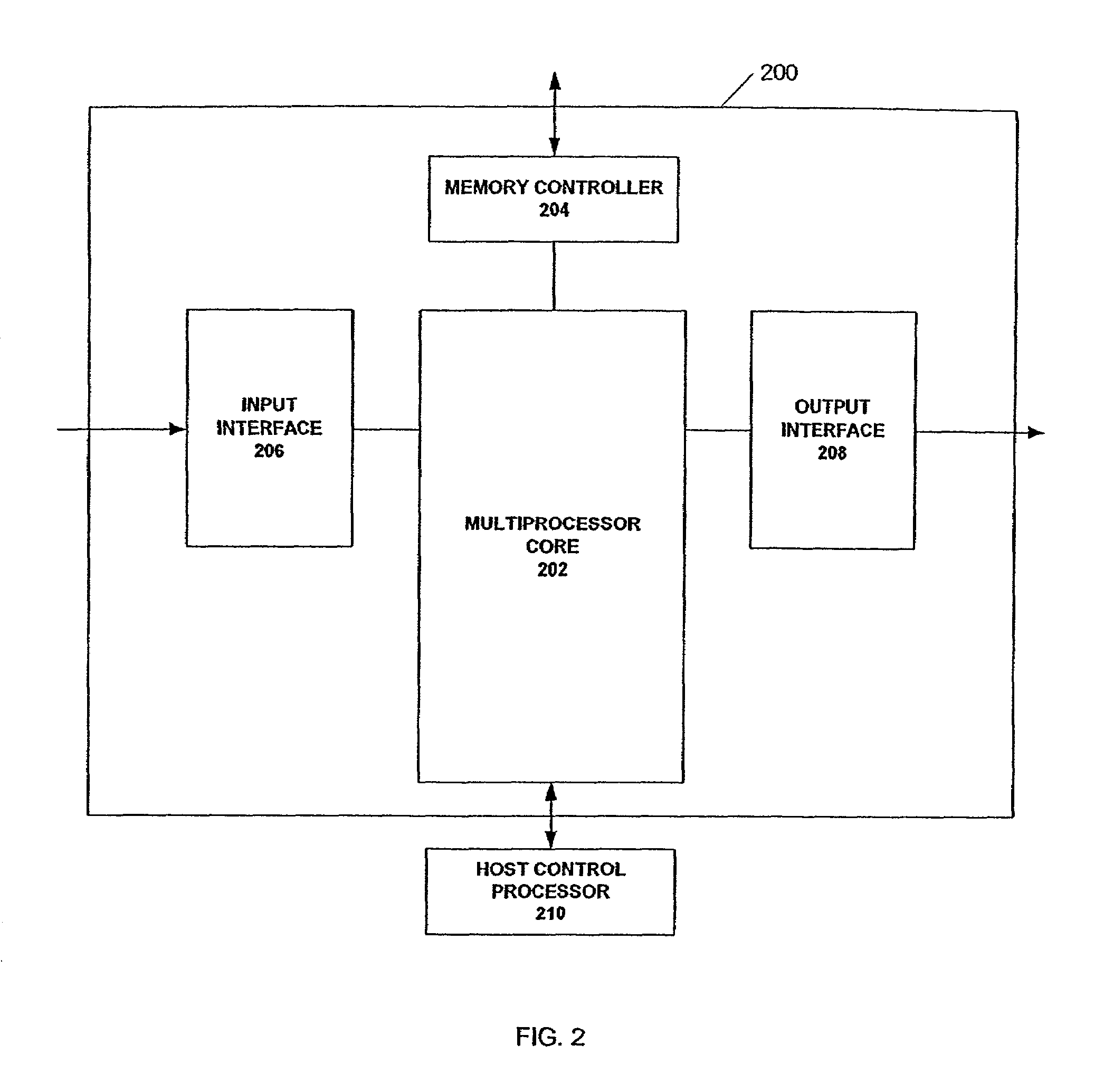

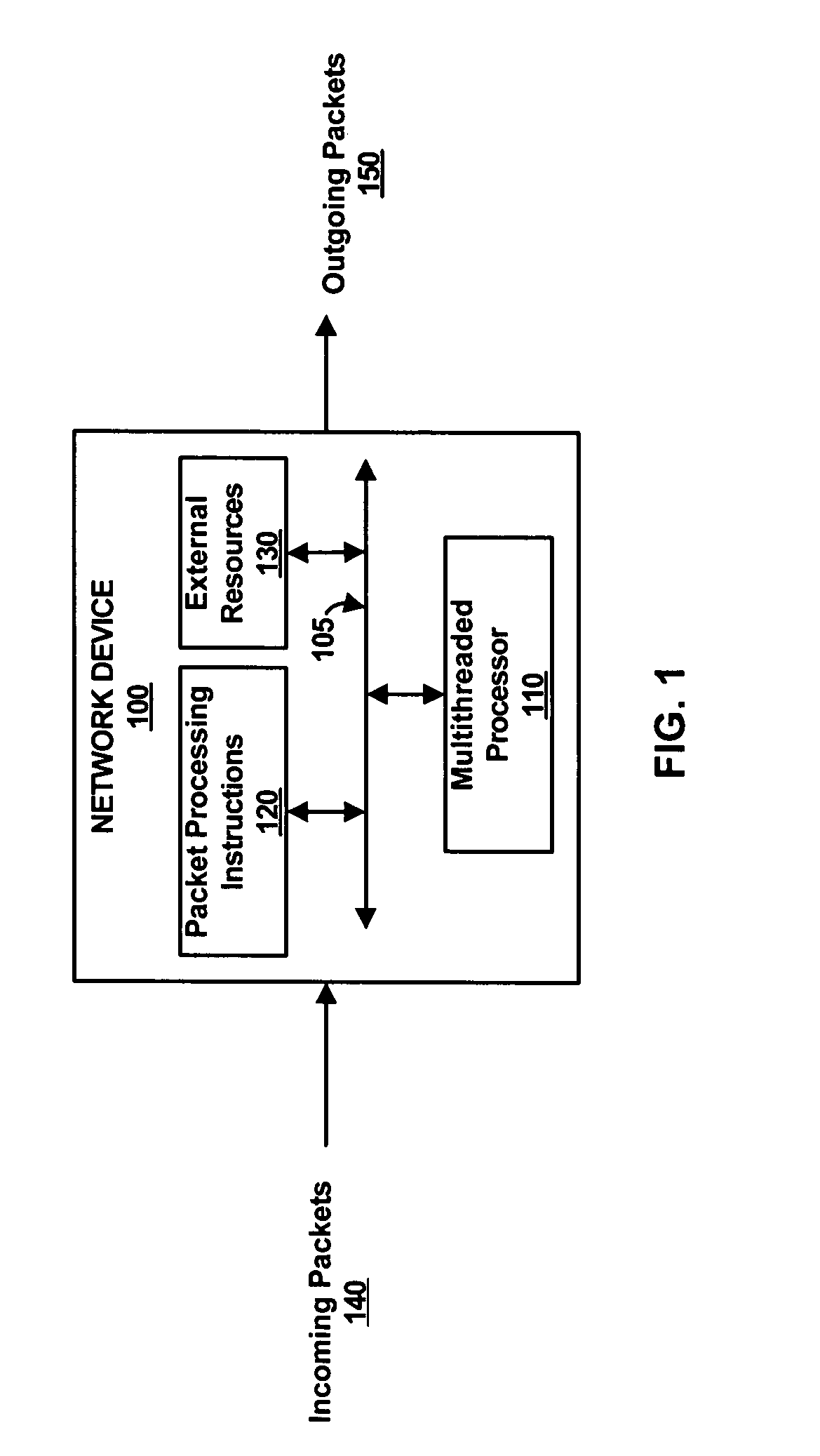

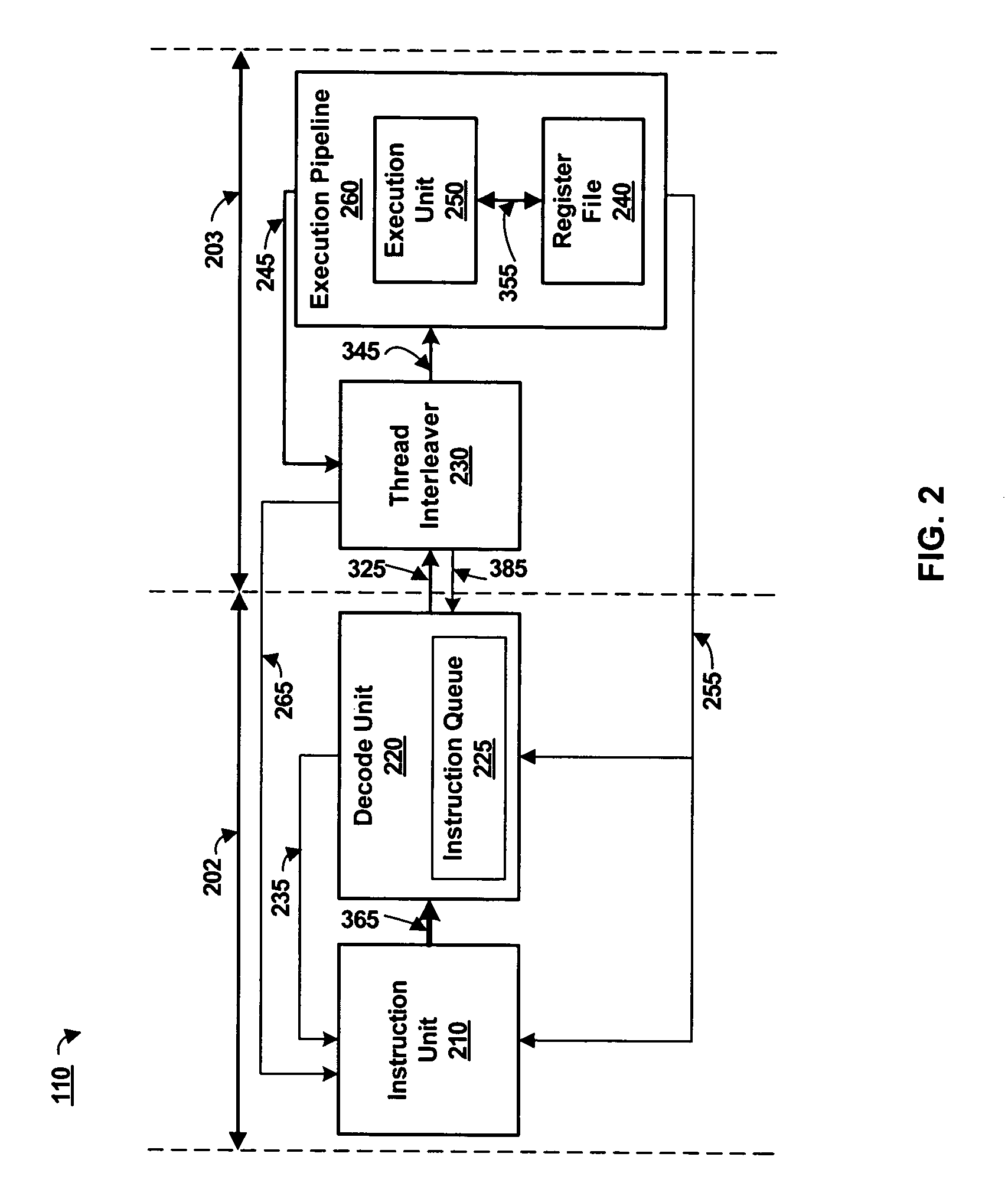

The present invention provides a network multithreaded processor, such as a network processor, including a thread interleaver that implements fine-grained thread decisions to avoid underutilization of instruction execution resources in spite of large communication latencies. In an upper pipeline, an instruction unit determines an instruction fetch sequence responsive to an instruction queue depth on a per thread basis. In a lower pipeline, a thread interleaver determines a thread interleave sequence responsive to thread conditions including thread latency conditions. The thread interleaver selects threads using a two-level round robin arbitration. Thread latency signals are active responsive to thread latencies such as thread stalls, cache misses, and interlocks. During the subsequent one or more clock cycles, the thread is ineligible for arbitration. In one embodiment, other thread conditions affect selection decisions such as local priority, global stalls, and late stalls.

Owner:CISCO TECH INC

System and method for instruction-level parallelism in a programmable multiple network processor environment

InactiveUS6950927B1Digital computer detailsConcurrent instruction executionInstruction unitExecution unit

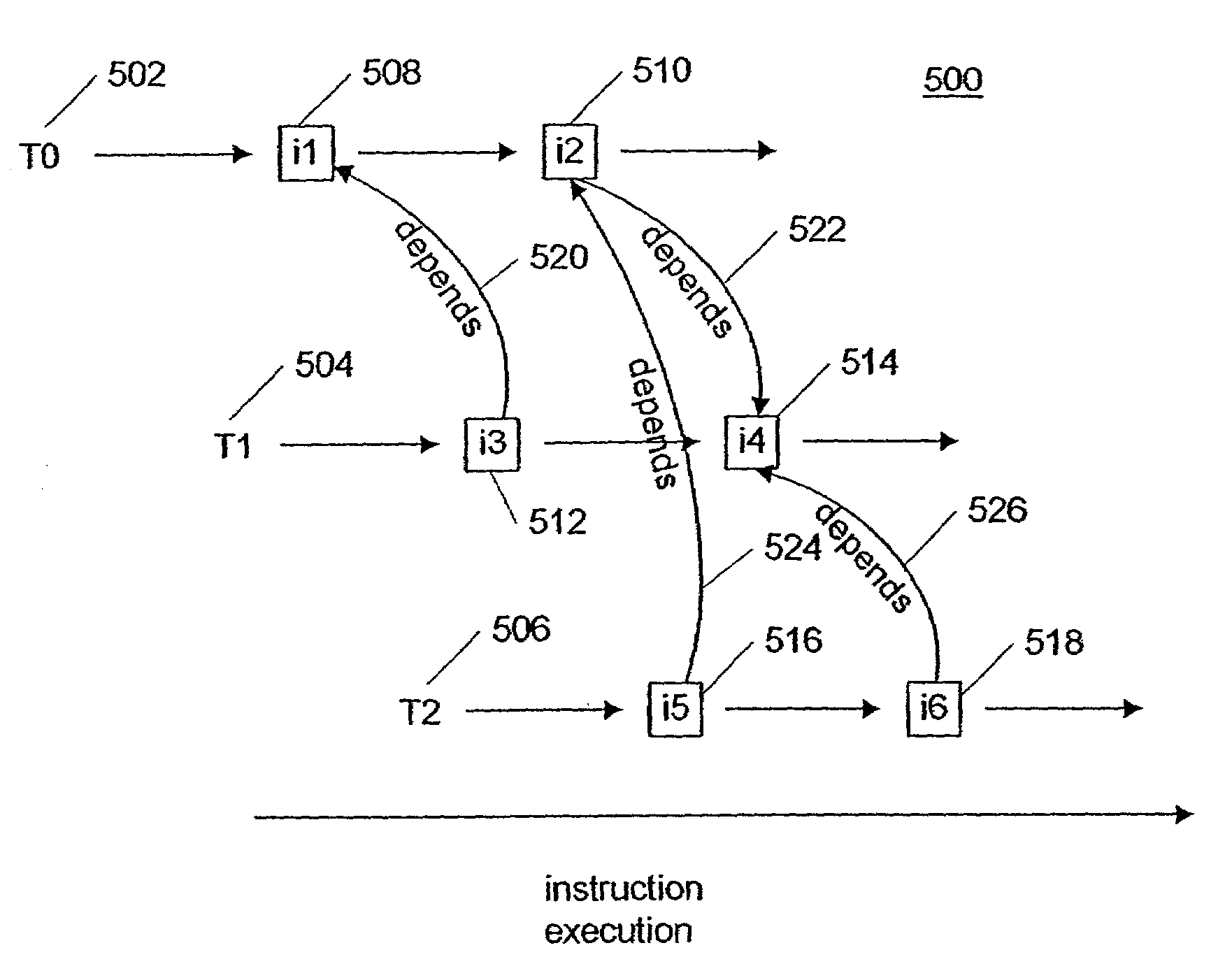

A system and method process data elements with instruction-level parallelism. An instruction buffer holds a first instruction and a second instruction, the first instruction being associated with a first thread, and the second instruction being associated with a second thread. A dependency counter counts satisfaction of dependencies of instructions of the second thread on instructions of the first thread. An instruction control unit is coupled to the instruction buffer and the dependency counter, the instruction control unit increments and decrements the dependency counter according to dependency information included in instructions. An execution switch is coupled to the instruction control unit and the instruction buffer, and the execution switch routes instructions to instruction execution units.

Owner:UNITED STATES OF AMERICA +1

Information processing apparatus and method, recording medium, and program

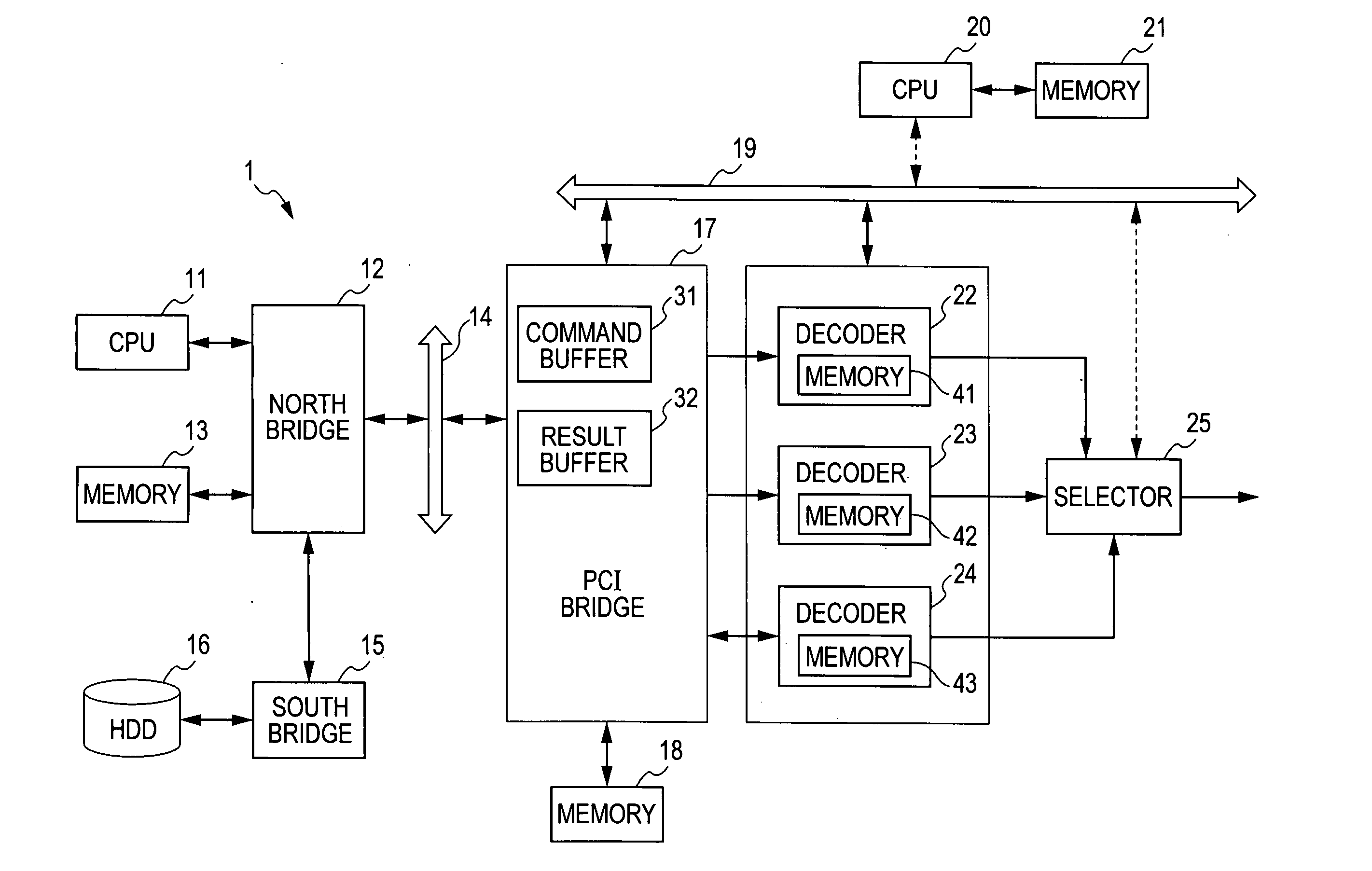

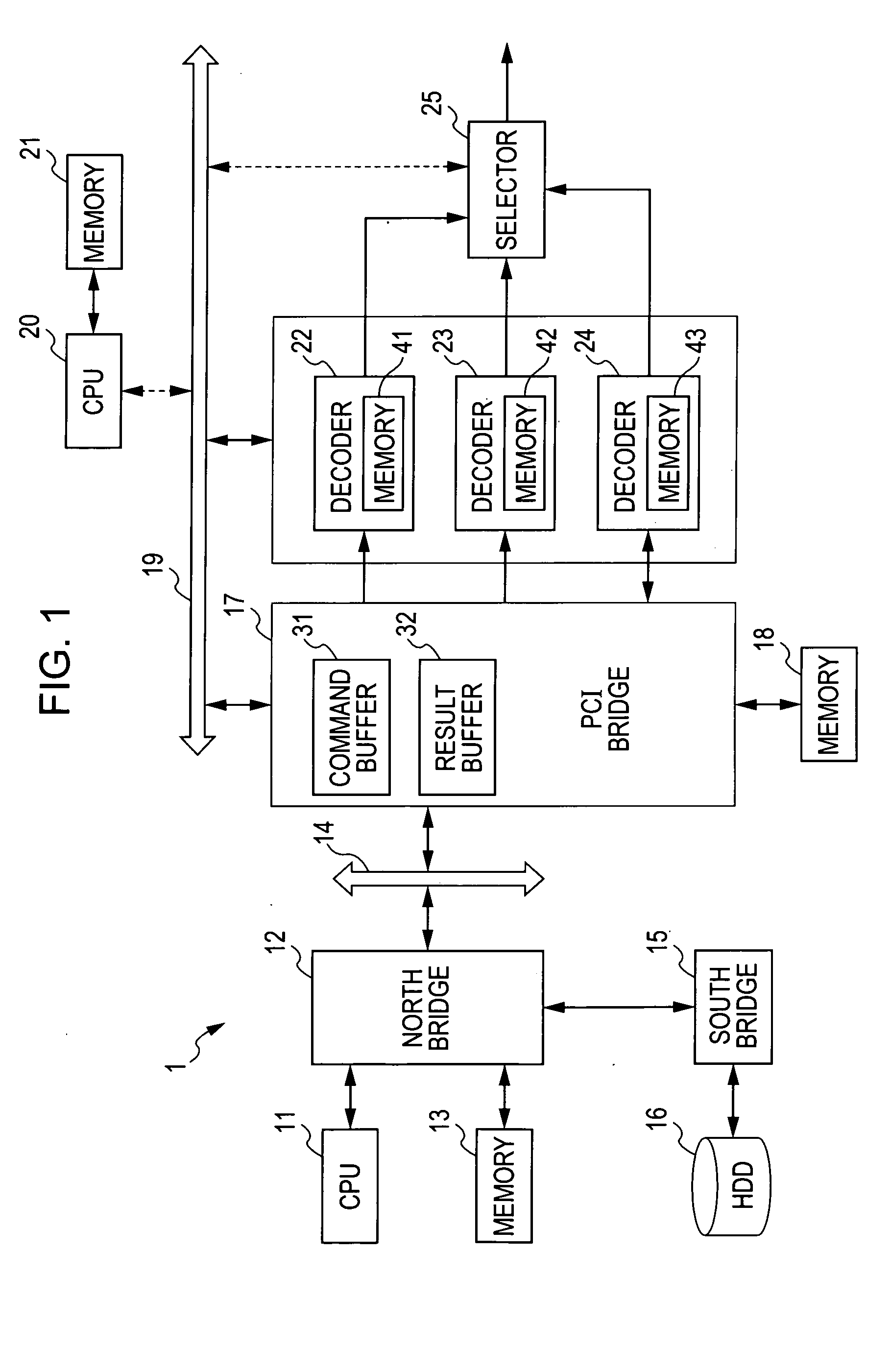

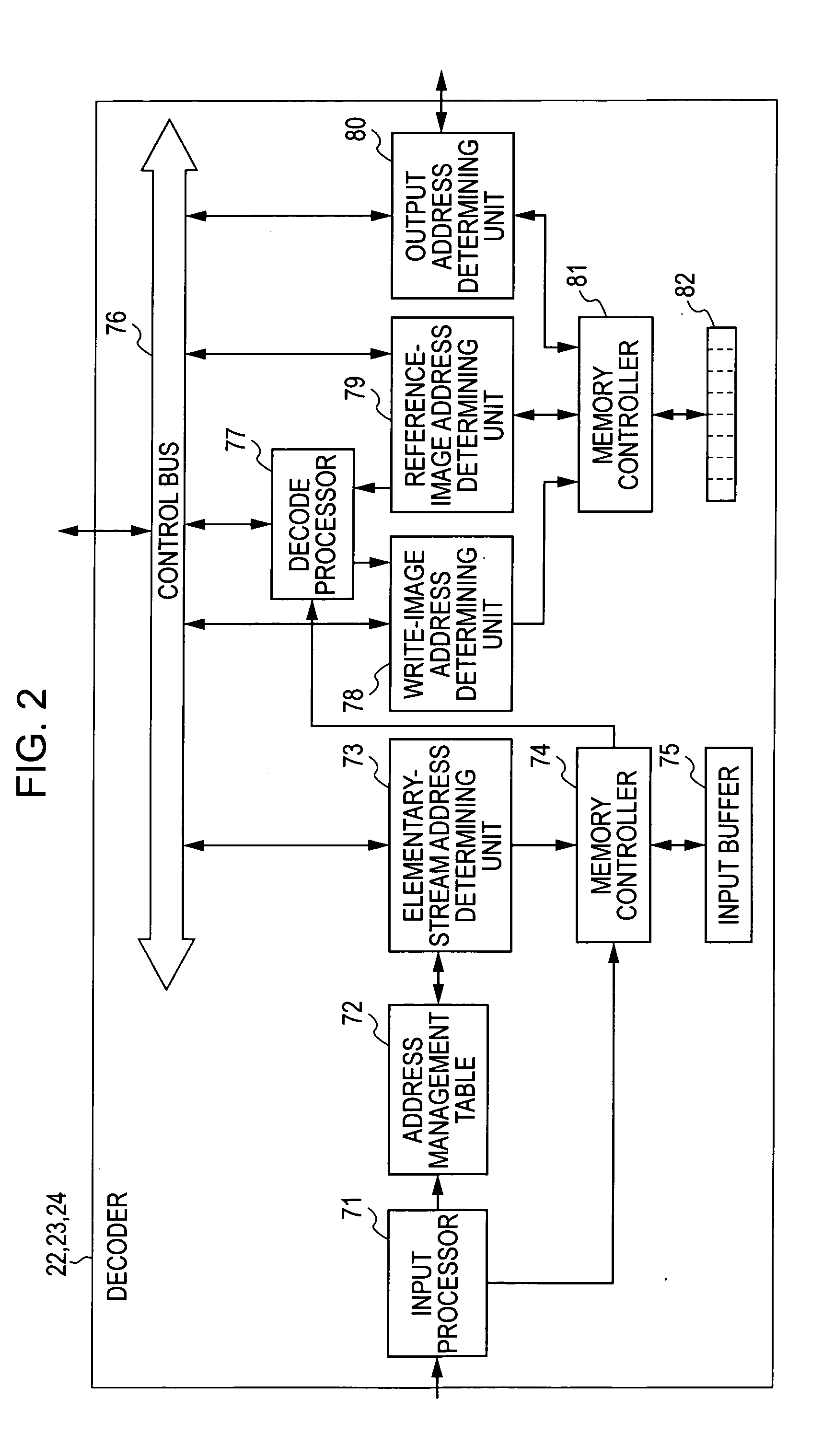

InactiveUS20060088286A1Control is complicatedSmoothly displaying imageTelevision system detailsDisc-shaped record carriersInformation processingInstruction unit

An information processing apparatus for decoding compression-coded video data includes at least one decoder decoding the compression-coded video data, a supply controller controlling the supply of the compression-coded video data to the decoder, and a controller controlling processing executed by the supply controller and the decoder. The controller determines the order of decoding processing performed by the decoder so that, among pictures contained in a decoding processing unit for the decoding processing performed by the decoder, I-pictures and P-pictures are decoded before B-pictures. The controller selects pictures to be output from the decoder from among the pictures contained in the decoding processing unit on the basis of a playback speed instruction provided by a playback speed instruction unit.

Owner:SONY CORP

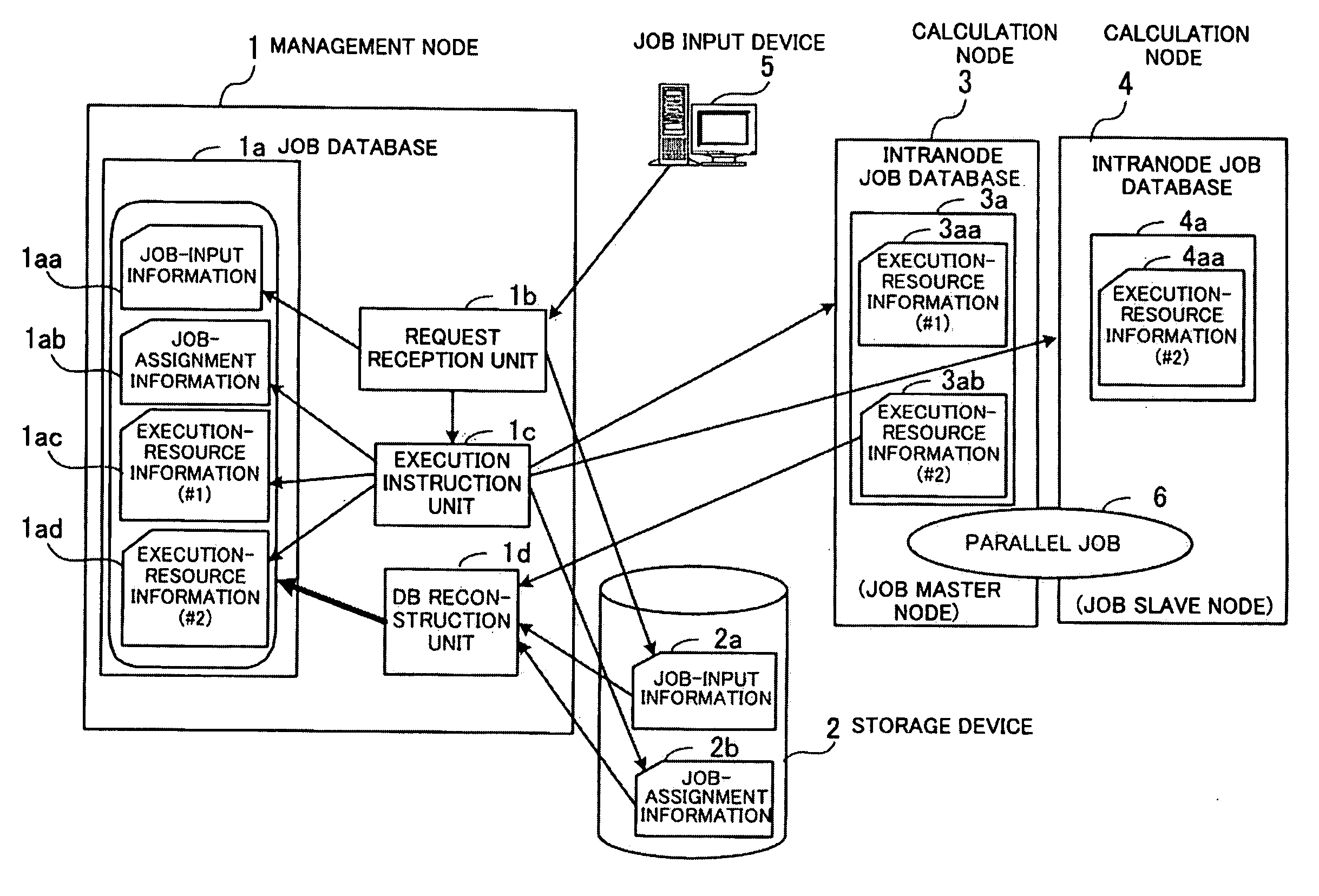

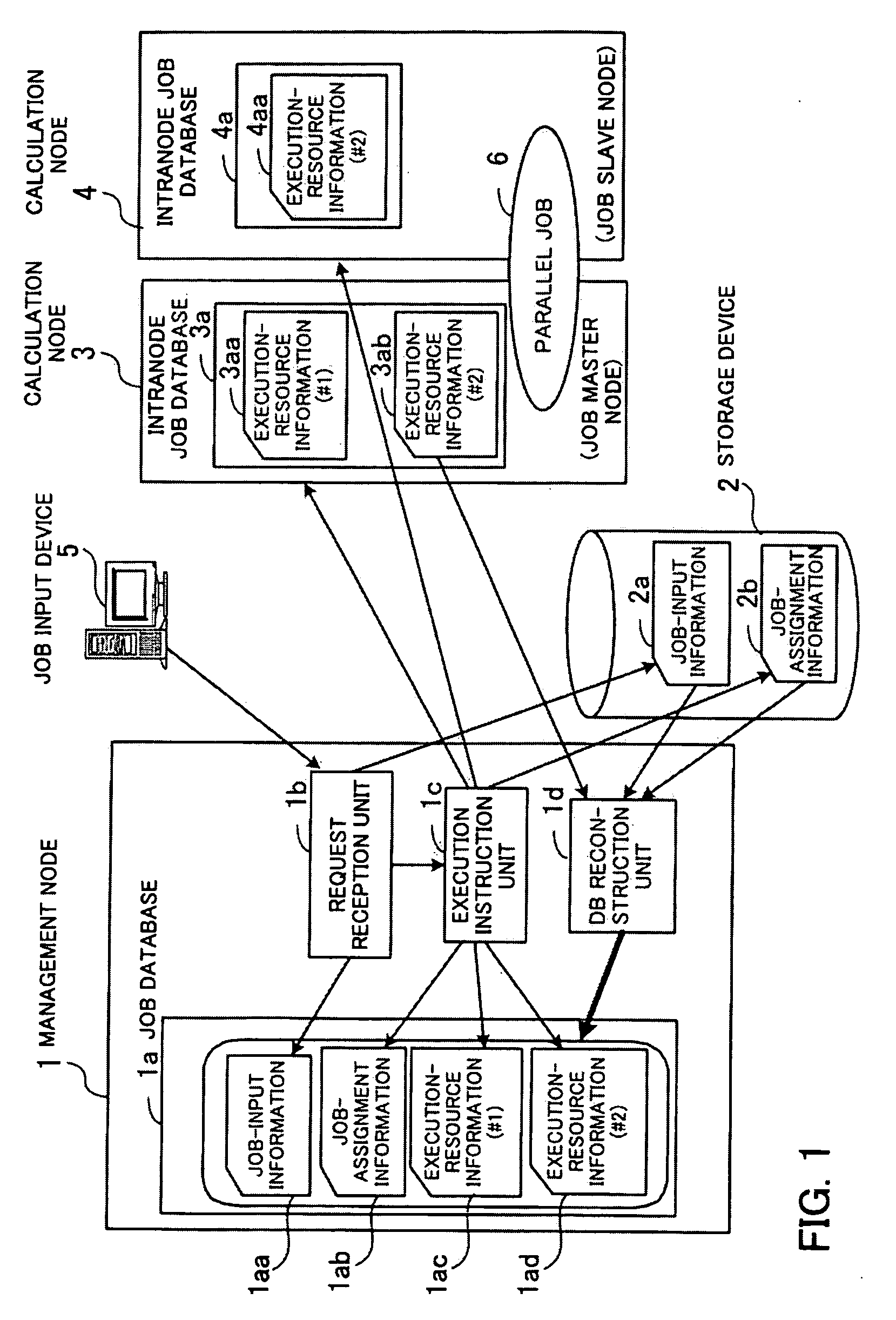

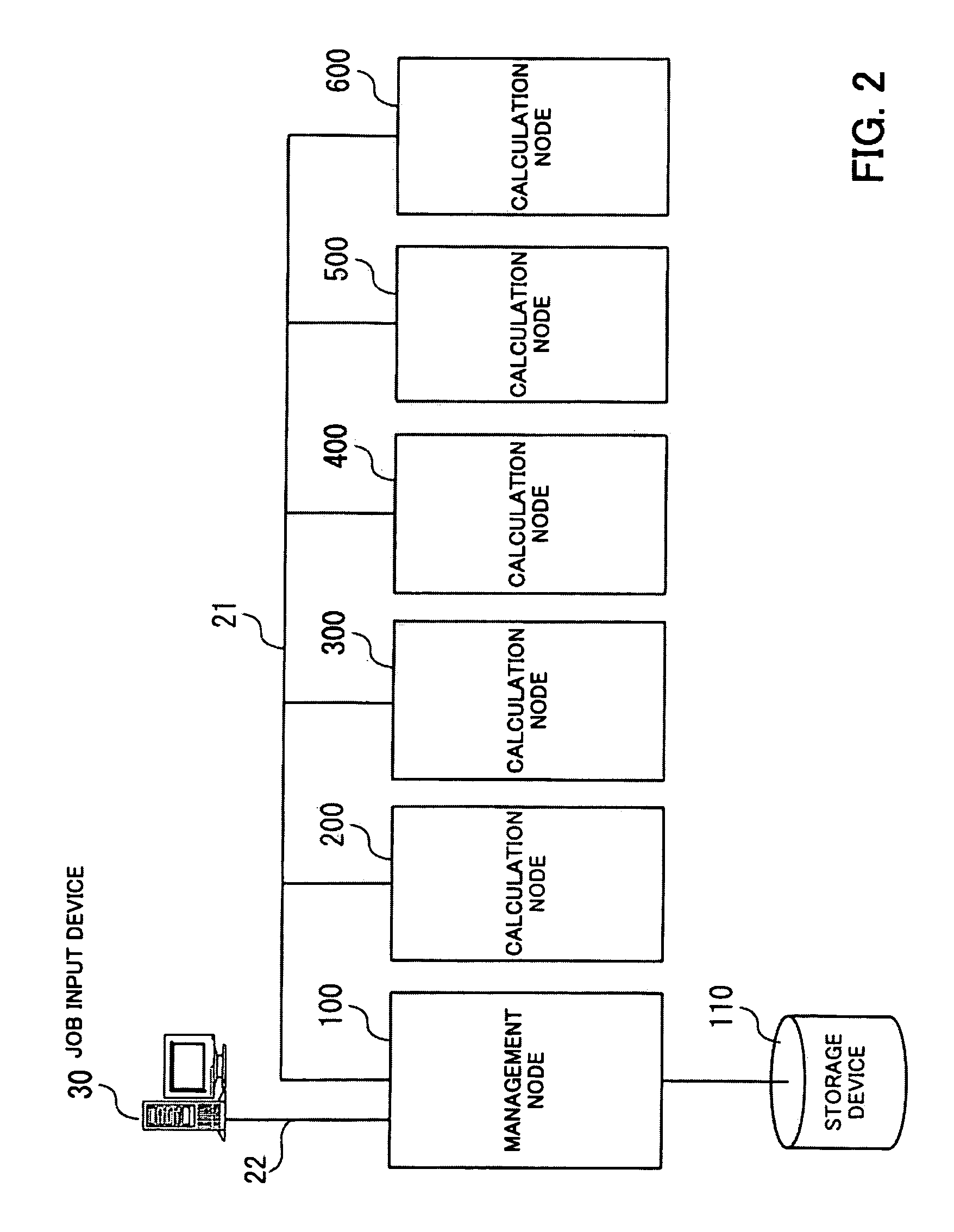

Job management device, cluster system, and computer-readable medium storing job management program

ActiveUS20080209423A1Ensure reliabilityEfficient processingError detection/correctionDigital data processing detailsInstruction unitResource information

In a job management device: a request reception unit stores job-input information in a storage device on receipt of a job-execution request; and an execution instruction unit sends to one or more job-assigned calculation nodes a job-execution instruction together with execution-resource information, and stores job-assignment information in the storage device in association with a job identifier. When the contents of the job database are lost by a restart of the job management device, a reconstruction unit collects the job-input information and the job-assignment information from the storage device, collects the execution-resource information from the one or more job-assigned calculation nodes, and reconstructs the job information in the job database.

Owner:FUJITSU LTD

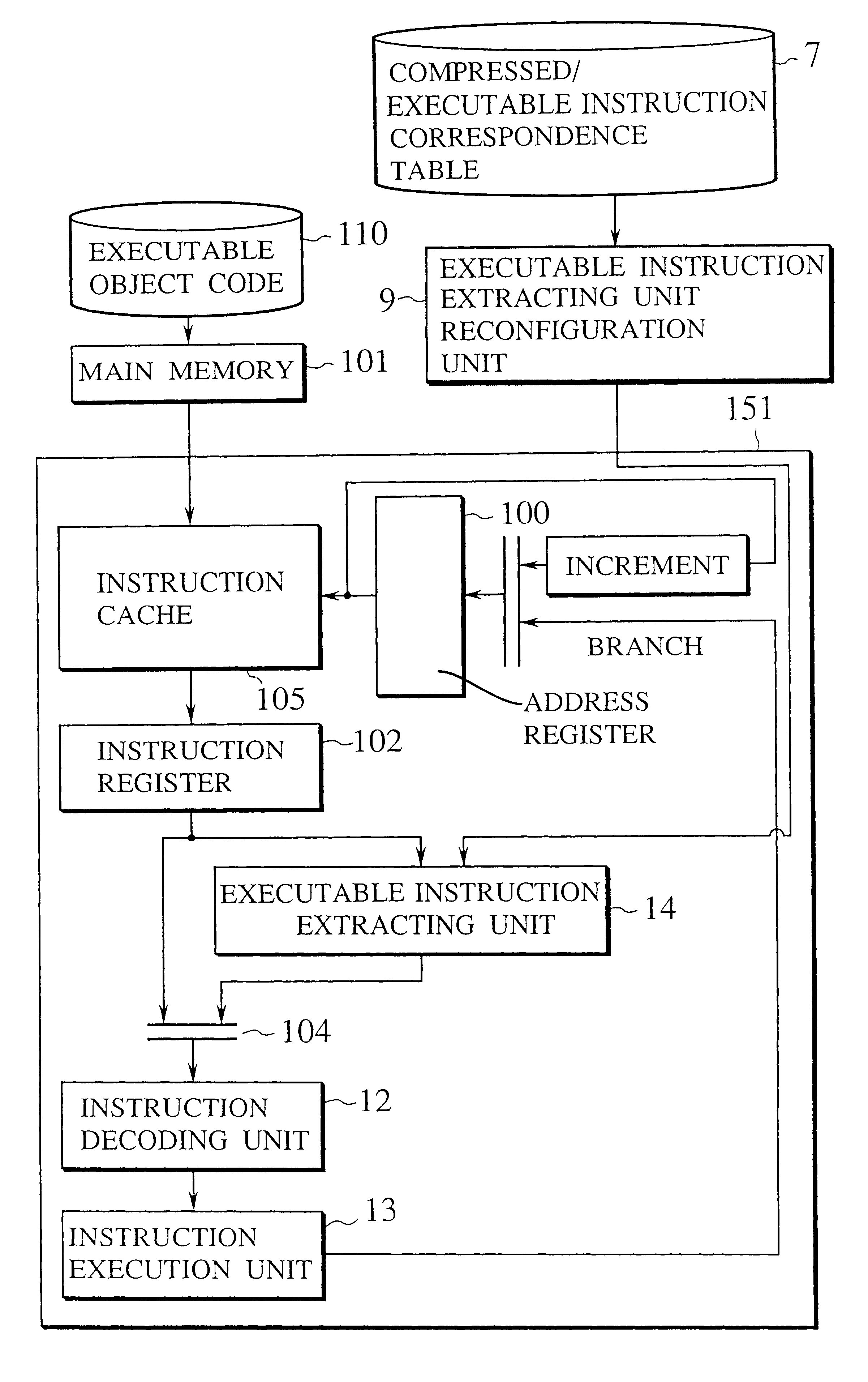

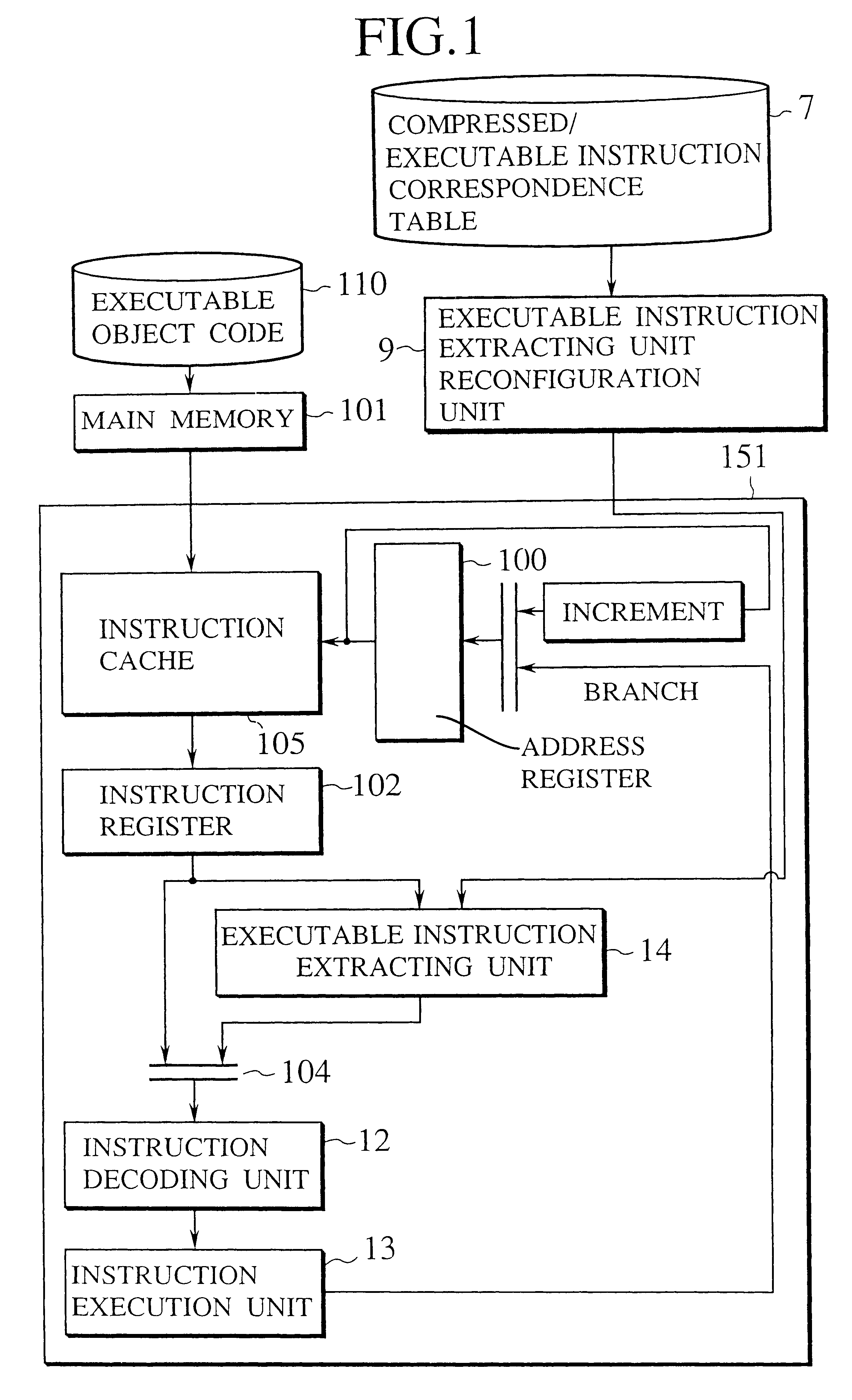

Information processing apparatus provided with an optimized executable instruction extracting unit for extending compressed instructions

InactiveUS6587939B1Reduce the numberData processing applicationsRuntime instruction translationInformation processingInstruction unit

An information processing apparatus is provided with a executable instruction extracting unit which is reconfigured by means of a executable instruction extracting unit reconfiguration unit with reference to a compressed / executable instruction correspondence table optimized for the respective executable program, which has been made up with an compressed instruction. The compressed instruction is extended into the corresponding executable instructions by means of the executable instruction extracting unit as reconfigured.

Owner:KK TOSHIBA

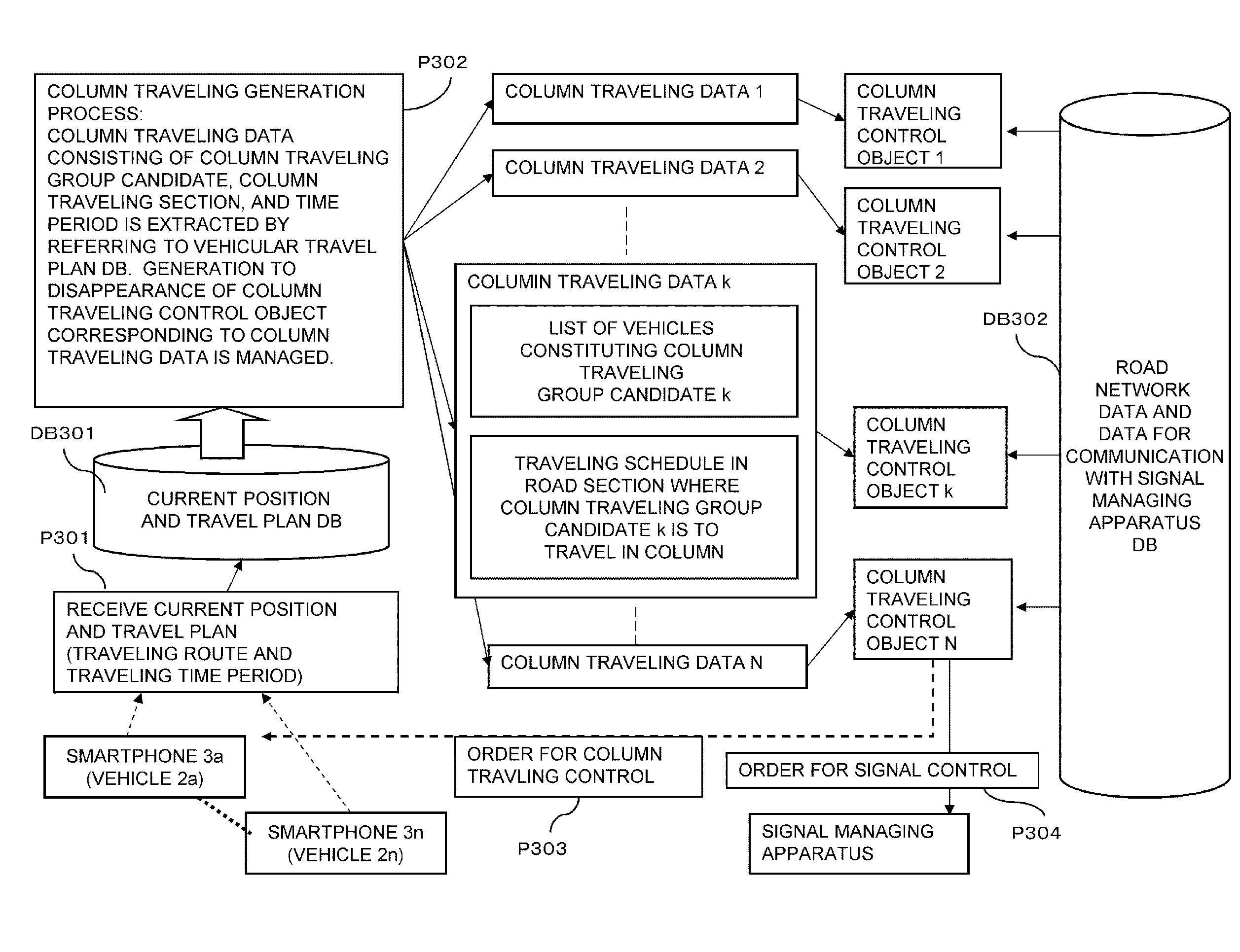

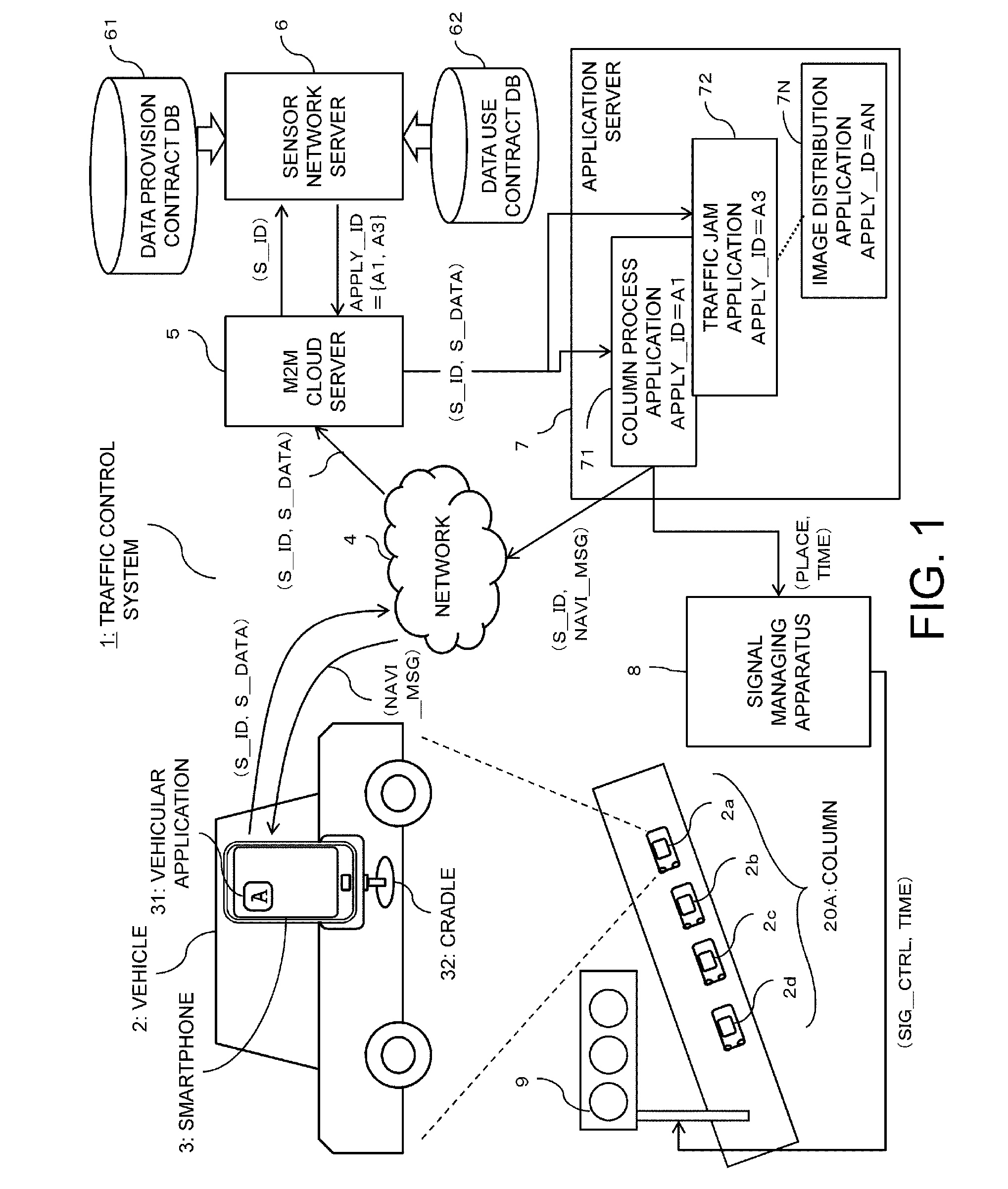

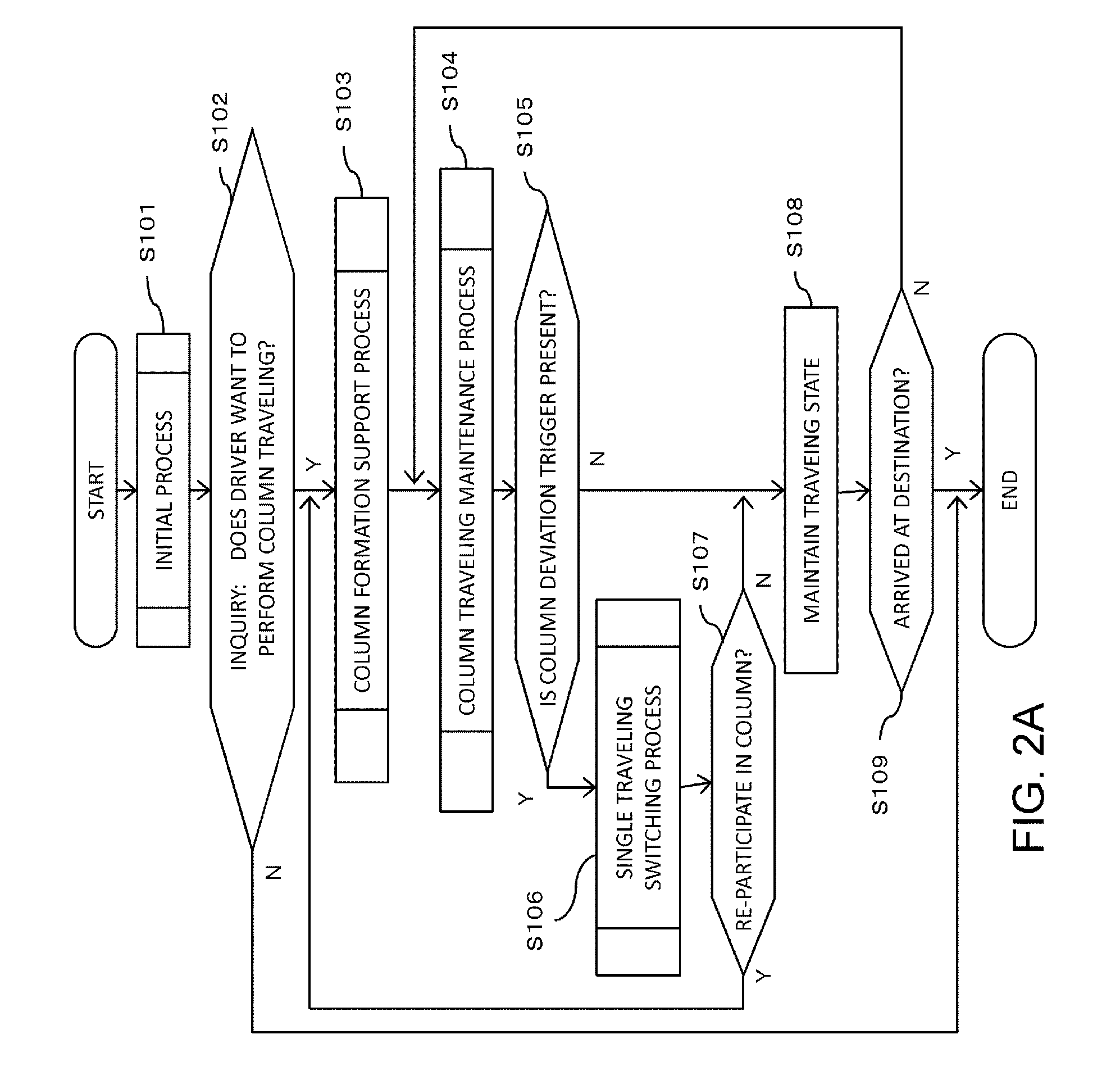

Data flow control order generating apparatus and sensor managing apparatus

ActiveUS20140372561A1Economic effectRequired data inexpensivelyMultiple digital computer combinationsPlatooningSensing dataInstruction unit

There is used a data flow control order generating apparatus that includes: a sensor side metadata acquisition unit acquiring sensor side metadata as information related to a sensor that outputs sensing data; an application side metadata acquisition unit acquiring application side metadata as information related to an application that provides a service by using the sensing data; a matching unit performing matching between the sensor side metadata and the application side metadata to extract the sensor capable of providing the sensing data that satisfies the request of the application; and an instruction unit transmitting a data flow control order that identifies the sensor extracted by the matching unit and the application to a sensor managing apparatus that manages the sensor.

Owner:ORMON CORP

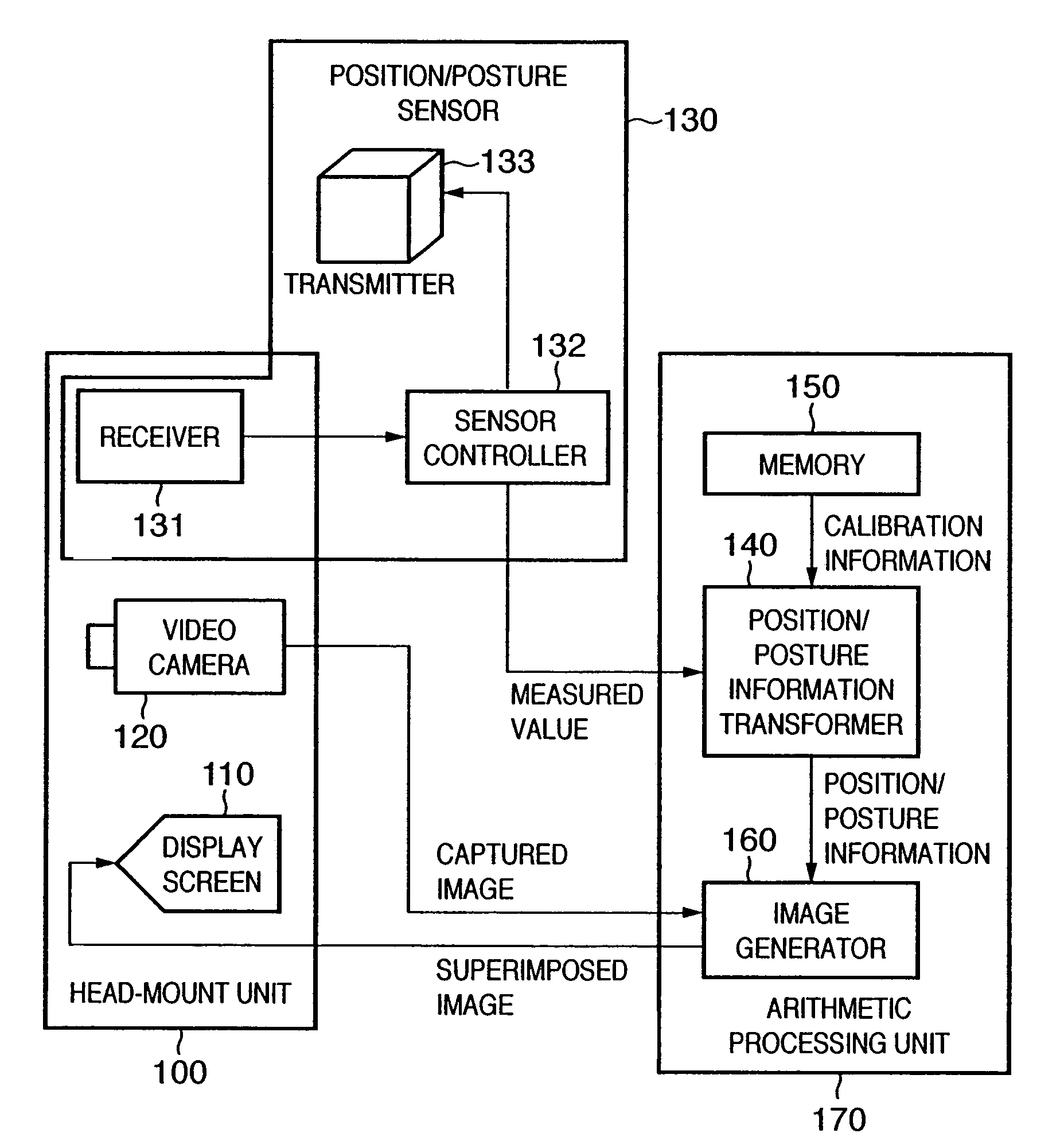

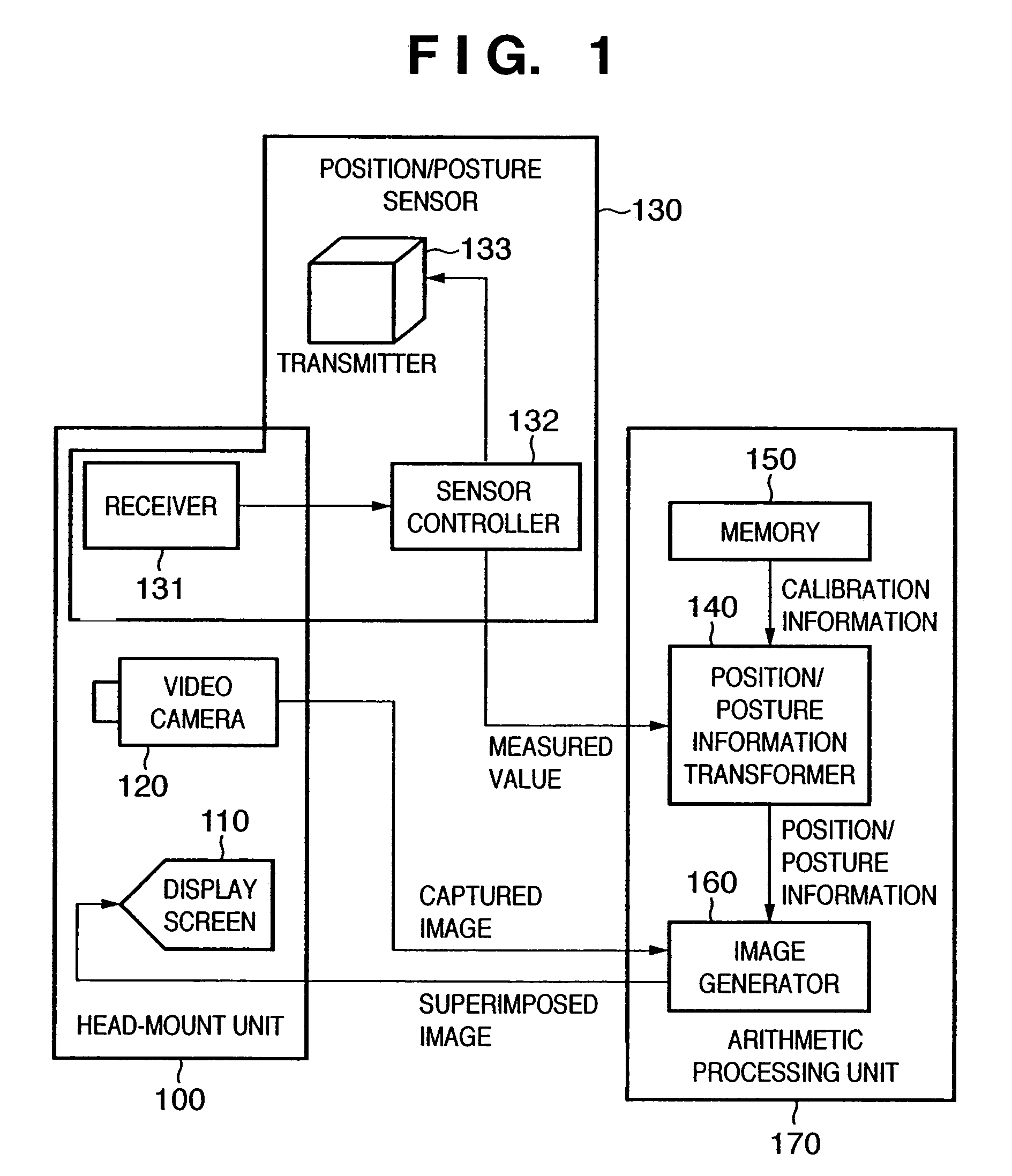

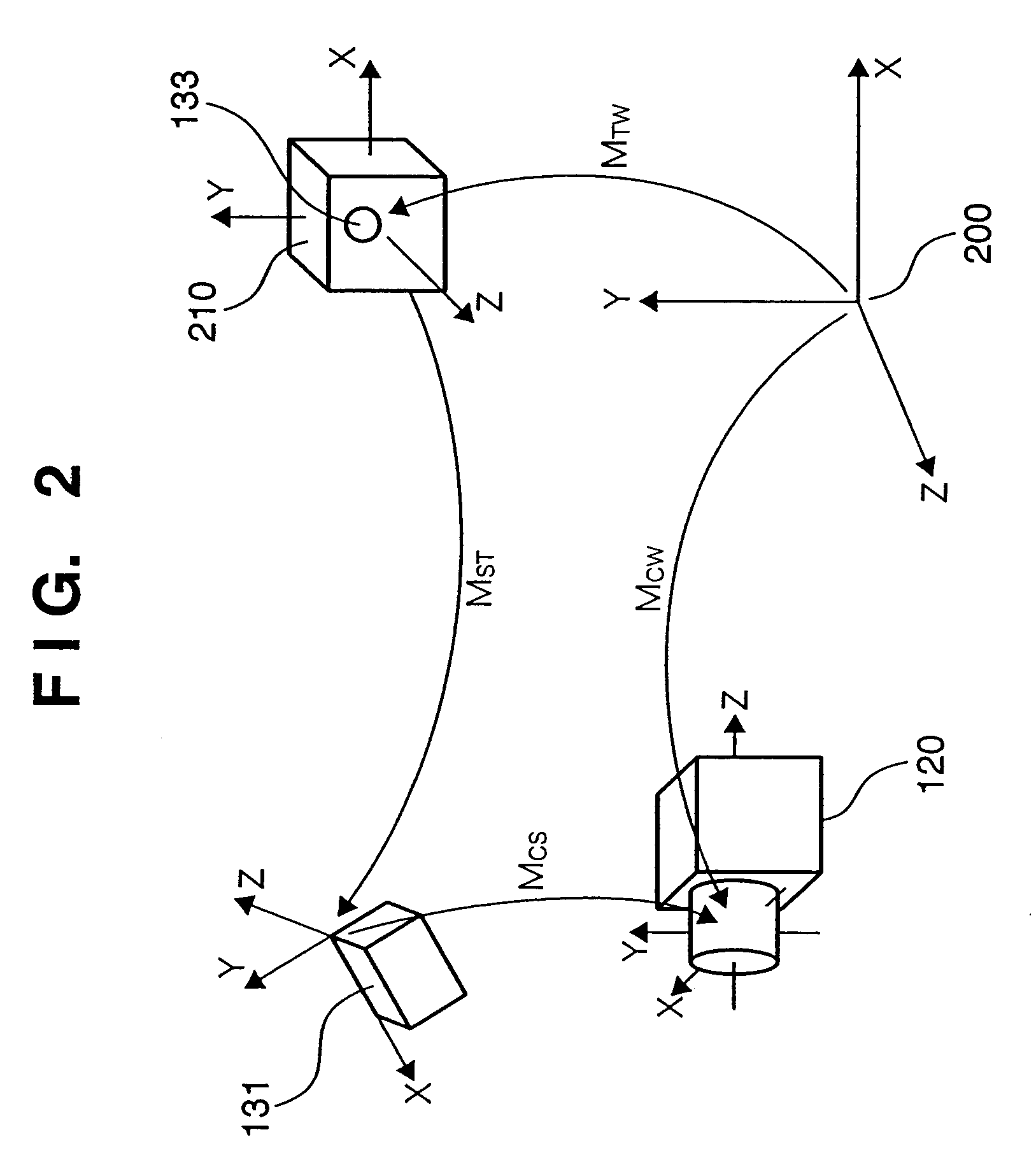

Sensor calibration apparatus, sensor calibration method, program, storage medium, information processing method, and information processing apparatus

A calibration information calculation unit 340 calculates the first coordinate positions of feature points included in images obtained by an image sensing apparatus at timings from an instruction unit 350 using position data, on world coordinate system, of a plurality of feature points held by a world coordinate holding unit 310 and the measured values of a position / posture sensor 130 input to a data management unit 330 at the timings. The unit 340 receives the second coordinate positions, which are acquired by an image coordinate acquisition unit 320, of the feature points included in the images obtained by the image sensing device at the timings. The unit 340 calculates calibration information using the first and second coordinate positions.

Owner:CANON KK

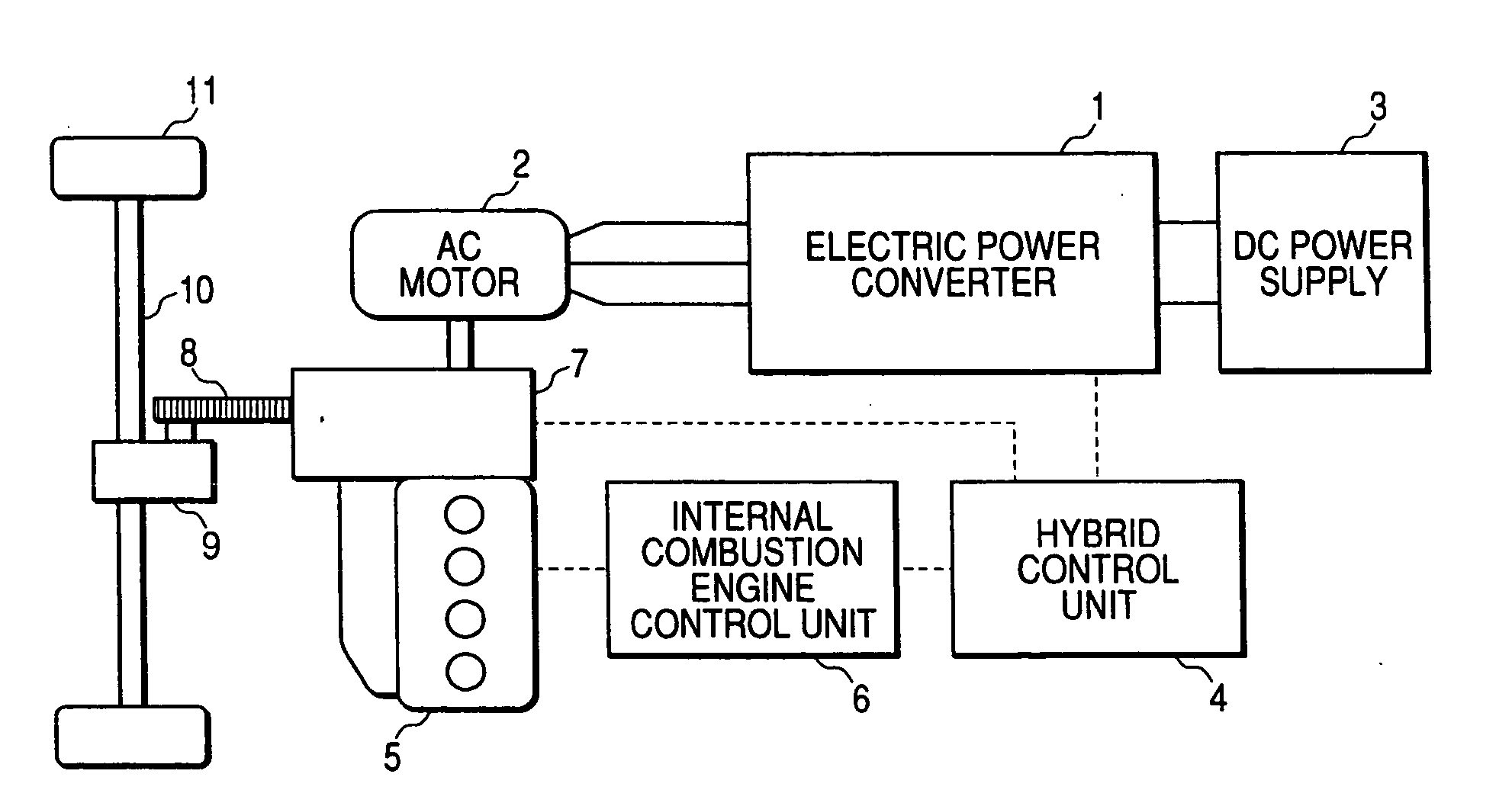

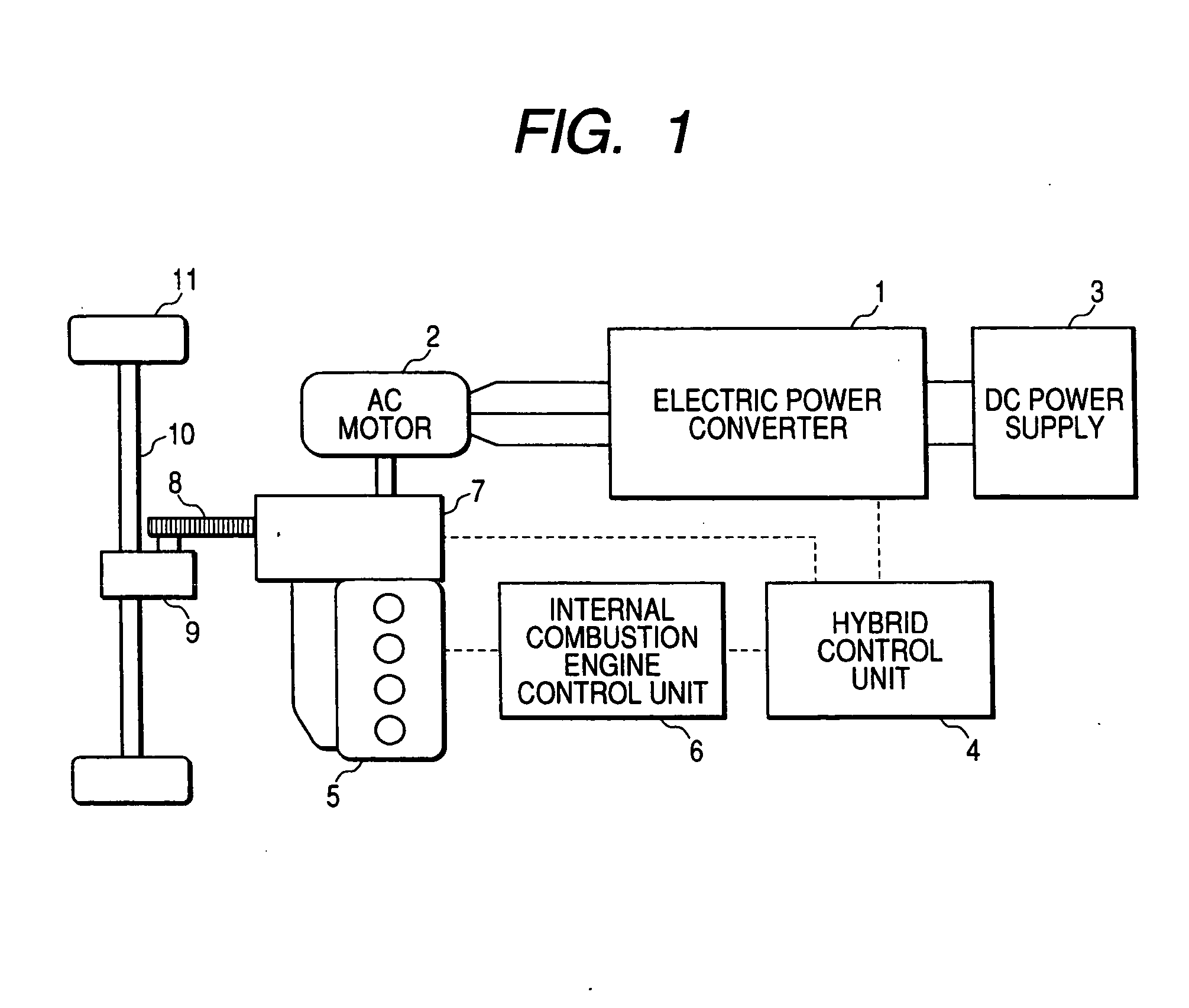

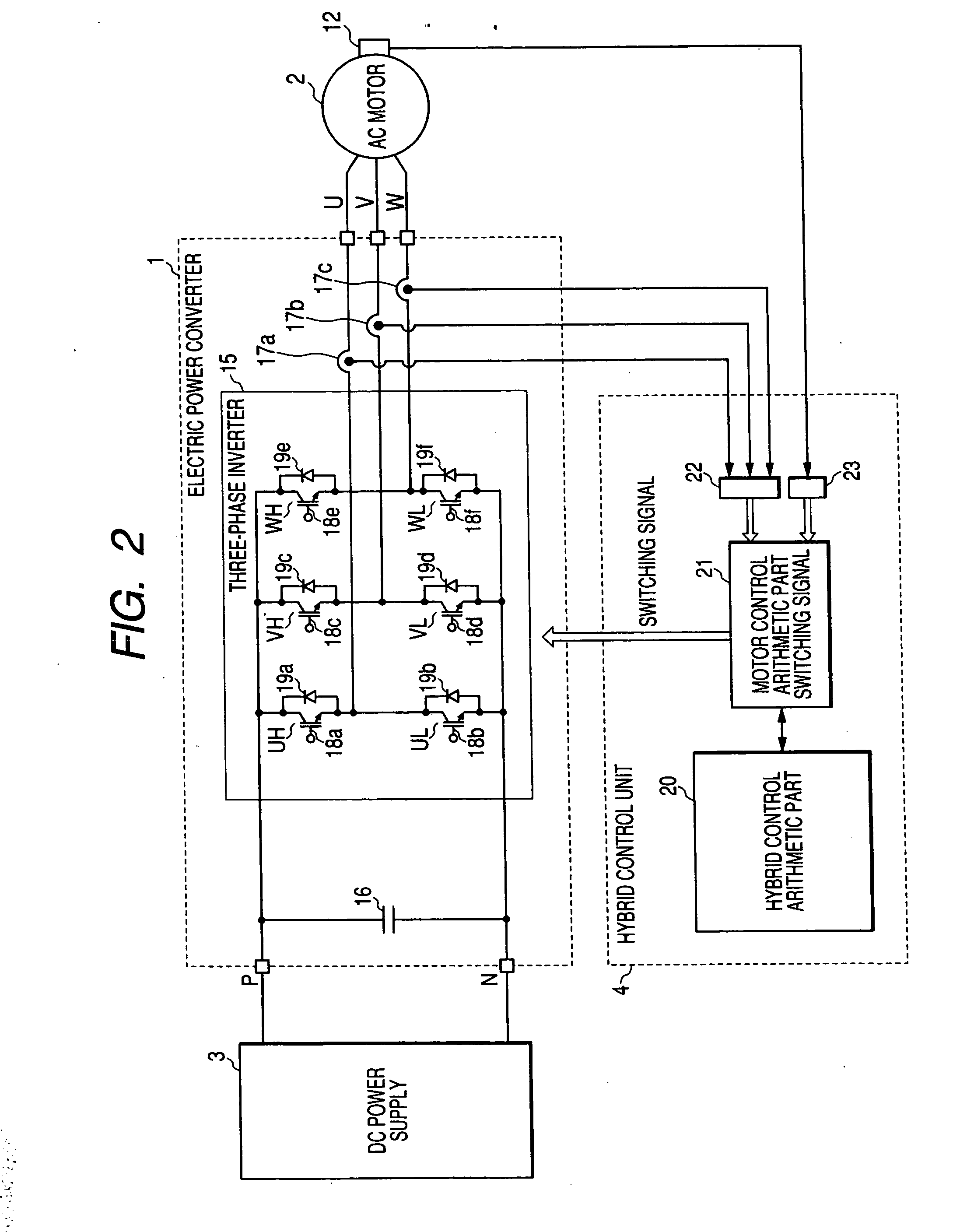

Vehicular power control apparatus

InactiveUS20070093359A1Not to damage safetyAvoid it happening againAC motor controlVector control systemsInstruction unitSwitching signal

A protection operation control part switches a gate signal interruption switch for protection of power elements to a gate signal interruption side, and invalidates a switching signal from a hybrid control unit to place transistors into a nonconducting operation. A motor current signal from a motor current detector is converted into a current value by a motor current calculation unit, and is inputted to a short-circuit abnormality detection unit through a motor control arithmetic part, and a short-circuit abnormality is detected. At a time of detecting the short-circuit abnormality, an internal combustion engine operation instruction unit gives an instruction to an internal combustion engine control unit so as to limit output of an internal combustion engine, and releases a conduction state of an abnormal motor current.

Owner:MITSUBISHI ELECTRIC CORP

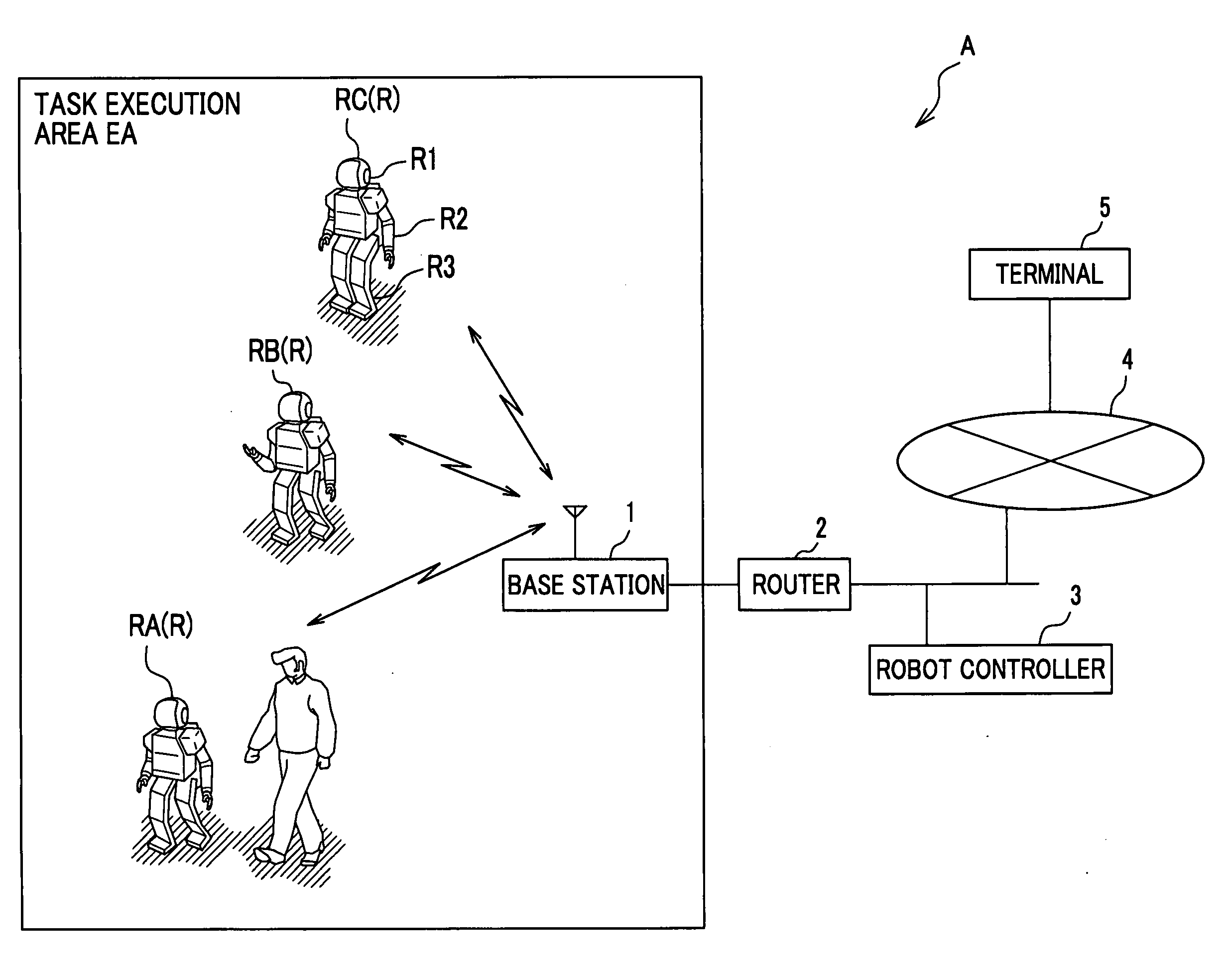

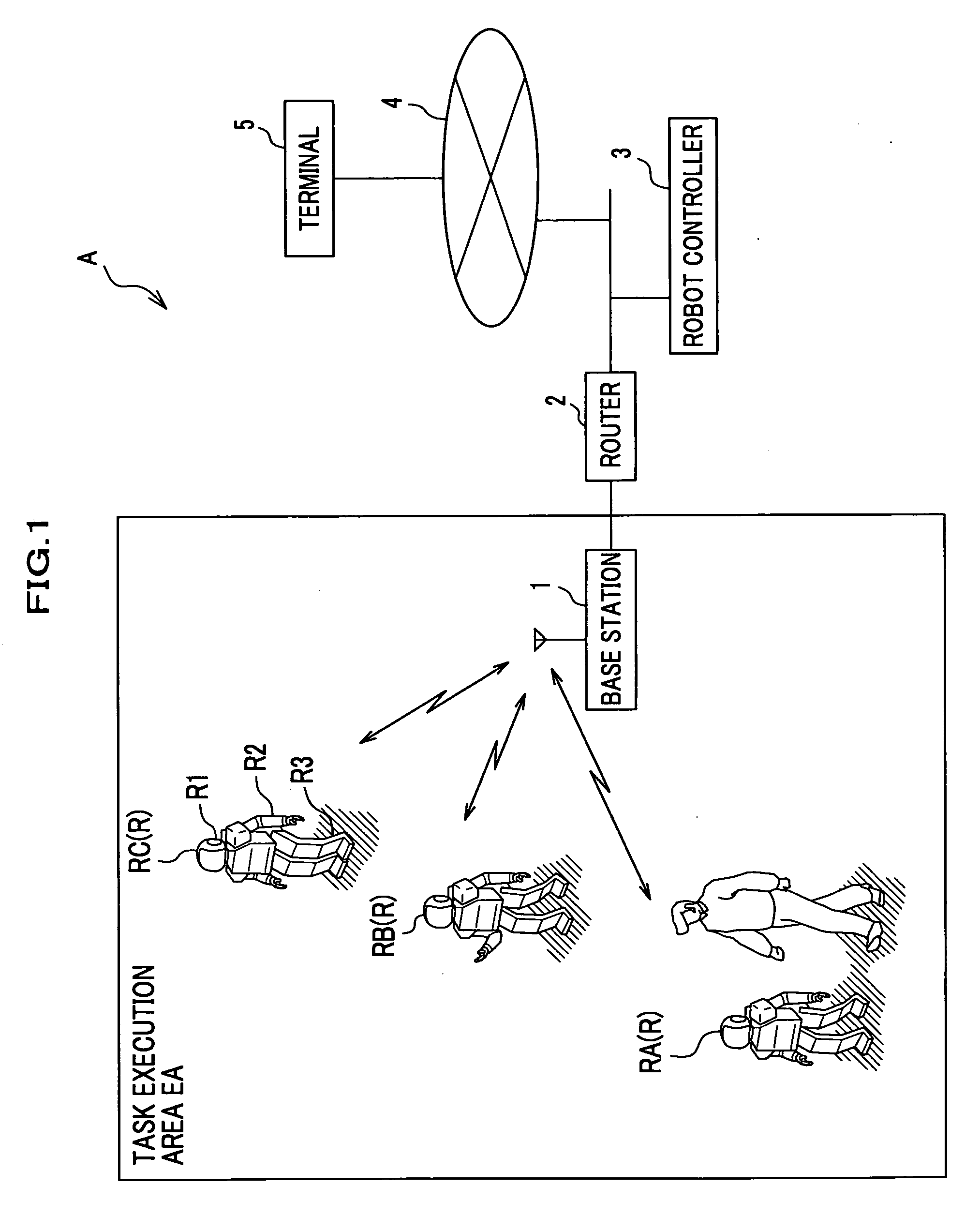

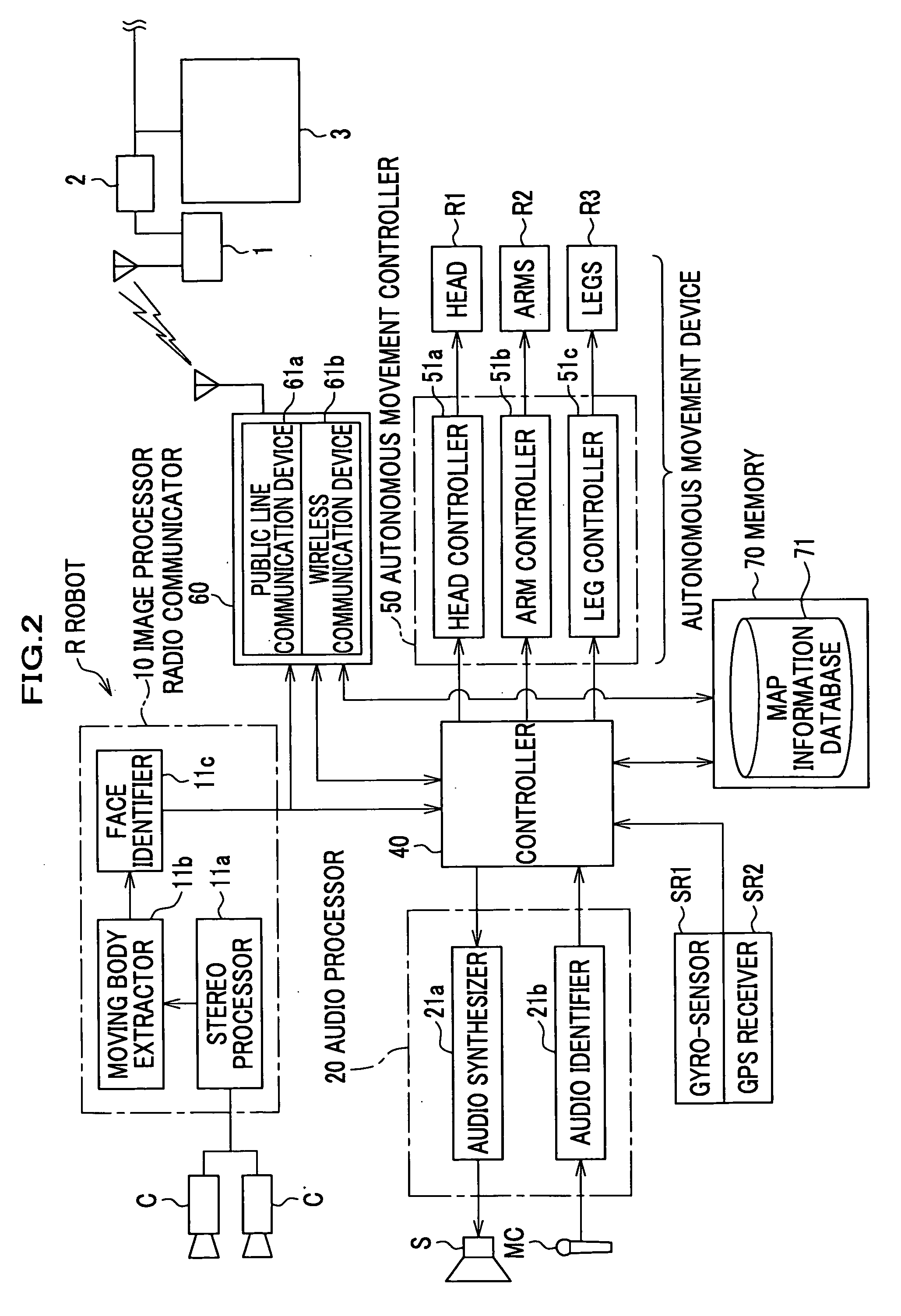

Robot controller

Disclosed is a robot controller which includes a map acquisition unit for obtaining map data on an active area where the routes are formed, a current location acquisition unit for obtaining current location data on current locations of the robots, a sub-goal acquisition unit for obtaining sub-goal data on sub-goals created on the routes, a collision possibility determination unit for determining whether two robots are likely to collide, a moving route change instruction unit for generating a moving route changing instruction signal, the moving route changing instruction signal for allowing at least one of the two robots to change its route, and a sending device for transmitting the moving route changing instruction signal to the corresponding one of the two robots. In this controller, the robots are controlled such that they move around without causing collisions.

Owner:HONDA MOTOR CO LTD

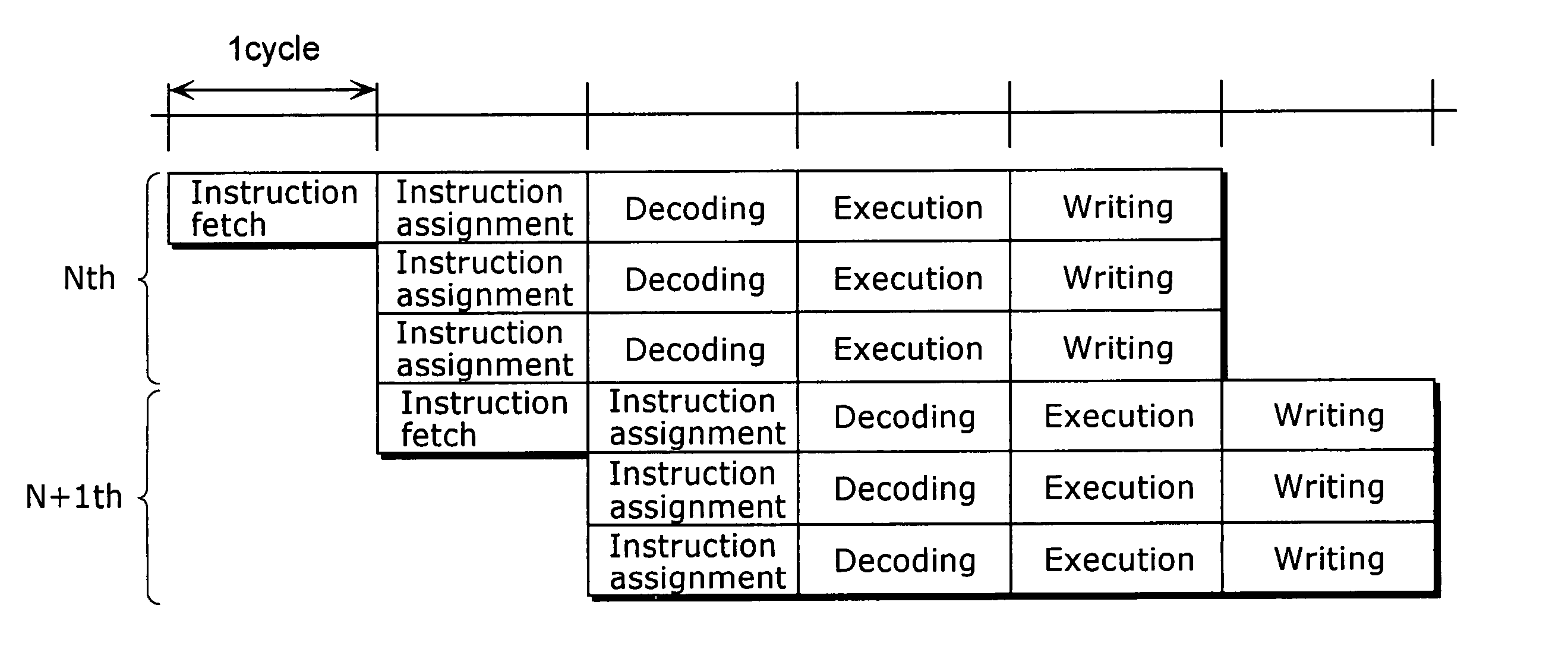

Compiler apparatus and compilation method

InactiveUS20040154006A1Avoid changeReduce power consumptionEnergy efficient ICTSoftware engineeringMachine instructionInstruction cycle

A compiler apparatus that is capable of generating instruction sequences for causing a processor with parallel processing capability to operate with lower power consumption is a compiler apparatus that translates a source program into a machine language program for the processor including a plurality of execution units which can execute instructions in parallel and a plurality of instruction issue units which issue the instructions executed respectively by the plurality of execution units, and includes: a parser unit operable to parse the source program; an intermediate code conversion unit operable to convert the parsed source program into intermediate codes; an optimization unit operable to optimize the intermediate codes so as to reduce a hamming distance between instructions placed in positions corresponding to the same instruction issue unit in consecutive instruction cycles, without changing dependency between the instructions corresponding to the intermediate codes; and a code generation unit operable to convert the optimized intermediate codes into machine language instructions.

Owner:SOCIONEXT INC

Image Display Apparatus and Control Method

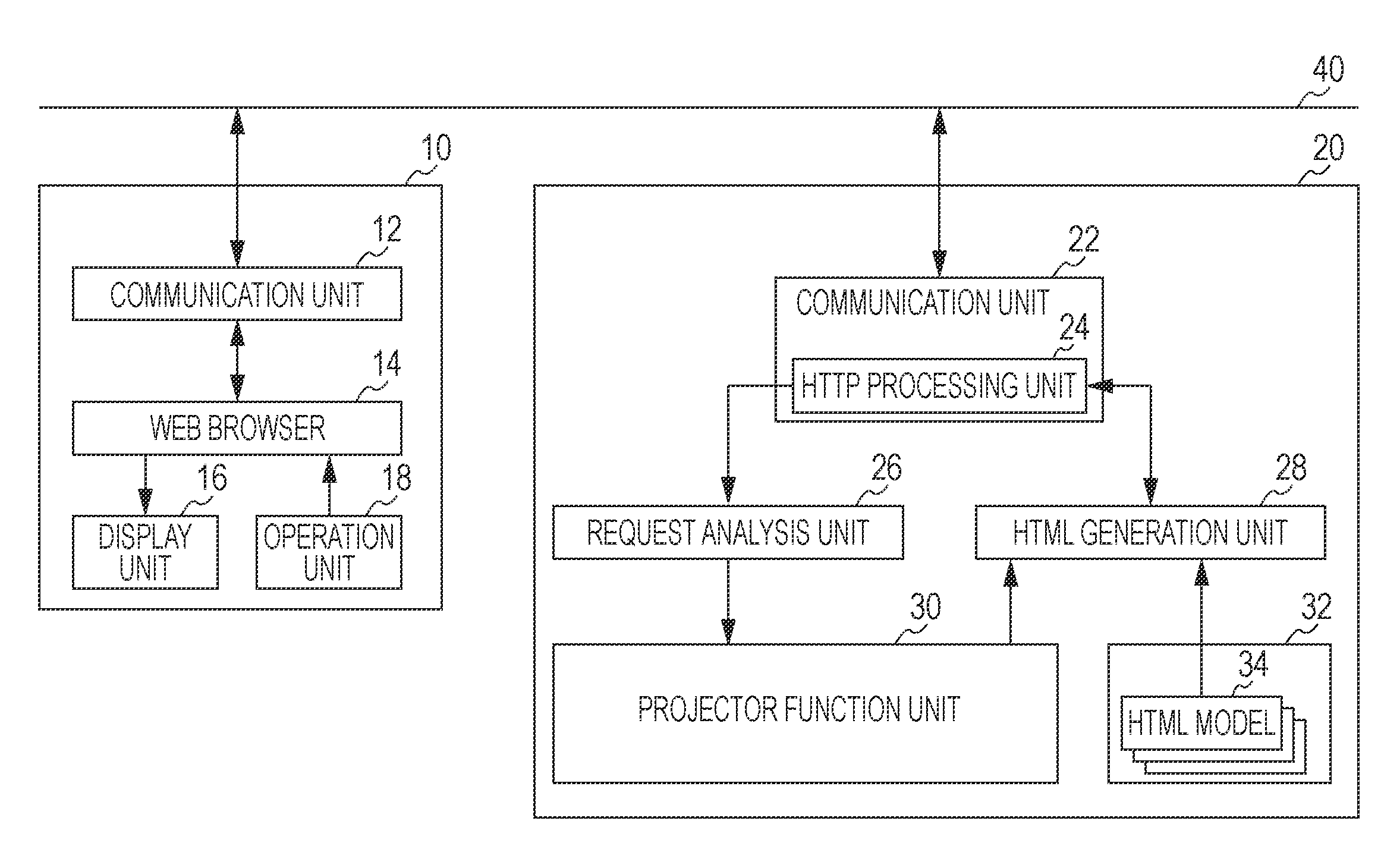

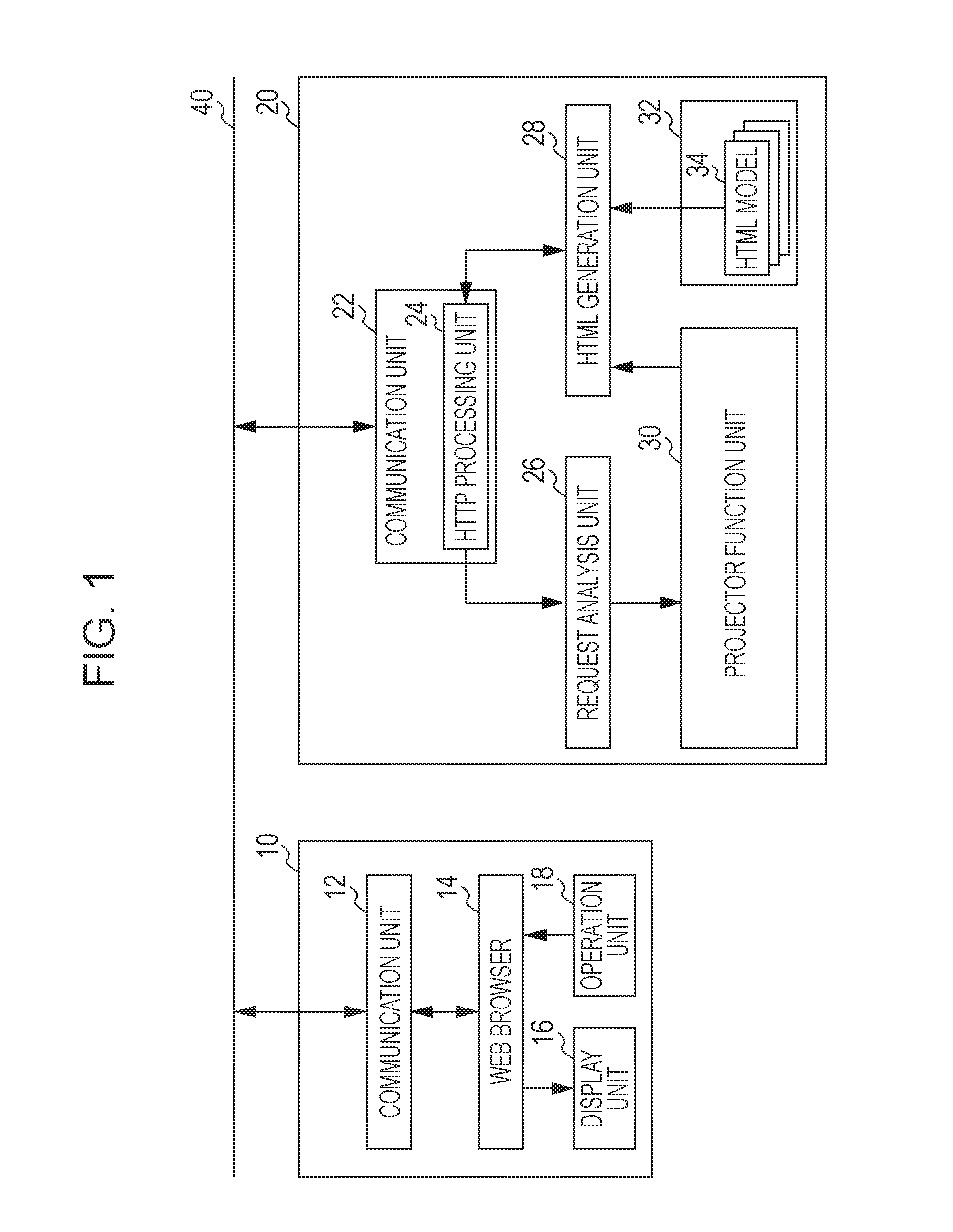

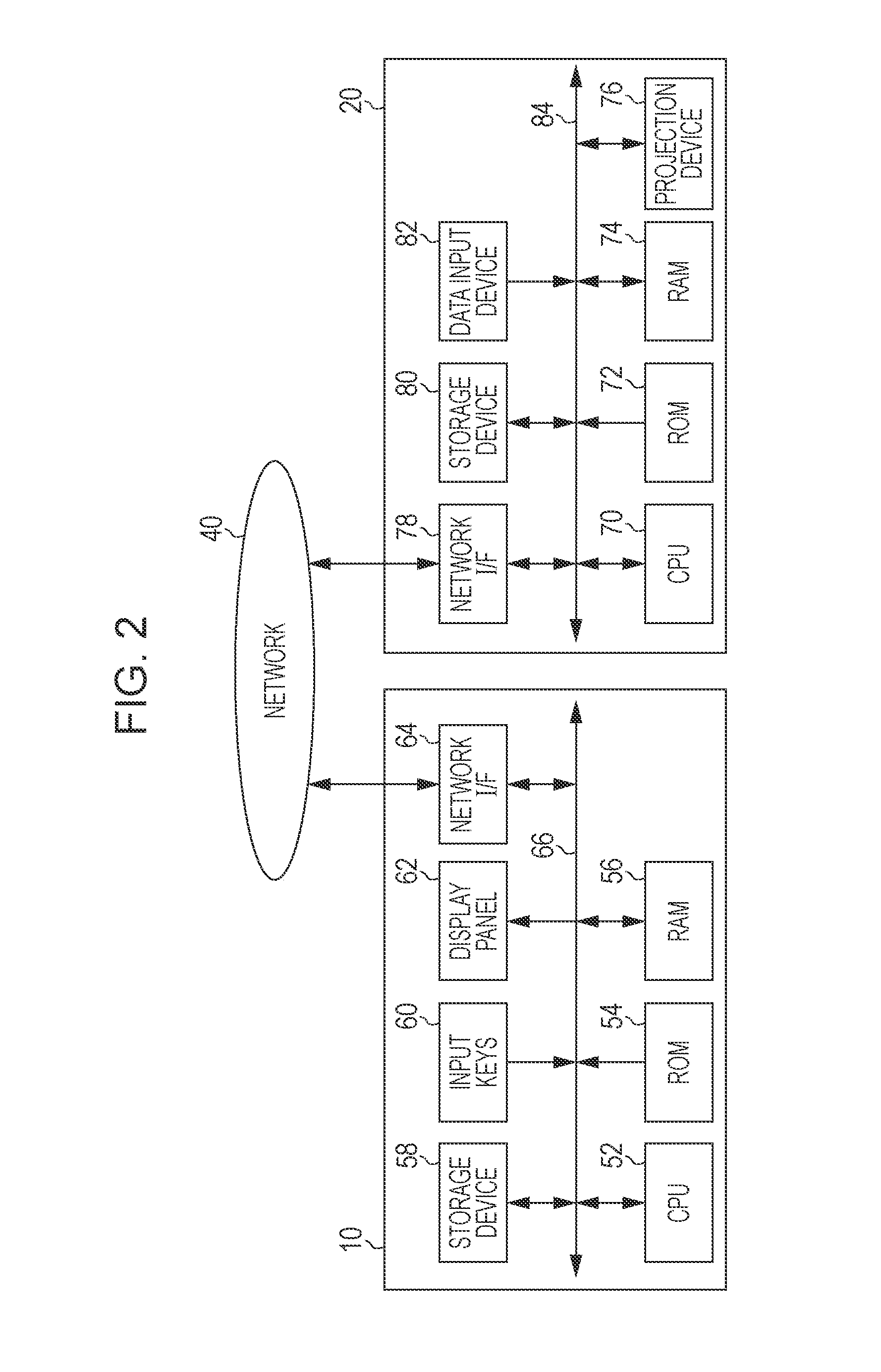

ActiveUS20110153799A1Digital computer detailsElectric digital data processingCommunication unitInstruction unit

A communication unit that communicates with the information terminal; an image display unit that forms and displays an image; a control unit that controls the image display unit; a storage unit that stores model data defining a model of web screen information for instructing the control of the image display unit; and a generation unit that generates the web screen information that can be displayed in the information terminal by selecting the model data stored in the storage unit, and configuring, in the model indicated by the model data, an instruction unit for instructing a control item that controls the display unit. The communication unit transmits the web screen information generated by the generation unit to the information terminal, and the control unit controls the control item of the image display unit based on an instruction signal transmitted as a result of specifying the instruction unit of the web screen information displayed in the information terminal.

Owner:SEIKO EPSON CORP

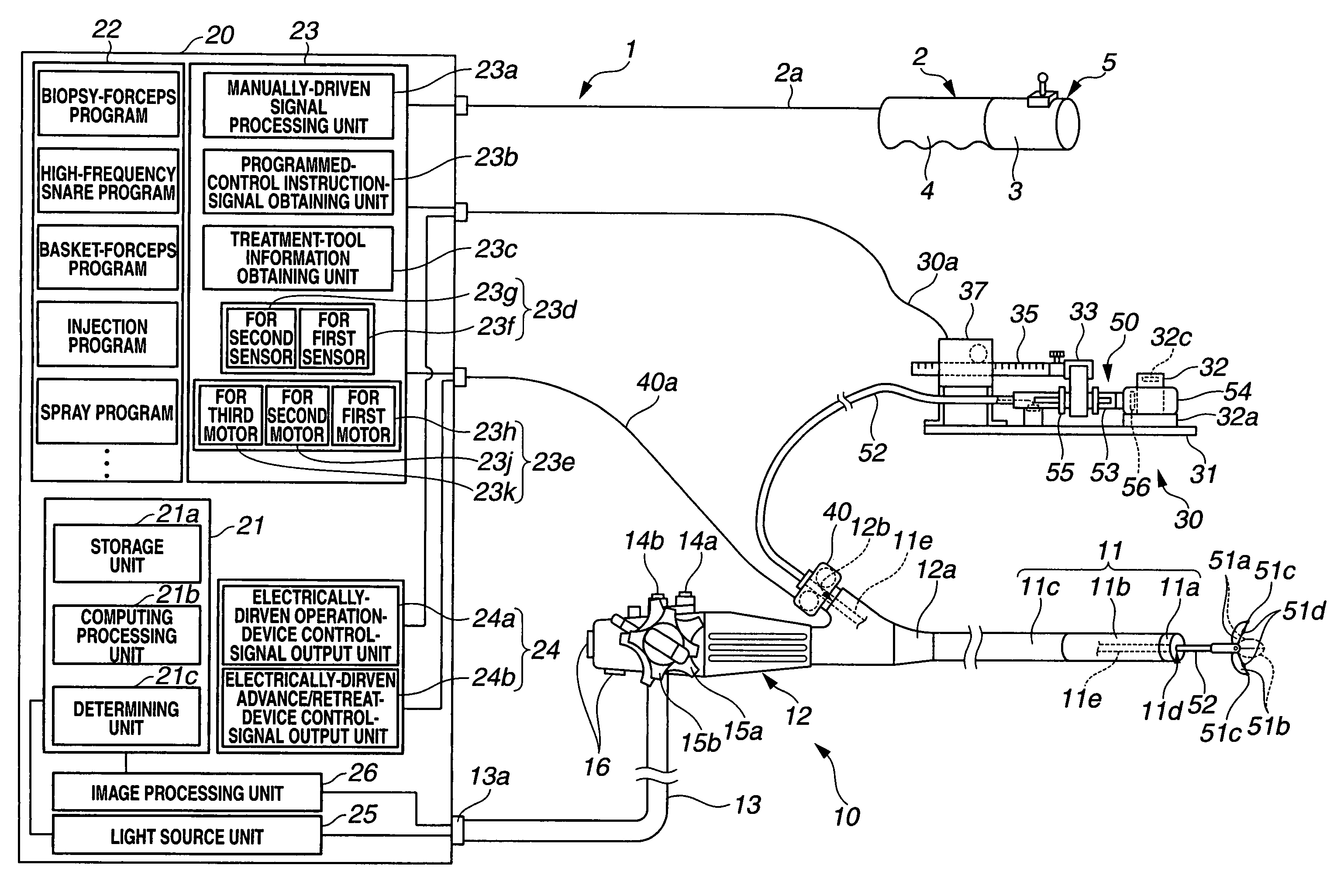

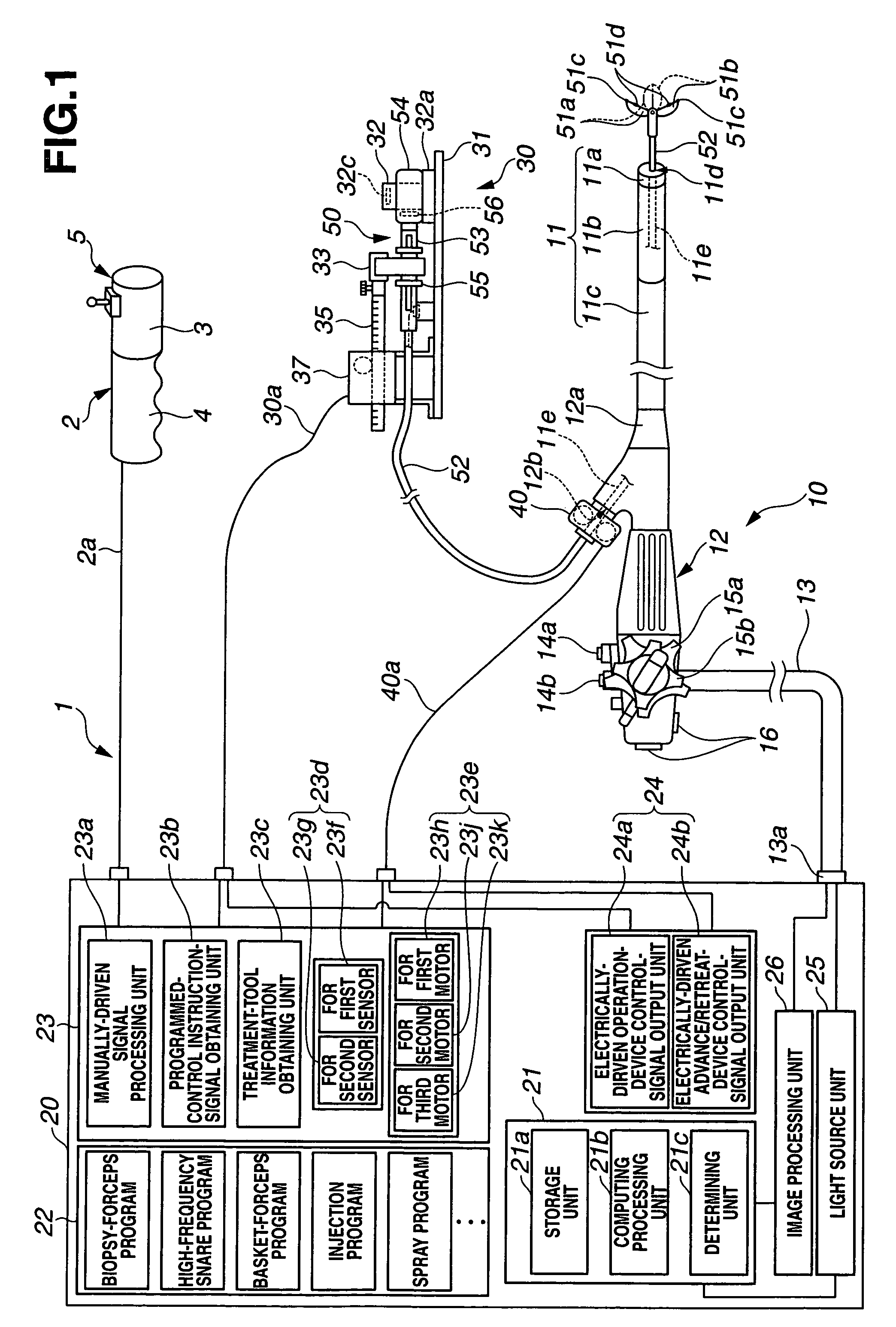

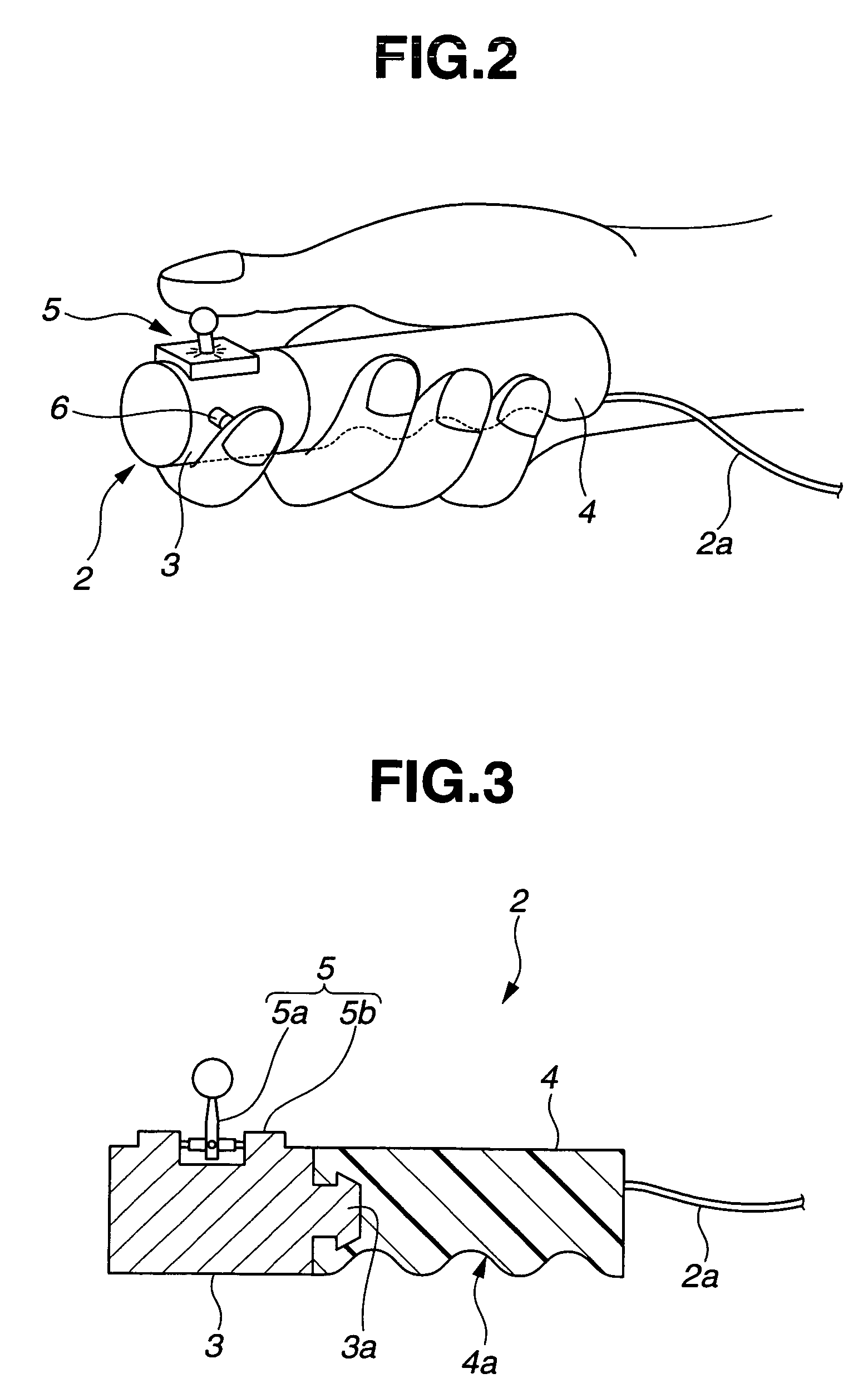

Endoscope system

An endoscope system comprises multiple types of treatment tools including a treatment-tool insertion unit, and a function unit having a function for performing treatment; an electrically-driven operation device which electrically drives the function unit; an electrically-driven advance / retreat device which electrically drives the treatment-tool insertion unit; a control device including at least one of a control unit for outputting a control signal to the electrically-driven advance / retreat device and the electrically-driven operation device, and an operating program corresponding to a treatment tool; and an operation instructing device including a first operating instruction unit for outputting an instruction signal for placing the electrically-driven operation device and the electrically-driven advance / retreat device into a manually-driven operating state, and a second operating instruction unit for outputting an instruction signal for placing the electrically-driven operation device and the electrically-driven advance / retreat device into a programmed-control state by the operating program. When receiving either of the signal from the first operating instruction unit or the signal from the second operating instruction unit, the control unit performs control for outputting the control signal corresponding to the received signal to at least one of the electrically-driven advance / retreat device and the electrically-driven operation device.

Owner:OLYMPUS CORP

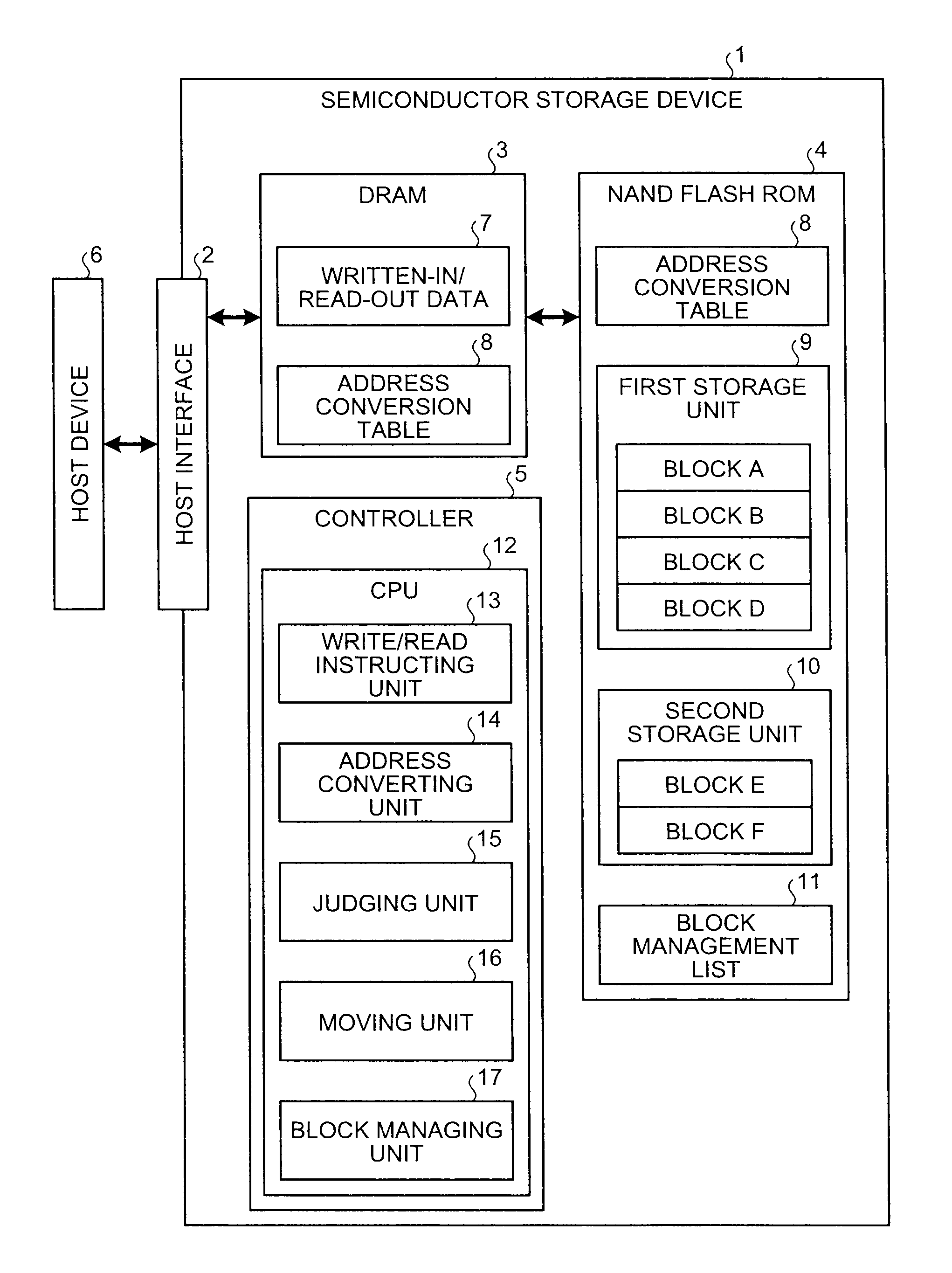

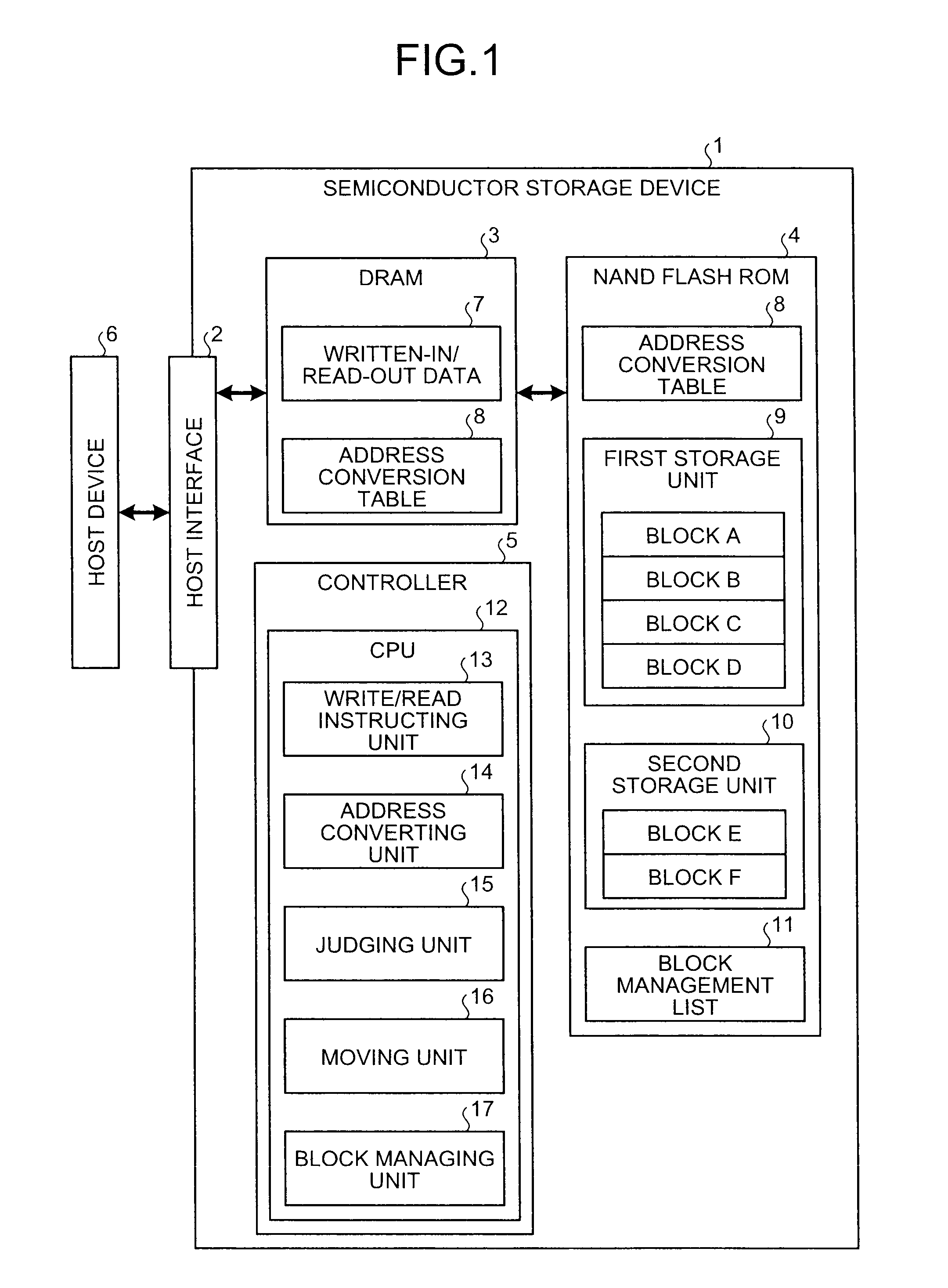

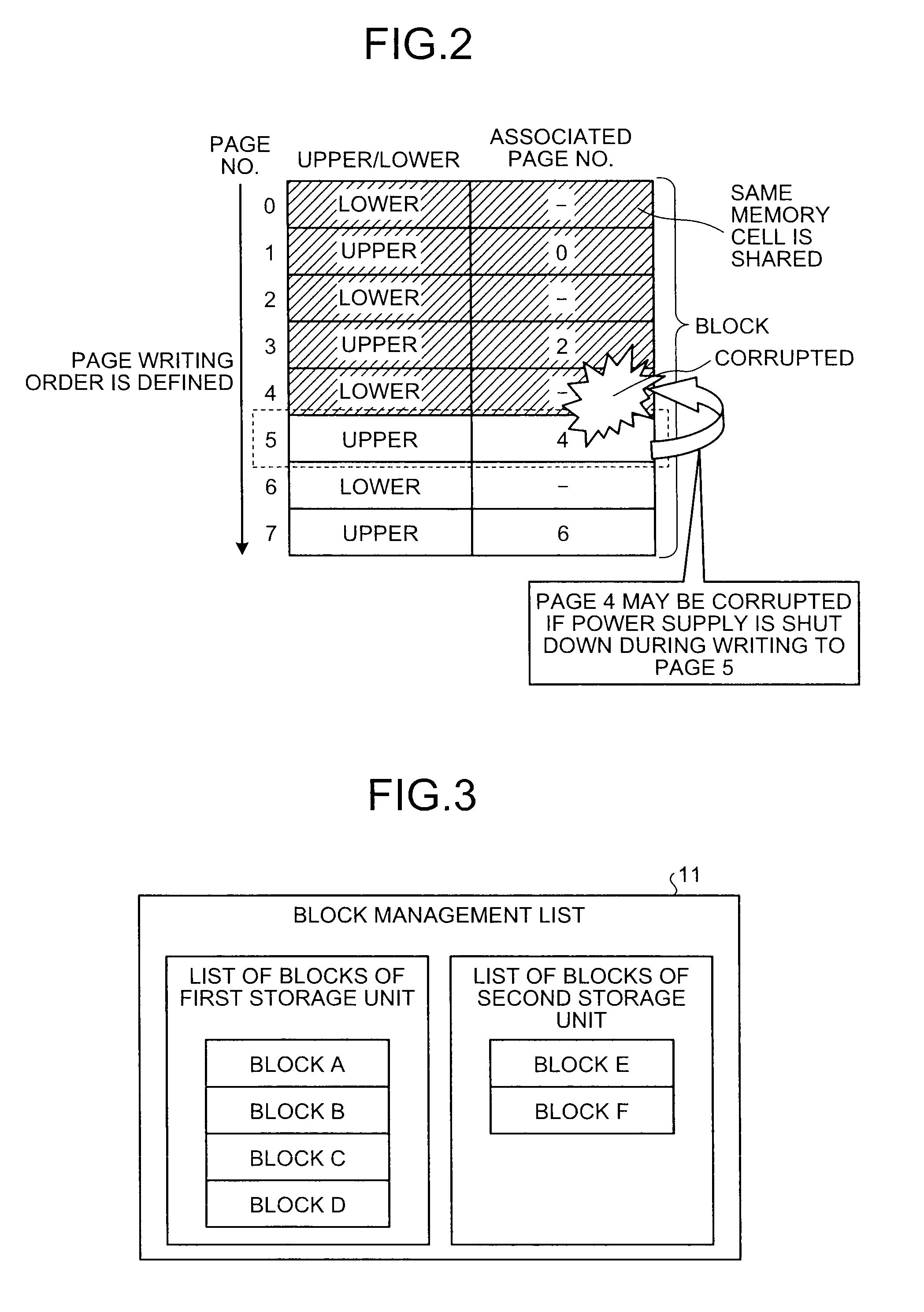

Semiconductor storage device and storage controlling method

InactiveUS20100161885A1Program control using stored programsMemory adressing/allocation/relocationInstruction unitSemiconductor storage devices

A semiconductor storage device includes a first storage unit having a plurality of first blocks as data write regions; an instructing unit that issues a write instruction of writing data into the first blocks; a converting unit that converts an external address of input data to a memory position in the first block with reference to a conversion table in which external addresses of the data are associated with the memory positions of the data in the first blocks; and a judging unit that judges whether any of the first blocks store valid data associated with the external address based on the memory positions of the input data, wherein the instructing unit issues the write instruction of writing the data into the first block in which the valid data is not stored, when any of the first blocks does not store the valid data.

Owner:KK TOSHIBA

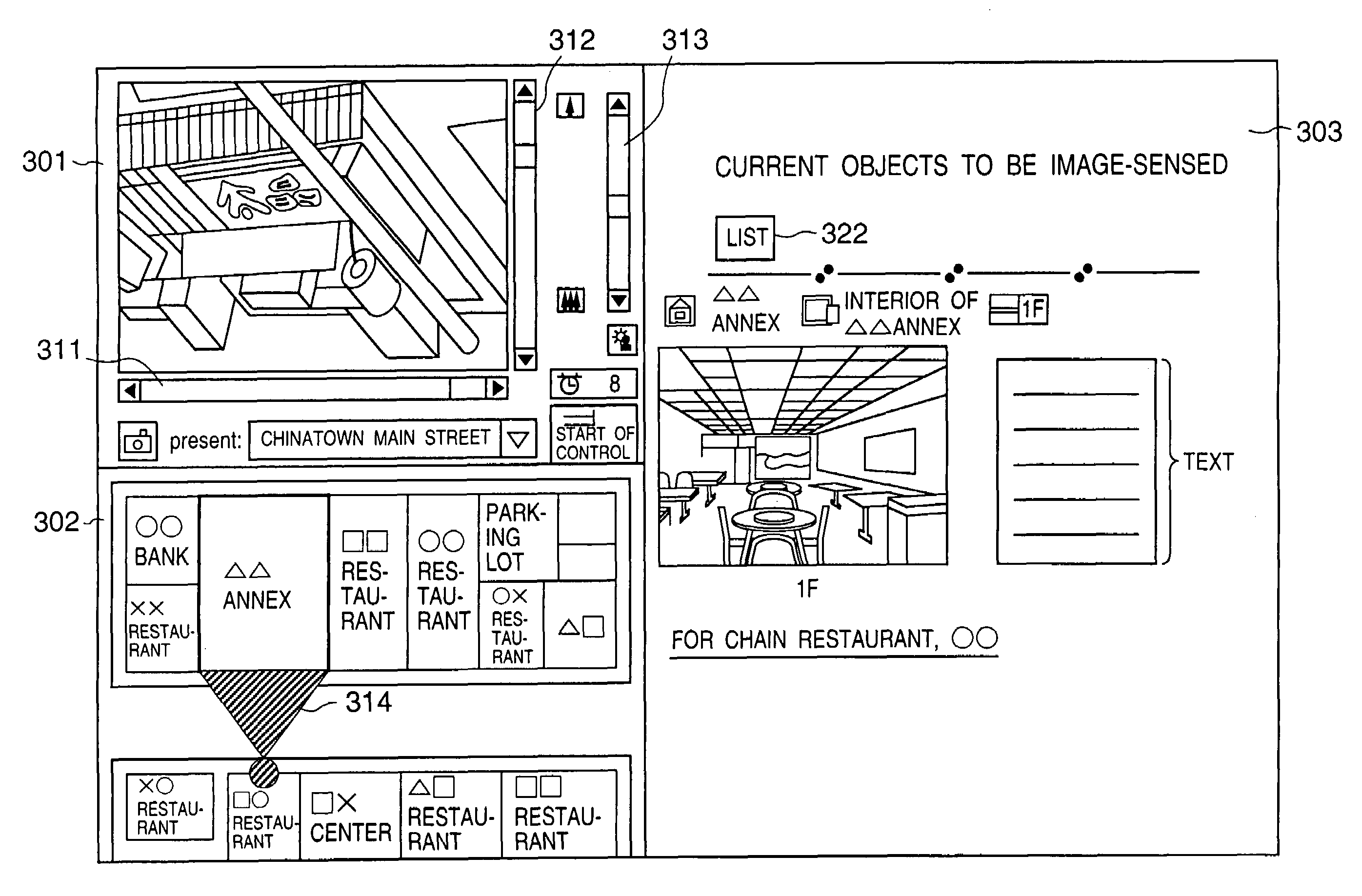

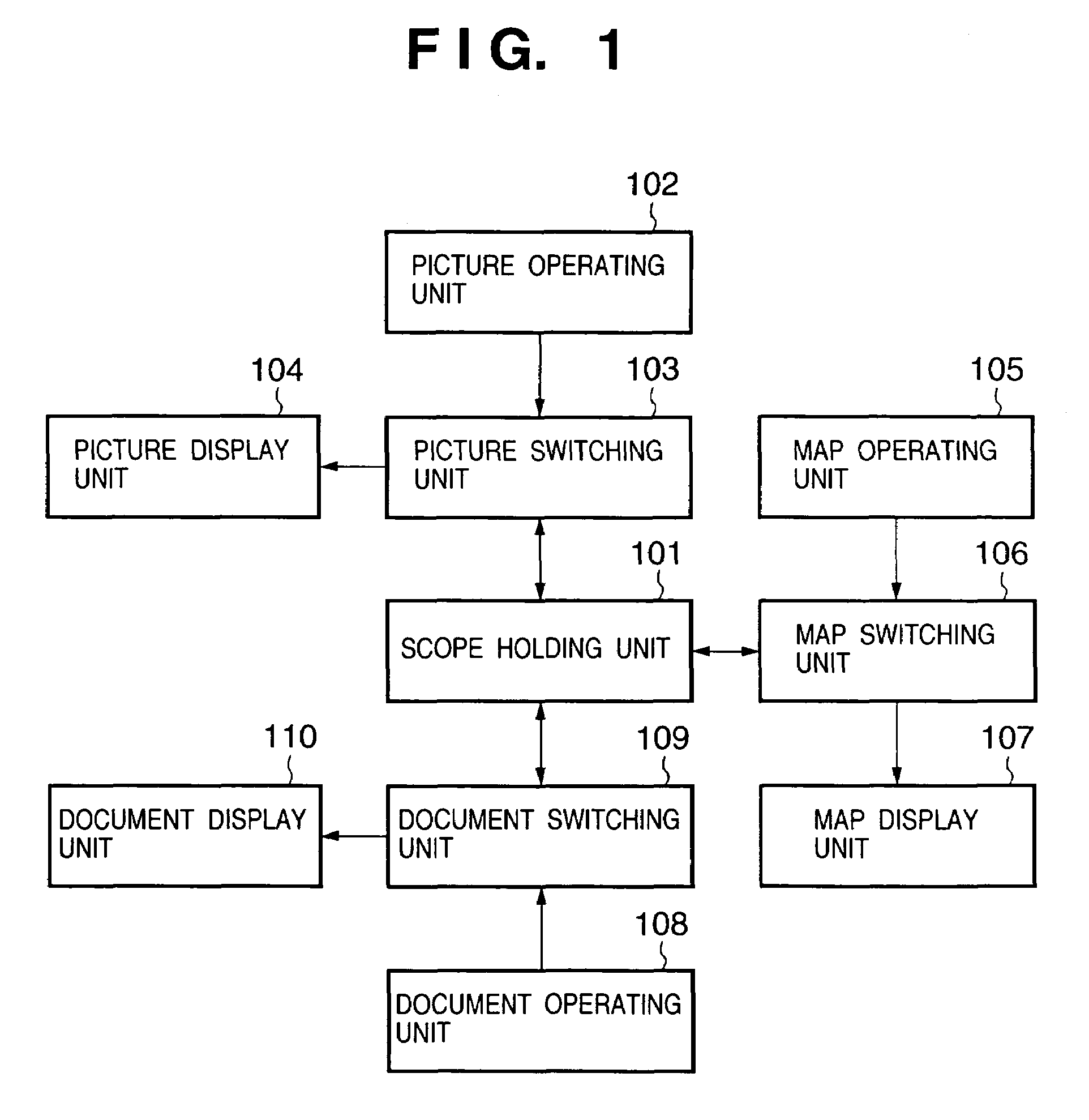

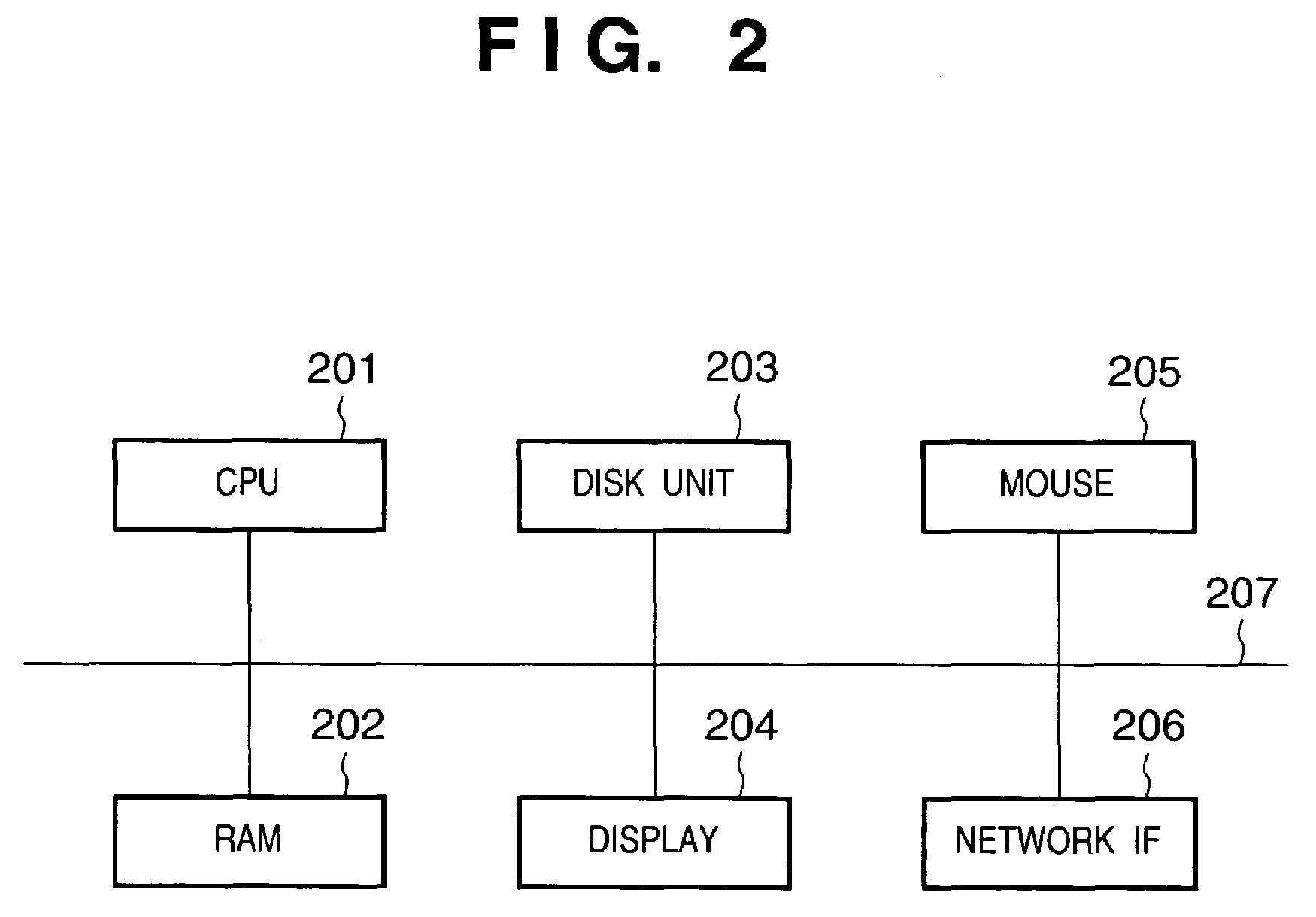

Information presenting apparatus, operation processing method therefor, storage medium storing program for executing operation processing

InactiveUS7136093B1Television system detailsDigital data information retrievalInstruction unitComputer graphics (images)

The present invention has as its object to automatically provide information about an object image-sensed by a camera and automatically image-sense and present an object described by browsed information while a user is browsing the information. To achieve this object, the present invention includes scope holding unit, picture operating unit, first instruction unit, picture display unit, map operating unit, second instruction unit, map display unit, document operating unit, third instruction unit, and document display unit.

Owner:CANON KK

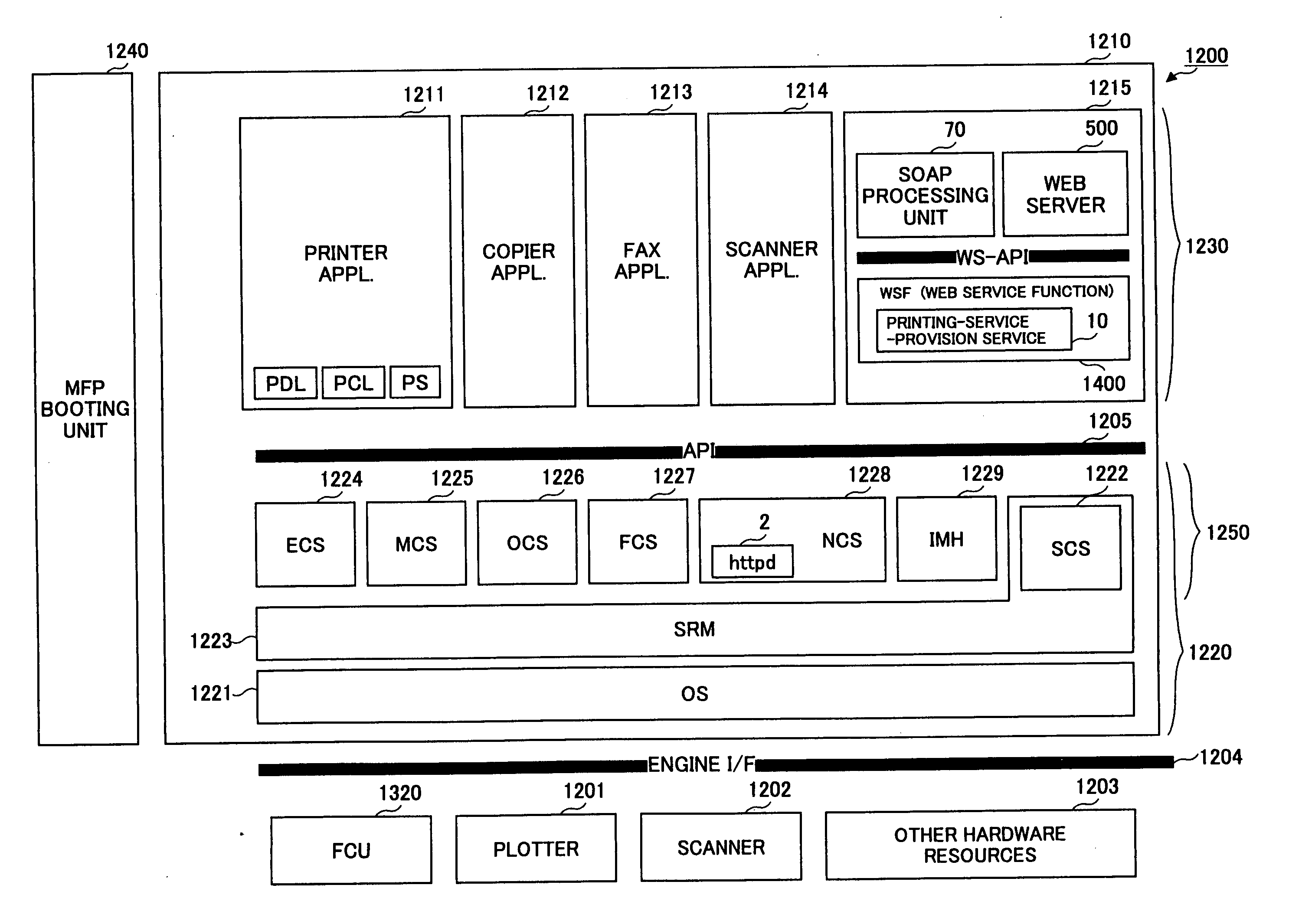

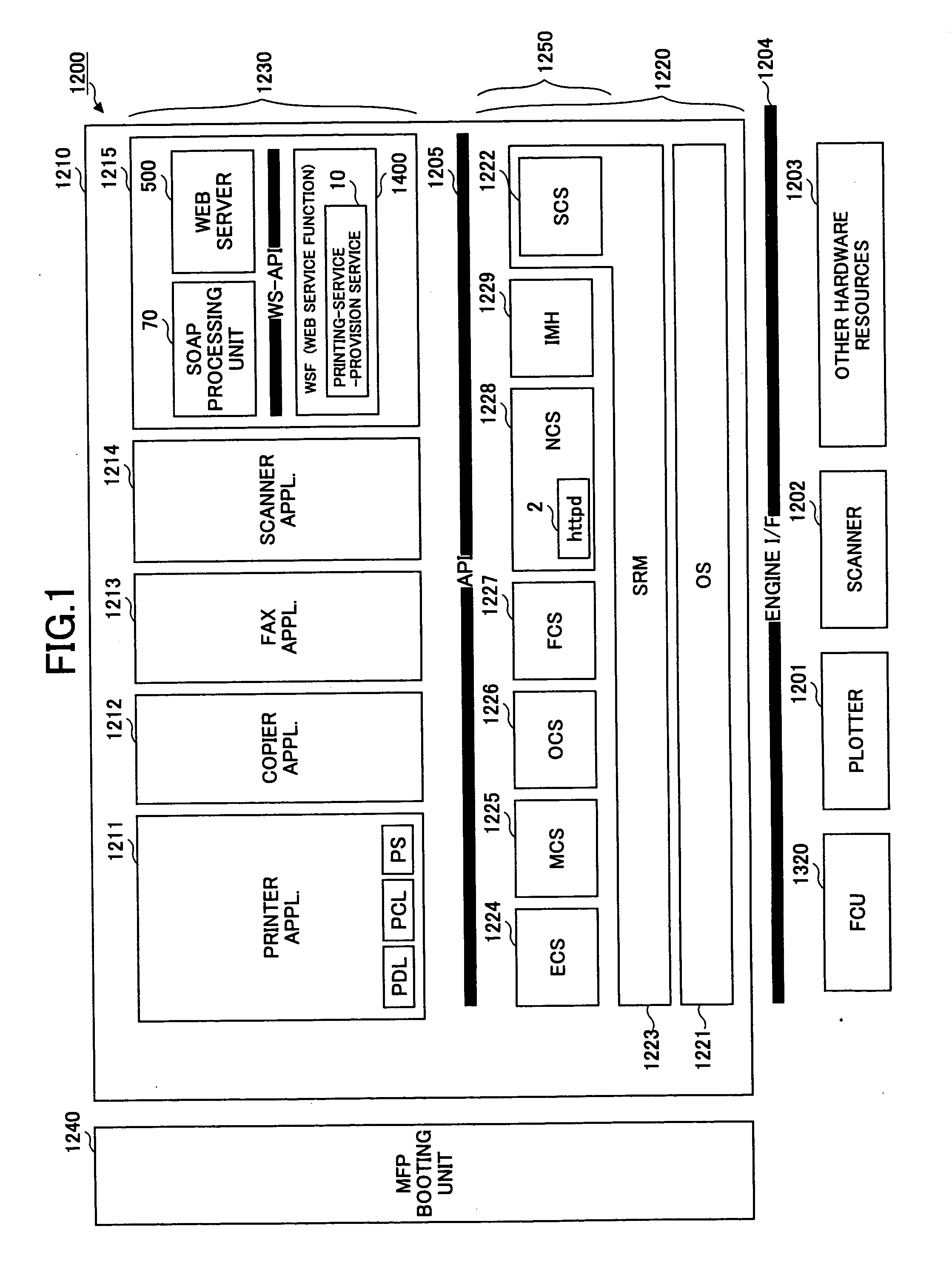

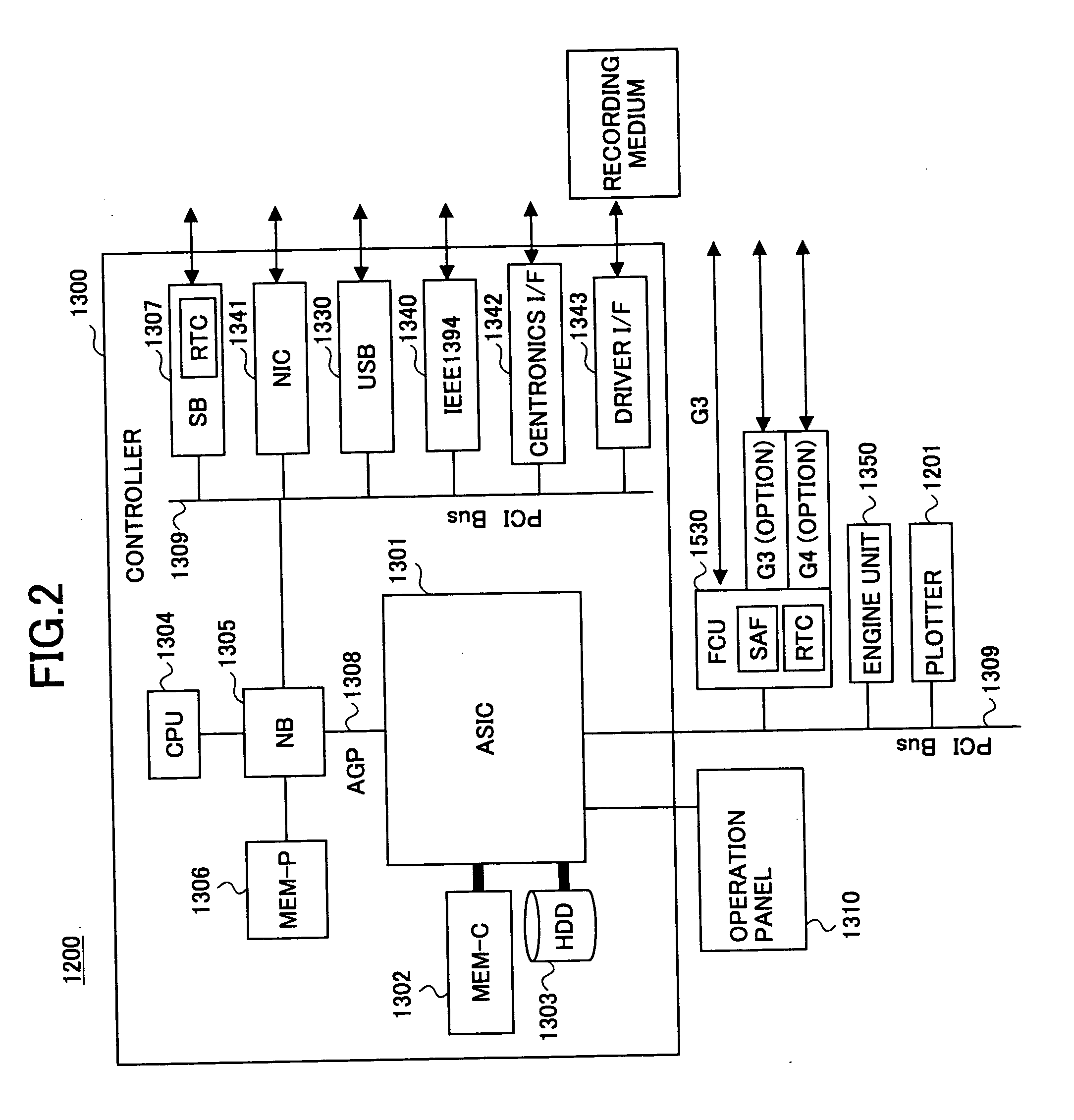

Service provision device, service provision program, recording medium, and service provision method

InactiveUS20050231755A1Efficiently provides userEffective serviceDigital computer detailsOther printing apparatusInstruction unitService provision

In a service provision device having a service provision unit which provides a user with a service, a receiving unit receives a request from a client which is connected through a network to the service provision unit and uses the service. A service unit provides the service which is created in response to the request from the client. An instruction unit provides an instruction, containing information concerning contents of processing related to the service, which is created in response to the request from the client. A job execution unit provides an interface to a service executor which performs the service-related processing, and performs a job related to the service-related processing.

Owner:RICOH KK

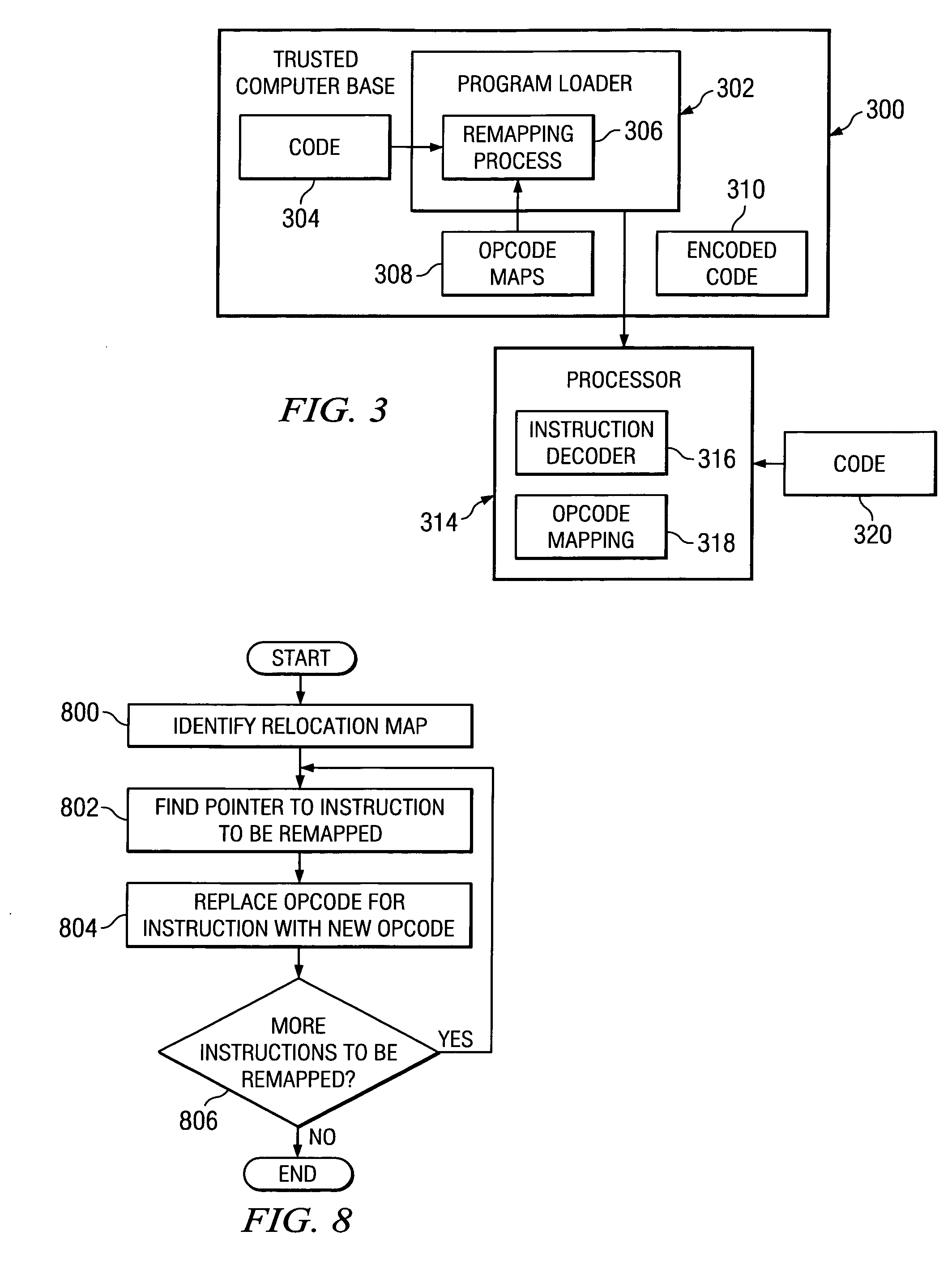

Method and apparatus to prevent vulnerability to virus and worm attacks through instruction remapping

InactiveUS20050188171A1Memory loss protectionInstruction analysisProcessing InstructionInstruction unit

A method, apparatus, and computer instructions for processing instructions by a processing unit. An instruction set is dynamically set for the processing unit using a selected instruction map. The selected instruction map is selected as one being different from a normal instruction map for the processing unit. The instructions are processed at the processor using the instruction set. A set of authorized instructions are encoded using the selected instruction map.

Owner:TREND MICRO INC

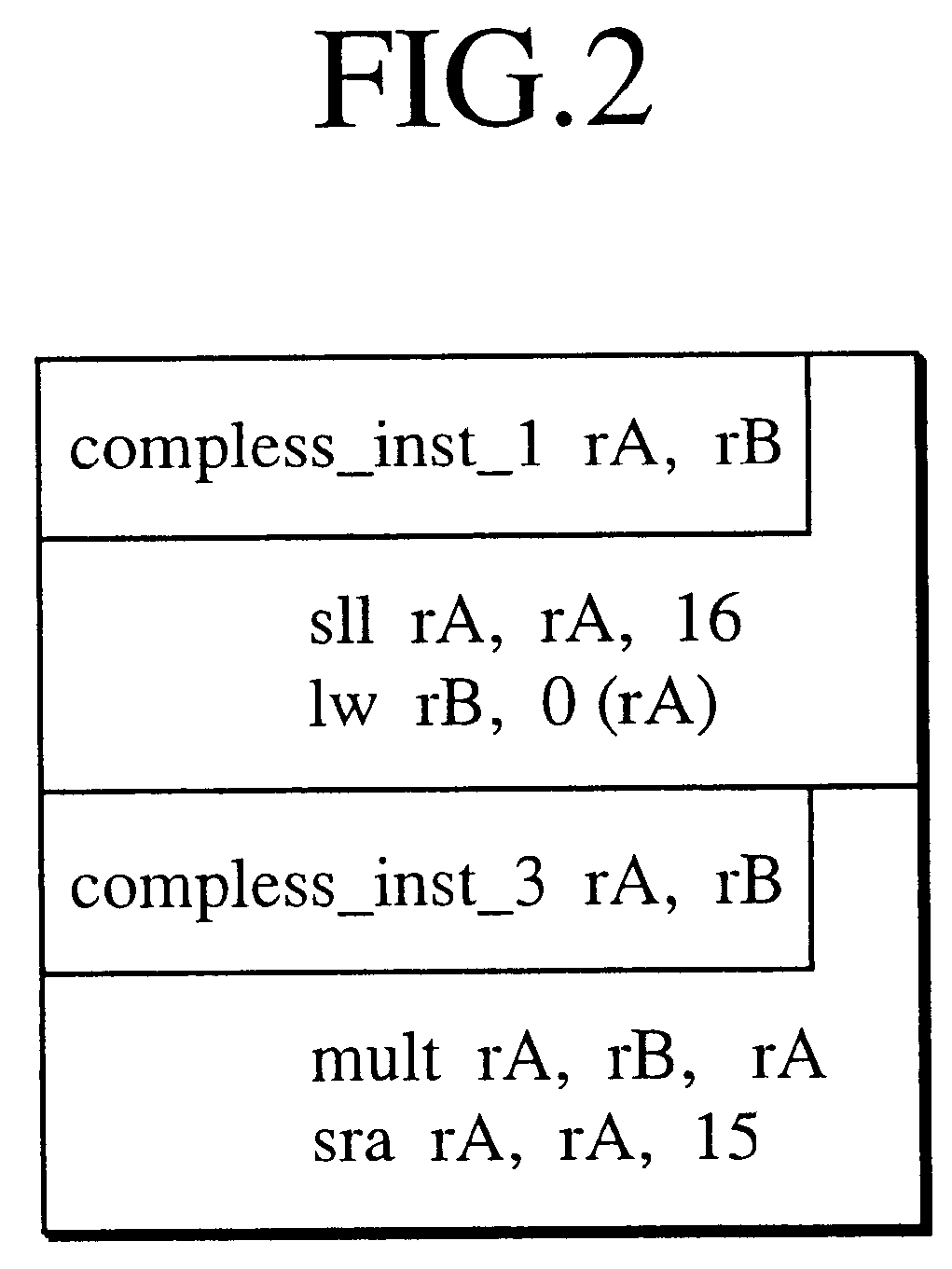

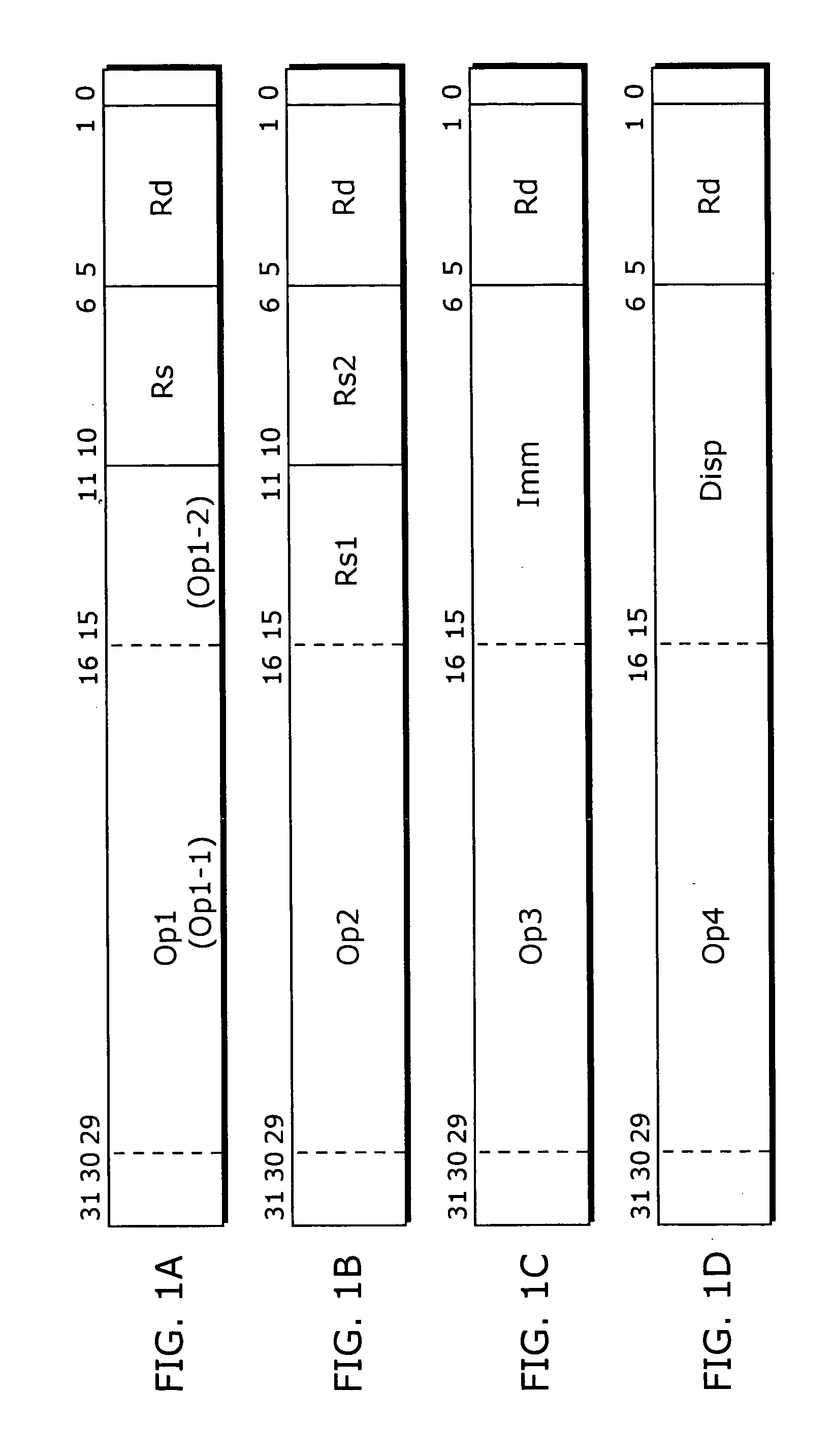

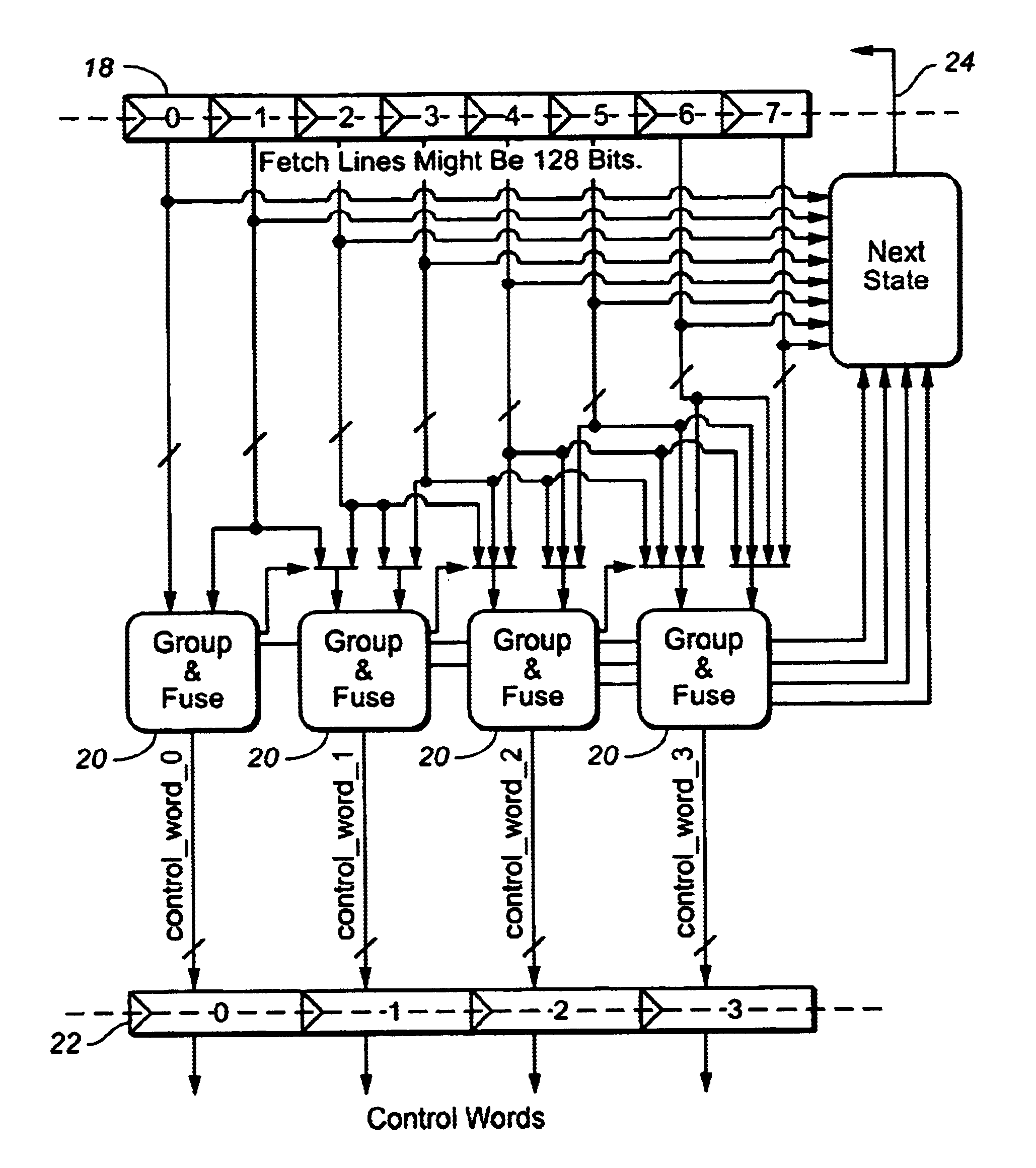

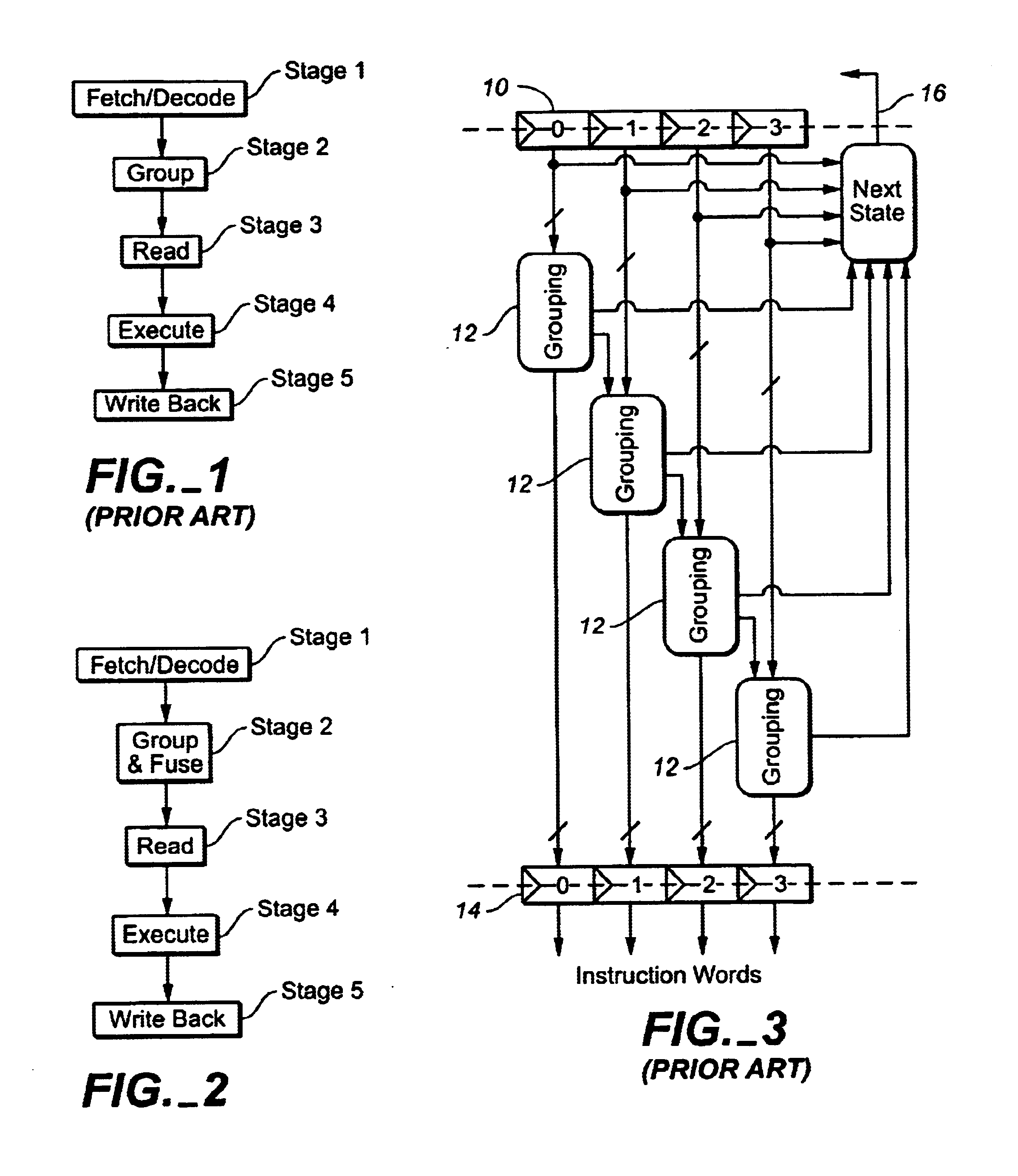

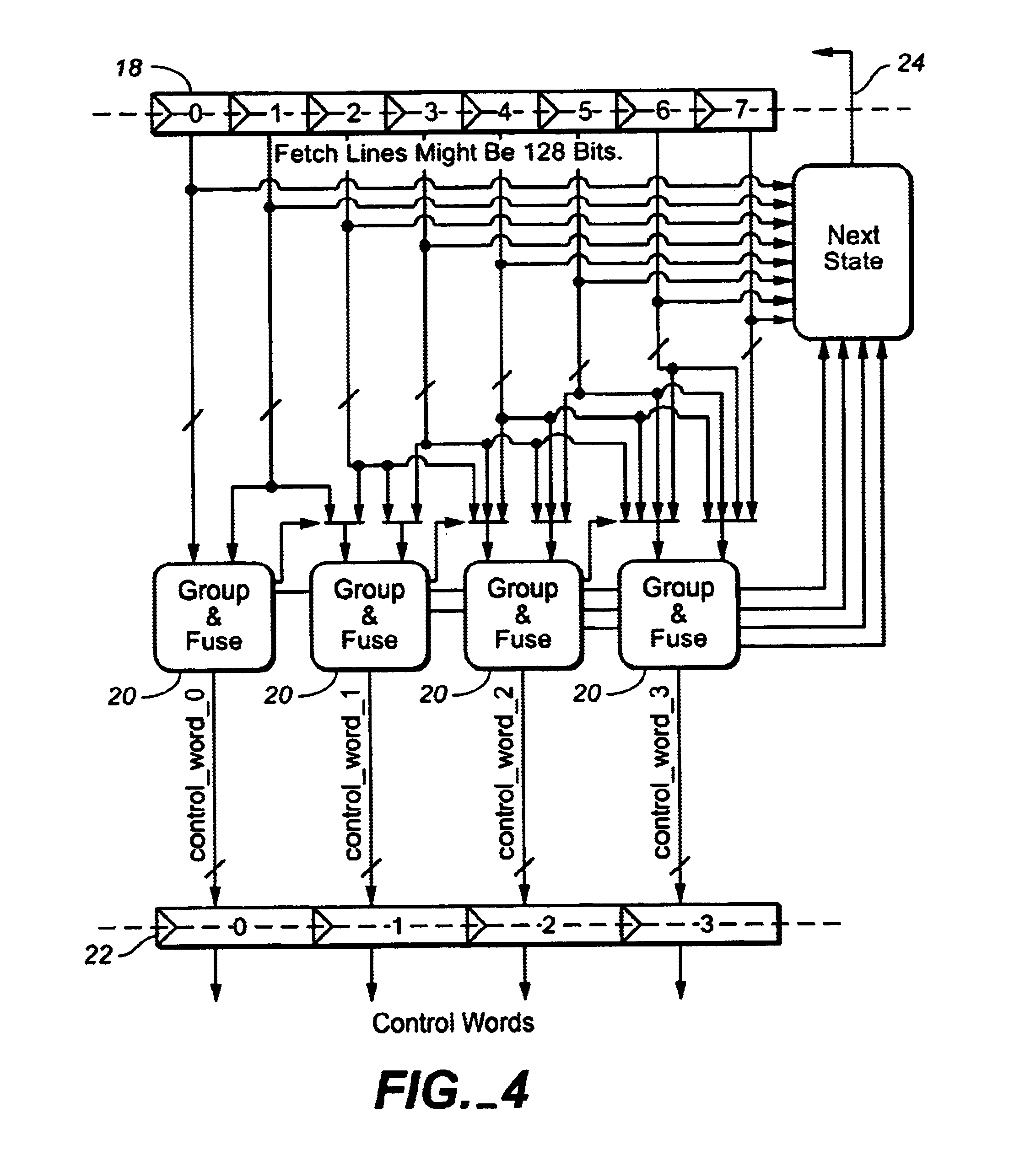

Instruction fusion for digital signal processor

InactiveUS6889318B1Digital computer detailsConcurrent instruction executionDigital signal processingInstruction unit

An instruction pipeline for a DSP with fusing logic for combining multiple instructions into a single control word which can be executed by one execution unit. The pipeline fetches a greater number of instructions than the number of execution units to which it can issue instructions. It applies grouping rules to the instructions and also identifies pairs, or larger groups, of instructions which can be combined, or fused, into a single control word which can be executed by one execution unit. Issuance of a fused control word to a single execution unit effectively allows two or more instructions to be executed simultaneously in one execution unit.

Owner:VERISILICON HLDGCO LTD

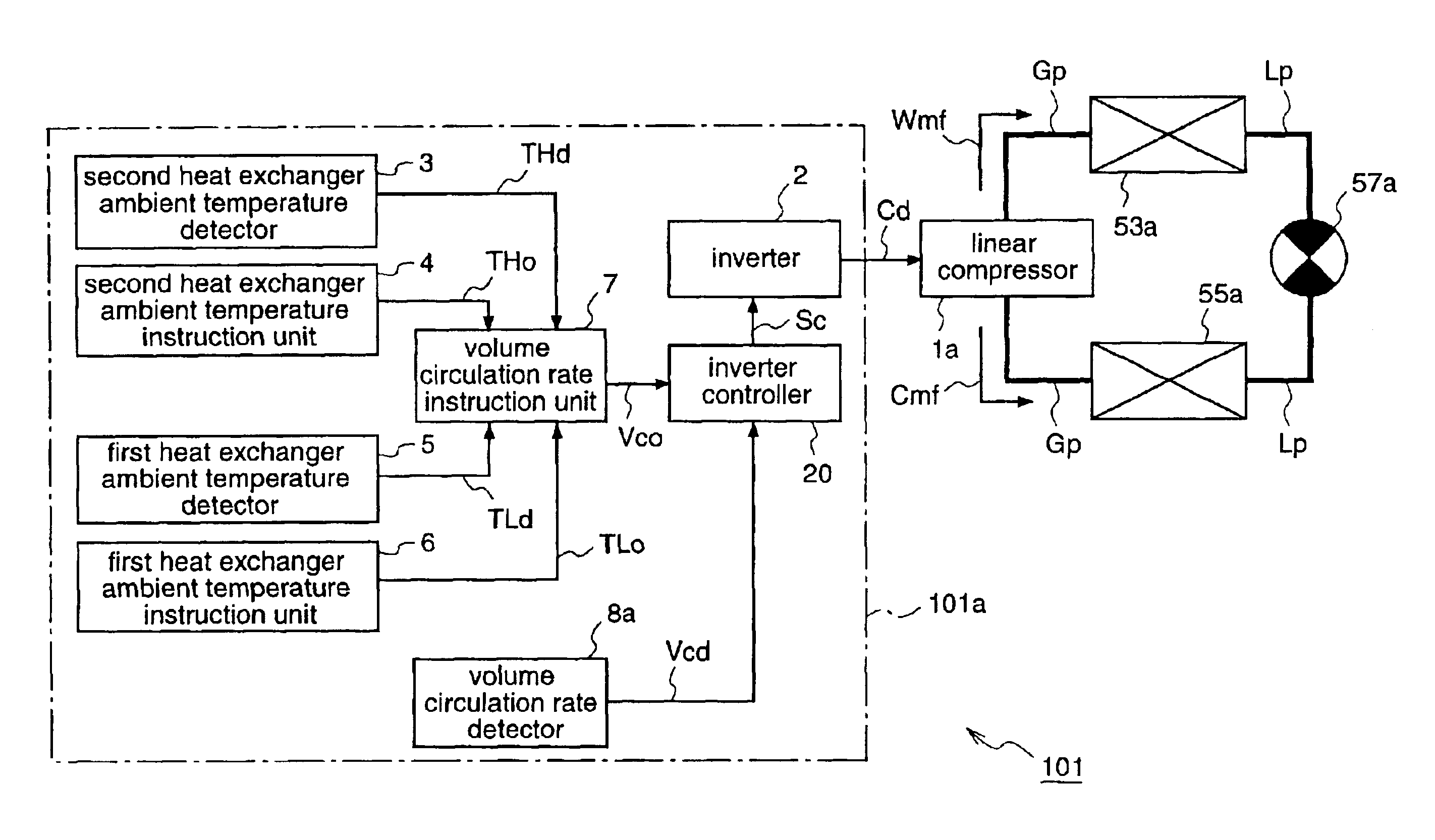

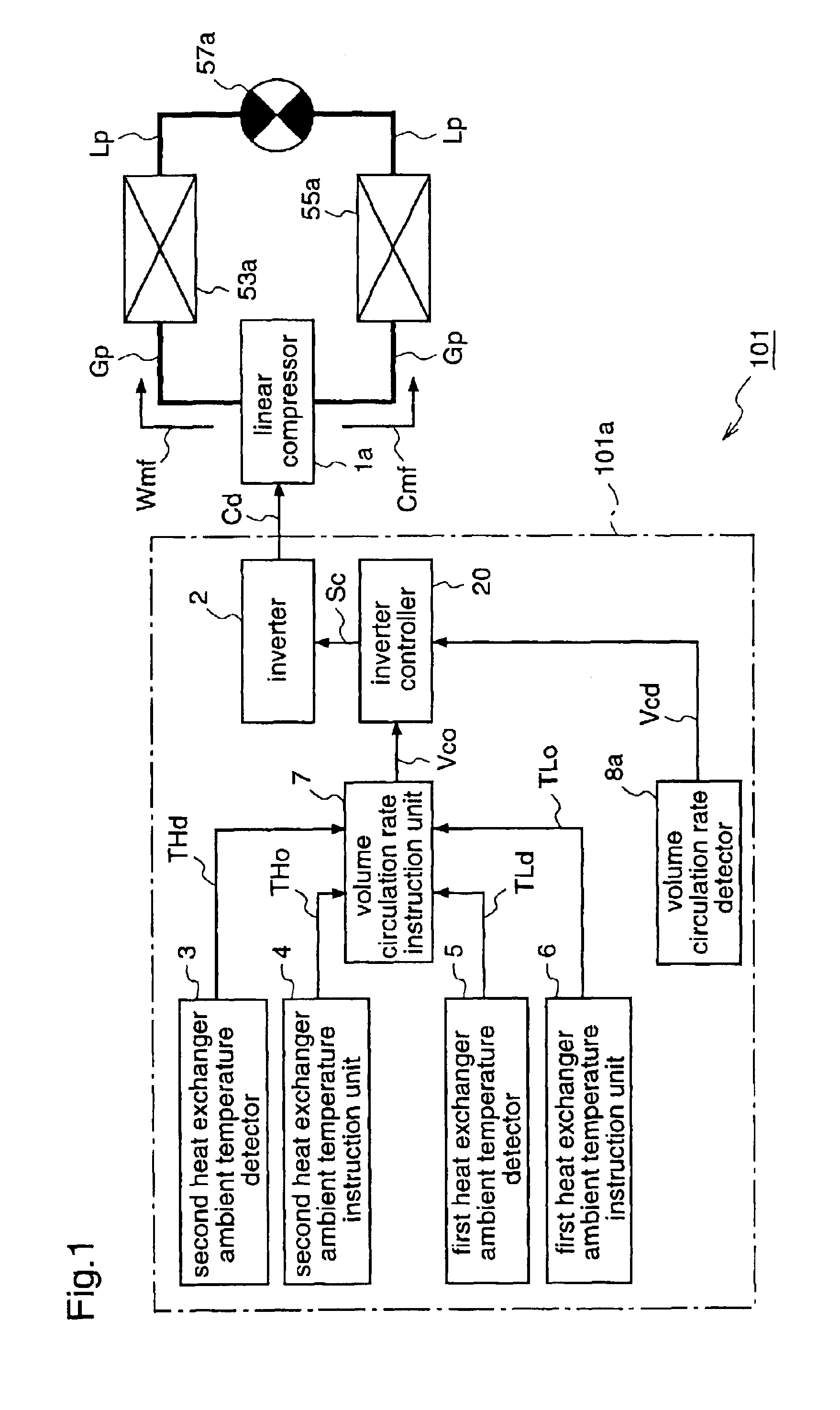

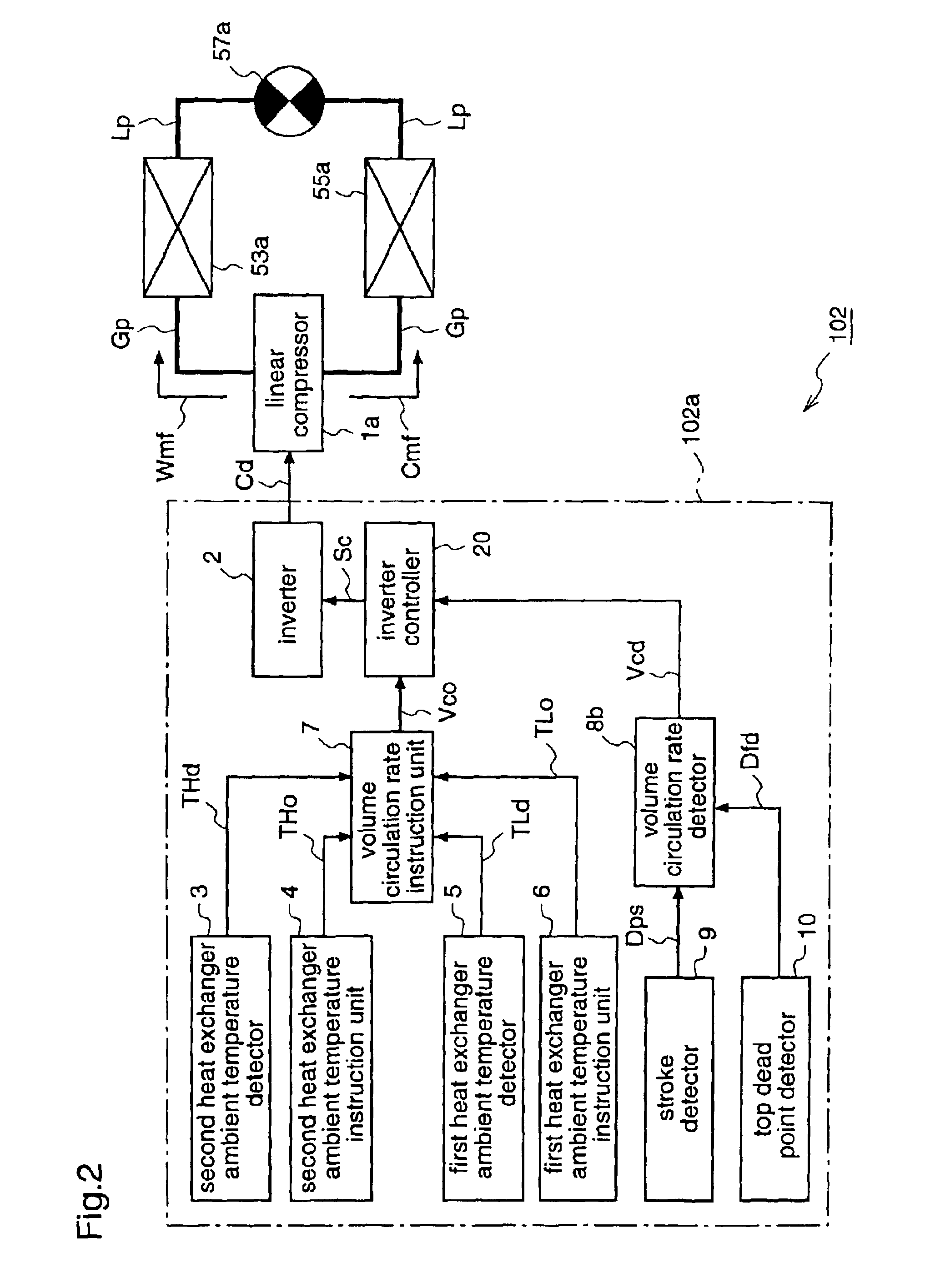

Refrigeration cycle apparatus

InactiveUS6868686B2Improve efficiencyShort timeHeat pumpsCompression machines with non-reversible cycleCycle rateInstruction unit

A refrigeration cycle apparatus having a linear compressor is provided with a volume circulation rate instruction unit for obtaining a volume circulation rate Vco of a refrigerant in accordance with refrigerating capacity required of the refrigeration cycle apparatus, on the basis of an ambient temperature of an indoor heat exchanger (evaporator), a target temperature set on the evaporator by the user, and an ambient temperature of an outdoor heat exchanger (condenser). A volume circulation rate detector is provided for detecting a volume circulation rate Vcd of the refrigerant that actually circulates in a refrigerant circulation path of the refrigeration cycle apparatus; and an inverter is provided for generating an AC current for driving the linear compressor. The inverter is controlled so as to decrease a difference between the volume circulation rate Vco and the volume circulation rate Vcd.

Owner:PANASONIC CORP

Dual thread processor

ActiveCN1841314ARegister arrangementsConcurrent instruction executionInstruction unitProcessor register

A pipeline processor architecture, processor, and methods are provided. In one implementation, a processor is provided that includes an instruction fetch unit operable to fetch instructions associated with a plurality of processor threads, a decoder responsive to the instruction fetch unit, issue logic responsive to the decoder, and a register file including a plurality of banks corresponding to the plurality of processor threads. Each bank is operable to store data associated with a corresponding processor thread. The processor can include a set of registers corresponding to each of a plurality of processor threads. Each register within a set is located either before or after a pipeline stage of the processor.

Owner:MARVELL ASIA PTE LTD

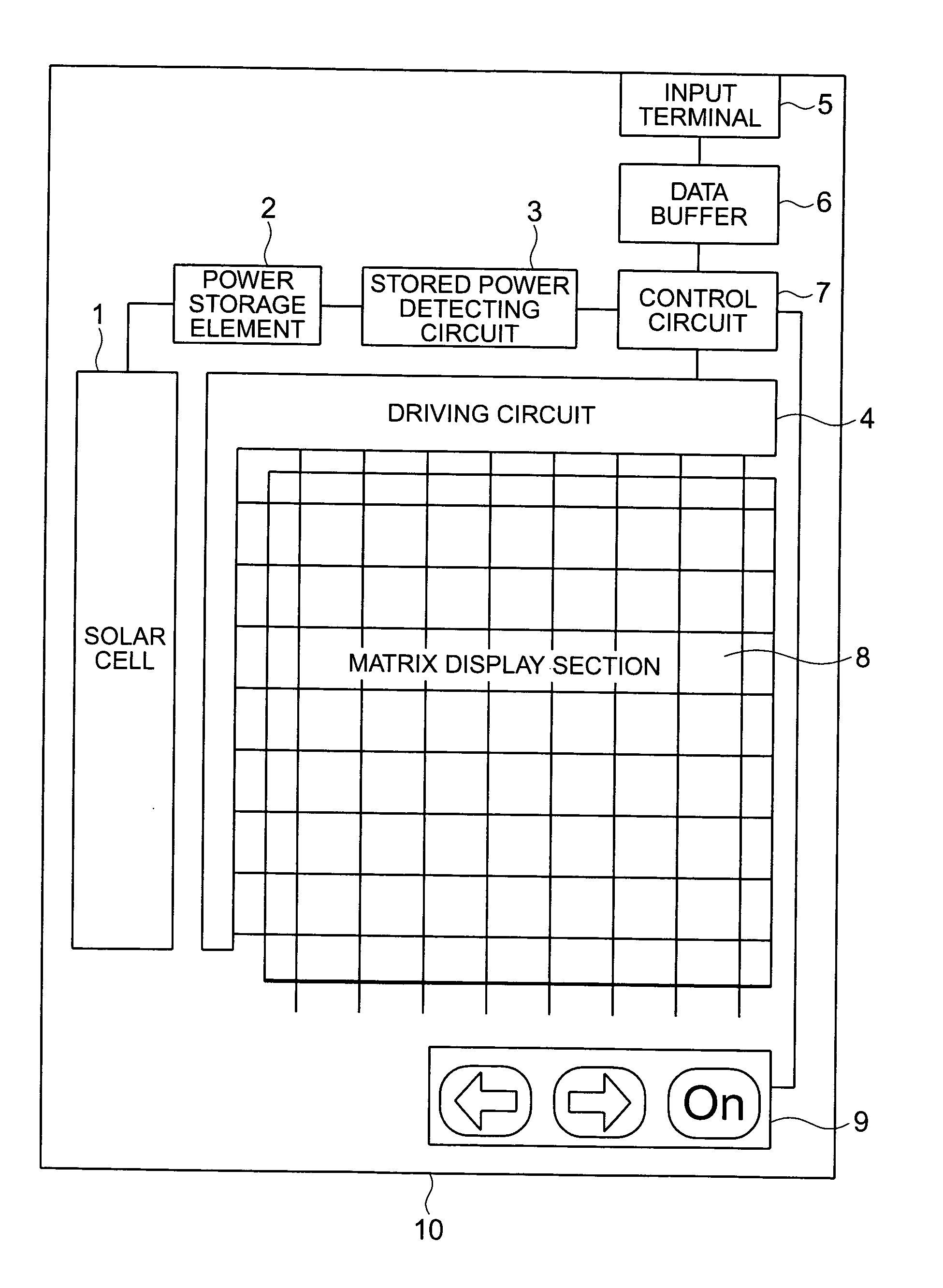

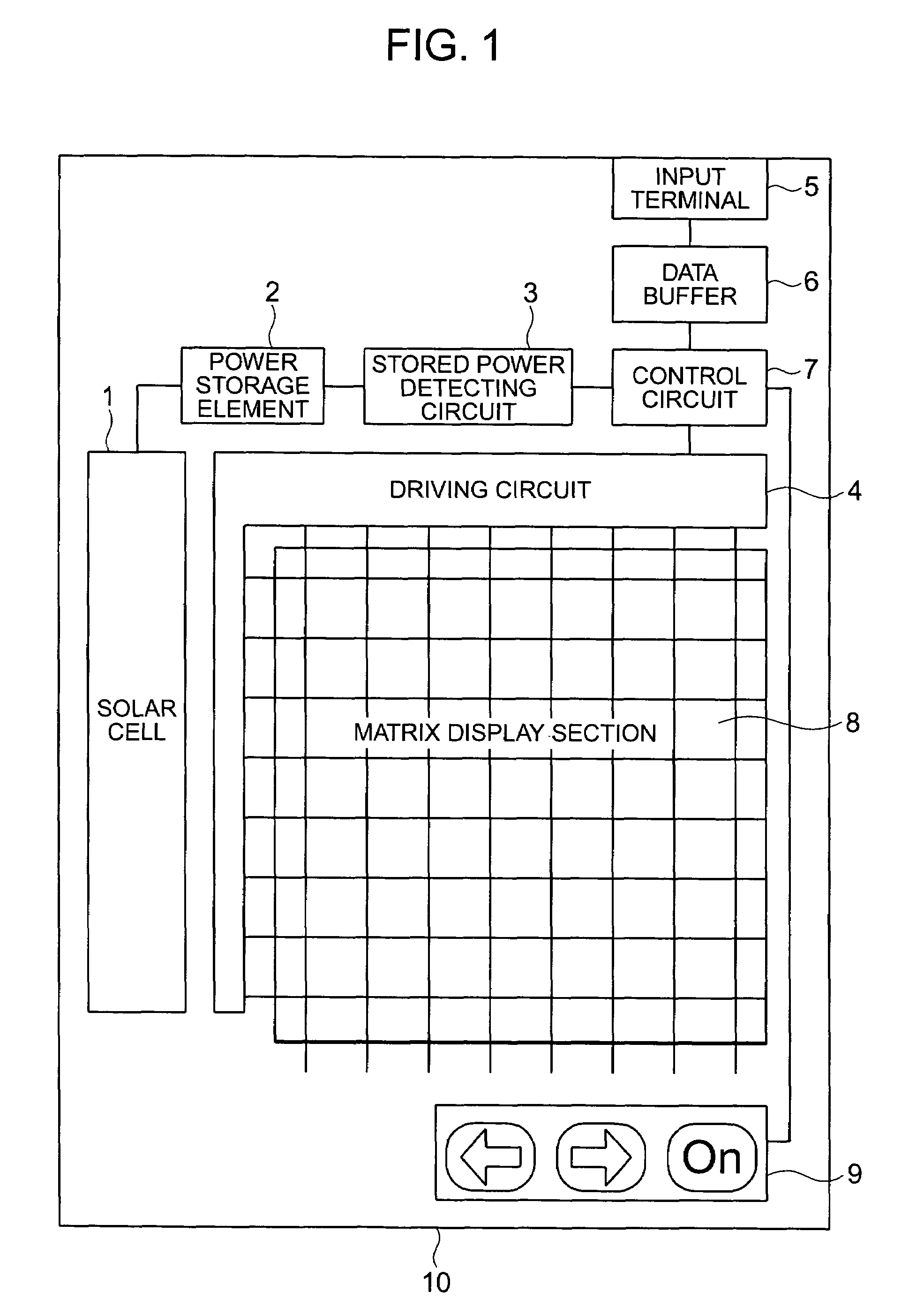

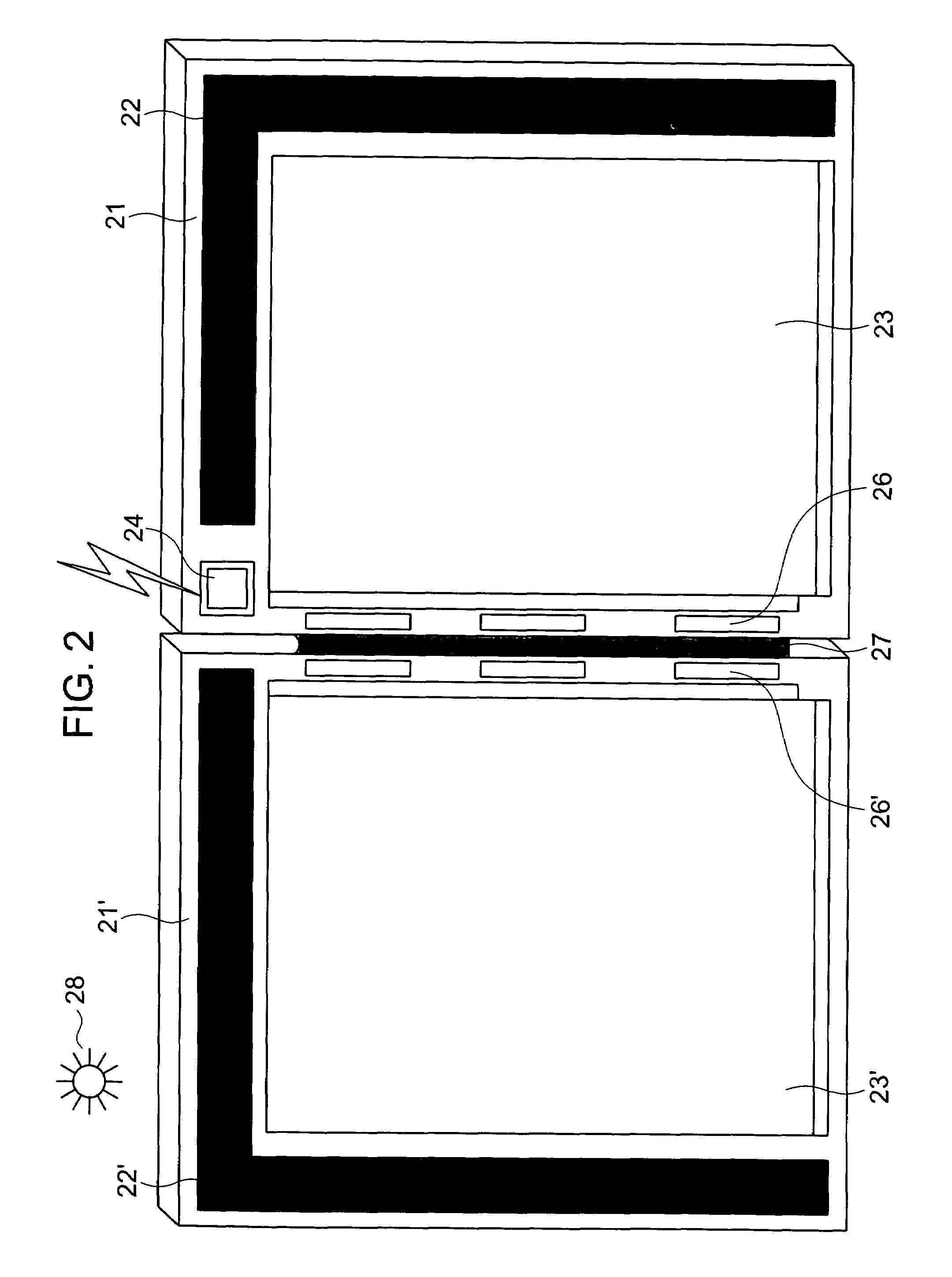

Low-power driven display device

InactiveUS7319465B2Reduce necessityCathode-ray tube indicatorsNon-linear opticsElectrical batteryDisplay device

For a display device having a solar cell and a power buffer for keeping stored electric power, a display system which has a low-power drive mode, self-contained power and no need for recharging or power wiring is provided. The display system includes a solar cell using a thin-film semiconductor, a power storage element for temporarily storing the produced power, a driving circuit, a matrix display unit, a display rewrite instruction unit for inputting screen rewrite and a control circuit and starts rewriting a display when power sufficient to rewrite an image screen is stored in the solar cell. The display device having remarkable portability and no limited battery life, which controls a display mode depending on the power produced by the solar cell, can display even when power generation is low and allows self-contained power even if the storage element has a small capacity, can be obtained.

Owner:HITACHI LTD

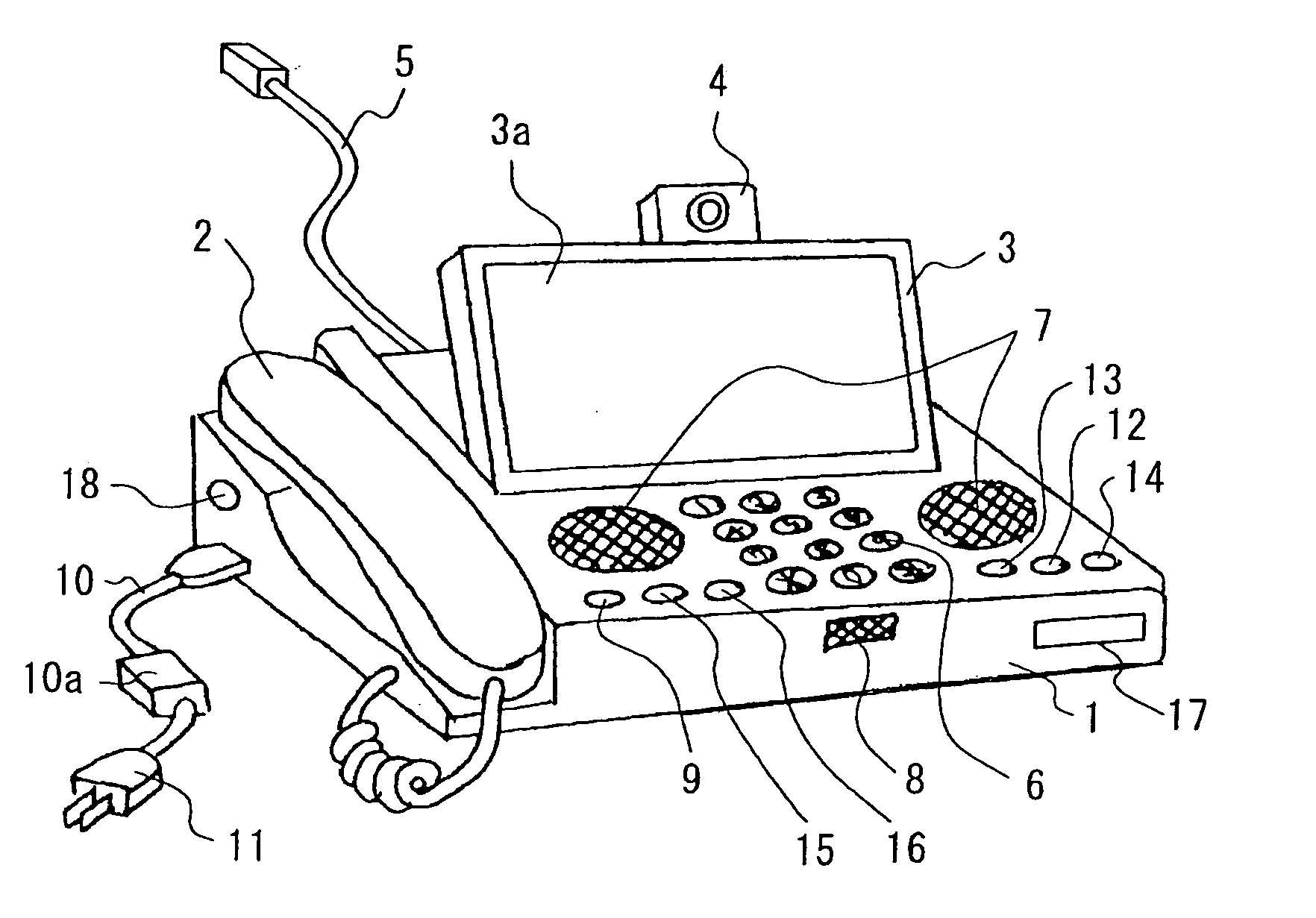

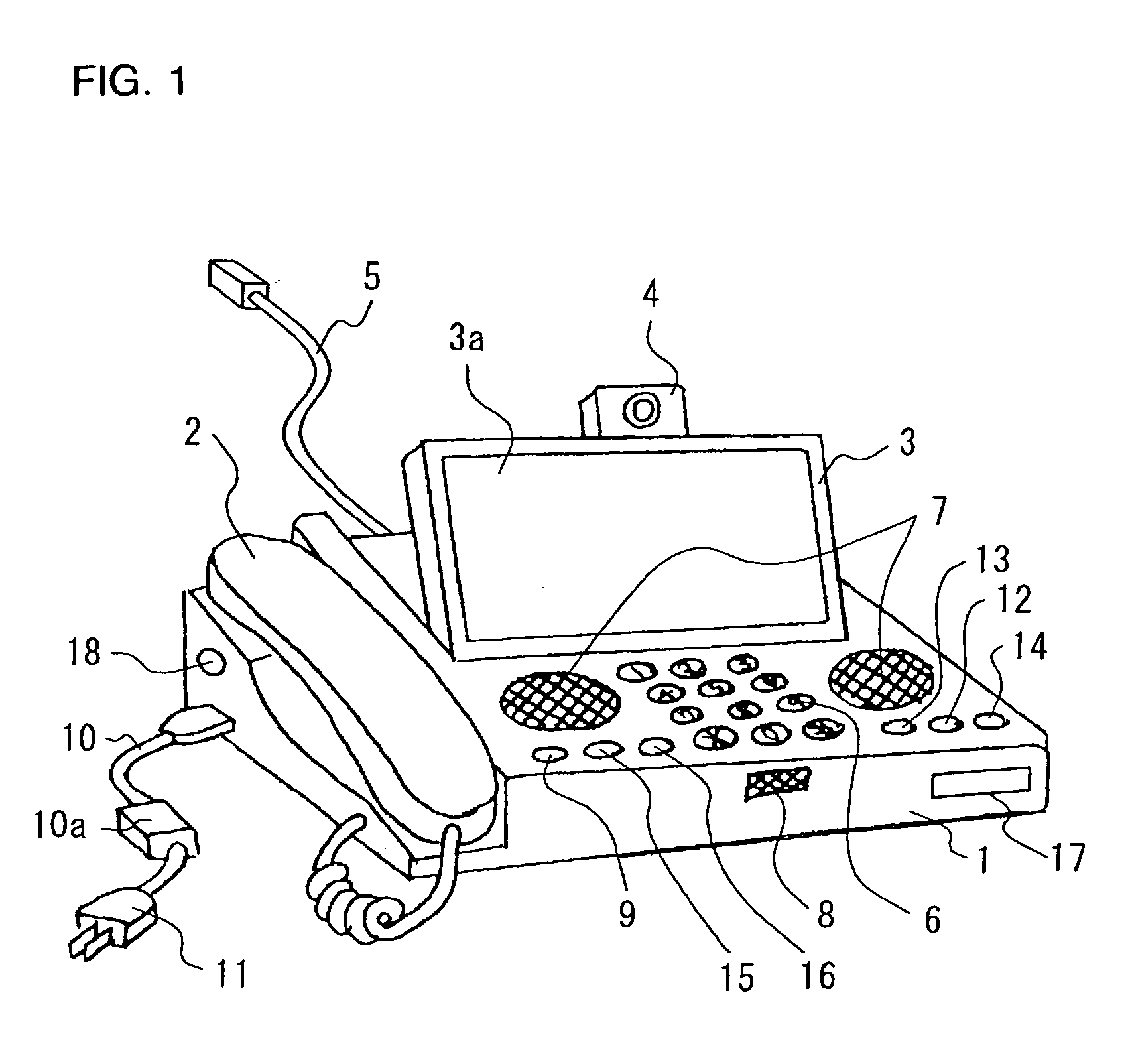

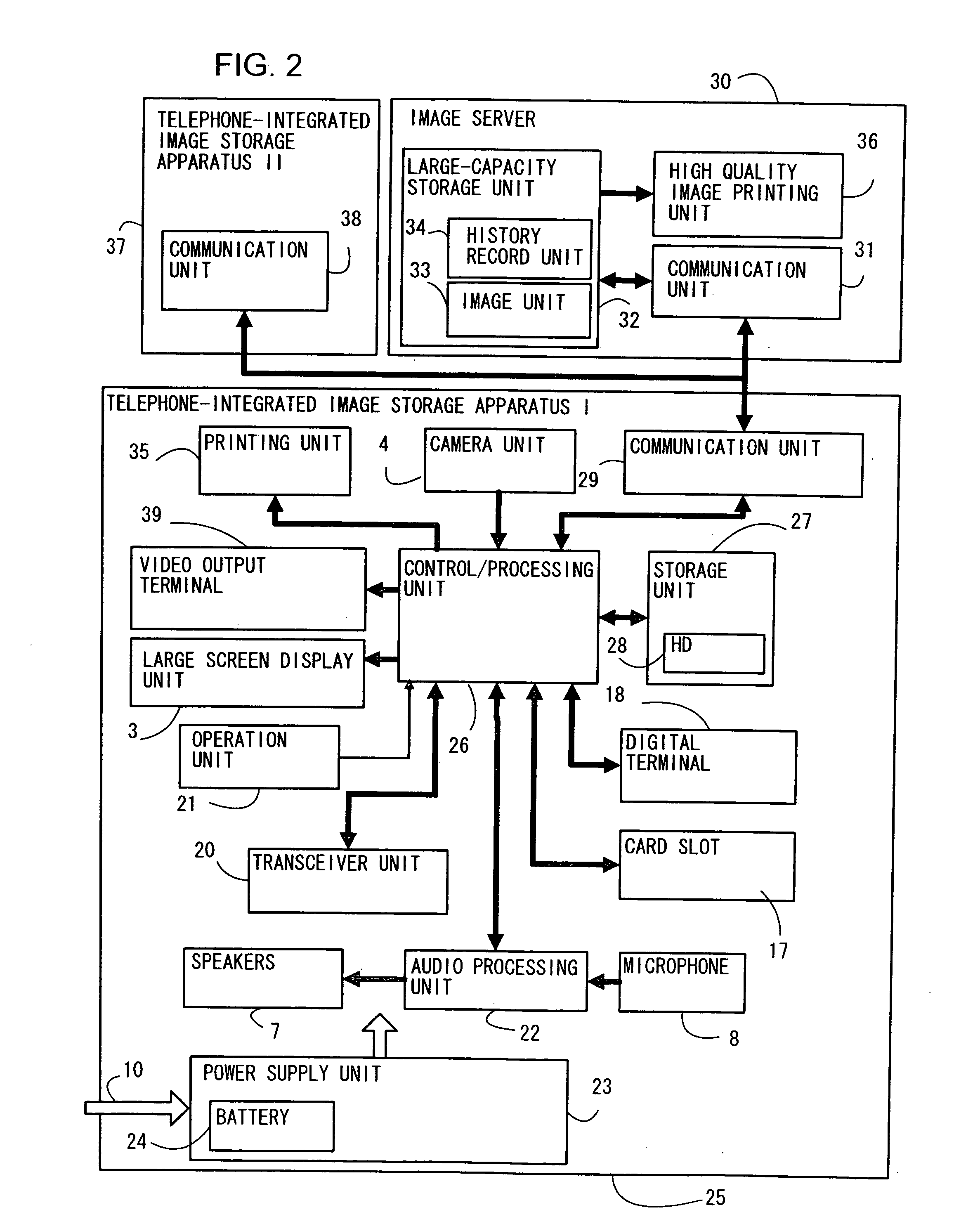

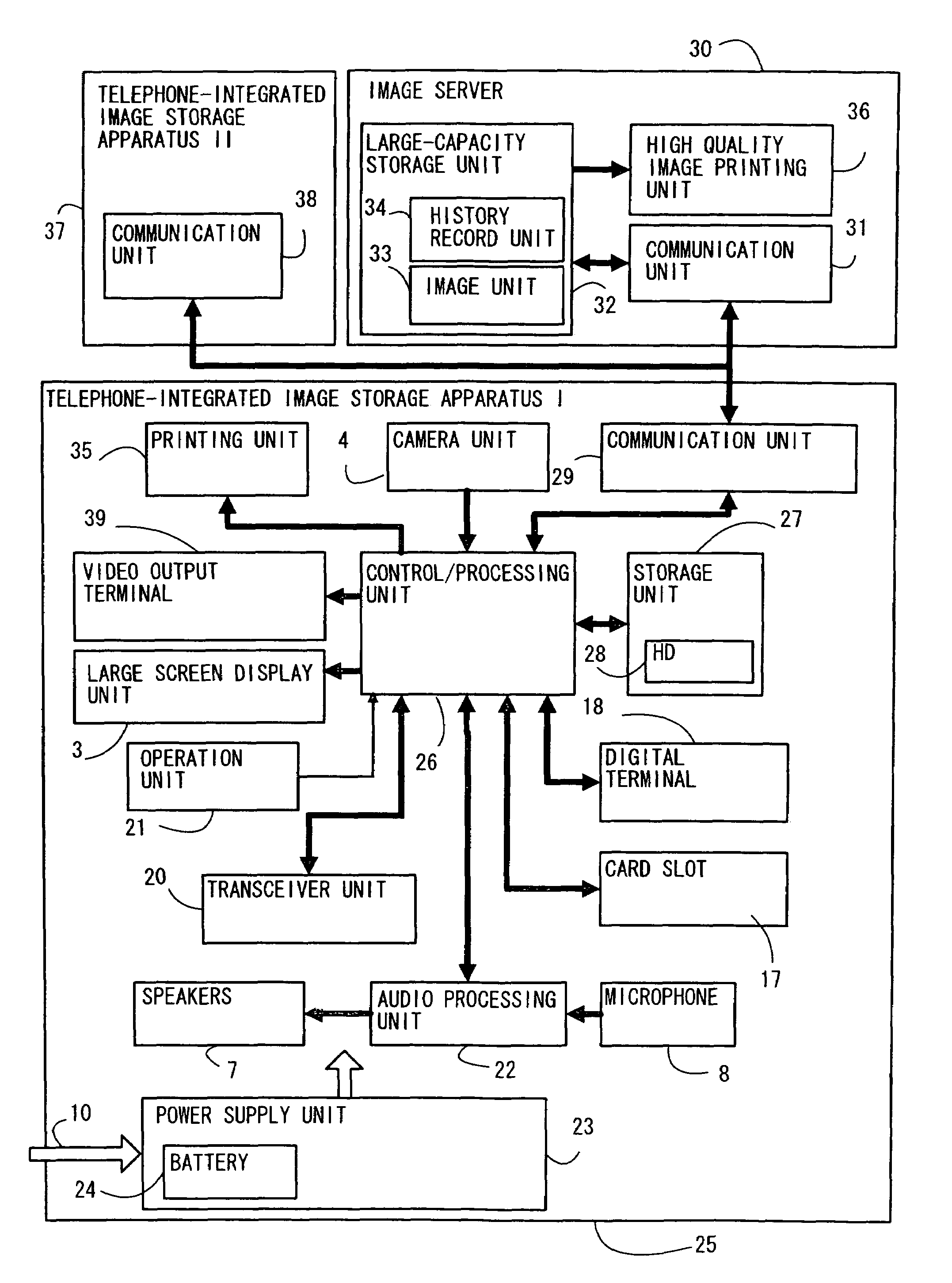

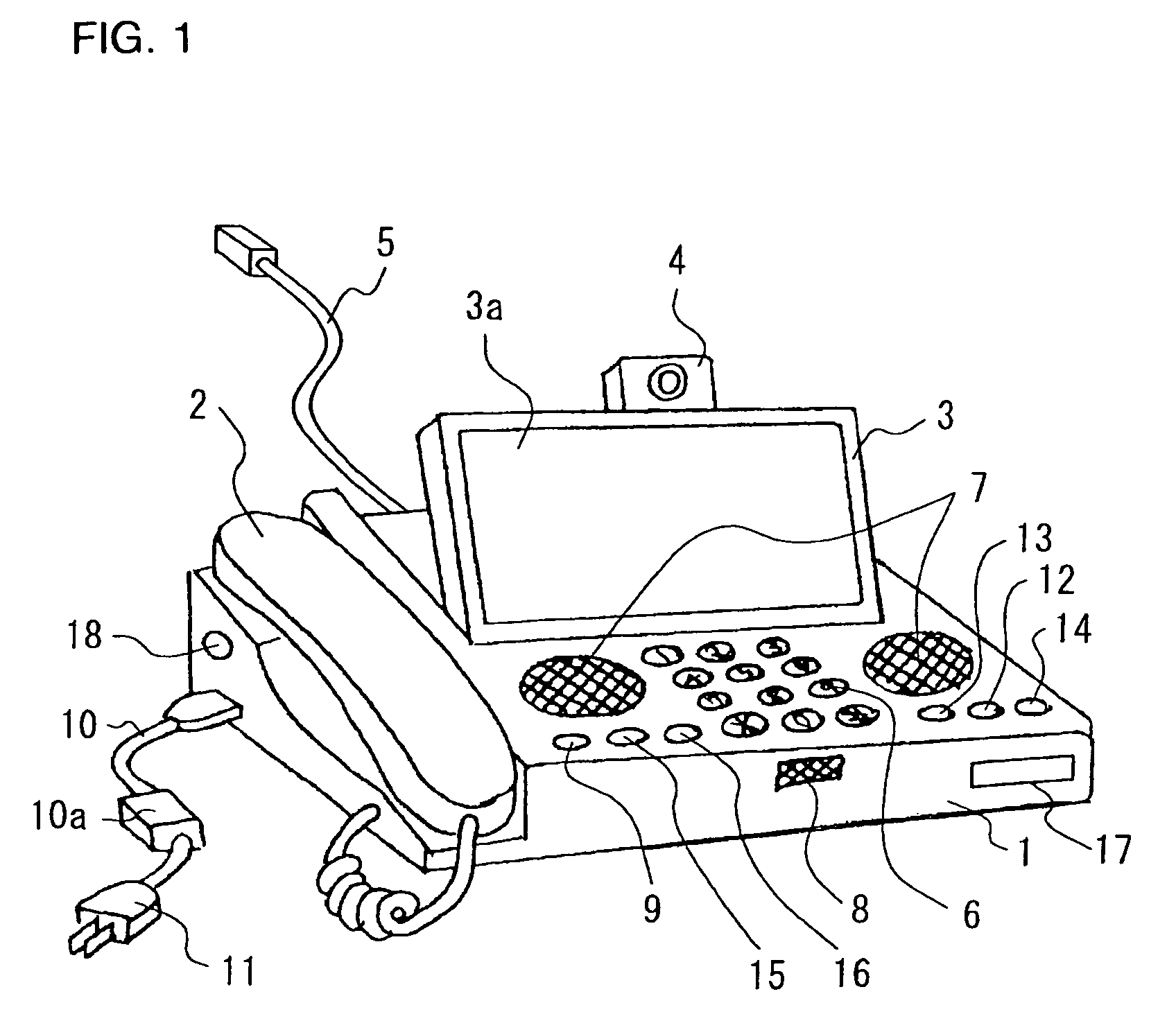

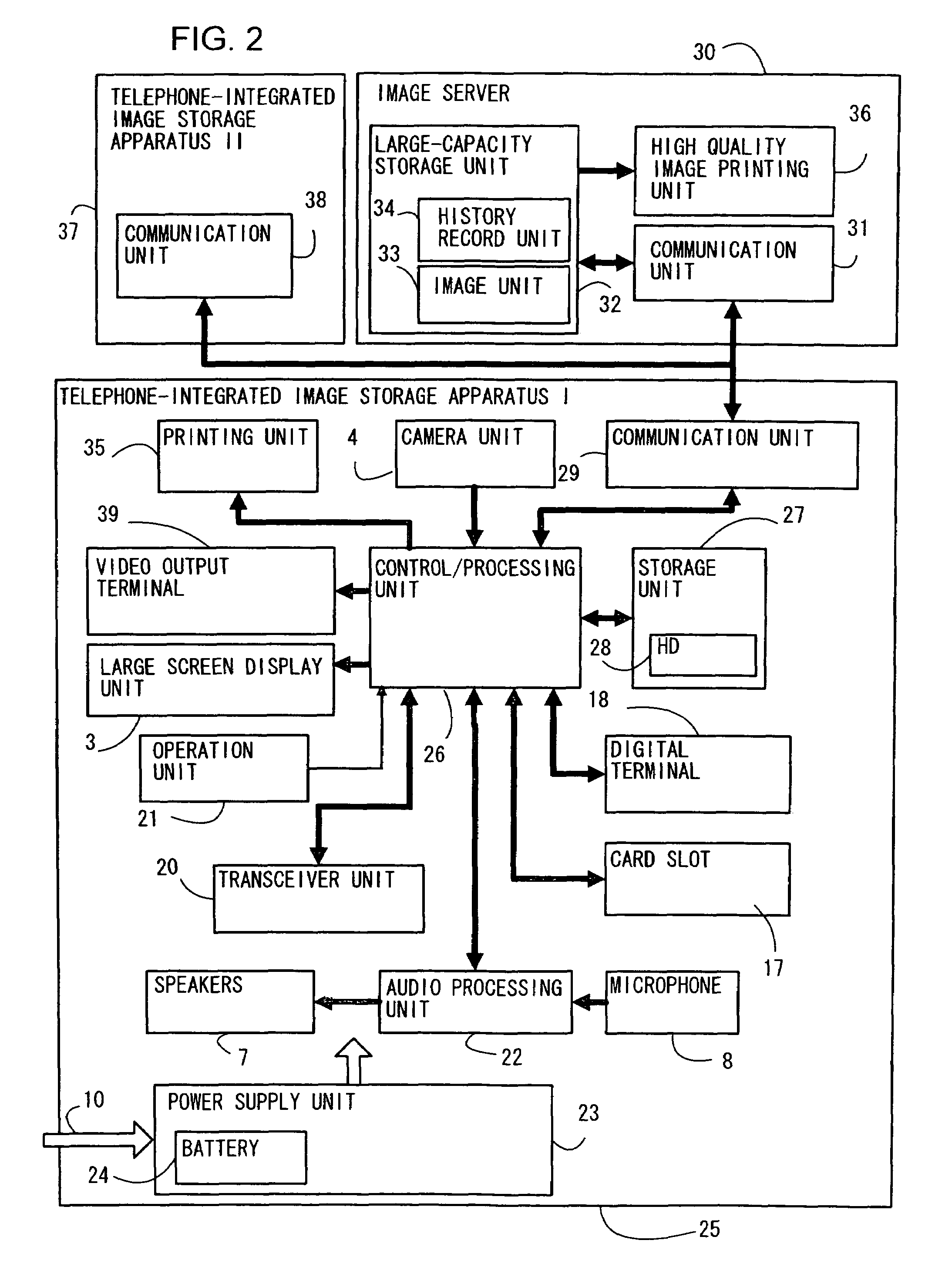

Image accumulating apparatus, image accumulation support apparatus, image accumulation system, image control apparatus, image storage apparatus

InactiveUS20050069107A1Improve reliabilityRaise security concernsTelephonic communicationTwo-way working systemsInstruction unitManagement unit

Owner:NIKON CORP

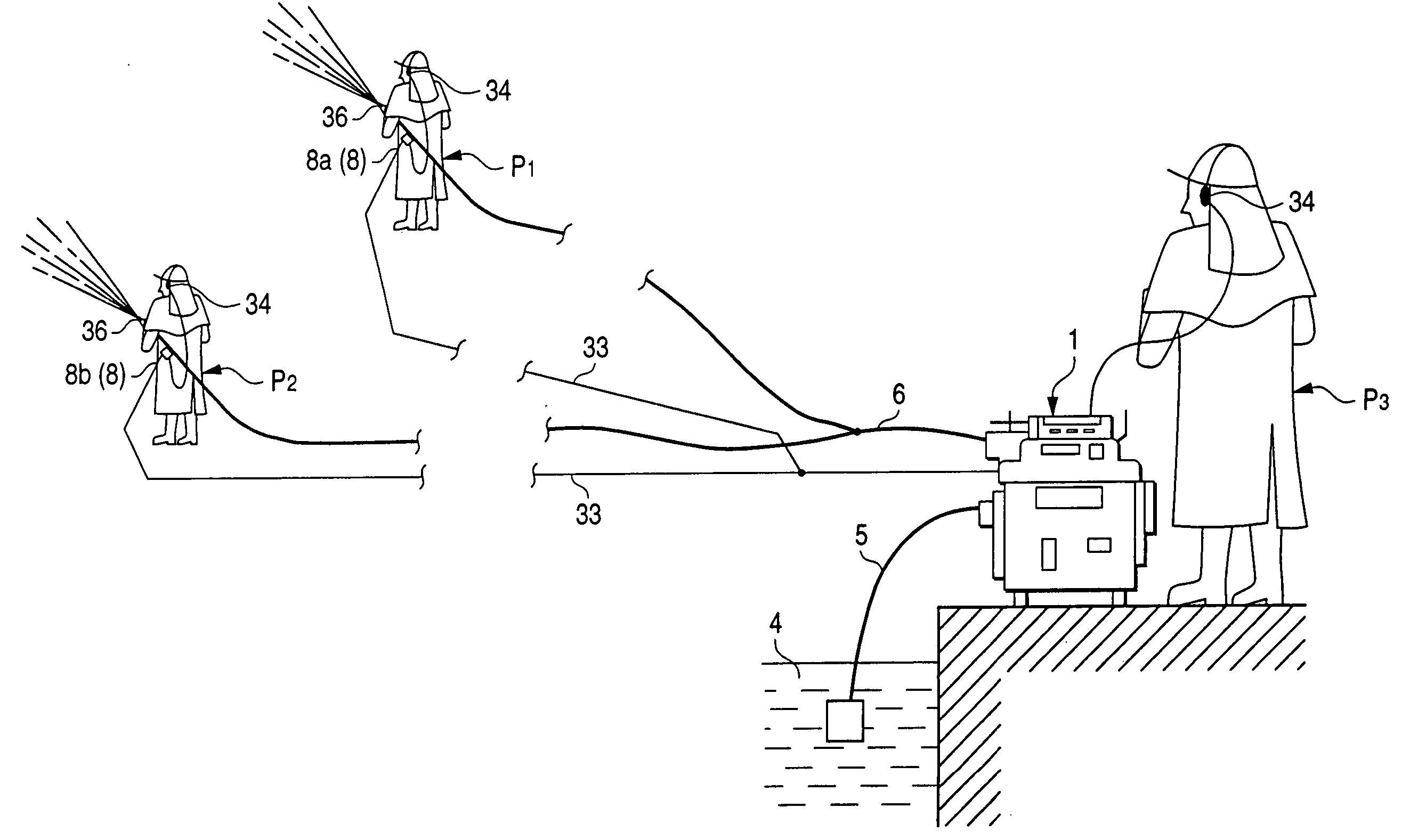

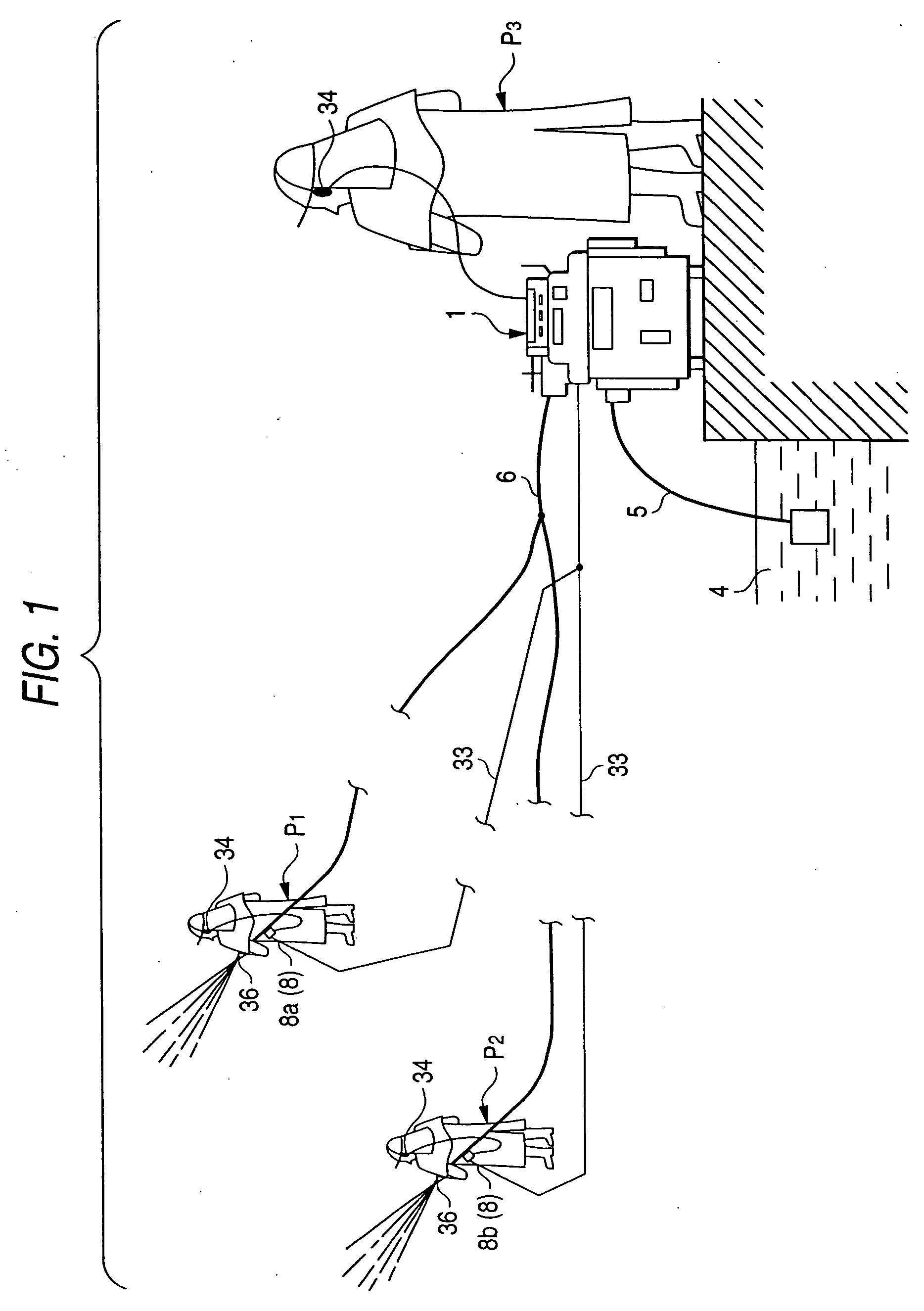

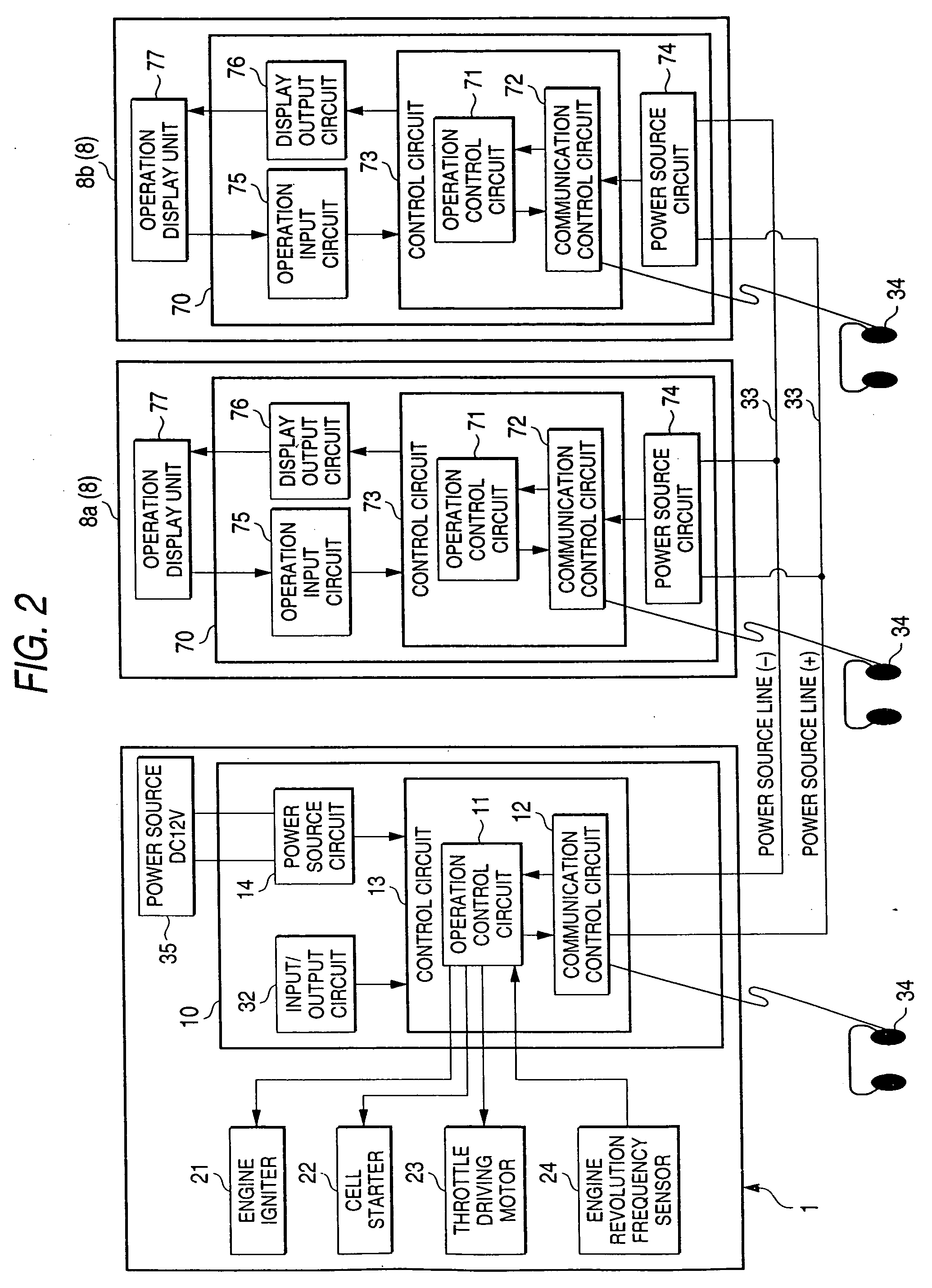

Control apparatus for a fire pump, operation display apparatus for a fire pump and operation mode control apparatus for a fire pump

InactiveUS20060180321A1Excellent operation controllability and information transfer capabilityGood safety and controllabilitySelf-acting watering devicesFire rescueInstruction unitControl signal

In a fire pump adapted to force out the water, which is pumped from a water source, from a nozzle provided at a front end portion of a delivery hose, a nozzle control unit 8 adapted to control the fire pump remotely is provided in the vicinity of the nozzle. The nozzle control unit 8 is connected to a body of the fire pump 1 by power source lines 33. On the nozzle control unit 8, a control instruction unit for instructing an operating mode of the pump 1, and a numerical value display unit for displaying the operation condition of the fire pump are provided. The transmitting and receiving of an operation control signal and a condition display signal are done between the pump 1 and nozzle control unit 8 by power line communication via the power source lines 33, whereby the operation condition of the pump 1 is feedback displayed in real time in response to a control operation of a nozzle operator.

Owner:YOSHIDA KENICHI

Display control device, display control method, computer product

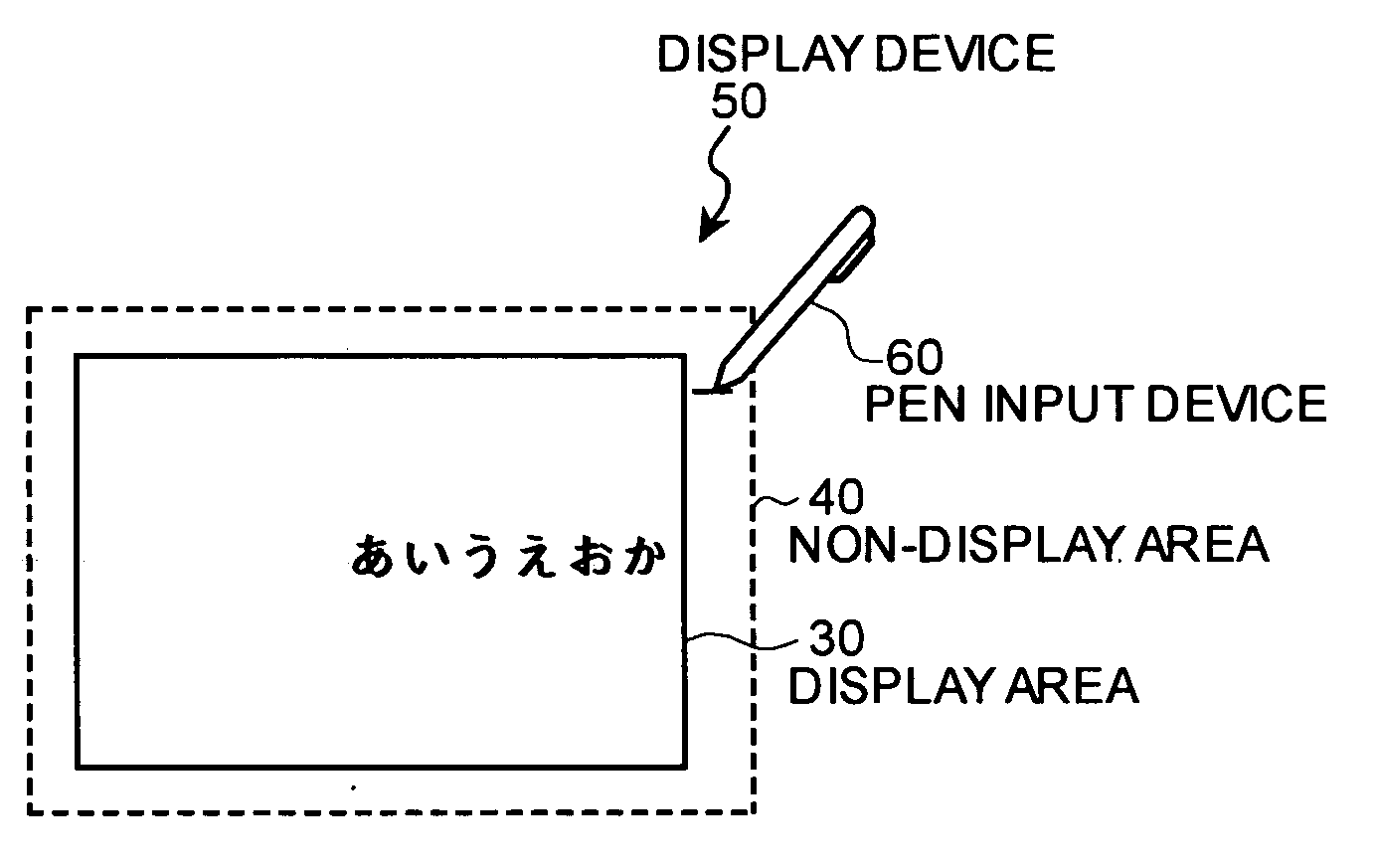

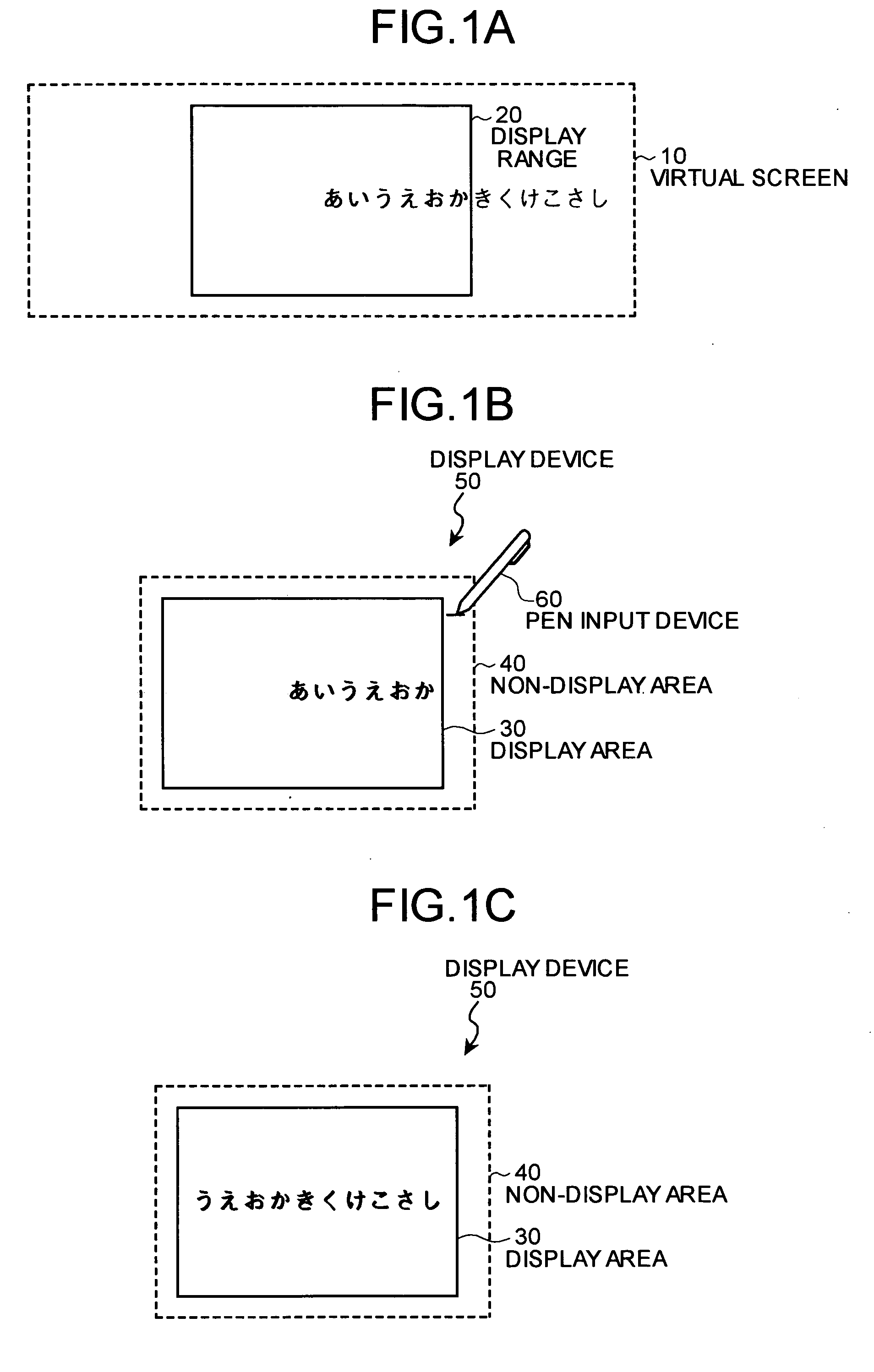

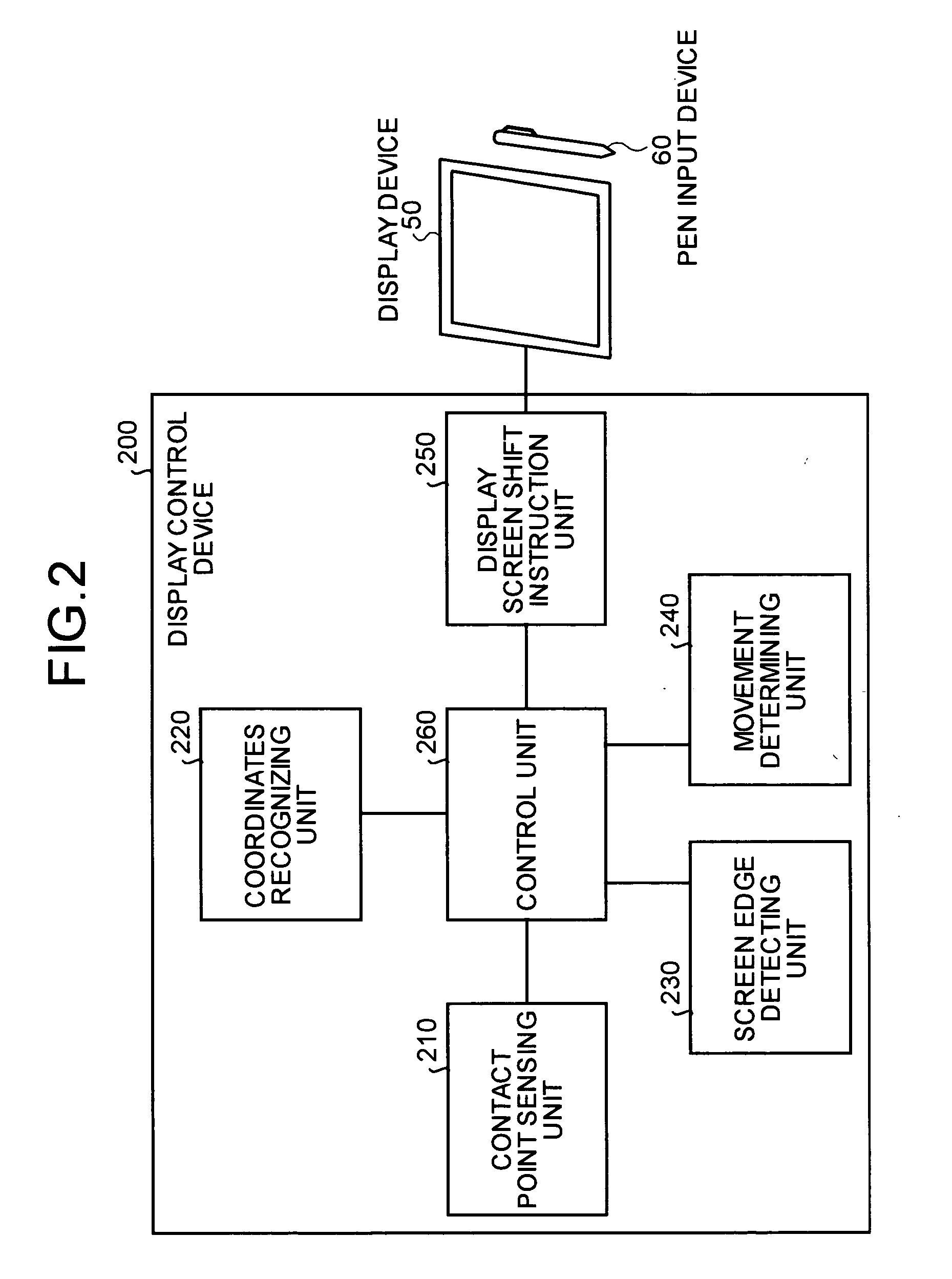

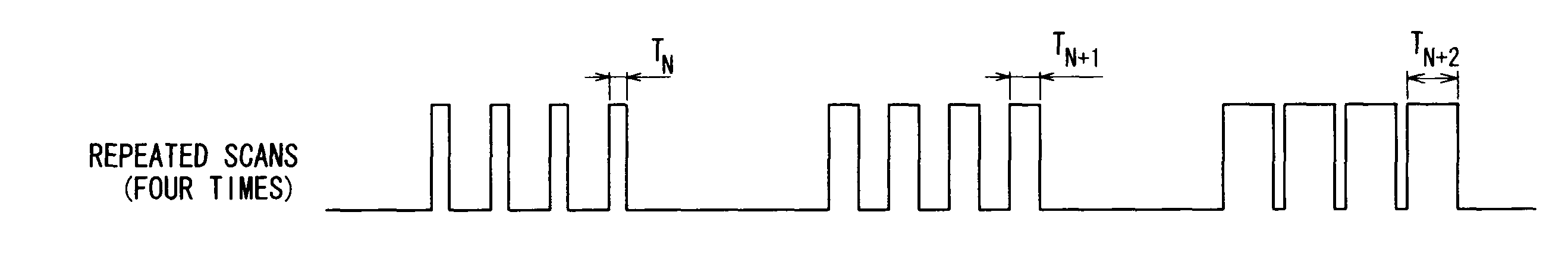

InactiveUS20050168441A1Cathode-ray tube indicatorsInput/output processes for data processingInstruction unitDisplay device

A display control device controls a display device that displays a screen area wider than a screen display area. The display control device includes a non-display area in the surrounding part of the screen display area, that receives pen input, but does not display the screen; a screen edge detecting unit that detects the touching of the non-display area by the pen; a movement determining unit that determines whether to start scrolling the display screen in a specific direction or whether to stop the scrolling based on whether the pen is touched in the non-display area, the direction of movement, and the amount of movement of the pen, and a display screen shift instruction unit that instructs the display device to start or stop scrolling the display screen.

Owner:FUJITSU LTD

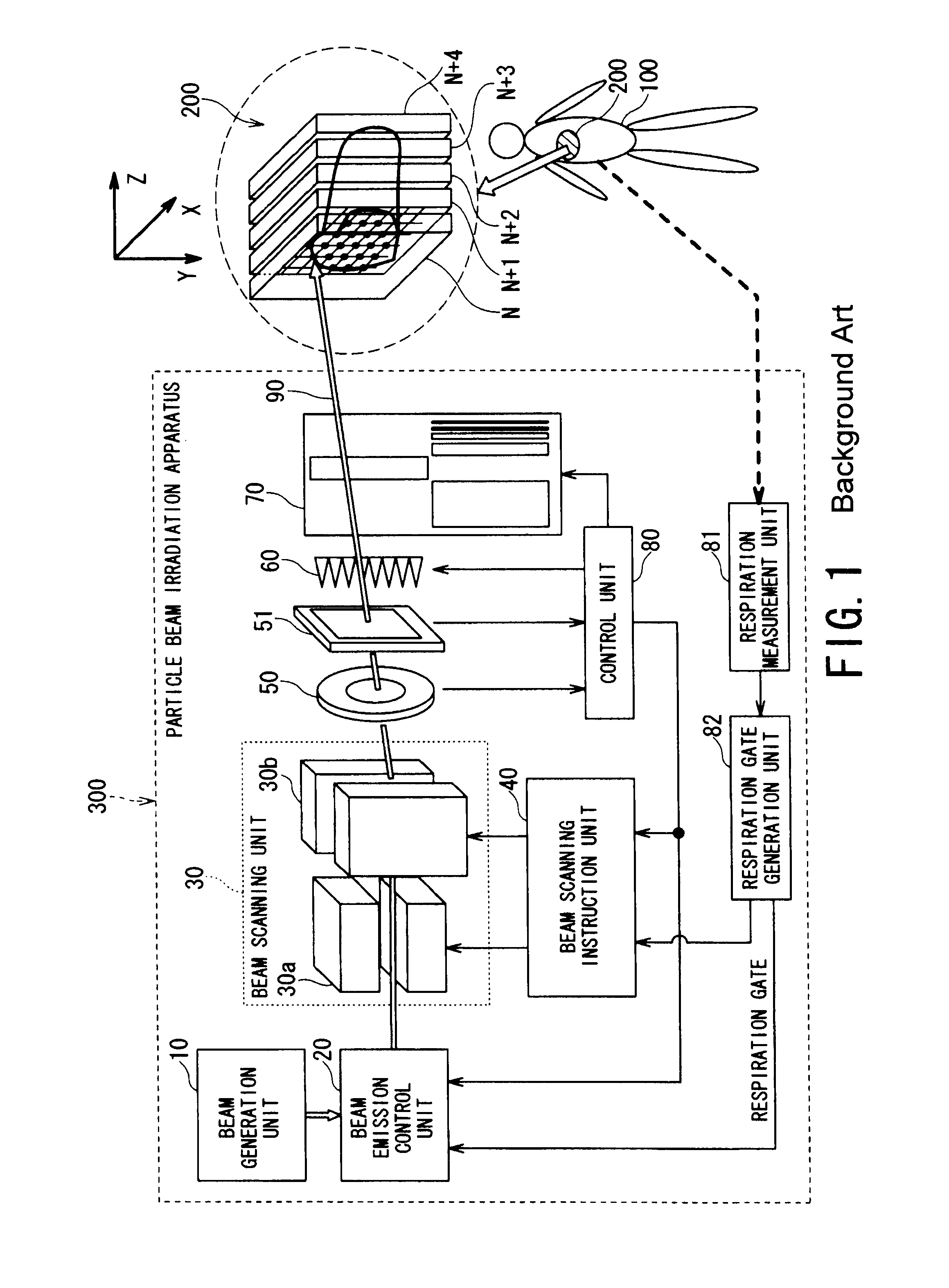

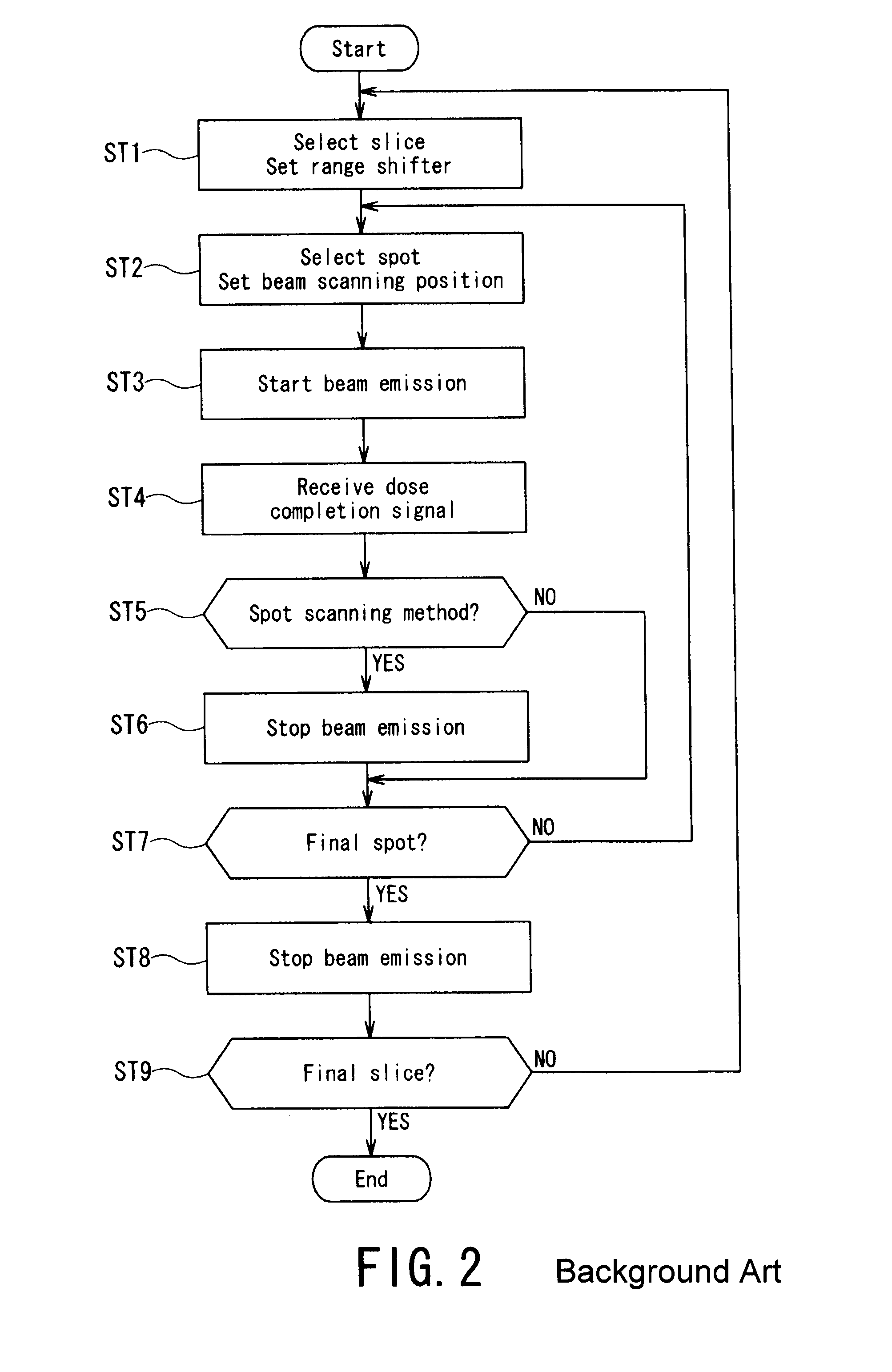

Particle beam irradiation apparatus and particle beam irradiation method

InactiveUS8436323B2Improve setting accuracyShorten treatment timeThermometer detailsBeam/ray focussing/reflecting arrangementsInstruction unitParticle beam

Owner:KK TOSHIBA

Image storage apparatus, image storage supporting apparatus, image storage system, image management apparatus and image saving apparatus

InactiveUS7336775B2Improve reliabilityRaise security concernsTelephonic communicationTwo-way working systemsInstruction unitCommunication unit

Owner:NIKON CORP

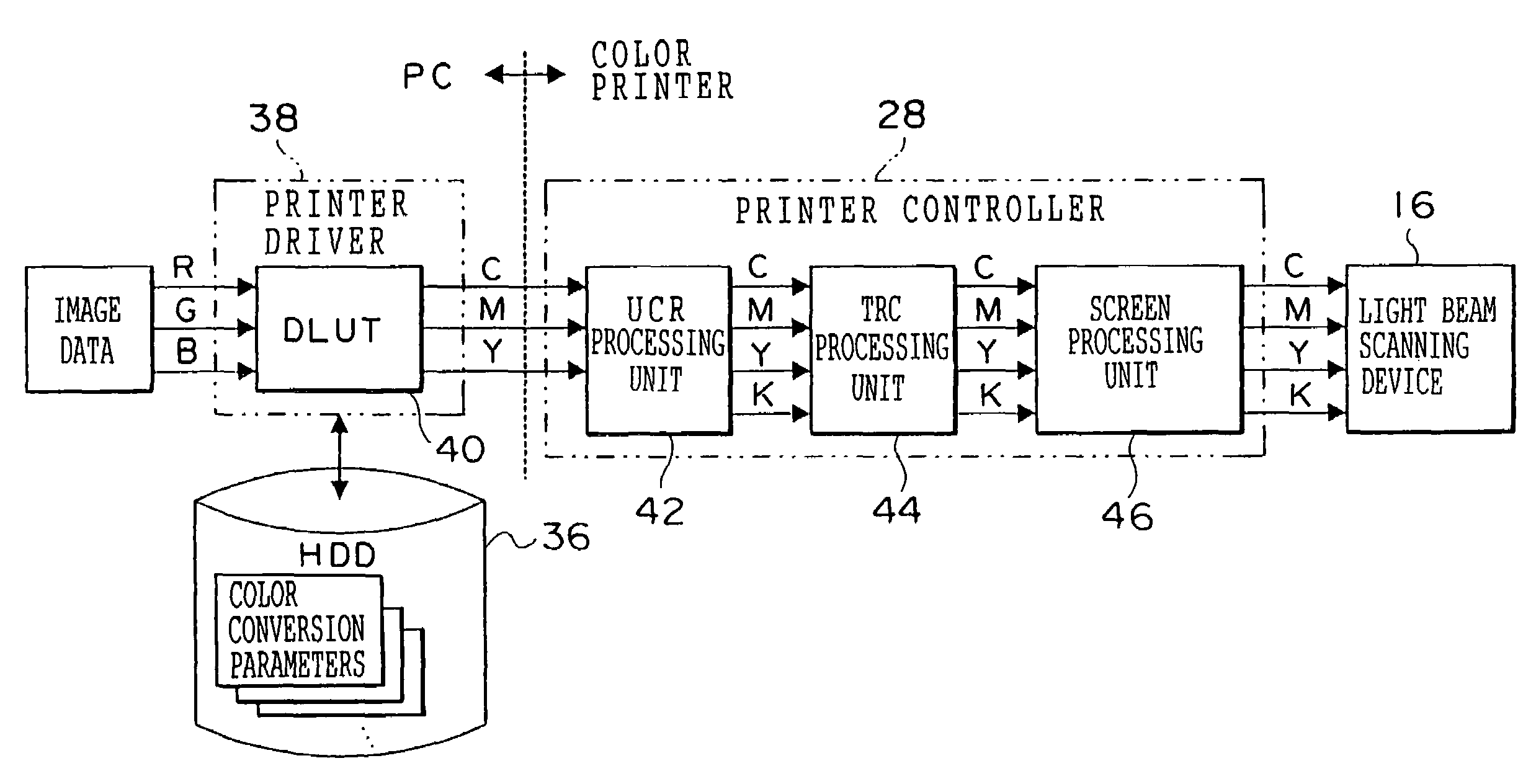

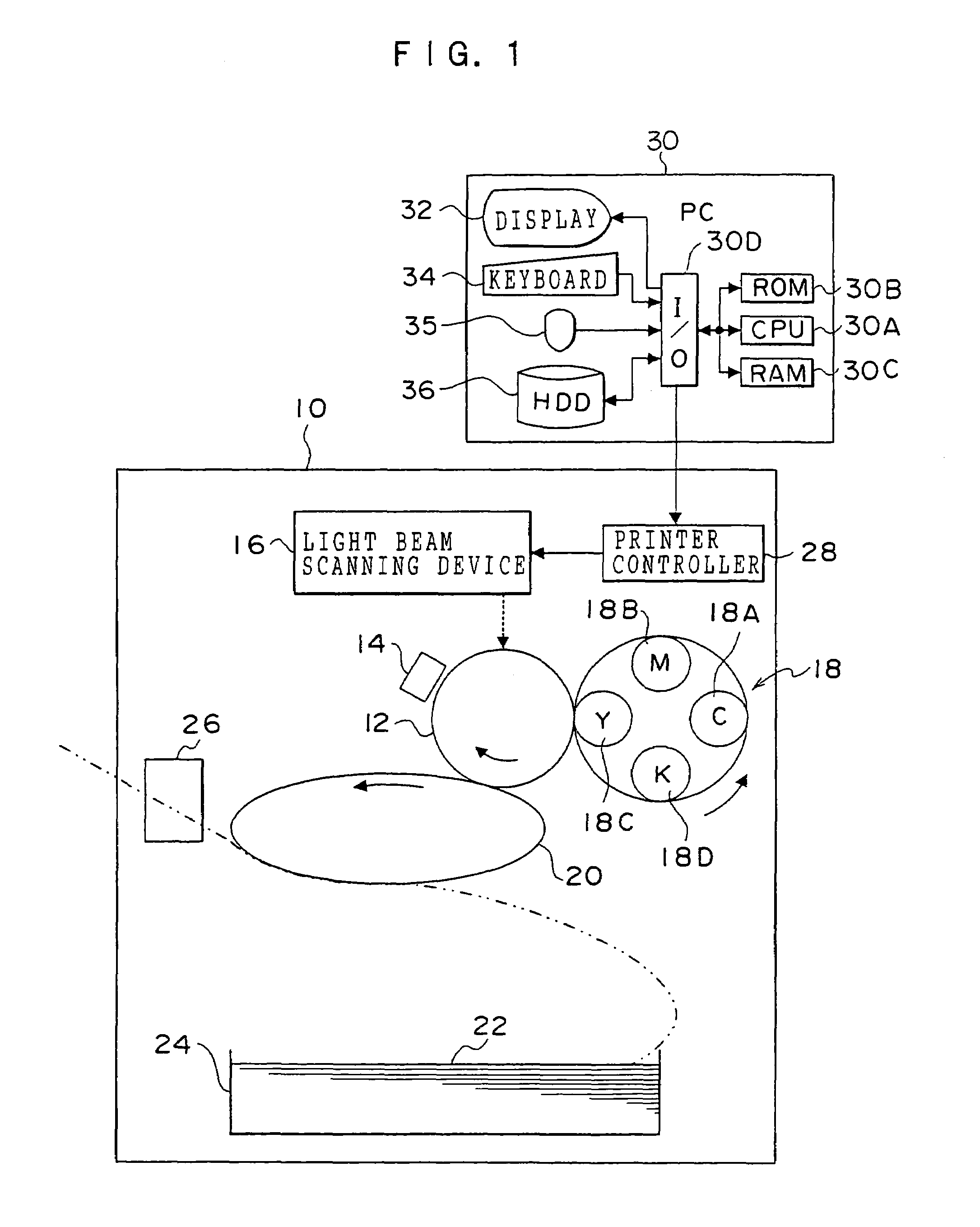

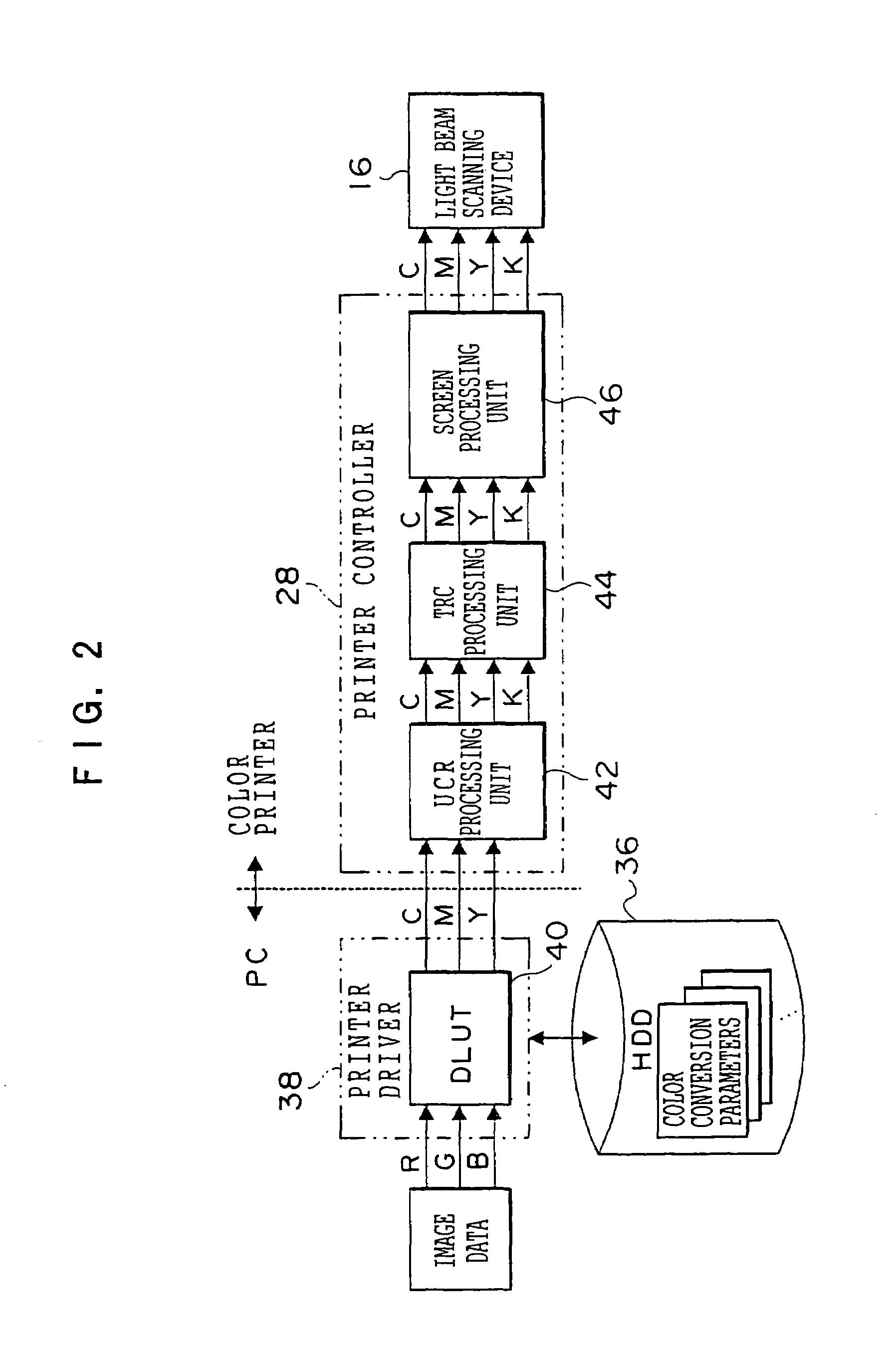

Image processing device and method

InactiveUS7492478B2Accurate color balanceIncrease costDigitally marking record carriersDigital computer detailsImaging processingInstruction unit

An image processing device including a storage unit which stores, for set moving-target-positions of a lightness or gray axis on an uniform color space in color balance correction, color correction parameters for performing color balance correction corresponding to moving the lightness or gray axis substantially parallel to a specific moving-target-position on the uniform color space to inputted color image data, and a correction unit which, when color balance correction to the target color image data is instructed via an instruction unit, reads a color correction parameter corresponding to the instructed color balance correction among the color correction parameters stored in the storage unit, to perform color balance correction to the target color image data using the read color correction parameter, is provided.

Owner:FUJIFILM BUSINESS INNOVATION CORP

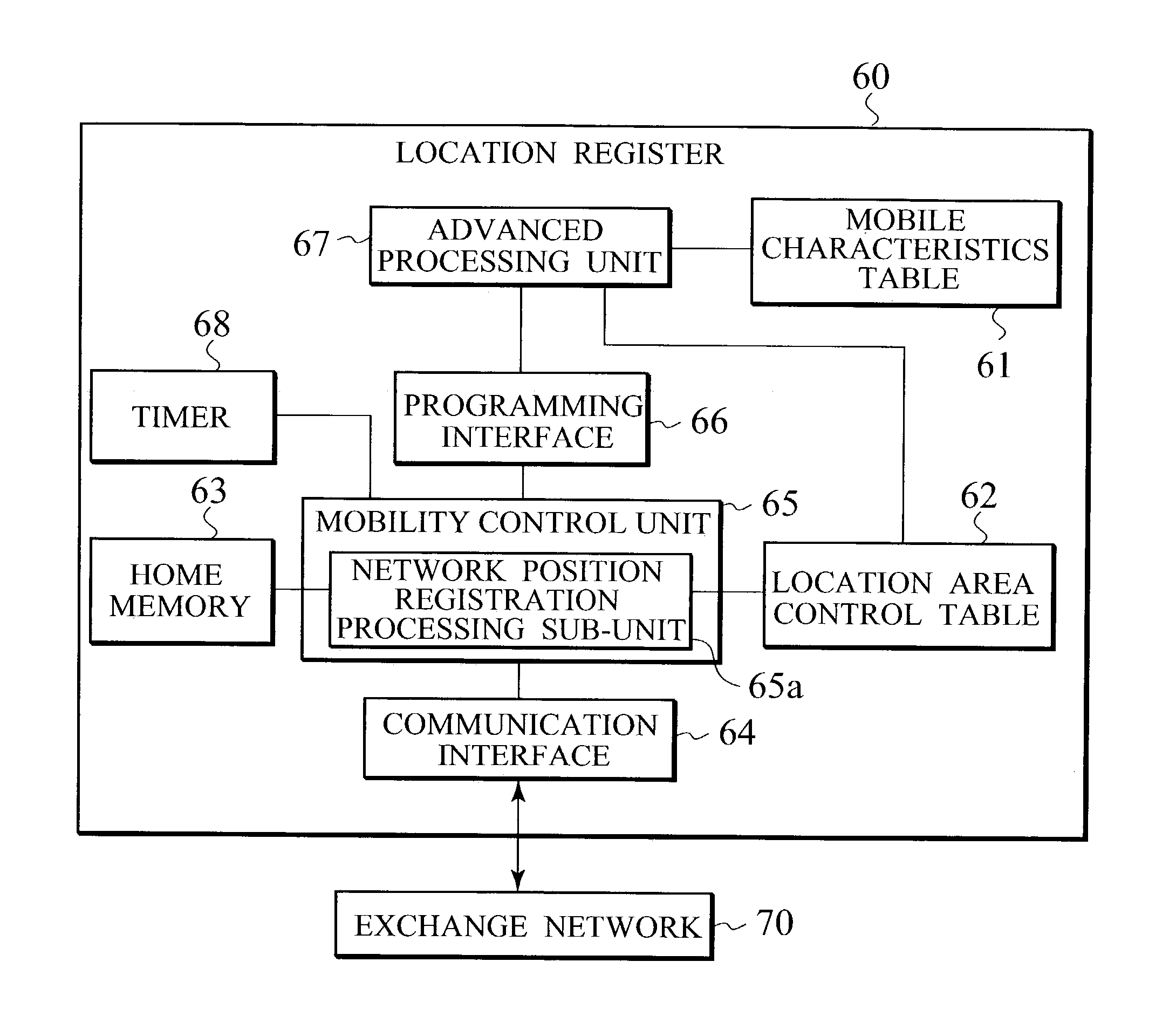

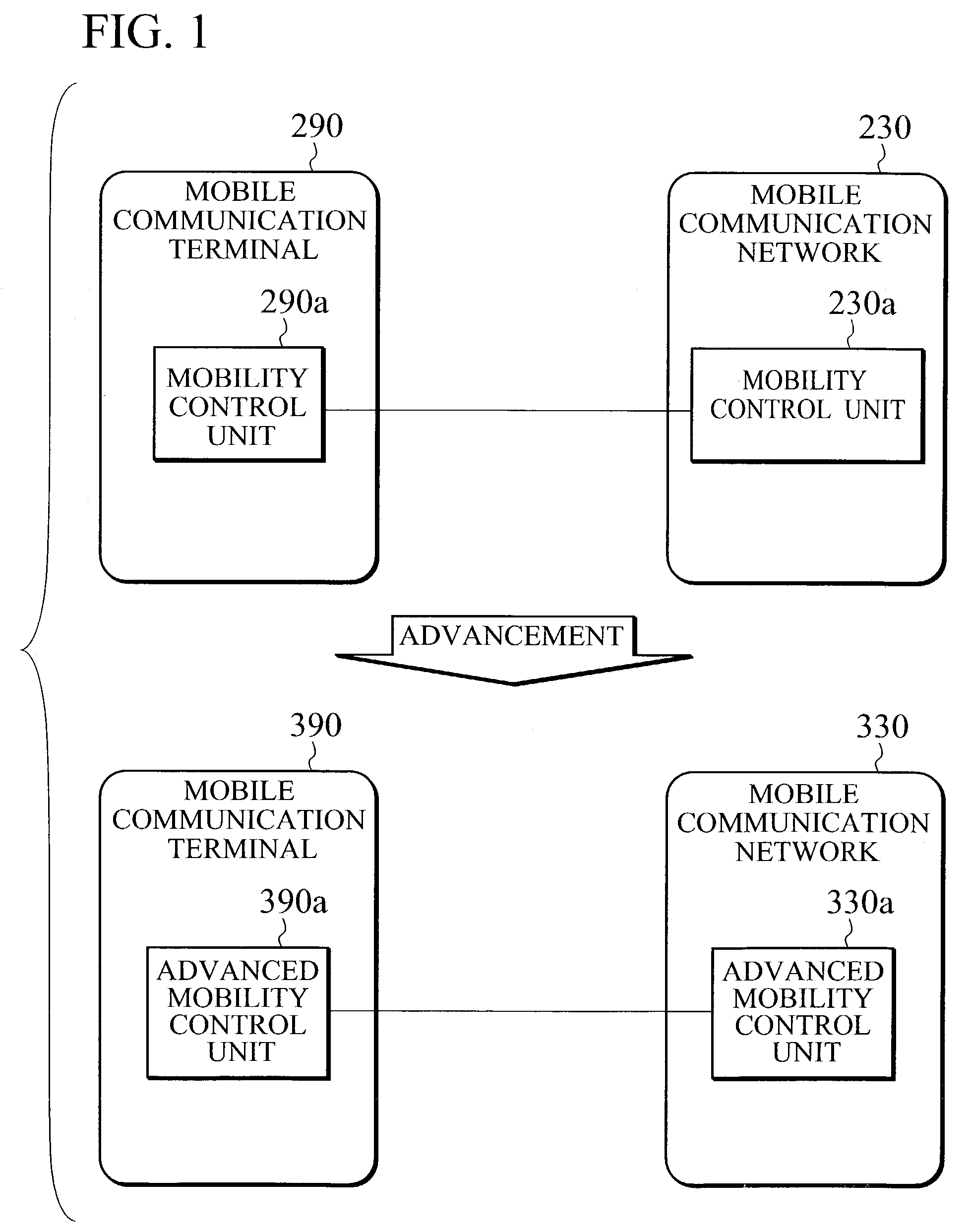

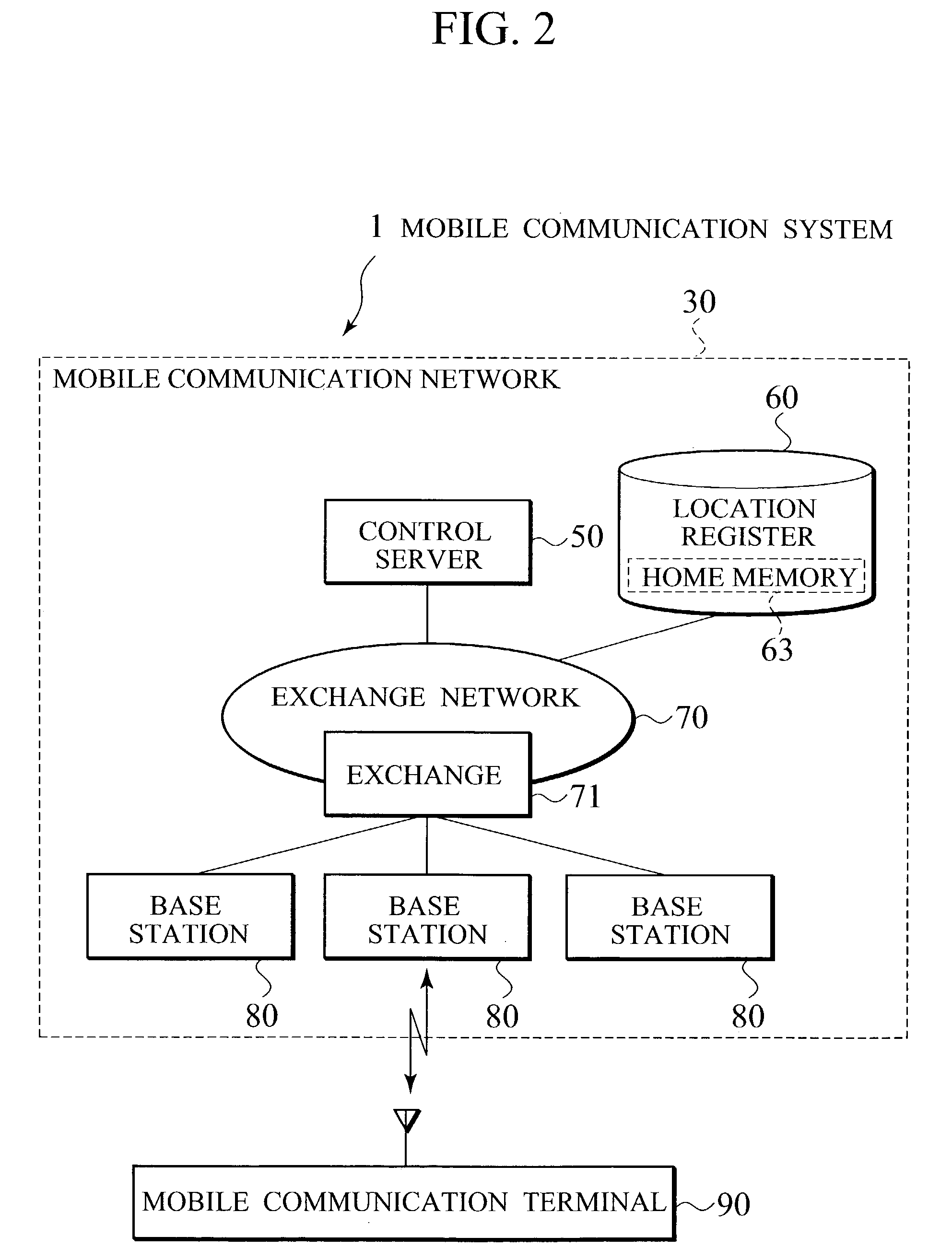

Mobility control apparatus, mobile communication terminal and mobile communication system

InactiveUS7120459B2Promote progressEasy mobile controlSubstation equipmentAutomatic exchangesInstruction unitMobile communication systems

A mobility control apparatus comprises: a mobility control unit configured to perform a first processing in accordance with movement of a mobile communication terminal and generate a notification related to the first processing; a processing unit configured to perform a second processing different from the first processing performed by the mobility control unit, based on the notification; and a notification providing unit configured to obtain the notification from the mobility control unit and provide the notification to the processing unit. Moreover, the mobility control apparatus comprises: an instruction unit configured to generate a command to a mobility control unit performing processing in accordance with movement of a mobile communication terminal; a command providing unit configured to obtain the command from the instruction unit and provide the command to the mobility control unit; and the mobility control unit configured to perform the processing based on the command.

Owner:NTT DOCOMO INC

Thread-aware instruction fetching in a multithreaded embedded processor

InactiveUS7441101B1Raise priorityLow priorityProgram initiation/switchingDigital computer detailsInstruction unitNetwork processor

The present invention provides a multithreaded processor, such as a network processor, that fetches instructions in a pipeline stage based on feedback signals from later stages. The multithreaded processor comprises a pipeline with an instruction unit in the early stage and an instruction queue, a thread interleaver, and an execution pipeline in the later stages. Feedback signals from the later stages cause the instruction unit to block fetching, immediately fetch, raise priority, or lower priority for a particular thread. The instruction queue generates a queue signal, on a per thread basis, responsive to a thread queue condition, etc., the thread interleaver generates an interleaver signal responsive to a thread condition, etc., and the execution pipeline generates an execution signal responsive to an execution stall, etc.

Owner:CISCO TECH INC