Dual thread processor

A processor and thread technology, applied in electrical digital data processing, instruments, register devices, etc., can solve problems such as consuming processor time

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

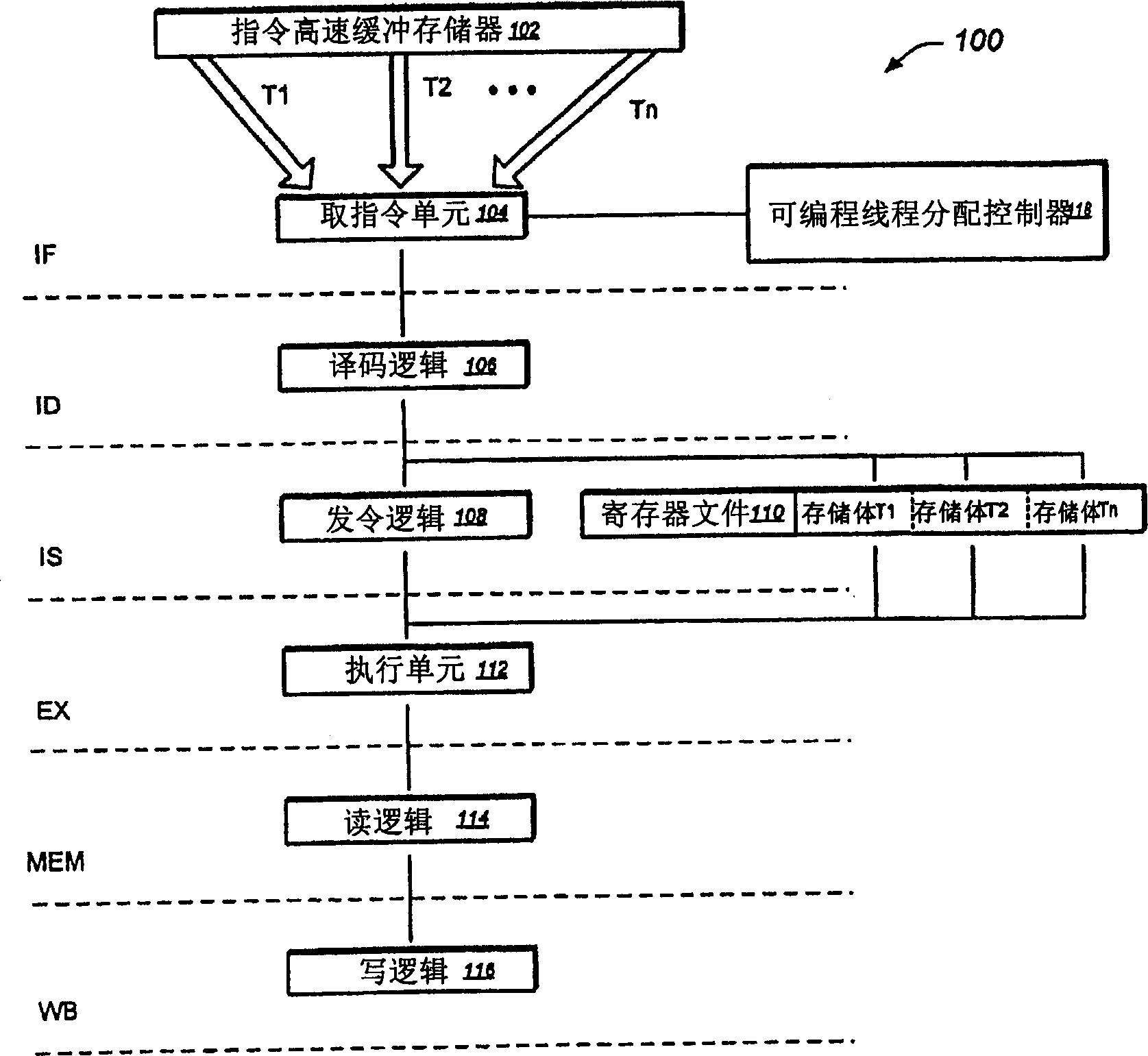

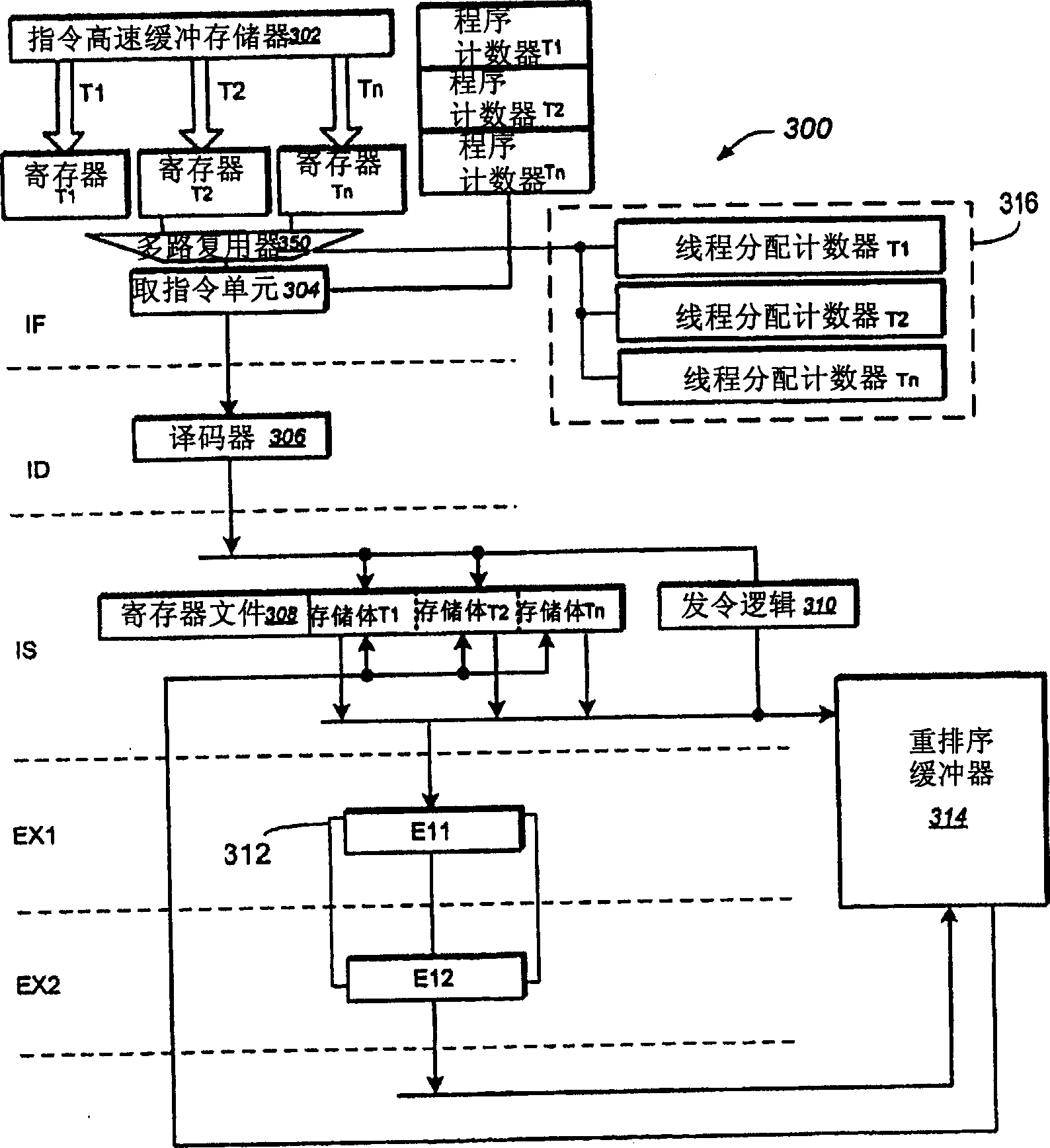

[0030] figure 1 is a block diagram of a pipelined processor architecture 100 operable to process two or more processor threads T1, T2...Tn. Processor threads T1 , T2 . . . Tn each represent an architectural state within pipeline processor architecture 100 that tracks the execution of a corresponding software program. Instructions for a software program may be retrieved, for example, from an instruction cache (eg, instruction cache 102). In one embodiment, pipelined processor architecture 100 includes two or more program counters (not shown), one for each processor thread T1, T2...Tn. Each program counter indicates the position of the pipelined processor structure 100 with respect to the sequence of instructions (for the corresponding processor thread T1, T2 . . . Tn). The program counter will be combined below image 3 and Figure 5 discussed in more detail.

[0031] In one embodiment, pipeline processor architecture 100 includes six pipeline stages. The six pipeline sta...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More