Patents

Literature

13157results about "Welding apparatus" patented technology

Efficacy Topic

Property

Owner

Technical Advancement

Application Domain

Technology Topic

Technology Field Word

Patent Country/Region

Patent Type

Patent Status

Application Year

Inventor

Pillar connections for semiconductor chips and method of manufacture

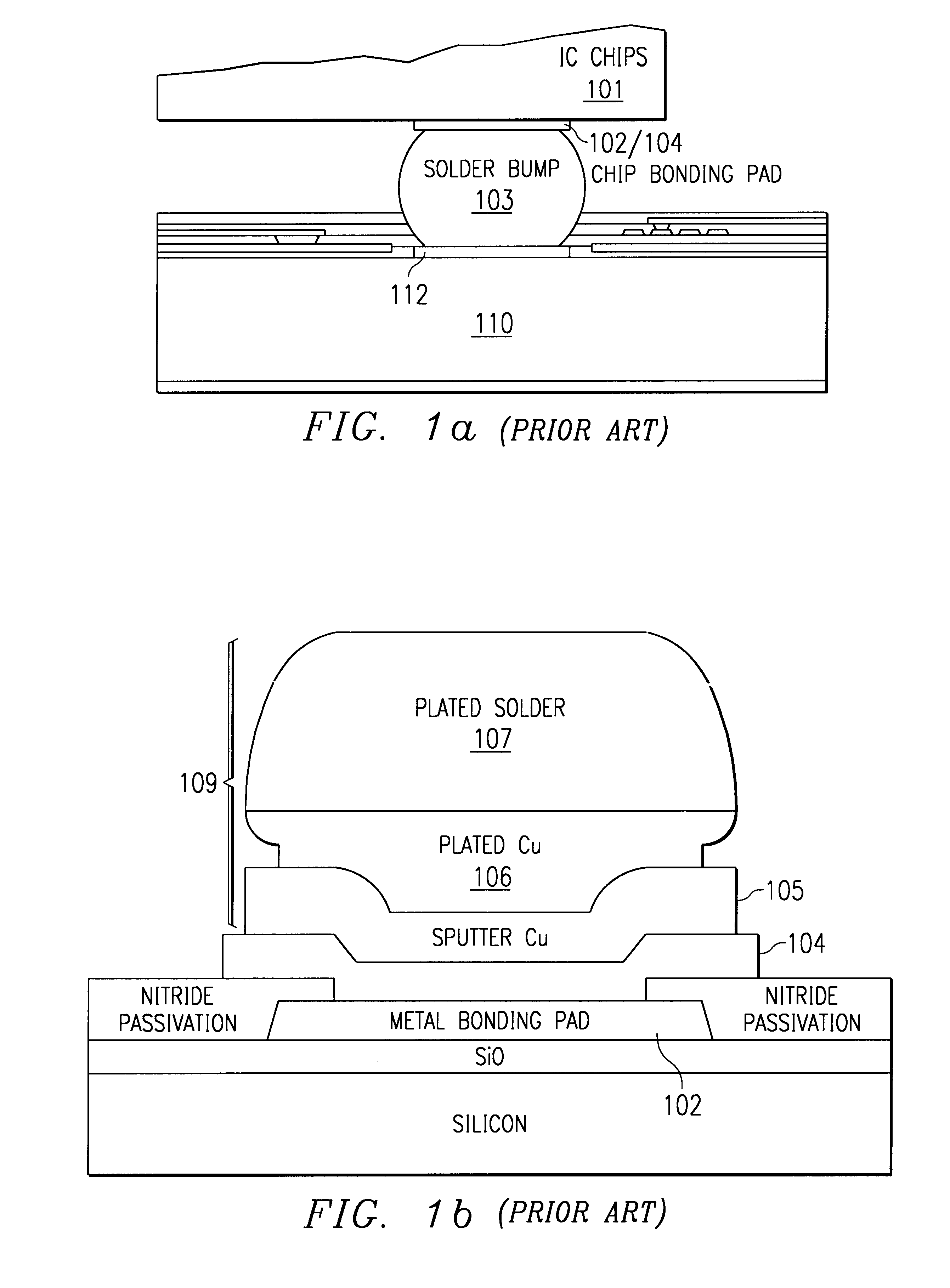

InactiveUS6578754B1Reduce chanceInduced in connectionSemiconductor/solid-state device detailsSolid-state devicesFlip chip interconnectSemiconductor chip

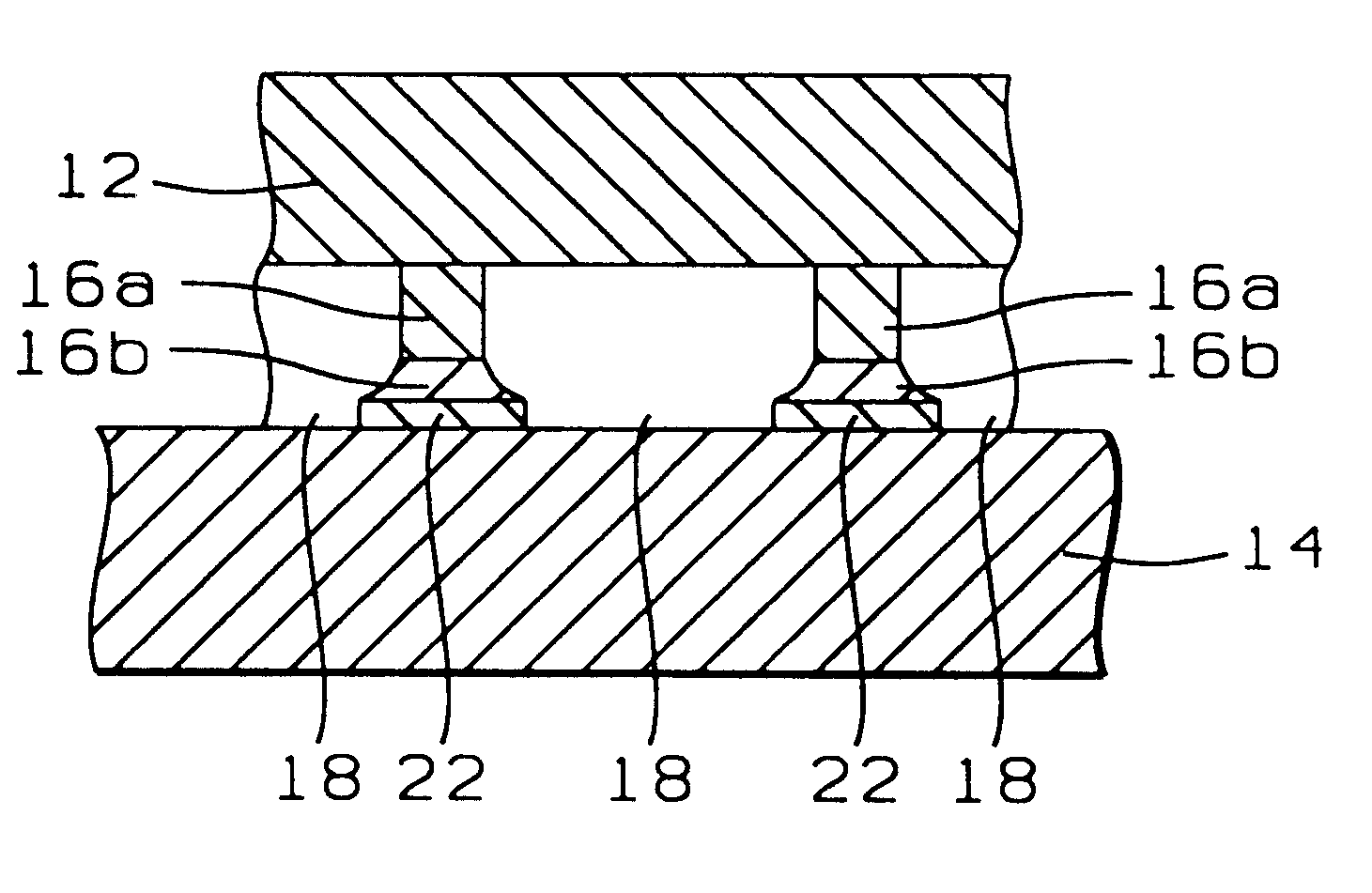

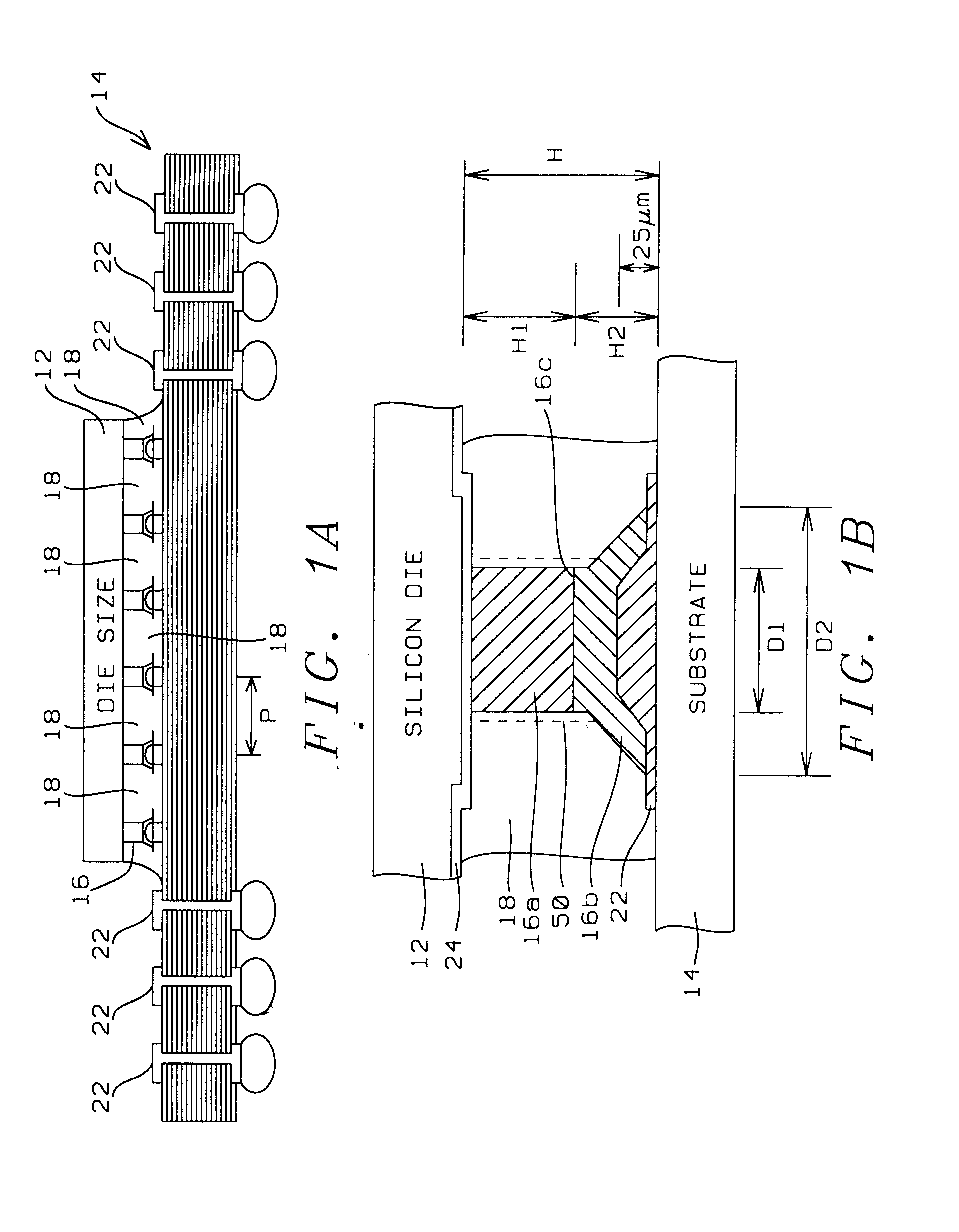

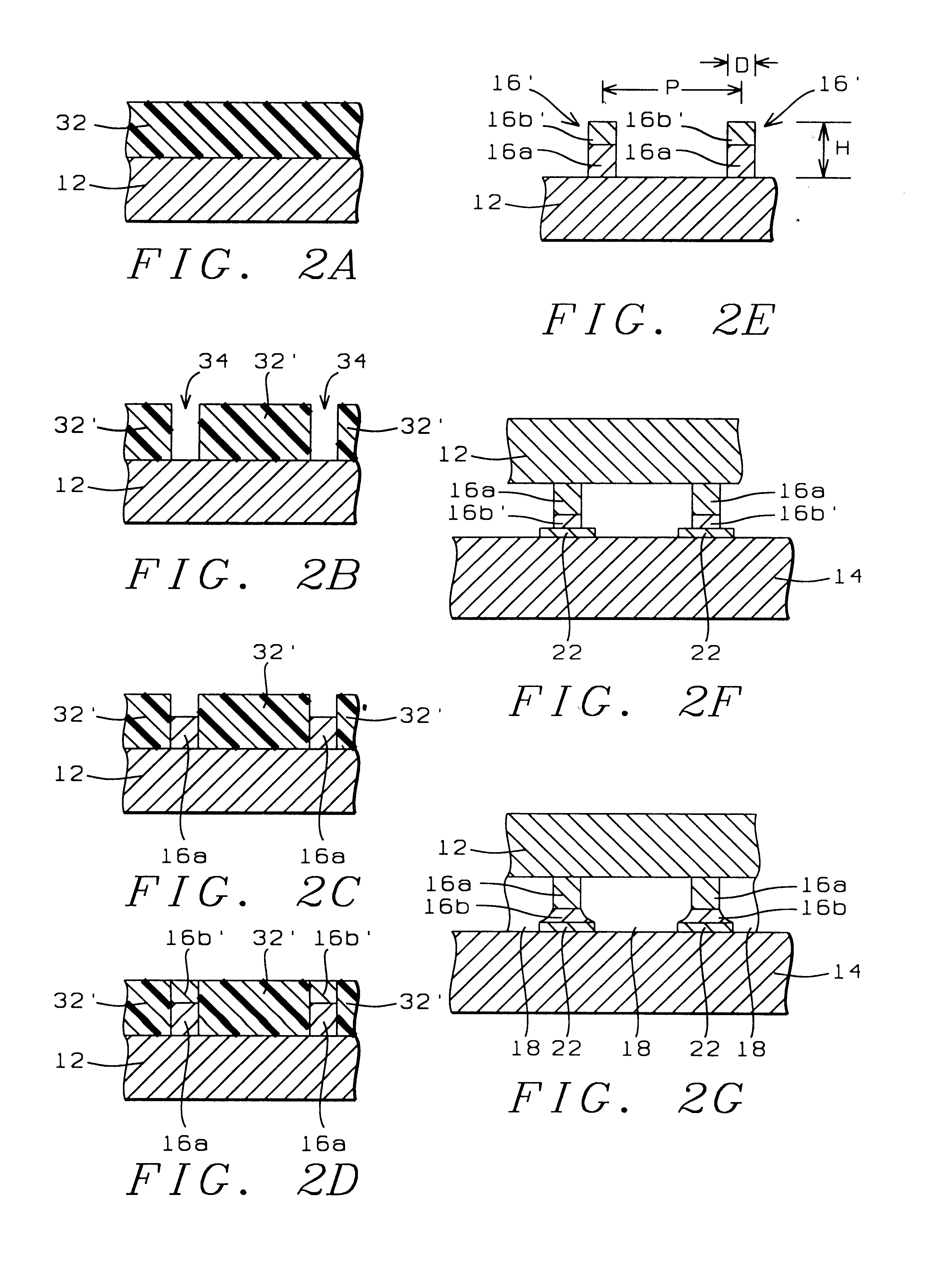

A flip chip interconnect system comprises and elongated pillar comprising two elongated portions, one portion including copper and another portion including solder. The portion including copper is in contact with the semiconductor chip and has a length preferably of more than 55 microns to reduce the effect of .alpha. particles from the solder from affecting electronic devices on the chip. The total length of the pillar is preferably in the range of 80 to 120 microns.

Owner:ADVANPAK SOLUTIONS PTE

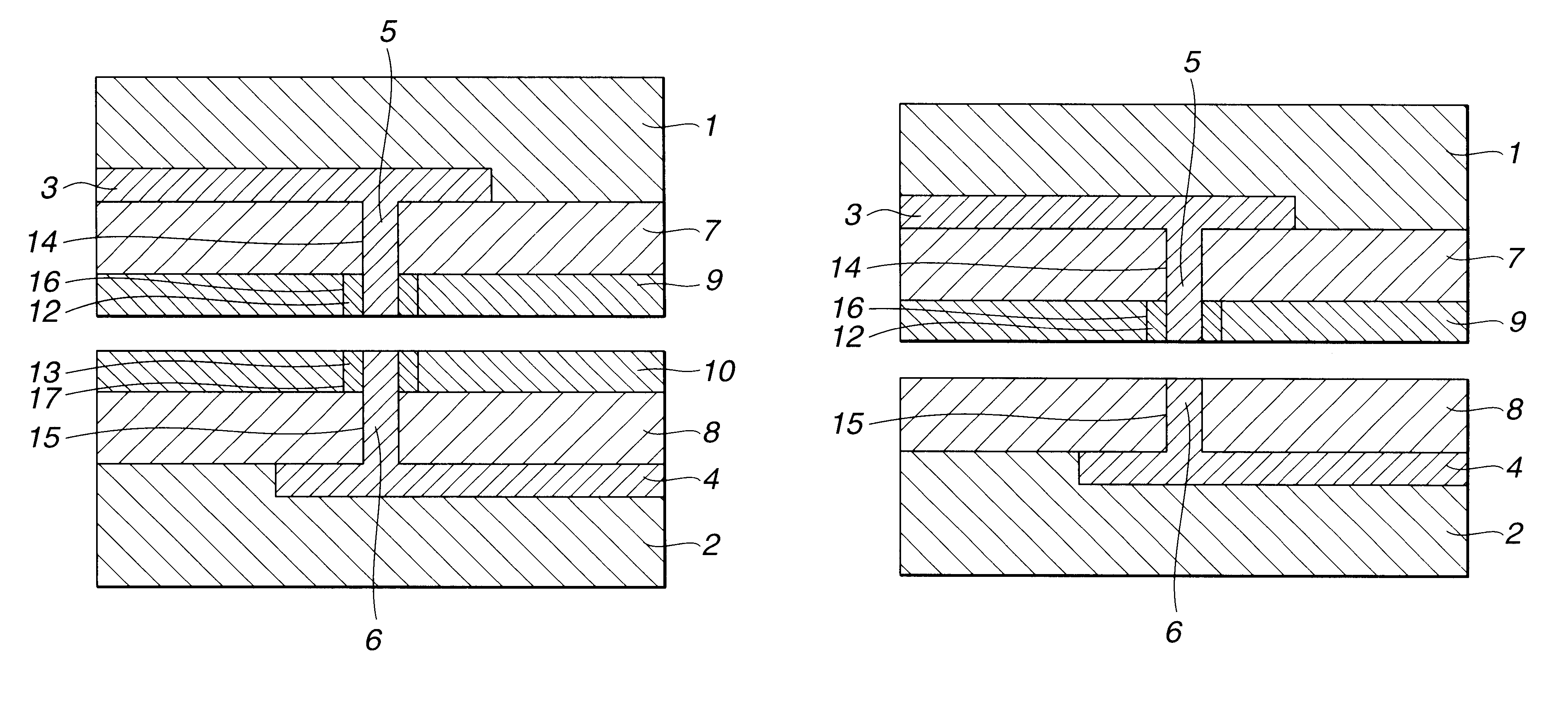

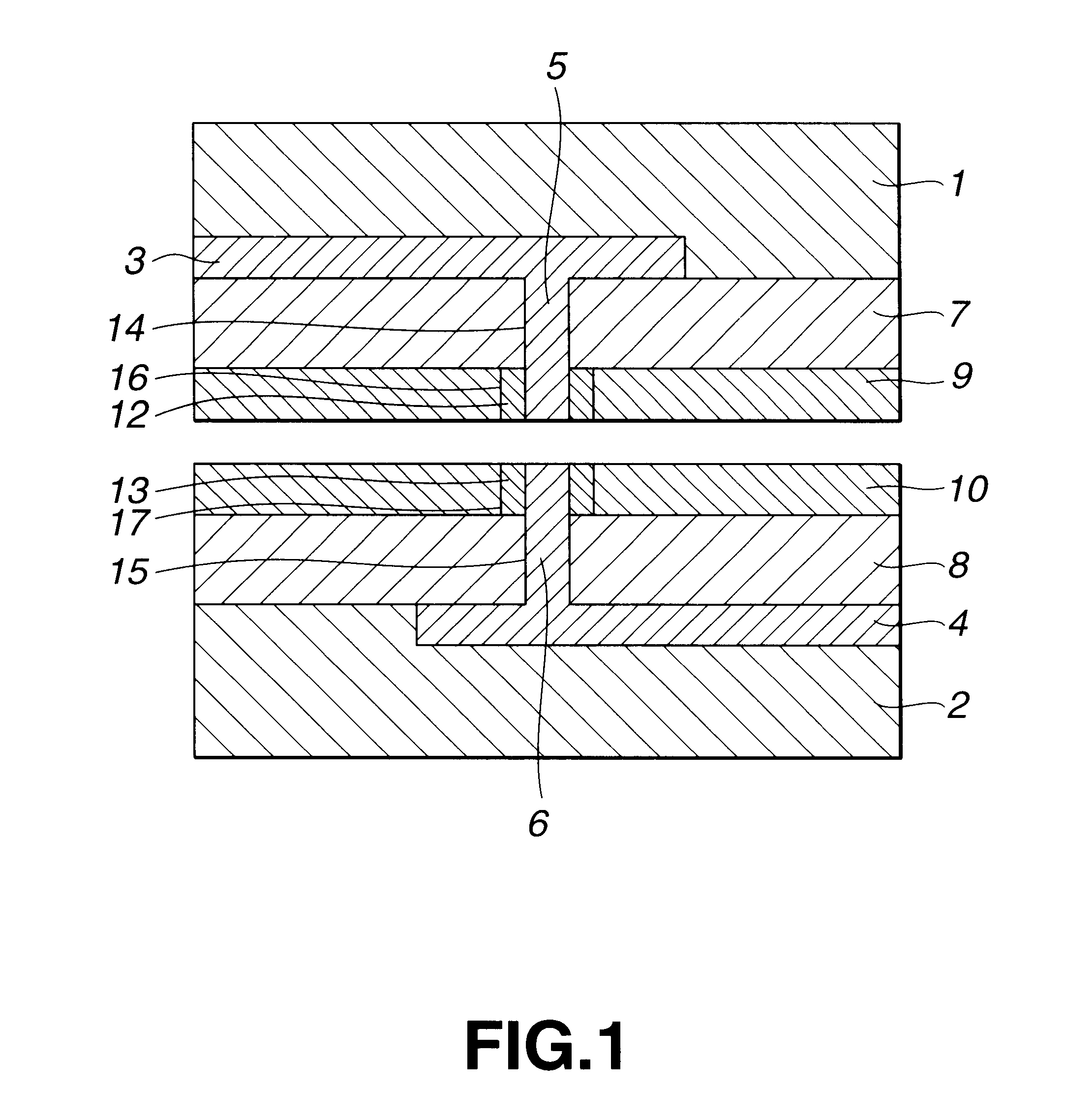

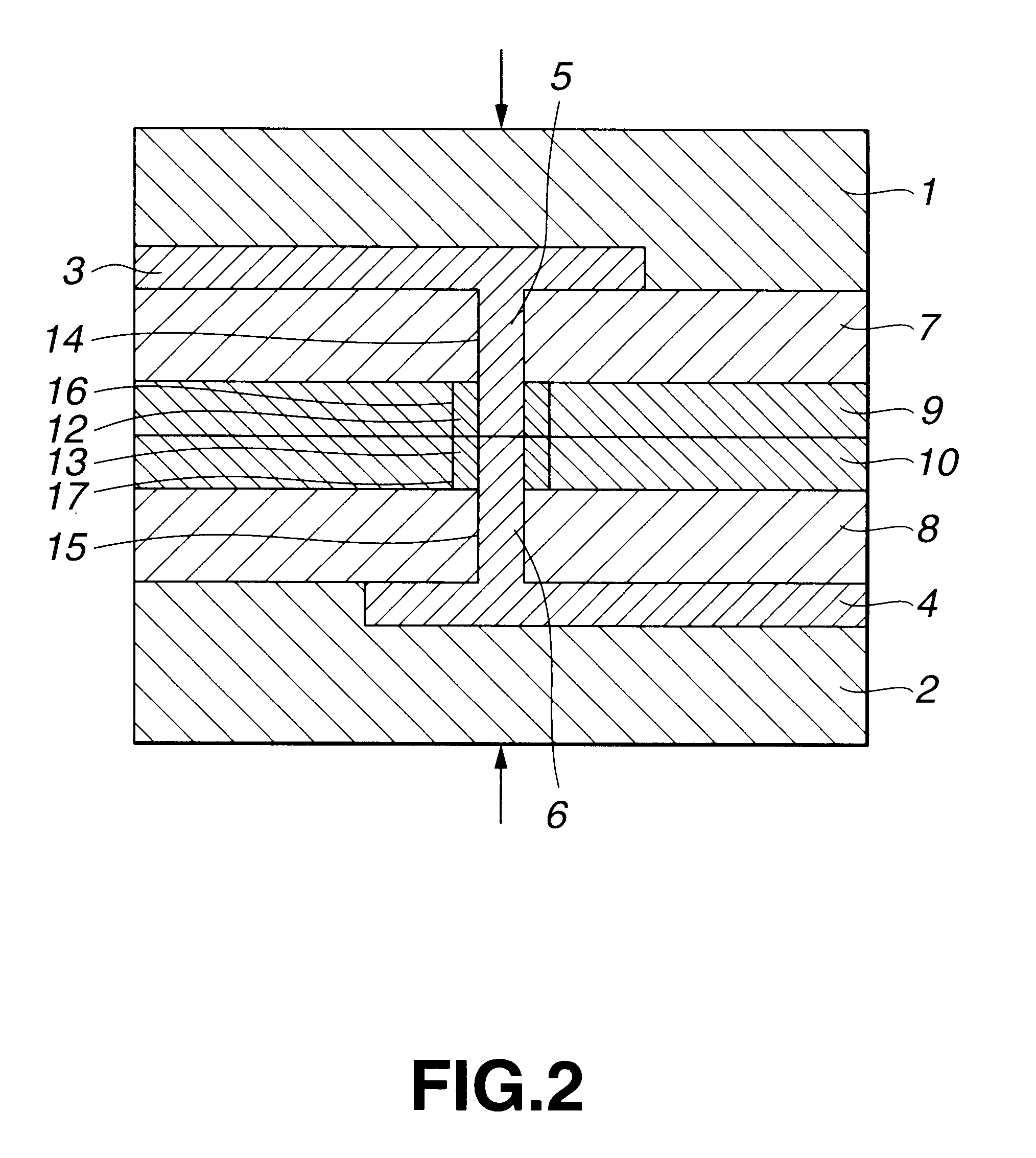

Interconnect structure for stacked semiconductor device

InactiveUS6465892B1Shorten the line lengthEasy to produceSemiconductor/solid-state device detailsSolid-state devicesDevice materialInterconnection

In a multi-layer interconnection structure, the wiring length is to be reduced, and the interconnection is to be straightened, at the same time as measures need to be taken against radiation noise. To this end, there is disclosed a semiconductor device in which plural semiconductor substrates, each carrying semiconductor elements, are bonded together. On each semiconductor substrate is deposited an insulating layer through which is formed a connection wiring passed through the insulating layer so as to be connected to the interconnection layer of the semiconductor element. On a junction surface of at least one of the semiconductor substrates is formed an electrically conductive layer of an electrically conductive material in which an opening is bored in association with the connection wiring. The semiconductor substrates are bonded together by the solid state bonding technique to interconnect the connection wirings formed on each semiconductor substrate.

Owner:LAPIS SEMICON CO LTD +9

Wafer-to-wafer transfer of microstructures using break-away tethers

InactiveUS6142358AReduce tensionSemiconductor/solid-state device detailsWelding/cutting auxillary devicesOptoelectronicsMicrostructure

Break-away tethers to secure electronic, mechanical, optical, or other microstructures, during release from one substrate and transfer to another. Microstructures are fabricated with integrated tethers attaching them to a first substrate. The structures are undercut by etching and contacted and bonded to a second substrate. First and second substrates are separated, breaking the tethers.

Owner:RGT UNIV OF CALIFORNIA

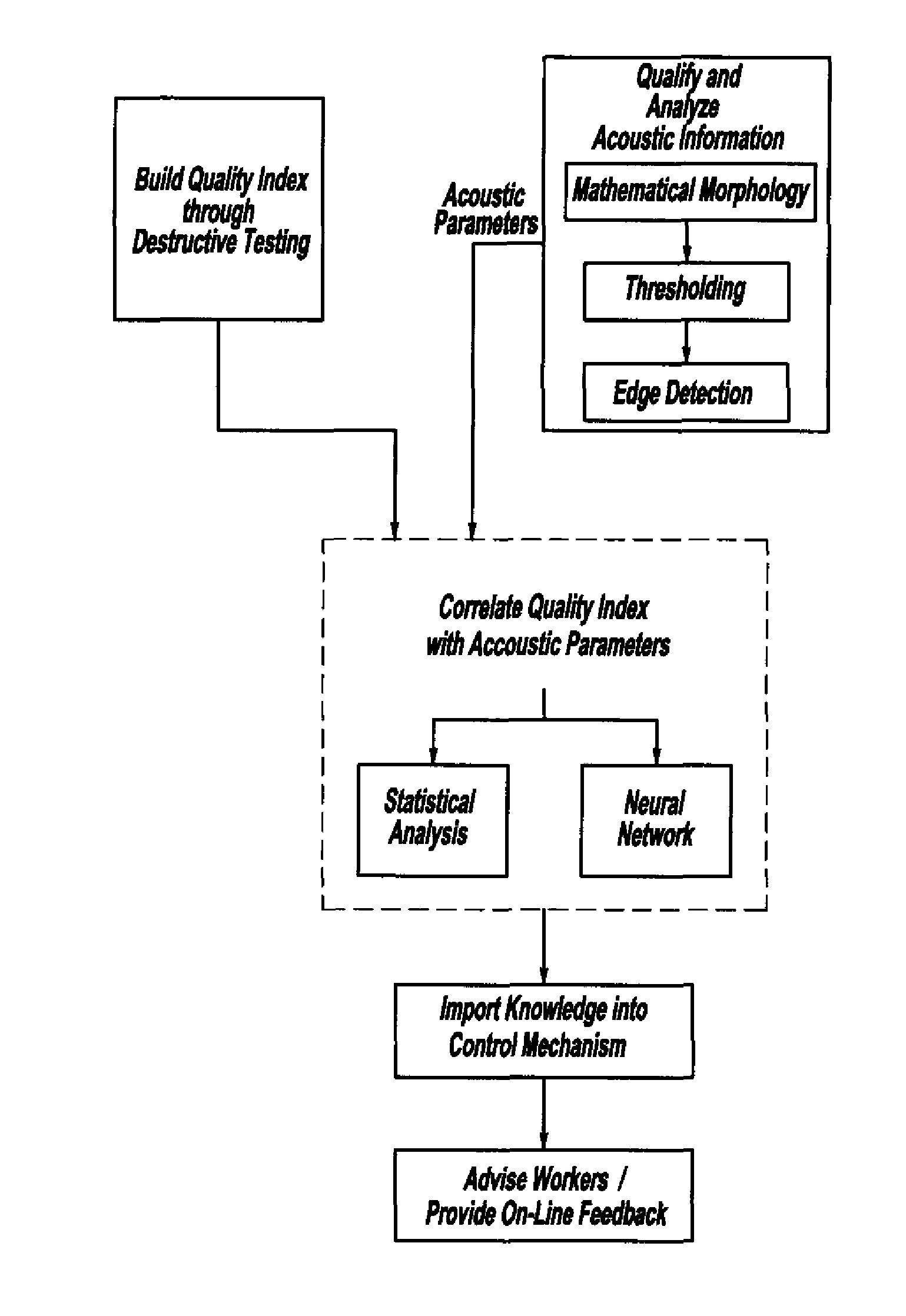

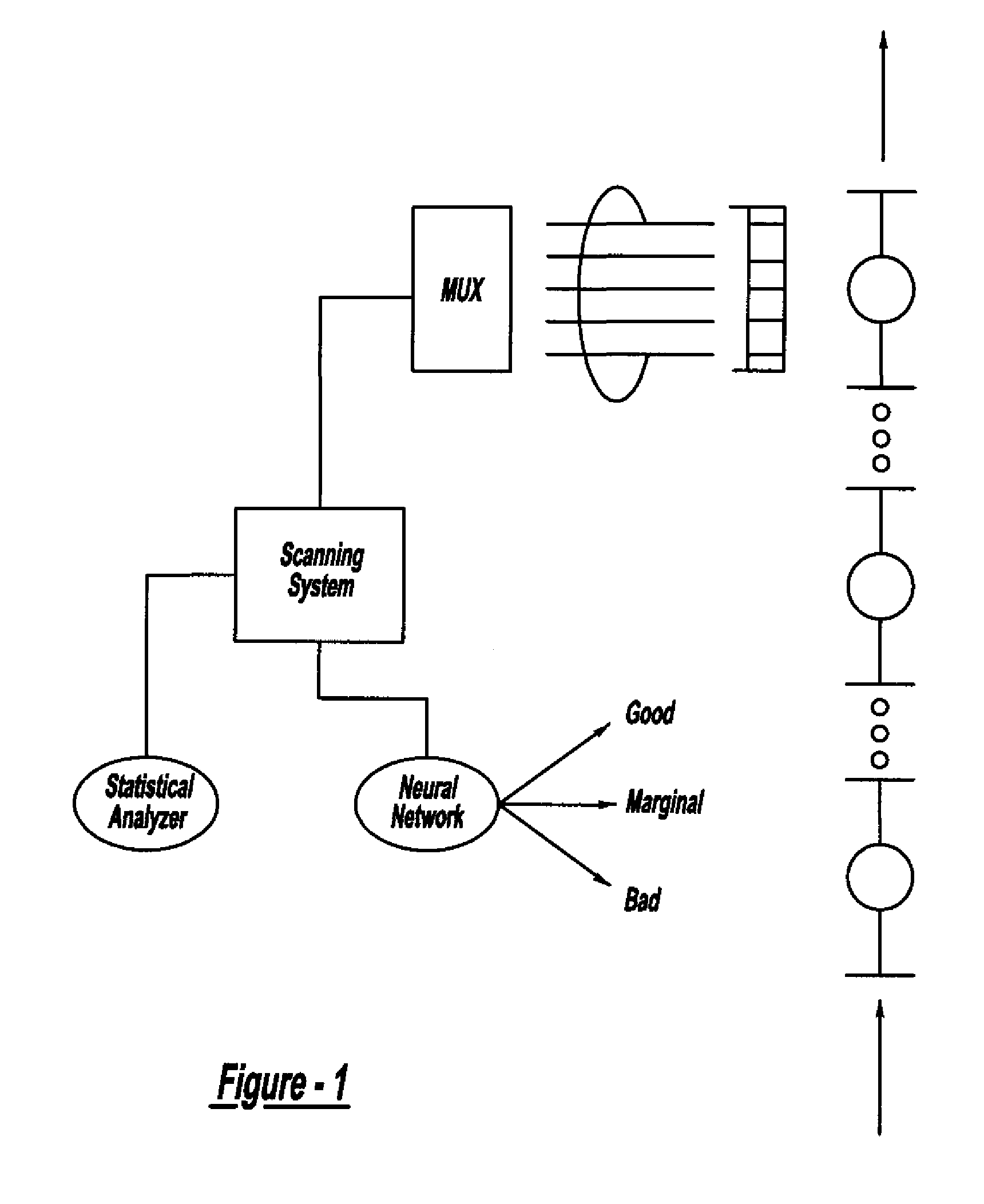

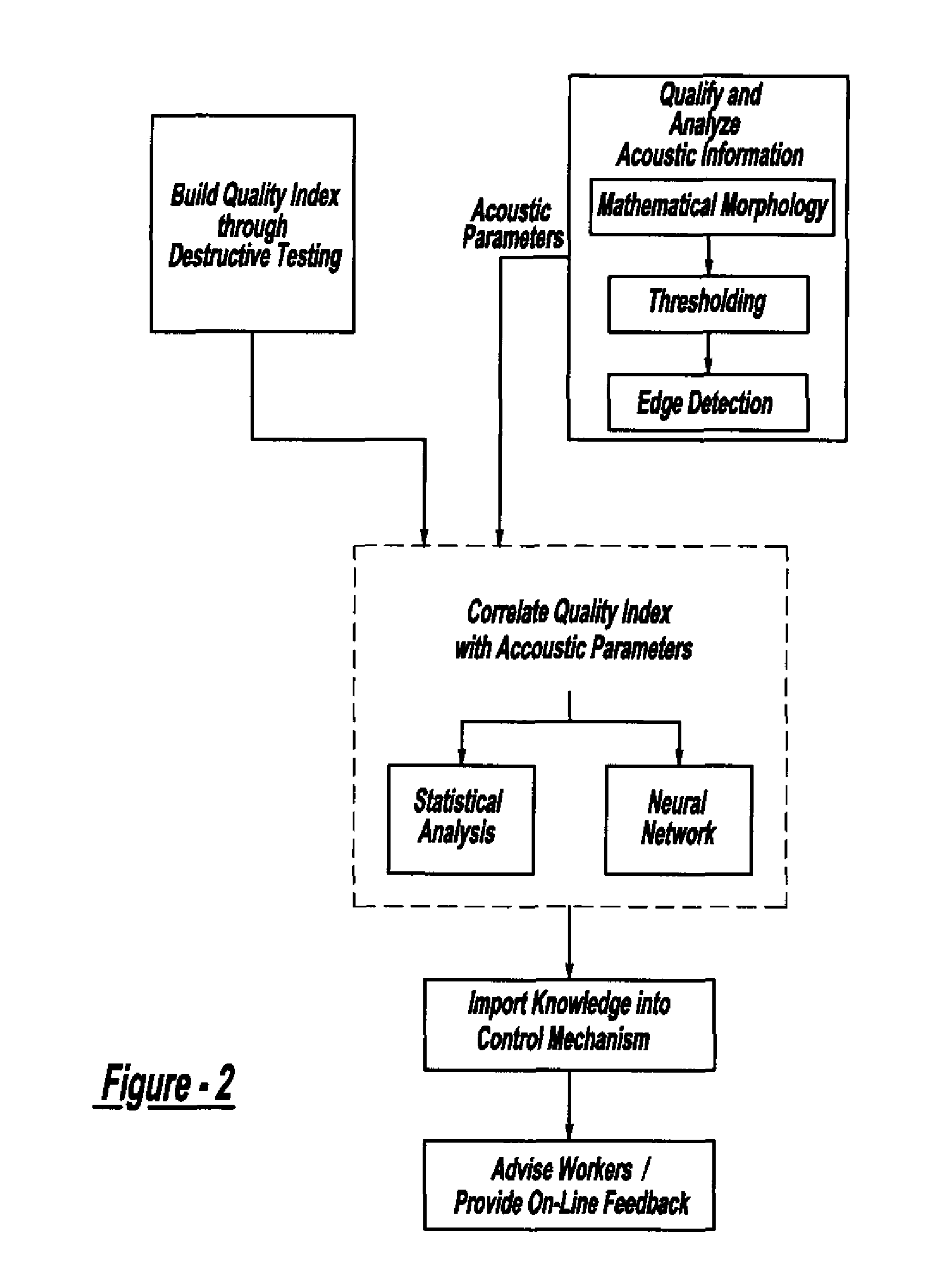

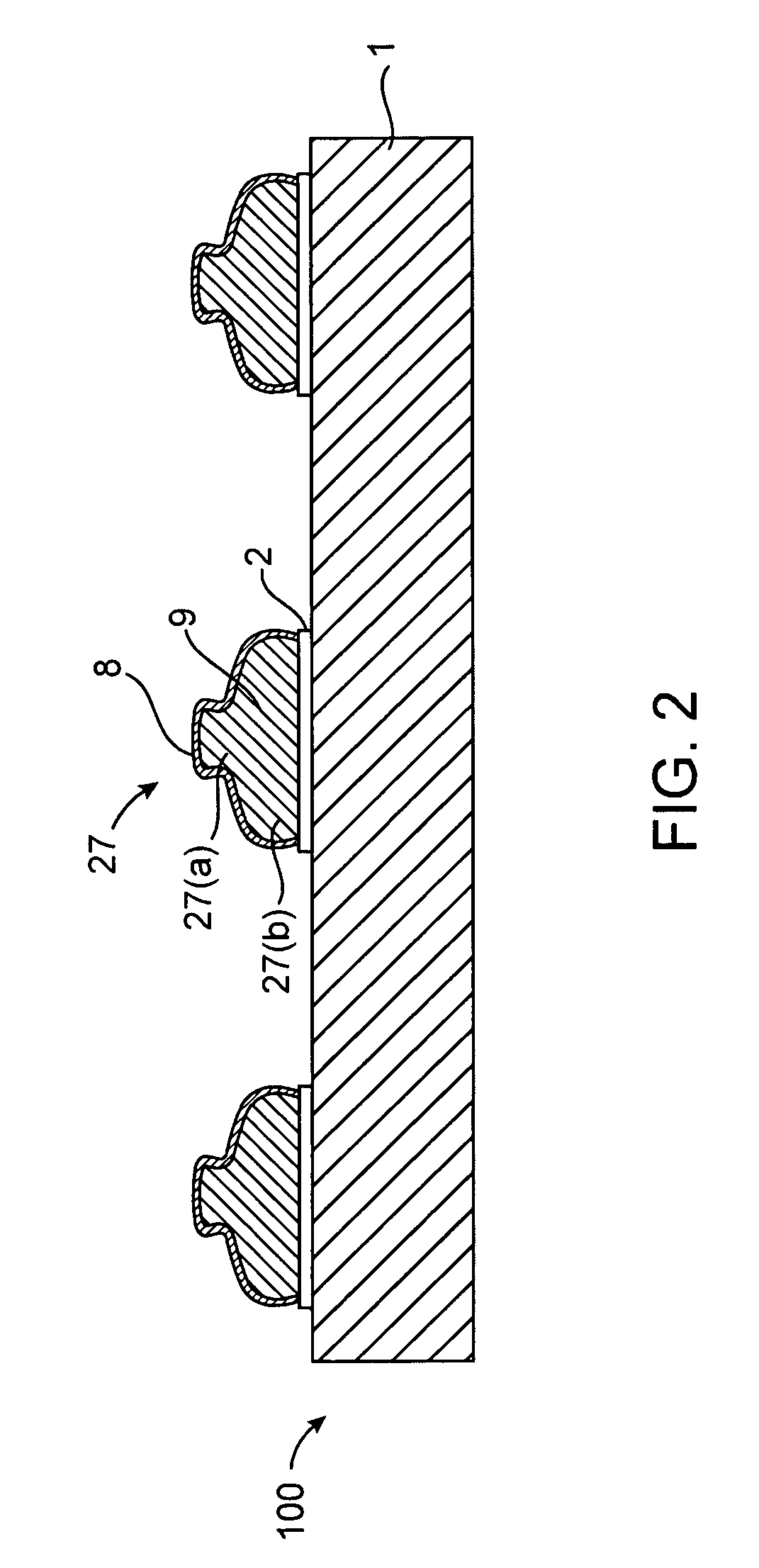

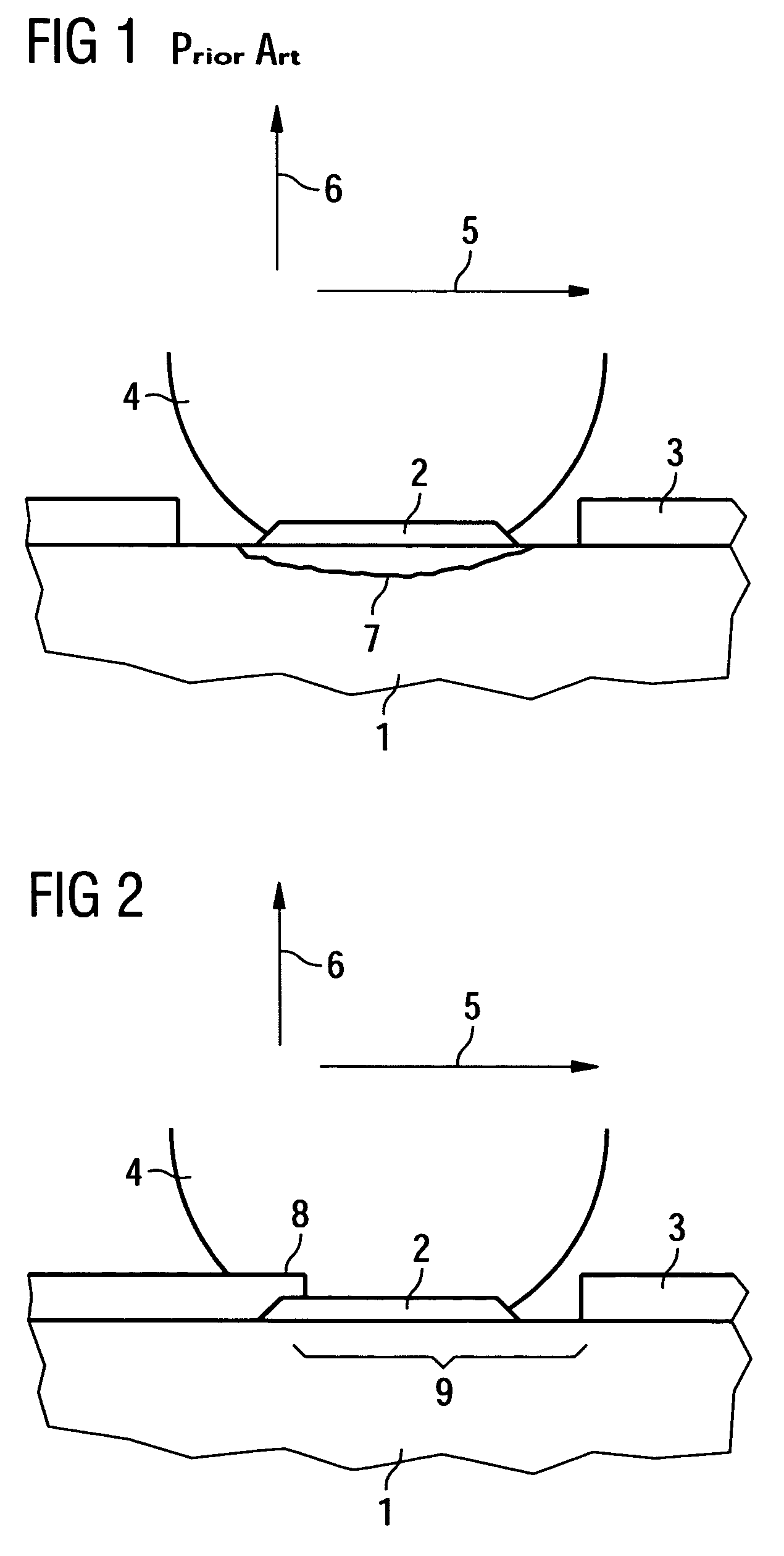

Method And System For Assessing Quality Of Spot Welds

InactiveUS20070038400A1Reduce in quantityReduce manufacturing costMultiple-port networksMagnetic property measurementsDigital dataSonification

A system and method for assessing the quality of spot weld joints between pieces of metal includes an ultrasound transducer probing a spot weld joint. The ultrasound transducer transmits ultrasonic radiation into the spot weld joint, receives corresponding echoes, and transforms the echoes into electrical signals. An image reconstructor connected to the ultrasound transducer transforms the electrical signals into numerical data representing an ultrasound image. A neural network connected to the image reconstructor analyzes the numerical data and an output system presents information representing the quality of the spot weld joint. The system is trained to assess the quality of spot weld joints by scanning a spot weld joint with an ultrasound transducer to produce the data set representing the joint; then physically deconstructing the joint to assess the joint quality.

Owner:FCA US

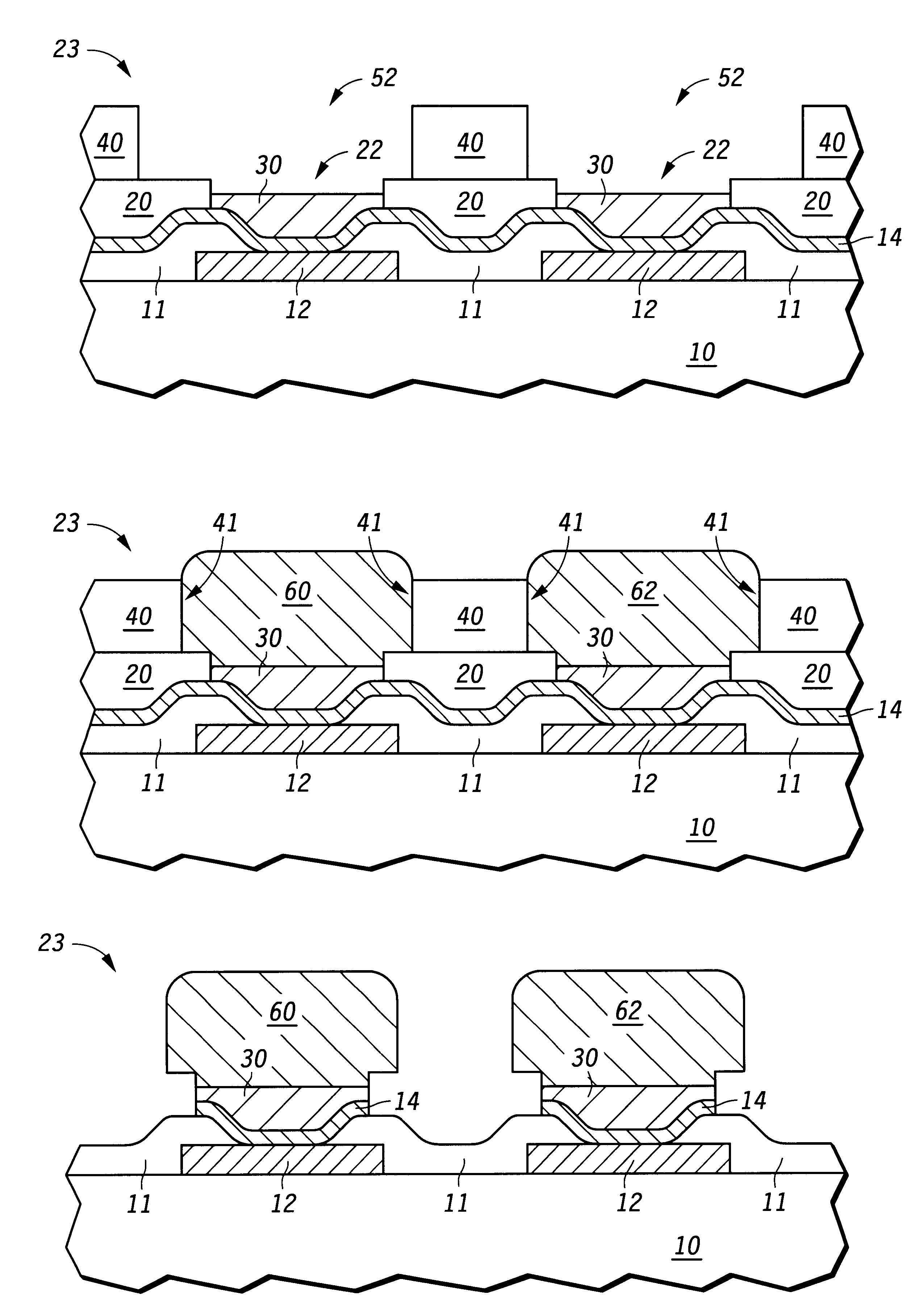

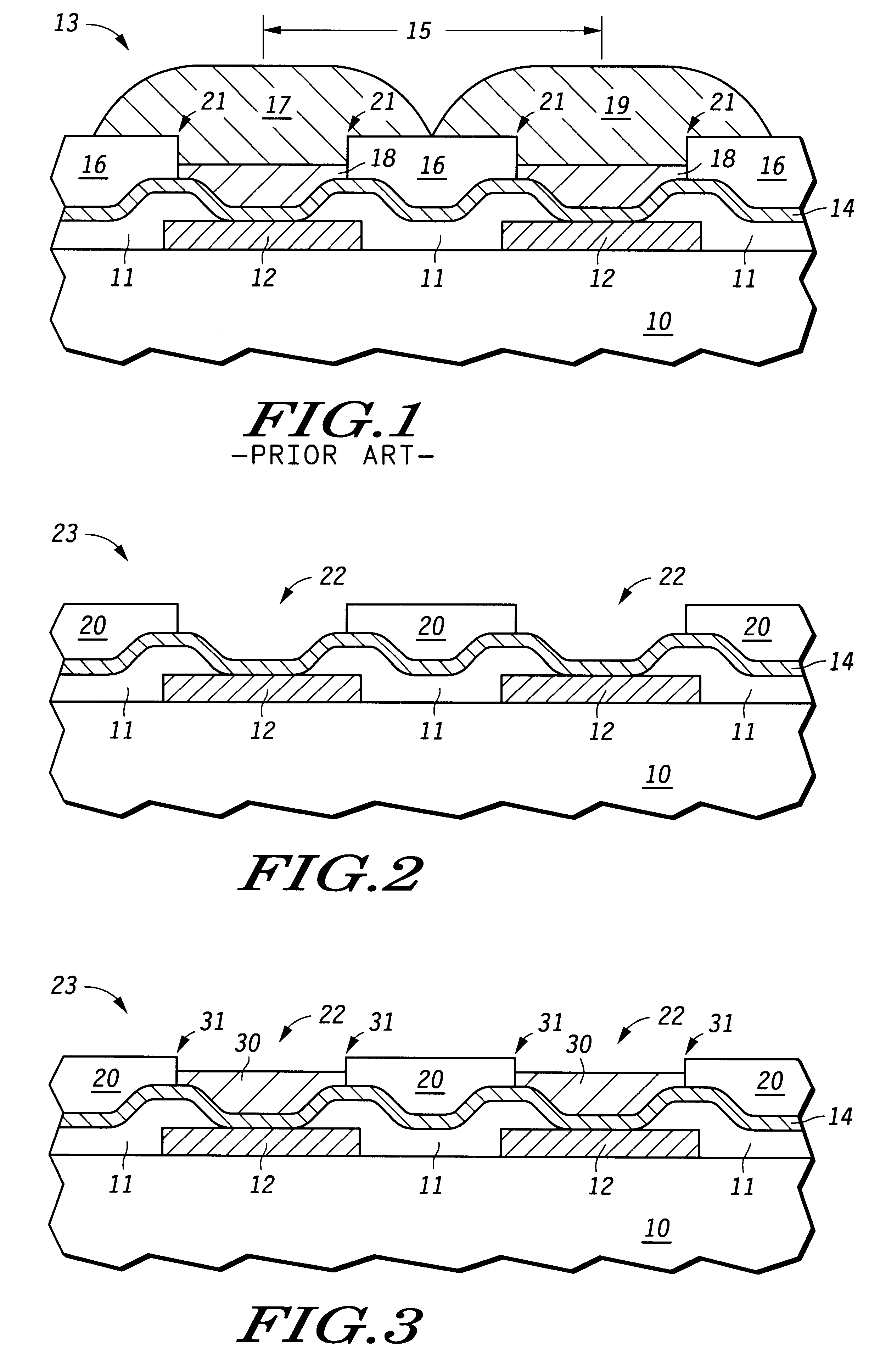

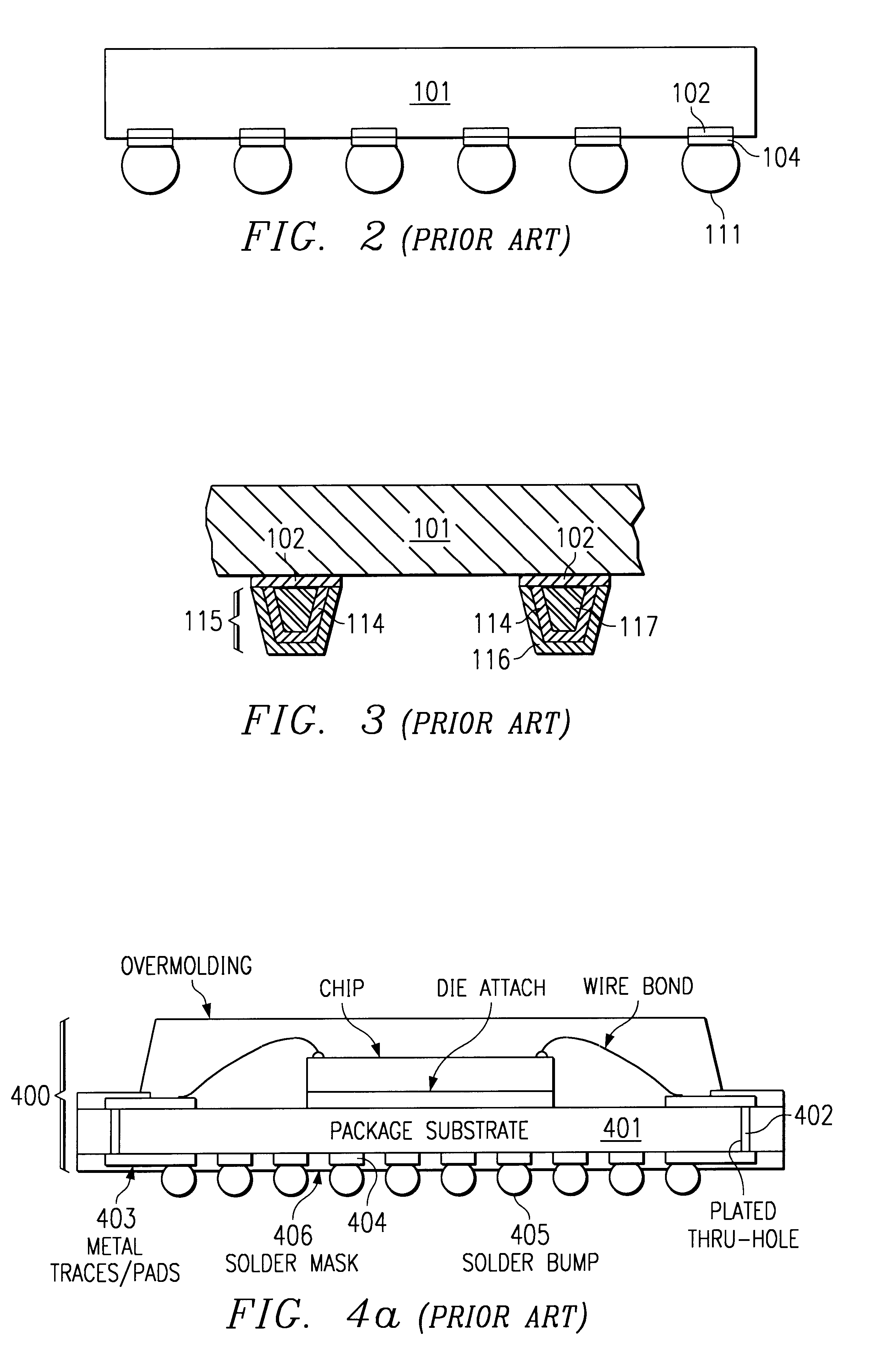

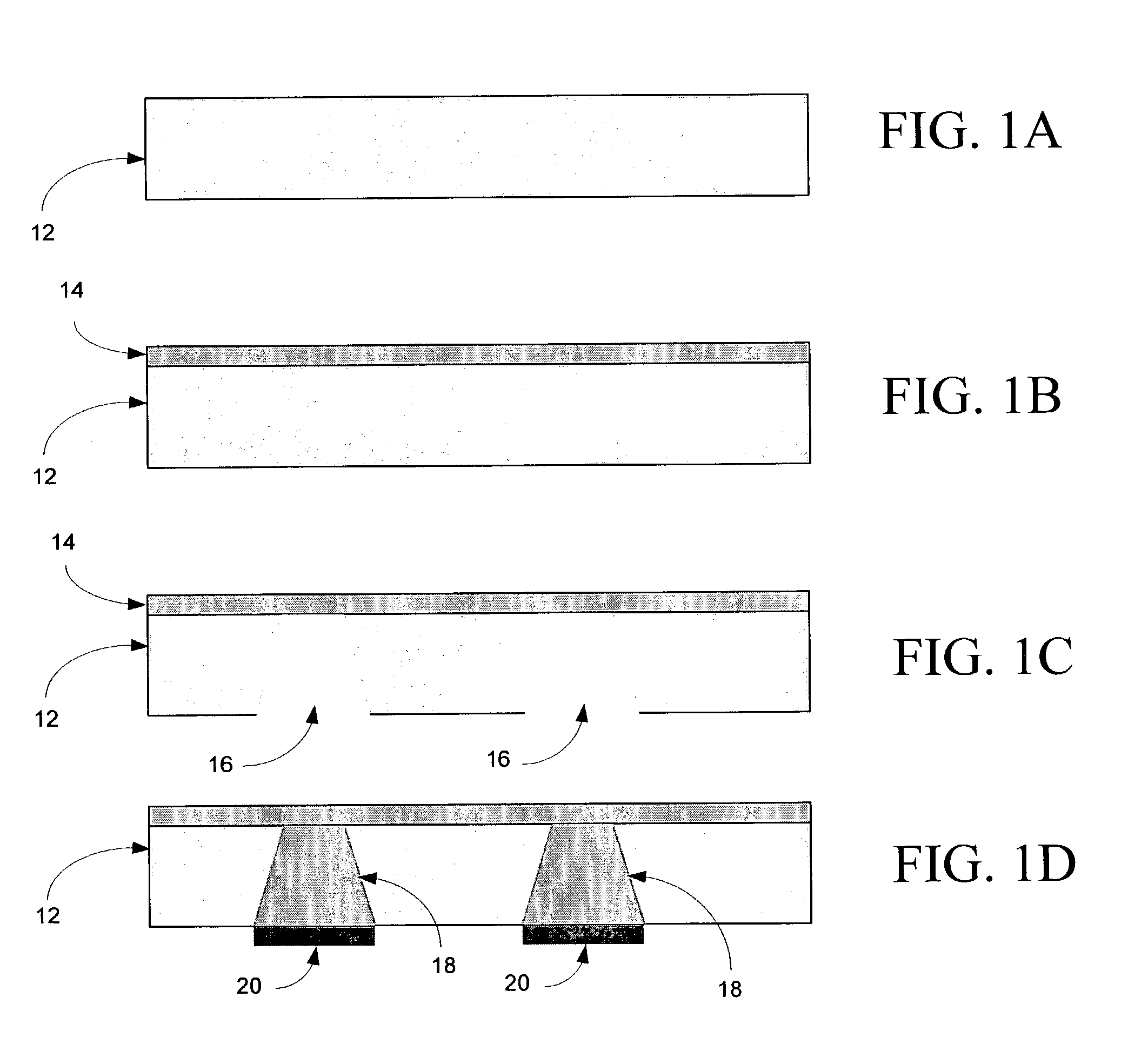

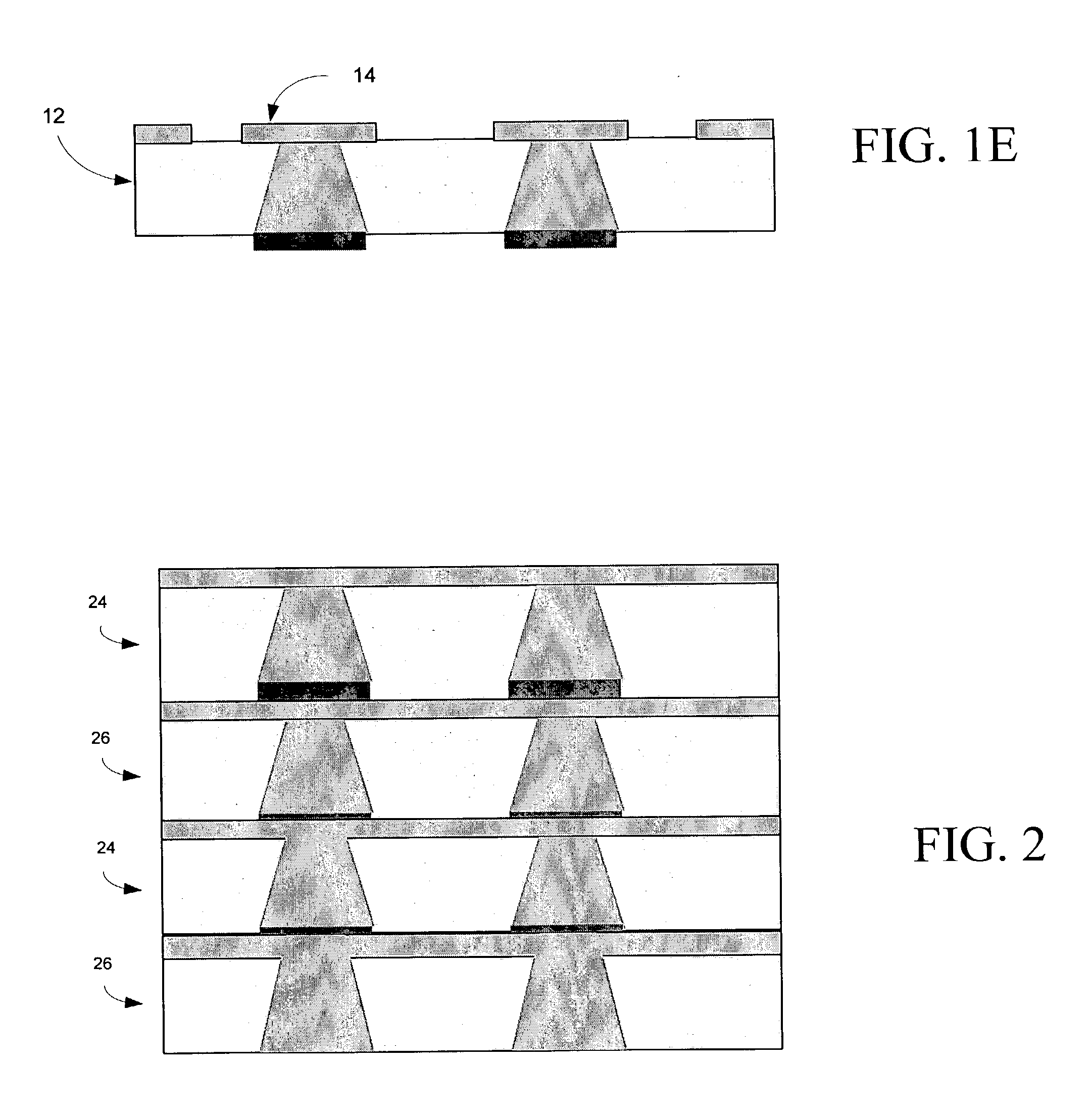

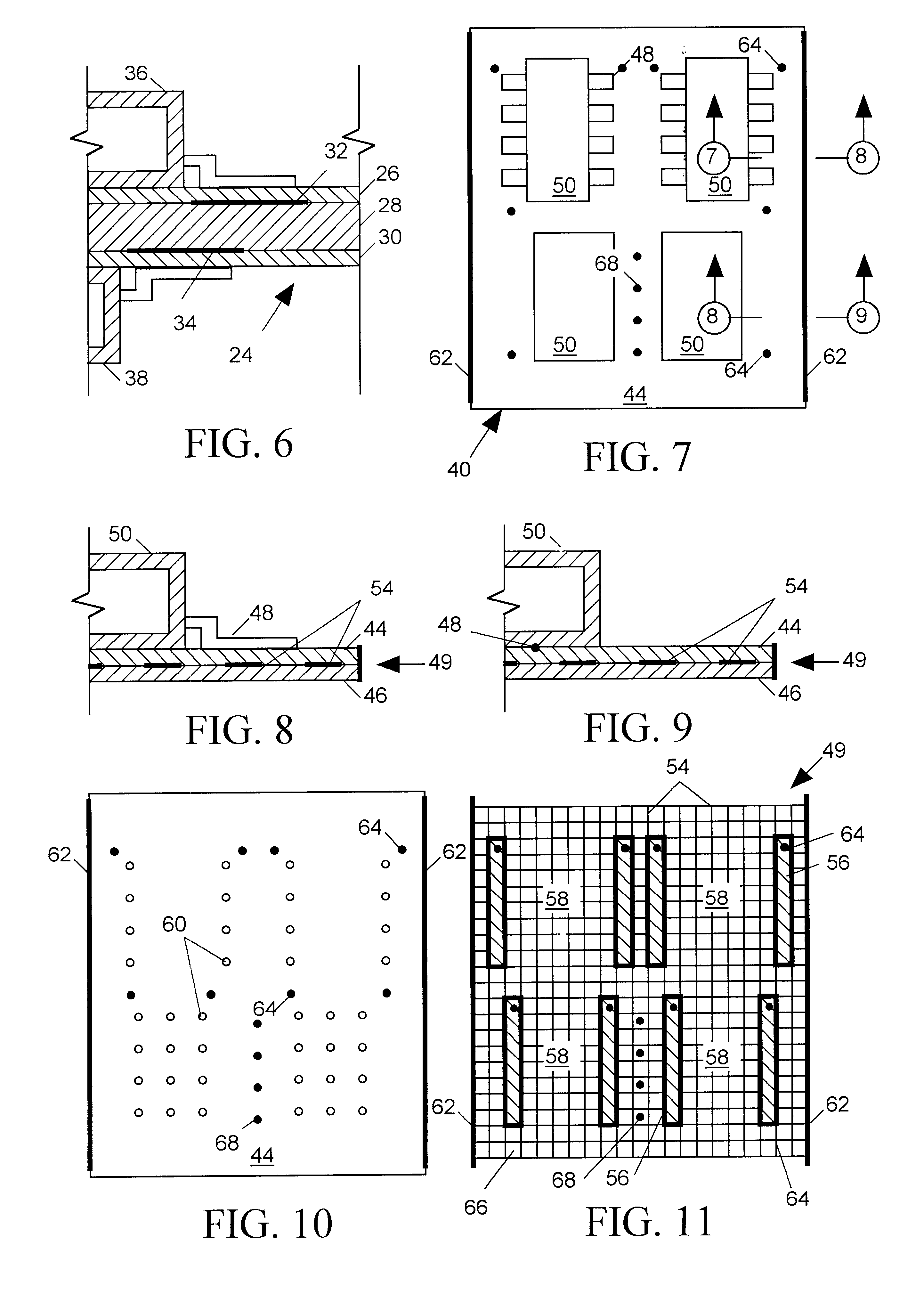

Fine pitch bumping with improved device standoff and bump volume

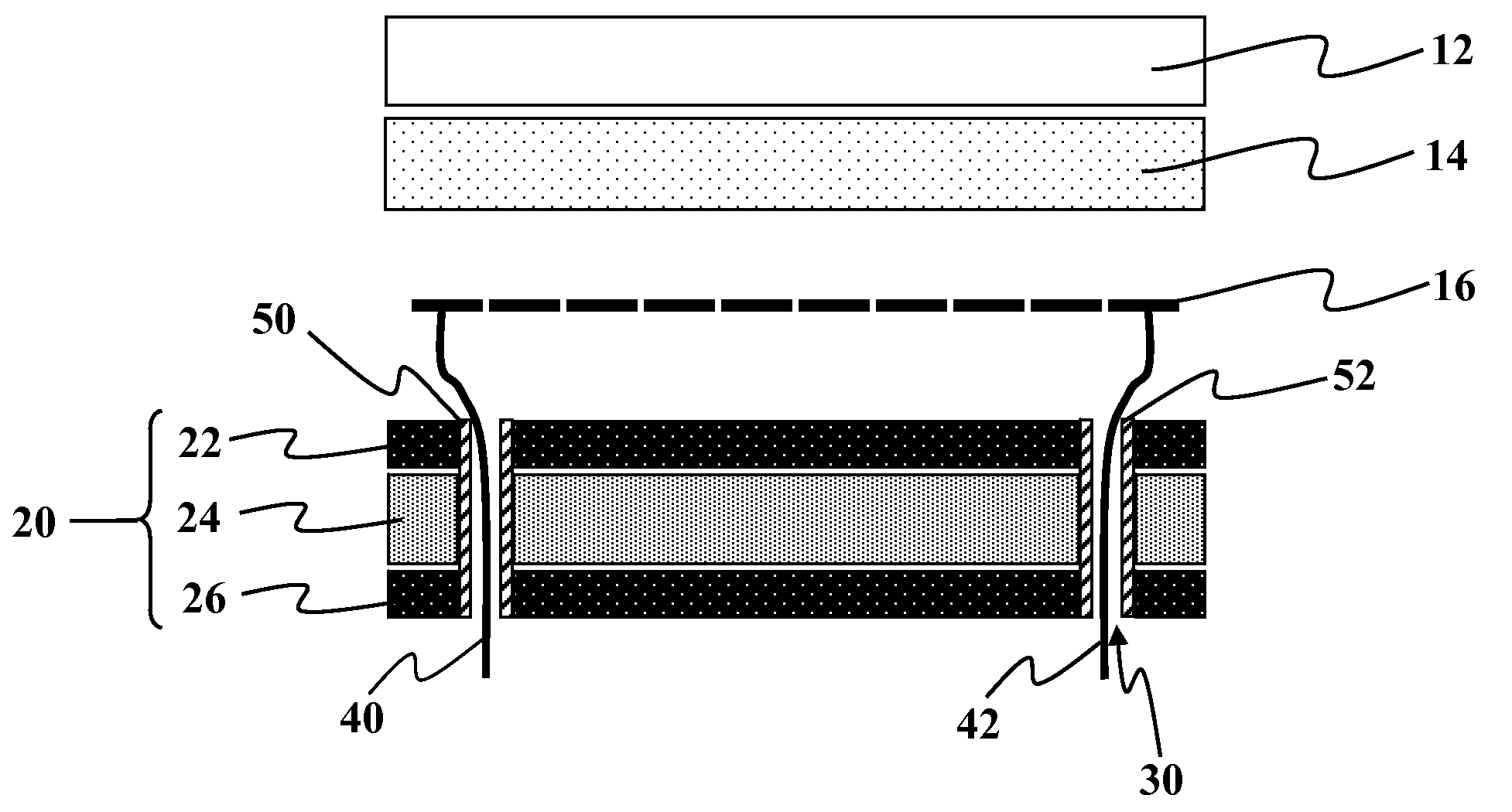

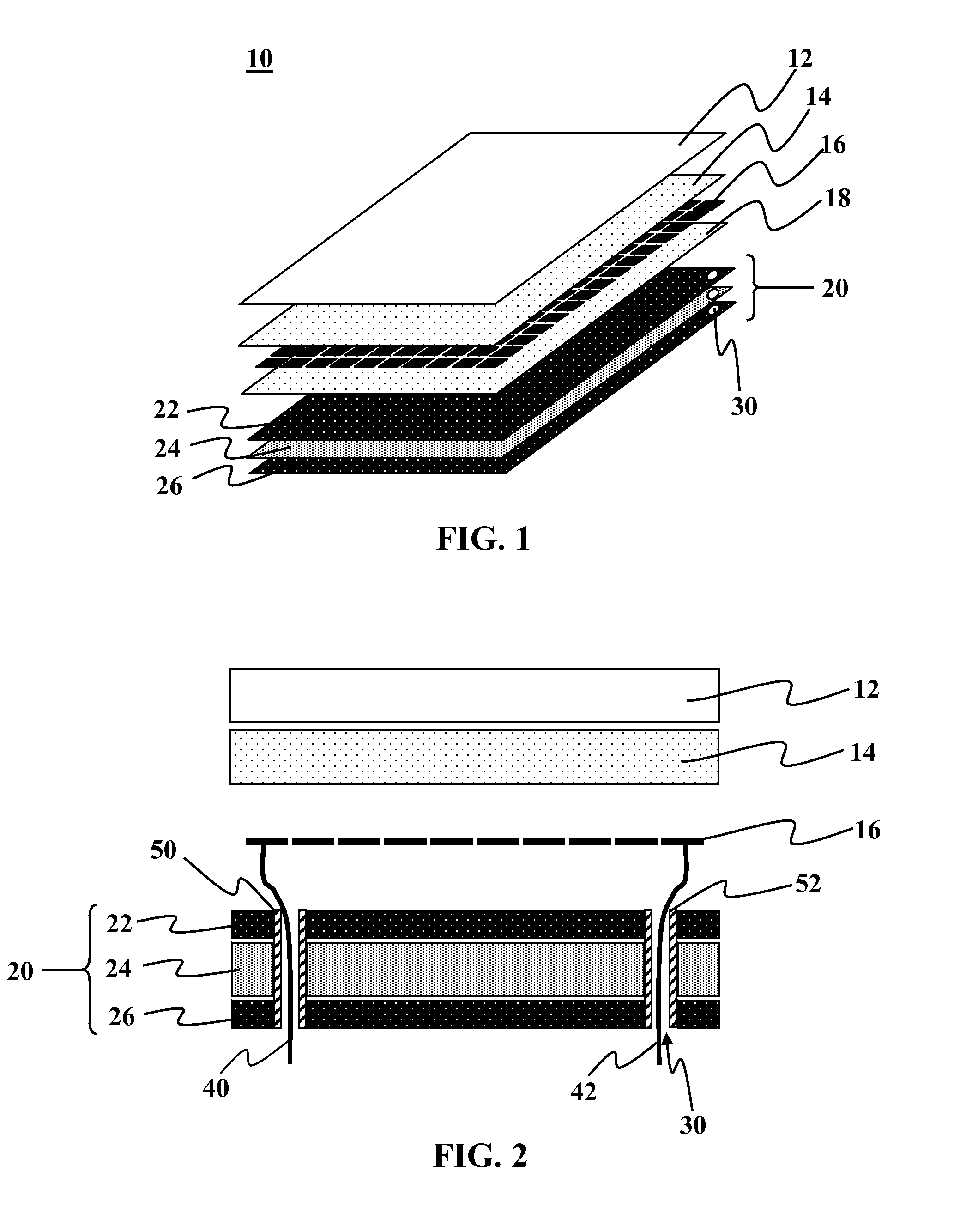

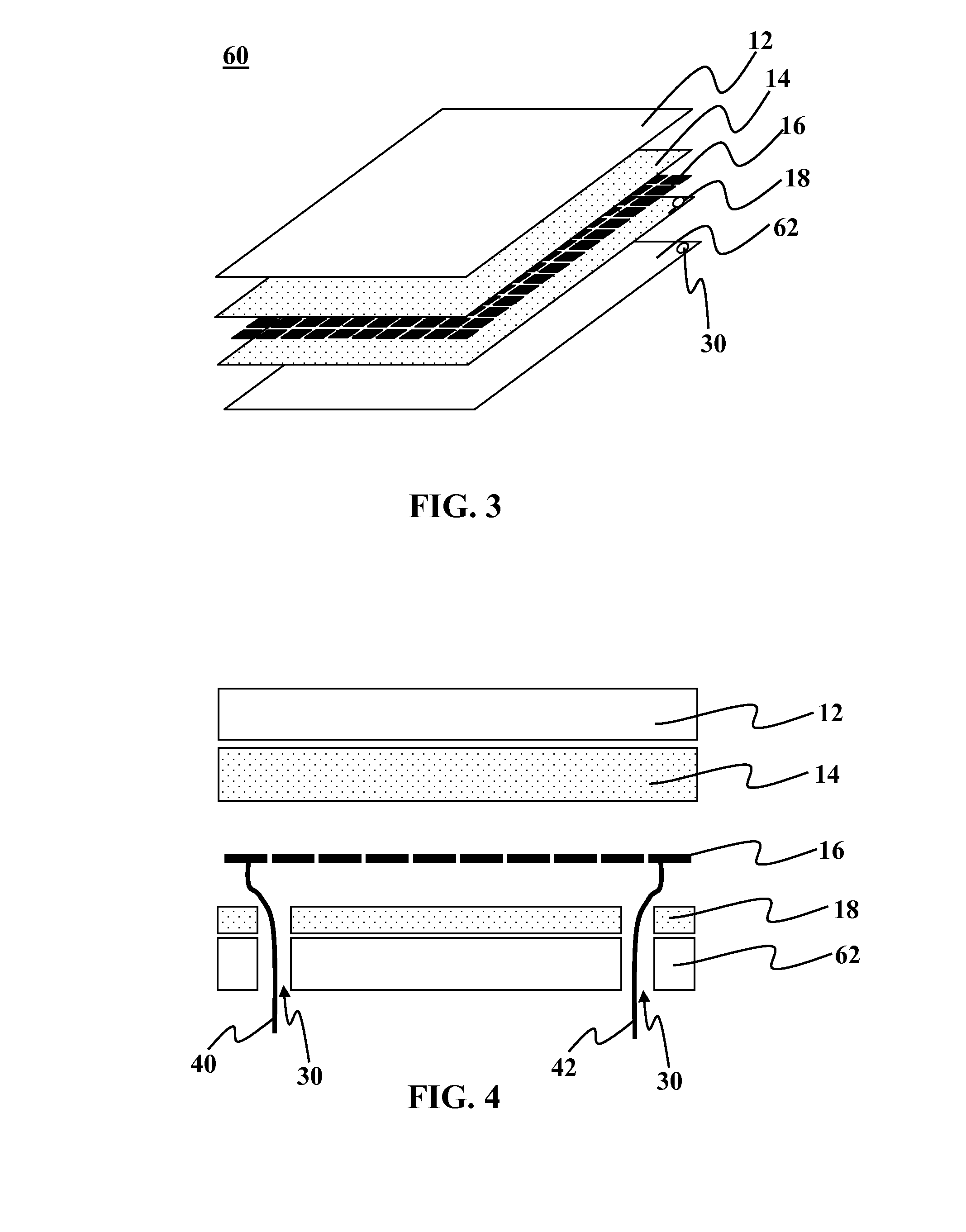

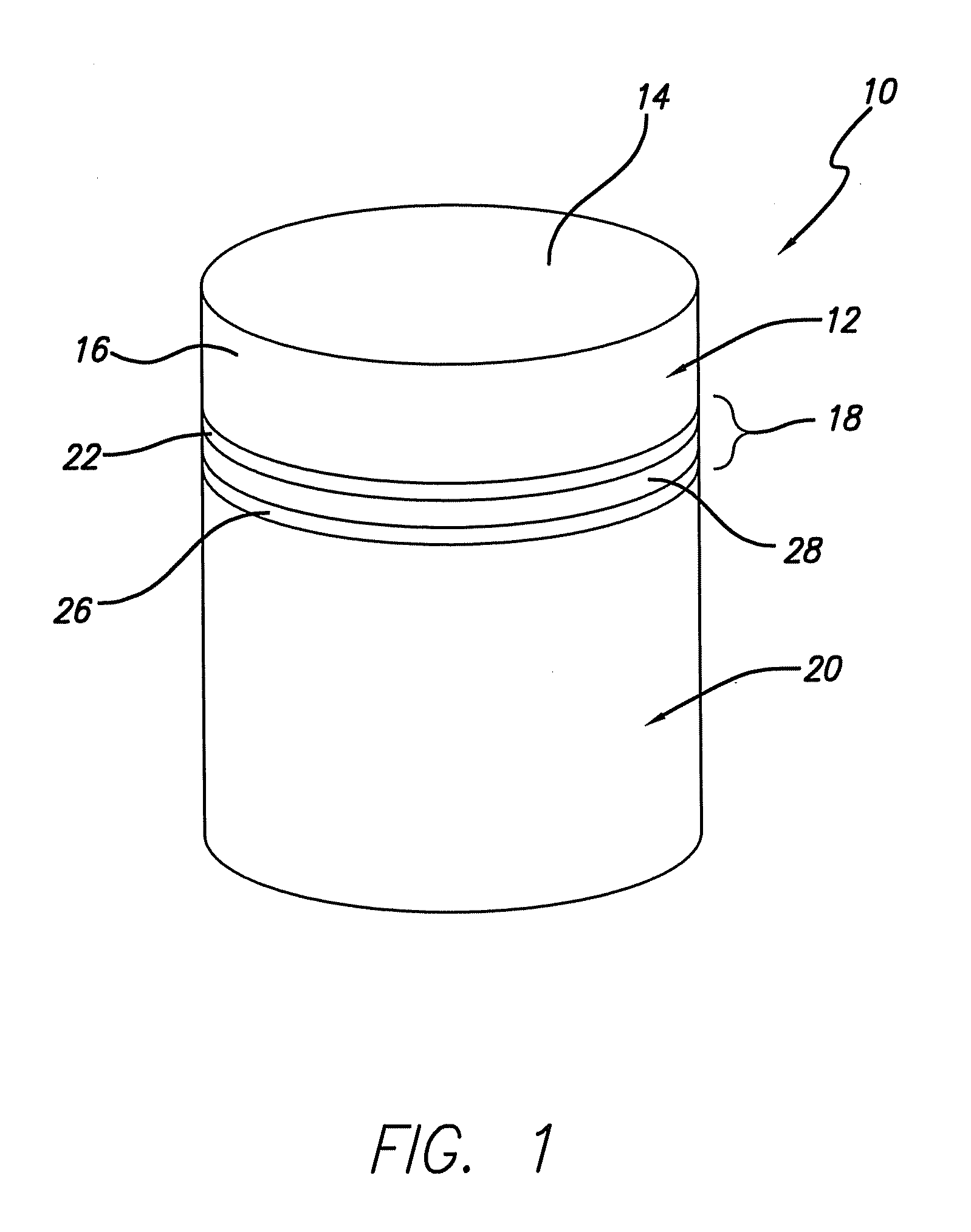

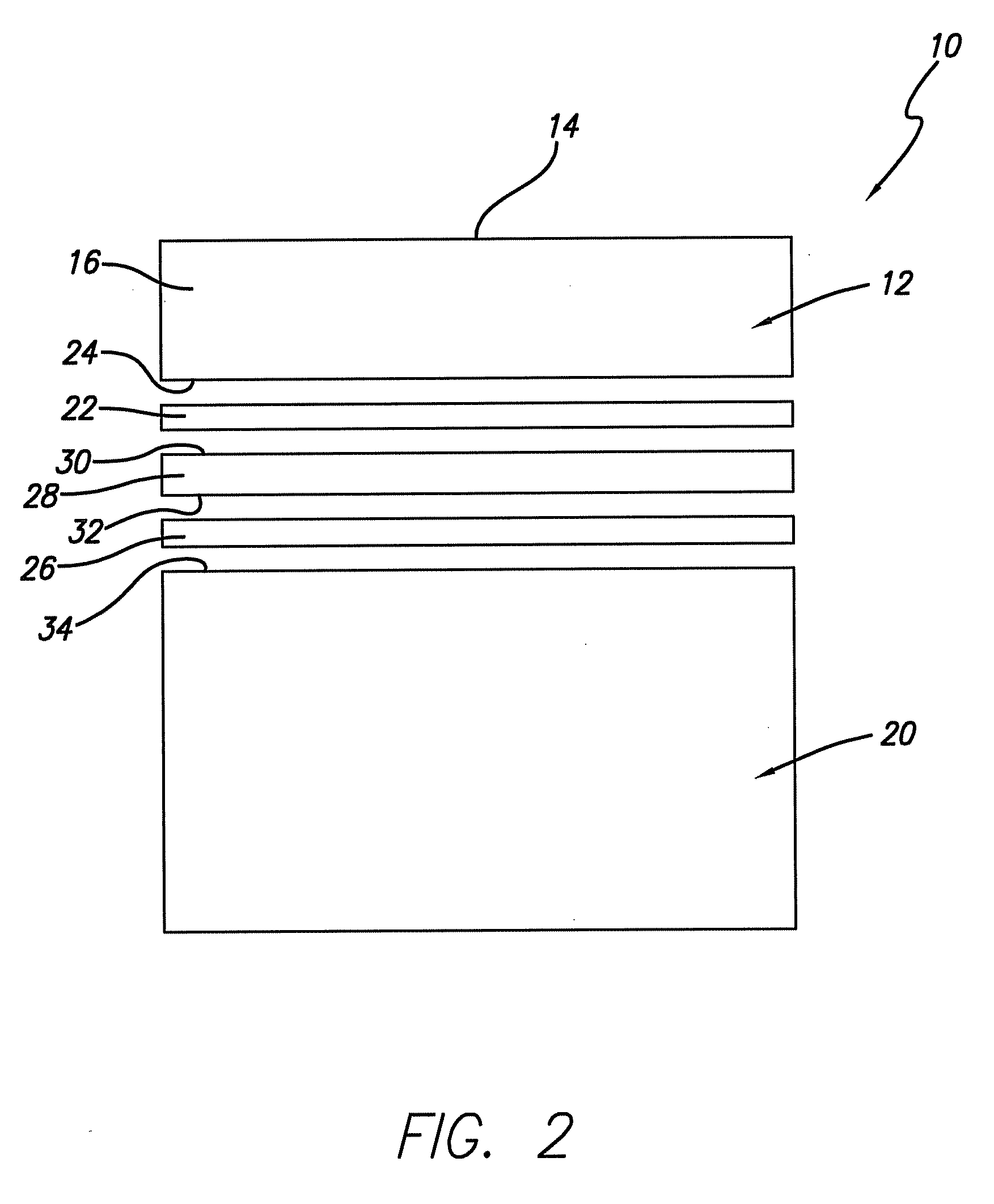

Embodiments of the present invention relate generally to solder bump formation and semiconductor device assemblies. One embodiment related to a method for forming a bump structure includes providing a semiconductor device (10) having a bond pad (12), and forming a first masking layer (20) overlying the bond pad (12). The first masking layer (20) is patterned to form a first opening (22) overlying at least a portion of the bond pad (12). A second masking layer (40) is formed overlying the first masking layer (20), and the second masking layer (40) is patterned to form a second opening (42) overlying at least a portion of the first opening (22). The method further includes forming a stud (30) at least within the first opening (22) and a solder bump (60) at least within the second opening (42).

Owner:NORTH STAR INNOVATIONS

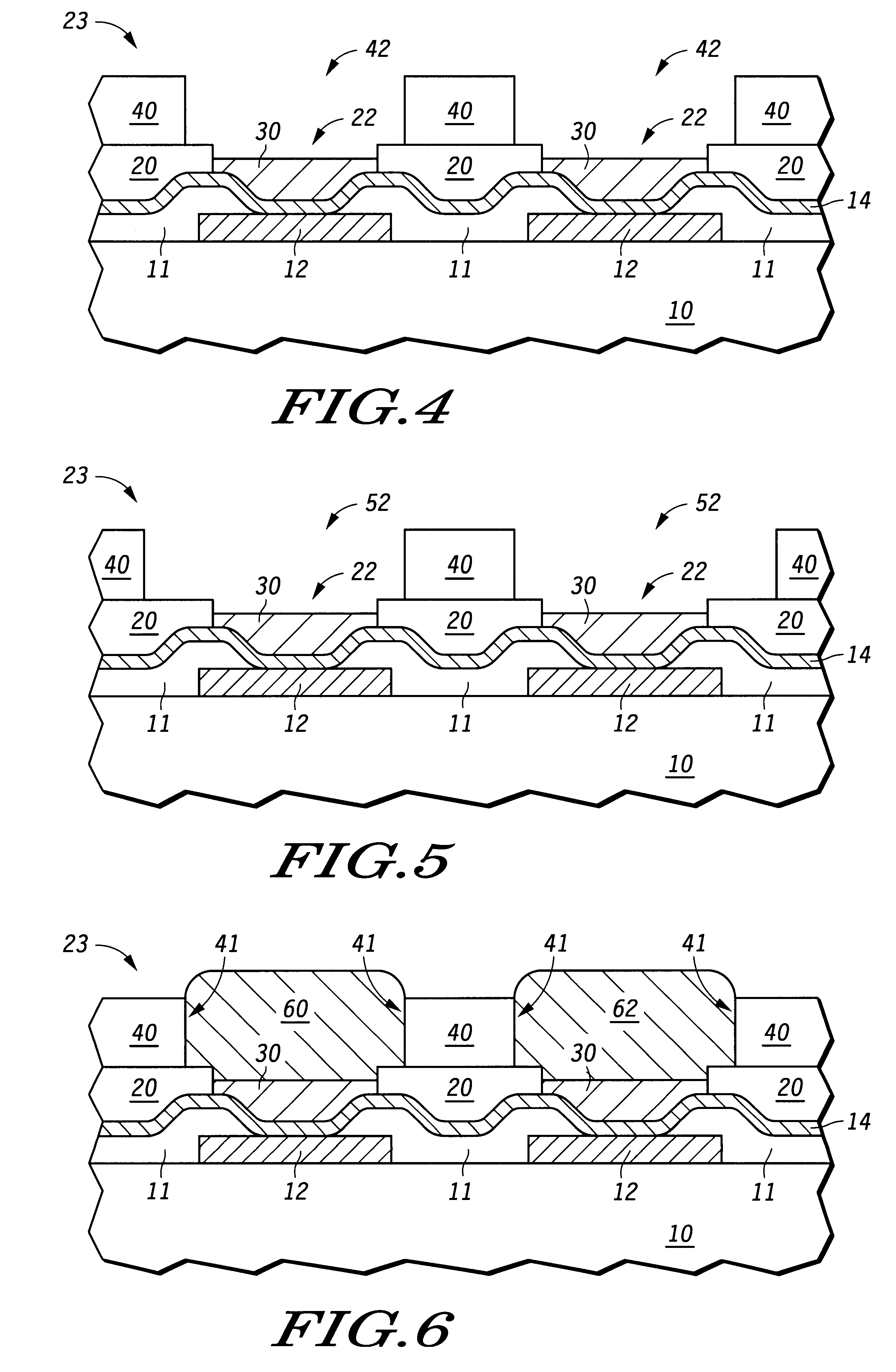

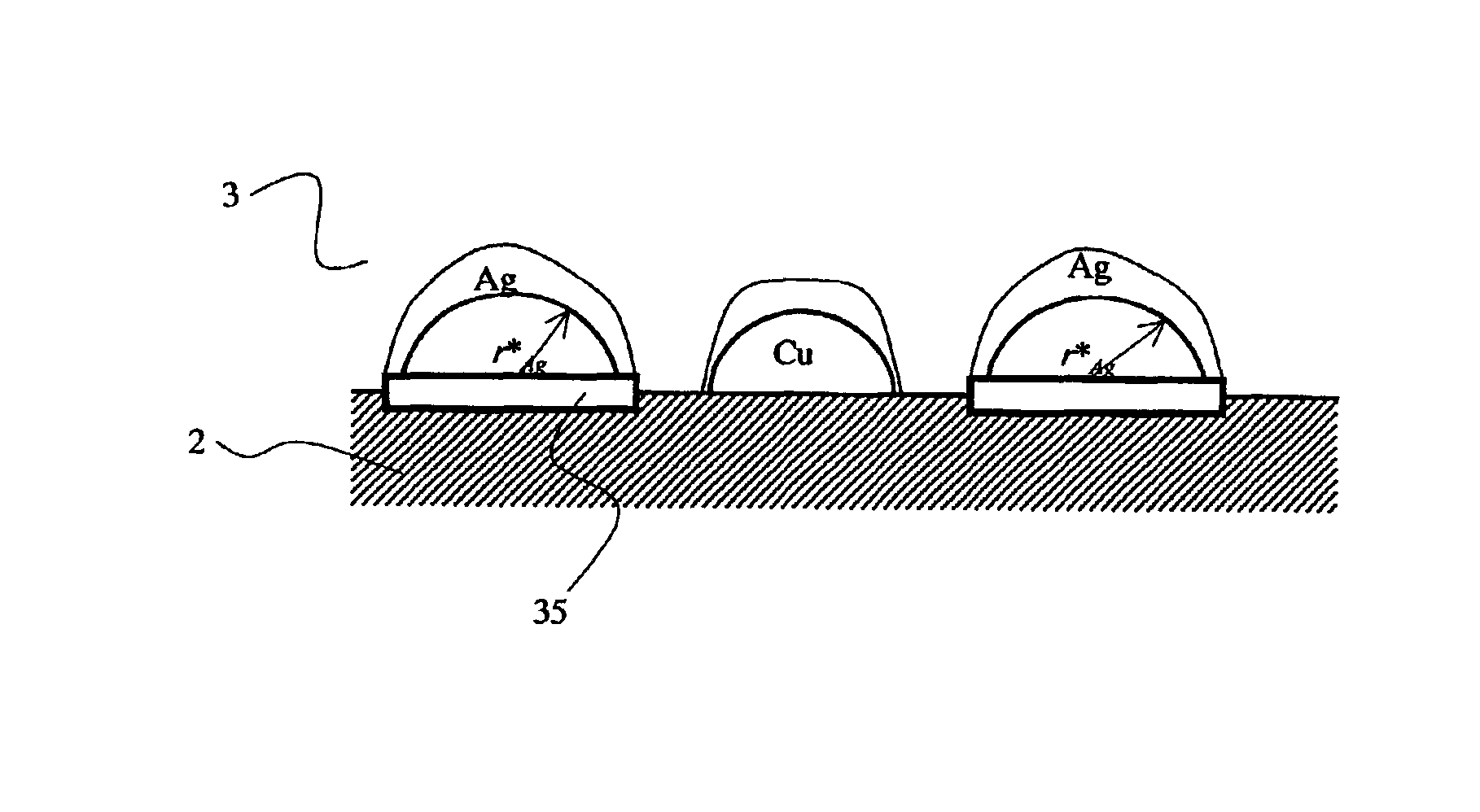

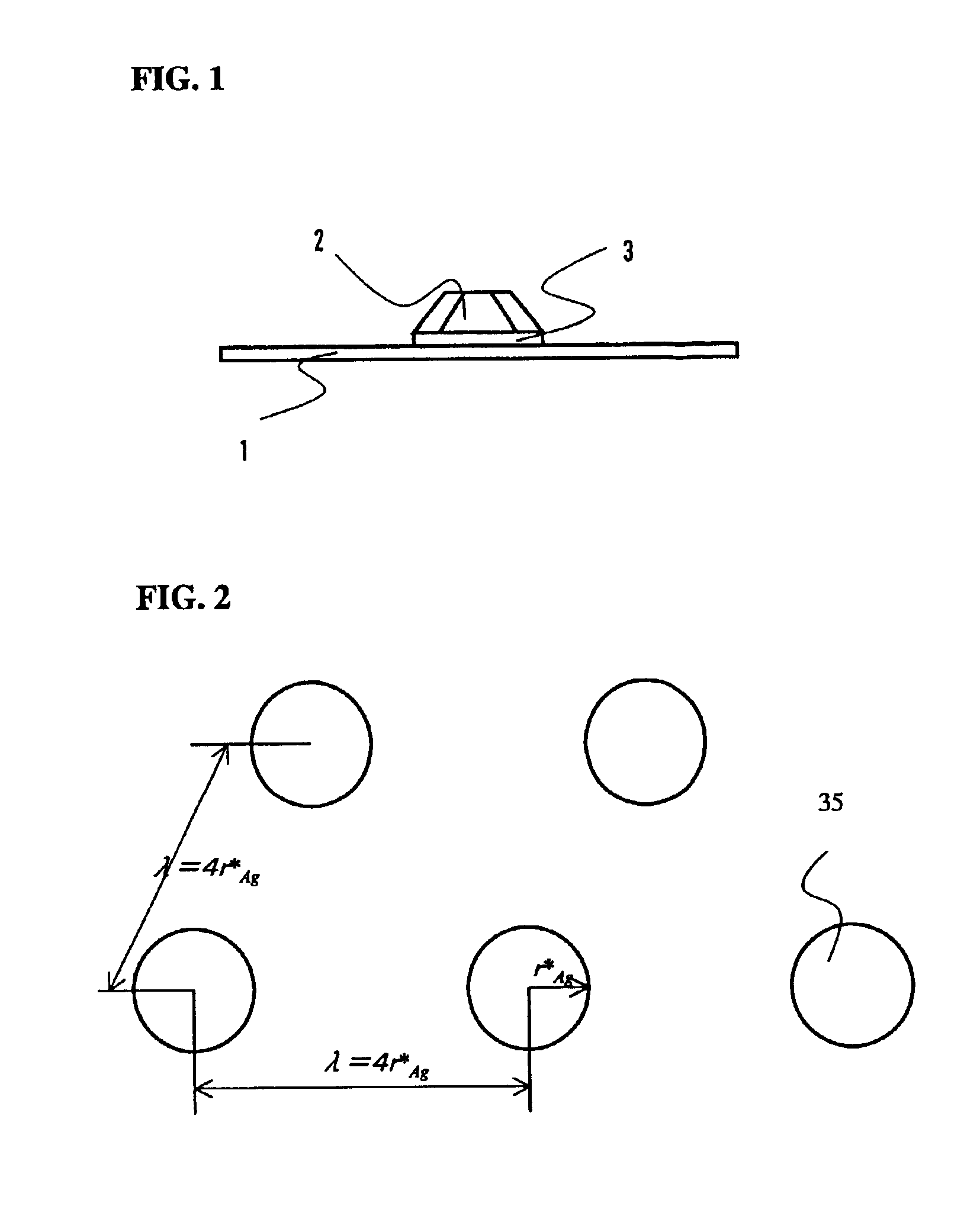

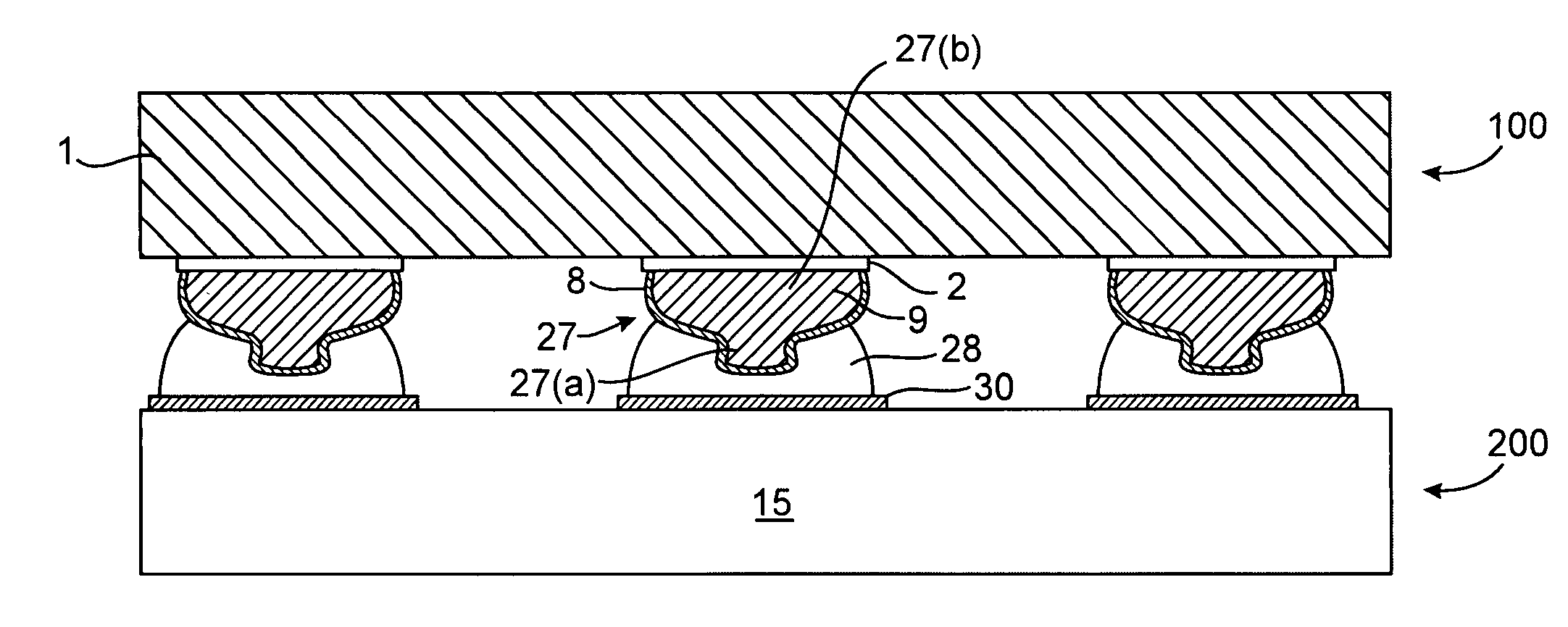

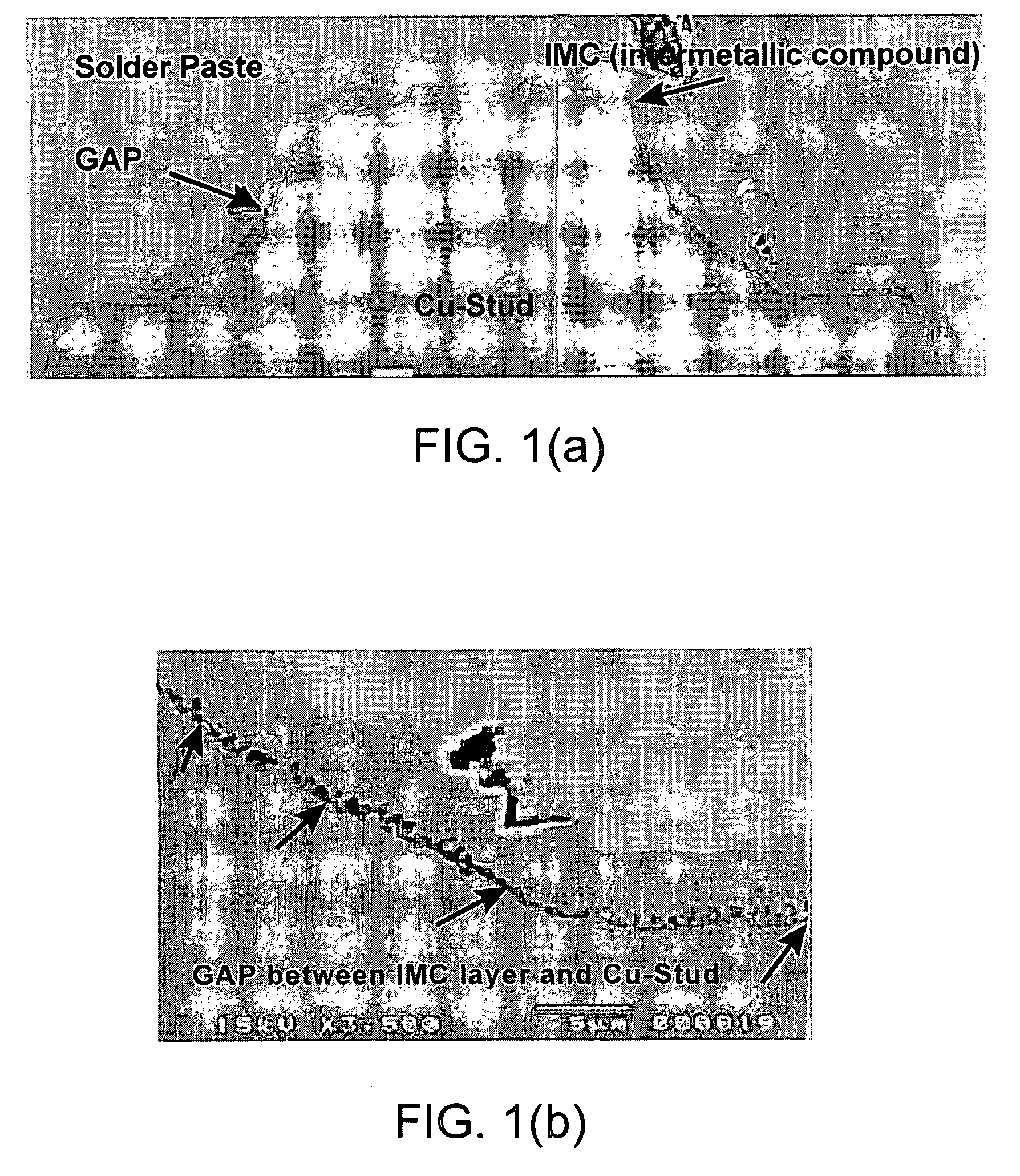

Composite connection structure and method of manufacturing

InactiveUS6337445B1Improve reliability and performanceImprove thermal conductivityPrinted circuit assemblingFinal product manufactureContact padSolder paste

A bump connection structure and a method of attachment to integrated circuits or packages is provided which comprises a prefabricated core structure coated with solderable metal layers to form a composite bump. Said composite bump is aligned to contact pads of the chip or package which have been coated with solder paste, and the assembly heated to form a metallurgical bond. The prefabricated core structures are comprised of metal, plastic or ceramic of the size and dictated by package standards. The connection structure is preferably lead free.

Owner:TEXAS INSTR INC

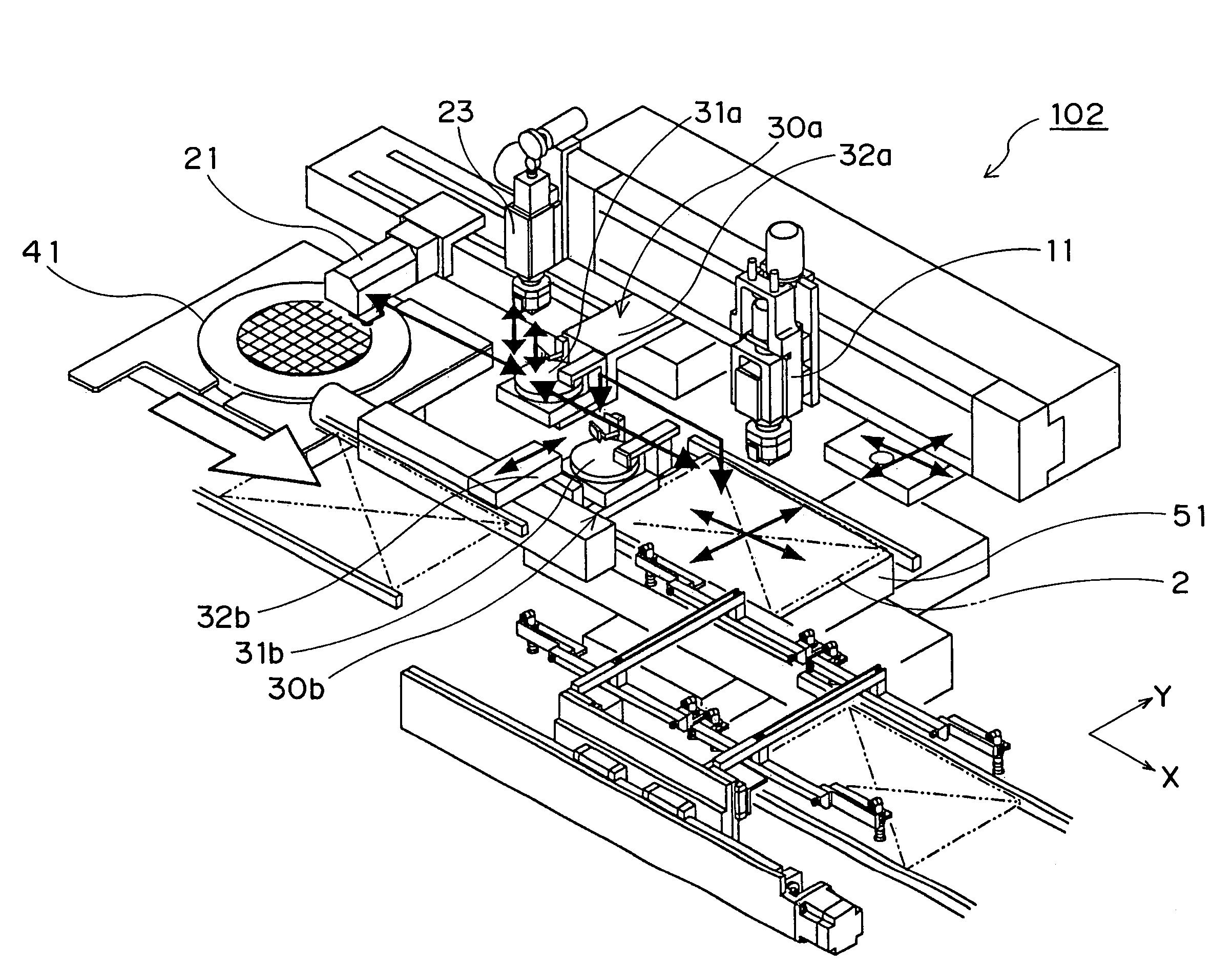

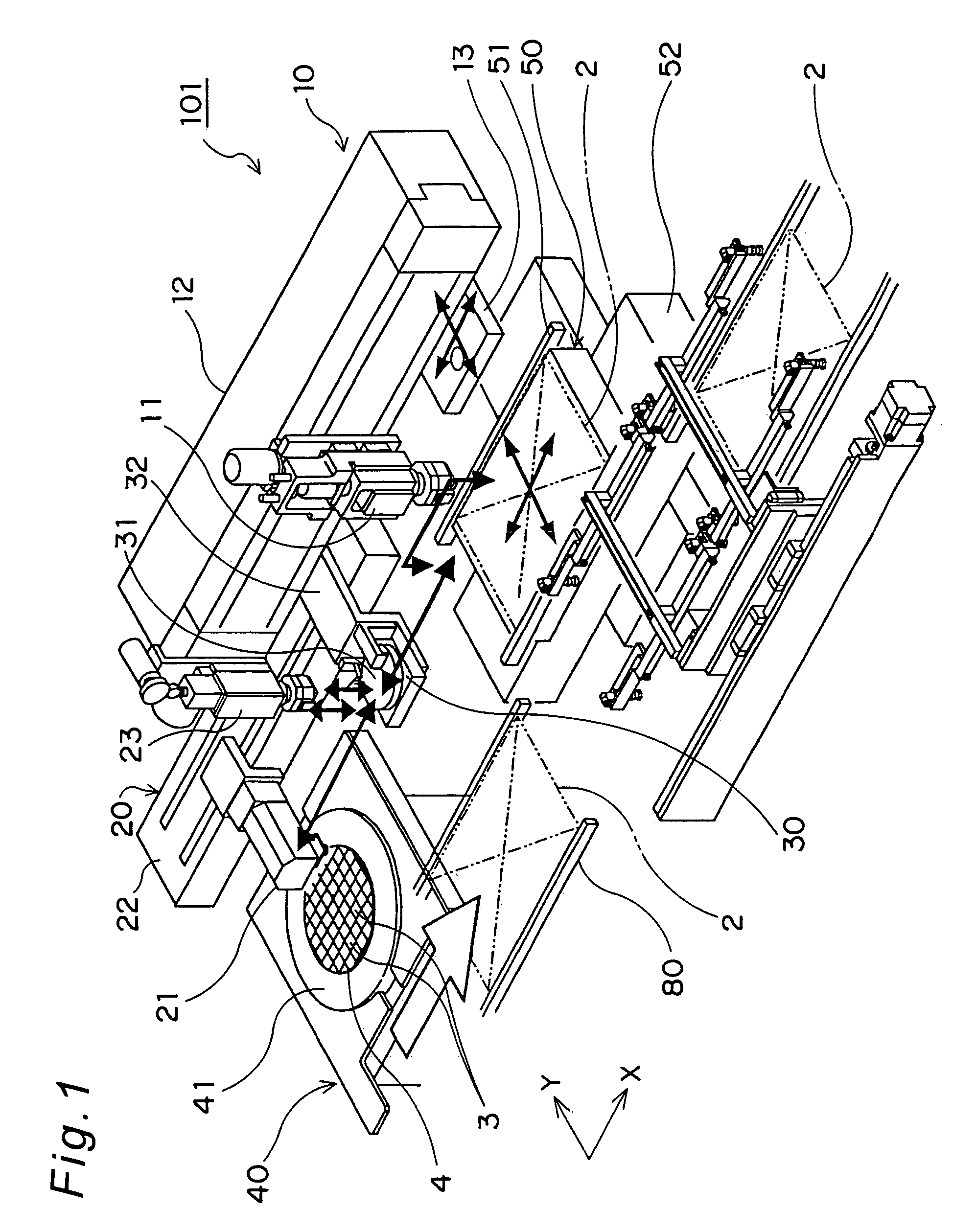

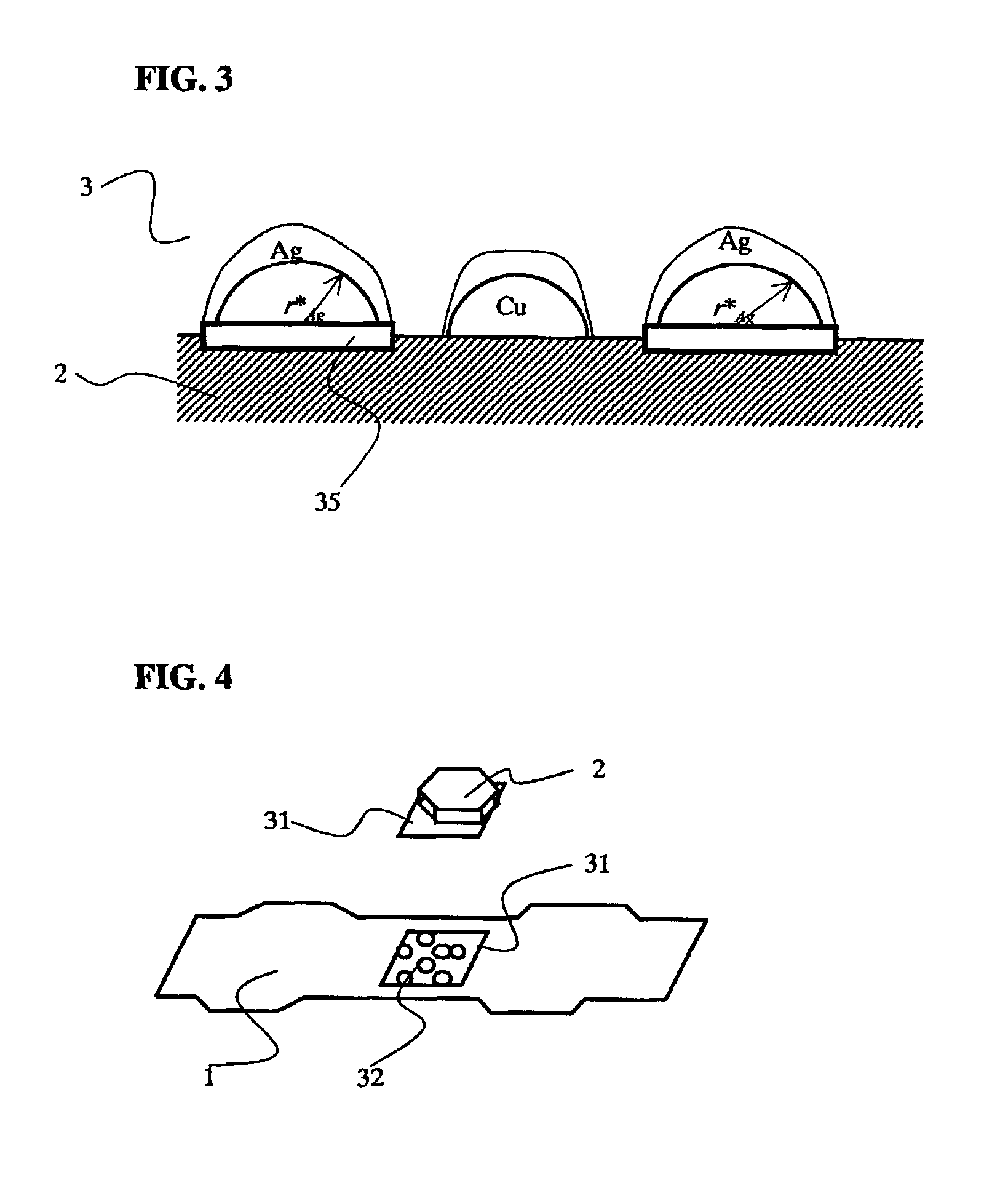

Component mounting method

InactiveUS7353596B2Shorten the timeComponents is relatively effectivePrinted circuit assemblingElectrically conductive connectionsEngineeringElectrical and Electronics engineering

In component mounting process for a plurality of components to be mounted onto a board, a plurality of bump electrode portions formed on mounting-side surfaces of the components to be mounted onto the board are brought into contact with a bonding-assistant agent so that the bonding-assistant agent is supplied thereto to allow the bonding-assistant agent-supplied components to be mounted onto the board. The component mounting process includes supplying the bonding-assistant agent to a first component among the plurality of components, and starting the supply of the bonding-assistant agent to a second component among the plurality of components before completion of the mounting of the bonding-assistant agent-supplied first component onto the board.

Owner:PANASONIC CORP

Brazing-filler material and method for brazing diamond

InactiveUS6889890B2Beautiful sceneryStable joint strengthLayered productsOther manufacturing equipments/toolsFilling materialsCopper

When a diamond is brazed to a metal substrate, while obtaining a stable joining strength, a joined interface of the diamond is not eroded to provide a good joint with a beautiful view. A brazing-filler material containing at least one selected from a group consisting of gold and silver, and copper as principal components, and further containing 0.001 to 5 mass % of vanadium is used. Preferably, a vanadium content is not more than 2.0 mass %, and more preferably not more than 0.5 mass %. Using this brazing-filler material, unidirectional solidification is performed from a side of diamond to form vanadium carbide in a joined interface in a shape of islands, and thereby an interface having a beautiful view with stable joining strength can be obtained. In addition, strong joining is possible also by a usual solidification method.

Owner:HOHOEMI BRAINS INC

Golf club

Owner:THE YOKOHAMA RUBBER CO LTD +1

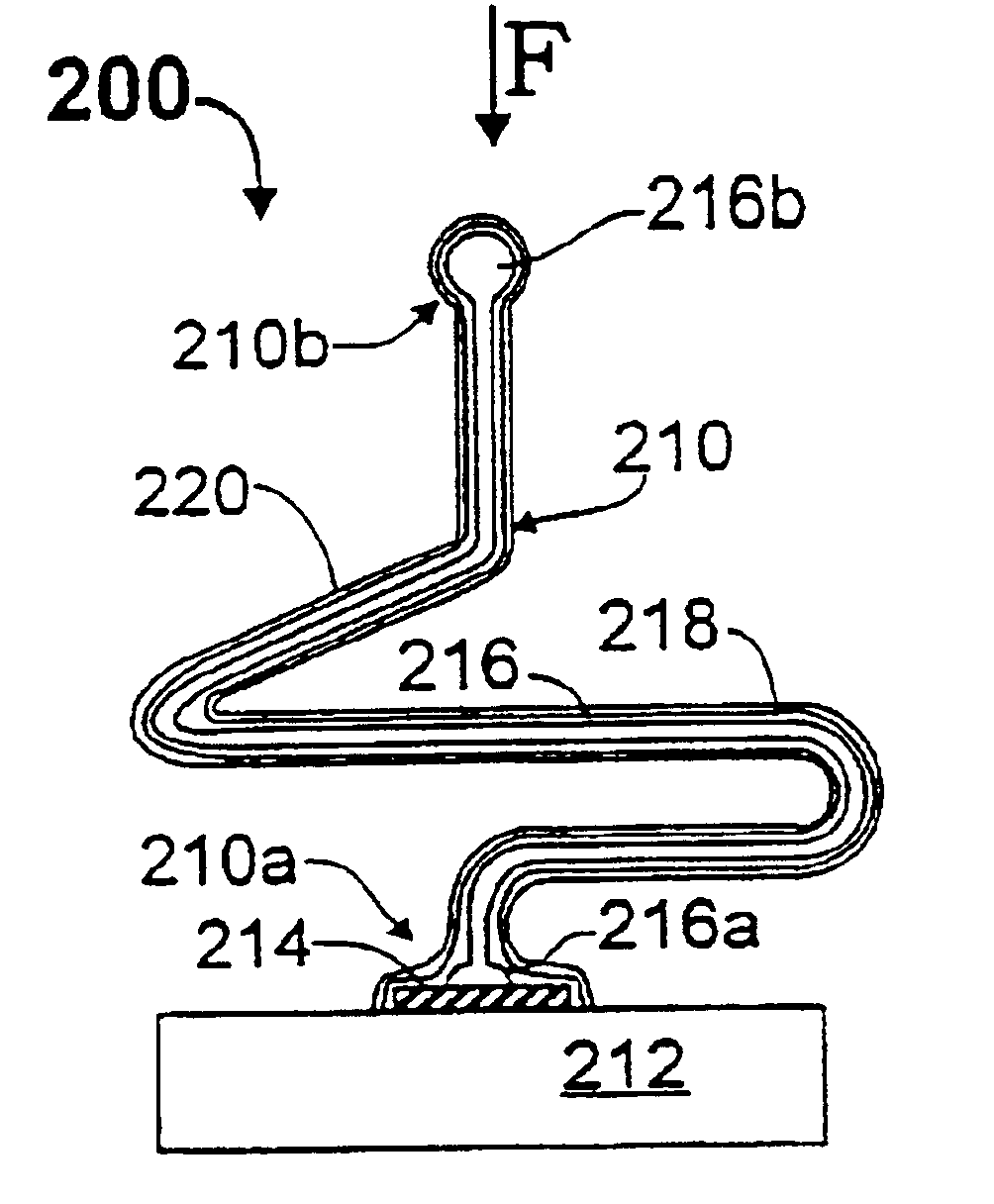

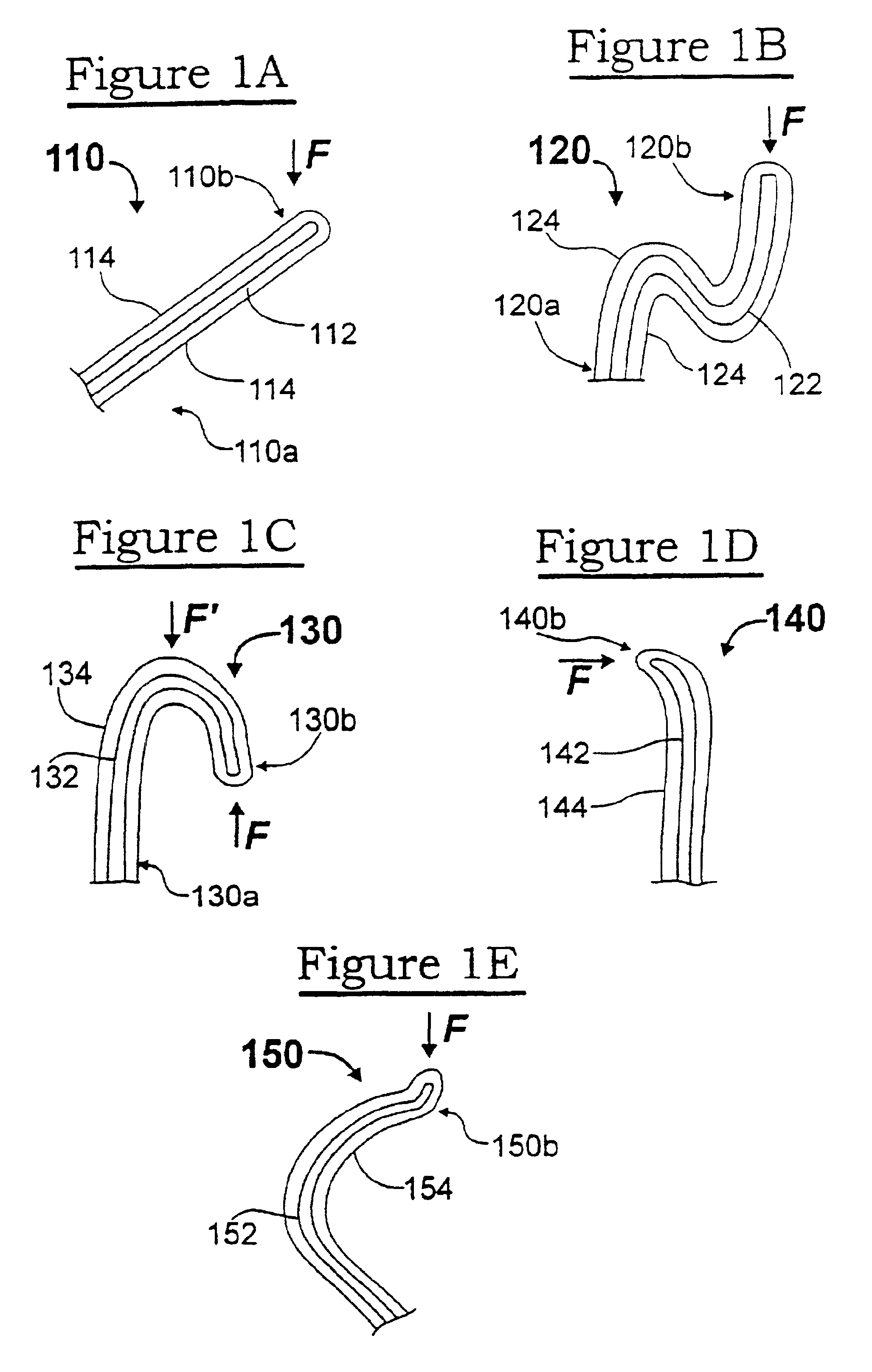

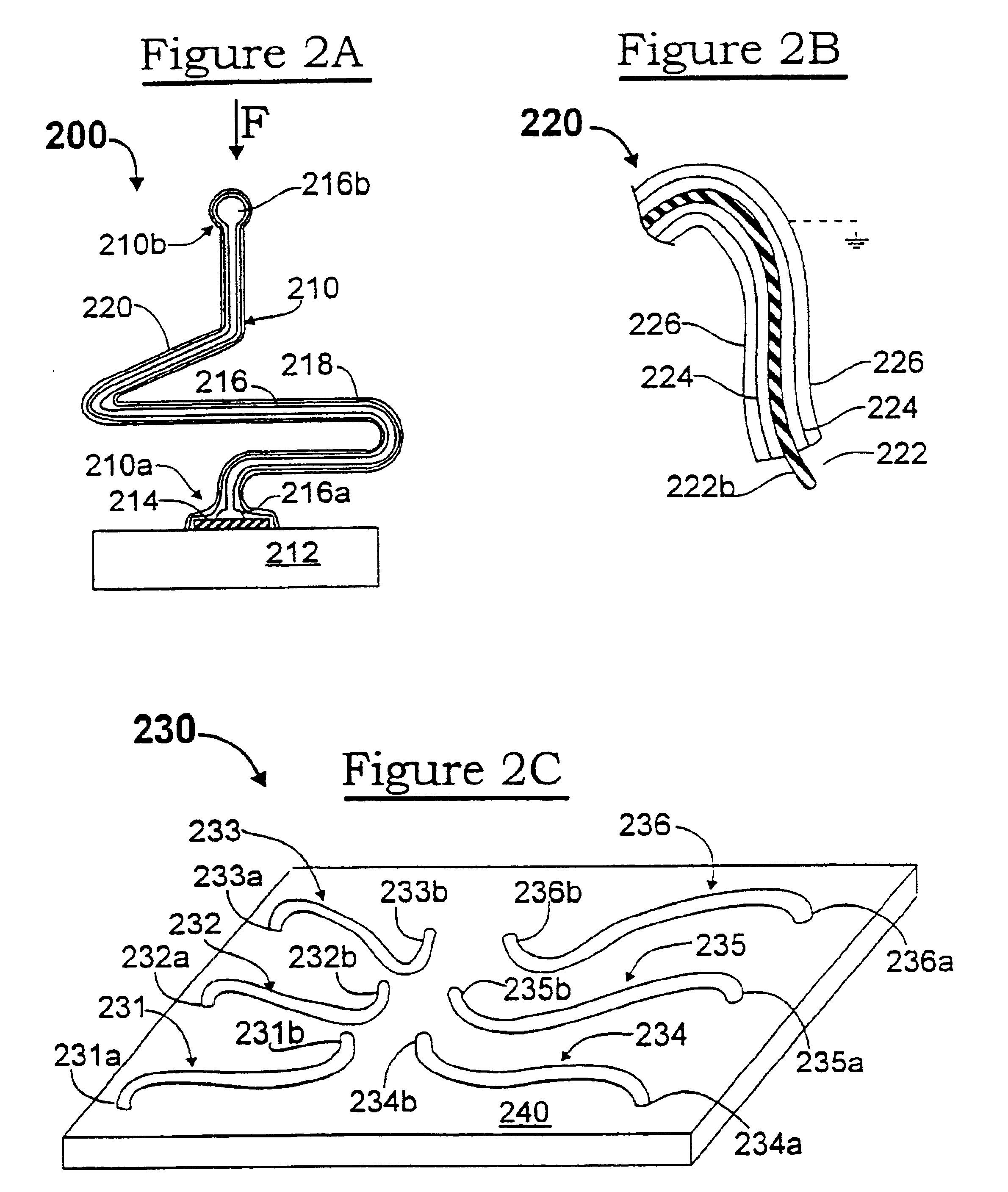

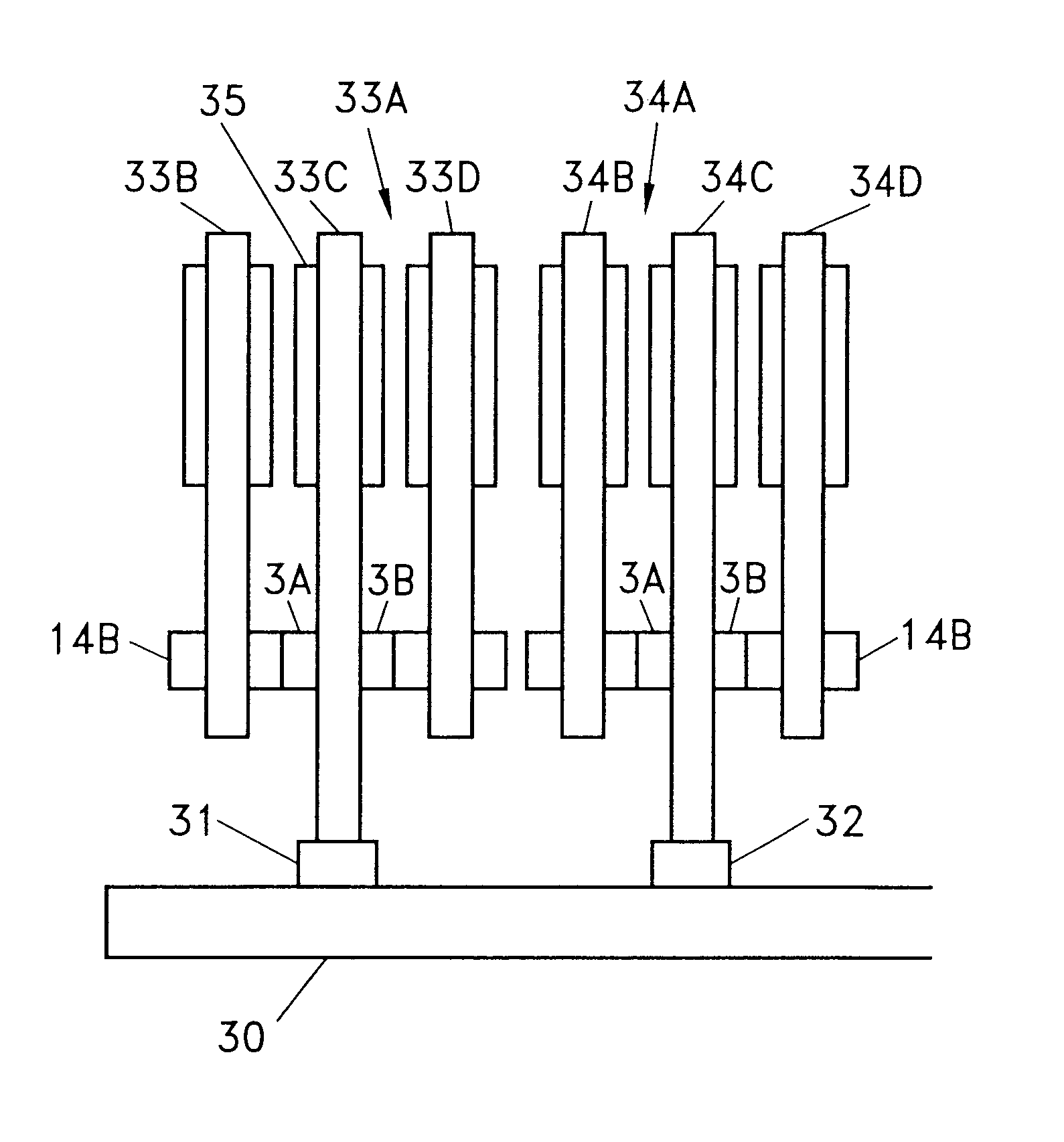

Method and apparatus for shaping spring elements

InactiveUS6836962B2Easy to disassembleEasy to manufactureElectrically conductive connectionsContact member assembly/disassemblyProbe cardCopper wire

Interconnection elements for electronic components, exhibiting desirable mechanical characteristic (such as resiliency, for making pressure contacts) are formed by using a shaping tool (512) to shape an elongate core element (502) of a soft material (such as gold or soft copper wire) to have a springable shape (including cantilever beam, S-shape, U-shape), and overcoating the shaped core element with a hard material (such as nickel and its alloys), to impart to desired spring (resilient) characteristic to the resulting composite interconnection element. A final overcoat of a material having superior electrical qualities (e.g., electrical conductivity and / or solderability) may be applied to the composite interconnection element. The resulting interconnection elements may be mounted to a variety of electronic components, including directly to semiconductor dies and wafers (in which case the overcoat material anchors the composite interconnection element to a terminal (or the like) on the electronic component), may be mounted to support substrates for use as interposers and may be mounted to substrates for use as probe cards or probe card inserts. The shaping tool may be an anvil (622) and a die (624), and may nick or sever successive shaped portions of the elongate elements, and the elongate element may be of an inherently hard (springy) material. Methods of fabricating interconnection elements on sacrificial substrates are described. Methods of fabricating tip structures (258) and contact tips at the end of interconnection elements are also described.

Owner:FORMFACTOR INC

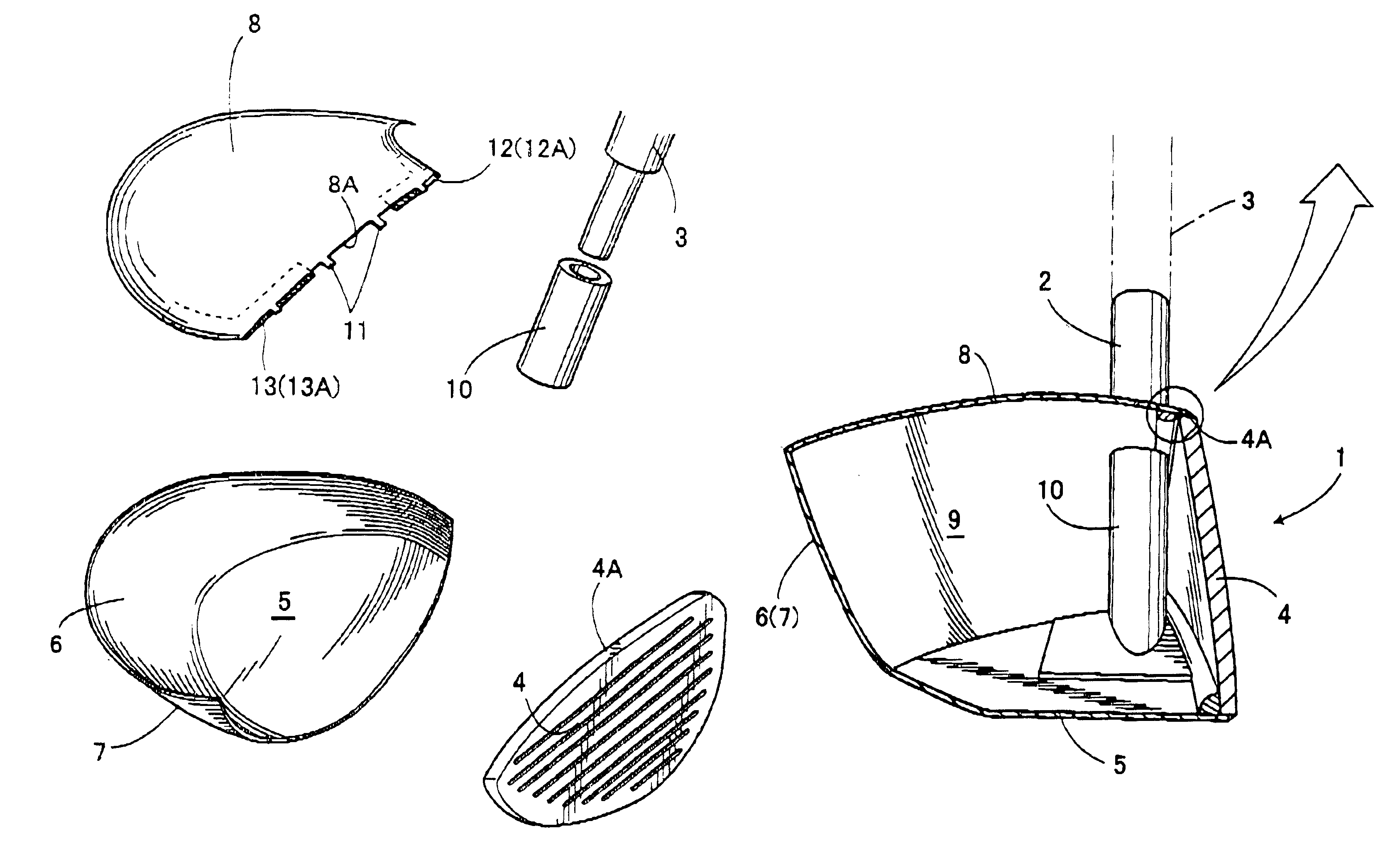

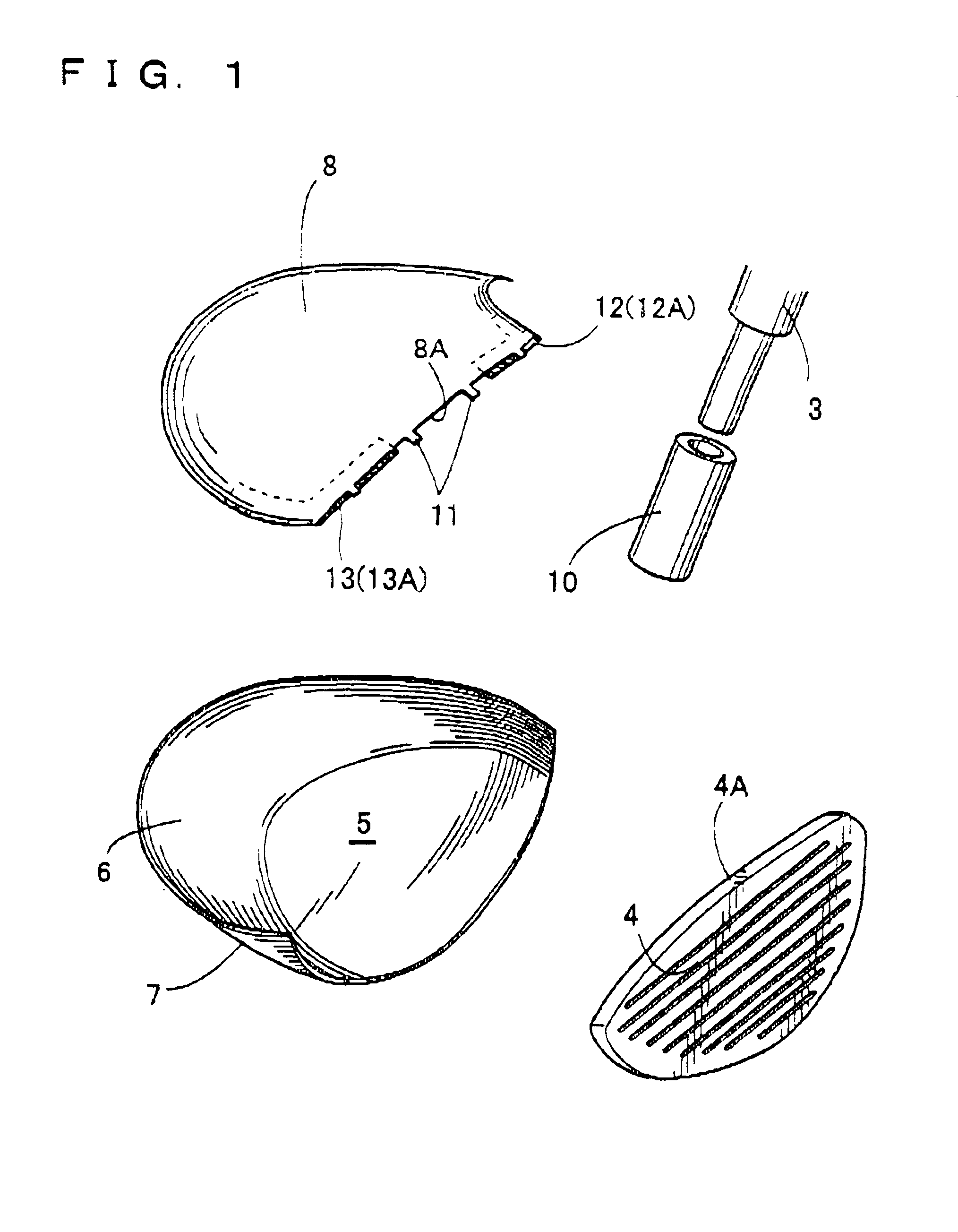

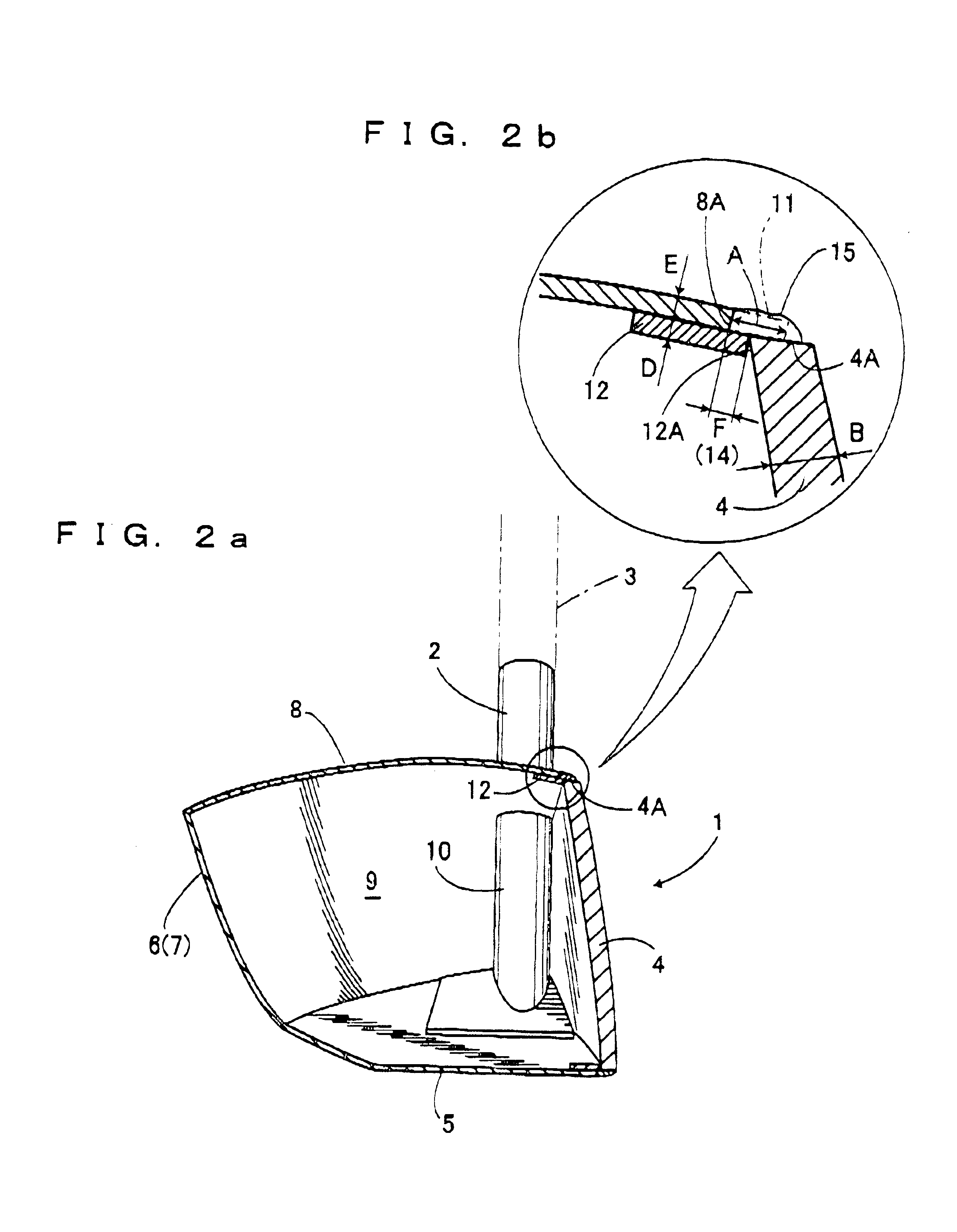

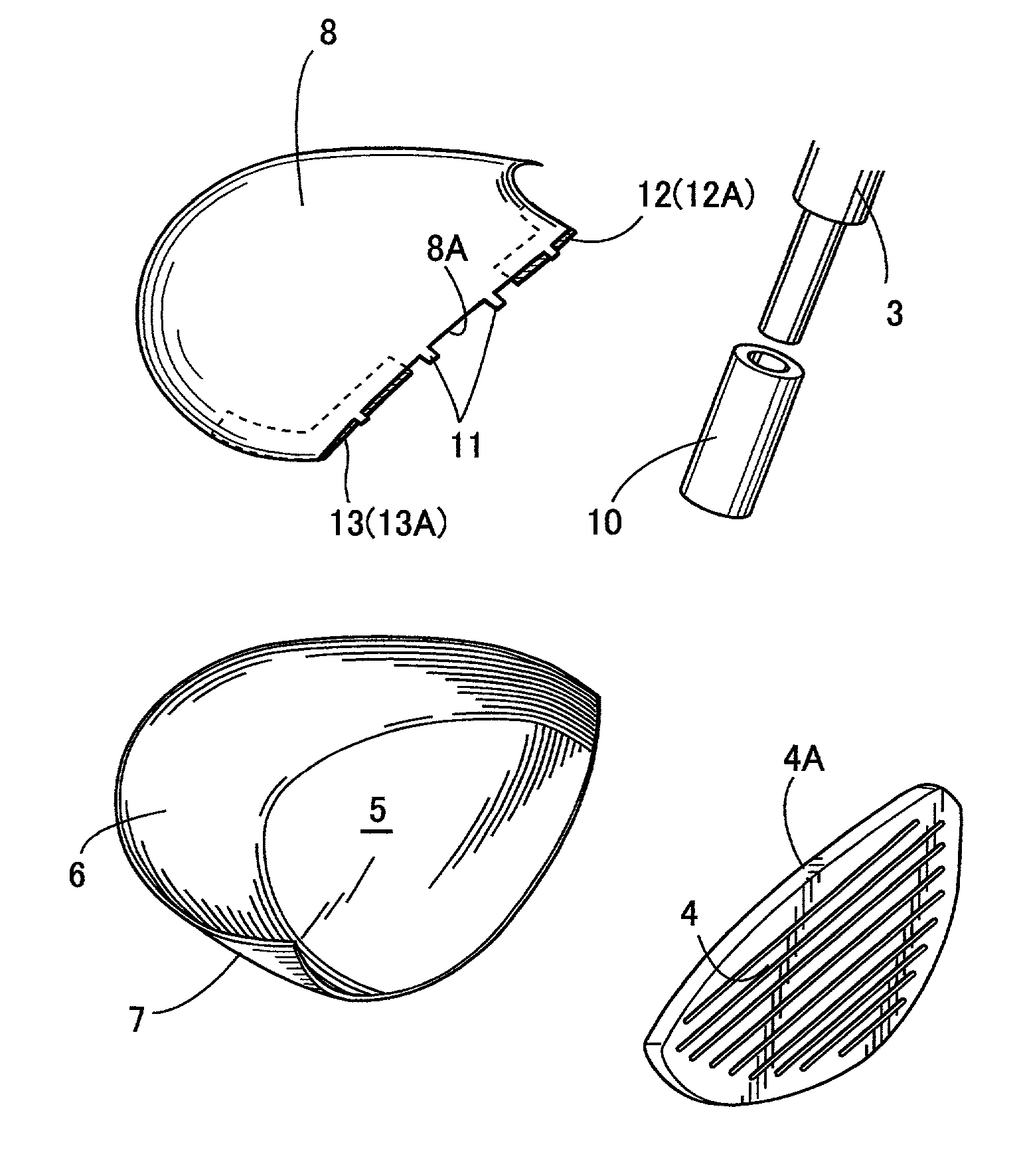

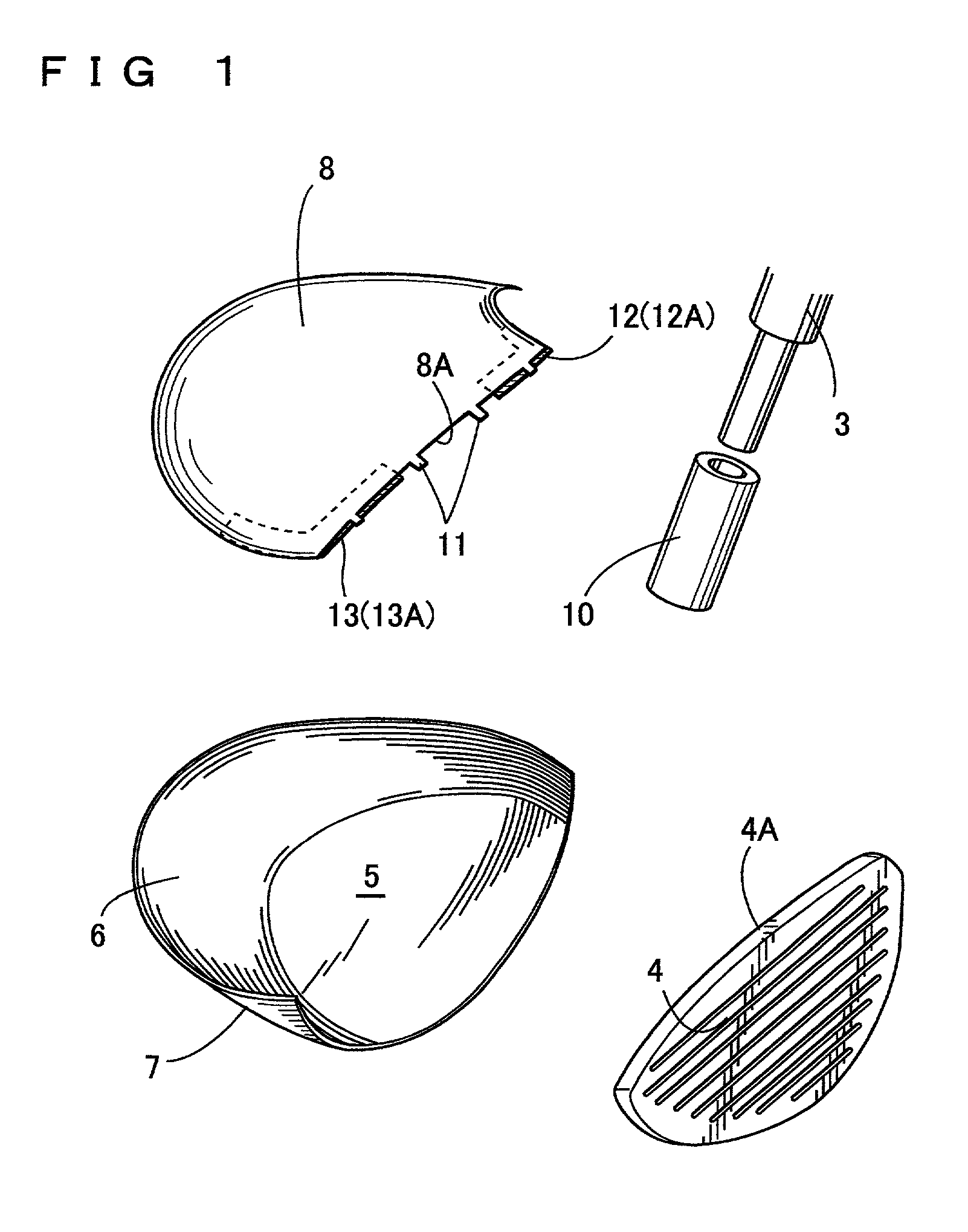

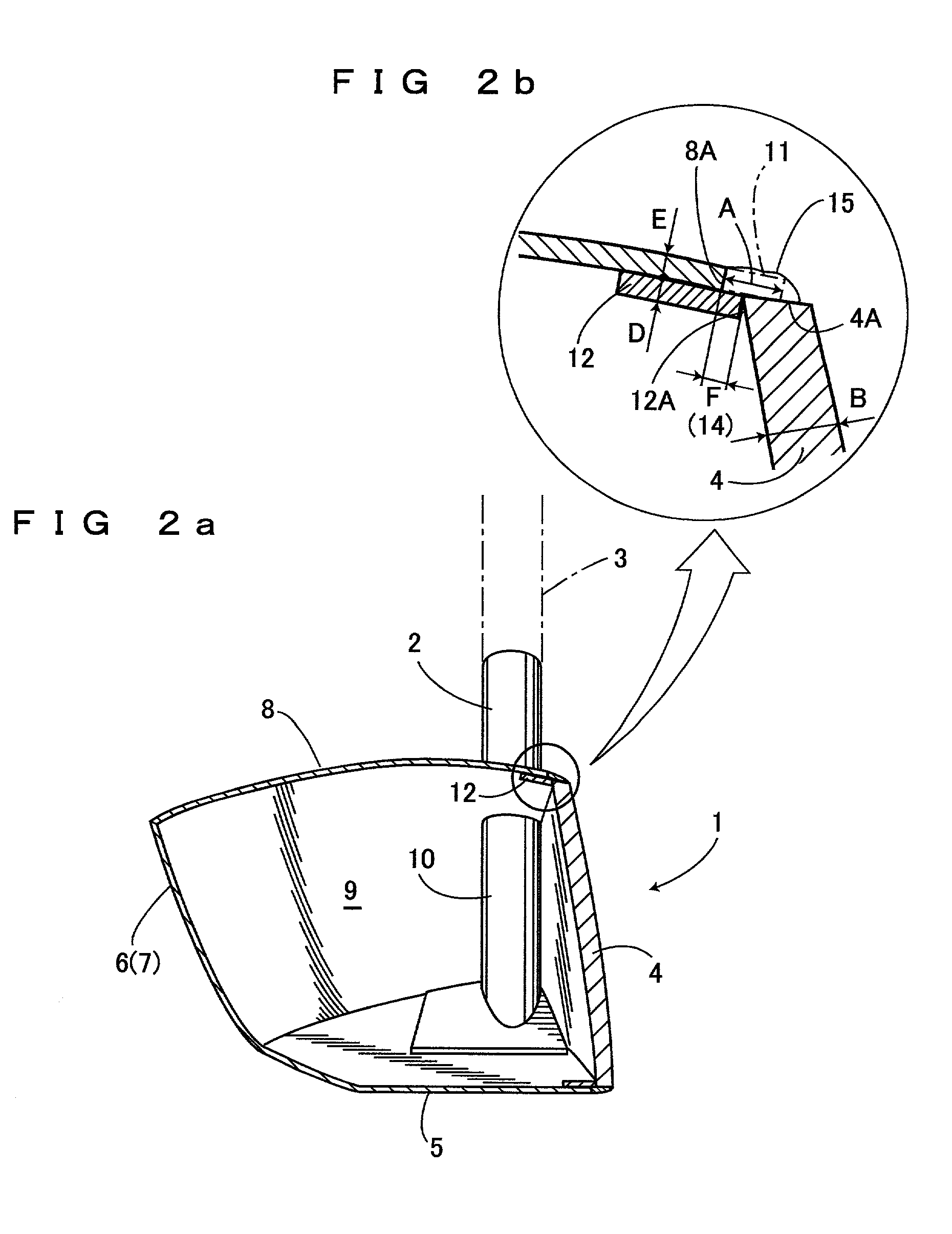

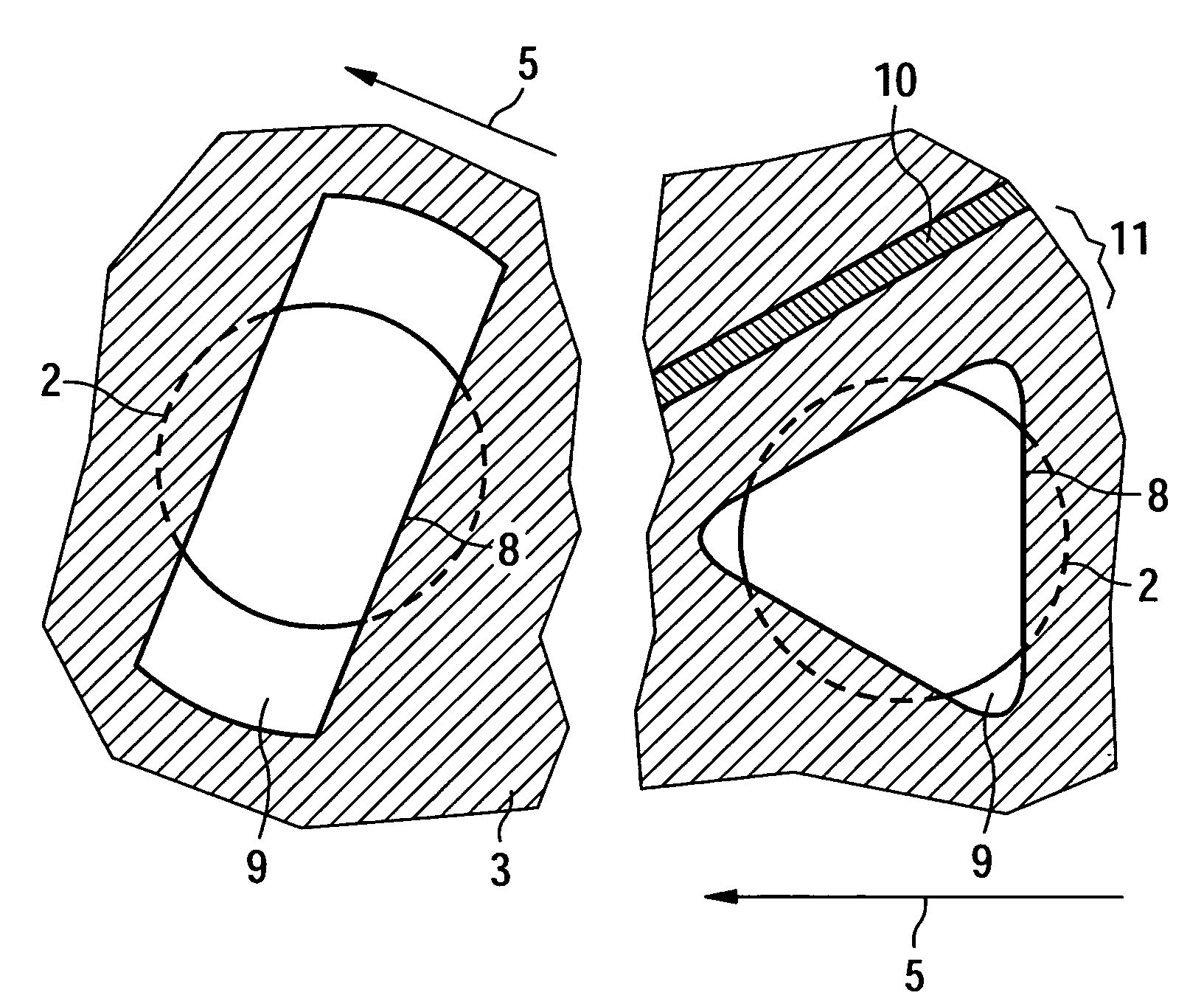

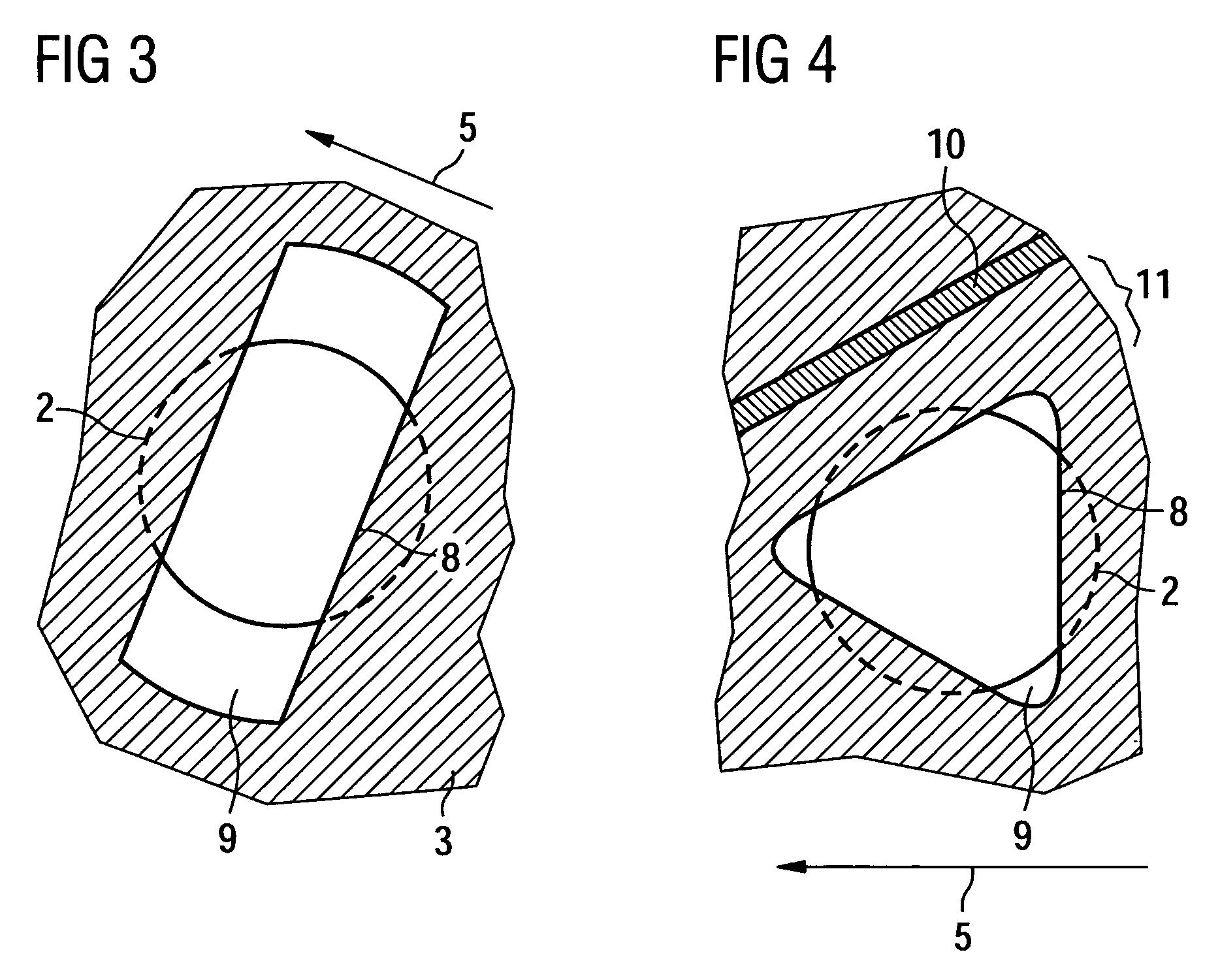

Golf club

A golf club which comprises a head which is less deformable by the heat in welding. Separate reinforcing members 12 and 13 are provided on inner surface of a front edge 8A of a crown shell 8. Thus, the front edge 8A side is thickened and then the upper edge 4A of the face shell 4 is joined to the front edge 8A of the crown shell 8, by welding. The front edge 8A of the crown shell 8 is formed with a plurality of projections 11 which are anchored by the upper edge 4A of the face shell 4. front edge 8A of the crown shell 8 is thickened by adding the thickness of the reinforcing members 12, 13 to the thickness of crown shell 8 itself. Thus, thermal deformation and the sinking of the front edge 8A at the time of welding can be prevented, thus enabling the upper edge 4A to be joined to the front edge 8A as designed.

Owner:THE YOKOHAMA RUBBER CO LTD +1

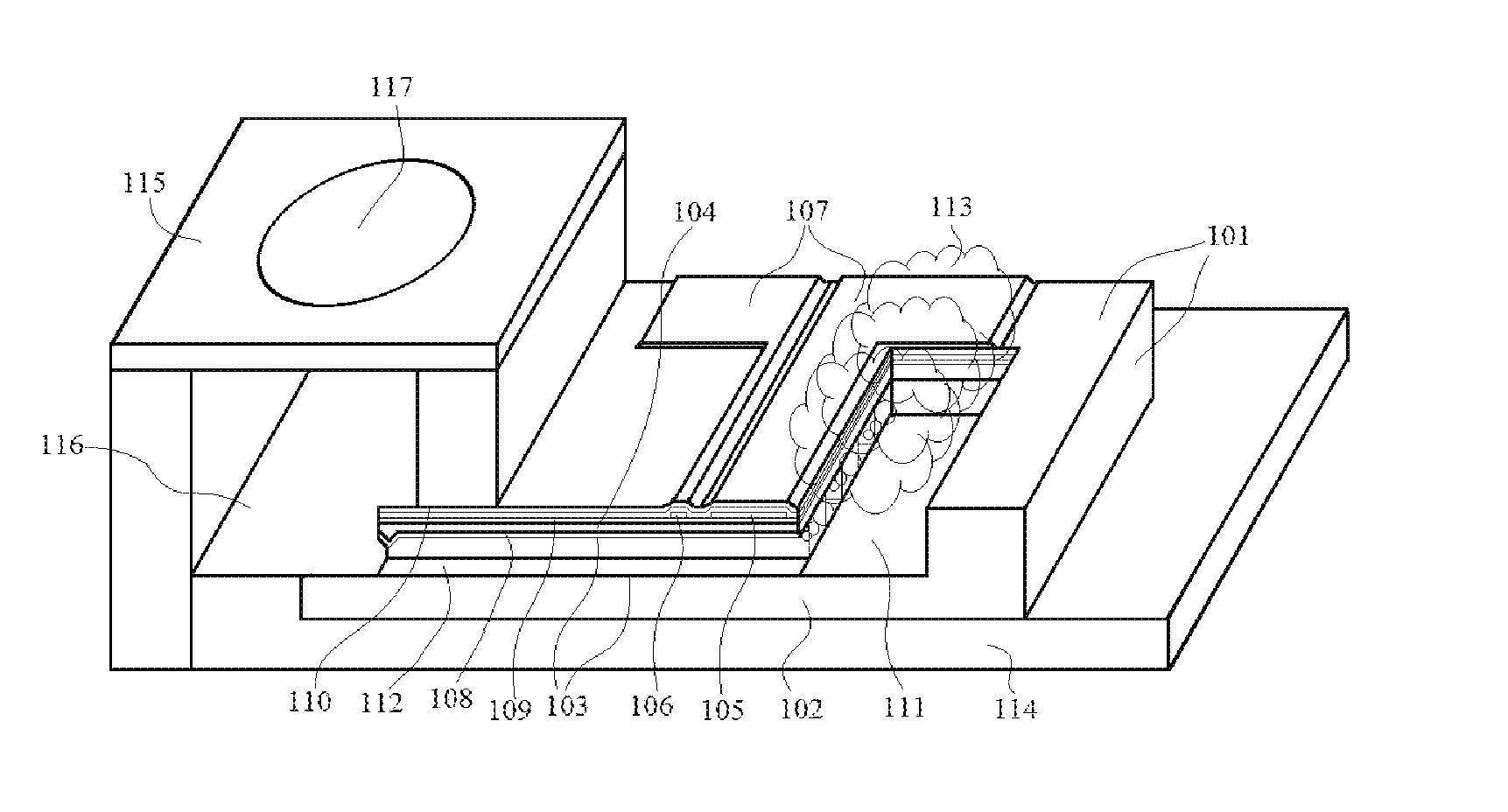

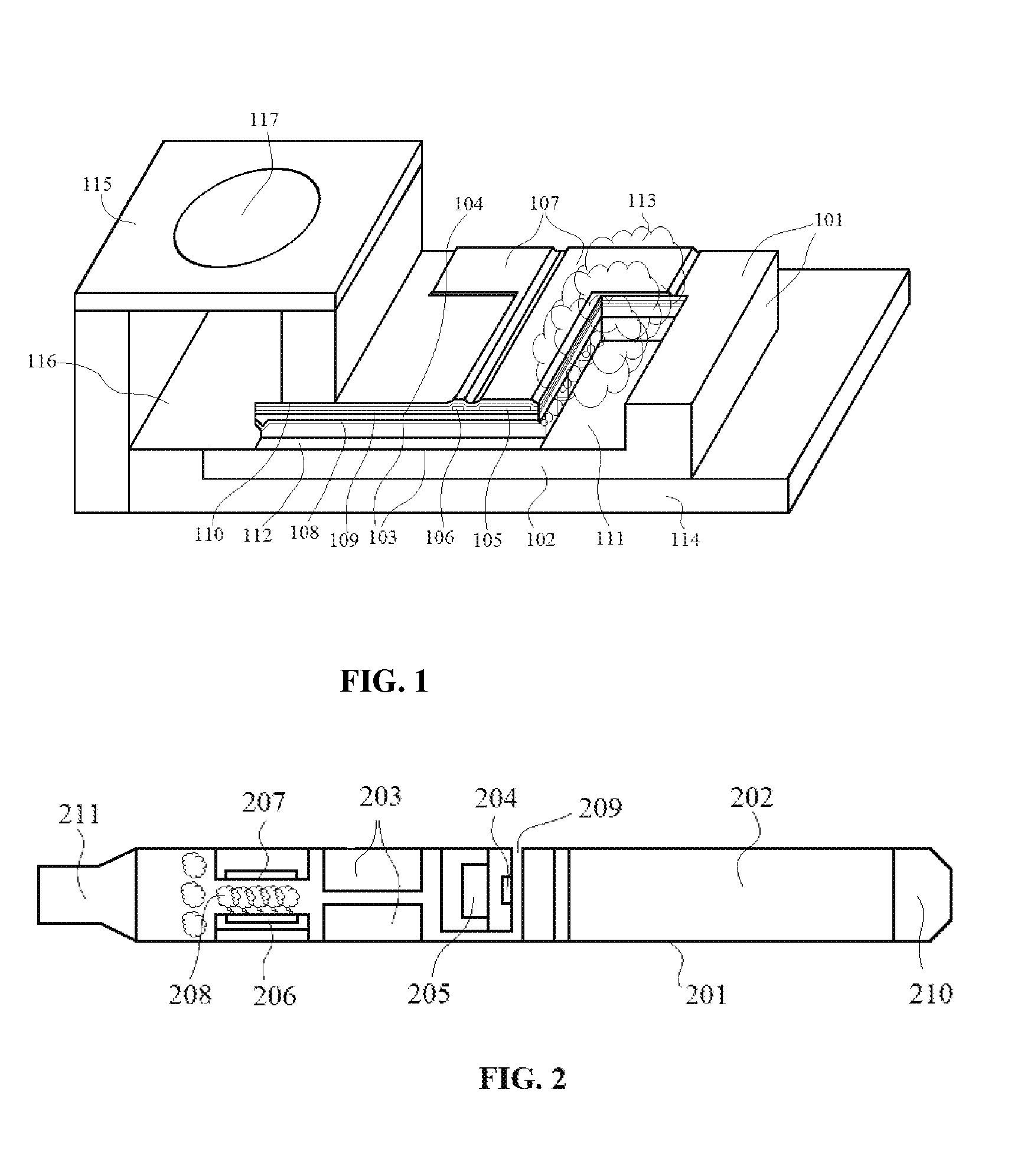

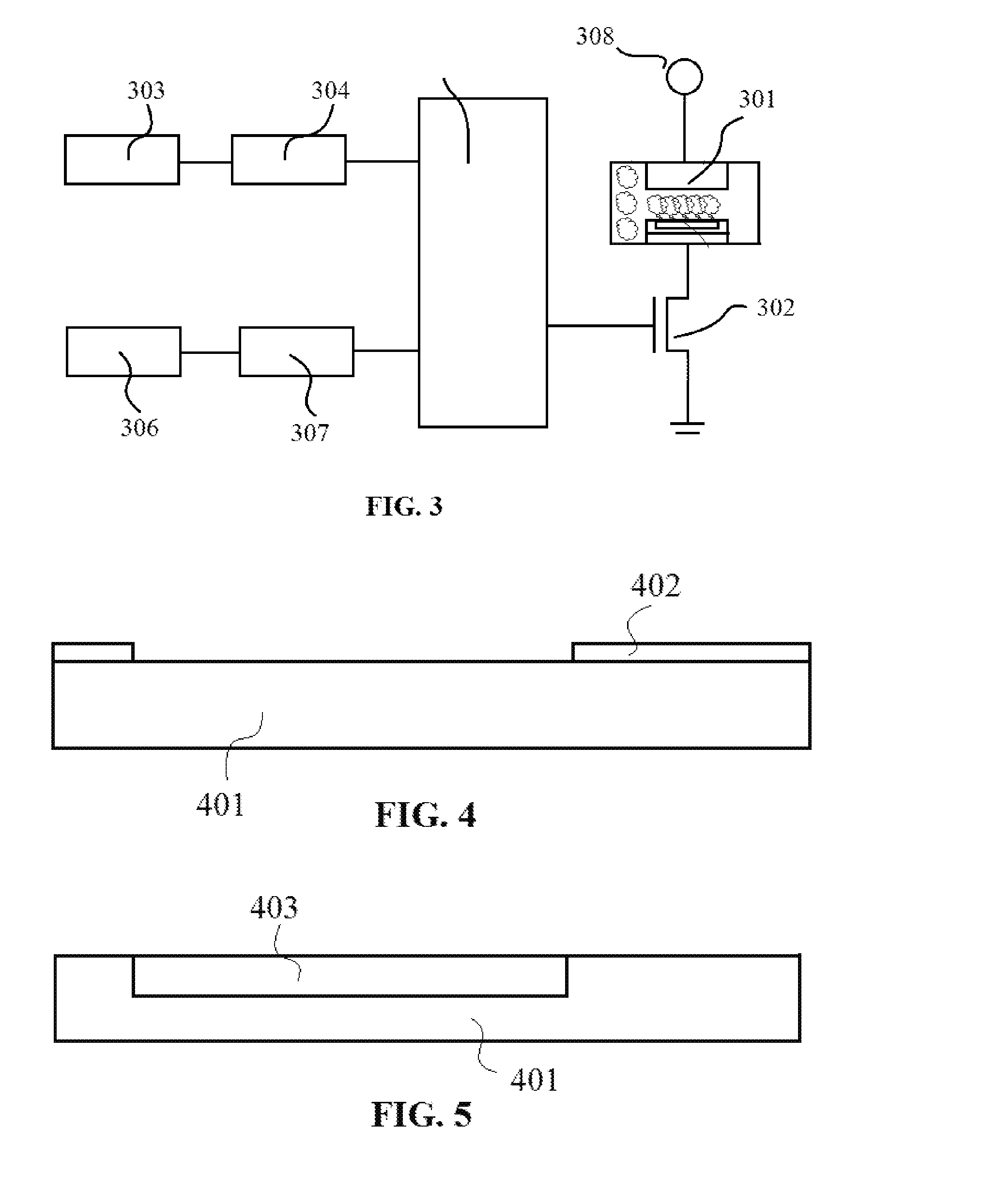

MEMS Vaporizer

ActiveUS20160007653A1Low costImprove reliabilityExhaust apparatusSemiconductor/solid-state device manufacturingEngineeringElectronic cigarette

A MEMS vaporizer is described which can be used for electronic cigarettes. The vaporizer mainly composes: a silicon substrate, a micro-channel array, a membrane suspending over the micro-channel array and supported by the silicon substrate, a resistance heater and a resistance temperature sensor are disposed on the membrane. Since the vaporizer is a silicon-based integrated actuator which provides advantages including small size, compact structure, lower power consumption, lower cost, increased reliability, higher precision, and more environmental friendliness.

Owner:POSIFA TECH LTD

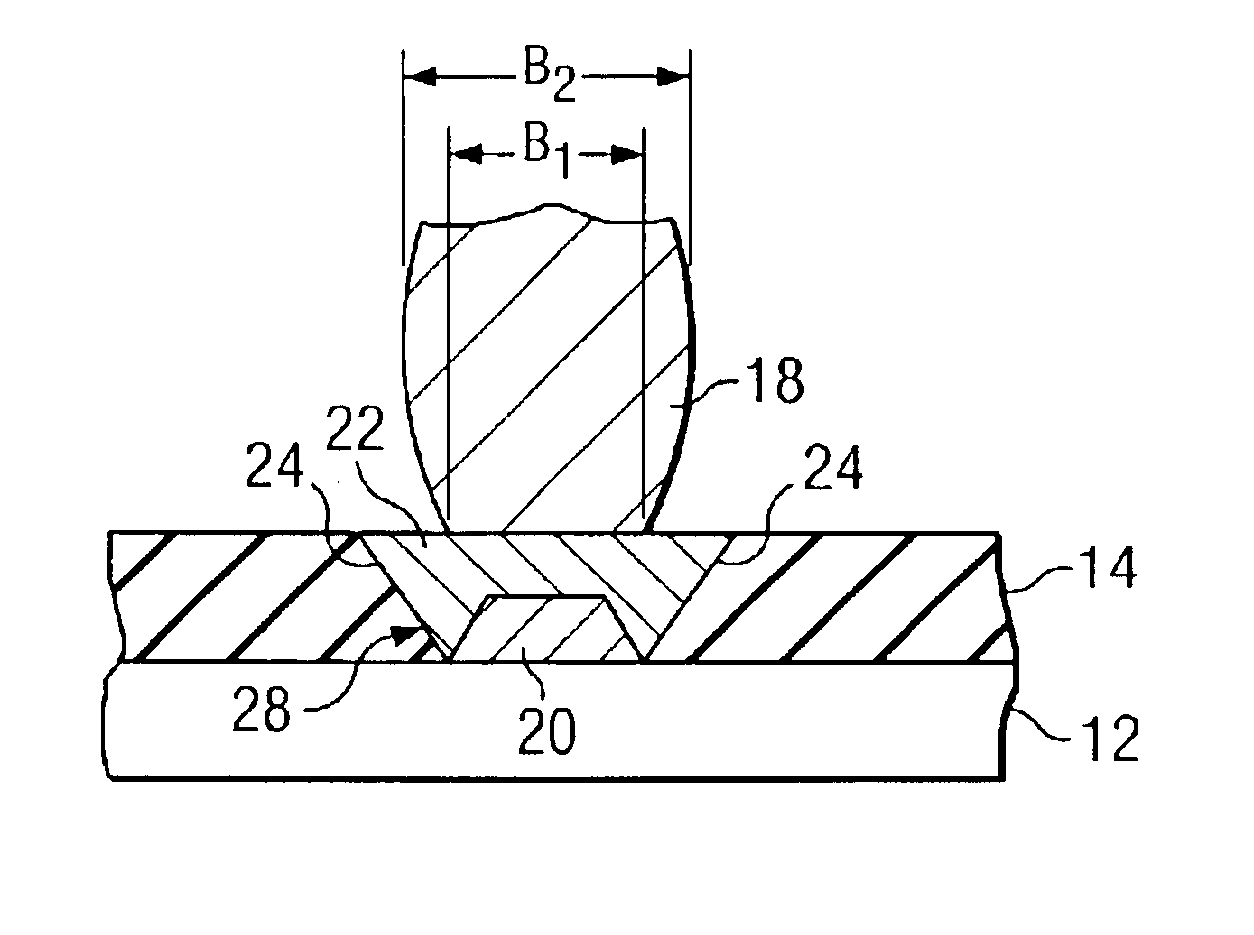

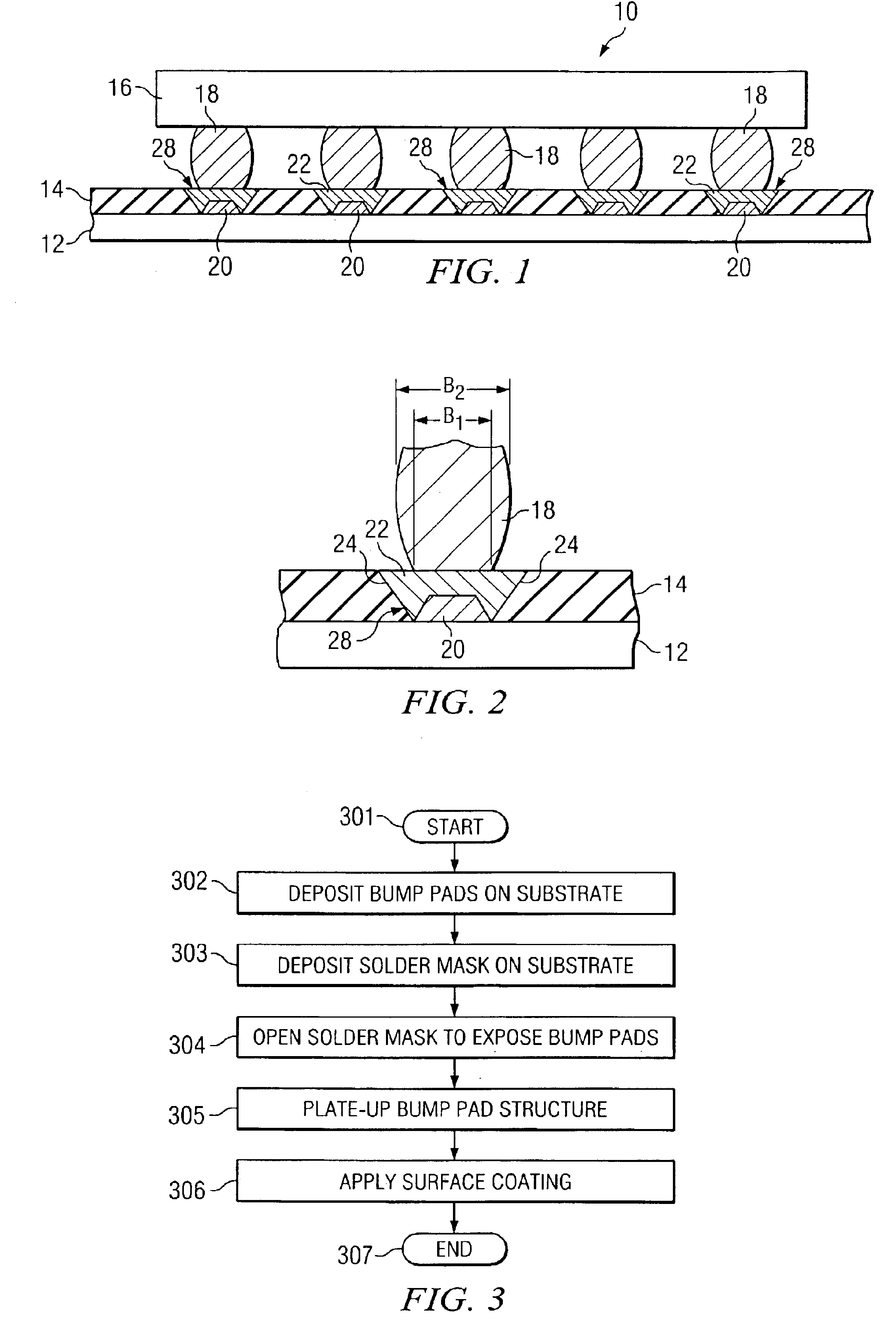

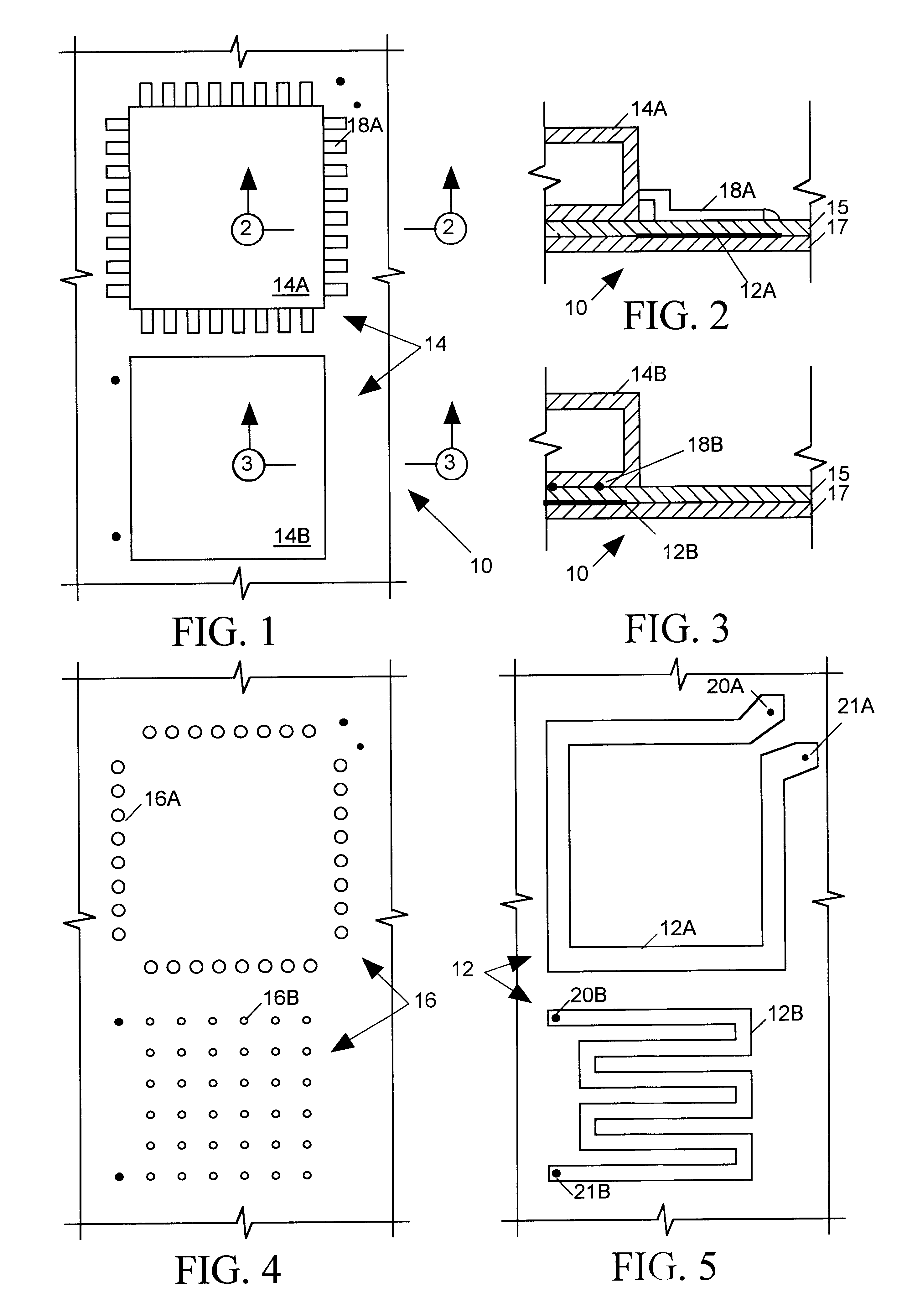

Built-up bump pad structure and method for same

InactiveUS6888255B2Reduce thicknessLess sensitivePrinted circuit assemblingFinal product manufactureSolder maskConductive materials

In accordance with the present invention, a built-up bump pad structure and method for the same are provided. The bump pad structure includes a substrate, a bump pad disposed upon the substrate, a solder mask disposed upon the substrate defining an opening around the bump pad, and a conductive material deposited upon the bump pad such that the conductive material at least partially fills the opening around the bump pad.

Owner:TEXAS INSTR INC

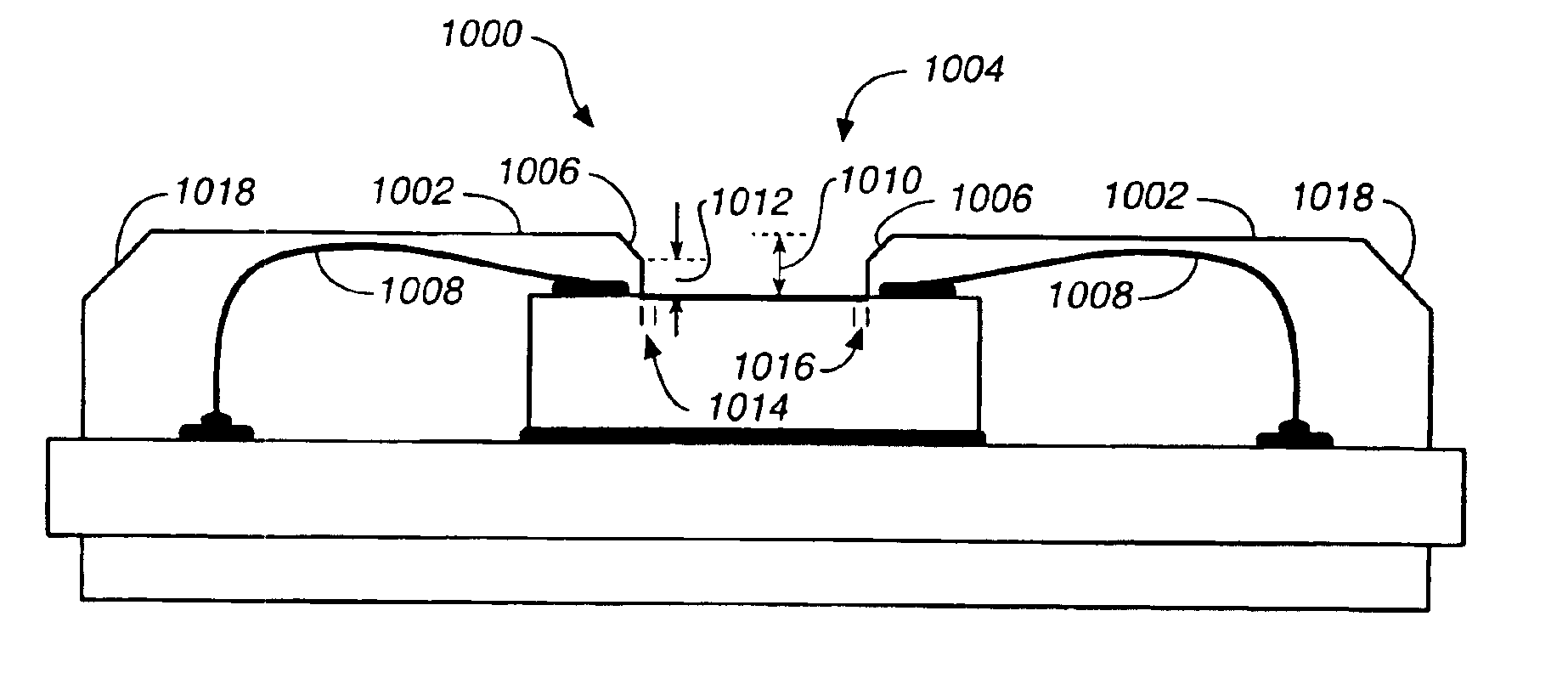

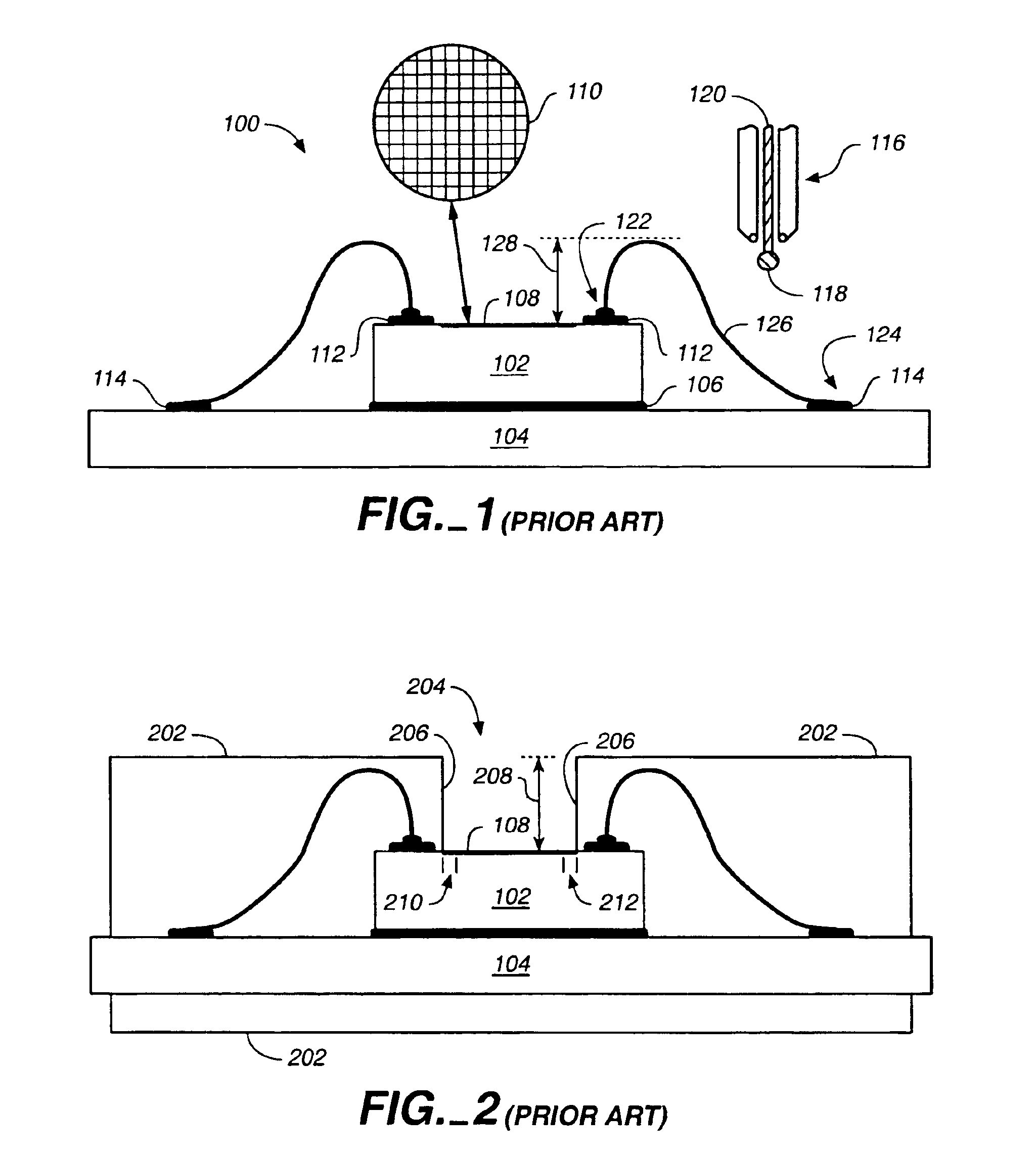

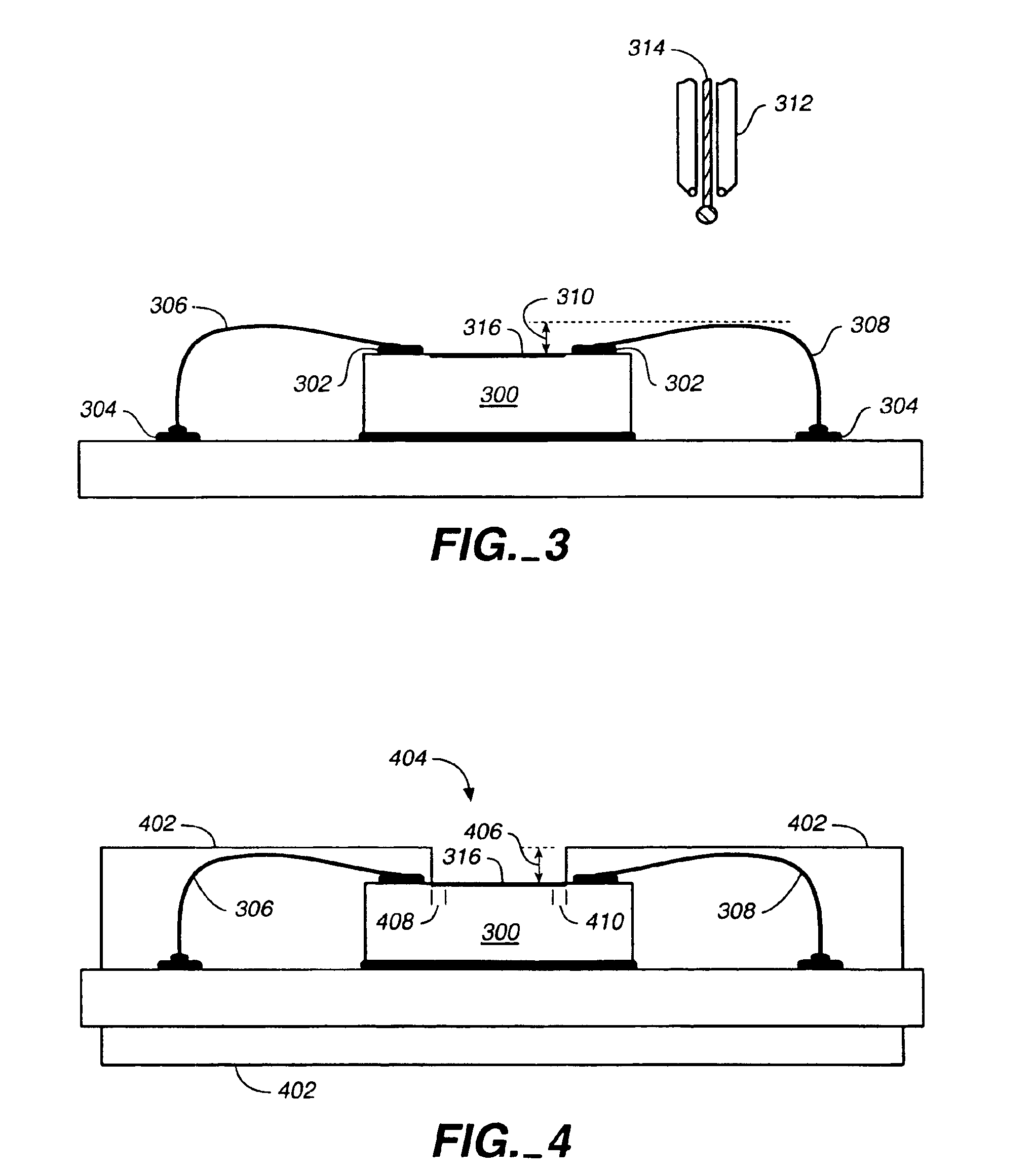

System for providing an open-cavity low profile encapsulated semiconductor package

InactiveUS6962282B2Small possible sizeReduce the overall heightPrinted circuit assemblingLine/current collector detailsSensor arrayLead bonding

System for providing an open-cavity semiconductor package. The system includes a method for wire bonding a finger sensor die to an external circuit. The finger sensor die includes a sensor array having one or more die contacts that are wire bonded to one or more external contacts of the external circuit so that a usable portion of the sensor array is maximized. The method comprises steps of forming a ball at a first end of a bonding wire, forming an electrically conductive connection between the ball and a selected external contact of the external circuit, extending the bonding wire to a selected die contact so as to form a wire loop having a low loop height, and forming an electrically conductive stitch connection between a second end of the bonding wire and the selected die contact.

Owner:SOCIONEXT INC

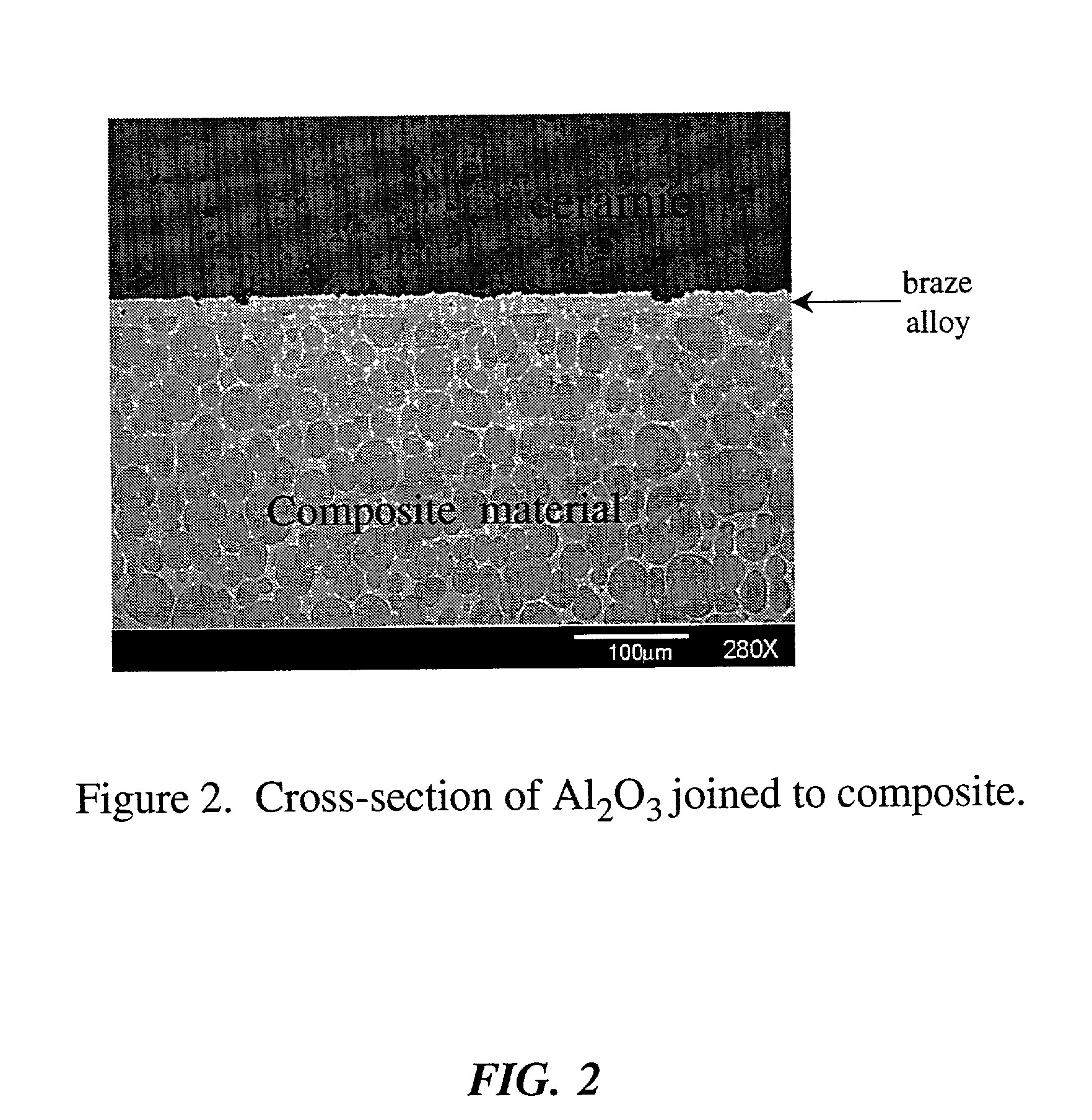

Braze system and method for reducing strain in a braze joint

A system for joining a pair of structural members having widely differing coefficients of thermal expansion is disclosed. A mechanically "thick" foil is made by dispersing a refractory metal powder, such as molybdenum, niobium, tantalum, or tungsten into a quantity of a liquid, high expansion metal such as copper, silver, or gold, casting an ingot of the mixture, and then cutting sections of the ingot about 1 mm thick to provide the foil member. These foil members are shaped, and assembled between surfaces of structural members for joining, together with a layer of a braze alloy on either side of the foil member capable of wetting both the surfaces of the structural members and the foil. The assembled body is then heated to melt the braze alloy and join the assembled structure. The foil member subsequently absorbs the mechanical strain generated by the differential contraction of the cooling members that results from the difference in the coefficients of thermal expansion of the members.

Owner:SANDIA NAT LAB

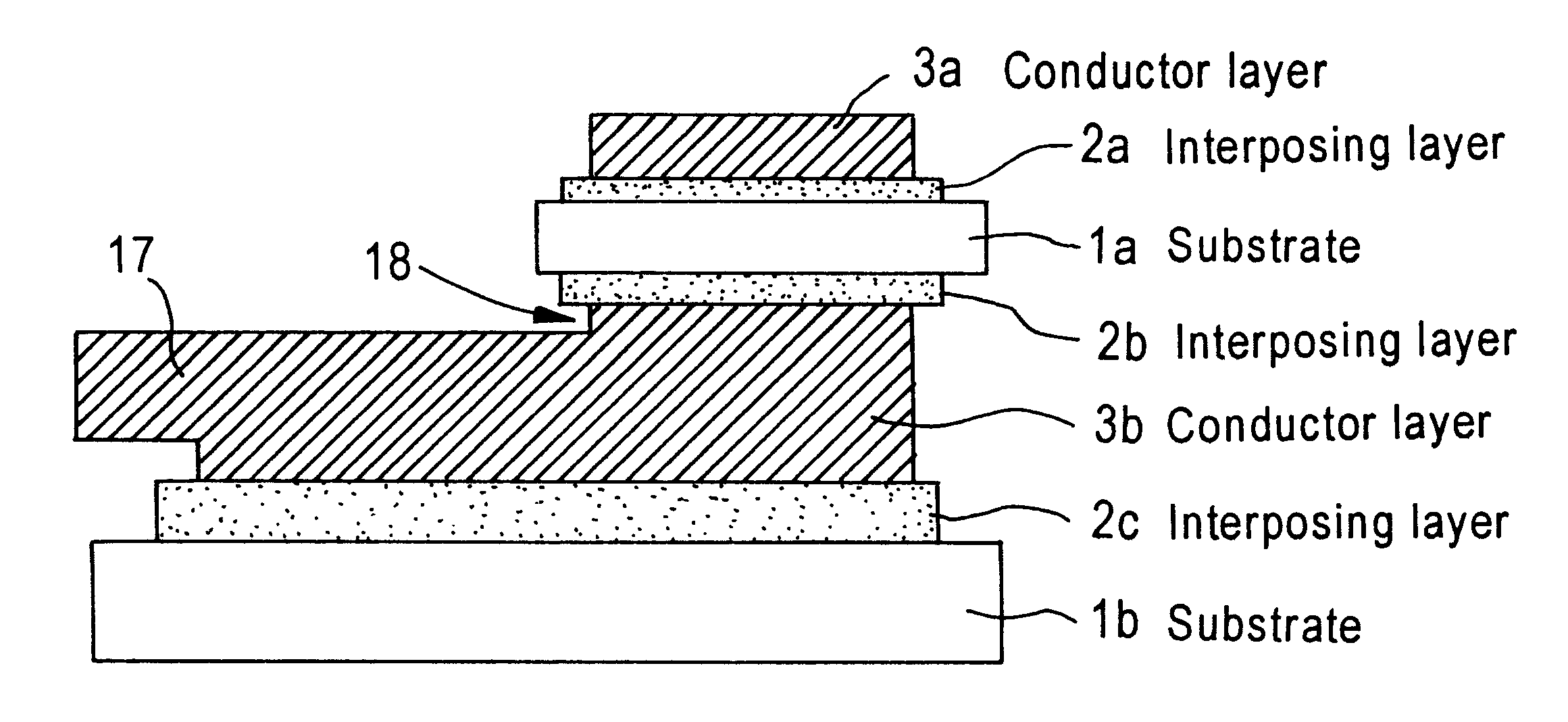

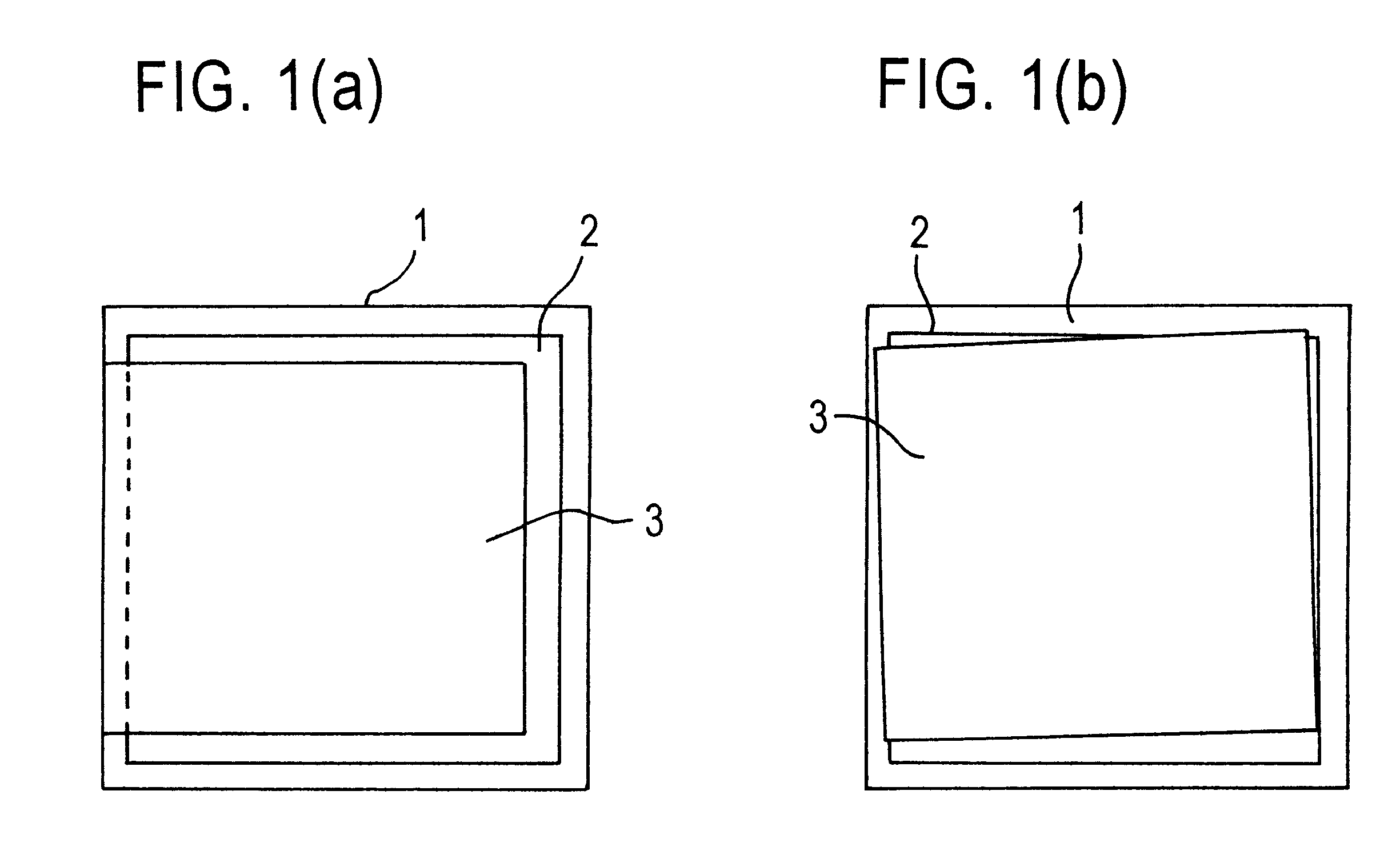

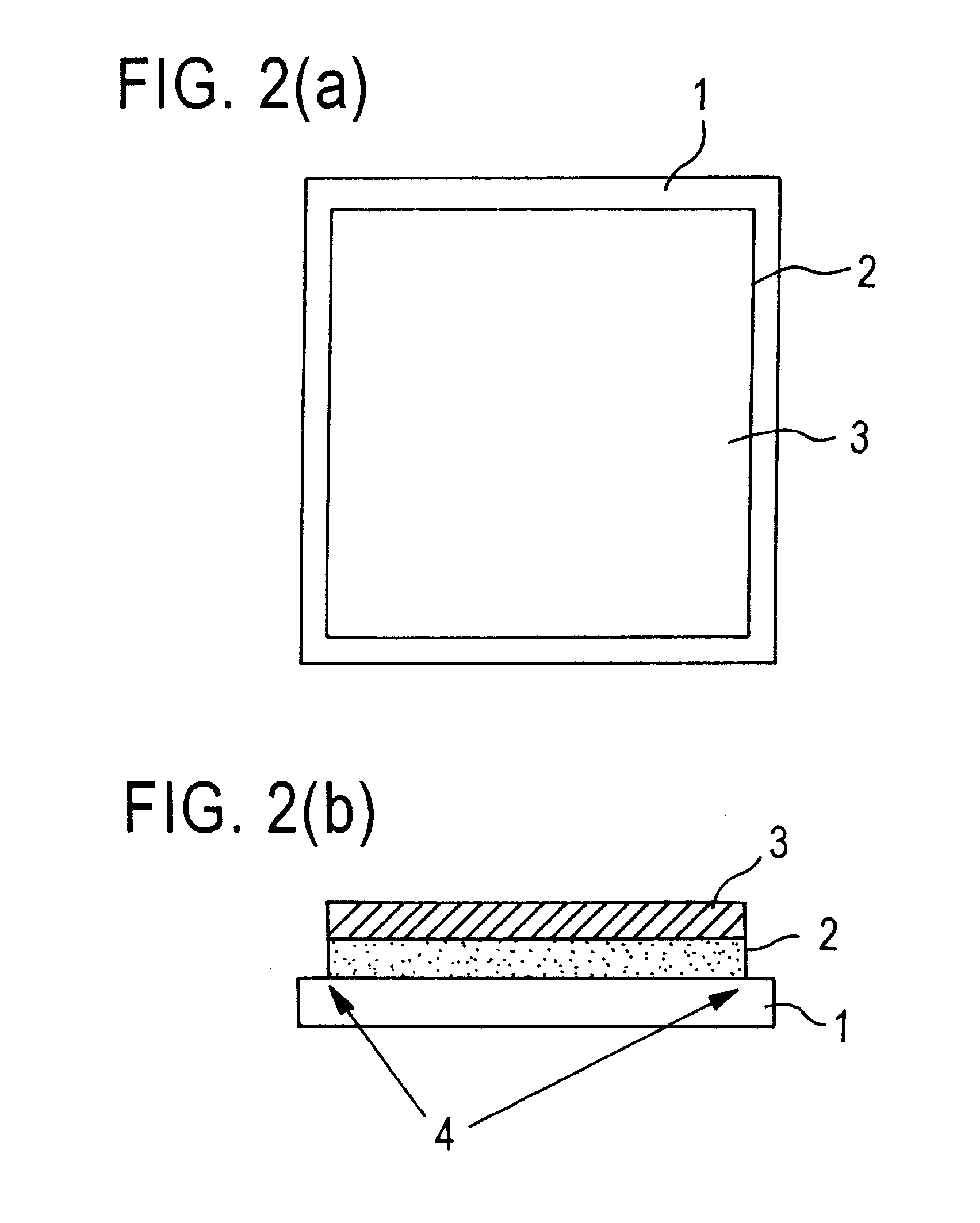

Copper circuit junction substrate and method of producing the same

InactiveUS6261703B1Avoid discharge phenomenonHigh concentration of thermal stressInsulating substrate metal adhesion improvementSemiconductor/solid-state device detailsElectrical conductorCopper oxide

A highly reliable copper circuit-joined board that, in mounting a semiconductor element, a lead frame or the like on a ceramic substrate, enables the semiconductor element, the lead frame or the like to be strongly joined to the substrate without breaking or deformation of the substrate found in conventional joining methods, such as brazing and joining using a copper / copper oxide eutectic crystal. Any one of an interposing layer comprising a brazing material layer comprising silver and / or copper as a main component and an active metal or an interposing layer having a two-layer structure comprising a first interposing layer comprising the brazing material layer or a high-melting metallizing layer and a second interposing layer, having a melting point of 1000.degree. C. or below, comprising Ni, Fe, Cu as a main component in that order from the substrate side, is formed on a ceramic substrate, and a conductor layer, comprising copper as a main component, which, in both the lengthwise and widthwise directions, is at least 0.05 mm shorter than the interposing layer, is formed on the interposing layer to prepare a copper circuit-joined board. The copper circuit-joined board may comprise the base board having thereon an outer layer comprising Ni as a main component. A semiconductor element is mounted on the copper circuit-joined board to prepare a semiconductor device.

Owner:SUMITOMO ELECTRIC IND LTD

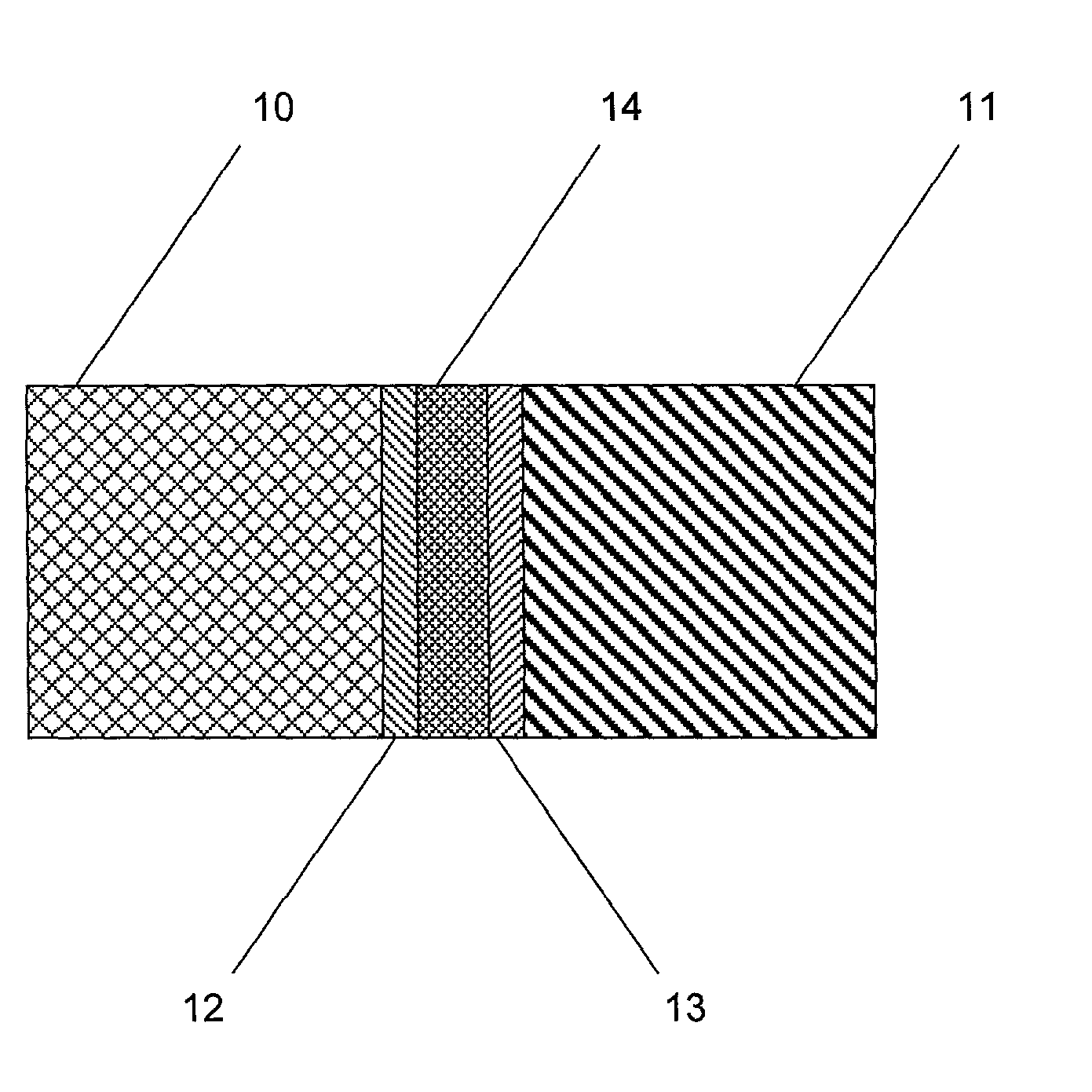

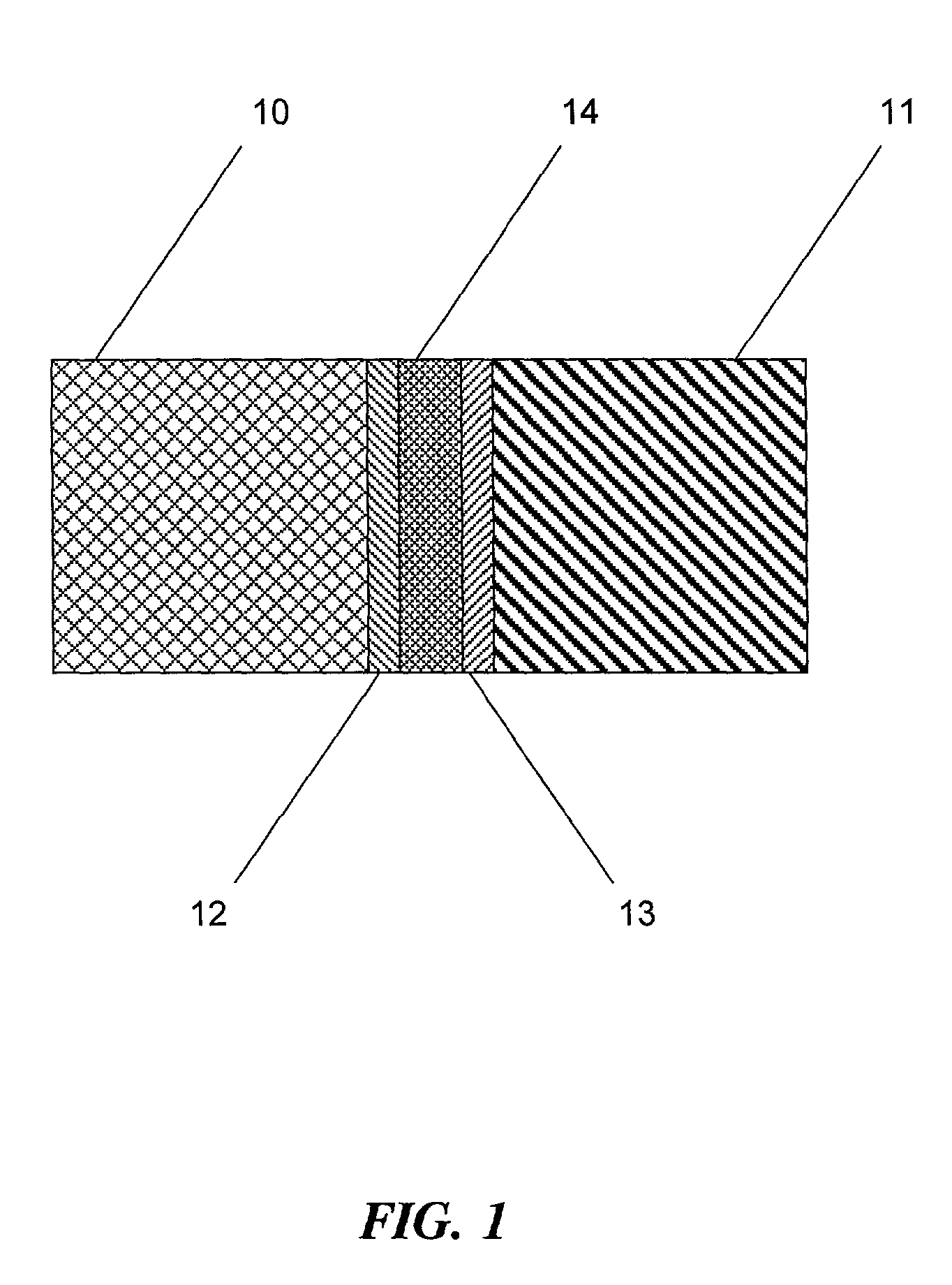

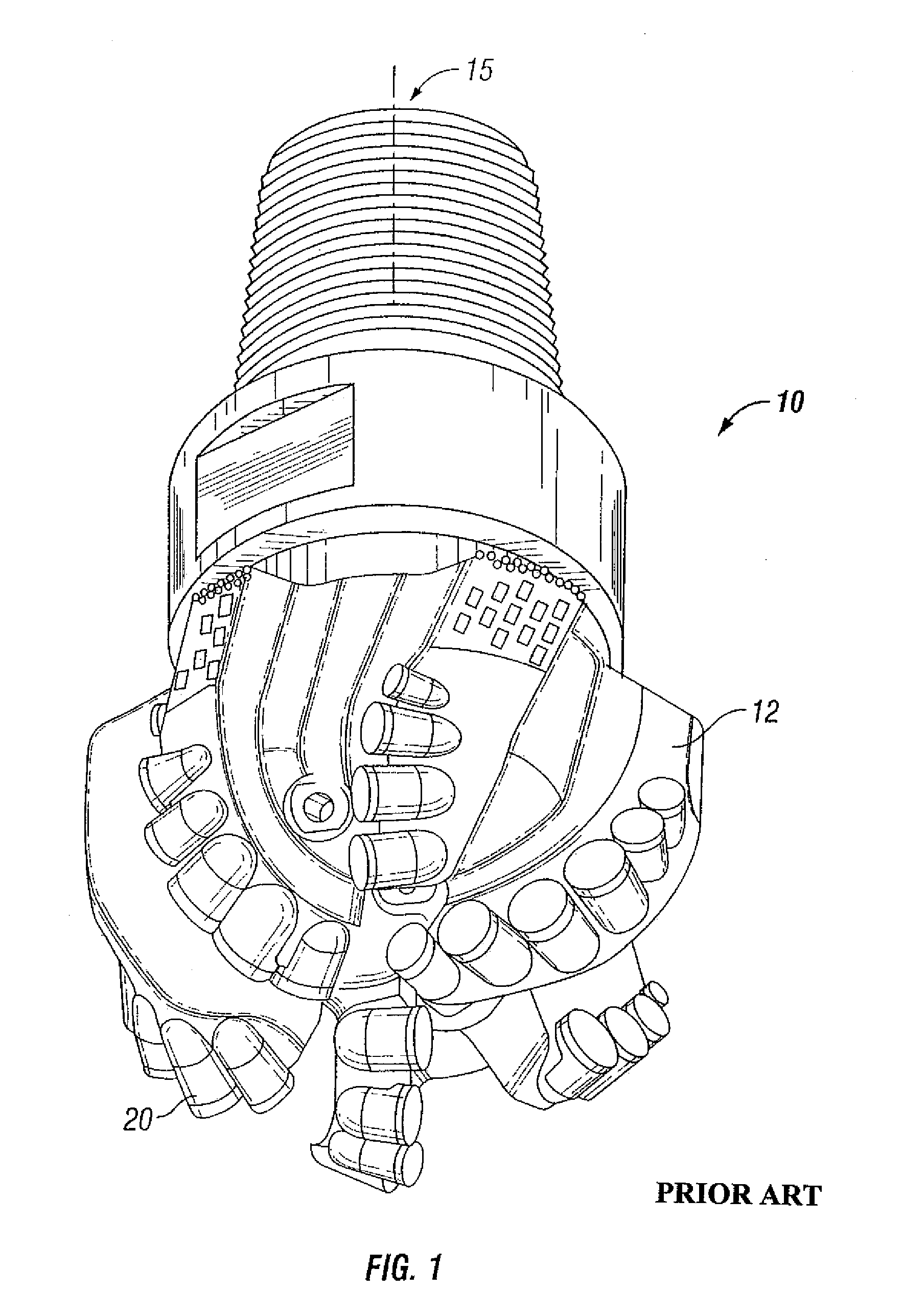

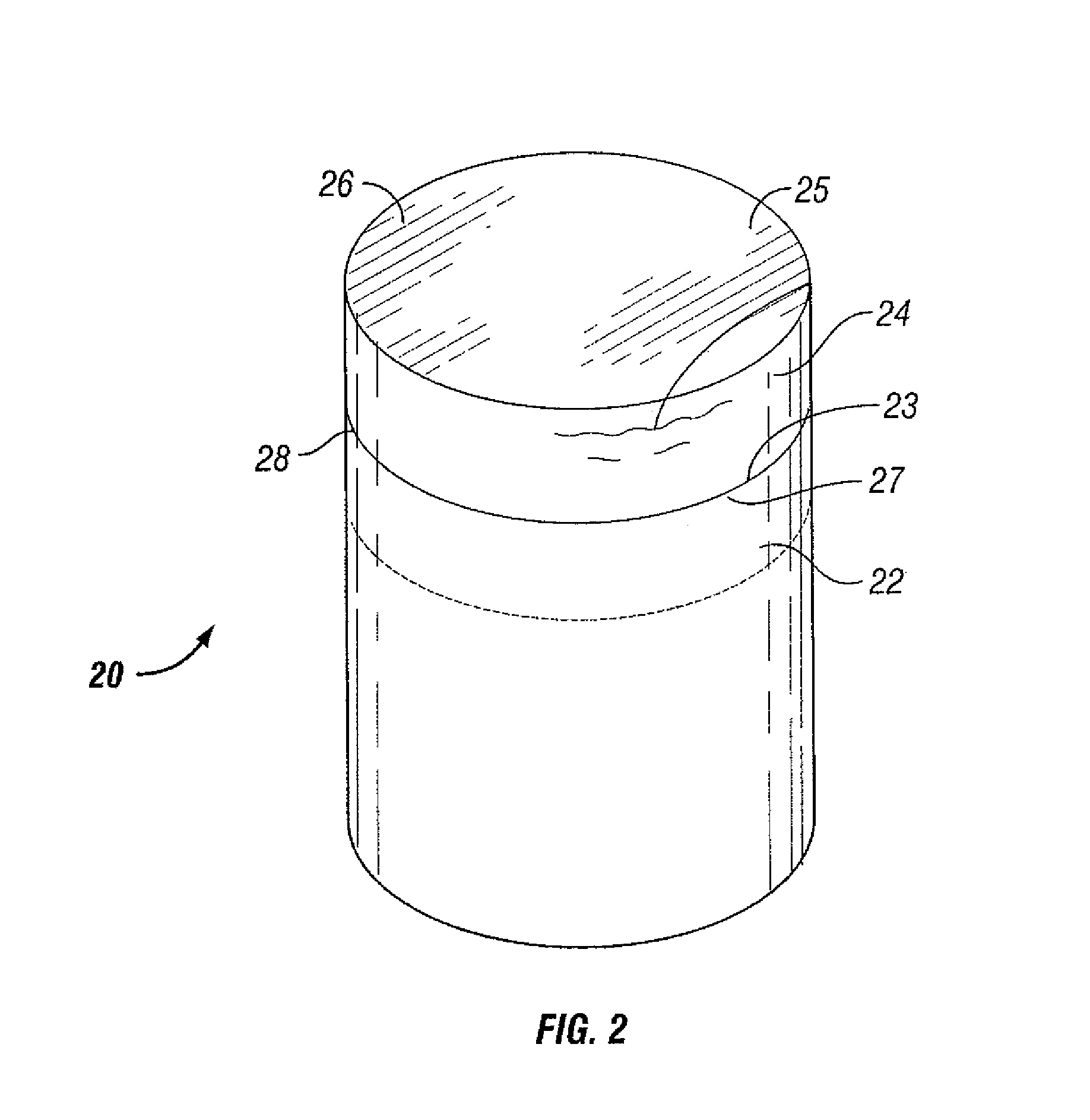

Thermally stable diamond brazing

A cutting element and a method for forming a cutting element is described and shown. The cutting element includes a substrate, a TSP diamond layer, a metal interlayer between the substrate and the diamond layer, and a braze joint securing the diamond layer to the substrate. The thickness of the metal interlayer is determined according to a formula. The formula takes into account the thickness and modulus of elasticity of the metal interlayer and the thickness of the TSP diamond. This prevents the use of a too thin or too thick metal interlayer. A metal interlayer that is too thin is not capable of absorbing enough energy to prevent the TSP diamond from fracturing. A metal interlayer that is too thick may allow the TSP diamond to fracture by reason of bending stress. A coating may be provided between the TSP diamond layer and the metal interlayer. This coating serves as a thermal barrier and to control residual thermal stress.

Owner:RADTKE ROBERT P

Dual metal stud bumping for flip chip applications

InactiveUS7271497B2ElectrotherapySemiconductor/solid-state device detailsOxidation resistantEngineering

A method for forming a stud bumped semiconductor die is disclosed. The method includes forming a ball at the tip of a coated wire passing through a hole in a capillary, where the coated wire has a core and an oxidation-resistant coating. The formed ball is pressed to the conductive region on the semiconductor die. The coated wire is cut, thereby leaving a conductive stud bump on the conductive region, where the conductive stud bump includes an inner conductive portion and an outer oxidation-resistant layer.

Owner:SEMICON COMPONENTS IND LLC

Substrate for producing a soldering connection

InactiveUS7271484B2Improve reliabilityReducing in fashionPrinted circuit assemblingSemiconductor/solid-state device detailsSolder maskEngineering

A solderable device includes a substrate and a soldering pad overlying the substrate. A solder mask overlies the substrate and portions of the soldering pad. The solder mask has an opening that exposes a portion of the soldering pad. The opening has at least two edges that symmetrically overlie portions of the soldering pad.

Owner:POLARIS INNOVATIONS LTD

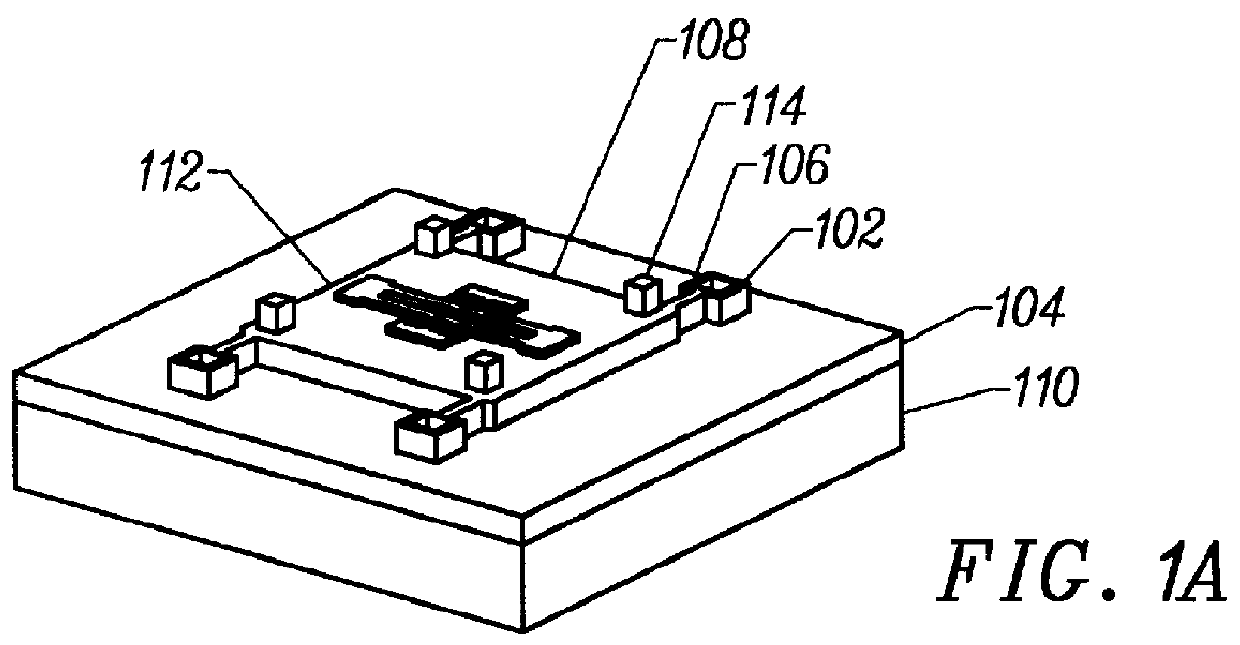

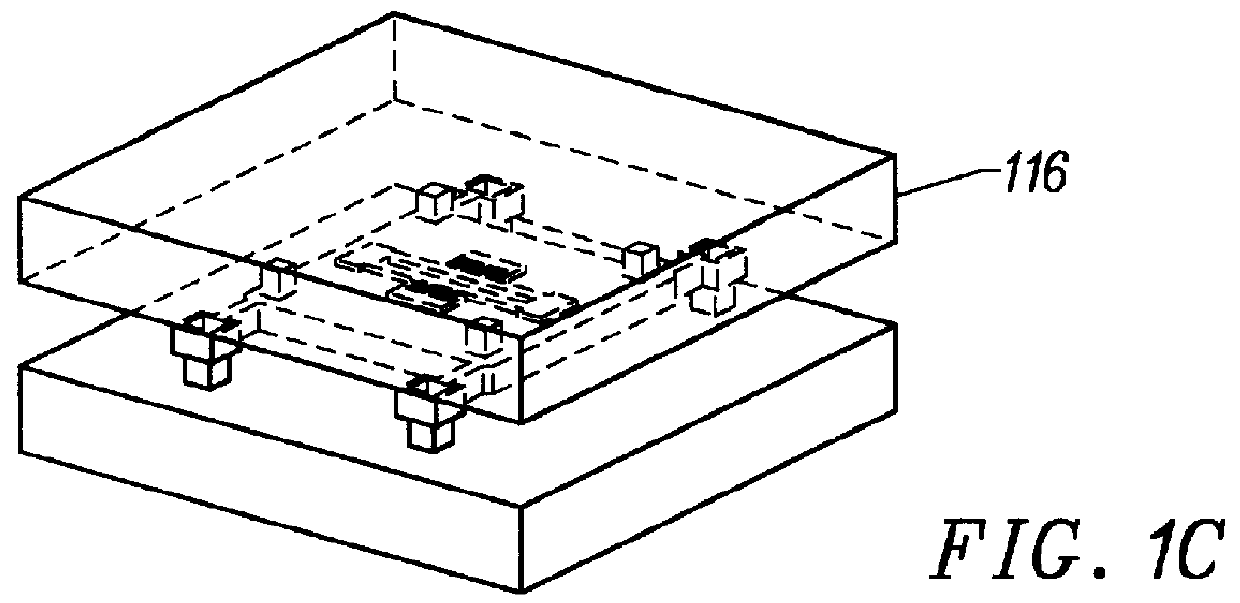

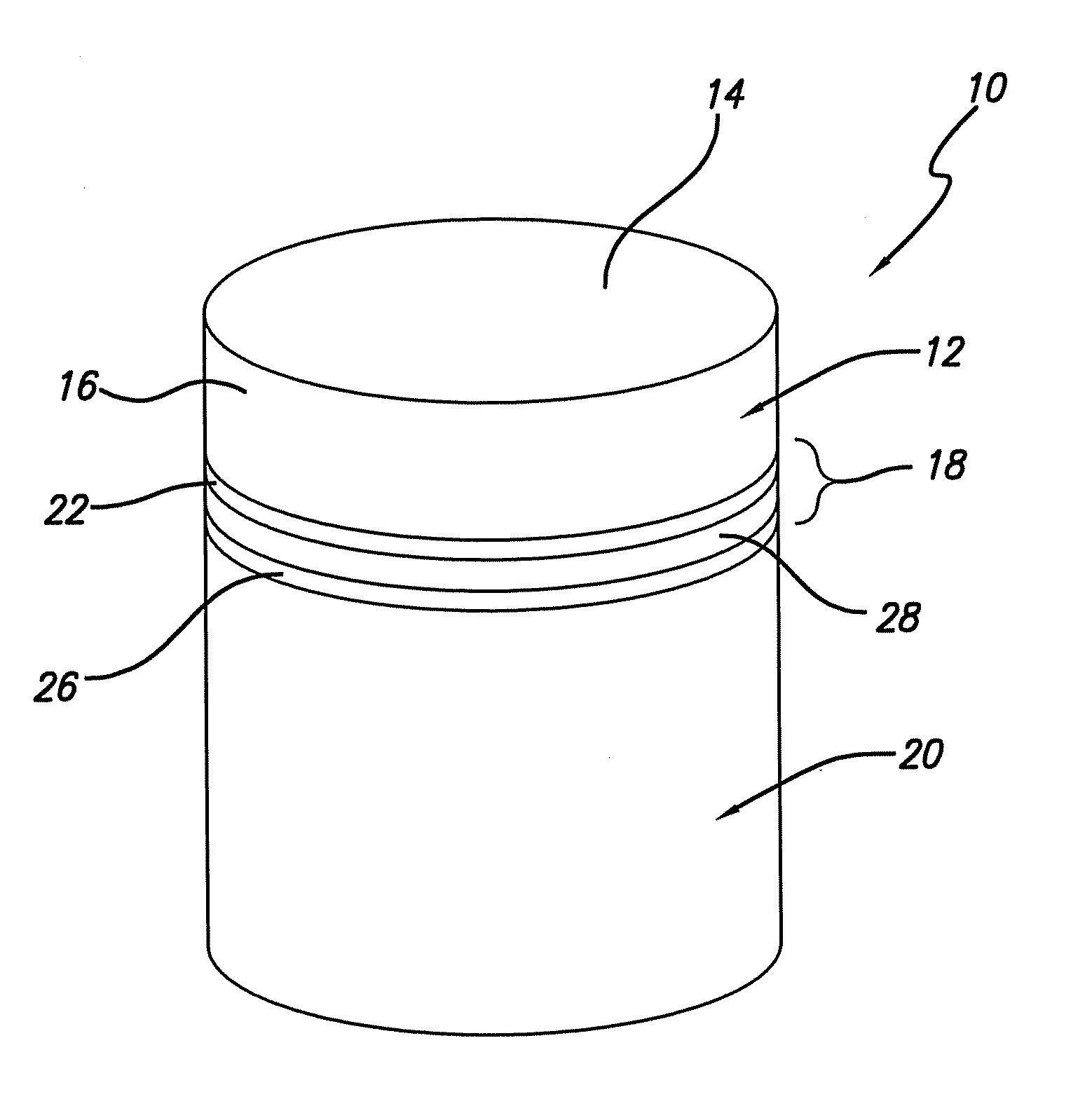

Stackable semiconductor device and method for manufacturing the same

InactiveUS6504241B1Semiconductor/solid-state device detailsSolid-state devicesMiniaturizationSemiconductor chip

There is provided a semiconductor device having a semiconductor chip in which a first protrusion electrode is formed on the semiconductor substrate; and an intermediate substrate which comprises a base substrate, a first external terminal provided in said base substrate, which is joined to said first protrusion electrode, a second external terminal provided in said base substrate, an electrode section being exposed on both surfaces of said base substrate, and a second protrusion electrode formed at one end face of said second external terminal, a plurality of said intermediate substrates being stacked in layers by joining said second protrusion electrode to the other end face of said second external terminal, thus enabling miniaturizing and lightening electronic equipment and realizing high reliability and high performance.

Owner:SONY CORP

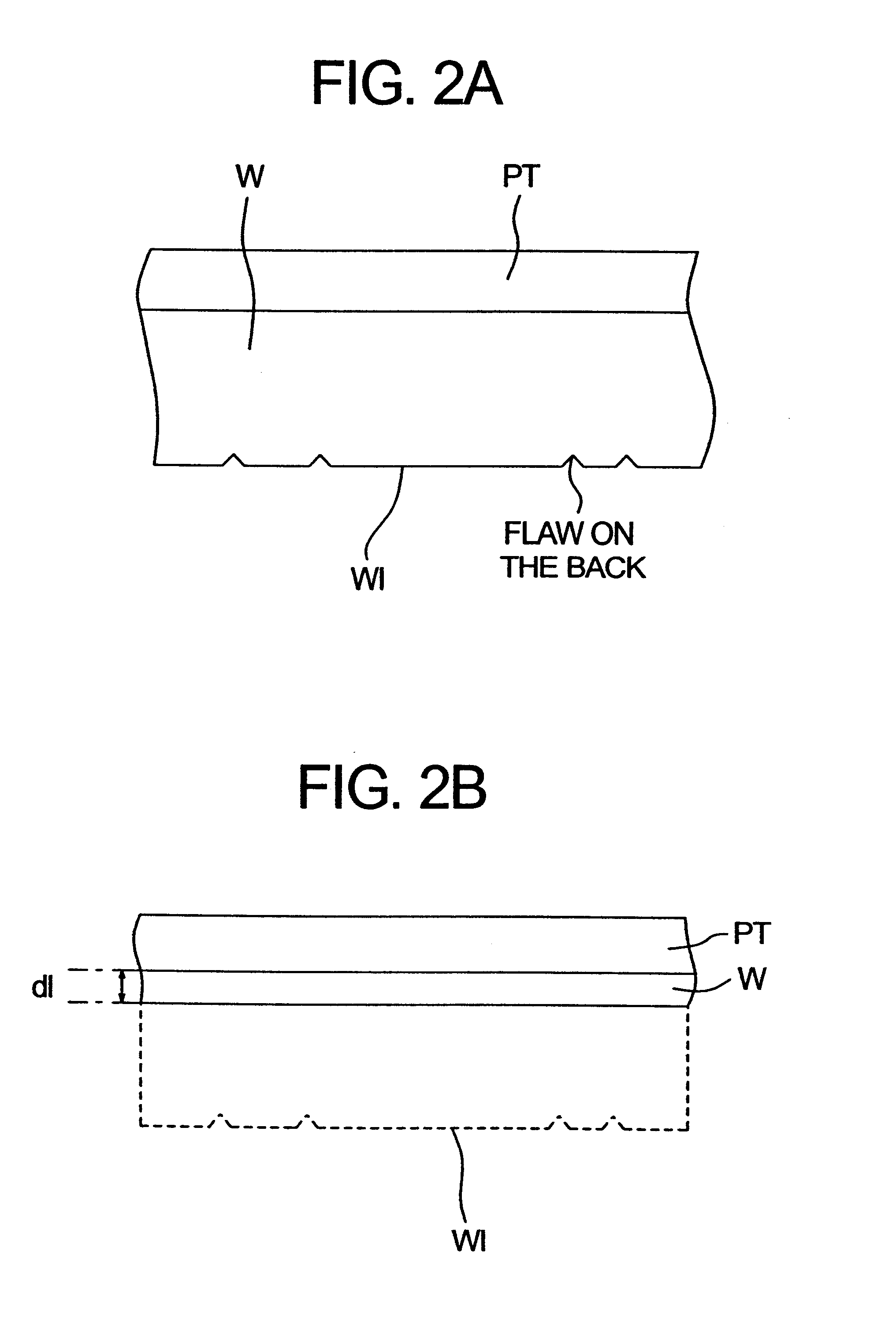

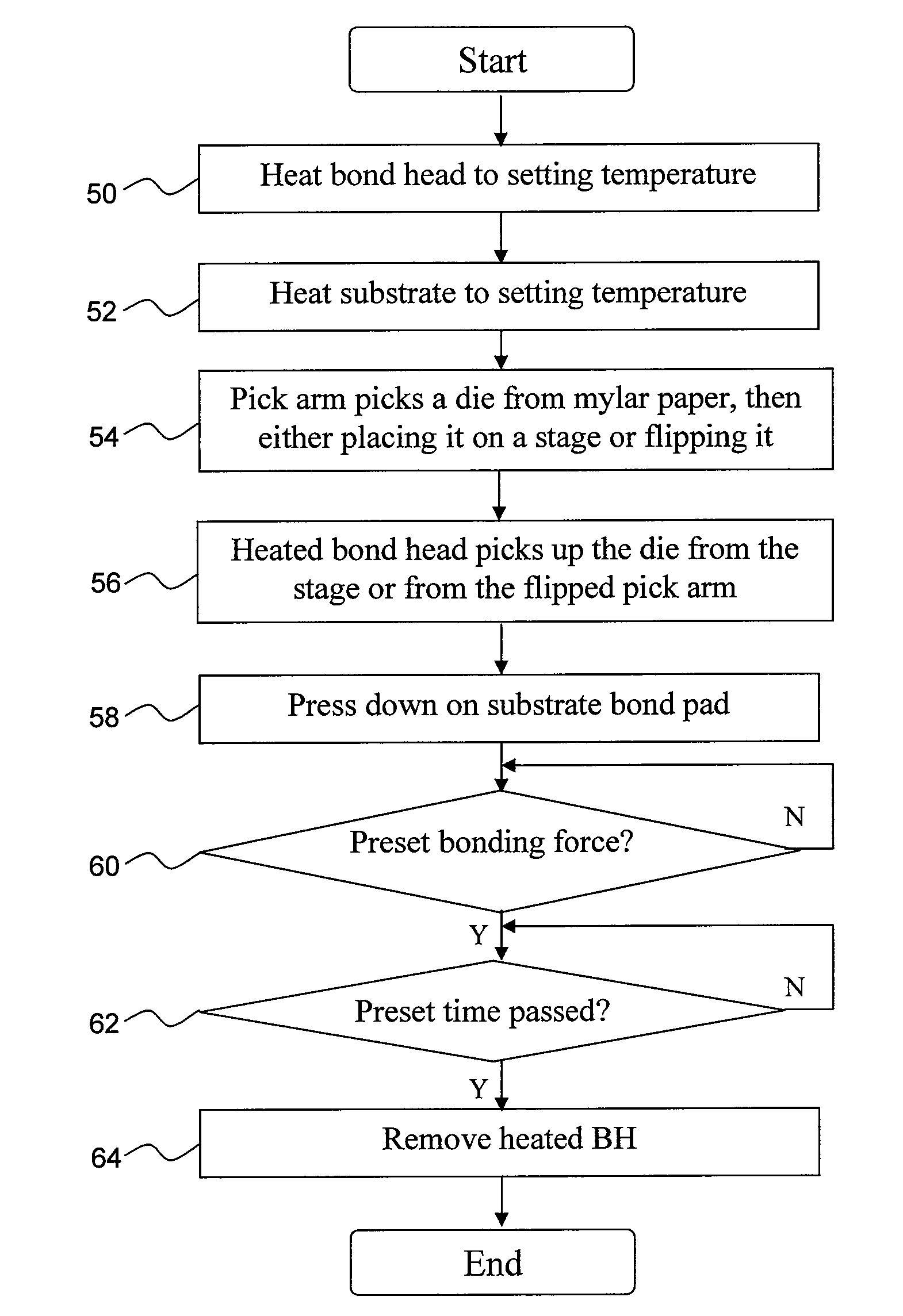

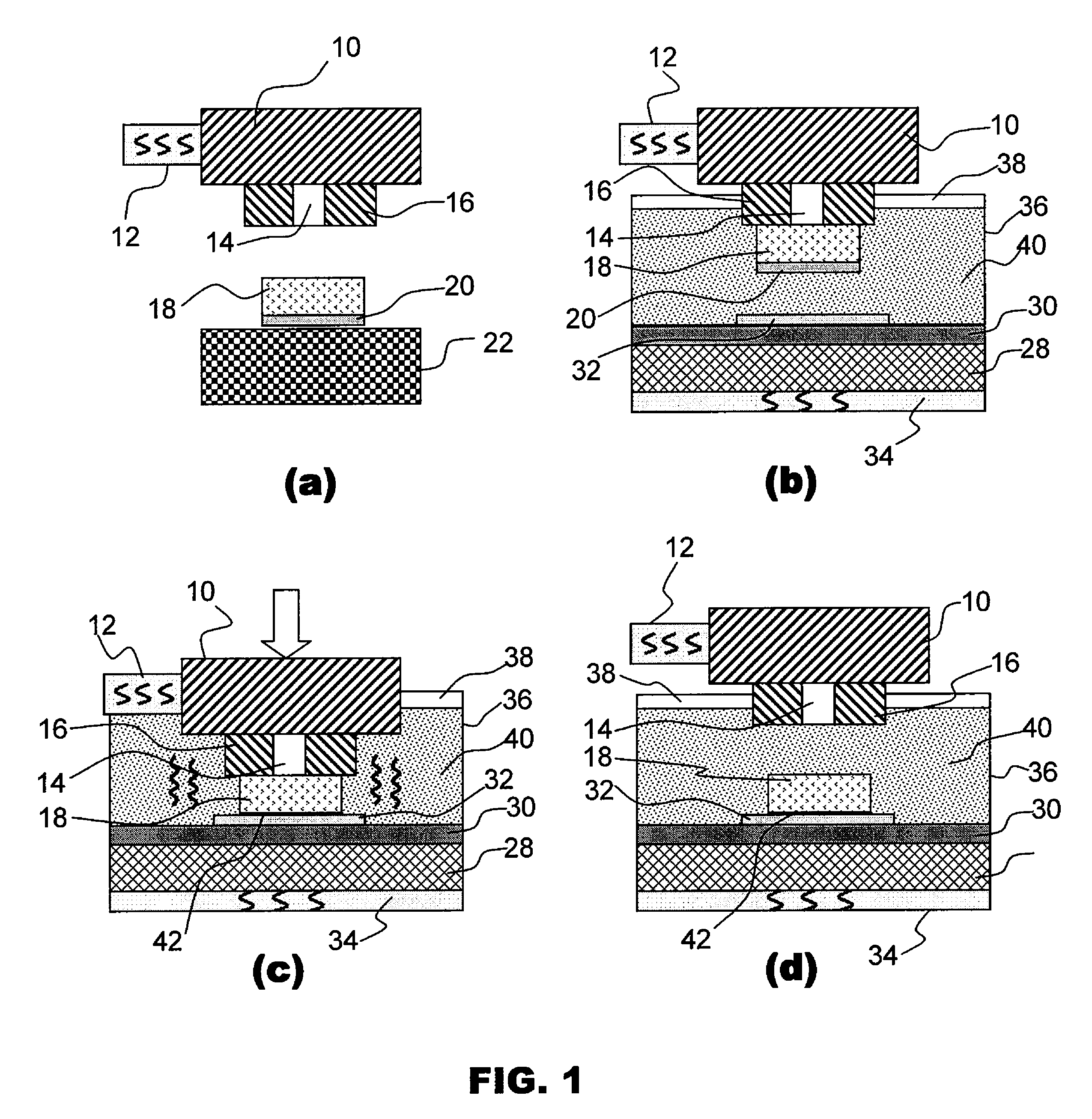

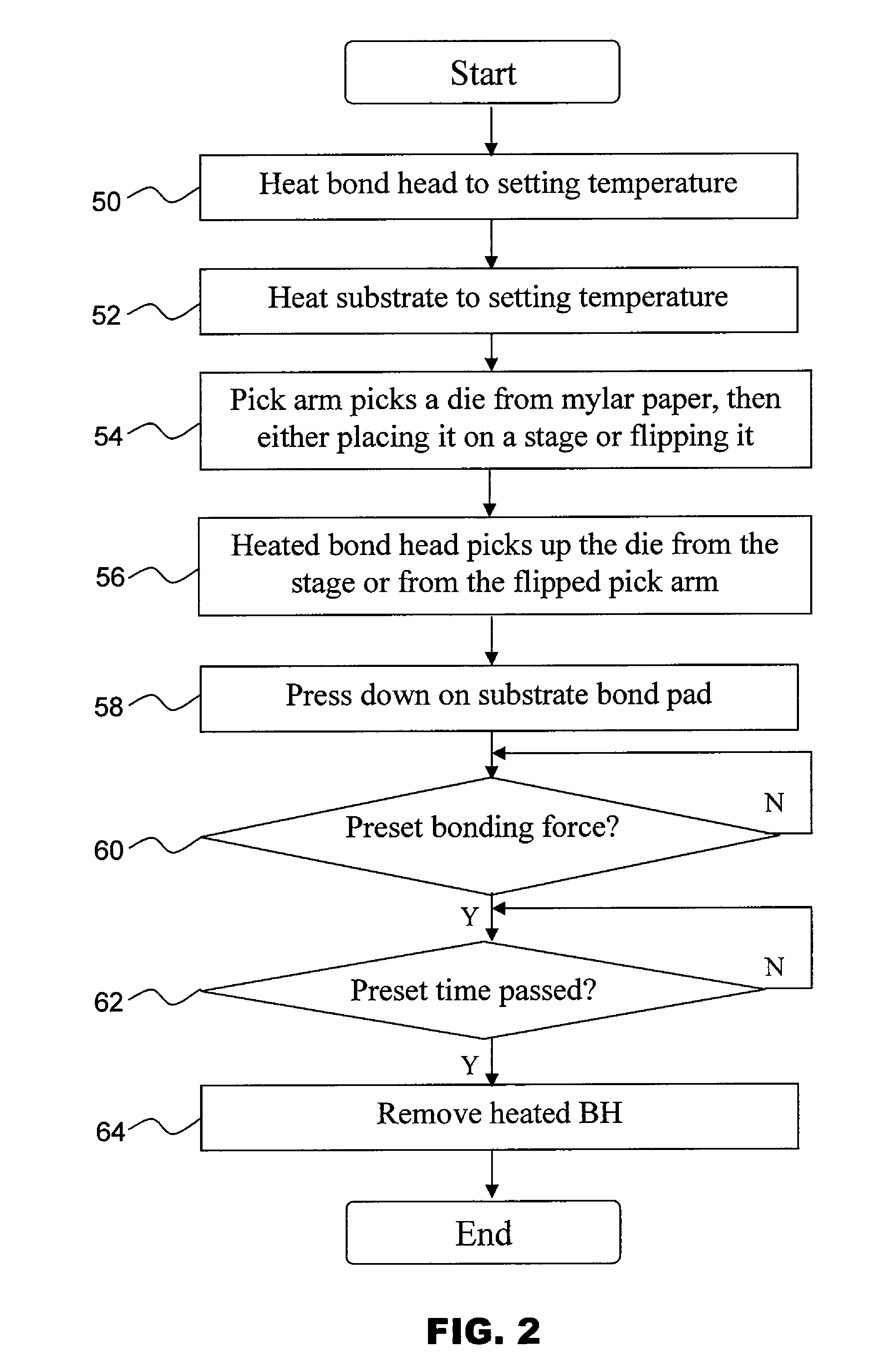

Direct die attach utilizing heated bond head

A method is provided for bonding a die comprising a solder layer which has a melting point Tm. A bond head is heated to a bond head setting temperature T1, which is higher than Tm, and a substrate is heated to a substrate setting temperature T2, which is lower than Tm. The bond head then picks up the die and heats the die towards temperature T1 so as to melt the solder layer. The solder layer of the die is pressed onto the substrate so as to bond the die to the substrate, and thereafter the bond head is separated from the die so that the solder layer is cooled towards T2 and solidifies.

Owner:ASMPT SINGAPORE PTE LTD

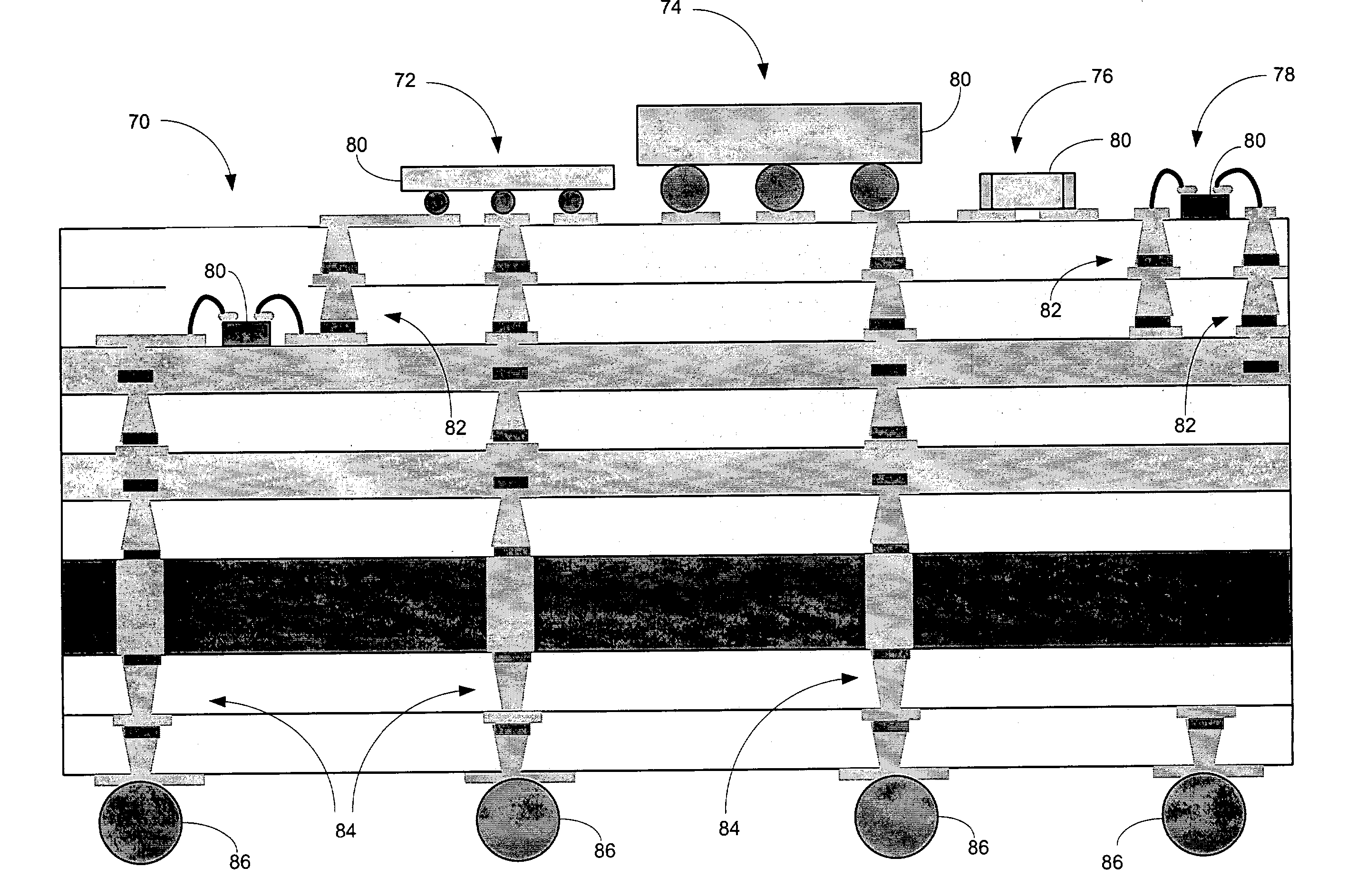

Methods and devices for large-scale solar installations

InactiveUS20080041434A1Reduce manufacturing costReduce redundant partsPV power plantsSoldering apparatusJunction boxSolar energy

Methods and devices are provided for improved large-scale solar installations. In one embodiment, a junction-box free photovoltaic module is used comprising of a plurality of photovoltaic cells and a module support layer providing a mounting surface for the cells. The module has a first electrical lead extending outward from one of the photovoltaic cells, the lead coupled to an adjacent module without passing the lead through a junction box. The module may have a second electrical lead extending outward from one of the photovoltaic cells, the lead coupled to another adjacent module without passing the lead through a junction box. Without junction boxes, the module may use connectors along the edges of the modules which can substantially reduce the amount of wire or connector ribbon used for such connections.

Owner:NANOSOLAR

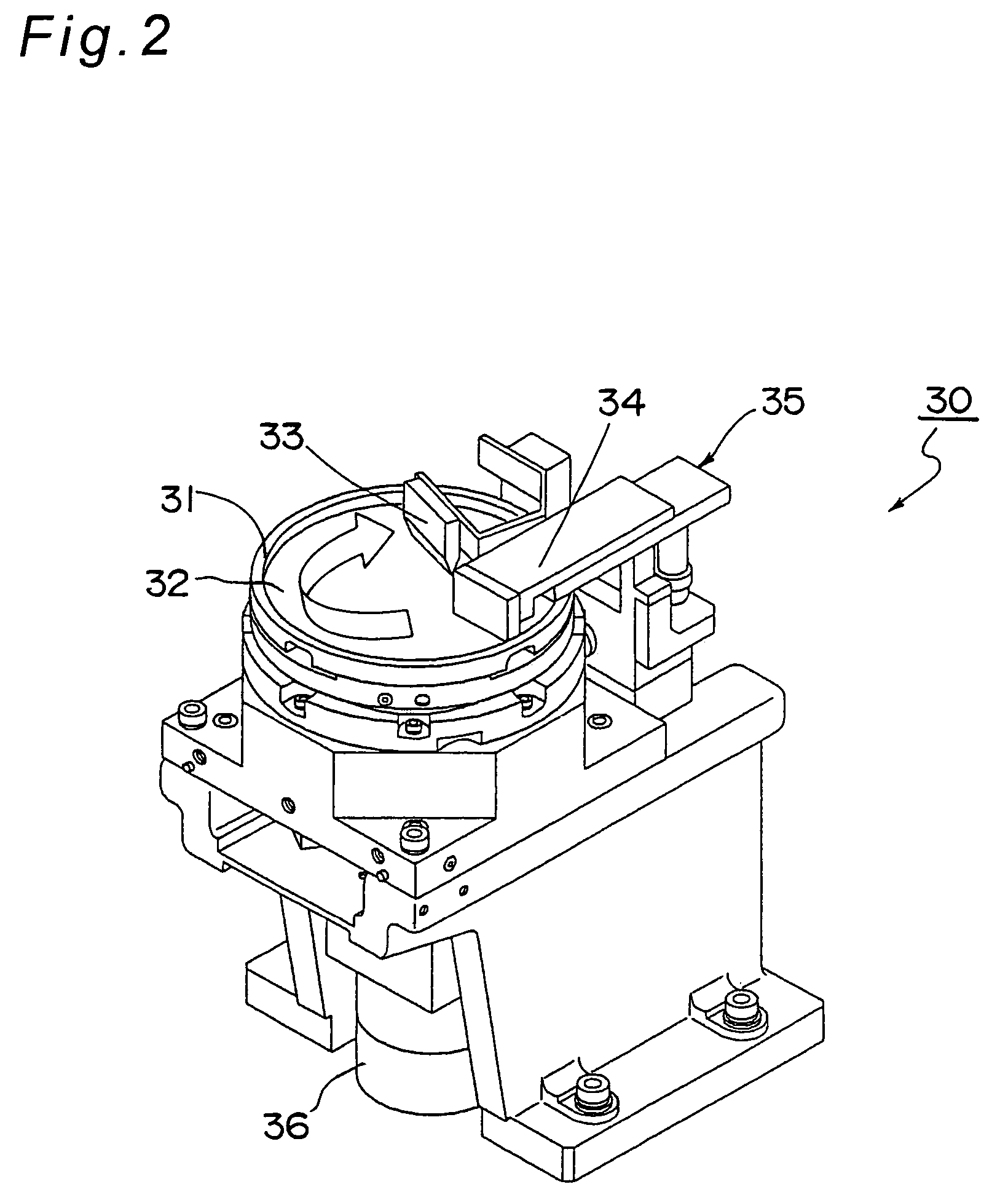

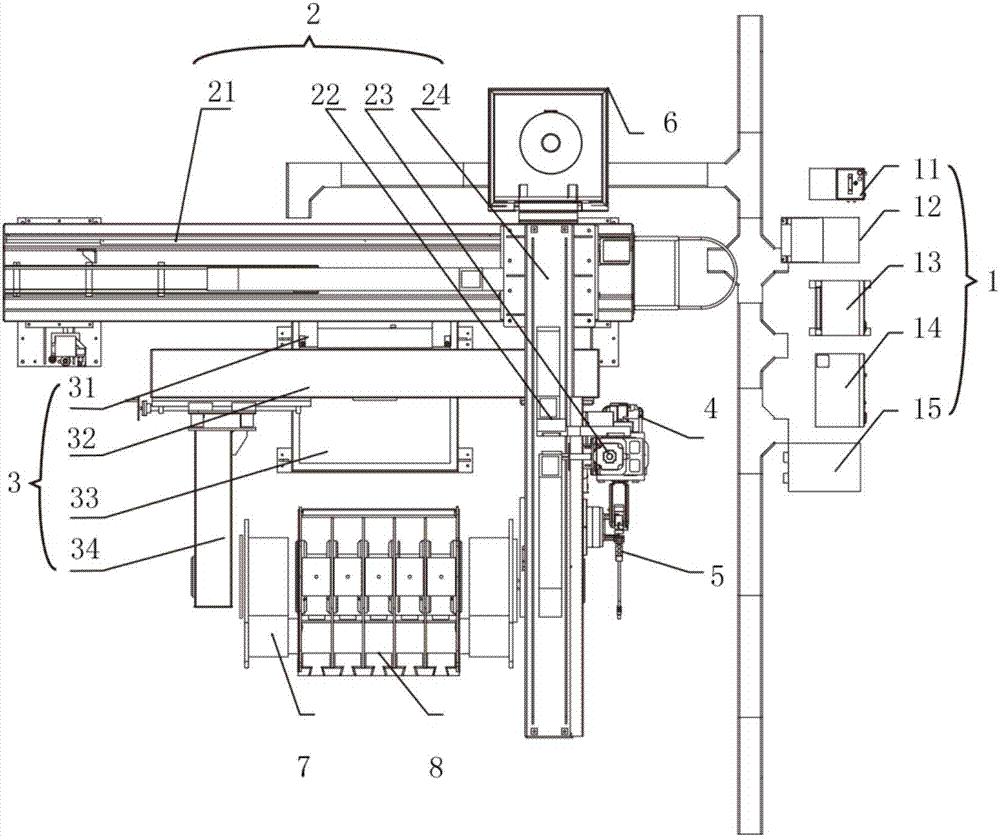

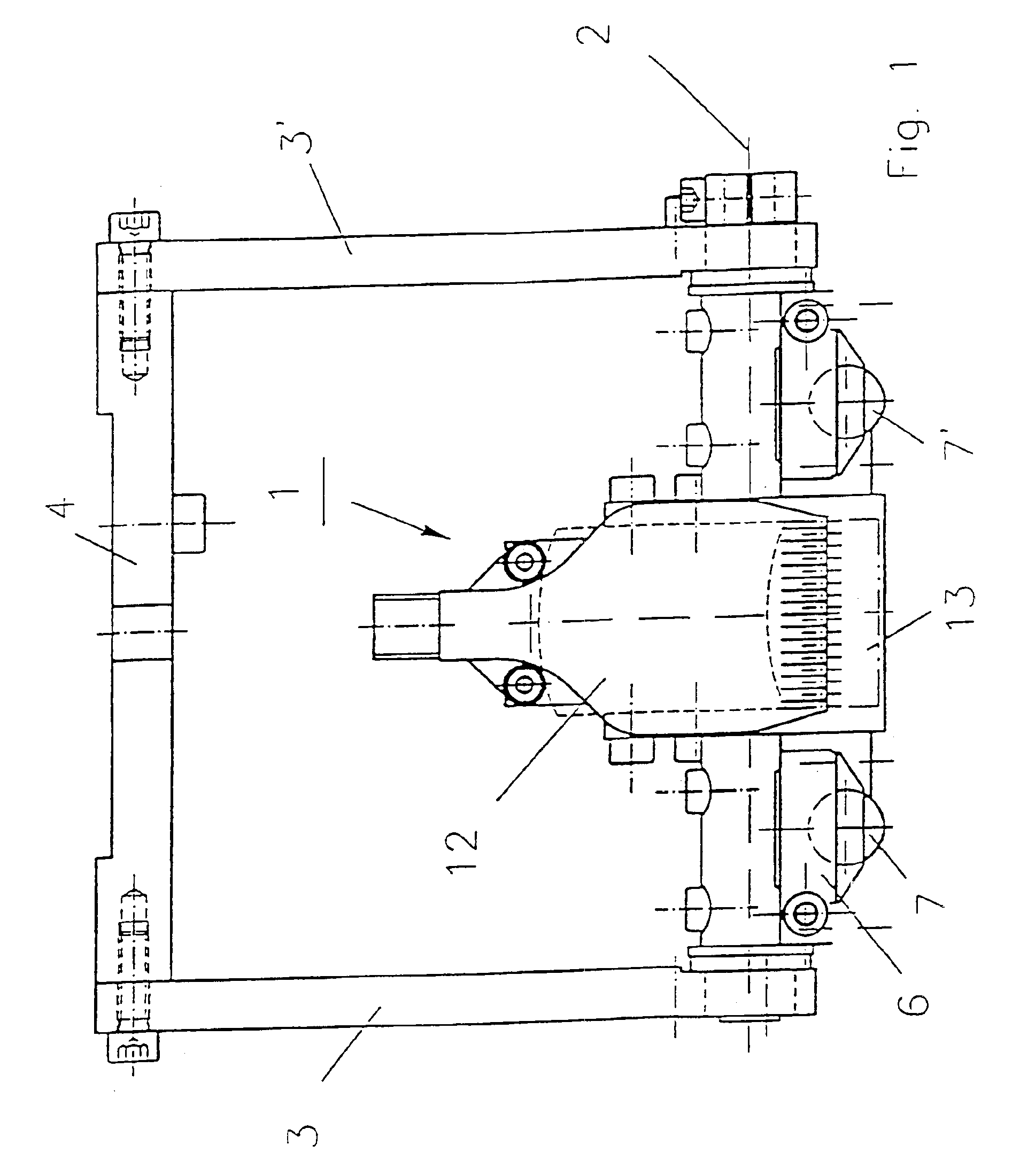

Welding robot device for welding of plunger pump power end shell

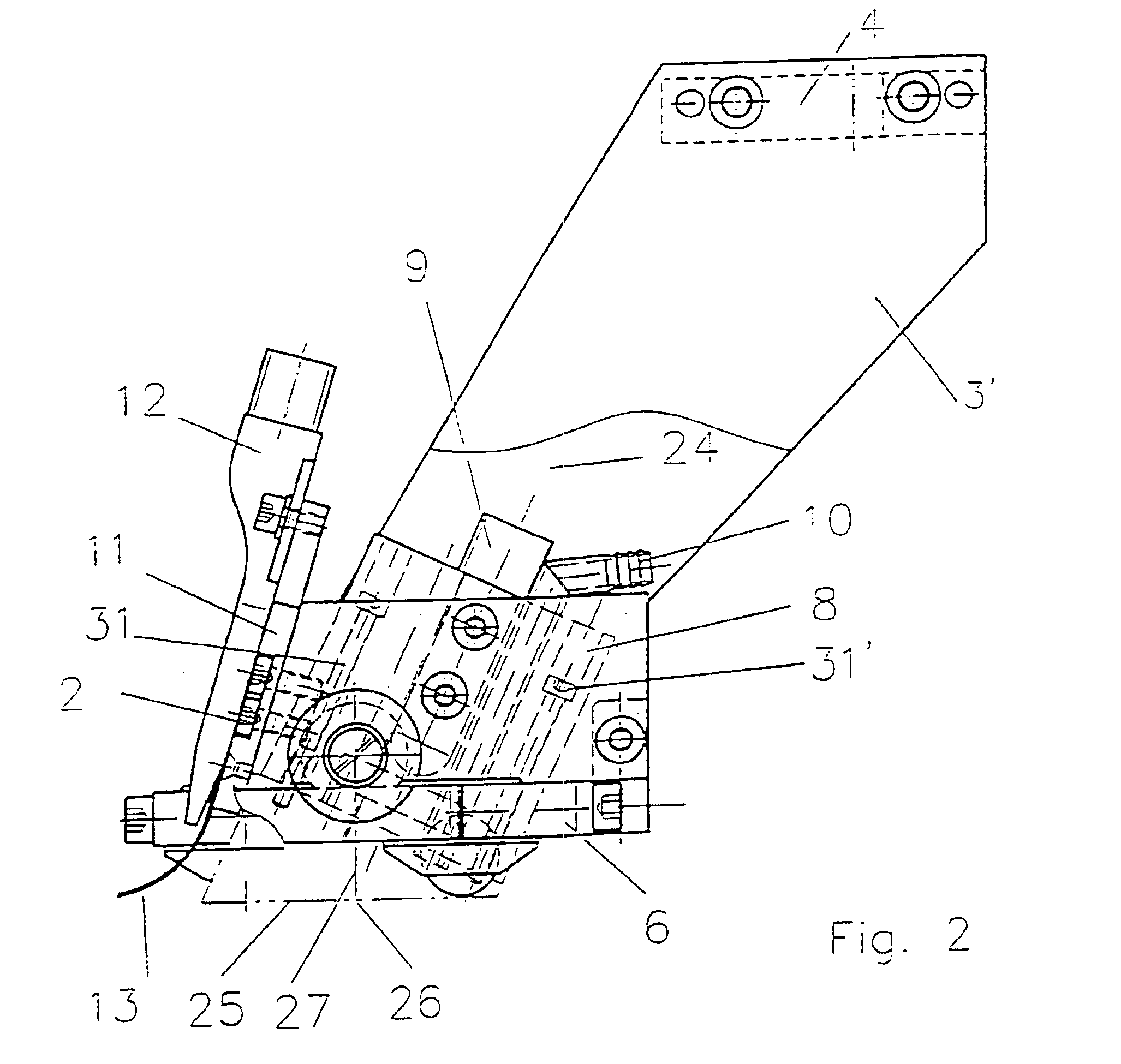

PendingCN107234358AGuarantee quality and efficiencyGuaranteed welding efficiencyWelding/cutting auxillary devicesAuxillary welding devicesFillet weldControl system

The invention provides a welding robot device for welding of a plunger pump power end shell. The welding robot device for welding of the plunger pump power end shell comprises a controlling system, a portal frame X-Y-Z coordinate system, a welding system, a space positioner and a tool clamp. The tool clamp is used for clamping the plunger pump power end shell, and a plunger pump shell can be one-time clamped; all welding joints of the plunger pump shell can be positionally changed to a flat welding position or a flat fillet welding position through the space positioner; a welding mechanical arm is connected with a coordinate Z-axis in the portal frame X-Y-Z coordinate system, and welding of welding joints in the different positions can be finished; and synchronized driving of the welding mechanical arm, a coordinate X-axis, a coordinate Y-axis, the coordinate Z-axis and the space positioner can be realized, so that continuity during the welding process is guaranteed, and welding quality and welding efficiency are ensured.

Owner:YANTAI JEREH PETROLEUM EQUIP & TECH CO LTD

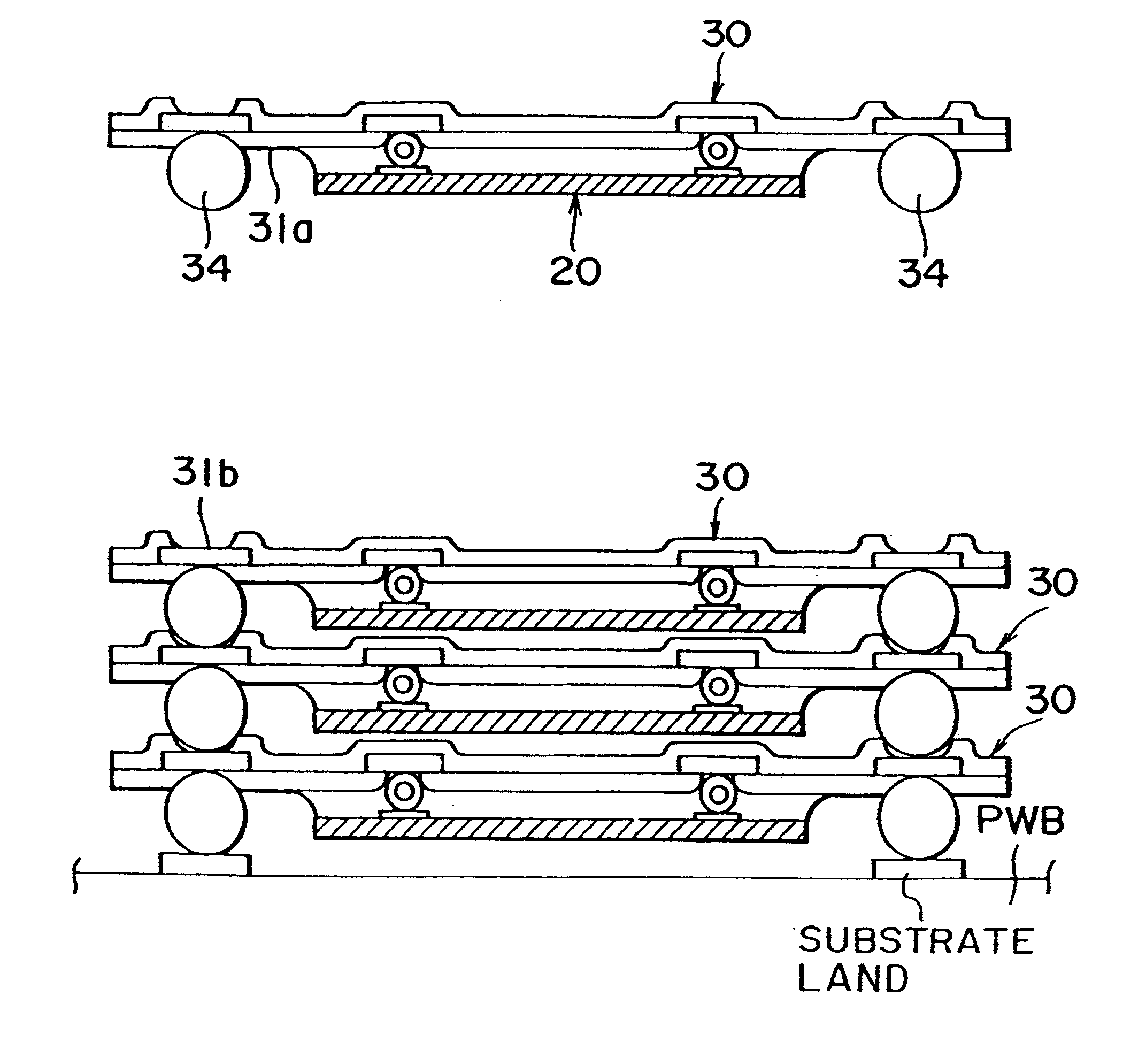

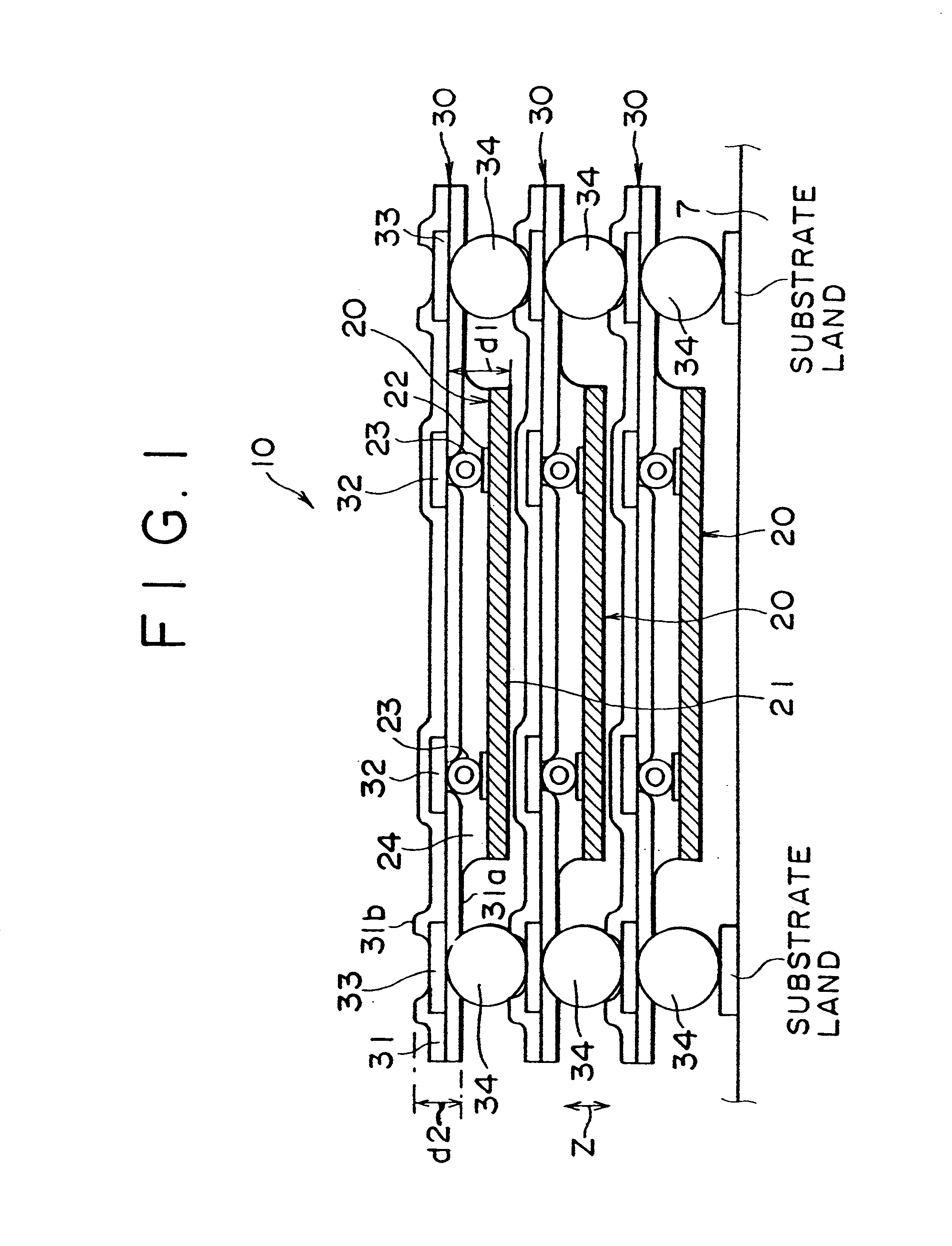

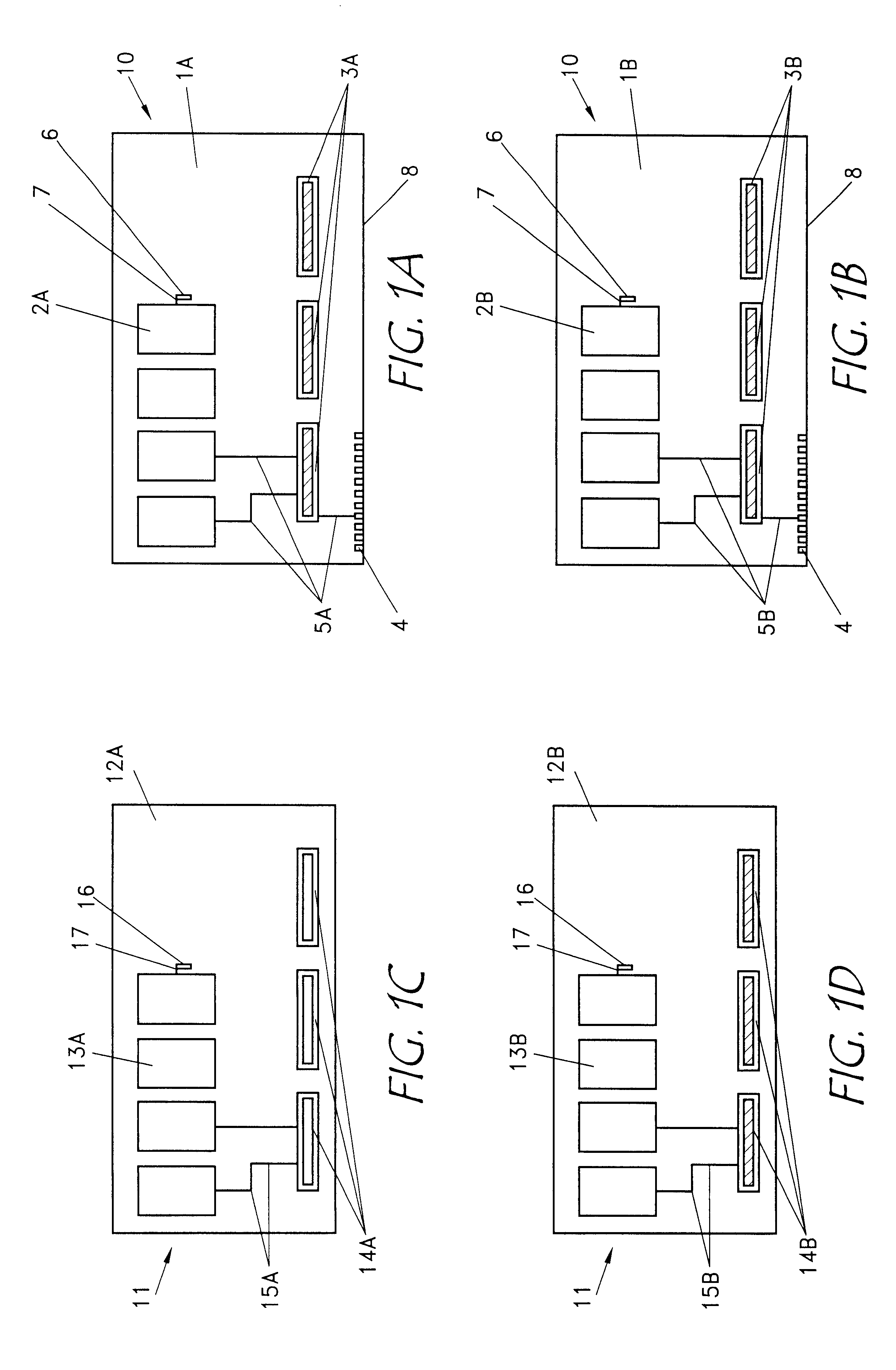

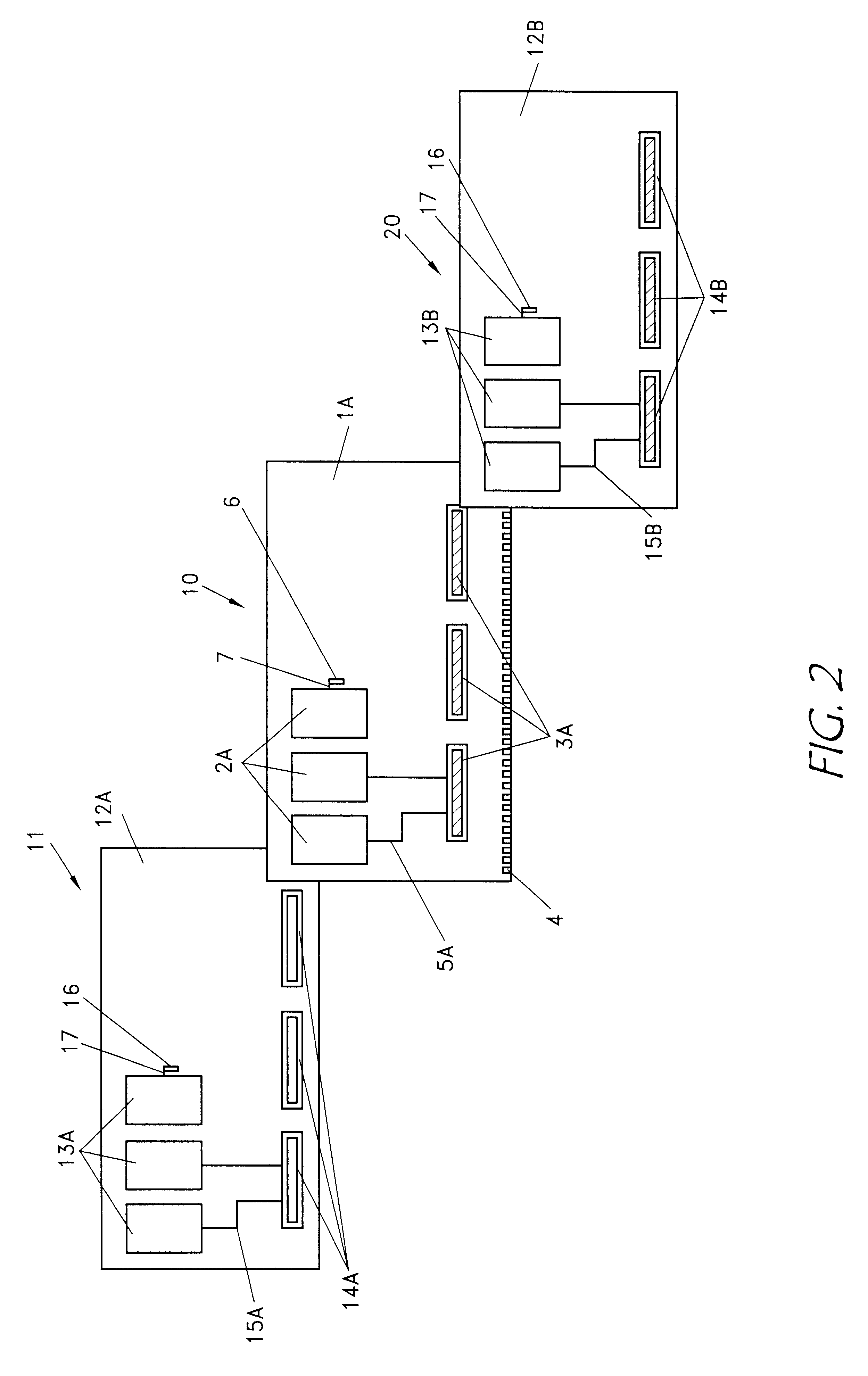

Stacked printed circuit board memory module and method of augmenting memory therein

InactiveUS6418034B1Coupling device connectionsElectrically conductive connectionsEngineeringPrinted circuit board

A stacked printed circuit board memory module in which a plurality of daughter circuit boards can be stacked onto a primary circuit board. The primary board and each of the plurality of daughter boards have electronic memory ICs mounted on the respective surfaces. The primary board and each of the daughter boards have mounted connectors so that the boards can be electronically and mechanically interconnected with another board.

Owner:MICRON TECH INC

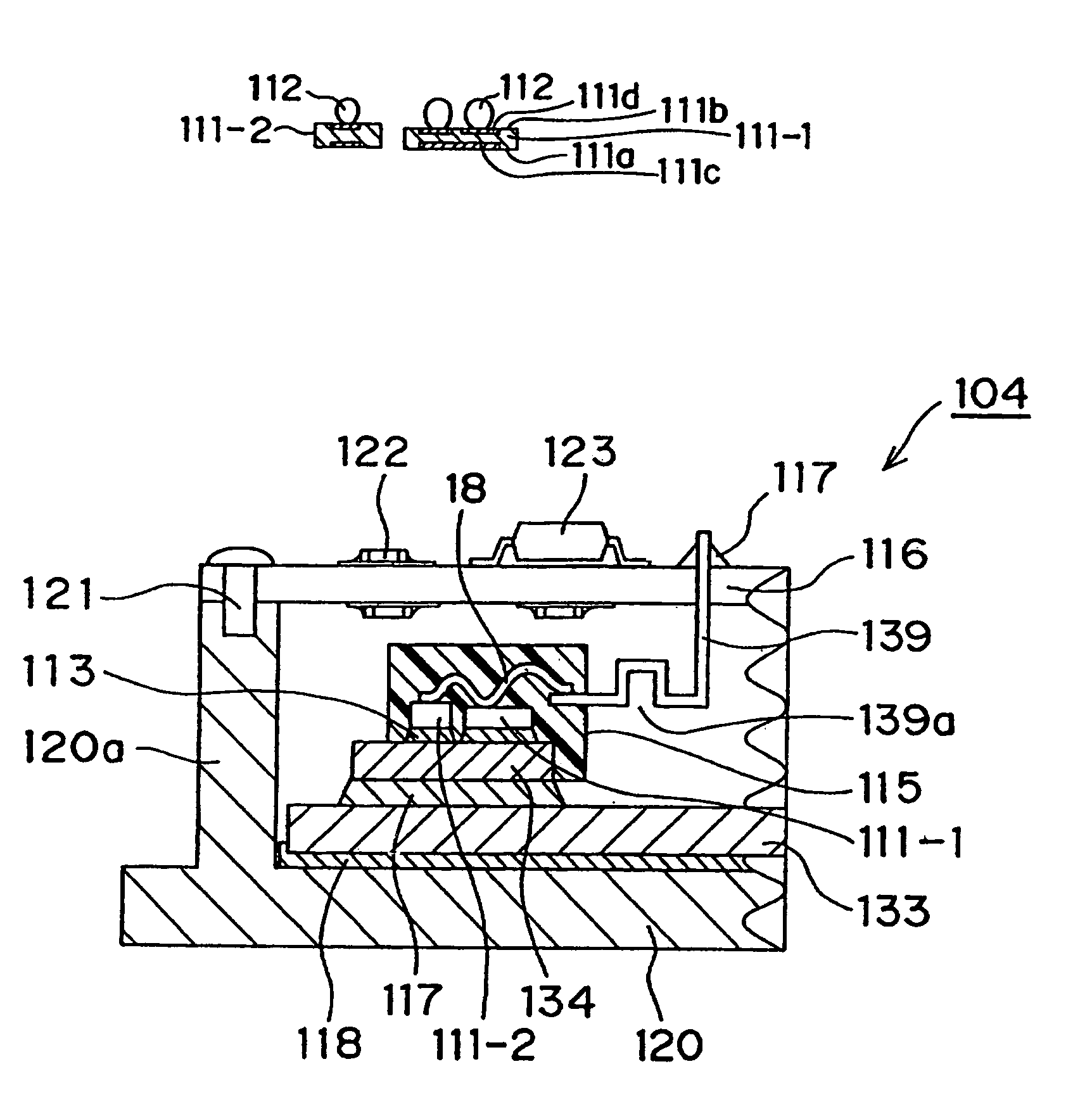

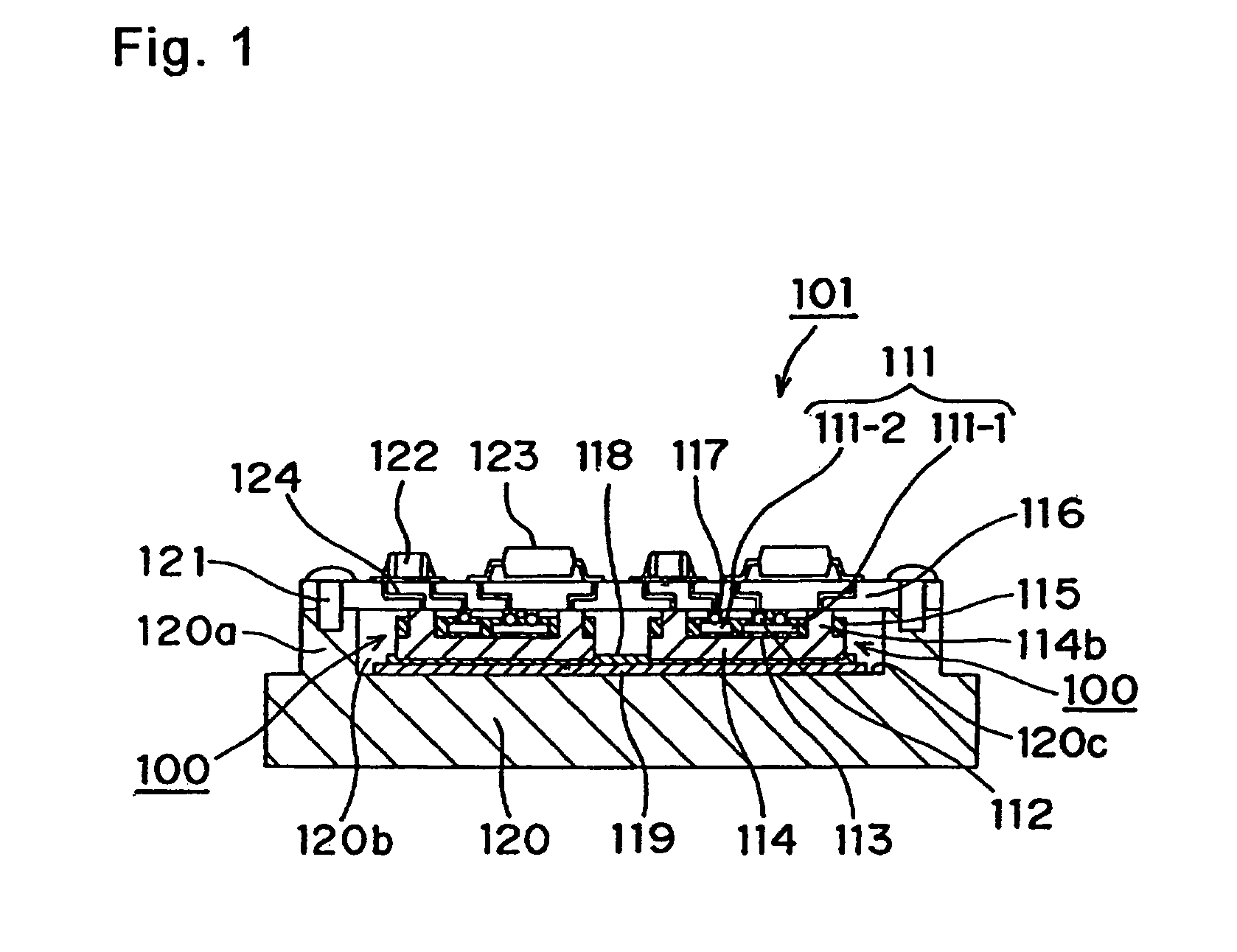

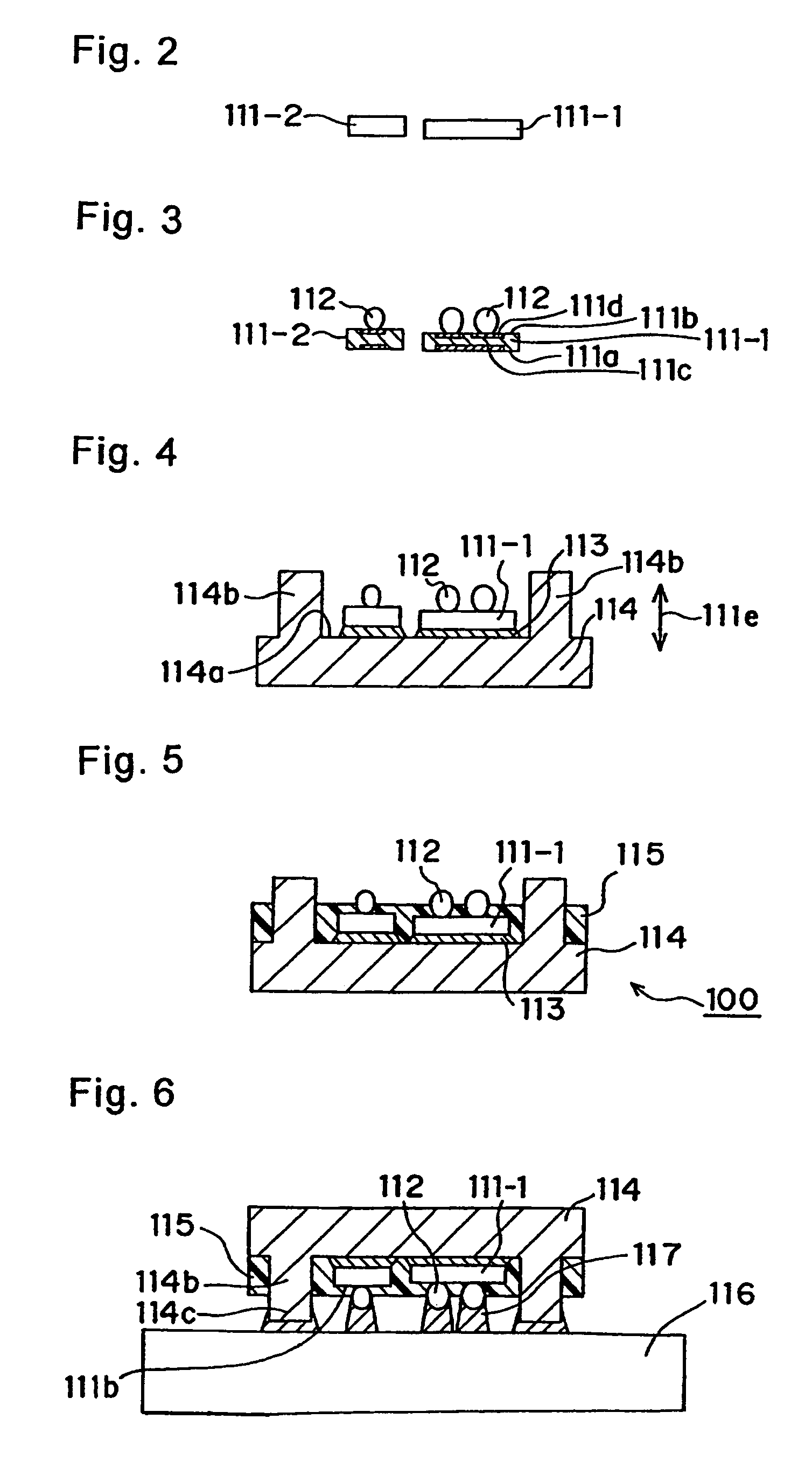

Electronic circuit device having circuit board electrically connected to semiconductor element via metallic plate

InactiveUS7208833B2Improve cooling efficiencyReduce resistanceSemiconductor/solid-state device detailsSolid-state devicesEngineeringControl circuit

An electronic circuit device comprises: a semiconductor element having a first surface and a second surface, with the first and second surfaces being on first and second sides of the semiconductor element, respectively, and facing in opposite directions; a first electrode on the first surface; a second electrode on the second surface; a first circuit board electrically connected to the first electrode via a metallic plate such that the metallic plate and the semiconductor element are on the first circuit board; a second circuit board on the second side of the semiconductor element, the second circuit board having a control circuit for the semiconductor element; and a metallic wire for directly electrically interconnecting the second electrode and the second circuit board.

Owner:PANASONIC CORP

Methods for fabricating three-dimensional all organic interconnect structures

InactiveUS20040000425A1Semiconductor/solid-state device detailsSolid-state devicesLiquid crystallineAdhesive

The present invention comprises methods for making three-dimensional (3-D) liquid crystalline polymer (LCP) interconnect structures using a high temperature singe sided liquid crystalline polymer, and low temperature single sided liquid crystalline polymer, whereas both the high temperature LCP and the low temperature LCP are drilled using a laser or mechanical drill or mechanically punch to form a z-axis connection. The single sided Conductive layer is used as a bus layer to form z axis conductive stud conductive stud within the high temperature and low temperature LCP, followed by deposition of a metallic capping layer of the stud that serves as the bonding metal between the conductive interconnects to form the z-axis electrical connection. High temperature and low temperature LCP circuit layers are etched or built up to form circuit patterns and subsequently bonded together to form final 3-D multilayer circuit pattern whereas the low temperature LCP melts to form both dielectric to dielectric bond to high temperature LCP circuit layer, and dielectric to conductive bond, whereas, metal to metal bonding occurs with high temperature metal capping layer bonding to conductive metal layer. The resultant structure is then packaged using two metallized organic cores that are laminated onto either side of the device using a low temperature adhesive with similar electrical properties and subsequently metallized to form the input output terminals and EM shielding.

Owner:GEORGIA TECH RES CORP

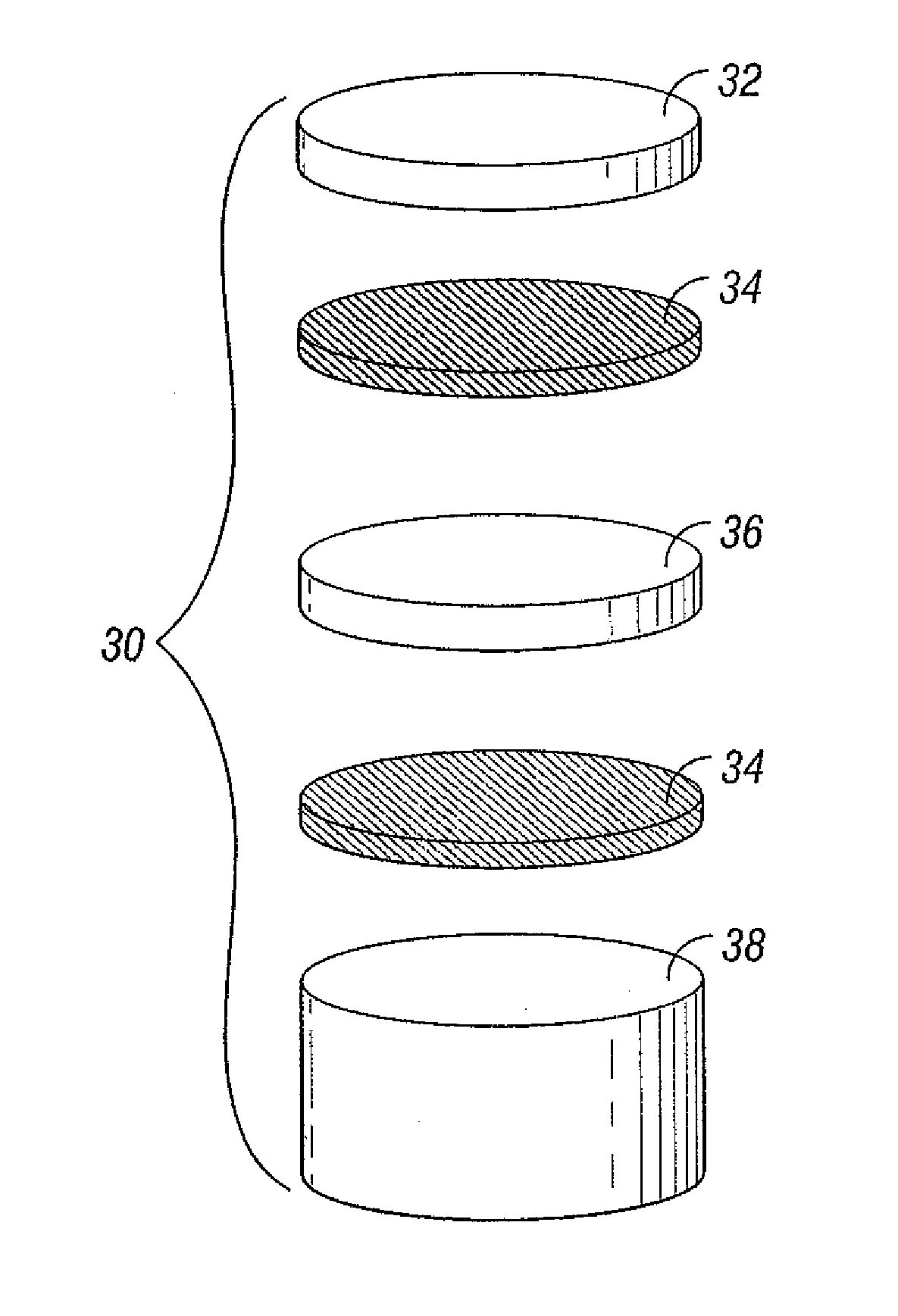

Ultra-hard and metallic constructions comprising improved braze joint

An ultra-hard and metallic construction comprises an ultra-hard component that is attached to a metallic component via a braze joint. The braze joint is interposed between the ultra-hard component and the metallic component, and comprises a first braze material bonded to a surface of the ultra-hard component. The braze joint includes an intervening layer in direct contact with the first braze material, and that is formed from a rigid material. The braze joint further comprises a second braze material that is interposed between the intervening layer and the metallic component, and that is different from the first braze material. Configured in this manner, the use of the braze joint operates to provide an optimum level of bond strength within the construction to enable its use in certain demanding wear and / or cutting applications.

Owner:SMITH INT INC

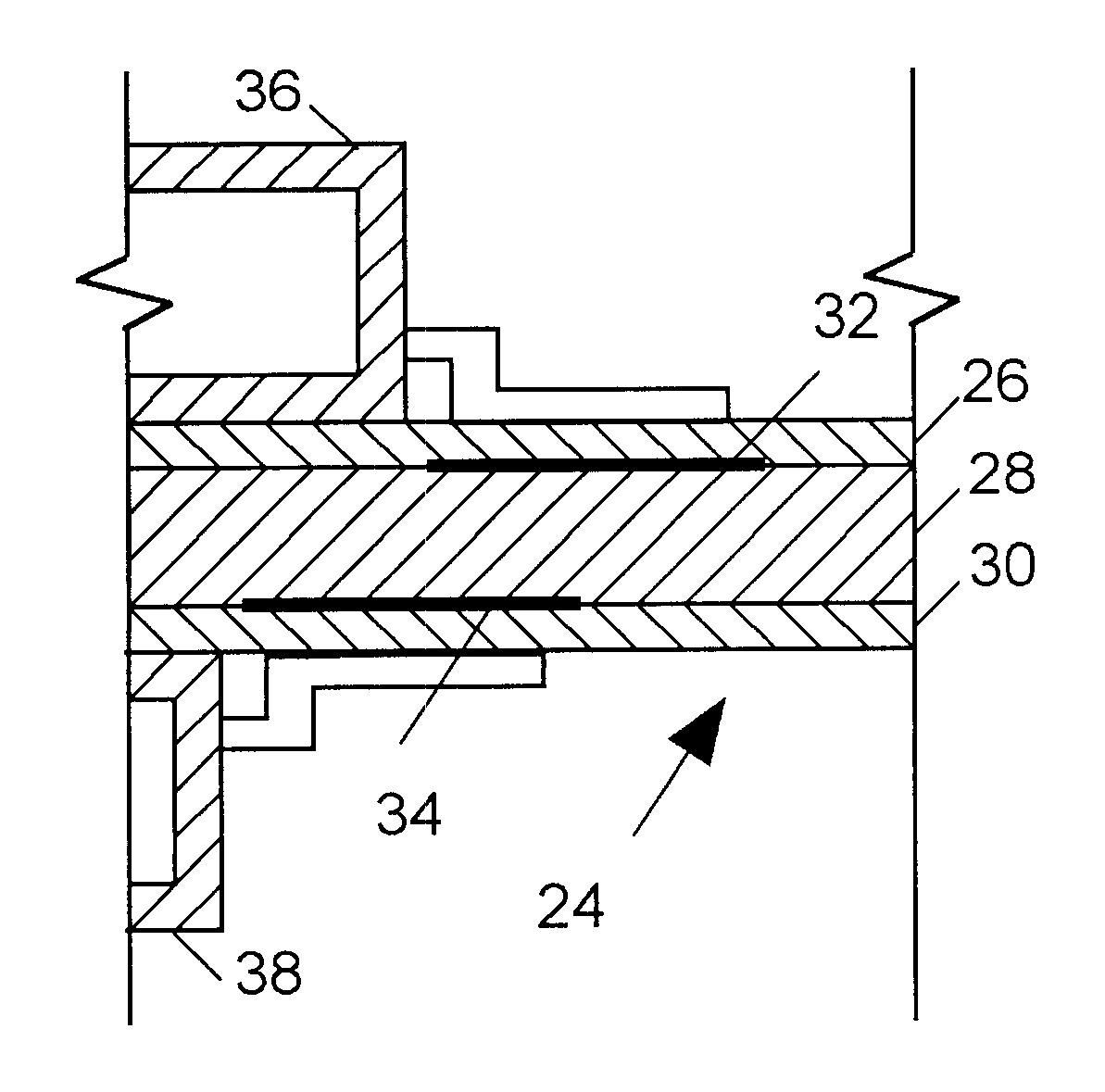

Device for ultrasonic weld seam testing of longitudinally welded pipes for longitudinal and transversal errors

InactiveUS6931931B2Simple adaptationSimplify workAnalysing solids using sonic/ultrasonic/infrasonic wavesMetal working apparatusEngineeringWeld seam

A device for ultrasonic weld seam testing of longitudinally includes two testing carriages swingably suspended and moveable on the pipe surface to the right and left of the weld seam for longitudinal flaw inspection, and one testing carriage swingably suspended in central relationship to the weld seam and moveable on the pipe surface for transverse flaw inspection. Each testing carriage has a mount for accommodating at least one testing head which includes an oscillator, and at least one coupling medium connection having a channel ending in the region of the oscillator and configured as nozzle in the outlet area. The test head for longitudinal flaw inspection can be arranged at various fixed and predefined angle positions at variable distance to the nozzle in the mount, and the test head for transverse flaw inspection can be arranged, together with the mount, at a variable distance to the pipe surface in a support element accommodating the mount.

Owner:MANNESMANN ROHRENWERKE

Self-heating circuit board

InactiveUS6396706B1Inexpensive and convenientSemiconductor/solid-state device detailsSolid-state devicesVoltage pulseAdhesive

Separate heating elements are embedded in a printed circuit board near integrated circuit (IC) packages or other parts mounted on the circuit board. Each heating element supplies heat to the part residing near it in response to an input voltage pulse. The heating elements are used to selectively melt solder or adhesives attaching the parts to the circuit board so that they can be easily removed or to temporarily melt solder or cure adhesive when the parts are mounted on the circuit board. The heating elements are also used to supply heat to IC packages for regulating their operating temperatures.

Owner:MA ZHONGXIN +1

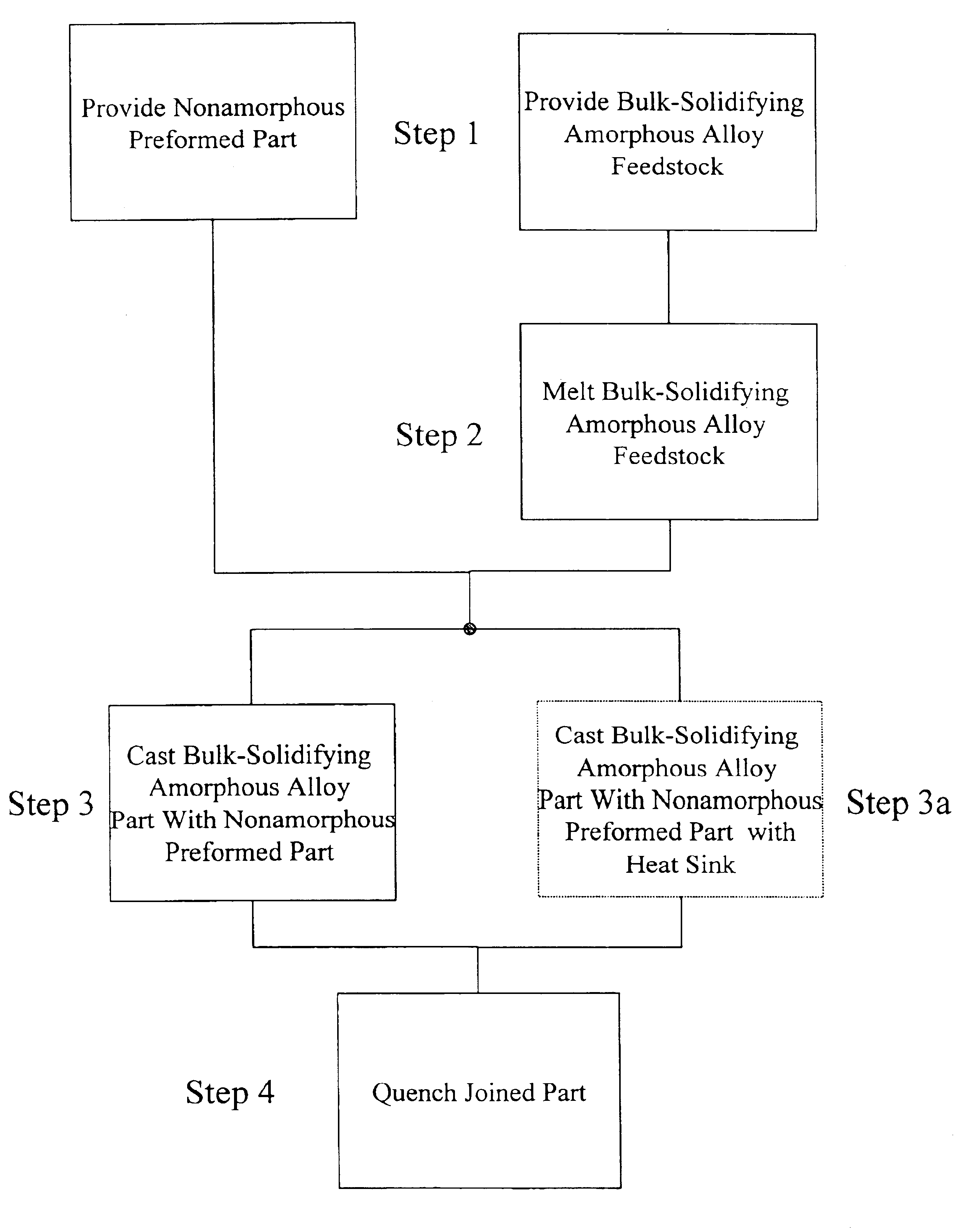

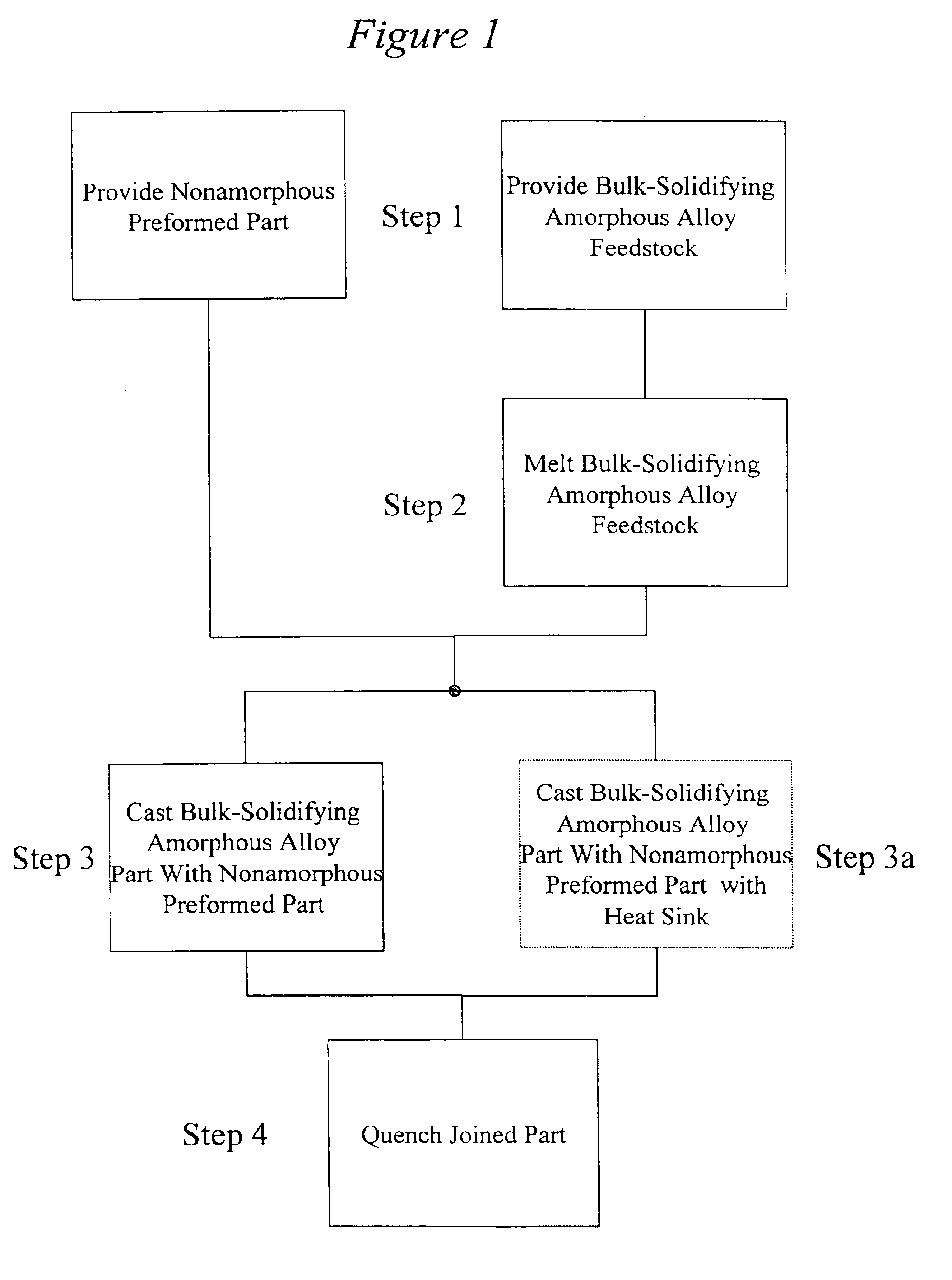

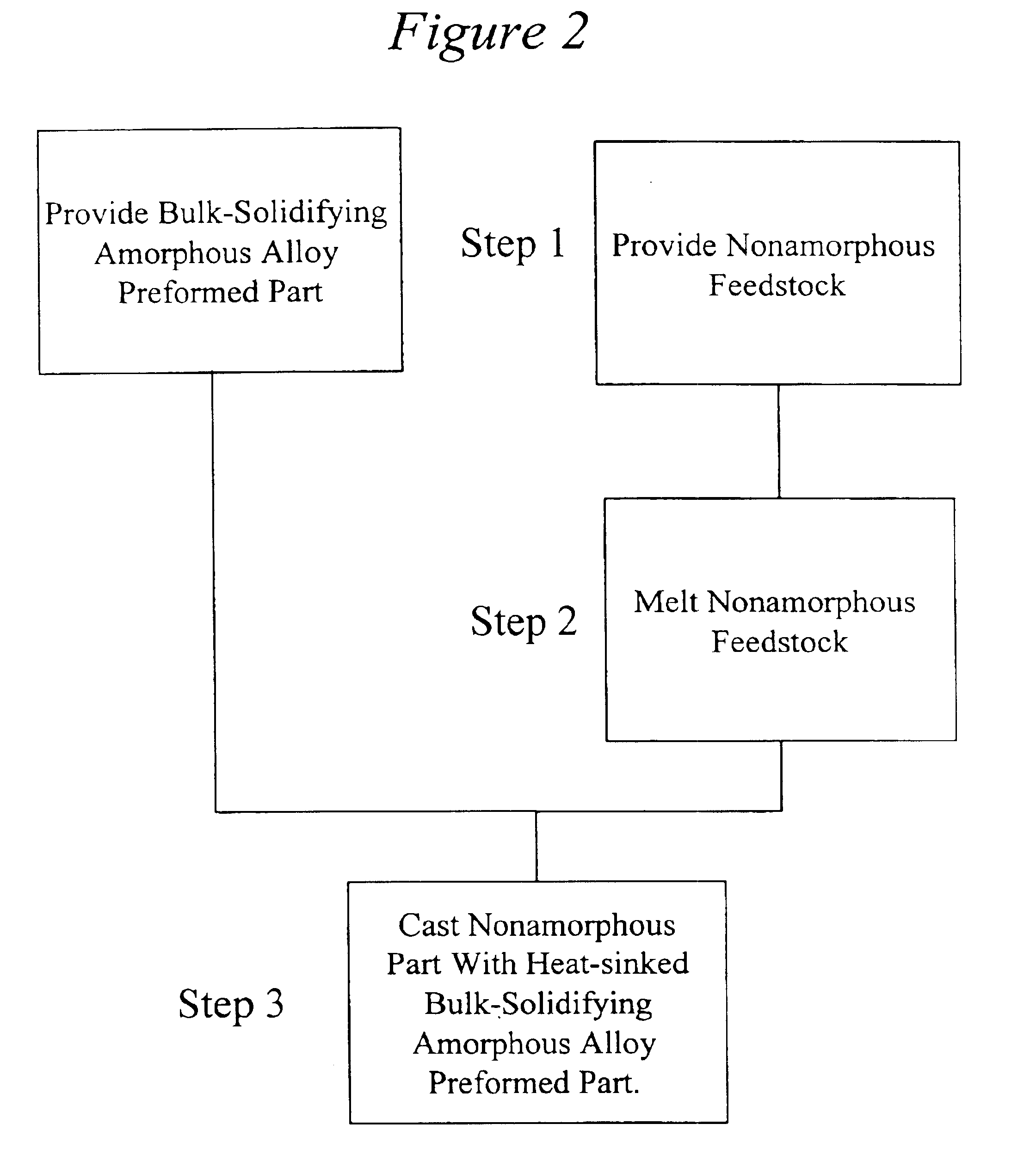

Joining of amorphous metals to other metals utilzing a cast mechanical joint

The present invention is directed to a method of joining an amorphous material to a non-amorphous material including, forming a cast mechanical joint between the bulk solidifying amorphous alloy and the non-amorphous material.

Owner:CRUCIBLE INTPROP LLC