Patents

Literature

177 results about "Indium gallium arsenide" patented technology

Efficacy Topic

Property

Owner

Technical Advancement

Application Domain

Technology Topic

Technology Field Word

Patent Country/Region

Patent Type

Patent Status

Application Year

Inventor

Indium gallium arsenide (InGaAs) (alternatively gallium indium arsenide, GaInAs) is a ternary alloy (chemical compound) of indium arsenide (InAs) and gallium arsenide (GaAs). Indium and gallium are (group III) elements of the periodic table while arsenic is a (group V) element. Alloys made of these chemical groups are referred to as "III-V" compounds. InGaAs has properties intermediate between those of GaAs and InAs. InGaAs is a room-temperature semiconductor with applications in electronics and photonics.

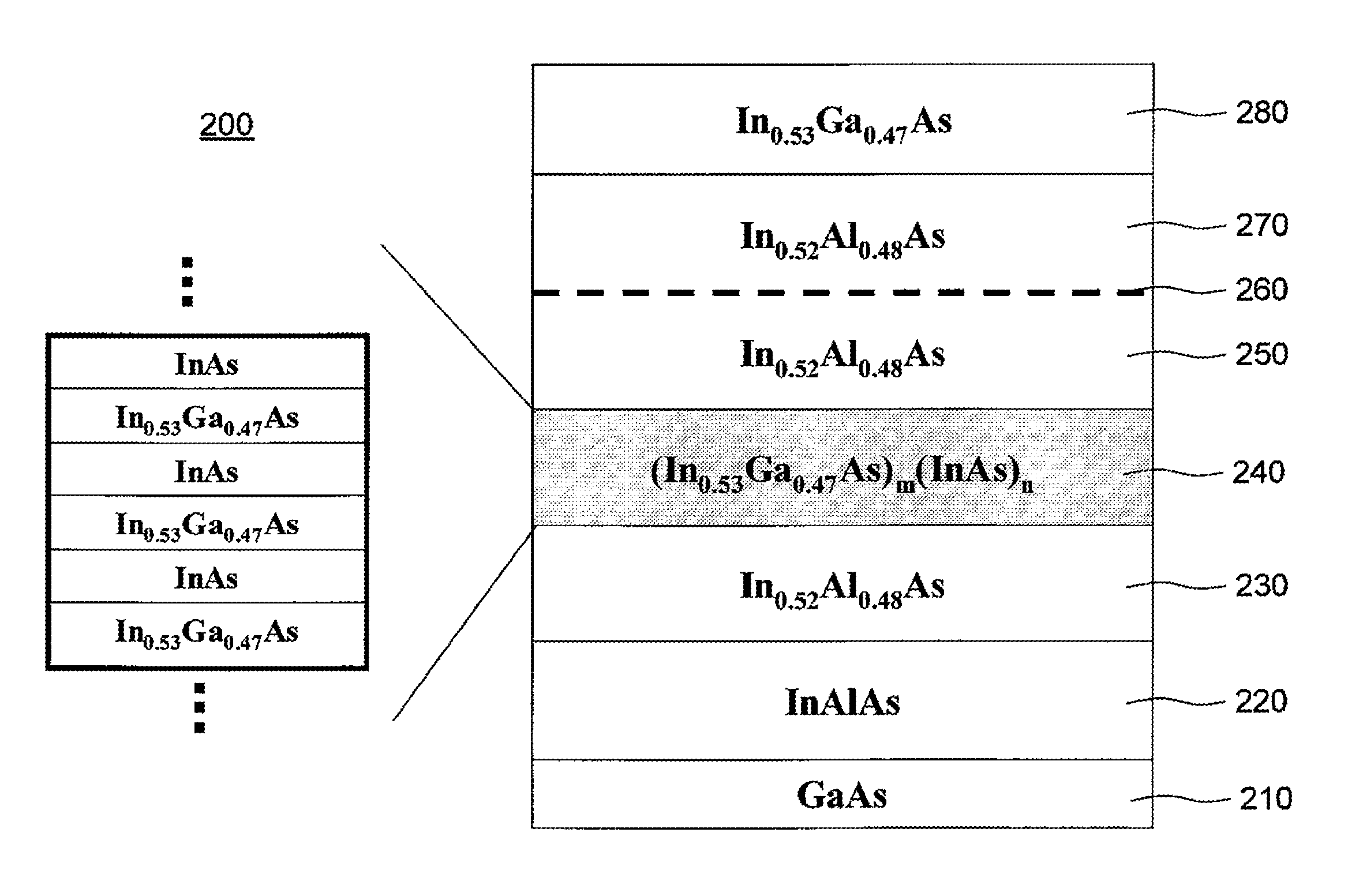

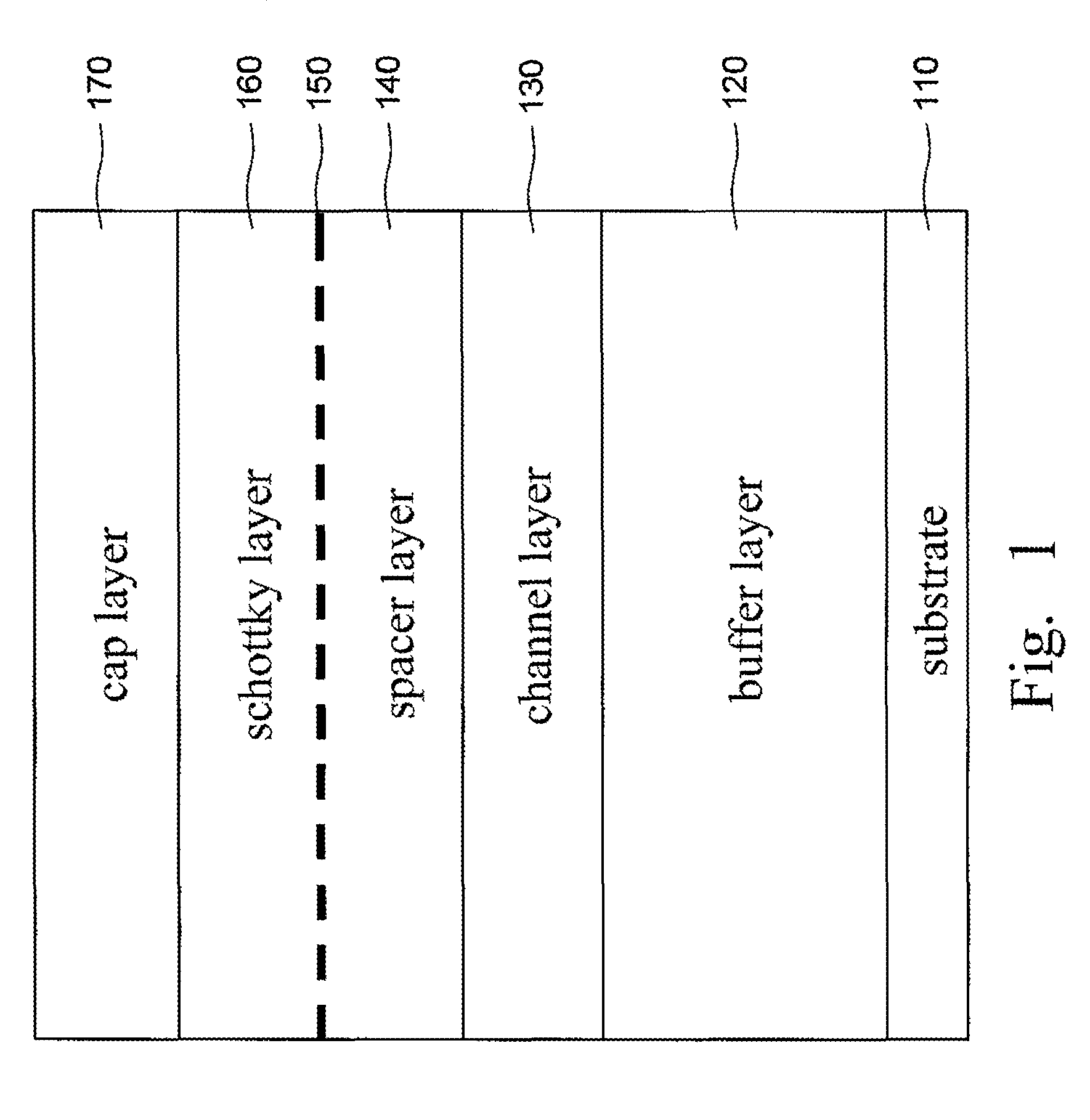

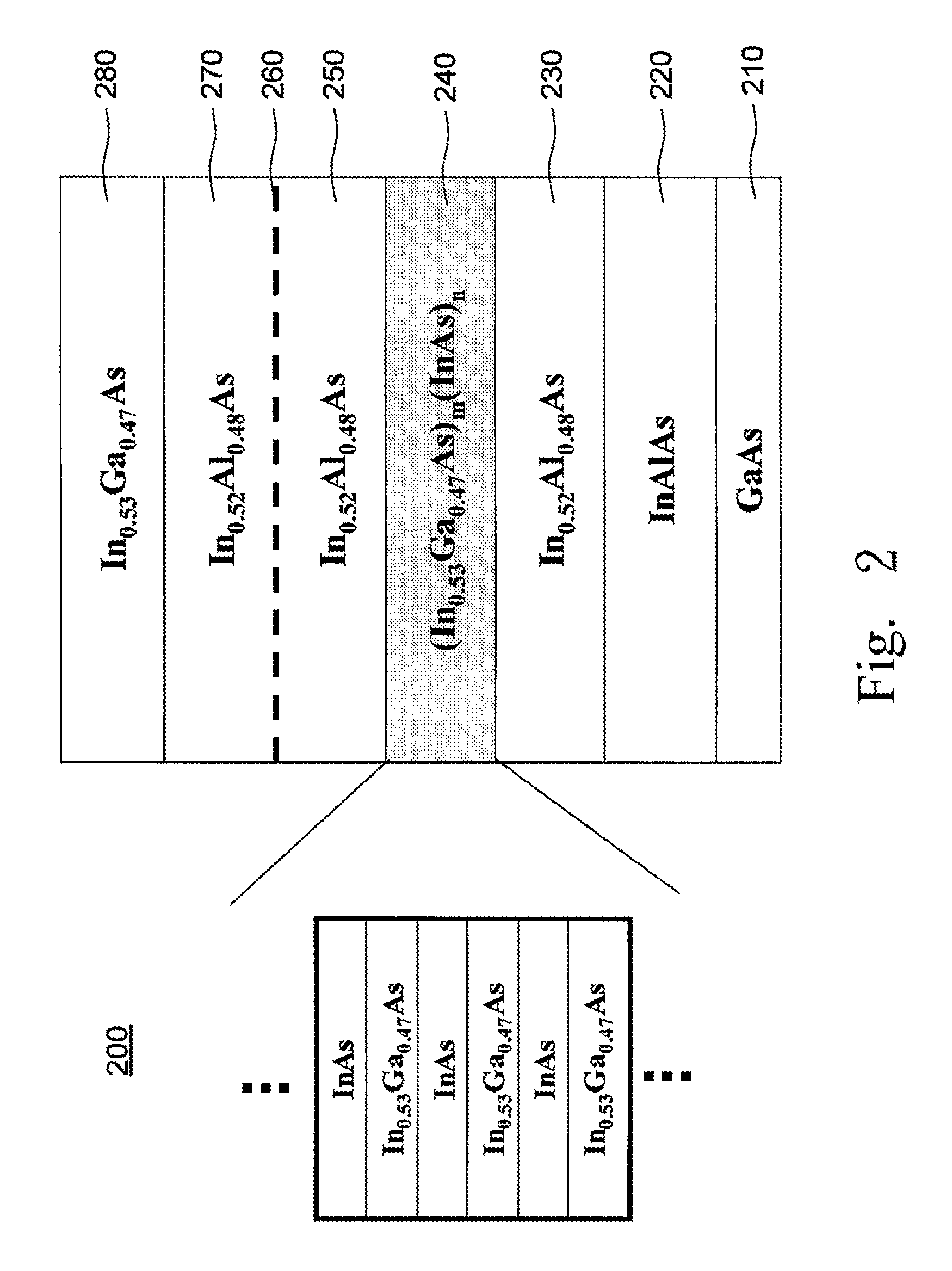

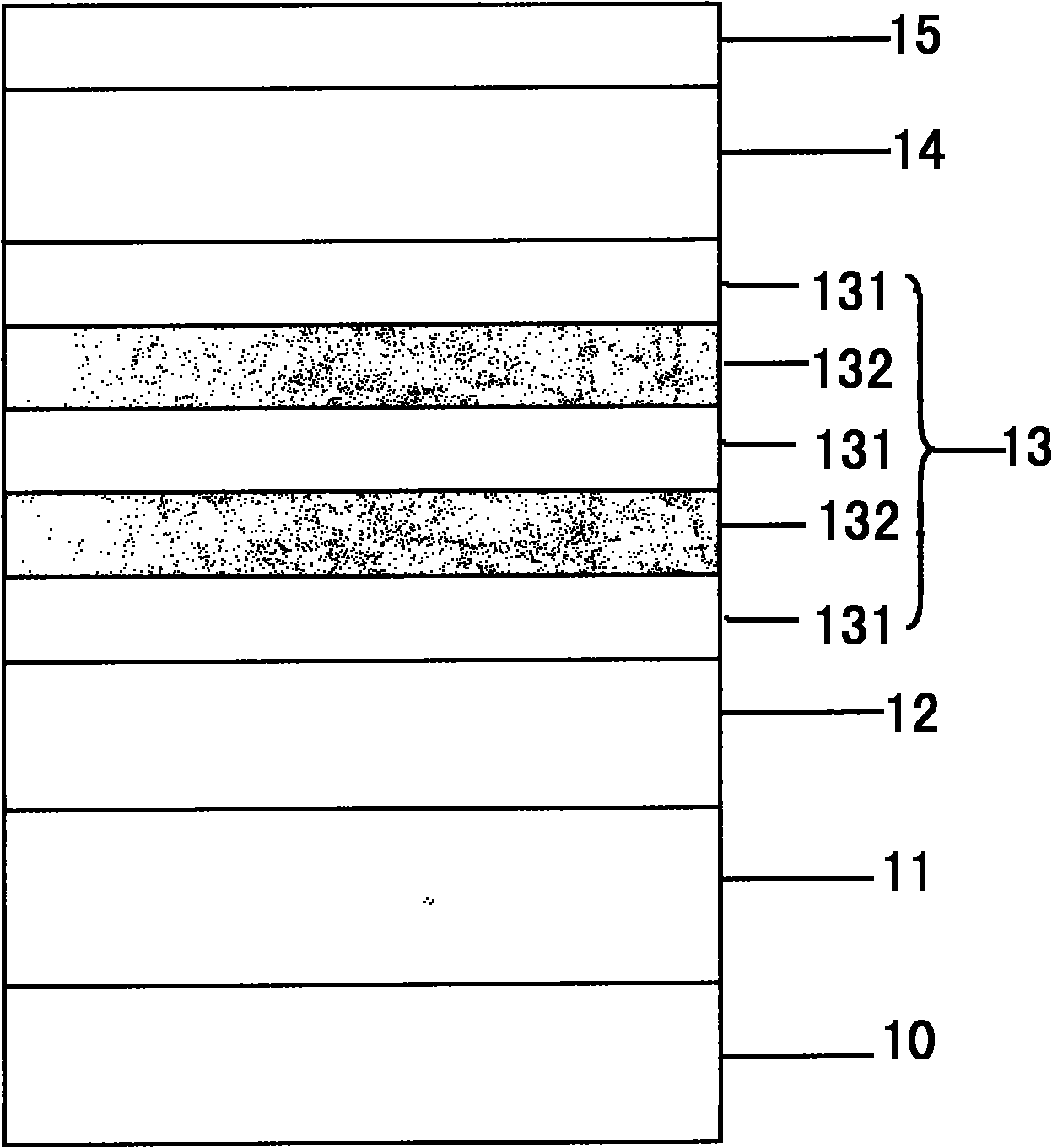

High electron mobility transistor and method for fabricating the same

ActiveUS8169002B2Improve high-frequency characteristicHigh electron mobilityTransistorNanoinformaticsIndium arsenideIndium gallium arsenide

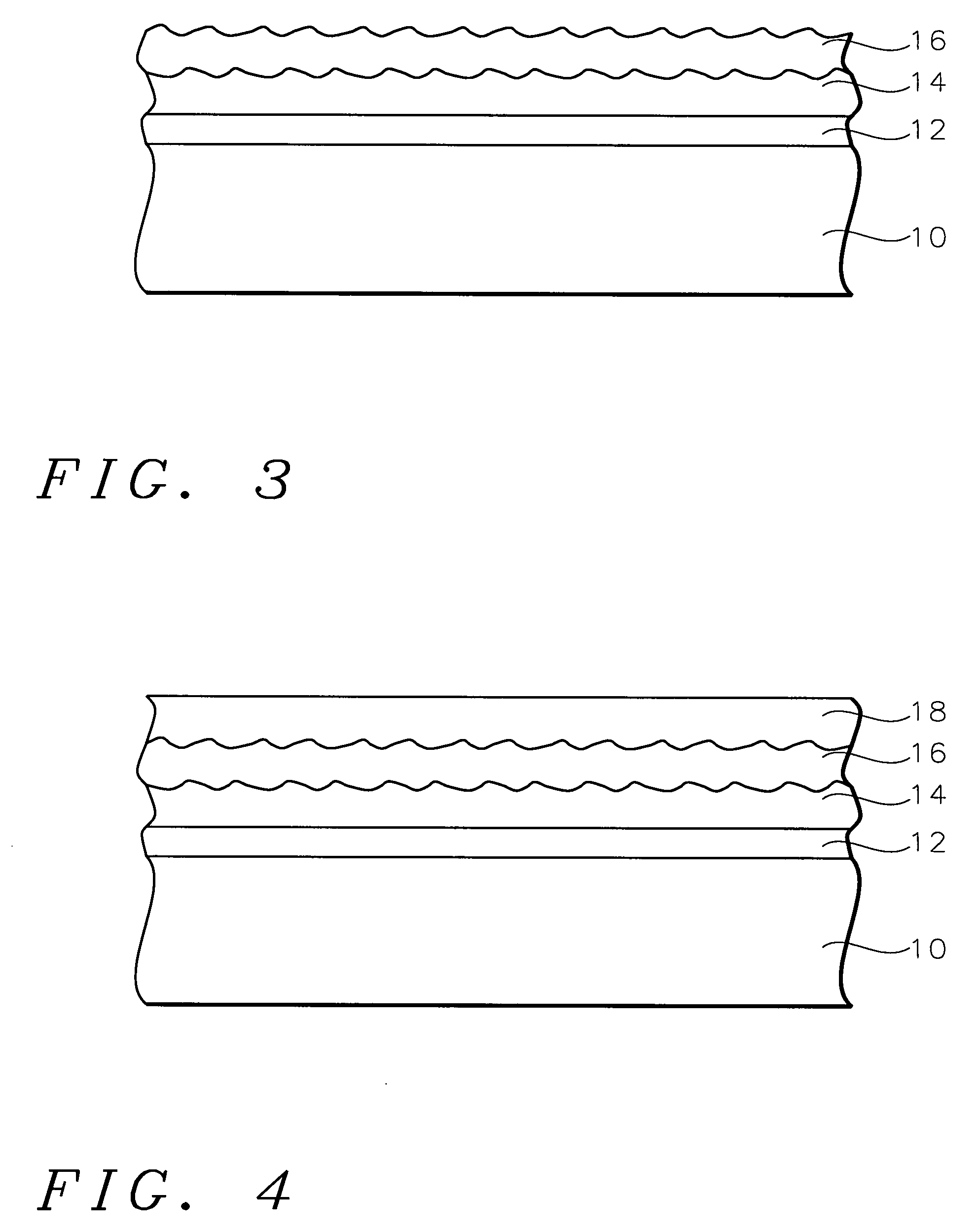

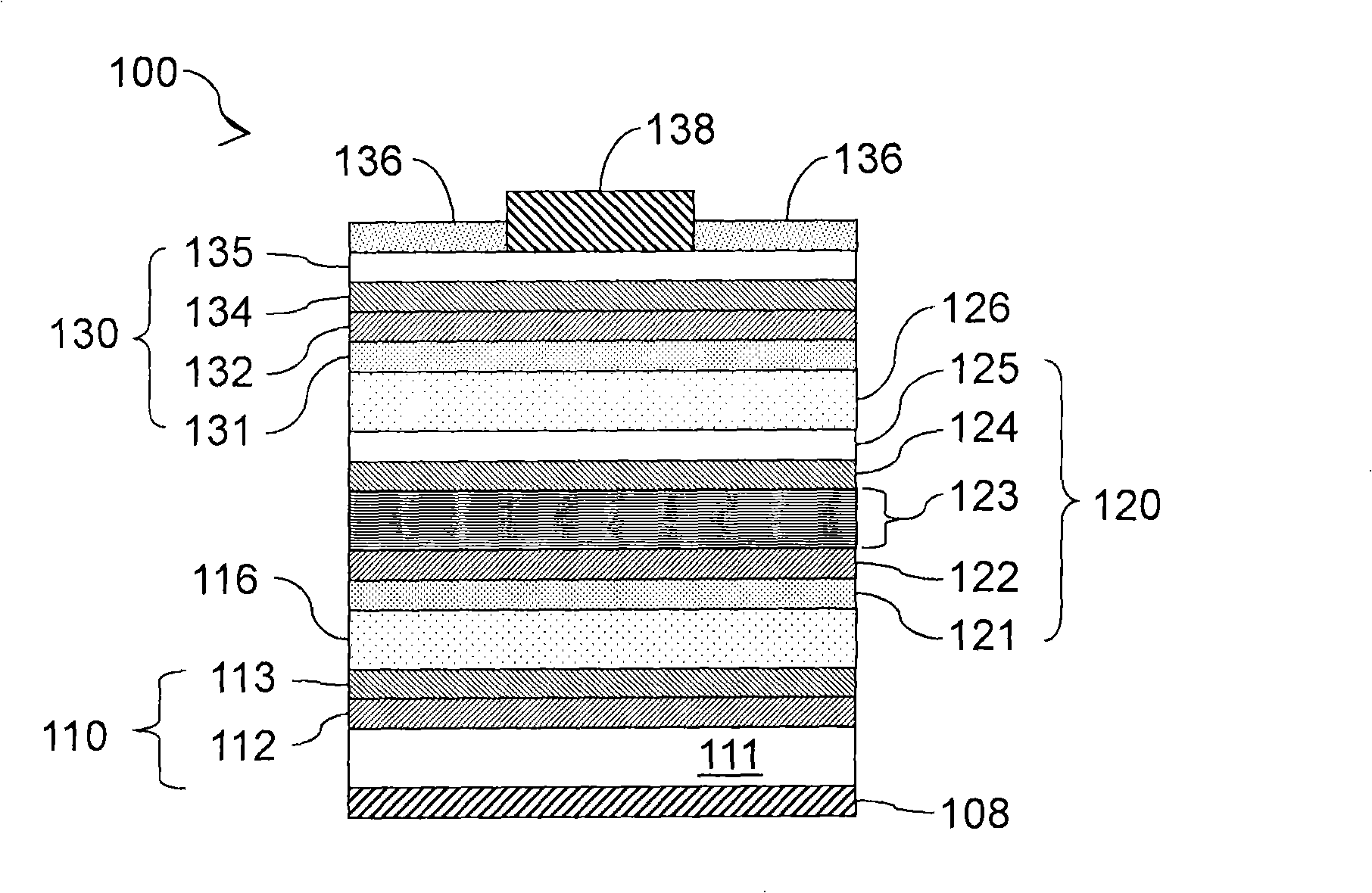

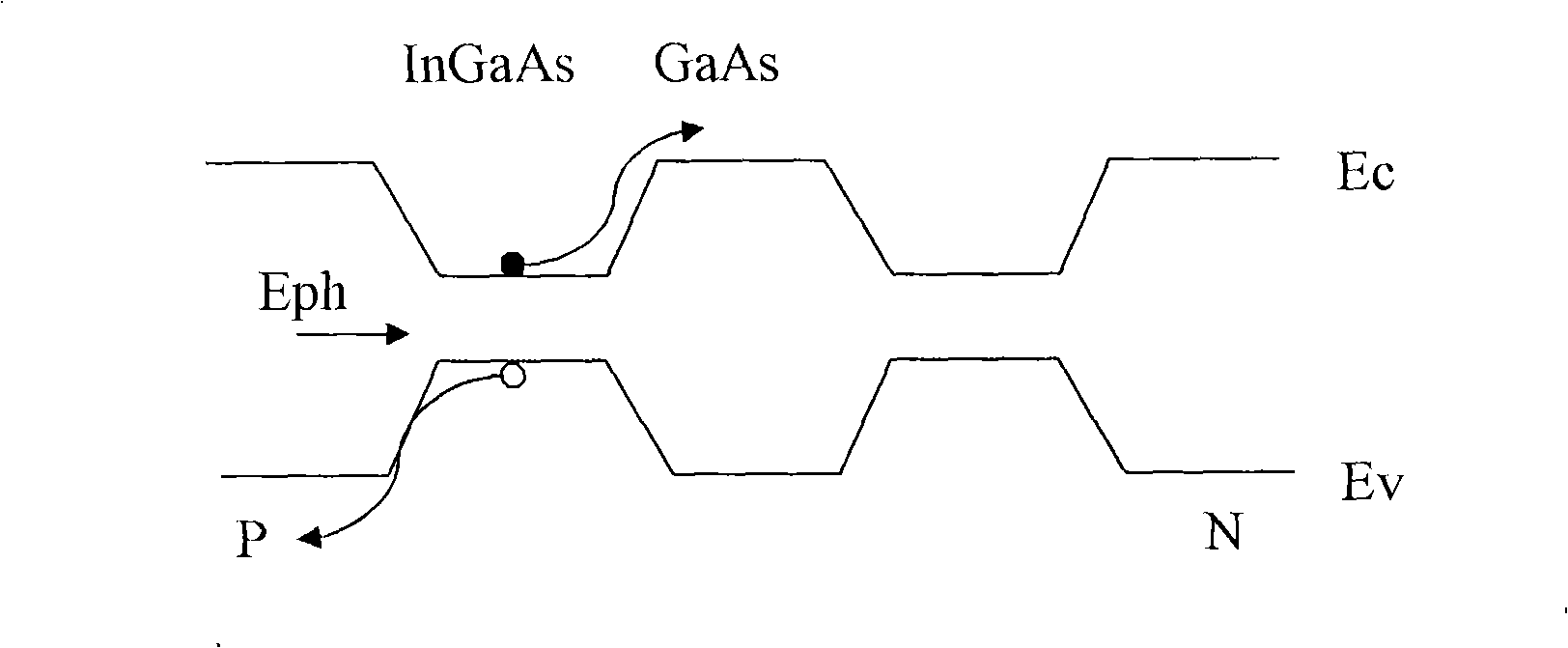

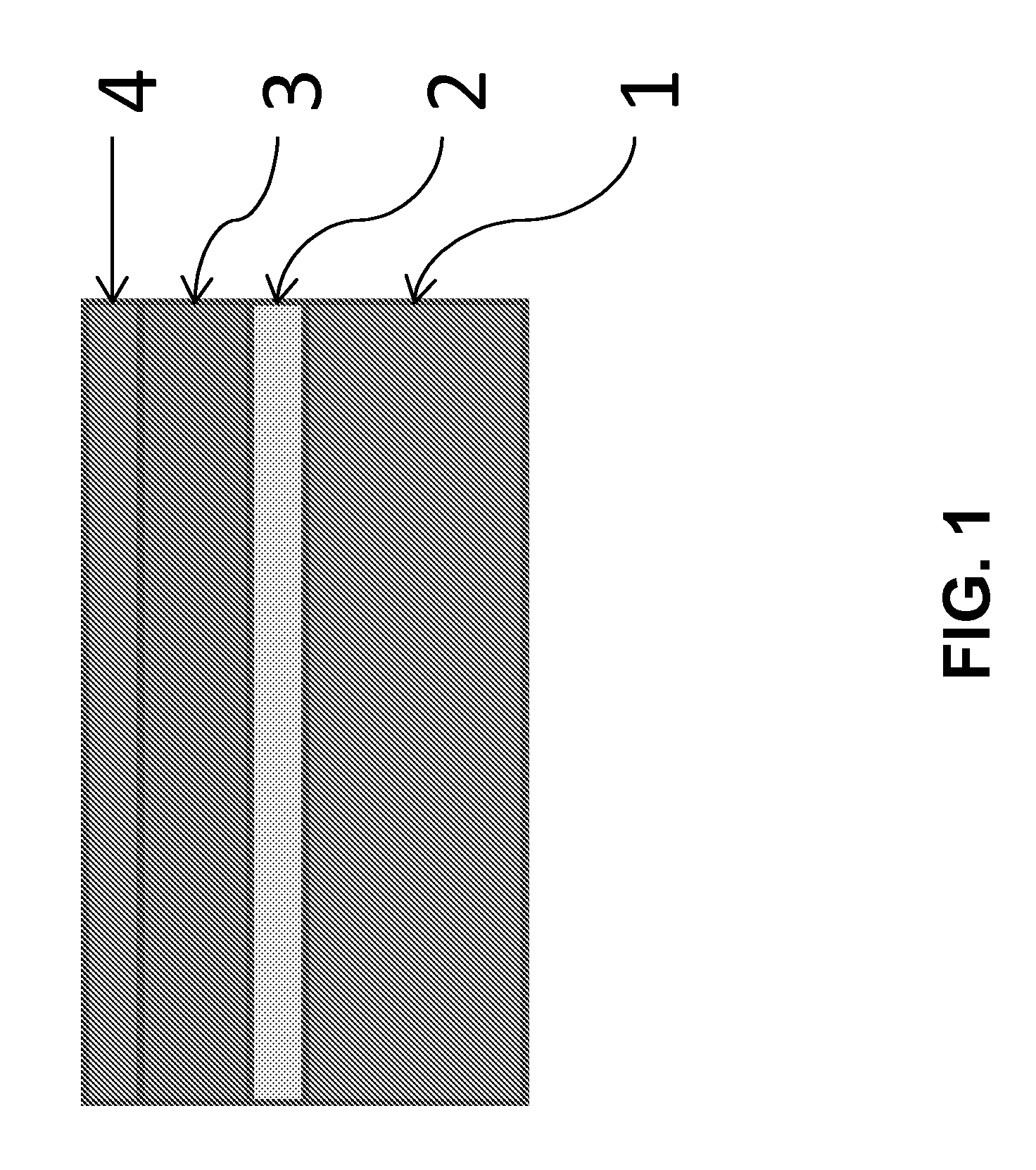

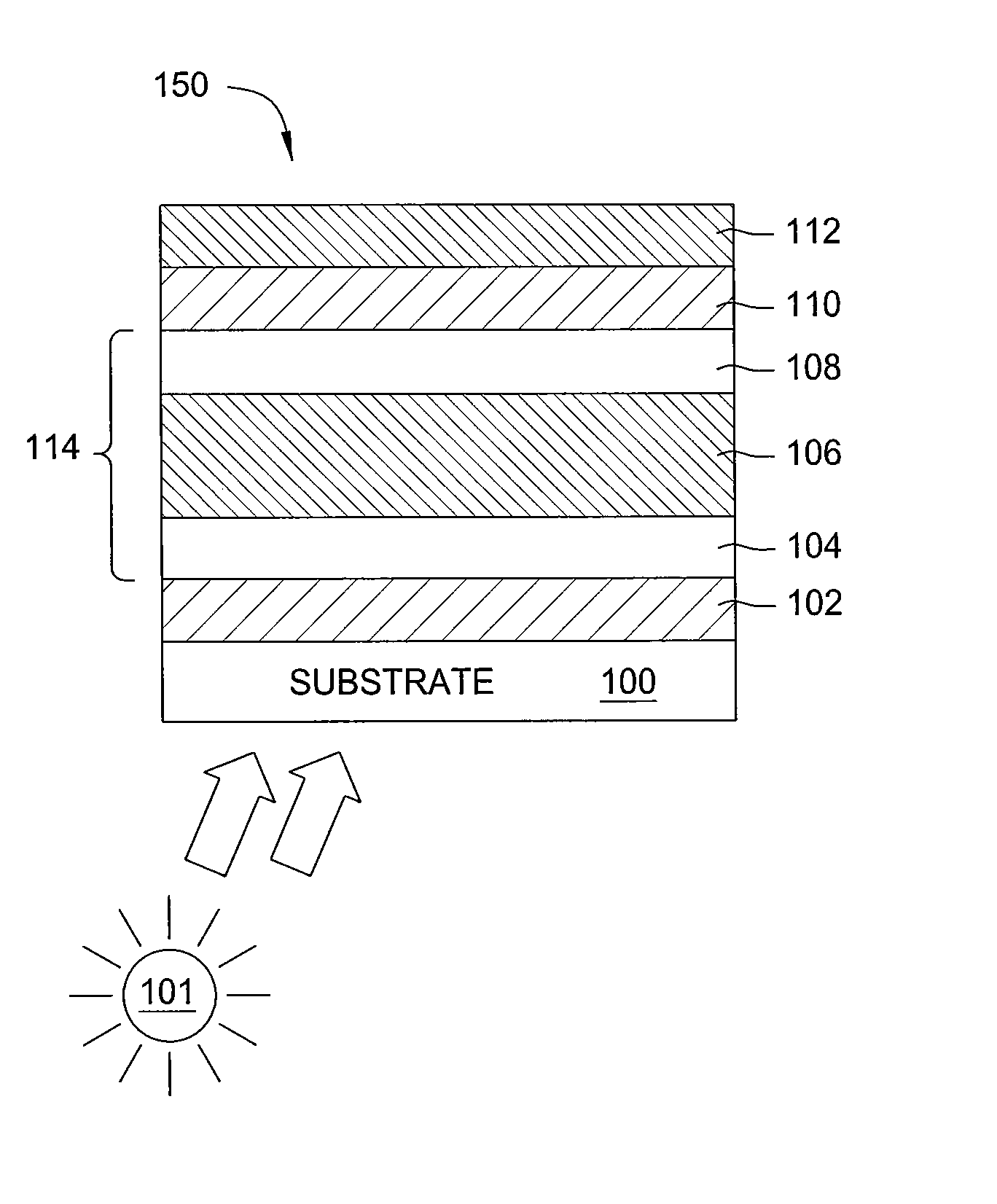

A high electron mobility transistor includes a substrate, a buffer layer, a channel layer, a spacer layer, a schottky layer and a cap layer. The buffer layer is formed on the substrate. The channel layer is formed on the buffer layer, in which the channel layer comprises a superlattice structure formed with a plurality of indium gallium arsenide thin films alternately stacked with a plurality of indium arsenide thin films. The spacer layer is formed on the channel layer. The schottky layer is formed on the spacer layer. The cap layer is formed on the schottky layer.

Owner:YLTLINK TECH CORP

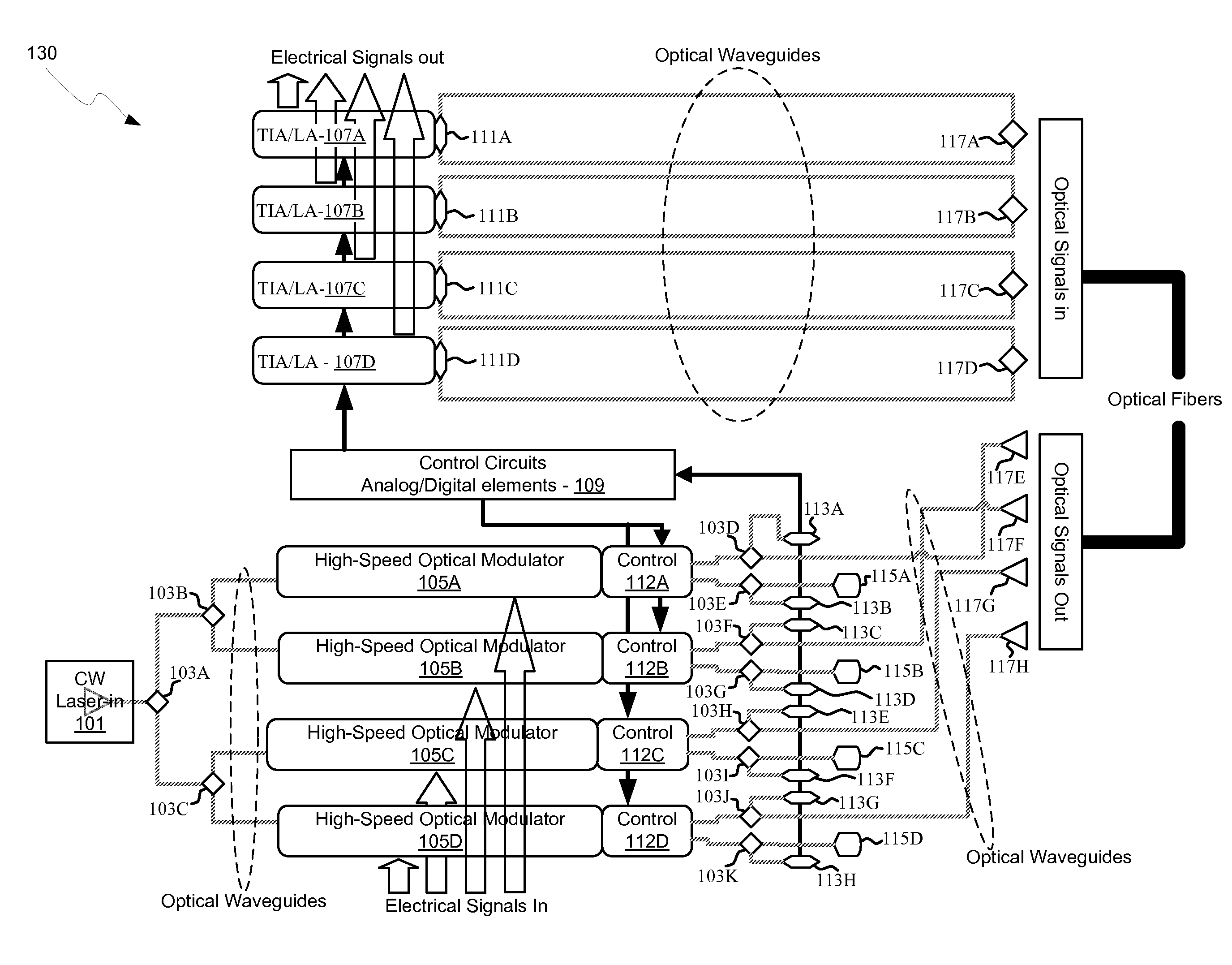

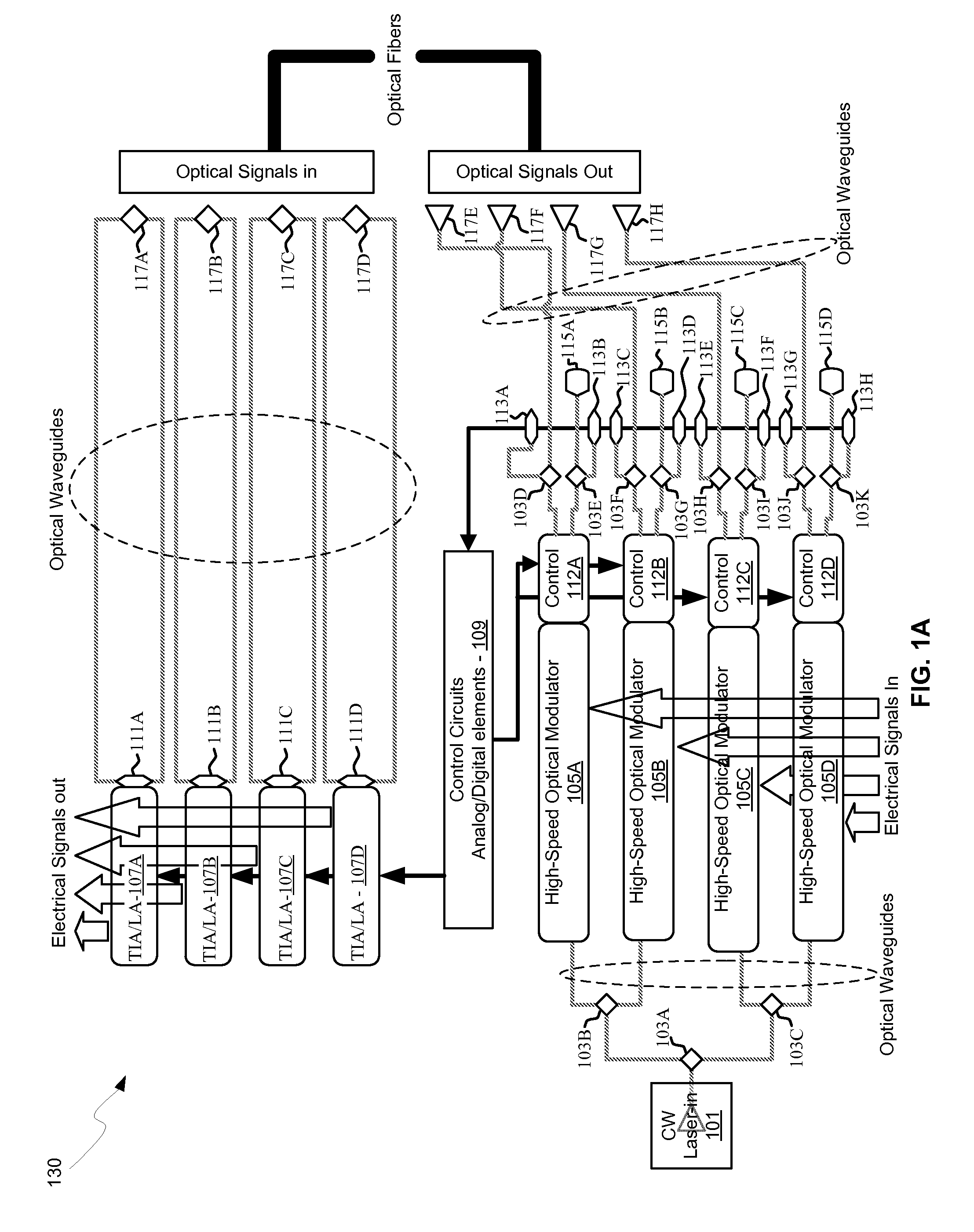

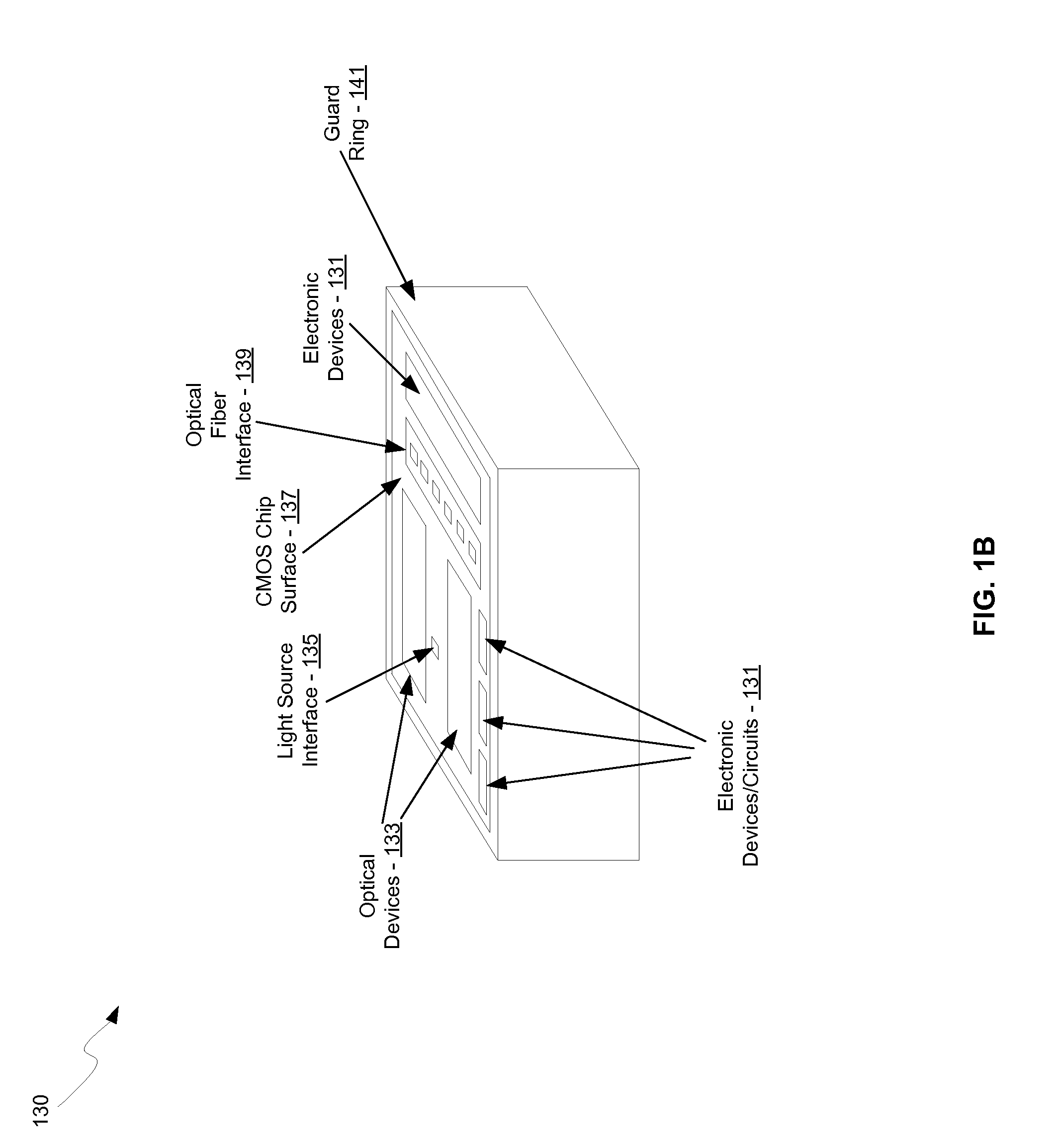

Method and circuit for encoding multi-level pulse amplitude modulated signals using integrated optoelectronic devices

ActiveUS20100060972A1Electromagnetic transmissionNon-linear opticsMach–Zehnder interferometerEngineering

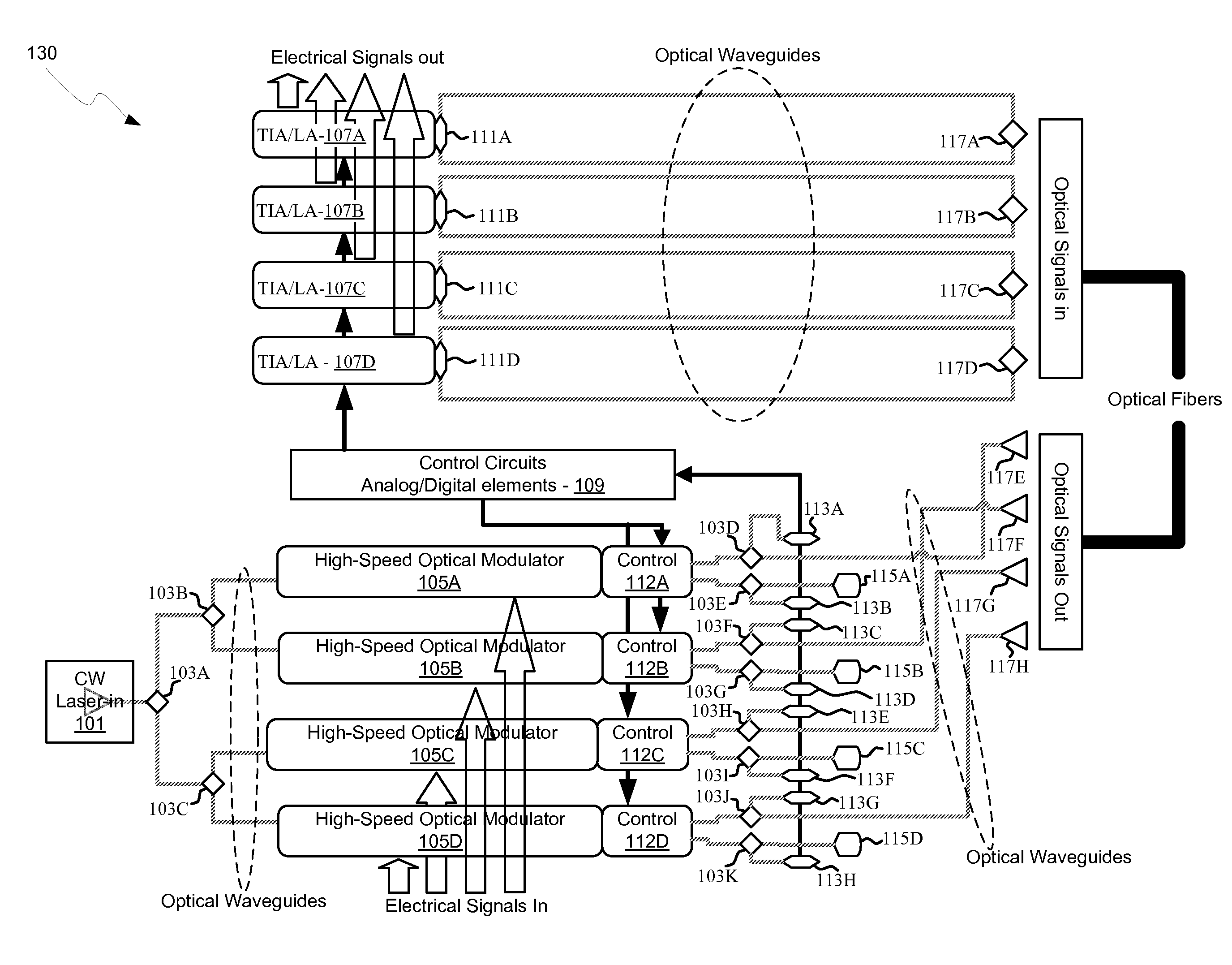

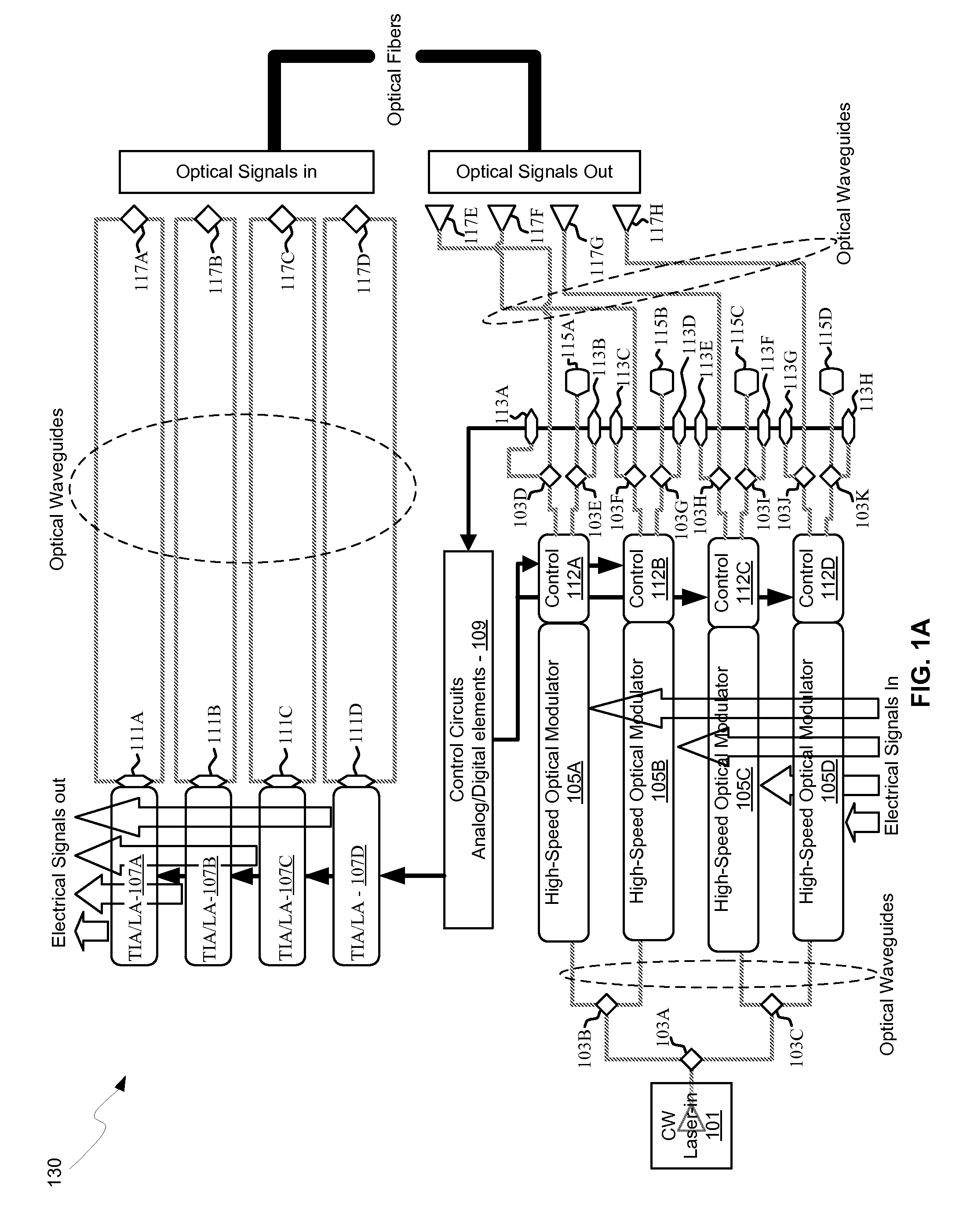

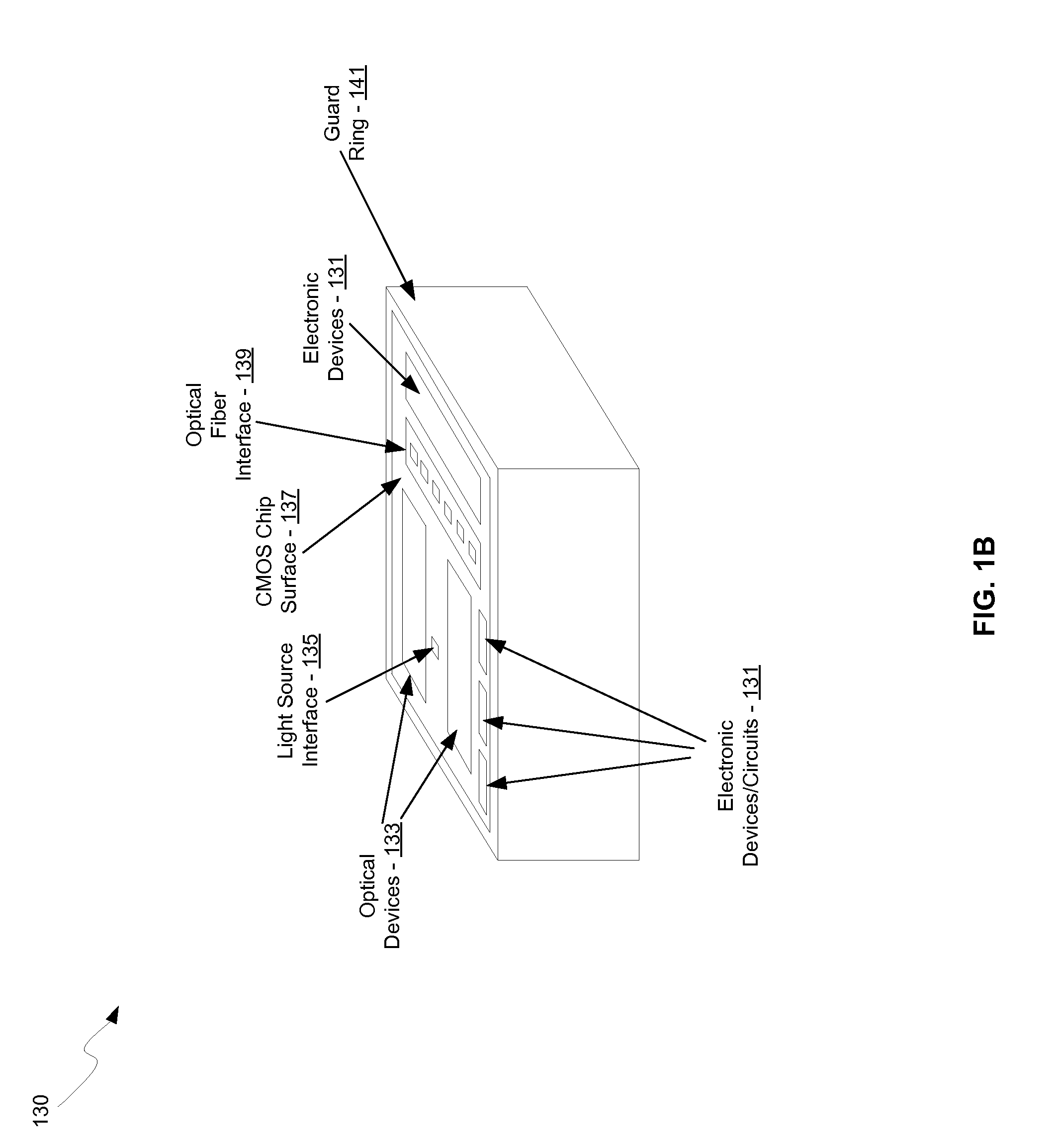

Methods and systems for encoding multi-level pulse amplitude modulated signals using integrated optoelectronics are disclosed and may include generating a multi-level, amplitude-modulated optical signal utilizing an optical modulator driven by two or more electrical input signals. The optical modulator may include optical modulator elements coupled in series and configured into groups. The number of optical modular elements and groups may configure the number of levels in the multi-level amplitude modulated optical signal. Unit drivers may be coupled to each of the groups. The electrical input signals may be synchronized before communicating them to the unit drivers utilizing flip-flops. Phase addition may be synchronized utilizing one or more electrical delay lines. The optical modulator may be integrated on a single substrate, which may include one of: silicon, gallium arsenide, germanium, indium gallium arsenide, polymers, or indium phosphide. The optical modulator may include a Mach-Zehnder interferometer or one or more ring modulators.

Owner:CISCO TECH INC

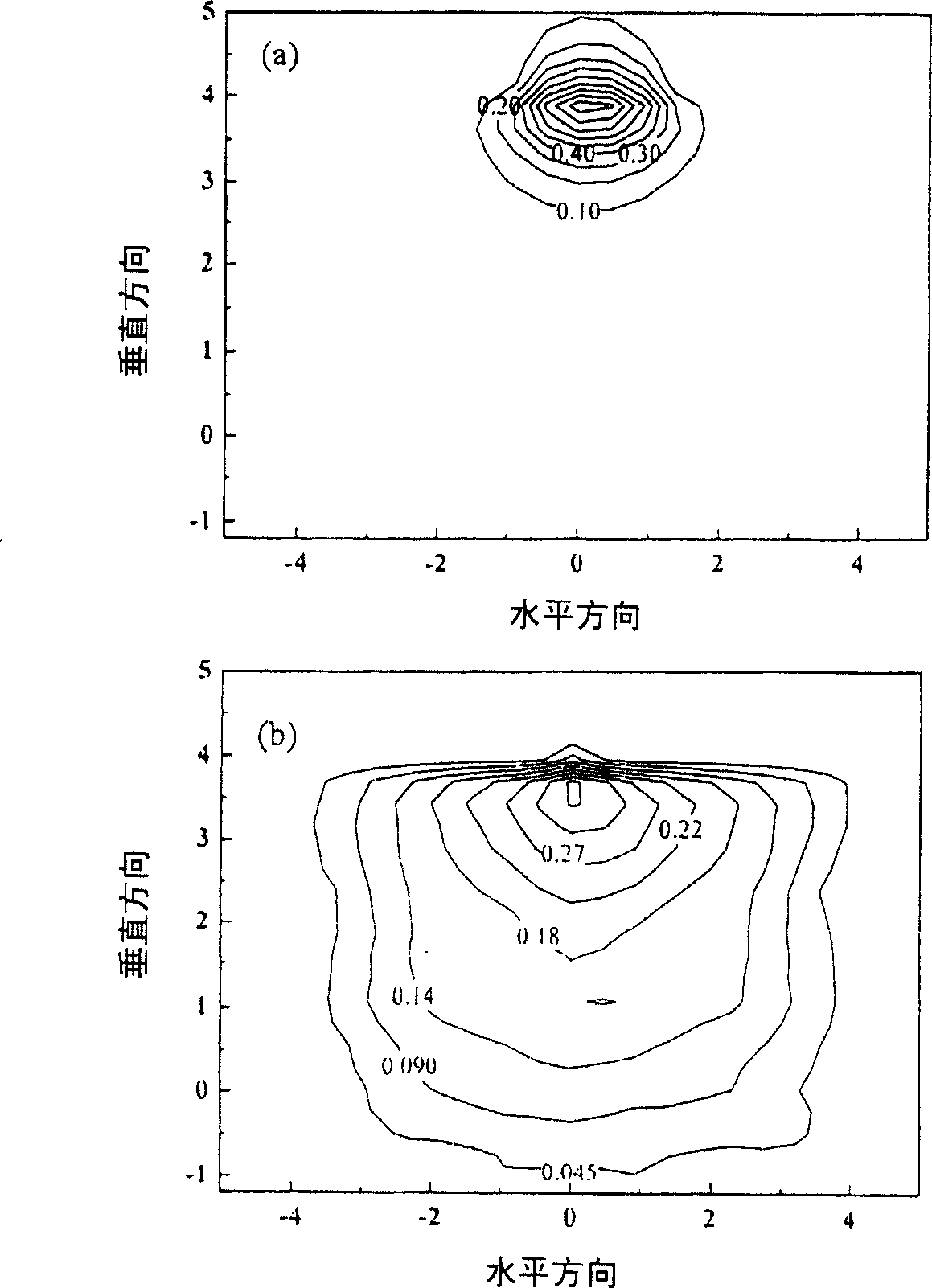

Growth of indium gallium nitride (InGaN) on porous gallium nitride (GaN) template by metal-organic chemical vapor deposition (MOCVD)

InactiveUS20090001416A1Increase indium incorporationLarge emissionsPolycrystalline material growthSemiconductor/solid-state device manufacturingIndiumGallium nitride

Si-doped porous GaN is fabricated by UV-enhanced Pt-assisted electrochemical etching and together with a low-temperature grown buffer layer are utilized as the template for InGaN growth. The porous network in GaN shows nanostructures formed on the surface. Subsequent growth of InGaN shows that it is relaxed on these nanostructures as the area on which the growth takes place is very small. The strain relaxation favors higher indium incorporation. Besides, this porous network creates a relatively rough surface of GaN to modify the surface energy which can enhance the nucleation of impinging indium atoms thereby increasing indium incorporation. It shifts the luminescence from 445 nm for a conventionally grown InGaN structure to 575 nm and enhances the intensity by more than two-fold for the growth technique in the present invention under the same growth conditions. There is also a spectral broadening of the output extending from 480 nm to 720 nm.

Owner:NAT UNIV OF SINGAPORE

Method and circuit for encoding multi-level pulse amplitude modulated signals using integrated optoelectronic devices

ActiveUS8238014B2Electromagnetic transmissionNon-linear opticsMach–Zehnder interferometerEngineering

Methods and systems for encoding multi-level pulse amplitude modulated signals using integrated optoelectronics are disclosed and may include generating a multi-level, amplitude-modulated optical signal utilizing an optical modulator driven by two or more electrical input signals. The optical modulator may include optical modulator elements coupled in series and configured into groups. The number of optical modular elements and groups may configure the number of levels in the multi-level amplitude modulated optical signal. Unit drivers may be coupled to each of the groups. The electrical input signals may be synchronized before communicating them to the unit drivers utilizing flip-flops. Phase addition may be synchronized utilizing one or more electrical delay lines. The optical modulator may be integrated on a single substrate, which may include one of: silicon, gallium arsenide, germanium, indium gallium arsenide, polymers, or indium phosphide. The optical modulator may include a Mach-Zehnder interferometer or one or more ring modulators.

Owner:CISCO TECH INC

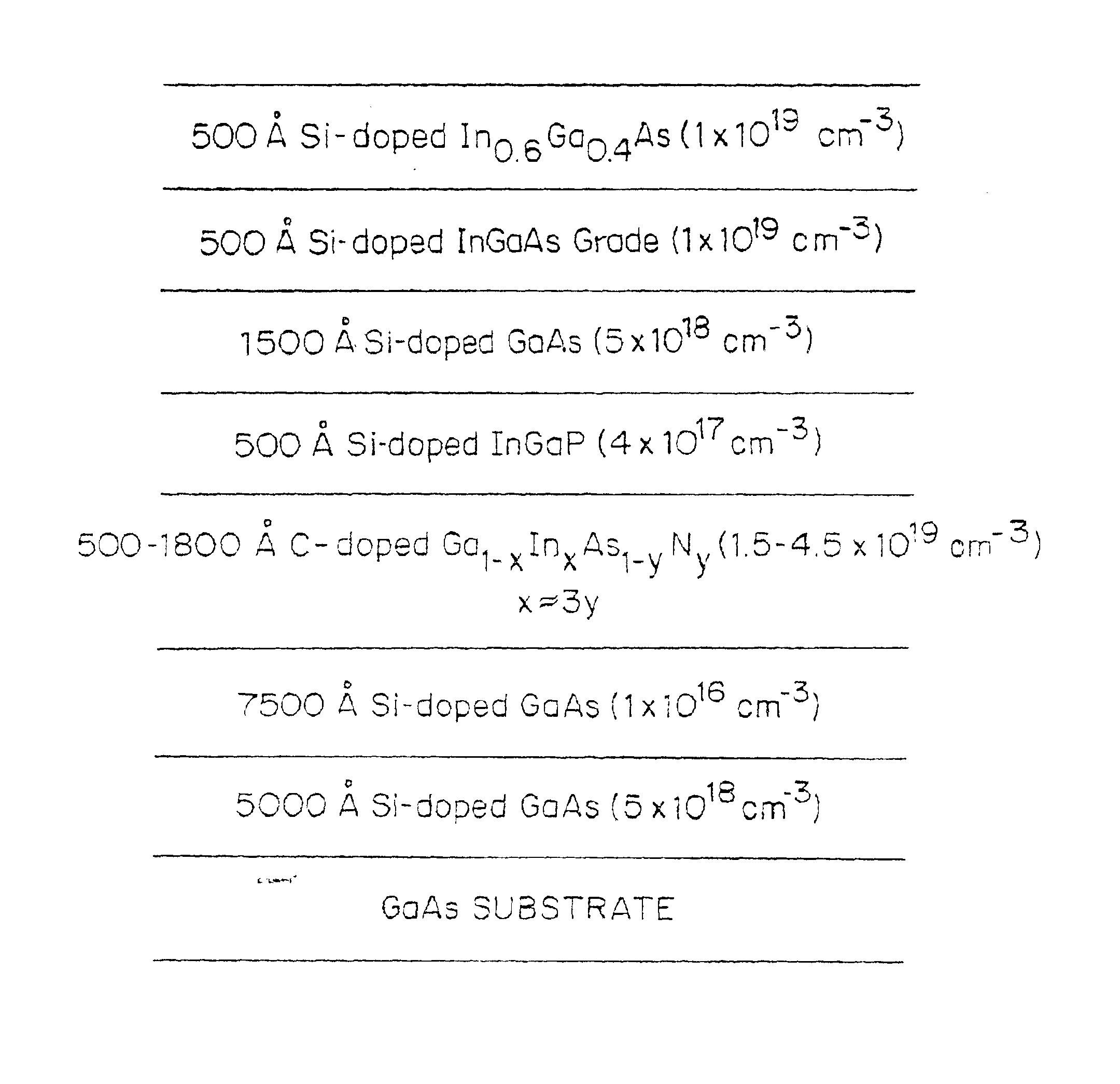

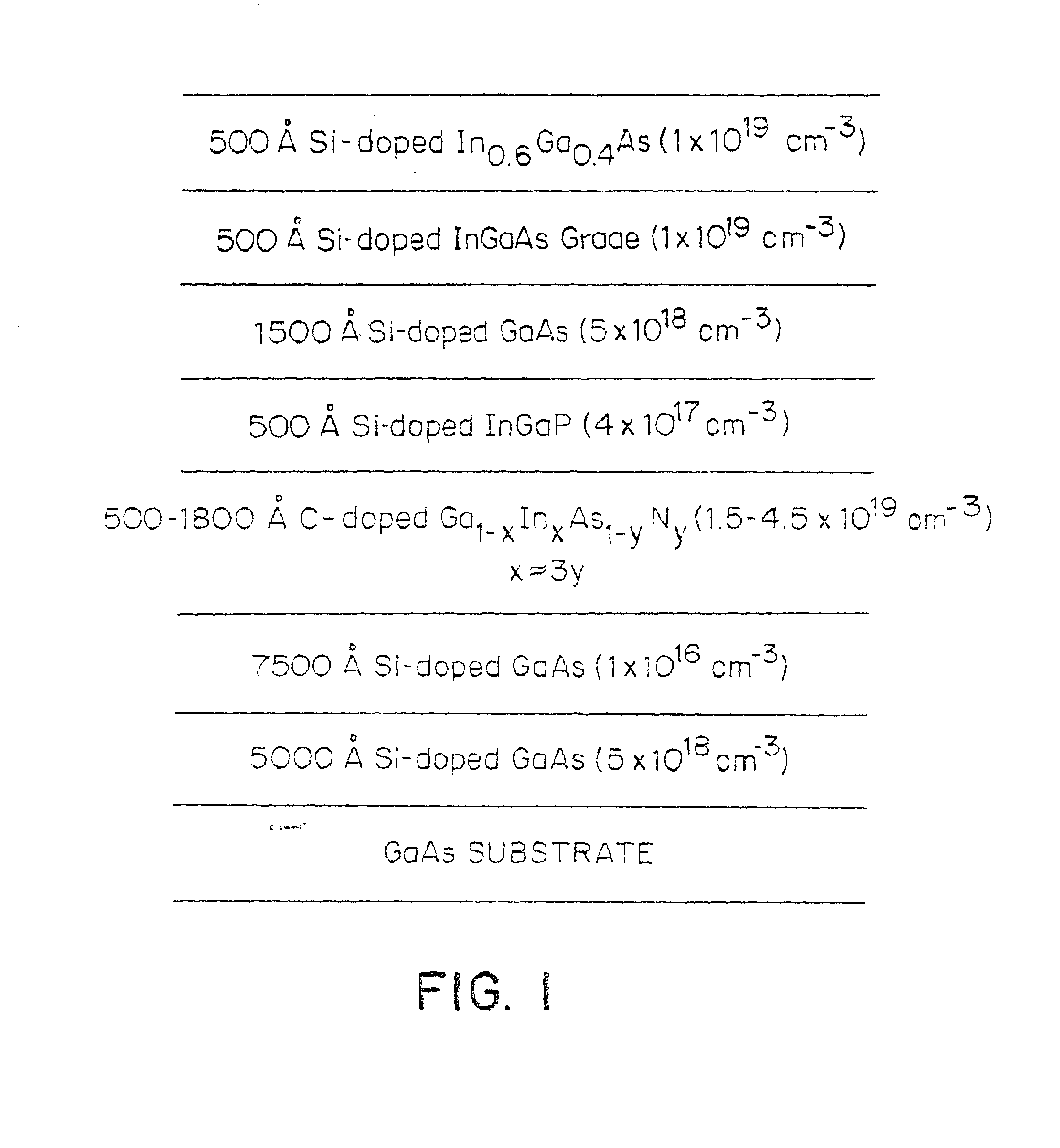

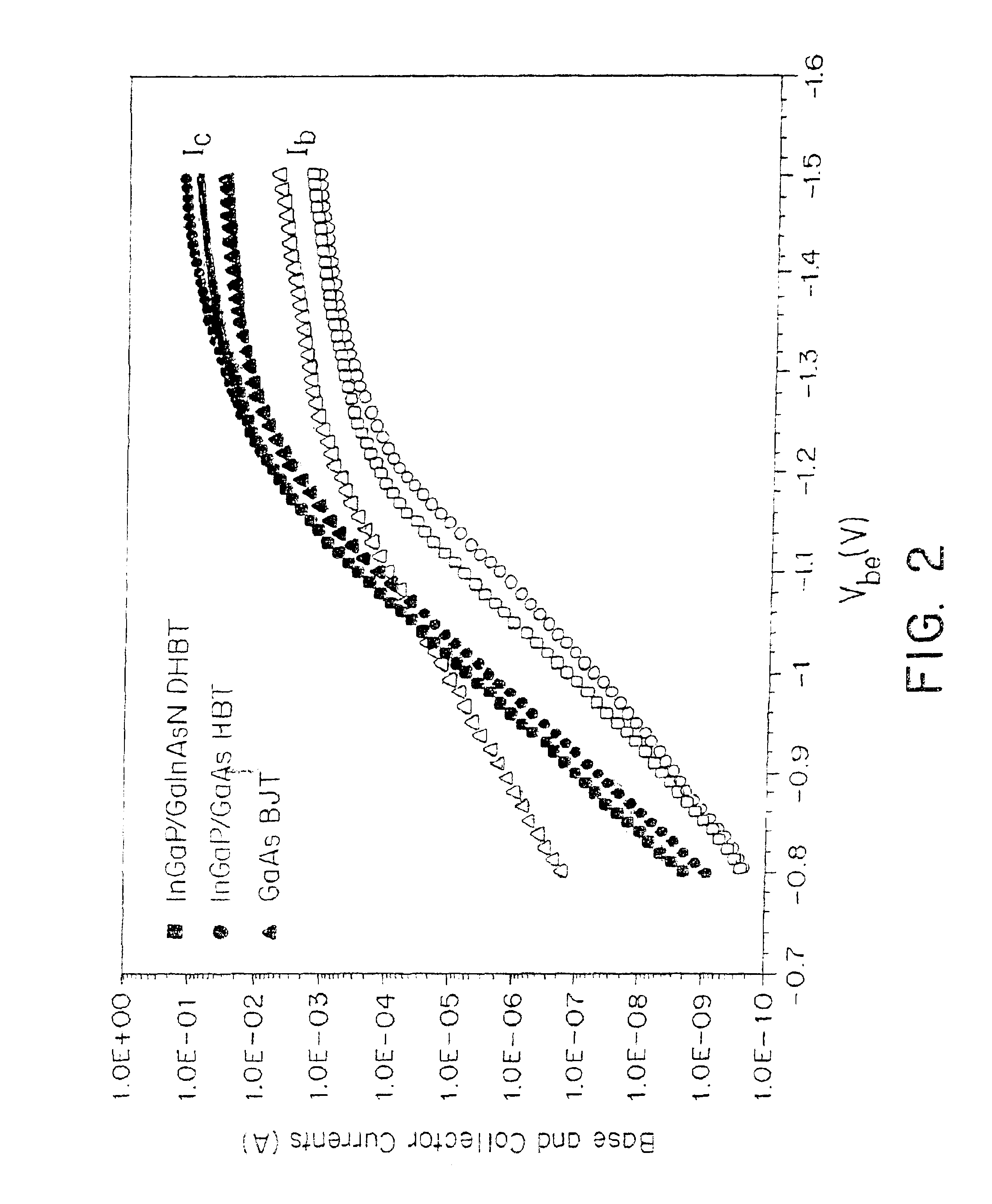

Bipolar transistor with graded base layer

InactiveUS6847060B2Easy to manageImprove RF performanceSemiconductor/solid-state device manufacturingThermoelectric device junction materialsHeterojunctionSemiconductor materials

A semiconductor material which has a high carbon dopant concentration includes gallium, indium, arsenic and nitrogen. The disclosed semiconductor materials have a low sheet resistivity because of the high carbon dopant concentrations obtained. The material can be the base layer of gallium arsenide-based heterojunction bipolar transistors and can be lattice-matched to gallium arsenide emitter and / or collector layers by controlling concentrations of indium and nitrogen in the base layer. The base layer can have a graded band gap that is formed by changing the flow rates during deposition of III and V additive elements employed to reduce band gap relative to different III-V elements that represent the bulk of the layer. The flow rates of the III and V additive elements maintain an essentially constant doping-mobility product value during deposition and can be regulated to obtain pre-selected base-emitter voltages at junctions within a resulting transistor.

Owner:IQE KC

Silica tube for growing semi-insulated gallium arsenide and method for doping carbon in gallium arsenide

InactiveCN101603208AGood electrical uniformityC concentration is easy to controlPolycrystalline material growthDiffusion/dopingCrucibleGraphite

The invention relates to a method for doping carbon in the gallium arsenide by using a silica tube for growing semi-insulated gallium arsenide. The method comprises the following steps: step 1: polycrystally synthesizing 7N Ga and 7N As to form a GaAs polycrystal; step 2: putting the synthesized GaAs polycrystal, seed crystal and B2O3 in a PBN crucible; step 3: putting the PBN crucible in a quartz body of the silica tube; step 4: fixing pure graphite in a silica groove on a silica cap of the silica tube; step 5: covering the quartz body and the silica cap, vacuumizing and welding the quartz body and the silica cap of the silica tube on oxyhydrogen flame; step 6: putting the welded silica tube in a VGF single crystal furnace for atmosphere doping and single crystal growth; and step 7: soaking the PBN crucible in methanol after the single crystal growth to obtain a GaAs single crystal and finish the preparation of the GaAs single crystal.

Owner:INST OF SEMICONDUCTORS - CHINESE ACAD OF SCI

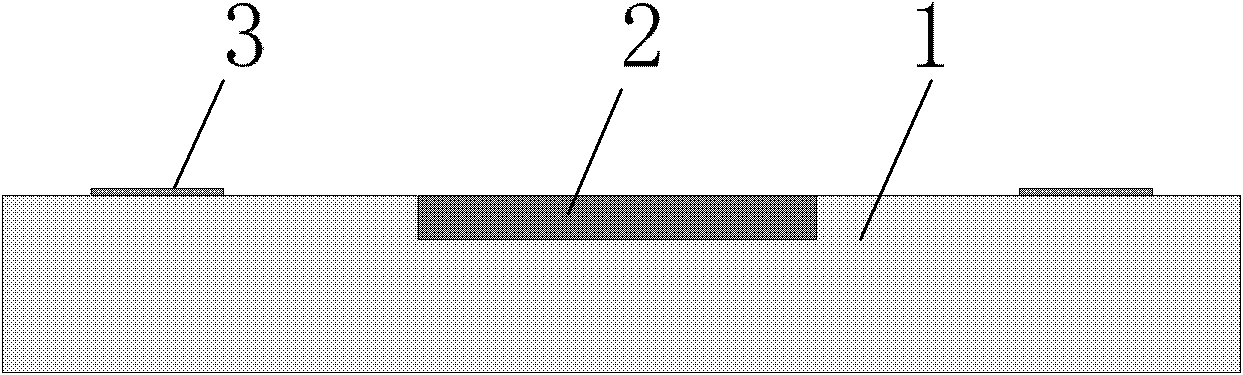

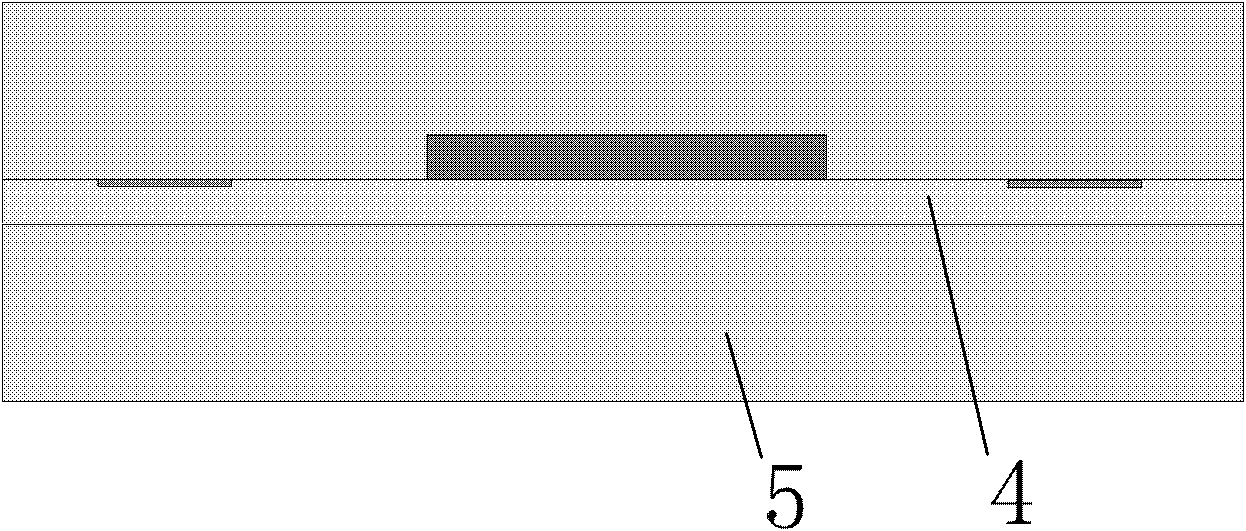

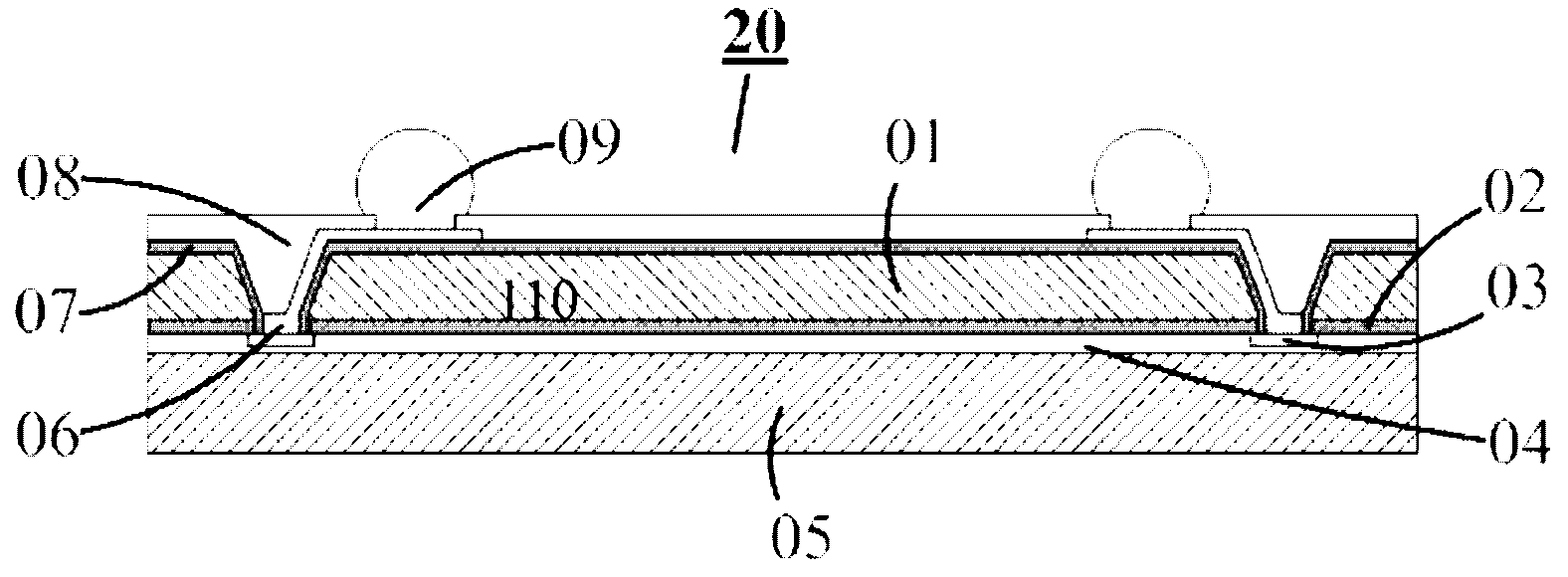

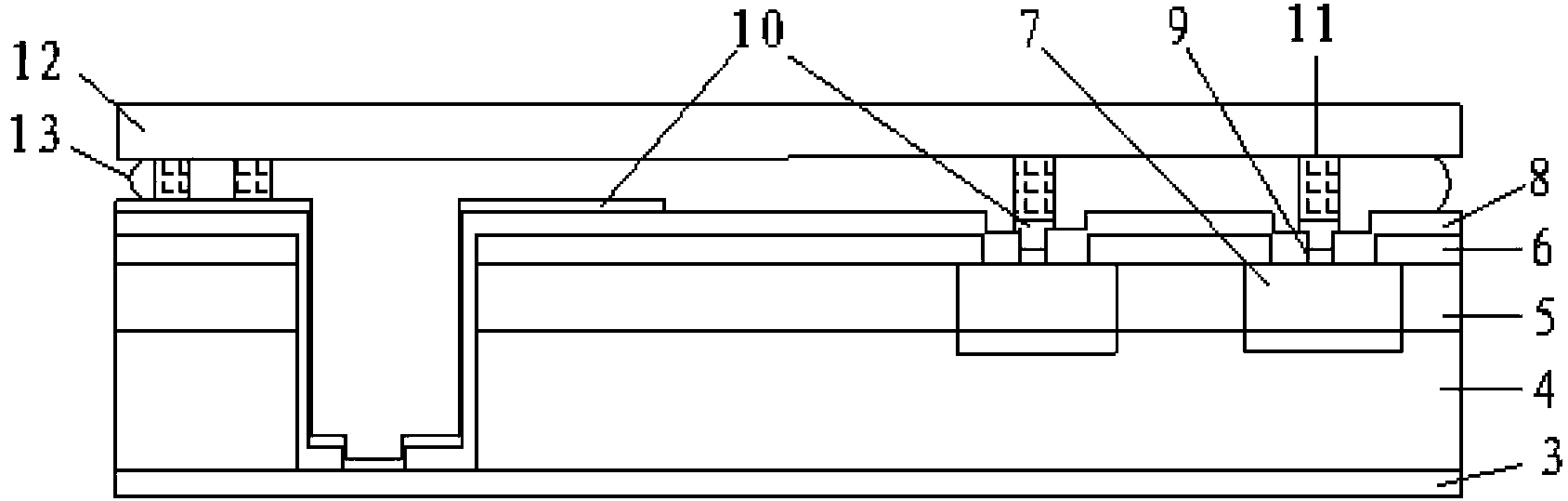

Method utilizing TSV (Through-Silicon-Via) to realize wafer level package of GaAs (gallium arsenide) image sensor

InactiveCN102544040AReduce volumeImprove package reliabilitySemiconductor/solid-state device manufacturingRadiation controlled devicesEtchingInterconnection density

The invention relates to a method utilizing TSV (Through-Silicon-Via) to realize wafer level package of a GaAs (gallium arsenide) image sensor. The method comprises the following steps: combining wet etching with mechanical machining to machine a groove; manufacturing a resin insulating layer in the groove; then manufacturing a through hole in resin by using a laser method; electroplating the inner part of the groove and the inner part of the through hole to realize the back extraction of the electrode of a front wafer surface; and making a passivating layer and solder bumps. The whole process is completed at a wafer level, and the interconnection density is high while the package cost is reduced. Meanwhile, a manufactured interconnection structure has high reliability.

Owner:SHANGHAI INST OF MICROSYSTEM & INFORMATION TECH CHINESE ACAD OF SCI

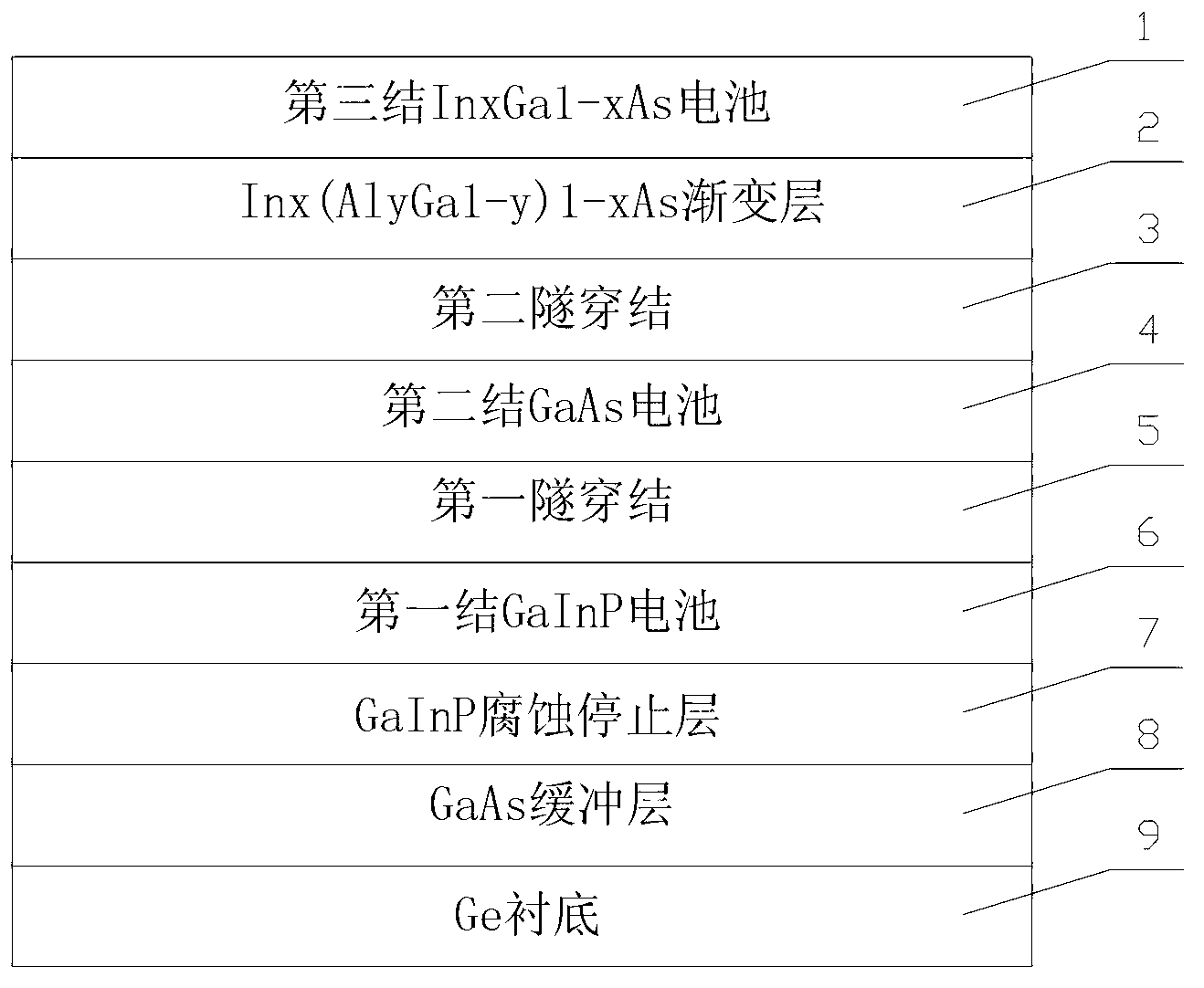

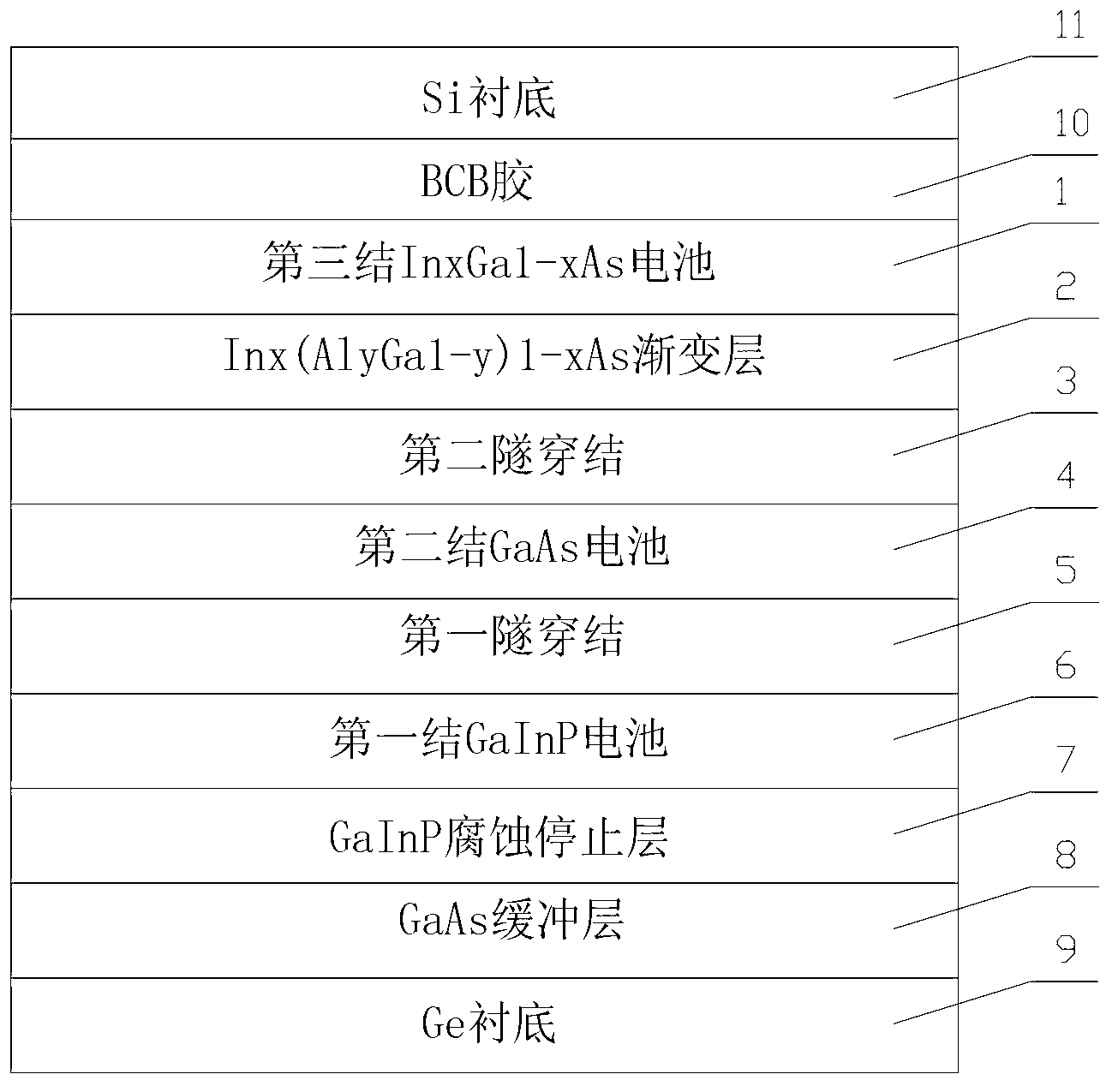

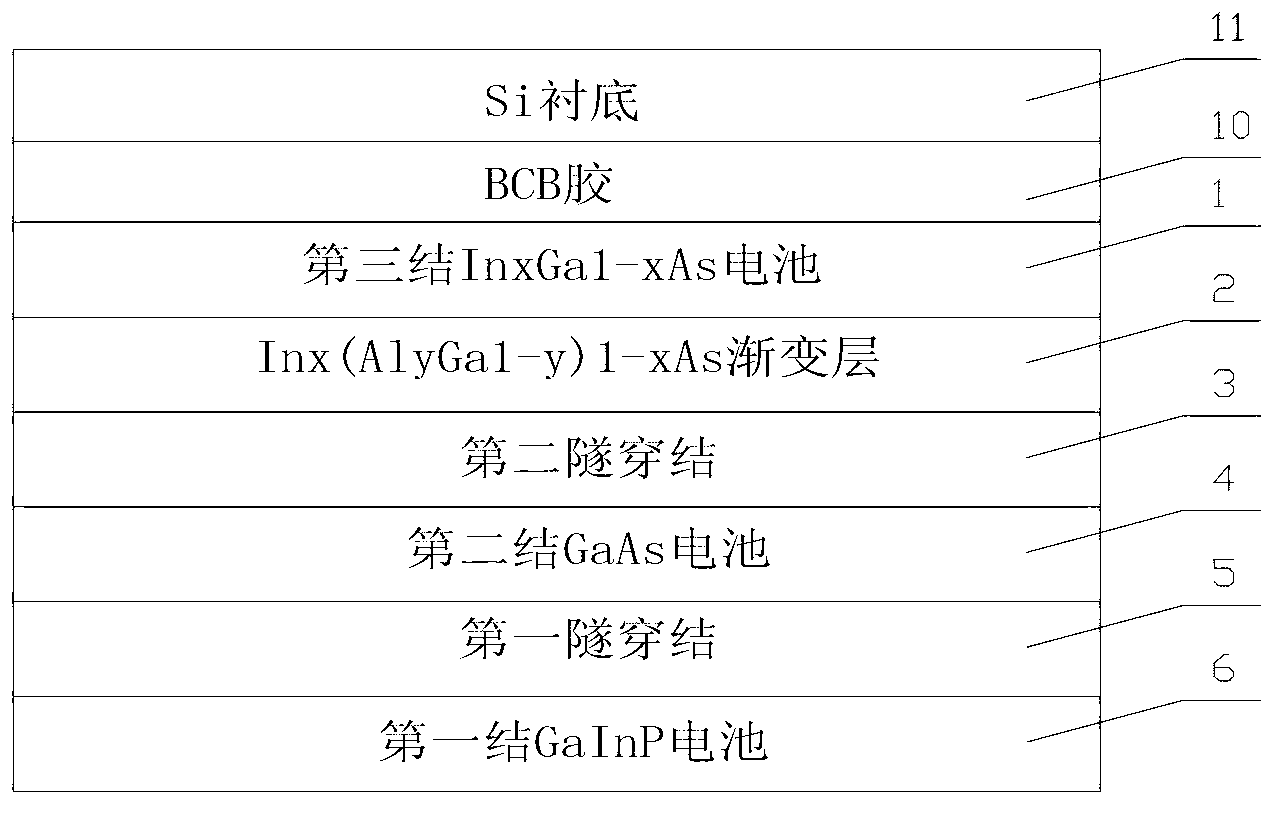

Preparation method of gallium arsenide thin-film multijunction stacked solar cells

ActiveCN103000759AImprove uniformityImprove reliabilityRenewable energy productsSemiconductor devicesIntermediate cellLow cost substrate

The invention relates to a preparation method of gallium arsenide thin-film multijunction stacked solar cells. The preparation method is characterized by including the steps of firstly, allowing for reverse growth of an epitaxial layer to prepare a GaAs three-junction solar cell; secondly, bonding the cell prepared in the step 1 to a Si substrate; thirdly, stripping a Ge substrate; fourthly, adhering a low-cost substrate; and fifthly, stripping the Si substrate. The preparation method allows for epitaxial growth of a top cell and an intermediate cell prior to growth of a bottom cell, and accordingly the lattice subjected to epitaxial growth firstly is guaranteed to match with perfect epitaxial growth of the top cell and the intermediate cell; doping uniformity and film reliability in large-area epitaxial thin films are increased, and photoelectric conversion efficiency is further improved; by the use of the low-cost support substrate lower than Ge in specific weight, the weight of the cells is reduced, the power ratio of the solar cells is increased, the cost of the cells is reduced effectively, and application prospect of the III-V compound solar cells is improved greatly.

Owner:TIANJIN LANTIAN SOLAR TECH +2

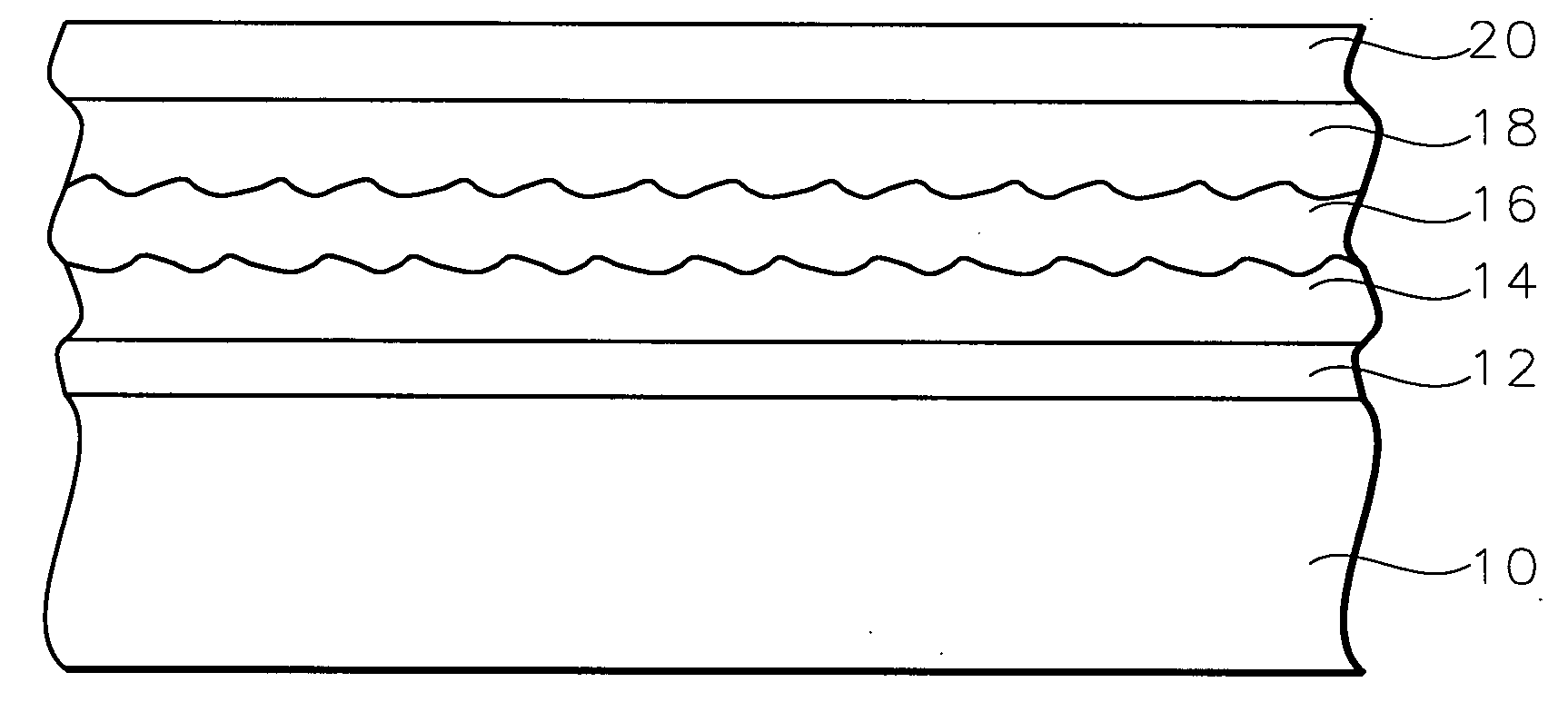

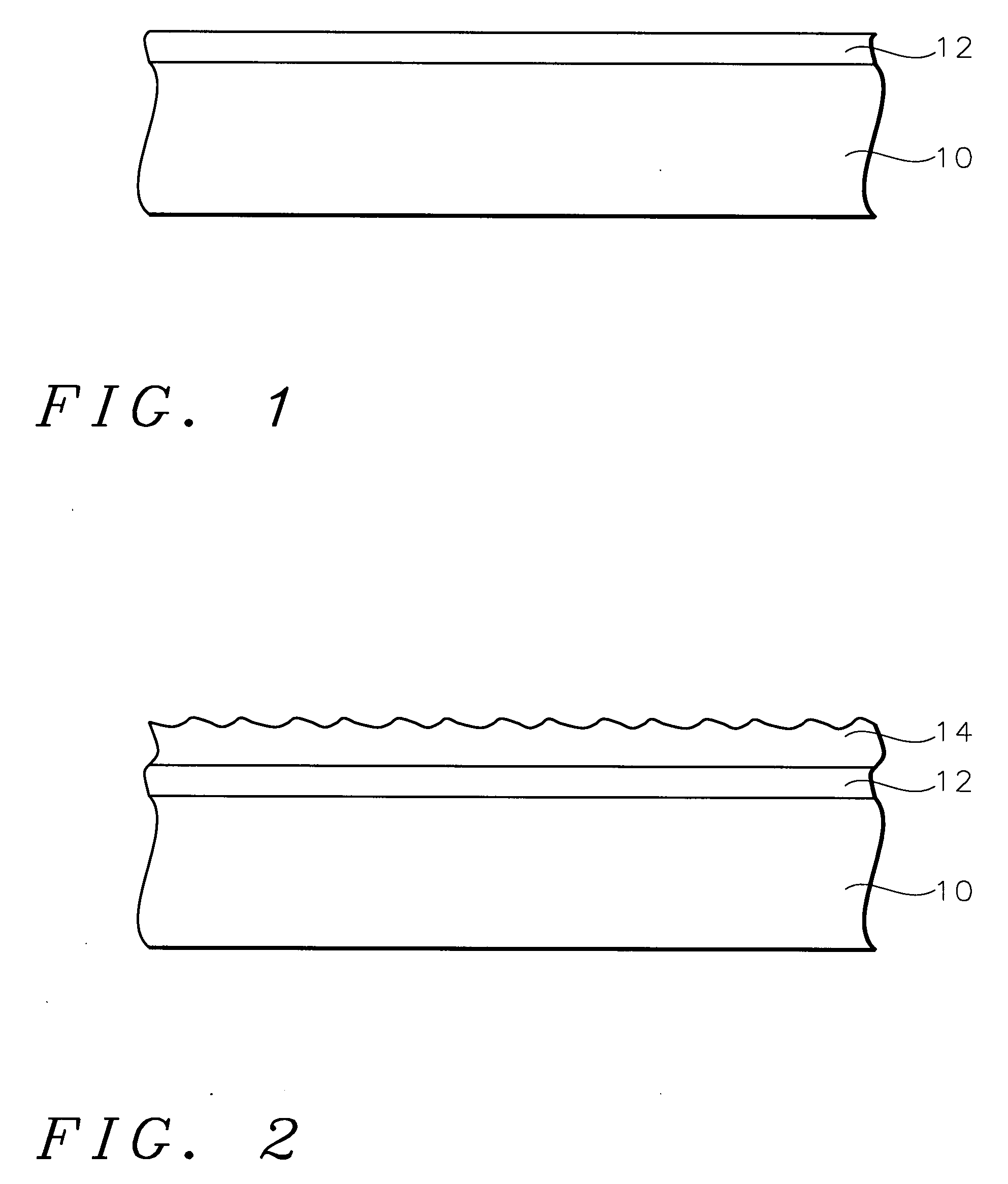

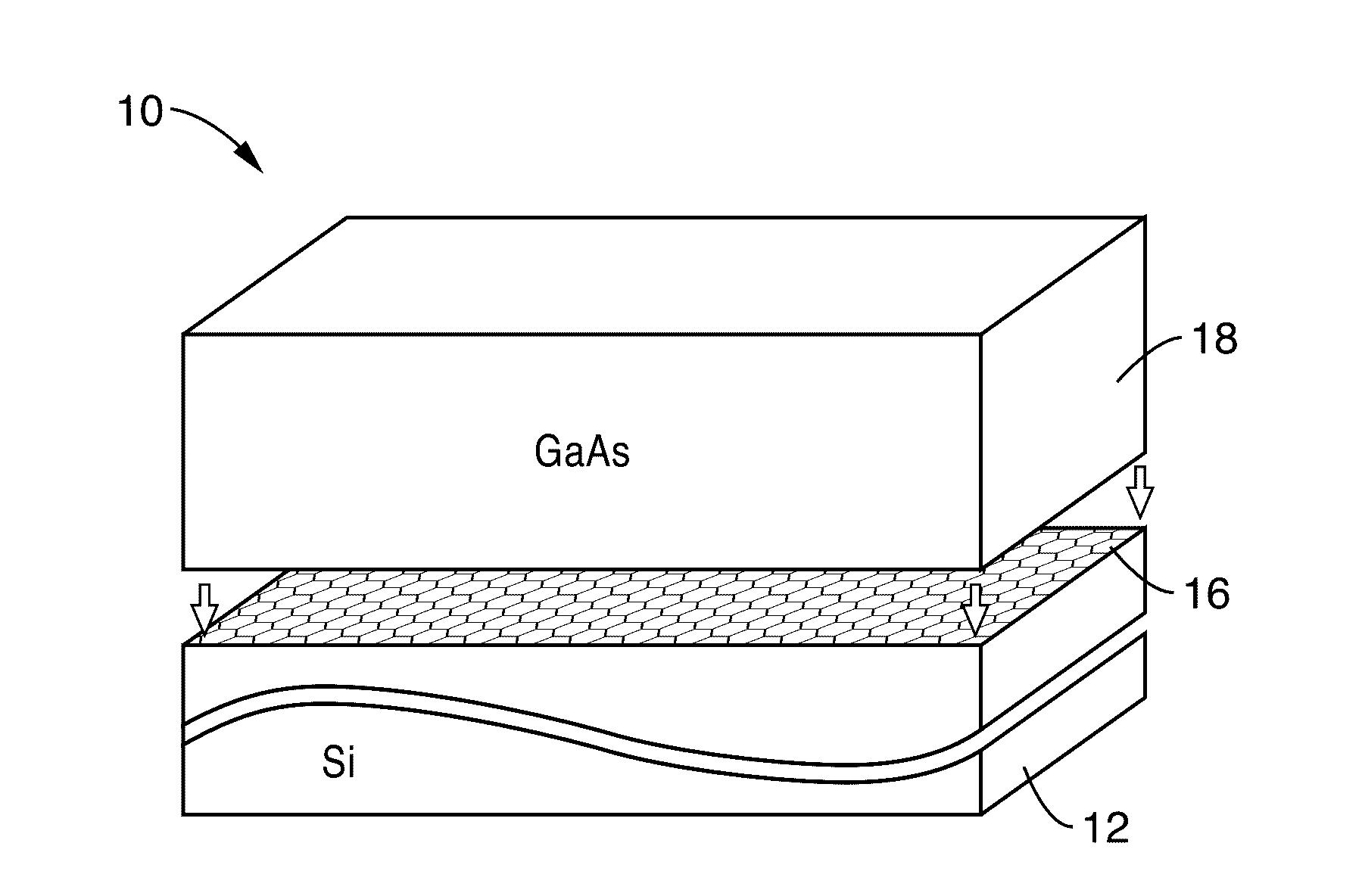

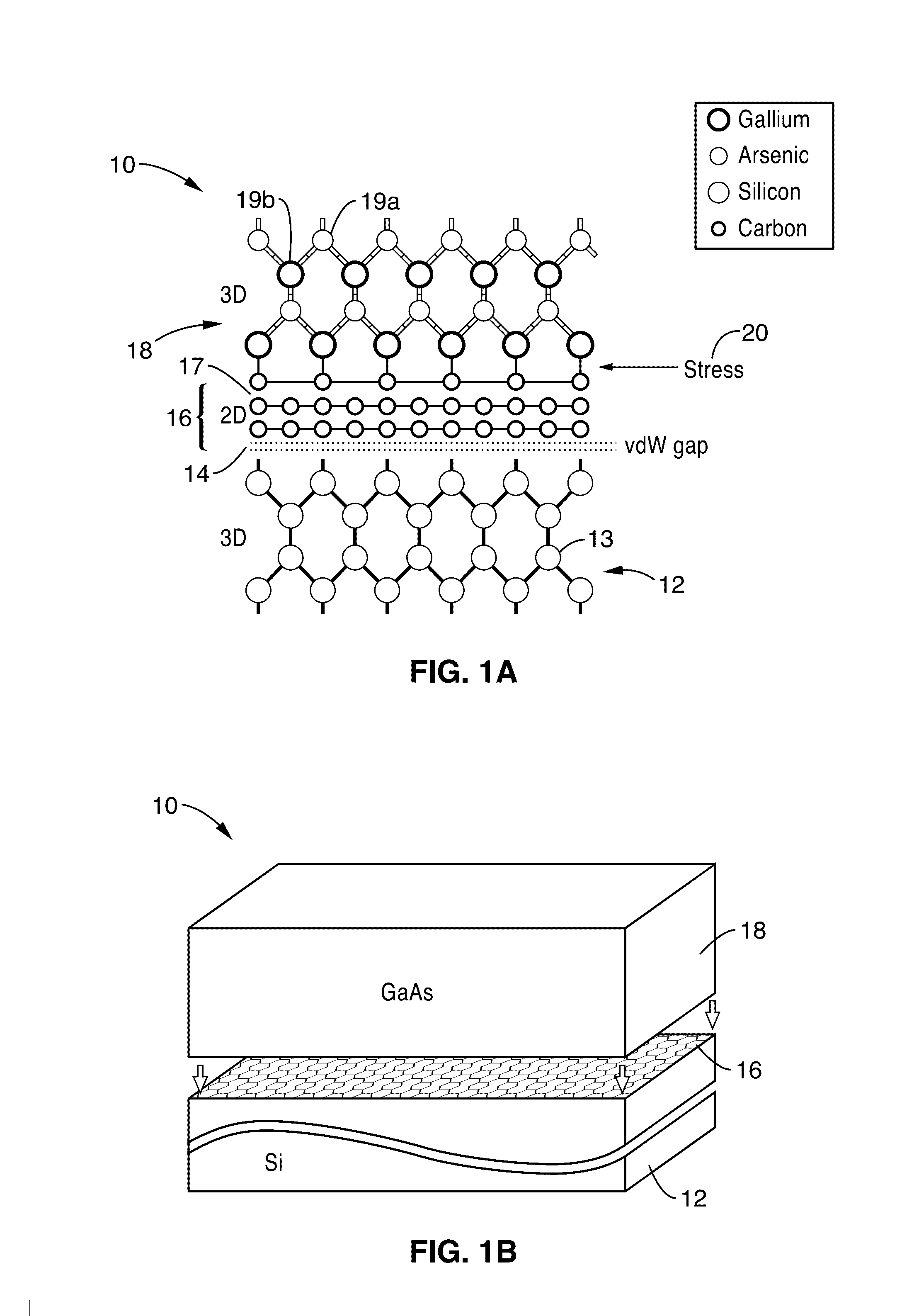

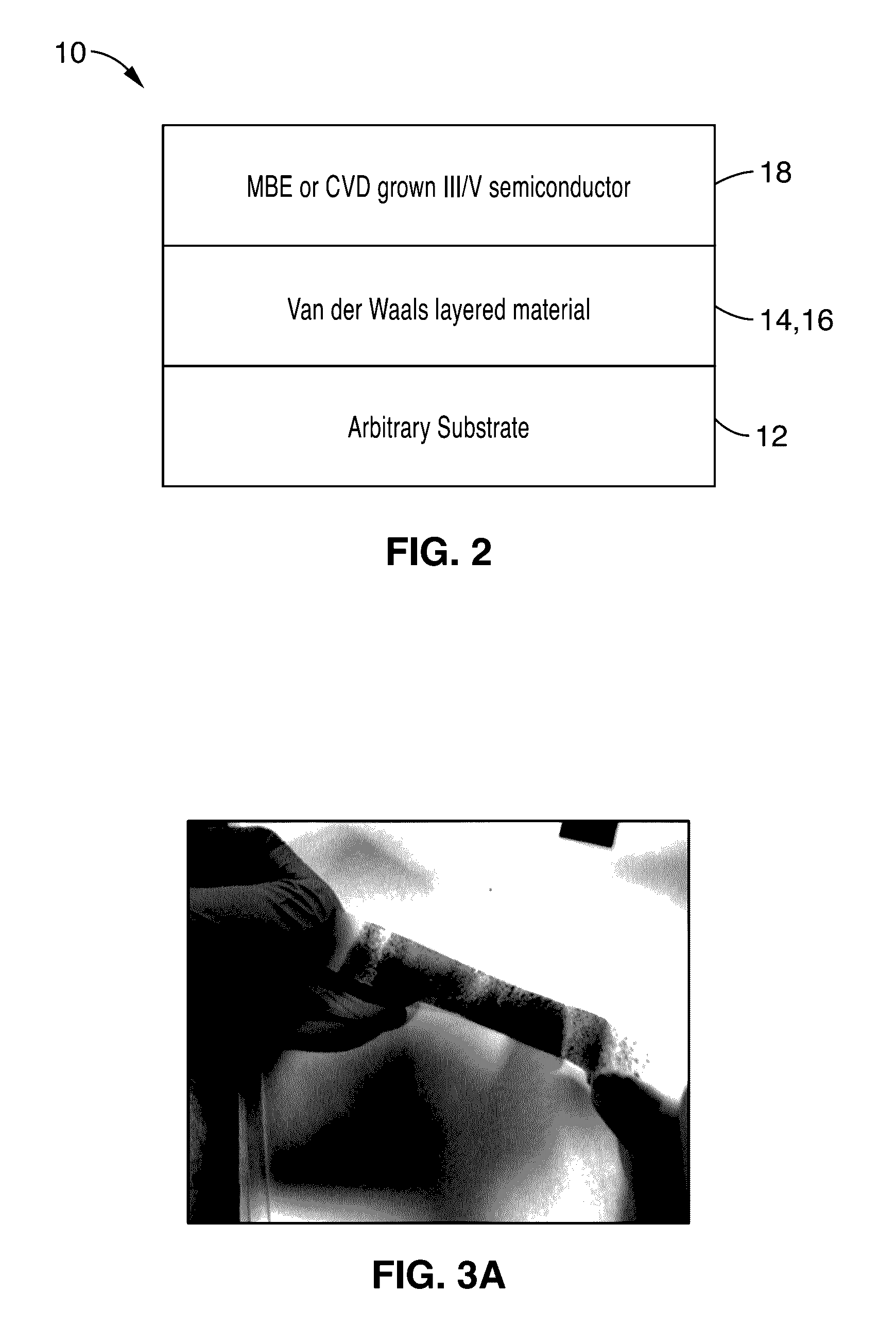

Epitaxial growth of gallium arsenide on silicon using a graphene buffer layer

InactiveUS20170047223A1Improve efficiencySemiconductor/solid-state device manufacturingSemiconductor devicesSemiconductor materialsLattice mismatch

Epitaxial growth of gallium arsenide (GaAs) on a semiconductor material (e.g., Si) using quasi-van der Waals Epitaxy (QvdWE). Prior to GaAs growth a buffer layer (e.g., graphene) is deposited which relieves lattice mismatch / thermal expansion. The low energy of the graphene surface and the GaAs / graphene interface is overcome through an optimized growth technique to obtain an atomically smooth low-temperature GaAs nucleation layer. The disclosure can be applied to optimize epitaxial thin film growth of other materials, (e.g., III-V semiconductors, such as InP, GaSb) on Si using van der Waals buffer layers such as graphene.

Owner:KING ABDULAZIZ CITY FOR SCIENCE AND TECHNOLOGY +1

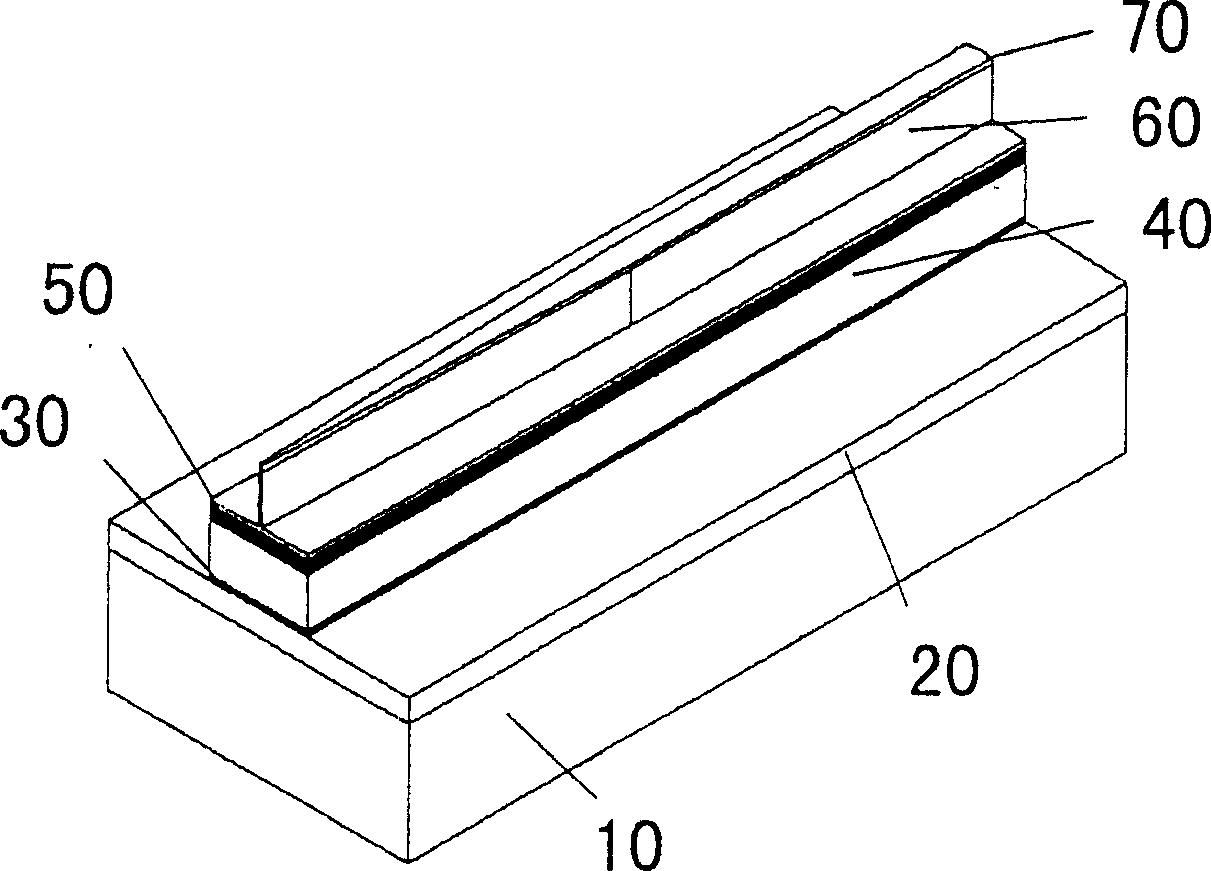

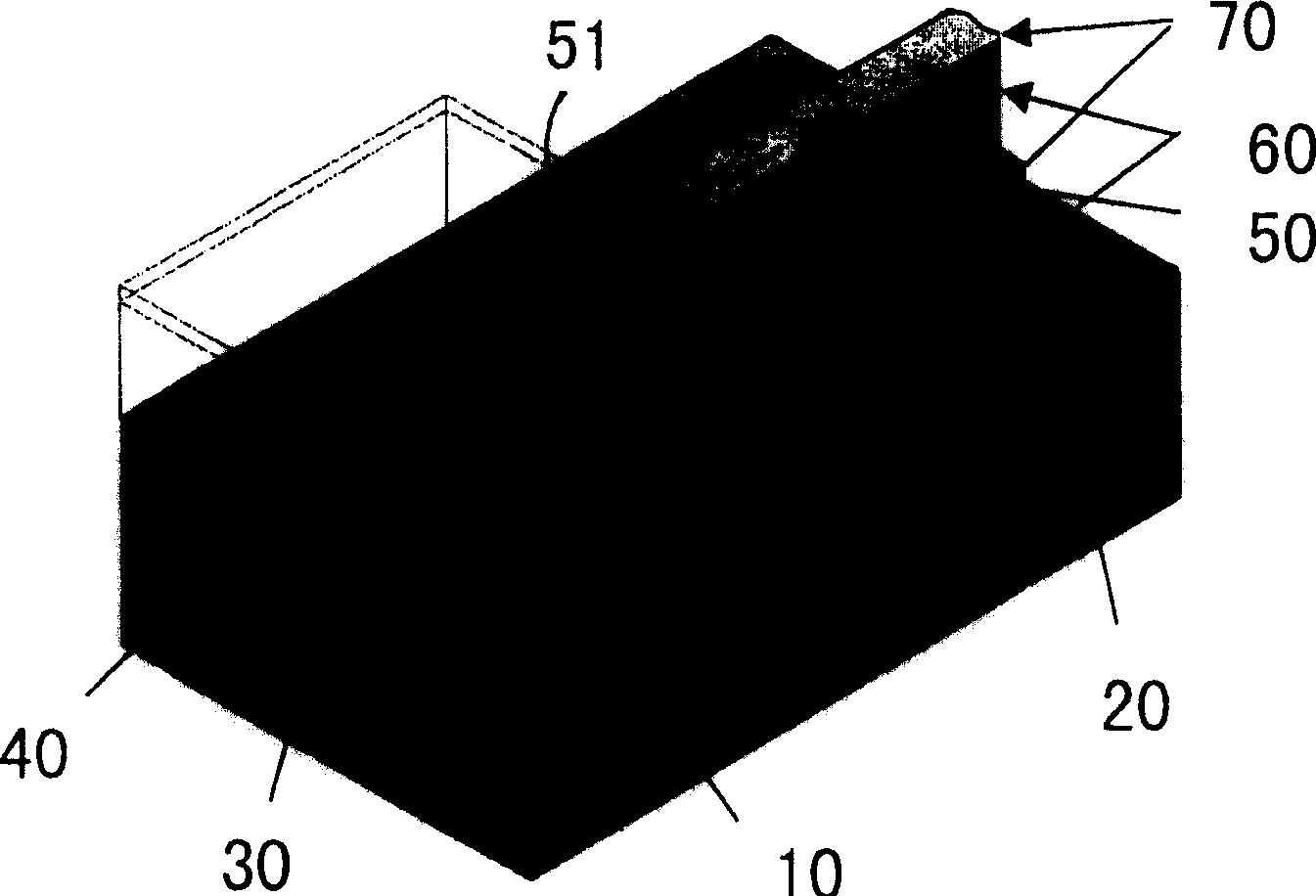

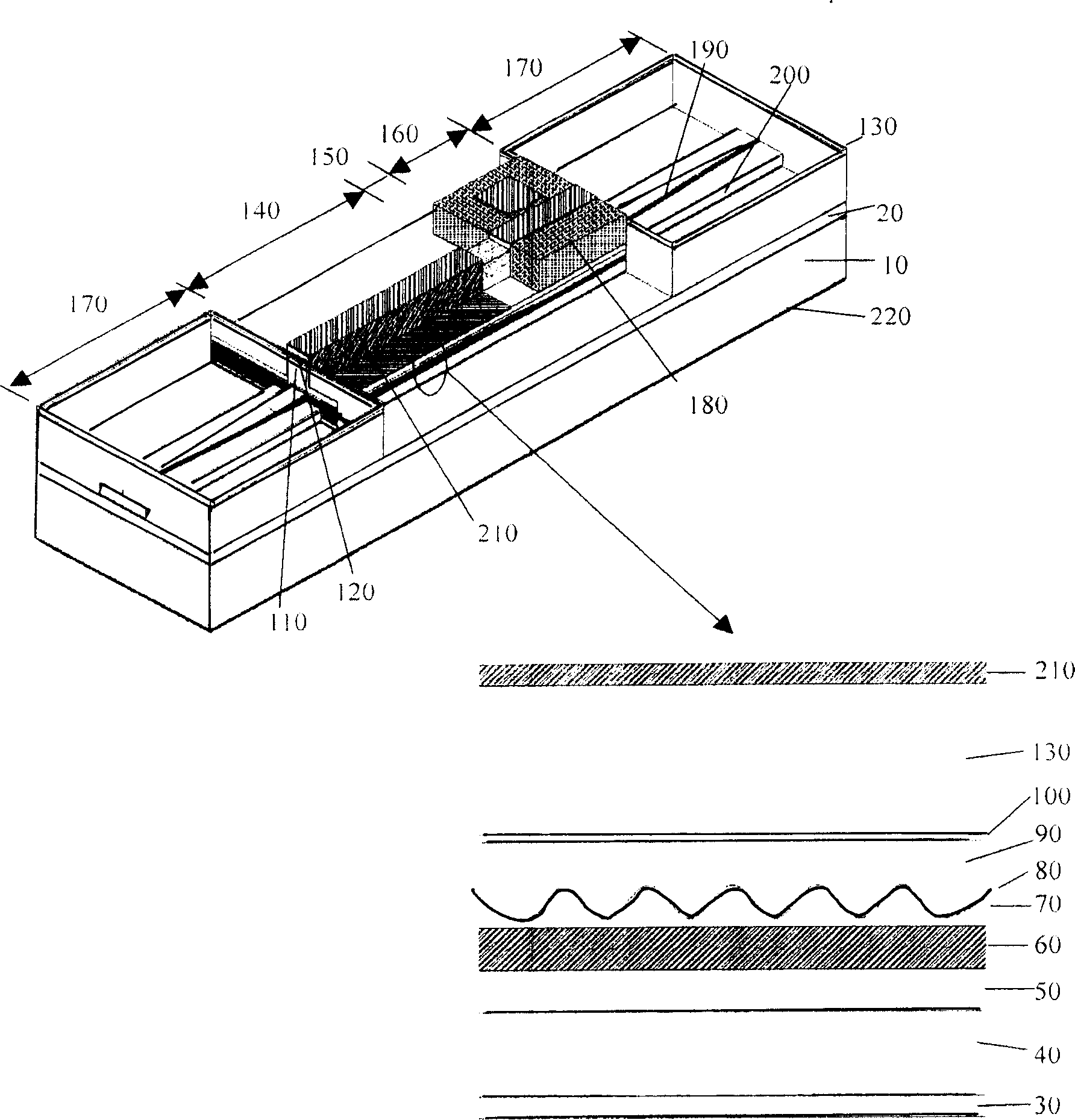

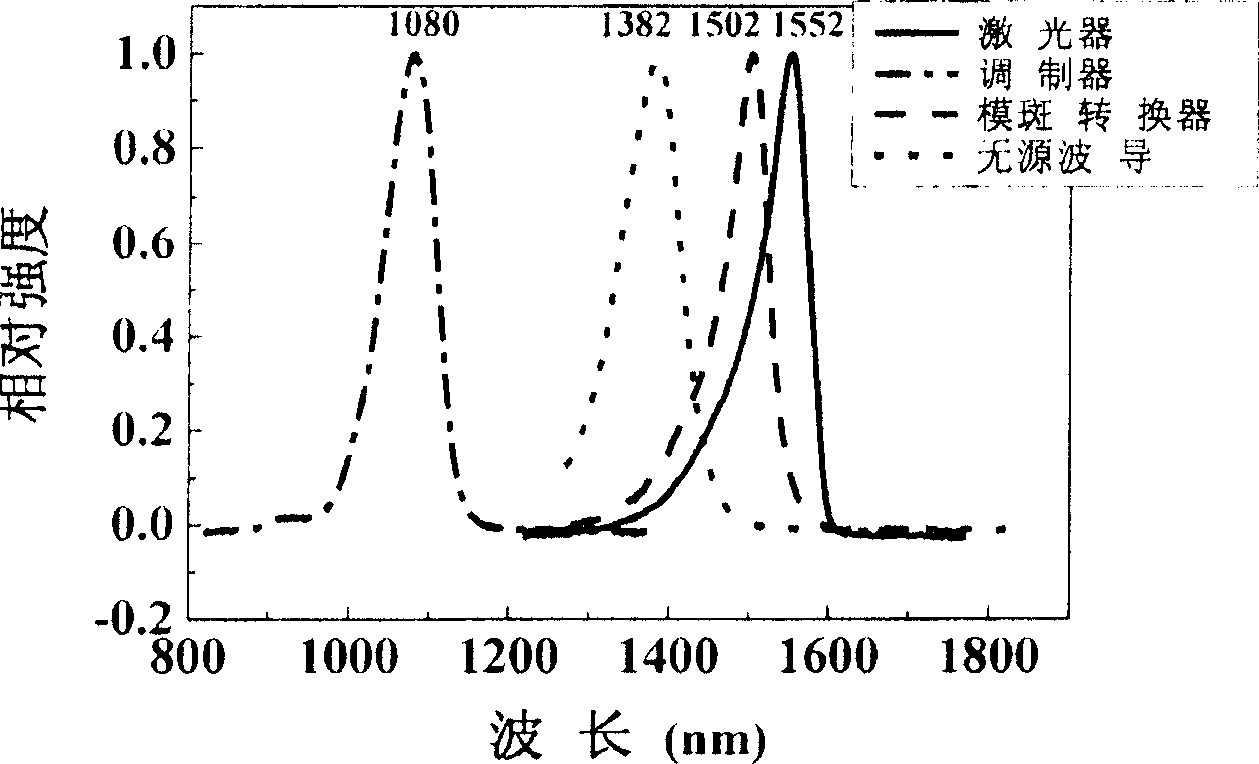

Method for forming semiconductor laser and spot-size converter by once epitaxy

InactiveCN1756008AReduce pollutionLow costLaser detailsSemiconductor lasersTime extensionSemiconductor package

Disclosed a method for one time extension forming the semiconductor laser and mode spot switch comprises following steps: (1), on the N type indium phosphide substrate, extending growing the N type indium phosphide breaker, a lower waveguide layer, a 2.4 ª–m indium phosphide space layer, a lower light-limited layer of active region, a compression strain quanta active region, a upper light-limited layer, a P type indium phosphide envelope, and a high doping P type indium gallium arsenide ohmic electrode contract layer; (2), utilizing the wet corrosion process to etch the upper carinate shape of laser and mode spot switch; (3) utilizing the auto-alignment process to etch the lower carinate shape; (4), growing the SiO2 insulating layer and opening a electrode window; (5) decreasing the substrate of extended plate to 100 ª–m, and manufacturing P / N electrodes to be scribed into the tube core of 250í‡600ª–m.

Owner:INST OF SEMICONDUCTORS - CHINESE ACAD OF SCI

RTD diode of indium gallium nitride emitting electrode ohmic contact layer and manufacturing method thereof

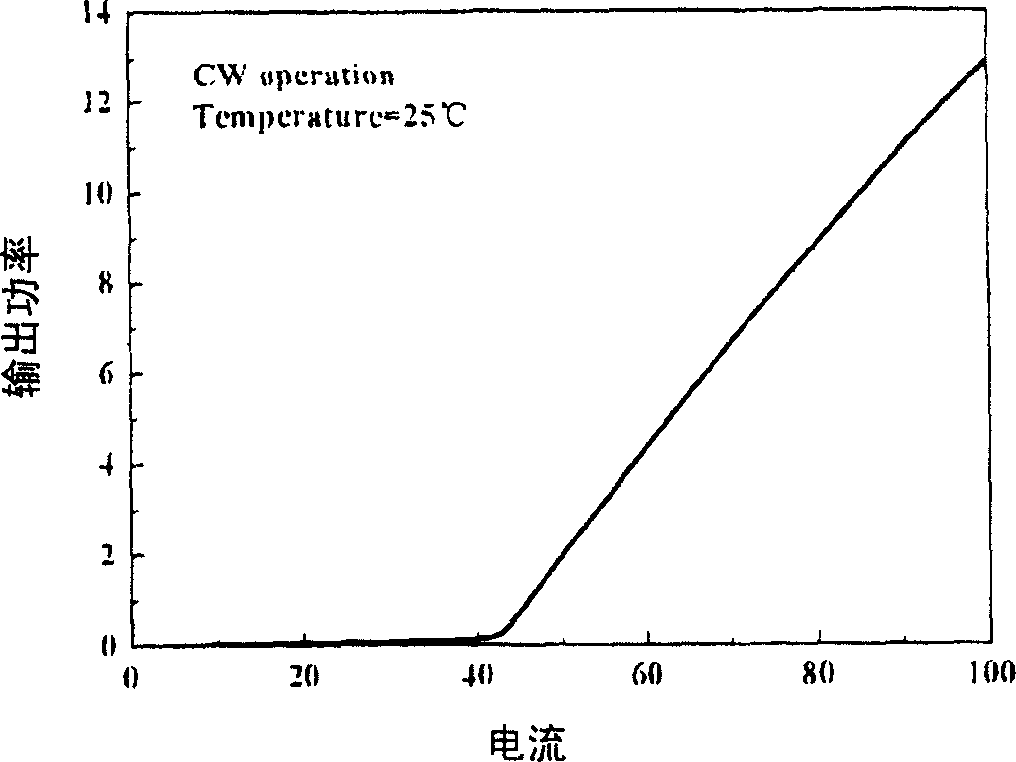

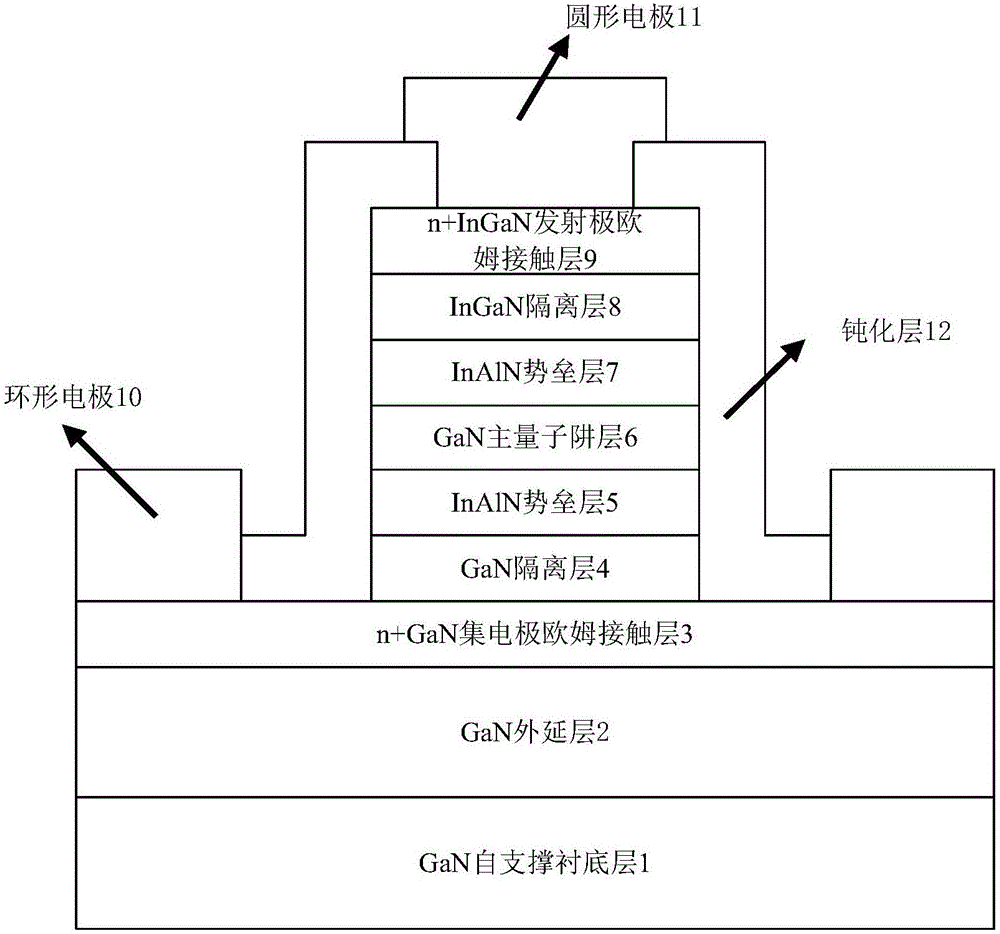

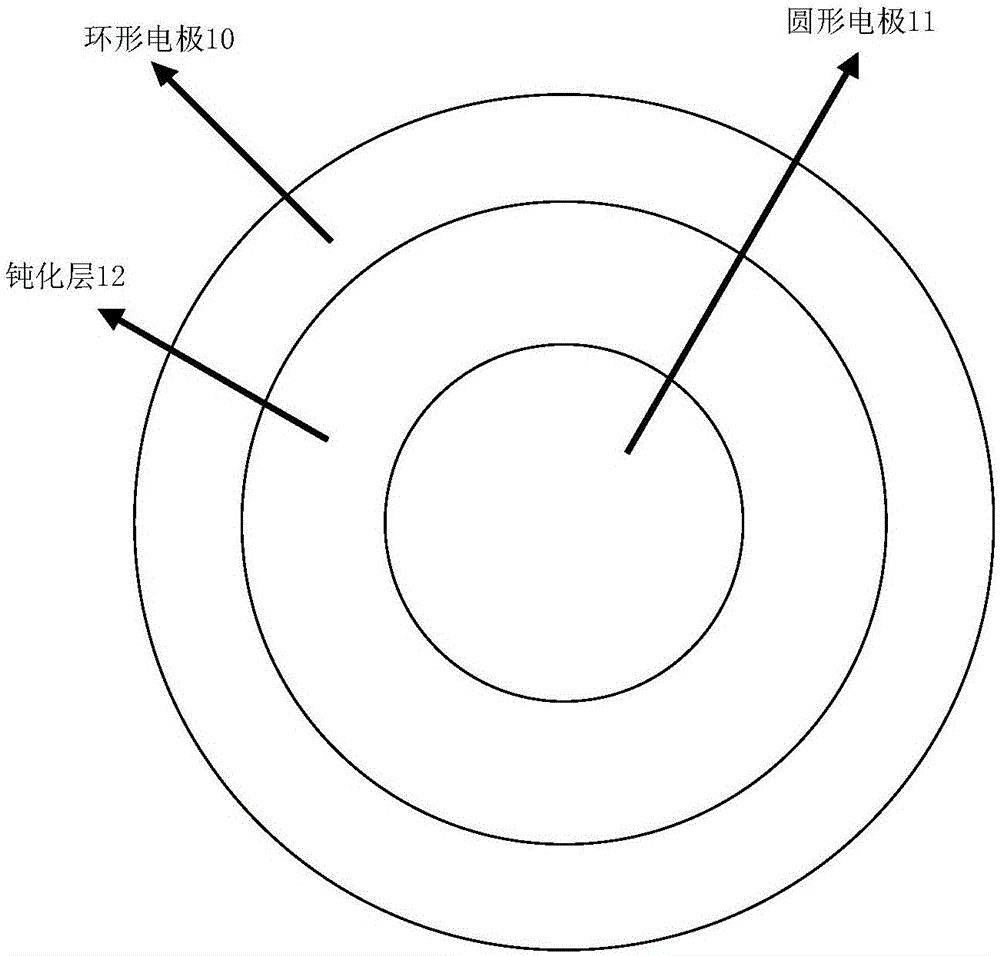

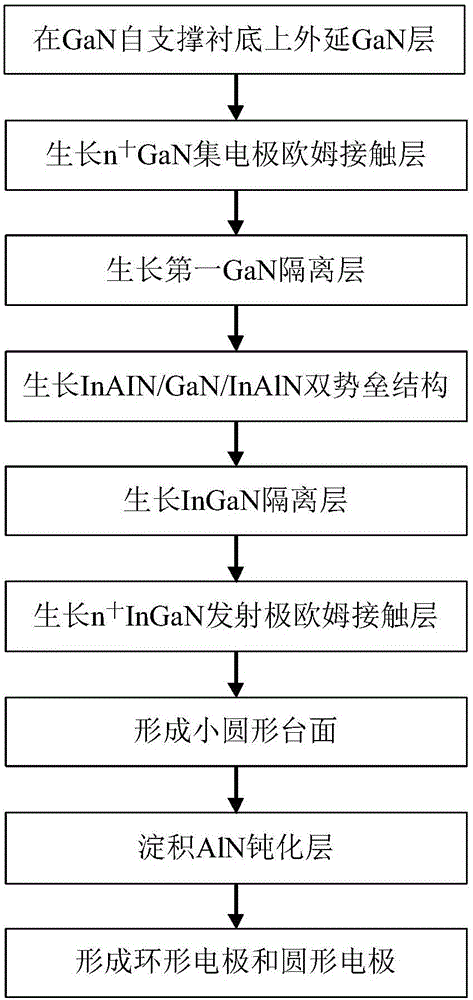

ActiveCN106057915AIncrease peak currentIncrease output powerSemiconductor/solid-state device manufacturingDiodeOhmic contactPeak value

The invention discloses an RTD diode of an indium gallium nitride emitting electrode ohmic contact layer and a manufacturing method thereof. The diode comprises a GaN epitaxial layer, an n+GaN collector electrode ohmic contact layer, a first GaN separating layer, a first InA1N barrier layer, a GaN main quantum well layer, a second InA1N barrier layer, an InGaN separating layer, an n+InGaN emitting electrode ohmic contact layer, a circular electrode, an annular electrode which is arranged above the n+GaN collector electrode ohmic contact layer and is not contacted with the first GaN separating layer and an A1N passivation layer located above the n+GaN collector electrode ohmic contact layer. The emitting electrode ohmic contact layer of the diode adopts an InGaN material so that a peak value current is increased and output power is increased too. In a diode manufacturing method, the InGaN is grown and then a high temperature technology is not needed, In precipitation does not exist and electric leakage of a device is reduced.

Owner:XIDIAN UNIV

Method for making semiconductor laser and spot-size converter by double waveguide technology

InactiveCN1756009AReduce the number of growthLow costLaser detailsSemiconductor lasersSemiconductor packageIntrinsics

Disclosed a method for utilizing the dual-waveguide technology to manufacture the semiconductor laser and mode spot switch comprises following steps: on the N type indium phosphide substrate, sequentially extending growing the N type indium phosphide breaker, a lower waveguide layer, a space layer, a active region, and a thinner indium phosphide intrinsic layer, wherein, the indium phosphide intrinsic layer can prevent the oxidation of active region; removing the highest indium phosphide intrinsic layer, partly covering the laser with SiO2, and utilizing the wet corrosion process to etch the upper carinate shape of mode spot switch; utilizing the auto-alignment process to etch the lower carinate shape which comprises a lower waveguide layer, a space layer, a second growth P type indium phosphide coating layer, and a high doping P type indium gallium arsenide ohmic electrode contract layer; utilizing the SiO2 to partly cover the mode spot switch and etching the upper and lower carnate shapes again while the upper carinate shape comprises a active region, a P type indium phosphide coating layer and a high doping P type indium gallium arsenide ohmic electrode contract layer; and decreasing the substrate of extended plate to 100 ª–m, and manufacturing P / N electrodes to be scribed into the tube core of 250í‡500ª–m.

Owner:INST OF SEMICONDUCTORS - CHINESE ACAD OF SCI

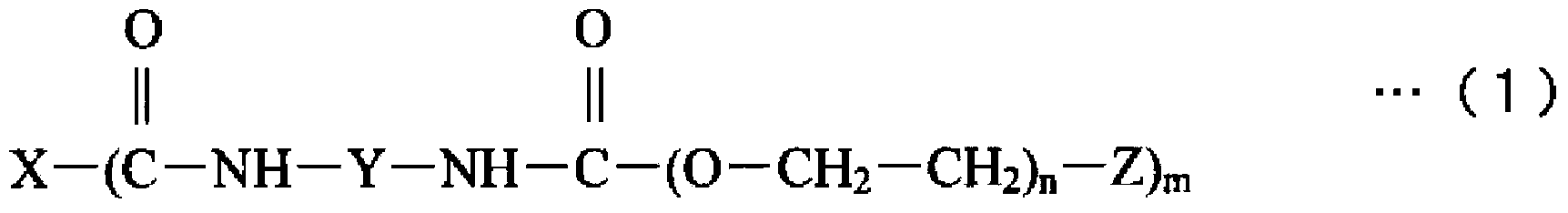

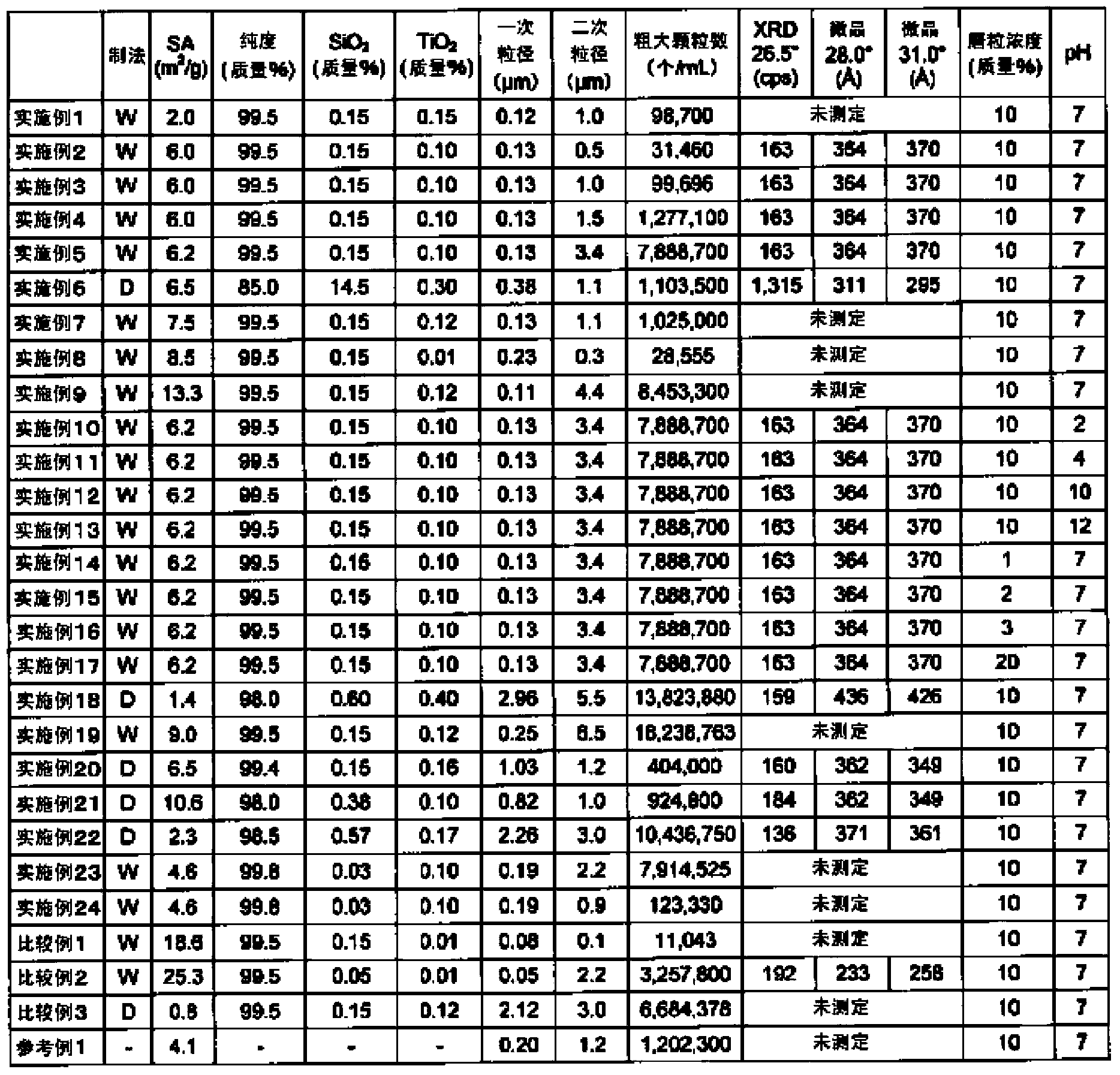

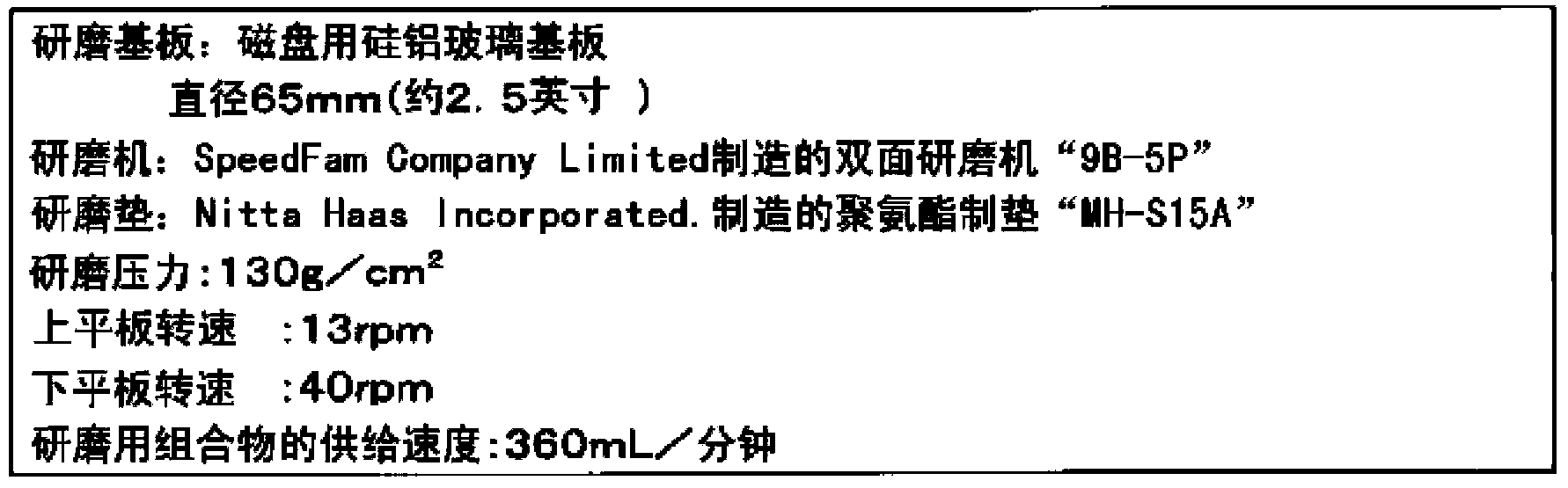

Polishing material and polishing composition

ActiveCN103402705ASuitable for useOther chemical processesLapping machinesIndium arsenideSilicon oxide

Provided is a polishing composition which contains a polishing material and water. The polishing composition contains the polishing material in an amount of 0.1% by mass or more. The polishing material contains zirconium oxide particles. Each zirconium oxide particle has a specific surface area of 1-15 m2 / g. It is preferable that the zirconium oxide particles has a purity of 99% by mass or more. For example, the polishing composition is used for the purpose of polishing hard-brittle materials such as sapphire, silicon nitride, silicon carbide, silicon oxide, glass, gallium nitride, gallium arsenide, indium arsenide and indium phosphide.

Owner:FUJIMI INCORPORATED

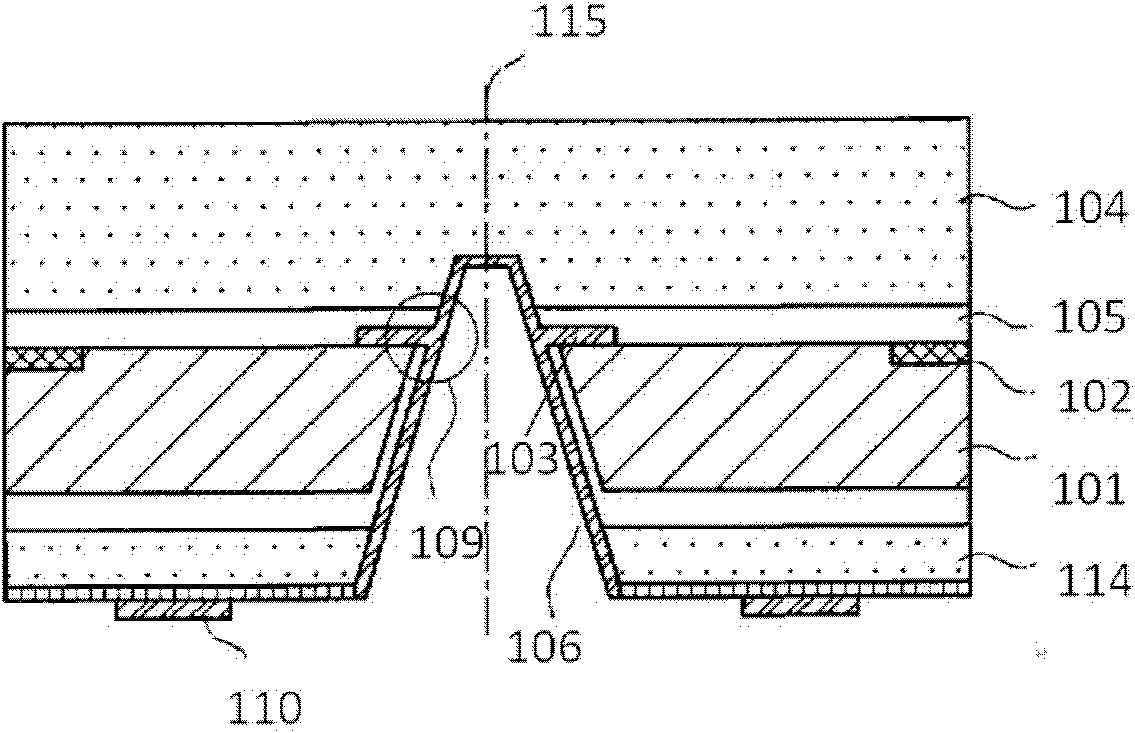

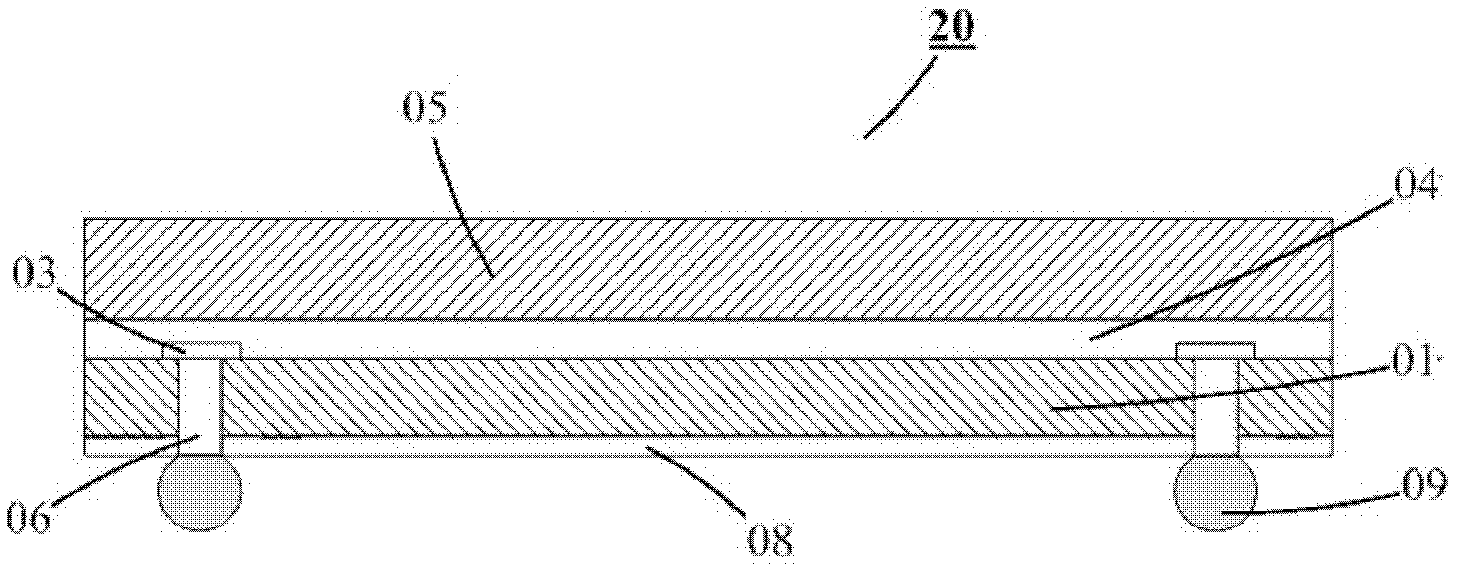

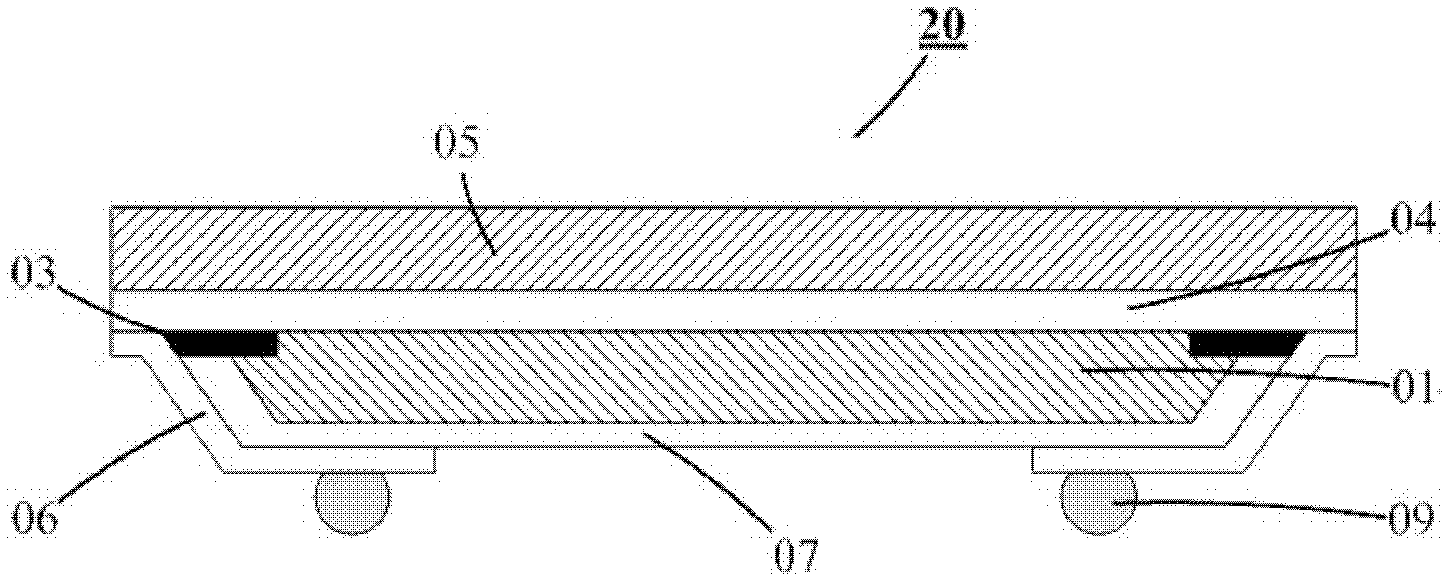

Wafer-level chip size encapsulation technology for GaAs (gallium arsenide) CCD (Charge Coupled Device) image sensor

ActiveCN102509718AImprove interconnect densityFirm packagingDecorative surface effectsSemiconductor/solid-state device manufacturingInterconnection densityCharge couple device

The invention relates to a wafer-level chip size encapsulation technology for a GaAs (gallium arsenide) CCD (Charge Coupled Device) image sensor. The technology is characterized by comprising the following steps of: (1) firstly bonding a glass wafer and a GaAs wafer through a resin adhesive so as to protect the active surface of a chip and improve the strength of a chip wafer; (2) manufacturing a trapezoidal-slot structure by a wet corrosion or physical method so as to reduce the lining thickness of a chip interconnection area; (3) manufacturing vertical interconnected through holes by a dry etching technology so as to expose a pad on the active surface of the chip; (4) sputtering seed-layer metal and electroplating, and manufacturing a hole metalizing and RDL layer to realize circuit interconnection from the active surface to the back surface of the chip; (5) manufacturing a passivation layer, a UBM layer and raised points; and (6) finally scribing to form an independent encapsulation chip. As the trapezoidal-slot structure on the back realizes thickness reduction only in the area with the pad, the cost is effectively lowered; and through the interconnection of the vertical through holes, the encapsulation interconnection density can be improved, and the signal transmission path is shortened.

Owner:SHANGHAI INST OF MICROSYSTEM & INFORMATION TECH CHINESE ACAD OF SCI

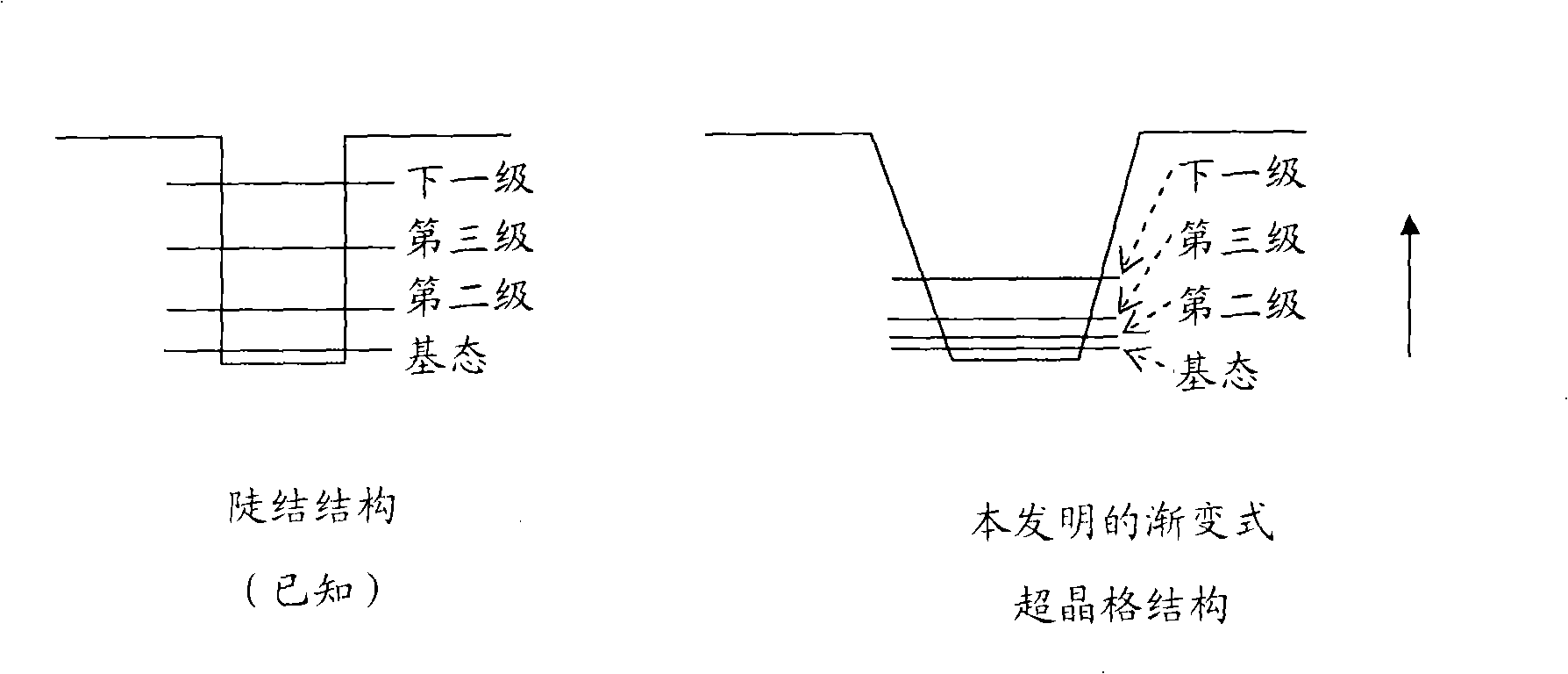

Solar cell with morphing type superlattice structure

InactiveCN101304051AImprove efficiencyReduced series resistancePhotovoltaic energy generationSemiconductor devicesFrequency spectrumSolar cell

The invention discloses a solar cell which consists of a plurality of stack 'pn' knot structures and a plurality of tunnel-through junction layers, wherein the tunnel-through junction layers are positioned between the stack 'pn' knot structures; moreover, one of the stack 'pin' knot structures comprises at least one p-typed semiconductor layer, one n-typed semiconductor layer, and one gradient superlattice structure positioned between the p-typed and the n-typed semiconductor layers. An energy gap of the gradient superlattice structure is between the energy gap of indium gallium phosphide (InGap) and the energy gap of gallium arsenide (GaAs). Therefore, a wavelength response range can be improved up to 1.0ev to add the wavelength response frequency spectrum; besides, owing to the gradient superlattice structure, a voltage barrier come up against by a current carrier in the area is relatively small and is easy to be stepped over, thus adding efficiency.

Owner:IND TECH RES INST

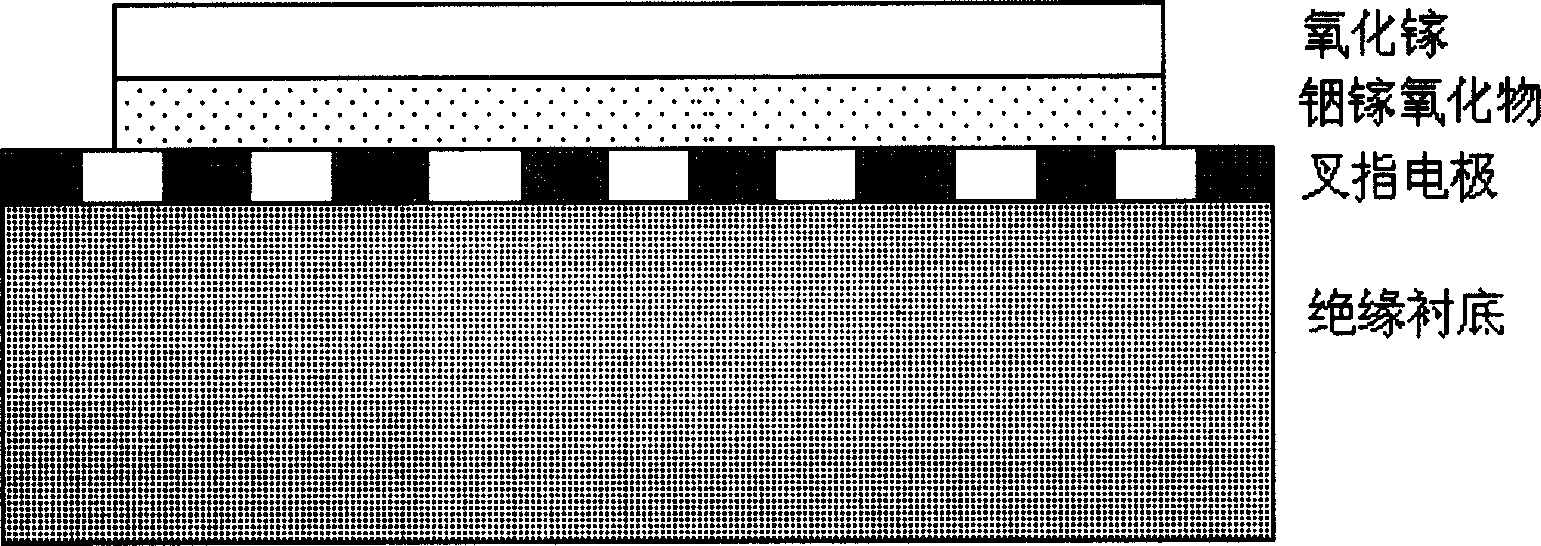

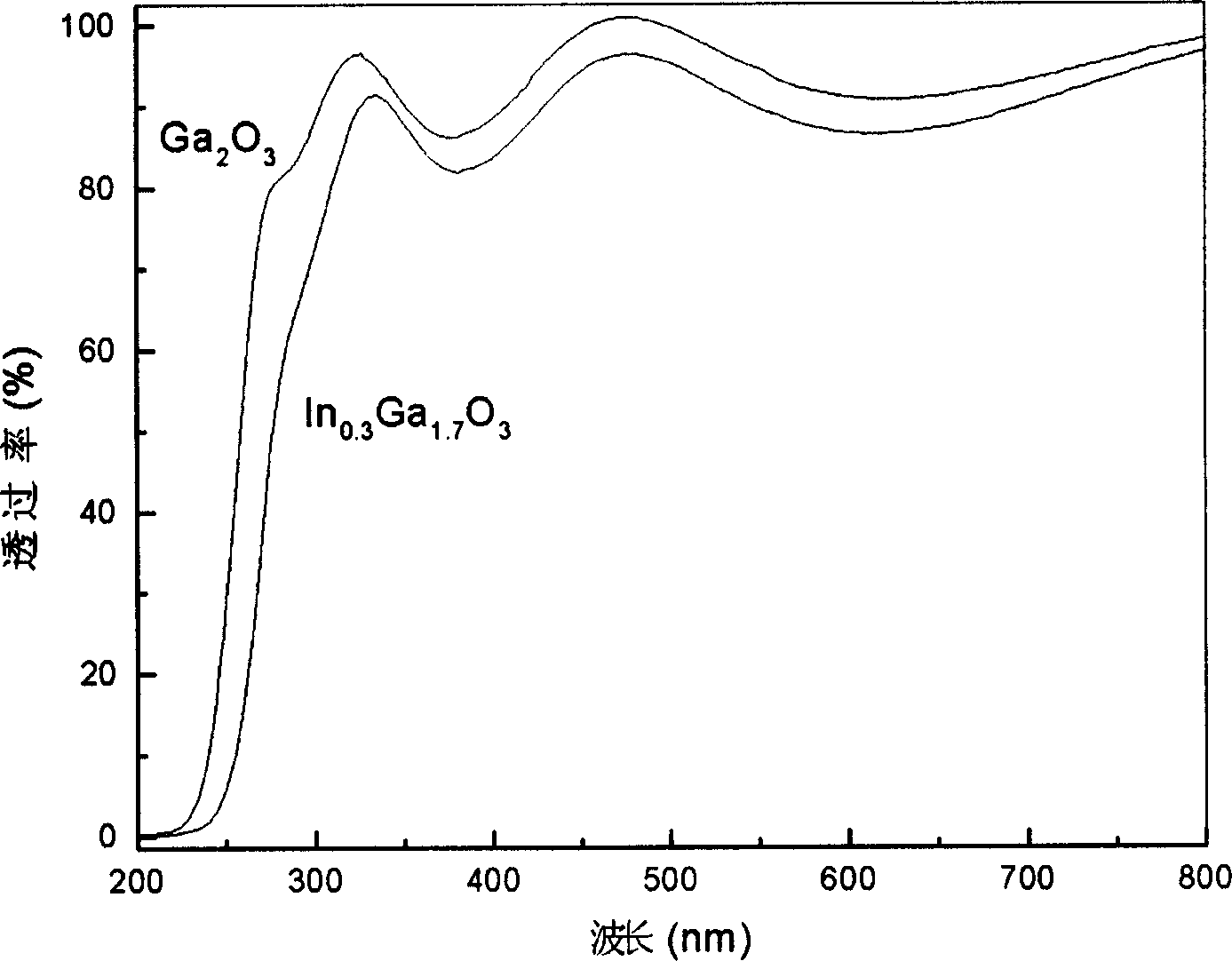

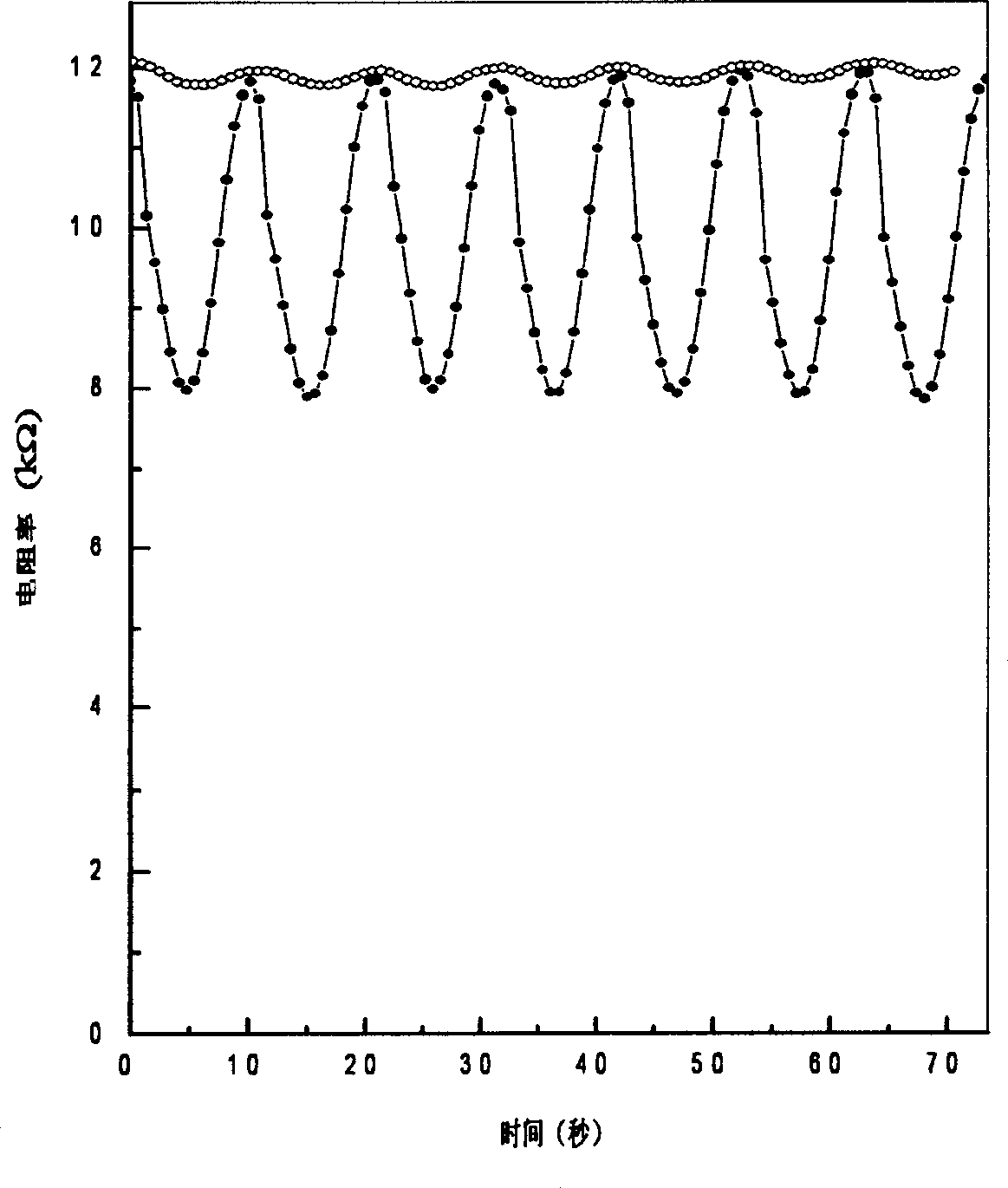

Photoconductive type ultraviolet detector

InactiveCN1587996AHigh sensitivitySimple structureColor/spectral properties measurementsPhotovoltaic energy generationIndiumUltraviolet detectors

The invention of light guide ultraviolet sensor consists of pure gallium oxide light filter, indium gallium oxide ultraviolet sensitive film, crossing electrode and insulating substrate from up to down. The ultraviolet sensor uses pure gallium oxide light filter as filtration layer, indium gallium oxide as ultraviolet sensitive layer, which can filter light whose wavelength is smaller than 240mm and make the probe only be sensitive to the light within sun blind area wavelength range. Besides, because of crossing electrode under sensitive film whose surface square receiving light is large, influence of crossing electrode in common light guide probe on surface square receiving light is avoided, resulting high sensitivity. The invention has the advantages of simple structure, high sensitivity and low cost.

Owner:ZHEJIANG UNIV

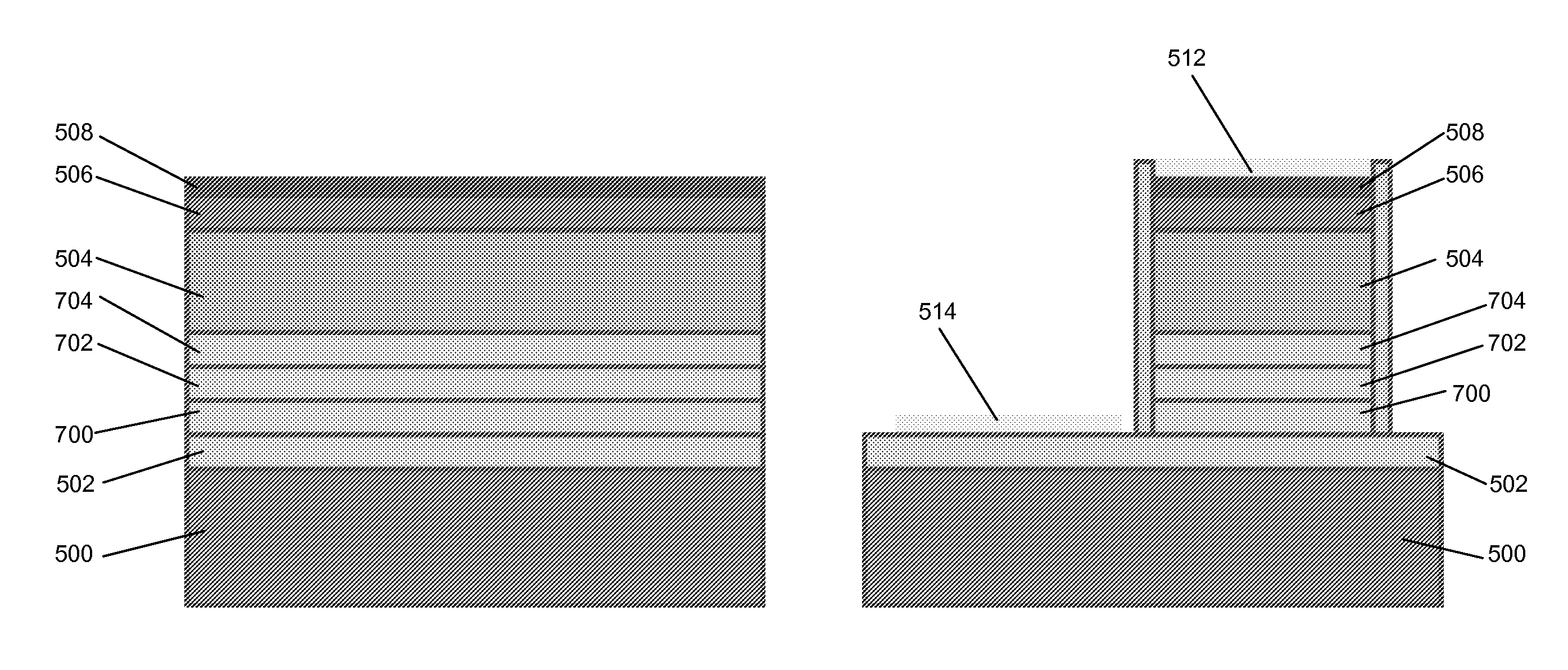

InGaAsSbN PHOTODIODE ARRAYS

Embodiments of detectors made using lattice matched photoabsorbing layers are disclosed. A photodiode apparatus in accordance with one or more embodiments of the present invention comprises an indium phosphide substrate, and a photoabsorbing region comprising at least an indium gallium arsenide antimonide nitride (InGaAsSbN) layer, wherein the InGaAsSbN layer has a thickness of at least 100 nanometers and is nominally lattice-matched to the indium phosphide substrate.

Owner:TELEDYNE FLIR LLC

Integration method for electric absorption modulation laser and modular spot converter

InactiveCN1909309AReduce the number of growthHas an effectLaser detailsSemiconductor lasersPhosphate ionSilicon dioxide

The invention relates to an integration method of electric adsorption modulation laser and mode speckle converter, which comprises: growing n-type indium phosphate buffer layer on the substrate; corroding the upper 1.1Q layer on the chip, to grow buffer layer; growing silica dioxide protective layer on the whole chip, and corroding the silica dioxide protective layer at two ends of mode speckle converter; pouring low-energy phosphate ion; growing the silica dioxide protective layer again; heating, keeping warm, anneal on the chip; corroding silica dioxide protective layer; using relative light etching plate to mask the laser and modulator, to form the upper ridge and lower ridge on the converter; growing p-type indium phosphate and indium gallium arsenic phosphate etching stop layer; etching ridge pilot structure; depositing medlin at two sides of laser and modulator; opening the electrode windows of laser and modulator; etching the electrode images on the laser and modulator to splash the P electrode and remove the P electrode; extending the substrate, and splashing n electrode; slicing the sample to form tubular chip.

Owner:INST OF SEMICONDUCTORS - CHINESE ACAD OF SCI

Method for stripping and transferring gallium arsenide based epitaxial layer

InactiveCN103904015AImprove uniformityBreak the inherent limitationsSolid-state devicesSemiconductor/solid-state device manufacturingPhotoresistSpin coating

The invention discloses a method for stripping and transferring a gallium arsenide based epitaxial layer. The method comprises the steps of (1) cleaning surfaces of a gallium arsenide based epitaxial piece and a temporary substrate through dilute hydrochloric acid; (2) spin-coating photoresist on the front surface of the gallium arsenide based epitaxial piece; (3) putting the gallium arsenide based epitaxial piece on a hot plate with the front surface upward to perform baking; (4) bonding the cooled front surface of the gallium arsenide based epitaxial piece with the front surface of the temporary substrate oppositely; (5) removing a gallium arsenide substrate of the gallium arsenide based epitaxial piece; (6) cleaning an objective substrate and the surface of an epitaxial piece supported by the temporary substrate through the dilute hydrochloric acid; (7) spin-coating BCB on the front surface of the epitaxial piece supported by the temporary substrate; (8) putting the epitaxial piece supported by the temporary substrate on the hot plate with the front surface upward to perform baking; (9) bonding the cooled front surface of the epitaxial piece supported by the temporary substrate with the front surface of the objective substrate oppositely; (10) immersing the bonded wafer in acetone, and automatically separating the objective substrate from the temporary substrate after the photoresist is dissolved. The method has the advantages that the epitaxial layer on the gallium arsenide based epitaxial piece can be transferred onto any objective substrate integrally, the process is simple, and the gallium arsenide based epitaxial layer cannot be damaged during transfer.

Owner:NO 55 INST CHINA ELECTRONIC SCI & TECHNOLOGYGROUP CO LTD

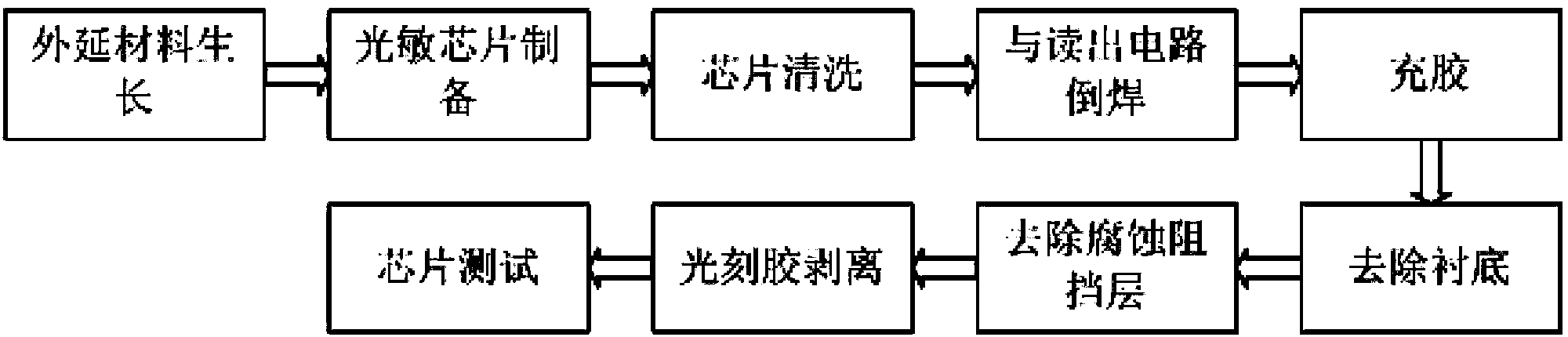

Method for manufacturing planar indium gallium arsenic infrared detector chip with extended wavelength

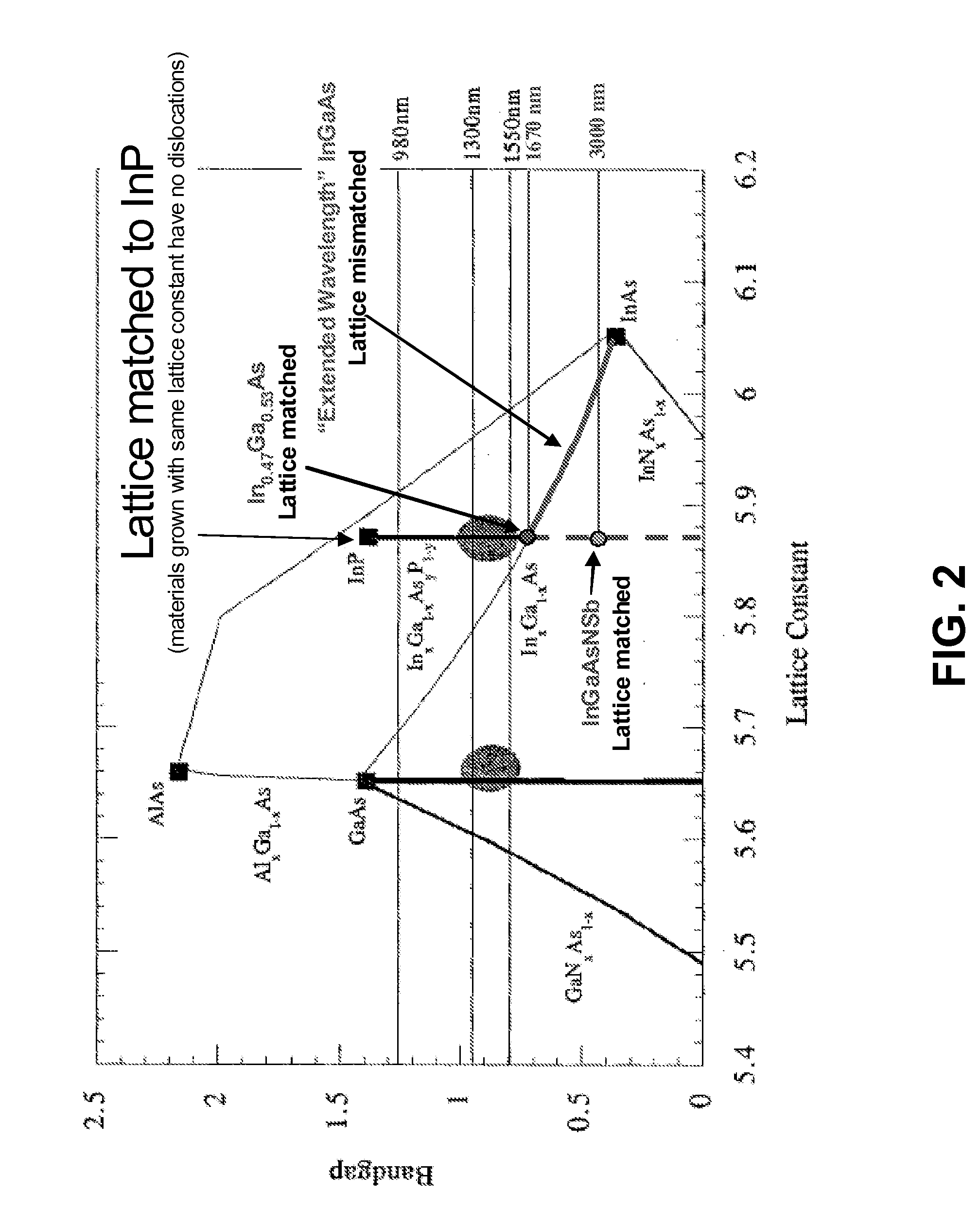

InactiveCN103413863AImprove quantum efficiencyControl thicknessFinal product manufactureSemiconductor devicesIndiumDetector array

The invention discloses a method for manufacturing a planar indium gallium arsenic infrared detector chip with an extended wavelength. According to a traditional PIN type indium gallium arsenic infrared detector, the quantum efficiency of the indium gallium arsenic infrared detector in the visible light band is limited due to absorption of an indium phosphide cap layer or absorption of a substrate. An indium gallium arsenic epitaxial material manufacuring device with a barrier layer is used in the method and coupled with a reading circuit after manufacturing of a detector array device, the substrate is thinned through the wet method and dry method combination technology, and the quantum efficiency of the device in the visible light band is improved. In addition, the planar indium gallium arsenic infrared detector chip manufactured through the novel method achieves wavelength extension, and meanwhile can also keep the quantum efficiency and dark current equivalent to those of the traditional indium gallium arsenic infrared detector at the regular band.

Owner:SHANGHAI INST OF TECHNICAL PHYSICS - CHINESE ACAD OF SCI

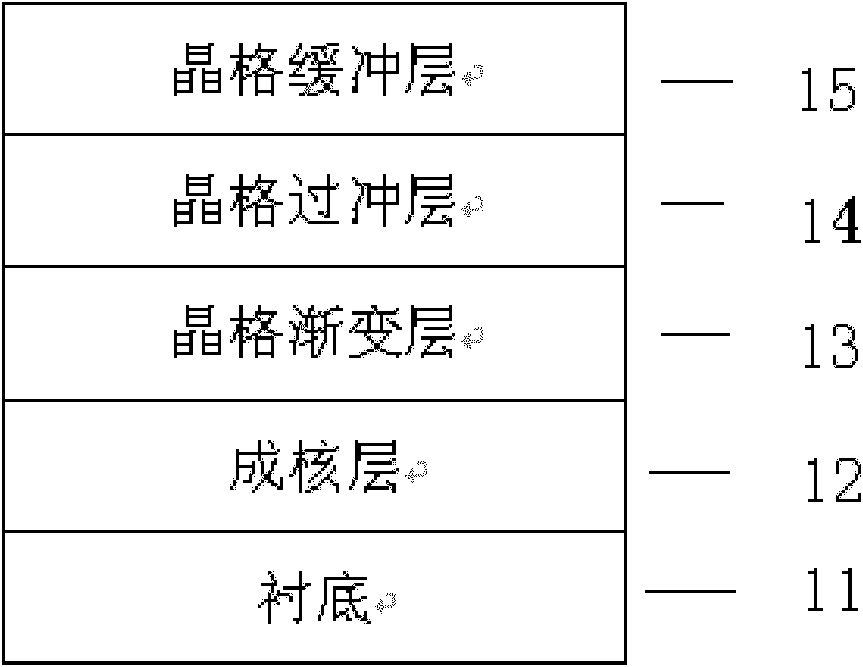

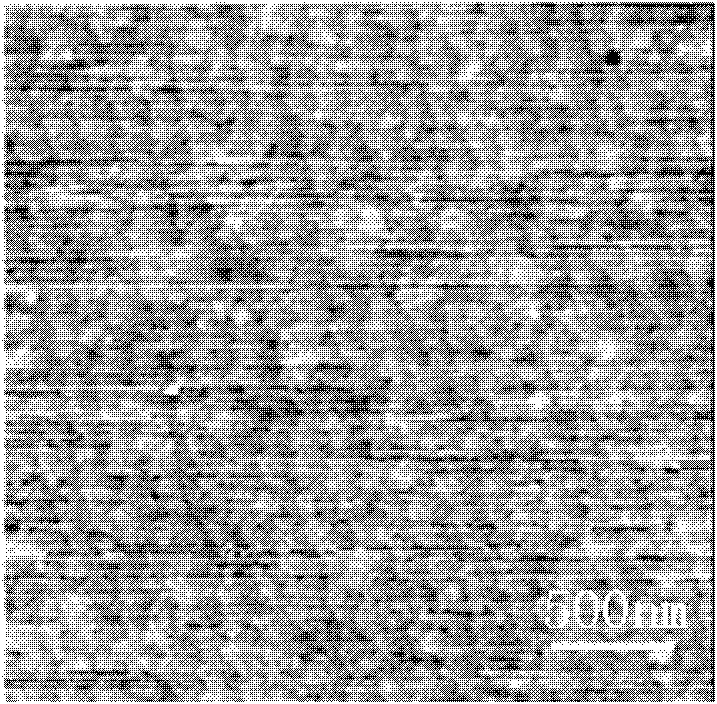

Method for manufacturing lattice graded buffer layer

ActiveCN102011182AControllable threading dislocation densityReduce dependenceFrom chemically reactive gasesThreading dislocationsEpitaxial material

The invention relates to a method for manufacturing a lattice graded buffer layer, which comprises the following steps of: (1) using a commercial germanium single crystal, arsenide gallium single crystal or indium phosphide single crystal as a substrate; (2) epitaxially forming a layer of material in lattice matching with the substrate material as a nucleation layer by utilizing epitaxial technology; (3) epitaxially growing a lattice graded layer on the nucleation layer until the lattice of the material of a top layer has an ideal lattice constant or a lattice constant slightly lower than theideal lattice constant, wherein the lattice graded layer consists of a plurality of indium gallium arsenide materials with gradually increased components; (4) epitaxially forming a layer of indium gallium arsenide material with the lattice constant more than the ideal lattice constant on the lattice graded layer as a lattice overshoot layer; and (5) epitaxially forming a layer of material which has the lattice constant equal to the ideal lattice constant and is the same as that grown on an adjacent upper layer thereof as the lattice buffer layer. The method solves the problem of influence of device appearance degradation caused by lattice mismatching between a conventional epitaxial material and the substrate, and can effectively control threading dislocation density on the surface of a device.

Owner:CHINA ELECTRONIC TECH GRP CORP NO 18 RES INST +1

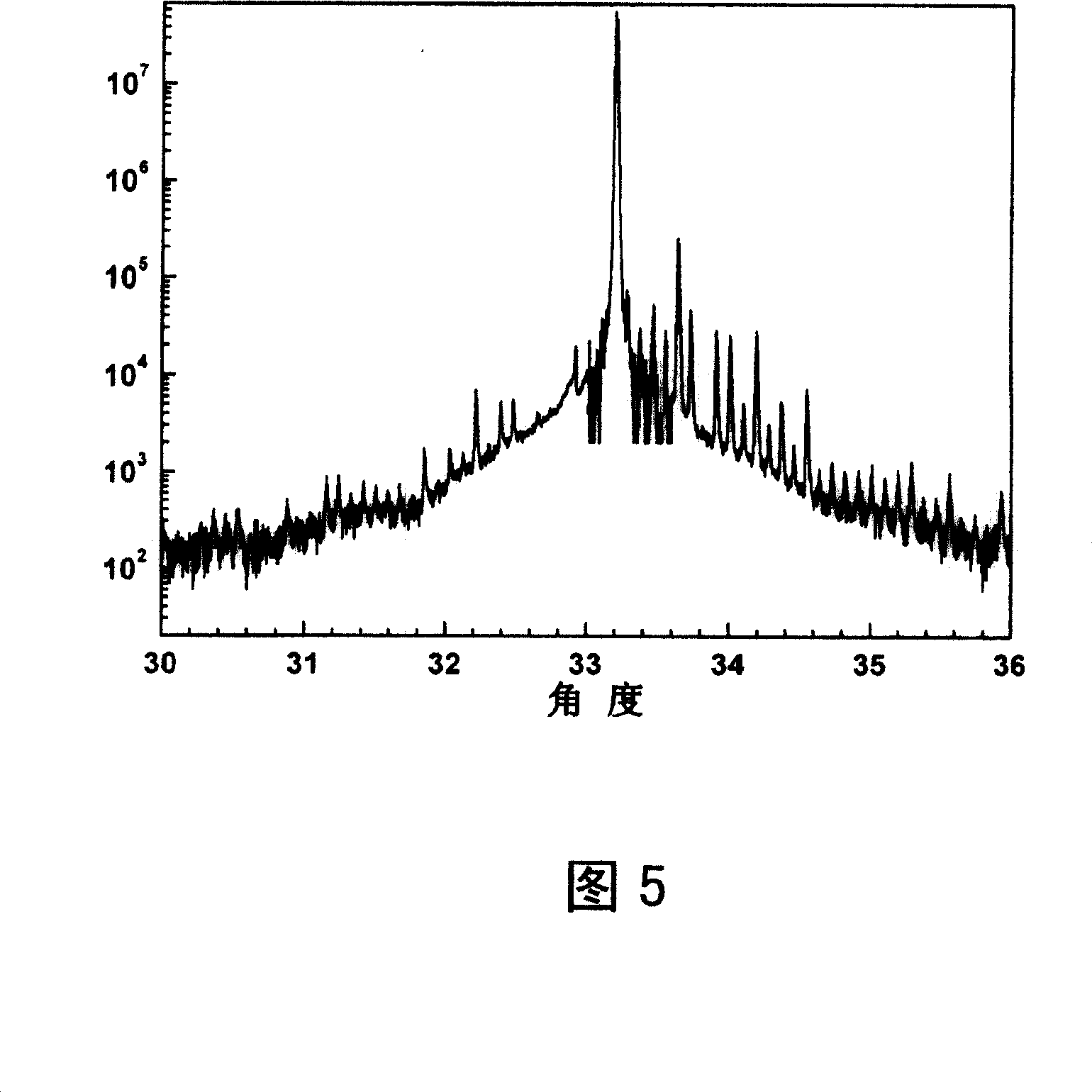

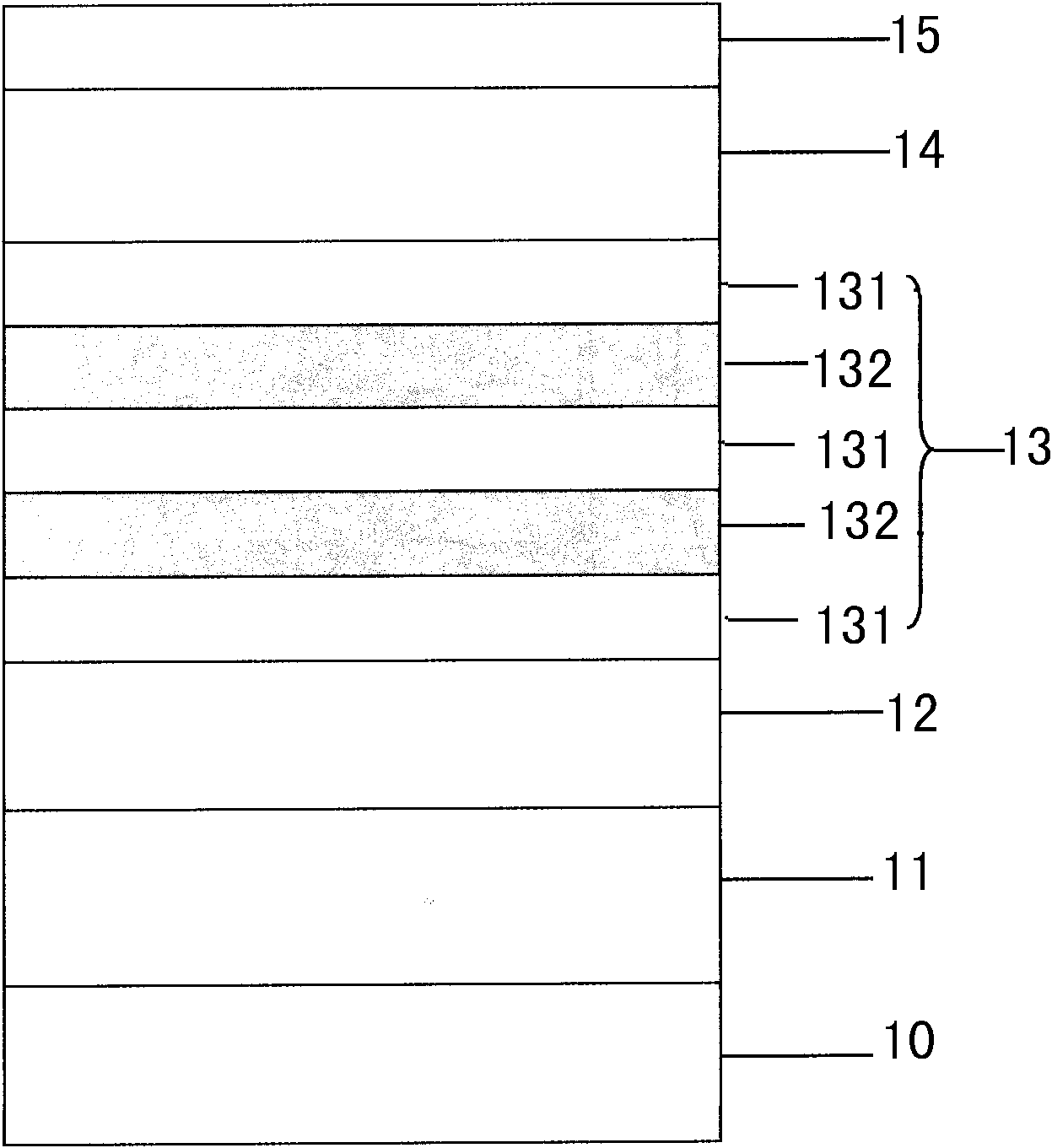

Ti Hz quanta cascaded semiconductor laser material and its growth method

InactiveCN101127432ASimple processImprove material qualityLaser detailsLaser active region structureOhmic contactQuantum

The utility model relates to a growth method of a THz quantum stage linked semiconductor laser material, which is characterized in comprising the following growth steps: step 1: A semiinsulating gallium arsenide substrate is adopted; step 2: N-shaped ohmic contact layer under the gallium arsenide is grown on the semiinsulating gallium arsenide substrate via the use of the molecular rays epitaxial technique to make a lower ohmic electrode; step 3: An active area is grown on the lower ohmic contact layer to form a luminous zone; step 4: An N-shaped gallium arsenide upper ohmic contact layer is grown on the active area to make a lower ohmic electrode to accomplish the growth of the THz quantum stage linked semiconductor laser material.

Owner:INST OF SEMICONDUCTORS - CHINESE ACAD OF SCI

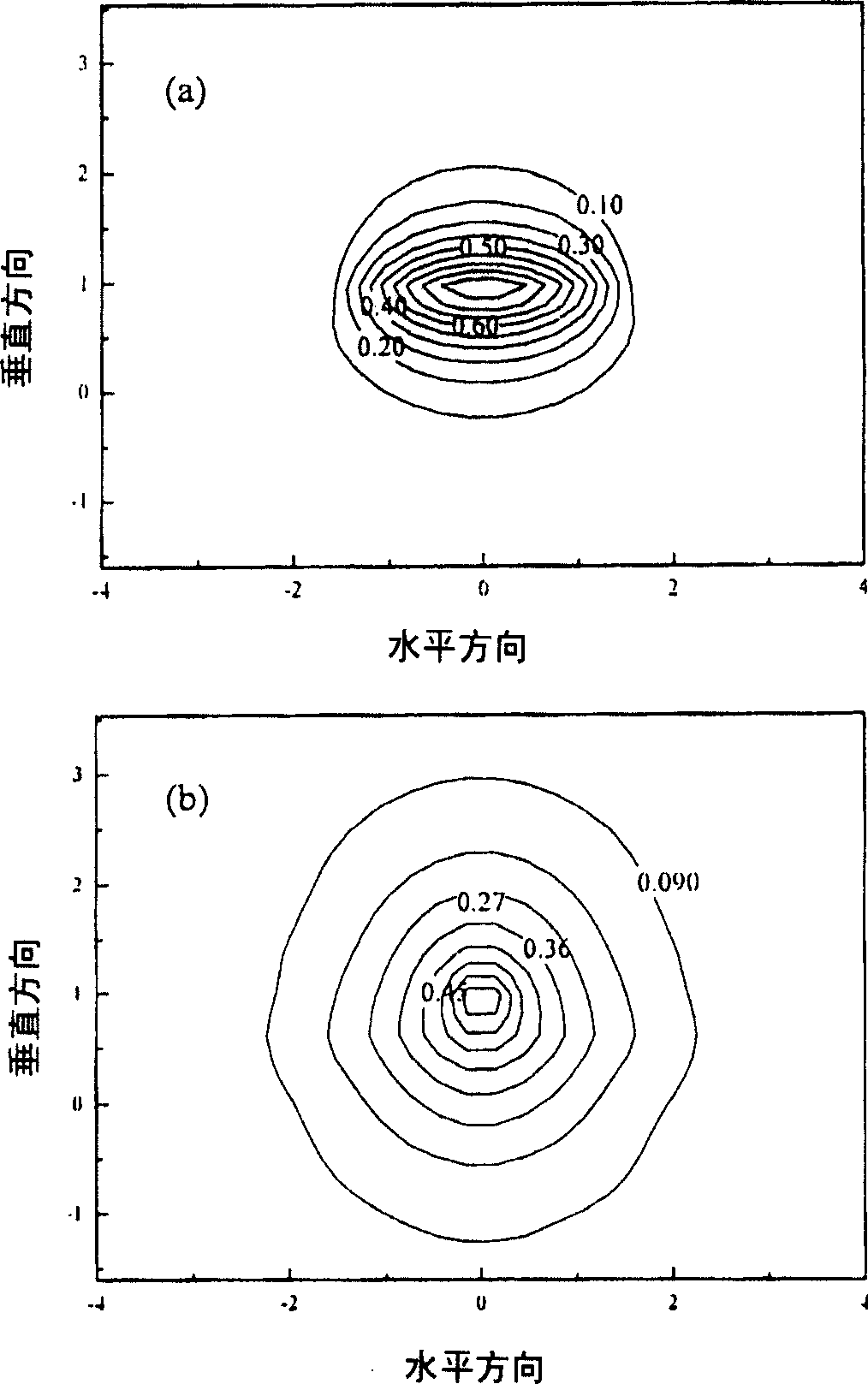

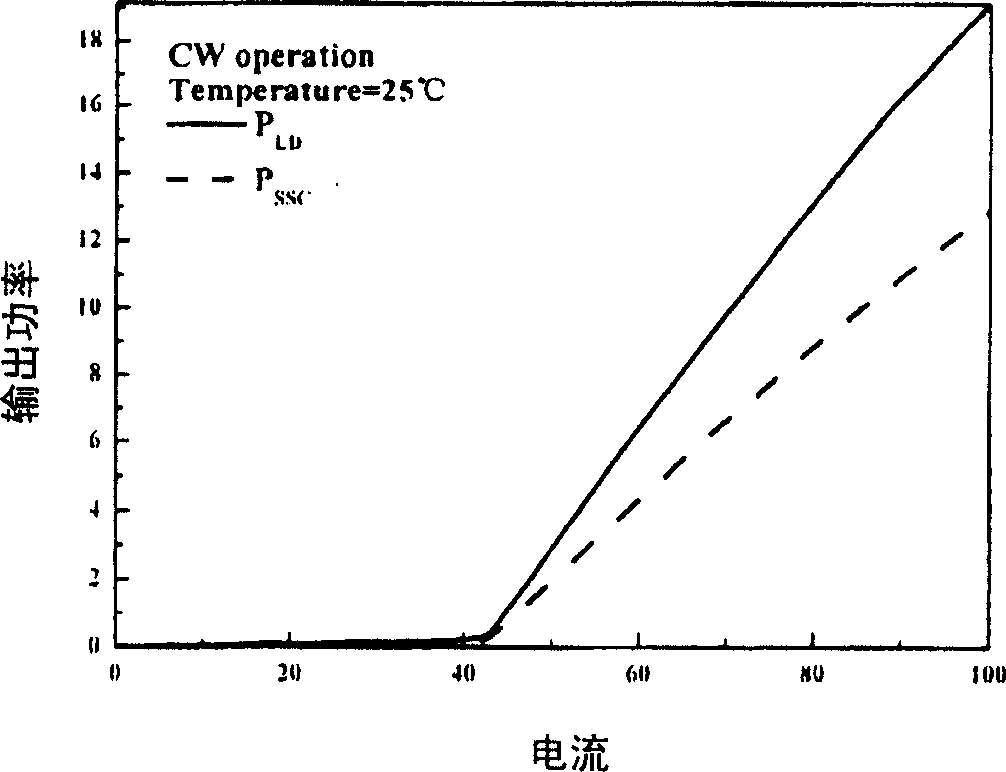

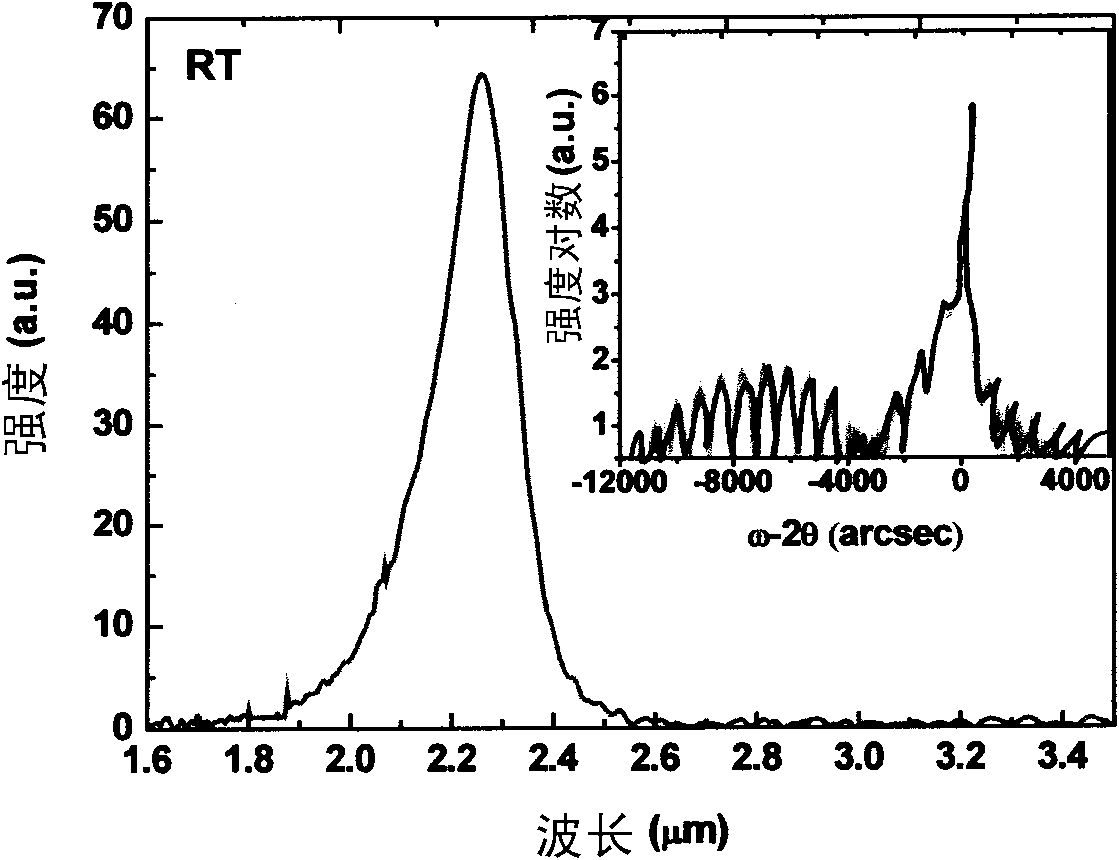

Method for growing indium arsenide/indium gallium arsenide quantum well material on indium phosphide substrate

ActiveCN102208756AReduce defectsIncrease the transition wavelengthLaser detailsSemiconductor lasersQuantum wellIndium arsenide

The invention discloses a method for growing indium arsenide / indium gallium arsenide quantum well material on an indium phosphide substrate. The method comprises the following steps of: 1, selecting the substrate; and 2, sequentially growing a buffer layer, a lower waveguide layer, a dual-quantum well structure, an upper waveguide layer and a cover layer to finish growing the indium arsenide / indium gallium arsenide quantum well material on the indium phosphide substrate. In the method, an InAs quantum well with a proper thickness is grown at relatively lower temperature to realize the functions of reducing shortcomings and increasing a transition wavelength to 2.3 mu m under high strain condition.

Owner:INST OF SEMICONDUCTORS - CHINESE ACAD OF SCI

Method for epitaxially growing strontium titanate (STO) thin film on gallium arsenide (GaAs) substrate

InactiveCN102181833AHigh thermodynamic stabilityImprove uniformityVacuum evaporation coatingSputtering coatingStrontium titanateAluminium arsenide

The invention relates to a method for epitaxially growing a strontium titanate (STO) thin film on a gallium arsenide (GaAs) substrate. The method comprises the following steps: 1. treating the surface of the GaAs substrate to form a flat atomically clean surface with Ga atoms as the final surface; 2. sending the GaAs substrate treated in the step 1 and an STO target to the vacuum chamber of laser molecular beam epitaxy (MBE) equipment and immobilizing the GaAs substrate and the STO target in the vacuum chamber; 3. heating the GaAs substrate immobilized in the step 2 to the temperature between 550-600; and 4. evaporating the STO target immobilized in the step 2 with laser beams to ensure the STO to be deposited on the GaAs substrate, using reflection high energy electron diffraction to monitor the growth process of the thin film in the deposition process and obtaining the STO epitaxial thin film when typical STO diffraction fringes appear on the diffraction patterns. The method has the following beneficial effect: the surface of the GaAs substrate is treated to form the flat atomically clean surface with Ga atoms as the final surface, thus overcoming the difficulty in growing the dielectric oxide thin film on the GaAs substrate binary compound.

Owner:UNIV OF ELECTRONICS SCI & TECH OF CHINA

Preparation method and light emitting diode (LED) structure of indium gallium nitride (InGaN) base multiple quantum well structure

ActiveCN103022289AImprove internal quantum efficiencyIncreases chance of radiative recombinationSemiconductor devicesIndiumGallium nitride

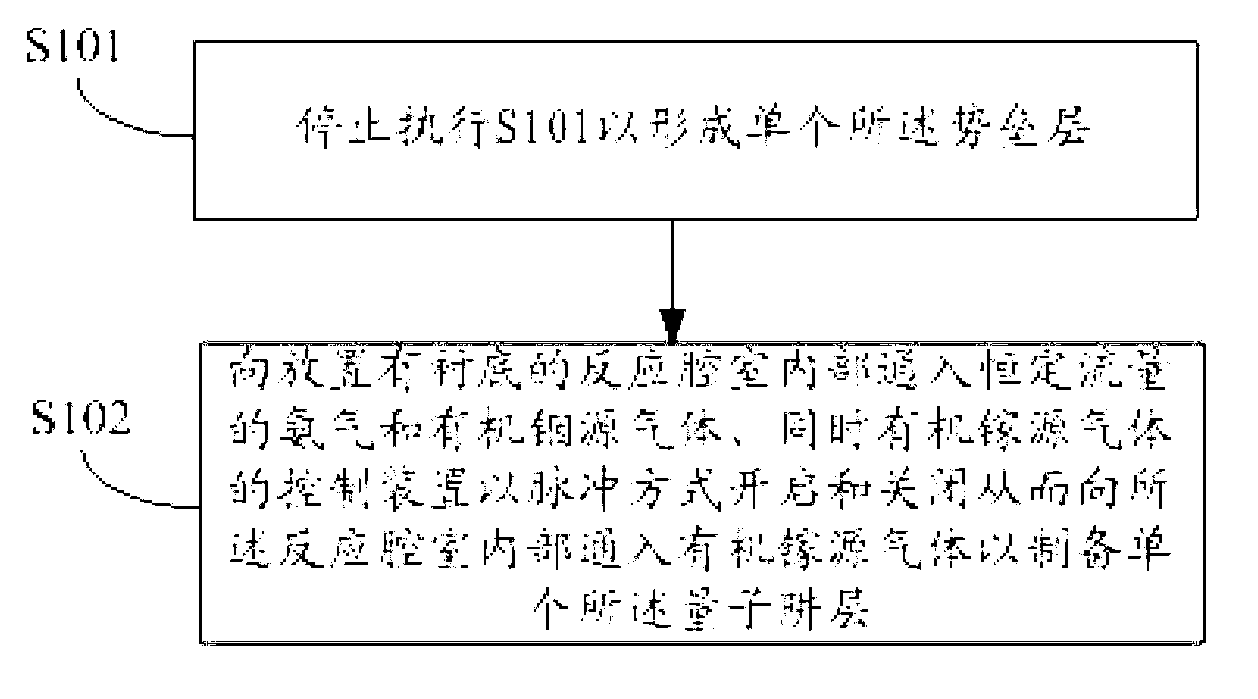

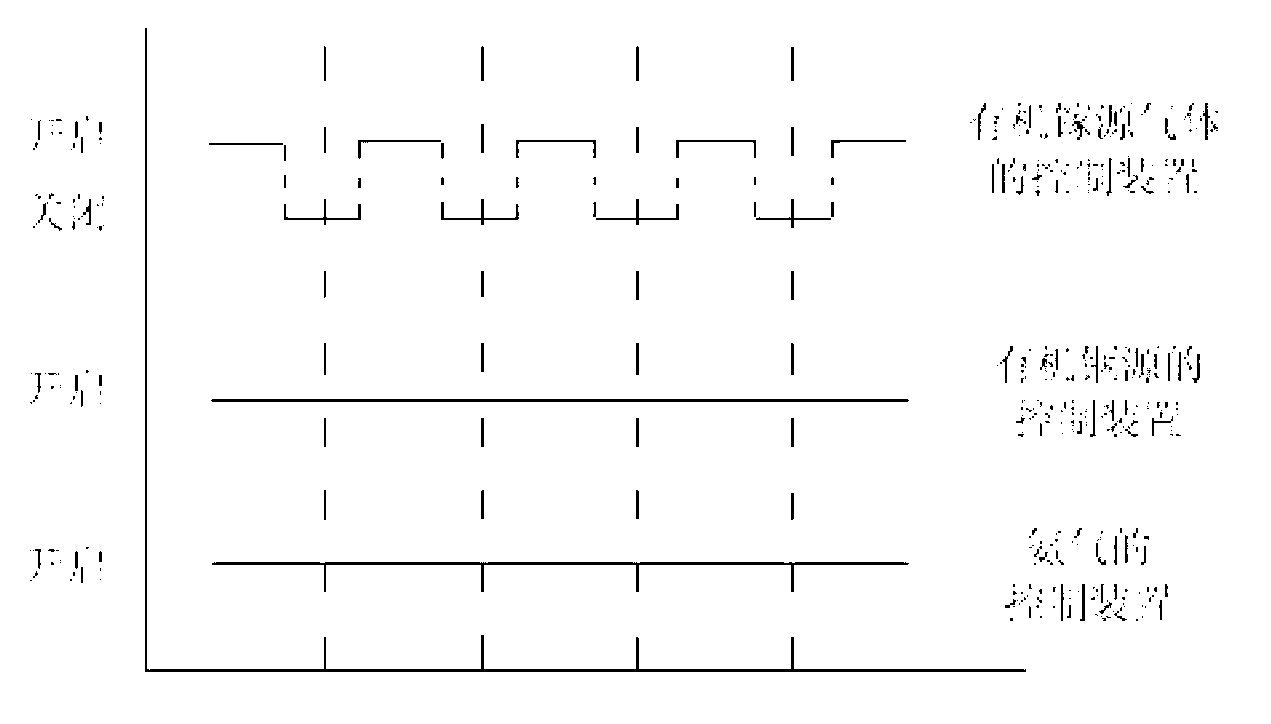

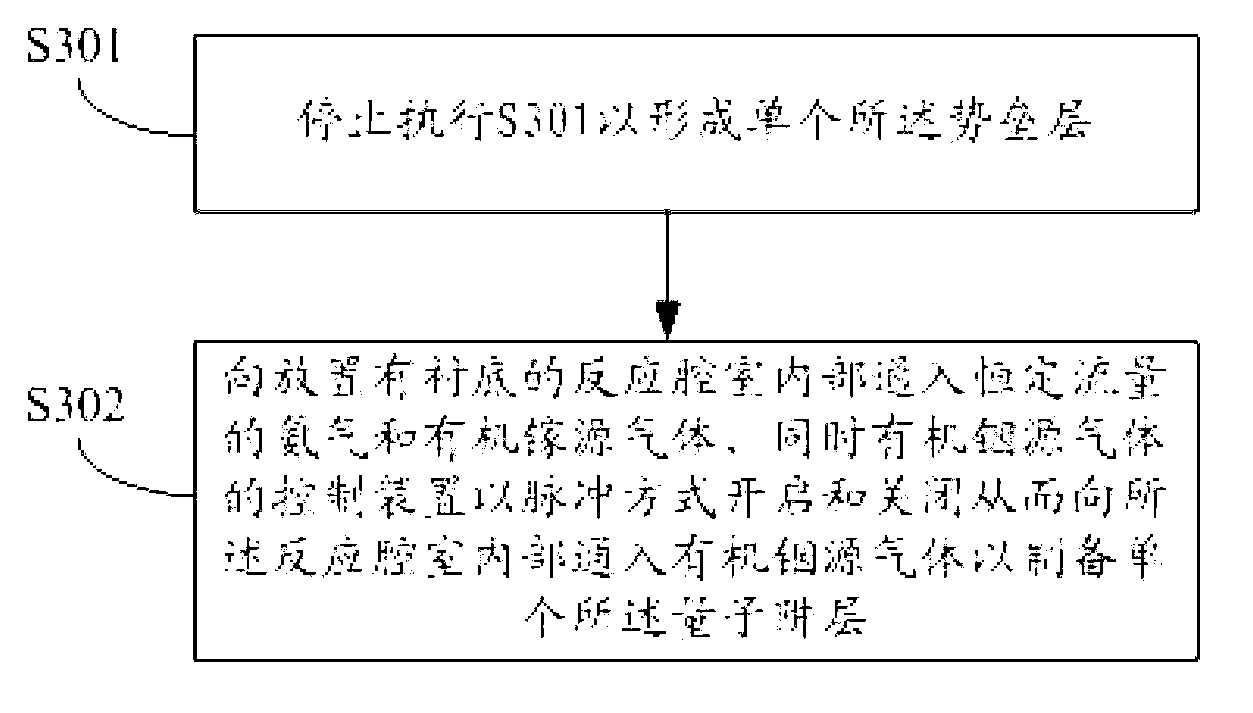

The invention provides a preparation method and a light emitting diode (LED) structure of an indium gallium nitride (InGaN) base multiple quantum well structure. The InGaN base multiple quantum well structure comprises a plurality of barrier layers and a plurality of quantum well layers, wherein the number of the barrier layers is M+1, and the number of the quantum well layers is M. A stage of preparing one barrier layer and one quantum well layer which are adjacent is set as a growth cycle, and the preparation method includes following steps which are performed in at least one growth cycle: step A, feeding ammonia with a constant flow rate and organic gallium source gas to the interior of a reaction chamber so as to form the single barrier layer; and step B, feeding organic indium source gas and the ammonia with the constant flow rate to the interior of a reaction chamber with a substrate placed, simultaneously opening and closing a control device of the organic gallium source gas in pulse mode, and accordingly feeding the organic gallium source gas to the interior of the reaction chamber to prepare the single quantum well layer. Luminous internal quantum efficiency of the InGaN base multiple quantum well structure can be increased by adopting the preparation method of the InGaN base multiple quantum well structure.

Owner:FOSHAN NATIONSTAR SEMICON

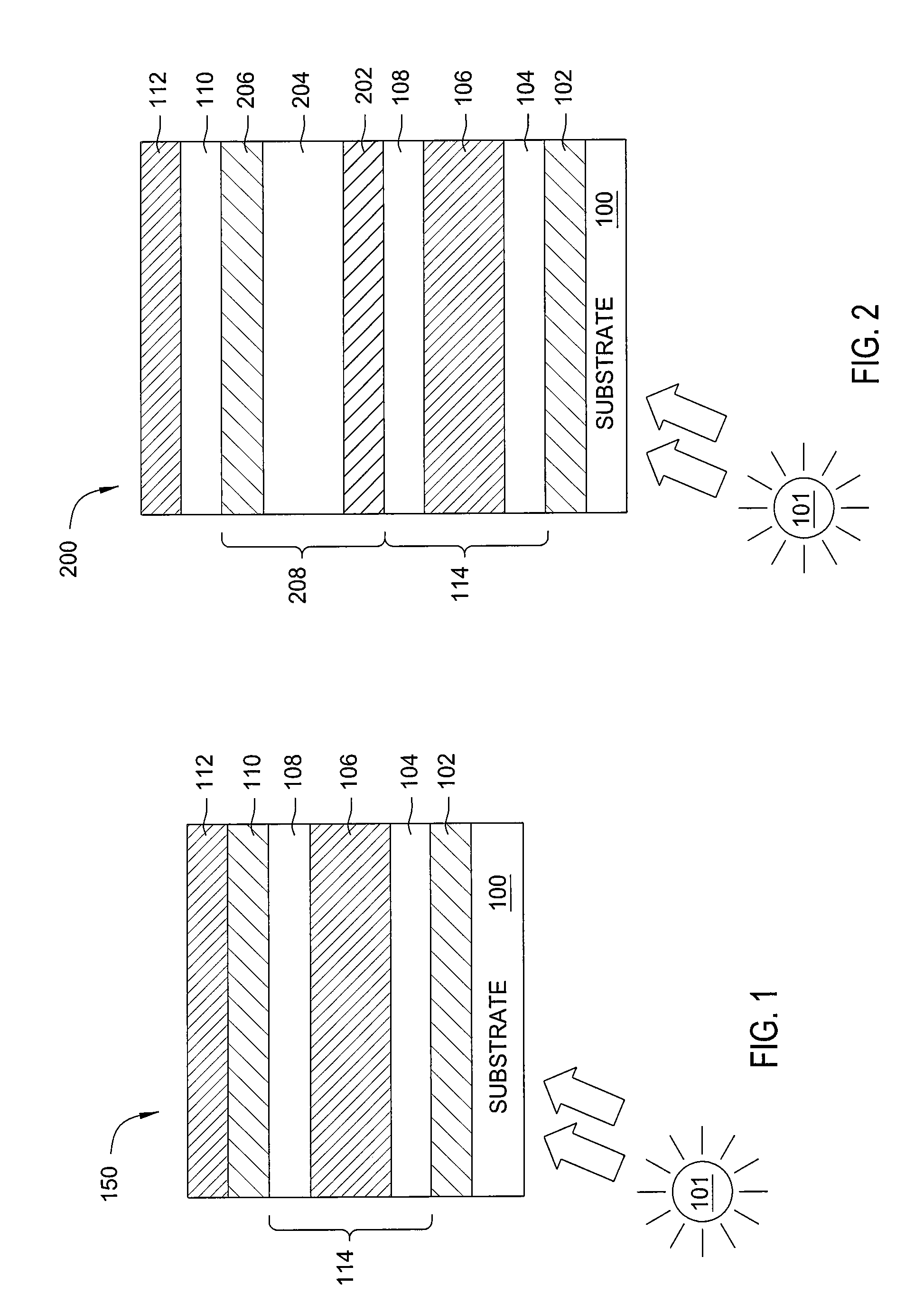

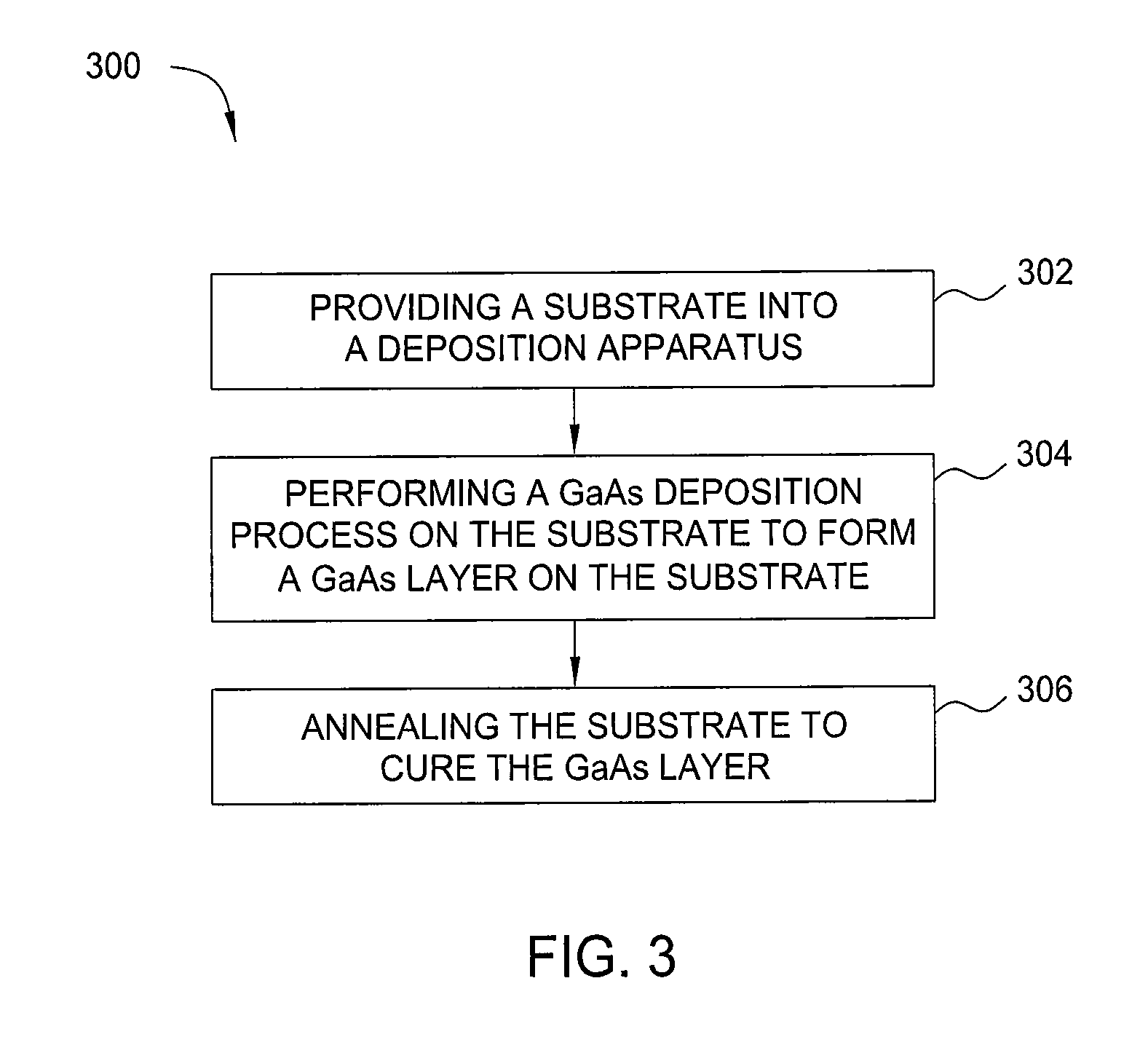

High efficiency thin film transistor device with gallium arsenide layer

InactiveUS8846437B2Light absorptionLight conversionMaterial nanotechnologyFinal product manufactureDopantSolar cell

Embodiments of the invention provide a method of forming a doped gallium arsenide based (GaAs) layer from a solution based precursor. The doped gallium arsenide based (GaAs) layer formed from the solution based precursor may assist solar cell devices to improve light absorption and conversion efficiency. In one embodiment, a method of forming a solar cell device includes forming a first layer with a first type of dopants doped therein over a surface of a substrate, forming a GaAs based layer on the first layer, and forming a second layer with a second type of dopants doped therein on the GaAs based layer.

Owner:APPLIED MATERIALS INC

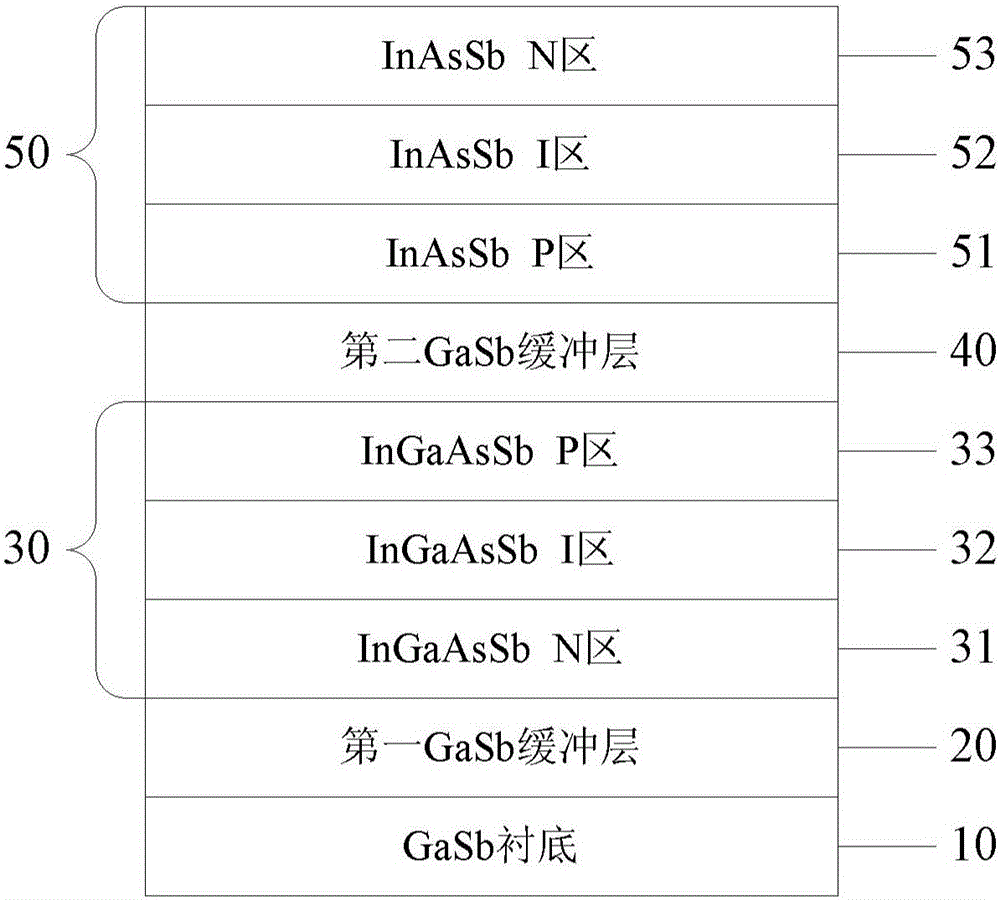

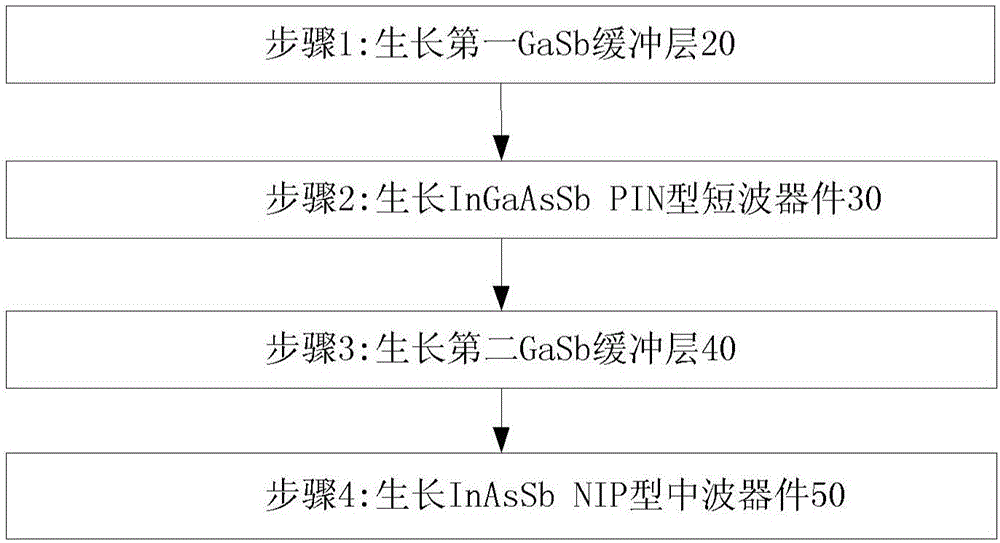

Indium arsenide antimony and indium gallium arsenide antimony two-waveband infrared detector and manufacturing method thereof

ActiveCN106298993AGuaranteed uniformityGuaranteed accuracyFinal product manufactureSemiconductor devicesIndiumIndium arsenide

The invention provides an indium arsenide antimony and indium gallium arsenide antimony two-waveband infrared detector and a manufacturing method thereof. The indium arsenide antimony and indium gallium arsenide antimony two-waveband infrared detector structurally comprises a GaSb substrate, a first GaSb buffer layer grown on the GaSb substrate, an InGaAsSb PIN type short-wave device grown on the first GaSb buffer layer, a second GaSb buffer layer grown on the InGaAsSb PIN type short-wave device and an InAsSb NIP type middle-wave device grown on the second GaSb buffer layer. The indium arsenide antimony and indium gallium arsenide antimony two-waveband infrared detector can realize signal detection on an infrared middle-wave waveband and a short-wave waveband.

Owner:INST OF SEMICONDUCTORS - CHINESE ACAD OF SCI

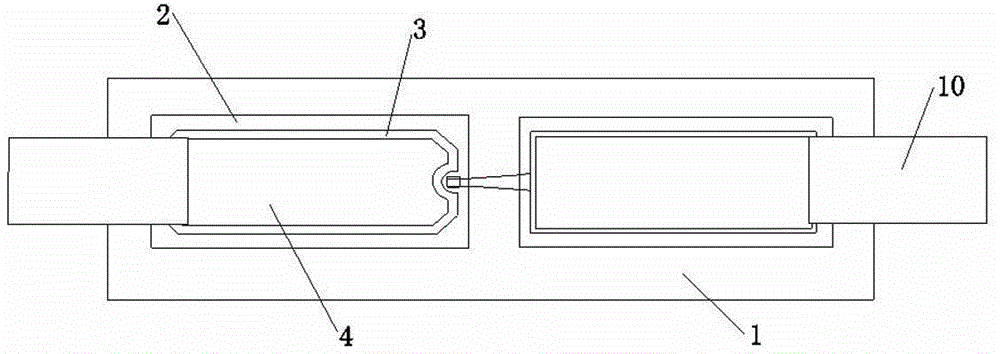

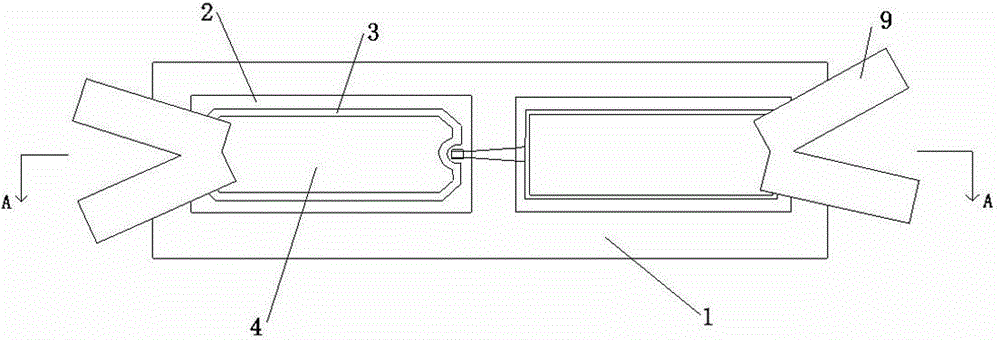

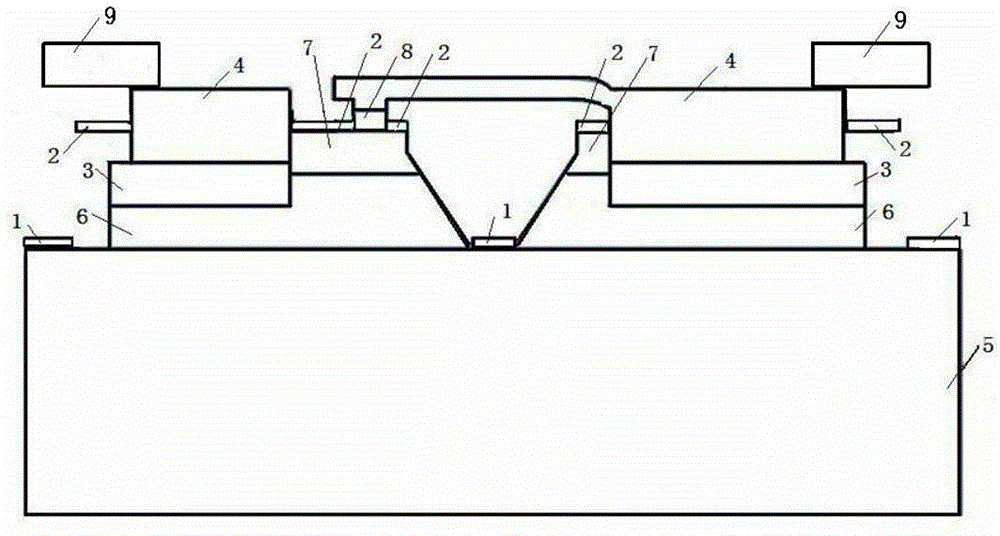

Gallium arsenide-based Schottky frequency-doubling diode with multi-beam leads

ActiveCN104795453AImprove securityImprove reliabilitySemiconductor/solid-state device detailsSolid-state devicesMicrometerMulti beam

The invention discloses a gallium arsenide-based Schottky frequency-doubling diode with multi-beam leads and relates to the technical field of semiconductor devices. The gallium arsenide-based Schottky frequency-doubling diode comprises a gallium arsenide-based Schottky frequency-doubling diode body. The multi-beam type leads are disposed at two ends of the gallium arsenide-based Schottky frequency-doubling diode body. Each multi-beam type lead comprises at least two beam type sub-leads with one ends connected, and the thickness of each beam type sub-lead is 2-4 micrometers. The gallium arsenide-based Schottky frequency-doubling diode has the advantages that the fact that the gallium arsenide-based Schottky frequency-doubling diode is normally mounted on a circuit is guaranteed, the safety and reliability of the Schottky frequency-doubling diode are increased, high mounting yield is achieved, mounting quality is guaranteed, production and scientific research costs are lowered greatly, the diode is simple in structure and convenient to use, and the service life of the diode is prolonged.

Owner:THE 13TH RES INST OF CHINA ELECTRONICS TECH GRP CORP

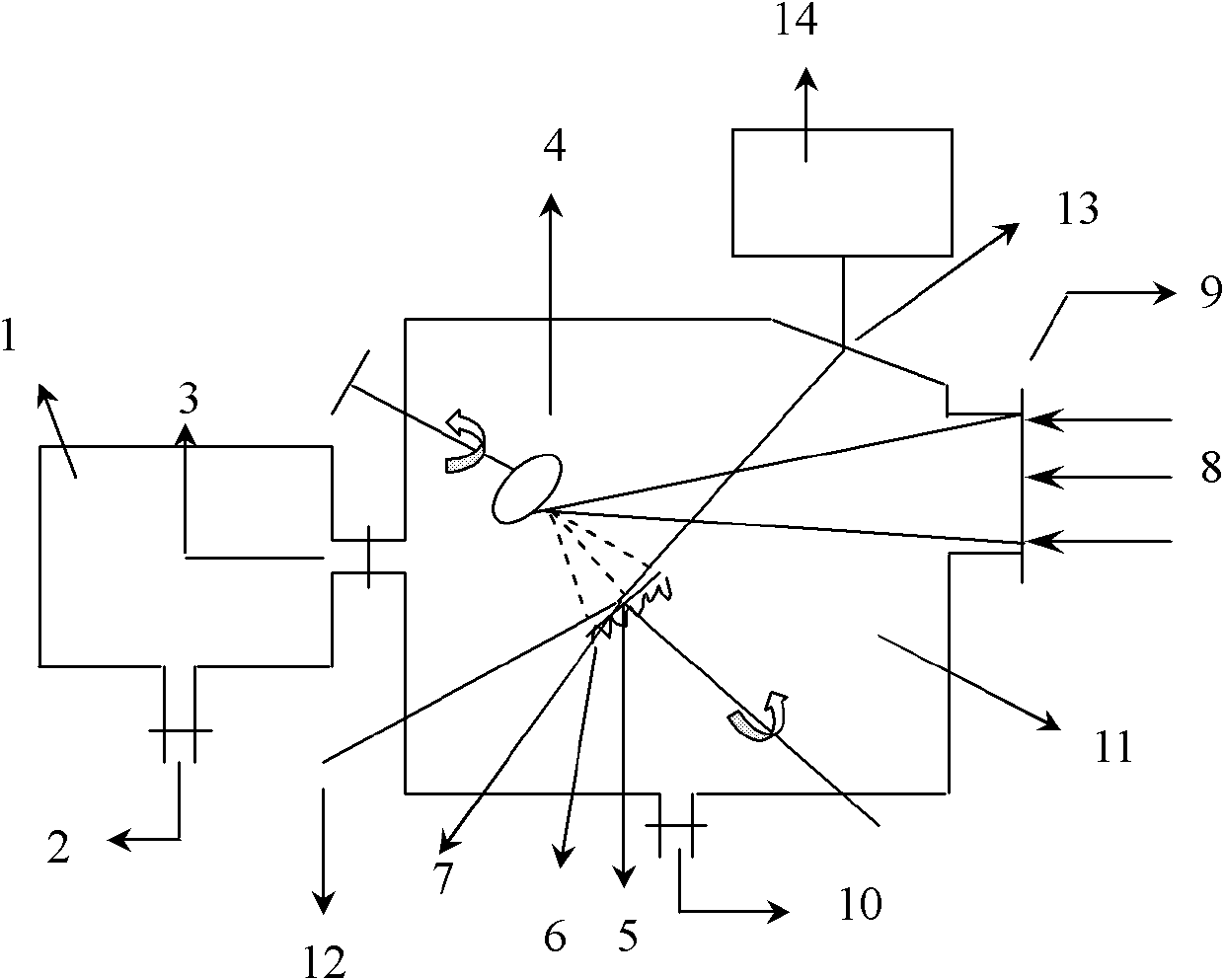

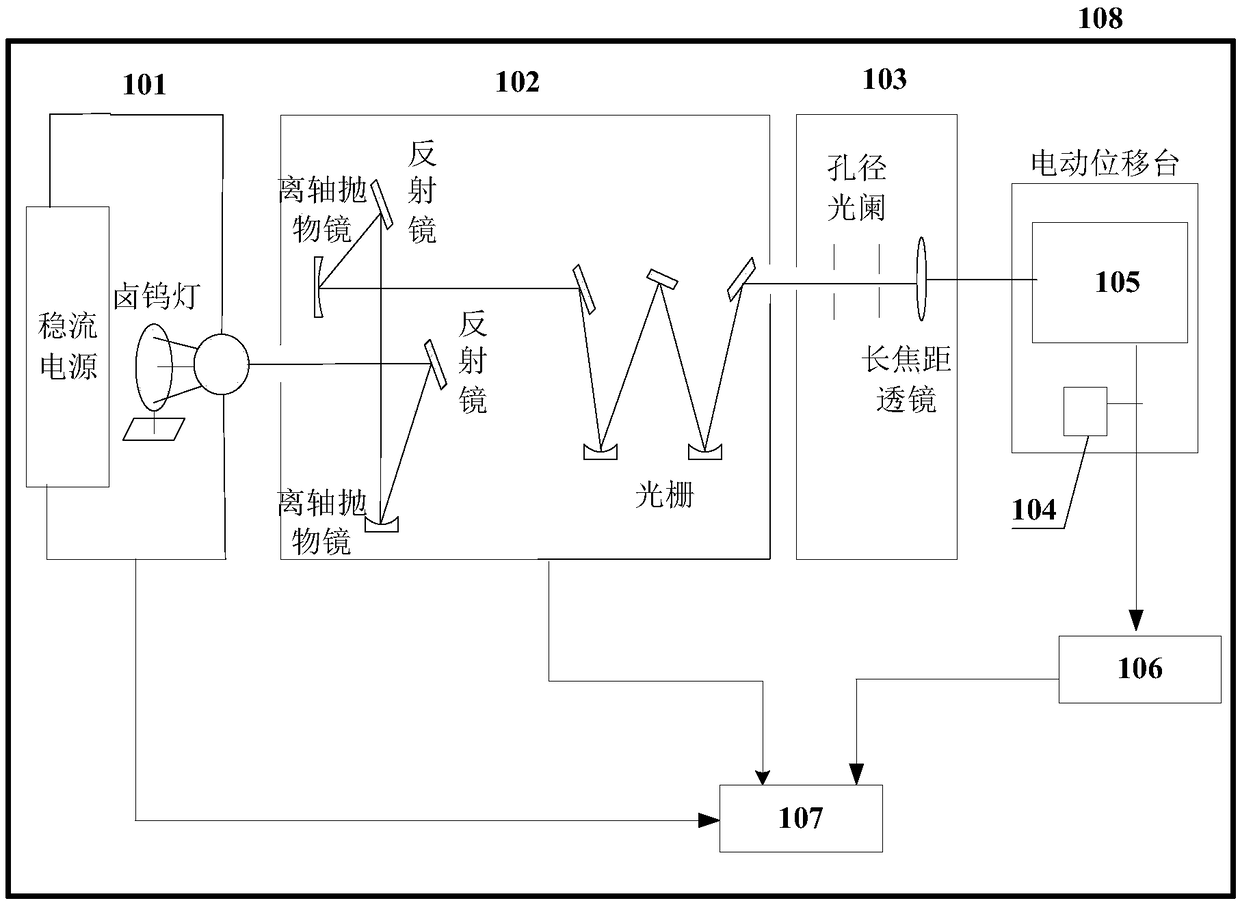

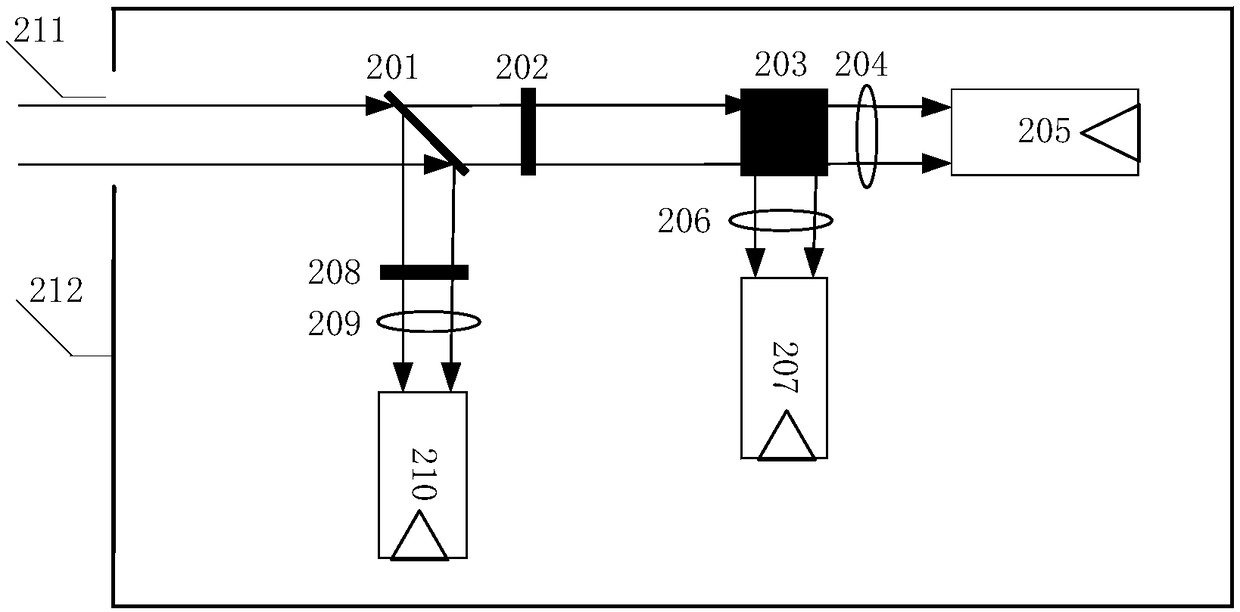

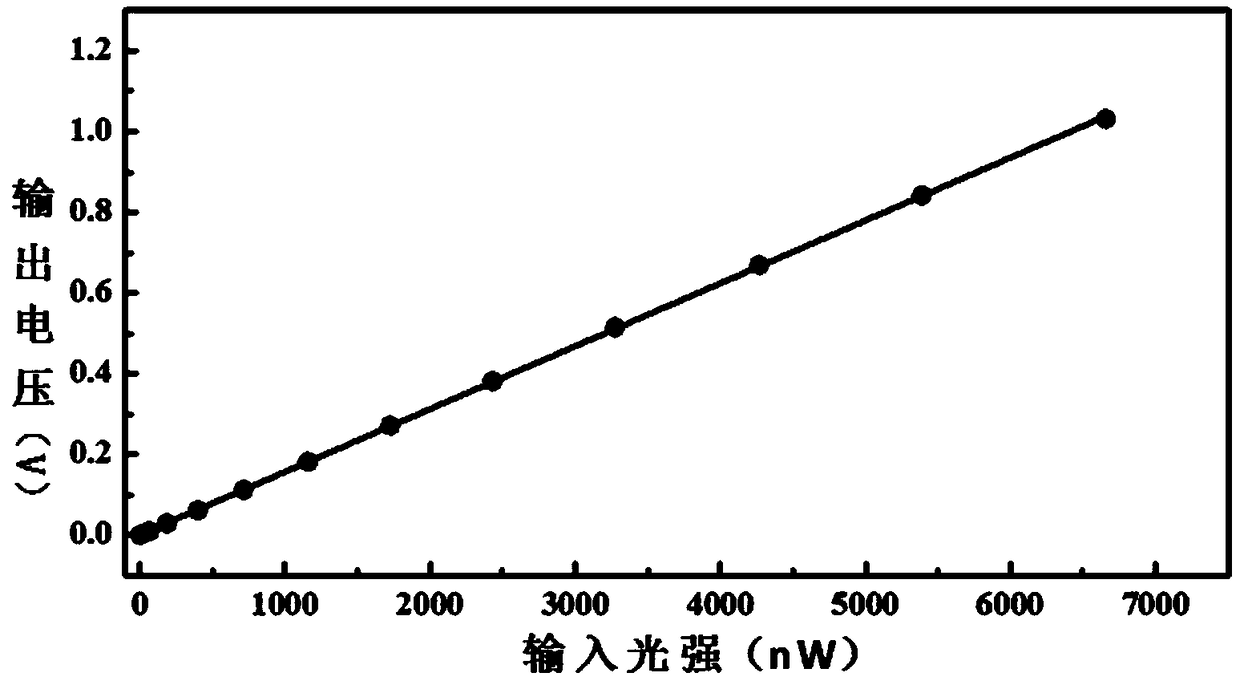

Detection performance testing method and device for photoelectric detection system of laser radar

InactiveCN108957426AImprove general performanceWide wavelength coverageWave based measurement systemsGratingPerformance index

The invention discloses a detection performance testing method and device for a photoelectric detection system of a laser radar. According to the invention, with a tungsten halogen lamp and a gratingmonochromator, a testing light signal with the precisely adjustable wavelength and strength is outputted; and an echo signal received actually by a laser radar is simulated from the aspects of wavelength and strength. On the basis of combination of silicon and indium-gallium-arsenide standard detectors, performance indexes like an optical transmittance, an input light intensity-output voltage response curve, and a linear response range of the photoelectric detection system of the laser radar are measured simultaneously. Relevant test results can be used for assisting in the parameter design ofthe photoelectric detection system of the laser radar, so that the installation and calibration quality of the photoelectric detection system of the laser radar is improved and the good quality of the measurement data during the application process of the laser radar is ensured.

Owner:CAS HEFEI INST OF TECH INNOVATION

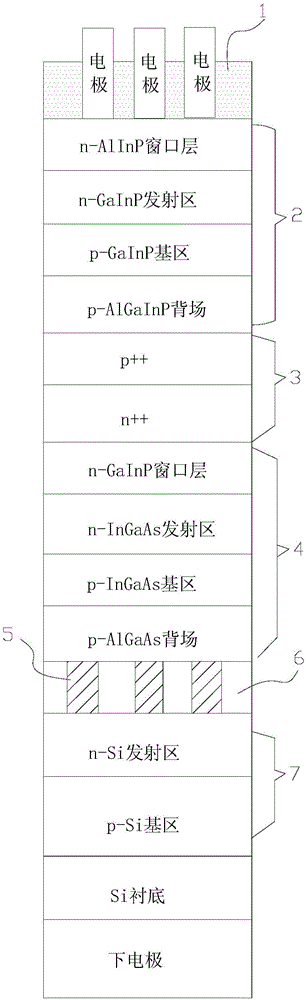

Preparation method for gallium arsenide-silicon multi-junction efficient solar battery

ActiveCN106653950AImprove photoelectric conversion efficiencyEfficient use ofFinal product manufacturePhotovoltaic energy generationEpoxyMultiplexing

The invention discloses a preparation method for a gallium arsenide-silicon multi-junction efficient solar battery. The preparation method is characterized by at least comprising the following steps of 101, preparing a Si solar battery through a diffusion or ion injection way; 102, preparing a GaAs solar battery; 103, preparing metal grid line electrodes with the same dimensions and used as contact electrodes on the Si solar battery and the GaAs solar battery respectively; 104, performing aligning and bonding on the Si solar battery and the GaAs solar battery by using transparent epoxy resin according to contact electrode patterns; 105, etching off an AlAs sacrificial layer by using HF acid by adopting a substrate stripping multiplexing technique to obtain GaInP / InGaAs / Si 3-junction laminated solar battery and a multiplexing GaAs substrate; 106, manufacturing upper and lower electrodes of the battery; and 107, preparing a battery antireflection film.

Owner:CHINA ELECTRONIC TECH GRP CORP NO 18 RES INST