Patents

Literature

40 results about "Low cost substrate" patented technology

Efficacy Topic

Property

Owner

Technical Advancement

Application Domain

Technology Topic

Technology Field Word

Patent Country/Region

Patent Type

Patent Status

Application Year

Inventor

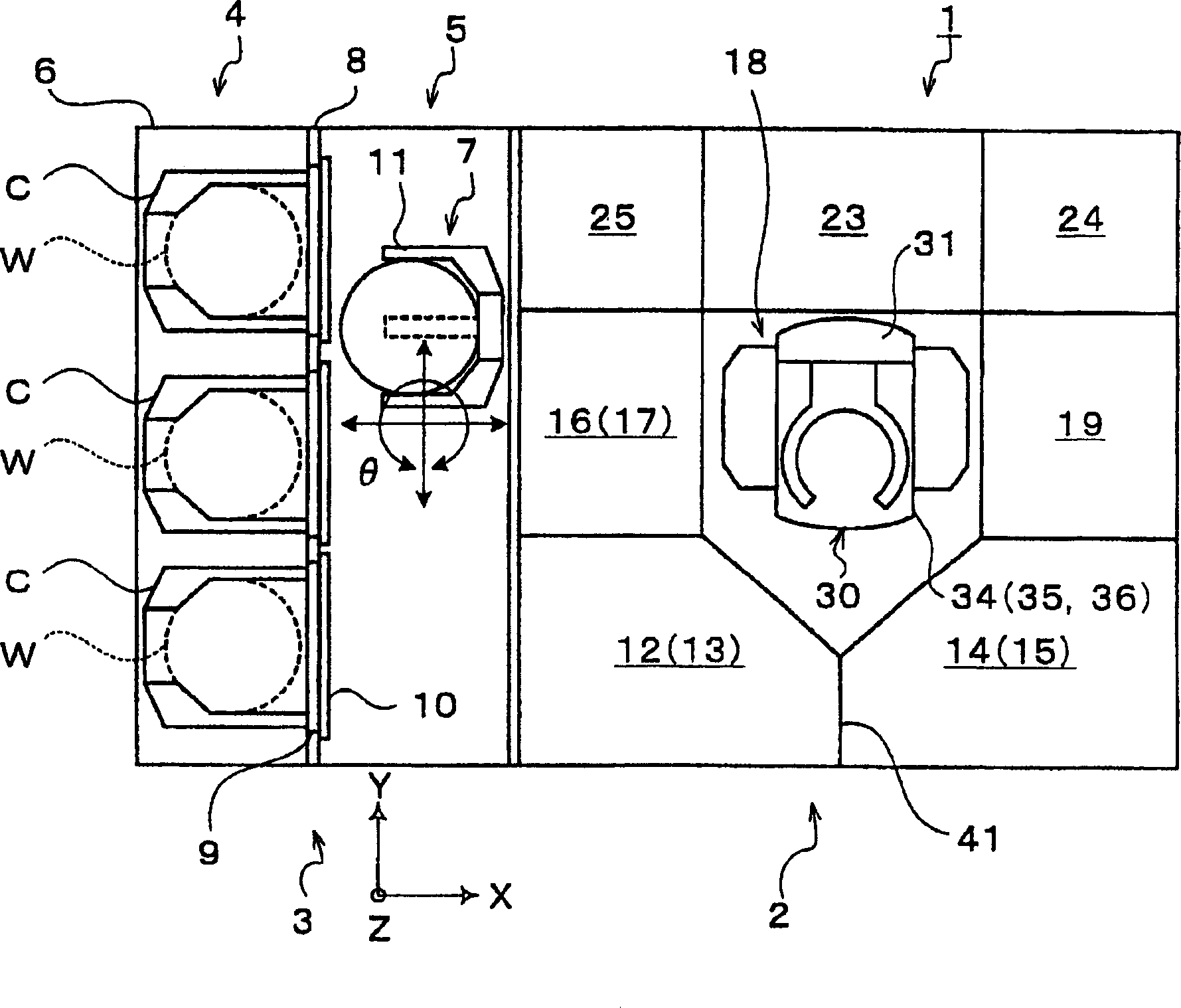

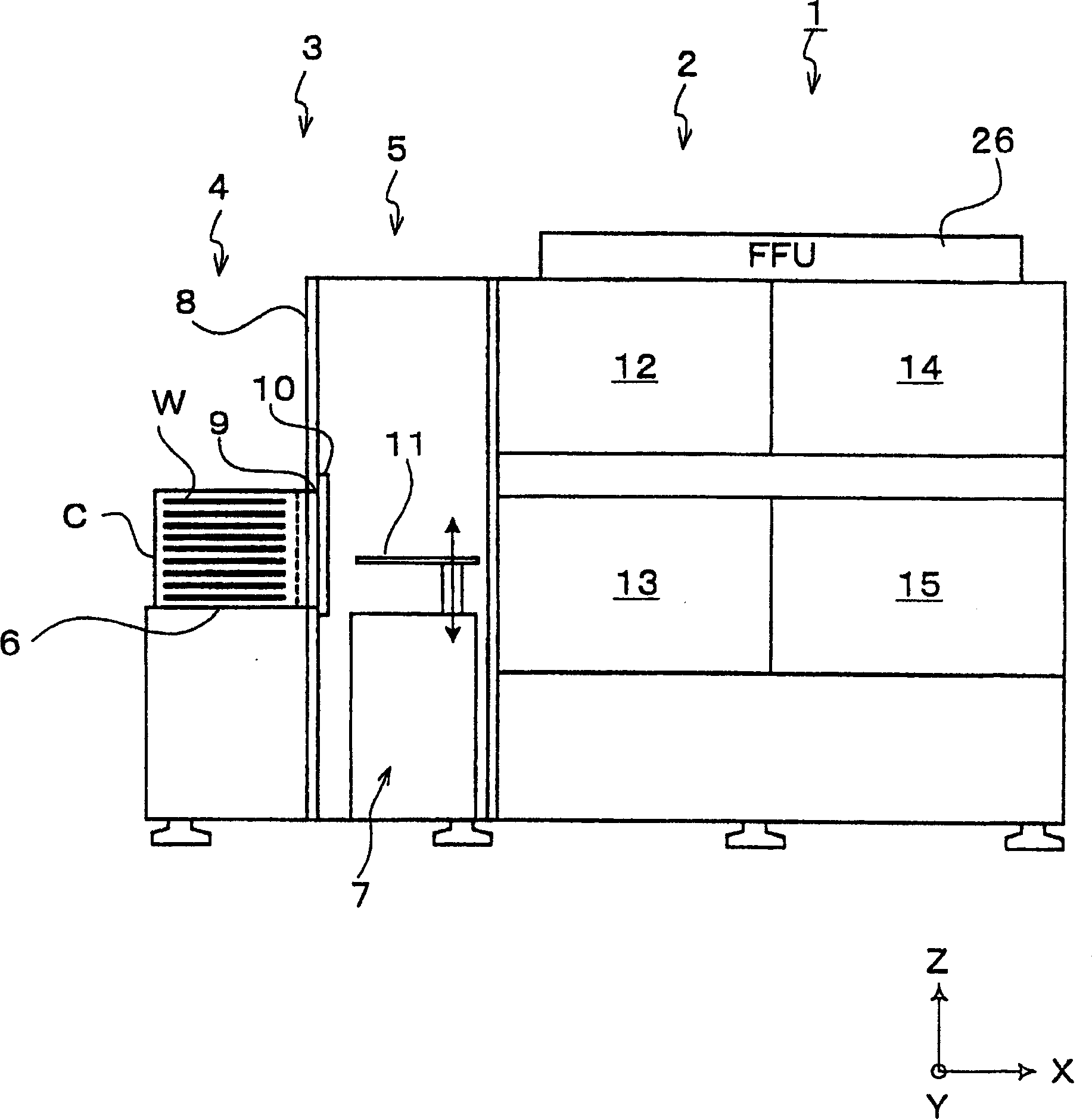

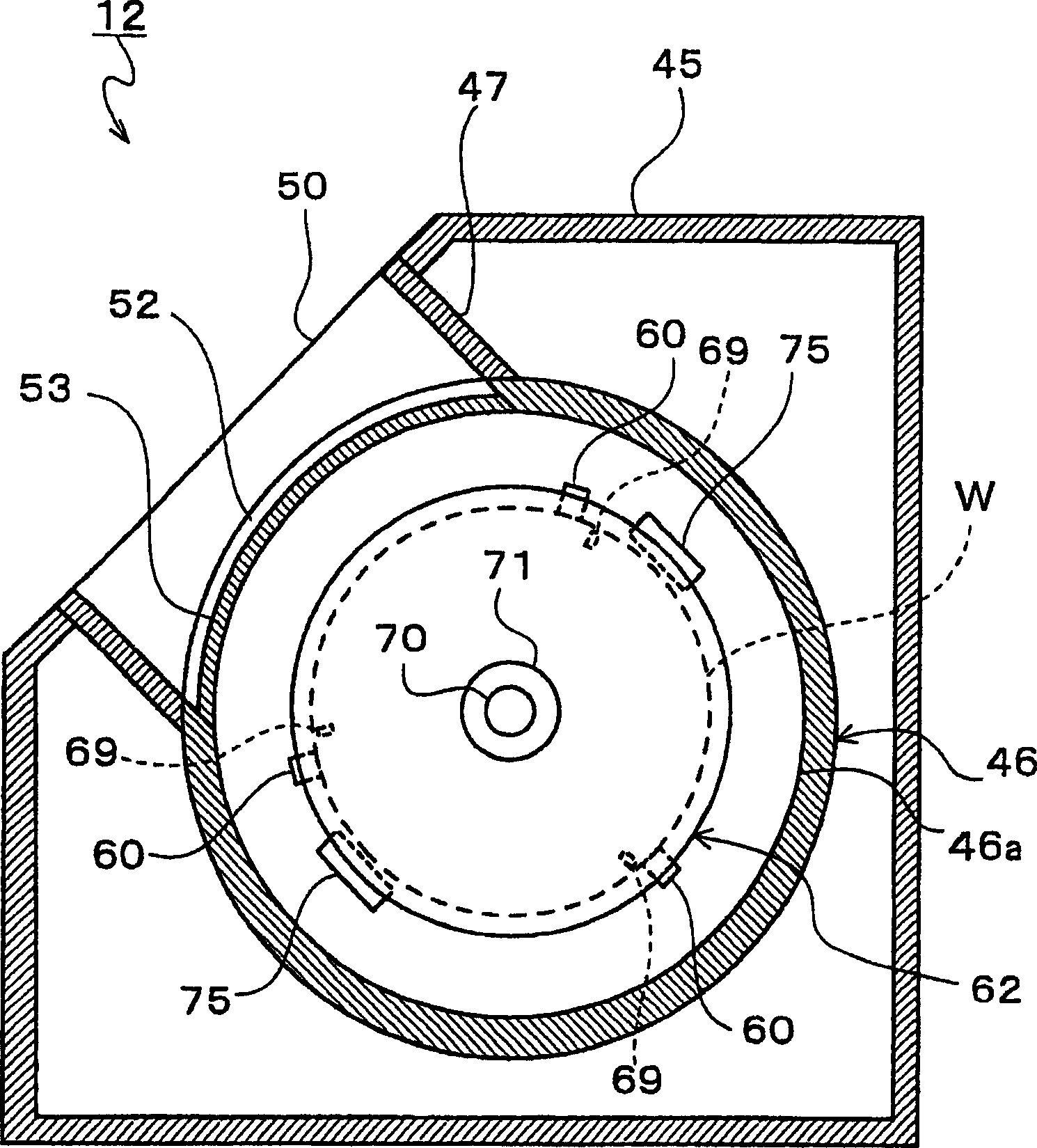

Processing apparatus and substrate processing method

InactiveUS7387131B2Reduce the impactLow costLiquid surface applicatorsSemiconductor/solid-state device manufacturingEngineeringLow cost substrate

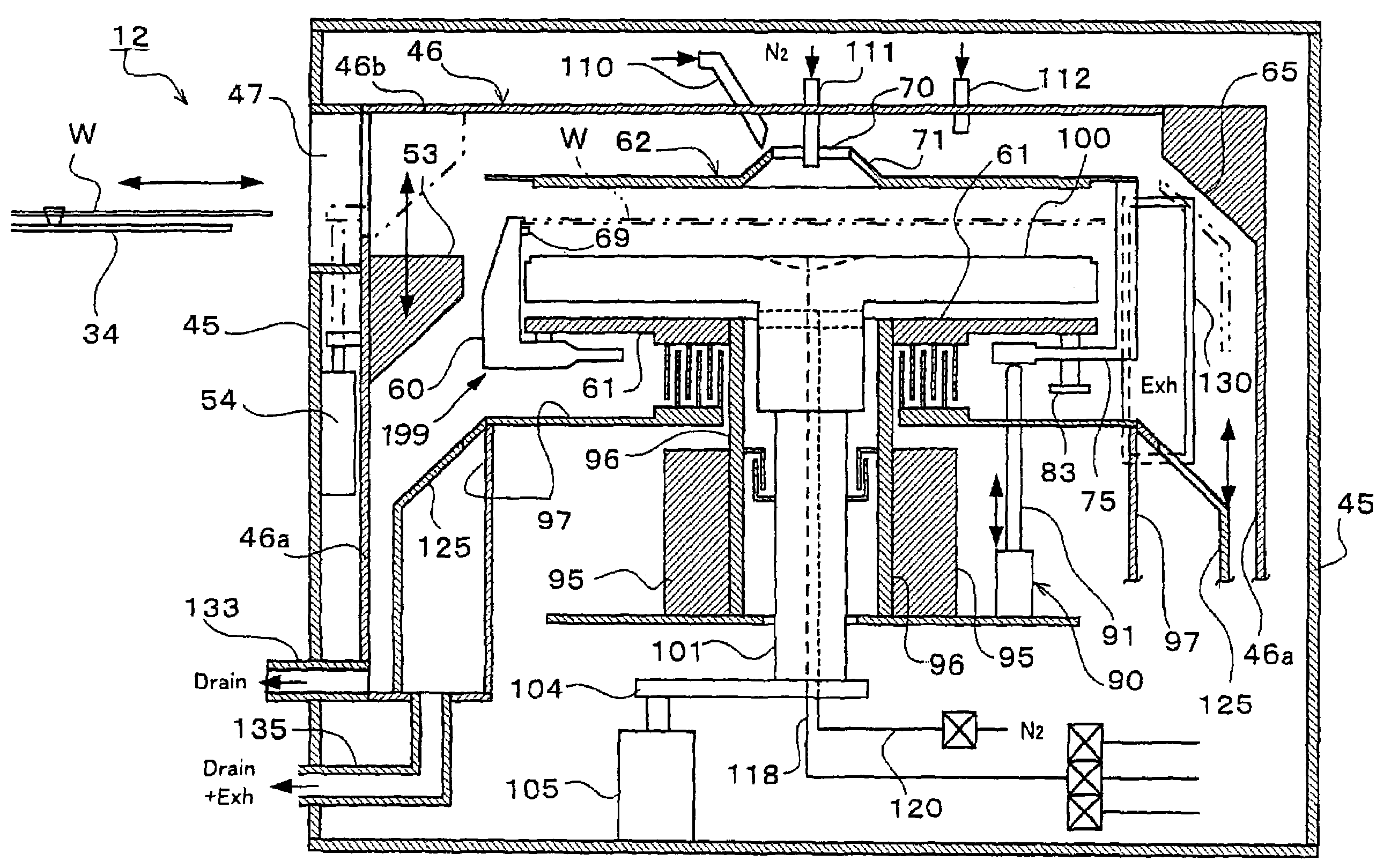

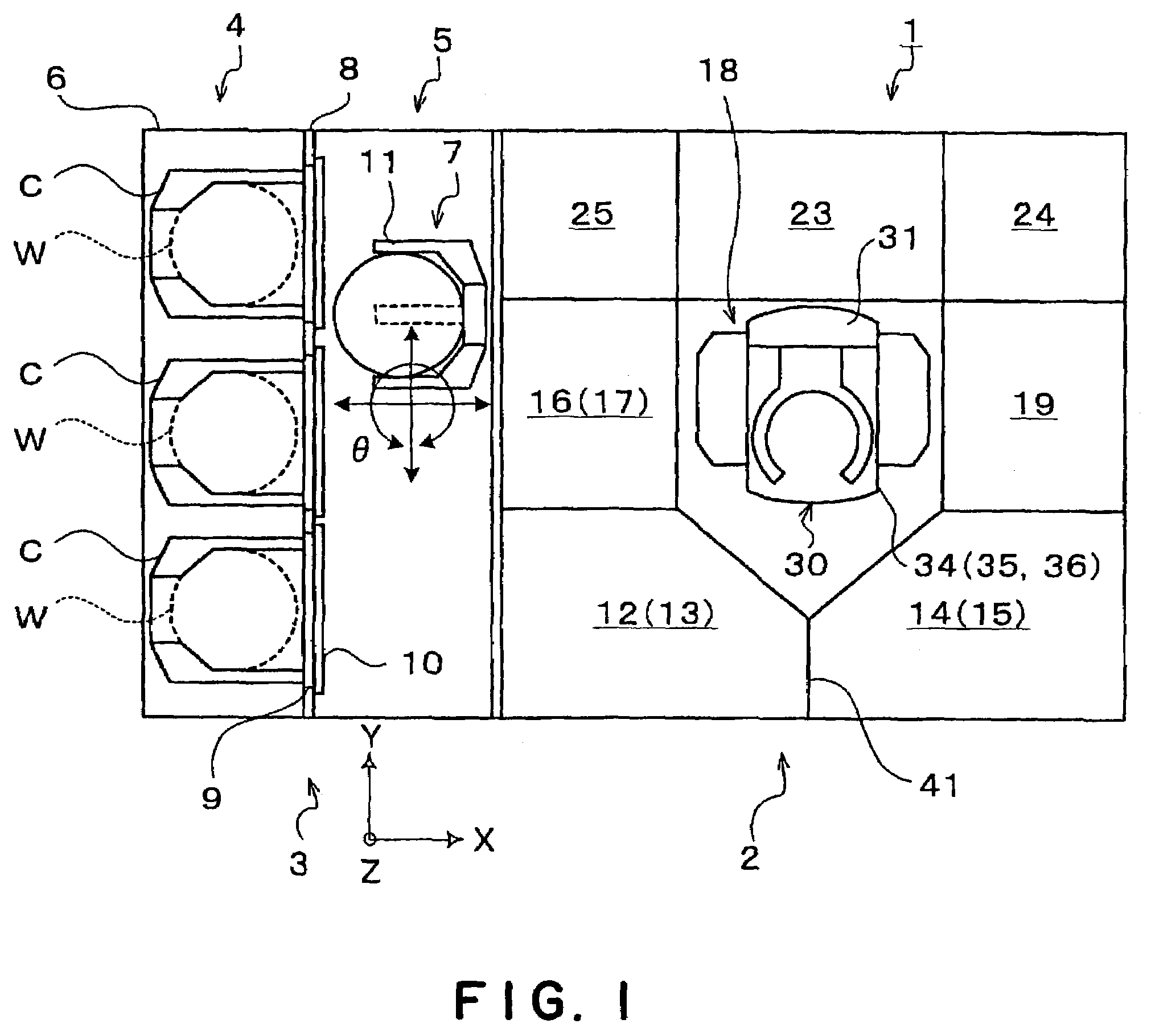

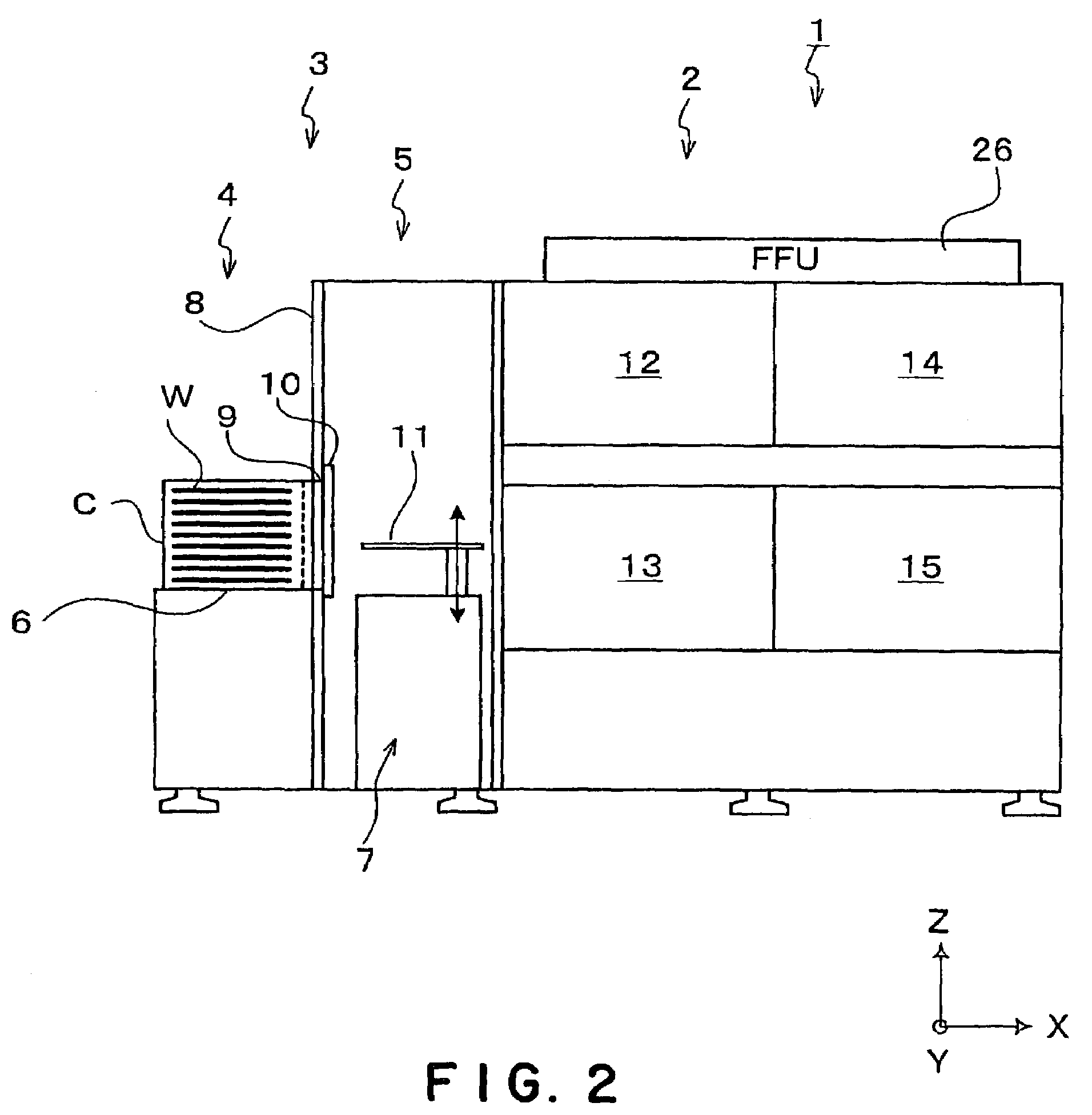

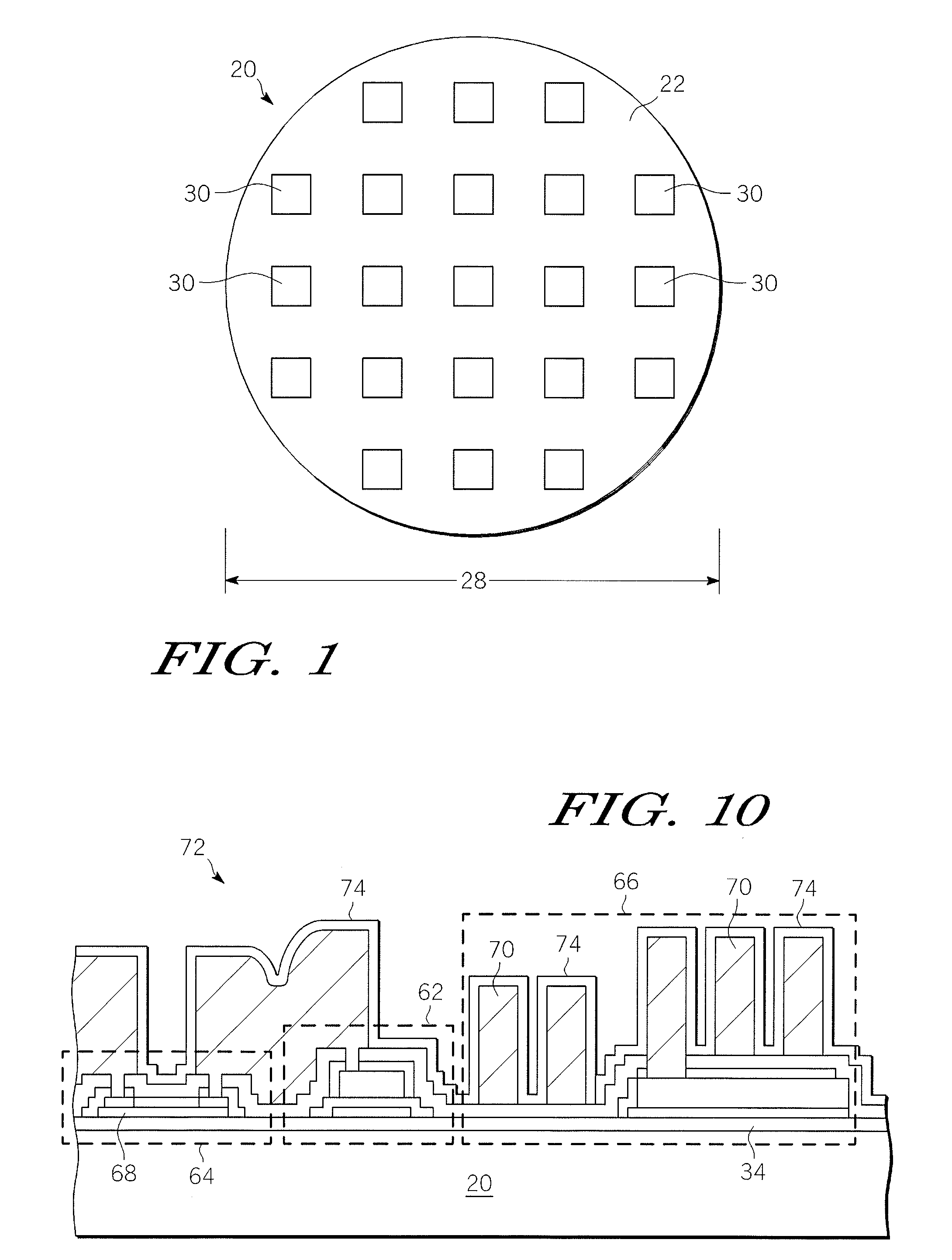

A substrate processing apparatus for processing a substrate With a processing fluid is provided. The apparatus includes holding members 60 for holding the substrate W, a chuck member 61 for supporting the holding members 60 and a top-face member 62 approaching the substrate W to cover its surface. In arrangement, since the top-face member 62 is supported by the chuck member 61, the holding members 60 can rotate together with the top-face member 62 in one body. With this structure, it is possible to reduce the influence of particles on the substrate W and also possible to provided a low-cost substrate processing apparatus occupied as little installation space as possible.

Owner:TOKYO ELECTRON LTD

High conductive water-based silver ink

Disclosed is a conductive composition which can be used to form an aqueous conductive ink with increased conductivity. The aqueous conductive composition contains conductive particles, preferably silver, an anionic wetting agent and a styrene-acrylic copolymer. The composition is highly conductive and requires reduced drying energy. In addition, it may be applied to low cost substrates by high speed printing processes.

Owner:SUN CHEM CORP

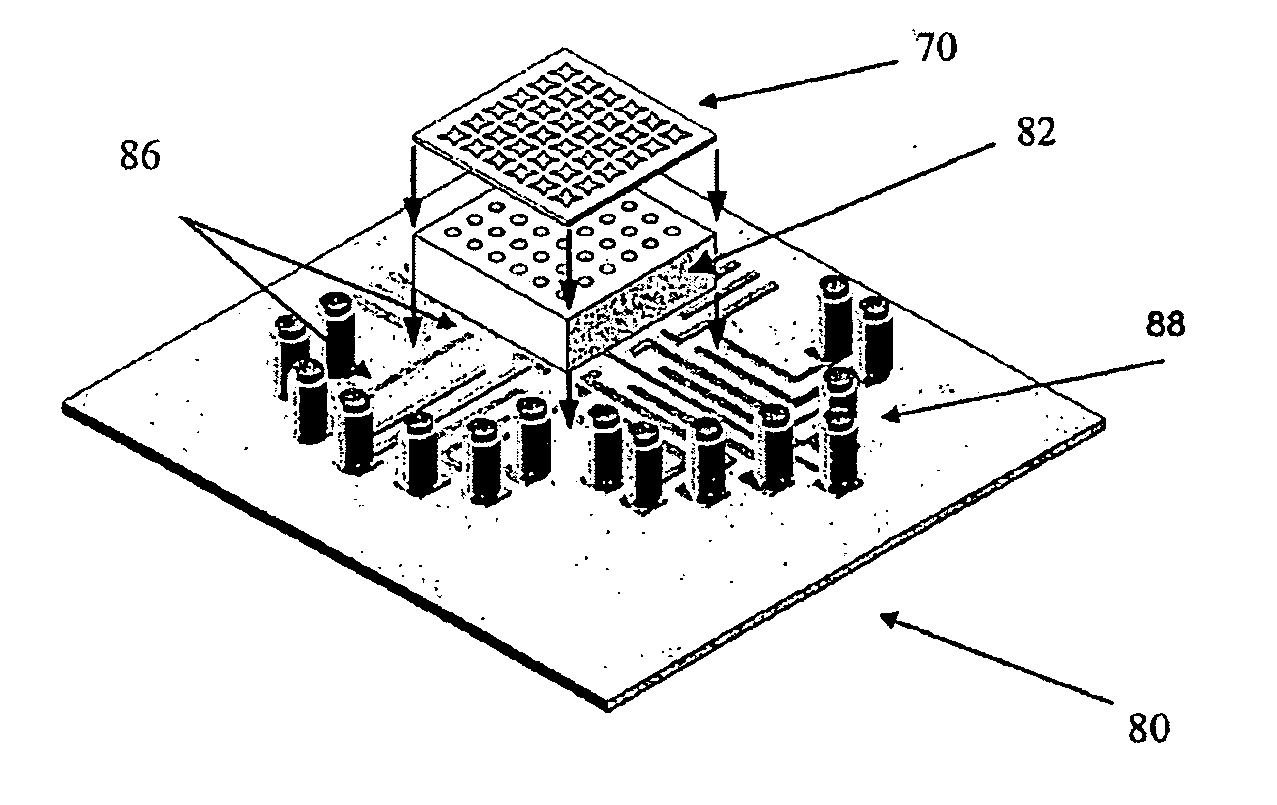

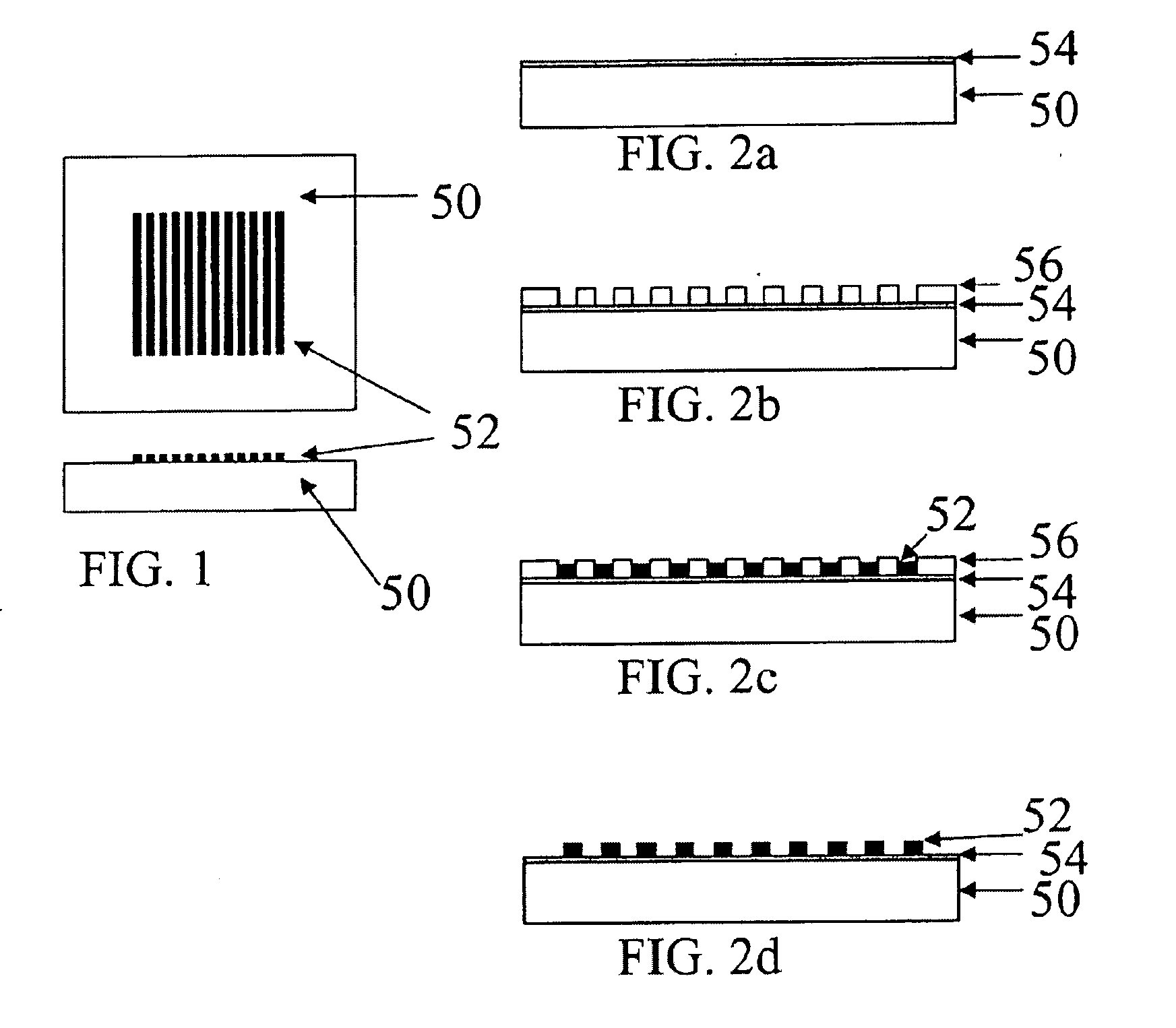

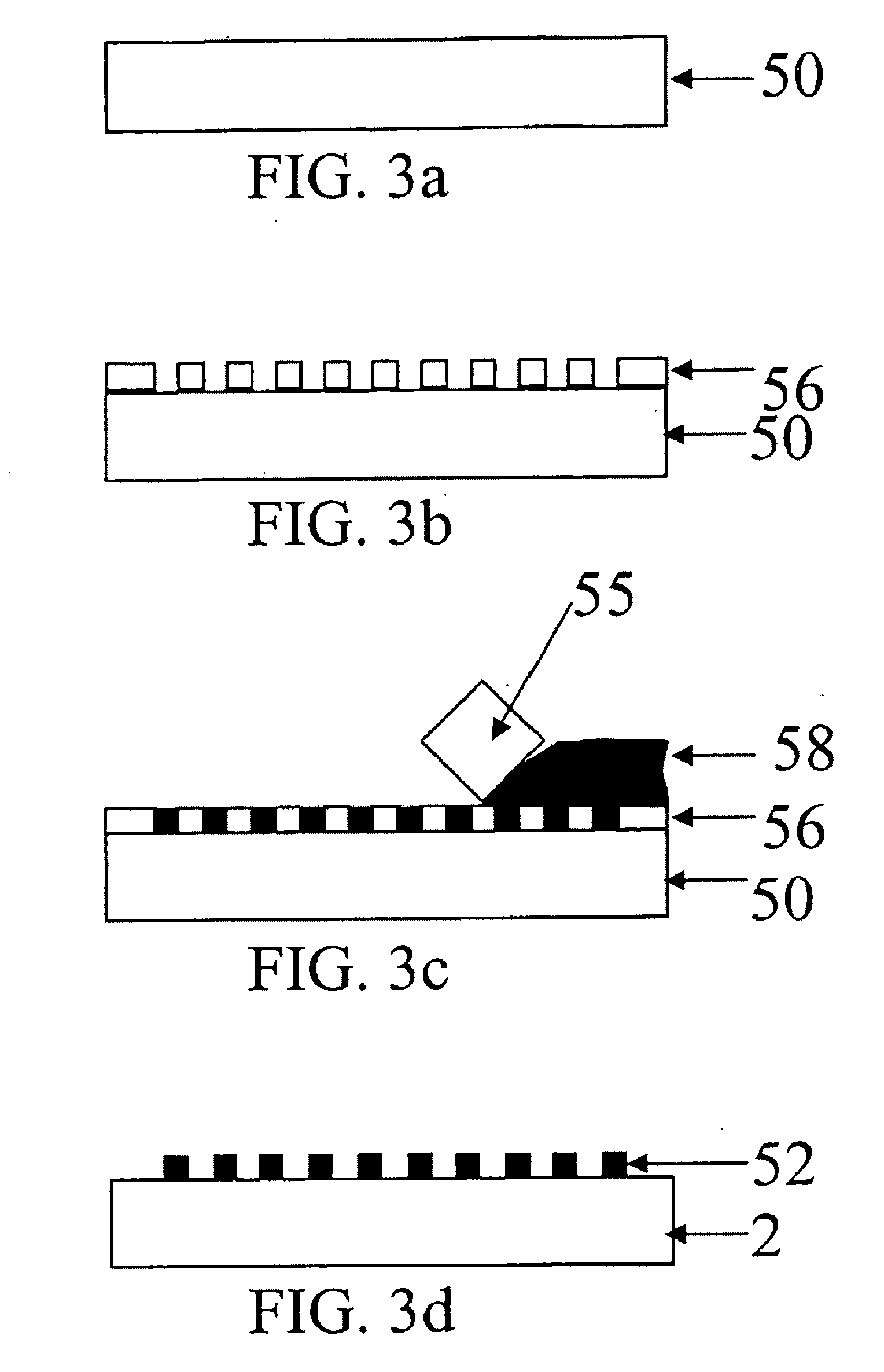

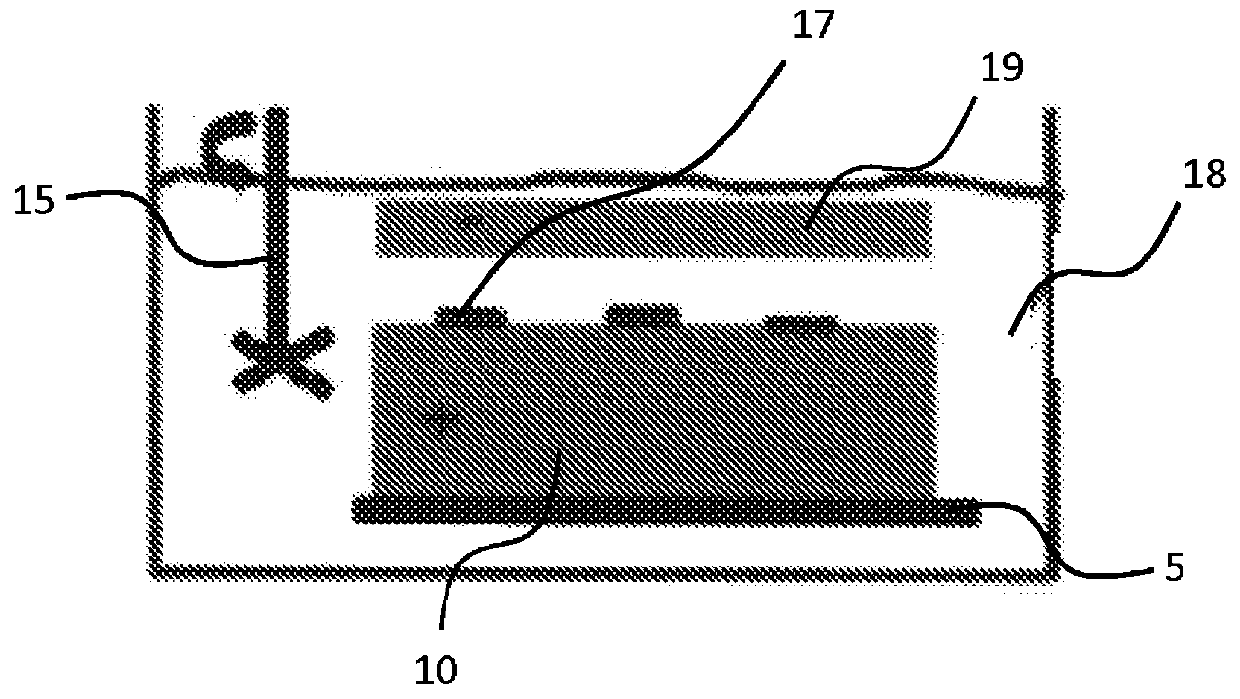

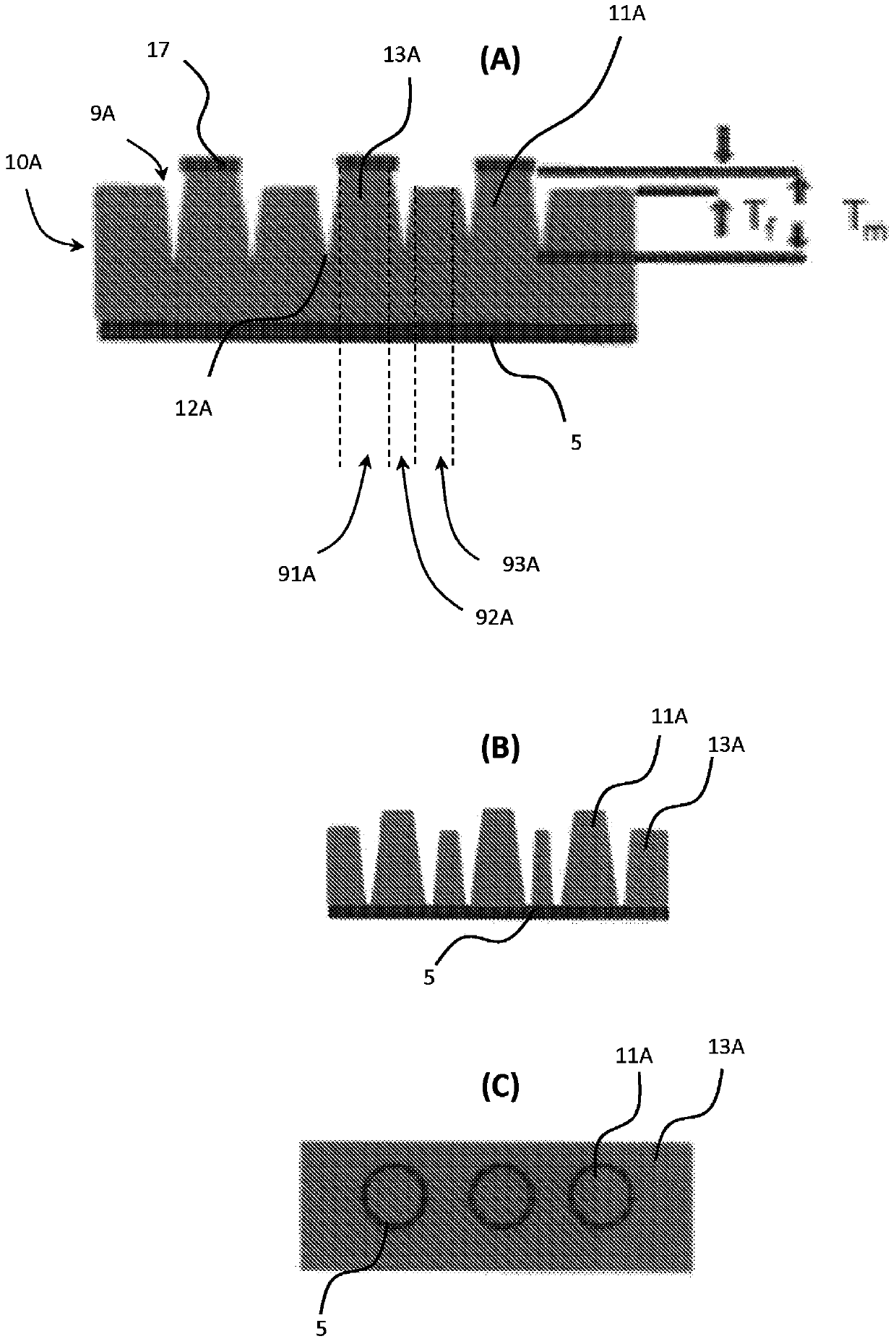

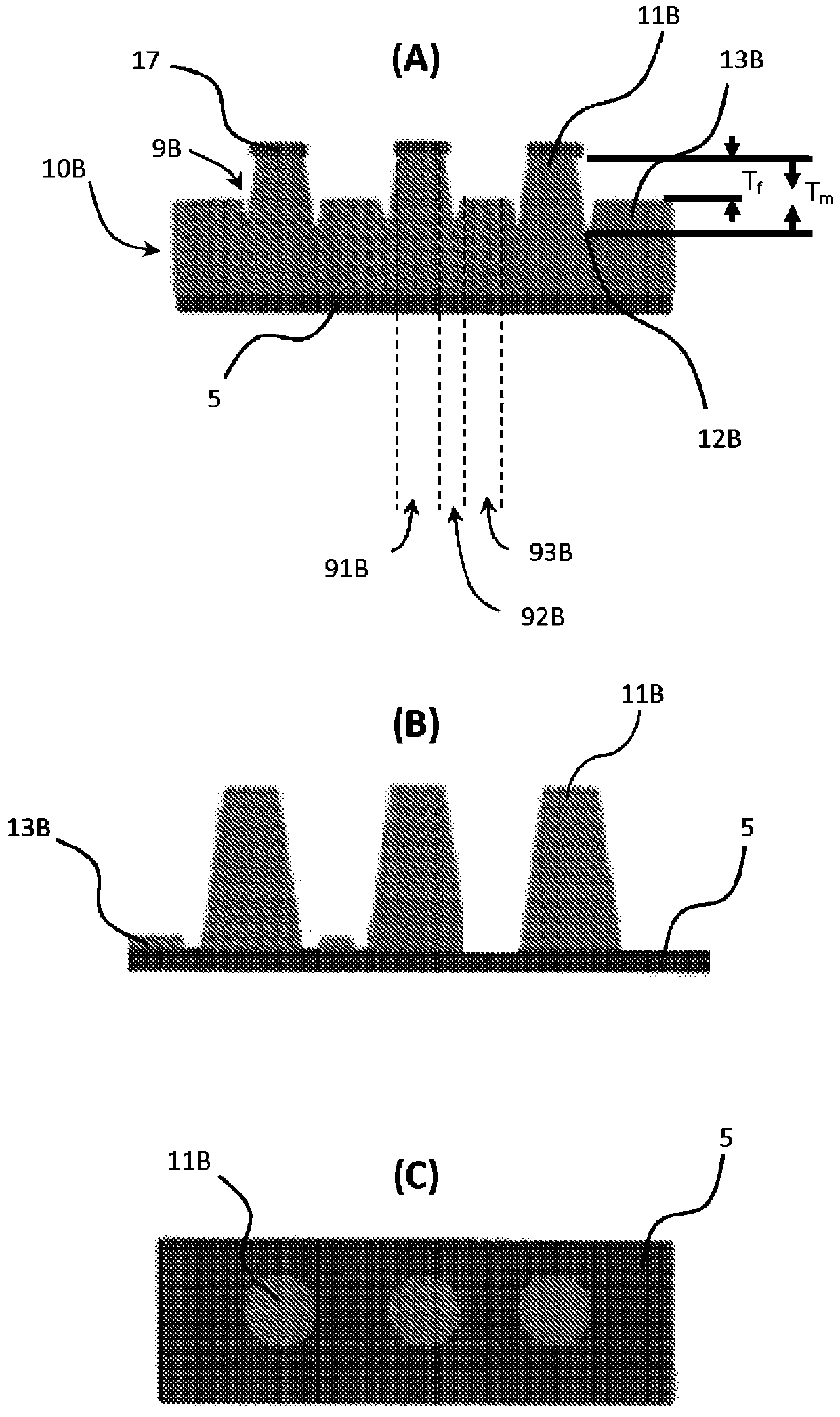

Magnetic bead-based arrays

InactiveUS20080187472A1Easy to separateEasy to replaceSequential/parallel process reactionsFlow mixersFluorescenceMagnetic bead

The present invention relates to magnetic particle separators using micromachined magnetic arrays and more particularly, to magnetic particle separators or manipulators using controlled magnetization on micromachined magnetic arrays for the separation of cells and other biological materials. The present invention also pertains to using such devices for the separation and analysis of biological materials for immunoassays, DNA sequencing, protein analysis, and biochemical detection applications. The present invention can also be viewed as a novel method for fabricating fully integrated permanent magnet components within any microelectromechanical system (“MEMS”) structures. The present invention also provides a magnetic particle separation and manipulation system for rapid separation and accurate manipulation of magnetic particles in two-dimensional electromagnetic arrays, which utilize high throughput biological analyses. A disposable cartridge can be produced in low cost using a low cost substrate such as plastic or other polymer, glass, or metal. Magnetic flux is generated by conventional or micromachined electromagnets a platform system consisting of magnetic flux sources, magnetic flux guidance, and a microprocessor control interface. By controlling direction of electric currents into inductors on the platform system, arbitrary magnetic poles can be generated on Permalloy structures of the cartridge to separate and manipulate magnetic particles. The magnetic particle separator and manipulator in the present invention can be easily combined with automated detection systems such as a fluorescent monitoring system.

Owner:AHN CHONG H +2

Substrate processor and substrate processing method

InactiveCN1440055ASemiconductor/solid-state device manufacturingCleaning using liquidsLow cost substrateEngineering

A substrate processing apparatus for processing a substrate with a processing fluid is provided. The apparatus includes holding members 60 for holding the substrate W, a chuck member 61 for supporting the holding members 60 and a top-face member 62 approaching the substrate W to cover its surface. In arrangement, since the top-face member 62 is supported by the chuck member 61, the holding members 60 can rotate together with the top-face member 62 in one body. With this structure, it is possible to reduce the influence of particles on the substrate W and also possible to provided a low-cost substrate processing apparatus occupied as little installation space as possible.

Owner:TOKYO ELECTRON LTD

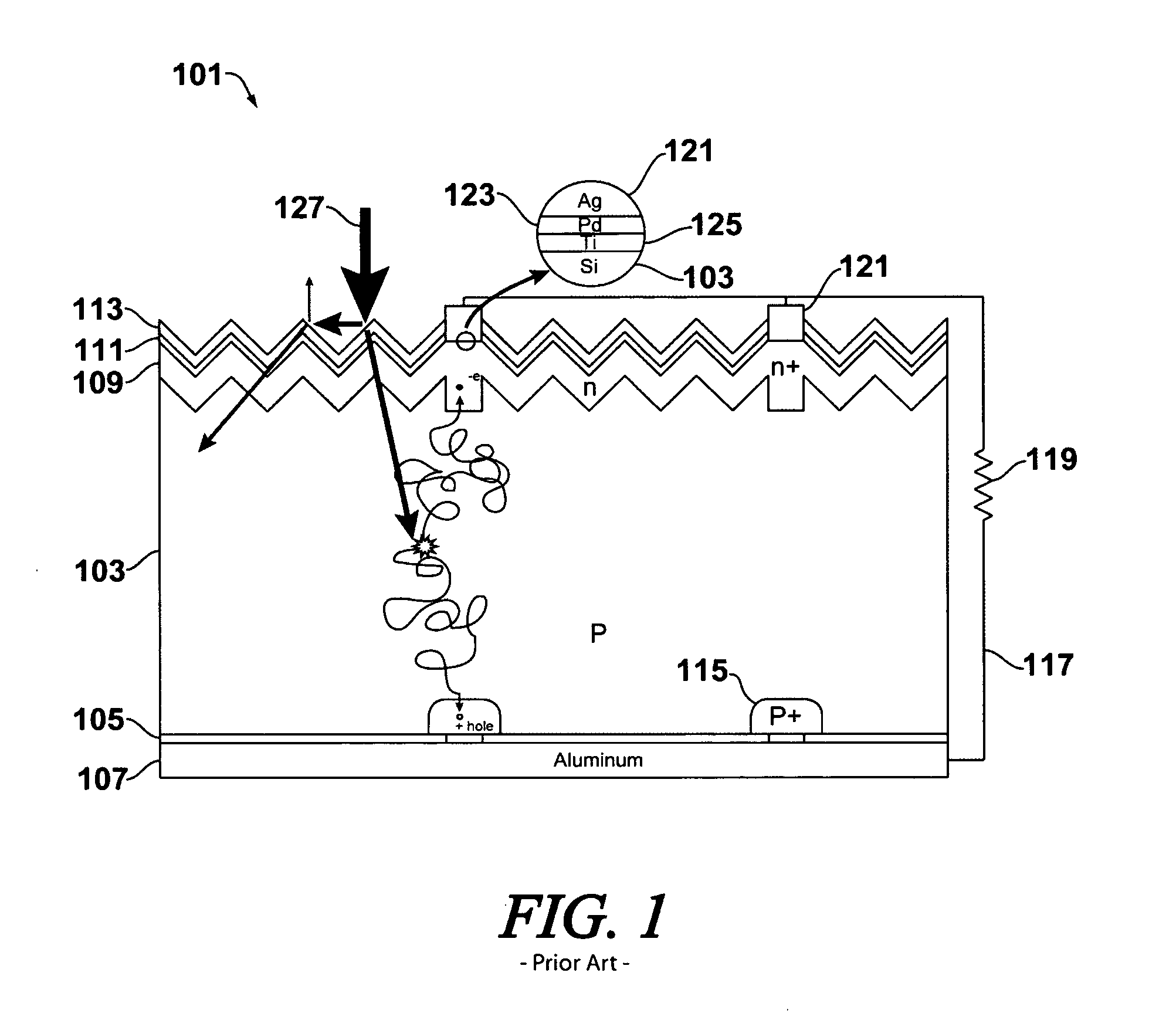

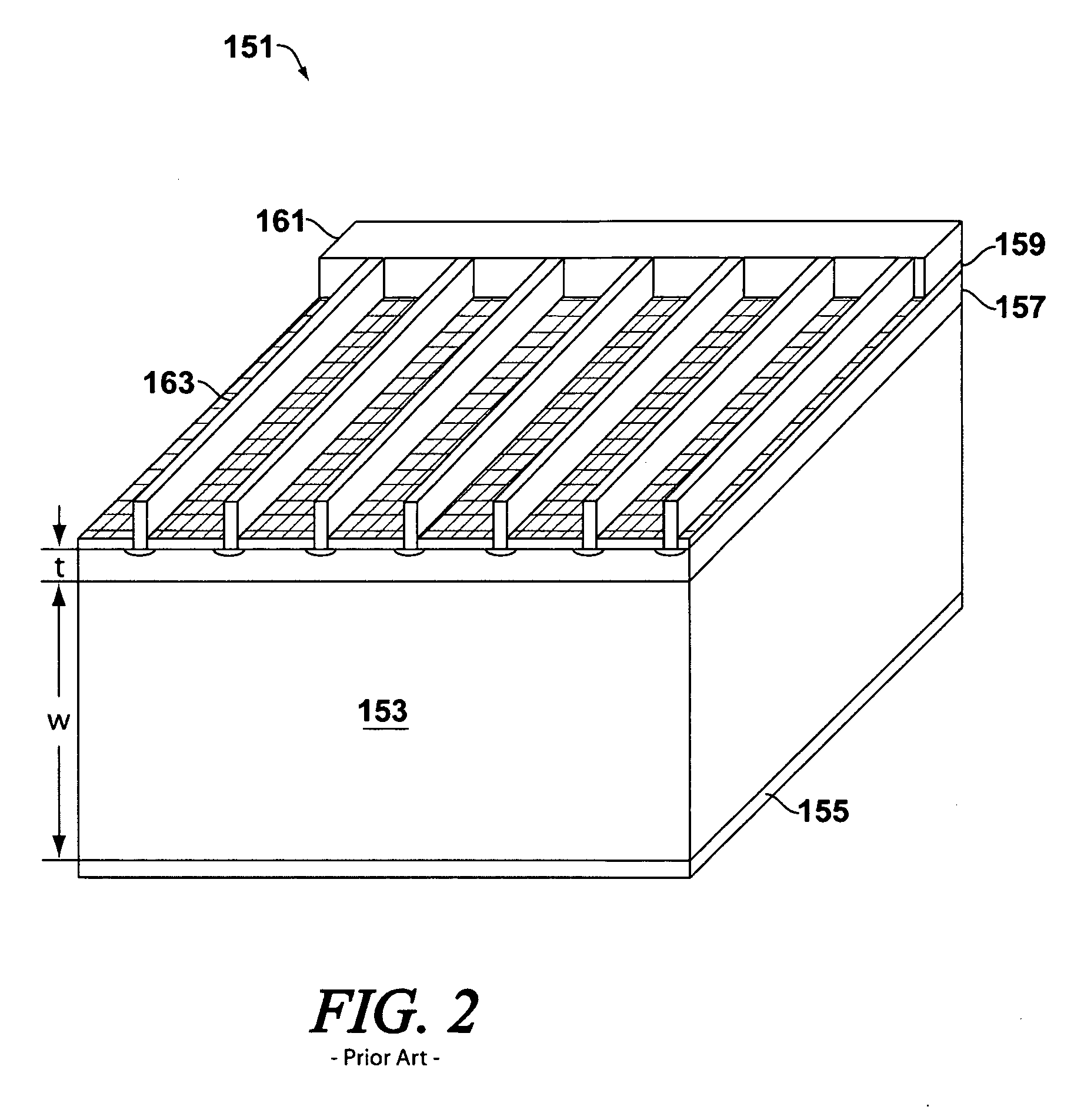

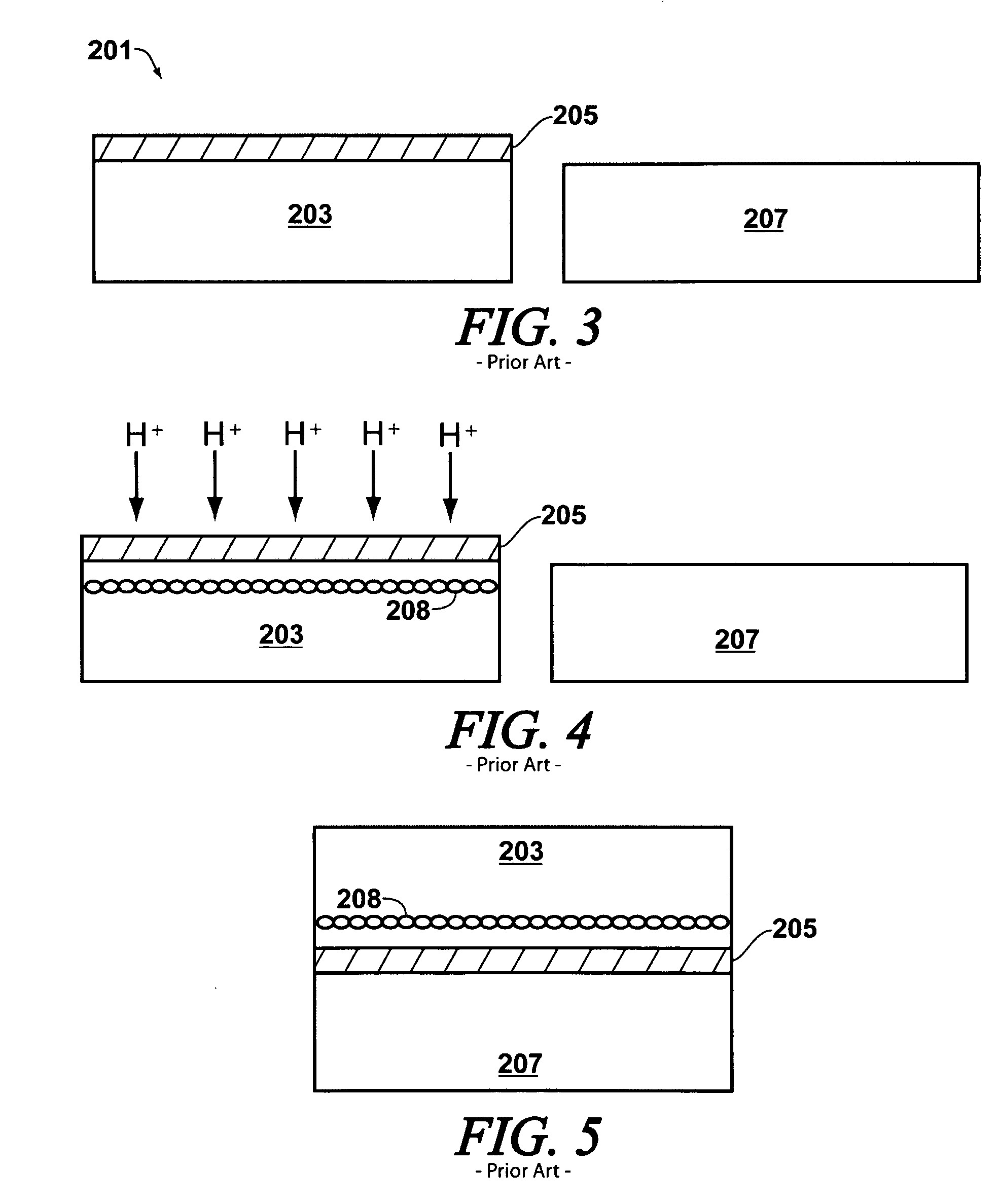

Photovoltaic device having a textured metal silicide layer

A semiconductor device is formed on a low cost substrate 312 onto which is deposited a metal film 314 that serves as an intermediate bonding layer with a transferred film 324 of semiconducting material from a bulk semiconductor substrate 322. The metal film forms an intermetallic compound such as a silicide 316 and functions as a bonding agent between the low cost substrate and the semiconducting substrate, as a back surface field for reflection of minority carriers, and as a textured optical reflector of photons. The silicide also forms a low resistivity back-side ohmic contact with the semiconductor layer. This results in a low cost, flexible, high efficiency, thin film solar cell device.

Owner:WOODSIDE GRP PTE LTD THE

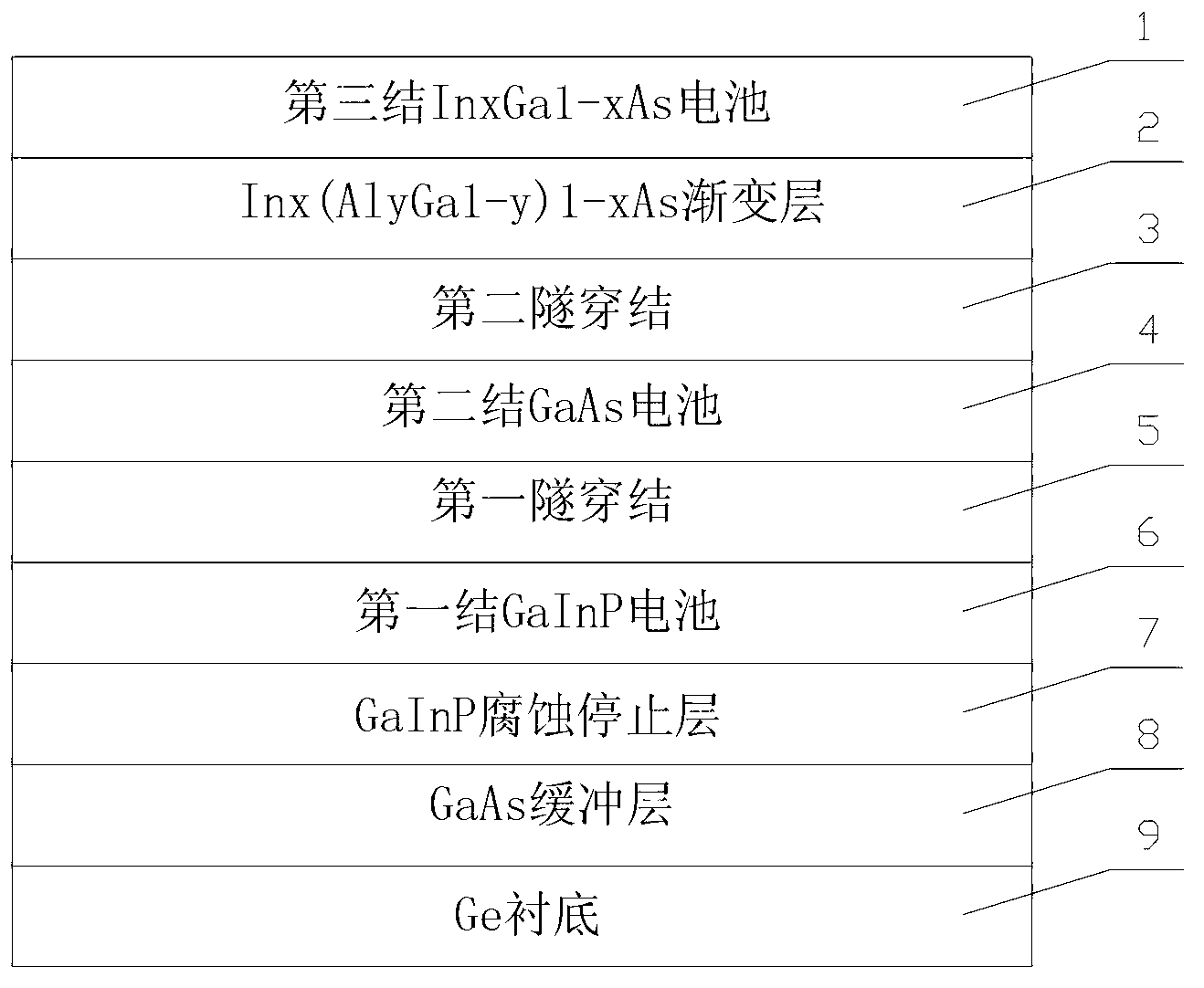

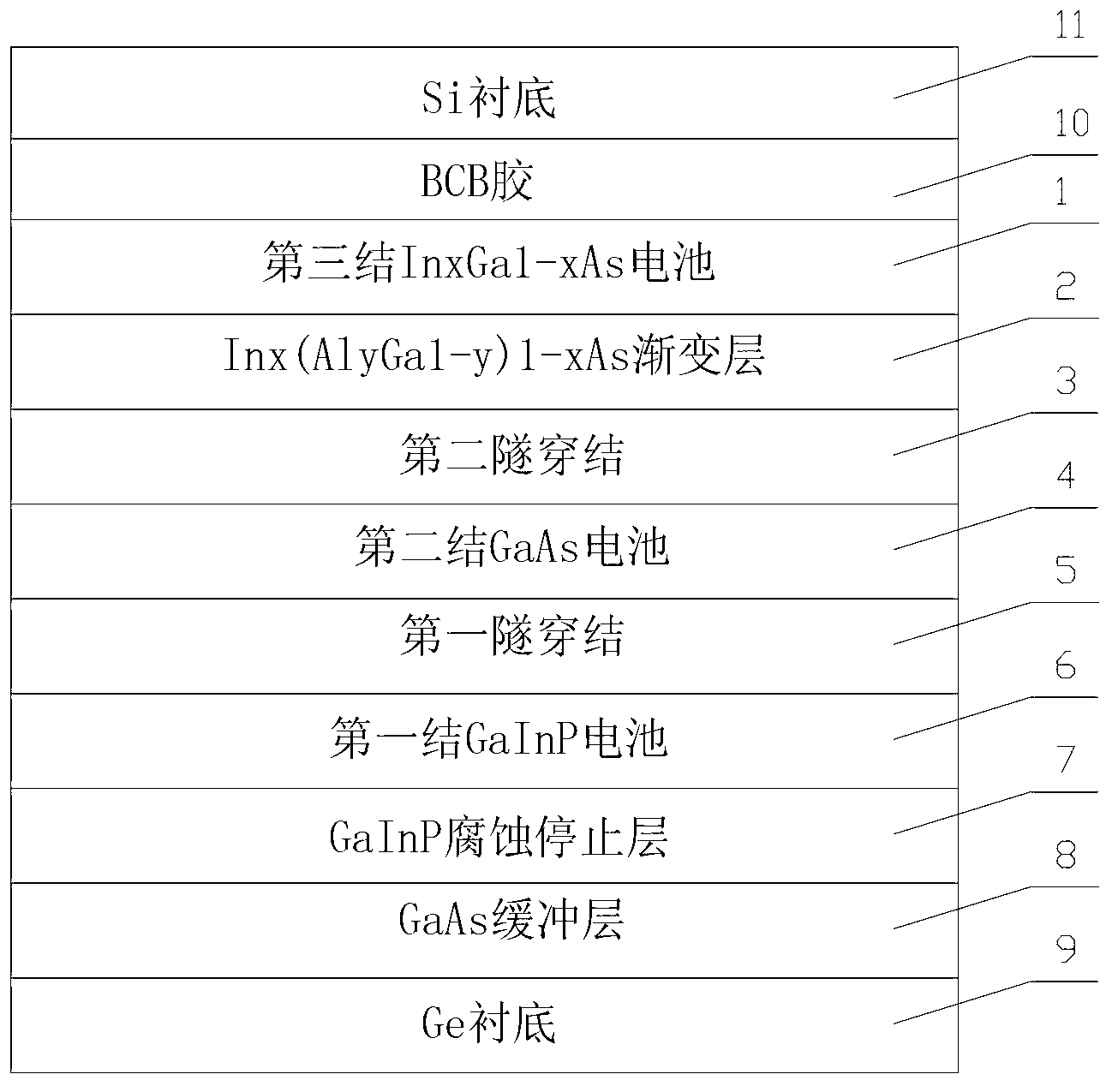

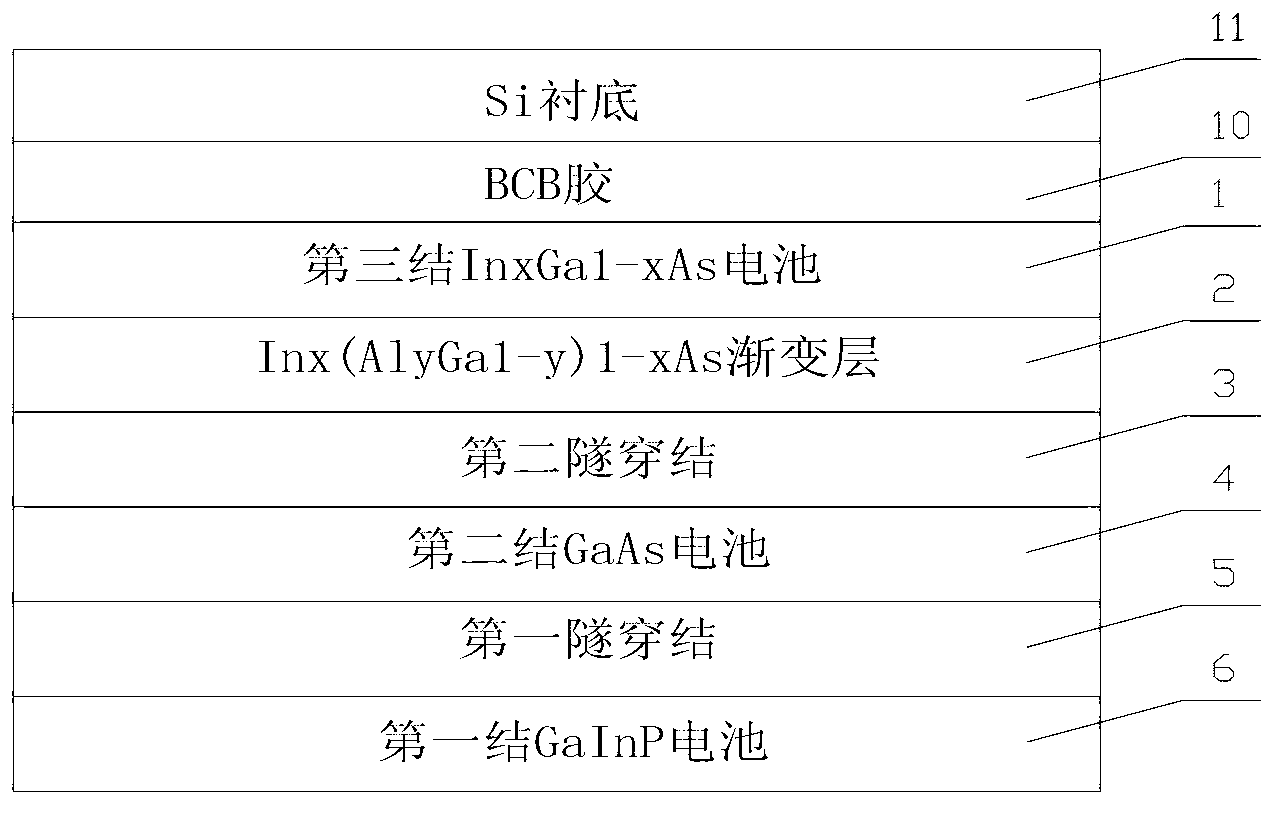

Preparation method of gallium arsenide thin-film multijunction stacked solar cells

ActiveCN103000759AImprove uniformityImprove reliabilityRenewable energy productsSemiconductor devicesIntermediate cellLow cost substrate

The invention relates to a preparation method of gallium arsenide thin-film multijunction stacked solar cells. The preparation method is characterized by including the steps of firstly, allowing for reverse growth of an epitaxial layer to prepare a GaAs three-junction solar cell; secondly, bonding the cell prepared in the step 1 to a Si substrate; thirdly, stripping a Ge substrate; fourthly, adhering a low-cost substrate; and fifthly, stripping the Si substrate. The preparation method allows for epitaxial growth of a top cell and an intermediate cell prior to growth of a bottom cell, and accordingly the lattice subjected to epitaxial growth firstly is guaranteed to match with perfect epitaxial growth of the top cell and the intermediate cell; doping uniformity and film reliability in large-area epitaxial thin films are increased, and photoelectric conversion efficiency is further improved; by the use of the low-cost support substrate lower than Ge in specific weight, the weight of the cells is reduced, the power ratio of the solar cells is increased, the cost of the cells is reduced effectively, and application prospect of the III-V compound solar cells is improved greatly.

Owner:TIANJIN LANTIAN SOLAR TECH +2

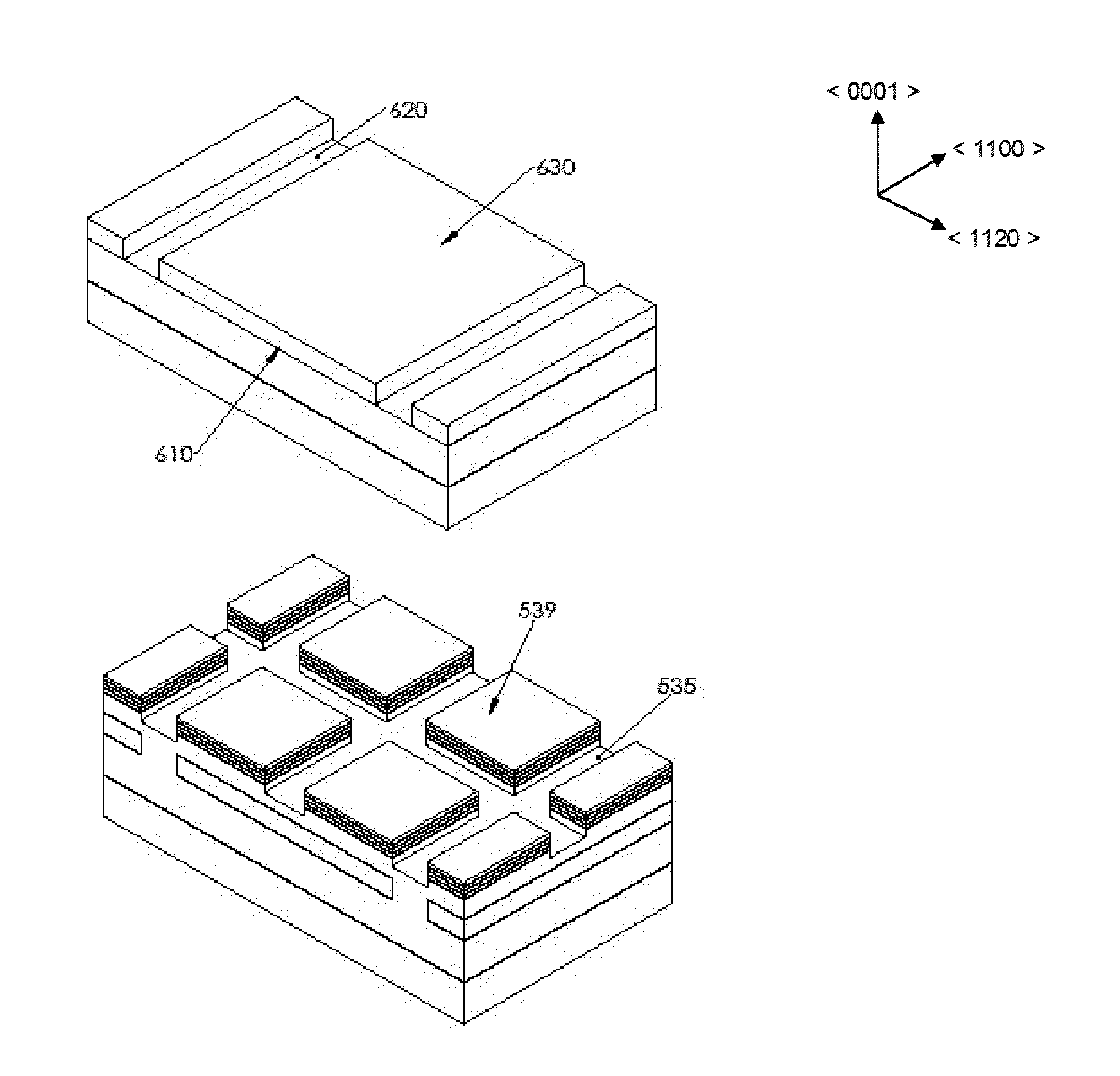

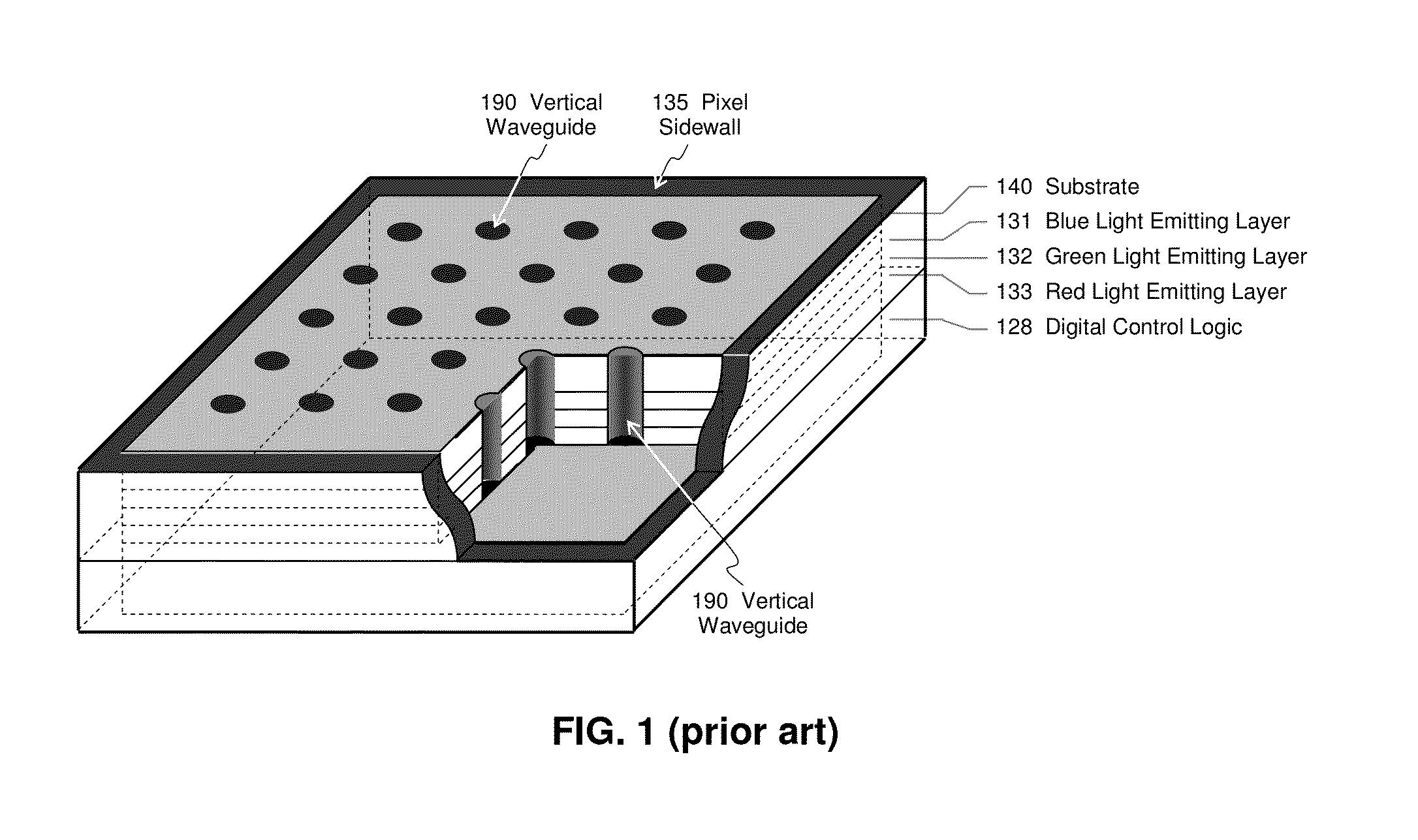

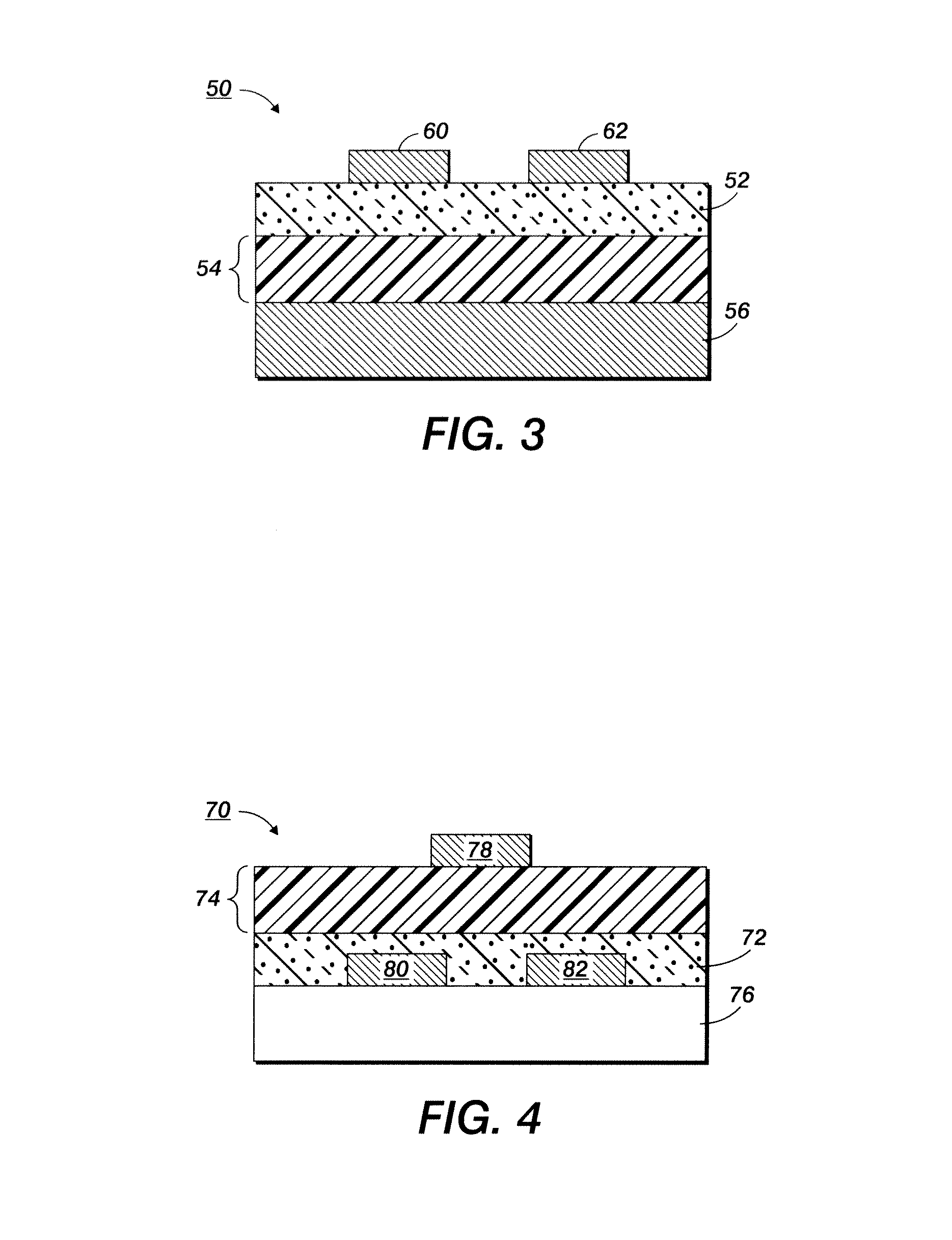

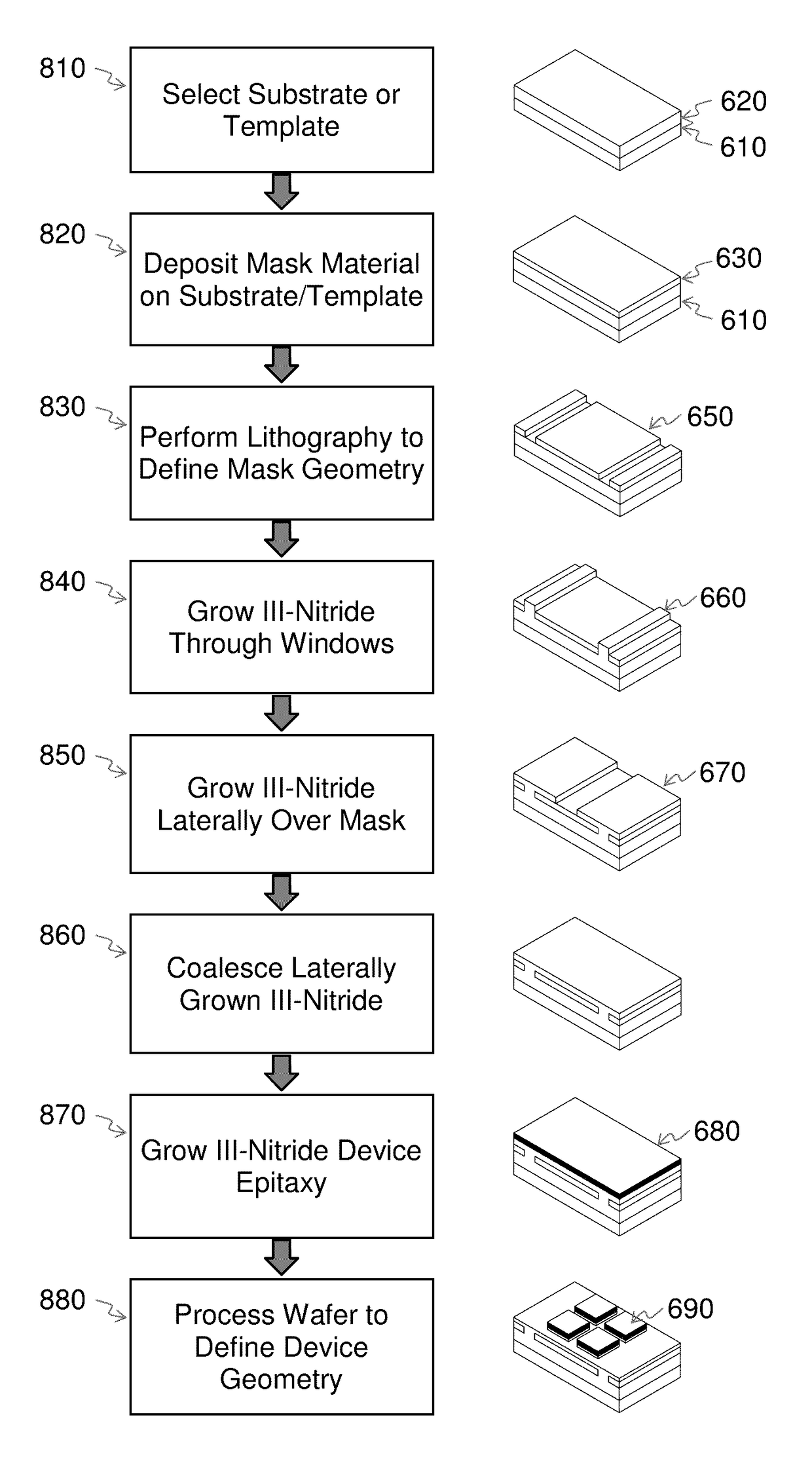

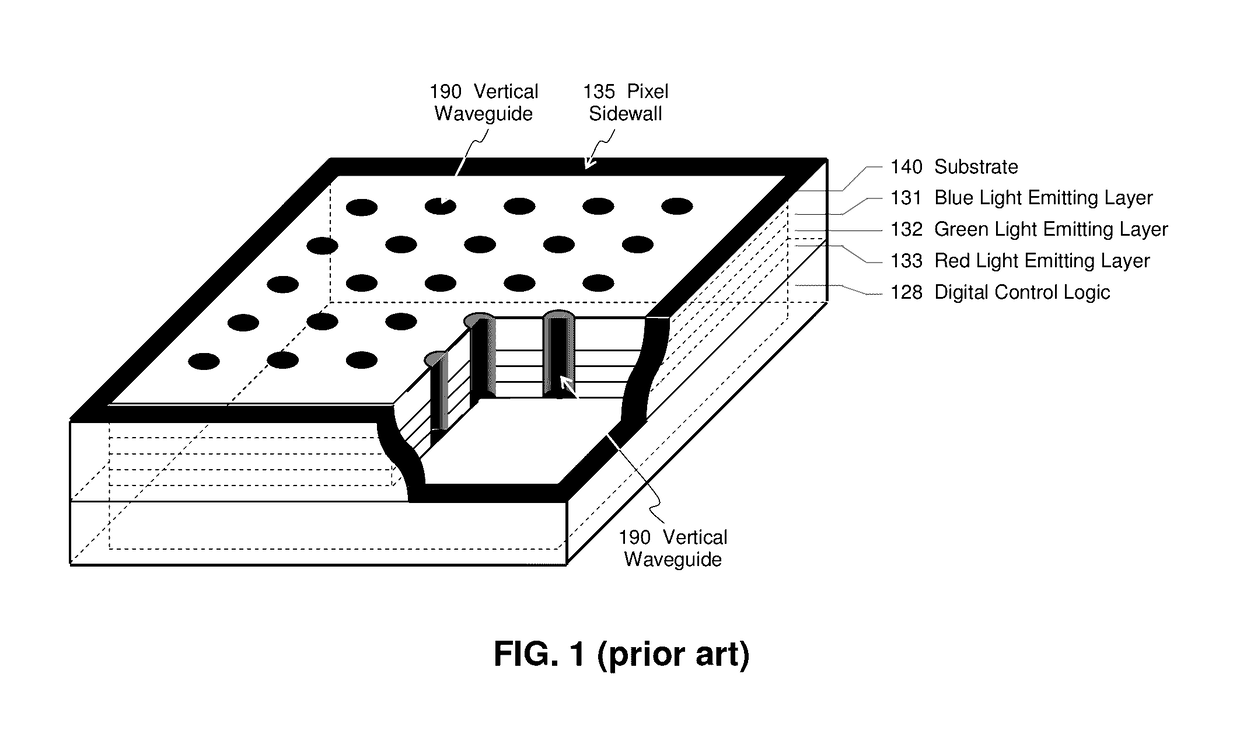

Enhanced Performance Active Pixel Array and Epitaxial Growth Method for Achieving the Same

Methods are described to utilize relatively low cost substrates and processing methods to achieve enhanced emissive imager pixel performance via selective epitaxial growth. An emissive imaging array is coupled with one or more patterned compound semiconductor light emitting structures grown on a second patterned and selectively grown compound semiconductor template article. The proper design and execution of the patterning and epitaxial growth steps, coupled with alignment of the epitaxial structures with the imaging array, results in enhanced performance of the emissive imager. The increased luminous flux achieved enables use of such images for high brightness display and illumination applications.

Owner:OSTENDO TECH INC

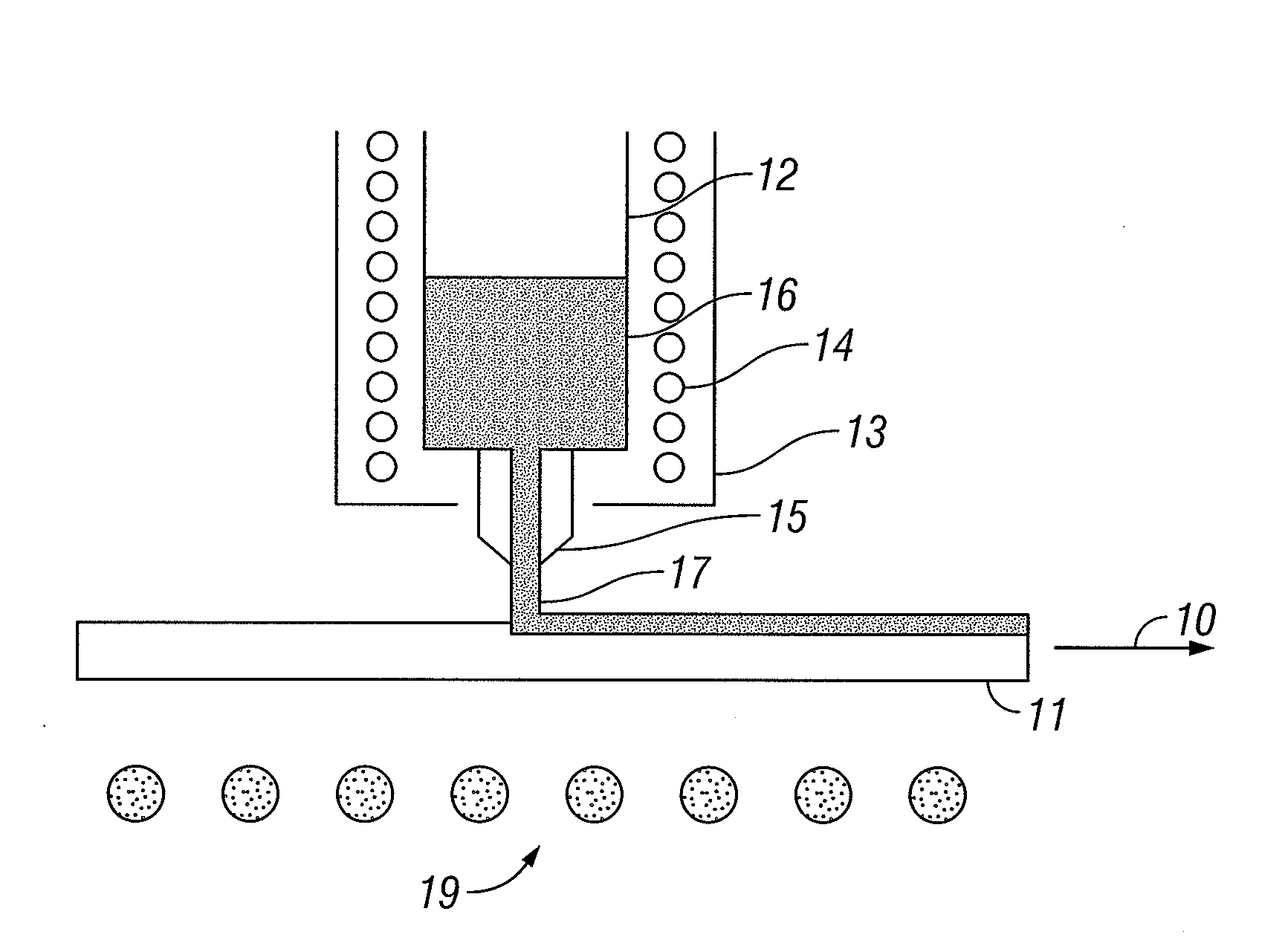

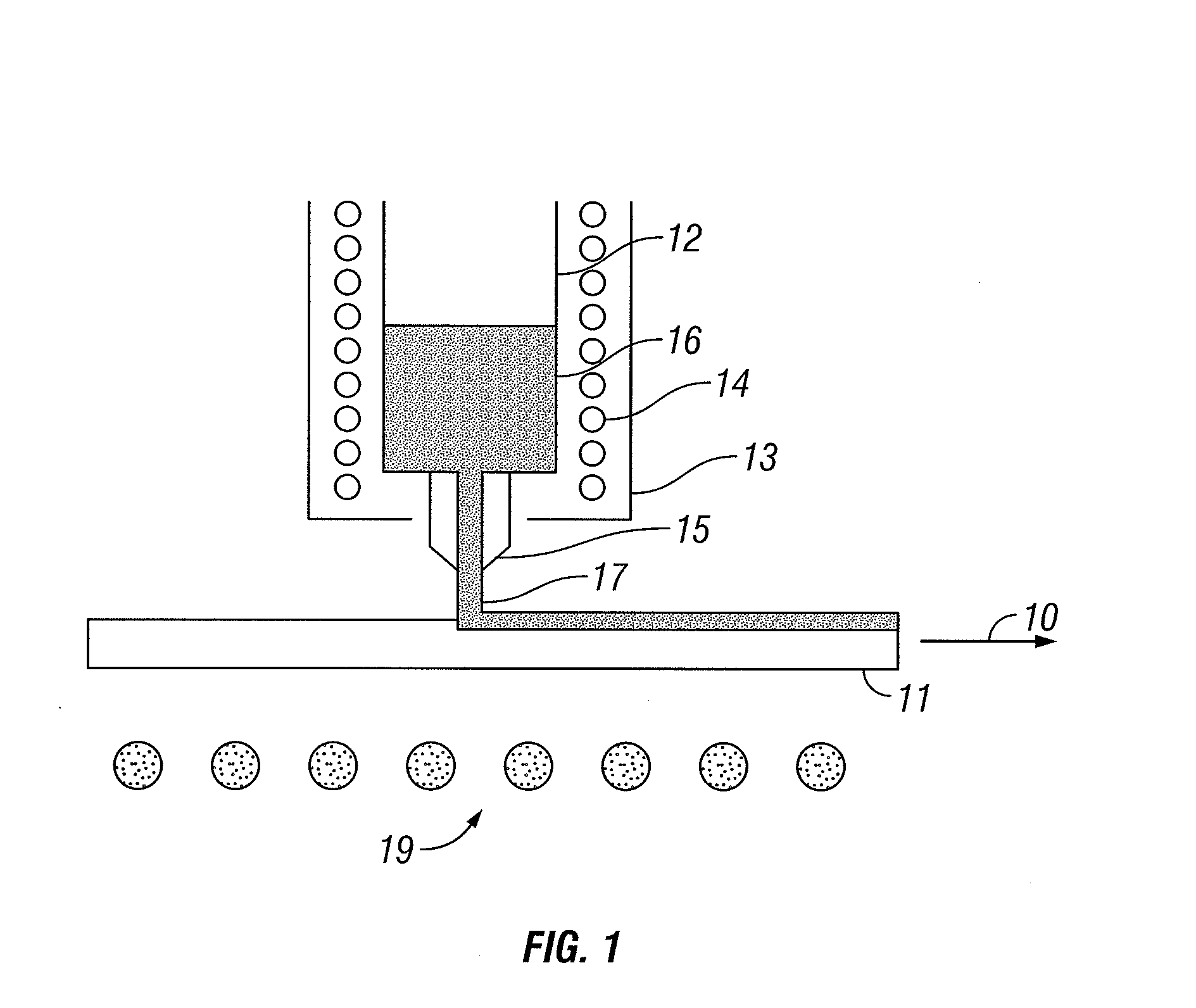

Method for Rapid Liquid Phase Deposition of Crystalline Si Thin Films on Large Glass Substrates for Solar Cell Applications

InactiveUS20080236665A1Improve efficiencyPropels solar electricity penetrationFinal product manufactureVacuum evaporation coatingElectrical batteryAmorphous silicon

A method for liquid phase deposition of crystalline silicon thin films, and a high efficiency solar cell that is fabricated using crystalline silicon thin film technology, has the performance of a crystal silicon solar cell, but at the cost level per unit area of a solar cell fabricated using an amorphous silicon thin film. The crystal thin film uses only 10% or less of the amount of silicon used in a wafer-based solar cell. Because of the maturity of silicon technology in semiconductor industry, this approach not only enables high volume, automated production of solar cells on a very large, low-cost substrate, but also increases the area throughput up to 10000 cm2 / min from 942 cm2 / min in case of CZ crystal growth.

Owner:SIERRA SOLAR POWER

Low cost substrate for an integrated circuit device with bondpads free of plated gold

InactiveUS6969638B2Printed circuit assemblingInsulating substrate metal adhesion improvementLead bondingLow cost substrate

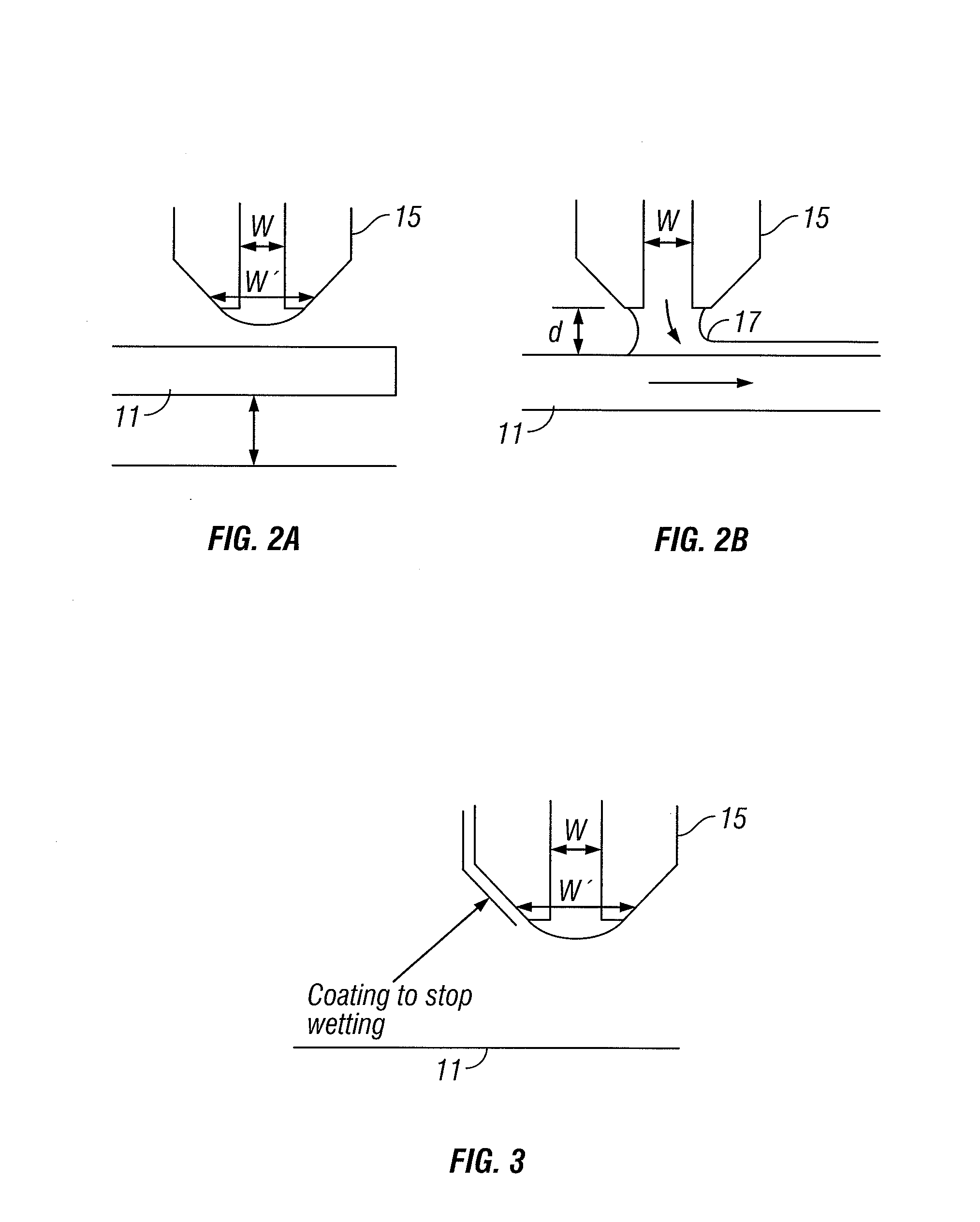

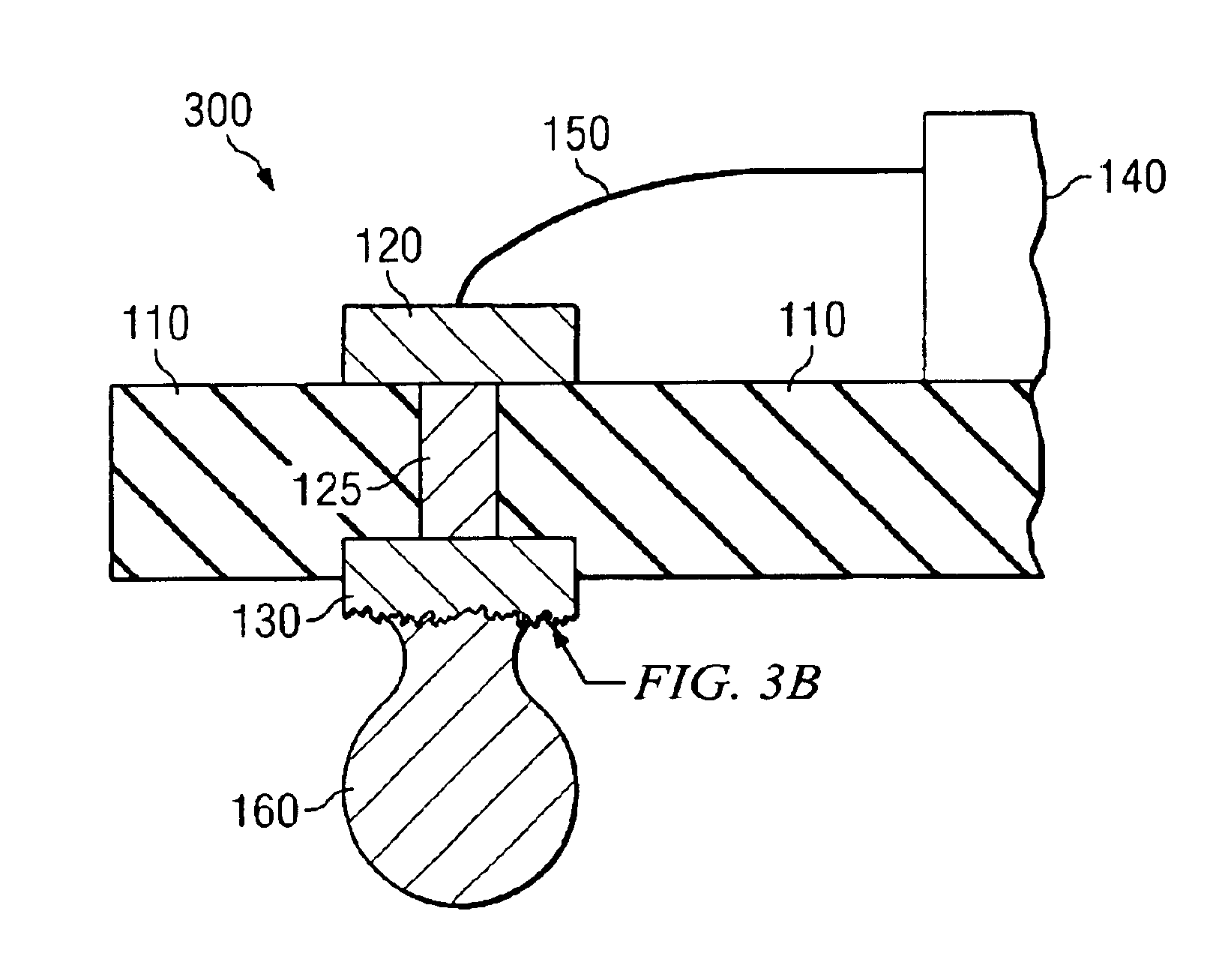

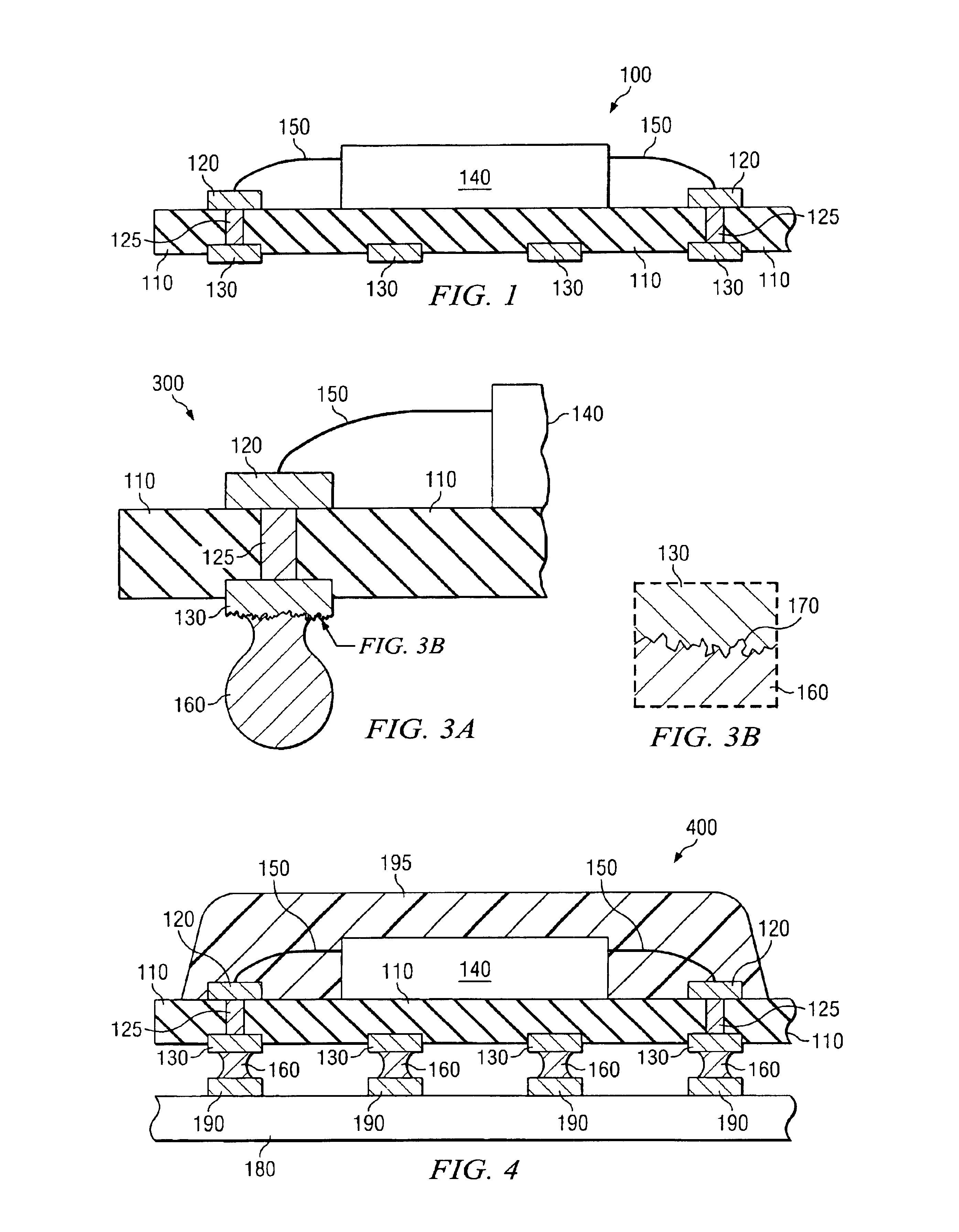

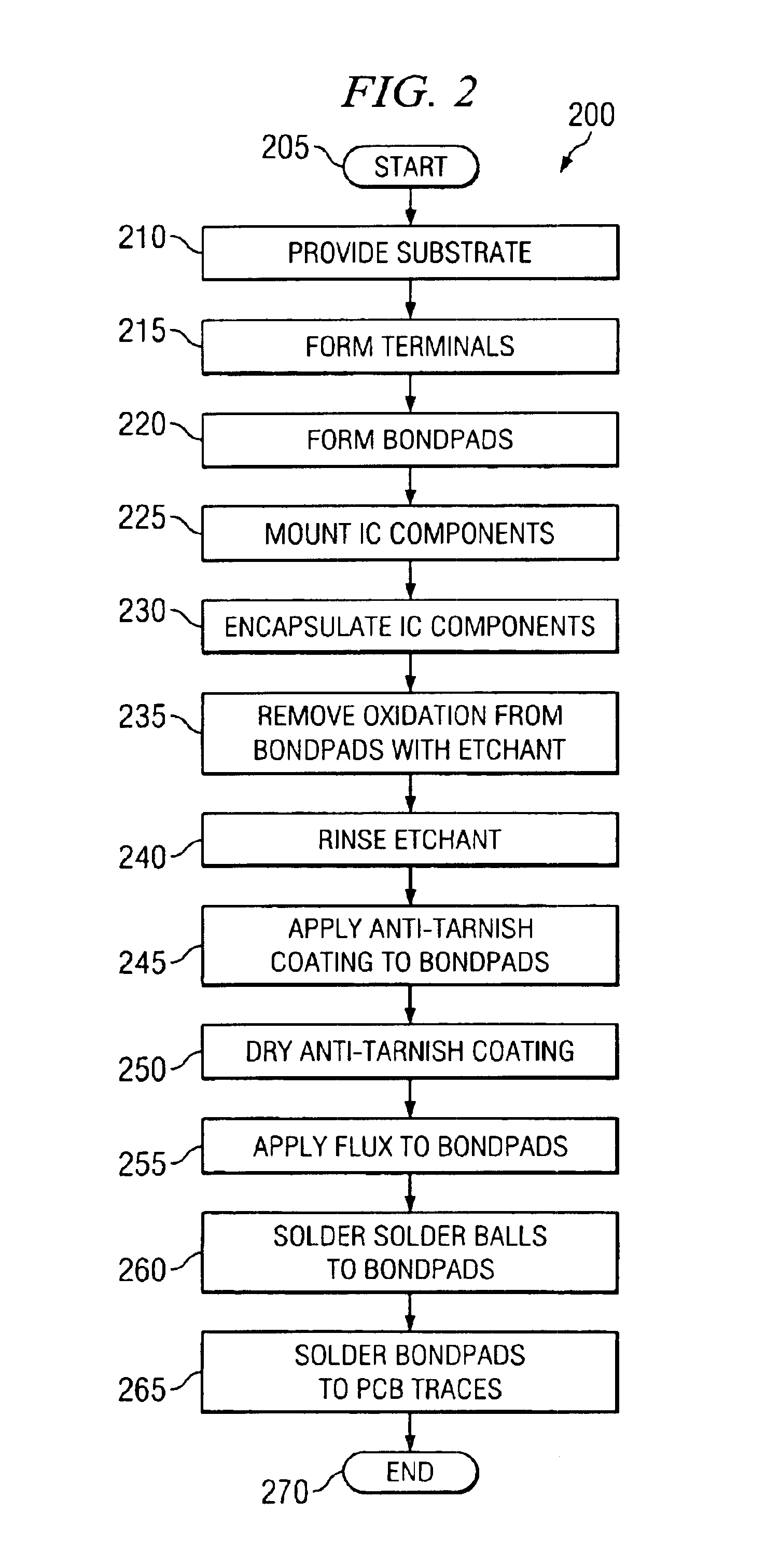

Disclosed herein is a process for assembling an integrated circuit, as well as the assembly resulting from the process, employing a surface treatment of bondpad surfaces. In one aspect, a method of assembling an integrated circuit includes providing a substrate having electrical terminals on a first side of the substrate and a bondpad on a second side of the substrate opposing the first side. In this embodiment, the bondpad is electrically coupled to at least one of the terminals on the first side. In addition, the method includes mounting an integrated circuit chip to the first side of the substrate, where the integrated circuit component has a lead adapted to be wire-bonded to the terminal. The method further includes removing oxidation from the bondpad, where the bondpad is adapted to be metallurgically bonded to a trace on a printed circuit board. Moreover, this embodiment of the method includes metallurgically bonding the bondpad to the trace.

Owner:TEXAS INSTR INC

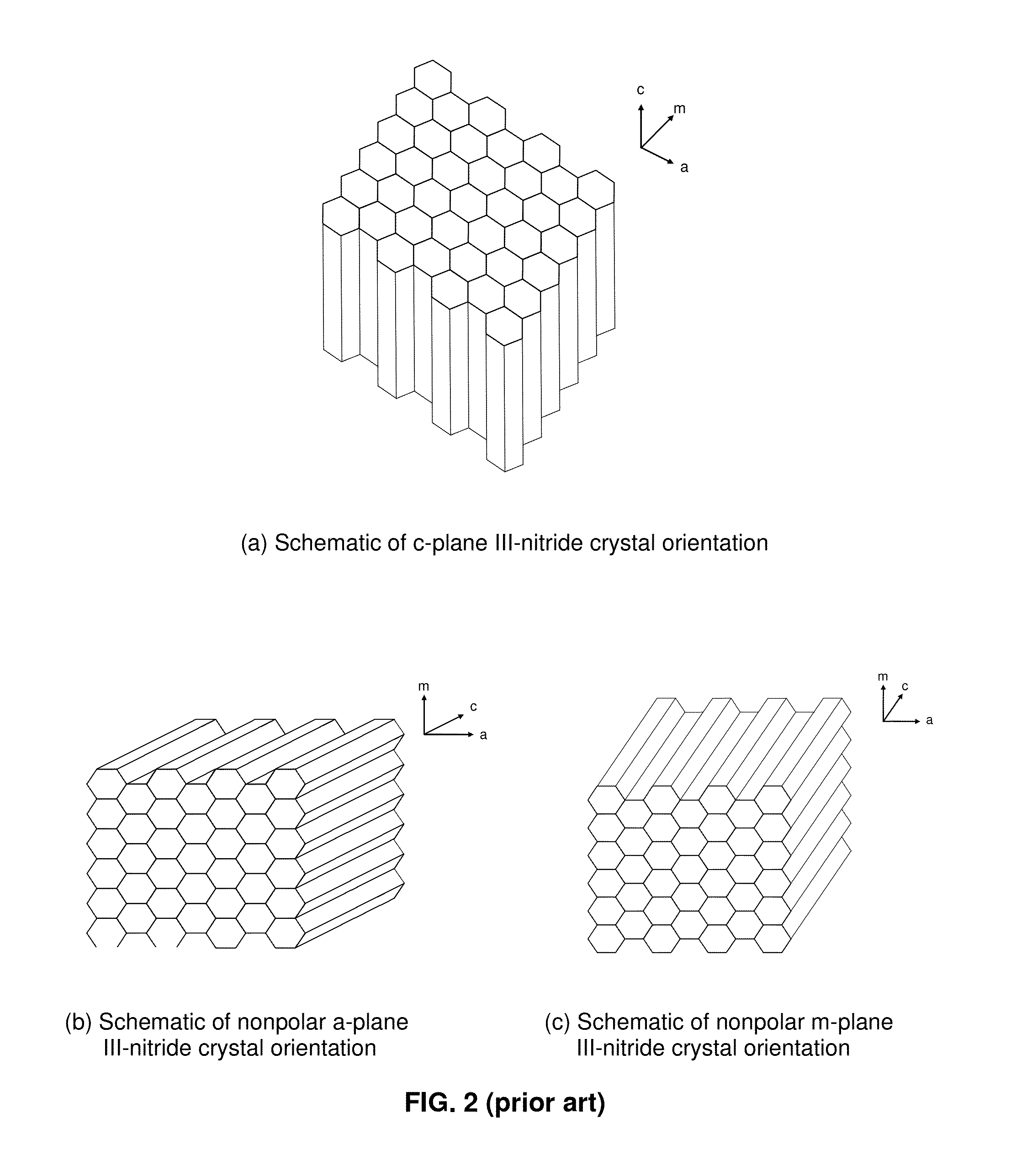

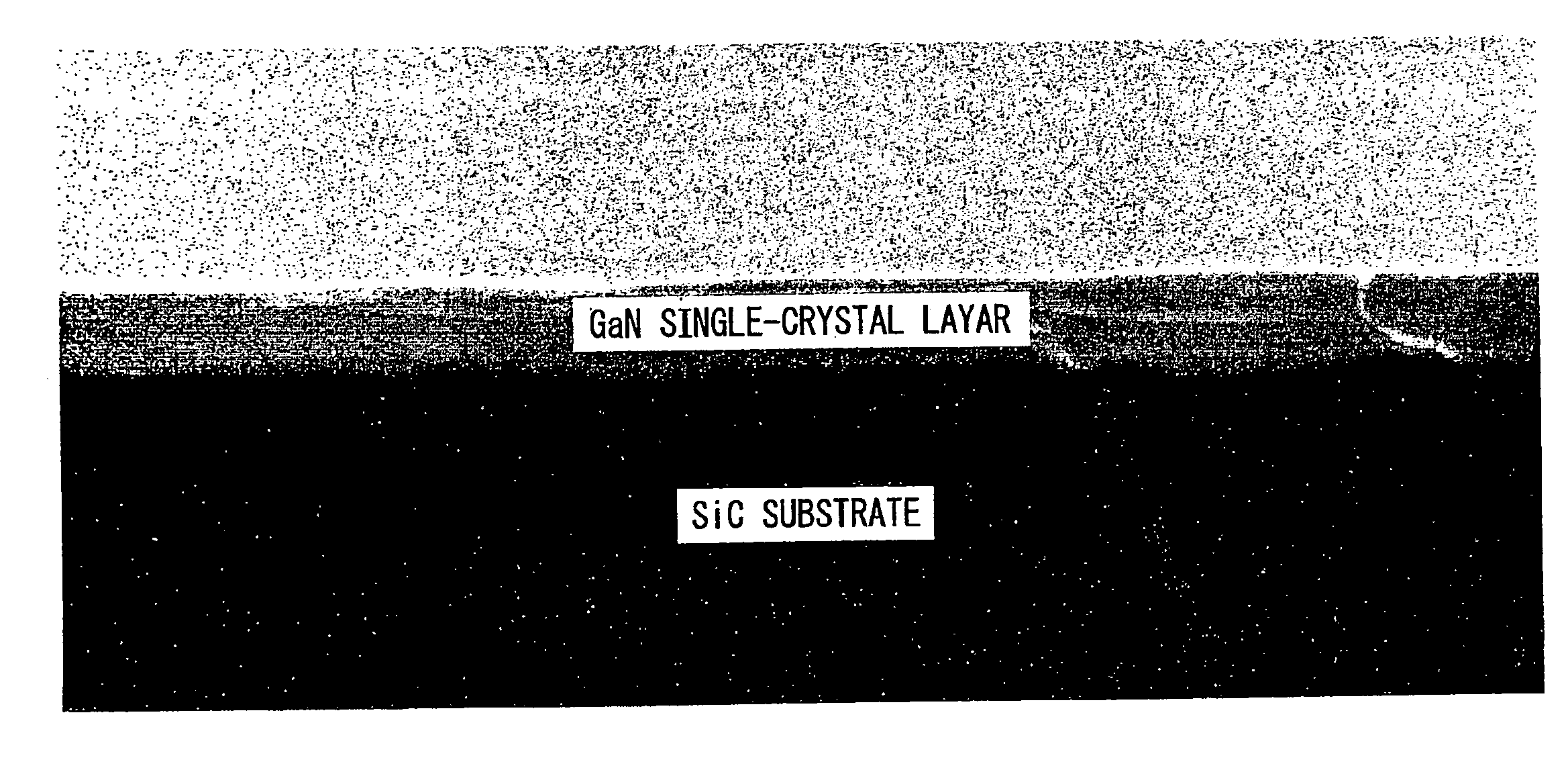

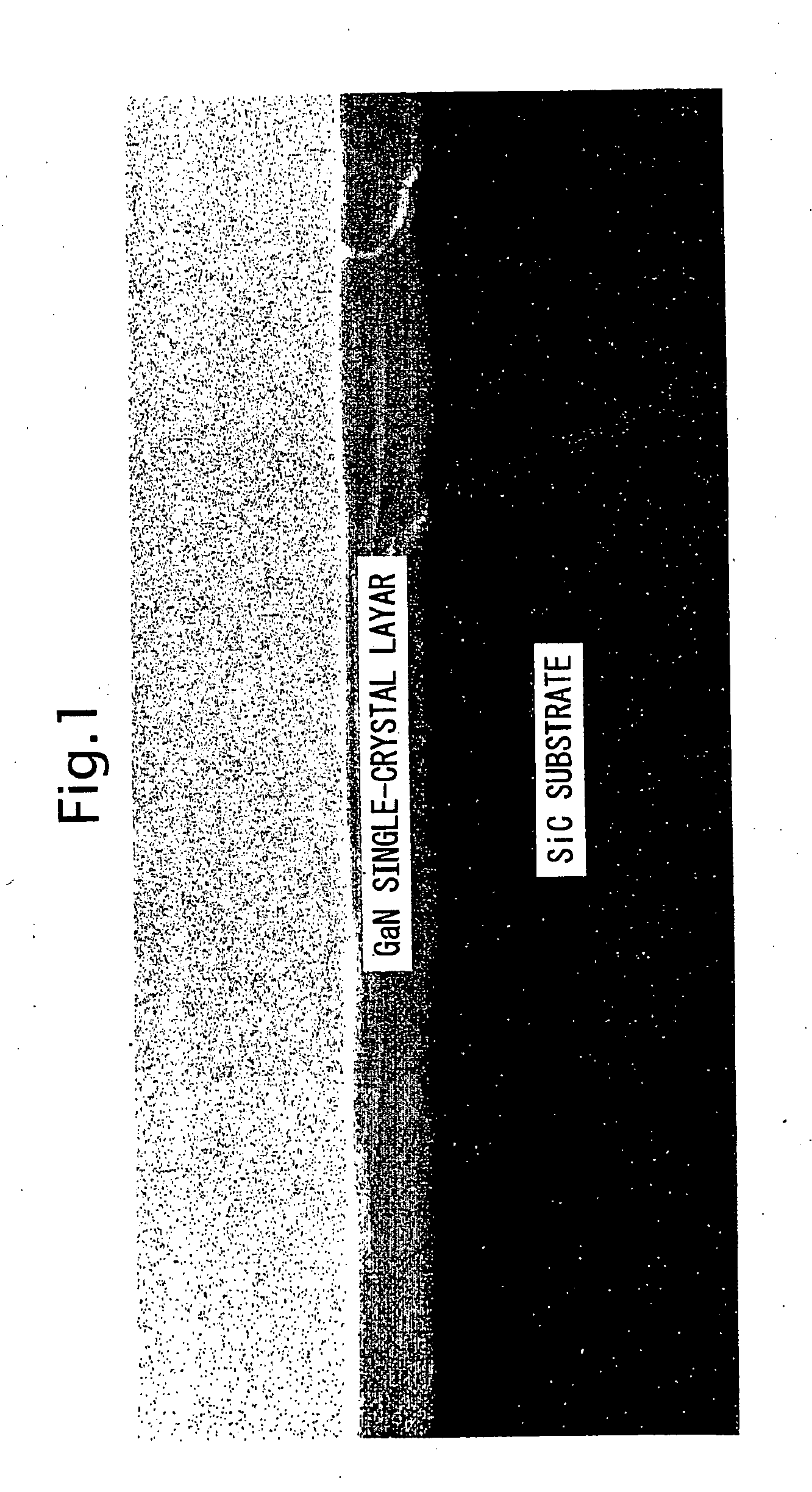

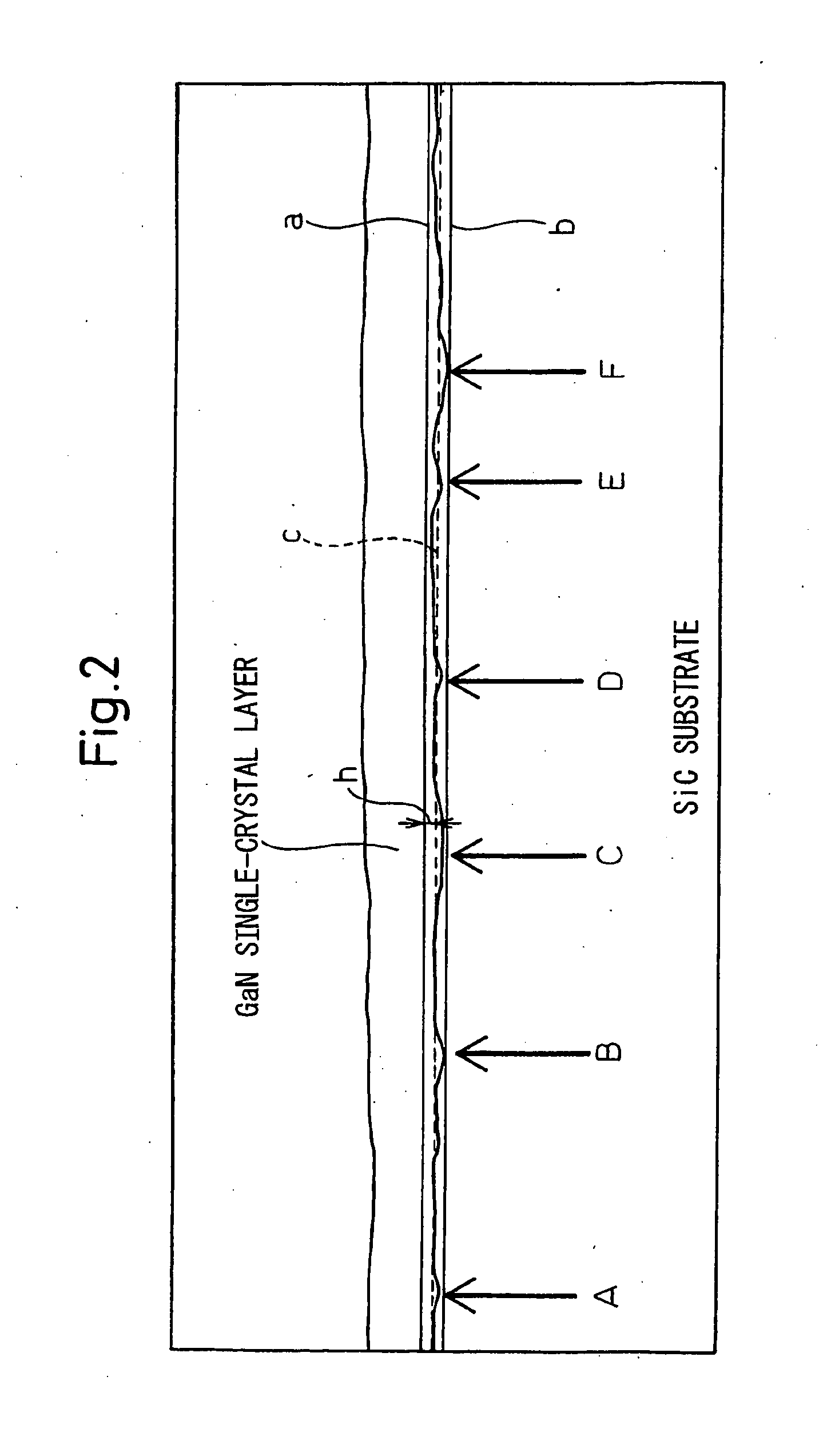

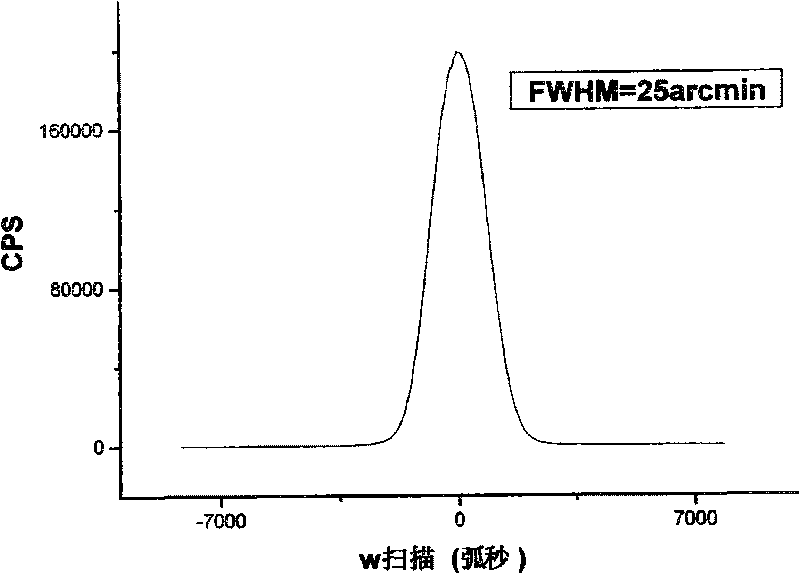

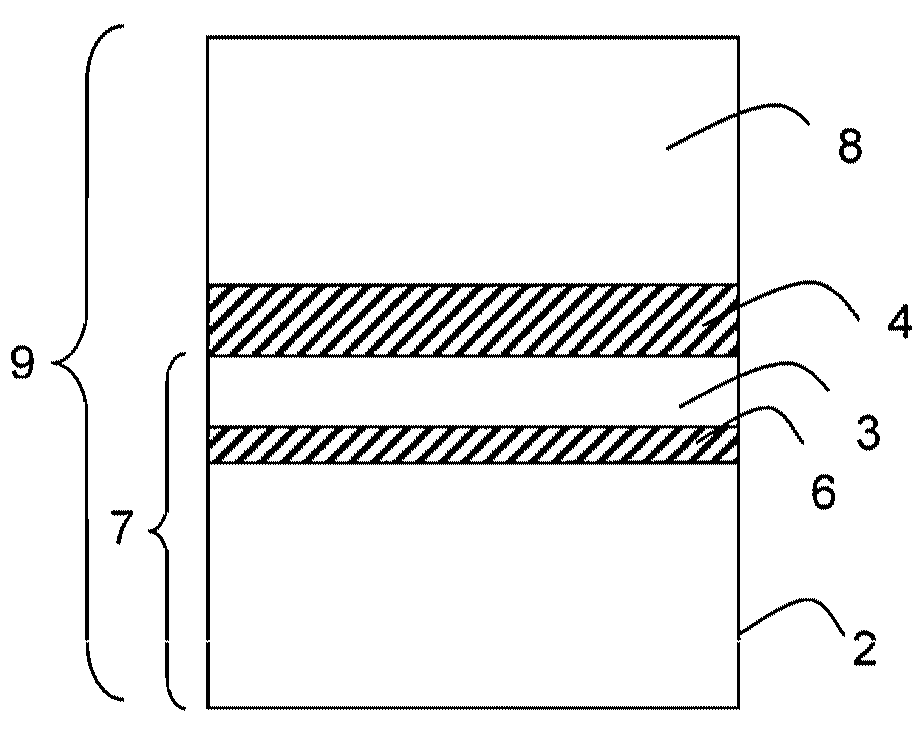

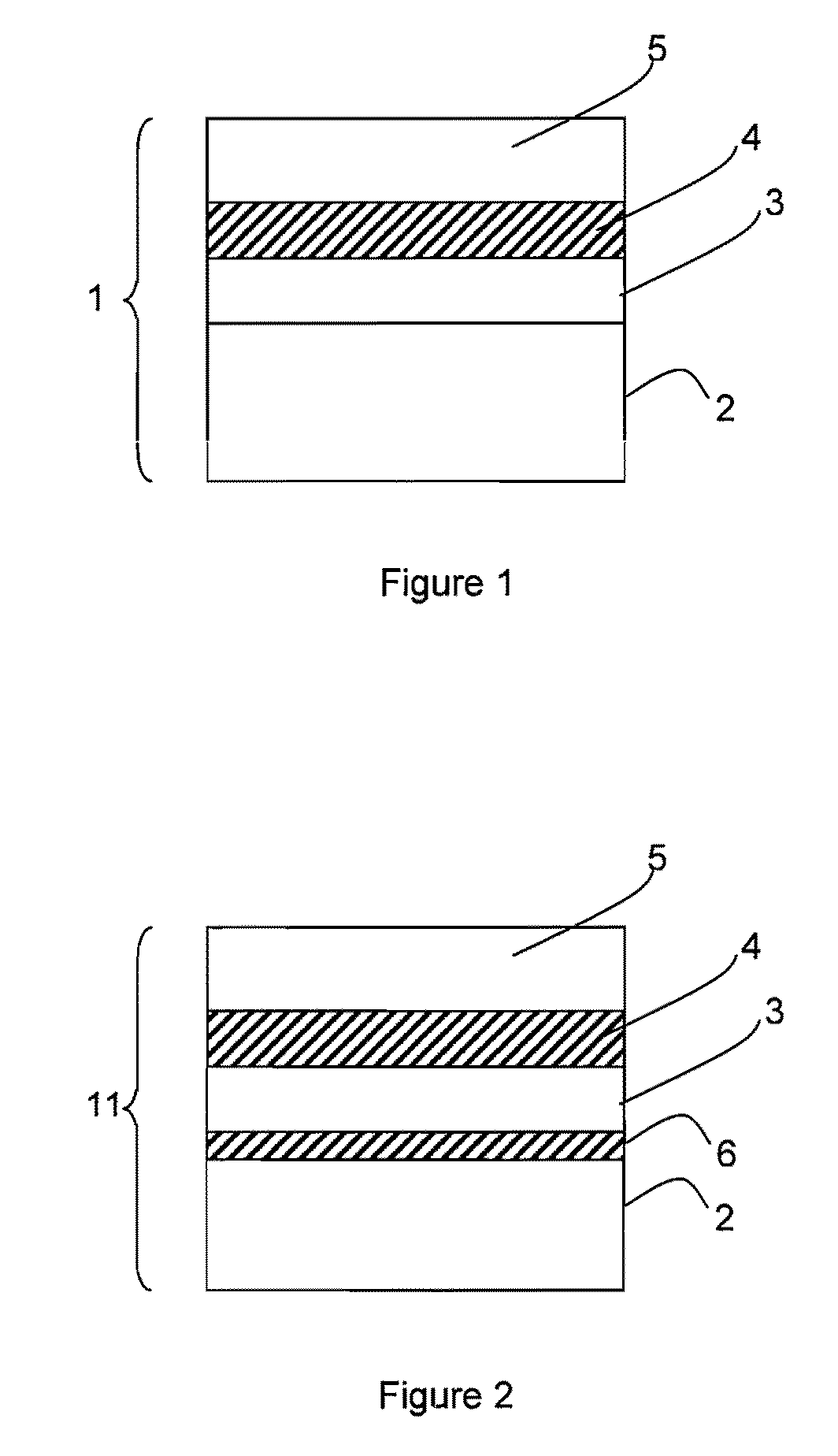

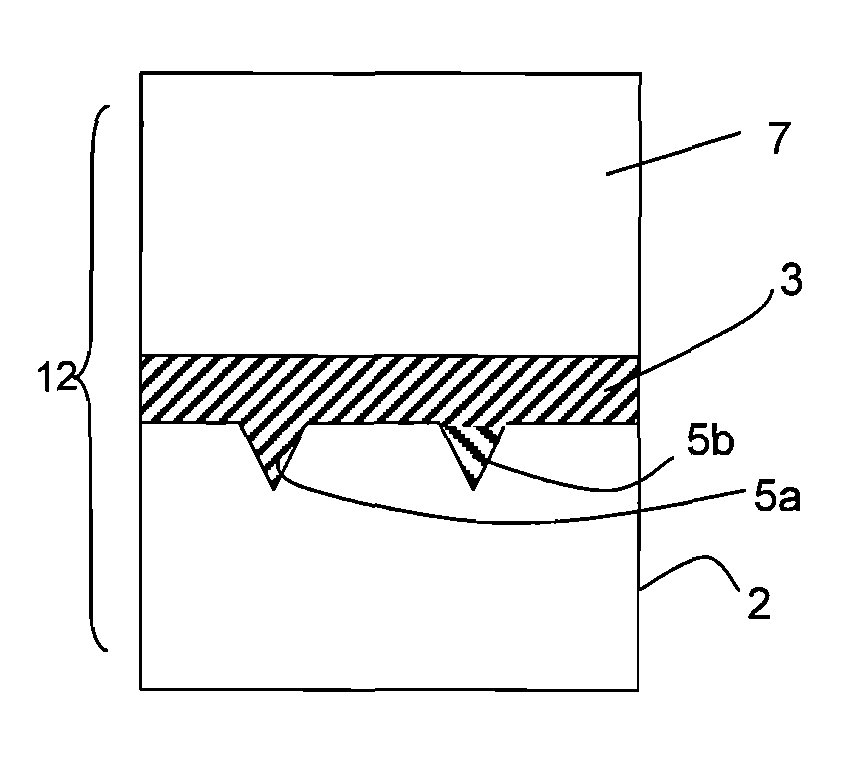

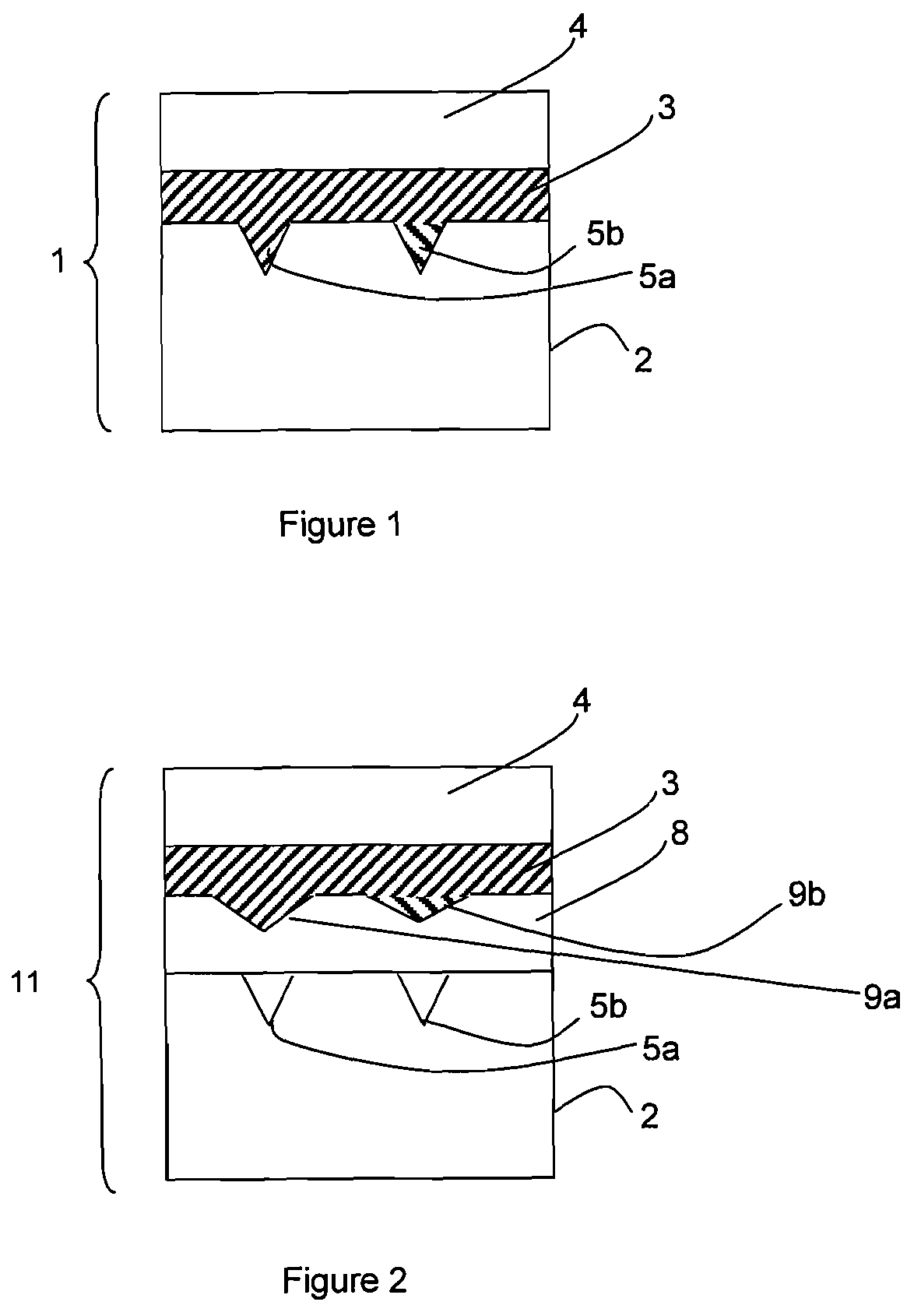

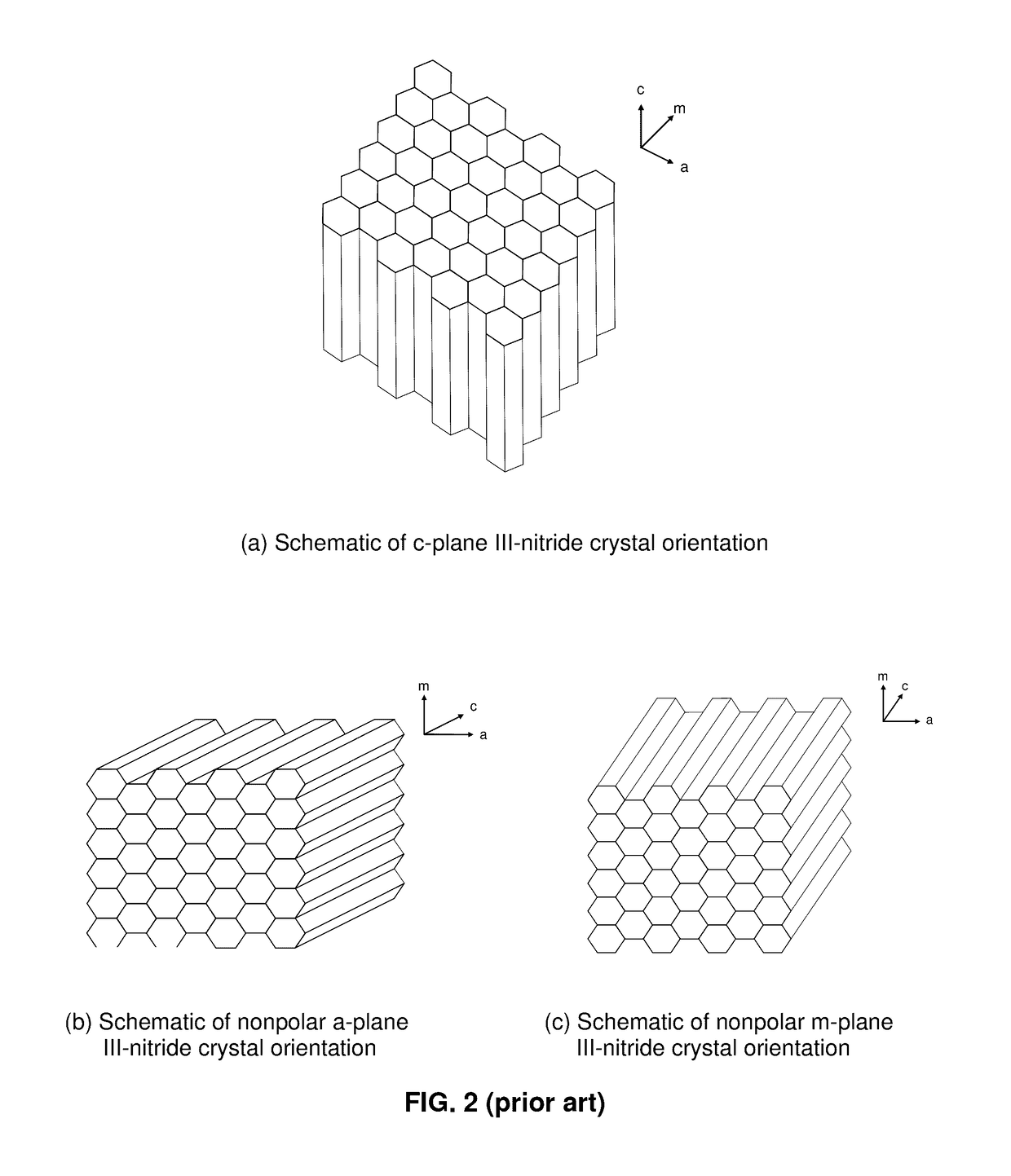

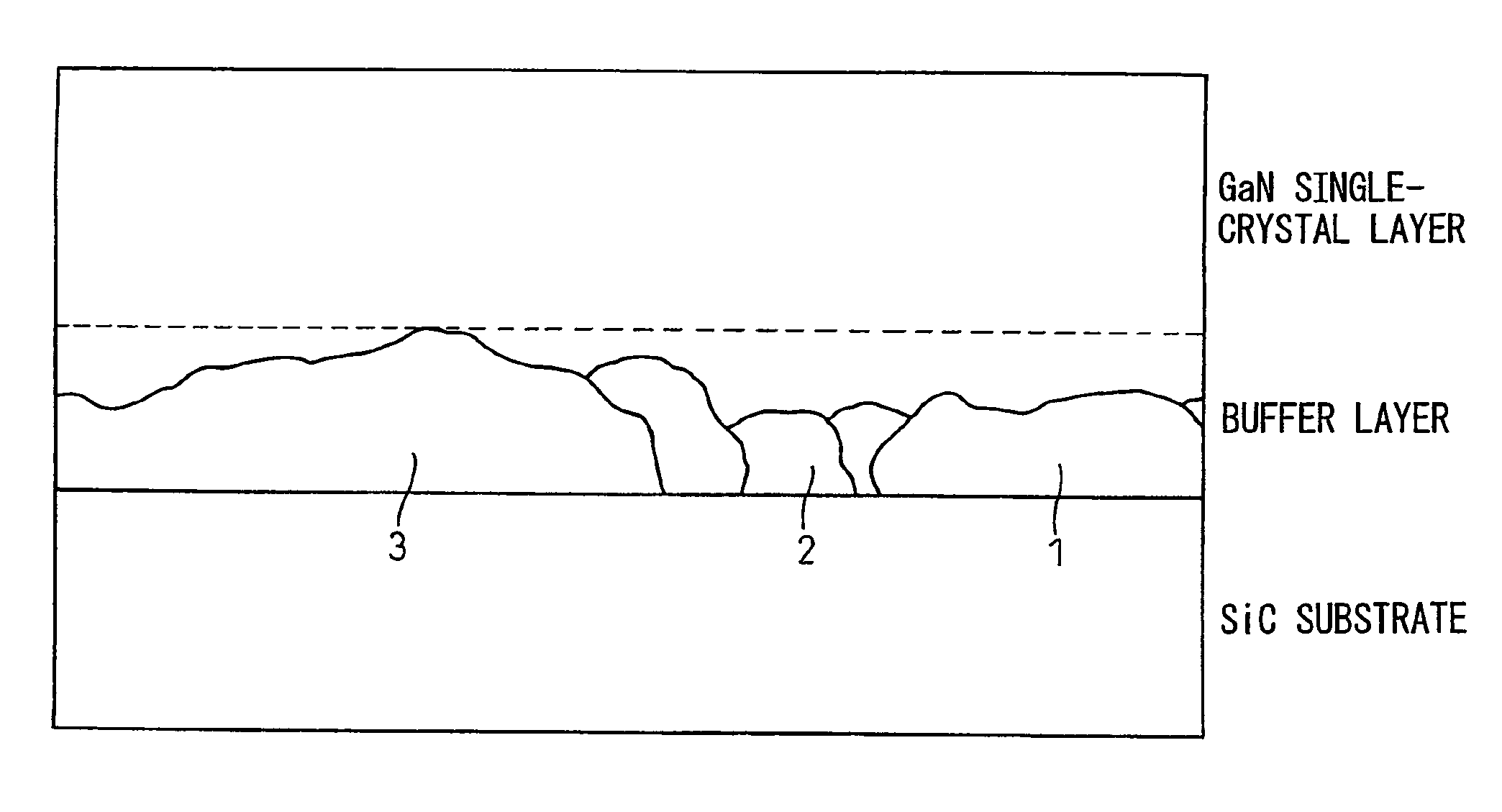

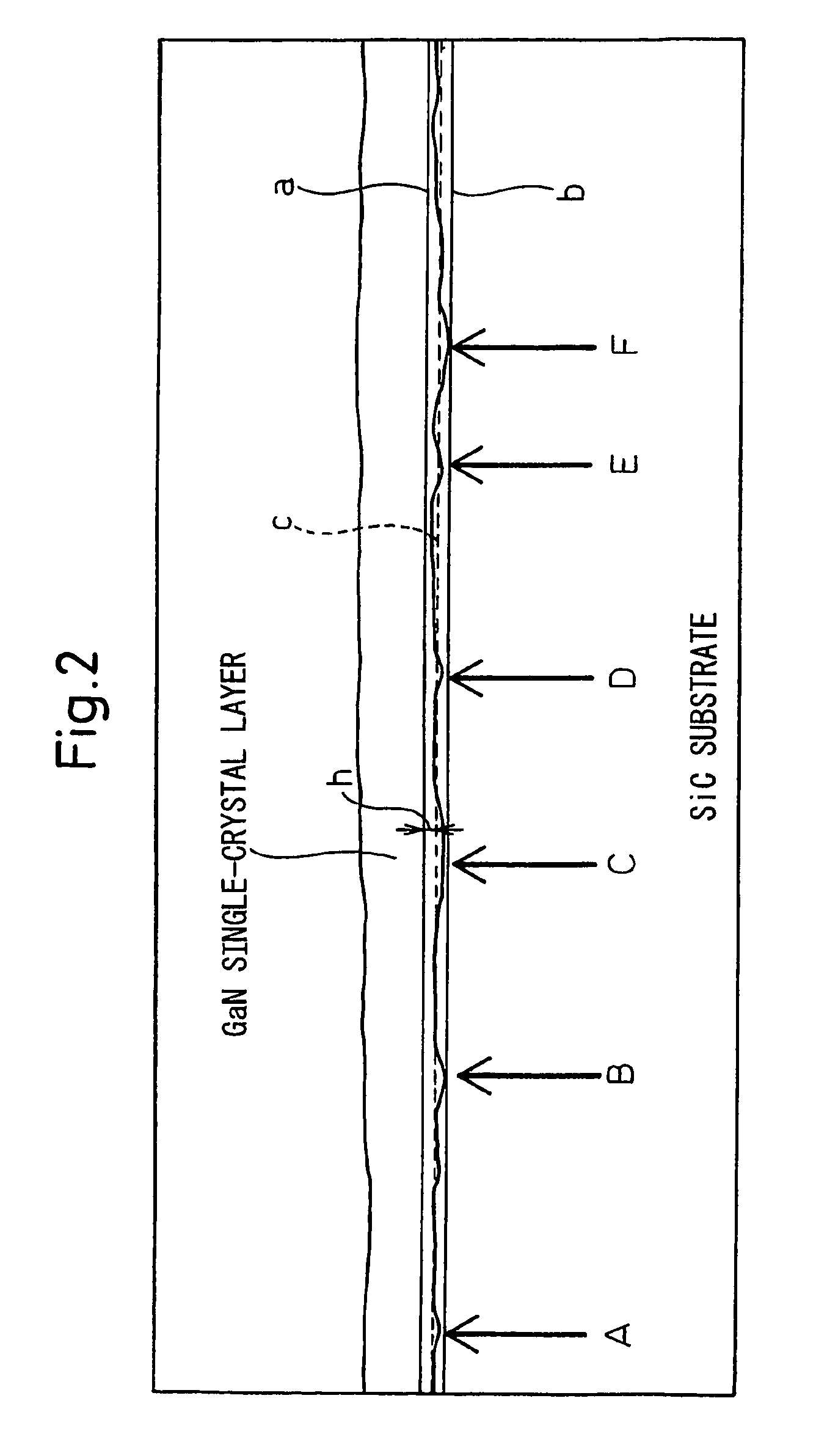

Group III Nitride Semiconductor Multilayer Structure

ActiveUS20080230780A1Easy to processHigh crystallinitySemiconductor/solid-state device manufacturingSemiconductor devicesCrystal structureLow cost substrate

An object of the present invention is to provide a Group III nitride semiconductor multilayer structure having a smooth surface and exhibiting excellent crystallinity, which multilayer structure employs a low-cost substrate that can be easily processed. Another object is to provide a Group III nitride semiconductor light-emitting device comprising the multilayer structure.The inventive Group III nitride semiconductor multilayer structure comprises a substrate; an AlxGa1-xN (0≦x≦1) buffer layer which is provided on the substrate and has a columnar or island-like crystal structure; and an AlxInyGa1-x-yN (0≦x≦1, 0≦y≦1, 0≦x+y≦1) single-crystal layer provided on the buffer layer, wherein the substrate has, on its surface, non-periodically distributed grooves having an average depth of 0.01 to 5 μm.

Owner:TOYODA GOSEI CO LTD

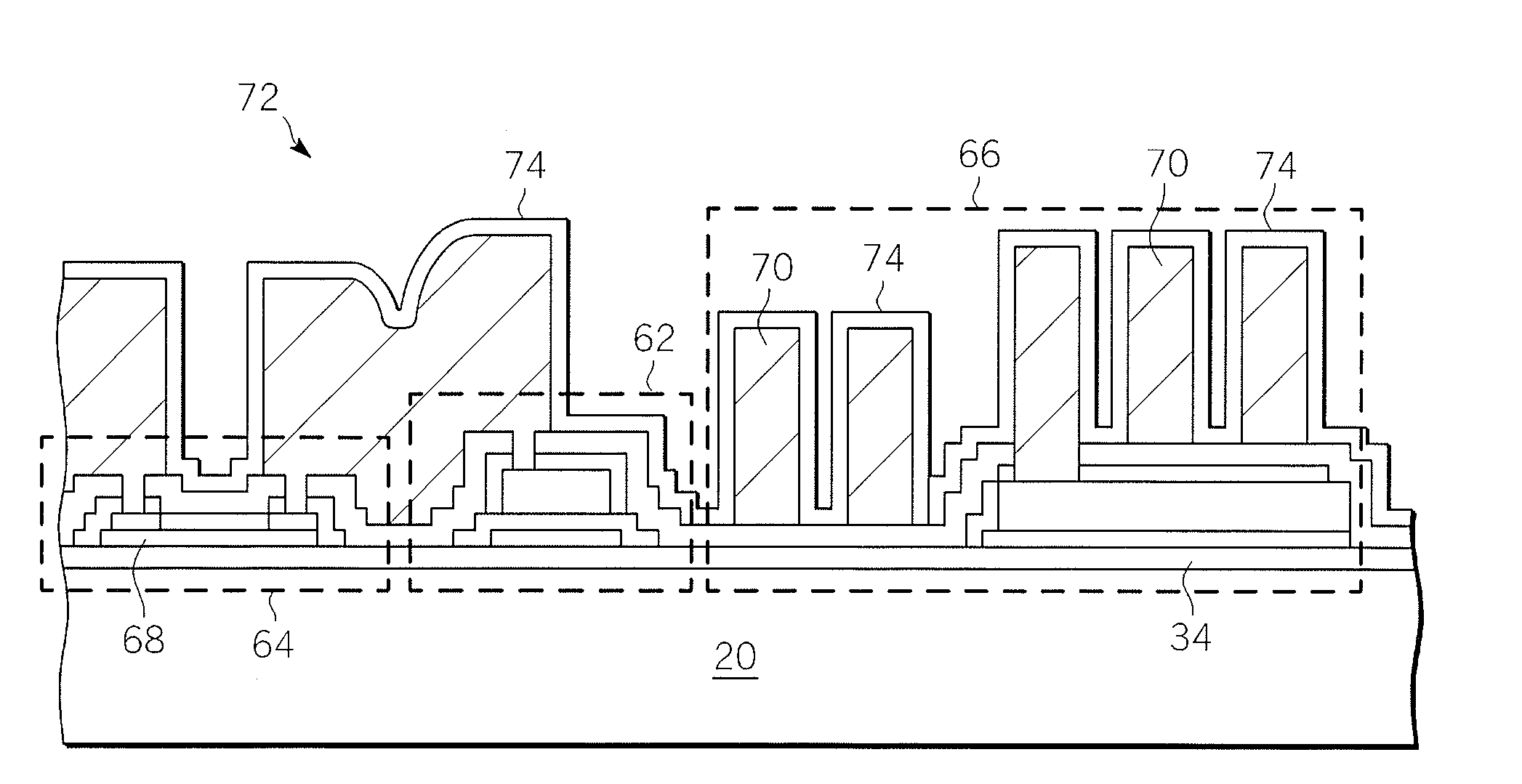

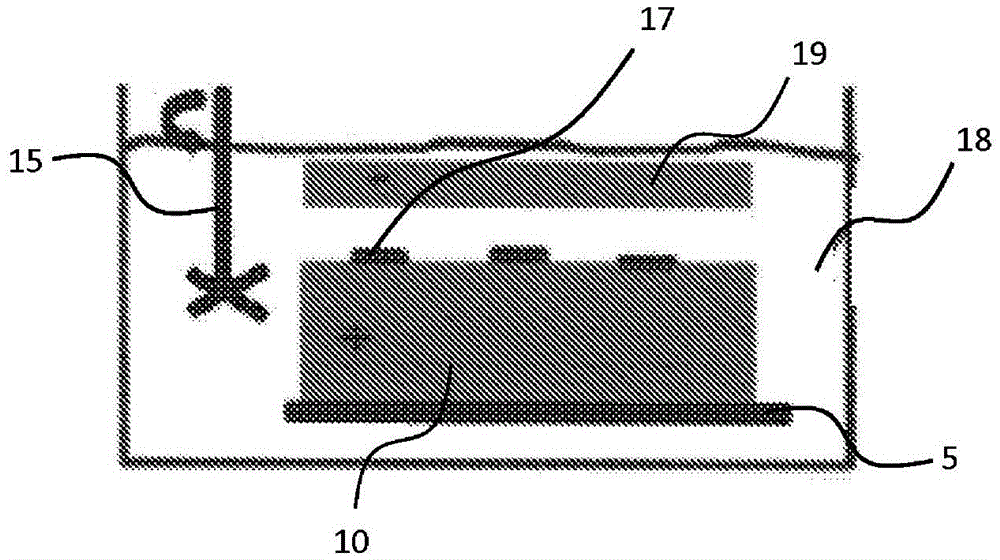

Integrated passive device and method with low cost substrate

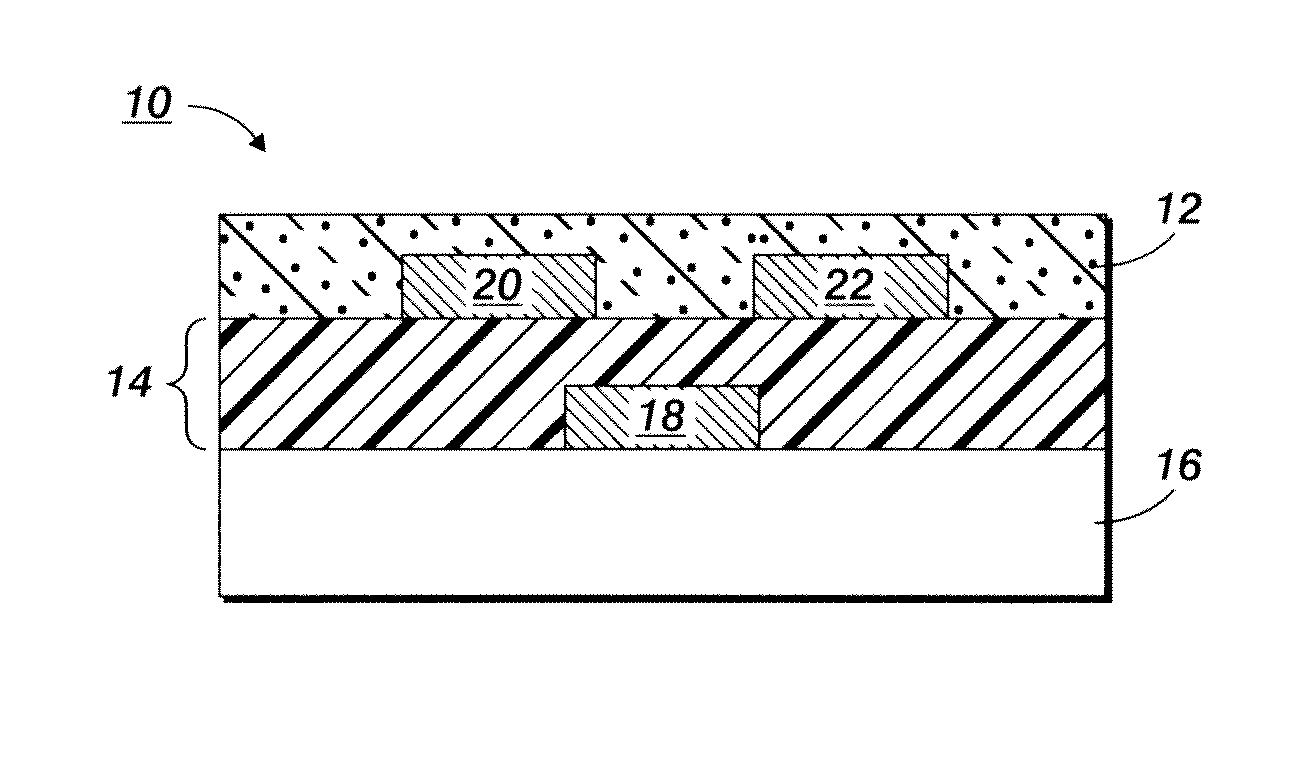

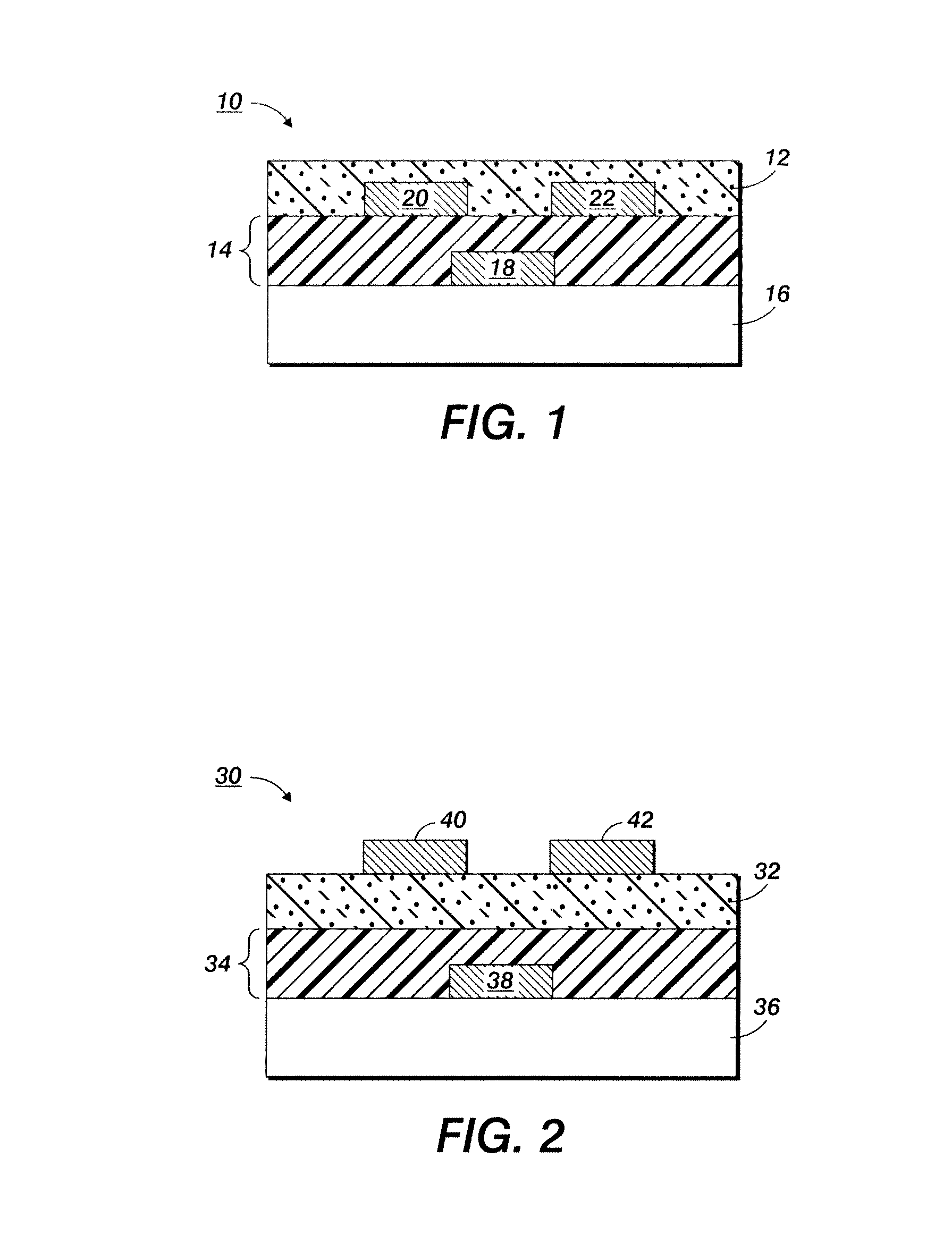

InactiveUS20090236689A1Effective resistivity is increasedHigh resistivitySemiconductor/solid-state device detailsSolid-state devicesTrappingLow cost substrate

According to one aspect of the present invention, a method of forming a microelectronic assembly, such as an integrated passive device (72), is provided. An insulating initial dielectric layer (32) comprising charge trapping films of, for example, aluminum nitride or silicon nitride or silicon oxide or a combination thereof, is formed over a silicon substrate (20). At least one passive electronic component (62) is formed over the initial dielectric layer (32). In an embodiment where silicon nitride or oxide is used in the initial dielectric layer (32) in contact with the silicon substrate (20), it is desirable to pre-treat the silicon surface (22) by exposing it to a surface damage causing treatment (e.g. an argon plasma) prior to depositing the initial dielectric layer, to assist in providing carrier depletion near the silicon surface around zero bias. RF loss in integrated passive devices using such silicon substrates is equal or lower than that obtained with GaAs substrates.

Owner:FREESCALE SEMICON INC

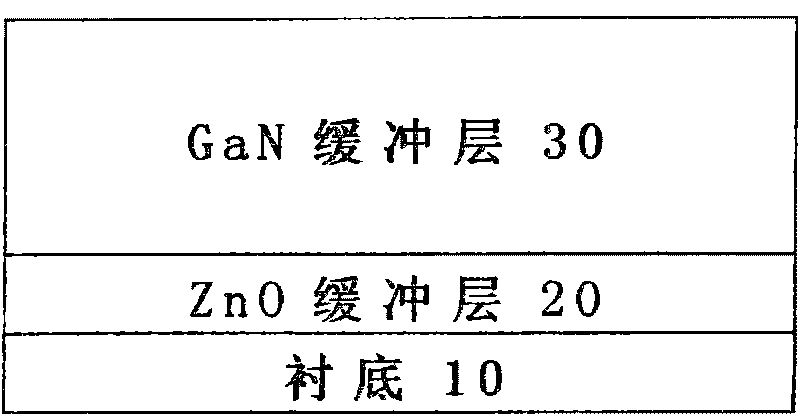

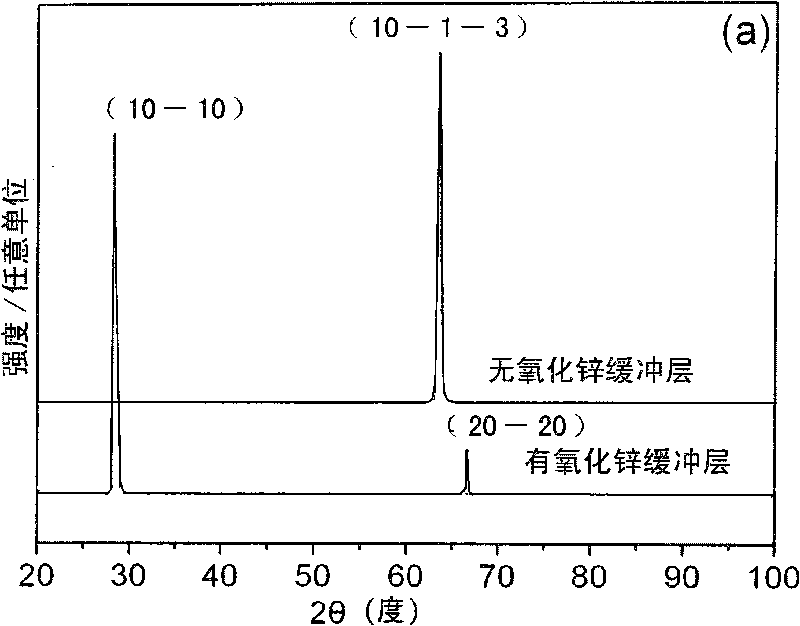

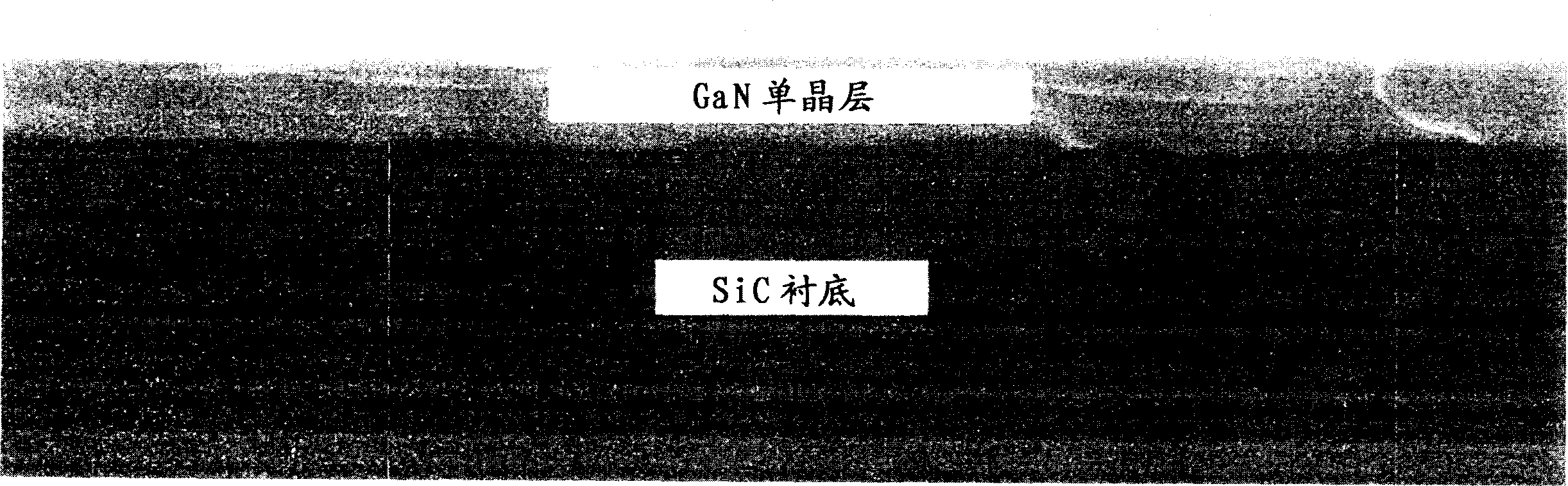

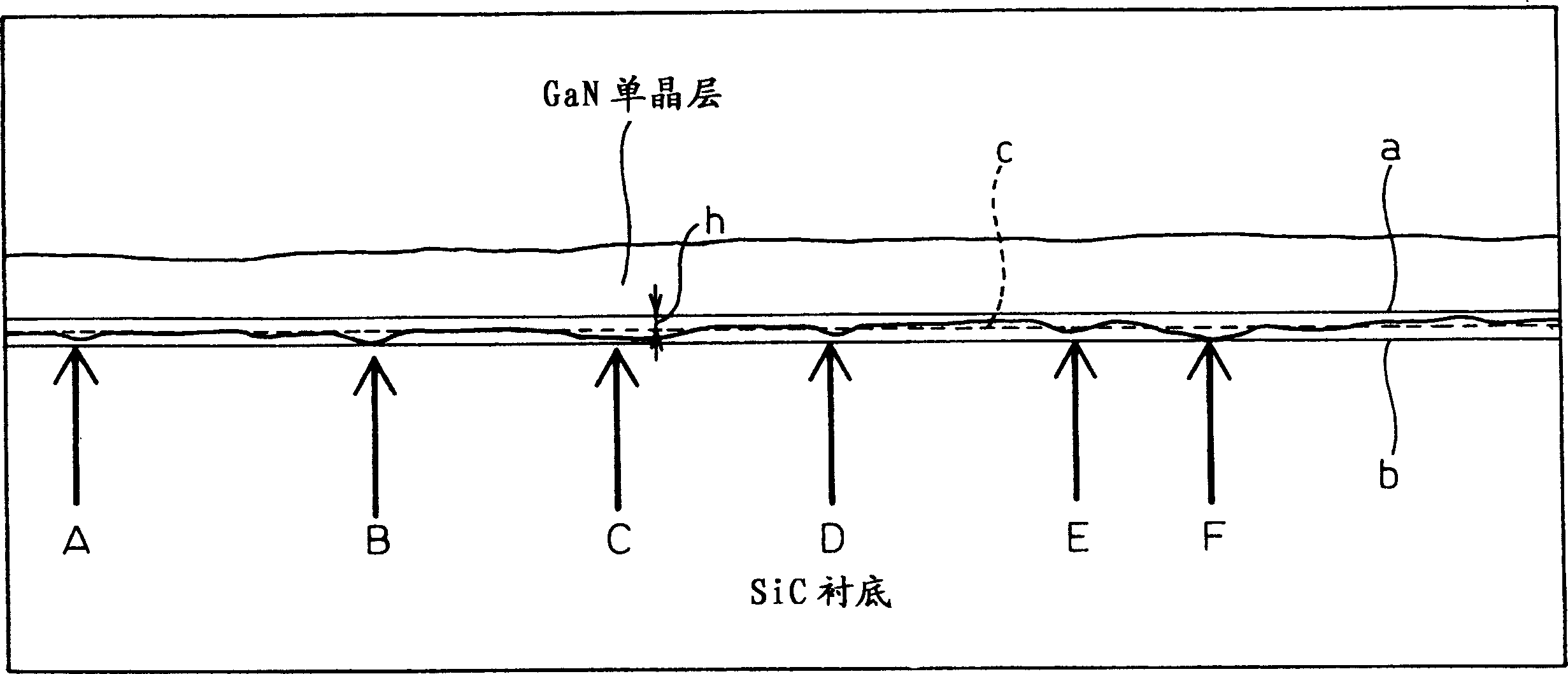

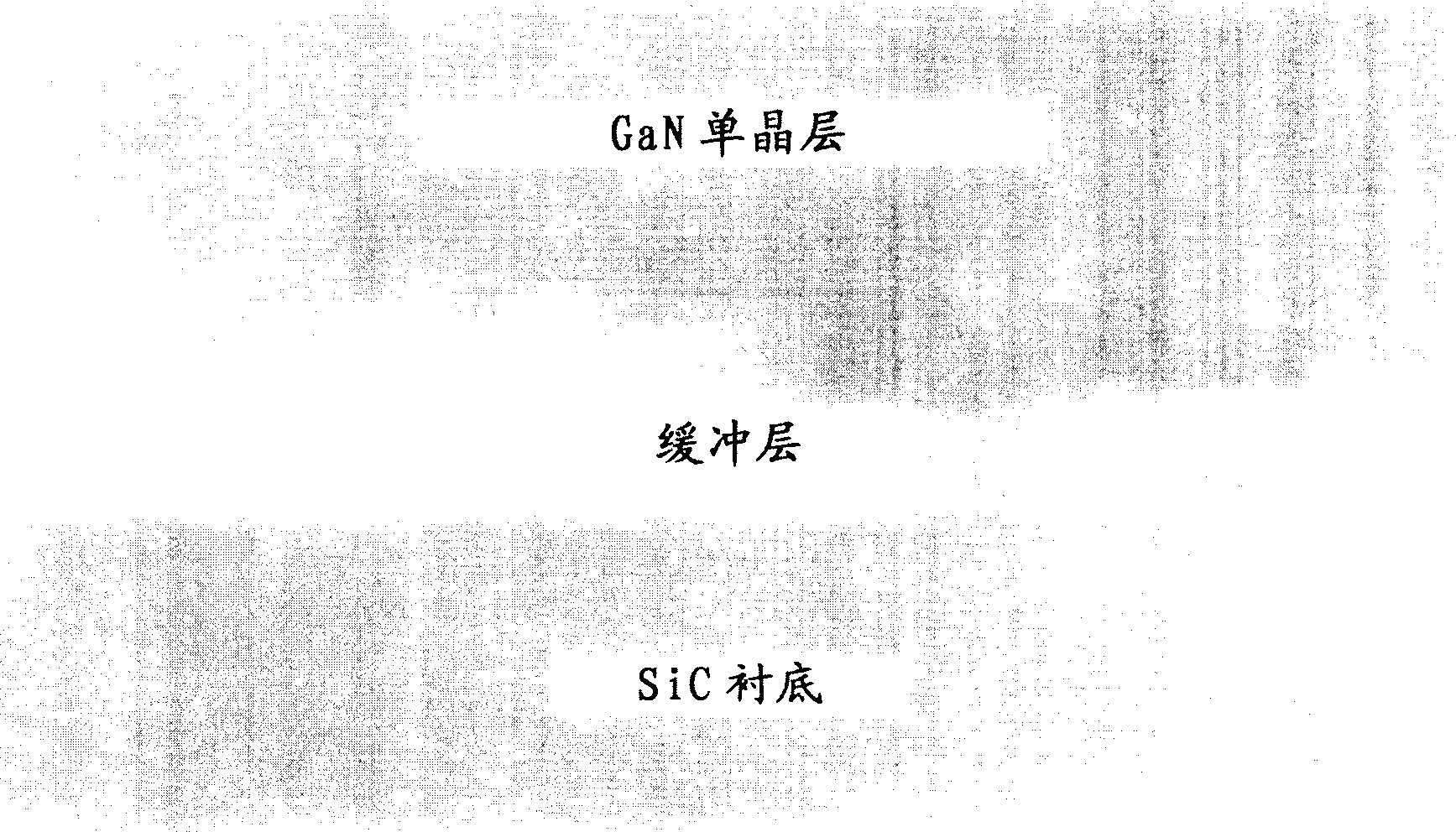

Growing method of gallium nitride

InactiveCN101728248AQuality improvementHighly controlled growthPolycrystalline material growthSemiconductor/solid-state device manufacturingSputteringElectrical polarity

The invention relates to a growing method of gallium nitride. The growing method is characterized by comprising the following steps of: (1) getting a substrate; (2) growing a buffer layer by adopting methods of magnetron sputtering, pulsed laser deposition or metal organic chemical vapor deposition (MOCVD); and (3) growing an epitaxial layer on the buffer layer by adopting methods of MOCVD, high voltage paper electrophoresis (HVPE) or pulsed laser deposition and magnetron sputtering. The growing method of gallium nitride can realize the high-quality growth and the polarity selection of a gallium nitride material and the use of a low cost substrate.

Owner:INST OF SEMICONDUCTORS - CHINESE ACAD OF SCI

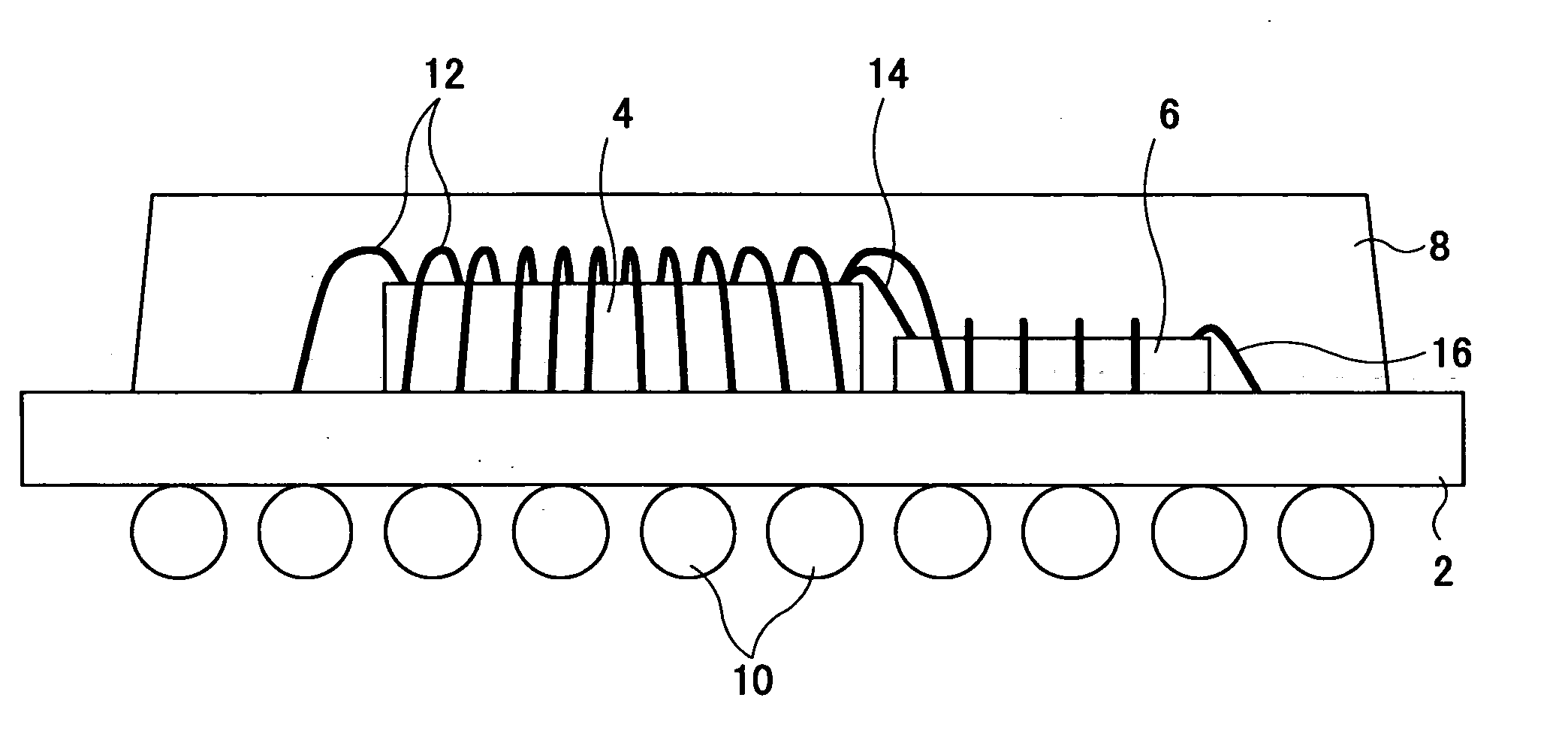

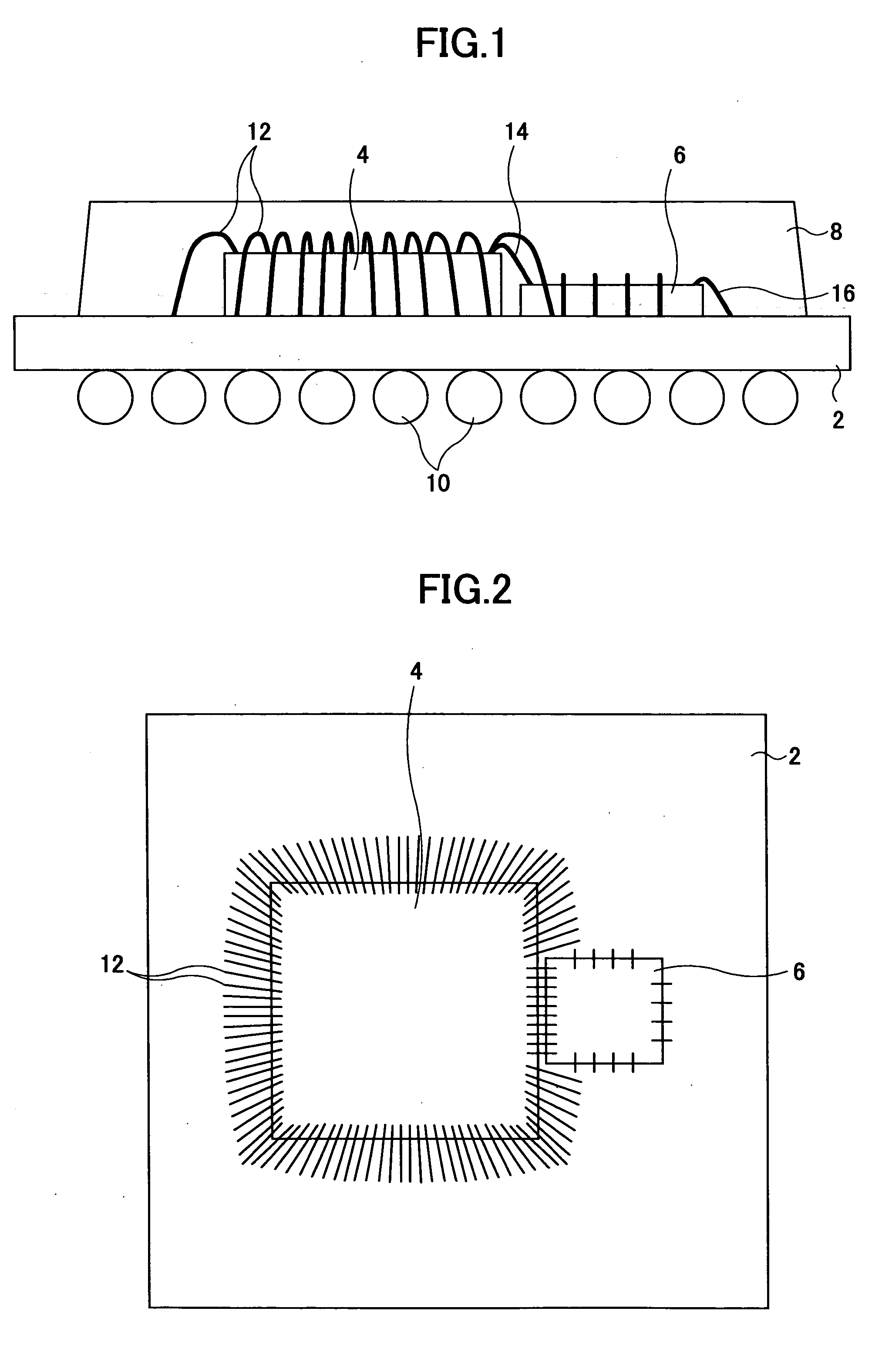

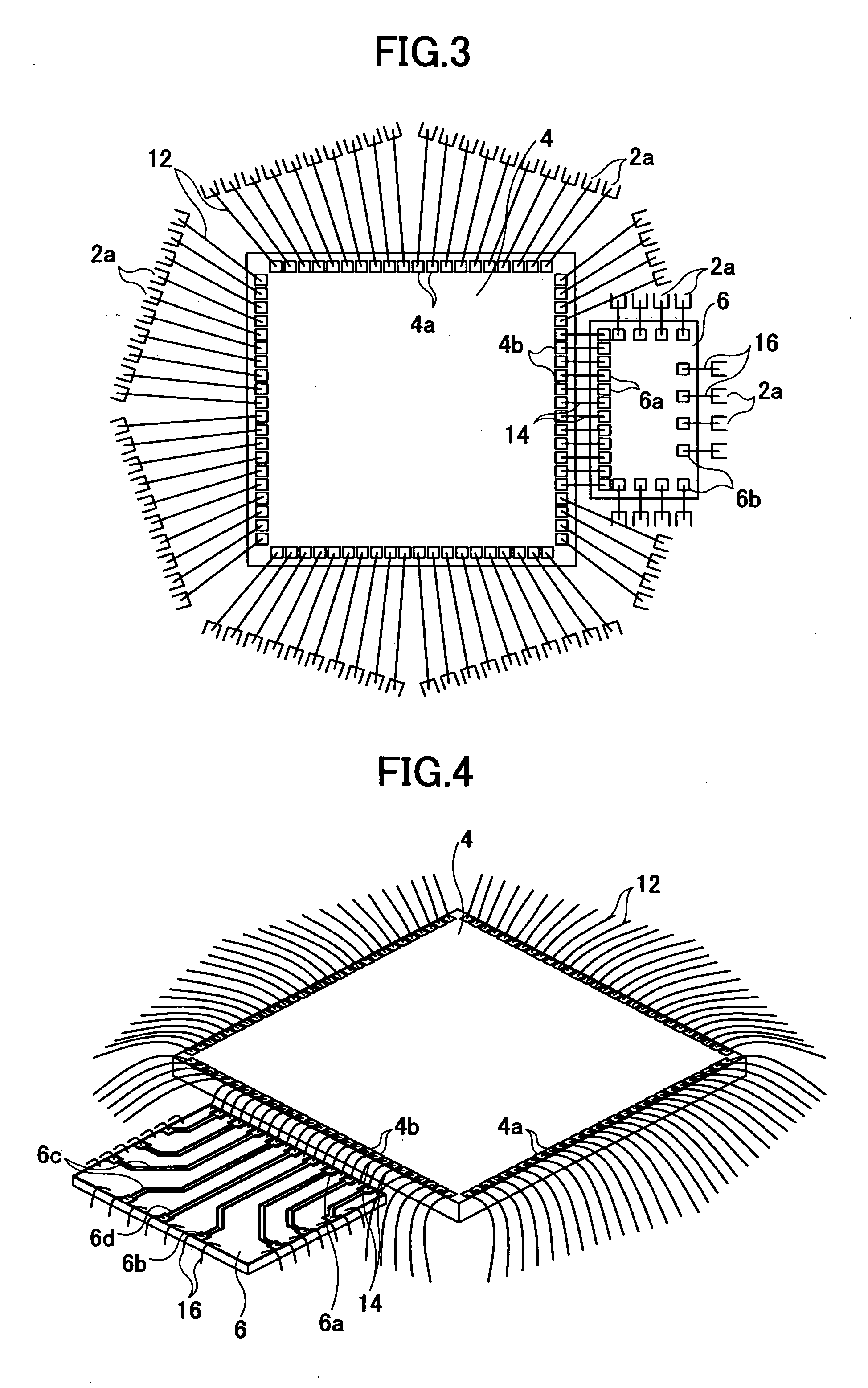

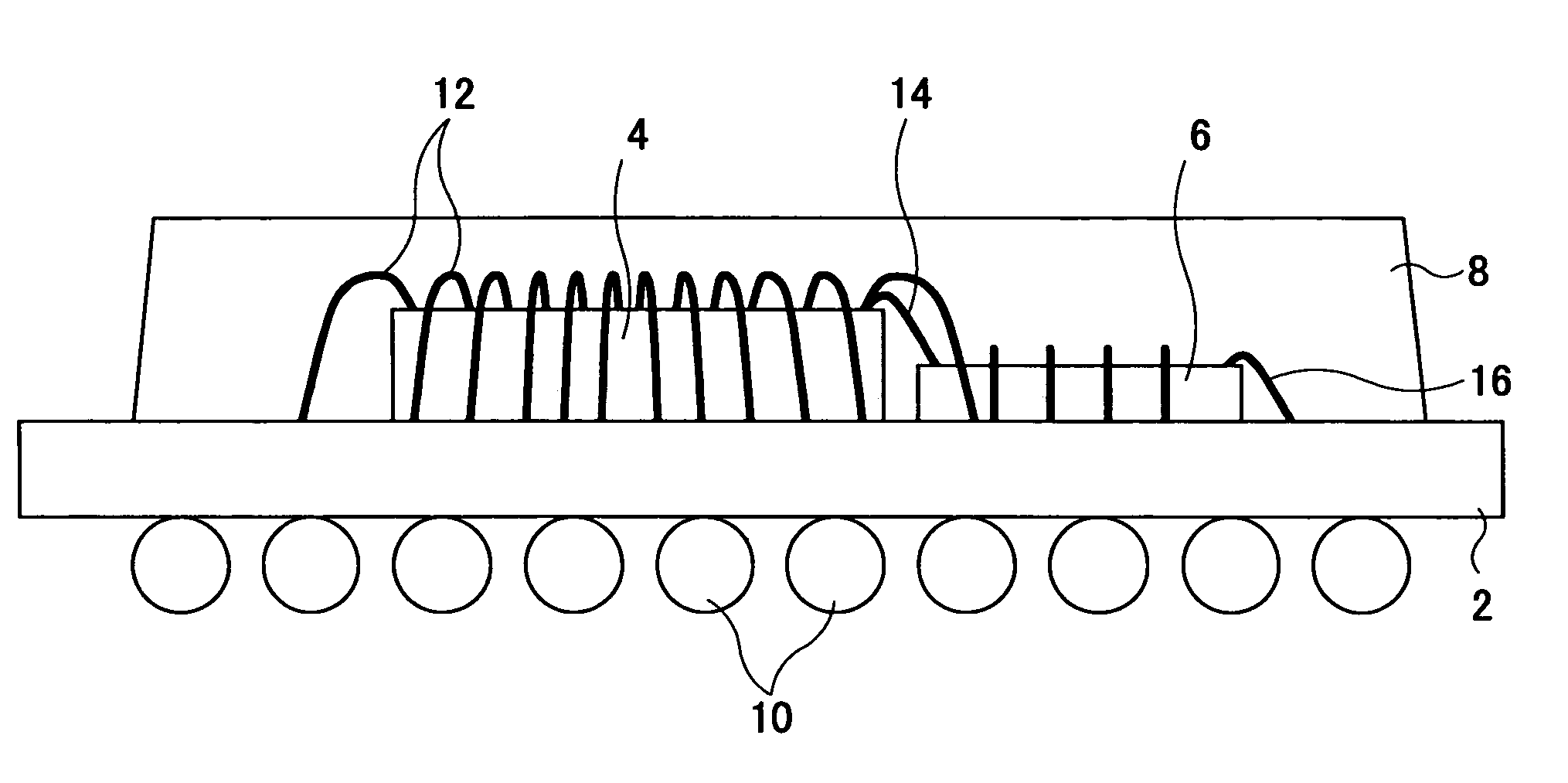

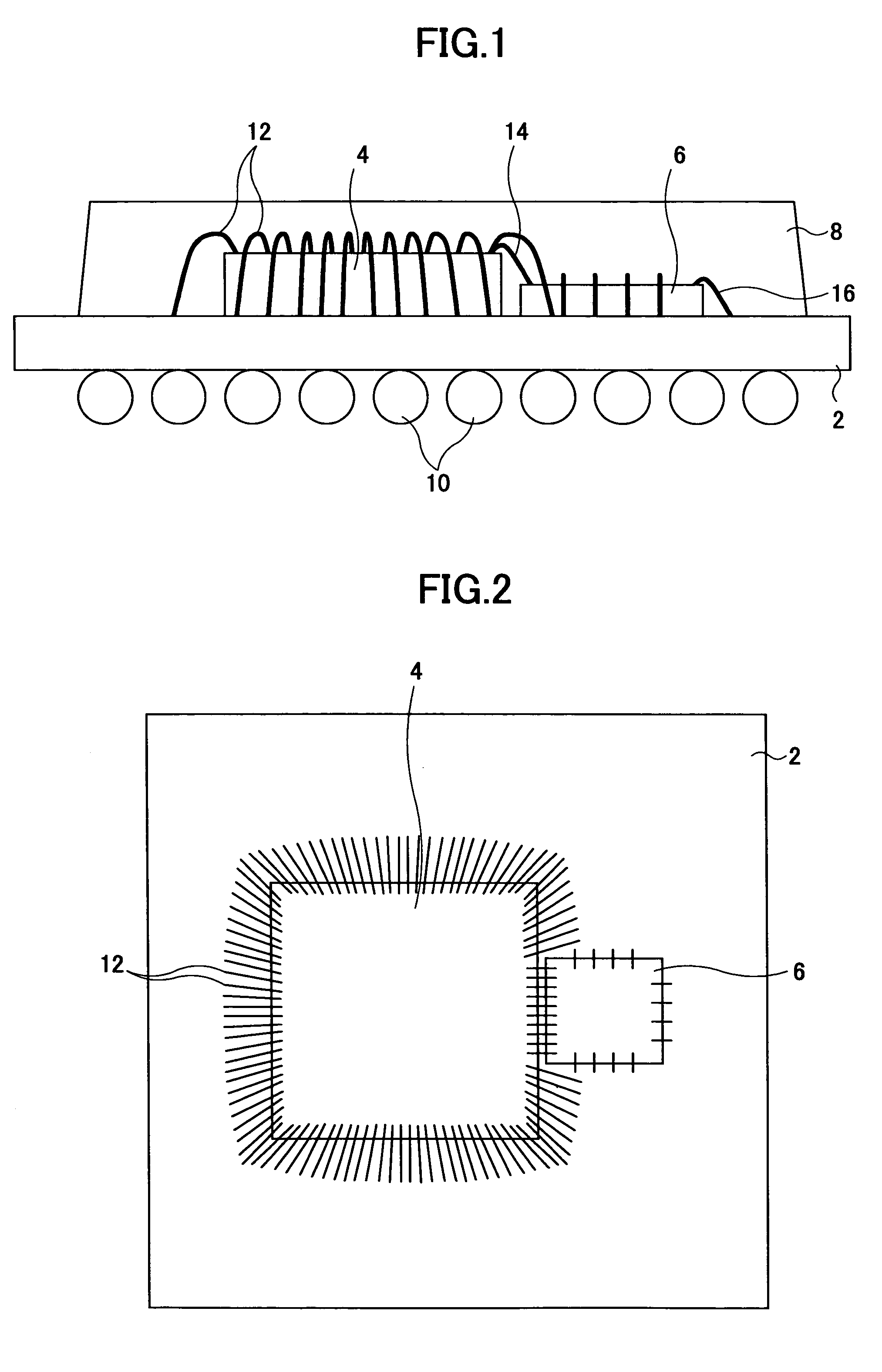

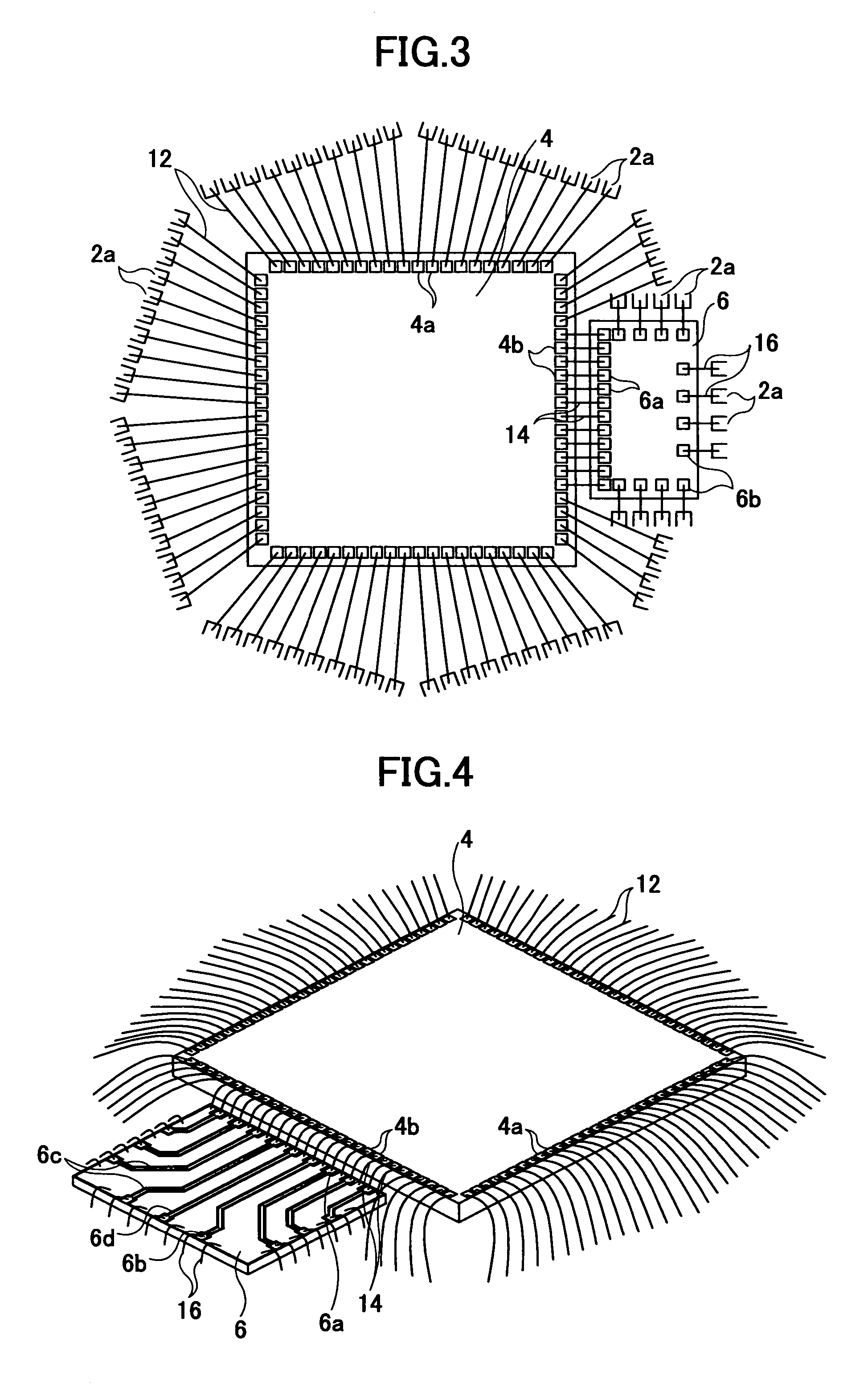

Semiconductor device

InactiveUS20050269701A1Improve accuracyLow accuracySemiconductor/solid-state device detailsSolid-state devicesDevice materialEngineering

In a semiconductor device, bonding-wires can be applied parallel to each other to electrodes of high-speed signal lines when mounting a highly densified semiconductor element on a low-cost substrate while reducing a length of the bonding-wires. An impedance-matched substrate having wiring that impedance-matched with circuits of a semiconductor element is mounted on a substrate. A plurality of first metal wires connect between first electrodes of the semiconductor element and electrodes of the substrate. A plurality of second metal wires connect between second electrodes of the semiconductor element and first electrodes of the impedance-matched substrate. A plurality of third metal wires connect between second electrodes of the impedance-matched substrate and electrodes of the substrate. The second metal wires extend parallel to each other, and the third metal wires also extend parallel to each other.

Owner:SOCIONEXT INC

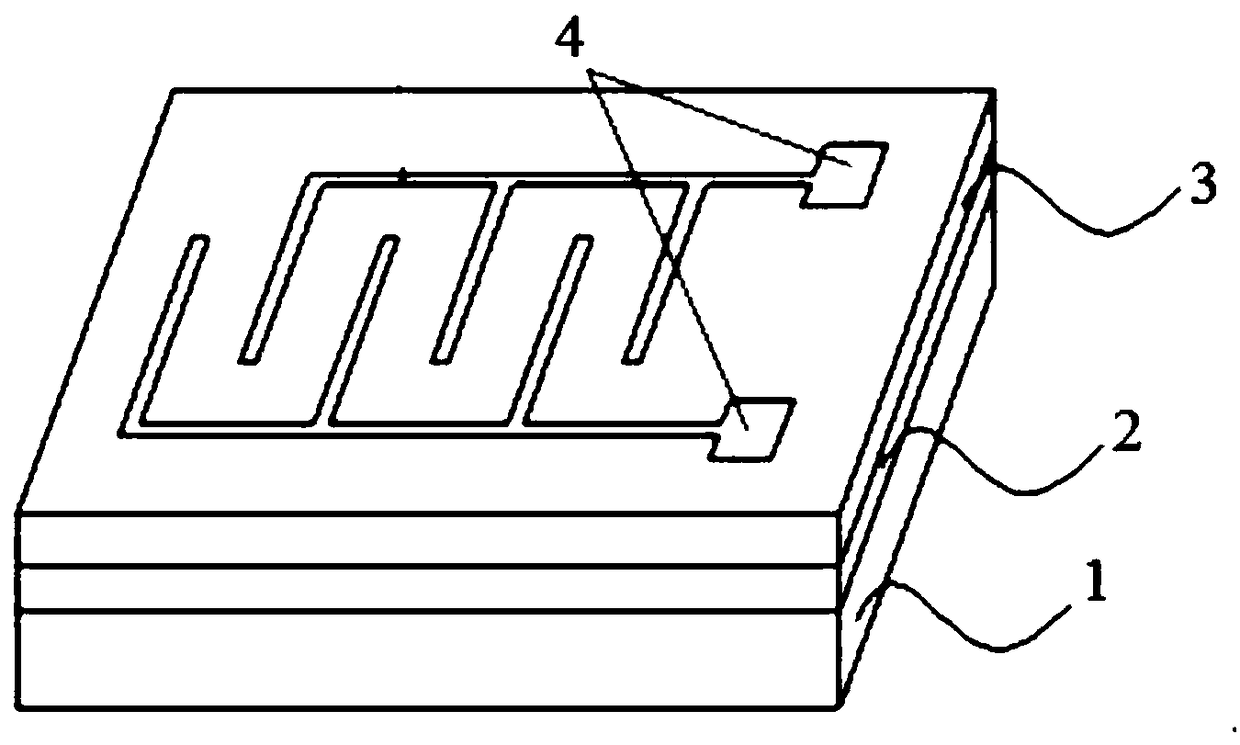

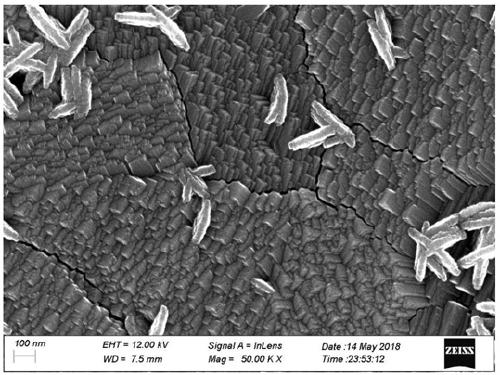

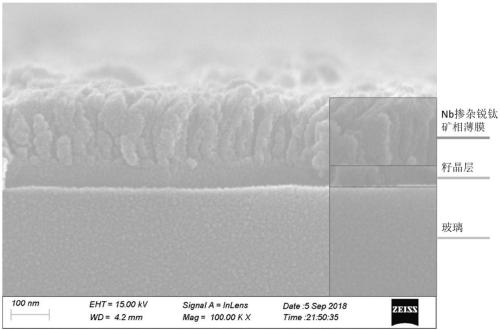

Titanium dioxide film gas sensor with niobium-doped anatase phase and manufacturing method for same

ActiveCN109298030AHigh sensitivityReduce manufacturing costVacuum evaporation coatingSputtering coatingNiobiumRoom temperature

The invention provides a titanium dioxide film gas sensor with a niobium-doped anatase phase and a manufacturing method for same, which belong to the field of sensor. The manufacturing method comprises the following steps: depositing a niobium-doped titanium dioxide seed layer on the surface of a substrate; forming a niobium-doped anatase phase titanium dioxide seed layer by annealing; growing a titanium dioxide gas sensitive film with the niobium-doped anatase on the seed layer by hydrothermal method; preparing a Pt interdigital electrode on the film after annealing again; and obtaining a titanium dioxide film gas sensor with the niobium-doped anatase phase. The manufacturing method prepares the titanium dioxide gas sensitive film with the niobium-doped anatase by hydrothermal method at one-step, so that the steps are simple; can make the sensor work at a room temperature by effective niobium-doped modification; and has both low detection limit and wide detection range. The sensor canuse a low cost substrate such as glass, which further reduces the manufacturing cost of the sensor.

Owner:HUBEI UNIV

High conductive water-based silver ink

Owner:SUN CHEM CORP

Group ó¾ nitride semiconductor multilayer structure

ActiveCN1910738AHigh crystallinityEasy to processSemiconductor/solid-state device manufacturingSemiconductor devicesCrystal structureLow cost substrate

An object of the present invention is to provide a Group III nitride semiconductor multilayer structure having a smooth surface and exhibiting excellent crystallinity, which multilayer structure employs a low-cost substrate that can be easily processed. Another object is to provide a Group III nitride semiconductor light-emitting device comprising the multilayer structure. The inventive Group III nitride semiconductor multilayer structure comprises a substrate; an AlxGa1-xN (0 <= x <= 1) buffer layer which is provided on the substrate and has a columnar or island-like crystal structure; and an AlxInyGa1-x-yN (0 <= x <= 1, 0 <= y <= 1, 0 <= x + y <= 1) single-crystal layer provided on the buffer layer, wherein the substrate has, on its surface, non-periodically distributed grooves having an average depth of 0.01 to 5 mum.

Owner:TOYODA GOSEI CO LTD

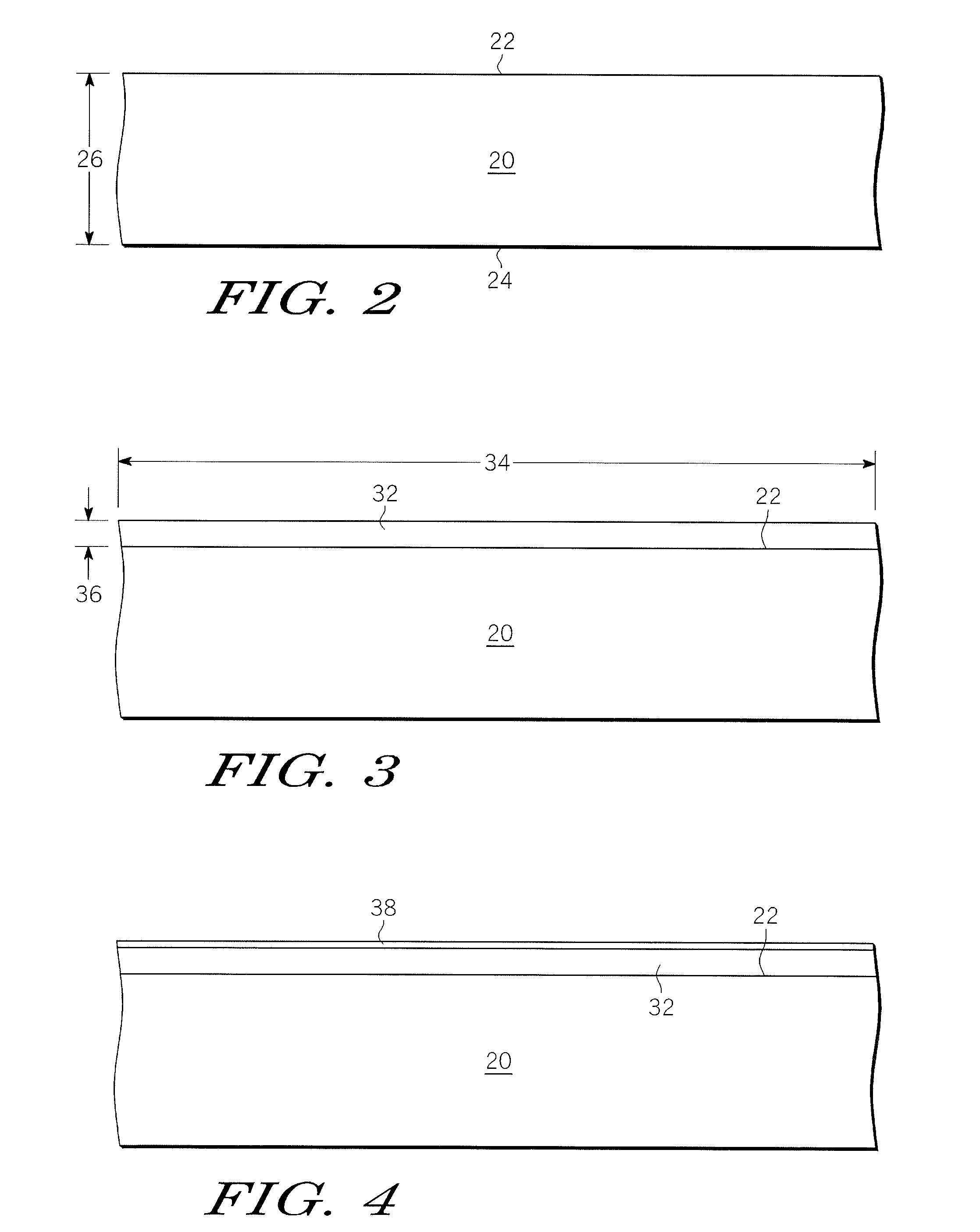

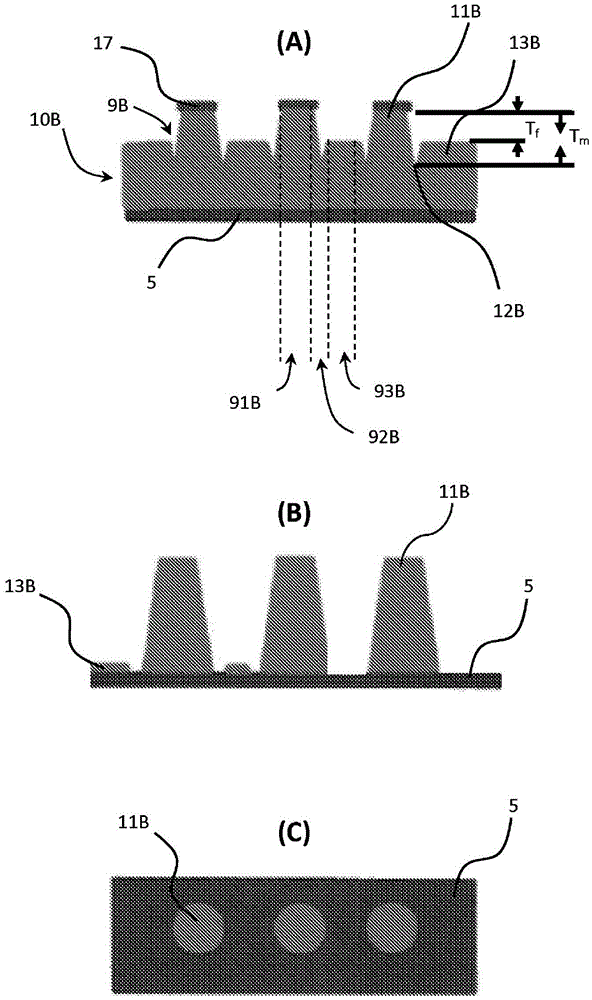

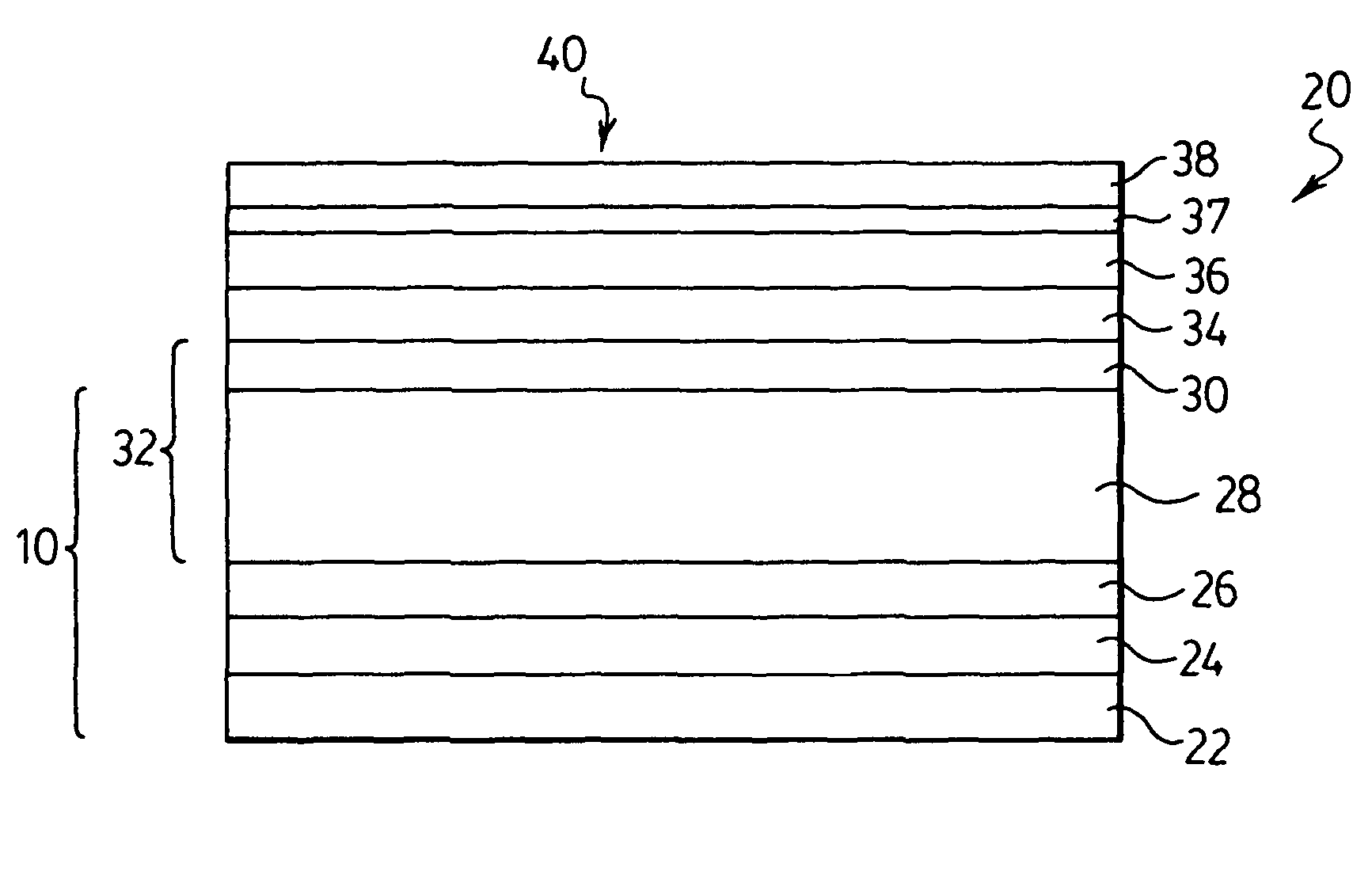

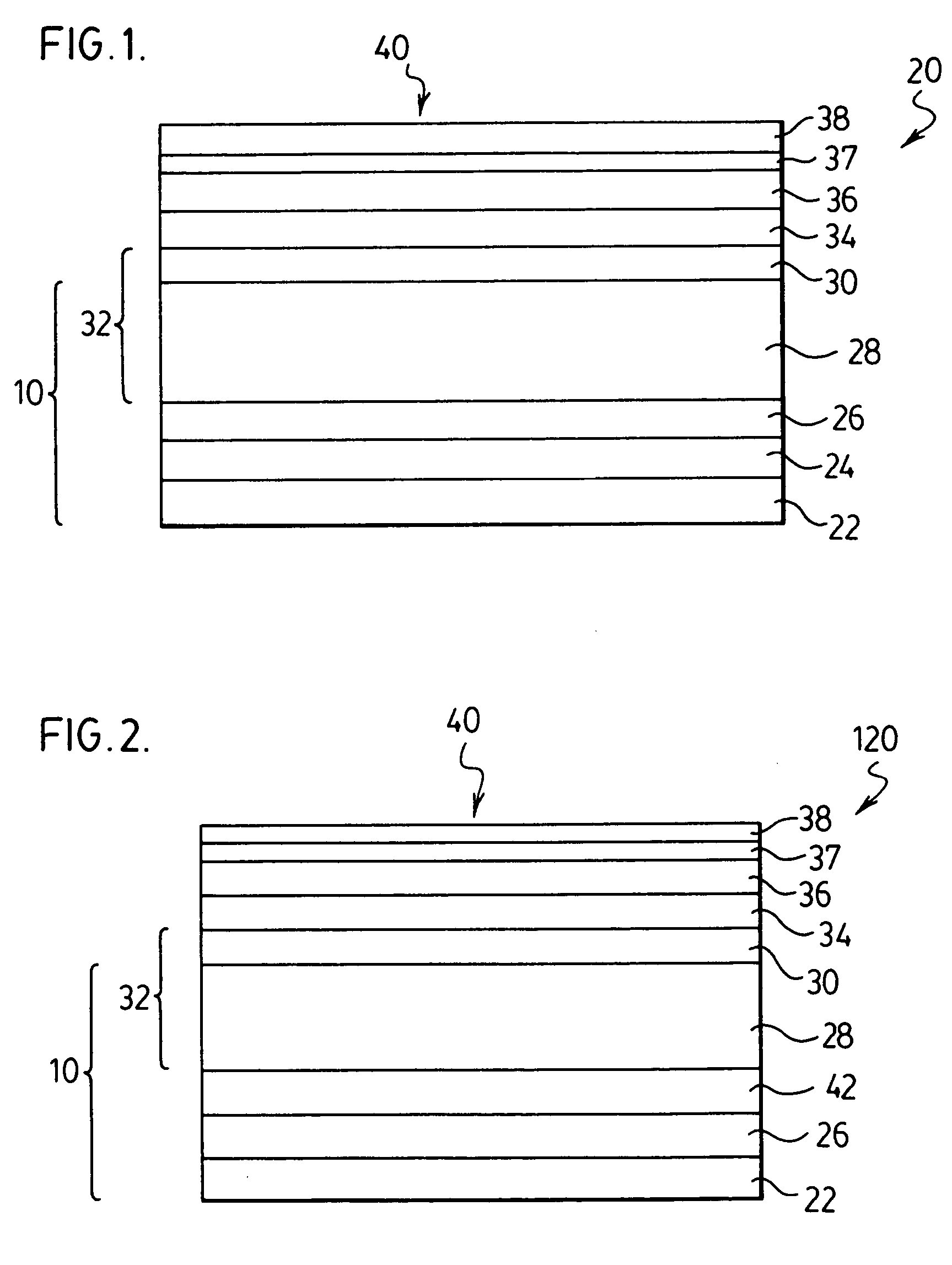

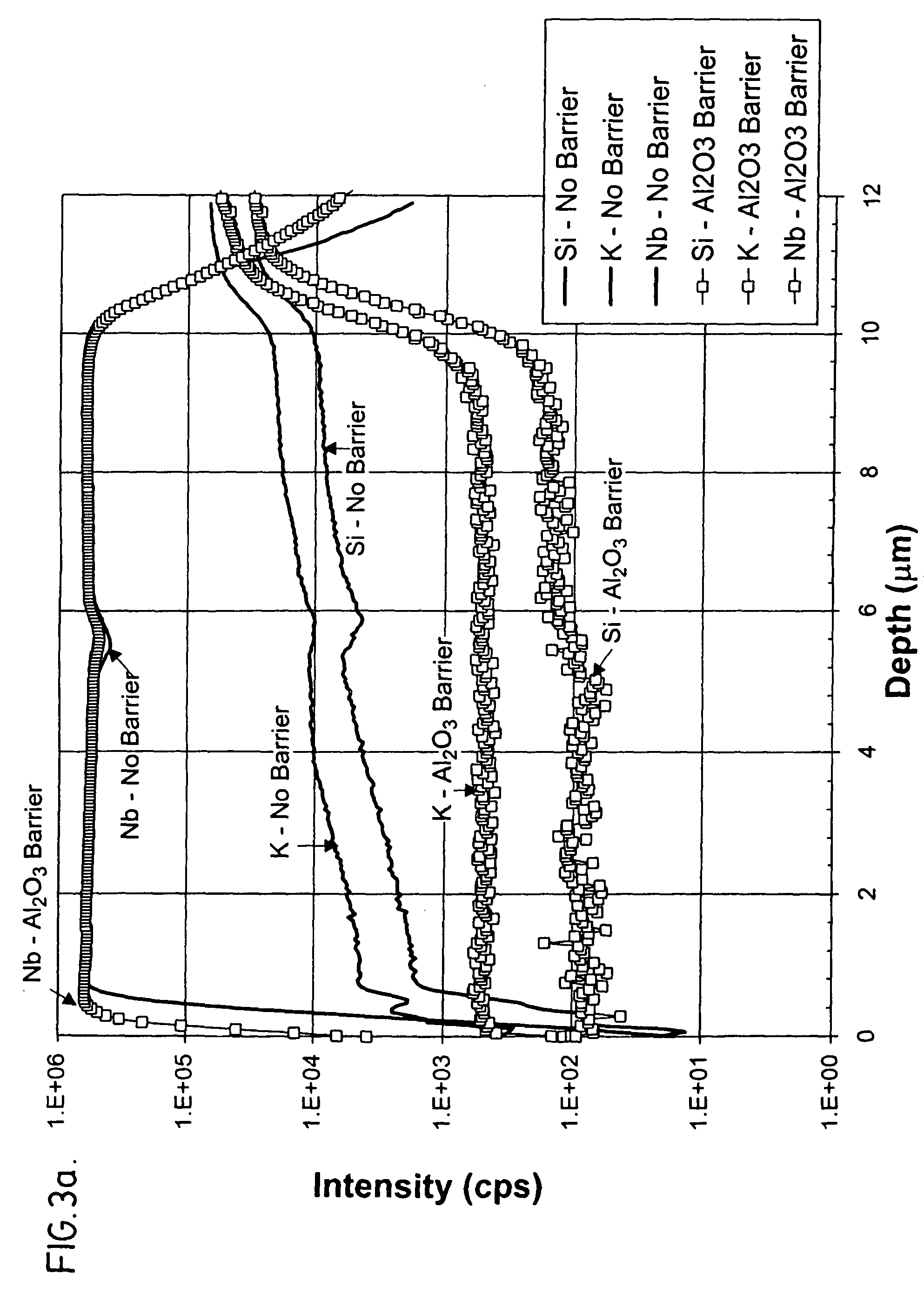

Low-cost substrates having high-resistivity properties and methods for their manufacture

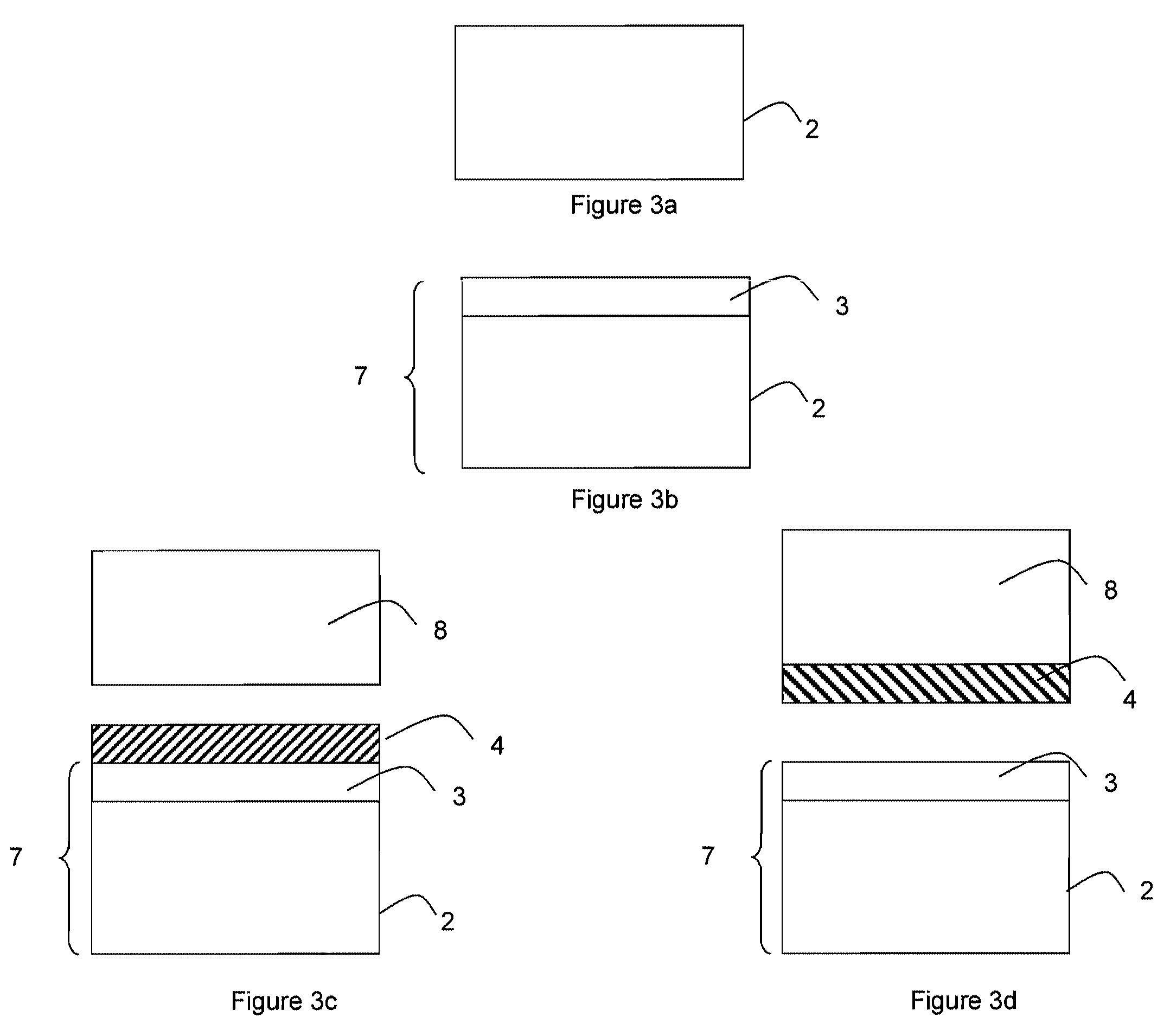

ActiveUS7977705B2Easy to manufactureLow costSolid-state devicesSemiconductor/solid-state device manufacturingHigh resistivityLow cost substrate

In one embodiment, the invention provides substrates that are structured so that devices fabricated in a top layer thereof have properties similar to the same devices fabricated in a standard high resistivity substrate. Substrates of the invention include a support having a standard resistivity, a semiconductor layer arranged on the support substrate having a high-resistivity, preferably greater than about 1000 Ohms-cm, an insulating layer arranged on the high-resistivity layer, and a top layer arranged on the insulating layer. The invention also provides methods for manufacturing such substrates.

Owner:SOITEC SA

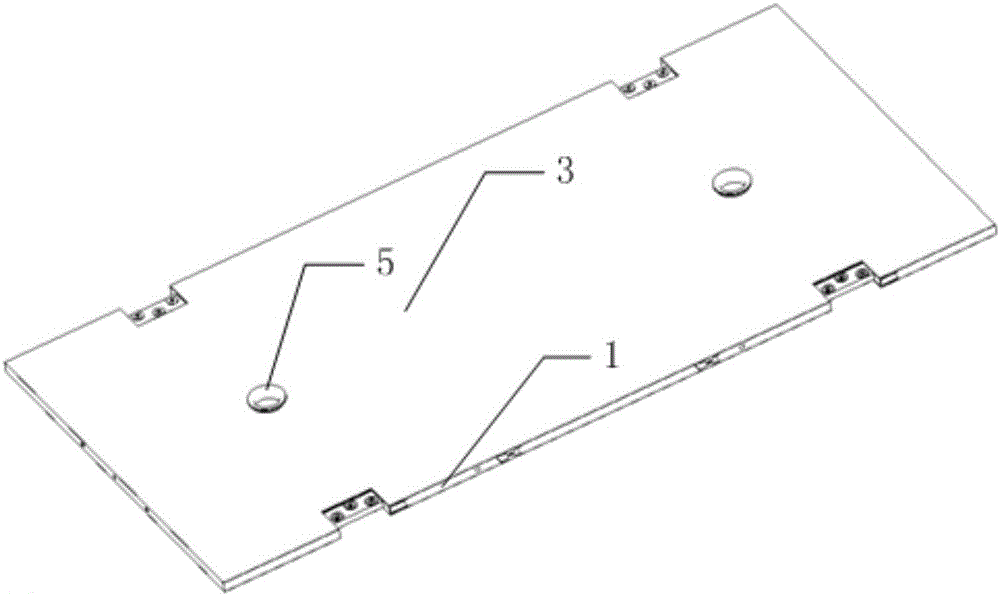

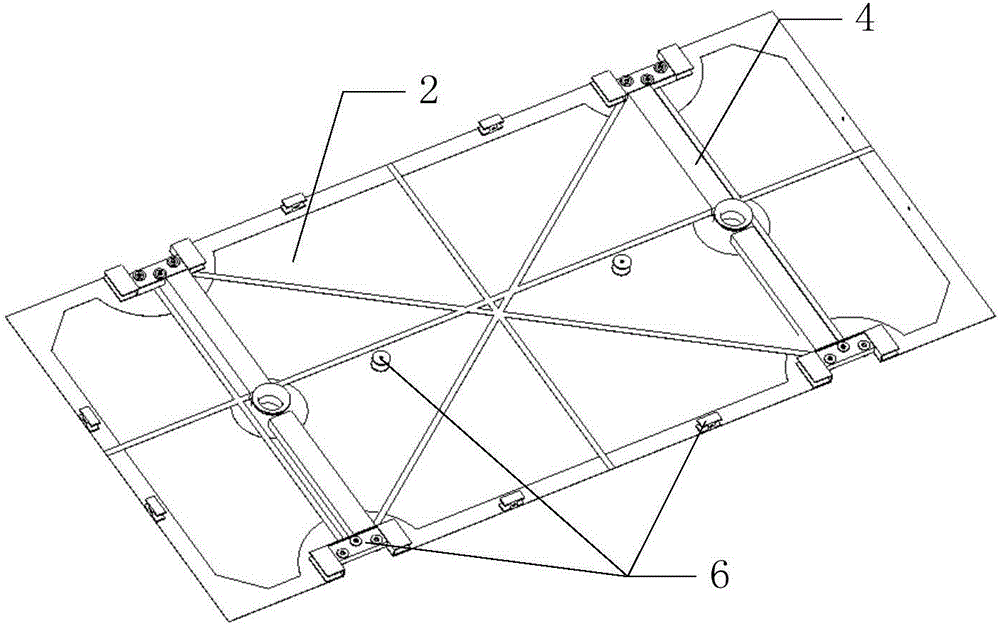

Light low-cost substrate for moonlet solar battery array

InactiveCN106452300AReduce envelope sizeLight in massPhotovoltaic supportsPhotovoltaic energy generationAluminum honeycombLow cost substrate

The invention discloses a light low-cost substrate for a moonlet solar battery array. The substrate comprises an aluminum honeycomb core, carbon fiber composite grid panels, a polyimide film, a built-in beam, a compressing liner and an embedded part, wherein the built-in beam is arranged in the aluminum honeycomb core along the direction of a connecting hinge; the built-in beam, the compressing liner and the embedded part are adhered to the interior of the aluminum honeycomb core through foam glue; the carbon fiber composite grid panels are respectively adhered to the front and rear sides of the aluminum honeycomb core; and the whole substrate is wrapped with the polyimide film through the glue and is once cured and formed. The solar battery array substrate has the characteristics of small enveloping volume, light weight, simple structure, short processing period, low manufacturing cost, and the like, and is the solar battery array substrate with higher application values in moonlets.

Owner:SHANGHAI SATELLITE ENG INST

Method for preparing low cost substrates

ActiveCN105612275ASemiconductor/solid-state device detailsPrinted circuit aspectsHigh rateLow cost substrate

A mask is formed over a first conductive portion of a conductive layer to expose a second conductive portion of the conductive layer. An electrolytic process is performed to remove conductive material from a first region and a second region of the second conductive portion. The second region is aligned with the mask relative to an electric field applied by the electrolytic process. The second region separates the first region of the second conductive portion from the first conductive portion. The electrolytic process is concentrated relative to the second region such that removal occurs at a relatively higher rate in the second region than in the first region.

Owner:INVENSAS CORP

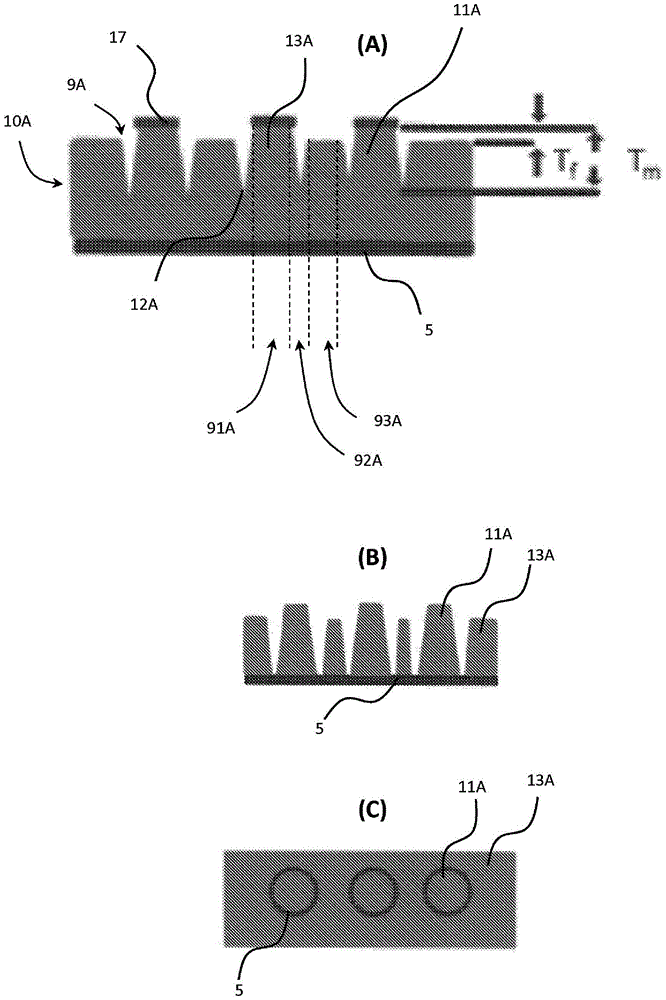

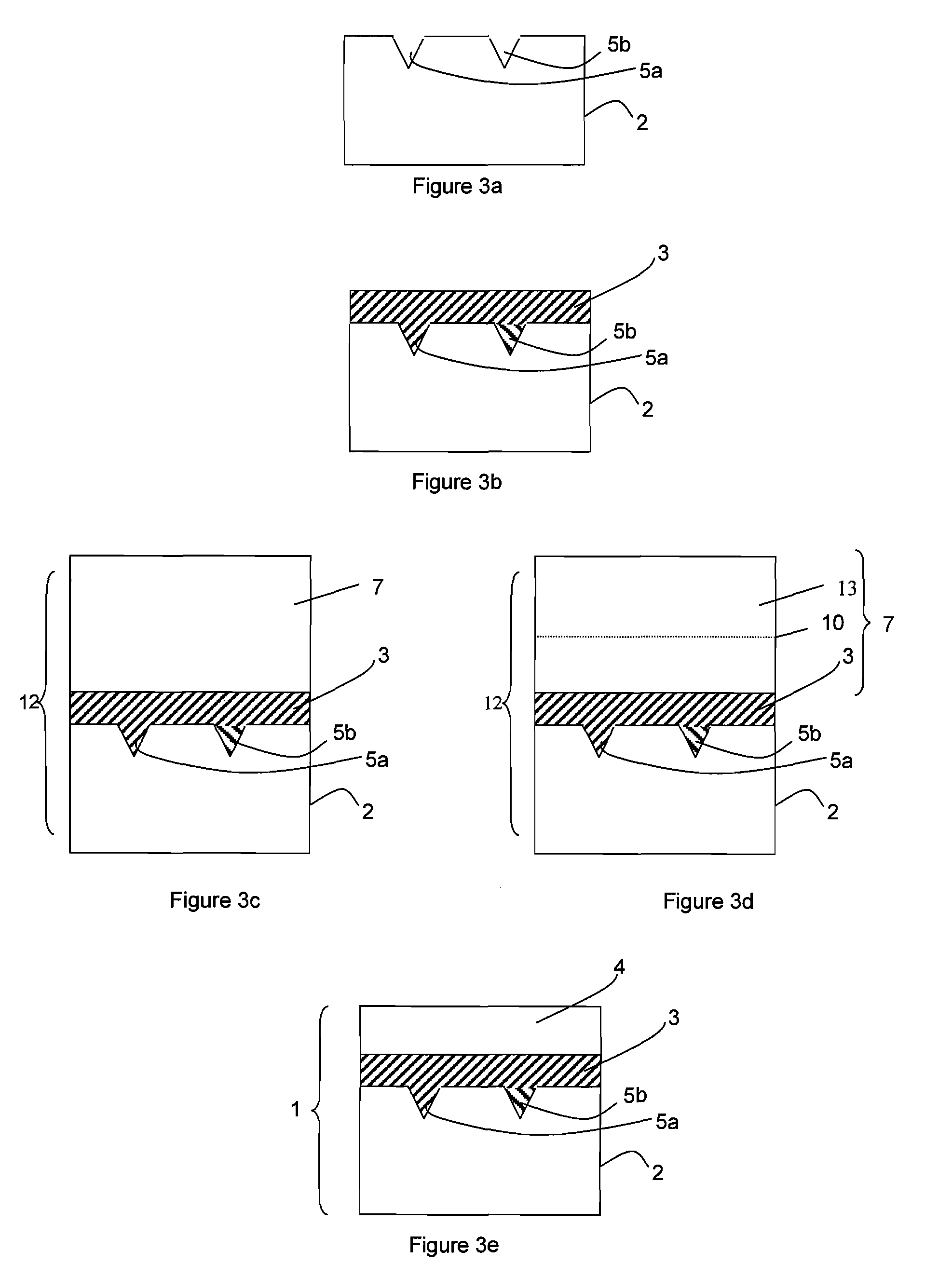

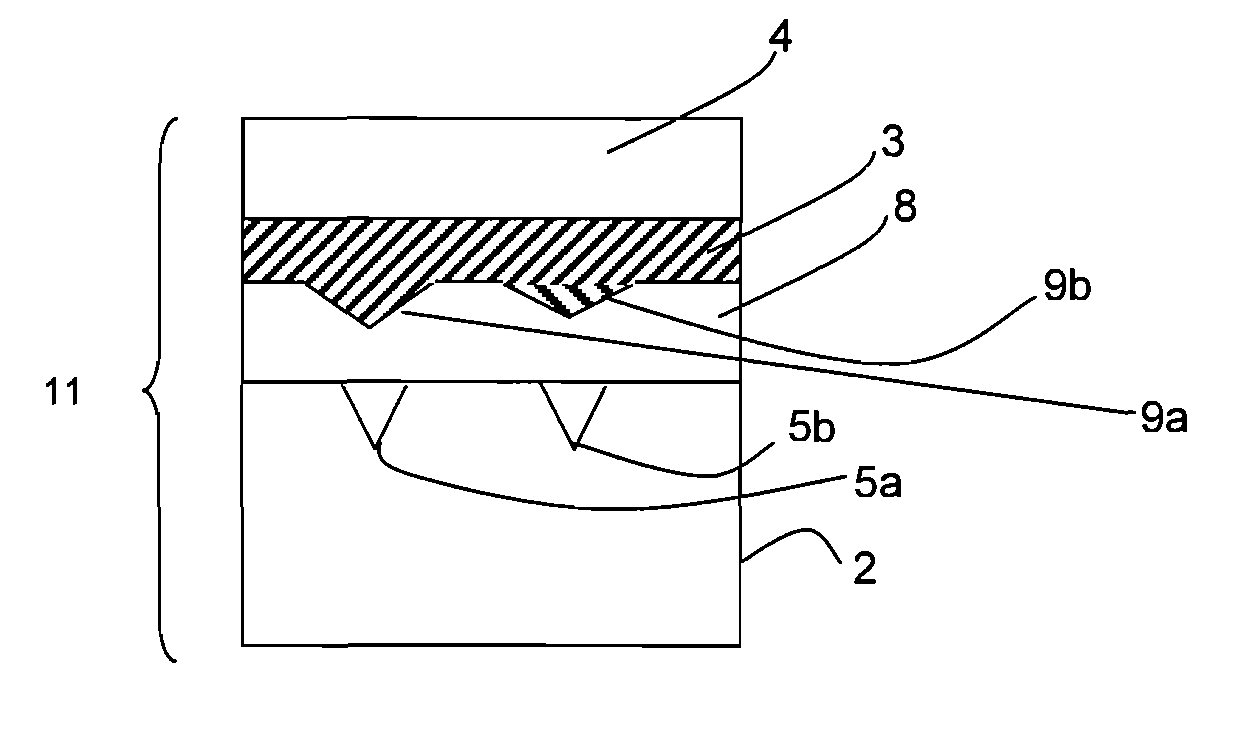

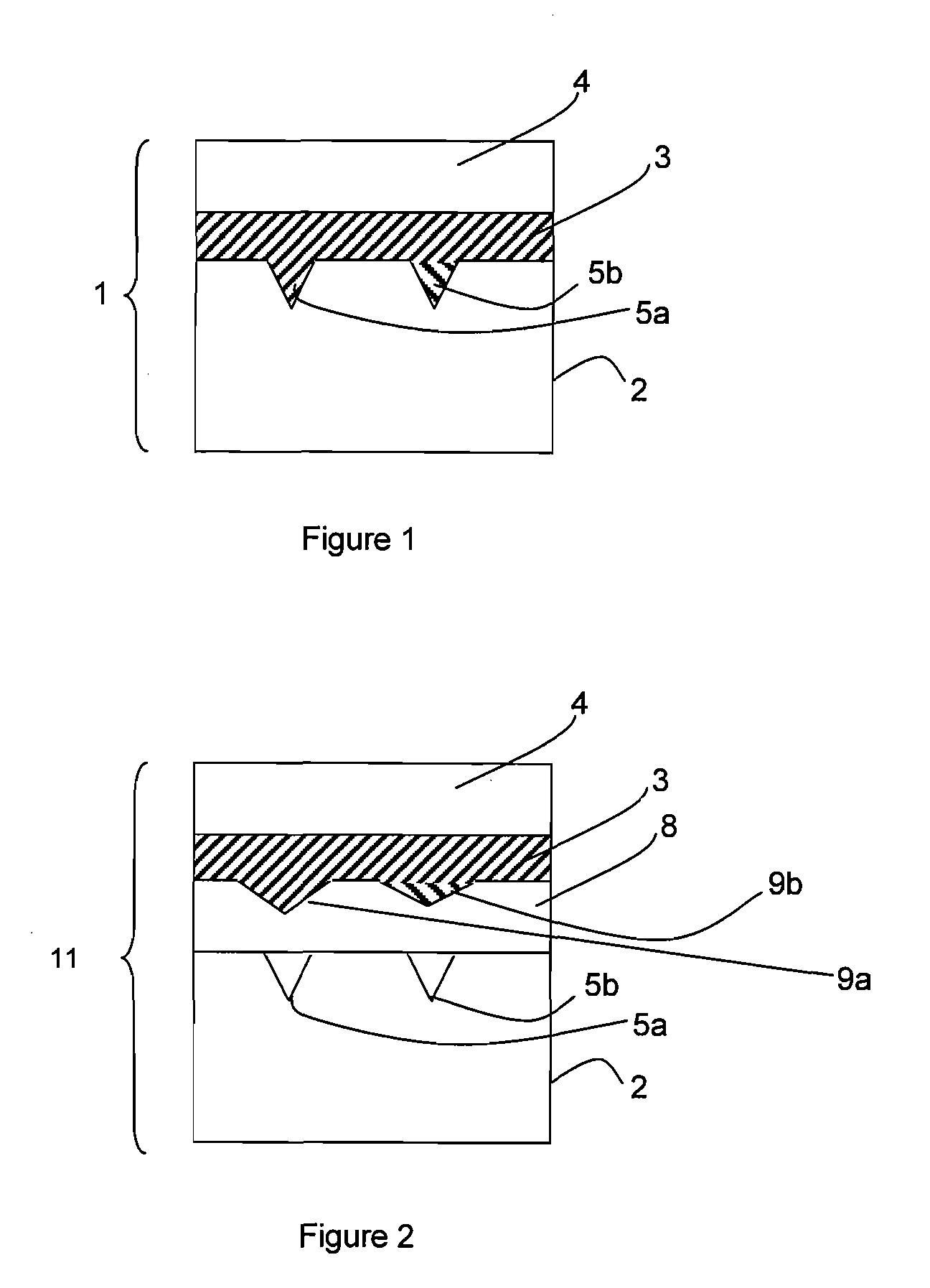

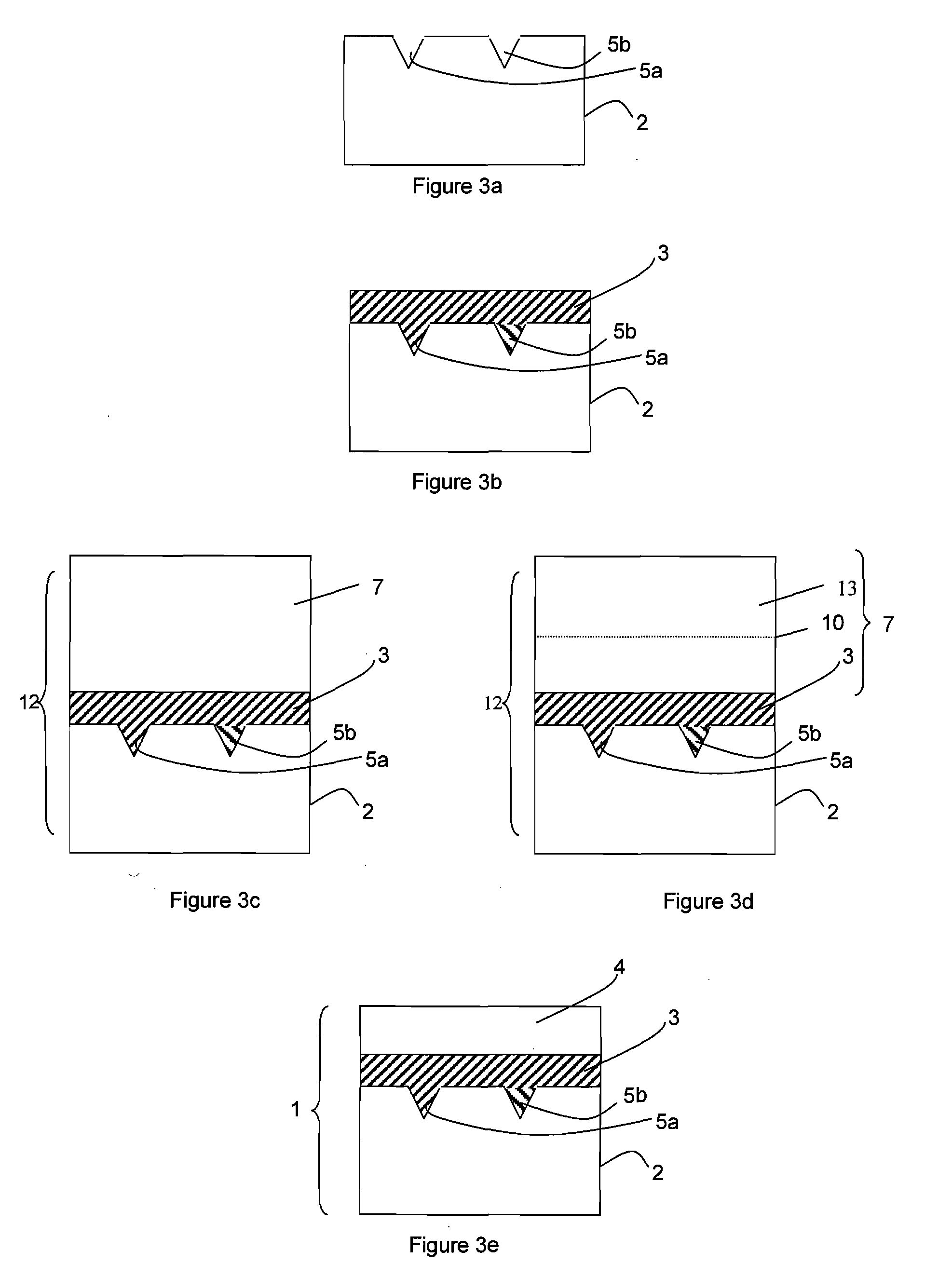

Low cost substrates and method of forming such substrates

In one embodiment, the invention provides engineered substrates having a support with surface pits, an intermediate layer of amorphous material arranged on the surface of the support so as to at least partially fill the surface pits, and a top layer arranged on the intermediate layer. The invention also provides methods for manufacturing the engineered substrates which deposit an intermediate layer on a pitted surface of a support so as to at least partially fill the surface pits, then anneal the intermediate layer, then assemble a donor substrate with the annealed intermediate layer to form an intermediate structure, and finally reduce the thickness of the donor substrate portion of the intermediate structure in order to form the engineered substrate.

Owner:SOITEC SA

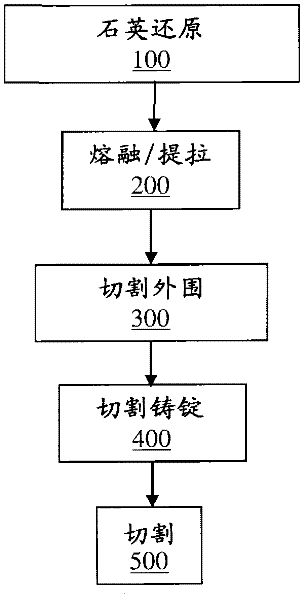

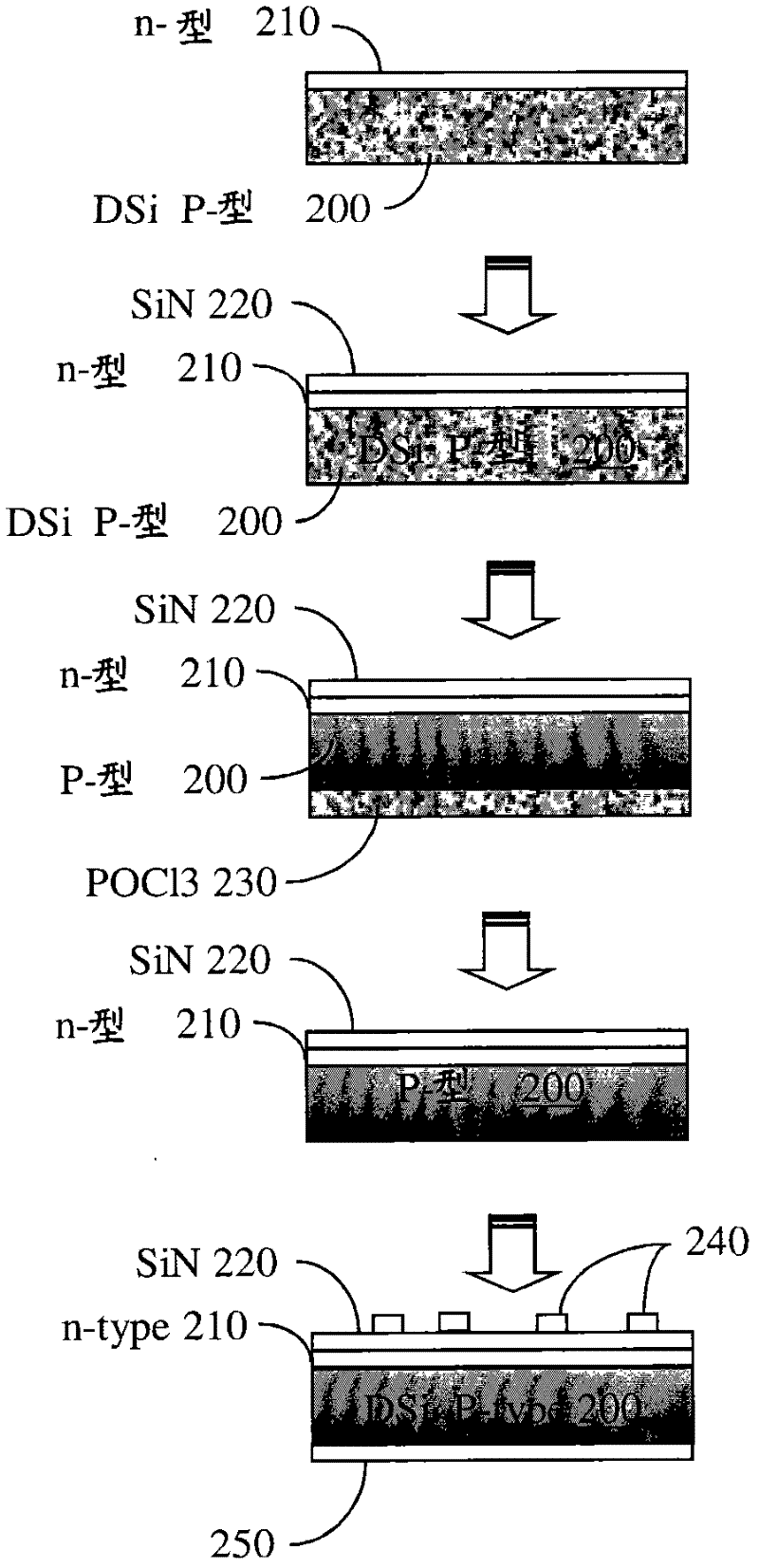

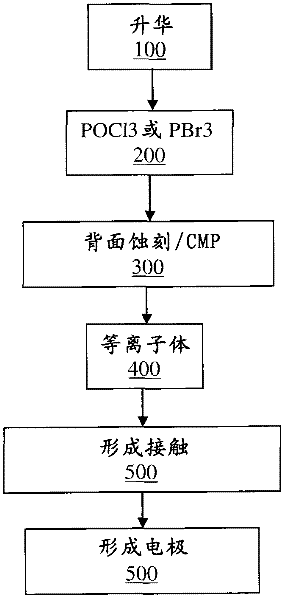

Low-cost solar cells and methods for fabricating low cost substrates for solar cells

InactiveCN102386285AAvoid harmLow costFinal product manufactureSemiconductor devicesWaferingLow cost substrate

The invention discloses low-cost solar cells and methods for fabricating low cost substrates for solar cells. Substrates for solar cells are prepared by etching a plurality of metallurgical grade wafers; depositing aluminum layer on backside of each wafer; depositing a layer of hydrogenated silicon nitride on front surface of each wafer; annealing the wafers at elevated temperature; removing the hydrogenated silicon nitride without disturbing the aluminum layer. A solar cell is then fabricated on the front surface of the wafer while the aluminum remains to serve as the back contact of the cell.

Owner:SUNPREME

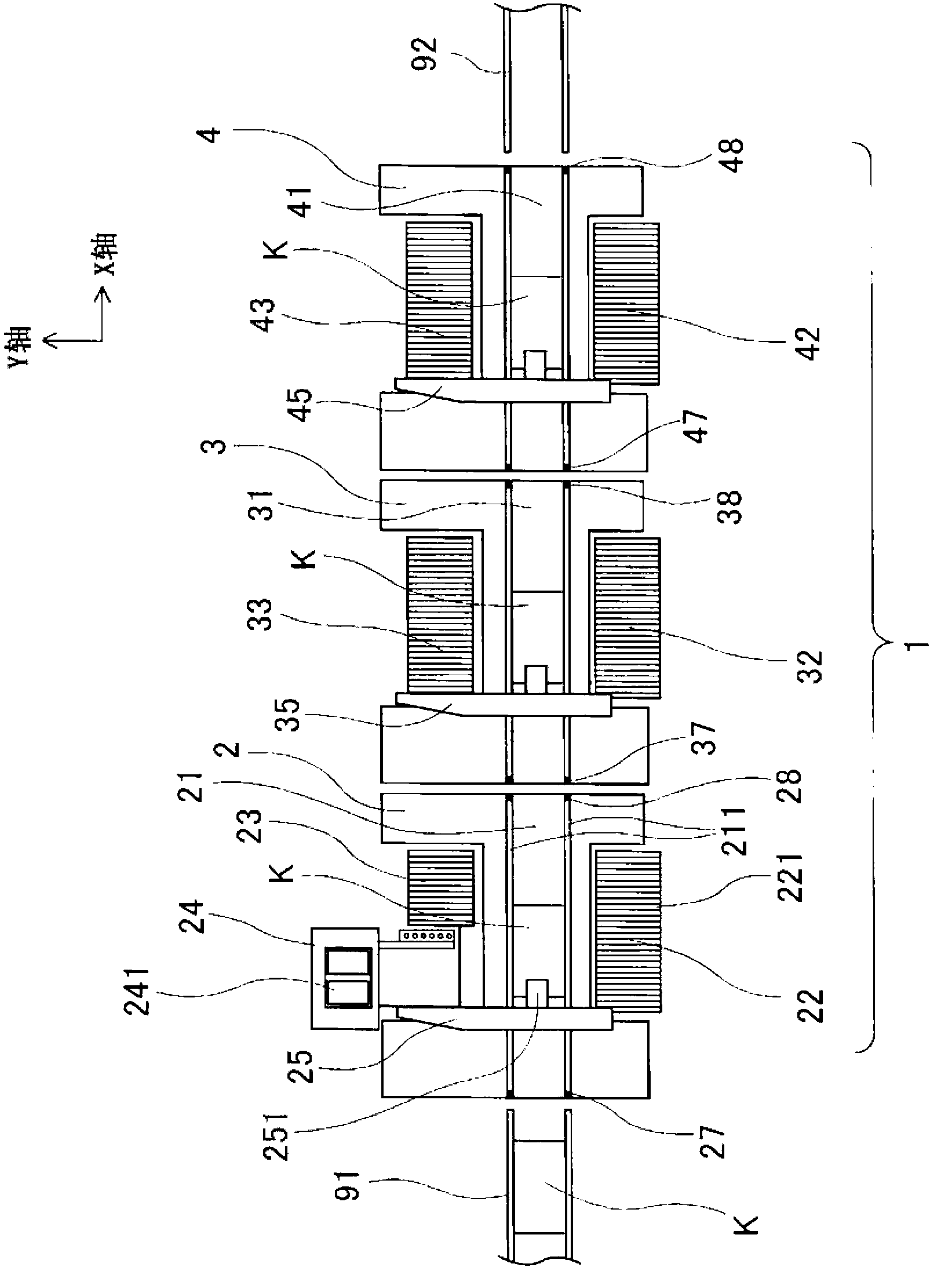

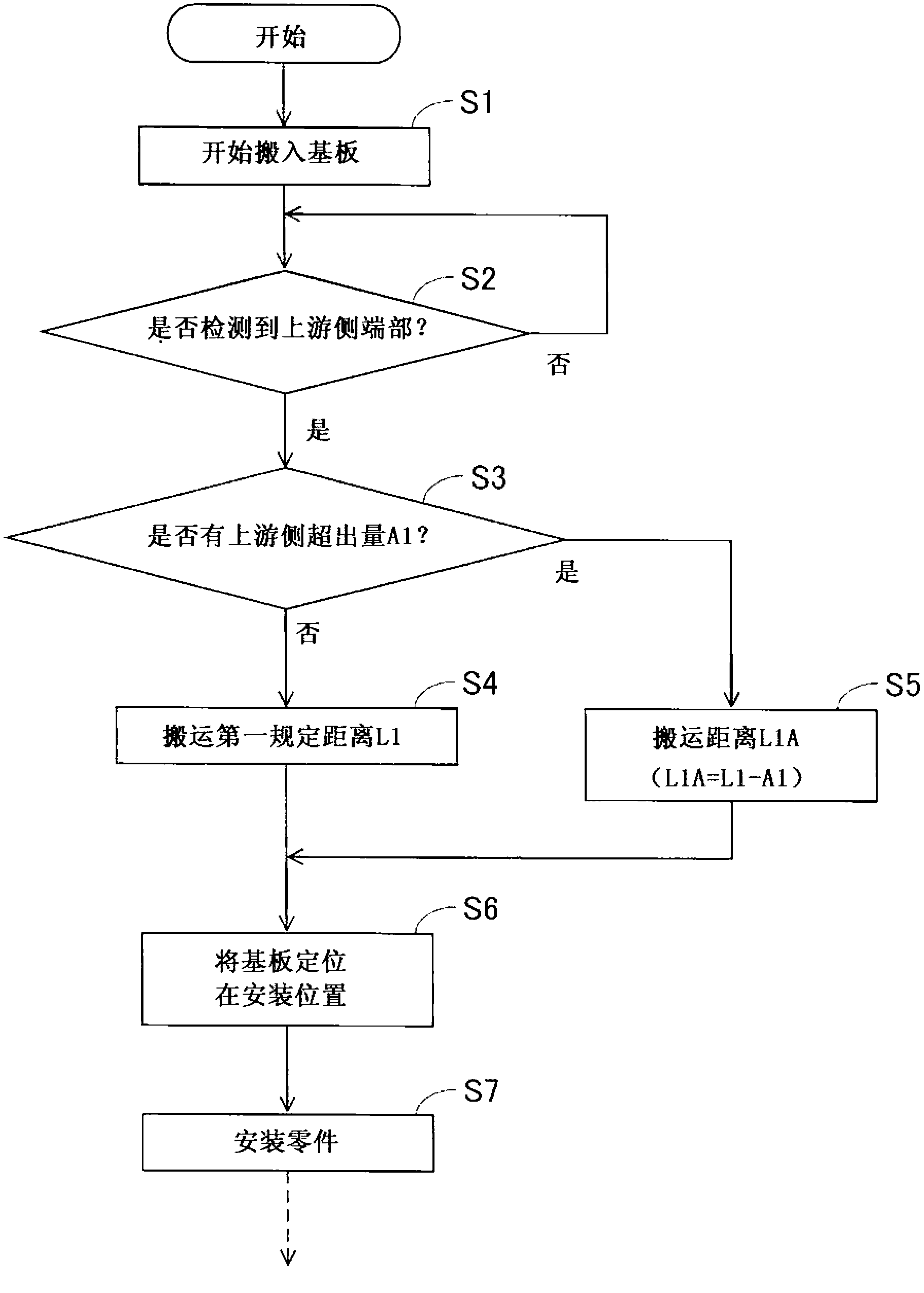

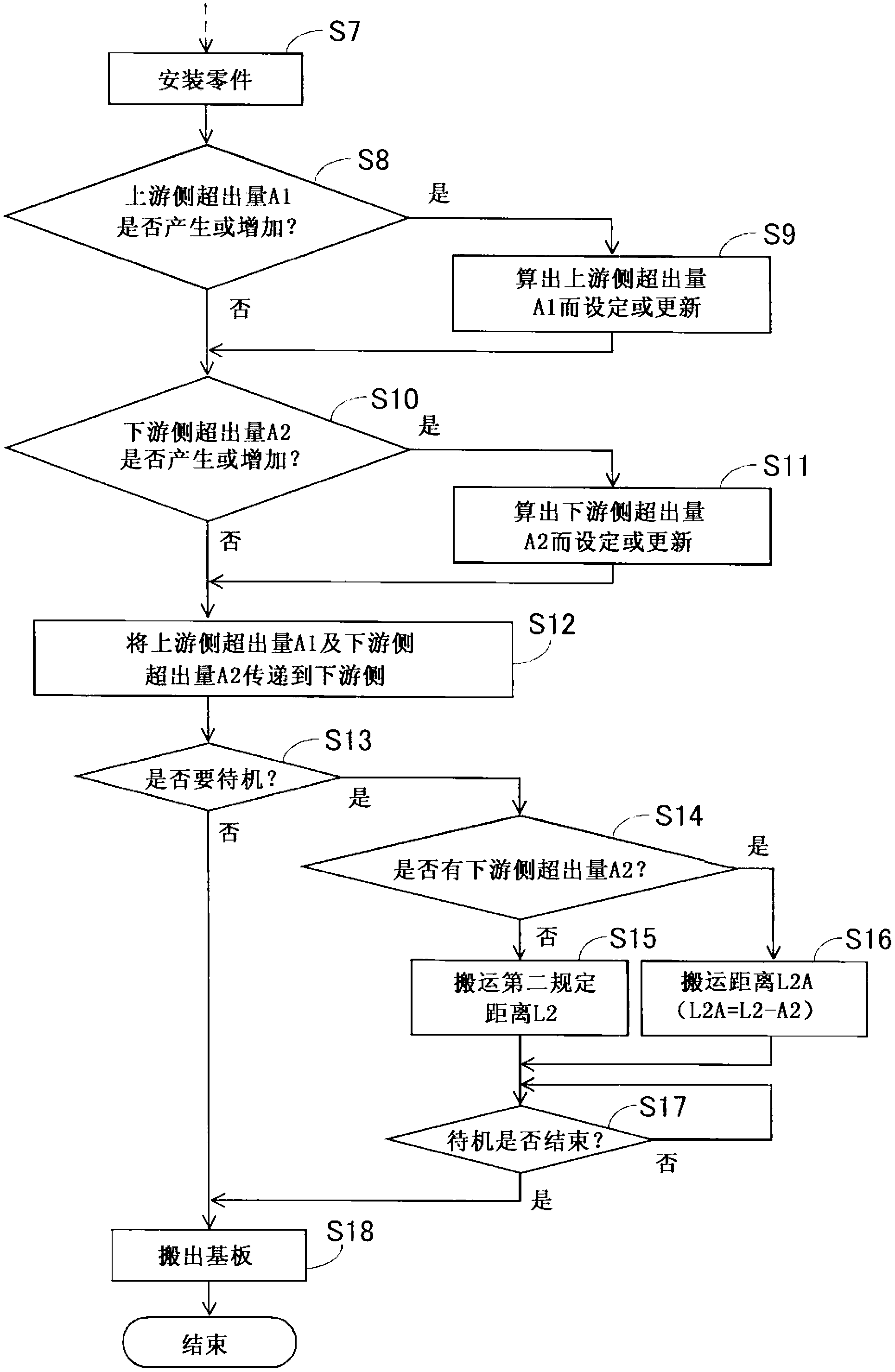

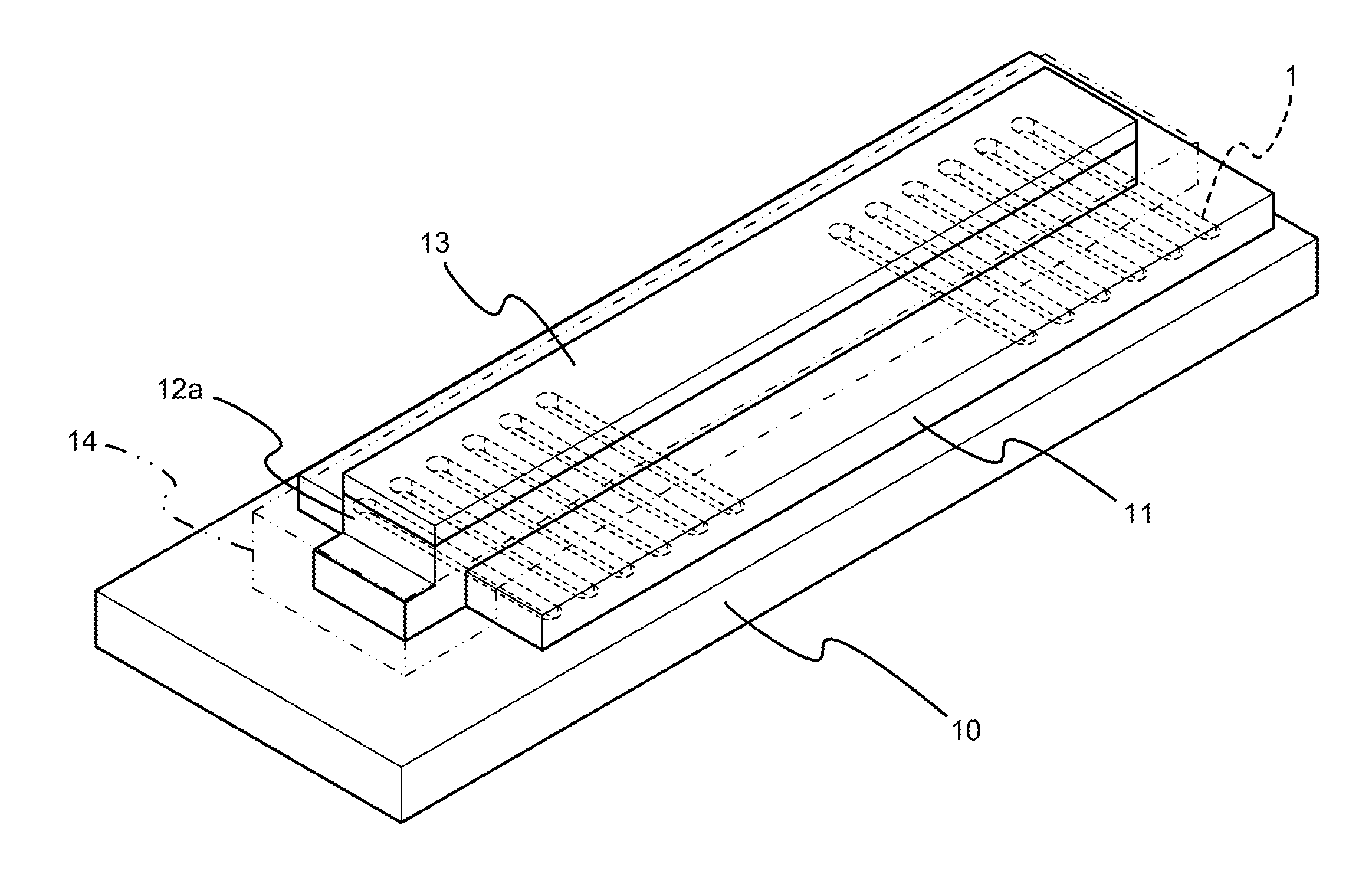

Substrate carrying control method and substrate carrying control device for part assembly line

ActiveCN102802396AReduce excessEliminate the effects ofElectrical componentsLow cost substrateAssembly line

Provided is a low-cost substrate carrying control method and a substrate carrying control device for a part assembly line, even for an overranging substrate that a part is arranged beyond an end portion of the substrate, the overranging substrate also can be accurately stopped at an assembling position and a standby position of a part assembling machine. The substrate carrying control method for the part assembly line formed by a plurality of part assembling machines which are arranged in a line comprises: an overranging amount calculating process for calculating an overranging amount when the part arranged on the substrate stopped at the assembling position is arranged beyond the end portion of the substrate in a carrying direction in the each part assembling machine; an overranging amount transmitting process for transmitting the overranging amount successively before carrying the overranging substrate successively towards the part assembling machines at a downstream side; and an overranging substrate carrying process for carrying the overranging substrate with a distance obtained by subtracting the overranging amount from a prescribed distance in the part assembling machines at a downstream side, so as to enable the overranging substrate to stop at a prescribed position.

Owner:FUJI KK

Hybrid optoelectronic device

InactiveUS20130196459A1Large yieldLarge productivityFinal product manufactureSemiconductor/solid-state device manufacturingGas phaseLow cost substrate

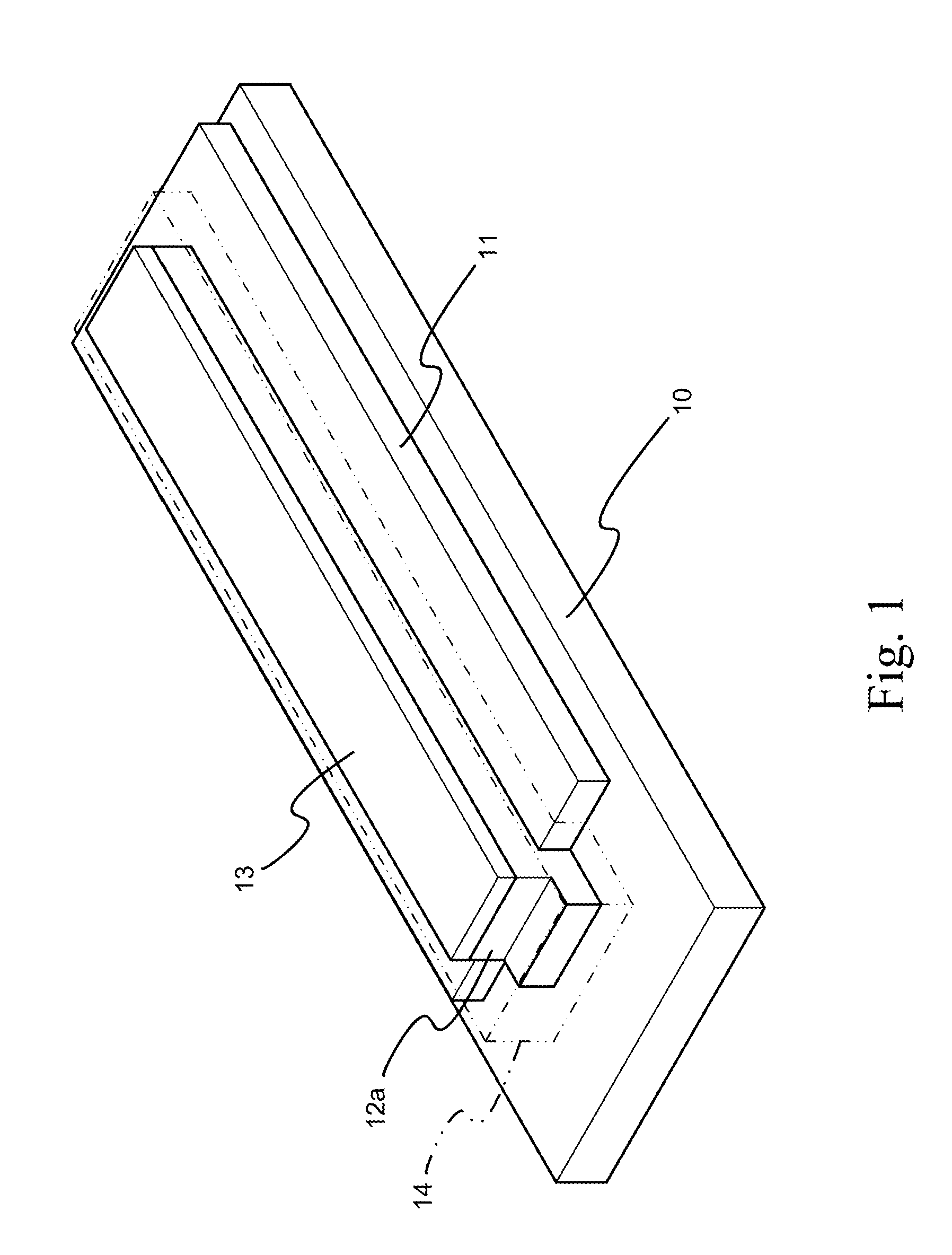

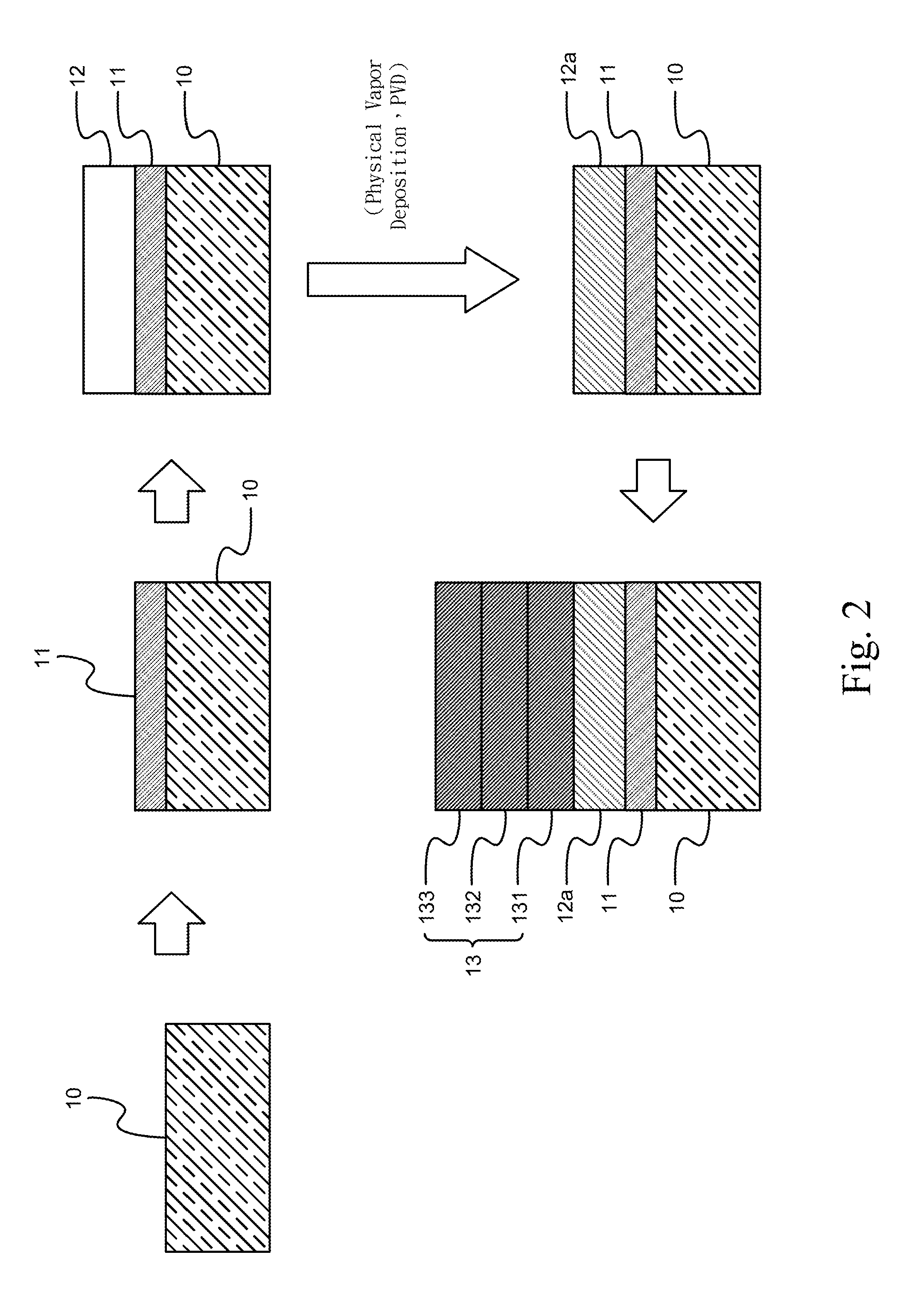

A hybrid optoelectronic device having Group III-V and Si composition on a low-cost substrate is disclosed. A photonic integrated circuit implemented by the hybrid optoelectronic device is much inexpensive and superior to those implemented by the conventional Group III-V optoelectronic device. In the hybrid optoelectronic device, a physical vapor deposition method is used to form a RMG structure with a smooth surface, and further produce a RE structure on the RMG structure. It relates a monolithic process. The wavelength and the material which attract interest can be adjusted. Thereby, the optoelectronic device can be manufactured with large yield and productivity. High optical coupling efficiency that can be offered comes from the Group III-V active device to the Si passive device (optical access). This would be beneficial to the application to the photonic integrated circuit and suitable for future development of high-performance electronic and optoelectronic devices.

Owner:NATIONAL TSING HUA UNIVERSITY

Dielectric composition for thin-film transistors

ActiveUS9076975B2Reduce distortionIncrease temperatureSolid-state devicesSemiconductor/solid-state device manufacturingLow cost substrateDielectric layer

An electronic device, such as a thin-film transistor, includes a substrate and a dielectric layer formed from a dielectric composition. The dielectric composition includes a dielectric material, a crosslinking agent, and an infrared absorbing agent. In particular embodiments, the dielectric material comprises a lower-k dielectric material and a higher-k dielectric polymer. When deposited, the lower-k dielectric material and the higher-k dielectric material form separate phases. The infrared absorbing agent allows the dielectric composition to attain a temperature that is significantly greater than the temperature attained by the substrate during curing. This difference in temperature allows the dielectric layer to be cured at relatively high temperatures and / or shorter time periods, permitting the selection of lower-cost substrate materials that would otherwise be deformed by the curing of the dielectric layer.

Owner:XEROX CORP

Enhanced performance active pixel array and epitaxial growth method for achieving the same

Owner:OSTENDO TECH INC

Barrier layer for thick film dielectric electroluminescent displays

InactiveUS7989088B2Minimize internal stressFree from crackingDischarge tube luminescnet screensElectroluminescent light sourcesCapacitanceChemical species

A novel sub-structure of a thick film dielectric electroluminescent display and a thick film dielectric electroluminescent display incorporating the same is provided. The sub-structure comprises a barrier layer between a substrate and a thick film dielectric layer. The barrier layer is chemically inert with respect to the substrate and the thick film dielectric layer and the barrier layer inhibits diffusion of at least one chemical species therethrough. This sub-structure results in a higher capacitance for the thick dielectric layer, which provides higher display luminance and a reduced tendency for dielectric breakdown of the thick dielectric layer. The barrier layer permits for lower cost substrates, such as glass, to be used.

Owner:IFIRE IP CORP +1

Group III nitride semiconductor multilayer structure

ActiveUS7935955B2Easy to processHigh crystallinitySemiconductor/solid-state device manufacturingSemiconductor devicesCrystal structureLow cost substrate

An object of the present invention is to provide a Group III nitride semiconductor multilayer structure having a smooth surface and exhibiting excellent crystallinity, which multilayer structure employs a low-cost substrate that can be easily processed. Another object is to provide a Group III nitride semiconductor light-emitting device comprising the multilayer structure.The inventive Group III nitride semiconductor multilayer structure comprises a substrate; an AlxGa1-xN (0≦x≦1) buffer layer which is provided on the substrate and has a columnar or island-like crystal structure; and an AlxInyGa1-x-yN (0≦x≦1, 0≦y≦1, 0≦x+y≦1) single-crystal layer provided on the buffer layer, wherein the substrate has, on its surface, non-periodically distributed grooves having an average depth of 0.01 to 5 μm.

Owner:TOYODA GOSEI CO LTD

Low cost substrates and method of forming such substrates

ActiveUS20090321872A1Reduce thicknessLayered productsSolid-state devicesInter layerLow cost substrate

In one embodiment, the invention provides engineered substrates having a support with surface pits, an intermediate layer of amorphous material arranged on the surface of the support so as to at least partially fill the surface pits, and a top layer arranged on the intermediate layer. The invention also provides methods for manufacturing the engineered substrates which deposit an intermediate layer on a pitted surface of a support so as to at least partially fill the surface pits, then anneal the intermediate layer, then assemble a donor substrate with the annealed intermediate layer to form an intermediate structure, and finally reduce the thickness of the donor substrate portion of the intermediate structure in order to form the engineered substrate.

Owner:SOITEC SA

Semiconductor device

InactiveUS7042102B2Shorten the lengthImprove compactnessSemiconductor/solid-state device detailsSolid-state devicesLow cost substrateImpedance matching

In a semiconductor device, bonding-wires can be applied parallel to each other to electrodes of high-speed signal lines when mounting a highly densified semiconductor element on a low-cost substrate while reducing a length of the bonding-wires. An impedance-matched substrate having wiring that impedance-matched with circuits of a semiconductor element is mounted on a substrate. A plurality of first metal wires connect between first electrodes of the semiconductor element and electrodes of the substrate. A plurality of second metal wires connect between second electrodes of the semiconductor element and first electrodes of the impedance-matched substrate. A plurality of third metal wires connect between second electrodes of the impedance-matched substrate and electrodes of the substrate. The second metal wires extend parallel to each other, and the third metal wires also extend parallel to each other.

Owner:SOCIONEXT INC

Method for preparing low-cost substrates

ActiveCN105612275BSemiconductor/solid-state device detailsPrinted circuit aspectsPhysical chemistryLow cost substrate

A mask is formed above the first conduction part of the conductive layer to expose the second conductive part of the conductive layer.The electrolytic process is performed to remove the conductive material from the first and second regions of the second and second regions of the second conductive part.Compared with the electric field applied by the electrolytic process, the second area is aligned with the mask.The first region of the second area is separated from the first area of the second conductive part from the first conduction part.Compared with the concentration of the second region, the electrolytic process is removed from a relatively higher ratio in the second area compared to the first area.

Owner:INVENSAS CORP