Method for preparing low cost substrates

A technology of equipment and conductive parts, which is applied in the field of packaging of microelectronic devices and can solve problems such as chip assembly

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0055] Components described herein, such as interposers, substrates, circuit panels, microelectronic elements, etc., may have one or both of insulating and dielectric structures at their outer surfaces in some arrangements. Thus, as used in this disclosure, a statement that a conductive element is "at" a surface of a component's dielectric structure means that when the component is not assembled with any other A theoretical point contact moving in the direction of the part surface from outside the part towards the part surface. Thus, a terminal or other conductive element at a surface of a component may protrude from such surface; may be flush with such surface; or may be recessed relative to such surface in the form of a hole or recess in the component.

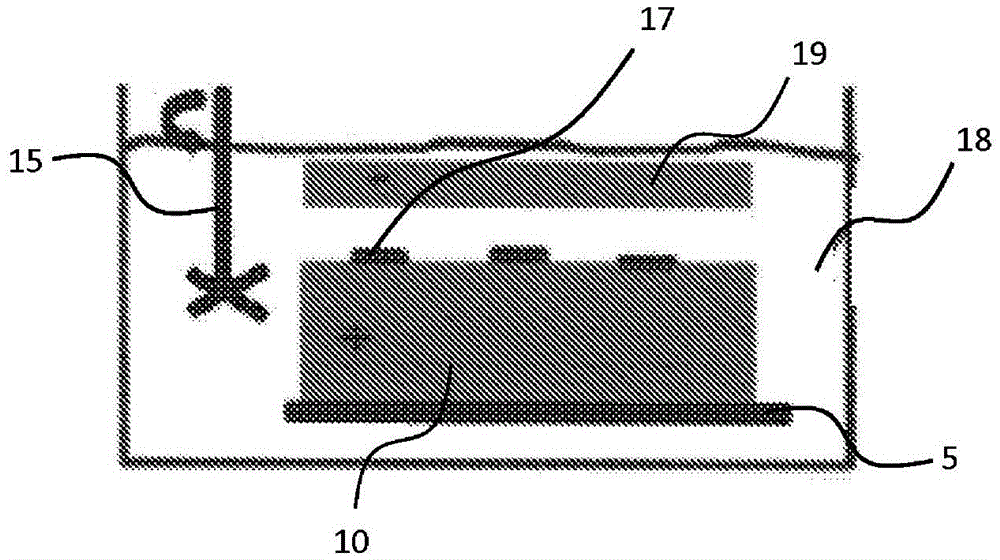

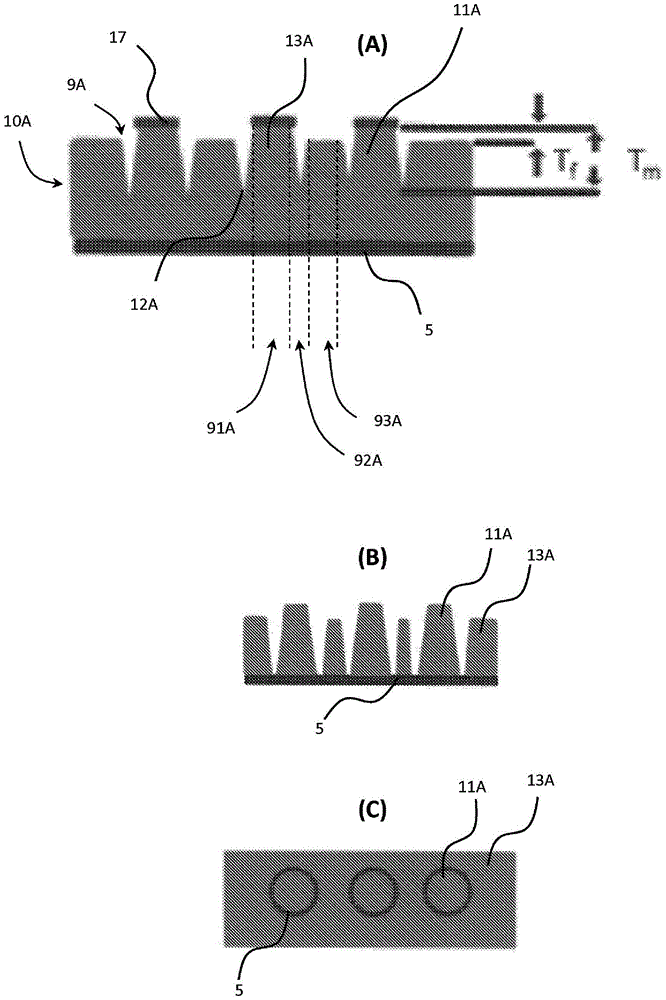

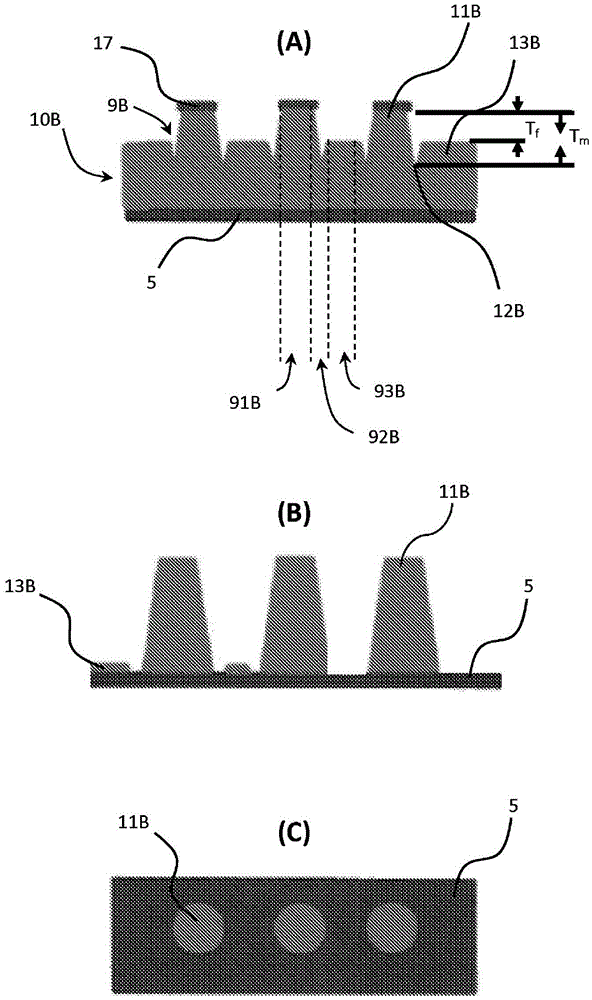

[0056] Now see attached picture, as figure 1 As shown, the conductive layer 10 can be attached to the support 5 together, or the conductive layer 10 can be attached to the support 5 . In one example, support 5 may comprise...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More