Multilayer composite membrane passivation structure of table top high-power semiconductor device and manufacturing technology of multilayer composite membrane passivation structure of table top high-power semiconductor device

A multi-layer composite film and semiconductor technology, applied in semiconductor/solid-state device manufacturing, semiconductor devices, semiconductor/solid-state device components, etc., can solve problems such as low reliability, inability to modulate, roughness, etc., and achieve a wide range of applications

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

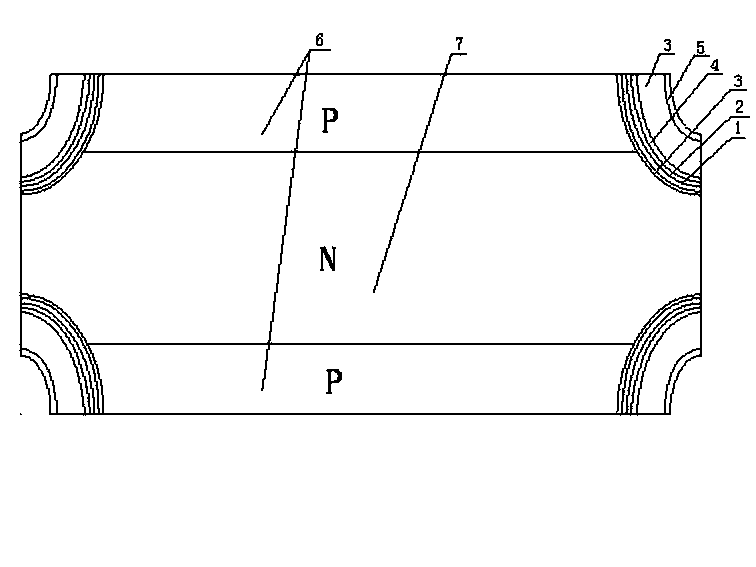

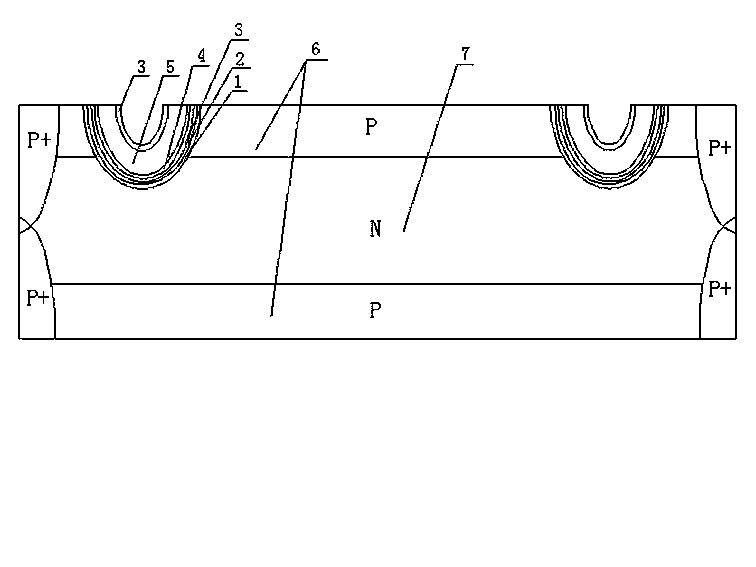

Image

Examples

Embodiment 1

[0025] A preparation process for a multilayer composite film passivation structure of a mesa high-power semiconductor device includes the following process steps in sequence:

[0026] a. Deposit α-polysilicon, using LPCVD deposition, the temperature is 570 ° C, the pressure is 0.3t, SiH 4 Flow rate 40cc / min, deposition time 4min;

[0027] b. Deposit semi-insulating polysilicon, using LPCVD deposition, the temperature is 650 ℃, the pressure is 0.3t, SiH 4 Flow 250cc / min, N 2 O flow rate 40cc / min, deposition time 40min;

[0028] c. Deposit a low-temperature thermal oxide layer, using LPCVD deposition, the temperature is 420 ° C, the pressure is 0.3t, SiH 4 Flow 150cc / min, O 2 Flow rate 40cc / min, deposition time 20min;

[0029] d. Deposit Si 3 N 4 , using LPCVD deposition, the temperature is 750 ° C, the pressure is 0.3t, SiH 2 Cl 2 Flow 150cc / min, NH 3 Flow rate 400cc / min, deposition time 20min;

[0030] e. Glass passivation, apply lead aluminosilicate glass by scrapi...

Embodiment 2

[0033] A preparation process for a multilayer composite film passivation structure of a mesa high-power semiconductor device includes the following process steps in sequence:

[0034] a. Deposit α-polycrystalline silicon by LPCVD at a temperature of 575°C and a pressure of 0.35t, SiH 4Flow rate 40cc / min, deposition time 4.5min;

[0035] b. Deposit semi-insulating polysilicon, using LPCVD deposition, the temperature is 660°C, the pressure is 0.3t, SiH 4 Flow 250cc / min, N 2 O flow rate 40cc / min, deposition time 45min;

[0036] c. Deposit a low-temperature thermal oxide layer, using LPCVD deposition, the temperature is 435 ° C, the pressure is 0.3t, SiH 4 Flow 150cc / min, O 2 Flow rate 40cc / min, deposition time 25min;

[0037] d. Deposit Si 3 N 4 , using LPCVD deposition, the temperature is 770 ℃, the pressure is 0.4t, SiH 2 Cl 2 Flow 150cc / min, NH 3 Flow rate 400cc / min, deposition time 25min;

[0038] e. Glass passivation, use the method of scraping to coat lead alumin...

Embodiment 3

[0041] A preparation process for a multilayer composite film passivation structure of a mesa high-power semiconductor device includes the following process steps in sequence:

[0042] a. Deposit α-polysilicon, using LPCVD deposition, the temperature is 580 ° C, the pressure is 0.4t, SiH 4 Flow rate 40cc / min, deposition time 5min;

[0043] b. Deposit semi-insulating polysilicon, using LPCVD deposition, the temperature is 670 ℃, the pressure is 0.3t, SiH 4 Flow 250cc / min, N 2 O flow rate 40cc / min, deposition time 50min;

[0044] c. Deposit a low-temperature thermal oxide layer, using LPCVD deposition, the temperature is 450 ° C, the pressure is 0.3t, SiH 4 Flow 150cc / min, O 2 Flow rate 40cc / min, deposition time 30min;

[0045] d. Deposit Si 3 N 4 , using LPCVD deposition, the temperature is 800 ℃, the pressure is 0.5t, SiH 2 Cl 2 Flow 150cc / min, NH 3 Flow rate 400cc / min, deposition time 30min;

[0046] e. Glass passivation, use the method of scraping to coat lead alum...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More