Patents

Literature

65results about How to "Avoid tunneling" patented technology

Efficacy Topic

Property

Owner

Technical Advancement

Application Domain

Technology Topic

Technology Field Word

Patent Country/Region

Patent Type

Patent Status

Application Year

Inventor

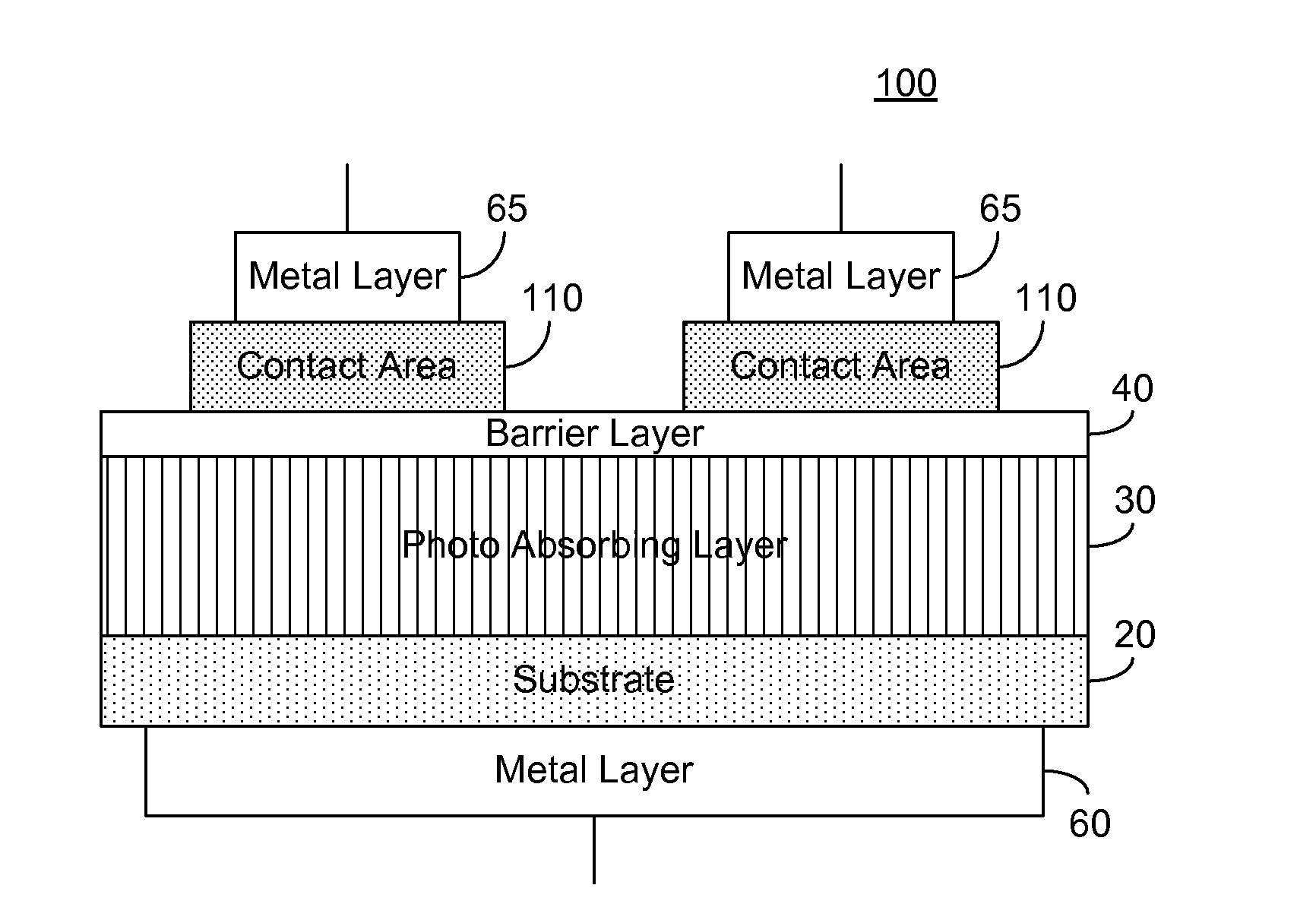

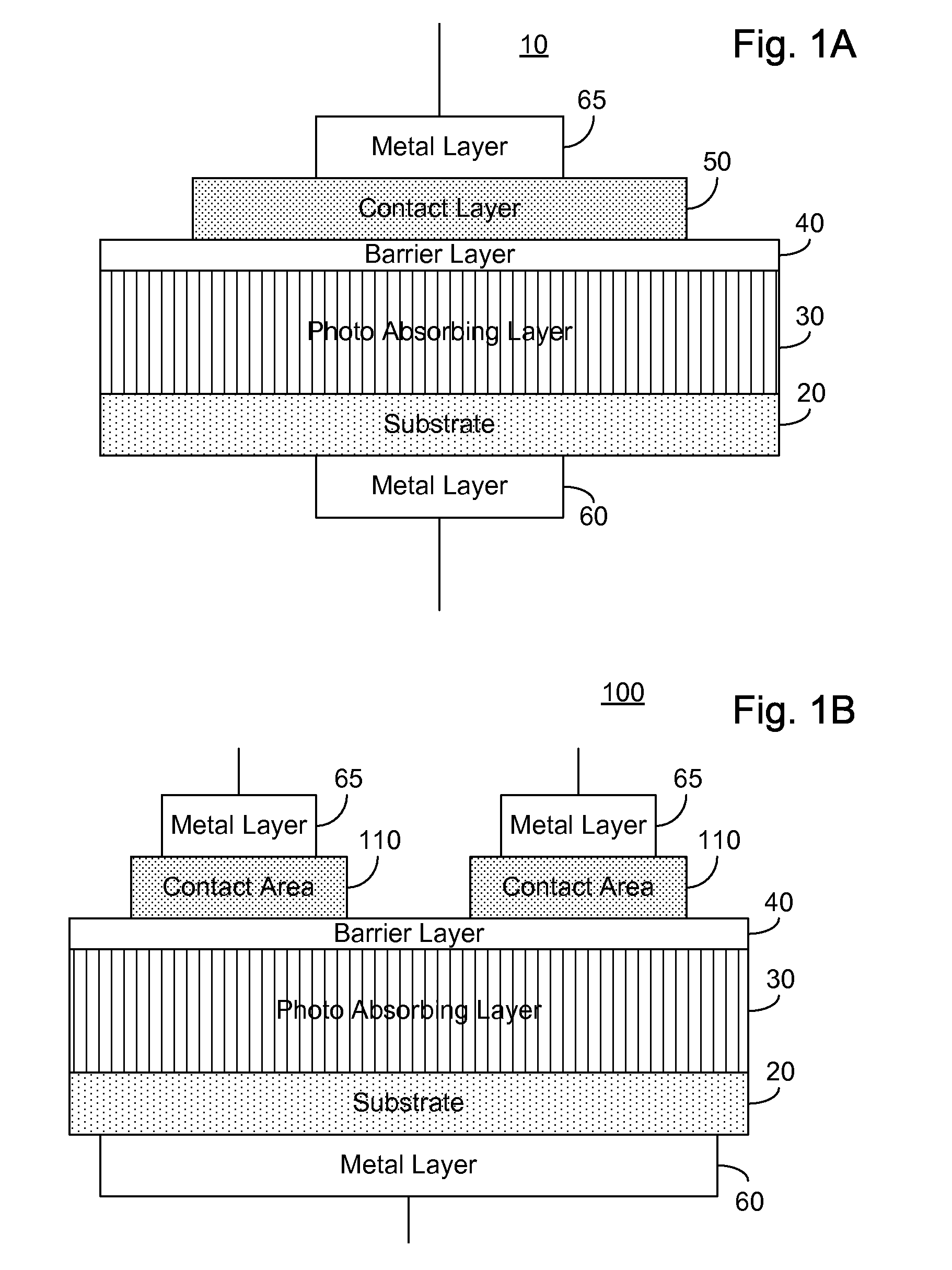

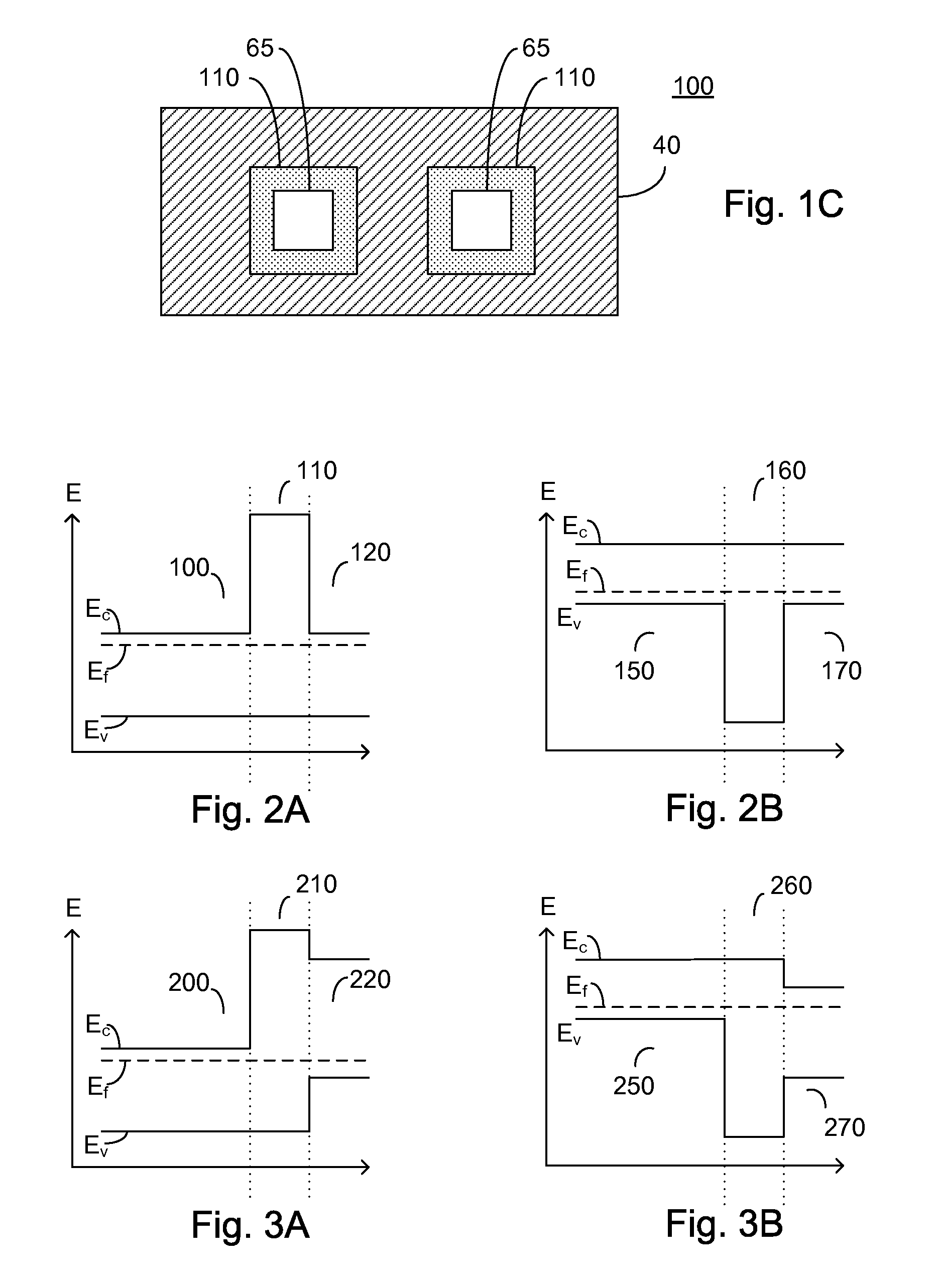

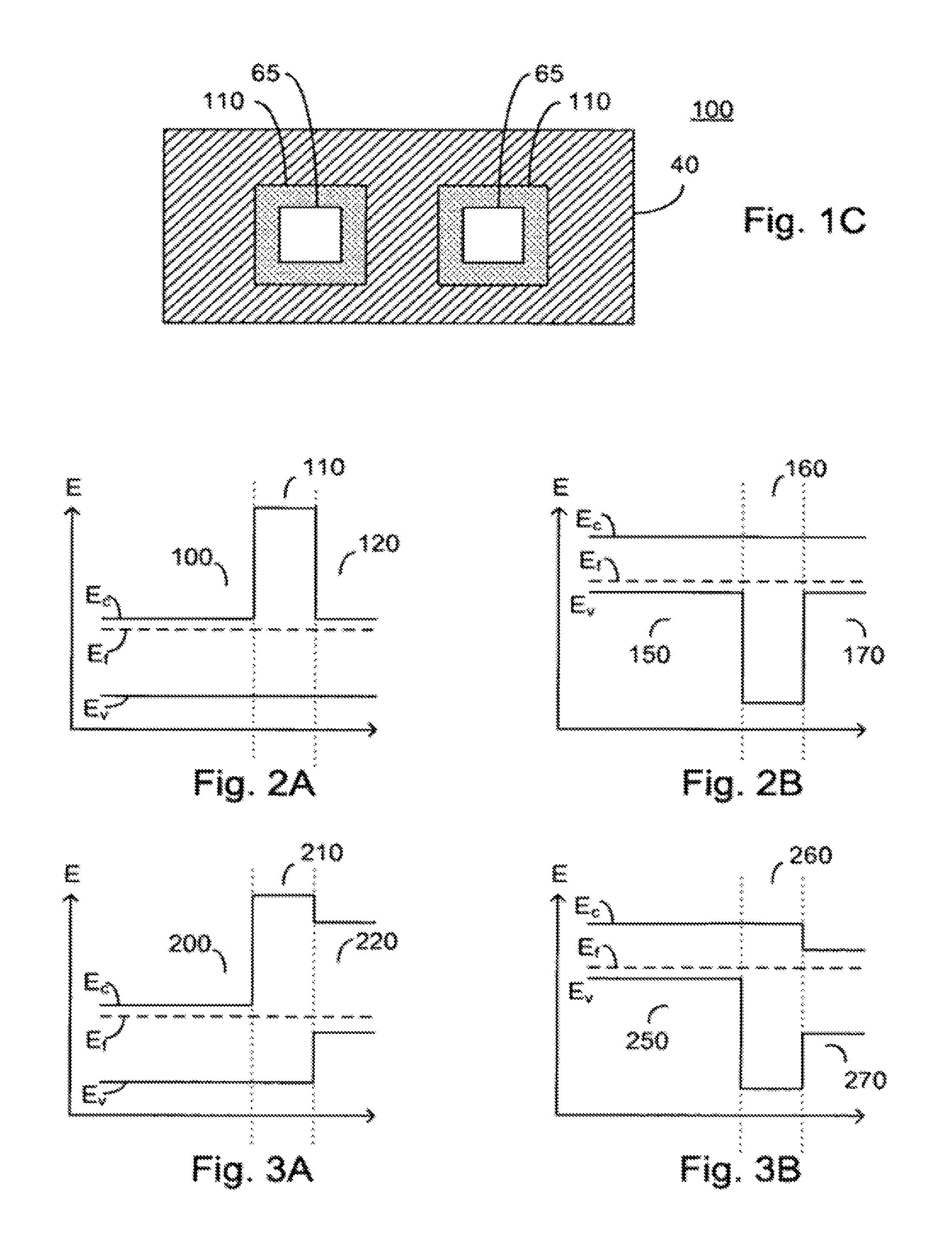

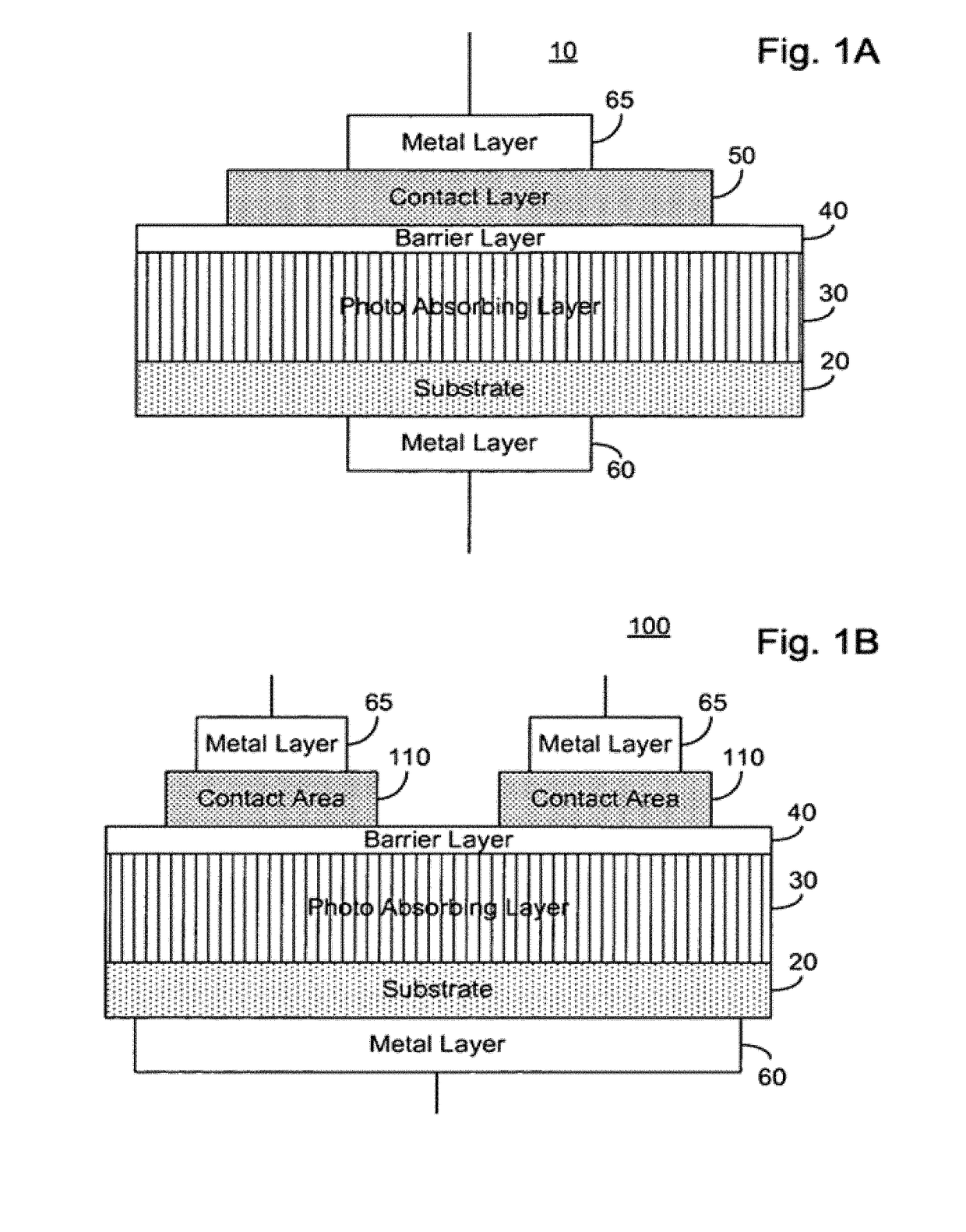

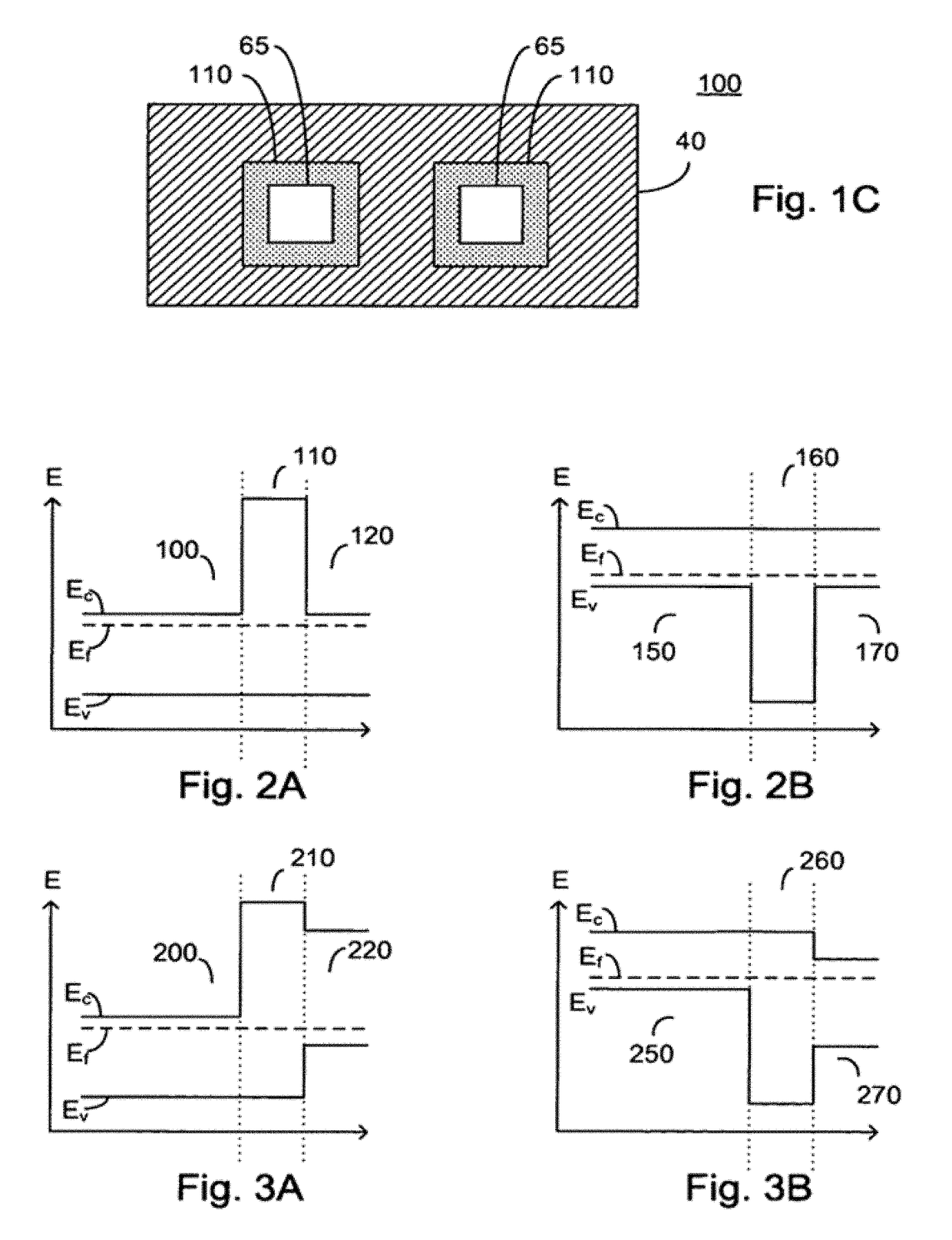

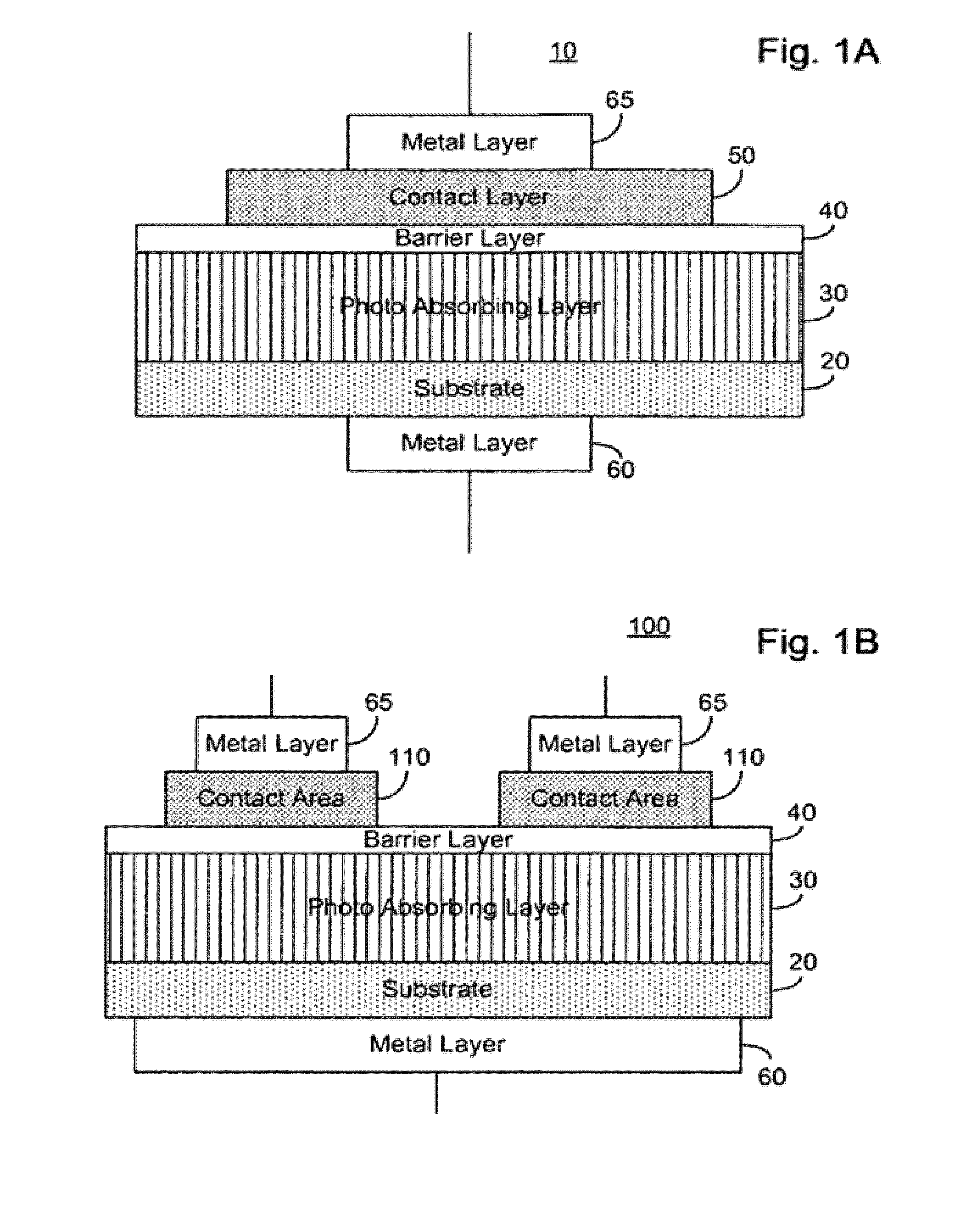

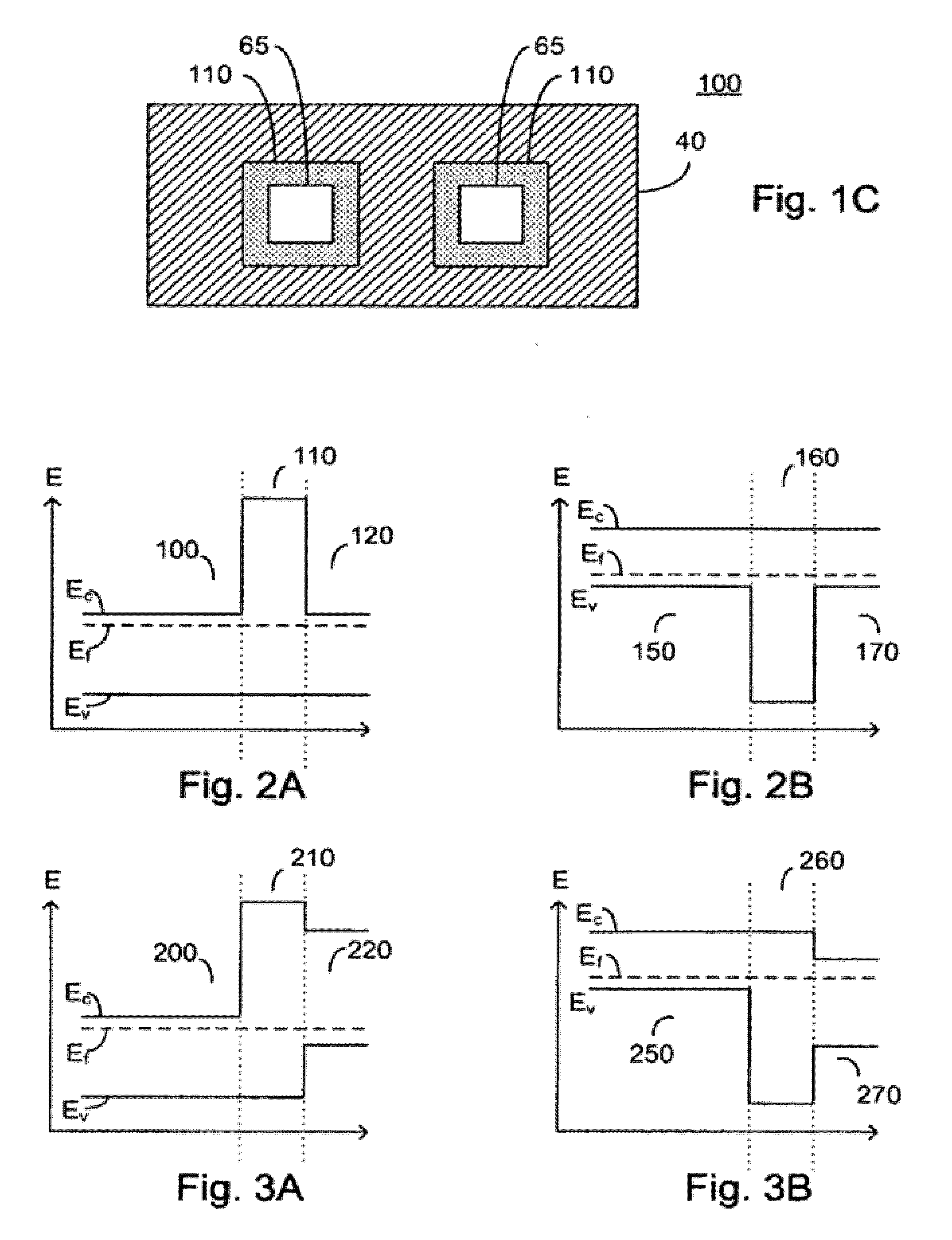

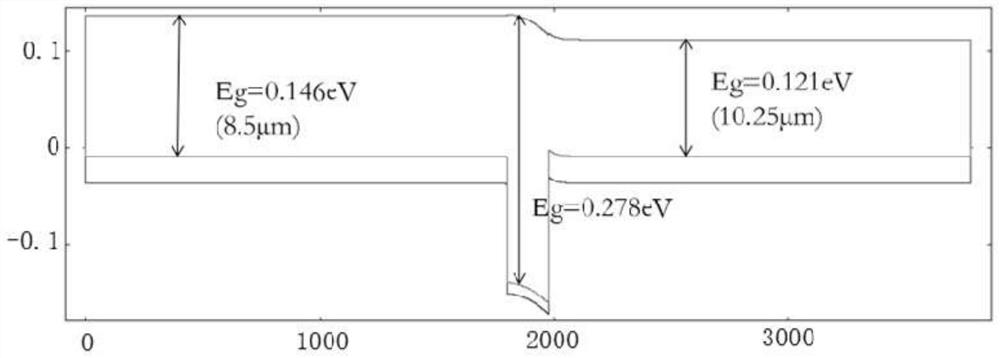

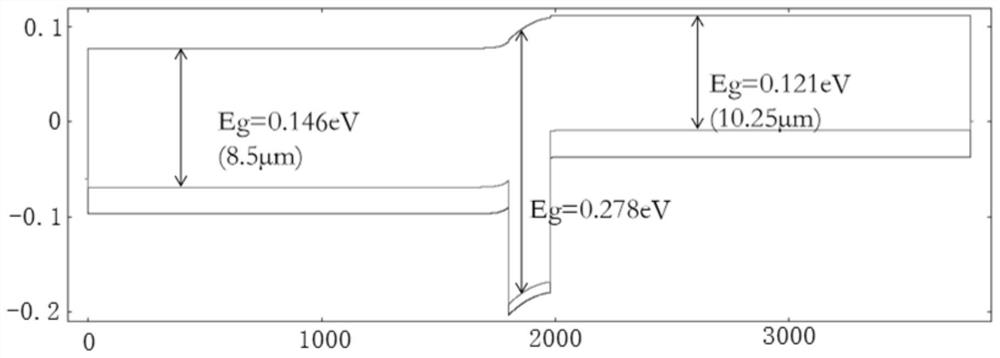

Reduced dark current photodetector

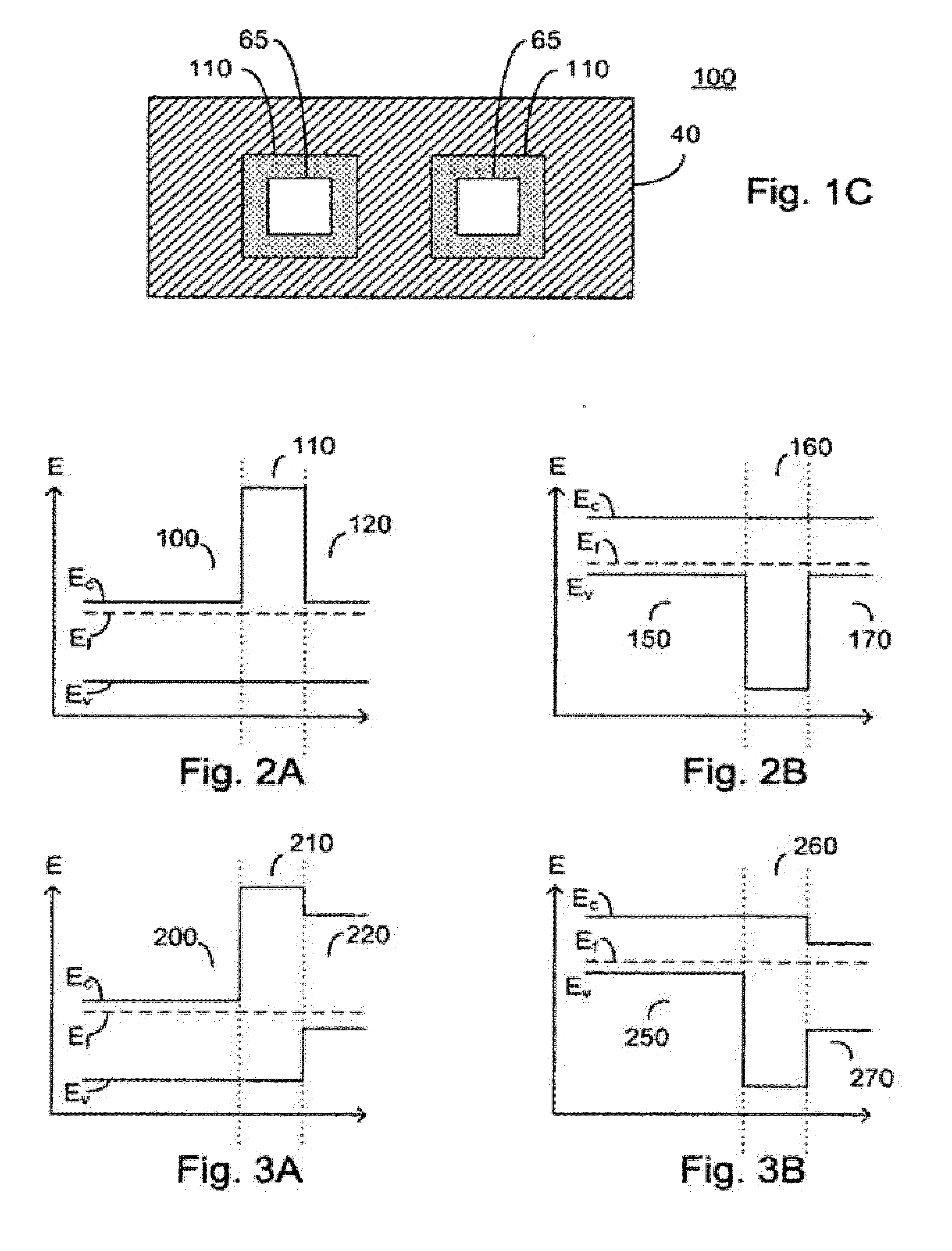

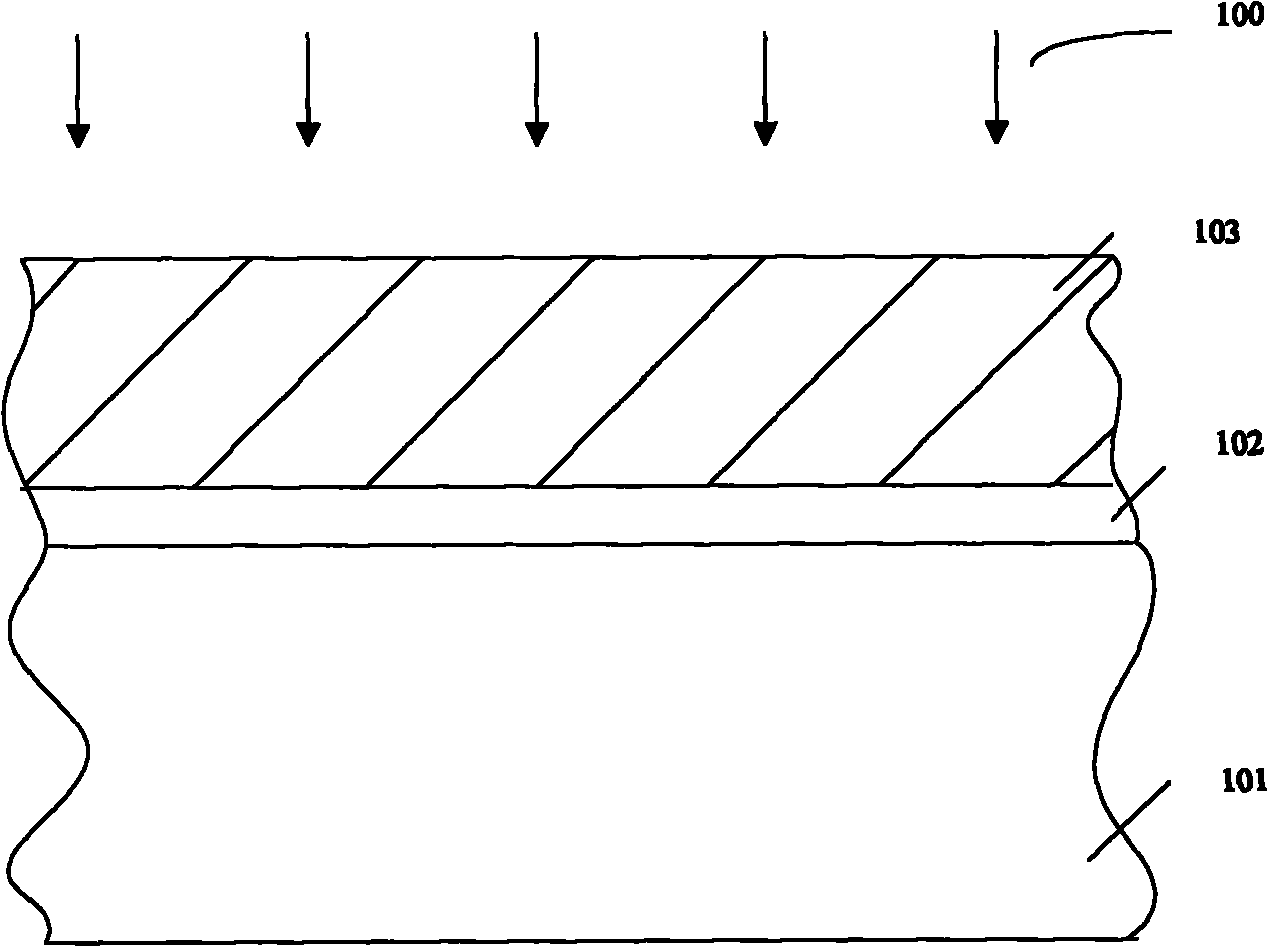

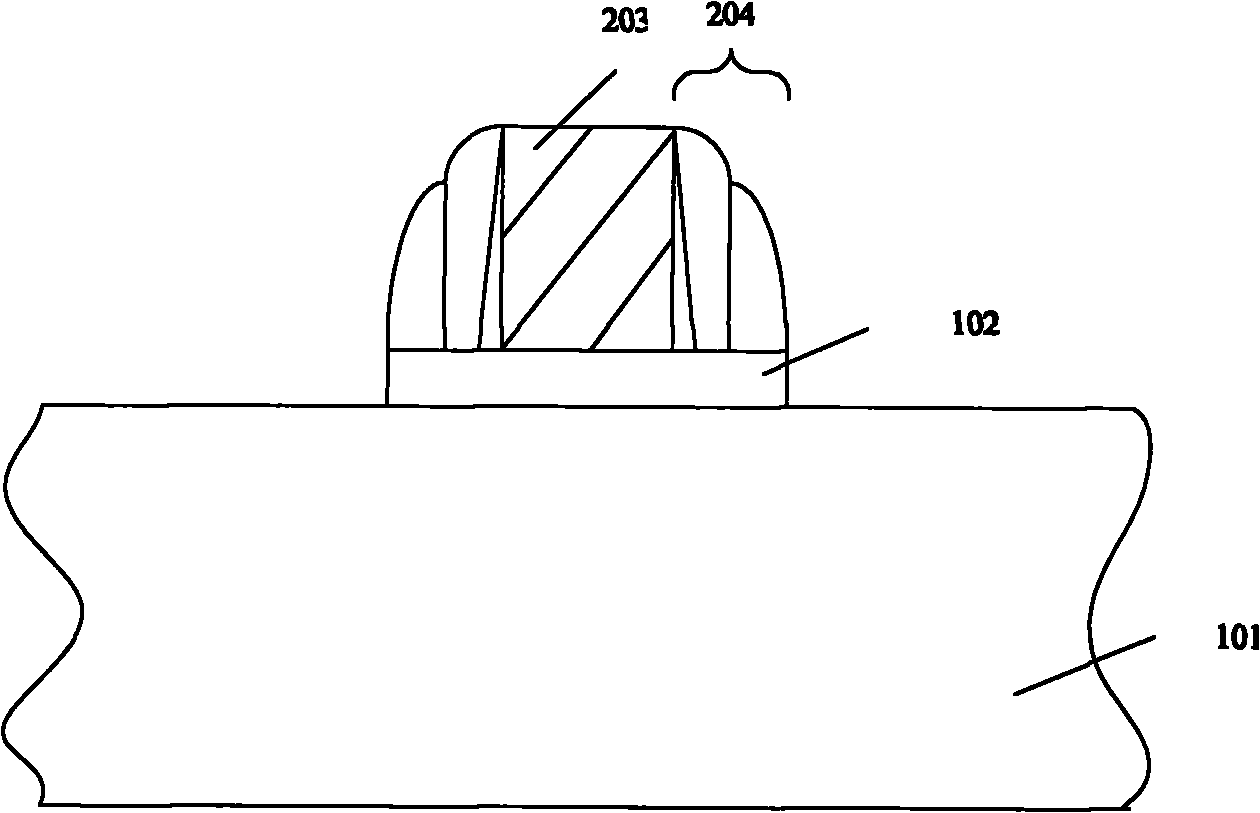

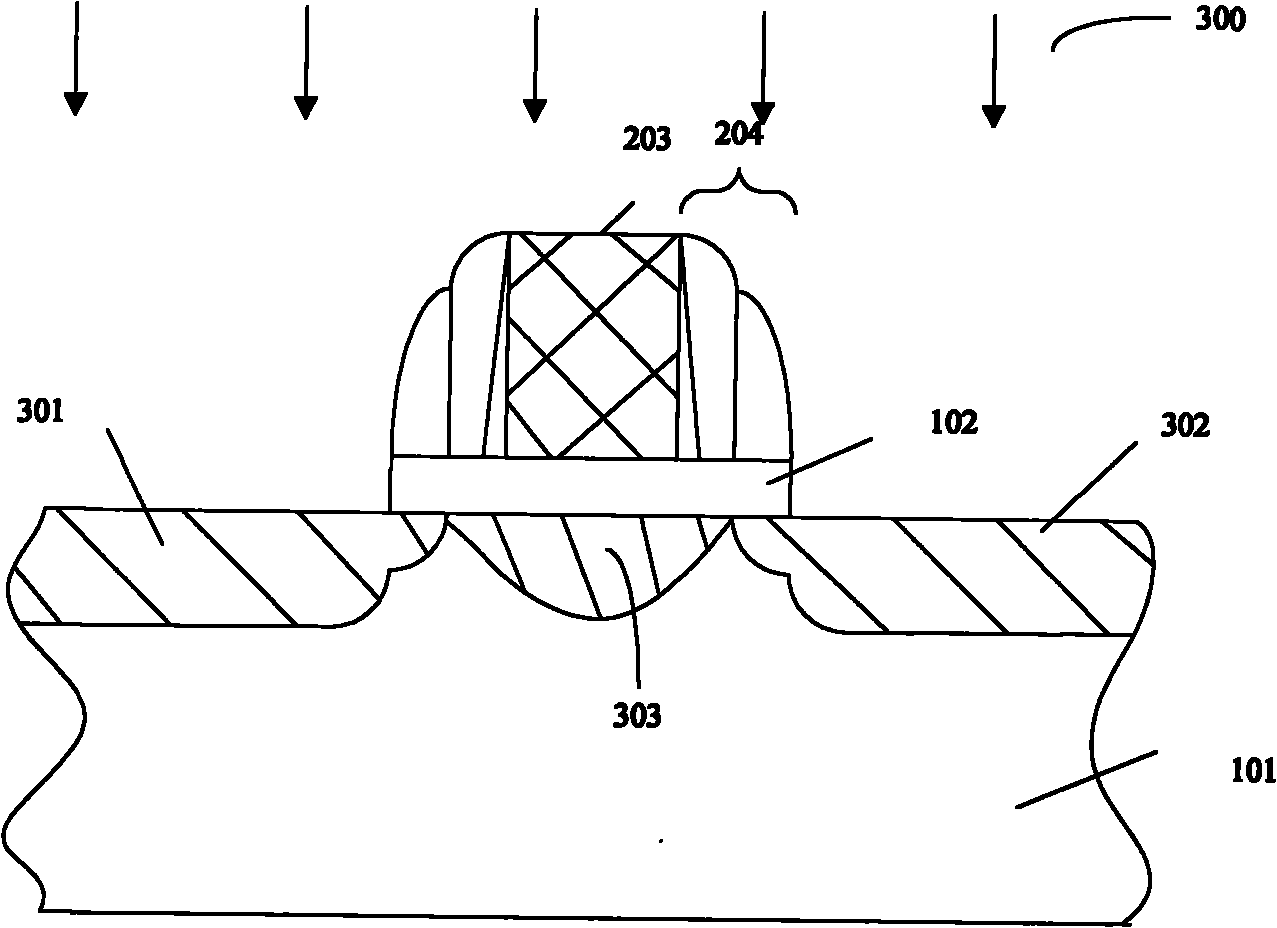

ActiveUS7687871B2Total current dropAvoid tunnelingFinal product manufactureSemiconductor/solid-state device manufacturingValence bandPhotodetector

Owner:MAIMON SHIMON

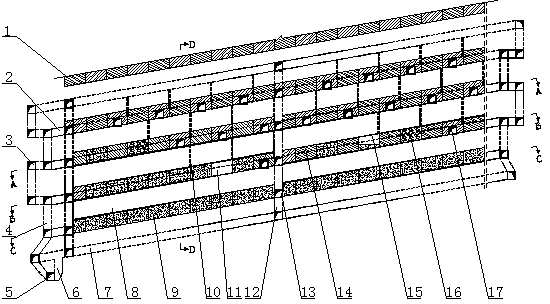

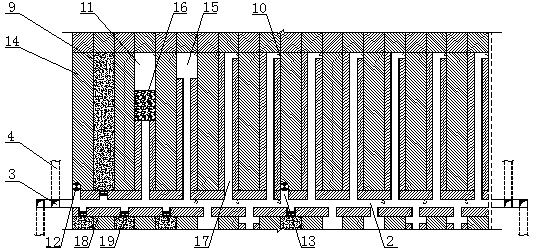

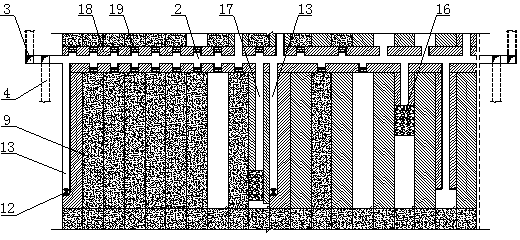

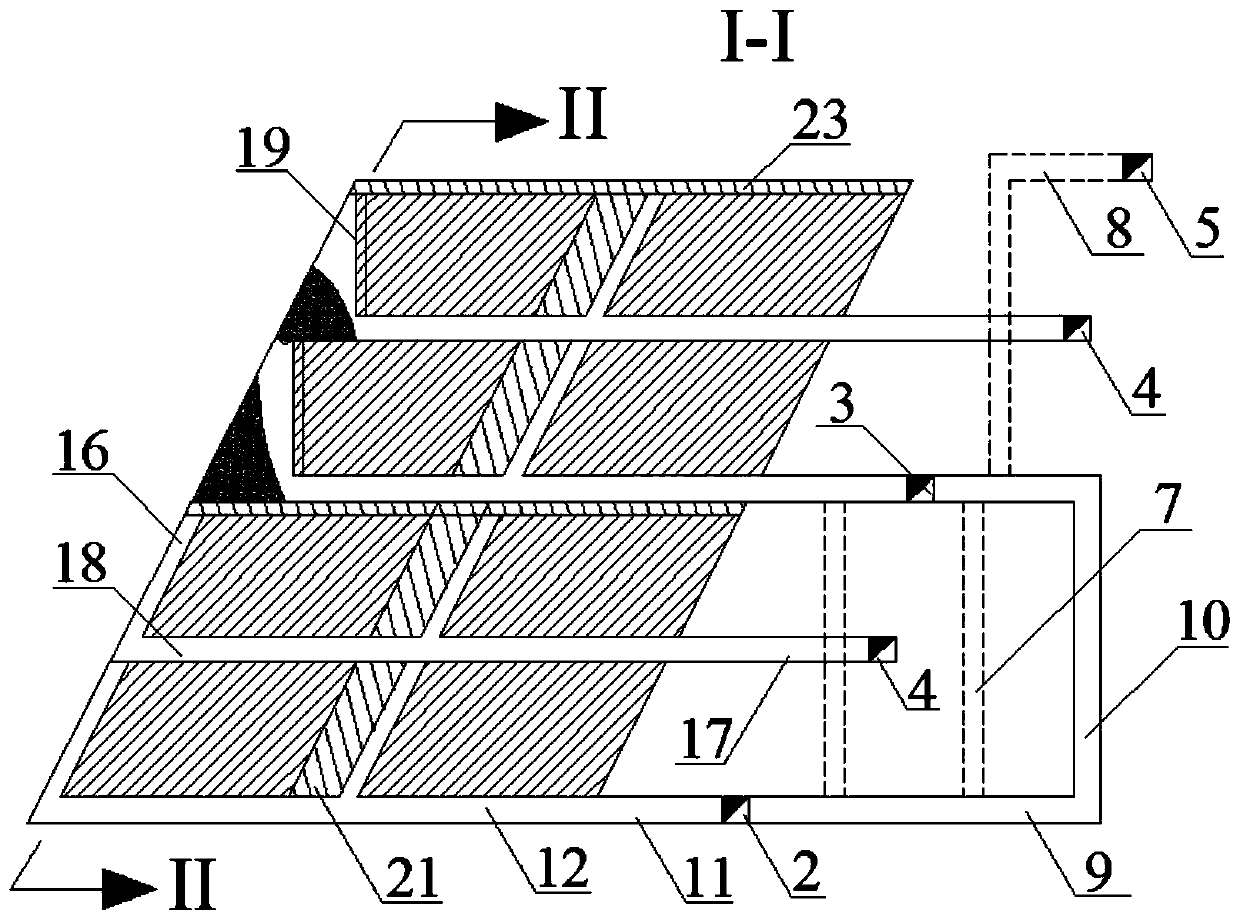

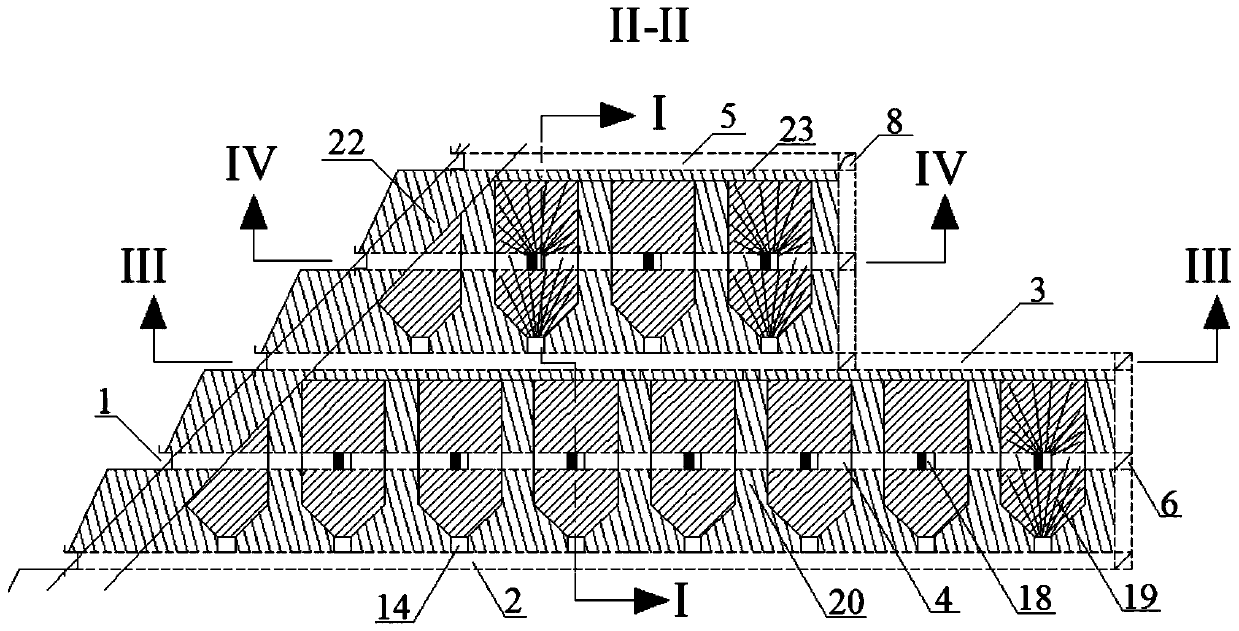

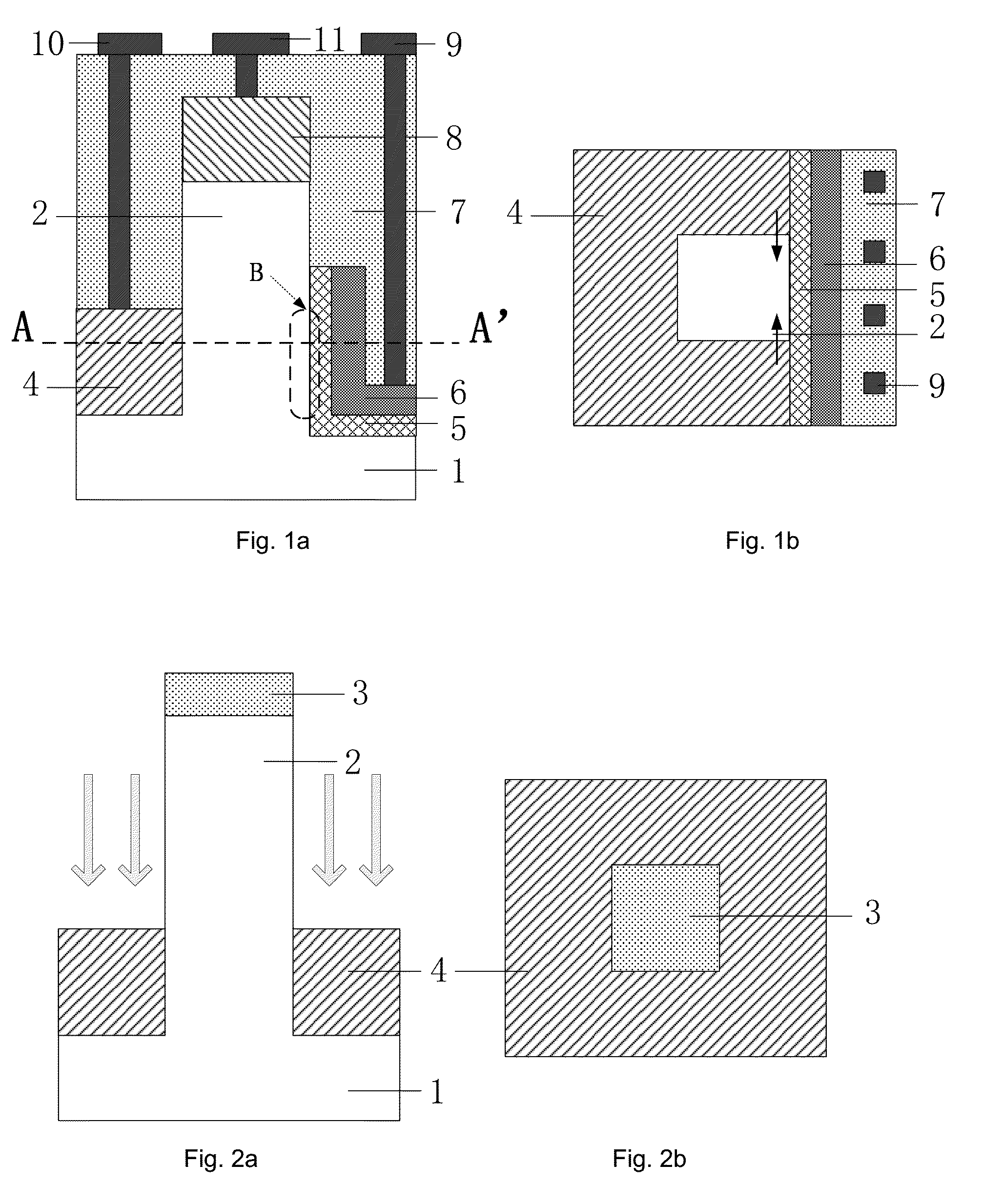

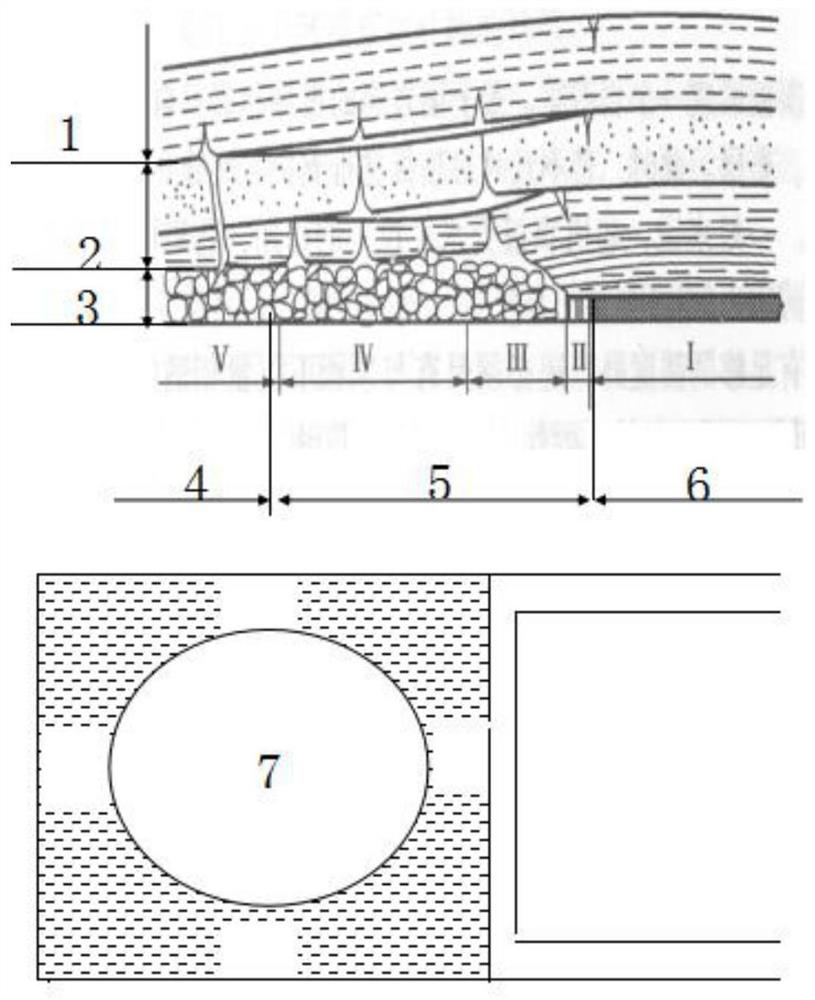

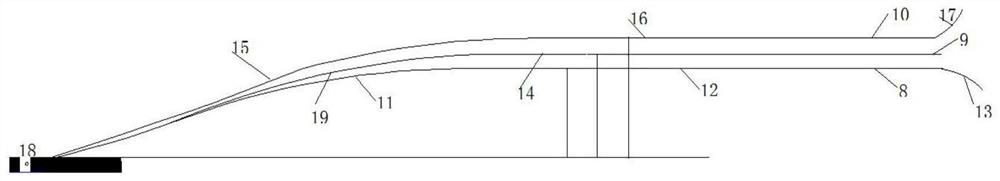

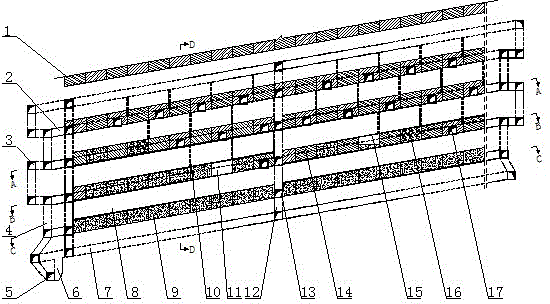

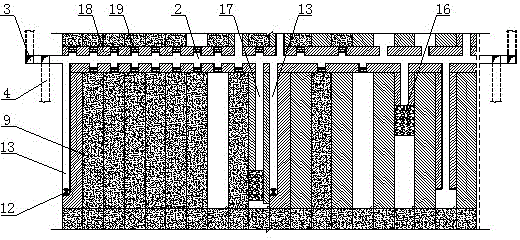

Multilayer gentle dip thin-medium ore deposit filling and mining method

ActiveCN103628877AContinuous high-intensity miningIncrease production capacityUnderground miningSurface miningMineralogyMineral deposit

The invention relates to a multilayer gentle dip thin-medium ore deposit filling and mining method. According to the technical scheme, the method comprises the following steps: dividing ore blocks, arranging mining and cutting projects, transporting, mining and filling. The step of dividing an ore deposit comprises the following sub-steps: dividing an ore body in the stage into a disc area, tunneling to uphill (2) at the bottom of an ore layer (1) along the inclined direction of the ore body, dividing the ore body on two sides into ore chambers (15) and ore columns (14) along the uphill (2), and reserving uphill ore columns (18) by taking the uphill (2) as the center. Three-step recovery is adopted in the disc area and comprises a first step of recovering the ore chambers (15), a second step of recovering the ore columns (14) and a third step of recovering the uphill ore columns (18); after the ore chambers (15) or the ore columns (14) are totally recovered, a goaf area (11) is downwards filled through the uphill (2) on the upper layer and via filling ventilation holes (10) communicated with a stope; finally, the uphill ore columns (18) are recovered within three steps from bottom to top along the uphill (2) by taking the disc area as a unit, and the uphill ore columns (18) in the next disc area are recovered after filling. The method has the characteristics of high mining intensity, high ore recovery rate, low ore dilution ratio and low mining cost.

Owner:WUHAN UNIV OF SCI & TECH

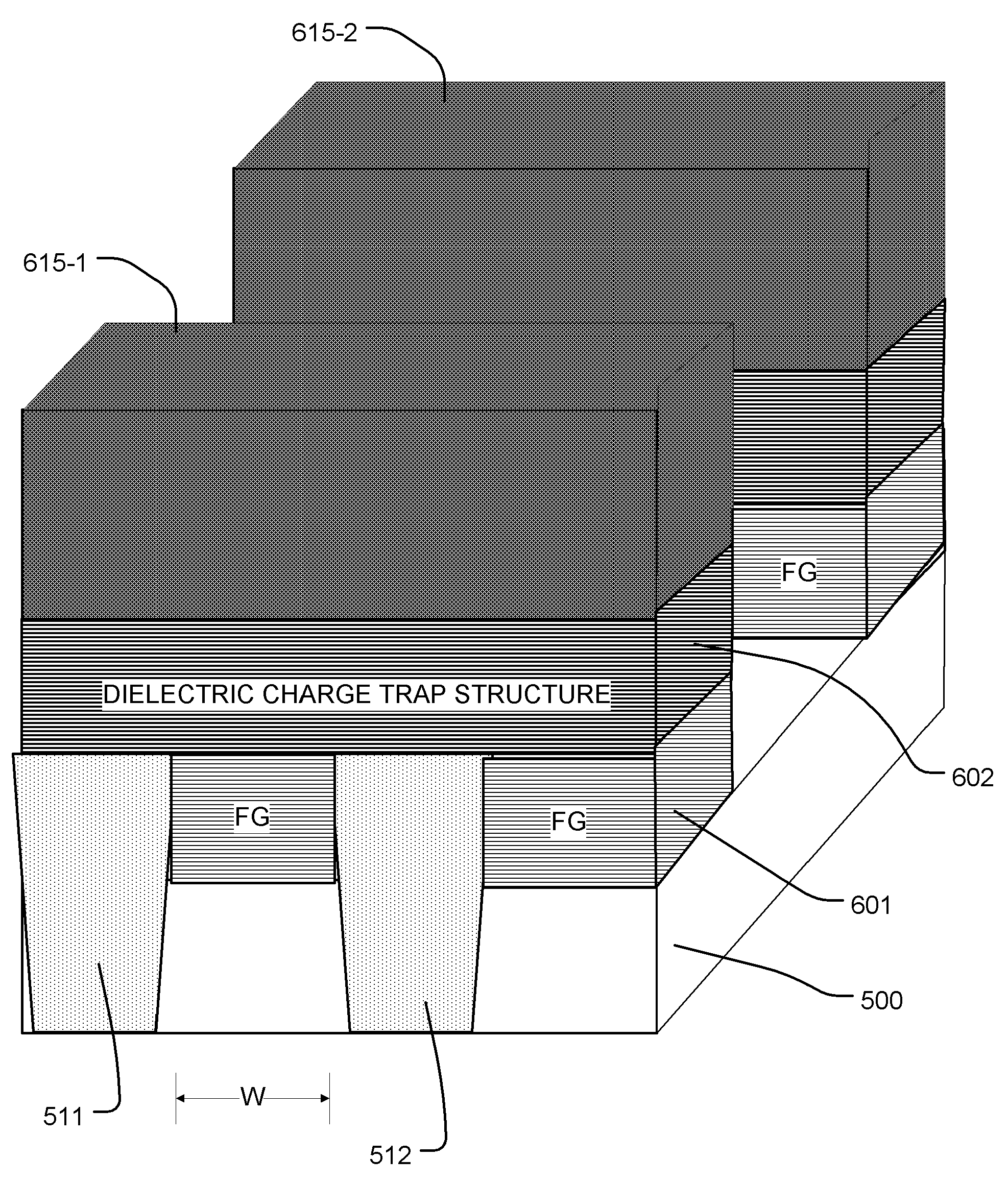

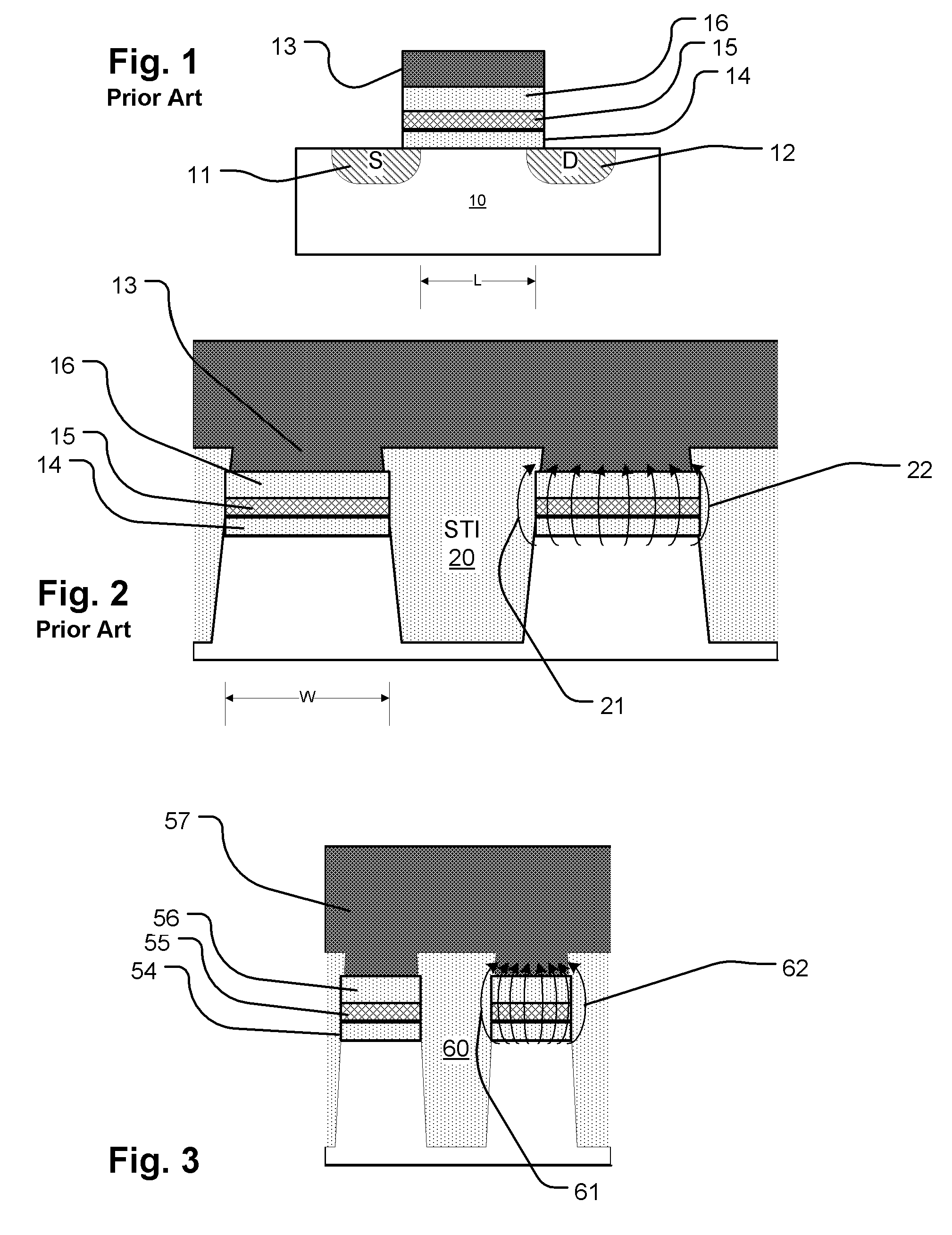

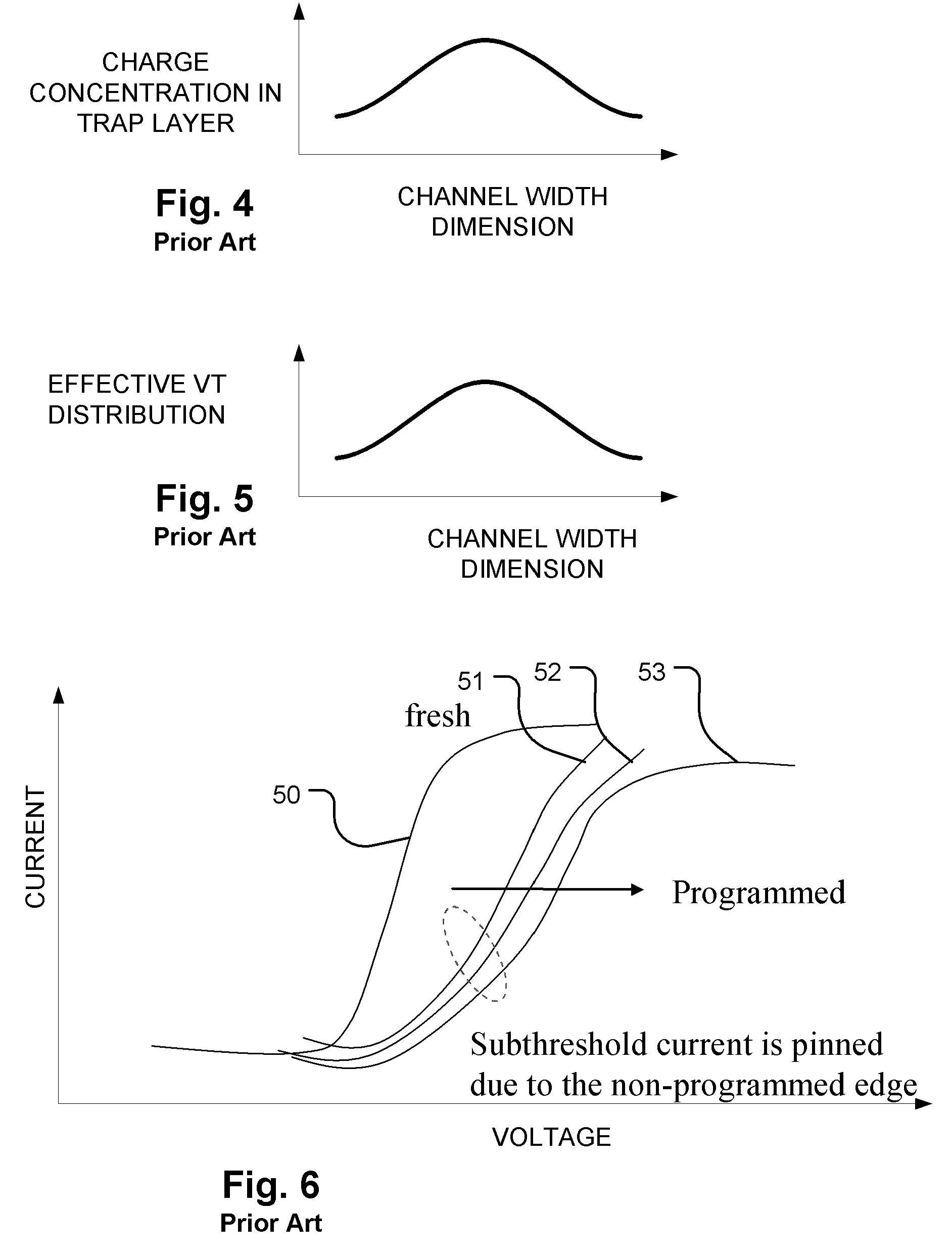

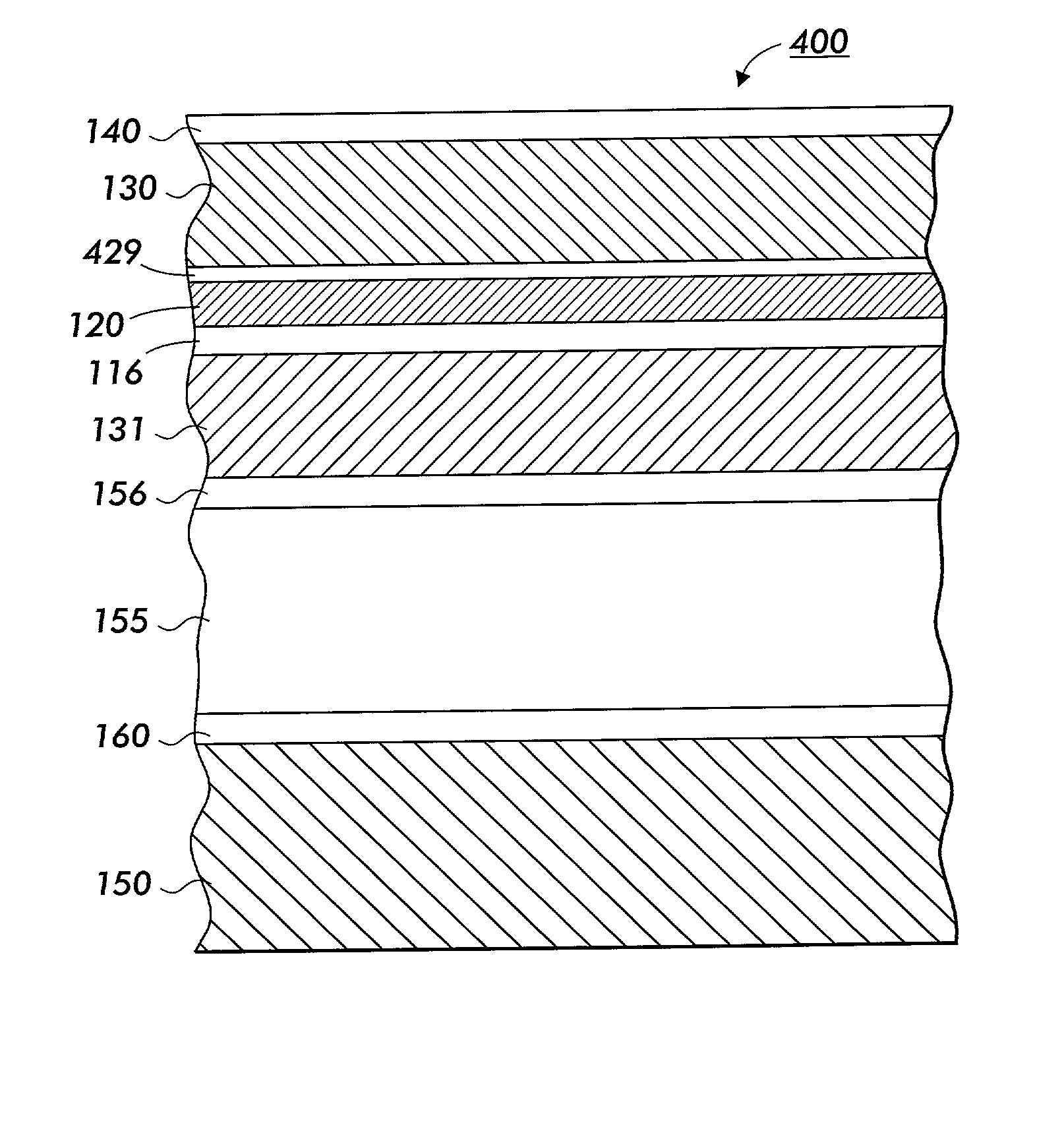

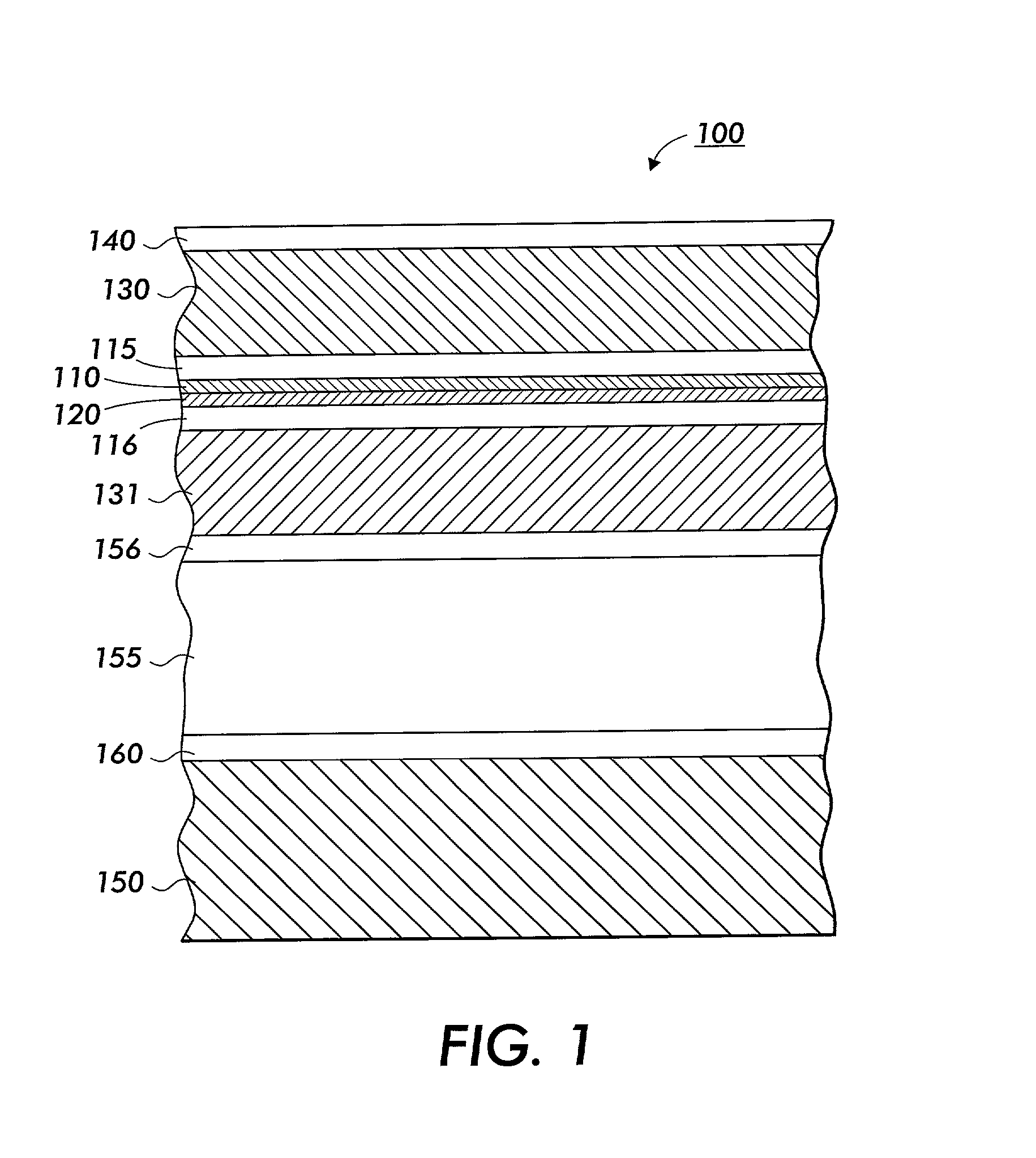

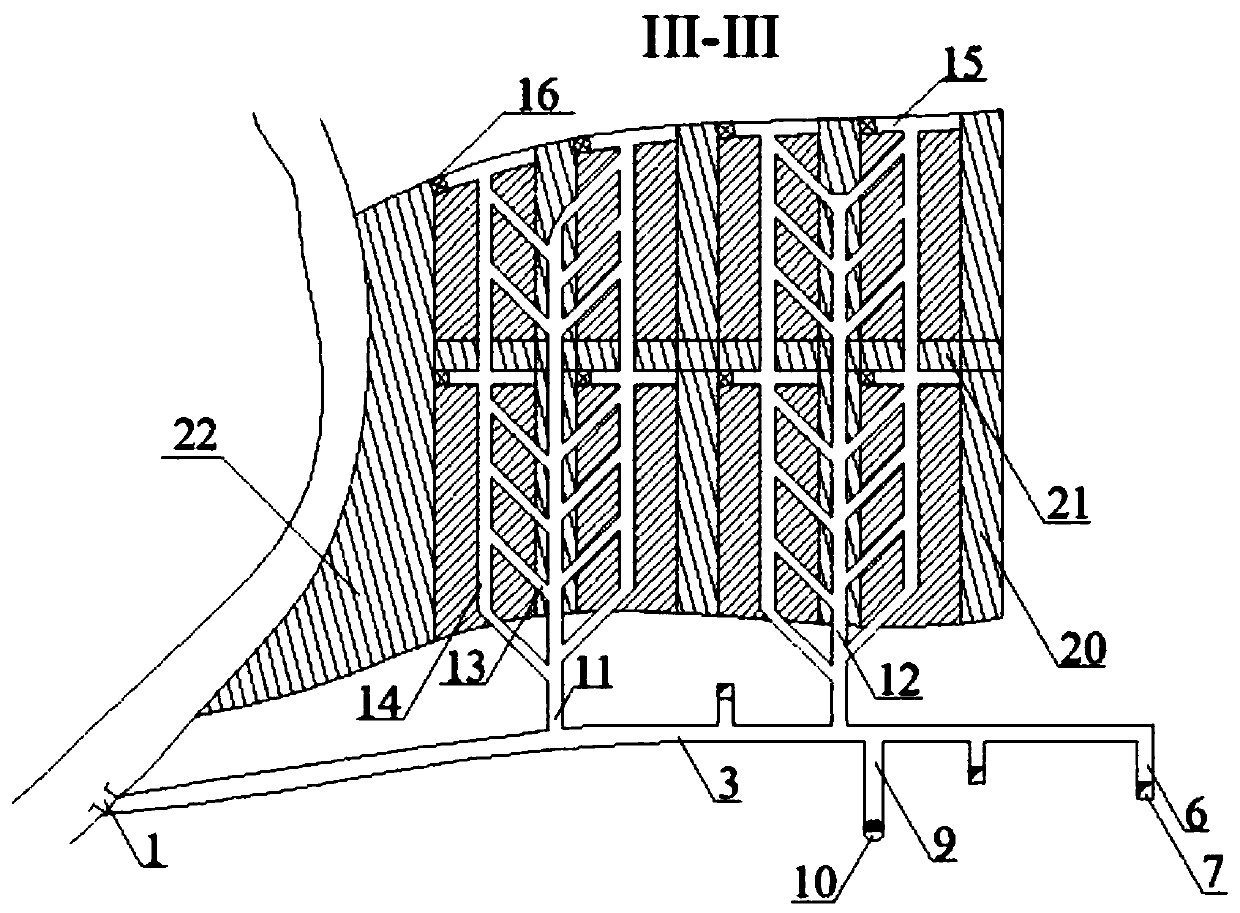

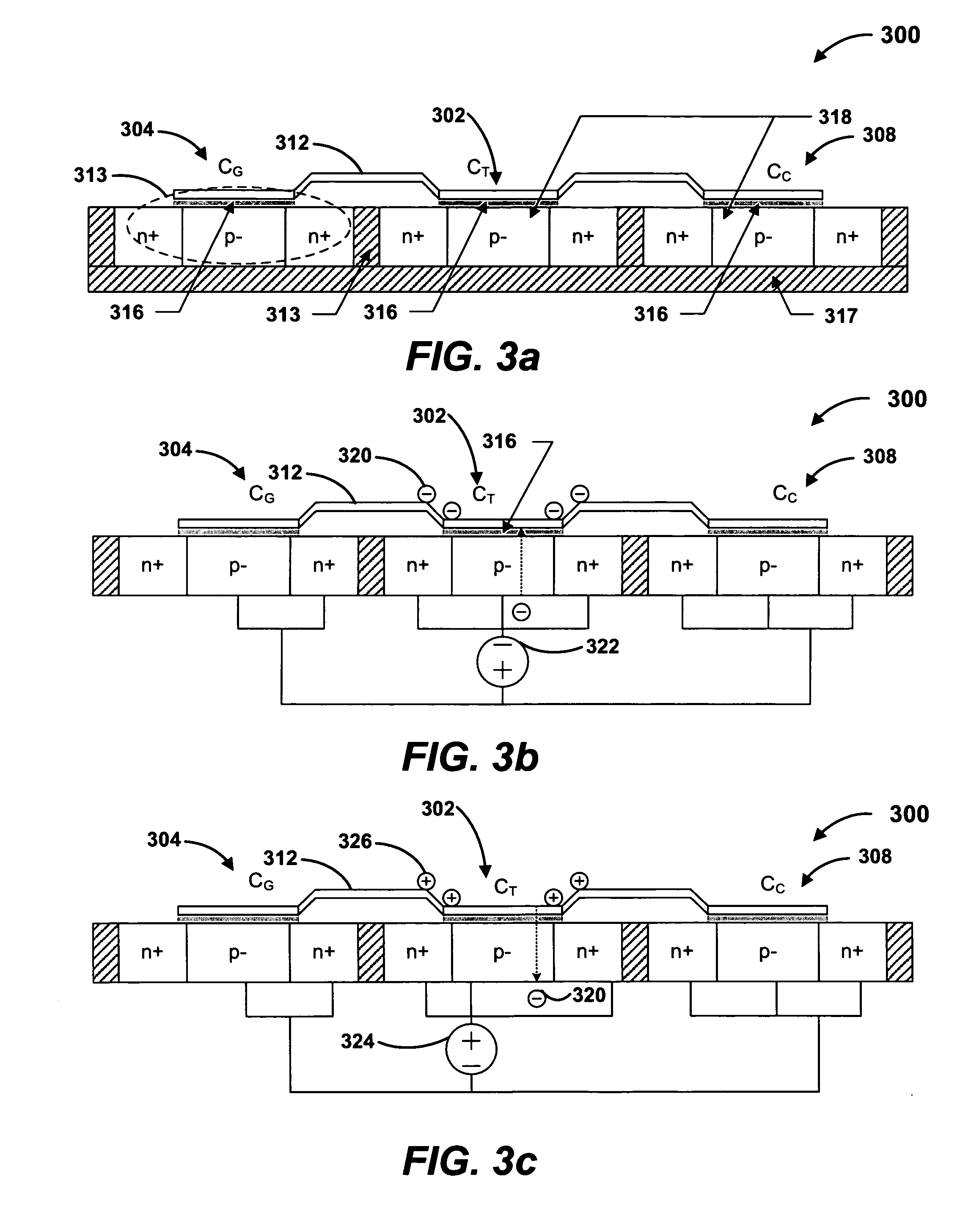

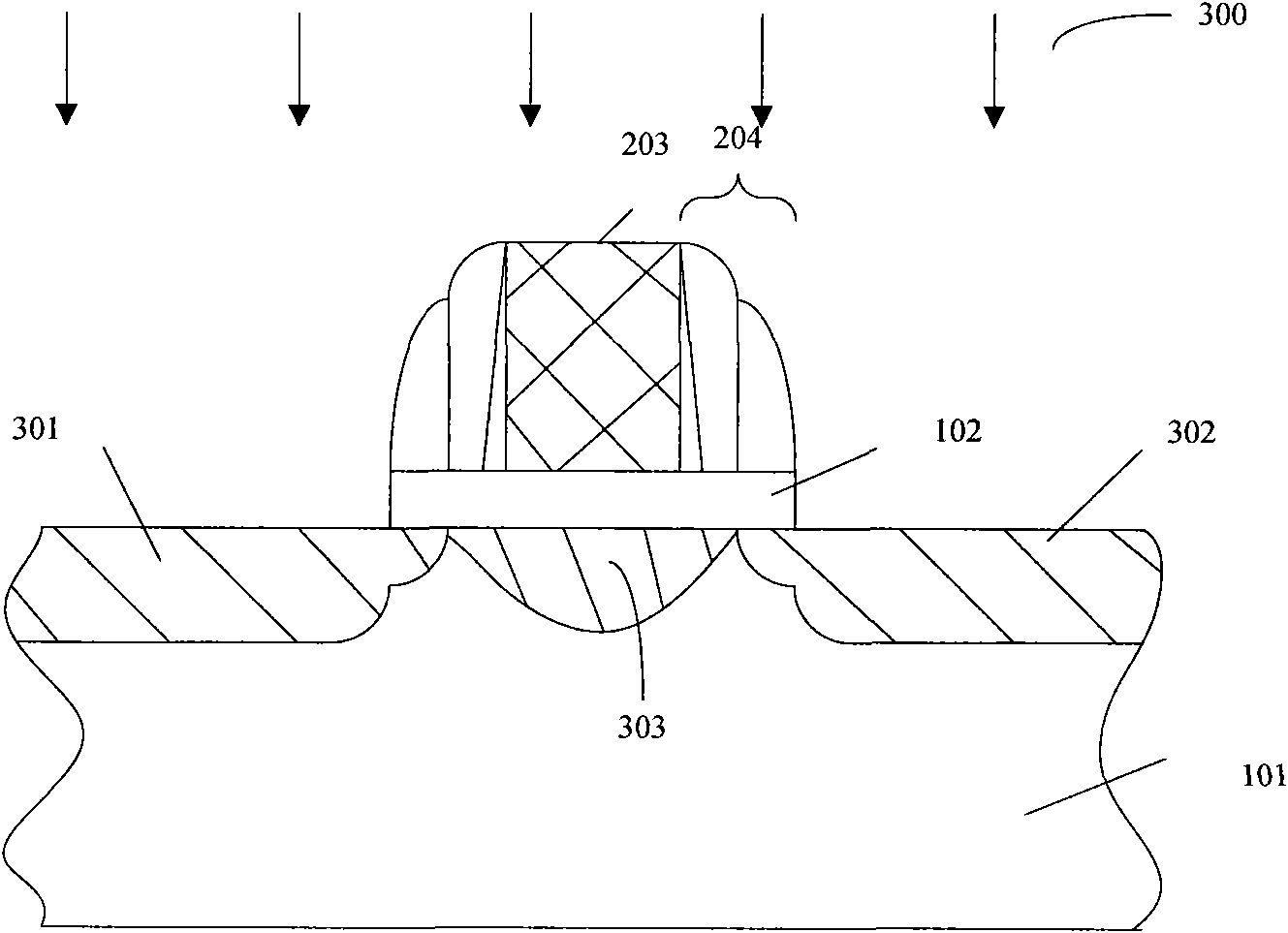

Floating gate memory device with interpoly charge trapping structure

ActiveUS8068370B2Reduce distractionsImprove data retentionTransistorSolid-state devicesPower flowElectrical conductor

A charge trapping floating gate is described with asymmetric tunneling barriers. The memory cell includes a source region and a drain region separated by a channel region. A first tunneling barrier structure is disposed above the channel region. A floating gate is disposed above the first tunneling barrier structure covering the channel region. A second tunneling barrier is disposed above the floating gate. A dielectric charge trapping structure disposed above the second tunneling barrier and a blocking dielectric structure is disposed above the charge trapping structure. A top conductive layer disposed above the top dielectric structure acts as a gate. The second tunneling barrier is a more efficient conductor of tunneling current, under bias conditions applied for programming and erasing the memory cell, than the first tunneling barrier structure.

Owner:MACRONIX INT CO LTD

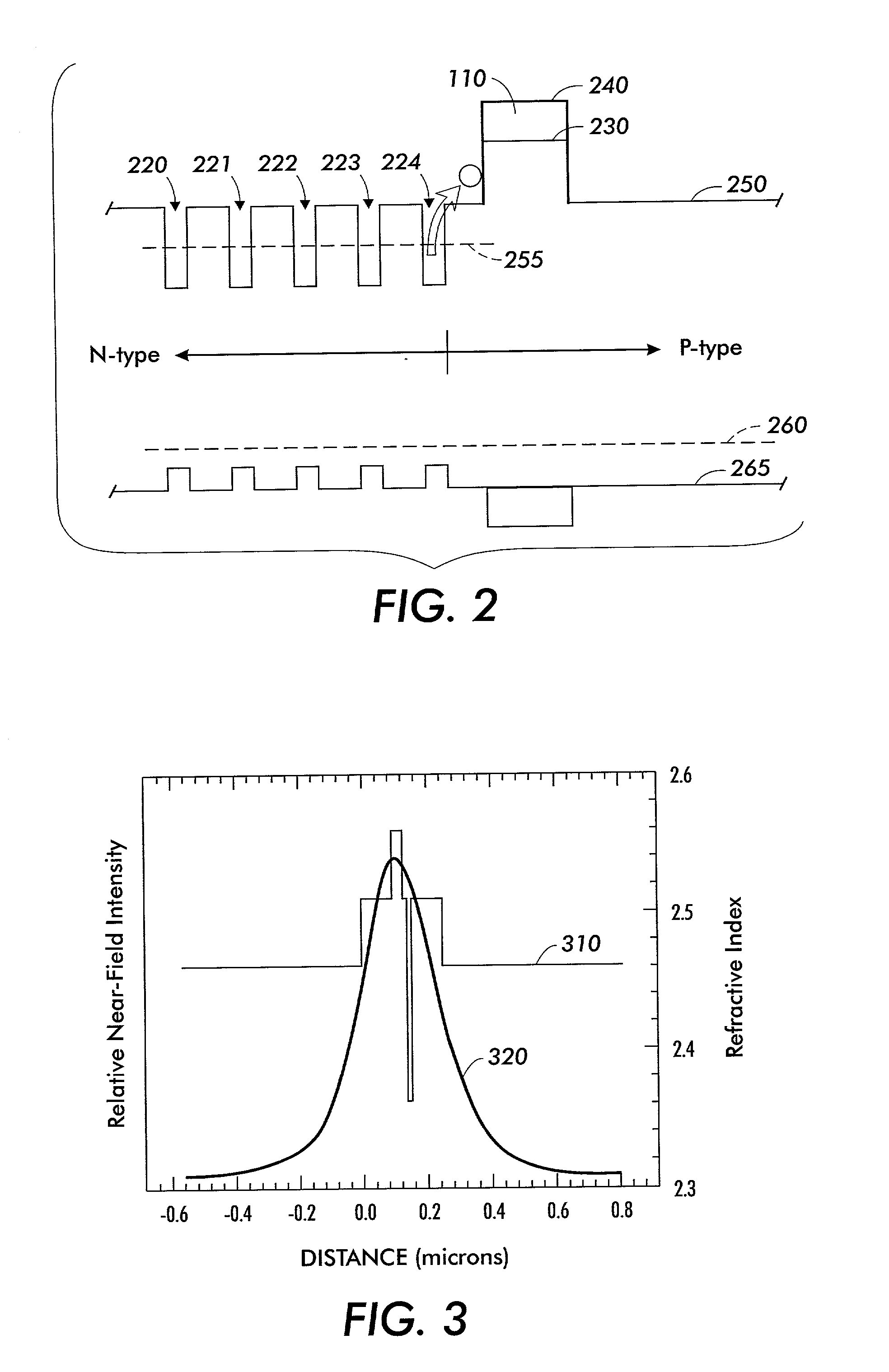

Method for forming an asymmetric nitride laser diode

InactiveUS20020054745A1Enhance carrier confinementAvoids tendencyOptical wave guidanceLaser detailsTunnel barrierLaser diode

A structure and method for an asymmetric waveguide nitride laser diode without need of a p-type waveguide is disclosed. The need for a high aluminum tunnel barrier layer in the laser is avoided.

Owner:XEROX CORP

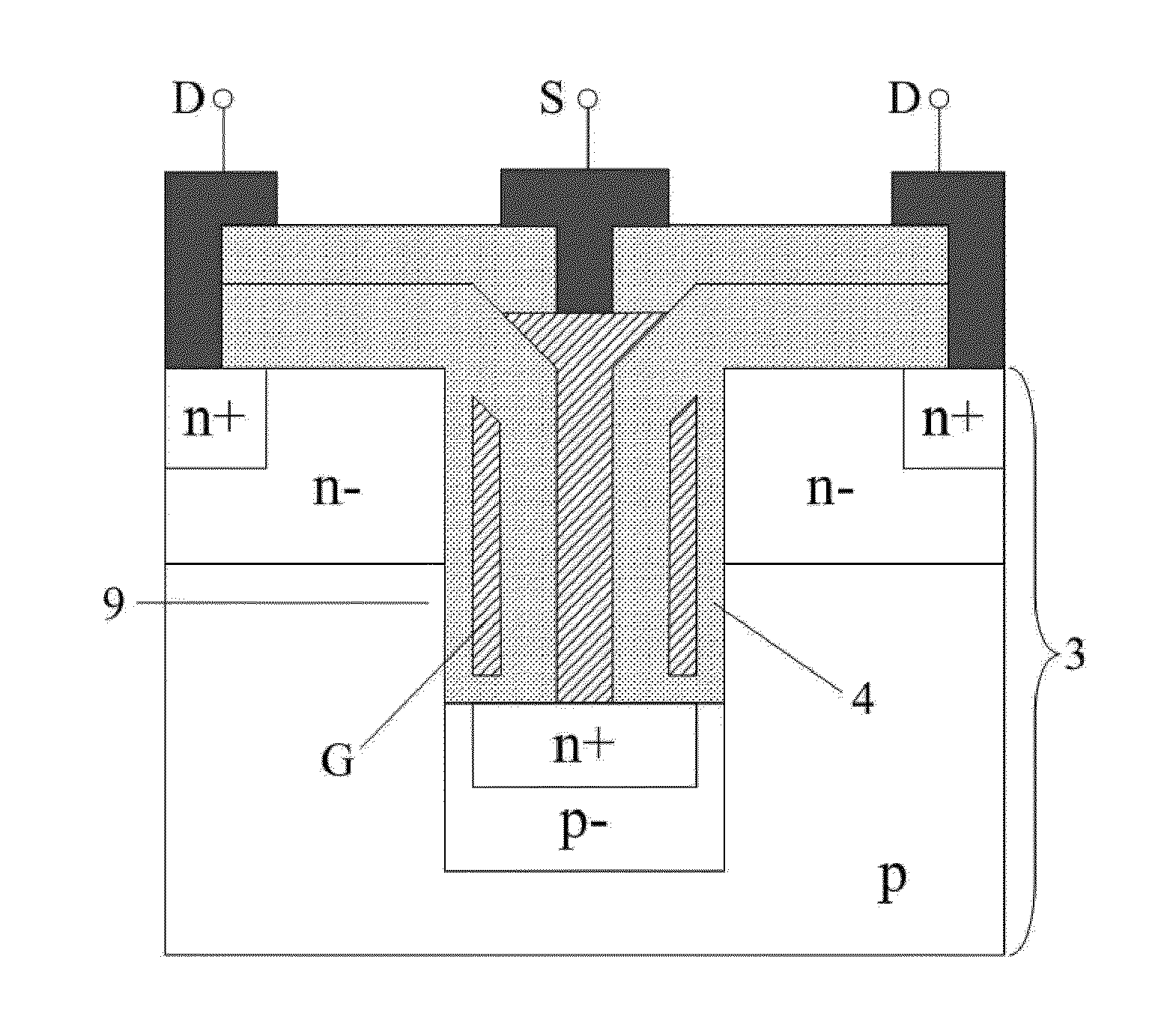

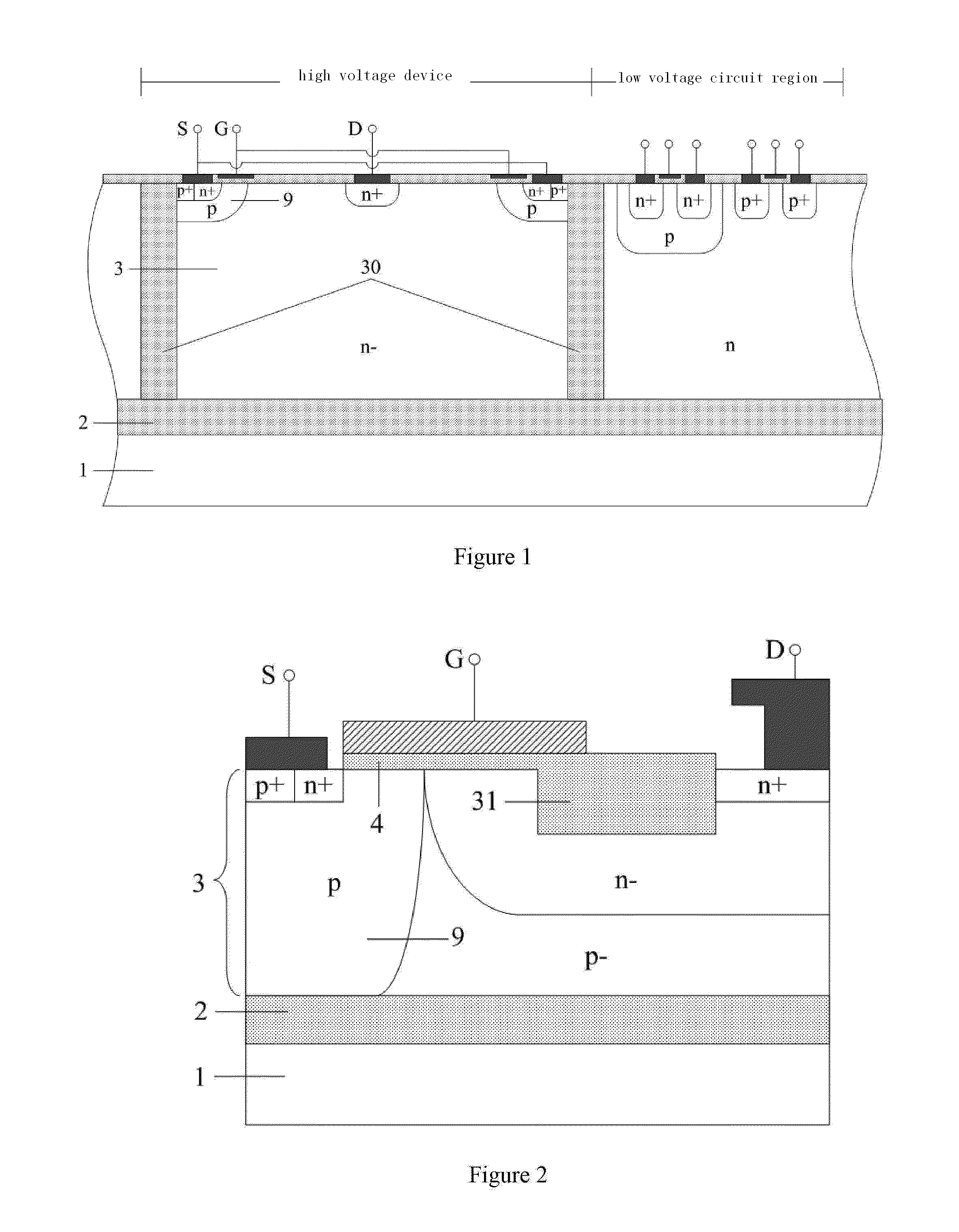

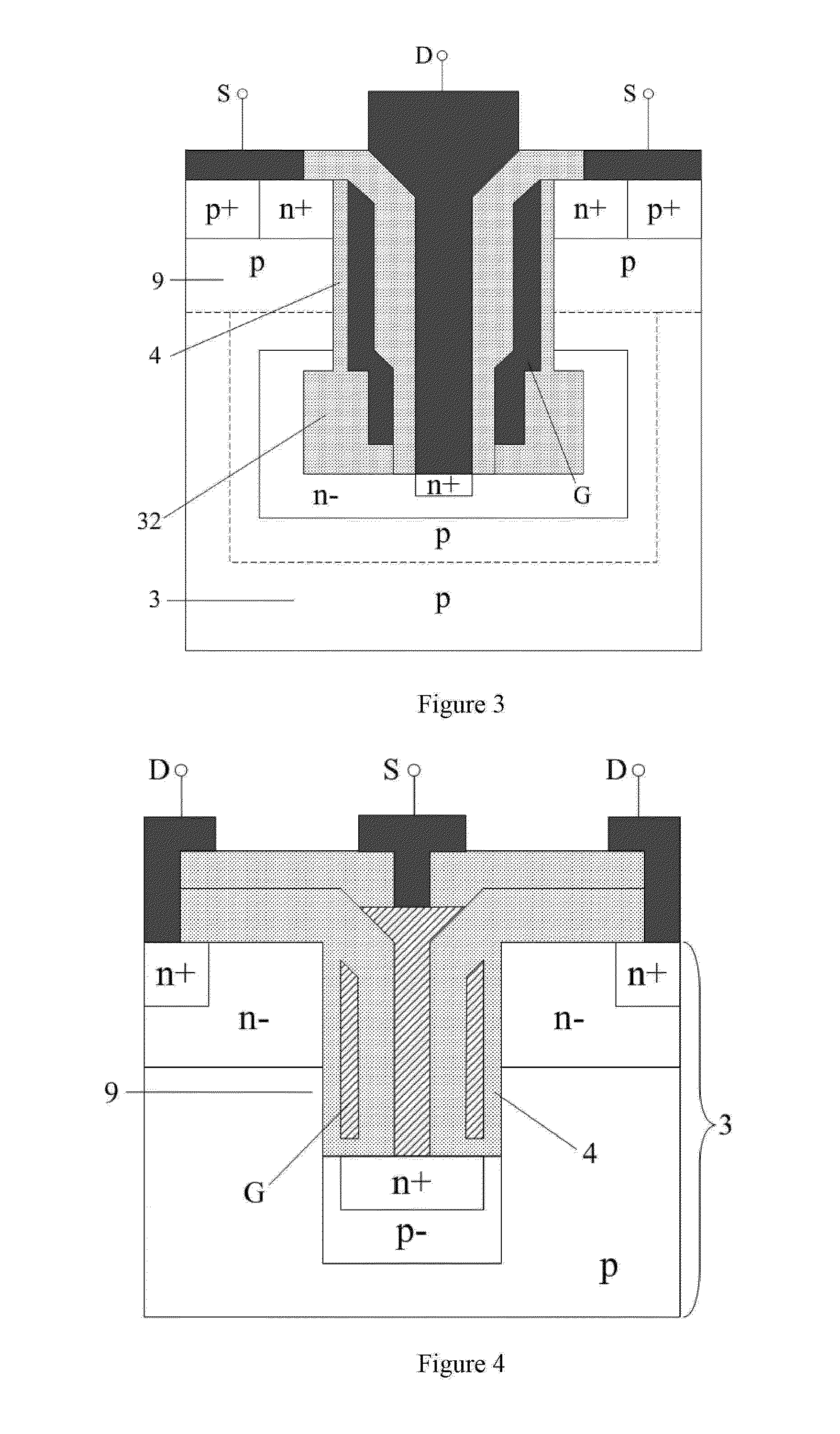

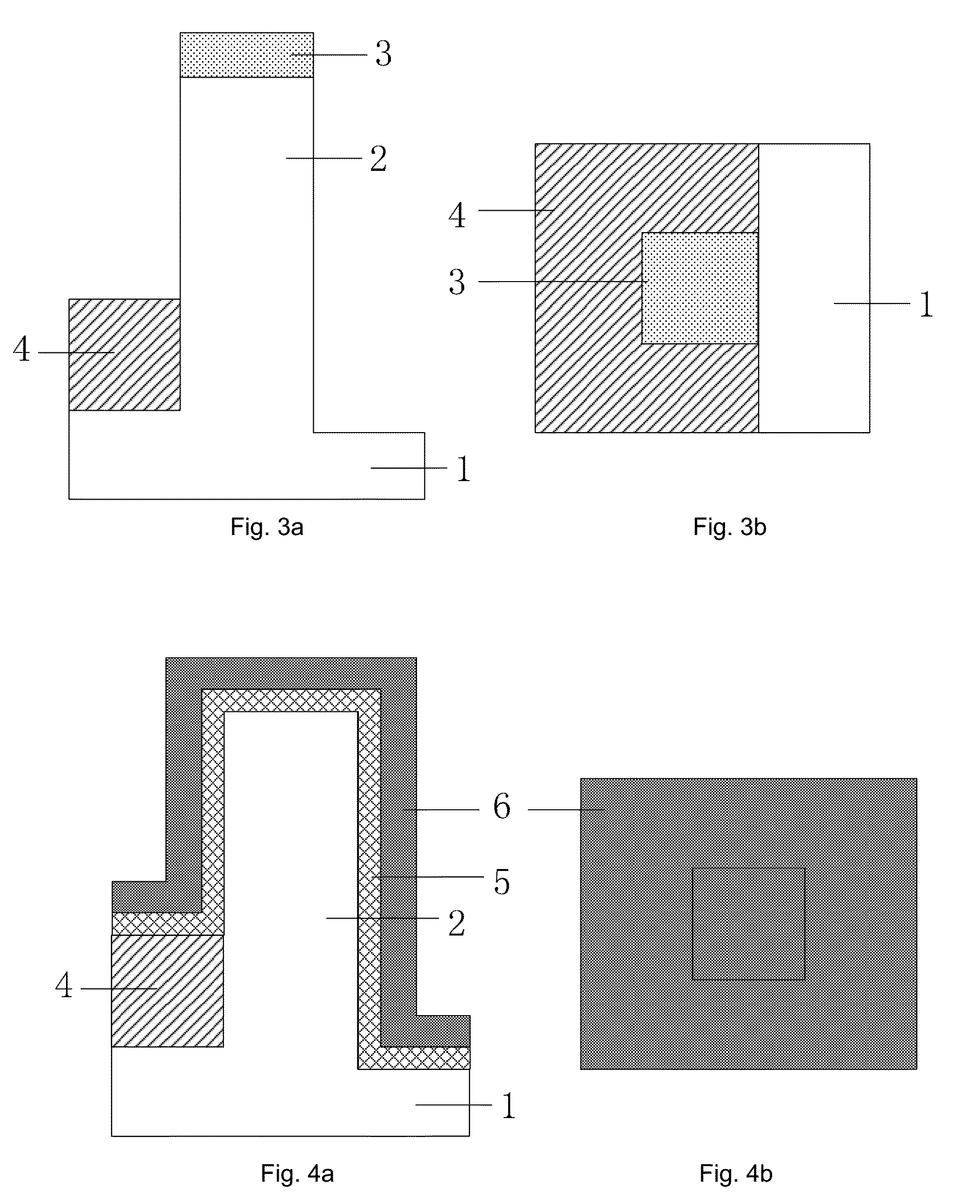

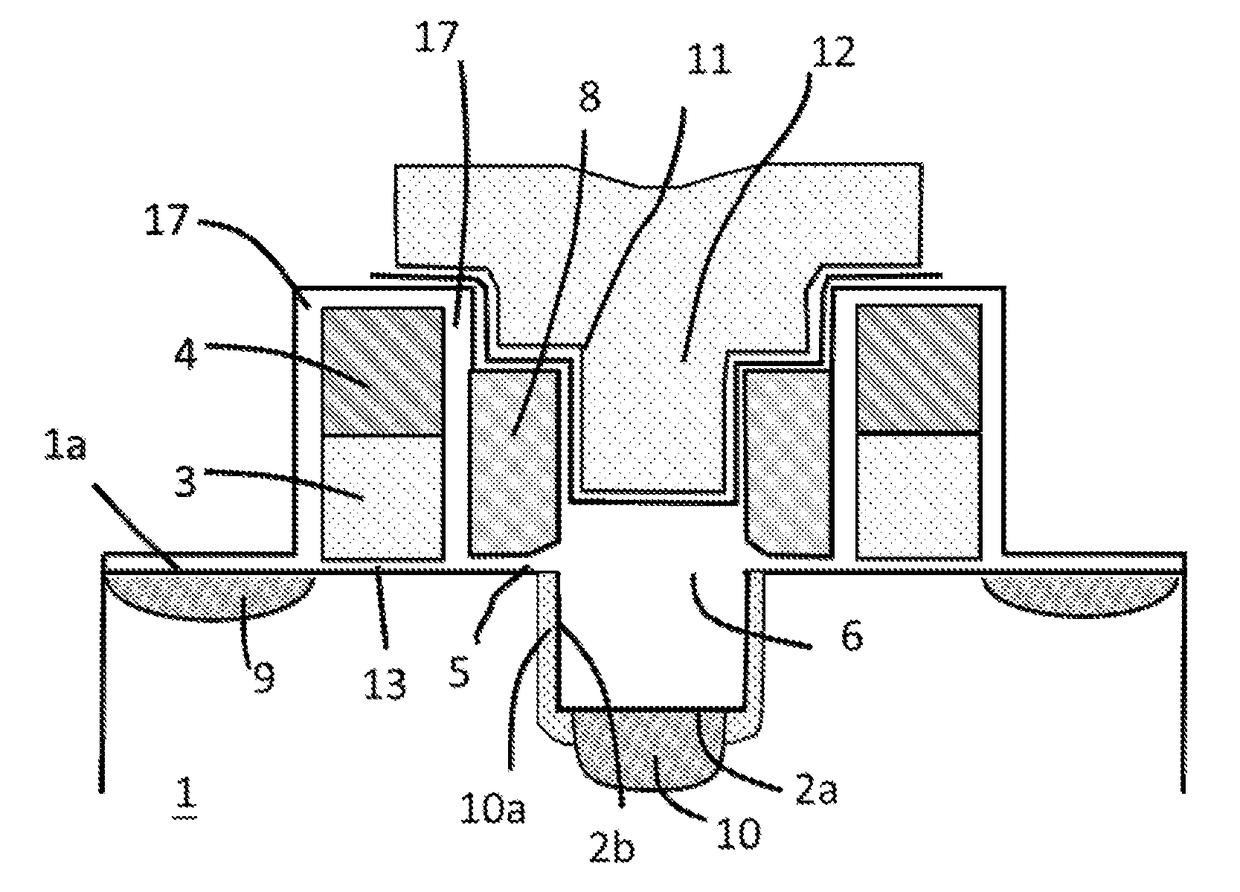

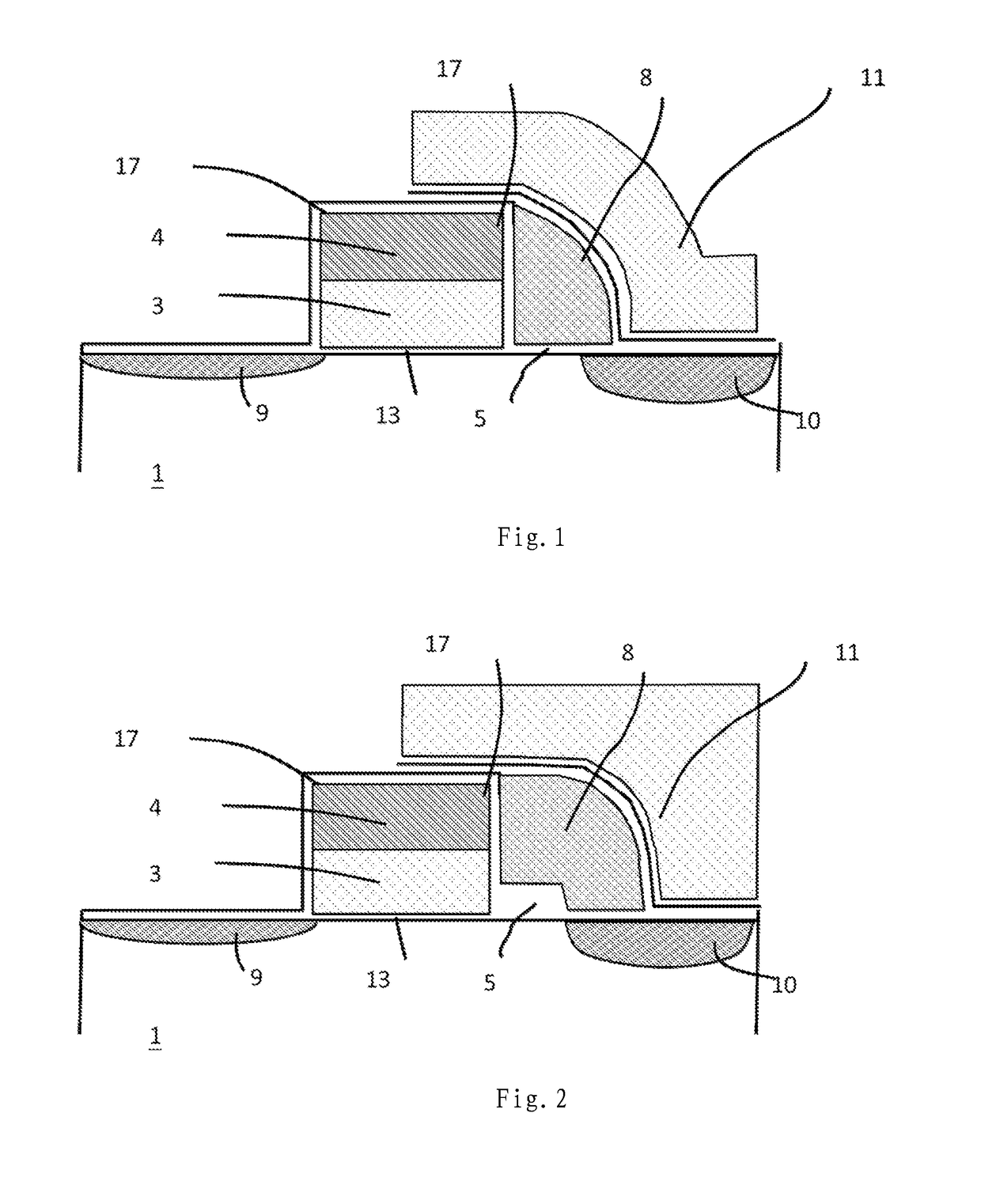

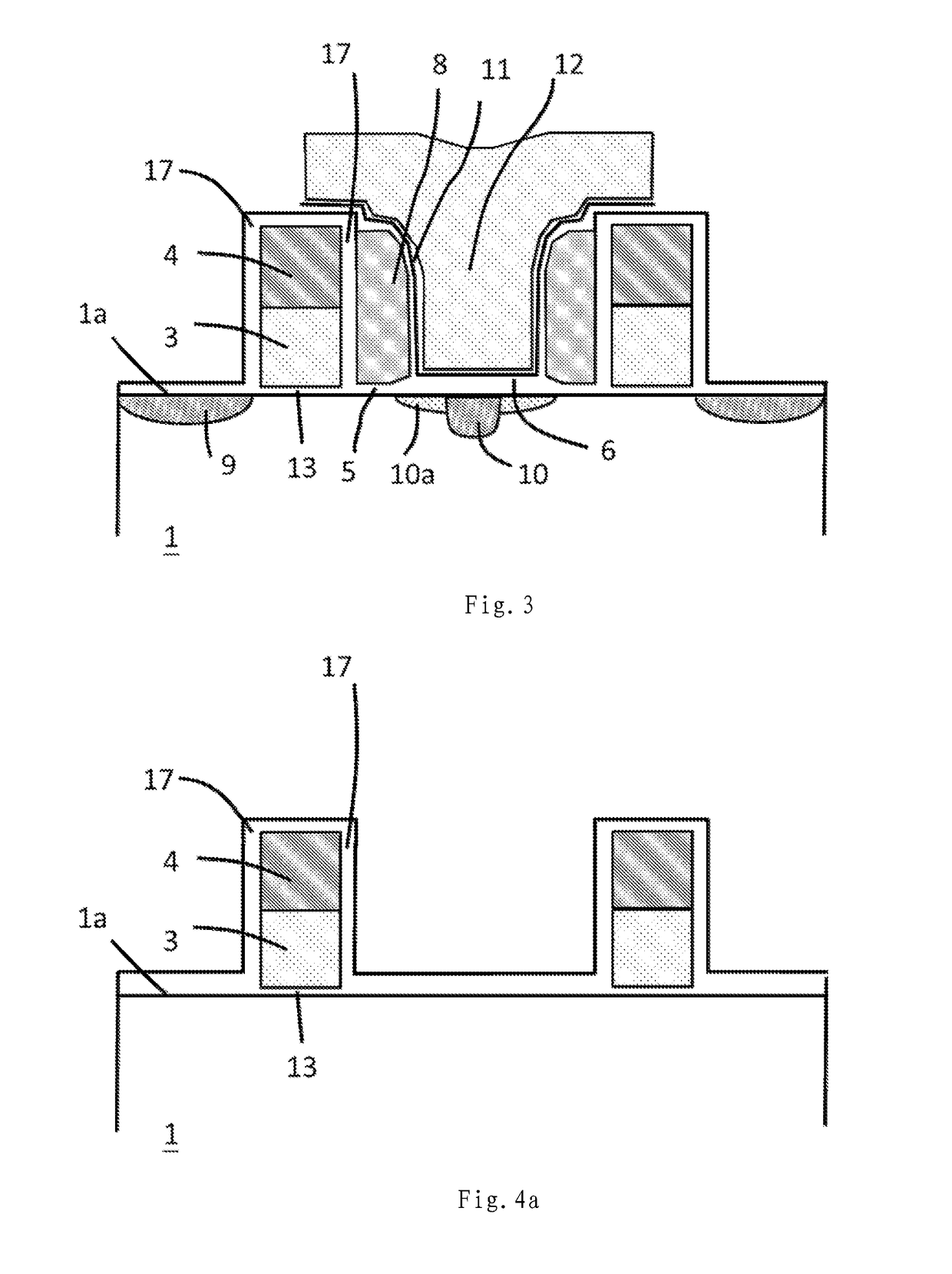

Soi lateral mosfet devices

InactiveUS20130193509A1High critical electric filedIncrease the electric field strengthSolid-state devicesSemiconductor devicesMOSFETPermittivity

The present invention relates to a semiconductor power device and power integrated circuits (ICs). The lateral SOI MOSFET in the present comprises a trench gate extended to the dielectric buried layer, one or multiple dielectric trenches in the drift region, and a buried gate in said dielectric trench. The permittivity of the dielectric in said dielectric trench is lower than that of said active layer. Firstly, said dielectric trench not only greatly improves breakdown voltage, but also reduces pitch size. Secondly, the trench gate widens the effective conductive region in the vertical direction. Thirdly, dual gates of said trench gate and buried gate increase channel and current densities. Thereby, specific on-resistance and the power loss are reduced. The device of the present invention has many advantages, such as high voltage, high speed, low power loss, low cost and ease of integration. The device in the present invention is particularly suitable for power integrated circuits and RF power integrated circuits.

Owner:UNIV OF ELECTRONICS SCI & TECH OF CHINA

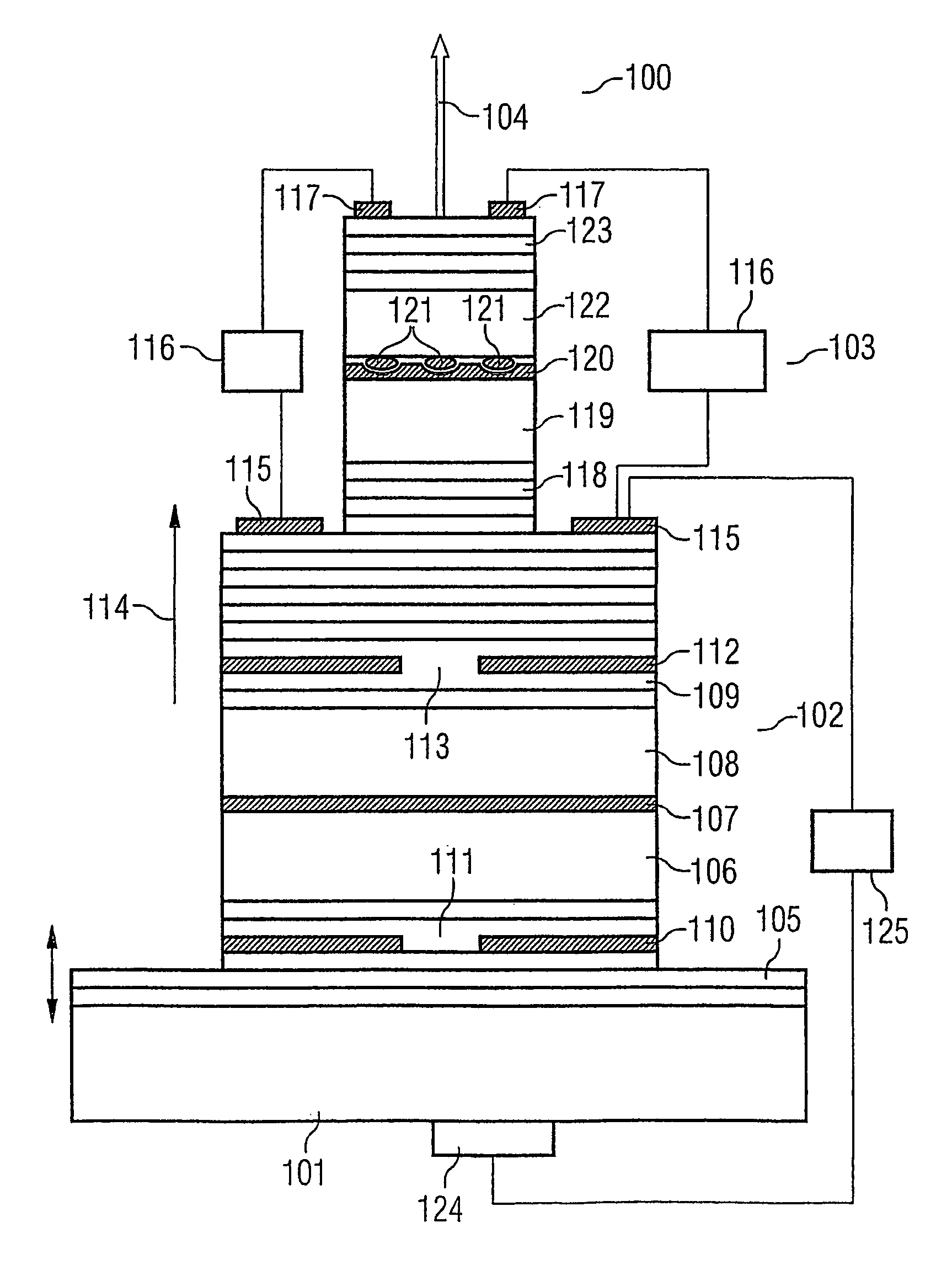

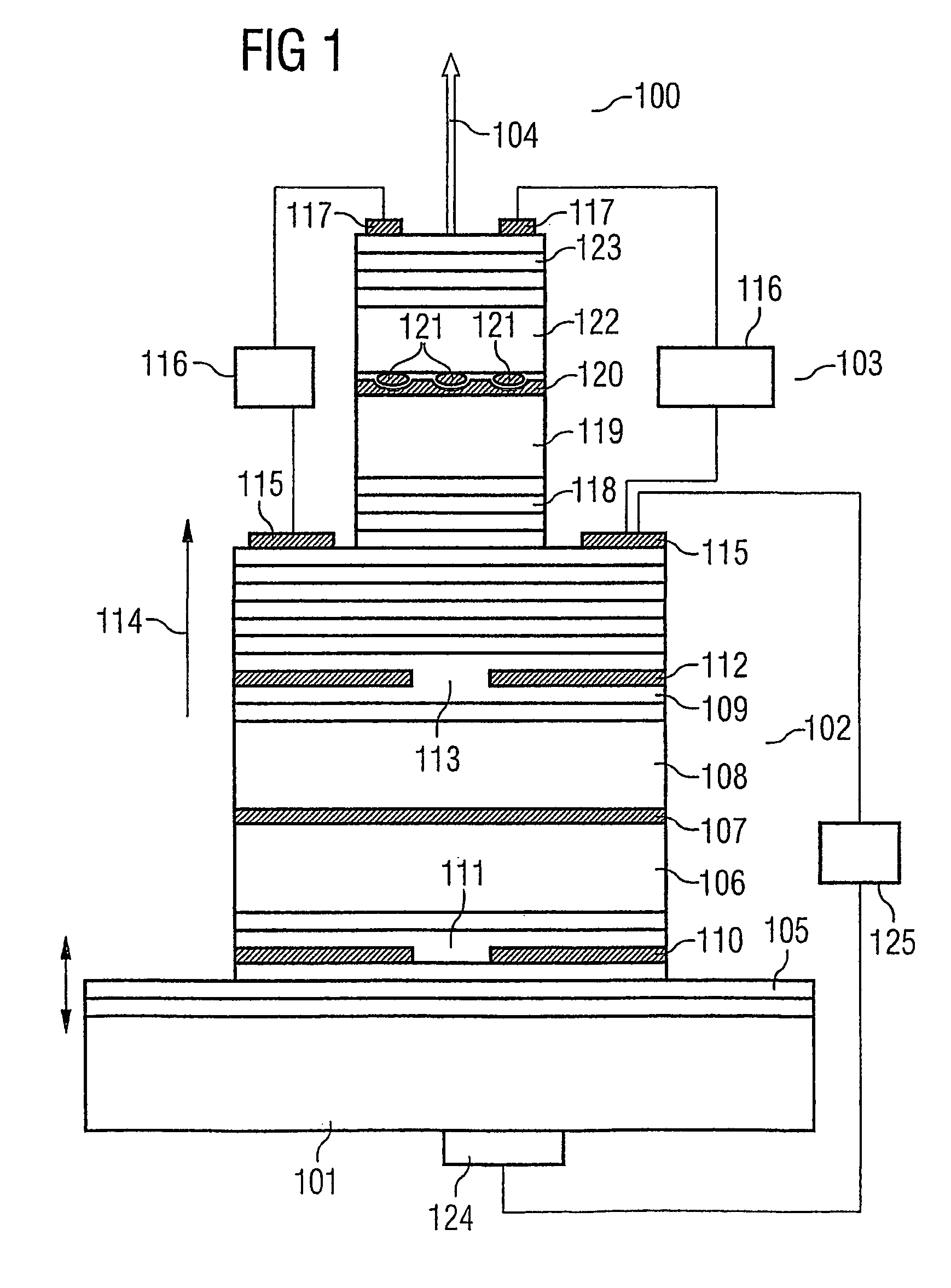

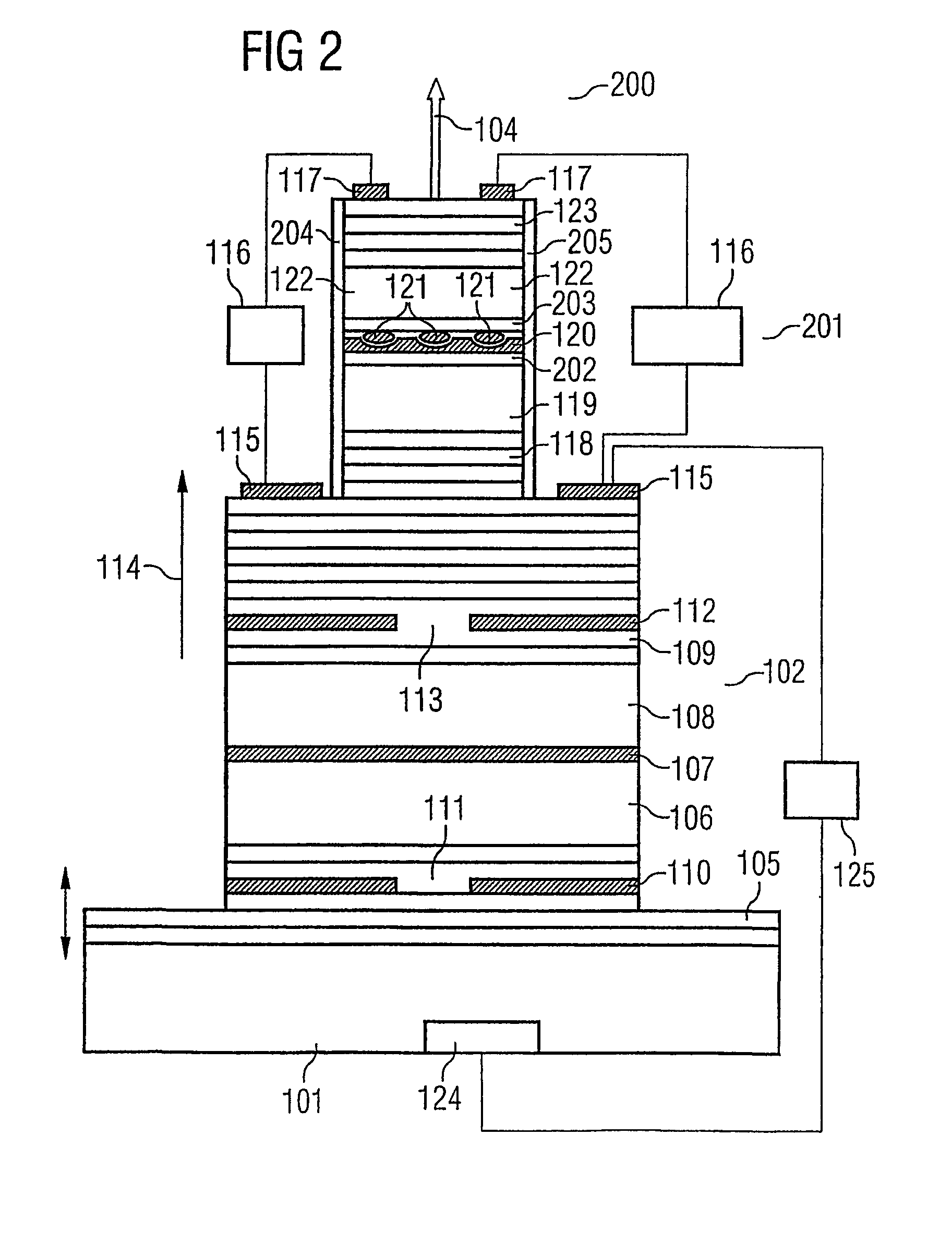

Photon emitter and data transmission device

InactiveUS7030407B2Avoid tunnelingImprove efficiencyLaser active region structureExcitation process/apparatusPhoton emissionResonance

Photon emitter and data transmission device wherein a second resonator is arranged in a direction of emission of a radiation-emitting first resonator in such a way that a quantum dot contained in the second resonator can be excited by energy of radiation emitted by the first resonator. A control unit brings the excitation ground state of the quantum dot into resonance with a prescribed resonator mode of the second resonator.

Owner:INFINEON TECH AG

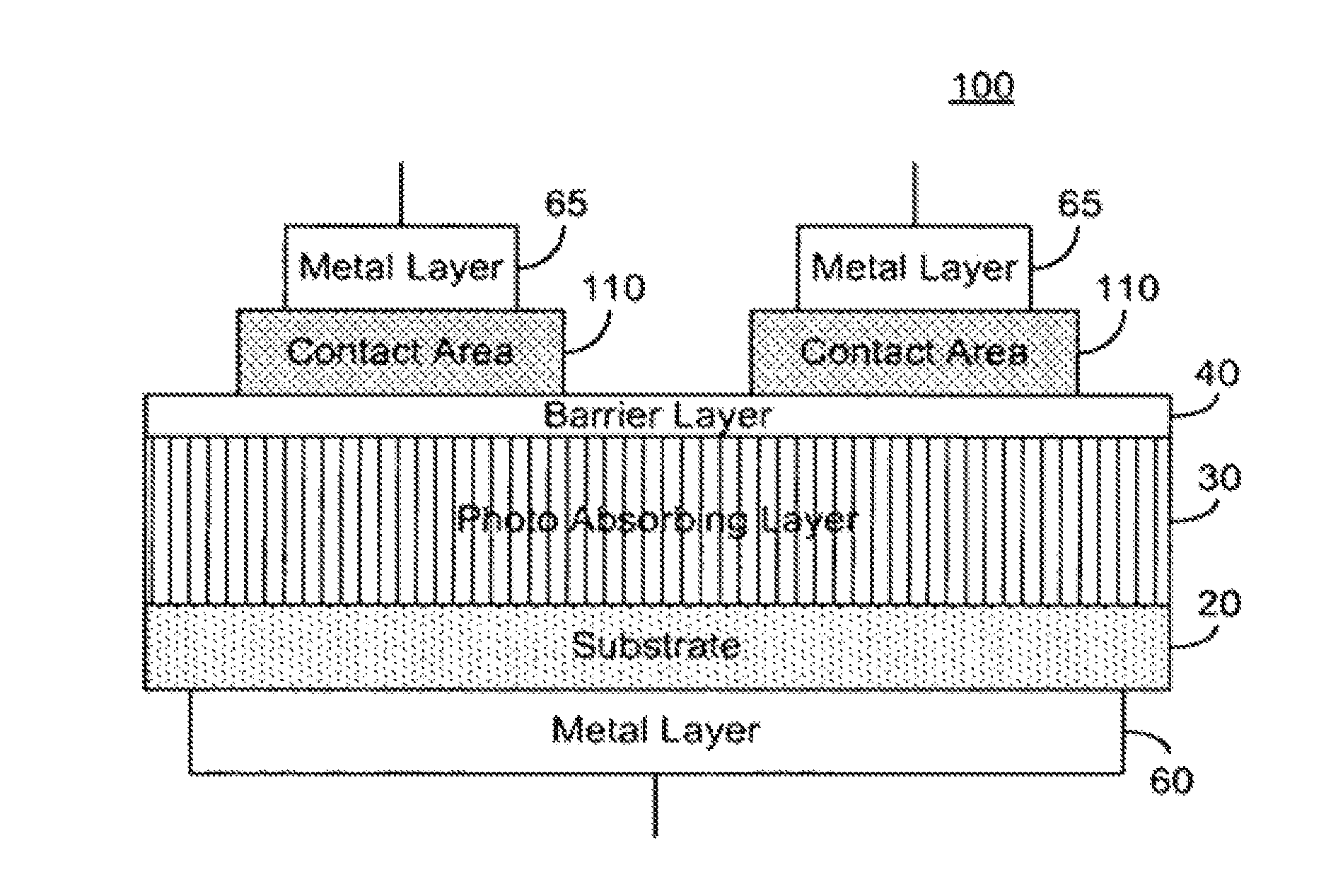

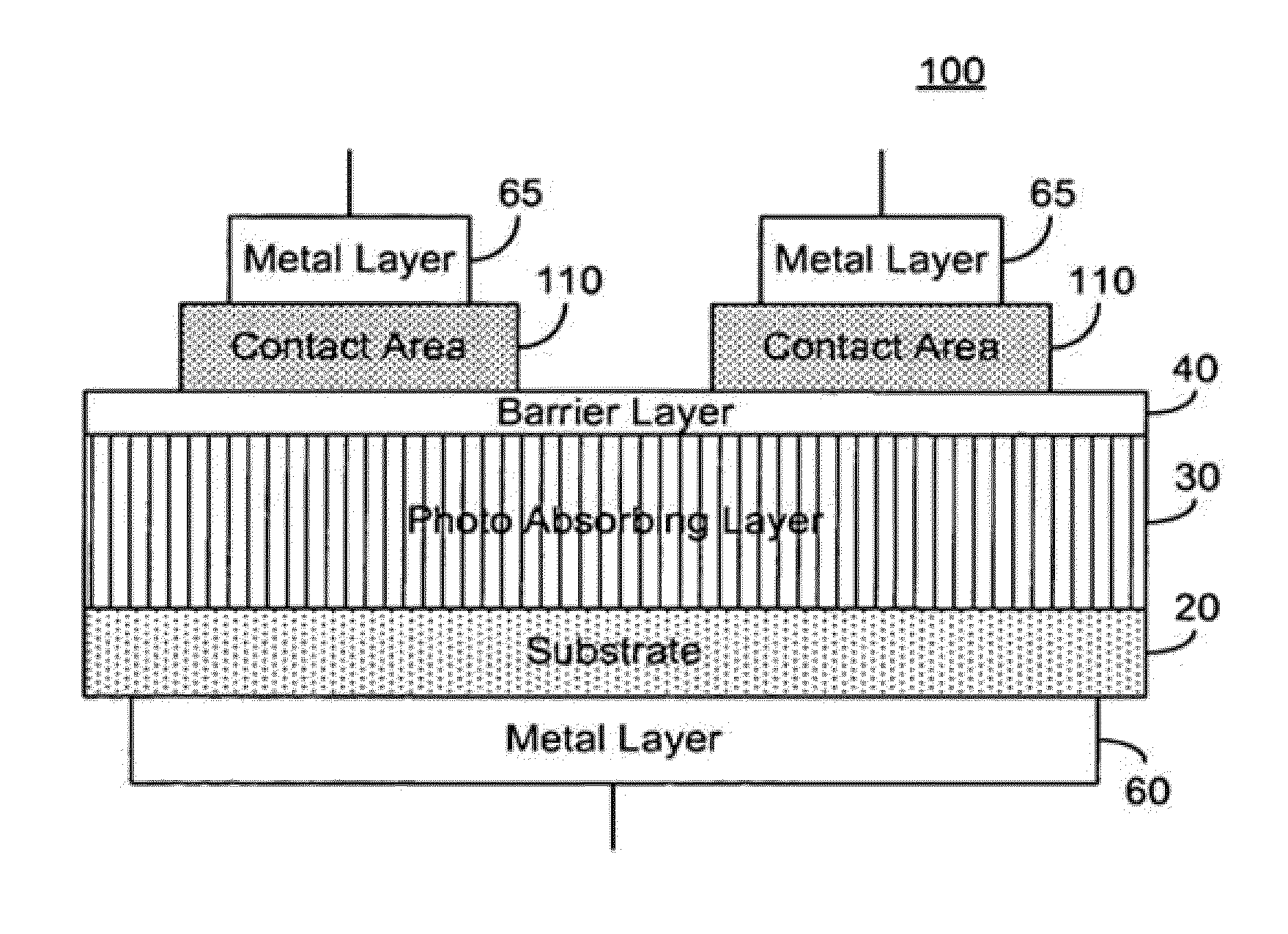

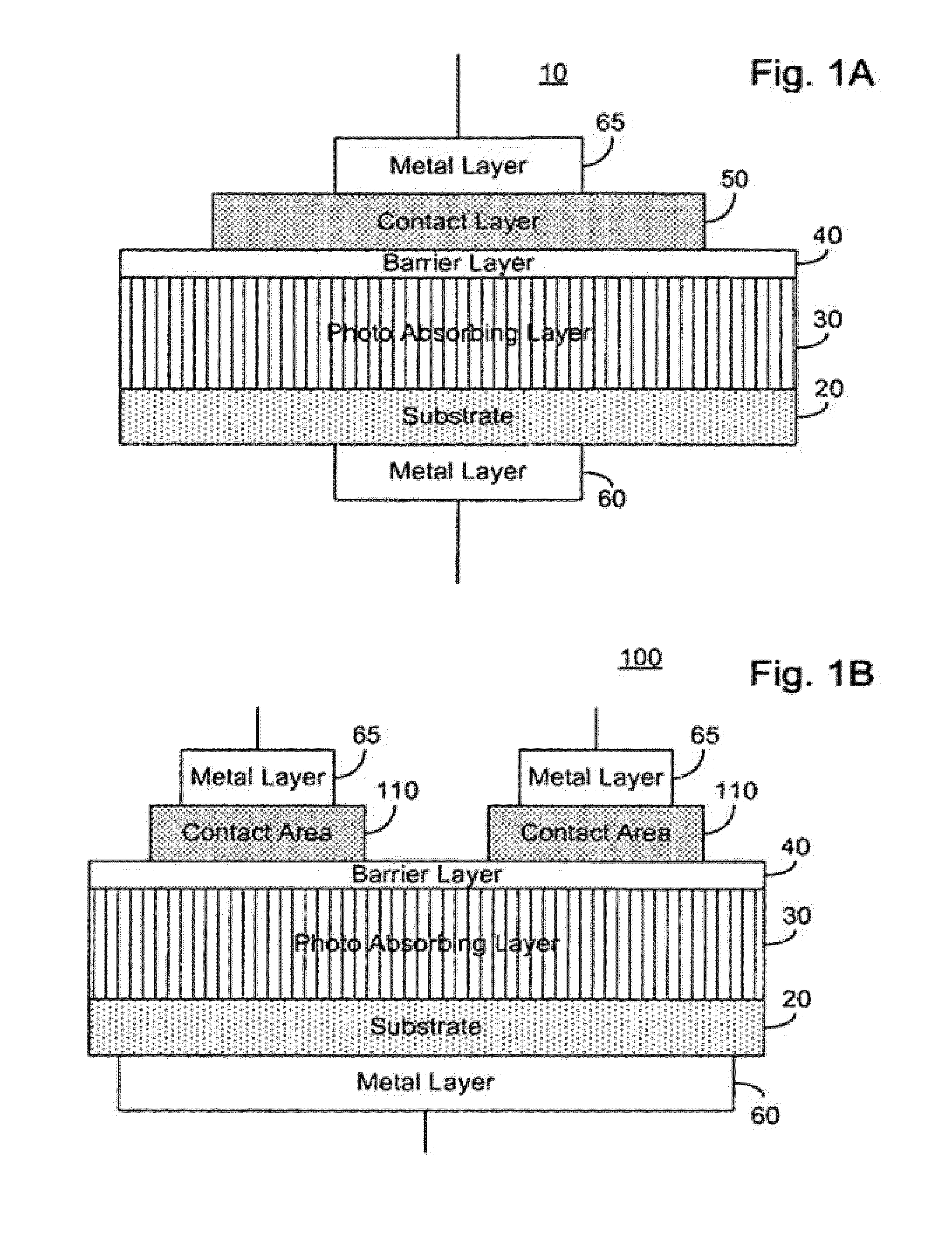

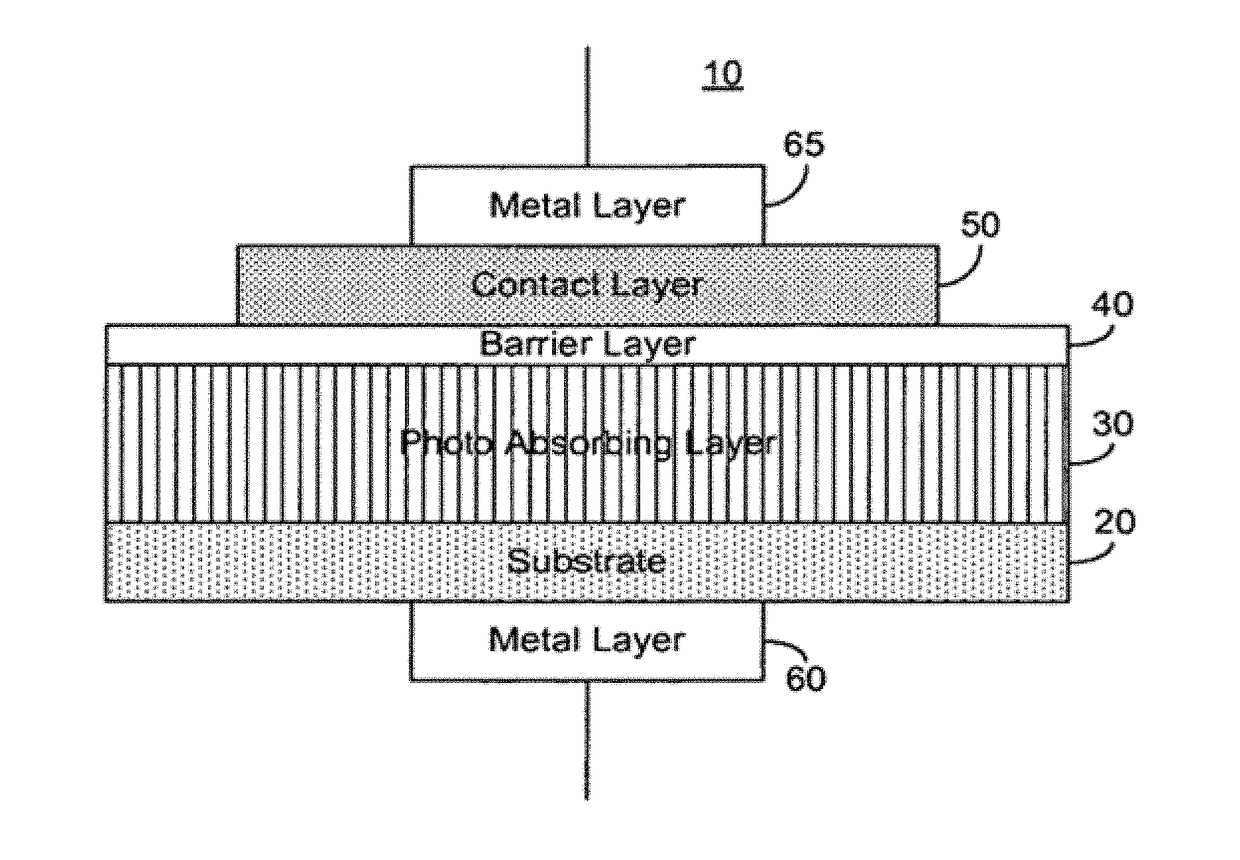

Application of reduced dark current photodetector

ActiveUS9117726B2Total current dropAvoid tunnelingRadiation pyrometrySemiconductor/solid-state device detailsValence bandPhotodetector

A IDCA system with internal nBn photo-detector comprising: a photo-absorbing layer comprising an n-doped semiconductor exhibiting valence band energy level; a barrier layer, a first side of the barrier layer adjacent a first side of the photo-absorbing layer, the barrier layer exhibiting a valence band energy level substantially equal to the valence band energy level of the doped semiconductor of the photo absorbing layer; and a contact area comprising a doped semiconductor, the contact area being adjacent a second side of the barrier layer opposing the first side, the barrier layer exhibiting a thickness and conductance band gap sufficient to prevent tunneling of majority carriers from the photo-absorbing layer to the contact area, blocking the flow of thermalized majority carriers from the photo-absorbing layer to the contact area. Alternatively, a p-doped semiconductor is utilized, equalizing barrier conductance band energy levels and photo-absorbing layers.

Owner:MAIMON SHIMON

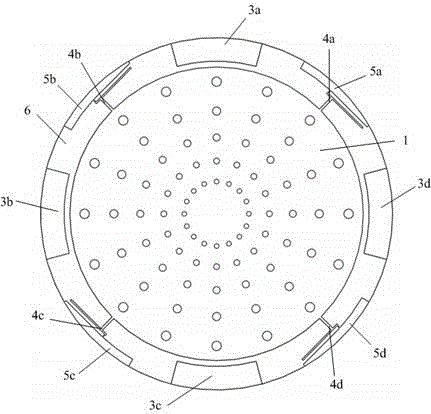

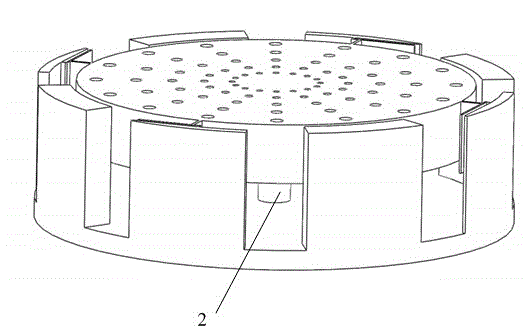

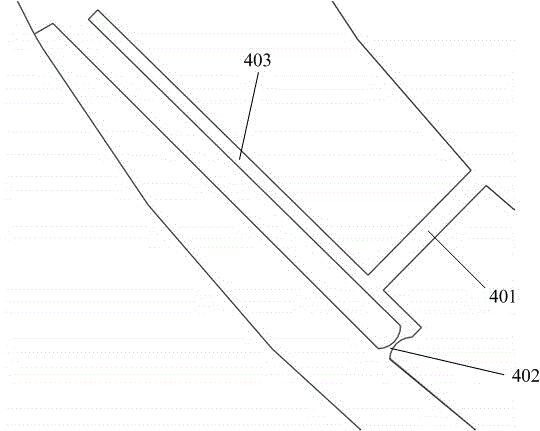

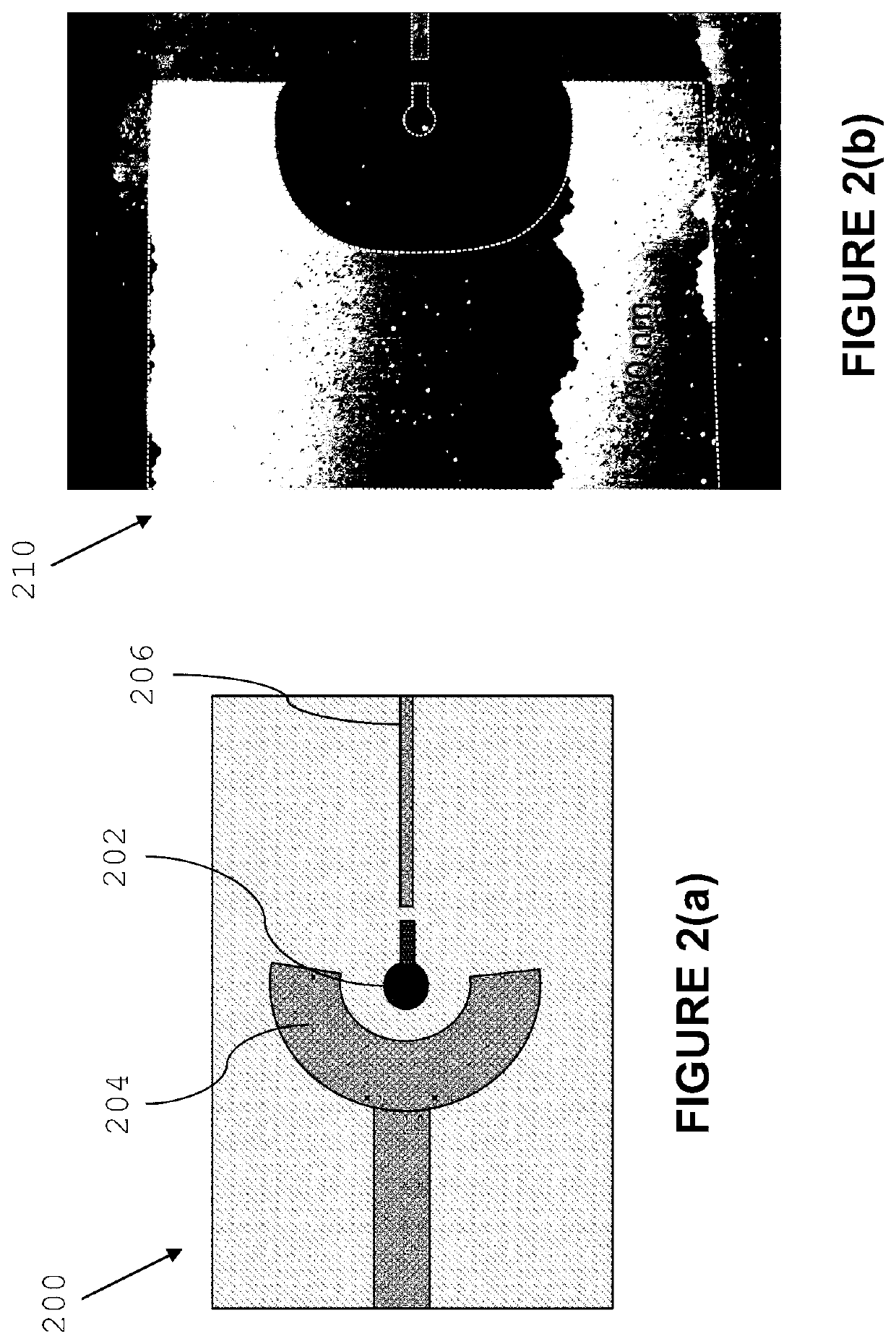

High-sensitivity bulk acoustic wave silicon microgyroscope

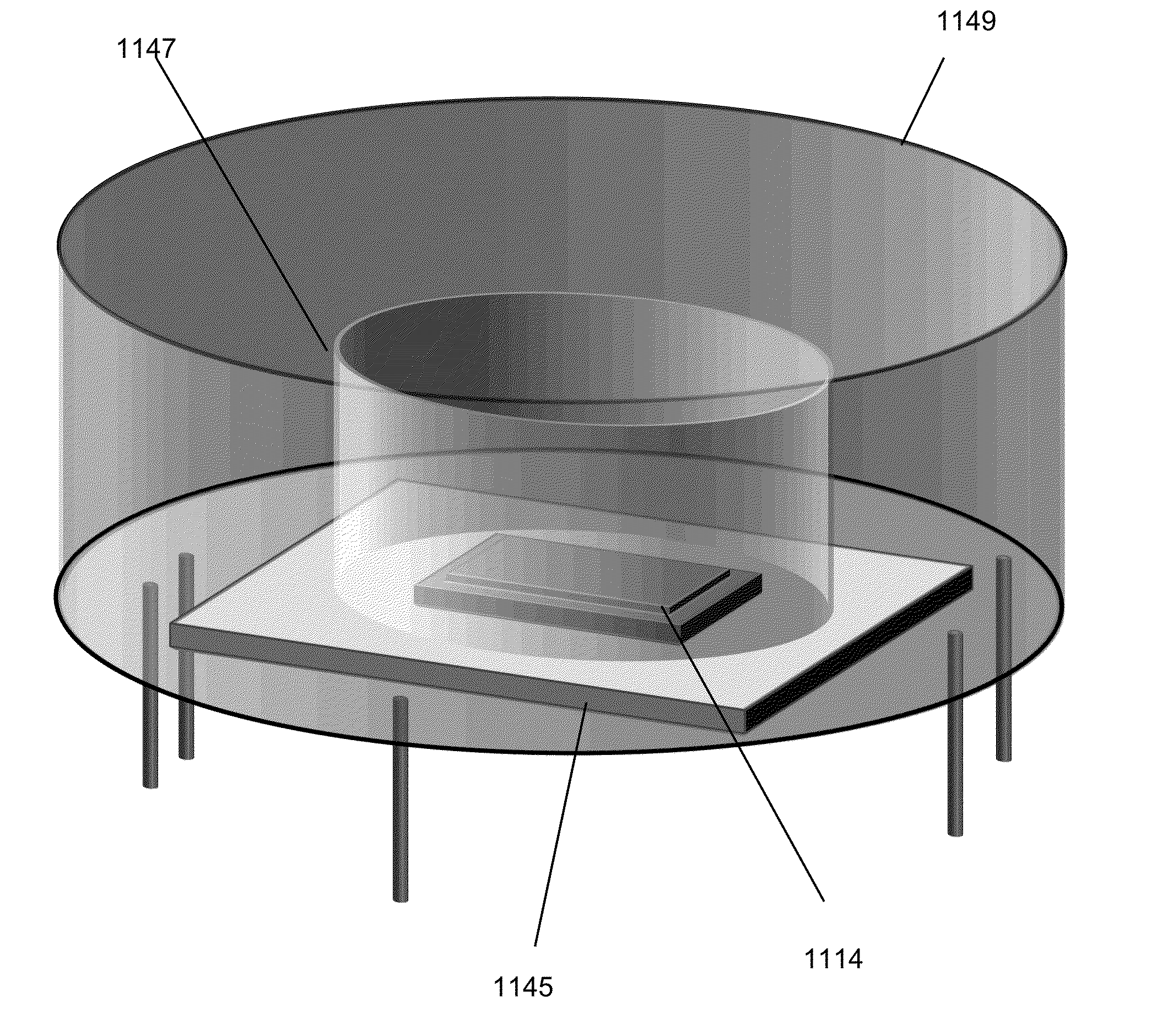

ActiveCN104457725AReduced Ultra High Aspect Ratio Gap RequirementsAvoid tunnelingSpeed measurement using gyroscopic effectsGyroscopes/turn-sensitive devicesHarmonic oscillatorMachining process

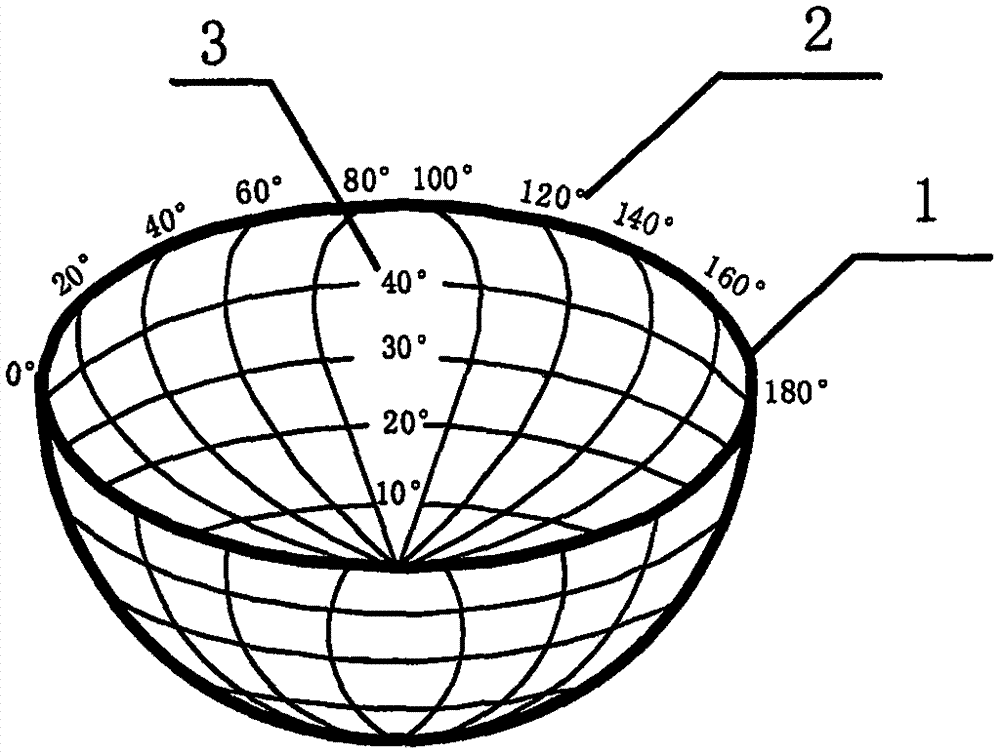

The invention discloses a high-sensitivity bulk acoustic wave silicon microgyroscope in the technical field of micro electro mechanical systems. The high-sensitivity bulk acoustic wave silicon microgyroscope comprises a disc-shaped harmonic oscillator, a supporting cylinder, a circular arc driving electrode, a detection electrode with a displacement mechanism, a detection electrode fixing boss and a base plate. A gyroscope utilizes four-amplitude wave node frequency matching modes of two surfaces of the disc-shaped harmonic oscillator as a driving mode and a detection mode, and all structures are completely realized by a micro electro mechanical machining process on a (111) silicon wafer. According to the high-sensitivity bulk acoustic wave silicon microgyroscope, a displacement enlargement mechanism based on a lever principle is used for outputting and enlarging infinitesimal displacement at the detection mode, so as to improve the sensitivity of the gyroscope, largely simplify the machining process of the bulk acoustic wave silicon microgyroscope, and reduce the production cost.

Owner:徐州雅居乐环保科技有限公司

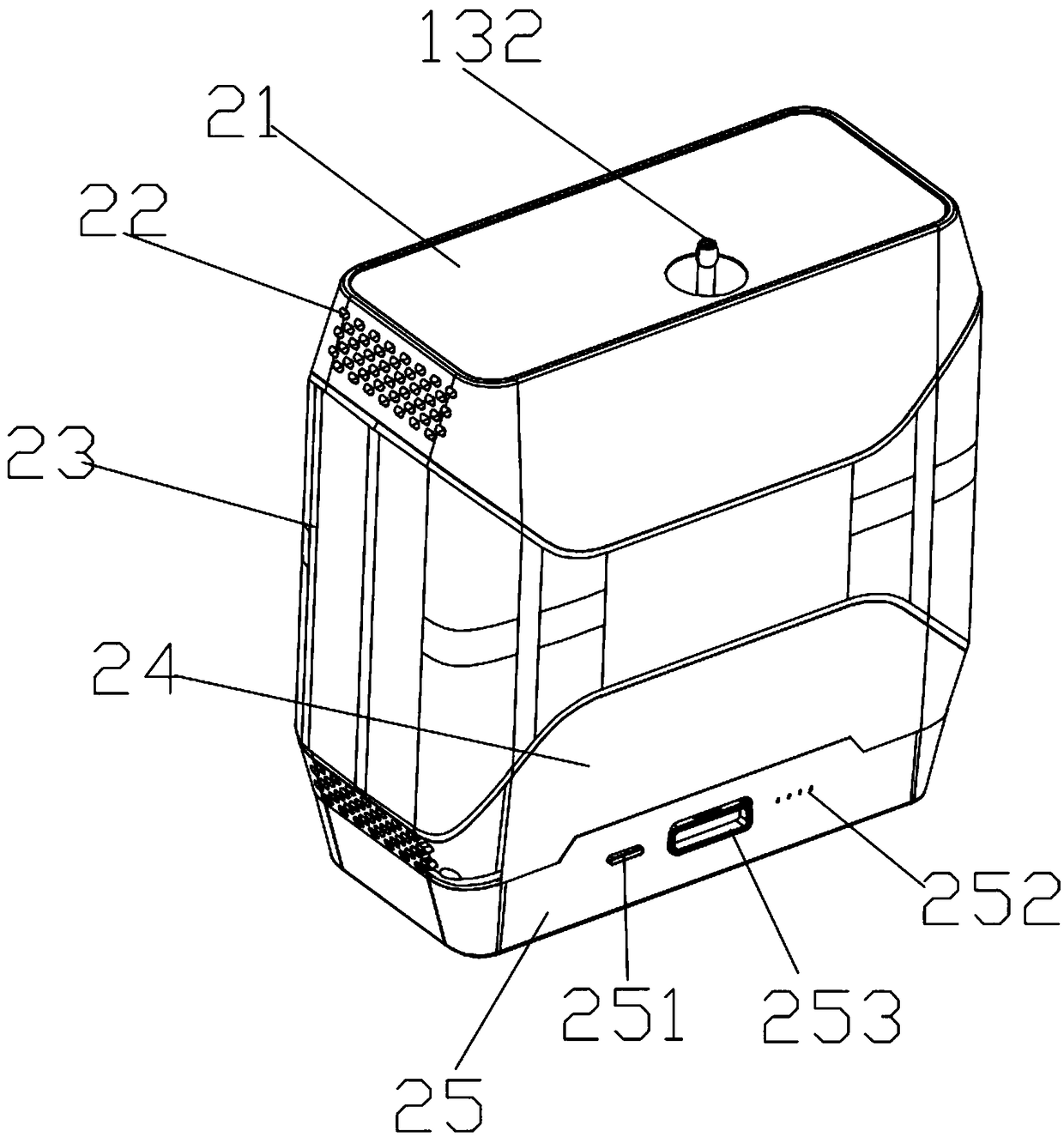

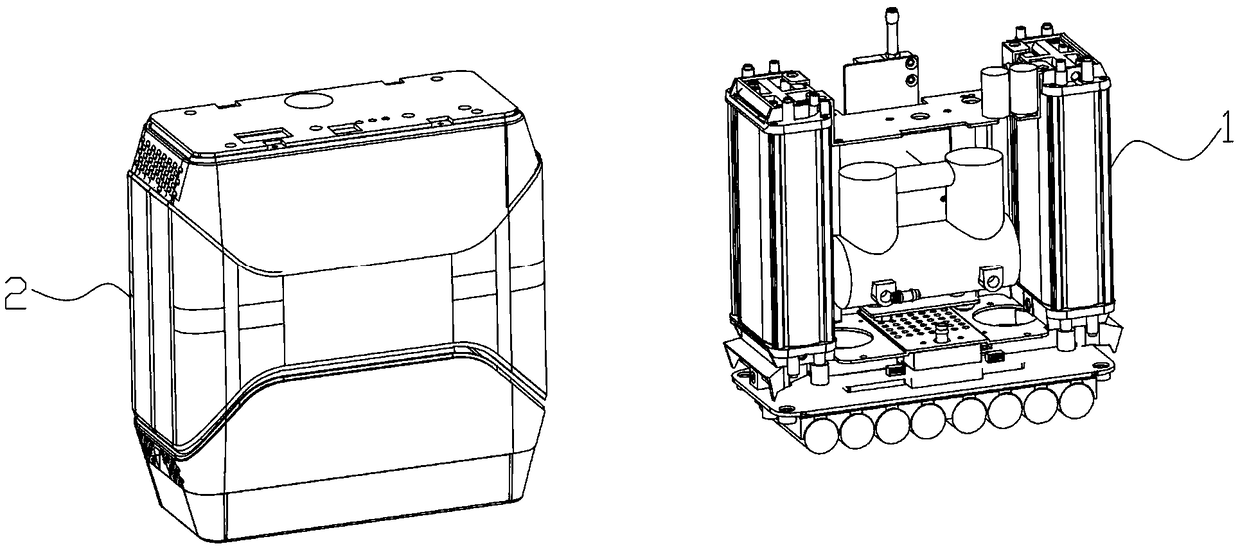

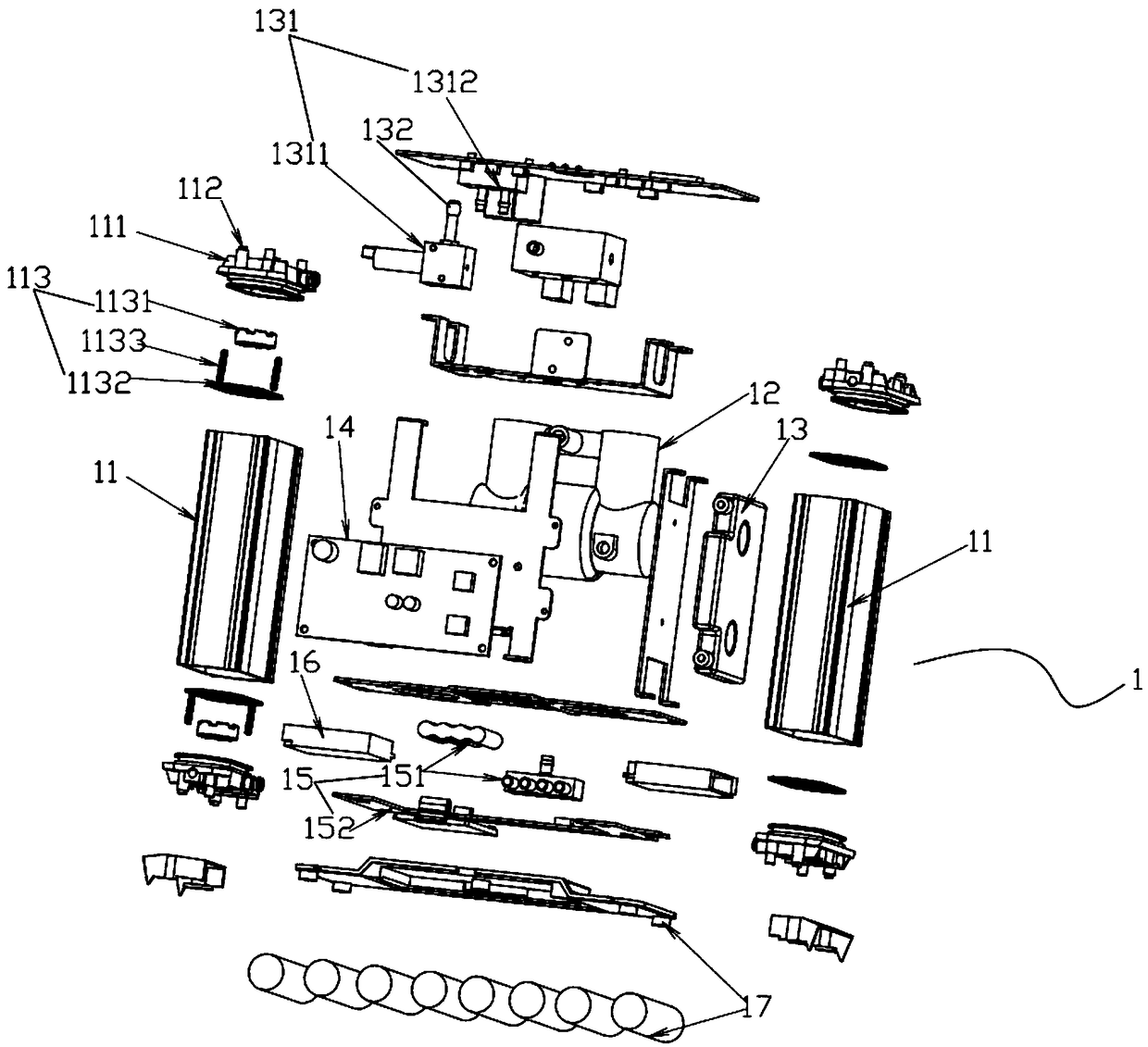

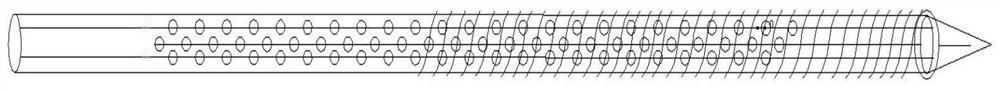

Portable oxygenerator

PendingCN109019519AIncrease productionQuality improvementRespiratorsMedical devicesMolecular sieveSpatial structure

The invention relates to the technical field of oxygenerators, in particular to a portable oxygenerator, which comprises a shell and an oxygenator main body placed in the shell. The oxygenator main body comprises two parallel adsorption towers, which are flat cylindrical structures and filled with molecular sieves in the inner cavities, the two adsorption towers are erected on both sides of the oxygenator main body oppositely, a compressor, an oxygen storage tank, a circuit board, an air intake module and a corresponding bracket and connection pipeline are placed between the two adsorption towers, air distribution structures are disposed between all adsorption tower air inlets and the molecular sieves, the air distribution structures include air distribution nozzles and flow equalization sieve plates for air distribution and flow equalization, so that the gas entering the adsorption towers can achieve a uniform pressure in the adsorption towers. The portable oxygenerator provided by the invention has the beneficial effects of compact space structure, small size, light weight and easy carrying, also the atmospheric pressure in the adsorption towers is uniform and the molecular sieveutilization rate is high.

Owner:西藏欧格斯医疗科技有限公司

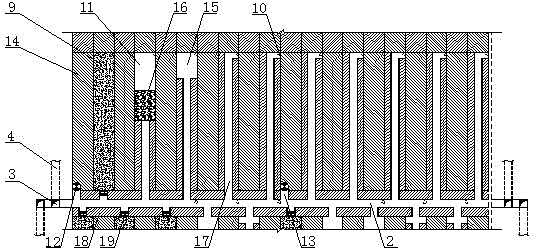

Medium-deep hole multi-stope and subsection common orepass mining method for mining hanging ore body

ActiveCN110700833AStable open air realmAvoid tunnelingUnderground miningSurface miningMineralogyMining engineering

The invention discloses a medium-deep hole multi-stope and subsection common orepass mining method for mining a hanging ore body. The method comprises the following steps that stage division and subsection division are carried out on the hanging ore body according to the height of an open-pit bench, and transverse and longitudinal spacing pillars and side slope safety pillars are reserved; transport roadways and sectional roadways are utilized to tunnel a connecting roadway to reach the ore body, and a mining structure and a sectional rock drilling roadway are constructed; during stoping of anore room, a plurality of stopes simultaneously carry out medium-deep hole blasting operation, a cutting groove is used as a free surface for lateral ore caving, ore in each stage is conveyed to the centralized stage transport roadways through an orepass, and then conveyed to the ground surface; and after the open-air production is finished, the spacing pillars and top pillars are recovered in time. By adopting the method, the mining and cutting cost and the difficulty of staff organization and management can be reduced, the ore drawing efficiency is improved, and the influence of transportation operation on the slope stability is reduced.

Owner:GUANGXI UNIV

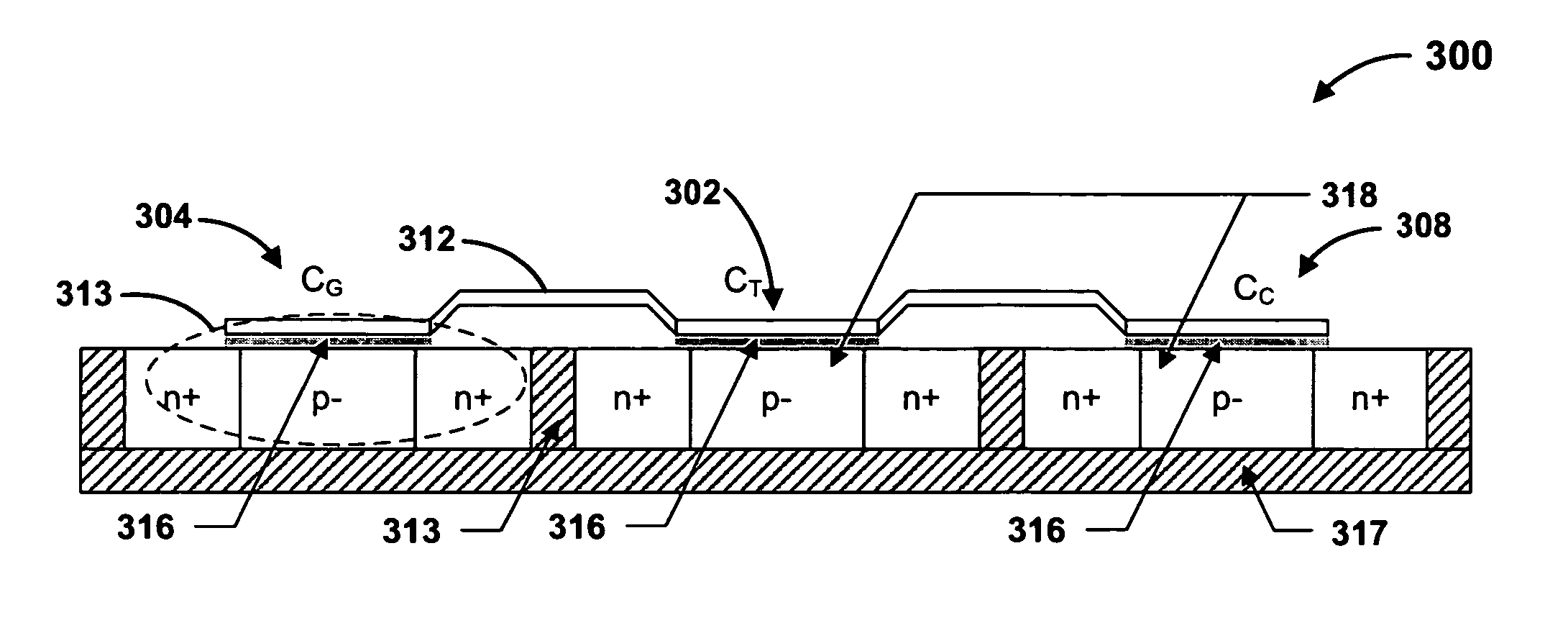

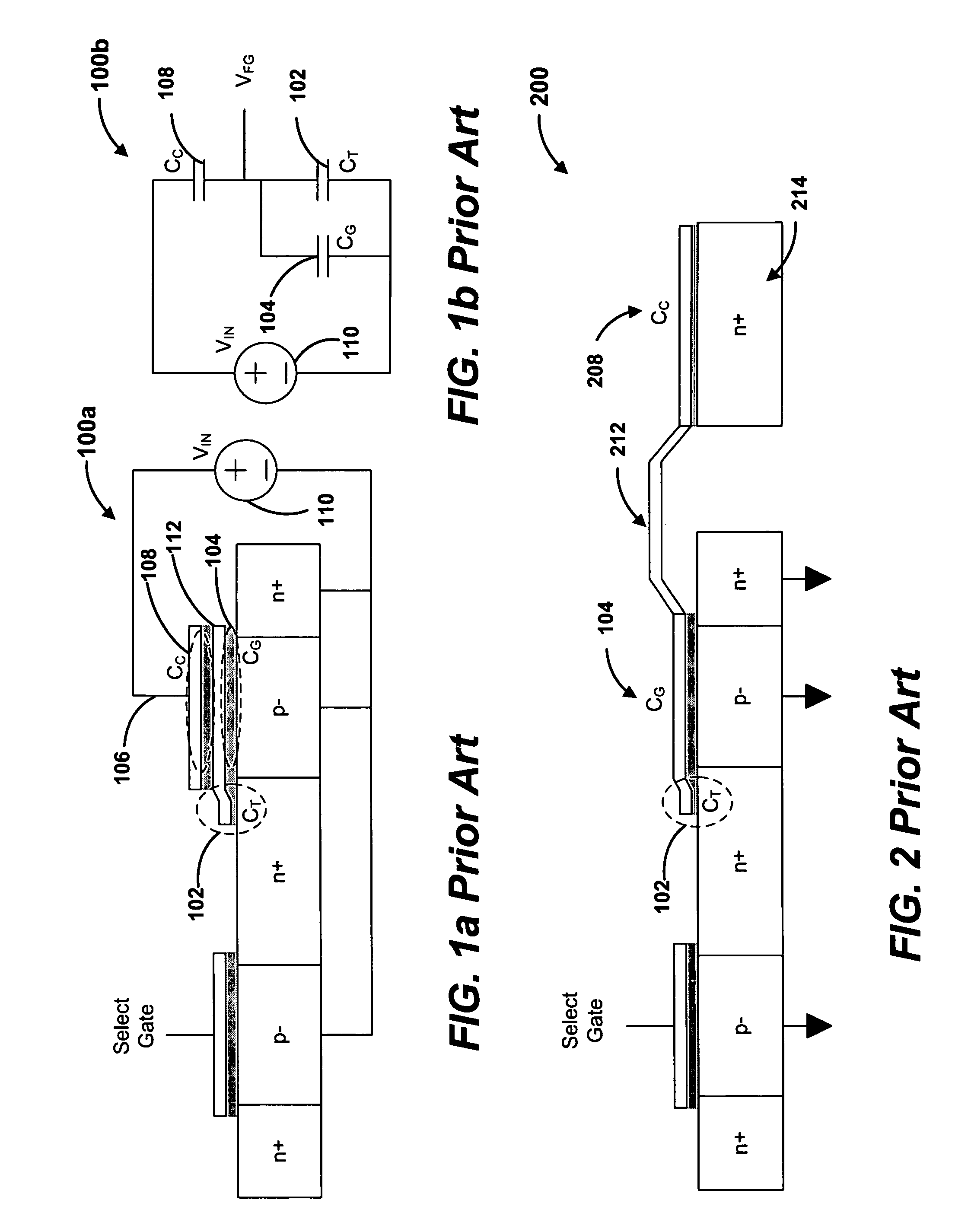

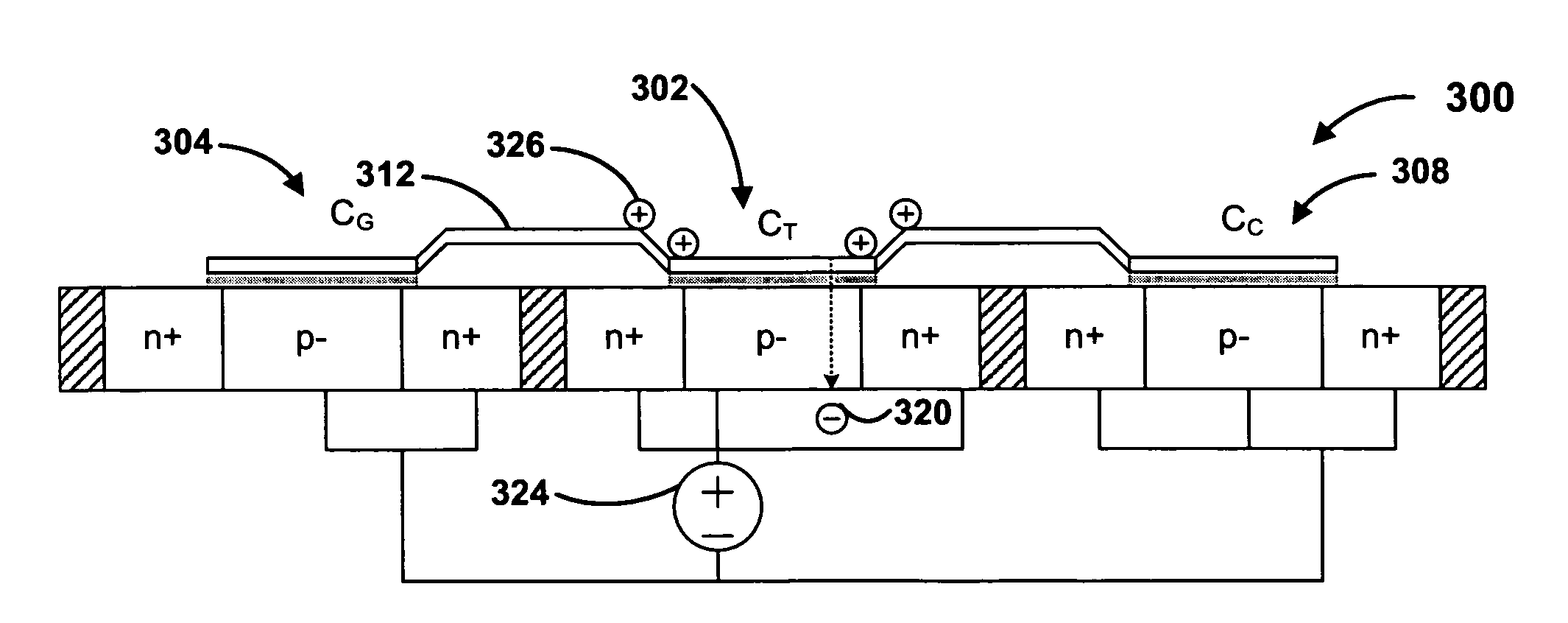

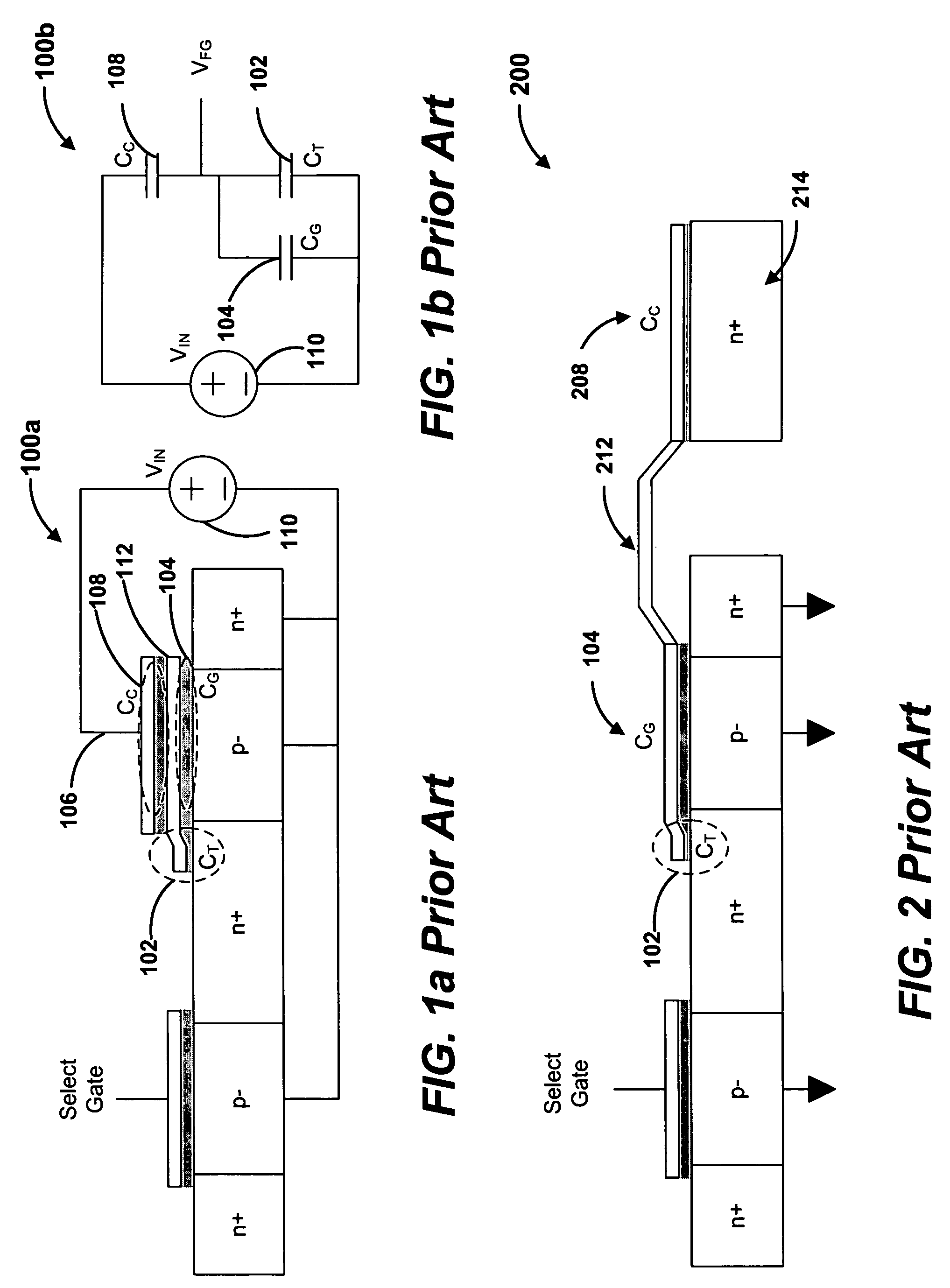

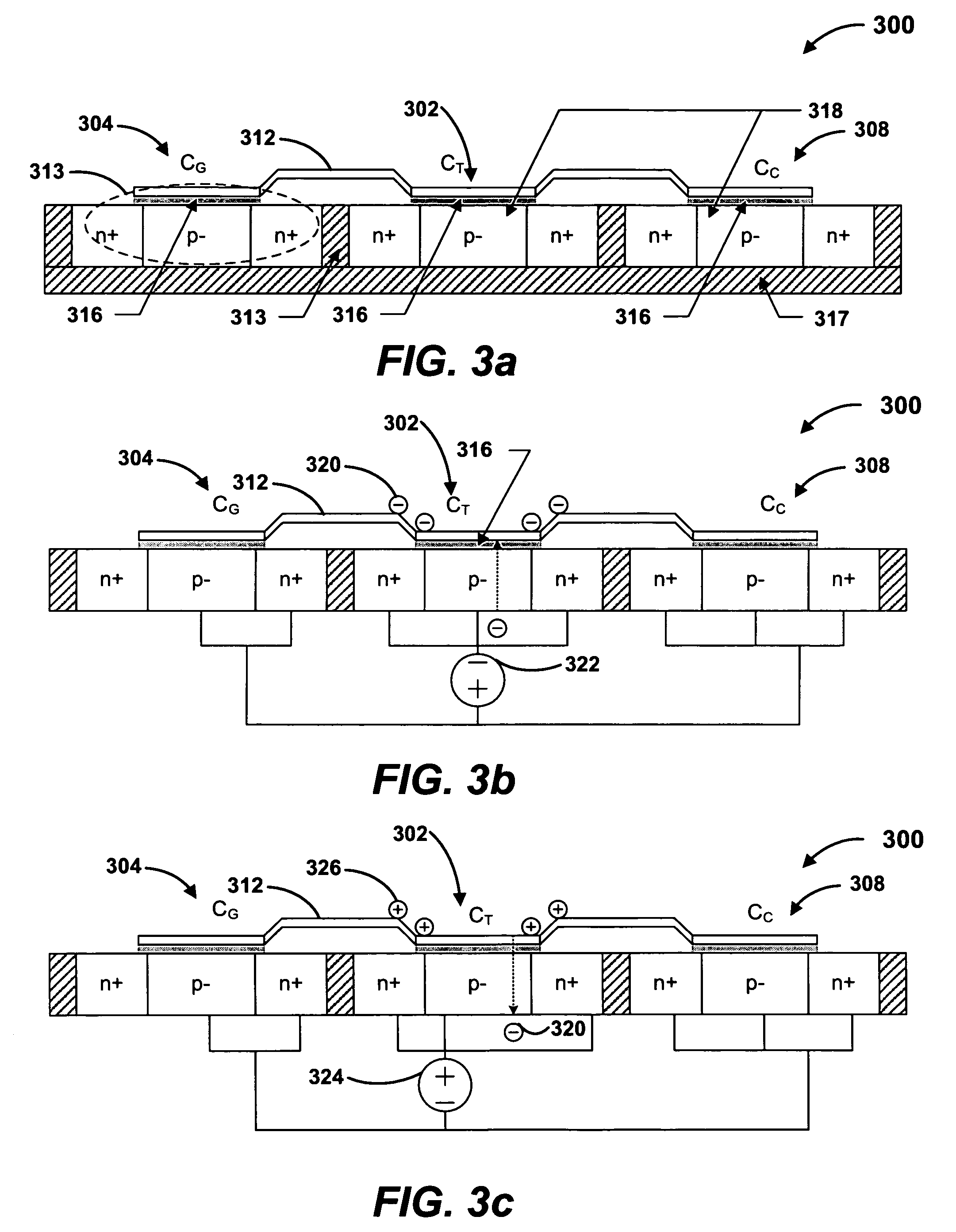

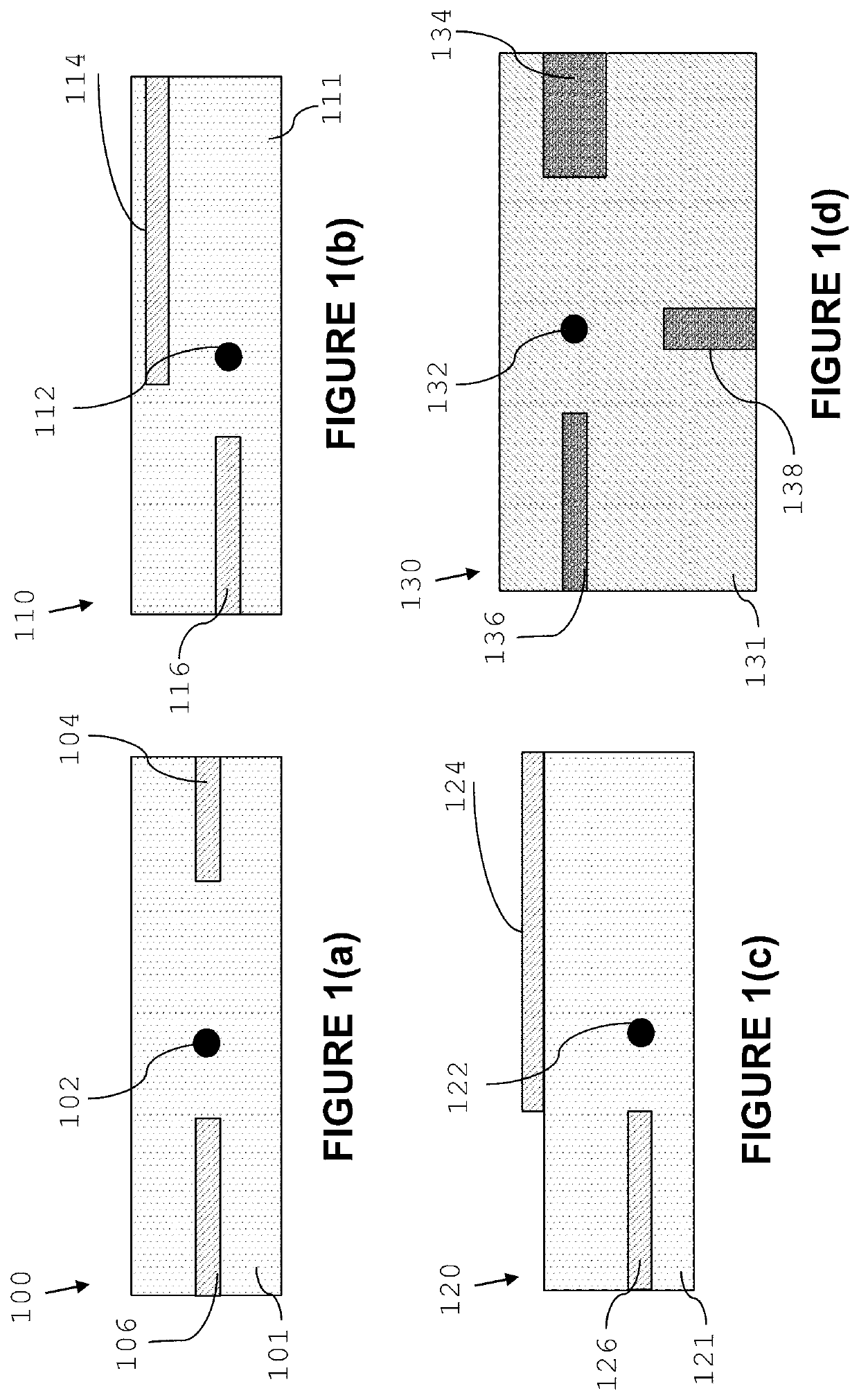

Single-poly EEPROM cell with lightly doped MOS capacitors

ActiveUS20070045710A1Reduce variationReduce needTransistorSolid-state devicesCapacitanceProgrammable read-only memory

An Electrically Erasable Programmable Read Only Memory (EEPROM) memory cell and a method of operation are disclosed for creating an EEPROM memory cell in a standard CMOS process. A single polysilicon layer is used in combination with lightly doped MOS capacitors. The lightly doped capacitors employed in the EEPROM memory cell can be asymmetrical in design. Asymmetrical capacitors reduce area. Further capacitance variation caused by inversion can also be reduced by using multiple control capacitors. In addition, the use of multiple tunneling capacitors provides the benefit of customized tunneling paths.

Owner:HONEYWELL INT INC

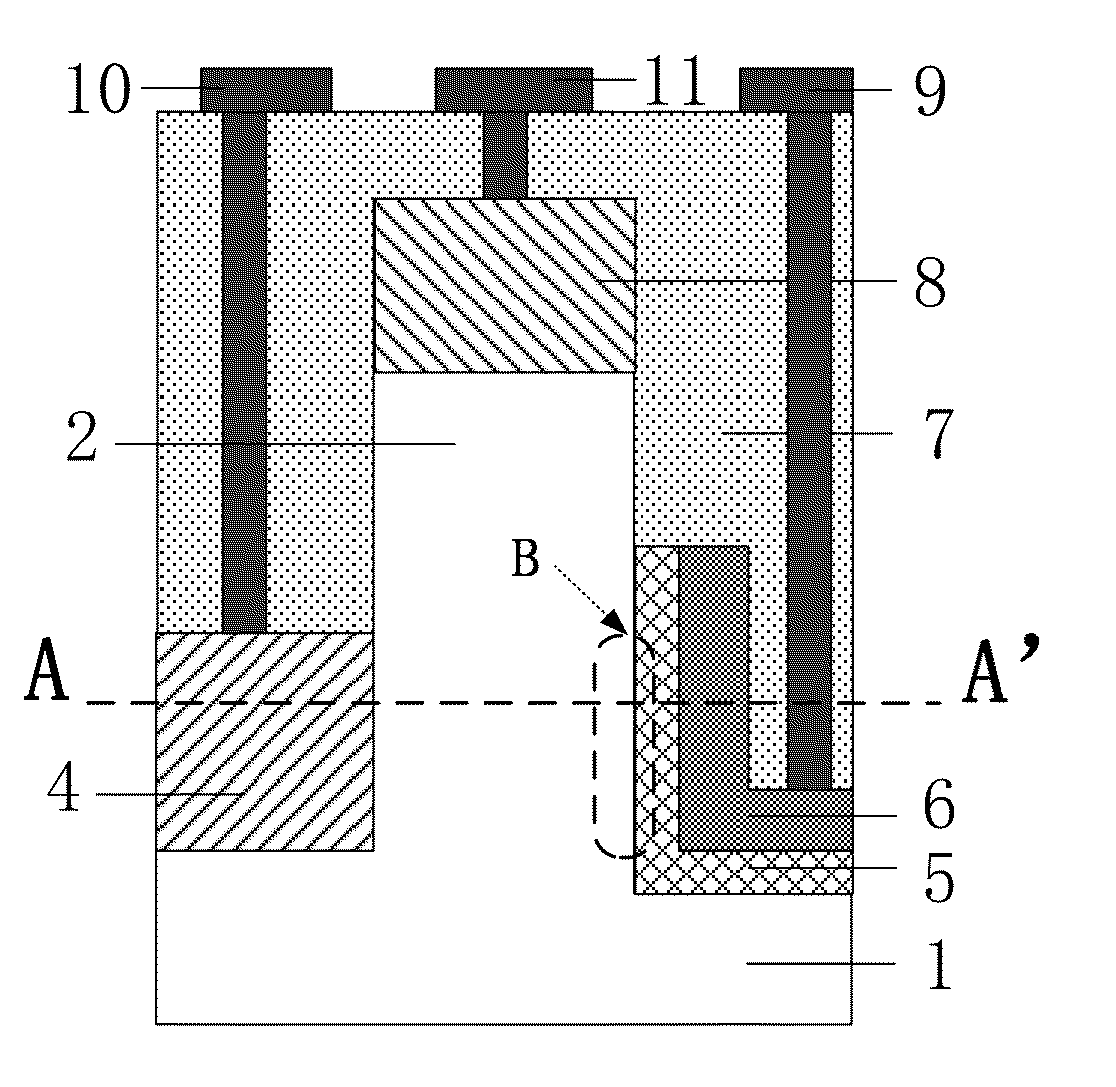

A junction-modulated tunneling field effect transistor and a fabrication method thereof

InactiveUS20160079400A1Improve featuresNarrow widthSemiconductor/solid-state device manufacturingDiodeEngineeringField-effect transistor

The present invention discloses a junction-modulated tunneling field effect transistor and a fabrication method thereof, belonging to a field of field effect transistor logic device and the circuit in connection with CMOS ultra large scale integrated circuit (ULSI). The PN junction provided by a highly-doped source region surrounding three sides of the vertical channel region of the tunneling field effect transistor can deplete effectively the channel region, so that the energy band of the surface channel under the gate is lifted, therefore the device may obtain a steeper energy band and a narrower tunneling barrier width than the conventional TFET when the band-to-band tunneling occurs, equivalently achieving the effect of a steep doping concentration gradient at the source tunneling junction, and thereby the sub-threshold characteristics are significantly improved while the turn-on current of the device is improved relative to the conventional TFET. Under the conditions that the device of the present invention is compatible with the existing CMOS process, on the one hand an ambipolar effect of the device can be inhibited effectively, while a parasitic tunneling current at a source junction corner in the small size device can be inhibited and thus can equivalently achieve an effect of a steep doping concentration gradient at the source junction.

Owner:PEKING UNIV

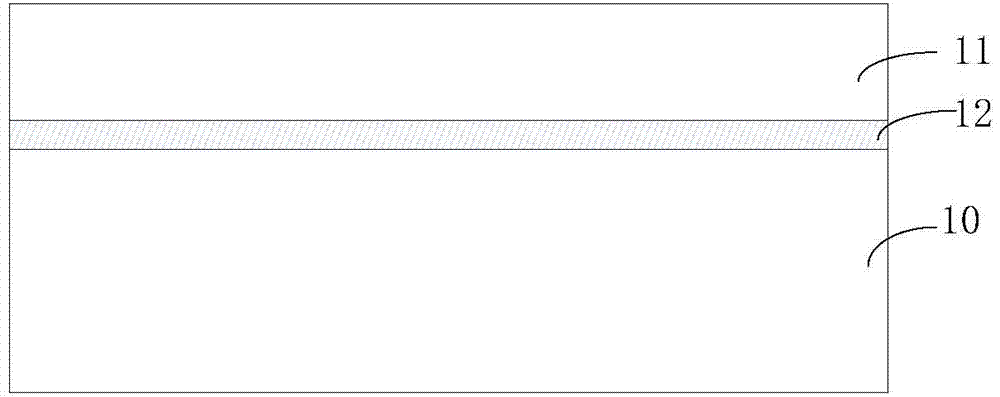

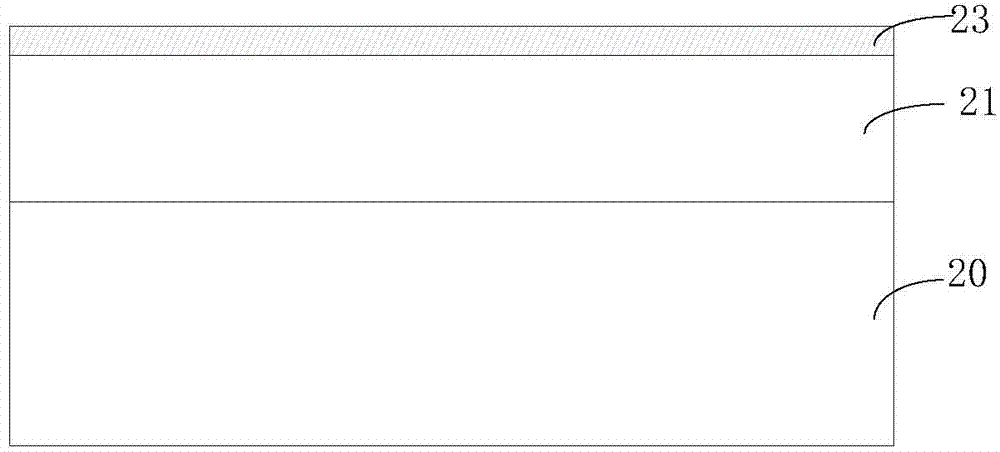

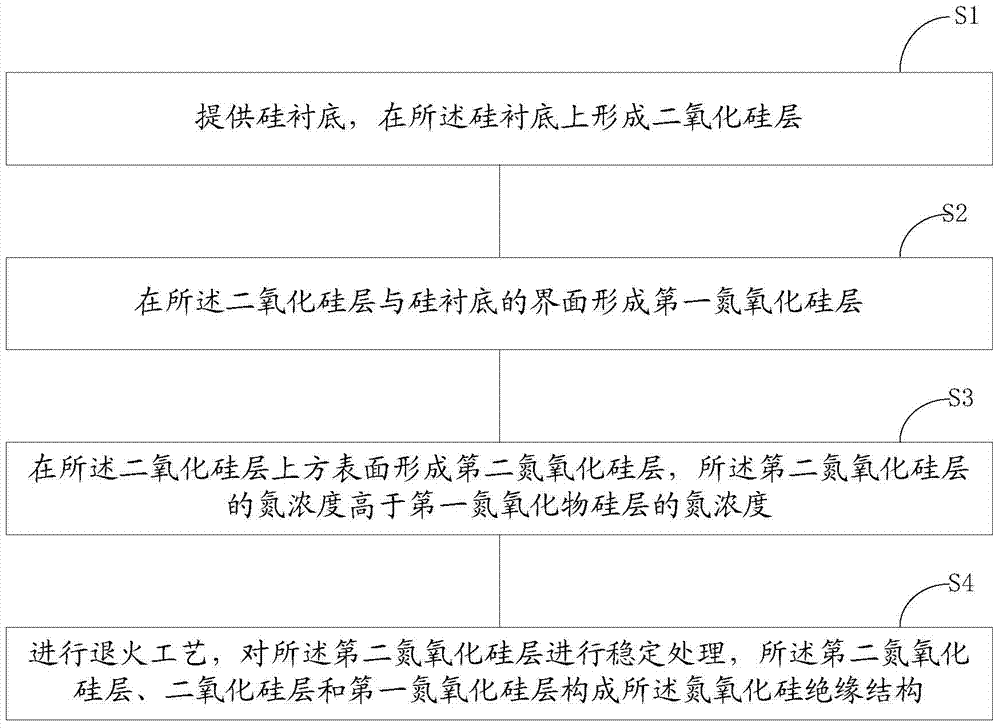

Silicon oxynitride insulation structure and manufacturing method thereof

InactiveCN103489771AAvoid tunnelingPrevent proliferationSemiconductor/solid-state device manufacturingSemiconductor devicesCharge carrierNitrogen

The invention provides a silicon oxynitride insulation structure and a manufacturing method of the silicon oxynitride insulation structure. The manufacturing method includes the steps that a silicon substrate is provided, and a silicon dioxide layer is formed on the silicon substrate; a first silicon oxynitride layer is formed on the interface between the silicon dioxide layer and the silicon substrate; a second ilicon oxynitride layer is formed on the upper surface of the silicon dioxide layer, and the nitrogen concentration of the second ilicon oxynitride layer is larger than that of the first silicon oxynitride layer; stabilizing processing is carried out on the second ilicon oxynitride layer by an annealing process, and silicon oxynitride insulation structure is composed of the second ilicon oxynitride layer, the silicon dioxide layer and the first silicon oxynitride layer and can prevent the tunnelling effect of carriers while preventing boron diffusion.

Owner:SHANGHAI HUALI MICROELECTRONICS CORP

Coal face fissure zone gas extraction method

PendingCN112302704AFully pumpedShort construction periodFluid removalGas removalMining engineeringGas concentration

The invention discloses a coal face fissure zone gas extraction method. According to the principle of the coal face fissure zone gas extraction method, before working face stoping, a drill hole arrangement method is determined through goaf overlying strata movement and gas seepage research, staggered high and low fissure zone directional long drill holes along the working face trend are arranged in a drilling field in a working face air return gate road, a main hole section of the high-position drill hole extends within the range of 30 m above a goaf formed after stoping of the working face, the low-position drill hole sinks properly at the position of the working face, a low negative pressure balanced extraction mode is adopted for the low-position drill hole, a high negative pressure balanced extraction mode is adopted for the high-position drill hole, and gas in a fissure zone and the goaf after stoping of the working face is extracted. According to the method, gas in the coal facefissure zone can be fully extracted, the gas concentration in the upper corner and the return air flow of the stoping face is reduced, meanwhile, the effect of treating goaf gas is achieved, gas treatment of the working face is achieved, and safe stoping of the coal face is guaranteed.

Owner:山西汾西矿业(集团)有限责任公司双柳煤矿

Application of Reduced Dark Current Photodetector

ActiveUS20140159188A1Total current dropAvoid tunnelingRadiation pyrometrySemiconductor/solid-state device detailsValence bandPhotodetector

A IDCA system with internal nBn photo-detector comprising: a photo-absorbing layer comprising an n-doped semiconductor exhibiting valence band energy level; a barrier layer, a first side of the barrier layer adjacent a first side of the photo-absorbing layer, the barrier layer exhibiting a valence band energy level substantially equal to the valence band energy level of the doped semiconductor of the photo absorbing layer; and a contact area comprising a doped semiconductor, the contact area being adjacent a second side of the barrier layer opposing the first side, the barrier layer exhibiting a thickness and conductance band gap sufficient to prevent tunneling of majority carriers from the photo-absorbing layer to the contact area, blocking the flow of thermalized majority carriers from the photo-absorbing layer to the contact area. Alternatively, a p-doped semiconductor is utilized, equalizing barrier conductance band energy levels and photo-absorbing layers.

Owner:MAIMON SHIMON

Doping method of semiconductor

ActiveCN101840854AAchieve dopingAvoid enteringSemiconductor/solid-state device manufacturingSemiconductor devicesAnti-reflective coatingIon implantation

The invention discloses a doping method of a semiconductor. After a grid is formed on a substrate, the method comprises the following steps of: coating bottom anti-reflective coatings (BARC) on the substrate surfaces at both sides of the grid; injecting ions into the substrates coated with BARCs, and ensuring that the ions can be injected into the substrates to realize doping, but can not penetrate through the substrates at the two sides of the BARC injection grid; removing the BARCs; re-injected ions into the substrate, the BARCs of which are removed, and ensuring that the ions can be injected into grid to realize doping and also can be injected into the substrate at both ends of the grid to realize doping so as to form a drain and a source. The invention can realize doping of the grid, the drain and the source at different concentration and avoid the tunneling effect.

Owner:SEMICON MFG INT (SHANGHAI) CORP

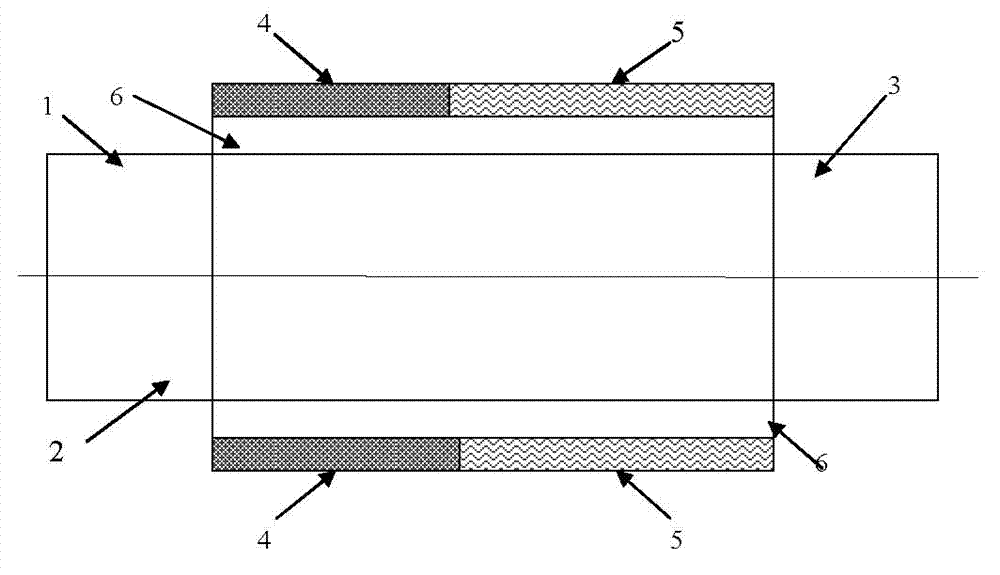

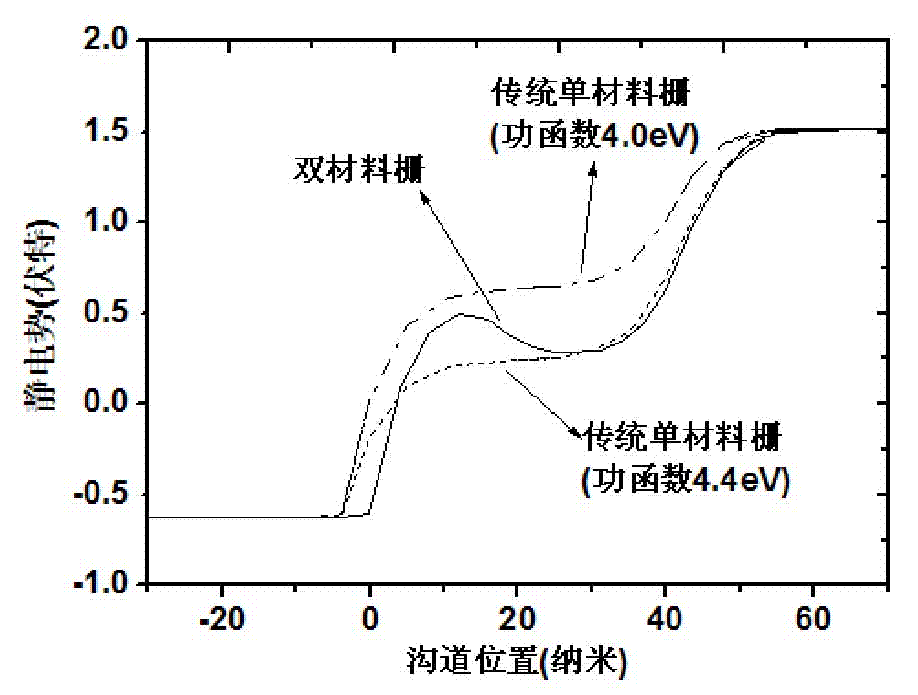

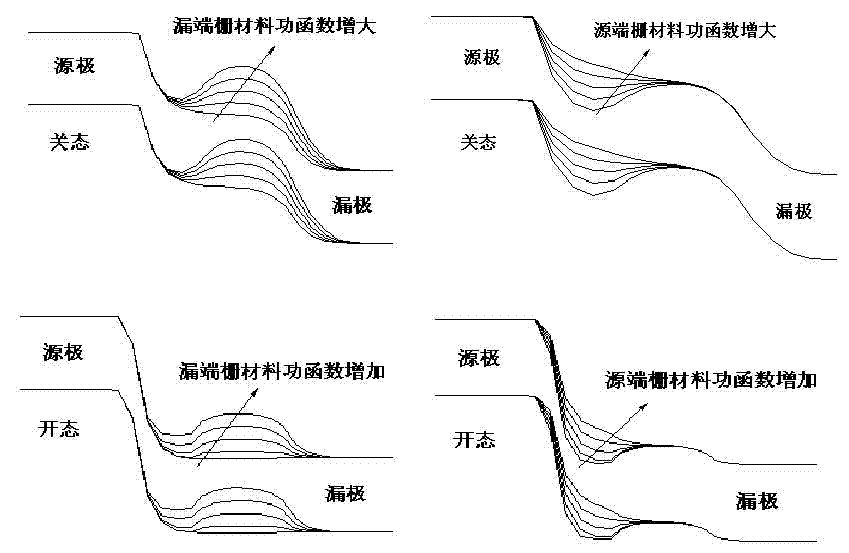

Bi-material railing nanowire tunneling field effect device and manufacturing method thereof

ActiveCN102956709AReduces off-state leakage currentHigh switching current ratioSemiconductor/solid-state device manufacturingSemiconductor devicesOxide semiconductorPhysics

The invention relates to a bi-material railing nanowire tunneling field effect device and a manufacturing method thereof. According to the bi-material railing nanowire tunneling field effect device, a channel is arranged at the center, and a source region and a drain region are respectively arranged at two ends, and an oxide and a gate electrode are covered at the periphery of the channel in sequence. The manufacturing method comprises the steps: SF6 etching a silicon column on a silicon wafer by using a round silicon nitride hard mask; conducting high-temperature oxidation, corroding and reducing the size of the silicon column to be a set diameter value of 6nm-30nm with HF aqueous solution, and conducting high-temperature oxidation to form a silicon column coated by an oxidation layer with set thickness; completing the preparation of a bi-material railing structure by adopting deposition and photoetching technology; and injecting boron and phosphorus of 1*10<20>cm<-2> / 10keV and 5*10<18>cm<-2> / 10keV at 120-150 DEG C respectively, and annealing at 900 DEG C / 10s-1100 DEG C / 10s to prepare the source region and the drain region; completing preparation of a metal electrode by CMOS (Complementary Metal-Oxide-Semiconductor) process; and manufacturing the bi-material railing nanowire tunneling field effect device.

Owner:PEKING UNIV SHENZHEN GRADUATE SCHOOL

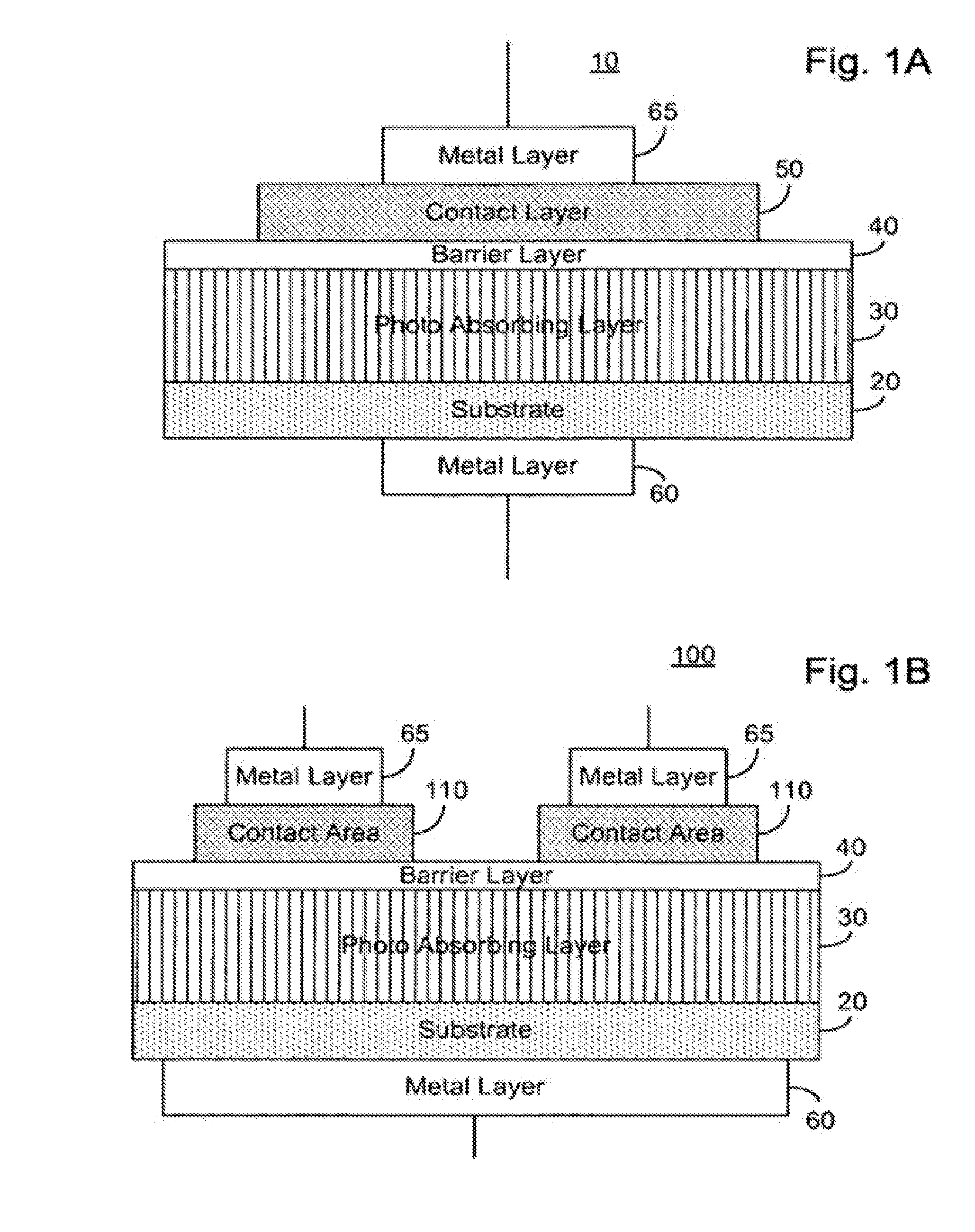

Application of reduced dark current photodetector with a thermoelectric cooler

ActiveUS9766130B2Total current dropAvoid tunnelingSemiconductor/solid-state device detailsSolid-state devicesValence bandThermoelectric cooling

A IDCA system combining thermo-electric cooler (TEC) and an internal nBn photo-detector having a photo absorbing layer comprising an n-doped semiconductor exhibiting a valence band energy level; and a contact layer comprising a doped semiconductor. A barrier layer is disposed between the photo absorbing layer and the contact layer, the barrier layer exhibiting a valence band energy level substantially equal to the valence band energy level of the doped semiconductor of the photo absorbing layer; the barrier layer exhibiting a thickness and a conductance band gap sufficient to prevent tunneling of majority carriers from the photo absorbing layer to the contact area and block the flow of thermalized majority carriers from the photo absorbing layer to the contact area. Alternatively, a p-doped semiconductor is utilized, and conductance band energy levels of the barrier and photo absorbing layers are equalized.

Owner:MAIMON SHIMON

Method for doping grid electrode, drain electrode and source electrode in semiconductor manufacturing process

ActiveCN101882574AAchieve dopingAvoid enteringSemiconductor/solid-state device manufacturingSemiconductor devicesIon implantationSemiconductor

The invention discloses a method for doping a grid electrode, a drain electrode and a source electrode in the semiconductor manufacturing process. The method comprises the following steps of: forming the grid electrode on a substrate, then coating bottom anti-reflective coating (BARC) on the surface of the grid electrode and the surfaces of the substrates at two sides of the grid electrode, wherein the BARC coated on the surface of the substrate is higher than the surface of the grid electrode; etching the BARC which is higher than the surface of the grid electrode, enabling the BARC on the surfaces of the substrates at two sides of the grid electrode to the surface of the grid electrode, and carrying out first ion implantation; eliminating the BARC; and carrying out ion implantation again. The method can realize the doping with the grid electrode, the drain electrode and the source electrode in different concentrations and prevent the tunneling effect.

Owner:SEMICONDUCTOR MANUFACTURING INTERNATIONAL (BEIJING) CORP

Single-poly EEPROM cell with lightly doped MOS capacitors

ActiveUS7378705B2Reduce variationReduce needTransistorSolid-state devicesCapacitanceProgrammable read-only memory

An Electrically Erasable Programmable Read Only Memory (EEPROM) memory cell and a method of operation are disclosed for creating an EEPROM memory cell in a standard CMOS process. A single polysilicon layer is used in combination with lightly doped MOS capacitors. The lightly doped capacitors employed in the EEPROM memory cell can be asymmetrical in design. Asymmetrical capacitors reduce area. Further capacitance variation caused by inversion can also be reduced by using multiple control capacitors. In addition, the use of multiple tunneling capacitors provides the benefit of customized tunneling paths.

Owner:HONEYWELL INT INC

Application of reduced dark current photodetector with a thermoelectric cooler

ActiveUS20150372035A1Reduce dark noiseLess powerSemiconductor/solid-state device detailsSolid-state devicesValence bandThermoelectric cooling

A IDCA system combining thermo-electric cooler (TEC) and an internal nBn photo-detector comprising: a photo absorbing layer comprising an n-doped semiconductor exhibiting a valence band energy level; a barrier layer, a first side of the barrier layer adjacent a first side of the photo absorbing layer, the barrier layer exhibiting a valence band energy level substantially equal to the valence band energy level of the doped semiconductor of the photo absorbing layer; and a contact area comprising a doped semiconductor, the contact area being adjacent a second side of the barrier layer opposing the first side, the barrier layer exhibiting a thickness and a conductance band gap sufficient to prevent tunneling of majority carriers from the photo absorbing layer to the contact area and block the flow of thermalized majority carriers from the photo absorbing layer to the contact area. Alternatively, a p-doped semiconductor is utilized, and conductance band energy levels of the barrier and photo absorbing layers are equalized.

Owner:MAIMON SHIMON

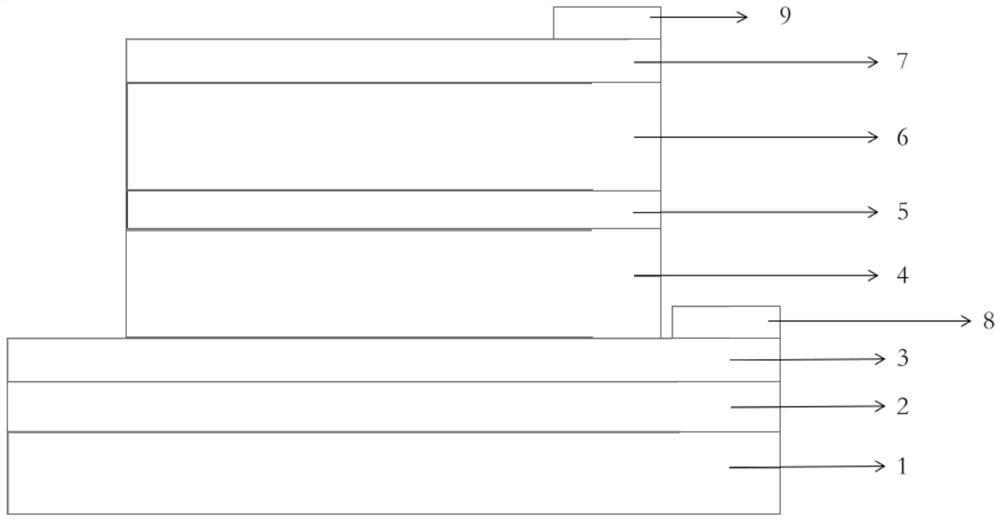

Barrier enhanced homotype heterojunction II type superlattice long/long wave two-color infrared detector

PendingCN114068738ALittle contributionImprove effective qualitySemiconductor devicesHeterojunctionDark current

The invention provides a barrier enhanced homotype heterojunction type II superlattice long / long wave double-color infrared detector. The infrared detector comprises a buffer layer, a P-type first ohmic contact layer, a P-type first long wave absorption layer, a P-type hole barrier layer, a P-type second long wave absorption layer and a P-type second ohmic contact layer which are sequentially epitaxially grown on a substrate, and the P-type first long-wave absorption layer and the P-type second long-wave absorption layer respectively form homotype doped heterojunctions with the P-type hole barrier layer. According to the structure disclosed by the invention, a bicolor detection function in a long wave band is realized through bias voltage modulation, and the structure is simple, through introduction of a homotype doped heterojunction and a single-barrier structure, compared with a traditional two-color detector of an NPPN structure, the two-color detector has the advantages that a space electric field in a long-wave absorption region is greatly reduced, composite dark current and tunneling dark current generated in the absorption region are effectively inhibited, and the signal-to-noise ratio and the detection rate of the device are improved.

Owner:中科爱毕赛思(常州)光电科技有限公司

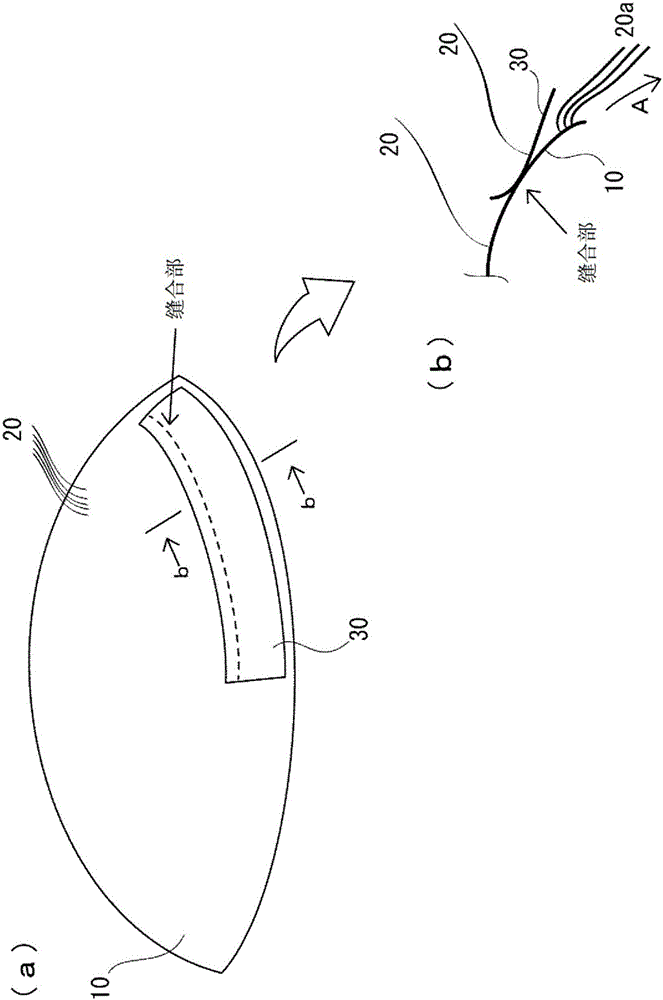

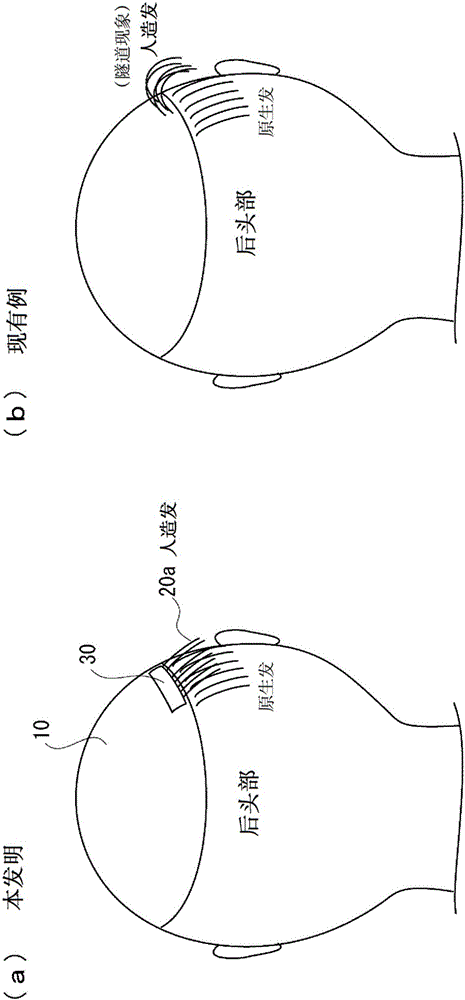

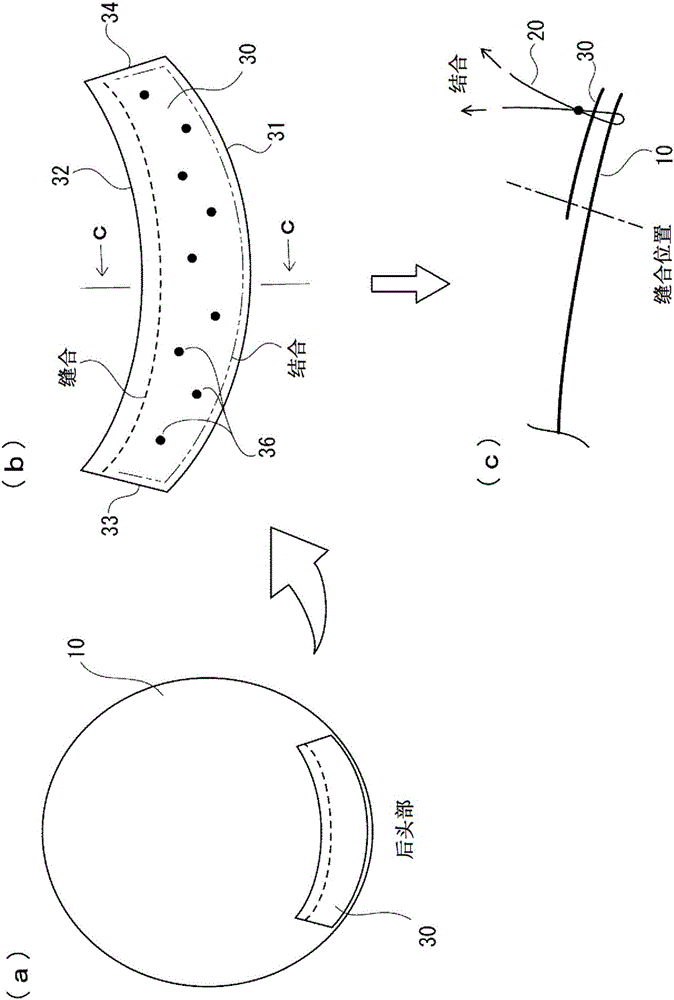

Wig

InactiveCN106659258AImprove coordinationAvoid tunnelingHair accessoriesToupeesEngineeringArtificial hair wig

The invention discloses a wig. In at least a portion of the peripheral region of a wig base (10) that is fitted to the head of a wearer, a pressing member (30) having a prescribed width is fixed to the wig base (10) so as to cover the root of an imitation hair (20a) that has been set in the wig base (10). The imitation hair (20a) in the wig periphery, said hair being held down by the pressing member (30), protrudes outwardly along the extension direction of the wig base (10), and this direction is close to the extension direction of the user's own hair which is remaining on the head. Consequently, a tunnel phenomenon can be prevented, and affinity between imitation hair (20a) and the user's own hair is improved.

Owner:ADERANS CO LTD

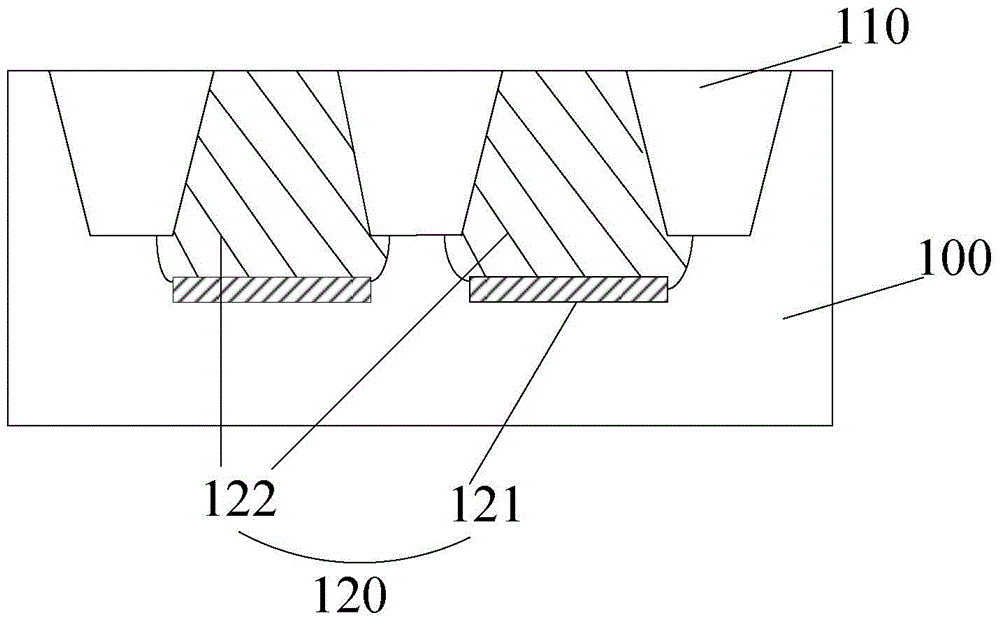

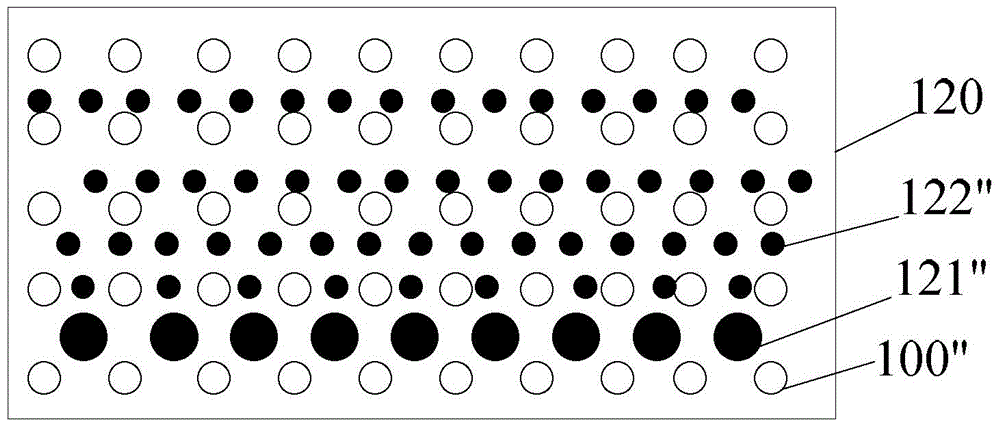

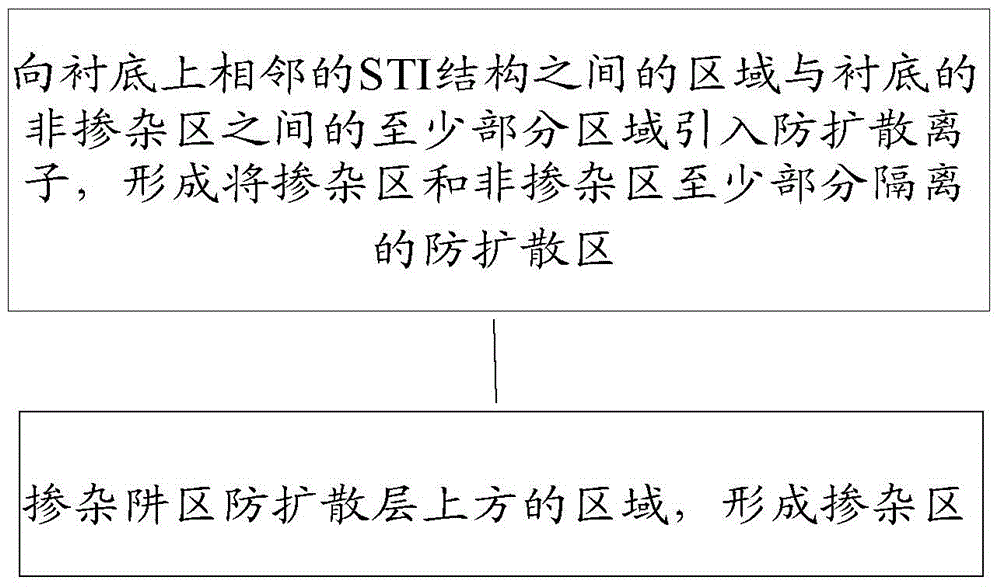

CMOS device and forming method thereof

InactiveCN105448913AReduce leakage currentEasy to useTransistorSemiconductor/solid-state device manufacturingCMOSLow leakage

The invention discloses a CMOS device and a forming method thereof. The CMOS device comprises STI structures and well region structures located between the adjacent STI structures. Each well region structure comprises a doping region and an anti-diffusion region, wherein the doping region is disposed in a substrate, and the anti-diffusion region is disposed between the doping region and a non-doping region of the substrate, and enables the doping region and the non-doping region to be at least separated. The anti-diffusion regions are additionally disposed below the doping regions in the well region structures of the CMOS device. The pre-formed anti-diffusion regions can prevent the movement of doping ions in the subsequent doping process and the power-on application process of the device, thereby preventing the doping ions from diffusing towards the substrate from a preset well region. The leakage of the doping ions to the substrate will be correspondingly reduced based on a condition that the diffusion of the doping ions towards the substrate from the well region is limited. Moreover, the lower leakage of the doping ions facilitates the tunneling effects between the well region and the substrate even between different well regions in the subsequent use process, thereby reducing the leaked current of the CMOS device, and enabling the device to be higher in usability.

Owner:SEMICON MFG INT (SHANGHAI) CORP +1

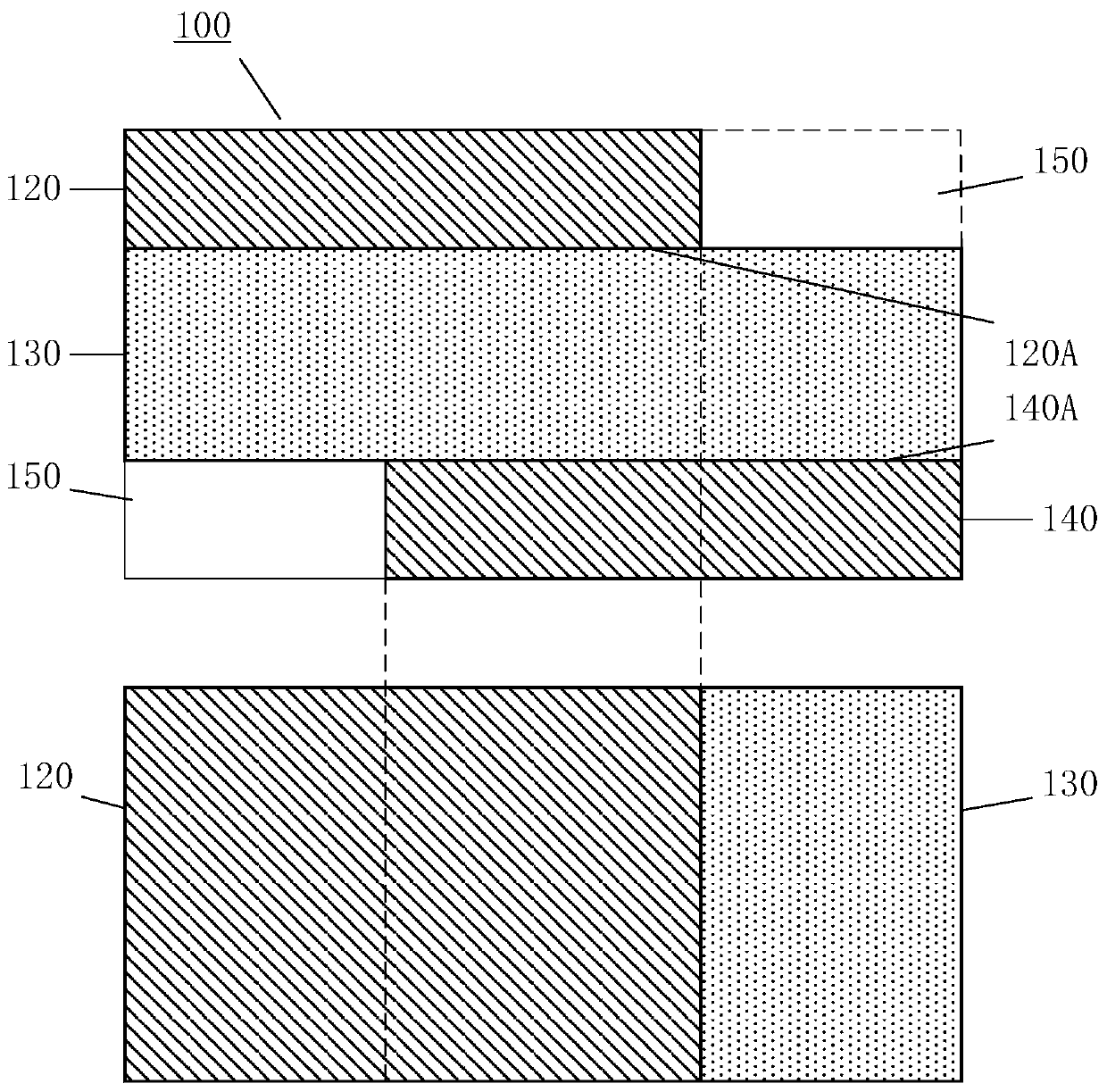

Vertical electrode configuration structure for nanoscale phase change memory cell

ActiveCN110635030AAvoid tunnelingExtend your lifeElectrical apparatusNon symmetricPhase-change memory

The invention discloses a vertical electrode configuration structure for a nanoscale phase change memory cell. The vertical electrode configuration structure comprises an upper electrode material layer, a middle phase change material layer and a lower electrode material layer, wherein the upper electrode material layer and the lower electrode material layer are of asymmetric upper and lower electrode structures and can perform source and drain end exchange, and insulating medium protection layers are arranged on the side of the lower electrode material layer and below the middle phase change material layer. For a low-resistance crystalline state, by constructing an asymmetric upper and lower electrode structure, compared with a structure directly facing a vertical electrode, the equivalentresistance R is increased, the working current is reduced, tunneling of a large current is avoided, and the service life of the device is prolonged, moreover, the non-opposite area component shunts the current of the series path, current diffusion in the series process is increased, the working current is reduced, and the smaller the working current is, the more difficult the metastable crystalline phase structure is broken down.

Owner:HUAZHONG UNIV OF SCI & TECH

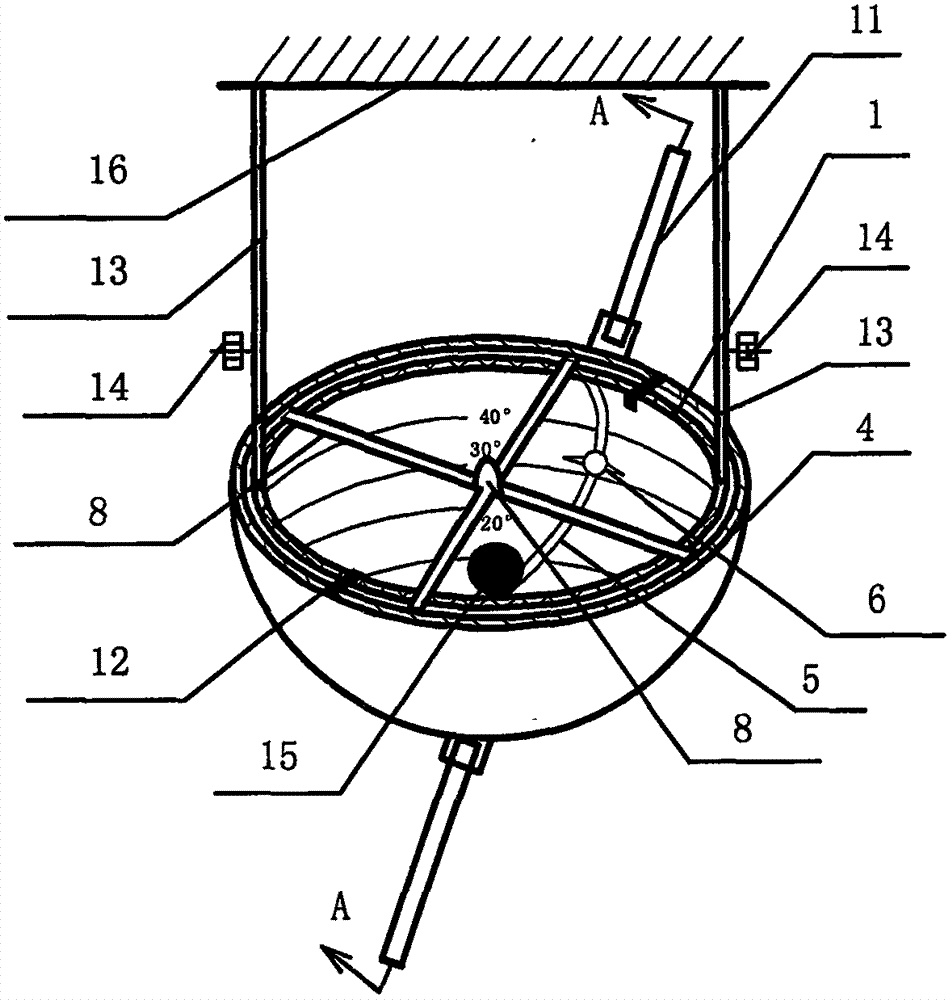

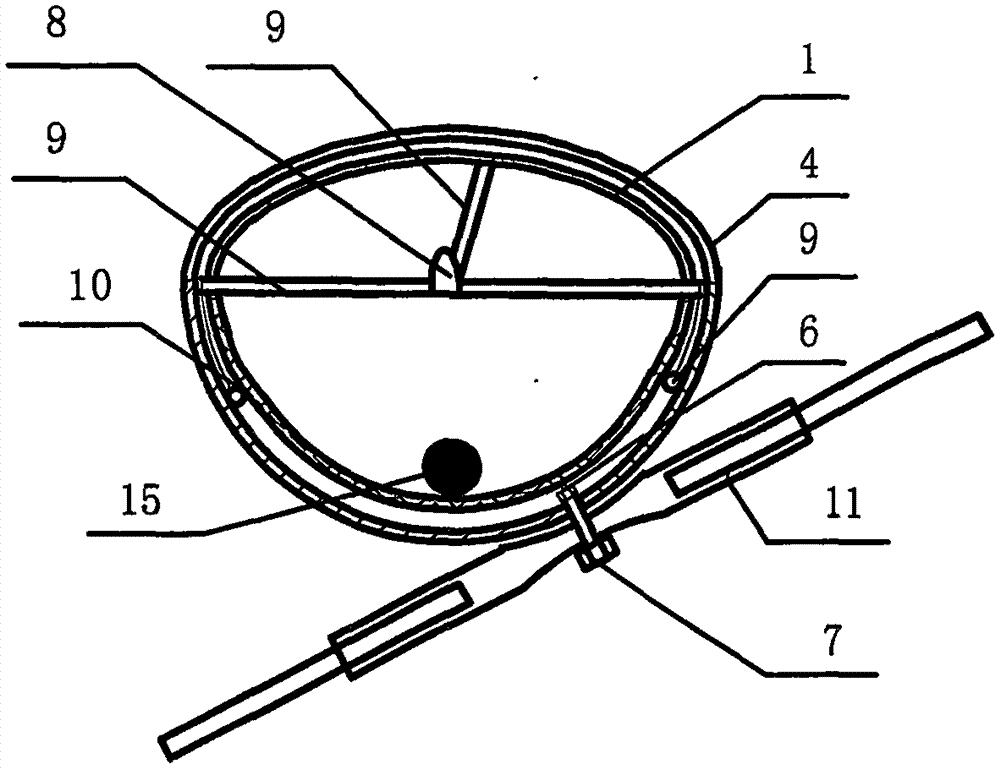

Bidimensional orientating device for coal mine underground roadway

The invention discloses a bidimensional orientating device for a coal mine underground roadway, which is composed of: a marking mechanism, a rotation mechanism, an indicating mechanism, an isolation mechanism and an assistant mechanism. The marking mechanism is composed of a longitude and latitude sphere shell (1), longitude scales (2) and latitude scales (3); the rotation mechanism is composed of a rotatable shell (4) and a warpwise groove (5); the indicating mechanism is composed of a screw rod pointer (6), a control nut (7), a telescopic rod (11) and a leveling ball (15); the isolation mechanism is composed of a control handle (8), a control panel (9) and an isolation ball (10); the assistant mechanism is composed of a connection board (12), an adjustable connection rod (13), an adjusting nut (14) and the leveling ball (15). The bidimensional orientating device works in a dead zone of a theodolite or a total station instrument and overcomes the defects of the theodolite or total station to some degree, avoids tunneling into an abandoned roadway and avoids safety and economic loss caused by constructing a waste hole and mis-penetrating a wasted and abandoned roadway.

Owner:HEBI AUTOMOTIVE ENG PROFESSIONAL COLLEGE

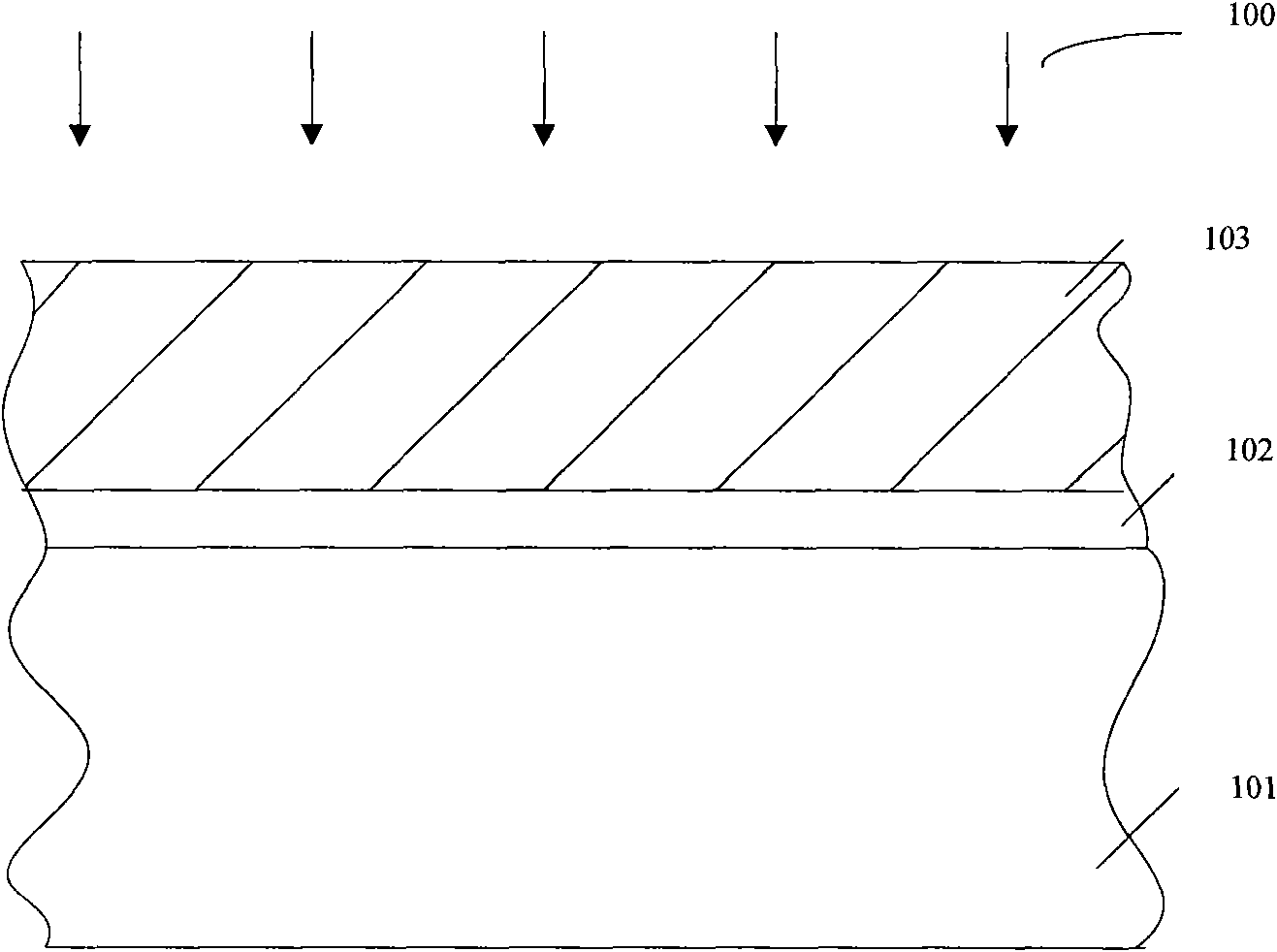

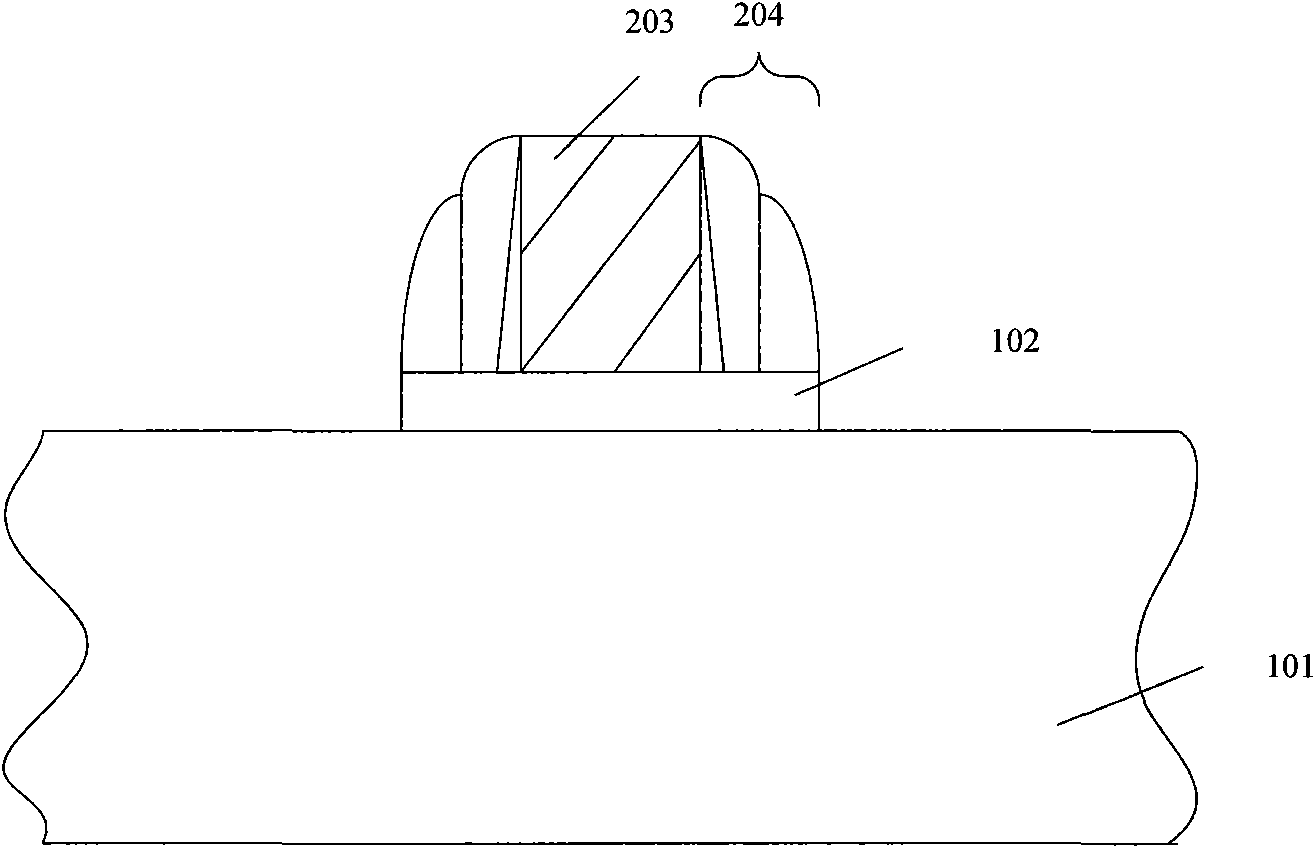

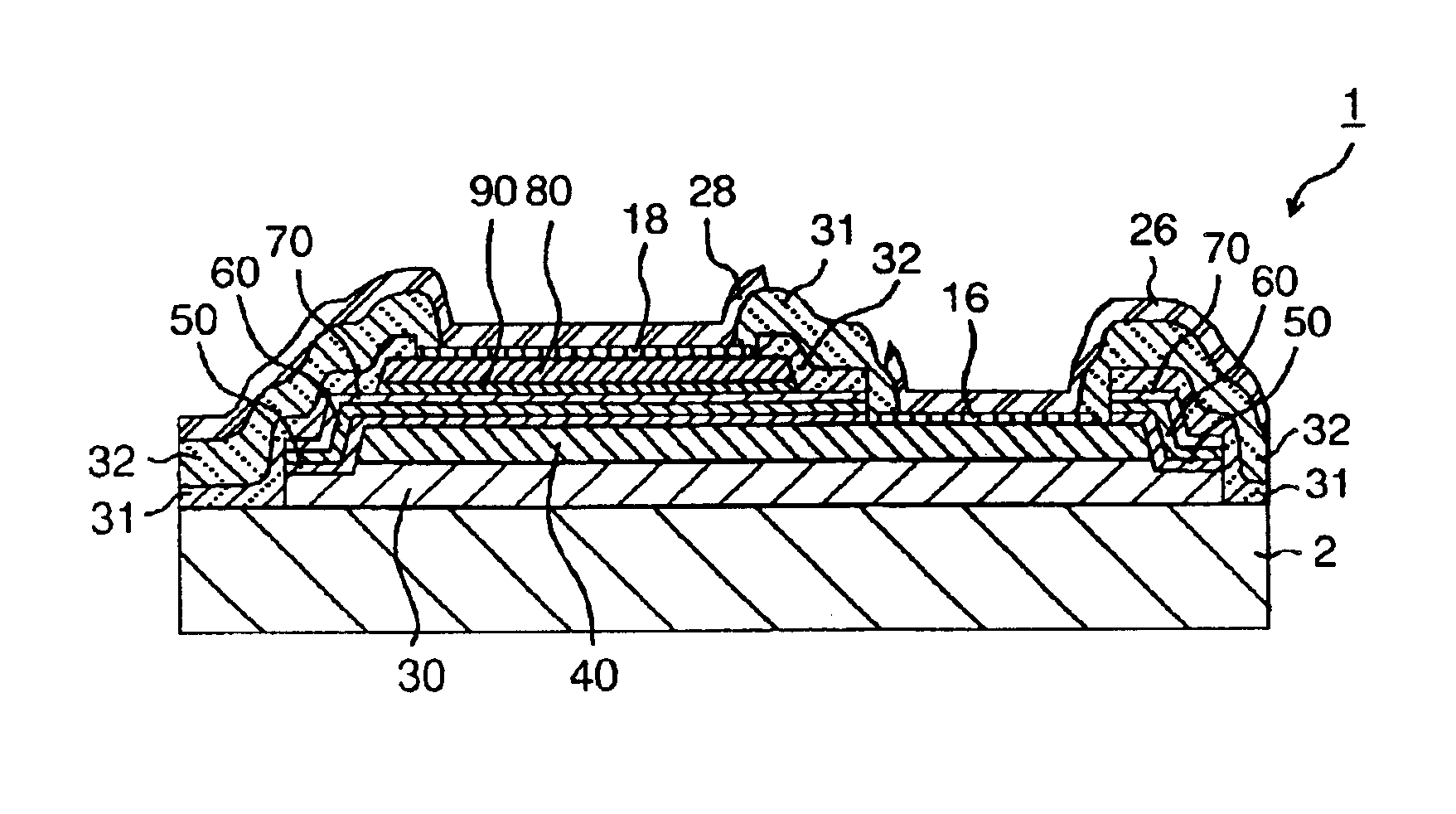

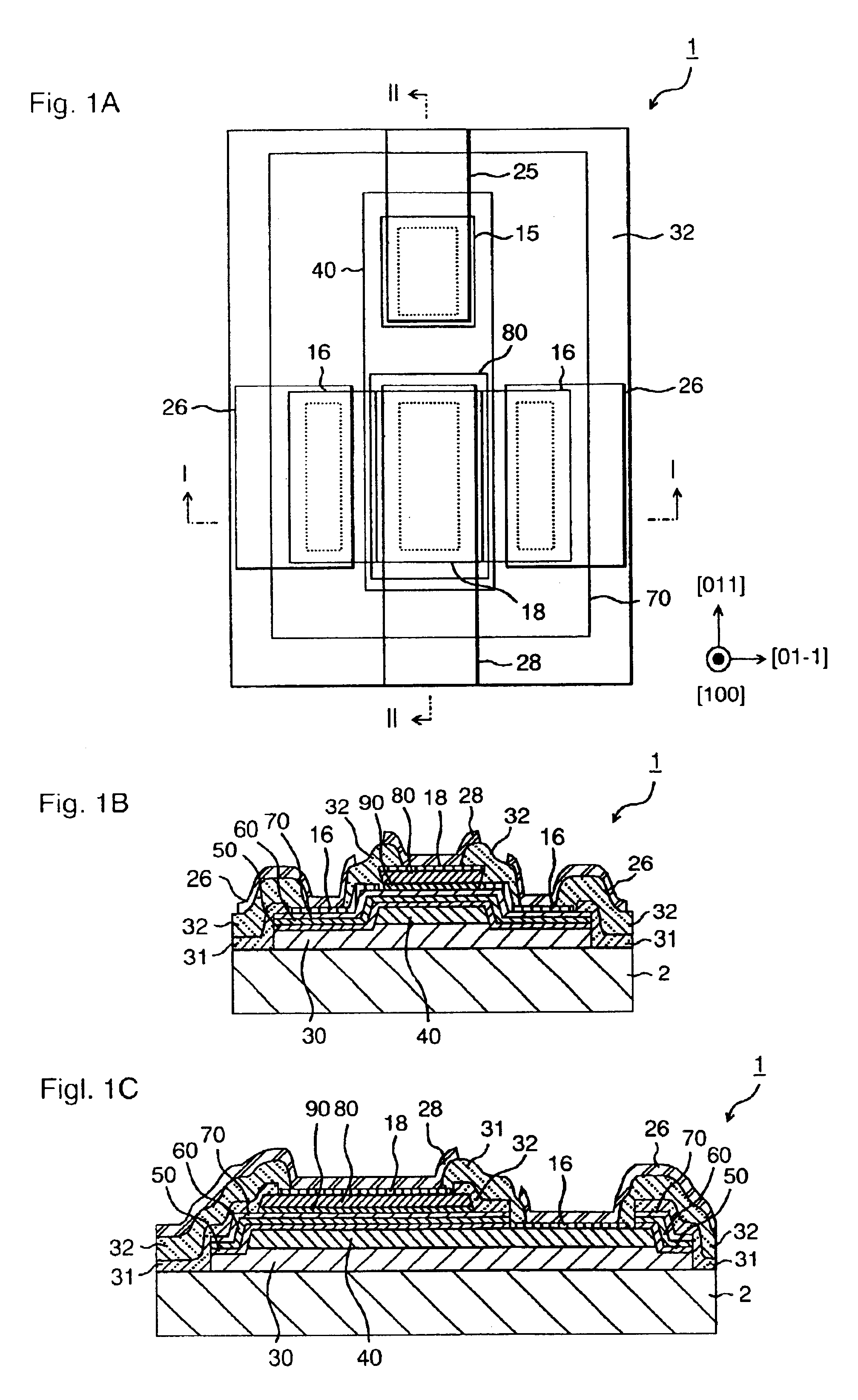

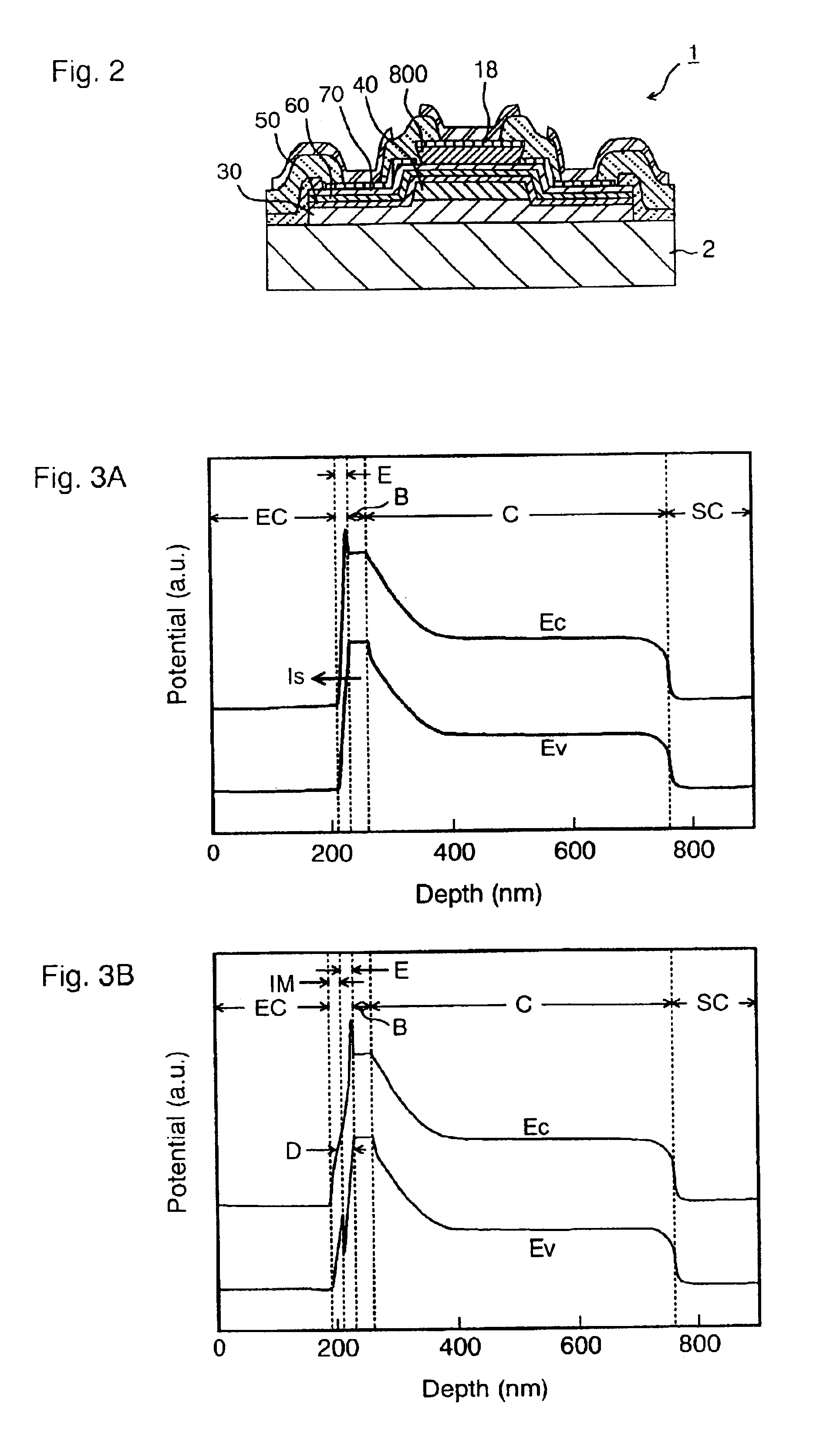

Hetero-bipolar transistor

InactiveUS6876012B2Increase current gainSuppress such carrier recombinationSemiconductor/solid-state device manufacturingSemiconductor devicesValence bandRecombination current

The present invention provides a Hetero-Bipolar Transistor that suppresses a recombination current between electrons in the conduction band of an emitter and holes in the valence band of a base, which results on an enhancement of the current gain of the transistor. The HBT according to the present invention comprises a semi-insulating semiconductor substrate and a series of semiconductor layers on the substrate. The semiconductor layers are a buffer layer, a sub-collector layer a collector layer, a base layer, an emitter layer, an emitter contact layer, and an intermediate layer between the emitter layer and the emitter contact layer. The emitter layer has a carrier concentation of 1.0×1019 cm−3.

Owner:SUMITOMO ELECTRIC IND LTD

Low electric field source erasable non-volatile memory and methods for producing same

ActiveUS9640403B2Overcomes drawbackAvoid tunnelingTransistorSolid-state devicesElectricityLower face

A low electric field source erasable non-volatile memory unit includes a substrate having a source diffusion region and a drain diffusion region. The source diffusion region includes a heavily-doped region and a lightly-doped region extending. A first dielectric layer and a tunnel dielectric layer are formed on the substrate. The tunnel dielectric layer includes a lower face contiguous to or partially overlapped with the lightly-doped region of the source diffusion region. A select gate and a floating gate are respectively formed on the first dielectric layer and the tunnel dielectric layer. The floating gate includes a source side edge contiguous to or partially overlapped with the lightly-doped region and misaligned from the heavily-doped region by a distance. A second dielectric layer and a control gate are formed on the floating gate. The control gate and the floating gate are insulating to each other by the second dielectric layer.

Owner:XINNOVA TECH

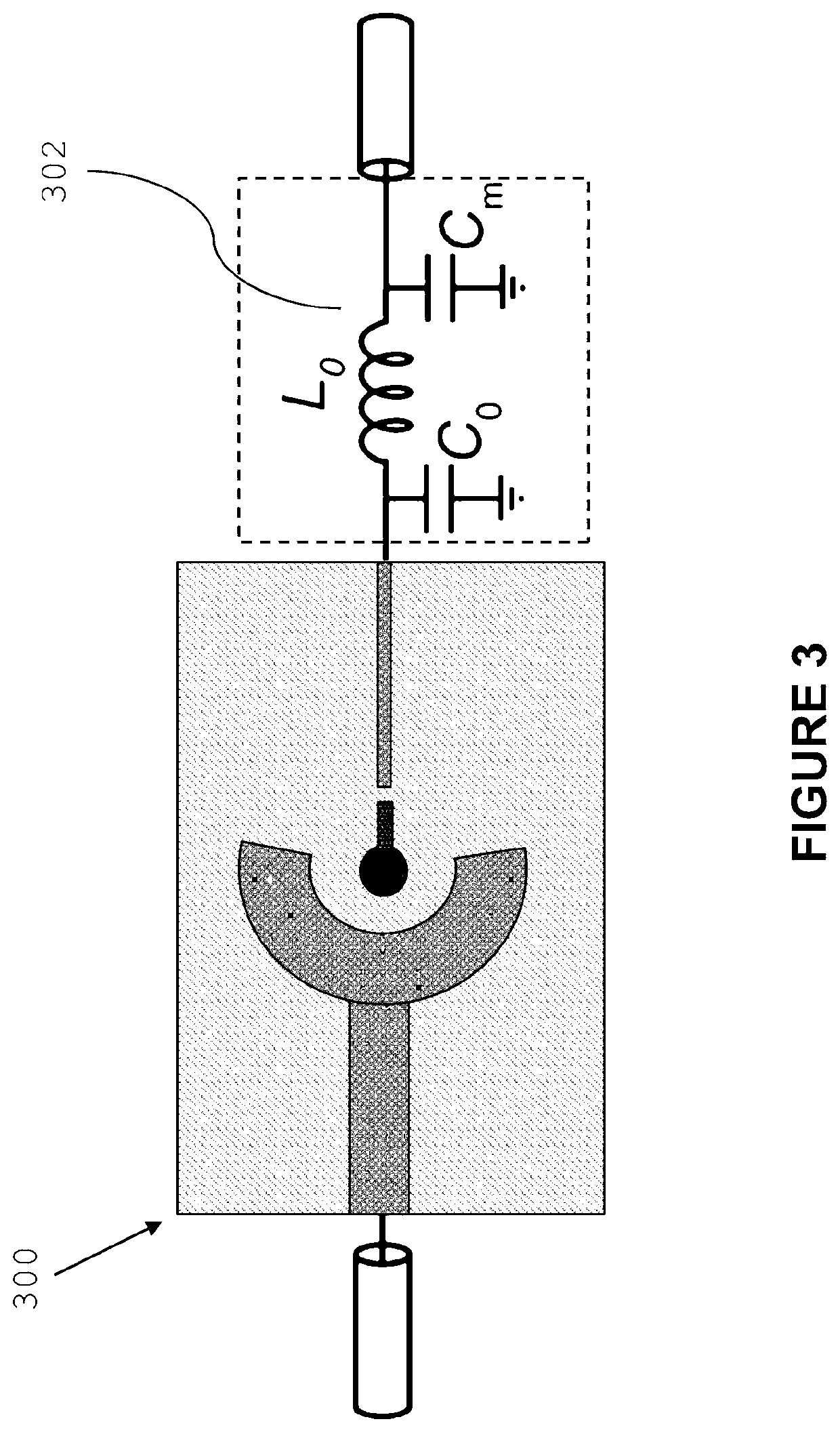

A parametric amplifier

ActiveUS20210135643A1Tunnelling of electrons to the quantum dot is preventedAvoid tunnelingNanoopticsVariable-capacitor element amplifiersCapacitanceQuantum dot

The present disclosure relates to parametric amplifiers that can be used in the presence of a magnetic field. In particular the present disclosure relates to an integrated signal amplifier that comprises: a quantum dot; a first conductive electrode arranged in a manner such that tunnelling of electrons to the quantum dot is prevented; and a second conductive electrode arranged in a manner such tunnelling of electrons to the quantum dot is permitted. When an oscillating signal is applied across the first and second electrodes, the equivalent capacitance across the first and the second electrodes oscillates at the frequency of the oscillating signal.

Owner:NEWSOUTH INNOVATIONS PTY LTD

A kind of filling mining method for multi-layer gently inclined thin-medium thick ore deposit

ActiveCN103628877BIncrease production capacityHigh recovery rateUnderground miningSurface miningMechanical engineeringMineralogy

The invention relates to a multilayer gentle dip thin-medium ore deposit filling and mining method. According to the technical scheme, the method comprises the following steps: dividing ore blocks, arranging mining and cutting projects, transporting, mining and filling. The step of dividing an ore deposit comprises the following sub-steps: dividing an ore body in the stage into a disc area, tunneling to uphill (2) at the bottom of an ore layer (1) along the inclined direction of the ore body, dividing the ore body on two sides into ore chambers (15) and ore columns (14) along the uphill (2), and reserving uphill ore columns (18) by taking the uphill (2) as the center. Three-step recovery is adopted in the disc area and comprises a first step of recovering the ore chambers (15), a second step of recovering the ore columns (14) and a third step of recovering the uphill ore columns (18); after the ore chambers (15) or the ore columns (14) are totally recovered, a goaf area (11) is downwards filled through the uphill (2) on the upper layer and via filling ventilation holes (10) communicated with a stope; finally, the uphill ore columns (18) are recovered within three steps from bottom to top along the uphill (2) by taking the disc area as a unit, and the uphill ore columns (18) in the next disc area are recovered after filling. The method has the characteristics of high mining intensity, high ore recovery rate, low ore dilution ratio and low mining cost.

Owner:WUHAN UNIV OF SCI & TECH