CMOS device and forming method thereof

A device, anti-diffusion technology, applied in semiconductor/solid-state device manufacturing, electrical components, transistors, etc., to achieve the effect of reducing leakage current and high performance

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

preparation example Construction

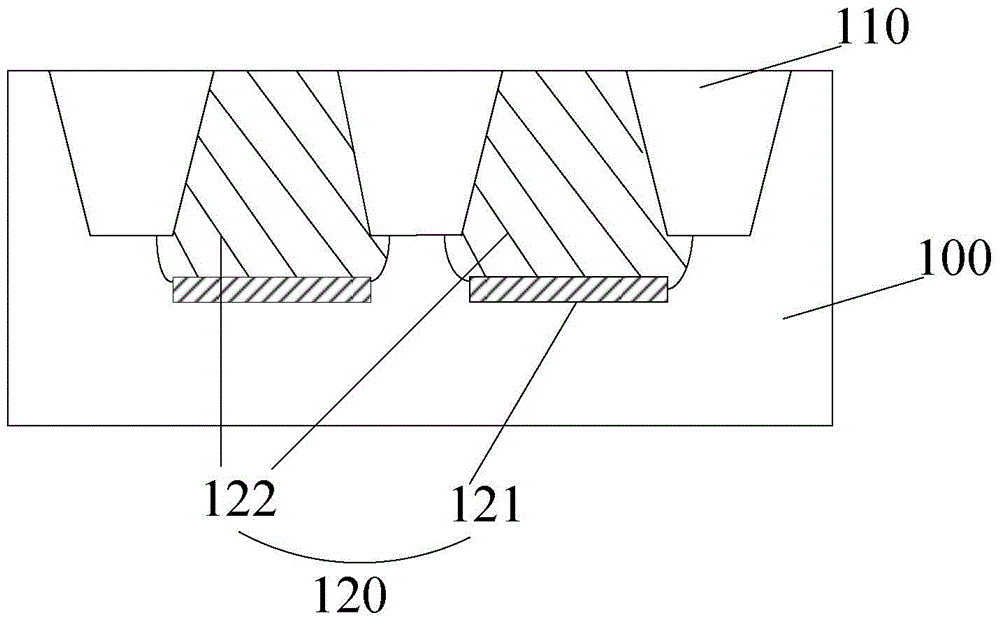

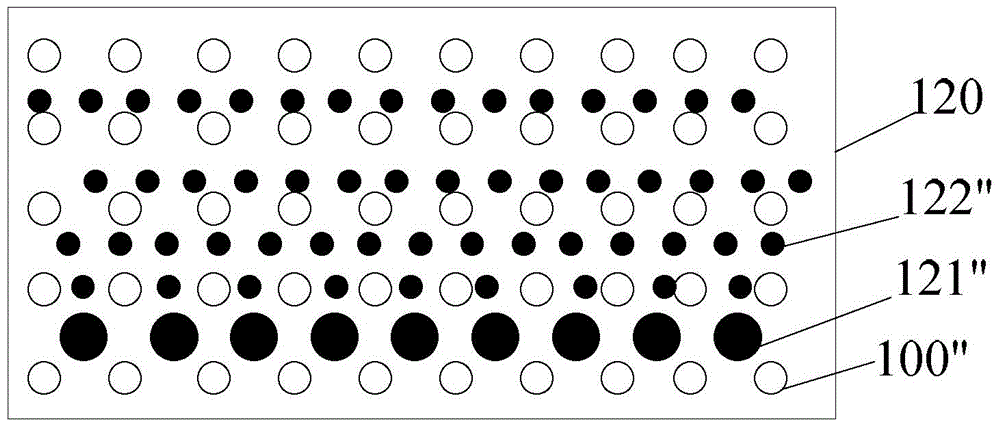

[0043] In the preparation process of the well structure, the area for forming the well structure is often set between adjacent STI structures, so as to isolate the well structures with different electrical properties and jointly form the functional area of the CMOS device. The method for forming the well region structure on the substrate forming the STI structure region (STI) will be described in detail below:

[0044] First, provide the Figure 4 In the substrate 100 shown, an STI structure 110 may be pre-formed therein. Wherein, the substrate 100 may be single crystal silicon, silicon on insulator (SOI) or silicon germanium (SiGe) or the like. As an example, in this embodiment, the substrate 100 is made of single crystal silicon.

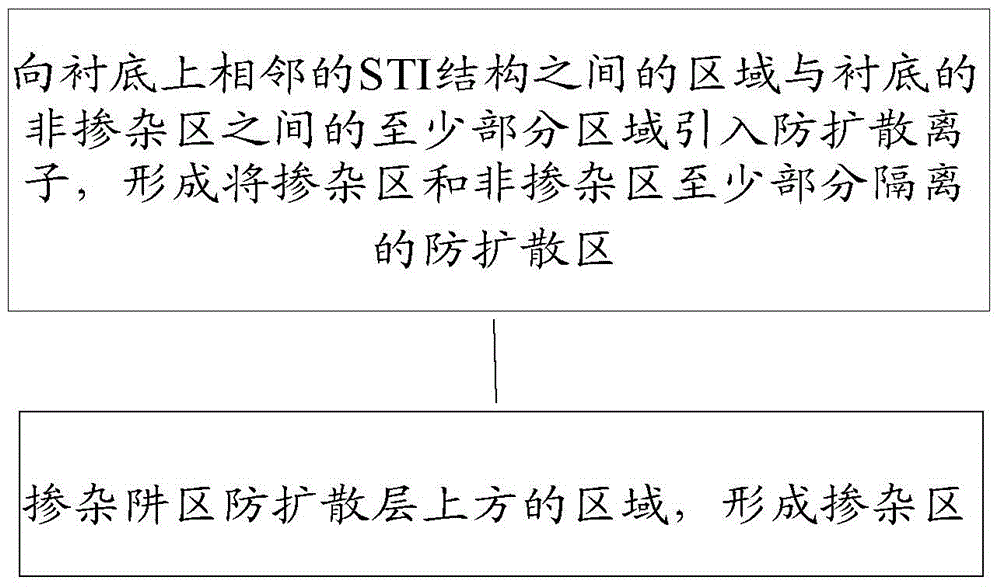

[0045] After completing the step of forming the STI structure 110 on the substrate 100, introduce anti-diffusion ions to the edge of the part of the area on the substrate 100 where the well structure 120 is to be formed (that is, the area betw...

Embodiment 1

[0050] This embodiment provides a method for manufacturing a CMOS device, comprising the following steps:

[0051] Form STI on a single crystal silicon substrate;

[0052] Xenon ions (Xe + ) into the substrate between some STIs, wherein the implantation energy is 500ev, and the implantation dose is 1×10 13 cm -2 , forming a depth of 500nm and a thickness of The anti-diffusion area of the well area;

[0053] Using the ion implantation method of 0° tilt angle / 0° twist angle, phosphorus is doped into the substrate above the anti-diffusion region of the well region, wherein the implantation energy is 200ev, and the implantation dose is 1×10 13 cm -2 , forming an N-type doped region;

[0054] Make the P well in the same way as above, and the P type element is boron;

[0055] A CMOS device is fabricated using the above-mentioned substrate on which the N well and the P well are formed.

Embodiment 2

[0057] This embodiment provides a method for manufacturing a CMOS device, comprising the following steps:

[0058] Form STI on a single crystal silicon substrate;

[0059] Xenon ions (Xe + ) into the substrate between some STIs, wherein the implantation energy is 50000ev, and the implantation dose is 2×10 12 cm -2 , forming a depth of 500nm and a thickness of The anti-diffusion area of the well area;

[0060] Using the ion implantation method of 0° tilt angle / 0° twist angle, phosphorus is doped into the substrate above the anti-diffusion region of the well region, wherein the implantation energy is 20000ev, and the implantation dose is 2×10 12 cm -2 , forming an N-type doped region;

[0061] Make the P well in the same way as above, and the P type element is boron;

[0062] A CMOS device is fabricated using the above-mentioned substrate on which the N well and the P well are formed.

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More