Thin film transistor with single-gate double-channel structure and manufacturing method thereof

A technology of thin film transistors and manufacturing methods, which is applied in the direction of transistors, semiconductor/solid-state device manufacturing, semiconductor devices, etc., can solve the problems of single function of thin film transistors, and achieve the effect of improving current driving ability

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment 1

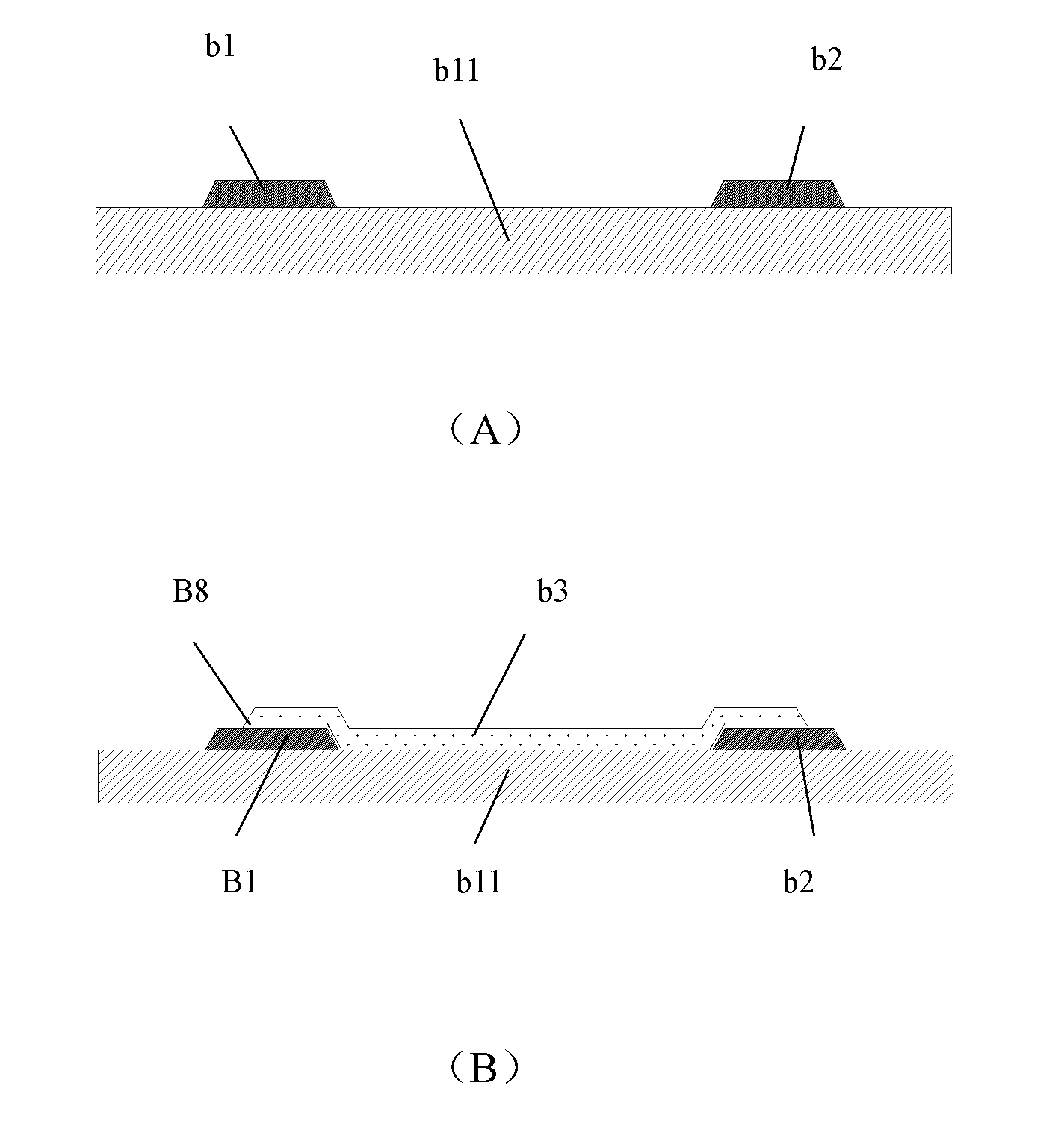

[0041] Please refer to A-G in 2, which show the process sectional view of the thin film transistor with single-gate and double-channel structure of the present invention. The thin film transistor with a single-gate double-channel structure of the present invention includes a substrate b11, a first source b1, a second source b9, a first drain b2, a second drain b10, a gate b5, and a first active layer b3, the second active layer b7; the first source b1 and the first drain b2 are formed on the substrate b11; the first active layer b3 is formed between the first source b1 and the first drain b2 between, the edges of which overlap with the edges of the first source b1 and the first drain b2; the first insulating layer b4 is formed on the first active layer b3; the gate b5 corresponds to the first active layer b3 and formed on the first insulating layer b4; the second insulating layer b6 is formed on the gate b5; the second active layer b7 corresponds to the first active layer b3 a...

Embodiment 2

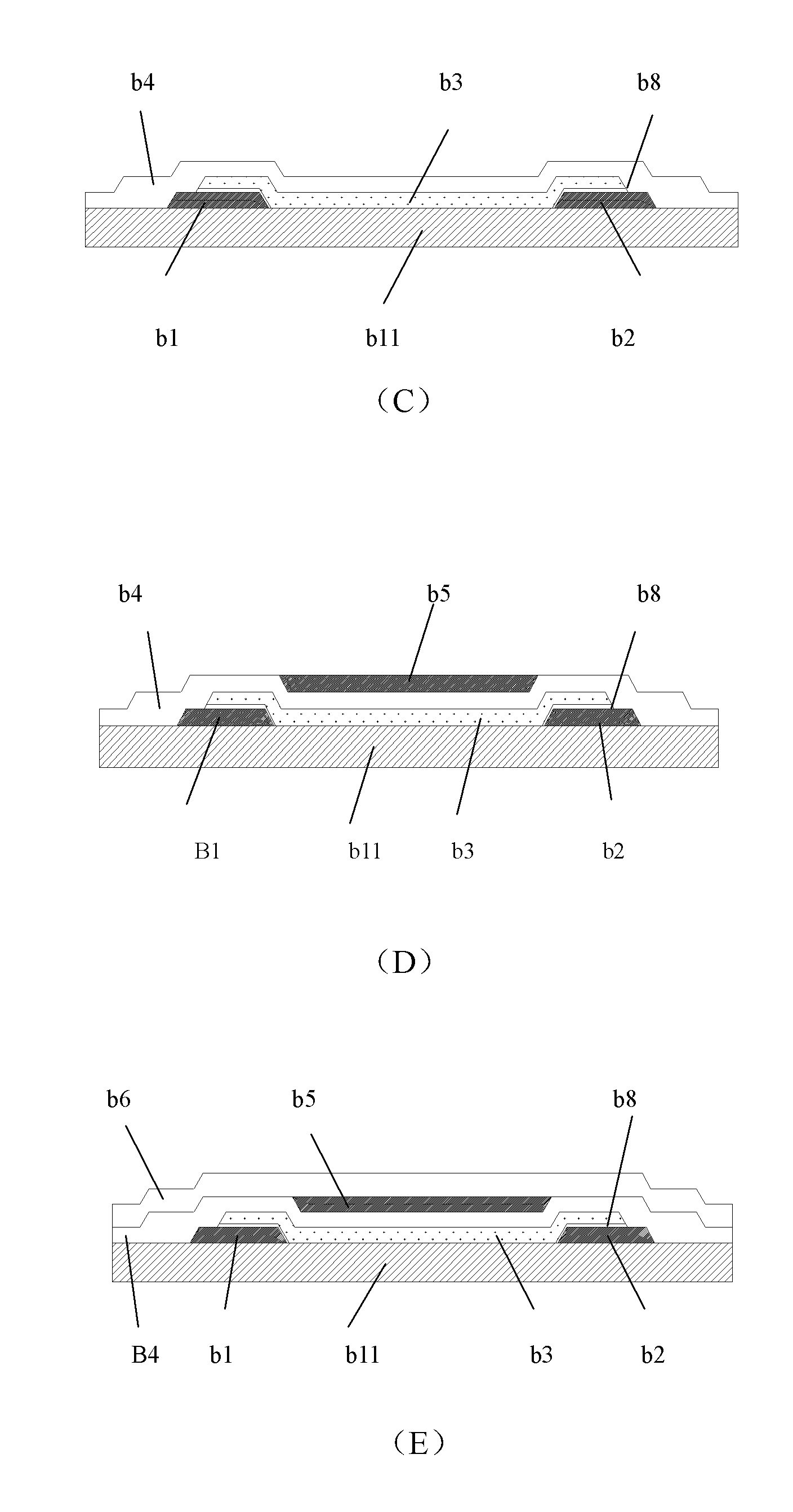

[0053] Please refer to Figs. A to G in Fig. 3, which show a cross-sectional process view of a thin film transistor with a single-gate and dual-channel structure according to Embodiment 2 of the present invention.

[0054] Such as image 3 Shown in Figure G. The thin film transistor with a single-gate double-channel structure of the present invention includes a substrate c11, a first source c1, a first drain c2, a gate c5, a first active layer c3, and a second active layer c7; The first part of the first source c1 and the first drain c2 are formed on the substrate c11; the first active layer c3 is formed between the first source c1 and the first part of the first drain c2, and its edge is in contact with the first part of the first drain c2. The edges of the first part of the first source c1 and the first drain c2 overlap; the first insulating layer c4 is formed on the first active layer c3 and the first source c1 and the first drain c2, and A through hole is left above the s...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More